STD6EX

STD6LE - link loader

MAP - memory map

default      BOUND      10008 - 16 K

BUILD

BOUND = LOW, HIGH

EVANS & SUTHERLAND COMPUTER CORP.

LINE DRAWING SYSTEM MODEL 2

SYSTEM REFERENCE MANUAL

*MIXED UP FOR HALFTONE SYS.*

Evans & Sutherland Computer Corporation

Three Research Road

Salt Lake City, Utah 84112

August 1, 1971

901002-100

COPY \_\_\_\_\_

Prepared by: Russell Athay

Copyright 1971

Evans & Sutherland Computer Corporation

## TABLE OF CONTENTS

|                                                   | <u>Page</u> |

|---------------------------------------------------|-------------|

| 1 SYSTEM OVERVIEW                                 | 1-1         |

| 1.1 System Configuration                          | 1-1         |

| 1.2 General Purpose Processing                    | 1-3         |

| 1.3 Graphic Processing                            | 1-3         |

| 1.3.1 Drawing Instructions                        | 1-3         |

| 1.3.2 Data Forms                                  | 1-5         |

| 1.3.3 Dimension Modes and Coordinate Data Storage | 1-5         |

| 1.3.4 The Display Processing Pipeline Units       | 1-7         |

| 1.4 Programming                                   | 1-7         |

| 2 THE CHANNEL CONTROL                             | 2-1         |

| 2.1 Function                                      | 2-1         |

| 2.2 Structure                                     | 2-1         |

| 2.2.1 Registers of the Channel Control            | 2-1         |

| 2.2.2 Memory Addressing                           | 2-1         |

| 2.3 General Computing Facilities                  | 2-4         |

| 2.3.1 General Purpose Instructions                | 2-4         |

| 2.3.2 The Stack                                   | 2-5         |

| 2.4 Graphic Facilities of the Channel Control     | 2-6         |

| 2.4.1 Display Instructions                        | 2-6         |

| 2.4.2 The X, Y, Z, and W Registers                | 2-6         |

| 2.4.3 Data Fetching for Display Instructions      | 2-7         |

| 2.4.4 Repeat Instructions                         | 2-8         |

| 2.4.5 The Data Sink                               | 2-9         |

| 2.4.6 Returning Output to Memory                  | 2-10        |

| 2.5 The I/O Structure                             | 2-10        |

| 2.5.1 Status Registers                            | 2-10        |

| 2.5.2 Interrupts                                  | 2-11        |

| 2.5.3 Real Time Clocks                            | 2-12        |

| 2.5.4 Memory Protection and Relocation            | 2-13        |

| 2.5.5 Special I/O Functions                       | 2-13        |

| 2.5.6 The Interface from the SEL-840 Side         | 2-14        |

|                                              | <u>Page</u> |

|----------------------------------------------|-------------|

| 3 THE MATRIX MULTIPLIER                      | 3-1         |

| 3.1 Function                                 | 3-1         |

| 3.2 Three-dimensional Matrix Transformations | 3-1         |

| 3.3 Two-dimensional Matrix Transformations   | 3-4         |

| 3.4 Composite Transformations                | 3-4         |

| 3.4.1 Nested Transformations                 | 3-4         |

| 3.4.2 Row-to-Row Moves                       | 3-6         |

| 3.4.3 Matrix Normalization                   | 3-6         |

| 3.5 Two-dimensional Curves                   | 3-6         |

| 3.6 Three-dimensional Curves                 | 3-6         |

| 3.7 Surface Patches                          | 3-9         |

| 3.8 Arithmetic Conventions                   | 3-9         |

| 3.9 Mode Control                             | 3-11        |

| 4 THE CLIPPING DIVIDER                       | 4-1         |

| 4.1 Function                                 | 4-1         |

| 4.2 The Current Point                        | 4-1         |

| 4.3 Relative Data                            | 4-1         |

| 4.4 Two-dimensional Clipping and Division    | 4-1         |

| 4.5 Three-dimensional Clipping and Division  | 4-3         |

| 4.6 Boxing                                   | 4-5         |

| 4.7 HIT and COUNT Functions                  | 4-7         |

| 4.8 Scope Control                            | 4-9         |

| 4.9 The NAME Register                        | 4-9         |

| 4.10 Graph Mode                              | 4-12        |

| 4.11 Mode Control                            | 4-12        |

| 5 THE LINE GENERATOR AND DISPLAY SCOPE       | 5-1         |

| 5.1 Function                                 | 5-1         |

| 5.2 Control                                  | 5-1         |

| 5.2.1 Intensity                              | 5-1         |

| 5.2.2 Scope Selection                        | 5-1         |

| 6 THE LDS-2 ASSEMBLER                        | 6-1         |

| 6.1 General Characteristics                  | 6-1         |

| 6.2 Syntax                                   | 6-1         |

| 6.2.1 Symbols                                | 6-1         |

| 6.2.2 Numbers                                | 6-1         |

| 6.2.3 Current Location Pointer               | 6-1         |

| 6.2.4 Expressions                            | 6-3         |

| 6.2.5 Text Strings                           | 6-3         |

| 6.2.6 Literals                               | 6-4         |

| 6.2.7 Subfields                              | 6-4         |

| 6.2.8 Fields                                 | 6-5         |

| 6.2.9 Statements                             | 6-5         |

|                                                       | <u>Page</u> |

|-------------------------------------------------------|-------------|

| 6.3 Assembler Directives                              | 6-7         |

| 6.3.1 Assembly-Control Directives                     | 6-7         |

| 6.3.2 Object-Control Directives                       | 6-9         |

| 6.3.3 Listing-Control Directives                      | 6-10        |

| 6.3.4 Storage-Allocation Directives                   | 6-10        |

| 7 LDS-2 INSTRUCTION SET                               | 7-1         |

| 7.1 Accessing Data for the Instructions               | 7-1         |

| 7.2 Notation                                          | 7-1         |

| 7.3 Loading and Storing the Channel Control Registers | 7-3         |

| 7.4 Program Control                                   | 7-5         |

| 7.5 Stack Control                                     | 7-10        |

| 7.6 Arithmetic and Logical Operations                 | 7-15        |

| 7.7 Compare Instructions                              | 7-22        |

| 7.8 Unary Instructions                                | 7-25        |

| 7.9 Shifting Instructions                             | 7-29        |

| 7.10 Masking Instructions                             | 7-33        |

| 7.11 Bit Manipulation                                 | 7-34        |

| 7.12 The IOT Instruction                              | 7-37        |

| 7.13 Load/Unload Pipeline Registers                   | 7-40        |

| 7.14 Drawing Instructions                             | 7-58        |

| 8 FORTRAN SUPPORT ROUTINES                            | 8-1         |

| 8.1 Function                                          | 8-1         |

| 8.2 Data Formats                                      | 8-1         |

| 8.3 Preparation Calls                                 | 8-2         |

| 8.4 Definition and Manipulation Calls                 | 8-5         |

| 8.5 Drawing Calls                                     | 8-25        |

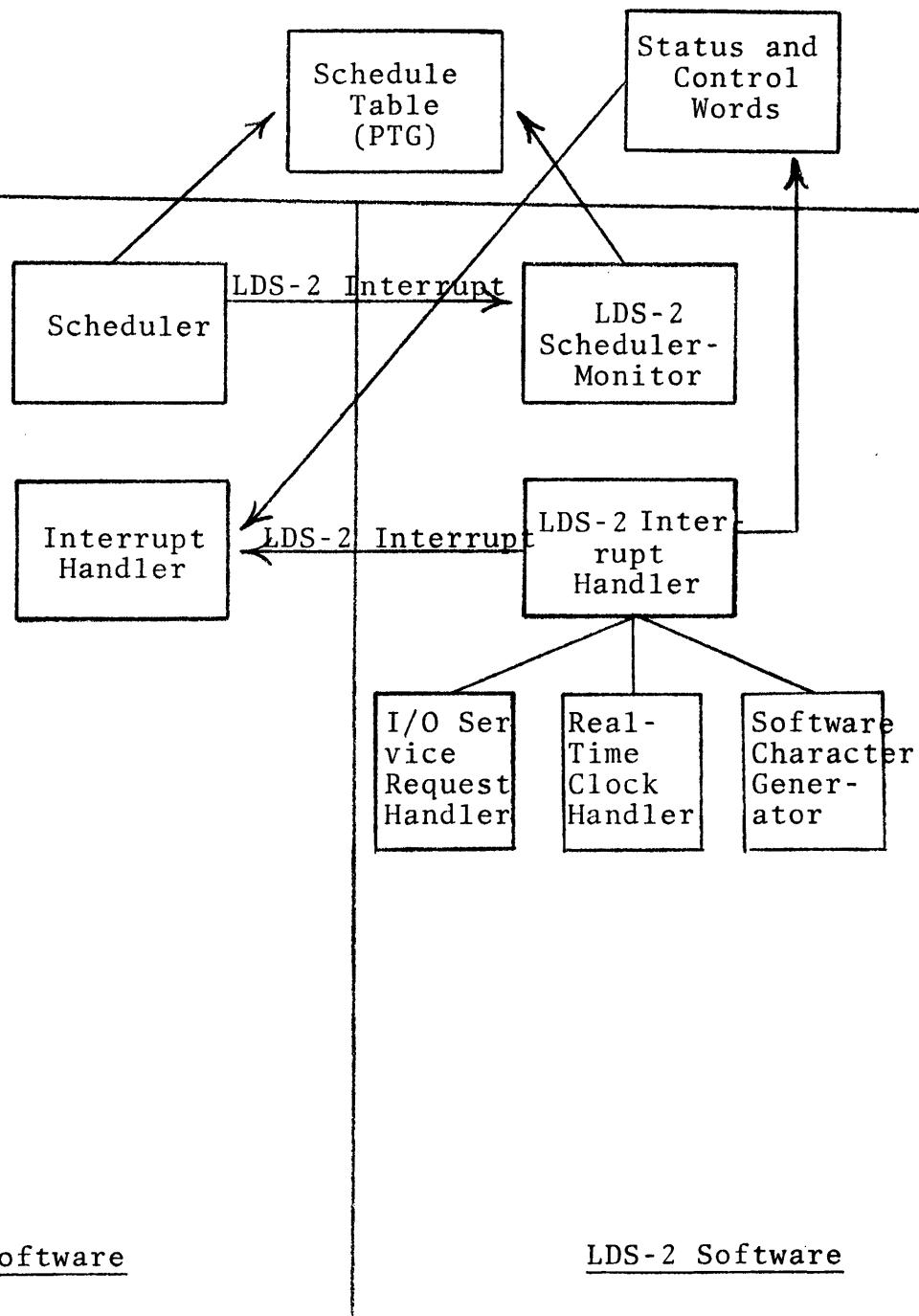

| 9 SOFTWARE INTERFACE                                  | 9-1         |

| 9.1 General                                           | 9-1         |

| 9.2 The Schedulers                                    | 9-1         |

| 9.3 Interrupt Handlers                                | 9-1         |

| APPENDIX I           LDS-2 Mnemonic Construction      | AI-1        |

| APPENDIX II          OPDEF's and EQU's                | AII-1       |

| APPENDIX III        A Note on Homogeneous Coordinates | AIII-1      |

## SYSTEM OVERVIEW

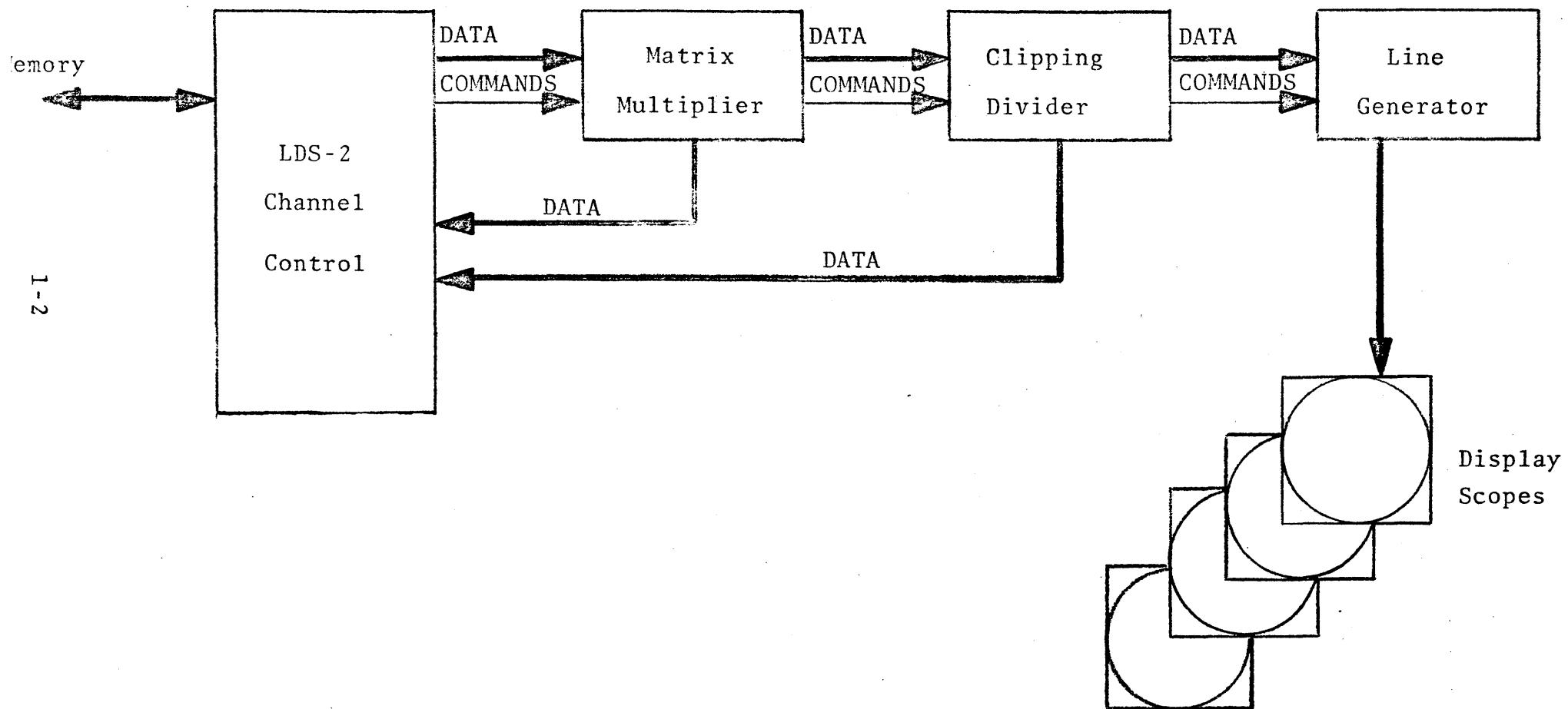

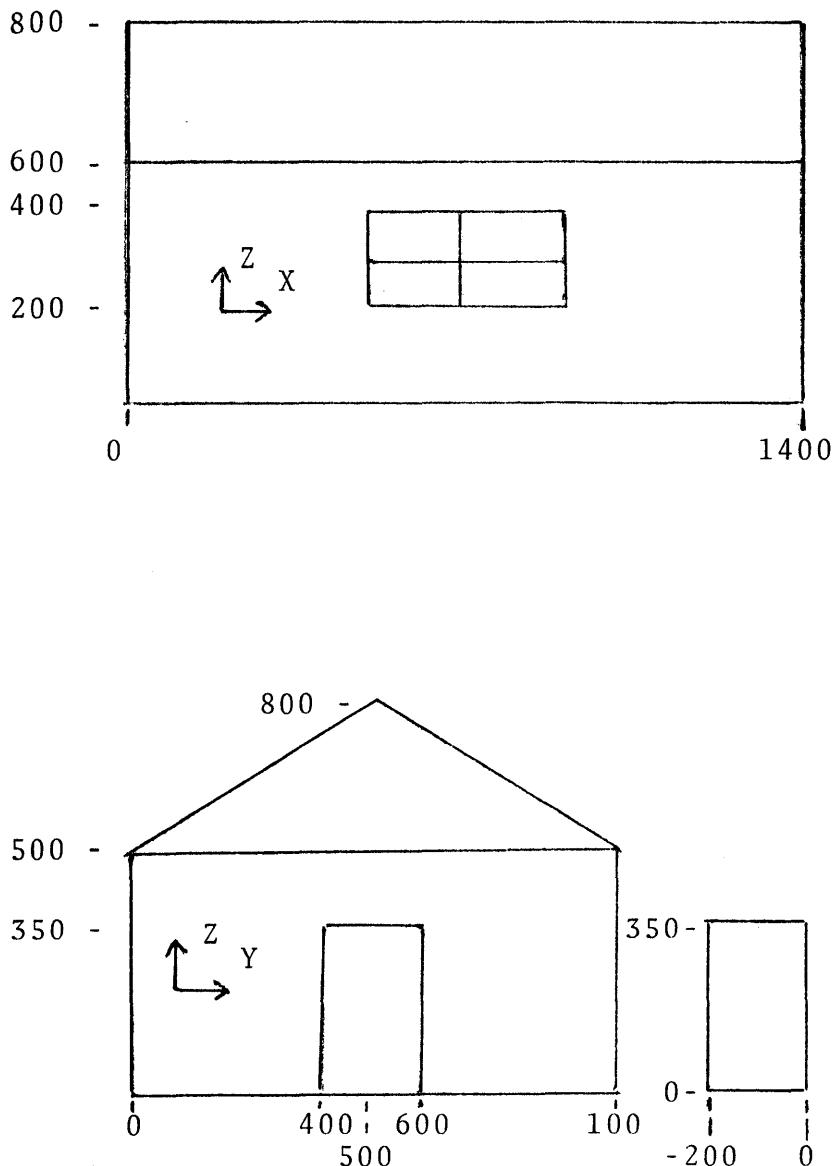

### 1.1 System Configuration

The LDS-2 is a general purpose computer with specialized facilities for graphic processing. In the shared memory configuration the LDS-2 operates as a second processor which shares memory with a host computer. In this configuration the LDS-2 is an independent processor in that it accesses and executes its own programs, but the LDS-2 is dependent upon the host computer for such functions as I/O and the regulation of its operation (i.e., starting and stopping the LDS-2, scheduling users, etc.). Figure 1.1 shows the configuration of the LDS-2. The following units make up the LDS-2:

The Channel Control. The Channel Control accesses memory to provide the instructions and data needed by the LDS-2. The Channel Control executes all of the general purpose processing instructions and interprets display instructions and provides commands and data to the display processing pipeline devices.

The Matrix Multiplier. The Matrix Multiplier can rotate, translate and scale the drawing to be displayed. The Matrix Multiplier also can iterate sets of difference equations to draw curves and families of curves.

The Clipping Divider. The Clipping Divider allows the user to specify the portion of the drawing he wishes to view. The Clipping Divider will automatically eliminate all portions of the drawing which lie outside the viewing area, and then scale and position the picture on the Display Scope. The Clipping Divider also performs three-dimensional perspective division.

The Line Generator and Display Scopes. The Line Generator converts the digital specification of endpoints into analog sweep voltages which are used to drive the deflection systems of the Display Scopes.

### 1.2 General Purpose Processing

The LDS-2 has a large and versatile instructions set, its own internal high-speed register memory, and facilities for interpreting complex data structures. Instructions are provided to perform the following tasks:

- Arithmetic and logical operations

- Shifting, masking, and bit manipulation

- Comparisons and conditional skips

- Program flow control and stack manipulation

## LDS-2 DISPLAY SYSTEM CONFIGURATION

Figure 1.1

The LDS-2 Channel Control has a high-speed register memory which is composed of sixteen registers. While all but four of these registers are used for special functions, all registers may be manipulated with equal ease, and when the special function to which a register is dedicated is not being used, that register may be used as a general purpose accumulator.

The LDS-2 provides facilities for direct, indirect, and indexed addressing, but it is also a stack machine with very powerful and versatile stack manipulation facilities. Special stacks are operated to hold return locations and parameter information from the display processing pipeline. The user may also set up and operate additional general purpose stacks.

### 1.3 Graphic Processing

In addition to its general computing capabilities, the LDS-2 can interpret drawing definitions, perform graphic transformations on the drawing and display a picture on the Display Scope. For the purposes of this manual, the following words will take on special meanings to avoid confusion.

Drawing. The drawing is the definition stored in memory which consists of two- or three-dimensional coordinate data and display instructions which determine how these coordinate values should be interpreted and how the points should be connected. The drawing is in "page coordinates."

Picture. The lines and dots which finally appear on the Display Scope are referred to as the picture. The picture is in "scope coordinates."

Page Coordinates. The page is a virtual drawing space which stretches from  $-2^{N-2}$  to  $+2^{N-2}$  in each coordinate axis. The LDS-2 performs all arithmetic and graphic processing using two's complement arithmetic, so one may think of the page as a fixed point, two's complement drawing space. Since the page is extremely large, no checking is done to detect overflow of the page boundaries.

Scope Coordinates. Scope coordinates are centered about zero and stretch from  $-2^{15}$  to  $+2^{15}$  in X and Y. Before the drawing is displayed, it is mapped into scope coordinates and becomes the picture.

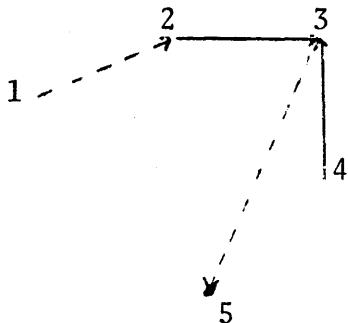

#### 1.3.1 Drawing Instructions

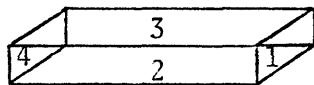

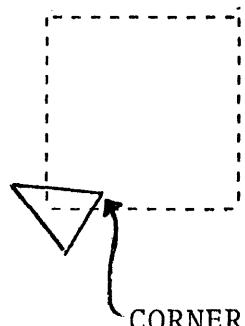

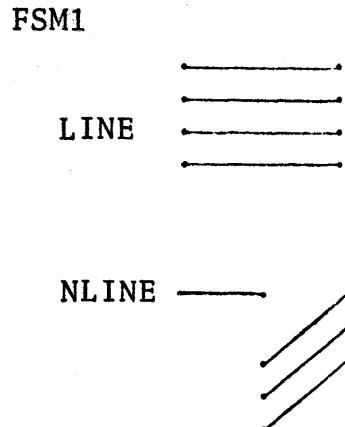

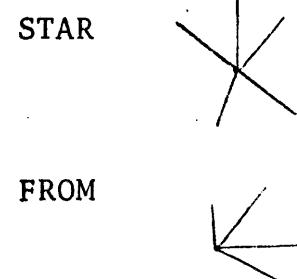

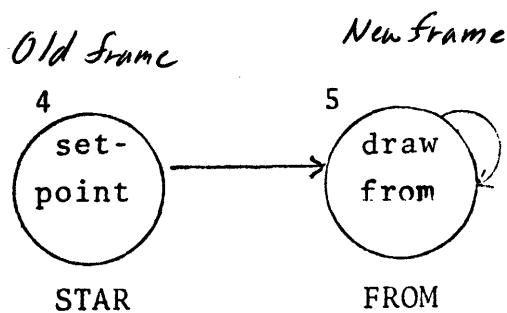

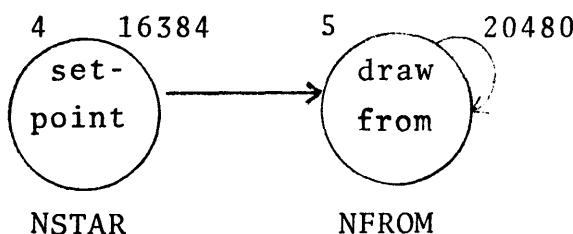

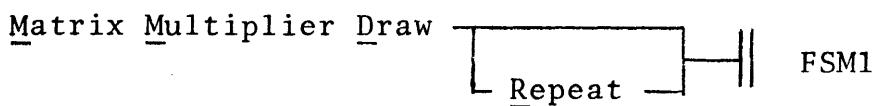

The drawing instructions generally result in some movement of the beam on the scope. The upper half of Figure 1.2

## DRAWING OPERATIONS

### Basic Drawing Operations

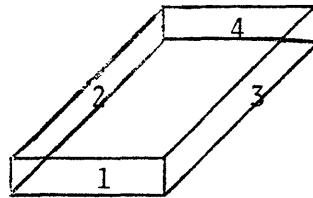

- 1 is current point

- "Set point" to 2 (2 becomes current point)

- "Draw to" 3 (3 becomes current point)

- "Draw from" 4 (3 remains current point)

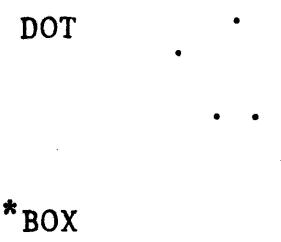

- "Dot" 5 (5 becomes current point)

### Complex Drawing Operations

"Polygon" = Set point, draw to, draw to, draw to...

"Star" = Set point, draw from, draw from...

"Lines" = Set point, draw to, set point, draw to, set point...

"Dots" = dot, dot, dot.

Figure 1. 2

1-4

illustrates the basic drawing operations that are available. These operations are done in relation to the "SAVE point" which indicates the current position of the beam on the scope. It is also possible to initiate a repeating series of the basic drawing operations with a single instruction, as shown on the lower half of Figure 1.2.

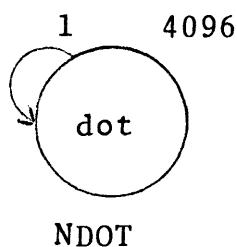

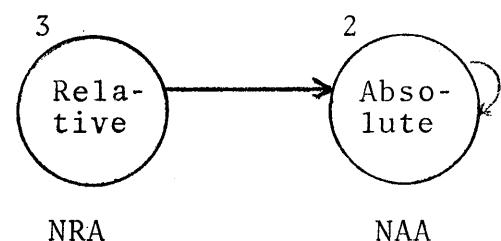

### 1.3.2 Data Forms

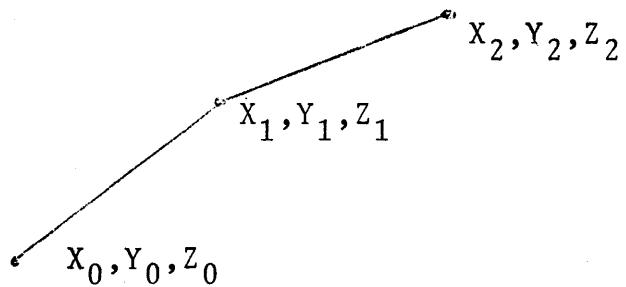

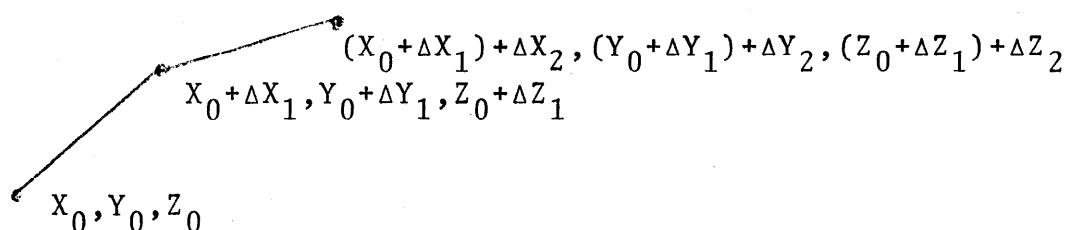

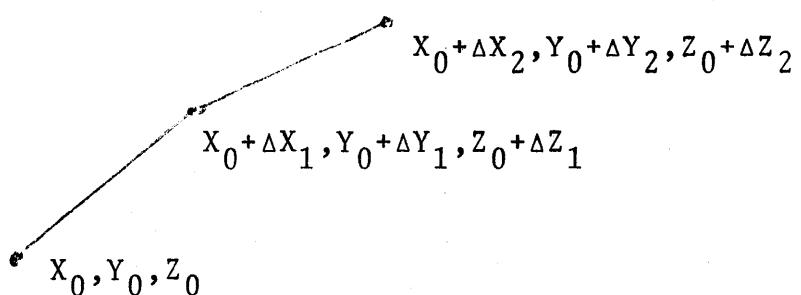

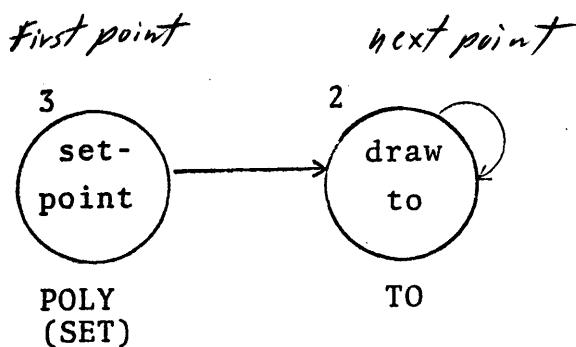

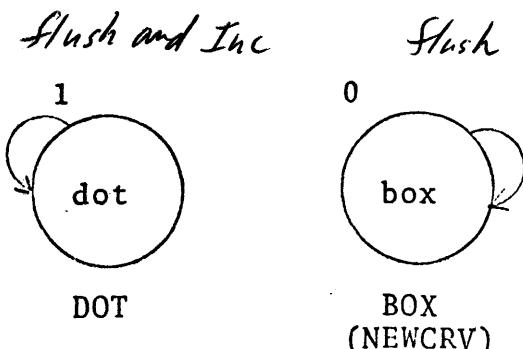

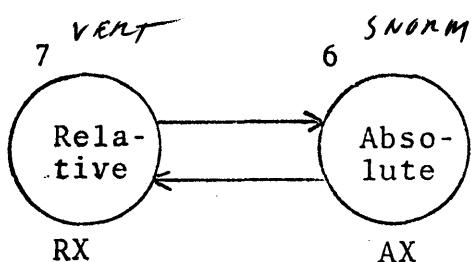

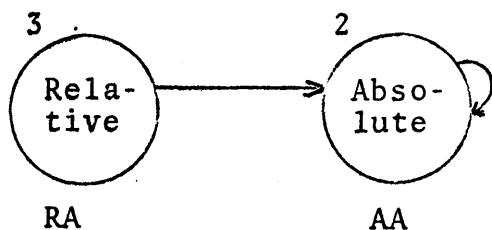

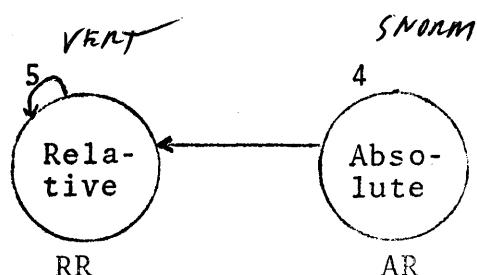

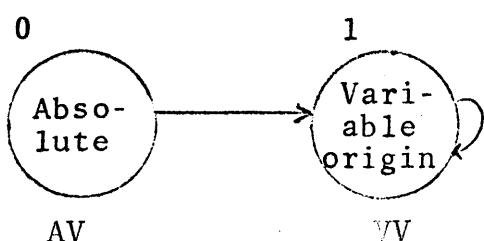

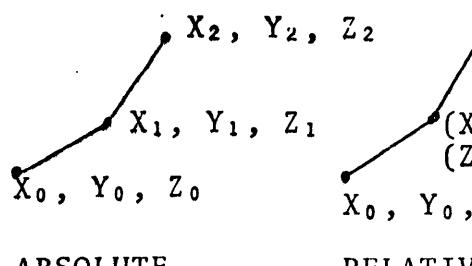

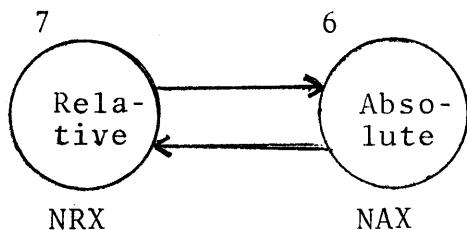

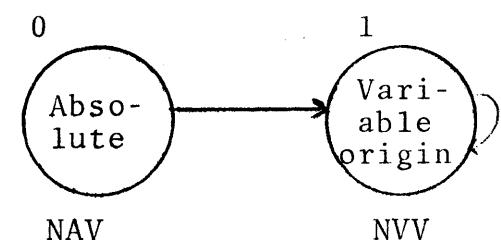

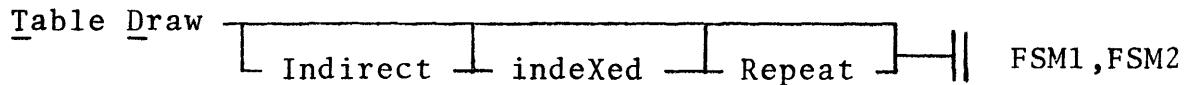

The coordinate data may be interpreted either as an absolute specification of the endpoint location, or as one of two forms of displacement specifications. The display instructions specify how the data are to be interpreted. Figure 1.3 illustrates the three manners of interpreting the coordinate data. "Absolute" data simply specify the position of the endpoint. "Relative" data are taken as an offset from the "current point." And "variable origin" causes the data to be taken as an offset from a user-specified "origin" which is held in the registers of the Channel Control.

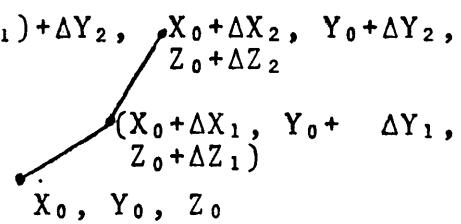

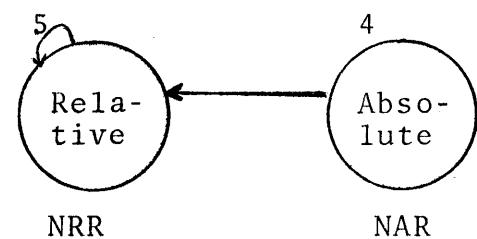

### 1.3.3 Dimension Modes and Coordinate Data Storage

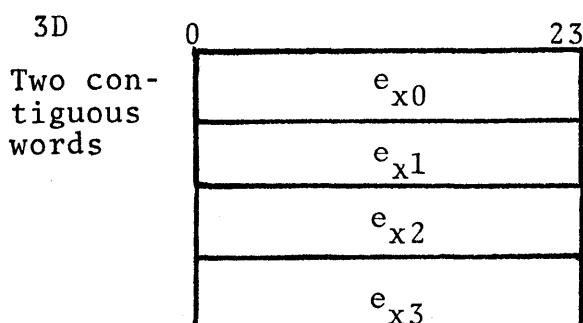

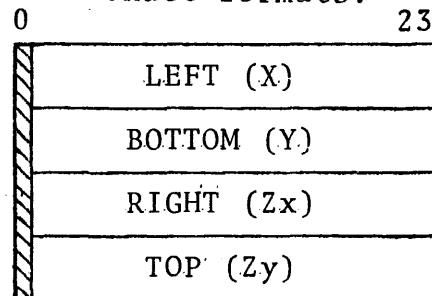

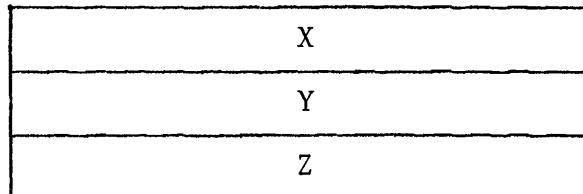

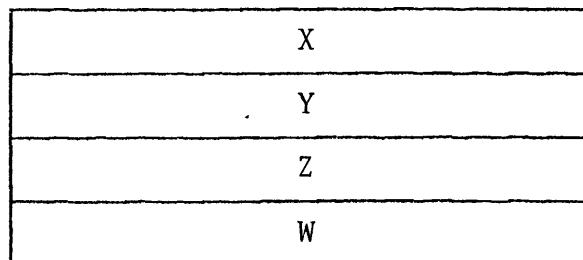

The LDS-2 is always in one of four dimension modes, and these modes affect how many words of data are fetched for display instructions (both drawing instructions and pipeline register load/unload instructions). The two-dimensional mode causes the LDS-2 to pick up two contiguous words of data which are interpreted as the X coordinate and the Y coordinate. In "homogeneous" mode (sometimes referred to as 4D) the LDS-2 picks up four words of data which are interpreted as X Y Z and W. This data format is known as homogeneous coordinates, where W is the homogeneous element and is used as a scale factor. Data fed through the Matrix Multiplier should be in homogeneous coordinates. (See Appendix III for a description of homogeneous coordinates and their usage.) If the Matrix Multiplier is turned off, the four words of data fetched by the LDS-2 will be interpreted as X Y Zx and Zy, where Zx and Zy are generally the same. This is the form in which the Clipping Divider expects data.

Two special three-dimension modes are provided to allow more compact storage of data. These modes apply only to drawing instructions (i.e., pipeline load/unload instructions still pick up four words). "Matrix Multiplier three-dimensions" (MM3D) causes the LDS-2 to pick up three words which are interpreted as X Y and Z. The LDS-2 then supplies the fourth word, which is the fractional approximation for "1" (223-1) to serve for the "W" element. Since W is often "1", when using homogeneous coordinates, MM3D may often be used to save storage. MM3D should only be used, however, if the Matrix Multiplier is active.

If the Matrix Multiplier is not active and data are being fed directly to the Clipping Divider, "Clipping Divider

DATA FORMS

ABSOLUTE

RELATIVE

VARIABLE ORIGIN

Figure 1.3

1-6

"three dimensions" (CD3D) may be used. This mode also causes the LDS-2 to pick up three words of data, but in this case the fourth word provided by the LDS-2 is a copy of the third word to give X Y Z Z, which is the form that the Clipping Divider expects.

#### 1.3.4 The Display Processing Pipeline Units

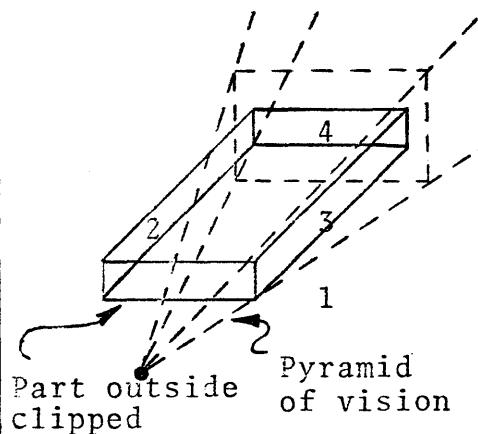

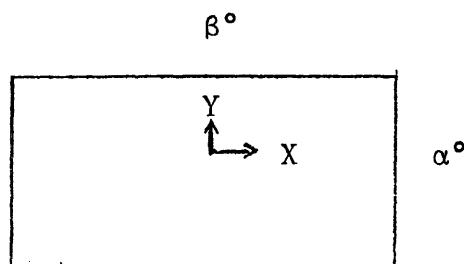

The display processing pipeline units perform graphic transformations on the coordinate data as they pass down the pipeline. The Matrix Multiplier and Clipping Divider contain their own internal storage registers to hold the parameters that are used in the graphic transformations. For instance, the Matrix Multiplier holds four  $4 \times 4$  matrices. When the Matrix Multiplier is active, the coordinate data are multiplied by the values in the first matrix as they pass down the pipeline. These matrix multiplications may be used to rotate, translate, and scale the drawing. Similarly, registers in the Clipping Divider hold the "window" and "viewport" values which are used to map the coordinate data from page coordinates into scope coordinates. Details of the operation of the pipeline devices are given in Chapters 3, 4 and 5. Figure 1.4 gives a pictorial representation for the graphic processing performed by the LDS-2.

Because the parameters for the graphic processing are held internally by the devices which perform this processing, the data base can remain "pure;" that is, motion and other transformations can be implemented by changing the parameters in the pipeline registers rather than changing the coordinate data as it is stored in memory. The registers of the pipeline devices may be loaded or unloaded with these parameters by LDS-2 instructions.

#### 1.4 Programming

The LDS-2 assembles its own programs and has its own assembly language (see Chapters 6 and 7 of this manual). Fortran callable support routines which generate code for the LDS-2 are also provided as an option. These routines allow the Fortran user to make use of the graphic capabilities of the LDS-2 through Fortran calls. The Fortran support routines are discussed in Chapter 8.

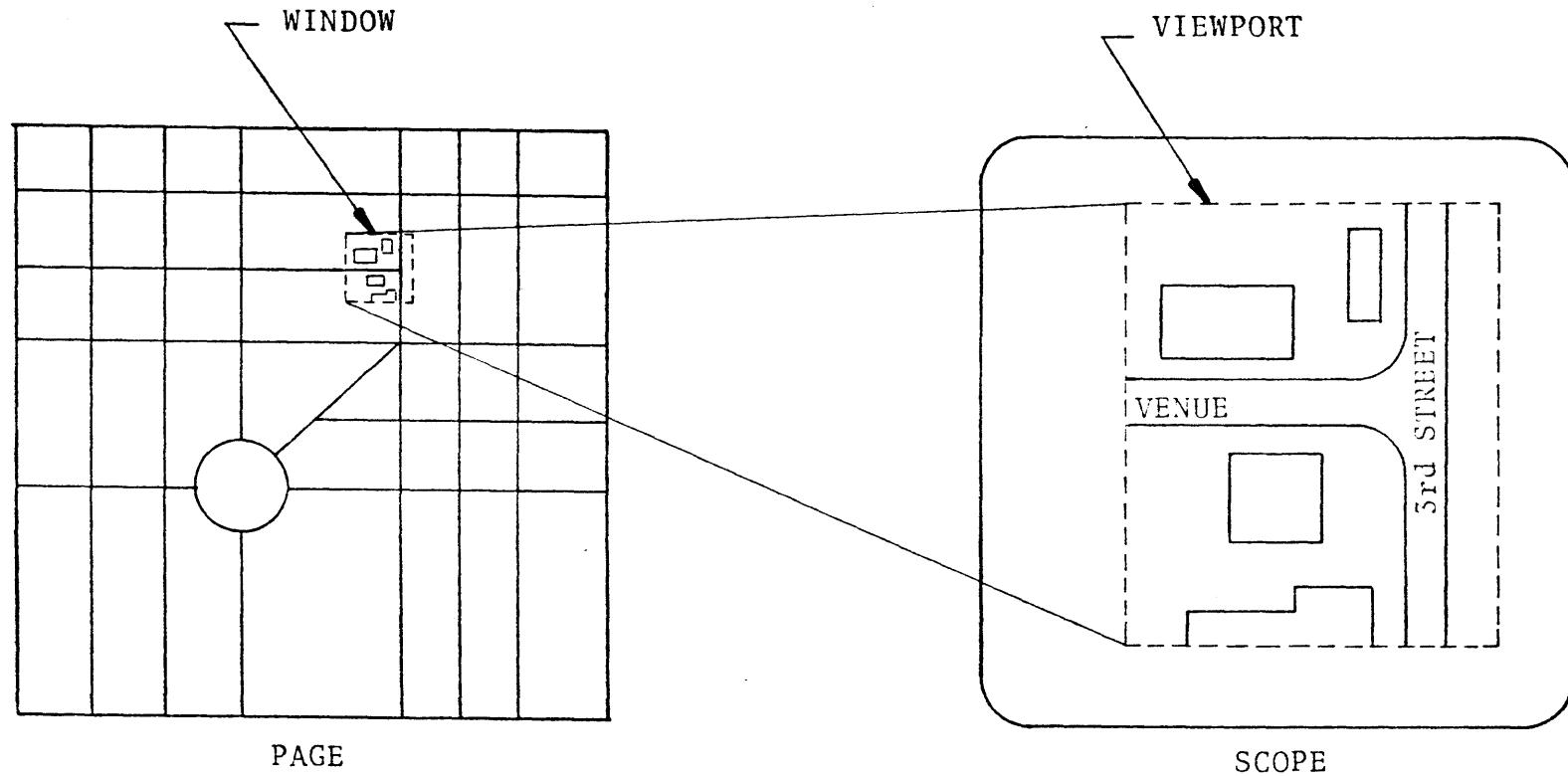

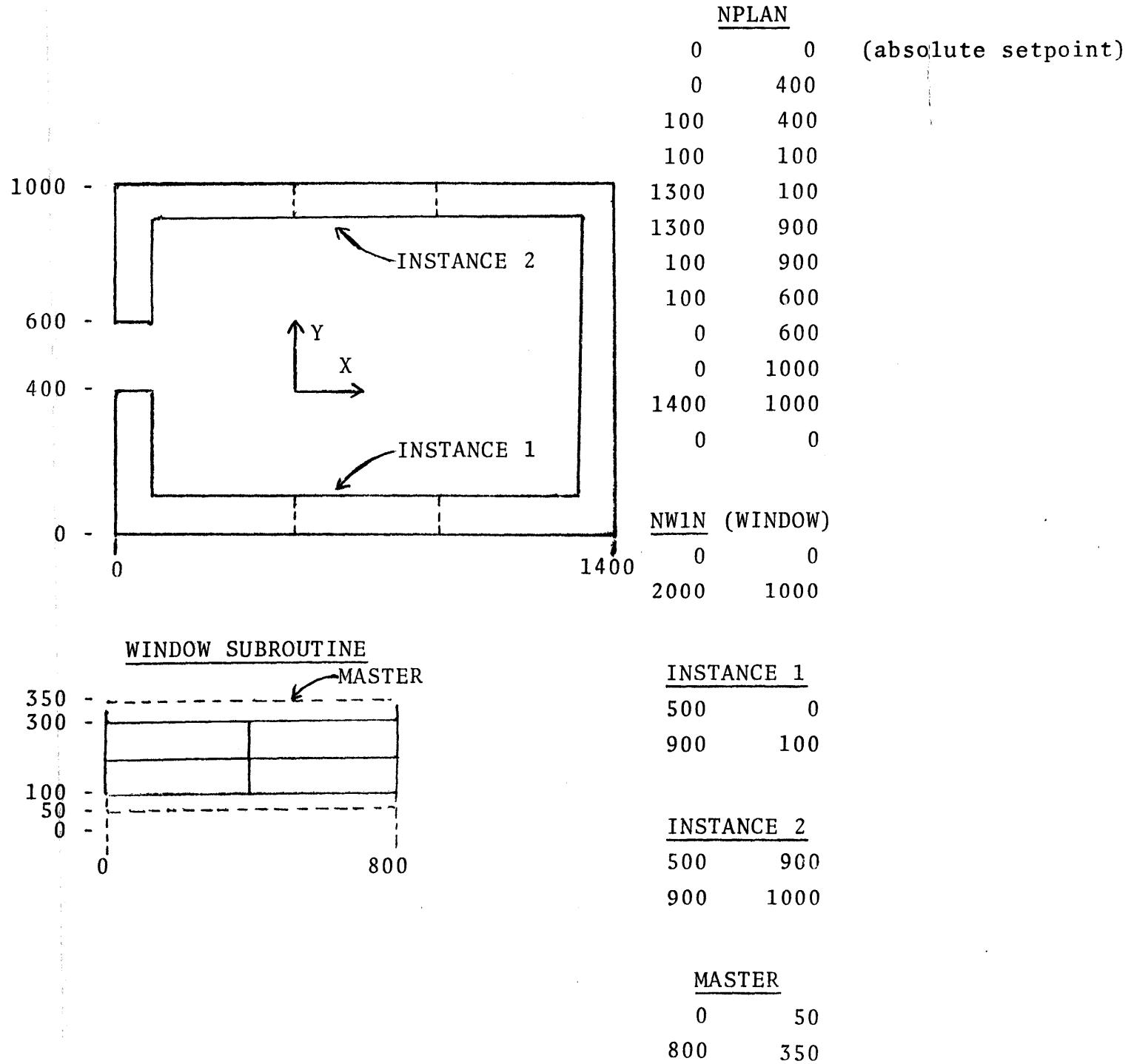

The drawing is defined in the user-chosen drawing space and a "window" is specified.

2. All parts of the drawing outside the "window" are eliminated by the Clipping Divider.

3. The clipped drawing is mapped onto the "viewport" on the Display Scope.

#### Two-dimensional windowing

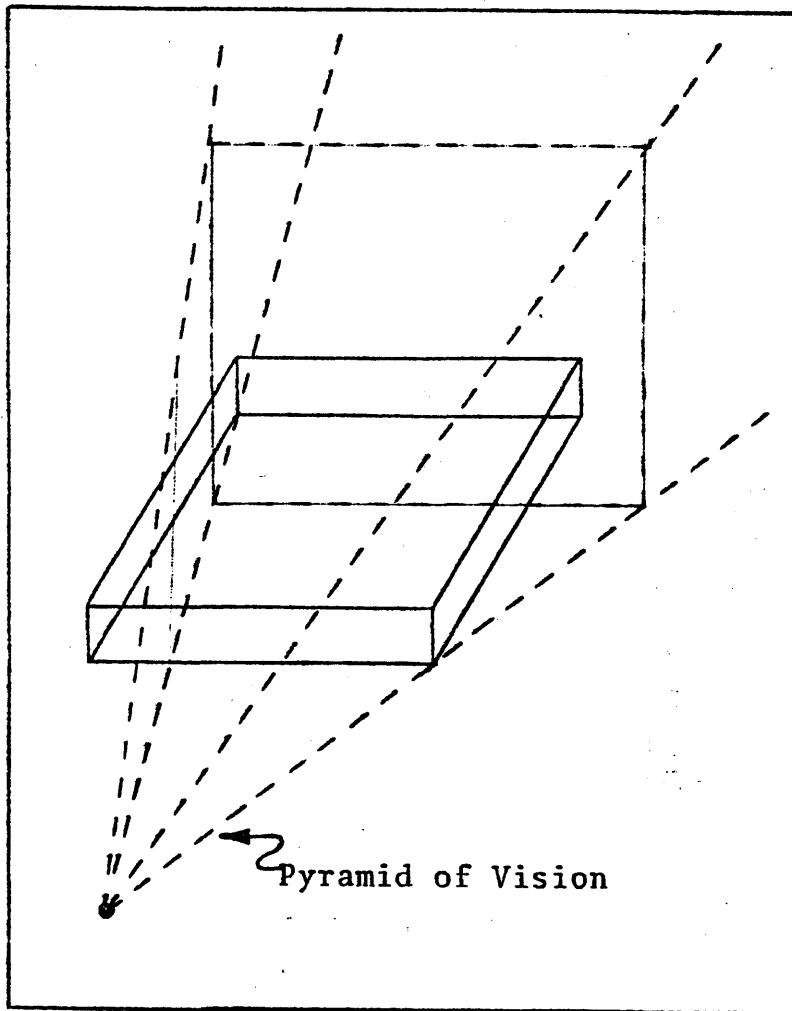

The drawing is defined in a three-dimensional drawing space.

2. The Matrix Multiplier rotates, translates, & scales the drawing.

3. The drawing is compared to a pyramid of vision by the Clipping Divider

4. The drawing is clipped, and put in perspective, then mapped onto the viewport of the Display Scope.

#### Three-dimensional processing

Figure 1.4

## CHAPTER 2

### THE CHANNEL CONTROL

#### 2.1 Function

The Channel Control functions as a general purpose processor and as the control unit for the LDS-2. The Channel Control has general computing capabilities which allow it to assemble its own programs and process both graphic and non-graphic data. But in addition to these general facilities, the Channel Control has special graphic capabilities which allow it to interpret display programs and to control the display processing pipeline units of the LDS-2.

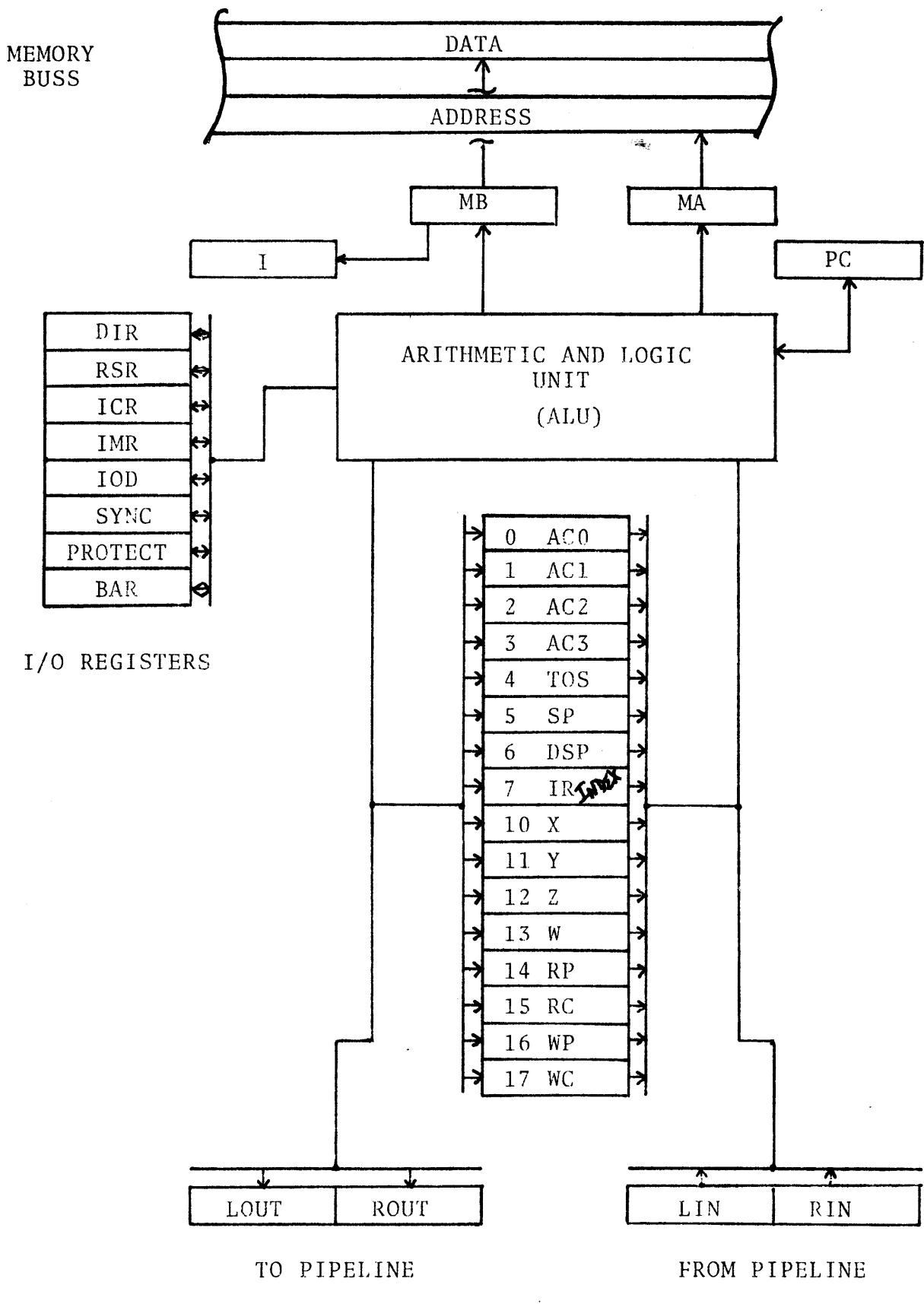

#### 2.2 Structure

A block diagram of the Channel Control is shown in Figure 2.1. The Channel Control operates out of the memory of the host computer by providing memory addresses and then either accepting or transmitting data or instructions. The Arithmetic and Logical Unit (ALU) provides the Channel Control with the ability to do general purpose data processing. The Channel Control has its own high-speed I/O buss which facilitates the communication between the Channel Control and several registers which function as I/O units to the Channel Control. These registers are described in Section 2.5.

#### 2.2.1 Registers of the Channel Control

The Channel Control is organized around sixteen registers which form a high-speed register memory. Four of these registers serve as general purpose accumulators while the other twelve are dedicated to special functions. However, all registers may be manipulated with equal ease and all registers may be used with most instructions. It is thus possible to use the dedicated registers as general purpose accumulators if the function to which they are dedicated is not being used. For instance, if the system is not returning processed data from the pipeline back into memory, the WP and WC registers can safely be used as general purpose accumulators. Table 2.2 lists the registers of the Channel Control and briefly describes their functions. The use of these registers is more fully described in the course of this chapter.

#### 2.2.2 Memory Addressing

The LDS-2 divides memory into pages of fixed length and fixed location. A page is  $2^{(n-8)}$  words long where n is the number of bits per memory word in the system. For a 24-bit LDS-2 the page is 64K words long so paging considerations generally disappear. The address specified in addressing

### STRUCTURE OF THE CHANNEL CONTROL

Figure 2.1

## CHANNEL CONTROL REGISTER MEMORY

| <u>Register</u> | <u>Mnemonic</u> | <u>Dedicated Use</u> | <u>Functional Characteristics</u>                        |

|-----------------|-----------------|----------------------|----------------------------------------------------------|

| 0               | AC0             | undedicated          | general purpose accumulator                              |

| 1               | AC1             | undedicated          | general purpose accumulator                              |

| 2               | AC2             | undedicated          | general purpose accumulator                              |

| 3               | AC3             | undedicated          | general purpose accumulator                              |

| 4               | TOS             | Top Of Stack         | top element of SP stack                                  |

| 5               | SP              | Stack Pointer        | decrements before writing in the old PC for a pushjump   |

| 6               | DSP             | Data Sink Pointer    | increments before writing in data from a sink operation  |

| 7               | IR              | Index                | index register                                           |

| 10              | X               | X current point      | updated automatically by drawing instructions            |

| 11              | Y               | Y current point      | updated automatically by drawing instructions            |

| 12              | Z               | Z current point      | updated automatically by drawing instructions            |

| 13              | W               | W current point      | updated automatically by drawing instructions            |

| 14              | RP              | Read Pointer         | points to the location of coordinate data tables         |

| 15              | RC              | Read Counter         | increments once per coordinate point read through the RP |

| 16              | WP              | Write Pointer        | increments after writing data from pipe.                 |

| 17              | WC              | Write Counter        | increments once per word written through WP              |

Table 2.2

instructions is taken as an address within the page and is added to the 8-high order bits of the Program Counter (PC) to obtain the effective address. Direct addresses may not cross page boundaries (i.e., they must be within the current page).

Indirect addressing may be specified with all addressing instructions. When the indirect bit of the instruction word is set, the effective address is the contents of the location directly addressed. The directly addressed location must be within the current page, but the indirect address may be anywhere within the total addressing space. Only one level of indirection is available.

Some addressing instructions may also be indexed. Indexing causes the contents of the Index Register (IR) to be added to the address specified in the instruction in order to calculate the effective address. Since the IR is a full word length register, the effective address may lie anywhere within the total addressing space. If both indirection and indexing are specified, the indirection is performed before the indexing. Examples of the addressing scheme of the LDS-2 are given in Section 7.4.

## 2.3 General Computing Facilities

The LDS-2 has a large and versatile instruction repertoire which makes it convenient for a large variety of general purpose processing tasks. The availability of the sixteen registers in register memory and the stack mechanism add to the processing power of the LDS-2.

### 2.3.1 General Purpose Instructions

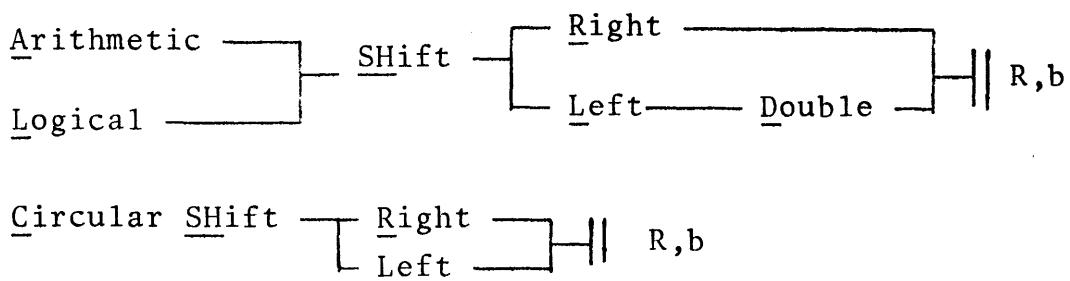

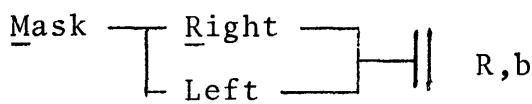

The general purpose instructions of the LDS-2 provide the following functions:

Load and store the Channel Control registers from memory or other registers

Program control (jump, pushjump, and execute)

Arithmetic and logical operations

Increment and decrement registers and skip on condition

Compare two registers and skip on condition

Arithmetic, logical and circular shifts

Masking

### Stack control (push and pop with increment or decrement)

The individual instructions are explained in detail in Chapter 7, but it is useful to keep these general functions in mind while attempting to understand the LDS-2.

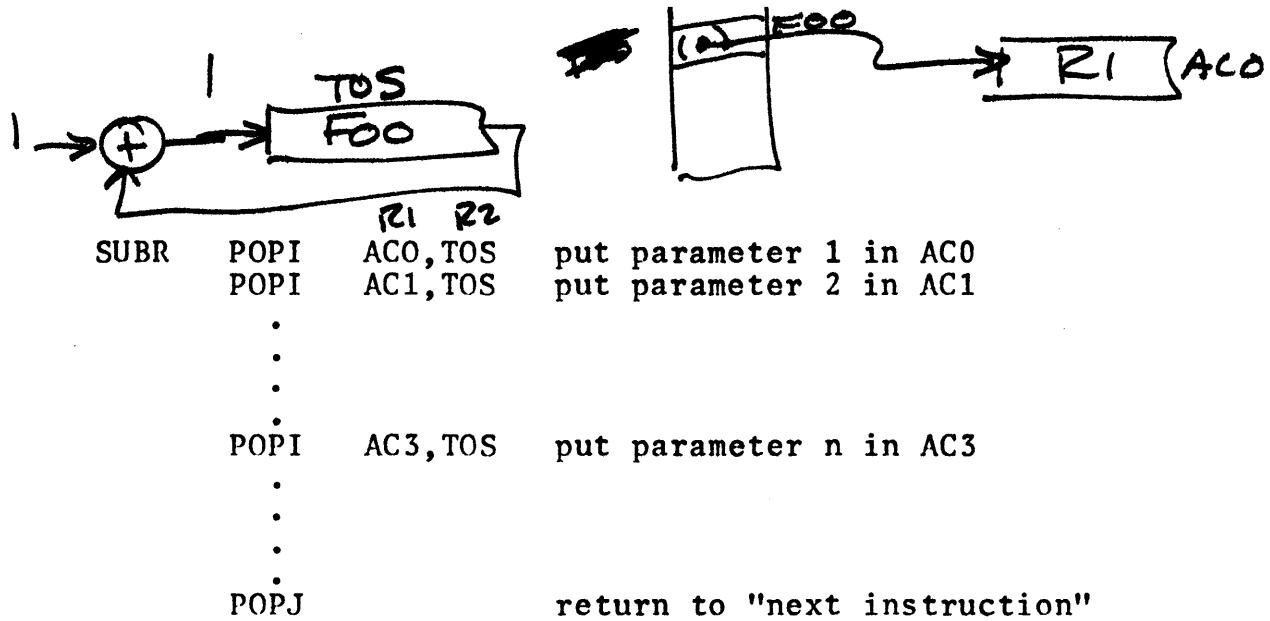

#### 2.3.2 The Stack

The LDS-2 operates two special purpose stacks and allows the user to operate additional general purpose stacks. One of the special purpose stacks is known as the "data sink" and is used to store parameters from the pipeline registers. The data sink is described in Section 2.4.5. The other special purpose stack is used for storing return locations (i.e., old PC values). This stack operates in a special way because the top element of the stack is held in the Channel Control's TOP OF STACK (TOS) register rather than in memory. Thus, the STACK POINTER (SP) points not to the top of the stack, but rather to the last element stored in the memory portion of the stack, which is effectively the second element in the stack. Since the top element in the stack is in the TOS register it is immediately available to the user. When pushing the old PC onto this stack, the following process occurs:

SP-1 → SP      decrement the stack pointer;

TOS → C(SP)      push the TOS;

PC → TOS      save the PC.

When the stack is popped to return the old PC the reverse path is followed:

TOS → PC      return old PC;

C(SP) → TOS      pop into the TOS;

SP+1 → SP      increment the stack pointer.

This whole process is invisible to the user so that he may simply consider the TOS as the top element in the stack.

In addition to these two special purpose stacks, the LDS-2 provides the user with convenient facilities for implementing other stacks which may be used and manipulated under program control. Any of the Channel Control's registers may be used as a stack pointer with which to push the value held in another register onto the stack, or to pop an element off of a stack back into a register. This "stack pointer" may be incremented or decremented either before or after the register is pushed or popped, so that the user has the full range of possibilities for stack control. Because the LDS-2 has such convenient stack-control facilities, it is often best to treat the LDS-2 as a stack machine.

## 2.4 Graphic Facilities of the Channel Control

In addition to its general purpose computing capabilities, the LDS-2 Channel Control has special facilities for interpreting display-oriented instructions and controlling the LDS-2 display processing pipeline.

### 2.4.1 Display Instructions

The display instructions of the Channel Control fall into two groups:

Drawing Instructions. The drawing instructions result in the transmission of the coordinate data to the processing pipeline. The drawing instructions define the topology of the drawing.

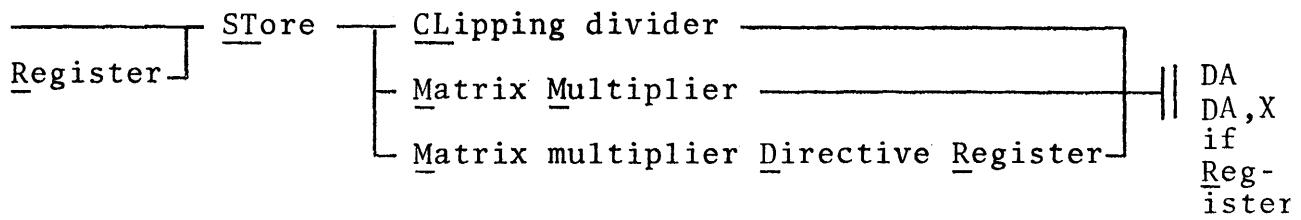

Pipeline Load/Unload Instructions. The display processing pipeline units contain parameter registers. The values in these registers are used to process the coordinate data and thus affect the picture that is displayed. The Channel Control loads and unloads these registers either singly or in groups.

All of the display instructions require the Channel Control to generate a command for the pipeline and provide the necessary data. The Channel Control can fetch this data from memory or from its own internal registers.

### 2.4.2 The X, Y, Z, and W Registers

The X, Y, Z, and W registers of the Channel Control maintain the coordinates of the current point which is used as the base for relative and variable origin drawing instructions. A relative drawing instruction causes the incoming data to be added to the values in these registers before it is sent down the pipeline and the contents of the registers to be updated to the computed value of the new point. Variable origin instructions also cause the additions to be performed, but the contents of the registers are not updated, so that the next point will also be relative to the "variable origin."

The point held in the X, Y, Z, and W registers of the Channel Control usually corresponds to the "current point" held in the SAVE registers of the Clipping Divider. When processing a "variable origin" instruction, however, the X, Y, Z, and W registers are not updated in order to make all data relative to the "variable origin." The SAVE registers of the Clipping Divider are updated, however, thus at the end of a variable origin sequence the two sets of registers will contain different values. Because of this, it is a good idea to follow all variable origin

instructions with either a "setpoint," a drawing operation in absolute mode, or another variable origin operation.

Note, that the relative pipeline load instructions do not use the X, Y, Z, and W registers as a base. For these instructions, data are sent to the pipeline in relative form and converted by the pipeline units themselves.

#### 2.4.3 Data Fetching for Display Instructions

Addresses for the coordinate data for drawing instructions may come from one of two sources. The single point drawing instructions (see Section 7.14) specify an address as part of the instruction word. This address may be either direct or indirect and may be indexed (remember that indexing is performed after indirection). The table draw instructions (see Section 7.14) rely on the contents of the READ POINTER (RP) for the address. The contents of the RP may be used either as the direct address or as an indirect address which contains the effective address. If indirection is specified, indexing is also available, but if indirection is not specified (i.e., the contents of the RP are taken as the direct address), then indexing may not be specified. When indirection and indexing are specified, the contents of the INDEX REGISTER (IR) are added to the contents of the word addressed by the RP, and the result is used as the effective address. The pipeline load/unload instructions (see Section 7.13) rely on the RP just as the table draw instructions, but only direct addressing is available.

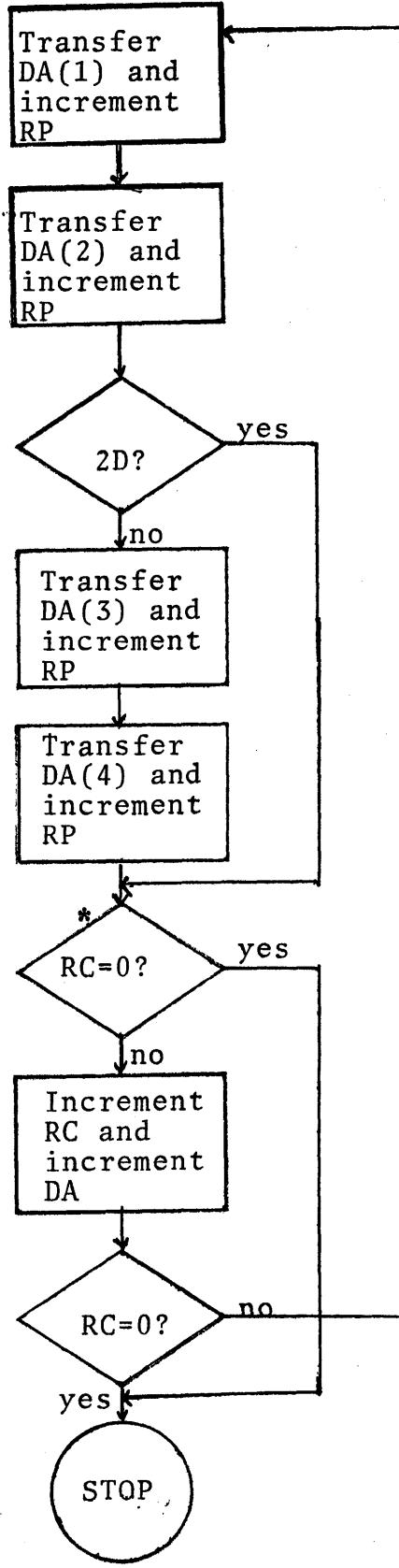

The RP is incremented after each use so that it can step through a contiguous table of data. The RP may be initialized to the beginning of a new table by loading it with the appropriate address.

The number of words of data fetched by the display instructions depends on the dimension mode of the Channel Control. The Channel Control has four modes:

Two Dimensions. In 2D two contiguous words of data are fetched which represent X and Y if the data are interpreted as coordinate data.

Three Dimensions for the Clipping Divider. This mode is abbreviated as CD3D. Three words are fetched for each point which represent X, Y, and Z. A fourth word is supplied to the pipeline by copying the last word which gives X, Y, Z, Z. This is the form that the Clipping Divider expects. Pipeline load/unload instructions behave as if the LDS-2 were in homogeneous mode.

Three Dimensions for the Matrix Multiplier. This second special three-dimensional mode (abbreviated MM3D) also fetches three words of data per coordinate point. In MM3D,

however, the fourth word is supplied as the fractional representation of "1" (37777777) to give X, Y, Z, "1" which corresponds to the homogeneous representation with the homogeneous element equal to "1". Pipeline load/unload instructions behave as if the LDS-2 were in homogeneous mode.

Homogeneous Mode. In homogeneous mode four words of data are fetched for each element. If the data are interpreted as coordinate data, these four words represent X, Y, Z, and W, where W is the homogeneous element.

It is very important to remember that the dimension mode of the LDS-2 affects all display instructions. Special care must be taken when using pipeline load/unload instructions or incorrect data will be loaded into the pipeline registers. The pertinent considerations are outlined in detail in Section 7.13 dealing with these instructions.

#### 2.4.4 Repeat Instructions

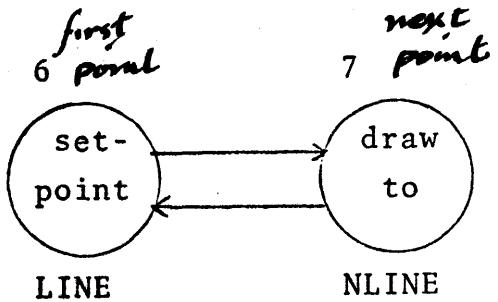

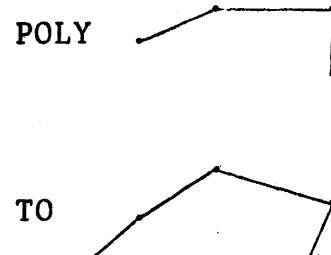

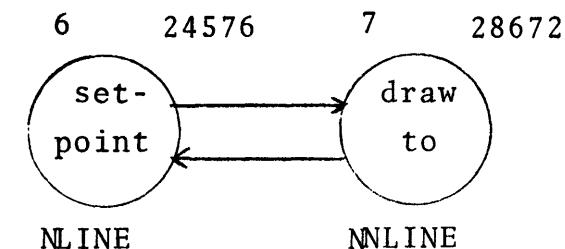

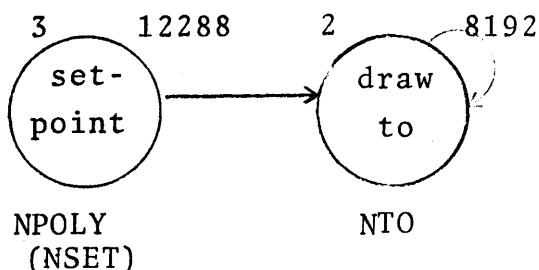

The Channel Control can generate a repeated series of simple drawing instructions in order to draw more complex figures with a single instruction. When a "repeat" drawing instruction is received which indicates a "draw to," "draw from," "polygon," "star," "lines," or "dots" operation, the Channel Control automatically generates the appropriate series of basic drawing instructions. Finite-state machines within the Channel Control update the command, so that a single repeat instruction causes a series of drawing instructions to be sent down the pipeline. The drawing sequences and absolute/relative/variable origin combinations that are available with these instructions are discussed in Section 7.14. Pipeline load/unload instructions are inherently repeat. The address of the register loaded or unloaded is incremented after each iteration, so that a series of registers may be loaded or unloaded with a single instruction.

The iterations of the repeat instructions are counted by the READ COUNTER (RC). The RC is initialized with the negative (two's complement) of the number of elements (e.g., the number of coordinate points or the number of registers) and is incremented once after each data element has been fetched and passed to the pipeline. When the count reaches zero, the process is stopped and another instruction is fetched. If the count is initially zero, only one iteration will be performed. The count will never increment past zero and, thus, should never contain a positive number unless it was loaded with a positive number initially.

When the RC is not being used for repeat mode instructions, or when no other registers are available, it is convenient to use the RC as a counter for other purposes. The programmer can increment (or decrement) the counter under program control

and test its results for zero. It is, of course, also possible to do this with any other of the Channel Control's internal registers.

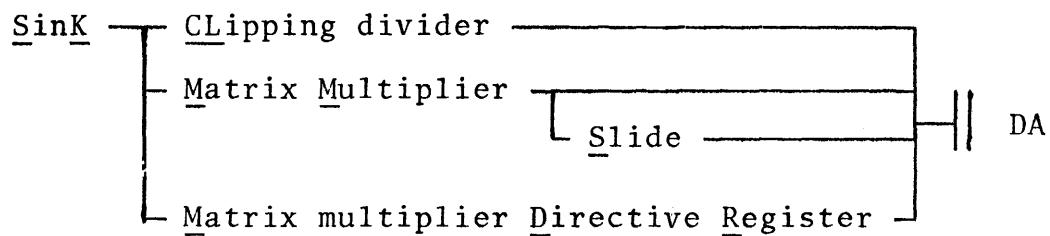

#### 2.4.5 The Data Sink

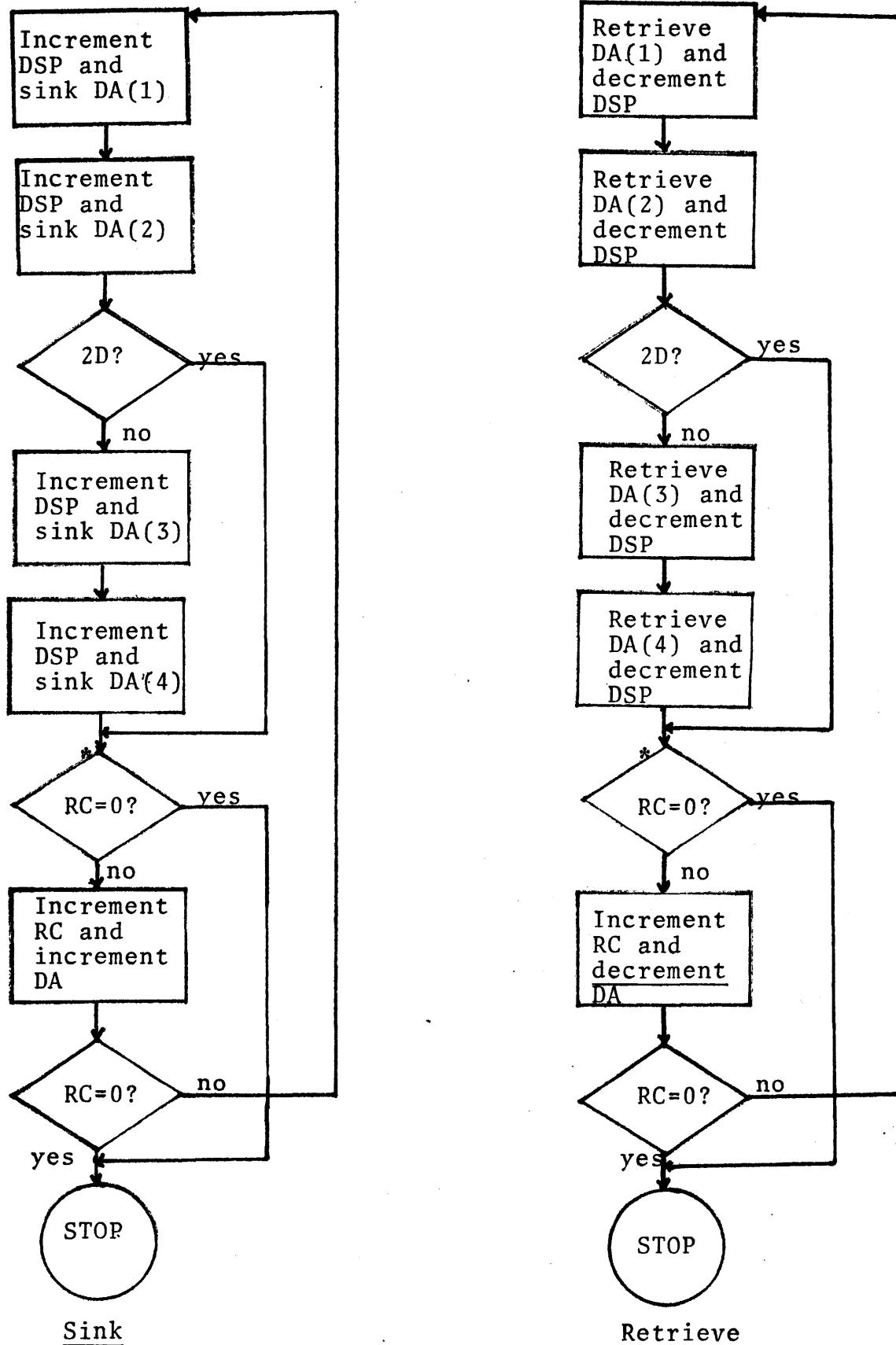

A special stack mechanism called the "data sink" is used to store information from the registers of the pipeline units. The DATA SINK POINTER (DSP) maintains the address of the last element written into the data sink. When pipeline registers are "sunked," the new information is written into memory and then the DSP is incremented. This information may then be "retrieved," in which case the DSP is decremented and then the register is reloaded. For retrieval operations the register addresses sent down the pipeline are decremented rather than incremented for repeat instructions, so that data are returned in the proper order.

#### 2.4.6 Returning Output to Memory

The processed output of the arithmetic devices may be returned to memory for use in further processing or for output to remote terminals. When one of the pipeline units has data ready to return to memory, it signals the Channel Control which stops its normal operation and records the data. The WRITE POINTER (WP) of the Channel Control is used to provide the memory address for recording the processed output. Since the WP is incremented after each use, the data are recorded in a contiguous table. The length of this table may be limited by loading the WRITE COUNT (WC) with the negative (two's complement) of the desired length of the table. When the WC reaches zero, the LDS-2 will be interrupted if the appropriate interrupt bit is enabled (see Section 2.5).

## 2.5 The I/O Structure

The Channel Control contains eight registers which are treated as I/O devices and manipulated with "input/output transfer" (IOT) instructions. IOT instructions are also used for special functions. All of the IOT instructions, except those indicated, are legal only when the LDS-2 is in executive mode.

The Channel Control is either in executive mode or user mode. In executive mode, all the implemented IOT instructions are legal, and the "permit" bits for scope selection (see Section 4.8) may be changed. Whenever an interrupt is received from either the LDS-2 itself or the host computer, the Channel Control goes to executive mode. The Interrupt Service Routine resets user mode before transferring control back to the user.

### 2.5.1 Status Registers

The DIRECTIVE register and REPEAT STATUS register hold information which controls the operation mode of the LDS-2 and the functioning of the pipeline devices. These are the only two registers available to the user. The DIRECTIVE register holds the dimension mode for the LDS-2, controls whether the pipeline devices are active, and contains status flags which are set by the pipeline.

| <u>DIRECTIVE</u> |                                                                                                                | <u>NEW BITS</u> |                                        |

|------------------|----------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------|

| <u>Bits</u>      | <u>Function</u>                                                                                                | 8               | SWITCHES NORMAL (READ ONLY)            |

| 0-1              | Unused                                                                                                         | 9               | VIDEO SETTLED (READ ONLY)              |

| 2                | Matrix Multiplier Active                                                                                       | 10              | SURFACE BITS<br>11 → NON SURFACE       |

| 3                | Clipping Divider Active                                                                                        | 11              | 01 → SURFACE<br>11 → SMOOTHED, SURFACE |

| 4                | No Overlap (i.e., each line is completely processed by all the pipeline devices before the next line is begun) |                 |                                        |

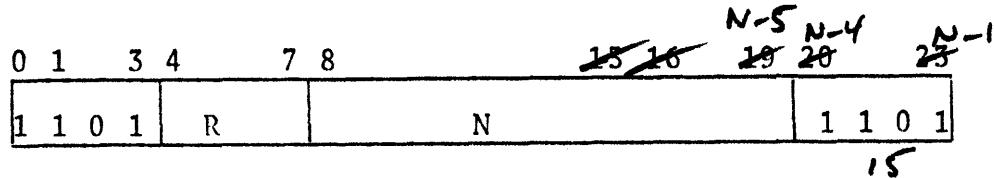

#### 5-6 Dimension modes

|    |                                   |

|----|-----------------------------------|

| 00 | 2D                                |

| 01 | Homogeneous mode (4D)             |

| 10 | MM3D (X Y Z with an assumed "1")  |

| 11 | CD3C (X Y Z with a copy of the Z) |

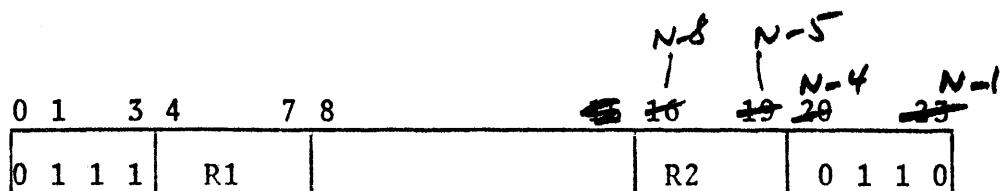

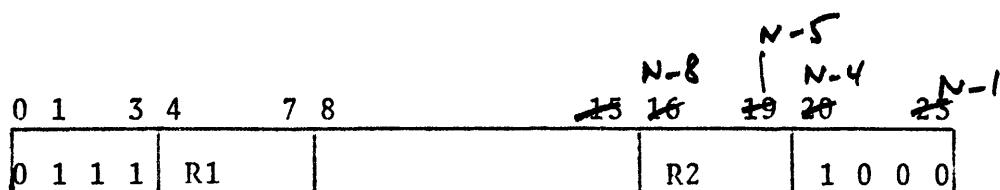

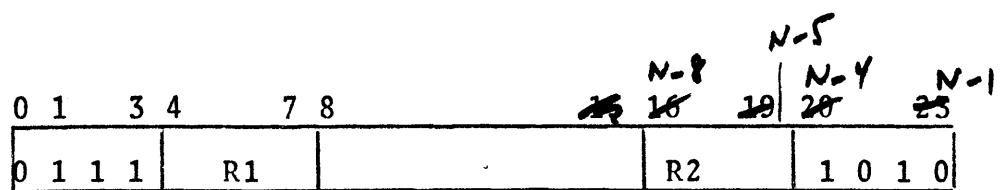

N-3 7

N-2 23

N-1 23

Interrupt on HIT

HIT (from the Clipping Divider)

Area In Common (from the Clipping Divider)

Settled (i.e., all of the pipeline units have finished processing pending data, and are waiting for input)

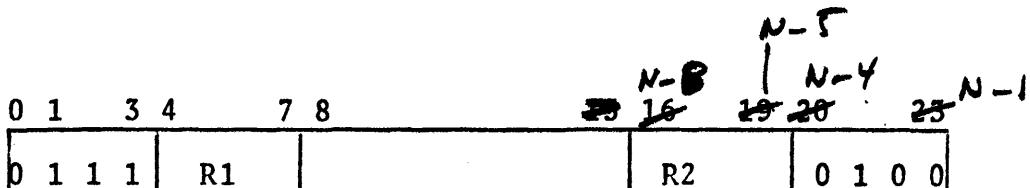

The REPEAT STATUS REGISTER (RSR) holds the pipeline load/unload and drawing commands that are sent down the pipeline, and is updated by the normal operation of the Channel Control. The RSR makes

it possible to interrupt a repeat drawing or load/unload sequence. If during the time interrupt is being serviced other drawing instructions will be executed, the RSR should be saved and then reloaded to restore the user. If the interrupt results in going to a new user, the repeat bit of the RSR must be cleared; otherwise, the first load/unload or drawing instruction executed by the new user will use the old RSR rather than the information in the instruction. The appropriate actions are taken by the LDS-2 Interrupt Handler, so that the user does not have to worry about the RSR.

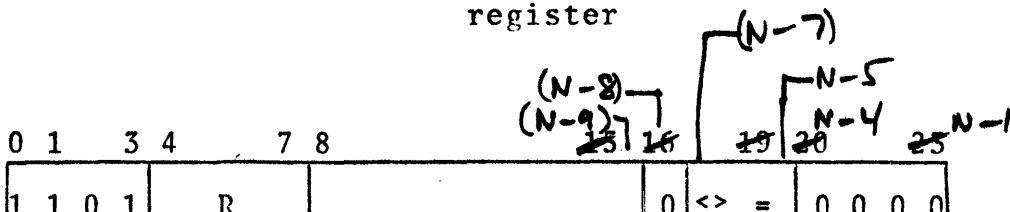

#### REPEAT STATUS REGISTER

| <u>Bits</u>      | <u>Function for Load/Unload</u>      | <u>Function for Drawing</u>                                    |

|------------------|--------------------------------------|----------------------------------------------------------------|

| 0-1              | Unused                               | Unused                                                         |

| 2-4              | Instruction Type (011 = load/unload) | Instruction Type (100 = drawing)                               |

| 5-6              | Load/Retrieve/Store/Sink             | ---                                                            |

| 5-7              | ---                                  | Present state of drawing operation finite-state-machine (FSM1) |

| 7, 16-18         | Device and Manner                    | ---                                                            |

| 16-18            | ---                                  | Present state of data form finite-state-machine (FSM2)         |

| <i>Ns to N-2</i> | 19-22 Address of Pipeline Register   | ---                                                            |

| <i>N-1</i>       | <i>23</i> Repeat                     | Repeat                                                         |

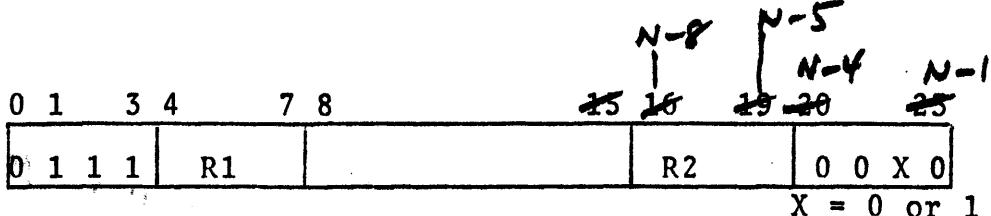

#### 2.5.2 Interrupts

The LDS-2 has a two-level interrupt system. High-level interrupts come only from the host computer and cause the execution of a hard-wired address. Low-level interrupts may be caused by a variety of internal conditions which the LDS-2 has detected. These interrupts also cause the execution of a hard-wired address which contains a "pushjump" to the Interrupt Handler. The condition which caused the interrupt will have set a bit in the INTERRUPT CONDITIONS REGISTER (ICR). The bits in the ICR are masked against the bits in the INTERRUPT MASK REGISTER (IMR). If the interrupt bit is set and the mask bit is set, the LDS-2 will be interrupted. The Interrupt Handler interrogates the ICR to determine the cause of the interrupt, so it can take appropriate action. If the Interrupt Handler returns control to the user, it is first necessary for it to decrement the TOS in order to return the instruction which was interrupted rather than the next instruction.

## INTERRUPT CONDITIONS REGISTER

| <u>Bits</u>       | <u>Meaning</u>                                                                        |

|-------------------|---------------------------------------------------------------------------------------|

| 6                 | Scope Protection Violation (TUT TUT FORBID)--Note that there is no mask for this bit. |

| 7                 | Memory Protection Violation                                                           |

| <del>N-7</del> 17 | Unimplemented Instruction (no mask)                                                   |

| <del>N-6</del> 18 | Nonexistent Memory                                                                    |

| <del>N-5</del> 19 | Nonexistent I/O Device                                                                |

| <del>N-4</del> 20 | Real Time Clock                                                                       |

| <del>N-3</del> 21 | Positive Write-Count Register (table overflow)                                        |

| <del>N-2</del> 22 | Overflow (caused by an arithmetic instruction)                                        |

| <del>N-1</del> 23 | Parity Error                                                                          |

## INTERRUPT MASK REGISTER

| <u>Bits</u>       | <u>Meaning</u>                |

|-------------------|-------------------------------|

| <del>N-8</del> 17 | Memory Protection Violation   |

| <del>N-7</del> 17 | High-level Interrupt Mask     |

| <del>N-6</del> 18 | Low-level Interrupt Mask      |

| <del>N-5</del> 19 | Nonexistent Memory            |

| <del>N-4</del> 20 | Nonexistent I/O Device        |

| <del>N-3</del> 21 | Real Time Clock               |

| <del>N-2</del> 22 | Positive Write-Count Register |

| <del>N-1</del> 23 | Overflow                      |

|                   | Parity                        |

When the LDS-2 is in user mode, most of the I/O devices are not accessible and are treated as "non-existent." The lower 8 bits of the device code of an illegal IOT are saved in the I/O DEVICE CODE ERROR REGISTER. If the interrupt mask is set, an interrupt will then be initiated. When the Interrupt Handler has determined that a nonexistent I/O device caused the interrupt, it checks the I/O DEVICE CODE ERROR REGISTER. The Interrupt Handler can then decide what to do on the basis of the information in this register. This mechanism provides a convenient communication between the user and the Interrupt Handler. For example, when the user's program needs input/output from the host computer, it can make the request by executing a specified "illegal" IOT (see Section 7.12).

### 2.5.3 Real Time Clocks

Four real time clock sources are available on the LDS-2. The LDS-2 itself has both a 60-cycle/second clock and a clock controlled by a variable potentiometer on the control panel which can be set between 10 and 100 cycles/second. In addition to these, the clock from the host computer is available and a clock from an external synchronization source. The selection of these clocks is made by setting the SYNC MASK REGISTER. This can only be done in executive mode.

### SYNC MASK REGISTER

| <u>Bits</u>       | <u>Function</u>                    |

|-------------------|------------------------------------|

| <del>N-5</del> 19 | External Sync                      |

| <del>N-4</del> 20 | Real Time Clock from Host Computer |

| <del>N-3</del> 21 | 60 Hz Real Time Clock              |

| <del>N-2</del> 22 | Adjustable Clock                   |

#### 2.5.4 Memory Protection and Relocation

For an LDS-2 which is interfaced to a ~~SEL-840, 512-word pages~~ can be protected. Each user is assigned an upper and lower bounds. The upper 8 bits of the bounds are loaded into the protection register.

*host computer*

### PROTECTION REGISTER

| <u>Bits</u> | <u>Function</u> |

|-------------|-----------------|

| 16-23       | Lower Bounds    |

| 8-15        | Upper Bounds    |

*host computer*

In order to facilitate the passing of addresses between the LDS-2 and the ~~SEL-840~~, the LDS-2 has been equipped with a BANK ADDRESS REGISTER (BAR) which is loaded at initialization with the same contents as the ~~SEL-840~~ BAR (except for the first two quarters which are reserved on the SEL-840). It is thus possible to pass addresses from software on the ~~SEL-840~~ to software on the LDS-2 without having to worry about BAR relocation. The BAR on the LDS-2 is active only when the LDS-2 is in user mode. In executive mode, addresses are interpreted as absolute.

### BANK ADDRESS REGISTER

| <u>Bits</u>       | <u>Function</u> |

|-------------------|-----------------|

| 2-5               | 00 Relocation   |

| 8-11              | 01 Relocation   |

| 14-17             | 10 Relocation   |

| (N-5)-(N-1) 20-23 | 11 Relocation   |

#### 2.5.5 Special I/O Functions

In addition to loading and unloading registers, IOT instructions are used for several special functions as listed below. Note: that only the "skip-on-settled" function is available to the user.

Enable Interrupts. When a low-level interrupt is being serviced, other low-level interrupts are automatically locked out. At the end of the interrupt routine, it is necessary to enable these interrupts again. Similarly, when a high-level interrupt is serviced, other high-level interrupts are locked out, so

that an "enable interrupt" IOT must be performed at the end of this routine also. The "enable interrupt" does not take effect until after the first "jump" instruction after the IOT.

Set User Mode. When an interrupt occurs, the LDS-2 goes into "executive" mode. In this mode, all of the defined IOT's are legal, and the scope selection registers can be set. User mode must be restored at the end of an interrupt service routine, or after the system has been initialized. User mode is not actually set until after the first "jump" instruction.

Sleep. Sleep is an idle state in which the LDS-2 does nothing but accept high-level interrupts.

Attention. When the LDS-2 needs to communicate with the host computer, the attention bit is raised. This IOT will cause an interrupt to the host computer.

Skip-on-Attention Clear. When the host computer has acknowledged the interrupt, it clears the attention bit. Before the LDS-2 issues another interrupt, it may want to check to see that the previous attention has been cleared. This is done by the "skip-on-attention clear" IOT.

Clear Protection Violation. When a protection violation occurs, a flip-flop is set which issues an interrupt. This flip-flop must be cleared by this IOT before going on to a new user.

Skip-On-Settled. This is the only special function IOT that is available to the user. Skip on settled causes the LDS-2 to skip the next instruction, if the pipeline is settled. This IOT is used when testing pipeline conditions (such as Area In Common) to insure that the pipeline is clear and the correct value for the condition can be read.

#### 2.5.6 The Interface from the ~~SEL-840~~ Side

##### ~~host computer~~ (HC)

The ~~SEL-840~~ receives and issues interrupts through the ~~SEL-840~~ I/O REGISTER of the LDS-2, which is an I/O device for the ~~SEL-840~~.

##### ~~Host Computer~~ ~~SEL-840 I/O REGISTER~~

~~host computer~~

~~host computer~~

| Bits        | Function                                                                                                                                         |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| N-5 29 '200 | Attention. When the LDS-2 issues an attention, this bit is set. It may also be loaded or unloaded from the <del>SEL</del> side of the interface. |

| N-4 20 '100 | Attention Interrupt Mask. If this bit is set, the Attention bit will cause an <del>SEL-840</del> interrupt.                                      |

| N-3 21      | Stop State. When the LDS-2 is in the "sleep"                                                                                                     |

state, this bit is set. It can be read, but not set, by the ~~SEL 840~~ <sup>HC</sup>.

~~N-2 22~~

Stop-State-Interrupt Mask. If this bit is set, the Stop-State bit will cause an ~~SEL 840~~ <sup>HC</sup> interrupt.

~~N-1 25~~

LDS-2 Interrupt. By setting the LDS-2 Interrupt bit, the ~~SEL 840~~ issues an interrupt to the LDS-2. This bit is cleared automatically, when the interrupt is serviced by the LDS-2.

## CHAPTER 3

### THE MATRIX MULTIPLIER

#### 3.1 Function

The Matrix Multiplier is the first arithmetic device in the LDS-2 display processing pipeline. The Matrix Multiplier performs rotations, translations, and scalings of the drawing by multiplying the coordinate data by an internally stored transformation matrix. The Matrix Multiplier can also compute the product of two such transformation matrices to give a composite transformation for substructures within the drawing definition. The third function of the Matrix Multiplier involves iterating a set of difference equations for drawing two- or three-dimensional curves which are drawn as a series of short line segments. Families of such curves can also be generated to draw a cross-hatched surface patch.

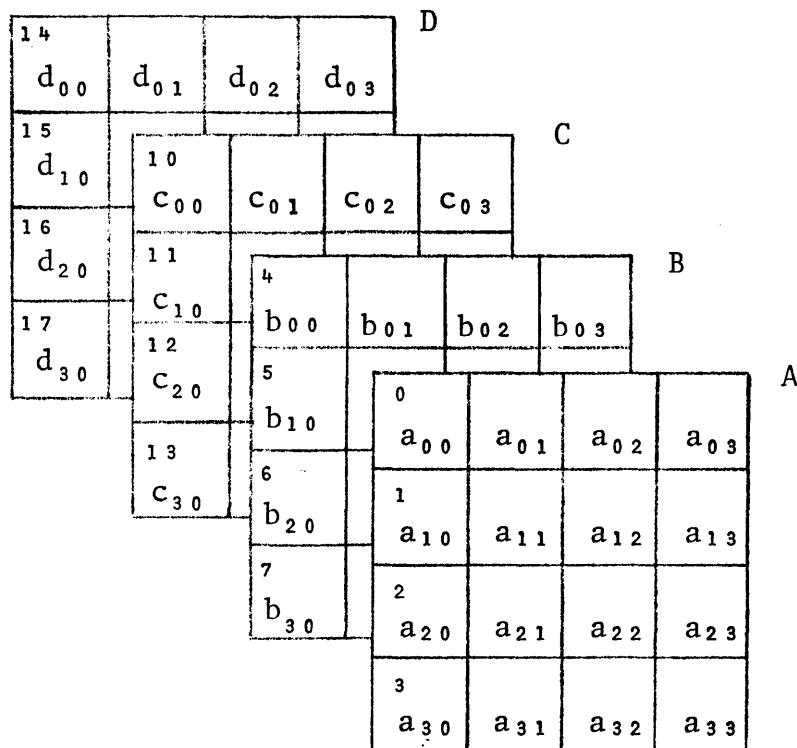

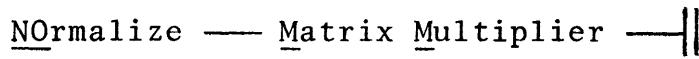

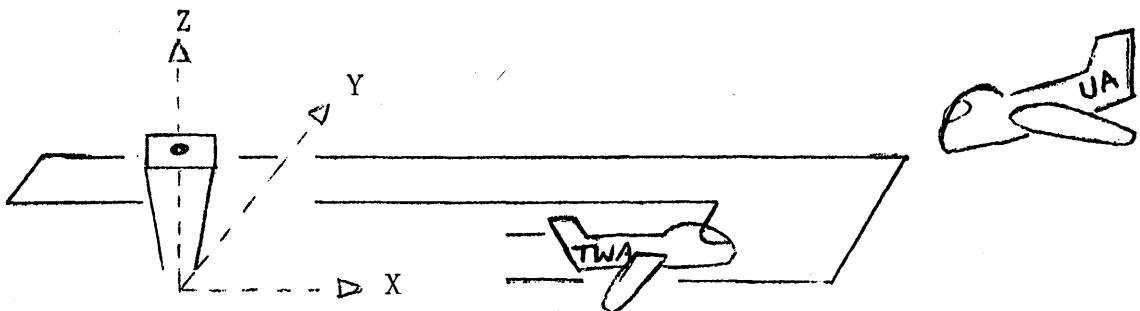

The basic configuration of the Matrix Multiplier and the addresses of the registers used for storing matrix elements are shown in Figure 3.1. Four matrices A, B, C, and D, each of dimension 4 x 4, are stored internally in a 4 x 4 x 4 matrix array of storage registers. The values in these registers may be manipulated by the "load," "store," "sink," and "retrieve" instructions. See Chapter 7. The matrix multiplications are performed by a high-speed array multiplier. Input data for the Matrix Multiplier are passed from the Channel Control, and the output is sent to the Clipping Divider, back to the memory of the host computer via the Channel Control, or both.

#### 3.2 Three-dimensional Matrix Transformations

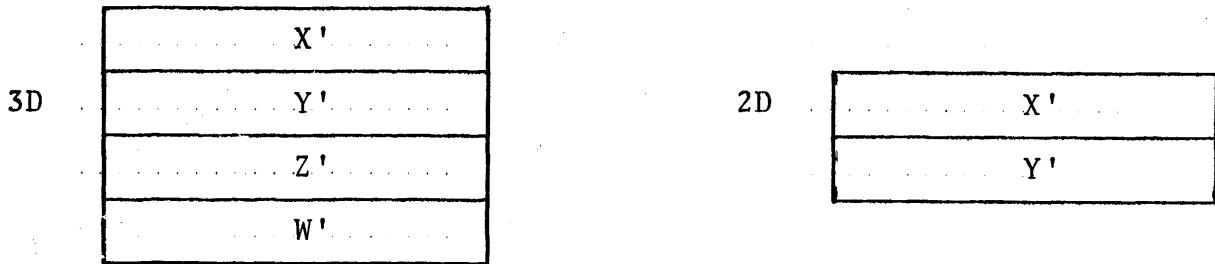

The Matrix Multiplier works on "homogeneous coordinates" (see Appendix III.) In homogeneous coordinates, three-dimensional coordinate data are represented by the four-component vector (X Y Z W), where X, Y, and Z are the normal orthogonal distances from the origin, and W is used as a scale factor. The transformation matrix is the 4 x 4 matrix in Position A. When the Matrix Multiplier is in three-dimensional operation and "active," all coordinate data values are multiplied by the matrix stored in Position A (see Figure 3.1). Note that this does not include parameter data for pipeline load/unload instructions. The form of the transformation and the equations which define this transformation are given in Figure 3.2. In 3D, entire rows of the matrices are affected by a "load," "store," "sink," or "retrieve" instruction (i.e., four components are loaded at a time).

It should be noted that, while the Matrix Multiplier expects input of the form (X Y Z W), the Clipping Divider expects (X Y  $Z_x Z_y$ ). The transform matrix can easily be structured so that it will make this change.

## MATRIX MULTIPLIER REGISTERS

Matrix data is stored in memory in the format:

x = number of row as indicated above

Note: In 2D ex2 and

e<sub>x3</sub> are inaccessible

Figure 3.1

3-2

### THREE-DIMENSIONAL MATRIX TRANSFORMATIONS

$$[X \ Y \ Z \ W] \begin{bmatrix} r_{00} & r_{01} & r_{02} & h_{03} \\ r_{10} & r_{11} & r_{12} & h_{13} \\ r_{20} & r_{21} & r_{22} & h_{23} \\ t_{30} & t_{31} & t_{32} & h_{33} \end{bmatrix} = [X' \ Y' \ Z' \ W']$$

Where

$$X' = r_{00}X + r_{10}Y + r_{20}Z + t_{30}W$$

$$Y' = r_{01}X + r_{11}Y + r_{21}Z + t_{31}W$$

$$Z' = r_{02}X + r_{12}Y + r_{22}Z + t_{32}W$$

$$W' = h_{03}X + h_{13}Y + h_{23}Z + h_{33}W$$

**r** = rotation terms

**t** = translation terms

**h** = homogenous terms

Figure 3.2

3-3

### 3.3 Two-dimensional Matrix Transformations

Two-dimensional coordinate data can also be transformed by the Matrix Multiplier. The "boxing" operation of the Clipping Divider (see Section 4.5) is, however, a more efficient way to effect two-dimensional transformations which do not involve rotations. For two-dimensional operation, the input is made up simply of the X and Y coordinate values. These values are augmented (by the Matrix Multiplier) to take the form:

$$[X \ Y \ 1]$$

Figure 3.3 shows the structure of the two-dimensional transformation matrix, the equation for the transformations performed, and the Trigonometric values for the elements.

In 2D, only the first two elements of each column in matrix A are loaded from a single word in memory. (See Figure 3.1.) The zeros and ones shown in the third column of the transformation matrix in Figure 3.3 are not actually present but shown only for expository purposes.

### 3.4 Composite Transformations

When an object within the drawing is to be transformed with respect to the drawing and the drawing itself is also to be transformed, a composite transformation of the form

$$[X \ Y \ Z \ W] \ [T_1] \ [T_0] \longrightarrow [X' \ Y' \ Z' \ W']$$

is required. Instead of generating the intermediate result,  $[X \ Y \ Z \ W] \ [T_1]$ , and then multiplying it by  $[T_0]$ , the Matrix Multiplier can form the composite transformation  $[T_1] \ [T_0]$ . This is done by executing a "load product" instruction (see Chapter 7). The load product instruction takes the matrix  $[T_1]$  which is stored in memory, and multiplies it by  $[T_0]$ , which can be specified as either matrix B, C, or D (but not A). The resulting matrix is left in matrix A.

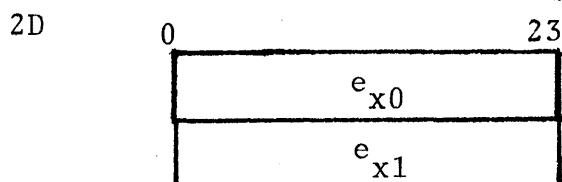

#### 3.4.1 Nested Transformations

This method of forming composite transformations generalizes to any level. The "data sink," operated by the Channel Control (see Section 2.4.5), serves as a pushdown stack for storing matrices in order to implement nested transformations. The sink and retrieve instructions for the Matrix Multiplier contain a "slide" option, which allows matrix A and some other matrix (usually B) to be operated as the first two matrices in a pushdown stack. The slide option copies matrix A into another matrix (e.g., B) as that matrix is "sunked" into the data sink. Then, when matrix B is retrieved from the data sink, the matrix in Position B is copied back into A. The slide versions of the "sink" and "retrieve" instructions, together with the "product load" facilitate a recursive subroutine call with only a few instructions.

## TWO-DIMENSIONAL MATRIX TRANSFORMATIONS

$$\begin{bmatrix} X & Y & (W) \end{bmatrix} \begin{bmatrix} r_{00} & r_{01} & 0 \\ r_{10} & r_{11} & 0 \\ t_{20} & t_{21} & 1 \end{bmatrix} = \begin{bmatrix} X' & Y' & (W') \end{bmatrix}$$

Where

$$X' = r_{00}X + r_{10}Y + t_{20}(W)$$

$$Y' = r_{01}X + r_{11}Y + t_{21}(W)$$

$W'$  is not computed

$r$  = rotation terms

$t$  = translation terms

$w$  = is not provided by input, but rather augmented by the Matrix Multiplier

$w = 1$  for absolute

$w = 0$  for relative

Form of 2D Transformation Matrix

$$\begin{bmatrix} \cos\alpha & \sin\alpha & 0 \\ -\sin\alpha & \cos\alpha & 0 \\ F_x & F_y & 1 \end{bmatrix}$$

Figure 3.3

### 3.4.2 Row-to-Row Moves

Rows of matrix A may be copied into another matrix by the "push Matrix Multiplier" instruction, and, similarly, rows of one of the other matrices can be copied back into matrix A by the "pop Matrix Multiplier" instruction, thus allowing matrices B, C, and D to be used as pushdown storage. This feature can be used in special cases, where subroutine depth is limited. The additional speed obtained in this manner by avoiding memory references is paid for by a loss of generality in the subroutine calls.

### 3.4.3 Matrix Normalization

Since the Clipping Divider performs perspective division yielding  $X/Z_x$  and  $Y/Z_y$ , homogeneous transformation matrices may be scaled without effecting the transformation performed. It is customary to normalize the matrices used, so that at least one element is between one-half and one in magnitude (taking matrix elements as signed fractions; see Section 3.8). The multiplication of two such matrices may result in a matrix which is no longer normalized. Renormalization of this matrix, before it is used in some subsequent concatenation, will assure that maximum precision is maintained in the new transformation matrix. The "normalize" instruction (see Section 7.3) is used to shift the elements of matrix A left until any element is greater than one-half in magnitude or until the "count" given in the normalize instruction runs out. The normalize instruction is disregarded in 2D.

## 3.5 Two-dimensional Curves

A two-dimensional curve is defined by the elements held in the first two columns of matrix A (see Figure 3.4a). When a Matrix Multiplier drawing instruction (other than "box") is received, a coordinate value is calculated by an iteration of the matrix according to the equations shown in Figure 3.4a, and the output is sent to the Clipping Divider (or memory, or both). Usually, a complete curve is drawn with a "polygon" instruction with the Channel Control in repeat mode. In this case the RC of the Channel Control should be loaded with the two's complement of the number of line segments that are to be in the curve (+1 for the initial setpoint). The class of curves that can be drawn includes all of the conic sections and a few other special curves, such as circular and elliptical spirals.

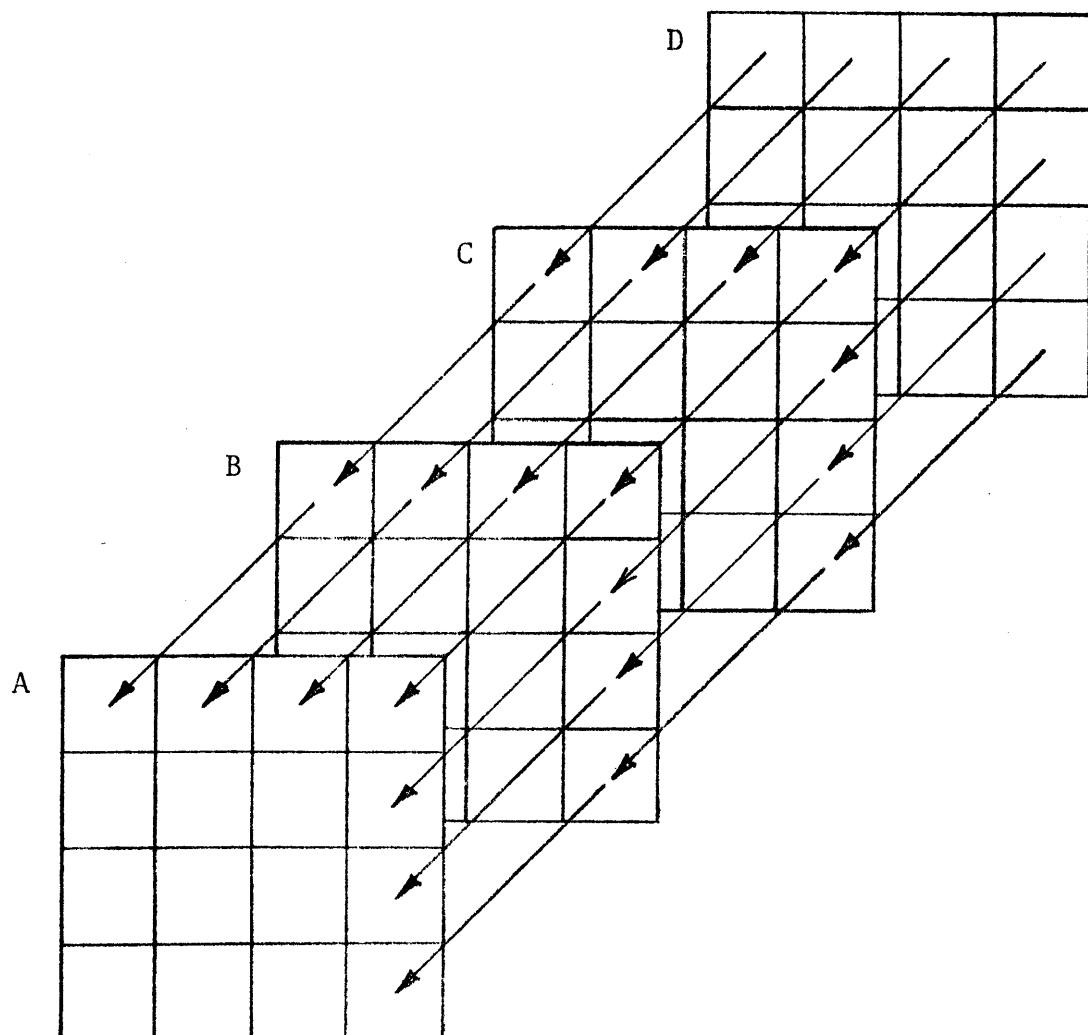

## 3.6 Three-dimensional Curves

Three-dimensional curves are defined using all of matrix A, as shown in Figure 3.4b. The coordinate values for the current location are held on the top row of matrix A. Dataless drawing instructions (other than "box") cause an iteration of the matrix to compute a new coordinate value and send it to the Clipping Divider. Following

## 2D CURVES

$$A = \begin{bmatrix} r_{00} & r_{10} \\ r_{10} & r_{11} \\ tx & ty \\ x & y \end{bmatrix}$$

Basic Representation

$[x, y] + [tx, ty] \rightarrow$  Clipping Divider

Set Curve Operation

$[x, y] [R] + [tx, ty] \rightarrow$  Clipping Divider

$[x, y] [R] \rightarrow [x, y]$

Other Drawing Instructions

### 3D CURVES

$$A = \begin{bmatrix} a_{00} & a_{01} & a_{02} & a_{03} \\ a_{10} & a_{11} & a_{12} & a_{13} \\ a_{20} & a_{21} & a_{22} & a_{23} \\ a_{30} & a_{31} & a_{32} & a_{33} \end{bmatrix}$$

top row specifies

current absolute

coordinate

Basic Representation

$$[a_{00} \ a_{01} \ a_{02} \ a_{03}] + Q[a_{10} \ a_{11} \ a_{12} \ a_{13}] \rightarrow [a_{00} \ a_{01} \ a_{02} \ a_{03}]$$

$$[a_{10} \ a_{11} \ a_{12} \ a_{13}] + Q[a_{20} \ a_{21} \ a_{22} \ a_{23}] \rightarrow [a_{10} \ a_{11} \ a_{12} \ a_{13}]$$

$$[a_{20} \ a_{21} \ a_{22} \ a_{23}] + Q[a_{30} \ a_{31} \ a_{32} \ a_{33}] \rightarrow [a_{20} \ a_{21} \ a_{22} \ a_{23}]$$

$$[a_{30} \ a_{31} \ a_{32} \ a_{33}] + 0 \rightarrow [a_{30} \ a_{31} \ a_{32} \ a_{33}]$$

$[a_{00} \ a_{01} \ a_{02} \ a_{03}] \rightarrow$  Clipping Divider

Iteration

Note: Q is taken from the right half of the MDIR

the perspective division performed by the Clipping Divider (see section 4.5), these cubic difference equations generate a very general class of curves called rational parametric cubics.

### 3.7 Surface Patches

Families of the curves generated in three-dimensional curve mode can be used to draw cross-hatched surface patches. The definition of the surface patch is stored in the matrix array as shown in figure 3.5. The "new curve" operation is used to generate each new curve of the surface patch.

### 3.8 Arithmetic Conventions

The word length of the Matrix Multiplier is 24 bits. The elements of input vectors and output vectors written into memory are all of this basic word length.

All arithmetic operations are performed treating elements as 2's complement signed (fixed point) fractions. Since the word length is 24 bits, the algebraically largest number that can be represented is  $1 - 2^{-23}$ , and the algebraically smallest number that can be represented is -1. In binary notation (with the binary point separating the sign bit from the fraction):

0.111111... is the algebraically largest number

0.000000... is the unique representation for zero

1.000000... is the algebraically smallest number (-10.)

The reader should note that the closest approximation to +1 is the fraction 0.111111..., which is close enough to +1 for practical cases.

Two's complement binary multiplication always invokes some questions. The Matrix Multiplier performs fractional multiplication, in which the 17 low-order bits of the product

## SURFACE PATCH ITERATION

$$\begin{aligned}

A + QB &\rightarrow A \\

B + QC &\rightarrow B \\

C + QD &\rightarrow C \\

D + 0 &\rightarrow D

\end{aligned}

\quad \left. \right\}$$

For all 16 elements of each matrix

Note:  $Q$  is taken from the MDIR

Figure 3.5

3-10

are lost. These bits are used, however, for rounding. Multiplication of -1 by -1 (1.000000...x1.000000...) yields a product of -1 (1.000000...). It is usually best to avoid -1 altogether.

The practical consequence of using fractional arithmetic is that at least one of the two numbers involved in a multiplication must be a fraction, and the other number may be thought of as having the binary point located at the user's discretion. Figure 3.6 shows a good way to think of the structure of the input vector and the transformation matrix. The advantage of this structure is that both multiplication of the input vector by the transformation matrix and multiplication of one transformation matrix by another results in an integer times a fraction or a fraction times a fraction. In addition, multiplication of one matrix by another gives a matrix of the same form.

### 3.9 Mode Control

The mode of operation of the Matrix Multiplier is controlled both by the Channel Control Directive register (DIR), and by a directive register internal to the Matrix Multiplier (MDIR). In general, the DIR specifies global operating modes, which may apply to several of the operating units in the display system, while the MDIR specifies those modes which apply only to the Matrix Multiplier.

The following bits in the Channel Control DIR have a direct effect on the operations of the Matrix Multiplier:

|       |                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MMA   | (Matrix Multiplier Active) -- When this bit is 0, the Matrix Multiplier is "transparent" -- that is, it simply passes its input data on to the Clipping Divider, and provides a level of data buffering in the computational pipeline. Matrix Multiplier load and store operations occur whether or not the MMA bit is set.                                                                           |

| 2D,3D | (LDS-2 Dimension Modes) -- These bits determine whether the Channel Control supplies the Matrix Multiplier with a two-component or four-component input. 2D indicates a two-component (i.e., two-word) input, while <u>all</u> of the three-dimensional modes (including "homogeneous mode") indicate a four-component input. These rules apply for both drawing and register load/unload operations. |

## FRACTIONAL MULTIPLICATION

$$[X, Y, Z, W] = [I, I, I, F]$$

$$\begin{bmatrix} r_{00} & r_{01} & r_{02} & 0 \\ r_{10} & r_{11} & r_{12} & 0 \\ r_{20} & r_{21} & r_{22} & 0 \\ tx & ty & tz & s \end{bmatrix} = \begin{bmatrix} F & F & F & 0 \\ F & F & F & 0 \\ F & F & F & 0 \\ I & I & I & F \end{bmatrix}$$

Where F = Fractions

I = Integers

The coordinates (X, Y, Z) are usually best regarded as integers, while the homogenous term W is usually considered to be a fraction.

The elements of the  $3 \times 3$  submatrix (R), the rotation matrix, are products of sines and cosines and are thus appropriately considered fractions. The translational elements (t) may be thought of as integers since W is a fraction. The "s" term is used to scale the matrix and is a fraction.

The directive information stored internally in the Matrix Multiplier MDIR register is the following:

MOC (Matrix Output to Clipper) -- causes the Matrix Multiplier to send its computational results to the Clipping Divider. This bit is ignored if MMA=0, in which case the Matrix Multiplier is "transparent" and always sends data to the Clipping Divider.

MOM (Matrix Output to Memory) -- causes the Matrix Multiplier to send its computational results to memory. This bit is ignored if MMA=0. The MOC and MOM bits are mutually independent, so it is possible to route the matrix output to the Clipping Divider, to memory, to both, or to neither.

Matrix Multiplier output to memory takes the following format:

CURVE (Curve Mode) -- causes the Matrix Multiplier to interpret drawing instructions as commands to iterate difference equations.

TR1, TR0 (Transpose Map) -- are interpreted as a 2-bit number which controls the addressing into the matrix scratchpad memory. They may be thought of as causing the array to be transposed about any one of its three diagonals. The matrix elements  $a_{00}$ ,  $b_{11}$ ,  $c_{22}$ , and  $d_{33}$  remain in the same place, for any transposition, but the other elements are reflected in the following way:

TR1 TR0

0 0 -- no transposition

0 1 -- rows and columns are exchanged (i.e. matrices A, B, C, and D are each transposed).

1 0 -- columns and rows are exchanged.

1 1 -- rods and rows are exchanged.

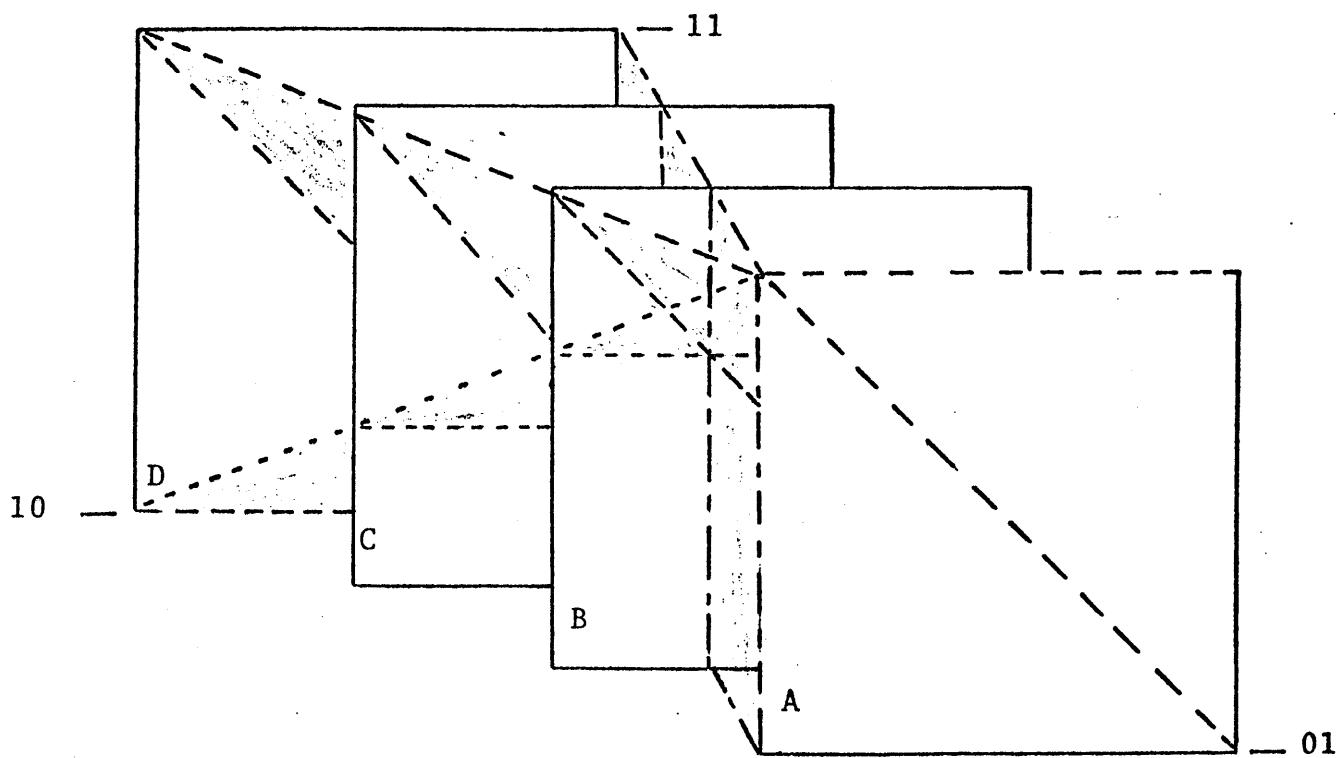

The planes about which the elements are reflected are shown in Figure 3.7.

## TRANSPOSITION PLANES

Rods

↔ Rows

↓

Columns

----- 01

----- 11

----- 10

Figure 3.7

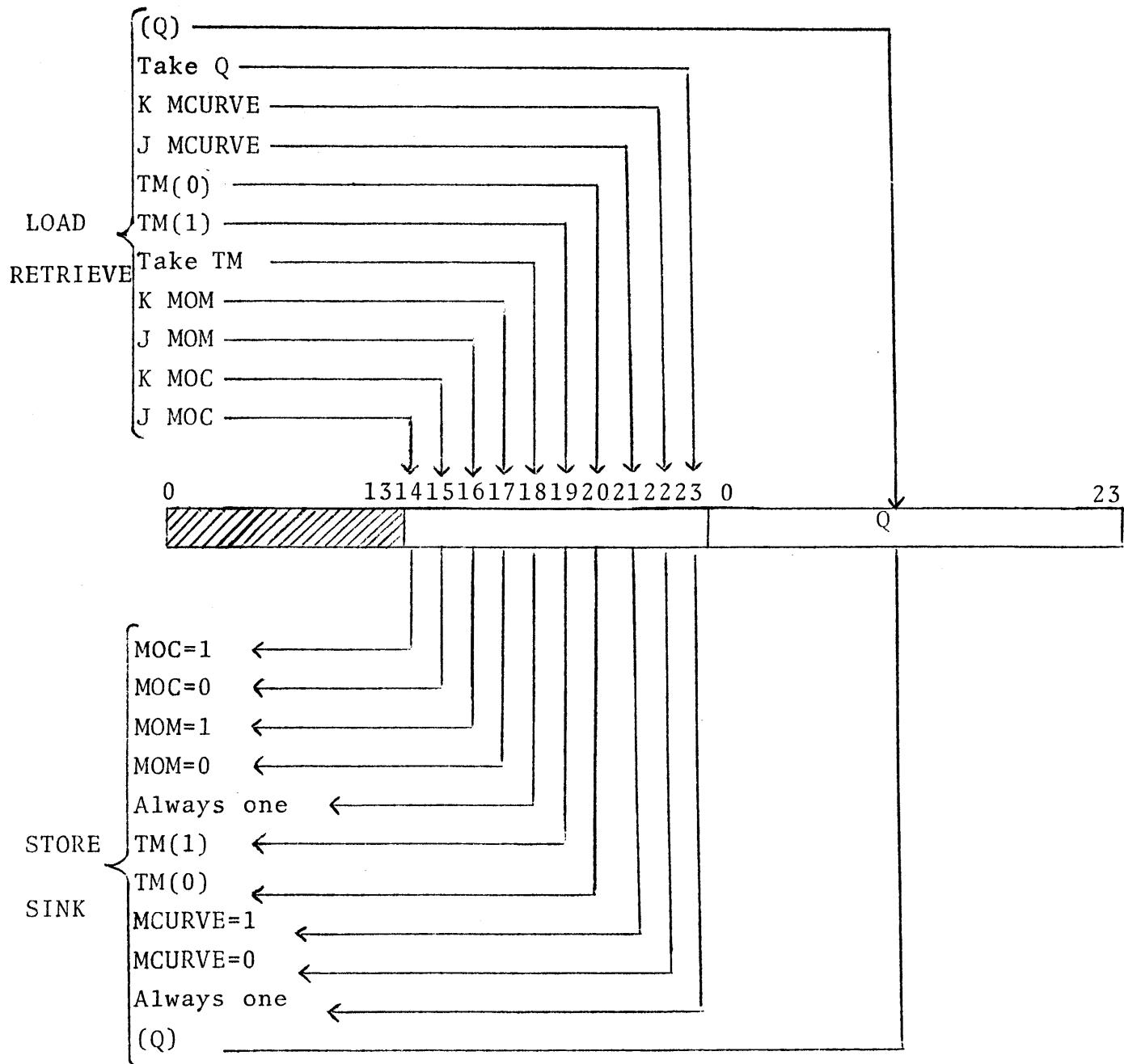

The MOC, MOM and CURVE bits and the transpose map are coded into the MDIR word in a special way, which permits the programmer to change one of them without knowing the values of the others. The right half of the MDIR is a numerical quantity, called Q, which is used in the 3D curve drawing operation. The left half of the MDIR register contains the actual directive coding, in the form shown in figure 3.8. Please note that if the MDIR register is stored (or sinked), and later is loaded (or retrieved) from data written, it will be restored to its original contents.

## THE MDIR REGISTER

Note: J K Next

|   |   |            |

|---|---|------------|

| 0 | 0 | no change  |

| 0 | 1 | 0          |

| 1 | 0 | 1          |

| 1 | 1 | complement |

Figure 3.8

## CHAPTER 4

### THE CLIPPING DIVIDER

#### 4.1 Function

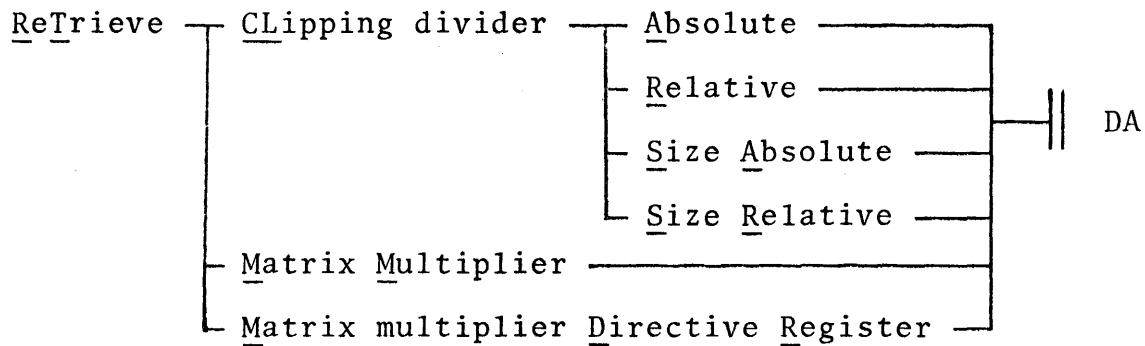

The Clipping Divider eliminates those portions of the drawing which lie outside the field of view, and maps the remaining portion of the drawing into scope coordinates. Input data come from the Matrix Multiplier\* (or the Channel Control if the Matrix Multiplier is not included in the system), and output goes to the Line Generator, back to memory via the Channel Control, or both.

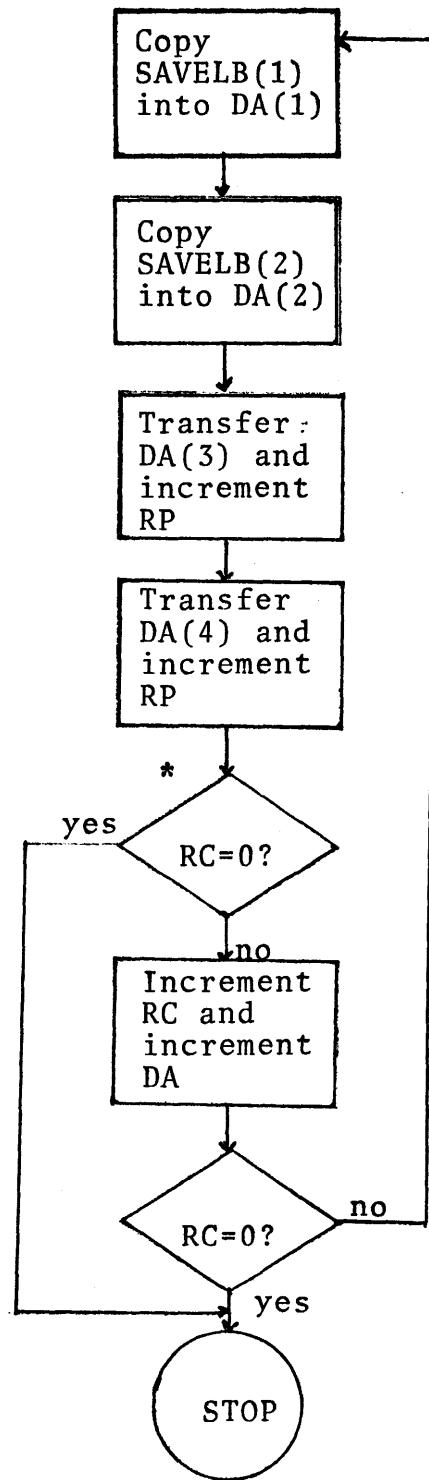

#### 4.2 The Current Point

The coordinates of the SAVE point which are retained by the LDS-2 are stored in the SAVE register of the Clipping Divider. The Clipping Divider processes lines (dots being treated as lines of zero length). In most cases, the SAVE point serves as one end of the line and the new point, defined by the incoming data, serves as the other end of the line. The SAVE register is automatically updated by drawing instructions as explained in Chapter 7. The address and structure of the SAVE register are shown in Figure 4.1.

#### 4.3 Relative Data

The SAVE point also serves as a reference point for relative loads. For relative parameter data (e.g., the window), data are first added to the contents of the SAVE register and the result is used to load the parameter register.

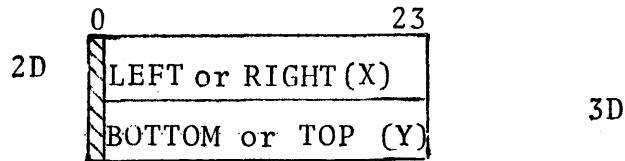

#### 4.4 Two-dimensional Clipping and Division

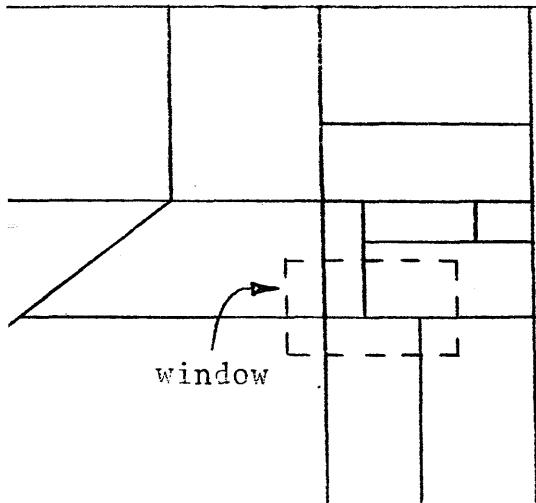

In two-dimensional operation, the Clipping Divider automatically eliminates portions of the drawing which lie outside a rectangular area of the drawing space or "page." This area on the drawing space is known as the WINDOW. The user is able to specify what part of the drawing space he wishes to view by specifying a window in page coordinates which covers that area. The window is specified by giving the page coordinates for its left, bottom corner and its right, top corner. These values are loaded into the WINDOW register of the Clipping Divider.

\* Note: The Clipping Divider accepts only 23-bits of data from the Matrix Multiplier. The high-order bit is a sign-extension. This is done to prevent overflow within the Clipping Divider. The page for the LDS-2 is thus effectively 23 bits rather than 24.

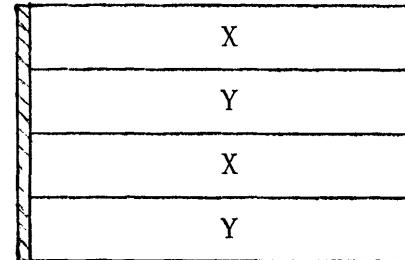

## CLIPPING DIVIDER REGISTER CONFIGURATION

| 4-component<br>addresses |                    | <u>2-component<br/>addresses</u>             |                                                          |

|--------------------------|--------------------|----------------------------------------------|----------------------------------------------------------|

| 14                       | SAVE               | 0 SAVELB<br>LEFT (X)<br>2 VIEWLB<br>LEFT (X) | 1 SAVERT<br>RIGHT (X or $Z_x$ )<br>3 VIEWRT<br>RIGHT (X) |

| 15                       | VIEW<br>(VIEWPORT) | 4 WINDLB<br>LEFT (X)<br>6 INSTLB<br>LEFT (X) | 5 WINDRT<br>RIGHT (X)<br>7 INSTRT<br>RIGHT (X)           |

| 16                       | WIND<br>(WINDOW)   | 10 NAME<br>NAME                              | 11 CDIR<br>CDIR                                          |

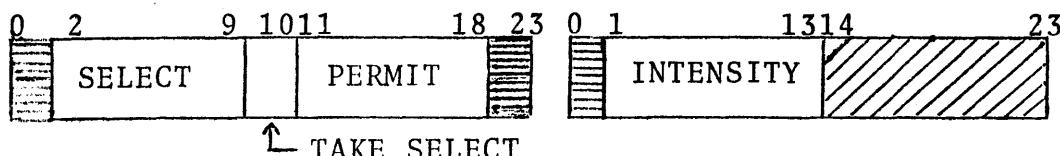

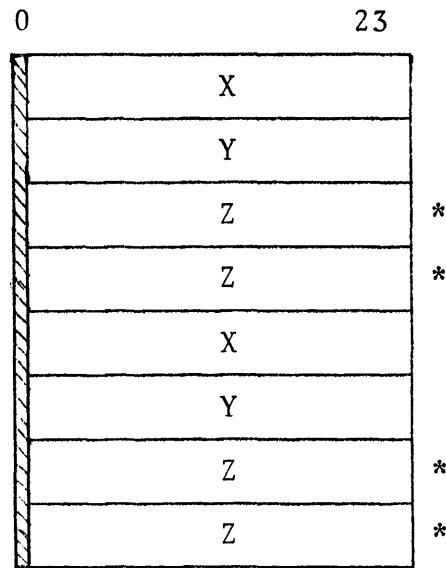

| 17                       | INST<br>(INSTANCE) | 12* HITANG<br>HIT, CORNER,<br>EDGE COUNTS    | 13* SELINT<br>SEL-<br>ECT PER<br>MIT<br>INTENSITY        |

### DATA FORMATS

3D

\* All bits not used,

see figure 4.5 for

exact formats.

Note: Bit 0 is a sign extention.

Note: The names associated with the registers are LDS-2 mnemonics which have been defined in the LDS-2 Assembly language.

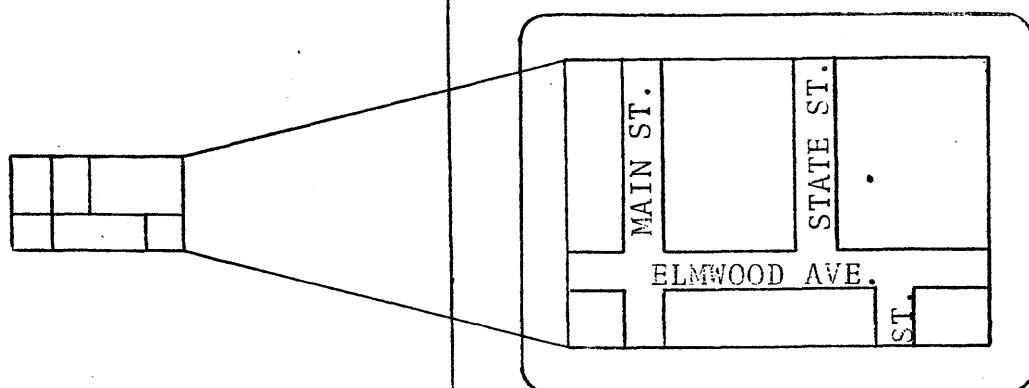

The user may specify the rectangular portion of the scope on which he wishes the picture to appear. This area on the scope is known as the viewport. The viewport is specified by loading the VIEWPORT register with the scope coordinates of its left, bottom corner and right, top corners. The scope coordinate system is centered about zero and stretches from -77777 to +77777 (i.e., 16 bits), but because the VIEWPORT register is a full 24-bit register and because only the 16 least significant bits are used to drive the scope, each boundary of the viewport should be specified to be between -77777 and +77777. Specifying a larger viewport results in wraparound, and specifying a smaller viewport results in the picture being drawn on less than the full viewing area on the scope.

The relation between the sizes of the window and viewport determines the scale of the drawing. A window specification of -17777777, +17777777 (in each axis) and a viewport specification of -77777, +77777 (each axis) will map the entire page onto the entire viewing area of the scope. If the window is only half as large (in each axis) and the viewport is the same size, only 1/4 of the drawing appears, and the scale is twice as large.

The window and viewport need not be the same "shape." When they are different, the scale will be different in X and Y (to "stretch" the picture in one direction). Furthermore, it is possible to create mirror images by specifying a "backward" viewport (i.e., where the value for the left edge is greater than the value for the right edge, or the value for the bottom edge is greater than the value for the top edge). Specifying a backward window, however, results in none of the drawing being displayed.

#### 4.5 Three-dimensional Clipping and Division

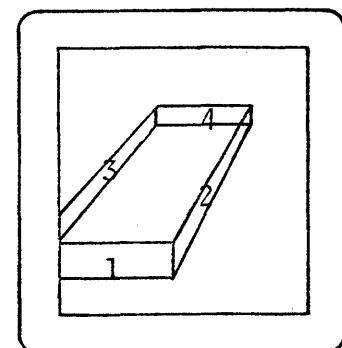

In three-dimensional operation the drawing is compared to a pyramid of vision rather than to the window. The pyramid of vision is defined for positive Z values by the planes  $X = +Z$ ,  $X = -Z$ ,  $Y = +Z$ , and  $Y = -Z$ , thus forming a right angle pyramid with its apex at an observation point about 5" from the face of the screen. Any portion of the drawing outside this pyramid of vision is eliminated. Thus, only those lines or portions of lines where  $|X| \leq Z_x$  and  $|Y| \leq Z_y$  are displayed, as shown in Figure 4.3. If Z is negative, the line is clipped. Since Bit 0 of the Clipping Divider is a sign extension, Z values should not be larger than 17777777, or the line will be clipped.

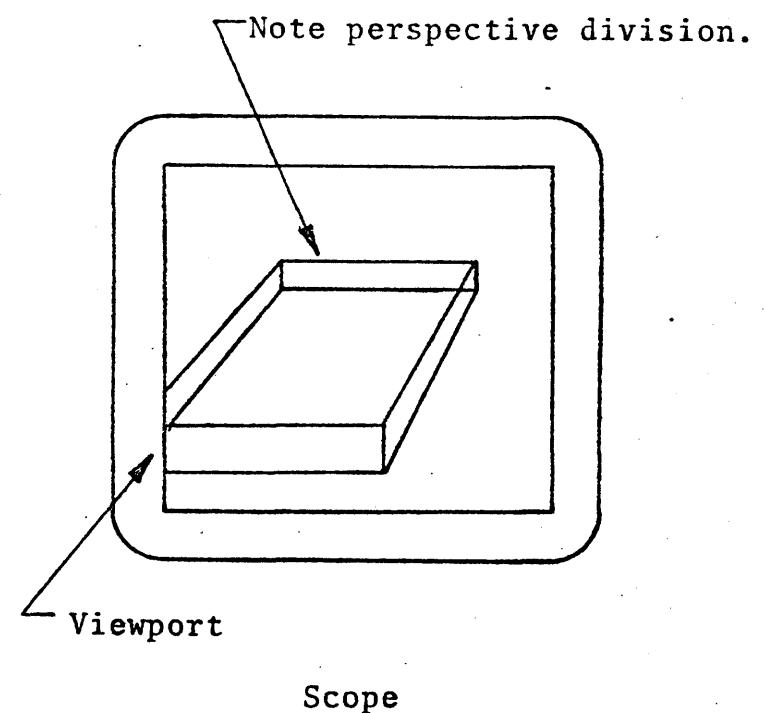

In three-dimensions, perspective division becomes part of the process of mapping the coordinate data into scope coordinates. This perspective division yields  $X/Z_x$  and  $Y/Z_y$ . The viewport operates just as in two-dimensions, controlling the portion of the viewing area of the Display Scope onto which the picture is mapped.

TWO-DIMENSIONAL CLIPPING AND DIVISION

4-4

Figure 4.2

It should be noted that because the pyramid of vision is right-angled, the perspective looks strange unless viewed from very close to the scope face (about 5"). Other viewing angles can be implemented by using the transformation

$$Z = Z \tan(\alpha/2)$$

where  $\alpha$  is the desired viewing angle.

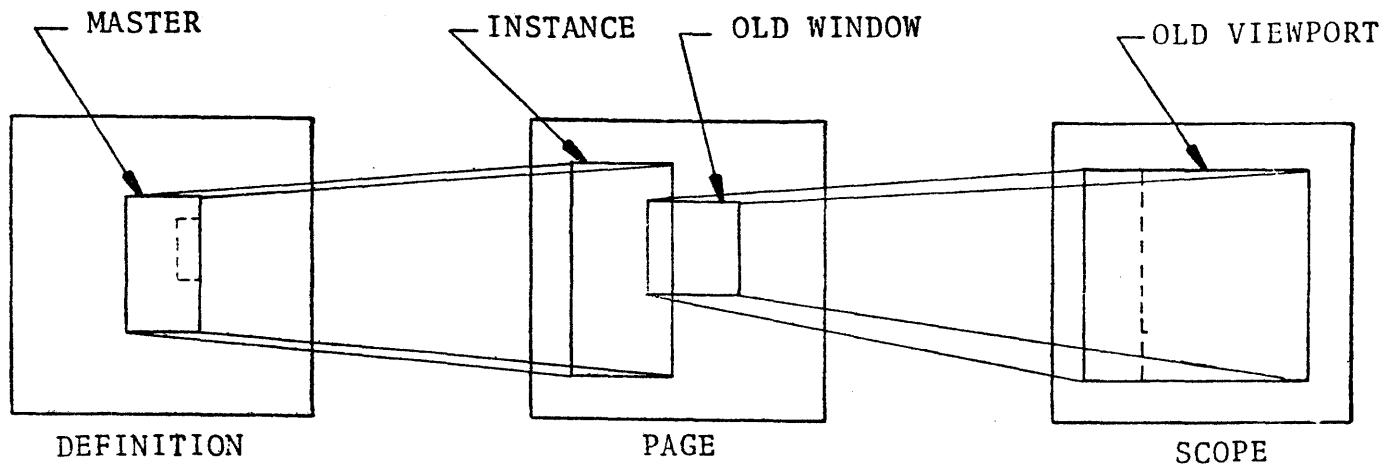

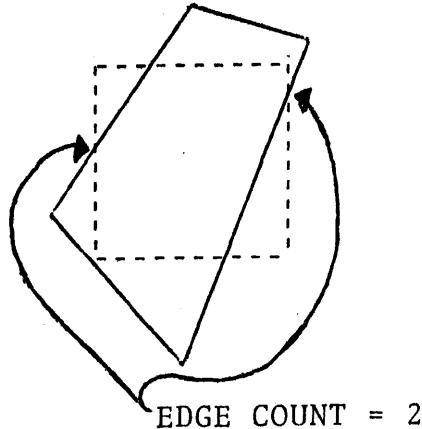

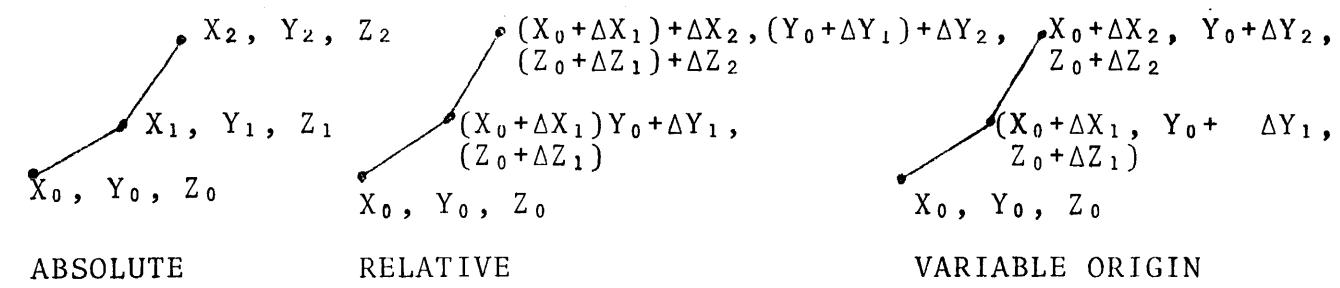

#### 4.6 Boxing

The boxing process is a special feature of the Clipping Divider which allows two-dimensional subpictures to be defined only once but appear in several different sizes and locations. In order to understand boxing it is useful to think of it conceptually as the concatenation of two mappings. The first mapping is from the subroutine definition space, a space similar to the page, onto the page. The second mapping is then the normal page to scope (window to viewport) mapping performed by the Clipping Divider. See Figure 4.4.

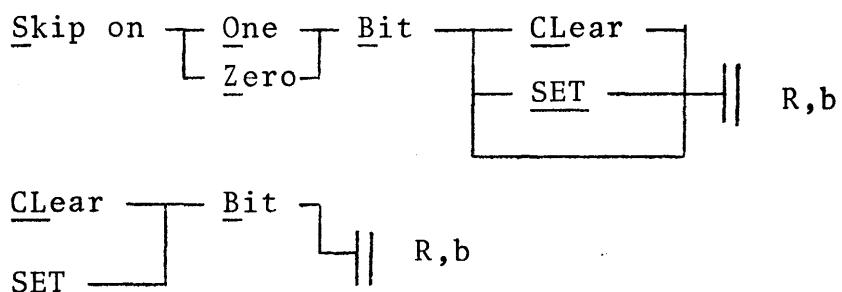

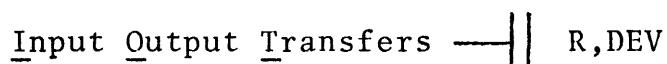

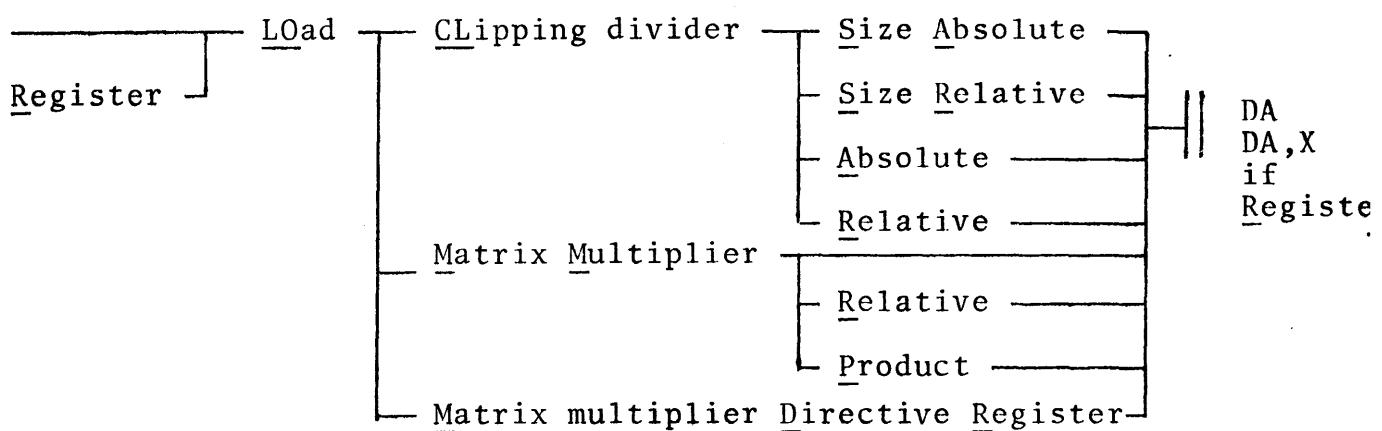

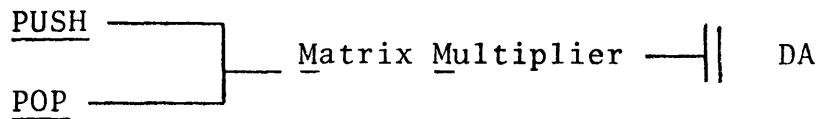

The area on this subroutine definition space which is to be the domain in the first mapping is delineated by the MASTER. The master specifies the rectangular portion of the subroutine definition space which is to be mapped onto the page. The area on the page onto which the MASTER is mapped is known as the INSTANCE. Once the subroutine has been mapped onto the page, the normal window-to-viewport mapping will eliminate any portion of the subroutine which lies outside the window and map the result onto the viewport, thus displaying the subroutine at the proper position and size.