PICTURE SYSTEM 2

Maintenance Manual

Volume 1

COPYRIGHT EVANS & SUTHERLAND COMPUTER CORPORATION

1977

Customer Engineering Dept.

Evans & Sutherland Computer Corporation

580 Arapeen Drive

Salt Lake City, Utah 84108

First Edition

July 1977

"All information contained herein together with all drawings, diagrams and specifications herein or attendant hereto are, and remain, the property of Evans & Sutherland Computer Corporation. Many of the intellectual and technical concepts described herein are proprietary to Evans & Sutherland and may be covered by U.S. and Foreign Patents or Patents Pending or are protected as trade secrets. Any dissemination of this information or reproduction of this material for commercial or other purposes other than the express purpose for which it has been made available are strictly forbidden unless prior written permission is obtained from Evans & Sutherland Computer Corporation".

Evans & Sutherland Computer Corporation assumes no responsibility for any errors that may appear in this manual. The information in this document is subject to change without notice.

## TABLE OF CONTENTS

|         |                                                |      |

|---------|------------------------------------------------|------|

| 1.0     | Introduction.....                              | 1-1  |

| 2.0     | Scope of the Manual.....                       | 2.1  |

| 3.0     | Installation.....                              | 3.1  |

| 3.1     | Picture Controller Interface Installation..... | 3-1  |

| 3.2     | Picture Display Installation.....              | 3-1  |

| 3.3     | Power Connections.....                         | 3-2  |

| 3.4     | Verifications of Proper Operation.....         | 3-2  |

| 4.0     | General Theory of Operation.....               | 4-1  |

| 4.1     | Picture Controller Interface.....              | 4-1  |

| 4.1.1   | Direct IO Path.....                            | 4-2  |

| 4.1.2   | Direct Memory Access Path.....                 | 4-2  |

| 4.2     | PSBUS Arbiter.....                             | 4-3  |

| 4.3     | Picture Processor.....                         | 4-4  |

| 4.4     | PICTURE SYSTEM Memory.....                     | 4-6  |

| 4.5     | Real Time Clock.....                           | 4-6  |

| 4.6     | Refresh Controller.....                        | 4-7  |

| 5.0     | Detailed Theory of Operation.....              | 5-1  |

| 5.1     | Picture Controller Interface.....              | 5-1  |

| 5.1.1   | PDP-11 Interface.....                          | 5-3  |

| 5.1.1.1 | Address Select & Control.....                  | 5-4  |

| 5.1.1.2 | DMA Address Register (DMABA).....              | 5-5  |

| 5.1.1.3 | DMA Word Count Register (DMAWC).....           | 5-5  |

| 5.1.1.4 | DMA Command Register.....                      | 5-5  |

| 5.1.1.5 | DMA Data In Register.....                      | 5-7  |

| 5.1.1.6 | I/O Status Register (IOST).....                | 5-8  |

| 5.1.1.7 | Direct IO Command Register.....                | 5-8  |

| 5.1.1.8 | CPU Data Out Register.....                     | 5-9  |

| 5.1.1.9 | Direct IO Data In Register.....                | 5-9  |

| 5.1.2   | Direct I/O Path.....                           | 5-11 |

| 5.1.2.1 | Direct IO Read.....                            | 5-13 |

| 5.1.2.2 | Direct IO Write.....                           | 5-17 |

| 5.1.2.3 | Reading the DIOPSA.....                        | 5-19 |

| 5.1.3   | Direct Memory Access Path (DMA).....           | 5-20 |

| 5.1.3.1 | DMA Block Transfer Initialization.....         | 5-20 |

| 5.1.3.2 | DMAIN Transfer.....                            | 5-21 |

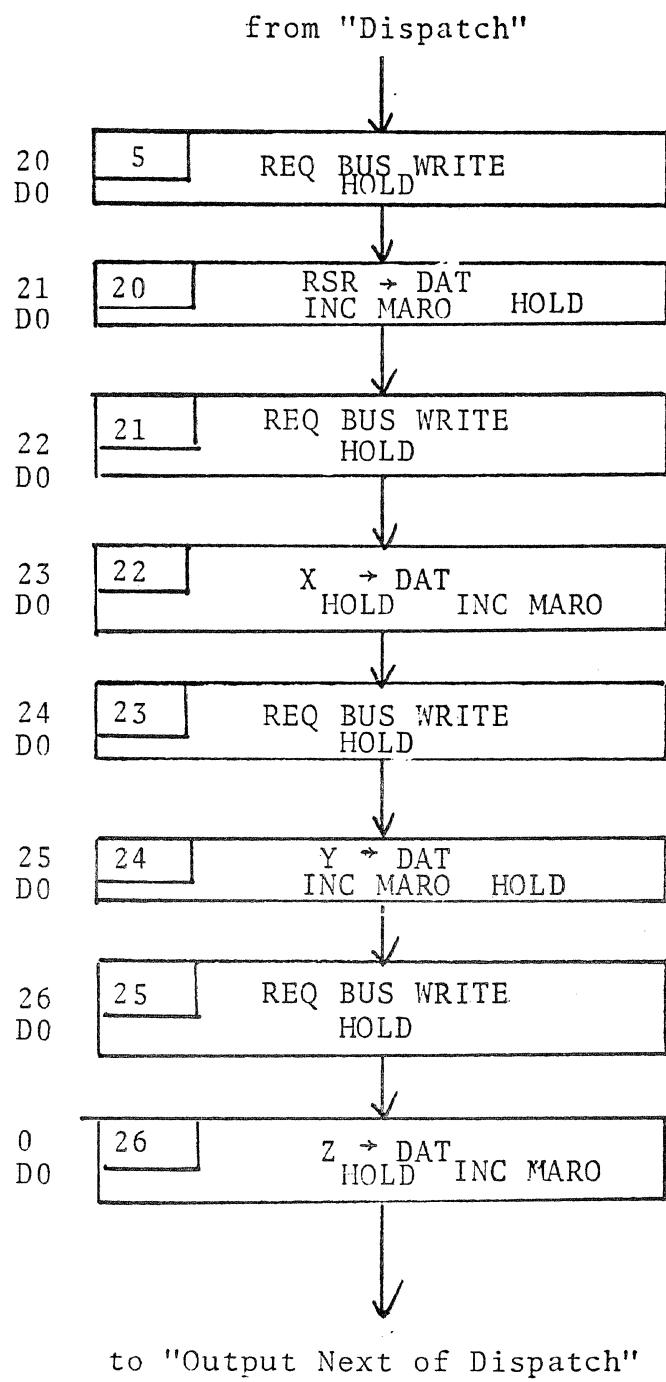

| 5.1.3.3 | DMAOUT Transfer.....                           | 5-25 |

|         |                                            |       |

|---------|--------------------------------------------|-------|

| 5.1.4   | Interrupt Sense and Control.....           | 5-27  |

| 5.1.4.1 | System Interrupts.....                     | 5-29  |

| 5.2     | PICTURE SYSTEM BUS - PSBUS.....            | 5-31  |

| 5.2.1   | PSBUS Structure.....                       | 5-31  |

| 5.2.2   | Active/Passive Devices.....                | 5-32  |

| 5.2.3   | PSBUS Timing.....                          | 5-33  |

| 5.2.4   | PSBUS Arbitration.....                     | 5-34  |

| 5.3     | Picture Processor.....                     | 5-39  |

| 5.3.1   | MAP Input Controller - Active.....         | 5-41  |

| 5.3.1.1 | MAP Input FIFO.....                        | 5-42  |

| 5.3.1.2 | MAP Input Sequencer.....                   | 5-42  |

| 5.3.2   | MAP Input Controller - Passive.....        | 5-48  |

| 5.3.3   | RSR Register and Update PROM.....          | 5-50  |

| 5.3.3.1 | GET RSR State.....                         | 5-50  |

| 5.3.3.2 | Control and DRAW Commands.....             | 5-51  |

| 5.3.3.3 | Drawing Sequences and Data.....            | 5-52  |

|         | Interpretation                             |       |

| 5.3.3.4 | Drawing Sequence Example.....              | 5-53  |

| 5.3.3.5 | RSR/Update PROM Hardware Description.....  | 5-55  |

| 5.3.3.6 | Reading the RSR.....                       | 5-56  |

| 5.3.3.7 | Writing the RSR.....                       | 5-56  |

| 5.3.4   | Extend Register.....                       | 5-57  |

| 5.3.5   | Matrix Arithmetic Processor (MAP).....     | 5-59  |

| 5.3.5.1 | MAP Data Store and ALU Unit.....           | 5-66  |

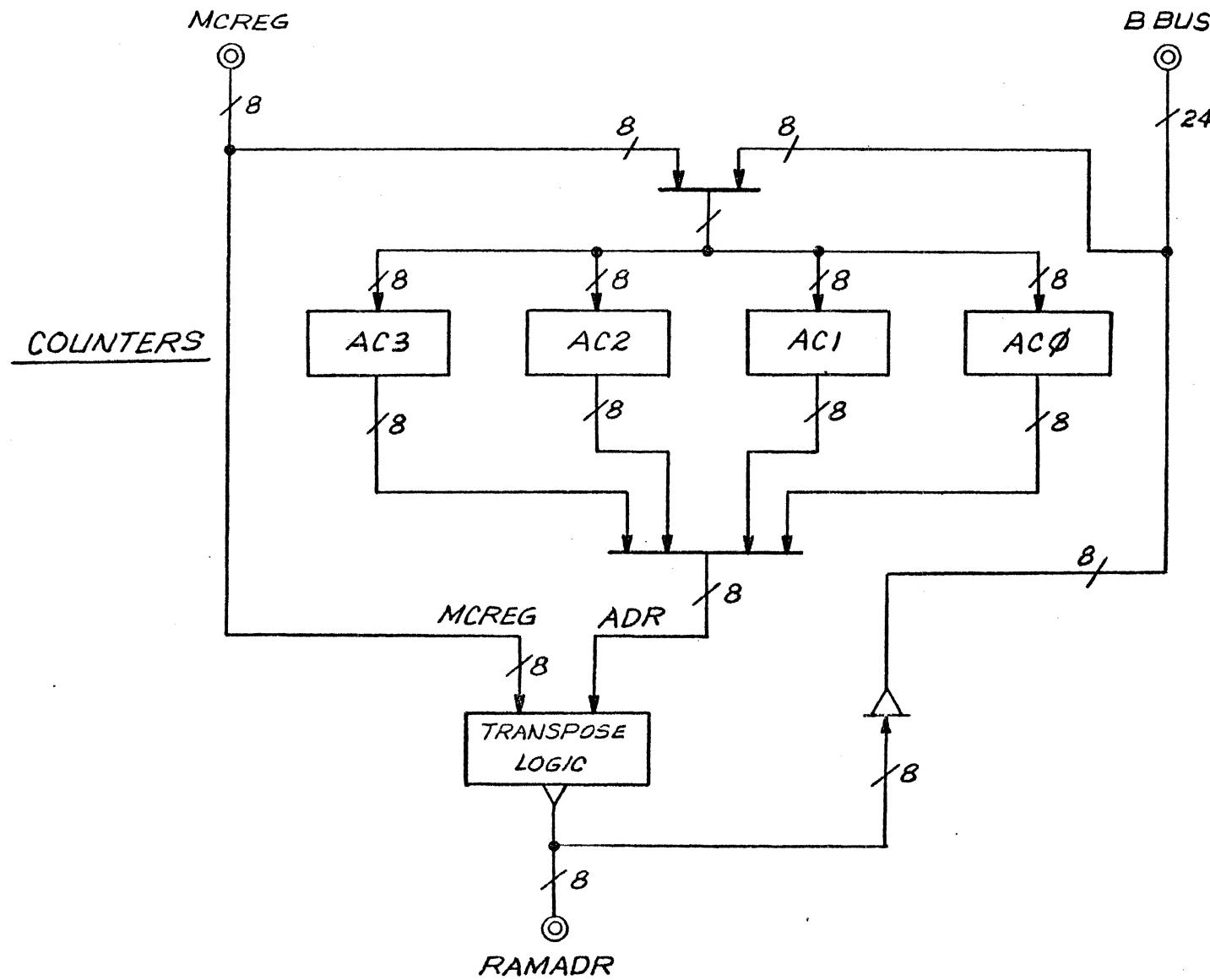

| 5.3.5.2 | MAP Address Counters.....                  | 5-70  |

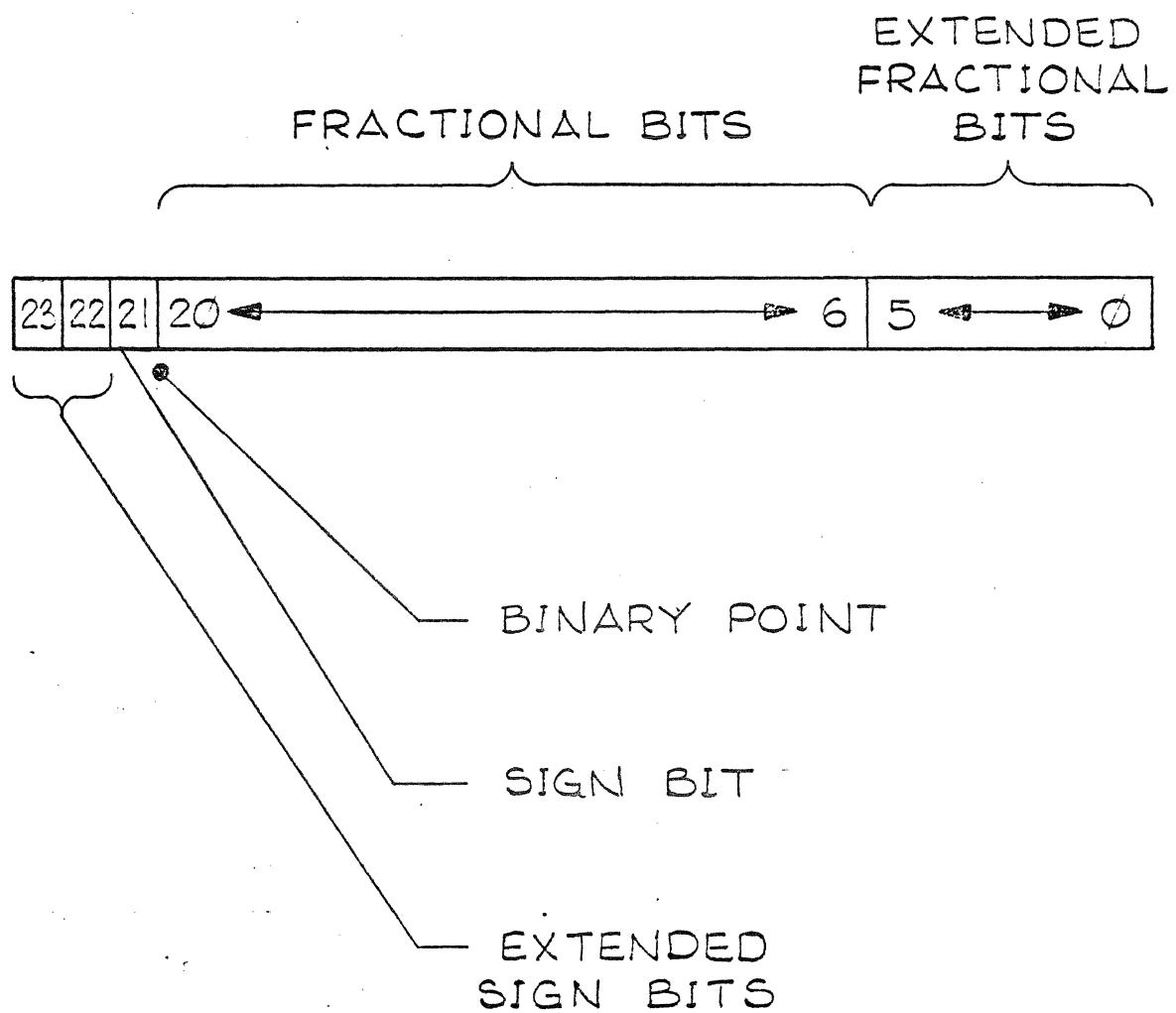

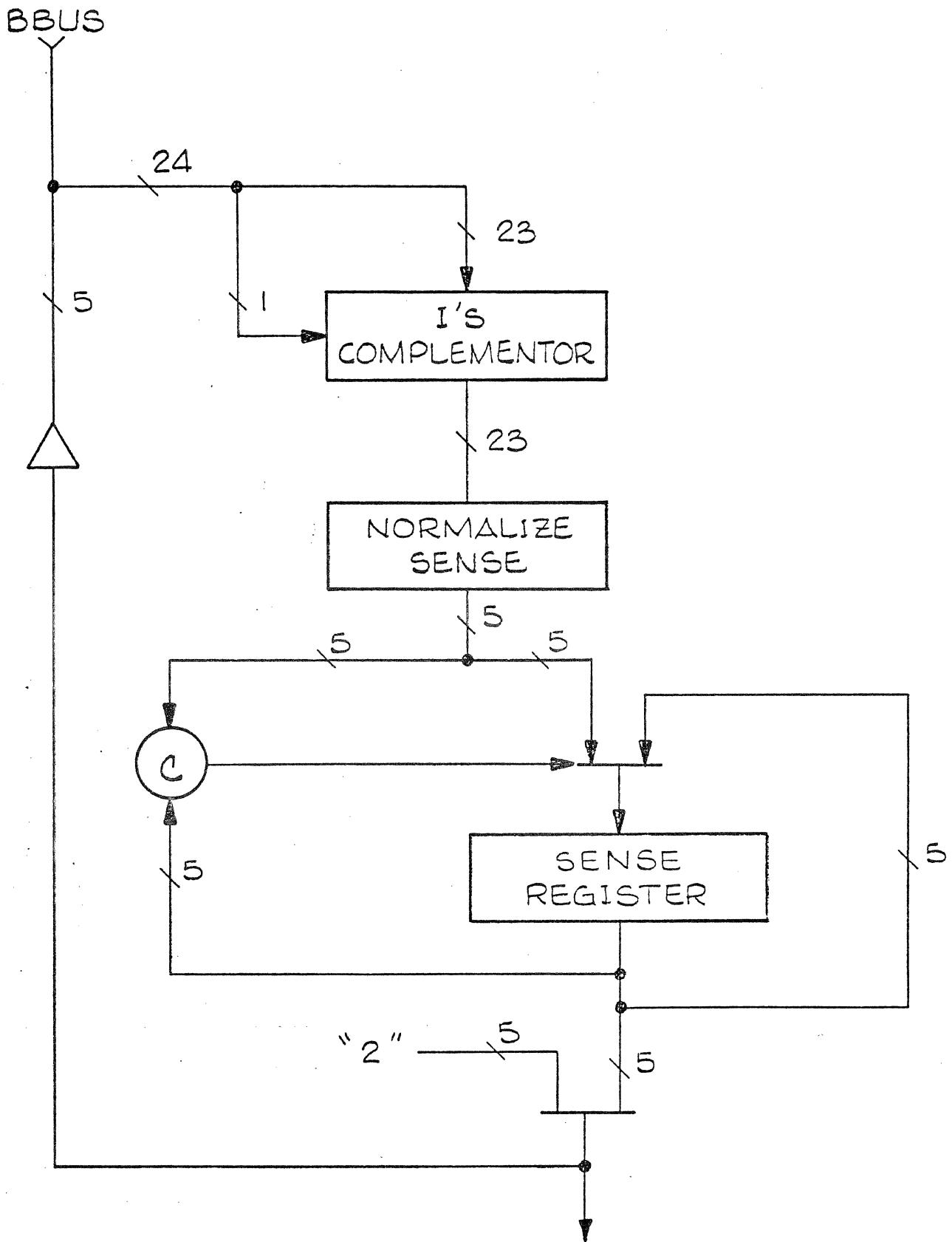

| 5.3.5.3 | Normalize Sense.....                       | 5-72  |

| 5.3.5.4 | Normalizer.....                            | 5-74  |

| 5.3.5.5 | Array Multiplier.....                      | 5-75  |

| 5.3.5.6 | Reciprocation.....                         | 5-76  |

| 5.3.5.7 | MAP Control Store.....                     | 5-80  |

| 5.3.5.8 | MAP System Clock.....                      | 5-82  |

| 5.3.5.9 | MAP Maintenance Structure.....             | 5-84  |

| 5.3.6   | MAP Output Formatter.....                  | 5-89  |

| 5.3.6.1 | Output Control Sequencer.....              | 5-90  |

| 5.4     | PICTURE SYSTEM Memory (PS MEMORY).....     | 5-92  |

| 5.4.1   | FIFO and Port Latch.....                   | 5-94  |

| 5.4.2   | Port Arbitration and Port Controllers..... | 5-95  |

| 5.4.3   | Sequence Controller.....                   | 5-96  |

| 5.5     | Real Time Clock.....                       | 5-99  |

| 5.6     | Refresh Controller.....                    | 5-101 |

| 5.6.1   | Refresh Control Command Words.....         | 5-102 |

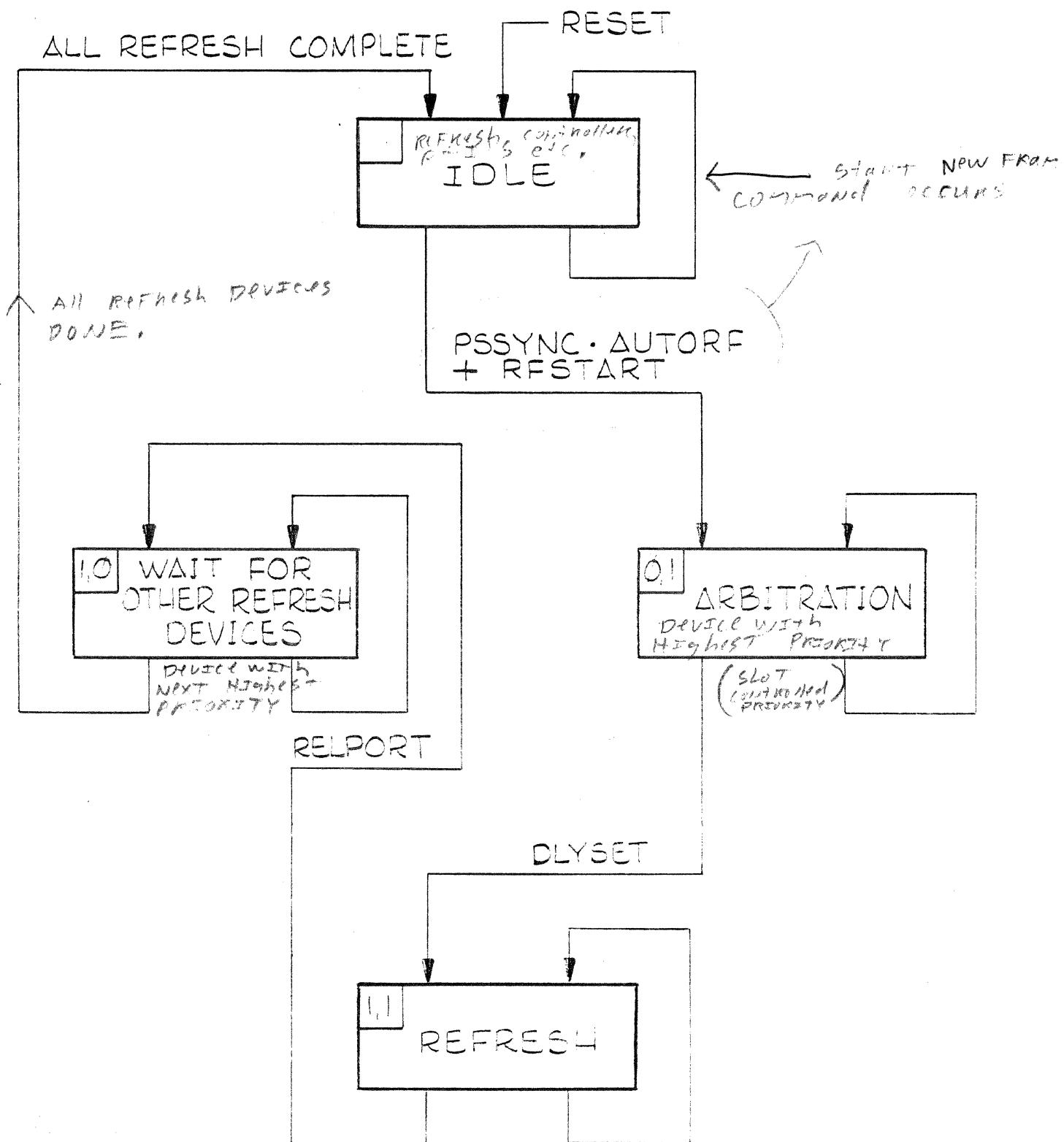

| 5.6.2   | Frame Synchronization.....                 | 5-102 |

| 5.6.2.1 | Arbitration of Refresh Devices.....        | 5-103 |

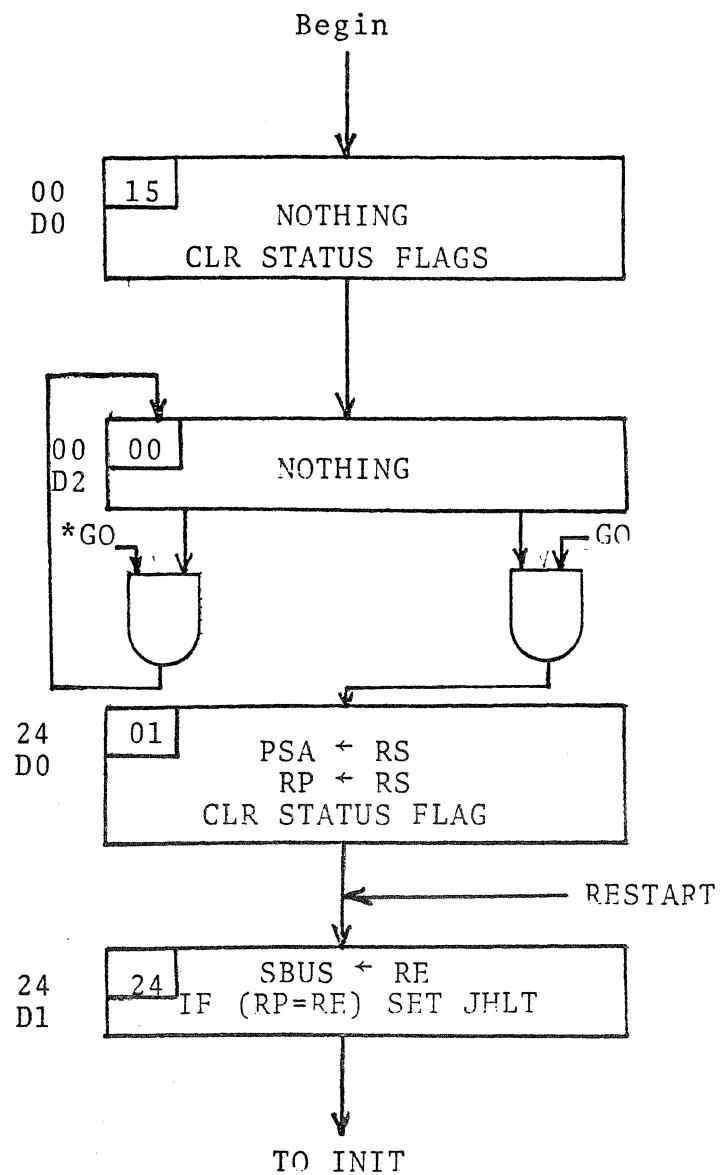

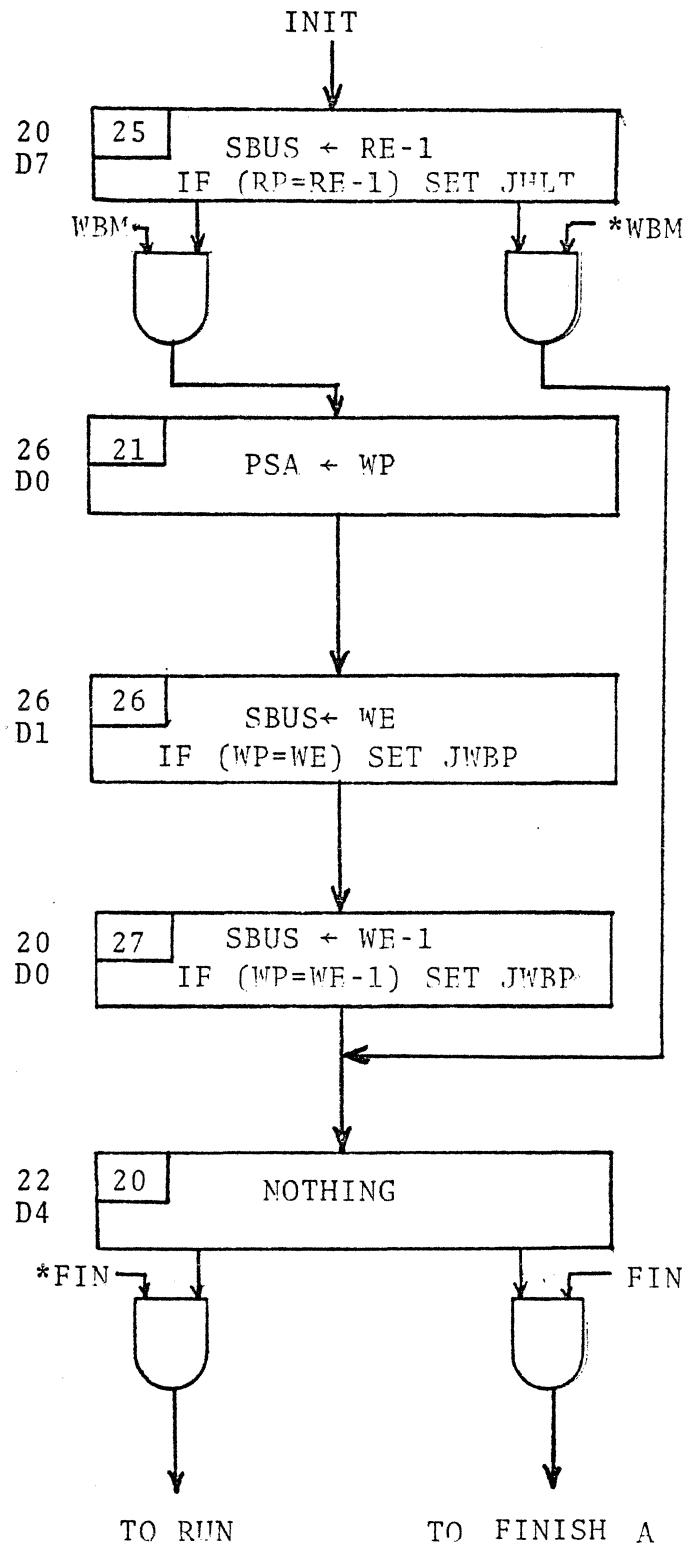

| 5.6.2.2 | Frame Sync State Machine.....              | 5-103 |

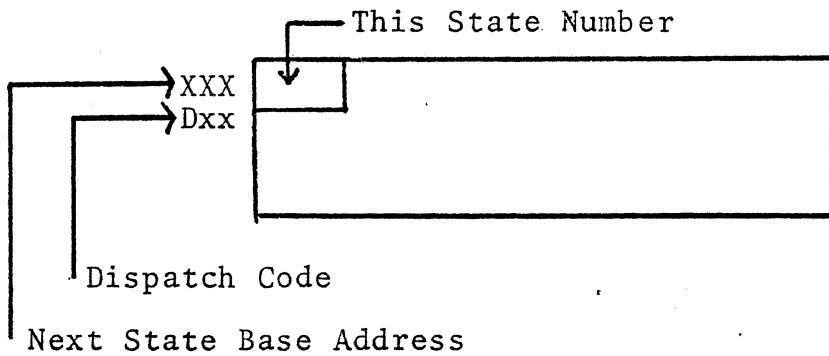

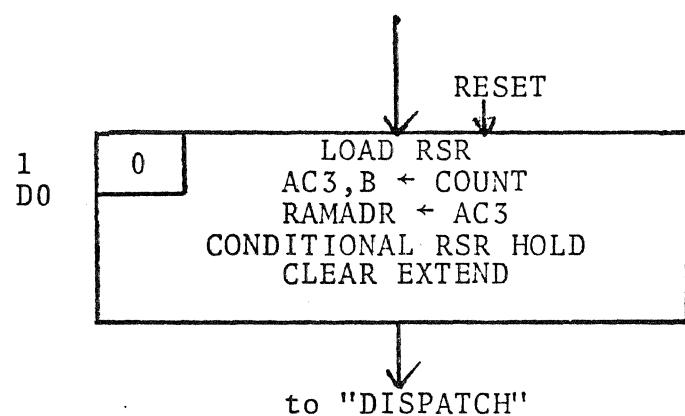

| 5.6.3   | Refresh Sequencer.....                     | 5-105 |

## APPENDIX

|            |                                           |      |

|------------|-------------------------------------------|------|

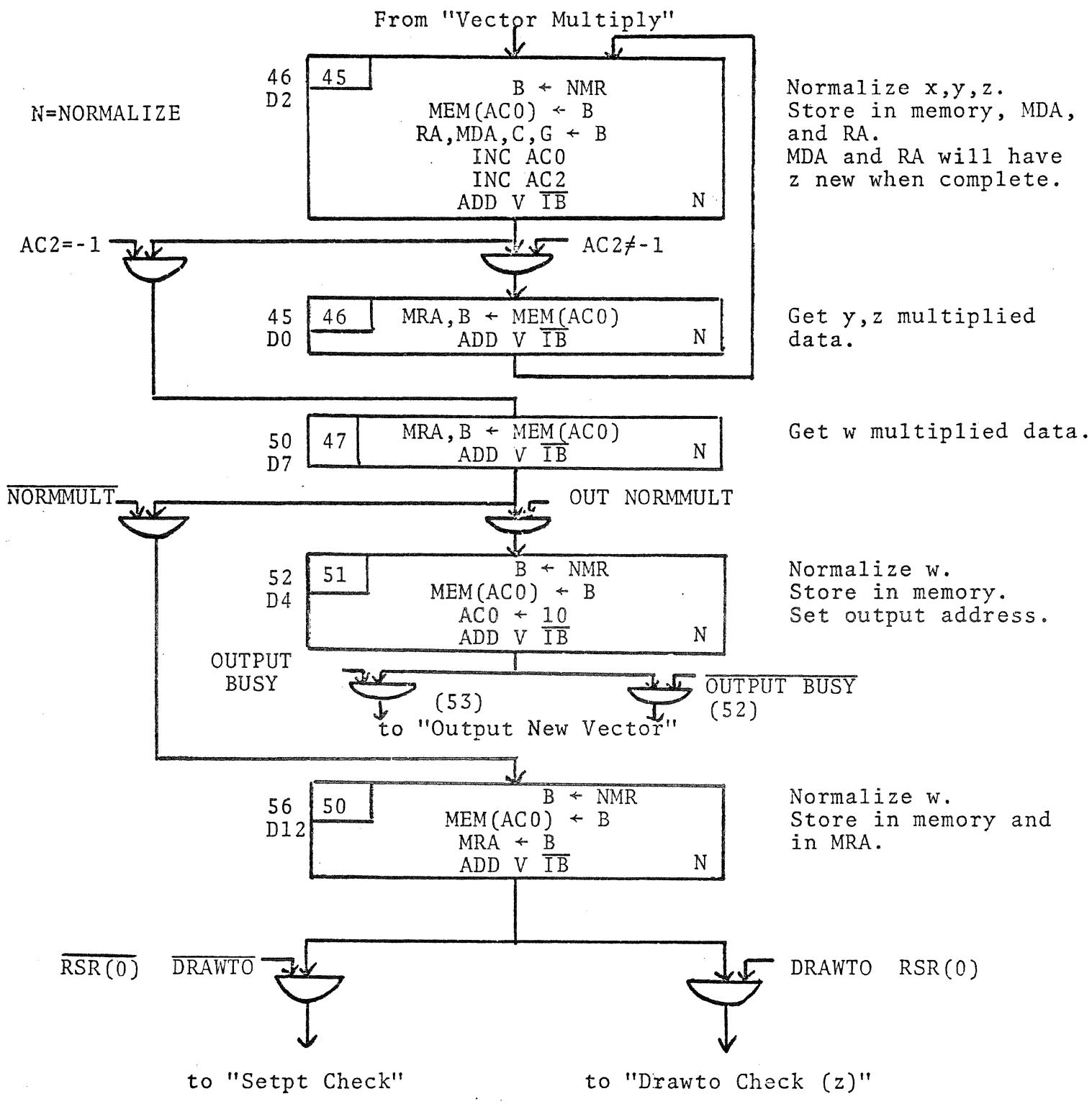

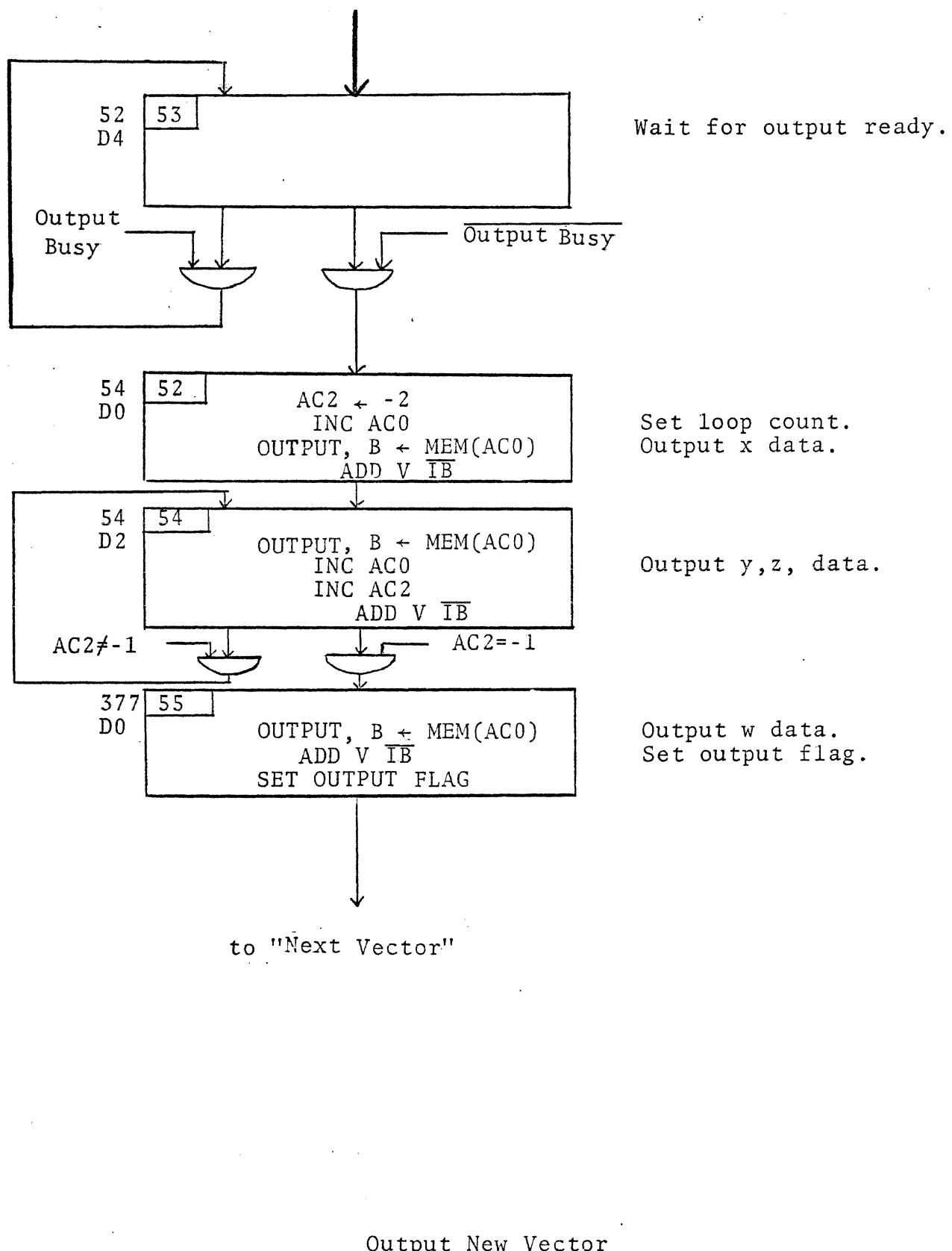

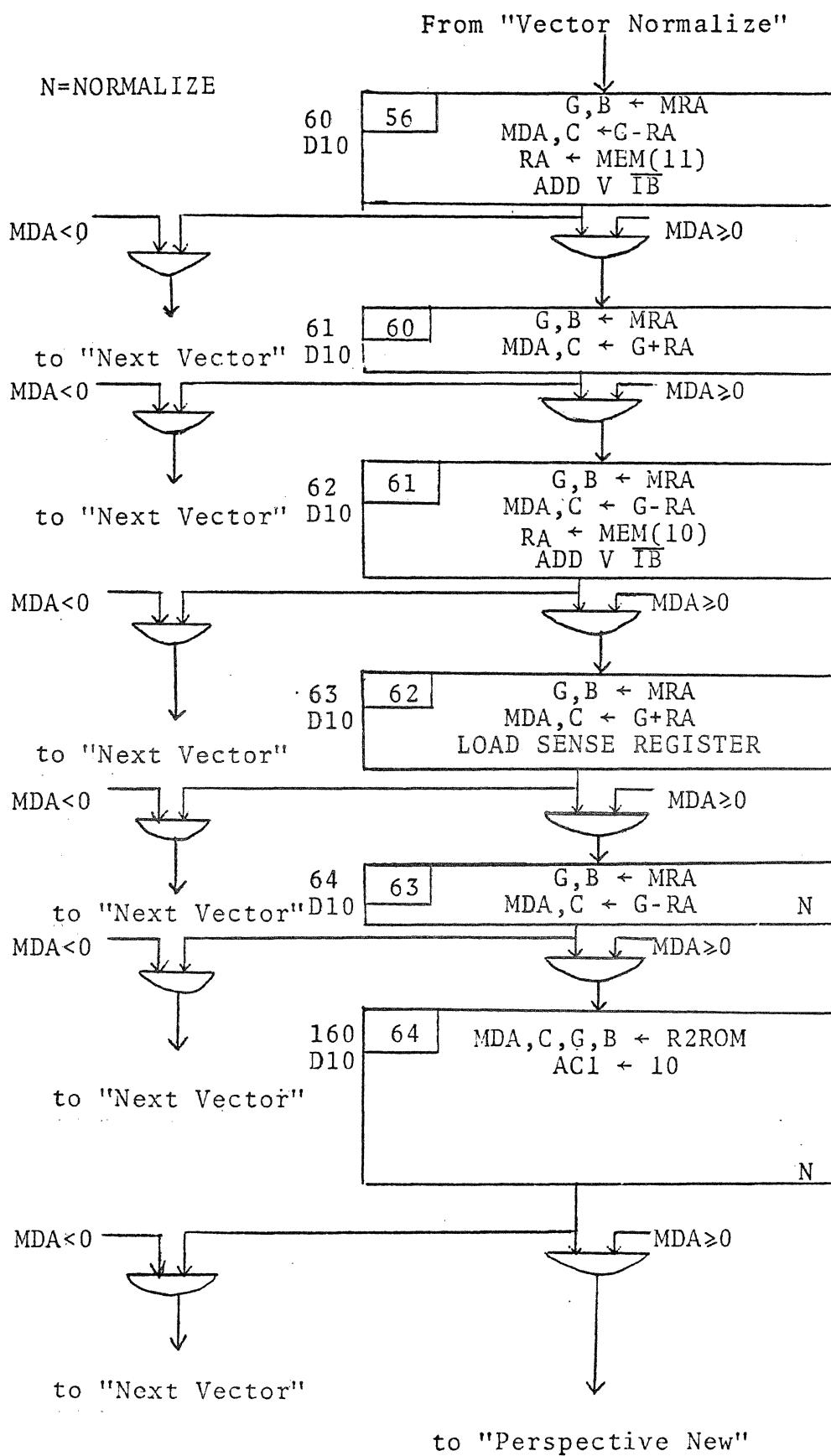

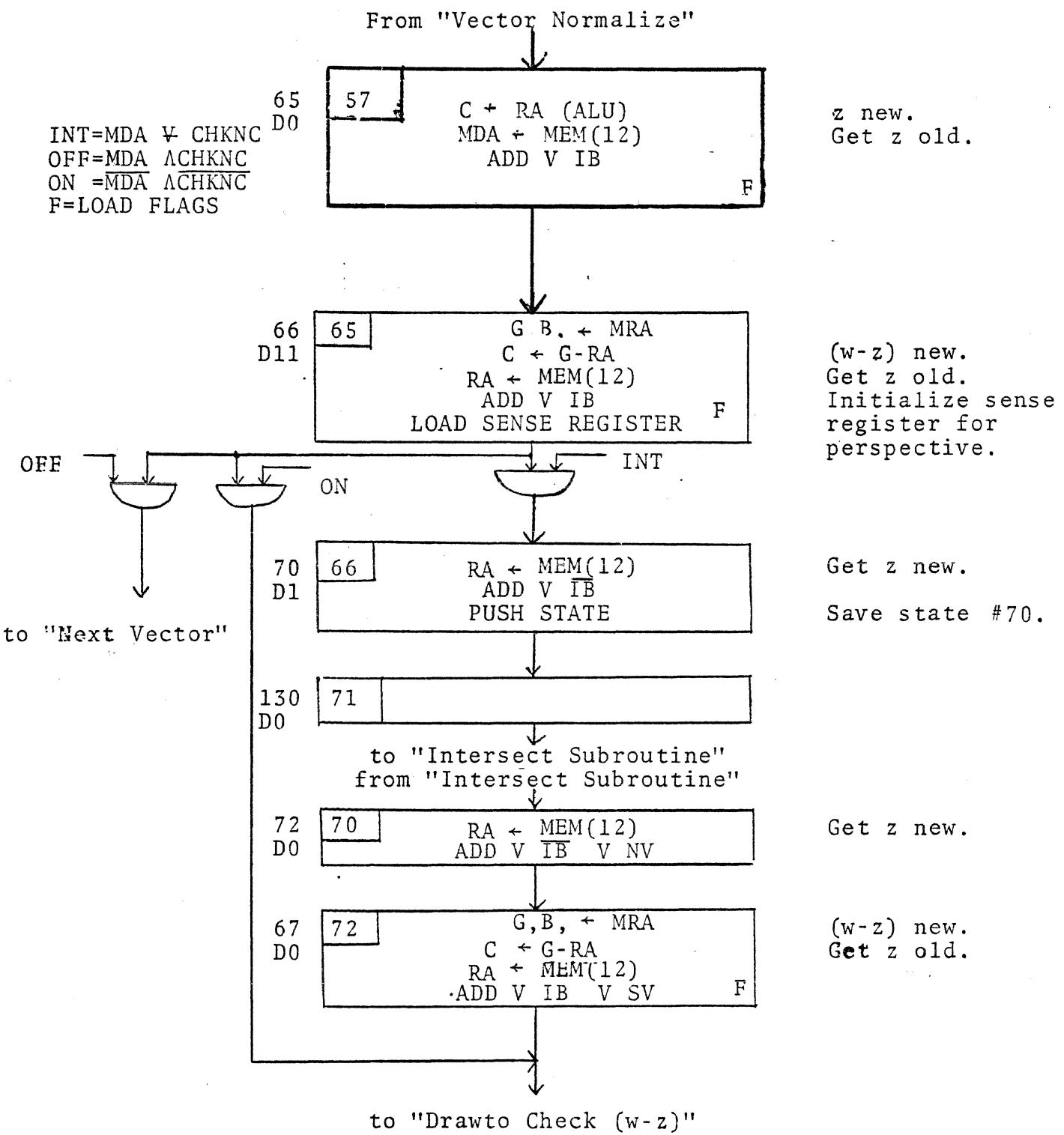

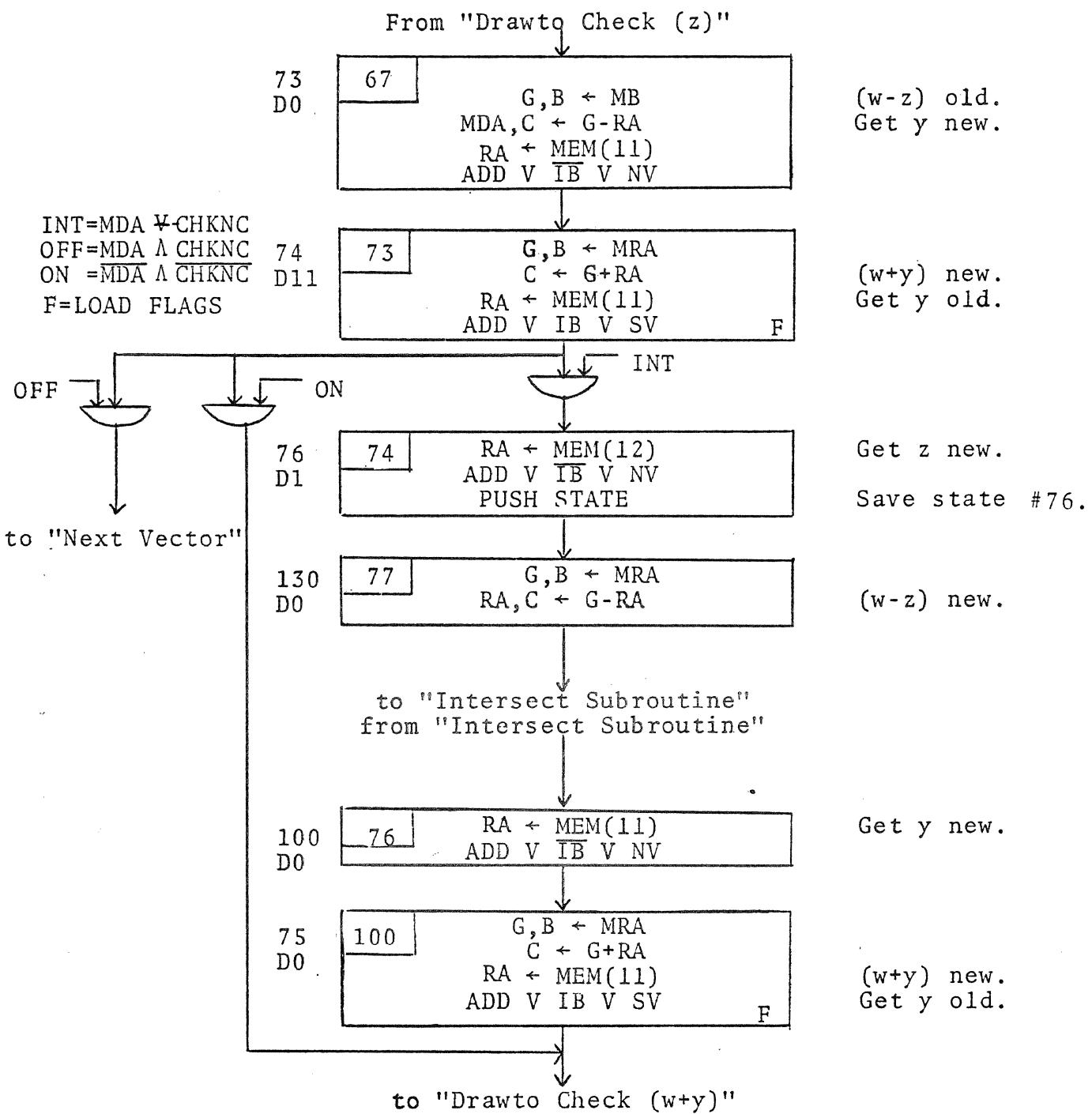

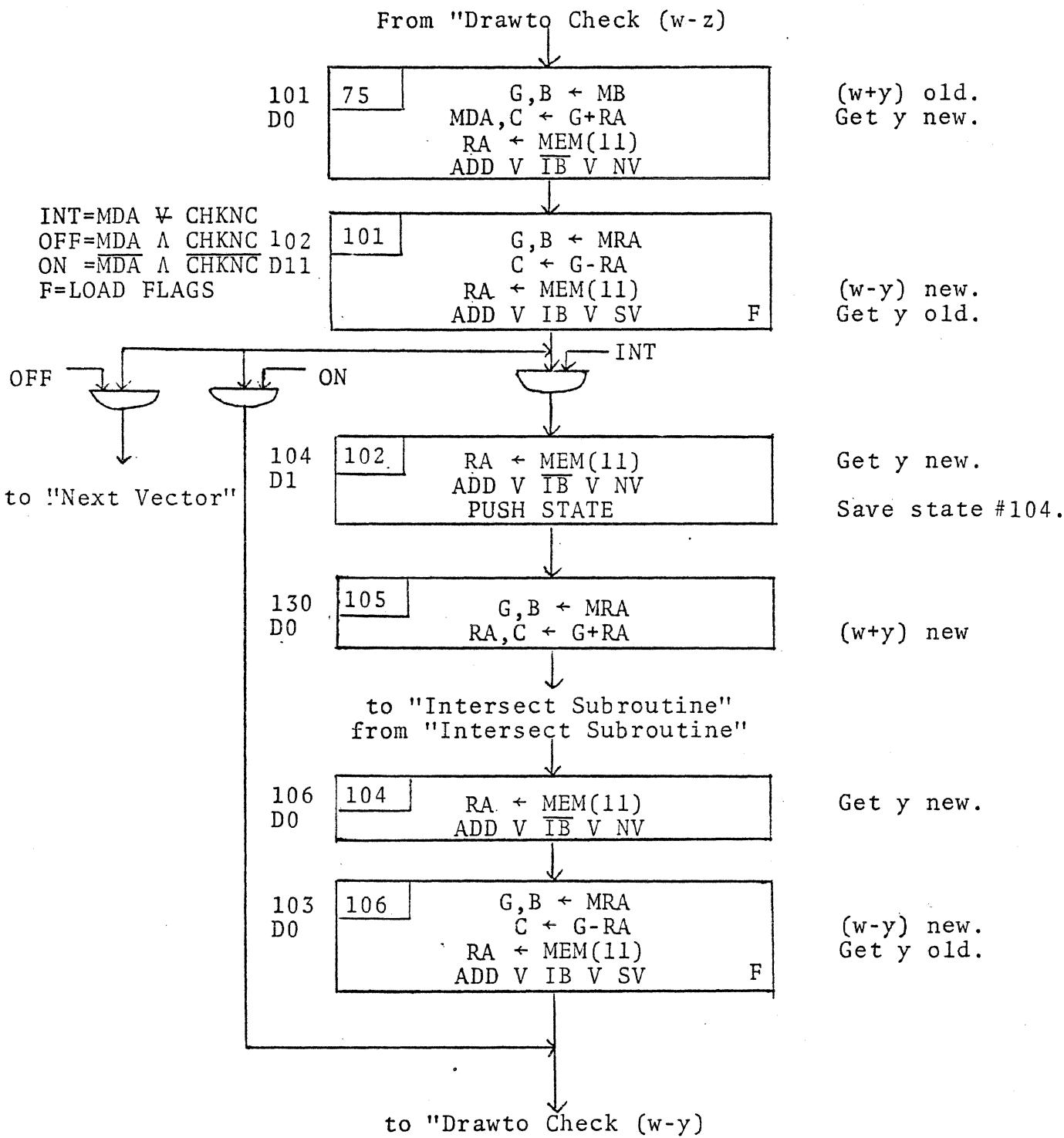

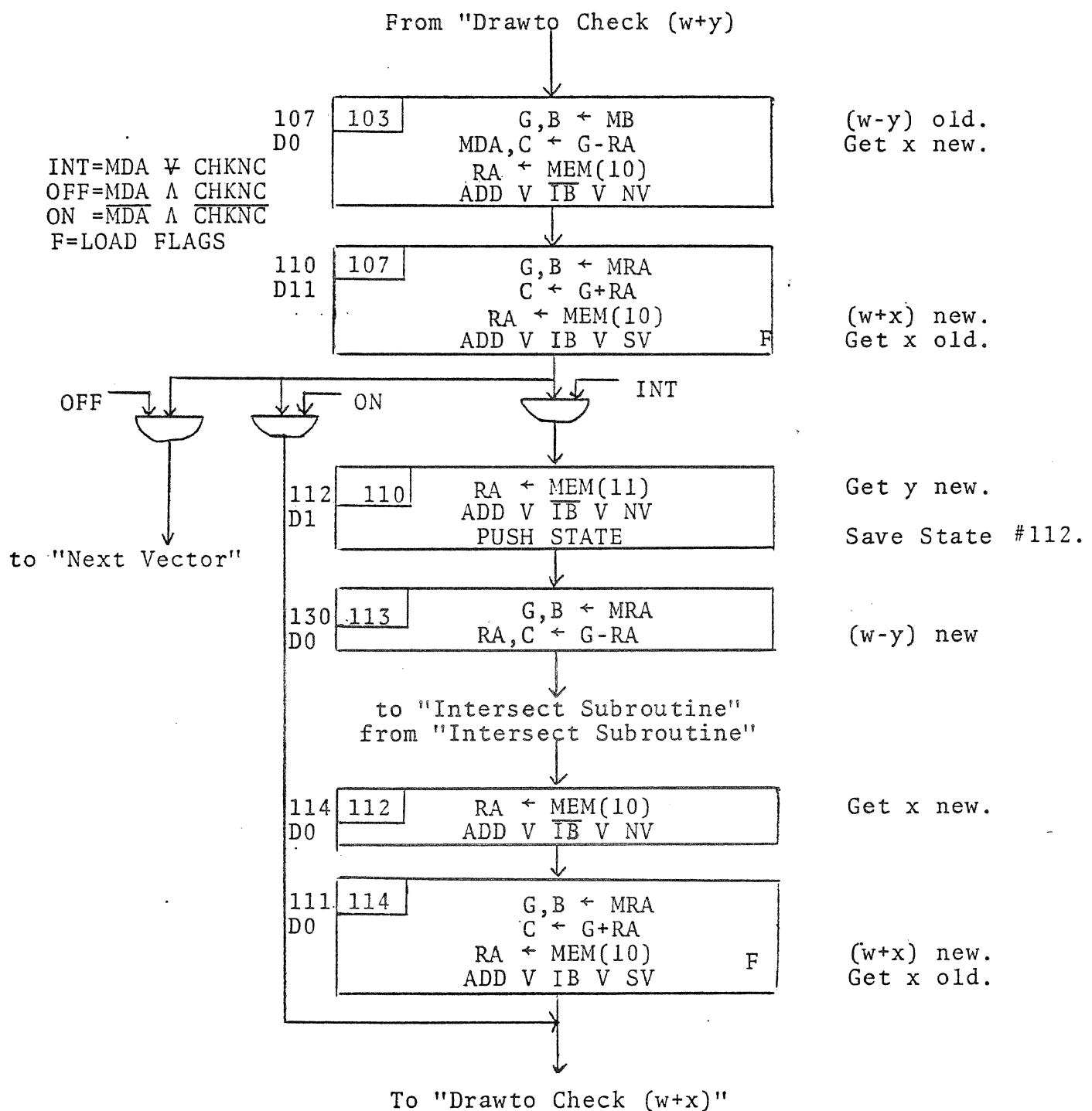

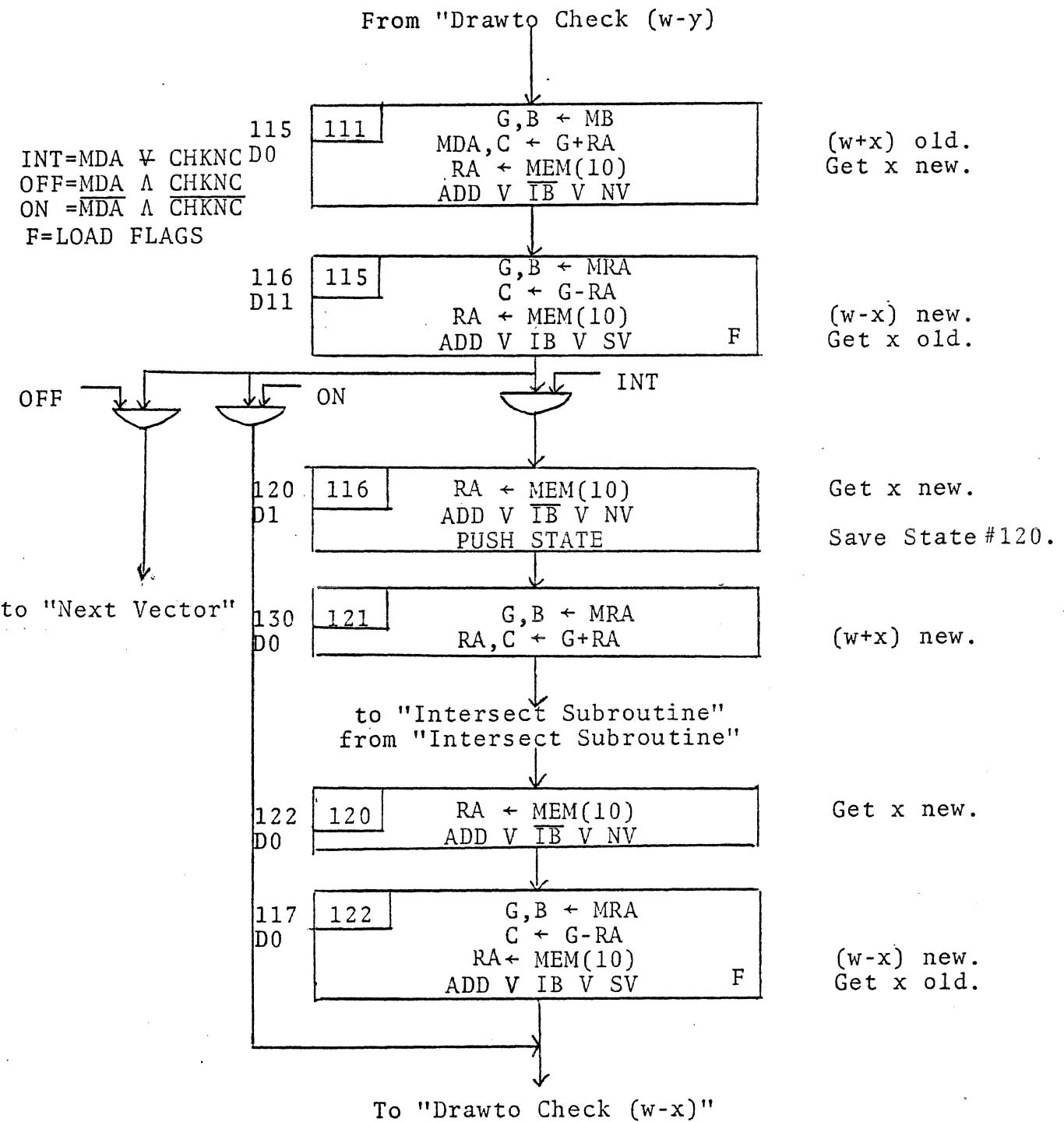

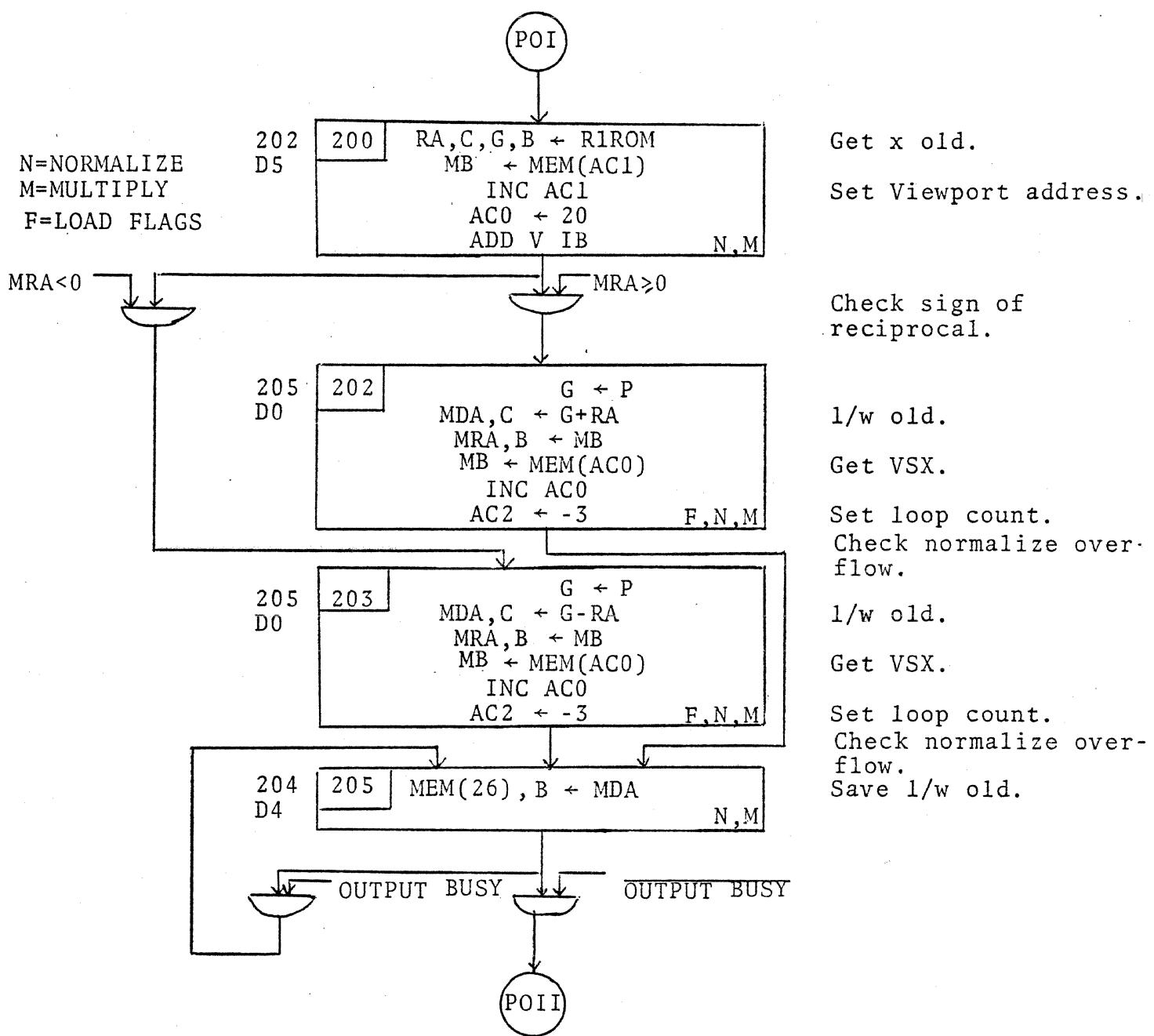

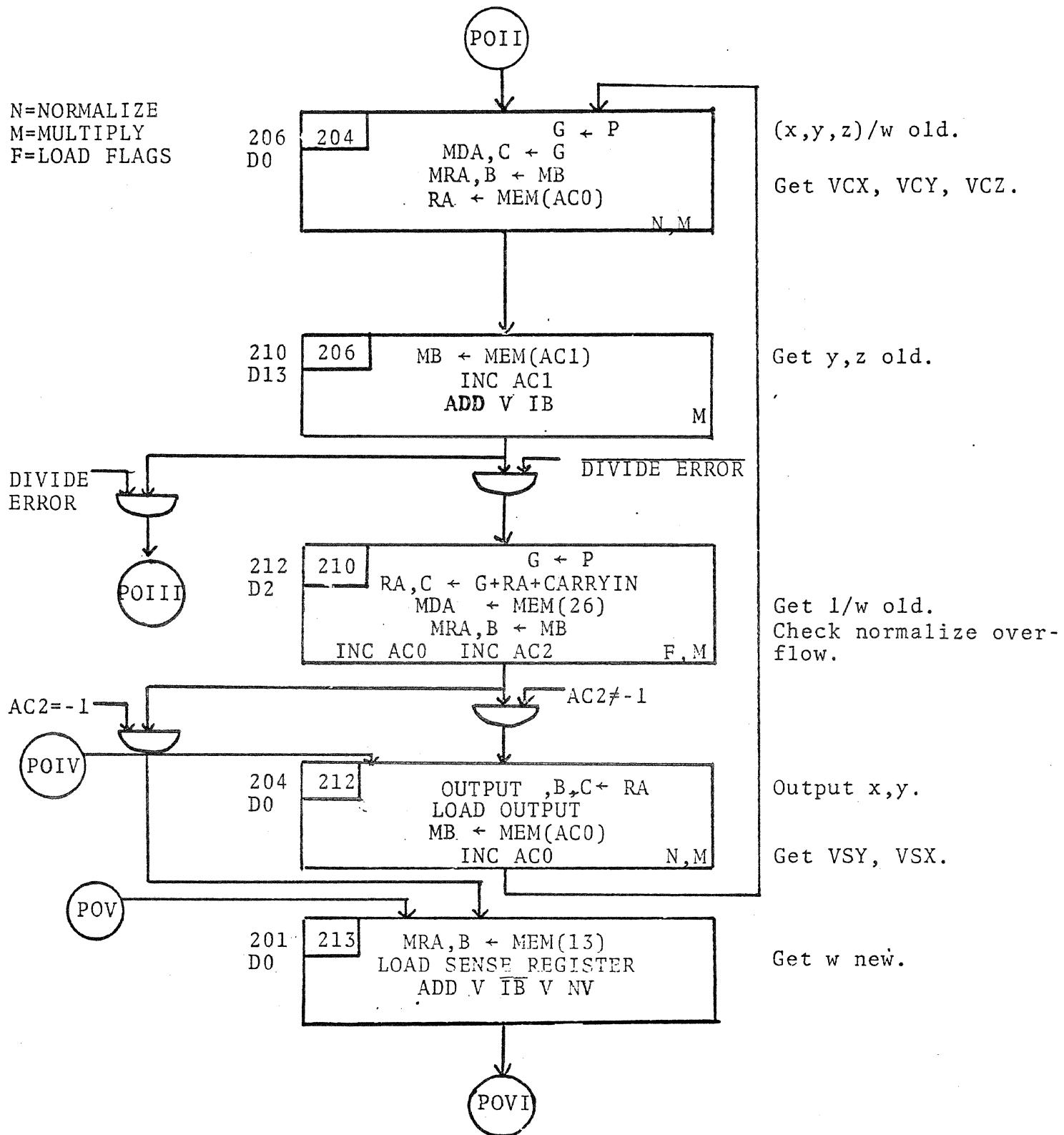

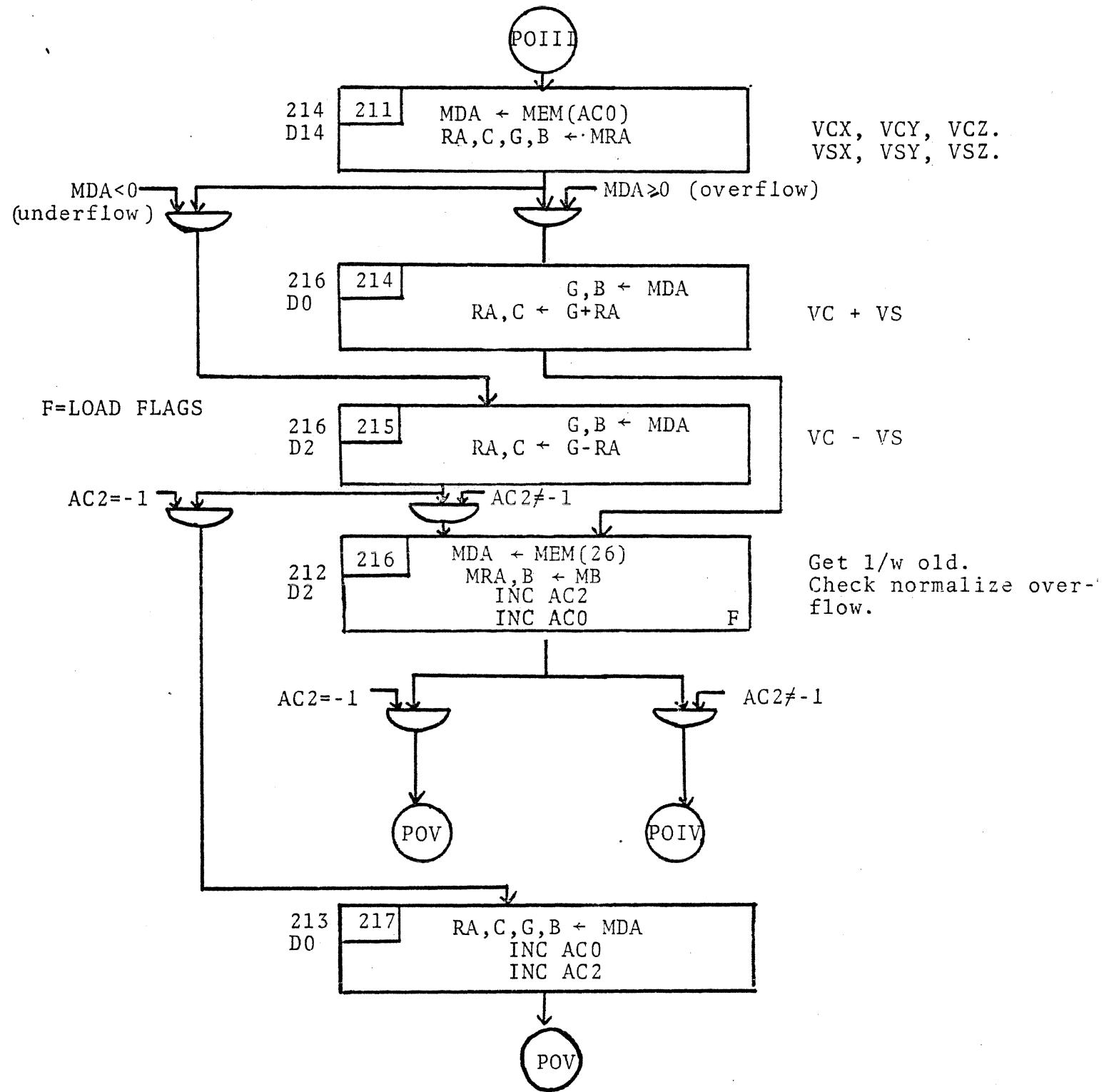

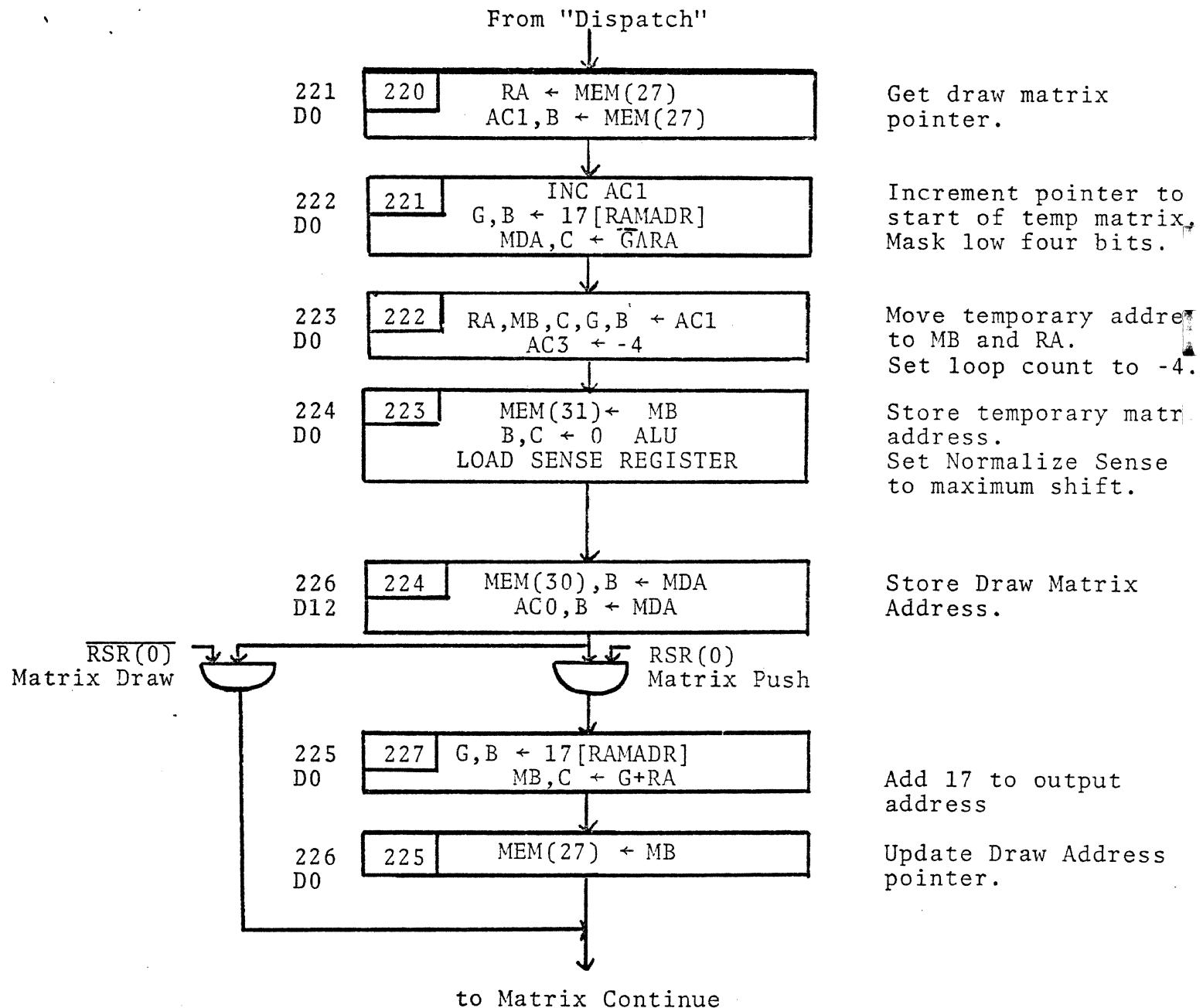

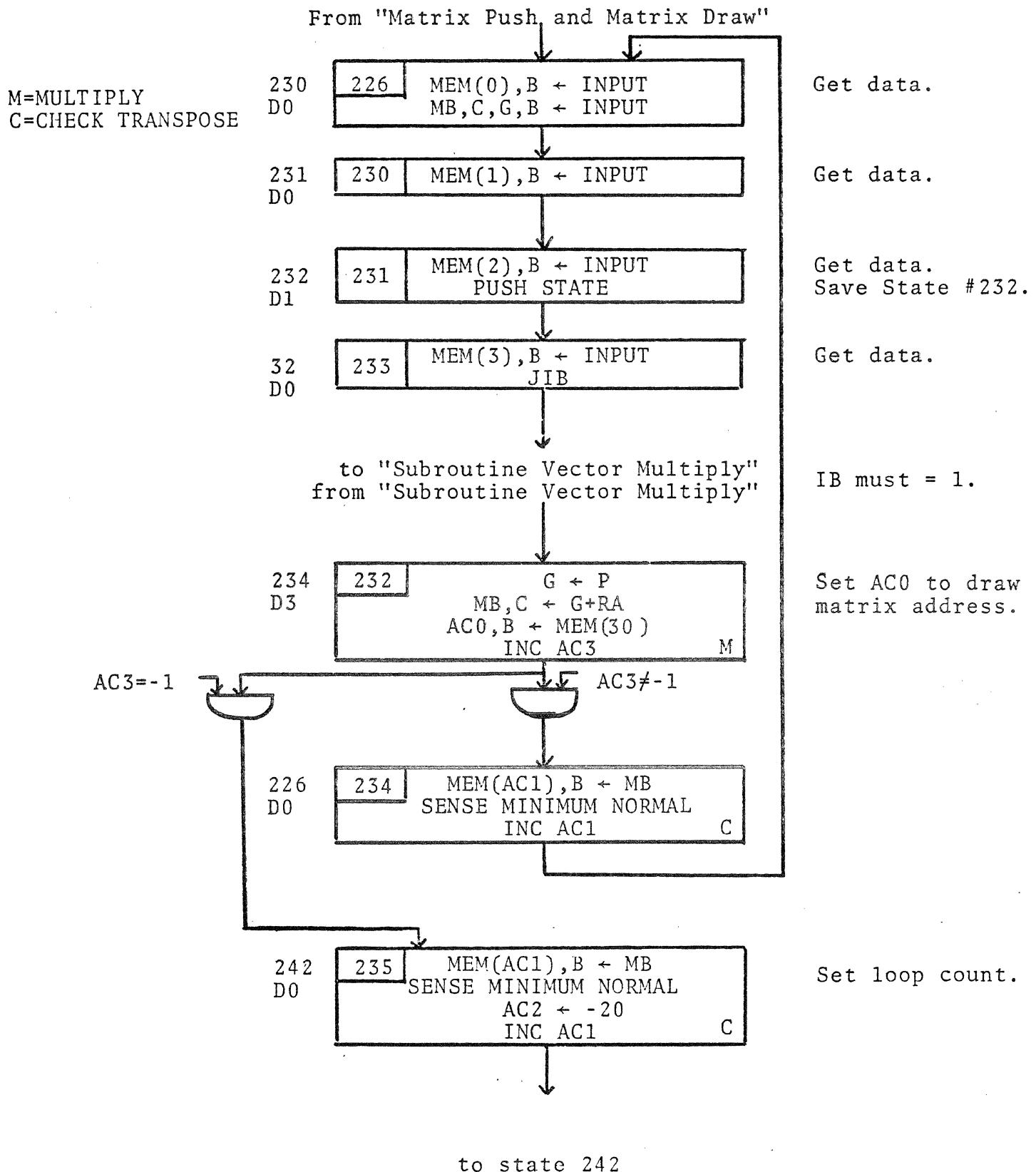

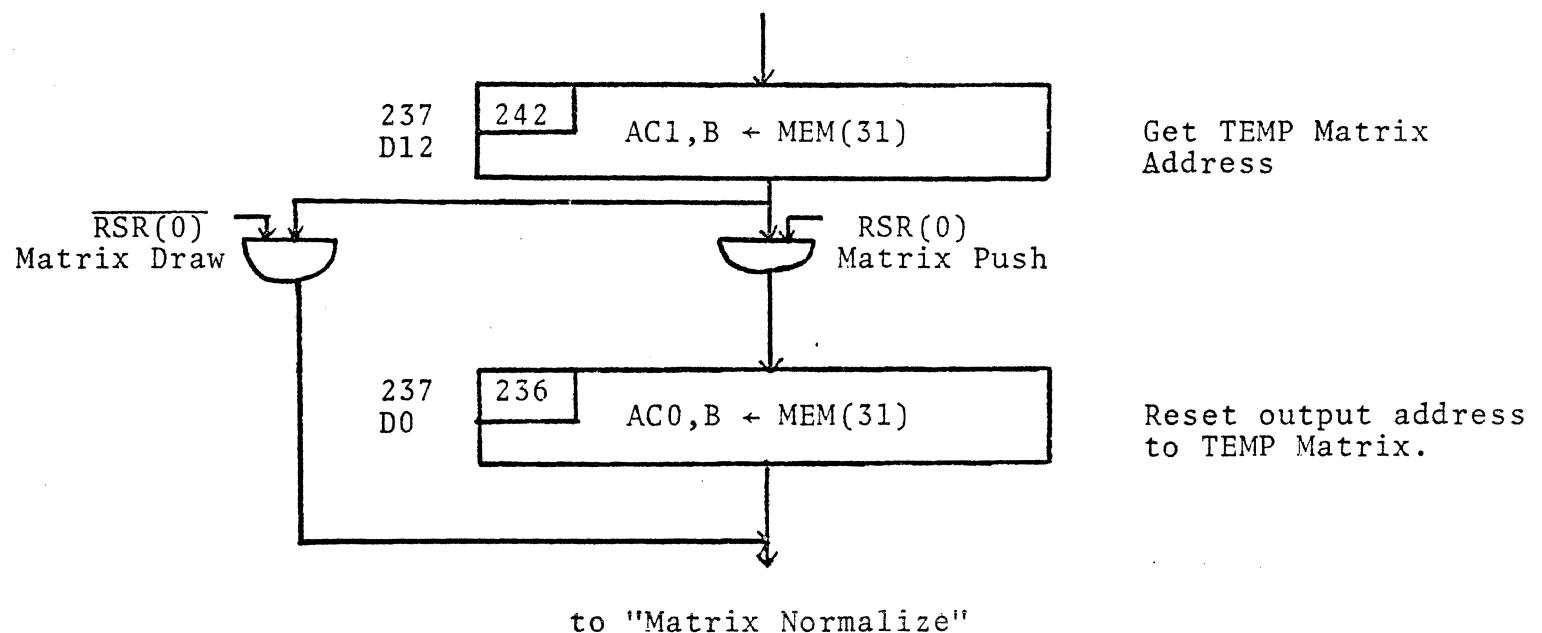

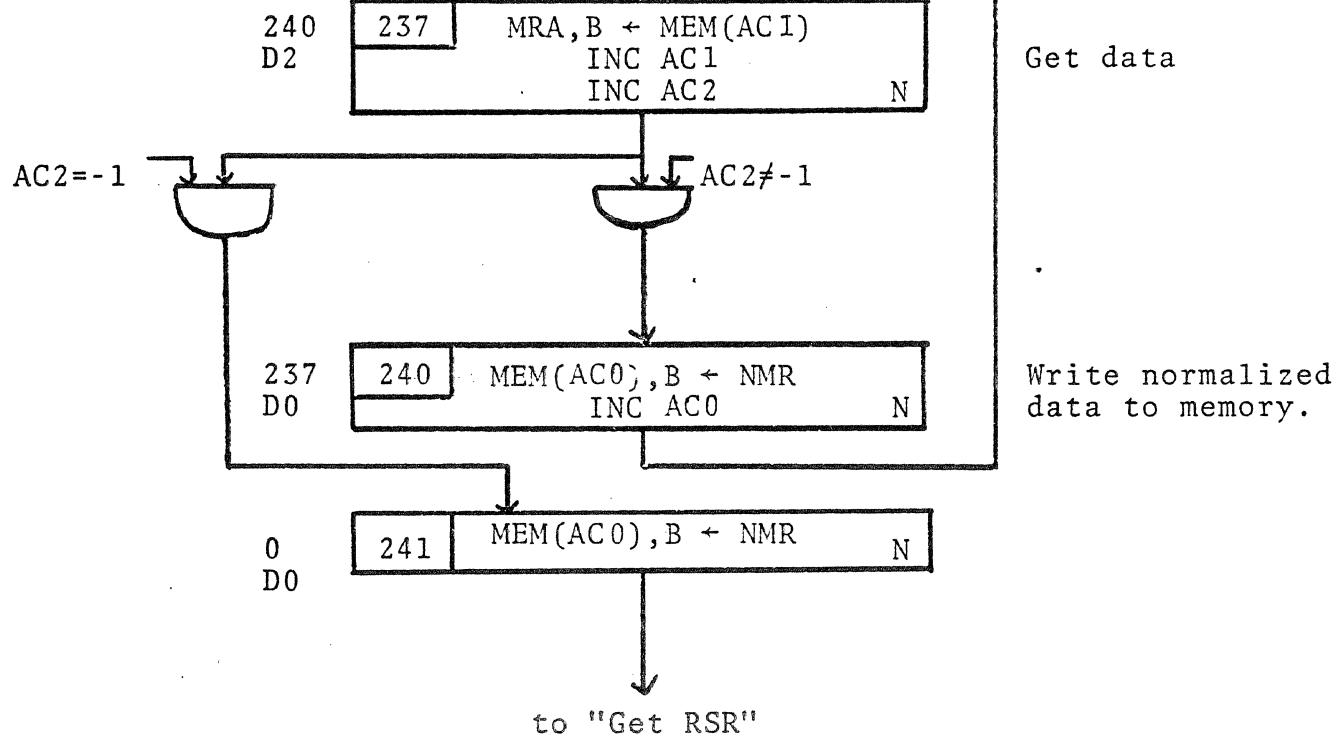

| Appendix A | MAP Algorithm State Diagram.....          | A-1  |

|            | MAP State/Name Cross-Reference Table..... | A-50 |

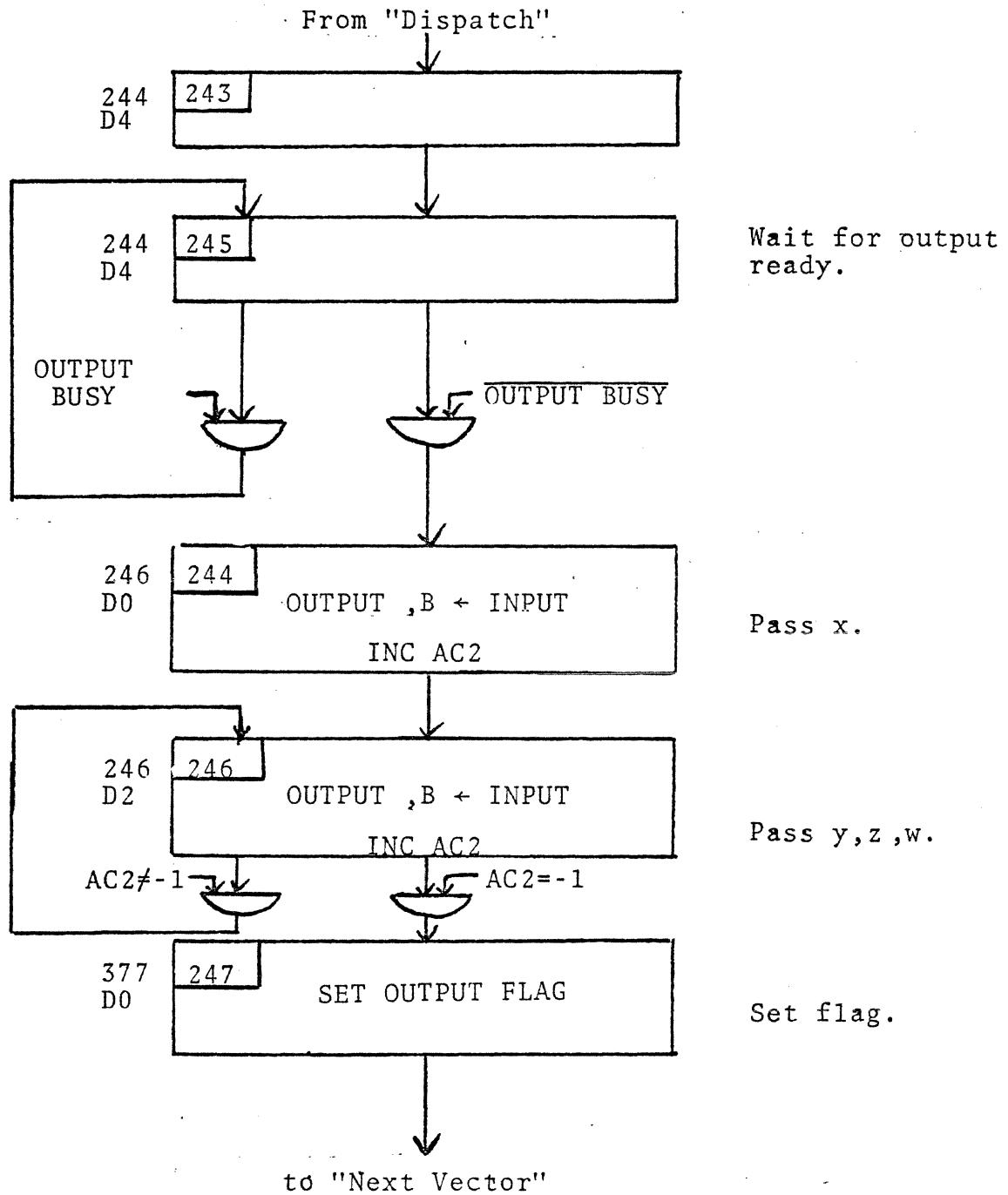

| Appendix B | MAP Output Sequencer State Diagram.....   | B-1  |

| Appendix C | RefreshSequencer State Diagram.....       | C-1  |

## 1.0 Introduction

This Maintenance Manual was created as a support item for both E&S Customer Engineers and on site maintenance personnel who have maintenance responsibility for the E&S PICTURE SYSTEM 2. To perform maintenance at the component level, a broad understanding of the operation and theory of the machine is a necessity. The PS2 diagnostics were designed to isolate hard failures to a functional unit within the system. To quickly isolate the problem to the component, the troubleshooter must understand the proper operation of the malfunctioning unit and the associated unit in which it is in communication with. The intent of the manual is to serve as both a theory of operation text and a hardware reference text for each functional unit in the standard PICTURE SYSTEM 2. It is assumed that the reader has a maintenance background and experience with troubleshooting TTL circuits.

The Picture Controller computer for PICTURE SYSTEM 2 may be one of many types; however, this manual assumes a Digital Equipment Corporation PDP-11 computer as the Picture Controller.

## 2.0 Scope of the Manual

Section 3 of the manual deals with installation of the PICTURE SYSTEM 2.

Section 4 outlines the general theory of operation of the standard PICTURE SYSTEM 2.

Section 5 details the theory of operation on a functional unit level and comprises the major portion of the manual. Exact Bit definitions for status and control registers as well as other register definitions are excluded; therefore, many references are made to the Picture System 2 Reference Manual where these definitions exist. When describing the detailed operation of specific circuits, references are made to the logic drawings contained in the PICTURE SYSTEM 2 Drawing Set.

Appendix A and B contain the MAP and Refresh Controller algorithms.

### 3.0 Installation

Installation of the PICTURE SYSTEM 2 involves the installment of a DEC PDP-11 computer by DEC personnel and the installment of the E&S equipment by an E&S Customer Engineer. The E&S equipment should be unpacked, set in place, and visually inspected for shipping damages.

#### 3.1 Picture Controller Interface Installation

The Picture Controller Interface consists of three cards:

195131-100

195106-100

195105-100

The 195131-100 is built on a DEC hex module and plugs into a peripheral slot in the DEC equipment. This slot should be wired for NPR operation. The 195105 and 195106 cards plug into the PICTURE SYSTEM backpanel as indicated by the stuffing chart, 195101-900 (see the drawing set).

#### 3.2 Picture Display Installation

The Picture Display connects to the scope driver card, 195211-100, by a coax cable set.

### 3.3 Power Connections

The power connection to the PS power controller should meet the following specifications:

- Primary Power - 115 volts, 60 Hz

- 30 Amp

- Single Phase

- Two wire + ground common to Picture Controller ground

- Hubbel 2610 or equivalent

The Picture Display Power card is plugged into the power control panel. Drawing 195100-100 illustrates the primary power connection to the power control panel and the power distribution to power supplies, clock assembly, etc.

Before applying power to the Picture System, check for shorts between all DC sources and ground. After power is applied, adjust all DC power sources to the correct level at the back-panel.

### 3.4 Verification of Proper Operation

To verify proper operation of the PICTURE SYSTEM, run the standard PS2 Acceptance Tests. This procedure is outlined in the PS2 Acceptance Tests document.

#### 4.0 General Theory of Operation

The standard PICTURE SYSTEM 2 contains the following functional units:

1. Picture Controller Interface

2. PICTURE SYSTEM Bus, PSBUS

3. PSBUS Arbiter

4. Picture Processor

5. PICTURE SYSTEM Memory, PSMEM

6. Real Time Clock, RTC

7. Refresh Controller

8. Picture Generator

This manual (volume 1) deals with all of the above functional units with the exception of the Picture Generator. Volume 2 deals with the Picture Generator.

##### 4.1 Picture Controller Interface

The Picture Controller Interface provides two data paths between the Picture Controller computer and the PSBUS. The interface also provides an interrupt link between the PICTURE SYSTEM and the Picture Controller. The two data paths are:

1. Direct IO Path (DIO)

2. Direct Memory Access Path (DMA)

#### 4.1.1 Direct IO Path

The DIO consists of a direct interface between the PDP-11 UNIBUS and the PSBUS. It is used for direct (processor controlled) transfers between UNIBUS address space and PICTURE SYSTEM address space. The interface consists of a Direct IO PICTURE SYSTEM Address register (DIOPSA) and a Direct IO PICTURE SYSTEM Data register, (PSDATA), both of which are UNIBUS addressable. Prior to the transfer of data between a UNIBUS address and a PSBUS address, the DIOPSA must be set up to point at a desired PSBUS address. The actual transfer is initiated by reading or writing the PSDATA register. The PSDATA register serves as a buffer to hold the data being either sent to the DIOPSA destination or retrieved from the DIOPSA source. The DIO is considered an active device, that is, no other PICTURE SYSTEM device can command it. The DIO, after commanded by the Picture Controller, always initiates either a read or write to a PICTURE SYSTEM passive device. The DIO initiates the transfer by requesting the PSBUS and when granted gates the DIOPSA (address) to the PSBUS, then either gates data to the bus or receives data from the bus depending on the nature of the transfer.

#### 4.1.2 Direct Memory Access Path

The DMA path also consists of an interface between the

UNIBUS and the PSBUS; however, it is used for data block (non processor controlled) transfers between UNIBUS address space and PICTURE SYSTEM address space. The DMA path may be programmed to be either an active or passive device; therefore, it can actively fetch data from UNIBUS address space and relay it to PS address space or it can passively wait for data from a PS device, then relay it to UNIBUS address space. In either mode of operation, it must be previously set up by the Picture Controller for a block transfer, then commanded to "GO". For each word transfer, the UNIBUS must be requested and granted; also, for word transfers to PS address destination, the PSBUS must be requested and granted. The PICTURE SYSTEM DMA Device contains a DMA PICTURE SYSTEM Address register (DMAPSA) which tracks the inter-block PS address. The UNIBUS DMA Device contains a UNIBUS Address register (DMABA) which tracks the inter-block UNIBUS address and a DMA Word Count register (DMAWC) which counts the number of words to be transferred. When the last word of the block has been transferred, the DMAWC register acclaims the DMA path to be READY for another block transfer.

#### 4.2 PSBUS Arbiter

The PSBUS Arbiter controls the use of the PSBUS. More than one PS device may need use of the bus at a given time; therefore, a round robin priority scheme is implemented to grant requesting devices. Eight active requests lines input to the

arbiter. A request line is hardwired to an active device and when the bus is needed, and active device inserts a request line to the arbiter. The eight requests are assigned a priority level and if granted, that request is rotated to the lowest priority level; therefore, all active devices, in general, have equal opportunity for the PSBUS.

#### 4.3 Picture Processor

The Picture Processor is a special purpose vector processor which receives commands and data from a PICTURE SYSTEM device and outputs processed commands and data to another device. Usually output data is directed to the Picture Generator for display; however, output may be directed to PS Memory or to the DMA as data to be stored in UNIBUS address space. Input to the Picture Processor may be sourced by either the Direct IO, DMA, or PS Memory. The Picture Processor input device may be either active or passive, that is, it may actively fetch input data or passively wait for data directed to it. The Picture Processor output may also be either active or passive. Also, input and output may be either 16 or 24 bit precision. These variables are programmably set up by writing a status word in the Picture Processor.

The Picture Processor operates on an instruction set. After inputting a command, appropriate action is performed on either incoming data or internal data. The instruction set is de-

tailed in the PS2 Reference Manual, pp 2-36 through 2-54.

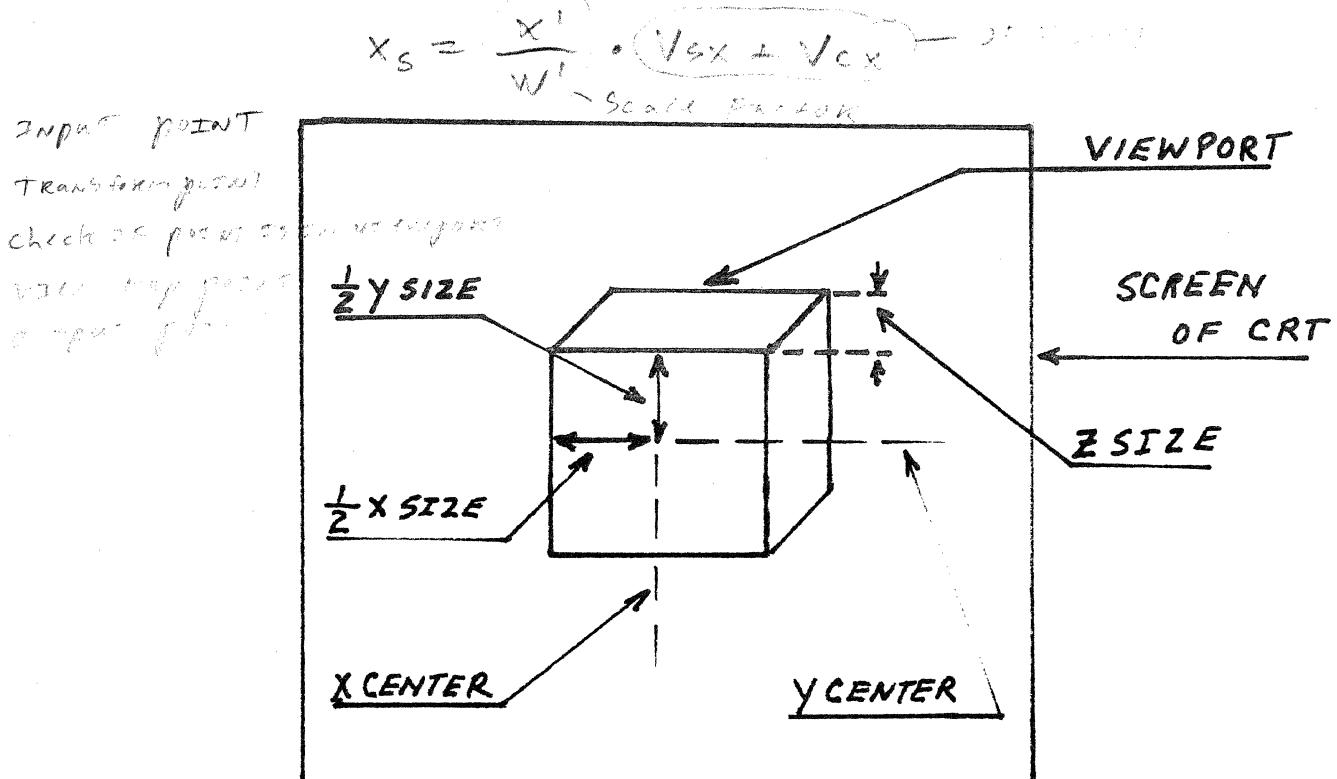

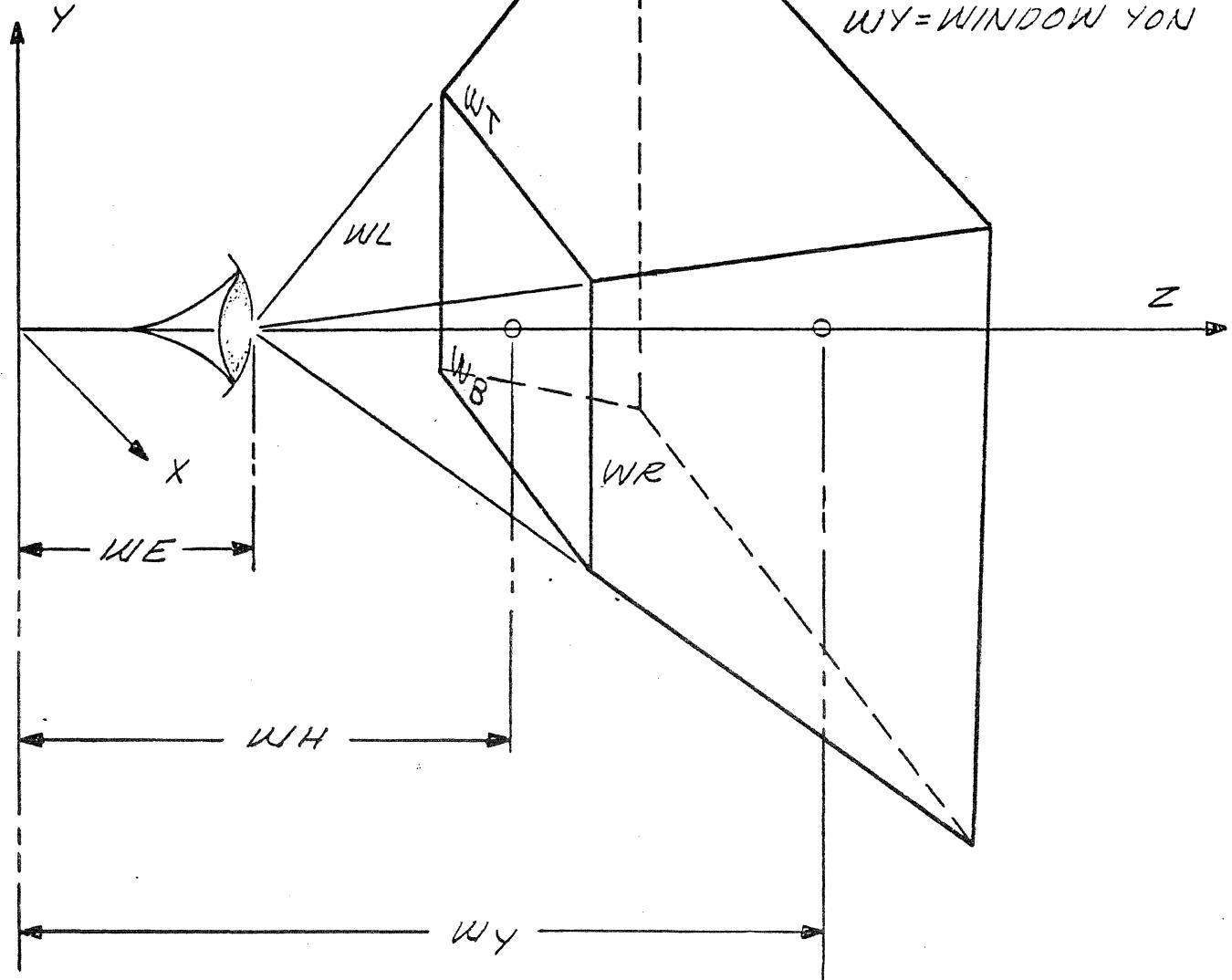

In general the Picture Processor receives commands and point vector data in the Data Space Coordinate system and transforms the point vector data into the Screen Coordinate system for subsequent display by the Picture Generator.

Functions performed on the input data include:

1. translation

2. rotation

3. clipping

4. perspective

5. view port mapping

6. zooming

7. matrix concatenation

8. pass data unformatted

9. pass data formated

These functions are performed by receiving a command, and traversing states of the MAP algorithm which operates on the data appropriately. The three main units of the Picture Processor are:

1. MAP Input Controller

2. MAP (Matrix Arithmetic Processor)

3. MAP Output Formatter

These units are described in detail in section 5, the detailed theory section of this manual.

#### 4.4 PICTURE SYSTEM Memory

The PICTURE SYSTEM Memory is a dual-port MOS memory (distinct from the Picture Controller's) organized as addressable 16-bit words. This memory is available in increments of 16K words, expandable to 64K words of memory, dependent upon user requirements.

PICTURE SYSTEM Memory may be used in a variety of ways to satisfy the user's application. Typically, a portion of the PICTURE SYSTEM Memory serves as a refresh buffer into which data, still in digital form, is deposited. This data represents information to be shown on the Picture Display. For each frame displayed, the Refresh Controller reads the data from the PICTURE SYSTEM Memory and channels this data to the Line Generator where the data are then converted to analog signals to drive the Picture Display.

#### 4.5 Real Time Clock

The Real Time Clock coordinates the picture update process with the picture refresh process by implementing a programmable interval at which a clock interrupt occurs. This interrupt causes the Picture Controller program to check the condition of the update and refresh process to determine if a new frame may be initiated. The basic timing of the clock is derived from two 60 Hz inputs to produce a 120 Hz

clocking signal which counts two counters. The two counters provide a interrupt interval and a refresh sync interval. At the interrupt interval, a request for interrupt is generated. At the sync interval, a sync pulse is generated for the refresh controller. This pulse is used by the refresh controller during automatic refresh mode.

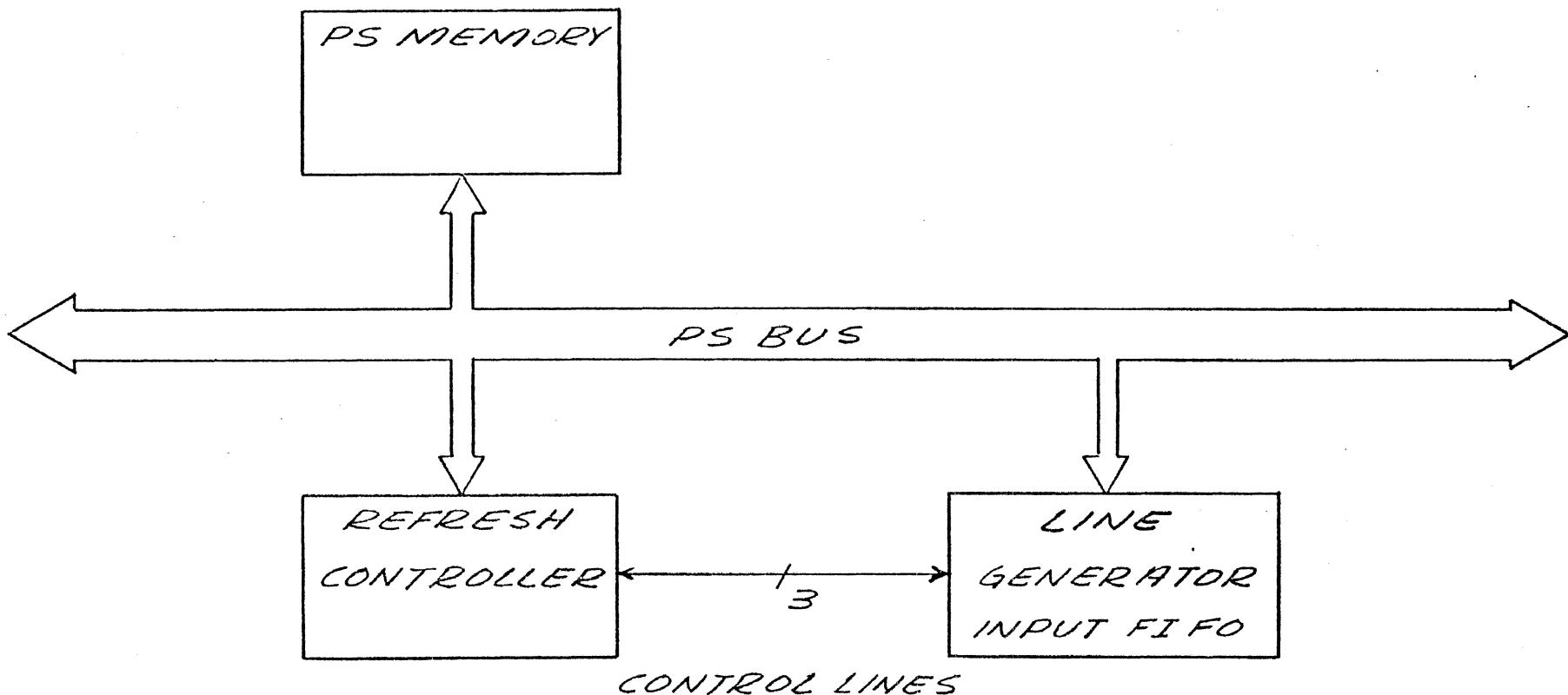

#### 4.6 Refresh Controller

The Refresh Controller is the unit of the Picture Generator that controls the refreshing of images on the Picture Display. The Refresh Controller reads data from the PICTURE SYSTEM Memory, a refresh buffer, and channels this data to the Line Generator for display. Under program supervision, the Refresh Controller is used to manage the organization of the PICTURE SYSTEM Memory. It also contains special-purpose hardware to facilitate memory segmentation and management.

In single-buffer mode, the entire refresh buffer is used to store a single display frame. In this mode, refresh may be initiated from a partially-updated display frame consisting of some lines from the new frame and some lines from the previous frame.

In double-buffer mode, one-half of the refresh buffer is designated as an old frame and one-half a new frame. Refresh is then initiated from the old frame while the new frame is

being constructed. When construction of the new frame is completed, the frame buffers are swapped and the newly-constructed frame is displayed. The space occupied by the old frame becomes available for new frame construction.

The segmented-buffer mode provides the most general use of the refresh buffer for the display and updating of data. Typically, a frame consists of portions which need not be updated as frequently as others. Ideally, these portions should be updated as separate parts, or segments, of the frame. The Refresh Controller facilitates the use of the refresh buffer in this mode by allowing each of the separate portions of the refresh buffer to be given a name by which the segment may be replaced, appended to, deleted, etc.

The Refresh Controller also improves the utilization of the refresh buffer by providing, in segmented-buffer mode, for the reclamation of unused portions of the refresh buffer that have been left by deleted segments. This prevents fragmentation of the refresh buffer into small, unuseable areas.

## 5.0 Detailed Theory of Operations

### 5.1 Picture Controller Interface

The Picture Controller Interface is the communication link between the host computer and the PICTURE SYSTEM. All command and data transfers between the two machines take place through this interface. The interface consists of three devices:

1. Direct I/O Path (DIO)

2. Direct Memory Access Path (DMA)

3. Interrupt Control

A DIO transfer is initiated by host computer control. Also, a DMA block transfer is set up and initiated by host control; however, individual word transfers within the block are initiated by the DMA control logic. This provides a mechanism by which the host computer may set up a block transfer, then execute other tasks while the DMA Controller manages the word transfers of the block. The DMA Controller gains access of the host transfer lines (data bus) for each word transfer, then releases control after each transfer.

The Interrupt Control monitors the DMA Interrupt Request and three interrupt request lines from the PICTURE SYSTEM.

1. Real Time Clock Interrupt

2. Device Interrupt

3. System Interrupt

The DMA Interrupt request, if enabled, requests an interrupt to be serviced when the DMA is ready or when a non-existent memory (NEXMEM) location was referenced by the DMA.

The Real Time Clock Interrupt request, if enabled, requests an interrupt at pre-defined programmable intervals. This program interrupt initiates a status check of the refresh process and update process by the program.

The Device Interrupt request occurs when a PICTURE SYSTEM Device needs servicing. Typical devices include: Function Switches, Keyboard, Tablet, etc.

The System Interrupt request occurs from designated PICTURE SYSTEM control functions such as: "Refresh Stopped", "MAP Stopped", "HIT Request", etc.

A detailed description of the interrupt requesting system exists in the PICTURE SYSTEM Reference Manual, pp. 2-130 thru 2-139.

The Interrupt Control, which monitors the four interrupt

requests, gains control of the host computer data bus, passes the interrupt vector for the honored request to the host computer data bus, and asserts the interrupt line to the host computer thus causing the host to execute the appropriate service routine.

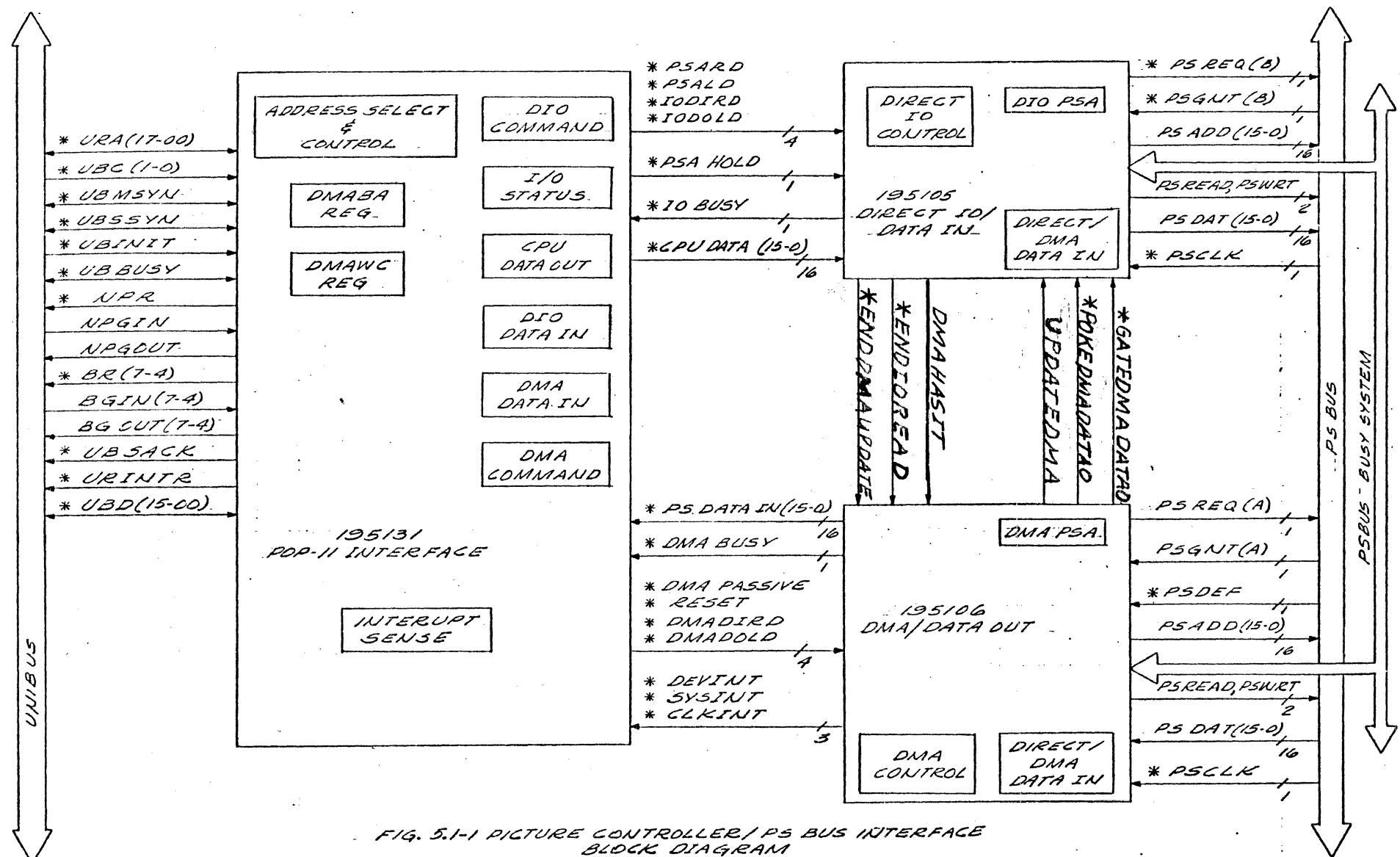

A block diagram of the Picture Controller Interface is illustrated in Figure 5.1-1. The interface is implemented on three cards.

1. 195131 PDP-11/PS Interface

2. 195105 Direct I/O/Data In

3. 195106 DMA/Data Out

The 195131 card is located in the host computer and the 195105 and 195106 are located in the PICTURE SYSTEM Backpanel.

A cable connects the 195105 and 195106 in the PICTURE SYSTEM to the PDP-11 Interface card in the host computer with 46 differential pairs of control and data lines.

#### 5.1.1 PDP-11 Interface

The 195131 PDP-11 Interface communicates with the PDP-11 UNIBUS with 57 lines. Communication with the UNIBUS is asynchronous, therefore; no synchronous clock

FIG. 5.1-1 PICTURE CONTROLLER/PS BUS INTERFACE

BLOCK DIAGRAM

signal exists on the 195131. Likewise communications between the 195131 and the PICTURE SYSTEM cards (195105-195106) is asynchronous; however, all communication between the 195105-195106 cards and the PICTURE SYSTEM Bus (PSBUS) is synchronous. The PSBUS contains a synchronous clock line which is input to both the 195105 and 195106 cards.

The PDP-11 Interface card consists of the following:

1. Address Select & Control

2. DMA Bus Address Register (DMABA)

3. DMA Word Count Register (DMAWC)

4. DMA Data In Register

5. DMA Command Register

6. Direct I/O Command Register

7. I/O Status Register

8. CPU Data Out Register

9. Direct I/O Data In Register

10. Interrupt Sense and Control

#### 5.1.1.1 Address Select & Control

The Address Select & Control monitors the UNIBUS address lines. If one of the five PDP-11 Interface register addresses exist on the UNIBUS the address select decodes which register the address is for and then waits for the UNIBUS MSYN signal which strobes the UNIBUS data in the selected register; else, enables the data out (to the UNIBUS) from the selected register. Whether the UNIBUS

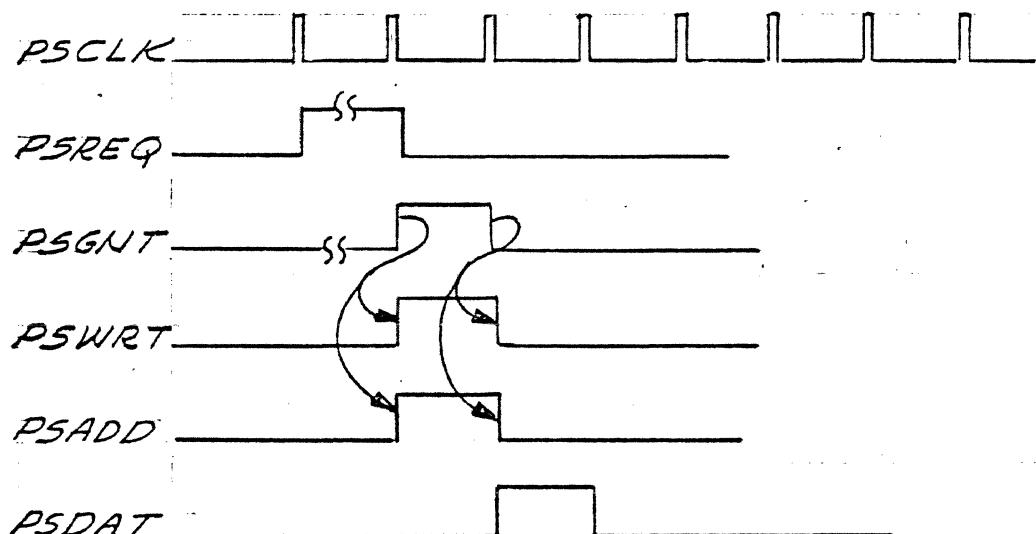

FIGURE 5.1-2 DIRECT I/O READ TIMING DIAGRAM

wants to write or read is decoded from the \*C1 line of the UNIBUS. This logic exists on sheet 3 of the 195131-600 drawings.

#### 5.1.1.2 DMA Bus Address Register (DMABA)

The DMABA register is used to address the UNIBUS during a DMA word transfer. This register is normally loaded with the beginning address of a data block and then incremented by one upon each word transfer. The DMABA register is only 15 bits and does not drive the LSB of the UNIBUS: therefore, incrementation by one effectively increments the UNIBUS address by two. Only word (not byte) addressing on the UNIBUS takes place during DMA transfers. The DMABA register is implemented on sheet 15 of the logic drawings.

#### 5.1.1.3 DMA Word Count Register (DMAWC)

The DMAWC register keeps track of the word count during a block transfer. It is initially loaded with a negative two's complement number of the words to be transferred. Upon each word transfer it is incremented by one. When the register overflows the last word has been transferred. The DMAWC is implemented on sheet 15 of the logic drawings.

#### 5.1.1.4 DMA Command Register

The DMA Command Register issues a DMA read or DMA write

command to the PICTURE SYSTEM DMA Controller. On the cable between the PDP-11 Interface and the PICTURE SYSTEM, these commands are named:

1. DMADIRD - DMA Data Input Read

2. DMADOLD - DMA Data Out Load

During a DMA write transfer from the UNIBUS to the PICTURE SYSTEM, the PDP-11 Interface performs the following steps:

1. Gains control of the UNIBUS.

2. Receives the UNIBUS data into the CPUDATA OUT register.

3. Releases control of the UNIBUS.

4. Issues a DMADOLD command to the PICTURE SYSTEM.

5. Waits for the PICTURE SYSTEM DMA Controller to go non-busy.

6. When the non-busy is received, goes to step 1 if the block transfer is not complete else goes to step 7.

7. Sets the DMA READY bit in the IOST register indicating the DMA is ready for program initiation of another block transfer.

During a DMA read transfer from the PICTURE SYSTEM to the UNIBUS, the PDP-11 Interface performs the following steps:

1. Issues a DMADIRD command to the PICTURE SYSTEM.

2. Waits for the PICTURE SYSTEM DMA Controller

to fetch the word. (waits for DMA BUSY TO go low).

3. Strobes the data from PSDATAIN (15-0) into the DMA DATA IN register.

4. Gains control of the UNIBUS.

5. Gates the DMA Data In register onto the UNIBUS and releases control of the UNIBUS when the destination device takes the data.

6. Goes to step 1 if the block transfer is not done; else goes to step 7.

7. Sets DMA READY in the IOST register, indicating ready for program initiation of another block transfer.

#### 5.1.1.5 DMA Data In Register

The DMA Data In Register, in the PDP-11 Interface, buffers data received from the PICTURE SYSTEM. During a DMA IN word transfer, the DMA Controller issues a DMADIRD command to the PICTURE SYSTEM's DMA Controller, which gains control of the PS BUS and fetches the data word pointed to by the DMAPSA register. The data is put on the PSDATA (15-0) lines to the PDP-11 Interface. The PICTURE SYSTEM clears DMA BUSY which strobes the data into the DMA Data In Register. The PDP-11 Interface issues a request for the UNIBUS and eventually, when the request is granted, gates the DMA Data In Register onto the UNIBUS.

The DMA Data In Register is on sheet 14 of the logic drawings.

#### 5.1.1.6 I/O Status Register (IOST)

The I/O Status Register implements status indicators of the DIO and DMA operations. It also contains a reset bit to initialize the DIO and DMA logic to their initial states and a GO bit to transfer control of a DMA block transfer to the DMA Controller after a block transfer has been set up under program control. A detailed description of the IO status bits exists in the PS2 Reference Manual, pp. 2-12 through 2-15.

DIO status bits are implemented on sheet 4 and DMA status bits on sheet 5 of the logic drawings.

#### 5.1.1.7 Direct IO Command Register

The Direct IO Command Register is updated when a new command from the UNIBUS is sensed by the Address Select & Control logic. Four Direct IO commands are possible:

IOPSARD - Read the Direct IO PICTURE SYSTEM Address Register (DIOPSA)

IOPSALD - Load the DIOPSA

IODATIRD - Read the Direct IO Data Input Register

IODATOLD - Load the CPU DATA OUT Register via the Direct IO.

The Direct IO Command Register is implemented by four F/F's on sheet 4 of the logic drawings. The four commands F/F's drive four differential command line pairs on the cable to the Direct IO/Data In Card, 195105. These drivers are on sheet 10 of the logic (195131-600).

#### 5.1.1.8 CPU Data Out Registers

The CPU Data Out Register buffers either DIO data or DMA data being sent to the PICTURE SYSTEM. This buffering enables the appropriate controller to store the data gathered from the UNIBUS and release control of the UNIBUS while waiting for the PICTURE SYSTEM to take the data. If the input data were not buffered, the UNIBUS would be tied up until the appropriate DIO or DMA logic interfaced to the PS BUS could take the data. The PICTURE SYSTEM Reference Manual refers to this register as the PSDATA Register when describing Direct IO write to the PICTURE SYSTEM.

The CPU DATA OUT Register is implemented on sheet 8 of the logic drawings.

#### 5.1.1.9 Direct IO Data In Register

The DIO Data In Register buffers data from the PICTURE SYSTEM to the UNIBUS upon completion of a IODATIRD command. The register is referred to in the PICTURE

SYSTEM Reference Manual as the PSDATA register. If a user wants to read a PS Memory location, he must first point the DIOPSA to the PS Memory location desired.

MOV #MEMLOC, DIOPSA

Execution of the PDP-11 instruction sets up the DIOPSA and initiates a read of the PS Memory location specified by DIOPSA. The contents of the specified memory location are fetched and stored in the DIO Data In (PSDATA) Register. To actually retrieve the desired data the user must read the PSDATA register.

MOV PSDATA, SAVE

This PDP-11 instruction moves the contents of the PSDATA register to the specified UNIBUS address (SAVE) and initiates a IODATIRD command to the PICTURE SYSTEM DIO Interface which increments the DIOPSA (unless inhibited) and fetches data from the next PS Memory location pointed to by the DIOPSA.

Successive PS Memory locations may be retrieved by successive reads of the PSDATA register.

While the DIO path is busy, another PSDATA read cannot be initiated; therefore, the user must test the IO READY bit in the IOST Register before initiating a read.

The DIO DATA IN Register is on sheet 14 of the 195131-600 logic drawings. The DIOPSA Register is on sheet 6 of the 195105-600 drawings.

#### 5.1.2 Direct IO Path

The Direct IO path interfaces the UNIBUS to the PICTURE SYSTEM to enable programmable Direct IO transfers between UNIBUS address space and PICTURE SYSTEM address space. The actual hardware for the Direct IO path consists of:

1. Direct IO control and buffering on the PDP-11 Interface Card (195131-100).

2. Direct IO control and "Data In" buffering on the 195105-100 card in the PS backpanel.

3. "Data Out" buffering on the 195106-100 card in the PS backpanel.

4. Cable driver and receiver lines between the PDP-11 Interface and the 195105-195106 cards.

5. Control lines on the PS backpanel between the 195105 and 195106 cards.

A Direct IO transfer can take place during a DMA block transfer. If the DMA is writing and the DIO is reading, or visa versa, there is no conflict of data line usage between the PDP-11 Interface and the PICTURE SYSTEM; because, there are two separate

groups of data lines. (See Fig. 5.1-1)

1. CPUDATA (15-0) - Data from UNIBUS to PICTURE SYSTEM.

2. PSDATAIN (15-0) - Data from PICTURE SYSTEM to UNIBUS.

Also, if both DMA and DIO are writing, there is no conflict in usage of the CPUDATA (15-0) lines because UNIBUS mastership arbitration insures only one user of the lines at one time.

For example, if the DMA controller is bus master and the program encounters a direct IO write instruction to the PICTURE SYSTEM, the requesting UNIBUS device must wait for the current DMA word transfer to complete before it becomes bus master. While it is master, the DMA process is held up and the CPUDATA (15-0) lines are solely dedicated to the UNIBUS master device using the Direct IO path.

However, if both the DMA and DIO are reading, the PSDATAIN (15-0) lines must be arbitrated between two devices.

For example, a DMA may be performing a block of read transfers and a UNIBUS device may desire to read the PSDATA register in the Direct IO path. The UNIBUS device again will not be granted bus

mastership until the current DMA word transfer is complete. Once bus master the UNIBUS device relays the read command to the PDP-11 Interface's Direct IO Controller. The controller responds by enabling the PSDATA register onto the UNIBUS, issues a read command to the PICTURE SYSTEM, and acknowledges the UNIBUS master. The master releases control of the UNIBUS and the DMA controller regains bus mastership; however, the read command to the PICTURE SYSTEM causes its Direct IO controller to increment the DIOPSA, (if not inhibited), and retrieve the data in PS address location pointed to by the DIOPSA. After fetching the desired data off the PSBUS, the controller must transfer it across the PSDATA (15-0) lines to the PSDATA register. Remember the DMA may still be performing read transfers on these lines; therefore, an arbiter in the PICTURE SYSTEM's Direct IO controller must arbitrate these lines between the DMA and DIO as necessary. This arbiter exists on the 195105-600, sheet 4.

#### 5.1.2.1 Direct IO Read

To read a PS address location(s) the user points the DIOPSA to the desired location:

```

MOV PSADD, DIOPSA

```

Loading the DIOPSA causes the PICTURE SYSTEM's Direct IO controller to retrieve the PS address data pointed to by the new DIOPSA contents and buffer it in the PDP-11 Interface PSDATA register. When the DIO becomes ready then the user may examine the PSDATA register:

MOV PSDATA, SAVE

Each read of the PSDATA register increments the DIOPSA by one (unless inhibited) and causes the Direct IO controller to retrieve the next sequential PS address contents and buffer the data in PSDATA. This enables the user to examine successive PS address locations by issuing successive PSDATA read commands.

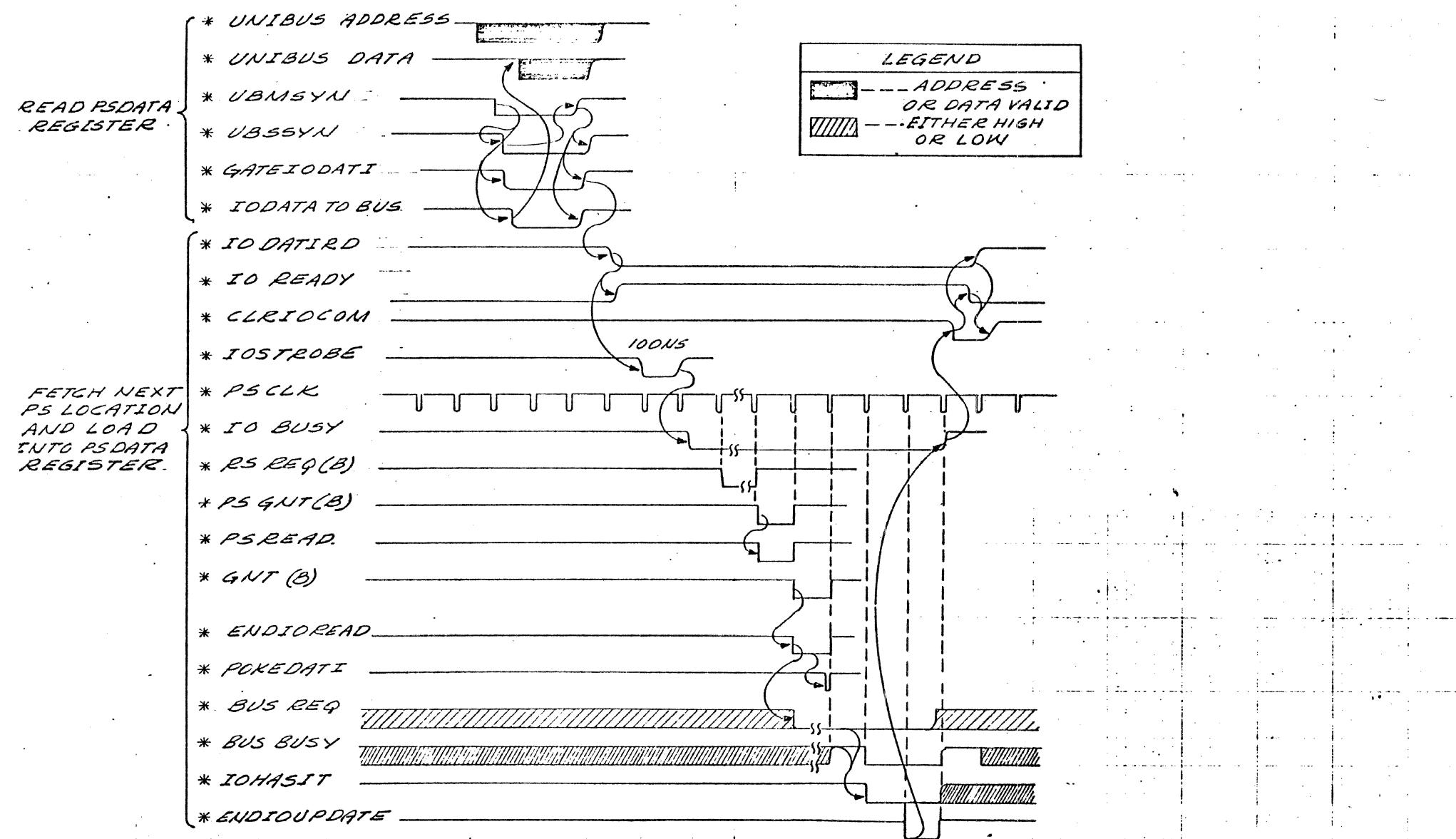

Execution of the above instruction causes the following sequence of events to occur. The sequence is illustrated in Direct IO Read Timing Diagram of Figure 5.1-2.

1. The UNIBUS master device asserts the address on PSDATA and sets up control lines C0 and C1 for a full word read onto the UNIBUS.

2. The UNIBUS master device asserts \*UBMSYN requesting the addressed device to respond.

3. The PDP-11 Interface's Direct IO control decodes the UNIBUS address and control lines and receives the master's request, \*UBMSYN, (195131-600 sheet 3).

4. The Direct IO control enables the DIO PS DATAIN register (PSDATA) through the mux on sheet 16 and \*IODATATOBUS asserts the data onto the UNIBUS.

5. \*UBSSYN acknowledges the UNIBUS master and \*GATEIODATI gets ready to issue a read command to the PICTURE SYSTEM. (sheet 4)

6. The trailing edge of \*GATEIODATI sets IODATIRD which clears IOREADY F/F indicating to the program that the DIO path is busy. IODATIRD drives a cable line to the PICTURE SYSTEM's Direct IO control on the 195105 card.

7. The Direct IO control in the PICTURE SYSTEM receives IODATIRD and generates \*IOSTROBE pulse of 100ns. (sheet 3 of 195105-600).

8. The trailing edge of \*IOSTROBE asserts the \*IOBUSY F/F which indicates to the PDP-11 Interface that the Direct IO is accessing a PS location for the PS DATA register. The trailing edge of \*IOSTROBE pulse also increments the contents of DIOPSA by one (if not inhibited).

9. IOBUSY sets the \*PSREQ(B) F/F in sync with the next \*PSCLK pulse which issues a request for the PSBUS.

10. The PS arbiter eventually responds (in sync with \*PSCLK) with \*PSGNT which gives the PSBUS to the Direct IO controller.

11. \*PSGNT will gate the contents of DIOPSA (PS address) and \*PSREAD to the PS BUS (sheet 6).

12. The next clock buffers \*PSGNT by setting \*GNT(B) F/F. (During the clock period with \*GNT(B) is set, the data from the destination location location is on the PS data lines of the PS BUS).

13. \*GNT(B) asserts \*ENDIOREAD which issues a request, BUSREQ, for the PSDATAIN (15-0) lines and the next clock pulse generates the \*POKEDATI pulse which strobes the data from the PSBUS into the DIO/DMA Data In register file on sheet 6 of the 195106 card which drives the PSDATAIN (15-0) lines.

14. When the PSDATAIN (15-0) lines are not busy (may be in use by the DMA) the IOHASIT F/F (sheet 4 of 195105-600) is set indicating that the lines now belong to the DIO.

15. IOHASIT enables the DIO word in the DIO/DMA Data In register file out to the PSDATAIN (15-0) lines to the PDP-11 Interface.

16. The next clock asserts \*ENDIOUPDATE which clears \*IOBUSY on the next clock.

17. The PDP-11 Interface's Direct IO control, which has been waiting for the trailing edge of \*IOBUSY, sets \*CLRIOCOM and the data on PSDATAIN (15-0) is strobed into the PSDATA register. (195131-600, sheet 14)

18. \*CLRIOCOM sets IOREADY, clears the read command F/F, IODATIRD (sheet 4), and the Direct IO path is ready for another transfer.

FIGURE 5.1-3 DIRECT I/O WRITE TIMING DIAGRAM

### 5.1.2.2 Direct IO Write

To write a PS address pointed to by DIOPSA, the user simply writes into the PSDATA register; therefore, data is moved to the PSDATA register.

MOV DATA, PSDATA

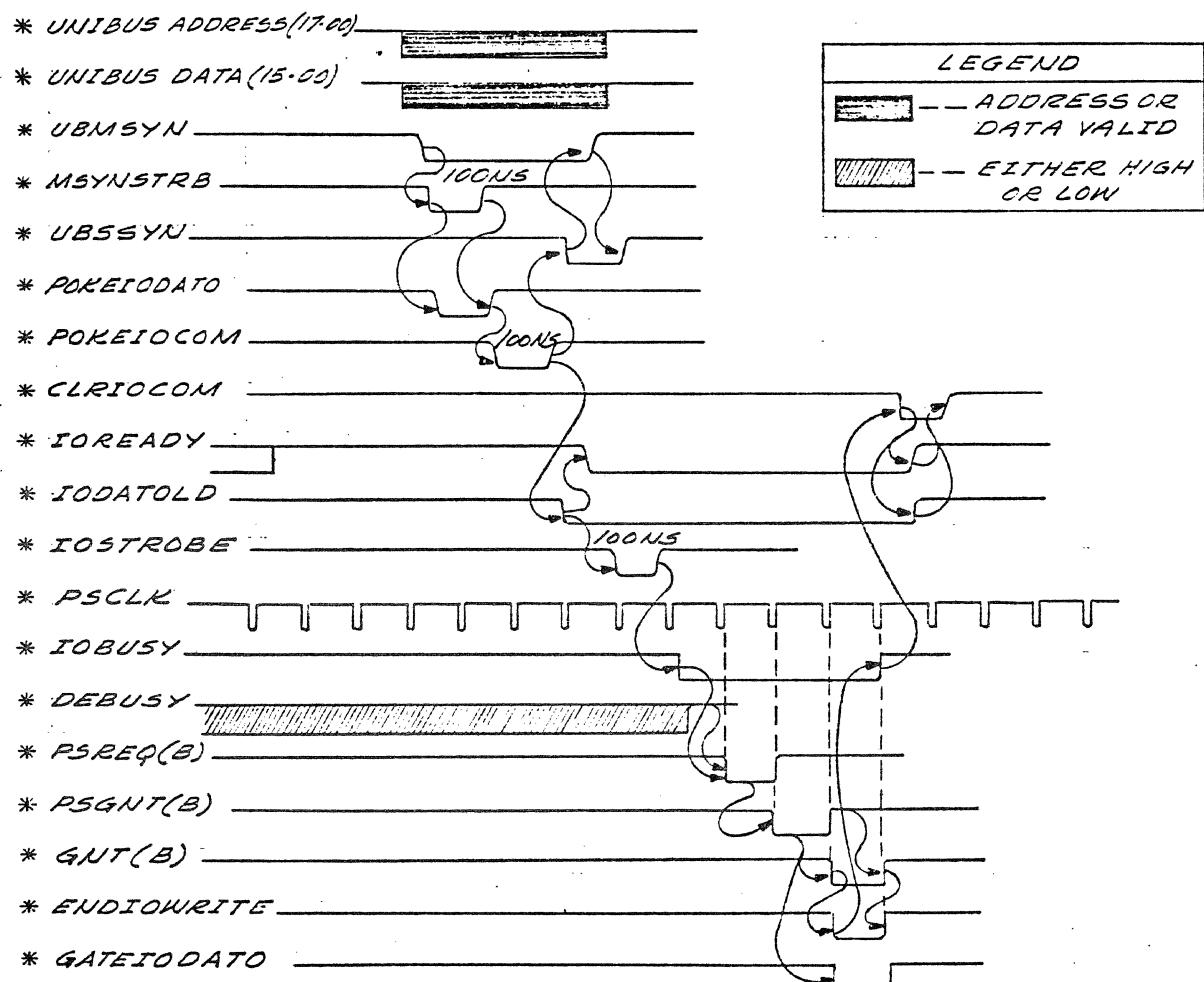

Execution of the above instruction causes the following sequence of events to occur. This sequence is illustrated in the Direct IO Write Timing Diagram of Figure 5.1-3.

1. The contents of location DATA are fetched and put on the UNIBUS data lines.

2. The address of PSDATA is asserted on the UNIBUS address lines.

3. UNIBUS control lines C1 and C0 are set up for a full word write.

4. After the data, address, and control lines of the UNIBUS have settled, the UNIBUS master asserts \*UBMSYN requesting the slave to respond.

5. The Address Select & Control logic on the PDP-11 Interface, 195131-600 sheet 3-4, received \*UBMSYN which generates \*MSYNSTRB pulse of 100ns duration.

6. \*MSYNSTRB enables the address decode's output \*POKEIODATO.

7. The trailing edge of \*MSYNSTRB terminates \*POKEIODATO which strobes the UNIBUS data into the CPU DATA OUT register on sheet 8

and generates \*POKEI0COM pulse of 100ns.

8. The trailing edge of \*POKEI0COM asserts \*UBSSYN, which acknowledges the UNIBUS Master, and sets the IODATOLD (IO DATA OUT LOAD) command F/F on sheet 4.

9. IODATOLD clears the IOREADY F/F which indicates to the program that the Direct IO path is busy.

10. IODATOLD and the data in the CPU DATA OUT register drive the cable drivers (on sheet 10) to the PICTURE SYSTEM Direct IO card.

11. The PICTURE SYSTEM DIO controller receives the command and data lines on the 195105 card, sheet 1 and 2.

12. \*IODATOLD generates the IOSTROBE pulse on sheet 3 which sets the IOBUSY F/F and strobes the incoming data into the DIO/DMA Data Out register, sheet 5.

13. IOBUSY sets the \*PSREQ(B) to the PSBUS if the destination device (location) pointed to by the DIOPSA is not busy. (This device busy monitor is on sheet 7 of the drawings).

14. The PSBUS Arbiter acknowledges the bus request with PSGNT(B) when the DIO controller can have the bus.

15. The PSGNT(B) gates the DIOPSA (destination address) onto the PSBUS address lines (sheet 6)

and the next clock buffers the PSGNT(B) by setting the GNT(B) F/F (sheet 4) and also sets the \*GATEIODATO F/F.

16. \*GATEIODATO gates the DIO/DMA DATA OUT register (destination data) onto the PSBUS and GNT(B) asserts \*ENDIOWRITE.

17. On the next clock, \*ENDIOWRITE clears \*IOBUSY indicating that the destination device has received the data.

18. \*IOBUSY is monitored back on the PDP-11 Interface (195131) and sets the \*CLRIOCOM F/F (sheet 4) which sets IOREADY and clears the command, IODATOLD F/F.

19. The Direct IO path is now ready for another DIO transfer.

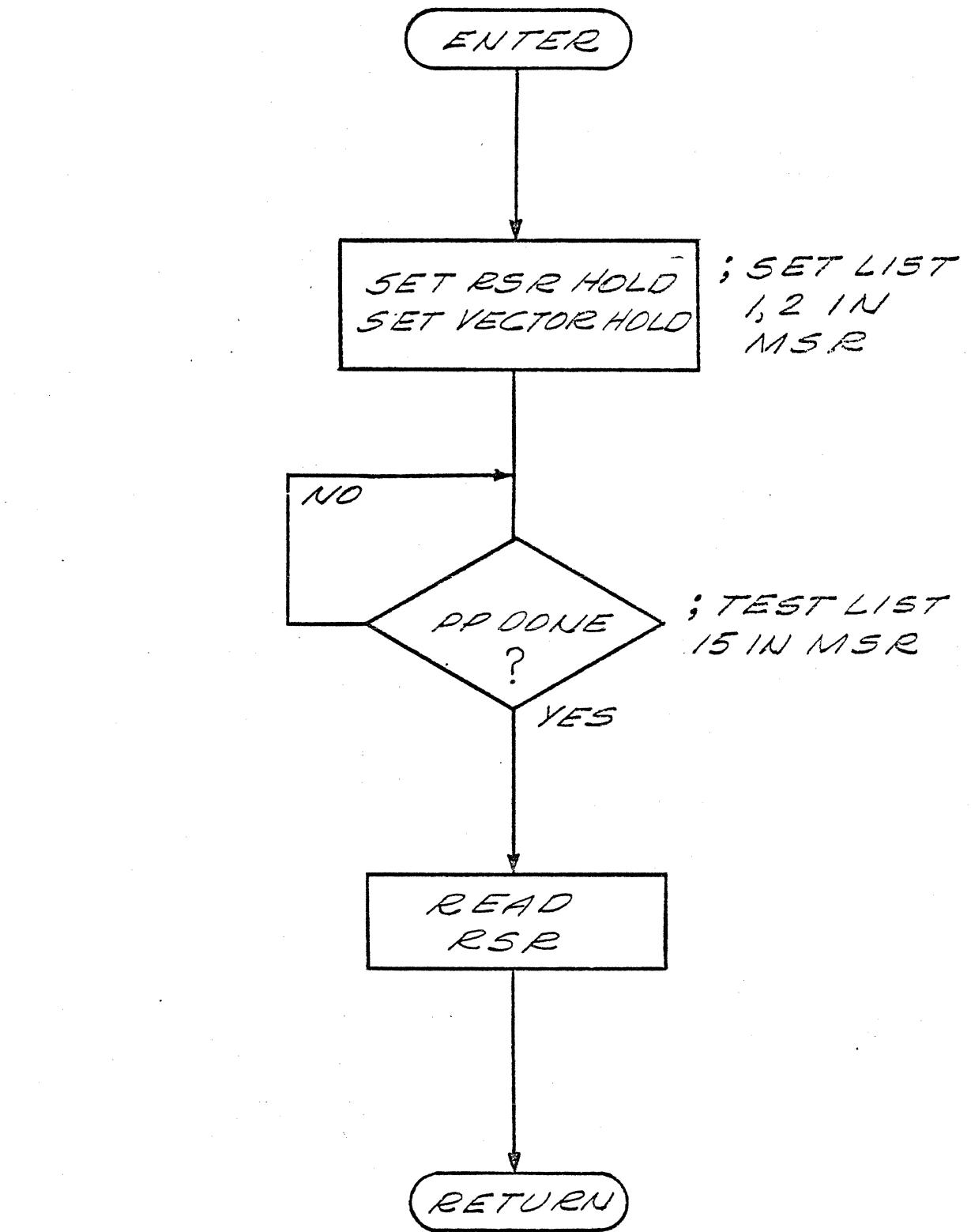

#### 5.1.2.3 Reading the DIOPSA

The DIOPSA is a write only register and cannot be read directly. Any attempt by the user to read the DIOPSA causes the contents of DIOPSA to be transferred to PSDATA register which is directly readable. The following code may be used to read the DIOPSA.

```

MOV DIOPSA, SAVE           ; Try to read the DIOPSA

TST IOST                  ; Test the DIOREADY bit

; in IOST

BPL .-4                   ; If not ready test again

MOV PSDATA, SAVE           ; Read contents of PSDATA

; into UNIBUS address SAVE.

```

### 5.1.3 Direct Memory Access PATH (DMA)

The Direct Memory Access Path Interfaces the UNIBUS to the PICTURE SYSTEM to enable programmable DMA block transfers between UNIBUS address space and PICTURE SYSTEM address space. The actual hardware for the DMA path consists of:

1. DMA control and buffering on the PDP-11 Interface card (195131-100).

2. DMA control and "Data Out" buffering on the 195106-100 card in the PS backpanel.

3. "Data In" buffering on the 195105-100 card in the PS backpanel.

4. Cable driver and receiver lines between the PDP-11 Interface and the 195105-195106 cards.

5. Control lines on the PS backpanel between the 195105 and 195106 cards.

A DMA block transfer between UNIBUS address space and PS address space is set up and initiated under program control. The transfer may be programmed to take place in either direction by setting or clearing the DMAIN bit of the IO status register (IOST).

#### 5.1.3.1 DMA Block Transfer Initialization

The program must interrogate bit 7 of the IOST register

to see if the DMA is ready (see page 2-13 of PICTURE SYSTEM Reference Manual) before manipulating any of the DMA registers. Upon finding the DMAREADY, (195131-600, sheet 5) the program may set up a data block transfer between UNIBUS address space and PS address space. A negative two's complement number of words in the block to be transferred is written into the word count register, DMAWC (sheet 15). The starting UNIBUS address of the block to be sent (or where the block is to be received) is written into the bus address register, DMABA (sheet 15). The direction of the block transfer is set up by writing a 1 or a 0 in the DMAIN bit of the IOST (sheet 5). The block transfer is started by setting bit 0 of the IOST (GO bit, sheet 5).

#### 5.1.3.2 DMAIN Transfer

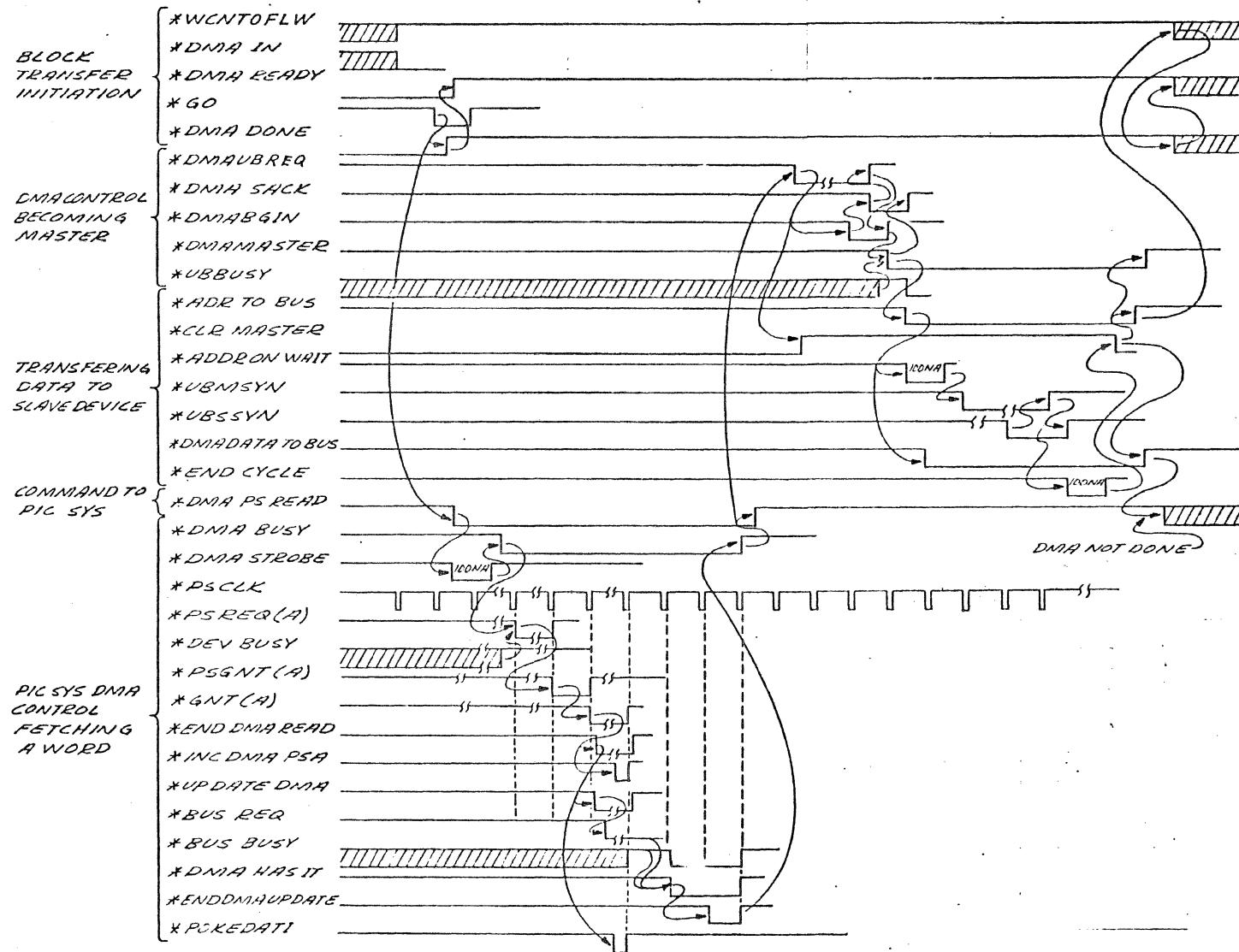

A DMAIN block transfer reads a block of data (one word at a time) from PS address space and stores it in UNIBUS address space. Assuming the block transfer has been set up according to section 5.1.3.1, the block transfer is executed as a series of word transfers. The timing sequence of a DMAIN word transfer is illustrated in Figure 5.1-4. The sequence is described as follows:

1. The \*GO pulse, generated by the program setting the GO bit in the IOST, clears \*DMADONE which

FIGURE 5.1-4

clears \*DMAREADY indicating the DMA path is busy (195131-600, sheet 5). \*GO also sets the \*DMAPSREAD command F/F which drives the \*DMADIRD (sheet 10) line to the PICTURE SYSTEM.

2. The PICTURE SYSTEM's DMA control receives \*DMADIRD (195106-600, sheet 2) and generates \*DMASTROBE pulse which sets the \*DMABUSY F/F (sheet 3). \*DMABUSY is monitored back on the PDP-11 Interface card.

3. \*DMABUSY generates a request for the PSBUS, \*PSREQ(A), in sync with the \*PSCLK when the source device is not busy, indicated by \*DEVBUSY (sheet 3).

4. The PS Arbiter eventually grants the request with \*PSGNT(A) which gates the DMAPSA register (source address) and PSREAD signal onto the PSBUS (sheet 5).

5. On the next clock, \*PSGNT is buffered by setting \*GNT(A) F/F, which is set for one clock period and enables \*ENDMAREAD. During the clock period when \*GNT(A) is set, the source device enables the data onto the PSBUS data lines, and \*ENDMAREAD enables \*UPDATEDMA which generates a \*BUSREQ (195105-600, sheet 4), requesting use of the PSDATAIN (15-0) lines to the PDP-11 Interface (see block diagram Figure 5.1-A).

6. The next clock pulse generates \*INCDMAPSA, which bumps the DMAPSA register by one (if not inhibited), and generates \*POKEDATI pulse which strobes the data off the PSBUS into

the Direct IO/DMA Data In register file (195106-600, sheet 6).

7. When \*BUSBUSY (195105-600, sheet 4), indicates the data lines between the PICTURE SYSTEM and the PDP-11 Interface are not in use, \*DMAHASIT is set in sync with the clock. \*BUSBUSY is asserted indicating the data lines are now in use by the DMA.

8. \*DMAHASIT stays asserted for two clock periods and gates the DMA source data from the input register file onto the data lines to the PDP-11 Interface. After the first clock period, \*ENDMAUPDATE is asserted and the next clock pulse clears the \*DMABUSY F/F (195106-600, sheet 3).

9. The PDP-11 Interface has been monitoring the \*DMABUSY F/F in the PICTURE SYSTEM. The trailing edge of \*DMABUSY clears the read command F/F, \*DMAPSREAD (195131-600, sheet 5) and the data from the PICTURE SYSTEM is strobed into the DMA DATA IN register (sheet 14). The DMA control generates a request for the UNIBUS, \*DMAUREQ (sheet 6).

10. The UNIBUS eventually responds with a grant, \*DMABGIN, which generates \*DMASACK acknowledging the grant and clearing the request.

11. The cleared request causes the UNIBUS to clear the grant which sets the \*DMAMASTER F/F when the UNIBUS becomes "not busy".

12. \*DMAMASTER clears \*DMASACK and asserts \*UBBUSY indicating the DMA is master of the UNIBUS. \*DMAMASTER gates the contents of the DMABA (destination address) onto the UNIBUS by asserting \*ADRTOBUS (sheet 13).

13. \*ADRTOBUS asserts \*DMADATATO BUS, which gates the data in the DMA DATA IN register onto the UNIBUS, and generates \*ADDRONWAIT pulse (sheet 7). The trailing edge of this pulse sets the MSYNOUT F/F which asserts \*UBMSYN to the UNIBUS.

14. The destination device on the UNIBUS eventually responds with \*UBSSYN, indicating it has taken the data. \*UBSSYN clears \*UBMSYN which generates \*ENDCYCLE pulse indicating the completion of a UNIBUS cycle.

15. The trailing edge of \*ENDCYCLE sets the \*CLRDAMASTER F/F (sheet 7) which clears the \*DMAMASTER F/F and unasserts \*ADRTOBUS and \*DMADATAOBUS.

16. The rising edge of \*ADRTOBUS increments the DMAWC (word count register, sheet 15). If the word count overflows (\*WCNTOFLW), the \*DMADONE F/F is set which asserts \*DMAREADY, indicating the DMA path is ready for another block transfer. The rising edge of \*DMADATATOBUS issues another command to the PICTURE SYSTEM (\*DMAPSREAD) if the block transfer is not complete, which commands another word to be fetched from the PICTURE SYSTEM.

### 5.1.3.3 DMAOUT Transfer

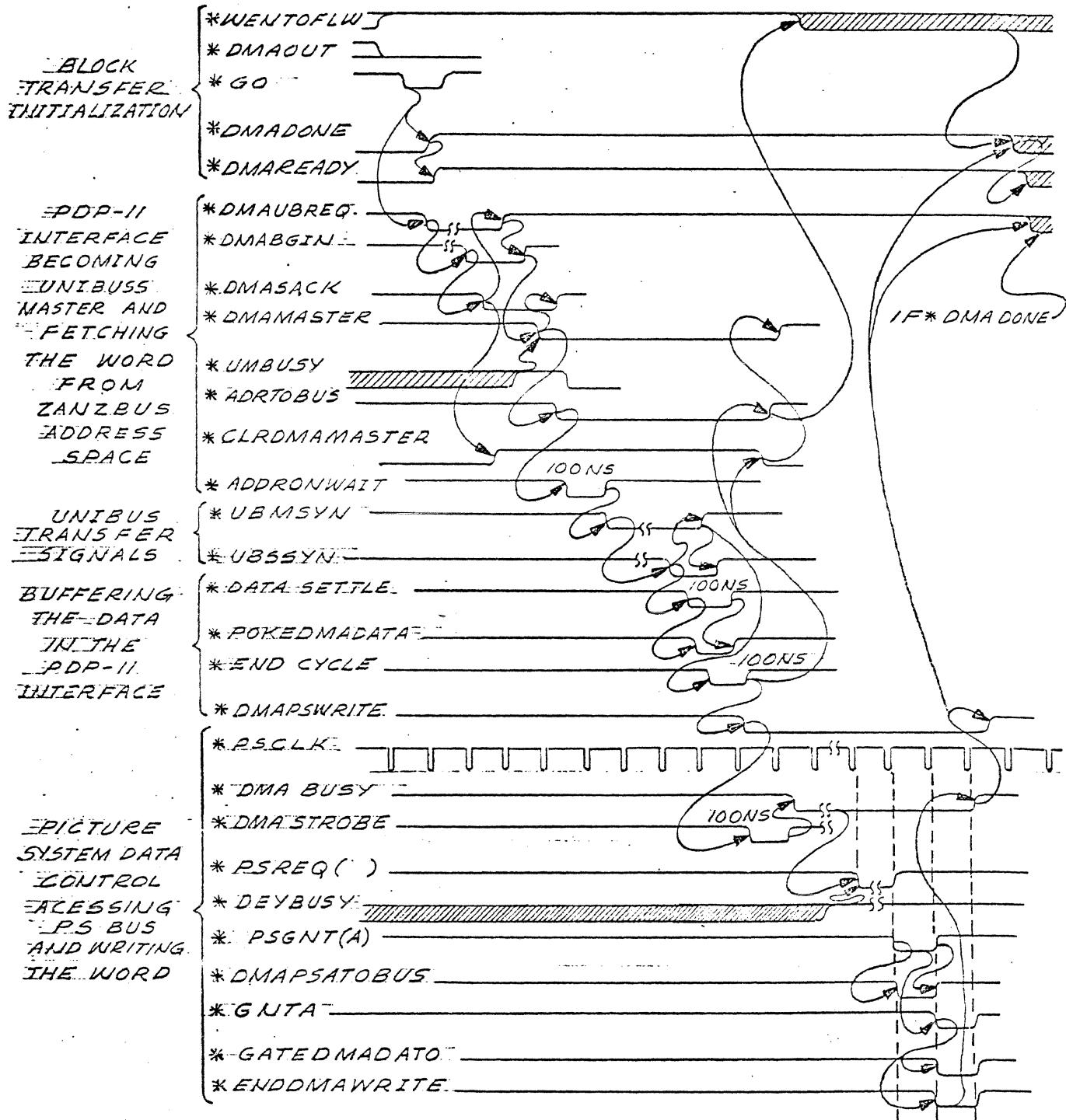

A DMAOUT transfer reads a block of data (one word at a time) from UNIBUS address space and stores it in PS address space. Assuming the block transfer has been set up according to section 5.1.3.1, the block transfer is executed as a series of word transfers. The timing sequence of a DMAOUT word transfer is illustrated in Figure 5.1-5. The sequence is described as follows:

1. The \*GO pulse clears \*DMADONE which clears \*DMAREADY, indicating to the program that the DMA path is busy. \*GO also sets the \*DMAUBREQ F/F (195131-600, sheet 6).

2. \*DMAUBREQ requests mastership of the UNIBUS and is eventually granted with \*DMABGIN which sets \*DMASACK acknowledging the grant.

3. \*DMASACK clears the request and eventually the UNIBUS grant is cleared which sets the \*DMAMASTER F/F when UNIBUS mastership is released by the current master.

4. \*DMAMASTER asserts \*ADRONBUS which gates the DMABA (source address) onto the UNIBUS and generates \*ADDRONWAIT pulse (sheet 7).

5. The trailing edge of \*ADDRONWAIT sets MSYNOUT F/F which asserts \*UBMSYN to the UNIBUS.

6. The slave device (usually memory) eventually responds with data on the UNIBUS by asserting \*UBSSYN which generates \*POKEDMADATA pulse and clears \*UBMSYN.

FIGURE 5.1-5 DMAOUT TIMING DIAGRAM

7. The trailing edge of \*POKEDMADATA strobes the data off the UNIBUS into the CPUDATAOUT register (sheet 8) and the trailing edge of \*UBMSYN generates \*ENDCYCLE pulse indicating the completion of a UNIBUS cycle.

8. The trailing edge of \*ENDCYCLE sets \*CLRDMMMASTER which clears \*ADRTOBUS and \*DMAMASTER.

9. The trailing edge of \*ADRTOBUS increments the DMAWC (word count) and DMABA (source address) and sets \*DMAPSWRITE (sheet 5) which is the write command to the PICTURE SYSTEM. \*DMAPSWRITE drives the DMADOLD line and CPUDATAOUT drives the data lines to the PICTURE SYSTEM.

10. \*DMAPSWRITE and the data is received (sheet 1 and 2, 195106-600) and generates \*DMASTROBE pulse which sets \*DMABUSY and strobes the data into the Direct IO/DMA data out register file (195105-600, sheet 5).

11. When the destination device is not busy (\*DEVBUSY), a request for the PSBUS is generated in sync with \*PSCLK.

12. The request is eventually granted with \*PSGNT(A) which gates the DMAPSA (destination address, 195106-100, sheet 5) onto the PSBUS.

13. The next clock buffers the grant by setting \*GNTA which gates the data from the DIO/DMA register file to the PSBUS and asserts \*ENDDMAWRITE.

14. The next clock clears \*DMABUSY which is the signal the PDP-11 Interface is monitoring.

15. The rising edge of \*DMABUSY clears the write command (\*DMAPSWRITE) and sets \*DMAUBREQ to request another UNIBUS cycle if the block transfer is not done. If \*WCNTOFLW (word count overflow) is asserted, then \*DMADONE is set which asserts \*DMAREADY indicating the DMA path is ready for another block transfer (195131-600, sheet 4).

#### 5.1.4 Interrupt Sense and Control

The PICTURE SYSTEM is equipped with an interrupt facility to enable program intervention by a requesting device. The possibility of more than one request for service at one time requires an arbitrator to decide which device is serviced first. A requesting device issues an interrupt request to the Interrupt Sense and Control which causes the following sequence of events:

1. The sense logic (195131-600, sheet 11) examines all interrupt request lines.

2. When one or more interrupt request are present, the Interrupt Control requests use of the UNIBUS (sheet 12).

3. Eventually, the UNIBUS is given to the Interrupt Control and it becomes bus master.

4. The Interrupt Control recognizes the interrupt request with the highest priority (sheet 11, bug 92), passes the appropriate interrupt vector address to the UNIBUS, and asserts the interrupt line, \*UBINTR, on the UNIBUS (sheet 12).

5. The PDP-11 Processor pushes the contents of the Processor Status Word and Program Counter (PSW,PC) onto the program stack and loads into the PC and PSW the first two consecutive words (interrupt vector) from memory pointed to by the interrupt vector address.

6. The Processor does a jump to the location in the PC and begins executing the interrupt service routine.

7. The last instruction of the routine is a RTI, return from interrupt, instruction. When executed, the RTI causes the Processor to pop two words from the program stack into the PC and PSW registers.

8. The Processor jumps to the new PC location and resumes execution of the interrupted task.

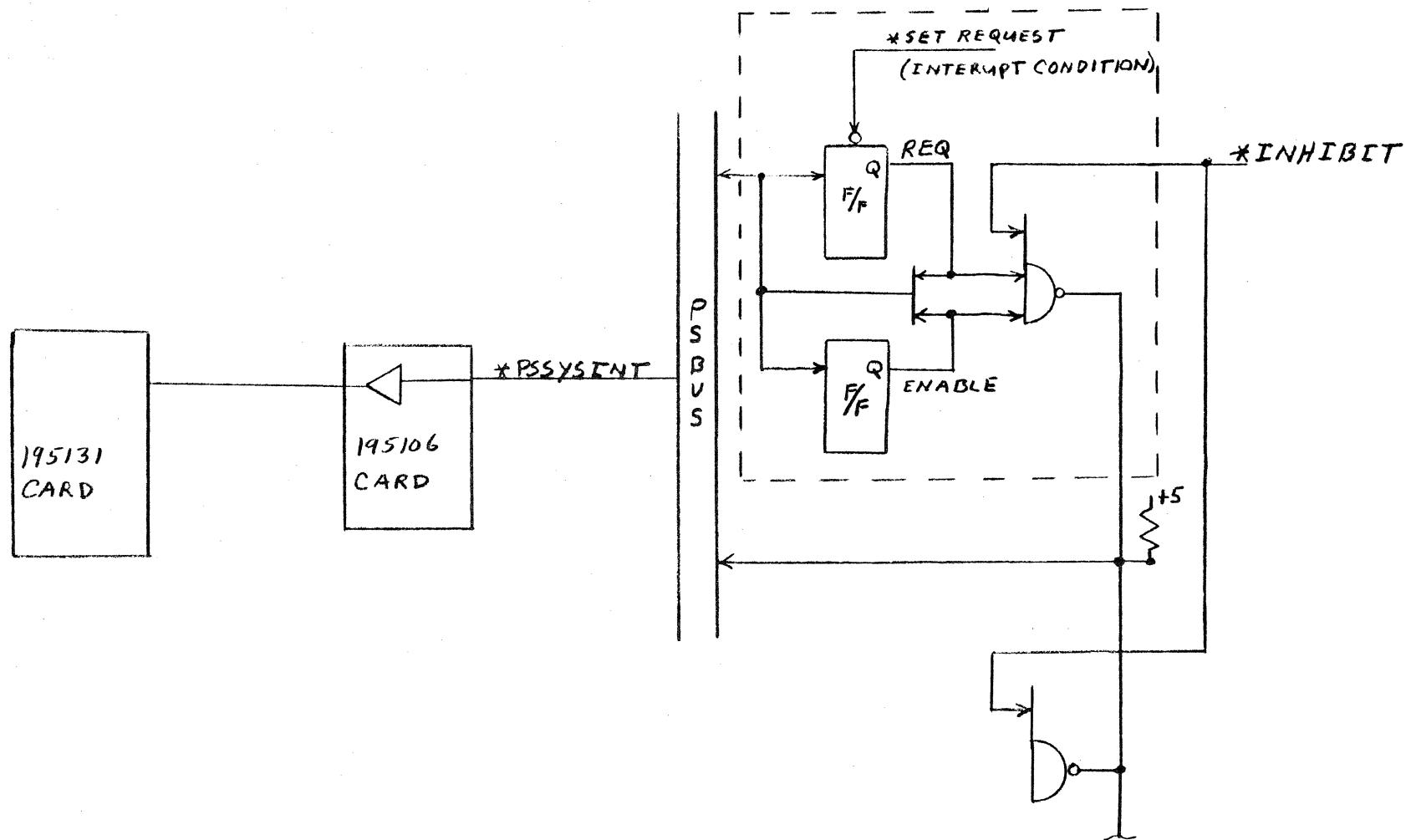

#### 5.1.4.1 System Interrupts

Any one of the following seven conditions will generate a system interrupt if the corresponding interrupt enable F/F is set.

1. MATCH REQ

2. WBSTOP REQ

3. RFSTOP REQ

4. MOSTOP REQ

5. JUMP REQ

6. HIT REQ

7. HALT REQ

These seven conditions are defined in the PS2 Reference Manual, pages 2-134 through 2-136. A circuit similar to the one surrounded by dashed lines in figure 5.1-6 exists for each system interrupt condition. \*PSSYSINT is the system interrupt line of the PSBUS driven by each system interrupt circuit. This line is relayed to the Interrupt Controller on the 195131 card by a differential driver on the 195106 card. A high to low transition of this line initiates action by the Interrupt Controller which will gain access of the UNIBUS and interrupt the Picture Controller (provided the PSIE bit of the IOST register is set). In order for a system interrupt circuit to assert \*PSSYSINT, both the interrupt enable F/F

SYSTEM INTERRUPT SCHEME

FIGURE 5.1-6

and the interrupt request F/F must be set. \*INHIBIT is a common line to all system interrupt circuits which inhibits any pending interrupt requests from asserting \*PSSYSINT while the program is clearing the particular request bit which generated the last interrupt. After the request bit is cleared, any other system interrupt request bit still set will generate another high to low transition of \*PSSYSINT; therefore, generating another system interrupt.

The interrupt circuits are found on the 195121-100 and 195151-100 cards.

## 5.2 PICTURE SYSTEM BUS - PSBUS

All PICTURE SYSTEM 2 devices connect and interact with each other on a single, high-speed, synchronous data bus. Memory, device registers, control and status registers all exist and are addressable memory locations on the PSBUS. By means of this PSBUS, coordinate data may be transferred from the Picture Controller host computer to the Picture Processor while data may concurrently be transferred to PS Memory. During the process, data may also be transferred from PS Memory to the Picture Generator for display. In addition, data may be entered from the data tablet, alphanumeric keyboard, function switches, etc., and read by the control program of the host computer. Data flow is supervised by a bus arbitration system which is an integral part of the PSBUS.

### 5.2.1 PSBUS Structure

The PSBUS consists of the following lines:

1. \*PSDAT (15-0) - 16 data lines

2. PSADD (15-0) - 16 address lines

3. \*PSREQ ( 7-0) - 8 request lines

4. \*PSGNT ( 7-0) - 8 grant lines

5. \*PSCLK ( 5-1) - 5 clock lines

6. \*PSDEF - 1 memory defer line

7. \*PSMEM - 1 memory busy line (FIFO Line)

|     |                                   |                          |

|-----|-----------------------------------|--------------------------|

| 8.  | *PSRST                            | - 1 reset line           |

| 9.  | *PSREAD/PSWRT                     | - 2 memory command lines |

| 10. | *PSDEVINT/*PSSYSINT/<br>*PSCLKINT | - 3 interrupt lines      |

| 11. | *PSBSY ( 7-0)                     | - 8 device busy lines    |

| 12. | *PSSYNC                           | - 1 sync line            |

---

TOTLA 70 lines

The five clock lines are all in sync and were implemented for driving capability. The \*PSSYNC line is used to arbitrate use of the Refresh Memory by the Refresh Controller and possible future console keyboard devices.

#### 5.2.2 Active/Passive Devices

Data transfers from device to device in the PICTURE SYSTEM are performed by an active device transferring data to or from a passive device via the PSBUS. The active device initiates and controls the transfer, and the passive device accepts or provides the data as commanded.

All devices are either active or passive; however, some devices may be programmed to be either active or passive at a given time. No device can be active and passive simultaneously.

A typical data transfer between active and passive devices involves the following sequence of events if the passive

device is not PS Memory:

1. The active device requests and is eventually granted use of the PSBUS.

2. When granted, the active device gates the address of the passive device and a read/write command onto the PSBUS.

3. The passive device is given one bus clock period (150 ns) to decode the address and command.

4. If the transfer is a write (active to passive), the active device gates data to the PSBUS. If the transfer is a read, the passive device gates data to the PSBUS. This data is held for one clock period.

5. The data on the PSBUS is taken by either the active or passive device depending on the direction of the transfer.

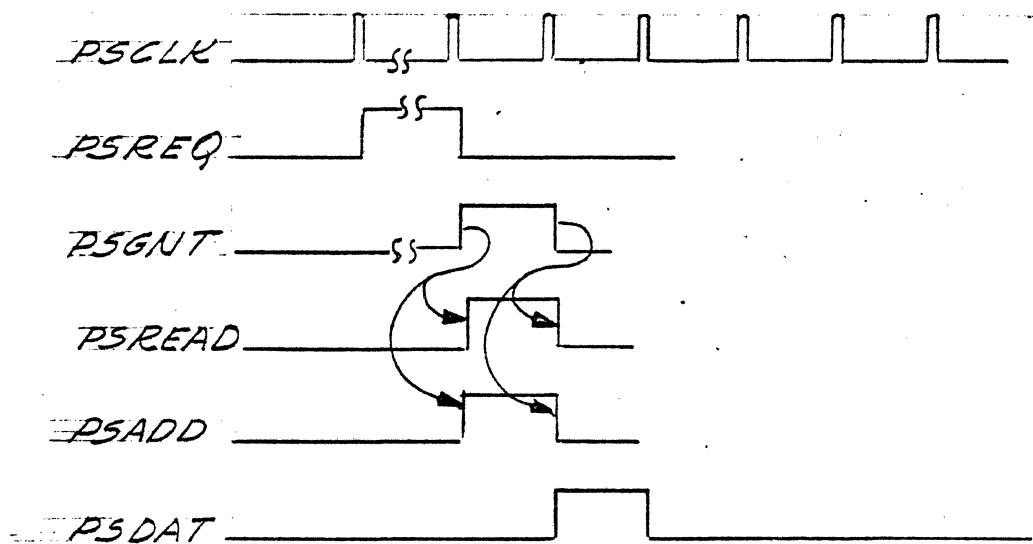

#### 5.2.3 PSBUS Timing

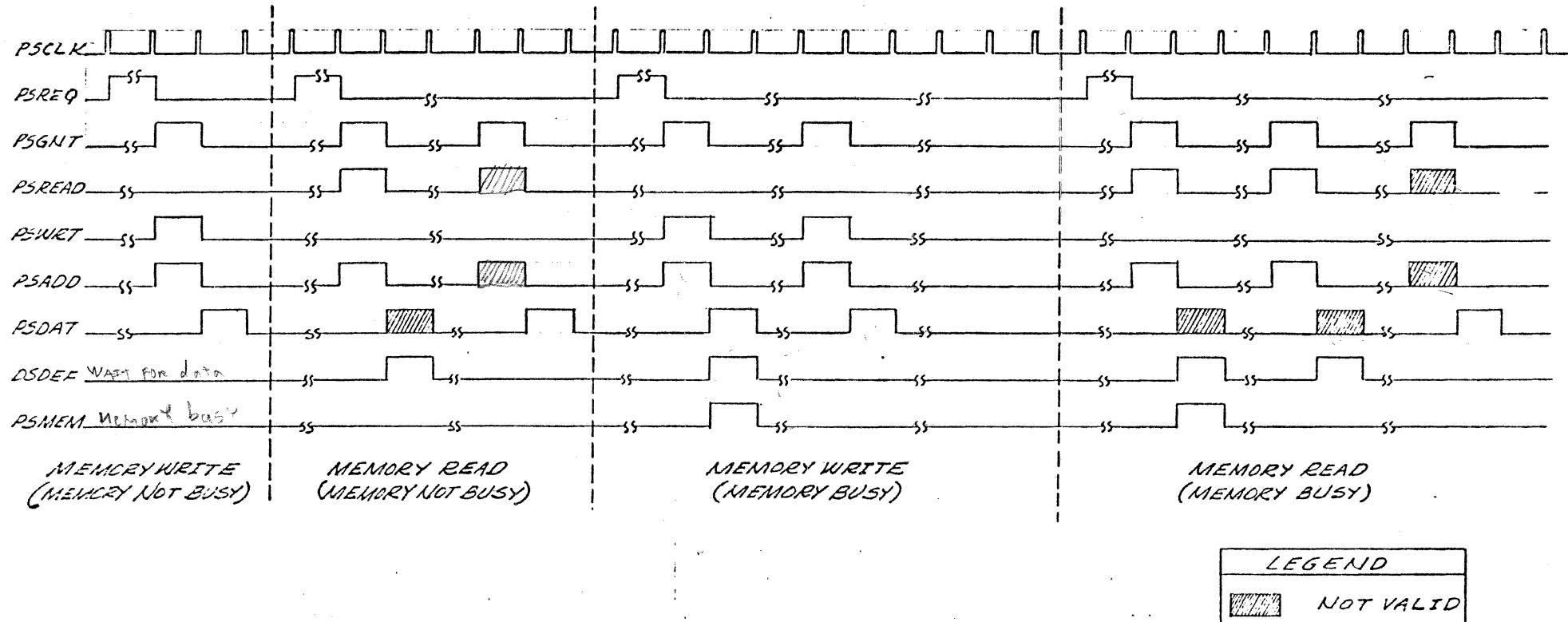

A timing diagram of typical non memory data transfers between active and passive devices as described in section 5.2.2 is illustrated in Figure 5.2-1. A special case exists when the passive device is the PICTURE SYSTEM Memory.

Any data transfer to or from PICTURE SYSTEM Memory requires

READ TRANSFER (ACTIVE ← PASSIVE)

WRITE TRANSFER (ACTIVE → PASSIVE)

FIG. 5.2-1 TIMING DIAGRAM FOR TYPICAL ACTIVE PASSIVE DATA TRANSFER

an active device initiating the transfer to or from the passive memory. More than one active devices may request concurrent use of the memory. The PSBUS Arbiter arbitrates use of the PSBUS, however, a memory read cycle is 450 ns and a read-write cycle is 750 ns; therefore, data from memory cannot be gated to the PSBUS during the clock after the memory receives the address. Also, the memory may be busy when addressed by an active device.

The Bus Arbiter always responds with a grant to a requesting (active) device when the PSBUS is not busy; however; if the memory access is a read, the memory controller simultaneously responds to the active device with a deferred signal (\*PSDEF). The deferred signal instructs the active device to wait till later for the data. If the memory is busy, it asserts the busy line (\*PSMEM) the same time it defers the active device. The device then waits for a second grant to give the memory the address, is again deferred and waits for a third grant which signifies data is valid on the next bus cycle. Typical data transfers between an active device and PICTURE SYSTEM Memory are illustrated by the timing diagrams in Figure 5.2-2.

#### 5.2.4 PSBUS Arbitration

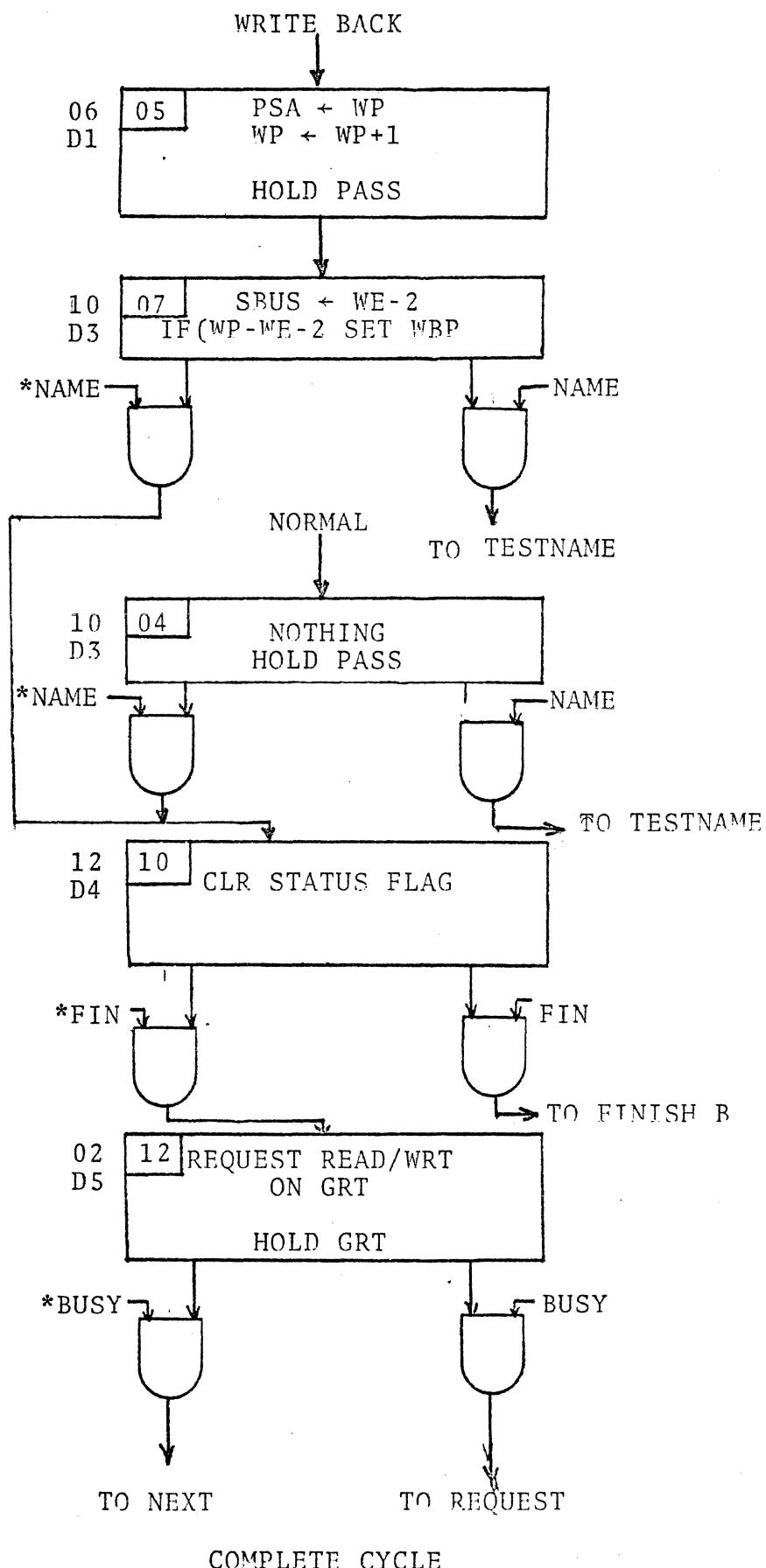

An Arbitration system for the PSBUS manages data

FIGURE 5.2-2 MEMORY DATA TRANSFER TIMING DIAGRAM

transfers between devices in such a way as to utilize the full bandwidth of the bus. Since the PSBUS is synchronous, a data transfer may take place every clock period if active devices are constantly requesting use of the bus; therefore, the bus can transfer 6.6 meg-a-words per second. The PS memory operates at a slower rate of 2.5 meg-a-words per second; therefore, a device accessing memory must wait for data; however, the device releases control of the bus to other devices while waiting. The arbitration system must recognize when memory is ready to output data, then give memory highest priority for use of the bus. This implies that memory has higher priority than the eight active request priority levels, \*PSREQ(7-0). Memory is always granted use of the bus the next bus cycle after requesting the bus.

The arbiter actually rotates priority of the eight active request levels. When one request is granted, that request level is changed to lowest priority, and the other seven levels are rotated appropriately for the next grant cycle; however, remember memory can override the highest requesting priority level if memory is in a data output state.

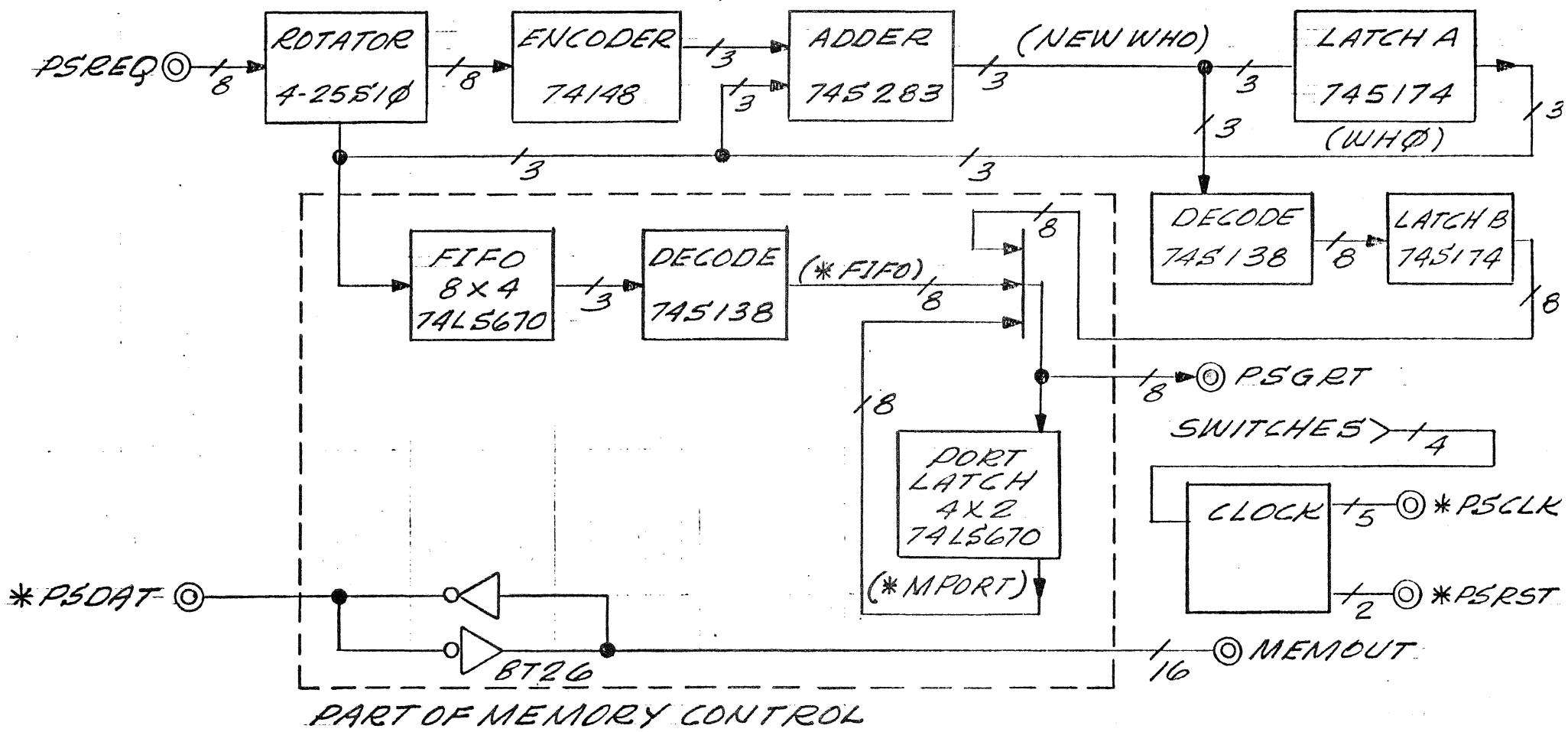

The PSBUS arbitration system receives eight active

requests from PICTURE SYSTEM devices. These requests are input into a priority rotater as illustrated in Figure 5.2-3. The rotator examines WHO, the last request level who was granted, and rotates the eight requests input to the priority encoder. The request corresponding to WHO is input to the encoder at the lowest priority level. The encoder outputs a 3 bit code corresponding to the highest level request on its inputs to the NEWWHO adder. The adder sums the result of the priority encoder with the number of places the encoder inputs are rotated to determine which Active Request is to be honored. This honored request, NEWWHO, waits for one of two events to occur before being saved in the WHO latch. The two events are:

1. A valid WHO does not exist in the WHO latch; therefore clock the latch until a valid NEWWHO is saved.

2. A valid WHO exists in the latch, a memory port does not need the PSBUS (not in data output state), and a free memory port does not need the FIFO.

Either event gates the decoded WHO out to the PSBUS as a grant, and on the next clock latches NEWWHO into the WHO latch which determines the rotation for the

FIGURE 5.2-3

PSBUS ARBITRATION SYSTEM BLOCK DIAGRAM

198107

next clock.

Further examination of event 2 leads to a clearer understanding of the request/grant timing on the PSBUS. Suppose that a valid WHO exists in the WHO latch, the memory FIFO contains a pending grant, and both memory port controllers are busy; however, neither port controller is in a data output state. This means event 2 is true and the PSBUS is free for a grant cycle. The decoded WHO which corresponds to the original active request that generated WHO, is gated out to the PSBUS as a grant. This grant is received by the active device which in turns gates the address and a read or write command to the passive device as depicted in the timing diagrams of Figure 5.2-2. The WHO latch is updated on the next clock, and if the address on the bus was for memory and the access is a read, the PS Memory Control asserts the deferred line which tells the active device that data will not be valid during this clock period. (If passive device is not memory data will be valid). Also, if the memory is busy, the PS Memory Control asserts \*PSMEM which tells the active device that the address was not accepted by the memory and will be asked for at a later time. If the active device is writing to memory, the device asserts data to the PSBUS during

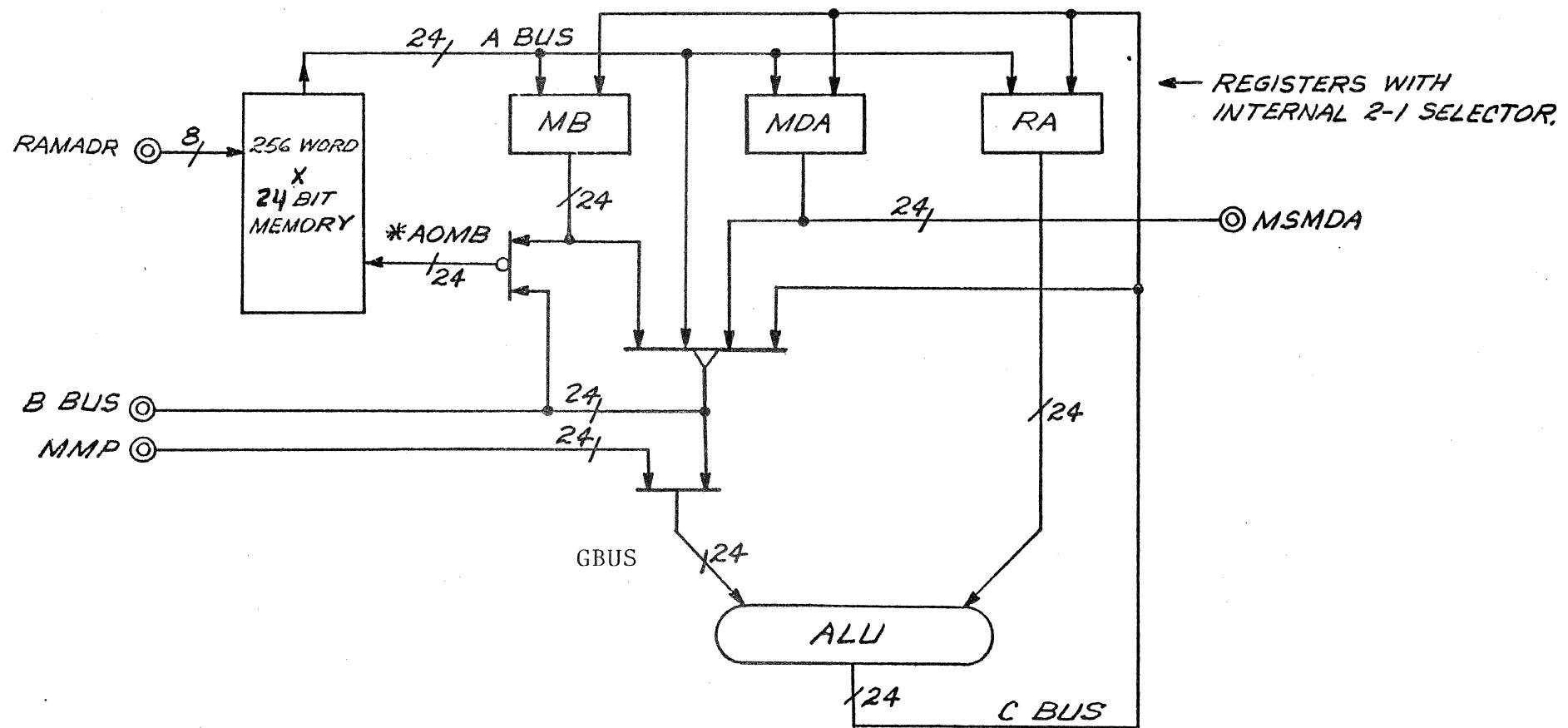

FIGURE 5.3-2 PS2 MAP BLOCK DIAGRAM

the clock period after memory latches the address.

If an active device receives the memory busy signal the device will receive a second grant at a later time from the memory. This implies that the memory must save the first grant. It does so in the memory FIFO, and if the FIFO is not empty when a memory port controller becomes idle, the FIFO is output to the grant lines as the second grant to a waiting active device. This second grant signals the device to repeat the address to the bus sense a free port controller can now begin access of the address. The PS Memory Control is also equipped with a port latch. This latch saves the particular grant that signals a device of the beginning of a read access by a port controller. When the port controller has data from memory (in data output state) it repeats the grant from the port latch which signals the device that data will be on the PSBUS during next clock cycle.

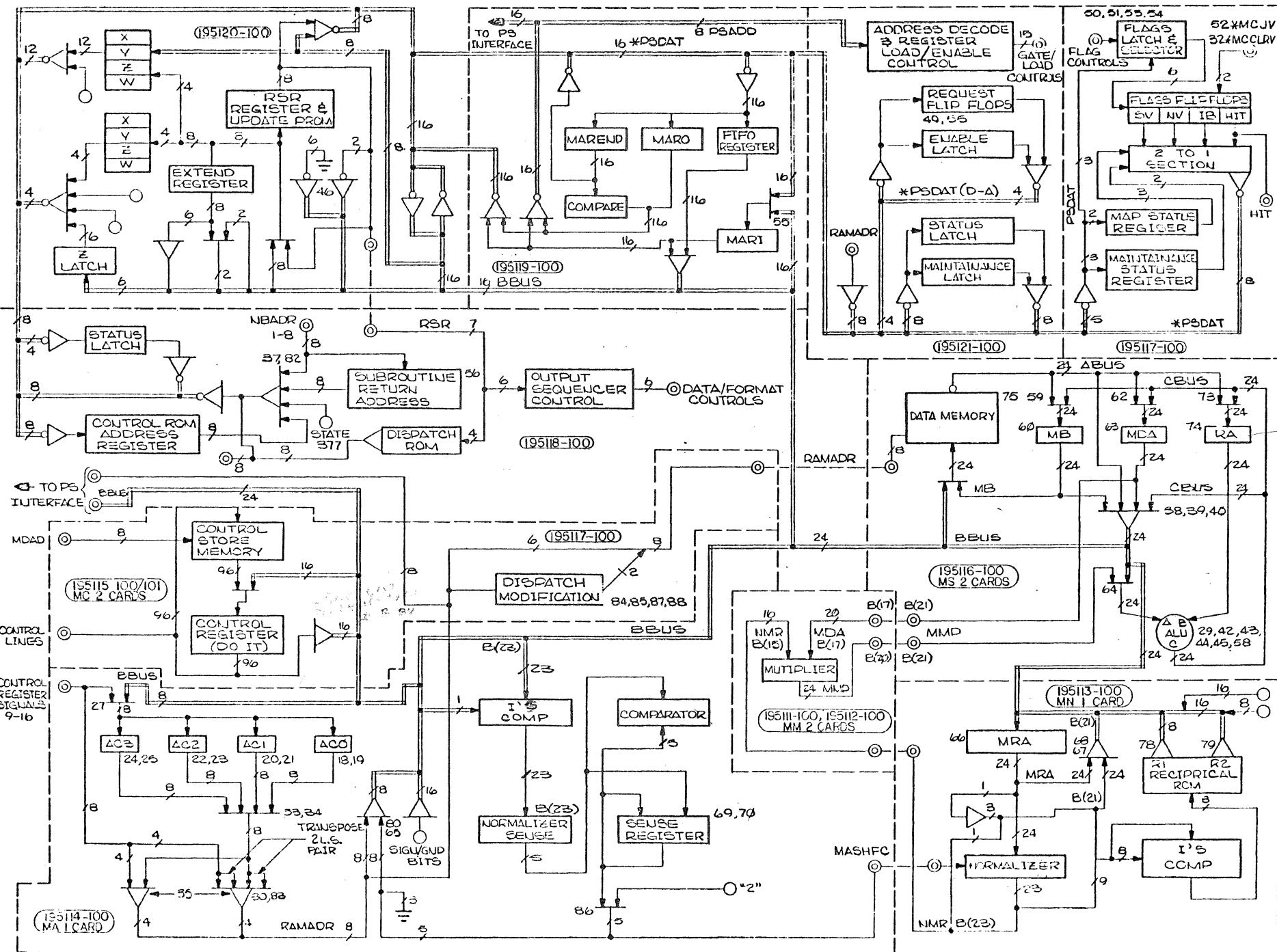

### 5.3 Picture Processor

The Picture Processor receives commands and data from the PSBUS, decodes the commands, operates on the data, and outputs data in a specified format to the PSBUS. Output from the Picture Processor may be directed to PS Memory, the Picture Generator, or the Picture Controller. The source of Picture Processor input and destinations of Picture Processor output is program controlled.

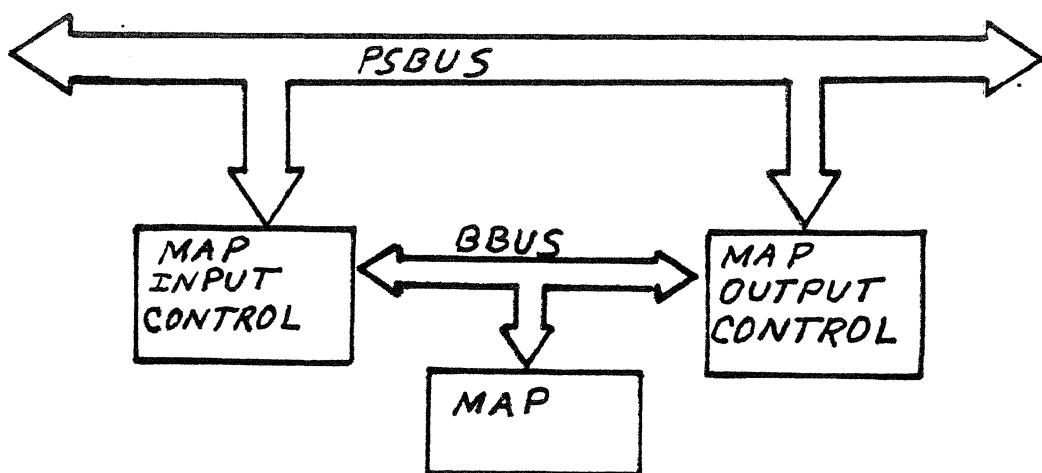

The Picture Processor consists of three units:

1. MAP Input Controller

2. Matrix Arithmetic Processor (MAP)

3. MAP Output Formatter

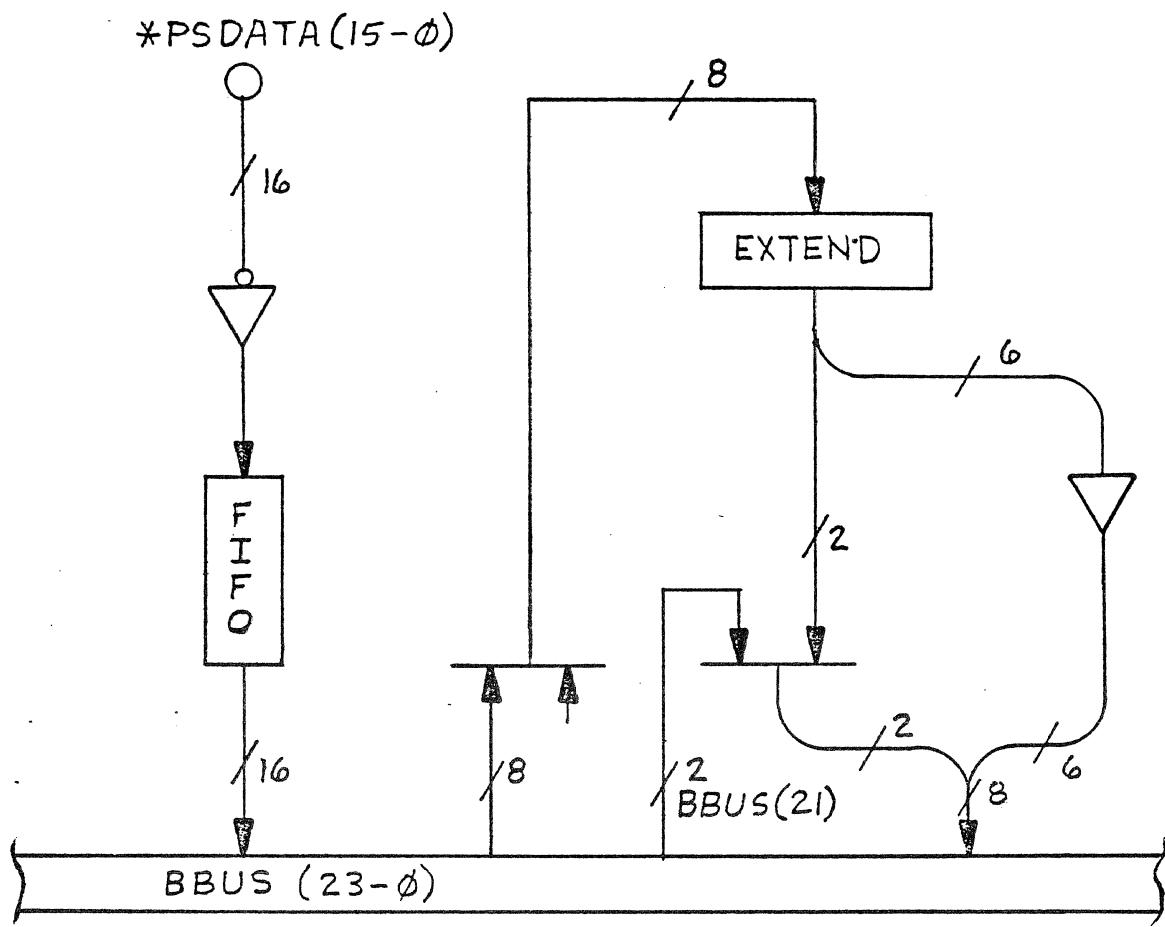

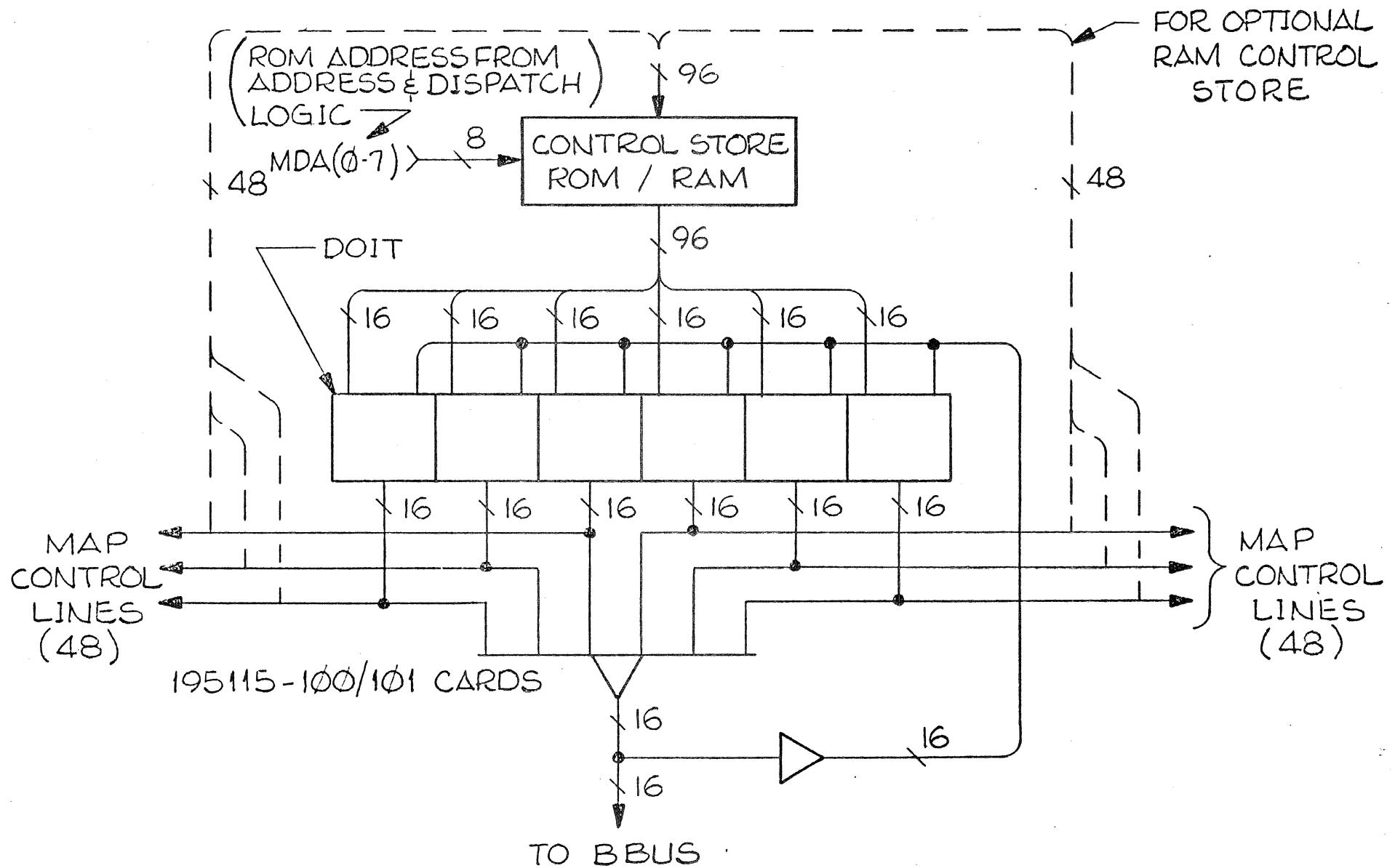

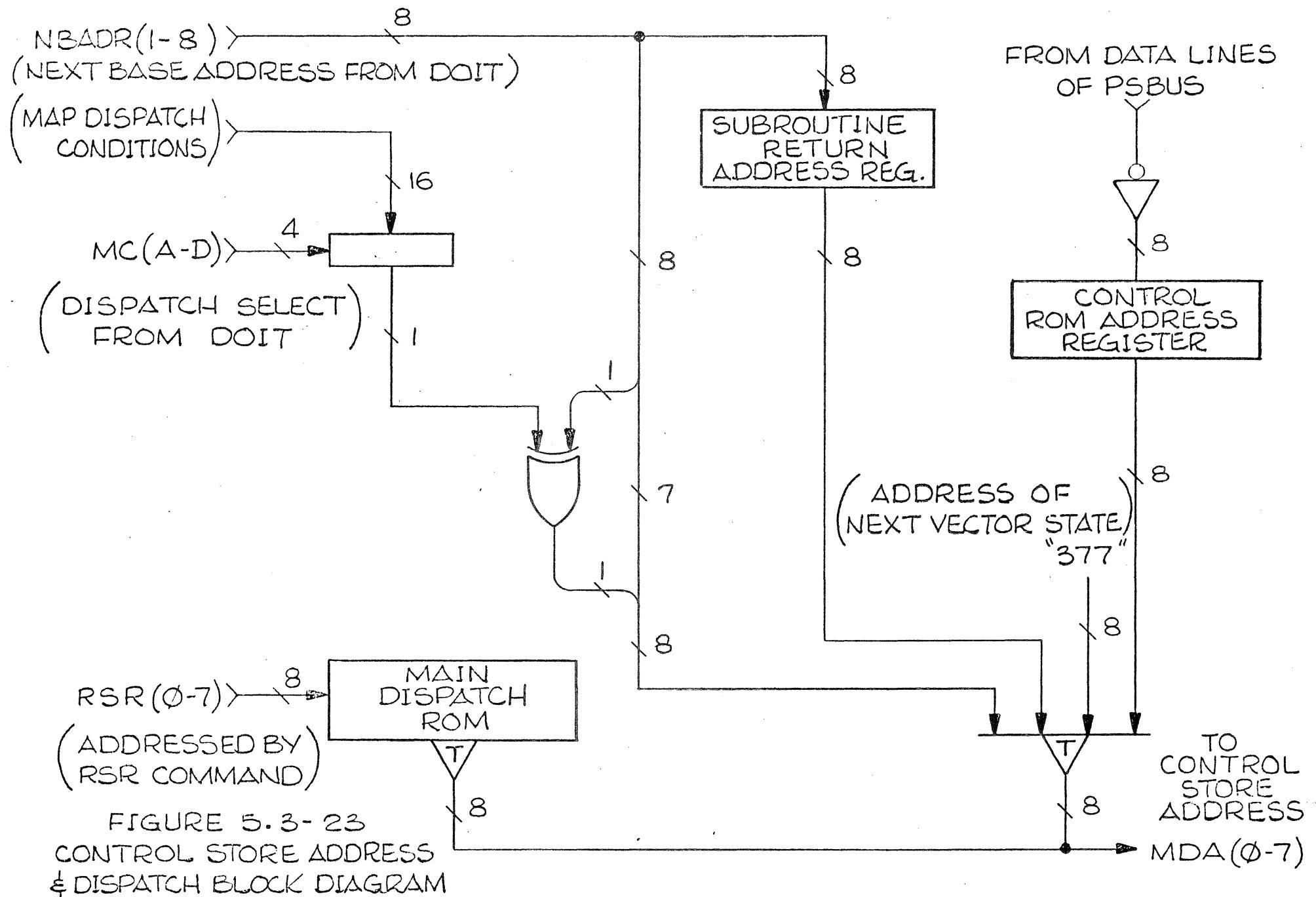

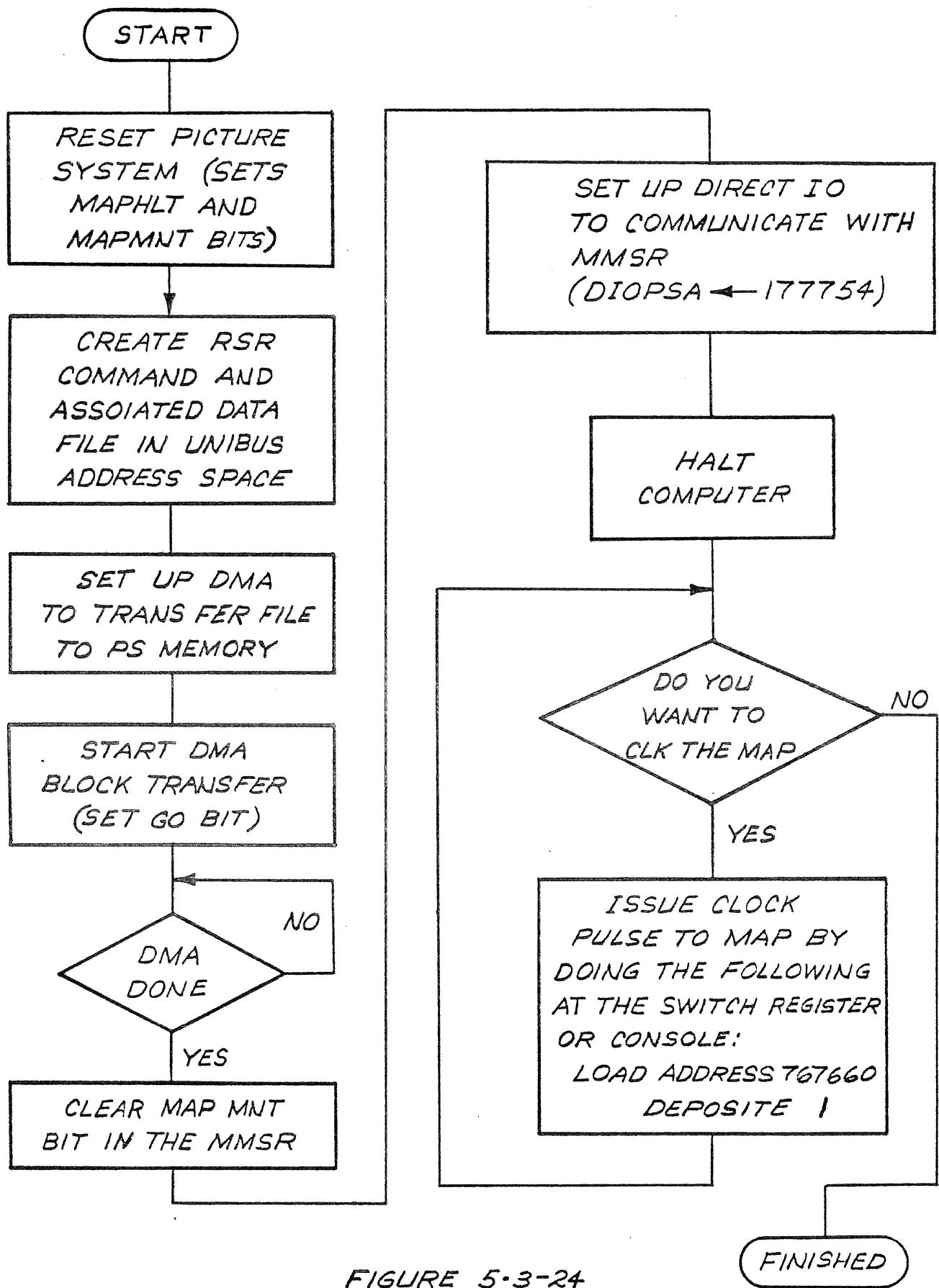

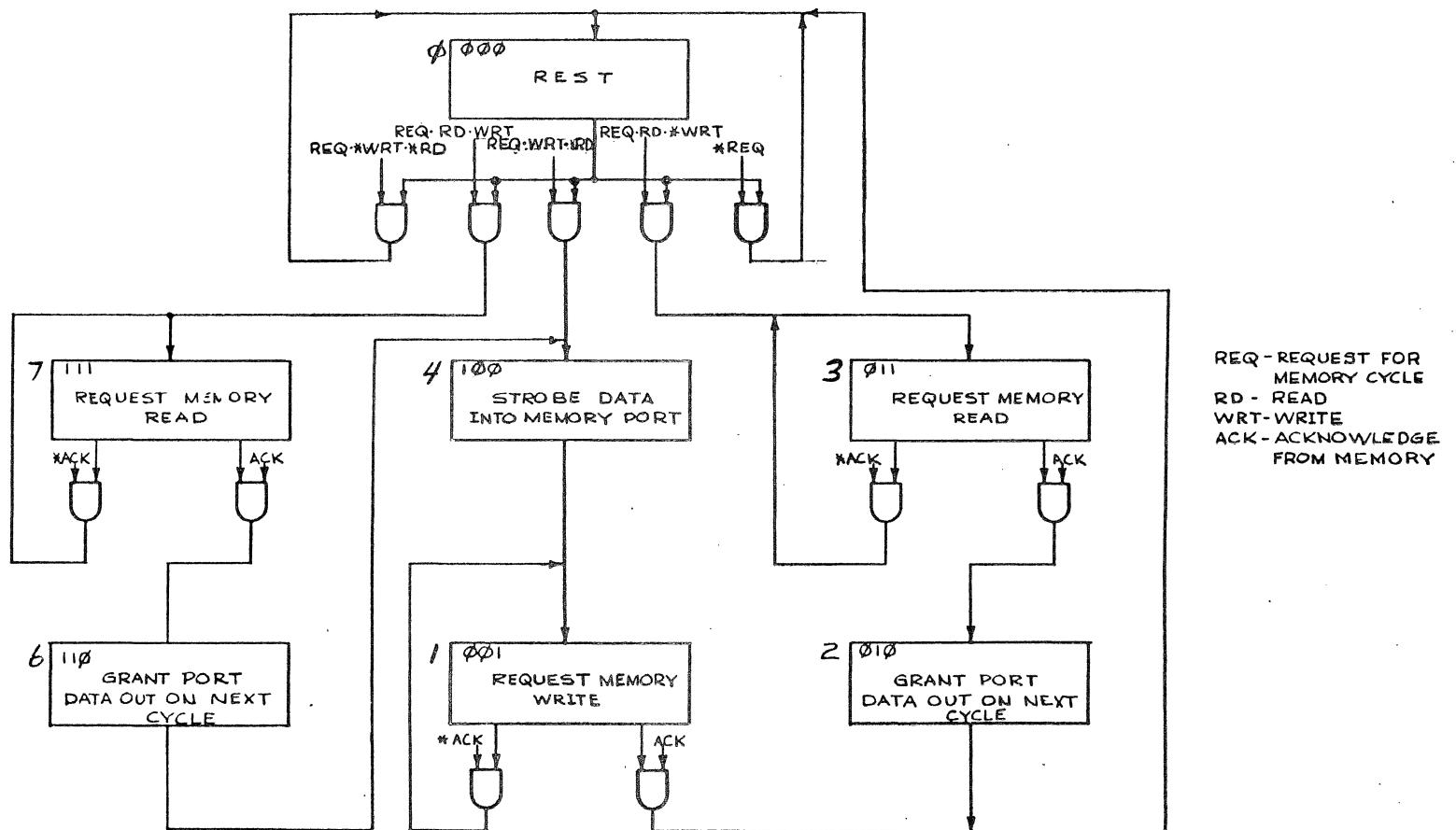

The three units interface to an internal bus, the BBUS. Data transfers between the three units occur on this bus; however, input and output occur on the PSBUS. Figure 5.3-1 illustrates a simplified block diagram of the Picture Processor interfaced to the PSBUS. A detailed block diagram is illustrated in Figure 5.3-2.

Figure 5.3-1

Simplified Block Diagram of Picture Processor

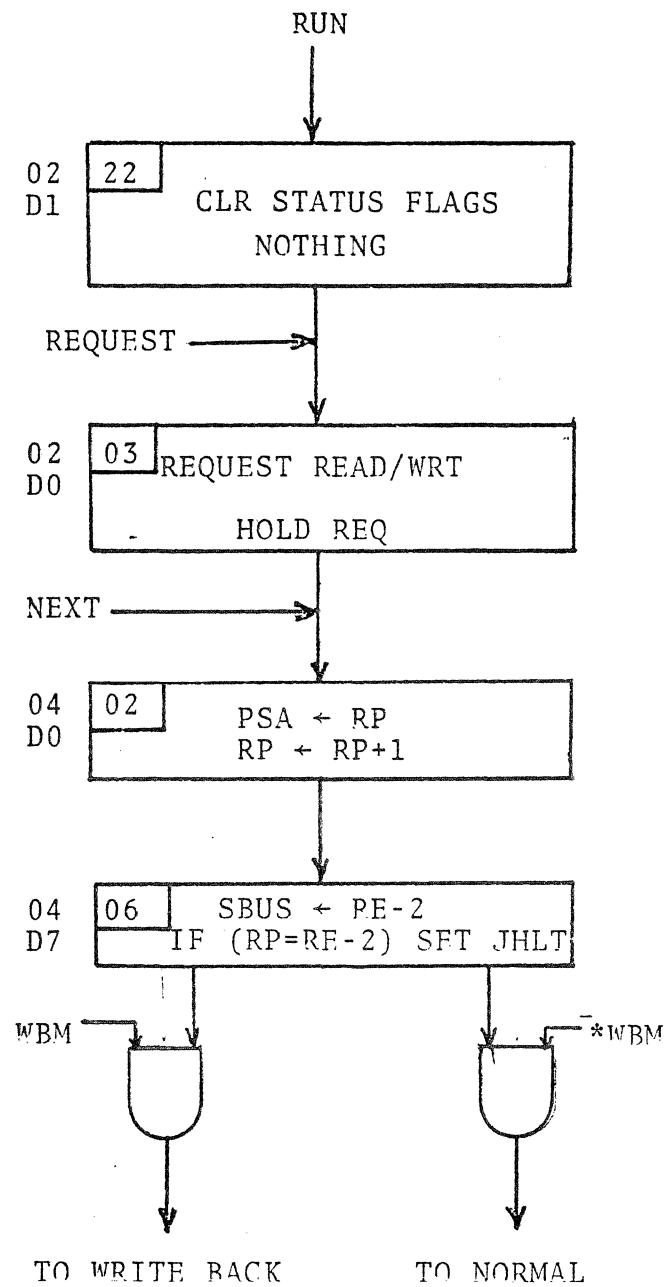

FIGURE 5.3-3

MAP INPUT STATE DIAGRAM

The Picture Processor contains eight, PSBUS, addressable, control registers which control status, input, and output.

These eight registers are:

1. MAOL - MAP Active Output Limit

2. MAOA - MAP Active Output Address

3. MAIA - MAP Active Input Address

4. MSR - MAP Status Register

5. MMSR - MAP Maintenance Status Register

6. MMRSR - MAP Maintenance Repeat Status Register

7. MMPAR - MAP Maintenance Prom Address Register

8. MMBUS - MAP Maintenance BBUS

The eight control registers are defined in Section 2.3 of the PS2 Reference Manual.

In addition to the eight control registers, the Picture Processor contains two additional PSBUS-addressable port registers. These registers act as input and output ports when input or output is functioning as a passive PSBUS device. The two passive port registers are:

1. MPIP - MAP Passive Input Port

2. MPOP - MAP Passive Output Port

The MPIP and MPOP are described in the PS2 Reference Manual on pages 2-28, 2-55 and 2-56.

The Picture Processor also includes 256, non-PSBUS-addressable, internal registers. These registers are

implemented as RAM Memory. They are used as parameters and working registers by the MAP during point vector transformation functions. They may be loaded from the PSBUS during MAP execution of LOAD, or LOAD STACK commands and may be output to the PSBUS during MAP execution of STORE or STORE STACK commands. These internal registers are described in the PS2 Reference Manual on pages 2-30 through 2-35.

The heart of the Picture Processor is the Matrix Arithmetic Processor (MAP). This processor is used to perform point-vector transformations, matrix concatenations, clipping, viewpoint mapping, perspective calculations, hit testing, etc. The MAP receives commands from the MAP Input Controller, operates on data as specified by the command, and outputs data to the MAP Output Formatter.

The MAP Output Formatter receives data from the MAP and formats it as specified by MSR bits 9 and 8 (See PS2 Reference Manual, page 22) in preparation for output to a PSBUS device.

#### 5.3.1 MAP Input Controller - Active

The MAP Input Controller is the device by which the Picture Processor inputs data from the PSBUS. It can be programmed to be either an active device or a passive device by modifications of bit 4 of the MSR. When operating

as an active device, the controller inputs data from the PS address specified by the MAIA register. The MAIA is incremented upon each PS address access; therefore, commands and data from a PSBUS-addressable file will stream into the MAP Input FIFO.

#### 5.3.1.1 MAP Input FIFO

The MAP Input FIFO consists of a four word register file which is simultaneously writeable and readable. The FIFO is monitored for full or empty status by the MSR; therefore, the program may sense the conditions of FIFO by testing bits 14 and 13 of the MSR. When the Input FIFO is full, further access to PS address locations by the Input Controller is inhibited. When the FIFO is empty further access to the FIFO by the MAP is inhibited.

The FIFO is implemented on sheet 2 of the 195119-600 drawings of the MAP BUFFER Card. Note the separate read and write address inputs.

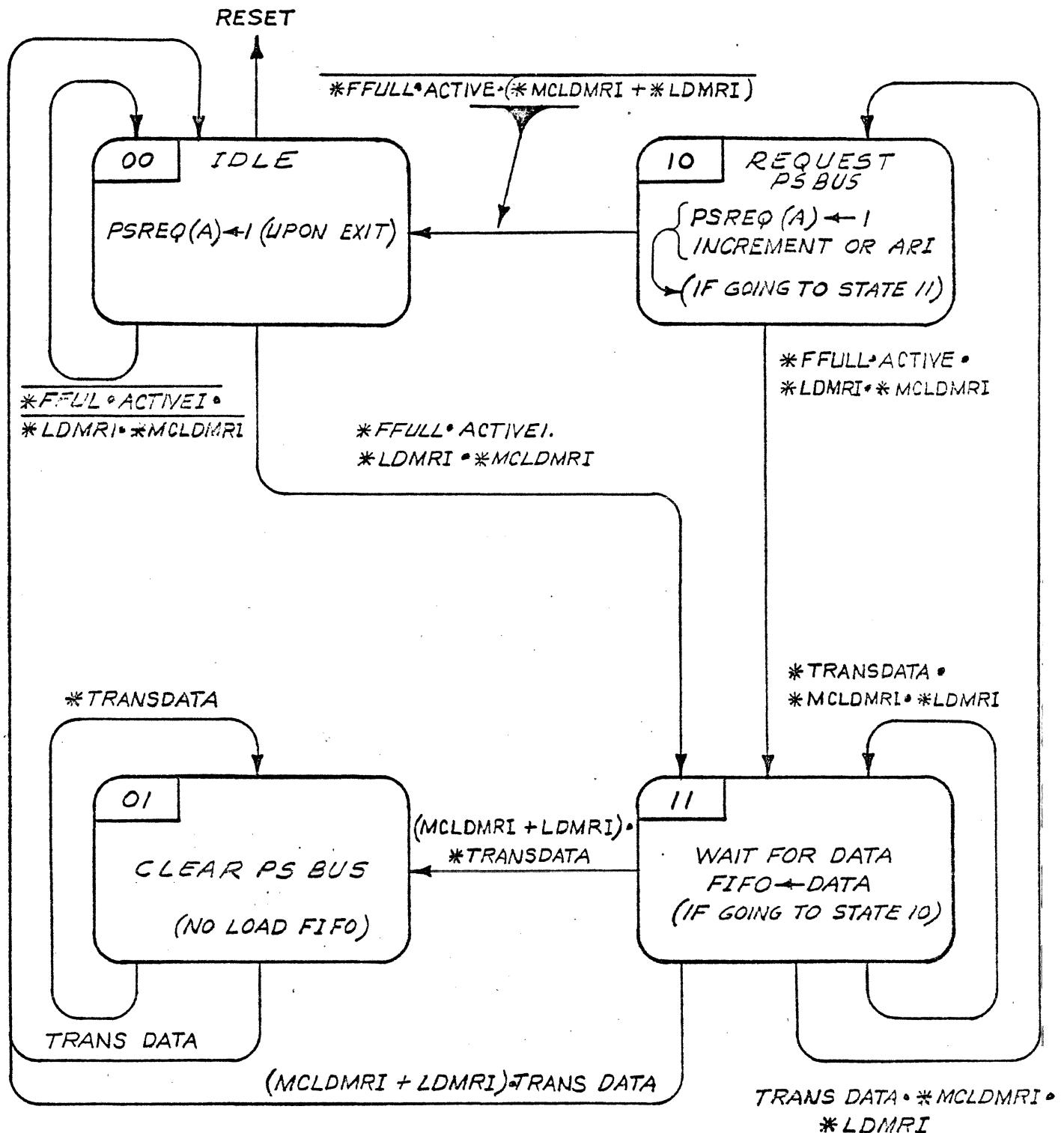

#### 5.3.1.2 MAP Input Sequencer

When operating as an active device, the MAP input is controlled by the MAP Input Sequencer. The sequencer is a four state machine which implements the following five tasks:

1. requests use of the PSBUS

2. passes the address specified by the MAIA to the PSBUS

3. loads data from the PSBUS into the MAP Input FIFO

4. controls automatic incrementation of the MAIA register

5. allows a current PSBUS cycle to clear if the program or the MAP changes the contents of the MAIA

The state diagram for the sequencer is illustrated in Figure 5.3-3. The four states are:

State 00 - IDLE

State 01 - PSBUS Clear

State 10 - Request PSBUS

State 11 - Wait for Data

State 00 is the initial state of the sequencer. When the MAP Input Controller is passive, this state is maintained; however, when functioning as an active device, exit from the "IDLE" state sets a request for the PSBUS. The dispatch from the "IDLE" state to the "Wait for Data" state occurs if the FIFO is not full, assuming the MAIA is not to be loaded. The MAIA may be loaded with a new address by command from the MAP or by command from the user program.

The "Wait for Data" state is maintained until the passive

FIGURE 5-3-6

ACTIVE DEVICE WRITE TO MAP PASSIVE INPUT PORT

device has data for the active Input Controller, unless the MAIA is to be loaded. During the time the sequencer remains in the "Wait for Data" state, a PSBUS cycle is in progress. The Input Controller gates the MAIA to the address lines of the PSBUS upon receiving a grant from the Bus Arbiter; the passive device gates the data onto the PSBUS; and, the data is strobed into the FIFO upon exit to the "Request PSBUS" state. If a command to change the MAIA content occurs when the passive device has data on the BUS, the data is not loaded into the FIFO and the "IDLE" state is entered. If the command to change the MAIA occurs while in the "Wait for Data" state and the passive device does not have data on the PSBUS, the "Clear PSBUS" state is entered. The "Clear PSBUS" state is maintained until the current PSBUS cycle is complete. Upon completion of the bus cycle the "IDLE" state is entered and the data from the bus cycle is not strobed into the FIFO.

The "Request PSBUS" state is maintained for only clock period and, upon exit, sets another request for the PSBUS only if going to the "Wait for Data" state. The "Wait for Data" state is entered only if the FIFO is not full and the MAIA is not to be loaded; else, the "IDLE" state is entered.

An example of the MAP Input Controller functioning as an

active device and fetching commands and data from a PS Memory file is described in the next few paragraphs.

Suppose the data file as depicted in Figure 5.3-4 exists in PS Memory.

|             |      |             |                                                                                        |

|-------------|------|-------------|----------------------------------------------------------------------------------------|

|             | 1000 | <u>MOVE</u> | RSR instruction with a count field of $12_8$ and a draw sequence of M,D,D,D,D (061764) |

|             | 1001 | <u>Ax</u>   |                                                                                        |

|             | 1002 | <u>Ay</u>   |                                                                                        |

|             | 1003 | <u>Bx</u>   |                                                                                        |

|             | 1004 | <u>By</u>   |                                                                                        |

|             | 1005 | <u>Cx</u>   |                                                                                        |

|             | 1006 | <u>Cy</u>   |                                                                                        |

| Partition A | 1007 | <u>Dx</u>   |                                                                                        |

|             | 1010 | <u>Dy</u>   |                                                                                        |

|             | 1011 | <u>Ax</u>   |                                                                                        |

|             | 1012 | <u>Ay</u>   |                                                                                        |

|             | 1013 | <u>JUMP</u> | RSR Jump command (002000)                                                              |

|             | 1014 | <u>4000</u> |                                                                                        |

|             |      |             |                                                                                        |

|             |      |             |                                                                                        |

|             |      |             |                                                                                        |

| Partition B | 4000 | <u>MOVE</u> | RSR instruction with a count field of 6 and a draw sequence of M,D,D,D (061772)        |

|             | 4001 | <u>Ex</u>   |                                                                                        |

|             | 4002 | <u>Ey</u>   |                                                                                        |

|             | 4003 | <u>Fx</u>   |                                                                                        |

|             | 4004 | <u>Fy</u>   |                                                                                        |

|             | 4005 | <u>Gx</u>   |                                                                                        |

|             | 4006 | <u>Gy</u>   |                                                                                        |

|             | 4007 | <u>HALT</u> | RSR Halt command (000000)                                                              |

Figure 5.3-4

PS Memory Data File

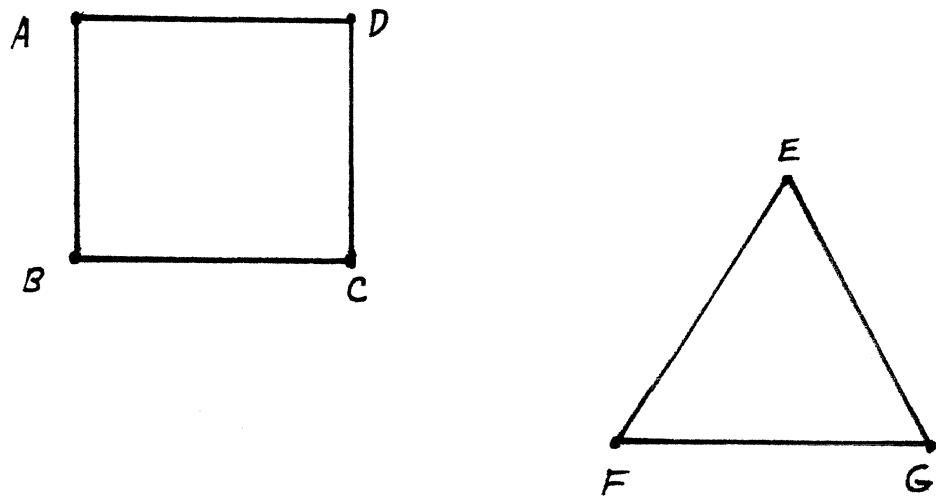

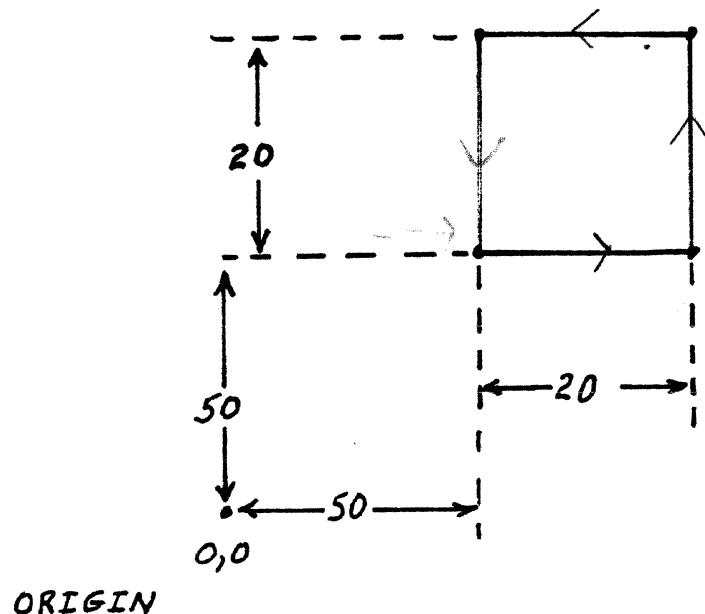

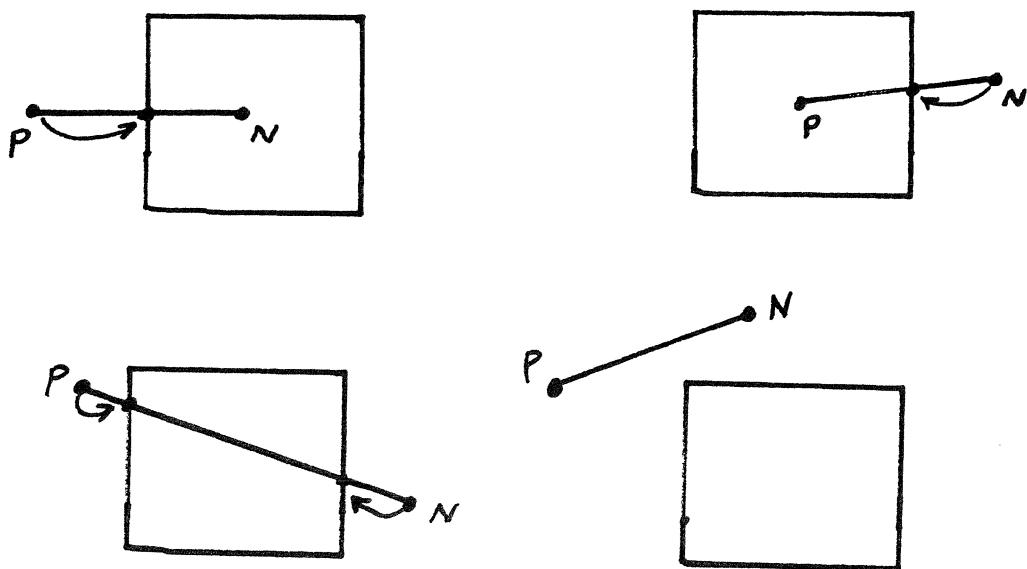

Assume the data words Ax.....Gy define the points of a square and a triangle as depicted in Figure 5.3-5.

Figure 5.3-5

Displayed Result of Data File

Notice that the file consists of two partitions. Partition A from locations 1000 to 1014 contains an RSR, 2-dimensional draw, sequence command of Move, Draw, Draw, Draw,... and a count of  $12_8$ . This partition also contains a JUMP command to the MAP. When executed it will cause the MAP Input Controller to fetch data starting at location 4000. Partition B contains the same RSR, 2-dimensional draw sequence command but with a count of only 6. The  $12_8$  data words of partition A define the points of the square and the 6 data

words of partition B define the points of the triangle.

The program initialized the MAIA to point at PS Memory location 1000. At the beginning of a frame update, the MAP Input Controller fetches the PS Memory location pointed to by the MAIA and puts the contents in the MAP Input FIFO. To do this the input sequencer requests the PSBUS upon exit of state 00 to state 11. In state 11 the sequencer waits for the word from PSMEM location 1000 to settle on the data lines of the PSBUS. Upon exit from state 11 to state 10 the word is strobed from the PSBUS into the FIFO. The MAP itself waits in the Load RSR State (see Appendix A, MAP Algorithm) until the FIFO is not empty. Since a word is in the FIFO, the MAP loads this word into its Repeat Status Register (RSR). The Input Sequencer tries to keep the FIFO full by accessing PS Memory locations and loading the data into the FIFO. This is accomplished by the input sequencer executing the loop consisting of state 10 and state 11. The MAP tries to empty the FIFO by unloading the FIFO contents and operating on the data. There will be a time when the MAP fetches the JUMP command from the FIFO. This JUMP command will be loaded from the FIFO into the RSR thus causing the MAP to execute the JUMP states of its algorithm. The JUMP command causes the MAP to fetch the next word from the FIFO and load it into the MAIA register; therefore, 4000 is fetched from the FIFO and loaded into the MAIA. The input will be in either state

10 or state 11 when the MAP issues the MAIA load signal; thus, dispatching the input sequencer to either state 00 or state 01 depending on whether the PSBUS is clear or not. The load signal, \*MCLDMRI, also clears the FIFO, therefore the input sequencer has an empty FIFO for the next command fetched from the PS Memory location 4000. At this point the MAP has received the data for the square and is waiting for the RSR Move command and data for the triangle. The Input Sequencer fetches the RSR Move command, data, and the Halt command, and the MAP unloads the commands and data from the FIFO. Upon execution of the Halt command, the MAP waits for the program to initiate the next frame update process.

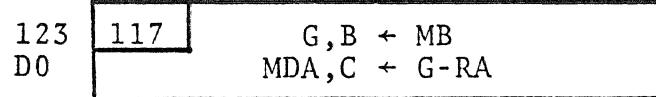

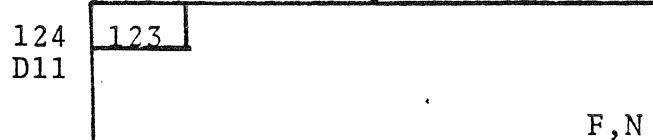

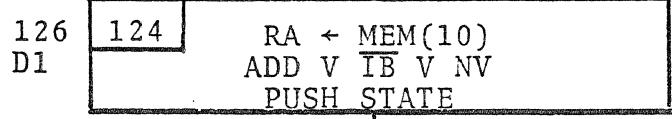

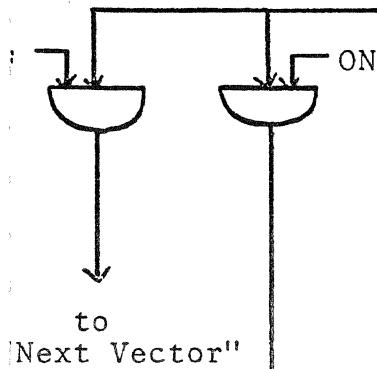

The implementation of the MAP Input Sequencer is shown on the MAP I/O Sequencer drawing, 195118-600, sheet 3. The four states are derived from two bits of the register in location 41. ISTATEA is the LSB and ISTATEB is the MSB (Refer to Figure 5.3-3, MAP Input Sequencer Diagram).

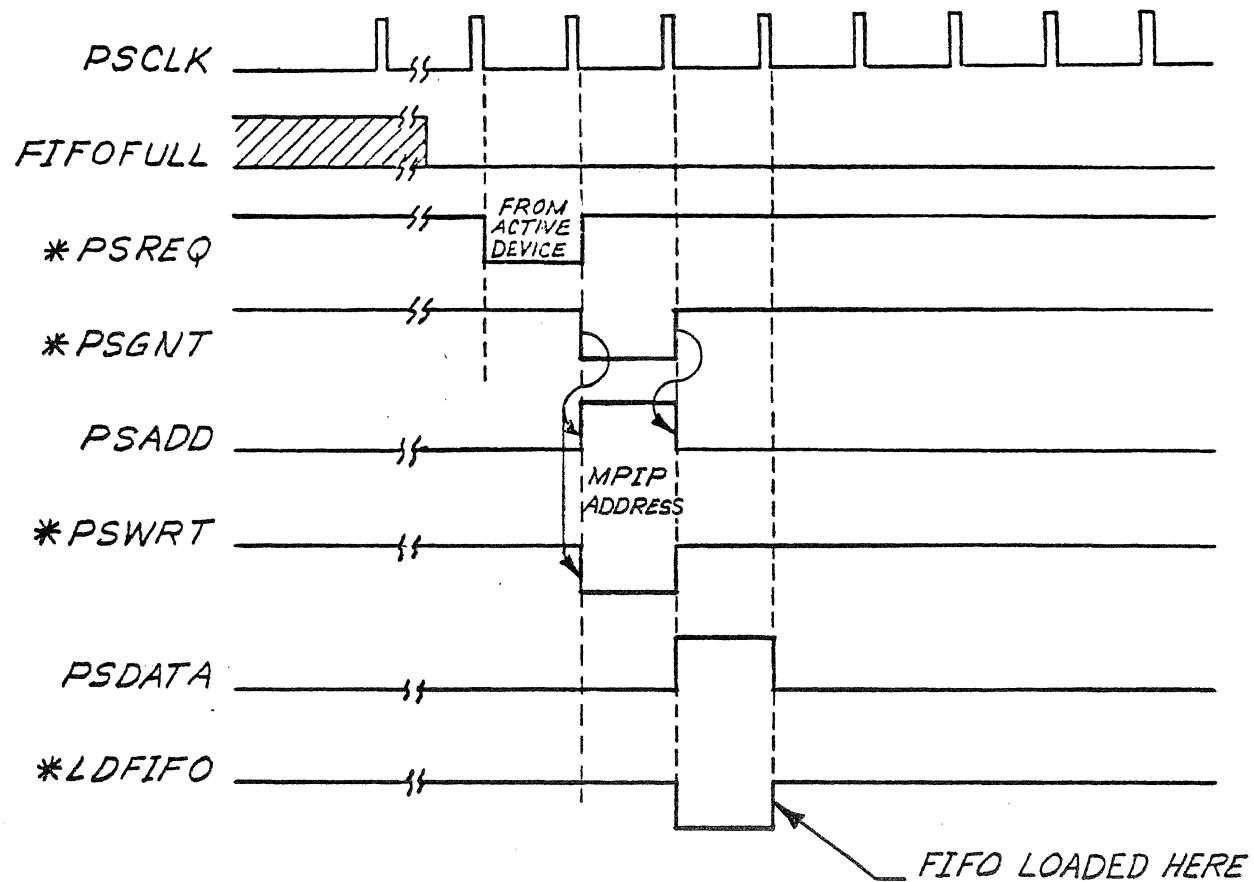

### 5.3.2 MAP Input Controller - Passive

When operating as a passive device, the MAP Input Sequencer is always "IDLE": Data transfers to the MAP Input Controller occur by an active device writing data to the MAP Passive Input Port (MPIP=177777). The MAP Input Controller passively waits for data directed to the MPIP and synchronously loads

the FIFO during the data cycle of the PSBUS. The timing diagram of Figure 5.3-6 illustrates an active device writing data to the MPIP.

The PSWRT line from the PSBUS is input on sheet 1 of the 195121-600 drawing. The MPIP address is decoded by bug 15 on sheet 2 and the PASIN bit of bug 26 is set at the beginning of the PSDATA period of the data transfer cycle. PASIN is input to the MAP I/O Sequencer Card, 195118-600, sheet 3, and generates LDFIFO. LDFIFO is input to the MAP Buffer Card, 195119-600, which contains the FIFO.

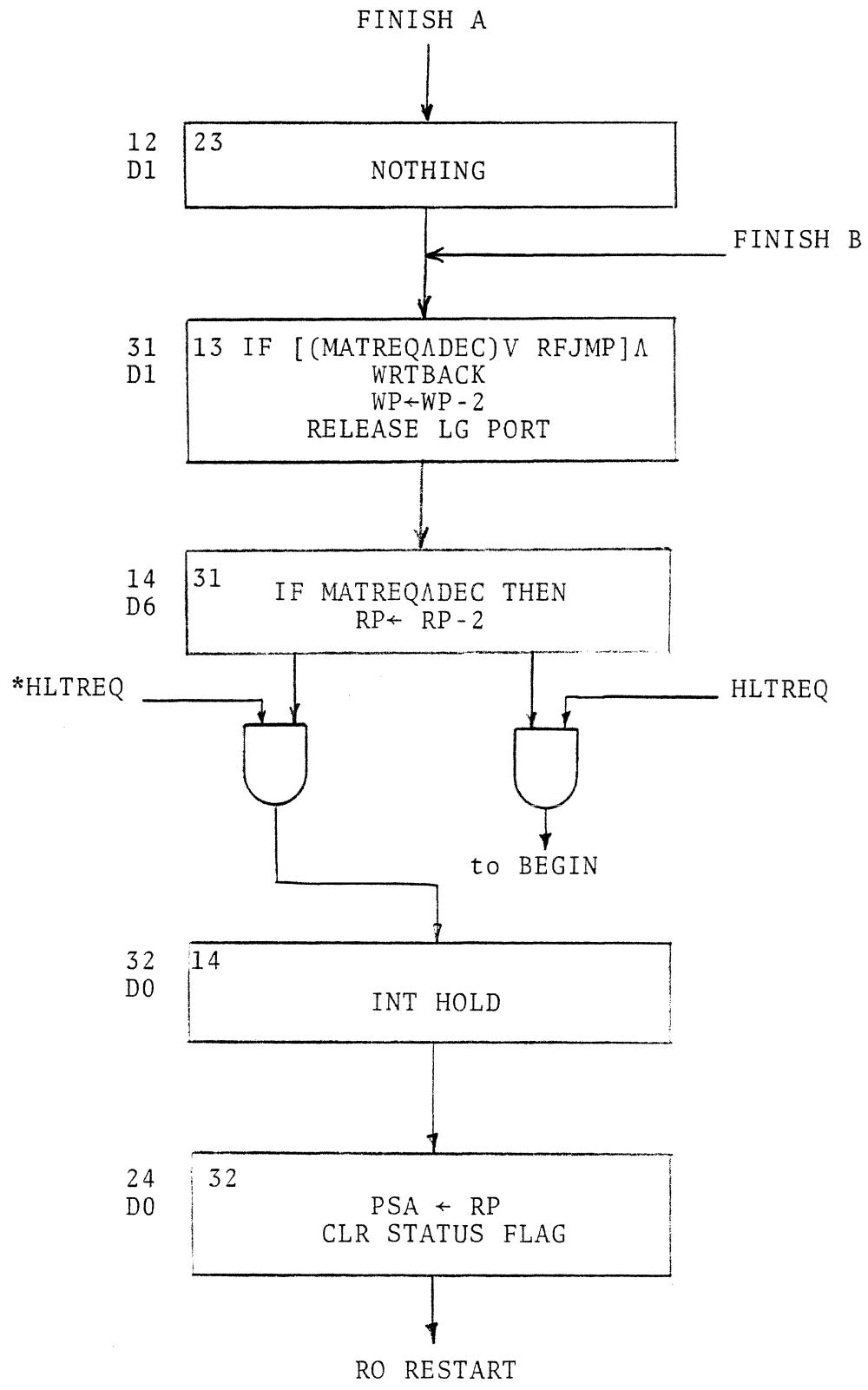

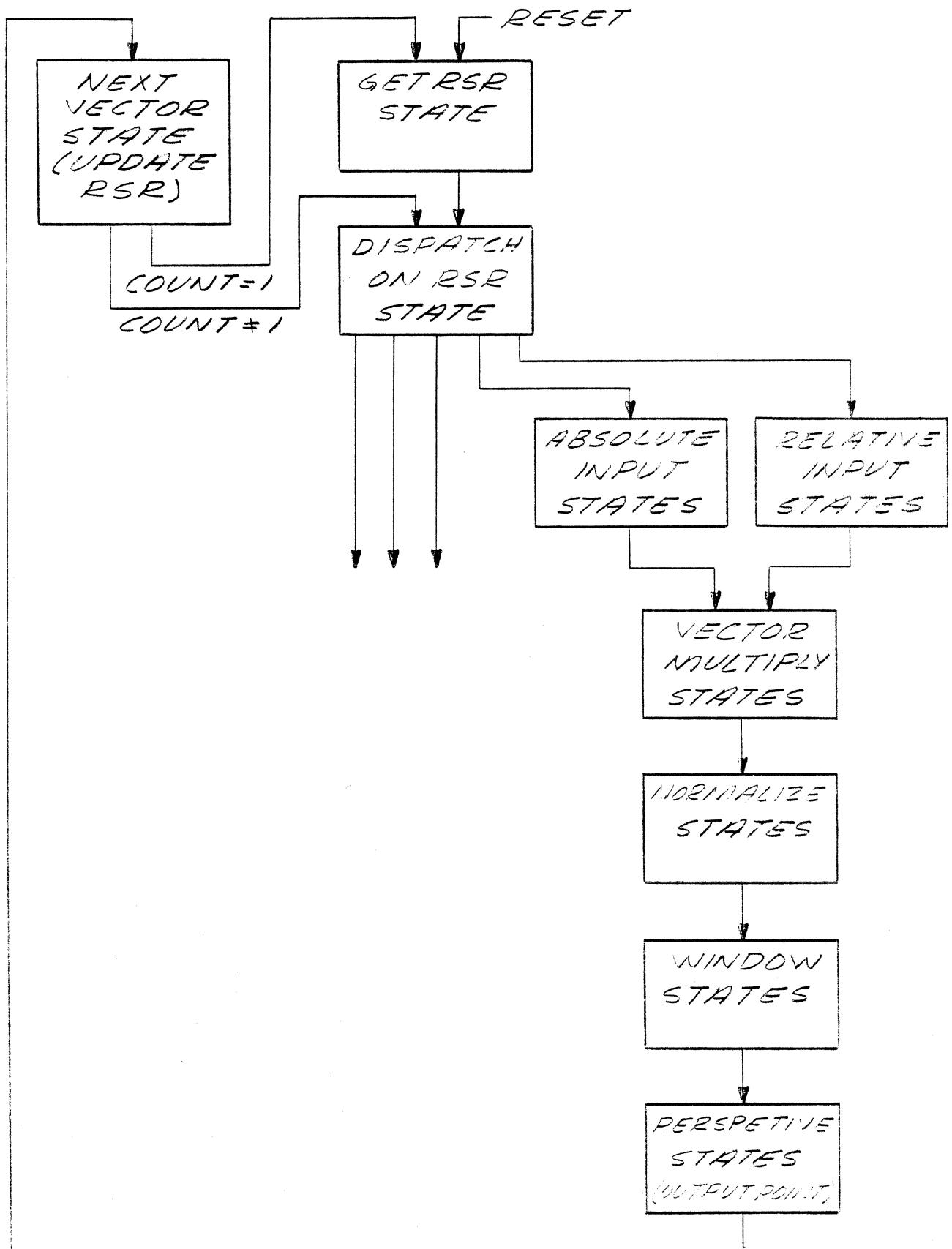

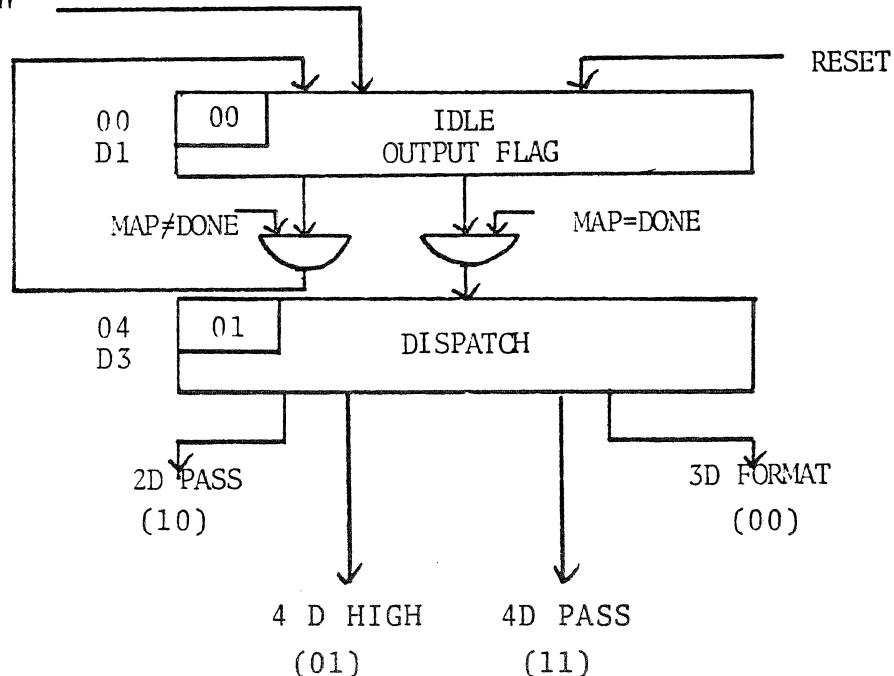

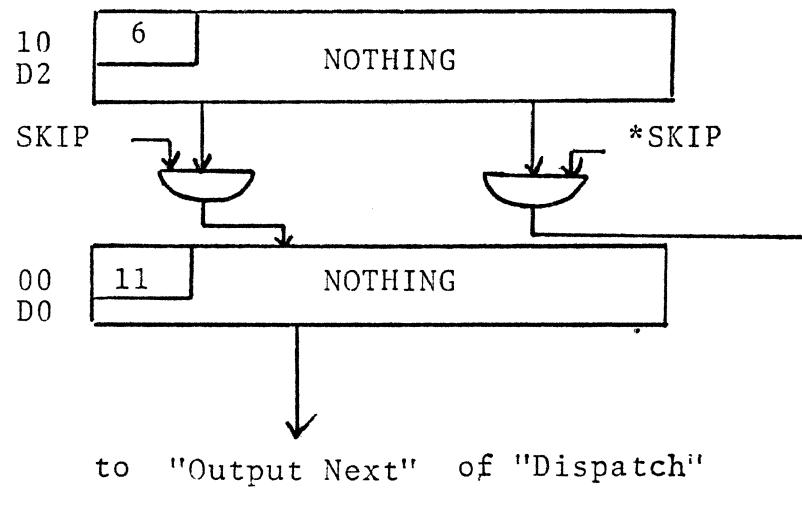

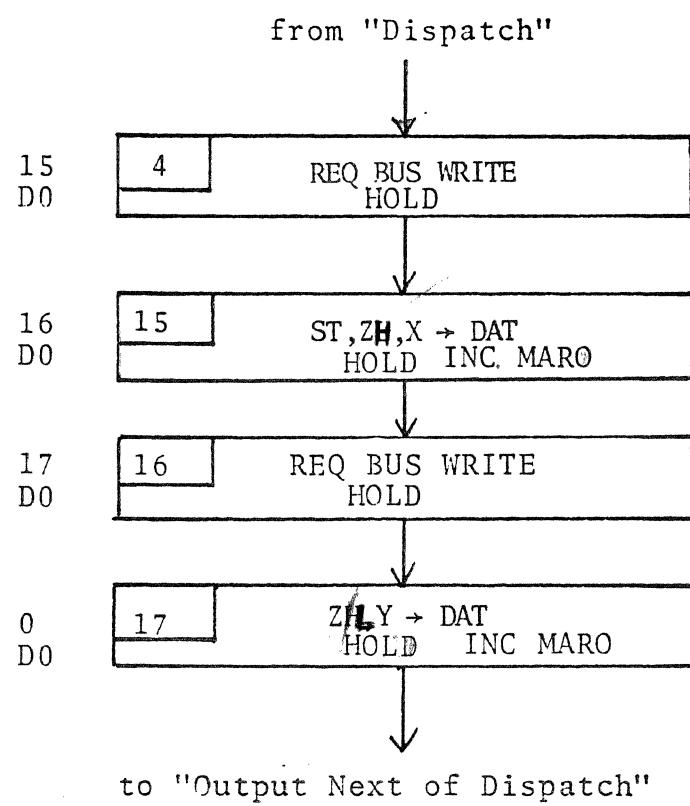

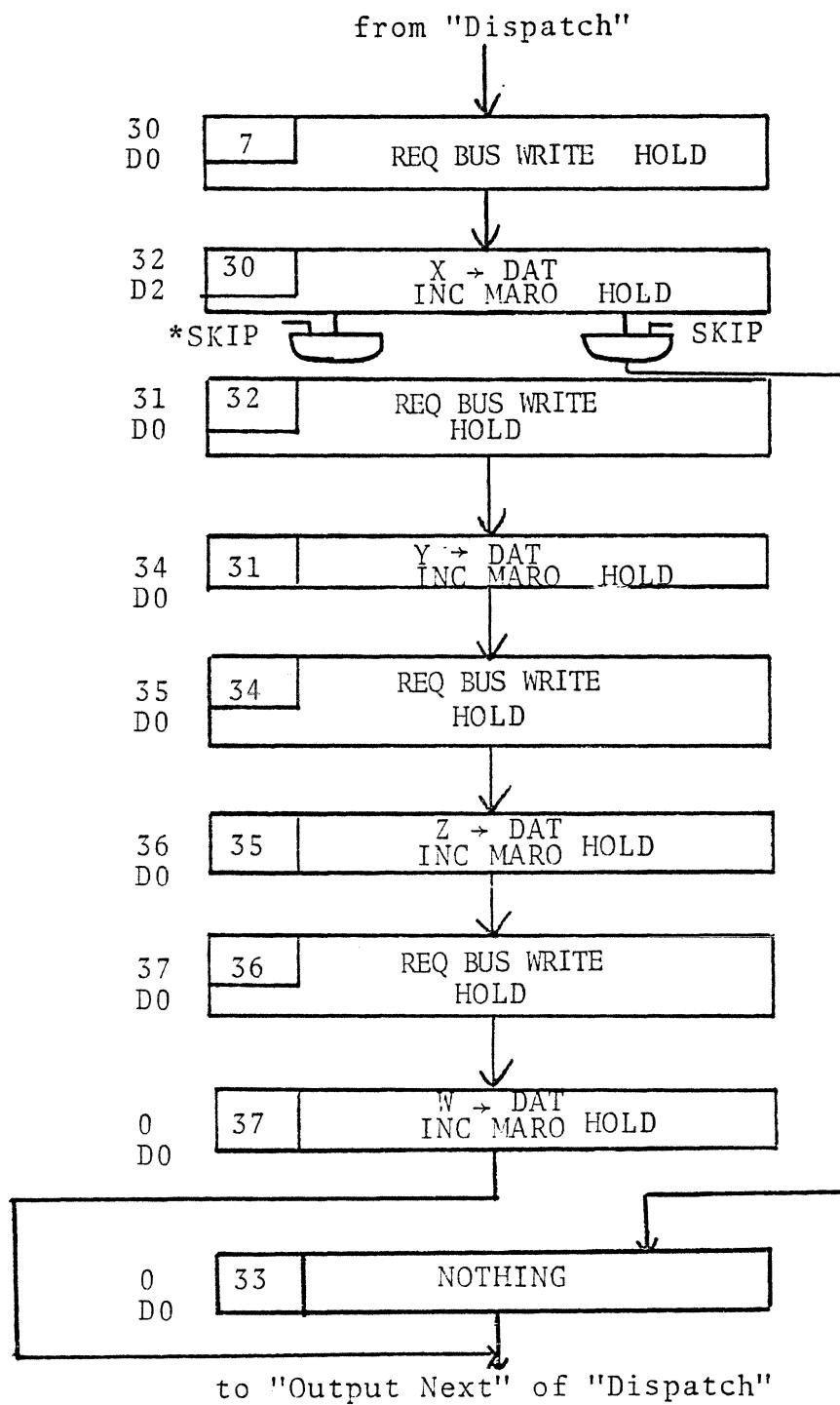

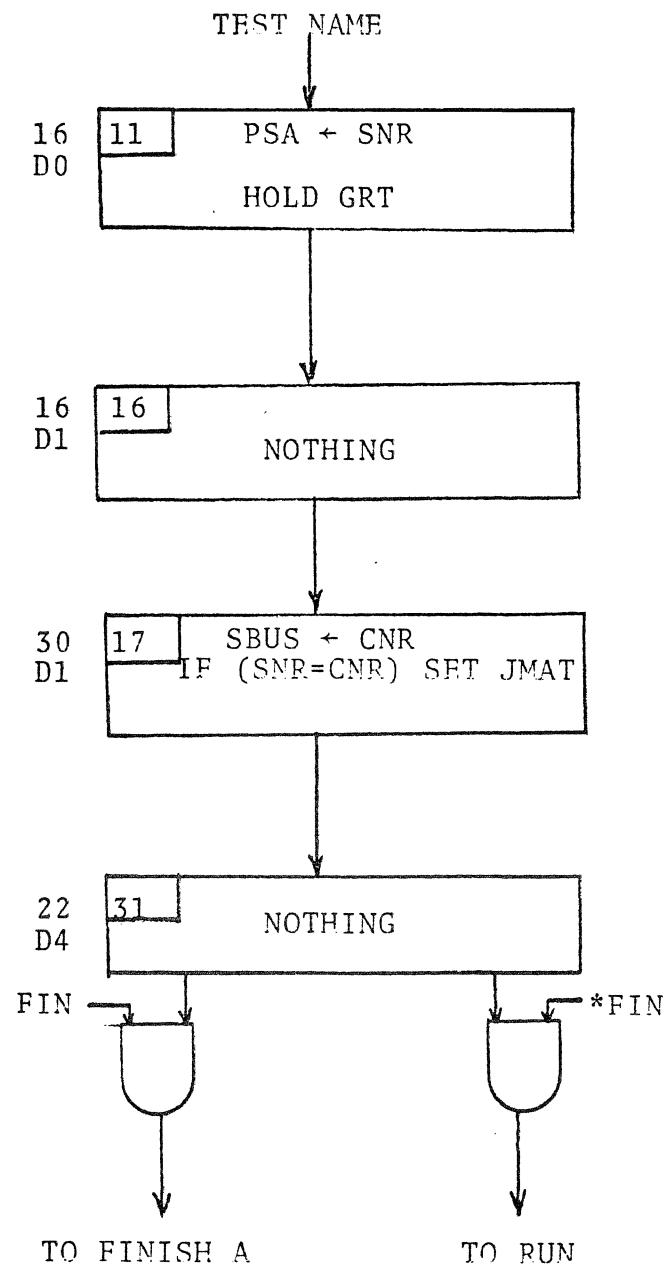

## SIMPLIFIED PARTIAL NHP STATE DIAGRAM

FIGURE 5.3-9

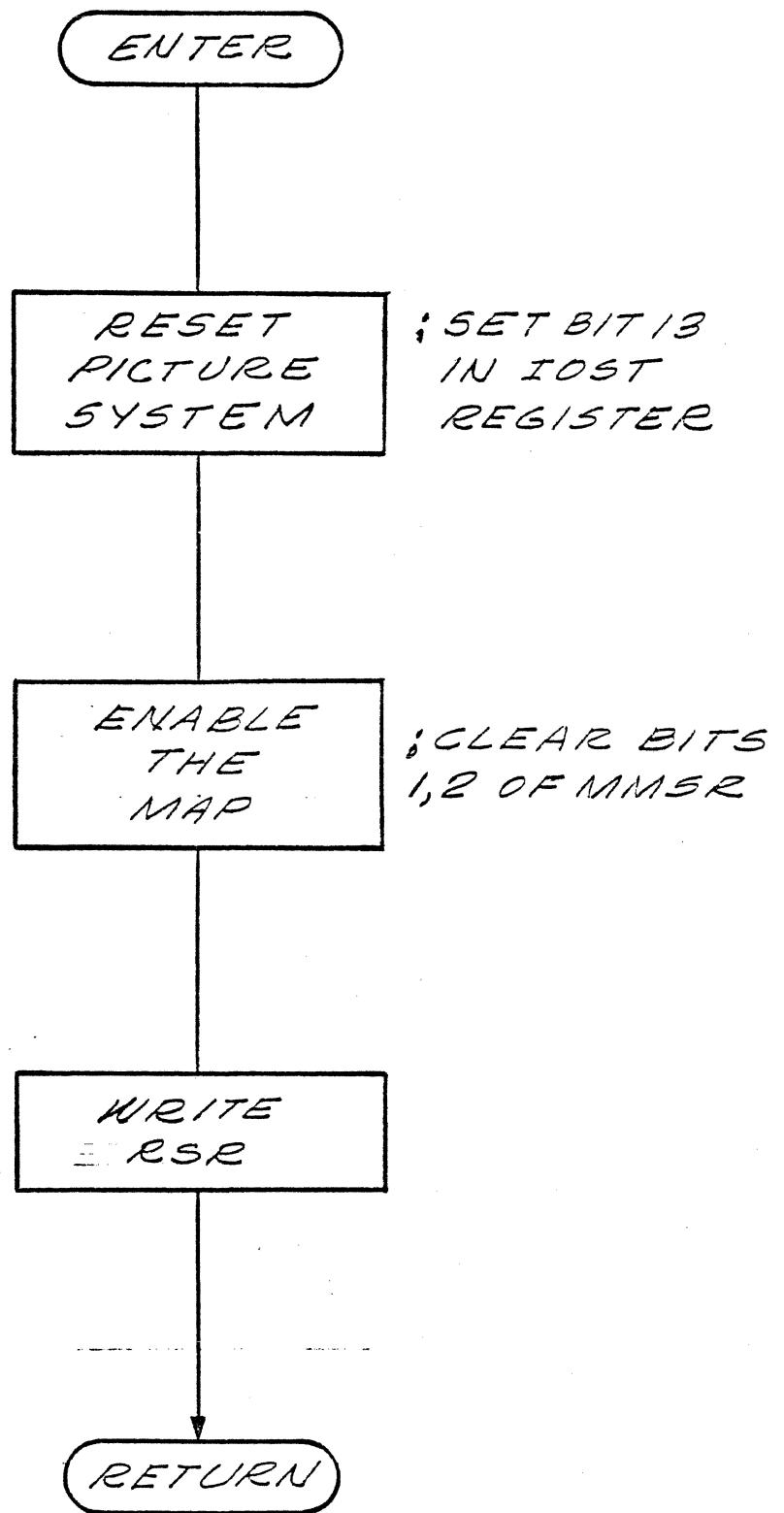

### 5.3.3 RSR Register and Update PROM