# EMONSTRA MAGROLOGIC LL

FAIRCHILD

# S Z O Ŷ, 00 MACRO 5

# INTRODUCTION

Macrologic is a family of cost-effective LSI circuits designed for use in high-performance digital systems. Bit-slice design makes Macrologic components particularly suitable as functional building blocks for microprocessor-oriented applications, processor emulation and microprogrammed replacement of hard-wired logic. Microprogramming concepts give Macrologic a greater flexibility for many applications not found in fixed instruction-set microprocessors. As a bonus to the designer, both bipolar and CMOS Macrologic circuits are available. For faster system operation, high-speed bipolar Macrologic is the logical choice. Where power is at a premium, use CMOS.

The Macrologic Demonstrator is an educational tool designed to familiarize the user with the processor-oriented devices in the Macrologic family, and demonstrate concepts used in microprogramming.

The system consists of three main functional blocks. The 8-bit wide data path contains an ALU, a LIFO stack, a 16-register scratch pad and miscellaneous logic. The microprogram controller contains the control memory as well as microprogram addressing and sequencing logic. The operator control and display panel provides the human interface and allows the operator to load and modify the control memory, run or step through his microprogram, and monitor system status and contents of various system busses. The Demonstrator is completely self-contained. The only item that is needed externally is a +5 V power supply capable of delivering about 2 A of current. The Macrologic Demonstrator also has an S-100 bus interface which enables its control memory (RAM) to be loaded by an 8080 based system. Using the Demonstrator, a user can write a microprogram sequence, load and execute it and observe various states of the machine via LEDs.

# TABLE OF CONTENTS

| SECTION 1                                         | BASIC THEORY OF MICROPROGRAMMING1-1                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                   | MICROPROGRAMMED SYSTEMS USING MACROLOGIC2-1<br>mple Processor Example2-6                                                                                                                                                                                                                                                                                                                                                           |

| Micr<br>Ope<br>Con<br>Misc<br>Ope                 | DESCRIPTION AND OPERATION OF THE         MACROLOGIC DEMONSTRATOR       .3-1         Data Path       .3-1         oprogram Control       .3-3         rator Panel       .3-5         trol Word Format       .3-7         ellaneous       .3-8         rating Procedure for Control Panel of                                                                                                                                         |

| SECTION 4<br>Exer<br>Exer<br>Exer<br>Exer<br>Exer | PROGRAMMING EXAMPLES AND EXERCISES       .4-1         cise 1 — Unconditional Branching in 9408       .4-4         cise 2 — Conditional Branching in 9408       .4-4         cise 3 — Rotate Function in the Demonstrator       .4-4         cise 4 — Timing Loop Example to Illustrate Branch to       .4-6         cise 5 — Timing Waveform Generation       .4-6         cise 6 — Setting Characteristics Measurement       .4-8 |

| B                                                 | <b>S</b><br>Microassembly Examples A-1<br>Sample Programming Sheets B-1<br>Macrologic Demonstrator Microword Format C-1                                                                                                                                                                                                                                                                                                            |

### Section 1

# BASIC THEORY OF MICROPROGRAMMING

The use of bit-slice bipolar Macrologic allows a machine to run at a higher speed than MOS microprocessors. Moreover, the modularity of Macrologic enables the data path width to be expandable in increments of four bits, allowing more flexibility than MOS microprocessors, whose data path width is fixed at 4, 8, 12 or 16 bits. However, unlike the fixed instruction set MOS microprocessors, Macrologic devices have to be microprogrammed. A prospective user has to become familiar with the concepts in microprogramming before he can utilize bit slices in his design effectively.

Basically, a microprogrammed machine is a 2-level machine. The machine command is known as the macrolevel. It takes a sequence of steps to execute a machine command; these steps are called microinstructions. In the case that the machine is a CPU, the basic machine command is the macroinstruction, which resides in main memory. After each macroinstruction is fetched, a corresponding sequence of microinstructions will be executed. Each microinstruction controls the machine for one clock cycle (called microcycle). A collection of microinstructions is called a microprogram. Microinstructions are stored in a memory called microprogram memory or control store. Usually PROMs are used for control store. However, the microprogram memory can be implemented using RAMs, which can be dynamically altered during machine execution; this is called writable control store.

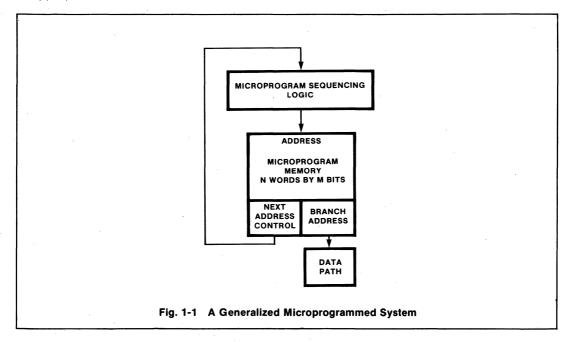

A microprogrammed system generally consists of two sections (Figure 1-1):

- 1. The controller section includes the microprogram memory and the sequencing logic required to provide the address to the microprogram memory.

- 2. The data path usually contains ALUs, general registers, stacks, etc. and is controlled by the appropriate bits fields of the microinstructions.

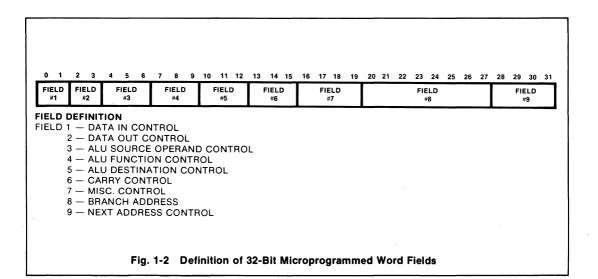

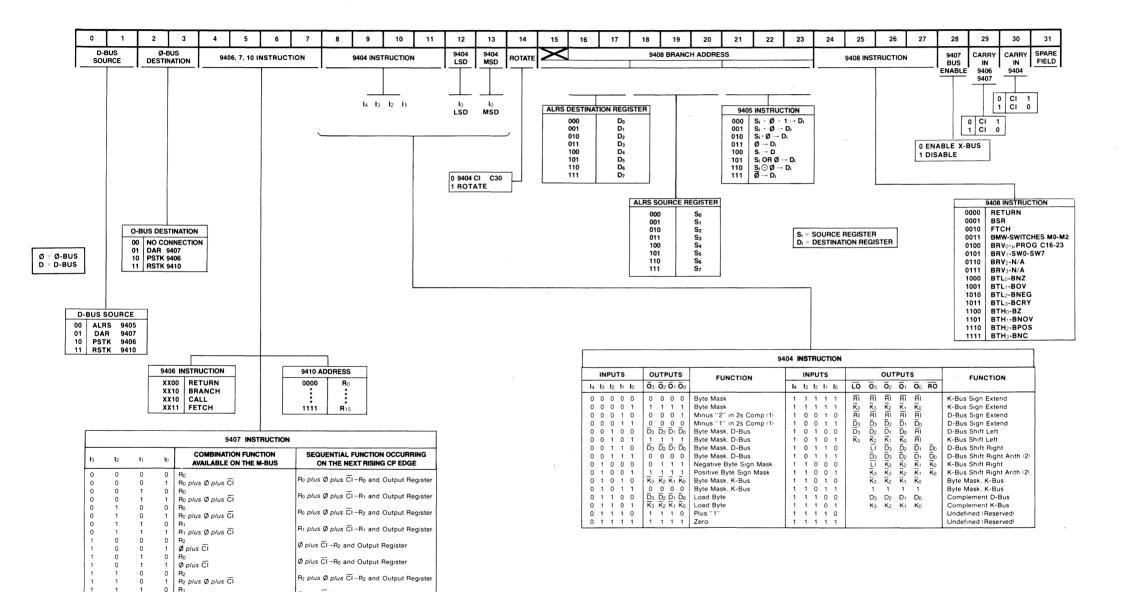

The microprogram memory is simply an N-word by M-bit memory used to hold the various microinstructions. Each word of the microprogram memory contains M bits, which are usually grouped into various fields. The field can consist of various numbers of bits. The definition of the various fields of microprogram word is referred to as FORMATTING. *Figure 1-2* illustrates the format of a 32-bit microprogram word containing nine fields.

In general, a microinstruction must contain the following information: First, the definition and control of the operations to be performed by the data path and other system logic. These include such things as ALU function, ALU source, destination registers, shift or rotate control, stack operations, data in, data out select and so forth. Second, the address of the next microinstruction to be performed. In some cases, it can be implicit, such as when next address is current address plus one. In other cases, the actual value of the address field has to be supplied.

The use of microprogramming allows the designer to employ memory as one of the functional building blocks in logic design. Unlike hard-wired logic approach, where a designer generates timing and control signals by using combinations of gates and flip-flops and prays he does not have to make major changes in the future, microprogramming enables highly ordered and structured designs. Therefore, implementation of design changes is easier. Instead of tearing up gates and flip-flops, a change can usually be accomplished by reprogramming the control store. With memory prices dropping the way they are, the increased use of microprogramming in logic design is imminent. Microprogramming will be used in such applications as:

Special purpose controllers High-speed (relative to MOS microprocessor) functions Extending computer instruction sets Emulations Diagnosis/fault tolerance Multiprocessors Multi-level hierarchies of processors Direct execution of high-level languages I/O controllers

# Section 2

# MICROPROGRAMMED SYSTEMS USING MACROLOGIC

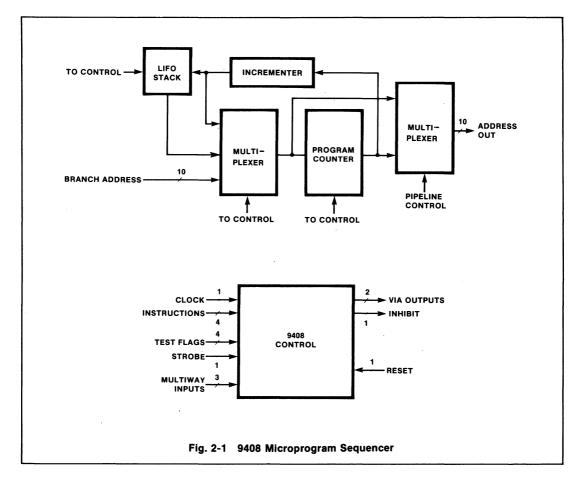

The controller part of the microprogrammed system can be implemented using the 9408 Microprogram Sequencer. The 9408 is based upon a 10-bit Program Counter (PC) and addresses 1K pages of microprogram memory (*Figure 2-1*). The basic instruction of the sequencer is FETCH, in which the program counter is incremented after each clock and, in effect, makes the next address the same as current address plus one. This type of addressing will cycle the microprogram memory sequentially, but will not be very adequate for most practical systems. The 9408 also has many provisions for branching.

The first type of branching is *unconditional branching*. Here a new address is placed on the 9408 input bus and loaded into the program counter. The new address can come from one of four different sources, selected by the BRV<sub>0</sub> to BRV<sub>3</sub> instructions.

The second type of branching is *conditional branching*. Here the 9408 performs a test on one of four available inputs. If test conditions are met, the program counter is loaded with the address at the input bus (BRANCH). If the conditions are not met, the program counter is incremented (FETCH).

The third type is the *multiway branch*. The multiway branch is similar to an unconditional branch in that a program counter will always be loaded into a specified address, i.e., a branch is certain to occur. However, the address of the branch is determined by substituting the three least significant bits of the branch address present at the input bus by the value of three multiway (test) inputs. The result is that the branch will be made to one of eight different locations.

The fourth type of branching is *subroutine branching*. In branching to a subroutine, the incremented value of the program counter is loaded into the on-chip LIFO stack. Then, the program counter is loaded with the address at the input bus. In returning from a subroutine, the program counter is loaded with the contents of the top level of the stack.

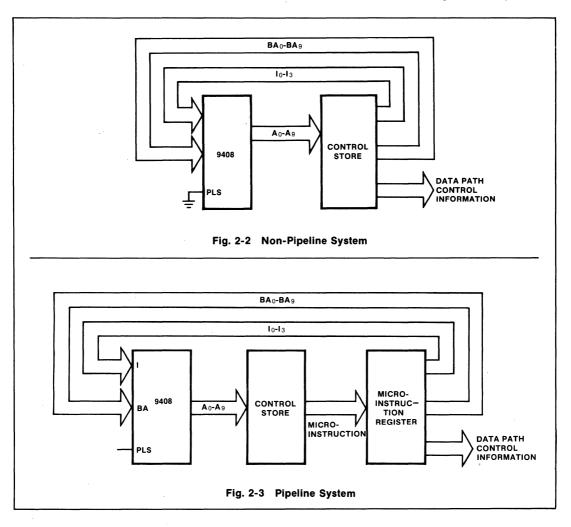

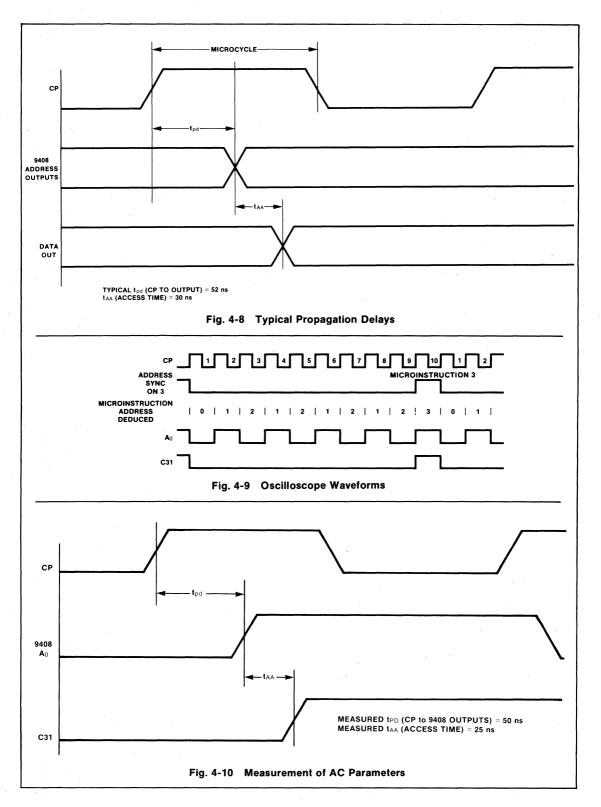

A microprogrammed system can be operated in either pipeline mode or non-pipeline mode. The non-pipeline controller is simply a 9408 and a control store (*Figure 2-2*). In a pipeline system, an edge-triggered microinstruction register is also needed (*Figure 2-3*). In a non-pipeline system, a microinstruction is read from the control store and executed before reading the next microinstruction. Since most microprogrammed systems are designed as synchronous machines, the maximum frequency the system will run at is indicated by the sum of the 9408 propagation delay (CP to address outputs), the memory access time, and the data path propagation delay.

In the non-pipeline system, the data path logic is idle during the part of the microcycle when the control store is being accessed. Similarly, the memory is not cycled and is sitting with the same outputs during the part of the cycle when the data path is used. A more efficient use of the resources will be overlapping the execution of the current microinstructions with the fetching of the next microinstruction. This requires holding the current microinstruction in a microinstruction register (*Figure 2-3*). Here, the control memory access time is hidden from the data path propagation delay. The system cycle time is the greater of the sum of the propagation, set-up, and access times of the controller or the data path worst case propagation delay. In many instances, a microprogram written for a non-pipeline system cannot be executed in pipeline mode. However, the 9408 architecture is chosen so that the same microprogram can be executed in pipeline or non-pipeline mode without any modification. In the Macrologic Demonstrator, the 9408 is designed to work in the non-pipeline mode.

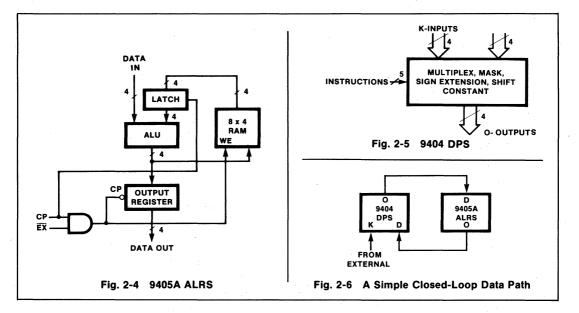

The data path logic generally consists of ALUs, general registers, stacks, etc., and can be readily implemented with Macrologic devices (ALRS, DPS, etc.). To provide logical, arithmetic and storage capabilities, the 9405A can be used (*Figure 2-4*). The 9405A is a 4-bit slice containing an eight-function ALU, eight general purpose registers, four conditional code flags (carry, negative, zero, overflow), an output register and the necessary decoding logic. It can be expanded in multiples of four bits without additional components, or can be expanded with a carry lookahead unit for greater speed.

Note the absence of a shifting network either before the RAM inputs or at the ALU outputs, which is quite common with other bit slice ALU designs. This is because Macrologic devices are designed to be functional building blocks in highly bus-organized systems so that sharing the input and output busses in the data path with the ALRS may be the hardware stack, general registers, etc. To eliminate the need for duplicating shifting capabilities in each Macrologic device, the shifting network is found in the 9404 Data Path Switch (DPS). The 9404 DPS is a combinational network consisting of two input busses and one output bus (*Figure 2-5*). It performs functions such as arithmetic or logic shifting, masking, sign extension and constant generations. In addition, when connected to other Macrologic devices (for example, the ALRS), it allows a closed-loop system to be formed, so that the output bus can communicate to the input bus. *Figure 2-6* depicts a simple closed-loop system in which the ALRS inputs and outputs are connected to the DPS outputs and inputs respectively. External data may be introduced into the system using the K inputs of the DPS.

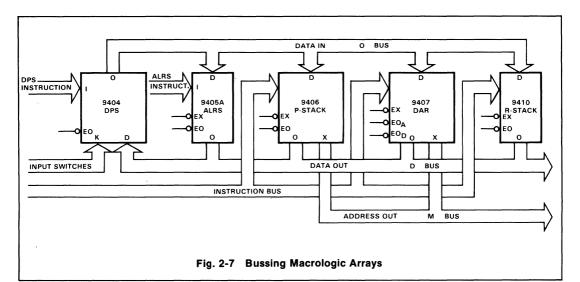

As Macrologic devices are designed to be used in bus-organized systems, all devices are provided with 3-state data outputs and an Output Enable  $(\overline{EO})$  input to control them. Therefore, the data outputs from the devices can be bussed together to obtain the output bus (D-bus) as in *Figure 2-7*. With a LOW level on the appropriate  $(\overline{EO})$  input, a Macrologic device can be made to source data onto the output bus. The data inputs of the Macrologic devices can also be bussed together to obtain the input bus. Except for the DPS, Macrologic devices used in the data path are provided with individual execute  $(\overline{EX})$  input and a device will not respond to the clock unless its  $\overline{EX}$  input is LOW. Thus, the instruction inputs can be bussed together to obtain an instruction bus. The result is that during a single clock cycle, information can be routed from any device in the data path to any other device (including itself) by controlling the proper  $\overline{EX}$  and  $\overline{EO}$  inputs.

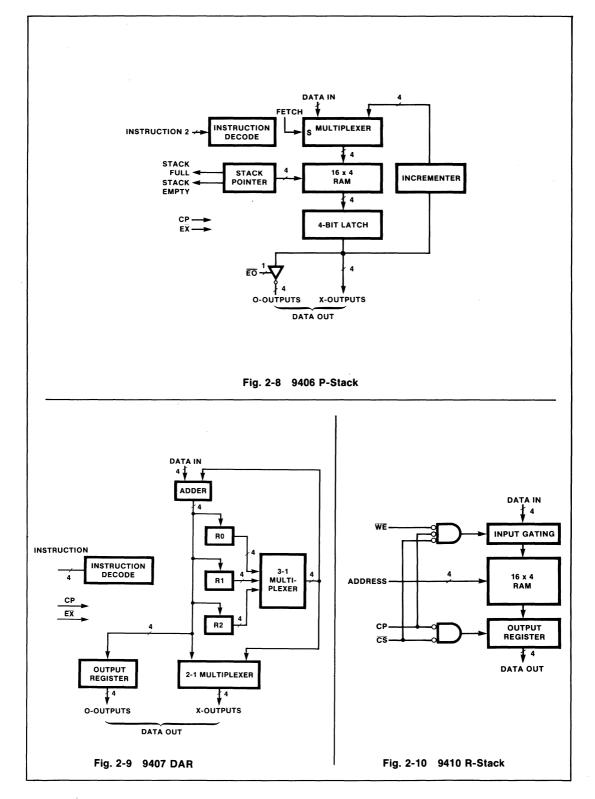

For some applications, a DPS and ALRS combination in the data path provides enough storage and computing power. For example, in an emulation design, one of the eight registers in the ALRS can be treated as the program counter, four can be accumulator registers, and the other three can be scratchpads. In some applications, this may be inadequate. If, for example, the emulation is for a machine with macrosubroutine nesting capabilities, the 9406 program stack can be added into the data path (*Figure 2-8*). The 9406 is a 16-level, last-in first-out hardware stack. The top of the stack can be used as the program counter and the other levels provide return address storage for nested subroutines. In addition, it provides two status outputs to indicate Stack Full ( $\overline{SF}$ ) and Stack Empty ( $\overline{SE}$ ) conditions.

But suppose someone needed more than 16 levels of stack, say for unlimited levels of subroutine nesting capability. In that case, fixed level hardware stack will not meet the requirement. The approach may be changed to put the stack out in RAM (Random Access Memory) and maintain it by pointers. The 9407 Data Access Register can be used for this purpose (*Figure 2-9*). Basically, the 9407 contains three registers with an adder network, an output register and a two-to-one multiplexer to select either the adder output or the individual register output. It is designed to perform memory address functions for RAM resident stack type applications. For example, the three registers can be used as program counter, stack pointers and operand address. The 9407 implements 16 instructions, which allows pre- or post-increment/decrement and register-to-register transfer in a single clock cycle. For applications which require more storage capacity than the eight registers the 9405A provides, the 9410 register stack (R-stack) can be added to the data path. The 9410 is a high speed 16-word by 4-bit memory with an edge-triggered output register (*Figure 2-10*).

#### A SIMPLE PROCESSOR EXAMPLE

One of the many possible Macrologic applications is to implement emulators for existing instruction sets. These complex functional LSIs offer improved cost and performance while retaining software compatibility with the target machine. A simple 16-bit processor is a good example to demonstrate the ease of use and versatility of Macrologic.

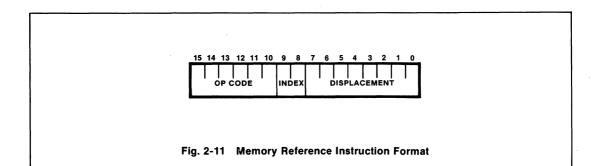

The 16-bit fixed word-length processor, with four accumulators (AC<sub>0</sub>-AC<sub>3</sub>) and 2's complement arithmetic, has a 16-word push/pop stack for subroutine nesting, as well as general use. The memory reference instruction format is shown in *Figure 2-11*. The 2-bit index field in the instruction specifies four addressing modes — base page, PC relative, AC<sub>2</sub> and AC<sub>3</sub> relative. For the base-page mode, the 8-bit displacement field of the instruction is taken as the absolute address, i.e., first 256 memory locations. For the relative mode, the 8-bit displacement is treated as a signed number in 2's complement notation and added to the Program Counter (PC relative) or one of the specified accumulators (AC<sub>2</sub> or AC<sub>3</sub> relative). The result is then used as the effective address for the operand.

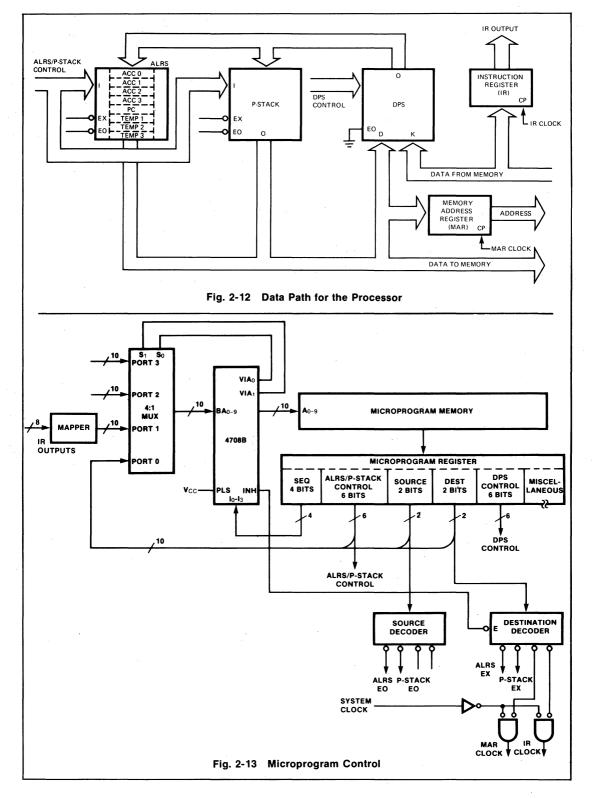

A data path suitable for this processor is shown in *Figure 2-12*. It consists of a 16-bit ALRS array, 16-bit P-stack array and 16-bit DPS array. The ALRS and DPS can perform all the arithmetic logic operations needed. The P-stack provides the required 16-level stack function. The ALRS has eight built-in accumulators, but only four are needed for this processor. The P-stack has the necessary features to implement the PC; however, if this feature is used, only 15 levels of nesting remain. This processor requires 16. Because the ALRS has four spare accumulators, one of these can be used as the PC, leaving three spares. Thus the PC feature of the P-stack is not needed and the address outputs are not used. The storage in the ALRS is allocated as follows:  $R_0 = AC_0$ ,  $R_1 = AC_1$ ,  $R_2 = AC_2$ ,  $R_3 = AC_3$ ,  $R_4 = PC$ ,  $R_5 = TEMP 1$ ,  $R_6 = TEMP 2$  and  $R_7 = TEMP 3$ . An edge-triggered Memory Address Register (MAR) on the output bus is provided. Data from the memory is introduced into the data path using one of the input ports of the DPS array. Data to the memory is obtained directly from the output bus. An edge-triggered Instruction Register (IR) is also provided to hold the OP code bits and index bits of the macroinstruction.

*Figure 2-13* illustrates the microprogram control section for the data path. This control is centered around the 9408 sequencer operating in the pipeline mode. The INH output of the 9408 is used to share the control fields. Thus, the source, destination, and ALRS/P-stack control fields provide the 10-bit address for branching when needed. A 6-bit DPS control field provides the instruction inputs for the DPS array while the 4-bit SEQ field provides the instruction inputs for the 9408. Other fields lumped as miscellaneous are used to control the memory, etc.

The source and destination fields are decoded to activate the  $\overline{EO}$  and  $\overline{EX}$  inputs (see *Figure 2-13*). Note that the IR clock and MAR clock signals are generated by gating the system clock with the appropriate destination decoder outputs. The Branch Address inputs (BA<sub>0</sub>-BA<sub>9</sub>) are obtained from a

4-way input multiplexer which, in turn, is controlled by the VIA<sub>0</sub> and VIA<sub>1</sub> outputs of the 9408. One of the inputs to this multiplexer consists of the address inputs for branching from the microinstruction register. The second part is fed by a mapper that may be a PROM or FPLA. It receives the IR outputs and translates them into a starting address in the control memory for emulation. *Figure 2-14* is a flow chart for the sequence of operations to accomplish macroinstruction fetch, while *Table 2-1* lists the operations performed by various data path elements and the 9408.

The first operation is to read the PC. Thus, the destination field specifies the ALRS and the destination decoder drives the  $\overline{\text{EX}}$  input of the ALRS LOW. The ALRS/P-stack control field specifies "Read R4." At the end of the microcycle, the contents of R4, i.e., the PC, are in the output register of the ALRS. The SEQ field of the first microinstruction is FETCH; therefore, the 9408 generates the address of the second microinstruction.

Here, the ALRS is specified as the source and the MAR as the destination. The source decoder activates the EO input of the ALRS, the destination decoder enables the gating for the MAR clock, and the microinstruction loads the PC into the MAR. In the miscellaneous field, a memory read is initiated. The third microinstruction is made to increment R4 by selecting ALRS as the destination specifying Add with Carry. The DPS outputs (ALRS inputs) are forced HIGH. This incrementation is in preparation for the next macroinstruction fetch. The result from the memory read operation, initiated during the second microinstruction, is now available on the K-bus of the DPS. The fourth microinstruction activates the IR clock so that the eight most significant bits of the memory data are loaded into the IR. Assuming the data is still on the bus, the sign extended displacement is loaded into R<sub>5</sub> (TEMP 1) of the ALRS in the fifth microcycle by selecting "Load R<sub>5</sub>" as the ALRS operation, and selecting the "K-Bus Sign Extended" for the DPS. It should be recalled that the data path has 16-bit fixed word length and the displacement must be treated as a 2's complement number. By using the sign extension capabilities of the DPS, the sign bits, i.e., most significant bits, can be aligned. At this point, the instruction is in the IR and the sign extended displacement is in TEMP 1. The sign of the least significant eight bits of the macroinstruction is extended in anticipation of a memory reference instruction. The sixth microcycle is intended to decode the IR. By specifying a BRV1 in the SEQ field, the VIA outputs of the 9408 select the mapper output as the source for next address. The mapper is designed to provide the starting address of the routine to emulate the instruction currently residing in the IR.

The total microprogram really consists of several simple routines. These easy steps can be converted into binary patterns to be loaded into the control store. Once a data path architecture and microinstruction format has been chosen for a given system design, the microprogram can be written to realize the desired function. It can then be assembled, using the microprogram assembler, to get the binary listing that specifies the control store address and contents. Using this information, the control store can be loaded with the program and the system is ready for operation.

Fig. 2-14 Flow Chart For Fetch Operation

| SOURCE     | DESTINATION | ALRS/<br>P-STACK CONTROL | DPS CONTROL          | SEQ  | MISCELLANEOUS |

|------------|-------------|--------------------------|----------------------|------|---------------|

| DON'T CARE | ALRS        | READ R4 (PC)             | DON'T CARE           | FTCH |               |

| ALRS       | MAR         | DON'T CARE               | DON'T CARE           | FTCH | READ MEMORY   |

| DON'T CARE | ALRS        | ADD WITH CARRY<br>TO R4  | ALL ZEROS            | FTCH |               |

| DON'T CARE | IR          | DON'T CARE               | DON'T CARE           | FTCH |               |

| DON'T CARE | ALRS        | LOAD R5 (TEMP 1)         | K-BUS SIGN<br>EXTEND | FTCH |               |

| DON'T CARE | DON'T CARE  | DON'T CARE               | DON'T CARE           | BRV1 |               |

#### Table 2-1 Operations for Fetch Instruction

# Section 3

# DESCRIPTION AND OPERATION OF THE MACROLOGIC DEMONSTRATOR

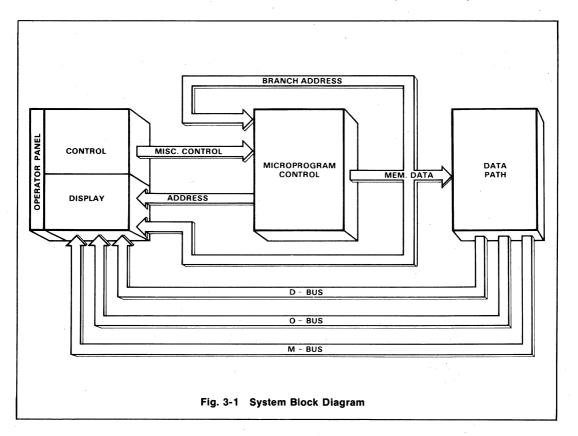

The Macrologic Demonstrator is an educational tool designed to familiarize the user with the processor-oriented devices in the Macrologic family. It consists of three main functional blocks (*Figure 3-1*). The 8-bit wide data path contains an ALU, a register file, LIFO stack and miscellaneous logic. The microprogram controller contains the control memory, as well as microprogram addressing and sequencing logic. The operator panel provides the human interface and allows the operator to load and modify the control memory, run or single-step the microprogram and look at system status and contents of various system busses. An S-100 bus interface is also provided for optional automatic loading of the control store by 8080 based system.

Schematics for the Macrologic Demonstrator are located at the end of this section.

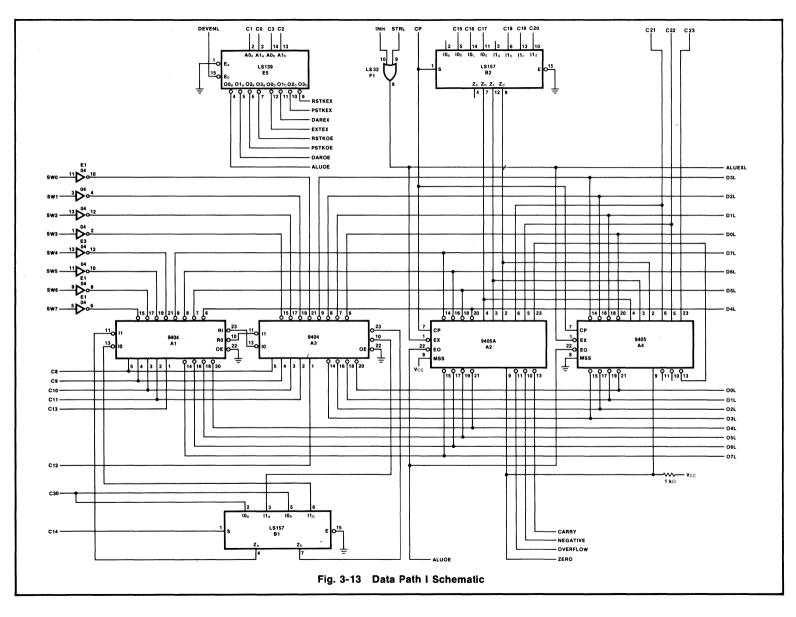

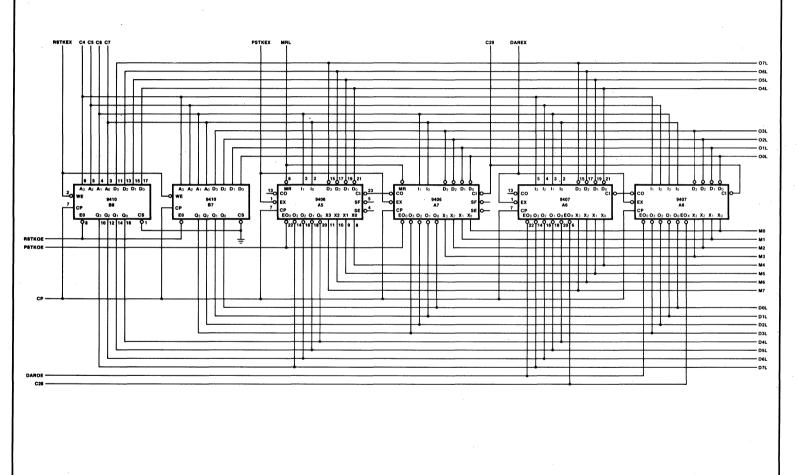

#### THE DATA PATH

Two 4-bit slices of the following Macrologic devices form the 8-bit wide data path (*Figure 3-2*). The Data Path Switch (9404 DPS) allows shifting, constant generation and other operations. An Arithmetic Logic Register Stack (9405A ALRS) performs eight arithmetic and logic functions and includes eight data registers. The Program Stack (9406 P-stack) contains a 16-level stack for last-in, first-out storage. The Data Access Register (9407 DAR) includes three general purpose registers and an adder network which can be used for RAM-resident stack-type functions. A Register Stack (9410 R-stack) provides 16 words of high-speed read/write memory for scratchpad area.

The data path illustrates the highly bus-organized configuration possible with Macrologic systems. The instruction inputs of the P-stack, DARs and R-stacks are bussed together to allow instruction field sharing. That is, the same 4-bit field (C4-C7) is used to control the devices, but only one of these devices is allowed to execute an instruction in a microcycle. The K-bus inputs of the DPSs are tied to the eight data input switches on the operator panel so external information can be introduced into the data path. Three other busses are also available — the D-bus, O-bus and M-bus. The D-bus is created by connecting the D-inputs of the DPSs to the corresponding O-outputs of the DPSs to the corresponding D-inputs of the ALRSs, P-stacks, DARs and R-stacks. The M-bus is created by wiring the X outputs of the P-stacks to the X outputs of the DARs.

Except for the DPS, all Macrologic devices in the data path are clocked by a common system clock. Each of these devices has an Execute input  $(\overline{EX})$  and the device will not respond to the clock unless  $(\overline{EX})$  is LOW. In addition, the 3-state outputs of the devices remain in the high impedance state except when the Output Enable  $(\overline{EO})$  is LOW. Thus, during a single clock cycle, information can be routed from any device in the data path to any other device (including itself) by controlling the proper  $\overline{EX}$  and  $\overline{EO}$  inputs.

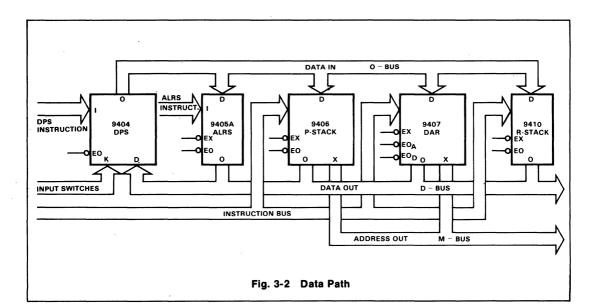

The manner in which the individual  $\overline{EX}$  and  $\overline{EO}$  inputs of the Macrologic devices are controlled is shown in *Figure 3-3*. Bits 0 and 1 of the microprogram control word (C0 and C1) are address inputs to an LS139 1-of-4 decoder. Its active LOW outputs are tied to the Output Enable ( $\overline{EO}$ ) inputs of the ALRSs, DARs, P-stacks and R-stacks, respectively. Therefore, a device can be selected to source data on to the Data Out bus (D-bus) in a clock cycle by appropriately selecting bit 0 and bit 1 of the microprogram control word. Similarly, bit 2 and 3 (C2, C3) of the microprogram control word are inputs to the other half of the LS139 package. Three of the four active LOW outputs are tied to the Execute ( $\overline{EX}$ ) inputs of the DARs, P-stacks, and R-stacks, respectively. Thus, bit 2 and 3 can select one of these three devices to be active and respond to input clocking, or none of them to be activated during a clock cycle. The ALRSs are operated in the general register mode. A two-to-one multiplexer routes the A field inputs of the 9405s to the source and destination registers during the HIGH and LOW periods of the clock respectively. The I<sub>0</sub> input of the most significant ALRS slice is used both to pass instructions and carry information from the least significant ALRS slice.

To extend the shifting capability in the data path, a two-to-one multiplexer selects data, originating from either a bit in the control memory (C30) or the right and left serial DPS outputs, and enters it into the left and right serial inputs of the DPSs (*Figure 3-4*).

The select input of the two-to-one multiplexer is controlled by a rotate select bit (C14). If this bit is HIGH during a right shift, the right serial output is shifted into the most significant DPS position which, in effect, makes the instruction a right rotation. For left rotation, the left serial output is shifted into the least significant DPS position. If the rotate select bit (C14) is LOW, then the value of the left or right shift carry in is under microprogram control and determined by control word bit 30 (C30). If C30 is HIGH during a right shift, a "0" will be shifted into the most significant DPS position since the DPS has active LOW inputs.

#### **MICROPROGRAM CONTROL**

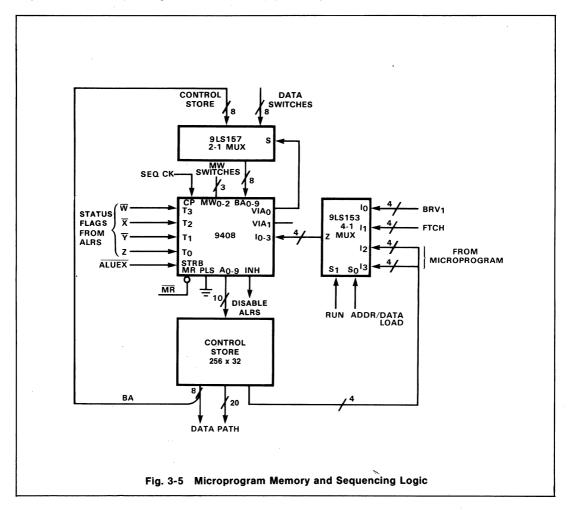

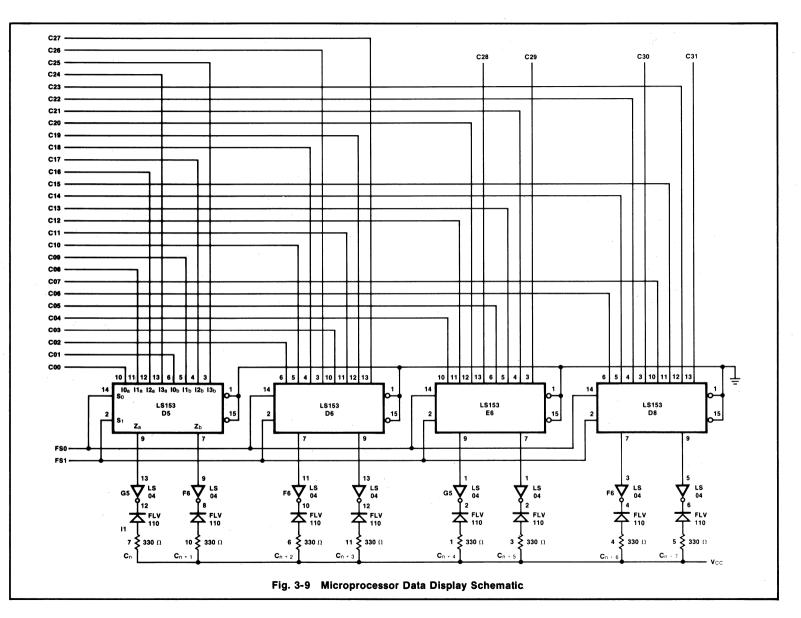

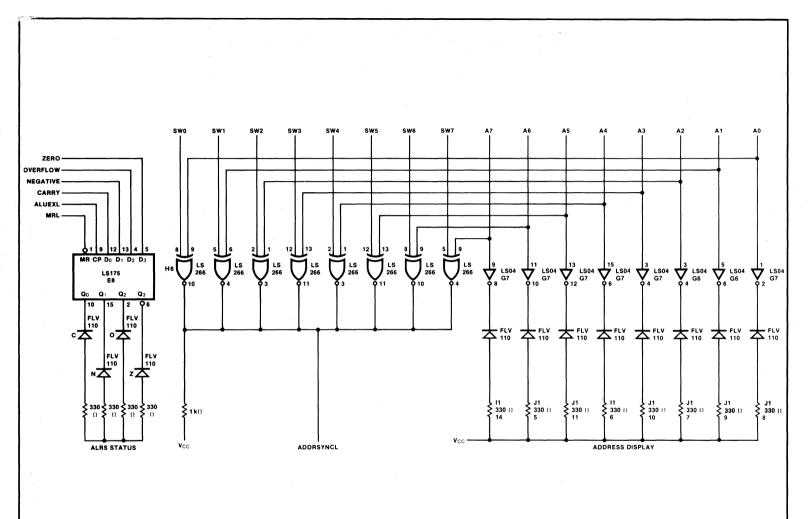

The microprogram memory is constructed using eight 1K 93L422 fully decoded RAMs organized as 256 words by 32 bits. A 9408 Microprogram Sequencer provides address inputs to the control memory (*Figure 3-5*).

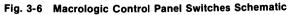

The clock input of the 9408 is a signal called SEQCK, which is the same as the system clock (CP) that goes to all other Macrologic devices in the data path when the system is in the Run or Single-Step mode. When the system is in the Halt mode, SEQCK is held HIGH and only goes LOW momentarily when either the Address Load switch is depressed, or the Deposit Next or Examine Next switch is depressed and Field Select (FS<sub>1</sub> and FS<sub>0</sub>) is "11" (to be described later).

The 9408 Branch Address inputs come from the outputs of two LS157 two-to-one multiplexers whose select input is tied to the VIA<sub>0</sub> output of the 9408. A Branch VIA<sub>0</sub> instruction will select control memory bits 16 to 23 (C16-C23) as the branch address, whereas the Branch VIA<sub>1</sub> instruction will load the microprogram address from the control panel input switches. Actually, the 9408 has the capability of selecting its branch address from up to four different sources through the BRV<sub>0</sub> to BRV<sub>3</sub> instructions. But in the Demonstrator design, only two branch address sources are implemented.

The Multiway switches (M0 to M2) on the control panel feed the 9408 MW<sub>0</sub>-MW<sub>2</sub> inputs for multiway branching. The four ALRSs status flags (zero, overflow, carry and negative) are strobed in the 9408 internal test register at the end of each microcycle in which the ALRSs are exercised by an active LOW signal called ALUEXL which also goes to the Execute ( $\overrightarrow{EX}$ ) input of the ALRSs. The PLS (Pipeline Select) input is grounded for non-pipeline operation.

The instruction inputs of the 9408 come from the outputs of two LS153 four-to-one multiplexers. *Table 3-1* depicts the manner in which the various combinations of the instruction inputs are selected. In the Run or Single-Step mode, S<sub>1</sub> of the multiplexer select input is HIGH and the 9408 instruction inputs are entered via the microprogram control memory output bits 24 to 27 (C24-C27). In the Halt mode, S<sub>1</sub> of the multiplexer select input is LOW and S<sub>0</sub> of the multiplexer input causes the 9408 to either increment the microprogram address by one (FETCH) or load the microprogram address from the control panel input switches (BRV<sub>1</sub>) when the 9408 is clocked. Normally, the clock input of the 9408 is disabled (held HIGH) and the S<sub>0</sub> input of the LS153 is HIGH, forcing the FETCH instruction of the 9408 instruction inputs. When Field Select (FS<sub>1</sub> and FS<sub>0</sub>) is "11" and either the microprogram address by one, allowing the next control word to be examined or loaded. Operation of the Load Address switch momentarily brings the S<sub>0</sub> input of the LS153 LOW, forcing the BRV<sub>1</sub> instruction on the 9408 instruction inputs, and selects the input switches as 9408 Branch Address inputs. The 9408 is again clocked once to match its address outputs to the input switch data.

#### **OPERATOR PANEL**

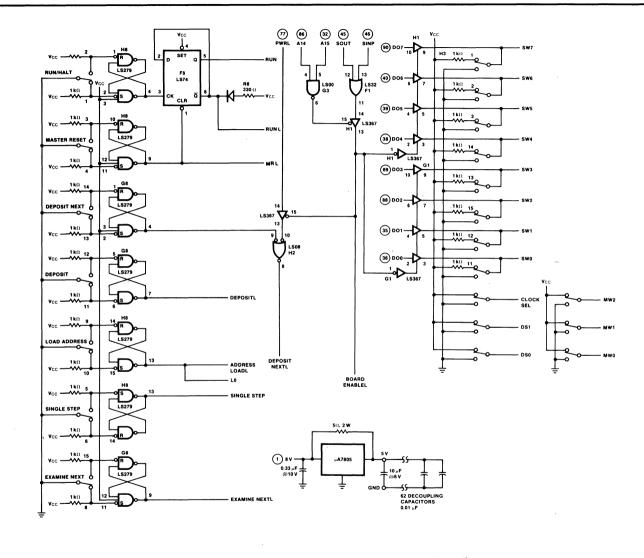

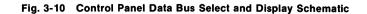

The operator panel consists of two sections — control and display. The control section provides the operator interface to the control memory and data path through a number of toggle switches. The display allows the operator to monitor the microprogram address and data, ALU status flags and the various system busses through LEDs. In addition, a number of turret terminals are provided to allow easy access to some important system signals.

#### Display

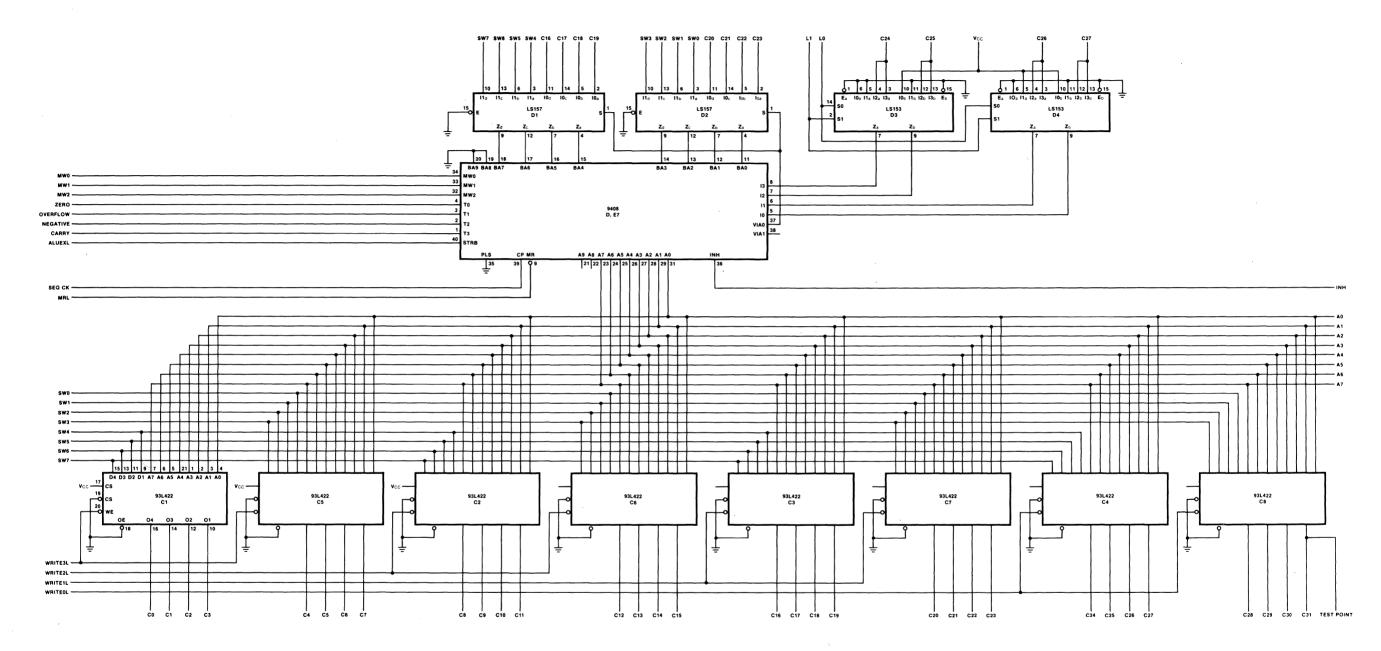

The display consists of two rows of eight LEDs which read the microprogram address and data; a row of eight bus status LEDs, four ALU status LEDs, two Field Select LEDs and a RUN indicator LED. Since the microprogram control word is 32 bits wide, two control inputs (FS<sub>1</sub> and FS<sub>0</sub>) select four separate fields to be displayed by a single set of eight data LEDs. Setting FS<sub>1</sub> and FS<sub>0</sub> to "00" produces the left most (most significant) eight bits of a control word. A setting of "01" produces the next eight bits, "10" the next, and "11" the right most (least significant) 8-bit field. The ALRS flags (zero, negative, carry and overflow) are latched into the four status LEDs so that ALU status can be continuously monitored.

#### Control

The panel control section, contains a group of eight toggle switches (SW0-SW7) for Branch Address or Data input to the system, as well as a number of miscellaneous control switches. The Clock Select switch selects between an internal 2 MHz oscillator or an external clock provided by

|                    |                | 5     |      |       |      |               |

|--------------------|----------------|-------|------|-------|------|---------------|

| S1                 | S <sub>0</sub> | I3    | · I2 | 11    | lo   | MEANING       |

| 0                  | 0              | . 0   | 1    | 0     | 1    | BRV1          |

| 0                  | 1              | 0     | 0    | 1     | 0    | FETCH         |

| 1                  | 0              | C24   | C25  | C26   | C27) | Controlled by |

| 1                  | 1              |       |      |       | C27) | Microprogram  |

| $S_1 = 0$          | Ha             | lt    |      |       |      |               |

| S <sub>1</sub> = 1 | Ru             | n or  | Sing | le St | tep  |               |

| $S_0 = 0$          |                | dress |      |       | •    |               |

| S <sub>0</sub> = 1 | Dat            | ta Lo | ad   |       |      |               |

the user. If an external clock (such as a pulse generator) is used, it should be attached to the EXT-CLK IN turret terminal on the board. A group of three Multiway switches (M0-M2) provides the multiway inputs to the 9408 for eight-way branching. Two Data Bus Select switches (DS1, DS0) select either a lamp test or the contents of one of three system busses (O, D, or M-bus) for display by the eight data-bus LEDs as illustrated by *Table 3-2*. The Master Reset switch halts the system and clears the microprogram address and field to zero.

The Run/Halt switch is a 2-function toggle switch that selects either the Run or Halt mode. If the processor is halted, pressing this switch returns the processor to the Run mode. The processor then executes the microprogram beginning with the instruction contained in the memory location pointed to by the microprogram address. It continues in this fashion until the Run/Halt switch is pressed again; however, the processor halts only after completion of the current microinstruction.

While the processor is in the Halt mode, a number of other switch functions can be activated. The Load Address switch loads input switch data as the microprogram address. The Deposit switch writes the 8-bit words, at the input switches, into the field of the memory location addressed by the 9408 address and Field Select (FS<sub>1</sub> and FS<sub>0</sub>) outputs. The Deposit Next switch operates similarly to Deposit; however, the field is incremented by one before the input switch data is written into memory. Moreover, if Field Select is "11," the field is recirculated to "00" and the 9408 address outputs are incremented by one before the input switch data is written into memory. Thus, the user can load a microprogram eight bits at a time without laboriously loading addresses by repeatedly setting up data switches and then pressing the Deposit Next switch.

The Examine Next switch displays the data in the next field by lighting the appropriate LEDs, and allows the operator to examine memory data field by field and location by location. The microprogram address LEDs display the memory location of the next processor instruction. Pressing the Single Step switch executes that instruction and then halts the processor. The Single Step switch is especially useful in program debug.

A number of turret terminals provide convenient access to some system signals as test points for viewing on the oscilloscope. The CP test point connects directly to the system clock line of the Demonstrator and represents the actual clock signal applied to the Macrologic devices in the data path. The ALUEXL test point is the LOW active signal which goes to the Execute  $(\overline{EX})$  input of the ALRS. The ADDR SYNC test point outputs a HIGH pulse whenever the microprogram address matches the input switch word. In this manner, the input switches can be used to select the microprogram address at which a sync pulse is desired. This provides a handy signal for use as a reference trace on the oscilloscope and signals in the vicinity of the synchronized instruction can be examined by placing the microprogram in a loop. The C31 test point is tied directly to control word bit 31, which is a spare bit at this time. However, it can be used as an additional marker to identify a microinstruction or provide another reference signal on the scope. A Ground point is also brought out to a turret terminal next to the ADDR SYNC test point so that the ground clip of an oscilloscope probe can be attached to it.

| DATA BUS | SELECT | BUS SELECTION |  |

|----------|--------|---------------|--|

| DS1      | DS0    | BUS SELECTION |  |

| 0        | 0      | O-Bus         |  |

| 0        | 1      | D-Bus         |  |

| 1        | 0      | M-Bus         |  |

| 1        | 1      | Lamp Test     |  |

#### Table 3-2 Data Bus Select Switches Operation

#### CONTROL WORD FORMAT

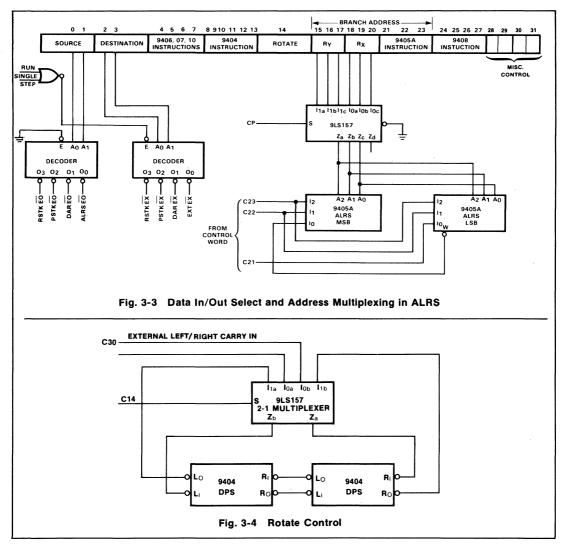

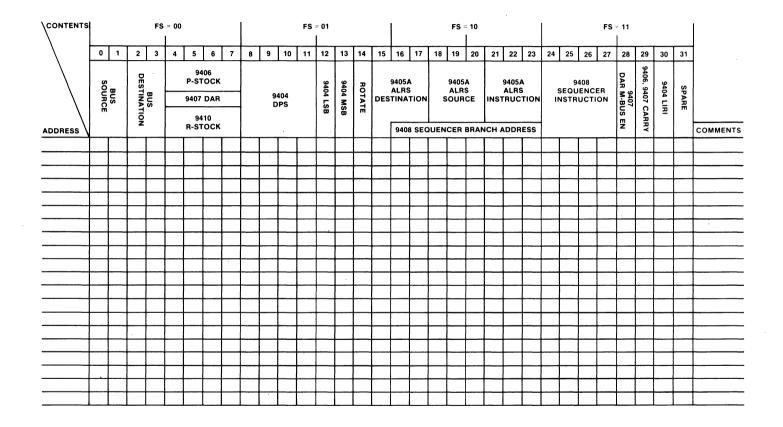

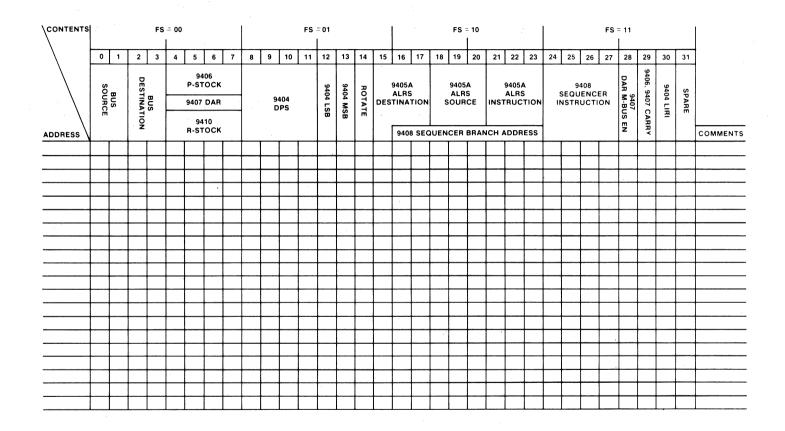

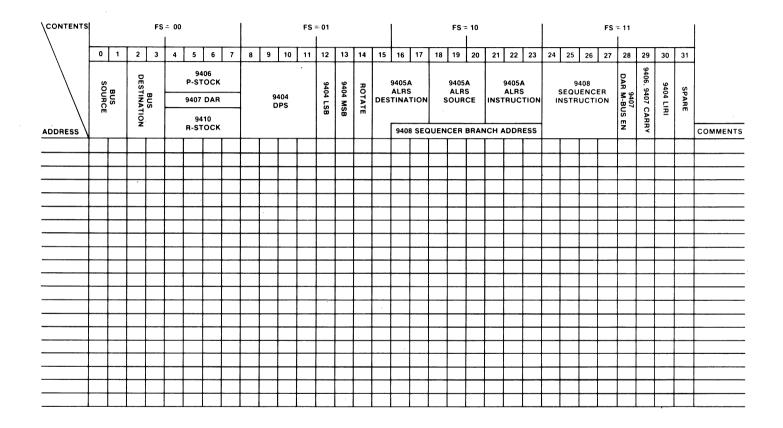

Choosing the width and format of the microprogram control word is a task which involves tradeoff between system performance and memory cost. A format which dedicates separate fields for each individual control function allows many independent operations to be done in one microcycle but also yields the widest control word. Usually, some sort of field sharing is implemented to reduce the control word width without sacrificing too much performance. The Macrologic Demonstrator uses a 32-bit control word reduced by the following overlapping and encoding techniques.

The control inputs for the ALRS and the Branch Address inputs of the 9408 are overlapped since most program structures consist of more fetches than branches. The address for the 9408 Microprogram Sequencer is implicit during Fetch (FTCH) and Return from Subroutine (RTS), which suggests that the branch address field of the 9408 can be overlapped with the instruction input field of another Macrologic element in the system. In this case, the 8-bit branch address field can be conveniently shared with the instruction and register fields of the ALRS. The 9408 Inhibit (INH) output simplifies field overlap; the EX input of the ALRS is simply disabled except during a FTCH or RTS.

Since the O-bus is 3-state, only one of the four Macrologic elements can drive this bus at any time. Thus the four O-bus sources can be encoded by two bits. Since the likelihood is small that more than one Macrologic element in the system will need to operate on the same input during the same microcycle, the four D-bus destinations can also be encoded by two bits. Actually, there are only three Macrologic device destinations and four possible permutations of two bits, which leaves a 'free' state "00." This state can be used to select an external device or to deactivate all three Macrologic elements. Note that the ALRS execution is controlled by the INH output of the 9408 and is unaffected by this field. The result is a 32-bit control word with field definition as shown in *Table 3-3*.

| BITS      | FUNCTION                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| C0 – C1   | O-bus source. These bits select the device driving the input bus of the DPS by activating th proper Output Enable $(\overline{EO})$ input. "00" – ALRS, "01" – DAR, "10" P-stack, "11" – R-stack                                                                                                                                                  |  |  |  |  |  |  |  |

| C2 – C3   | D-bus destination. These bits specify device to be activated and respond to C4 – C7 by ena the proper Execute $(\overline{EX})$ input. "00" – EXT*, "01" – DAR, "10" – P-stack, "11" – R-stack                                                                                                                                                    |  |  |  |  |  |  |  |

| C4 – C7   | Shared between P-stack, DAR and R-stack, these bits are Instruction inputs to the P-stack an DAR and Address inputs to the R-stack.                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| C8 – C13  | Instruction inputs to the DPS.                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| C14       | Rotate control. Specifies source of carry in (external or rotate) during DPS shifts.                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| C15 — C23 | Shared between the 9408 Sequencer and ALRS. When the 9408 instruction $(C24 - C27)$ is neither a Fetch or a Return, these bits are the Branch Address. Otherwise, C15 - C17 select one ALRS register for destination of ALU operations, C18 - C20 select one ALRS register as source of ALU operations, C21 - C23 become ALRS Instruction inputs. |  |  |  |  |  |  |  |

| C24 – C27 | 9408 Sequencer Instruction inputs.                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| C28       | 9407 X-bus enable input. When the 9406 is executing a FETCH instruction, C28 should be held<br>HIGH for microcycle to prevent both the 9406 and 9407 from driving the M-bus at the same time                                                                                                                                                      |  |  |  |  |  |  |  |

| C29       | 9406 and 9407 carry in input.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| C30       | 9404 carry in input for shift function. If rotate control (C14) is LOW, the value of C30 (active LOW will be shifted into the least or most significant position of the DPS following a left or right shift, respectively.                                                                                                                        |  |  |  |  |  |  |  |

| C31       | Spare. This bit is brought out to a turret terminal and can be used as a marker to identify one or a group of microinstructions.                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

#### **MISCELLANEOUS**

The Demonstrator is pretty much self-contained. The only additional equipment needed for its operation is a 5 V power supply capable of delivering about 2 A of current to be attached to the  $V_{CC}$  and GND turret terminals in the lower left hand corner of the board.

Instead of hand loading the microprogram through input switches, a user who has an S-100 bus 8080 based system can choose to have the control store of the Demonstrator loaded by the 8080. The Demonstrator card edge connector plugs directly into the S-100 bus. A  $\mu$ A7805 voltage regulator in TO-220 package is used to obtain Vcc from the 8 V which come from pin 1 of the S-100 bus. A 5  $\Omega$ , 2 W resistor is required between the input and output terminal of the regulator to provide enough current for the board.

#### OPERATING PROCEDURE FOR CONTROL PANEL OF MACROLOGIC DEMONSTRATOR

The following operations are possible when the system is in the Halt mode. To place the system in the Halt mode, use either the Run/Halt switch or press the Master Reset switch momentarily.

#### Loading In Microprogram

- 1. Press Master Reset. Make sure system is in Halt mode by verifying Run light is off.

- 2. Set up starting address via the eight data input switches.

- 3. Hit Load Address switch momentarily and verify the address lights show the same data as the input switch settings.

- 4. Verify Field Select (FS<sub>1</sub> and FS<sub>0</sub>) lights="00." Set up data for first field in data input switches.

- 5. Depress Deposit switch and verify the data lights show the same data as the input switch setting.

- 6. Set up data for the next field through the input switches.

- 7. Depress Deposit Next switch and verify:

- a. The Field Select (FS<sub>1</sub>, FS<sub>0</sub>) lights are incremented by one.

- b. If the Field Select lights = "11," the address light will be incremented by one and the Field Select lights will go to "00."

- c. The data lights are the same as the input switch settings.

- 8. Repeat steps 6 and 7 to input data sequentially, field by field, location by location.

#### Verifying Program

- 1. Press Master Reset to get into the Halt mode.

- 2. Set up desired starting address of microprogram by input switches. Press Load Address switch momentarily and verify the address lights show the same data as the input switch settings.

- 3. By continuing depressing the Examine Next switch, one can sequentially examine the contents of the microprogram, 8-bit field at a time, location by location.

۵

#### **Modifying Program**

- 1. Hit Master Reset to clear out address and field lights.

- 2. Enter starting address via input switches and depress Load Address switch.

- 3. Get to desired field using Examine Next switch.

- 4. Verify old data is displayed on data lights. Set up new desired data through input data switches.

- 5. Hit Deposit switch and verify new data is deposited.

- 6. Repeat above steps for other fields to be modified or use Examine Next switch to advance to the next field to be modified and repeat step 4 and 5.

#### Single Stepping Microprogram

- 1. Make sure system is in Halt mode. Set up starting microprogram address via the eight data input switches.

- 2. Press Load Address switch and verify the address lights display the same data as input switches.

- 3. Depressing Single Step switch momentarily will cause the microinstruction pointed to by the microprogram address LEDs to be executed. The system will then be halted.

- 4. Repeat step 3 to execute the microprogram one microinstruction at a time.

#### Running the Microprogram

- 1. Set up starting address via input switches and hit Load Address switch.

- 2. Depress Halt/Run switch and the RUN light will come on, verifying the system has begun execution starting from the microinstruction specified in the microprogram address.

#### Loading the Microprogram Memory Through the S-100 Bus

The Macrologic Demonstrator has the provision for an S-100 bus system to load its control memory. The write signal from the 8080 Processor (PWRL) is simply made to act like the Deposit Next switch. The Demonstrator board decodes the two higher order bits of the 8080 address bus and makes sure they are equal to "11" before its control memory is loaded, i.e., the Demonstrator can have a hexadecimal memory address of CXXX up to FXXX. To load the microprogram memory, 8-bit field at a time, do the following:

- 1. Halt the 8080 system. Plug the Macrologic Demonstrator into the S-100 bus connector.

- 2. Press Master Reset and verify the address and field lights are zero and the system is halted.

- 3. Set up the starting microprogram address via the input switches and press the Load Address switch.

- 4. Set up the first field of the microprogram through the input switches. Depress Deposit momentarily. Verify the data lights are the same as the input switch settings.

- 5. Put all eight data switches in the Up position.

- 6. Any subsequent write by the 8080 Processor to memory address CXXX through FXXX will increment the field by one first before writing the data, i.e., it generates the same action as if the Deposit Next switch is depressed.

This gives the user an alternative to loading the microprogram memory through input switches. A user can now, say, read in a microprogram through the paper tape reader of the 8080 system and transfer it to the control memory of the Macrologic Demonstrator.

10 LS74 F8 LS20 LS04 1 G6 12 ā СК CLR 13 Vcc 3 4 ÷ PE Po P P<sub>2</sub> CEP 10 LS161 G2 СЕТ тс - 15 • СР SYS CLOCK MR Q0 Q1 Q2 Q3 14 13 12 11 MRL LS04 LS51 LS08 ADDRESS LOADL SEQ CK FS11 Vcc CP 3 4 5 13 LS00 ÷ DE P0 P1 D<sub>o</sub> DEPOSIT NEXTL G3 EP EXAMINE NEXTL 10 LS161 LS00 СЕТ тс F2 G3 LS00 Q0 Q1 Q2 Q3 WR 14 13 12 11 G DEPOSITL -FS0 Vcc LS08 LS20 FS11 H2 E2 LS04 3 LS04 19 SYS CLOCKL G5 E3 7 FS1 Е A0 A1 LS139 E4 \$ 11 \$ 330 Ω \$ 11 \$ 330 Ω **O**<sub>0</sub> **O**<sub>1</sub> **O**<sub>2</sub> **O**<sub>3</sub> 59 6 Vcc WRITE OL WRITE 1L WRITE 2L WRITE 3L Fig. 3-8 Examine, Deposit, and Address Load Logic Schematic

M7 M6 MS M D7L DBI D5i D4L D3L D2L D11 DOL 07L OGL O5L 041 031 O2L 01L OOL 10 11 12 13 6 4 3 10 11 12 13 10 11 12 13 6 10 11 12 13 5 5 10a 11a 12a 13a 10b 11b 12b 13b 10a 11a 12a 13a 10b 11b 12b 13b 10a 11a 12a 13a 10b 11b 12b 13b 10a 11a 12a 13a 10b 11b 12b 13c 01 015 14 14 LS153 86 L\$153 B3 LS153 B4 LS153 B5 15 15 Zr Z۲ Ζb Ζb DS0 DS1-本 🔛 夲 本 圡 厺  $\Delta$ \$ J1 330 Ω 14 ↓ J1 330 Ω 12 330 Ω 13 \$ J1 330 Ω 3 ↓ J1 330 Ω 2 J1 330 11 15 ≩ J1 ≩ 330 Ω | 4 J1 330 Ω 14 Vcc

Fig. 3-11 Address Sync, ALRs Flags and Address Display Schematic

Fig. 3-14 Data Path II Schematic

3-20

## Section 4

# **PROGRAMMING EXAMPLES AND EXERCISES**

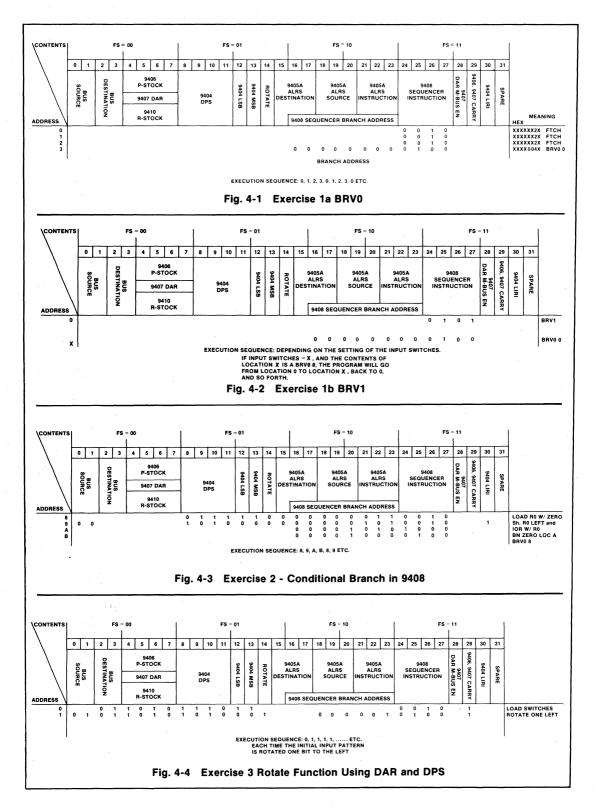

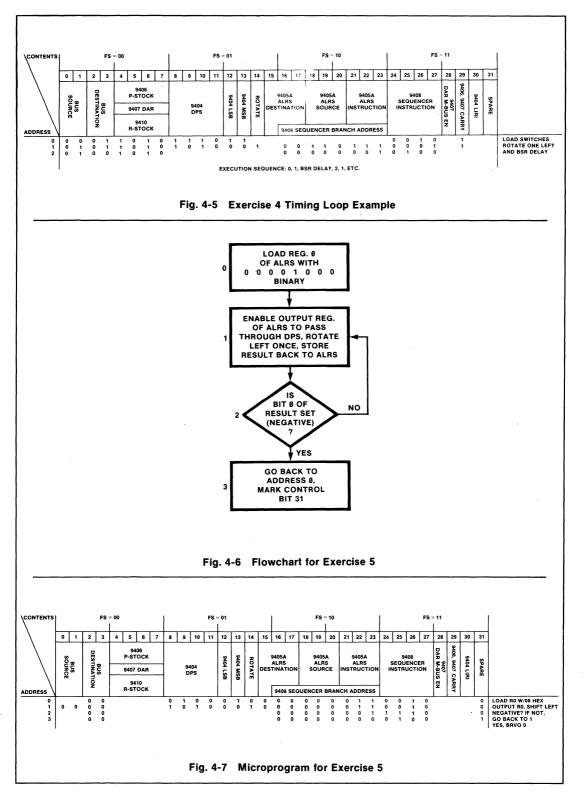

The previous section described the data path architecture and the 32-bit microinstruction format of the Macrologic Demonstrator. This section will show some programming examples and exercises geared to demonstrate the uses of the Macrologic devices and to involve the user in the microprogramming of these devices. The binary information which specifies the control store address and contents can be realized by either hand-coding the various fields of each control word or using a microprogram assembler. (Fairchild offers a choice of assembler software, the microprogram assembler and DAPL, available through time sharing networks.)

After a microprogram is loaded, the user can single step through it. In this mode, the user can observe the various states of the machine at each microcycle. Alternatively, the user can evaluate the dynamic behavior of the machine by putting it in the Run mode. This allows the Macrologic devices to be tested under operating conditions and some switching characteristics to be measured by an oscilloscope.

*Table 4-1* provides a summary of the instruction set definitions for the various Macrologic devices. However, users should refer to the Macrologic Data Book for detailed device information.

|                |                                                                                                         |                         | ,              |                                                                                                                        |                         |

|----------------|---------------------------------------------------------------------------------------------------------|-------------------------|----------------|------------------------------------------------------------------------------------------------------------------------|-------------------------|

|                |                                                                                                         |                         | 9404           |                                                                                                                        |                         |

| INPUTS         | OUTPUTS                                                                                                 |                         | INPUTS         | OUTPUTS                                                                                                                |                         |

| 14 13 12 11 10 | $\overline{o_3} \ \overline{o_2} \ \overline{o_1} \ \overline{o_0}$                                     | FUNCTION                | 14 13 12 11 10 | $\overline{LO}$ $\overline{O_3}$ $\overline{O_2}$ $\overline{O_1}$ $\overline{O_0}$ $\overline{RO}$                    | FUNCTION                |

| LLLL           | LLLL                                                                                                    | Byte Mask               | HLLLL          | RI RI RI RI RI                                                                                                         | K-Bus Sign Extend       |

| н              | нннн                                                                                                    | Byte Mask               | нсссн          | $\overline{K_3}$ $\overline{K_3}$ $\overline{K_2}$ $\overline{K_1}$ $\overline{K_0}$                                   | K-Bus Sign Extend       |

| L L L H L      | LLLH                                                                                                    | Minus "2" in 2s Comp    | нсснс          |                                                                                                                        | D-Bus Sign Extend       |

| с с с н н      | LLLL                                                                                                    | Minus "1" in 2s Comp    | нсснн          | $\overline{D_3}$ $\overline{D_3}$ $\overline{D_2}$ $\overline{D_1}$ $\overline{D_0}$                                   | D-Bus Sign Extend       |

| L L H L L      | $\overline{D_3}$ $\overline{D_2}$ $\overline{D_1}$ $\overline{D_0}$                                     | Byte Mask, D-Bus        | нгнгг          | $\overline{D_3}$ $\overline{D_2}$ $\overline{D_1}$ $\overline{D_0}$ $\overline{RI}$                                    | D-Bus Shift Left        |

| ссн с н        | нннн                                                                                                    | Byte Mask, D-Bus        | нснсн          | $\overline{K_3}$ $\overline{K_2}$ $\overline{K_1}$ $\overline{K_0}$ $\overline{RI}$                                    | K-Bus Shift Left        |

| L L Н Н L      | $\overline{D_3}$ $\overline{D_2}$ $\overline{D_1}$ $\overline{D_0}$                                     | Byte Mask, D-Bus        | нсннс          | $\overline{LI}$ $\overline{D_3}$ $\overline{D_2}$ $\overline{D_1}$ $\overline{D_0}$                                    | D-Bus Shift Right       |

| ггнн           |                                                                                                         | Byte Mask, D-Bus        | нсннн          | $\overline{D_3}$ $\overline{D_3}$ $\overline{D_2}$ $\overline{D_1}$ $\overline{D_0}$                                   | D-Bus Shift Right Arith |

| ιнιιι          | с н н н                                                                                                 | Negative Byte Sign Mask | ннццц          | $\overline{\text{LI}} \ \overline{\text{K}_3} \ \overline{\text{K}_2} \ \overline{\text{K}_1} \ \overline{\text{K}_0}$ | K-Bus Shift Right       |

| LHLLH.         | нннн                                                                                                    | Positive Byte Sign Mask | ннссн          | $\overline{K_3}$ $\overline{K_3}$ $\overline{K_2}$ $\overline{K_1}$ $\overline{K_0}$                                   | K-Bus Shift Right Arith |

| ь н ь н ц      | $\overline{K_3}$ $\overline{K_2}$ $\overline{K_1}$ $\overline{K_0}$                                     | Byte Mask, K-Bus        | ннснс          | $\overline{K_3}$ $\overline{K_2}$ $\overline{K_1}$ $\overline{K_0}$                                                    | Byte Mask, K-Bus        |

| ь н ь н н      | LLLL                                                                                                    | Byte Mask, K-Bus        | ннснн          | нннн                                                                                                                   | Byte Mask, K-Bus        |

| L Н Н L L      | $\overline{D_3}$ $\overline{D_2}$ $\overline{D_1}$ $\overline{D_0}$                                     | Load Byte               | нннгг          | D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub>                                                            | Complement D-Bus        |

| L H H L H      | $\overline{\mathbf{K}_3} \ \overline{\mathbf{K}_2} \ \overline{\mathbf{K}_1} \ \overline{\mathbf{K}_0}$ | Load Byte               | нннсн          | к <sub>3</sub> к <sub>2</sub> к <sub>1</sub> к <sub>0</sub>                                                            | Complement K-Bus        |

| L H H H L      | нннг                                                                                                    | Plus "1"                | ннннг          |                                                                                                                        | Undefined (Reserved)    |

| L Н Н Н Н      | нннн                                                                                                    | Zero                    | ннннн          |                                                                                                                        | Undefined (Reserved)    |

Comp = Complement Arith = Arithmetic

### Table 4-1 Instruction Sets for Macrologic Devices

|                | 9405A |   |                                                    |                          |                                                              |                                      |  |  |  |  |  |  |  |  |

|----------------|-------|---|----------------------------------------------------|--------------------------|--------------------------------------------------------------|--------------------------------------|--|--|--|--|--|--|--|--|

| I              | INPUT | s |                                                    |                          | GENERAL REGISTER MODE (R <sub>v</sub> ≠ R <sub>v</sub> )     |                                      |  |  |  |  |  |  |  |  |

| <sup>1</sup> 2 | 1     |   |                                                    | MODE ( $R_x = R_y$ )     | GENERAL REGISTER MODE                                        | : (n <sub>X</sub> - n <sub>γ</sub> ) |  |  |  |  |  |  |  |  |

| L              | L     | L | $R_x plus D-Bus plus 1 \rightarrow R_x$            | Accumulate and Increment | $R_{\chi} plus \overline{D-Bus} plus 1 \rightarrow R_{\chi}$ | Add with Carry                       |  |  |  |  |  |  |  |  |

| L              | L     | н | $R_x plus \overline{D-Bus} \rightarrow R_x$        | Accumulate               | $R_x plus \overline{D-Bus} \rightarrow R_y$                  | Add                                  |  |  |  |  |  |  |  |  |

| L              | н     | L | $R_{\chi} \overline{D-Bus} \rightarrow R_{\chi}$   | Logical AND              | $R_x \overline{D-Bus} \rightarrow R_y$                       | Logical AND                          |  |  |  |  |  |  |  |  |

| L              | н     | н | $\overline{\text{D-Bus}} \rightarrow \text{R}_{x}$ | Load                     | $\overline{\text{D-Bus}} \rightarrow \text{R}_{y}$           | Load                                 |  |  |  |  |  |  |  |  |

| н              | L     | L | R <sub>x</sub> → Output Register                   | Read                     | $R_x \rightarrow R_y$                                        | Transfer                             |  |  |  |  |  |  |  |  |

| н              | Ł     | н | $R_{\chi} + \overline{D-Bus} \rightarrow R_{\chi}$ | Logical OR               | $R_{x} + \overline{D-Bus} \rightarrow R_{y}$                 | Logical OR                           |  |  |  |  |  |  |  |  |

| н              | н     | L | $R_x \oplus \overline{D-Bus} \to R_x$              | Exclusive OR             | $R_x \oplus \overline{D-Bus} \to R_y$                        | Exclusive OR                         |  |  |  |  |  |  |  |  |

| н              | н     | н | D-Bus $\rightarrow R_{\chi}$                       | Load Complement          | D-Bus $\rightarrow R_{\gamma}$                               | Load Complement                      |  |  |  |  |  |  |  |  |

NOTES:

$R_x$  is the RAM location addressed by  $A_0 - A_2$  when CP is HIGH.  $R_y$  is the RAM location addressed by  $A_0 - A_2$  when CP is LOW. The result of any operation is always loaded into the Output Register at the end of the cycle provided that  $\overline{EX}$  is LOW.

|        |                         |                                                                                | 9406                                                                                                                          |                                                                                                                                                                                                                                                         |

|--------|-------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUTS | INSTRUCTION             | INTERNAL OPERATION                                                             | X-BUS                                                                                                                         | O-BUS (WITH EO <sub>0</sub> LOW)                                                                                                                                                                                                                        |

| L L    | Return (Pop)            | Decrement Stack Pointer                                                        | Disabled                                                                                                                      | Depending on the relative timing of $\overline{EX}$ and CP, the outputs will reflect the current program counter or the new value while CP is LOW. When CP goes HIGH again, the output will reflect the new value.                                      |

| ιн     | Branch (Load PC)        | Load D-Bus into Current<br>Program Counter Location                            | Disabled                                                                                                                      | Current Program Counter until CP goes<br>HIGH again, then updated with newly<br>entered PC value.                                                                                                                                                       |

| нц     | Call (Push)             | Increment Stack Pointer and<br>Load D-Bus into New Program<br>Counter Location | Disabled                                                                                                                      | Depending on the relative timing of $\overline{EX}$ and CP, the outputs will reflect the current program counter or the previous contents of the incremented SP location. When CP goes HIGH again, the outputs will reflect the newly entered PC value. |

| нн     | Fetch<br>(Increment PC) | Increment Current Program<br>Counter if CI is LOW                              | Current Program Counter while both CP and $\overline{\text{EX}}$ are LOW, disabled while CP or $\overline{\text{EX}}$ is HIGH | Current Program Counter until CP goes<br>HIGH again, then updated with<br>incremented PC value.                                                                                                                                                         |

9407

|     | INPUTS |   |    | COMBINATORIAL FUNCTION        | SEQUENTIAL FUNCTION OCCURRING                                                   |  |  |  |  |  |  |  |

|-----|--------|---|----|-------------------------------|---------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 13  | I2     | 1 | 10 | AVAILABLE ON THE X-BUS        | ON THE NEXT RISING CP EDGE                                                      |  |  |  |  |  |  |  |

| L   | L      | L | L  | R <sub>0</sub>                |                                                                                 |  |  |  |  |  |  |  |

| , L | L      | L | н  | R <sub>0</sub> plus D plus CI | R <sub>0</sub> , <i>plus</i> D <i>plus</i> Cl→R <sub>0</sub> and Output Registe |  |  |  |  |  |  |  |

| L   | L      | н | L  | R <sub>0</sub>                |                                                                                 |  |  |  |  |  |  |  |

| L   | L      | н | н  | R <sub>0</sub> plus D plus CI | R <sub>0</sub> <i>plus</i> D <i>plus</i> Cl→R <sub>1</sub> and Output Registe   |  |  |  |  |  |  |  |

| £.  | н      | L | L  | R <sub>0</sub>                | R <sub>0</sub> plus D plus CI +R <sub>2</sub> and Output Register               |  |  |  |  |  |  |  |

| L   | н      | L | н  | R <sub>0</sub> plus D plus CI | no plus of plus of magaine output negiste                                       |  |  |  |  |  |  |  |

| L   | н      | н | Ł  | B <sub>1</sub>                | $R_1 plus \overline{D} plus \overline{CI} \rightarrow R_1$ and Output Register  |  |  |  |  |  |  |  |

| L   | н      | н | н  | R <sub>1</sub> plus D plus CI | 1 plus o plus ci-ri and output negiste                                          |  |  |  |  |  |  |  |

| н   | L      | L | L  | B <sub>2</sub>                | $\overline{D} p / us \overline{CI} \rightarrow R_2$ and Output Register         |  |  |  |  |  |  |  |

| н   | L      | L | н  | D plus CI                     |                                                                                 |  |  |  |  |  |  |  |

| н   | L      | н | L  | R <sub>0</sub>                | $\overline{D} plus \overline{CI} \rightarrow R_0$ and Output Register           |  |  |  |  |  |  |  |

| н   | L      | н | н  | D plus Cl                     | D plus CI-AQ and Output Register                                                |  |  |  |  |  |  |  |

| н   | н      | L | L  | R <sub>2</sub>                | R <sub>2</sub> plus D plus Cl·+R <sub>2</sub> and Output Registe                |  |  |  |  |  |  |  |

| н   | н      | L | н  | R <sub>2</sub> plus D plus Cl | 12 plus of plus Clience and Output Registe                                      |  |  |  |  |  |  |  |

| н   | н      | н | L  | R1                            | $\overline{D} plus \overline{CI} \rightarrow R_1$ and Output Register           |  |  |  |  |  |  |  |

| н   | н      | н | н  | D plus CI                     |                                                                                 |  |  |  |  |  |  |  |

### Table 4-1 Instruction Sets for Macrologic Devices (Cont.)

9408

|                       | MNEMONIC         | DEFINITION                | INPUTS<br>13121110 | T3T2T1T0 | 0 <sub>9</sub> 0 <sub>8</sub> 070 <sub>2</sub> 0 <sub>1</sub> 0 <sub>0</sub> | VIA1VIA0 | INH | DESCRIPTION OF<br>OPERATION                                                               |

|-----------------------|------------------|---------------------------|--------------------|----------|------------------------------------------------------------------------------|----------|-----|-------------------------------------------------------------------------------------------|

|                       | BRVO             | Branch VIA <sub>O</sub>   | LHLL               | XXXX     | BA9 BA8BA1 BA0                                                               | LL       | н   | BA <sub>O</sub> - BA <sub>9</sub> →PC                                                     |

| Unconditional         | BRV1             | Branch VIA1               | LHLH               | XXXX     | BA9 BA8BA1 BA0                                                               | LH       | н   | BA <sub>0</sub> BA <sub>9</sub> →PC                                                       |

| Branch                | BRV2             | Branch VIA2               | LHHL               | XXXX     | BA9 BA8BA1 BA0                                                               | ΗL       | н   | BA <sub>0</sub> - BA <sub>9</sub> →PC                                                     |

|                       | BRV3             | Branch VIA3               | LHHH               | XXXX     | BA9 BA8BA1 BA0                                                               | нн       | н   | $BA_0 - BA_9 \rightarrow PC$                                                              |

| Instructions          | BMW              | Branch<br>Multiway        | LLHH               | x        | BA9 BA3MW2 MW0                                                               | LL       | н   | MW <sub>0</sub> - MW <sub>2</sub> ,<br>BA <sub>3</sub> - BA <sub>9</sub> →PC              |

|                       | BSR              | Branch to<br>Subroutine   | LLLH               | x        | BA9 BA8BA1 BAO                                                               | LL       | н   | BA <sub>O</sub> - BAg → PC &<br>Push the Stack                                            |

|                       | втн <sub>о</sub> | Branch on TO              | HHLL               | хххн     | BA9 BA8BA1 BA0                                                               | LL       | н   | If Test Register 0 is HIGH:                                                               |

|                       |                  | HIGH                      |                    | XXXL     | PC+1                                                                         |          |     | BA <sub>0</sub> - BA <sub>9</sub> → PC<br>If Test Register 0 is LOW:<br>PC $\cdot$ 1 → PC |

|                       | BTH1             | Branch on T1              | ннгн               | ххнх     | BA9 BA8BA1 BA0                                                               | LL       | н   | If Test Register 1 is HIGH:                                                               |

|                       |                  | HIGH                      | -                  | XXLX     | PC+1                                                                         |          |     | BA <sub>O</sub> - BAg → PC<br>If Test Register 1 is LOW:<br>PC+1 → PC                     |

|                       | BTH <sub>2</sub> | Branch on T2              | HHHL               | хнхх     | BA9 BA8BA1 BA0                                                               | LL       | н   | If Test Register 2 is HIGH:                                                               |

|                       |                  | нідн                      |                    | XLXX     | PC+1                                                                         |          |     | BA <sub>0</sub> - BA <sub>9</sub> → PC<br>If Test Register 2 is LOW<br>PC+1 → PC          |

|                       | BTH3             | Branch on T3              | нннн               | нххх     | BA9 BA8BA1 BA0                                                               | LL       | н   | If Test Register 3 is HIGH:                                                               |

| Conditional<br>Branch |                  | нідн                      |                    | LXXX     | PC+1                                                                         |          |     | BA <sub>O</sub> - BA <sub>9</sub> → PC<br>If Test Register 3 is LOW:<br>· PC+1 → PC       |

| Dranch                | btlo             | Branch on TO              | HLLL               | XXXL     | BA9 BA8BA1 BA0                                                               | LL       | н   | If Test Register 0 is LOW:                                                                |

| Instructions          |                  | LOW                       |                    | хххн     | PC+1                                                                         |          |     | BA <sub>O</sub> - BAg→PC<br>If Test Register O is HIGH:<br>PC+1→PC                        |

|                       | BTL1             | Branch on T <sub>1</sub>  | HLLH               | XXLX     | BA9 BA8BA1 BA0                                                               | LL       | н   | If Test Register 1 is LOW:                                                                |

|                       |                  | LOW                       |                    | ххнх     | PC+1                                                                         |          |     | BA <sub>O</sub> - BAg → PC<br>If Test Register 1 is HIGH:<br>PC+1 → PC                    |

|                       | BTL2             | Branch on T <sub>2</sub>  | HLHL               | XLXX     | BA9 BA8BA1 BA0                                                               | LL       | н   | If Test Register 2 is LOW:                                                                |

|                       |                  | LOW                       |                    | хнхх     | PC+1                                                                         |          |     | BA <sub>O</sub> - BAg → PC<br>If Test Register 2 is HIGH:<br>PC+1 → PC                    |

|                       | BTL3             | Branch on T3              | нгнн               | LXXX     | BA9 BA8BA1 BA0                                                               | LL       | н   | If Test Register 3 is LOW:                                                                |

|                       |                  | LOW                       |                    | нххх     | PC+1                                                                         |          |     | BA <sub>0</sub> - BA <sub>9</sub> → PC<br>If Test Register 3 is HIGH:<br>PC+1 → PC        |

| Miscellaneous         | RTS              | Return from<br>Subroutine | LLLL               | XXXX     | Contents of the<br>Stack Addressed<br>by Read Pointer                        | LL       | L   | Pop the Stack                                                                             |