# THE

# FAIRCHILD FST-1

**COMPUTER**

Part Number 67095031

Issued: September, 1973

### **TABLE OF CONTENTS**

# Chapter I General System Description

|                                                                            |                                                                                                                                                                                                                                                                                                                                                 | Page                                                                                                 |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| SECTION :                                                                  | 1 GENERAL INFORMATION                                                                                                                                                                                                                                                                                                                           | I-1-1                                                                                                |

| 1.0<br>1.1<br>1.1.1<br>1.2<br>1.2.1<br>1.2.1.1<br>1.2.2<br>1.2.3           | Memory Interface                                                                                                                                                                                                                                                                                                                                | I-1-1<br>I-1-6<br>I-1-6<br>I-1-6<br>I-1-12<br>I-1-14<br>I-1-16                                       |

| SECTION                                                                    | 2 CONTROLS AND INDICATORS                                                                                                                                                                                                                                                                                                                       | I-2-1                                                                                                |

| 2.1                                                                        | GENERAL                                                                                                                                                                                                                                                                                                                                         | I-2-1                                                                                                |

|                                                                            | Chapter II<br>Central Processing Unit                                                                                                                                                                                                                                                                                                           |                                                                                                      |

| SECTION                                                                    | 1 GENERAL INFORMATION                                                                                                                                                                                                                                                                                                                           | II-1-1                                                                                               |

| 1.0                                                                        |                                                                                                                                                                                                                                                                                                                                                 | II-1-1<br>II-1-1                                                                                     |

| SECTION                                                                    | 2 INDIVIDUAL BOARD DESCRIPTION                                                                                                                                                                                                                                                                                                                  | II-2-1                                                                                               |

| 2.0<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10 | TWO-BIT SLICE (97166001-04, 2 pages)  DATA BUS (97340203-04, 2 pages)  CPU CLOCK (97166004-04, 1 page)  CONTROL FF (97166003-04, 1 page)  P COUNTER (97166005-04, 1 page)  INSTRUCTION DECODE (97166008-04, 1 page)  GATE CONTROL #1 (97166006-04, 1 page)  GATE CONTROL #2 (97166007-04, 1 page)  MISCELLANEOUS REGISTERS (97166009-04,1 page) | II-2-1<br>II-2-1<br>II-2-3<br>II-2-5<br>II-2-7<br>II-2-9<br>II-2-10<br>II-2-11<br>II-2-13<br>II-2-13 |

|           |                                        | Page    |

|-----------|----------------------------------------|---------|

| SECTION 3 | INSTRUCTION REPERTOIRE                 | 11-3-1  |

| 3.0       | INTRODUCTION                           | II-3-1  |

| 3.1       | ABBREVIATIONS AND MNEMONICS            | II-3-1  |

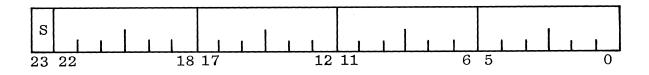

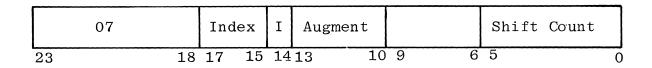

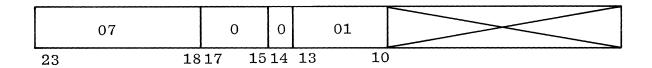

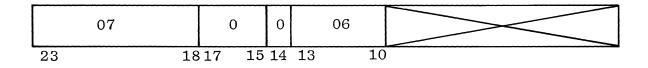

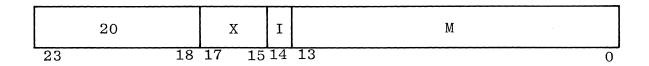

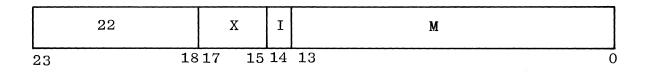

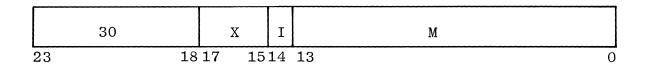

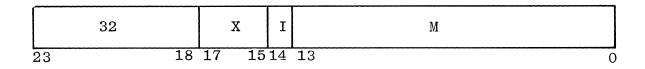

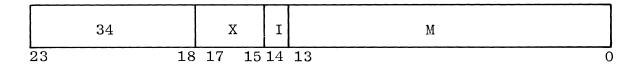

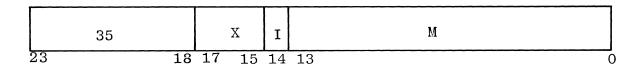

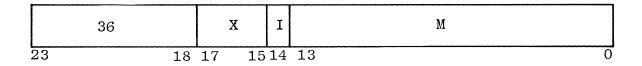

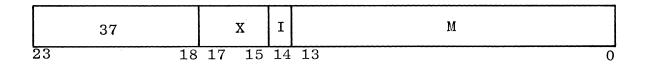

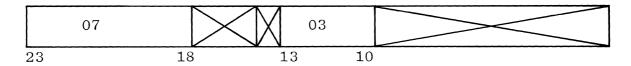

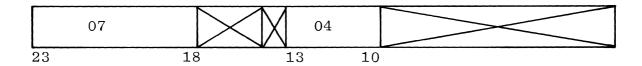

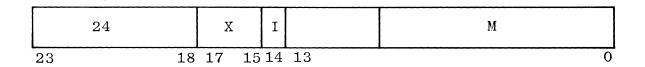

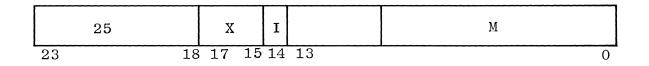

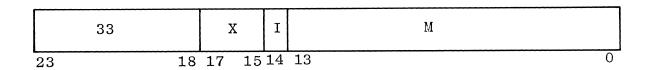

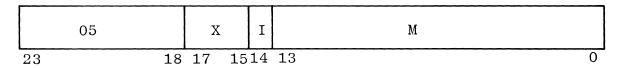

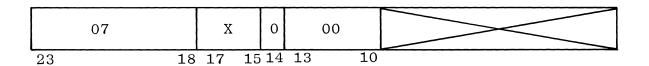

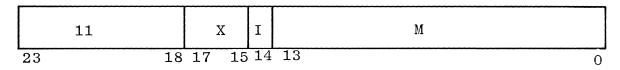

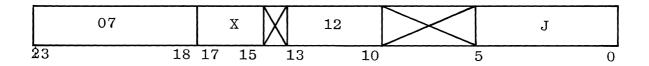

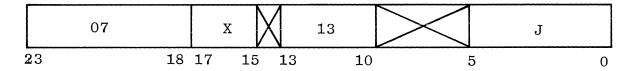

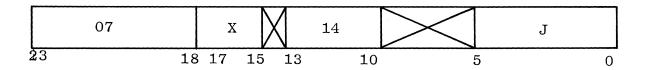

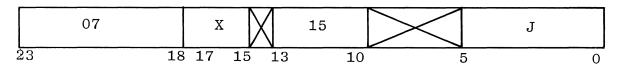

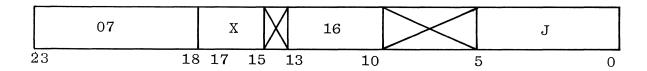

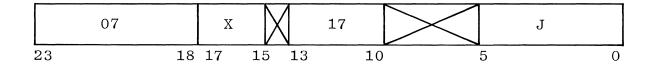

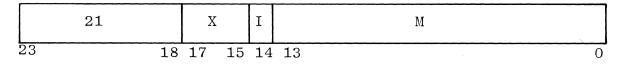

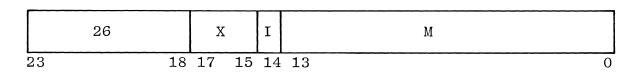

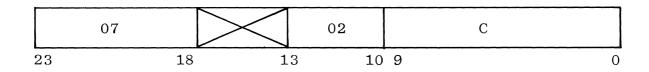

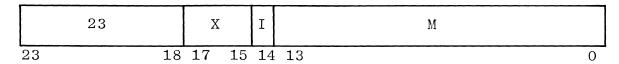

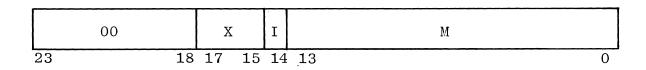

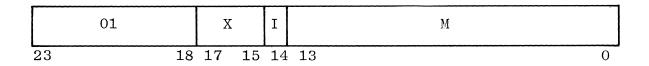

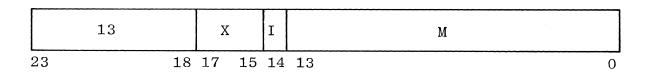

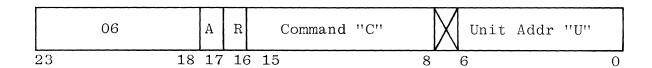

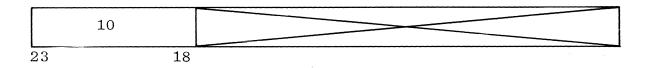

| 3.2       | INSTRUCTION FORMATS                    | II-3-1  |

| 3.2.1     | Word Format                            | II-3-1  |

| 3.2.2     | Standard Instruction Word Format       | II-3-2  |

| 3.2.3     | Augmented Instruction Word Format      | II-3-2  |

| 3.3       | ASSEMBLER FORMATS                      | II-3-2  |

| 3.4       | CYCLES REQUIRED                        | II-3-3  |

| 3.5       | ARITHMETIC INSTRUCTIONS                | II-3-4  |

| 3.5.1     | TCA Two's Complement A Register        | II-3-4  |

| 3.5.2     | DTC Double Two's Complement            | II-3-4  |

| 3.5.3     | ADD Addition                           | II-3-5  |

| 3.5.4     | SUB Subtraction                        | II-3-5  |

| 3.5.6     | DSUB Double Subtraction                | II-3-6  |

| 3.5.7     | MUL Multiply                           | II-3-7  |

| 3.5.8     | DIV Division                           | II-3-7  |

| 3.5.9     | AOM Add One To Memory                  | II-3-8  |

| 3.5.10    | SOM Subtract One From Memory           | 11-3-8  |

| 3.6       | DATA TRANSFER INSTRUCTIONS             | II-3-9  |

| 3.6.1     | RSR Read Switch Register               | 11-3-9  |

| 3.6.2     | EXC Exchange A And E                   | 11-3-9  |

| 3.6.3     | STA Store A                            | II-3-10 |

| 3.6.4     | STE Store E                            | II-3-10 |

| 3.6.5     | LDA Load A                             | II-3-11 |

| 3.6.6     | LDE Load E (The Accumulator Extension) | II-3-11 |

| 3.6.7     | DLD Double E Load A And E              | II-3-11 |

| 3.6.8     | DST Double Store                       | II-3-12 |

| 3.7       | INDEX INSTRUCTIONS                     | II-3-12 |

| 3.7.1     | LDX Load Index                         | II-3-13 |

| 3.7.2     | LXA Load Index From A                  | II-3-13 |

| 3.7.3     | ATX Add To Index                       | II-3-14 |

| 3.7.4     | STX Store                              | II-3-14 |

| 3.7.5     | LAX Load A From Index                  | II-3-15 |

| 3.8       | SHIFT INSTRUCTIONS                     | II-3-15 |

| 3.8.1     | DSN Double Shift Normalize             | II-3-16 |

| 3.8.2     | SR Shift Right                         | II-3-16 |

| 3.8.3     | LS Logical Shift                       | II-3-17 |

| 3.8.4     | SA Shift Around                        | II-3-17 |

| 3.8.5     | SL Shift Left                          | II-3-18 |

| 3.8.6     | DSE Double Shift Right                 | II-3-18 |

| 3.8.7     | LDS Logical Double Shift               | II-3-19 |

| 3.8.8     | DSA Double Shift Around                | II-3-19 |

| 3 8 9     | DSL Double Shift Left                  | TT_3_90 |

|                  |                                                      | Page               |

|------------------|------------------------------------------------------|--------------------|

| 3.9              | LOGICAL INSTRUCTIONS                                 | II-3-20            |

| 3.9.1            | RUM Replace Under Mask                               | II-3-20            |

| 3.9.2            | EOR Exclusive OR                                     | II-3-21            |

| 3.9.3            | AND Logical And                                      | II-3-21            |

| 3.9.4            | OR Logical Or (Inclusive OR)                         | II-3-22            |

| 3.10             | STATE CONTROL INSTRUCTIONS                           | II-3-22            |

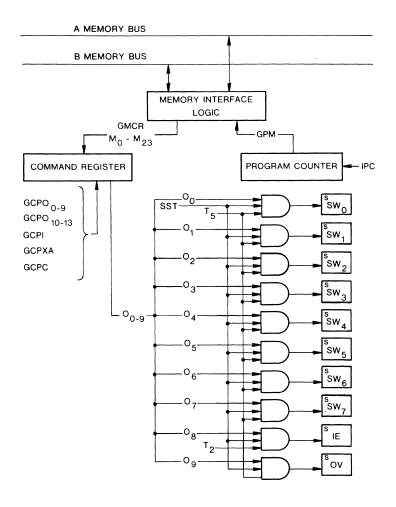

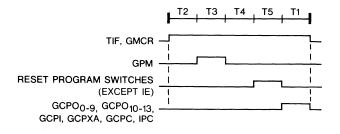

| 3.10.1           | SST Set State                                        | II-3-23            |

| 3.10.2           | RST Reset State                                      | II-3-24            |

| 3.11             | COMPARE INSTRUCTION                                  | II-3-24            |

| 3.11.1           | CAM Compare A With Memory                            | II-3-24            |

| 3.12             | TRANSFER OF CONTROL INSTRUCTIONS                     | II-3-25            |

| 3.12.1           | BAH Branch And Halt                                  | II-3-25            |

| 3.12.2           | BRU Branch Unconditionally                           | II-3-26            |

| 3.12.3           | BAT Branch A Register Test                           | 11-3-27            |

| 3.12.4           | BOI Branch On Indicator                              | II-3-28            |

| 3.12.5           | BOS Branch On State                                  | II-3-28            |

| 3.12.6<br>3.12.7 | BSM Branch Store Return At M                         | II-3-29<br>II-3-30 |

| 3.13             | BSZ Branch Store Return At Zero                      | II-3-30<br>II-3-31 |

| 3.13.1           | INPUT/OUTPUT INSTRUCTIONS SPU Select Peripheral Unit | II-3-31            |

| 3.14             | NO OPERATION INSTRUCTION                             | II-3-31            |

| 3.14.1           | NOP No Operation                                     | II-3-32            |

|                  | -                                                    | 11-0-02            |

| APPENDIX A       | - FST-1 ABBREVIATIONS                                | II-3-33            |

| APPENDIX B       | - INSTRUCTION MNEMONICS                              | II-3-34            |

| SECTION 4        | FST-1 INSTRUCTION EXECUTION AND TIMING               | II-4-1             |

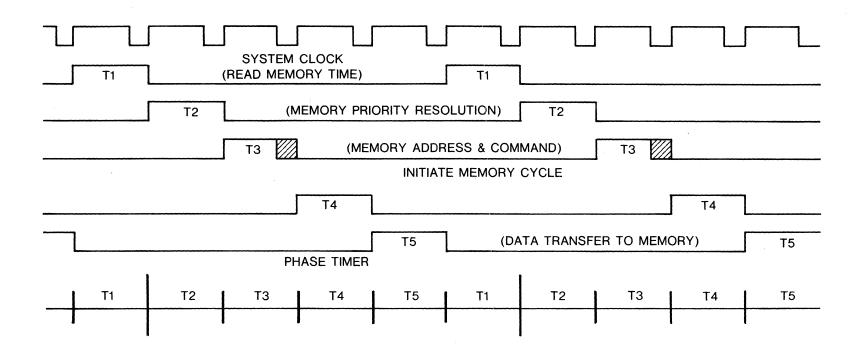

| 4.1              | INTRODUCTION                                         | II-4-1             |

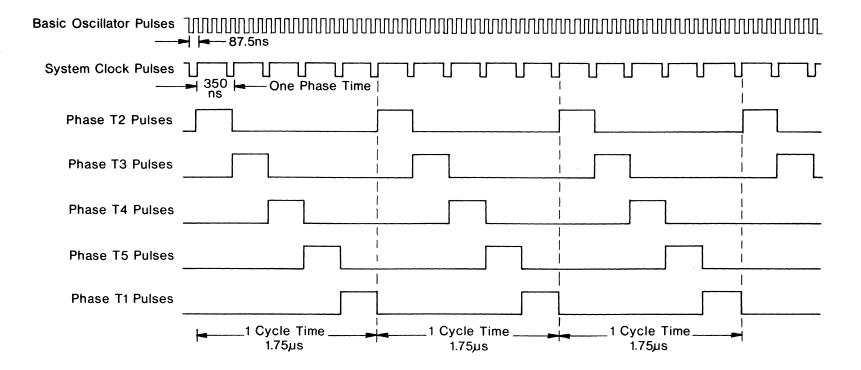

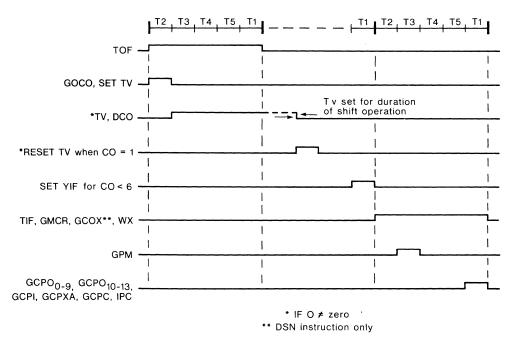

| 4.2              | PHASE TIMER                                          | II-4-1             |

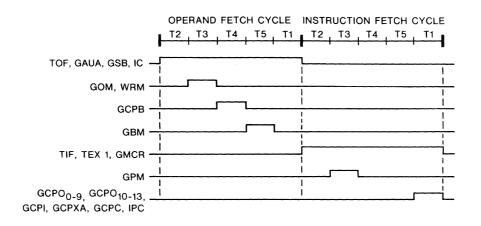

| 4.3              | TIMING DIAGRAMS                                      | II-4-3             |

| 4.4              | OPERAND & INSTRUCTION FETCH CYCLE                    | II-4-3             |

| 4.4.1            | Instruction Fetch Cycle                              | II-4-3             |

| 4.4.2            | Operand Fetch Cycle                                  | II-4-5             |

| 4.4.3            | Address Modification                                 | II-4-6             |

| 4.4.3.1          | Indexing                                             | II-4-6             |

| 4.4.4            | Indirect Addressing                                  | II-4-7             |

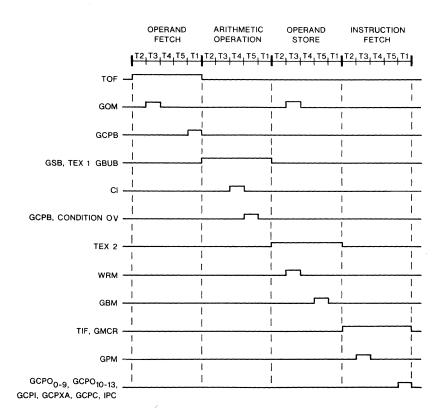

| 4.5              | INSTRUCTION EXECUTION AND TIMING                     | II-4-9             |

| 4.5.1            | Add Instruction                                      | II-4-9             |

| 4.5.2            | Sub Instruction                                      | II-4-9             |

| 4.5.3            | EOR Instruction                                      | II-4-12            |

| 4.5.4            | CAM Instruction                                      | II-4-12            |

| 4.5.5            | LDA Instruction                                      | II <b>-</b> 4-15   |

| 4.5.6            | LDE Instruction                                      | II-4-15            |

| 4.5.7            | RIM. AND and OR Instruction                          | TT-4-15            |

|                                                                                                                                                                                                                                                                                                                                                                                                    | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATX Instruction DTC Instruction BSM Instruction BSZ Instruction STA Instruction STE Instruction STE Instruction TCA Instruction LDX Instruction LDX Instruction LXA Instruction EXC Instruction EXC Instruction SST Instruction SST Instruction SPU Instruction BRU Instruction BRU Instruction BAH Instruction BAT Instruction BOS Instruction BOI Instruction BOI Instruction SHIFT Instructions | Page  II-4-22 II-4-24 II-4-27 II-4-27 II-4-30 II-4-30 II-4-34 II-4-34 II-4-34 II-4-34 II-4-39 II-4-39 II-4-43 II-4-43 II-4-43 II-4-43 II-4-43 II-4-49 II-4-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AOM Instruction                                                                                                                                                                                                                                                                                                                                                                                    | II <b>-</b> 4-53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SOM Instruction DADD Instruction DSUB Instruction DLD Instruction DST Instruction MUL Instruction DIV Instruction                                                                                                                                                                                                                                                                                  | II-4-55<br>II-4-58<br>II-4-58<br>II-4-61<br>II-4-61<br>II-4-64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                    | DTC Instruction BSM Instruction BSZ Instruction STA Instruction STE Instruction STX Instruction TCA Instruction LDX Instruction LXA Instruction EXC Instruction EXC Instruction EXC Instruction SST Instruction SPU Instruction BRU Instruction BRU Instruction BAH Instruction BOS Instruction BOI Instruction BOI Instruction SOM Instruction SOM Instruction DADD Instruction DSUB Instruction |

# Chapter III Memory System

| SECTION 1 | MEMORY SYSTEM                      | III-1-1 |

|-----------|------------------------------------|---------|

| 1.0       | INTRODUCTION                       | III-1-1 |

| 1.1       | GENERAL DESCRIPTION                | III-1-1 |

| 1.1.1     | Basic Storage Module (BSM)         | III-1-4 |

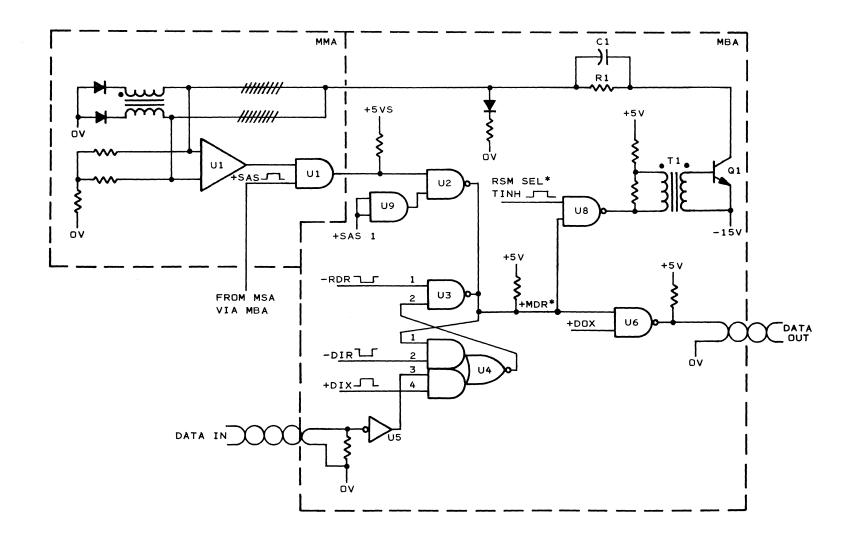

| 1.1.2     | The Memory Magnetic Assembly (MMA) | III-1-4 |

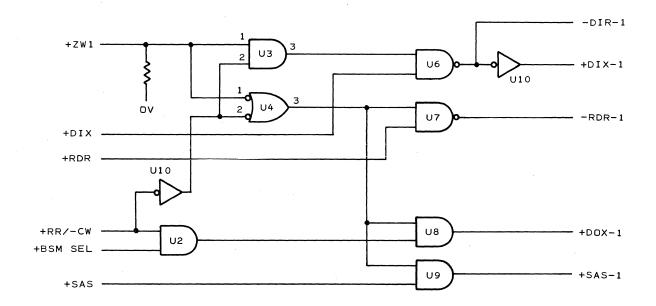

| 1.1.3     | The Memory Switch Assembly (MSA)   | III-1-4 |

|                                     |                                                                                                                           | Page                                                   |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| SECTION 2                           | PRINCIPLES OF OPERATION                                                                                                   | III-2-1                                                |

| 2.0<br>2.1<br>2.1.1                 | INTRODUCTION THE RANDOM-ACCESS, DIGITAL STORAGE DEVICE                                                                    | III-2-1<br>III-2-1                                     |

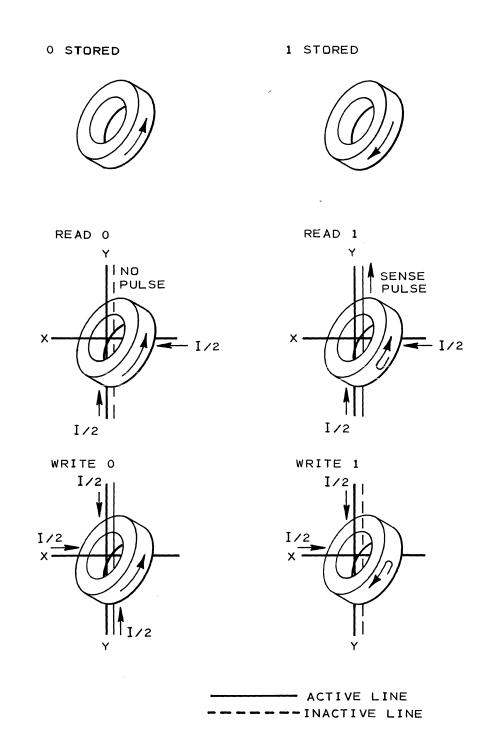

| 2.1.1<br>2.1.2<br>2.1.3             | Magnetic Characteristics of the<br>Ferrite Core<br>The 3D System<br>Operation                                             | III-2-2<br>III-2-2<br>III-2-4                          |

| SECTION 3                           | THEORY OF OPERATION                                                                                                       | III-3-1                                                |

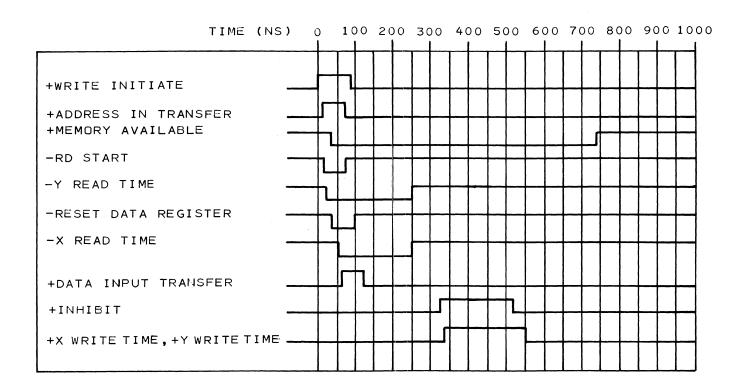

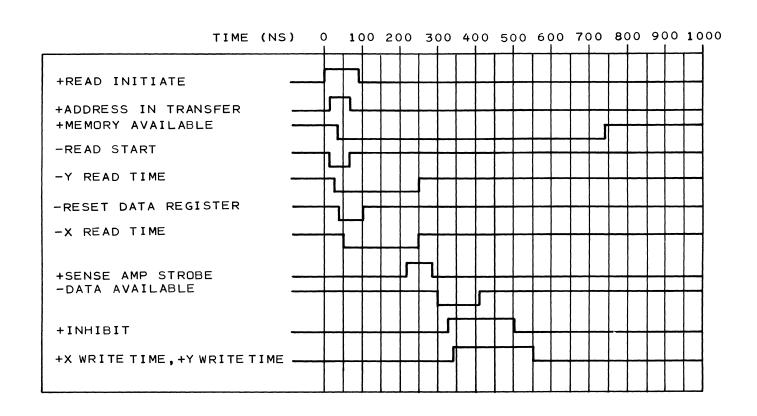

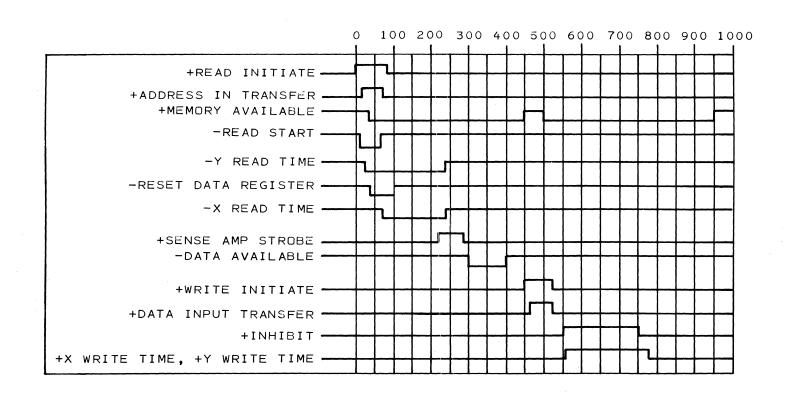

| 3.0<br>3.1<br>3.1.1                 | INTRODUCTION GENERAL DESCRIPTION Operating Modes                                                                          | III-3-1<br>III-3-1<br>III-3-4                          |

| SECTION 4                           | CIRCUIT DESCRIPTION                                                                                                       | III-4-1                                                |

| 4.0<br>4.1<br>4.1.1<br>4.1.2<br>4.2 | INTRODUCTION MEMORY SWITCH ASSEMBLY (MSA) Memory Magnetic Assembly The Memory Bit Assembly SIGNAL NAMES AND ABBREVIATIONS | III-4-1<br>III-4-1<br>III-4-12<br>III-4-14<br>III-4-17 |

# LIST OF ILLUSTRATIONS

|        |          | I                                            | Page    |

|--------|----------|----------------------------------------------|---------|

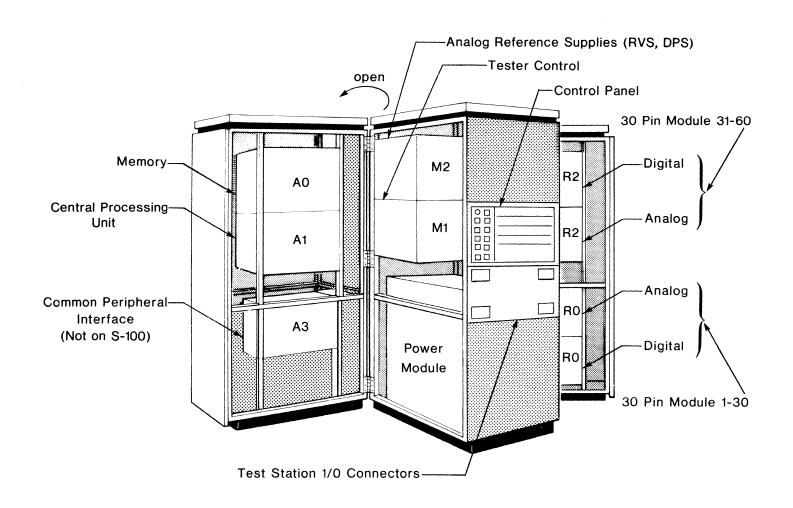

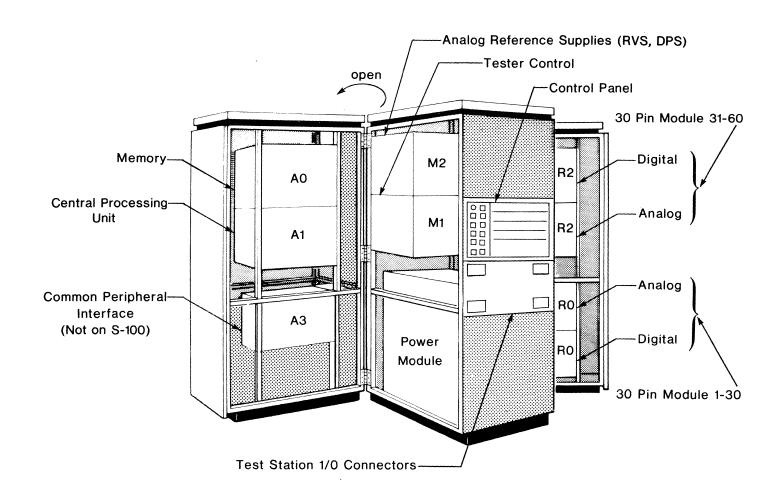

| Figure | I-1-1.   | Sentry Systems Mainframe                     | I-1-2   |

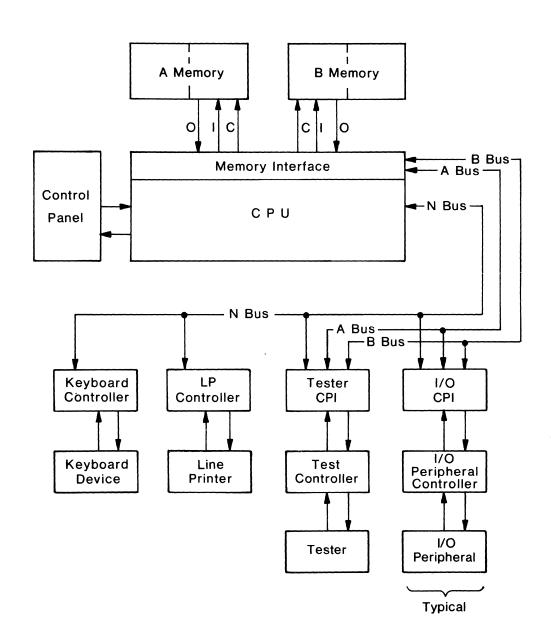

| Figure | I-1-2.   | Basic FST-1 System Configuration             | I-1-4   |

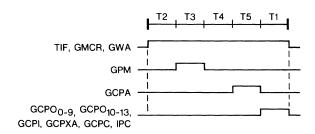

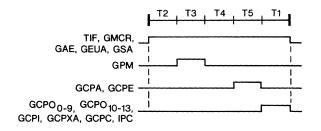

| Figure | I-1-3.   | Basic FST-1 Timing Diagram                   | I-1-5   |

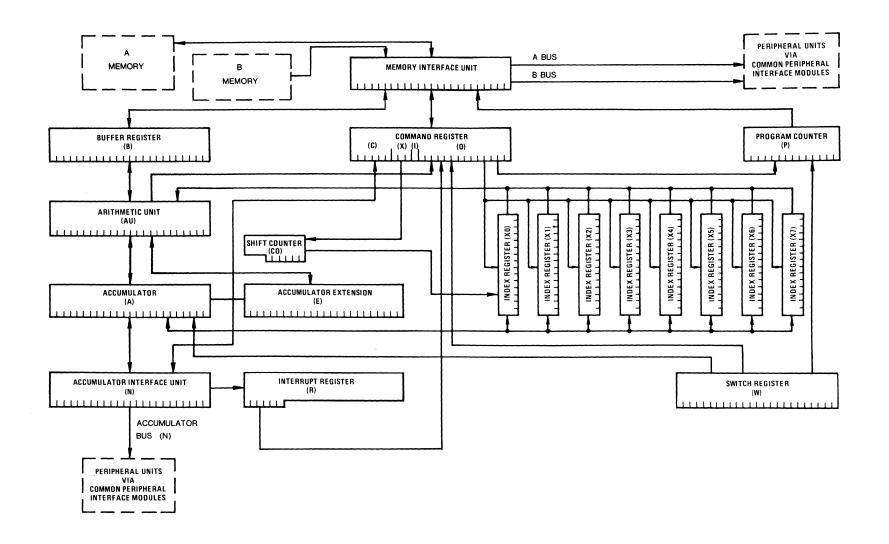

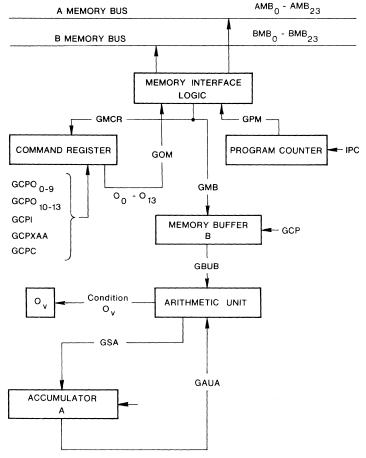

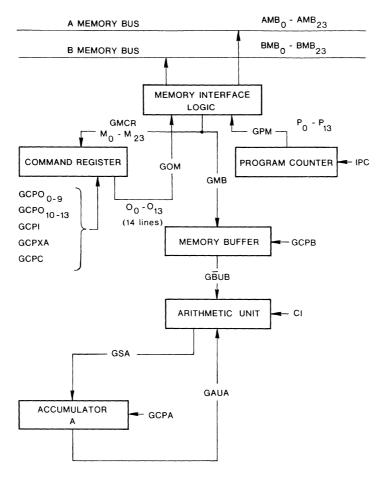

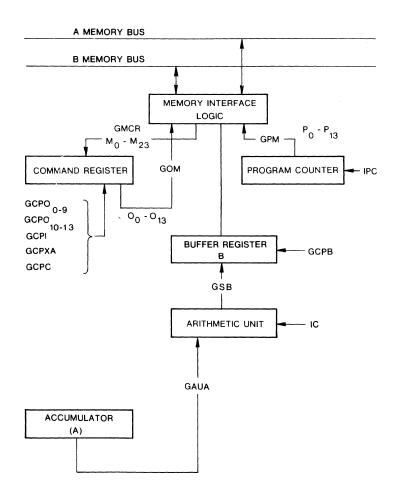

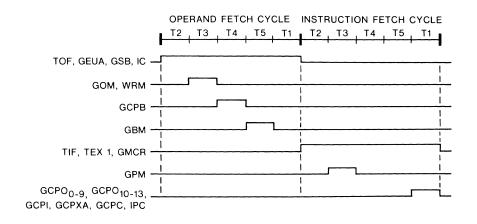

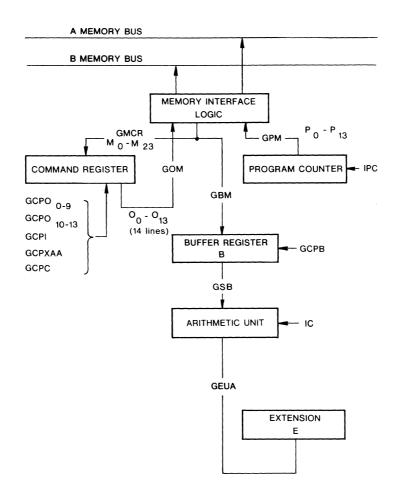

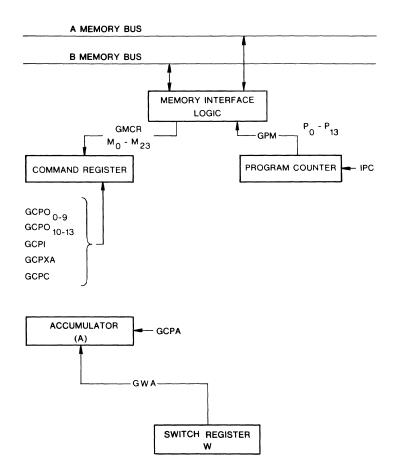

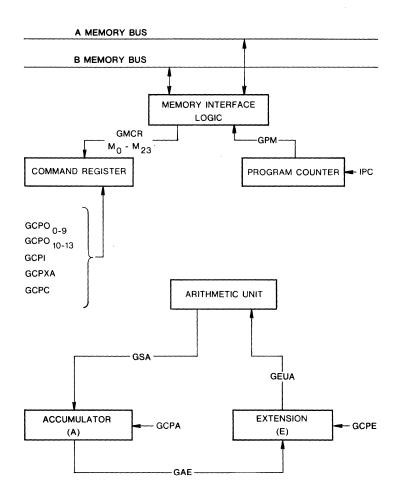

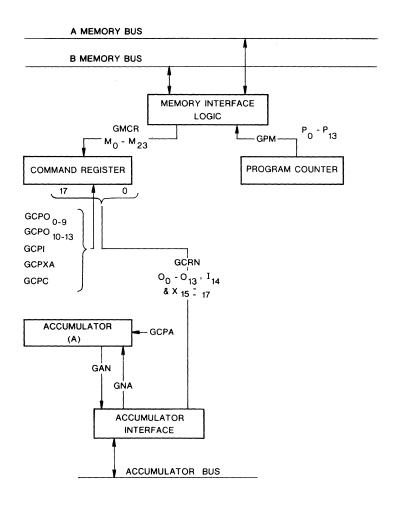

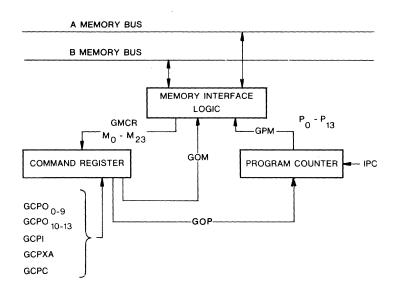

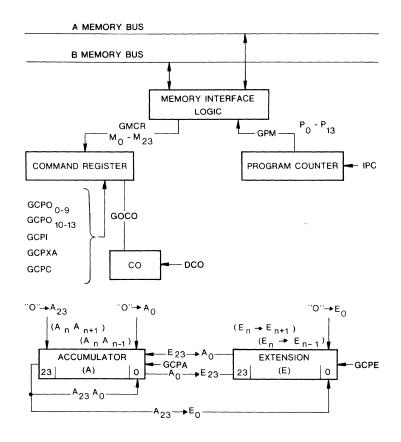

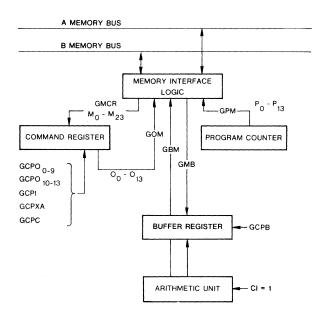

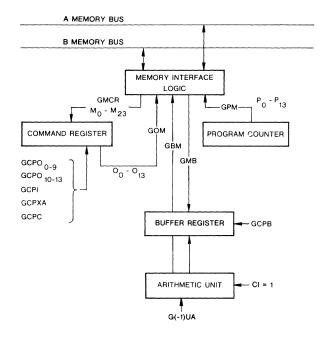

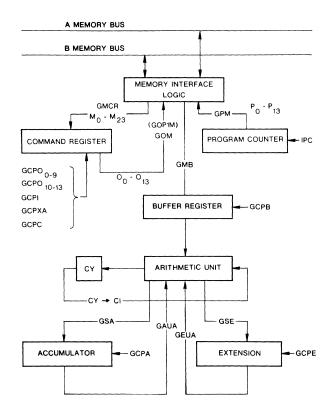

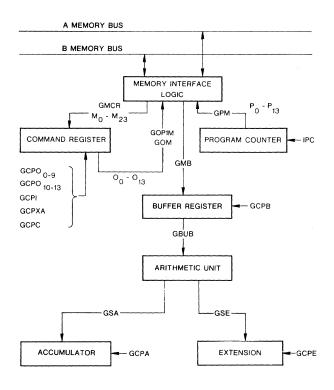

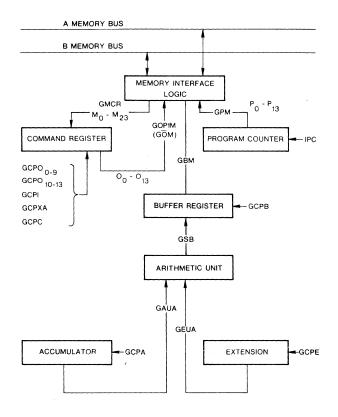

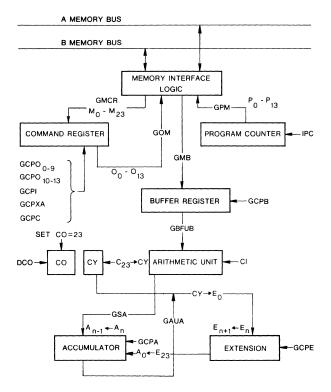

| Figure | I-1-4.   | FST-1 Simplified Block Diagram               | I-1-7   |

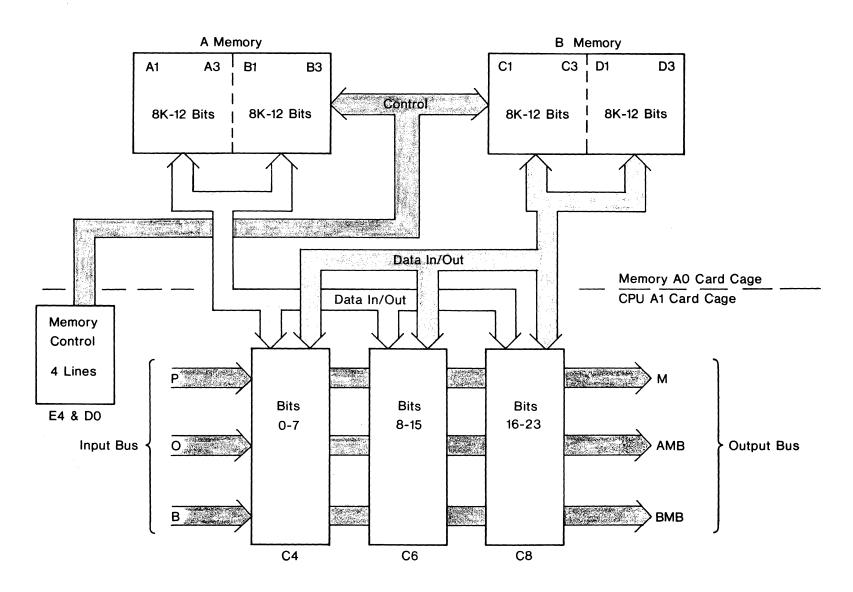

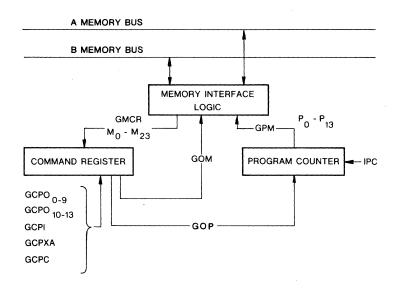

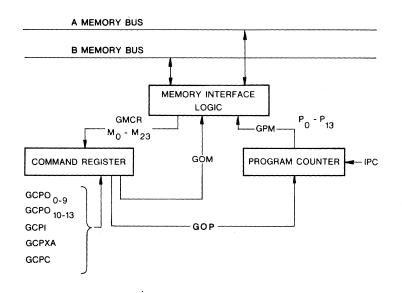

| Figure | I-1-5.   | Memory Interface                             | I-1-13  |

| Figure | I-1-6.   | One Bit Memory Dataflow                      | I-1-15  |

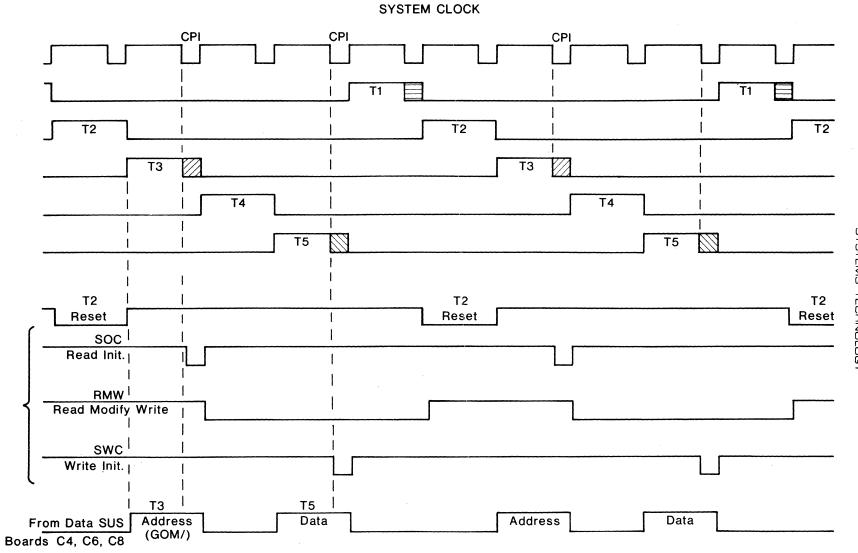

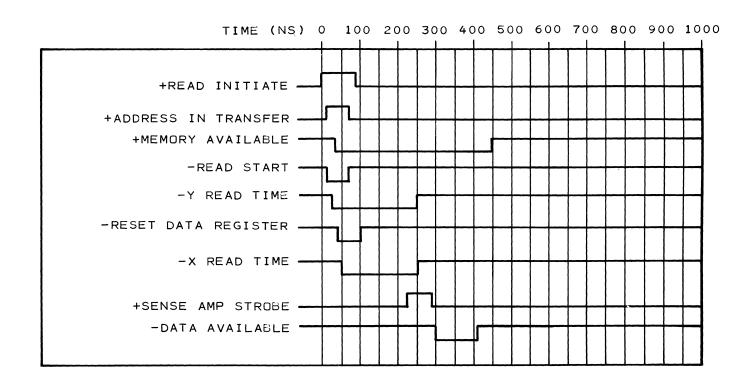

| Figure | I-1-7.   | Memory Read Cycle                            | I-1-17  |

| Figure | I-1-8.   | Memory Write Cycle                           | I-1-18  |

| Figure | I-2-1.   | FST-1 Front Panel Controls & Indicators      | I-2-10  |

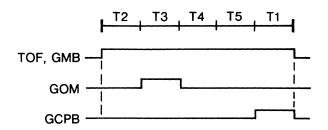

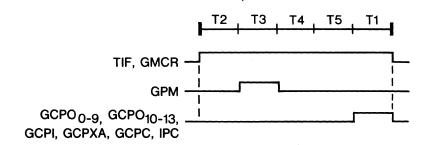

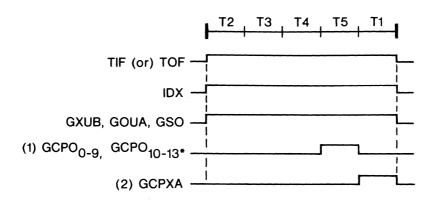

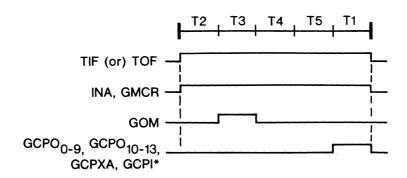

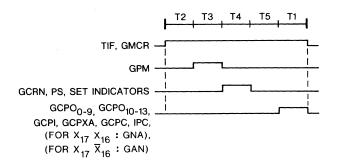

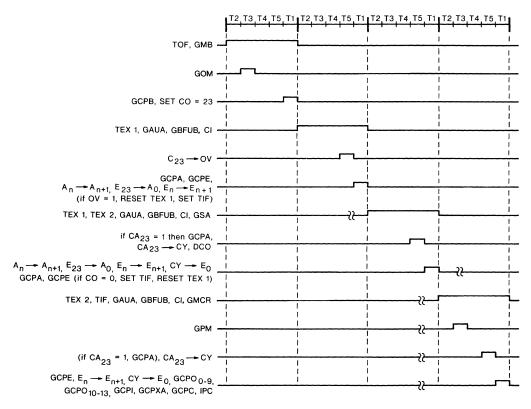

| Figure | II-4-1.  | System Clock & Phase Timer                   | II-4-2  |

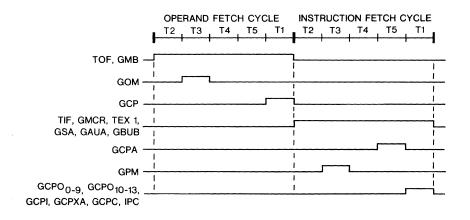

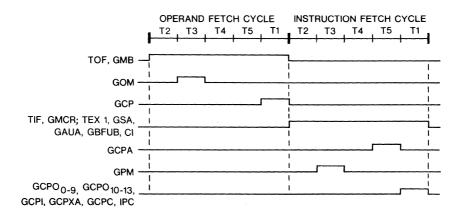

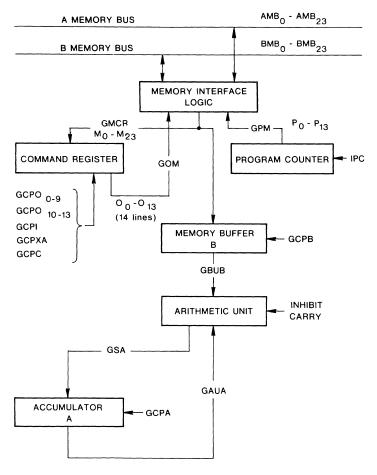

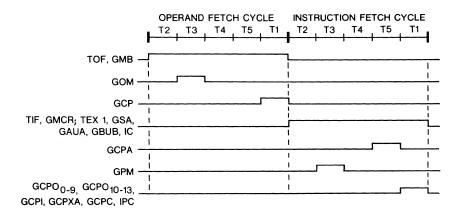

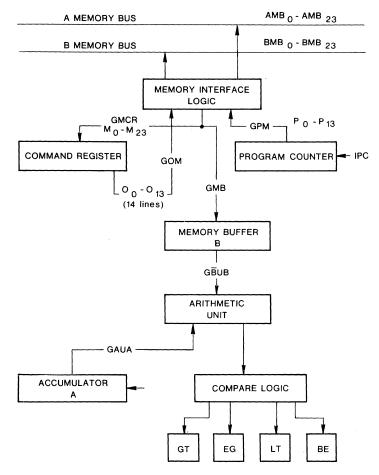

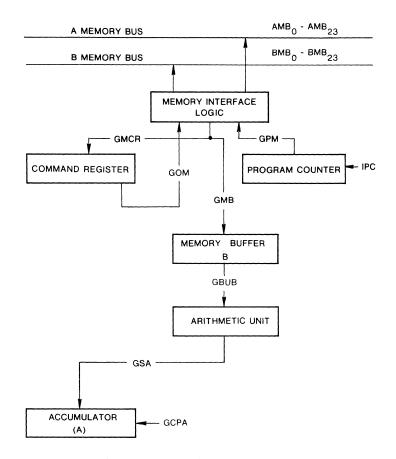

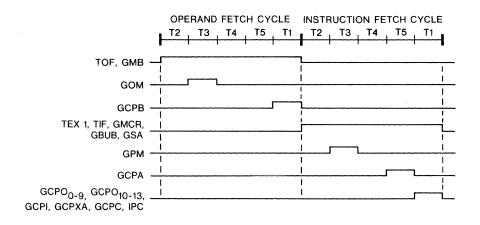

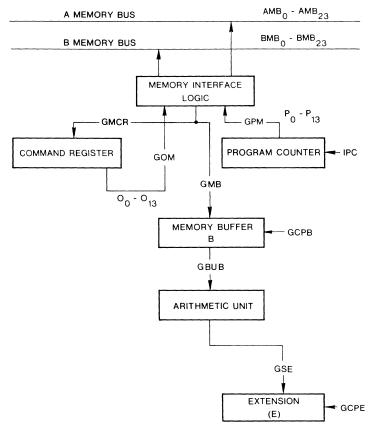

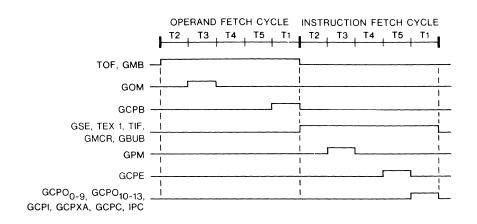

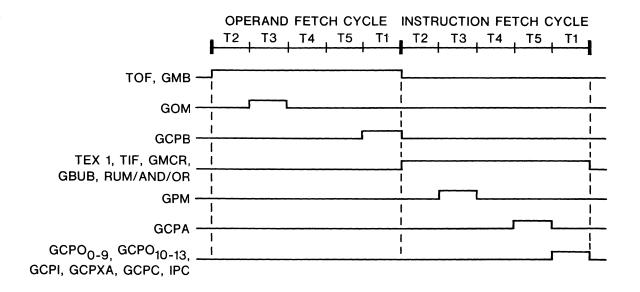

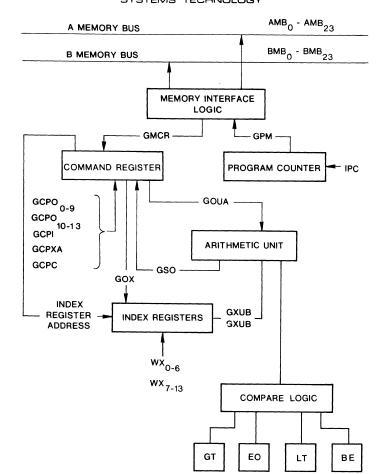

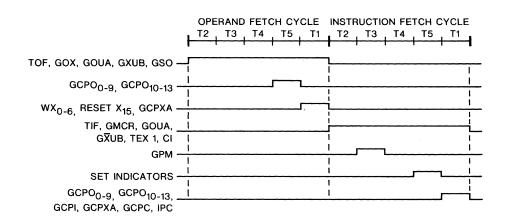

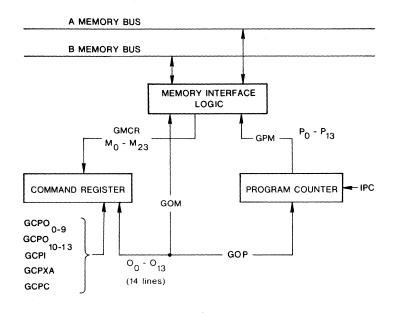

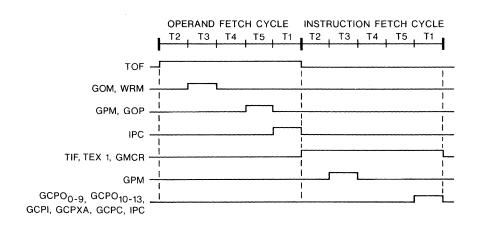

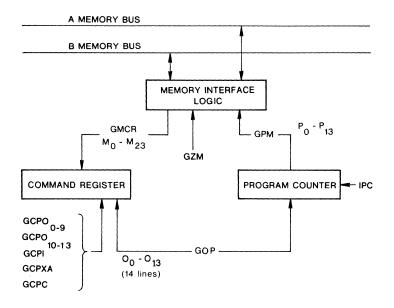

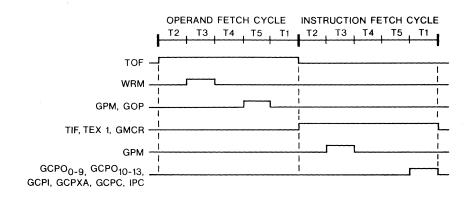

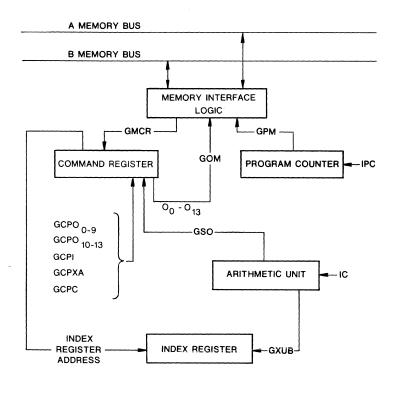

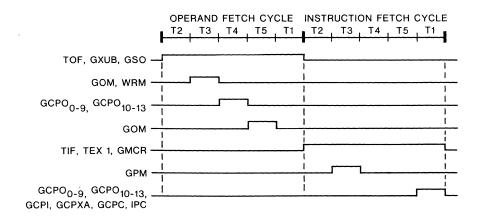

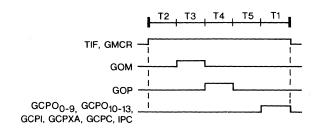

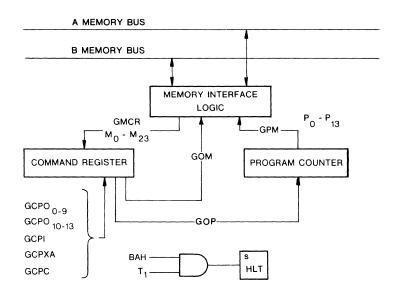

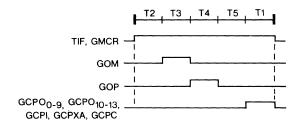

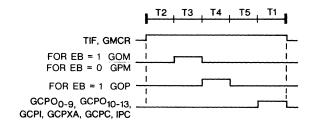

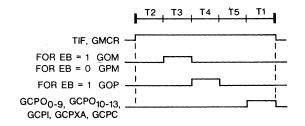

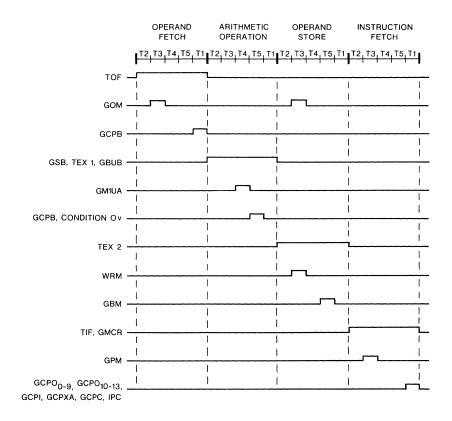

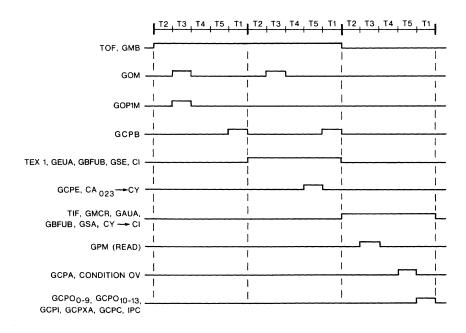

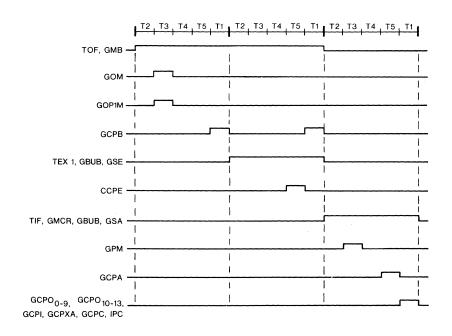

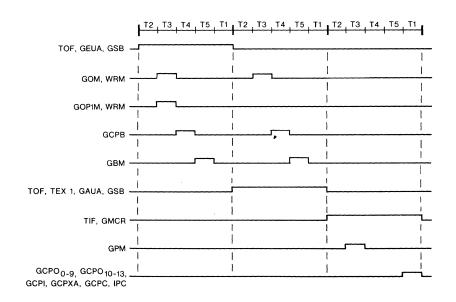

| Figure | II-4-2.  | Operand & Instruction Fetch Cycle            | II-4-4  |

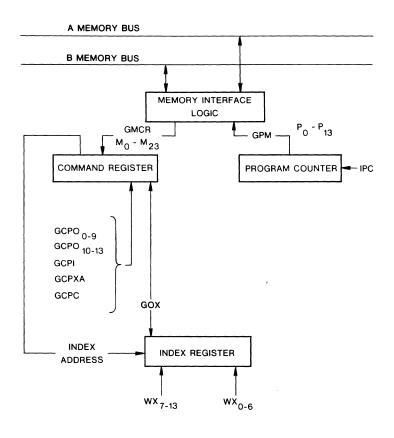

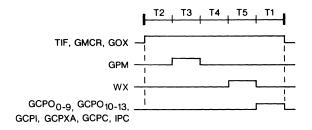

| Figure | II-4-3.  | Indexing Address Modification Timing Diagram | II-4-8  |

| Figure | II-4-4.  | Indirect Address Modification                | 11 1 0  |

| rigure | 11 1 1.  | Timing Diagram                               | II-4-8  |

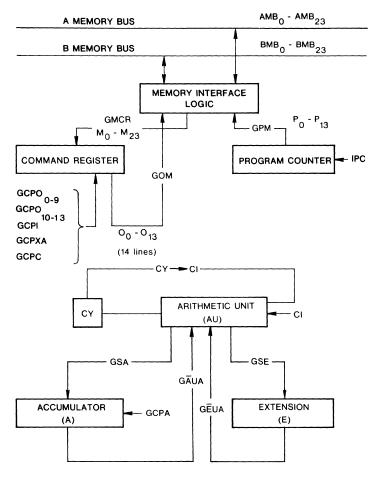

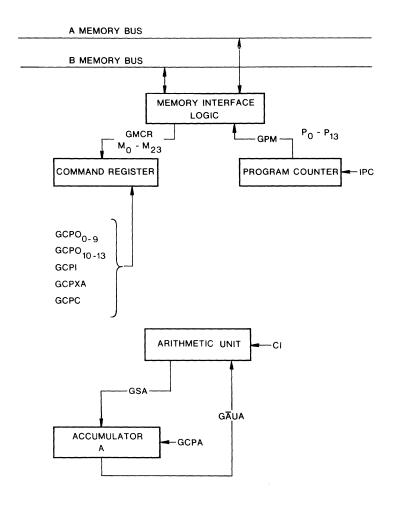

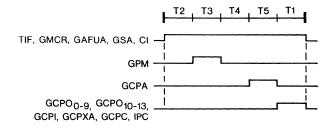

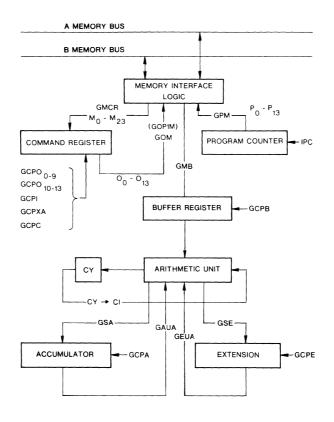

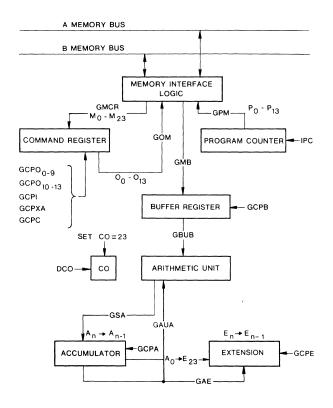

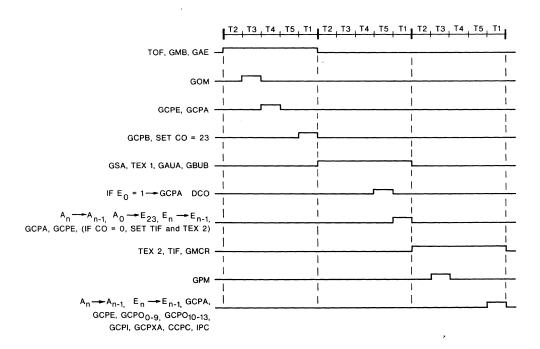

| Figure | II-4-5.  | Add Instruction Flow Diagram                 | II-4-10 |

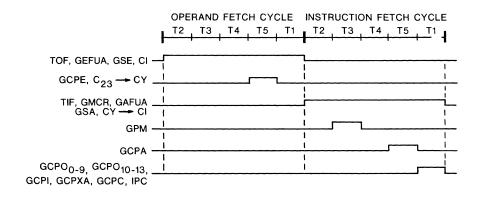

| Figure | II-4-6.  | Add Instruction Timing Diagram               | II-4-10 |

| Figure | 11-4-7   | SUB Instruction Flow Diagram                 | II-4-11 |

| Figure | II-4-8.  | SUB Instruction Timing Diagram               | II-4-11 |

| Figure | II-4-9.  | EOR Instruction Flow Diagram                 | II-4-13 |

| Figure | II-4-10. |                                              | II-4-13 |

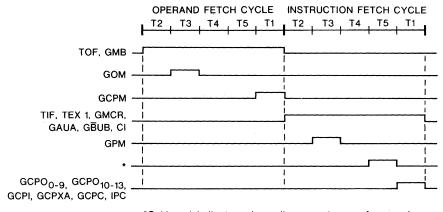

| Figure | II-4-11. | CAM Instruction Flow Diagram                 | II-4-14 |

| Figure | II-4-12. | CAM Instruction Timing Diagram               | II-4-14 |

| Figure | II-4-13. | LDA Instruction Flow Diagram                 | II-4-16 |

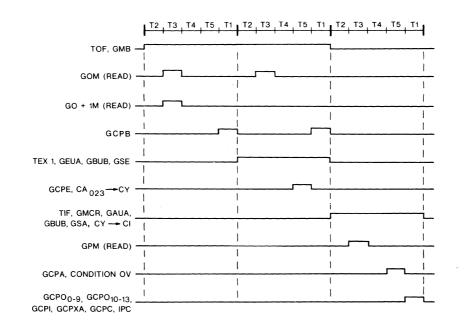

| Figure | II-4-14. | LDA Instruction Timing Diagram               | II-4-16 |

| Figure | II-4-15. | LDE Instruction Flow Diagram                 | II-4-17 |

| Figure | II-4-16. |                                              | II-4-17 |

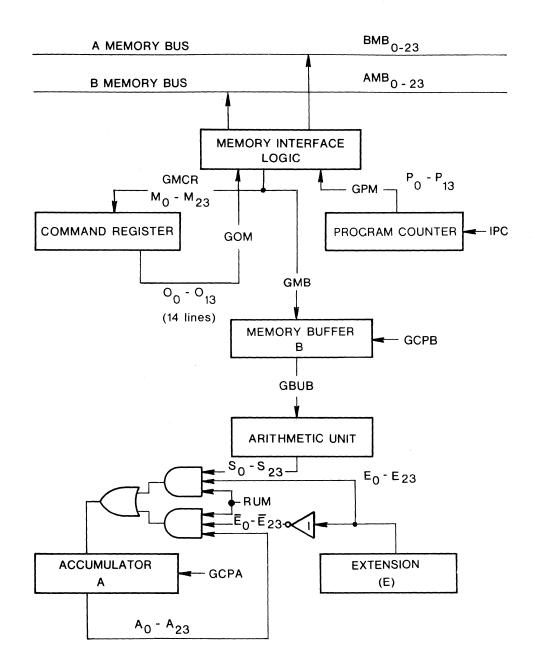

| Figure | II-4-17. | RUM Instruction Flow Diagram                 | II-4-18 |

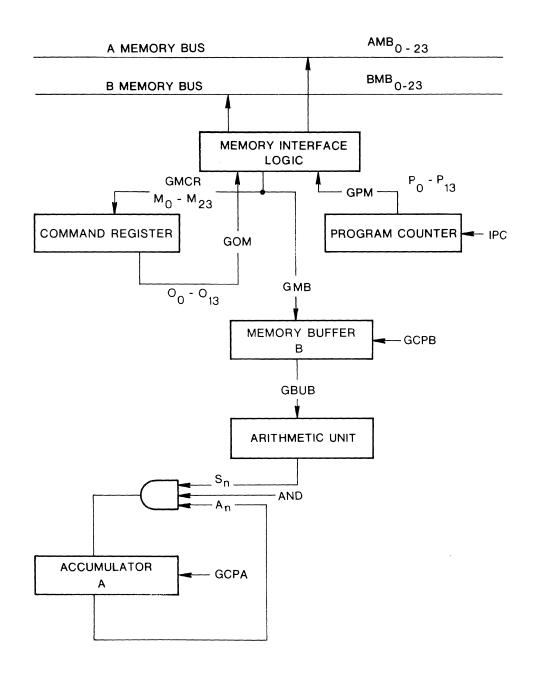

| Figure | II-4-18. | AND Instruction Flow Diagram                 | II-4-19 |

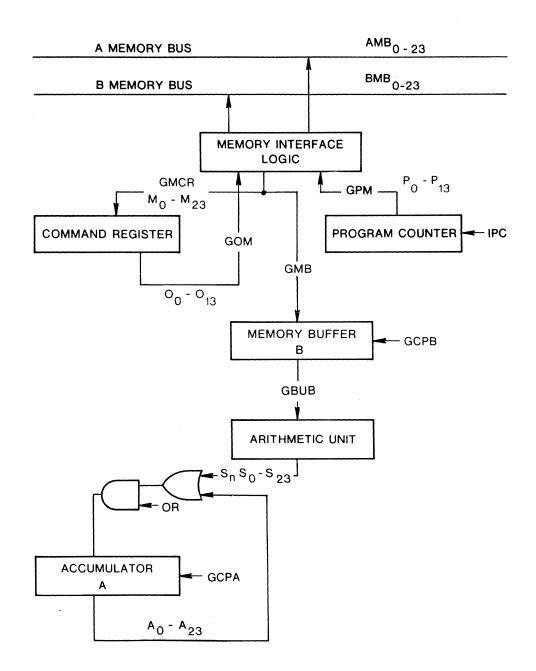

| Figure | II-4-19. |                                              | II-4-20 |

| Figure | II-4-20. | •                                            | II-4-21 |

| Figure | II-4-21. | , ,                                          | II-4-23 |

| Figure | II-4-22. |                                              | II-4-23 |

| Figure | II-4-23. |                                              | II-4-25 |

| Figure |          | DTC Instruction Timing Diagram               | II-4-25 |

| Figure |          | BSM Instruction Flow Diagram                 | II-4-26 |

| Figure |          | BSM Instruction Timing Diagram               | II-4-26 |

| Figure | II-4-27. |                                              | II-4-28 |

| Figure | II-4-28. | 9                                            | II-4-28 |

| Figure | II-4-29. |                                              | II-4-29 |

| Figure | II-4-30. |                                              | II-4-29 |

| Figure | II-4-31. | STE Instruction Flow Diagram                 | II-4-31 |

| Figure | II-4-32. |                                              | II-4-31 |

| Figure | II-4-33. | 3                                            | II-4-32 |

| Figure |          | STX Instruction Timing Diagram               | TT-4-32 |

## List of Illustrations (Continued)

|           |           |                                                             | Page                      |

|-----------|-----------|-------------------------------------------------------------|---------------------------|

| Ti mumo   | TT 4 95   | TCA Instruction Flow Diagram                                | II-4-33                   |

| Figure    |           | TCA Instruction Flow Diagram TCA Instruction Timing Diagram | II-4-33                   |

| Figure    |           | LDX Instruction Flow Diagram                                | II-4-35                   |

| Figure    |           | LDX Instruction Timing Diagram                              | II-4-35                   |

| Figure    |           |                                                             | II-4-36                   |

| Figure    |           | LXA Instruction Flow Diagram                                | II-4-36                   |

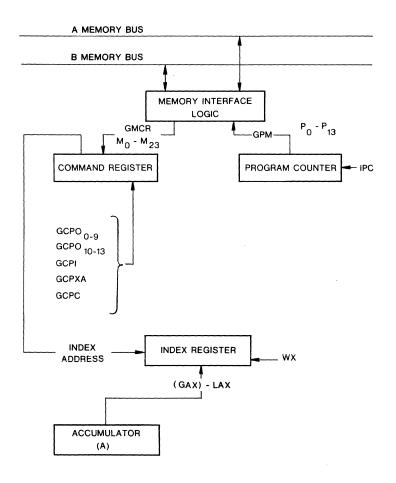

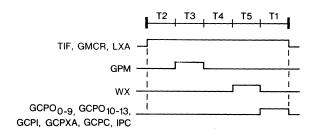

| Figure    |           | LXA Instruction Timing Diagram                              |                           |

| Figure    |           | RSR Instruction Flow Diagram                                | II-4-37                   |

| Figure    |           | RSR Instruction Timing Diagram                              | II-4-37                   |

| Figure    | II-4-43.  |                                                             | II-4-38                   |

| Figure    | II-4-44.  |                                                             | II-4-38                   |

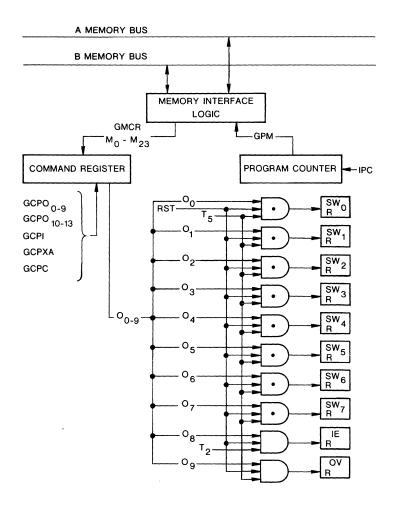

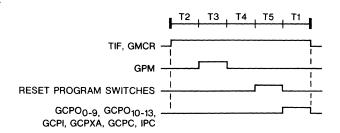

| Figure    |           | RST Instruction Flow Diagram                                | II-4-40                   |

| Figure    | II-4-46.  |                                                             | II-4-40                   |

| Figure    | II-4-47.  | •                                                           | II-4-41                   |

| Figure    | II-4-48.  |                                                             | II-4-41                   |

| Figure    | II-4-49.  | G                                                           | II-4-42                   |

| Figure    | II-4-50.  |                                                             | II-4-42                   |

| Figure    | II-4-51.  | •                                                           | II-4-44                   |

| Figure    | II-4-52.  | BRU Instruction Timing Diagram                              | II-4-44                   |

| Figure    | II-4-53.  | BAH Instruction Flow Diagram                                | II <b>-</b> 4 <b>-</b> 45 |

| Figure    | II-4-54.  | BAH Instruction Timing Diagram                              | II <b>-</b> 4-45          |

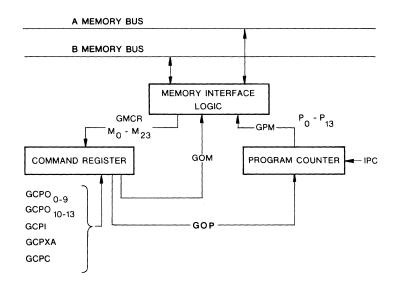

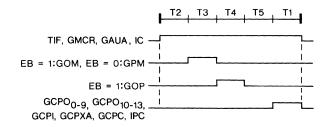

| Figure    | II-4-55.  | BAT Instruction Flow Diagram                                | II-4-47                   |

| Figure    | II-4-56.  | BAT Instruction Timing Diagram                              | II-4-47                   |

| Figure    | II-4-57.  | BOS Instruction Flow Diagram                                | II-4-48                   |

| Figure    | II-4-58.  | BOS Instruction Timing Diagram                              | II-4-48                   |

| Figure    | II-4-59.  | BOI Instruction Flow Diagram                                | II-4-50                   |

| Figure    | II-4-60.  |                                                             | II-4-50                   |

| Figure    | II-4-61.  |                                                             | II-4-51                   |

| Figure    | II-4-62.  |                                                             | II-4-51                   |

| Figure    | II-4-63.  |                                                             | II-4-52                   |

| Figure    | II-4-64.  |                                                             | II-4-54                   |

| Figure    | II-4-65.  |                                                             | II <b>-</b> 4-54          |

| Figure    | II-4-66.  | <u> </u>                                                    | II-4-56                   |

| Figure    |           | SOM Instruction Timing Diagram                              | II <b>-</b> 4-56          |

| Figure    |           | DADD Instruction Flow Diagram                               | II-4-57                   |

| Figure    | II-4-69.  |                                                             | II-4-57                   |

| Figure    |           | DSUB Instruction Flow Diagram                               | II-4-59                   |

| Figure    |           | DSUB Instruction Timing Diagram                             | II-4-59                   |

| Figure    |           | DLD Instruction Flow Diagram                                | II-4-60                   |

| Figure    |           | DLD Instruction Timing Diagram                              | II-4-60                   |

| Figure    |           | DST Instruction Flow Diagram                                | II-4-62                   |

| Figure    |           | DST Instruction Timing Diagram                              | II-4-62                   |

| Figure    | II-4-76.  |                                                             | II-4-63                   |

| Figure    | 11-4-77.  | <u> </u>                                                    | II-4-63                   |

| Figure    | II-4-78.  |                                                             | II-4-65                   |

| Figure    |           | DIV Instruction Flow Diagram                                | II-4-66                   |

| Figure    |           | DIV Instruction Flow Bragram DIV Instruction Timing Diagram | II-4-66                   |

| * +8 U1 G | .11-1-00. | DIV INSCINCTION TIMING DIAGRAM                              | 11-4-00                   |

# List of Illustrations (Continued)

| Figure III-1-1. Sentry Systems Mainframe Figure III-1-2. Memory System With Full Complement of Modules Figure III-1-3. Basic Storage Module Figure III-1-4. The Memory Magnetic Assembly Figure III-1-5. The Memory Switch Assembly Figure III-1-6. The Memory Bit Assembly Figure III-2-1. Hysterises Loop Of A Ferrite Memory Core Figure III-2-2. Ferrite Core Memory Element With Three Wires Figure III-2-3. Sense Winding Output Curve Figure III-2-4. Read And Write Operations Figure III-3-1. Memory System Block Diagram Figure III-3-2. Internal Timing Clear/Write Figure III-3-2. Internal Timing Read/Restore Figure III-3-5. Internal Timing Read/Restore Figure III-4-1. Timing And Control Logic Figure III-4-2. Internal Timing Relationship Figure III-4-3. Address Register Figure III-4-5. Addressing Decoding Figure III-4-5. Sense, Inhibit And Data Circuitry Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-9. Zone Control Circuitry  LIST OF TABLES  Table II-3-1. Clear/Write Table III-3-2. Read/Modify/Write Table III-3-3. Read/Modify/Write Table III-3-3. Read/Modify/Write Table III-3-3. Read/Modify/Write Table III-3-3. Read/Modify/Write Tible III-3-3. Read/Modify/Write Tible III-3-3. Read/Modify/Write Table III-3-4. Read Only TIII-3-15 Table III-3-4. Read Only TIII-3-15 Table III-3-4. Read Only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |          |                                       | Page                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|---------------------------------------|---------------------------|

| Figure III-1-2. Memory System With Full Complement of Modules Figure III-1-3. Basic Storage Module Figure III-1-4. The Memory Magnetic Assembly Figure III-1-5. The Memory Switch Assembly Figure III-1-6. The Memory Switch Assembly Figure III-1-7. The Memory Switch Assembly Figure III-2-1. Hysterises Loop Of A Ferrite Memory Core Figure III-2-2. Hysterises Loop Of A Ferrite With Three Wires Figure III-2-3. Sense Winding Output Curve Figure III-2-4. Read And Write Operations Figure III-3-1. Memory System Block Diagram Figure III-3-2. Internal Timing Clear/Write Figure III-3-3. Internal Timing Read/Restore Figure III-3-4. Internal Timing Read/Modify/Write Figure III-3-5. Internal Timing - Read Only Figure III-4-1. Timing And Control Logic Figure III-4-2. Internal Timing Relationship Figure III-4-3. Address Register Figure III-4-3. General Reset Circuit Figure III-4-4. General Reset Circuit Figure III-4-6. Simplified View Of Current Sources Figure III-4-7. Voltage Regulator Figure III-4-7. Voltage Regulator Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-18. Sense, Inhibit And Data Circuitry Figure III-4-19. Zone Control Circuitry  LIST OF TABLES  Table II-1-1. A1 Card Cage  Table II-1-1. A2 Card Cage  Table III-3-1. Clear/Write Table III-3-2. Read/Restore Table III-3-3. Read/Modify/Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Figure | II-4-81. | Simplified Division Example           | II-4-69                   |

| Complement of Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |          |                                       | III-1-2                   |

| Figure III-1-3. Basic Storage Module Figure III-1-4. The Memory Magnetic Assembly Figure III-1-5. The Memory Switch Assembly Figure III-1-6. The Memory Bit Assembly Figure III-1-6. The Memory Bit Assembly Figure III-2-1. Hysterises Loop Of A Ferrite Memory Core Figure III-2-2. Ferrite Core Memory Element With Three Wires Figure III-2-3. Sense Winding Output Curve Figure III-2-4. Read And Write Operations Figure III-3-1. Memory System Block Diagram III-3-2 Figure III-3-2. Internal Timing Clear/Write Figure III-3-3. Internal Timing Read/Modify/Write Figure III-3-4. Internal Timing - Read/Modify/Write Figure III-3-5. Internal Timing - Read Only Figure III-4-1. Timing And Control Logic Figure III-4-2. Internal Timing Relationship Figure III-4-3. Address Register Figure III-4-4. General Reset Circuit Figure III-4-5. Address Register Figure III-4-6. Simplified View Of Current Sources Figure III-4-7. Voltage Regulator Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-9. Zone Control Circuitry Figure III-4-9. Zone Control Circuitry Figure III-4-1. Clear/Write Table II-1-1. A1 Card Cage  Table II-1-1. Clear/Write Table III-3-1. Clear/Write Table III-3-2. Read/Restore Table III-3-3. Read/Modify/Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figure | III-1-2. | · ·                                   |                           |

| Figure III-1-4. The Memory Magnetic Assembly III-1-6 Figure III-1-5. The Memory Switch Assembly III-1-6 Figure III-1-6. The Memory Bit Assembly III-1-7 Figure III-2-1. Hysterises Loop Of A Ferrite    Memory Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |          |                                       |                           |

| Figure III-1-5. The Memory Switch Assembly III-1-6 Figure III-1-6. The Memory Bit Assembly III-1-7 Figure III-2-1. Hysterises Loop Of A Ferrite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |          | Basic Storage Module                  | III <b>-</b> 1-3          |

| Figure III-1-6. The Memory Bit Assembly Figure III-2-1. Hysterises Loop Of A Ferrite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure | III-1-4. | The Memory Magnetic Assembly          | III <b>-1-</b> 6          |

| Figure III-2-1. Hysterises Loop Of A Ferrite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure | III-1-5. | The Memory Switch Assembly            | III <b>-</b> 1-6          |

| Memory Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure | III-1-6. | The Memory Bit Assembly               | III-1-7                   |

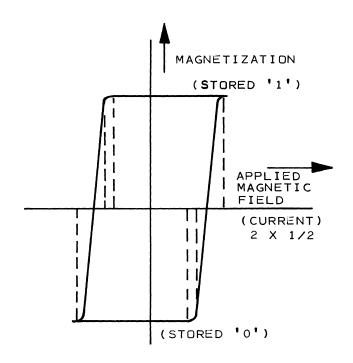

| Figure III-2-2. Ferrite Core Memory Element With Three Wires Figure III-2-3. Sense Winding Output Curve Figure III-2-4. Read And Write Operations Figure III-3-1. Memory System Block Diagram Figure III-3-2. Internal Timing Clear/Write Figure III-3-3. Internal Timing Read/Restore Figure III-3-4. Internal Timing - Read/Modify/Write Figure III-3-5. Internal Timing - Read Only Figure III-4-1. Timing And Control Logic Figure III-4-2. Internal Timing Relationship Figure III-4-3. Address Register Figure III-4-4. General Reset Circuit Figure III-4-5. Addressing Decoding Figure III-4-6. Simplified View Of Current Sources Figure III-4-7. Voltage Regulator Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-9. Zone Control Circuitry  LIST OF TABLES  Table II-1-1. A1 Card Cage  Table III-3-1. Clear/Write Table III-3-2. Read/Restore Table III-3-3. Read/Modify/Write  III-3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure | III-2-1. | Hysterises Loop Of A Ferrite          |                           |

| With Three Wires Figure III-2-3. Sense Winding Output Curve Figure III-2-4. Read And Write Operations Figure III-3-1. Memory System Block Diagram III-3-2 Figure III-3-2. Internal Timing Clear/Write Figure III-3-3. Internal Timing Read/Restore Figure III-3-3. Internal Timing - Read/Modify/Write Figure III-3-5. Internal Timing - Read/Modify/Write Figure III-3-5. Internal Timing - Read Only Figure III-4-1. Timing And Control Logic Figure III-4-2. Internal Timing Relationship Figure III-4-3. Address Register Figure III-4-5. Addressing Decoding Figure III-4-6. Simplified View Of Current Sources Figure III-4-7. Voltage Regulator Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-9. Zone Control Circuitry  LIST OF TABLES  Table II-1-1. A1 Card Cage  Table III-3-1. Clear/Write Table III-3-2. Read/Restore Table III-3-3. Read/Modify/Write  III-3-5 Table III-3-3. Read/Modify/Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |          | Memory Core                           | III-2-3                   |

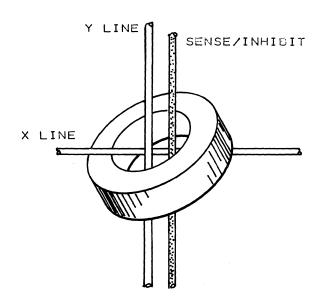

| Figure III-2-3. Sense Winding Output Curve Figure IIII-2-4. Read And Write Operations Figure III-3-1. Memory System Block Diagram Figure III-3-2. Internal Timing Clear/Write Figure III-3-3. Internal Timing Read/Restore Figure III-3-3. Internal Timing Read/Modify/Write Figure III-3-4. Internal Timing - Read/Modify/Write Figure III-3-5. Internal Timing - Read Only Figure III-4-1. Timing And Control Logic Figure III-4-2. Internal Timing Relationship Figure III-4-3. Address Register Figure III-4-4. General Reset Circuit Figure III-4-5. Addressing Decoding Figure III-4-6. Simplified View Of Current Sources Figure III-4-7. Voltage Regulator Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-9. Zone Control Circuitry  LIST OF TABLES  Table II-1-1. A1 Card Cage  Table III-3-1. Clear/Write Table III-3-2. Read/Restore Table III-3-3. Read/Modify/Write  III-3-5 Table III-3-3. Read/Modify/Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure | III-2-2. | Ferrite Core Memory Element           |                           |

| Figure III-2-4. Read And Write Operations Figure IIII-3-1. Memory System Block Diagram Figure III-3-2. Internal Timing Clear/Write Figure III-3-3. Internal Timing Read/Restore Figure III-3-3. Internal Timing Read/Modify/Write Figure III-3-4. Internal Timing - Read/Modify/Write Figure III-3-5. Internal Timing - Read Only Figure III-4-1. Timing And Control Logic Figure III-4-2. Internal Timing Relationship Figure III-4-3. Address Register Figure III-4-4. General Reset Circuit Figure III-4-5. Addressing Decoding Figure III-4-6. Simplified View Of Current Sources Figure III-4-7. Voltage Regulator Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-9. Zone Control Circuitry  LIST OF TABLES  Table II-1-1. A1 Card Cage  Table III-3-1. Clear/Write Table III-3-2. Read/Restore Table III-3-3. Read/Modify/Write  III-3-5 Table III-3-3. Read/Modify/Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |          | With Three Wires                      | III <b>-</b> 2 <b>-</b> 3 |

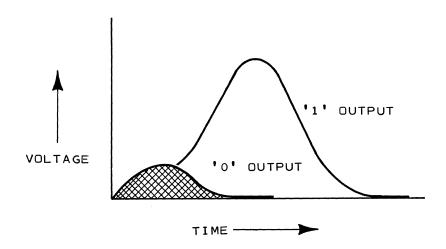

| Figure III-3-1. Memory System Block Diagram Figure III-3-2. Internal Timing Clear/Write Figure III-3-3. Internal Timing Read/Restore Figure III-3-4. Internal Timing - Read/Modify/Write Figure III-3-5. Internal Timing - Read/Modify/Write Figure III-3-5. Internal Timing - Read Only Figure III-4-1. Timing And Control Logic Figure III-4-2. Internal Timing Relationship Figure III-4-3. Address Register Figure III-4-4. General Reset Circuit Figure III-4-5. Addressing Decoding Figure III-4-6. Simplified View Of Current Sources Figure III-4-7. Voltage Regulator Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-9. Zone Control Circuitry Figure III-4-9. Zone Control Circuitry  LIST OF TABLES  Table II-1-1. A1 Card Cage  Table III-3-1. Clear/Write Table III-3-3. Read/Modify/Write  III-3-5 Table III-3-3. Read/Modify/Write  III-3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure | III-2-3. | Sense Winding Output Curve            | III <b>-</b> 2 <b>-</b> 5 |

| Figure III-3-2. Internal Timing Clear/Write Figure III-3-3. Internal Timing Read/Restore Figure III-3-4. Internal Timing - Read/Modify/Write Figure III-3-5. Internal Timing - Read/Modify/Write Figure III-4-1. Timing And Control Logic Figure III-4-2. Internal Timing Relationship Figure III-4-3. Address Register Figure III-4-4. General Reset Circuit Figure III-4-5. Addressing Decoding Figure III-4-6. Simplified View Of Current Sources Figure III-4-7. Voltage Regulator Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-9. Zone Control Circuitry  LIST OF TABLES  Table II-1-1. A1 Card Cage  Table III-3-1. Clear/Write Table III-3-2. Read/Restore Table III-3-3. Read/Modify/Write  Timing Read/Modify/Write  III-3-6 III-3-7 III-3-7 III-3-7 III-3-7 III-3-8 III-3-8 III-3-1. Read/Modify/Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Figure | III-2-4. | Read And Write Operations             | III-2-6                   |

| Figure III-3-2. Internal Timing Clear/Write Figure III-3-3. Internal Timing Read/Restore Figure III-3-4. Internal Timing - Read/Modify/Write Figure III-3-5. Internal Timing - Read/Modify/Write Figure III-4-1. Timing And Control Logic Figure III-4-2. Internal Timing Relationship Figure III-4-3. Address Register Figure III-4-4. General Reset Circuit Figure III-4-5. Addressing Decoding Figure III-4-6. Simplified View Of Current Sources Figure III-4-7. Voltage Regulator Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-9. Zone Control Circuitry  LIST OF TABLES  Table II-1-1. A1 Card Cage  Table III-3-1. Clear/Write Table III-3-2. Read/Restore Table III-3-3. Read/Modify/Write  Timing Read/Modify/Write  III-3-6 III-3-7 III-3-7 III-3-7 III-3-7 III-3-8 III-3-8 III-3-1. Read/Modify/Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Figure | III-3-1. | Memory System Block Diagram           | III-3-2                   |

| Figure III-3-3. Internal Timing Read/Restore Figure III-3-4. Internal Timing - Read/Modify/Write Figure III-3-5. Internal Timing - Read Only Figure III-4-1. Timing And Control Logic Figure III-4-2. Internal Timing Relationship Figure III-4-3. Address Register Figure III-4-3. Address Register Figure III-4-5. Addressing Decoding Figure III-4-6. Simplified View Of Current Sources Figure III-4-7. Voltage Regulator Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-9. Zone Control Circuitry  LIST OF TABLES  Table II-1-1. A1 Card Cage  Table III-3-1. Clear/Write Table III-3-2. Read/Restore Table III-3-3. Read/Modify/Write  III-3-11  III-3-11  III-3-11  III-3-11  III-3-11  III-3-11  III-3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |          |                                       |                           |

| Figure III-3-4. Internal Timing - Read/Modify/Write Figure III-3-5. Internal Timing - Read Only Figure III-4-1. Timing And Control Logic Figure III-4-2. Internal Timing Relationship Figure III-4-3. Address Register Figure III-4-4. General Reset Circuit Figure III-4-5. Addressing Decoding Figure III-4-6. Simplified View Of Current Sources Figure III-4-7. Voltage Regulator Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-9. Zone Control Circuitry Figure III-4-11 Figure III-4-9. Zone Control Circuitry  LIST OF TABLES  Table II-1-1. A1 Card Cage  Table III-3-1. Clear/Write Table III-3-2. Read/Restore Table III-3-3. Read/Modify/Write  III-3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |          | <del>-</del> ,                        |                           |

| Figure III-3-5. Internal Timing - Read Only Figure III-4-1. Timing And Control Logic Figure III-4-2. Internal Timing Relationship Figure III-4-3. Address Register Figure III-4-4. General Reset Circuit Figure III-4-5. Addressing Decoding Figure III-4-6. Simplified View Of Current Sources Figure III-4-7. Voltage Regulator Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-9. Zone Control Circuitry Figure III-4-9. Zone Control Circuitry  LIST OF TABLES  Table II-1-1. A1 Card Cage  Table III-3-1. Clear/Write Table III-3-2. Read/Restore Table III-3-3. Read/Modify/Write  III-3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |          |                                       |                           |

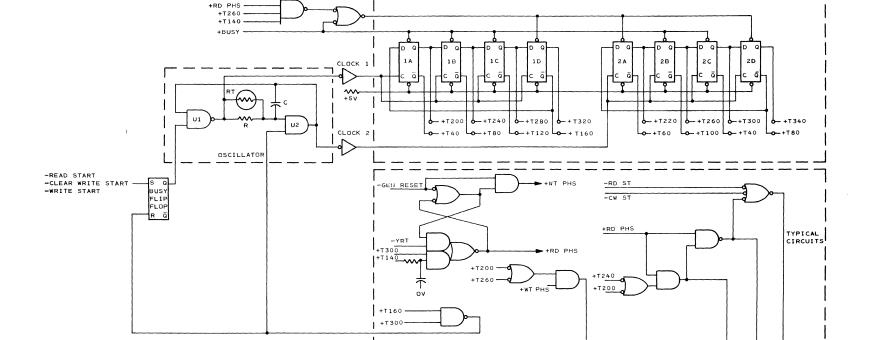

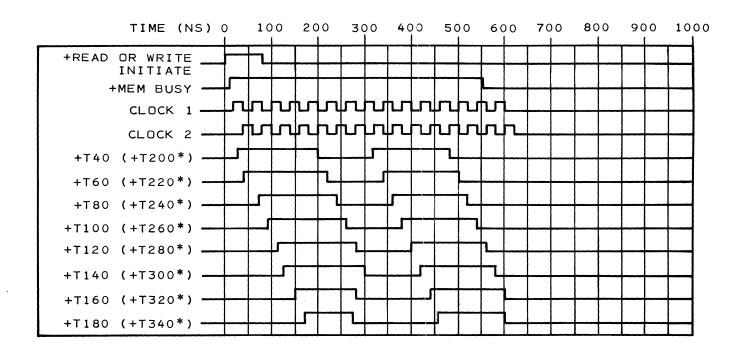

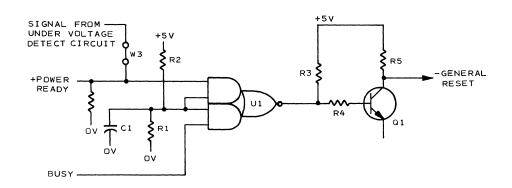

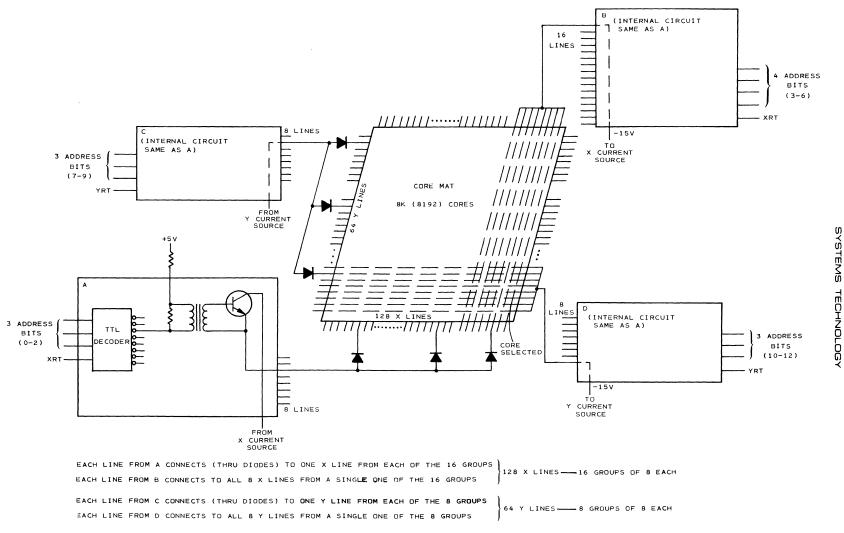

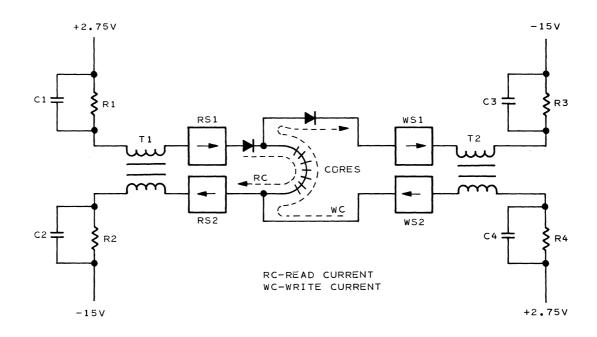

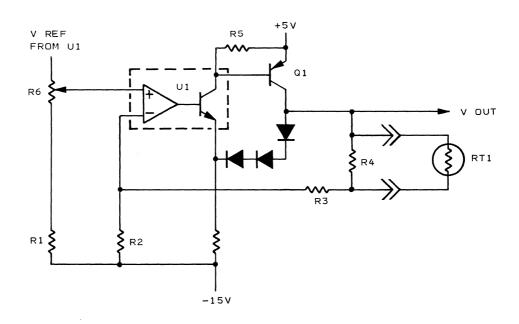

| Figure III-4-1. Timing And Control Logic III-4-3 Figure III-4-2. Internal Timing Relationship III-4-4 Figure III-4-3. Address Register III-4-7 Figure III-4-4. General Reset Circuit III-4-7 Figure III-4-5. Addressing Decoding III-4-9 Figure III-4-6. Simplified View Of Current Sources III-4-11 Figure III-4-7. Voltage Regulator III-4-15 Figure III-4-8. Sense, Inhibit And Data Circuitry III-4-15 Figure III-4-9. Zone Control Circuitry III-4-18  LIST OF TABLES  Table II-1-1. A1 Card Cage II-1-3  Table III-3-1. Clear/Write III-3-5 Table III-3-2. Read/Restore III-3-8 Table III-3-3. Read/Modify/Write III-3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |          |                                       |                           |

| Figure III-4-2. Internal Timing Relationship  Figure III-4-3. Address Register  Figure III-4-4. General Reset Circuit  Figure III-4-5. Addressing Decoding  Figure III-4-6. Simplified View Of Current Sources  Figure III-4-7. Voltage Regulator  Figure III-4-8. Sense, Inhibit And Data Circuitry  Figure III-4-9. Zone Control Circuitry  LIST OF TABLES  Table II-1-1. A1 Card Cage  Table III-3-1. Clear/Write  Table III-3-2. Read/Restore  Table III-3-3. Read/Modify/Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |          | · · · · · · · · · · · · · · · · · · · |                           |

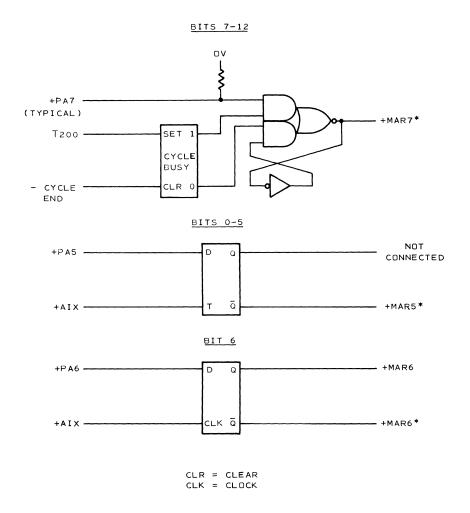

| Figure III-4-3. Address Register Figure III-4-4. General Reset Circuit Figure III-4-5. Addressing Decoding Figure III-4-6. Simplified View Of Current Sources Figure III-4-7. Voltage Regulator Figure III-4-8. Sense, Inhibit And Data Circuitry Figure III-4-9. Zone Control Circuitry Figure III-4-9. Zone Control Circuitry  LIST OF TABLES  Table II-1-1. A1 Card Cage II-1-3  Table III-3-1. Clear/Write Table III-3-2. Read/Restore Table III-3-3. Read/Modify/Write  III-4-7  III-4-7  III-4-7  III-4-7  III-4-7  III-4-9  III-4-9  III-4-11  III-4-7  III-4-7  III-4-7  III-4-7  III-4-7  III-4-7  III-4-7  III-4-9  III-4-9  III-4-11  I |        |          |                                       |                           |