# SPARC CPU-2CE TECHNICAL REFERENCE MANUAL

REVISION NO. A1 JANUARY 1994

FORCE COMPUTERS Inc./GmbH All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless express permission has been granted.

Copyright by FORCE COMPUTERS

## NOTICE

The information in this document has been carefully checked and is believed to be entirely reliable. FORCE COMPUTERS makes no warranty of any kind with regard to the material in this document, and assumes no responsibility for any errors that may appear in this document. FORCE COMPUTERS reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance or design.

FORCE COMPUTERS assumes no responsibility for the use of any circuitry other than circuitry which is part of a product of FORCE COMPUTERS GmbH/Inc.

FORCE COMPUTERS does not convey to the purchaser of the product described herein any license under the patent rights of FORCE COMPUTERS GmbH/Inc. nor the rights of others.

| FORCE COMPUTERS Inc.                                                                                                  | FORCE COMPUTERS GmbH                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 2001 Logic Drive                                                                                                      | ProfMesserschmitt-Str. 1                                                                                      |

| San Jose, CA 95124                                                                                                    | D-85579 Neubiberg/Munich                                                                                      |

| U.S.A.                                                                                                                | Germany                                                                                                       |

| Phone : (408) 371-5900<br>FAX : (408) 371-3382                                                                        | Phone : (089) 608 14-0<br>Telex : 524190 forc-d<br>FAX : (089) 609 77 93                                      |

| FORCE COMPUTERS FRANCE S.A.R.L.<br>Le Volta<br>17-19 rue Jeanne Braconnier<br>F-92366 Meudon La Foret Cedex<br>France | FORCE COMPUTERS (U.K.) Ltd.<br>No. 1 Holly Court<br>3 Tring Road<br>Wendover<br>Buckinghamshire HP<br>England |

| Phone : (1) 41 07 95 15                                                                                               | Phone : (0296) 625456                                                                                         |

| FAX : (1) 45 37 06 19                                                                                                 | Telex : 838033                                                                                                |

FORCE COMPUTERS strives to contribute to the safety and preservation of the environment with the same care it applies to the performance and quality of its products.

FAX : (0296) 624027

To support this effort, this Product Manual has been printed on paper that is completely chlorine free and conservation friendly.

## TABLE OF CONTENTS

## Section 1

| 0 INTRODUCTION                              | 1-1 |

|---------------------------------------------|-----|

| 1.1 The Processor                           | 1-4 |

| 1.2 The Memory Subsystem                    | 1-4 |

|                                             | 1-4 |

|                                             | 1-5 |

|                                             | 1-5 |

|                                             | 1-5 |

| Keyboard/Mouse Port                         | 1-5 |

|                                             | 1-5 |

|                                             | 1-5 |

|                                             | 1-6 |

| 1.7 Small Computer Systems Interface (SCSI) | 1-6 |

|                                             | 1-6 |

|                                             | 1-6 |

| 1.10 SBus Interface                         | 1-7 |

|                                             | 1-7 |

|                                             | 1-7 |

| 1.11.2 Slave Interface                      | 1-8 |

|                                             | 1-8 |

| •                                           | 1-8 |

|                                             | 1-8 |

|                                             | 1-9 |

| 1.14 Sun Tools                              | 1-9 |

| 1.15 Graphical User Interface               | 1-9 |

| 1.16 Real-Time                              | -11 |

| 1.17 Networking                             | -11 |

| 1.18 Determining Revision Level 1           | -13 |

| ection 2                                    |     |

| ISTALLATION and DIAGNOSTICS                 | 2-1 |

|                                                  | 2-1 |

|--------------------------------------------------|-----|

| 2.1 Power Up                                     | 2-2 |

| 2.2 Post Power Up Procedures                     | 2-4 |

| 2.2.1 How to Talk to the CPU-2CE On-Board Memory | 2-4 |

| 2.2.1.1 Memory Test Command One                  | 2-4 |

| 2.2.1.2 Memory Test Command Two                  | 2-4 |

| 2.2.1.3 Memory Test Command Three                | 2-5 |

| 2.2.2 Test the Ethernet Port                     | 2-5 |

| 2.2.3 How to Talk to the SPARC CPU-2CE Buses     | 2-6 |

| 2.2.3.1 Mapping Memory                           | 2-6 |

| 2.2.3.2 Accessing Memory                         | 2-6 |

| 2.2.4 How to Talk to the SBus                    | 2-6 |

|                                                  |     |

| 2.3 Running PROM Diagnostics         | 2-6  |

|--------------------------------------|------|

| 2.4 Running Functional Tests         | 2-7  |

|                                      | 2-7  |

| 2.6 Diagnostics                      | 2-7  |

| 2.6.1 Main Categories of Diagnostics |      |

| 2.6.2 Diagnostic Selections          |      |

| 2.6.3 Boot PROM Diagnostics 2        |      |

| 2.6.3.1 POST 2                       |      |

| 2.6.3.2 On Board Diagnostics         | 2-13 |

| 2.6.4 Sundiag System Exerciser       |      |

| 2.6.5 Monitor and Forth Toolkit      | 2-13 |

| 2.7 SPARC CPU-2CE NVRAM Parameters   | 2-16 |

|                                      |      |

#### Section 3

| HARDWARE                                             |

|------------------------------------------------------|

| 3.1 Card Landmarks                                   |

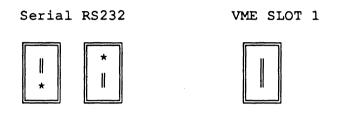

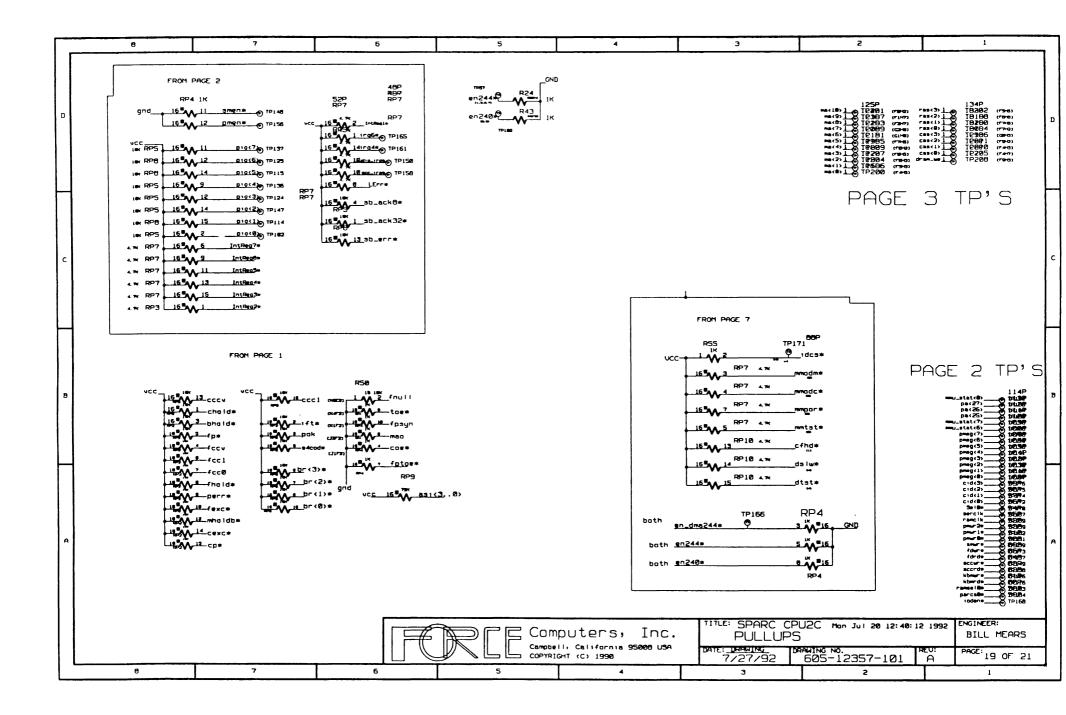

| 3.1.1 Card Jumpers 3-5                               |

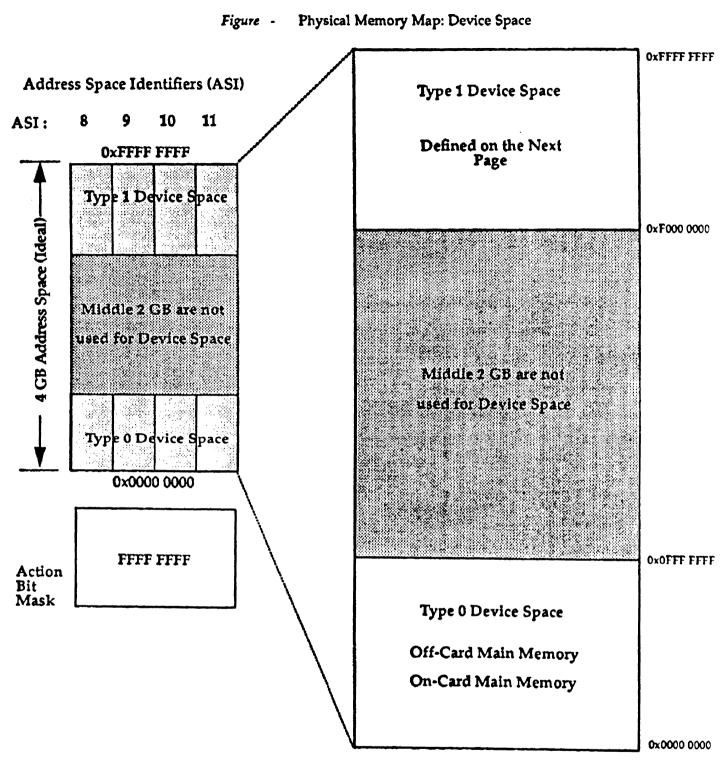

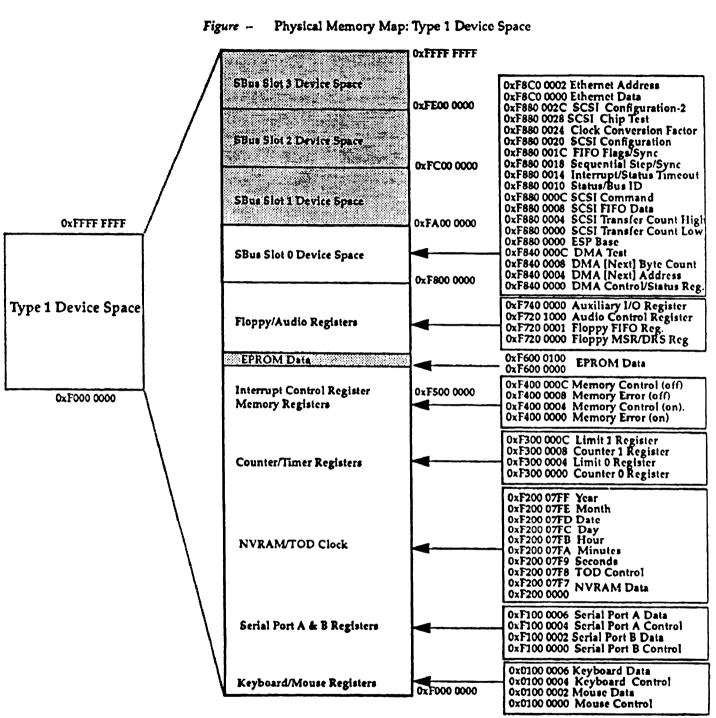

| 3.1.2 Device Space                                   |

| 3.1.3 Control Space 3-12                             |

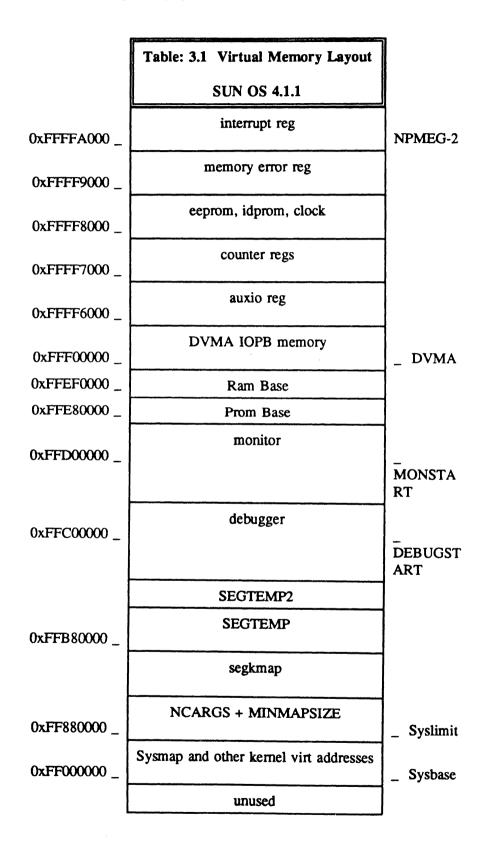

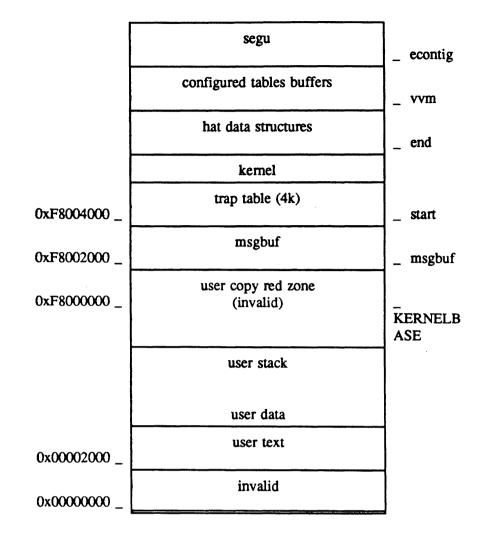

| 3.1.4 The Memory Map Page 3-15                       |

| 3.1.5 Interrupt Map 3-17                             |

| 3.2 Custom Chips                                     |

| 3.2.1 Cache+                                         |

| 3.2.2 RAM+ 3-18                                      |

| 3.2.3 DMA+ 3-18                                      |

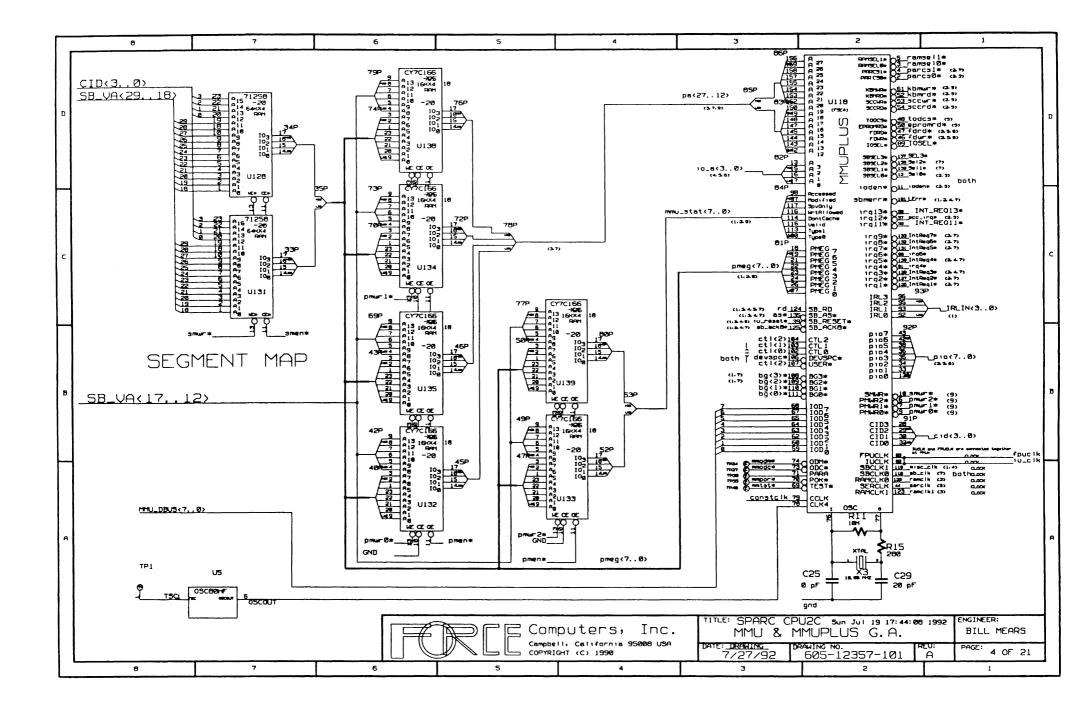

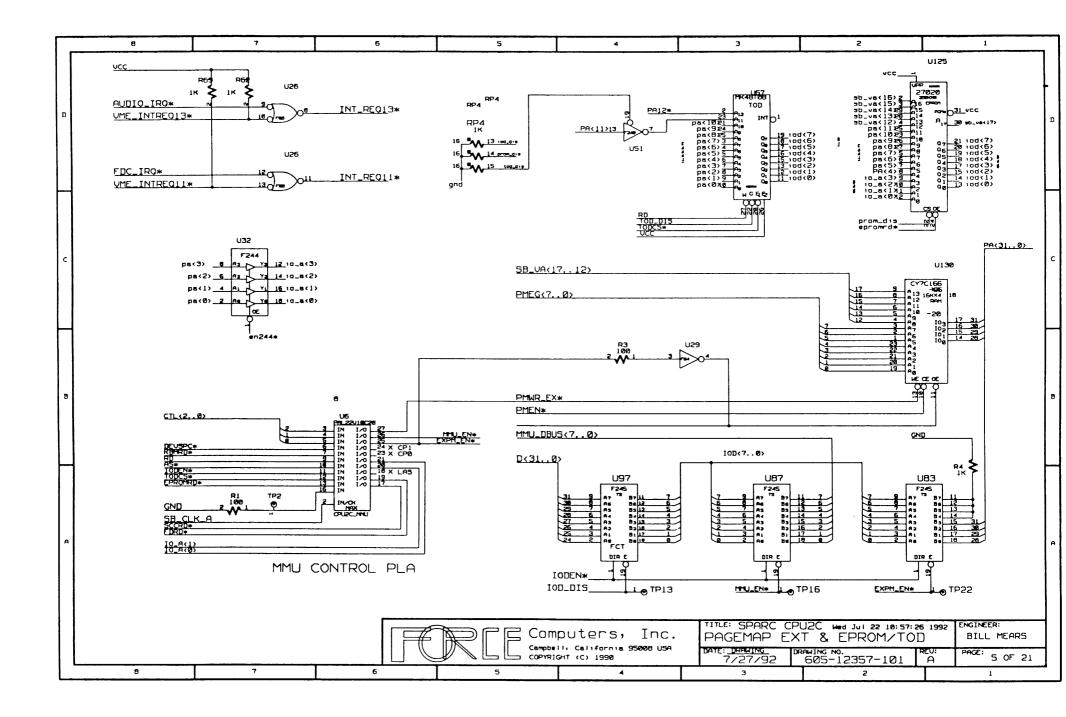

| 3.2.4 MMU+                                           |

| 3.2.5 SPARC CPU-2CE CACHE Controller 3-18            |

| The Cache Controller features:                       |

| The Cache Controller functions:                      |

| Function of Write Through Cache Control              |

| 3.3 SPARC Expansion Connector 3-22                   |

| 3.3.1 Overview                                       |

| 3.3.1.1 Intent of the Expansion Connector            |

| 3.3.2 Reconciling the Differences 3-22               |

| 3.3.2.1 Pa26 3-22                                    |

| 3.3.2.2 Pa25 3-22                                    |

| 3.3.2.3 РОК 3-23                                     |

| 3.3.2.4 Ramclk $N$                                   |

| 3.3.2.5 Ramsel* vs. ramsel1* 3-23                    |

| 3.3.2.6 ParityN vs parcs1*, ramclk1, pa25, and perr* |

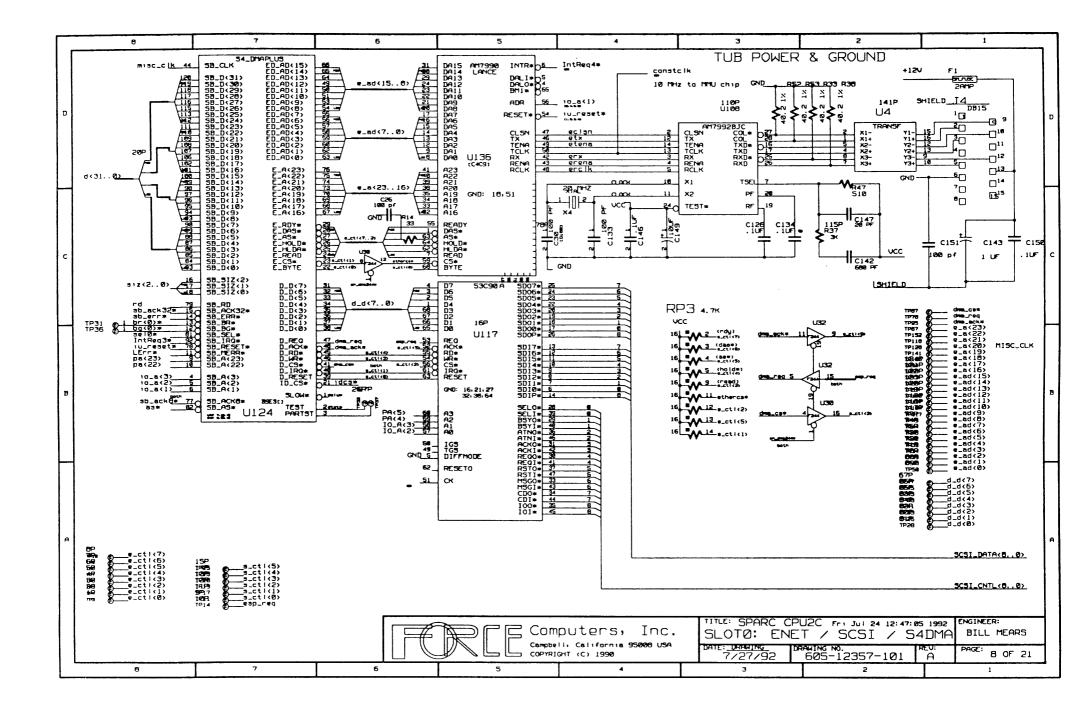

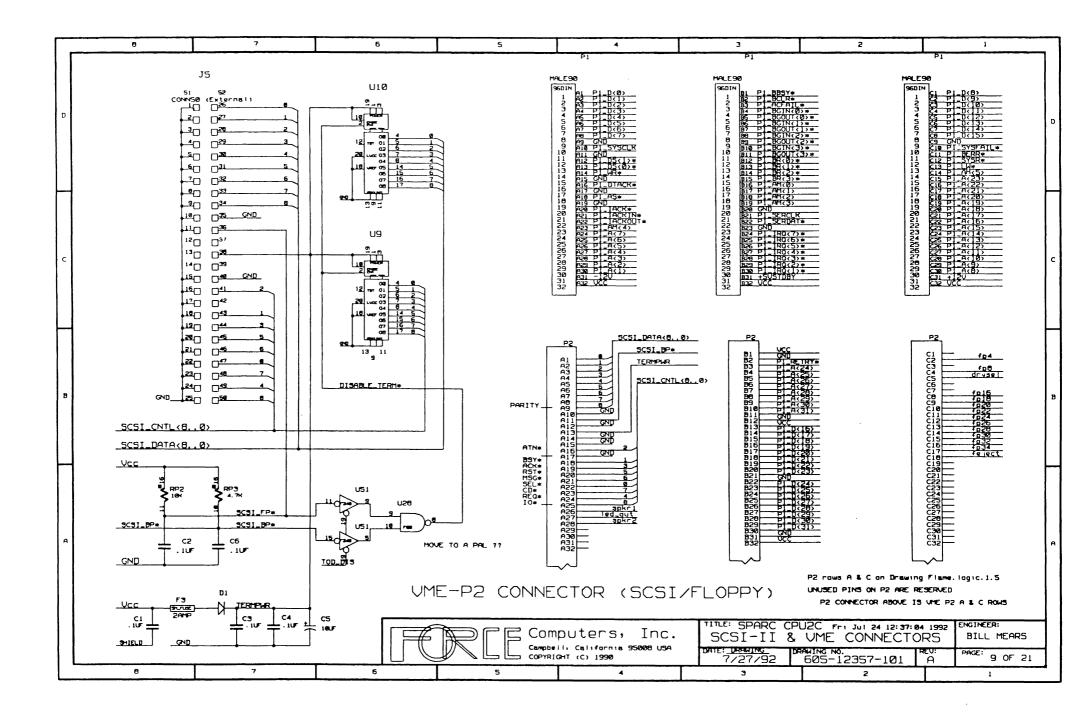

| 3.4 | SCSI Int  | erface                                      | 3-24 |

|-----|-----------|---------------------------------------------|------|

|     | 3.4.1     | SCSI Definition                             | 3-24 |

|     | 3.4.2     | SCSI Performance                            | 3-24 |

|     | 3.4.3     | SCSI Addresses                              | 3-25 |

|     | 3.4.4     | SCSI Interrupt                              | 3-25 |

|     | 3.4.5     | Interface Programming                       | 3-26 |

| 3.5 |           | Interface                                   |      |

|     | 3.5.1     | Ethernet Interface Definition               | 3-27 |

|     |           | 3.5.1.1 Ethernet Transmits and Receives     | 3-27 |

|     |           | 3.5.1.2 Ethernet Buffer                     | 3-27 |

|     | 3.5.2     | Ethernet Performance                        | 3-27 |

|     | 3.5.3     | Ethernet Interrupt                          | 3-27 |

|     | 3.5.4     | Ethernet Addresses                          | 3-28 |

|     | 3.5.5     | Ethernet Interface Programming              | 3-28 |

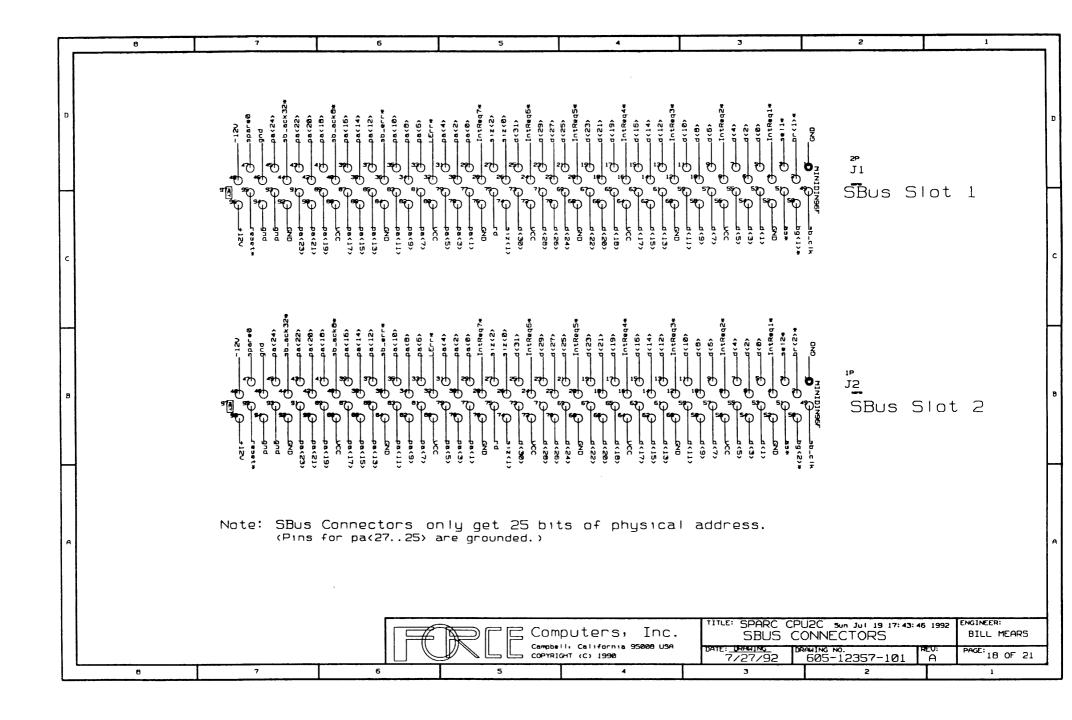

| 3.6 | SBus Int  | erface                                      | 3-31 |

|     | 3.6.1     | Introduction                                | 3-31 |

|     | 3.6.2     | SBus Connections                            | 3-31 |

|     | 3.6.3     | SBus Slot Addresses                         | 3-32 |

|     | 3.6.4     | SBus Slot 0 Devices                         | 3-33 |

|     |           | 3.6.4.1 Card ID                             | 3-33 |

|     |           | 3.6.4.2 DMA Registers                       | 3-34 |

|     |           | DMA Control/Status Register                 | 3-35 |

|     |           | DMA Address Register                        |      |

|     |           | DMA Byte Count Register                     |      |

|     |           | DMA Diagnostic Register                     |      |

|     | 3.6.5     | SBus Slot 1 Devices and Slot 2 Devices      |      |

|     |           | 3.6.5.1 SPARC Assembly Language Example     |      |

|     |           | 3.6.5.2 Forth Example                       |      |

|     |           | 3.6.5.3 C/SunOS Example                     |      |

| 3.7 |           |                                             |      |

|     |           | FEATURES                                    |      |

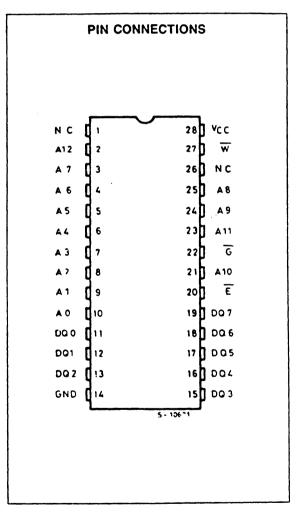

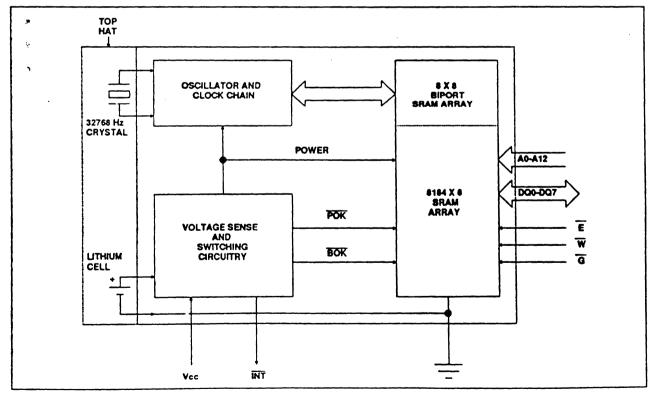

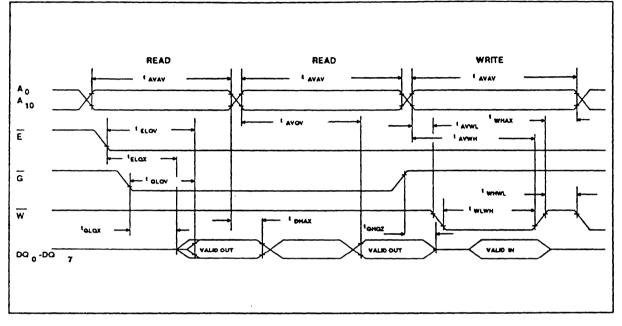

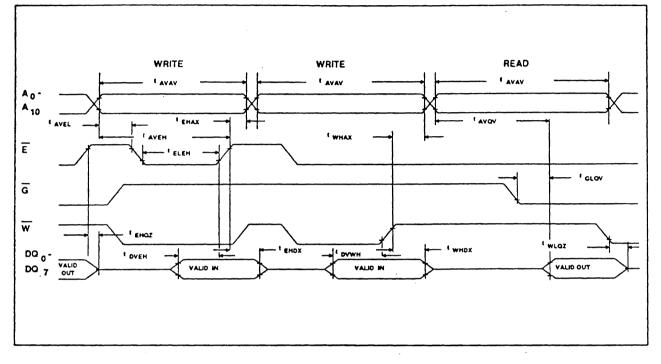

|     | 3.7.2     | PIN DESCRIPTION                             |      |

|     |           | 3.7.2.1 Sbus Interface                      |      |

|     |           | 3.7.2.2 DRAM Interface                      |      |

|     |           | 3.7.2.3 Power/Ground                        |      |

|     |           | 3.7.2.4 LSI Logic Buffer Naming Conventions |      |

|     | 3.7.3     | SBus INTERFACE                              |      |

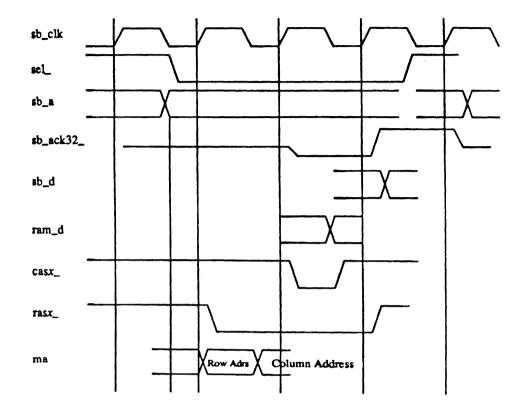

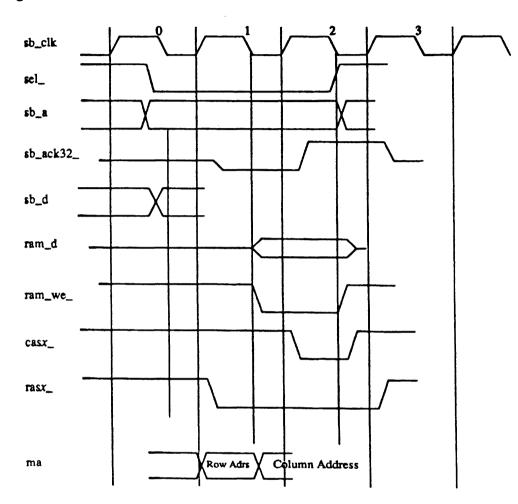

|     |           | 3.7.3.1 DRAM Access                         |      |

|     |           | • Word Read                                 |      |

|     |           | • Word Write - Buffered                     |      |

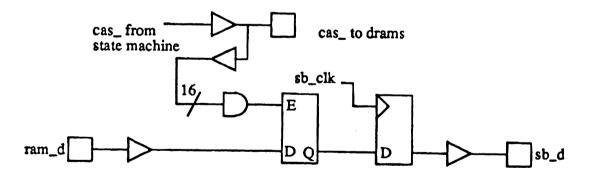

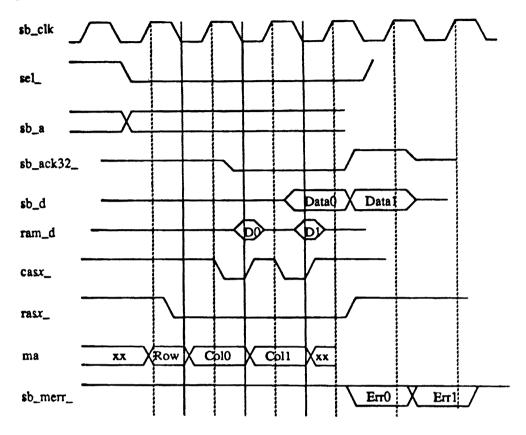

|     |           | • Burst Read                                |      |

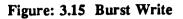

|     |           | • Burst Write                               |      |

|     | <b></b> . | 3.7.3.2 Address Mapping                     |      |

|     | 3.7.4     | DETAILED TIMING                             |      |

|     |           | 3.7.4.1 DRAM Timing                         |      |

|     |           | DRAM Errors                                 |      |

|     |           | DRAM                                        | 3-48 |

|                                            | 3-49 |

|--------------------------------------------|------|

| 3.8.1 Features                             | 3-49 |

| 3.8.2 Pin Description                      | 3-50 |

| 3.8.2.1 SBus Interface                     | 3-50 |

| 3.8.2.2 MMU Interface                      | 3-50 |

| 3.8.2.3 Decodes                            | 3-51 |

| 3.8.2.4 Miscellaneous                      | 3-52 |

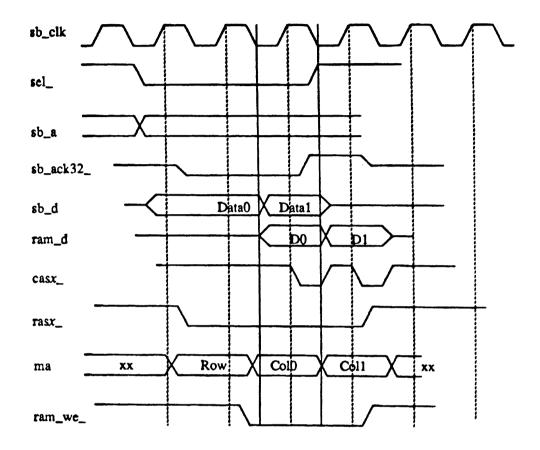

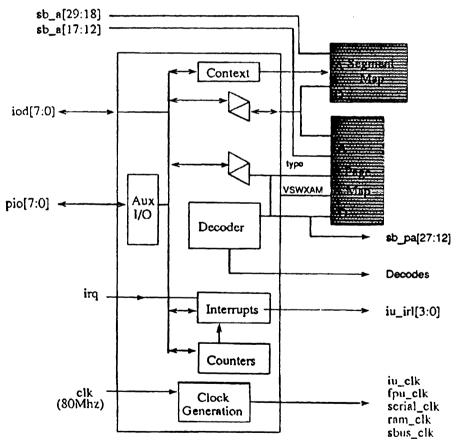

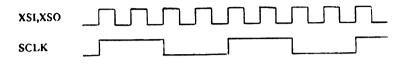

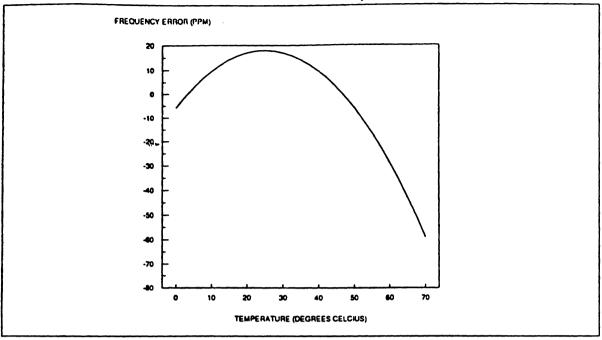

| 3.8.3 Clock Generation                     | 3-52 |

| 3.8.3.1 General Description                | 3-52 |

| 3.8.3.2 Constant Clock                     | 3-53 |

| 3.8.3.3 Serial Clock                       | 3-53 |

| 3.8.4 Decodes                              | 3-53 |

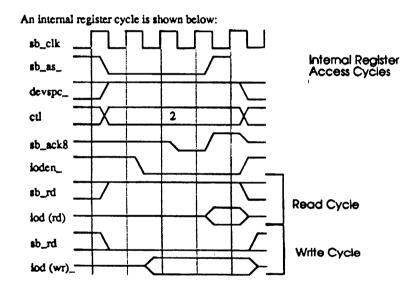

| 3.8.4.1 Control Space                      | 3-53 |

| • CTL mappings                             | 3-53 |

| Context Register Access                    | 3-54 |

| • SCC Bypass                               | 3-54 |

| • EPROM Bypass                             | 3-54 |

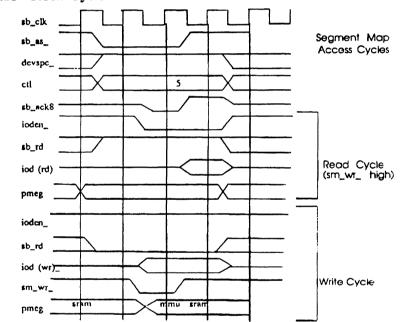

| Segment Map Access                         | 3-55 |

| • Page Map Access                          | 3-56 |

| • Page Type Bits                           | 3-56 |

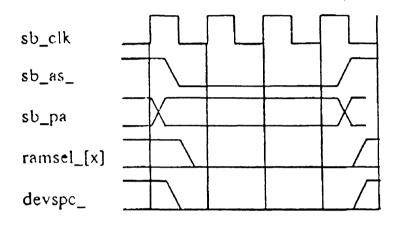

| 3.8.4.2 Device Space                       | 3-57 |

|                                            | 3-58 |

|                                            | 3-59 |

|                                            | 3-60 |

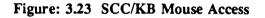

| SCC/KB Mouse Access                        | 3-60 |

| 3.8.5 Protection Checking                  | 3-61 |

| 3.8.6 Statistics Updates                   | 3-61 |

| -                                          | 3-62 |

| 3.8.8 Counters                             | 3-62 |

| 3.8.9 I/O Register                         | 3-63 |

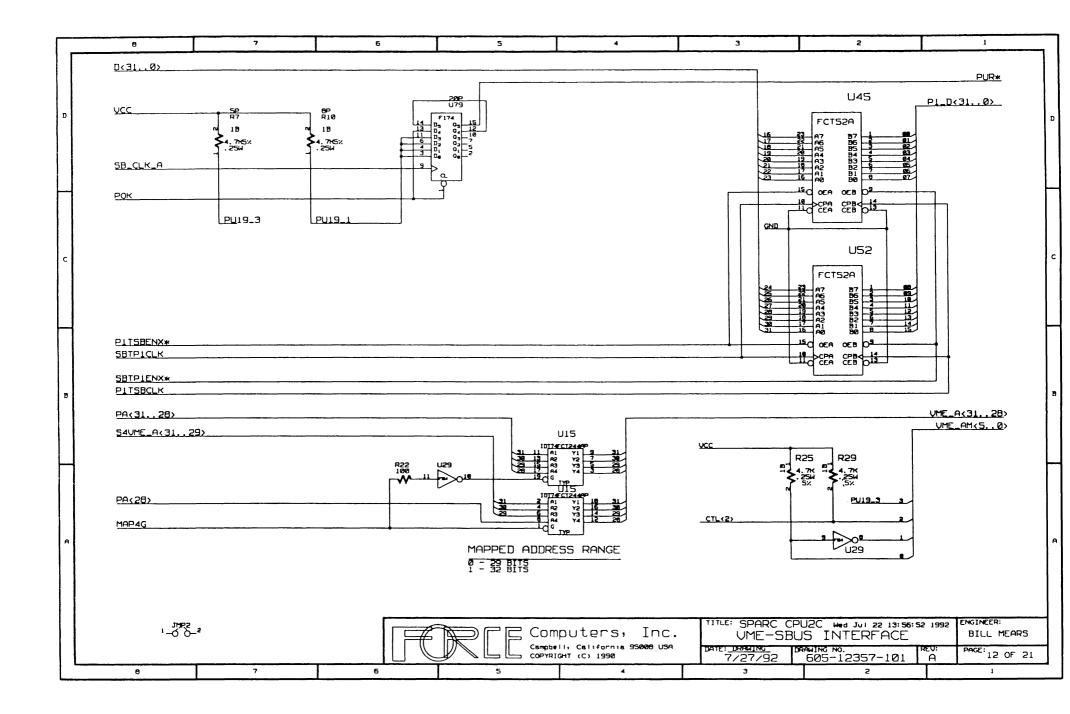

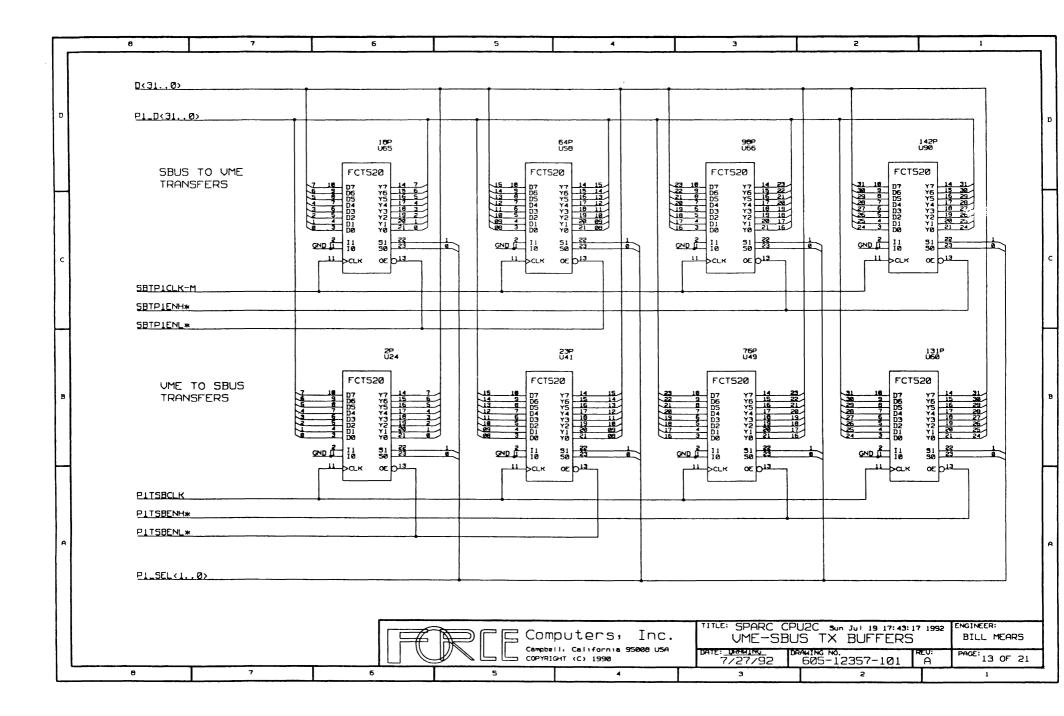

| 3.9 P2 Bus Interface Overview              | 3-64 |

| 3.9.1 P1/P2 Connector Numbering            | 3-64 |

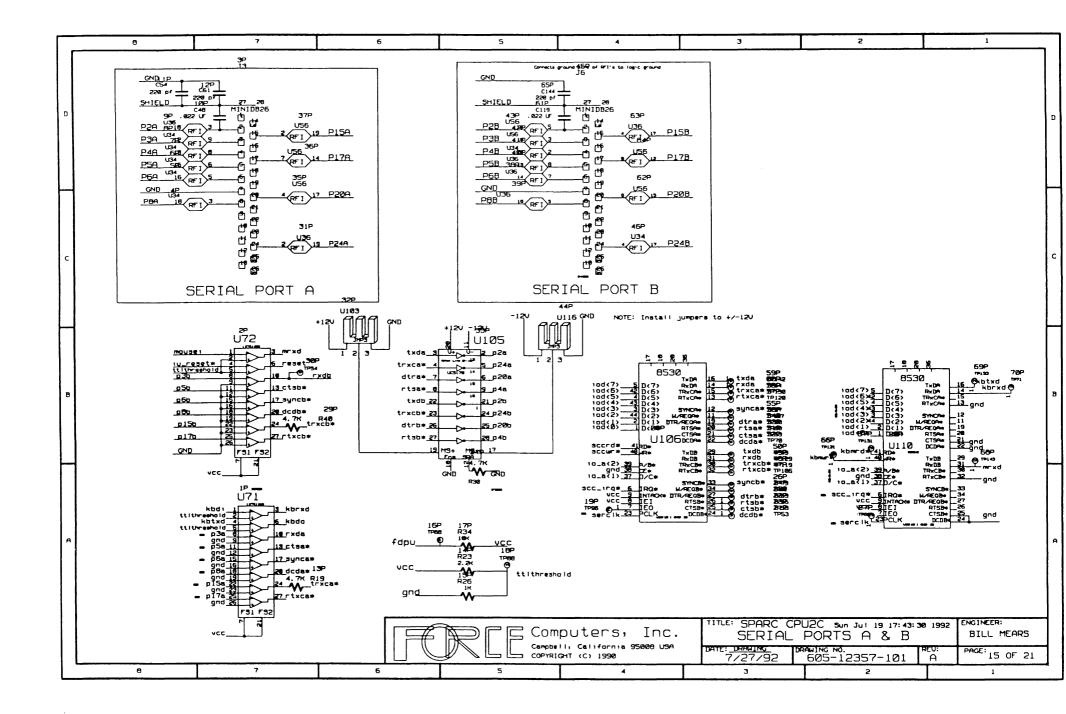

| 3.10 Serial Interface A and B              | 3-64 |

|                                            | 3-64 |

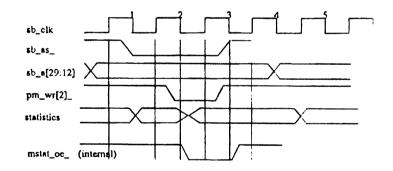

| 3.10.1.1 RS232/RS423 Jumper Selection      | 3-64 |

| 3.10.2 Serial Interface A/B Definition     | 3-64 |

| 3.10.3 Serial Interface A/B Performance    | 3-64 |

| 3.11 Keyboard/Mouse Interface              | 3-66 |

| 3.11.1 Keyboard/Mouse Device Address       | 3-66 |

| 3.11.2 Keyboard/Mouse Interface Definition | 3-66 |

| 3.11.3 Specifications                      | 3-66 |

#### Section 4

| APPENDICES TO THE HARDWARE USER'S MANUAL | 4-1 |

|------------------------------------------|-----|

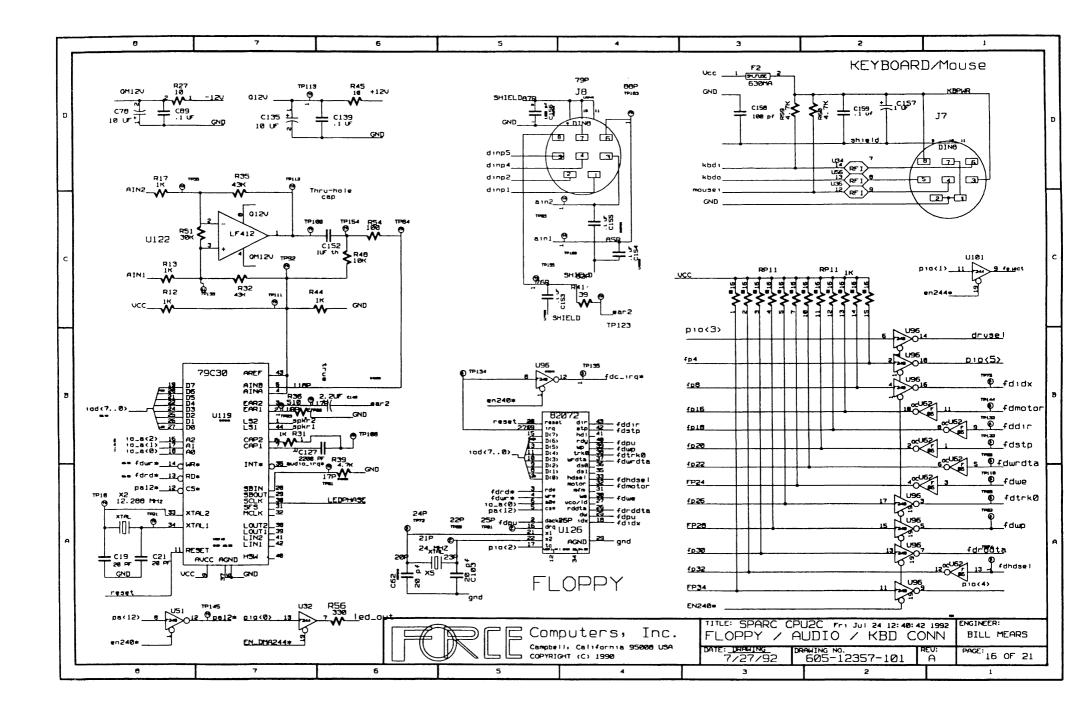

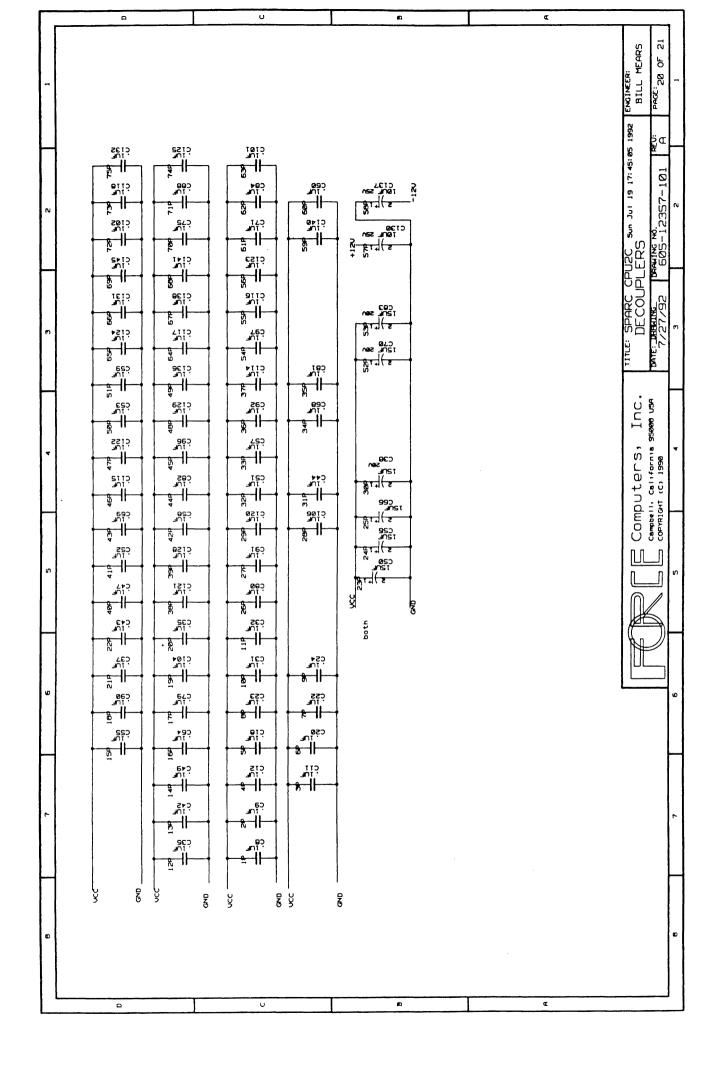

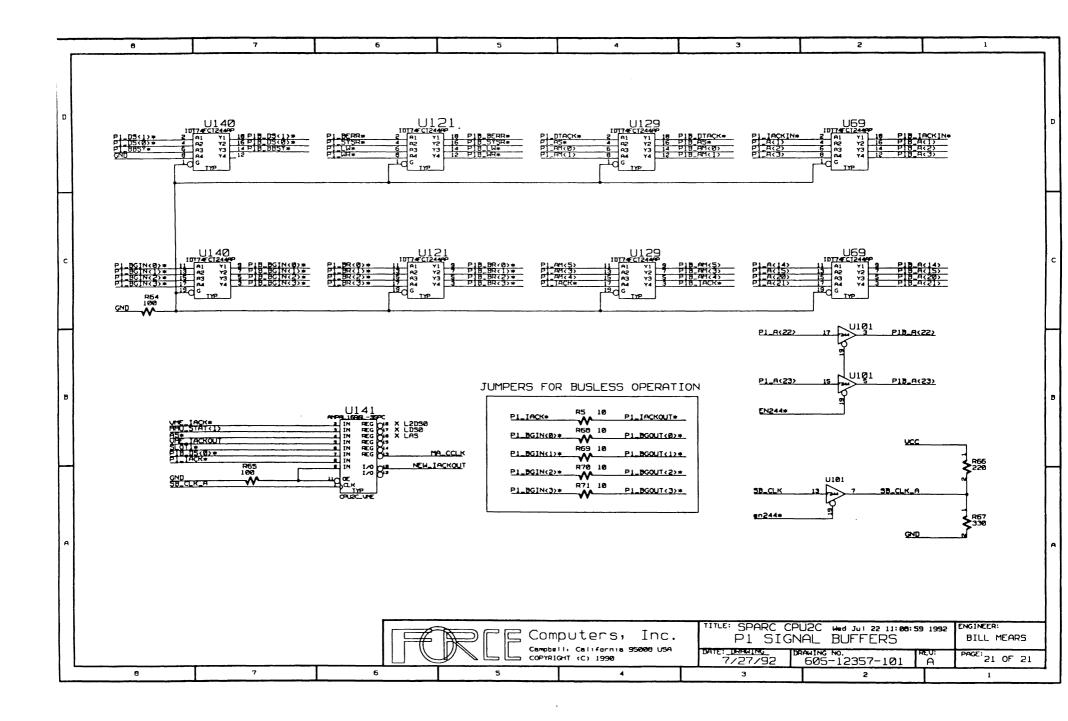

| The CPU Card Schematic Diagrams          |     |

| DWG Schematics                           |     |

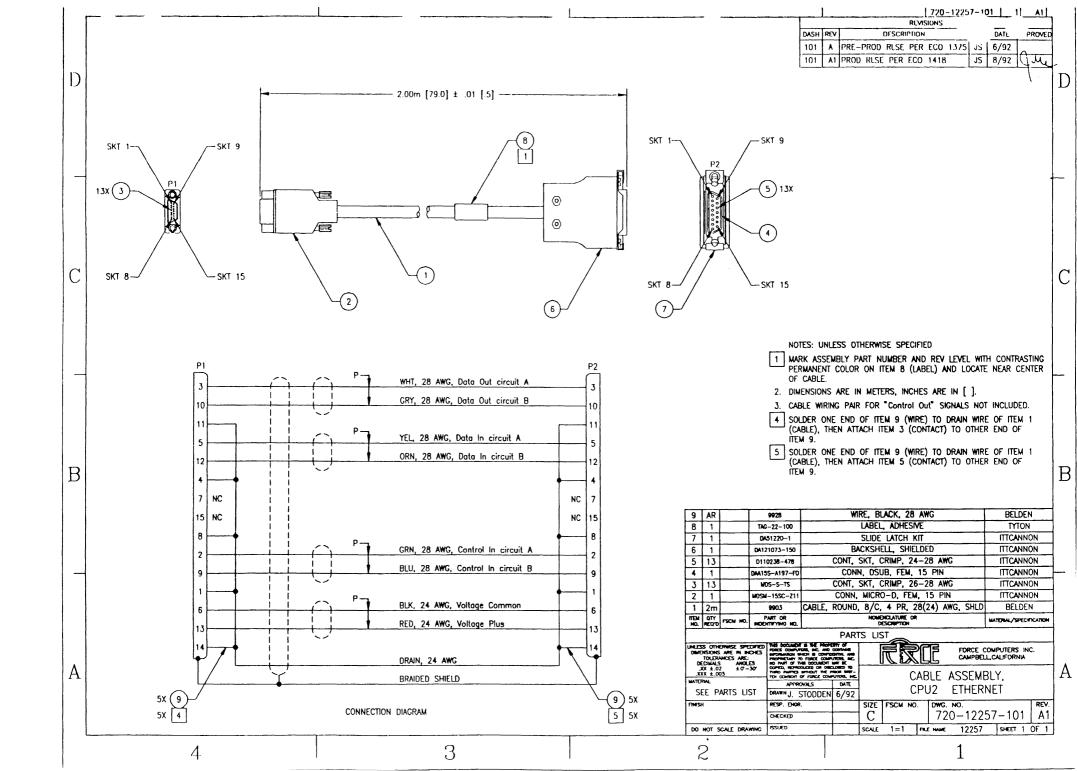

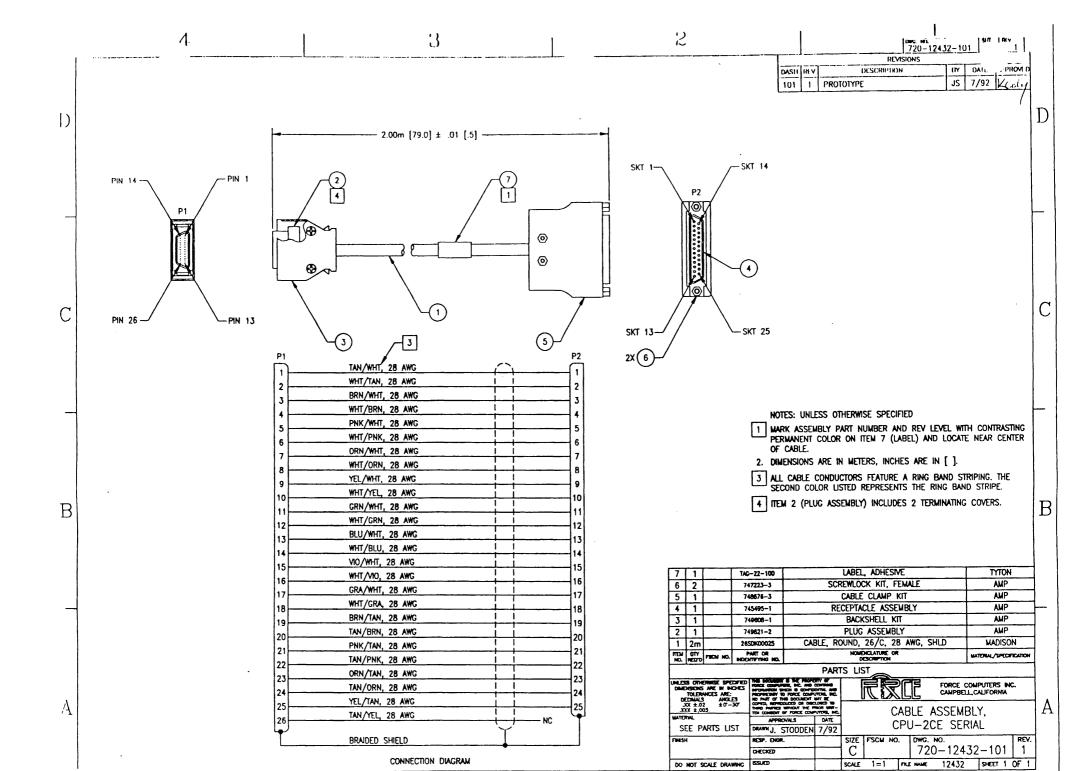

| Serial Cable Drawing                     |     |

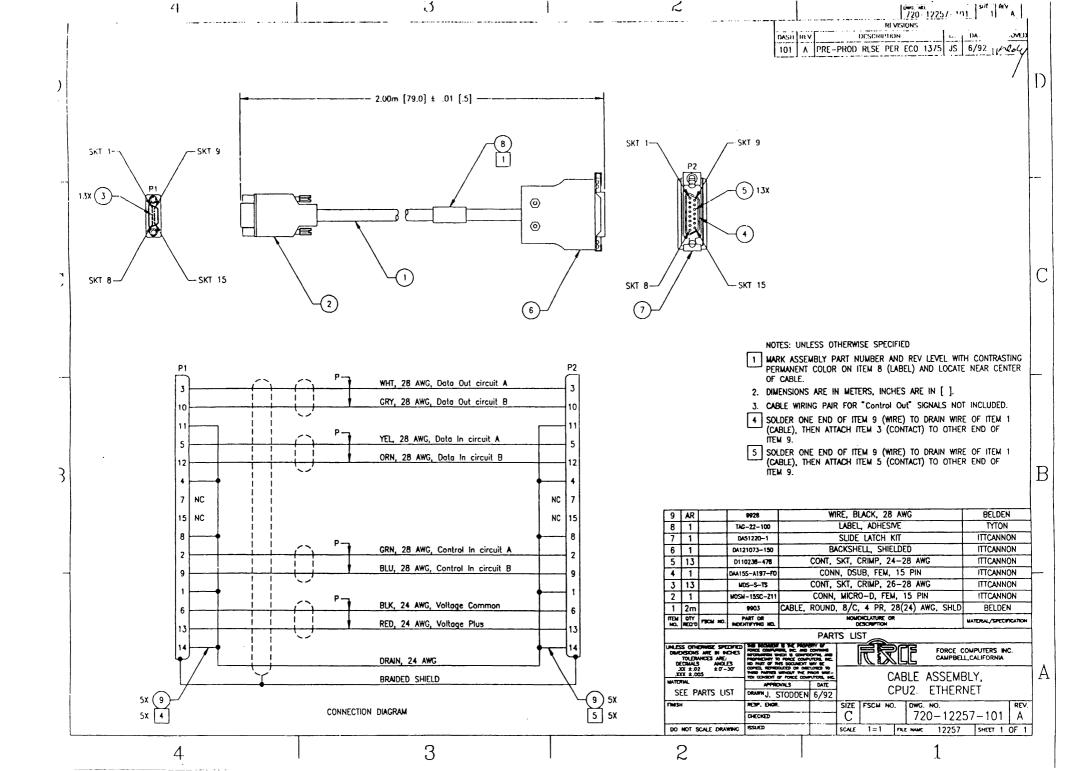

| Ethernet Cable Drawing                   |     |

| Reader Comment Card                      |     |

| Product Error Report                     |     |

| Section 5                                |     |

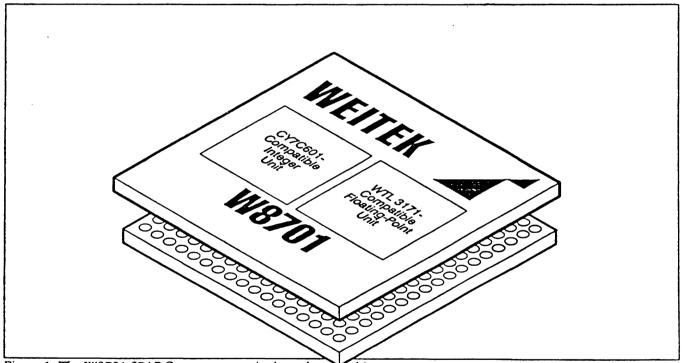

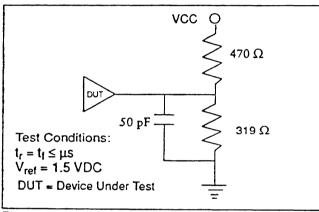

| ABSTRACT COPIES OF DATA SHEETS |  | 5-1 |

|--------------------------------|--|-----|

|--------------------------------|--|-----|

## Section 6

| PROGRAMMING & FIRMWARE MANUAL                    | 6-1  |

|--------------------------------------------------|------|

| 6.0 Programming                                  | 6-1  |

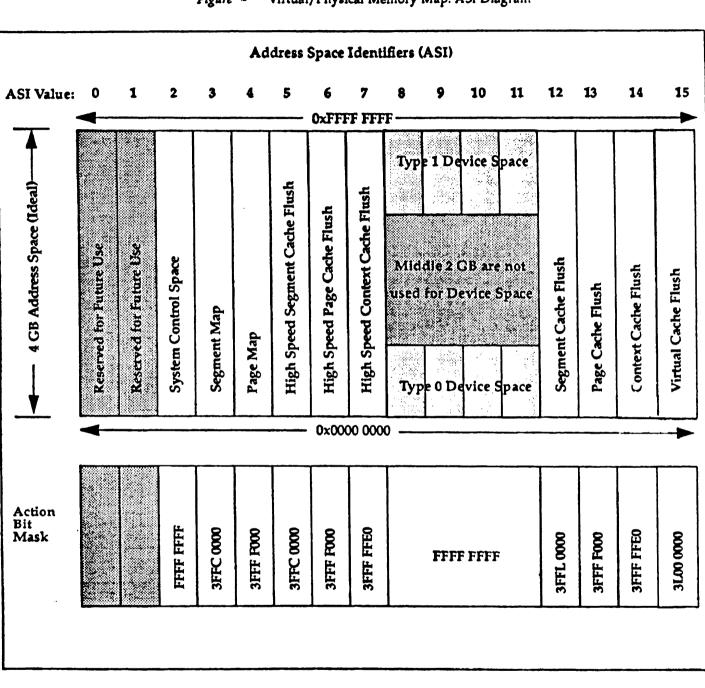

| 6.1 Address Spaces                               | 6-1  |

| 6.1.1 Control Space                              |      |

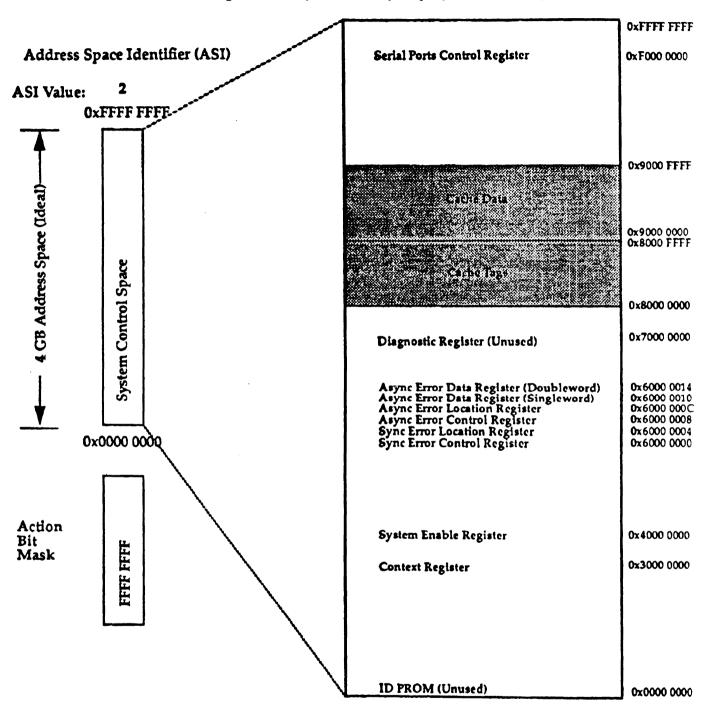

| 6.1.2 System Space (ASI = 2)                     | 6-2  |

| 6.1.3 Device Space                               | 6-7  |

| 6.2 Memory Management                            |      |

| 6.2.1 Address Translation                        | 6-13 |

| 6.2.2 Modifying the MMU                          | 6-13 |

| 6.2.3 MMU Protection Criteria                    | 6-13 |

| 6.3 Programming LED's                            | 6-14 |

| 6.3.1 SPARC CPU-2CE LED Programming Example      | 6-15 |

| 6.3.1.1 Example of the ce-misc.h file            | 6-16 |

| 6.4 Additional Forth Commands for LEDs/Hexswitch |      |

| Section | 7 |

|---------|---|

|---------|---|

| VME |                                                | 7-1 |

|-----|------------------------------------------------|-----|

| 7.0 | VMEbus Interface                               | 7-1 |

| 7.1 | Features of the SPARC CPU-2CE VMEbus Interface | 7-1 |

| 7.2 | VMEbus Basics - An Introduction                | 7-3 |

| 7.3 | VME Performance                                | 7-3 |

| 7.4 | VME Addresses                                  | 7-4 |

| 7.5 | VME Implementation                             | 7-5 |

| 7.6 Major VME Register Groups                        | 7-6  |

|------------------------------------------------------|------|

| 7.6.1 Accesses To Byte Registers                     | 7-7  |

| 7.7 Master Interface                                 | 7-8  |

| 7.7.1 A32 Map Register Base Location                 | 7-8  |

| 7.7.2 A32 Map Register Initialization                | 7-8  |

| 7.7.3 VME Registers Programming Example              | 7-10 |

| 7.8 Slave Interface                                  | 7-12 |

| 7.8.1 Slave Transfer Control                         | 7-12 |

| 7.8.2 Slave Map Register                             | 7-12 |

| 7.8.2.1 Slave Map Register Initialization            | 7-13 |

| 7.9 Mail Box                                         | 7-14 |

| 7.9.1 Mail Box Register Base Location                | 7-15 |

| 7.9.1.1 Mail Box Register Initialization             | 7-15 |

| 7.9.1.2 Mail Box Register Interrupt Level            | 7-15 |

| 7.10 Mailbox Interrupt Level - Rerun Length Register | 7-16 |

| 7.11 Bus Locker                                      | 7-17 |

| 7.11.1 VME Bus Locker Register                       | 7-17 |

| 7.11.2 Initialization                                | 7-18 |

| 7.12 Interrupt Handler                               | 7-19 |

| 7.12.1 Interrupt Enable/Bus Arbiter Mode Register    | 7-19 |

| 7.12.1.1 Interrupt Enable Register Initialization    | 7-19 |

| 7.13 Bus Requester                                   | 7-20 |

| 7.13.1 Bus Arbiter                                   | 7-20 |

| 7.14 Bus Time Out Period                             | 7-20 |

| 7.14.1 Rerun Time Out                                | 7-20 |

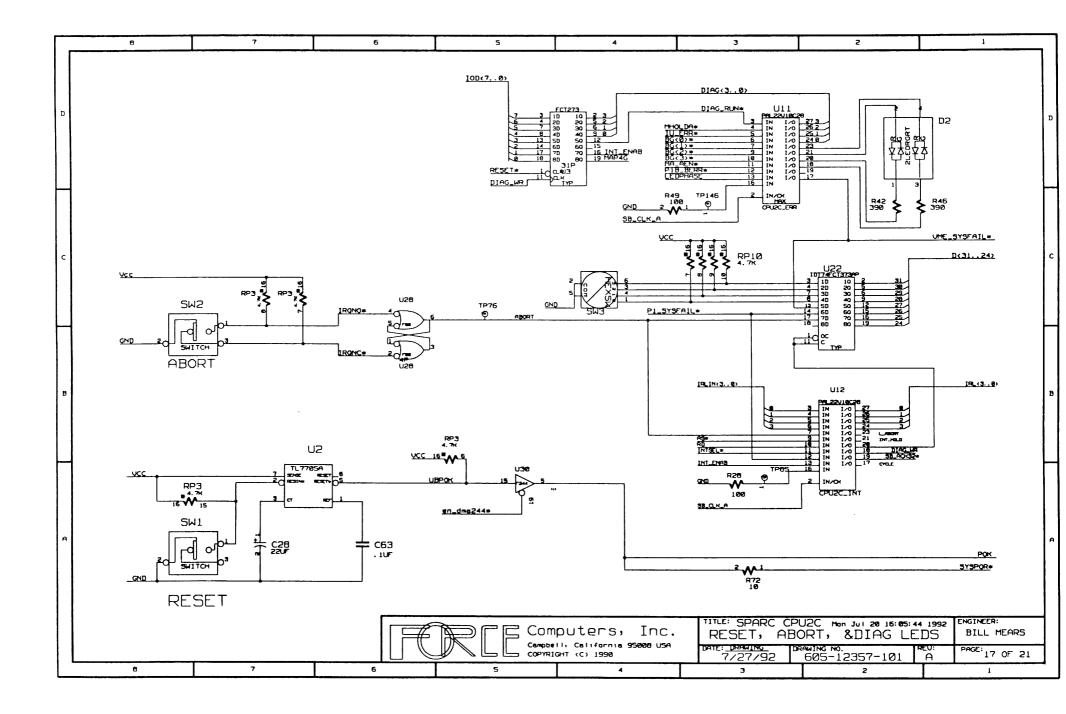

| 7.14.2 Abort                                         | 7-20 |

| 7.15 VMEbus Watchdog Timer                           | 7-21 |

| 7.16 System Reset and the Reset Switch               | 7-21 |

| 7.16.1 Sources for a System Reset                    | 7-21 |

| "The Power-On Reset"                                 | 7-21 |

| "The Reset Switch"                                   | 7-21 |

| "The Watchdog Reset"                                 | 7-22 |

| "The Software Reset"                                 | 7-22 |

| 7.17 Jumper                                          | 7-22 |

| 7.18 Programmable Register Settings                  | 7-22 |

| 7.19 VME Interrupt Monitor Register                  | 7-23 |

| 7.19.1 Fair Mode Requester                           | 7-23 |

| 7.20 VME IACK Cycles                                 | 7-23 |

| 7.20.1 Daisy Chain IACK Driver                       | 7-24 |

| 7.20.2 Master Cycles                                 | 7-25 |

| 7.20.3 Slave Cycles                                  | 7-25 |

| 7.21 Bus Arbitration                                 | 7-25 |

| 7.22 Interrupts                                      | 7-26 |

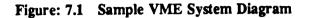

| 7.23 Example of a VME System                         |      |

| 7.24 VMEbus Device Driver                            | 7-28 |

| 7.24.1 VMEbus Device Driver System Calls             | 7-28 |

.

| 7.24.2 VMEbus Address Modifiers               | 7-30 |

|-----------------------------------------------|------|

| Program/Data/Block Transfer Address Modifiers | 7-30 |

| Supervisory/Non-Privileged Address Modifiers  | 7-31 |

| Extended/Standard/Short Address Modifiers     | 7-31 |

| 7.24.3 VMEbus Device Driver Limitations       | 7-31 |

| Floppy and Audio Interrupt Conflicts          | 7-31 |

| Potential for SunOS Patches to Conflict       | 7-32 |

| GENERIC.VME versus GENERIC_SMALL.VME          | 7-32 |

| 7.25 VME Programming Examples                 | 7-32 |

| 7.25.1 FORTH Programming Examples             | 7-32 |

| Map the VMEbus to a Virtual Address           | 7-32 |

| Map Local Memory to the VMEbus                | 7-33 |

| Map an SBUS Address to a Virtual Address      | 7-36 |

| 7.25.2 C Programming Example                  | 7-36 |

## Section 8

| ONC/VME |                                          | 8-1 |

|---------|------------------------------------------|-----|

| 8.1     | Capabilities                             | 8-1 |

|         |                                          | 8-1 |

| 8.3     | Booting Over the VMEbus Backplane        | 8-2 |

|         | 8.3.1 Installation Example               | 8-2 |

|         | 8.3.2 Hardware Configuration             | 8-3 |

|         |                                          | 8-3 |

|         | •                                        | 8-3 |

|         | 8.3.4.1 vme-slavemap                     | 8-4 |

|         |                                          | 8-4 |

|         |                                          | 8-4 |

|         | 8.3.4.4 vm-server-addr                   | 8-4 |

|         | 8.3.4.5 vm-ip-addr                       | 8-4 |

|         |                                          | 8-5 |

|         | 8.3.6 Files To Edit on the Server        | 8-5 |

|         | 8.3.6.1 /sys/sun4c/conf/GENERIC.VME      | 8-5 |

|         |                                          | 8-5 |

|         |                                          | 8-5 |

|         |                                          | 8-6 |

|         |                                          | 8-6 |

|         |                                          | 8-6 |

|         |                                          | 8-6 |

|         | 8.3.7.3 /export/root/client-vm/etc/fstab | 8-7 |

|         | 8.3.7.4 /export/root/client-vm/etc/hosts | 8-7 |

|         |                                          | 8-7 |

|         | 8.3.8 System Start-Up                    | 8-7 |

| 8.4     |                                          | 8-7 |

|         |                                          | 8-8 |

| 8.5     |                                          | 8-9 |

|         |                                          |     |

| 8.6 Memory Usage                                                                                                                                                                                                                                                                                                                                     | 8-9                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 8.6.1 Addressing Scheme                                                                                                                                                                                                                                                                                                                              | 8-9                                                  |

| 8.6.2 ONC/VME Region Layout                                                                                                                                                                                                                                                                                                                          |                                                      |

| 8.6.2.1 Magic Number                                                                                                                                                                                                                                                                                                                                 | 8-11                                                 |

| 8.6.2.2 Packet-Ready Flags                                                                                                                                                                                                                                                                                                                           | 8-11                                                 |

| 8.6.2.3 Host States                                                                                                                                                                                                                                                                                                                                  | 8-11                                                 |

| 8.6.2.4 IP Addresses                                                                                                                                                                                                                                                                                                                                 | 8-11                                                 |

| 8.6.2.5 Valid-Host Flags                                                                                                                                                                                                                                                                                                                             | 8-11                                                 |

| 8.6.2.7 Packet Contents                                                                                                                                                                                                                                                                                                                              | 8-11                                                 |

| 8.7 Protocol Operation                                                                                                                                                                                                                                                                                                                               | 8-11                                                 |

| 8.7.1 Initialization                                                                                                                                                                                                                                                                                                                                 | 8-12                                                 |

| 8.7.1.1 Initializing the Hardware                                                                                                                                                                                                                                                                                                                    | 8-12                                                 |

| 8.7.1.2 Initializing the Local Region                                                                                                                                                                                                                                                                                                                | 8-12                                                 |

| 8.7.1.3 Probing for Remote Hosts                                                                                                                                                                                                                                                                                                                     | 8-12                                                 |

| 8.7.2 Sending a Packet                                                                                                                                                                                                                                                                                                                               | 8-12                                                 |

| 8.7.2.1 Broadcast Packets                                                                                                                                                                                                                                                                                                                            | 8-13                                                 |

| 8.7.3 Receiving a Packet                                                                                                                                                                                                                                                                                                                             | 8-13                                                 |

| 8.7.3.1 Shutting Down                                                                                                                                                                                                                                                                                                                                | 8-14                                                 |

| 8.7.3.2 Error Handling                                                                                                                                                                                                                                                                                                                               | 8-14                                                 |

| OPTIONS AND APPLICATIONS                                                                                                                                                                                                                                                                                                                             | 9-1                                                  |

| GLOSSARY                                                                                                                                                                                                                                                                                                                                             | 10-1                                                 |

| SPARC CPU-2CE Hardware Documentation Glossary                                                                                                                                                                                                                                                                                                        | 10-1                                                 |

| SPARC Reference Materials Available from Sun         Documentation Available Other Places         Suggested Reference Material for the SCSI Interface         Ethernet Interface         Suggested Reference Material for Serial Interface A/B         Suggested Reference Material for Keyboard/Mouse Interface         Suggested Reading for FORTH | 10-1<br>10-1<br>10-2<br>10-2<br>10-2<br>10-2<br>10-3 |

| Section 11                                                                                                                                                                                                                                                                                                                                           |                                                      |

| CPU-2CE OPEN BOOT SUPPLEMENT                                                                                                                                                                                                                                                                                                                         | 11-1                                                 |

## LIST OF TABLES

| Table: 1.1 Board Function & Specification       1                         | -11  |

|---------------------------------------------------------------------------|------|

|                                                                           | 1-13 |

| Table: 2.1 Diagnostic Tools                                               |      |

| Table: 2.2 Diagnostic Switches    2                                       | 2-11 |

| Table: 2.3 Non-Volatile System Configuration Parameter Defaults         2 |      |

| Table: 2.4 NVRAM VME Configuration Parameters         2                   |      |

| Table: 2.5 Front Panel         Front Panel         2                      |      |

| Table: 2.6 CPU-2CE Connectors         2                                   |      |

| Table: 2.7 SCSI Pinout List         2                                     |      |

| Table: 2.8 Ethernet Pinout List    2                                      |      |

| Table: 2.9 Serial Pinout List    2                                        |      |

| Table: 2.10    Audio Connector (Din 8)    2                               |      |

| Table: 2.11    Keyboard/Mouse    Connector    Pinout    List    2         |      |

| Table: 2.12    SBus Connector Pinout    2                                 |      |

| Table: 2.13 P1 Bus Pinout List    2                                       |      |

| Table: 2.14    P2 Bus Pinout List    2                                    |      |

| Table: 2.15 Expansion Connector Electrical Pinout    2                    |      |

| Table: 3.1    Virtual Memory Layout                                       |      |

| Table: 3.2 Address Space Indicator Contents       3                       |      |

|                                                                           | 3-17 |

| Table: 3.4 SBus Bandwidth Estimation       3                              |      |

| Table: 3.5       SCSI Register Addresses       3                          |      |

| Table: 3.6 Ethernet Registers    3                                        |      |

| ▲ · · · · · · · · · · · · · · · · · · ·                                   | 3-31 |

| Table: 3.8 SBus Slot Addresses       3                                    |      |

| Table: 3.9 SBus Slot 0 Addresses    3                                     |      |

| <b>.</b>                                                                  | 3-34 |

| Table: 3.11    Address Ranges    3                                        |      |

| Table: 3.12 DRAM maps physical addresses to SIMM Locations         3      |      |

| Table: 3.13 CTL mappings    3                                             |      |

|                                                                           | 8-56 |

|                                                                           | 3-57 |

|                                                                           | 6-2  |

|                                                                           | 6-3  |

|                                                                           | 6-3  |

|                                                                           | 6-4  |

| Table: 6.5    Synchronous Error Register                                  | 6-4  |

| $\mathbf{v}$                                                              | 6-5  |

| Table: 6.7 Synchronous Error Register                                     | 6-5  |

| Table: 6.8    Synchronous Error Register                                  | 6-5  |

| Table: 6.9    Asynchronous Error Register                                 | 6-6  |

| Table: 6.10    Cache Tags                                                 | 6-6  |

| Table: 6.11   Type One Space                                              | 6-8  |

| Table: 6.12   TOD/NVRAM                                                   | 6-9  |

| Table: 6.13 Counters timers    Counters timers                            | 6-9  |

## LIST OF TABLES "continued"

| Table: 6.14 PError   PError                                         | 6-10 |

|---------------------------------------------------------------------|------|

| Table: 6.15 Type 1 Space for off Board DRAM                         | 6-11 |

| Table: 6.16 Interrupt Control Register                              | 6-11 |

| Table: 6.17 Aux I/O Register                                        | 6-12 |

| Table: 6.18 LED/SW3 Register (Longword access only)                 | 6-14 |

| Table: 7.1 VME Concept Definitions                                  |      |

| Table: 7.2 VME Addresses                                            |      |

| Table: 7.3 VME Address Spaces                                       | 7-5  |

| Table: 7.4 VME Registers                                            |      |

| Table: 7.5 A32 Map Register                                         |      |

| Table: 7.6 A32 Map Register Address Bits                            |      |

| Table: 7.7    A32    Map Register Bit Definitions                   | 7-9  |

| Table: 7.8    Slave Map Register Address                            | 7-13 |

| Table: 7.9    Slave Map Register Address Bits                       |      |

| Table: 7.10       Slave Master Register Bit Definitions             | 7-14 |

| Table: 7.11    Mail Box Register Address                            | 7-15 |

| Table: 7.12    Mail Box Register Address Bits                       | 7-15 |

| Table: 7.13 Mail Box Register Bit Definitions                       | 7-16 |

| Table: 7.14    Bus Locker Register Bit Definitions                  |      |

| Table: 7.15    Interrupt Enable Register Address                    | 7-19 |

| Table: 7.16 Interrupt Enable Register Bit Definitions               | 7-19 |

| Table: 7.17    Slot 1 Jumper & Functions                            | 7-22 |

| Table: 7.18 Programmable Register Settings                          | 7-22 |

| Table: 7.19 VME Interrupt Monitor Register Address                  | 7-23 |

| Table: 7.20 Interrupt Monitor Register Address Definitions          | 7-23 |

| Table: 7.21    Mail Box Register Address                            | 7-24 |

| Table: 7.22       VME IACK Cycles Register Address Bits             | 7-24 |

| Table: 7.23       VME IACK Cycles Interrupt Responses               |      |

| Table: 7.24         Slave Cycles Duration and Theoretical Bandwidth |      |

| Table: 7.25 Bus Arbitration                                         |      |

| Table: 7.26    VME Interrupt Levels and Sources                     |      |

| Table: 7.27    A16 - only    Address    Decode                      |      |

| Table: 7.28    A24 - Only Address Decode                            | 7-31 |

| Table: 7.29    Address Modifier Codes                               | 7-32 |

| Table: 8.1    Example Server Configuration                          | 8-2  |

| Table: 8.2    Example Client Configuration                          | 8-3  |

| Table: 8.3       ONC/VME Region Layout                              | 8-10 |

| Table: 11.1 SPARC Reference Materials Available from Sun            | 11-1 |

| Table: 11.2 Documentation Available Other Places    Other Places    | 11-1 |

.

## LIST OF FIGURES

| Figure: 1.1 Block Diagram                                  | 1-2  |

|------------------------------------------------------------|------|

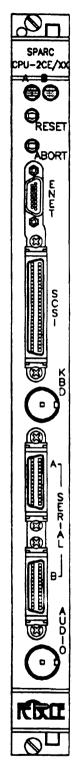

| Figure: 1.2 Photo Page                                     | 1-3  |

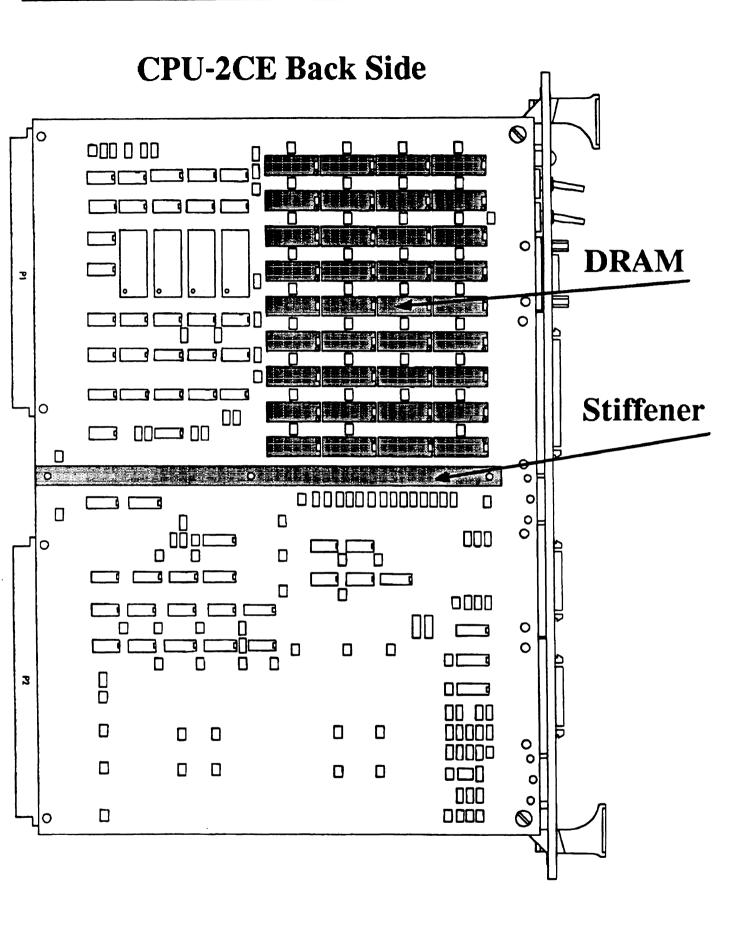

| Figure: 2.1 RS-232/423 Jumper Blocks                       | 2-3  |

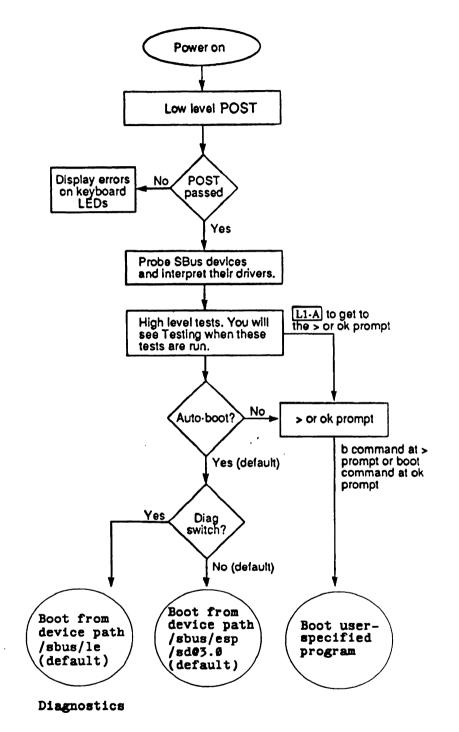

| Figure: 2.2 POST                                           | 2-9  |

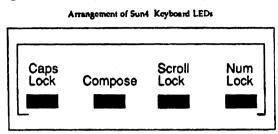

| Figure: 2.3 Keyboard LED Diagnostic Codes                  |      |

| Figure: 2.4 Font Panel                                     | 2-18 |

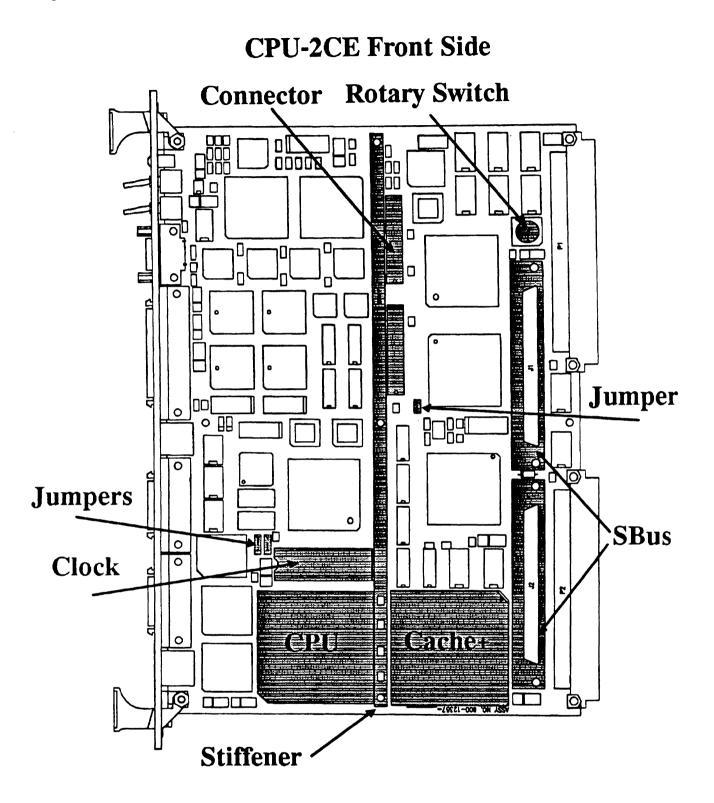

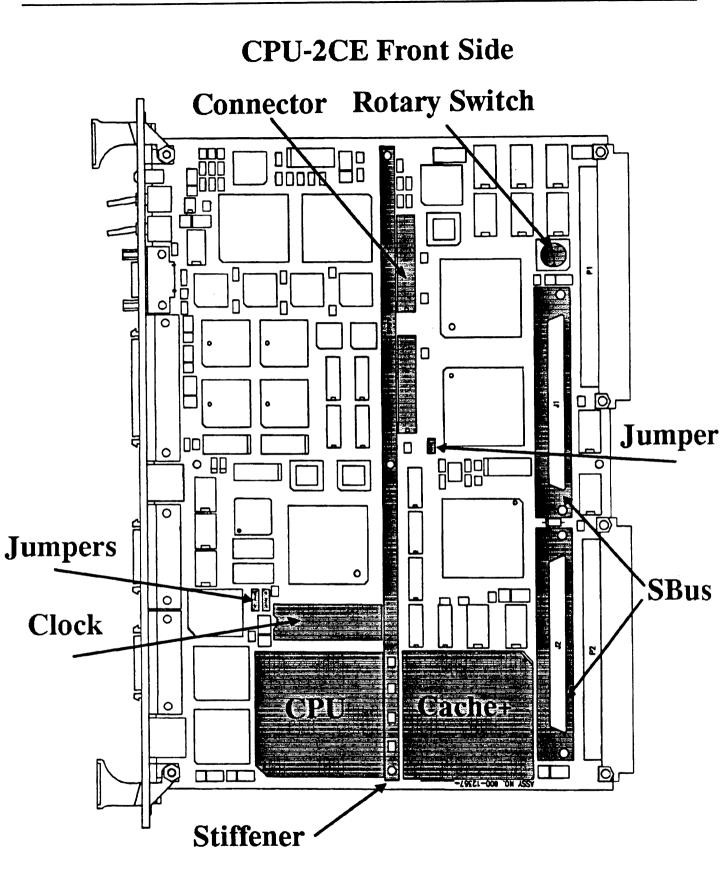

| Figure: 2.5 Component Side                                 | 2-19 |

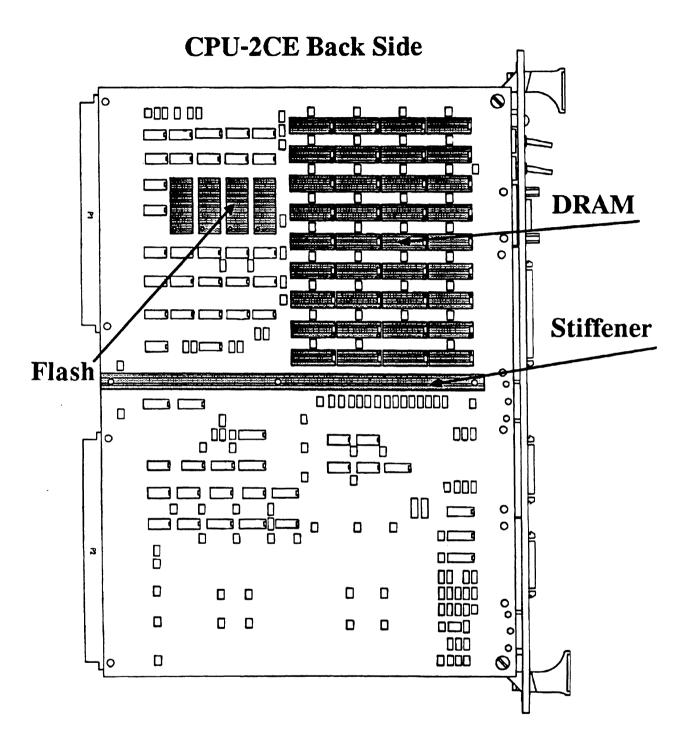

| Figure: 2.6 Solder Side                                    | 2-20 |

| Figure: 2.7 SCSI Connector and Pins (Front View)           |      |

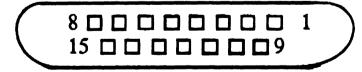

| Figure: 2.8 Ethernet Cable Connector and Pins (Front View) | 2-22 |

| Figure: 2.9 Ethernet Cable                                 |      |

| Figure: 2.10 Serial Cable                                  | 2-25 |

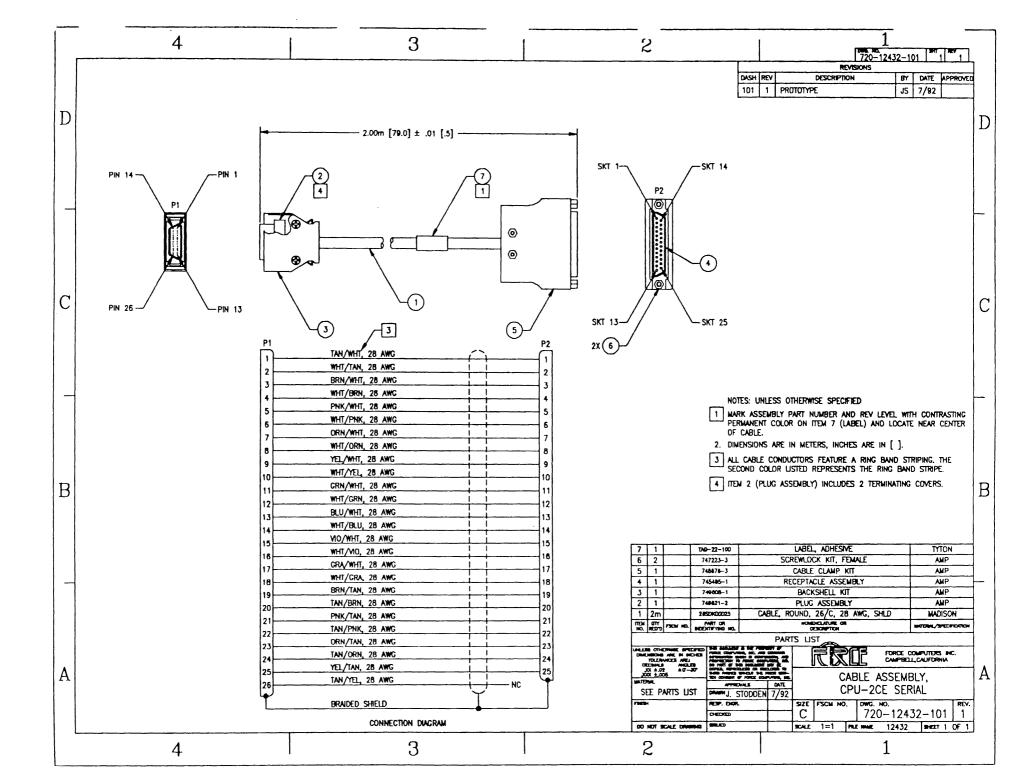

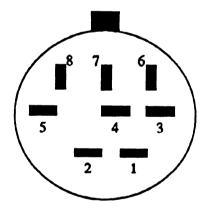

| Figure: 2.11 Audio Connector                               |      |

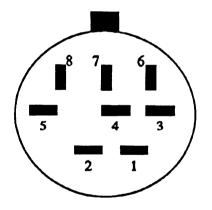

| Figure: 2.12 Keyboard/Mouse Connector                      | 2-27 |

| Figure: 2.13 Sun Expansion Connector Pin Orientation       |      |

| Figure: 3.1 Shows the Front Panel                          |      |

| Figure: 3.2 Shows the component-side                       |      |

| Figure: 3.3 Shows the solder                               |      |

| Figure: 3.4 RS-232/423 Jumper Blocks                       |      |

| Figure: 3.5 SPARC/CPU-2CE ADDRESS SPACE VIRTUAL            |      |

| Figure: 3.6 Physical Memory Map                            |      |

| Figure: 3.7 Virtual/Physical Memory Map ASI Diagram        |      |

| Figure: 3.8 Type 1 Space (On-Board I/O) (obio)             |      |

| Figure: 3.9 Type 0 Space (Main Memory) (obmem)             |      |

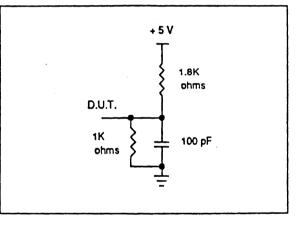

| Figure: 3.10 Safe Decode Circuit                           |      |

| Figure: 3.11 Word Read                                     | 3-43 |

| Figure: 3.12 Word Read 2                                   |      |

| Figure: 3.13 Word Write                                    |      |

| Figure: 3.14 Burst Read                                    |      |

| Figure: 3.15 Burst Write                                   |      |

| Figure: 3.16 Segment Map & Page Map                        |      |

| Figure: 3.17 Internal Register Cycle                       |      |

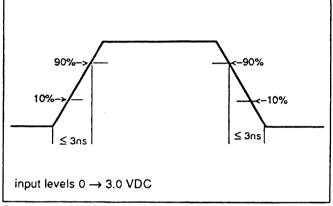

| Figure: 3.18 Clock Cycle                                   |      |

| Figure: 3.19 SBus or DRAM Access                           |      |

| Figure: 3.20 Scan EPROM Access                             |      |

| Figure: 3.21 2nd EPROM Access                              | 3-59 |

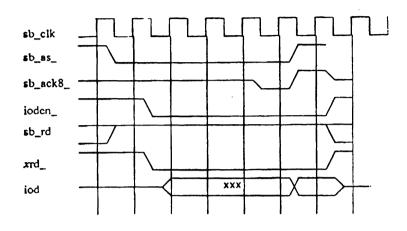

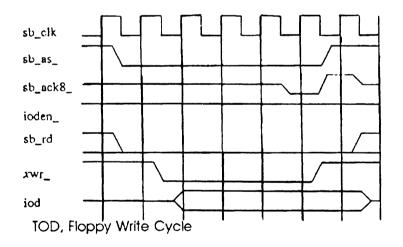

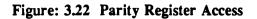

| Figure: 3.22 Parity Register Access                        | 3-60 |

| Figure: 3.23 SCC/KB Mouse Access                           | 3-60 |

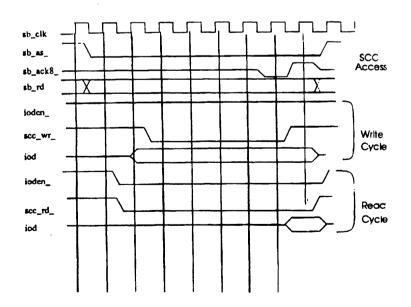

| Figure: 3.24 Statistics Updates                            | 3-61 |

| Figure: 3.25 Counter                                       | 3-63 |

| Figure: 3.26 2nd Counter                                   | 3-63 |

| Figure: 3.27 RS-232/423 Jumper Blocks                      | 3-65 |

| Figure: 6.1 Illustration Memory Management                 | 6-12 |

| Figure: 7.1 Sample VME System Diagram                      | 7-28 |

|                                                            | 1-20 |

Section 1

#### **1.0 INTRODUCTION**

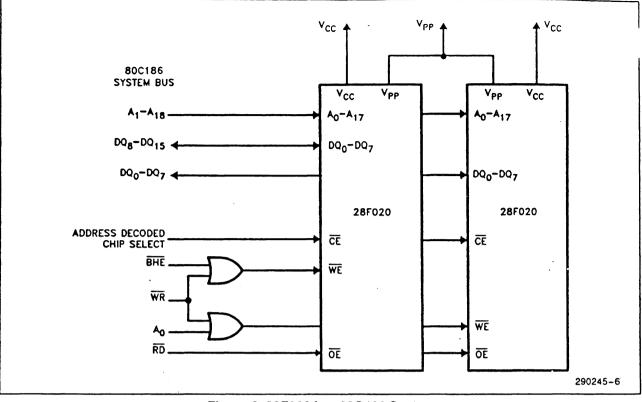

A complete VMEbus-based SPARCstation<sup>TM</sup> 2 architecture with Sbus expansion. The SPARC CPU-2CE is the latest innovation resulting from the technology partnership of FORCE COMPUTERS and Sun Microsystems. Combining a true SPARCstation 2 architecture with FORCE COMPUTERS expertise and experience in standard 6U Eurocards has resulted in a faithful SPARCstation 2 implementation in a single VMEbus slot.

The SPARC CPU-2CE<sup>™</sup> offers the same I/O interfaces as the SPARC station 2, including DMA supported SCSI and Ethernet ports along with audio, keyboard/mouse, and two serial channels with full modem support. Two Sbus sockets allow the installation of standard, off-the-shelf Sbus modules such as graphic frame buffers or accelerators or any other of over 300 Sbus cards available from third-party vendors.

Through its binary compatibility with the Sun SPARC station 2 family, the SPARC CPU-2CE runs current versions of SunOS<sup>™</sup>/Solaris<sup>™</sup> as well as the more than 4,000 shrink-wrapped SPARCware<sup>™</sup> applications available today. In addition, a variety of real-time operating systems will be available.

Its IEEE 1014 compatible VMEbus interface enables the SPARC CPU-2CE user to build high-performance embedded UNIX® systems, SPARC®- based real-time systems and hybrid UNIX/real-time systems linked via the VMEbus or local- and/or wide-area networks.

The SPARC CPU-2CE is a compact single board computer that brings the power and functionality of the popular Sun SPARC station 2 to the industry-standard VMEbus for use in UNIX and real-time applications.

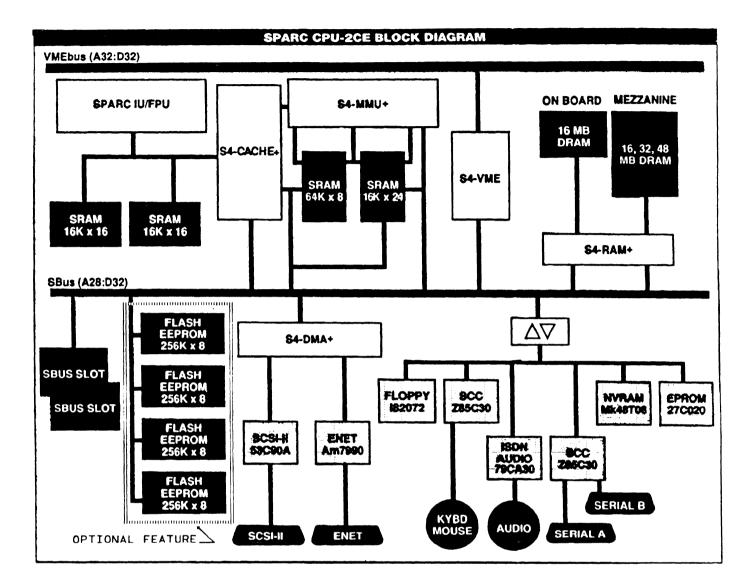

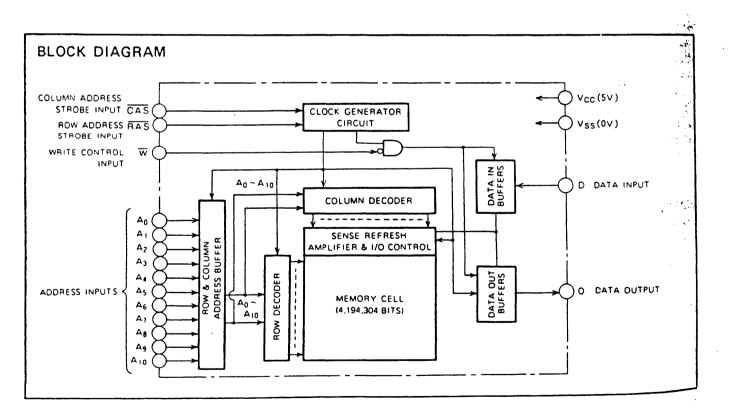

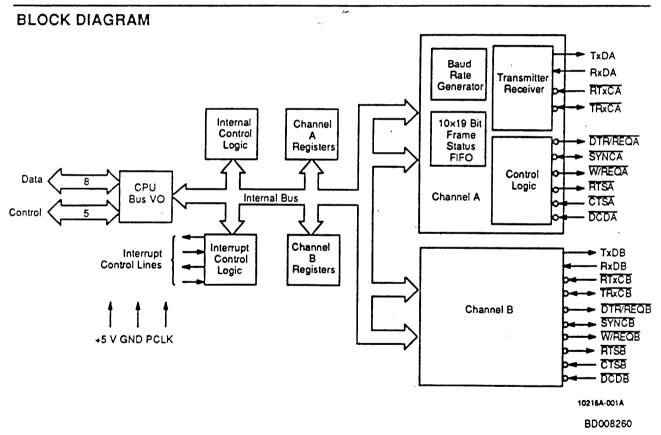

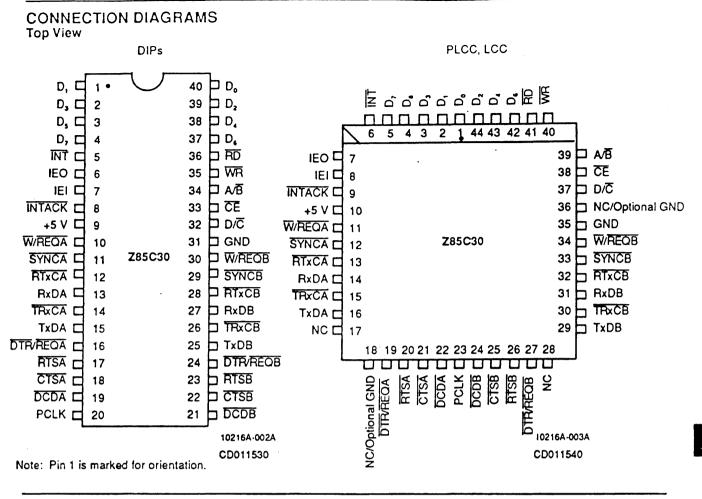

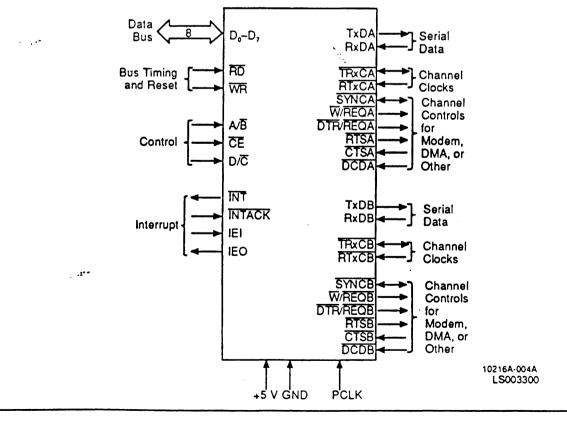

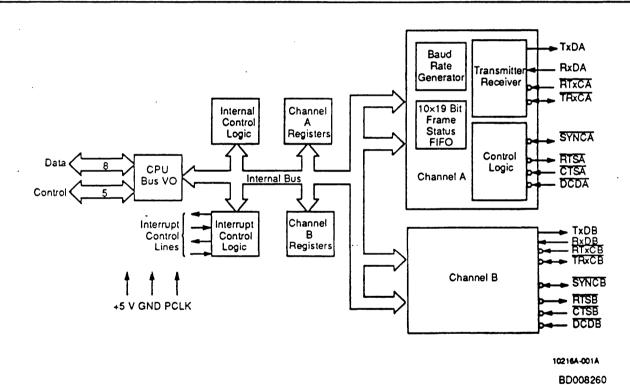

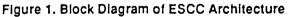

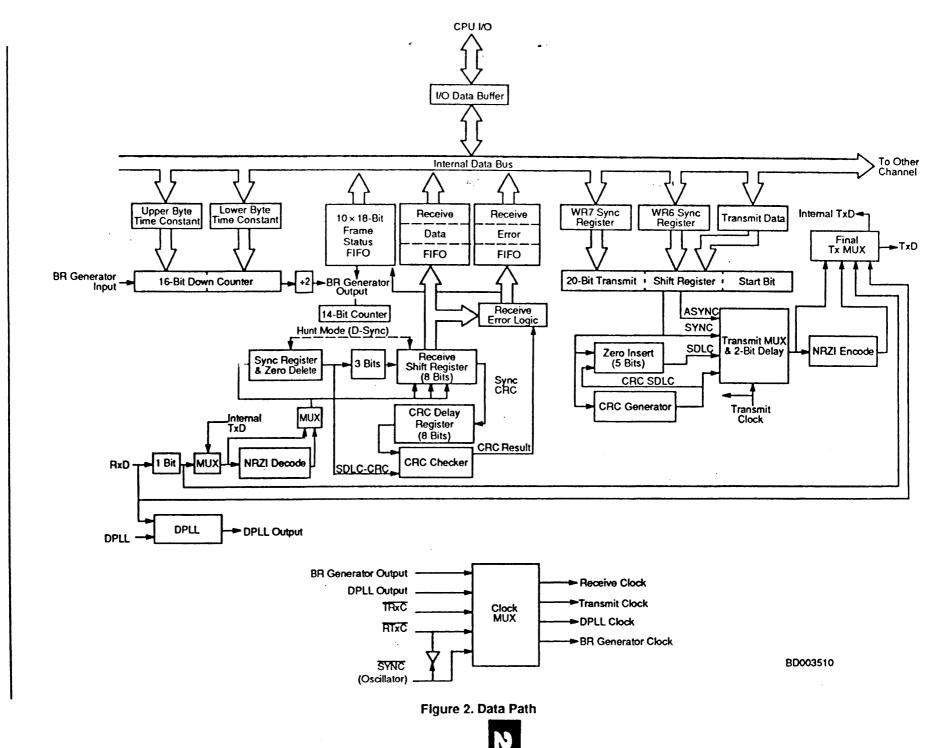

#### Figure: 1.1 Block Diagram

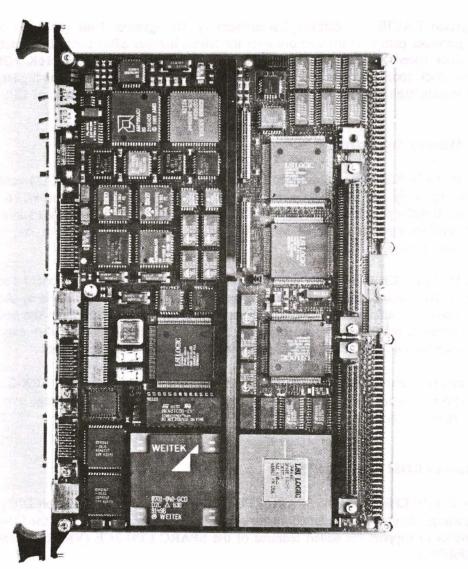

#### Figure: 1.2 Photo Page

TURRE LOT STOLES

a Sadar Sirki Capadabb Basusar ARC setatan) 32 GrBASC provem dig tata da a sata - sear te Shefici CE bettike da is maptica af ar imgaart fangar Unit/Poeng Court (Calas - a da a da a taugar Unit/SRAM based Moorry Management Scratche), a Cadar Courtific (Calas - affine) affine Sata daga. Operanty at 40 Marche Courties 23,3 Milla mager performance of the Cal tautang point realizations. The Cooke Courties is provided a 120 Will wave affine to site to self the Scratche mager and cal

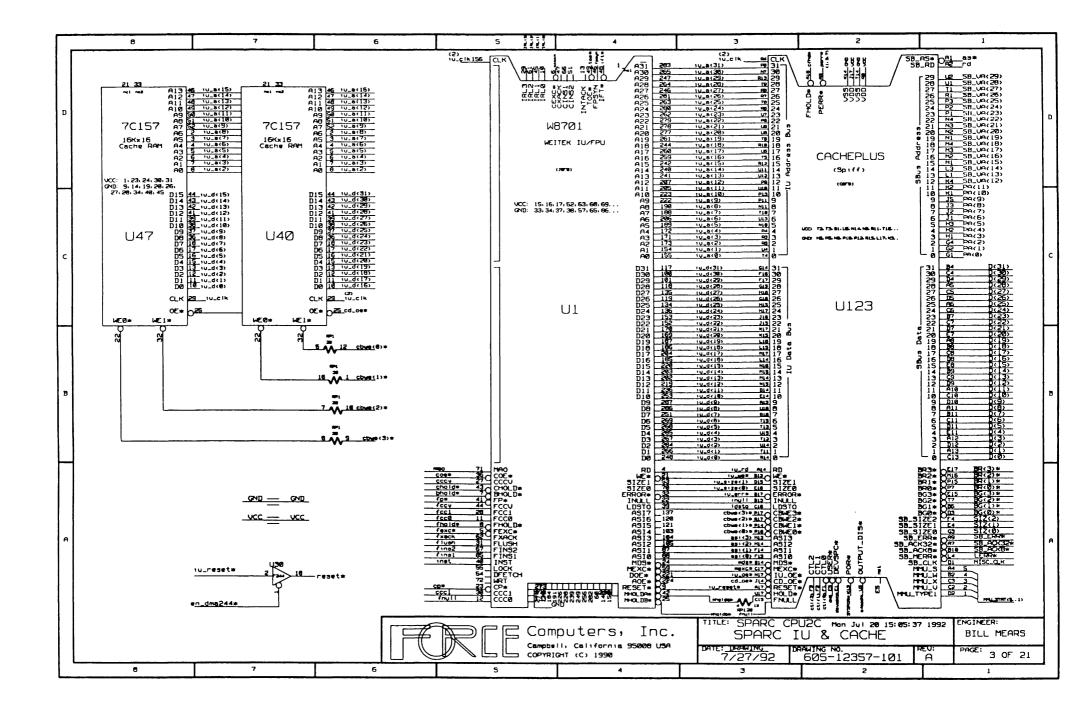

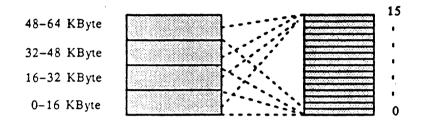

#### 1.1 The Processor

A 40-Mhz SPARC (Scalable Processor ARChitecture) 32-bit RISC processor chip set is at the core of the SPARC CPU-2CE. It is comprised of an integrated Integer Unit/Floating Point Unit (IU/FPU), a Sun standard SRAM-based Memory Management Unit (MMU+), a Cache Controller (Cache+) and two Cache RAM chips. Operating at 40 Mhz, the IU/FPU provides 28.5 MIPS integer performance and 4.2 MFLOPS floating point performance. The Cache Controller provides a 2-Kbyte tag array for a 64-Kbyte, virtual, write-through cache.

The integrated CACHE+ Controller Cache/Memory Management Unit (CMMU) handles the cache memory, provides path to main memory over the SBus, handles SBus controller function, and works at 40 MHz clock speed. The SPARC CPU-2CE has two cache RAMs that are 16K x 16 devices and run at 40 MHz clock speed. The large cache and double word write buffer means higher hit ratios and the ability to sustain high I/O DMA bandwidths with only a small reduction in local CPU performance.

#### **1.2 The Memory Subsystem**

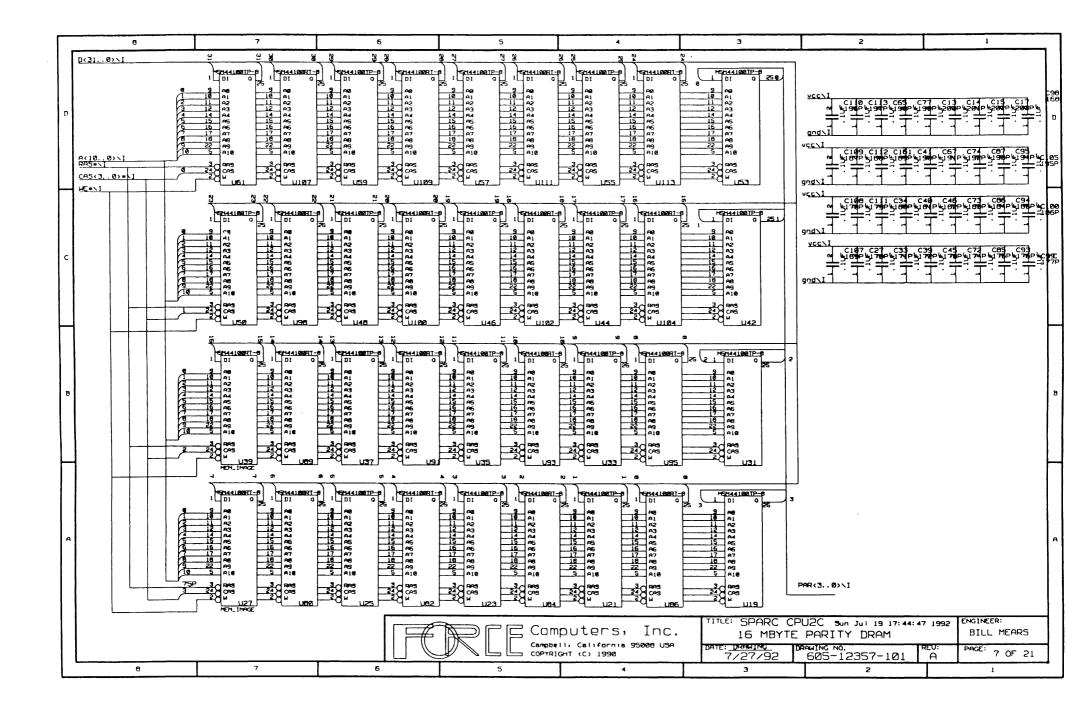

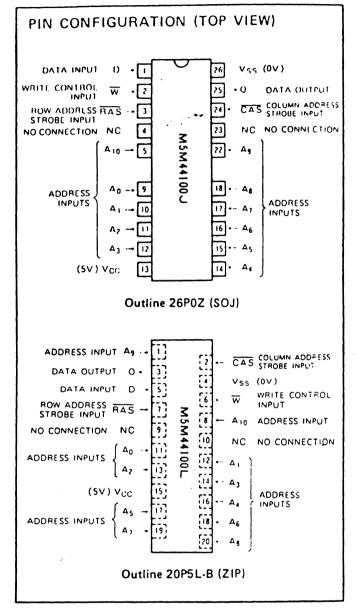

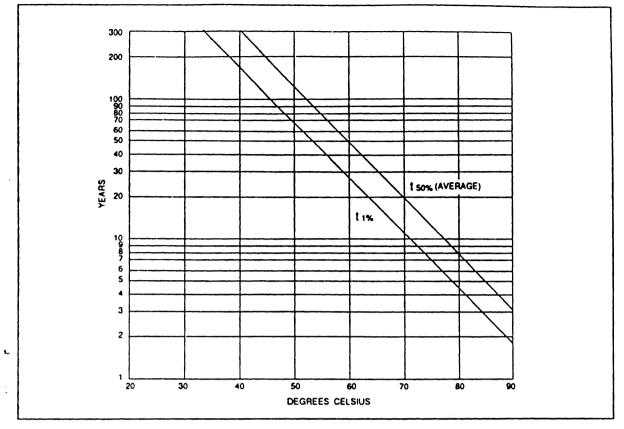

The SPARC CPU-2CE chip set includes the RAM+, an Sbus-compatible DRAM controller with single clock burst capability. RAM+ operates the DRAM in fast page mode to support 8-, 16-, 32-, and 64-byte bursts at one transfer per clock after an initial access latency of 4 clocks for reads and 2 clocks for writes. The configuration supports up to 64 Mbytes of 32-bit wide DRAM on board and incorporates parity generation and parity error detection.

The SPARC CPU-2CE is available with 16-, 32-, 48-, or 64-Mbytes of on-board DRAM. 16 Mbytes reside on the base-board and are implemented using high-reliability TSOP devices. Additional capacity, up to 64 Mbytes, is achieved using separate mezzanine modules which retain the single-slot capability without interfering with Sbus expandability on the SPARC CPU-2CE. Memory capacity upgrades are possible since the DRAM mezzanine modules are designed for field installation.

Memory can be expanded beyond the 64-Mbyte on-board limit via an SBus SRX-2 card. This option expands Type0 memory space by up to 64 Mbytes and is cacheable, an advantage over other Sbus-based memory expansion modules.

#### **1.3** System EPROM Open Boot<sup>™</sup>:

The Open Boot<sup>TM</sup> EPROM on the SPARC CPU-2CE is located in a single 32 bit DIP socket that enables easy upgrading. It provides the functionality of the boot device supplied with the SPARCstation 2, with enhancements to support the added features of the SPARC CPU-2CE (VMEbus interface and optional Flash EEPROM).

There is an EPROM-based monitor/debugger called Open Boot<sup>™</sup>. Open Boot is a trademark by Sun.

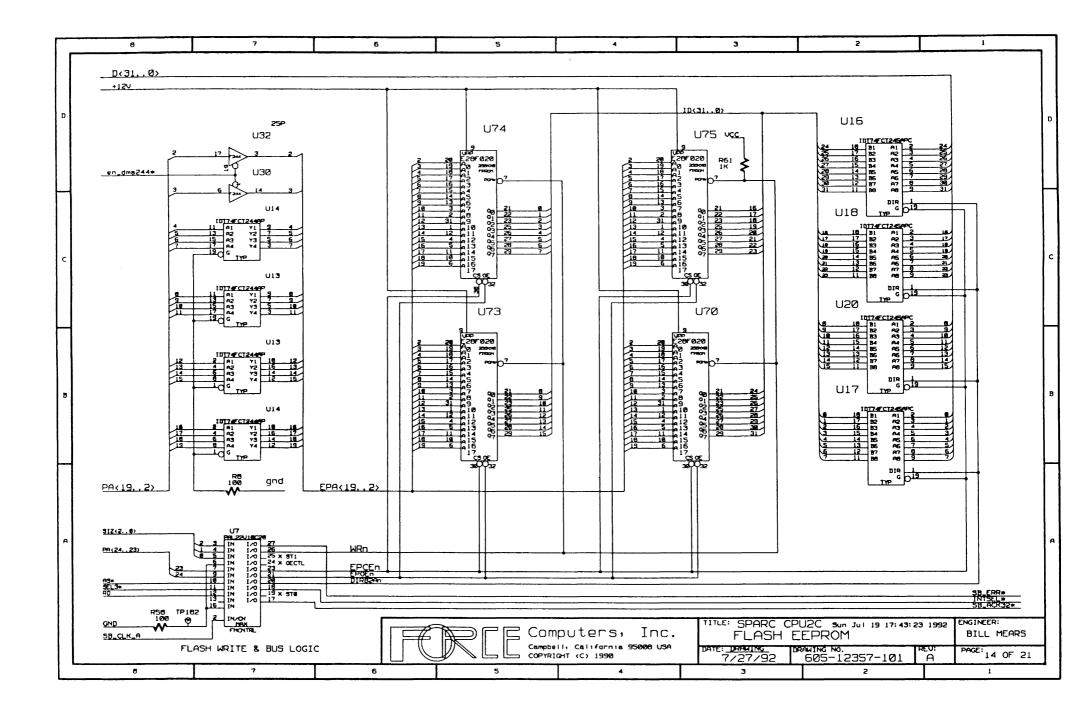

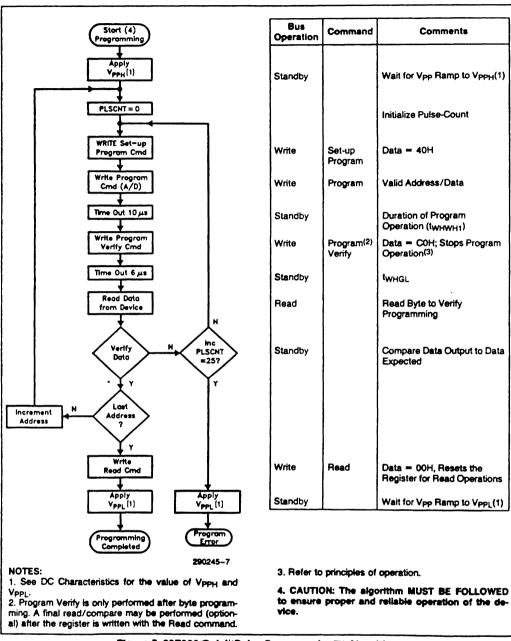

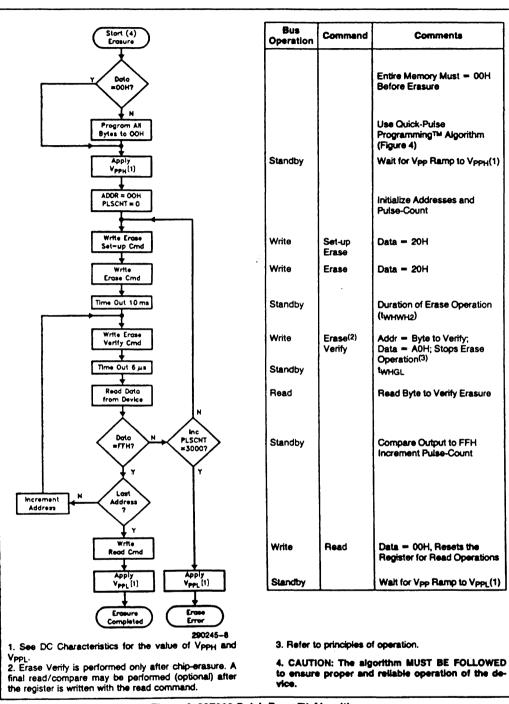

#### **1.4 FLASH EEPROM (Optional Feature)**

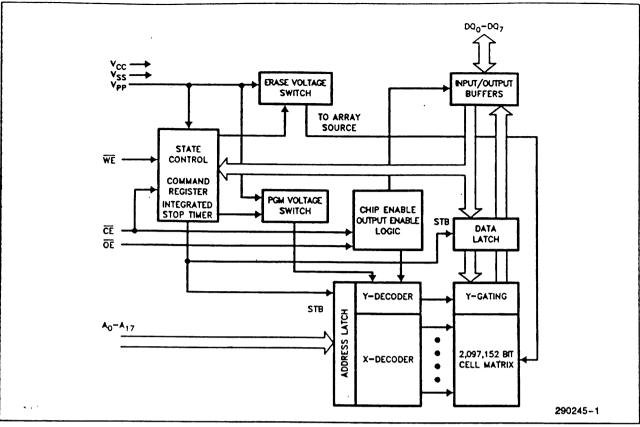

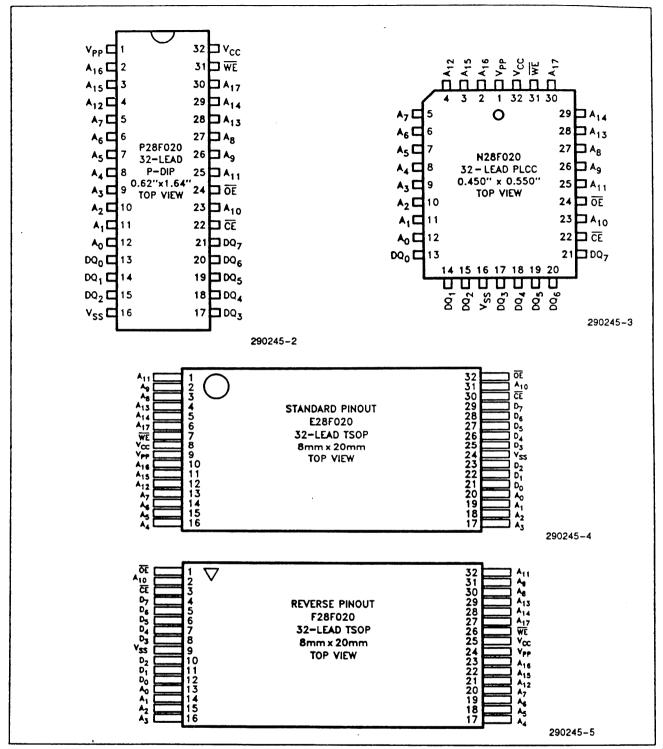

In addition to the boot device, the SPARC CPU-2CE employs 4 FLASH EEPROMs in TSOP packages for flexibility and customization. This 1-Mbyte FLASH EEPROM is organized to be 32-bits wide and is mapped in place of the Sun SPARC station 2 Sbus Slot 3.

These EEPROMs are erasable and writable by the user and allow the system integrator to incorporate FCODE drivers for system specific VME-based products using routines supplied in the boot ROM. With 150 ns EEPROMs, the access time is 4 clocks.

The SPARC CPU-2CE allows integrators to specify their product as the console or boot device without having to modify the on-board firmware. It also allows them to take advantage of SunOS loadable drivers for their VME products. This feature provides a path to firmware-assisted system auto-configuration.

#### 1.5 Local I/O

Ethernet, SCSI interfaces, two serial interface ports, a keyboard specific serial port, a mouse specific serial port, a floppy disk controller, and an audio input / output port are provided.

#### Serial Interface Ports

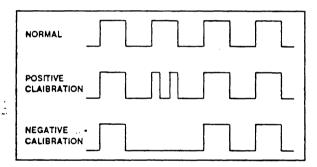

The Zilog Z85C30 Serial Communications Controller (SCC) supports two serial interface ports using 26-pin connectors on the front panel for synchronous and asynchronous communications. Data rates up to 64 Kbaud are supported and are user configurable, with a pluggable shunt for either RS-232C or RS-423C, and offer full modem control and interrupt capability. Both ports must be set identical as either RS-232 or RS-423.

#### Keyboard/Mouse Port

The connector for the keyboard/mouse port uses a SPARCstation Type 2 8-pin Mini-circular DIN connector on the front panel. The Z85C30 SCC for the keyboard/mouse specific port is terminated with TTL buffers and uses all TTL-compatible data signals. The interface is fully compatible with Sun SPARCstation 2 keyboard and mouse product offerings and uses the same cables.

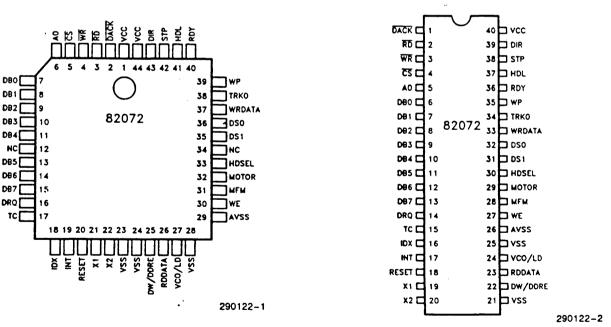

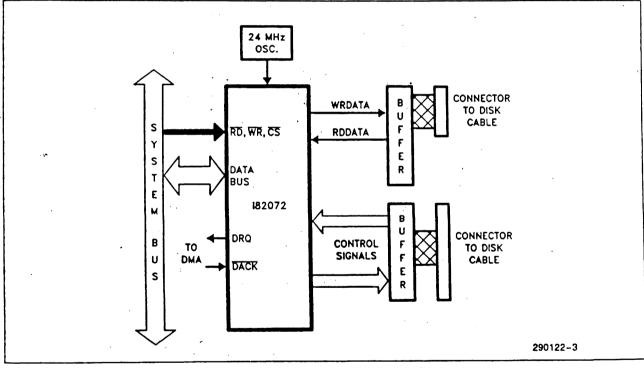

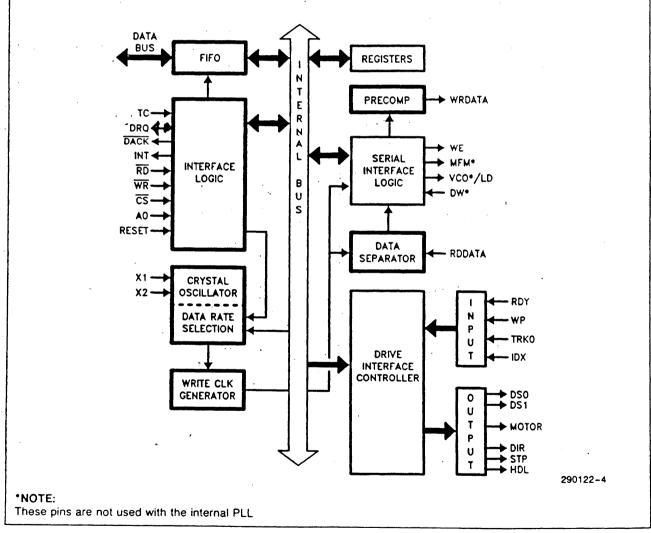

#### Floppy Disk Controller

An Intel i82072 functions as the floppy disk controller and is fully compatible with the Sun SPARCstation 2. The floppy disk controller signals are available on the User I/O lines of the P2 connector.

#### Audio Port

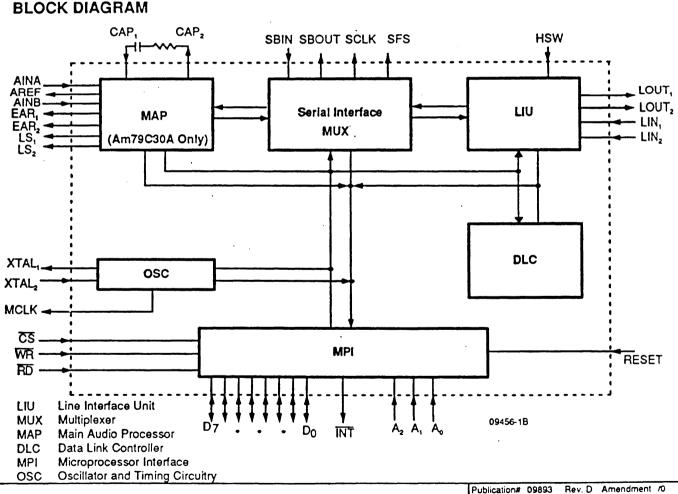

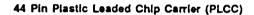

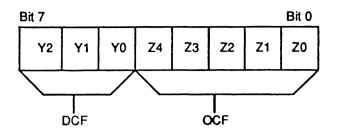

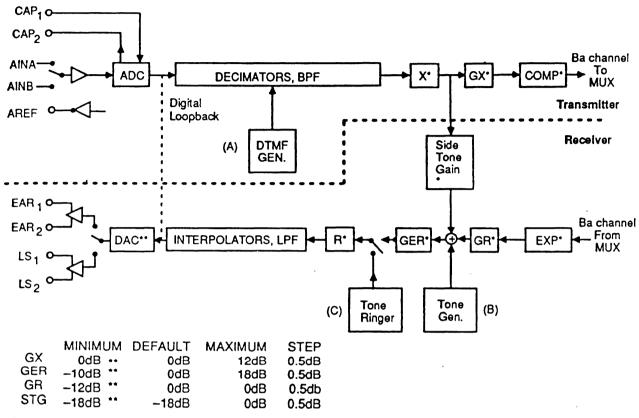

The audio interface is implemented with an AMD Am79CA30 ISDN/audio controller device and is fully compatible with the Sun SPARCstation 2. The audio connector on the front panel is an 8-pin Mini-circular DIN connector. As in the SPARCstation 2, the ISDN functionality of the Am79CA30 is not implemented.

#### 1.6 DMA+

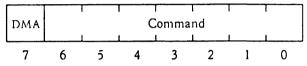

The DMA ASIC provides DMA and data assembly-disassembly functions for both the Ethernet and SCSI interfaces. The ASIC contains a 32 byte FIFO for each interface and performs DMA in 16 byte bursts when alignment and transfer length permit.

#### 1.7 Small Computer Systems Interface (SCSI)

The SCSI interface provides a standard interface to a wide variety of mass storage devices, such as hard disks, tapes, and CD-ROMs.

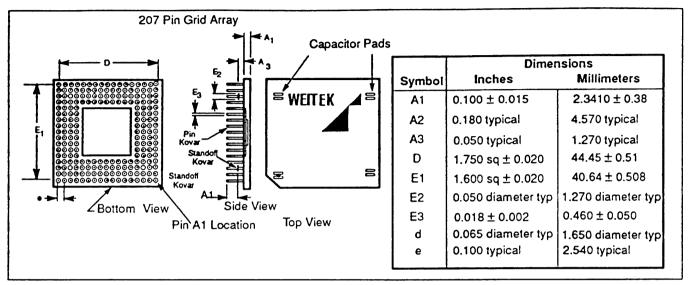

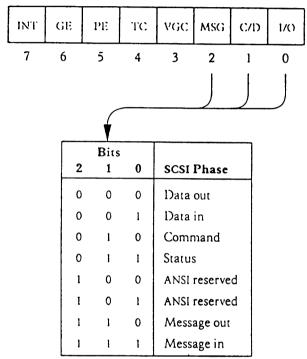

The SPARC CPU-2CE board features a Small Computer System Interface (SCSI) controller device using the NCR 53C90A controller chip augmented by the DMA+(D-channel). This provides SCSI-I functionality and can transfer at up to 5 Mbytes/sec, depending on the speed of the target.

The SCSI controller on the SPARC CPU-2CE acts as a SCSI initiator. Up to seven SCSI target devices can be connected to a SPARC CPU-2CE board. The SCSI bus is properly buffered and terminated on the SPARC CPU-2CE, so that the connection of SCSI devices is simple and straight forward. Just attach a terminated SCSI device with a cable and the CPU-2CE will automatically adjust for proper termination.

The DMA features full SCSI specification, ANSI X3.131/1986, compatibility. It supports both synchronous and asychronous operation with SCSIbus signals connected to the front panel connector and VMEbus P2 connector. Single ended mode is supported only.

The SCSI bus is routed to both the front panel, via a 50-pin SCSI-II connector, and to the board's P2 User I/O pins.

#### **1.8 Ethernet Interface**

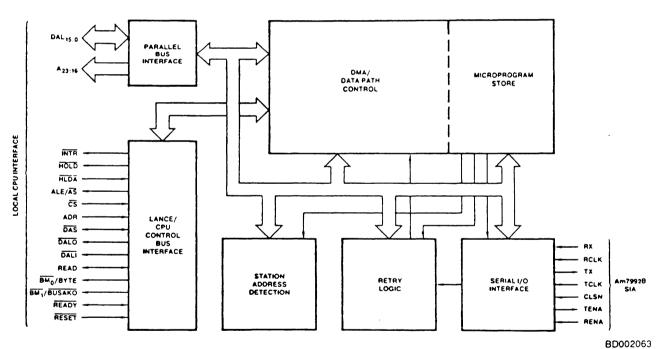

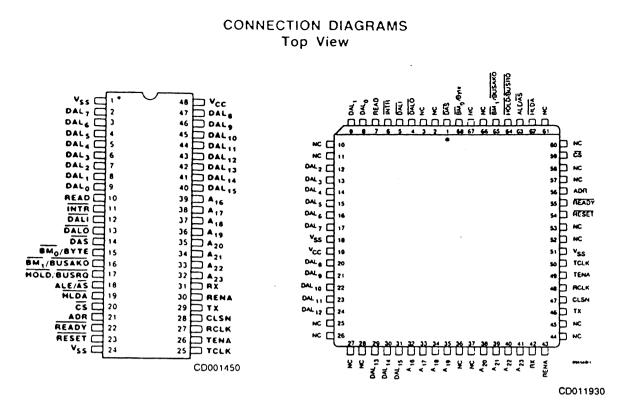

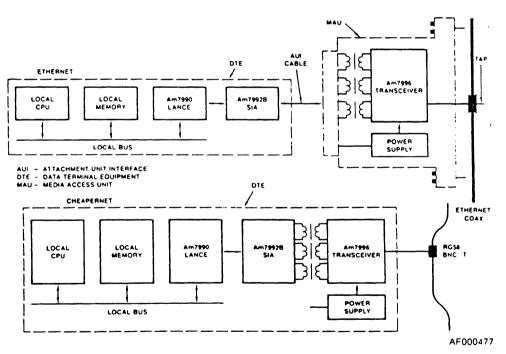

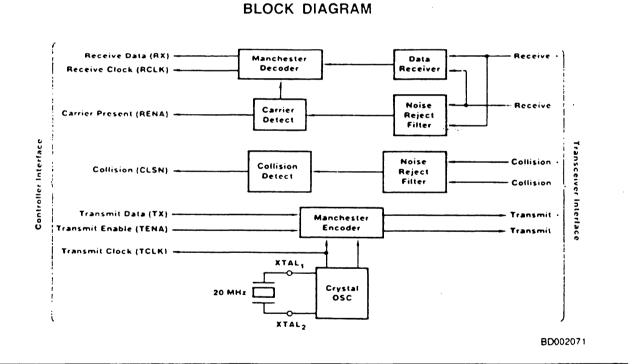

The Ethernet interface is comprised of the DMA+ interface chip for DMA, the AMD Am7990 Local Area Network Controller (LANCE) chip and the AMD Am7992B Serial Interface Adapter (SIA). The IEEE 802.3 Ethernet interface is available via a 15-pin Micro-D connector on the front panel. An adapter cable for the Micro-D to the regular DB15 is available. The DMA+ chip contains a 32-byte FIFO and increases performance through its 16-byte DMA burst capability.

The Ethernet interface features compatibility to the IEEE 802.3 Ethernet specification, DMA burst capability, data rate of up to 10 Mbit/sec, interrupt generation (Level 6), and utilization of up to 128 Kbytes of memory.

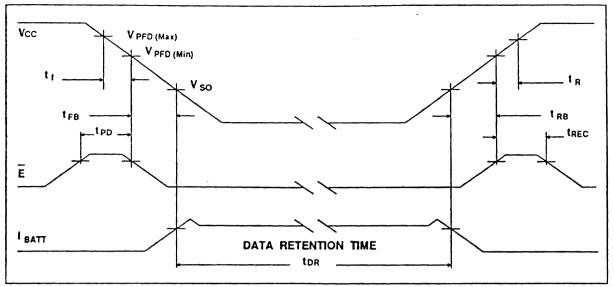

#### 1.9 Real-Time Clock/NVRAM

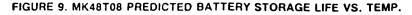

The SPARC CPU-2CE board uses the Mostek MK48T08 RTC-NVRAM chip. This device includes an 8-Kbyte non-volatile static RAM, of which 2 Kbyte is user programmable, and a clock/calendar circuit. Both are supported by a 10-year shelf-life lithium battery, in order to retain data when the board is powered down.

#### 1.10 SBus Interface

The SBus is a high performance CMOS bus and the basic interconnection mechanism for the system between the CPU and main memory and I/O devices. Two Sbus connectors are available for I/O expansion into the next VME slot.

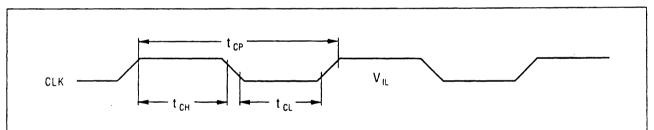

The Sbus is a high-performance expansion bus with a bandwidth of over 50 Mbytes/sec. The Sbus forms the local memory and I/O bus for the SPARC CPU-2CE and features 32-bit virtual addressing, 28-bit physical addressing, 32-bit data path, synchronous data transfer and master/slave capability. The SPARC CPU-2CE incorporates two Sbus sockets for I/O expansion. These provide support and compatibility with the hundreds of third-party Sbus expansion products on the market, including products for video and graphics, connectivity and networking, manufacturing and process control, engineering, and scientific instrumentation.

FORCE offers a 6U VMEbus Front Panel with two SBus board cutouts used to mount SBus boards to the CPU-2CE.

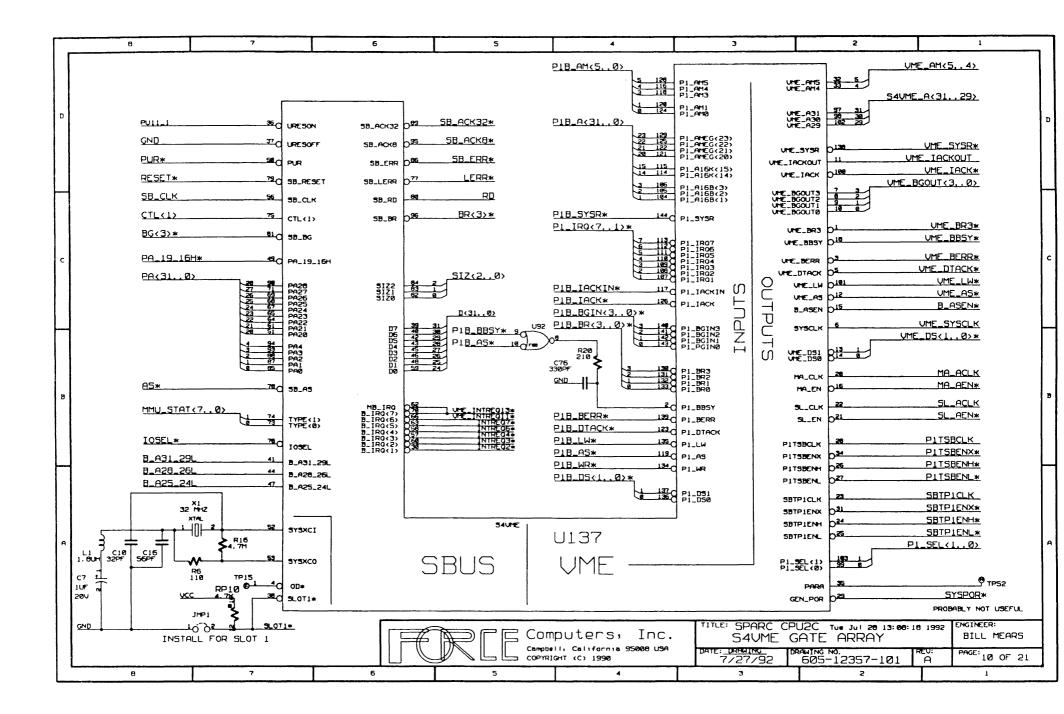

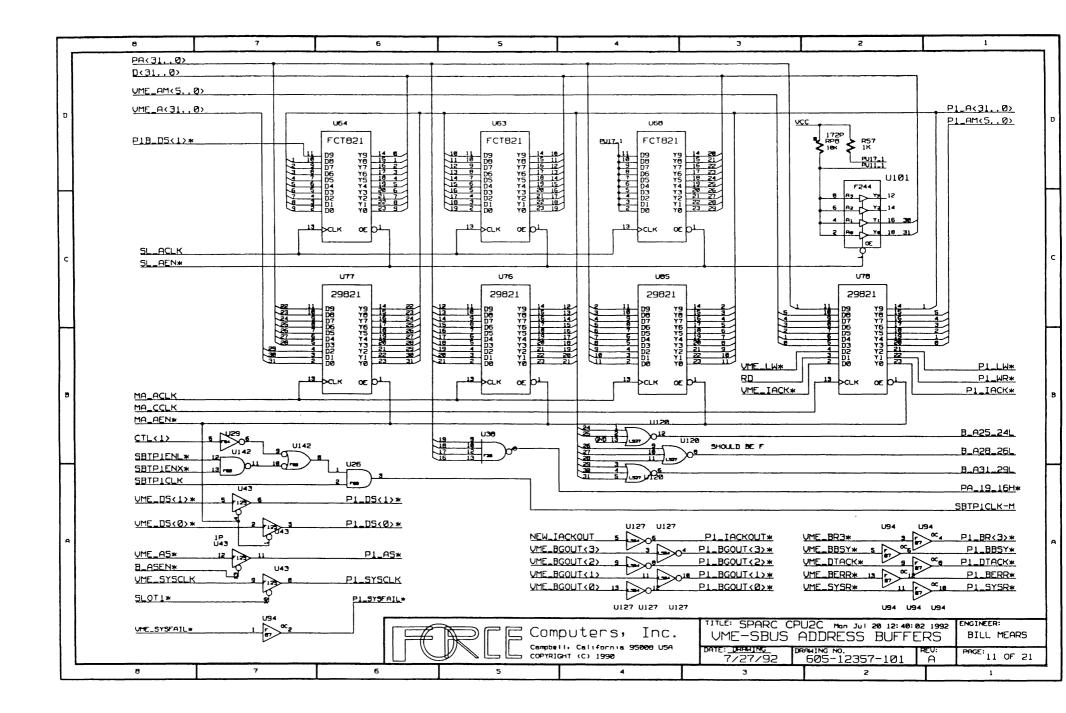

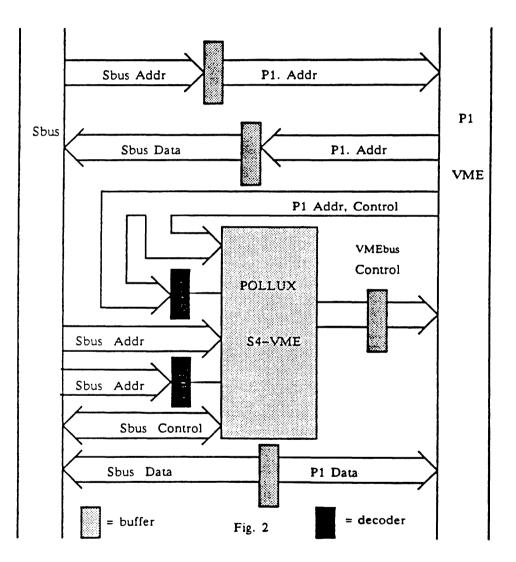

#### 1.11 VMEbus Interface

The SPARC CPU-2CE utilizes the Sun VME Chip to provide a complete 32-bit VMEbus interface. Since this is the same device used on the SPARC CPU-1E from FORCE COMPUTERS system performance upgrades with minimal software changes are guaranteed. Supported functions include master and slave data transfer capabilities, and VMEbus interrupt handling and arbitration functions. Additional VMEbus utility functions and a special loop-back cycle for standalone testing of the interface are provided.

The VMEbus interface on the SPARC CPU-2CE is fully supported by a driver for the SunOS/Solaris operating system. The software support also includes an implementation of the ONC/VME protocol which supports standard networking protocols such as TCP/IP, NFS and RPCs across the VMEbus backplane. The VME Driver is needed to implement VME software.

#### 1.11.1 Master Interface

The VMEbus master interface allows 16-, 24-, and 32-bit addressing with 8-, 16-, and 32-bit data transfers. A full 4-GByte address range is available and may be mapped contiguously without the 512-Mbyte limitation typically imposed by the 28-bit Sbus definition. This is done by directing normally unused MMU signals to VMEbus decoding logic, external to the VME chip. A software switch enables the standard VME 512-Mbyte address mode with window mapping registers. This 28-bit mode emulates the SPARC CPU-1E VMEbus addressing scheme, allowing customers a migration path to help preserve a previous investment in custom VMEbus drivers.

Read-modify-write cycles are supported for master accesses, and a 300 µsec VMEbus timer is included.

NOTE: Unaligned transfers are not supported by the VME chip.

#### 1.11.2 Slave Interface

Access to the on-board DRAM is allowed to a 1-Mbyte page configurable on 1-Mbyte boundaries within the local address space. Addressing is recognized for both 32- and 24-bit standard accesses, with 16-bit accesses reserved for the mail box interrupt. Address modifiers are supported, and any slave access as a Direct Virtual Memory Access (DVMA) device is set to the local supervisor mode in accordance with the Sun-4<sup>TM</sup> architecture. The 1-Mbyte VME address space selected is always mapped to the highest megabyte in the virtual address space in accordance with the Sun-4 architecture. Unaligned slave accesses are not supported by the VME chip. See the chapter on the VMEbus Interface for more details.

A mail box interrupt function allows other VMEbus devices to interrupt the SPARC CPU-2CE. This mail box detects accesses to the specific A16 address space set in the mail box register. Mail box accesses are acknowledged as standard VMEbus cycles, and trigger an on-board level 13 interrupt.

#### 1.11.3 Interrupts

The on-board interrupt handler selectively supports all seven VMEbus interrupt levels which are routed directly to the MMU interrupt logic. Control of interrupts is handled via software in the interrupt enable register.

#### 1.11.4 System Controller

The SPARC CPU-2CE is capable of providing Slot 1 system controller functions. The VMEbus requestor is a release on request (ROR) requestor. Bus requests are made on BR3.

The VMEbus arbiter function is used when the SPARC CPU-2CE is configured for system controller functions (Slot 1 jumper). Both single-level (SGL) and round robin (RRS) arbitration are provided. Bus timer logic is included to prevent a VMEbus lockup to a non-responding bus requestor or to a non-existent slave device.

Additional system controller functions are automatically activated, when the Slot 1 jumper is enabled. These capabilities include: IACK Daisy Chain Driver, SYSRESET, SYSFAIL and VMEbus system clock.

#### 1.12 Software Description

With full SPARCstation 2 architecture compatibility, the SPARC CPU-2CE runs the Solaris operating system, including enhancements specific to the a SPARCstation product line. Solaris provides an advanced development and run-time environment for the SPARC CPU-2CE. As the first "shrink-wrapped" distributed computing solution, Solaris is comprised of SunOS, ONC© networking environments, OpenWindows<sup>TM</sup>, OPEN LOOK® and DeskSet<sup>TM</sup>. SunOS is the highest quality and most widely supported enriched UNIX implementation available today.

By carefully merging the most robust functionality of UNIX System V<sup>TM</sup>, Berkeley BSD<sup>TM</sup>, and Xenix<sup>TM</sup>; SunOS offers the optimum balance of UNIX capability, reliability, and performance. Further functionality includes:

- Standards Conformance (POSIX, X/Open, XPG, SVID and FIPS)

- The OpenWindows "Look and Feel" Graphical User Interface

• Hierarchical and consistent format file system that includes support for MS-DOS®, CD-ROM and RFS, among others

- ONC networking environment for distributed computing across multivendor networks

- Enhanced UNIX kernel with internationalization, system accounting, security and redundancy

• A comprehensive range of third-party software that include databases, design automation and artificial intelligence

• VMEbus driver configured for Sun-4/SPARCserver<sup>™</sup> type expansion interface allowing the use of existing Sun-compatible VMEbus device drivers

ONC is the industry standard for heterogeneous networking. OpenWindows is the network-extensible graphical application development platform. OPEN LOOK is an intuitive graphical user interface, and Deskset is a suite of personal and workgroup productivity applications.

#### 1.13 Development

By using the SPARC CPU-2CE as both the development and the target system, equipment costs and time-to-market can be reduced. Solaris on the SPARC CPU-2CE provides all the tools necessary to take a project from conception through delivery. This includes: project planning aids (e.g. mail, diary, print facilities, etc.); design aids (e.g. compilers, assemblers, debuggers, and libraries); test facilities (e.g. compliance checkers, performance monitors, profilers, and system diagnostics); documentation tools (e.g. text formatters, print filters, and PostScript® interfaces); archiving and maintenance (e.g. source-code control systems, archivers, and backup systems); and others.

Optimizing compilers available from Sun include: C, C++, FORTRAN-77, Pascal, Modula-2, and Common Lisp. Independent software developers furnish many other languages, including Ada, APL, BASIC, COBOL, Forth, Mainsail, PL/I, and Prolog. Sun languages have full access to systems, graphics, networking, and user interface packages. Third-party cross compilers allow C, FORTRAN, or Pascal programmers to produce executable binary code for multiple architectures from a single FORCE SPARC CPU-2CE.

#### 1.14 Sun Tools

Standard software provided with Solaris includes a powerful user interface. This allows access to Solaris resource management functions, as well as industry- standard UNIX editors, command shells, and all UNIX commands for file management and manipulation, system administration, I/O system control, and other software development tools.

#### 1.15 Graphical User Interface

OpenWindows is a full-featured windowing environment based on the X-Window Standard and the Network extensible Windowing System (NeWS<sup>TM</sup>). OPEN LOOK is a graphical user interface that uses X-Windows and NeWS to provide an intuitive, "look and feel" desktop. The DeskSet is a group of personal productivity tools and system service applications which includes a File Manager, Calendar, Debugger, Mailer, and others.

#### 1.16 Real-Time

The SPARC CPU-2CE with Solaris, which supports a wide range of VMEbus and SBus-based hardware and software solutions, creates an ideal embedded system. New releases of Solaris will provide the SPARC CPU-2CE with real-time extension for use in "soft" real-time applications. These extensions include: fixed priority processes, priority manipulation, pre-emptive scheduling, process priority inheritance, guaranteed dispatch latency and memory locking.

Several hard real-time operating systems are available for or are being ported to the SPARC CPU-2CE. These typically provide high-speed multi-tasking, pre-emptive scheduling, and fast interrupt response. They include facilities for intertask communications and synchronization, efficient memory management, system clock and timing, optimized floating point support, and high-performance I/O and file systems. Real-time development tools usually include an interactive debug Shell, a linking loader, symbolic debugger, performance monitor, exception and signal handling, libraries, utility routines, extensive system and task information utilities, and source level debuggers.

#### 1.17 Networking

ONC networking environment is a suite of software modules and services that are the de facto standard for distributed computing. FORCE COMPUTERS provides a VMEbus driver utility as a standard item in conjunction with the Solaris operating system. This driver combines the standard Sun-4 SPARCserver treatment of the VMEbus expansion interface with the additional capability to run ONC over the VMEbus backplane. This provides an optimal platform for both tightly coupled networking and distributed processing applications, as well as the ability to utilize existing drivers for add-in VMEbus peripheral controllers.

The Remote Procedure Call (RPC) is the core of ONC and is used to build services such as the Network File System (NFS<sup>TM</sup>), Network Information Service (NIS) and Network System Boot.

Solaris also supports an extensive set of networking tools that allow developers to take advantage of industry standards. Solaris supports internet protocols, including raw (IP), datagram (UDP/IP) and stream (TCP/IP). User-accessible interfaces allow development of custom interfaces and protocols. Sun will also offer a Solaris Serial Line Internet Protocol (SLIP) for serial line\_based wide-area networks (WANs).

Optional software provides support for: DECnet; SNA, including IBM's Advanced Program-to-Program Communications (APPC) and Document Interchange Architecture (DIA); OSI support which adheres to MAP 2.1 and TOP 1.0 specifications, Layers 1 through 7 for MAP applications; FTAM (File Transfer Access and Management); and CASE (Common Application Services Elements).

| Central Processing Unit              | SPARC RISC                                 |

|--------------------------------------|--------------------------------------------|

| Clock Frequency                      | 40 MHz                                     |

| Integer Performance                  | 28.5 MIPS                                  |

| Floating Point                       | 4.2 MFLOPS @ 40 MHz Double Precision       |

| Block Transfer DMA                   | 50 Mbytes/sec (80 Mbyte/sec peak)          |

| Cache: Data & Instruction            | 64 Kbytes                                  |

| Basic DRAM TSOP Capacity             | 16 Mbytes                                  |

| Error Detection                      | Byte Parity                                |

| Local DRAM Expansion (Single Slot)   | 16, 32, 48 via mezzanine                   |

| Maximum On-Board DRAM                | 64 Mbytes                                  |

| SRAM (Battery Backed Up)             | 8 Kbytes                                   |

| MMU                                  | Sun-4 MMU ASIC                             |

| SBus Expansion                       | 2 Slots                                    |

| VMEbus                               | 32-bit IEEE/ANSI-standard                  |

| VMEBus Master                        | A32, A24, A16: D8, D16, D32, RMW           |

| VMEBus Slave                         | A32, A24: D8, D16, D32, RMW, BLT           |

| VMEBus Interrupt Handler             | 1 through 7 (Selectable)                   |

| VMEBus Arbiter                       | 4 level SGL                                |

| Multiprocessor Mailbox               | Yes (A16 access)                           |

| Ethernet (IEEE 802.3)                | 7990 Lance, AMD 7992B SIA                  |

| Ethernet Transfer Rate               | 10 Mbits/sec                               |

| SCSI Controller                      | NCR 53C90A and DMA+                        |

| SCSI Transfer Rate                   | ASYC 1.5 Mbyte/sec, SYNC up to 5 Mbyte/sec |

| Serial Ports                         | 2 Async/Sync; RS-232-C/RS-423              |

| Serial Data Rates                    | 64 Kbaud                                   |

| NVRAM TOD Clock/Calendar             | MK 48T08                                   |

| EPROM Size                           | 2 Mbyte, 8-bit wide                        |

| FLASH EEPROM Size (Optional Feature) | 1 Mbyte, 32-bit wide                       |

| Reset Switch                         | Yes                                        |

| Abort Switch                         | Yes                                        |

| Table: 1.1 | Board | Function | & | Specification |

|------------|-------|----------|---|---------------|

|------------|-------|----------|---|---------------|

| Hex Rotary Switch, switch input port        | 1                                |

|---------------------------------------------|----------------------------------|

| LEDs                                        | 2 (bi-color Red/Green)           |

| Programmable Timers                         | 2                                |

| Watchdog                                    | Yes                              |

| Keyboard/Mouse Port                         | Sun-4 Standard                   |

| Floppy Disk Controller                      | Intel 82072                      |

| Audio Controller                            | AMD 79C30                        |

| CD ROM Support                              | Yes                              |

| Front Panel                                 | Yes                              |

| Power Requirements + 5V                     | 4 Amps (W/O Optional SBus Cards) |

| +12 V                                       | 0.1 Amp /max .6 Amp              |

| -12 V                                       | 0.1 Amp /max 0.2 Amp             |

| 2A Minifuse                                 | Schurter P/N 3402.0012.xx        |

| 630ma Minifuse                              | Schurter P/N 3402.0008.xx        |

| Number of VME Slots Used                    | 1                                |

| Board                                       | 14 Layers                        |

| Board Dimensions                            | 6.29" X 9.18" (160 x 233 mm)     |

| SunOS or UNIX <sup>™</sup> Operating System | Solaris                          |

See the ordering information table on the next page for adapters available from FORCE. Contact your local sales office for additional options.

| Tape Drive   | Archive 2150s    | 1/2" cartridge drive      |

|--------------|------------------|---------------------------|

| Tape Drive   | Exabyte 8200     | 8mm cartridge 2.5 GB      |

| Tape Drive   | Exabyte 8500     | 8mm cartridge 5 GB***     |

| Floppy Drive | Sony F17W-FP     | 3 1/2" 1.44 MB            |

| Hard Drive   | Maxtor LXT-213SY | 210 MB 3 1/2 inch SUN 207 |

| Hard Drive   | Segate ST1480N   | 424 MB 3 1/2 inch SUN424* |

| Hard Drive   | SEgate ST4766N   | 669 MB 5 1/4 inch SUN669  |

| Hard Drive   | Segate ST41200N  | 1.GB 5 1/4 inch SUN1.0G** |

| Hard Drive   | Segate ST41600N  | 1.3 GB SUN1.3G*           |

| CDROM        | Sony CDU-8012    |                           |

#### Table: 1.2 Compatible Peripherals

\* Not in SUNOS 4.1e

**\*\*** Not in SUNOS 4.1.1b

\*\*\* Only Supported in SUNOS 4.12

## 1.18 Determining Revision Level

You can determine the revision code and serial number of a SPARC CPU-2CE by inspecting the label attached to the P1 connector of each card.

#### Section 2

#### **INSTALLATION and DIAGNOSTICS**

## WARNING

TO AVOID MALFUNCTIONS AND COMPONENT DAMAGE, PLEASE READ THE COMPLETE INSTALLATION PROCEDURE BEFORE THE BOARD IS INSTALLED IN A SYSTEM ENVIRONMENT.

# **STATIC KILLS**

#### 2.1 Power Up

This chapter will cover the instructions and considerations for powering up to insure proper operation of the CPU-2CE.

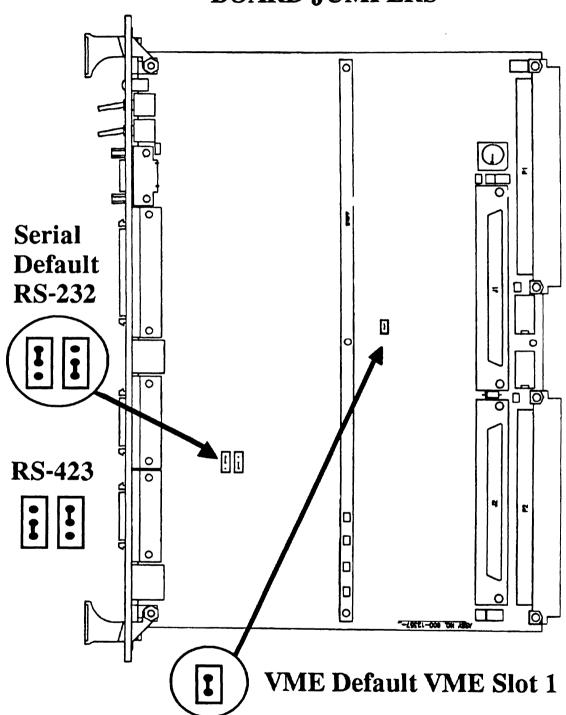

The only mechanical jumper blocks for the CPU-2CE are to configure the serial ports and to configure the VME. The serial ports are RS-232-C or RS-423 with the default being RS-232-C. If RS-423 is needed, set the block before power up. Move the jumpers position to set RS-423. Both ports must be set identical as either RS-232 or RS-423. The VME default is VME slot 1 device with the jumper installed in JMP1. Removing Jumper 1 selects the card to be non-slot 1 VME device. VME backplane must be terminated according to spec.

#### **Backplane Slot Configuration Requirements**

The SPARC CPU-2CE can be plugged into any VMEbus slot. If a SPARC CPU-2CE is installed in a slot other than 1 with empty slots between it and the slot 1 controller. Each of the empty slots must be configured as described below. See your backplane manual for documentation on the location of these jumpers.

Jumper IACKIN\* to IACKOUT\* on the backplane:

Pins A21 and A22 on the backplane must be jumpered together.

The signals Bus Grant [0:3] must be jumpered across empty slots, as follows:

BGO: jumper pins 4 and 5 Row B

BG1: jumper pins 6 and 7 Row B

BG2: jumper pins 8 and 9 Row B

BG3: jumpered pins 10 and 11 Row B

The CPU-2CE can power up without a computer terminal and keyboard, but you cannot enter the appropriate commands to test the card without a means to enter commands and view the results. FORCE recommends the initial power up to be performed with a computer terminal connected to serial port A of the CPU-2CE. By using the computer terminal, additional possible error producing factors; a nonfunctioning SBus card, SBus frame buffer ca. connector, or monitor can be detected. Connecting a terminal is simpler than connecting a frame buffer, monitor, and keyboard. The optional serial cable is available by ordering the accessories kit.

NOTE: Make sure you use a terminal type serial cable. See your terminal manual for ordering or building the proper cable.

The power-up sequence consists of a series of component functional tests and initialization, followed by booting. Turn on the power to the backplane.

In the default autoboot mode, the SPARC CPU-2CE attempts to boot SunOS from an attached SCSI disk. If a disk is not attached, the Open PROM displays an identification banner and enters the command mode of the "PROM Monitor" (a program that monitors the activity of the keyboard). The PROM displays a > prompt.

#### 2.2 Post Power Up Procedures

#### 2.2.1 How to Talk to the SPARC CPU-2CE On-Board Memory

At the > prompt type n to enter "New Mode" the FORTH/OpenBoot interpreter.

FORTH displays the ok prompt. Basic Assembly PROM commands are available to the SPARC CPU-2CE in this interpreter. Enter the following command at the OK prompt.

0 obmem 0 map-page <cr> to map in the first 4K bytes of main memory.

There is at least 16MB of onboard memory available to the SPARC CPU-2CE card. The first test of the SPARC CPU-2CE PROM validates correct operation of this memory. Use one of the three commands explained below:

#### 2.2.1.1 Memory Test Command One

Perform a LOOP/READ that validates that the on-board memory is functional:

At the ok prompt type 100 50 dump <cr>

RESULTS: If the PROM and the on-board memory are functional, the contents of the 80 bytes (50 hex) of memory starting at address 100 (hex) are displayed. If the PROM or the on-board memory is not working, you receive one of a number of possible error messages indicating a problem with the memory.

#### 2.2.1.2 Memory Test Command Two

Perform a LOOP/WRITE that writes a number pattern to memory, validating memory and memory response:

At the ok prompt type 100 50 78 fill <cr>

RESULTS: If the SPARC CPU-2CE is working correctly, the number pattern "78" is written to 80 bytes of memory starting at address 100, and you will receive the ok prompt. The fill command fills byte by byte. If the PROM or the on-board memory is not working correctly, you receive one of a number of possible error messages indicating a problem.

#### 2.2.1.3 Memory Test Command Three

Perform a memory test that exercises the on-board memory. This test does not reside in the PROM, and must be keyed in at the FORTH prompt. (Memory must be mapped according to section 2.2.1)

Key in the following program:

;

```

: memory-test ( -- )

150 100 do

\from 0x100 to 0x150

\longword write

12345678

i 1!

\longword read (result left

i 10 dup

\on stack)

\compare

12345678 <>

if ." obs = "

." exp = " 12345678.

." adr = " i . cr

then

drop

4 +loop

```

When this code has been correctly entered, you can perform the memory test:

memory-test <cr>

Also, the following command runs the Open Boot memory test:

test /memory or test-memory

This test is the same as the Open Boot POST test and will take approximately 4 minutes for 32 megabytes.

RESULTS: If the SPARC CPU-2CE is working correctly, the memory is erased and tested, and you will receive the ok prompt. If the PROM or the on-board memory is not working correctly, you receive one of a number of possible error messages indicating a problem.

Connect the cables for the additional devices you wish to test with the SPARC CPU-2CE: SCSI, Keyboard, Ethernet, Serial Ports A and B. (Make sure the power is off before connecting any cables to the CPU-2CE.)

#### 2.2.2 Test the Ethernet Port

Test the Ethernet port by connecting a MAU (Medium Access Unit) to the Ethernet port and while in Forth/OpenBoot and typing:

test net <net>

FORCE COMPUTERS

## 2.2.3 How to Talk to the SPARC CPU-2CE Buses

Access to the devices available on the SPARC buses in general requires mapping, reading, and writing the device. This test is performed only when testing an SBus memory card. The procedure below can be used to map in memory. Devices are mapped in two stages:

## 2.2.3.1 Mapping Memory

Select unused segments, virtual address range and size. Map in the segments, e.g., seg# = 0x80, va = 0x1000000, size = 0x4000.

## 80 1000000 0x4000 map-segments <cr>

Select a physical address range and space (SBus Slot2). Map in the page e.g., pa = 0xFC000000, space = SBus.

FC000000 sbus 1000000 4000 map-pages <cr>

## 2.2.3.2 Accessing Memory

To dump out memory at the ok prompt type 1000 000 50 Dump <cr>

## 2.2.4 How to Talk to the SBus