## GE-PAC® 3010/2

# CENTRAL PROCESSOR REFERENCE MANUAL

## **REVISION RECORD**

PUBLICATION: GET-6174, GE-PAC 3010/2 Central Processor Reference Manual

| REVISION OR PAGE NO. | DATE  | REVISION OR PAGE NO. | DATE |

|----------------------|-------|----------------------|------|

| ii                   | 4/72  |                      |      |

| iv                   |       |                      |      |

| 2-8                  |       |                      |      |

| 2-12                 |       |                      |      |

| 2-13/2-14            |       |                      |      |

| 4-22                 |       |                      |      |

| 5-12                 |       |                      | -    |

| 5-13                 |       |                      |      |

| 5-16                 |       |                      |      |

| 5-17                 |       |                      |      |

| 5-23                 |       |                      |      |

| 5-49 Added           |       |                      |      |

| 5-50 Added           |       |                      |      |

| 5-51 Added           |       |                      |      |

| 5-52 Added           |       |                      |      |

| 5-53 Added           |       |                      |      |

| 5-54 Added           |       |                      |      |

| 5-55 Added           |       |                      |      |

| A5-1                 |       |                      |      |

| A5-2                 |       |                      |      |

| 2-2                  | 10/72 |                      |      |

| 2-12                 |       |                      |      |

| 4-24                 |       |                      |      |

| 5-5                  |       |                      |      |

| 5-34                 |       |                      |      |

|                      |       |                      |      |

|                      |       |                      |      |

|                      |       |                      |      |

# GE-PAC® 3010/2 COMPUTER SYSTEM

# CENTRAL PROCESSOR REFERENCE MANUAL

General Electric reserves the right to make changes in the equipment or software, and its characteristics or functions, at any time without notice.

|        |                                                                       | Page                                                    |

|--------|-----------------------------------------------------------------------|---------------------------------------------------------|

| INTROD | UCTION                                                                | 1-1                                                     |

| 1.1    | Major Features                                                        | . 1-1                                                   |

| 1.2    | Core Memory Parity Option                                             | . 1-2                                                   |

| 1.3    | Memory Protect Option                                                 | . 1-2                                                   |

| 1.4    | 1.4.1 Multiplexor Channel                                             | <ul><li>1-2</li><li>1-2</li><li>1-2</li></ul>           |

| 1.5    | Software                                                              | . 1-3                                                   |

| 1.6    | Process I/O                                                           | . 1-3                                                   |

| 1.7    | Peripheral Devices                                                    | . 1-3                                                   |

| SYSTEM | DESCRIPTION                                                           | . 2-1                                                   |

| 2.1    | Introduction                                                          | . 2-1                                                   |

| 2.2    | 2.2.1       Processor                                                 | . 2-1<br>. 2-3<br>. 2-4<br>. 2-4<br>. 2-4               |

|        | 2.2.3.2 Interleaved Data Channel                                      | . 2-5                                                   |

| 2.3    | 2.3.1 Program Status Words                                            | . 2-5<br>. 2-6                                          |

| 2.4    | 2.4.1 Interrupt Procedure                                             | . 2-9<br>. 2-10<br>. 2-10<br>. 2-10<br>. 2-10<br>. 2-11 |

|        | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>SYSTEM<br>2.1<br>2.2 | 1.2   Core Memory Parity Option                         |

| Chapter |         |                                        | *: 7                                                                       |                                                          |                                                                                 | * *           |                                       |            |             |      |       |      |       |                                         | Page                                                 |

|---------|---------|----------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------|---------------|---------------------------------------|------------|-------------|------|-------|------|-------|-----------------------------------------|------------------------------------------------------|

|         |         | 2.4.4                                  | 2.4.3.2<br>2.4.3.3<br>2.4.3.4<br>Special Inte<br>2.4.4.1<br>2.4.4.2        | External In<br>Automatic I<br>Automatic I<br>Automatic I | terrupt I/O Serv I/O Terr | ice . ninatio | on Inton Qu                           | errupeue C | ot<br>Overt | flow | Inte  | rru  | pt.   | • • • • • • • • • • • • • • • • • • • • | 2-12<br>2-12<br>2-12<br>2-13<br>2-13<br>2-13<br>2-13 |

| 3       | DATA AN | ID INSTRUC                             | CTION FORM                                                                 |                                                          |                                                                                 |               | _                                     |            |             |      | -     |      |       |                                         |                                                      |

|         | 3.1     | Introduction                           | on                                                                         |                                                          |                                                                                 | • *• • •      |                                       |            |             |      |       |      |       |                                         | 3-1                                                  |

|         | 3.2     | 3. 2. 1<br>3. 2. 2<br>3. 2. 3          | nats Hexadecima Fixed-Point 3.2.2.1 Floating-Po Logical Dat                | l Notation . Data 2's Comple int Data                    | ment No                                                                         | tation        |                                       |            |             | • •  |       |      | • •   | • • •                                   | 3-1<br>3-1<br>3-1<br>3-3                             |

|         | 3.3     | Instruction                            | n Formats                                                                  |                                                          |                                                                                 |               |                                       |            |             | • •  |       |      | • •   |                                         | 3-5                                                  |

|         | 3.4     | General Re                             | egister Usag                                                               | ge                                                       |                                                                                 |               |                                       |            |             | • •  | ••    | •; • | , ·   |                                         | 3-6                                                  |

|         | 3.5     | Storage Ad                             | ddressing.                                                                 |                                                          |                                                                                 |               |                                       | • ,•••     |             | • •, |       |      | • • • |                                         | 3-7                                                  |

| 4       | INSTRUC | TION REPE                              | ERTOIRE .                                                                  |                                                          |                                                                                 |               |                                       |            | • . •       | · •  | • • . | • •  |       |                                         | 4-1                                                  |

|         | 4.1     | Introduction                           | on                                                                         |                                                          |                                                                                 | • • •         | • • • .                               |            |             | • •  |       |      |       |                                         | 4-1                                                  |

|         | 4.2     | 4.2.1<br>4.2.2<br>4.2.3                | nt Load/Stor<br>Load Halfwo<br>Load Multip<br>Store Halfwo<br>Store Multip | ord<br>le<br>ord                                         |                                                                                 |               | • • •                                 |            |             | • •  |       |      |       | : :                                     | 4-4<br>4-5<br>4-5                                    |

|         | 4.3     |                                        | nt Arithmeti                                                               | e Instructio                                             | ns                                                                              |               |                                       |            |             |      |       |      |       |                                         | 4-7                                                  |

|         |         | 4.3.2<br>4.3.3                         | Add Halfwor<br>Add with Ca<br>Subtract Ha<br>Subtract wit                  | rry Halfwoilfword                                        | rd                                                                              | • • , •       |                                       |            |             | • •  |       |      |       |                                         | 4-9<br>4-10                                          |

|         |         | 4.3.5<br>4.3.6<br>4.3.7<br>4.3.8       | Compare Lo<br>Compare Ha<br>Multiply Ha<br>Multiply Ha                     | ogical Halfw<br>alfword<br>lfword<br>lfword Unsi         | ord gned                                                                        | • • •         | · · · · · · · · · · · · · · · · · · · |            | • •         | • •  |       | • •  | • •   | • •                                     | 4-12<br>4-13<br>4-14<br>4-14                         |

|         | 4.4     | Logical Ins<br>4.4.1<br>4.4.2<br>4.4.3 | Divide Halfvestructions AND Halfwor OR Halfwor Exclusive O                 |                                                          |                                                                                 |               |                                       |            |             |      |       |      | • •   |                                         | 4-16<br>4-17<br>4-18<br>4-19                         |

|         |         | 4.4.4                                  | Test Halfwo                                                                | ra immedia                                               | пе                                                                              |               |                                       |            |             | • •  | • •   | • •  | • •   | • •                                     | 4-20                                                 |

| Chapter |       |                                      | Page       |

|---------|-------|--------------------------------------|------------|

|         | 4.5   | Deta Hay Nivy I at yet a             | 4 01       |

|         | 4.5   | Byte Handling Instructions           | 4-21       |

|         |       | 4.5.1 Load Byte                      | 4-22       |

|         |       |                                      | 4-22       |

|         |       | 4.5.3 Exchange Byte                  | 4-23       |

|         |       | 1                                    | 4-23       |

|         | 4.6   | Floating-Point Instructions          | 4-24       |

|         |       | 4.6.1 Floating-Point Load            | 4-25       |

|         |       | 4.6.2 Floating-Point Store           | 4-25       |

|         |       | 4.6.3 Floating-Point Add             | 4-20       |

|         |       | 4.6.4 Floating-Point Subtract        | 4-27       |

|         |       | 4.6.5 Floating-Point Compare         | 4-28       |

|         |       | 4.6.6 Floating-Point Multiply        | 4-29       |

|         |       | 4.6.7 Floating-Point Divide          | 4-30       |

|         | 4.7   | Shift/Rotate Instructions            | 4-31       |

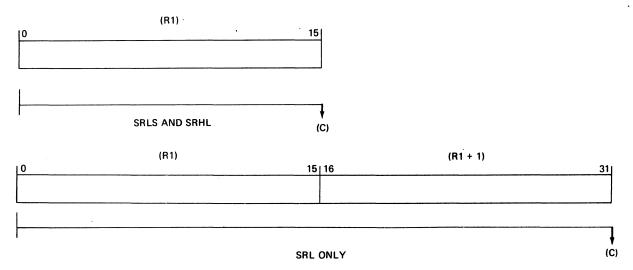

|         |       | 4.7.1 Shift Left Logical             | 4-32       |

|         |       | 4.7.2 Shift Right Logical            | 4-33       |

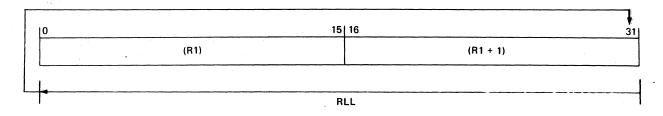

|         |       | 4.7.3 Rotate Left Logical            | 4-34       |

|         |       | 4.7.4 Rotate Right Logical           | 4-35       |

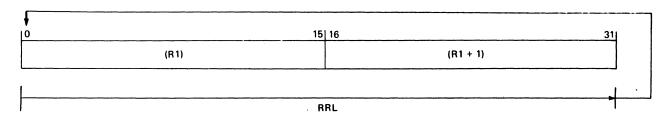

|         |       | 4.7.5 Shift Left Arithmetic          | 4-36       |

|         |       | 4.7.6 Shift Right Arithmetic         | 4-37       |

|         | 4.8   | Branch Instructions                  | 4-38       |

|         | -     | 4.8.1 Branch on True Condition       | 4-39       |

|         |       | 4.8.2 Branch on False Condition      | 4-40       |

|         |       | 4.8.3 Branch on Index                | 4-41       |

|         |       | 4.8.4 Branch and Link                | 4-42       |

|         | 4.9   | List Instructions                    | 4-43       |

|         | -, -  | 4.9.1 Add to Top/Bottom of List      | 4-44       |

|         |       | 4.9.2 Remove From Top/Bottom of List | 4-45       |

|         | 4.10  | Input/Output Instructions            | 4-46       |

|         | 4.10  | 4.10.1 Acknowledge Interrupt         | 4-47       |

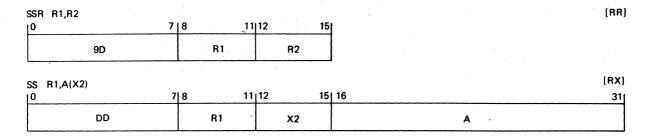

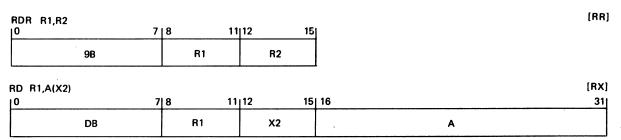

|         |       | 4.10.2 Sense Status                  | 4-48       |

|         |       | 4.10.3 Output Command                | 4-49       |

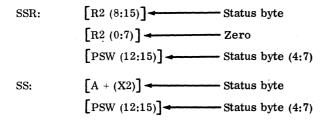

|         |       | 4.10.4 Read Data                     | 4-49       |

|         |       | 4.10.5 Write Data                    | 4-50       |

|         |       | 4.10.6 Read Block                    | 4-51       |

|         | ,     | 4.10.7 Write Block                   | 4-52       |

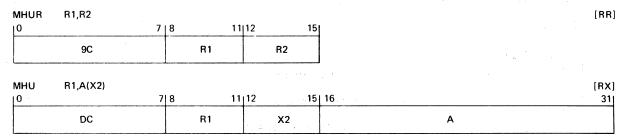

|         |       | 4.10.8 Read Halfword                 | 4-53       |

|         |       | 4.10.9 Write Halfword                | 4-54       |

|         |       | 4.10.10 Autoload                     | 4-55       |

|         | 4.11  | System Control Instructions          |            |

|         | 4.11  | System Control Instructions          | 4-56       |

|         |       |                                      | 4-56       |

|         |       |                                      | 4-57       |

|         |       |                                      | 4-57       |

|         |       | 4.11.4 Supervisor Call               | 4-58       |

| 5       | IN PU | T/OUTPUT SYSTEM                      | 5-1        |

|         | 5.1   | Introduction                         | 5-1        |

|         | 5.2   |                                      |            |

|         | 0. 4  | Systems Interface                    | 5-1<br>5-1 |

|         |       |                                      | .,-1       |

| Chapter |      |                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                                               |

|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

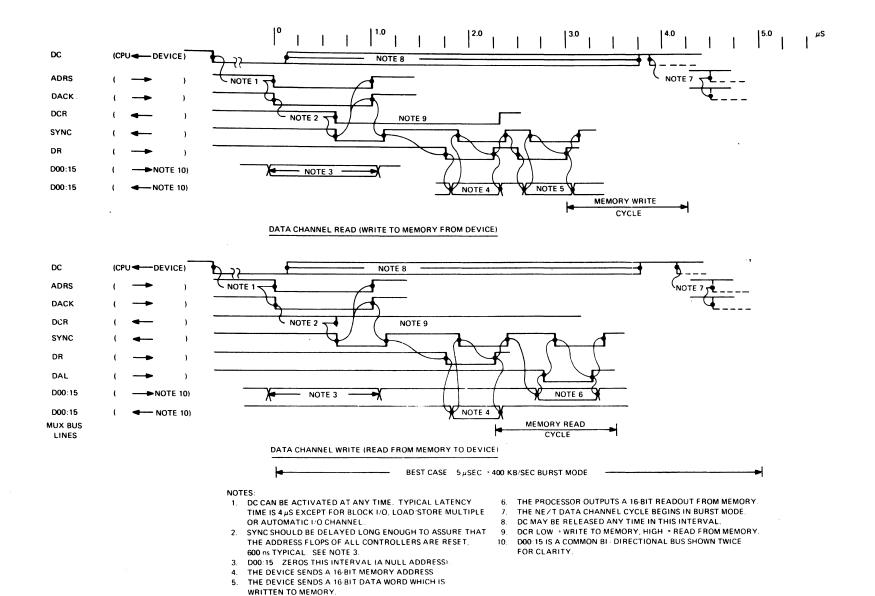

|         |      | 5.2.2 Interleaved Data Channel                                                                                                                                                                                                                                                                                                                                                                                         | 5 <b>-</b> 4<br>5 <b>-</b> 5                                                       |

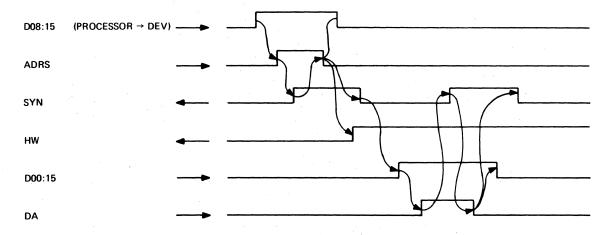

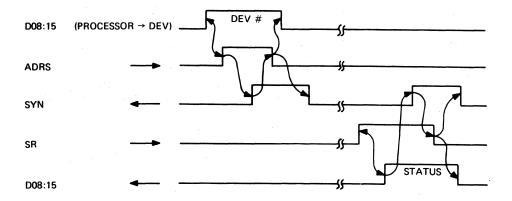

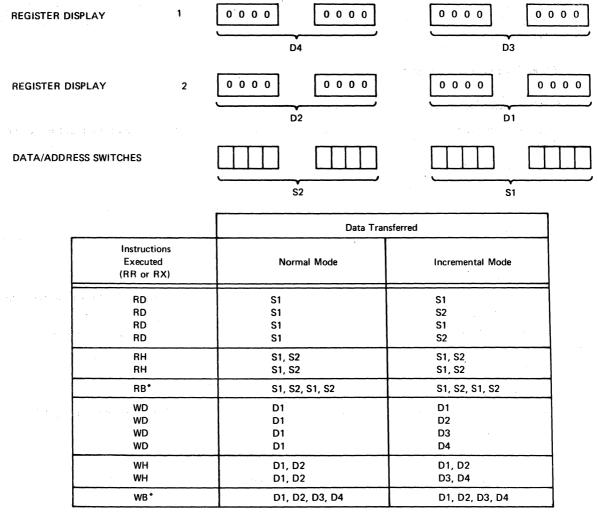

|         | 5.3  | Input/Output Instructions  5.3.1 Read Data (RD) Instruction.  5.3.2 Read Halfword (RH) Instruction  5.3.3 Write Data (WD) Instruction.  5.3.4 Write Halfword (WH) Instruction.  5.3.5 Sense Status (SS) Instruction.  5.3.6 Output Command (OC) Instruction  5.3.7 Acknowledge Interrupt (AI) Instruction.  5.3.8 Read Block (RB) Instruction.  5.3.9 Write Block (WB) Instruction.  5.3.10 Autoload (AL) Instruction. | 5-9<br>5-9<br>5-11<br>5-14<br>5-16<br>5-19<br>5-21<br>5-22<br>5-24<br>5-26<br>5-28 |

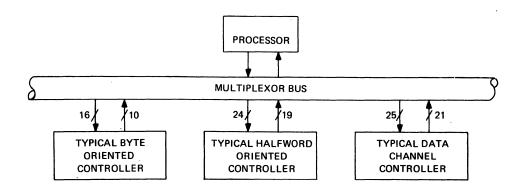

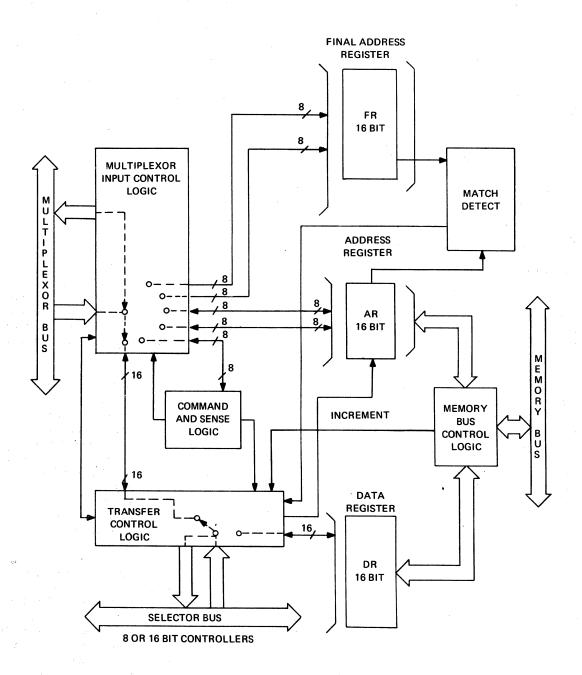

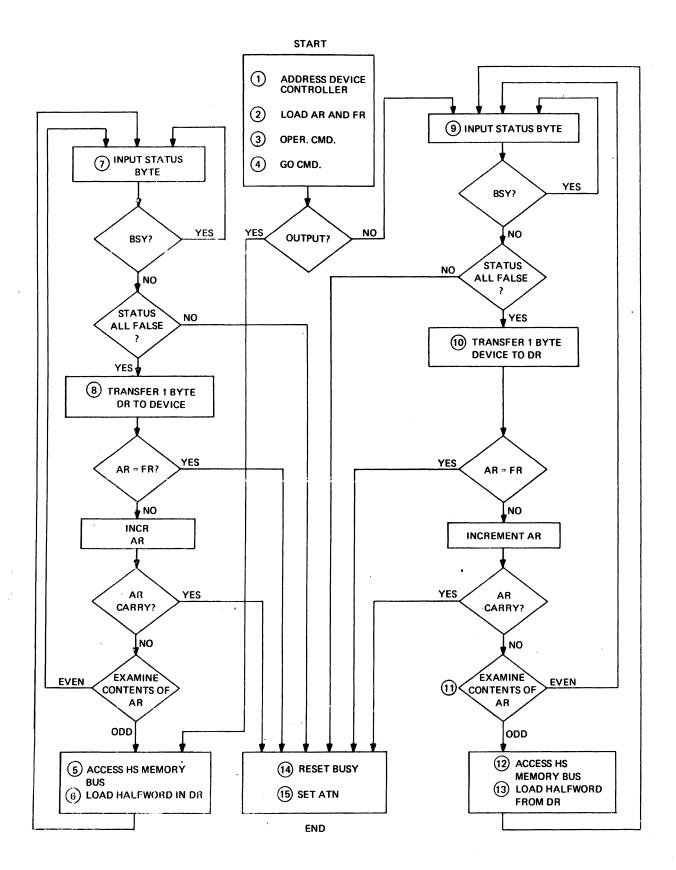

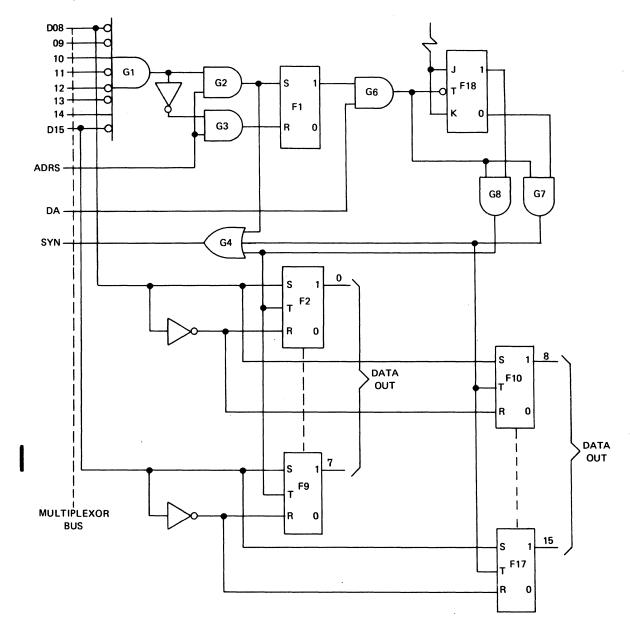

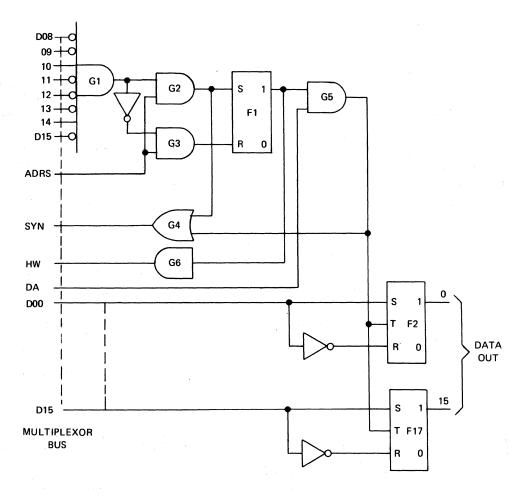

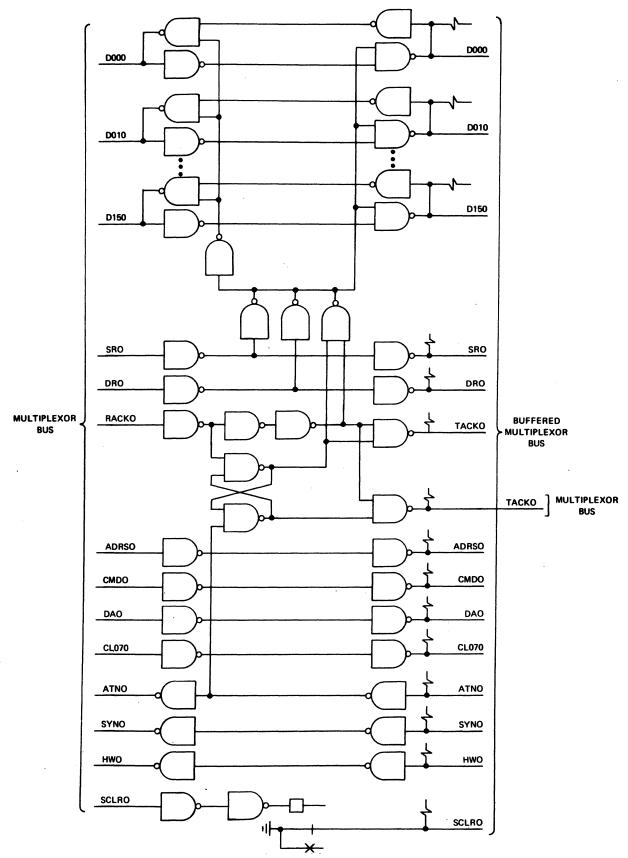

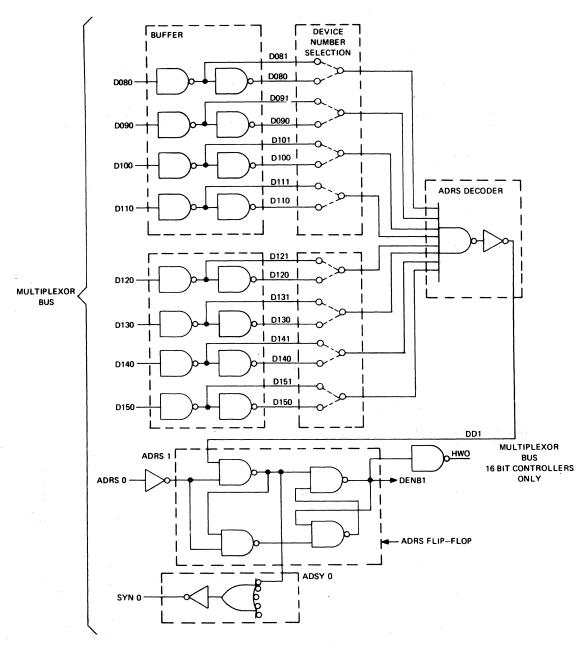

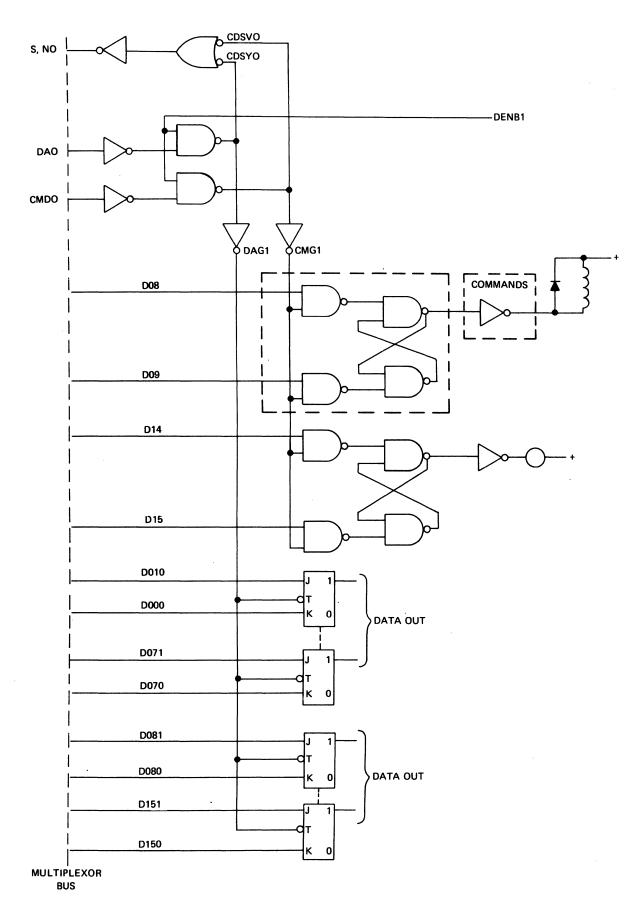

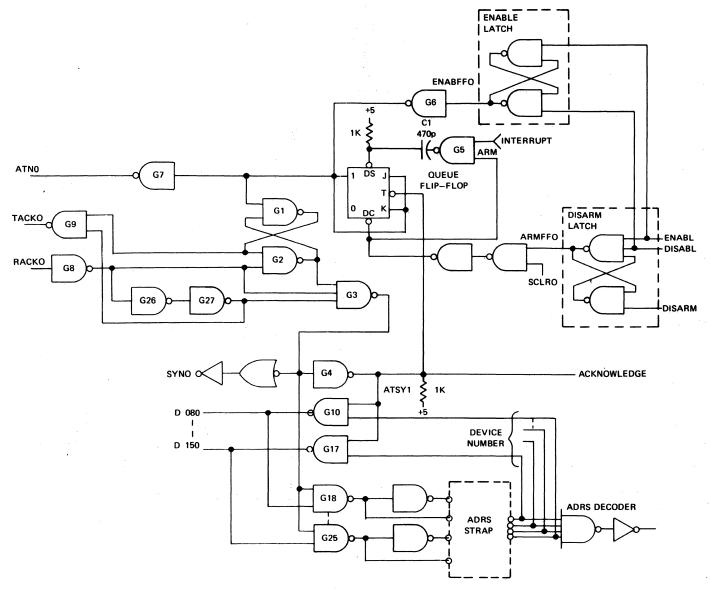

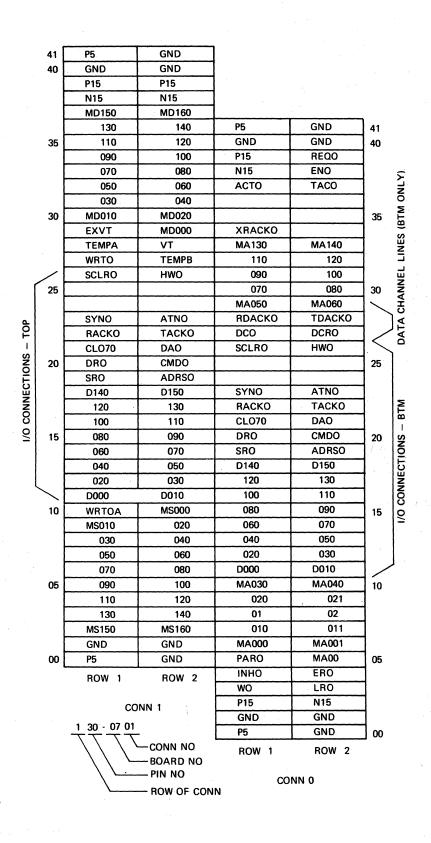

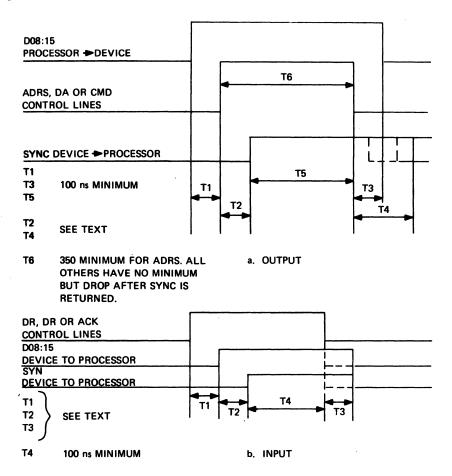

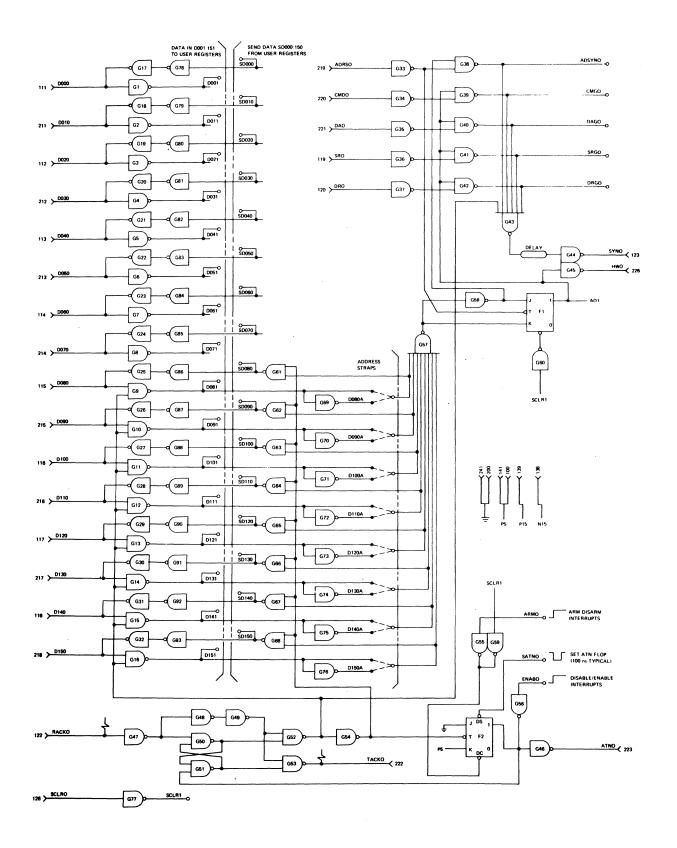

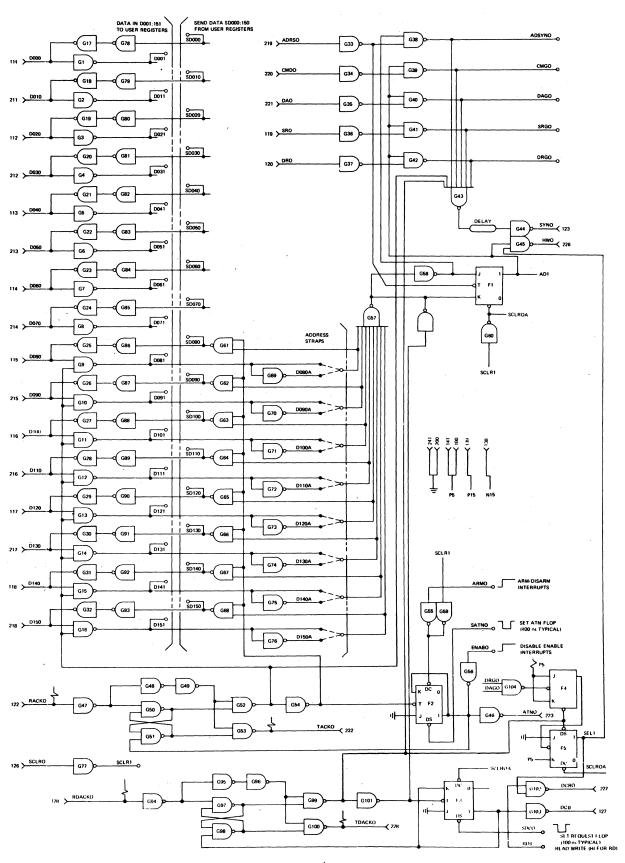

|         | 5.4  | Device Controller Logic Design  5.4.1 Multiplexor Bus  5.4.2 Device Controller Addressing.  5.4.3 Data and Status Input/Output  5.4.3.1 Data  5.4.3.2 Status                                                                                                                                                                                                                                                           | 5-30<br>5-30<br>5-34<br>5-34<br>5-34<br>5-36                                       |

|         |      | 5.4.4 Data and Command Output                                                                                                                                                                                                                                                                                                                                                                                          | 5-38<br>5-38                                                                       |

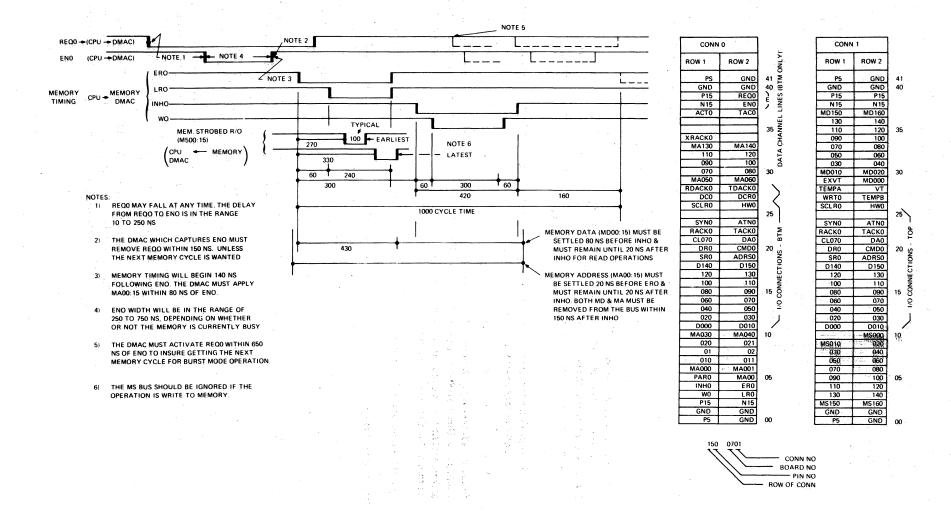

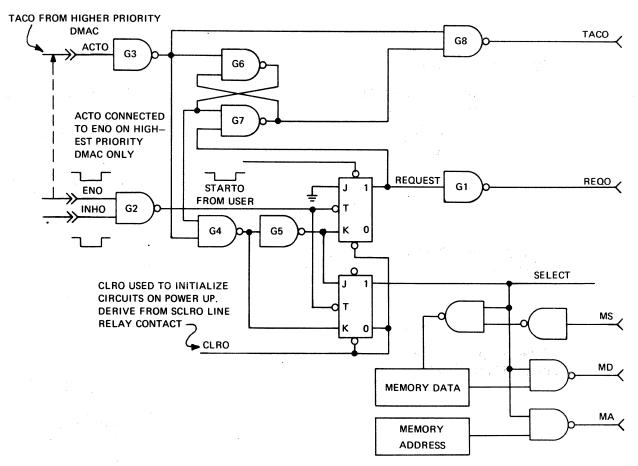

|         |      | 5.4.4.2 Command  5.4.5 Interrupt Control  5.4.6 Multiplexor Bus Wiring  5.4.7 Multiplexor Channel Timing  5.4.8 Typical Device Controller Interface  5.4.9 Data Channel Interface Design                                                                                                                                                                                                                               | 5-38<br>5-38<br>5-41<br>5-41<br>5-44<br>5-44                                       |

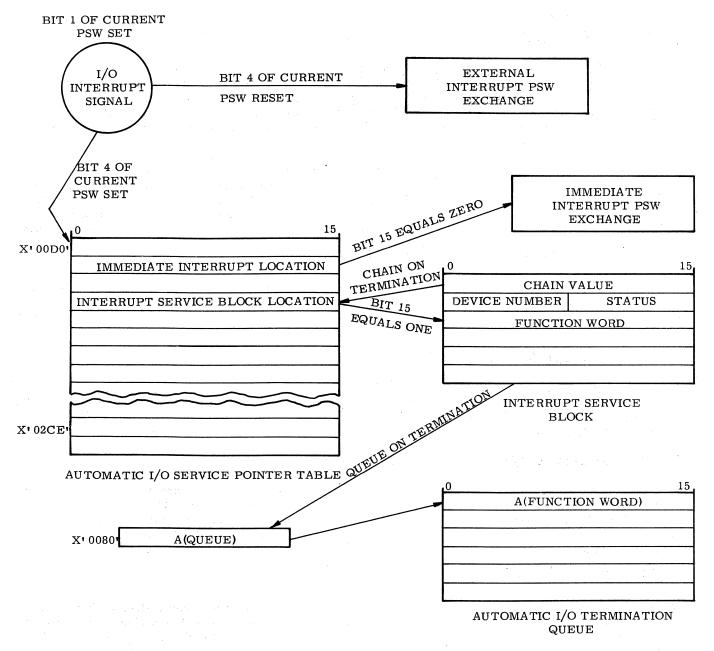

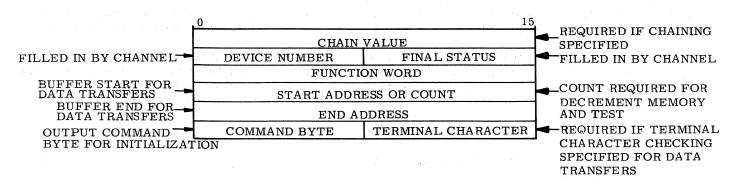

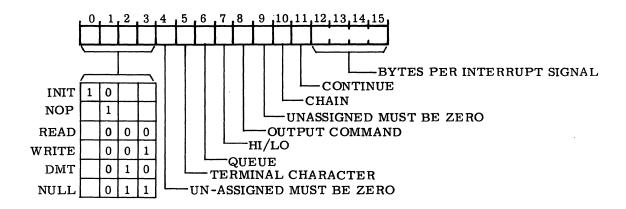

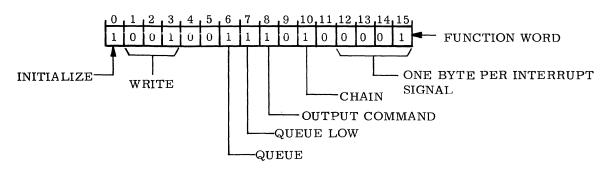

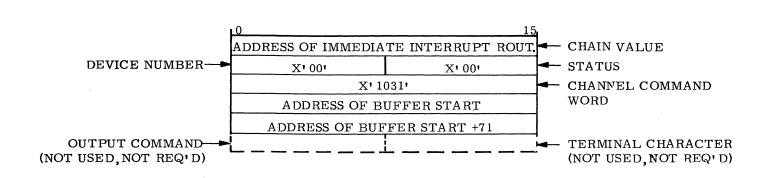

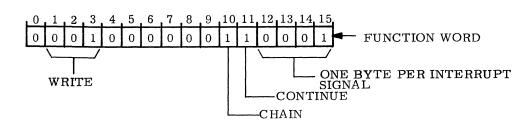

|         | 5.5  | Automatic I/O  5. 5. 1 Automatic I/O Service Pointer Table  5. 5. 2 Interrupt Service Block  5. 5. 3 Automatic I/O Termination Queue  5. 5. 4 General Operation  5. 5. 5 Function Words  5. 5. 6 Initialization  5. 5. 7 I/O Operation  5. 5. 8 Termination  5. 5. 9 Example of Channel I/O Programming                                                                                                                | 5-49<br>5-49<br>5-49<br>5-49<br>5-5<br>5-5<br>5-5<br>5-5                           |

| 6       | CORE | MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-1                                                                                |

|         | 6.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                           | 6-1                                                                                |

|         | 6.2  | Core Memory Modules                                                                                                                                                                                                                                                                                                                                                                                                    | 6-2                                                                                |

|         | 6.3  | Parity Option                                                                                                                                                                                                                                                                                                                                                                                                          | 6-2                                                                                |

|         | 6.4  | Memory Bus                                                                                                                                                                                                                                                                                                                                                                                                             | 6-3<br>6-4<br>6-4<br>6-7                                                           |

| Jnapter |       | P                                             | 'age       |

|---------|-------|-----------------------------------------------|------------|

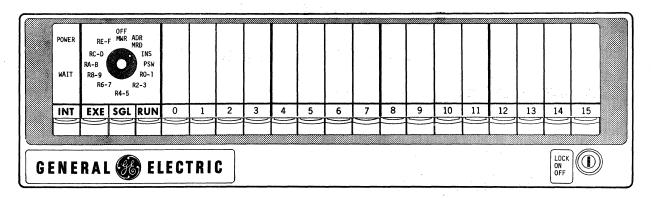

| 7       | CON   | TROL CONSOLE                                  | 7-1        |

|         | 7.1   | Introduction                                  | 7-1        |

|         | 7.2   | Control Console Description.                  | 7-1        |

|         | . • - | 7.2.1 Key Operated Security Lock              | 7-1        |

|         |       | 7.2.2 Control Switches                        | 7-1        |

|         |       | 7.2.3 Function Switches                       | 7-2        |

|         | 7.3   | Control Console Operating Procedures          | 7-3        |

|         |       | 7.3.1 Power Up                                | 7-3        |

|         |       | 7.3.2 Power Down                              | 7-5<br>7-5 |

|         |       | 7.3.4 Program Execution                       | 7-6        |

|         |       | 7.3.5 Program Termination                     | 7-7        |

|         |       | 7.3.6 Manually Initiated Memory Operations    | 7-7        |

|         |       | 7.3.6.1 Memory Read                           | 7-7        |

|         |       | 7.3.6.2 Memory Write                          | 7-7        |

|         | 7.4   | Programming Considerations                    | 7-8        |

|         |       | 7.4.1 Control Console I/O                     | 7-8<br>7-9 |

|         |       | 7.4.2 Console Interrupt                       | 7-9        |

|         |       | 7.4.4 Power Fail                              | 7-9        |

| Append  | lix   |                                               |            |

| 1       |       | STRUCTION SUMMARY - ALPHABETICAL              | A1-1       |

| 2       | IN    | STRUCTION SUMMARY - NUMERICAL                 | A2-l       |

| 3       | E     | XTENDED BRANCH MNEMONICS                      | A3-l       |

| 4       | O     | P CODE MAP                                    | A4-l       |

| 5       | IN    | STRUCTION EXECUTION TIMES                     | A5-l       |

| 6       | AI    | RITHMETIC REFERENCES                          | A6-l       |

| 7       | I/0   | O AUTOMATIC SERVICE OPERATION AND TIMING DATA | A7-1       |

| 8       | т //  | O REFERENCES                                  | A8-1       |

|         | 1/1   | . J. B. D. D. D. D. D. L. D. D.               | ~~-1       |

#### **CHAPTER 1**

#### **INTRODUCTION**

The GE-PAC\* 3010/2 process computer system is a flexible, modular process control system based upon a powerful and reliable Central Processor. A GE-PAC 3010/2 system may implement a full line of process input and output interfaces and peripheral devices. The Central Processor includes a Processor, a Core Memory, and an input/output Multiplexor Channel and Bus. The Central Processor is normally installed in a Central Systems Cabinet (CSC).

The advanced circuitry and packaging utilized in the system and the Central Processor provide an optimized price/performance ratio. The GE-PAC 3010/2 system is upwardly compatible with other GE-PAC computer systems, including the GE-PAC 30-1, 30-2, 30-2E and 3010. The user instruction sets, interrupt handling scheme, input and output formats, and control sequences are similar in all of these machines. Programs which run on these earlier systems will run on 3010/2 systems with no changes or with only minor changes. Absolute upward program compatibility from the 3010 to the 3010/2 is maintained.

The basic Central Processor consists of only five printed wire boards which provide the control logic, a read-only memory (ROM) and 8, 192 bytes of Core Memory. This simple Central Processor has a functional capability similar to much larger and more complex computers because the non-volatile ROM allows great simplification of the Processor logic, by executing micro-instruction subroutines, which in turn, emulate the user instructions, and execute other valuable functions simplifying I/O and housekeeping operations.

Core Memory is addressable at the 8-bit byte or 16-bit halfword level. This memory is expandable from the basic 8,192 bytes to 65,536 bytes. All of core is directly addressable with the user instructions, and no paging or indirect addressing is required.

The Processor hardware includes sixteen 16-bit General Registers which may be used as accumulators. Fifteen of the General Registers may also be used as index registers. Several register to register user instructions permit direct register-to-register operations, eliminating redundant loading and storing in Core Memory.

Up to four Direct Memory Access Channels may be implemented in the Central Processor. These channels operate over a common Core Memory bus on a cycle stealing basis, through a Direct Memory Access Port, which is built into the Processor. Two types of Direct Memory Access Channels may be implemented: The first is the Selector Channel, which permits direct data transfers between any standard device controller and core. The second direct channel may be custom designed for special applications.

#### 1.1 MAJOR FEATURES

The user instruction set consists of 113 instructions including:

Floating-Point Instructions

Arithmetic and Logical Instructions

Byte Processing Instructions

Both Single-Word and Double-Word Shift Instructions

List Processing Instructions

Short Branch Instructions for local branches

Single-Byte, Double-Byte, and Block I/O Instructions

Simulate Interrupt Instruction, for sophisticated I/O control

Supervisor Call Instruction, for communication with the operating system (RTMOS-30)

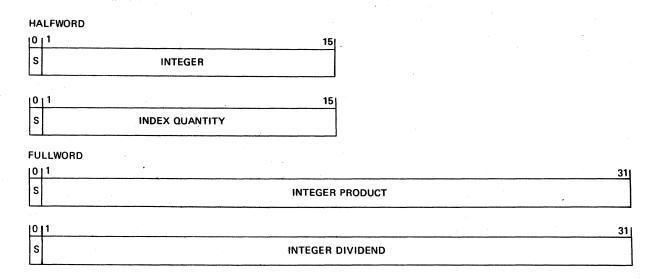

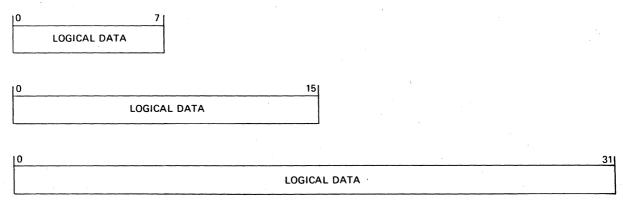

The instruction words are 16 bits and 32 bits in length. Data transfers are in the form of 8-bit bytes, 16-bit halfwords and 32-bit fullwords.

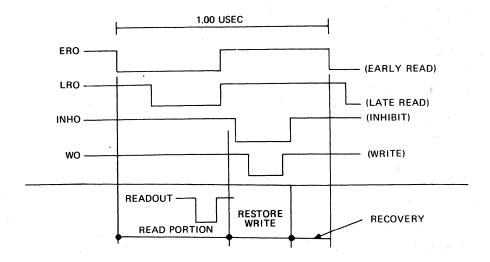

The Core Memory features a 1.0 microsecond cycle time and the access time is 300 nanoseconds. Because the Read-Only Memory is faster than in earlier GE-PAC mini-based computer systems, instruction execution times in this machine are considerably reduced.

<sup>\*</sup>Registered Trademark of General Electric Company

The Processor may respond to up to 256 interrupt levels. The interrupt scheme and the micro-program are combined effectively to permit an Automatic I/O Service mode, wherein much of the overhead required for I/O service is handled by the Processor, simplifying programming and saving memory space.

The Central Processor includes a compact but complete Control Console which permits manual operation of the system by programming and maintenance personnel. The console permits reading from and writing in core, displays any of the General Purpose Registers, allows an operator to manually step through programs, and features a keyswitch to prohibit unauthorized tampering with the controls.

#### 1.2 CORE MEMORY PARITY OPTION

Preservation of memory integrity is provided by a memory Parity option. During Write operations, an odd parity bit is generated, and is appended to each 16-bit halfword. When data is fetched from memory, parity is again calculated and compared with the parity bit originally stored during the Write operation. In the event the parity bit originally stored and the recalculated parity bit are different, the Processor is interrupted via the Machine Malfunction Interrupt.

#### 1.3 MEMORY PROTECT OPTION

The preservation of specific programs and data stored in Core Memory is provided by the Memory Protect option. The Memory Protect option permits available memory to be divided into blocks of 512, 1,024, or 2,048 bytes. Any combination of from 1 up to 64 blocks may be selected for protection under program control. The Memory Protect option permits the Processor to read data from any core location, but to write data only into unprotected locations. Any attempt to write into a protected block of memory is aborted and the Memory Protect hardware generates an I/O interrupt as an indication to the Processor that an illegal write was attempted.

#### 1.4 INPUT/OUTPUT METHODS

#### 1.4.1 Multiplexor Channel

The Multiplexor Channel provides an extremely reliable Input/Output System capable of communicating directly with up to 255 peripheral devices. Data transfers over the Multiplexor Channel can be either 8-bit or 16-bit to accommodate both byte and halfword oriented devices.

#### 1.4.2 Multiplexor Channel I/O Techniques

The flexible structure of the Multiplexor Channel provides a repertoire of built-in I/O techniques. These techniques provide an important benefit in the ease of use, since an appropriate I/O technique can be chosen and matched to the speed and transfer requirements for a variety of peripheral devices. The various Multiplexor Channel I/O techniques include: Program-Controlled I/O, Interrupt Driven I/O, Automatic I/O Service, and Burst Mode I/O.

#### 1.4.3 Interleaved Data Channel (IDC)

The Interleaved Data Channel is a high speed autonomous memory port. It provides a convenient method for customer-designed device controllers, requiring direct access to memory, to transfer data at 440K bytes in the Burst Mode or 280K bytes in the Single Cycle Mode.

#### 1.4.4 Direct Memory Access Port

The built-in Direct Memory Access Port accepts up to four DMA Channels. This port operates on a cycle-steal basis with core memory, allowing simultaneous processing and I/O data transfers. The maximum transfer rate over a DMA Channel is 2,000,000 bytes per second. The Direct Memory Access Port may be used through the Selector Channel, which permits block transfers between memory and up to 16 devices, or by interfacing special devices directly to the port.

#### 1.5 SOFTWARE

The GE-PAC 3010/2 system features a full line of standard software packages to support the available functional subsystems. The Real-Time Operating System, RTMOS-30, supports all process I/O and peripheral device operations on a real-time multiprogrammed basis. RTMOS-30 operates in a protected mode, wherein the operating system is protected from user level programs by the Processor hardware, which implements a "privileged instruction" concept. The privileged instructions are the system control and I/O instruction subsets, which are reserved for use by the operating system. User level programs interface with the operating system via a subset of Supervisor Call instructions (SVC).

In addition, core areas occupied by RTMOS-30 and other critical programs and data may be protected if the Memory Protect Option is implemented (1.3).

The standard software includes both on-line and off-line loaders, assemblers, editors, and debugging programs. The standard software packages are described in the GE-PAC 30/3010 Programming Reference Manual, GET-6171.

A complete line of hardware test programs is also provided with 3010/2 systems. These programs are part of the maintenance documentation provided with each system.

#### 1.6 PROCESS I/O

An Analog Input/Output Subsystem, which includes an Analog Input Scanner, Absolute Analog Output Voltages, and Variable Analog Output Current Pulses, is available. The Digital I/O Subsystem provides digital inputs, digital outputs, and pulse train outputs. All process I/O subsystems are described in detail in the 3010/2 General Description.

#### 1.7 PERIPHERAL DEVICES

The peripheral device complement may include TermiNet\* 300 Printers, teletypewriters, a paper tape reader, a card reader, a paper tape punch, video display terminals, and bulk memory units. Serial-bit communications interfaces, suitable for remote communications via digital data sets are available as is a High Speed Data Link, which provides a parallel 8-bit byte interface with another GE-PAC 3010 or 4000 series computer. Refer to the GE-PAC 3010/2 General Description for detailed descriptions of these devices.

<sup>\*</sup> Trademark of General Electric Company

# CHAPTER 2 SYSTEM DESCRIPTION

#### 2.1 INTRODUCTION

The GE-PAC 3010/2 is a 16-bit halfword-oriented digital computer useful in a wide variety of applications such as scientific, industrial process control, business, data collection, communications, and general purpose processing. The Processor is modularly constructed using the latest Large Scale Integrated (LSI) Circuits and state of the art computer technology.

The GE-PAC 3010/2 provides the user with more computing power per dollar than any machine available today. The Processor uses 16- and 32-bit instructions for efficient coding and optimum core utilization.

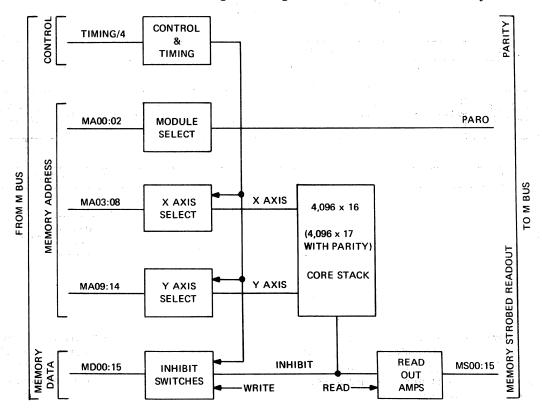

The Processor is designed around highly reliable 4,096 by 16-bit core memory modules. An optional 4,096 by 17-bit parity core memory is available. Both types of memory modules may be intermixed for a total of 65,536 bytes of storage (eight modules).

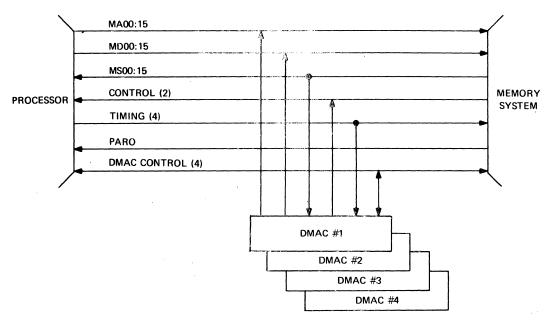

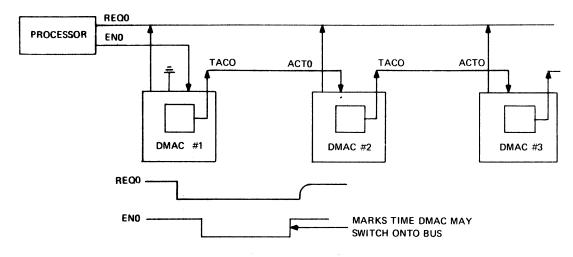

A Direct Memory Access Port is built into the Memory System. Up to four Direct Memory Access (DMA) Channels may be plugged into the port. The DMA Channels cycle-steal memory from the Processor at a maximum rate of 2,000,000 bytes per second. Two kinds of DMA Channels can be used with the Memory System; a Selector Channel available from General Electric for use with standard peripheral device controllers, and a direct Memory Connection custom designed by the user for special applications.

Input/Output operations between the GE-PAC 3010/2 and the peripheral device controllers ordinarily occur over the Multiplexor Bus. Up to 255 device controllers may be connected to this bus. The Processor implements eight Input/Output instructions plus Read Block and Write Block Instructions for high speed data transfer over the Multiplexor Bus. The Multiplexor Bus is fully hardware plug compatible with all peripheral device controllers developed and field proven on the existing line of GE-PAC 3010 Processors.

A parallel, character buffered, Teletypewriter adapter is standard on the GE-PAC 3010/2 Processor. This provides a very economical method for interfacing to a Teletypewriter.

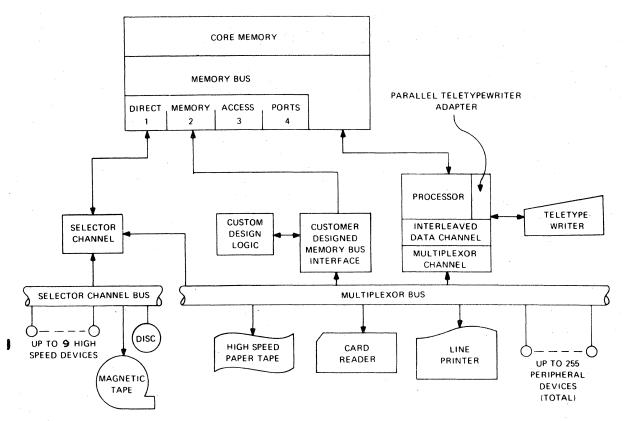

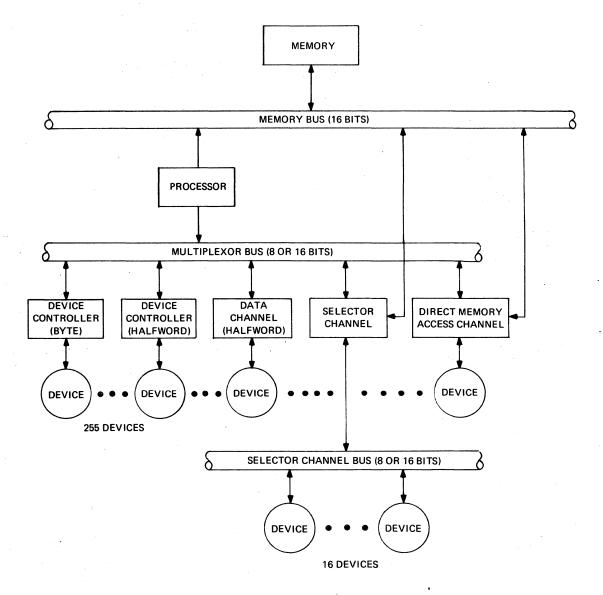

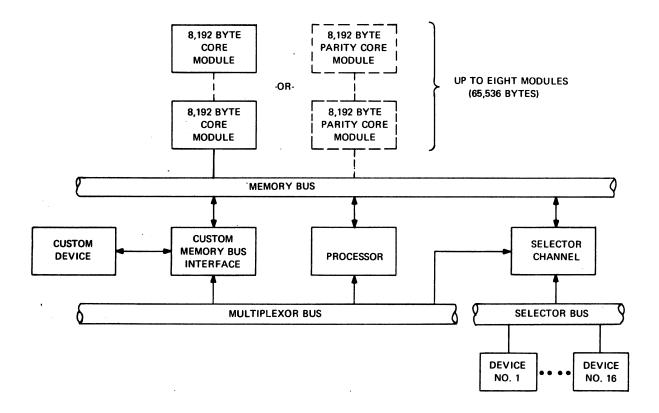

The Processor is presented in this chapter in block diagram form. A System block diagram is shown in Figure 2-1 and a general block diagram of the Processor is shown in Figure 2-2. The major elements of the system are described in the following paragraphs.

#### 2.2 ELEMENTS OF THE SYSTEM

#### 2.2.1 Processor

The various elements of the system are organized around the Processor, as shown in Figure 2.1. The Processor contains facilities for:

- 1. Sequencing of instructions in the required order.

- 2. Arithmetic and logical data processing.

- 3. Initiating or controlling communications with external devices.

- 4. Servicing interrupts.

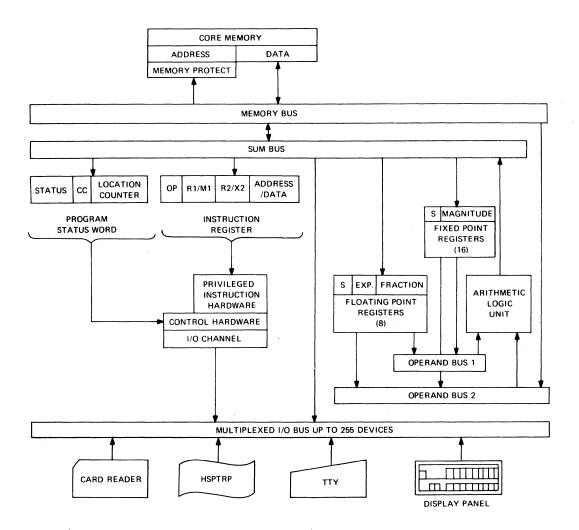

The basic elements of the Processor are: a set of 16 General Registers, an Arithmetic and Logic unit, a Control unit, and connections to the Memory and I/O Buses. See Figure 2-2.

The Processor operates under the direction of the Control unit which has a micro-program contained in a Read-Only Memory (ROM). The micro-program is a sequence of micro-operations which fetches the Processor instructions, decodes them, and processes the operands located in the General Registers and core memory locations. Such micro-programs are often referred to as "firmware" because they operate in a plane between "hardware" and "software".

Figure 2-1. System Block Diagram

The instruction set of the GE-PAC 3010/2 is described in Chapter 4. All memory is directly addressable with the primary instruction word; no paging or indirect addressing is required. The 16-bit General Registers can be used as fixed-point accumulators, link registers for subroutine returns, or pointers for program branching. Of the 16 General Registers, 15 can be used as index registers for address modification.

The Protect Mode is enabled in the Processor under program control. In this mode, the Memory Protect is activated, and the Privileged instructions are detected and their execution is prevented. Privileged instructions are I/O instructions and any Control instruction whose execution could change the status of the system. In the Protect Mode, the execution of any Privileged instruction causes an Illegal Instruction Interrupt. Privileged instructions are discussed in detail in Chapter 4.

In general, fixed-point operations are performed upon one operand in a General Register, with the other operand in either a General Register or a core memory location.

Multiple-precision arithmetic operations are possible using two's complement representation, and by recognition of the carry/borrow from one operation to another.

The Standard Floating-Point instructions manipulate floating-point data using eight unique Floating-Point Registers which are resident in core memory.

The standard format for 32-bit single-precision floating-point data is identical to that used in the IBM System/360. This format represents numbers in the range of 5.4  $\times$  10<sup>-79</sup> to 7.2  $\times$  10<sup>75</sup>, with six digits of precision.

Figure 2-2. Processor Block Diagram

#### 2.2.2 Core Memory

The GE-PAC 3010/2 can have from 8K to 65K bytes of Core Memory, where a byte refers to eight binary bits. The byte designation is used to describe memory size, since the memory reference instructions address memory at the byte level. The hardware memory modules are actually 16-bit oriented, and each Read or Write operation on the memory transfers 16-bits in one memory cycle. The maximum memory size, therefore, is 65,536/8-bit bytes or 32,768/16-bit halfwords.

When executing instructions, all 16-bit instructions and 16-bit data are handled in a single memory cycle. Multiple halfword data requires an additional memory cycle for each 16-bit halfword. Byte operations are performed by selectively manipulating the right or left 8-bits of the 16-bit halfword.

The Memory Write Control can be divided into two types. These two types have meaningful differences when used in conjunction with the Memory Protect. The first type is Standard Memory Write, the performance of which is subject to Memory Protect. That is, if the Processor is in the Protect Mode, any memory write into a protected area is inhibited, and a Memory Protect Controller Interrupt is generated. Memory, in this case is not altered. This type of memory write is used by all instructions which store data of any kind into memory. In Chapter 4, all instructions of this type are noted as being "subject to Memory Protect". Note that the Memory Protect does not affect reading from memory.

The other type of Memory Write Control, referred to as Privileged Write, overrides the Memory Protect circuit. This type of control is used by various internal Processor functions which must be allowed to write

into core memory, even in the Protect Mode. Examples of this operation are Processor access of dedicated registers in low core, and the register save sequence which is used on power failure. Other Privileged Write operations are noted where applicable in this manual.

In systems equipped with less than 65K bytes of memory, it is possible to address memory at an address greater than that of the last actual memory location. In this case, memory Read operations cause all zero data to be read, and Write operations proceed normally, but the data is lost.

#### 2.2.2.1 Memory Bus

The Memory Bus provides the path for communication between the memory modules, the Processor, and up to four parallel Direct Memory Access Ports. The ports operate on a cycle stealing basis where the maximum latency time is one memory cycle or 1.0 microsecond. Memory service is granted on a priority basis where the Processor is always lowest in priority. The assigning of priority for a port is on a serial daisy-chain basis with the port closest to the Processor having the highest priority. The Selector Channel is used with standard device controllers for high speed devices.

#### 2.2.2.2 Selector Channel

The Selector Channel is a Direct Memory Access device which provides high speed block-oriented data transfer at a rate of up to 2000K bytes. Up to 16 devices can be accommodated by the Selector Channel. Once initiated, the block transfer proceeds on a cycle stealing basis independent of the Processor. To initiate a data transfer, the Processor specifies the device address, the starting address in memory, the type of operation (Read or Write), and the ending address in memory. The data transfer is then completed without further direction or intervention by the Processor. Upon completion of the data transfer or termination due to a fault, the Processor is notified via a Selector Channel generated external interrupt.

#### 2.2.2.3 Customer Designed Direct Memory Access Channel

Customers wishing to design their own Direct Memory Access Channel (DMAC) interfaces directly to the Memory Bus can do so with data transfer rates of up to 2,000,000 bytes per second in the Burst Mode through a custom-built DMAC. This is accomplished by using a general purpose wire wrapped circuit board available from General Electric. In addition to the circuits required for the Memory Bus and the user's device, his DMAC must include a 16-bit Memory Address Register and a 16-bit Memory Data Register, which are switched onto the Memory Bus when the DMAC captures the daisy-chain response for a request for service.

#### 2.2.3 Multiplexor Channel

The Multiplexor Channel provides an Input/Output system for communicating directly with up to 255 peripheral device controllers. Operation over the Multiplexor Channel can be to either 8-bit byte devices or 16-bit half-word devices. The Multiplexor Channel consists of 30 lines:

- Sixteen bi-directional data lines for transferring either bytes or halfwords of data between the device and Processor.

- Eight control lines are used to identify the type of data transferred over the bi-directional data lines, such as status, command, address, or data.

- Five test lines are used to interrupt the Processor, and to synchronize the Input/Output system with the Processor.

- One initialize line is used to initalize the Input/Output system when power is turned On to the system.

The Multiplexor Channel operates on a request/response basis to allow simple reliable device controller design. Priority on the Multiplexor Channel is assigned on a party line basis where the device controller with the closest electrical proximity to the Processor has the highest priority. The Processor responds to an interrupt by swapping Program Status Words. The interrupt response time is 8.0 microseconds. The latency time for most instructions except Store Multiple and Load Multiple (which have a latency time of 20 microseconds) is 4 microseconds to 8 microseconds.

#### 2.2.3.1 Multiplexor Channel I/O Techniques

The task-oriented structure of the Multiplexor Channel provides a repertoire of built-in I/O techniques. These techniques provide an important benefit in the ease of use of the GE-PAC 3010/2 since the appropriate I/O technique can be chosen and matched to the speed and transfer requirements of various devices. The Multiplexor Channel I/O techniques include:

Program-Controlled I/O Using normal programmed I/O, a program can interrogate the status of any device, and control the transfer of data (either 8-bit or 16-bit) to or from a device when the device indicates it is ready.

Interrupt Driven I/O Provides an interrupt facility with which any device can indicate a device "ready" condition to the Processor by interrupting the running program. Interrupt acknowledgements are achieved using "daisy chain" hardware logic, which avoids any programmed device polling to determine which device interrupted. Interrupt programming, therefore, can efficiently transfer data to or from multiple devices simultaneously.

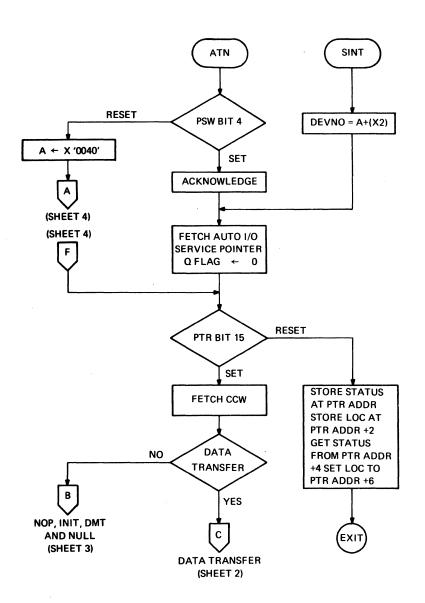

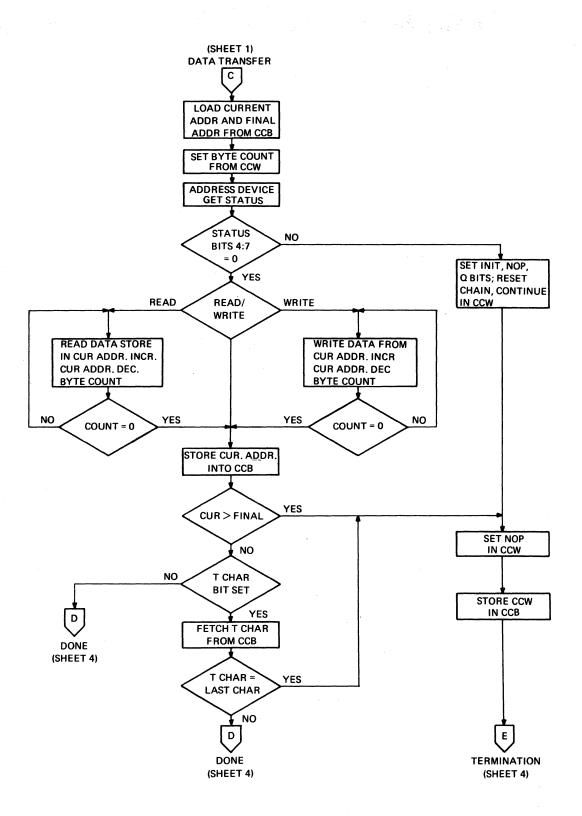

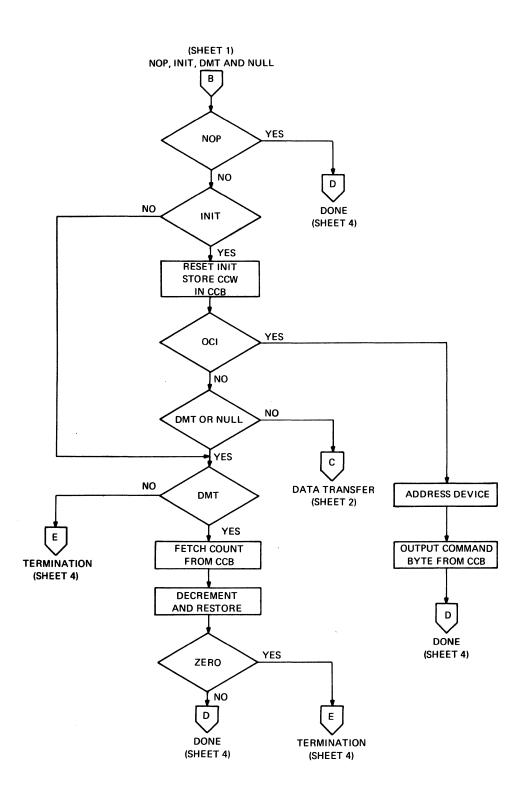

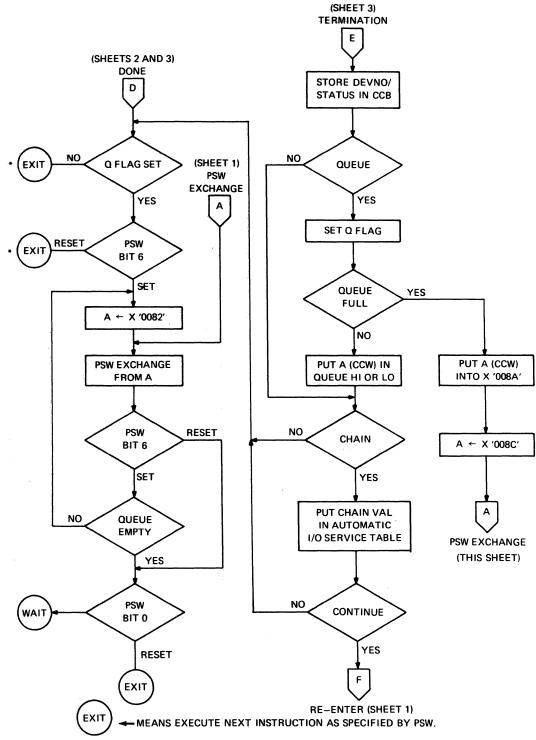

Automatic I/O Interrupt programming is simplified by an Automatic I/O Service Mode, in which the Processor performs much of the overhead associated with each interrupt. This Automatic I/O Service Mode can be disabled under program control, which makes the I/O compatible with the other GE-PAC 30's and 3010's. With the Automatic I/O Service in use, the I/O Channel capability can also be used. The I/O Channels, which are commanded via specified Channel Control Blocks (CCB) in memory, perform signal counting or data transfers without interrupting the running program. When the I/O channel completes a specified sequence, a variety of automatic command chaining and interrupt queuing operations can take place.

Burst Mode I/O This incorporates Read Block/Write Block instructions. These instructions permit the Processor to achieve transfer rates in excess of 330K bytes by momentary dedication to a particular device.

#### 2.2.3.2 Interleaved Data Channel

The Interleaved Data Channel (IDC) is an inexpensive direct to memory I/O system, which operates on an instruction steal basis, as compared with a memory cycle steal technique for the Direct Memory Access Channels. Data is transferred over the Multiplexor Channel autonomously with respect to the current program. Internal registers in the Processor are used as buffer registers between memory and the data channel device controller.

The Interleaved Data Channel controller is set up by the program over the Multiplexor Channel. Once initiated, the data transfer proceeds without further direction from the Program. For each Interleaved Data Channel cycle, the Processor inputs a 16-bit memory address from the Interleaved Data Channel controller along with a command to Read or Write. If the command is Write, the Processor reads the the memory location and outputs the 16-bit halfword of data to the Interleaved Data Channel controller. If the command is Read, the Processor inputs the 16-bit halfword of data and writes that data to memory.

The Interleaved Data Channel operates in the Burst Mode at 440K bytes, or at speeds up to 280K bytes in the Single Cycle Mode.

#### 2.3 PROCESSOR OPERATION

#### 2.3.1 Program Status Words

The focal point of control for the Processor is the Current Program Status Word (PSW). This 32-bit register contains the information required to direct program execution; a 12-bit Status field, a 4-bit Condition Code field, and a 16-bit Location Counter. See Figure 2-3.

The left half of the PSW defines Program Status, the right half is the Location Counter. The Current PSW controls instruction sequencing, and maintains the status of the system in relation to the program currently being executed. A program can change the Processor status by loading a New PSW. This is accomplished

| 1 | o 11   | 12 15 | 116              | 1 |

|---|--------|-------|------------------|---|

|   | STATUS | сс    | LOCATION COUNTER |   |

Figure 2-3. Program Status Word Format

by executing a Load Program Status Word (LPSW) or Exchange Program Status (EPSR) instruction. These instructions are described in Chapter 4.

The interrupt mechanism also involves the PSW. When an interrupt takes place, the Current PSW is stored at a unique four-byte location called the Old PSW. After the Current PSW is stored, the Current PSW register is loaded from another four-byte location called the New PSW. Each and every interrupt class has a unique set of Old and New PSWs. The PSW swap takes place automatically, and after the PSW swap, program execution will begin at the location specified by the Location Counter of the New PSW. The reserved core locations for Old and New PSWs for all interrupts are defined in Section 2.3.3.

The meaning of each bit in the left half of the PSW, Status and Condition Code, is explained in Table 2-1, and shown in Figure 2-4. The particular meaning or function of each bit applies when the bit is 1.

| 10 | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8 | 9 | 10 | 11 | 12 | 1 3 | 14 | 15 |

|----|----|----|----|----|----|----|----|---|---|----|----|----|-----|----|----|

| WT | ΕI | мм | DF | AS | FP | СТ | РМ | 0 | 0 | 0  | 0  | С  | >   | G  | L  |

Figure 2-4. Program Status Bits

#### 2.3.2 Instruction Execution

The 16-bit Location Counter field of the Program Status Word specifies the location of the next instruction to be fetched and processed. The 16-bit address field has the capability of directly addressing the maximum core memory of 65K bytes, or 32K halfwords.

Note that since instructions are aligned on halfword boundaries the value of the Location Counter must be even. That is, Bit 15 of the Location Counter must be zero.

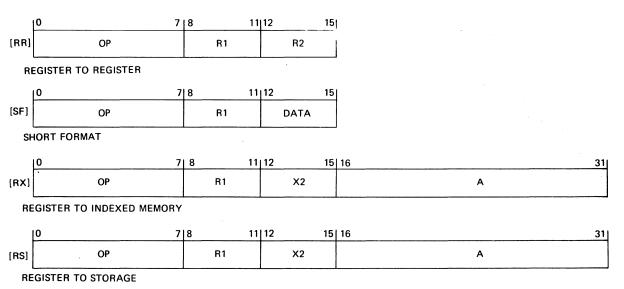

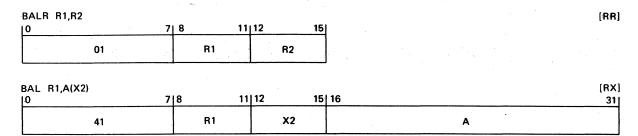

During the normal processing of a program, an instruction is fetched from the location specified by the Location Counter, the instruction is executed, the Location Counter is incremented, and another fetch and execute cycle begins. After instruction execution, (except for Branch or Control instructions) the Location Counter is incremented by two if the executed instruction is of the halfword (RR or SF) 16-bit format, or by four if the executed instruction is of the fullword (RX or RS) 32-bit format.

Following Branch instructions or System Control instructions, the Location Counter is adjusted as a function of the particular instruction. See Section 4.8 for a summary of Branch instructions, and Section 4.11 for a summary of System Control instructions.

The sequencing of instructions during program execution is also changed if an interrupt occurs. In this case, the PSW swap procedure saves the Current PSW in core memory so that, after an interrupt is processed, execution can resume at the correct location.

TABLE 2-1. PROGRAM STATUS BIT DEFINITIONS

| Bit                  |                  | Name                                                            | Comments                                                                                                                                                                                                                                                            |

|----------------------|------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                    | WT               | Wait State                                                      | The Wait bit is set to halt program execution. When this bit is set in the Current PSW, no program execution takes place, but the Processor will respond to all I/O and Machine Malfunction Interrupts, if they are enabled.                                        |

| 1                    | EI               | External<br>Interrupt Enable                                    | The External Interrupt Enable bit is set to make the Processor responsive to interrupt signals from the Multiplexor Bus. External interrupts are discussed in detail in Section 2.4.3.1.                                                                            |

| 2                    | MM               | Machine Malfunction<br>Interrupt Enable                         | The Machine Malfunction Enable bit allows an interrupt to occur if a power fail is detected, if the machine is equippped with the Memory Parity Option and a memory parity error occurs, or during the restart process following a power down. See Section 2.4.2.3. |

| 3                    | DF               | Fixed Point Divide<br>Fault Interrupt<br>Enable                 | The Divide Fault Interrupt Enable bit allows the Processor to interrupt when a Fixed-Point Divide instruction is attempted and the result cannot be expressed in 16-bits. See Section 2.4.2.1.                                                                      |

| 4                    | AS               | Automatic Input/<br>Output Service<br>Enable                    | The Automatic I/O Service Enable bit allows the Processor to acknowledge I/O Interrupts and service them automatically as described in Section 2.4.3.2.                                                                                                             |

| 5                    | FP               | Floating-Point<br>Arithmetic Fault<br>Interrupt Enable          | The Floating-Point Arithmetic Fault Interrupt Enable bit allows the Processor to interrupt if exponent overflow or underflow occurs during any floating-point operation. See Section 2.4.2.2.                                                                       |

| 6                    | CT               | Channel Termination<br>Interrupt Enable                         | Channel Termination Interrupt Enable bit pertains to the Automatic I/O Channel, which can be used in conjunction with the Automatic I/O Service as described in Section 2.4.3.3.                                                                                    |

| 7                    | РМ               | Protect Mode                                                    | The Protect Mode bit enables Memory Protect and detection of Privileged instructions. When the Protect Mode is not enabled the Processor is said to be in the Supervisor Mode. See Section 2.4.4.2.                                                                 |

| 8-11                 |                  | Unused                                                          | Must be zero.                                                                                                                                                                                                                                                       |

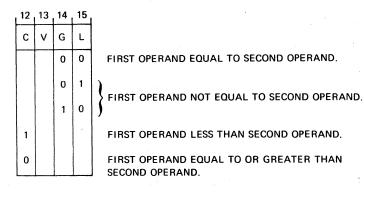

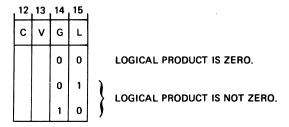

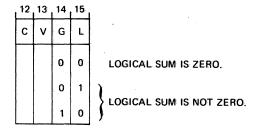

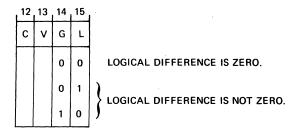

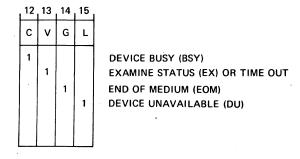

| 12<br>13<br>14<br>15 | C<br>V<br>G<br>L | Carry/Borrow<br>Overflow<br>Greater than Zero<br>Less than Zero | The Condition Code bits are set or adjusted after the execution of instructions by the Processor.  See Chapter 4 for details.                                                                                                                                       |

#### TABLE 2-2 CORE MEMORY ALLOCATION

| Function                                | Hexadecimal<br>Memory Address                                                                                                  | Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Floating-Point Registers                | 00-03<br>04-07<br>08-0B<br>0C-0F<br>10-13<br>14-17<br>18-1B                                                                    | Floating-Point Register, R0 Floating-Point Register, R2 Floating-Point Register, R4 Floating-Point Register, R6 Floating-Point Register, R8 Floating-Point Register, R10 Floating-Point Register, R12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Power-Fail Locations                    | 1C-1F<br>20-21<br>22-23<br>24-27                                                                                               | Floating-Point Register, R14  Unassigned Register Save Pointer Current PSW Save Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Interrupt PSWs                          | 28-2B<br>2C-2F<br>30-33<br>34-37<br>38-3B<br>3C-3F<br>40-43<br>44-47<br>48-4B<br>4C-4F                                         | Old PSW FLPT Arithmetic Fault Interrupt New PSW FLPT Arithmetic Fault Interrupt Old PSW Illegal Instruction Interrupt New PSW Illegal Instruction Interrupt Old PSW Machine Malfunction Interrupt New PSW Machine Malfunction Interrupt Old PSW External Interrupt New PSW External Interrupt Old PSW Fixed-Point Divide Fault Interrupt New PSW Fixed-Point Divide Fault Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Reserved                                | 50-7F                                                                                                                          | Bootstrap Loader and Device Definition Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Automatic I/O Termination<br>Parameters | 80-81<br>82-85<br>86-89<br>8A-8B<br>8C-8F                                                                                      | Termination Queue Pointer Old PSW Automatic I/O Termination Interrupt New PSW Automatic I/O Termination Interrupt Overflow Termination Pointer Old PSW Termination Queue Overflow Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Supervisor Call                         | 90-93<br>94-95                                                                                                                 | New PSW Termination Queue Overflow Interrupt Supervisor Call Argument Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Automatic I/O Service                   | 96-99 9A-9B 9C-9D 9E-9F A0-A1 A2-A3 A4-A5 A6-A7 A8-A9 AA-AB AC-AD AE-AF B0-B1 B2-B3 B4-B5 B6-B7 B8-B9 BA-BB BC-CF  D0-D1 D2-D3 | Old PSW Supervisor Call New PSW (Status and Condition Code) Supervisor Call New PSW (Location Counter) Supervisor Call 0 New PSW (Location Counter) Supervisor Call 1 New PSW (Location Counter) Supervisor Call 2 New PSW (Location Counter) Supervisor Call 3 New PSW (Location Counter) Supervisor Call 3 New PSW (Location Counter) Supervisor Call 4 New PSW (Location Counter) Supervisor Call 5 New PSW (Location Counter) Supervisor Call 6 New PSW (Location Counter) Supervisor Call 7 New PSW (Location Counter) Supervisor Call 8 New PSW (Location Counter) Supervisor Call 9 New PSW (Location Counter) Supervisor Call 10 New PSW (Location Counter) Supervisor Call 11 New PSW (Location Counter) Supervisor Call 11 New PSW (Location Counter) Supervisor Call 12 New PSW (Location Counter) Supervisor Call 13 New PSW (Location Counter) Supervisor Call 14 New PSW (Location Counter) Supervisor Call 15 Reserved  Service Pointer, Device 0 Service Pointer, Device 1 |

| Table                                   | D4-D5  0 0 2CC-2CD 2CE-2CF                                                                                                     | Service Pointer, Device 2  Service Pointer, Device 254 Service Pointer, Device 255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### 2.3.3 Core Memory Allocation

The GE-PAC 3010/2 Processor requires certain locations in core memory for Floating-Point Registers, register save areas, and interrupt processing. These locations are defined in Table 2-2 and described in the following paragraphs.

| Floating-Point Registers              | - | These eight 32-bit registers are used by the Floating-Point instructions. See Section 4.6 for details of the Floating-Point instructions.                                                                                                                                                                                                                               |

|---------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Fail Locations                  | - | The Register Save Pointer at location X'22', points to the first of 16 consecutive halfword locations in memory where the General Registers are saved in the event of power failure. When power is restored, the General Registers are restored automatically from these locations. The Current PSW is saved and restored in similar fashion from location X'24'-X'27'. |

| Interrupt PSWs                        | - | These locations are reserved for the Old and New PSWs for the various internal and external interrupts. These are discussed further in Sections 2.4.2 and 2.4.3.1 respectively.                                                                                                                                                                                         |

| Bootstrap Loader                      | - | The Bootstrap Loader is called the 50 sequence and is used to load the more sophisticated loaders.                                                                                                                                                                                                                                                                      |

| Channel I/O Termination<br>Parameters | - | These locations are used in conjunction with Termination interrupts from channel I/O operation. Refer to Sections 2.4.3.3 and 2.4.3.4 for details.                                                                                                                                                                                                                      |

| Supervisor Call Parameters            | - | These locations are used for the PSW exchange associated with the Supervisor Call (SVC) instruction. This instruction is described in Section 4.11.4.                                                                                                                                                                                                                   |

| Automatic I/O Service Table           | - | This table of 256 halfwords is used in the Automatic I/O Service Mode of operation. The Processor uses this table to uniquely service each interrupting device. See Section 2.4.3.2.                                                                                                                                                                                    |

#### 2.4 INTERRUPT SYSTEM

#### 2.4.1 Interrupt Procedure

The Interrupt structure of the GE-PAC 3010/2 provides rapid response to internal and external events that require service by special software routines. In the interrupt response procedure, the Processor preserves the current state of the machine, and branches to the required service routine. The service routine may optionally restore the previous machine state upon completion of its service. The types of interrupts with their associated enable/disable PSW bits are listed in Table 2-3. Interrupts without a controlling PSW bit are always enabled.

Interrupts can occur at various times during processing. The Arithmetic Fault Interrupts occur during execution of user instructions. The Illegal instruction and Protect Mode Interrupt occur as soon as the offending instruction is recognized. The Supervisor Call Interrupt occurs as part of the execution of the Supervisor Call instruction. The Machine Malfunction and I/O Service Interrupts occur following instruction execution. The Channel Termination Interrupt can also occur during a Load Program Status Word or Exchange Program Status instruction.

The Interrupt Procedure is based on the concepts of Old, Current, and New Program Status Words. The Current PSW, contained in a hardware register, defines the operating status of the machine. When this status must be interrupted, the Current PSW becomes an Old PSW and is stored in a core location dedicated

TABLE 2-3. INTERRUPTS

| Interrupt                          | PSW Control Bit    |

|------------------------------------|--------------------|

| External                           | 1                  |

| Machine Malfunction                | 2                  |

| Fixed Point Divide Fault           | 3                  |

| Automatic I/O Service              | 4                  |

| Floating-Point Arithmetic Fault    | 5                  |

| Channel Termination                | 6                  |

| Protect Mode                       | 7                  |

| Illegal Instruction                | Cannot be disabled |

| Channel Termination Queue Overflow | Cannot be disabled |

| Supervisor Call                    | Cannot be disabled |

to the type of interrupt that has occurred. The New PSW becomes the Current PSW by being loaded from a dedicated core location into the hardware PSW Register. The status portion of the Current PSW now contains the operating status for the interrupt service routine, and the Location Counter points to the first instruction in the service routine. New Program Status Words for interrupts controlled by PSW bits should disable interrupts of their own class. Interrupts controlled by Bits 1 and 6 must disable interrupts of their own class to prevent the Processor from going into an endless loop. The dedicated core locations for Old and New Program Status Words are shown in Table 2-2 of Section 2.3.2. The Program Status Word exchange procedure does not change the contents of the New PSW location, and subsequent interrupts of the same type are treated in the same way.

#### 2.4.2 Internal Interrupts

The GE-PAC 3010/2 can generate six Internal Interrupts. Of these, the Illegal instruction and the Supervisor Call cannot be inhibited. Inhibited Internal Interrupts are not queued.

#### 2.4.2.1 Fixed-Point Divide Fault Interrupt

The Fixed-Point Divide Fault Interrupt, enabled by Bit 3 of the Program Status Word, is indicative of division by zero or quotient overflow. Quotient overflow is defined as quotient magnitude greater than  $2^{15}$ -1. The interrupt takes place before modification of the operand registers. After a Fixed-Point Divide Fault Interrupt, the Old PSW Location Counter points to the next instruction following the Divide instruction.

#### 2.4.2.2 Floating-Point Arithmetic Fault Interrupt

The Floating-Poirt Arithmetic Fault Interrupt enabled by Bit 5 of the Current PSW, occurs on exponent overflow or underflow as well as on division by zero. In the case of division by zero, the interrupt takes place prior to alteration of the operand register. An exponent overflow sets the result to  $\pm X'7FFF$  FFFF'. An exponent underflow sets the result to X'0000 0000'. The Location Counter of the Old PSW points to the next instruction. Refer to Section 4.6 for an explanation of Floating-Point instructions.

#### 2.4.2.3 Machine Malfunction Interrupt

Bit 2 of the Current Program Status Word controls the Machine Malfunction Interrupt. This error can occur on either a primary power failure, a memory parity error, or during the restart process following a power shutdown. If the memory is equipped with the Parity Option, the parity bit of each memory word is set to maintain odd parity. This bit is recomputed during each memory read; if the computed bit is not equal to the bit read out of memory and if Bit 2 of the current PSW is set, the Current Program Status Word is stored at the Machine Malfunction Old PSW location, and the Current PSW is loaded from the Machine Malfunction New PSW

location. The Condition Code field of the Current PSW is then adjusted by setting the G flag (PSW 14) if the parity error occurred on instruction read, or setting the V flag (PSW 13) if the error occurred on an operand read. It is not possible to guarantee programmed recovery from a parity error.

NOTE

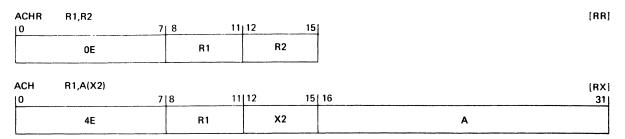

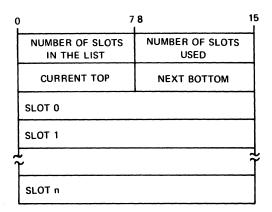

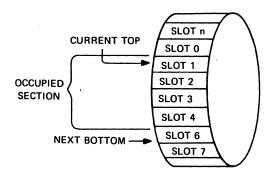

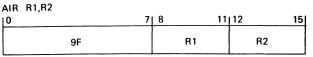

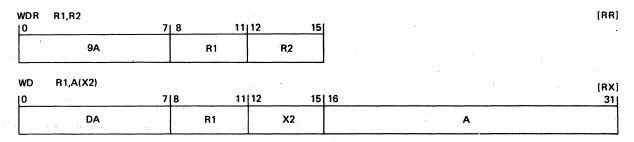

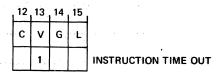

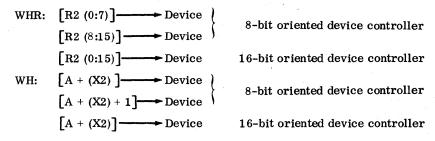

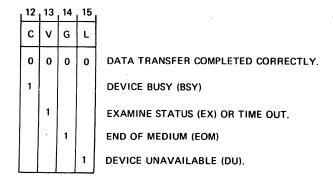

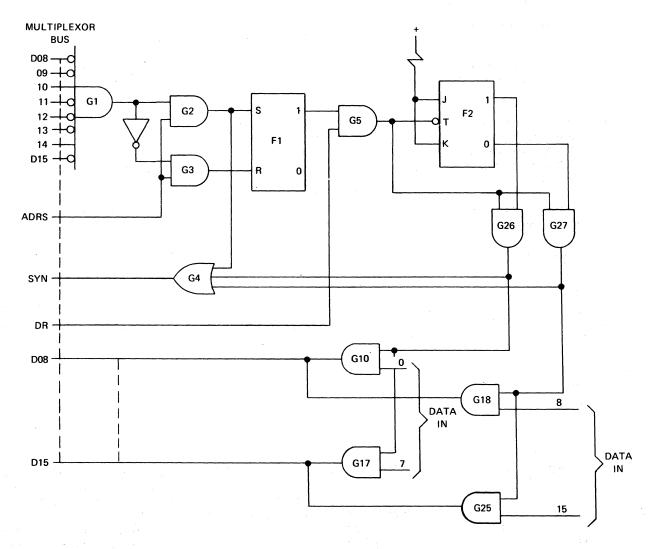

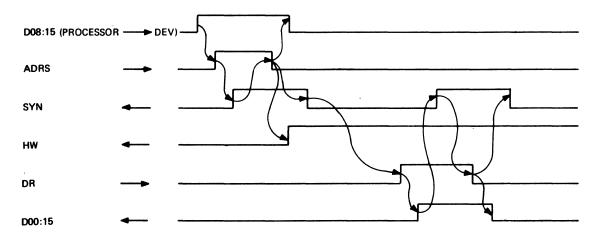

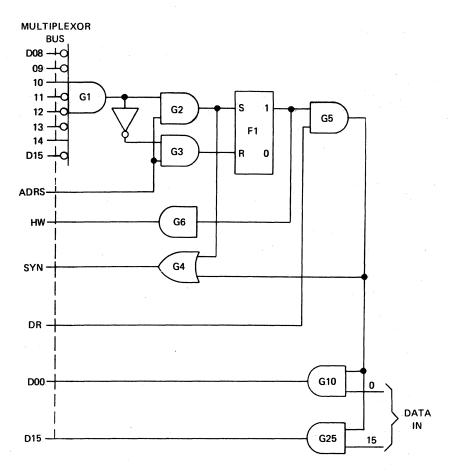

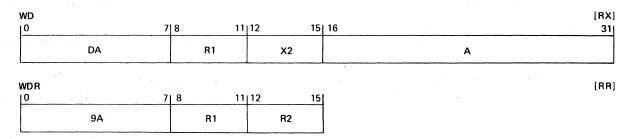

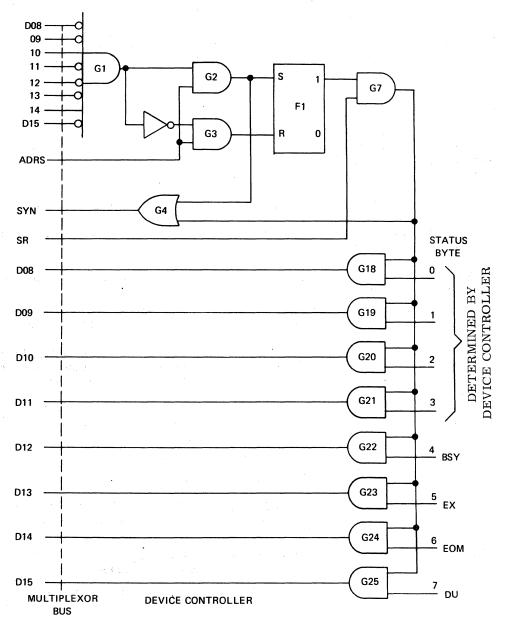

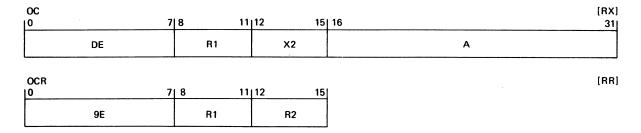

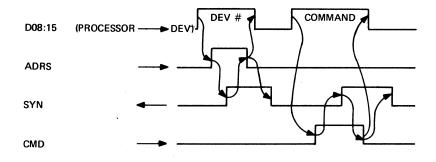

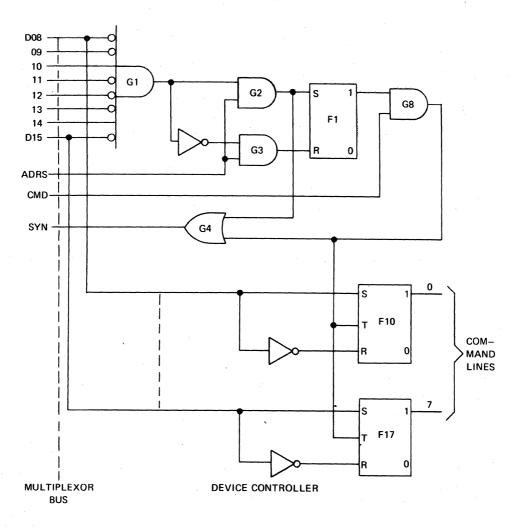

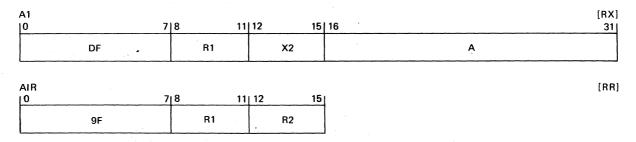

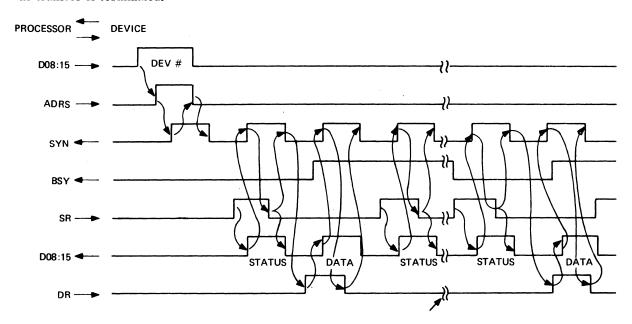

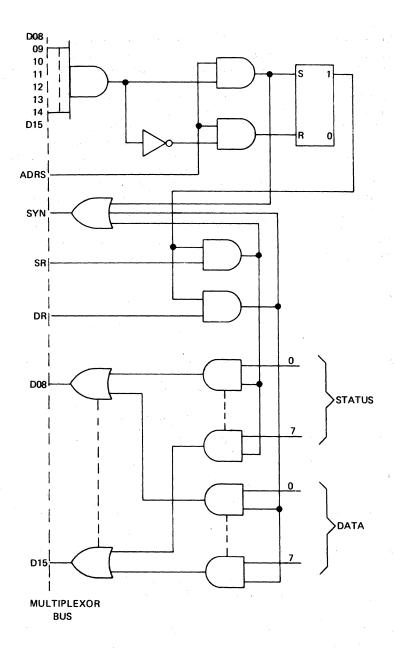

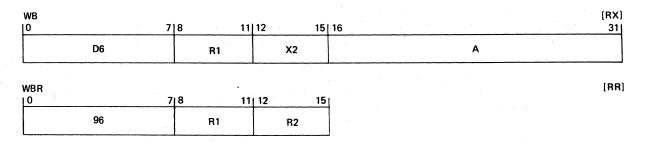

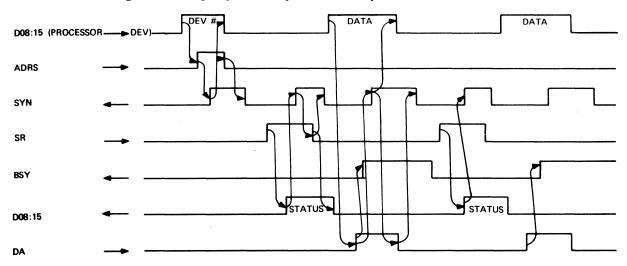

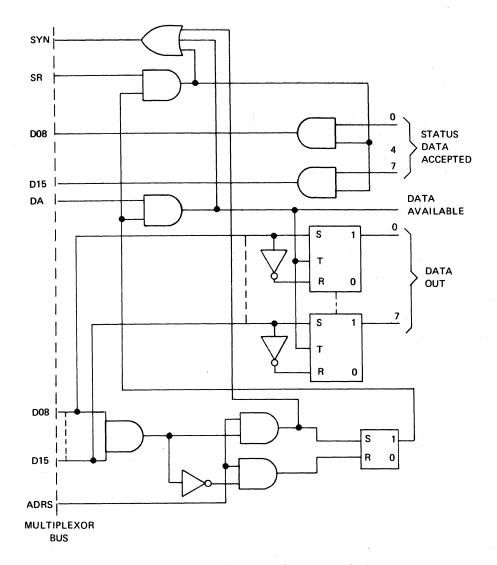

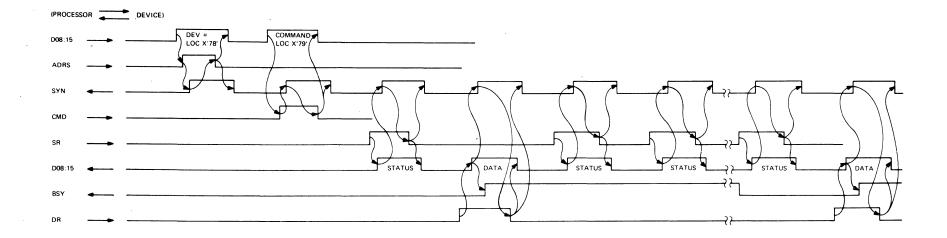

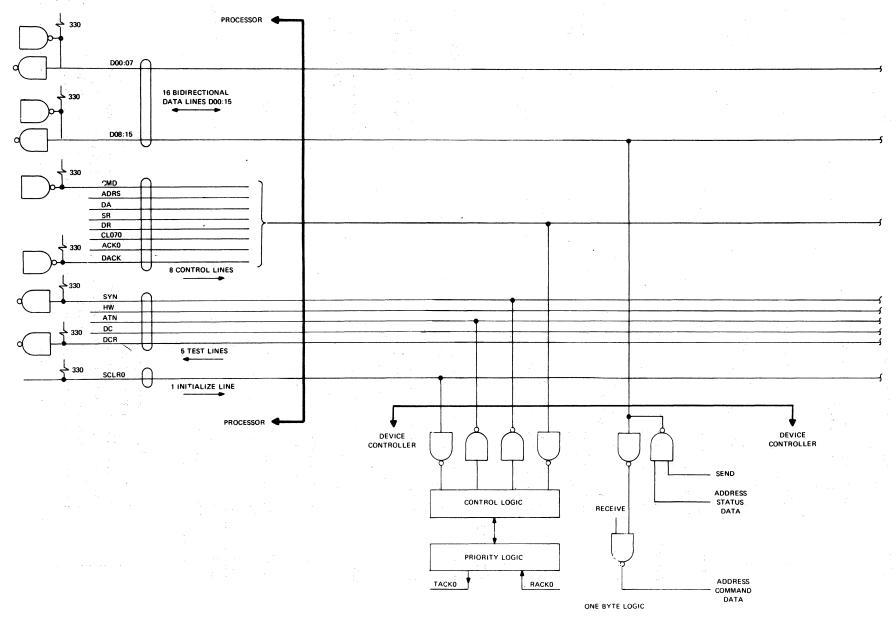

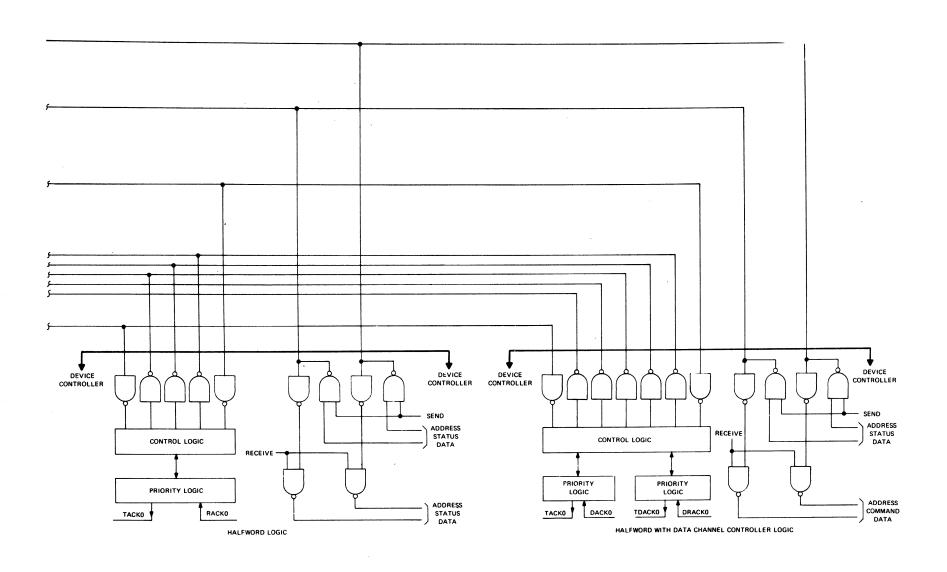

The Condition Code field of the Machine Malfunction New PSW location in memory must be zero.