# HONEYWELL

# DPS 8 & DPS 88 ASSEMBLY

**INSTRUCTIONS**

# SUBJECT

Description of the Assembly Instructions for the CP-6 and DPS 8/DPS 88 Information Systems

# SPECIAL INSTRUCTIONS

This is the first revision to DH03-00, dated April 1980. Because of extensive changes, change bars have not been used.

# SOFTWARE SUPPORTED

CP-6, Software Release B03 GCOS 8, Software Release 2300

ORDER NUMBER DH03-01

June 1984

#### PREFACE

This manual contains information that enables the user to code programs in symbolic machine language which is then translated into binary machine instructions.

This manual is directed to users who are experienced in coding within the environment of a large-scale computer installation. Considerable knowledge and practical experience is required in the use of address modification with indirection, hardware indicators, fault interrupts and recovery routines, macro operations, pseudo-operations, and other features normally encountered in a large computer with a flexible instruction repertoire under control of a master executive program. It is assumed that the user is familiar with the twos complement number system as employed in a sign-number machine (see Appendix F).

This manual includes the processor capabilities, modes of operation, detailed descriptions of machine instructions, virtual memory addressing, paging, and the representation of data. It should prove useful to programmers who are responsible for analyzing conditions that cause system failures.

Related manuals:

GCOS 8 OS GMAP User's Guide, Order Number DH01.

The information and specifications in this document are subject to change without notice. Consult your Honeywell Marketing Representative for product or service availability.

©Honeywell Information Systems Inc., 1984

File No.: 1Q23, 1V23, 1W23

#### LISTING OF MANUALS

A listing of large system software manuals is available to any Honeywell user who has access to an uppercase and lowercase ASCII terminal with a line length of 80 or more characters. The manuals are categorized both by software release and by software category. This listing is updated regularly to enable ordering of manuals as soon as they are published. Instructions on how to order manuals are output with the listing.

To obtain the listing:

1. Dial appropriate telephone number to connect your terminal with the Multics system in Phoenix.

| 1200-baud                 | 300-baud             |          | 150-baud  |  |

|---------------------------|----------------------|----------|-----------|--|

| terminals                 | terminals            |          | terminals |  |

| (602)249-5356<br>249-6430 | 249-7501<br>249-7701 | 249-7801 | 249-7554  |  |

System response - computer system identification

Example: Multics MR10.1: Honeywell LCPD Phoenix, System M Load=35.0 out of 125.0 units: users=35

2. Enter the following login command: login Sam (the identifier "Sam" must be used - it is not a sample for any proper name)

Press carriage return key.

System response - request for password

#### Example: <u>Password</u>: **BEREFERENCE** (password strikeover mask)

3. Enter the password:

Multics

Press carriage return key.

System response - Welcome message followed by a query and "r" message

Example: Welcome to the Multics system For services available online type: :list rllll.7 Thu (ready message)

To obtain a list of commands, enter:

Press carriage return Key.

:list

System response - list of commands available for specific topics and "r" message.

5. Enter command selected and press carriage return key.

6. To log off Multics system, enter: | logout

System response - logout message

Example: Sam SRB logged out 02/04/84 1110.3 mst fri CPU usage 3 sec, memory usage 22.4 units .

# CONTENTS

| s | ec | t | ion | I |

|---|----|---|-----|---|

|   |    |   |     |   |

| Section I | Ι |

|-----------|---|

|-----------|---|

. . .

Section III

Section IV

|                                              | Page |

|----------------------------------------------|------|

| Introduction                                 | 1-1  |

| Introduction                                 | 1-1  |

| Functional Units                             | 1-2  |

| Address Modification                         | 1-2  |

| Faults And Interrupts                        | 1-2  |

| Execution Of Interrupts                      | 1-3  |

|                                              | 1-4  |

|                                              | 1-6  |

| Addressing Modes                             | 1-6  |

|                                              | 1-6  |

|                                              | 1-6  |

| Interval Timer                               | 1-0  |

| Representation Of Data                       | 2-1  |

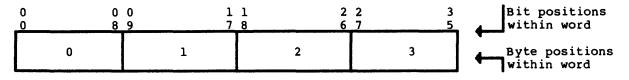

| Bit Groupings                                | 2-1  |

| Position Numbering                           | 2-1  |

|                                              | 2-1  |

| Character-Strings                            | 2-2  |

| Character Positions                          | 2-2  |

| Bit Positions                                | 2-3  |

| Literals                                     | 2-3  |

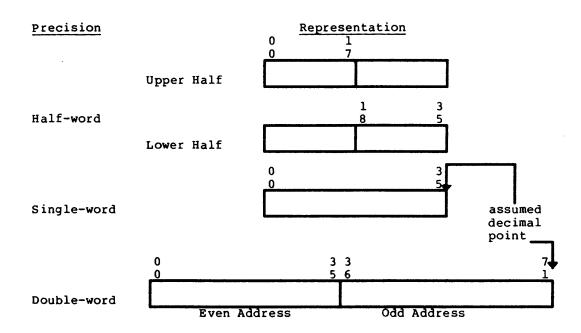

| Binary Numbers                               | 2-4  |

| Fixed-Point Numbers                          | 2-4  |

|                                              | 2-6  |

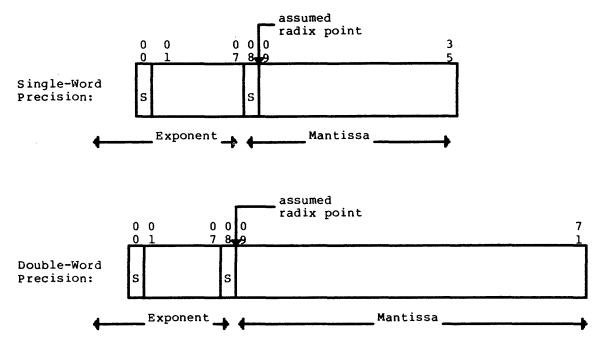

| Normalized Binary Floating-Point Numbers     | 2-6  |

| Hexadecimal Floating-Point Numbers           | 2-0  |

| Binary Representation Of Fractional          | 2-7  |

|                                              | 2-8  |

|                                              |      |

|                                              | 2-8  |

| Decimal Data Character Codes                 | 2-9  |

| Floating-Point Decimal Numbers               | 2-10 |

| Decimal Number Ranges                        | 2-11 |

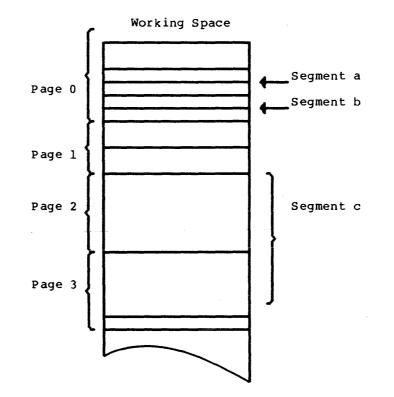

| Memory Characteristics                       | 3-1  |

| General Description                          | 3-1  |

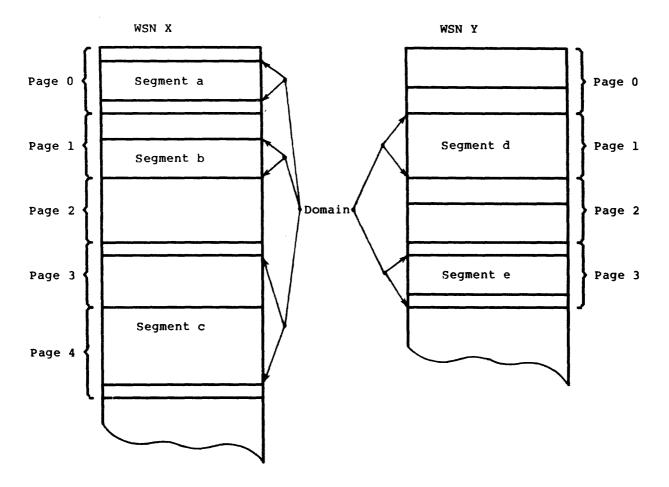

| Virtual Memory                               | 3-2  |

| Working Spaces And Pages                     | 3-2  |

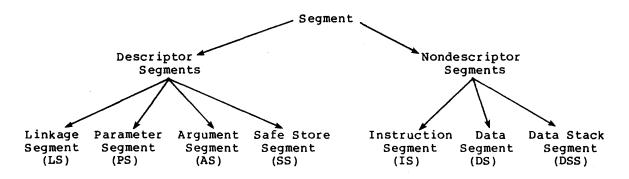

| Segments                                     | 3-3  |

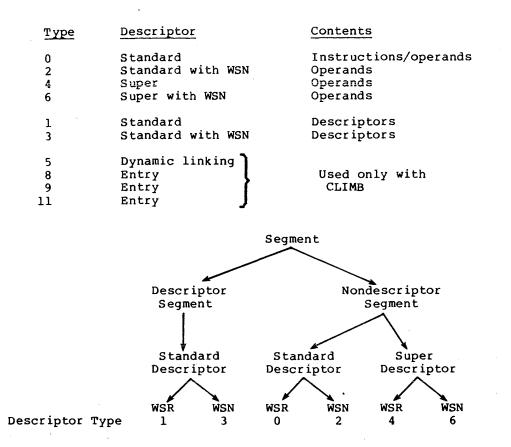

| Descriptors                                  | 3-4  |

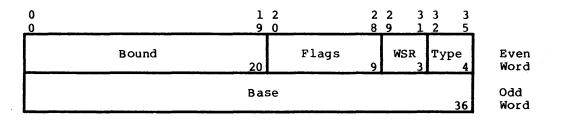

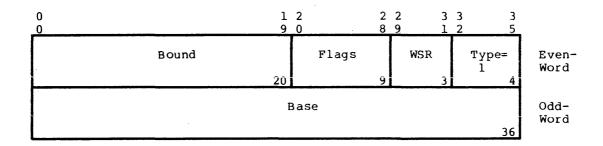

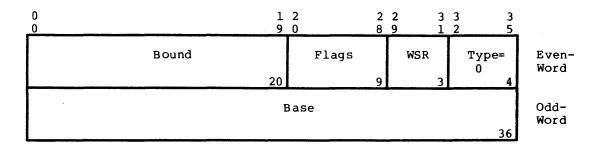

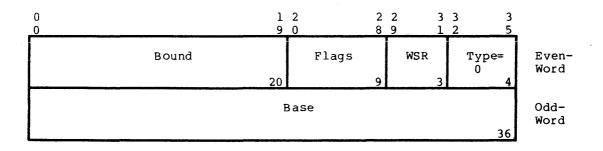

| Standard Descriptor                          | 3-5  |

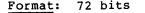

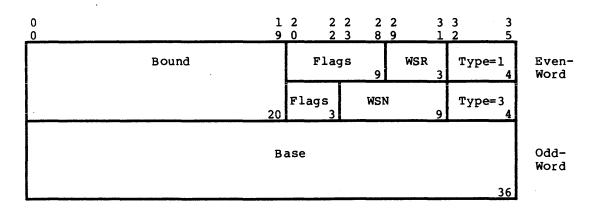

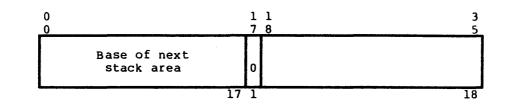

| Standard Descriptor With Working Space       | 5 5  |

|                                              | 3-7  |

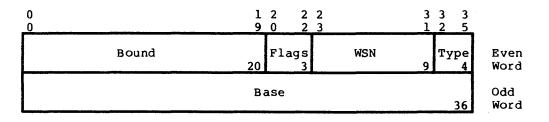

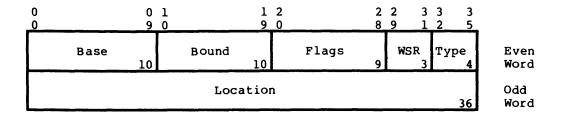

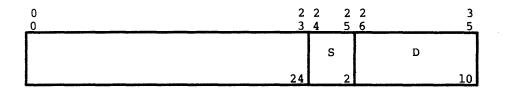

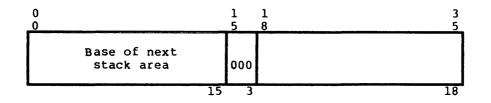

| Super-Descriptor                             | 3-8  |

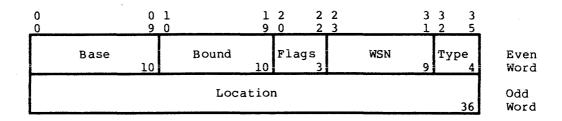

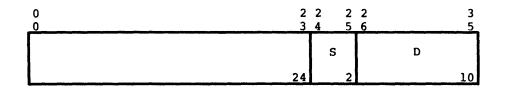

| Super-Descriptor With Working Space          | 5.0  |

|                                              | 3-9  |

| Number                                       |      |

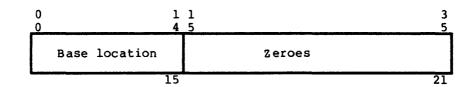

| Domains                                      | 3-10 |

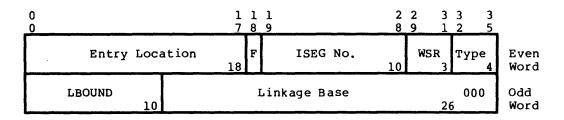

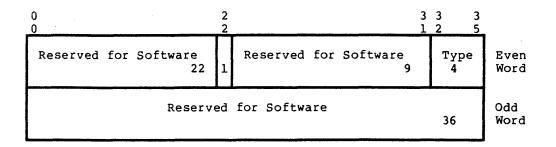

| Entry Descriptor                             | 3-12 |

| Dynamic Linking Descriptor                   | 3-13 |

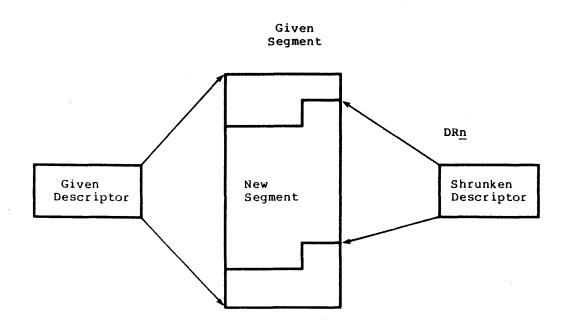

| Shrinking                                    | 3-13 |

| Processor Accessible Registers               | 4-1  |

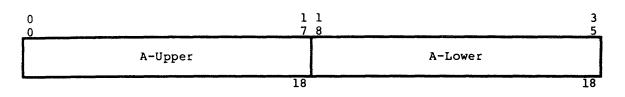

| Accumulator Register (A)                     | 4-3  |

| Quotient Register (Q)                        | 4-4  |

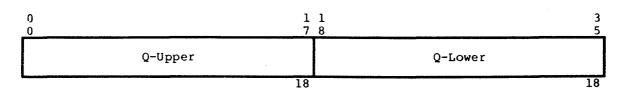

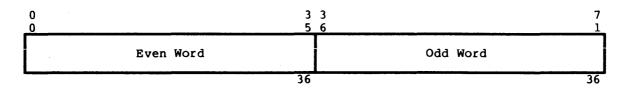

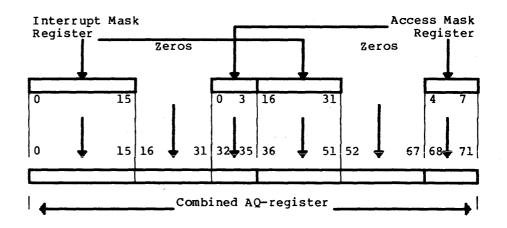

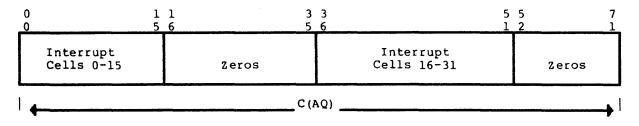

| Accumulator-Quotient Register (AQ)           | 4-4  |

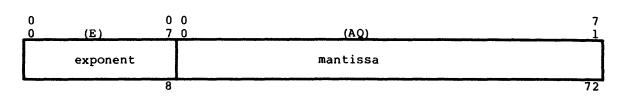

| Exponent Register (E)                        | 4-5  |

| Exponent-Accumulator-Quotient Register (EAQ) | 4-6  |

| Index Registers (Xn)                         | 4-6  |

| Index Registers (Xn)                         | 4-7  |

|                                              | - 1  |

Page

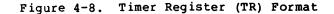

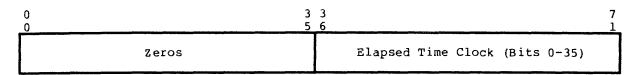

| Timer Register (TR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

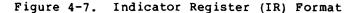

| Timer Register (TR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

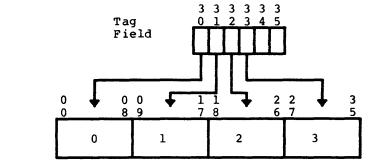

| Address Registers (ARn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

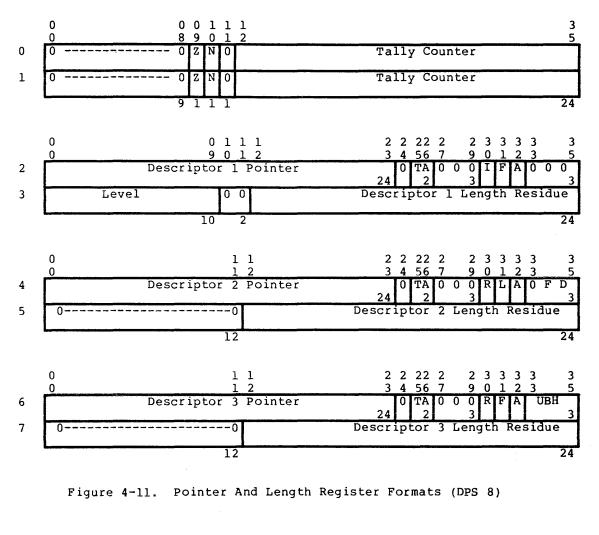

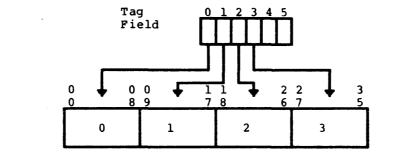

| Pointer And Length Registers (DPS 8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Pointer And Length Registers (DPS 88)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Node Desights (MD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Mode Register (MR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

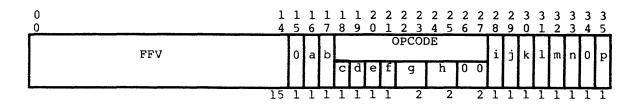

| Cache Mode Register (CMR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Fault Register (FR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Fault Register Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Control Unit History Registers (CUn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Operations Unit History Registers (OUn)<br>Decimal Unit History Registers (DUn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Decimal Unit Highers Decistors (DUR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Decimal Unit History Registers (DUn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |