## **HONEYWELL SERIES 200**

Models 200/1200/2200 PROGRAMMERS' REFERENCE MANUAL

**ELECTRONIC DATA PROCESSING**

Copyright 1965 Honeywell Inc. Electronic Data Processing Division Wellesley Hills, Massachusetts 02181

## **HONEYWELL SERIES 200**

## Models 200/1200/2200 PROGRAMMERS' REFERENCE MANUAL

FIRST EDITION

First Printing September, 1965

Second Printing December, 1965

# Honeywell ELECTRONIC DATA PROCESSING

PRICE .....\$4.50

Questions and comments regarding this manual should be addressed to:

Honeywell Electronic Data Processing Information Services 60 Walnut Street Wellesley Hills, Massachusetts 02181 The purpose of this text is to provide a detailed reference source containing:

- 1. a functional description of the Honeywell Series 200 Models 200, 1200, and 2200 and their components.

- 2. a definition of the Series 200 Assembly System (Easycoder).

- a detailed explanation of machine operation codes.

The only prerequisite for a thorough understanding of the information presented in this manual is a familiarity with basic data processing terminology. No previous knowledge of the Series 200 is assumed.

The equipment characteristics reported herein remain subject to change in order to allow the introduction of design improvements.

The following publications are hereby superseded:

Honeywell 200 Programmers' Reference Manual (DSI-214), Honeywell 2200 Programmers' Reference Manual (DSI-304), Easycoder 8K Assembly Language (DSI-409), and Easycoder 12K Assembly Language (DSI-313).

# TABLE OF CONTENTS

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                                                                                                                              |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Section 1 | Series 200 Components Central Processor Standard Processing Mode Interrupt Processing Mode Processing Power. Peripheral Equipment Peripheral Equipment Peripheral Control Punched Card Equipment High-Speed Printers. Magnetic Tape Units Mass Memory File Random Access Drum File Paper Tape Equipment. Data Communication Equipment Peripheral Data Transfer Operation Input/Output Trunk Read/Write Channel Optional Features Advanced Programming Program Interrupt Edit Instruction Additional Input/Output Trunks and Read/Write Channels Scientific Unit | 1-1<br>1-3<br>1-3<br>1-4<br>1-6<br>1-6<br>1-7<br>1-7<br>1-8<br>1-9<br>1-9<br>1-10<br>1-11<br>1-13<br>1-15<br>1-15<br>1-16<br>1-16 |

| Section 2 | Storage Protect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-17 2-1 2-1 2-4 2-6 2-7 2-7 2-8 2-8 2-9 2-10                                                                                     |

| Section 3 | Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-1<br>3-1<br>3-2<br>3-2<br>3-2<br>3-3<br>3-4                                                                                     |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Section 3 (cont) | Fields Items Records Summary  Magnetic Tape Data Format Punched Card Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-4<br>3-5<br>3-6<br>3-6<br>3-7<br>3-8                                                                          |

| Section 4        | Addressing.  Basic Concepts Registers Used in Addressing Sequence Register (SR). Change Sequence Register (CSR). External Interrupt Register (EIR). Internal Interrupt Register (IIR) A-Address Register (AAR). B-Address Register (BAR). Summary. Addressing Modes Two-Character Addressing Mode Three-Character Addressing Mode Four-Character Addressing Mode Address Modification. Three-Character Address Indirect Addressing Indexed Addressing Four-Character Addressing Mode Indirect Addressing Explicit Addressing, Implicit Addressing, and Chaining. | 4-1<br>4-3<br>4-3<br>4-3<br>4-4<br>4-4<br>4-4<br>4-5<br>4-5<br>4-6<br>4-8<br>4-9<br>4-9<br>4-12<br>4-13<br>4-14 |

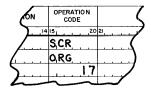

| Section 5        | Easycoder Programming Introduction Easycoder Symbolic Language. Easycoder Assembly Program. Coding Form Card Number (Card Columns 1-5) Type (Card Column 6) Mark (Card Column 7) Location (Card Columns 8-14) Operation Code (Card Columns 15-20) Operands (Card Columns 21-62) Additional Coding Rules Address Codes Absolute Symbolic Self Reference Relative Blank Literals                                                                                                                                                                                   | 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8<br>5-9<br>5-9<br>5-9<br>5-10<br>5-11<br>5-12               |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Section 5 (cont) | Decimal Literals  Binary Literals  Octal Literals  Alphanumeric Literals  Area Defining Literals  Address Literals  Variant Character  Input/Output Control Characters  Address Modification Codes  Indexed  Indirect                                                                                                                                                                                                                                         | 5-12<br>5-13<br>5-13<br>5-14<br>5-14<br>5-15<br>5-16<br>5-16<br>5-16                                                       |

| Section 6        | Data Formatting Statements Introduction  Define Constant with Word Mark — DCW  Numeric Constants  Decimal Constants  Binary Constants  Octal Constants  Alphanumeric Constants  Blank Constants  Define Constant — DC  Reserve Area — RESV  Define Symbolic Address — DSA  Define Area — DA                                                                                                                                                                   | 6-1<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-4<br>6-5<br>6-5<br>6-6                                                         |

| Section 7        | Assembly Control Statements Introduction Program Header — PROG Easycoder A. Easycoder B. Easycoder C. Segment Header — SEG Easycoder C. Execute — EX. Easycoder B. Easycoder B. Easycoder B. Easycoder B. Easycoder C. Origin — ORG. Easycoder B. Easycoder A. Easycoder B. Easycoder B. Easycoder B. Easycoder C. Modular Origin — MORG Easycoder A, B, and C. Literal Origin — LITORG Easycoder B. Easycoder C. Set Address Mode — ADMODE Easycoder A and B | 7-1<br>7-2<br>7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4<br>7-5<br>7-6<br>7-6<br>7-7<br>7-7<br>7-7<br>7-7<br>7-7<br>7-8<br>7-9 |

|                  |                        | Page          |

|------------------|------------------------|---------------|

| Section 7 (cont) | Easycoder C            | 7-10          |

|                  | Equals — EQU           | 7-10          |

|                  | Easycoder A and B      | 7-10          |

|                  | Easycoder C            | 7-11          |

|                  | Control Equals — CEQU  | 7-11          |

|                  | Easycoder A and B      | 7-11          |

|                  | Easycoder C            | 7-12          |

|                  | Memory Dump — HSM      | 7-12          |

|                  | Easycoder A            | 7-12          |

|                  | Skip — SKIP            | 7-13          |

|                  | Easycoder C            | 7-13          |

|                  | Suffix — SFX           | 7-13          |

|                  | Easycoder C            | 7-14          |

|                  | Repeat — REP           | 7-14          |

|                  | Easycoder C            | 7-14          |

|                  | Generate — GEN         | 7-14          |

|                  | Easycoder C            | 7-15          |

|                  | Clear — CLEAR          | 7-15          |

|                  | Easycoder A            | 7-16          |

|                  | Easycoder B            | 7-16          |

|                  | Easycoder C            | 7-17          |

|                  | End — END              | 7-17          |

|                  | Easycoder A            | 7-17          |

|                  | Easycoder B            | 7-18          |

|                  | Easycoder C            | 7-19          |

|                  | •                      | 1-1/          |

| Section 8        | Instructions           | 8-1           |

|                  | Introduction           | 8-1           |

|                  | Arithmetic Operations  | 8-6           |

|                  | Binary Addition        | 8-6           |

|                  | Binary Subtraction     | 8-6           |

|                  | Decimal Addition       | 8-9           |

|                  | True Add               | 8-9           |

|                  | Complement Add         | 8-9           |

|                  | Decimal Subtraction    | 8-10          |

|                  | Indicators             | 8-11          |

|                  | Multiplication         | 8-11          |

|                  | Division               | 8-13          |

|                  | Add — A                | 8 <b>-</b> 16 |

|                  | Subtract — S           | 8-18          |

|                  | Binary Add — BA        | 8-20          |

|                  | Binary Subtract — BS   | 8-21          |

|                  | Zero and Add — ZA      | 8-23          |

|                  | Zero and Subtract — ZS | 8-24          |

|                  | Multiply — M           | 8-26          |

|                  | Divide — D             | 8-29          |

|                  | Logic                  | 8-33          |

|                  | Extract — EXT          | 8-34          |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

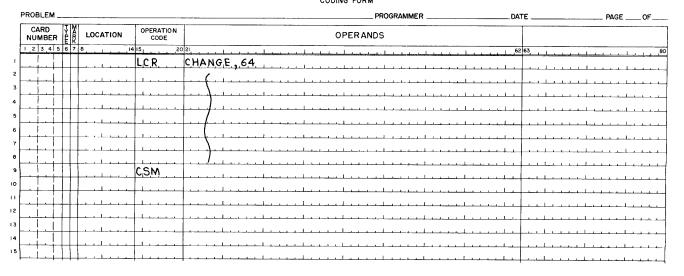

| Section 8 (cont) | Half Add — HA  Substitute — SST  Compare — C  Branch — B  Branch on Condition Test — BCT  Branch on Character Condition — BCC  Branch if Character Equal — BCE  Branch on Bit Equal — BBE  Control  Set Word Mark — SW  Set Item Mark — SI  Clear Word Mark — CW  Clear Item Mark — CI  Halt — H  No Operation — NOP  Move Characters to Word Mark — MCW  Load Characters to A-Field Word Mark — LCA  Store Control Registers — SCR  Load Control Registers — LCR  Change Addressing Mode — CAM  Change Sequencing Mode — CSM  Extended Move — EXM  Move and Translate — MAT  Move Item and Translate — MIT  Load Index/Barricade Indicator — LIB  Store Index/Barricade Indicator — SIB  Interrupt Control  Store Variant and Indicators — RVI  Monitor Call — MC  Resume Normal Mode — RNM  Editing.  Move Characters and Edit — MCE  Input/Output  Peripheral Data Transfer — PDT  Peripheral Data Transfer — PDT  Peripheral Control and Branch — PCB  Peripheral Control and Branch — PCB | 8-37<br>8-38<br>8-40<br>8-41<br>8-45<br>8-51<br>8-53<br>8-54<br>8-55<br>8-56<br>8-58<br>8-59<br>8-61<br>8-62<br>8-63<br>8-67<br>8-69<br>8-74<br>8-77<br>8-80<br>8-84<br>8-93<br>8-91<br>8-91<br>8-102<br>8-102<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103<br>8-103 |

| Appendix A       | Octal-Decimal Conversion Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Appendix B       | Miscellaneous Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Appendix C       | Instruction Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | C-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Appendix D       | Interrupt Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            |                                               | Page |

|------------|-----------------------------------------------|------|

| Appendix E | Storage Protect Feature                       | E-1  |

|            | Internal Interrupt                            | E-1  |

|            | Violations of Storage Protection              |      |

|            | Proceed Indicator                             |      |

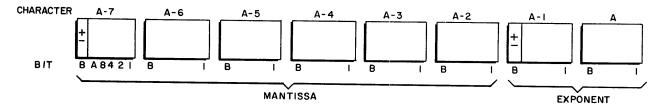

| Appendix F | Scientific Unit for Models 1200 and 2200      | F-1  |

|            | Data Format                                   | F-1  |

|            | Floating-Point Registers                      | F-1  |

|            | Floating-Point Indicators                     |      |

|            | Automatic Formatting In Arithmetic Operations |      |

|            | Symbology                                     |      |

|            | Timing Notes                                  |      |

# LIST OF ILLUSTRATIONS

|              |                                                              | Page         |

|--------------|--------------------------------------------------------------|--------------|

| Figure 1-1.  | Type 1201 Control Panel                                      | 1-2          |

| Figure 1-2.  | Type 220-1 Console                                           | 1-3          |

| Figure 1-3.  | Type 220-2 Console                                           | 1-3          |

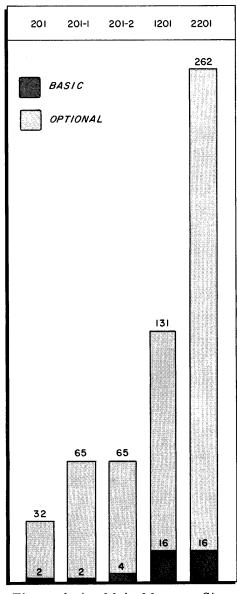

| Figure 1-4.  | Main Memory Size                                             | 1-5          |

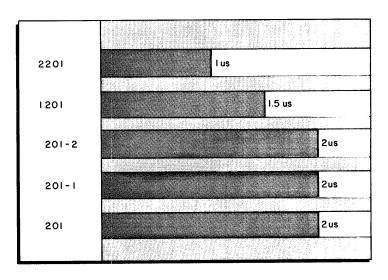

| Figure 1-5.  | Main Memory Speed                                            | 1 - 5        |

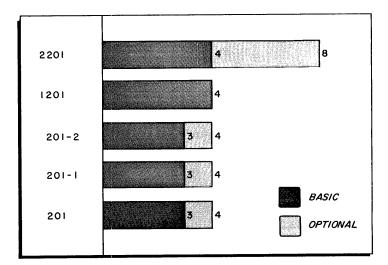

| Figure 1-6.  | Peripheral Simultaneity                                      | 1-5          |

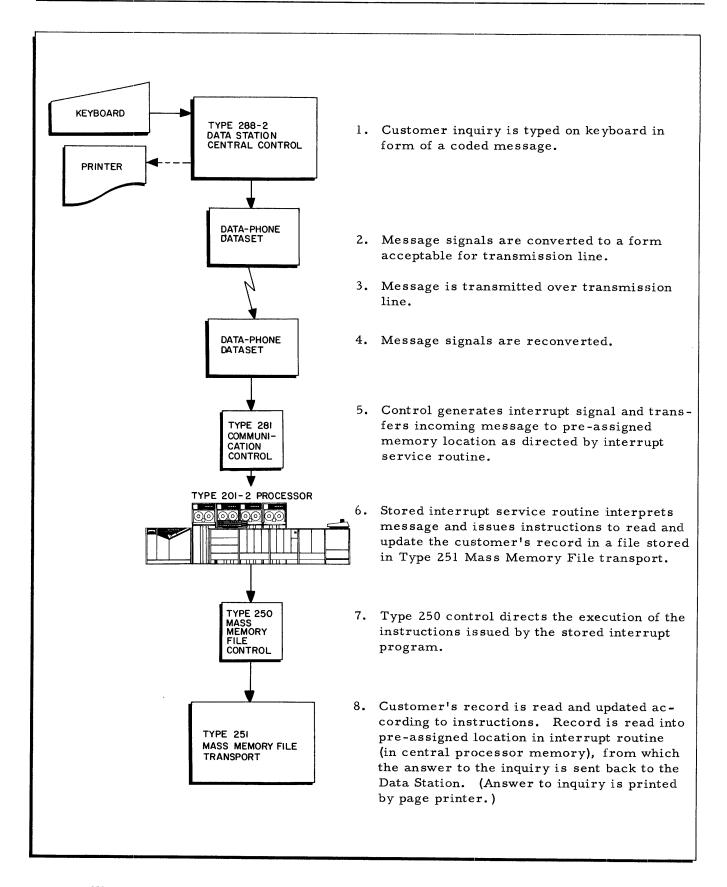

| Figure 1-7.  | Customer Inquiry Handling via Typical Communications Network | 1-12         |

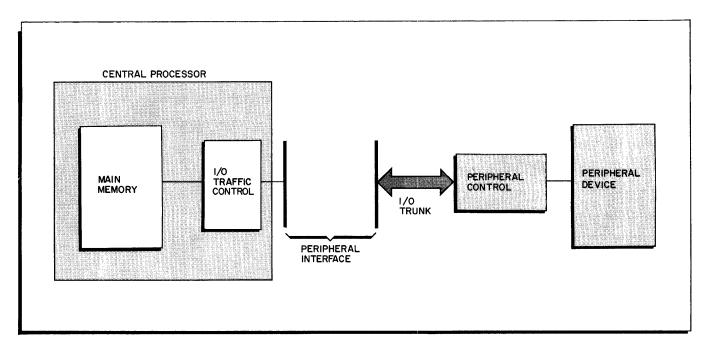

| Figure 1-8.  | Basic Input/Output Data Path                                 | 1-13         |

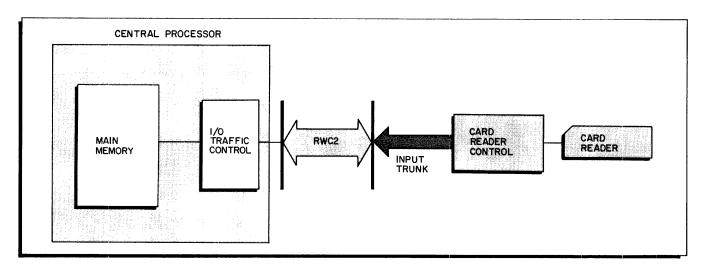

| Figure 1-9.  | Data Path During Card Read Operation                         | 1-14         |

| Figure 1-10. | Data Path Components of Series 200 Processors                | 1-14         |

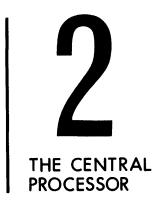

| Figure 2-1.  | Logical Division of Series 200 Central Processor             | 2-1          |

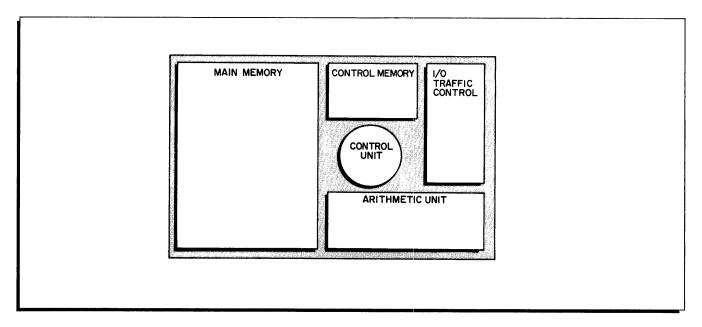

| Figure 2-2.  | Main Memory Functions                                        | 2-2          |

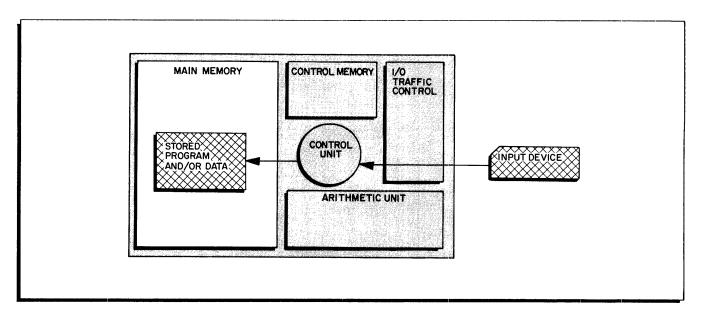

| Figure 2-3.  | Main Memory Core Plane                                       | 2-2          |

| Figure 2-4.  | One Memory Position                                          | 2-3          |

| Figure 2-5.  | Representation of Characters in Magnetic Core Storage        | 2-3          |

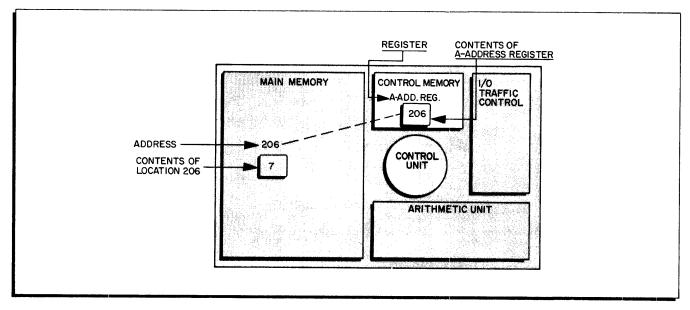

| Figure 2-6.  | Typical Control Register Function                            | 2-4          |

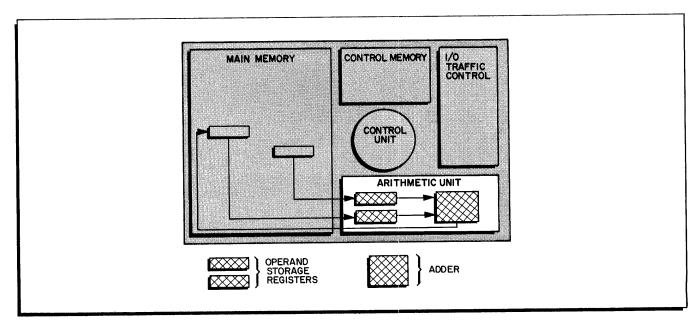

| Figure 2-7.  | Data Flow Between Main Memory and Arithmetic Unit            | 2-7          |

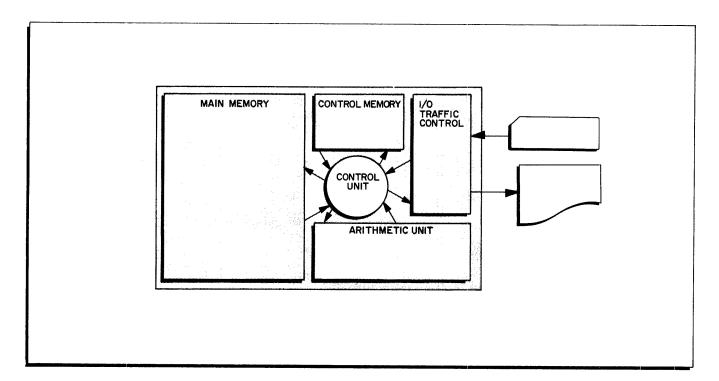

| Figure 2-8.  | Control Unit Activities                                      | 2-8          |

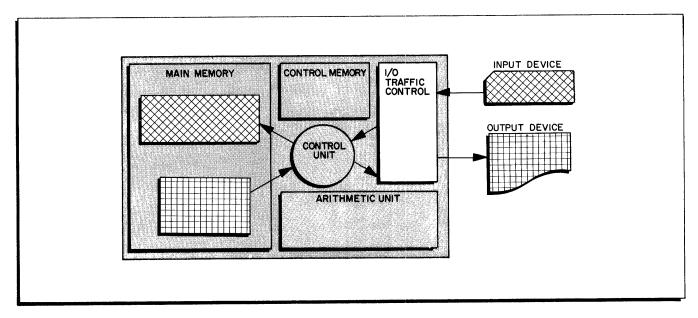

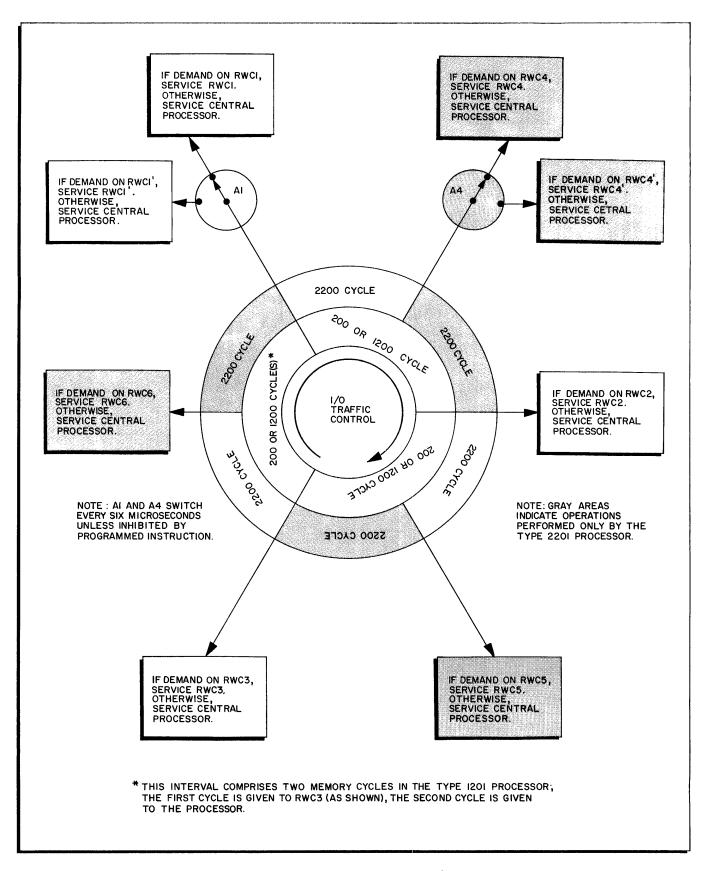

| Figure 2-9.  | Input/Output Traffic Control Activities                      | 2-9          |

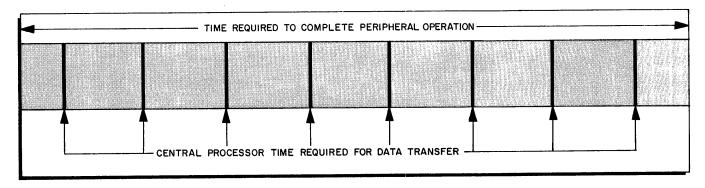

| Figure 2-10. | Data Transfer Intervals During One Peripheral Operation      | 2-9          |

| Figure 2-11. | Symbolic Representation of Input/Output Traffic Control      | 2-11         |

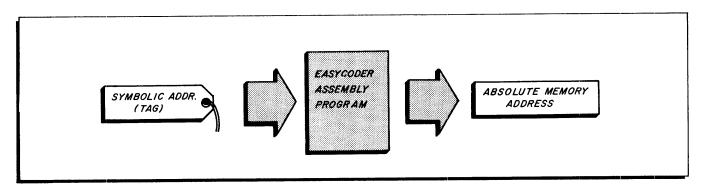

| Figure 3-1.  | Conversion of Symbolic Tags to Absolute Memory Addresses     | 3-2          |

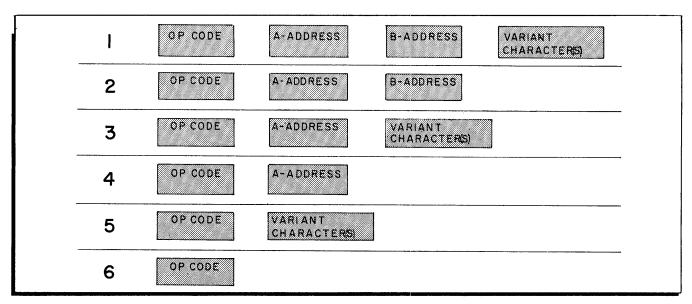

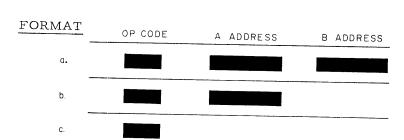

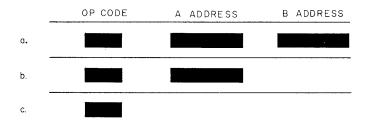

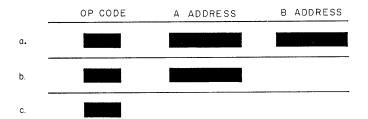

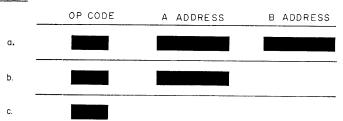

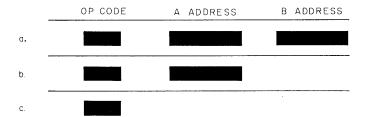

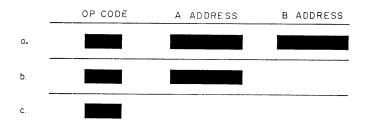

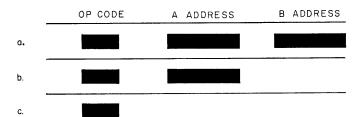

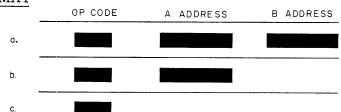

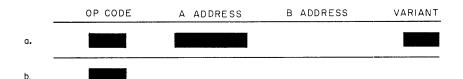

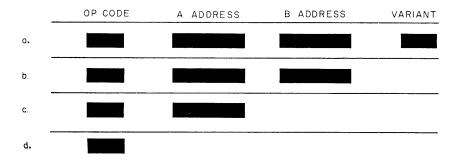

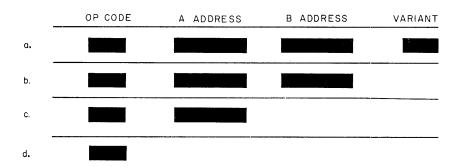

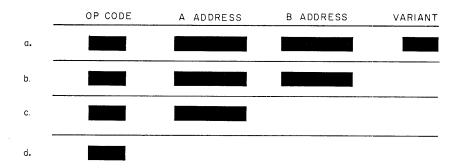

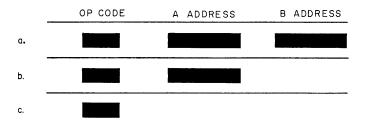

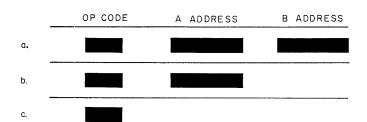

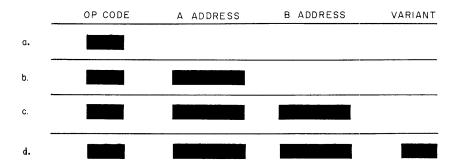

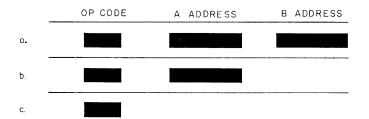

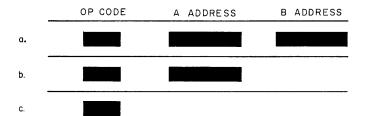

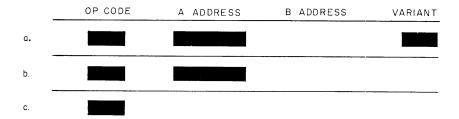

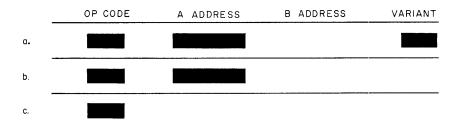

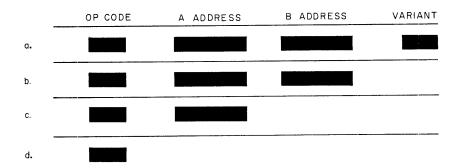

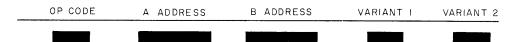

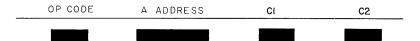

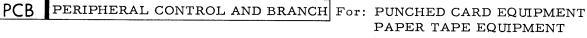

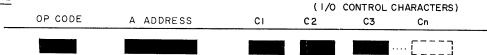

| Figure 3-2.  | Series 200 Instruction Formats                               | 3-3          |

| Figure 3-3.  | Symbolic Representation of Series 200 Instructions           | 3-4          |

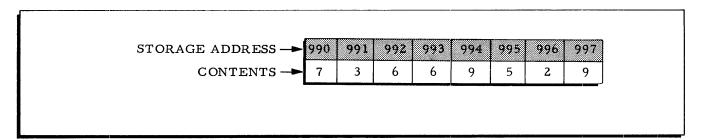

| Figure 3-4.  | Consecutive Storage Locations in Main Memory                 | 3-4          |

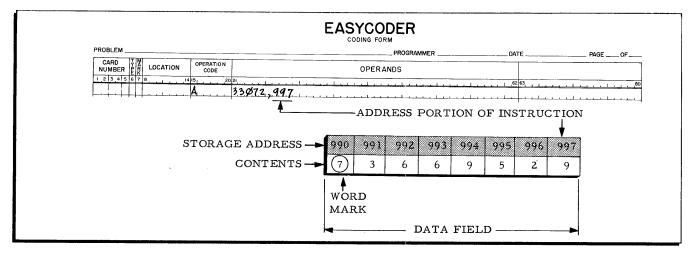

| Figure 3-5.  | Data Field Format in Main Memory                             | 3-5          |

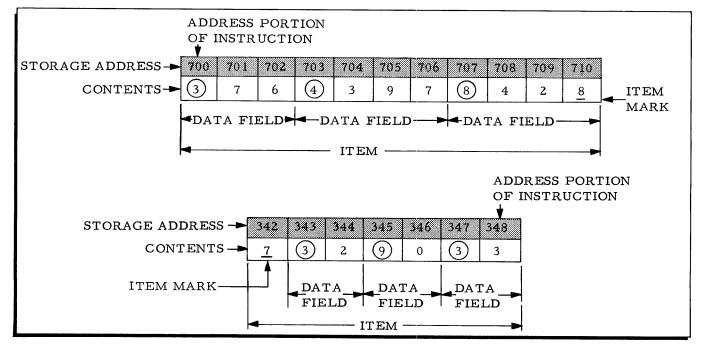

| Figure 3-6.  | Two Item Formats in Main Memory                              | 3-5          |

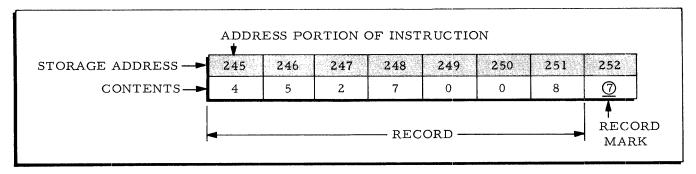

| Figure 3-7.  | Record Format in Main Memory                                 | 3-6          |

| Figure 3-8.  | Summary of Internal Data Formats                             | 3-6          |

| Figure 3-9.  | Character Representation on Magnetic Tape                    | 3-7          |

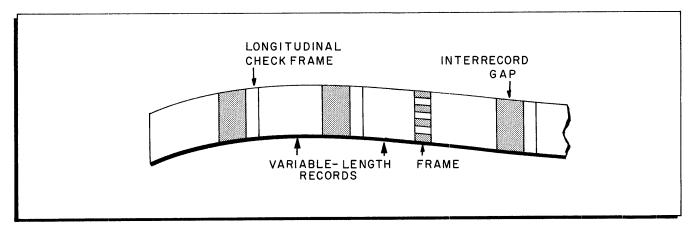

| Figure 3-10. | Data Format on Magnetic Tape                                 | 3-8          |

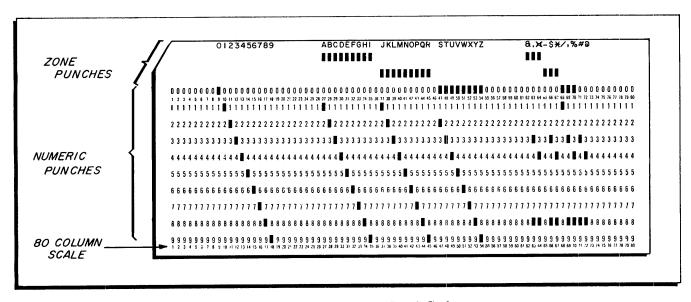

| Figure 3-11. | Punched Card Codes                                           | 3-9          |

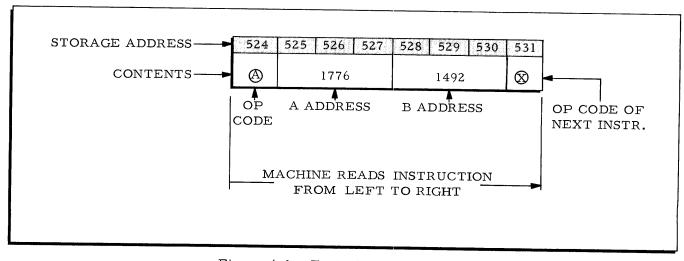

| Figure 4-1.  | Typical Add Instruction                                      | 4-1          |

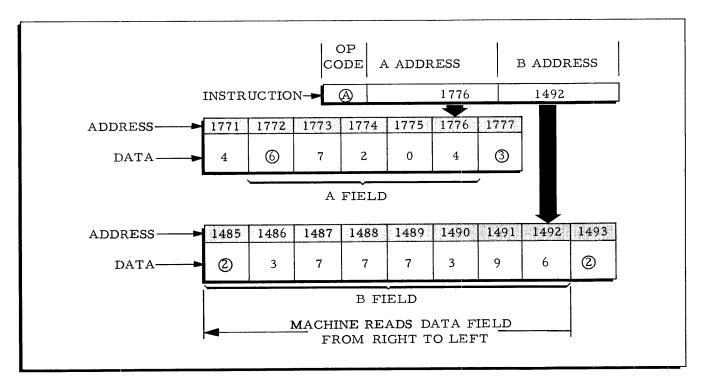

| Figure 4-2.  | Extraction of Data Fields in Typical Add Instruction         | 4-2          |

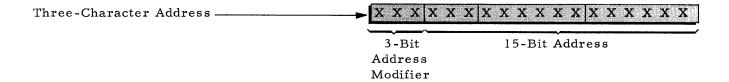

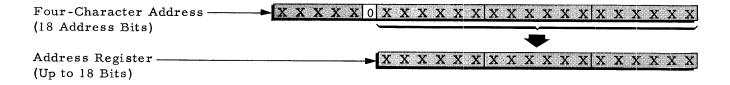

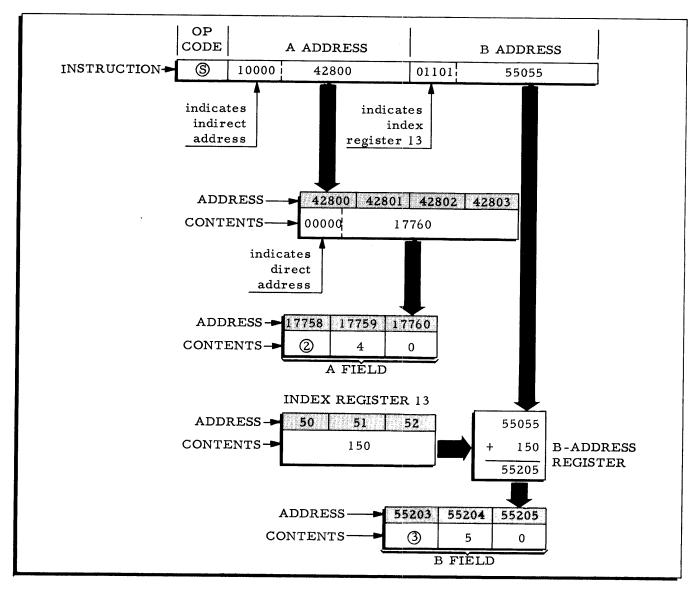

| Figure 4-3.  | Extraction of Three-Character Indirect Address               | 4-10         |

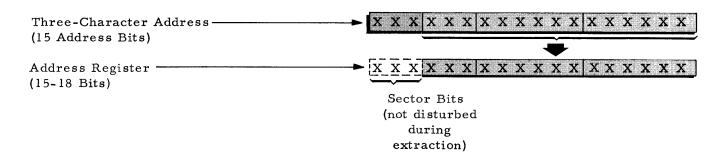

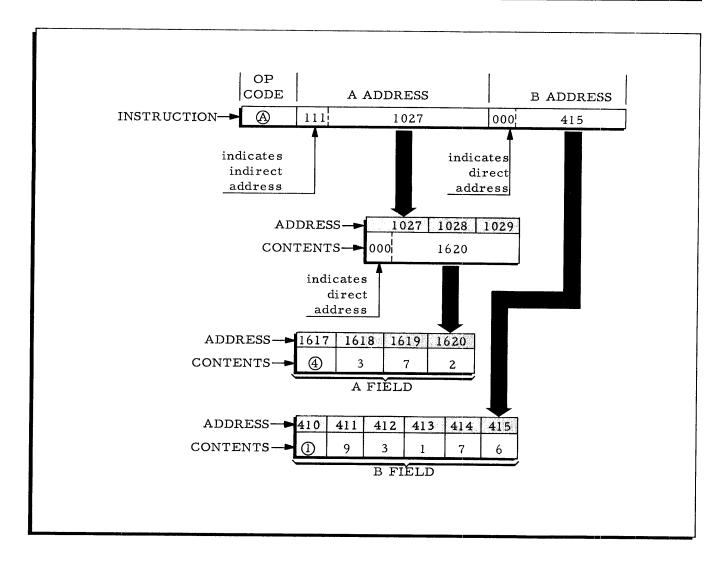

| Figure 4-4.  | Extraction of Indexed Address in Three-Character Mode        | 4-12         |

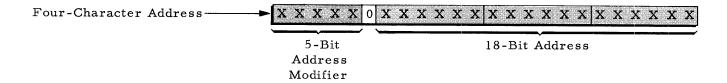

| Figure 4-5.  | Extraction of Indirect and Indexed Four-Character Addresses  | <b>4-</b> 15 |

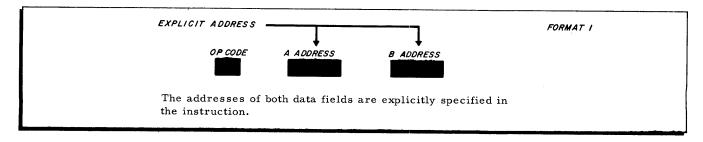

| Figure 4-6.  | Series 200 Instruction Format 1                              | 4-15         |

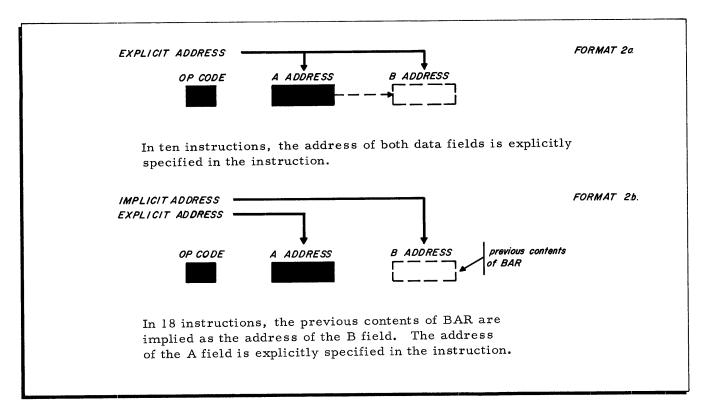

| Figure 4-7.  | Series 200 Instruction Format 2                              | <b>4-</b> 16 |

| Figure 4-8.  | Series 200 Instruction Format 3                              | 4-17         |

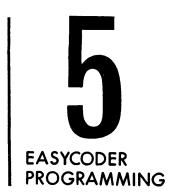

| Figure 5-1.  | Relationship of Source, Assembly, and Object Programs        | 5-2          |

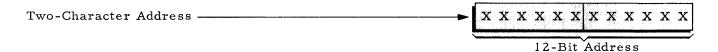

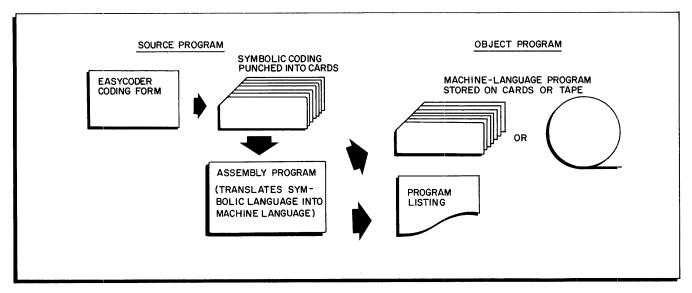

| Figure 5-2.  | Two-Character Address Assembly                               | 5-3          |

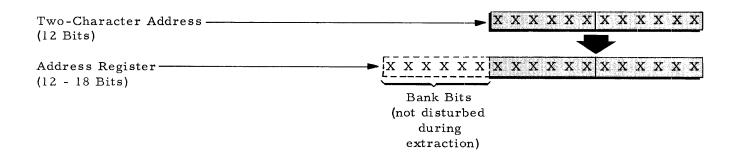

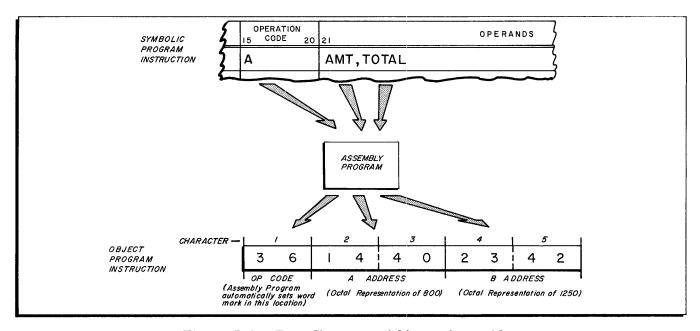

| Figure 5-3.  | Three-Character Address Assembly                             | 5-3          |

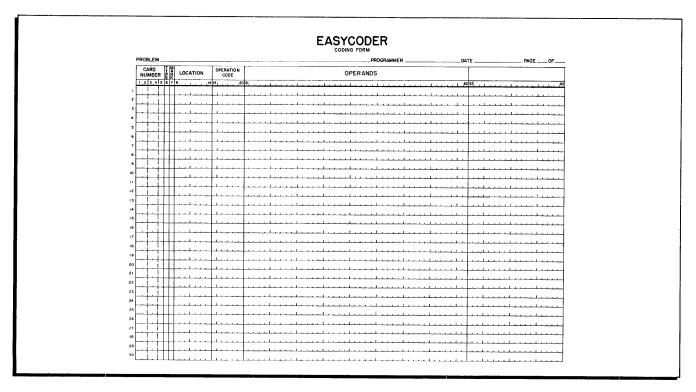

| Figure 5-4.  | Easycoder Coding Form                                        | 5-4          |

#### LIST OF ILLUSTRATIONS (cont)

|           | Page                                                                 |

|-----------|----------------------------------------------------------------------|

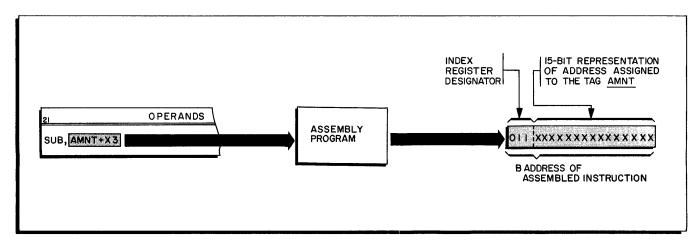

| Figure 5- | Assembly of Indexed Address in Three-Character Addressing Mode 5-17  |

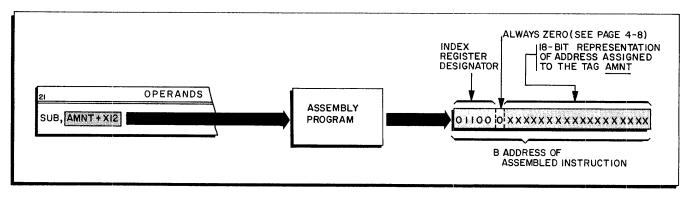

| Figure 5- | Assembly of Indexed Address in Four-Character Addressing Mode 5-18   |

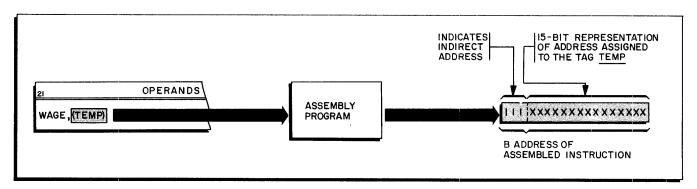

| Figure 5- | Assembly of Indirect Address in Three-Character Addressing Mode 5-18 |

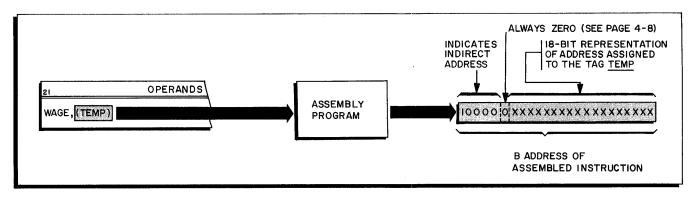

| Figure 5- | Assembly of Indirect Address in Four-Character Addressing Mode 5-19  |

| Figure 8- | True Add Examples 8-9                                                |

| Figure 8- | Complement Add Examples 8-10                                         |

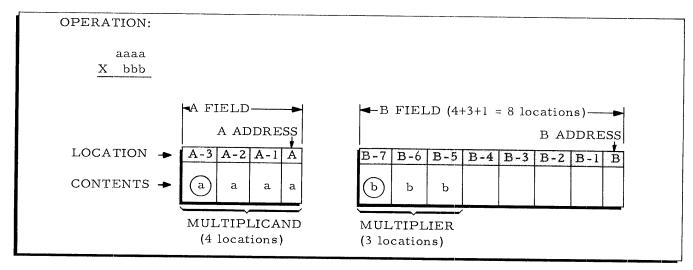

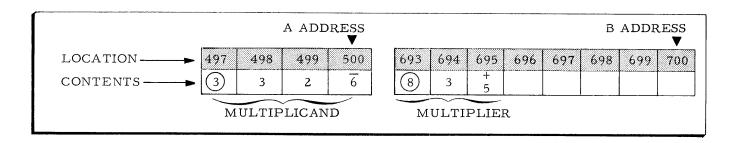

| Figure 8- | A and B Fields in Multiply Operation 8-12                            |

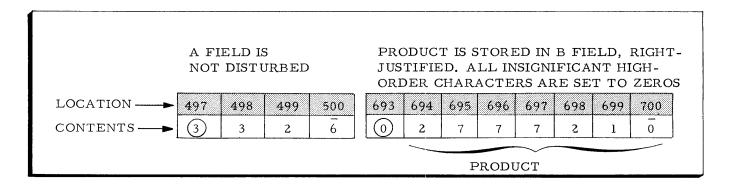

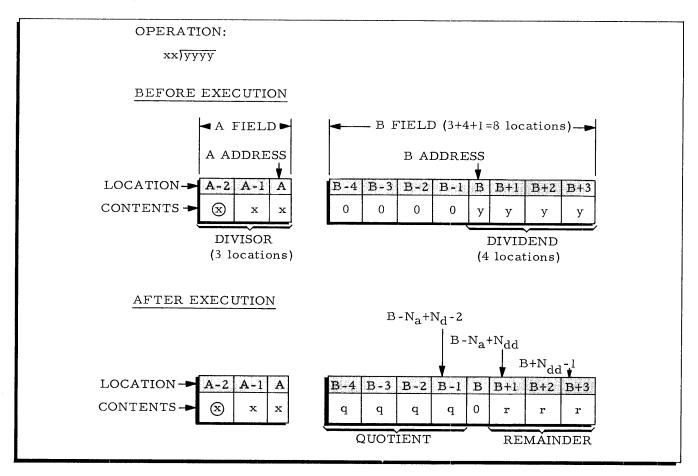

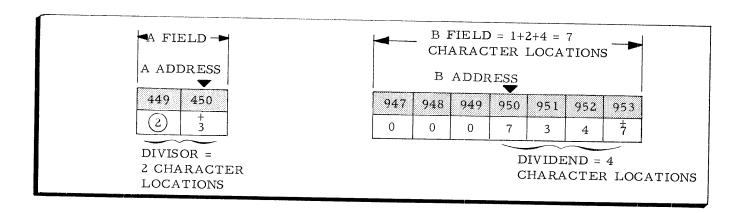

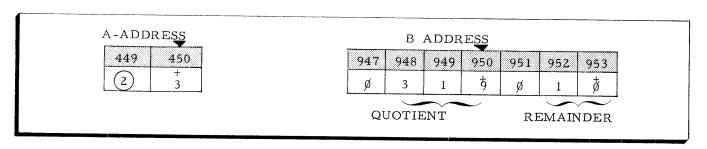

| Figure 8- | Factor Locations in Divide Operation 8-14                            |

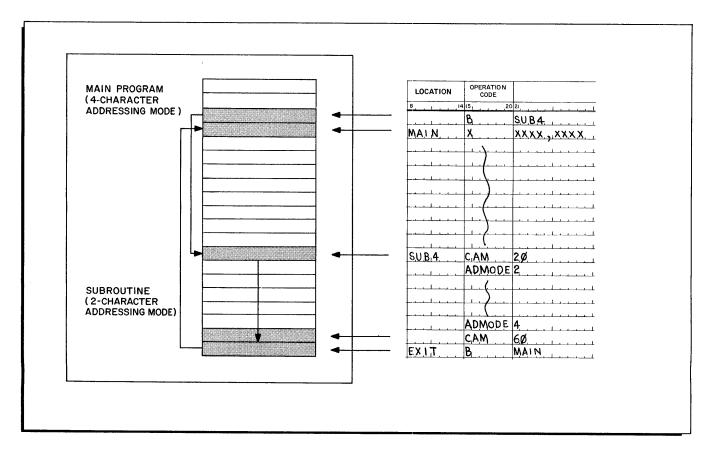

| Figure 8- | Changing Addressing Modes via CAM Instruction 8-71                   |

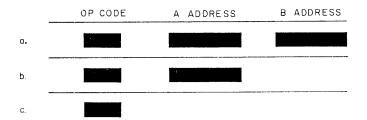

| Figure 8- | MAT Operation 8-79                                                   |

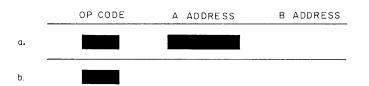

| Figure 8- | MIT Operation 8-84                                                   |

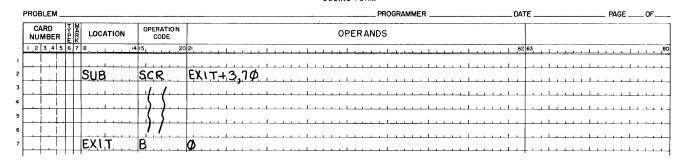

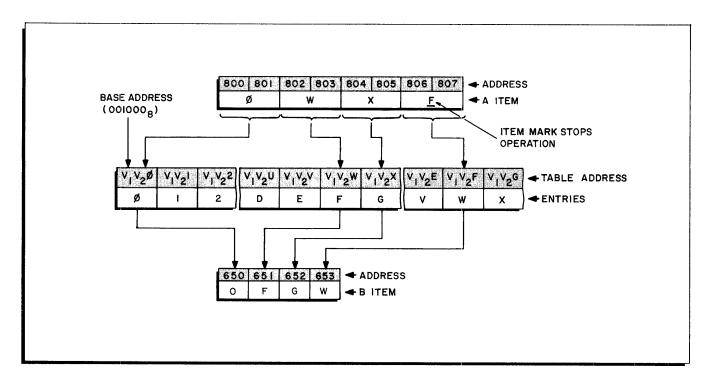

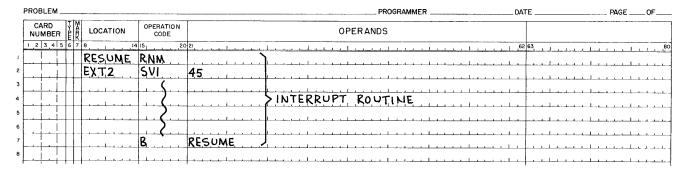

| Figure D. | Sample Coding for External Interrupt Routine D-3                     |

| Figure D. | Sample Coding for Internal Interrupt Routine D-4                     |

### LIST OF TABLES

|                       |                                                              | Page          |

|-----------------------|--------------------------------------------------------------|---------------|

| Table 1-1. Table 1-2. | Series 200 Punched Card Equipment                            | 1-7<br>1-8    |

| Table 1-3.            | Series 200 Magnetic Tape Units                               | 1-8           |

| Table 1-4.            | Series 200 Mass Memory File Units                            | 1-9           |

| Table 1-5.            | Series 200 Magnetic Drum File Units                          | 1-9           |

| Table 1-6.            | Series 200 Paper Tape Equipment                              | 1-10          |

| Table 1-7.            | Series 200 Data Communication Equipment                      | 1-10          |

| Table 1-8.            | Series 200 Optional Features                                 | 1-15          |

| Table 1-9.            | Model 200 Advanced Programming Feature                       | 1-16          |

| Table 2-1.            | Size of Control Memory Registers                             | 2-5           |

| Table 2-2.            | Control Memory Registers                                     | 2-5           |

| Table 2-3.            | Summary of Central Processor Characteristics                 | 2-12          |

| Table 4-1.            | Number of Index Registers Available to Series 200 Processors | 4-10          |

| Table 4-2.            | Index Register Addresses in Three-Character Addressing Mode  | 4-11          |

| Table 4-3.            | Index Register Addresses in Four-Character Addressing Mode   | 4-13          |

| Table 4-4.            | Active Address Bits in Series 200 Processors                 | 4-14          |

| Table 5-1.            | Set I Punctuation Indicators                                 | 5 <b>-</b> 5  |

| Table 5-2.            | Set II Punctuation Indicators (Easycoder Only)               | 5-6           |

| Table 6-1.            | Data Formatting Statements                                   | 6-1           |

| Table 7-1.            | Assembly Control Statements                                  | 7-2           |

| Table 8-1.            | Symbology Used in Series 200 Instruction Descriptions        | 8-2           |

| Table 8-2.            | Series 200 Add and Subtract Operations                       | 8-6           |

| Table 8-3.            | Binary Addition Table                                        | 8-6           |

| Table 8-4.            | Algebraic Signs in Decimal Addition                          | 8-9           |

| Table 8-5.            | Decimal Arithmetic Sign Conventions                          | 8-11          |

| Table 8-6.            | Multiply Sign Conventions                                    | 8-12          |

| Table 8-7.            | Divide Sign Conventions                                      | 8-15          |

| Table 8-8.            | SENSE Switch Conditions for BCT Instruction                  | 8-42          |

| Table 8-9.            | Indicator Test Conditions for BCT Instruction                | 8-43          |

| Table 8-10.           | Basic Test Conditions for BCC Instruction                    | 8 <b>-4</b> 6 |

| Table 8-11.           | BCC Test Conditions with Advanced Programming Feature        | 8-47          |

| Table 8-12.           | Control Register Contents Stored by SCR Instruction          | 8-65          |

| Table 8-13.           | Control Registers Stored by SCR Instruction                  | 8-66          |

| Table 8-14.           | Control Register Contents Loaded by LCR Instruction          | 8-67          |

| Table 8-15.           | Modes Specified by Variant Character in CAM Instruction      | 8-69          |

| Table 8-16.           | Extended Move Conditions                                     | 8-74          |

| Table 8-17.           | Size of Information Units in MIT Operation                   | 8-80          |

| Table 8-18.           | Leftmost Boundaries of Protected Memory                      | 8-85          |

| Table 8-19.           | Information Stored by SVI Instruction                        | 8-90          |

| Table 8-20.           | Information Restored by RVI Instruction                      | 8-94          |

| Table 8-21.           | Special Characters in MCE Instruction                        | 8-103         |

| Table 8-22.           | Description of PDT I/O Control Characters C1 and C2          | 8-109         |

| Table 8-23.           | Summary of PDT I/O Control Characters                        | 8-112         |

#### LIST OF TABLES (cont)

|              |                                                           | Page         |

|--------------|-----------------------------------------------------------|--------------|

| Table 8-24.  | C3 Coding for Type 209 Paper Tape Reader                  | 8-114        |

| Table 8-25.  | C3 Coding for Type 210 Paper Tape Punch                   |              |

| Table 8-26.  | C3 Coding for Types 206 and 222 Printers                  |              |

| Table 8-27.  | C3 Coding for Type 270 Random Access Drum                 |              |

| Table 8-28.  | Summary of PDT I/O Control Characters for Type 286 Multi- | 00           |

|              | Channel Communication Control                             | 8-116        |

| Table 8-29.  | Type 286 Line Control Instructions                        |              |

| Table 8-30.  | Summary of PCB I/O Control Characters                     |              |

| Table 8-31.  | Summary of PCB I/O Control Characters for Type 286 Multi- | 0-11/        |

|              | Channel Communication Control                             | 8_134        |

| Table A-l.   | Binary Octal Equivalents                                  |              |

| Table A-2.   | Decimal Octal Conversion Table                            |              |

| Table B-1.   | Control Register Designations                             |              |

| Table B-2.   | Extended Move (EXM) Conditions                            |              |

| Table B-3.   | Branch on Condition Test (BCT) SENSE Switch Conditions    |              |

| Table B-4.   | Branch on Condition Test (BCT) Indicator Conditions       |              |

| Table B-5.   | Branch on Character Condition (BCC) Conditions            |              |

| Table B-6.   | Series 200 Character Codes                                |              |

| Table B-7.   | Binary, Octal, and Decimal Equivalents                    |              |

| Table B-8.   | Powers of 2                                               | D=0          |

| Table C-1.   |                                                           |              |

| Γable C-1.   | Instruction Summary                                       |              |

| Labie F - I. | Summary of Scientific Instructions                        | r <b>-</b> 4 |

Honeywell's Series 200 Data Processing System is a set of modularly designed, compatible models, three of which — the Models 200, 1200, and 2200 — are the subject of this manual. Each model consists of two basic elements: a central processor, and an array of peripheral devices connected to that processor. The peripheral equipment in the system can be attached to any processor, and the number of connectable devices is limited only by the number of trunks available with any one processor.

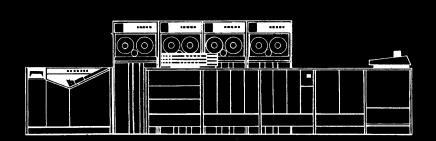

The initial member of Series 200 was the Model 200. The capabilities of the Model 200 processor have twice been extended since its introduction. Thus, five central processors are described herein: the three processors of Model 200 (Types 201, 201-1, and 201-2); the Type 1201; and the Type 2201. The processing power of any one of these types can be increased at any time by the addition of peripheral devices and/or optional hardware features. This section describes: (1) the two basic elements of a Series 200 model (processor and peripheral devices); (2) the manner in which these elements communicate with one another; and (3) the expansion of processing power that is possible through the addition of optional hardware features to a processor.

#### CENTRAL PROCESSOR

The central processor is the computing and control center of a Series 200 model; instructions processed within the central processor control the operations of the entire computer. A Series 200 processor is functionally divided into three units: storage, control, and arithmetic. The storage unit provides magnetic core storage for both the program instructions and the data to be processed according to these instructions; it is also used to contain the resultant

data. The control unit directs the operation of the entire computer by selecting, interpreting, and controlling the execution of all program instructions. It controls not only the flow of information within the central processor but also the flow of data between the central processor and all peripheral equipment. The arithmetic unit performs such operations as addition, subtraction, multiplication, division, and comparison, as directed by the control unit.

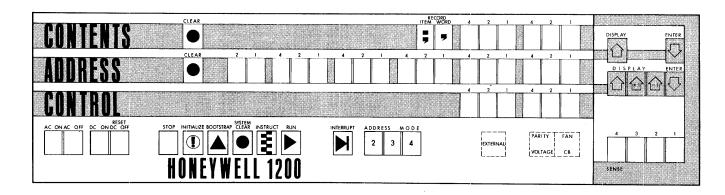

Included as a part of the central processor is a control panel (see Figure 1-1) which provides for easy communication between an operator and the computer. By using various control switches, the operator can start and stop the machine and can load and interrogate memory locations. The control panel also includes from four to eight SENSE switches which may be used in conjunction with programmed instructions to stop processing or to select predetermined program paths. The use of these switches increases the flexibility of a program, allowing it to be used in several different applications.

Figure 1-1. Type 1201 Control Panel

Another communication medium between the operator and the central processor is the Type 220 console, of which three versions are available. The Type 220-1 console (Figure 1-2) contains a typewriter which may be used as a peripheral device, operating under program control, or as a logging typewriter by which the operator can make essential notes about the program in progress. The central processor control panel remains situated on the processor cabinetry and is used for the functions described above.

In the Type 220-2 and Type 220-3 consoles (Figure 1-3), most of the control panel functions, including that of direct access to the processor, are performed by means of the console type-writer. In addition, the typewriter can perform the peripheral and logging functions described for the Type 220-1. The central processor control panel is replaced by a smaller control panel containing only the main power switches, the SENSE switches, and certain check condition

indicators which are located in the bottom row of the control panel shown in Figure 1-1. The Type 220-3 control panel contains additional indicators used with the Storage Protect Feature (see page 1-17) and the additional SENSE switches used with the larger Series 200 processors.

Figure 1-2. Type 220-1 Console

Figure 1-3. Type 220-2 Console

#### STANDARD PROCESSING MODE

The central processor performs arithmetic and logical operations as directed by the instructions of an internally stored program. These instructions are read into memory from an input medium such as punched cards, magnetic tape, or punched paper tape. Control circuitry within the processor then selects, interprets, and executes these instructions. Normally, the instructions are executed sequentially. Branch instructions are provided, however, which make it possible to skip over a group of instructions or otherwise change the sequence of the program.

#### INTERRUPT PROCESSING MODE

Sequential instruction execution is changed temporarily when the processor is interrupted. Any one of four sources (see below) can "demand" access to the central processor by generating an interrupt signal; this signal turns on a central processor interrupt indicator. An automatic hardware response is made to this condition: information concerning the current status of the processor is stored, and a branch is made to a stored routine which identifies and services the demand. Thus, programmed tests need not be made to detect the presence of an interrupt condition — the entire process of detecting and responding to an interruption is automatic. When the stored service routine has been executed, control is returned to the main program at the point where the interruption occurred.

The four sources of processor interruption are:

- 1. Peripheral Control The control connected to any Series 200 peripheral device can generate an interrupt signal under program control (peripheral controls are described on page 1-6). For instance, a data communication control which services one or a number of communication lines and devices may generate a real time demand on central processor time to handle a customer inquiry from a remote terminal. The current operations of the processor are temporarily interrupted so that the inquiry may be serviced. A routine to read the inquiry and to answer the question from a stored customer file is automatically executed, and a response is sent back to the terminal.

- 2. Operator's Control Panel or Console The operator can interrupt the central processor by pressing the INTERRUPT button on the control panel or console. The source of such "on-site" interruptions is made available to the program by the execution of a single instruction at the beginning of the interrupt service routine.

- 3. Program Instruction One instruction in the Series 200 repertoire, the Monitor Call instruction, is used to generate an interrupt condition. For programming convenience, the activation (or "calling") of the monitor program can be accomplished by means of this instruction.

- 4. Storage Protect Violation The above-mentioned sources cause an external interrupt condition. When a processor contains the Storage Protect Feature (Types 1201 and 2201 only), an internal interrupt condition, caused by certain "violations" to storage protection, can also occur. Internal interruptions are of lower priority than external interruptions, so that a processor executing an external interrupt service routine cannot be interrupted by an internal interruption until the routine is completed. The nature of storage protect violations is described in Appendix E.

#### PROCESSING POWER

The power of any processor within Series 200 can be defined as the sum of its main memory <u>size</u>, its internal <u>speed</u>, its degree of peripheral <u>simultaneity</u>, and the number of <u>optional features</u> which may be added to it.

Main memory <u>size</u> within the Models 200/1200/2200 ranges from a minimum of 2,048 character locations (Types 201 and 201-1) to 262,144 locations (Type 2201). Figure 1-4 shows the modular main memory structures of the five processor types.

The internal <u>speed</u> of a processor is measured in terms of a memory cycle (i.e., the time required to read and restore the contents of a single character location). These speeds range from two microseconds to one microsecond for the five processors (see Figure 1-5).

The Types 201 and 201-1 processors cannot be interrupted by sources 2. and 3. above.

Peripheral <u>simultaneity</u> is a key feature of Series 200 processors. Among the processors described in this manual, from three (Model 200 processors) to eight (Type 2201 processor) simultaneous input/output operations can be performed concurrently with internal computing (see Figure 1-6).

A number of optional features can be included in the Series 200 processors to provide complete flexibility in specializing any one processor to a user's particular application. Since some of these features refer to the peripheral capabilities of a processor, they are summarized at the conclusion of this section.

Figure 1-4. Main Memory Size

Figure 1-5. Main Memory Speed

Figure 1-6. Peripheral Simultaneity

#### PERIPHERAL EQUIPMENT

The array of peripheral devices available with Series 200 processors includes over 40 units: punched card equipment, high-speed printers, magnetic tape units, paper tape equipment, magnetic tape strip mass memory units, random access drum units, and various data communication equipment. Also included are computer-to-computer adapters, an interval timer, a time of day clock, MICR reader/sorter

controls, and magnetic tape switching units which provide extremely flexible Series 200 configurations.

Information is transferred between any one of these devices and the central processor by means of a single stored-program instruction — the Peripheral Data Transfer instruction described in Section 8. By coding various control characters in this instruction, the programmer specifies the direction of data transfer (into or out of the processor), the specific device involved in the transfer, the data path over which information is to be transferred, and any other information necessary to define the input/output operation (e.g., the number of lines to be spaced during printer operations). The actual communication with the central processor is not made by the particular peripheral device but by the peripheral control connected to that device.

#### PERIPHERAL CONTROL

A peripheral control regulates the transfer of data between a processor and a peripheral device. The control compensates for the difference in the data transfer rates of the processor and the peripheral device by temporarily storing each character of transmitted information until either the processor or the device is ready to receive the character. The control also converts each character into the code used by the intended recipient (e.g., the card reader control converts a character from Hollerith code to the internal six-bit code of the central processor). As each character is transferred to the control, it is also checked for accuracy by the control. One particularly significant feature of the peripheral control is that it operates independently of the central processor and requires access to the main memory only when information transfers are performed. In particular, all of the previously mentioned activities of the control — temporarily storing, converting, and checking the information — do not involve the central processor in any way. When each character of information is transferred, one main memory cycle is allocated for the transfer.

Some peripheral devices require one peripheral control per device (e.g., a card reader). Other devices can be connected in multiple fashion to a single peripheral control (e.g., up to eight 1/2-inch magnetic tape units can be directed by a single control). The number of Series 200 devices connectable to a peripheral control is shown in the following tables.

#### PUNCHED CARD EQUIPMENT

Series 200 includes a wide variety of peripheral devices not only of different kinds but also on several performance levels for the same kind. For instance, six different punched card units are offered: a card reader, a card punch, and four reader/punches. Table 1-1 lists the card devices available within Series 200. Note that a card device requires either one or two "I/O trunks," depending on the number of functions the device performs. The significance of the I/O trunk is explained on page 1-13.

Table 1-1. Series 200 Punched Card Equipment

| Device |                   |                                                       | No. Devices Per Control | No. I/O Trunks<br>Required by |

|--------|-------------------|-------------------------------------------------------|-------------------------|-------------------------------|

| Type   | Function          | Data Transfer Rate                                    |                         | Control                       |

| 223    | Card Reader       | 800 cards/minute                                      | 1                       | 1                             |

| 214-1  | Card Punch        | 100-400 cards/minute                                  | 1                       | 1                             |

| 224-1  | Card Reader/Punch | Read: 300 cards/minute Punch: 50-270 cards/minute     | 1                       | 2                             |

| 224-2  | Card Reader/Punch | Read: 400 cards/minute<br>Punch: 90-360 cards/minute  | 1                       | 2                             |

| 214-2  | Card Reader/Punch | Read: 400 cards/minute<br>Punch: 100-400 cards/minute | 1                       | 2                             |

| 227    | Card Reader/Punch | Read: 800 cards/minute<br>Punch: 250 cards/minute     | 1                       | 2                             |

#### HIGH-SPEED PRINTERS

Five types of printers (see Table 1-2) produce printed reports, listings, etc., at speeds which vary from 450 to 1,300 lines per minute. Processed information is printed from any programmer-assigned area in memory. A single program instruction — the Move Characters and Edit instruction — allows the programmer to punctuate the output data, suppress zeros, and insert identifying symbols in the data prior to printing.

Table 1-2. Series 200 High-Speed Printers

| . Type                             | Data Transfer Rate     | No. Printers<br>Per Control | No. I/O Trunks Required by Control |

|------------------------------------|------------------------|-----------------------------|------------------------------------|

| 222-1 (96 print positions)         | 650-1,300 lines/minute | 1                           | 1                                  |

| 222-2 (108 print positions)        | 650-1,300 lines/minute | 1                           | 1                                  |

| 222-3 (120 or 132 print positions) | 650-1,300 lines/minute | 1                           | 1                                  |

| 222-4 (120 or 132 print positions) | 950-1,266 lines/minute | 1                           | 1                                  |

| 222-5 (120 print positions)        | 450 lines/minute       | 1                           | 1                                  |

#### MAGNETIC TAPE UNITS

Magnetic tape is a compact and highly versatile medium for the storage of programs and data files. Two complete families of industry-acclaimed tape units are available with Series 200 processors (see Table 1-3): 1/2-inch tape units (10 types) transfer data at speeds ranging from 7,200 to 83,300 characters per second; three types of 3/4-inch tape units read/write from 32,000 to 88,800 characters per second.

Table 1-3. Series 200 Magnetic Tape Units

| Type               | Data Transfer Rate                         | No. Devices<br>Per Control | No. I/O Trunks Required by Control |

|--------------------|--------------------------------------------|----------------------------|------------------------------------|

|                    | 1/2-Inch Magnetic Ta                       | pe Units                   |                                    |

| 204B-1<br>204B-2   | 7,200/20,000 characters/second             | 1-8                        | 2                                  |

| 204B-3<br>204B-4   | 16,000/44,400 characters/second            | 1 -8                       | 2                                  |

| 204B-5             | 24,000/66,700 characters/second            | 18                         | 2                                  |

| 204B-6             | 30,000/83,300 characters/second            | 1 8                        | 2                                  |

| 204B-7             | 7,200/20,000/28,800 characters/<br>second  | 1-8                        | 2                                  |

| 204B-8             | 16,000/44,400/64,000 characters/<br>second | 18                         | 2                                  |

| 204B-11<br>204B-12 | 13,300 characters/second                   | 1-4                        | 2                                  |

|                    | 3/4-Inch Magnetic Tap                      | e Units                    |                                    |

| 204A-1             | 32,000 characters/second                   | 1-4                        | 2                                  |

| 204A-2             | 64,000 characters/second                   | 1-4                        | 2                                  |

| 204A-3             | 88,800 characters/second                   | 1-4                        | 2                                  |

#### MASS MEMORY FILE

Honeywell's reputation for reliable magnetic tape control is inherited by the new member of Series 200, the Mass Memory File. Three types of transports, varying in access time and capacity, use magnetic tape strips to store programs and data files and thereby complement the main memory storage capacities of the central processor (see Table 1-4). A single control can provide access to over two billion characters of stored information. Data transfer rate is 100,000 characters per second, and average access times are as low as 95 milliseconds.

|      | Device                                                 |                           |      | No. I/O Trunks<br>Required by |  |

|------|--------------------------------------------------------|---------------------------|------|-------------------------------|--|

| Туре | Function                                               | Data Transfer Rate        |      | Control                       |  |

| 251  | Magnetic Tape Strip Transport (15 million characters)  | 100,000 characters/second | 1-8  | 2                             |  |

| 252  | Magnetic Tape Strip Transport (60 million characters)  | 100,000 characters/second | 1-8  | 2                             |  |

| 253  | Magnetic Tape Strip Transport (300 million characters) | 100,000 characters/second | 1 -8 | 2                             |  |

Table 1-4. Series 200 Mass Memory File Units

#### RANDOM ACCESS DRUM FILE

The Series 200 drum file features a control unit which can direct from one to eight magnetic drums, each capable of storing over two million characters of information (see Table 1-5). Thus, a single drum file subsystem can have a total capacity of over 20 million characters. Any record stored on the drum can be accessed in 27.5 milliseconds (average) and can be transferred at the rate of 102,000 characters per second.

| Type                      | Device<br>Function                     | Data Transfer Rate        | No. Devices<br>Per Control | No. I/O Trunks<br>Required by<br>Control |  |

|---------------------------|----------------------------------------|---------------------------|----------------------------|------------------------------------------|--|

| 270-1<br>through<br>270-8 | Magnetic Drum (2.6 million characters) | 102,000 characters/second | 1-8                        | 2                                        |  |

Table 1-5. Series 200 Magnetic Drum File Units

#### PAPER TAPE EQUIPMENT

Paper tape is an ideal medium for recording data which originates at locations distant from a central Series 200 installation and, as such, becomes particularly significant in data communication networks. A variety of standard commercial codes may be used with this relatively inexpensive medium. Two paper tape devices are offered in Series 200 (see Table 1-6).

Table 1-6. Series 200 Paper Tape Equipment

| Туре | Device<br>Function | Data Transfer Rate    | No. Devices<br>Per Control | No. I/O Trunks<br>Required by<br>Control |

|------|--------------------|-----------------------|----------------------------|------------------------------------------|

| 209  | Paper Tape Reader  | 600 characters/second | 1                          | 1                                        |

| 210  | Paper Tape Punch   | 120 characters/second | 1                          | 1                                        |

#### DATA COMMUNICATION EQUIPMENT

The immediate and automatic response to an external interrupt source by the Series 200 processor was described previously (page 1-3). A common source of external interruption is the communication control, of which two different types are available in Series 200. These controls allow the Series 200 processor to communicate with distant locations (e.g., branch offices, warehouses, etc.) by receiving and transmitting data over toll and leased lines. Both single-channel and multi-channel data communication controls are offered; these controls adapt themselves to a broad selection of lines, speeds, and terminal devices. One such terminal device is Honeywell's Data Station (see Table 1-7).

Table 1-7. Series 200 Data Communication Equipment

| Device |                                            |                                      |             | No. I/O Trunks                          |  |

|--------|--------------------------------------------|--------------------------------------|-------------|-----------------------------------------|--|

| Туре   | Function                                   | Data Transfer Rate                   | rer Control | Required by Control                     |  |

|        |                                            | Communication Controls               |             |                                         |  |

| 281    | Single-Channel Control                     | Up to 5,100 characters/second        | l line      | 2                                       |  |

| 286    | Multi-Channel Control                      | Up to 300 characters/second/<br>line | 1-63 lines  | 2                                       |  |

|        |                                            | Remote Terminal Device               |             | 100000000000000000000000000000000000000 |  |

| 288-1  | Data Station Central<br>Control            | 120 characters/second                | n/a         | n/a                                     |  |

| 288-2  | Data Station Central<br>Control & Keyboard | 120 characters/second                | n/a         | n/a                                     |  |

| 289-2  | Data Station Page<br>Printer & Keyboard    | 10 characters/second                 | n/a         | n/a                                     |  |

| 289-2A | Keyboard                                   | 10 characters/second                 | n/a         | n/a                                     |  |

| 289-3  | Data Station Page<br>Printer & Keyboard    | 40 characters/second                 | n/a         | n/a                                     |  |

| 289-4  | Data Station Paper Tape<br>Reader          | 120 characters/second                | n/a         | n/a                                     |  |

| 289-5  | Data Station Paper Tape<br>Punch           | 120 characters/second                | n/a         | n/a                                     |  |

|        |                                            |                                      |             | المستحدث                                |  |

| Table 1-7 (cont). | Series | 200 | Data | Communication | Equipment |

|-------------------|--------|-----|------|---------------|-----------|

|-------------------|--------|-----|------|---------------|-----------|

| Device Type Function |                                         |                        |     | No. I/O Trunks<br>Required by<br>Control |  |

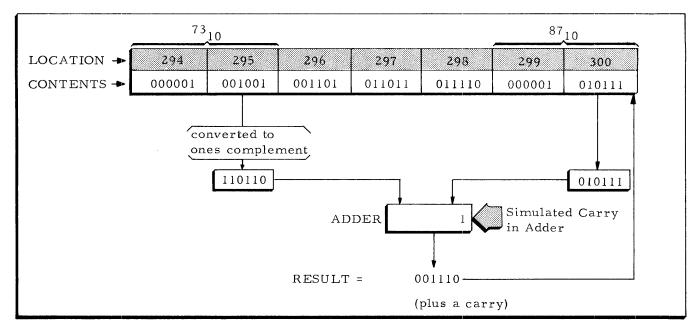

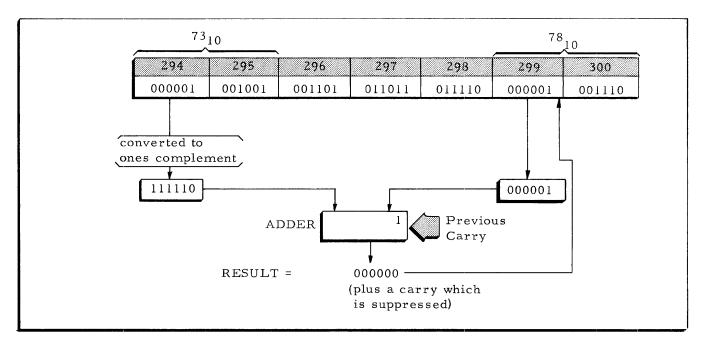

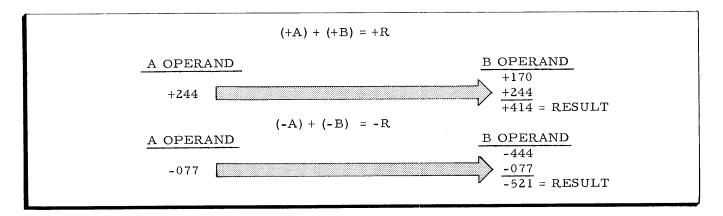

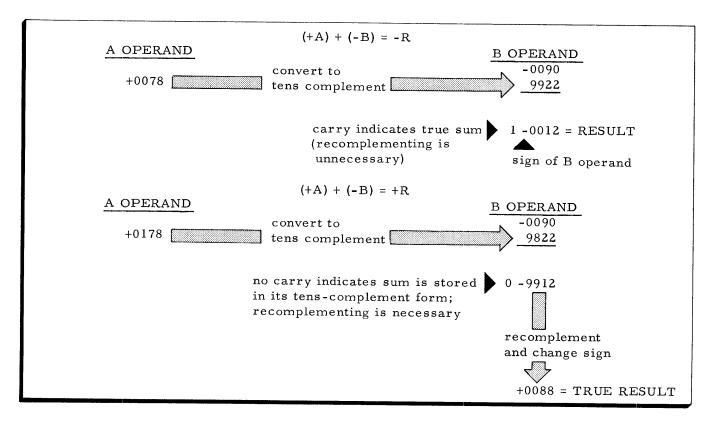

|----------------------|-----------------------------------------|------------------------|-----|------------------------------------------|--|