## MEMORY PARITY CHECK for 2114A COMPUTER

model 12598A

OPERATING AND SERVICE MANUAL 1 FEB 1969

### 1. MEMORY PARITY CHECK.

2. Memory Parity Check option Model 12598A provides the HP 2114A Computer with "odd" parity (an odd total of true bits, including the parity bit, in each computer memory word). The parity of all words transferred from memory is also checked. If a bit is either dropped or added in the transfer process, a parity error indication is generated. The manner in which the Computer responds to the parity error is selectable by the user (by reversing the top connector on the Parity Error board). The Computer may be set to the halt mode, which halts the Computer and lights the front panel PARITY indication, or it may be set to the interrupt mode in which the Computer interrupts to location 5 in addition to giving the PARITY indication. The address of the memory location containing the parity error is stored and may be loaded into the A, B, or S Registers for identification regardless of the mode of operation. The use of a parity error subroutine accessed through interrupt location 5 allows the computer user to correct the lost or added bit and then return to the main program at the point at which the parity error occurred.

### 3. INSTALLATION.

- 4. Installation of the option is easily accomplished in the field with one plug-in unit, Parity Error printed circuit board 12598-6001. This board may be installed in the factory when ordered as part of the initial computer system. To install Memory Parity Check option HP 12598A, perform the following:

- a. Make certain that the computer POWER switch is in the "off" position.

- b. Install the Parity Error printed circuit board in slot A5 of the HP 2114A. The components mounted on the board should face to the left as you face the front of the Computer.

- c. Install the top connector, 12580-6002 on the top edge of the board. When this connector is in the normal position (extractor handle aligned with those of adjacent connectors), the Parity Halt function is enabled. When the top connector is installed in the reverse position (extractor handle off-set with respect to adjacent connectors) the Computer will interrupt on detection of a parity error.

- d. If there is no subroutine to service the interrupt, location 5 should contain a HLT instruction.

e. If the Computer has previously been run without the parity error board it will be necessary to correct the parity bits in memory. The Basic Binary Loader should have its parity bits corrected first to facilitate the correction of other programs stored in memory. This may be done by putting the LOADER PROTECT switch in the ENABLED position. Load the starting address of the Basic Binary Loader program (the last 64 locations in memory) and step through the Loader program using the DISPLAY MEMORY button. Return the LOADER PROTECT switch to NORMAL position and reload any programs that were stored in memory. The Parity Error circuits will automatically assign the correct parity to any programs loaded. If the Computer is run for even a short time with the Parity Error board removed, all programs that have been stored in memory should be reloaded to assign proper parity.

### 5. OPERATION.

- 6. Operation of the Memory Parity Check option is completely automatic during normal Computer operation and requires no special attention by the Computer operator. The option may be operated in the Parity Error Halt mode or in the Parity Error Interrupt mode. The Parity Error Interrupt mode is enabled by reversing the 48-pin top connector of the Parity Error board. If a parity error occurs during the Computer's operation it is recommended that the complete program be reloaded before resuming normal Computer operation. However, it is possible to continue Computer operation without reloading the program (see Paragraph 10).

- 7. HALT FUNCTION. When the 48-pin top connector is in the normal position the Halt mode of the option is enabled. If a parity error occurs the parity error card will cause the Computer to halt, as indicated by the illumination of the PARITY lamp on the Computer front panel. In this case the option does not cause an interrupt of the Computer program but halts at the location following the error instead. Again, it is recommended that the complete program be reloaded. However, if it should be desired to continue the program in operation without reloading, proceed in the following manner:

- a. First ensure that the instruction executed during the parity error has not altered the contents of any of the registers or the contents of any memory location. To do this, read the information contained in the T-Register as visible on the Computer front panel and check the phase status of this information. By using this data and a program listing it is possible

to determine what operations have taken place during execution of the information that had the parity error. Affected memory locations may now be checked, and any errors may be corrected by loading the proper data into the respective memory locations.

- b. After correcting the parity error and any register or memory contents that it may have affected return the Computer to the location in the program at which the parity error occurred and resume normal operation.

- INTERRUPT FUNCTION. When the top con-8. nector described above is reversed, the Parity Error Interrupt mode is enabled. The Parity Error card will then cause an interrupt to location 00005 (octal) on detecting a parity error. Memory location 00005 may contain any type of instruction as desired by the Computer user. The interrupt capability of the Parity Error Interrupt card is enabled when Computer power is turned on, and unlike external I/O devices does not have to be initialized by the computer program. However, if desired by the Computer user, the interrupt capability of the Parity Error card may be reinitialized by program control following the occurrence of a parity error interrupt by use of an STF 05 instruction in a parity error subroutine. Table 1 provides a sample interrupt subroutine (a JSB instruction referencing the subroutine is assumed to be stored in location 00005) which could be used to automatically present both the offending data and its program location to the Computer user. Again the same procedure used in the Halt mode (Paragraph 7) should be used to ensure that the parity error has not affected other parts of the program or data. When this check is complete, normal operation may be resumed.

- 9. PARITY ERROR ADDRESS. The memory address at which the parity error occurred is stored

- in the Parity Error Address Register on the Parity Error card. By using LIA 5 and OTA 1 (Load Into the A-Register the contents of the Parity Error Address Register and Output the contents of the A-Register to the S-Register) the address of the parity error can be read on the front panel.

- 10. It may be desirable to continue operation without reloading the complete program. To do this, use the following procedure:

- a. Using the address of the parity error obtained in Paragraph 9 above, determine what operations have taken place during the execution of the instruction that experienced the parity error. Affected memory locations may be checked, and any errors may be corrected by loading the proper information into the proper memory locations. It may also be necessary to correct the program if it too has been affected by the error.

- b. Now with the Computer in the same state that it was in when the error occurred it is possible to resume normal operation.

### 11. THEORY OF OPERATION.

### 12. BASIC OPERATION.

13. In order to ensure that the total number of true bits in each Computer word is always odd, it is necessary to control the value (true or false) of the parity bit. The Parity Error card does this by monitoring the T-Register bits to determine if each Computer word (16 bits plus the parity bit) transferred from memory, has an odd number of true bits. If even parity is detected, an error signal is generated on the Parity Error card which interrupts or halts Computer operation as determined by the placement of the 48-pin connector on the Parity Error card.

| Table 1. Sample Parity Error Interrupt Subroutine |                                                                                 |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|---------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LABEL                                             | OPCODE                                                                          | OPERAND                                                                                 | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| PESR                                              | NOP STA STB LIA STA LIA AND LDB OTA HLT OTB HLT LIB STB LDA OTA LDA LDA LDB STF | SVA<br>SVB<br>01<br>SVS<br>5<br>RSET<br>0,1<br>01<br>01<br>01<br>01<br>SVS<br>01<br>SVS | Enter P.E. Subroutine Save the contents of the A-Register Save the contents of the B-Register Load the contents of the S-Register Save the contents of the S-Register Load the address of the P.E. Reset the Parity indicator bit (15) Load the incorrect data into B-Register Display the address of the P.E.  Display the incorrect data Correct the data, Register and Memory contents affected by P.E. Load corrected data into B-Register Store corrected data  Restore S-Register Restore A-Register Restore B-Register Turn on P.E. Interrupt |  |  |  |

| RSET                                              | JMP<br>OCT                                                                      | PESR, I<br>077777                                                                       | Exit P.E. Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

Table 1. Sample Parity Error Interrupt Subroutine

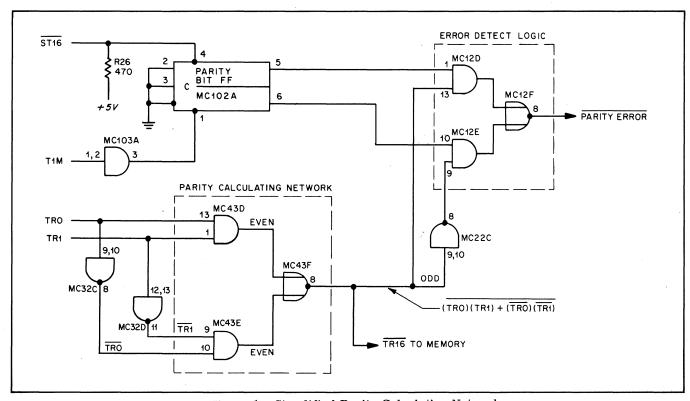

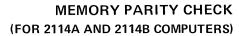

- PARITY CALCULATING NETWORK. The pur-14. pose of the Parity Calculating Network is to determine whether the sum of all true bits in the T-Register is odd or even, during both the read and write operations. It produces one output signal, TR16. During write operations if the number of bits in the T-Register, not including the parity bit (TR16), is odd then TR16 will be high indicating that the number of true bits held in the T-Register is odd without need of a true parity bit. Similarly if the number of bits in the T-Register is even the TR16 signal will go false writing a true parity bit into memory at T5 to provide odd parity in the memory word. During read operations, the TR16 signal generated by the Parity Calculating Network is compared with the previously stored parity bit for that memory word. The Parity Bit Flip-Flop is set by an ST16 signal, which is generated on the Sense Amplifier board during the memory read cycle, and causes the Parity Bit Flip-Flop to follow the state of the parity bit read out of memory. MC12D/E and F compare the parity bit read out of memory and the parity bit generated by the Parity Calculating Network. If the two disagree, a false Parity Error signal is generated indicating an error.

- 15. In order to simplify explanation of the Parity Calculating Network, Figure 1 has been provided to show its basic operation by using only two input data signals. The resulting output signifies whether the sum of true bits in a hypothetical 2-bit T-Register is odd or even. This output, now the new parity bit, is checked with the previously stored parity bit to generate a Parity Error signal (Paragraph 14).

- 16. Refer to Figure 1 while reading the following circuit explanation. In Figure 1, "and" gate MC43D

- in the Parity Calculating Network receives the TRO and TR1 signals from the T-Register as input data signals. If both of these signals are true, there will be a true output to ''nor'' gate MC43F indicating that there is an even number of true bits in the T-Register (11). Inverting gates MC32C and MC32D provide TR0 and TRI inputs to "and" gate MC43E. If both of these inputs are true there will be a true output to 'nor" gate MC43F indicating an even number of true bits in the T-Register (00). If either of the inputs to 'nor" gate MC43F is true the gate will output a false TR16 signal to memory to generate odd parity during the "write" operation or to the Error Detect Logic to indicate an even sum of bits during the read operation. If both ''nor'' gate inputs are false (01 or 10) a true TR16 signal will be generated to maintain odd parity during the memory write operation and to indicate an odd sum of bits to the Error Detect Logic during the memory read operation. During the memory read cycle the TR16 signal is compared with the contents of the Parity Bit Flip-Flop MC102A in the Error Detect Logic.

- 17. During memory read operations, the Error Detect Logic MC22C and MC12D/E/F performs a comparison between what the T-Register contents indicate the parity bit should be and the actual state of the parity bit stored in memory. To do this the output bit of the Parity Bit Sense Amplifier, ST16, is applied to the Parity Bit Flip-Flop, MC102A. This signal, if false (true parity bit in memory), sets the flip-flop and is applied as a true input to pin 1 of MC12D and a false (inhibit) input to MC12E. The sum of data bits must therefore be even to inhibit MC12D. With a true TR16 signal from the Parity Calculating Network (odd sum) applied to pin 13 of MC12D, a true

Figure 1. Simplified Parity Calculating Network

input will be applied to "nor" gate MC12F giving a false  $\overline{PE}$  signal indicating a parity error. A false  $\overline{TR16}$  signal from the Parity Calculating Network (even sum) applied to pin 13 of MC12D will cause a false input to be applied to "nor" gate MC12F and provides a true  $\overline{PE}$  signal at pin 8 of MC12F indicating no parity error.

### 18. <u>DETAILED LOGIC</u>.

- 19. PARITY ERROR SIGNAL. (Refer to Figure 3, Parity Error Interrupt card.) Table 2 summarizes the functions of command lines to the Parity Error card. When a true input is applied to either input of "nor" gate MC12F a false PE signal (a parity error), is generated. A false input is then applied to "nor" gate MC76E. In order for the output of MC76E to be true, propagating the Parity Error signal, the following conditions must first exist:

- a. Either the ISZ (Increment and Skip if Zero) signal and the PH3 (Phase 3) signal applied to pins 2 and 1 of MC73A respectively must be true causing a false input to pin 1 of MC76C or the MWL (Memory Write Level) signal applied to pin 13 of MC76C must be false, providing a false input to "nor" gate MC76E. This allows the parity to be checked during the ISZ instruction, which utilizes a normal memory read cycle.

- b. Both the AAF (A Addressable Flip-Flop) and the BAF (B Addressable Flip-Flop) signals, pins 55 and 56, must be false. This prevents the generation of extraneous parity errors during AAF or BAF operations since the A and B registers do not contain a stored parity bit.

Table 2. Control Signals to the Parity Error Card

| CONTROL<br>SIGNALS        | DESCRIPTION                                                                                                                             |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| IOG,<br>SCM(0),<br>SCL(5) | Enables control commands to the Parity Error card.                                                                                      |

| STF(05)                   | Enables the interrupt capability of the Parity Error card.                                                                              |

| CLF(05)                   | Disables the interrupt capability of the Parity Error card.                                                                             |

| IAK                       | Will reset the Parity Error Flag at time T1 following a parity interrupt to prevent more than one interrupt from the same parity error. |

| IOI(05)                   | Generated by an input group instruction with the Select Code 05; allows retrieval of the address of the parity error.                   |

20. When the conditions described above are met, a true output signal is obtained on pin 8 of MC76E and applied to pin 3 of MC75A. When MTE is true (MTE is normally true except when the Loader Enable

switch is in the NORMAL position and the LOAD Flip-Flop is clear) and timing signal T3 is true the three inputs to MC75A are all true, giving a false  $\overline{PE}$  output. The false  $\overline{PE}$  signal goes to pin 11 of MC102B to clock in  $\overline{M12}$ , the most significant bit of the parity error address. The  $\overline{PE}$  is also inverted by MC103C and D and sent to pins 4 and 13 of each of quad-latching flip-flops MC96, 106, and 26. These flip-flops then clock in the remaining bits of the parity error address. Since the "not" outputs of the M-Register are used to provide the input data to the Parity Error Address Register, the address bits are taken from the reset sides of the address flip-flops when the address is retrieved.

- The true PE signal from MC103C is also 21. applied to pin 2 of MC84A. The false output resets the Flag Buffer Flip-Flop. If the Computer is set for the Halt mode, the output of the Flag Buffer Flip-Flop is inverted by MC42C and sent as a false PEH signal to halt the Computer. The output of the Flag Buffer Flip-Flop is also sent to enable MC84D (Flag gate) and to provide a true input to MC74B (Interrupt Request gate). The Flag Flip-Flop is set via MC84D by the ENF (T2) signal in the machine phase following the resetting of the Flag Buffer Flip-Flop. The output of the Flag Flip-Flop causes the PEI (Parity Error Indicator) signal to go true, turning on the PARITY indicator on the Computer front panel. The true output of the Flag Flip-Flop is also used to provide a true input to MC73B. The other input is provided by the set Control Flip-Flop. This gives a false output to MC85A, breaking the priority signal to the I/O Control card to keep interrupts from other devices from being generated. It also provides a false input to MC22D. MC22D then provides a true output to pin 9 of MC74B (the second of four required enabling signal for interrupt request). At time T5 the SIR signal from the Timing Generator card goes true (third signal), and a high PRL 4 signal from the I/O Control card (fourth signal) sets the IRQ Flip-Flop, generating the IRQ5 signal. This signal is inverted by MC42B to form a false PINT signal to the I/O Control card. The set IRQ Flip-Flop puts a true input on pin 2 of MC92A. At T1 of the next machine phase the IAK signal makes the other input of MC92A true resetting the Flag Buffer Flip-Flop. The false output from the Flag Buffer Flip-Flop results in a true output from MC74B. This allows the IRQ Flip-Flop to be reset by the ENF (T2) signal from the Timing Generator card.

- INTERRUPT IDENTIFICATION. When a Parity Error occurs and causes an interrupt to memory location 00005 (octal), the instruction contained in location 00005 may tell the Computer to execute a subroutine. Contained in the subroutine must be an LIA, MIA, LIB, or MIB instruction which when executed causes a true IOI signal input to pin 64 of the Parity Error card to be applied to pin 6 of MC85B. At the same time execution of one of these instructions causes the SCM0 (Select Code Most significant digit 0), SCL5 (Select Code Least significant digit 5), and the IOG signals from pins 59, 66, and 57 respectively to go true. This causes a true output from "and" gate MC86C, since PEI (Parity Error Indicator signal) is also true. MC85B then provides a true output to enable the output gates MC83A/B, MC15A/B, MC16A/B,

MC105A/B, MC104A/B, MC95A/B, and MC94A/B of the Parity Error Address Register. This allows the address of the parity error to be read onto the IOB (Input/Output Bus) line under program control. MC83A outputs a true bit 15 onto the IOB line whenever the contents of the Parity Error Address Register are read. Bit 15 is used to indicate that the address is that of a parity error.

- 23. CLF. The CLF (Clear Flag signal at pin 32 of the Parity Error card becomes true when a CLF instruction is executed during the Parity Error Interrupt subroutine. This signal is applied to pin 10 of MC73D. This causes the Control Flip-Flop to be reset putting a false input on pin 4 of MC73B. The output of MC84B provides the other false input to MC73B. The true output of MC73B causes MC22D to provide a false input to MC74B. This action inhibits the interrupt circuitry during the execution of the interrupt subroutine.

- 24. STF. The STF (Set Flag) signal at pin 19 of the Parity Error card becomes true when an STF instruction is executed by the interrupt subroutine. This signal together with the 05 Select Code causes MC72D to output a false signal to MC75C of the Flag Flip-Flop and MC74A of the Flag Buffer Flip-Flop, enabling the interrupt system. The STF 05 instruction

also provides a true input to MC72B, causing a false input to MC75A of the Control Flip-Flop. This causes a true output from the Control Flip-Flop to pin 4 of MC73B, enabling the interrupt request circuits.

- 25. POPIO. When the Computer power is turned on, or whenever the PRESET button on the Computer front panel is pushed, the POPIO (Power On Pulse to the I/O section) signal is applied to pin 45 of the Parity Error card. In order to initialize the card's interrupt capability, the inverted POPIO signal is applied to the following places:

- a. Pin 13 of MC75A to set the Control Flip-Flop.

- b. Pin 11 of MC75C to set the Flag Flip-Flop.

- c. Pin 1 of MC74A to set the Flag Buffer Flip-Flop.

### 26. REPLACEABLE PARTS.

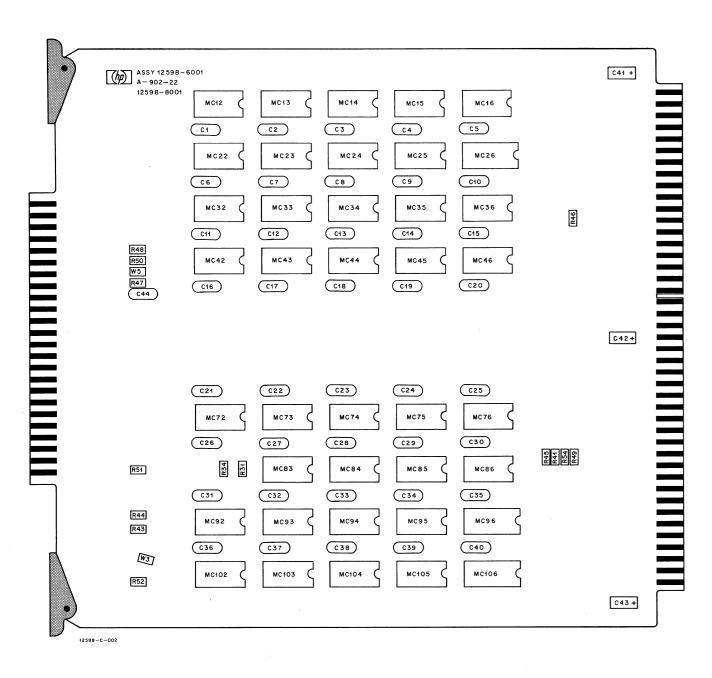

27. Table 3 lists replaceable parts in alphanumeric order of their reference designations, with a description and HP part number for each part. Figure 2 shows the location of all parts on the Parity Error board. To order a replacement part, address the order or inquiry to your local Hewlett-Packard field office.

| REFERENCE             | нР        |                                          | MFR.           |                        |     |

|-----------------------|-----------|------------------------------------------|----------------|------------------------|-----|

| DESIGNATION           | PART NO.  | DESCRIPTION                              | CODE           | MFR. PART NO.          | QTY |

|                       |           | ~                                        |                |                        |     |

| C1-40                 | 0150-0093 | C:fxd cer 0.01 uf, +80-20%,              | 91418          | TA                     | 40  |

| G41 40                | 0100 0155 | 100 VDCW                                 | F.C.0.00       | 150D005370000 A 0 D370 | 2   |

| C41-43                | 0180-0155 | C:fxd elect $2.2$ uf, $20\%$ , $20$ VDCW | 56 <b>2</b> 89 | 150D225X0020A2-DYS     | 4   |

| C44                   | 0160-0938 | C:fxd, Mica, 1000 pf, 5%                 | 72136          | RDM15E102J1C           | 1   |

| MC12, 13, 24, 35, 36, | 1820-0378 | Integrated Circuit: TTL                  | <b>2</b> 8480  | 1820-0378              | 8   |

| 43,45,46              |           |                                          |                |                        |     |

| MC14, 22, 23, 25, 32  | 1820-0370 | Integrated Circuit: TTL                  | <b>2</b> 8480  | 1820-0370              | 8   |

| 33,34,44              |           | _                                        |                | •                      |     |

| MC15, 16, 83, 85, 93, | 1820-0974 | Integrated Circuit: CTL                  | <b>2</b> 8480  | 1820-0974              | 9   |

| 94,95,104,105         |           |                                          |                |                        |     |

| MC26,96,106           | 1820-0301 | Integrated Circuit: TTL                  | <b>2</b> 8480  | 1820-0301              | 3   |

| MC42                  | 1820-0327 | Integrated Circuit: TTL                  | <b>2</b> 8480  | 1820-0327              | 1   |

| MC72,73,84,92,103     | 1820-0054 | Integrated Circuit: TTL                  | <b>2</b> 8480  | 1820-0054              | 5   |

| MC74                  | 1820-0069 | Integrated Circuit: TTL                  | <b>2</b> 8480  | 18 <b>2</b> 0-0069     | 1   |

| MC75                  | 1820-0068 | Integrated Circuit: TTL                  | <b>2</b> 8480  | 18 <b>20-0</b> 068     | 1   |

| MC76                  | 1820-0074 | Integrated Circuit: TTL                  | <b>2</b> 8480  | 1820-0074              | 1   |

| MC86                  | 1820-0973 | Integrated Circuit: TTL                  | <b>2</b> 8480  | 1820-0973              | 1   |

| MC102                 | 1820-0077 | Integrated Circuit: TTL                  | 28480          | 1820-0077              | 1   |

| R26,31,41,42,44,      | 0683-4715 | R:fxd comp 470 ohm, $5\%$                | 01121          | CB 4715                | 7   |

| 45,48                 |           | 1/4W                                     |                |                        |     |

| R34,43,49,50,51,      | 0683-1025 | R:fxd comp 1K, $5\%$ , $1/4$ W           | 01121          | CB 1025                | 6   |

| 52                    |           |                                          |                |                        | _   |

| R40,46,54             | 0683-1525 | R:fxd comp 1.5K, 5%,<br>1/4W             | 01121          | CB 15 <b>2</b> 5       | 3   |

| R47                   | 0683-4705 | R:fxd comp 47 ohm, 5%, 1/4W              | 01121          | CB 4705                | 1   |

| W3,5                  | 8159-0005 | Jumper: Wire, Insulated                  | 04404          |                        | 2   |

Table 3. Replaceable Parts List

Figure 2. Part Location Diagram

Figure 3. Parity Error Interrupt Card

# DIAGNOSTIC TEST AND PROCEDURE MEMORY PARITY CHECK

model 12598A

DIAGNOSTIC SUPPLEMENT 5 FEB 1969

### INTRODUCTION. 1.

The information contained in this supplement provides the computer user with procedures for testing the operation of the Memory Parity Check Option HP 12598A. By performing these diagnostic tests the user can determine which circuits and functions of the option are operating correctly and which are malfunctioning. This supplement is to be used in conjunction with the 12598A Memory Parity Check operating manual.

### MEMORY PARITY CHECK DIAGNOSTIC. 3.

Memory Parity Check diagnostic, HP 20345A, furnishes the computer user with a method of testing the operational and programmable features of Memory Parity Check. The routine includes 17 separate checks of the Parity Error card operation. (Order information for the diagnostic tape is contained in Paragraph 24 of this supplement.)

### 5. TEST PROCEDURE.

- Make certain that the Computer POWER switch is in the "OFF" position. The Parity Error board should be properly installed in slot A5 with the components facing to the left from the front of the Computer. Place the top connector hood in the Interrupt position. Restore power to the Computer. Load all zeros (NOP) in location 00005 to permit loading the diagnostic tape without generating unwanted parity halts. This procedure also assigns proper parity to the Basic Binary Loader program if this has not already been done.

- When the loading of the diagnostic tape is complete, turn off power to the Computer and remove the Parity Error board in order to insert parity errors into memory for test purposes. Restore power to the Computer and press the PRESET button. Set the address to 7000 (octal) and press RUN. This sets up data patterns with both correct and incorrect parity bits for use later in the test. The Computer should halt with the T-Register set to 102072.

- A jumper should now be placed from pin 52 (TR16) of slot A5 to ground. This will cause a true bit 16 to be written back into memory for each word read out regardless of the word's true parity. When a machine with a 4K memory is used set Switch Register bit 15. Press the PRESET and RUN buttons. The Computer should halt with the T-Register set to 102074.

- When the parity bit test patterns have been loaded into memory the ground jumper should be removed and the Parity Error board replaced in slot A5 observing the same power precautions used in the above procedures. The top connector hood should be set to halt on detecting a parity error. Load 7033 into P-Register. Press PRESET, press RUN. The Computer should halt with the T-Register set to 0 and the PARITY light on.

- Reverse the top connector hood so that the Computer will interrupt on detection of a parity error. Press the PRESET and RUN buttons. The next section of the diagnostic will test the Parity Error board's ability to interrupt on the detection of a parity error. The 0 (NOP) loaded into location 5 allows the Computer to return to the diagnostic routine without operator intervention. If the Computer fails to interrupt properly an error halt (HLT 21) is generated indicating a failure to interrupt.

### DIAGNOSTIC TEST. 11.

- The diagnostic program performs the tests in sequential order. Each test assumes that the previous test was completed without failure. A list of the error halts and their descriptions is given in Table 1. By using the error halt description and the contents of the various registers it is possible in most cases to isolate the malfunction.

- The diagnostic test checks the contents of the Parity Error Address Register. If the contents of this register do not compare with the stored address of the parity error a HLT 22 is generated, indicating a failure of the Parity Error Address circuitry.

- The ability to turn the Parity Error circuitry on and off is tested by a programmed CLF 05 instruction to disable the Parity Error board. A parity error is then introduced. If the Parity Error board has failed to turn off, a parity error interrupt will be generated causing the test program to execute a HLT 23. Normal control operation will cause the diagnostic program to proceed to the next test.

- The A and B Registers do not contain a parity bit and therefore parity errors detected during an addressable A or B Register function should be disregarded. Also during the memory write cycle there is no need to generate a parity error. If any occurred they should have been detected during the memory read cycle. The diagnostic program tests these conditions by addressing first the A and then the B Registers. Data is placed in the registers such that a

Table 1. Diagnostic Halt Codes

| HALT CODE | DESCRIPTION                                                                                          |  |

|-----------|------------------------------------------------------------------------------------------------------|--|

| 102021    | Did not interrupt on bad parity.                                                                     |  |

| 102022    | Error address incorrect (Register contents not 7402).                                                |  |

| 102023    | Control not cleared by CLF 5.                                                                        |  |

| 102024    | Interrupted on (AAF + MWL) (Bad Parity)                                                              |  |

| 102025    | Interrupted on (BAF + MWL) (Bad Parity)                                                              |  |

| 102026    | Interrupted on (AAF) (Bad Parity)                                                                    |  |

| 102027    | Interrupted on (BAF) (Bad Parity)                                                                    |  |

| 102030    | Interrupted on (ISZ) (PH3) (AAF) (Bad Parity)                                                        |  |

| 102031    | Interrupted on (ISZ) (PH3) (BAF) (Bad Parity)                                                        |  |

| 102032    | Did not interrupt (ISZ) (PH3) (AAF + BAF) (Bad Parity)                                               |  |

| 102033    | Error address incorrect. Register contents not 11200 (if a 4K machine, register contents not 01200). |  |

| 102034    | Interrupted on (MWL) (ISZ) (Bad Parity).                                                             |  |

| 102035    | Did not interrupt on (MWL) (Bad Parity).                                                             |  |

| 102036    | Interrupted to I/O 10 after CLF 5 (PRL5).                                                            |  |

| 102037    | Did not interrupt to I/O 10 after STF 5 (PRL5).                                                      |  |

| 102040    | Test sequence error - Reload program.                                                                |  |

| 102044    | Interrupt on good parity (A = Data B = Address)                                                      |  |

| 102055    | Did not interrupt on bad parity (A = Data B = Address)                                               |  |

| 102066    | Error address incorrect (A = Error Address Register - B = Program Address)                           |  |

parity error would normally be generated. If a parity error is generated during the execution of these functions or while the MWL (Memory Write Level) signal is true a HLT 24 or HLT 25 is generated. The next sequential test checks the A and B Addressable functions again, separately from the MWL signal. A failure of the A or B addressable functions will generate a HLT 26 or HLT 27 respectively.

- 16. The diagnostic program next checks the ISZ (Increment and Skip if Zero) instruction. This command is normally used as a memory reference instruction but when used with the A or B addressable registers could produce an incorrect parity error indication. Data containing parity errors is placed in the A and B Registers and then referenced by an ISZ instruction. The parity halt circuitry should inhibit parity error generation under these conditions. If it fails to do so a HLT 30 or HLT 31 is produced for the A and B functions respectively.

- 17. The ISZ instruction should be allowed to generate a parity error under normal memory reference conditions. The parity error should be generated during the Phase 3 machine cycle. The diagnostic first checks to see if the parity error is allowed to cause an interrupt and then checks to see that the parity error address is correct. Failure of one of these tests will cause the program to execute an error halt HLT 32 or HLT 33 respectively.

- 18. When the MWL signal is true and the ISZ signal is false a parity error should not be allowed to cause an interrupt or halt Computer operation. The diagnostic tests this function and on failure generates a HLT 34. Next the MWL signal is tested alone. When the MWL signal is false the Computer should interrupt on detection of a parity error. If the Computer fails to do so an error halt HLT 35 is generated.

- 19. The ability of the Parity Error board to hold off interrupts while processing a parity error is tested by inducing a parity error and then causing an interrupt from I/O slot 10. If the test fails then the PRL5 (Priority Low) signal did not drop inhibiting lower priority devices from interrupting. A failure of this test produces an error halt HLT 36. The CLC 00 instruction should clear the parity error indication causing the PRL5 signal to go true. The STF 00 instruction turns the interrupt system back on. If the induced interrupt from I/O slot 10 does not occur after the parity error indication has been cleared an error halt HLT 37 is generated.

- 20. Error halt HLT 40 provides for errors in the program procedure or test sequence. The diagnostic procedure should be repeated from the beginning as well as reloading the diagnostic program.

- 21. The Parity Calculating Network is checked by using a series of data patterns which exercise differ-

- ent parity configurations. By observing the data or address that generated a failure the group of gates responsible can be isolated. A parity error interrupt that is generated by correct data will cause an error halt HLT 44. A failure to interrupt on incorrect data will cause an error halt HLT 55.

- 22. When a parity error occurs the address of the error is stored in the Parity Error Address Register on the Parity Error board. When the artificial parity errors are tested the program compares the address read out of the Parity Error Address Register with the actual address of the parity error. If the two disagree an error halt HLT 66 is generated.

- 23. When an error halt HLT 44, HLT 55, or HLT 66 occurs the contents of the A and B Registers (Error Address Register and parity error address respectively) can be displayed by single cycling twice and viewing the Switch Register (first the B and then the A Register is displayed). After successful completion of the diagnostic the program corrects the test parity data in memory. The Computer should then execute a normal HLT 77 (102077 octal).

- 24. To order a replacement tape, address the order or inquiry to your local Hewlett-Packard field office. See the list at rear of the Memory Parity Check operating manual for field-office addresses.

| 0001         |                 | ASFd, A.B.L, T | 2-4-69 ERH   |

|--------------|-----------------|----------------|--------------|

| Вх           | 007344          |                | 4 2 2 W (11) |

| DMP          | 001057          |                |              |

| EHR          | 196047          |                |              |

| FIX          | 947333          |                |              |

| FPE          | ศลาย51          |                |              |

| K2           | W91035          |                |              |

| K3           | 4410 <b>3</b> 6 |                |              |

| K 4          | 991937          |                |              |

| K 5          | 701040          |                |              |

| MIK          |                 |                |              |

| NDT          | Ø <b>9734</b> 5 |                |              |

| PEG          | 901100          |                |              |

| RPE          | 401043          |                |              |

|              | VIØ1062         |                |              |

| RRR          | Ø30050          |                |              |

| T1           | 007112          |                |              |

| T10          | 307236          |                |              |

| T11          | 007255          |                |              |

| T12          | 007302          |                |              |

| T13          | 007311          |                |              |

| T14          | 007320          |                |              |

| 15           | 907126          |                |              |

| 13           | 007134          |                |              |

| T 4          | 007143          |                |              |

| <b>T</b> 5   | M07160          |                |              |

| T 6          | 007172          |                |              |

| 17<br>70     | 007177          |                |              |

| T8           | uu7246          |                |              |

| T9           | NA7225          |                |              |

| ADDR         | 001047          |                |              |

| BADP         | 007251          |                |              |

| BKT14        | MM7327          |                |              |

| BKTP         | 000042          |                |              |

| CLEAN        | 707346          |                |              |

| EH21         | 991000          |                |              |

| EH22         | 001001          |                |              |

| EH23         | 901002          |                |              |

| EH24         | 001003          |                |              |

| EH25         | 001004          |                |              |

| EH26         | PU1005          |                |              |

| EH27         | HO1006          |                |              |

| EH30         | 091007          |                |              |

| EH <b>31</b> | 001010          |                |              |

| EH32         | 001011          |                |              |

| EH33         | 991912          |                |              |

| EH34         | w01013          |                |              |

| EH35         | 001014          |                |              |

| EH36         | 001015          |                |              |

| <b>ЁНЗ</b> 7 | 901016          |                |              |

| EH40         | B01017          |                |              |

| EH44         | 001020          |                |              |

| EH55         | 001021          |                |              |

| ЕН6 <b>6</b> | 001022          |                |              |

| FURK         | @01050          |                |              |

| FUUR         | 091934          |                |              |

| ISZA1        | @ 41 Ø 25       |                |              |

| JAPBK        | 001026          |                |              |

|              |                 |                |              |

| K3.9  | 001041    |

|-------|-----------|

| K5.9  | MØ1042    |

| K7401 | 000041    |

| K7404 | 1411023   |

| MASK1 | 001024    |

| MASK2 | 201027    |

| PE10  | 031045    |

| PE12  | 991046    |

| PESU  | 097000    |

| PICUP | M00051    |

| PTRN1 | 301030    |

| PTRN2 | 001031    |

| PTRN3 | au1032    |

| THREE | 801033    |

| ** N  | O ERRURS* |

v1≈57\*

```

ASMB, A.B.L.T

2-4-69 ERH

0001

8002×

PARITY ERROR DIAGNUSTIC FOR 12580B

0003*

N004+

1259RA

0005+

TEST PROCEDURE

0006*

0007*

0008*

A BUARD WITH STANDARD INTERRUPT CIRCUITRY MUST BE IN I/O 10.

0009*

0010×

---TURN OFF PUWER BEFORE REMOVING OR INSERTING BUARD---

1. PLUG PET BOARD IN A5 - INSTALL HOOD IN INTERRUPT MODE.

6611 *

2. LUAD & IN ADDRESS 5.

@012*

No 13 *

3. LUAU PRUGRAM.

4. REMOVE PEL BOARD. IF 4K MACHINE, SET SWITCH 15.

0014×

0015±

5. PRESET, SA 7000 CCTAL, RUN.

(SHOULD FALL T = 102072 OCTAL).

0016*

6. GROUND PIN 52 OF A5. IF 4K MACHINE, SET SW.REG. AIT 15.

0 w 17 *

7. RUNI (SHOULD HALT T = 142474 OCTAL).

0018*

8. REPLACE PEL BUARL IN AB - PUT HOOD IN PARITY HALT MODE.

8019*

-REMOVE GRUUND FROM PIN 52 OF A5-.

0620*

9. PRESET, RUN (SHOULD HALT I = 0, PARITY LIGHT ON.)

9W21 *

10. TURN HOUD TO INTERRUPT MODE.

0022*

11. PRESET, RUN (SHOULE HALT T = 102077 OCTAL)

0023*

0024×

Ø025*

ERRUR HALTS

0026×

HALT 21

DID NOT INTERRUPT ON BAD PARTTY

Ø⊌27*

HALT 22

ERROR AUDRESS INCORRECT (REGISTER CONTENTS NOT 7402)

0028 ×

MØ29*

HALT 23

CONTROL NOT CLEARED BY CLF 5

INTERRUPTED ON (AAF TRUE + MWL TRUE) (BAD PARITY)

HALT 24

0030*

HALT 25

INTERRUPTEL ON (HAF TRUE + MWL TRUE) (BAD PARITY)

0031 *

HALT 26

INTERRUPTEL ON (AAF) (BAD PARITY).

0632*

HALT 27

0 M33 +

INTERRUPTEL ON (HAF) (RAD PARTTY).

HALT 30

INTERRUPTEL ON (ISZ) (PH3) (AAF) (BAD PARITY)

06,34 +

HALT 31

0035*

INTERRUPTEL UN (ISZ)(PH3)(BAF)(BAD PARITY)

DID NOT INTERRUPT (ISZ)(PH3)(BAD PARTTY)

HALT 32

0036×

HALT 33

0037*

ERROR ADDRESS INCORRECT - REG. CONTENTS NOT 11200.

(SHOULD BE 1200 ON 4K MACHINE).

9438 ×

0039+

HALT 34

INTERRUPT ON (MWL) (ISZ NOT) (BAD PARITY)

0040*

HALT 35

DID NOT INTERRUPT (MAL NOT) (BAD PARITY)

HALT 36

INTERRUPT TO I/O 10 AFTER CLF 5 (PRL5 NOT)

0041 *

HALT 37

FAILURE TO INTERRUPT TO IZO 10 AFTER STF 5.

8842*

HALT 40

TEST SEWLENCE ERROR - RELOAD PROGRAM!

0043*

0044*

HALT 44

INTERRUPTED ON GOOD PARITY

(A = DATA B = ADDR_{\bullet})

0245*

0046*

HALT 55

FAILURE TO INTERMUPT ON BAD PARITY

0047*

(A = UATA B = ABER_{\bullet})

HALT 66

ERROR ADDRESS REGISTER DOES NOT AGREE

6648*

WITH PRUGRAM AUDRESS.

0049*

(A = AUDRESS REG. B = PROGRAM ADDRESS)

0050×

--AFTER ERRUR MALIS 44, 55, 8 66, 8 & A REGISTER

0051 ×

CONTENTS MAY BE OBSERVED BY SINGLE CYCLING TWICE

0 N 52*

AND VIEWING IN THE SWITCH REGISTER (B THEN A)

8653×

PARITY ERROR HALT/INTERHOPT =

0054*

V×55*

(EAU MARITY)(M)c)(T3)((AAF MOT)(BAF NOT)(MWE) +

(AAF BOT) (BAF NOT) (PH3) (182))

V v. 56*

```

```

0 u 58 *

0059*

0060×

TRAP

CELL

CONSTANTS

0061

00002

URG 28

6062

00002 102002

HL 1 28

ERROR HLT

00003 102003

0063

HLI 3B

0064

90004 103004

HLT 48,C

ERROR HALT

0065

00005 102005

HLT 5B

TRAP CELL

0066

60006 162006

HLI 6B

ERROR HALT

00007 102607

HLI 78

0v67

NUNIU 102010

0068

HLT 10B

INTR.

0069

00011 102011

HL 118

0070

00012 102012

HLI 128

FROM

00013 102013

0071

HL1 13B

0072

00014 102014

HLI 148

SOME

8e73

00015 102015

HL1 158

0074

0M916 102M16

HLT 16B

1/0

00017 102017

2075

HLT 178

WW76

000020 102020

HLT 20B

DEVICE

めしフフォ

INDIRECT ADDRESS CUNSTANTS

0078

00040

URG 408

0679

00040 007112

DEF T1

00741 007401

K7401 UCT 7401

0800

0081

00042 007160

BKIP

DEF 15

0082

00043 007172

DEF T6

0083

00044 00/225

DEF T9

00045 007255

0084

LEF T11

0085

00046 007302

BEF T12

0086

00047 015051

EHK

JSE FPE

LINK TO PE ROUTINE

RRR

JSE RPE

0087

6445W 015662

LINK TO RECOVER R.

PICUP JSE 40B, I

8899

00051 114040

0089*

ERRUR HALTS

0090

01000

URG 1000m

01000 102021

EH21

0091

HLI 218

0092

01001 102022

EH22

HLT 22H

0093

01002 102023

EH23

hL1 238

0094

01003 102024

EH24

HLT 24B

01004 102025

HL1 258

N 4 9 5

EH25

0096

01405 102026

EH26

HLI 26B

0097

01096 102027

EH27

HLI 27B

0098

01007 102030

EH30

HLI 30B

01010 102031

EH31

0099

HLI 31B

0100

01011 102032

EH32

HLT 328

0101

01012 102033

EH33

HLI 33R

0102

01413 102034

EH34

nLI 34R

0103

01014 102035

EH35

HLT 358

0104

01015 102036

EH36

HL1 369

01016 102037

0105

EH37

HL1 378

01217 102040

HLT 40B

0106

EH40

W107

01420 102044

EH44

HL1 448

0108

01021 102055

EH55

HL1 558

0109

01022 102066

EH66

HLT 668

6110=

CONSTANTS

9111

01923 007404

K7404 UC1 7404

0112

01024 107402

MASKI UCT 107402

W1025 W374WW

152A1 UC1 37400

(ISZ 1400)

Ø113

JMPBK JMF BKTP.I

JUMP BACK TO PROGRAM

6114

61026 124042

```

171

```

Ø115

£1327 617777

MASK2 UCT 1777/

01030 007400

PTHN1 UCT 7400

6116

0117

01931 170526

PTKN2 UC1 170526

UDD PARITY PATTERN

0118

01032 015705

PTHN3 UCT 015745

EVEN PARITY PATTERN

91033 000003

THREE UCT

0119

3

0120

01034 000004

FULR

UCT 4

01035 002000

0121

K 2

UCI

200n

390v

0122

01036 003000

K 3

UCI

01037 004000

V123

K4

UCT 4000

01940 005000

9124

K5

UC1 5000

0125

01041 003777

K3.9

UCT

3777

0126

01042 005777

UCT

K5.9

5777

Ø127

01043 011200

PES

UCT 11200

01944 011290

1128

UCT 11200

9129

01045 000000

PEIU

UCT

0130

01046 000000

PE12

UCT

Ø

0131

01747 011290

ADDR

UCT 11200

0132

01350 001230

FORK

GC1 1260

W133*

FAIL RUUTINE

01951 000000

W134

FPE

NUP

01952 102044

Ø135

HLT

44B

BEADDR, AEDATA

W136

01053 106601

OTE 1

ADDRESS

01054 102601

W137

UTA 1

DATA

0138

01055 071057

STA

DMP

TREE CHECK

2139

01056 125051

JMP FPE, 1

RETURN

0140

01357 0000A0

DMP

NOP

0141 *

RECOVER ROUTINE

0142

01960 007326

DEF BKT14-1

0143

W1061 WW7327

LEF BKT14

01062 000000

W144

RPE

NOF

0145

01063 102505

LIA 5B

GET REG.

0146

01364 011827

ANL MASKO

REMOVE BIT 15

CPA 18

0147

01065 050001

REG=AUDR.

0148

01066 002001

RSS

YES

01967 102066

0149

HLT 66B

NO-REGEA, ADDREB

0150

01070 106601

OTB 1

ADDRESS

01071 102601

0151

UTA 1

REG. CONT.

LDA RPE

0152

01072 061062

0153

01073 051060

CPA RPE-2

DID WE COME FROM TEST 14?

9154

01074 125061

JMF RPE-1, I

YES GO BACK

01075 102601

0155

OTA 1

NOI

SW. REG. = LOCATION OF SAD

vi 156

01076 102040

HLT 408

CAME FROM WRONG PLACE

Ø157

01077 025076

JMF #-1

0158*

FAIL TO DET PE

%159

01130 000000

NDT

NOP

01101 102055

HLT 558

2169

B=ADDR. A=DATA

3161

W1102 106601

OTE 1

ADDRESS

01103 102601

UTA 1

DATA

J162

STA DMP

1163

01104 071057

TREE CHECK

9164

01135 125100

JMF NDT, I

√ 165 ★

SET UP PARITY EKROKS IN MEMORY

Ø166★

0167★

PE

BOARD****

£168 *

****REMOVE

1169*

URG 7000H

170

07400

17 400 061031

PESU

LDA PTRNO

```

```

0172

07001 005035

LDE K2

0173

07002 017333

JSH FIX

SET UP PB=U, ODD PTRN.

07903 061032

9174

LDA PTRNS

0175

W7W04 065040

LDE K5

0176

07905 017333

JSE FIX

SET UP PB=0, EVEN PTRN.

0177

07006 002400

LLA

W178

07007 071045

STA PEIR

FIX

0179

W7010 W71046

STA PE12

BAD

07011 171044

0180

STA PE9+1, I

PARITY

Ø181

07912 073490

5TA 74000

67013 073401

0182

STA 74018

0183

07314 473442

STA 7402H

LDA BADP

0184

Ø7315 Ø63251

PARITY ISTH.

6185

07016 102072

HL1 728

V186*

Ø187*

****PUI GND ON PIN 52****

Ø188*

W189

67917 102501

LIA 1

W19W

W7020 002021

SSA, RSS

CHANGE ADDRESS

Ø7021 Ø27024

JMF *+3

0191

FOR 4K

0192

67022 061950

LDA FORK

MACHINE ..

0193

07023 071047

STA ADDR

67024 861632

LDA PTRN3

W194

W195

07025 065036

LDE K3

W196

W7026 W17333

JSE FIX

SET UP PB=1, EVEN PTRM.

0197

07027 061031

LDA PTRNO

0198

07030 065037

LDB K4

JSE FIX

W199

67031 617333

SET UP PB=1, UDD PTRN.

07032 102074

HL1 74P

0200

0201 *

0202*

**** PLUG IN RUARD ****

0203*

0204

W7033 W271WW

JMF 71008

BEGIN TESTS

07100

CRG 7100H

0205

07100 063400

LDA 7400R

W246

8297

67141 666666

NOF

97102 000000

0208

NOF

0209

07143 000446

NOF

0210×

TEST THAT IT IS PUSSIBLE TO INTERRUPT

0211

67104 802400

LLA

07105 071400

STA 1400H

0212

0213

47146 142135

STF 5B

6214

27137 P60051

LUA PICUP

0215

67110 070005

STA 5B

SET UP RETURN

W216

87111 027402

JMF 74028

0217

07112 @00000

11

NOF

0218

07113 102505

LIA 5B

CLF 58

0219

07114 103135

0220

07115 102601

UTA 81

REG. CONTENTS

LPA MASKI

VID WE COME FROM 7402

0221

87116 B51824

0222

07117 V42801

K S S

07120 102022

NO! ERROR HALT

0223

HLI 22B

0224

07121 064290

LDE 8

W225

w7122 853112

LUA 11

LPA K7494

CHECK VALUE OF P

@226

07123 051023

W227

0/124 602001

KSS

HL1 218

6228

47125 102021

NO NOT FROM 7402

```

```

0229*

TEST THAT CAN TURN CONTROL OFF

0230

07126 103105

12

CLF 58

0231

W7127 061002

LUA EH23

0232

U7130 U70005

STA 5B

SET UP EH

0233

07131 103175

LLF 58

READY

0234

07132 160041

LDA K7401, I

0235

07133 WWWWWW

NOF

0236*

CHECK ADUR. A & B

Ø237

07134 U61033

LDA EH24

13

SET UP EH

0238

67135 670015

STA 58

W239

07136 002400

LLA

0240

07137 102135

STF 58

READY -

W7148 064000

0241

LUE W

TEST

0242

W7141 200000

NOP

0243

07142 103105

LLF 58

INTERRUPT OFF ...

07143 061004

0244

T 4

LDA EH25

0245

67144 070665

STA 58

SET EH

07145 006400

0246

CLE

0247

07146 102105

STF 58

READY -

0248

07147 460001

TEST

LDA 18

0249

67150 000000

NOF

INTERRUPT OFF ...

0250

07151 1031W5

CLF 58

0251 *

CHECK ADDR. A & B 15Z

0252

07152 461495

LDA EH26

0253

W7153 W7WW95

STA 58

SET EH

0254

07154 061025

LDA ISZAI

SET UP INST.

0255

07155 065026

SET UP RETURN

LDE JMPBK

0256

07156 102105

STF 58

READY -

0257

07157 024000

JMP 0

TEST

0258

07160 000000

15

NOF

07161 103105

CLF 58

0259

INTERRUPT OFF ...

LDA EH27

W261

07162 061096

0261

07163 070005

STA 5B

SET EH

9262

67164 065025

LUB ISZAT

SET UP INSTR.

0263

07165 061026

LDA JMPBK

0264

07166 002004

INA

0265

07167 070002

STA 2B

SET UP RETURN

0266

07170 102105

STF 58

READY -

07171 024001

0267

JMP 1

TEST

0268

07172 000000

16

NOF

INTERRUPT OFF ...

0269

07173 103105

CLF 58

0270

07174 003400

LCA

07175 040003

0271

ADA 38

07176 070002

0272

STA 28

RETURN LOC. 2 TO HLT 2

CHECK ADDR. A & B ISZ PH 3

0273×

6274

07177 061907

LDA EH30

17

6275

07200 070005

STA 58

SET EH

0276

07201 002400

CLA

W277

07202 102105

STF 58

READY -

0278

07203 U34000

152 0

TEST

0279

07204 000000

NOF

0280

07205 103105

CLF 58

INTERRUPT OFF...

W281

07206 061010

LDA EH31

18

5TA 58

0282

Ø7247 Ø78645

SET EH

W283

07210 W35400

LLE

3284

07211 162105

READY -

STF 58

07212 034 has

0285

152 13

TEST

```

```

0286

07213 000000

NOF

0287

07214 103105

CLF 5B

INTERRUPT OFF ...

0288*

TEST

ISZ PHASE 3

0289

07215 061426

LDA JMPBK

0290

07216 002004

INA

0291

07217 002004

INA

SET UP RETURN

0292

07220 070005

STA 5B

07221 102105

0293

STF 58

READY -

0294

07222 135043

ISZ PE9, I

0295

07223 000000

NOF

07224 102032

ERROR HALT

0296

HLT 328

0297

07225 102505

LIA 58

0298

07226 103105

LLF 5B

INTERRUPT OFF ...

07227 011027

0299

AND MASKS

0300

07230 065047

LDE ADDR

GET CORRECT ADDR.

0301

67231 051047

CPA ADDR

CHECK REG.

0302

07232 002001

RSS

07233 102033

HLT 33B

0303

ERROR HALT - REG. WRONG

0304

07234 106601

OTE VI

ADDR

07235 102601

OTA 01

0305

REG.

CONTENTS

0306*

CHECK STORE

07236 061013

LDA EH34

0307

TIE

0308

07237 070005

STA 58

SET EH

07240 002400

0309

CLA

0310

07241 102105

STF 58

READY -

07242 071045

STA PE10

TEST

0311

07243 000000

0312

NOF

0313

07244 103105

CLF 58

INTERRUPT OFF ...

0314*

CHECK ISZ PHASE 1

V315

07245 Ø61426

LDA JMPBK

0316

07246 041033

ADA THREE

0317

07247 079095

STA 58

SET UP RETURN

9318

07250 102105

STF 58

READY -

BALP

0319

07251 035500

IS2 1500H

07252 0000AA

0320

NOF

07253 000000

0321

NUF

0322

07254 102035

ERROR HALT

HLT 35B

07255 103105

0323

711

CLF 5B

INTR. OFF

0324*

CHECK PRIORITY CHAIN

0325

07256 061015

LDA EH36

07257 070010

0326

STA 10B

07250 002400

0327

CLA

07261 070005

0328

STA 5B

0329

07262 102105

STF 5B

6330

07263 061046

LDA PE12

67264 8000000

W331

NOF

07265 000000

0332

NOF

07266 106790

0333

CLC 0

CLEAR ALL CONTROLS

0334

U7267 102710

STC 10B

TURN ON 1/0 10

07270 102110

STF 10B

0335

SET FLAG 10

TURN INTR SYST ON

9336

67271 102100

STF 0

0337

07272 000000

FAIL TEST IF INTR TO 10

NOP

6338

07273 061026

LDA JMPBK

07274 041034

ADA FOUR

0339

STA 10B SET UP RETURN

0340

07275 070010

9341

07276 102105

STF 58

07277 0000000

TEST IF CAN INTR TO 14

NOF

J342

```

```

0343

07340 000000

NOF

0344

07301 102037

HLT 37B

ERROR HALT

0345

W7342 0W3400

T12

CCA

07303 107700

0346

CLC 0,C

TURN INTR SYSTEM OFF

0347

07304 040011

ADA 118

0348

07305 070010

STA 108

FIX

TRAP CELL UP

0349*

CHECK PARITY TREE

(GOOD PARITY)

0350

67346 868847

LDA EHR

07307 070005

0351

STA 58

SET PE FAIL LINK

0352

07310 065035

LDE K2

SET START ADDR.

U353

07311 102105

STF 5B

READY

113

0354

67312 160001

LDA 1.I

TEST

NOF

0355

07313 000000

0356

07314 055041

CPE K3.9

DONE ?

07315 027320

Ø357

YES- GO TO TEST 14

JMF T14

0358

07316 006004

INE

NO

Ø359

07317 @27311

JMF T13

GO BACK

0360*

CHECK PARITY TREE

(BAU PARITY)

0361

07320 060050

T14

LDA RRR

07321 070005

SET PE RECOVER LINK

9362

STA 58

07322 065037

0363

LDE K4

SET START ADDR.

0364

07323 102135

STF 58

READY -

0365

07324 160001

LDA 1, I

TEST

0366

0/325 0000000

NOF

0367

07326 615100

JS6 NOT

07327 055042

BK114 UPE K5.9

DONE ?

Ø368

0369

67330 027346

JMF CLEAN

YES- GO TO CLEAN UP

0370

07331 006404

INE

NO

07332 027323

0371

JMF 714+0

GO BACK

PARITY ERROR FIX RUUTINE

0372*

07333 000000

FIX

PATTERN IN A

0373

NOF

0374

07334 170001

STA 1.I

FIRST ADDR. IN B

07335 001200

0375

RAL

ROTATE PATTERN

0376

07336 006004

INB

NEXT ADDR.

0377

07337 037344

ISZ BX

6378

07340 027334

JMF FIX+1

07341 063345

LDA MIK

0379

FINISHED

0380

67342 673344

STA BX

INITALIZE COUNTER

0381

07343 127333

JMF FIX, 1

RETURN TO PRG

07344 177000

UCT -1000

6382

COUNTER

ВΧ

67345 177000

MIK

UC1 -1000

0383

REMOVE ANY PARITY EXRCRS FROM MEMORY

6384*

TURN OFF INTR.

0385

07346 103105

CLEAN CLF 58

07347 006400

0386

CLE

LDA 1, I

0387

07350 160001

CORRECT PARITY BIT

@388

07351 006004

INE

NEXT ADDRESS

CPE MASKO

67352 655027

DONE ?

0389

0390

07353 002001

HSS

YES

0391

67354 027350

NO-LOOP BACK

JMF *-4

07355 003400

CCA

0392

0393

07356 040006

ADA 68

07357 070005

STA 58

FIX UP TRAP CELL

0394

0395

07360 102105

STF 58

0396

07361 102077

HLT 778

DONE (AT LAST)

JMP 7090H

07362 W27WAW

0397

LRG 7400B

0398

07430

UCT 0

9399

07400 000000

```

| 0400 | 07401 | DUNHUND | UCT | Ø   |

|------|-------|---------|-----|-----|

| 0401 | 67402 | BRABBO  | 100 | 0   |

| 0402 | 07473 | 000000  | 001 | e   |

| 0483 | 07494 | 102021  | HLT | 21B |

| 0444 | 07405 | นิดถอดด | ÜCT | 0   |

| 0405 |       |         | ENL |     |

|      |       | 30.     |     |     |

# DIAGNOSTIC TEST AND PROCEDURE for MEMORY PARITY CHECK

model

12598A

UPDATING SUPPLEMENT 2 JULY 69

MANUAL IDENTIFICATION

Manual Serial Prefixed:

Manual Printed:

Manual Part Number:

### **SUPPLEMENT DESCRIPTION**

The purpose of this supplement is to correct manual errors (Errata) and to adapt the manual to instruments containing production improvements made subsequent to the printing of the manual. Enter the new information (or the Change Number, if more convenient) into the appropriate places in the manual, identified at left.

**ASSEMBLY CHANGES**

| Prefix-Serial | Changes |

|---------------|---------|

| ALL           | 1,2     |

|               |         |

|               |         |

|               |         |

INSTRUMENT CHANGES

| Ref Des | Description                                                                                                     | HP Part No. |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------|-------------|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         | The second se |             |  | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| -       |                                                                                                                 |             |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|         |                                                                                                                 |             |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |