# 21MX Computer Series

**Reference Manual**

# 21MX COMPUTER SERIES

reference manual

HEWLETT-PACKARD COMPANY

11000 WOLFE ROAD, CUPERTINO, CALIFORNIA, 95014

Printed: JUN 1976 Printed in U.S.A.

# **CONTENTS**

| Section I                        | Page  | Input/Output Instructions                   |

|----------------------------------|-------|---------------------------------------------|

| SYSTEM FEATURES                  |       | Extended Arithmetic Memory                  |

| Microprogramming Capabilities    | . 1-2 | Reference Instructions                      |

| System Speed                     |       | Extended Arithmetic Register                |

| Memory Space                     | _     | Reference Instructions                      |

| Special Functions and Security   | _     | Extended Instruction Group Coding           |

| Additional Hardware Facilities   |       | Index Register Instructions                 |

| Hewlett-Packard Software         |       | Jump Instructions                           |

| Input/Output                     |       | Byte Manipulation Instructions              |

| Specifications                   |       | Bit Manipulation Instructions               |

| System Expansion and Enhancement | 1-4   | Word Manipulation Instructions              |

|                                  |       | Floating Point Instruction Coding           |

|                                  |       | Dynamic Mapping System                      |

| Section II                       | Page  | Memory Addressing                           |

| OPERATING FEATURES               | rage  |                                             |

| Hardware Registers               | 9 1   | Map Register Loading                        |

| A-Register                       |       | Status and Violation Registers              |

| B-Register                       |       | Map Segmentation                            |

|                                  |       | Power Fail Characteristics                  |

| M-Register                       |       | DMS Instruction Coding                      |

| T-Register                       |       | Sample Map Load/Enable Routine              |

| P-Register                       |       | Additional DMS Definitions                  |

| S-Register                       |       | Alternate Map                               |

| Extend Register                  |       | Protected Mode                              |

| Overflow Register                |       | MEM Violations                              |

| Display Register                 |       | DCPC Operation In a DMS Environment 3-34    |

| X- and Y-Registers               |       | Instruction Execution Times                 |

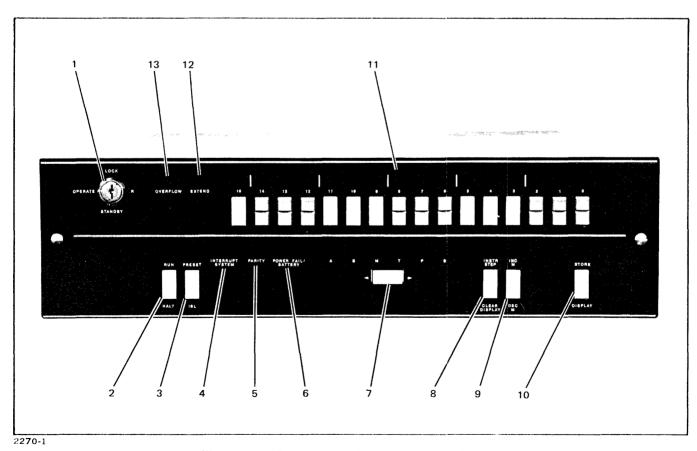

| Control and Indicators           | . 2-2 | Interrupt System                            |

| Operator Panel                   | . 2-2 | Power Fail Interrupt                        |

| Rear Panel                       |       | Parity Error Interrupt                      |

| Internal Switches                | . 2-2 | Memory Protect/DMS Interrupt                |

| Basic Operating Examples         | . 2-5 | Dual-Channel Port Controller Interrupt 3-41 |

| Cold Start Procedure             |       | Input/Output Interrupt                      |

| Manual Loading                   |       | Central Interrupt Register                  |

| Running Programs                 | . 2-6 | Interrupt System Control                    |

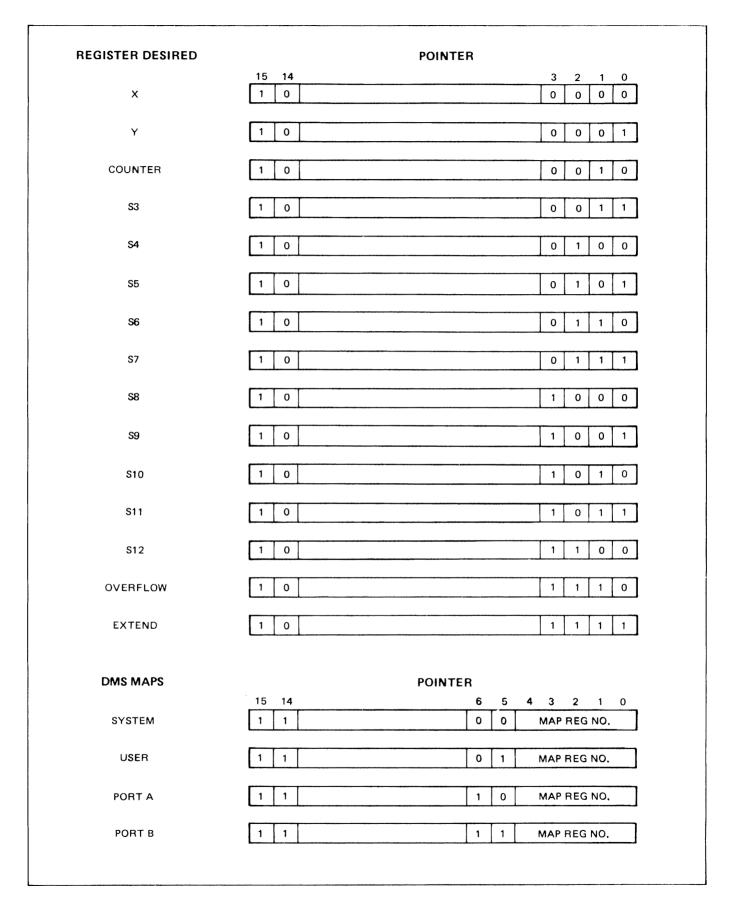

| Special Register Display Mode    | . 2-6 |                                             |

|                                  |       | Section IV Page                             |

| Section III                      | Dogo  | NPUT/OUTPUT SYSTEM                          |

| PROGRAMMING INFORMATION          | Page  | Input/Output Addressing 4-1                 |

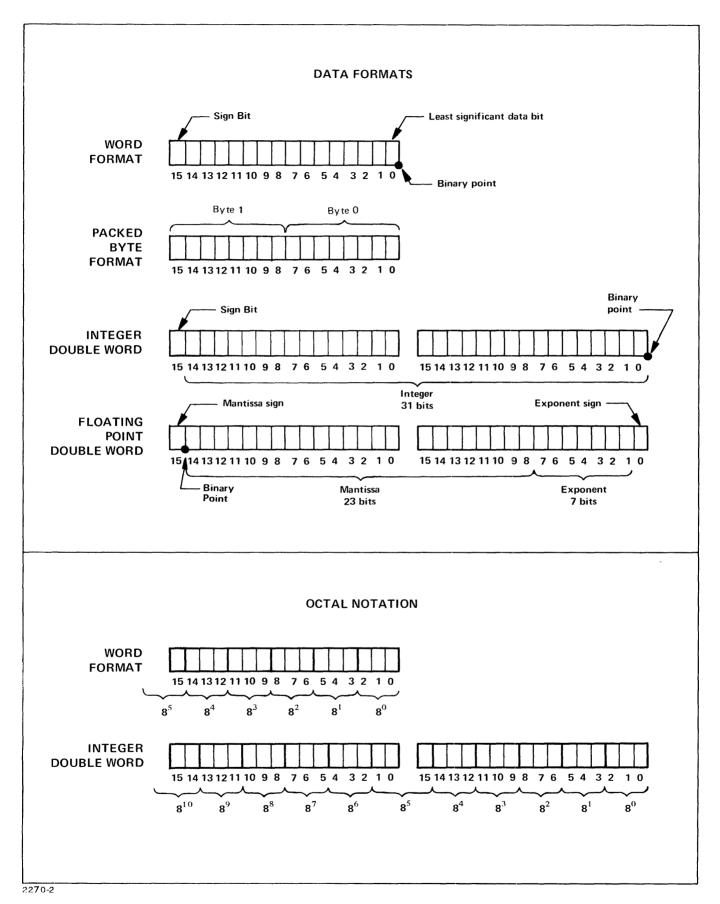

| Data Formats                     | 0.1   | Input/Output Priority 4-1                   |

|                                  |       | Interface Elements 4-3                      |

| Memory Addressing                | . 3-1 | Control Bit 4-3                             |

| Paging                           |       | Flag Bit                                    |

| Direct and Indirect Addressing   |       | Buffer 4-4                                  |

| Reserved Memory Locations        |       | Input/Output Data Transfer 4-4              |

| Nonexistent Memory               | . 3-4 | Input Data Transfer (Interrupt Method) 4-4  |

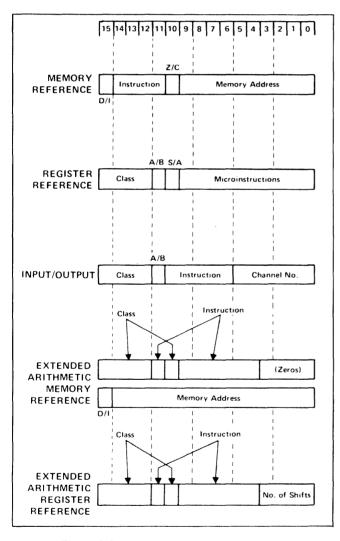

| Base Set Instruction Formats     |       | Output Data Transfer (Interrupt Method) 4-5 |

| Memory Reference Instructions    |       | Noninterrupt Data Transfer 4-5              |

| Register Reference Instructions  |       | Input                                       |

| Input/Output Instructions        | . 3-4 | Output                                      |

| Extended Arithmetic Memory       |       | Dual-Channel Port Controller 4-6            |

| Reference Instructions           | . 3-5 | DCPC Operation 4-6                          |

| Extended Arithmetic Register     |       | DCPC Initialization                         |

| Reference Instructions           |       |                                             |

| Base Set Instruction Coding      |       |                                             |

| Memory Reference Instructions    | . 3-5 | Appendix Page                               |

| Register Reference Instructions  | . 3-7 | Computer Physical Layout                    |

| Shift/Rotate Group               |       | Character Codes                             |

| Alter/Skip Group                 |       | Octal Arithmetic                            |

# **CONTENTS** (continued)

| Octal/Decimal Conversions     |     |     |    |  |  |  | A-5  | Extended Instruction Group Codes in Binary          |  | . A-11 |

|-------------------------------|-----|-----|----|--|--|--|------|-----------------------------------------------------|--|--------|

| Mathematical Equivalents .    |     |     |    |  |  |  | A-6  | Dynamic Mapping System Instruction                  |  |        |

| Octal Combining Tables .      |     |     |    |  |  |  | A-8  | Codes in Binary                                     |  | . A-12 |

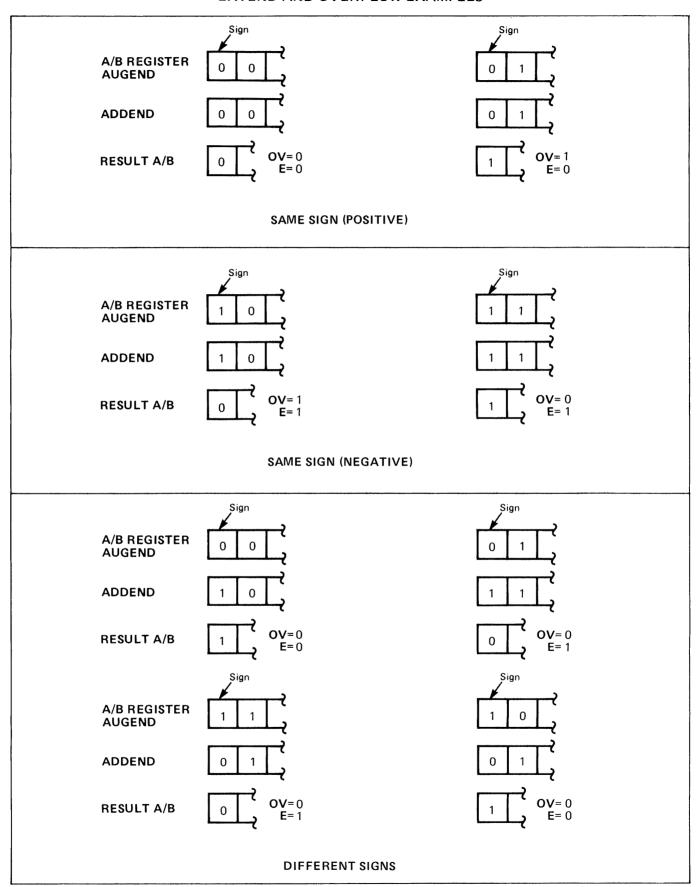

| Instruction Codes in Octal    |     |     |    |  |  |  | A-9  | Extend and Overflow Examples                        |  | . A-13 |

| Base Set Instruction Codes in | ı B | ina | ry |  |  |  | A-10 | Interrupt and I/O Control Summary $\cdot$ . $\cdot$ |  | . A-14 |

## **ILLUSTRATIONS**

| Title                                      | Page   | Title                                   | Page |

|--------------------------------------------|--------|-----------------------------------------|------|

| Microprogrammable Processors               | . 1-0  | Map Segmentation                        | 3-26 |

| Operator Panel Controls and Indicators     | . 2-2  | Input/Output System                     | 4-1  |

| Special Register Display Mode Pointers     | . 2-7  | I/O Address Assignments                 | 4-2  |

| Data Formats and Octal Notation            | . 3-2  | Priority Linkage                        | 4-2  |

| Base Set Instruction Formats               |        | Interrupt Sequences                     |      |

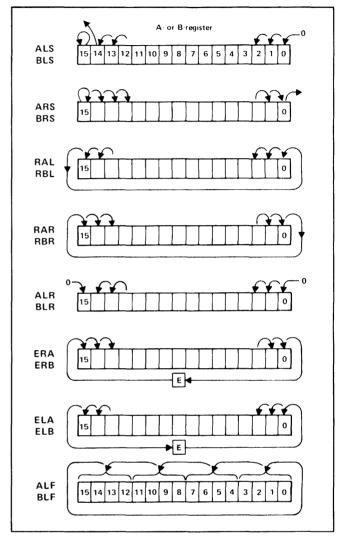

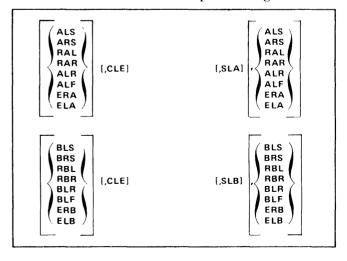

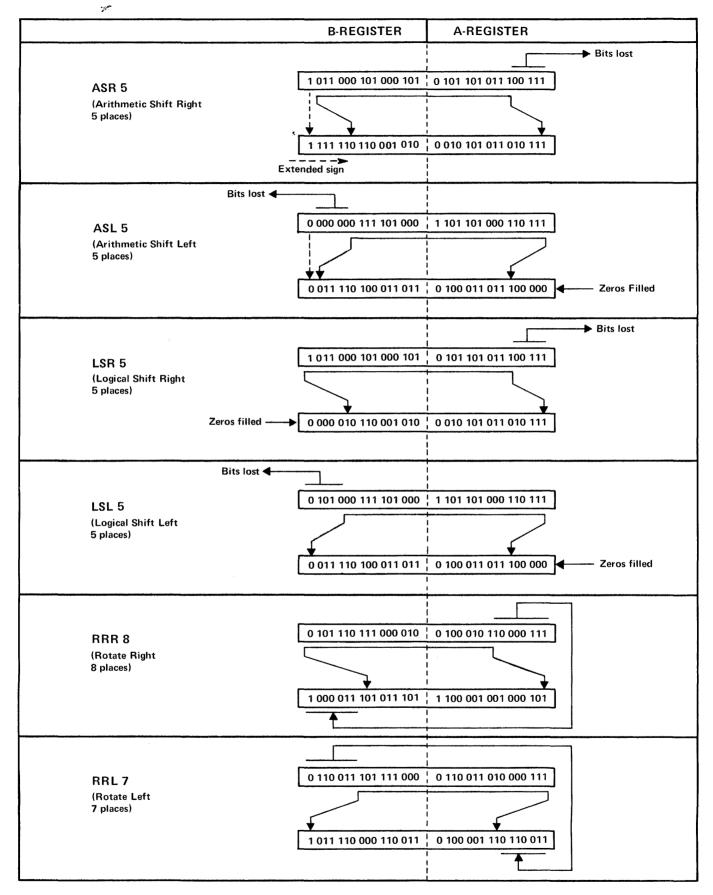

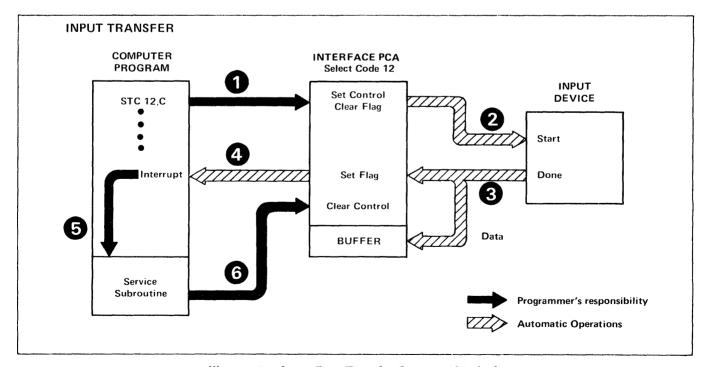

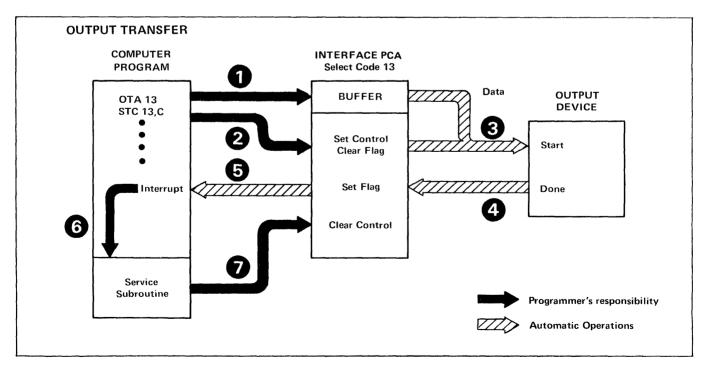

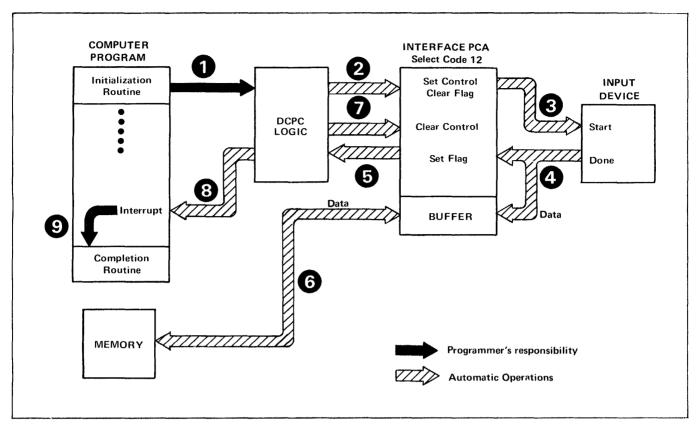

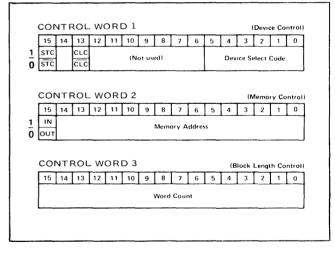

| Shift and Rotate Functions                 | . 3-7  | Input Data Transfer (Interrupt Method)  | 4-4  |

| Examples of Double-Word Shifts and Rotates | . 3-15 | Output Data Transfer (Interrupt Method) | 4-   |

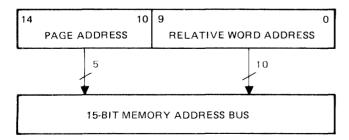

| Basic Memory Addressing Scheme             | . 3-24 | DCPC Input Data Transfer                | 4-   |

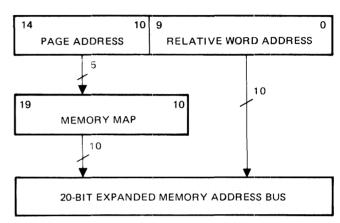

| Expanded Memory Addressing Scheme          |        | DCPC Control Word Formats               | 4-   |

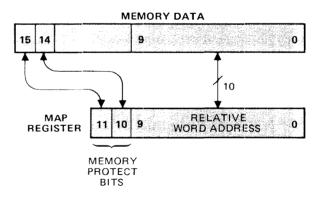

| Basic Word Format Vs Man Register Format   | 3-24   |                                         |      |

# **TABLES**

| Γitle                                            | Page   | Title                                           | Page   |

|--------------------------------------------------|--------|-------------------------------------------------|--------|

| Specifications                                   | . 1-5  | MEM Status Register Format                      | . 3-25 |

| Options and Accessories                          | . 1-9  | MEM Violation Register Format                   | . 3-25 |

| Operator Panel Control and Indicator Functions . | . 2-3  | Sample DMS Load/Enable Routine                  | . 3-35 |

| Special Register Display Mode                    |        | Instruction Execution Times                     | . 3-36 |

| Switch Operation                                 | . 2-8  | HP 2105A Interrupt Assignments                  | . 3-38 |

| Effects of Storing/Displaying Special            |        | HP 2108A Interrupt Assignments                  |        |

| Registers                                        |        | HP 2112A Interrupt Assignments                  |        |

| Memory Paging                                    |        | Sample Power Fail Subroutine                    |        |

| Reserved Memory Locations                        |        | Sample Memory Protect/Parity Error Subroutine . |        |

| Shift/Rotate Group Combining Guide               |        | Noninterrupt Transfer Routines                  | . 4-6  |

| Alter/Skip Group Combining Guide                 | . 3-10 | DCPC Initialization Program                     |        |

|                                                  |        |                                                 |        |

### ALPHABETICAL INDEX OF STANDARD INSTRUCTIONS

| Instruct                                                    | ion                                                    | Page | Instruc                                                     | ition                                             | Page                      |

|-------------------------------------------------------------|--------------------------------------------------------|------|-------------------------------------------------------------|---------------------------------------------------|---------------------------|

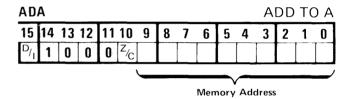

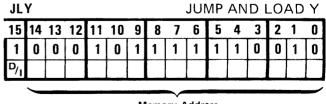

| ADA                                                         | Add to A                                               |      | JLY                                                         | Jump and Load Y                                   | 3-19                      |

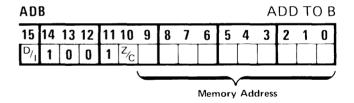

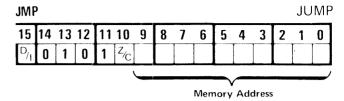

| ADB                                                         | Add to B                                               | 3-5  | JMP                                                         | Jump                                              | 3-6                       |

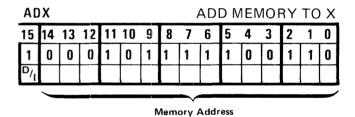

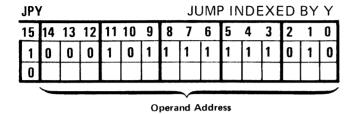

| ADX                                                         | Add Memory to X                                        |      | JPY                                                         | Jump Indexed by Y                                 |                           |

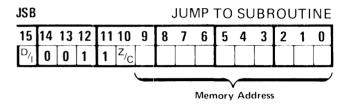

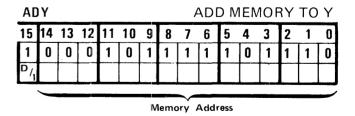

| ADY                                                         | Add Memory to Y                                        |      | JSB                                                         | Jump to Subroutine                                |                           |

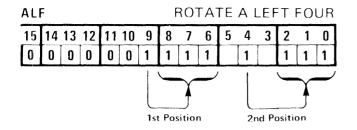

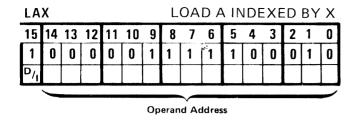

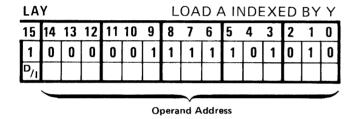

| ALF                                                         | Rotate A Left Four                                     |      | LAX<br>LAY                                                  | Load A Indexed by X Load A Indexed by Y           |                           |

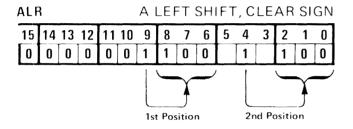

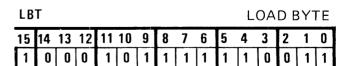

| ALR                                                         | A Left Shift, Clear Sign                               |      | LBT                                                         | Load Byte                                         |                           |

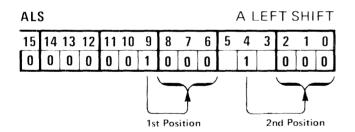

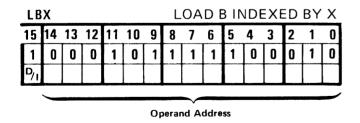

| ALS                                                         | A Left Shift                                           |      | LBX                                                         | Load B Indexed by X                               | 3-18                      |

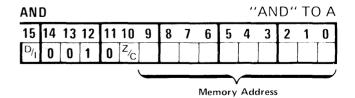

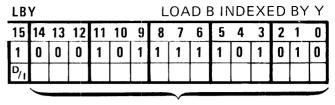

| AND                                                         | "And" to A                                             |      | LBY                                                         | Load B Indexed by Y                               |                           |

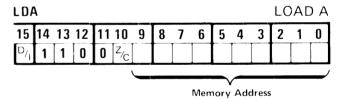

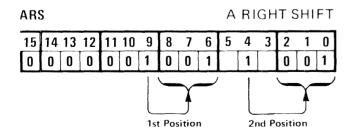

| ARS                                                         | A Right Shift                                          |      | LDA                                                         | Load A                                            |                           |

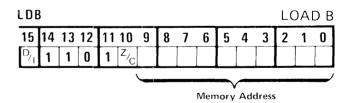

| ASL<br>ASR                                                  | Arithmetic Shift Left (32) Arithmetic Shift Right (32) |      | LDB                                                         | Load B                                            |                           |

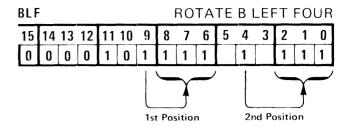

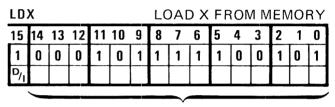

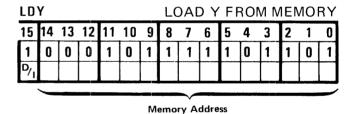

| BLF                                                         | Rotate B Left Four                                     |      | $rac{	ext{LDX}}{	ext{LDY}}$                                | Load X from Memory Load Y from Memory             |                           |

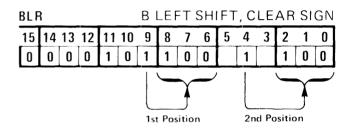

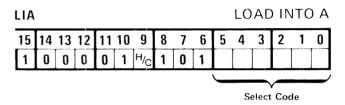

| BLR                                                         | B Left Shift, Clear Sign                               |      | LIA                                                         | Load Input to A                                   |                           |

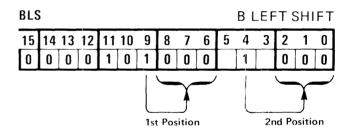

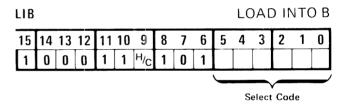

| BLS                                                         | B Left Shift                                           |      | LIB                                                         | Load Input to B                                   |                           |

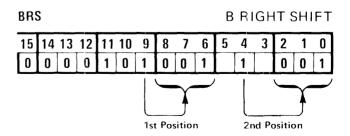

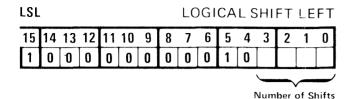

| BRS                                                         | B Right Shift                                          |      | LSL                                                         | Logical Shift Left (32)                           | 3-16                      |

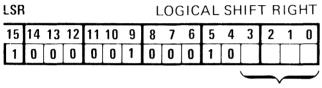

| CAX                                                         | Copy A to X                                            | 3-17 | LSR                                                         | Logical Shift Right (32)                          | 3-16                      |

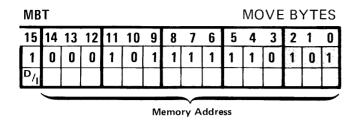

| CAY                                                         | Copy A to Y                                            | 3-17 | MBT                                                         | Move Bytes                                        | 3-21                      |

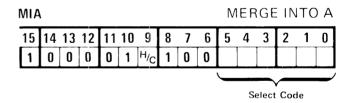

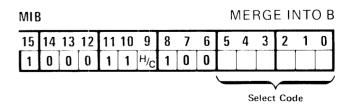

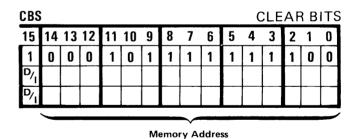

| CBS                                                         | Clear Bits                                             |      | MIA                                                         | Merge Into A                                      |                           |

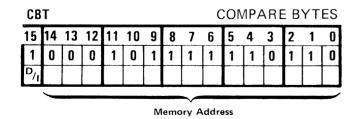

| $\begin{array}{c} \mathrm{CBT} \\ \mathrm{CBX} \end{array}$ | Compare Bytes                                          |      | MIB<br>MPY                                                  | Merge Into B                                      |                           |

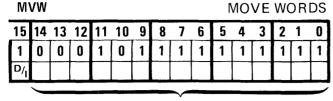

| CBX                                                         | Copy B to Y                                            |      | MVW                                                         | Move Words                                        |                           |

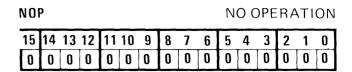

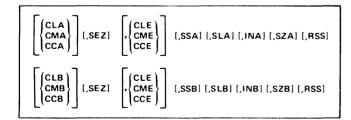

| CCA                                                         | Clear and Complement A                                 |      | NOP                                                         | No Operation                                      |                           |

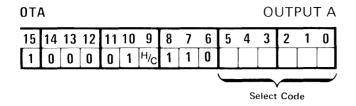

| CCB                                                         | Clear and Complement B                                 |      | OTA                                                         | Output A                                          | 3-13                      |

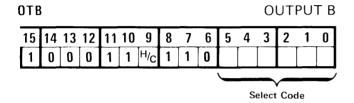

| CCE                                                         | Clear and Complement E                                 |      | OTB                                                         | Output B                                          |                           |

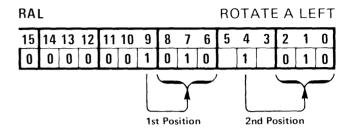

| CLA                                                         | Clear A                                                |      | RAL                                                         | Rotate A Left                                     |                           |

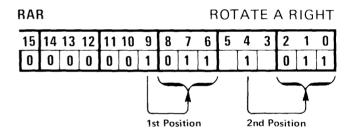

| CLB                                                         | Clear B                                                |      | RAR                                                         | Rotate A Right                                    |                           |

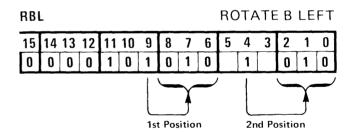

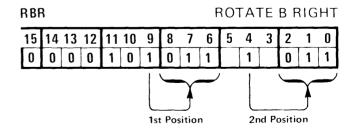

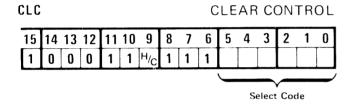

| $\begin{array}{c} \mathrm{CLC} \\ \mathrm{CLE} \end{array}$ | Clear Control                                          |      | RBL<br>RBR                                                  | Rotate B Left                                     |                           |

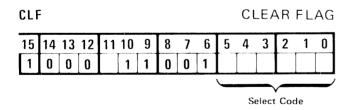

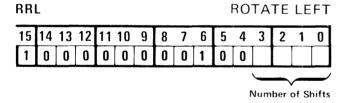

| CLE                                                         | Clear Flag                                             |      | RRL                                                         | Rotate B Right                                    | 5-9<br>3-16               |

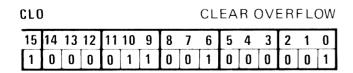

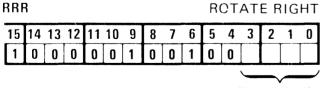

| CLO                                                         | Clear Overflow                                         |      | RRR                                                         | Rotate Right (32)                                 |                           |

| CMA                                                         | Complement A                                           |      | RSS                                                         | Reverse Skip Sense                                |                           |

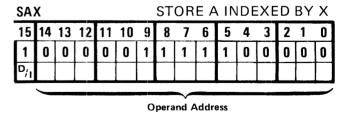

| CMB                                                         | Complement B                                           | 3-10 | SAX                                                         | Store A Indexed by X                              | 3-18                      |

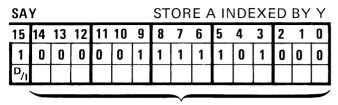

| CME                                                         | Complement E                                           |      | SAY                                                         | Store A Indexed by Y                              |                           |

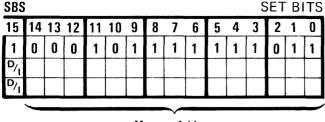

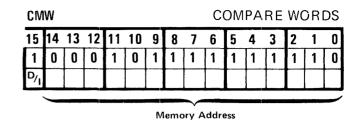

| CMW                                                         | Compare Words                                          |      | SBS                                                         | Set Bits                                          |                           |

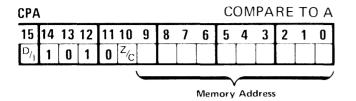

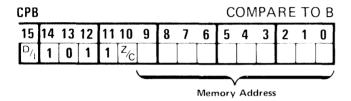

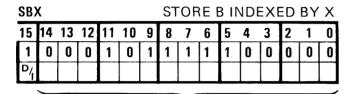

| CPA<br>CPB                                                  | Compare to A                                           |      | SBT<br>SBX                                                  | Store Byte                                        |                           |

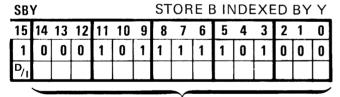

| CXA                                                         | Copy X to A                                            |      | SBY                                                         | Store B Indexed by Y                              | 3-19                      |

| CXB                                                         | Copy X to B                                            |      | SEZ                                                         | Skip if E is Zero                                 |                           |

| CYA                                                         | Copy Y to A                                            | 3-17 | SFB                                                         | Scan For Byte                                     | 3-21                      |

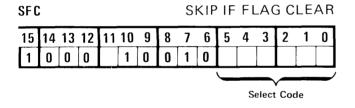

| CYB                                                         | Copy Y to B                                            |      | $\mathbf{SFC}$                                              | Skip if Flag Clear                                |                           |

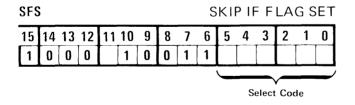

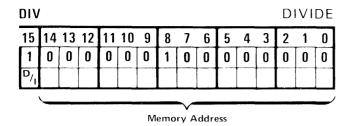

| DIV                                                         | Divide                                                 |      | SFS                                                         | Skip if Flag Set                                  | 3-13                      |

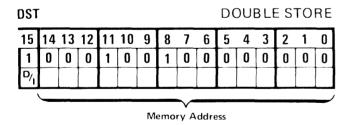

| DLD<br>DST                                                  | Double Load                                            | 3-14 | $\begin{array}{c} \mathrm{SLA} \\ \mathrm{SLB} \end{array}$ | Skip if LSB of A is Zero Skip if LSB of B is Zero |                           |

| DSX                                                         | Decrement X and Skip if Zero                           |      | SOC                                                         | Skip if Overflow Clear                            |                           |

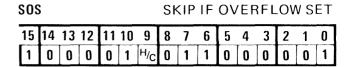

| DSY                                                         | Decrement Y and Skip if Zero                           |      | SOS                                                         | Skip if Overflow Set                              |                           |

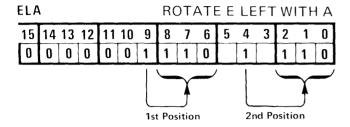

| ELA                                                         | Rotate E Left with A                                   | 3-9  | SSA                                                         | Skip if Sign of A is Zero                         | 3-11                      |

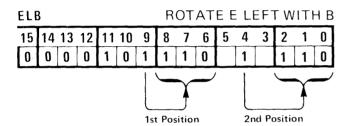

| ELB                                                         | Rotate E Left with B                                   |      | SSB                                                         | Skip if Sign of B is Zero                         |                           |

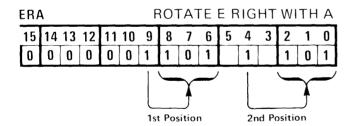

| ERA                                                         | Rotate E Right with A                                  |      | STA                                                         | Store A                                           |                           |

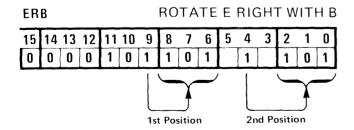

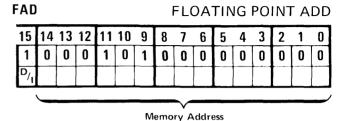

| ERB<br>FAD                                                  | Rotate E Right with B                                  |      | STB                                                         | Store B                                           |                           |

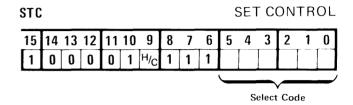

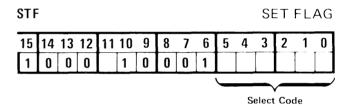

| FDV                                                         | Floating Point Add                                     |      | STC<br>STF                                                  | Set Control                                       | 3-13                      |

| FIX                                                         | Floating Point to Integer                              |      | STO                                                         | Set Overflow                                      |                           |

| FLT                                                         | Integer to Floating Point                              |      | STX                                                         | Store X to Memory                                 |                           |

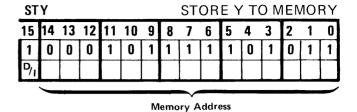

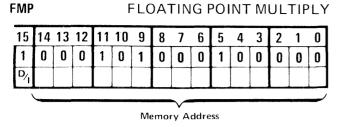

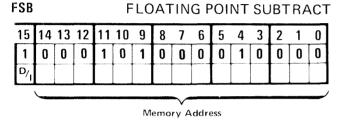

| FMP                                                         | Floating Point Multiply                                | 3-24 | STY                                                         | Store Y to Memory                                 | 3-19                      |

| FSB                                                         | Floating Point Subtract                                |      | SZA                                                         | Skip if A is Zero                                 | 3-11                      |

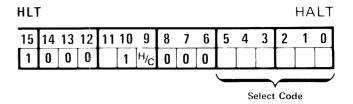

| HLT                                                         | Halt                                                   |      | SZB                                                         | Skip if B is Zero                                 |                           |

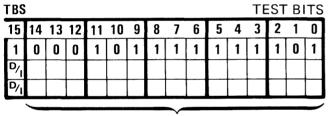

| INA<br>INB                                                  | Increment A                                            |      | ${ m TBS} \ { m XAX}$                                       | Test Bits                                         |                           |

| INB                                                         | Increment B                                            |      | XAX<br>XAY                                                  | Exchange A and X                                  | 3-19<br>9 <sub>-</sub> 19 |

| ISX                                                         | Increment X and Skip if Zero                           |      | XBX                                                         | Exchange B and X                                  |                           |

| ISY                                                         | Increment Y and Skip if Zero                           |      | XBY                                                         | Exchange B and Y                                  |                           |

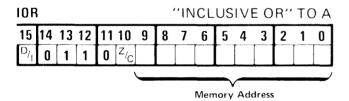

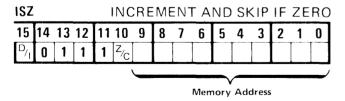

| ISZ                                                         | Increment and Skip if Zero                             |      | XOR                                                         | "Exclusive Or" to A                               |                           |

### ALPHABETICAL INDEX OF DYNAMIC MAPPING SYSTEM INSTRUCTIONS

| Instruct | tion                            | Page | Instruc | tion                              | Page   |

|----------|---------------------------------|------|---------|-----------------------------------|--------|

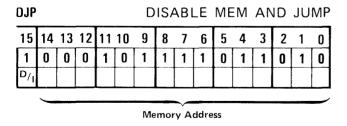

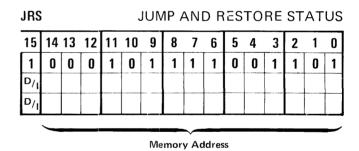

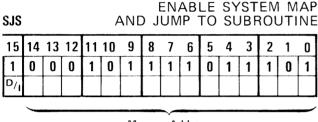

| DJP      | Disable MEM and JMP             | 3-26 | SJP     | Enable System Map and JMP         | . 3-29 |

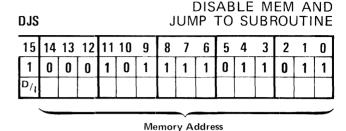

| DJS      | Disable MEM and JSB             | 3-26 | SJS     | Enable System Map and JSB         |        |

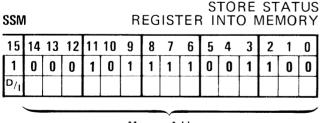

| JRS      | Jump and Restore Status         | 3-26 | SSM     | Store Status Register Into Memory | . 3-30 |

| LFA      | Load Fence From A               | 3-27 | SYA     | Load/Store System Map per A       | . 3-30 |

| LFB      | Load Fence From B               | 3-27 | SYB     | Load/Store System Map per B       | . 3-30 |

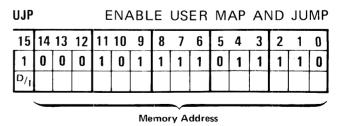

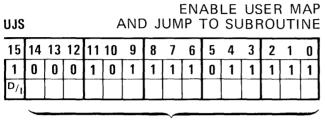

| MBF      | Move Bytes From Alternate Map   | 3-27 | UJP     | Enable User Map and JMP           | . 3-30 |

| MBI      | Move Bytes Into Alternate Map   | 3-27 | UJS     | Enable User Map and JSB           | . 3-31 |

| MBW      | Move Bytes Within Alternate Map | 3-28 | USA     | Load/Store User Map per A         | . 3-31 |

| MWF      | Move Words From Alternate Map   | 3-28 | USB     | Load/Store User Map per B         |        |

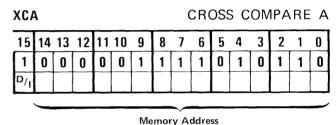

| MWI      | Move Words Into Alternate Map   | 3-28 | XCA     | Cross Compare A                   |        |

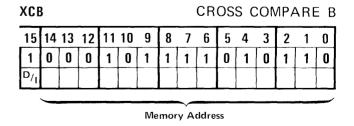

| MWW      | Move Words Within Alternate Map | 3-28 | XCB     | Cross Compare B                   |        |

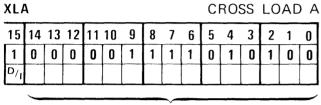

| PAA      | Load/Store Port A Map per A     | 3-28 | XLA     | Cross Load A                      |        |

| PAB      | Load/Store Port A Map per B     | 3-29 | XLB     | Cross Load B                      | . 3-32 |

| PBA      | Load/Store Port B Map per A     | 3-29 | XMA     | Transfer Maps Internally per A    | . 3-32 |

| PBB      | Load/Store Port B Map per B     | 3-29 | XMB     | Transfer Maps Internally per B    | . 3-32 |

| RSA      | Read Status Register Into A     | 3-29 | XMM     | Transfer Maps or Memory           | . 3-32 |

| RSB      | Read Status Register Into B     | 3-29 | XMS     | Transfer Maps Sequentially        | . 3-33 |

| RVA      | Read Violation Register Into A  | 3-29 | XSA     | Cross Store A                     |        |

| RVB      | Read Violation Register Into B  | 3-29 | XSB     | Cross Store B                     |        |

System Features 21MX

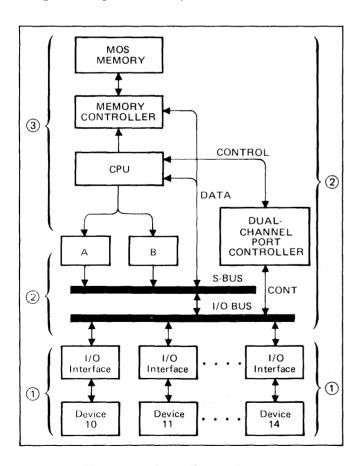

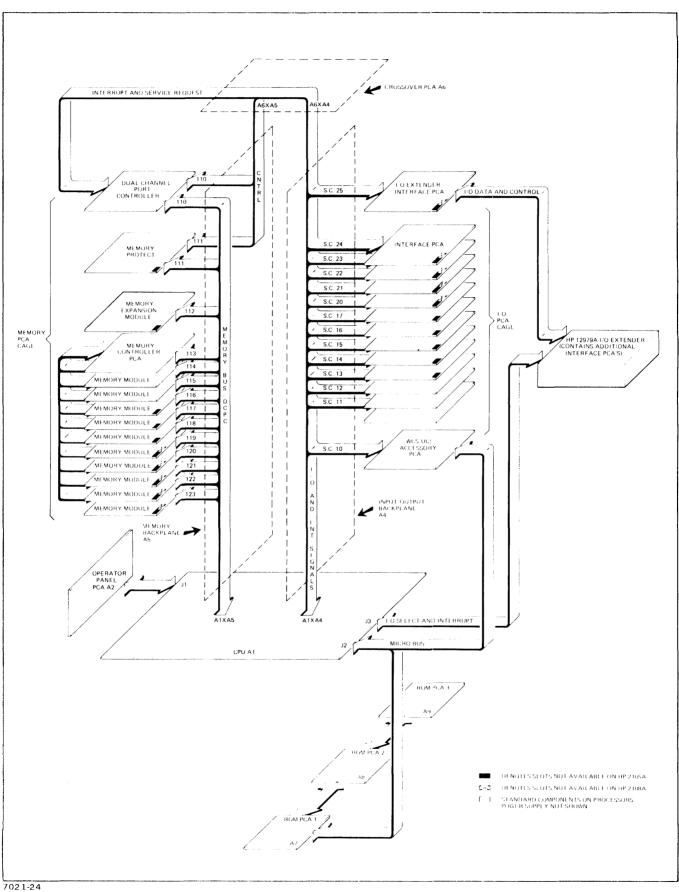

Figure 1-1. Microprogrammable Processors

### SECTION

## 1

## **SYSTEM FEATURES**

The microprogrammable processors shown in figure 1-1 accommodate a variety of memory configurations and processor options to form the new and powerful HP 21MX Computer Series. Salient features of these computers, which utilize the latest developments in semiconductor technology, are as follows.

#### PROCESSOR

- Powerful user-microprogrammable processor with 178 micro-orders and 4K of control store space.

- 128 standard instructions including 80 instructions which emulate the HP 2100 Series Computer; 42 new instructions for indexing, byte and bit manipulation, byte and word moves, and byte string scanning; and 6 single-precision floating point instructions.

- 4 general-purpose registers, two of which may be used as index registers.

- Fully microprogrammed processor, including all arithmetic functions, input/output, and operator panel control.

- Initial binary loader is ROM resident and callable by a pushbutton switch on the operator panel. A paper tape loader ROM is standard; provision is made for up to three additional loader ROM's, which are available as options or may be user-generated.

- Operator panel is standard.

- Writable Control Store (WCS) is optional.

- Programmable ROM (pROM) Writer available as a supporting product.

- Dynamic Mapping System (DMS) is optional on HP 2108A and HP 2112A Processors.

#### POWER SUPPLY

- Power module supplies power for the processor and all processor options, the memory system and all memory options, all standard and optional microcode packages, and a wide range of I/O controller configurations.

- Power module operates over a wide range of line voltage and line frequency variations; operates through a line loss of 2.5 cycles at 60 hertz.

- Over-current and over-voltage protection on all power supply outputs.

- Input voltage protection.

- Line standby mode for memory integrity.

#### MEMORY

N-channel MOS semiconductor memory with 650nanosecond cycle time; expandable as follows:

HP 2101A Memory — expandable in mainframe to 32K in HP 2105A; 64K in HP 2108A, and 128K in HP 2112A.

HP 2102A Memory — expandable in mainframe to 32K in HP 2105A; 64K in HP 2108A, and 128K in HP 2112A.

- Memory parity generation and checking are standard.

- Up to 2 hours of memory sustaining power with optional power fail recovery system; this option provides an automatic restart capability.

- Optional Dual-Channel Port Controller (DCPC) with bidirectional input/output transfer; provides for direct memory access, program assignable, to any I/O channel.

- Memory, I/O, and infinite indirect addressing protection by the memory protect or DMS option (not available for HP 2105A Processor).

- Memory integrity is maintained through a line loss of 160 milliseconds.

- Optional HP 12990A Memory Extender adds space and power for eight semiconductor memory modules.

#### INPUT/OUTPUT

- Fully microprogrammed I/O instructions.

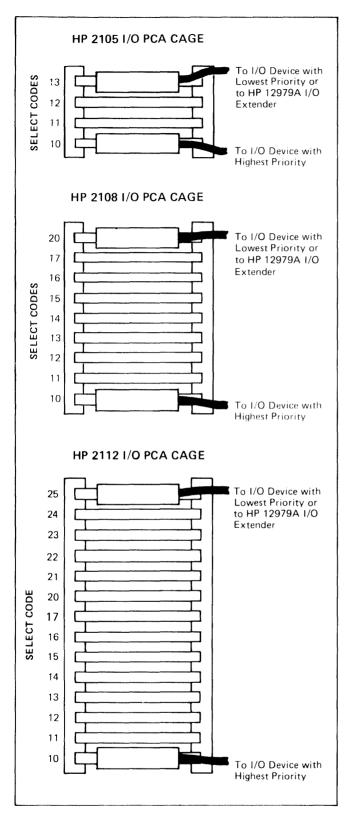

- HP 2105A has four I/O channels in mainframe.

- HP 2108A has nine I/O channels in mainframe.

- HP 2112A has 14 I/O channels in mainframe.

- I/O channels can be increased with one or two optional HP 12979A I/O Extenders (16 additional channels each).

- Compatibility maintained with existing HP 2100 Series Computer I/O interfaces.

System Features 21MX

These compact data processors are supplied with a comprehensive set of software, including assemblers, compilers, and operating systems. A full line of Hewlett-Packard peripherals and I/O interface kits are available to provide a flexible and efficient systems package. The programming languages are those commonly encountered in data processing and control.

All three processors are microprogrammed and microprogrammable, which allows program-structured commands to be coded into a more concise language than is possible using machine language. The ROM modules in which microprograms are stored are referred to collectively as *control store*. Standard control store consists of 1,024 directly addressable locations configured into four modules of 256 locations each. Each control store location accommodates one microinstruction, which in turn consists of a 24-bit word encompassing six micro-orders. The control store address space of each processor is 4,096 words

Microprograms in standard control store for executing the various machine functions are as follows:

- Base instruction set (modules 0 and 1)

- Floating point instructions (module 14)

- Extended instruction group (module 15)

Unused modules of control store are available for user-supplied microprograms. Microprogramming capabilities from a hardware standpoint are provided in *Microprogramming HP 21MX Computers Operating and Reference Manual*, part no. 02108-90008. This manual covers in detail the following:

- a. HP Microassembler

- b. HP Micro Debug Editor

- c. HP Programmable ROM Writer

- d. HP Writable Control Store (WCS) I/O Utility Routine

- e. Basic Control System (BCS) and Disc Operating System (DOS) versions of a through d above.

Some of the more important benefits of microprogramming are presented in following paragraphs.

#### 1-2. SYSTEM SPEED

Microprogramming can increase the system speed in many ways. Since microinstructions are executed from 5 to 10 times faster than machine language instructions, a frequently used software subroutine will execute much

faster when in the form of a microprogram. With 14 additional registers available to a microprogram, the number of main memory accesses can be greatly reduced. This is particularly significant in real-time systems which are compute-bound (i.e., systems in which the I/O is performed faster than the computation).

#### 1-3. MEMORY SPACE

By converting software routines into microprograms, main memory space is freed for other purposes. The routines remain instantly callable, as opposed to routines which are relegated to disc or drum storage.

#### 1-4. SPECIAL FUNCTIONS AND SECURITY

The computer instruction set can be expanded to perform functions that are oriented to specific applications. Thus, the general-purpose computer can become a special-purpose machine uniquely adapted to a particular environment. Because of the relative inaccessibility of microprograms as compared to conventional software in main memory, proprietary packages which are coded as microprograms inherently have a high degree of security.

#### 1-5. ADDITIONAL HARDWARE FACILITIES

Microinstructions in control store are 24 bits long whereas machine language instructions residing in main memory are 16 bits long. In addition, microinstructions have access to many internal registers and logic functions that machine language instructions cannot use. Software can be invented and implemented in control store to reference these registers as required by the microprogram.

1-6. WRITABLE CONTROL STORE. The Writable Control Store (WCS) option provides a read-write control store module which can be used for the development and execution of user-supplied microprograms. Microprograms in WCS are executed at the same speed as those in the read-only control store. Four WCS cards may be used with HP 2112A, two WCS cards may be used in an HP 2108A, and one WCS card may be used in an HP 2105A. The module containing the basic instruction set must always be in the form of Read-Only-Memory (ROM) integrated circuit chips. Each WCS module consists of a single card which plugs into the I/O PCA cage, thus eliminating the need for extensive cabling or an additional power supply. A WCS card contains 256 24-bit locations of Random-Access-Memory (RAM), including all necessary address and read/write circuits. WCS can be written into or read under computer control using standard input/output instructions. An I/O utility routine makes it possible for FORTRAN and ALGOL programs to write into or read from a WCS module using a conventional subroutine call.  $\Lambda$  WCS module is read at full speed by way of a flat cable connecting it to the control section of the processor. Software supplied with the WCS card includes a microassembler, a micro debug editor, a WCS I/O driver, a WCS I/O utility routine, and a WCS diagnostic.

21MX System Features

1-7. PROGRAMMABLE ROM WRITER. The Programmable ROM Writer option makes it possible for the user to permanently transfer microprograms to programmable Read-Only-Memory chips which can then be physically added to the control section of the computer. The Programmable ROM Writer consists of a single card which plugs into a computer I/O slot, thus eliminating the need for extensive cabling or an additional power supply. A small box is connected to the Programmable ROM Writer card by way of a cable; the programmable ROM chip to be burned is mounted on the box by the computer operator. A stand-alone computer program, supplied with the Programmable ROM Writer, burns and verifies the chip using punched tape input.

1-8. DYNAMIC MAPPING SYSTEM. The Dyanmic Mapping System (DMS) option gives the user the capability to address physical memory configurations larger than the standard 32,768 word limitation. The DMS provides a 20-bit-wide memory address bus which allows an addressing space of 1,048,576 words of main memory and allows the user to specify each 1,024-word page within physical memory to be read and/or write protected for program security. Separate memory translation maps provide isolation of user from system and user from user. All systems using the DMS execute with the same memory cycle time as those systems having 32K words or less of memory.

The DMS consists of a Memory Expansion Module (MEM) and a Memory Protect PCA which plug into the memory PCA cage; microcode for implementing the additional 38 machine language instructions associated with the DMS is mounted in the control store section of the Central Processor Unit (CPU).

1-9. FAST FORTRAN PROCESSOR. The Fast FORTRAN Processor (FFP) option provides the system with 13 subroutines implemented in three control store ROM modules (modules 3, 4, and 5). Included are five fast FORTRAN subroutines (.GOTO, ..MAP, .ENTR, .ENTP, and .SETP) and eight extended precision subroutines (DBLE, SNGL, .XMPY, .XDIV, .DFER, .XFER, .XADD, and .XSUB). These subroutines are executed up to 28 times faster than the same routines executed under software control.

Software for the HP 21MX Computer Series includes four high-level programming languages: HP FORTRAN, HP FORTRAN IV, HP ALGOL, and HP BASIC, plus an efficient, extended assembler which is callable by FORTRAN and ALGOL. Utility software includes a debugging routine, a symbolic editor, and a library of commonly used computational procedures such as Boolean, trigonometric, and plotting functions, real/integer conversions, natural log, square root, etc.

Hewlett-Packard provides several systems built around BASIC interpreters. The single-terminal BASIC system allows the user to prepare and run BASIC language programs conversationally through a teleprinter. Programs can also be entered through a tape reader and punched out on tape punches. A similar system, Educational BASIC, allows BASIC programs to be translated from marked cards. The time-shared BASIC systems provide an extended version of the BASIC language to 16 or 32 users simultaneously. The extensions to BASIC allow the user to store and access large amounts of data in an external mass memory, to manipulate strings of characters, and to store and retrieve programs in mass memory.

Several operating systems are available, covering a wide range of applications. The Basic Control System, which simplifies the control of input/output operations, also provides relocatable loading and linking of user programs. The time-shared systems, using conversational BASIC language, permit up to 32 terminals to be connected to the system, either directly or by telephone lines via Dataphones. The Hewlett-Packard Real-Time Executive (RTE) system permits several programs to run in real-time concurrently with general-purpose background programs. This allows multiple data-processing capabilities where separate computers are not economically feasible. The user can write programs in HP Assembly, FORTRAN, or ALGOL languages. A Magnetic Tape System and a Disc Operating System are also available. These systems greatly increase the speed and simplicity of assembling, compiling, loading, and executing user programs.

The Hewlett-Packard User Library includes over 800 tested and documented BASIC programs contributed for users. The library is segmented into the following five categories:

- Data Handling and Programming Utilities

- Scientific and Numerical Analyses

- Operations Research and Business Applications

- Education

- Demonstration Routines

Interfacing of peripheral devices is accomplished by plug-in interface printed-circuit assemblies (PCA's). The HP 2105A, HP 2108A, and HP 2112A mainframes can accommodate four, nine, and fourteen interface PCA's, respectively. The I/O capability can be increased with one or two optional HP 12979A Input/Output Extenders (16 additional channels each). Interface PCA's are available for a wide variety of peripheral devices, and virtually all interfaces developed for use with HP 2100 Computers may be used with the HP 21MX Computer Series.

System Features 21MX

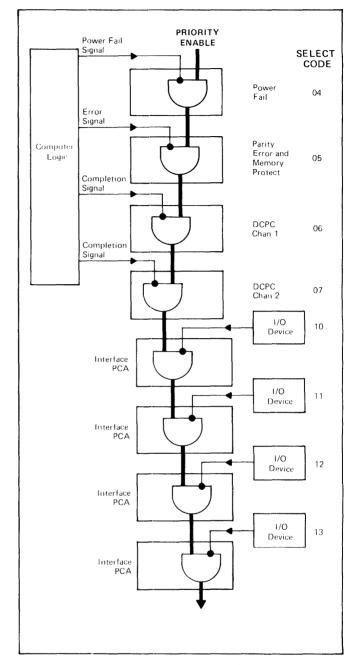

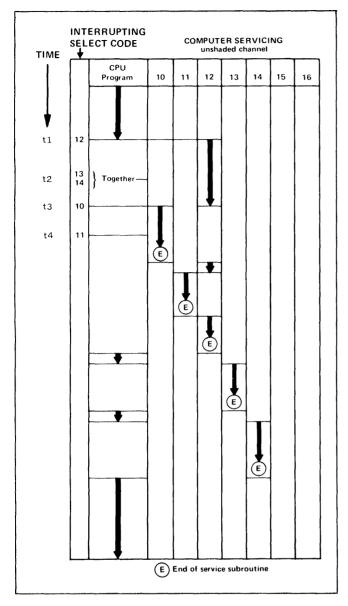

All I/O channels are buffered and bidirectional, and are serviced through a multilevel vectored priority interrupt structure. The two Dual-Channel Port Controller (DCPC) channels are program-assignable to any two of the I/O channels in the mainframe, expandable to all I/O channels if a DCPC is installed in the I/O extender. DCPC transfers occur on an I/O cycle-stealing basis, not subject to the I/O priority structure. The total bandwidth through both DCPC channels is 616,666 words per second. It is possible for the CPU to interleave memory cycles while the DCPC is operating at full bandwidth.

Table 1-1 lists the specifications of the HP 2105A, HP 2108A, and HP 2112A Microprogrammable Processors

and the HP 2101A and HP 2102A Memory Systems. All three processors have been approved by the Underwriters' Laboratories (UL) and the Canadian Standards Association (CSA).

Table 1-2 lists the options and accessories available to expand or enhance the computer system. On an original order, specify the desired system configuration by option number. For a field upgrade of an existing system, specify the system addition by accessory number.

#### Table 1-1. Specifications

#### **PROCESSOR**

CONTROL STORE

Type: Size: Bipolar LSI ROM semiconductor. Up to sixteen 256-word modules.

CONTROL PROCESSOR

Address Space: Word Size: Word Formats: Word Fields: ROM Cycle: 4,096 words. 24 bits.

Four. Five.

325 nanoseconds.

REGISTERS

Index:

Accumulators:

implicitly addressable as memory. Two (X and Y), 16 bits each.

Two (X

Memory Control: Supplementary: Manual Data: Scratch Pads: Two (T and P), 16 bits each; one (M) 15 bits. Two (overflow and extend), one bit each.

One (display), 16 bits. Twelve, 16 bits each.

DYNAMIC MAPPING SYSTEM (OPTION)

Installation:

Plugs into slots 111 and 112 of HP 2108A and HP 2112A memory PCA cage; control store module mounts on bottom of CPU.

Two (A and B), 16 bits each. Explicitly addressable; also

Address Space: Program Security:

1,048,576 words.

Memory Cycle Time: System Control: Memory Maps: Read and write protection; programmable base page fence protection.

650 nanoseconds.

38 machine instructions.

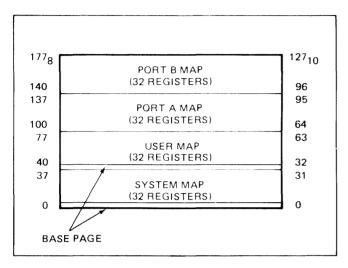

Map Registers: Parity Error Interrupt: Four dynamically alterable maps; two for program execution and two for Dual-Channel Port Controller. Allows DCPC to communicate to an area separate from program space; loading and unloading may be done from noncontiguous memory segments.

32 registers per map; 12 bits per register. Yes

Yes.

Program Compatibility:

Compatible with existing software for HP 21MX and HP 2100 Computers.

Operating system may be given complete control of I/O

logic.

I/O Control:

MEMORY PARITY CHECK HP 2105A Processor:

Monitors all words read from memory. Switch selectable to either halt or ignore parity when detected. A parity indication is displayed on operator panel.

HP 2108A and HP 2112A Processors:

Same as for HP 2105A. With memory protect or DMS option, interrupt on parity error occurs.

POWER FAIL INTERRUPT

Priority: Power Failure: Highest priority interrupt.

Detects power failure and generates an interrupt to trap cell for user-written power-failure routine. A minimum of 500  $\mu$ s is available for the routine. Automatic restart is provided as a memory system option.

Table 1-1. Specifications (Continued)

### PROCESSOR (Continued)

**PROTECTION**

Loaders:

All loaders reside in special ROM's separate from control ROM and are loaded into last 64 words of logical main memory by activating operator panel switches. Paper tape loader is standard; three additional switch-selectable loader spaces are provided to accommodate other modes of operation as a user option. User-generated loaders may be written in Assembly Language.

Mains ac standby mode and sustaining power for line loss of 2.5 cycles at 60 Hz before entering power fail routine. Power fail recovery is a memory system option.

Volatility:

INPUT/OUTPUT

Priority Interrupt:

I/O Channels:

Current Available to I/O:

Multilevel vectored priority interrupt determined by interface channel assignment.

HP 2105A: four internal I/O channels; expandable to 36 channels with two I/O extenders.

HP 2108A: nine internal I/O channels; expandable to 41 channels with two I/O extenders.

HP 2112A: 14 internal I/O channels; expandable to 46 channels with two I/O extenders.

| SUPPLY             | HP 2105A             | HP 2108A              | HP 2112A              |

|--------------------|----------------------|-----------------------|-----------------------|

| +5V<br>-2V<br>+12V | 6.0V<br>2.0A<br>1.0A | 13.0A<br>4.0A<br>1.5A | 18.0A<br>9.1A<br>3.0A |

| - 12V              | 1.0A                 | 1.5A                  | 3.0A                  |

Note: Current availability to I/O assumes maximum memory in mainframe, Dual-Channel Port Controller, and maximum available control store mounted to CPU.

#### PHYSICAL CHARACTERISTICS

Width:

Depth:

Height:

Weight:

16-3/4 inches (42.55 cm) behind rack mount; 19 inches (48.26 cm) operator panel width on sides.

23-1/2 inches (59.69 cm); 23 inches (58.42 cm) behind operator panel.

HP 2105A: 5-1/4 inches (13.31 cm) in rack mount. HP 2108A: 8-3/4 inches (22.23 cm) in rack mount. HP 2112A: 12-1/4 inches (30.87 cm) in rack mount.

HP 2105A: 39 pounds (17.69 kg). HP 2108A: 45 pounds (20.41 kg). HP 2112A: 75 pounds (34.02 kg).

#### **ELECTRICAL CHARACTERISTICS**

Input Line Voltage: Line Frequency:

Power:

110V or 220V ac ( $\pm$ 20%), single phase. 47 to 66 Hz.

HP 2105A: 400W maximum. HP 2108A: 525W maximum. HP 2112A: 800W maximum.

Line Overvoltage Protect:

Output Protect:

Output Voltage Regulation:

Thermal Sensing:

Input crowbar in series with line breaker.

All voltages protected against overvoltage and overcurrent.

±5%.

Monitors internal temperature and automatically shuts down if temperature exceeds specified level.

#### Table 1-1. Specifications (Continued)

#### PROCESSOR (Continued)

**ENVIRONMENTAL LIMITATIONS**

Ambient Temperature:

Relative Humidity:

Operating: 32° to 131° F (0° to 55°C).

Nonoperating:  $-40^{\circ}$  to  $167^{\circ}$  F ( $-40^{\circ}$  to  $75^{\circ}$  C).

Operating: 15,000 feet (4,573 meters). Nonoperating: 25,000 feet (7,622 meters). 20 to 95% at  $77^{\circ}$  to  $104^{\circ}$  F ( $25^{\circ}$  to  $40^{\circ}$  C).

Tested for 30g shock for 11 milliseconds over a 1/2 sine

wave shape.

Can withstand vibration of 1g at 44 cycles per second.

Vibration: **VENTILATION**

Altitude:

Shock:

Air Flow:

Heat Dissipation:

Intake on left-hand side; exhaust on right-hand side. HP 2105A: 1365 BTU's (344 kilocalories)/hour, max. HP 2108A: 1795 BTU's (452 kilocalories)/hour, max. HP 2112A: 2732 BTU's (688 kilocalories)/hour, max.

MEMORY SYSTEMS

**HP 2101A MEMORY**

Density:

Configuration:

High density; 16K words per module.

Available in 8K or 16K configuration; only one 8K module

allowed per system.

HP 2102A MEMORY

Density:

Configuration:

Medium or high density:

Available in 4K, 8K, and 16K configurations; only one 4K

module allowed per system.

MEMORY ORGANIZATION

Type: Word Size:

Configuration:

Page Size: Address Space:

System Cycle Time:

Volatility Protection:

4K chip N-channel MOS/RAM semiconductor.

16 bits plus parity bit.

Controller and multiple plug-in memory modules.

1,024 words. 1.048,576 words.

650 nanoseconds.

Mains ac standby mode and sustaining power for line loss of 160 milliseconds is standard. Power fail recovery system

is optional.

MEMORY PROTECT

Fence Register:

Installation:

Priority:

Operation:

Interrupt:

Plugs into slot 111 of HP 2108A or HP 2112A memory PCA cage.

Second highest priority interrupt (shared with memory

parity).

Initiated under programmed control; protects any amount of memory, I/O, or privileged instruction whem imple-

mented in the HP 2108A or HP 2112A Processor.

Set under program control; memory below fence is protected. Interrupts to trap cell for subroutine when user program (1) attempts to alter a protected location, (2) attempts to jump into the protected area, or (3) attempts to execute

an I/O instruction.

Violation Register: Contains memory address of violating instruction.

Provides interrupt signal when parity error is detected; saves

address of error in violation register.

Infinite Indirect Protect: Interrupts are enabled after three levels of indirect

addressing.

Parity Error Interrupt:

System Features 21MX

#### Table 1-1. Specifications (Continued)

#### MEMORY SYSTEMS (Continued)

DUAL-CHANNEL PORT CONTROLLER

Installation: Plugs into slot 110 of memory PCA cage.

Number of Channels: Two.

Number of Memory Ports: One.

Registers/Channel: Two (word count and address).

Word Size: 16 bits.

Maximum Block Size: 32,768 words.

I/O Assignable: Assignable to any two I/O channels; all logic necessary to

facilitate bidirectional direct memory to and from I/O is

contained on this controller.

Transfer Rate: 616,666 words per second maximum.

Priority: Highest: DCPC Channel 1.

Middle: DCPC Channel 2.

Lowest: Processor.

POWER FAIL RECOVERY SYSTEM

Power Restart: Detects resumption of power and generates an interrupt to

trap cell for user-written restart program which has been

protected in memory by the sustaining battery.

Power Control and Charge Unit: Monitors battery charge status and provides trickle charge.

Sustaining Battery: Type: 12V nickel cadmium.

Charging rate: 350 milliamperes.

Capacity: 4 ampere-hours; will sustain 128K of HP 2101A

or 64K of HP 2102A main memory for 2 hours.

21MX System Features

Table 1-2. Options and Accessories

| DESCRIPTION                                        | OPTION NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ACCESSORY NO     |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| HP 2105A PROCESSOR                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |

| Fast FORTRAN Processor (FFP)                       | -003                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12977A           |

| Writable Control Store (WCS)                       | -005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12978A           |

| Disc Loader ROM                                    | -005<br>-014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12976A<br>12992A |

|                                                    | i i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

| 230V, 50-Hz Operation                              | -015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |

| User Control Store Board                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12945A           |

| Programmable ROM (pROM) Writer                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12909B           |

| Slide Mounting Kit                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12903A           |

| HP 2108A and HP 2112A PROCESSORS                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |