# 21MX M-Series and E-Series Computer I/O Interfacing Guide

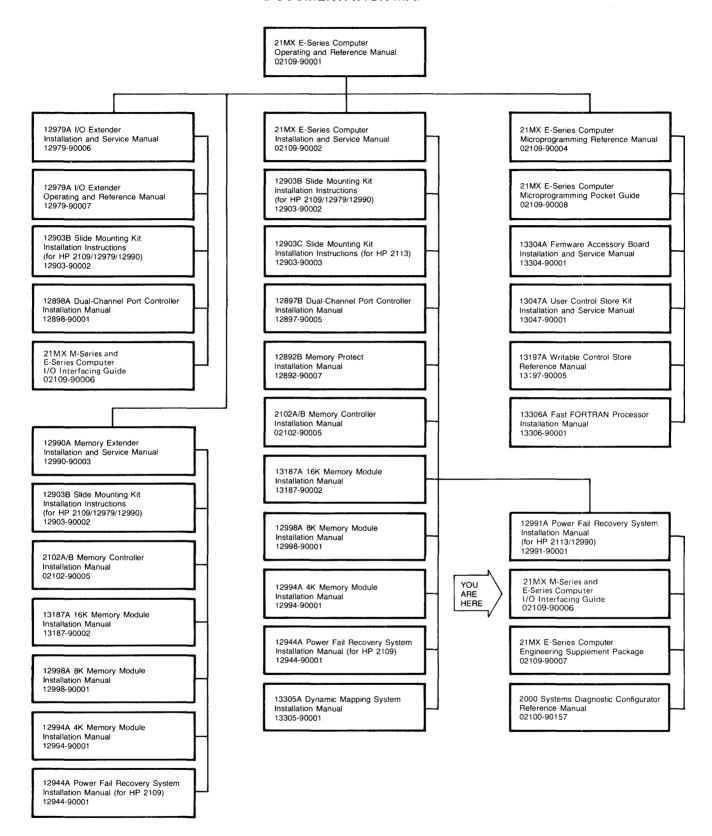

#### **DOCUMENTATION MAP**

## 21MX M-SERIES AND E-SERIES COMPUTERS

I/O interfacing guide

HEWLETT-PACKARD COMPANY

11000 WOLFE ROAD, CUPERTINO, CALIFORNIA, 95014

#### LIST OF EFFECTIVE PAGES

Changed pages are identified by a change number adjacent to the page number. Changed information is indicated by a vertical line in the outer margin of the page. Original pages do not include a change number and are indicated as change number 0 on this page. Insert latest changed pages and destroy superseded pages.

Change 0 (Original . . . . . . . . . . . July 1977

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another program language without the prior written consent of Hewlett-Packard Company.

## **CONTENTS**

| Section I<br>INTRODUCTION                | Page   | I/O Section Timing                        |             |

|------------------------------------------|--------|-------------------------------------------|-------------|

| Introduction to Interfacing              | 1-1    | Sample Programs                           | 4-8         |

| and Differences                          | 1-1    | Dual-Channel Port Controller              |             |

| User Interface Requirements              |        | (DCPC) Timing                             | 4-14        |

| Levels of Hardware Interfacing           |        | -                                         |             |

| Available Documentation                  | 1-4    |                                           |             |

| Section II                               | Page   | Section V                                 | Page        |

| COMPUTER CHARACTERISTICS                 | 1 age  | DESIGNING INTERFACE PCA'S                 |             |

| Computer Overview                        | 2-1    | Introduction                              |             |

| Control Processor Section                |        | I/O Section Interfacing                   |             |

| Arithmetic/Logic Section                 |        | I/O Interface PCA Specifications          |             |

| Main Memory Section                      |        | I/O Interface PCA Design                  |             |

| I/O Section                              |        | I/O Interface FCA Design                  | ט-ט         |

| Section III                              | Page   |                                           |             |

| I/O SYSTEM FUNDAMENTALS                  | J      | Section VI                                | Page        |

| Purpose                                  | 3-1    | ADVANCED INTERFACING TECHNIQUES           |             |

| I/O Section Control                      | 3-1    | Party-Line I/O                            |             |

| General                                  |        | Principles of Operation                   |             |

| I/O Data Transfer Instructions           |        | Controller Hardware Design                |             |

| Interrupt Requests                       |        | Input Programming Using Noninterrupt Mode |             |

| Interface PCA's                          |        | Output Programming Using Noninterrupt Mod | e . 6-5     |

| I/O Timing                               |        | I/O Programming Using Interrupt Mode      | 6-5         |

| I/O Addressing                           |        | DCPC Transfers                            |             |

| Interrupt System                         |        | Microprogrammed I/O                       |             |

| Interrupt Priority                       |        | Microprogrammed Block I/O Transfers       | 6-9         |

| Interrupt Generation                     |        | Microprogrammable Processor               |             |

| Interrupt Processing                     | 3-6    | Port Interfacing                          | 6-18        |

| I/O Data Transfers                       |        |                                           |             |

| Noninterrupt Transfers                   |        |                                           |             |

| Interrupt Transfers                      |        |                                           | _           |

| Dual-Channel Port Controller             | . 3-12 | Appendix A INTERFACE KITS                 | Page<br>A-1 |

| Section IV                               | Page   |                                           |             |

| COMPUTER TIMING                          |        |                                           | _           |

| Control Processor Timing (21MX M-Series) |        | Appendix B                                | Page        |

| Control Processor Timing (21MX E-Series) | 4-1    | I/O SIGNAL DEFINITIONS                    | B-1         |

## **ILLUSTRATIONS**

| Title Page                                   | Title Page                                        |

|----------------------------------------------|---------------------------------------------------|

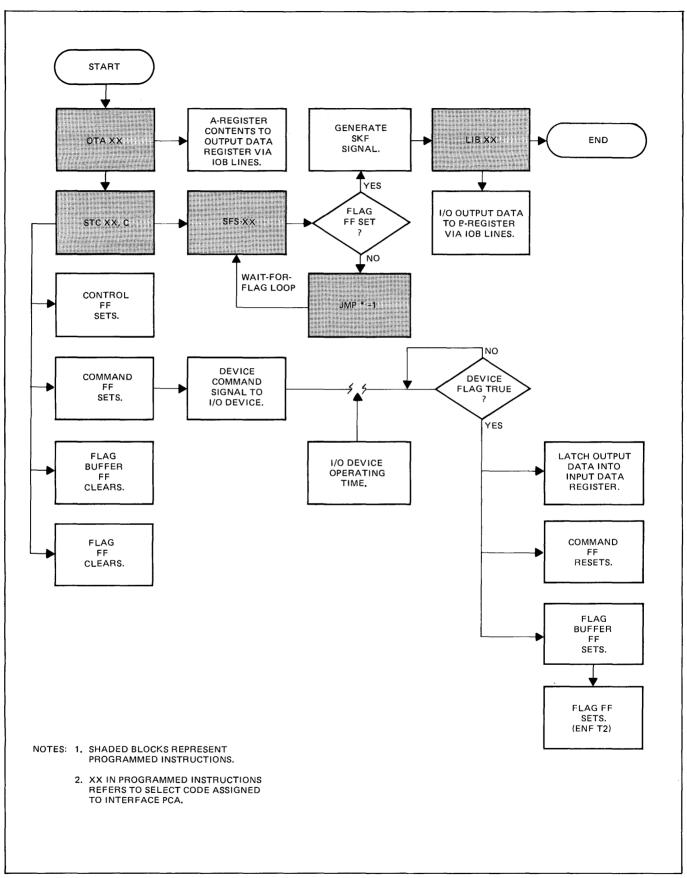

| Computer Functional Sections 2-1             | Interface PCA Functional Operation Flowchart 4-13 |

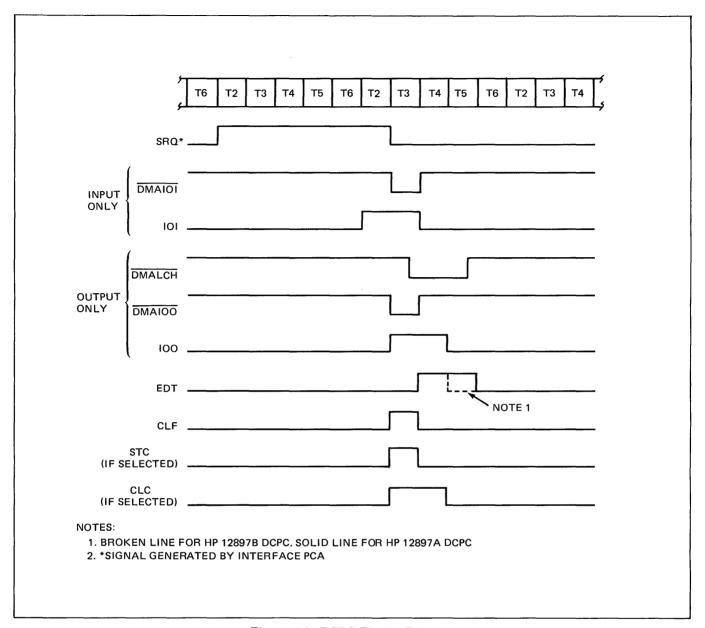

| Computer Functional Block Diagram2-2         | DCPC Timing Diagram                               |

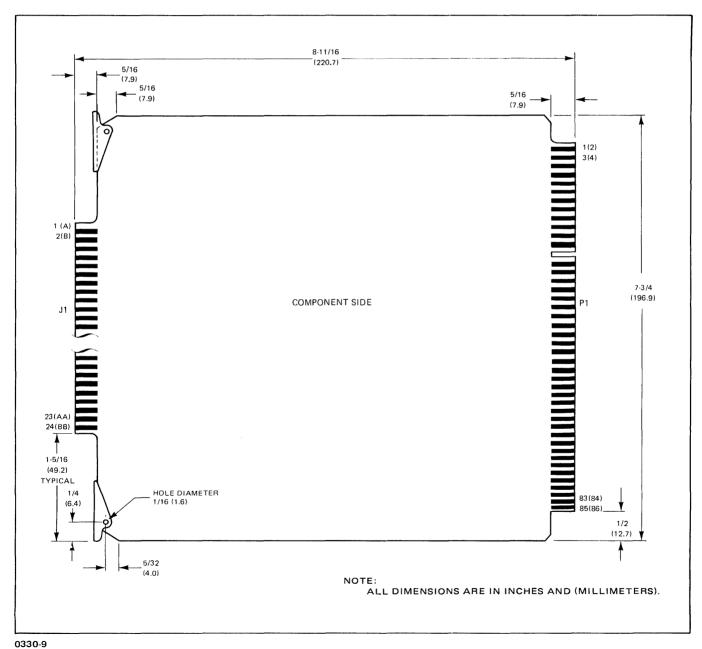

| HP 21MX M-Series Computer Block Diagram2-4   | I/O Interface PCA Dimensions 5-2                  |

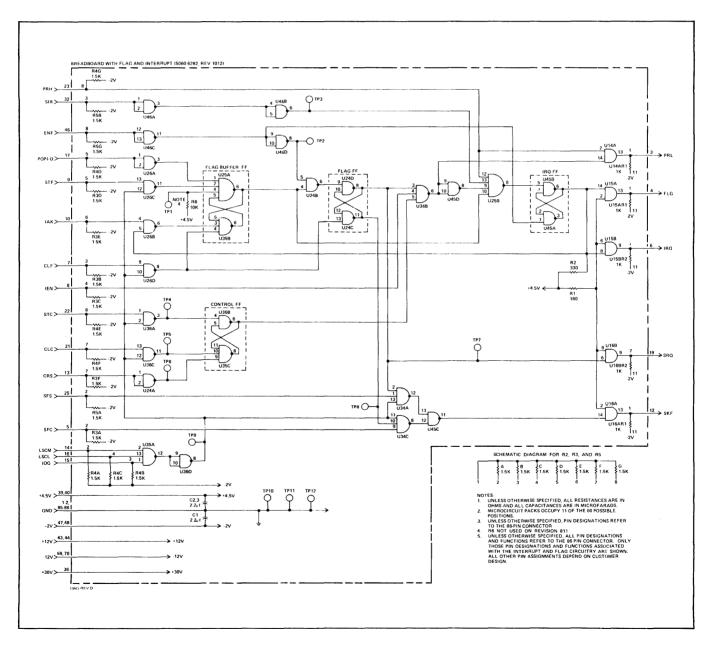

| HP 21MX E-Series Computer Block Diagram 2-6  | Flag and Interrupt Circuits Logic Diagram 5-4     |

| Input/Output System                          | Valid Interface PCA TTL Receiver 5-5              |

| I/O Address Assignments                      | Valid Interface PCA Driver Circuit5-5             |

| I/O Slot Connector Select Code Wiring3-5     | Valid Interface PCA PRL and SRQ                   |

| Interrupt Priority Network                   | Line Drivers                                      |

| Input Data Transfer (Interrupt Method) 3-10  | Remote Computer Halt Drive Circuit 5-6            |

| Output Data Transfer (Interrupt Method) 3-11 | Typical I/O Device Controller Simplified          |

| DCPC Input Data Transfer 3-12                | Logic Diagram6-4                                  |

| DCPC Control Word Formats3-13                | Critical DCPC Interface Design 6-8                |

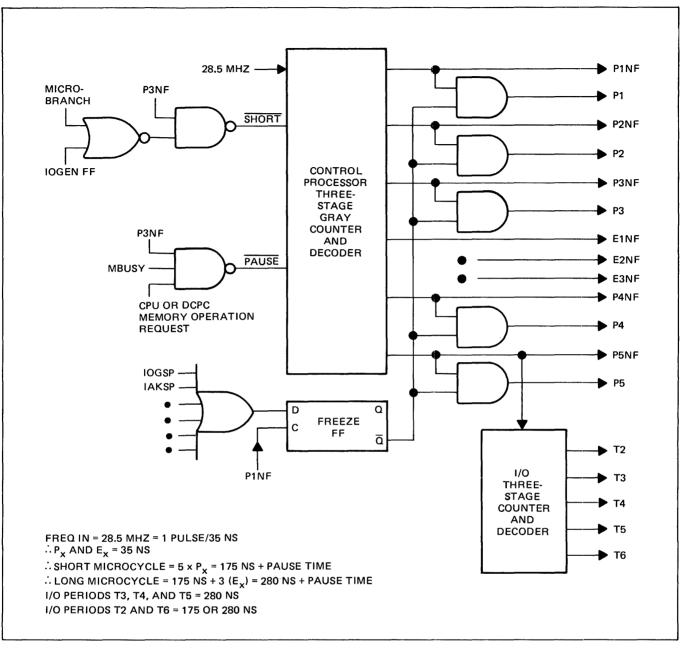

| HP 21MX M-Series Computer                    | Microprogrammed Block I/O Input                   |

| Timing Configuration4-2                      | Data Transfer                                     |

| HP 21MX M-Series Control Processor           | Microprogrammed Block I/O Flow Diagram 6-10       |

| Timing Diagram4-3                            | Interface PCA Flag and Interrupt Circuit          |

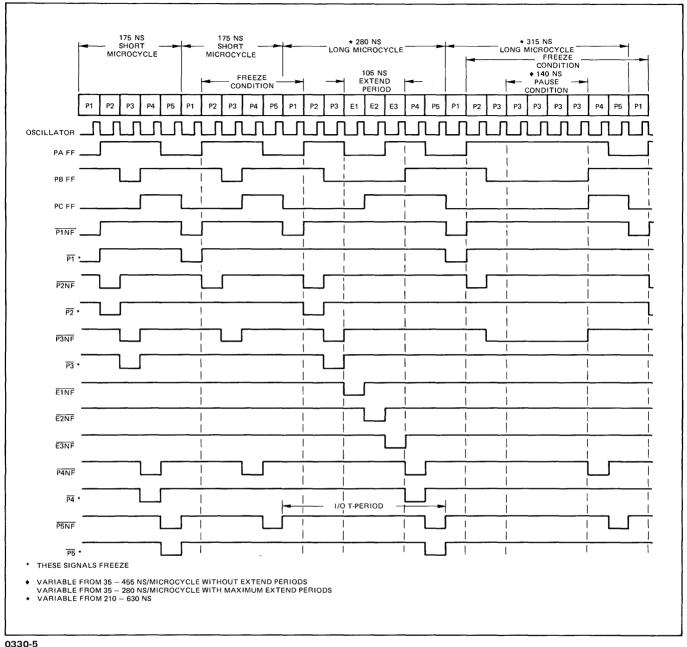

| HP 21MX E-Series Computer                    | Modifications Required For Microprogrammed        |

| Timing Configuration4-4                      | I/O Transfers6-11                                 |

| HP 21MX E-Series Control Processor           | Typical Microprogrammed Block I/O                 |

| Timing Diagram4-5                            | Interface Circuits6-13                            |

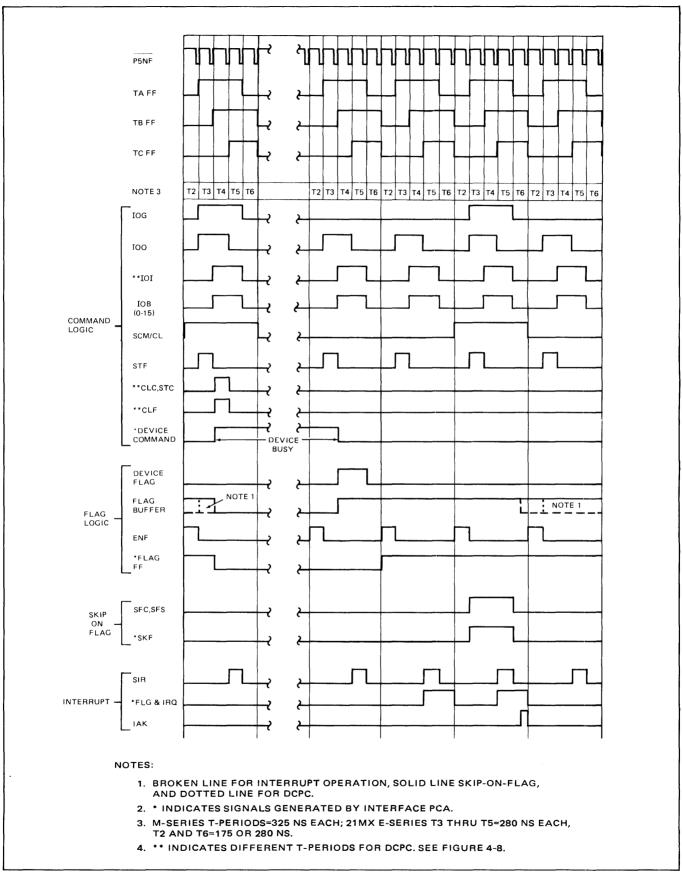

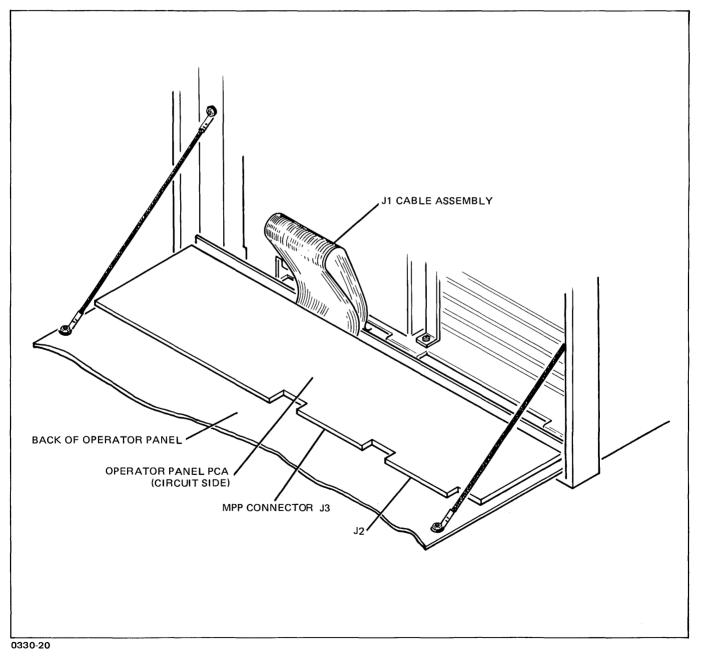

| I/O Section Timing Diagram 4-6               | MPP Connector Location 6-19                       |

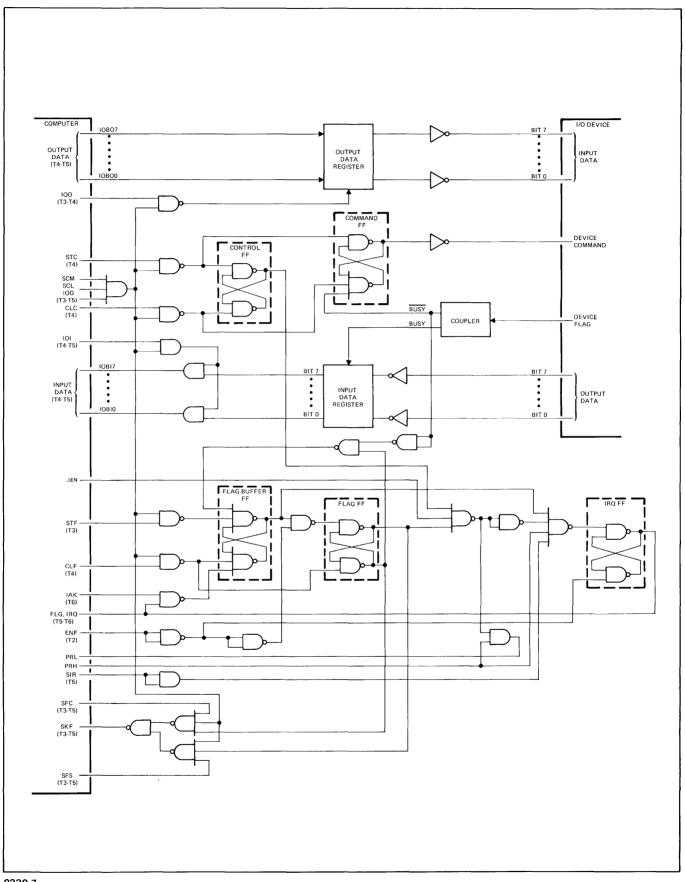

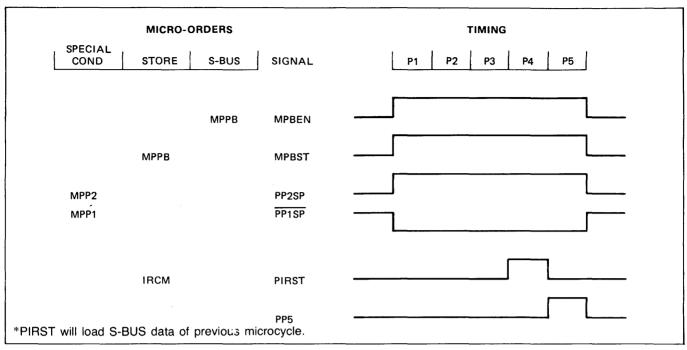

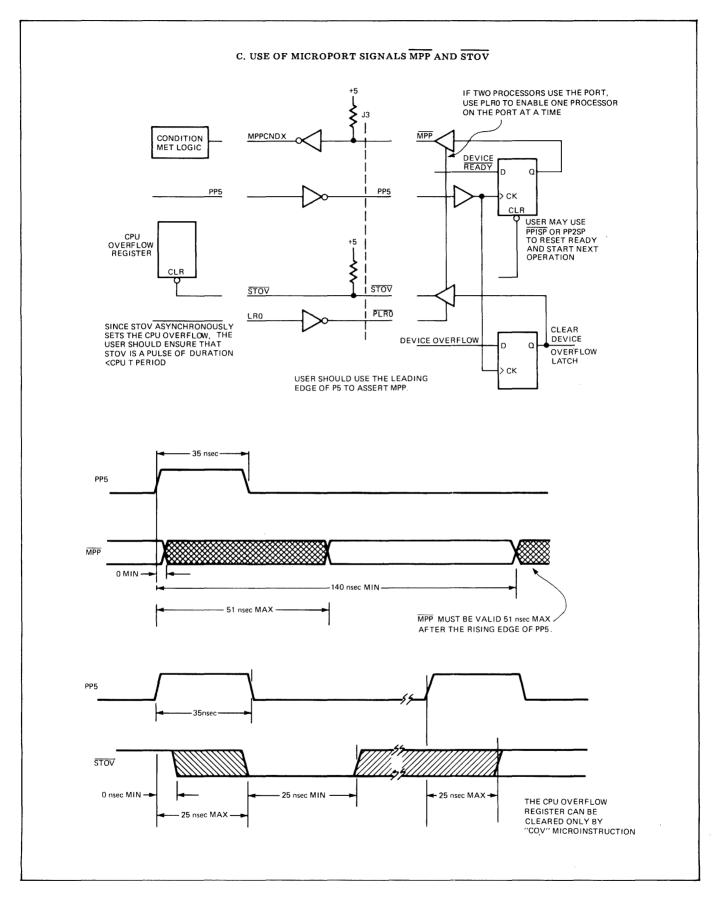

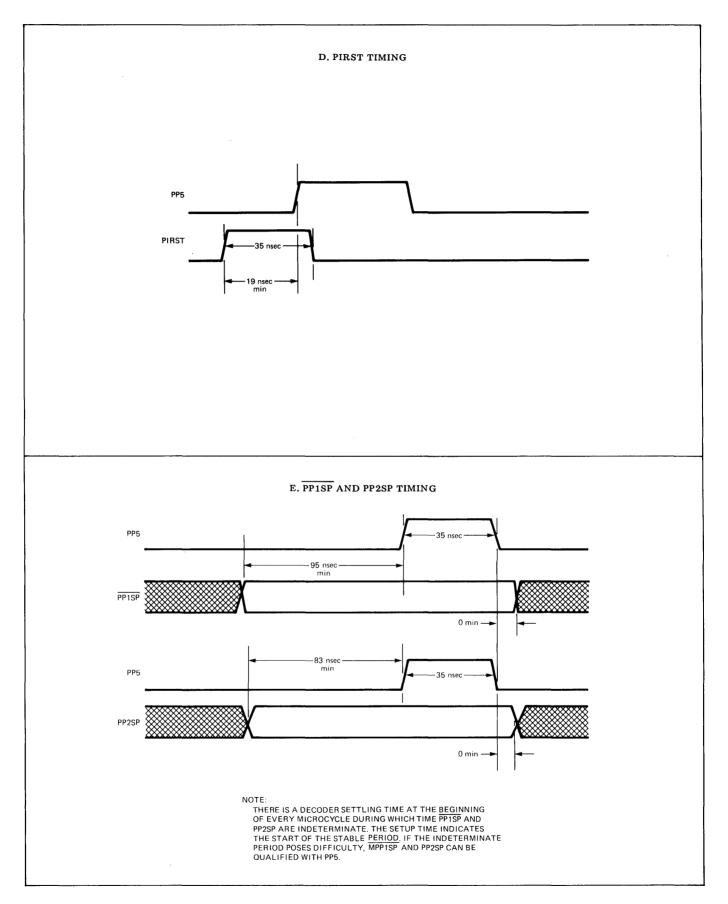

| Duplex Register Interface PCA Simplified     | MPP Timing Diagram6-21                            |

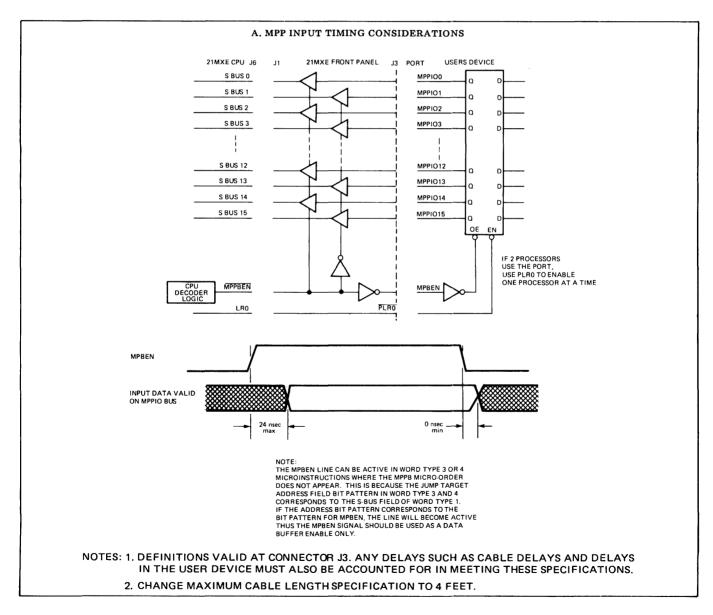

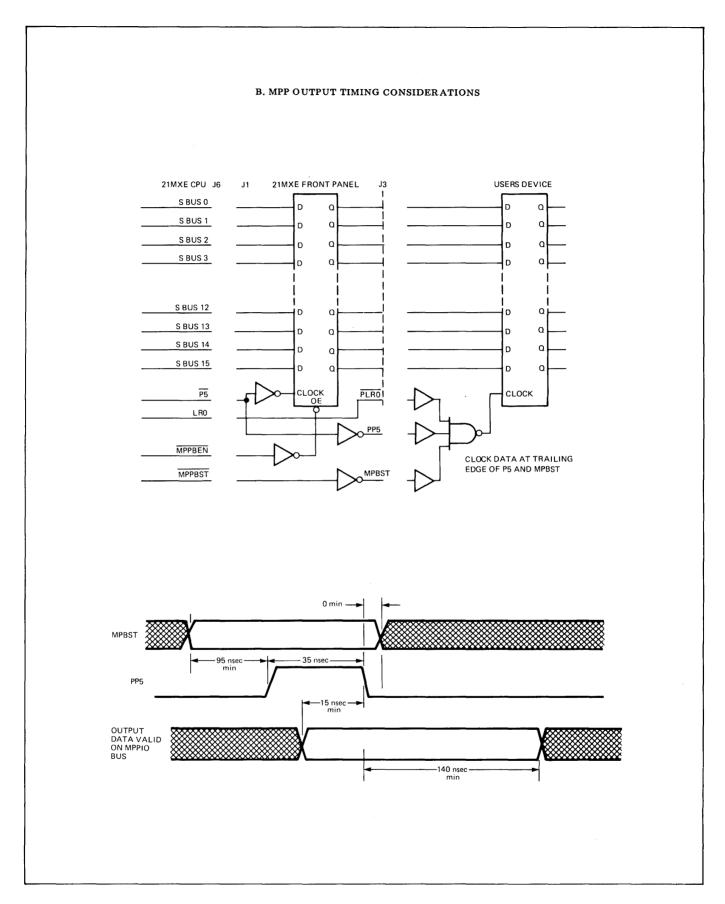

| Logic Diagram4-9                             | MPP Timing Considerations 6-22                    |

## **TABLES**

| Title Pa                                  | ge        | Title                                      | Page |

|-------------------------------------------|-----------|--------------------------------------------|------|

| HP 21MX M- and E-Series Computers         |           | I/O Current Availability From I/O Extender | 5-6  |

| Interface Specifications                  | <b>-2</b> | Interface PCA Test Program                 |      |

| I/O Interface Related Reference Manuals 1 | l-5       | Interrupt Test Program                     | 5-9  |

| Select Code Assignments 3                 | 3-4       | Command and Status Bit Assignments         |      |

| Interrupt and I/O Control Summary         |           | Party-Line Noninterrupt Input Routine      |      |

| Noninterrupt Transfer Routines            |           | Party-Line Noninterrupt Output Routine     |      |

| DCPC Initialization Program3-             | 14        | Party-Line Interrupt Input Routine         | 6-6  |

| I/O Signal Definitions and Connector      |           | Master Interrupt Subroutine                | 6-7  |

| Pin Assignments4                          | L-7       | Specific Device Interrupt Subroutine       | 6-7  |

| Sample Input and Output Programs4-        | 10        | Forming and Executing Microprogrammed      |      |

| Sample Combined I/O Programs4-            | 10        | I/O Instructions                           | 6-12 |

| Interrupt-Method Input Routine4-          | 11        | Block I/O Output Microprogram              | 6-14 |

| Flag and Interrupt Circuit Test           |           | Block I/O Input Microprogram               | 6-16 |

| Point Definitions 5                       | 5-3       | MPP Connector J3 Signal Definitions and    |      |

| Flag and Interrupt Logic Component        |           | Connector Pin Assignments                  | 6-20 |

| Identification 5                          | 5-5       | MPP Word Burst Input Microprogram          | 6-21 |

|                                           |           |                                            |      |

## INTRODUCTION

ı

This manual is provided as an aid for design engineers and programmers to design and program special-purpose interfaces for the HP 21MX M-Series and HP 21MX E-Series Computers. The content of this manual is presented as a supplement to the HP 21MX Computer Series Reference Manual and to the HP 21MX E-Series Computer Operating and Reference Manual and the user should therefore have a thorough understanding of the applicable reference manual contents prior to reading this manual. It is also suggested that the user read this manual in its entirety and become completely acquainted with its contents before attempting to use the information presented in any one particular section.

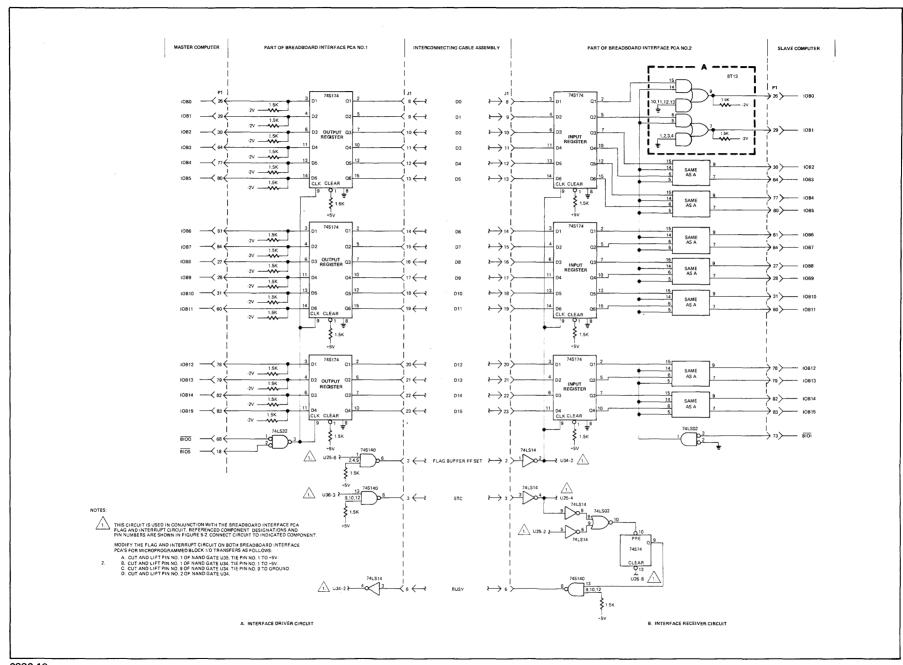

#### 1-1. INTRODUCTION TO INTERFACING

Interfacing a peripheral device with HP 21MX M- and E-Series Computers involves both hardware and software. Except for the Microprogrammable Processor Port (MPP) interfacing discussed in Section VI, the hardware interface is accomplished by inserting one or more interface printed-circuit assemblies (PCA's) into easily accessible input/output (I/O) slots in the computer and connecting a cable between the interface PCA(s) and the peripheral device. As discussed in Section III, the computer provides a unique channel identification and service priority interrupt for every I/O channel used. Priority levels for the peripheral devices connected to the computer can be reassigned by simply changing the position of the interface PCA's in the computer I/O slots. (Specifications for I/O-type interface PCA's are discussed in Section V.) The software interface is accomplished by updating the existing computer I/O software system which may necessitate creating a new peripheral device driver.

## 1-2. HP 21MX M-SERIES AND E-SERIES BASIC FEATURES AND DIFFERENCES

The HP 21MX M-Series and E-Series are microprogrammable, high-performance computers. The HP 21MX E-Series Computers (HP 2109 and HP 2113) are enhanced versions of the HP 21MX M-Series Computers (HP 2105, HP 2108, and HP 2112) featuring faster system cycle and instruction execution times, faster I/O transfer rates, and increased microprogram routine efficiency. Pertinent interfacing specifications for the computers are contained in table 1-1. For more detailed specifications, refer to the applicable reference manuals listed in paragraph 1-5. A discussion of control processor and I/O section timing for the computers is contained in Section IV.

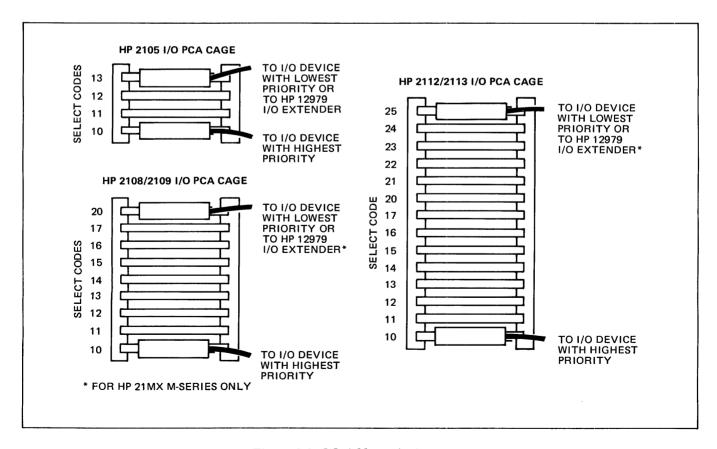

The I/O systems for the HP 21MX M- and E-Series Computers are generally compatible with each other. Individual differences between the I/O systems are discussed throughout this manual. The computer I/O system features a multilevel, vectored priority interrupt structure. There are 60 distinct interrupt levels, each of which has a unique priority assignment. Any I/O device can be selectively enabled or disabled, or the entire interrupt system (except for power fail and parity error interrupts) can be enabled or disabled under program control. (Refer to Section III.) The HP 2105 computer has four I/O channels in its mainframe; the HP 2108 and HP 2109 computers have nine; and the HP 2112 and HP 2113 have 14. The number of available I/O channels for the HP 21MX M-Series computer can be increased by adding one or two HP 12979 I/O Extenders that provide 16 additional I/O channels each. All I/O channels are fully powered, buffered, and bidirectional.

Data transfers between HP 21MX M- or E-Series Computers and I/O devices can take place under program control or, for faster transfer rates, under Dual- Channel Port Controller (DCPC) control. The DCPC provides two direct links between computer memory and I/O devices and is program assignable to any two devices. DCPC data transfers occur on an I/O cycle-stealing basis and are independent of the I/O priority structure. For applications where even faster transfer rates are desirable, the HP 21MX E-Series Computers have special microprogrammed I/O capabilities that are discussed in Section VI.

#### 1-3. USER INTERFACE REQUIRE-MENTS

This manual assumes that the user wishes to interface a device which is not a standard peripheral supplied by Hewlett-Packard along with its software I/O driver subroutine. Therefore, two objectives must be accomplished: some sort of general-purpose or special I/O interface PCA must be selected to plug into the computer and accept the device interface cable, and I/O software must be configured so that the computer can control the device. There are several possible methods of accomplishing these objectives. For hardware, the methods range from using available HP general-purpose interface PCA's to designing and building special interface PCA's from the drawingboard level. For software, writing a short assembly-language subroutine may suffice, or full Basic Control System (BCS), Real-Time Executive (RTE) system, or Disc Operating System (DOS) drivers may have to be written. For software development information, refer to the applicable software system documentation listed in table 1-2.

Table 1-1. HP 21MX M- and E-Series Computers Interface Specifications

| FEATURE                                                                                                                                     |                                                     | CAPABILITY                                                                                                  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                             | HP 21MX M-SERIES                                    | HP 21MX E-SERIES                                                                                            |  |  |  |

| MAX. MAINFRAME MEMORY SIZE:  (Optional HP 12990A Memory Extender adds space and power for additional 144K.)                                 | HP 2105 to 32K<br>HP 2108 to 80K<br>HP 2112 to 160K | HP 2109 to 80K<br>HP 2113 to 160K                                                                           |  |  |  |

| WORD SIZE:                                                                                                                                  | 16 bits                                             | 16 bits                                                                                                     |  |  |  |

| SYSTEM CYCLE TIME (nS):                                                                                                                     | 650                                                 | 560                                                                                                         |  |  |  |

| INPUT/OUTPUT INSTRUCTION GROUP EXECUTION TIME ( $\mu$ S): (Depends on which I/O time period the instruction begins; T2, T3, T4, T5, or T6.) | 2.59 to 3.89                                        | 1.58 to 2.66                                                                                                |  |  |  |

| * INTERRUPT LATENCY (μS):                                                                                                                   | 85 (max.)                                           | 45 (max.)                                                                                                   |  |  |  |

| DUAL-CHANNEL PORT CONTROLLER                                                                                                                |                                                     |                                                                                                             |  |  |  |

| Number of Channels:                                                                                                                         | 2                                                   | 2                                                                                                           |  |  |  |

| Word Size:                                                                                                                                  | 16 bits                                             | 16 bits                                                                                                     |  |  |  |

| Maximum Block Size:                                                                                                                         | 32,768 words                                        | 32,768 words                                                                                                |  |  |  |

| Maximum Input Transfer Rate (Words/Second):                                                                                                 | 616,666                                             | 1,000,000                                                                                                   |  |  |  |

| Maximum Output Transfer Rate (Words/Second):                                                                                                | 616,666                                             | Without DMS: 890,000<br>With DMS: 860,000                                                                   |  |  |  |

| ** DCPC LATENCY (Channel 1)                                                                                                                 |                                                     |                                                                                                             |  |  |  |

| Input Latency Time (μS):                                                                                                                    | Worst Case: 2.93<br>Typical: 2.22                   | Worst Case with DMS: 3.22 Typical with DMS: 1.78 Worst Case without DMS: 3.05 Typical without DMS: 1.68     |  |  |  |

| Output Latency Time (μS):                                                                                                                   | Worst Case: 3.25<br>Typical: 2.54                   | Worst Case with DMS: 3.395 Typical without DMS: 1.855 Worst Case without DMS: 3.225 Typical with DMS: 1.960 |  |  |  |

| MICROPROGRAMMABLE BLOCK I/O TRANSFERS<br>(HP 21MX E-Series Only)                                                                            |                                                     |                                                                                                             |  |  |  |

| Input (256 words or less):                                                                                                                  | 1.59M words/sec (maximum)                           |                                                                                                             |  |  |  |

| Output (256 words or less):                                                                                                                 | 1.36M words/sec (maximum)                           |                                                                                                             |  |  |  |

| MICROPROGRAMMABLE PROCESSOR PORT (MPP) I/O TRANSFERS (HP 21MX E-Series Only)                                                                |                                                     |                                                                                                             |  |  |  |

| Burst (16 words or less):                                                                                                                   | 5.7M words/sec (maximum)                            |                                                                                                             |  |  |  |

| Continuous:                                                                                                                                 | 1.59M words/sec (maxin                              | num)                                                                                                        |  |  |  |

M/E Introduction

| Table 1-1. | HP 21MX M- | and E-Series | Computers | Interface | Specifications | (Continued) |

|------------|------------|--------------|-----------|-----------|----------------|-------------|

|            |            |              |           |           |                |             |

MAXIMUM CURRENT AVAILABLE FOR MEMORY, ACCESSORIES, AND I/O CARDS

| SUPPLY VOLTAGE | 2105A | 2108A | 2109A | 2112A | 2113A |

|----------------|-------|-------|-------|-------|-------|

| + 5V           | 12.8A | 24.8A | 24.6A | 38.2A | 38.0A |

| -2V            | 1.5A  | 4.5A  | 4.5A  | 9.5   | 9.5   |

| +12V           | 1.0A  | 1.5A  | 1.5A  | 3.0A  | 3.0A  |

| -12V           | 1.0A  | 1.5A  | 1.5A  | 3.0A  | 3.0A  |

NOTES: \* Interrupt latency is defined as the time interval between the generation of an Interrupt Request (IRQ) signal by an I/O device and entry into the service routine.

## 1-4. LEVELS OF HARDWARE INTERFACING

For purposes of this manual, the approaches to interfacing break down into three levels: Level 1 — Using HP General-Purpose Interface PCA's, Level 2 — Party-Line I/O, and Level 3 — Fabricating Interface PCA's.

Level 1 assumes that the specifications of off-the-shelf HP general-purpose interface PCA's are satisfactory to operate your device. These interface PCA's cover a wide range of applicability: receiving or transmitting signals with characteristics suitable for microcircuits, transistors, or relays. Appendix A of this manual contains a condensed, general description of the general-purpose interface kits available from Hewlett-Packard as of this printing. A data sheet providing the features, specifications, and a list of product support documentation and software either supplied with or available for the applicable interface kit is available at your nearest Hewlett-Packard Sales and Service Office. (A list of Sales and Service Offices is provided at the back of this manual). Economics in design and manufacture can frequently be achieved by using these general-purpose interfaces. If a large number of devices, or devices of a special type are required to be serviced by the computer, or if exceptionally fast transfer rates are desired, Level 2 or Level 3 may have to be considered.

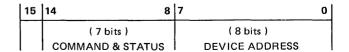

Level 2 provides a party-line method of servicing a large number of I/O devices. The number of devices serviceable by party-line I/O is dependent on the addressing word format you choose. Assuming seven bits are used for command and status information, eight bits would be left to address 256 devices. (One bit must be reserved for indirect addressing.) This is a typical example, but the quantity limit can vary by factors of the powers of two (128, 256, 512, etc.). A detailed discussion of party-line I/O is contained in Section VI.

Level 3 is the most basic level; designing and building an interface PCA that will permit the computer to service special-type devices or, for the HP 21MX E-Series Computers only, an interface that permits the faster microprogrammed I/O capabilities. Hewlett-Packard can furnish a breadboard interface PCA with the Flag and Control logic required by the computer's I/O section to facilitate these procedures. Refer to Sections V and VI for more detailed information. It should be noted that the HP 21MX E-Series Computer has provisions for two types of microprogrammed I/O data transfers: transfers via a block I/O interface PCA connected to the I/O Section and transfers via an interface PCA connected to the Microprogrammable Processor Port (MPP). As an aid toward determining whether block I/O or MPP transfers are best for your particular application, the following features and limitations should be considered. Generally, MPP transfers are easier to microprogram and provide faster data transfer rates. Block I/O transfers are more difficult to microprogram because the microcode must be written to simulate I/O instructions and the data transfer rates are slower because the I/O control instructions must be synchronized to I/O Section timing. The MPP is totally independent of the I/O Section and, therefore, does not require

<sup>\*\*</sup> DCPC latency is defined as the time interval between the generation of a Service Request (SRQ) signal by an I/O device through the initiation of a DCPC channel 1 cycle to the actual completion of the I/O data transfer to or from the I/O interface PCA.

Introduction M/E

the use of an I/O Section connector slot or select code. Also, since MPP transfers are affected through bus drivers and receivers, the MPP has the capability of driving cables up to six feet (1.83 meters) in length. Conversely, block I/O transfers do require the use of an I/O Section connector slot and do require a select code. Therefore, block I/O transfers can be used to combine the speed of microprogrammed I/O transfers with the capabilities of the interrupt system discussed in Section III. The MPP has no interrupt capability. Therefore, the computer must determine when the I/O device requires service by polling the device in the microprogram and then initiating the required data transfer. Refer to Section VI for more detailed information.

At all levels, the user should keep in mind that Hewlett-Packard warranties and responsibilities apply only to those items produced and quality controlled by Hewlett-Packard. This manual is intended as a guide only, and the effectiveness of devices or programs created according to the recommendations outlined herein are purely the responsibility of the user.

#### 1-5. AVAILABLE DOCUMENTATION

Supporting hardware documentation is provided with each Hewlett-Packard computer shipped to a customer. Hardware documentation is also supplied for optional and accessory add-ons as well as for off-the-shelf I/O interface PCA's. Basic hardware manuals for the HP 21MX M- and E-Series Computers are listed in table 1-2. Hardware manuals are also available for the I/O interface PCA's described in Appendix A of this manual. Consult your local Hewlett-Packard Sales and Service Office for additional hardware documentation related to the HP 21MX M- and E-Series Computers. If your computer was supplied as part of an HP computer system, a complete list of related hardware documentation is contained in the Manual and Software Record supplied with the system.

All software supplied with any HP computer system is supported by complete user documentation. General types of software manuals include language manuals, operating system manuals, software operating procedures, user manuals, applications manuals, and small program manuals. The Manual and Software Record supplied with each system lists all software furnished with the original equipment and provides an index to the software documentation. Software and software documentation supplied with standard HP I/O interface PCA's are listed in the individual data sheets. Reference manuals that contain basic information for writing system software drivers are listed in table 1-2. Consult your local Hewlett-Packard Sales and Service Office for additional software documentation related to the HP 21MX M- and E-Series Computers.

A complete list of microprogramming manuals available for the 21MX M- and E-Series Computers is contained in table 1-2.

Table 1-2. I/O Interface Related Reference Manuals

| TITLE                                                                   | HP PART NUMBER      |

|-------------------------------------------------------------------------|---------------------|

| HARDWARE                                                                |                     |

| HP 21MX Computer Series Reference Manual                                | 02108-90002         |

| HP 21MX Computer Series Operator's Manual                               | 02108-90004         |

| HP 21MX Computer Series Installation and Service Manual                 | 02108-90006         |

| HP 21MX E-Series Computer Operating and Reference Manual                | 02109-90001         |

| HP 21MX E-Series Computer Installation and Service Manual               | 02109-90002         |

| MICROPROGRAMMING                                                        |                     |

| HP 21MX M-Series Computer BCS and DOS Microprogramming Reference Manual | 02108-90008         |

| HP 21MX M-Series Computer RTE Microprogramming Reference Manual         | 02108-90032         |

| HP 21MX E-Series Computer Microprogramming Reference Manual             | 02109-90004         |

| SOFTWARE                                                                |                     |

| Basic Control System                                                    | 021 <b>\</b> 6-9017 |

| DOS-III Data Communications Drivers Reference Manual                    | 24307-90012         |

| DOS-III Standard Drivers Reference Manual                               | 24307-90073         |

| HP 24307B/C DOS-III Disc Operating System Reference Manual              | 24307-90006         |

| Real-Time Executive Operating System Drivers and Device Subroutines     | 92200-93005         |

| RTE-II Programming and Operating Manual                                 | 92001-93001         |

| RTE-III Programming and Operating Manual                                | 92060-90004         |

## **COMPUTER CHARACTERISTICS**

As an aid toward more successful I/O interface design, this section contains a general discussion of the HP 21MX M-and E-Series Computer's operation and architecture. Unless otherwise specified, the contents of this section apply equally to the HP 21MX M-Series and HP 21MX E- Series Computers.

#### 2-1. COMPUTER OVERVIEW

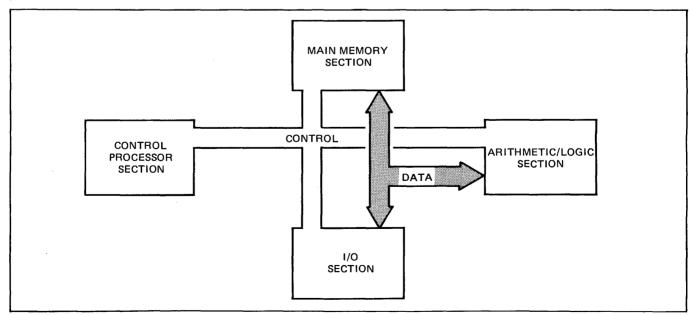

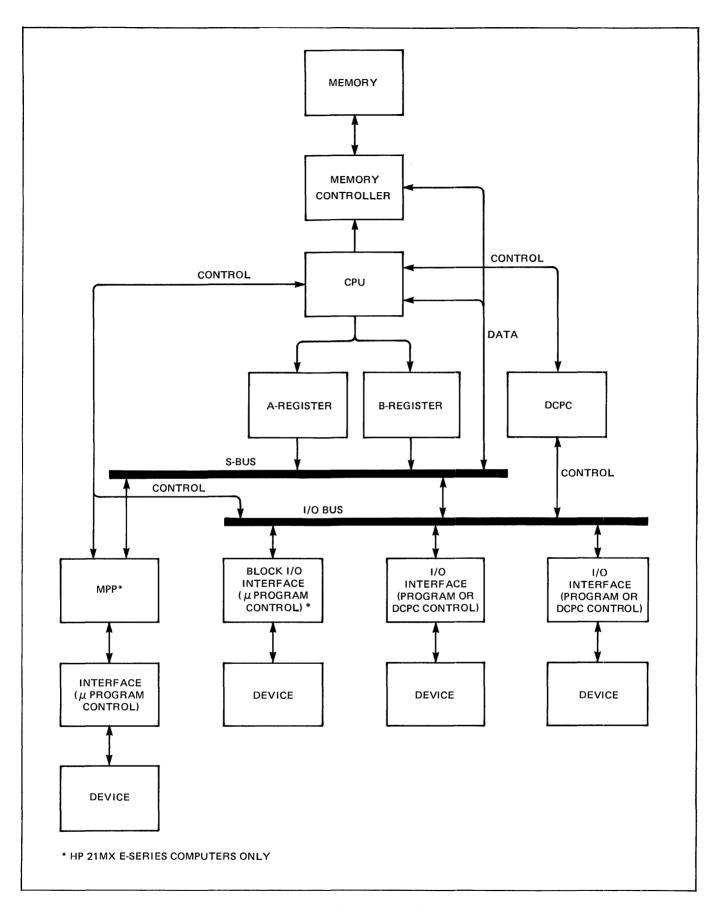

As shown in figure 2-1, the computer functionally consists of four major sections: a Control Processor Section, Main Memory Section, I/O Section, and Arithmetic/Logic Section. These four sections and the computer's Operator Panel are interconnected by a network of signal paths. Data processing programs and data are stored in the Main Memory Section. Parameters, status, commands, and computer results (data) are exchanged with external peripherals via the I/O Section. Mathematical functions such as add, subtract, and multiply and logical functions such as "and", "or", and shift are performed by the Arithmetic/Logic Section. The Operator Panel registers and switches provide direct operator communication. Each section operates under direction of the Control Processor Section by means of a microprogram. The Control Processor Section interprets the user's program stored in the Main Memory Section and directs the appropriate hardware in each of the other sections to perform the required operations. Control commands (or microinstructions) spell out which signal paths the data is to follow and what modifications or tests are to be performed.

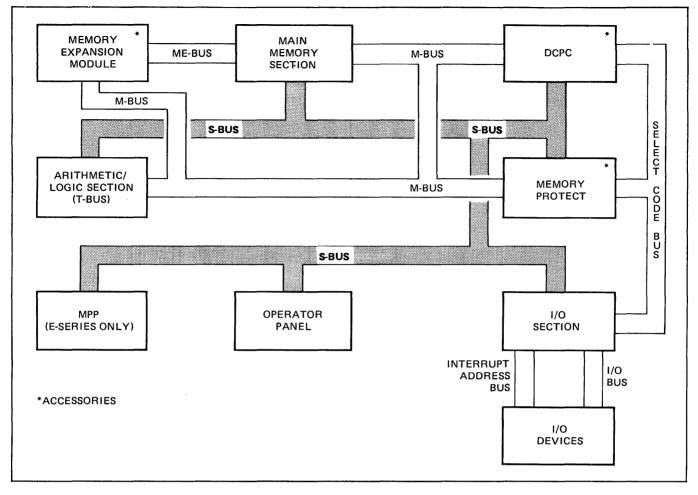

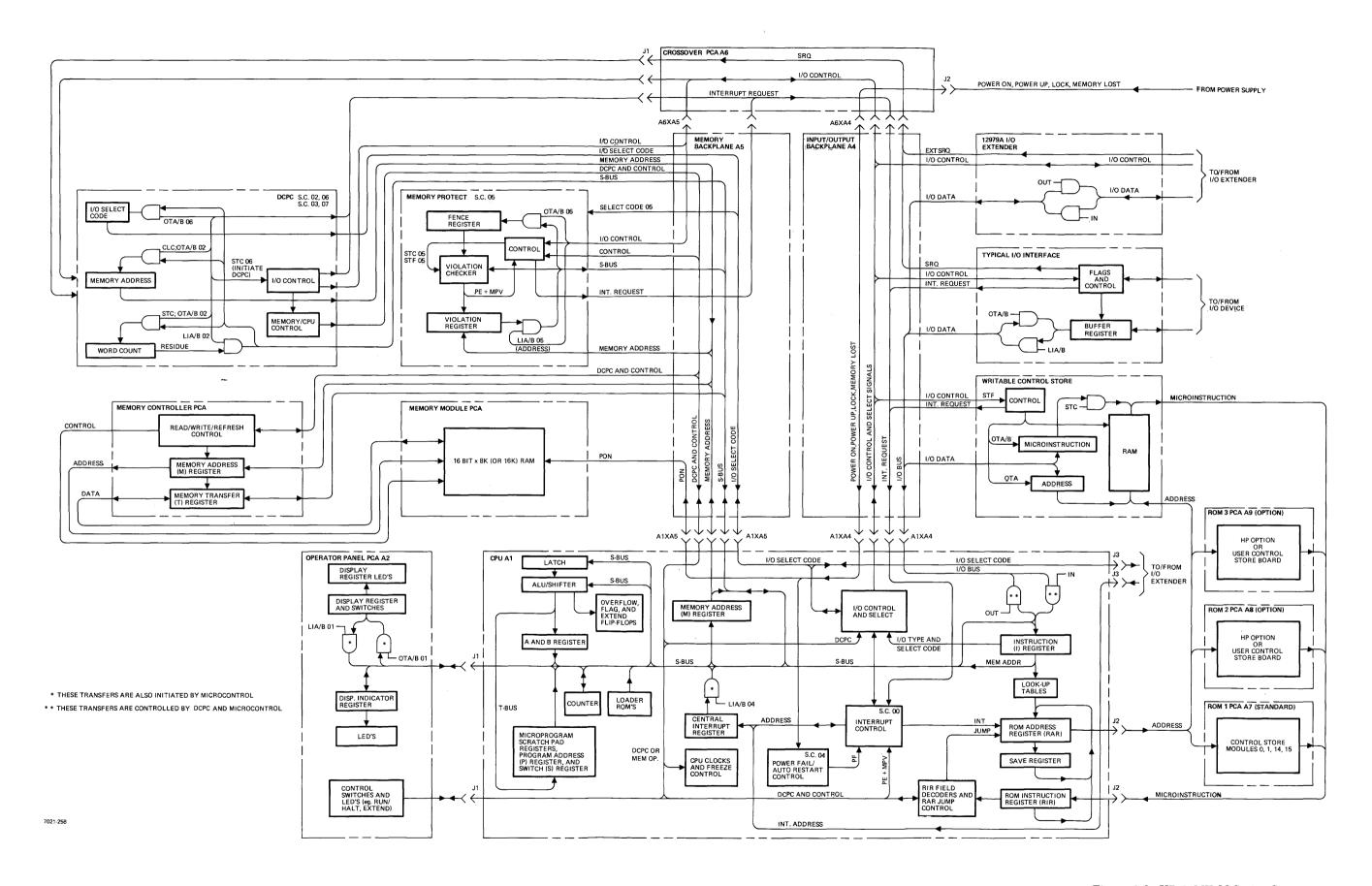

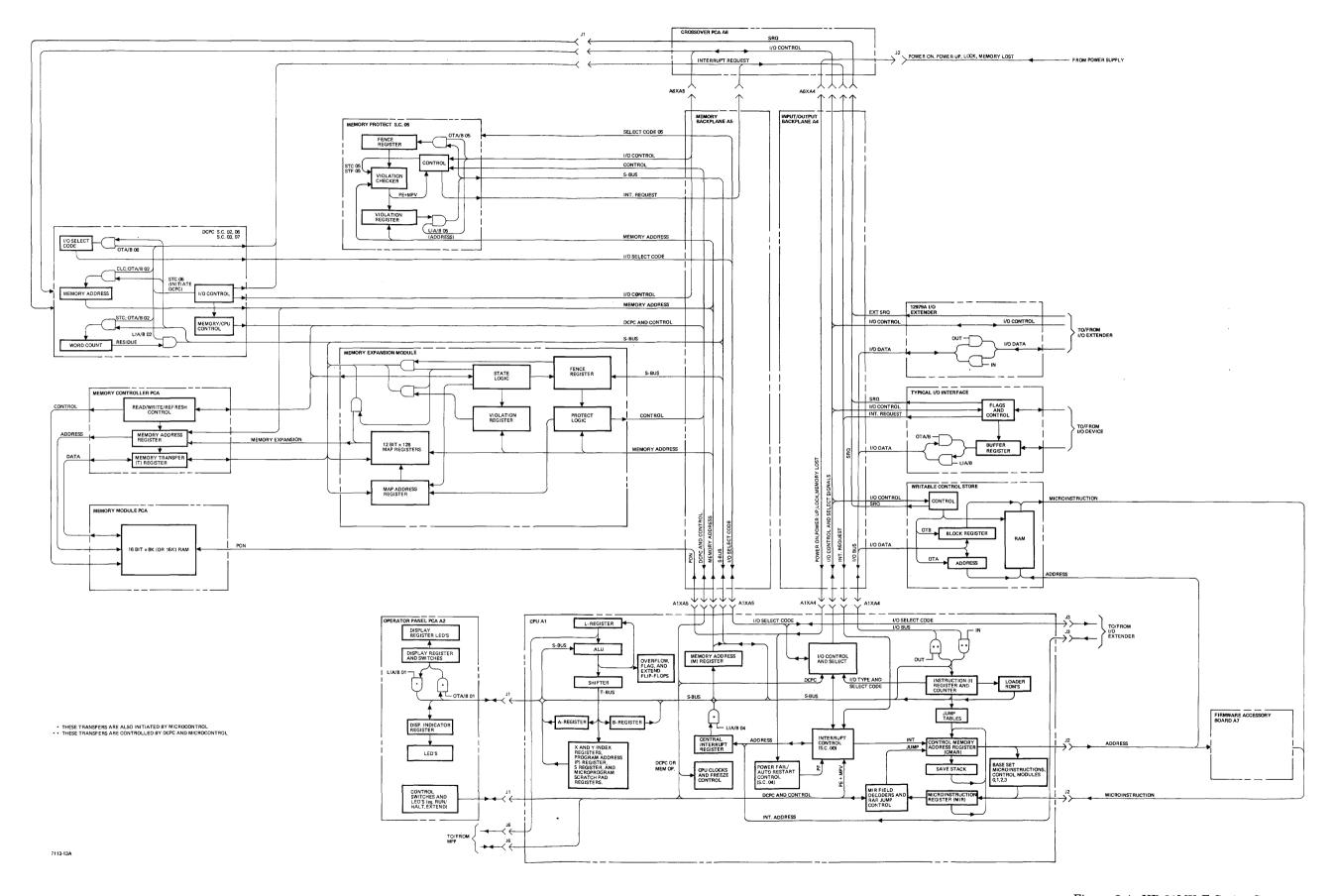

Control and data paths between the computer's major sections and add-on accessories are provided by a bus system. The structure of the bus system is shown in figure 2-2 which illustrates the main communication paths between major computer sections and accessories. The S-bus is a 16-bit, tri-state, TTL-compatible bus and is the major data transfer bus in the computer. The T-bus is a 16-bit, bistate, TTL-compatible bus. The T- bus is a resultant data bus and is completely internal to the Arithmetic/Logic Section. The M-bus is a 16-bit, tri-state, TTL-compatible bus. The M-bus holds the address to be referenced by memory and is driven by either the Arithmetic/Logic Section M-register or the DCPC address registers. The ME-bus is a 10-bit, tri-state, TTL-compatible bus. The ME-bus holds the upper-ten bits of the expanded memory address and is driven by the Memory Expansion Module. For interfacing, the select code bus, interrupt address bus, and I/O bus are of prime importance. The select code bus is a 6-bit, CTL-compatible, control bus. The select code bus holds the select code for the I/O device being referenced by either the I/O Section or DCPC. The interrupt address bus is a 6-bit, open-collector, TTL-compatible control bus. The interrupt address bus holds the select code of any interrupt-requesting I/O interface PCA. The I/O bus is a 16-bit, bi-directional, CTL-compatible, data communication bus for the I/O Section. All plug-in I/O interface PCA's transmit and receive data via the I/O bus. A more detailed discussion of the three I/O-related buses is contained in Sections III and IV of this manual. Block diagrams of the HP 21MX M-Series and HP 21MX E-Series Computers are contained in figures 2-3 and 2-4, respectively at the end of this section.

Figure 2-1. Computer Functional Sections

Computer Characteristics M/E

Figure 2-2. Computer Functional Block Diagram

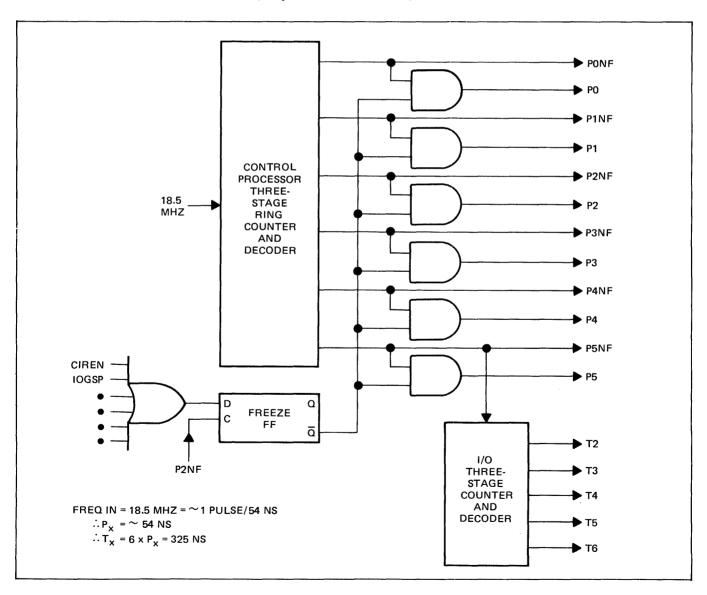

#### 2-2. CONTROL PROCESSOR SECTION

The Control Processor Section is the heart of the computer and contains the registers, control logic, control memory, and timing logic required to execute microprograms and fetch and execute programs stored in the Main Memory Section. This section initializes and controls, either directly or indirectly, the other computer sections. The primary tasks of the Control Processor Section are as follows:

- Control the execution sequence of computer microprograms.

- b. Decode microinstruction fields.

- c. Control the computer data manipulations.

- d. Initiate I/O signal sequences.

- e. Control the Operator Panel.

- f. Communicate with Memory Protect.

- g. Provide system timing for all other computer sections.

- h. Provide control processor synchronization with memory and I/O timing as required.

- i. Provide effective execution of computer instructions.

#### 2-3. ARITHMETIC/LOGIC SECTION

The Arithmetic/Logic Section contains all the computer's working registers and the necessary logic to perform arithmetic and logical operations on data. Resultant data is transferred between elements in this section via the T-bus. Data is transferred between this section and the rest of the computer via the S-bus. The primary tasks of the Arithmetic/Logic Section are as follows:

- a. Provide temporary register storage of memory data.

- b. Perform arithmetic and logical operations on data received from other computer registers and to modify and manipulate this data as instructed by the computer program.

- Provide status indications of computed results as an operations aid (overflow, extend, and special flags).

M/E Computer Characteristics

#### 2-4. MAIN MEMORY SECTION

The Main Memory Section consists of a memory controller and one or more memory module boards with which the controller is designed to operate. The memory module boards contain semiconductor memory arrays that are switch selectable to various address spaces. The memory controller is the interface to and from the Main Memory Section and responds to read/write requests, generates proper timing and enabling signals for the memory modules, and controls memory refresh timing and addressing. The primary tasks of the Main Memory Section are as follows:

- a. Sustain memory data. Since dynamic semiconductor memory is used, the memory module boards must be refreshed to retain stored data. The memory controller initiates and controls the refresh cycles to fit around read/write requests and Dual-Channel Port Controller (DCPC) cycles.

- b. Respond to read and write requests. The memory controller generates the proper timing and enabling signals to perform read or write data transfers. The memory address is obtained from the M-bus and the addressed data is transferred on the S-bus.

- c. Inhibit memory cycles upon receipt of violation flags from the Memory Protect. (Memory cycles received from the DCPC are not inhibited.)

#### 2-5. I/O SECTION

Except for the MPP (E-Series computers only), the I/O Section provides the hardware link for communication between the computer and all peripheral devices. (The MPP provides direct interfacing under microprogrammed control and is discussed in more detail in Section VI of this manual.) The I/O Section contains the I/O control and select code addressing logic, I/O bus control logic, interrupt control logic, and I/O interface PCA slots required to carry out computer initiated transfer operations and I/O device interrupting transfer operations. (Refer to Section III.) The primary tasks of the I/O Section are as follows:

- a. Generate control signals for the I/O interface PCA's.

- Provide data and status paths for the I/O interface PCA's.

- c. Determine select codes of interrupting peripheral devices.

- d. Resolve interrupt request priority conflicts.

- e. Generate pending interrupt signals for the Control Section.

- f. Provide control interface signals for special computer accessories such as the DCPC, Memory Protect, etc.

- g. Provide communication lines for I/O extenders.

M/E

Figure 2-3. HP 21MX M-Series Computer Block Diagram

Figure 2-4. HP 21MX E-Series Computer Block Diagram

#### 111

## I/O SYSTEM FUNDAMENTALS

This section contains a general discussion of the HP 21MX M- and E-Series Computer I/O system. Unless otherwise specified, the contents of this section apply equally to the HP 21MX M-Series and HP 21MX E-Series Computers.

#### 3-1. PURPOSE

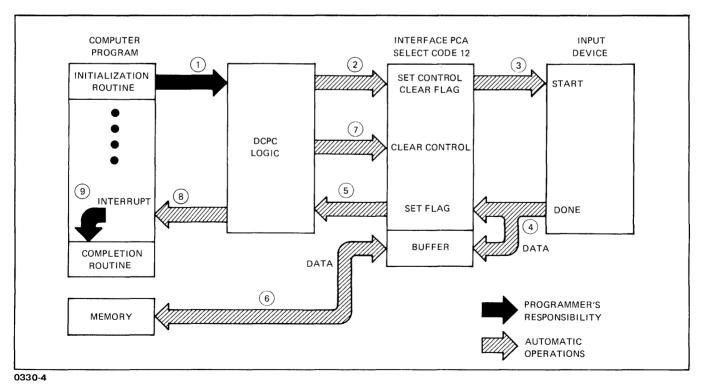

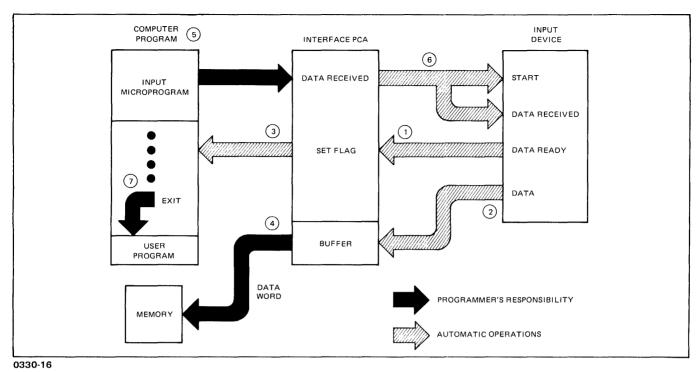

The purpose of the I/O system is to transfer data between the computer and external peripheral devices. As shown in figure 3-1, data is normally transferred through the A-or B-register. An input transfer of this type occurs in three distinct steps: (1) between the external device and its interface PCA in the computer, (2) between the interface PCA and the A- or B-register via the I/O bus and CPU, and (3) between the A- or B-register and memory via the S-bus and memory controller. This three-step process also applies to an output transfer except in reverse order. This type of transfer, which is executed under machine instruction program control, allows the computer logic to manipulate the data during the transfer process.

As shown in figure 3-1, data may also be transferred automatically under control of the Dual-Channel Port Controller (DCPC). Once the DCPC has been initialized. no programming is involved and the transfer is reduced to a two-step process: (1) between the external device and its interface PCA in the computer and (2) between the interface PCA and memory via the I/O bus, S-bus, and memory controller. The two DCPC channels are program assignable to operate with any two device interface PCA's. Since a DCPC transfer eliminates programmed loading and storing via the accumulators, the time involved is very short. Also, since DCPC operates on a cycle-stealing basis, instruction execution can occur concurrently with DCPC operation. Therefore, the DCPC is normally used with high-speed external devices capable of transferring data at the rates specified in table 1-1. Additional information on DCPC I/O transfers is contained in paragraph 3-25.

Also shown in figure 3-1, data may be transferred under microprogram control in the HP 21MX E-Series Computers. Two types of data transfer are available under microprogram control: transfer via a user-designed block I/O PCA connected to the I/O bus or via a user-designed interface PCA connected to the Microprogrammable Processor Port (MPP). Design of the MPP permits external devices to be connected directly to the CPU and interfaced under microprogrammed control. For microprogrammed block I/O operations, an input transfer occurs in two steps: (1) between the external device and its interface PCA in the computer, and (2) between the interface PCA and memory via the I/O bus, S-bus, and memory controller. This two-step process also applies to an output transfer except in reverse order. For MPP I/O operations, an input

transfer also occurs in two steps: (1) between the external device and its interface PCA and (2) between the interface PCA and memory via the MPP, S- bus, and memory controller. This two step process also applies to an output transfer except in reverse order. Microprogrammed I/O operations can be used with exceptionally fast external devices capable of transferring data at the rates specified in table 1-1. Additional information on microprogrammed I/O transfers is contained in Section VI.

#### 3-2. I/O SECTION CONTROL

#### 3-3. GENERAL

Functionally, the I/O Section allows the computer to select and communicate with each of the I/O device's associated interface PCA(s) through I/O control and address logic and through direct bus wiring. The structure of the I/O Section also provides a means by which I/O devices can interrupt the computer program in order to be serviced by the computer. When more than one I/O device requests an interrupt, the computer processes the requests on a priority basis. Figure 3-1 illustrates the main sections of the computer concerned with the control of I/O operations All sections shown are contained in the computer mainframe except for the I/O devices. Although the S-bus is represented as a single line, it actually consists of 16 individual hardwired lines.

#### 3-4. I/O CONTROL INSTRUCTIONS

I/O instructions generate signals that are translated into appropriate control, flag, and select code signals. The control signals are used to enable the I/O interface PCA and the flag signals are used to monitor the status of the associated I/O device. The control and flag signals are routed to the various I/O interface PCA's as determined by the select code signals. The control and flag signals are used to set or clear the Control and Flag flip-flops on the interface PCA's and to test the flip-flop's set or clear states. Each I/O slot is permanently assigned to an individual select code through the computer's hardware design. This allows the select code logic to individually address each I/O interface PCA and its associated I/O device on a priority basis.

### 3-5. I/O DATA TRANSFER INSTRUCTIONS

Data transfer instructions initiate either an input or output data transfer between the computer and an I/O device

I/O System Fundamentals

Figure 3-1. Input/Output System

by generating either an I/O Input (IOI) signal or an I/O Output (IOO) signal. The IOI signal strobes all interface PCA's for input data as a result of a Load Into A (LIA), Load Into B (LIB), Merge Into A (MIA), or Merge Into B (MIB) instruction. Only the data from the interface PCA addressed by the select code is enabled. The data is strobed by IOI into either the A- or B-register via the I/O bus and S-bus. The IOO signal is applied to the interface PCA's as a result of an Output From A (OTA) or Output From B (OTB) instruction. This signal, when combined with the appropriate select code signal, strobes data from either the A- or B-register into the addressed interface PCA via the S-bus and I/O bus.

#### 3-6. INTERRUPT REQUESTS

If a specific instruction (STF 00) has previously enabled the interrupt system, an external I/O device can request an interrupt to the computer program at any time. (Refer to paragraph 3-10.) To request an interrupt, the I/O device applies an Interrupt Request (IRQ) signal to the computer via its interface PCA. The I/O Section determines the address of the interrupting device and causes an interrupt to the main computer program. The computer services the interrupt by setting the M-register to the memory location corresponding to the address or select code of the interrupting device. (Memory locations corresponding to interrupt addresses are commonly referred to as "trap cells".) Generally, the trap cell will contain a Jump to Subroutine Indirect (JSB,I) instruction to be executed. The subroutine accepts and/or prepares input data from the I/O device or applies output data from the computer to the I/O device. Upon completion of the service request, the subroutine causes a return to the proper location in the main computer program.

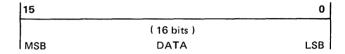

#### 3-7. INTERFACE PCA'S

The interface PCA's provide data transfer channels between the computer and the external I/O devices, and provide control (via computer commands) of the I/O device's operation. The interface PCA's usually contain flag and interrupt logic circuits and registers for temporary storage of data being transferred to or from the computer. Requirements for the use of the flag and interrupt logic circuits and the number of storage registers designed into the interface PCA depend on the type of I/O device to which it is connected. (Refer to Section V for a detailed discussion of interface PCA design.)

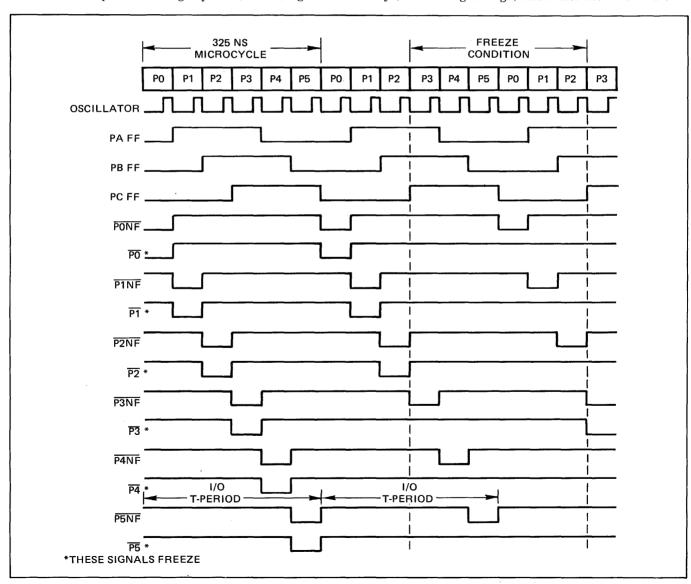

#### 3-8. I/O TIMING

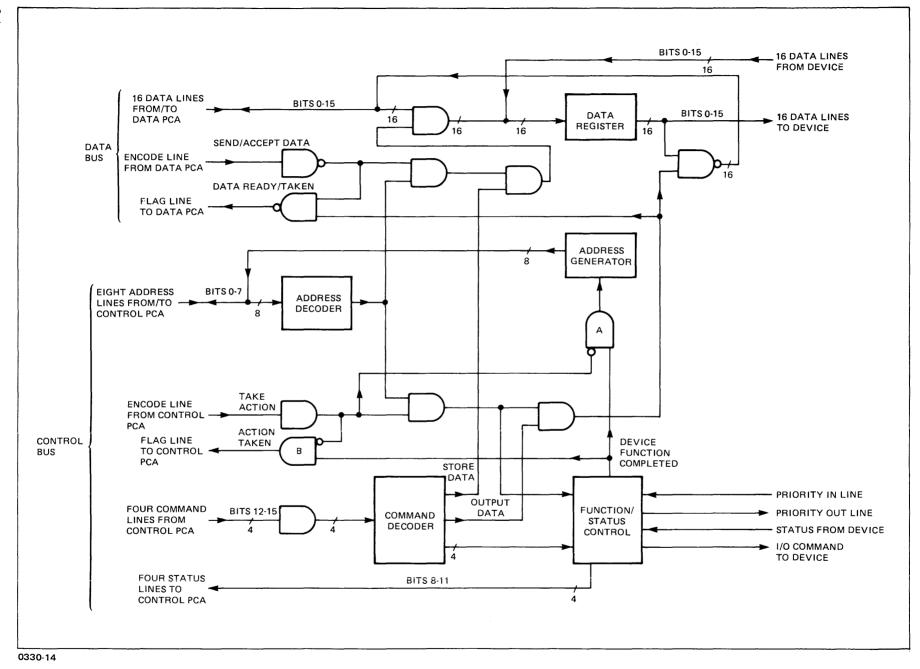

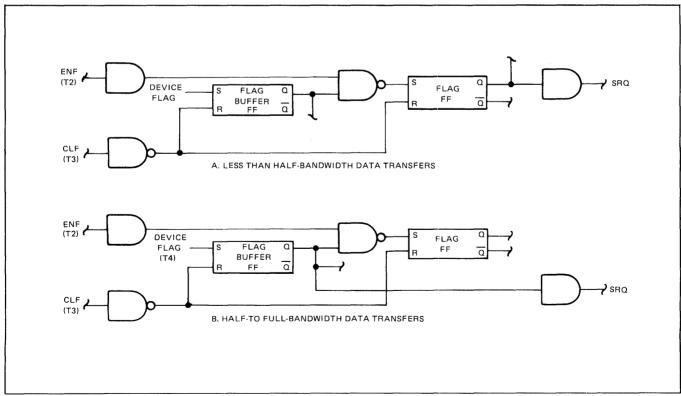

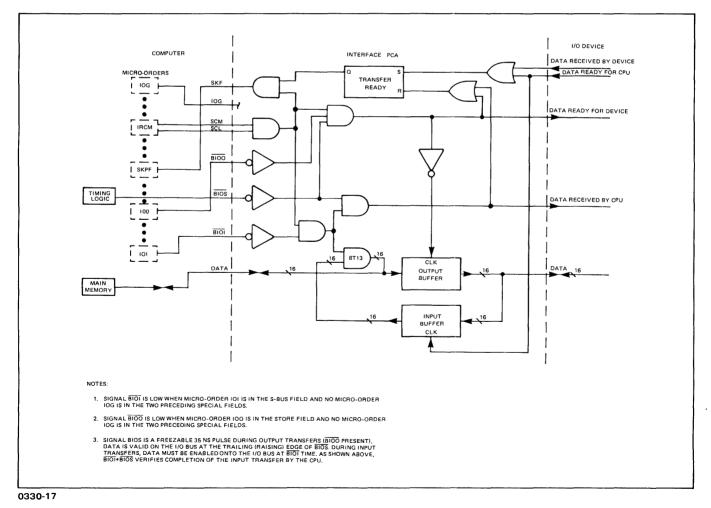

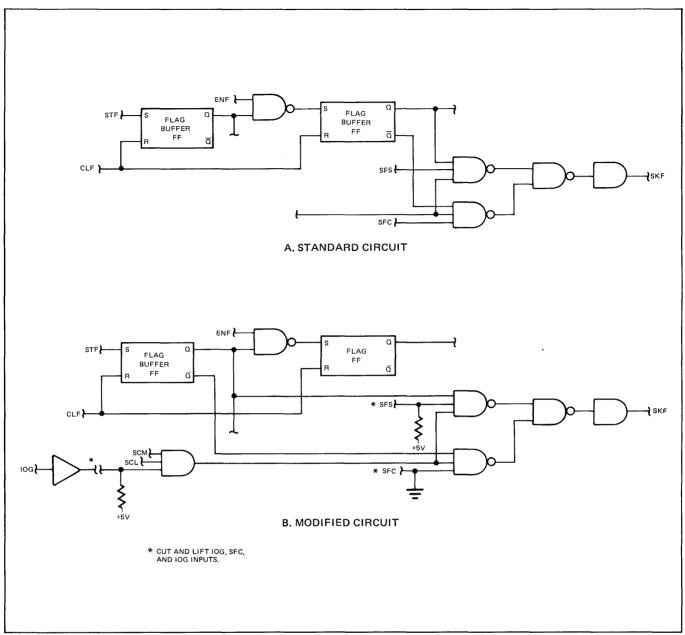

An I/O cycle is the time required to generate all I/O signals necessary to execute an I/O instruction. Each I/O cycle is divided into five T-periods designated T2, T3, T4, T5, and T6. The control processor provides the required gating signals for the I/O signals resulting from decoded I/O instructions and interrupt requests. Timing of the I/O signals in relation to the I/O time periods is discussed in Section IV. Two I/O time period signals, Enable Flag

(ENF) and Set Interrupt Request (SIR), are buffered to provide control signals for interrupt processing. I/O time period T2 is buffered to form the ENF signal which is routed to all computer I/O slots. The ENF signal is used during I/O operations to time the setting of the interface PCA's Flag flip-flop. I/O time period T5 is buffered to form the SIR signal which is routed to all computer I/O slots. The SIR signal is used during interrupt processing to time the setting of the interface PCA's Interrupt Request (IRQ) flip-flop.

#### 3-9. I/O ADDRESSING

Communication between the interface PCA's and the computer is accomplished by specific I/O addresses called select codes. The select codes specify one of 64 possible I/O devices or functions. Select code signals are transferred to the I/O slot of the selected I/O device to permit program control of the device. Table 3-1 lists the select codes and their assignments, and indicates the corresponding interrupt location (i.e., the memory location containing the instruction to be executed when an interrupt occurs). Figure 3-2 illustrates the I/O slots in the computer for the associated interface PCA's. Each I/O slot is assigned two select codes in order to service I/O devices that contain both input and output logic circuits. The input section and output section of an interface PCA may require separate select codes. When a single interface PCA contains both addressable input and output logic circuits, its I/O slot must provide both select codes. The second interface PCA maintains priority continuity. Since I/O slot wiring determines the select codes for the slot, and interface PCA's can be inserted into any I/O slot, the interface PCA assumes the select codes of the I/O slot into which it is inserted.

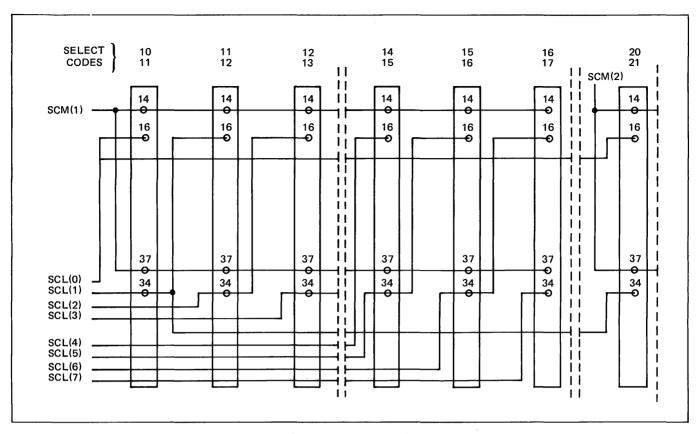

The Select Code Most Significant Digit (SCM) and Select Code Least Significant Digit (SCL) signal combination determines the I/O slot to which the instruction portion of the I/O instruction word is to be directed. As previously discussed, each I/O slot and therefore each interface PCA contains two octal select codes. Figure 3-3 illustrates the SCM and SCL signal paths to the I/O slot connectors. Note that the SCM(1) signal is applied to most-significant-digit input pins on the I/O slot connectors with select codes of 10 through 17 and that the SCM(2) signal is applied to the I/O slot connectors with select codes of 20 through 25. The SCM(0) and SCL(0) through SCL(7) signals are used to form select code address signals SC0 through SC7. The functions of these select codes are contained in table 3-2. It should be noted that the SCM and SCL signals are applied to the same numbered pins on all I/O slot connectors as follows:

- a. Pin 14 lower select code, most significant digit.

- b. Pin 16 lower select code, least significant digit.

- c. Pin 37 higher select code, most significant digit.

- d. Pin 34 higher select code, least significant digit.

Table 3-1. Select Code Assignments

| SELECT CODE<br>(OCTAL) | INTERRUPT<br>MEMORY LOCATION<br>(OCTAL) | ASSIGNMENT                                                                       |

|------------------------|-----------------------------------------|----------------------------------------------------------------------------------|

| 00                     | None                                    | Interrupt System Enable/Disable                                                  |

| 01                     | None                                    | Display Register or Overflow                                                     |

| 02                     | None                                    | DCPC Initialization Channel 1                                                    |

| 03                     | None                                    | DCPC Initialization Channel 2                                                    |

| 04                     | 00004                                   | Power Fail Interrupt/Central Interrupt Register                                  |

| 05                     | 00005                                   | Parity Error Interrupt/Memory Protect Interrupt/Dynamic Mapping System Interrupt |

| 06                     | 00006                                   | DCPC Channel 1 Completion Interrupt                                              |

| 07                     | 00007                                   | DCPC Channel 2 Completion Interrupt                                              |

| 10 thru 77             | 00010 thru 00077                        | I/O Devices                                                                      |

Figure 3-2. I/O Address Assignments

Figure 3-3. I/O Slot Connector Select Code Wiring

#### 3-10. INTERRUPT SYSTEM

The interrupt system provides the means for an external I/O device to interrupt the program in progress when data is available for input or when additional output data can be accepted. An interrupt request from an I/O device occurs when the following conditions are met:

- The interrupt system is enabled.

- b. The specific I/O device's interface PCA Flag flip-flop is

- The specific I/O device's interface PCA Control flipflop is set.

- d. No instruction that affects priority (STF, CLF, STC, or CLC) is in progress.

- e. The priority network is not disabled by gaps between interface PCA's as discussed in paragraph 3-13.

- No higher priority I/O devices have met the conditions stated in a through d above.

The computer program determines if interrupt requests from the external I/O devices will be recognized by enabling or disabling the interrupt system. A Set Flag (STF) instruction with a select code of 00 (octal) enables the

interrupt system. A Clear Flag (CLF) instruction with a select code of 00 (octal) disables the interrupt system. When power is initially applied to the computer, the interrupt system is disabled. Initial power application also clears all I/O interface PCA's Control flip-flops and sets all Flag Buffer and Flag flip-flops. Therefore, to operate any I/O device under interrupt system control, it is first necessary to clear the addressed I/O interface PCA's Flag Buffer and Flag flip-flops and to set the Control flip-flop.

#### 3-11. INTERRUPT PRIORITY

The interrupt system contains a priority network that establishes an orderly sequence of granting interrupt requests. The following paragraphs contain discussions of priority assignments, network operation, continuity, and instructions.

**3-12. PRIORITY ASSIGNMENTS.** A priority circuit on the I/O interface PCA's allows only one I/O device to interrupt the computer program regardless of the number of I/O devices requesting an interrupt. The priority network assigns the highest priority to select code 04 (octal) which is reserved for power fail interrupt and decreasing priority to select codes 05 through 77 (octal) as listed in table 3-1. Each I/O interface PCA connector in the computer is assigned two interrupt priorities corresponding to the two select codes assigned each connector. This

I/O System Fundamentals M/E

provides an interrupt priority for both the input and output circuits of an I/O interface PCA in case they are to be separately addressable. The interrupt priority assignments for each I/O interface PCA connector are fixed but, since any I/O interface PCA can be inserted into any connector slot, the interrupt priority of any I/O device can be easily changed simply by inserting the device's associated I/O interface PCA into another connector slot.

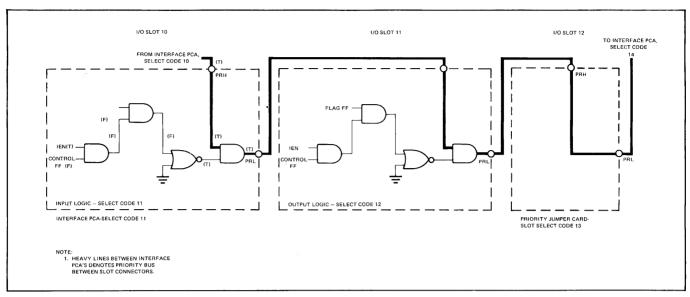

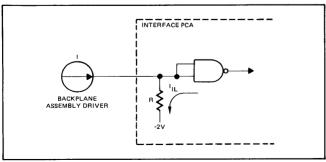

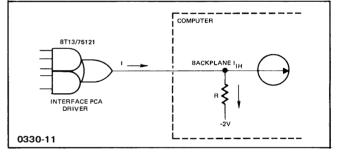

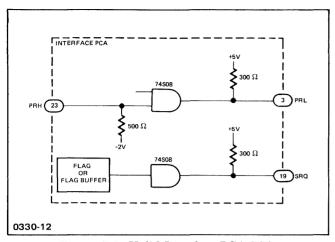

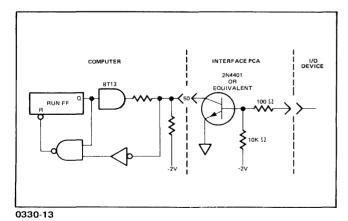

3-13. PRIORITY NETWORK OPERATION. As shown in figure 3-4, priority is established by a hardwired priority network on both the individual I/O interface PCA's and on each I/O connector slot. The true/false logic levels for an I/O interface PCA that is not requesting an interrupt are indicated by parenthesis (T) or (F) on the first I/O interface PCA (select code 11) illustrated in figure 3-4. Figure 3-4 also indicates that the interrupt system is enabled (i.e., IEN input signal is true). Also, figure 3-4 indicates that an I/O device with a higher priority is not requesting an interrupt (i.e., PRH input signal from select code 10 is true). In this case, the priority chain is not broken and a true PRL signal is applied to the next I/O interface PCA (select code 12) as a true PRH signal.

If an I/O interface PCA contains both input and output logic circuits, each circuit may have a separate select code and corresponding interrupt priority with the priority chain connected internally on the PCA. Usually, for I/O interface PCA's that contain both input and output logic circuits, the output logic circuit is assigned a higher priority than the input logic circuit. Since the I/O interface PCA uses both select codes assigned to its connector, the second I/O interface PCA (if required) must provide continuity for the priority network. There can be no gaps in the priority network if it is to function properly. If only one I/O interface PCA which operates from two select codes is required for an I/O device, a priority jumper PCA must be installed to maintain priority continuity for the lower priority I/O devices.

If the output logic circuit of the I/O interface PCA (figure 3-4) requests an interrupt, the PRL signal to the input logic circuit of the PCA goes false and the priority chain is broken, preventing any I/O interface PCA with a lower priority from interrupting the computer program. A service subroutine can now be entered to process the interrupt requested by the output logic circuit. A service subroutine for any I/O device can be interrupted by any I/O device(s) with a higher priority. Then, after the I/O device(s) with a higher priority has been serviced, the subroutine for the I/O device with the lower priority can continue. Therefore, several service subroutines can be in an interrupted state at one time. Each subroutine will continue from its interrupted point when the next higher priority subroutine is completed.

Interrupt priority can also be program controlled. Since an interrupt cannot occur unless the I/O interface PCA's Control flip-flop is set, all Control flip-flops on I/O interface PCA's with a higher priority than the one desired can be cleared by a CLC instruction. This prevents the higher priority I/O interface PCA's from requesting an interrupt

and establishes the desired I/O interface PCA as the highest priority device. However, the I/O interface PCA's disabled by the CLC instruction must now be monitored for service by testing the state of their Flag flip-flops or by resetting the Control flip-flops with an STC instruction. (Refer to paragraph 3-19.)

**3-14. PRIORITY CONTINUITY.** When an I/O interface PCA requests an interrupt, the PRL signal applied to the next lower priority I/O interface PCA as PRH goes false which prevents that I/O interface PCA from requesting an interrupt. This sequence continues from PCA to PCA until the last (lowest priority) I/O interface PCA receives a false PRH signal.

**AFFECTING** 3-15. INSTRUCTIONS ORITY. Four instructions (STC, CLC, STF, and CLF) affect the I/O interface PCA's priority network. Whether an I/O device can or cannot request an interrupt depends on whether its I/O interface PCA's Control flip-flop is set (STC) or cleared (CLC) and whether its Flag flip-flop is set (STF) or cleared(CLF). If an I/O device cannot request an interrupt, all succeeding lower priority devices assume a priority of one higher in the priority network. The four instructions also inhibit all interrupts during the computer cycle in which they occur. This prevents interrupts from occuring during entry and exit from subroutines. Also, a combination of two of the four instructions is normally the next-to-last instruction in a service subroutine processing an interrupt. (The last instruction is a JMP,I instruction to return to the main program or to an address of another subroutine.) If another I/O device could interrupt the subroutine immediately after the combination of the two instructions and before the JMP, I instruction, the possibility would exist that the first I/O device could interrupt a second time before the JMP,I instruction. In this case, the first main program address or the other service subroutine address would be destroyed, preventing a return to the main program or to the other service subroutine.

#### 3-16. INTERRUPT GENERATION

A detailed discussion of the sequence of events that take place during an interrupt request is contained in paragraphs 4-4 through 4-8 and paragraph 5-4 of this manual.

#### 3-17. INTERRUPT PROCESSING

Initially, during an interrupt, the computer decrements the P-register to ensure that the proper location in the main program will be returned to after the interrupt is processed. Also, the computer places the service request address (always equal to the select code of the interrupting I/O device) into the M-register. This addresses the memory location having the same number as the service request address (select code). This location in memory is referred to as the "trap cell" and is reserved for one particular I/O device. For example, an I/O device specified by select code 10 (octal) will interrupt to (i.e., cause execution of the

| INST  | S.C. 00                                                                                      | S.C. 01                                              | S.C. 02                                                                                                                                                                                                | S.C. 03                                                                                                                                                                                                | S.C. 04                                                                                                                      | S.C. 05                                                                                              | S.C. 06                                                                                          | S.C. 07                                                                                                    | S.C. 10-77                                                                   |

|-------|----------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| STC   | NOP                                                                                          | NOP                                                  | Prepares DCPC channel 1 to receive and store the block length in 2's complement form.                                                                                                                  | Prepares DCPC channel 2 to receive and store the block length in 2's complement form.                                                                                                                  | Re-initializes power-fail<br>logic and restores inter-<br>rupt capability to lower<br>priority functions.                    | Turns on memory protect.                                                                             | Sets Control FF on DCPC channel 1 (activates DMA).                                               | Sets Control FF on DCPC channel 2 (activates DMA).                                                         | Sets PCA Control FF and<br>turns on device on chan-<br>nel specified by S.C. |

| CLC   | Clears all Control FF's<br>from S.C. 06 and up;<br>effectively turns off<br>all I/O devices. | NOP                                                  | Prepares DCPC channel 1 to receive and store the direction of data flow and the starting memory address.                                                                                               | Prepares DCPC channel 2 to receive and store the direction of data flow and the starting memory address.                                                                                               | Re-initialize power-fail<br>logic and restores inter-<br>rupt capability to lower<br>priority functions.                     | NOP                                                                                                  | Clears Control FF on DCPC channel 1 (reestablishes priority with STF; does not turn off DCPC).   | Clears Control FF on<br>DCPC channel 2<br>(reestablishes priority<br>with STF; does not turn<br>off DCPC). | Clears PCA Control FF and turns off device.                                  |

| STF   | Turns on interrupt system.                                                                   | STO sets overflow bit.                               | NOP                                                                                                                                                                                                    | NOP                                                                                                                                                                                                    | Flag FF sets auto-<br>matically when power<br>comes up. (No pro-<br>gram control<br>possible.)                               | Turns on parity error interrupt capability.                                                          | Aborts DCPC channel 1 data transfer.                                                             | Aborts DCPC channel 2 data transfer.                                                                       | Sets PCA Flag FF.                                                            |

| CLF   | Turns off interrupt system except power fail (S.C. 04) and parity error (S.C. 05).           | CLO clears overflow bit.                             | NOP                                                                                                                                                                                                    | NOP                                                                                                                                                                                                    | Flag FF clears auto-<br>matically when power<br>fail occurs. (No pro-<br>gram control<br>possible.)                          | Turns off parity error interrupt capability and clears violation register bit 15.                    | Clears Flag FF on DCPC channel 1.                                                                | Clears Flag FF on DCPC channel 2.                                                                          | Clears PCA Flag FF.                                                          |

| SFS   | Skip if interrupt system is on.                                                              | sos                                                  | NOP                                                                                                                                                                                                    | NOP                                                                                                                                                                                                    | NOP                                                                                                                          | Skip if Dynamic Map-<br>ping System (DMS)<br>interrupt.                                              | Tests if DCPC channel 1 data transfer is complete.                                               | Skip if DCPC channel 2 data transfer is complete.                                                          | Skip if I/O channel Flag FF is set.                                          |

| SFC   | Skip if interrupt system is off.                                                             | soc                                                  | NOP                                                                                                                                                                                                    | NOP                                                                                                                                                                                                    | Skip if power fail has occurred.                                                                                             | Skip if memory protect interrupt.                                                                    | Tests if DCPC channel 1 data transfer is still in progress.                                      | Skip if DCPC channel 2 data transfer is still in progress.                                                 | Skip if I/O channel Flag FF is clear.                                        |

| LIA/B | Loads A/B register with all zeros. (Equivalent to CLA/B instruction.)                        | Loads display register contents into A/B register.   | Loads present contents of DCPC channel 1 word count register into A/B register.                                                                                                                        | Loads present contents of DCPC channel 2 word count register into A/B register.                                                                                                                        | Loads contents of central interrupt register (S.C. of last interrupting device) into least-significant bits of A/B register. | Loads contents of<br>violation register into<br>A/B register:<br>Bit 15 = 1 = PE<br>Bit 15 = 0 = MPV | Loads A/B register with all ones. (Equivalent to CCA/CCB instruction.)                           | Loads A/B register with all ones. (Equivalent to CCA/CCB instruction.)                                     | Loads contents of PCA data buffer into A/B register.                         |

| MIA/B | Equivalent to a NOP.                                                                         | Merges display register contents into A/B register.  | Merges present contents<br>of DCPC channel 1<br>word count register into<br>A/B register.                                                                                                              | Merges present contents<br>of DCPC channel 2<br>word count register into<br>A/B register.                                                                                                              | Merges contents of central interrupt register into least-significant bits of A/B register.                                   | Merges contents of violation register into A/B register.                                             | Same as LIA/B 06 above.                                                                          | Same as LIA/B 07 above.                                                                                    | Merges contents of PCA data buffer into A/B register.                        |

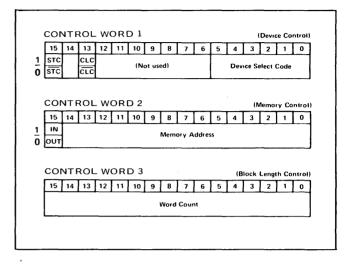

| OTA/B | NOP                                                                                          | Outputs A/B register contents into display register. | 1. Outputs to DCPC channel 1 the block length in 2's complement form (previously prepared by an STC 02 instruction).  2. Outputs to DCPC channel 1 the direction of data flow and the starting memory. | 1. Outputs to DCPC channel 2 the block length in 2's complement form (previously prepared by an STC 03 instruction).  2. Outputs to DCPC channel 2 the direction of data flow and the starting memory. | NOP                                                                                                                          | Outputs first address of unprotected memory to fence register.                                       | Outputs to DCPC channel 1 the S.C. of I/O channel. Specify STC after each word; CLC after block. | Outputs to DCPC channel 2 the S.C. of I/O channel. Specify STC after each word; CLC after block.           | Outputs data from A/B register into PCA data buffer.                         |

|       |                                                                                              |                                                      | the starting memory address (previously prepared by a CLC 02 instruction).                                                                                                                             | the starting memory address (previously prepared by a CLC 03 instruction).                                                                                                                             |                                                                                                                              |                                                                                                      |                                                                                                  |                                                                                                            |                                                                              |

0330-1

Figure 3-4. Interrupt Priority Network

contents of) memory location 00010. The computer fetches the instruction in the trap cell which is usually a jump to a subroutine (JSB,I) instruction. (Any legal instruction can be placed in the trap cell.) The contents of the P-register plus one are then stored in the first location (X) of the subroutine. (Since the previous contents of the first memory location are destroyed when P+1 is stored, the first instruction of the subroutine should always be a nooperation (NOP) instruction or equivalent.) Next, the location of the subroutine (X+1) is placed in the P- and M-registers and the computer resumes operation in the subroutine. Thus, the instruction stored in location X+1 is the first instruction of the subroutine to be executed. It should be noted that the contents of the working registers that were in use in the main program should be stored when entering the subroutine and restored before exiting from the subroutine. Exit from the subroutine is accomplished with a JMP,I instruction to location X. This places the address of the interrupted program instruction in the P- and M-registers and allows normal program operation to resume.

#### 3-18. I/O DATA TRANSFERS

The following paragraphs describe how data is transferred between memory and I/O devices. A summary of I/O group instructions pertinent to the computer's interrupt and control functions is contained in table 3-2. The sequences presented for noninterrupt and interrupt methods of data transfer are highly simplified in order to present an overall view without the involvement of software operating systems and device drivers. For additional information, refer to Sections IV through VI of this manual and to the documentation supplied with the appropriate software system or I/O subsystem.

#### 3-19. NONINTERRUPT TRANSFERS

It is possible to transfer data without using the interrupt system. This involves a "wait-for-flag" method in which the computer commands the device to operate and then waits for the completion response. In using this method to transfer data, it is assumed that the computer time is relatively unimportant. The programming is very simple, consisting of only four words of in-line coding as shown in table 3-3. Each of these routines will transfer one word or character of data. It is also assumed that the interrupt system is disabled (STF 00 not previously given).

Table 3-3. Noninterrupt Transfer Routines

| INSTRUCTIONS                                    | COMMENTS                                                                                                                |  |  |  |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| INPUT ROUTINE                                   |                                                                                                                         |  |  |  |

| STC 12,C<br>SFS 12<br>JMP *–1<br>LIA 12         | Start device. Is input ready? No, repeat previous instruction. Yes, load input into A-register.                         |  |  |  |

| С                                               | OUTPUT ROUTINE                                                                                                          |  |  |  |

| OTA 13<br>STC 13,C<br>SFS 13<br>JMP *- 1<br>NOP | Output A-register to buffer. Start device. Has device accepted the data? No, repeat previous instruction. Yes, proceed. |  |  |  |

I/O System Fundamentals M/E

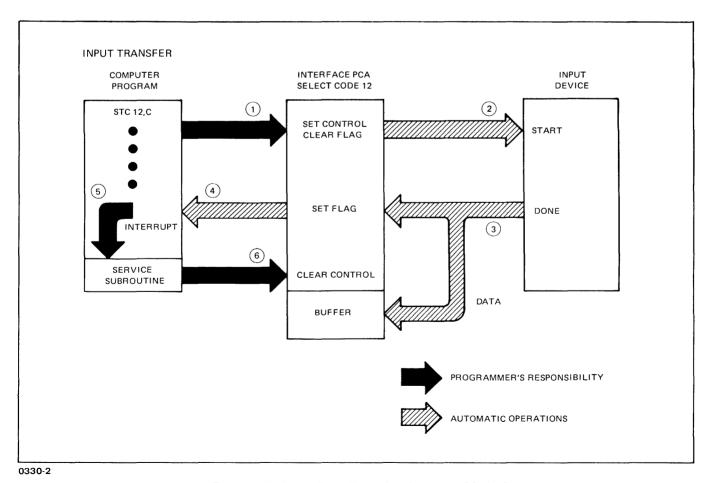

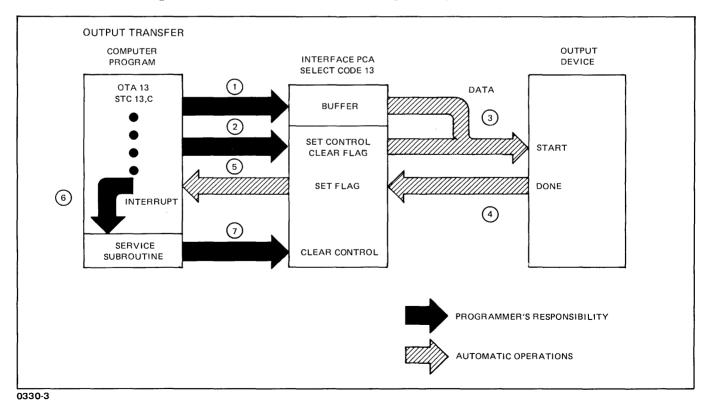

INPUT DATA. The operation begins with a 3-20. programmed STC 12,C instruction which sets the Control flip-flop and clears the Flag flip-flop on the interface PCA. The computer then goes into a waiting loop, repeatedly checking the status of the PCA Flag flip-flop. Setting the Control flip-flop causes the PCA to output a Start signal to the I/O device. The Start signal causes the device to output a data character and then a Done signal to the PCA which sets the PCA Flag flip-flop. (A more detailed discussion of interface PCA operations is contained in Sections IV and V.) If the Flag flip-flop is not set, the JMP \*-1 instruction causes a jump back to the SFS instruction. (The \*-1 operand is assembler notation for "this location minus one".) When the Flag flip-flop is set, the skip condition for SFS is met and the JMP instruction is skipped. The computer then exits from the waiting loop and the LIA 12 instruction loads the device input data into the A-register.