### MAINTENANCE MANUAL

# 30051A

#### UNIVERSAL INTERFACE (DIFFERENTIAL)

(FOR HP 3000 COMPUTER SYSTEMS) Manual Part No. 30051-90001 Microfiche Part No. 30051-90005

> Printed in U.S.A. 10/72 Update 5/76

**Printed-Circuit Assembly:**

30051-60001

Note

This manual should be retained with the documentation covering the subsystem in which this interface printed-circuit assembly is used.

### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATER-IAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

Copyright @ 1976 by HEWLETT-PACKARD COMPANY

# LIST OF EFFECTIVE PAGES

The List of Effective Pages gives the most recent date on which the technical material on any given page was altered. If a page is simply re-arranged due to a technical change on a previous page, it is not listed as a changed page. Within the manual, changes are marked with a vertical bar in the margin.

| Pages                                         | Effective Date | Pages          | Effective Date |

|-----------------------------------------------|----------------|----------------|----------------|

| Title                                         | . May 1976     | 3-29 thru 3-34 | . Oct 1972     |

| ii thru v · · · · · · · · · · · · · · · · · · | . May 1976     | 3-35 thru 3-36 | . Mar 1975     |

| vi thru ix                                    | 0 . 10.50      | 3-37 thru 3-41 | . Oct 1972     |

| Blank                                         | . Oct 1972     | Blank          | . Oct 1972     |

| 1-1 thru 1-2                                  | . Oct 1972     | 3-43           | . Oct 1972     |

| 2-1 thru 2-7                                  | . Oct 1972     | Blank          | . Oct 1972     |

| Blank                                         | . Oct 1972     | 3-45           | . Oct 1972     |

| 3-1 thru 3-15                                 | . Oct 1972     | Blank          | . Oct 1972     |

| Blank                                         | . Oct 1972     | 4-1            | . Mar 1975     |

| 3-17                                          | . Oct 1972     | 4-2 thru 4-3   | . Oct 1972     |

| Blank                                         | . Oct 1972     | 4-4            | . Mar 1975     |

| 3-19 thru 3-21                                | . Oct 1972     | 4-5            | . Oct 1972     |

| Blank                                         | . Oct 1972     | Blank          | . Oct 1972     |

| 3-23 thru 3-27                                | . Oct 1972     |                |                |

| Blank                                         | . Oct 1972     |                |                |

## **PRINTING HISTORY**

New editions incorporate all update material since the previous edition. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The date on the title page and back cover changes only when a new edition is published. If minor corrections and updates are incorporated, the manual is reprinted but neither the date on the title page and back cover nor the edition change.

Note: This update is for the purpose of referencing the HP 3000 Series II documentation.

This manual contains maintenance information for the HP 30051A Universal Interface (Differential). The interface described in this manual is used as an integral part of the HP 3000 Computer System to provide I/O capability between the system and parallel data transfer devices requiring differential-logic signals.

The contents of this manual are organized in four sections as follows:

- a. Section I contains general information relative to the interface physical features and specifications.

- b. Section II contains operating parameters for the interface including a description of control word and status word formats.

- c. Section III contains theory of operation for the interface.

- d. Section IV contains servicing instructions with preventive and corrective maintenance information.

This manual should be retained and used with related documentation for the HP 3000 Series II Computer System or the pre-Series II HP 3000 Computer System. The related documentation for the HP 3000 Series II Computer System includes the following:

- a. HP 3000 Series II Computer System Service Manual, part no. 30000-90018.

- b. HP 3000 Series II Computer System Signal and Power Distribution Manual, part no. 30000-90021.

- c. HP 3000 Series II Computer System Stand-Alone Universal Interface PCA, Card Reader/Punch PCA Diagnostic, part no. 30050-90012.

- d. HP 3000 Computer Systems Support Log, part no. 03000-90117.

The related documentation for the pre-Series II HP 3000 Computer System includes the following:

- a. HP 30001A CPU/IOP Maintenance Manual, part no. 30001-90003.

- b. HP 30005A/30006A Memory Maintenance Manual, part no. 30005-90001.

- c. HP 3000 Computer System Manuals of Diagnostics (MOD).

- d. HP 3000 Computer System Detailed Diagrams Manual, part no. 03000-90023 (Diagram Set DD-501, part no. 30051-90004).

- e. HP 3000 Computer System Illustrated Parts Breakdown (IPB) Manual, part no. 03000-90021.

- f. HP 3000 Computer System PCA Cage Maintenance Manual, part no. 30002-90002.

- g. HP 3000 Computer System Installation Manual, part no. 03000-90032.

- h. System Configuration Package.

- Note: Do not use the equipment described in this manual to interface serial data transfer or parallel data transfer devices requiring DTL/TTL compatible signals.

# CONTENTS

| tion |

|------|

|      |

|      |

| I  | GENER          | AL INFORMATION                             |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|----|----------------|--------------------------------------------|-------|-----|---|---|---|-----|---|---|---|-----|---|---|---|---|---|---|---|---|------------|

| 1  | 1-1.           | Introduction                               |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 1.1        |

|    | 1-3.           | General Description                        |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 1-0.<br>1-8.   | Specifications                             |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 1-0.<br>1-10.  | Identification                             |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 1-10.          |                                            | •     | ••• | • | · | • | • • | • | • | • | ••• | • | · | · | · | • | · | · | · | 1-1        |

|    |                |                                            |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

| П  | OPER A         | TING PARAMETERS                            |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

| 11 | 2-1.           | Introduction                               |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2.1        |

|    | 2-1.<br>2-3.   | General Information .                      |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 2-0.           | System Parameters                          |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 2-9.           | CIO Instruction                            |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-1<br>2-1 |

|    | 2-3.<br>2-10.  | RIO Instruction                            |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-1        |

|    | 2-10.<br>2-11. | SIN Instruction                            | •     |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-1        |

|    | 2-11.<br>2-12. | SIO Instruction .                          | -     |     |   |   |   |     |   |   |   |     |   |   |   |   | - |   |   |   | 2-2        |

|    | 2-12.<br>2-13. | SMSK Instruction                           |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-2        |

|    | 2-13.<br>2-14. |                                            |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 2-14.<br>2-15  | TIO Instruction .                          |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 2-15.<br>2-16. | WIO Instruction .                          |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | • •            | Direct I/O                                 | •     | • • | • | • | • | ••• | • | • | • | ••• | • | • | · | • | · | · | • | • | 4-4<br>0.0 |

|    | 2-18.          | Programmed I/O                             |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 2-20.          | Control Order                              |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 2-21.          | End Order                                  |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 2-22.          | Interrupt Order .                          |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 2-23.          | Jump Order                                 |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-3        |

|    | 2-24.          |                                            | •     |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-3        |

|    | 2-25.          | Return Residue Or                          |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 2-26.          | Sense Order                                |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-3        |

|    | 2-27.          | Write Order                                |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 2-28.          | Control Word Format .                      |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 2-30.          | Master Clear                               |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-3        |

|    | 2-31.          | Clear All Interrupt                        |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 2-32.          | Selective Interrupt                        |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   |            |

|    | 2-33.          | Initiate Data Trans                        | fer   |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-3        |

|    | 2-34.          | Device Control .                           |       |     |   |   |   |     | • |   |   |     |   |   |   |   |   |   |   |   | 2-3        |

|    | 2-35.          | Data Transfer Inter                        | rupt  |     |   |   |   |     | • |   |   |     |   |   |   |   |   |   |   |   | 2-4        |

|    | 2-36.          | Interrupt/Device S                         | tatus |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-4        |

|    | 2-37.          | Byte Transfer                              |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-4        |

|    | 2-38.          | Enable Interrupt R                         | eque  | st. |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-4        |

|    | 2-39.          | Start Transfer Tim                         | er    |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-4        |

|    | 2-40.          | Status Word Formats .                      |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-4        |

|    | 2-43.          | Interface Status Byte                      |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-5        |

|    | 2-45.          | SIO OK                                     |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   |   | 2-5        |

|    | 2-46.          | RIO, WIO OK.                               |       | · · |   |   | ÷ |     |   | ÷ | • |     |   |   |   |   |   |   |   | Ż | 2-5        |

|    | 2-47.          | Interrupt Pending                          |       |     |   |   |   |     |   | • | • | ••• | • | • | • | • | · |   | • | • | 2-5        |

|    | 2-48.          | Sequence Counter                           |       |     |   |   |   |     |   |   |   |     |   |   |   |   | • | • | • | • | 2-5        |

|    | 2-49.          | Device Flag.                               |       |     |   |   |   |     |   |   |   |     |   |   |   |   | · | • | • | • | 2-5        |

|    | 2-50.          | Interrupt/Device St                        |       |     |   |   |   |     |   |   |   |     |   |   |   |   | • | • | • | • | 2-5        |

|    | 2-50.<br>2-51. | Permanent Zero                             |       |     |   |   |   |     | • |   | • | ••• | • | • | · | • | • | · | • | • | 2-5        |

|    | 2-51.<br>2-52. | Interrupt Status Byte                      | •     |     | • |   |   |     |   | • | • | • • | • | • | • | • | • | • | • | • | 2-5<br>2-6 |

|    | 2-52.<br>2-54. | Device Status Inter                        | •     |     | • | - | - | • • |   | · | • | • • | · | • | · | • | · | • | • | • | 2-0<br>2-6 |

|    | 2-54.<br>2-55. | Device Status Inter<br>Data Transfer Inter |       |     | • | • | • | • • | • | - | - | • • | • | - | • | • | · | · | · | · | 2-0<br>2-7 |

|    |                |                                            | -     |     | ٠ | - | - | • • | • | • | - | ••• |   | • | · | • | · | · | · | · | 2-7<br>2-7 |

|    | 2-56.          | Clear Interface Inte                       | •     |     |   |   |   |     | • |   |   |     | • | • | • | · | · | · | · | · |            |

|    | 2-57.          | I/O System Interru                         |       |     |   |   |   |     | • |   |   |     | • | • | • | • | • | · | · | · | 2.7        |

|    | 2-58.          | Transfer Error Inte                        | -     |     |   |   |   |     | • |   |   |     |   |   |   |   |   | · | • | • | 2-7        |

|    | 2-59.          | Time Out Interrup                          |       |     |   |   |   |     |   |   |   |     |   |   |   |   |   |   |   | • | 2-7        |

|    | 2-60.          | Device Status Byte .                       | •     |     | • | • | • |     | • |   | • |     |   | • | • | • | , | • |   | • | 2 - 7      |

### **CONTENTS** (Continued)

| SPC | tion |

|-----|------|

|     |      |

4-13.

4-14.

4-15.

4-16.

4-17.

4-18.

4-20.

4-1

4-1 .

4-1 .

4-1

4-3

. .

| ш   | THEOF          | RY OF OPERATION                                                                   |

|-----|----------------|-----------------------------------------------------------------------------------|

|     | 3-1.           | Introduction                                                                      |

|     | 3-3.           | System-Level Description                                                          |

|     | 3-11.          | Functional-Level Description                                                      |

|     | 3-13.          | Command Function                                                                  |

|     | 3-15.          | Direct Commands                                                                   |

|     | 3-13.<br>3-23. | Program Commands                                                                  |

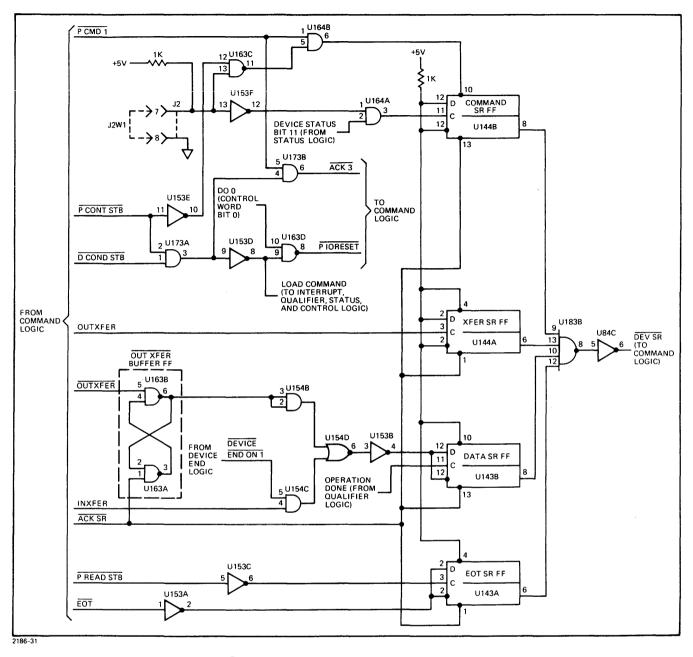

|     | 3-23.<br>3-24. | Program Control Strobe Operation                                                  |

|     | 3-24.<br>3-29. | Program Read Strobe Operation.                                                    |

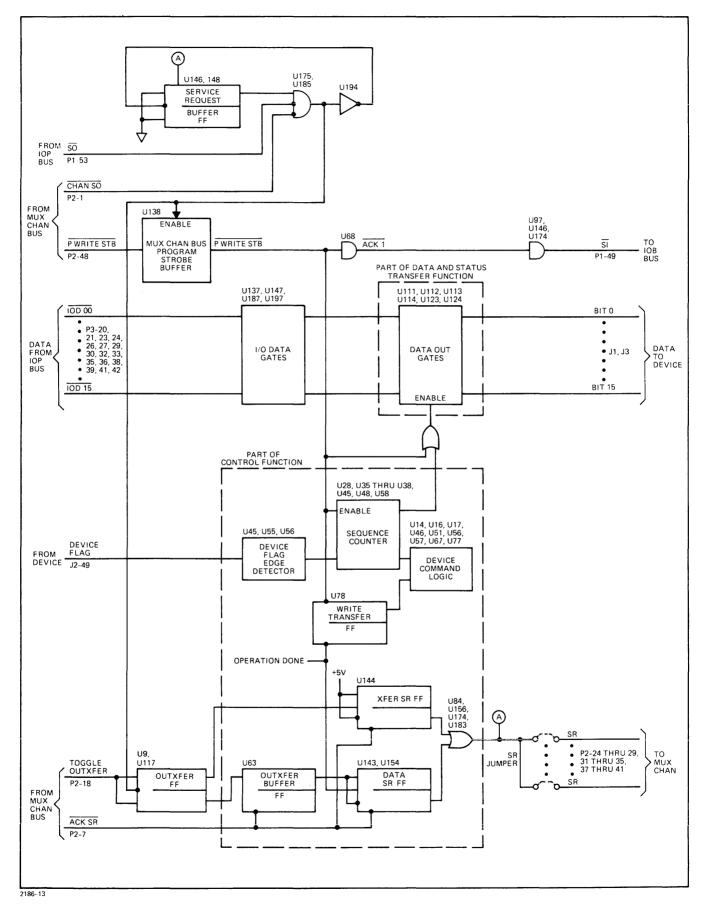

|     | 3-29.<br>3-33. | Program Write Strobe Operation.                                                   |

|     | 0.001          |                                                                                   |

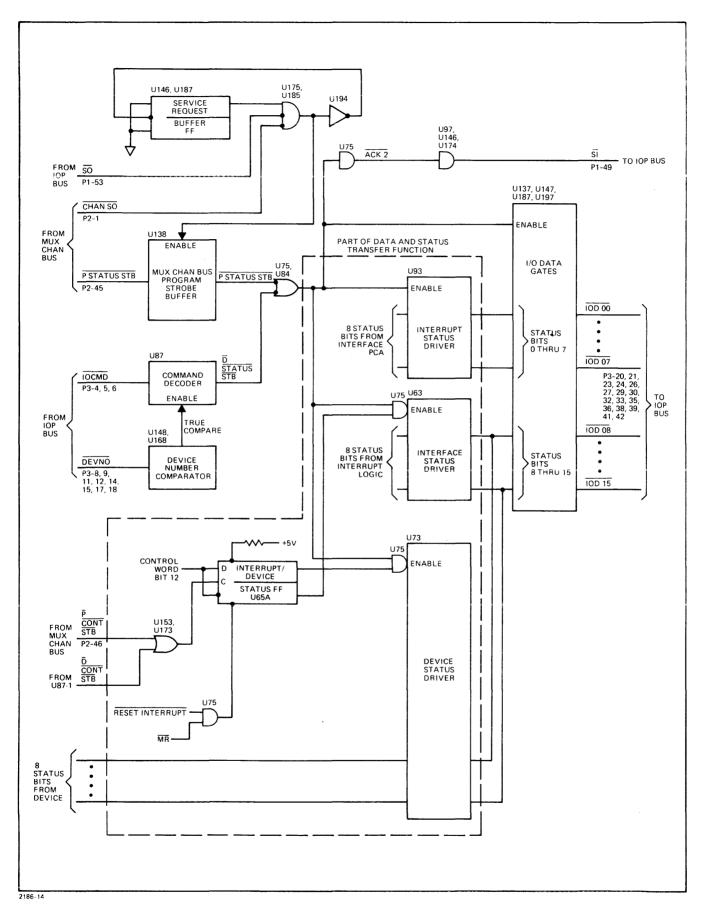

|     | 3-36.          | Direct/Program Status Strobe Operations                                           |

|     | 3-39.          | "Not" Set Interrupt                                                               |

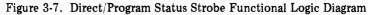

|     | 3-40.          | Interrupt Processing                                                              |

|     | 3-45.          | I/O Data Gates                                                                    |

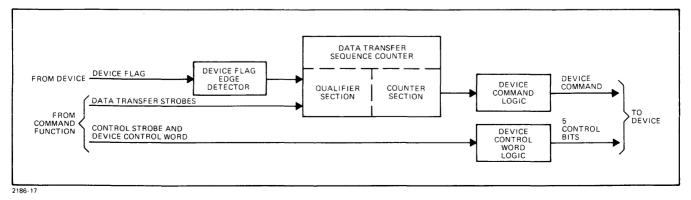

|     | 3-49.          | Control Function                                                                  |

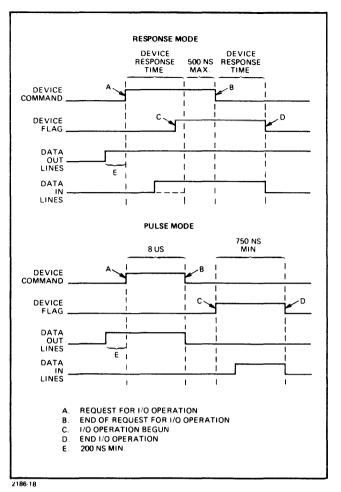

|     | 3-51.          | Device Control Logic                                                              |

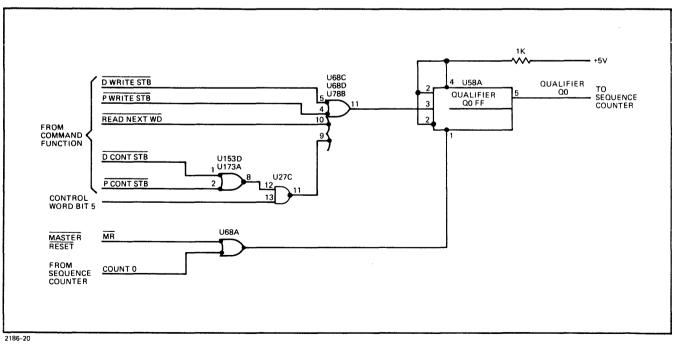

|     | 3-53.          | Sequence Counter Qualifier Logic                                                  |

|     | 3-60.          | Sequence Counter                                                                  |

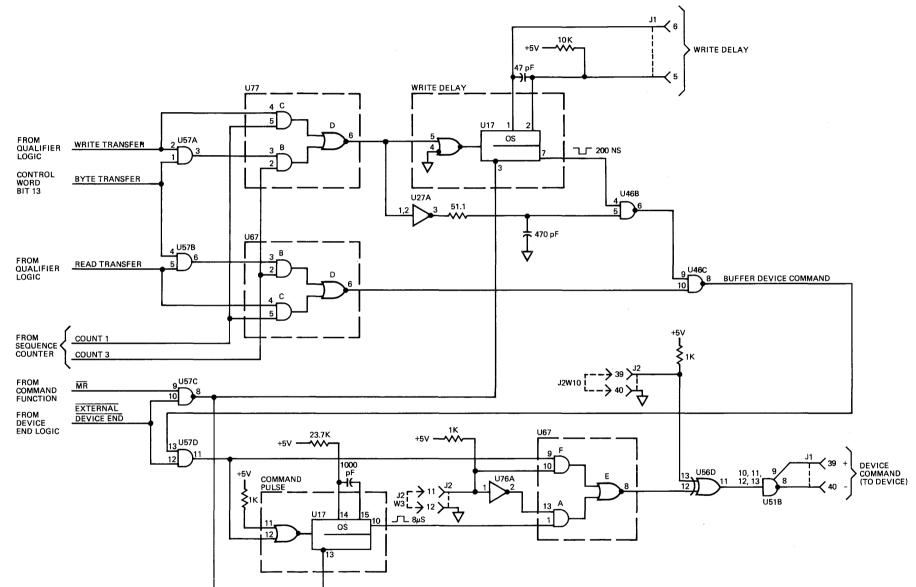

|     | 3-62.          | Device Command Logic                                                              |

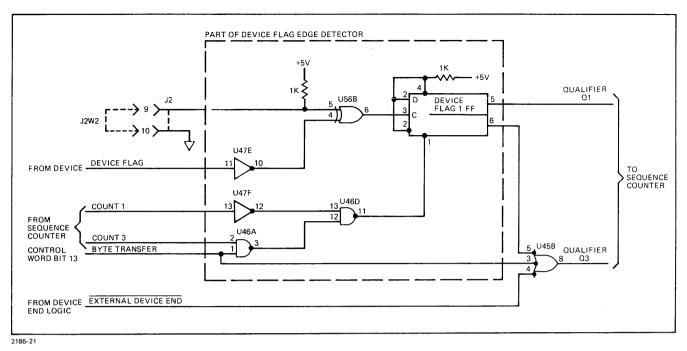

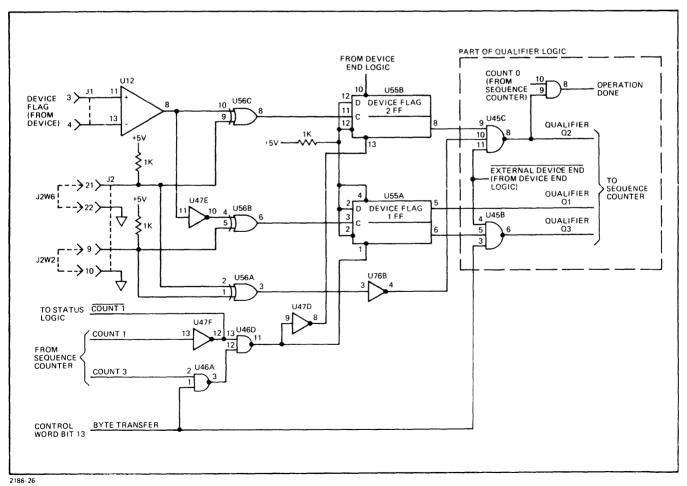

|     | 3-63.          | Device Flag Edge Detector                                                         |

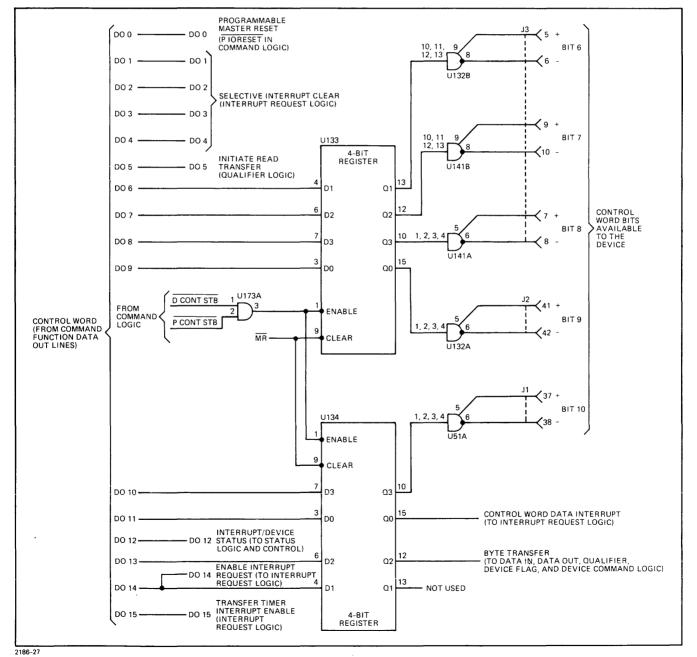

|     | 3-65.          | Device Control Word Logic                                                         |

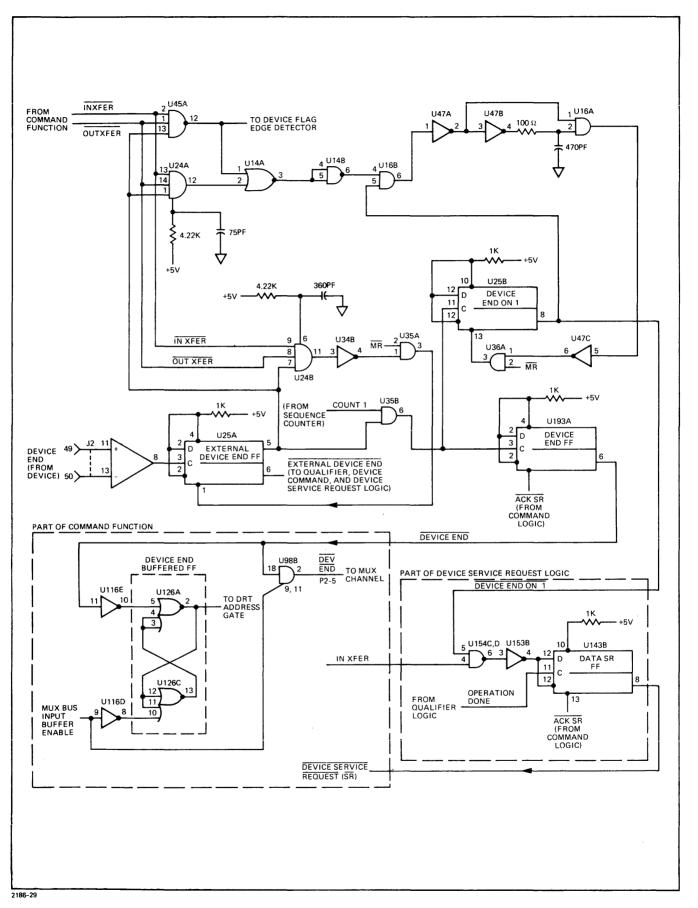

|     | 3-67.          | Device End Logic                                                                  |

|     | 3-68.          | Device End During a One-Word Data Transfer                                        |

|     | 3-69.          | Device End During a Two-Byte Data Transfer                                        |

|     | 3-70.          | Device Service Request Logic                                                      |

|     | 3-72.          | Interrupt Request Logic                                                           |

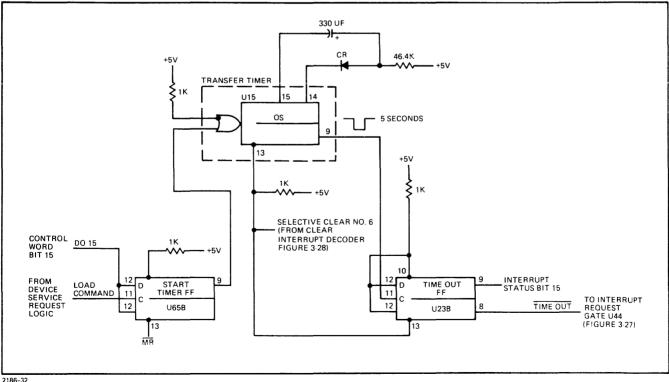

|     | 3-74.          | Data Transfer Timer                                                               |

|     | 3-76.          | Device Interrupt Request Logic                                                    |

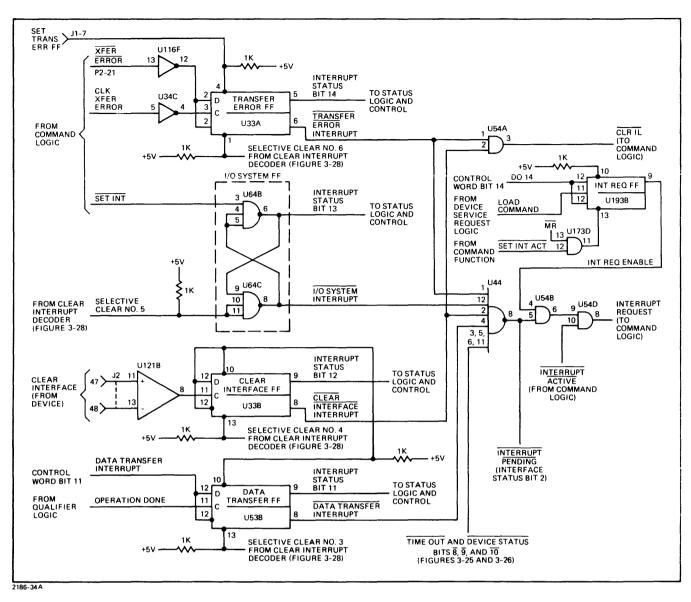

|     | 3-77.          | I/O System and Interface Interrupt Request Logic                                  |

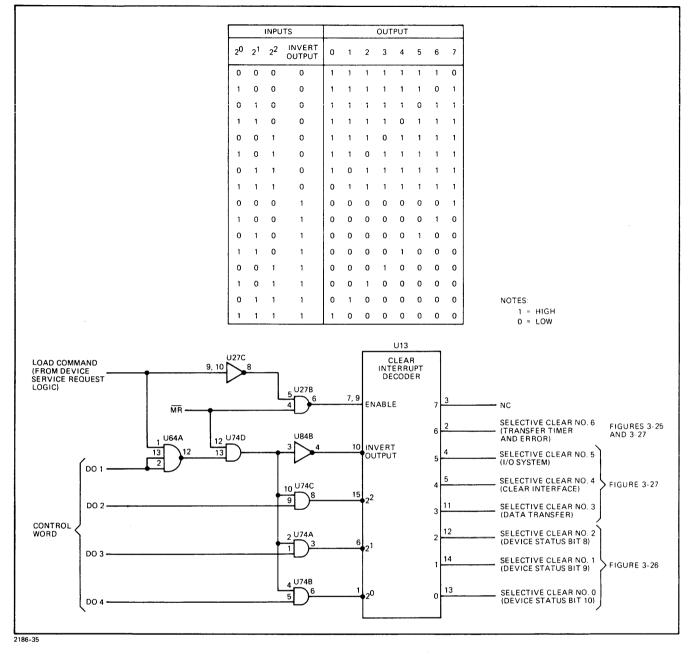

|     | 3-78.          | Clear Interrupt Decoder Logic                                                     |

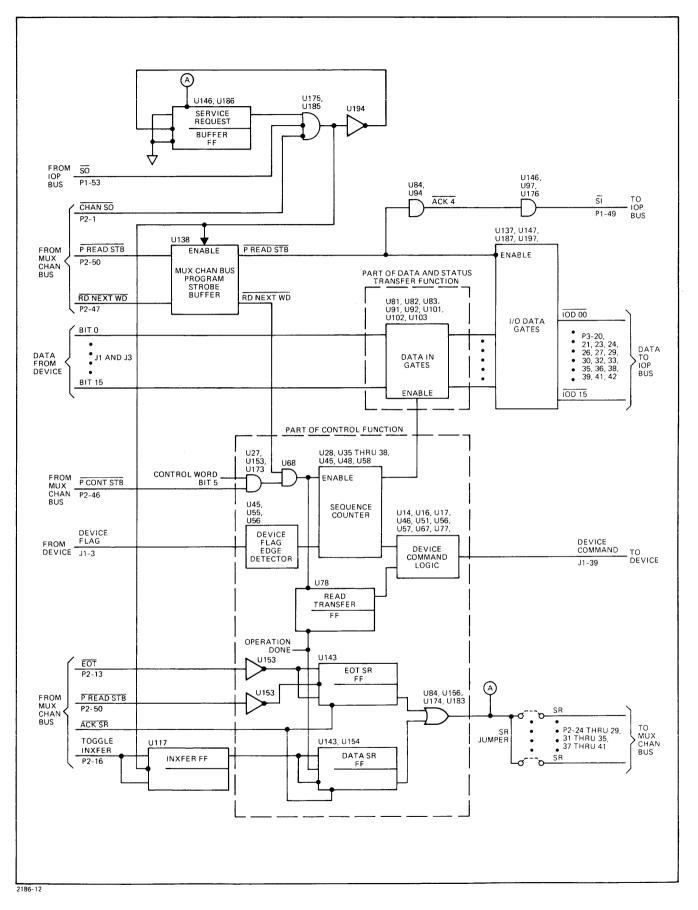

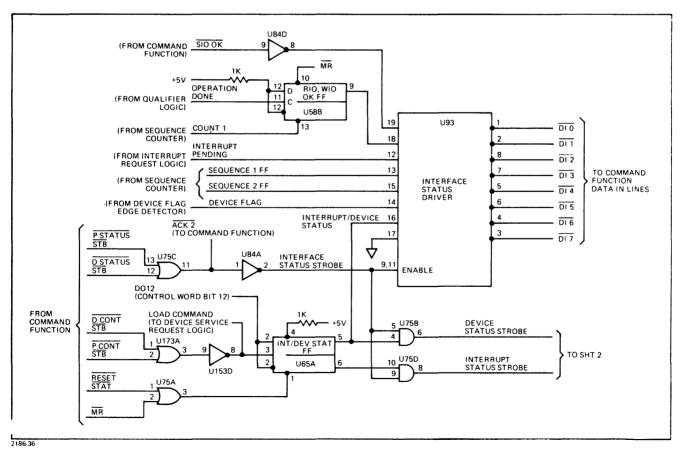

|     | 3-80.          | Data and Status Transfer Function.                                                |

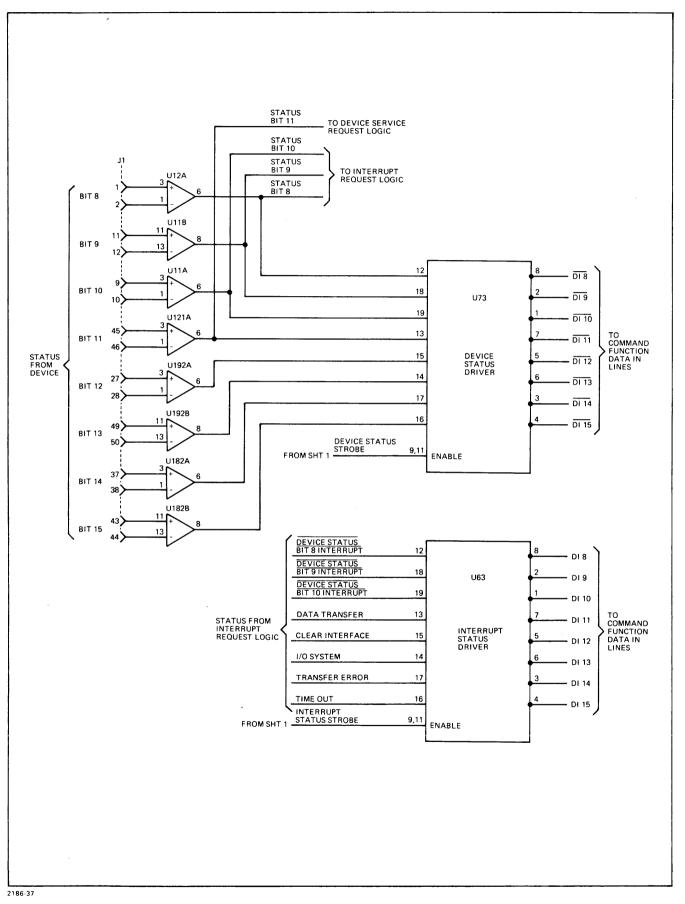

|     | 3-82.          | Status Logic and Control                                                          |

|     | 3-83.          | Interface Status Byte                                                             |

|     | 3-91.          | Device Status Byte                                                                |

|     | 3-92.          | Interrupt Status Byte                                                             |

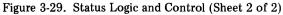

|     | 3-93.          | Data In Logic                                                                     |

|     | 3-94.          | One-Word Data Transfer                                                            |

|     | 3-95.          | Byte Transfer                                                                     |

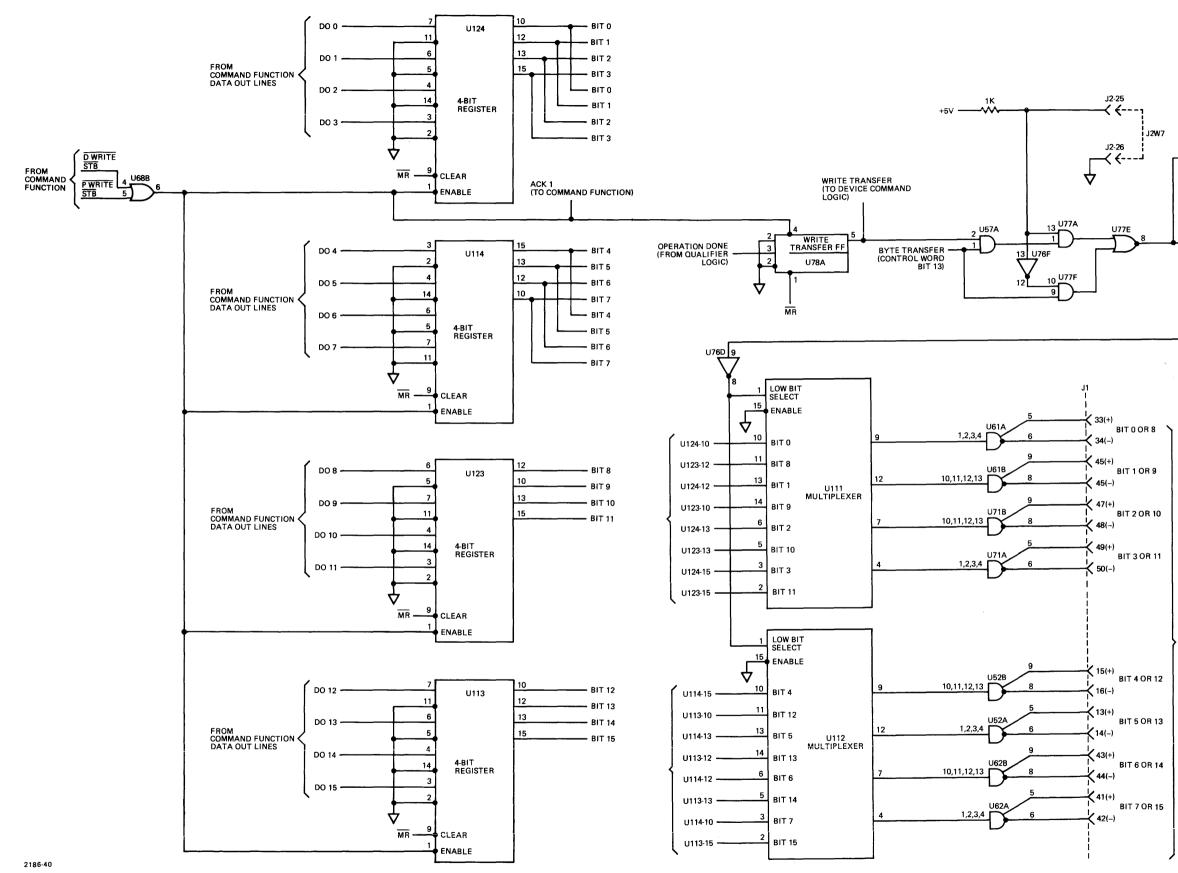

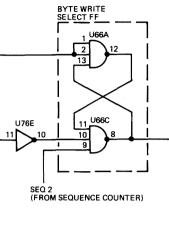

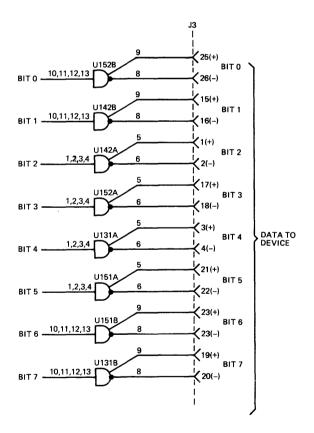

|     | 3-96.          | Data Out Logic                                                                    |

|     | 3-97.          | Normal Write                                                                      |

|     | 3-98.          | Test Write                                                                        |

|     |                |                                                                                   |

| IV  | ΜΔΙΝΤ          | ENANCE                                                                            |

| - · | 4-1.           | Introduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $4-1$ |

|     | 4-1.<br>4-3.   | General Servicing Information                                                     |

|     | 4-5.<br>4-5.   | Safety Precautions                                                                |

|     | 4-5.<br>4-9.   |                                                                                   |

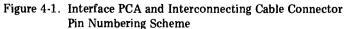

|     | 4-9.<br>4-11.  | Jumper Wire Configuration                                                         |

|     | ·±•⊥1,         |                                                                                   |

Required Servicing Equipment

Page

# CONTENTS (Continued)

#### Section

| 4-23. | Preventive Maintenance.        |   |   |  |  |   |  |  |  |  |  |  |   | 4-3 |

|-------|--------------------------------|---|---|--|--|---|--|--|--|--|--|--|---|-----|

| 4-25. | Troubleshooting                |   |   |  |  |   |  |  |  |  |  |  | - | 4-4 |

| 4-28. | <b>Corrective Maintenance.</b> | • | • |  |  | • |  |  |  |  |  |  |   | 4-4 |

# ILLUSTRATIONS

| Figure | Title                                                                  | Page   |

|--------|------------------------------------------------------------------------|--------|

| 1-1.   | HP 30051A Universal Interface (Differential)                           | . 1-1  |

| 2-1.   | Control Word Format                                                    | 2-4    |

| 2-2.   | Status Word Format                                                     |        |

| 2-3.   | Interface/Interrupt Status Word Format                                 |        |

| 2-4.   | Interface/Device Status Word Format                                    | . 2-7  |

| 3-1.   | Overall System Block Diagram                                           | . 3-2  |

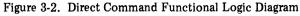

| 3-2.   | Direct Command Functional Logic Diagram                                | . 3-4  |

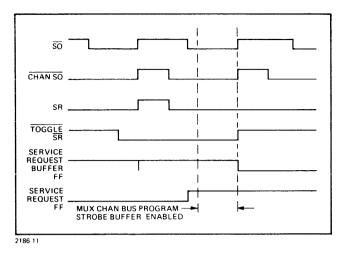

| 3-3.   | Program Control Strobe Command Functional Logic Diagram                | . 3-7  |

| 3-4.   | Program Strobe Timing.                                                 |        |

| 3-5.   | Program Read Strobe Functional Logic Diagram                           | . 3-9  |

| 3-6.   | Program Write Strobe Functional Logic Diagram                          |        |

| 3-7.   | Direct/Program Status Strobe Functional Logic Diagram                  |        |

| 3-8.   | Interrupt Processing Functional Logic Diagram.                         |        |

| 3-9.   | Command Function I/O Data Gates Functional Logic Diagram               | 3-17   |

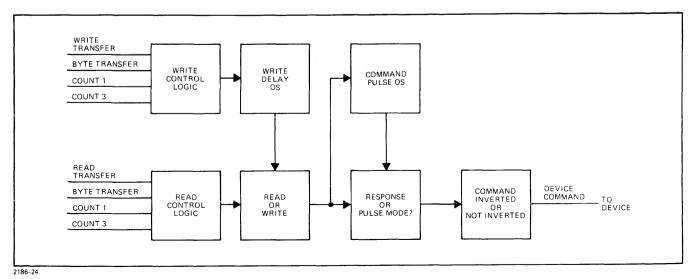

| 3-10.  | Device Control Logic Block Diagram                                     |        |

| 3-11.  | Response Mode and Pulse Mode Timing Diagrams.                          |        |

| 3-12.  | Qualifier Q0 Simplified Diagram                                        |        |

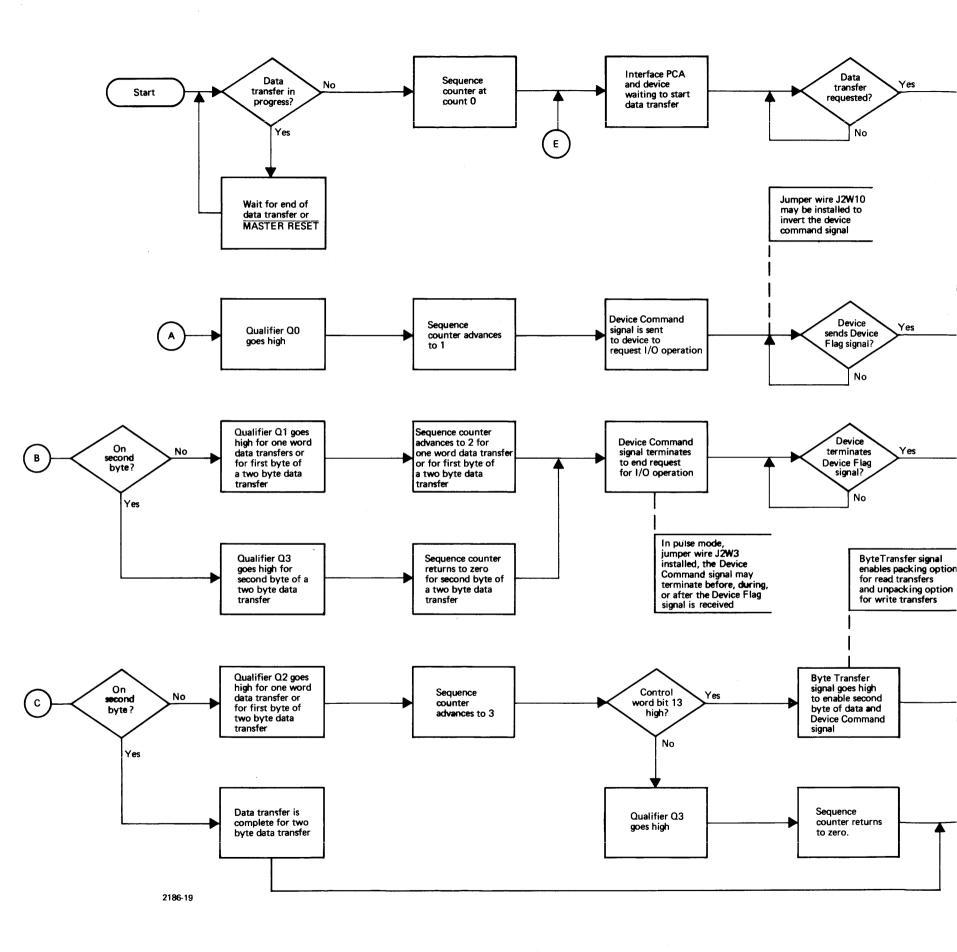

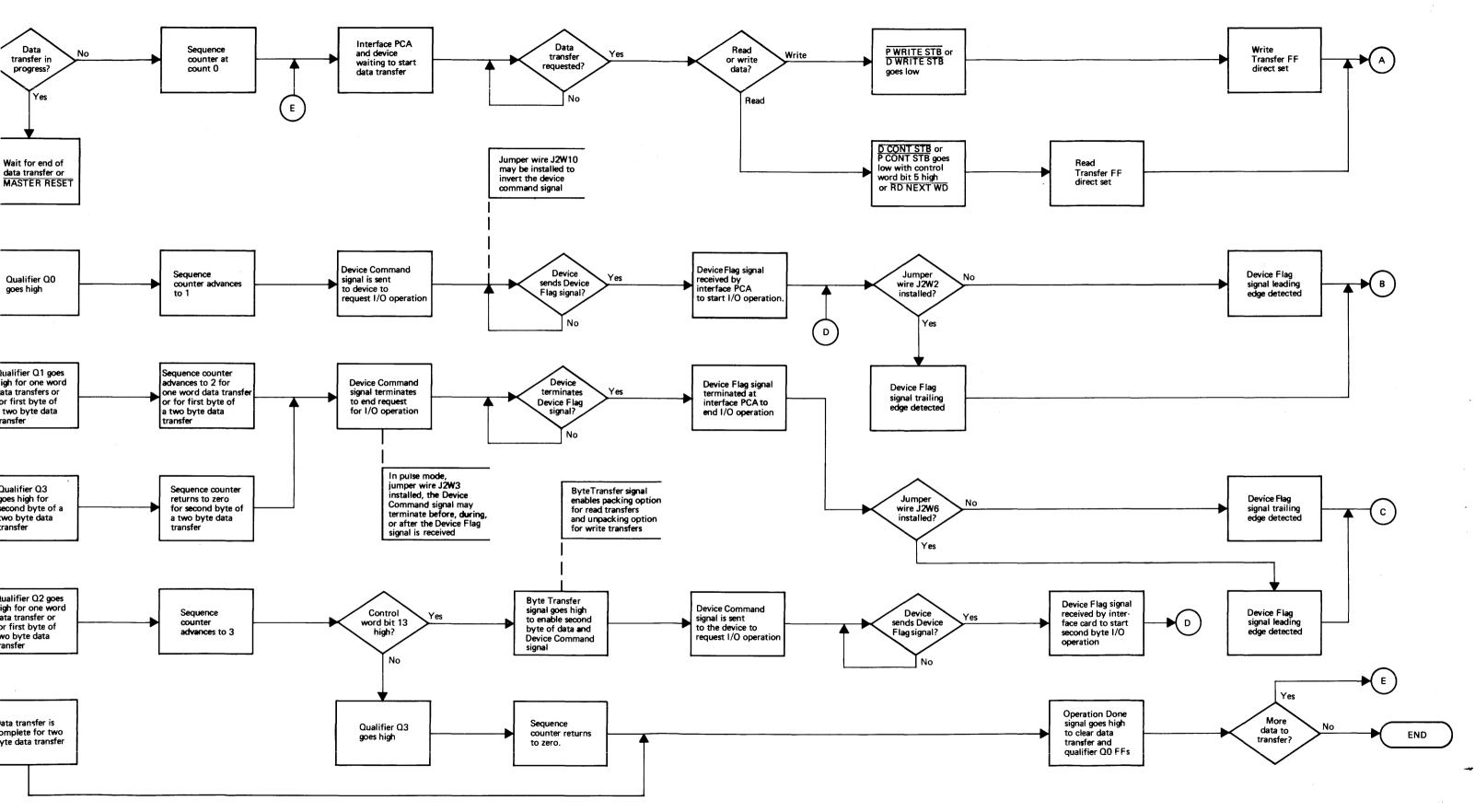

| 3-13.  | Control Function Sequence Counter Operational Flow Diagram             | . 3-21 |

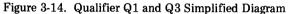

| 3-14.  | Qualifier Q1 and Q3 Simplified Diagram                                 |        |

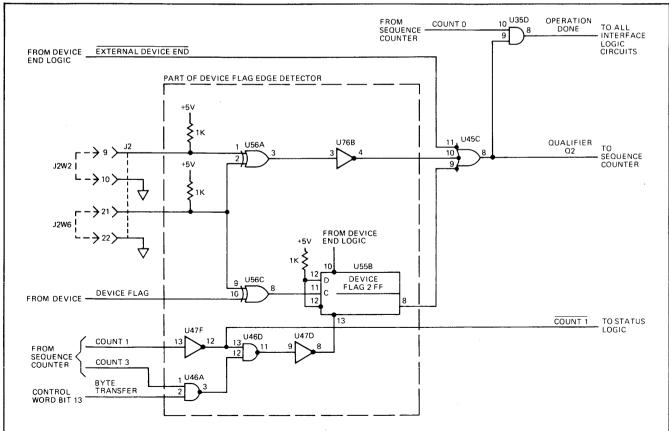

| 3-15.  | Qualifier Q2 Simplified Diagram                                        | 3-23   |

| 3-16.  | Sequence Counter Simplified Diagram.                                   |        |

| 3-17.  | Device Command Logic Block Diagram                                     |        |

| 3-18.  | Device Flag Edge Detector                                              |        |

| 3-19.  | Device Command Logic                                                   |        |

| 3-20.  | Device Control Word Logic                                              |        |

| 3-21.  | Discrete Device Control Signals                                        |        |

| 3-22.  | Device End Logic                                                       |        |

| 3-23.  | Device End Signal Timing Diagrams                                      |        |

| 3-24.  | Device Service Request Logic                                           |        |

| 3-25.  | Data Transfer Timer Interrupt Request Logic                            |        |

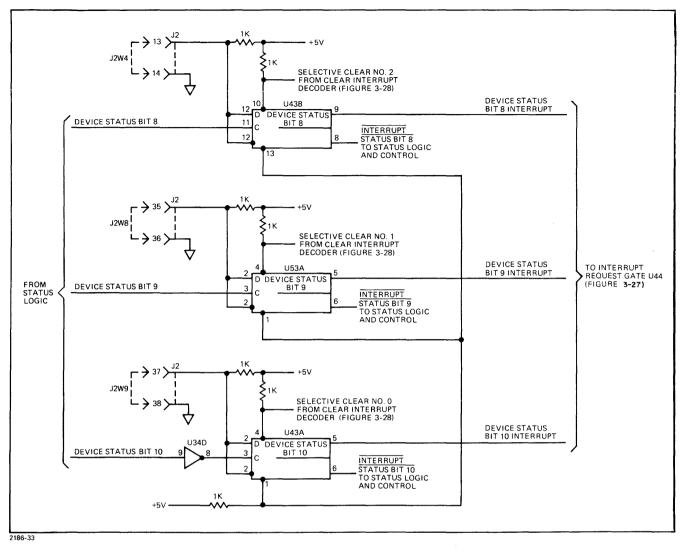

| 3-26.  | Device Interrupt Request Logic                                         |        |

| 3-27.  | I/O System and Interface Interrupt Request Logic                       |        |

| 3-28.  | Clear Interrupt Decoder Logic                                          |        |

| 3-29.  | Status Logic and Control                                               |        |

| 3-30.  | Data In (from Device) Transfer Logic.                                  |        |

| 3-31.  | Data Out (to Device) Transfer Logic                                    |        |

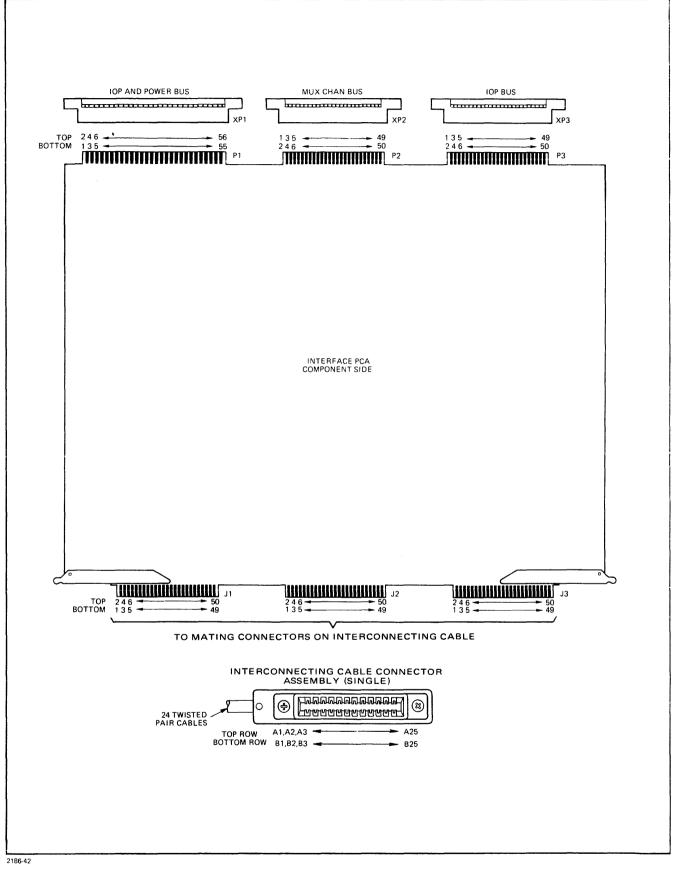

| 4-1.   | Interface PCA and Interconnection Cable Connector Pin Numbering Scheme |        |

| 4-2.   | Interface PCA Jumper Wire Locations                                    |        |

| Table | Title                                                  | Page |

|-------|--------------------------------------------------------|------|

| 1-1.  | Interface PCA Specifications                           |      |

| 2-1.  | Sample Program to Read Data                            |      |

| 2-2.  | Sample Program to Write Data                           |      |

| 2-3.  | Direct I/O Command Codes                               |      |

| 2-4.  | Interrupt Request Selective Clear                      |      |

| 2-5.  | Interrupt Service Routine                              |      |

| 2-6.  | Sequence Counter Status Bit Decoding                   |      |

| 3-1.  | Direct I/O Commands Decoding Table                     |      |

| 3-2.  | Command Function External Signal List                  |      |

| 4-1.  | Interface PCA to Interconnecting Cable Connector Pin ( |      |

|       | Function Index                                         |      |

| 4-2.  | Connector J2 Jumper Wire Functions                     |      |

#### 1-1. INTRODUCTION.

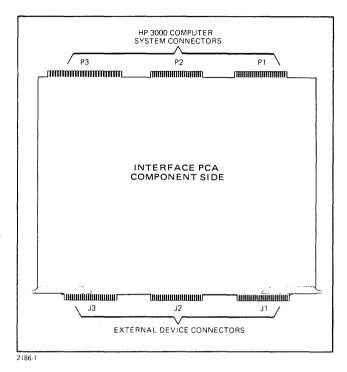

1-2. This section describes the physical features and provides specifications and identification data for the HP 30051A Universal Interface (Differential) (figure 1-1). Related publications that may be required for operation of this interface are listed in the preface to this manual.

#### 1-3. GENERAL DESCRIPTION.

1-4. The HP 30051A Universal Interface (Differential) provides interface capability between the HP 3000 Computer System and an external I/O device that uses parallel data transfer through differential logic circuits. Typical devices used with the HP 3000 Computer System include line printers, card punches, and paper tape readers and punches. The HP 30051A Universal Interface (Differential) consists of the following items:

- a. Universal interface (differential) printed-circuit assembly, part no. 30051-60001.

- b. Maintenance Manual, part no. 30051-90001.

1.5. The universal interface (differential) printed-circuit assembly (interface PCA) contains logic circuits for decoding and executing programmed instructions from the computer system. Executing programmed instructions includes sending 16-bit data and status words from the device to the computer system and 16-bit data and control words from the computer system to the device. When transferring data to the device, the interface PCA accepts up to 16 bits from the computer system and transfers these bits to the device in one word or in two bytes of up to 8 bits each. When accepting data from the device, the interface PCA receives either one word of up to 16 bits or two bytes of up to 8 bits each. These two bytes are then packed into one 16-bit word before transfer to the computer system. Software control of the interface PCA can be either direct (CPU-tointerface PCA) mode or SIO (IOP-to-multiplexer channelto-interface PCA) mode. In both cases, the I/O operations performed between the device and interface PCA are identical.

1-6. Status information is transferred to the computer system in either of two 16-bit word formats. In both formats the high order eight bits (0 through 7) indicate status of the interface PCA logic circuits. The low order bits (8 through 15) are programmed through the control word format to indicate status of either the external device or the interrupt request circuit. Eight different actions of the device can be monitored through the device status byte. The interrupt request circuit contains eight different methods for the device and interface PCA to request an

Figure 1-1. HP 30051A Universal Interface (Differential)

interrupt for service from the computer and each interrupt request provides a separate bit in the interrupt status byte.

1-7. The 16-bit control word contains 5 bits that are transferrable directly to the device. The remaining bits are used on the interface PCA to control data and status transfers and interrupt request logic.

#### 1-8. SPECIFICATIONS.

1-9. Specifications for the interface PCA are listed in table 1-1. Data transfer rates given in table 1-1 were measured between successive programmed strobes with the diagnostic hardware (self-test connector), part no. 30049-60001, installed and a clock rate of 200 nanoseconds. These rates are affected by interconnecting cable length and I/O circuit capacitance so that cables longer than 30 feet and/or increased capacitance will decrease the data transfer rate.

#### 1-10. IDENTIFICATION.

1-11. Printed-circuit assemblies (PCA's) are identified by a part number etched on the PCA. Revisions to the PCA are

identified by a letter, a series code, and a division code (A-0000-00) marked beneath the part number on the PCA. The letter identifies the version of the etched trace pattern on the unloaded PCA. The four-digit series code pertains

to the electrical characteristics and the positions of the components on the PCA. The two-digit division code identifies the division of Hewlett-Packard that manufactured the PCA.

| Table 1-1. | Interface | PCA | Specifications |

|------------|-----------|-----|----------------|

|------------|-----------|-----|----------------|

| CURRENT REQUIRED FROM<br>COMPUTER POWER SUPPLIE<br>+5-volt supply: |                                                         | DATA TRANSFER RATE:<br>(Refer to paragraph 1-9.)<br>Read Order: |                           |

|--------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------|---------------------------|

|                                                                    | 3.5 amperes                                             | Packing Disabled                                                | 300k words per second     |

|                                                                    |                                                         | Packing Enabled                                                 | 230k words per second     |

|                                                                    |                                                         | Write Order:                                                    |                           |

|                                                                    |                                                         | Unpacking Disabled                                              | 210k words per second     |

| METHOD OF DATA<br>TRANSFER:                                        |                                                         | Unpacking Enabled                                               | 180k words per second     |

| To and from Device:                                                | 16-bit parallel, or two 8-bit                           | DIMENSIONS:                                                     |                           |

|                                                                    | bytes using byte transfer,<br>through differential line | Depth:                                                          | 11-1/2 in. (292.1 mm)     |

|                                                                    | drivers and receivers                                   | Width:                                                          | 13-11/16 in. (352.425 mm) |

| To and from Computer:                                              | 16-bit parallel                                         | Thickness<br>(with Components):                                 | 5/8 in. (15.875 mm)       |

| Logic 1 level (high):                                              | +2.5 Vdc minimum                                        | WEIGHT:                                                         |                           |

| Logic 0 level (low):                                               | +0.5 Vdc maximum                                        | Net:                                                            | 1 lb, 4 oz (0.558 kg)     |

|                                                                    |                                                         |                                                                 |                           |

.

#### 2-1. INTRODUCTION.

2-2. This section contains information regarding operation of the interface PCA in the HP 3000 Computer System. Descriptions are included for I/O instructions, direct I/O commands, and programmed I/O orders used by the interface PCA. The control word and status word formats are also described along with sample programming information. All information in this section is general in regard to programming data transfers with a particular device. To determine specific parameters for a particular device, refer to the applicable subsystem manual.

#### 2-3. GENERAL INFORMATION.

2-4. The interface PCA permits bidirectional data transfer between an external device and the HP 3000 Computer System. This interface PCA operates under direct I/O commands from the CPU or under programmed I/O orders initiated through an SIO routine. In either case, the interface PCA performs the same functions and operation is identical to the external device.

2-5. The interface PCA has two sets of jumper wires that determine operating parameters. One set of jumper wires is located on the interface PCA and is used to select the device number, service request priority, group interrupt mask, and DRT address parity (see figure 4-2). The other set of jumper wires is located on the device cable connector which connects to connector J2 on the interface PCA. These jumpers select various operating features of the interface PCA (refer to table 4-2).

2-6. All required control information, data, and status is transferred between the HP 3000 Computer System and the interface PCA by way of the IOP and MUX buses. A block diagram showing the connections for these buses is provided in figure 3-1.

#### 2-7. SYSTEM PARAMETERS.

2-8. Operation of the interface PCA is controlled by machine language I/O instructions. These instructions are supplied by a user program or the operating system. From either source, the response to any given instruction is the same. I/O instructions initiate either direct I/O operations (operations under direct control of the CPU) or programmed I/O operations (operations under control of the multiplexer channel). The following paragraphs describe the I/O instructions that affect the interface PCA and the resultant direct and/or programmed I/O operation.

2-9. CIO INSTRUCTION. The CIO instruction causes a 16-bit control word to be sent from the top-of-stack (TOS) register in the CPU/IOP module to the interface PCA. All 16 bits of the control word are sent with the CIO instruction, therefore, each command modifies all bits in the interface PCA control word buffers. The control word format is described in paragraph 2-28. If the CIO instruction is executed successfully, condition code CCE is set in the computer system.

2-10. RIO INSTRUCTION. The RIO instruction strobes a data word from the interface PCA data input buffers to the computer system memory (refer to table 2-1). The RIO instruction is preceded by a CIO instruction to transfer data

| Table 2-1. Sample Program to Re | ead Data |

|---------------------------------|----------|

|---------------------------------|----------|

|           | TOS←DEVICENUMBER;                                      |                                                            |

|-----------|--------------------------------------------------------|------------------------------------------------------------|

|           | TOS <del>&lt;-%</del> 002004;                          | < <enable data="" transfer="">&gt;</enable>                |

|           |                                                        | < <enable option="" packing="">&gt;</enable>               |

|           | ASSEMBLE (CIO 1);                                      |                                                            |

| SELF:     | IF $<>$ THEN GO SELF;                                  | < <test cio="" completed="" for="">&gt;</test>             |

| TRYAGAIN: | ASSEMBLE (RIO Ø);                                      |                                                            |

| HANGUP:   | IF $\leq$ THEN GO HANGUP;                              | < <device does="" not="" respond="">&gt;</device>          |

|           | IF = THEN GO ONWARD;                                   | < <rio continue="" executed="" o.k.,="">&gt;</rio>         |

|           | ASSEMBLE (DEL);                                        | < <data in="" progress="" still="" transfer="">&gt;</data> |

|           | GO TRY AGAIN;                                          | << DELETE STATUS WORD & TRY AGAIN>>                        |

| ONWARD:   | DATA←TOS;                                              | << 2 BYTES IN PACKED FORMAT>>                              |

|           | < <continue main="" program="" with="">&gt;</continue> |                                                            |

(control word bit 5). The interface PCA accepts a 16-bit word of data (or two 8-bit bytes if byte transfer is enabled) from the device and stores the data in the input buffer. If bit 1 of the status word is high, the RIO instruction reads the buffer contents into the computer system memory. When the RIO instruction is executed successfully, condition code CCE is set in the computer system.

2-11. SIN INSTRUCTION. The SIN instruction sets the I/O system interrupt (bit 13 of the interrupt status word) and causes an interrupt request to be initiated. If control word bit 14 is high and no other interrupts are active, the interface PCA will request an interrupt.

2-12. SIO INSTRUCTION. The SIO instruction initiates a microprogram routine that switches control of the interface PCA away from the CPU and allows the multiplexer channel to control I/O operations. This frees the CPU to do other word during routine I/O operations.

2-13. SMSK INSTRUCTION. The SMSK instruction sends a 16-bit mask word from the top-of-stack (TOS) register in the CPU/IOP module through the interface PCA data out lines. The mask word sets up all interface PCA's in the mask group to allow interrupts. Interface PCA's are assigned to mask groups by a jumper wire (see figure 4-2).

2-14. TIO INSTRUCTION. The TIO instruction causes the interface PCA to send a status word to the computer system. If the TIO instruction is internally microprogrammed as part of an RIO, WIO, or SIO instruction, the status word is sent to scratch pad 2 in the CPU. If the TIO instruction is part of the program code, the status word is sent to the TOS register in the CPU/IOP module. The status word format is described starting in paragraph 2-40.

2-15. WIO INSTRUCTION. The WIO instruction causes a 16-bit data word (or two 8-bit bytes if byte transfer is enabled) to be transferred from the computer system to the external device (refer to table 2-2). Bit 1 of the status word must be high before the WIO instruction is issued or the instruction is rejected. If the WIO instruction is executed successfully, condition code CCE is set in the computer system.

#### 2-16. **DIRECT I/O.**

2-17. Direct I/O operations are under control of the CPU and result from decoding and executing machine language instructions. These instructions each cause the CPU to issue a 12-bit word over the IOP bus to all PCA's. This 12-bit word consists of a 3-bit direct I/O command (IOCMD), an 8-bit device number (DEVNO), and a service out (SO) bit. The IOCMD bits indicate which operation is required by a PCA (refer to table 2-3), the DEVNO bits indicate the PCA being addressed, and the SO bit indicates that a direct I/O command is on the IOP bus. The addressed PCA acknowledges receipt of the direct I/O command by returning a service in (SI) signal over the IOP bus.

#### 2-18. PROGRAMMED I/O.

2-19. The I/O program is initiated as a result of a direct SIO instruction and once initiated is controlled by the multiplexer channel through the IOP and IOP bus. The multiplexer channel accepts the programmed I/O command orders one-at-a-time from the IOP, decodes the command orders and sends control strobe signals to the interface PCA. There are eight programmed I/O command orders that affect operation of the interface PCA. The command orders are CONTROL, END, INTERRUPT, JUMP, READ, RETURN RESIDUE, SENSE, and WRITE. How these command orders affect operation of the interface PCA is described in the following paragraphs.

2-20. CONTROL ORDER. This order causes a transfer of a 16-bit control word in the IOAW field from memory to the interface PCA. The control word format is identical to the CIO instruction control word format and is described in paragraph 2-28. To prevent loss of control word bits, all bits must be restored with each control word.

2-21. END ORDER. This order indicates the termination of an I/O program and causes the interface PCA to send a status word to the computer system memory location specified by the IOAW. The status word format is described in paragraph 2-40.

| Tabla  | 2.2  | Sample | Program | to | Write | Data |

|--------|------|--------|---------|----|-------|------|

| I able | 4-4. | Sample | riogram | w  | write | Data |

|         | TOS←DEVICENUMBER;              |                                                |

|---------|--------------------------------|------------------------------------------------|

|         | TOS <b>←%00000</b> 4;          | < <enable option="" unpacking="">&gt;</enable> |

|         | ASSEMBLE (CIO 1);              |                                                |

| SELF:   | IF $<>$ THEN GO SELF;          | < <test cio="" completed="" for="">&gt;</test> |

|         | TOS←DATA;<br>ASSEMBLE (WIO 1); | << 2 BYTES IN PACKED FORMAT>>                  |

| HANGUP: | IF <> THEN GO HANGUP;          | < <test completed="" for="" wio="">&gt;</test> |

Table 2-3. Direct I/O Command Codes

| COMMAND  | IOCMD |    | ō  | DESCRIPTION                                                                                                                                                                   |  |

|----------|-------|----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| COMMAND  | 00    | 01 | 02 | DESCRIPTION                                                                                                                                                                   |  |

| CIO      | 1     | 1  | 0  | Control I/O. Transfers a 16-bit con-<br>trol word from the computer sys-<br>tem to the interface PCA (see<br>figure 2-1).                                                     |  |

| RESETINT | 0     | 1  | 1  | Reset Interrupt. Clears the inter-<br>face PCA interrupt active condition<br>but does not clear the conditional<br>logic that specifies the cause of an<br>interrupt request. |  |

| RIO      | 0     | 0  | 0  | Read I/O. Transfers a 16-bit data<br>word from the interface PCA to the<br>computer system.                                                                                   |  |

| SIN      | 1     | 1  | 1  | Set Interrupt. Sets the I/O system interrupt and causes an interrupt request to be initiated.                                                                                 |  |

| SIO      | 1     | 0  | 1  | Start I/O. Initiates a microprogram<br>routine that allows the multiplexer<br>channel to control operation of the<br>interface PCA.                                           |  |

| SMSK     | 0     | 0  | 1  | Set Mask. Transfers a mask word<br>from top of stack (TOS) to all<br>interface PCA's.                                                                                         |  |

| TIO      | 0     | 1  | 0  | Test I/O. Transfers a 16-bit status<br>word from the interface PCA to the<br>computer system (see figures 2-2,<br>2-3, and 2-4).                                              |  |

| WIO      | 1     | 0  | 0  | Write I/O. Transfers a 16-bit data word from the computer system to the interface PCA.                                                                                        |  |

2-22. INTERRUPT ORDER. This order sets the I/O system interrupt (bit 13 of the interrupt status word) and causes an interrupt request to be initiated. Then, if control word bit 14 is high and no other interrupts are active, the interface PCA will request an interrupt. There is no effect on the external device.

2-23. JUMP ORDER. This order causes the multiplexer channel to jump unconditionally to the address given in the IOAW for the next IOCW to be executed.

2-24. READ ORDER. This order causes the transfer of a block of data from the device to the computer system memory. The starting address in memory is specified by the IOAW. This transfer terminates normally if the device sends a Device End signal or the word count has gone to zero.

2-25. RETURN RESIDUE ORDER. This order has no effect on the interface PCA. The order returns the remainder of the word count to the IOAW. This information is used to determine the number of words transferred if

the device terminates a READ or WRITE order before word count has gone to zero.

2-26. SENSE ORDER. This order causes a 16-bit status word to be transferred from the interface PCA to the computer by the IOAW. The status word format is described in paragraph 2-40.

2-27. WRITE ORDER. This order causes the transfer of a block of data from the computer system memory to the external device. The starting address of the block is specified by the IOAW. This transfer terminates normally if the device sends a Device End signal or the word count has gone to zero.

#### 2-28. CONTROL WORD FORMAT.

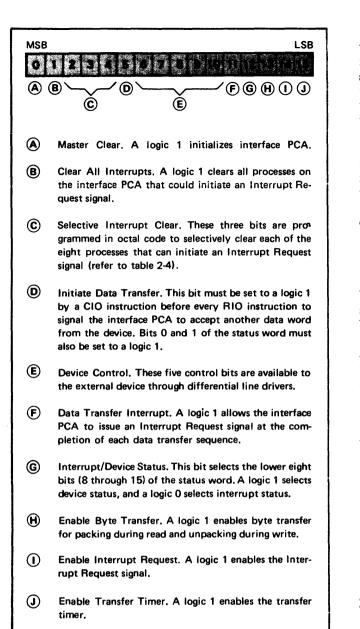

2-29. The control word is a 16-bit word that is sent from the computer system to the interface PCA over the IOP bus data out lines. This control word is sent to the interface PCA after execution of a direct CIO instruction or I/O program CONTROL order. To ensure against loss of control bits, all of the control bits must be restored each time a control word is sent to the interface PCA. Figure 2-1 shows the control word format and the separate bits are explained in the following paragraphs.

2-30. MASTER CLEAR. When high (logic 1), this bit initializes the interface PCA. Its action on the interface PCA is similar to pushing the I/O reset switch on the computer system console. Master clear should be used only when the condition of the interface PCA is unknown or when it is necessary to clear one of the interface status bits.

2-31. CLEAR ALL INTERRUPTS. This bit, when high, clears all processes on the interface PCA that could initiate an interrupt request. Master clear has the same effect on the interrupt processing logic. After this bit is issued, the interrupt pending bit (bit 2 of the status word) should be low indicating that all interrupt requests were cleared.

2-32. SELECTIVE INTERRUPT CLEAR. These three bits may be programmed to separately clear each of the eight conditions that can cause an interrupt request. Table 2-4 lists the bits configurations required to clear each interrupt request.

2-33. INITIATE DATA TRANSFER. This bit must be set high with a CIO instruction before every RIO instruction to signal the interface PCA to fetch another data word from the device. Set this bit high only when bits 0 and 1 of the status word are both high to indicate that an SIO is not in progress and data is not being transferred.

2-34. DEVICE CONTROL. These five bits are made available to the device through differential line drivers. On the interface PCA, these bits are stored in a buffer that is modified by every control word.

2186-4

Figure 2-1. Control Word Format

|   | CONTROL<br>WORD BITS |   | INTERRUPT PROCESS CLEARED                                               |  |  |

|---|----------------------|---|-------------------------------------------------------------------------|--|--|

| 2 | 3                    | 4 | ]                                                                       |  |  |

| 0 | 0                    | 0 | Inactive state, no action                                               |  |  |

| 0 | 0                    | 1 | Transfer Timer and Transfer Error, inter-<br>rupt status bits 15 and 14 |  |  |

| 0 | 1                    | 0 | I/O System, interrupt status bit 13                                     |  |  |

| 0 | 1                    | 1 | Clear Interface, interrupt status bit 12                                |  |  |

| 1 | 0                    | 0 | Data Transfer, interrupt status bit 11                                  |  |  |

| 1 | 0                    | 1 | Device Status bit 8, interrupt status bit 8                             |  |  |

| 1 | 1                    | 0 | Device Status bit 9, interrupt status bit 9                             |  |  |

| 1 | 1                    | 1 | Device Status bit 10, interrupt status<br>bit 10                        |  |  |

2-35. DATA TRANSFER INTERRUPT. This bit, when high, causes the interface PCA to issue an interrupt request at the completion of each data transfer sequence. Its purpose is to allow programming of data transfer instructions (WIO and RIO) to the device, continue with some other operation, and then return to transfer more data when signaled by the interrupt.

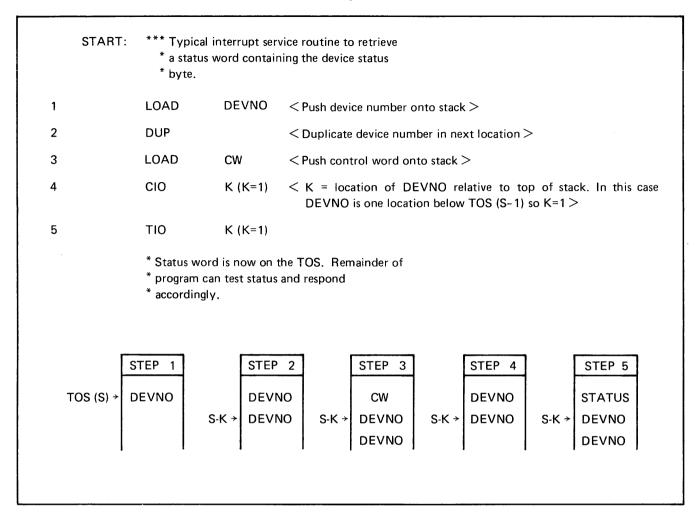

2-36. INTERRUPT/DEVICE STATUS. When this bit is low the interrupt status byte is enabled and when this bit is high the device status byte is enabled. Table 2-5 provides a typical interrupt service routine with changes in the stack shown for each step.

2-37. BYTE TRANSFER. When high, this bit allows the interface PCA to accept two data bytes of up to 8 bits each from the device and to pack them into a single word of up to 16 bits. This data word can then be transferred to the computer system memory. Also, the high byte transfer bit allows the interface PCA to accept a single word of up to 16 bits from the computer system memory and to transfer the word to the device in two bytes of up to 8 bits each.

2-38. ENABLE INTERRUPT REQUEST. This bit, when high, enables the interrupt request logic so that the interface PCA may request an interrupt.

2-39. START TRANSFER TIMER. This bit, when high, starts the data transfer timer. If the transfer timer is not cleared by a control word (see table 2-4) within 5 seconds, an interrupt request is initiated.

#### 2-40. STATUS WORD FORMATS.

2-41. The status word is a 16-bit word that is fetched from the interface PCA after executing a TIO instruction or a SENSE order in an I/O program. When the TIO instruction is internally microprogrammed as 'part of an RIO, WIO, or SIO instruction, the status word is sent to scratch pad 2 of the CPU. If the TIO instruction is part of the program code, the status word is sent to the TOS register in the CPU/IOP module. The SENSE order is always the first part of an I/O program doubleword and results in the status word being stored in the second part of the same doubleword.

2-42. The 16-bit status word has two different formats with the upper eight bits (bits 0 through 7) being the same for either format. The lower eight bits (8 through 15) indicate either interrupt status or device status depending on control word bit 12. With control word bit 12 low, the status word contains the interrupt status byte and with control word bit 12 high, the status word contains the device status byte.

#### 2-43. INTERFACE STATUS BYTE.

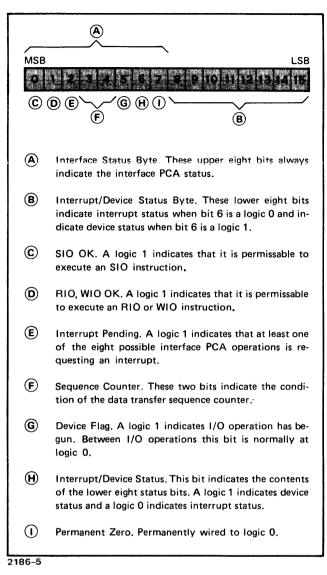

2-44. The interface status byte is contained in the upper eight bits (0 through 7) of every status word. These bits indicate the condition of several interface PCA functions (see figure 2-2). Each bit is explained in the following paragraphs.

2-45. SIO OK. When high, this status bit indicates that it is permissable to execute an SIO command. A low in this bit position indicates that an SIO routine is in progress or that the multiplexer channel cannot service the interface PCA.

2-46. RIO, WIO OK. This bit, when high, indicates that it is permissable to execute an RIO or WIO instruction to transfer data between the device and computer system. During data transfers this bit is held low to indicate that a data transfer is in progress.

2-47. INTERRUPT PENDING. A high in this bit position indicates that at least one of the eight possible interface PCA functions is requesting an interrupt. When this bit is low it indicates that there are no active interrupt requests. Even when the interrupt pending bit is high, the interrupt request may be inhibited if control word bit 14 is low.

2-48. SEQUENCE COUNTER. These two bits indicate the condition of the interface PCA data transfer sequence counter. They are used primarily for troubleshooting the interface PCA during diagnostic routines. The two bits are decoded as described in table 2-6.

2-49. DEVICE FLAG. This bit is supplied by the external device in response to a request for operation. When high, it indicates that the I/O operation at the device is complete. Between I/O operations, this bit is normally low.

2-50. INTERRUPT/DEVICE STATUS. This bit is controlled by bit 12 of the control word and is used to indicate the content of the lower eight status bits (7 through 15). When this bit is high, the lower eight status bits are device status and when this bit is low, the lower eight status bits are interrupt status. Interrupt and device status bits are explained in the following paragraphs.

2-51. PERMANENT ZERO. Status bit 7 is permanently wired low.

| Table 2-6.  | Sequence | Counter | Status | Rit | Decoding |

|-------------|----------|---------|--------|-----|----------|

| 1 abie 2-0. | Sequence | Counter | Status | DIL | Decounig |

| STATUS BIT |   | DESCRIPTION                                                |  |

|------------|---|------------------------------------------------------------|--|

|            |   | DESCRIPTION                                                |  |

| 0          | 0 | Sequence counter at rest.                                  |  |

| 1          | 0 | Request for operation to device.                           |  |

| 1          | 1 | Begin operation from device.                               |  |

| 0          | 1 | Request for operation to begin transfer<br>of second byte. |  |

#### 2-52. INTERRUPT STATUS BYTE.

2-53. The interrupt status byte is contained in bits 8 through 15 of the status word when bit 6 of the status word is low. Each bit of the interrupt status byte indicates a function on the interface PCA that can request an

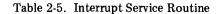

interrupt (see figure 2-3). When one or more of these bits are high, indicating an interrupt request, bit 2 of the status word is also high to indicate that an interrupt request is waiting for service. Also, each of the interrupt request conditions and its associated status bit can be cleared individually to ensure that no interrupt requests will be lost. Selective clearing of the interrupt requests is described in paragraph 2-32. The following paragraphs describe each of the interrupt status bits.

2-54. DEVICE STATUS INTERRUPTS. The device status interrupts are three independent bits in the interrupt status word. These bits (8, 9, and 10) are enabled by the same signals from the device that provide device status bits 8, 9, and 10. To activate the interrupt requests from the device status lines, the appropriate jumper wire must be

| MSB |                                                                                                                                                                                                                                                              |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ۲   | Interface Status Byte. These upper eight bits always indicate the interface PCA status.                                                                                                                                                                      |

| B   | Interrupt Status Byte. These lower eight bits indicate interrupt status when bit 6 is a logic 0.                                                                                                                                                             |

| ©   | Interrupt/Device Status. This bit indicates content of the lower eight status bits and must be a logic 0 for interrupt status.                                                                                                                               |

| D   | Device Status Interrupts. Device status bits 8, 9, and<br>10 can be used to initiate interrupt requests. When<br>used to initiate an interrupt request, device status bits<br>8, 9, and 10 also initiate interrupt status bits 8, 9, and<br>10 respectively. |

| E   | Data Transfer Interrupt. A logic 1 indicates that con-<br>trol word bit 11 is a logic 1 and that an interrupt re-<br>quest will occur after each data transfer.                                                                                              |

| F   | Clear Interface Interrupt. A logic 1 indicates that an I/O program was cancelled by the external device.                                                                                                                                                     |

| G   | I/O System Interrupt. A logic 1 indicates that a direct SIN command or I/O program INTERRUPT code was executed.                                                                                                                                              |

| θ   | Transfer Error Interrupt. A logic 1 indicates that an error has occurred in the transfer of data between the interface PCA and the computer system.                                                                                                          |

| 0   | Transfer Timer Interrupt. A logic 1 indicates that the transfer timer was enabled by control word bit 15 and the time expired before the timer was cleared.                                                                                                  |

2186-6

Figure 2-3. Interface/Interrupt Status Word Format

installed in the mating connector to connector J2. The jumper wires designation are J2W4, J2W8, and J2W9 for interrupt status bits 8, 9, and 10 respectively (refer to table 4-2). When the appropriate jumper wire is installed, interrupt status bits 8 and 9 are enabled by the leading edge of device status signals 8 and 9, and interrupt status bit 10 is enabled by the trailing edge of device status bit 10.

2-55. DATA TRANSFER INTERRUPT. The data transfer interrupt is enabled by control word bit 11 and when enabled causes an interrupt request after each data transfer. Refer to paragraph 2-35.

2-56. CLEAR INTERFACE INTERRUPT. A clear interface interrupt is valid only during an I/O program when the multiplexer channel is controlling the interface PCA. The external device can completely abort the I/O program and enable this interrupt by sending a Clear Interface signal to the interface PCA.

2-57. I/O SYSTEM INTERRUPT. This bit, when high, indicates that a direct SIN instruction or an I/O program INTERRUPT order was executed and an interrupt requested.

2-58. TRANSFER ERROR INTERRUPT. This bit, when high, indicates that an error has occurred in the transfer of data between the interface PCA and the computer system. Once enabled, this bit must be cleared before another data transfer can occur. The conditions that cause this bit to go high are as follows:

- a. Illegal address.

- b. Memory parity error.

- c. Parity error on data transfer to or from computer system memory.

2-59. TIME OUT INTERRUPT. This bit goes high if the transfer timer delay expires. The transfer timer is first

started by control word bit 15 and then expires 5 seconds later if the timer is not cleared by a control word with bit 4 at a logic 1. If the timer is not cleared within the preset time limit, an interrupt is requested.

#### 2-60. DEVICE STATUS BYTE.

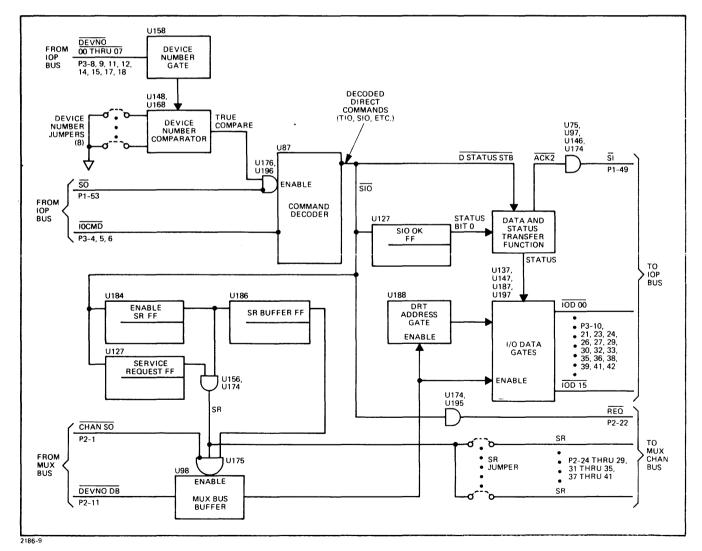

2-61. The device status byte is contained in bits 8 through 15 of the status word when bit 6 of the status word is high. Each bit of the device status word indicates an input signal from the external device (see figure 2-4). Three of the bits (8, 9, and 10) are also connected to the interrupt status lines to enable the device to request an interrupt (refer to paragraph 2-54).

|     | (A) (B)                                                                                                                                     |  |  |  |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MSB | LSB                                                                                                                                         |  |  |  |  |  |

| 0   | <u>1 2 3 4 5 6 7 8 9 10 11 12 13 14 15</u><br>C                                                                                             |  |  |  |  |  |

| ۸   | Interface Status Byte. These upper eight bits always indicate the interface PCA status.                                                     |  |  |  |  |  |

| ₿   | Device Status Byte. When connected to an external device and bit 6 is a logic 1, these lower eight bits in-<br>dicate status of the device. |  |  |  |  |  |

| C   | Interrupt/Device Status. This bit indicates content of the lower eight status bits and must be a logic 1 for device status.                 |  |  |  |  |  |

2186-7

Figure 2-4. Interface/Device Status Word Format

#### 3-1. INTRODUCTION.

3-2. This section contains system-level and functionallevel descriptions of operation for the HP 30051A Universal Interface (Differential) PCA. The system-level description briefly describes interface PCA operations in relation to the HP 3000 Computer System. The functional-level description divides the interface PCA into functional circuit groups and provides a description of operation for each group.

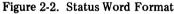

#### 3-3. SYSTEM-LEVEL DESCRIPTION.

3-4. The interface PCA is combined with any compatible device such as a line printer to form a subsystem of the HP 3000 Computer System (see figure 3-1). This subsystem can be any one of sixteen subsystems connected to each multiplexer channel in the overall system. Operation of the subsystem requires the transfer of commands, data, and status information between the interface card and the following system components:

- a. Memory Module

- b. Central Processor Unit (CPU)

- c. Input/Output Processor (IOP)

- d. Multiplexer Channel

3-5. The memory module contains the I/O drivers that are executed by the CPU, I/O programs that are transferred by the IOP to the multiplexer channel, and the device reference tables (DRT). I/O drivers contain direct instructions such as Read I/O (RIO), Write I/O (WIO), and Start I/O (SIO). As an I/O driver instruction is executed by the CPU, the CPU issues direct commands through the IOP and IOP bus directly to the addressed interface PCA. When the interface PCA accepts a direct command, it returns an acknowledge signal and performs the command. If the direct instruction was an SIO, the multiplexer channel assumes control of the interface PCA and the CPU is free to perform other functions.

3-6. An SIO instruction calls a routine that permits the IOP to transfer an I/O program, one instruction at a time, from the memory module to the multiplexer channel. The multiplexer channel then controls operation of the interface PCA. Instructions contained in the I/O program are similar to the instructions contained in the I/O driver and they perform many of the same functions such as Read I/O and Write I/O.

3-7. The multiplexer channel is a controller for up to 16 subsystems and contains a one-word storage location for each subsystem. Program instructions from the IOP are stored one at a time in the storage location for the addressed subsystem. Each program word is then decoded by the multiplexer channel and sent through the MUX CHAN bus to the appropriate interface PCA. When the interface PCA accepts the decoded program instruction, it returns an acknowledge signal to the IOP and performs the instruction. The interface PCA and multiplexer channel exchange signals that monitor progress in performing instructions.

3-8. Data are transferred to and from the device through the interface PCA and IOP bus. This transfer occurs in response to either direct or program I/O instructions. The device number (address) and interrupt priority are determined by relocateable jumper wires on the interface PCA. An interrupt to transfer data to or from the device can be initiated by the operating program or by an interrupt request from the device and interface PCA. Interrupt requests are also initiated due to several different status conditions.

3-9. Status conditions for the interface PCA and device, including the conditions that cause an automatic request for interrupt, are transferred from the interface PCA through the IOP bus data lines. These status conditions are transferred as either of two 16-bit status words. One status word indicates the interface PCA status and the status of eight interrupt conditions. The second status word indicates the same interface PCA status as the first status word. However, the eight interrupt status bits are replaced by eight device status bits. Bit 12 of the control word determines which status word is transferred.

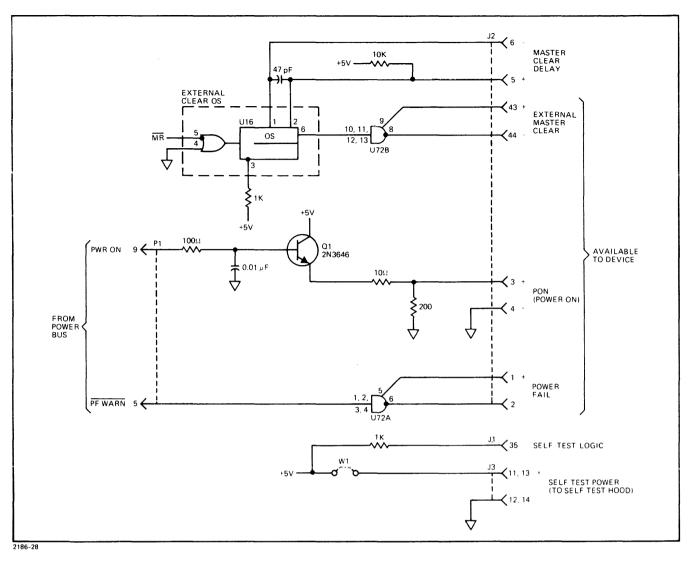

3-10. The device control word is a 16-bit word that is sent to the interface PCA through the IOP bus data lines. Five bits of the control word are available at output pins to control device operations. The remaining bits control functions on the interface PCA such as selecting the interrupt status or device status word. The interface card also has three discrete signals available for the device. These three discrete signals are Master Clear, Power Fail Warning, and Power On.

#### 3-11. FUNCTIONAL-LEVEL DESCRIPTION.

3-12. The interface PCA performs three interrelated functions. These functions are (1) command, (2) control, and (3) data and status transfer (see figure 3-1). Each of these functions is divided in circuit groups and operation of the circuit groups is described in the following paragraphs. Simplified and detailed diagrams for the interface PCA are contained in the HP 3000 Computer System diagrams manuals. The simplified diagrams are set number SD-131 and the detailed diagrams are set number DD-501. Functional block diagrams, timing diagrams and partial schematics contained in this manual are referred to by figure number.

Figure 3-1. Overall System Block Diagram

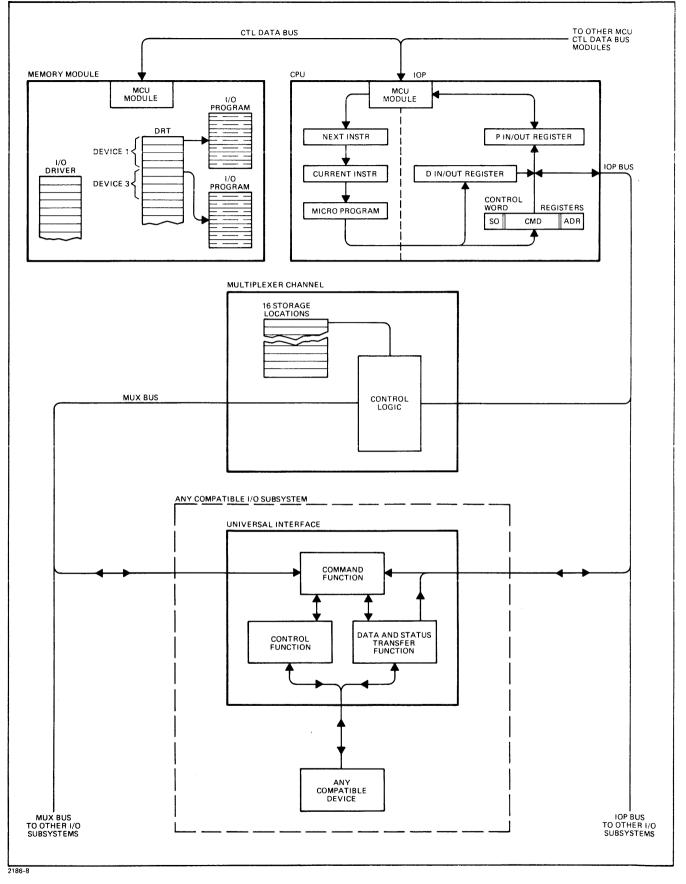

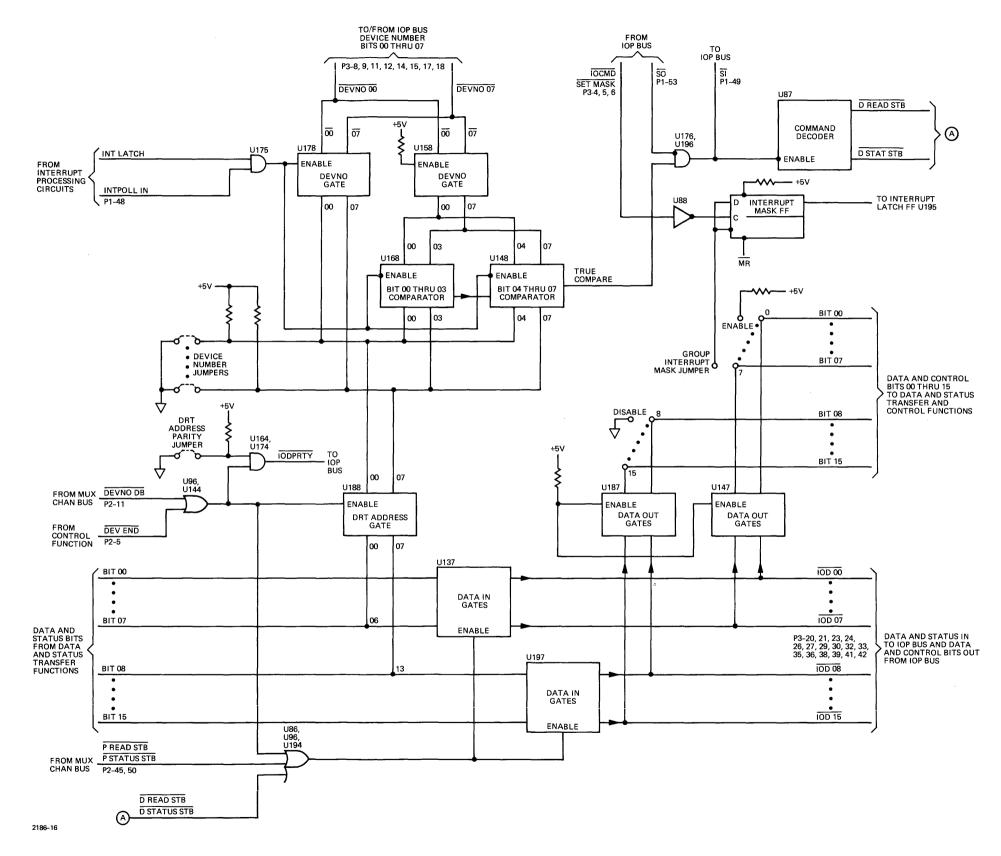

#### 3-13. COMMAND FUNCTION.

3-14. The interface PCA command function is performed by the circuits that receive and process the direct commands from the CPU and the decoded program commands from the multiplexer channel. In addition, an interrupt processing circuit and the I/O data gates are contained with the command function circuits. Operation of these circuits is described in the following paragraphs.

3-15. DIRECT COMMANDS. Direct commands are executed by the CPU and sent through the IOP and IOP bus to the interface PCA. The interface PCA receives the direct commands as three bits of the I/O command (IOCMD) word. These three bits are decoded as shown in table 3-1. To enable the command decoder and initiate the command operation requires a series of interlocking operations. Since decoding of each direct command is similar, only the decoding of the SIO command is described in the following paragraphs.

3-16. When the CPU executes an SIO command, the resulting CPU microcode assembles a device address word, microcode test I/O, and service out. This combined 12-bit word, is sent through the S-bus to the IOP control word registers (see figure 3-1). The IOP, in turn, sends the 12-bit word through the IOP bus to the interface PCA command function circuits (see figure 3-2). These circuits receive the 12-bit word as  $\overline{\text{DEVNO}}$ , 8 bits;  $\overline{\text{IOCMD}}$ , 3 bits; and  $\overline{\text{SO}}$ , 1 bit. (Refer to table 3-2 for a list of external signal names and abbreviations.) The  $\overline{\text{DEVNO}}$  bits are compared with the device number relocateable jumper wire configuration. Coincidence of the compared signals provides a True Compare signal that is combined with the SO signal to enable the command decoder.

3-17. The command decoder then decodes the  $\overline{IOCMD}$  bits as a TIO which provides a  $\overline{D}$  STATUS STB command to the status transfer function on the interface PCA. This command strobes a 16-bit status word onto the IOP bus. At the same time, the status transfer function provides an acknowledge signal (ACK 2) that results in sending an  $\overline{SI}$  signal to the IOP. The IOP then terminates the  $\overline{SO}$  signal that was enabling the command decoder and transfers the 16-bit status word to scratch pad 2 of the CPU.

3-18. In the CPU, the microcode checks bit 0 of the status word to determine if the device and interface PCA are ready to transfer data. If the status indicates that data transfer can proceed, the microcode again assembles a  $\overline{\text{DEVNO}}$ ,  $\overline{\text{SO}}$ , and  $\overline{\text{IOCMD}}$  command word that is sent through the IOP and IOP bus to the interface PCA. The interface PCA command decoder is again enabled. However, the decoded command is now  $\overline{\text{SIO}}$ .

3-19. When a direct strobe command such as  $\overline{D}$  WRITE STB is decoded, the interface PCA performs the commanded function and returns an acknowledge signal to the CPU. The acknowledge signal must be received before the CPU can proceed to the next command. However, decoding

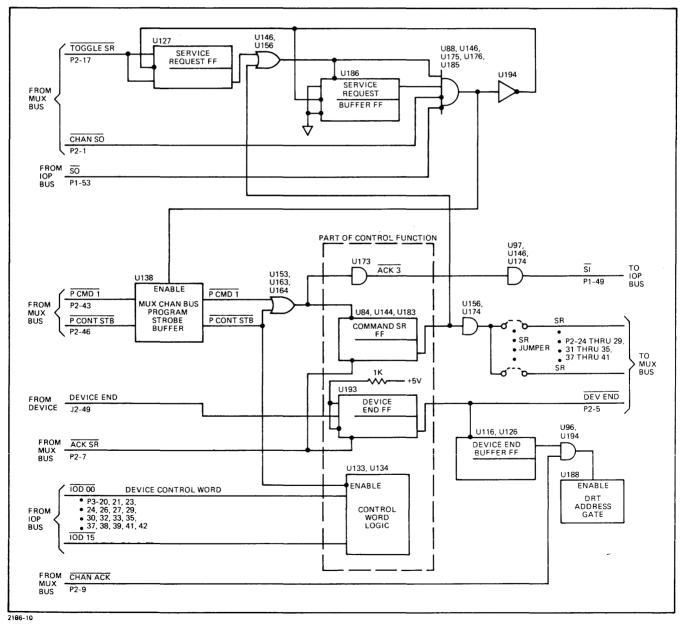

a  $\overline{SIO}$  command starts a routine that allows the IOP to control the interface PCA operations and frees the CPU to perform other operations. Decoding the  $\overline{SIO}$  command direct sets the  $\overline{SIO}$  OK, Service Request, Enable Service Request, and Service Request Buffer flip-flops. Setting the  $\overline{SIO}$  OK FF causes status bit 0 to go to logic 0. This indicates, during any subsequent status checks, that an SIO operation is in progress and prevents the CPU from sending another  $\overline{SIO}$  command until the first operation is complete.

3-20. Setting the Service Request and Enable Service Request FF's causes an SR signal to be enabled. This SR signal can be jumper wired to any one of 16 output pins. The location of this jumper wire determines which device will be serviced by the multiplexer channel. Each interface PCA connected to the same multiplexer channel must have the jumper wire connected to a different output pin. The SR signal and a  $\overline{\text{REQ}}$  signal are sent through to MUX bus to the multiplexer channel. At the multiplexer channel, the  $\overline{REQ}$  signal causes an  $\overline{SI}$  signal to be sent to the IOP. The IOP then terminates the  $\overline{SO}$  signal to the interface PCA. Terminating the  $\overline{SO}$  signal disables the interface PCA command decoder. Also, the  $\overline{REQ}$  signal puts the multiplexer channel in the DRT fetch mode. The SR signal from the interface PCA causes the multiplexer channel to send a high Service Request signal to the IOP. This high Service Request signal starts the multiplexer channel DRT fetch operation and causes the IOP to issue a DATAPOLL IN signal on the IOP bus. The DATAPOLL IN signal propogates through each multiplexer channel until the highest priority multiplexer channel that is requesting service breaks the priority chain.

3-21. Once the multiplexer channel is being serviced by the IOP, the multiplexer channel overrides the SR signal from the interface PCA and at the same time sends a CHAN SO signal through the MUX bus to the interface PCA. This allows the set-side output from the Service Request Buffer FF, set when the  $\overline{SIO}$  command was decoded, to enable eight of the MUX bus buffer gates on the interface PCA. Enabling these MUX bus buffer gates allows the DEVNO  $\overline{\text{DB}}$  signal from the multiplexer channel to enable the DRT address and data gates so that the DRT address is available on the I/O data lines (IOD 00 thru IOD 15) to the IOP bus. The DRT address is developed by sending device number bits 00 through 07 (DEVNO 00 thru DEVNO 07) through the DRT address gates to I/O data lines IOD 06 thru IOD 13. This shift in bit positions multiplies the device number by four to provide the DRT address.

3-22. The multiplexer channel then sends an  $\overline{SI}$  signal and a DRT fetch command to the IOP and the IOP accepts the DRT address from the IOP bus. The content of this address is a pointer to the first I/O program command. I/O program commands are then transferred one-at-a-time to the multiplexer channel where they are decoded and the decoded program commands are sent on to the interface PCA. Operation of the I/O program commands is described in the following paragraphs.

|    | IOCMD<br>BITS |    | I/O DRIVER | DECODED COMMAND             |              |  |

|----|---------------|----|------------|-----------------------------|--------------|--|

| 00 | 01            | 02 | COMMAND    | NAME                        | ABBREVIATION |  |

| 1  | 1             | 1  | SIN        | "Not" Set Interrupt         | SET INT      |  |

| 0  | 1             | 1  | RESET INT  | "Not" Reset Interrupt       | RESET INT    |  |

| 1  | 0             | 1  | SIO        | "Not" Start Input/Output    | SIO          |  |

| 0  | 0             | 1  | SMSK       | "Not" Set Mask              | SMSK         |  |

| 1  | 1             | 0  | СЮ         | "Not" Direct Control Strobe | D CONT STB   |  |

| 0  | 1             | 0  | TIO        | "Not" Direct Status Strobe  | D STATUS STB |  |

| 1  | 0             | 0  | WIO        | "Not" Direct Write Strobe   | D WRITE STB  |  |

| 0  | 0             | 0  | RIO        | "Not" Direct Read Strobe    | D READ STB   |  |

Table 3-1.

Direct I/O Commands Decoding Table

| NO. | SIGNAL<br>NAME                                 | ABBREVIATION              | BUS |     | CONNECTOR                                                          |

|-----|------------------------------------------------|---------------------------|-----|-----|--------------------------------------------------------------------|

|     |                                                |                           | MUX | IOP | AND PIN NO.                                                        |

| 1   | "Not" Acknowledge<br>Service Request           | ACK SR                    | ×   |     | P2-7                                                               |

| 2   | "Not" Channel Service<br>Out                   | CHAN SO                   | ×   |     | P2-1                                                               |

| 3   | "Not" Device Number<br>00 thru 07              | DEVNO 00 thru<br>DEVNO 07 |     | х   | P3-8,9,11,12,<br>14,15,17,18                                       |

| 4   | "Not" Device End                               | DEV END                   | x   |     | P2-5                                                               |