HP64000 Logic Development System

# Model 64271A General Purpose Control Card

HEWLETT PACKARD

## CERTIFICATION

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### WARRANTY

This Hewlett-Packard system product is warranted against defects in materials and workmanship for a period of 90 days from date of installation. During the warranty period, HP will, at its options, either repair or replace products which prove to be defective.

Warranty service of this product will be performed at Buyer's facility at no charge within HP service travel areas. Outside HP service travel areas, warranty service will be performed at Buyer's facility only upon HP's prior agreement and Buyer shall pay HP's round trip travel expenses. In all other cases, products must be returned to a service facility designated by HP.

For products returned to HP for warranty service, Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country.

HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instructions when properly installed on that instrument. HP does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTIBILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### EXCLUSIVE REMEDIES

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HP SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### ASSISTANCE

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office. Addresses are provided at the back of this manual.

гого неве

NO POSTAGE NECESSARY IF MAILED IN THE UNITED STATES

# BUSINESS REPLY CARD FIRST CLASS PERMIT NO. 1303 COLORADO SPRINGS, COLORADO

POSTAGE WILL BE PAID BY ADDRESSEE

HEWLETT PACKARD

# HEWLETT-PACKARD Logic Product Support Dept.

Attn: Technical Publications Manager Centennial Annex - D2 P.O. Box 617 Colorado Springs, Colorado 80901-0617

FOLD HERE

Your cooperation in completing and returning this form will be greatly appreciated. Thank you.

# **READER COMMENT SHEET**

Service Manual General Purpose Control Card 64271-90902, November 1983

Your comments are important to us. Please answer this questionaire and return it to us. Circle the number that best describes your answer in questions 1 through 7. Thank you.

1. The information in this book is complete:

| Doesn't cover enough<br>(what more do you need?) | 1   | 2    | 3 | 4 | 5 | Covers everything       |

|--------------------------------------------------|-----|------|---|---|---|-------------------------|

| 2. The information in this book is accurate:     |     |      |   |   |   |                         |

| Too many errors                                  | 1   | 2    | 3 | 4 | 5 | Exactly right           |

| 3. The information in this book is easy to find  | :   |      |   |   |   |                         |

| I can't find things I need                       | 1   | 2    | 3 | 4 | 5 | I can find info quickly |

| 4. The Index and Table of Contents are useful:   |     |      |   |   |   |                         |

| Helpful                                          | 1   | 2    | 3 | 4 | 5 | Missing or inadequate   |

| 5. What about the "how-to" procedures and ex     | amp | les: |   |   |   |                         |

| No help                                          | 1   | 2    | 3 | 4 | 5 | Very helpful            |

| Too many now                                     | 1   | 2    | 3 | 4 | 5 | I'd like more           |

| 6. What about the writing style:                 |     |      |   |   |   |                         |

| Confusing                                        | 1   | 2    | 3 | 4 | 5 | Clear                   |

| 7. What about organization of the book:          |     |      |   |   |   |                         |

| Poor order                                       | 1   | 2    | 3 | 4 | 5 | Good order              |

| 8. What about the size of the book:              |     |      |   |   |   |                         |

| too big/small                                    | 1   | 2    | 3 | 4 | 5 | Right size              |

| Comments:                                        |     |      |   |   |   |                         |

| Particular pages with errors?                    |     |      |   |   |   |                         |

| Name (optional):                                 |     |      |   |   |   |                         |

| Company!                                         |     |      |   | _ |   |                         |

Note: If mailed outside U.S.A., place card in envelope. Use address shown on other side of this card.

FOLD HERE

NO POSTAGE NECESSARY IF MAILED IN THE UNITED STATES

# BUSINESS REPLY CARD FIRST CLASS PERMIT NO. 1303 COLORADO SPRINGS, COLORADO

POSTAGE WILL BE PAID BY ADDRESSEE

HEWLETT PACKARD

# **HEWLETT-PACKARD**

Logic Product Support Dept. Attn: Technical Publications Manager Centennial Annex - D2 P.O. Box 617 Colorado Springs, Colorado 80901-0617

FOLD HERE

Your cooperation in completing and returning this form will be greatly appreciated. Thank you.

# **READER COMMENT SHEET**

Service Manual General Purpose Control Card 64271-90902, November 1983

Your comments are important to us. Please answer this questionaire and return it to us. Circle the number that best describes your answer in questions 1 through 7. Thank you.

1. The information in this book is complete:

| Doesn't cover enough<br>(what more do you need?) | 1   | 2    | 3 | 4 | 5 | Covers everything              |

|--------------------------------------------------|-----|------|---|---|---|--------------------------------|

| 2. The information in this book is accurate:     |     |      |   |   |   |                                |

| Too many errors                                  | 1   | 2    | 3 | 4 | 5 | Exactly right                  |

| 3. The information in this book is easy to find: |     |      |   |   |   |                                |

| I can't find things I need                       | 1   | 2    | 3 | 4 | 5 | I can find info quickly        |

| 4. The Index and Table of Contents are useful:   |     |      |   |   |   |                                |

| Helpful                                          | 1   | 2    | 3 | 4 | 5 | Missing or inadequate          |

| 5. What about the "how-to" procedures and ex     | amp | les: |   |   |   |                                |

| No help                                          | 1   | 2    | 3 | 4 | 5 | Very helpful                   |

| Too many now                                     | 1   | 2    | 3 | 4 | 5 | I'd like more                  |

| 6. What about the writing style:                 |     |      |   |   |   |                                |

| Confusing                                        | 1   | 2    | 3 | 4 | 5 | Clear                          |

| 7. What about organization of the book:          |     |      |   |   |   |                                |

| Poor order                                       | 1   | 2    | 3 | 4 | 5 | Good order                     |

| 8. What about the size of the book:              |     |      |   |   |   |                                |

| too big/small                                    | 1   | 2    | 3 | 4 | 5 | Right size                     |

| Comments:                                        |     |      |   |   |   |                                |

|                                                  |     |      |   |   |   |                                |

| Particular pages with errors?                    |     |      |   |   |   |                                |

| · · ·                                            |     |      |   |   |   |                                |

| Name (optional):                                 |     |      |   |   |   |                                |

| Company:Address:                                 |     |      |   |   |   | the set of the set of the card |

Note: If mailed outside U.S.A., place card in envelope. Use address shown on other side of this card.

SERVICE MANUAL

# MODEL 64271A GENERAL PURPOSE CONTROL CARD

#### REPAIR NUMBERS

This manual applies to 64271A Emulators with a repair number prefix of 2124A. For further information on repair numbers refer to "Instruments Covered by This Manual" in Section I.

© COPYRIGHT HEWLETT -PACKARD COMPANY 1981, 1983 LOGIC SYSTEMS DIVISION COLORADO SPRINGS, COLORADO, U.S.A.

ALL RIGHTS RESERVED

Manual Part No. 64271-90902

## **PRINTED: NOVEMBER 1983**

# SAFETY SUMMARY

The following general safety precautions must be observed during all phases of operation, service, and repair of this instrument. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the instrument. Hewlett-Packard Company assumes no liability for the customer's failure to comply with these requirements.

#### GROUND THE INSTRUMENT.

To minimize shock hazard, the instrument chassis and cabinet must be connected to an electrical ground. The instrument is equipped with a three-conductor ac power cable. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

#### DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE.

Do not operate the instrument in the presence of flammable gases or fumes. Operation of any electrical instrument in such an environment constitutes a definite safety hazard.

#### KEEP AWAY FROM LIVE CIRCUITS.

Operating personnel must not remove instrument covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with the power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### DO NOT SERVICE OR ADJUST ALONE.

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### DO NOT SUBSTITUTE PARTS OR MODIFY INSTRUMENT.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the instrument. Return the instrument to a Hewlett-Packard Sales and Service Office for service and repair to ensure that safety features are maintained.

## DANGEROUS PROCEDURE WARNINGS.

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

#### WARNING

Dangerous voltages, capable of causing death, are present in this instrument. Use extreme caution when handling, testing, and adjusting.

#### SAFETY SYMBOLS

#### General Definitions of Safety Symbols Used on Equipment or in Manuals.

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect against damage to the instrument.

는 OR (느

Indicates dangerous voltage (terminals fed from the interior by voltage exceeding 1000 volts must be so marked).

) Protective conductor terminal. For protection against electrical shock in case of a fault. Used with field wiring terminals to indicate the terminal which must be connected to ground before operating equipment.

Low-noise or noiseless, clean ground (earth) terminal. Used for a signal common, as well as providing protection against electrical shock in case of a fault. A terminal marked with this symbol must be connected to ground in the manner described in the installation (operating) manual, and before operating the equipment.

Frame or chassis terminal. A connection to the frame (chassis) of the equipment which normally includes all exposed metal structures.

- Alternating current (power line).

- Direct current (power line).

$\sim$

CAUTION

, OR\_

Alternating or direct current (power line).

WARNING

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, condition or the like, which, if not correctly performed, could result in injury or death to personnel.

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, practice, condition or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product.

NOTE: The NOTE sign denotes important information. It calls attention to procedure, practice, condition or the like, which is essential to highlight.

# **PRINTING HISTORY**

Each new edition of this manual incorporates all material updated since the previous edition. Manual change sheets are issued between editions, allowing you to correct or insert information in the current edition.

The part number on the back cover changes only when each new edition is published. Minor corrections or additions may be made as the manual is reprinted between editions.

First Edition.....June 1981 (P/N 64271-90901) Second Edition.....November 1983 (P/N 64271-90902)

# TABLE OF CONTENTS

| Section                                                                                                                                                                                                                                                                                                                                                         | Page                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| I GENERAL INFORMATION                                                                                                                                                                                                                                                                                                                                           | 1-1                                                                                                                   |

| <ul> <li>1-1. INTRODUCTION.</li> <li>1-4. ORGANIZATION.</li> <li>1-6. INSTRUMENTS COVERED BY THIS MANUAL.</li> <li>1-10. DESCRIPTION.</li> <li>1-11. EMULATION OVERVIEW.</li> <li>1-14. GP CONTROL BOARD.</li> <li>1-23. ADDITIONAL EQUIPMENT REQUIRED.</li> <li>1-25. POWER SUPPLY LOADS.</li> </ul>                                                           | 1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-2                                                                                |

| II INSTALLATION                                                                                                                                                                                                                                                                                                                                                 | 2-1                                                                                                                   |

| <ul> <li>2-1. INTRODUCTION.</li> <li>2-3. INITIAL INSPECTION.</li> <li>2-5. INSTALLATION.</li> <li>2-9. RFI GROUND BRACKET INSTALLATION.</li> <li>2-14. OPERATING ENVIRONMENT.</li> <li>2-16. STORAGE AND SHIPMENT.</li> <li>2-17. ENVIRONMENT.</li> <li>2-19. ORIGINAL PACKAGING.</li> <li>2-21. OTHER PACKAGING.</li> </ul>                                   | 2-1<br>2-1<br>2-5<br>2-8<br>2-8<br>2-8<br>2-8<br>2-8                                                                  |

| III OPERATION                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                       |

| 3-1. INTRODUCTION.                                                                                                                                                                                                                                                                                                                                              | 3-1                                                                                                                   |

| IVPERFORMANCE TESTS.4-1. INTRODUCTION.4-4. 64271A PERFORMANCE VERIFICATION.4-7. CONTROL BOARD TEST (Figure 4-4).4-9. RAM OUTPUT SHORT TESTS (VCC/GND).4-15. MAPPER WRITE TEST.4-21. INTERRUPT AND BREAK TESTS.4-21. INTERRUPT AND BREAK TESTS.4-27. ADDRESS LINE SHORT TO GND TEST.4-33. ADDRESS LINE SHORT TO VCC TEST.4-39. ADDRESS LINE TO LINE SHORTS TEST. | $\begin{array}{c} & 4-1 \\ & 4-1 \\ & 4-2 \\ & 4-2 \\ & 4-3 \\ & 4-3 \\ & 4-4 \\ & 4-4 \\ & 4-4 \\ & 4-5 \end{array}$ |

| V ADJUSTMENTS                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                       |

# TABLE OF CONTENTS (Cont'd)

| Sectio | on                                       | Page |

|--------|------------------------------------------|------|

| VI     | REPLACEABLE PARTS                        | 6-1  |

|        | 6-1. INTRODUCTION.                       |      |

|        | 6-3. EXCHANGE ASSEMBLIES.                |      |

|        | 6-5. ABBREVIATIONS                       |      |

|        | 6-7. REPLACEABLE PARTS                   |      |

|        | 6-9. ORDERING INFORMATION.               | 6-1  |

|        | 6-12. DIRECT MAIL ORDER SYSTEM.          | 6-2  |

| VII    | MANUAL CHANGES                           | 7-1  |

|        | 7-1. INTRODUCTION.                       |      |

| VIII   | SERVICE                                  |      |

|        | 8-1. INTRODUCTION.                       | 8-1  |

|        | 8-3. SAFETY                              | 8-1  |

|        | 8-5. THEORY OF OPERATION.                | 8-1  |

|        | 8-6. GENERAL                             | 8-1  |

|        | 8-8. EMULATION OVERVIEW.                 | 8-1  |

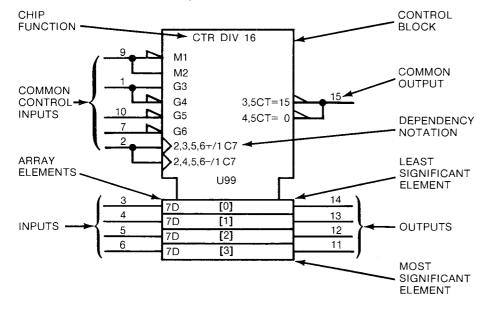

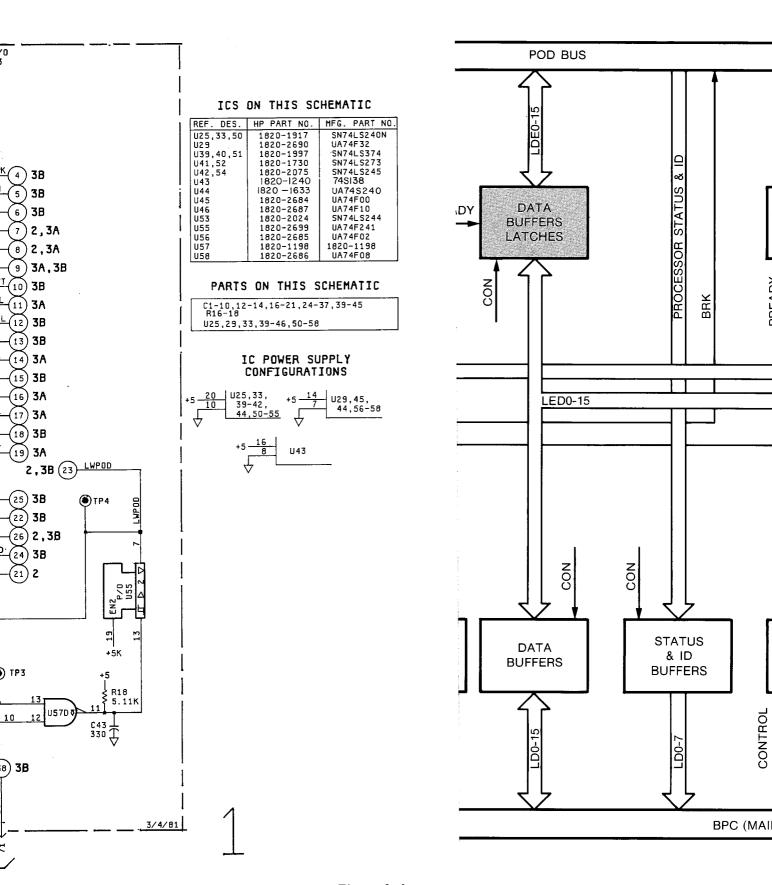

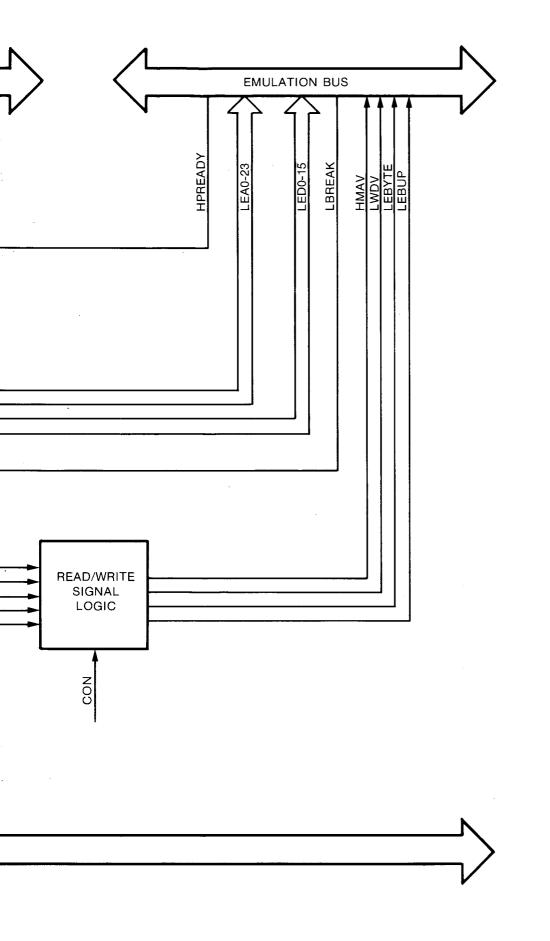

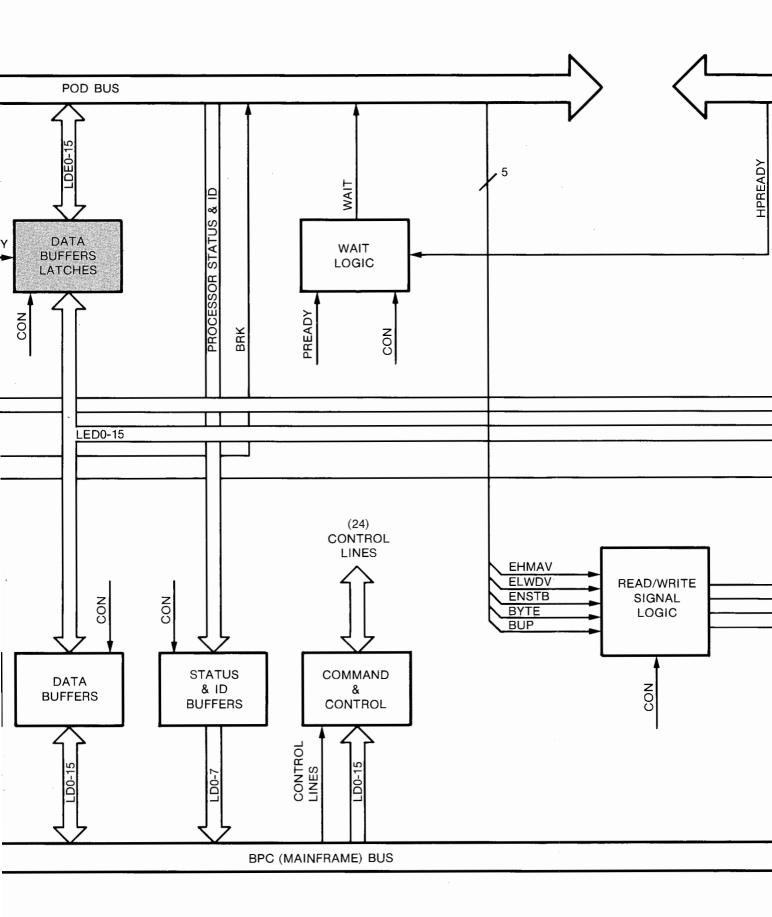

|        | 8-13. EMULATION SUBSYSTEM BLOCK DIAGRAM. | 8-2  |

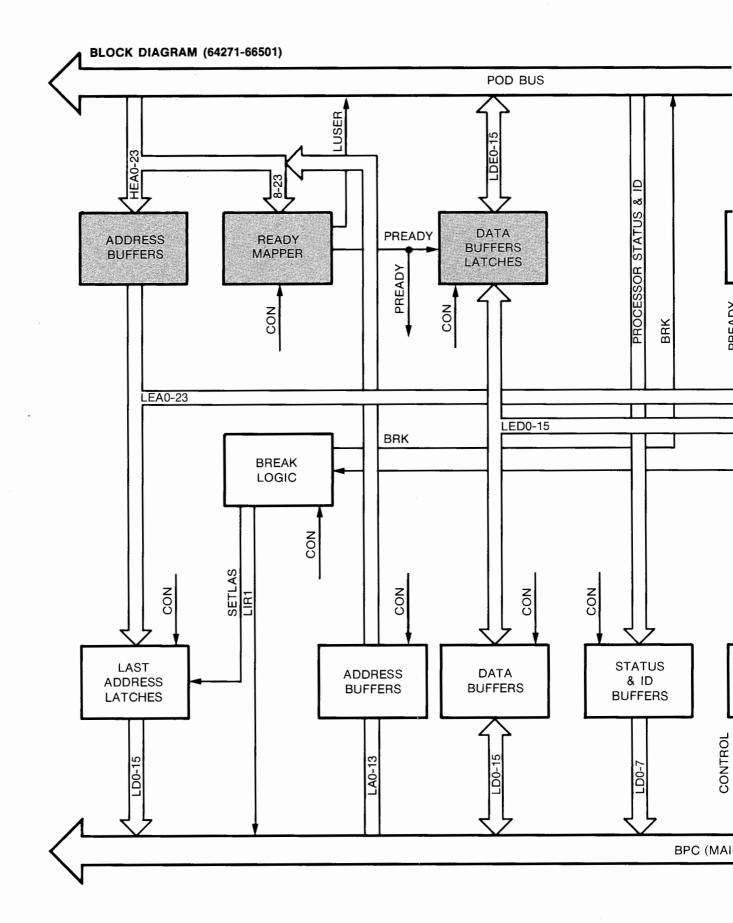

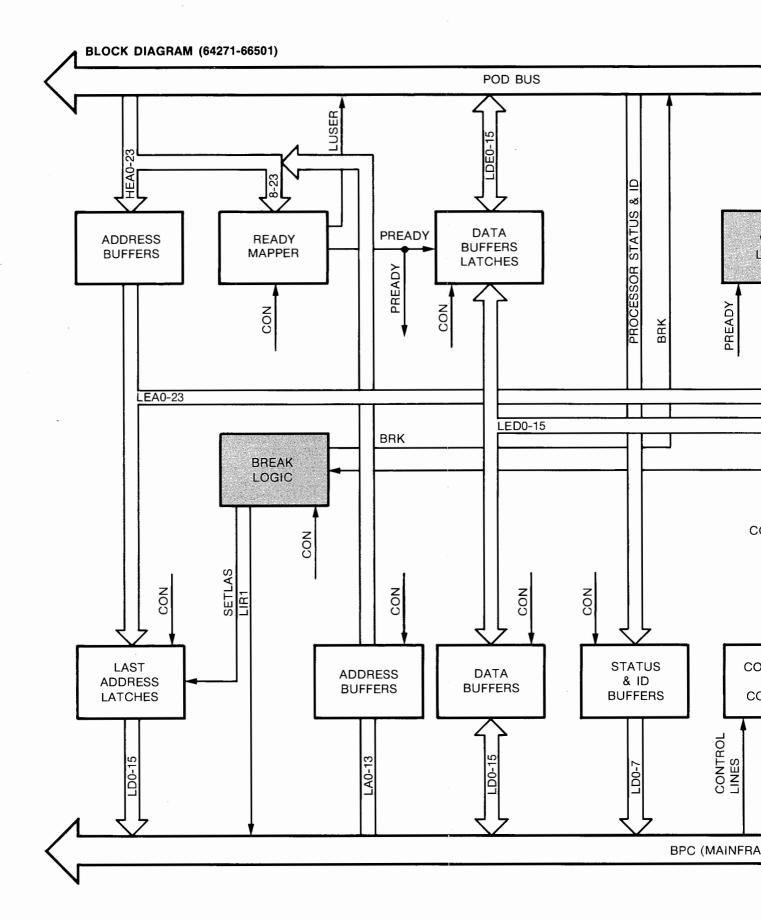

|        | 8-20. GP CONTROLLER BLOCK DIAGRAM.       | 8-5  |

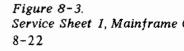

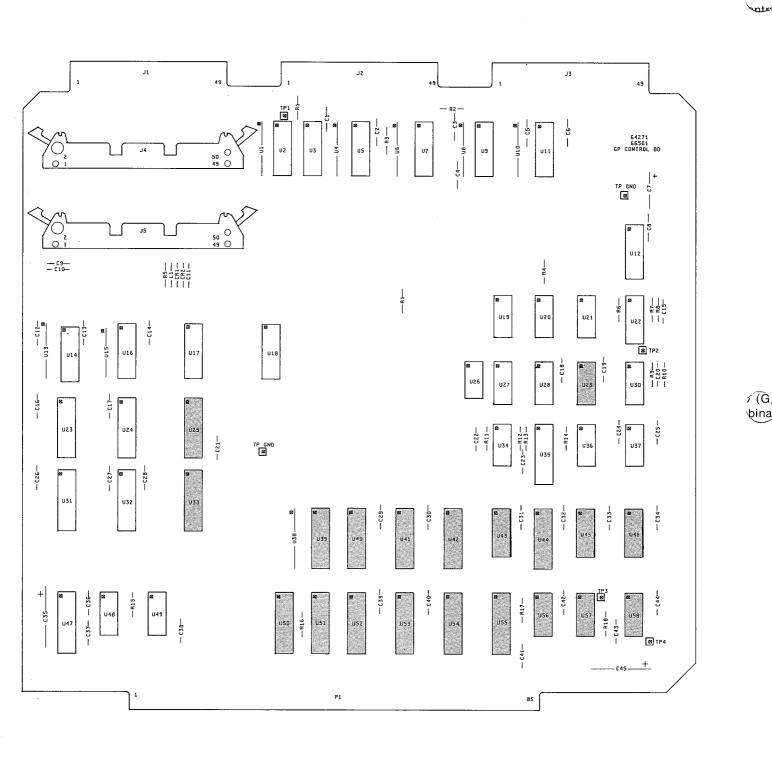

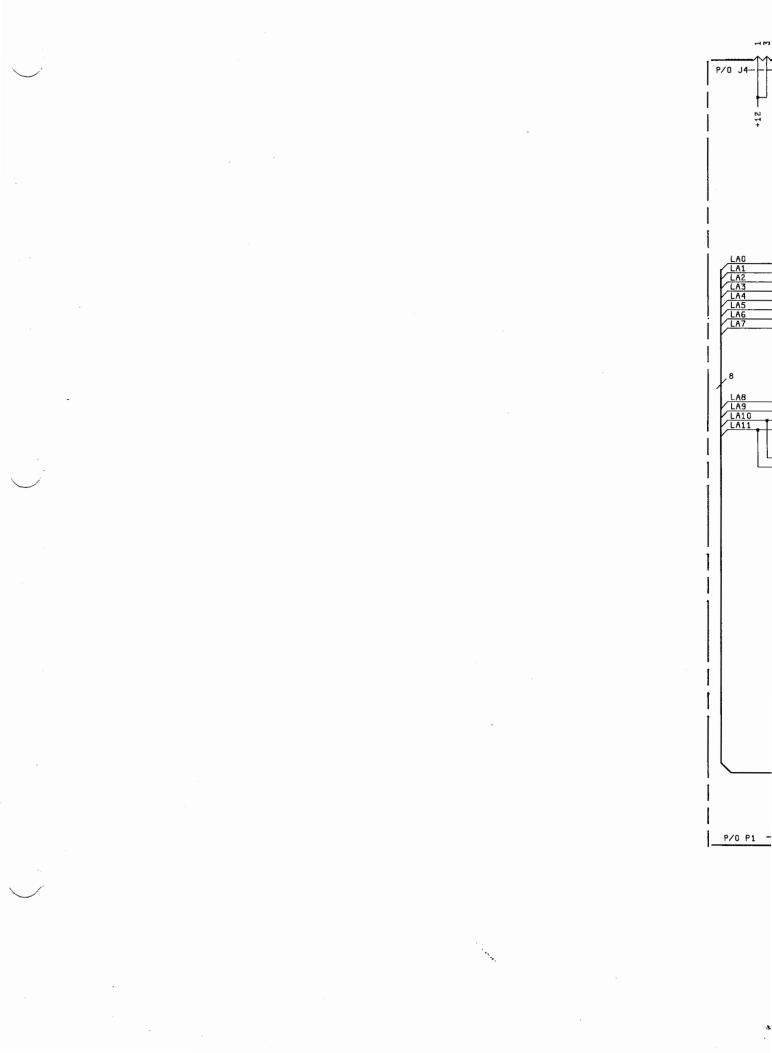

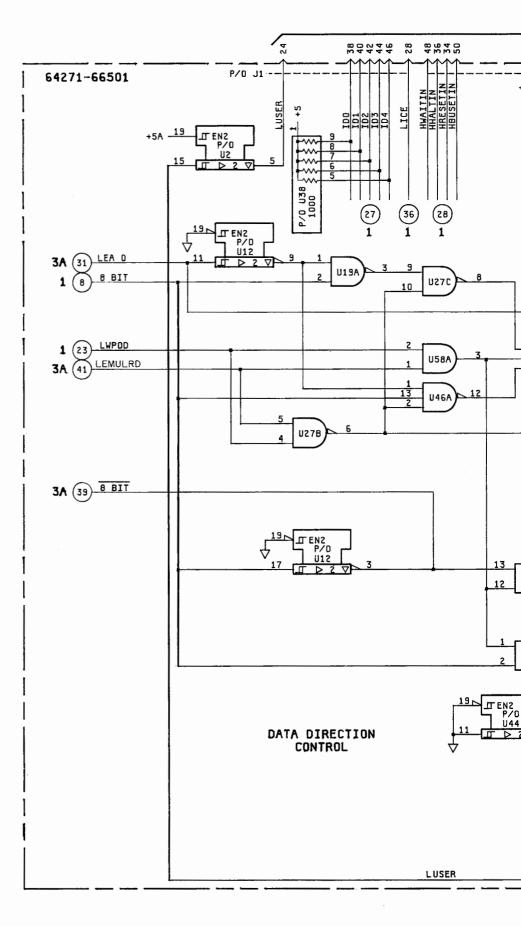

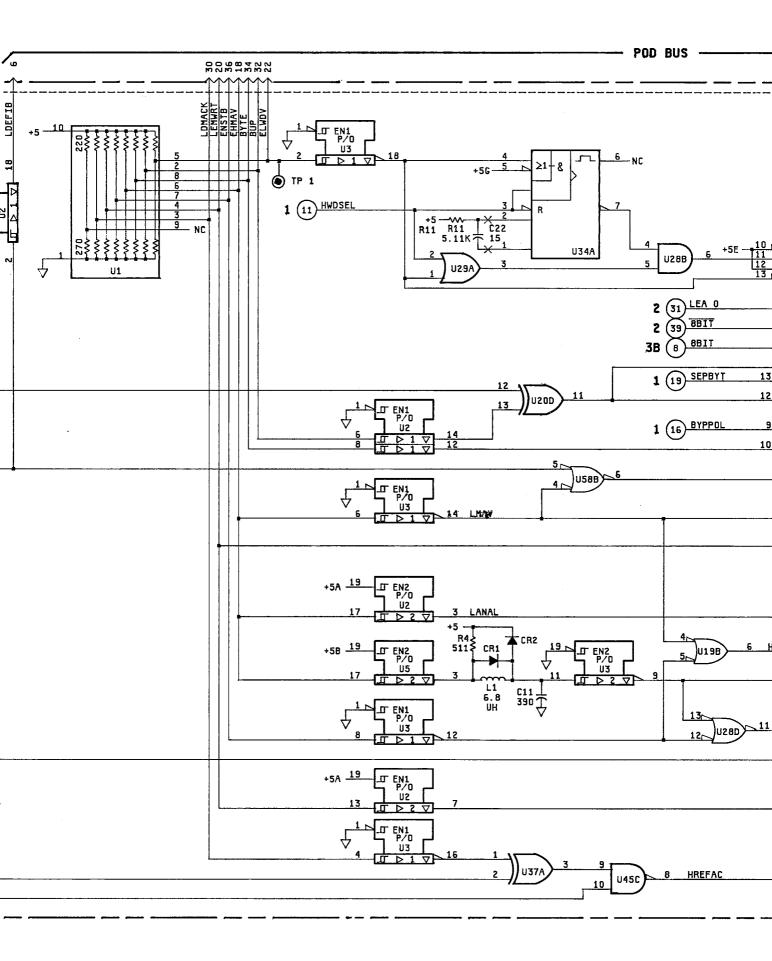

|        | 8-29. SERVICE SHEET 1                    | 8-6  |

|        | 8-39. SERVICE SHEET 2                    | 8-7  |

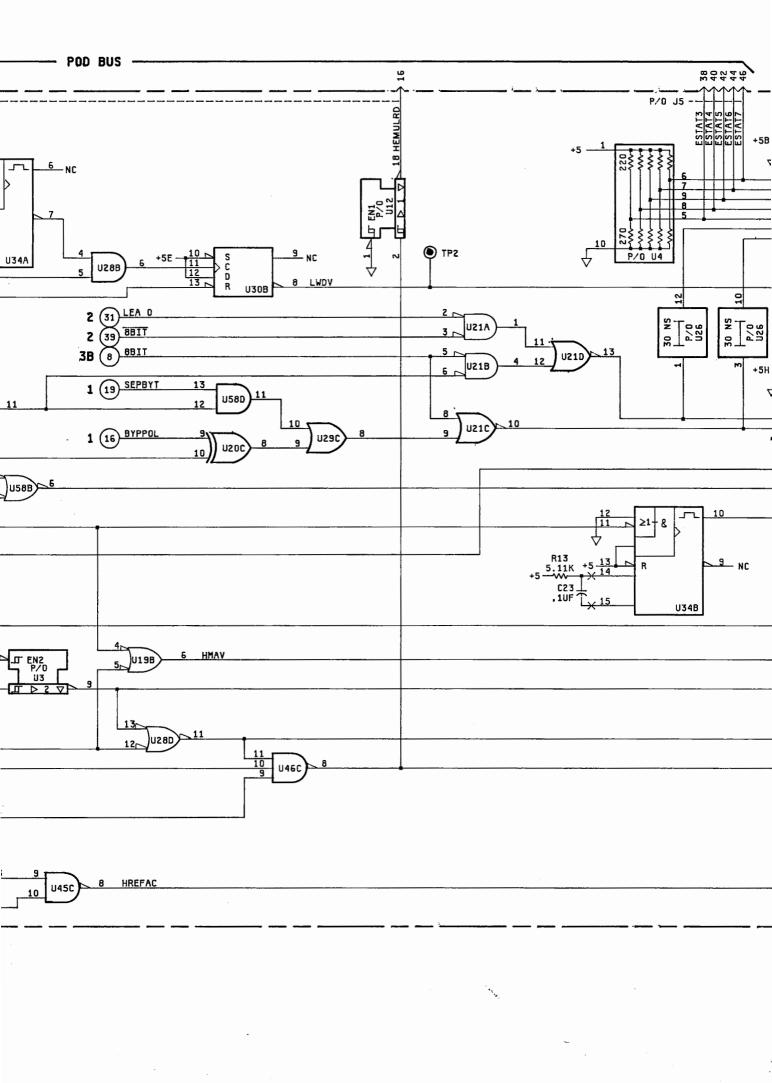

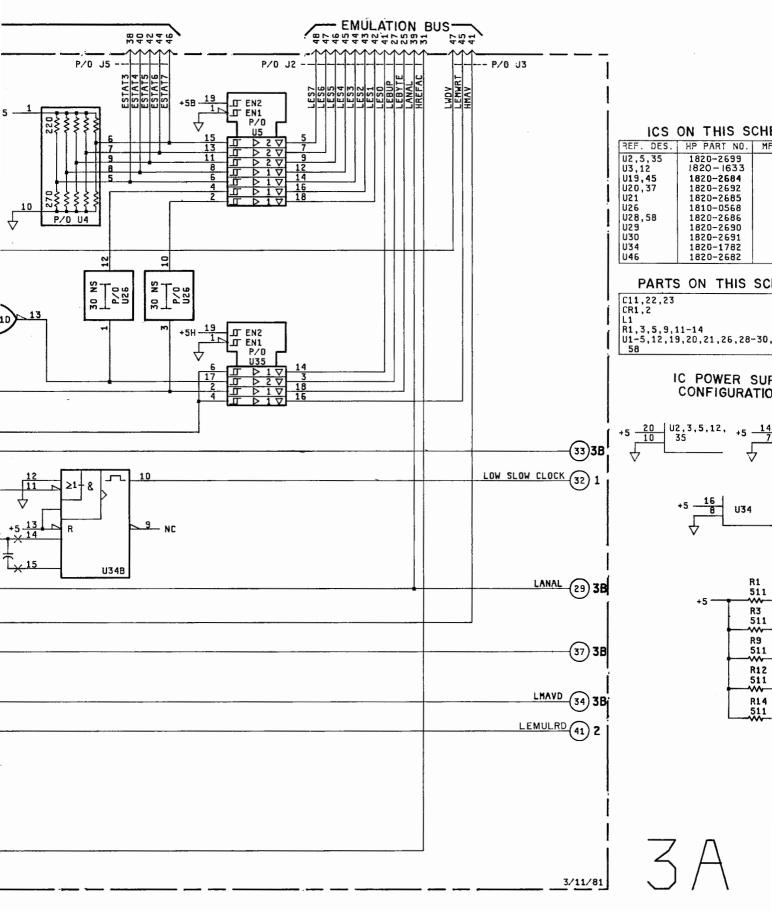

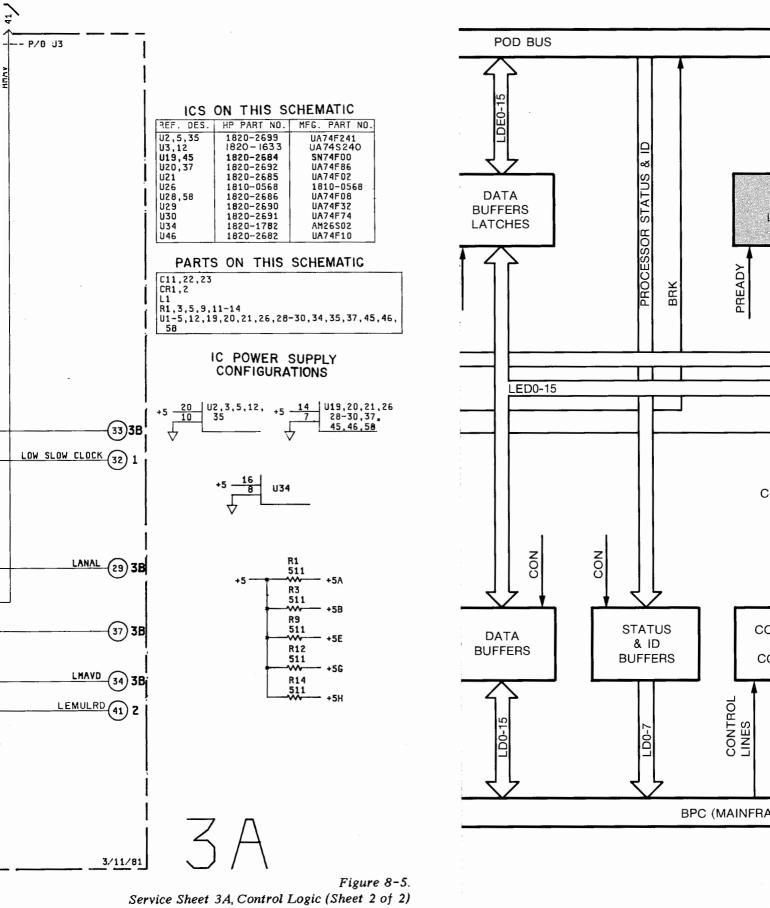

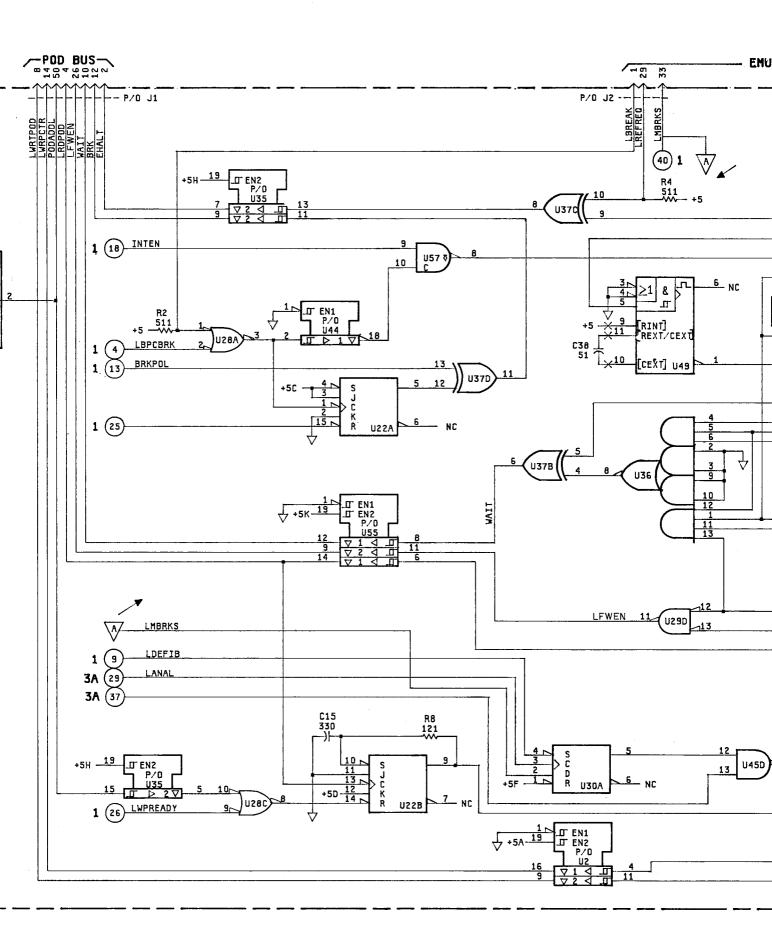

|        | 8-45. SERVICE SHEET 3A                   | 8-8  |

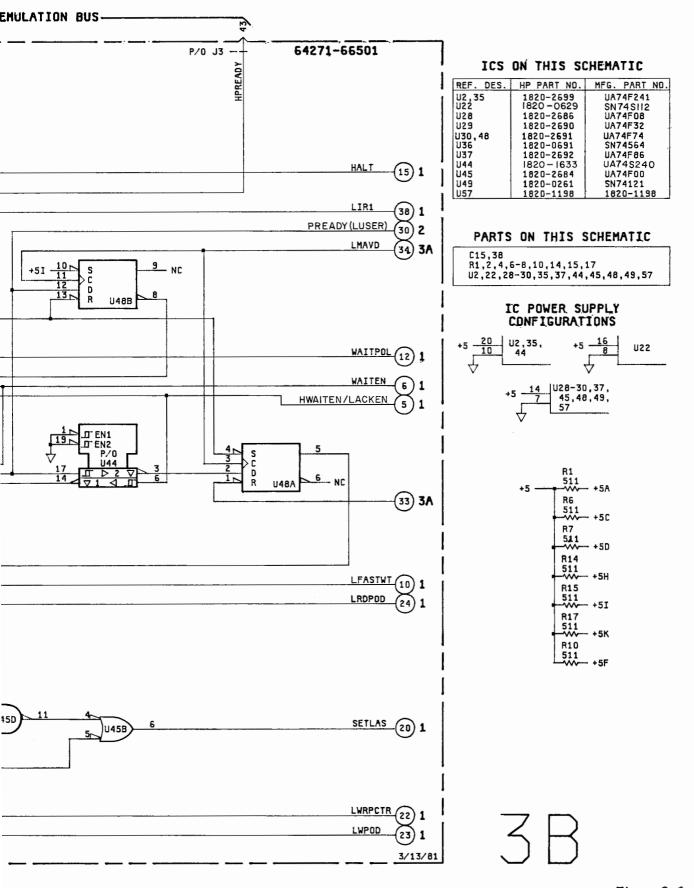

|        | 8-53. SERVICE SHEET 3B                   |      |

|        | 8-60. LOGIC CONVENTION.                  | 8-12 |

|        | 8-64. MNEMONICS                          | 8-12 |

# LIST OF ILLUSTRATIONS

| Figure       |                                          | Page |

|--------------|------------------------------------------|------|

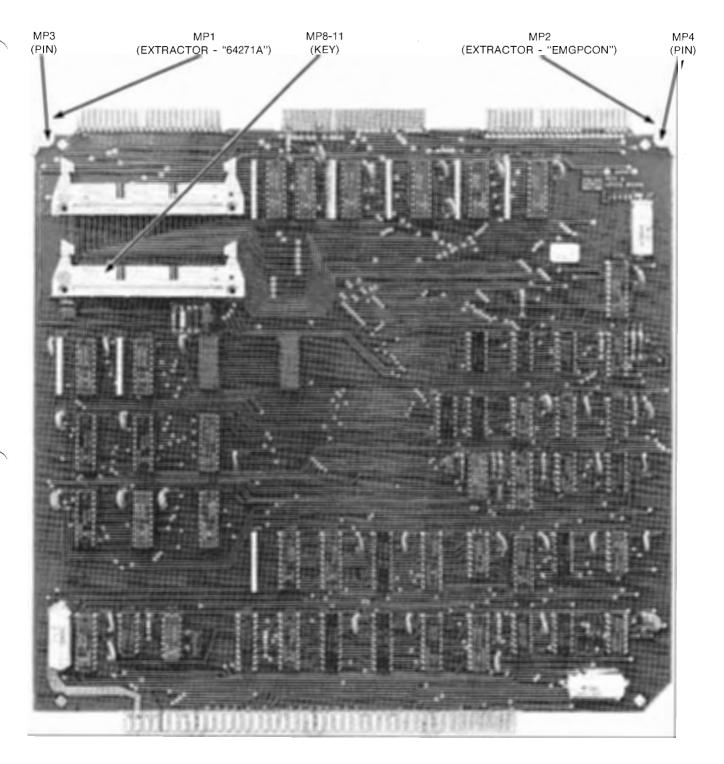

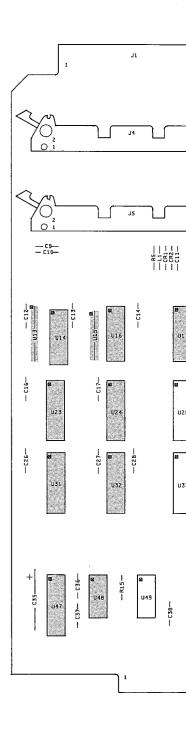

| 1-1.         | 64271A General Purpose Control Card      | 1-0  |

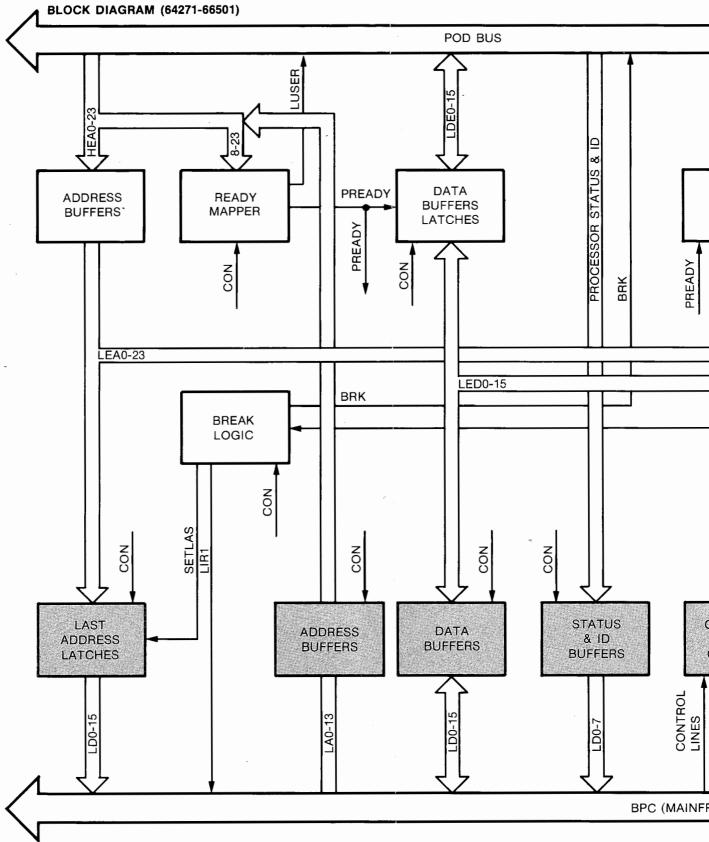

| 1-2.         | Emulation Subsystem Block Diagram        |      |

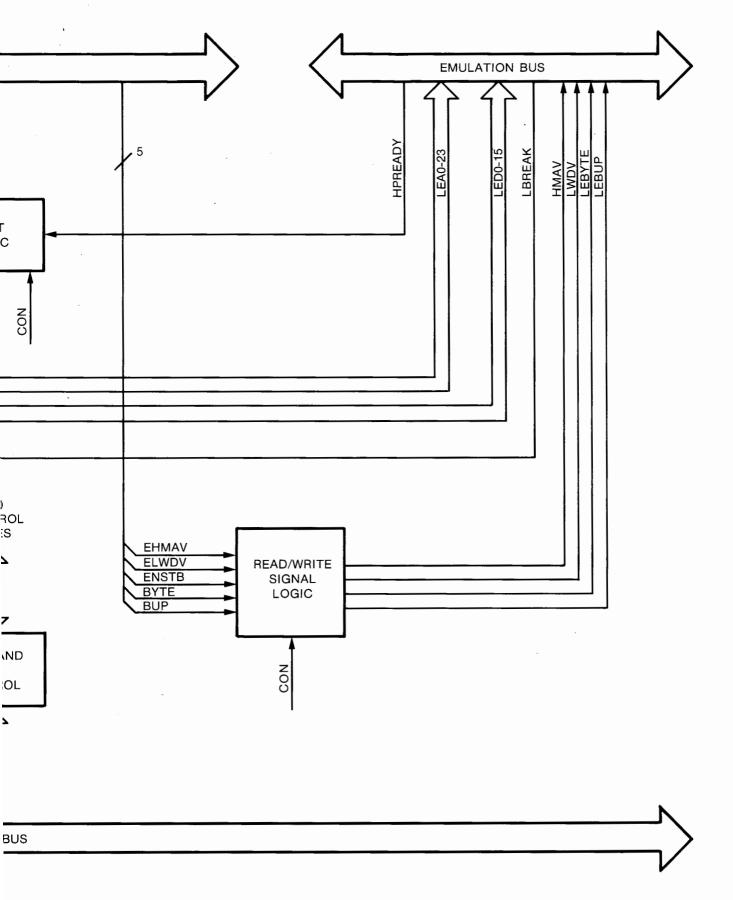

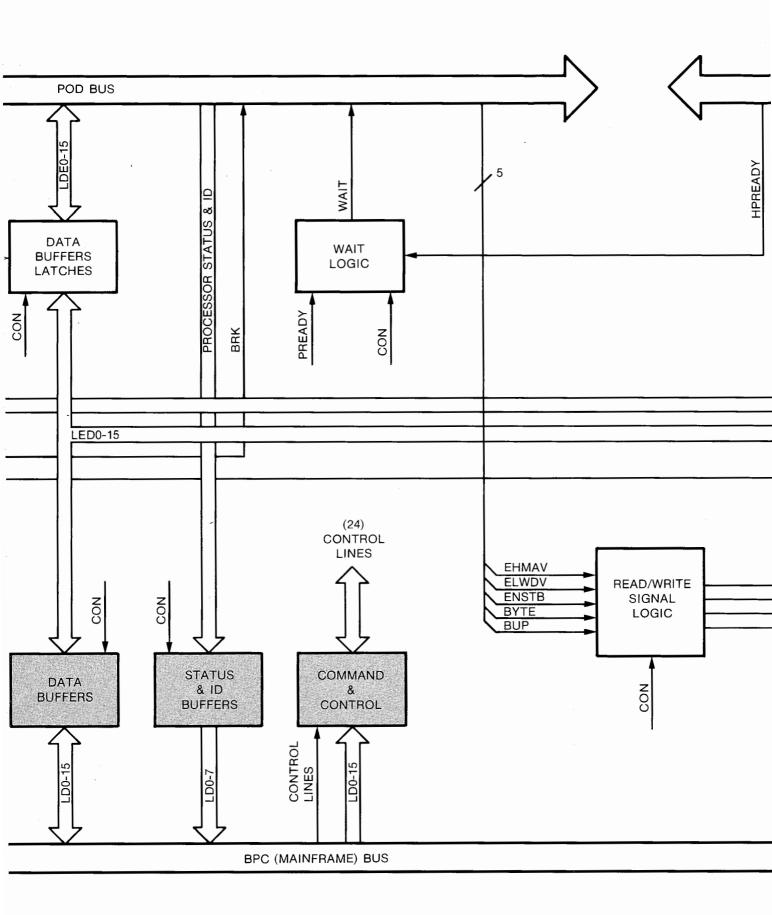

| 1-3.         | GP Control Board Block Diagram           |      |

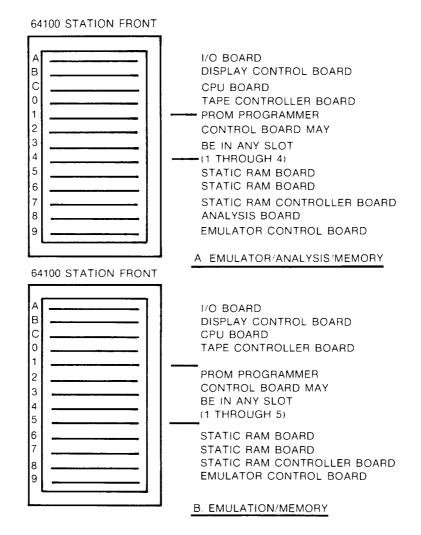

| 2-1.         | 64100A Card Cage Configuration           | 2-2  |

| 2-2.         | 64110A Card Cage Configuration           | 2-3  |

| 2-3.         | RFI Ground Bracket Assembly Parts        |      |

| 2-4.         | RFI Ground Bracket Installation (64100A) |      |

| 2-5.         | Ground Bar Clamp Installation (64100A)   | 2-7  |

| 2-6.         | Ground Bar Clamp Installation (64110A)   |      |

| 4-1.         | Awaiting Command Status                  | 4-8  |

| <b>4-</b> 2. | Option Test Card Slot Listing            |      |

| 4-3.         | Mapper Control Test Overview             |      |

| 4-4.         | Control Board Test Display               |      |

| <b>6-</b> 1. | Illustrated Parts Breakdown              | 6-3  |

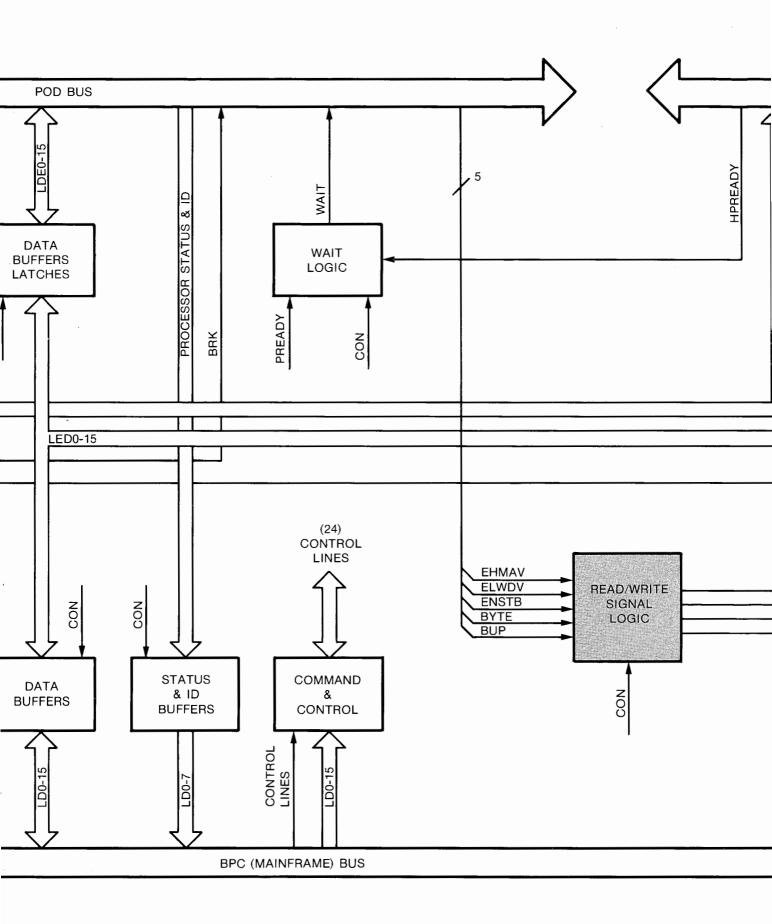

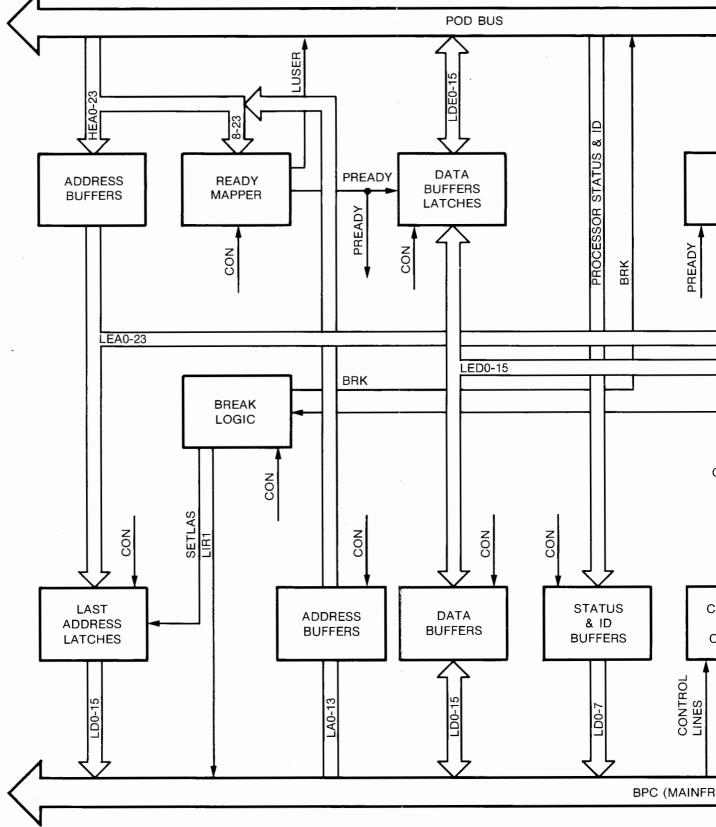

| 8-1.         | Emulation Subsystem Block Diagram        | 8-3  |

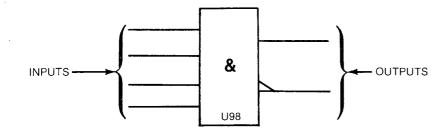

| 8-2.         | 64271A Block Diagram                     |      |

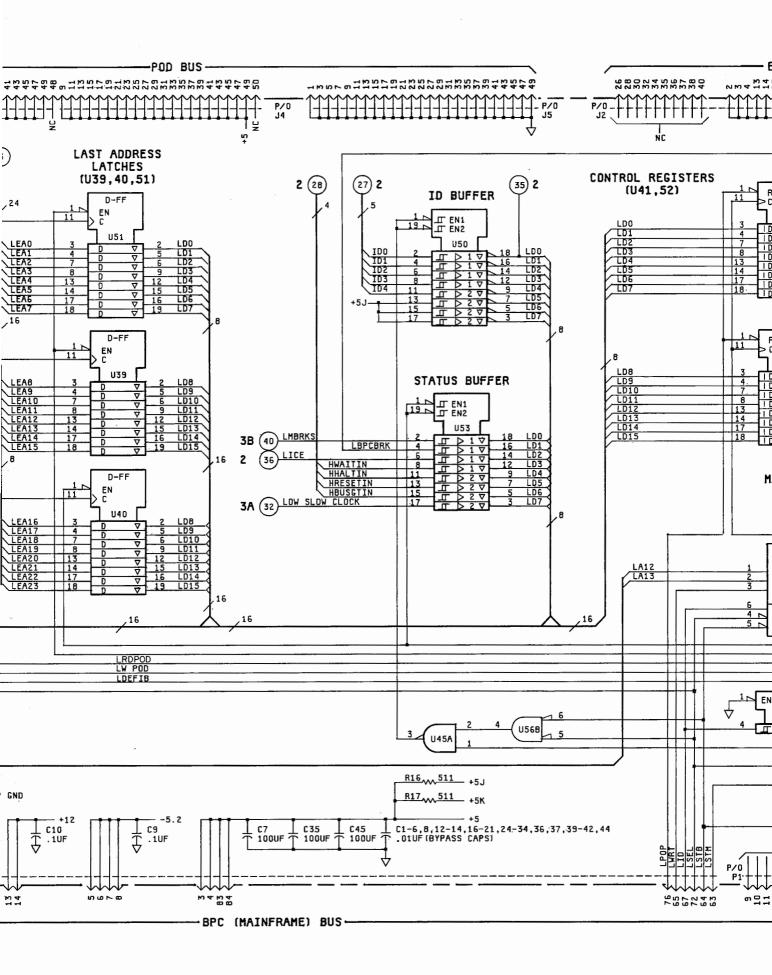

| 8-3.         | Service Sheet 1, Mainframe CPU Interface |      |

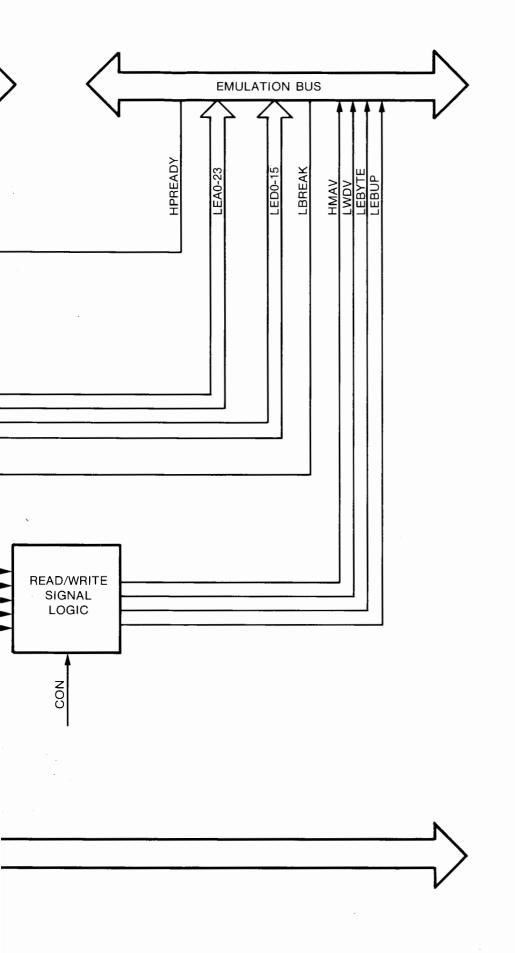

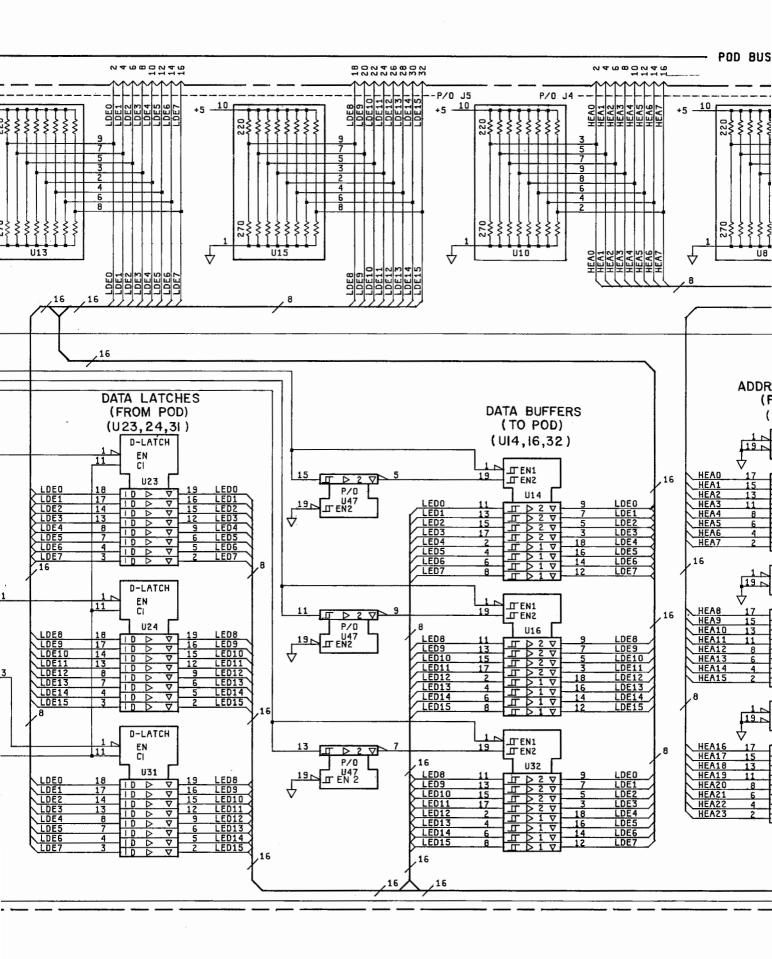

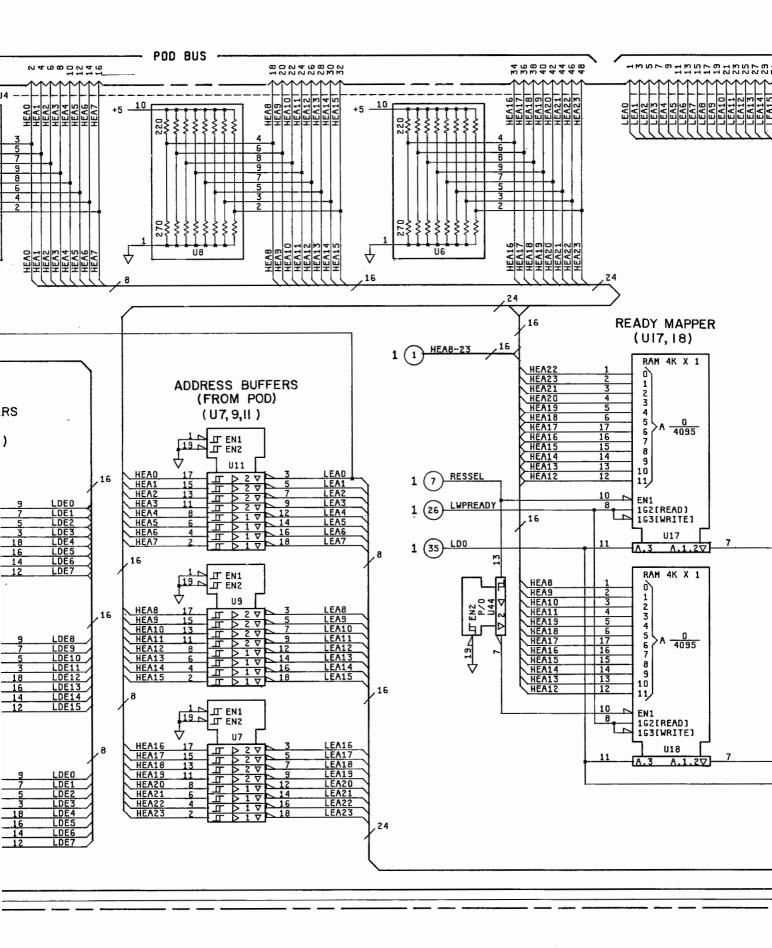

| 8-4.         | Service Sheet 2, Emulation Pod Interface |      |

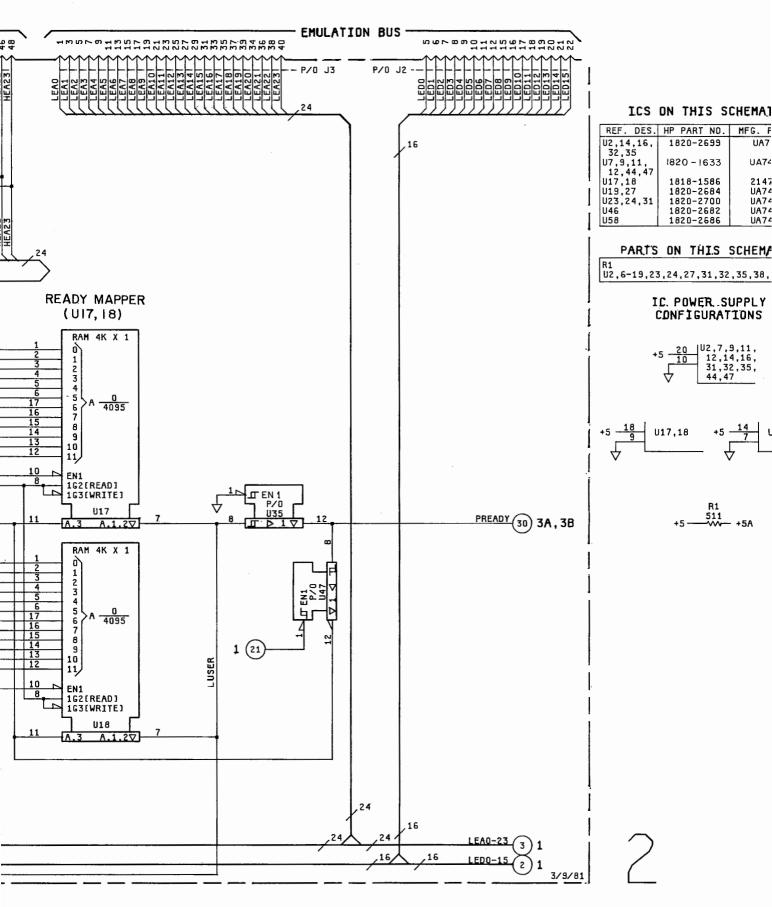

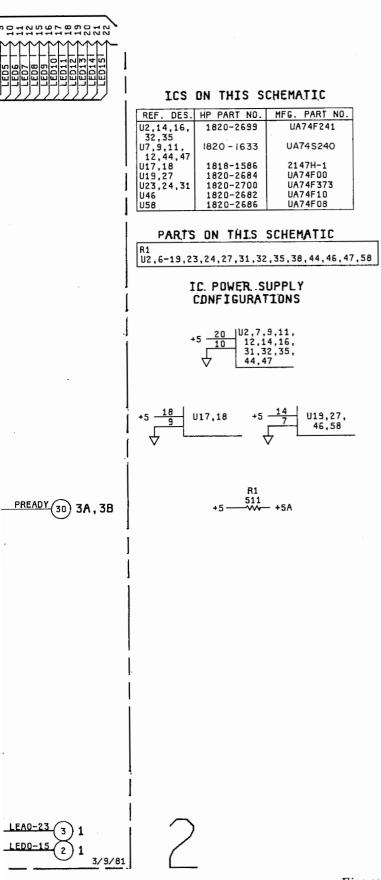

| 8-5.         | Service Sheet 3A, Control Logic          |      |

| 8-6.         | Service Sheet 3B, Control Logic          |      |

|              |                                          |      |

## LIST OF TABLES

| Table |                                         | Page |

|-------|-----------------------------------------|------|

| 2-1.  | Emulation Bus Cables                    |      |

| 2-2.  | RFI Ground Bracket Assembly Parts       |      |

| 6-1.  | Reference Designators and Abbreviations |      |

| 6-2.  | Replaceable Parts                       |      |

| 6-3.  | Manufacturer's Codes                    |      |

| 8-1.  | Mnemonics                               |      |

| 8-2.  | Schematic Diagram Notes                 |      |

| 8-3.  | Logic Symbology                         |      |

.

Figure 1-1. 64271A General Purpose Control Card

# SECTION I

# GENERAL INFORMATION

# 1-1. INTRODUCTION.

1-2. This Abbreviated Service Manual contains installation information, parts lists, component locators, and schematics for the 64271A General Purpose Control Card. It does not contain information for operating or servicing the 64271A. Refer to the applicable Emulation Subsystem manuals for information on operation and troubleshooting.

1-3. Shown on the title page is a microfiche part number. This number can be used to order 4X6-inch microfilm transparencies of the manual. Each microfiche contains up to 96 photoduplicates of the manual pages.

# 1-4. ORGANIZATION.

1-5. This manual is organized into eight sections:

Section I, General Information, contains information regarding manual applicability, instrument usage, instrument characteristics, and equipment requirements.

Section II, Installation, explains how to unpack and install the Model 64271A; it also gives information on environmental limits of operation, and packing instructions should the 64271A ever need to be shipped.

Section III, Operation, refers the user to the proper manuals for operation of the 64271A in an emulation system.

Section IV, Performance Verification, describes how to run the option\_test Performance Verification procedures for the 64271A board only; and indicates general methods for troubleshooting failures during these verification procedures.

Section V, Adjustments, normally contains calibration information; however, this section is blank since the 64271A requires no parametric adjustments.

Section VI, Replaceable Parts, contains information for ordering spare parts, along with parts lists for the 64271A board and diagrams showing the correspondence between the physical location of the part on the 64271A and the reference designator.

Section VII, Manual Changes, normally contains information required to modify the manual for other versions of the 64271A. However, no major electrical or functional changes have been made to the 64271A since its introduction; therefore, this section is blank.

Section VIII, Service, contains reference information for servicing a defective 64271A, including block diagrams, schematics, component locators, and theory of operation. A complete list of signal names (mnemonics) is also included here, with definitions of each signal's function provided.

# 1-6. INSTRUMENTS COVERED BY THIS MANUAL.

1-7. Attached to the 64271A is a repair number tag. The repair number is in the form: 0000A00000. It is in two parts; the first four digits and the letter are the prefix and the last five are the suffix. The prefix is the same for all identical General Purpose Control Cards; it only changes when a change is made to the card. The suffix is assigned sequentially and is different for each General Purpose Control Card. This manual applies to those 64271A's with repair number prefixes listed on the title page.

1-1

1-8. 64271A's manufactured after the printing of this manual may have a repair number not listed on the title page. The manual for the newer General Purpose Control Card will be accompanied by a yellow manual change supplement. The supplement explains how to adapt the manual to the newer 64271A.

1-9. In addition to change information, the supplement may contain information for correcting errors in the manual. To keep this manual as current and as accurate as possible, Hewlett-Packard recommends that you periodically request the latest manual changes supplement. The supplement is identified by the manual print date and part number, both of which appear on the manual title page. Complimentary copies of the supplement are available from Hewlett-Packard Sales/Service office.

# 1-10. DESCRIPTION.

# 1-11. EMULATION OVERVIEW.

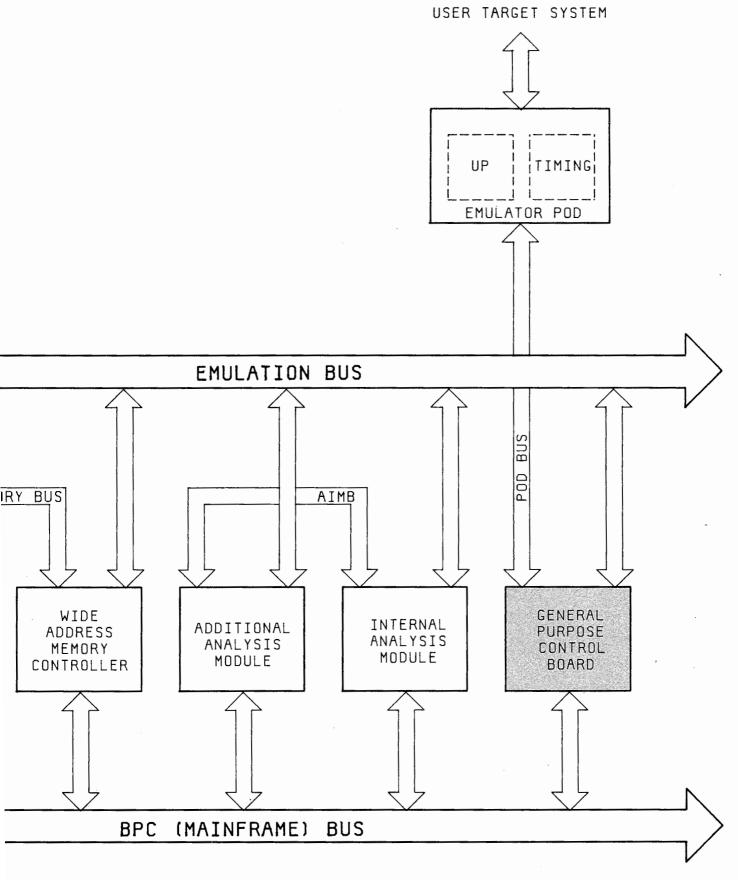

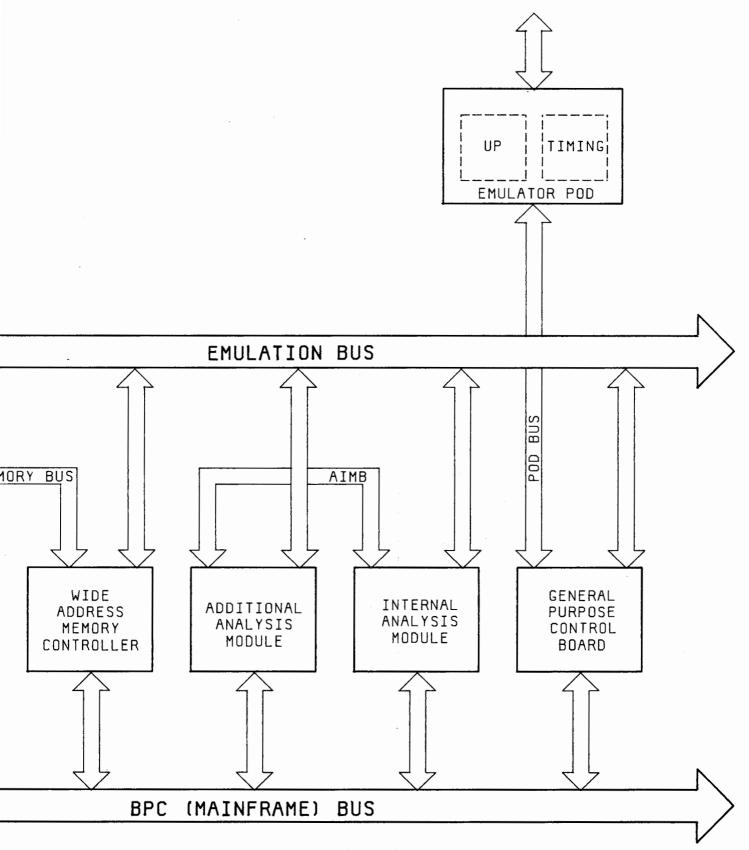

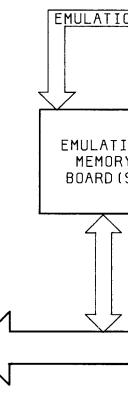

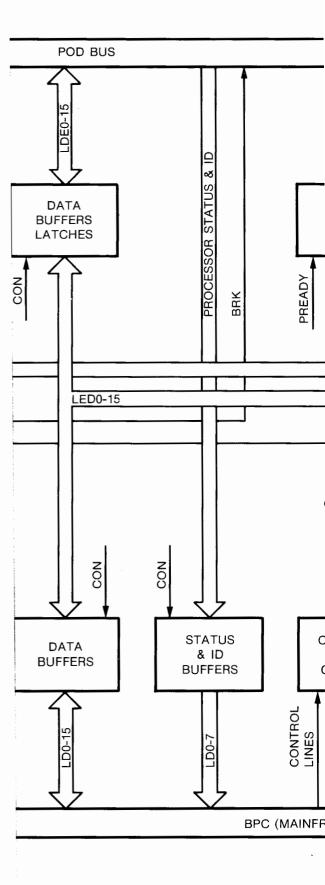

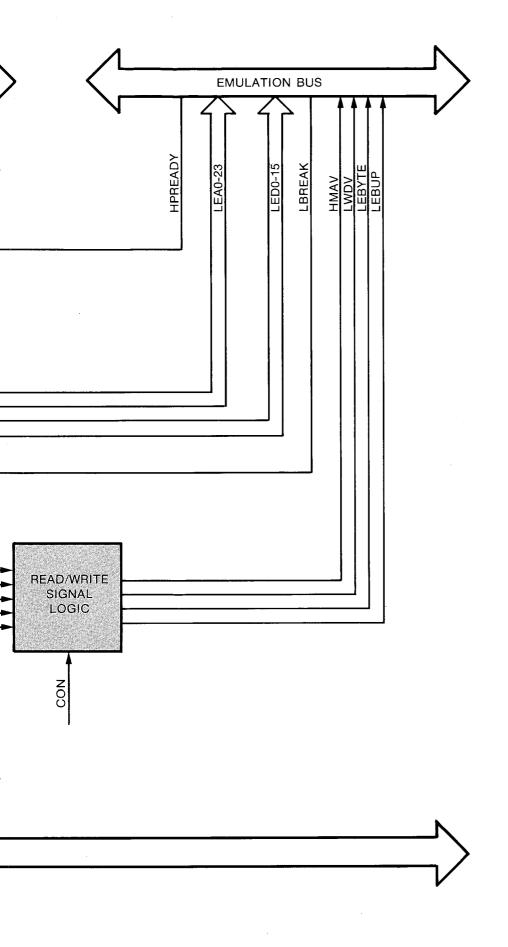

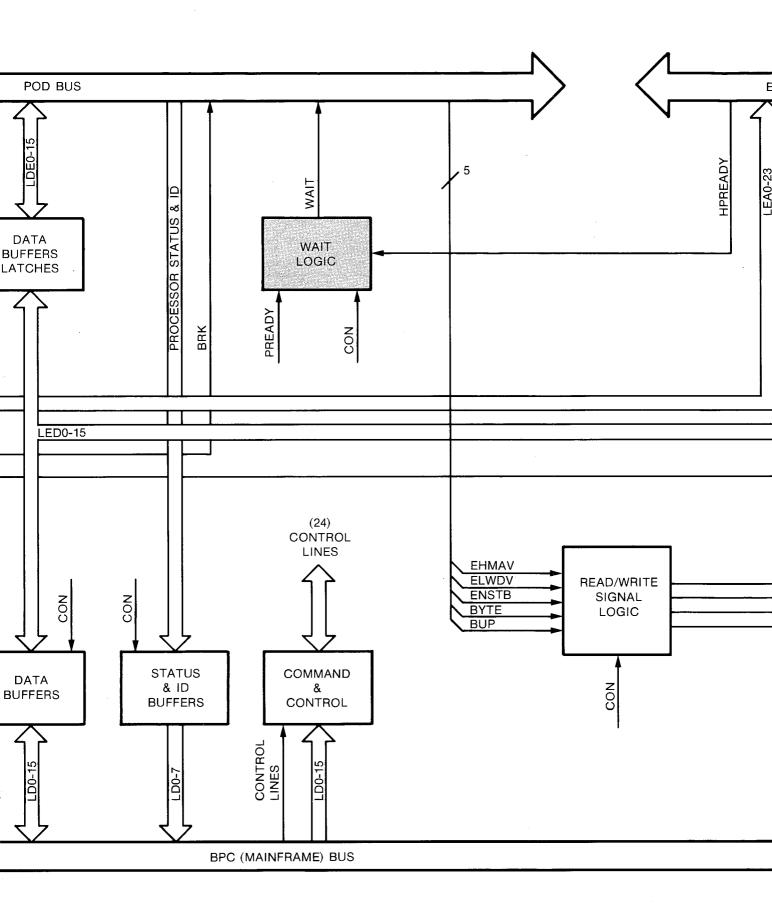

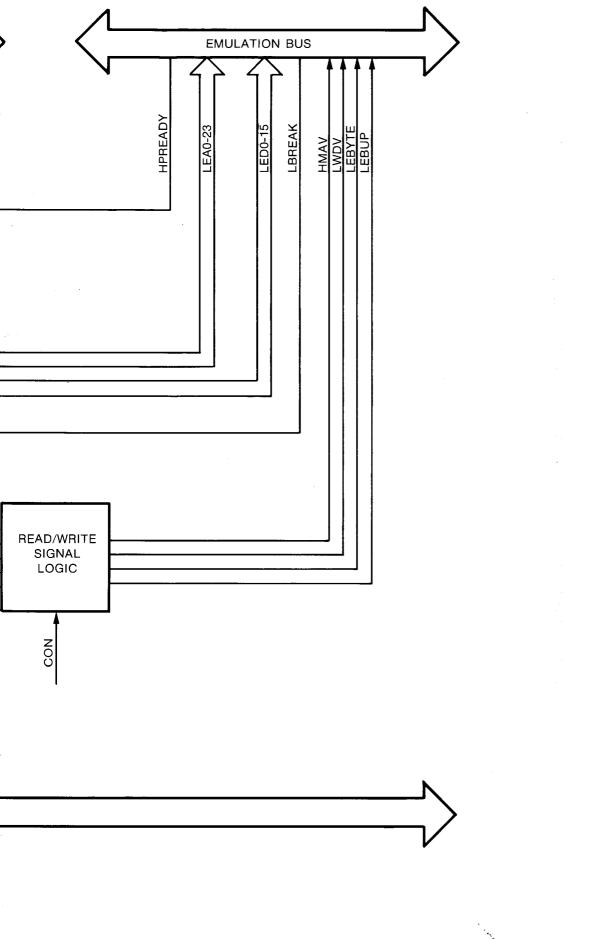

1-12. Refer to Figure 1-2, which is a basic block diagram of the emulation subsystem. The shaded portion is the area occupied by the Model 64271A General Purpose Control Board. The emulator may be used without a target system by developing software on the 64000 development stations via the editor and relocatable linker utilities; then this software may be uploaded into the emulation memory modules and executed by the emulation processor within the emulation pod. Analysis of software execution is also available. Note that the emulation processor transmits address information and transmits or receives data information to and from emulation memory and analysis via the emulation bus; this allows the processor to run at full speed without having to share the resources of the development station CPU bus.

1-13. The user probe of the emulator may also be inserted into the space which would be occupied by the microprocessor in a user's target system. The probe will then emulate the actions of that processor inserted into the system, with the added benefits of being able to access both the user's memory or emulation memory in any combination, plus allowing real-time analysis of software execution.

## 1-14. GP CONTROL BOARD.

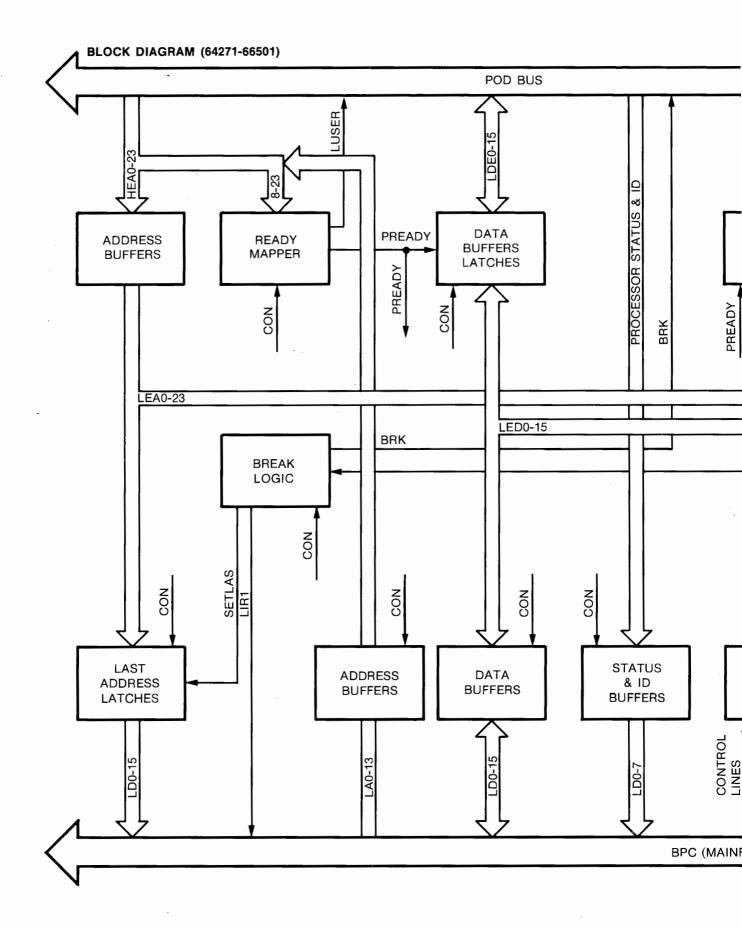

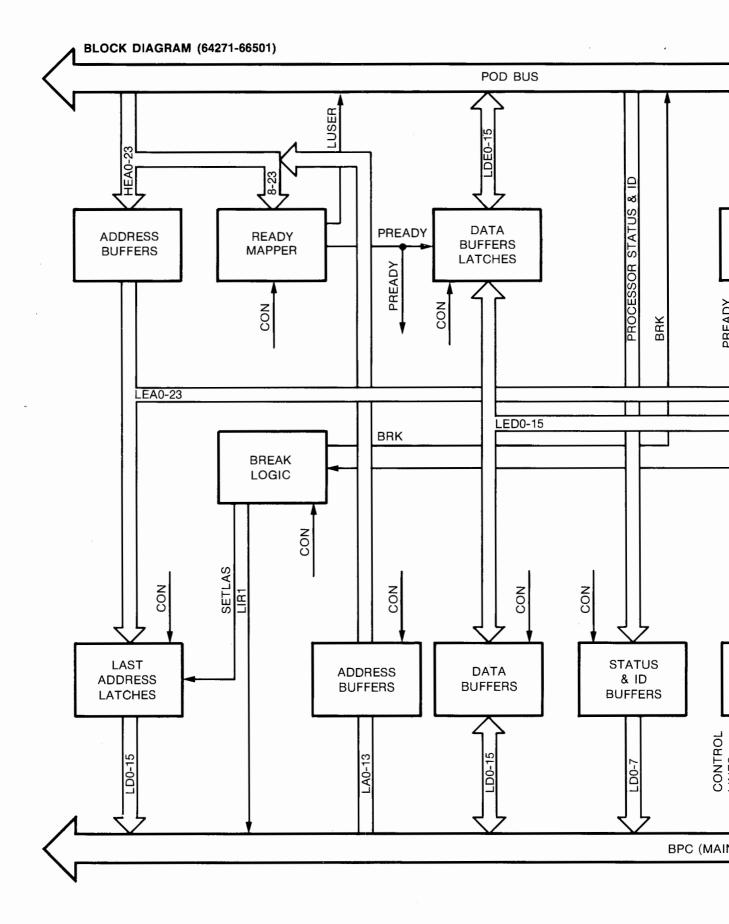

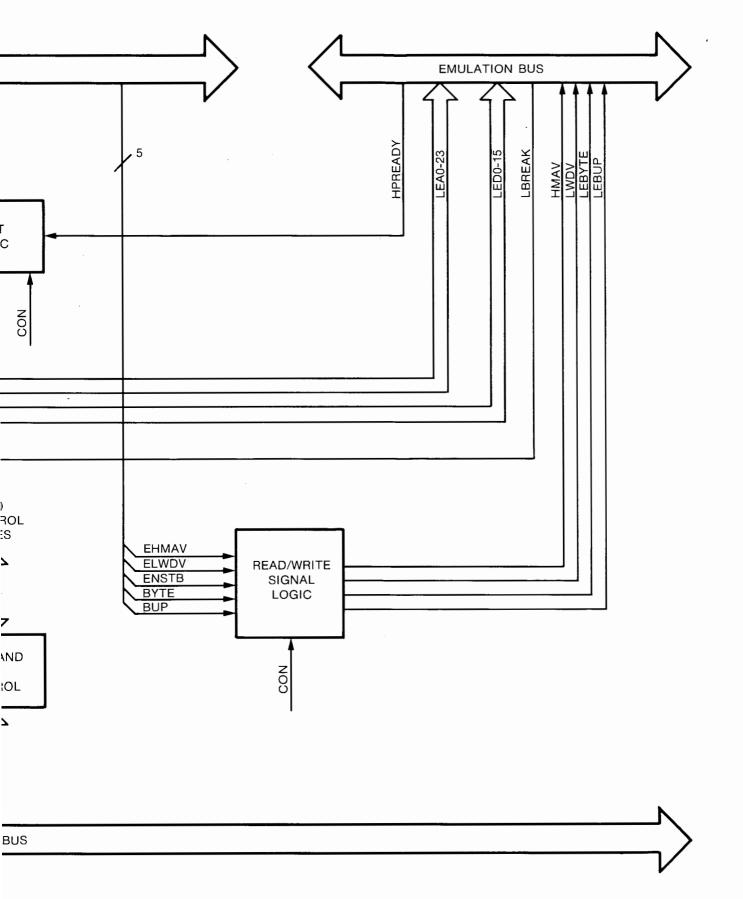

1-15. The 64271A General Purpose Control Board performs the interface functions between the emulator pod, the emulation system, and the mainframe CPU. See Figure 1-3.

1-16. Last Address and Break Logic. Pod address HEA 0-23 is buffered to the emulation bus and the last address latches by address buffers. The last address latches are loaded on a low-to-high transition on the SETLAS line. If an emulation break (LBREAK) or a mainframe break (LBPCBRK) occurs, BRK is asserted. This causes an interrupt or break to be sent to the pod, and also allows the last address latches to hold the break address.

1-17. Ready Mapper. The ready mapper determines whether the current address on the pod bus (HEA 0-23) is within space mapped to user or emulation (mainframe) memory. Output from the mapper are two signals which are identical in logic function but have different uses. They are:

a. LUSER-- Output to the pod. When low, current address is within space mapped to user memory.

b. PREADY-- Internal use on control board. Used by the wait state generator and also used to enable the correct data buffers for a data transaction.

The mapper is programmed during the emulation defib (reset) mode.

"`**\***.

#### Figure 1-2. Emulation Subsystem Block Diagram 1-3

Model 64271A

$\langle -----$

.

#### General Information

1-4

1-18. Three Port Data Bus. Three separate data buses are used on the 64271A. They are:

- a. Mainframe (mainframe CPU) data bus.

- b. Pod data bus.

- c. Emulation data bus.

The data bus enabling logic uses ready mapper signal PREADY and various signal lines from the command & control logic to determine which buffers to enable or disable for the data transaction.

1-19. Status and ID Buffers. The status buffer is used to gate emulation processor status onto the mainframe data bus. Also included is an ID (identification) buffer which, when enabled, tells the mainframe which emulator pod is connected to the control board, as well as identifying the control board itself.

1-20. Wait Logic. The wait logic functions as a programmable wait state generator, using PREADY (ready mapper), HPREADY (emulation memory controller), and various control lines to determine whether to insert wait states or acknowledges into the current memory cycle.

1-21. Command and Control. This section uses the mainframe data bus, address lines LA 12 & 13, and certain mainframe control lines to determine which functions are selected on the 64271A.

1-22. Read/Write Signal Logic. This section includes logic for:

a. Determining whether or not memory is being accessed (HMAV).

b. Inserting a delay into the ELWDV (Emulator Low Write Data Valid) line.

c. Determining polarity and function of the BYTE and BUP lines, which are used to enable lower and upper byte banks of memory.

#### 1-23. ADDITIONAL EQUIPMENT REQUIRED.

1-24. The Model 64271A must be plugged into a 64000 mainframe to operate. It must also be connected to an in-circuit emulation pod and a wide address memory controller with at least 8K of memory to have a minimum emulation subsystem.

#### 1-25. POWER SUPPLY LOADS.

1-26. Power supplies used by the 64271A and current draws are as follows:

+5 V -- Draws 3.1A -5 V -- Routed to pods via the GP board, not used on board. +12 V -- Routed to pods via the GP board, not used on board. -12 V -- Not used. +17 V -- Not used. +40 V -- Not used. -3 V -- Not used.

1-27. The current drawn by the selected Emulator Pod must be added to that of the 64271A to determine the current drawn by the combination.

1-5/(1-6 blank)

## SECTION II

#### INSTALLATION

#### **2-1. INTRODUCTION.**

2-2. This section contains information necessary to install the Model 64271A in the Model 64100A mainframe. Also included is information concerning initial inspection, damage claims, environmental considerations, storage and shipment.

#### 2-3. INITIAL INSPECTION.

2-4. Inspect the shipping container for damage. If the shipping container or cushioning material is damaged, it should be kept until the contents have been checked for completeness and the 64271A has been checked mechanically and electrically. If the contents are incomplete, if there is mechanical damage or defect, or if the 64271A does not pass performance verification, notify the nearest Hewlett-Packard office. If the shipping container or cushioning material is damaged, notify the carrier as well as the Hewlett-Packard office. Keep the shipping materials for carrier's inspection. The HP office will arrange for repair or replacement at HP option without waiting for claim settlement.

## 2-5. INSTALLATION.

2-6. Figure 2-1 shows a top view of the 64100A mainframe card cage. The recommended card slot for the 64271A is the rearmost one, as this will maximize free cable length outside the mainframe to the in-circuit emulation pod.

WARNING

Read the Safety Summary at the front of this manual before installing the 64271A.

2-7. To install the 64271A, proceed as follows:

a. Turn off power to the 64100 station.

CAUTION

Power to the 64000 development station must be removed before installation or removal of option cards (emulation, etc.) to avoid damage to the option cards and the development station.

b. Loosen the two hold-down screws and remove the card cage access cover (64100A). (Refer to the 64110A Mainframe Service Manual for information on removing the card cage access cover of a 64110A.)

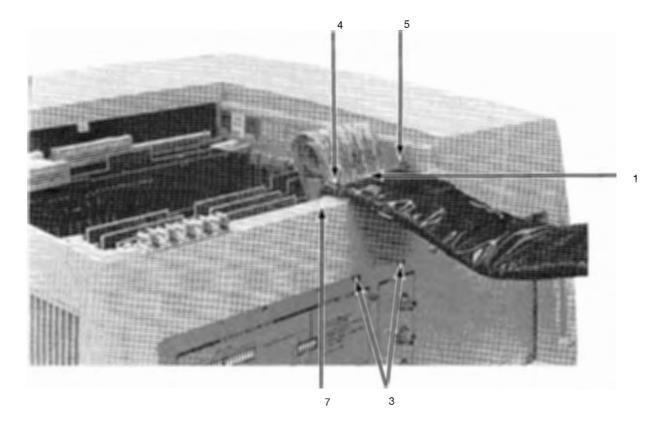

c. If you are installing the 64271A in a 64100A development station along with an emulator pod that uses a shielded cable assembly, verify that the RFI Ground Bracket (item 7 in Figure 2-3) has been installed in the mainframe as shown in Figure 2-4. If it has not been installed, go to the paragraphs entitled "RFI Ground Bracket Installation" in this section to install the bracket. After installation, proceed with step d.

#### 64110A STATION TOP

CPU/I-O BOARD DISPLAY CONTROLLER EMULATION MEMORY EMULATION MEMORY EMULATION MEMORY CONTROL EMULATION CONTROL ANALYSIS

#### A. EMULATOR/ANALYSIS/MEMORY

64110A STATION TOP

CPU/I-O BOARD DISPLAY CONTROLLER EMULATION MEMORY EMULATION MEMORY EMULATION MEMORY CONTROL EMULATION CONTROL BLANK

B. EMULATOR/MEMORY

Figure 2-2. 64110A Card Cage Configuration

Figure 2-1. 64100A Card Cage Configuration

and on into the RFI ground bracket. Attach a nut (item 5) to the free end of the screw (inside the top cover of the development station at this point) and tighten firmly enough to hold the bar clamp in place but not so tight as to damage the emulator pod cables.

4. Tighten the nut placed on the stud in Step 2, being sure to observe the cautions given in Step 3.

5. Up to two sets of emulator pod cables can be grounded in this fashion, using the procedure described above.

#### 64110A

1. Insert a screw (item 2) through the single hole end (NOT the slot end) of the ground bar clamp (item 1). Continue with the screw through the right most perforation of the emulator pod cable shield braid and the right most hole of the sheet metal in the rear of the mainframe. (Right most as viewed from the rear of the mainframe. Refer to Figure 2-6 for details.)

2. Repeat the procedure with another screw; this time, use the slot end of the bar clamp and the holes in the shield braid and sheet metal immediately left of the right most position (refer to Figure 2-6).

h. The emulation bus cables are next installed across the Control Card, the emulation memory controller, and the analysis options. (Refer to Table 2-1 for a list of available emulation bus cables.) The cables are keyed so that they will seat on the edge connector in only one position.

#### Table 2-1. Emulation Bus Cables

| Cable           | HP Part Number |

|-----------------|----------------|

| Two Connector   | 8120-3351      |

| Three Connector | 8120-3352      |

| Four Connector  | 8120-3353      |

| Five Connector  | 8120-3345      |

i. Reinstall the card cage access cover and tighten the two screws (64100A). (Refer to the 64110A Mainframe Service Manual for information on replacing the card cage access cover of the 64110A.)

2-8. To remove the 64271A, reverse the installation procedure.

# 2-9. RFI GROUND BRACKET INSTALLATION.

2-10. An RFI Ground Bracket must be installed in the 64100A mainframe when installing the 64271A Control Board with any emulator pod that uses a shielded cable assembly for RFI suppression. The purpose of this ground bracket is to connect the emulator pod cable shield braid to earth ground. This effectively prevents the emission of radio frequency interference components from the pod cables.

2-11. No ground bracket is required on the 64110A development station, since the bar clamp holding the shield braid to the mainframe bolts into existing sheet metal which is at ground potential.

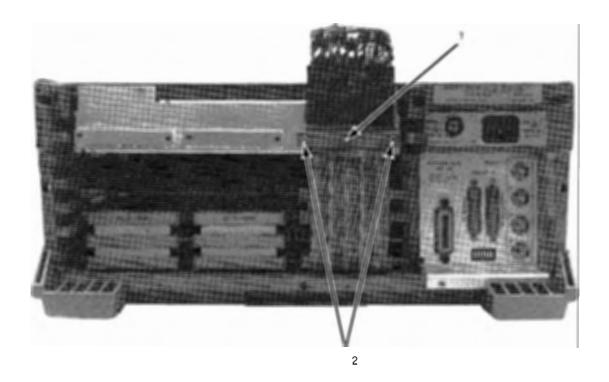

2-12. The RFI ground bracket parts are included with the emulator pod. For convenience, a photograph depicting all the parts is reproduced here; Table 2-2 gives a listing of the parts included in the ground bracket assembly.

d. If the Control Board has previously been installed in the development station, it must be removed to remove or install the emulator pod. To remove the 64271A, grasp both board extractor levers (at the top of the card) and pull up until the card disengages from the motherboard and clears the card guide rails.

e. Before installing the 64271A in the card cage, connect the selected Emulator Pod to the 64271A. Three multi-colored ribbon cables (within a shielded cable assembly) are used to connect the Emulator Pod to the Control Board. One cable is terminated in a female card-edge connector; the other two are terminated in female socket type connectors. Pin 1 is indicated by a triangle molded into each connector. The mating male connectors are at the top left corner of the 64271A (as you face the component side of the board). Pin 1 of the card-edge connector is indicated by a "1" etched on the board surface; Pin 1 of the two block connectors is indicated by a triangle molded into the connector block. The two block connectors and their female counterparts have matching colored dots on their surfaces. Also, the block connectors on the board are a latching type. Make sure the connectors are open (tips spread towards outside edges of board) before installing the emulator pod cables. Making sure to align Pin 1 of the male and female connectors, connect the pod to the control board by joining the three connector sets. When installing the block connectors, push down on the female connector until the latching tips snap over the top of the connector.

#### NOTE

To help prevent scuffing the pod cables when installing or removing the Control Board, try to keep the cables as flat and as close to the board as possible. When sliding the board into the development station, care should be used to prevent the cables from rubbing against the back side of the board installed in front of the Control Board.

f. Next install the 64271A in the 64100 card cage. To do this, grasp the control card by the extractor levers with the component side of the board towards the front of the develop- ment station and the card edge connector labeled "P1" towards the bottom of the card cage. Insert the card into the guide rails; making sure the connector "P1" and the edge connector socket on the Motherboard are aligned, push the card down until it seats firmly in the socket.

g. If the 64271A is installed with an emulator pod that uses a shielded cable assembly for RFI suppression, a ground bar clamp must now be installed to ground the shielded cable assembly to the mainframe sheet metal. Refer to Figure 2-3 for an illustration of the clamp (item 1); refer to either Figure 2-5 (64100A) or Figure 2-6 (64110A) as appropriate for details on how the clamp is installed while following the procedures given below.

#### 64100A

1. The emulator pod cable shield braid has two perforations. Place the perforation nearest the RFI ground bracket stud over the stud and press down gently until the cable lays flat across the top rear of the mainframe.

2. Place the single hole end (NOT the slot end) of the ground bar clamp (item 1) over the RFI ground bracket stud in such a manner that the open end of the slot points in a clockwise direction as viewed from the top of the development station. Thread a single nut (item 5) onto the stud. Do not tighten the nut at this point.

3. Insert the long screw (item 4 in Figure 2-3) into the slot end of the ground bar clamp. Continue by inserting the screw through the free end of the ground shield braid

Figure 2-5. Ground Bar Clamp Installation (64100A)

Figure 2-6. Ground Bar Clamp Installation (64110A)

Table 2-2. RFI Ground Bracket Assembly Parts

| REF DES | DESCRIPTION         | PART #      |

|---------|---------------------|-------------|

| ITEM 0  | GROUND BRACKET ASSY | 64100-62102 |

| ITEM 1  | GROUND BAR CLAMP    | 1531-0273   |

| ITEM 2  | SCREW 4-40 3/4"     | 2200-0151   |

| ITEM 3  | SCREW 6-32 3/8"     | 2360-0117   |

| ITEM 4  | SCREW 6-32 1"       | 2360-0129   |

| ITEM 5  | NUT 6-32            | 2420-0001   |

| ITEM 6  | WASHER              | 3050-0235   |

| ITEM 7  | RFI GROUND BRACKET  | 64100-01207 |

2-13. To install the ground bracket on the 64100A development station, proceed as follows:

a. If no ground bracket is installed in the mainframe, then the old U-shaped cable strain relief bracket on the rightmost side of the mainframe top cover (as viewed from the rear) must be removed. Loosen the two screws; remove the bracket; discard the bracket and the screws (they will not be needed for the RFI bracket).

b. Place the RFI bracket on the top rear cover of the mainframe in the rightmost cable position (as viewed from the rear of the station) with the threaded stud on the bracket pointing upwards and the U-shaped portion of the bracket to the inside of the card cage. Refer to Figure 2-4 for details.

c. Refer to Figure 2-5. Thread two screws (item 3) into the RFI bracket from the outside of the development station rear panel sheet metal. Tighten the screws securely.

d. To remove the bracket, reverse the installation procedure.

# 2-14. OPERATING ENVIRONMENT.

2-15. The 64271A may be operated in environments within the following limits:

| Temperature | 0 <sup>°</sup> to +55 <sup>°</sup> C |

|-------------|--------------------------------------|

| Humidity    | Up to 95% relative humidity at +40°C |

| Altitude    |                                      |

It should be protected from temperature extremes which cause condensation within the instrument.

# 2-16. STORAGE AND SHIPMENT.

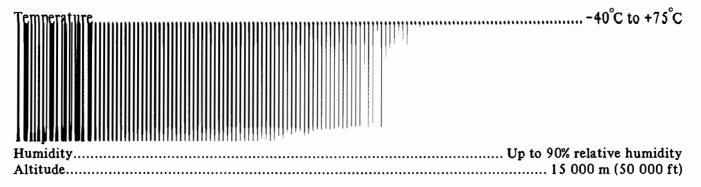

## 2-17. ENVIRONMENT.

2-18. The 64271A may be stored or shipped in environments within the following limits:

## 2-19. ORIGINAL PACKAGING.

2-20. Containers and packing materials identical to those used in factory packaging are available through Hewlett-Packard offices.

#### 2-21. OTHER PACKAGING.

2-22. The following general instructions should be used for re-packing with commercially available materials:

a. Wrap the 64271A in heavy paper or plastic.

b. Use a strong shipping container. A double-wall carton made of 350-pound test material is adequate.

c. Use a layer of shock-absorbing material 70 to 100 mm (3 to 4- inch) thick around all sides of the 64271A to provide firm cushioning and prevent movement inside the container.

d. Seal shipping container securely.

e. Mark shipping container FRAGILE to ensure careful handling.

f. In any correspondence, refer to instrument by model number and full serial number.

.

# SECTION III

# **OPERATION**

# **3-1. INTRODUCTION.**

3-2. This section contains no operating information. Refer to the applicable Emulation Subsystem Operator's Guide for information relating to the operation of the 64271A.

3-1/(3-2 blank)

# SECTION IV

# PERFORMANCE TESTS

# 4-1. INTRODUCTION.

4-2. This section describes the Performance Verification for the General Purpose Emulation Control Card. The scope of the Performance Verification is to detect problems at the board level only. Board level troubleshooting is in support of the Blue Stripe Program.

4-3. For convenience, the figures for the Performance Verification are grouped together at the end of this section.

# 4-4. 64271A PERFORMANCE VERIFICATION.

4-5. The Performance Verification (P.V.) for the 64271A General Purpose Control Board is a subsection of the Option Test P.V. The Option Test P.V. tests all possible option modules that can be configured within the expansion slots of the Mainframe.

The option\_test P.V. can either be run with a 64000 development station configured in a network arrangement (hard disk based); or it may be run from a 64000 station in a stand-alone configuration (mini disk based). When running the option\_test performance verification on a Model 64271A Control board from a stand-alone 64000 configuration, the following modules must be present on the current local disk system:

> FLOPPY\_OP\_SYS OPTION\_TEST PV\_EMUL\_UDE

4-6. To test the 64271A, proceed as follows:

a. With the operating system initialized and awaiting a command, use the softkey (or manually type the lower case command):

option\_\_test RETURN

Refer to Figure 4-1.

b. The P.V. will now display a directory of the installed option boards and their card slot number (Figure 4-2). Locate the General Purpose Controller - No Pod and enter the card slot number. For example, in Figure 4-2 the 64271A is in slot 9. Therefore, enter:

#### 9 RETURN

c. A menu will now be displayed showing the test available to exercise the 64271A. This is the Mapper Control Test (refer to Figure 4-3). The following softkeys will appear at the bottom of the display:

<end>

Returns the user to the option test card slot listing.

4-1

| <disptest></disptest> | Advances the user to the detailed view of the mapper control test; that is, the test execution display. |

|-----------------------|---------------------------------------------------------------------------------------------------------|

| <print></print>       | Copies the display to the system line printer (if one is attached).                                     |

d. Press the <disp\_test> softkey. This will advance the P.V. to the Control Board test execution display (refer to Figure 4-4). The following softkeys are listed at the bottom of the display:

| <start></start>         | Begins execution of the tests listed.                                              |

|-------------------------|------------------------------------------------------------------------------------|

| <exit_test></exit_test> | Returns the user to the Mapper Control Test overview display described previously. |

| <print></print>         | Copies the display to the system line printer (if one is attached).                |

e. To initiate testing of the General Purpose Control Card, press the <start> softkey. The key will be highlighted in inverse video on the display and test execution will proceed. If all tests pass, testing can be terminated as described in the next paragraph. However, if any failures occur, refer to the description of the Control Board Test in the following sections.

f. Termination of testing on the 64271A is possible in one of two ways:

1) The <start> softkey may be pressed. The test will terminate at the end of the current test cycle and the start softkey on the display will return to normal video. To completely exit the performance verification from this point, press the <exit\_test> softkey. This returns the user to the Mapper Control Test display. Press the <end> softkey while in this display. This returns the user to the option\_test card slot listing, at which point the <end> softkey can be pressed to exit the performance verification software.

2) The <exit\_test> softkey may be pressed. The test will terminate at the end of the current test cycle and the display will be returned to the Mapper Control Test overview display. At this point, the user may press the <end> softkey, returning the display to the option\_test card slot listing level. When the <end> softkey is pressed at this point, the option\_test performance verification is completely exited and the display is returned to the "Awaiting command" status.

## 4-7. CONTROL BOARD TEST (Figure 4-4).

4-8. The Control Board Test consists of six tests. Each will be discussed in the order that they appear on the menu.

#### 4-9. RAM OUTPUT SHORT TESTS (VCC/GND).

4-10. Purpose -- to make sure that the high speed ready mapper RAMs can output zeroes and ones throughout their address range.

4-11. What -- the mainframe CPU writes zeroes to all locations in the mapper RAMs and verifies that all locations can be read back correctly. The test is then repeated by writing ones to all locations and reading them back.

4-12. How -- the mainframe CPU address bus is translated through buffers U25 and U33 to the address bus HEA 8-23 of the mapper RAMs (U17,18). This is done by asserting LSEL from the mainframe bus and LDEFIB from control register U52. The mapper RAMs are selected in turn by the state of RESSEL. If RESSEL is high, U17 will be enabled; if low, U18 will be enabled. The write strobe for the RAMs is provided by LWPREADY from the function select decoder U43. LD0 from the mainframe CPU provides the data input for the RAMs. All locations in each RAM are written as a zero, and read back by negating LWPREADY and lowering U47 pin 1. This allows the mapper output to be passed through U35 and U47 out onto the mainframe data bus LD0. All other conditions remain the same for a read as they do for a write. The process is repeated by writing ones to all locations in the mapper RAMs and reading back the result.

4-13. Results -- If both RAMs fail at all locations, one of the following messages appears on the status line:

"Ram output stuck at VCC or defective (always on) write circuit"

"Ram output stuck at GND"

The test assumes that at least one RAM is good; it is also assumed that at least one RAM is present. If one of the RAMs has all failures it is assumed that the RAM is missing or defective.

4-14. Troubleshooting -- failures in this test are most likely caused by problems with the General Purpose Control Board; however, the emulator pod may be causing problems on the emulation address lines during the writes to the mapper RAM (if an emulator pod is left attached to the control board). To determine whether or not this is the case, disconnect the Emulator Pod from the Control Board and re-run the test. If the test still fails, the problem is with the Control Board; if the test passes, the problem is with the Emulator Pod. A probable reason for this failure is an improper DEFIB of the address buffers driving the bus to the 64271A.

#### 4-15. MAPPER WRITE TEST.

4-16. Purpose -- to verify that the mapper RAM write circuitry is functional.

4-17. What -- the mainframe CPU writes zeroes to all locations in the mapper RAMs and then verifies that all locations were written correctly. The process is repeated by writing ones to all locations in the RAMs and verifying that correct data was written. If both write sequences show some failures, that is, the RAM will not write all zeroes and it also will not write all ones, another test is run which checks that writing a zero or one to each address returns the same result. If this test indicates that writing a zero or one to every location returns the same result, it is assumed that the write circuitry is defective.

4-18. How -- this test is performed in a similar manner to the preceding one. The mainframe CPU address bus is translated through buffers U25 and U33 to the address bus HEA 8-23 of the mapper RAMs (U17,18). This is done by asserting LSEL from the mainframe bus and LDEFIB from control register U52. The mapper RAMs are selected in turn by the state of RESSEL. If RESSEL is high, U17 will be enabled; if low, U18 will be enabled. The write strobe for the RAMs is provided by LWPREADY from the function select decoder U43. LD0 from the mainframe CPU provides the data input for the RAMs. All locations in each RAM are written as a zero, and read back by negating LWPREADY and lowering U47 pin 1. This allows the mapper output to be passed through U35 and U47 out onto the mainframe data bus LD0. All other conditions remain the same for a read as they do for a write. The process is repeated by writing ones to all locations in the mapper RAMs and reading back the result.

4-19. Results -- if an error is detected in either the first or second test then the status line will read:

"Defective (inactive) write circuitry"

4-20. Troubleshooting -- problems in this test are most likely to occur on the General Purpose Control Board; however, the emulator pod may be causing interference with the emulation address lines during the write sequences to the mapper RAMs (if an emulator pod is left attached to the control board). To determine whether or not this is the case, disconnect the Emulator Pod from the Control Board and re-run the test. If the test fails, the problem is with the Control Board; if the test passes, the problem is with the Emulator Pod. A probable reason for this failure is an improper DEFIB of the pod address buffers driving the bus to the 64271A.

#### 4-21. INTERRUPT AND BREAK TESTS.

4-22. Purpose -- this test verifies that the mainframe CPU can cause an emulator break, and that the emulator control board can assert a mainframe CPU interrupt.

4-23. What -- in the first test, the mainframe CPU toggles the control register break line and reads it back. In the second test, the mainframe CPU enables interrupts and toggles the break line, then verifies that a mainframe interrupt is asserted.

4-24. How -- in the first test, the mainframe CPU sets the LBPCBRK line (output of control register U52) to a high and a low state in turn, and reads back the state of the line by enabling the output of status buffer U53. In the second test, the mainframe CPU sets the INTEN line (output of control register U41) to the high state and then toggles the LBPCBRK line to the low state. This propagates through U28 and U44 to force the output of U57 (LIR 1) low, which will cause a mainframe interrupt to occur.

4-25. Results -- if the first test fails, one of the following messages will be displayed on the status line:

"Break appears to be stuck at ground" "Break appears to be indeterminately failing"

The mainframe CPU assumes that the second test has failed if a jump to an interrupt service routine does not occur (this routine negates an error flag). If the test fails, the following message will be displayed on the status line:

"Break does not cause a mainframe CPU interrupt"

4-26. Troubleshooting -- Failures in this test are most likely to be caused by problems with the General Purpose Control Board, so it is recommended that this board be replaced first.

4-27. ADDRESS LINE SHORT TO GND TEST.

4-28. Purpose -- to make sure that address lines HEA 8-23 are not shorted to ground and can be read by the last address registers.

4-29. What -- the mainframe CPU performs a series of mapper RAM writes to appropriate addresses. The last address registers are clocked every time that a mapper write is done. The mainframe CPU then reads back the status of the last address registers and compares it with what was written.

4-30. How -- the mainframe CPU address bus is translated through buffers U25 and U33 to the address bus HEA 8-23 of the mapper RAMs (U17,18). This is done by asserting LSEL from the mainframe bus and LDEFIB from control register U52. The write strobe for the RAMs is provided by LWPREADY from the function select decoder U43. This signal is also input to AND gate U28C, which drives the reset input of flip-flop U22. When a mapper write is done (LWPREADY toggles low), U22 is cleared. The output of U22 is used to drive U45B, which provides the SETLAS signal to the last address registers. A low-to-high transition on this line clocks the mapper address into the last address registers (U39,U40). The mainframe CPU then reads the desired register by enabling it via function select decoder U43. 4-31. Results -- if an difference is detected between the address that was written and the address that was read, the following message will appear on the status line:

"Lines (HEA23 - HEA8)=XXXXH Appear to be fixed low"

This status information is decoded as follows:

| HEX  | BINARY    |      |      | SIGNAL |

|------|-----------|------|------|--------|

| 0000 | 0000 0000 | 0000 | 0000 |        |

|      |           |      |      |        |

|      |           |      | 1    | HEA8   |

|      |           |      | 1-   | HEA9   |

|      |           |      | -1   | HEA10  |

|      |           |      | 1    | HEA11  |

|      |           | 1    |      | HEA12  |

|      |           | 1-   |      | HEA13  |

|      |           | -1   |      | HEA14  |

|      |           | 1    |      | HEA15  |

|      | 1         |      |      | HEA16  |

|      | 1-        |      |      | HEA17  |

|      | 1         |      |      | HEA18  |

|      | 1         |      |      | HEA19  |

|      | 1         |      |      | HEA20  |

|      | 1         |      |      | HEA21  |

|      | -1        |      |      | HEA22  |

|      | 1         |      |      | HEA23  |

|      |           |      |      |        |

For example, if the message reads (HEA23 - HEA8)=1248H, then HEA20, HEA17, HEA14, and HEA11 are bad.

4-32. Troubleshooting -- failures in this test are most likely caused by problems with the General Purpose Control Board; however, the emulator pod may be causing interference on the emulation address lines (if an emulator pod is left attached to the control board). To determine whether or not this is the case, disconnect the Emulator Pod from the Control Board and re-run the test. If the test fails, the problem is with the control board; if the test passes, the problem is with the Emulator Pod. The emulator pod address buffers which drive the 64271A should be checked to verify that they are tri-stated by the DEFIB signal from the Control Board.

#### 4-33. ADDRESS LINE SHORT TO VCC TEST.

4-34. Purpose -- to make sure that address lines HEA 8-23 are not shorted to the +5 volt supply and can be read by the last address registers.

4-35. What -- the mainframe CPU performs a series of mapper RAM writes to appropriate addresses. The last address registers are clocked every time that a mapper write is done. The mainframe CPU then reads back the status of the last address registers and compares it with what was written.

4-36. How -- the mainframe CPU address bus is translated through buffers U25 and U33 to the address bus HEA 8-23 of the mapper RAMs (U17,18). This is done by asserting LSEL from the mainframe bus and LDEFIB from control register U52. The write strobe for the RAMs is provided by LWPREADY from the function select decoder U43. This signal is also input to AND gate U28C, which drives the reset input of flip-flop U22. When a mapper write is done (LWPREADY toggles low), U22 is cleared. The output of U22 is used to drive U45B, which provides the SETLAS signal to the last address registers. A low-to-high transition on this line clocks the mapper address into the last address registers (U39,U40). The mainframe CPU then reads the desired register by enabling it via function select decoder U43. 4-37. Results -- if an difference is detected between the address that was written and the address that was read, the following message will appear on the status line:

"Lines (HEA23 - HEA8)=XXXXH Appear to be fixed high or open"

This status information is decoded as follows:

| HEX  | 2 | BINAR | ۲Y   |      |      | SIGNAL |

|------|---|-------|------|------|------|--------|

| 0000 |   | 0000  | 0000 | 0000 | 0000 |        |

|      |   |       |      |      | 1    | HEA8   |

|      |   |       |      |      | 1-   | HEA9   |

|      |   |       |      |      | -1   | HEA10  |

|      |   |       |      |      | 1    | HEA11  |

|      |   |       |      | 1    |      | HEA12  |

|      |   |       |      | 1-   |      | HEA13  |

|      |   |       |      | -1   |      | HEA14  |

|      |   |       |      | 1    |      | HEA15  |

|      |   |       | 1    |      |      | HEA16  |

|      |   |       | 1-   |      |      | HEA17  |

|      |   |       | -1   |      |      | HEA18  |

|      |   |       | 1    |      |      | HEA19  |

|      |   | 1     |      |      |      | HEA20  |

|      |   | 1-    |      |      |      | HEA21  |

|      |   | -1    |      |      |      | HEA22  |

|      |   | 1     |      |      |      | HEA23  |

|      |   |       |      |      |      |        |

For example, if the message reads (HEA23 - HEA8)=1248H, then HEA20, HEA17, HEA14, and HEA11 are bad.

4-38. Troubleshooting -- failures in this test are most likely to be caused by problems with the General Purpose Control Board; however, the emulator pod may be causing interference on the emulation address lines (if an emulator pod is left attached to the control board). To determine whether or not this is the case, disconnect the Emulator Pod from the Control Board and re-run the test. If the test fails, the problem is with the Control Board; if the test passes, the problem is with the Emulator Pod. The emulator pod address buffers which drive the 64271A should be checked to verify that they are being set to the high-impedance off state by the DEFIB signal from the Control Card.

#### 4-39. ADDRESS LINE TO LINE SHORTS TEST.

4-40. Purpose -- to make sure that address lines HEA 8-23 are not shorted to each other and can be read by the last address registers.

4-41. What -- the mainframe CPU performs a series of mapper RAM writes to appropriate addresses. The last address registers are clocked every time that a mapper write is done. The mainframe CPU then reads back the status of the last address registers and compares it with what was written.

4-42. How -- the mainframe CPU address bus is translated through buffers U25 and U33 to the address bus HEA 8-23 of the mapper RAMs (U17,18). This is done by asserting LSEL from the mainframe bus and LDEFIB from control register U52. The write strobe for the RAMs is provided by LWPREADY from the function select decoder U43. This signal is also input to AND gate U28C, which drives the reset input of flip-flop U22. When a mapper write is done (LWPREADY toggles low), U22 is cleared. The output of U22 is used to drive U45B, which provides the SETLAS signal to the last address registers. A low-to-high transition on this line clocks the mapper address into the last address registers (U39,U40). The mainframe CPU then reads the desired register by enabling it via function select decoder U43. 4-43. Results -- if an difference is detected between the address that was written and the address that was read, the following message will appear on the status line:

"Lines (HEA23 - HEA8)=XXXXH Appear to have line to line shorts"

This status information is decoded as follows:

| HE X | = | BINARY              | SIGNAL |

|------|---|---------------------|--------|

| 0000 |   | 0000 0000 0000 0000 |        |

|      |   | 1                   | HEA8   |

|      |   | 1-                  | HEA9   |

|      |   | 1                   | HEA10  |

|      |   | 1 1                 | HEA11  |

|      |   | <u>1</u>            | HEA12  |

|      |   | 1                   | HEA13  |

|      |   | 1                   | HEA14  |

|      |   | 1                   | HEA15  |

|      |   | 1                   | HEA16  |

|      |   | 1                   | HEA17  |

|      |   | 1                   | HEA18  |

|      |   | 1                   | HEA19  |

|      |   | 1                   | HEA20  |

|      |   | 1                   | HEA21  |

|      |   | -1                  | HEA22  |

|      |   | 1                   | HEA23  |

For example, if the message reads (HEA23 - HEA8)=1248H, then HEA20, HEA17, HEA14, and HEA11 are bad.

4-44. Troubleshooting -- failures in this test are most likely to be caused by problems with the General Purpose Control Board; however, the emulator pod may be causing interference on the emulation address lines which will cause the test to fail (if an emulator pod is left attached to the control board). To determine whether or not this is the case, disconnect the Emulator Pod from the Control Board and re-run the test. If the test fails, the problem is with the Control Board; if the test passes, the problem is with the Emulator Pod. The emulator pod address buffers which drive the bus to the 64271Å should be checked to verify that they are being set to the high-impedance off state by the DEFIB signal from the Control Card.

| ADRS<br>0 | DEVICE<br>13037 DISC CONTROLLER       |               |       |

|-----------|---------------------------------------|---------------|-------|

| 1         | UNIT 0 7906 DISC MEMO<br>2631 PRINTER | JKX F0=0 F0=T |       |

| 6         | 64000                                 |               |       |

| 7         | THIS 64000, MASTER CONTROL            | DLLER         |       |

|           |                                       |               |       |

| STATU     | S: Awaiting command                   | userid        | 13:44 |

| optio     | n_test_                               |               |       |

|           |                                       |               |       |

Figure 4-1. Awaiting Command Status

| 9       | OOFFH                                                               | General Purpo  | se Controlle | r - No Pod |       |

|---------|---------------------------------------------------------------------|----------------|--------------|------------|-------|

| -       |                                                                     | -              |              |            |       |

|         |                                                                     |                |              |            |       |

|         |                                                                     |                |              |            |       |

|         |                                                                     |                |              |            |       |

|         |                                                                     |                |              |            |       |

|         |                                                                     |                |              |            |       |

| STATUS: | Awaiting                                                            | option_test co | mmand        |            | <br>  |

| 9_      |                                                                     |                |              |            |       |

| end     | <slot< td=""><td>#&gt;</td><td></td><td></td><td>print</td></slot<> | #>             |              |            | print |

|         |                                                                     |                |              |            | <br>  |

Figure 4-2. Option Test Card Slot Listing

| Mapper control test 0                 | ance Verification<br># Fail # Tests |

|---------------------------------------|-------------------------------------|

| Test #Fail #<br>Mapper control test 0 | # Fail # Tests                      |

| Mapper control test 0                 | # Fail # Tests                      |

|                                       |                                     |

| STATUS: Awaiting option_test command  | 0 0                                 |

| STATUS: Awaiting option_test command  |                                     |

| STATUS: Awaiting option_test command  |                                     |

| STATUS: Awaiting option_test command  |                                     |

| -                                     |                                     |

|                                       |                                     |

| end disp test pr                      | print                               |

Figure 4-3. Mapper Control Test Overview

| Test<br>Mapper RAM output short tests (to VCC or GND) | # Fail<br>0 | # Tests<br>0 |       |

|-------------------------------------------------------|-------------|--------------|-------|

| Mapper write test                                     | 0           | 0            |       |

| Interrupt and break tests                             | 0           | 0            |       |

| Address line short to GND test                        | 0           | 0            |       |

| Address line short to VCC test                        | 0           | 0            |       |

| Address line short to each other test                 | 0           | 0            |       |

| STATUS: Awaiting option_test command                  |             |              | 8:32  |

|                                                       | test        |              | print |

|                                                       |             |              |       |

Figure 4-4. Control Board Test Display

•

# SECTION V

## ADJUSTMENTS

## 5-1. INTRODUCTION.

5-2. The 64271A has no adjustments.

5-1/(5-2 blank)

## SECTION VI

## REPLACEABLE PARTS

## 6-1. INTRODUCTION.

6-2. This section contains information for ordering parts. Section 6-3 lists exchange assemblies (Blue Stripe Program). Table 6-1 lists abbreviations used in the parts list and throughout the manual. Table 6-2 lists all replaceable parts in reference designator order. Table 6-3 contains a list of manufacturer code numbers and corresponding names and addresses.

## 6-3. EXCHANGE ASSEMBLIES.

6-4. The Model 64271A is available through the Hewlett-Packard Corporate Parts Center by Blue Stripe Exchange. Exchange, factory repaired and tested assemblies are available only on a trade-in basis. Therefore, 64271A's required for spare parts stock must be ordered by the new assembly part number, found in Table 6-2, "Replaceable Parts". To order a Blue Stripe Exchange assembly, use Part Number 64271-69501.

## 6-5. ABBREVIATIONS.

6-6. Table 6-1 lists abbreviations used in the parts list, the schematics, and component locators.

## 6-7. REPLACEABLE PARTS.

6-8. Table 6-2 is the list of replaceable parts and is organized as follows:

- a. Electrical assemblies and their components in alphanumeric order by reference designation.

- b. Miscellaneous parts.

The information given for each part consists of the following:

- a. The Hewlett-Packard part number and the check digit (for HP internal use).

- b. The total quantity (Qty) in the instrument.

- c. The description of the part.

- d. A typical manufacturer of the part in a five-digit code.

- e. The manufacturer's number for the part.

The total quantity for each part is given only once - at the first appearance of the part number in the list.

#### 6-9. ORDERING INFORMATION.

6-10. To order a part listed in the replaceable parts table, quote the Hewlett-Packard part number and check digit, indicate the quantity required, and address the order to the nearest Hewlett-Packard Sales/Service office.

6-11. To order a part that is not listed in the replaceable parts table, include the instrument model number, instrument serial number, description and function of the part and the number of parts required. Address the order to the nearest Hewlett-Packard Sales/ Service office.

## 6-12. DIRECT MAIL ORDER SYSTEM.

6-13. Within the USA, Hewlett-Packard can supply parts through a direct mail order system. Advantages of using the system are as follows:

a. Direct ordering and shipment from the HP Parts Center in Mountain View, California.

b. No maximum or minimum on any mail order (there is a minimum order amount for parts ordered through a local HP office when the orders require billing and invoicing).

c. Prepaid transportation (there is a small handling charge for each order).

d. No invoices- to provide these advantages, a check or money order must accompany each order.

6-14. Mail-order forms and specific ordering information are available through your local HP office. Addresses and phone numbers are located at the back of this manual.

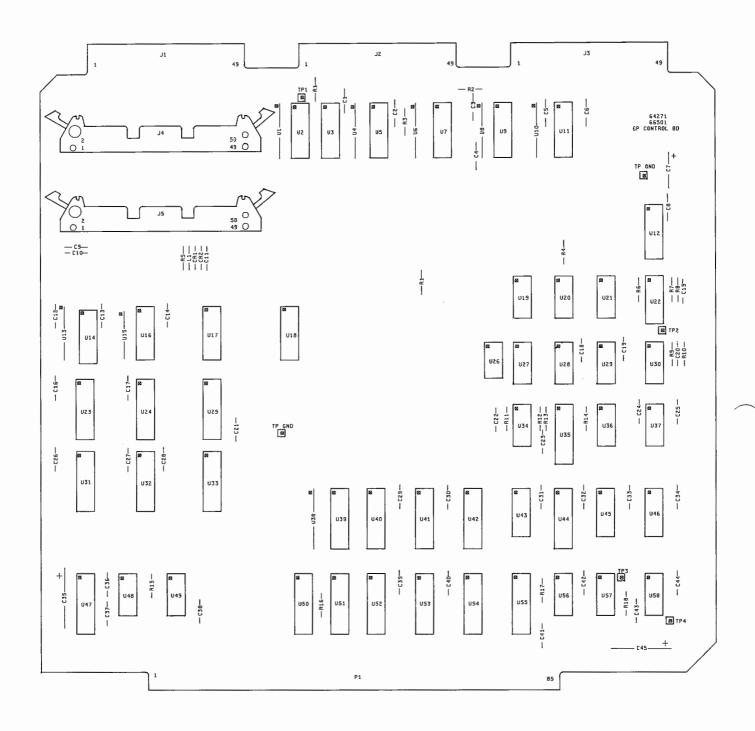

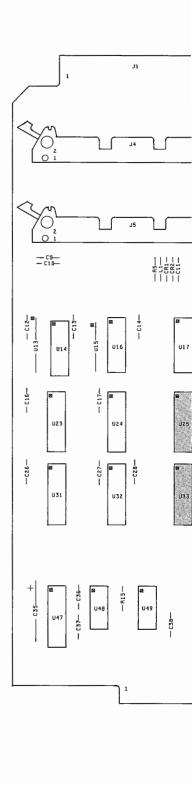

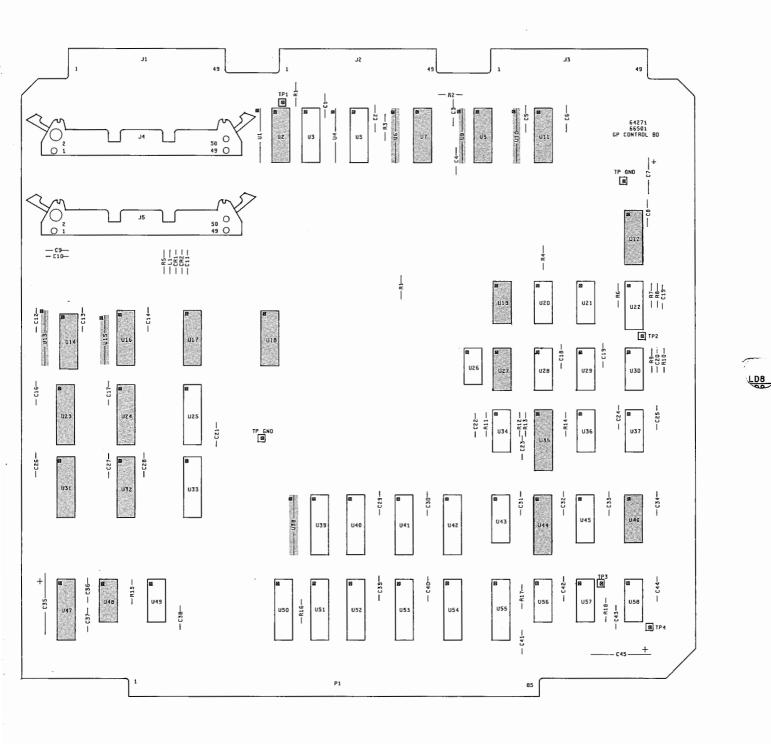

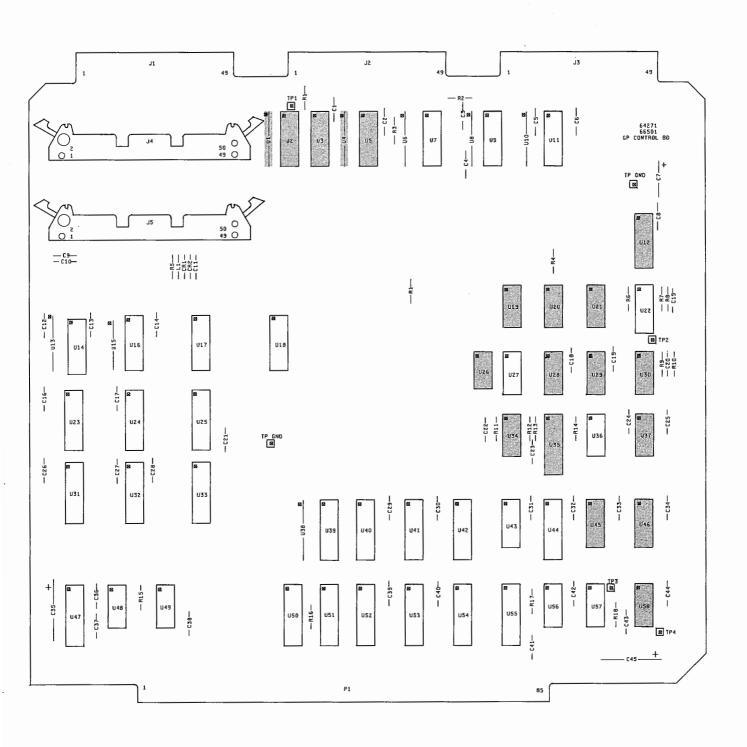

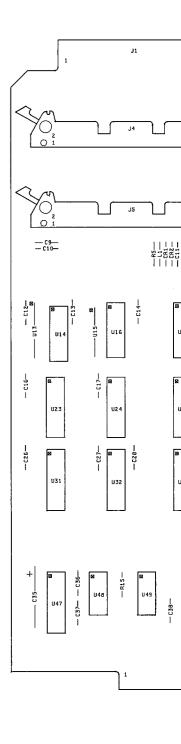

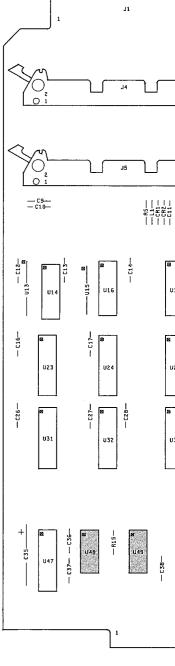

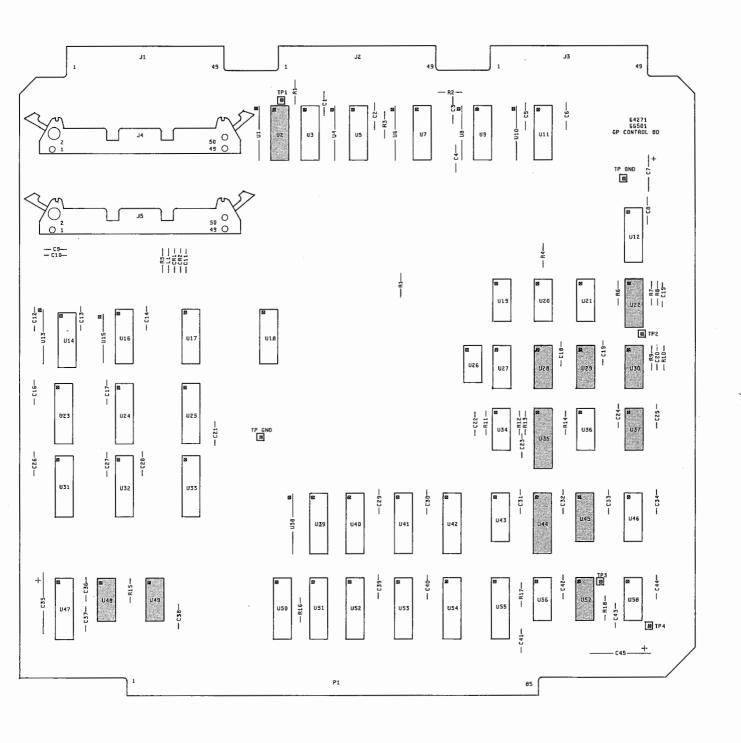

Figure 6-1. Illustrated Parts Breakdown (Sheet 1 of 2)

Figure 6-1. Illustrated Parts Breakdown (Sheet 2 of 2)

| Table 6-1. Reference Designators and Abbreviation | ons |

|---------------------------------------------------|-----|

|---------------------------------------------------|-----|

|       |                                                     |         | REFERENCE                        | DESIGNAT  | ORS                                    |         |                                     |

|-------|-----------------------------------------------------|---------|----------------------------------|-----------|----------------------------------------|---------|-------------------------------------|

| A     | = assembly                                          | F       | = fuse                           | MP        | = mechanical part                      | U       | = integrated circuit                |

| В     | = motor                                             | FL      | = filter                         | P         | = plug                                 | v       | = vacuum, tube, neon                |

| вт    | = battery                                           |         | = integrated circuit             | Q.        | = transistor                           |         | bulb, photocell, etc                |

| c.    | = capacitor                                         | J       | = jack                           | R         | = resistor                             | VR      | = voltage regulator                 |

| CP    | = coupler                                           | ĸ       | = relay                          | BT        | = thermistor                           | w       | = cable                             |

| CR    | = diode                                             | L       | = inductor                       | S         | = switch                               | x       | - socket                            |

| DL    | = delay line                                        | LS      | = loud speaker                   | Ť         | = transformer                          | Ŷ       | = crystal                           |

| DS    | = device signaling (lamp)                           | M       | = meter                          | тв        | = terminal board                       | z       | = tuned cavity network              |

| E     | = misc electronic part                              | MK      | = microphone                     | тр        | = test point                           | 2       | toned outry network                 |

| -     | inter clothenic part                                |         |                                  | EVIATIONS |                                        |         |                                     |

|       |                                                     |         | ABBR                             | EVIATIONS |                                        |         |                                     |

| Α     | = amperes                                           | н       | = henries                        | N/O       | = normally open                        | RMO     | = rack mount only                   |

| AFC   | <ul> <li>automatic frequency<br/>control</li> </ul> | HDW     | = hardware                       | NOM       | = nominal                              | RMS     | = root-mean square                  |

| AMPL  | = amplifier                                         | HEX     | = hexagonal                      | NPO       | = negative positive zero               | RWV     | = reverse working                   |

|       |                                                     | HG      | = mercury                        |           | (zero temperature                      |         | voltage                             |

| BFO   | = beat frequency oscillator                         | HR      | - hour(s)                        |           | coefficient)                           |         |                                     |

| BE CU | = beryllium copper                                  | HZ      | = hertz                          | NPN       | <ul> <li>negative-positive-</li> </ul> | S-B     | - slow-blow                         |

| BH    | = binder head                                       |         |                                  |           | negative                               | SCR     | - screw                             |