# 64000 LOGIC DEVELOPMENT SYSTEM

# ASSEMBLER SUPPLEMENT Z80

#### CERTIFICATION

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### WARRANTY

This Hewlett-Packard system product is warranted against defects in materials and workmanship for a period of 90 days from date of installation. During the warranty period, HP will, at its options, either repair or replace products which prove to be defective.

Warranty service of this product will be performed at Buyer's facility at no charge within HP service travel areas. Outside HP service travel areas, warranty service will be performed at Buyer's facility only upon HP's prior agreement and Buyer shall pay HP's round trip travel expenses. In all other cases, products must be returned to a service facility designated by HP.

For products returned to HP for warranty service. Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country.

HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instructions when properly installed on that instrument. HP does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### EXCLUSIVE REMEDIES

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HP SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### ASSISTANCE

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office.

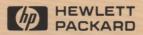

## Model 64000 Reference Manuals

The following block diagram shows the documentation scheme for the HP Model 64000 Logic Development System. The interconnecting arrows show the recommended progression through the manuals as a way of gaining familiarity with the system.

For a detailed map showing specific manuals and their part numbers, refer to the Manual Map in the System Overview Manual.

# **Printing History**

Each new edition of this manual incorporates all material updated since the previous edition. Each new or revised page is indicated by a revision (rev) date. Manual change sheets are issued between editions, allowing you to correct or insert information in the current edition.

The part number on the back cover changes only when each new edition is published. Minor corrections or additions may be made as the manual is reprinted between editions.

First Printing . . . March 1980 Second Printing . . . September 1980

.

## Z80 Assembler Supplement

HP Model 64000 Logic Development System

© COPYRIGHT HEWLETT-PACKARD COMPANY/COLORADO SPRINGS DIVISION 1980 1900 GARDEN OF THE GODS ROAD, COLORADO SPRINGS, COLORADO, U.S.A.

ALL RIGHTS RESERVED

The information in this supplement has been checked for accuracy and is believed to be correct; however, no responsibility is assumed for inaccuracies. When discrepancies are noted, refer to the manufacturer's Microprocessor Programming Manual for clarification.

## **Table of Contents**

#### Chapter 1: General Information

| Introduction                       |

|------------------------------------|

| Programming Considerations1-1      |

| Z80 Architecture                   |

| Accumulator and Flag Registers1-1  |

| General Purpose Registers1-1       |

| Program Counter Register1-2        |

| Index Registers                    |

| Stack Pointer Register             |

| Interrupt Page Address Register1-2 |

| Memory Refresh Register            |

| Modes of Addressing                |

| Immediate Addressing1-3            |

| Immediate Extended Addressing1-3   |

| Relative Addressing1-3             |

| Extended Addressing1-3             |

| Indexed Addressing1-4              |

| Register Addressing1-4             |

| Register Indirect Addressing1-4    |

| Implied Addressing1-4              |

| Bit Addressing                     |

| Modified Page Zero Addressing1-4   |

| Condition Flags                    |

| Zero (Z) Flag                      |

| Sign (S) Flag                      |

| Parity/Overflow (P/V) Flag1-5      |

| Carry (CY) Flag                    |

| Half Carry (HC) Flag               |

| Add/Subtract (N) Flag              |

## Chapter 2: Operand Rules and Conventions

| Types of Information             |     |

|----------------------------------|-----|

| Identifying Types of Information | 2-2 |

#### Chapter 3: Special Pseudo Instructions

| Introduction     | 1 |

|------------------|---|

| DEFB Instruction | 2 |

| DEFS Instruction | 3 |

| DEFW Instruction | 4 |

# Table of Contents (Cont'd)

#### Chapter 4: Assembler Output Listing

| General                | . 4-1 |

|------------------------|-------|

| Input/Output Files     | . 4-1 |

| Source Input File      | .4-1  |

| Assembler Output Files | . 4-1 |

| Output Listing         | . 4-2 |

|                        |       |

### Chapter 5: Z80 Instruction Set Summary

| General            | ĺ |

|--------------------|---|

| Predefined Symbols | 3 |

# **List of Tables**

| 4-1. | Source Program Format Example | . 4-3 |

|------|-------------------------------|-------|

| 4-2. | Assembler Output Listing      | . 4-4 |

| 4-3. | Assembler Output with Errors  | . 4-6 |

# Chapter **1** General Information (Z80)

## Introduction

This chapter contains general information about the Z80 microprocessor. It briefly discusses the microprocessor's architecture, addressing modes, and condition codes. For a detailed description of the microprocessor refer to the manufacturer's Z80 User's Manual.

#### NOTE

If you are unfamiliar with assembly language or assemblers, read Chapter 6 in the Assembler/Linker Reference Manual. That chapter briefly reviews assemblers, assembly language, and the numbering systems.

# **Programming Considerations**

## **Z80** Architecture

There are eighteen 8-bit registers and four 16-bit registers available in the Z80 microprocessor for control of external memory and peripheral devices that may be associated with the target system. These registers are discussed briefly in the following paragraphs.

## **Accumulator and Flag Registers**

The microprocessor contains two independent 8-bit registers (accumulators) with associated 8-bit flag registers. They are referred to as register A and register A'. The F flag register is associated with the A register and the F' flag register is associated with the A' register. The A or A' register holds the result of 8-bit arithmetic or logical operations while the flag register (F or F') indicates the specific effect of those operations.

## **General Purpose Registers**

There are two sets of general purpose registers with each set containing six 8-bit registers that may be addressed individually or as 16-bit register pairs. One set contains register pairs BC, DE, and HL while the second set contains register pairs BC', DE', and HL'.

## **Program Counter Register**

The program counter (PC) is a two-byte (16-bit) register that points to the current program address. After each instruction the program counter will be automatically incremented. When a program branch is required, the branch address will be placed into the program counter, overriding the incremental operation.

## **Index Registers**

The two index registers (IX and IY) are special-purpose 16-bit registers that may be used as pointers to memory locations where data may be retrieved or stored. When using the indexed addressing mode, an additional byte may be included in the instructions to indicate an offset from the register content. The offset must be specified as a two's complement signed integer.

## **Stack Pointer Register**

The stack pointer (SP) register is another special-purpose 16-bit register that allows the microprocessor to use a section of external memory as a last-in, first-out (LIFO) file. Data may be pushed onto the stack or pulled off the stack by using the PUSH and POP instructions.

## Interrupt Page Address Register

The microprocessor may be operated whereby an indirect call to any memory location can be accomplished in response to an interrupt. The interrupt address (1) register may be used to store the high-order 8 bits of the indirect address while the interrupting device provides the low-order 8 bits.

## **Memory Refresh Register**

The microprocessor has a memory refresh register that allows dynamic memories to be used in the same fashion as static memories. The data in the refresh counter will be sent out on the address bus along with a refresh control signal while the microprocessor is executing an instruction.

## Modes of Addressing

A number of instructions, such as the "compare" instruction, require data to be operated on. The method of specifing or locating the data is generally referred to as the mode of addressing. The Z80 microprocessor uses ten addressing modes to reference the data stored in memory or in registers. The addressing modes are briefly explained in the following paragraphs.

## **Immediate Addressing**

In this mode of addressing, the operand field of the instruction contains the value to be used in the operation or computation. The value is an 8-bit quantity that immediately follows the opcode.

## **Immediate Extended Addressing**

This mode of addressing is the same as the immediate addressing mode except that the data is a 16-bit quantity (two bytes) that immediately follows the opcode.

## **Relative Addressing**

Branch instructions are somewhat different from other instructions in that their selected addresses do not indicate the location of data. Instead, the addresses indicate the location of the next instruction. This location will be relative to the current setting of the program counter (plus 2).

For the relative addressing mode to be valid, the branch distance (range) between the instruction and the destination of the branch must fall in the value range of -128 to +127 bytes. This relationship between the relative address and the absolute address of the destination of the branch may be expressed by:

$$\mathsf{DA} = (\mathsf{PC+2}) + \mathsf{R}$$

where:

DA = address of the destination of the branch instruction.

PC = content of the lowest 8 bits of the program counter.

R = the 8-bit, two's complement, binary number stored in the second byte of the instruction.

## **Extended Addressing**

In the extended addressing mode, the instruction uses three bytes of memory with the first byte containing the opcode of the instruction, the second byte containing the low-order 8 bits of the absolute numerical address, and the third byte containing the high-order 8 bits.

The second and third bytes of an extended address instruction may be an address to which a program can jump or it may be an address where an operand is located. To indicate an operand location as opposed to a jump address, enclose the second and third bytes of the instruction in brackets. The use of brackets always means that the enclosed value is to be used as a pointer to a memory location.

#### NOTE

Do not use parentheses as enclosing symbols. The Model 64000 assembler decodes parentheses as enclosing expressions.

### Indexed Addressing

The byte of data following the opcode contains an offset that is added to the designated index register to form a pointer to a memory location. The instruction will specify which index register (IX or IY) that is to be used. The content of the index register will not be altered by this operation.

### **Register Addressing**

The instruction itself specifies the register that contains the data.

## **Register Indirect Addressing**

The instruction specifies a 16-bit register that contains the memory address where the data is located.

### Implied Addressing

In a number of instructions, the opcode specifies one or more registers that contain operands or where results are to be stored. For example, there are a number of arithmetic instructions where the accumulator is always implied to be the destination of the results of the operation.

## **Bit Addressing**

The instruction set for the Z80 contains many set, reset, and test instructions. These instructions permit any memory location or register to be specified for a bit operation. Three bits in the opcode designates the specific bit to be manipulated or tested.

## Modified Page Zero Addressing

The Z80 microprocessor has a special call instruction that may specify any one of eight locations in page zero of memory. These locations may be used to initialize restart subroutines.

# **Condition Flags**

There are six condition flags associated with each flag register. The state of each flag will be established by the execution of various instructions. Unless the description of an instruction states otherwise (see Chapter 5), the condition flags associated with a specified register are affected as described in the following paragraphs.

## Zero (Z) Flag

If the result of the instruction has the value of 'zero', the zero flag will be set to 'one'; otherwise, it will be reset. The zero flag is assigned to bit-position 6 in the flag register.

## Sign (S) Flag

After an operation, if the most significant bit in the register has the value of 'one', the sign flag will be set to 'one'; otherwise, it will be reset. The sign flag is assigned to bit-position 7 in the flag register.

## Parity/Overflow (P/V) Flag

For logical operations, if the result of the instruction indicates even parity, the parity/overflow flag will be set; otherwise, it will be reset. For signed two's complement arithmetic operation, the parity/overflow flag will be set if the two's complement number in the associated register is in error. The error indicates that the resulting number of the arithmetic operation exceeds the maximum possible number (-128 to +127) that can be represented by the two's complement notation. The parity/overflow flag is assigned to bit-position 2 in the flag register.

## Carry (CY) Flag

If the result of the instruction is a carry (from addition) or a borrow (from subtraction) out of the high-order bit, the carry/borrow flag will be set to 'one'; otherwise, it will be reset. The carry flag is assigned to bit-position  $\emptyset$  in the flag register.

## Half Carry (HC) Flag

If the instruction causes a carry out of bit 3 into bit 4 of the resulting value, the auxiliary carry flag will be set to 'one'; otherwise, it will be reset. The half carry flag is assigned to bit-position 4 in the flag register.

## Add/Subtract (N) Flag

This flag is used to specify the type of instruction that was executed last so that a following decimal adjust operation will be executed correctly by the microprocessor. For all 'add' instructions, the N flag will be reset. For all 'subtract' instructions, the N flag will be set. The add/subtract flag is assigned to bit-position 1 in the flag register.

### NOTE

The first four flags (Z, S, P/V, and C) may be checked and - used as conditions for jump, call, or return instructions. Bitpositions 3 and 5 in the flag register are not used.

# **Operand Rules and Conventions**

# **Types of Information**

There are five types of information that may be used as data in the operand field:

a. Register Information - operands may reference directly, data contained in the processor registers such as the stack, register A, or data memory registers B,C,D,E,H, and L.

A.RØ

#### Example:

LD

;LOAD CONTENTS OF ;REGISTER Ø INTO ;REGISTER A

b. Register Pair Information - operands may reference directly data contained in register pairs such as the BC and DE registers.

#### Examples:

| LD | SP,HL    | ;LOAD REGISTER PAIR<br>;HL INTO STACK<br>;POINTER  |

|----|----------|----------------------------------------------------|

| LD | DE,5FFFH | ;LOAD IMMEDIATE DATA<br>;INTO REGISTER PAIR<br>;DE |

c. Immediate Data - operands may contain immediate data. The required value is inserted directly into the operand field. The value may be in the form of numbers, an expression to be evaluated at assembly time, a symbol, or an ASCII constant enclosed in quotation marks.

#### **Examples:**

| LD | D,ØFFH | ;LOAD "FF" HEX INTO<br>;REGISTER D                                 |

|----|--------|--------------------------------------------------------------------|

| LD | В,"А"  | ;LOAD VALUE OF ASCII<br>;CONSTANT A (Ø1ØØØØØ1)<br>;INTO REGISTER B |

d. 16-bit Memory Address - operands may reference a 16-bit absolute memory address within the range of  $\emptyset$  to 65,535 that contains the operand data.

#### Example:

- LD IX,[HL]

- e. Dual Operands when the operand field contains two operands, the first operand listed is the destination and the second operand is the source.

#### **Example:**

LD

;LOAD REGISTER H ;INTO REGISTER A

# **Identifying Types of Information**

A,H

There are nine ways to define the types of information that can be presented in the operand field. These ways are discussed in the following paragraphs.

a. Binary Data - each binary number must be followed by the letter B.

#### Example:

- SAM LD H,10010011B

- b. Octal Data each octal number must be followed by either the letter O or the letter Q.

| Example: |    |    |       |

|----------|----|----|-------|

| SAM      |    | LD | H,55O |

| SAM      | or | LD | H,55Q |

c. Hexadecimal Data - each hexadecimal number must begin with a number and be followed by the letter H.

Example:

- SAM LD H,ØF1H

- d. Decimal Data each decimal number may be followed by the letter D or it may stand alone. Any number not specifically identified as binary, octal, or hexadecimal is assumed to be decimal.

#### Example:

| SAM |    | LD | H,55D |

|-----|----|----|-------|

|     | or |    |       |

| SAM |    | LD | H,55  |

#### NOTE

Leading zeros are appended or truncated from constants to produce 8- or 16-bit values as required by the particular operand. Spaces are not permitted within a numeric constant. e. ASCII Constants - one or more ASCII characters enclosed in quotation marks or apostrophes identify an ASCII constant.

#### Example:

SAM

| l | _D  | Н,'Т'          | ;LOADS H REG WITH<br>;8-BIT ASCII CODE<br>;FOR LETTER T |

|---|-----|----------------|---------------------------------------------------------|

|   | ASC | "FULTON'S FOLL | _Y"                                                     |

f. Location Counter - The dollar symbol (\$) refers to the content of the program counter. The program counter contains the address of the current instruction or data statement being assembled.

#### Example:

JP

;JUMP TO ADDRESS ;3 BYTES BEYOND ;FIRST BYTE OF THIS ;INSTRUCTION

g. Label Assigned Values - The EQU directives can be used to assign values to labels.

\$+3

#### Example:

SAM EQU 6AH

h. Labels of Instruction or Data. The label assigned to an instruction or a data definition has as its value the address of the first byte of the instruction or data. Instructions elsewhere in the program can refer to this address by its symbolic name.

#### Example:

| SAM  | JP | FRED  | JUMP TO INSTRUC;<br>IION AT FRED; |

|------|----|-------|-----------------------------------|

|      | •  | •     |                                   |

|      | •  | •     |                                   |

|      | •  | •     |                                   |

|      | •  | •     |                                   |

| FRED | LD | B,6AH |                                   |

i. Expressions. The operand field may contain an expression consisting of one or more terms acted on by the expression operators. A term may be either a symbol, a string constant, a numeric constant, or an expression. The assembler reduces the entire expression to a single value.

Terms within expressions may be connected by the following arithmetic operators:

- a. The plus operator (+) produces the arithmetic sum of its operands.

- b. The minus operator (-) produces the arithmetic difference of its operands or the arithmetic negative of its operand when used alone.

- c. The asterisk operator (\*) produces the arithmetic product of the operands.

- d. The slant operator (/) produces the quotient of its operands, discarding any remainder.

- e. An instruction enclosed in parentheses is a legal expression in the operand field. For expressions in parentheses, the deepest expression in parentheses is evaluated first.

Care should be taken when using the arithmetic operators since their operational results may affect the condition flags in the condition code register.

ASSEMBLER SUPPLEMENT Z80

# Chapter 3

# **Special Pseudo Instructions**

# Introduction

This chapter supplements Chapter 3 in the HP Model 64000 Assembler/Linker Reference Manual. It lists and defines in detail those assembler instructions that are applicable to the Z80 microprocessor only.

÷

| DEFB                   |           |            | MODEL 64000<br>ASSEMBLER SUPPLEMENT<br>Z80 |

|------------------------|-----------|------------|--------------------------------------------|

| Define Byte<br>SYNTAX: |           |            |                                            |

| Label                  | Operation | Operand    |                                            |

| [Name]                 | DEFB      | expression |                                            |

The DEFB pseudo instruction will store data in consecutive memory locations starting with the current setting of the program counter. The operand field may contain an expression that evaluates to one-byte (8 bits) numbers in the range Ø through 255.

The label name is optional. If the label name is present, it is assigned the starting value of the program counter, and will reference the first byte stored by the DEFB instruction.

#### Example:

| Label | Operation | Operand |

|-------|-----------|---------|

| SAM   | DEFB      | CHARLIE |

| MODEL 64000<br>ASSEMBLER SUPPLEMENT<br>Z80 |           |            | DEFS                 |

|--------------------------------------------|-----------|------------|----------------------|

|                                            |           |            | Define Storage Block |

| SYNTAX:                                    |           |            |                      |

| Label                                      | Operation | Operand    |                      |

| [Name]                                     | DEFS      | expression |                      |

|                                            |           |            |                      |

The DEFS pseudo instruction may be used to define a block of memory space. The value of the expression in the operand field specifies the number of bytes to be reserved.

Any symbol appearing in the operand field must be predefined. If the value of the operand expression is zero, no memory will be reserved; however, if the optional label name is present, it will be assigned the current value of the program counter.

The DEFS instruction reserves space in memory by incrementing the program counter by the value in the operand expression.

Example:

| Label | Operation | Operand | Comment           |

|-------|-----------|---------|-------------------|

| SAM   | DEFS      | 15      | ;RESERVE 15 BYTES |

|       |           |         | FOR SAM ROUTINE   |

|             |           |            | MODEL 64000<br>ASSEMBLER SUPPLEMENT<br>Z80 |

|-------------|-----------|------------|--------------------------------------------|

| Define Word |           |            |                                            |

| SYNTAX:     |           |            |                                            |

| Label       | Operation | Operand    |                                            |

| [Name]      | DEFW      | expression |                                            |

The DEFW pseudo instruction will store a 16-bit value from the expression as an address. The value is stored in memory starting at the current setting of the program counter.

Expressions evaluate to one-word (16 bits) numbers, typically addresses. If an expression evaluates to a single byte, it is assumed to be the low-order byte of a l6-bit word where the high-order byte is all zeros.

If the label name is present, it is assigned the starting address of the program counter, and thus will reference the first byte stored by the DEFW instruction.

Example:

| Label | Operation | Operand |

|-------|-----------|---------|

| SAM   | DEFW      | ØB123H  |

# Chapter **4**

# **Assembler Output Listing**

# General

The assembler processes source program modules and produces an output that consists of a source program listing, a relocatable object file, and a symbol cross-reference list. Errors detected by the assembler will be noted in the output listing as error messages. Refer to Appendix D in the Assembler/Linker Manual for a listing of all error codes and their definitions.

## Input/Output Files

## **Source Input File**

Input to the assembler is a source file that is created through the editor. It consists of the following:

| Example | Description                                                                   |

|---------|-------------------------------------------------------------------------------|

| "Z80"   | - Assembler directive                                                         |

|         | - Source statements consisting of:                                            |

|         | Assembler Pseudos - refer to Chapter 3<br>(Assembler/Linker Reference Manual) |

|         | Assembler Instructions - refer to Chapter 5, this Supplement                  |

## **Assembler Output Files**

The assembler produces relocatable object modules that are stored under the same name as the source file but in a format that can be processed by the linker. If an object file does not exist at assembly time, the assembler will create one. If an object file does exist, the assembler will replace it. **List File** - The list file is a formatted file that is output to a line printer. It can also be stored in another file or applied to the system CRT display. The list may include:

- a. Source statements with object code.

- b. Error messages.

- c. Summary of errors with a description list.

- d. Symbol cross-reference list.

**Symbol Cross-reference List** - All symbols are cross-referenced except local macro labels and parameters. A cross-reference listing contains:

- a. Alphabetical list of program symbols.

- b. Line numbers where symbols are defined.

- c. All references (by line numbers) to symbols in the program.

## **Output Listing**

An example of an assembler output listing is given in table 4-2, using the source program example listed in table 4-1. To illustrate an assembler output listing that contains error messages refer to table 4-3.

#### NOTE

The source program example was not written as a specific program. It merely lists a group of mnemonics to present a formatted example.

| "Z80" LIST XREF |          |                    |

|-----------------|----------|--------------------|

|                 | EXT      | DSPL8,KYBD8        |

|                 | ORG      | Ø8ØØH              |

| EXEC8           | LD       | HL,ØCØØH           |

|                 | LD       | SP,HL              |

|                 | LD       | HL,Ø8Ø5H           |

|                 | LD       | A,Ø3H              |

| LP1             | LD       | [HL],A             |

|                 | DEC      | HL                 |

|                 | LD       | B,Ø6H              |

| LP2             | CALL     | KYBD8              |

|                 | JP       | C,LIGHT            |

|                 | PUSH     | AF                 |

|                 | DJNZ     | LP2                |

|                 | LD       | B,Ø1H              |

|                 | LD<br>LD |                    |

| GO              | LD       | DE,Ø8Ø4H<br>A,[DE] |

| GO              | CPDR     | A,[DE]             |

|                 | JP       | Z,LP2              |

|                 | DEC      | L,2,2,2            |

|                 | DEC      | E                  |

|                 | JP       | NZ,GO              |

|                 | POP      | AF                 |

|                 | CPD      |                    |

|                 | JP       | Z,LIGHT            |

|                 | LD       | [HL],A             |

|                 | DEC      | L                  |

| LIGHT           | CALL     | DSPL8              |

|                 | JP       | LP1                |

|                 | END      |                    |

## Table 4-1. Source Program Format Example

| Table | 4.0           | A         | <b>•</b> •••••• | 1 1 - 41 |

|-------|---------------|-----------|-----------------|----------|

| rable | 4- <u>Z</u> . | Assembler | Output          | LISTING  |

| LINE | LOC  | CODE | ADDR |                 | SOURC | E STATEMENT |

|------|------|------|------|-----------------|-------|-------------|

|      |      |      |      |                 |       |             |

| 1    |      |      |      | "Z80" LIST XREF |       |             |

| 2    |      |      |      |                 | EXT   | DSPL8,KYBD8 |

| 3    | Ø8ØØ |      |      |                 | ORG   | Ø8ØØH       |

| 4    | Ø8ØØ | 21   | ØCØØ | EXEC8           | LD    | HL,ØCØØH    |

| 5    | Ø8Ø3 | F9   |      |                 | LD    | SP,HL       |

| 6    | Ø8Ø4 | 21   | Ø8Ø5 |                 | LD    | HL,Ø8Ø5H    |

| 7    | Ø8Ø7 | 3E   | ØЗ   |                 | LD    | А,ØЗН       |

| 8    | Ø8Ø9 | 77   |      | LP1             | LD    | [HL],A      |

| 9    | Ø8ØA | 2B   |      |                 | DEC   | HL          |

| 1Ø   | Ø8ØB | Ø6   | Ø6   |                 | LD    | B,Ø6H       |

| 11   | Ø8ØD | CD   | ØØØØ | LP2             | CALL  | KYBD8       |

| 12   | Ø81Ø | DA   | Ø831 |                 | JP    | C,LIGHT     |

| 13   | Ø813 | F5   |      |                 | PUSH  | AF          |

| 14   | Ø814 | 1ØF7 |      |                 | DJNZ  | LP2         |

| 15   | Ø816 | Ø6   | Ø1   |                 | LD    | B,Ø1H       |

| 16   | Ø818 | 21   | Ø8Ø5 |                 | LD    | HL,Ø8Ø5H    |

| 17   | Ø81B | 11   | Ø8Ø4 |                 | LD    | DE,Ø8Ø4H    |

| 18   | Ø81E | 1A   |      | GO              | LD    | A,[DE]      |

| 19   | Ø81F | EDB9 |      |                 | CPDR  |             |

| 2Ø   | Ø821 | CA   | Ø8ØD |                 | JP    | Z,LP2       |

| 21   | Ø824 | 2D   |      |                 | DEC   | L           |

| 22   | Ø825 | 1D   |      |                 | DEC   | E           |

| 23   | Ø826 | C2   | Ø81E |                 | JP    | NZ,GO       |

| 24   | Ø829 | F1   |      |                 | POP   | AF          |

| 25   | Ø82A | EDA9 |      |                 | CPD   |             |

| 26   | Ø82C | CA   | Ø831 |                 | JP    | Z,LIGHT     |

| 27   | Ø82F | 77   |      |                 | LD    | [HL],A      |

| 28   | Ø83Ø | 2D   |      |                 | DEC   | L           |

| 29   | Ø831 | CD   | ØØØØ | LIGHT           | CALL  | DSPL8       |

| 3Ø   | Ø834 | C3   | Ø8Ø9 |                 | JP    | LP1         |

| 31   |      |      |      |                 | END   |             |

| FILE: EXEC | FILE: EXEC8:SAVE |      | CROSS REFERENCE TABLE |  |  |

|------------|------------------|------|-----------------------|--|--|

| LINE#      | SYMBOL           | TYPE | REFERENCES            |  |  |

|            | А                | R    | 7,8,18,27             |  |  |

|            | В                | R    | 10,15                 |  |  |

|            | С                | R    | 12                    |  |  |

|            | DE               | R    | 17,18                 |  |  |

| 2          | DSPL8            | E    | 29                    |  |  |

|            | E                | R    | 22                    |  |  |

| 4          | EXEC8            | А    |                       |  |  |

| 18         | GO               | А    | 23                    |  |  |

|            | HL               | R    | 4,5,6,8,9,16,27       |  |  |

| 2          | KYBD8            | Е    | 11                    |  |  |

|            | L                | R    | 21,28                 |  |  |

| 29         | LIGHT            | Α    | 12,26                 |  |  |

| 8          | LP1              | А    | 30                    |  |  |

| 11         | LP2              | А    | 14,2Ø                 |  |  |

|            | NZ               | А    | 23                    |  |  |

|            | SP               | R    | 5                     |  |  |

|            | Z                | А    | 20,26                 |  |  |

|            |                  |      |                       |  |  |

### Table 4-2. Assembler Output Listing (Cont'd)

- **NOTE:** In the cross-reference table, the letter listed under the TYPE column has the following definition:

- A = Absolute

- C = Common (COMN)

- D = Data (DATA)

- E = External

- M = Multiple Defined

- P = Program (PROG)

- R = Predefined Register

- U = Undefined

٦

### Table 4-3. Assembler Output with Errors

| FILE: EXEC8:SAVE                      |          |         | HEWLETT-PACKARD: ZILOG Z80 ASSEMBLER |                 |          |             |

|---------------------------------------|----------|---------|--------------------------------------|-----------------|----------|-------------|

| LINE                                  | LOC      | CODE    | ADDR                                 | SC              | OURCE ST | ATEMENT     |

| 1                                     |          |         |                                      | "Z80" LIST XREF |          |             |

| 2                                     |          |         |                                      |                 | EXT      | DSPL8,KYBD8 |

| 3                                     | Ø8ØØ     |         |                                      |                 | ORG      | Ø8ØØH       |

| 4                                     | Ø8ØØ     | 21      | ØCØØ                                 | EXEC8           | LD       | HL,ØCØØH    |

| 5                                     |          |         |                                      |                 | LB       | SP,HL       |

| ERR                                   | OR-UO    |         |                                      |                 | $\wedge$ | ,           |

| 6                                     | Ø8Ø3     | 21      | Ø8Ø5                                 |                 | LD       | HL,0805H    |

| 7                                     | Ø8Ø6     | 3E      | Ø3                                   |                 | LD       | А,Ø3Н       |

| 8                                     | Ø8Ø8     | 77      |                                      | LP1             | LD       | [HL],A      |

| 9                                     | Ø8Ø9     | 2B      |                                      |                 | DEC      | HL          |

| 1Ø                                    | Ø8ØA     | Ø6      | FF                                   |                 | LD       | B,Ø6FFH     |

| ERR                                   | OR-LR,s  | ee line | 5                                    |                 |          | $\wedge$    |

| 11                                    | Ø8ØC     | CD      | ØØØØ                                 | LP2             | CALL     | KYBD8       |

| 12                                    | Ø8ØF     | DA      | Ø83Ø                                 |                 | JP       | C,LIGHT     |

| 13                                    | Ø812     | F5      |                                      |                 | PUSH     | AF          |

| 14                                    | Ø813     | 1ØF7    |                                      |                 | DJNZ     | LP2         |

| 15                                    | Ø815     | Ø6      | Ø1                                   |                 | LD       | B,Ø1H       |

| 16                                    | Ø817     | 21      | Ø8Ø5                                 |                 | LD       | HL,Ø8Ø5H    |

| 17                                    | Ø81A     | 11      | Ø8Ø4                                 |                 | LD       | DE,Ø8Ø4H    |

| 18                                    | Ø81D     | 1A      |                                      | GO              | LD       | A,[DE]      |

| 19                                    | Ø81E     | EDB9    |                                      |                 | CPDR     |             |

| 2Ø                                    | Ø82Ø     | CA      | ØØØØ                                 |                 | JP       | Z,LP3       |

| ERRO                                  | R-US,see | e line  | 1Ø                                   |                 |          | $\wedge$    |

| 21                                    | Ø823     | 2D      |                                      |                 | DEC      | L           |

| 22                                    | Ø824     | 1D      |                                      |                 | DEC      | E           |

| 23                                    | Ø825     | C2      | Ø81D                                 |                 | JP       | NZ,GO       |

| 24                                    | Ø828     | F1      |                                      |                 | POP      | AF          |

| 25                                    | Ø829     | EDA9    |                                      |                 | CPD      |             |

| 26                                    | Ø82B     | CA      | Ø83Ø                                 |                 | JP       | Z,LIGHT     |

| 27                                    | Ø82E     | 77      |                                      |                 | LD       | [HL],A      |

| 28                                    | Ø82F     | 2D      |                                      |                 | DEC      | L           |

| 29                                    | Ø83Ø     | CD      | ØØØØ                                 | LIGHT           | CALL     | DSPL8       |

| 3Ø                                    | Ø833     | C3      | Ø8Ø8                                 |                 | JP       | LP1         |

| 31                                    |          |         |                                      |                 | END      |             |

| Errors = 3, previous error at line 20 |          |         |                                      |                 |          |             |

| <ul> <li>US - Undefined Symbol, The indicated symbol is not defined as a (wrap around: label or declared as an external)</li> <li>LR - Legal Range, Address or displacement is out of range of the (wrap around: instruction's addressing capability)</li> <li>UO - Unidentified Opcode, Opcode encountered is not defined for (wrap around: this micro-processor)</li> </ul> |        |         |                 |        |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|-----------------|--------|--|

| FILE: EXEC                                                                                                                                                                                                                                                                                                                                                                    | B:SAVE | CROSS I | REFERENCE TABLE | PAGE 2 |  |

| LINE                                                                                                                                                                                                                                                                                                                                                                          | SYMBOL | TYPE    | REFERENCES      |        |  |

|                                                                                                                                                                                                                                                                                                                                                                               | А      | R       | 7,8,18,27       |        |  |

|                                                                                                                                                                                                                                                                                                                                                                               | В      | R       | 10,15           |        |  |

|                                                                                                                                                                                                                                                                                                                                                                               | С      | R       | 12              |        |  |

|                                                                                                                                                                                                                                                                                                                                                                               | DE     | R       | 17,18           |        |  |

| 2                                                                                                                                                                                                                                                                                                                                                                             | DSPL8  | E       | 29              |        |  |

|                                                                                                                                                                                                                                                                                                                                                                               | Е      | R       | 22              |        |  |

| 4                                                                                                                                                                                                                                                                                                                                                                             | EXEC8  | А       |                 |        |  |

| 18                                                                                                                                                                                                                                                                                                                                                                            | GO     | А       | 23              |        |  |

|                                                                                                                                                                                                                                                                                                                                                                               | HL     | R       | 4,6,8,9,16,27   |        |  |

| 2                                                                                                                                                                                                                                                                                                                                                                             | KYBD8  | E       | 11              |        |  |

|                                                                                                                                                                                                                                                                                                                                                                               | L      | R       | 21,28           |        |  |

| 29                                                                                                                                                                                                                                                                                                                                                                            | LIGHT  | А       | 12,26           |        |  |

| 8                                                                                                                                                                                                                                                                                                                                                                             | LP1    | А       | 30              |        |  |

| 11                                                                                                                                                                                                                                                                                                                                                                            | LP2    | А       | 14,20           |        |  |

| * * *                                                                                                                                                                                                                                                                                                                                                                         | LP3    | U       | 2Ø              |        |  |

|                                                                                                                                                                                                                                                                                                                                                                               | NZ     | А       | 23              |        |  |

|                                                                                                                                                                                                                                                                                                                                                                               | Z      | А       | 20,26           |        |  |

**NOTE:** Error messages are inserted immediately following the statement where the error occurs. All error messages (after the first error message) will contain a statement which points to the statement where the last error occurred. At the end of the source program listing, an error summary statement will be printed. The summary will contain a statement as to the total number of errors noted, along with a line reference to the previous error. It will also define all error codes listed in the source program listing.

The primary purpose of the error statement that points to the line number where the previous error occurred is to facilitate location of errors. Since some programs may be many pages in length, this feature helps the programmer locate errors quickly (as opposed to thumbing through each page of the program).

Chapter 5

# **Z80** Instruction Set Summary

## General

This chapter describes the instruction set for the Z80 microprocessor. It briefly explains the individual instructions and gives formatted examples and object codes. For a detailed description of the instruction set, refer to the manufacturer's User's Manual.

Each Z80 instruction consists of a mnemonic code and up to two operands. The descriptive symbols used in this chapter to represent items in mnemonic definitions are as follows:

| Symbol      |   | Description                                    |  |

|-------------|---|------------------------------------------------|--|

| Α           | - | Register A accumulator                         |  |

| Ā           | - | Complement of Register A                       |  |

| В           | - | Register B                                     |  |

| b           | - | Specifies one bit in the range Ø-7             |  |

| [BC]        | - | Memory location pointed to by register pair BC |  |

| С           | - | Register C                                     |  |

| СС          | - | Specifies the state of the condition flags for |  |

|             |   | certain conditional branch jump instructions   |  |

| CY          | - | Carry/borrow flag bit                          |  |

| CY          | - | Complement of carry/borrow flag bit            |  |

| D           | - | Register D                                     |  |

| d           | - | Specifies a one-byte expression in the range   |  |

|             |   | -128 to +127                                   |  |

| [DE]        | - | Memory location pointed to by register pair DE |  |

| E           | - | Register E                                     |  |

| е           | - | Specifies a one-byte expression in the range   |  |

|             |   | -126 to +129                                   |  |

| н           | - | Register H                                     |  |

| HC          | - | Half carry flag bit                            |  |

| [HL]        | - | Memory location pointed to by register pair HL |  |

| H subscript | - | High-order byte of a 16-bit word               |  |

| I           | - | Interrupt Vector Register                      |  |

| IFF         | - | Content of interrupt enable flip-flop          |  |

| IX          | - | X Index Register                               |  |

| [IX+d]               | - | Memory location pointed to by the X Index<br>Register plus d displacement |

|----------------------|---|---------------------------------------------------------------------------|

| IY                   | - | Y Index Register                                                          |

| [IY+d]               | - | Memory location pointed to by the Y Index<br>Register plus d displacement |

| L                    | - | Register L                                                                |

| L (subscript)        | - | Low-order byte of a 16-bit word                                           |

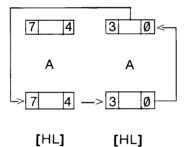

| m                    | - | Specifies any register r or memory location [HL],<br>[IX+d], or [IY+d]    |

| n                    | - | Specifies a one-byte expression in the range $\emptyset$ to 255           |

| nn                   | - | Specifies a two-byte expression in the range $\emptyset$ to 65,535        |

| PC                   | - | Program Counter Register                                                  |

| P/V                  | - | Conditional flag symbol indicating parity/overflow notation               |

| р                    | - | Page zero memory location                                                 |

| рр                   | - | Any register pair BC, DE, IX, or SP                                       |

| qq                   | - | Any register pair BC, DE, HL, or AF                                       |

| R                    | - | Memory Refresh Register                                                   |

| r                    | - | Any of the following registers: A, B, C, D, E, H, or L                    |

| rr                   | - | Any register pair BC, DE, IY, or SP                                       |

| S                    | - | Specifies any register r, value n, or memory location                     |

|                      |   | [HL], [IX+d], or [IY+d]                                                   |

| SP                   | - | Stack Pointer Register                                                    |

| SS                   | - | Any register pair BC, DE, HL, or SP                                       |

| <                    | - | Transfer into                                                             |

| <>                   | - | Exchange register content                                                 |

| •                    | - | Boolean AND                                                               |

| $\oplus$             | - | Exclusive OR                                                              |

| $\overline{\bullet}$ | - | Inclusive OR                                                              |

| +                    | - | Addition                                                                  |

| _                    | - | Subtraction                                                               |

| Ø                    | - | Condition flag is reset                                                   |

| 1                    | - | Condition flag is set                                                     |

# **Predefined Symbols**

The following symbols are reserved. They have special meaning to the assembler and cannot appear as user-defined symbols.

| Symbol | Definition                |

|--------|---------------------------|

| A      | Register A                |

| AF     | Register pair AF          |

| В      | Register B                |

| BC     | Register pair BC          |

| С      | Register C                |

| D      | Register D                |

| DE     | Register pair DE          |

| Е      | Register E                |

| Н      | Register H                |

| HL     | Register pair HL          |

| 1      | Interrupt Vector Register |

| IX     | X Register Index          |

| IY     | Y Register Index          |

| L      | Register L                |

| PC     | Program Counter Register  |

| R      | Memory Refresh Register   |

| SP     | Stack Pointer Register    |

**Z80** Instruction Set Summary

ASSEMBLER SUPPLEMENT Z80 MODEL 64000 ASSEMBLER SUPPLEMENT Z80

Add with carry to Register A

ADC A,\_ \_

| SYNTAX: |           |          |                     |

|---------|-----------|----------|---------------------|

| Label   | Operation | Operand  | Object<br>Code(hex) |

|         | ADC       | A,A      | 8F                  |

|         | ADC       | A,B      | 88                  |

|         | ADC       | A,C      | 89                  |

|         | ADC       | A,D      | 8A                  |

|         | ADC       | A,E      | 8B                  |

|         | ADC       | A,H      | 8C                  |

|         | ADC       | A,L      | 8D                  |

|         | ADC       | A,n      | CE(n)               |

|         | ADC       | A,[HL]   | 8E                  |

|         | ADC       | A,[IX+d] | DD8E(d)             |

|         | ADC       | A,[IY+d] | FD8E(d)             |

The ADC  $A_{,--}$  instruction will add the content of the designated register or memory location plus the carry flag bit (from register F) to the content of register A. The result of the operation will be stored in register A.

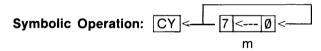

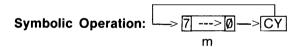

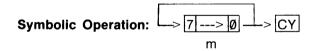

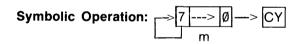

Symbolic Operation: A <--- A+s+CY

Condition codes affected: CY, N, P/V, HC, Z, and S.

Example:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | ADC       | A,A     |         |

This instruction will double the content of register A, plus the carry flag bit.

# ADC HL,\_\_

| YNTAX: |           |         |           |

|--------|-----------|---------|-----------|

|        |           |         | Object    |

| Label  | Operation | Operand | Code(hex) |

|        | ADC       | HL,BC   | ED4A      |

|        | ADC       | HL,DE   | ED5A      |

|        | ADC       | HL,HL   | ED6A      |

|        | ADC       | HL,SP   | ED7A      |

The ADC HL,  $\_\_$  instruction will add the content of the designated register pair plus the carry flag bit (from register F) to the content of register pair HL. The result of the operation will be stored in register pair HL.

Symbolic Operation: HL <--- HL+ss+CY

Condition codes affected: CY, N, P/V, HC, Z, and S.

Example:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | ADC       | HL,DE   |         |

This instruction will add the content of register pair DE to the content of register pair HL, plus the carry flag bit.

Add to Register A

ADD A,\_ \_!

## SYNTAX:

| Label | Operation | Operand  | Object<br>Code (hex) |

|-------|-----------|----------|----------------------|

|       | •         | •        | · · ·                |

|       | ADD       | A,A      | 87                   |

|       | ADD       | A,B      | 8Ø                   |

|       | ADD       | A,C      | 81                   |

|       | ADD       | A,D      | 82                   |

|       | ADD       | A,E      | 83                   |

|       | ADD       | A,H      | 84                   |

|       | ADD       | A,L      | 85                   |

|       | ADD       | A,n      | <b>C6</b> (n)        |

|       | ADD       | A,[HL]   | 86                   |

|       | ADD       | A,[IX+d] | DD86(d)              |

|       | ADD       | A,[IY+d] | FD86(d)              |

The ADD  $A_{,-}$  instruction will add the content of the designated register or memory location to the content of register A. The result of the operation will be stored in register A.

Symbolic Operation: A <--- A+s

Condition codes affected: CY, N, P/V, HC, Z, and S.

Example:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | ADD       | A,[HL]  |         |

This instruction will add the content of memory location addressed by register pair HL to the content of register A.

# ADD HL,\_\_I

# Add Register Pair to Register Pair HL

| Operation | Operand           | Object<br>Code (hex)                |

|-----------|-------------------|-------------------------------------|

| ADD       | HL,BC             | Ø9                                  |

| ADD       | HL,DE             | 19                                  |

| ADD       | HL,HL             | 29                                  |

| ADD       | HL,SP             | 39                                  |

|           | ADD<br>ADD<br>ADD | ADD HL,BC<br>ADD HL,DE<br>ADD HL,HL |

The ADD HL,\_\_ instruction will add the content of the designated register pair to the content of register pair HL. The result of the operation will be stored in register pair HL.

Symbolic Operation: HL <--- HL+ss

Condition codes affected: CY, N, and HC.

Example:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | ADD       | HL,DE   |         |

This instruction will add the content of register pair DE to the content of register pair HL.

MODEL 64000 ASSEMBLER SUPPLEMENT

Add Register Pair to Index Register IX

ADD IX,\_\_

| SYNTAX: |           |         |                      |

|---------|-----------|---------|----------------------|

| Label   | Operation | Operand | Object<br>Code (hex) |

|         | ADD       | IX,BC   | DDØ9                 |

|         | ADD       | IX,DE   | DD19                 |

|         | ADD       | IX,IX   | DD29                 |

|         | ADD       | IX,SP   | DD39                 |

|         |           |         |                      |

The ADD  $IX_{--}$  instruction will add the content of the designated register pair to the content of index register IX. The result of the operation will be stored in index register IX.

Symbolic Operation: IX <--- IX+pp

Condition codes affected: CY, N, and HC.

Example:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | ADD       | IX,IX   |         |

This instruction will double the value of the content of index register IX.

# ∎ADD IY,\_ \_I

| Add | Register | Pair | to | Index | Register | IY |  |

|-----|----------|------|----|-------|----------|----|--|

|     |          |      |    |       |          |    |  |

| SYNTAX: |           |         |            |

|---------|-----------|---------|------------|

|         |           |         | Object     |

| Label   | Operation | Operand | Code (hex) |

|         | ADD       | IY,BC   | FDØ9       |

|         | ADD       | IY,DE   | FD19       |

|         | ADD       | IY,IY   | FD29       |

|         | ADD       | IY,SP   | FD39       |

The ADD IY,\_\_ instruction will add the content of the designated register pair to the content of index register IY. The result of the operation will be stored in index register IY.

Symbolic Operation: IY <--- IY+rr

Condition codes affected: CY, N, and HC.

Example:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | ADD       | IY,BC   |         |

This instruction will add the content of register pair BC to the content of index register IY.

AND s

Logical 'AND' with Register A

## SYNTAX:

| Label | Operation | Operand | Object<br>Code (hex)   |

|-------|-----------|---------|------------------------|

|       |           | oporana | ,                      |

|       | AND       | A       | A7                     |

|       | AND       | В       | AØ                     |

|       | AND       | С       | A1                     |

|       | AND       | D       | A2                     |

|       | AND       | E       | A3                     |

|       | AND       | Н       | A4                     |

|       | AND       | L       | A5                     |

|       | AND       | n       | <b>E6</b> ( <b>n</b> ) |

|       | AND       | [HL]    | A6                     |

|       | AND       | [IX+d]  | DDA6(d)                |

|       | AND       | [IY+d]  | FDA6(d)                |

|       |           |         |                        |

A logical 'AND' operation will be performed between the byte specified by the operand field and the byte contained in register A. The result of the operation will be stored in register A.

Symbolic Operation: A <--- A • s

Condition codes affected: CY, N, P/V, HC, Z, and S.

Example:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | AND       | [HL]    |         |

This instruction performs a logical 'AND' operation using the content of memory location addressed by register pair HL and the content of register A.

# BIT b,\_ \_

Test Bit b

SYNTAX:

|     |                  | <b>.</b>  | <b>.</b>           |     | Object             |

|-----|------------------|-----------|--------------------|-----|--------------------|

|     | Label            | Operation | Operand            |     | Code (hex)         |

|     |                  | BIT       | b,reg o            | r   | (see below)        |

|     |                  |           | [addr]             |     |                    |

| bit | Ø,A=CB47         | bit       | 3,A=CB5F           | bit | 6,A=CB77           |

|     | Ø,B=CB4Ø         |           | 3,B=CB58           |     | 6,B=CB7Ø           |

|     | Ø,C=CB41         |           | 3,C=CB59           |     | 6,C=CB71           |

|     | Ø,D=CB42         |           | 3,D=CB5A           |     | 6,D=CB72           |

|     | Ø,E=CB43         |           | 3,E=CB5B           |     | 6,E=CB73           |

|     | Ø,H=CB44         |           | 3,H=CB5C           |     | 6,H=CB74           |

|     | Ø,L=CB45         |           | 3,L=CB5D           |     | 6,L=CB75           |

|     | Ø,[HL]=CB46      |           | 3,[HL]=CB5E        |     | 6,[HL]=CB76        |

|     | Ø,[IX+d]=DDCB(d) | )46       | 3,[IY+d]=DDCB(d)5E |     | 6,[IX+d]=DDCB(d)76 |

|     | Ø,[IY+d]=FDCB(d) | 46        | 3,[IY+d]=FDCB(d)5E |     | 6,[IY+d]=FDCB(d)76 |

|     | 1,A=CB4F         |           | 4,A=CB67           |     | 7,A=CB7F           |

|     | 1,B=CB48         |           | 4,B=CB6Ø           |     | 7,B=CB78           |

|     | 1,C=CB49         |           | 4,C=CB61           |     | 7,C=CB79           |

|     | 1,D=CB4A         |           | 4,D=CB62           |     | 7,D=CB7A           |

|     | 1,E=CB4B         |           | 4,E=CB63           |     | 7,E=CB7B           |

|     | 1,E=CB4C         |           | 4,H=CB64           |     | 7,H=CB7C           |

|     | 1,L=CB4D         |           | 4,L=CB65           |     | 7,L=CB7D           |

|     | 1,[HL]=CB4E      |           | 4,[HL]=CB66        |     | 7,[HL]=CB7E        |

|     | 1,[IX+d]=DDCB(d) | 4E        | 4,[IX+d]=DDCB(d)66 |     | 7,[IX+d]=DDCB(d)7E |

|     | 1,[IY+d]=FDCB(d) | 4E        | 4,[IY+d]=FDCB(d)66 |     | 7,[IY+d]=FDCB(d)7E |

MODEL 64000 ASSEMBLER SUPPLEMENT Z80

| 2,A=CB57           | 5,A=CB6F           |

|--------------------|--------------------|

| 2,B=CB5Ø           | 5,B=CB68           |

| 2,C=CB51           | 5,C=CB69           |

| 2,D=CB52           | 5,D=CB6A           |

| 2,E=CB53           | 5,E=CB6B           |

| 2,H=CB54           | 5,H=CB6C           |

| 2,L=CB55           | 5,L=CB6D           |

| 2,[HL]=CB56        | 5,[HL]=CB6E        |

| 2,[IX+d]=DDCB(d)56 | 5,[IX+d]=DDCB(d)6E |

| 2,[IY+d]=FDCB(d)56 | 5,[IY+d:=FDCB(d)6E |

|                    |                    |

### NOTE

BI

n

(Cont'd)

The expression (d) in the object codes listed above is the register offset assigned by the user. The hexadecimal value of the offset will be a one-byte expression in the range of -128 to +127.

The BIT  $b_{,-}$  instruction will test a specific bit (b) in the designated register or memory location and then adjust the zero (Z) flag accordingly.

Symbolic Operation: Z <--- s<sub>h</sub>

Condition Codes affected: N, HC, and Z.

Example:

| Label | Operation | Operand            | Comment |

|-------|-----------|--------------------|---------|

|       | BIT       | 4, <b>[</b> IX+3H] |         |

Assume the content of index register IX is  $\emptyset$ 5FAH. The instruction will check bit 4 of memory location  $\emptyset$ 5FDH and if the bit is set (1), the zero (Z) flag in register F will be reset (Z= $\emptyset$ ).

# CALL cc,nn

#### **Conditional Call of Subroutine**

|        |                   |         | Object                  |

|--------|-------------------|---------|-------------------------|

| Label  | Operation         | Operand | Code (hex)              |

|        | CALL              | C,nn    | DC(nn)                  |

|        | CALL              | M,nn    | FC(nn)                  |

|        | CALL              | NC,nn   | D4(nn)                  |

|        | CALL              | NZ,nn   | <b>C4</b> ( <b>nn</b> ) |

|        | CALL              | P,nn    | <b>F4</b> ( <b>nn</b> ) |

|        | CALL              | PE,nn   | EC(nn)                  |

|        | CALL              | PO,nn   | <b>E4</b> ( <b>nn</b> ) |

|        | CALL              | Z,nn    | CC(nn)                  |

| where: | C = carry         |         |                         |

|        | M = sign negative |         |                         |

|        | NC = non carry    |         |                         |

|        | NZ = non zero     |         |                         |

|        | P = sign positive |         |                         |

|        | PE = parity even  |         |                         |

|        | PO = parity odd   |         |                         |

|        | Z = zero          |         |                         |

The CALL cc,nn instruction will cause the condition flags in register F to be tested for the condition designated by the cc section of the operand. If the condition is true, the microprocessor will push the current content of the program counter (PC) onto the stack. It will then load the nn section of the operand into the program counter to point to the address in memory that contains the first opcode of a subroutine.

If condition cc is false, program execution will continue with the next instruction.

#### Condition codes affected: none.

#### Example:

| Labei | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | CALL      | C,Ø5FAH |         |

If the carry flag in register F is set (1), this instruction will call the subroutine located at memory address Ø5FAH.

| MODEL 64000<br>ASSEMBLER SUPPLEMENT<br>Z80 |           |         | CALL nn                      |

|--------------------------------------------|-----------|---------|------------------------------|

|                                            |           | Unco    | nditional Call of Subroutine |

| SYNTAX:                                    |           |         |                              |

| Label                                      | Operation | Operand | Object<br>Code (hex)         |

|                                            | CALL      | nn      | CD(nn)                       |

The CALL nn instruction will push the current content of the program counter (PC) onto the stack. It will then load operand nn into the program counter, pointing to the memory address that contains the first opcode of a subroutine.

**Symbolic Operation:** [SP-1] <--- PC<sub>H</sub> [SP-2] <--- PC<sub>L</sub> PC <---nn

Condition codes affected: none.

Example:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | CALL      | Ø5FAH   |         |

This instruction will perform an unconditional branch to memory location Ø5FAH by loading the operand address into the program counter.

|                    |           |         | MODEL 6400<br>ASSEMBLER SUPPLEMEN<br>Z8 |

|--------------------|-----------|---------|-----------------------------------------|

| Complement Carry F | lag       |         |                                         |

| SYNTAX:            |           |         |                                         |

| Label              | Operation | Operand | Object<br>Code (hex)                    |

|                    | CCF       |         | 3F                                      |

The CCF instruction will invert the carry (CY) flag in register F.

Symbolic Operation: CY <---  $\overline{CY}$

Condition codes affected: CY and N.

Compare with Register A

СР

### SYNTAX:

|       |           |         | Object     |

|-------|-----------|---------|------------|

| Label | Operation | Operand | Code (hex) |

|       | CP        | А       | BF         |

|       | CP        | В       | B8         |

|       | CP        | С       | B9         |

|       | CP        | D       | BA         |

|       | CP        | E       | BB         |

|       | CP        | Н       | BC         |

|       | CP        | L       | BD         |

|       | СР        | n       | FE(n)      |

|       | СР        | [HL]    | BE         |

|       | СР        | [IX+d]  | DDBE(d)    |

|       | СР        | [IY+d]  | FDBE(d)    |

The CP  $\_$  \_ instruction will compare the content of the designated register or memory location with the content of register A. If the comparison is true, the zero (Z) flag will be set. The content of register A will not be affected by this operation.

#### Symbolic Operation: A-s

Condition codes affected: CY, N, P/V, HC, Z, and S.

#### Example:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | СР        | D       |         |

This instruction will compare the content of register D with the content of register A. The condition flags are set or reset according to the result of the operation.

| PD <b>man</b> |                          |         | MODE<br>ASSEMBLER SUPPL |

|---------------|--------------------------|---------|-------------------------|

| are Memory L  | ocation [- HL] with Regi | ister A |                         |

| SYNTAX:       |                          |         |                         |

| Label         | Operation                | Operand | Object<br>Code (hex)    |

|               |                          |         |                         |

The CPD instruction will compare the content of memory location addressed by the HL register pair with the content of register A. If the comparison is true, the zero (Z) condition flag will be set. The HL and BC register pairs will then be decremented.

The contents of memory location [HL] and register A will not be affected by this operation.

Symbolic Operation: A - [HL]; HL <---HL-1, BC <---BC-1

| MODEL 64000<br>ASSEMBLER SUPPLEME<br>280 | NT        |                        | CPD                      |

|------------------------------------------|-----------|------------------------|--------------------------|

|                                          | Com       | pare Memory Block (dec | cremented) with Register |

| SYNTAX:                                  |           |                        |                          |

|                                          |           |                        |                          |

| Label                                    | Operation | Operand                | Object<br>Code (hex)     |

The CPDR instruction will compare the content of memory location addressed by the HL register pair with the content of register A. If the comparison is true, the zero (Z) condition flag will be set. The HL and BC register pairs will then be decremented. If register A = [HL], the instruction will be terminated. If the BC register pair is not zero and if register A  $\neq$  [HL], the program counter will be decremented by 2 and the instruction will repeat itself.

#### NOTE

If the BC register pair is zeroed prior to executing the CPDR instruction, the microprocessor will loop through 64K bytes if no true comparison is found.

Symbolic Operation: A - [HL]; HI <--- HL-1, BC <--- BC-1; Repeat until A=[HL] or BC=Ø

| ;PI             |                         |         | ASSEMBLER SUPPLEMEN<br>Za |