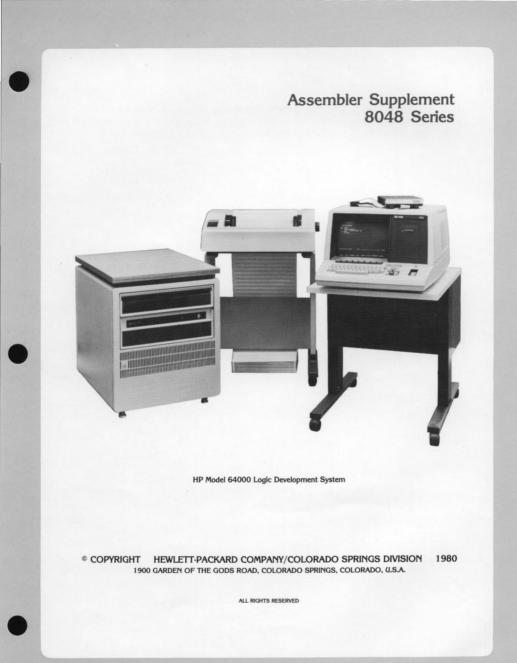

## 64000 EF LOGIC DEVELOPMENT SYSTEM

## ASSEMBLER SUPPLEMENT 8048 SERIES

#### CERTIFICATION

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### WARRANTY

This Hewlett-Packard system product is warranted against defects in materials and workmanship for a period of 90 days from date of installation. During the warranty period, HP will, at its options, either repair or replace products which prove to be defective.

Warranty service of this product will be performed at Buyer's facility at no charge within HP service travel areas. Outside HP service travel areas, warranty service will be performed at Buyer's facility only upon HP's prior agreement and Buyer shall pay HP's round trip travel expenses. In all other cases, products must be returned to a service facility designated by HP.

For products returned to HP for warranty service. Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country.

HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instructions when properly installed on that instrument. HP does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HP SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### ASSISTANCE

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office.

CW&A 9/79

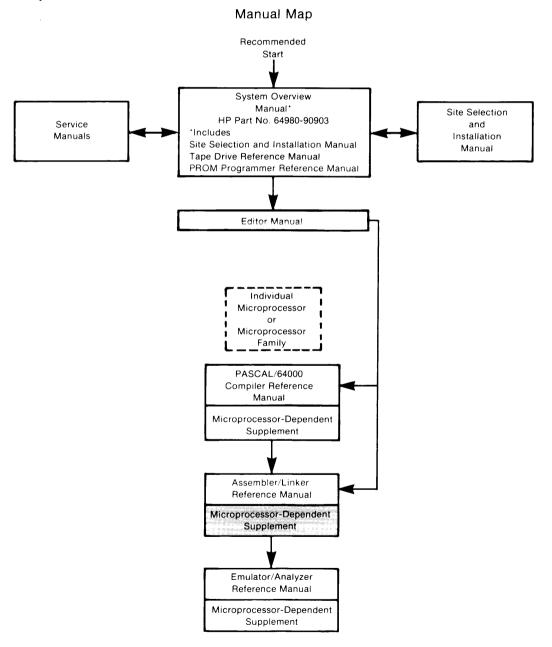

### Model 64000 Reference Manuals

The following block diagram shows the documentation scheme for the HP Model 64000 Logic Development System. The interconnecting arrows show the recommended progression through the manuals as a way of gaining familiarity with the system.

For a detailed map showing specific manuals and their part numbers, refer to the Manual Map in the System Overview Manual.

## **Printing History**

Each new edition of this manual incorporates all material updated since the previous edition. Each new or revised page is indicated by a revision (rev) date. Manual change sheets are issued between editions, allowing you to correct or insert information in the current edition.

The part number on the back cover changes only when each new edition is published. Minor corrections or additions may be made as the manual is reprinted between editions.

First Printing ...... April 1980 (Part Number 64846-90902) Reprinted ..... November 1980

The information in this supplement has been checked for accuracy and is believed to be correct; however, no responsibility is assumed for inaccuracies. When discrepancies are noted, refer to the manufacturer's Microprocessor Program Manual for clarification.

## **Table of Contents**

#### Chapter 1. General Information

| Introduction                             |

|------------------------------------------|

| Microprocessor Architecture1-2           |

| Program Memory                           |

| Data Memory1-2                           |

| Program Counter and Stack1-3             |

| Program Status Word1-4                   |

| Functional Description                   |

| General                                  |

| Memory Differences                       |

| Interrupt Differences                    |

| Hardware Differences                     |

| Chapter 2. Operand Rules and Conventions |

| General Information                      |

| Identifying Types of Information2-2      |

| Invalid Operand Instructions2-5          |

| Chapter 3. Special Pseudo Instructions   |

####

#### Chapter 4. Assembler Output Listing

| General                      | -1 |

|------------------------------|----|

| nput/Output Files            |    |

| Source Input File            |    |

| Assembler Output Files       | -2 |

| List File                    | -2 |

| Symbol Cross-Reference List4 | ·2 |

| Output Listing               | -2 |

#### Chapter 5. Instruction Set Summary

| General            | 5-1 |

|--------------------|-----|

| Predefined Symbols | 5-3 |

## List of Tables

| 4-1. | Source Program Format Example        | 1-3 |

|------|--------------------------------------|-----|

| 4-2. | Assembler Output Listing             | 1-4 |

| 4-3. | Assembler Output Listing with Errors | 1-6 |

.

## Chapter 1

## General Information (8048 Series)

### Introduction

This chapter contains general information about the 8048 series of microprocessors/microcomputers and briefly discusses their architecture, addressing modes, and condition codes. For a detailed description of a particular device, refer to the manufacturer's User's Manual.

#### NOTE

The term "microprocessor" will be used in this manual for both microcomputers and microprocessors.

#### NOTE

If you are unfamiliar with assembly language or assemblers, read Chapter 6 in the Assembler/Linker manual for a brief review of assemblers, assembly language, and numbering systems.

#### NOTE

The following discussion on "Microprocessor Architecture" applies primarily to the 8048/8021 microprocessors. Differences between the 8048, 8041, and 8021 will be noted. Otherwise, the descriptions apply to all 8048-series devices. The 8041 differs somewhat from the 8048 in hardware and software design due to its external bus configuration. Therefore, a functional description of the 8041 microprocessor and how it differs from the 8048 is presented at the end of this chapter. (Any reference to the 8041 also applies to the 8741.)

Use the following assembler directives to specify the 8048series devices.

"8048" = 8048, 8049, 8748, 8749. "8021" = 8021, 8022, 8035, 8039. "8041" = 8041, 8042, 8741.

### **Microprocessor Architecture**

#### **Program Memory**

Resident program memory in the 8048 microprocessor consists of a 1K by 8-bit ROM (2K by 8-bit in 8049) which is divided into 256-byte pages. Program memory can be expanded up to 4K using additional ROMs (not applicable to the 8021). This additional memory can be addressed directly since the 8048 contains a 12-bit program counter. Bits Ø-1Ø of the program counter address up to 2K memory locations. Bit 11, when set by mnemonic instruction SEL MB1, permits addressing to 4K memory locations.

#### NOTE

The 8035 and 8039 do not have internal program memories. Otherwise, they are identical to the 8048 and 8049 respectively.

There are three reserved locations in program memory:

- Location Ø- Initializing the Reset function of the microprocessor causes the first instruction to be brought from location Ø. Therefore, the first instruction to be executed after initialization should be stored in location Ø.

- Location 3- Initializing the Interrupt function of the microprocessor (if enabled) causes a jump to location 3. Therefore, the first word of an external interrupt service subroutine should be stored in location 3.

- Location 7 An interrupt resulting from a timer/counter overflow (if enabled) causes a jump to location 7. Therefore, the first word of a timer/counter service routine should be stored in location 7.

#### **Data Memory**

The 8048, in addition to resident program memory, contains a 64 by 8-bit RAM data memory (128 by 8-bit in 8049). The memory is made up of eight working registers plus an additional eight registers selectable by register bank switch instruction SEL RB (not applicable to the 8021), an eight-level program counter stack, and a scratch-pad area. The amount of scratch-pad memory available will depend on the number of addresses in the stack and the number of working registers selected.

The working registers are assigned to data memory locations Ø-7. The additional working registers, when selected, are assigned to data memory locations 24-31 (not applicable to the 8021). Working registers in RAM memory can be addressed directly by specifying a register number. Other locations in RAM memory are addressed indirectly by using data memory registers RØ and R1 to specify the location desired. The symbol "@" (commercial at) indicates the indirect addressing mode of operation.

Since all 64 locations can be addressed by 6 bits ( $\emptyset$ -5), the most significant bits (6 and 7) of the addressing registers (R $\emptyset$  and R1) are ignored on the 8048 (not applicable to the 8049). However, all 8 bits of register R $\emptyset$  and register R1 can be used in combination with the MOVX instructions (not applicable to the 8021) to indirectly address up to 256 locations when external data memory is used.

#### **Program Counter and Stack**

The program counter is an independent counter and is not directly accessible. It is initialized to zero by activating the Reset function.

The program counter stack is implemented using pairs of registers in the data memory area. Locations 8-23 are used to provide an 8-level stack. When program execution branches to a subroutine or an interrupt service routine, the 12-bit program counter and bits 4-7 of the program status word (PSW) are stored in two stack locations.

The program counter stack is addressed by stack pointer (STP) bits  $\emptyset$ -2 in the program status word. The setting of the STP bits indicates the location to be loaded the next time the program counter is stored. The STP is incremented each time the program counter is stored and decremented each time the program counter is restored. Unused locations in the stack may be used as a scratch pad area.

#### Program Status Word

The program status word (PSW) contains 8 bits of status information used by the microprocessor. The PSW bit definitions are as follows:

| Bits Ø-2 | - | Stack Pointer address location                                                                                             |  |

|----------|---|----------------------------------------------------------------------------------------------------------------------------|--|

| Bit 3    | - | Not used                                                                                                                   |  |

| Bit 4    | - | Working register bank switch:<br>bank $\emptyset$ (RØ-R7) = bit 4 reset ( $\emptyset$ )<br>bank 1 (R24-31) = bit 4 set (1) |  |

| Bit 5    | - | Flag Ø (user controlled)                                                                                                   |  |

| Bit 6    | - | Auxiliary Carry (AC) bit                                                                                                   |  |

| Bit 7    | - | Carry (C) bit                                                                                                              |  |

The carry flag (C) bit is affected by addition, decimal adjust instructions, and certain rotation operations and generally indicates a carry out of the bit 7 position of register A (accumulator). It can be complemented, reset to zero, and tested by a conditional jump instruction.

The auxiliary carry (AC) bit indicates a carry out of bit 3 in register A and is only applicable when decimal arithmetic is being performed. It cannot be tested or altered directly.

## **Functional Description**

#### General

The main difference between the 8048 and the 8041 is that the 8041 includes handshaking capabilities and interface protocols that enable it to function as a programmable peripheral in a large microcomputing system.

#### **Memory Differences**

In a large microcomputer system, handshaking protocol requires the 8041 to use the BUS port for interfacing with the master computer. Therefore, the 8041 program memory cannot be expanded beyond 1K and data memory cannot be expanded beyond 64 locations.

#### **Interrupt Differences**

The external interrupt function of the 8041 is also committed to a master computer interface and the EN I and DIS I instructions have a different function.

When the master computer is transferring data to the 8041, it can generate an interrupt each time the 8041's data bus buffer is filled to ensure that two writes are not given before the buffer is cleared. The EN I and DIS I instructions enable and disable this interrupt. When initiated, the interrupt passes control to program memory location 3 as in the 8048.

The master computer must check special status bits to determine if the data bus buffer is empty when data is being transferred from the 8041 to it. No interrupt is possible except by dedicating I/O lines.

Pin 1 (TØ) cannot be used as a clock output in the 8041. It can only be used as a test input.

#### Hardware Differences

The 8041 has two special registers that are not available in the 8048. These registers are the data bus buffer (DBB) and the status register. A description of each follows:

- a. Data Bus Buffer: the 8-bit data bus buffer provides a temporary storage facility for data passing between the master computer and the 8041. This transfer of data can be implemented with or without program interference by using the EN I and DIS I instructions.

- b. **Status Register:** this is a 4-bit register that indicates the status of the flags FØ, F1, and two special 8041 flags. The two special flags, input buffer flag (IBF) and output buffer flag (OBF), indicate the condition of the data bus buffer and are initially cleared. The two special flags are used when transferring data to or from the master computer.

ASSEMBLER SUPPLEMENT 8048 Series

# Chapter 2

## **Operand Rules and Conventions**

## **General Information**

There are three types of data that may be needed as items in the operand field:

a. Register Information - operands can reference directly data contained in the processor registers such as the stack, register A, or data memory registers RØ, R1, R2, R3, R4, R5, R6, and R7. In addition, operands can reference data contained on input/output ports.

#### Example:

MOV A,RØ

;MOVE CONTENTS OF ;REGISTER Ø TO ;REGISTER A

b. **Immediate Data** - operands can contain immediate data. The required value is inserted directly into the operand field. The value can be in the form of numbers, an expression to be evaluated at assembly time, a symbol, or an ASCII constant enclosed in quotation marks. The immediate data indicator is the pound (#) symbol.

#### Examples:

| MOV | R1,#ØFFH | ;MOVE "FF" HEX TO<br>;REGISTER R1                                   |

|-----|----------|---------------------------------------------------------------------|

| MOV | R4#"A"   | ;MOVE VALUE OF ASCII<br>;CONSTANT A (Ø1ØØØØØ1)<br>;INTO REGISTER R4 |

c. **Memory Addressing** - working registers can be addressed directly in data memory by specifying a register number. Other locations in data memory can be addressed indirectly by using either register RØ or register R1 to specify the addressed location. Because all 64 locations in data memory (including registers RØ through R7) can be addressed by six bits; bits seven and eight are ignored. However, all eight bits are used by registers RØ and R1 during certain microprocessor instructions which require up to 256 locations in external data memory.

| NOTE |

|------|

|------|

The "commercial at" (@) symbol indicates that indirect addressing is desired.

#### Examples:

| MOV | A,@R1   |

|-----|---------|

| MOV | R4,#ØFH |

## **Identifying Types Of Information**

There are nine ways to define the types of information that can be presented in the operand field. These ways are discussed in the following paragraphs.

a. Binary Data. Each binary number must be followed by the letter B.

Example:

SAM MOV R3,#10010011B

b. Octal Data. Each octal number must be followed by either the letter O or the letter Q.

Example:

| SAM | MOV | R3,#55O |

|-----|-----|---------|

|     | or  |         |

| SAM | MOV | R3,#55Q |

c. **Hexadecimal Data.** Each hexadecimal number must begin with a number and be followed by the letter H.

#### Example:

- SAM MOV R3,#ØF1H

- d. **Decimal Data.** Each decimal number may be followed by the letter D or it may stand alone. Any number not specifically identified as binary, octal, or hexadecimal is assumed to be decimal.

| Example: |     |     |         |

|----------|-----|-----|---------|

|          | SAM | MOV | R3,#55D |

|          |     | or  |         |

|          | SAM | MOV | R3,#55  |

e. **ASCII Constants.** One or more ASCII characters enclosed in quotation marks identify an ASCII constant.

#### Example:

|     | MOV | R3,#'T'   | ;LOADS REG R3 WITH<br>;8-BIT ASCII CODE<br>;FOR LETTER T |

|-----|-----|-----------|----------------------------------------------------------|

| SAM | DB  | "FULTON'S | FOLLY"                                                   |

f. Location Counter. The dollar symbol (\$) refers to the current location counter. The location counter contains the address where the current instruction or data statement is being assembled.

#### Example:

| JUMP | JMP | \$+3 | ;JUMP TO ADDRESS<br>;3 BYTES BEYOND |

|------|-----|------|-------------------------------------|

|      |     |      | ;FIRST BYTE OF THIS<br>;INSTRUCTION |

g. Label Assigned Values. The EQU directives can be used to assign values to labels. Example:

SAM EQU 6AH

h. Labels of Instruction or Data. The label assigned to an instruction or a data definition has as its value the address of the first byte of the instruction or data. Instructions elsewhere in the program can refer to this address by its symbolic name.

#### Example:

| SAM  | JMP | FRED    | ;JUMP TO INSTRUC-<br>;TION AT FRED |

|------|-----|---------|------------------------------------|

|      |     |         |                                    |

|      | •   |         |                                    |

|      |     |         |                                    |

|      | •   |         |                                    |

|      |     |         |                                    |

| FRED | MOV | RØ,#6AH |                                    |

Expressions. The operand field may contain an expression consisting of one or more terms acted on by the expression operators listed in Chapter 2 of the Assembler/Linker Manual. A term may be either a symbol, a string constant, a numeric constant, or an expression. The assembler reduces the entire expression to a single value.

Terms within expressions can be connected by the following arithmetic operators:

- a. The plus operator (+) produces the arithmetic sum of its operands.

- b. The minus operator (-) produces the arithmetic difference of its operands or, when used alone, the arithmetic negative of its operand.

- c. The asterisk operator (\*) produces the arithmetic product of the operands.

- d. The slant operator (/) produces the quotient of its operands and discards any remainder.

- e. An instruction enclosed in parentheses is a legal expression in the operand field. For expressions in parentheses, the deepest expression in the parentheses is evaluated first.

Be careful when using the arithmetic operators because their operational results may affect the condition flags of the processor registers.

## **Byte Selection Operator**

The assembler's relocation characteristic treats all external and relocatable symbols as 16-bit addresses. When one of these symbols appears in the operand expression of an immediate instruction, it must be followed by the high operator (H) if the high-order byte is required. The default condition is the low-byte value. For example, if the symbol SAM has a value of 1FDBH, then the operand expression SAM would default to the low-order byte ØDBH. The operand expression SAM,H will select the high-order byte 1FH.

#### NOTE

Since the low-order byte is assumed in all cases not specified as high-order bytes, no error messages will be generated if an address or number is too large.

## **Invalid Operand Instructions**

There are certain operand field instructions that are not recognized by the Model 64000 macroassembler and should be avoided. A list of the invalid instructions are as follows:

a. Shift Operators:

| SHL | - | shift ( | operand | left  |

|-----|---|---------|---------|-------|

| SHR | - | shift o | operand | right |

b. Logical Operators:

| NOT | - | logical 1's complement |

|-----|---|------------------------|

| AND | - | logical AND            |

| OR  | - | logical OR             |

| XOR | - | logical EXCLUSIVE OR   |

c. Compare Operators:

| EQ  | - | equal                          |

|-----|---|--------------------------------|

| NE  | - | not equal                      |

| LT  | - | less than                      |

| LE  | - | less than or equal             |

| GT  | - | greater than                   |

| GE  | - | greater than or equal          |

| NUL | - | test for null macro parameters |

ASSEMBLER SUPPLEMENT 8048 Series

1

# Chapter **3**

## **Special Pseudo Instructions**

## Introduction

This chapter provides supplemental information to Chapter 3 in the HP Model 64000 Assembler/Linker Manual. Assembler instructions that are applicable only to the 8048 series of microprocessors are defined herein.

|          | MODEL  | 64000  |

|----------|--------|--------|

| SSEMBLER | SUPPLE | MENT   |

|          | 8048   | Series |

Δ

#### **Define Byte**

DB

| SYNTAX: |           |                    |            |

|---------|-----------|--------------------|------------|

| ••••••  |           |                    | Object     |

| Label   | Operation | Operand            | Code (hex) |

| [Name]  | DB        | expression<br>list |            |

Applicable to: 8048, 8041, and 8021 microprocessors.

The DB pseudo instruction will store data in consecutive memory locations starting with the current setting of the program counter. The operand field may contain expressions or text strings or both.

Expressions will evaluate to one-byte numbers (8 bits) in the range Ø through 255 (ØØH through ØFFH).

#### NOTE

If the first hex number in an expression is an alpha character, it must be preceded by a zero.

The label name is optional. If a label name is present, it will be assigned the starting value of the program counter, and will reference the first byte stored by the DB directive. Therefore, the label SAM, in the following example, refers to the letter P in the string "PRICE".

#### Example:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

| SAM   | DB        | "PRICE" |         |

| MODEL 64000<br>ASSEMBLER SUPPLEME<br>8048 Series | NT        |            | DŜI                  |

|--------------------------------------------------|-----------|------------|----------------------|

|                                                  |           |            | Define Storage Block |

| SYNTAX:                                          |           |            |                      |

| Label                                            | Operation | Operand    | Object<br>Code (hex) |

| [Name]                                           | DS        | expression |                      |

|                                                  |           |            |                      |

Applicable to: 8048, 8041, and 8021 microprocessors.

The DS pseudo instruction can be used to define a block of memory space. The value of the expression in the operand field specifies the number of bytes to be reserved in memory.

Any symbol appearing in the operand field must be predefined. If the value of the operand expression is zero, no memory will be reserved; however, if the optional label name is present, it will be assigned the current value of the program counter.

The DS directive reserves memory by incrementing the program counter by the value in the operand expression.

#### Example:

| Label | Operation | Operand | Comment                       |

|-------|-----------|---------|-------------------------------|

| SAM   | DS        | 15      | ;RESERVE 15<br>;BYTES FOR SAM |

;ROUTINE

|          | MODEL 64000 |

|----------|-------------|

| SSEMBLER | SUPPLEMENT  |

|          | 8048 Series |

Comment

#### **Define Word**

DW

| SYNTAX: |           |            |            |

|---------|-----------|------------|------------|

|         |           |            | Object     |

| Label   | Operation | Operand    | Code (hex) |

| [Name]  | DW        | expression |            |

|         |           | list       |            |

Applicable to: 8048, 8041, and 8021 microprocessors.

The DW pseudo instruction will store each 16-bit value from the expression list as an address. The values will be stored in memory starting at the current setting of the program counter.

The most significant eight bits of the first value in the expression list will be stored at the current setting of the program counter; the least significant eight bits will be stored at the next higher location. This process will be repeated for each item in the expression list.

Expressions evaluate to one-word numbers (16 bits), typically addresses. If an expression evaluates to a single byte, it is assumed to be the low-order byte of a 16-bit word where the high-order byte is all zeros. Strings are limited to one or two characters.

If the label name is present, it will be assigned the starting address of the program counter, and thus reference the first byte stored by the DW directive.

Example:

| Label | Operation | Operand |

|-------|-----------|---------|

| SAM   | DW        | ØB123H  |

## **Assembler Output Listing**

### General

The assembler processes the source program modules and produces an output that consists of a source program listing, a relocatable object file, and a symbol cross-reference list. Errors detected by the assembler will be noted in the output listing as error messages. Refer to Appendix D in the Assembler/Linker Manual for a listing of all error codes and their definitions.

## Input/Output Files

#### **Source Input File**

The input to the assembler is a source file that is created through the editor. It consists of the following:

| Example     | Description                                                             |

|-------------|-------------------------------------------------------------------------|

| "8048"      | - Assembler directive.                                                  |

| Source Code | - Source statements consisting of:                                      |

|             | Assembler Psuedos - refer to<br>Chapter 3 (Assembler/<br>Linker Manual) |

|             | Assembler Instructions - refer                                          |

|             | to Chapter 5, this                                                      |

|             | Supplement                                                              |

|             |                                                                         |

#### **Assembler Output Files**

The assembler produces relocatable object modules that are stored under the same name as the source file but in a format that can be processed by the linker. If an object file does not exist at assembly time, the assembler creates one. If an object file does exist, the assembler replaces it.

**List File.** The list file is a formatted file designed for output to a line printer. It can also be stored in a file or applied to the display. The list can include:

- a. Source statements with object code.

- b. Error messages.

- c. Summary of errors with a description list.

- d. Symbol cross-reference list.

**Symbol Cross-Reference List.** All symbols are cross-referenced except local macro labels and parameters. A cross-reference listing contains:

- a. Alphabetical list of program symbols.

- b. Line numbers where symbols are defined.

- c. All references (by line numbers) to symbols in the program.

### **Output Listing**

An example of an assembler output listing is given in table 4-2 using the source program example listed in table 4-1. To illustrate an assembler output listing that contains error messages refer to table 4-3.

#### NOTE

The source program example was not written as a specific program. It merely lists a group of mnemonics to present a formatted example.

| "8048" LIST XR | EF                       |                             |   |

|----------------|--------------------------|-----------------------------|---|

|                | EXT<br>ORG<br>STRT       | DSPL4,KYBD4<br>ØBØØH<br>CNT |   |

|                | SPHL<br>SEL<br>SEL<br>EN | MBØ<br>RBØ                  |   |

|                | EN                       | TCNTI                       |   |

| EXEC           | MOV<br>MØV               | А,#ØFFH<br>RØ,#ØØH          | 1 |

|                | MOV<br>MOV               | R1,#1ØH<br>T,A<br>          |   |

| LOOP_A         | STRT<br>IN<br>JZ         | T<br>A,P1<br>EXIT_A         | : |

|                | MOV                      | @RØ,A<br>RØ                 |   |

|                | DJNZ                     | R1,LOOP_A                   |   |

| EXIT_A         | MOV<br>MOV<br>JFØ        | A,R2<br>PSW,A<br>DSPL4      |   |

|                | JF1<br>CLR               | KYBD4<br>FØ                 |   |

|                | JTF<br>DEC               | EXEC<br>RØ                  |   |

|                | MOV<br>OUTL<br>DJNZ      | A,@RØ<br>BUS,A<br>RØ,EXIT_A |   |

|                | END                      | ØBØØH                       |   |

#### Table 4-1. Source Program Format Example

| Table | 4-2. | Assembler | Output | Listing |

|-------|------|-----------|--------|---------|

|-------|------|-----------|--------|---------|

| FILE:  | EXEC4:S | AVE  |      | HEWLETT-PA       | CKARD:  | INTEL 8048 ASSEMBLER |

|--------|---------|------|------|------------------|---------|----------------------|

| LINE   | LOC     | CODE | ADDR | SOU              | RCE STA | TEMENT               |

|        |         |      |      | "8048" LIST XREF |         |                      |

| 1      |         |      |      |                  |         |                      |

| 2      |         |      |      |                  | EXT     | DSPL4,KYBD4          |

| 3      | ØBØØ    |      |      |                  | ORG     | ØBØØH                |

| 4      | ØBØØ    | 45   |      |                  | STRT    | CNT                  |

| 5      | ØBØ1    | E5   |      |                  | SEL     | MBØ                  |

| 6      | ØBØ2    | C5   |      |                  | SEL     | RBØ                  |

| 7      | ØBØ3    | Ø5   |      |                  | EN      | 1                    |

| 8      | ØBØ4    | 25   | _    |                  | EN      | TCNTI                |

| 9      | ØBØ5    | 23   | FF   | EXEC             | MOV     | A,#ØFFH              |

| 1Ø     | ØBØ7    | B9   | ØØ   |                  | MOV     | R1,#ØØH              |

| 11     | ØBØ9    | 62   |      |                  | MOV     | T,A                  |

| 12     | ØBØA    | 55   |      |                  | STRT    | Т                    |

| 13     | ØBØB    | _    |      | LOOP_A           | IN      | A,P1                 |

| 14     | ØBØC    | C6   | 12   |                  | JZ      | EXIT_A               |

| 15     | ØBØE    | AØ   |      |                  | MOV     | @RØ,A                |

| 16     | ØBØF    | 18   |      |                  | INC     | RØ                   |

| 17     | ØB1Ø    | E9   | ØВ   |                  | DJNZ    | DR1,LOOP_A           |

| 18     | ØB12    | FA   |      | EXIT_A           | MOV     | A,R2                 |

| 19     | ØB13    | D7   |      |                  | MOV     | PSW,A                |

| 2Ø     | ØB14    | B6   | ØØ   |                  | JFØ     | DSPL4                |

| 21     | ØB16    | 76   | ØØ   |                  | JF1     | KYBD4                |

| 22     | ØB18    | 85   |      |                  | CLR     | FØ                   |

| 23     | ØB19    | A5   |      |                  | CLR     | F1                   |

| 24     | ØB1A    | 16   | Ø5   |                  | JTF     | EXEC                 |

| 25     | ØB1C    | C8   |      |                  | DEC     | RØ                   |

| 26     | ØB1D    | FØ   |      |                  | MOV     | A,@RØ                |

| 27     | ØB1E    | Ø2   |      |                  | OUTL    | BUS,A                |

| 28     | ØB1F    | E8   | 12   |                  | DJNZ    | RØ,EXIT_A            |

| 29     |         |      | ØØ   |                  | END     | ØBØØH                |

| Errors | s=Ø     |      |      |                  |         |                      |

| 33     |         |      |      |                  | END     |                      |

| FILE: EXE | EC4:SAVE | CROSS-REFE                                                                           | RENCE TABLE                                                         | PAGE 2  |

|-----------|----------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------|

| LINE#     | SYMBOL   | TYPE                                                                                 | REFERENCES                                                          |         |

|           | A        | А                                                                                    | 9,11,15,18,19,26,27                                                 |         |

|           | BUS      | А                                                                                    | 27                                                                  |         |

|           | CNT      | А                                                                                    | 4                                                                   |         |

| 2         | DSPL4    | E                                                                                    | 2Ø                                                                  |         |

| 9         | EXEC     | А                                                                                    | 24                                                                  |         |

| 18        | EXIT_A   | Α                                                                                    | 14,28                                                               |         |

|           | FØ       | А                                                                                    | 22                                                                  |         |

|           | F1       | Α                                                                                    | 23                                                                  |         |

|           | I        | Α                                                                                    | 7                                                                   |         |

| 2         | KYBD4    | E                                                                                    | 21                                                                  |         |

| 13        | LOOP_A   | А                                                                                    | 17                                                                  |         |

|           | MBØ      | Α                                                                                    | 5                                                                   |         |

|           | PSW      | А                                                                                    | 19                                                                  |         |

|           | RØ       | А                                                                                    | 15,16,25,26,28                                                      |         |

|           | R1       | Α                                                                                    | 10,17                                                               |         |

|           | R2       | Α                                                                                    | 18                                                                  |         |

|           | RBØ      | Α                                                                                    | 6                                                                   |         |

|           | т        | А                                                                                    | 11,12                                                               |         |

|           | TCNTI    | А                                                                                    | 8                                                                   |         |

| NO        |          | has the following<br>A = Absolution C = Com D = Data E = Extent M = Multion P = Prog | olute<br>mon (COMN)<br>(DATA)<br>rnal<br>ple Defined;<br>ram (PROG) | ne TYPE |

|           |          | R = Pred<br>U = Unde                                                                 | efined Register<br>efined                                           |         |

#### Table 4-2. Assembler Output Listing (Cont'd)

|       | EXCT:        |             |            |                  |         | INTEL 8048 ASSEMBLER |

|-------|--------------|-------------|------------|------------------|---------|----------------------|

| LINE  | LOC          | CODE        | ADDR       | SOU              | RCE STA | TEMENT               |

|       |              |             |            | "8048" LIST XREF |         |                      |

| 1     |              |             |            |                  |         |                      |

| 2     |              |             |            |                  | GLB     | DSPL                 |

| 3     | ØFFF         |             |            |                  | ORG     | ØFFFH                |

| 4     | ØØØØ         |             |            |                  | DATA    |                      |

| 5     | ØØØØ         | 2D          |            | DSPL             | XCH     | A,R5                 |

| 6     | ØØØ1         | 94          |            |                  | MOVX    | @R4,A                |

| ERRO  | R-IO         |             |            |                  |         |                      |

| 7     | ØØØ2         | 21          |            |                  | XCH     | A,@R1                |

| 8     | ØØØ3         | E6          | ØØ         |                  | JNC     | DSPL                 |

| 9     | ØØØ5         | 86          | ØB         |                  | JNI     | LOOP_C               |

| 1Ø    | ØØØ7         | 6Ø          |            |                  | ADD     | A,@RØ                |

| 11    | ØØØ8         | 51          |            |                  | ANL     | A,@R1                |

| 12    | ØØØ9         | FF          |            |                  | ANL     | A,ØFFH               |

| ERRC  | R—IO, s      | ee line 6   |            |                  |         |                      |

| 13    | ØØØA         | 8F          |            |                  | ORLD    | P7,A                 |

| 14    | ØØØB         | E7          |            | LOOP_C           | RL      | A                    |

| 15    | ØØØC         | DC          |            |                  | XRL     | A,R4                 |

| 16    | ØØØD         | F7          |            |                  | RLC     | Α                    |

| 17    | ØØØE         | D1          |            |                  | XRL     | A,@R1                |

| 18    | ØØØF         | 3Ø          |            |                  | XCHD    | A,@RØ                |

| 19    | ØØ1Ø         | 26          | ØØ         |                  | JNTØ    | DSPL                 |

| 2Ø    | ØØ12         | 46          | 18         |                  | JNT1    | END_C                |

| 21    | ØØ14         | 36          | ØØ         |                  | JTØ     | LOOP_C               |

| 22    | ØØ16         | 56          | ØØ         |                  | JT1     | DSPL                 |

| 23    | ØØ18         | 83          |            | END_C            | RET     |                      |

| 24    |              |             |            |                  | END     |                      |

| Error | s = 2, pre   | vious error | at line 12 | 2                |         |                      |

|       | , <b>,</b> - |             |            |                  |         |                      |

#### Table 4-3. Assembler Output Listing with Errors

| FILE: EXC | CT:    | CROSS-REF | ERENCE TABLE                     | PAGE 2 |

|-----------|--------|-----------|----------------------------------|--------|

| LINE#     | SYMBOL | TYPE      | REFERENCES                       |        |

|           | A      | A         | 5,6,7,10,11,12,13,14,15,16,17,18 |        |

| 5         | DSPL   | D         | 2,8,19,22                        |        |

| 23        | END_C  | D         | 20                               |        |

| 14        | LOOP_C | D         | 9,21                             |        |

|           | P7     | А         | 13                               |        |

|           | RØ     | А         | 18                               |        |

|           | R1     | А         | 7,11,17                          |        |

|           | R4     | А         | 6,1518                           |        |

|           | R5     | А         | 5                                |        |

| Table 4-3. Assembler Output Listing with Errors (Co | ont'd) |

|-----------------------------------------------------|--------|

|-----------------------------------------------------|--------|

**NOTE:** Error messages are inserted immediately following the statement where the error occurs. All error messages (after the first error message) will contain a statement which points to the statement where the last error occurred. At the end of the source program listing, an error summary statement will be printed. The summary will contain a statement as to the total number of errors noted, along with a line reference to the previous error. It will also define all error codes listed in the source program listing.

The primary purpose of the error statement that points to the line number where the previous error occurred is to facilitate location of errors. Since some programs may be many pages in length, this feature helps the programmer locate errors quickly (as opposed to thumbing through each page of the program).

# Chapter 5

## **Instruction Set Summary**

## General

All mnemonic instructions are summarized in this chapter in alphabetical order.

Each instruction consists of a mnemonic code and up to two operands. Descriptive symbols used in this chapter to represent items in mnemonic definitions are as follows:

| Symbol | Description                          |

|--------|--------------------------------------|

| Ā      | Complement of Register A             |

| AC     | Auxiliary Carry                      |

| addr   | 12-bit ROM address                   |

| Bb     | Bit identifier $(b = \emptyset - 7)$ |

| BS     | Bank switch                          |

| C      | Complement of carry flag             |

| CRR    | Conversion Result Register           |

| D      | 4-bit expression                     |

| data   | 8-bit expression                     |

| DBF    | Memory bank flip-flop                |

| FØ     | Complement of Flag Ø                 |

| F1     | Complement of Flag 1                 |

| Symbol   | Description                                 |

|----------|---------------------------------------------|

| Р        | 'In page' operation                         |

| PC       | Program counter                             |

| Рр       | Port designator $(p = 1,2 \text{ or } 4-7)$ |

| Rr       | Register designator $(r = \emptyset-7)$     |

| SP       | Stack pointer                               |

| т        | Timer                                       |

| ТØ       | Test Ø                                      |

| T1       | Test 1                                      |

| TF       | Timer flag                                  |

| <        | Transfer into                               |

| <>       | Exchange content                            |

|          | Boolean AND                                 |

| $\oplus$ | Exclusive OR                                |

| $\odot$  | Inclusive OR                                |

|          |                                             |

## **Predefined Symbols**

The following symbols are reserved. They have special meaning to the assembler and cannot appear as user-defined symbols.

| Symbol | Definition             |

|--------|------------------------|

| A      | Register A             |

| BUS    | BUS port               |

| С      | Carry flag             |

| CLK    | Clock                  |

| CNT    | Counter register       |

| DBB    | Data bus buffer        |

| FØ     | Flag Ø                 |

| F1     | Flag 1                 |

| I      | Interrupt              |

| IBF    | Input buffer flag      |

| MBØ    | Memory bank Ø          |

| MB1    | Memory bank 1          |

| OBF    | Output buffer flag     |

| P1-P7  | Ports P1 through P7    |

| PSW    | Program Status Word    |

| RØ-R7  | Register R1 through R7 |

| RBØ    | Register bank Ø        |

| Symbol | Definition              |

|--------|-------------------------|

| RB1    | Register bank 1         |

| TCNT   | Timer/Counter           |

| TCNTI  | Timer/Counter interrupt |

| @      | Indirect address prefix |

| #      | Immediate data prefix   |

| \$     | Program counter content |

| (_)    | Content of _            |

### **8048 Series Instruction Set Summary**

### ADD

#### Add to Register A

SYNTAX:

|          |                   | Object                                                                   |

|----------|-------------------|--------------------------------------------------------------------------|

| peration | Operand           | Code (hex)                                                               |

| ADD      | A,RØ              | 68                                                                       |

| ADD      | A,R1              | 69                                                                       |

| ADD      | A,R2              | 6A                                                                       |

| ADD      | A,R3              | 6B                                                                       |

| ADD      | A,R4              | 6C                                                                       |

| ADD      | A,R5              | 6D                                                                       |

| ADD      | A,R6              | 6E                                                                       |

| ADD      | A,R7              | 6F                                                                       |

| ADD      | A,@RØ             | 6Ø                                                                       |

| ADD      | A,@R1             | 61                                                                       |

| ADD      | A,#data           | Ø3                                                                       |

|          |                   |                                                                          |

|          | ADD<br>ADD<br>ADD | ADDA,RØADDA,R1ADDA,R2ADDA,R3ADDA,R4ADDA,R5ADDA,R6ADDA,R7ADDA,@RØADDA,@R1 |

The ADD  $A_{,-}$  instruction adds the content of the designated register, memory location, or immediate data to the content of register A. The result of the operation will be stored in register A.

Symbolic Operation: (A) <--- (A)+(Rr) where r=0-7; (A) <--- (A)+((Rr)) where r=0-1; (A) <--- (A)+data

#### Example:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | ADD       | A,R6    |         |

This instruction adds the content of register 6 to the content in register A. The following instruction:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | ADD       | A,@RØ   |         |

will add the content of the memory location address by the first 6 bits ( $\emptyset$ -5) in register R $\emptyset$  to the content of register A.

Cont'd

###

#### Add with carry to Register A

SYNTAX:

| Label | Operation | Operand | Object<br>Code (hex) |

|-------|-----------|---------|----------------------|

|       | ADDC      | A,RØ    | 78                   |

|       | ADDC      | A,R1    | 79                   |

|       | ADDC      | A,R2    | 7A                   |

|       | ADDC      | A,R3    | 7B                   |

|       | ADDC      | A,R4    | 7C                   |

|       | ADDC      | A,R5    | 7D                   |

|       | ADDC      | A,R6    | 7E                   |

|       | ADDC      | A,R7    | 7F                   |

|       | ADDC      | A,@RØ   | 7Ø                   |

|       | ADDC      | A,@R1   | 71                   |

|       | ADDC      | A,#data | 13                   |

The ADDC  $A_{,-}$  instruction adds the content of the carry flag bit to the content of register A. The carry flag bit will then be reset to zero. The content of the designated register, memory location, or immediate data, will then be added to the content of register A. The result of the operation will be stored in register A.

The carry flag bit will be affected by the result of the operation.

#### Example:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | ADDC      | A,R2    |         |

This instruction adds the carry flag bit and the content of register 2 to the content of register A. The carry flag bit will indicate the result of operation (overflow).

Δ

(Cont'd)

MODEL 64000 ASSEMBLER SUPPLEMENT 8048 Series

# ANL A,\_ \_

| Logical A | ١ND | Register | A | with | Designated | Mask |

|-----------|-----|----------|---|------|------------|------|

|-----------|-----|----------|---|------|------------|------|

SYNTAX:

| Label | Operation | Operand | Object<br>Code (hex) |

|-------|-----------|---------|----------------------|

|       | ANL       | A,RØ    | 58                   |

|       | ANL       | A,R1    | 59                   |

|       | ANL       | A,R2    | 5A                   |

|       | ANL       | A,R3    | 5B                   |

|       | ANL       | A,R4    | 5C                   |

|       | ANL       | A,R5    | 5D                   |

|       | ANL       | A,R6    | 5E                   |

|       | ANL       | A,R7    | 5F                   |

|       | ANL       | A,@RØ   | 5Ø                   |

|       | ANL       | A,@R1   | 51                   |

|       | ANL       | A,#data | . 53                 |

A logical "AND" operation will be performed between the byte specified by the operand field and the content of register A. The result of the operation will be stored in register A.

Symbolic Operation: (A) <--- (A) (Rr) where r=Ø-7; (A) <--- (A) ((Rr)) where r=Ø-1; (A) <--- (A) data

Example:

This instruction will perform a logical "AND" operation on the data in register A and the mask contained in the memory location referenced by bits Ø-5 in register RØ.

ÂNI

Cont'd

#### NOTE

A mask for a logical operation can reside anywhere in resident data memory. Logical operations cannot reference external memory.

## ANL BUS,#data

MODEL 64000 ASSEMBLER SUPPLEMENT 8048 Series

#### Logical AND BUS with Immediate Data

| SYNTAX: |           |           |                      |  |

|---------|-----------|-----------|----------------------|--|

| Label   | Operation | Operand   | Object<br>Code (hex) |  |

|         | ANL       | BUS,#data | 98                   |  |

|         |           |           |                      |  |

Not applicable to 8021, 8022, 8041, 8741.

This instruction will logically "AND" the byte of data on the BUS port with the immediate data specified in the operand field. The result of the operation will remain on the BUS port.

Symbolic Operation: (BUS) <--- (BUS) data

Example:

| Label | Operation | Operand   | Comment |

|-------|-----------|-----------|---------|

|       | ANL       | BUS,#ØFØH |         |

This instruction will logically "AND" the data on the BUS port with the binary mask 11110000.

|         |           | Logical AN | D Port_ with Immed   |

|---------|-----------|------------|----------------------|

| SYNTAX: |           |            |                      |

| Label   | Operation | Operand    | Object<br>Code (hex) |

|         | ANL       | P1,#data   | 99                   |

|         | ANL       | P2,#data   | 9A                   |

Not applicable to 8021, 8022.

This instruction will perform a logical "AND" operation on the data at the designated port (P1 or P2) using the immediate data given in the operand field. The result of the operation will remain on the specified port.

**Symbolic Operation:** (Pp) <--- (Pp) data where p = 1-2

Example:

| Label | Operation | Operand | Comment |

|-------|-----------|---------|---------|

|       | ANL       | P1,#ØFH |         |

This instruction will logically "AND" the data at P1 with the binary mask ØØØØ1111.

### ANLD

#### Logical AND Port\_ with Register A

| YNTAX: |           |         |                      |

|--------|-----------|---------|----------------------|

| Label  | Operation | Operand | Object<br>Code (hex) |

|        | ANLD      | P4,A    | 9C                   |

|        | ANLD      | P5,A    | 9D                   |

|        | ANLD      | P6,A    | 9E                   |

|        | ANLD      | P7,A    | 9F                   |

This instruction will logically "AND" the data at the designated port with the binary mask in register A. The result of the operation will remain on the specified port.

Symbolic Operation: (Pp) <--- (Pp) (A BØ-3) where p = 4-7

### CALL

**Call Subroutine**

|       |           |          | Object     |

|-------|-----------|----------|------------|

| _abel | Operation | Operand  | Code (hex) |

|       | CALL      | address  | 14         |

|       |           | (page Ø) |            |

|       | CALL      | address  | 34         |

|       |           | (page 1) |            |

|       | CALL      | address  | 54         |

|       |           | (page 2) |            |

|       | CALL      | address  | 74         |

|       |           | (page 3) |            |

|       | CALL      | address  | 94         |

|       |           | (page 4) |            |

|       | CALL      | address  | B4         |

|       |           | (page 5) |            |

|       | CALL      | address  | D4         |

|       |           | (page 6) |            |

|       | CALL      | address  | F4         |

|       |           | (page 7) |            |

**NOTE:** page = 256 bytes

This instruction is used for entering subroutines. It will push the program counter and bits 4-7 of the program status word (PSW) onto the stack. The stack pointer (bits  $\emptyset$ -2 of the PSW) will be updated. Program control will then be passed to the address specified in the operand field.

Upon return from the subroutine, execution of the program will continue at the instruction following the CALL instruction routine.

Symbolic Operation: ((SP)) <--- (PC), (PSW B4-7); (SP) <--- (SP)+1; (PC B8-10) <--- addr B8-10; (PC B0-7) <--- addr B0-7; (PC B11) <--- memory bank flip-flop

|           |         | MODEL<br>ASSEMBLER SUPPLE<br>8048 |

|-----------|---------|-----------------------------------|

|           |         |                                   |

|           |         |                                   |

| Operation | Operand | Object<br>Code (hex)              |

| CLR       | Α       | 27                                |

|           |         |                                   |

This instruction will reset the content of register A to zero (clears the register).

Symbolic Operation: A <--- Ø

# ICLR CI

#### **Clear Carry Flag Bit**

| SYNTAX: |           |         |                      |  |

|---------|-----------|---------|----------------------|--|

| Label   | Operation | Operand | Object<br>Code (hex) |  |

|         | CLR       | С       | 97                   |  |

|         |           |         |                      |  |

This instruction will reset the carry flag bit to zero.

#### Symbolic Operation: C <--- Ø

| Label            | Operation                      | Operand                  | Object<br>Code (hex) |

|------------------|--------------------------------|--------------------------|----------------------|

|                  | CLR<br>CLR                     | FØ<br>F1                 | 85<br>A5             |

| ot applicable to | ວ 8021, 8022.                  |                          |                      |

|                  | will clear (reset to zero      | ) the flag designated in | the operand field.   |

|                  | eration: (FØ) < Ø;<br>(F1) < Ø |                          |                      |

|                  | peration: (FØ) < Ø;            |                          | CPL                  |

|                  | peration: (FØ) < Ø;            |                          | CPL                  |

|                  | peration: (FØ) < Ø;            |                          |                      |

| Symbolic Op      | peration: (FØ) < Ø;            | Operand                  | Object<br>Code (hex) |

| 9 | <b>7</b> 11 | ID 1 |  | hei | and | ///. | $(\mathbf{n})$ | ~- |

|---|-------------|------|--|-----|-----|------|----------------|----|

|   |             |      |  |     |     |      |                |    |

Example:

| Label | Operation | Operand | Comment                                                       |

|-------|-----------|---------|---------------------------------------------------------------|

|       | CPL       | A       | ;prior to instruction<br>;content of register<br>;A=10101010B |

This instruction will replace the current content of register A (10101010B) with 01010101B.

| Label                                 | Operation                                     | Operand                        | Object<br>Code (hex)         |

|---------------------------------------|-----------------------------------------------|--------------------------------|------------------------------|

|                                       | CPL                                           | С                              | A7                           |

|                                       | vill complement the carry<br>I be set to one. | y flag bit. If it was a one, i | it will be reset to zero. If |

|                                       | $\overline{(0)}$                              |                                |                              |

| Symbolic Op                           | eration: (C) < (C)                            |                                |                              |

| Symbolic Op                           |                                               |                                |                              |

| Symbolic Op                           |                                               |                                |                              |

|                                       | eration: (C) < (C)                            |                                |                              |

| Symbolic Op                           |                                               |                                |                              |

|                                       | eration: (C) < (C)                            |                                |                              |

|                                       | eration: (C) < (C)                            |                                |                              |

|                                       |                                               |                                |                              |

| PL F1                                 |                                               |                                |                              |

| PLF                                   |                                               |                                |                              |

| PLFI<br>plement Flag<br>SYNTAX:       |                                               | Operand                        | Object<br>Code (bex)         |

| PLF                                   |                                               | Operand                        | Object<br>Code (hex)         |

| PLFI<br>plement Flag<br>SYNTAX:       |                                               | <b>Operand</b><br>FØ           |                              |

| <b>PLF</b><br>plement Flag<br>SYNTAX: | Operation                                     |                                | Code (hex)                   |

was set to one, it will be reset to zero. If the flag was zero, it will be set to one.

Symbolic Operation:  $(F\emptyset) < --- \overline{(F\emptyset)};$

(F1) <--- (F1)

|                                                                               |                                                                                                  | ·······                                                    | ······································                                                                                        |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| SYNTAX:                                                                       |                                                                                                  |                                                            |                                                                                                                               |

| Label                                                                         | Operation                                                                                        | Operand                                                    | Object<br>Code (hex)                                                                                                          |

|                                                                               | DA                                                                                               | А                                                          | 57                                                                                                                            |

| f the low-order<br>egister A will be<br>f the high-order<br>order nibble will | digits.<br>nibble (bits Ø-3) is greate<br>e incremented by six.<br>r nibble (bits 4-7) is greate | er than nine, or if the aux<br>er than nine, or if the car | m two 4-bit binary coded<br>kiliary carry flag bit is one,<br>ry flag bit is one, the high-<br>y flag bit will be set to one; |

|                                                                               | uxiliary carry flags will be                                                                     | e affected by this operati                                 | on.                                                                                                                           |

|                                                                               |                                                                                                  | e affected by this operati                                 | on.                                                                                                                           |

Α

This instruction will decrement the content of register A by one.

DEC

Symbolic Operation: (A) <--- (A)-1

Ø7

### DEC R\_I

#### Decrement Register R\_

|       |           |         | Object     |

|-------|-----------|---------|------------|

| Label | Operation | Operand | Code (hex) |

|       | DEC       | RØ      | C8         |

|       | DEC       | R1      | C9         |

|       | DEC       | R2      | CA         |

|       | DEC       | R3      | СВ         |

|       | DEC       | R4      | CC         |

|       | DEC       | R5      | CD         |

|       | DEC       | R6      | CE         |

|       | DEC       | R7      | CF         |

Not applicable to 8021, 8022.

This instruction will decrement the content of the register designated in the operand field by one.

**Symbolic Operation:** (Rr) <--- (Rr)-1 where  $r = \emptyset$ -7

|                   |                            |                                                      | Disable External Inter     |

|-------------------|----------------------------|------------------------------------------------------|----------------------------|

| SYNTAX:           |                            |                                                      |                            |

| Label             | Operation                  | Operand                                              | Object<br>Code (hex)       |

|                   | DIS                        | 1                                                    | 15                         |

|                   | 2001                       |                                                      |                            |

| ot applicable to  | 8021.                      |                                                      |                            |

|                   |                            | rrupts in the 8048 micro                             | processor.                 |

| nis instruction w | vill disable external inte |                                                      |                            |

| nis instruction w | vill disable external inte | rrupts in the 8048 micro<br>errupt in the 8041 micro |                            |

| nis instruction w | vill disable external inte |                                                      |                            |

| nis instruction w | vill disable external inte |                                                      |                            |

| nis instruction w | vill disable external inte |                                                      |                            |

| nis instruction w | vill disable external inte |                                                      |                            |

| nis instruction w | vill disable external inte |                                                      | processor.                 |

| nis instruction w | vill disable external inte |                                                      |                            |

| nis instruction w | vill disable external inte | errupt in the 8041 microp                            | processor.                 |

| nis instruction w | vill disable external inte | errupt in the 8041 microp                            | Drocessor.                 |

| nis instruction w | vill disable external inte | errupt in the 8041 microp                            | Drocessor.                 |

| nis instruction w | vill disable external inte | errupt in the 8041 microp                            | sable Timer/Counter Interr |

This instruction will disable timer/counter interrupts and any timer interrupt request will be cleared. The interrupt sequence will not be initiated by an overflow, but the timer flag will be set and time accumulation continued.

### DJNZ

#### **Decrement Register and Test**

|       |           |            | Object     |

|-------|-----------|------------|------------|

| Label | Operation | Operand    | Code (hex) |

|       | DJNZ      | RØ,address | E8         |

|       | DJNZ      | R1,address | E9         |

|       | DJNZ      | R2,address | EA         |

|       | DJNZ      | R3,address | EB         |

|       | DJNZ      | R4,address | EC         |

|       | DJNZ      | R5,address | ED         |

|       | DJNZ      | R6,address | EE         |

|       | DJNZ      | R7,address | EF         |

This instruction will decrement the register in the operand field. If the register contains all zeros, program execution will continue with the next instruction. If the designated register contents are not zero when tested, program control will jump to the specified address.

**Symbolic Operation:**  $(Rr) \leq (Rr) - 1$  where  $r = \emptyset - 7$

If Rr = Ø: (PC BØ-7) <--- addr

**Examples:**

| Label | Operation   | Operand        | Comment |

|-------|-------------|----------------|---------|

|       | DJNZ<br>ADD | R3,SAM<br>A,R1 |         |

This instruction will decrement register R3. If the content of R3 is not all zeros, a jump will occur to a location designed by SAM. If the content of register R3 is all zeros, program execution will continue with the ADD instruction.

|                   |           |                           | Enable External Inter     |

|-------------------|-----------|---------------------------|---------------------------|

|                   |           | <u></u>                   | Enable External Inter     |

| SYNTAX:           |           |                           |                           |

|                   |           |                           | Object                    |

| Label             | Operation | Operand                   | Code (hex)                |

|                   | EN        | I                         | Ø5                        |

|                   |           |                           |                           |

|                   |           | rrupts in the 8048 microp |                           |

|                   |           |                           |                           |

|                   |           |                           | rocessor.                 |

|                   |           | rrupt in the 8041 microp  | rocessor.                 |

|                   |           | rrupt in the 8041 microp  | rocessor.                 |

| his instruction v |           | rrupt in the 8041 microp  | able Timer/Counter Interr |

| nis instruction v |           | rrupt in the 8041 microp  | rocessor.                 |

Not applicable to 8021.

This instruction will enable the timer/counter interrupts. An overflow of the timer/counter will initiate the interrupt sequence.

# ENTO CLKI

#### Enable Clock Output

| Operation | Operand | Object<br>Code (hex) |                              |

|-----------|---------|----------------------|------------------------------|

| ΕΝΤΟ      | CLK     | 75                   |                              |

|           |         |                      | Operation Operand Code (hex) |

Not applicable to 8021, 8022, 8041, 8741.

This instruction will enable the test Ø pin so that it will act as the clock output. This function will be disabled by a system reset.

### IN A,DBB

#### Input DBB Data to Register A

| SYNTAX: |           |         |                      |

|---------|-----------|---------|----------------------|

| Label   | Operation | Operand | Object<br>Code (hex) |

|         | IN        | A,DBB   | 22                   |

|         |           |         |                      |

Applicable to 8041, 8741 only.

This instruction will transfer data from the data bus buffer to register A.

| IN A,P                    |         | MODEL 64000<br>ASSEMBLER SUPPLEMENT<br>8048 Series |         |

|---------------------------|---------|----------------------------------------------------|---------|

| out Port Data to Register | Inpu    |                                                    |         |

|                           |         |                                                    | SYNTAX: |

| Object<br>Code (hex)      | Operand | Operation                                          | Label   |

| Ø8 (8021, 8022 only       | A,PØ    | IN                                                 |         |

| <b>40</b>                 | A,P1    | IN                                                 |         |

| Ø9                        |         |                                                    |         |

This instruction will transfer the data on the designated port into register A.

Symbolic Operation: (A) <--- (Pp) where p = 1-2

#### **Increment Register**

SYNTAX:

|     | Operand | Code (hex) |

|-----|---------|------------|

| INC | А       | 17         |

| INC | RØ      | 18         |

| INC | R1      | 19         |

| INC | R2      | 1A         |

| INC | R3      | 1B         |

| INC | R4      | 1C         |

| INC | R5      | 1D         |

| INC | R6      | 1E         |

| INC | R7      | 1F         |

| INC | @RØ     | 1Ø         |

| INC | @R1     | 11         |

This instruction will increment the content of the designated register or resident memory location by one.

NOTE

External data memory content cannot be incremented directly.

|                  |                                                     | Strobe In                                           | put of BUS Data to Regist                                                       |

|------------------|-----------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------|

| SYNTAX:          |                                                     |                                                     |                                                                                 |

| Label            | Operation                                           | Operand                                             | Object<br>Code (hex)                                                            |