# IBM 1401 Symbolic Programming Systems: SPS-1 and SPS-2 Specifications and Operating Procedures

This manual provides programmers with the information necessary to code a 1401 program in SPS language and assemble a machine-language object-program. It is assumed that the programmer has a basic knowledge of 1401 machine language programming.

It describes symbolic programming principles and concepts and gives detailed specifications of the 1401 Symbolic Programming Systems, SPS 1 and SPS 2.

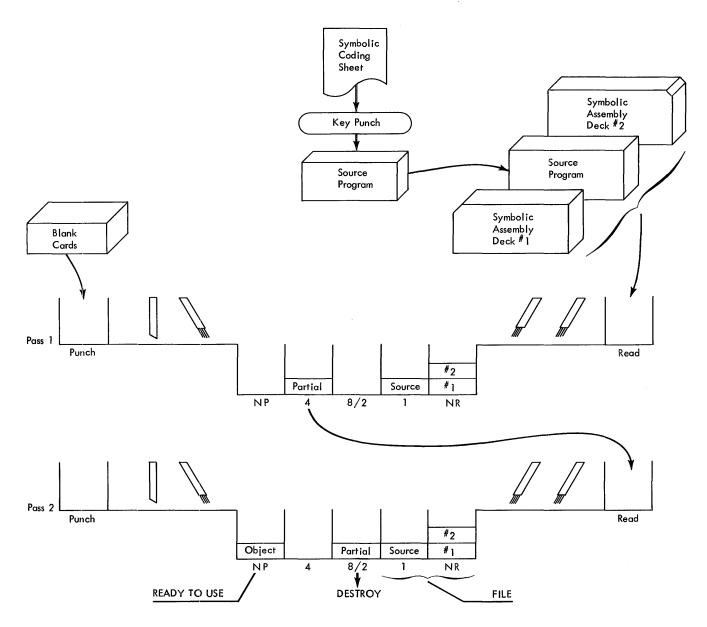

Operating instructions for processing the SPS source program are enumerated. The SPS processor program can assemble a machine language program on configurations of the 1401 Data Processing System equipped with a 1402 Card Read-Punch.

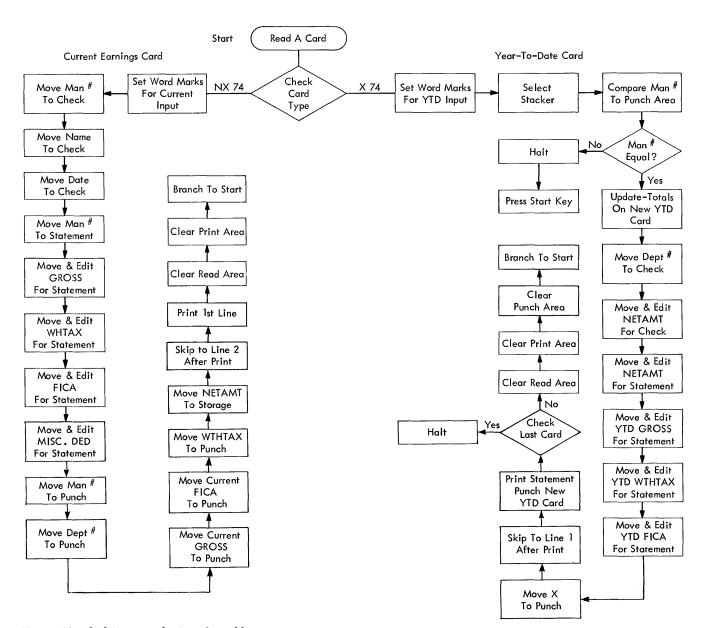

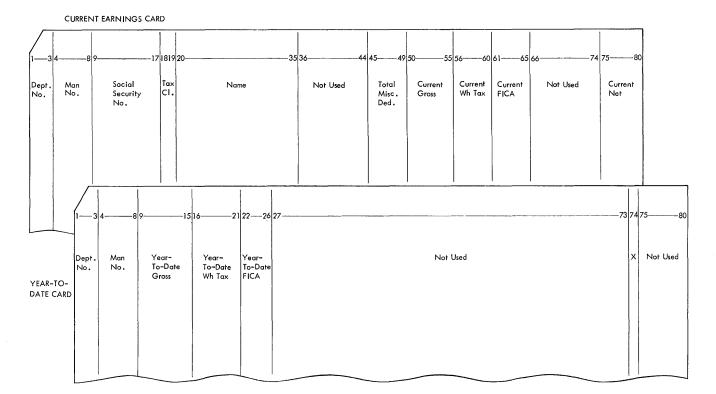

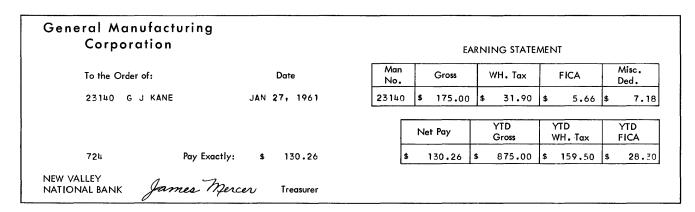

A sample program is included for the convenience of the beginning SPS programmer. Input and output forms, a block diagram of the program procedure, the symbolic program, and SPS output listings of the symbolic and machine-language programs are shown.

# Preface

This manual describes the language specifications and operating procedures for the IBM 1401 Symbolic Programming Systems SPS-1 and SPS-2.

This manual is designed for programmers who know the input, output, and processing characteristics, as well as the basic functions and operations of the IBM 1401 Data Processing system.

The language is presented in a special format that:

- describes generally each type of SPS statement

- describes specifically the construction of the statement

- describes generally the processing and assembly functions

- shows an example of how each statement can be used in a program.

The operating procedures are presented in detail with descriptions of deck assemblies, error notes, etc.

A sample problem shows a simple payroll listing including input and output documents, the SPS source program, and the output from assembly.

This SRL publication, C24-1480, obsoletes the IBM 1401 Data Processing System Bulletins: IBM 1401 Symbolic Programming System: Preliminary Specifications, J24-0200, and IBM 1401 Symbolic Programming Systems: SPS-1 and SPS-2, J24-1412.

# Contents

| Introduction                         | 5  |

|--------------------------------------|----|

| IBM 1401 Symbolic Programming System | 6  |

| Advantages of IBM 1401 SPS           | 6  |

| Programming with SPS                 | 7  |

| Symbolic Language                    | 7  |

| Processor Program                    | 7  |

| Information Requirements             | 7  |

| Coding Sheet                         | 7  |

| Address Assignment                   | 12 |

| Declarative Operations               | 13 |

| Imperative Operations                | 17 |

| Special Mnemonic Operation Codes     | 17 |

| Processor Control Operations         | 19 |

| SPS Processor Operations             | 21 |

| Pre-Process Listing Routine          | 21 |

| Processor Assembly Program           | 22 |

| Processor Output                     | 26 |

| Post-Process Listing Routine         | 28 |

| Condensing Routine                   | 29 |

| IBM 1401 SPS Sample Program          | 30 |

| Index                                | 38 |

With the increasing capability of data processing systems, programming in the actual machine language of a system has become more complex. Not only does machine-language coding require memorization of a great many numeric and alphabetic codes but also the length and intricate design of programs written in machine language make them prone to logical and clerical errors.

Also, the problem of correcting errors in an actual machine-language program is intensified because of the difficulty in tracing the steps of a machine-language program to include corrections and relocate the problem in storage.

Symbolic programming, the use of mnemonic characters to write a program, has been developed to facilitate computer programming. When mnemonic instructions are used, data may be referred to in terms which are logical to the layman, as well as to the experienced programmer. Another advantage of symbolic programming is that the checking of each program may be performed by a person other than the programmer.

In a symbolic system, a routine to add current withholding tax to total miscellaneous deductions, subtract the total from gross pay, and store the amount as net pay might look like this:

| Operation Code |        | <b>Operands</b> |

|----------------|--------|-----------------|

| ZA             | CURWTX | ACCUM           |

| Α              | TOTMDN | ACCUM           |

| ZA             | GROSS  | NETPAY          |

| S              | ACCUM  | NETPAY          |

The first instruction in this routine sets to zero a machine storage area, which is arbitrarily labeled ACCUM. It then adds the current withholding tax (an area called CURWTX) into this area. The next instruction, total miscellaneous deductions (TOTMDN), is added to the contents of ACCUM, which is CURWTX.

Then a storage location, labeled NETPAY, is set to zero, and gross pay (GROSS) is added into it. In the last step the contents of ACCUM (CURWTX + TOTMDN) is subtracted from the contents of NETPAY (GROSS). This puts (GROSS-CURWTX-TOTMDN) in a suitably labeled location (NETPAY), to which the programmer may refer later in the program.

Once the data and working areas have been defined and labeled, it is easier to follow the logic of this short routine written in symbolic form than to comprehend the same routine written in machine language, which might look like this:

| OPERATION CODE                             | Opei | ANDS |

|--------------------------------------------|------|------|

| 2                                          | 060  | S93  |

| $\frac{\overline{\mathbf{A}}}{\mathbf{a}}$ | 045  | S93  |

| <u>7</u>                                   | 050  | A95  |

| <u>S</u>                                   | S93  | A95  |

A program written in symbolic programming language (the source program) requires translation into an actual machine-language program (the object program) before a computer can execute it. This translation is done by a machine-language program called a *processor*. In general, the translation is "one-forone." That is, for each instruction written in symbolic form, one machine-language instruction is produced.

The processor, sometimes called an assembly system, generally utilizes the machine for which the symbolic program is written. It analyzes all symbolic entries and converts them to actual machine operating data and instructions, establishing specified relationship between them.

As an additional feature, assembly programs also indicate various types of errors such as coding, out-ofsequence cards, etc. Symbolic programming saves time and simplifies coding. Because actual machine addresses of data and instructions are assigned automatically by the processor, the programmer need not concern himself with this detail. He can, however, refer to these addresses symbolically.

Once there is an agreement on label terminology, subroutines (short programs or routines common to a number of programs) may be easily incorporated in any program, and a major program may be written in independent parts with no loss of efficiency in the final program. Corrections and modifications of program instructions also entail no reassignment of addresses by the programmer. Finally, the automatic assignment of addresses makes programs and subroutines readily relocatable, i.e., they can be placed in varying machine locations as desired.

Because of the advantages in symbolic programming for the IBM 1401 Data Processing System, IBM has developed the 1401 Symbolic Programming Systems (SPS-1 and SPS-2).

# IBM 1401 Symbolic Programming System

The IBM 1401 basic Symbolic Programming System, SPS-1, operates on the 1400-character machine with the 1402 Card Read-Punch and the 1403 Printer, but it can assemble programs for any object machine configuration up to 4000 positions of storage. An expanded Symbolic Programming System, SPS-2, can assemble programs for any size object machine (1,400 to 16,000 positions of storage), but requires assembly on a 1401 system that has at least 4,000 storage positions and the 1402 Card Read-Punch, and the 1403 Printer. The general description and operating procedure of both systems are the same; however, any characteristics that apply only to the expanded programming system, because of its larger machine storage requirements, will be noted throughout the manual.

### Advantages of IBM 1401 SPS

Some significant advantages of the IBM 1401 Symbolic Programming System are:

- Simplifies program writing and organization. For example, it is easier to write and refer to an instruction such as s WHTAX GROSS (Subtract Withholding Tax from Gross) than to look up the addresses of withholding tax and gross for an instruction like S 599 618.

- Provides continuity for group programming efforts. Upon agreement of labeling terminology, program routines can be written independently and efficiently and can be combined for assembling because addresses are automatically assigned by the processor.

- Simplifies program adjustment. If programs require partial revision, only the affected routines need to be rewritten.

- Detects coding errors. Illegal operation codes, invalid addresses, sequence errors, etc., are detected by the SPS listing routine before the program is actually assembled.

- Facilitates program testing. Explanatory comments may be listed next to program instructions.

### **Programming with SPS**

Effective programming in IBM 1401 requires a knowledge of the methods of programming in machine language. Before the programmer begins to code his program in symbolic language, (as when writing in actual machine language) he draws a block diagram of the procedure the program must take to accomplish a desired end result. From this block diagram he must determine which constants and work areas are needed.

Constants are fixed data, such as a standard FICA LIMIT calculation. Work areas are locations within core storage where the data can be manipulated, such as input and output areas, accumulator fields, etc. Then he writes the instructions for the program.

### Symbolic Language

The symbolic language includes a standard set of *mnemonics*. These mnemonics are standardized abbreviations for operation code descriptions, and are usually easier to remember than the machine-language codes. For example:

|                 |          | MACHINE       |

|-----------------|----------|---------------|

| DESCRIPTION     | MNEMONIC | LANGUAGE CODE |

| Multiply        | Μ        | @             |

| Clear Word Mark | CW       | Ē             |

A list of mnemonic operation codes is shown in Figure 38. Also included as part of the symbolic language are standard methods for defining areas and entering constants, comments, etc.

By using the symbolic language, the programmer can control the locations of record and work areas if he so chooses, or he can leave this job to the processor program.

### **Processor Program**

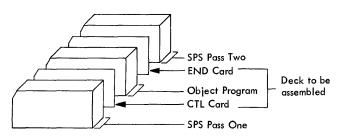

A standard deck of cards furnished by IBM contains the processor program that produces the *object program* (actual machine-language program) from the *source program* (symbolic language program). The SPS processor, also called an assembly program, assembles the object program from information given in the source program statements. The object program is then punched in one-instruction-per-card format. The punched output deck is then used to load the assembled machine-language program into core storage prior to its execution.

### Information Requirements

The information that the processor program requires to assemble the object program is divided into three major categories:

Area Definition (Declarative Operations) Instructions (Imperative Operations) Processor Controls (Process Control Operations)

### Area Definition

These statements assign sections of storage space for work areas. The assigned areas will be used by the object program and may contain the data to be processed and/or the constants required to execute the object program. Area definition statements in most cases do not result in instructions to be executed as part of the object program. However, the processor program does produce for these statements cards containing constants and their assigned machine addresses. These constants cards are loaded with the object program each time the program is used.

#### Instructions

Most of the statements on the program sheet are the instructions for the data processing job to be performed. These statements are translated by the processor program into their machine-language equivalents in the object program.

### **Processor Controls**

These statements are special signals to the processor program. They allow the programmer to adjust certain portions of the assembly process. These statements are never executed in the object program.

These three types of information are presented to the processor program in the form of SPS statements written originally on a special Symbolic Program Coding Sheet.

### **Coding Sheet**

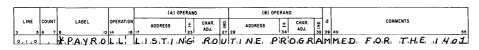

The IBM 1401 Symbolic Program Coding Sheet (Figure 1) is fixed-form. A special field is provided for each item of information required by the processor. Each statement is written on a separate line.

Before assembly, each line of the coding sheet is key punched into a card. These cards make up the source program deck which is the input to the processor program.

Column numbers on the coding sheet indicate the punching format for all source program cards.

To facilitate key punching, IBM makes available a special card, electroplate C55369, for use with the 1401 SPS. This card is also used to contain the object program as it is punched as output from the assembly process.

The function of each portion of the coding sheet is explained in the following paragraphs.

### Page Number (Columns 1 and 2)

This two-character entry provides sequencing for coding sheets. Only numerical characters may be used. Standard collating sequence for the IBM 1401 should be followed when sequencing pages.

### Line Number (Columns 3-5)

A three-character line number sequences entries on each coding sheet. The first 20 lines are prenumbered 010-200. The third position is punched zero, the lowest number in the collating sequence. The six unnumbered lines at the bottom of each sheet can be used to continue line numbering or to make insertions between entries elsewhere on the sheet. The units position of the line number indicates the sequence of inserts. Any numerical character can be used, but standard collating sequence should be used. For example, if an insert is to be made between lines 020 and 030, it could be numbered 021. Line numbers do not necessarily have to be consecutive, but the deck should be in collating sequence, for sorting purposes.

The programmer should note that insertions can affect address adjustment. An insertion might make it necessary to change the adjustment factor in the operand of one or more entries. All insertions should be placed in their proper sequence in the source program deck before assembly.

### Count Field (Columns 6 and 7)

The number of characters the assembled actual machine instruction or defined area is to contain is punched into this field. The processor uses this number to allocate storage locations for data and instructions. For example, if the count field of an area definition statement contains a 6, six storage locations will be allocated for that area. The processor will also use this number to assign an address for the area. See Address Assignment.

Because the processor can determine the length of an instruction from the information presented in the statement, the programmer can leave the count field blank for instruction entries. The processor will develop and punch the count in the count field of the object program deck in any case. For instructions, the processor will override any punching in the count field.

#### Label Field (Columns 8-13)

The label is a symbol or descriptive term selected by the programmer to identify the specific area or instruction represented by the source program statement in which the label appears. The label may then be used elsewhere in the program, i.e., in an operand of another source program statement, to refer to the area or instruction which it identifies.

It is advantageous to devise a label that suggests the meaning of the area or instruction, so that the source program can be easily interpreted by anyone concerned with the program. For example:

| Type of Statement | MEANING         | LABEL  |

|-------------------|-----------------|--------|

| Area definition   | Withholding Tax | WHTAX  |

| Instruction       | Update          | UPDATE |

Labels are used only with area definition and instruction statements. Remember that core storage is allocated, and an address is assigned for all instructions and most area definitions. If the statement is labeled, the assigned address is known as the "equivalent address" of the label. The processor maintains during assembly a table of labels and their equivalent addresses. When a label appears in the *operand* of a statement, its equivalent address may be found and substituted for the label in the assembled statement.

The equivalent address of the label of an instruction is made equal to the leftmost, or high-order, corestorage position of those positions allocated to the instruction. The equivalent address of the label of a defined area or constant is made equal to the rightmost, or low-order, core-storage position of those positions allocated to the area or constant.

No two labels in the source program may be identical.

The label is punched beginning in column 8 of the label field. It can be as many as six alphamerical characters in length and the first, or leftmost, character must be alphabetic. No actual machine addresses or special characters should be used for this purpose. Blanks must not appear *within* a label.

#### **Operation (Columns 14-16)**

This field contains the operation code for the statement. Area-definition and processor control statements always have mnemonic operation codes. Instruction statements can have either mnemonic or actual operation codes. If the mnemonic op code is used, it is written and punched beginning in column 14 of the operation field. Actual op codes are punched in column 16.

### Operands (Columns 17-27 and 28-38)

In the (A) and (B) operand fields are placed the programmer's designations of:

1. For instruction statements: the addresses of the

data to be operated upon, or the input-output units to be operated.

- 2. For area definition statements: the constant being defined, the address at which the constant is to be stored, or the address or input-output unit which is to be the equivalent of the label.

- 3. For processor control operations: the address which is to be used with the particular control of the processor being invoked by the programmer at that point in the program.

It is evident, then, that each entry in the operand fields serves one of the following purposes:

- 1. It designates a core-storage address.

- 2. It designates an input-output unit.

- 3. It provides the constants being defined.

#### **Core-Storage Address Operands**

These are designated by using the Address, Character Adjustment, and Indexing portions of the operand field.

There are four types of core-storage address operands: Symbolic, Actual, Asterisk, and blank.

#### SYMBOLIC ADDRESSES

A symbolic address can be composed of as many as six letters or digits (no special characters), but the first (high-order) character must be a letter. It refers to an instruction or area definition statement in the source program whose label is identical to it. For example, if ENTRYA is used as the label for an instruction in the source program, ENTRYA can be used as the symbolic operand of another instruction which references it such as B ENTRYA (Branch to the instruction whose label is ENTRYA).

Each symbol used must have a corresponding label because the processor substitutes the address assigned to the label wherever the symbol appears in the operand field of another source program statement. If character adjustment or indexing is associated with the

| ' <b>BM</b><br>rogram |              |                                               |          |                                       | IBM               |                   | SYMB                 | OL        | IC P     | MACHINES CO<br>ROGRAMA<br>SHEET |            |               | м           |         | Page No.                                                     |

|-----------------------|--------------|-----------------------------------------------|----------|---------------------------------------|-------------------|-------------------|----------------------|-----------|----------|---------------------------------|------------|---------------|-------------|---------|--------------------------------------------------------------|

| rogramr               | ned by       | /                                             |          |                                       |                   |                   | 1                    | Dat       | e        |                                 |            |               |             |         | Identification 76 80                                         |

|                       |              |                                               | ·        | 1                                     | (A) OP            | ERAND             | )                    |           |          | (8) (                           | PERAN      | D             |             |         |                                                              |

|                       | COUNT<br>6 7 | LABEL<br>813                                  | OPERATIO | ADD                                   | RESS              | :55 ±             |                      | ONI 27    | 28       | ADDRESS                         | ±<br>34    | CHAR.<br>Adj. | 0 N I<br>38 | d<br>39 | COMMENTS                                                     |

| 0 1 1 0               |              |                                               |          |                                       |                   |                   |                      |           |          | _ <u>+_</u>                     | 1          |               |             |         |                                                              |

| 0 2 0                 | [            |                                               | <u> </u> | ++++                                  |                   | <u>   </u>        |                      | 1_        |          |                                 |            | LL.           |             |         |                                                              |

| 0 3 0                 | ļ            |                                               |          | <u></u>                               |                   | $\frac{1}{1}$     | le le                | -         | - L-     |                                 |            | ليستلير       | 1-          |         |                                                              |

| 0,4,0                 |              |                                               | <u> </u> |                                       | <b>i</b> i        | ÷÷                |                      | ╞         |          |                                 | <u> </u>   | - I - I       | -           |         |                                                              |

| 5,0                   |              |                                               |          | +                                     | ll                | <u>i i</u>        |                      | +         |          |                                 |            | <b>I</b>      |             |         |                                                              |

| 6 0                   | ļ            |                                               | <u> </u> |                                       | I                 | $\frac{1}{1}$     |                      |           |          |                                 | <u>i</u> i |               | -           |         |                                                              |

| 7 0                   |              |                                               | li-      |                                       |                   | <u>i i</u><br>1 i |                      |           | . I.     |                                 |            | II            |             |         | <u>┥</u> <u></u>                                             |

| 8 0                   |              |                                               |          | · · · · · · · · · · · · · · · · · · · |                   | $\frac{1}{1}$     |                      | + -       |          |                                 | 1 1        |               | +           |         | <u>┤</u> <u></u>                                             |

| 0,9,0                 |              |                                               |          | 4                                     |                   | $\frac{1}{1}$     |                      | -         | <u> </u> |                                 |            |               | +           | L.,     |                                                              |

| 0,0                   |              |                                               |          |                                       | <u> </u>          | 1 1               | <u>I</u>             |           |          | <u></u>                         | <u>   </u> |               |             |         |                                                              |

| , 1 , 0               |              |                                               |          |                                       | ll                | ++                |                      | +         | 4        |                                 | 1 1        |               |             |         |                                                              |

| 1 2 0<br>1 3 0        | 11           | kkkk                                          |          |                                       | L                 |                   |                      | -         |          |                                 | 1 1        | 1             | +           | -       |                                                              |

| 1,4,0                 |              |                                               | <u></u>  |                                       | l                 |                   |                      | +         |          |                                 |            |               | +           |         |                                                              |

| 1 5 0                 |              |                                               |          |                                       |                   | $\frac{1}{1}$     |                      | -         |          |                                 | 11         | ll            | +           | -       | ╋ <u>┯┥</u> ╾┙┉ <u>┤╴</u> ┋╾┨╴┟ <u>╼</u> ┞ <u>╶</u> ┠╶┨╸┠╼╉╸ |

| 1 6 0                 |              | ittttt                                        |          |                                       |                   | 1 1               |                      |           |          |                                 | 1 1        | ( ]           | 1           |         |                                                              |

| 1,8,0                 | ┟╌┵──        | <u>↓</u>                                      | 1-1-1-   | 1 - 1 1 1                             | └ <u>─</u> ┹──┤── | 11                |                      |           | <u> </u> | <u>_</u>                        | !!         |               | +           | -       |                                                              |

| 1,8,0                 |              |                                               |          |                                       |                   |                   |                      | $\square$ | <u> </u> |                                 |            | I I<br>       |             | -       |                                                              |

| 1 9 0                 |              |                                               |          |                                       |                   | 1 1               |                      | 1         |          |                                 |            |               | +           |         |                                                              |

| 2 0 0                 |              |                                               |          |                                       |                   |                   | ····                 | 1         |          | · · · · ·                       |            |               | 1           |         |                                                              |

| <u> </u>              | ┟╾╍┞╍╍       |                                               |          |                                       | ╘╼╼┻              | 1 1               | مر ما <u>مسامر م</u> |           |          |                                 |            |               | +-          |         |                                                              |

| <u></u>               |              |                                               |          |                                       | L                 | 11                |                      |           |          |                                 | 1 1        |               | 1           | -       |                                                              |

|                       |              |                                               |          |                                       | LL                |                   |                      | 1         |          | · · · · ·                       |            |               |             |         |                                                              |

|                       |              |                                               |          | 1                                     | L                 |                   |                      | 1         |          |                                 |            |               | -           |         |                                                              |

|                       |              |                                               |          |                                       | ·ł                |                   |                      | 1         |          |                                 |            |               |             | _       |                                                              |

|                       | 1            | <u>  -                                   </u> | +        | 1                                     | LL                | $\frac{1}{1}$     |                      | +         | <u>↓</u> |                                 |            |               | +           |         |                                                              |

Figure 1. IBM 1401 Symbolic Program Coding Sheet

symbolic address, the processor will modify the address assigned to the label accordingly.

The programmer may write a symbolic address in a statement that precedes the labeled statement in the source program, because the processor does not assign addresses until all source program statements have been examined and the entire label table has been created.

#### ACTUAL ADDRESSES

In SPS-1 an actual address is a four-digit number written and punched beginning in column 17 of the A-operand field or in column 28 of the B-operand field.

In SPS-2 actual addresses can be either four or five digits, depending upon machine size, and are written and punched beginning in column 17 of the A-operand field or in column 28 of the B-operand field.

Figure 2 shows the use of one symbolic and one actual address in the source program.

| 1 |             | I |      |         |   |        |    |           |     | (A) OPE | RAN | )             |        | (B) OP  | ERAND | )             | ٦                | Π       |

|---|-------------|---|------|---------|---|--------|----|-----------|-----|---------|-----|---------------|--------|---------|-------|---------------|------------------|---------|

|   | LINE<br>3 5 | Ľ | :0UI | 1T<br>7 | 8 | LABEL  | 13 | OPERATION |     | ADDRESS | ±   | CHAR.<br>ADJ. | ONI 27 | ADDRESS | ±     | CHAR.<br>ADJ. | 0<br>1<br>3<br>9 | d<br>39 |

|   | 0,110       | Ī |      | -       |   | L L l. |    | B.WZ      | U.P | DATE    |     | 1.1           |        | 0.0.7.4 | 11    | . I           |                  | K       |

Figure 2. SPS Instruction with Symbolic and Actual Addresses

#### ASTERISK ADDRESSES

An asterisk address is the character "\*" left-justified in the address field. Like symbolic addresses, it has a core-storage equivalent, but this equivalent address is simply the rightmost, or low-order, position in the instruction or data field defined by the statement.

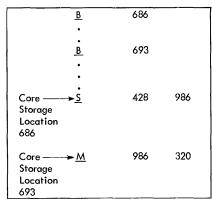

Figure 3 shows an SPS statement with an asterisk address. In this example, the instruction was assigned the address 0906 during assembly. Because the instruction is seven characters in length, the low-order position of the instruction is 0912. The processor substitutes this address in the A-operand of the statement shown in Figure 3 and assembles it: <u>M</u> 912285. Thus, the actual machine-language instruction will appear in core storage as shown in Figure 4 after the object program has been loaded.

| 1 |       |       |          |           | (A) OP  | RANC |               |        | (B) OPE | RAND            |          | ٦       |

|---|-------|-------|----------|-----------|---------|------|---------------|--------|---------|-----------------|----------|---------|

|   | LINE  | COUNT | LABEL (3 | OPERATION | ADDRESS | ±    | CHAR.<br>ADJ. | ONI 27 | ADDRESS | ± CHAR.<br>ADJ. | 39<br>19 | d<br>39 |

|   | 0,1,0 |       |          | M.C.W     | *       |      | 1 . 1         |        | 02.85   |                 | T        | ٦       |

Figure 3. SPS Statement with an Asterisk Address

| Character                | M   | 9   | 1   | 2   | 2   | 8   | 5   |

|--------------------------|-----|-----|-----|-----|-----|-----|-----|

| Core-Storage<br>Location | 906 | 907 | 908 | 909 | 910 | 911 | 912 |

Figure 4. Assembled Instruction in Core Storage

BLANK ADDRESSES

Blank addresses are valid in instructions where no operand is needed. (See *Imperative Operations*.)

### Input-Output Operands

The three-character addresses of tape units, disk storage units, and other input-output or storage units requiring special addresses are written left-justified in the A-operand field.

For example, the three-character address of tape unit 1 is the A-operand of the SPS statement shown in Figure 5.

### **Constant Operands**

A constant operand is valid only in an area-definition statement which contains a constant to be loaded with the assembled object program. The constant should be written and punched exactly as it is to be loaded and stored. It must begin at column 24 and may extend to column 55.

Figure 6 shows a constant operand. The field to be defined is labeled FICALT. The constant is 480000.

Character Adjustment (Columns 23-26 and 34-37). It is possible to reduce the number of labels required in a source program by using a character-adjustment factor with an actual, asterisk or symbolic address in the operand field of an SPS source program statement.

The adjustment factor is written and punched as a plus or minus (& or -) in the  $\pm$  column (23 or 34) and the number of positions of adjustment (as many as 3 digits) right-justified in the Char. Adj. field (columns 24-27 or 35-38).

During the assembly of the machine-language object program entry, this adjustment factor is added to or subtracted from the actual address assigned to the label by the processor. Thus, one label can

|   |       |       |               | (A) OPE | RAND    |               |      | (B) OPE | RAND  |      | Τ           |

|---|-------|-------|---------------|---------|---------|---------------|------|---------|-------|------|-------------|

|   | LINE  | COUNT | <br>OPERATION | ADDRESS | ±<br>23 | CHAR.<br>Adj. | IND. | ADDRESS | ± CHA | . 15 | s d<br>8 39 |

| ľ | 0,1,0 | . ,   |               | 10.UI   | 1       | 1.1.          |      | INPUT   |       |      | R           |

Figure 5. Addressing a Tape Unit in an SPS Statement

|   |      | Τ |       |     |       |    |       |      | (A) OPERAND |    |       |     | (B) OPERAND |     |       |    |    |

|---|------|---|-------|-----|-------|----|-------|------|-------------|----|-------|-----|-------------|-----|-------|----|----|

| l | LINE | Į | COUNT |     | LABEL |    | OPERA | TION |             | ±  | CHAR. | NO. | ADDRESS     | ±   | CHAR. | Ū. | d  |

|   | 3    | 5 | 67    | 8   |       | 13 | 14    | 16   | 17          | 23 | ADJ.  | 27  | 28          | 34  | ADJ.  |    | 39 |

| J |      | . | 0L    | E I | CAL   | т  | nc    | 5    | <b>/</b>    | 1  | 480   | 2   | 00          | 1 1 |       |    |    |

Figure 6. Constant Operand

|         |          |                   |           | (A) OPE            | RAN        | D             |   | (8) 090           | RAND    | )             |      |

|---------|----------|-------------------|-----------|--------------------|------------|---------------|---|-------------------|---------|---------------|------|

|         | COUNT    |                   | OPERATION | ADDRESS            | ±<br>23    | CHAR.<br>ADJ. |   | ADDRESS           | ±<br>34 | CHAR.<br>ADJ. | d 31 |

| 0,1,0   |          |                   | B         | ENTRYA             |            |               |   |                   |         | 1             |      |

| 0 2 0   |          |                   | •         |                    |            |               |   | where the barry   |         |               |      |

| 0,3,0   | 1        | L                 | · .       |                    | 1.1        |               |   | and the local law |         |               | 1    |

| 0,4,0   |          | L L L L L L L L L | •         | and and and a sub- | 1.1        |               |   | - t . 1 . 1 . 1   | 11      |               | +    |

| 0, 8, 0 |          |                   | B         | ENTRYB             | <u>   </u> |               |   |                   | 1.1     |               | 1    |

| 0,6,0   |          |                   | ·         |                    |            |               |   |                   |         |               | 1    |

| 0 7 0   |          |                   | •         | and the standards  | 11         |               |   |                   |         | - landard     |      |

| 0,8,0   | <u> </u> |                   | • <u></u> |                    |            |               |   |                   |         |               | 4.   |

| 0,9,0   |          | ENTRYA            | S.        | DISCNT             | Ц          |               |   | TOTAL             |         |               |      |

| 1,0,0   |          | E N.T. R.N.B      | IMC:W     | TOTAL              | 11         | 1.4           | l | PRINT1            | 1 1     |               |      |

Figure 7. Two Labels Used

serve as a reference point for more than one address. For example, if ENTRYA is the label for an instruction which precedes the instruction, which could be called ENTRYB, the programmer can use ENTRYA as the reference point for ENTRYB.

If the instruction whose label is ENTRYA is 7 characters long, the symbolic entry operand ENTRYA +007 will produce an actual address equal to the address that would have been created if ENTRYB had been used as the label for the second instruction. Figure 7 shows a section of a source program in which two separate labels are used. Figure 8 shows the same section in which one label is used. Both sections produce the same result in the object program (Figure 9).

Figure 10 shows how character adjustment can be used to address a location within a labeled field.

DATE is a twelve-character constant. The character adjusted operand will cause only the first six digits of the date (i. e., DEC 28, rather than DEC 28, 1961) to be moved to 0243.

Because the number of labels used in a source program can have a significant effect on the amount of time required to assemble an SPS program, character

|             |       |                        |           | (A) OP   | RA         | ID            |          | (B) OP                                  | ERAND                                   |               |         |         |

|-------------|-------|------------------------|-----------|----------|------------|---------------|----------|-----------------------------------------|-----------------------------------------|---------------|---------|---------|

| LINE<br>3 5 | COUNT |                        | OPERATION | ADDRESS  | ±<br>23    | CHAR.<br>ADJ. | 01<br>27 | ADDRESS<br>28                           | ±<br>34                                 | CHAR.<br>ADJ. | SE IND. | d<br>39 |

| 0,1,0       |       |                        | B. !      | ENTRYA   | l          |               |          |                                         |                                         | -1            |         |         |

| 0,2,0       |       | And and a local sector | · ·       |          | <u> </u>   |               |          |                                         | 1.1.                                    |               |         | -       |

| 0,3,0       |       | [                      |           |          | <u> </u>   |               |          |                                         | <u>i - i</u>                            |               | -       | -       |

| 0,4,0       |       | I                      |           | Chim and | ÷-         |               |          | - · - · - · - · - · - · - · - · - · - · | <u>i -</u>                              |               |         | -       |

| 0,5,0       |       |                        | B         | ENTRYF   | <b>i</b> + | 0.0.7         |          | a la k il alandari                      | <u>i i</u>                              | - I - Jacob   |         | -       |

| 0 6 0       |       |                        | • j       |          | L          | i takun       |          |                                         | $\frac{1}{1}$                           |               | -       |         |

| 0,7,0       | f     | i tet destadad         |           |          | 1          | l<br>l        |          |                                         | ++                                      |               |         | ┝       |

| 0,8,0       |       | ENTRYA                 | c         | DISCNT   | -          |               |          | TATAL                                   | +++++++++++++++++++++++++++++++++++++++ |               |         | -       |

| 0,9,0       |       |                        | MCW       | TOTAL    | 1          | · ·           | -        | PRINTI                                  | 11                                      |               |         |         |

Figure 8. One Label Used with Character Adjustment

Figure 9. Assembled Instructions

|   |       |   |     | 1       |     |       |    |           |    | (A)     | OPER | AND     |               |        | Γ  | (8) 01  | PER | AND |               | _      | Π       |

|---|-------|---|-----|---------|-----|-------|----|-----------|----|---------|------|---------|---------------|--------|----|---------|-----|-----|---------------|--------|---------|

|   |       |   | 60U | 11<br>7 | 8   | LABEL | 13 | OPERATION | 17 | ADDRESS |      | ±<br>23 | CHAR.<br>ADJ. | . UND. | 28 | ADDRESS |     | ±   | CHAR.<br>ADJ. | S IND. | d<br>39 |

| 1 | 0,1,0 | Ì |     |         | - L |       |    | M.C.W     | D/ | AT E    | -    | -1      | . 6           |        | 02 | .4.3    | l   | 1   |               |        |         |

Figure 10. Character Adjustment Used in Addressing a Location within a Field

adjustment is especially recommended in source programs which require a considerable amount of labeling. The number of labels that can be processed in one pass of SPS assembly depends upon the size of the processing 1401. Details are given in the operating section of this publication.

Note: The programmer must be careful when making insertions in a source program where character adjustment has been used. The insertion could necessitate changing the adjustment factor in one or more SPS statements. This same caution also applies to patching.

Indexing (Columns 27 and 38). If the advancedprogramming feature is available in the machine that executes the object program (object machine), the programmer may indicate that an actual, symbolic, or asterisk address is to be indexed. He does this by writing the SPS index code in the index column of an SPS statement.

The index codes are 1, 2, and 3. A code 1 in an index column specifies that the address in the same operand field is to be indexed by the contents of index location 1 (core-storage locations 087-089) when the object program is executed. A code 2 specifies index location 2 (core-storage locations 092-094) and a code 3 specifies index location 3 (core-storage locations 097-099).

When the processor program encounters an indexed operand, it puts tag bits over the tens position of the assembled three-character machine address as follows:

| INDEX CODE | Tag Bits<br>Tens Position | Zone Punch |

|------------|---------------------------|------------|

| 1          | A-bit                     | 0          |

| 2          | B-bit                     | 11         |

| 3          | A and B-bits              | 12         |

|            |                           |            |

For example, the source program statement shown in Figure 11 specifies that the B-operand is to be modified by the contents of index location 1. The processor will assemble an instruction that will cause TOTAMT to be moved to a field whose address is equal to 596 plus the contents of index location at program execution time. If index location 1 contains 100 when the instruction is executed, TOTAMT will be moved to 696. Assume that the equivalent address of TOTAMT is 428. The machine-language instruction produced by the SPS processor program will be: <u>M</u> 428 5Z6.

|   |       | T |          |     |    |       |    | (A) OPE | RAN | D             |      | (B) OPE | RAN | 0             |    |    |

|---|-------|---|----------|-----|----|-------|----|---------|-----|---------------|------|---------|-----|---------------|----|----|

|   | LINE  | ł | COUNT    |     | -  | RATIO | 1  | ADDRESS | ±   | CHAR.<br>ADJ. | IND. | ADDRESS | ±   | CHAR,<br>ADJ. | ġ  | d  |

| 1 | 3 0   | Ľ | <u> </u> | 8 3 | 14 | 14    | 17 |         | 23  |               | 27   | 28      | 341 |               | 38 | 39 |

| 1 | 0,1,0 | l |          |     | M. | C'h   | T. | OTAMT   | 1   |               |      | 0.5.9.6 |     |               | 1  |    |

Figure 11. SPS Statement Specifying Indexing

Note: Character adjustment and indexing entries are valid only with core-storage address operands, and then only when the address field of the operand is actual, symbolic, or asterisk. These entries are not valid with input-output unit operands or constant operands, nor are they valid when a core-storage address operand designates the address at which a defined area or constant is to be stored.

### d-Character (Column 39)

Some 1401 instructions require a special modifier to the operation code called a *d-character*. It is a single alphabetic, numerical, or special character written and punched in column 39. The d-characters are always written in machine-language and are simply transferred by the processor to the d-character position of the assembled machine-language instruction.

### Comments (Columns 40-55)

This field is reserved for programmer's notes or comments about a particular entry. A source program that contains a complete set of comments can be more easily understood and traced by all persons concerned with a given program. The comments have no effect on the object program as it is assembled or executed. Columns 56-75 of source program cards must be left blank, or incorrect processing will occur.

### COMMENTS CARD

To provide the programmer with the ability to insert more extensive descriptive information in the program listing than is possible by using the comments field on a program entry card, a comments card may be included in the source program deck.

Comments cards will not be assembled nor will they affect the assembling procedure. When encountered by the processor, they will be reproduced unaltered in the SPS output deck, and will be bypassed when the object program is being loaded.

#### The Programmer:

- 1. Indicates with an asterisk in the first position of the label field (column 8) that the card is a comments card.

- 2. May write the comment beginning at any position (columns 9-55). Comments extending beyond position 55 may cause an error during processing.

- The Processor: Reproduces (unaltered) the comment in proper sequence in the program listing.

*Example:* In the sample program, the entry in Figure 12 is a comments card entry.

### Identification (Columns 76-80)

This field may contain any 1401 characters which the programmer selects to identify the program.

### **Address Assignment**

To assign addresses to instruction and area-definition entries, the 1401 SPS processor uses a "storage assignment counter." This counter stands at 333 at the beginning of assembly (333 is the first available storage location beyond the standard read punch and print areas). However, the programmer can force the processor to begin assigning addresses elsewhere. See Origin.

During the first pass of assembly, the processor allocates storage for constants, work areas, and instructions. The amount of storage needed for each such entry is determined by the number in the count field. This number is simply added to the storage-address assignment-counter to develop addresses.

If the statement being processed has a label, the processor transfers it and its equivalent address to the label table.

During the second pass the processor converts these addresses to three-character machine addresses and stores them in the object program statements where corresponding symbols appeared in the operand fields of the source program statements. If character adjustment and indexing are specified, addresses are modified before they are stored.

Addresses for asterisk operands in instructions are determined by the address assigned to the low-order position of the instruction. This information is part of the loading data and is thus available when instructions are assembled for the object program deck.

Note: Actual addresses in area-definition statements do not affect the storage assignment counter and the count field in these statements is ignored. However, labels and the actual addresses associated with them are stored in the label table. The programmer must be careful that the locations specified in these statements are not the same locations that will be allocated by the processor to other statements in the source program. Otherwise, the processor will re-allocate them, and part of the object program will be destroyed at program load time.

Figure 12. Typical Entry on an SPS Comments Card

### **Declarative Operations**

### (Area-Definition Statements)

The IBM 1401 SPS provides four different declarative operations for reserving work areas and constants.

| MNEMONIC OP   | Code | Purpose                        |

|---------------|------|--------------------------------|

| DCW           |      | Define Constant with Word Mark |

| $\mathbf{DC}$ |      | Define Constant (no Word Mark) |

| DS            |      | Define Symbol                  |

| DSA           |      | Define Symbol Address          |

#### DCW – Define Constant With Word Mark

General Description: A DCW statement causes a constant to be loaded into a core-storage area and a word mark to be set in the high-order position of this area at program load time.

#### The Programmer:

- 1. writes DCW in the operation field.

- 2. writes in the count field the number of core-storage positions needed to store the constant or work area.

- 3. writes a symbol in the label field if he wishes to refer later to the address of the field where the constant is stored.

- 4. writes the address of the area in which the constant is to be stored. If the programmer wishes to let the processor assign the address, he simply writes an asterisk (\*) in column 17. Otherwise, he writes an actual address beginning in column 17. In any case the address will refer to the low-order (units) position of the defined area.

- 5. writes the constant beginning in column 24 of the coding sheet. The constant may extend to the end of the comments field (column 55). Thus, the maximum size of a constant is 32 core-storage positions.

- 6. may write a comment in columns 40-55 if these positions are outside the range of the constant itself as specified in the count field.

NOTE: In SPS-1, comments in DC and DCW statements are never listed. DCW and DC operands may not have character adjustment or indexing.

#### NUMERICAL CONSTANTS

A plus or minus sign can precede a numerical constant. A plus sign causes AB-bits to be placed over the units position of the constant; a minus sign causes a B-bit to be put there. The plus or minus sign is written and punched in column 23. If no plus or minus sign appears in column 23, the constant is stored at program load time as an unsigned field.

|   |       |      |      |       |         |    |    | (A)     | OPERAN | D         |    |      |    | (B) OPE | RAN | D     |      |    |

|---|-------|------|------|-------|---------|----|----|---------|--------|-----------|----|------|----|---------|-----|-------|------|----|

|   | LINE  | COUN | LAB  |       | OPERATI |    |    | ADDRESS | ŧ      | CH/<br>AD | 4  | IND. |    | ADDRESS | ±   | CHAR. | IND. | d  |

|   | 3 5   | 6    | 8    | 13    | 14      | 16 | 17 |         | 23     |           |    | 27   | 28 |         | 134 |       | 38   | 39 |

| ļ | 0,1,0 | 0.2  | CONS | 5.T.I | DC      | W  | 3  | 9.8.7   | . 4    | 1.0       | ), |      |    | 1       |     |       | -    |    |

Figure 13. Numerical Constant (Signed)

*Example:* Figure 13 shows the numerical constant +10 defined in a pcw statement. The programmer has selected core-storage positions 3986 and 3987 as the location for the constant. It will be stored 1?.

Figure 14 shows an unsigned numerical constant (designed for use as a work area). In this example seven zeros are loaded to initialize the work area to 0000000. The asterisk indicates that the processor is to assign the address of the constant.

|   |       |   | [  |     |   |    |      |       |     |       | T   |    | (A) 0           | PERA | ND |               |         | (8) 05  | ERAN | D             |       |         |

|---|-------|---|----|-----|---|----|------|-------|-----|-------|-----|----|-----------------|------|----|---------------|---------|---------|------|---------------|-------|---------|

|   | LINE  | 5 | C( | DUN | 7 |    | LABI |       | 0PE | RATIO |     | 7  | ADDRESS         | ±    | Γ  | GHAR.<br>ADJ. | 0 NI 27 | ADDRESS | ±    | CHAR.<br>ADJ. | SIND. | d<br>39 |

| ł | 9,1,0 | 0 | Č  | ).' | ĺ | NE | J.A  | A.M.T | D   | c١    | - 1 | ¥. | ملديدا بدراسر ا | 1    | 10 | 0.0.0         | 0       | 0.0.0   | 1    |               |       | Ĵ       |

Figure 14. Work Area Defined by a DCw Statement

#### ALPHAMERICAL CONSTANTS

An alphamerical constant can consist of any valid 1401 characters. Alphamerical constants are always unsigned.

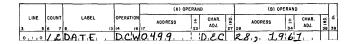

Example: Figure 15 shows the alphamerical constant DATE defined by a DCW statement. The programmer has selected 0499 as the address of the constant. Because DATE is now equivalent to address 0499, the constant can be referred to as either DATE or 0499. The constant will be loaded as  $\underline{D}EC$  28, 1961.

Figure 16 shows the alphamerical constant EDTWD1 defined in a DCW statement. The constant §bb,bb0.bb will appear in core storage as a field whose units position is determined by the processor.

Figure 15. Alphamerical Constant

| ł |       |       |        |           | (A      | ) OPERAN | )             |    | (B) OPI | ERAND |               | 7  |    |

|---|-------|-------|--------|-----------|---------|----------|---------------|----|---------|-------|---------------|----|----|

|   | LINE  | COUNT |        | OPERATION | ADDRESS | ±        | CHAR.<br>ADJ. | Ň  | ADDRESS | ±     | CHAR.<br>ADJ. | ġ  | d  |

| 1 | 3 5   | 6 7   | 8 13   | 14 16     | 17      | 23       |               | 27 | 20      | 1341  |               | 38 | 38 |

| 1 | 0.1.0 | 1.0   | EDTWD1 | DCW       | *       |          | \$5           |    | 0,-,    | 11    |               |    |    |

Figure 16. Edit Control Word Defined by a DCw Statement

#### BLANK CONSTANTS

A blank constant appears as blanks in the constant field (columns 24 through the length of the area as specified by the count field).

|       |       |       |           | (A) OPE  | RAN | D             |     | (B) OPE     | RAND   |   | T    | ٦  |

|-------|-------|-------|-----------|----------|-----|---------------|-----|-------------|--------|---|------|----|

| LINE  | COUNT | LABEL | OPERATION | ADDRESS  | ±   | CHAR.<br>ADJ. | GNI | ADDRESS     | + CHAP |   | ġ    | d  |

| 3 5   | 6 7   | 8 13  | 14 16     | 17       | 23  |               | 27  | 28          | 34     | 3 | 58 3 | 39 |

| 0,1,0 | 05    | EMPTY | DCW       | <b>X</b> |     |               |     | 1 1 1 1 1 1 |        |   |      |    |

Figure 17. Blank Constant

*Example:* Figure 17 shows a blank constant <u>b</u>bbbb coded in a DCW statement and labeled EMPTY. The processor assigns the address.

### The Processor:

- 1. allocates a field in core storage to store the constant. The number in the count field determines the number of positions allocated.

- 2. adds the number in the count field to the number that was standing in the storage assignment counter if there is an \* in column 17. The result becomes the address of the constant. This address is made equivalent to the label, and the two are stored in the label table.

If the programmer has specified the address, this address is equated to the label before it is stored in the label table. The count field is examined and used to create the loading data for the DCW card, but the storage assignment counter is undisturbed.

- 3. substitutes the equivalent addresses of labels in the operands of symbolic program statements which have corresponding symbolic addresses during assembly of the object program.

- 4. produces a card, as part of the object program, containing the data defined, with a sign if required, and instructions to load the constant into core storage with a word mark in the high-order position. This card is loaded with the object program, and the constant is stored exactly as the DCW source program statement defined it. For blank constants, the area is cleared of all existing word marks except the high-order word mark for the DCW constant.

### DC - Define Constant (No Word Mark)

General Description: This statement is the same as a pew statement except that the processor does not set a word mark in the high-order position of the constant.

NOTE: The storage area to which the constant is to be moved should be cleared of word marks.

### **DS** – Define Symbol

General Description: DS statements cause the processor to assign equivalent addresses to labels or to assign storage for work areas. DS statements differ from DCW and DC statements in that no data is loaded into the defined area at program load time. A DS-defined area is unaffected during the loading of the object program. Data, word marks, instructions, previously put in the area, remain unaltered. Thus, if DS statements are used only to define areas, using a clear storage routine before loading the program is recommended.

Some ps statements affect the storage assignment counter. These can be used to bypass areas needed for independent routines (instructions or data not included in the source program being assembled) or for storing constants for which the programmer has selected the actual storage locations.

### The Programmer:

- 1. writes DS in the operation field.

- 2. writes a symbol in the label field if he wishes to refer symbolically to the low-order position of the area.

- 3. writes the address of the area.

If the processor is to assign the address, he writes an asterisk in column 17 and writes a number in the count field to indicate the size of the area.

If the programmer wants to equate the label to an actual address or I/O unit operand, he writes the address or I/O operand beginning in column 17. In this case no storage will be allocated by the processor, so the count field is left blank.

NOTE: DS statements cannot be character-adjusted or indexed.

- The Processor:

- 1. adds the number in the count field to the storage assignment counter and equates the resulting address to the label if one appears in the ps statement if there is an asterisk in column 17. If an asterisk or I/O unit operand appears in the ps statement, the processor equates the label to the operand.

- 2. substitutes the equivalent addresses of labels in the operands of symbolic program statements which have corresponding symbolic addresses during the assembly of the object program.

- 3. leaves the defined area unaltered during object program loading.

- *Examples:* Figure 18 shows a DS statement with an asterisk address. This 8-position area which can be referred to as INPUTA will be assigned an actual address which will be the low-order core-storage position occupied by the area when the program has been loaded.

Figure 19 shows a DS statement used to equate a label to an actual core-storage address. (This type of DS statement is used for assembly only, and does not require any storage space in the object machine. Thus,

|      |     |       |         | Τ         |    | (A)     | OPERAND |       |          | (B)     | OPERAND | ,             |       |    |

|------|-----|-------|---------|-----------|----|---------|---------|-------|----------|---------|---------|---------------|-------|----|

| LINI | ε.  | COUNT |         | OPERATION | 17 | ADDRESS | ±<br>23 | CHAR. | . GNI 27 | ADDRESS | ±<br>34 | CHAR.<br>ADJ. | SIND. | d  |

| 0.1  | . 0 | 0.8   | INPUT A | DS!       | *  |         |         |       | 21       |         |         |               | 30    | 29 |

Figure 18. Defining an Area with a DS Statement

| 1 |       | ٦ |          |          |     |     |      |   |          | Ĩ        | (       | A) OPI | RAN     | 0             |        | (B) OF        | ERANC   | >             |         |         |

|---|-------|---|----------|----------|-----|-----|------|---|----------|----------|---------|--------|---------|---------------|--------|---------------|---------|---------------|---------|---------|

| Ì | LINE  |   | COL<br>6 | INT<br>7 | 8   | ι   | ABEL |   | OPERATIO | он<br>16 | ADDRESS | 1      | ±<br>23 | CHAR.<br>Adj. | QN1 27 | ADDRESS<br>20 | ±<br>34 | CHAR.<br>ADJ. | 9<br>30 | d<br>39 |

|   | 0,1,0 | , |          | L        | C.L | ) R | GR   | 0 | DS       |          | 00.4.4  |        |         |               |        |               | 1.1     |               |         |         |

Figure 19. Ds Statement Equating a Symbolic Address to an Actual Address

it is very useful in creating symbols for addresses that must be referenced often in the source program.) An input card contains current gross in card columns 40-44. When the card is read into 1401 core-storage, current gross will be in positions 0040-0044. The programmer wants to refer to current gross as curcre so that he does not have to remember the actual address (0044). The statement shown in Figure 19 allows him to use curcro as a symbolic address for 0044.

Figure 20 shows how a DS statement can label a tape unit. The programmer can now use TAPE1 instead of % U1 in the A-operand of a magnetic tape instruction.

Figure 21 shows how a ps statement can bypass 20 positions of core storage. The constants of the storage assignment counter will be increased by 20 when the processor encounters this statement. The processor will not re-allocate these 20 storage positions. However, an actual address in another area-definition statement or an instruction patch card can cause data to be loaded into them. For example, if the counter contained 0936 before this statement was processed, it would contain 0956 afterward. The pcw statement shown in Figure 21 would cause const2 (1875) to be loaded into storage positions 0953-0956 at object program load time.

| ٢ |       |           |       |    |        |            | (A)     | OPERA | ND |               |       | (8)     | OPERA | AND   |          | Ι |         |

|---|-------|-----------|-------|----|--------|------------|---------|-------|----|---------------|-------|---------|-------|-------|----------|---|---------|

|   |       | COUNT     | LABEL | 13 | OPERAT | 110N<br>16 | ADDRESS | ±     | Ţ  | CHAR.<br>Adj. | 0N 27 | ADDRESS | 13    | CHAR. | 02<br>38 |   | d<br>39 |

|   | 0,1,0 | <u>, </u> | TAPE: | 1  | DS     |            | U.I.    |       | ł  |               |       |         | 1     | 1     | _        | 1 | _       |

Figure 20. Assigning a Label to a Tape Unit

|             |              |          | (A) (   | (A) OPERAND |               |        |               | (B) OPERAND |         |  |  |  |  |

|-------------|--------------|----------|---------|-------------|---------------|--------|---------------|-------------|---------|--|--|--|--|

| LINE<br>3 5 | COUNT<br>6 7 | OPERATIO | ADDRESS | 23          | CHAR.<br>ADJ. | 0K1 27 | ADDRESS<br>28 | - AD1       | 9<br>38 |  |  |  |  |

| 0.1.0       | 2.0          | D.S.     | ¥       | 11          | 1-1           |        |               |             | _       |  |  |  |  |

Figure 21. Advancing the Storage Assignment Counter and Using the Bypassed Area

#### **DSA – Define Symbol Address**

General Description: A DSA statement causes the threecharacter machine address which the processor has assigned to a label to be stored as a constant when the object program is loaded. This three-character address is called an *address constant*. Address constants are used to modify addresses during the *execution* of an object program.

### The Programmer:

- 1. writes DSA in the operation field.

- 2. may leave the count field blank because an address constant is automatically assigned three core-storage positions by the processor.

- 3. may write a symbol in the label field if he wishes to refer later to the address of the address constant.

- 4. writes the address of the area in which the address constant is to be stored. If the programmer wishes to let the processor assign the address, he writes an asterisk (\*) in column 17. In any case, the address will refer to the units position of the three-character address constant.

- 5. writes the symbol whose equivalent address is to be the address constant beginning in column 28 of the (B) operand field. This operand may have character adjustment and indexing.

#### The Processor:

- 1. allocates a three-position field in core storage in which will be stored the address constant at program-load time.

- 2. adds three to the number that was standing in the core storage assignment counter if there is an \* in column 17. The result becomes the address of the address constant. This address is made equivalent to the label, and the two are stored in the label table. If the programmer has specified the address, this address is equated to the label before it is stored in the label table. The storage assignment counter is not affected when an actual address is used.

- 3. looks up in the label table, the equivalent address of the symbol in the B-operand and uses this address as the address constant.

- 4. produces a DSA card containing the address constant and instructions to load this constant into core storage with a word mark in the high-order position of the three-character field.

- Examples: Figure 22 shows how a DSA statement can develop an address constant. In another part of his source program, the programmer has used the symbol WHTAX. During assembly, the processor will assign a three-character machine address to WHTAX, but the programmer does not know what that address will be. Yet for an address modification operation he needs this machine address (stored as a constant)

| 1 |       |       |       |           | (A) OP  | ERAND   | )             | _      | (B) OP        | ERAND   |               |         |         |

|---|-------|-------|-------|-----------|---------|---------|---------------|--------|---------------|---------|---------------|---------|---------|

|   | LINE  | COUNT |       | OPERATION | ADDRESS | ±<br>23 | CHAR.<br>ADJ. | 0H1 27 | ADDRESS<br>26 | ±<br>34 | CHAR.<br>ADJ. | .0N1 36 | d<br>39 |

|   | 0,1,0 | 0.2   | WHTAX | DCW       | *       |         | 18,           |        | WHTAX         |         |               |         | H       |

Figure 22. Area Definition Entries

so that he can write an instruction that will move it into the A- or B-operand of another instruction at program *execution* time. The programmer wishes to refer to the address of the address constant as a ADCONA.

For the example shown in Figure 22 assume that the storage assignment counter is standing at 584 when the DCW statement is encountered.

The processor will assign 586 as the address of WHTAX and 589 as the address of ADCONA. These two constants will appear in core storage as shown in Figure 23, after the object program has been loaded.

Figure 24 shows another section of the source program that uses ADCONA.

Assume that the equivalent address of INSTR is 829 and WORKAR has an equivalent address of 763. The processor will assemble these two instructions. <u>M</u> 589 832 <u>A</u> 000 763. When the first instruction is executed in the object program, the second instruction will be modified to <u>A</u> 586 763. When the second instruction is executed, WHTAX (18) will be moved to WORKAR.

Figure 25 shows a DSA statement with an actual address in the B-operand. In this case the programmer knows the actual address he wants to store as an address constant, but he does not want to bother to translate the actual address to a three-character machine address. The DSA statement causes the machine address of 12332 (<u>33B</u>) to be stored as an address constant in core-storage locations 14088-14090. The programmer can refer to the address constant as 14090 or as ADDRS1.

|                          | WXTAX    |     | A   | DCON | NA  |  |

|--------------------------|----------|-----|-----|------|-----|--|

| Character                | <u> </u> | 8   | 5   | 8    | 6   |  |

| Core–Storage<br>Location | 585      | 586 | 587 | 588  | 589 |  |

Figure 23. Constants in Core Storage

Figure 24. Instructions Using an Address Constant

|       |       |        |           | (A) OP  | ERANI | )             |      | (8) OP  | ERAND |               |    |    |

|-------|-------|--------|-----------|---------|-------|---------------|------|---------|-------|---------------|----|----|

| LINE  | COUNT | LABEL  | OPERATION | ADDRESS | ±     | CHAR.<br>ADJ. | IND. | ADDRESS | ±     | CHAR.<br>ADJ. | ŝ  | d  |

| 3 5   | 6 7   | 8      | 3 14 16   | 17      | 1231  |               | 27   | 28      | 1341  |               | 38 | 39 |

| 0.1.0 |       | ADDRSY | DSD       | 14090   | 1 1   |               |      | 42332.  | 1     |               | Г  | Г  |

Figure 25. DSA Statement with Actual B-address

### Imperative Operations (Instructions)

General Description: SPS imperative operations are direct commands to the object machine to act upon data, constants, auxiliary devices, or other instructions. Thus, they are the symbolic statements for the instructions to be executed in the object program. Most of the statements in the source program will be imperative instructions. The programmer must be careful to write instructions that use only the features and devices that are included in the machine that will execute his program.

#### The Programmer:

- 1. writes the operation code for the instruction in the operation field. Mnemonic op codes are written left-justified in the operation field. Actual op codes are written in column 16. (Also, see *Coding Sheet*).

- 2. leaves the count field blank if he so desires.

- 3. writes a symbol in the label field if the instruction is an entry point for a branch instruction elsewhere in the program or, if he wishes to make other reference to it. This label is assigned an address equal to the core-storage location occupied by the operation code of the associated instruction at program load time. Thus, the programmer can use this label as a symbolic address in another SPS instruction.

- 4. writes in the (A) and (B) operand fields, core-storage addresses or I/O Unit Addresses.

Core Storage Addresses. These are symbolic, actual, asterisk, or blank addresses representing the A/I or B addresses of actual machine-language instructions. Symbolic, actual, or asterisk operands may have character adjustment and indexing.

NOTE: Blank operands are valid:

- a. in an instruction that does not require an operand (such as a read instruction).

- b. in instructions in which useful A- or B-addresses are supplied by the chaining method such as MCW FIELDA FIELDB MCW MCW.

If an instruction is to have addresses stored by other instructions, the operand or operands affected must not be left blank. Zeros are recommended as shown in the DSA example.

Input/Output Unit-Addresses. An I/O unit operand is valid only in the A-operand field of an SPS statement. It is the three-character address of an auxiliary device such as tape unit (% Ux).

5. writes the d-character in column 39 if one is needed for the instruction. The d-character is always written in actual machine language.

NOTE: Blank is not a significant d-character except in the Branch-If-Character-Equal instruction. A Branch-

If-Bit-Equal (BBE) instruction with a blank d-character will be assembled as a seven-character instruction.

### The Processor:

- 1. substitutes the actual machine-language operation code in place of the mnemonic operation code and transfers it to the operation-code position of the assembled machine-language instruction. Actual op codes are simply transferred as they are written in an SPS instruction statement.

- 2. counts the number of characters that will appear in the assembled instruction and adds this number to the number that was standing in the storageassignment counter.

- 3. allocates a field in core storage that will be occupied by the assembled machine-language instruction.

- 4. stores the label (if one appears in the label field) and its equivalent address in the label table. Remember that an equivalent address assigned to a label in an instruction statement is the address assigned to the position occupied by the operation code when the instruction is loaded in the object machine.

- 5. looks up in the label table the equivalent addresses of symbols used in the operand fields of an instruction and inserts them in the actual machine-language instructions.

Converts actual addresses to three-character machine addresses and transfers them to the machinelanguage instruction.

Replaces asterisk addresses with the address occupied by the low-order position of the instruction in object-core storage, and transfers them to the machine-language instruction.

Transfers an input-output unit operand to the Aaddress portion of the machine-language instruction.

6. produces a card, as part of the object program, which contains the machine-language instruction, and the information necessary to load it with a word mark in the op-code position.

NoTE: All instruction operations: Arithmetic, Data Control, Logic Control, and System Control are explained in the *IBM 1401 Data Processing System Reference Manual*, Form A24-1403. Operations requiring special features (noted by an asterisk in Figure 38) are also described in this manual. The programmer should thoroughly review the operation code functions before attempting to program in SPS.

### **Special Mnemonic Operation Codes**

Three special mnemonic instruction operation codes are included for use with SPS-1 and SPS-2: Modify Address (MA), Load Unit (LU), and Move Unit (MU).

#### MA – Modify Address