File No. S360-50 Form C28-2008-0

# IBM System/360 Time Sharing System

# System Programmer's Guide

IBM System/360 Time Sharing System (TSS/360) makes a distinction between user and system programmers. This publication is specifically intended for persons responsible for maintaining, modifying, or extending the system and discusses:

- Operating environment

- Program structure

- Coding practices and conventions

- Privileged supervisor call instructions

- Serviceability aids

- System macro definitions

- Changing TSS/360

- Privilege Class E

This publication will aid you -- as a system programmer -- extend and modify IBM System/360 Time Sharing System. We'll discuss the programming capabilities available to you and the conventions followed in developing the programs that are already part of TSS/360. We'll also cover a number of examples designed to give you a feeling for what is involved in changing the system.

There are four sections to this publication. The <u>Introduction</u>, Section 1, contains a reader's guide to help you find your way through the publications devoted to system programming. In Section 2, <u>Resident Programs</u>, we'll discuss some of the factors that go into writing resident TSS/ 360 programs. The same topics are discussed for <u>Nonresident Programs</u> in Section 3. Section 4, <u>Defining Macro Instructions</u>, discusses the types of macro instrunctions used in TSS/360 and the techniques you can use in writing them. Section 5, <u>Generating</u> and <u>Maintaining TSS/360</u>, shows some sample changes to the system. Finally, in Section 6, <u>Programming with Privilege Class E</u>, the additional facilities that are available to the System Monitor are discussed.

You may be reading this publication just for interest; you may have no intention to modify TSS/360. If this is the case, be sure and see the reader's guide -- it will help you in selecting those publications most beneficial to you. If you plan to change TSS/360, you should be an experienced programmer who knows the overall design of the system. You should have read -- or have handy -- most of the user-programmer publications. Finally, you should thoroughly understand <u>IBM System/360</u> <u>Principles of Operation</u>, Form A22-6821, and <u>IBM System/360 Model 67 Functional Characteristics</u>, Form A27-2719.

#### First Edition (October 1967)

Significant changes or additions to the specifications contained in this publication will be reported in subsequent revisions or Technical Newsletters.

This publication was prepared for production using an IBM computer to update the text and to control the page and line format. Page impressions for photo-offset printing were obtained from an IBM 1403 Printer using a special print chain.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form is provided at the back of this publication for reader's comments. If the form has been removed, comments may be addressed to IBM Corporation, Time Sharing System/360 Programming Publications, Department 561, 2651 Strang Blvd., Yorktown Heights, N.Y. 10598

© International Business Machines Corporation 1967

| SECTION 1. INTRODUCTION                                                                                                                             |             | _      | _        | _   | _          | _ | 7              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|----------|-----|------------|---|----------------|

| Peader's Cuide                                                                                                                                      |             |        |          |     | •          |   | 7              |

| Reduer 5 Gurue                                                                                                                                      | • •         | •      | •        | •   | •          | • | 7              |

| SECTION 1: INTRODUCTION .<br>Reader's Guide<br>Program Logic Manuals<br>Assembler Language Manu                                                     | • •         | •      | ٠        | •   | •          | ٠ | <u>′</u>       |

| Assembler Language Manu                                                                                                                             | als         | •      | ٠        | •   | •          | • | 7              |

| Assembler Language Manu<br>System Programming With TSS<br>Who                                                                                       | /36         | )      | •        | •   | •          | ٠ | 8              |

| Who                                                                                                                                                 | • •         | •      | •        | •   | •          | ÷ | 8              |

| Why                                                                                                                                                 |             |        |          |     |            |   | 8              |

| TSS/360 Organization                                                                                                                                |             | -      | -        | -   | -          |   | 8              |

| TSS/360 Organization<br>Format And Notation                                                                                                         |             | -      | -        | •   | •          | 7 | ğ              |

| Nome Hield                                                                                                                                          | • •         | •      | •        | •   | •          | • | á              |

|                                                                                                                                                     | ••.         | •      | •        | •   | •          | • | 9<br>9         |

| Operation Field                                                                                                                                     | • •         | •      | ٠        | •   | •          | • | 9              |

| Operand Field                                                                                                                                       | • •         | •      | •        | •   | •          | • | -9             |

| Name Field Operation Field                                                                                                                          |             | ٠      | •        | • . | •          | • | 13             |

|                                                                                                                                                     |             |        |          |     |            |   |                |

| SECTION 2: RESIDENT PROGRA                                                                                                                          | MS          | ٠      | •        | •   | •          | ٠ | 16             |

| Operating Environment                                                                                                                               | • •         | ٠      | •        | •   | •          | ٠ | 16             |

| Operating Environment<br>Getting Started<br>Normal Operation<br>Extended Control PSW .<br>The Prefixed Storage Ar                                   | • •         | ٠      | •        | •   | •          | • | 16             |

| Normal Operation                                                                                                                                    |             | •      | •        | •   | •          | • | 16             |

| Extended Control PSW .                                                                                                                              |             | -      |          |     | <b>.</b> , |   | 16             |

| The Prefixed Storage Ar                                                                                                                             | ea          | -      | -        | -   | -          |   | 17             |

| Cummary                                                                                                                                             | cu          | -      | •        | •   | •          | • | 10             |

|                                                                                                                                                     | • •         | •      | •        | •   | •          | • | 10             |

| Summary<br>Dummy Sections<br>Purpose<br>Use<br>Module Structure                                                                                     | • •         | •      | •        | •   | •          | ٠ | 19             |

| Purpose                                                                                                                                             | • •         | ٠      | •        | •   | •          | ٠ | 19             |

| Use                                                                                                                                                 | • •         | •      | •        | •   | •          | • | 19             |

| Module Structure                                                                                                                                    |             |        |          |     |            |   | 20             |

| System Control Blocks<br>Module Design Consideration                                                                                                |             | -      | _        |     | -          | - | 21             |

| Module Design Consideration                                                                                                                         | 9           |        |          |     |            |   | 22             |

| Enabling And Disabling Inte                                                                                                                         |             | •      |          | •   | •          | • | 22             |

| Enabling And Disabling inte                                                                                                                         | rru         | pτs    | 5        | •   | •          | • | 22             |

| Naming Conventions                                                                                                                                  | • •         | ٠      | •        | •   | •          | ٠ | 23             |

| Program Module Names                                                                                                                                | • •         | •      | •        | •   | •          | • | 23             |

| System Control Block Name                                                                                                                           | s.          |        |          |     |            |   | 23             |

| Secondary Entry Points                                                                                                                              |             | _      |          | -   | -          |   | 24             |

| Secondary Entry Points .<br>Supervisor Linkage Conventi                                                                                             | one         |        | -        | •   |            | • | 25             |

| Supervisor Linkage convence                                                                                                                         | ons         | •      | •        | •   | •          | • | 25             |

| Getting Resident Working Sp<br>Programming Convention Comm                                                                                          | ace         | •      | •        | •   | •          | • | 23             |

| Programming Convention Comm                                                                                                                         | ent         | 3      | •        | •   | •          | • | 20             |

| SECTION 3: NONRESIDENT PRO                                                                                                                          | 007         | AC     |          |     |            |   | 28             |

|                                                                                                                                                     |             |        |          |     |            |   |                |

| Virtual Machine Structure                                                                                                                           | • •         | ٠      | •        | •   | •          | ٠ | 28             |

| Virtual Program Status Wo<br>Interrupt Storage Area .<br>Linkage Conventions<br>Type-I Linkage<br>Use of the Save Area .<br>Contents of the General | rd          | •      | •        | •   | •          | • | 28             |

| Interrupt Storage Area .                                                                                                                            | • •         | •      | •        | •   | •          | • | 28             |

| Linkage Conventions                                                                                                                                 |             | •      | •        | •   |            | • | 30             |

| Type-I Linkage                                                                                                                                      |             | -      | <u>.</u> |     | -          |   | 30             |

| lice of the Save Area                                                                                                                               |             | -      | •        | •   | •          | • | 32             |

| Ose of the Save Area .                                                                                                                              | • •         |        |          | •   | •          | • | 72             |

| Contents of the General                                                                                                                             | Reg         | JIS    | ce       | rs  |            | • | 22             |

| Transfer of Control .                                                                                                                               | • •         | •      | •        | •   | ٠          | ٠ | 33             |

| Type-II Linkage                                                                                                                                     | • •         | •      | •        | •   | •          | ٠ | 34             |

| Transfer of Control .<br>Type-II Linkage<br>The Save Area<br>Content and Usage of th                                                                |             |        | •        | •   |            | • | 34             |

| Content and Usage of th                                                                                                                             | e Ge        | ene    | ra       | 1   |            |   |                |

| Registers                                                                                                                                           |             |        |          |     |            |   | 35             |

|                                                                                                                                                     | • •         | •      | •        | •   | •          | • | 35             |

|                                                                                                                                                     | • •         |        | ٠        | •   | •          | • |                |

|                                                                                                                                                     | • •         |        | •        | •   | •          |   | 36             |

| Type-III Linkage                                                                                                                                    | • •         | •      | •        | •   | •          | • | 36             |

| The Save Area                                                                                                                                       |             | •      | •        | •   | •          | • | 36             |

| Content and Usage of                                                                                                                                |             |        |          |     |            |   |                |

| General-Purpose Registe                                                                                                                             |             |        | -        | _   |            | _ | 37             |

|                                                                                                                                                     | rs          |        |          | -   | -          | - |                |

|                                                                                                                                                     |             | •      | -        |     |            |   | 27             |

| Transfer of Control .                                                                                                                               | • •         | •      | •        | •   | •          | • | 37             |

| Transfer of Control .<br>Type-IV (Restricted) Link                                                                                                  | • •         | •      | •        | •   | •          | • |                |

| Transfer of Control .<br>Type-IV (Restricted) Link<br>Conventions                                                                                   | age         | •      | •        | •   | •          | • | 38             |

| Transfer of Control<br>Type-IV (Restricted) Link<br>Conventions<br>Use of the General Regi                                                          | age<br>     | •<br>• | •        | •   | •          | • | 38<br>38       |

| Transfer of Control .<br>Type-IV (Restricted) Link<br>Conventions                                                                                   | age<br>     |        | •        | •   | •          | • | 38             |

| Transfer of Control<br>Type-IV (Restricted) Link<br>Conventions<br>Use of the General Regi<br>Transfer of Control                                   | age<br>stei | •      | •        | •   | •          | • | 38<br>38<br>38 |

| Transfer of Control<br>Type-IV (Restricted) Link<br>Conventions<br>Use of the General Regi                                                          | age<br>stei | •      | •        | •   | •          | • | 38<br>38       |

| System Programmer Authority Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | 40                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •     | 40                                                                          |

| Privileged SVCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •     |                                                                             |

| Program Checkout System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •     | 40                                                                          |

| Dynamic Loader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •     | 41                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •     | 42                                                                          |

| I/O Device Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •     | 42                                                                          |

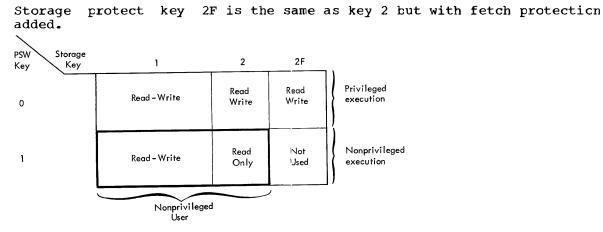

| Storage Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | 44                                                                          |

| Timekeeping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | 45                                                                          |

| Initial Virtual Storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •     | 45                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •     | 75                                                                          |

| Privileged Supervisor Call                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                                                                             |

| Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •     | 45                                                                          |

| CRTSI Create Task Status Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |                                                                             |

| (R)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •     | 47                                                                          |

| SCRTSI Special Create Task                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                                                                             |

| Status Index (R)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _     | 48                                                                          |

| DLTSI Delete Task Status Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •     |                                                                             |

| (7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | 48                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •     | 40                                                                          |

| SETUP Set Up Task Status Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |                                                                             |

| Field (R)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 48                                                                          |

| XTRCT Extract Task Status Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |                                                                             |

| Field (R)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | 50                                                                          |

| SETXTS Set Up Extended Task                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |                                                                             |

| Status Index Field (R)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | 51                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •     | 51                                                                          |

| XTRXTS Extract Extended Task                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |                                                                             |

| Status Index Field (R)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •     | 52                                                                          |

| CHAP Change Task Priority (R) .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •     | 52                                                                          |

| XTRTM Extract Accumulated CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                                                                             |

| Time (nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | 53                                                                          |

| SETSYS Set System Table Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -     |                                                                             |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | 53                                                                          |

| $(\mathbf{R}) \qquad \qquad$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •     | 55                                                                          |

| XTRSYS Extract System Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |                                                                             |

| Field (R)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 54                                                                          |

| RSTTIM Reset System Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •     |                                                                             |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 54<br>55                                                                    |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55                                                                          |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     |                                                                             |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55<br>56                                                                    |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55                                                                          |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55<br>56<br>56                                                              |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55<br>56                                                                    |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55<br>56<br>56<br>56                                                        |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55<br>56<br>56                                                              |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • • • | 55<br>56<br>56<br>56<br>57                                                  |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55<br>56<br>56<br>56                                                        |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • • • | 55<br>56<br>56<br>56<br>57<br>57                                            |

| RSTTIM Reset System Time<br>(nonstandard)<br>ALLTI Allow Task Initiation (R)<br>SETYMD Set Year, Month, and Day<br>(nonstandard)<br>SETTOD Set Time of Day<br>(nonstandard)<br>RDI Reset Drum Interlock<br>(nonstandard)<br>SETTU Set User Timer (R)<br>SETTU Set Real Time Interval<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                   | •     | 55<br>56<br>56<br>56<br>57                                                  |

| RSTTIM Reset System Time<br>(nonstandard)<br>ALLTI Allow Task Initiation (R)<br>SETYMD Set Year, Month, and Day<br>(nonstandard)<br>SETTOD Set Time of Day<br>(nonstandard)<br>RDI Reset Drum Interlock<br>(nonstandard)<br>SETTU Set User Timer (R)<br>SETTU Set Real Time Interval<br>(nonstandard)<br>REDTIM Read Elapsed Real Time                                                                                                                                                                                                                                                                                                                  |       | 55<br>56<br>56<br>57<br>57<br>57<br>58                                      |

| RSTTIM Reset System Time<br>(nonstandard)<br>ALLTI Allow Task Initiation (R)<br>SETYMD Set Year, Month, and Day<br>(nonstandard)<br>SETTOD Set Time of Day<br>(nonstandard)<br>RDI Reset Drum Interlock<br>(nonstandard)<br>SETTU Set User Timer (R)<br>SETTR Set Real Time Interval<br>(nonstandard)<br>REDTIM Read Elapsed Real Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                 | •     | 55<br>56<br>56<br>57<br>57<br>57<br>58<br>58                                |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55<br>56<br>56<br>57<br>57<br>58<br>58<br>58                                |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55<br>56<br>56<br>57<br>57<br>57<br>58<br>58                                |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55<br>56<br>56<br>57<br>57<br>58<br>58<br>58                                |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55<br>56<br>56<br>57<br>57<br>58<br>58<br>58<br>58<br>59                    |

| RSTTIM Reset System Time<br>(nonstandard)<br>ALLTI Allow Task Initiation (R)<br>SETYMD Set Year, Month, and Day<br>(nonstandard)<br>SETTOD Set Time of Day<br>(nonstandard)<br>RDI Reset Drum Interlock<br>(nonstandard)<br>SETTU Set User Timer (R)<br>SETTU Set Real Time Interval<br>(nonstandard)<br>REDTIM Read Elapsed Real Time<br>(nonstandard)<br>REDTIM Force Time Slice End (R)<br>AWAIT Wait for an Interrupt (R)<br>TWAIT Wait for Terminal I/O<br>Interrupt (R)                                                                                                                                                                           | •     | 55<br>56<br>56<br>57<br>57<br>58<br>58<br>58                                |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 555<br>56<br>56<br>57<br>57<br>58<br>58<br>58<br>58<br>59<br>59             |

| RSTTIM Reset System Time<br>(nonstandard)<br>ALLTI Allow Task Initiation (R)<br>SETYMD Set Year, Month, and Day<br>(nonstandard)<br>RDI Set Time of Day<br>(nonstandard)<br>RDI Reset Drum Interlock<br>(nonstandard)<br>SETTU Set User Timer (R)<br>SETTR Set Real Time Interval<br>(nonstandard)<br>REDTIM Read Elapsed Real Time<br>(nonstandard)<br>REDTIM Force Time Slice End (R)<br>AWAIT Wait for an Interrupt (R)<br>TWAIT Wait for Terminal I/O<br>Interrupt (R)<br>ADDPG Add Virtual Storage Pages<br>(R)                                                                                                                                    | •     | 55<br>56<br>56<br>57<br>57<br>58<br>58<br>58<br>58<br>59                    |

| RSTTIM Reset System Time<br>(nonstandard)<br>ALLTI Allow Task Initiation (R)<br>SETYMD Set Year, Month, and Day<br>(nonstandard)<br>RDI Set Time of Day<br>(nonstandard)<br>RDI Reset Drum Interlock<br>(nonstandard)<br>SETTU Set User Timer (R)<br>SETTW Set Real Time Interval<br>(nonstandard)<br>REDTIM Read Elapsed Real Time<br>(nonstandard)<br>REDTIM Force Time Slice End (R)<br>AWAIT Wait for an Interrupt (R)<br>TWAIT Wait for Terminal I/O<br>Interrupt (R)<br>ADDPG Add Virtual Storage Pages<br>(R)<br>ADSPG Add Shared Virtual                                                                                                        | •     | 555<br>56<br>56<br>57<br>57<br>58<br>58<br>58<br>59<br>59<br>60             |

| RSTTIM Reset System Time<br>(nonstandard)<br>ALLTI Allow Task Initiation (R)<br>SETYMD Set Year, Month, and Day<br>(nonstandard)<br>RDI Set Time of Day<br>(nonstandard)<br>RDI Reset Drum Interlock<br>(nonstandard)<br>SETTU Set User Timer (R)<br>SETTU Set Real Time Interval<br>(nonstandard)<br>REDTIM Read Elapsed Real Time<br>(nonstandard)<br>REDTIM Read Elapsed Real Time<br>(nonstandard)<br>SETTO Force Time Slice End (R)<br>AWAIT Wait for an Interrupt (R)<br>TWAIT Wait for Terminal I/O<br>Interrupt (R)<br>ADDPG Add Virtual Storage Pages<br>(R)<br>ADSPG Add Shared Virtual<br>Storage Pages (R)                                  | •     | 555<br>56<br>56<br>57<br>57<br>58<br>58<br>58<br>58<br>59<br>59             |

| RSTTIM Reset System Time<br>(nonstandard)<br>ALLTI Allow Task Initiation (R)<br>SETYMD Set Year, Month, and Day<br>(nonstandard)<br>RDI Set Time of Day<br>(nonstandard)<br>RDI Reset Drum Interlock<br>(nonstandard)<br>SETTU Set User Timer (R)<br>SETTU Set Real Time Interval<br>(nonstandard)<br>SETTR Set Real Time Interval<br>(nonstandard)<br>REDTIM Read Elapsed Real Time<br>(nonstandard)<br>TSEND Force Time Slice End (R)<br>AWAIT Wait for an Interrupt (R)<br>TWAIT Wait for Terminal I/O<br>Interrupt (R)<br>ADDPG Add Virtual Storage Pages<br>(R)<br>DELPG Delete Virtual Storage                                                    | •     | 555<br>56<br>56<br>57<br>57<br>58<br>58<br>58<br>58<br>59<br>59<br>60<br>61 |

| RSTTIM Reset System Time<br>(nonstandard)<br>ALLTI Allow Task Initiation (R)<br>SETYMD Set Year, Month, and Day<br>(nonstandard)<br>RDI Set Time of Day<br>(nonstandard)<br>RDI Reset Drum Interlock<br>(nonstandard)<br>SETTU Set User Timer (R)<br>SETTU Set Real Time Interval<br>(nonstandard)<br>SETTR Set Real Time Interval<br>(nonstandard)<br>REDTIM Read Elapsed Real Time<br>(nonstandard)<br>TSEND Force Time Slice End (R)<br>AWAIT Wait for an Interrupt (R)<br>TWAIT Wait for Terminal I/O<br>Interrupt (R)<br>ADDPG Add Virtual Storage Pages<br>(R)<br>DELPG Delete Virtual Storage                                                    | •     | 555<br>56<br>56<br>57<br>57<br>58<br>58<br>58<br>59<br>59<br>60             |

| RSTTIM Reset System Time<br>(nonstandard)<br>ALLTI Allow Task Initiation (R)<br>SETYMD Set Year, Month, and Day<br>(nonstandard)<br>SETTOD Set Time of Day<br>(nonstandard)<br>RDI Reset Drum Interlock<br>(nonstandard)<br>SETTU Set User Timer (R)<br>SETTU Set Real Time Interval<br>(nonstandard)<br>SETTR Set Real Time Interval<br>(nonstandard)<br>REDTIM Read Elapsed Real Time<br>(nonstandard)<br>TSEND Force Time Slice End (R)<br>AWAIT Wait for an Interrupt (R)<br>TWAIT Wait for Terminal I/O<br>Interrupt (R)<br>ADDPG Add Virtual Storage Pages<br>(R)<br>DELPG Delete Virtual Storage<br>Pages (R)                                    | •     | 555<br>56<br>56<br>57<br>57<br>58<br>58<br>58<br>58<br>59<br>59<br>60<br>61 |

| RSTTIM Reset System Time<br>(nonstandard)<br>ALLTI Allow Task Initiation (R)<br>SETYMD Set Year, Month, and Day<br>(nonstandard)<br>SETTOD Set Time of Day<br>(nonstandard)<br>RDI Reset Drum Interlock<br>(nonstandard)<br>SETTU Set User Timer (R)<br>SETTU Set Real Time Interval<br>(nonstandard)<br>SETTR Set Real Time Interval<br>(nonstandard)<br>REDTIM Read Elapsed Real Time<br>(nonstandard)<br>TSEND Force Time Slice End (R)<br>AWAIT Wait for an Interrupt (R)<br>TWAIT Wait for Terminal I/O<br>Interrupt (R)<br>ADDPG Add Virtual Storage Pages<br>(R)<br>DELPG Delete Virtual Storage<br>Pages (R)<br>CNSEG Connect Segment to Shared | •     | 555<br>56<br>56<br>57<br>57<br>58<br>58<br>58<br>59<br>60<br>61<br>63       |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 555<br>56<br>56<br>57<br>57<br>58<br>58<br>58<br>58<br>59<br>59<br>60<br>61 |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55556<br>56557<br>5757<br>585859<br>5960<br>6163<br>63                      |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 555<br>56<br>56<br>57<br>57<br>58<br>58<br>58<br>59<br>60<br>61<br>63       |

| RSTTIM Reset System Time<br>(nonstandard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | 55556<br>56557<br>5757<br>585859<br>5960<br>6163<br>63                      |

CKCLS -- Check Protection Class (R) ADDEV -- Add Device to Task 65 Symbolic Device List (R) . . 66 RMDEV -- Remove Device from Task Symbolic Device List (R) . . . . . 67 PURGE -- Purge I/O Operations (R) . 67 RESET -- Reset Device Suppression SPATH -- Set I/O Device Path (R) . . 69 PGOUT -- Write Virtual Storage Pages to External Storage . . . . 75 SETXP -- Set External Page Table VSEND -- Send Message to Another Task (R) ..... ERROR -- Indicate Supervisor 79 Detected Error (nonstandard) . . . . 79 SYSER -- Indicate Nonresident-Program Detected Error Privileged Program Naming Conventions 83 Writing Privileged System Programs . . 84 Program Design Considerations . . . . 87 Nonprivileged Supervisor Call . . . 88 Instructions . . . . . . . . . . ENTER -- Enter Privileged Service Routine (R) DLINK -- Transfer to Dynamic . . . . . 88 Loader for External Symbol Resolution (R) . . . . . . . . . . . 89 DELET -- Enter Delete Program . . . 89 (nonstandard) . . . . . . . . PCSVC -- Enter Program Checkout Subsystem (nonstandard) .... 90 CLIC -- Read Command From SYSIN (conditional) (nonstandard) . . . 90 CLIP -- Read Command From SYSIN (unconditional) (nonstandard) . . . 91 RTRN -- Enter Command Language Director to End RUN (R) ... 91 RSPRV -- Restore Privilege (R) . . 92 SECTION 4: DEFINING MACRO INSTRUCTIONS 93 addrx ..... 93 93 integer ..... 94 9/1 value . . . . . . . . . . . . . . . . . . 94 94 Linkage . . . . . . . . . . . . . . . . . . 95 S-Type Macro Definitions 97 Standard-form S-type macro definition 98 integer, absexp, and value . . . . 98

L-form S-type macro definition . . . . 99 E-form S-type macro definitions . . .101 integer, absexp, and value . . . . 102 Linkage . . . . . . . . **. . . .**102 Modified R-type macro definitions . .104 Modified S-type macro definitions . .104 Nonstandard macro definitions ....104 Techniques used in writing macro Defining Inner Macro Instructions . .106 Naming the First Executable Processing a Single Apostrophe . . . . 108 Terminal Apostrophe and Size . . .110 Limitation . . . . . . . . . . Keyword Operands and Standard Values .110 Substring Notation Processing . . . .110 N'&SYSLIST Handling in Mixed Mode Subscripts and Sublists ......... Logical Terms in Relational CHDINNRA -- Generate Type-1 or Type-2 Linkage (nonstandard) . . . . 112 CHDERMAC -- Generate Error Message (nonstandard) CHDPSECT -- Reserve Storage for Parameter List (nonstandard) . . . .116 SECTION 5: GENERATING AND MAINTAINING Program Checkout Subsystem (PCS) . . .121 SECTION 6: PROGRAMMING WITH PRIVILEGE Designating Devices for MSAM . . . . .125 Designating Devices for TAM . . . .126 Controlling I/O Devices For BSAM . . . .126 CNTRL -- Control On-Line Input/Output Devices (R) .....126 PRTOV -- Test for Printer Carriage Multiple Sequential Access Method DDEF Command and Macro Instruction . .134 General Service Macro Instructions . .134 OPEN -- Prepare the Data Control

| CLOSE Disconnect Data Set from<br>User's Problem Program (S)        | <ul> <li>FINDJFCB Locate JFCB and Ensure</li> <li>Volume Mounting (S)</li></ul> |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------|

| APPENDIX A: SYSTEM MACRO INSTRUCTIONS .15<br>ATPOL Poll for Pending | APPENDIX E: CODES FOR SYSER MACRO<br>8 INSTRUCTION PARAMETERS                   |

| Attention Interrupt (nonstandard) .15                               | 8 Index                                                                         |

# FIGURES

Figure 1. Extended Control Program Status Word . . . . . . . . . 17 Figure 2. Virtual Program Status TSS/360 Program Modules, CSECT, CSECT Attributes, Sharability, and Storage Key Assignment .... 43 of Input/Output Request Control Block as Set Before IOCAL . . . . . 73 List Entry Before IOCAL is Issued . 74 Figure 11. Fixed Area of I/O Request Control Block as Set by List Entry After Task I/O Interrupt -

| Figure 13. I/O Paging Control     |           |

|-----------------------------------|-----------|

| Block                             | . 76      |

| Figure 14. Coding addrx Operands  |           |

| Figure 15. Determining the Length | • 55      |

| of a Character String             | . 99      |

| Figure 16. Standard and L-form    | •         |

| S-type Macro Description          | . 101     |

| Figure 17. Parameter List         | • • • •   |

| Generated by L-form               | .101      |

| Figure 18. E-form S-type Macro    | • • • •   |

| Description                       | .103      |

| Figure 19. Packing Two Halfword   | • • • • • |

| Parameters Into Register 1        | .105      |

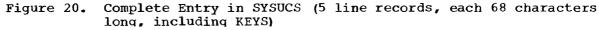

| Figure 20. Complete Entry in      |           |

| SYSUCS (5 line records, each 68   |           |

| characters long, including KEYS)  | .141      |

| Figure 21. Complete Entry in      | ••••      |

| SYSURS (4-line record, each 68    |           |

| characters long, including KEY) . | - 141     |

| Figure 22. DECB Format            |           |

| Figure 23. Flag Field of the DECB |           |

| Figure 24. Organization of IBM    |           |

|                                   | .164      |

| Figure 25. Organization of IBM    | ••••      |

|                                   | .165      |

| Figure 26. Format of IBM 2311     |           |

| 5                                 | .166      |

|                                   |           |

# TABLES

| Table 1. Effect of Authority                       |    |

|----------------------------------------------------|----|

| Code in Dynamic Loader Processing . 4              | 42 |

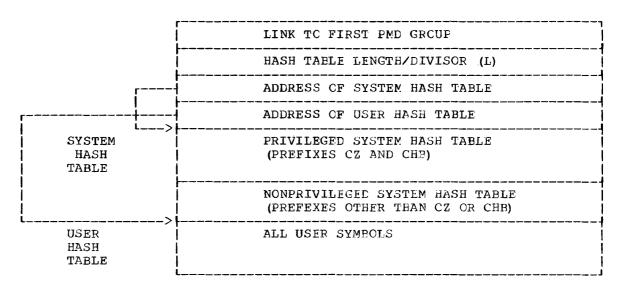

| Table 2. Main Storage Page Key                     |    |

| Assignments                                        | 44 |

| Table 3. Processing Unit and                       |    |

| bucu channer hey hoorymained to to to              | 44 |

| Table 4. Privileged Supervisor                     |    |

| Calls (SVC 128-255) (Part 1 of 2) . 4              | 46 |

| Table 4. Privileged Supervisor                     |    |

| curre (510 (100 500) (100 5 0) -                   | 47 |

| TUDIC 5. Byseem Hiror beace                        | 80 |

| Table 6. Dump Option Codes for                     |    |

| Dyseem Hrist Hessesser                             | 80 |

| Table 7. Resident Supervisor                       |    |

| Module couch a s s s s s s s s s s s s s s s s s s | 81 |

| Table 8. Nonprivileged                             |    |

| Supervisor Calls (SVC 64-127)                      | 88 |

| Table 9. Error Messages Issued    |

|-----------------------------------|

| by CHDERMAC (Part 1 of 2) 115     |

| Table 9. Error Messages Issued    |

| by CHDERMAC (Part 2 of 2) 116     |

| Table 10. Sources of DCB          |

| Information for MSAM              |

| Table 11. Return Codes for SETUR  |

| Macro                             |

| Table 12. Return Codes for MSAM   |

| GET Macro Instruction             |

| Table 13. Return Codes for MSAM   |

| PUT Macro Instruction             |

| Table 14. Return Codes for MSAM   |

| FINISH Macro Instruction          |

| Table 15. Character Set Codes 152 |

| Table 16. Input Formats Accepted  |

| ha mine Company Pointing 162      |

| by Time Conversion Routine 162    |

| Table 17. Results of Time         |

| Conversion                        |