GC28-1160-4 File No. S370-34

# **Program Product**

à

**MVS/Extended Architecture** Planning: Recovery and Reconfiguration

**MVS/System Products:**

| JES2 | Version | 2 | 5740-XC6 |

|------|---------|---|----------|

| JES3 | Version | 2 | 5665-291 |

#### | Fifth Edition (June, 1987)

- This is a major revision of, and obsoletes, GC28-1160-3. See the Summary of Amendments following the Contents for a summary of the changes made to this manual. Technical changes or additions to the text and illustrations are indicated by a vertical line to the left of the change.

- This edition applies to Version 2 Release 2.0 of MVS/System Product (5665-291 and 5740-XC6), and to Data Facility Product (5665-284 and 5665-XA2), and to all subsequent releases until otherwise indicated in new editions or Technical Newsletters. Changes are made periodically to the information herein; before using this publication in connection with the operation of IBM systems, consult the latest *IBM System/370 Bibliography*, GC20-0001, for the editions that are applicable and current.

References in this publication to IBM products or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM product in this publication is not intended to state or imply that only IBM's product may be used. Any functionally equivalent product may be used instead.

Publications are not stocked at the address given below. Requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be addressed to IBM Corporation, Information Development, Department D58, Building 921-2, PO Box 390, Poughkeepsie, N.Y. 12602. IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation to you.

© Copyright International Business Machines Corporation 1984, 1987

## Preface

### What to Expect From This Publication

The emphasis of this publication is on maintaining system availability after an abnormal event. This publication is intended for the programmers and planners who develop recovery and reconfiguration procedures tailored to their installation's requirements. This publication does not contain ready-to-use procedures; rather it contains hardware and software information and guidelines needed to develop procedures that the installation can use to control the system after an error situation has resulted in a loss of system availability or any hardware unit. This publication addresses recovery and reconfiguration considerations for both UPs and MPs but not to the same degree for the two types of processor complex. It talks about recovery for both UPs and MPs. However, it talks about reconfiguration for MPs only, since there's very little on a UP system that can be taken offline without bringing down the whole system. For example, only on an MP can a CPU or a channel controller (e.g., an EXDC on a 308x) be taken offline.

This publication does **not** address software recovery from software errors. For example, recovery procedures for the following subsystems/components are outside the scope of this publication:

- Global Resource Serialization

- JES2

- JES3

- CICS

- IMS

- ACF/VTAM

### How This Publication is Organized

The contents of each chapter are described in the following paragraphs.

Chapter 1: Introduction to Recovery and Reconfiguration provides overview information concerning the processes of recovery and reconfiguration.

**Chapter 2: Pre-Installation Planning for Reconfiguration** provides guidelines to an installation on how to set up its I/O configuration.

**Chapter 3: Recovery** describes what the hardware and software facilities do to recover from a hardware failure. This information helps the installation understand the system's attempt to recover from a hardware failure and the effect the recovery attempt has on the system.

Chapter 4: Reconfiguration describes the process of adding hardware units to, or removing hardware units from, a configuration.

### **Bibliography**

The following publications are either referred to in this manual or contain further information on a topic described in this manual.

MVS/Extended Architecture

Message Library: System Messages, Volume 1, GC28-1376

Message Library: System Messages, Volume 2, GC28-1377

Message Library: System Codes, GC28-1157

Operations: System Commands, GC28-1206

System Programming Library: Initialization and Tuning, GC28-1149

System Programming Library: System Modifications, GC28-1152

Installation: System Generation, GC26-4009

MVS Configuration Program Guide and Reference, GC28-1335

IBM System/370 Extended Architecture Principles of Operation, SA22-7085

Input/Output Configuration Program User's Guide and Reference, GC28-1027

*IBM 3090 Processor Input/Output Configuration Program User's Guide and Reference*, SC38-0038

IBM Disk Storage Management Guide: Error Handling, GA26-1672

EREP User's Guide and Reference, GC28-1378

Data Facility Data Set Services User's Guide and Reference, SC26-3949

Device Support Facilities, GC35-0033

IBM 3081, 3083, 3084 Messages for the System Console, GC38-0035

IBM 3081 Operator's Guide for the System Console, GC38-0034

IBM 3083 Operator's Guide for the System Console, GC38-0036

IBM 3084 Operator's Guide for the System Console, GC38-0037

IBM 3090 Channel Characteristics, SA22-7120

(Includes all base and E models)

IBM 3090 Functional Characteristics, SA22-7121

(Includes all base and E models)

*IBM 3090 Processor Complex: Operator Controls for the System Console for Models 150/150E/180/180E/200/200E/400/400E*, SC38-0040

IBM 3090 Processor Complex: Operator Tasks for the System Console for Models 200 and 200E, SC38-0041

IBM 3090 Processor Complex Operator Tasks for the System Console for Models 150/150E/180/180E, SC38-0049

IBM 3090 Processor Complex: Operator Tasks for the System Console for Models 400 and 400E, SC38-0050

IBM 3090 Processor Complex Recovery Guide, SC38-0051

IBM 3090 Processor Complex Operator Tasks for the System Console for Model 300E, SC38-0054

*IBM 3090 Processor Complex Operator Tasks for the System Console for Model* 600E, SC38-0056

*Note:* The following package applies to the 3090 Model 200 (without the Vector Facility), although much of the controls and task information should also be useful for a 3090 Model 400.

*IBM 3090 Processor Complex Operator Training Package* (3 volumes), GG24-1740 through GG24-1742

IBM 3081 Functional Characteristics, GA22-7076

IBM 3083 Functional Characteristics, GA22-7083

IBM 3084 Functional Characteristics, GA22-7088

IBM 4381 Processor Model Group 3 Functional Characteristics, GA24-4021

IBM 4381 Processor Operations Manual, GA24-3949

### **Contents**

Chapter 1. Introduction to Recovery and Reconfiguration 1-1 Terminology and Definitions 1-1 Introduction to Recovery 1-3 Hardware Recovery 1-3 System Recovery 1-3 **Operator Intervention** 1-3 Introduction to Reconfiguration 1 - 3Chapter 2. Pre-Installation Planning for Reconfiguration 2 - 1I/O Configuration Considerations 2-1 Channel Subsystem Considerations for 308x Processors 2 - 22-2 Channel Subsystem Considerations for 3090 Processors Channel Designations on 3090 Models 200, 200E, and 300E 2 - 3Channel Designations on 3090 Models 400, 400E, 600E 2-3 **Configuration Guidelines** 2-4Channel Subsystem Considerations for a 4381 Model 3 Processor Configuring Devices for a Nonpartitionable Processor Complex I/O Configuration Guidelines for a Partitionable Processor Complex in Single-Image Mode 2-10 String Switching 2 - 10Master Console Configuration Guidelines 2 - 12**IOCP** Considerations 2-12 MVS/XA Configuration Program or SYSGEN Considerations 2 - 13**RSU** Parameter 2 - 14**RSU** Implementation 2 - 14**RSU** Parameter Specifications 2-15 Chapter 3. Recovery 3-1 Hardware/Operating System Recovery Actions 3-2 Information Provided with Machine Checks 3-4 **Central Processing Unit Errors** 3-4 Soft CPU Errors 3-5 Hard CPU Errors 3-5 Terminating CPU Errors 3-6 Vector Facility Recovery 3-7 Vector Facility Source Error Machine Check 3-7 Vector Facility Failure Machine Check 3-8 Alternate CPU Recovery (ACR) 3-8 Terminating Errors on Multiple CPUs 3-9 Service Processor Damage 3-9 Storage Errors 3-9 Soft Storage Errors 3-10 Hard Storage Errors 3-10 Effects of Storage Errors 3-11

2-4

2-5

Storage Element Failure 3-12 **Channel Subsystem Errors** 3-12 Channel Report Words (CRWs) 3-12 **Channel Path Recovery** 3-12 **Channel Path Alert Conditions** 3-14 Subchannel Recovery 3 - 14Monitoring Facility Recovery 3-14 I/O Errors 3-14 Master Console Failure 3-15 Missing Interrupts 3 - 15Unconditional Reserve/Alternate Path Recovery (APR) 3-16 Hot I/O 3-16 Sample Parameters for Hot I/O Recovery in Parmlib Member **IECIOSxx** 3-17 3880/3380 Considerations 3 - 173380 Enable/Disable Switch 3-17 Recovery from an Out-of-Sync Condition 3-18 DASD Maintenance and Recovery 3-18 **Operator Recovery Actions** 3-19 Recovery by CPU Restart 3-19 Continuing a Vector Job If a Vector Facility is Offline 3-20 Hardware Instruction Tracing (Loop Trace) 3-20 Recovery from Wait States 3-21 **Disabled Wait States** 3-21 **Enabled Wait States** 3-21 Uncoded Wait States 3-21 Spin Loop Recovery 3-21 Spin Loops 3-22 **Operator Notification** 3-22 Processing Messages at the System Console 3-23 ACR Considerations 3-23 **Recovery Actions** 3-24 3-24 Example of Recovery Procedure for Spin Loop Message Recovery for X'09x' Wait State 3-25 Additional Recovery Actions 3-26 **Restart Procedures** 3-26 Procedure to Restart from Message IEE331A 3-26 Procedure to Restart from Wait State 091, 092, 095, 097, or 09E 3-26 Determining the Cause of a Spin Loop 3-27 Analysis of Excessive Spin LOGREC Records 3-27 Chapter 4. Reconfiguration 4 - 1Logical and Physical Reconfiguration 4 - 2General Considerations for Reconfiguration 4-2 Reconfiguration Support According to Processor Types 4-2 Recommended Sequence for Partitioning and Merging 4-3 **DISPLAY** Command Considerations 4-4 D U Command 4-4 D M Command 4-4 **Program Properties Table Considerations** 4-5 Real Storage Reconfiguration 4-6 Extended Storage Reconfiguration on Partitionable 3090 Models 4-9 Processor Reconfiguration 4-10 Reconfiguring a Processor with a Vector Facility 4 - 10

VIII MVS/XA Planning: Recovery and Reconfiguration

Removing the Last Vector Facility 4-11

Channel Measurements 4-11

Vector Facility Reconfiguration Examples 4-12

Channel Path Reconfiguration 4-14

I/O Device Reconfiguration 4-15

Examples of Partitioning and Merging a 3084 4-15

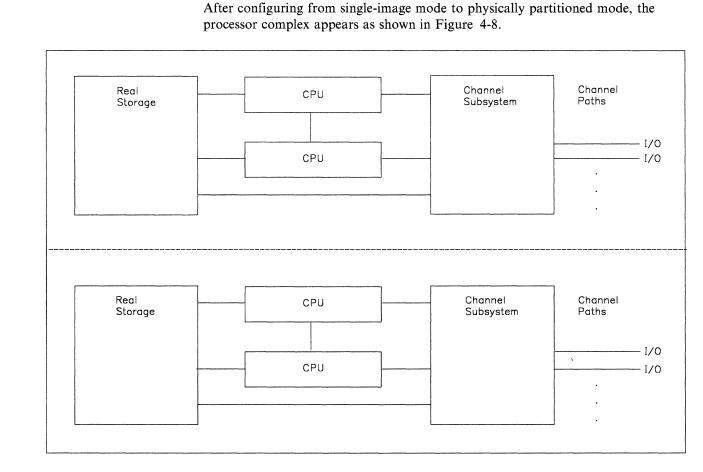

Partitioning from Single-Image Mode to Physically Partitioned Mode (Side B to Be Configured Offline) 4-17

Merging from Physically Partitioned Mode to Single-Image Mode (Side B To Be Configured Online) 4-25

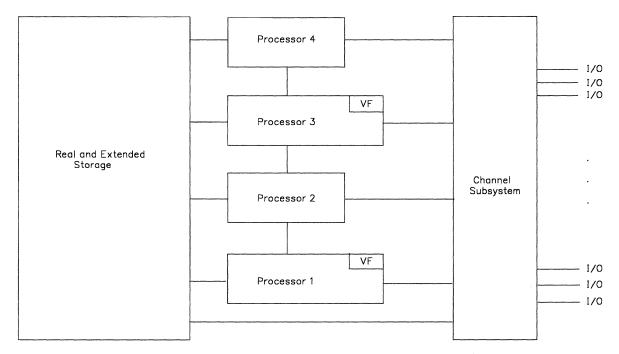

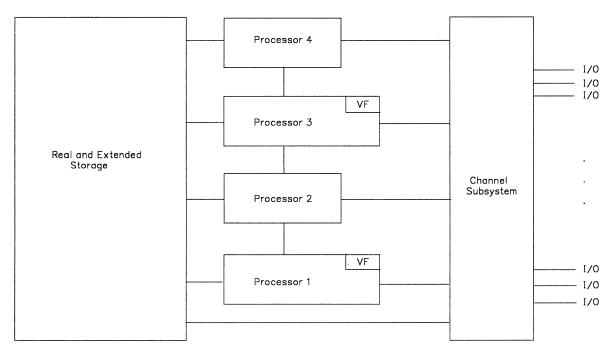

Examples of Partitioning and Merging a Partitionable 3090 4-32

Partitioning from Single-Image Mode to Physically Partitioned Mode (Side 1 to Be Configured Offline) 4-33

Merging from Physically Partitioned Mode to Single-Image Mode (Side 1 To Be Configured Online) 4-42

Index X-1

### **Figures**

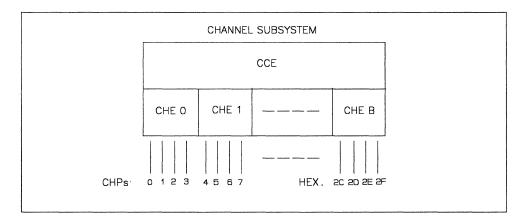

- 2-1. 308x Channel Subsystem 2-2

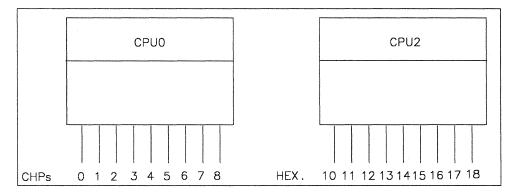

- 2-2. 3090 Channel Subsystem Configuration 2-3

- 2-3. Channel Paths and Channel Elements on Partitionable 3090

Systems 2-3

- 2-4. 4381 Dual-Processor Channel Subsystem Configuration 2-4

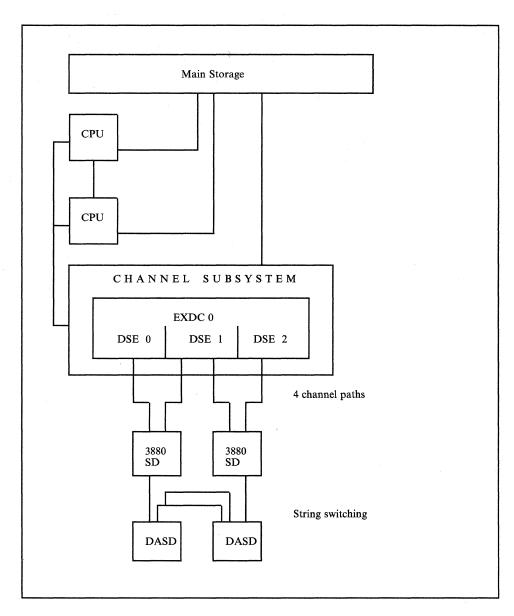

- 2-5. DASD Configuration for Maximum Availability with a 308x

Complex 2-6

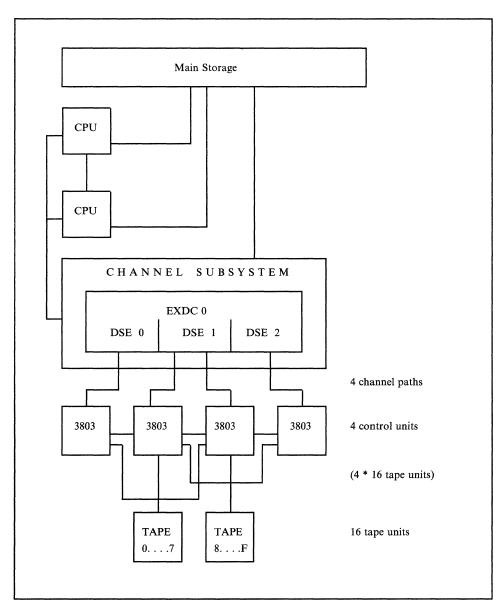

- 2-6. Tape Configuration for Maximum Availability (308x Complex) 2-7

- 2-7. Configuration of a 3725 for Maximum Availability (308x Complex) 2-8

- 2-8. Unit Record or Local TP Device Configuration for Maximum Availability (308x Complex) 2-9

- 2-9. DASD Configuration for Maximum Availability (3084 in Single-Image Mode) 2-11

- 2-10. Calculation of RSU Value for the 3084 and Reconfigurable 3090 Models 2-15

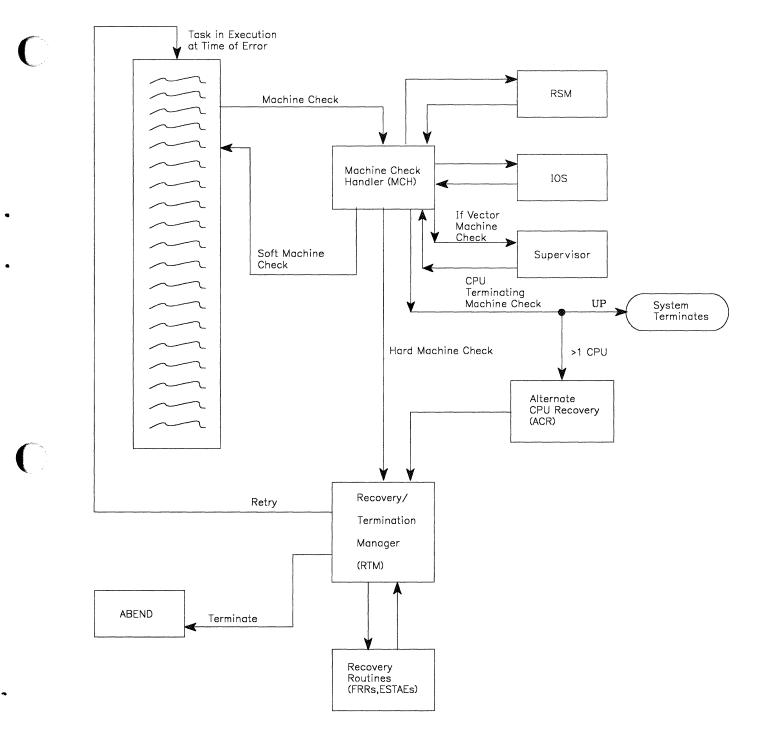

- 3-1. Operating System Handling of Machine Checks 3-3

- 3-2. Recovery Actions for Each Message Insert or Wait State 3-24

- 4-1. A Logical View of Real Storage (3084 Example) 4-6

- 4-2. A Physical View of Real Storage (3084) 4-7

- 4-3. Real Storage Differences Between 308x and 3090 Systems 4-8

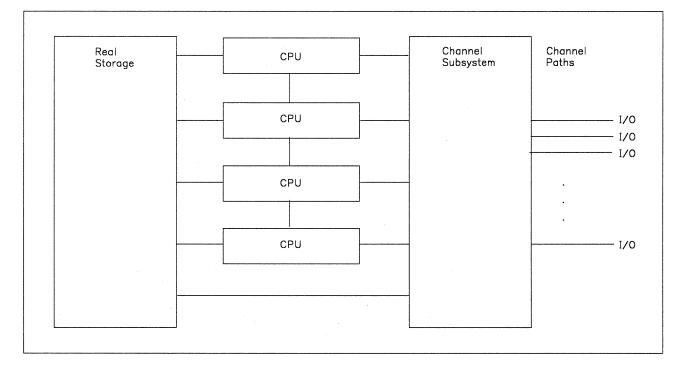

- 4-4. Single-Image Mode of a 3084 4-17

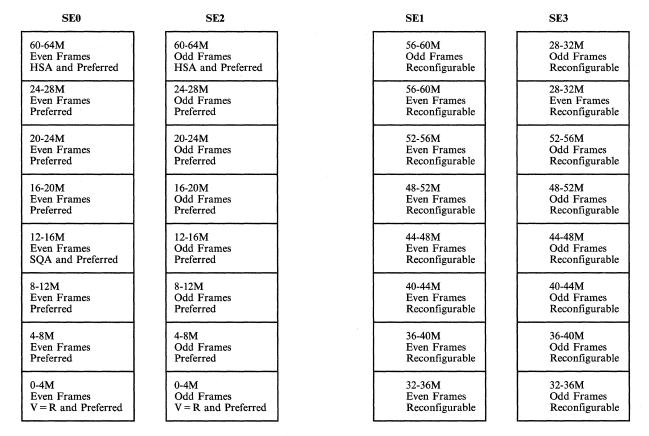

- 4-5. Storage Layout in Single-Image Mode (3084) 4-18

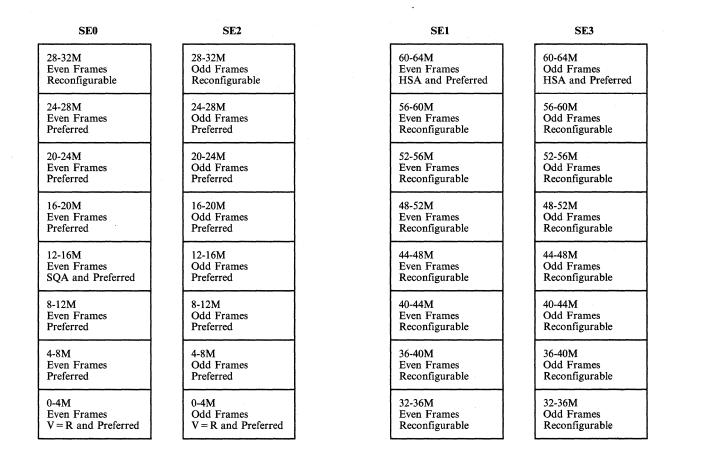

- 4-6. Storage Layout SE1 Configured Offline (3084) 4-21

- 4-7. Storage Layout SE1 and SE3 Configured Offline (3084) 4-22

- 4-8. Physically Partitioned Mode of the 3084 4-23

- 4-9. Examples of D M Displays 3084 System in Physically Partitioned Mode 4-24

- 4-10. Storage Layout SE1 and SE3 Configured Offline (3084) 4-25

- 4-11. Storage Layout SE3 Configured Online (3084) 4-27

- 4-12. Storage Layout SE1 and SE3 Configured Online 4-28

- 4-13. Single-Image Mode of a 3084 4-30

- 4-14. Examples of D M Displays 3084 System in Single-Image Mode 4-31

- 4-15. Differences Between the 3084 and the 3090 Models 400, 400E, and 600E 4-32

- 4-16. Single-Image Mode of a 3090 Model 400 4-33

- 4-17. Sample Real Storage Layout of 3090 Model 400 Before Partitioning 4-34

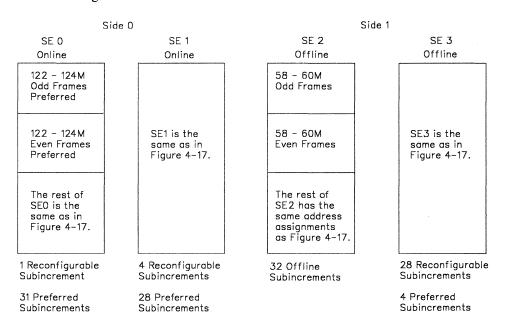

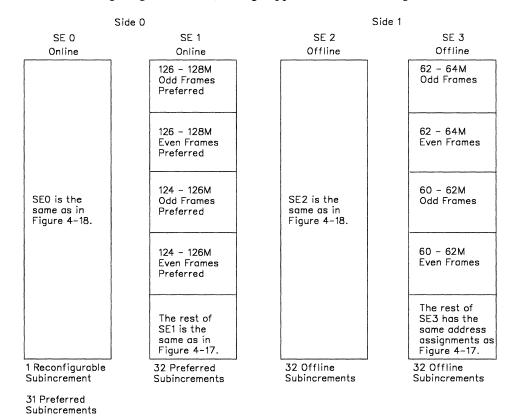

- 4-18. Real Storage Layout SE2 Configured Offline (3090 Model 400) 4-37

- 4-19. Real Storage Layout SE3 Configured Offline (3090 Model 400) 4-39

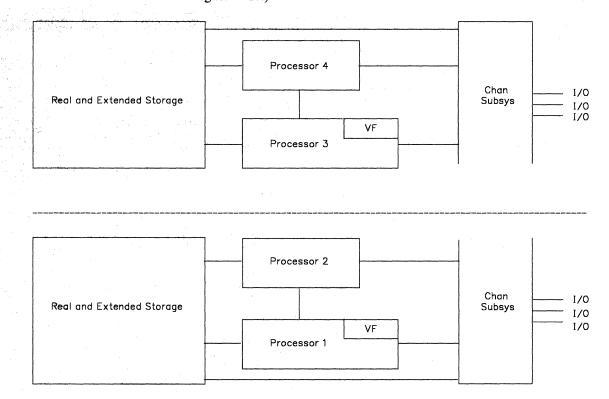

- 4-20. Physically Partitioned Mode of the 3090 Model 400 4-40

- 4-21. Examples of D M Displays 3090 Model 400 System in Physically Partitioned Mode 4-41

- 4-22. Single-Image Mode of a 3090 Model 400 4-45

4-23. Examples of D M Displays - 3090 Model 400 System in Single-Image Mode 4-46

### **Summary of Amendments**

Summary of Amendments for GC28-1160-4 for MVS/System Product Version 2 Release 2.0

This major revision includes the following new and changed information:

- Information in the various chapters to reflect support of the 3090 models 200E, 300E, and 600E.

- In Chapter 2 a description and summary table of channel path IDs and channel element IDs for the 3090 Models 400, 400E, and 600E.

- In Chapter 2 a description of the real storage increment size for the 3084 and the 3090 models 400, 400E, and 600E.

- In Chapter 3 additional details on subchannel recovery.

- In Chapter 3 additional comparison of 3090 hardware instruction tracing with that on a 308x.

- In Chapter 4 a table that describes real storage for the 3081, 3084, and various 3090 models: the storage element IDs, storage element size, storage increment size, storage subincrement size, and maximum storage size.

- Minor technical and editorial corrections throughout the manual.

Changes are indicated by change bars () in the left margin.

### Summary of Amendments for GC28-1160-3 for MVS/System Product Version 2 Release 1.7

This major revision contains changes to support reconfiguration of the 3090 Model 400 in MVS/System Product Version 2 Release 1.7. The changes include:

- The addition of a new CONFIG parameter to configure extended storage elements offline and online.

- Changes to the reconfiguration examples and DISPLAY M examples in Chapter 4 to illustrate differences between the 3084 and the 3090 Model 400 during partitioning and merging.

- Change of message ID for the D M display message. It used to be IEE490I; it is now IEE174I.

- In Chapter 4, a description of the recommended sequence of issuing CONFIG commands, aimed at allowing channel measurements during partitioning and merging and at reducing resource contention.

- In Chapter 4, addition of a procedure to get a storage element to come online when it does not respond in the normal manner to CONFIG STOR(E=X),ONLINE.

- In Chapter 4, addition of a separate section of partitioning and merging examples to illustrate the reconfiguration of the 3090 Model 400.

- In Chapter 4, changes to the 3084 sample D M displays to reflect programming changes that make the 3084 displays more consistent with the 3090 Model 400 displays.

Changes are indicated by change bars (|) in the left margin.

#### Summary of Amendments for GC28-1160-2 for MVS/System Product Version 2 Release 1.3

This major revision, which supports MVS/System Product Version 2 Release 1.3, includes the following new and changed information:

- In Chapter 2, additional guidance on how to increase availability for devices configured across 3090 channel elements.

- In Chapter 4, a table of real storage differences between a 3090 and a 308x.

- For MVS/System Product Version 2 Release 1.3 Vector Facility Enhancement:

- In Chapter 3, modifications to the machine check handler processing.

- In Chapter 4, a new VF parameter for the CONFIG command, and sample CONFIG commands and D M displays that illustrate the use of this parameter.

- Minor technical and editorial corrections.

Changes are indicated by change bars (|) in the left margin.

### **Chapter 1. Introduction to Recovery and Reconfiguration**

To each installation, the approaches to recovery and reconfiguration may be different depending on its recovery philosophy. For example, one installation decides that continuous system operation (as long as work can be done) is one of its priorities. In this case, after a malfunction the installation keeps the system operational as long as possible, even at the risk of lost diagnostic data, and defers maintenance. Another installation, however, decides that immediate repair of a failing unit is one of its priorities. In this case after a malfunction, the installation takes as much of the system as is necessary out of operation to perform the maintenance.

An installation should base its recovery and reconfiguration procedures on its operational priorities. Each installation may need several procedures because the operational priorities may change with workload or time-of-day. For example, priorities and procedures may change during a shift to accommodate a heavier or lighter workload. Also, priorities and procedures that apply to first shift may not apply to third shift.

### **Terminology and Definitions**

To resolve any conflicts concerning terms used in this publication, the following list defines the meaning and usage of those terms.

Configuration - a set of hardware units that can support a single operating system.

Dual Processor - A non-partitionable multiprocessor that has two CPUs, each having its own integrated channel paths. That is, each CPU's channel paths work only with that CPU and cannot be accessed by the other CPU.

Hardware Unit - a CPU, storage element, channel path, device, etc.

Master Console - the console used for communications between the operator and the software system.

MP or Multiprocessor - a processor complex that has more than one CPU.

Partition - one of the configurations formed by partitioning.

Partitioning - the process of forming multiple configurations from one.

**Note:** A processor complex that supports partitioning is termed partitionable; a processor complex that does not support partitioning is termed nonpartitionable. These types of processor complex are partitionable: the 3084 and the 3090 Models 400, 400E, and 600E.

Physical Partition - a hardware implementation of a partition.

Physically Partitioned Mode - the state of a processor complex when its hardware units are divided into multiple configurations.

Processor - a central processing unit (CPU)

Processor Complex - the maximum set of hardware units that support a single operating system.

Service Processor (equivalent to "processor controller) - that part of a processor complex that provides for the maintenance of the complex and may perform:

- Some or all of the functions associated with operator facilities

- Recovery actions associated with machine-check handling

- Reconfiguration operations

Side - equivalent to the term "Physical Partition".

Single-Image Mode - the state of a processor complex when all of its hardware resources are in a single configuration.

System - the interactive combination of a configuration and the operating system (software).

System Console - the console used by the operator to enter hardware commands and to receive hardware messages.

UP or Uniprocessor - a processor complex that has one CPU.

VF or Vector Facility - an optional processing facility to do vector mathematics, available for all 3090 models. There can be one or more Vector Facilities for each processor complex, but only one Vector Facility is associated with each central processor unit.

## **Introduction to Recovery**

Recovery is the attempt by the hardware, the operating system, the operator, or any combination of the three, to correct system malfunctions and return the system to a state in which it can do productive work.

#### Hardware Recovery

Many temporary hardware errors are recovered by the hardware and do not require operating system or operator intervention.

#### System Recovery

System recovery involves both the hardware and the operating system, because many hardware malfunctions are communicated to the operating system for retry and recovery. When a malfunction occurs, it may cause the machine check handler (MCH), alternate CPU recovery (ACR), I/O Supervisor (IOS), or another operating system function to be invoked. That operating system function may retry in an attempt to recover or may determine that recovery from the particular malfunction is not feasible and configure the failing unit offline.

#### **Operator Intervention**

For some hardware failures, operator intervention is required to attempt recovery to keep the system in operation. For example, if a channel path fails, the operator can configure it offline. If the system is operating in single-image mode, the operator can reconfigure to physically partitioned mode to allow maintenance to be performed on a partition. In addition, other system errors may require operator intervention to attempt recovery. Those errors include wait states, loops, excessive spin loop timeouts, Hot I/O, etc. (Refer to Chapter 3 for detailed information.)

### **Introduction to Reconfiguration**

Reconfiguration is the process of adding hardware units to, or removing hardware units from, a configuration. Operational units (for example, CPUs, storage elements, and channel paths) can be added to the configuration (configured online) to make them available to the system. Failing units can be removed from the configuration (configured offline) to make them unavailable to the system and (possibly) allow the system to continue operation.

One facet of system reconfiguration is **partitioning** — changing from single-image mode to physically partitioned mode. This capability is available only on a 3084 and 3090 Models 400, 400E, and 600E systems. An installation can use partitioning as an operational convenience or as an aid to recovery. In the first case, partitioning allows one operating system to run in one partition and another one in the other partition. For example, an installation could run MVS/XA in one partition; MVS/370, VM/SP, or a test system in the other partition. In the second case, an installation could give the failing partition to service personnel for diagnosis and repair and still have the system continue operation.

Another facet of system reconfiguration on a 3084 and the 3090 Models 400, 400E, and 600E is **merging** -- changing from physically partitioned mode to single-image mode. An installation uses merging to create a single more powerful MP system from the two systems that exist in physically partitioned (or PP) mode. One of the two PP-mode systems must be stopped and the partition (side) on which it was running be merged with the MVS/XA system that is running on the other partition (side).

## **Chapter 2.** Pre-Installation Planning for Reconfiguration

Prior to placing a system into operation, an installation should plan the configuration for maximum availability, or to state it in terms of reconfiguration — to provide the maximum capability for reconfiguration. Also, since reconfiguration is a consideration for recovery, the planning serves a dual purpose.

There are two aspects of the planning — one focuses on the I/O configuration and the other on the operating system. For the I/O configuration, an installation should focus on such things as device attachment (which devices are attached to which paths) and master console configuration. For the operating system, an installation should focus on such things as system generation considerations and SYS1.PARMLIB updates.

## I/O Configuration Considerations

This section deals with the following areas:

- Channel subsystem considerations for the various processor types

- Sample I/O configurations illustrated on a 308x system

- I/O configuration guidelines for a 3084 complex in single-image mode

- Master console configuration guidelines

- IOCP considerations

I/O configuration planning will enhance system availability and recovery. This involves the consideration of the number of paths to each device and the hardware elements in each path. MULTIPLE PATHS TO A DEVICE SHOULD INCLUDE AS FEW COMMON HARDWARE ELEMENTS AS POSSIBLE TO MINIMIZE THE EFFECT OF A MALFUNCTION; THAT IS, TO PREVENT A SINGLE MALFUNCTION FROM DISABLING ALL THE PATHS TO A DEVICE. Multiple paths to some devices may require the installation of two-channel switches, or switching devices such as a 3814 or 2914.

The illustrations that follow in this chapter show examples of I/O configurations that will give an installation maximum availability in case of a hardware element failure. Each illustration shows the hardware elements in the path to a device and shows how the device should be connected.

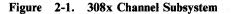

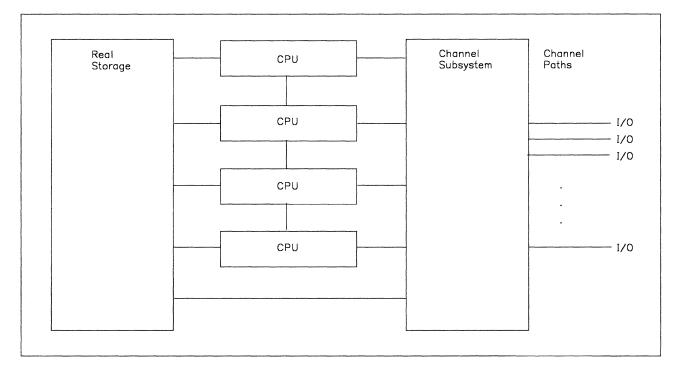

### Channel Subsystem Considerations for 308x Processors

The hardware elements in a path from a 308x to a device are:

- External data controller (EXDC)

- Data server element (DSE)

- Control unit

- Channel path (CHP)

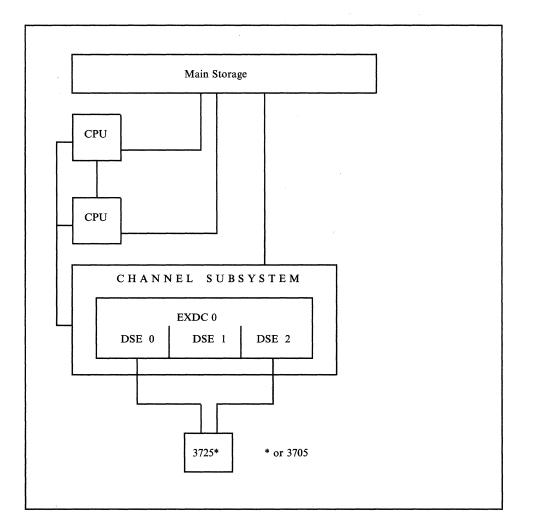

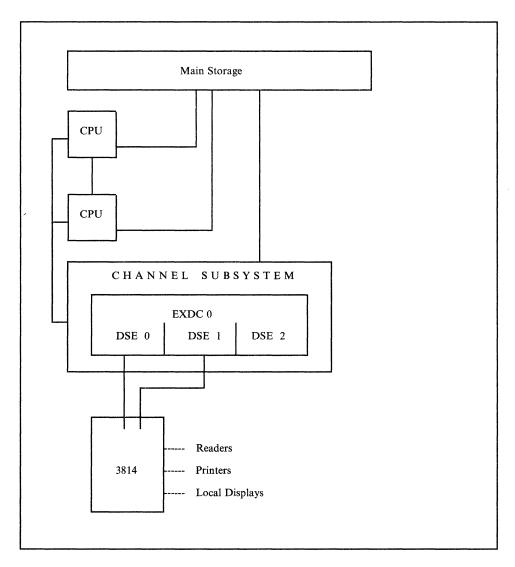

Figure 2-1 shows the relation among the hardware elements that make up the 308x channel subsystem.

To maintain maximum availability in case of a CHP or DSE failure, an installation should configure multi-path devices to CHPIDs on different DSEs. On systems with multiple EXDCs (i.e., 3084), the installation should configure multi-path devices across the EXDCs.

#### **Channel Subsystem Considerations for 3090 Processors**

The hardware elements in a path from a 3090 to a device are:

- Channel control element (CCE)

- Channel element (CHE)

- Channel path (CHP)

- Control unit

Figure 2-2 shows the relation among the hardware elements that make up the 3090 channel subsystem.

Figure 2-2. 3090 Channel Subsystem Configuration

#### Channel Designations on 3090 Models 200, 200E, and 300E

The nonpartitionable models of the 3090 (for example, models 200, 200E, and 300E) have 32 standard CHPs numbered 00 -- 1F. The model 200 can have 8 or 16 additional CHPs, numbered 20 -- 2F, and the models 200E and 300E can have up to 32 additional CHPs, numbered 20 -- 3F. Note that unlike the 308x CHPIDs, the CHPs on the nonpartitionable models of the 3090 are consecutively numbered with no gaps in the numbering.

A channel element (CHE) has four consecutively numbered channel paths. The CHEs numbered 0 -- 7 relate to the 32 standard CHPs on all three nonpartitionable models. For the optional CHPs, the CHEs are numbered 8 -- B on the model 200, and 8 -- F on the models 200E and 300E. Figure 2-3 summarizes CHP and CHE numbering for several 3090 models.

#### Channel Designations on 3090 Models 400, 400E, 600E

Figure 2-3 shows the channel path (CHP) designations and the channel element (CHE) designations for the 3090 models 400, 400E, and 600E.

| Model Number       | Model 400 | Model 400E | Model 600E |

|--------------------|-----------|------------|------------|

| Max Number of CHPs | 96        | 128        | 128        |

| CHPIDs - Side A    | 0 - 2F    | 0 - 3F     | 0 - 3F     |

| CHPIDs - Side B    | 40 - 6F   | 40 - 7F    | 40 - 7F    |

| Max Number of CHEs | 24        | 32         | 32         |

| CHE IDs - Side A   | 0 - B     | 0 - F      | 0 - F      |

| CHE IDs - Side B   | 10 - 1B   | 10 - 1F    | 10 - 1F    |

Figure 2-3. Channel Paths and Channel Elements on Partitionable 3090 Systems

#### **Configuration Guidelines**

When you configure a device with multiple paths to the same system, the following guidelines allow for maximum availability of the device:

- 1. Attach each path from the device to a separate CHE.

- Distribute paths across both odd and even numbered CHEs. Thus, one path from the device could include any of these channel paths: 0--3, 8--B, 10--13, 18--1B. The other path (assuming two per device) could be selected from channel paths 4--7, C--F, 14--17, or 1C--1F.

- 3. If optional channel paths (20--2F) are installed, distribute the paths to a device across both optional and standard channel paths. When doing this, also follow the configuration pattern of odd and even CHEs (point #2 in this list).

- 4. For a Model 400, 400E, or 600E, distribute the paths across channel control elements (CCEs). (A CCE is analogous to an EXDC on a 308x.)

#### Channel Subsystem Considerations for a 4381 Model 3 Processor

The hardware elements in the path from a 4381 dual processor to a device are:

- Channel path (CHP)

- Control unit

Figure 2-4 shows the relation among the hardware elements that make up the 4381 dual-processor channel subsystem.

#### Figure 2-4. 4381 Dual-Processor Channel Subsystem Configuration

*Note:* The Model 3 and 14 have 6 standard channels on each processor, with 6 optional channels: 3 extra for each processor, as shown. The model 24 (not shown) has up to 24 channels, 12 on each processor.

Where possible, I/O devices should be connected to channel paths on both CPUs of the processor complex. It is particularly important for recovery that system DASD devices be accessible from either CPU and that at least one operator console be attached to each CPU. This is especially necessary if a CPU failed, since the associated channel paths would become unusable.

It is desirable to attach an MVS operator console to both CPUs. The MVS operator console for 4381 Model 3 is connected through a local channel adapter only to channel path zero on CPU zero. It is desirable to have at least one operator console device attached through a local 3274 control unit on a channel path belonging to CPU 1. This configuration would still allow the operator to communicate with MVS if either CPU 0 or channel path zero were to fail.

### **Configuring Devices for a Nonpartitionable Processor Complex**

The following device-type configurations are shown:

- DASD

- Tape

- 3725

- Unit record, local displays, etc.

Figure 2-5 on page 2-6 through Figure 2-8 on page 2-9 show, respectively, the DASD, tape, 3725, and unit record configurations for maximum availability on a 308x complex. Although these figures illustrate the 308x, the general concepts apply to all MVS/XA-supported processor types.

Figure 2-5. DASD Configuration for Maximum Availability with a 308x Complex

String switching (or a 3380 model AA4) is chosen so all devices can be accessed, even if a control unit fails.

•

÷

Figure 2-6. Tape Configuration for Maximum Availability (308x Complex)

Figure 2-7. Configuration of a 3725 for Maximum Availability (308x Complex)

.

...

Figure 2-8. Unit Record or Local TP Device Configuration for Maximum Availability (308x Complex)

### I/O Configuration Guidelines for a Partitionable Processor Complex in Single-Image Mode

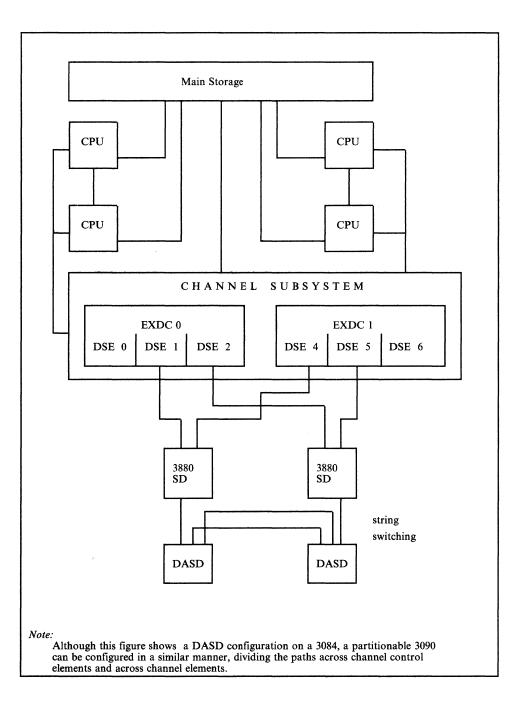

The partitionable processor complexes are the 3084 and the 3090 models 400, 400E, and 600E. When an installation plans its I/O configuration for one of these complexes in single-image mode, the plan should address not only that mode, but physically partitioned mode as well. The resulting I/O configuration should provide maximum availability in either mode of operation.

Some general recommendations for an I/O configuration are:

- Attach control units symmetrically, whenever possible, so they can be accessed from both sides.

- Attach critical unit record or local TP device control units through a 3814 (2914) switch, so they can be switched to either side.

- Attach a tape or DASD device to one channel path from each side and operate with two channel paths online. (To provide the same availability in physically partitioned mode, attach the device to four channel paths, two from each side.)

Figure 2-9 illustrates a configuration for single-image mode for maximum availability. The example shows a DASD configuration on a 3084. However, tape, TP-controller, and unit record configurations on a 3084 (and all device configurations on a 3090) should be done similarly, using features like two-channel switches and switching units, to attach the devices to different channel paths on different sides.

#### **String Switching**

String switching features are used so that all devices can be accessed if a control unit fails.

2-10 MVS/XA Planning: Recovery and Reconfiguration

### **Master Console Configuration Guidelines**

When attaching the master console (and its alternate) to a complex, an installation should implement the following guidelines. Following these guidelines provides a high degree of access to the consoles and helps increase the availability of the system:

- Dedicate a control unit to the master console and a different one to its alternate.

- Ensure that in a string of control units on the channel path, the control unit for the master/alternate console is the first terminal control unit on the channel path. Also, ensure that the control unit is set for *high* priority (performed by the service rep).

- Attach the master console and its alternate such that they share the least number of common hardware elements. For systems that can be physically partitioned, attach the master and alternate consoles to channel paths on different sides.

If the master and alternate consoles are NOT on dedicated control units, the ability of the operator to communicate with the operating system in certain recovery situations is impacted.

During system recovery processing for situations such as Hot I/O and Spin Loop Timeout, the Disabled Console Communications Facility (DCCF) is used to communicate with the operator. If DCCF is unable to issue a message to the MVS master console or its alternate, it attempts to issue the message to the system console. If the message cannot be issued to the system console, either the entire system or one CPU (depending on the problem) will be put into a restartable wait state. To recover from the wait state, the operator must use recovery procedures which may require modification of real storage. By providing the master console with its own dedicated control unit, the chances of encountering a restartable wait state, as a result of DCCF processing, are reduced significantly, and the operator may not need to display or modify real storage.

### **IOCP** Considerations

When operating in single-image mode, the 'Dual Write' function allows an installation to define duplicate copies of a new I/O configuration on each partition with a single execution of IOCP. The installation can then physically partition the complex and have the new I/O configuration available to either partition. In this way, for example, the installation can use either partition to test the new I/O configuration, or act as a common back-up.

## **MVS/XA Configuration Program or SYSGEN Considerations**

The MVS configuration program is to be used by installations that have installed MVS/System Product Version 2 Release 2.0 (MVS/SP2.2.0) or a later release. These installations use the MVS configuration program to:

- Define new I/O configurations or eligible device tables

- Replace existing I/O configurations or eligible device tables

- Define the consoles that the nucleus initialization program (NIP) can use

- Migrate I/O configurations or eligible device tables that were previously defined through the SYSGEN process so they can be used on the MVS/SP2.2.0 or a subsequent release.

FEATURE = SHAREDUP is an optional parameter on the IODEVICE statement in the MVS/XA configuration program and in the pre-SP2.2.0 sysgen program. The specification of this feature:

- Eliminates the overhead of the hardware device reserve/release logic when a device is attached only to partitions operating in single-image mode.

- Indicates that the device reserve/release logic is to be used only when operating in physically partitioned mode and allows the sharing of the device between partitions.

*Note:* Specify FEATURE = SHARED (not FEATURE = SHAREDUP) if a device is attached to more than one processor complex.

FEATURE = ALTCTRL is an optional parameter on the IODEVICE statement in the MVS/XA configuration program. The specification of this feature allows a device to be accessed through an alternate control unit.

For additional information regarding SHAREDUP and ALTCTRL, refer to *MVS/XA Configuration Program Guide and Reference* or the *MVS/XA System Generation* manual.

### **RSU** Parameter

The RSU parameter specifies the number of storage increments that the operating system tries to keep available for storage reconfiguration. (The size of a storage increment depends on the processor model and sometimes on the system engineering change (SEC) level.) At system initialization (IPL-time), when the RSU parameter is processed, the operating system assigns the number of storage increments specified in the RSU parameter to 'non-preferred' status (non-preferred for long-term page fixes for a non-swappable job). 'Non-preferred' storage is also called 'reconfigurable' storage. The operating system uses storage frames from both non-preferred and preferred storage to satisfy normal page allocation requests and requests for short-term page fixes.

Normally, the operating system assigns long-term fixed pages for a non-swappable job only to storage frames in the preferred area. However, if a long-term fixed page for a non-swappable job requires storage space but the preferred area is full, the operating system may convert some non-preferred storage to preferred storage. If some non-preferred storage is converted to preferred, the amount of storage available for reconfiguration is less than that specified in the RSU parameter. The operating system informs the operator of the condition by issuing message IAR005I.

When the operating system is requested to configure storage offline, it attempts to free the amount of real storage required to support the request. The physical real storage and the address ranges assigned to that storage cannot be configured offline either logically or physically until the required amount of storage is available.

The RSU parameter is specified in the IEASYSxx member of SYS1.PARMLIB or as an IPL parameter. The default value assigned to the RSU parameter is 0 -indicating that all storage is designated as preferred (that is, non-reconfigurable). (See *SPL: Initialization and Tuning* for detailed information.)

### **RSU** Implementation

At IPL-time, the specification of RSU = x is satisfied from the total amount of installed real storage (both online and offline). Therefore, a specification of RSU = 0 indicates that the operating system will designate <u>ALL</u> installed real storage as preferred. As a result, an installation must specify the proper RSU value at IPL-time to be able to physically partition a complex during the life of the IPL. This is true regardless of whether the system is IPLed in single image or physically partitioned mode.

The requirement to always specify the proper RSU value may appear to penalize a complex operating in physically partitioned mode for long periods of time. However, such is not the case. Reconfigurable real storage is allocated logically as though the total amount of installed real storage was online at IPL-time. For example, if a 3084 Q64 is initialized in physically partitioned mode with RSU=4

(assuming a real storage increment size of 8MB), the operating system allocates the required 32MB of reconfigurable real storage from real storage addresses not owned by the initialized partition. If an installation subsequently configures the offline partition into the system to operate in single-image mode, the real storage owned by that partition is automatically designated as reconfigurable and the RSU requirement is met.

### **RSU** Parameter Specifications

1

An installation specifies a value for the RSU parameter according to the type of complex and the mode of operation of that complex. The recommended values to ensure the least system overhead and maximum capability for reconfiguration are as follows:

- Uniprocessor (for example a 3090 Model 180E) specify RSU = 0

- Nonpartitionable multiprocessor (for example a 3090 Model 200E) specify RSU=0

- Single-image mode with the capability to physically partition the complex, specify RSU according to the following formula:

On a 3084 the increment size is either 4M if the system has 64M or less of real storage, or is 8M if the system has more than 64M. On a 3090 the increment size is 2M on the Model 400, and 4M on Models 400E and 600E.

*Note:* Figure 2-10 lists RSU values calculated from real storage sizes and storage increment sizes for the 3084 and the reconfigurable 3090 models.

| Processor<br>Type | Installed<br>Real Storage<br>(MB) | Storage<br>Increment<br>(MB) | RSU Value |

|-------------------|-----------------------------------|------------------------------|-----------|

| 3084              | 32                                | 4                            | 4         |

| 3084              | 48                                | 4                            | 6         |

| 3084              | 64                                | 4                            | 8         |

| 3084              | 96                                | 8                            | 6         |

| 3084              | 128                               | 8                            | 8         |

| 3090 Mod 400      | 128                               | 2                            | 32        |

| 3090 Mod 400E     | 128                               | 4                            | 16        |

| 3090 Mod 400E     | 256                               | 4                            | 32        |

| 3090 Mod 600E     | 128                               | 4                            | 16        |

| 3090 Mod 600E     | 256                               | 4                            | 32        |

Figure 2-10. Calculation of RSU Value for the 3084 and Reconfigurable 3090 Models

## Chapter 3. Recovery

Recovery is the attempt by the hardware, operating system, the operator, or any combination of the three, to correct system malfunctions and return the system to a state in which it can do productive work. Some recovery actions are 'automatic'; that is, the hardware recovers from a malfunction without any intervention by the operator or any action by the operating system. Other recovery situations require overt actions by the system and/or the operator. For example, to keep the system in operation, the operator or the system can configure offline a failing component, such as a storage element, a processor, or a channel path. The system continues processing, possibly with some degradation.

The process of recovery includes the following:

- Hardware/operating system communication and corrective actions

- Operator/operating system communication and recovery actions

This chapter describes the following categories of hardware malfunctions:

- Central processing unit errors

- Service processor damage

- Storage errors

- Channel subsystem errors

For each of the preceding categories, the discussion includes the effect on system operation and the recovery actions taken (if any).

This chapter also includes some recommended operator actions for responding to such events as wait states, loops, spin loops, missing interrupts, etc.

Additionally, this chapter presents some recommendations for DASD maintenance and recovery.

## Hardware/Operating System Recovery Actions

The following categories of hardware errors are discussed:

- Central processing unit errors

- Service processor damage

- Storage errors

- Channel subsystem errors

When any of the preceding errors, except for some I/O errors, occurs, the hardware notifies the operating system with a machine check interruption. Machine check interruptions fall into one of three classes depending on the severity of the error. The classes are:

- soft (or repressible) errors least severe type. Generally do not affect the operation of the task currently in control. Soft errors can be disabled (repressed) so that they do not cause a machine check interruption.

- hard errors malfunctions that affect the execution of the current instruction or invalidate the contents of hardware areas (such as registers).

- terminating errors malfunctions that affect the operation of a CPU.

Hard and terminating errors are also referred to as "exigent" errors.

Refer to Figure 3-1 for an illustration of how the operating system handles machine checks.

Figure 3-1. Operating System Handling of Machine Checks

.

## Information Provided with Machine Checks

When the hardware detects a failure, it stores the following types of information about the failure:

- The machine check interrupt code (MCIC), which contains information about the severity of the error, the time of the error (in relation to the current instruction stream), and an indication of whether the processor has successfully stored additional information about the error. The interrupt code is the major interface between the hardware and the operating system that uses the MCIC to determine what action to take.

- The model-independent fixed logout, which contains the values of the general purpose, floating point, and control registers at the time of error. It also contains the CPU timer and clock comparator values.

- The model-dependent extended logout, which contains diagnostic information needed by service personnel. The operating system does not use this information; it writes the information to SYS1.LOGREC along with the other information pertaining to the error.

- The machine check old PSW, which contains the PSW at the time of error.

The format and content of these storage areas are described in detail in IBM System/370 Extended Architecture Principles of Operation.

After storing the preceding types of information, the hardware gives control to the machine check handler (MCH) by loading the machine check new PSW. MCH gathers the information about the error into a buffer for later recording to SYS1.LOGREC. Next, MCH assesses the severity of the error by checking the machine check interrupt code and determines the appropriate course of action.

# **Central Processing Unit Errors**

Central processing unit (CPU) errors result from a malfunction of a hardware element such as a timing facility, instruction-processing hardware, or microcode. When a CPU error occurs, the recovery processing has, in general, two stages depending on the severity and type of error:

- 1. When possible, the hardware retries the failing operation a certain number of times. If the retry works, the hardware may issue a recovery machine check interruption (which is repressible) so that the operating system can record the error to SYS1.LOGREC. After recording, the operating system returns control to the interrupted task.

- 2. If the error is too severe for hardware retry or the retries fail, the hardware issues either a hard or terminating machine check interruption. The machine check handling routines determine the severity of the error and take the appropriate action that may range from terminating the interrupted task to terminating the entire system.

# Soft CPU Errors

The CPU errors that can result in a soft machine check are:

- System Recovery (SR) a malfunction has occurred, but the hardware has successfully corrected or circumvented it.

- Degradation (DG) continuous degradation of system performance has been detected.

The operating system does not inform the operator about the occurrence of soft machine checks until the "threshold" for a given type is reached. The threshold set by MCH for each soft machine check is four. The operator can change the threshold for either an SR or a DG machine check with the MODE command. When a threshold for a type of machine check is reached, MCH issues message IGF931E.

When a threshold is reached, the operator can allow the system to remain in quiet mode or enter the MODE command to reenable system recovery or degradation machine checks by setting a new threshold value. If the operator specifies RECORD = ALL for a particular type of machine check, the system does not enter quiet mode; it records all instances of system recovery and degradation machine checks in SYS1.LOGREC. The operating system issues message IGF931E when the number of machine checks is a multiple of the threshold. For example, if REPORT = 3 is specified, message IGF931E appears after the third, sixth, ninth, twelfth machine checks, and so on.

Numerous IGF931E messages appearing on the operator's console might indicate a performance degradation. In this case, the installation might want to configure offline the processor that is experiencing the errors. Maintenance on the offline processor can be done by service personnel as indicated by installation procedures.

## Hard CPU Errors

A hard machine check indicates that the current instruction could not complete. When MCH receives a hard machine check, it records the error on SYS1.LOGREC, issues message IGF972E, and passes control to the Recovery/Termination Manager (RTM) that either terminates the interrupted task or retries the interrupted task at a pre-defined retry point. Even though the task may be terminated, the system usually continues to run.

The CPU errors that cause hard machine checks are:

- System Damage (SD) a malfunction has caused the processor to lose control over the operation it was performing to the extent that the cause of the error cannot be determined.

- Instruction Processing Damage (PD) a malfunction has occurred in the processing of an instruction.

- Invalid PSW or Registers (IV) the hardware was unable to store the PSW or registers at the time of error, as indicated by validity bits in the MCIC. Any error (even a soft machine check) associated with these validity bits is

treated as a hard machine check because the operating system does not have a valid address to use to resume operation. The error goes through recovery processing.

• Timing Facility Damage – damage to the TOD clock (TC), processor timer (PT), or clock comparator (CC) has been detected.

To overcome the effects of numerous hard machine checks, the MODE command allows the operator to define machine check thresholds for each type which, when reached, cause the failing processor to be configured offline by ACR. (The default threshold is five machine checks in five minutes.) Thus, the operator can control whether, and to what extent, the system monitors the frequency of hard machine checks, and can define a separate threshold and time interval for each.

If installation thresholds have been established but numerous IGF972E messages are generated, (RECOVERY INITIATED FOR PROCESSOR FAILURE ON CPUx), the installation should consider configuring CPUx offline prior to the expiration of the threshold.

## **Terminating CPU Errors**

A terminating machine check occurs when the operating system or the hardware considers a failure severe enough that a processor cannot continue operation.

In a UP environment, the operating system terminates with a disabled wait state (such as A01, A26), and issues the following message:

IGF910W UNRECOVERABLE MACHINE FAILURE, RE-IPL SYSTEM

In a multiprocessor environment, the action taken is as follows:

- If the hardware determines that a processor cannot continue operation, it places the processor in a check-stop state and attempts to signal the other processor(s) by issuing a malfunction alert (MFA) external interrupt. The hardware issues an MFA when:

- it cannot store the machine check logout data about the error

- it cannot load the machine check new PSW

- it is disabled for machine checks

- If the operating system determines that a processor cannot continue operation, it attempts to signal the other processor(s) by issuing a SIGP emergency-signal (EMS) instruction to cause an external interrupt. The operating system issues an EMS when:

- MCH is processing one machine check when another machine check occurs that cannot be handled

- A hard-machine-check threshold (installation option), established by issuing the MODE command, has been reached

- Channel subsystem damage is detected

- The content of the MCIC is invalid

When a processor receives either an MFA or EMS external interruption (relative to the preceding stated conditions), the External Interruption handler gives control to MCH. MCH, in turn, invokes Alternate CPU Recovery (ACR) processing which takes the malfunctioning processor offline and initiates recovery processing for that processor.

In a multiprocessor environment, an MFA or EMS is received by all the other online processors. On the first processor to receive the signal, MCH tests and sets a flag before starting to process the error. When the other processors receive the interruption, MCH on those processors sees that the error is already being processed and returns to the interrupted task.

## **Vector Facility Recovery**

If the Vector Facility on a 3090 has a malfunction, it will present one of two types of machine check:

- Vector facility source error

- Vector facility failure

These machine checks are represented by two newly defined bits in the machine check interrupt code (MCIC).

### Vector Facility Source Error Machine Check

A vector facility source error is a hard machine check presented with the PD bit and the VF source bit set in the MCIC. Vector facility source errors are not counted as processor damage machine checks for threshold purposes against the CPU but are counted toward a separate vector source (VS) threshold count. The VS threshold can be set by the operator via the MODE command VS parameter.

For a vector facility source error, the MCH performs these steps:

- Tries to save the vector environment for possible retries during RTM processing (that is, during handling of an '0F3' ABEND.)

- Increases by one the threshold count of vector source machine checks.

- Routes the current work to RTM with an '0F3'ABEND code, for possible recovery or ABEND processing.

- If the threshold of vector source machine checks has not been reached (default is five in five minutes), the MCH takes no further action.

- If, however, the vector source threshold has been reached, the MCH indicates in the common system data area (CSD) that a Vector Facility is logically offline, requests the service processor to physically disconnect the Vector Facility, and issues this message:

IGF970I VFn NOW OFFLINE. UNRECOVERABLE ERROR DETECTED.

#### **Vector Facility Failure Machine Check**

A Vector Facility failure is a soft machine check presented with the Vector Facility failure bit set in the MCIC. In this case, if the interrupted task is a vector task, its vector status (such as vector registers and clock) are invalidated, and the Vector Facility (but not the CPU) is taken offline. The interrupted unit of work is terminated only if it attempts to issue another vector operation. In this case, the work is terminated because, even if there are other operational Vector Facilities, the user's vector status at the time of failure cannot be guaranteed.

## Alternate CPU Recovery (ACR)

ACR is a function that is initiated on an operative CPU when that CPU receives a signal that another CPU has had a terminating error. ACR has two major functions:

1. To configure offline the malfunctioning CPU

2. To initiate the release of system resources held on the malfunctioning CPU

If the failing CPU has a Vector Facility, the Vector Facility is also taken offline.

ACR initiates the release of any resources held on the failing CPU by invoking RTM which initiates the functional recovery routines (FRRs) of the work on the failing CPU. ACR allows the operating system to continue its normal operation on the remaining CPU(s) although the task that was interrupted by the error on the failing CPU may be terminated.

When ACR is complete, it sets up message IEA858E stating that ACR is complete and identifying the CPU that was configured offline. At this point, the operator can try to configure the failing CPU back online using a CONFIG CPU(x),ONLINE command. The configuration 'online' may, or may not, be successful depending on the error that caused the CPU to be configured offline.

Some hardware malfunctions may cause a subsequent CONFIG CPU,ONLINE command to that CPU to fail, or may cause the problem to reoccur when the CPU is brought back online. In these cases, hardware service is necessary before the CPU can be successfully brought back into the system.

However, if a CPU was configured offline because a threshold was reached or because of an operating system problem, a subsequent request to configure the CPU back online may work. Since online processing does hardware resets and rebuilds the CPU-related control blocks, the cause of the problem may be eliminated.

On the 4381 Model 3 and Model Group 14 processors, the channel paths physically attached to the failing CPU will be configured offline during ACR. In addition to a malfunction alert (MFA) external interrupt, the hardware also presents a channel report pending machine check interrupt which indicates permanent errors for all channel paths attached to the failing CPU. In response to the channel errors, MVS physically takes offline all channel paths attached to the failing CPU. If the failing CPU is returned online in response to a CONFIG CPU,ONLINE command, the operator should also use the CONFIG CHP,ONLINE command to try to configure online the channel paths.

## **Terminating Errors on Multiple CPUs**

In a multiprocessor environment, failure of some hardware elements may cause a terminating error on more than one CPU. It is also possible that a terminating error may occur on a CPU while ACR is still processing a terminating error on another CPU. In either case, MCH issues message IGF973W indicating that an ACR is already in progress and puts the entire system into a '050' nonrestartable wait state.

# Service Processor Damage

In a 308x complex (excluding 3081D), when the system detects that the service processor is failing, the system:

- Generates a service processor damage machine check

- Informs the subsystems (such as IMS) so that they can perform an orderly shutdown

In a 3081D complex *only*, when the system detects the unique hardware malfunction called 'service processor stall', it:

- Generates a service processor damage machine check

- Logically but not physically configures one processor offline

In all 308x complexes the system issues message IEA470W so that the operator can perform an orderly shutdown of the system. Processing can continue until functions of the service processor are required; at that time, the system becomes inoperative. To recover, the operator performs an IML.

*Note:* This is also true for a 3084 complex in single image mode if the backup service processor is not available, or if a successful switchover to the backup does not occur when the active service processor goes down.

# **Storage Errors**

The hardware detects and corrects storage errors where possible. The machine check handler (MCH) is informed of the error by a machine check interrupt, and MCH invokes recovery routines through RSM. If the storage error is detected during an I/O operation, however, the operation is terminated with either a channel data check or a channel control check, depending on whether the error was encountered during data transfer or CCW/IDAW fetching. No machine check interrupt is generated in this case. Error recovery procedures (ERPs) recover from this type of error.

### Soft Storage Errors

The soft storage errors are system recovery (SR) errors with the 'storage error corrected' flag set in the MCIC to indicate that the storage controller was able to repair the error.

When a 'storage error corrected' condition occurs, MVS attempts to stop using the affected frame. This action eliminates performance degradation that would result from the hardware's correction of later occurrences of the same error. It also minimizes the chance that the same problem will later occur as a 'storage error uncorrected'. If the frame contains pageable data, MVS moves that data to another frame, and the original frame is marked offline. If the data in the frame cannot be moved, the frame is marked 'pending offline', and is subsequently taken offline if the frame is released or if its contents are made pageable. (Before MVS takes a frame offline, it tests the frame and if it has no errors, the frame is returned to available status.)

The threshold for SR machine checks affects the ability of MVS to deal with 'storage error corrected' conditions. When the threshold for SR machine checks is reached, MVS disables SR machine checks. This action prevents subsequent 'storage error corrected' from being presented. MVS then does not take any action to remove the affected frame.

Because the default threshold for SR machine checks is 4, you should consider using the MODE command to raise the SR threshold to 50 for all the CPUs. The increased SR threshold allows MVS recovery functions to handle more 'storage error corrected' for any given IPL. If the revised threshold is eventually reached, MVS issues message IGF931E to inform the operator, and disables this class of machine check.

You can raise the SR threshold to 50 by means of this operator command:

MODE SR, RECORD = 50

Note that although this recovery technique applies to all systems supported by MVS/XA, it is especially pertinent to 3090 systems. Because the 3090 performs double-bit error correction, a larger percentage of its storage errors is presented as 'storage error corrected'.

### Hard Storage Errors

This section deals with these types of hard storage errors:

- Storage error uncorrected indicates that the hardware could not repair a storage error.

- Key in storage error uncorrected indicates that the hardware could not repair a storage key that was in error.

When a hard storage error occurs, MCH invokes the real storage manager (RSM) to attempt recovery. If RSM cannot repair the error, it either takes the storage frame (4K) offline or marks it pending offline (which means that RSM will take the frame offline when the frame becomes free). MCH processing issues message IGF971E that indicates which processor is handling the error; and if possible, the address of the storage. If the operator receives message IGF971E for numerous storage addresses within an identifiable range, configuring that range offline using a CONFIG STOR command may be warranted.

Because a 'storage error uncorrected' condition represents the potential loss of critical data, MVS in most cases will terminate the affected unit of work. If the recovery routines in this termination complete successfully, and cause the freeing of the affected storage frame, the frame is marked offline and system processing continues. The recovery processing, however, could try to refer to the storage that originally caused the machine check, thus causing further errors. Such action could result in the PD threshold for machine checks being reached, thus taking a CPU offline.

You can reduce the chance of having a storage error take a CPU offline by using the following MODE command to raise the threshold for PD machine checks on all CPUs to 25 machine checks in 5 minutes:

MODE PD, RECORD = 25, INTERVAL = 300

### **Effects of Storage Errors**

Errors in critical areas of storage may cause the hardware system or the operating system to become inoperative. Those areas of storage and the effect of an error are as follows:

Hardware Storage Area (HSA): An uncorrectable storage error in the HSA causes the system to enter a check-stop state. The system can be recovered by these two steps:

- 1. Power-on-reset or SYSIML CLEAR

- 2. IPL

**HIGH SPEED BUFFER:** A processor high speed buffer error can result in the loss of the processor and possibly the system. The real storage frame corresponding to any changed data in the high speed buffer is marked with an uncorrectable storage error. Since the high speed buffer may contain critical system data, recovery may require an IPL.

**NUCLEUS:** A storage error in nucleus pages requires an IPL for recovery. If the IPL fails, recovery requires either a power-on-reset or SYSIML CLEAR, followed by IPL.

**LPA/SQA/LSQA**: A storage error in SQA could have the same effects as a nucleus storage error.

For a storage error in LPA, the operating system handles recovery. Normally, only the associated job is terminated with the remainder of the system unaffected.

### **Storage Element Failure**

If a storage element fails and sufficient usable storage is available, the operator can recover by:

- 1. Releasing the configuration (via the CONFIG frame), then deselecting the failing storage element (if this function is supported).

- 2. Issuing a storage validation function either SYSIML CLEAR or a power-on-reset.

- 3. Re-IPLing.

# **Channel Subsystem Errors**

If the channel subsystem fails, the hardware generates a 'channel subsystem damage' machine check interrupt. MCH invokes IOS to handle the interrupt.

IOS puts the entire system into an A19 nonrestartable wait state and issues message IOS019W.

## **Channel Report Words (CRWs)**

When the channel subsystem detects an error, it

- builds a CRW that describes the error

- queues the CRW for retrieval by IOS

- generates a machine check interrupt with 'CRW pending' indicator set in the machine check interrupt code (MCIC).

MCH invokes IOS to handle the interrupt.

IOS retrieves the CRW by issuing the Store CRW (STCRW) instruction and records the CRW in SYS1.LOGREC. The CRW contains a code that indicates the source of the error: the channel path, the subchannel, channel configuration alert, or the monitoring facility. (For additional information on CRWs, see *System/370 Extended Architecture Principles of Operation*.)

#### **Channel Path Recovery**

If the CRW indicates that a channel path caused the machine check, IOS attempts to recover the channel path or route I/O down an alternate channel path. (If multiple CRWs indicate errors on different channel paths, a failure in the hardware elements common to those channel paths may be indicated.)

The channel path conditions identified in the CRW are:

- A permanent error on the channel path; a system reset to the channel path has not been done (reserved devices are still reserved and the path groups for devices that have dynamic pathing active are still intact)

- A permanent error on the channel path; a system reset to the channel path has been done (devices reserved on this path are no longer reserved and the path groups for devices that have dynamic pathing active are not intact)

- The channel path is in a terminal error condition

- The channel path is recovered (initialized); a system reset to the channel path has been done (devices reserved on this path are no longer reserved and the path groups for devices that have dynamic pathing active are not intact)

The channel path conditions fall into two categories: expected and unexpected. An expected channel path condition occurs as a result of a previous recovery action taken for an unexpected channel path error, and indicates the result of the action. An unexpected channel path error occurs with no warning.

The permanent errors can be either expected or unexpected. The terminal error condition is only unexpected; it is never the result of a previous recovery action. The initialized condition can only be expected; it means that a previous recovery action has successfully recovered the channel path and the channel path is available for use.

A permanent error condition means that the channel path cannot be recovered.

A terminal error condition means that the channel path is not permanently lost but cannot be used in its current condition. IOS attempts to recover the channel path by issuing the Reset Channel Path (RCHP) instruction to initiate hardware recovery processing. This action by IOS results in another CRW with "expected" error status.

A recovered or initialized condition means that a previous recovery action has been successful in recovering the channel path.

During channel path recovery processing, IOS communicates with the operator by issuing IOSxxx messages. These messages may be issued to:

- request a specific operator action during or after recovery processing

- inform the operator of the recovery status

- inform the operator of the actions taken by IOS

## **Channel Path Alert Conditions**

IOS communicates with the operator when two other indicators are set in a CRW – 'configuration alert temporary' or 'channel path temporary'. In either case, IOS performs no recovery processing.

- For 'channel path temporary', IOS issues message IOS162A to inform the operator that the channel subsystem could not identify the device requesting service.

- For 'configuration alert temporary', IOS issues message IOS163A to inform the operator that the channel subsystem could not associate a valid subchannel with the device requesting service.

## **Subchannel Recovery**

If the CRW indicates that a subchannel caused the machine check, IOS examines the error recovery code in the CRW. If the CRW indicates that the subchannel is available, the channel subsystem has recovered from a previous malfunction. I/O functions in progress and presentation of status by the device have not been affected. No program action is required.

If the CRW indicates that the subchannel is "installed parameter initialized", IOS determines if the device associated with the subchannel is still valid. If it is, IOS reenables the subchannel. If, however, the device related to the subchannel is not valid, IOS marks the device as unusable and issues message IOS1511.

## **Monitoring Facility Recovery**

IOS does not do any recovery for the monitoring facility. IOS schedules the system resource manager's (SRM's) recovery routine.

### **I/O Errors**

The channel subsystem generates an I/O interrupt for the following I/O error conditions:

- if the device is not operational on any path

- for any device status errors (for example, unit check)

- for any subchannel status errors (for example, interface control check, channel control check)

IOS processing of the interrupt may be:

- invoking a driver exit

- interfacing with attention routines and volume verification processing

- invoking a device-dependent ERP for error recovery processing

- unconditional reserve processing

- redriving the I/O request on a channel path other than the one that generated the interrupt

- entering a restartable wait state (115) if a paging device is not operational and waiting for the operator to RESTART a processor. (The RESTART reason is ignored.)

- issuing message IOS050I to inform the operator that a subchannel status error occurred.

## **Master Console Failure**

If the master console becomes unavailable (cannot be accessed), the operating system normally switches automatically to an alternate without a re-IPL. If the alternate master console cannot be used, MVS tries to write to the hardware system console. (Refer to "Processing Messages at the System Console" on page 3-23.)

## **Missing Interrupts**

A missing interrupt condition exists when IOS expects an interrupt that does not occur within a specified time interval. For example, the IBM-default time interval between checks for missing interrupts varies from 15 seconds for paging DASD devices (other than 3330V) to 12 minutes for the 3330V and 3851 devices. An installation can define, in parmlib member IECIOSxx, time intervals for all devices in its I/O configuration and override the IBM-supplied defaults. (Refer to *SPL: Initialization and Tuning* for additional information.

The missing interruption handler (MIH) determines whether an expected interrupt has failed to occur within a specified time interval. Some possible missing interrupt conditions are:

- an idle UCB with I/O requests queued that should be started

- an outstanding I/O operation that should have completed

- an outstanding mount for a tape or disk

If an expected condition does not occur, MIH informs the operator and tries to correct the situation before system performance is affected. In addition, missing interrupt incidents are recorded in SYS1.LOGREC.

For missing interrupts, MIH issues message IOS071I or IOS076E to inform the operator of the particular condition that exists. Message IOS076E also describes the operator actions required to reset some of the conditions.

*Note:* If there are missing interrupts on the devices that contain SYSRES or page volumes, the operator may not receive any message, because the MIH message writer and the CONSOLE address space (Comm Task) are pageable. The operator can learn about the missing interrupts by initiating the RESTART function with REASON 1.

For recurring missing interrupts, MIH issues message IOS075E together with message IOS076E or IOS077E to inform the operator of the recurring condition on a particular device.

## Unconditional Reserve/Alternate Path Recovery (APR)

Alternate path recovery (APR) permits recovery from control unit or channel path failures that cause a DASD device, or a string of DASD devices, to no longer be accessible to the system. APR is performed only after IOS guarantees ownership of the device; that is, the device is reserved to this system.

APR issues an UNCONDITIONAL RESERVE command along each online path, one at a time, to the device. If an alternate path is available, APR issues message IEA428I. If no alternate paths are available, APR issues message IEA429I. IOS then boxes the device and terminates all subsequent requests to that device with a permanent error.

If IOS cannot guarantee ownership of the device, it issues message IEA427A, which gives the operator three recovery options. However, before replying with one of the options, the operator should ensure that the device is owned (reserved) to this system.

# Hot I/O

A Hot I/O condition occurs when a device, control unit, or channel path causes continuous unsolicited I/O interrupts. If the Hot I/O condition goes undetected, it can cause the system to enter a loop or it can exhaust the system queue area (SQA). IOS attempts to recover from a Hot I/O condition so that a re-IPL is not required. For diagnostic purposes, IOS records all Hot I/O incidents on SYS1.LOGREC.

IOS first tries recovery at the device level by issuing the Clear Subchannel instruction in an attempt to clear the Hot I/O condition. If the condition is cleared, processing continues normally. If the condition persists, the next recovery action is determined by one of the following:

- the parameters the installation defined in parmlib member IECIOSxx for Hot I/O recovery

- operator response to the appropriate Hot I/O message or restartable wait state:

- IOS110A or wait state 110 (non-DASD),

- IOS111A or wait state 111 (unreserved DASD), or

- IOS112A or wait state 112 (reserved DASD).

3-16 MVS/XA Planning: Recovery and Reconfiguration

Because IPLs related to Hot I/O are generally caused by incorrect operator actions, an installation should use the IECIOSxx parmlib member to make Hot I/O recovery more automatic and reduce the need for immediate operator intervention. The following sample parameters, when defined in the IECIOSxx parmlib member, tell IOS how to handle automatic recovery from Hot I/O for three classes of devices: non-DASD, non-reserved DASD, and reserved DASD. (Additional information on Hot I/O parameter specification is discussed in *SPL: Initialization and Tuning*, and *SPL: System Modifications*.)

#### Sample Parameters for Hot I/O Recovery in Parmlib Member IECIOSxx

The following entries are an example of how to specify the Hot I/O recovery parameters in the IECIOSxx parmlib member. As of SP2.2.0, the values shown are also the IBM default values.

#### HOTIO DVTHRSH = 100

Specifies 100 repeated interrupts as the threshold for IOS recognizing the condition.

HOTIO DFLT110 = (BOX,)

Box the non-DASD device on the first occurrence of this condition and prompt the operator for the recursive condition.

HOTIO DFLT111=(CHPK,BOX)

Attempt channel path recovery for non-reserved DASD on first occurrence. On recursion, box the device.

HOTIO DFLT112=(CHPK,OPER)

Attempt channel path recovery for reserved DASD on first occurrence, but prompt the operator for the recursive condition.

### 3880/3380 Considerations