GC28-1348-0 File No. S370-34

# MVS/Extended Architecture Overview

# **Systems**

.(

#### First Edition (March, 1984)

This edition applies to:

ſ

MVS/System Product - JES2 Version 2 (5740-XC6) MVS/System Product - JES3 Version 2 (5665-291) MVS/XA Data Facility Product<sub>2</sub>(DFP) (5665-284)

and to all subsequent releases until otherwise indicated in new editions or Technical Newsletters. Changes are made periodically to the information herein; before using this publication in connection with the operation of IBM systems, consult the latest *IBM System/370 Bibliography*, GC20-0001, for the editions that are applicable and current.

References in this publication to IBM products, programs, or services do not imply that IBM intends to makes these available in all countries in which IBM operates. Any reference to an IBM program product in this publication is not intended to state or imply that only IBM's program products may be used. Any functionally equivalent program may be used instead.

Publications are not stocked at the address given below; requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for reader's comments is provided at the back of this publication. If the form has been removed, comments may be addressed to IBM Corporation, Information Development, Department D58, Building 920-2, PO Box 390, Poughkeepsie, New York 12602. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

© Copyright International Business Machines Corporation 1984

# **Preface**

í

The *MVS/Extended Architecture Overview* is an introduction to MVS/Extended Architecture (MVS/XA), the operating system that manages IBM System/370-XA computers. This book expects readers to have a general understanding of how computers work. That is, it assumes some background knowledge of the components of a computer system, the role of an operating system, and computer programming concepts.

Chapter 1 describes the environment in which MVS/XA runs and the attributes that allow MVS/XA to govern complex computer configurations. It presents MVS/XA interpretations of computer terms and concepts.

The remaining chapters give an overview of how MVS/XA works. Chapters 2 and 3 explain how MVS/XA manages and makes use of two key system resources: real storage and virtual storage. Subsequent chapters explain how MVS/XA accomplishes the primary operating system functions of:

- Chapter 4: Managing the hardware

- Chapter 5: Monitoring system resource use

- Chapter 6: Processing units of work

- Chapter 7: Reading and writing code and data

- Chapter 8: Identifying, tracking, and allocating resources to jobs

- Chapter 9: Preventing and tracing system errors

- Chapter 10: Recovering from system errors

- Chapter 11: Initializing the system

There are no prerequisite MVS/XA reading materials for using this book. Additional documentation of MVS/XA appears in the MVS/XA library. The MVS/XA Library User's Guide, GC28-1339, gives a complete list of related publications.

iv MVS/Extended Architecture Overview

í

## Contents

Chapter 1. Introduction to MVS/Extended Architecture 1-1 The MVS/XA Environment 1-1 Virtual Storage 1-2 Address Spaces 1-3 Task Management 1-3 Control Blocks 1-4 Program Status Word 1-5 Interruptions 1-6 Macro Instructions 1-6 Resource Management 1-6 System Parameters 1-7 Exit Routines 1-7 **Operator Console 1-7** I/O and Data Management 1-8 Job Management 1-8 **Recovery Management 1-9** Summary 1-9

Chapter 2. Multiple Virtual Storage 2-1 Addressing Mode and Residence Mode 2-1 Virtual and Real Storage 2-3 Dynamic Address Translation (DAT) 2-4 Virtual Address 2-5 Segment and Page Tables 2-5 Two-Level Lookup 2-6 The Paging Process 2-7 Page Stealing 2-9 Swapping 2-11 Storage Protection 2-11 Storage Protect Keys 2-11 Key Assignments 2-12 Key Switching 2-13 MVS/XA Storage Managers 2-13 Real Storage Manager (RSM) 2-13 Auxiliary Storage Manager (ASM) 2-14 Virtual Storage Manager (VSM) 2-14

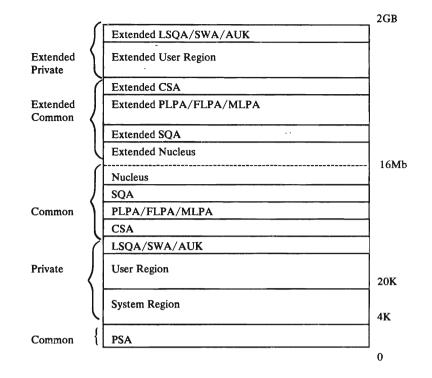

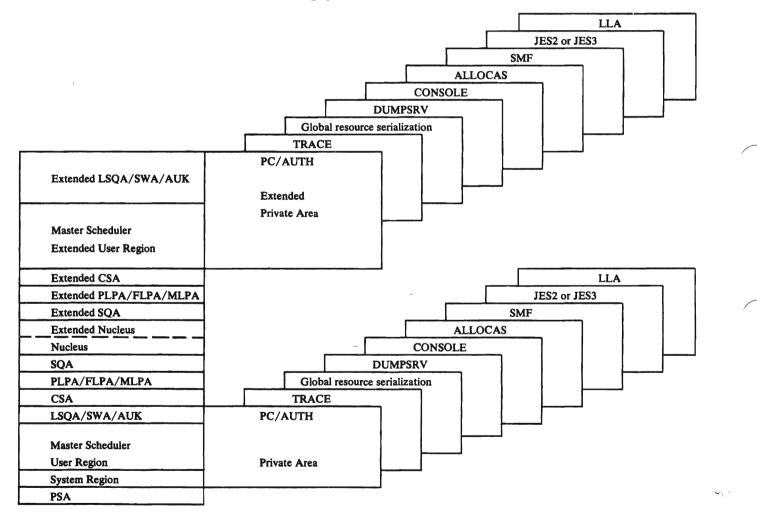

Chapter 3. MVS/XA Address Spaces 3-1 Virtual Storage Areas 3-1 Prefixed Save Area 3-2 The Private Area and Extended Private Area 3-2 System Region 3-3 User Region/Extended User Region 3-3 Authorized User Key (AUK)/Extended AUK 3-4 Scheduler Work Area (SWA)/Extended SWA 3-4 Local System Queue Area (LSQA)/Extended LSQA 3-5 The Common Area and Extended Common Area 3-5 Common Service Area (CSA)/Extended CSA 3-5 Pageable Link Pack Area (PLPA)/Extended PLPA 3-5 Fixed Link Pack Area (FLPA)/Extended FLPA 3-5 Modified Link Pack Area (MLPA)/Extended MLPA 3-6 System Queue Area (SQA)/Extended SQA 3-6 Nucleus/Extended Nucleus 3-6 MVS/XA System Component Address Spaces 3-7 Inter-Address Space Communication 3-9 Cross Memory 3-9

#### Chapter 4. Multiprocessing 4-1

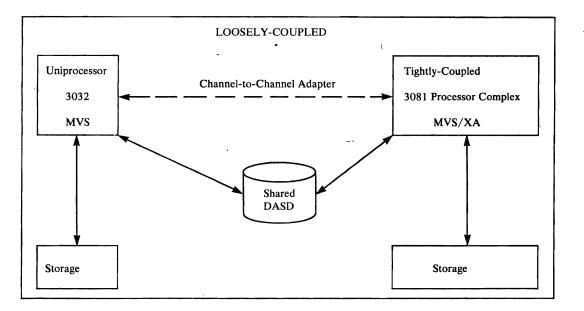

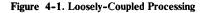

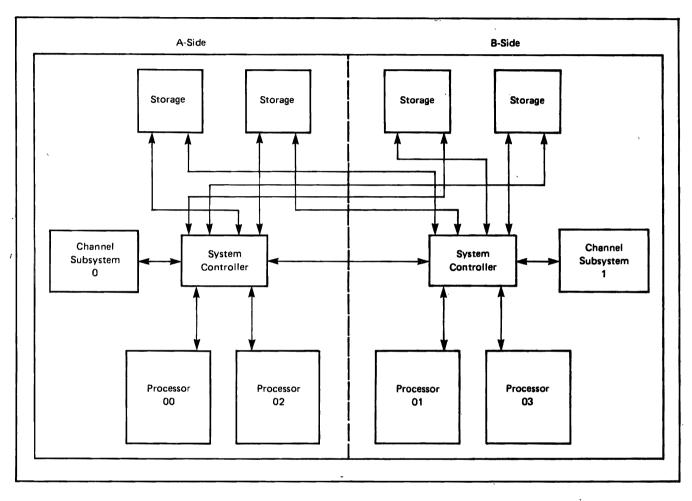

Types of Multiprocessing 4-1 Loosely-Coupled Multiprocessing 4-1 Tightly-Coupled Multiprocessing 4-2 Configuring a Tightly-Coupled Processor 4-2 Dyadic Tightly-Coupled Multiprocessing 4-4 Control of Processing in a Tightly-Coupled MP System 4-4 Communication Among Processors in an MP System 4-5

MVS/XA-Initiated Communication 4-5 Hardware-Initiated Communication 4-6 Chapter 5. Managing System Resources 5-1 SRM Decisions 5-1 Functional Areas of SRM 5-1 Communicating with SRM 5-2 SRM Control 5-3 Swap Analysis 5-3 The Workload Manager 5-4 The Resource Manager 5-4 Storage Management 5-5 I/O Management 5-6 Processor Management 5-6 **Resource Monitoring 5-7** Chapter 6. Supervising the Execution of Work 6-1 Interruption Processing 6-1 The Program Status Word 6-2 The Interruption Handlers 6-3 Creating Dispatchable Units of Work 6-5 Task Control Blocks (TCBs) 6-6 Service Request Blocks (SRBs) 6-7 **Dispatching Work 6-8** Serializing the Use of Resources 6-9 Enqueuing 6-9 Global Resource Serialization 6-10 Locking 6-10 Lock Hierarchy 6-10 Chapter 7. Satisfying I/O Requests 7-1 How I/O Data Moves Through the System 7-2 How an I/O Request Moves Through MVS/XA 7-5 A Closer Look at How an I/O Request Moves Through MVS/XA 7-7 User Program Functions 7-8 **OPEN Processing 7-8** Requesting I/O 7-9 Access Method Exit Appendages 7-9 CLOSE Processing 7-10 Access Method Functions 7-10 Building the Channel Program 7-11 **Building Control Blocks 7-11** Invoking EXCP 7-11 EXCP and IOS Functions 7-12 EXCP Processor Front End 7-13 IOS I/O Initiation 7-13 Channel Subsystem Functions 7-14 IOS Interruption Handling<sup>-</sup> 7-14 **EXCP Exit Processing 7-14 IOS Post Status 7-15** EXCP Processor Back End 7-15 Summary 7-15 Virtual Input/Output (VIO) 7-16 Virtual Fetch 7-18 Access Methods 7-18 Access Techniques 7-18 Access Method Categories 7-19 **Conventional Access Methods 7-19 Telecommunication Access Methods 7-20** Virtual Storage Access Method (VSAM) 7-21 Chapter 8. Entering and Scheduling Work 8-1 The Role of the Job Entry Subsystem 8-1 Job Entry/Output Processing 8-2 Entry 8-2 Conversion/Interpretation 8-3

Device Allocation 8-3 Job Step Allocation 8-4

1

JES3 Device Allocation 8-5 Dynamic Allocation 8-6 Scheduling a Job for Execution 8-6 JES2 Job Scheduling 8-6 JES3 Job Scheduling 8-7 Additional Job Scheduling Functions 8-8 Output 8-9 Purge 8-9 Job Entry Subsystems in a Multi-System Environment. 8-9 Job Networking 8-12 Comparing JES2 and JES3 Features 8-14

#### Chapter 9. Monitoring System Activity 9-1

System Management Facilities 9-2 **Resource Measurement Facility 9-4 Dumping Facilities 9-7** SNAP Dump 9-8 ABEND Dump 9-9 SVC Dump 9-10 Stand-Alone Dump 9-10 **Trace Facilities 9-13** System Trace 9-14 Generalized Trace Facility 9-16 Master Trace 9-19 Serviceability Level Indication Processing (SLIP) 9-20 Program Event Recording Events 9-21 Error Events 9-21 SLIP Actions 9-22 Using SLIP Traps 9-22 SYS1.LOGREC Error Recording 9-24

#### Chapter 10. Recovering From Errors 10-1

1.

Software Recovery: Recovery Termination Manager 10-1 Recovery Routines 10-1 Task Recovery Routines 10-2 Functional Recovery Routines 10-2 Hardware Recovery Facilities 10-3 Machine Check Handler 10-3 Alternate CPU Recovery 10-3 Subchannel Logout Handler 10-4 Dynamic Device Reconfiguration 10-5 Missing Interruption Handler 10-5

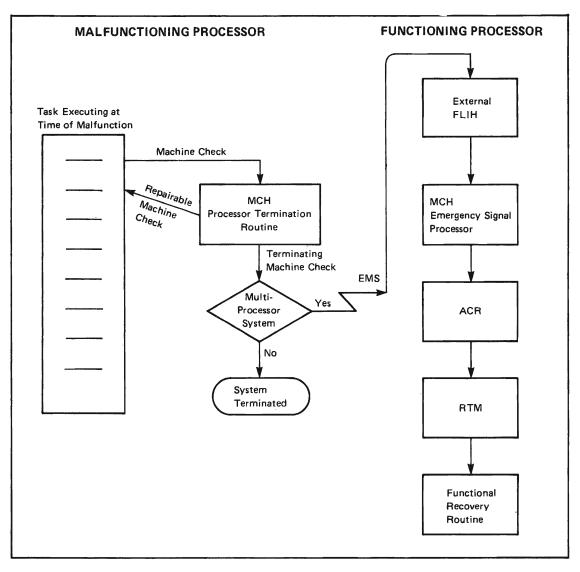

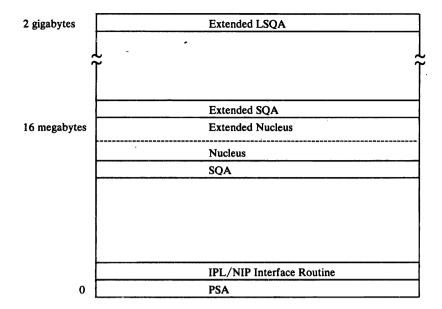

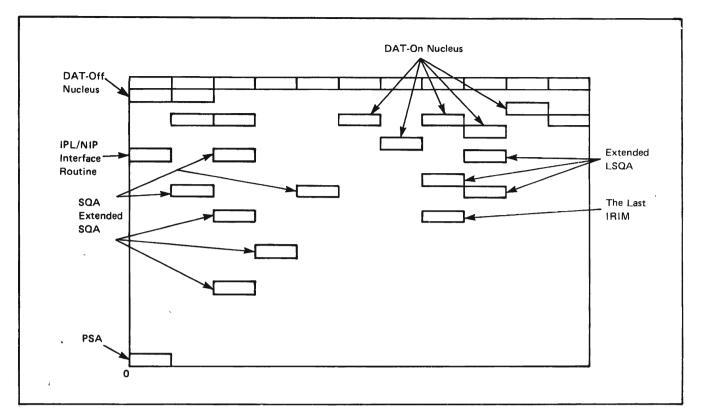

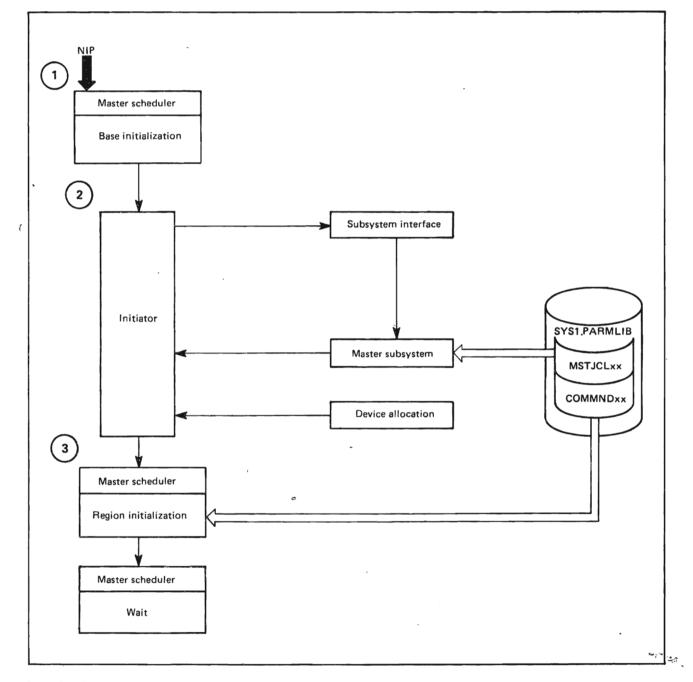

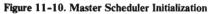

Chapter 11. Initializing the System 11-1 Loading the Nucleus 11-2 Initializing System Resources 11-2 Initializing the Resource Managers 11-3 Initializing the Master Scheduler Address Space 11-3 Initializing a Job Entry Subsystem 11-3 The Initialization Process 11-3 **Required Resources 11-5** Initial Program Load (IPL) 11-6 The IPL Program 11-7 The Work of the IRIMs 11-7 Loading the Nucleus 11-7 Initializing Virtual Storage 11-8 Initializing Real Storage 11-9 Initializing the IPL Device 11-10 Nucleus Initialization Program (NIP) 11-10 Establishing the Master Scheduler Address Space 11-11 Processing System Parameters 11-11 System Parameter Lists 11-12 System Operator 11-12 Initializing System Resources and Resource Managers 11-13 Initializing I/O Devices 11-13 Initializing the Master Catalog 11-14 Initializing the Auxiliary Storage Manager 11-15 Initializing Page Data Sets 11-16 Initializing Swap Data Sets 11-16

Initializing the Master Scheduler 11-17 Initializing the Master Scheduler Base 11-18 Initiating the Master Scheduler 11-18' Initializing the Master Scheduler Region 11-18 Initializing the Job Entry Subsystem 11-19 Creating an Address Space for JES 11-19 Initializing the Region Control Task 11-19 Initializing the Time Sharing Option (TSO) 11-19 Creating User Address Spaces 11-20

\*

Index X-1

## **Figures**

1

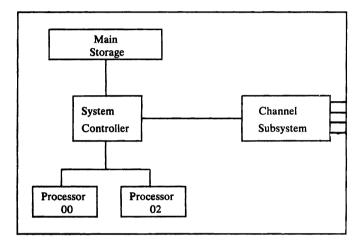

- 1-1. The 3081 Processor Complex 1-2

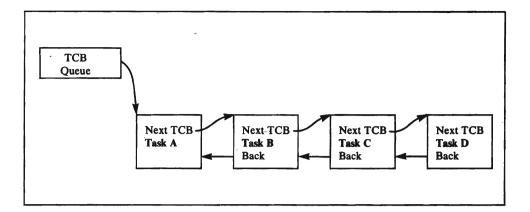

- 1-2. A Queue of Task Control Blocks 1-5

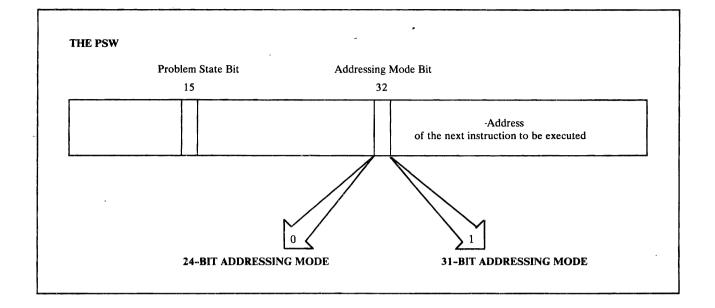

- 1-3. The MVS/XA PSW 1-6

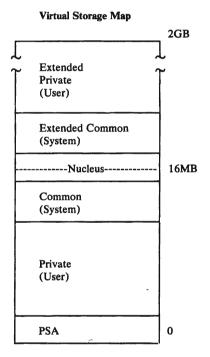

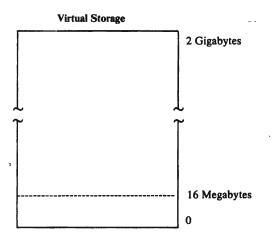

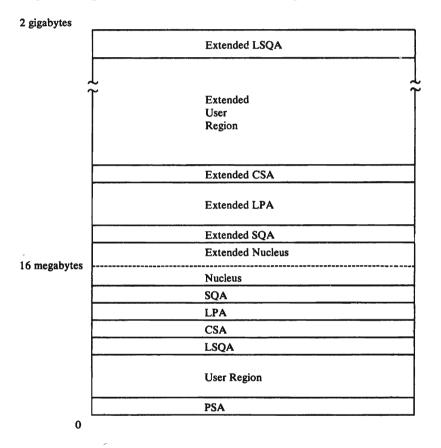

- 2-1. The MVS/XA Address Space 2-1

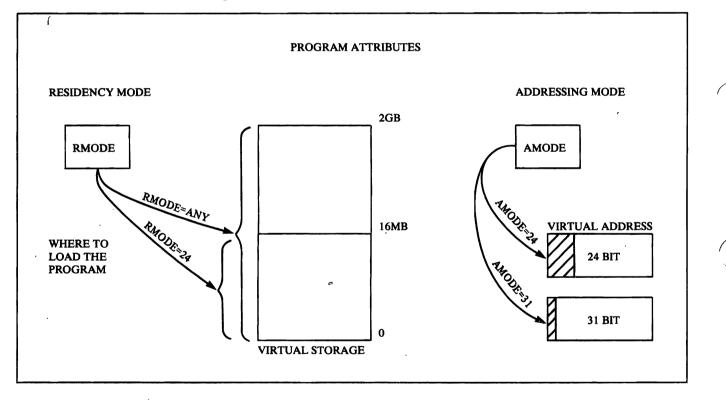

- 2-2. AMODE and RMODE Attributes 2-2.

- 2-3. Valid AMODE and RMODE Combinations 2-3

- 2-4. Virtual Storage Page Movement 2-4

- 2-5. Virtual Storage Address 2-5

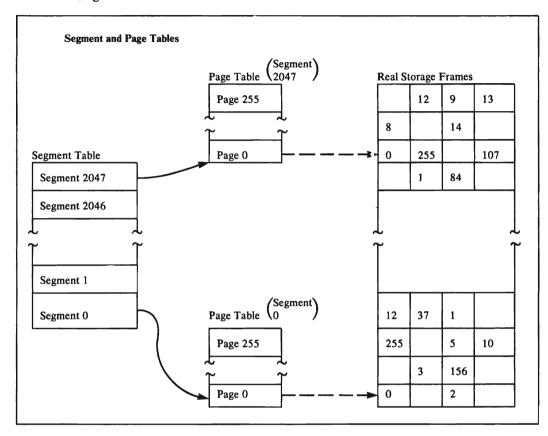

- 2-6. Segment Table and Page Tables 2-6

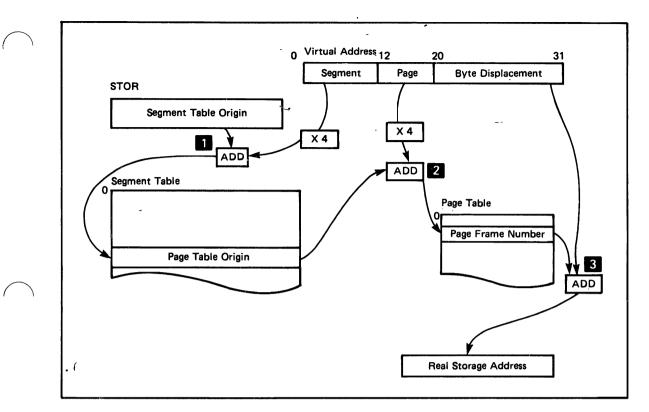

- 2-7. Dynamic Address Translation 2-7

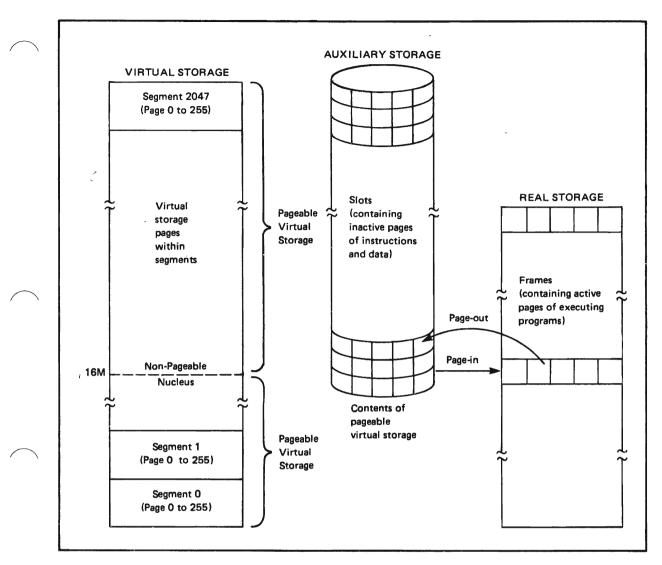

- 2-8. Page-Out and Page-In 2-9

- 2-9. Page Frame Table 2-11

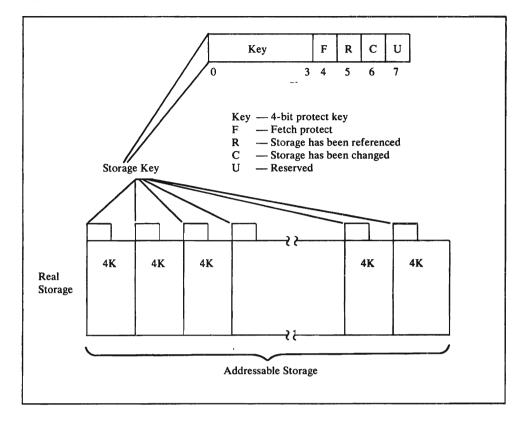

- 2-10. The Key in Storage 2-12

- 2-11. Storage Protect Key Assignment 2-13

- 3-1. A Logical Representation of Virtual Storage 3-1

- 3-2. Virtual Storage Layout 3-2

- 3-3. V=R Storage Mapping 3-4

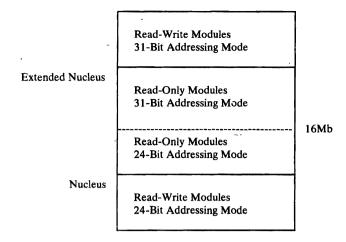

- 3-4. The DAT-on Nucleus 3-7

- 3-5. Virtual Storage Layout For Key MVS/XA Components. 3-8

- 4-1. Loosely-Coupled Processing 4-2

- 4-2. Tightly-Coupled Multiprocessing 4-3

- 4-3. Dyadic Processor Complex 4-4

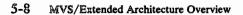

- 6-1. The Use of Program Status Words (PSWs) in Interruption Processing 6-3

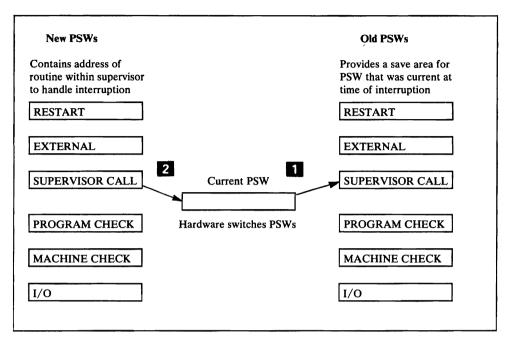

- 6-2. Summary of Interruption Processing 6-5

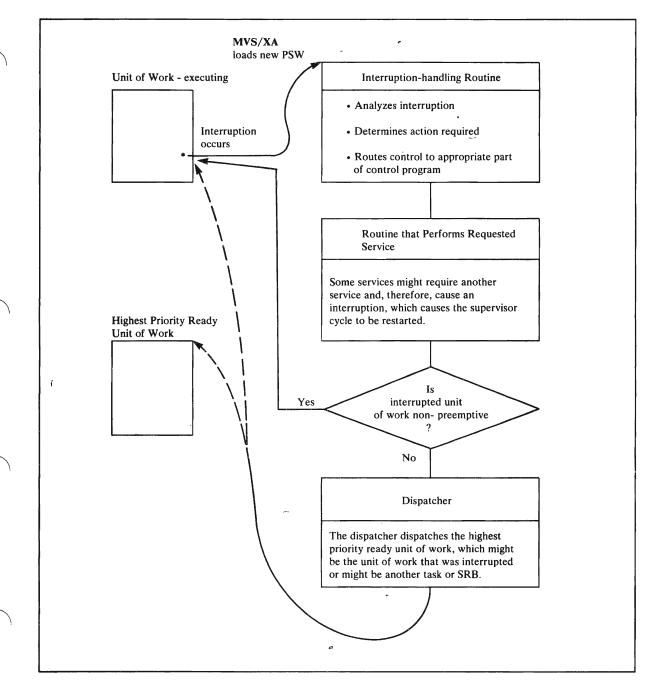

- 6-3. Address Space Task Control Block (TCB) Dispatching Queues 6-7

- 6-4. Definition and Hierarchy of Locks 6-11

- 7-1. Components of the I/O Request 7-2

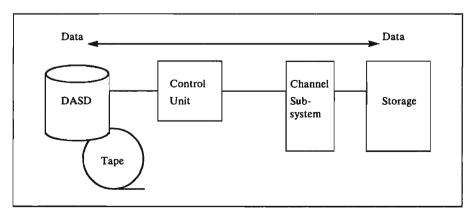

- 7-2. Conventional Input/Output 7-2

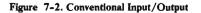

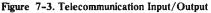

- 7-3. Telecommunication Input/Output 7-3

- 7-4. Multiple I/O Channel Paths 7-4

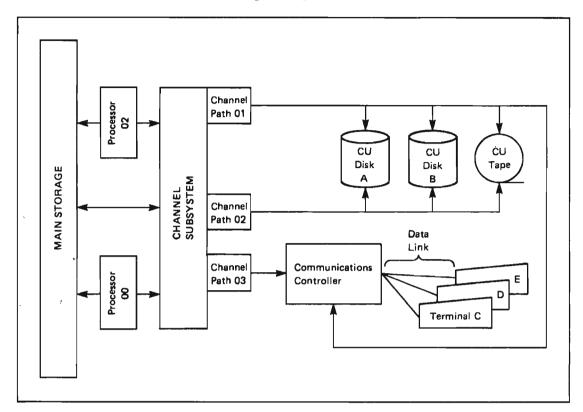

- 7-5. Logical Control Units 7-5

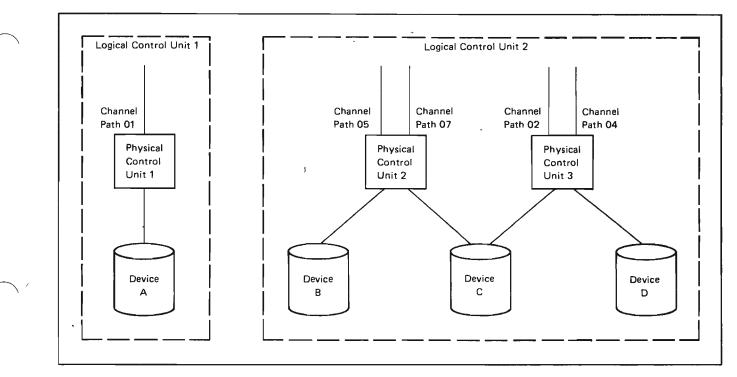

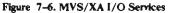

- 7-6. MVS/XA I/O Services 7-6

- 7-7. Relationships Established by OPEN 7-9

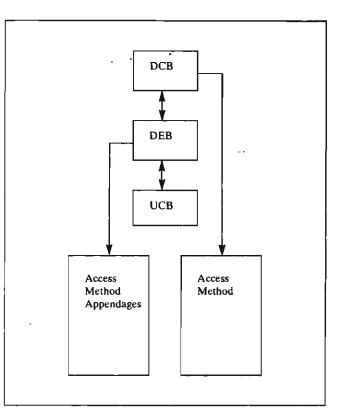

- 7-8. CLOSE Processing Summary 7-10

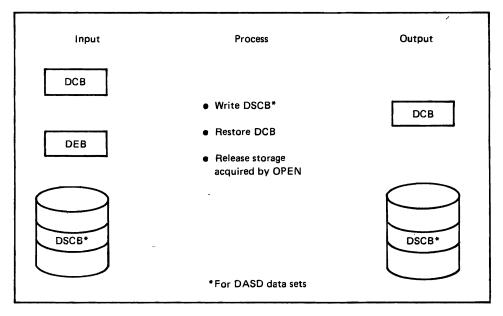

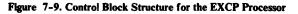

- 7-9. Control Block Structure for the EXCP Processor 7-11

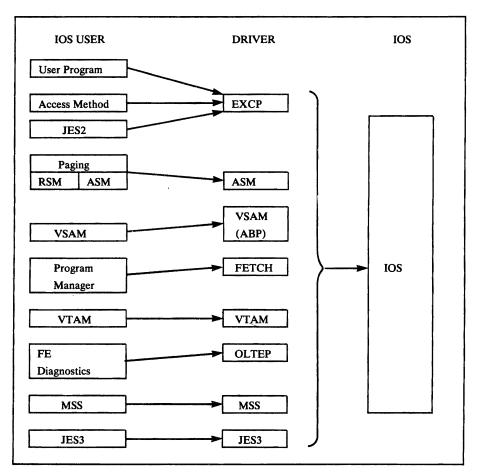

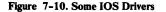

- 7-10. Some IOS Drivers 7-12

- 7-11. MVS/XA I/O Processing 7-16

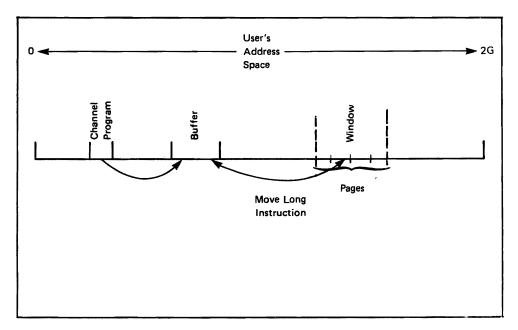

- 7-12. VIO Window 7-17

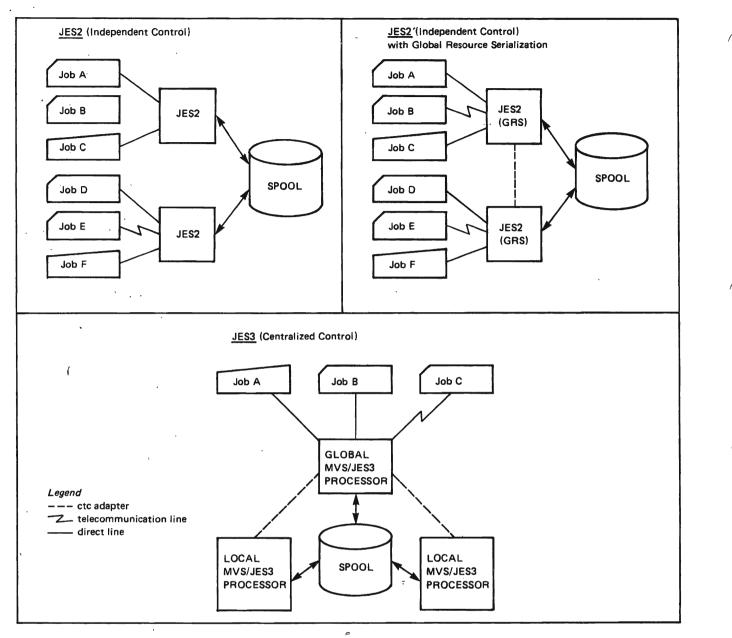

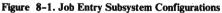

- 8-1. Job Entry Subsystem Configurations 8-12

8-2. Job Networking 8-13

- 8-3. JES2 and JES3 Features 8-14

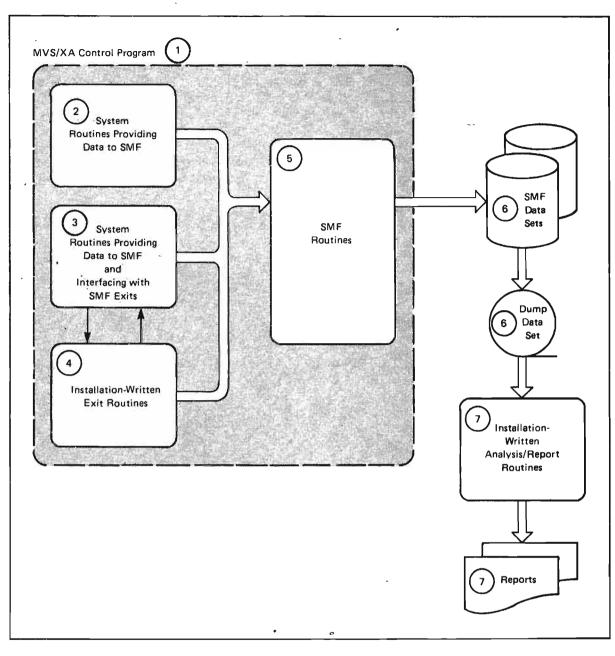

- 9-1. System Management Facilities Overview 9-4

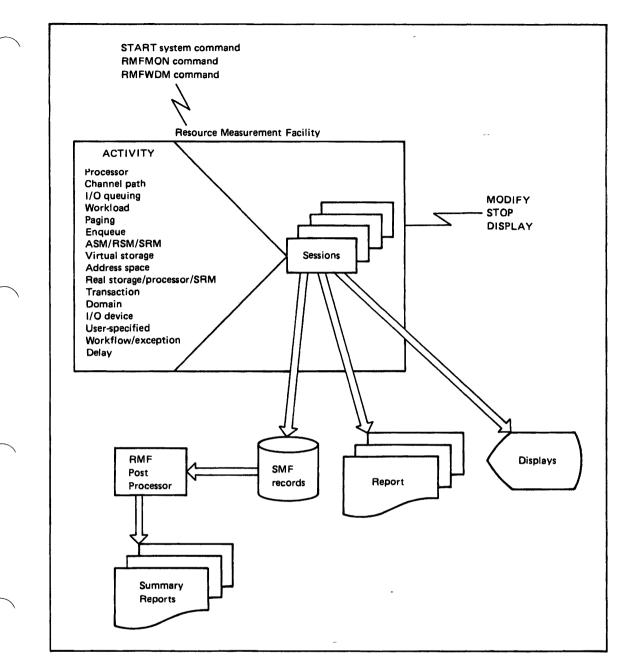

9-2. Summary of RMF 9-7

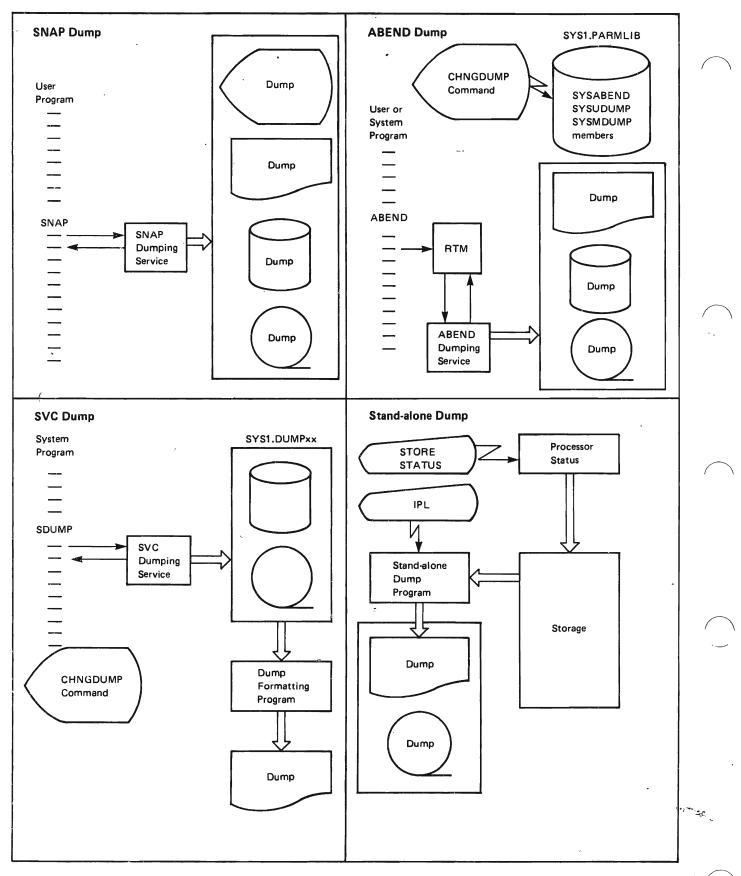

- 9-3. Summary of MVS/XA Dumping Services 9-12

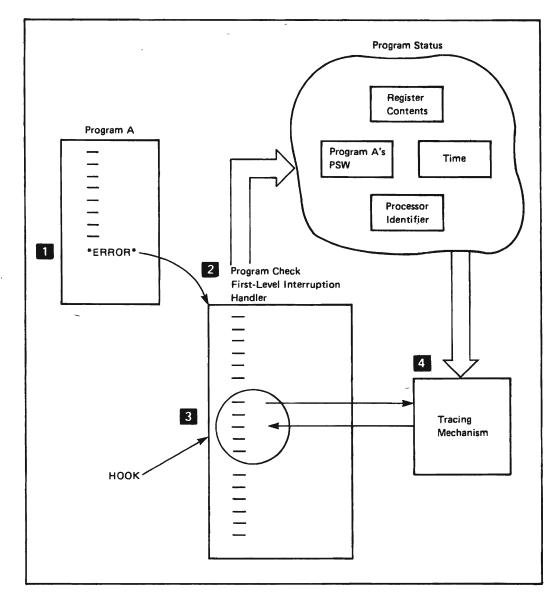

- 9-4. The HOOK Concept 9-14

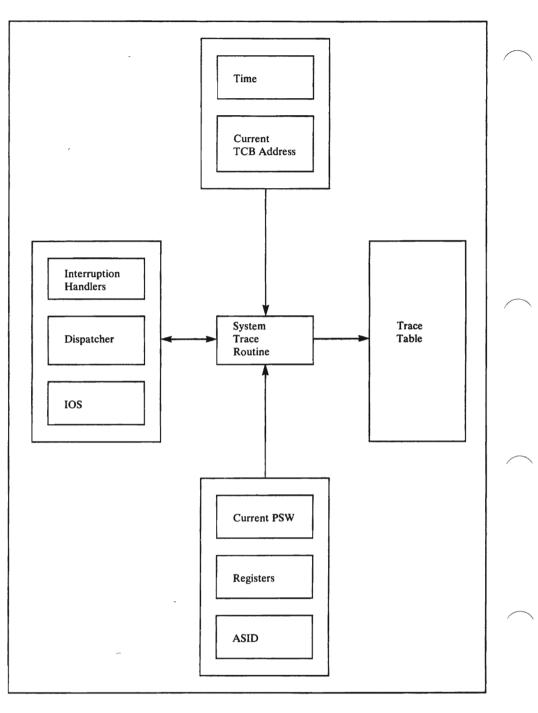

- 9-5. System Trace Overview 9-16

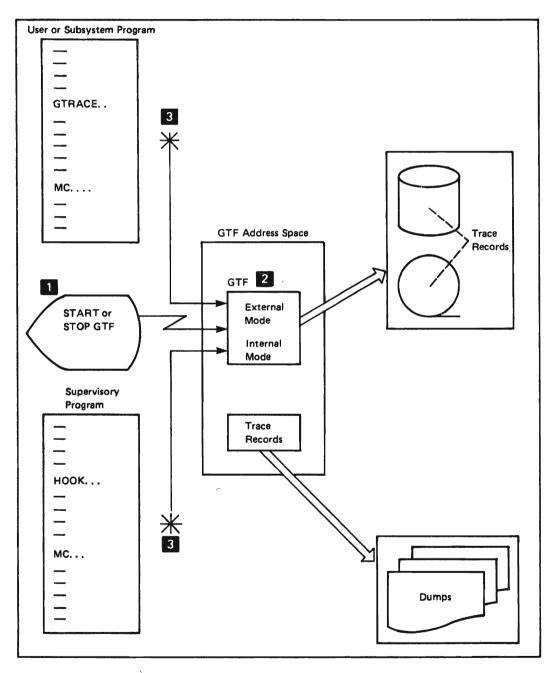

- 9-6. Generalized Trace Facility Summary 9-18

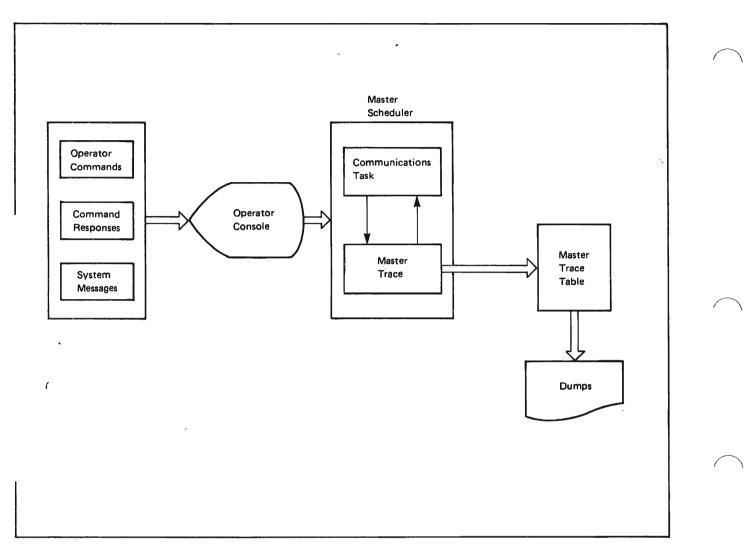

- 9-7. Master Trace Overview 9-20

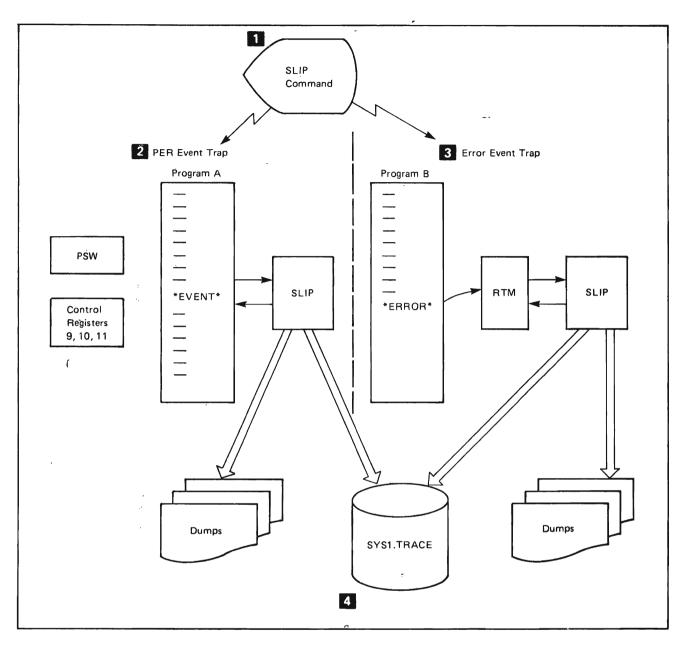

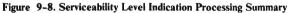

- 9-8. Serviceability Level Indication Processing Summary 9-24

- 9-9. SYS1.LOGREC Error Recording Overview 9-26

- 10.1. O TELEOGREC ENDI Recording Overview

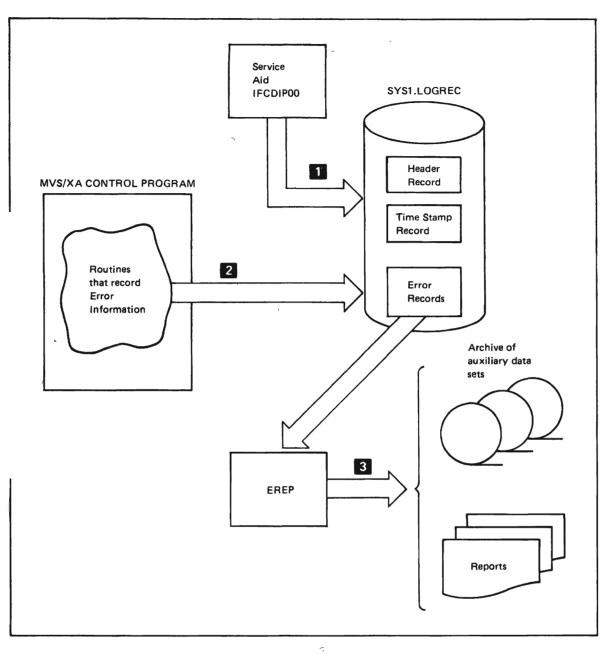

- 10-1. Control Flow for MCH and ACR 10-4

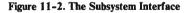

- 11-1. The Initialization Process 11-2

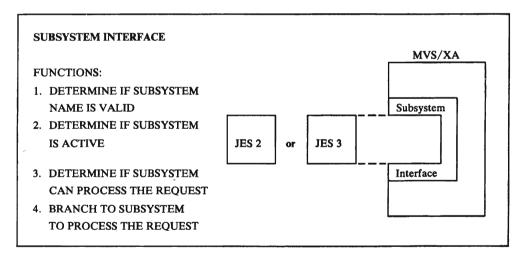

- 11-2. The Subsystem Interface 11-3

- 11-3. System Initialization Summary 11-4

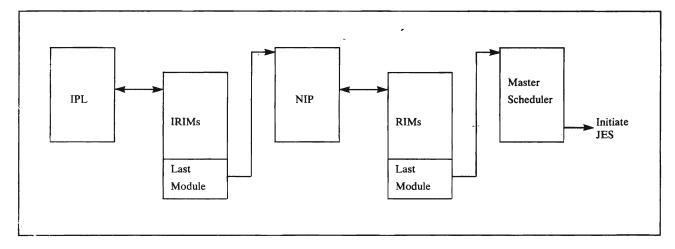

- 11-4. Loading the IPL Control Program 11-7

- 11-5. Virtual Storage at Exit from the IPL Phase of Initialization 11-9

- 11-6. Real Storage at Exit from IPL 11-10

- 11-7. Virtual Storage at Exit from NIP 11-11

- 11-8. Initializing Channel Paths 11-14

- 11-9. Locating the Master Catalog 11-15

- 11-10. Master Scheduler Initialization 11-17

- 11-11. Creating an Address Space 11-21

X MVS/Extended Architecture Overview

\_

P

\_ \_

1

An operating system is a group of related programs that govern the computer system. The operating system controls the execution of programs and provides services they need to make use of the computer system hardware. MVS/XA is the operating system that takes advantage of the IBM System/370 extended architecture (System/370-XA).

A computer's architecture consists of the functions the computer system provides. It is distinct from the physical design, and, in fact, different machine designs may conform to the same computer architecture. In a sense, the architecture is the computer as seen by the user such as a system programmer. For example, part of the architecture is the set of machine instructions that the computer can recognize and execute.

System/370-XA, as its name implies, is an extension of the System/370 computer architecture. Similarly, MVS/XA is an extension of the MVS/370 operating system that supports the System/370 architecture. Thus, MVS/XA, despite the fact that it supports significant changes to System/370 architecture, includes much that is familiar to MVS/370 users.

The differences between MVS/370 and MVS/XA center on taking advantage of the continuing high performance enhancements to computer system hardware and improving the reliability, availability, and serviceability of the system. The two most significant changes are:

31-bit addressing

MVS/370 provides a 24-bit addressing scheme. MVS/XA provides both a 31-bit and a 24-bit addressing scheme. This change extends the storage available to any one user from 16 million bytes (16 megabytes) to two billion bytes (two gigabytes).

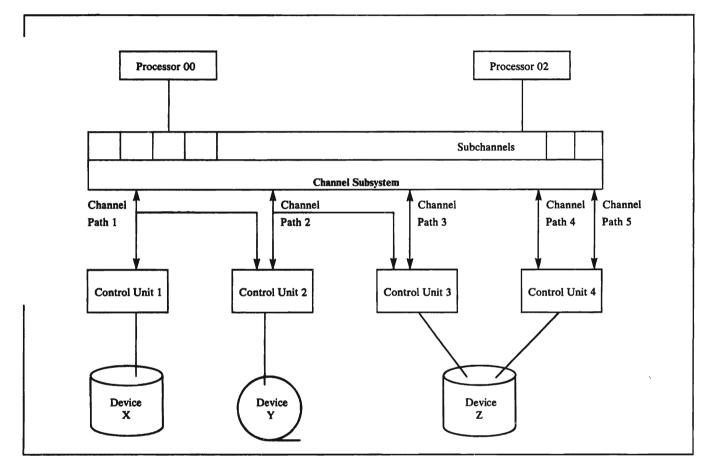

• The channel subsystem

The channel subsystem handles input and output (I/O) operations independently of the processors in the MVS/XA system. MVS/370 also allows overlap of I/O operations with instruction processing, but the MVS/XA channel subsystem increases the amount of overlap and allows all of the processors to access all of the I/O devices without the need for multiple tasks or for switches.

Neither of the changes, however, creates the need for users to change existing application programs. Application programs written for 24-bit addressing can run under MVS/XA, and there have been no changes to the way programs invoke I/O operations.

## The MVS/XA Environment

To understand how and why MVS/XA functions as it does, it is important to understand the environment in which it functions. The special features that make MVS/XA unique reflect the features of the computer environments that MVS/XA manages. By way of contrast, consider a simple, single user, computer system. Its operating system is a simple one that reads in one job, finds the data and devices it needs, lets the job run to completion, and then reads in another job.

The computer systems that MVS/XA manages are capable of **multiprogramming**, or executing many programs concurrently. By means of multiprogramming the system can, for example, run hundreds of jobs simultaneously for users who might be at distant geographical locations.

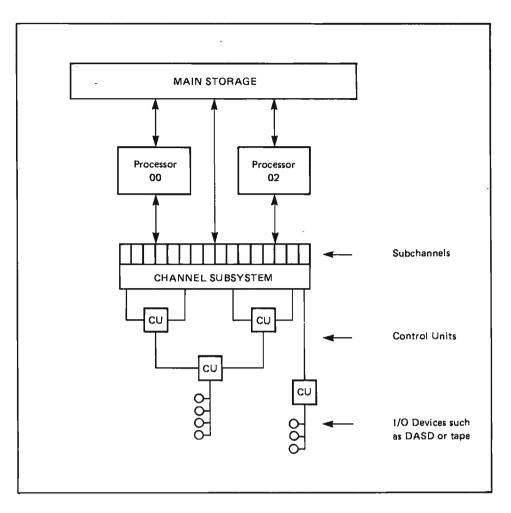

MVS/XA can also manage multiprocessing, which is the simultaneous operation of two or more processors that share the various system hardware devices. Figure 1-1 illustrates the IBM 3081 Processor Complex; two central processors share main storage and the channel subsystem. Chapter 4, "Multiprocessing" gives more detail on the MVS/XA multiprocessing environment.

Figure 1-1. The 3081 Processor Complex

Many users running many separate programs means that, along with large amounts of complex hardware, MVS/XA users need large amounts of storage to ensure suitable system performance. They run sophisticated application programs that access large data bases and program modules. Such applications require the operating system to provide routines to protect privacy as well as routines for sharing the data bases and software services.

Thus, multiprogramming, multiprocessing, and the need for large amounts of storage mean that MVS/XA must provide function beyond simple job-to-job transition. The following introduction describes, in a general way, the attributes that enable MVS/XA to manage complex computer configurations. Subsequent chapters explain these features in more detail.

## Virtual Storage

The MVS in MVS/XA stands for multiple virtual storage to indicate that each user has access to virtual, rather than only real (physical), main storage. Virtual storage means that each running program can assume it has access to all of the main storage that the addressing scheme allows. The only limit is the number of bits in a storage address. This ability to use a large number of storage locations is important because a program may be long and complex and, both the program's code and the data it requires must be in main storage in order for the processor to access them.

The 31-bit address supported by MVS/XA allows a program to address up to 2,147,483,648 (two gigabytes) storage locations. In contrast, the system has much less real storage. How much less depends upon the model of computer and the installation's configuration.

To allow each user to behave as though he had much more real storage than really exists in the computer system, MVS/XA keeps only the active portions of each program in real storage and the rest of its code and data in special data sets, usually on high-speed direct access storage devices (DASDs).

Virtual storage, then, is this combination of real and auxiliary storage. MVS/XA requires billions of bytes of auxiliary storage to make virtual storage possible. It uses a system of tables and bit settings to relate the DASD locations to real storage locations and keep track of the identity and authority of each program. Chapter 2, "Multiple Virtual Storage," explains how MVS/XA manages virtual and real storage.

A complete two-gigabyte range of 31-bit virtual storage addresses is known as an address space. MVS/XA provides each user (batch job initiator, TSO user, or started task) with a unique address space and maintains the distinction between the code and data belonging to each address space. MVS/XA also includes cross memory services, that permit a single user to access other address spaces when necessary.

The ability of many users to share the same resources implies the need to protect users from one another and to protect the operating system itself. Along with such methods as "keys" for protecting real storage and code words for protecting data files and programs, separate address spaces ensure that users' programs and data do not overlap. Chapter 3, "MVS/XA Address Spaces," describes the virtual storage areas within each address space and which address spaces are created during system initialization.

# **Task Management**

MVS/XA breaks each job into separate units of work known as tasks and attempts to process each one as efficiently as possible. The tasks for one job compete with one another, and with tasks related to other jobs, for use of system resources. Responsibility for controlling the progress of tasks through the system lies with the **supervisor**, a component of the operating system. The supervisor allocates resources (other than I/O devices) and maintains current information about each task so that processing can resume from the appropriate point in case of an interruption.

MVS/XA includes several mechanisms to enable the supervisor and other system components to maintain control. This section describes four control mechanisms: control blocks, the program status word, interruptions, and macro instructions. Chapter 6, "Supervising the Execution of Work," describes other key features of MVS/XA task management.

**Address Spaces**

í

# **Control Blocks**

MVS/XA modules normally store the information needed to control a particular unit of work or manage a resource in defined storage areas called control blocks. Generally speaking, there are three types of MVS/XA control blocks:

System

Each system-related control block represents one MVS/XA system. These contain system-wide information such as how many processors are functioning.

• Resource

Each resource-related control block represents one resource such as a processor or auxiliary storage device.

Task

Each task-related control block represents one unit of work.

Control blocks work as vehicles for communication throughout MVS/XA. Such communication is possible because the structure of a control block is known to all of its users, and thus all can find needed information about the unit of work or resource. The MVS/XA system control blocks, for example, are all documented in the multi-volume MVS/XA Debugging Handbook.

Control blocks representing many units of the same type may be chained together on **queues**, with each control block pointing to the next one in the chain. A program can search the queue to find the data for a particular unit of work or resource, which might be:

- An address (of a control block or a required routine)

- Actual data, such as a value, a quantity, a parameter, or a name

- Status flags (usually single bits in a byte, where each bit has a specific meaning)

All fields in a control block are defined and identified in the documented structure of the specific control block.

Control blocks have many sizes and formats. Usually, a control block consists of a series of fullword fields, but some fields can be longer (such as the name of a data file) or shorter (such as a flag byte). Important points to remember about control blocks are that they are structured, documented, and usually chained together. Figure 1-2 illustrates a queue of task control blocks (TCBs).

L

Figure 1-2. A Queue of Task Control Blocks

#### **Program Status Word**

The program status word (PSW) is a 64-bit data area in the processor that, along with control registers, timing registers, and the prefix registers, provides details crucial to both the hardware and the software. The current PSW includes the address of the next program instruction and control information about the program that is running, such as whether it is running in 24-bit or 31-bit addressing mode or whether or it is running in the **problem program** state or **supervisor** state.

Supervisor state programs are authorized to issue all instructions, including those that, for example, change the PSW. Problem programs may be IBM-distributed programs, such as language translators, or user-written application programs. They are not authorized to use all operating system instructions. Only when the problem state bit in the PSW is off can the program execute all instructions.

Each processor has only one current PSW. Thus, only one task can execute on a processor at any one time. Multiprogramming is possible, however, because an **interruption** causes the processor to save the contents of the current PSW and insert new PSW information in order to process the interruption. Figure 1-3 illustrates the MVS/XA PSW and some of its most important bits.

**~**,~ ,~

#### Figure 1-3. The MVS/XA PSW

## Interruptions

An interruption is a request for attention from a processor. It indicates that an event, such as the completion of an I/O operation, expiration of a time interval, a program error, or a request for high-priority system services has taken place, and the system must reassess the mix of work to be done. When an interruption occurs, the processor temporarily ceases execution of the current task and begins executing an MVS/XA interruption handler.

First level interruption handlers (FLIHs) store the crucial information (such as the contents of the PSW) about the status of the interrupted task and give control to second level interruption handlers (SLIHs), which actually respond to the reason for the interruption.

After the interruption handlers complete their processing, a system component called the **dispatcher** might be called to select the highest priority ready unit of work (not necessarily the one that had been interrupted) and give it control until it completes or until another interruption occurs. An interruption thus allows the dispatcher to reassess the priorities of the tasks at hand.

# Macro Instructions

Communication between MVS/XA programs occurs because system programmers follow established programming conventions and use common **macro** instructions. These instructions invoke segments of program code that map frequently used control blocks or perform frequently used system functions. MVS/XA macros, many of which are available to application programmers, exist for such functions as opening and closing data files, loading and deleting programs, and sending messages to the computer system operator.

#### **Resource Management**

Multiprogramming and multiprocessing create the need to measure the activity of the system and to adjust the workload to fit changing conditions. MVS/XA, for

example, monitors how much each active address space uses the processors, I/O devices, and real storage locations. The system resources manager, the MVS/XA component known as SRM, uses this information when it determines whether an address space should remain resident in real storage or whether a new address space should be created.

The system resources manager also takes into account the workload goals and priorities for users and equipment that the installation specifies in the installation performance specification (IPS). SRM, described in Chapter 5, "Managing System Resources," is the primary means by which the system and the installation manage the system resources.

MVS/XA provides other tools that allow the installation to control use of system resources. These include system parameters, exit routines, and the operator console.

#### System Parameters

System parameters are values specified by IBM or the installation and stored in the system data set named SYS1.PARMLIB. Each member of this data set contains parameters that the operator selects to control processing. For example, member IEASYS00 contains the default system parameters that tailor MVS/XA at start-up; the system uses these parameters and other values during the system initialization process.

#### Exit Routines

An exit is a defined point in system processing where a system program calls another program. The called program that IBM supplies performs standard default processing; it is designed to be replaced by a user version of the exit routine. The user exit routine performs user-defined functions appropriate to that particular point in MVS/XA processing.

## **Operator** Console

The installation controls MVS/XA by entering system commands through one or more devices defined to MVS/XA as operator consoles. There is also a system console for use by IBM customer engineers in diagnosing and correcting hardware problems.

Through system commands issued at the operator console, the operator or system programmer can control MVS/XA or respond to a condition MVS/XA detects. System commands can:

- Change the status of hardware units, such as devices, between online (available) and offline (not available) to the system

- Monitor the status of various units of work in the system

- Change those system parameters that can be referenced after system initialization

- Start and stop system functions

- Set a trap for a recurring error condition

## I/O and Data Management

Nearly all tasks involve some amount of data input or data output. The channel subsystem manages the use of I/O devices, such as disks, tapes, and printers, while MVS/XA, through software, associates the data for the task at hand with a device.

MVS/XA manages data by means of **data sets**. Data sets can hold information usually thought of as file data like the patients' records in a doctor's office. Or, data sets can hold information the computer needs, like parameters or programs.

The records in data sets may be organized in various ways, depending upon how the information will be accessed. Data sets can be organized for sequential access or direct access.

In a sequential data set organized for sequential access, records are data items that are stored consecutively. To retrieve the tenth item in the data set, for example, the system first passes by the preceding nine items. Data items that must all be used in sequence, like the alphabetical list of names in a seating chart, are best stored in sequential access data sets.

In a data set organized for direct access, also called random access, records are data items stored with control information so that the system can retrieve an item without searching all preceding items in the data set. Data items that are used frequently and in an unpredictable order are best stored in **direct access data sets**.

**Partitioned data sets** combine the features of sequential and direct access. The data set consists of a directory and **members**. The directory holds the address of each member and thus makes it possible to access each member directly. A member, however, consists of sequentially stored records.

Partitioned data sets are often called libraries. Programs are stored as members of partitioned data sets so that, even though they generally execute sequentially when running, the operating system can access them directly when selecting one for execution.

MVS/XA supports many different devices for data storage. Disks or tape are most frequently used for storing data sets on a long term basis. Disk drives are known as **direct access storage devices** (DASDs) because, even though some of the data sets on them might be stored sequentially, these devices can handle direct access. Tape drives are known as sequential access devices because data sets on tape must be accessed sequentially.

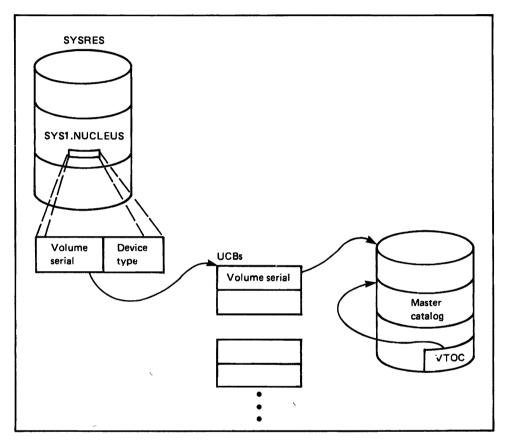

To enable the system to locate a specific data set quickly, MVS/XA includes a a data set known as the master catalog that permits access to any of the data sets in the computer system or to other catalogs of data sets. MVS/XA requires that the master catalog reside on a DASD that is always mounted on a drive that is online to the system. Certain other key data sets needed by the operating system reside on a particular DASD known as SYSRES, or the system residence volume, and must also always be on line. Chapter 7, "Satisfying I/O Requests," gives more details on how MVS/XA manages I/O operations and the transfer of data within the computer system.

## Job Management

MVS/XA provides several ways to enter work into the computer system. With **batch processing**, a user enters a job through a local terminal or, by means of

.\_\_\_\_\_

remote job entry (RJE), through a remote terminal, or from tape, card reader, or disk, and the system processes the job at a later time. The operating system follows installation-defined guidelines as it chooses the time and resources for the job. With **interactive** job entry, such as the time sharing option (TSO), the system responds to terminal users while they are actually logged-on to the system. MVS/XA also permits the computer operator to enter a job by means of the START command; such jobs are called started tasks.

For MVS/XA, a job is more than the work to be done; it is the work to be done embedded in a stream of job control language (JCL) statements supplied by the user or the installation. JCL identifies such things as the system resources and data the job needs. The **job entry subsystem** (JES) processes the JCL, organizes the necessary programs, data, and resources, and presents MVS/XA with a job that is ready to be processed. Upon completion of the job, JES releases resources used for processing and schedules job output.

There are two IBM-supplied job entry subsystems: JES2 and JES3. Chapter 8, "Entering and Scheduling Work," describes how each one manages jobs.

### **Recovery Management**

A data processing system must be available for use when it is needed. For a large system, this means that the system can function even if one component fails and can, possibly, diagnose the cause and correct or compensate for the failure. MVS/XA includes recovery mechanisms to prevent a user error from causing the failure of the computer system, to isolate and recover from operating system errors, and to protect the system from hardware errors. It also has programs that trace system activity and display the status and contents of various system resources. Chapter 9, "Monitoring System Activity," describes how MVS/XA monitors system activity; Chapter 10, "Recovering From Errors," describes the recovery mechanisms.

#### Summary

The operating system called MVS/XA is a combination of program and data modules. Large groups of modules that make a particular MVS/XA function possible are known as system components. Other groups of modules that provide added function that is dependent on MVS/XA are known as subsystems. MVS/XA includes a subsystem interface (SSI) for communication with IBM subsystems (such as the job entry subsystems) or user-supplied subsystems.

The motto, "divide and conquer", aptly describes how MVS/XA manages a computer configuration. MVS/XA gets work done by dividing it into pieces and giving portions of the job to components and subsystems that function interdependently. At any point in time, one component or another gets control of the processor, makes its contribution, and then passes control along to a user program or another component. There is no one entity that is MVS/XA. Rather, what exists is a collection of specialists acting according to accepted guidelines to get work done.

The remainder of this book describes important aspects of MVS/XA processing and gives an overview of what various components do and how they do it. It finishes with Chapter 11, "Initializing the System," which shows how components work together. ſ

w;~ ..

# **Chapter 2.** Multiple Virtual Storage

The two gigabytes of storage in an MVS/XA address space are shared between user programs and MVS/XA system programs. System areas include the prefixed save area (PSA), which holds critical information unique to each processor in the system, the nucleus portion of the system control program that must always be in storage, and the commonly used system programs and subsystems. The map of an address space showing the addresses allocated for these areas is the same for all users. It is shown in Figure 2-1.

The organization of the MVS/XA virtual storage address space map arose from the need to maintain compatibility with programs written for MVS/370. Because of its 24-bit addressing scheme, MVS/370 provides address spaces with a maximum of 16 million bytes of virtual storage to be shared among user and system programs. Thus, maintaining compatibility means that MVS/XA must provide portions of each region at addresses below 16 megabytes as well as extended portions of these regions above the 16-megabyte line.

Figure 2-1. The MVS/XA Address Space

#### Addressing Mode and Residence Mode

To maintain compatibility with MVS/370, MVS/XA recognizes 24-bit addresses. Whether it interprets an address as 24 or 31 bit depends upon the setting of the addressing mode bit in the current PSW at the time an instruction executes. If this bit, bit 32, is set on, all addresses are interpreted as 31-bit addresses. Programs running in 31-bit mode can access locations zero to two gigabytes of virtual storage.

If the addressing mode bit is zero, the processor uses the 24 right-hand bits of an address. Programs running in 24-bit addressing mode can address the first 16 megabytes of virtual storage. MVS/XA allows programs to switch from one mode to another during execution in order to access data or call modules running in the

other mode. Thus, new programs can take advantage of 31-bit addressing and still be compatible with ones written for 24-bit addresses.

All MVS/XA program modules have an addressing mode (AMODE) attribute that indicates which addressing mode is to take affect when a module is given control. The AMODE attribute is assigned to an MVS/XA program module by the programmer, as input to the assembler or the linkage editor, or by default. The default is 24-bit addressing mode.

MVS/XA modules also have a residence mode (RMODE) attribute that indicates whether they must be loaded below the 16-megabyte address line or can be loaded anywhere in virtual storage. RMODE=24 modules require residency below 16-megabytes. RMODE=ANY allows the operating system to load a module anywhere in virtual storage.

A program that must be directly addressable by 24-bit callers must reside below the 16-megabyte line. A program that does not have 24-bit callers, or whose 24-bit callers call it indirectly, can reside anywhere. The RMODE attribute is assigned as input to the assembler or linkage editor, or established by default. RMODE=24 is the default residence mode.

Figure 2-2 shows the meaning of the AMODE and RMODE program attributes.

#### Figure 2-2. AMODE and RMODE Attributes

The AMODE and RMODE attributes can be assigned to modules in various combinations depending on the location of the code and data they use. Not all of the possible combinations make sense, however. The combination of AMODE=24 and RMODE=ANY, for example, is invalid because a program using 24-bit addresses cannot function in locations above the 16-megabyte line where more than 24 bits are needed to denote an address. The AMODE=ANY and RMODE=ANY combination can be specified, but the system translates it to

| AMODE | RM<br>24 | IODE<br>ANY |

|-------|----------|-------------|

| 24    | valid    | invalid     |

| 31    | valid    | valid       |

| ANY   | valid    | invalid     |

AMODE=31, RMODE=ANY at execution time. Figure 2-3 shows the possible combinations of program attributes and indicates which are ones are valid.

#### Virtual and Real Storage

Virtual storage is the MVS/XA mechanism that makes it possible for a user to access the maximum amount of storage that can be addressed in 31 bits even though the system might have much less real storage. Virtual storage works because MVS/XA keeps active portions of each address space in real storage and inactive portions on high-speed DASD (auxiliary storage). It moves them back and forth as necessary to ensure that the program code and data for each user are in real storage when they are needed.

To enable the parts of a program in virtual storage to move between real storage and auxiliary storage, MVS/XA breaks real storage, virtual storage, and auxiliary storage into blocks:

- A block of real storage is a frame.

- A block of virtual storage is a page.

- A block of auxiliary storage is a slot.

A page, a frame, and a slot are all the same size: each is 4096 (4K) bytes. An active virtual storage page resides in a real storage frame; a virtual storage page that becomes inactive resides in an auxiliary storage slot.

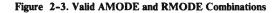

Moving pages between real storage frames and auxiliary storage slots is called paging. Figure 2-4 shows how MVS/XA performs paging for a program that has been running in virtual storage. At point 1, parts A, B, and C of a three-page program are in virtual storage. Page A is active and executing in a real storage frame, while pages B and C are inactive since they have been moved to auxiliary storage slots. At point 2, page B is required; the system brings B in from auxiliary storage and puts it in an available real storage frame. At point 3, page C is required; the system brings C in from auxiliary storage and puts it in an available real storage frame. If page A had not been used recently and the system needed its frame in real storage, page A would be moved to an auxiliary storage slot, as shown at point 4.

Figure 2-4. Virtual Storage Page Movement

Thus, the entire program resides in virtual storage; the system copies pages of the program between real storage frames and auxiliary storage slots to ensure that the pages that are currently active are in real storage as they are required. Note also that neither the frames nor the slots allocated to a program need to be contiguous; thus, a page could occupy several different frames and several different slots during the execution of a program. That is, if page A in the example became active again, MVS/XA would move it to any available frame.

Each address space competes with all other active address spaces for the use of real storage and other system resources, and the work being performed in each address space is paged between real and auxiliary storage. In order for this paging activity to take place quickly and efficiently, the system must be able to translate a virtual address (the address of a specific instruction or data item in virtual storage) into a real address (the address of the corresponding location in real storage). The solution is dynamic address translation.

#### **Dynamic Address Translation (DAT)**

ſ

**Dynamic address translation (DAT)** is a hardware feature that plays an important role in making virtual storage possible. The DAT hardware feature works with MVS/XA system software to translate a virtual address into a real address.

# Virtual Address

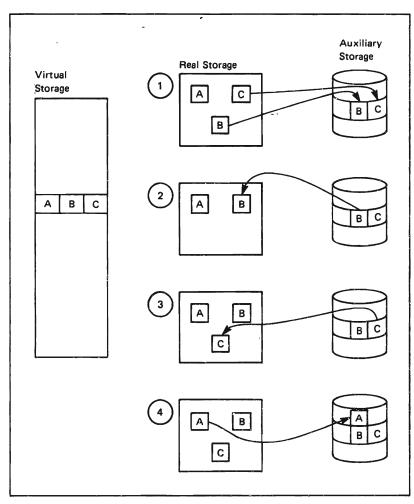

In order to denote a location in virtual storage (create a virtual address), MVS/XA breaks the two gigabytes of virtual storage into 2048 segments, numbered 0 through 2047. Each segment consists of 1,048,576 bytes (one megabyte). The bytes in each segment are further broken down into 256 pages, numbered 0 through 255. Each page, as stated earlier, consists of 4K bytes. Within each page, a specific location is addressed by its byte displacement, that is, the number of bytes between the page origin and the specific location.

A virtual address, therefore, consists of the segment number, the page number within that segment, and the byte displacement within that page. Figure 2-5 shows how virtual storage is broken down to provide a 31-bit virtual address that consists of an eleven-bit segment number, an eight-bit page number and a twelve-bit byte displacement.

Figure 2-5. Virtual Storage Address

Segment and Page Tables

To translate a virtual address into a 31-bit real address, the DAT feature uses a control register, the **segment table origin register (STOR)** and one **segment table** and 2048 **page tables** for each address space. The segment table has one entry for each of the 2048 segments in the address space; each entry contains, among other things, a pointer to the page table for that particular segment. When address translation occurs, the STOR points to the segment table for the address space. This provides the distinction between a virtual address for one address space and the same virtual address for any others.

The page table for each segment has one entry for each of the 256 pages in the segment. If a page is currently in a real storage frame, the entry includes the page frame real address (PFRA) for the frame that corresponds to that page. If a copy of a page is not currently in a frame in real storage, the entry indicates this; the

invalid bit is set on, and the system must copy the page from auxiliary storage to real storage and update the page table before the virtual address can be successfully translated. The MVS/XA page table also contains a page protection bit that, when set, marks the corresponding frame as read-only. The system uses this bit to protect against unexpected modification of code and data. Figure 2-6 shows the relationship between the segment table, the page tables, and the pages in real storage.

Figure 2-6. Segment Table and Page Tables

## Two-Level Lookup

To translate a virtual address into a real address, DAT looks in two tables. Figure 2-7 illustrates this process. The first table lookup 1 adds the address of the start of the segment table, in the segment table origin register (STOR), to the segment number from the virtual address (multiplied by 4 bytes, the length of each segment table entry) to locate the proper segment table entry. This entry contains the origin address of the page table for that segment. The second table lookup 2 adds the page table origin to the page number in the virtual address (also multiplied by 4 bytes, the length of each page table entry) to locate the required entry in the page table. Unless the page is invalid, the page table entry contains the address of the real storage frame that holds the page specified in the virtual address. The final step 3 in dynamic address translation adds the address of the real storage frame to... the byte displacement within the frame. The byte displacement is the 12 rightmost bits of the virtual address. The result of this addition is the 31-bit real address.

Figure 2-7. Dynamic Address Translation

Each time a virtual address is successfully translated into a real address, the system saves the address of the real storage frame in a special hardware buffer called the translation lookaside buffer (TLB). The TLB contains, an address space identifier, the segment number and page number from the virtual address, and the corresponding real storage address for the most active virtual pages. The DAT hardware checks the TLB before beginning the process of address translation, and, because a very high percentage of addresses can be found in the TLB, address translation time is significantly reduced by bypassing the two-level table lookup process most of the time.

When the first step of the table look up process encounters a segment table entry that has no corresponding page table in real storage, the DAT cannot translate the virtual address and a segment translation exception, or **segment fault** occurs. If the page table for the segment exists, paging is required to bring the page table into real storage. If the page table does not exist, one is built before paging occurs.

Similarly, when the second step of the table lookup process encounters an invalid page table entry, it means the required page is not in a real storage frame. The DAT hardware thus cannot translate the virtual address, and a page-translation exception, known as a **page fault**, occurs. If the page has been defined in the page table, **demand paging** - the transfer of a slot in auxiliary storage to a page in real storage on demand - is required to bring the page into real storage. If the page is not backed by a frame, a frame is assigned to the page and demand paging occurs.

#### The Paging Process

In addition to the DAT hardware and the segment and page tables required for address translation, paging activity involves a number of system components to handle the movement of pages and several additional tables to keep track of the most current version of each page at any particular time.

To understand how paging works, assume that DAT encounters an invalid page table entry during address translation, indicating that a page is required that is not in a real storage frame. To resolve this page fault, the system must bring the page in from auxiliary storage. First, however, it must locate an available real storage frame. If there is no available frame, the request must be saved and an assigned frame must be freed. To free a frame, the system copies its contents to auxiliary storage and marks its corresponding page table entry as invalid. This operation is called a **page-out**. Actually, the system performs a page-out only when the contents of the frame have been changed since the page was copied into real storage. If the contents have not changed, the frame is freed by simply setting on the page table entry invalid bit.

After a frame is located for the required page, the contents of the page are copied from auxiliary storage to real storage and the page table invalid bit is set off. This operation is called a **page-in**. Actually, in order to avoid unnecessary I/O, the processor checks, before doing a page-in, to see if the frame that previously held the contents of the page has the same information and ownership as the slot on DASD indicating that the frame has not been changed. If so, the frame is **reclaimed** by setting the page table invalid bit off, and no actual data transfer occurs.

Figure 2-8 summarizes the paging process, showing how pages move between real and auxiliary storage in response to a page fault or to fill the need for an adequate supply of real storage frames.

Figure 2-8. Page-Out and Page-In

Paging can also take place when the program loader loads a program into virtual storage. The program loader brings an entire program into virtual storage. MVS/XA obtains virtual storage for the user program, and allocates a real storage frame to each page. Each page is then active and subject to the normal paging activity; that is, the most active pages are retained in real storage while the pages not currently active might be paged out to auxiliary storage.

MVS/XA tries to keep an adequate supply of available real storage frames constantly on hand. When a program refers to a page that is not in real storage, the system uses a real storage page frame from a supply of available frames. When this supply becomes low, the system uses page stealing to replenish it.

## **Page Stealing**

Page stealing occurs when the system takes a frame assigned to an active user and makes it available for other work. The decision to steal a particular page is based on the activity history of each page currently residing in a real storage frame. Pages that have not been accessed for a relatively long time are good candidates for page stealing.

To determine which pages are to be stolen, MVS/XA examines the activity history of the pages that are currently in real storage. This information is held in the **page frame table**. There is one page frame table for the entire system, and it has an entry for each frame of real storage. Each entry identifies a page frame and includes the address space identifier and the virtual address within the address space for the page that is currently using the frame.

Other information in the entry describes the activity history of the page. The available frame field indicates whether the frame is currently in use or is available. Two additional bits associated with the frame, the reference bit and the change bit, are relevant when the frame is in use. (Note: These bits are actually part of a control field associated with each 4K block of storage. They are maintained by the hardware and used by the software to make paging decisions; they are therefore described here as if they were physically part of the page frame table.)

The unreferenced interval count indicates how long it has been since a program referenced the frame. The reference bit is set on by the hardware whenever a page frame is referenced. At regular intervals, the system checks the reference bit for each page frame. If the reference bit is not on -- that is, the frame has not been referenced -- the system adds to the page frame's unreferenced interval count. It adds the number of seconds since this address space last had the reference count checked. If the reference bit is on, the frame has been referenced and the system turns it off and sets the unreferenced interval count for the page frame to zero. Those page frames with the highest unreferenced interval counts are most likely to be stolen.

The change bit is set to zero when a page is initially brought into a real storage frame. When the contents of the page are changed the change bit is set on. Setting the change bit on tells the system that it must copy the contents of the frame to auxiliary storage before making the frame available for other work. Checking the change bit ensures that no changes made during program execution are lost during the paging process.

Figure 2-9 shows a portion of the page frame table and illustrates how the entries are set up and how the reference, change information, and unreferenced interval count are used to determine which pages will be stolen. All example frames are in use; the available frame bits are set to zero. The system checks the unreferenced interval count and finds two pages that have not been referenced recently. These two pages will be stolen. The first page that not been changed since it was brought in from auxiliary storage; therefore, no physical page-out is required to save its contents because the copy of the page in real storage is the same as the copy of the page in auxiliary storage. The second page 2 has been changed; therefore the system performs a page-out before it steals the page, and the contents of the page are written to auxiliary storage. The system is thus able to steal two pages, only one of which requires a page-out. (The first page will be the first one selected for stealing because of its higher unreferenced interval count.)

1

| Change<br>lit |

|---------------|

| 1             |

| 0             |

| 0             |

| 1             |

| 1             |

| 1             |

| 1             |

| 1             |

| 0             |

| -             |

Figure 2-9. Page Frame Table

# Swapping

Swapping is the process of transferring all of the most recently valid private pages of an address space between virtual storage and auxiliary storage. This has the effect of moving an entire address space into or, out of, virtual storage. It is one of several methods MVS/XA employs to balance the system workload, as well as to ensure that an adequate supply of available real storage frames is maintained. Address spaces that are **swapped-in** are active, having pages in real storage frames and pages in auxiliary storage slots. Address spaces that are **swapped-out** are inactive; the address space resides on auxiliary storage and cannot execute until it is swapped in. Swapping is performed in response to recommendations from the system resources manager (SRM), described in Chapter 5, "Managing System Resources."

# **Storage Protection**

Figure 2-4 showed how virtual storage works for one program; in reality, of course, many programs or users would be competing for use of the system. MVS/XA uses two techniques to preserve the integrity of each user's work: (1) a private address space for each user, as described in Chapter 3, "MVS/XA Address Spaces," and (2) multiple storage protect keys, as described in the following topic.

# Storage Protect Keys

Under MVS/XA, the information in real storage is protected from unauthorized use by means of multiple storage protect keys. A control field in storage called a key is associated with each 4K frame of real storage. This field, or key, is not itself addressable except by special operating system instructions.

The key in storage contains the protect key that the user of the frame must have as well as a fetch protect bit. The **protect key** controls which, if any, users can modify the frame. (A bit in the page table, the **protection bit**, makes the frame read-only and thereby prevents modification by **any** user.) The **fetch-protect bit** also protects

a frame. When it is set, a program must have the same key as the frame or have key 0. Otherwise, it can neither modify the frame nor read, or fetch, its contents. Figure 2-10 shows the format of the key in storage.

Figure 2-10. The Key in Storage

When a request is made to modify the contents of a real storage location, the key is compared to the storage protect key associated with the request, which appears in the current program status word (PSW). If the keys match or the program is executing in key 0, the request is satisfied. If the key associated with the request does not match the storage key, the system rejects the request and issues a program exception interruption.

When a request is made to read (or fetch) the contents of a real storage location, the request is automatically satisfied unless the fetch protect bit is on, indicating that the frame is fetch-protected. When a request is made to access the contents of a fetch-protected real storage location, the key in storage is compared to the key associated with the request. If the keys match, or the requestor is in key 0, the request is satisfied. If the keys do not match, and the requestor is not in key 0, the system rejects the request and issues a program exception interruption.

## Key Assignments

ſ

j

There are sixteen possible storage protect keys available. A specific key is assigned according to the type of work being performed. Figure 2-11 summarizes the assignment of storage protect keys.

Storage protect keys 0 through 7 are reserved for the MVS/XA control program and various subsystems. Storage protect key 0 is the master key. Its use is restricted to those parts of the control program that require almost unlimited store and fetch capabilities. With two limitations, a storage protect key of 0 associated with a request to access or modify the contents of a real storage location means that the request is satisfied. The limitations on the ability of key 0 to modify real storage are: first, no program can store into real storage locations 0 to 511; second, no program can store into real storage frames for which the page table protection bit is set on.

Storage protect keys 8 through 15 are assigned to users. Because all users are isolated in private address spaces, most users - those whose programs run in a virtual region - can use the same storage protect key. These users are called V=V (virtual=virtual) users and are assigned a key of 8. Some users, however, must run in a real storage region. These users are known as V=R (virtual=real) users and require individual storage protect keys because their addresses are not protected by the DAT process that keeps each address space distinct. Without separate keys, V=R users might reference each other's code and data. These keys are in the range of 9 through 15.

| Key  | Use                                                   |

|------|-------------------------------------------------------|

| 0    | MVS/XA system control program                         |

| 1    | Job scheduler and job entry subsystems (JES2 or JES3) |

| 2    | Virtual Storage Personal Computing (VSPC)             |

| 3-4  | Reserved                                              |

| 5    | Data management                                       |

| 6    | TCAM and VTAM                                         |

| 7    | IMS                                                   |

| 8    | V=V users running in virtual storage                  |

| 9-15 | V=R users requiring real storage                      |

# Key Switching

í

)

Frequently, a user program requests a service from a system (or subsystem) program; with the request the program passes the address of an area in storage to be modified by the system program. This area should belong to the user. However, if an error occurs and the area really belongs to the system instead of the user, the system could be destroyed. Thus, the system program does a key switch before performing the service for the user. A key switch means that the system program uses the storage protect key of the user program rather than its own storage protect key while performing the requested service.

## **MVS/XA Storage Managers**

Real storage frames, auxiliary storage slots and the virtual storage pages that they support, are managed by separate components of MVS/XA. They are the real storage manager, the auxiliary storage manager, and the virtual storage manager.

## Real Storage Manager (RSM)

The real storage manager (RSM) keeps track of the contents of real storage. It maintains the entries in the system's page frame table, and in each address space's page tables and associated **external page tables** that relate the virtual storage page to a page data set slot. It manages the paging activities described earlier such as page-in, page-out, and page stealing. RSM also assists with swapping an address space in or out, verifies the storage protect keys, and does **page fixing** (marking pages as unavailable for stealing).

#### Auxiliary Storage Manager (ASM)

)

The auxiliary storage manager (ASM) keeps track of the contents of the page data sets, the swap data sets and the VIO data sets (described in Chapter 7, "Satisfying I/O Requests"). Page data sets contain slots representing virtual storage pages that are not currently occupying a real storage frame. They also contain slots representing pages that do currently occupy a real frame but, because the frame's contents have not been changed, the slots are still valid.

Swap data sets contain the **working set** of an address space. Generally speaking, the working set is a subset of pages that were in real storage and associated with the address space when the swap out occurred. The working set includes the most recently referenced pages, pages fixed in real storage, and the segment and the page tables.

When a page-in or page-out is required, ASM works with RSM to locate the proper real storage frame and auxiliary storage slots. For a page-in, RSM reads the entries in the external page table to determine the slot location of a page, locates an available frame, and passes this information to ASM, which uses it to bring the slot into real storage. For a page-out, ASM locates an available slot on auxiliary storage, copies the page from real storage to auxiliary storage, and sends RSM the information needed to update the external page table.

## Virtual Storage Manager (VSM)

The virtual storage manager (VSM) responds to requests to obtain and free virtual storage. It also manages storage allocation for any program that must run in real, rather than virtual storage. Storage is allocated to code and data when they are loaded in virtual storage. As they run, programs can request additional storage by means of the GETMAIN macro; they request the release of storage with the FREEMAIN macro instruction.

VSM keeps track of the map of virtual storage for each address space. In so doing, it sees an address space as a collection of 256 subpools. Subpools are logically related areas of virtual storage identified by numbers (0 to 255). Being logically related means the storage areas within a subpool share characteristics such as:

- Storage protect key

- Whether or not they are fetch protected

- Whether or not they are pageable

- Whether or not they are swappable

- Where they must reside in virtual storage (above or below the 16 megabyte line)

- Whether they can be shared by more than one task

Some subpools (with numbers 128 to 255) are predefined for use by system programs. Subpool 252, for example, is for authorized programs from authorized program libraries. Others (numbered 0 to 127) are defined by user programs.

Within an address space, VSM keeps track of:

• Unallocated areas:

Virtual storage that is not allocated to a subpool

• Allocated areas:

Virtual storage that is allocated to a subpool

• Free areas:

ſ

Virtual storage within a subpool that is not being used

ſ

MVS/Extended Architecture Overview 2-16

Conceptually, an MVS/XA address space consists of the two gigabytes of virtual storage available to each user. Figure 3-1 shows an address space as the rectangular description of virtual storage.

Figure 3-1. A Logical Representation of Virtual Storage

An MVS/XA address space contains the system prefix save area, private areas, and common areas. Each user has an entire address space and thus has access to all three kinds of areas. MVS/XA effectively isolates one address space from another by means of segment and page tables. Through the common areas of the address space, users can share programs and data areas. Thus, MVS/XA balances both the need to share resources and the need to maintain users' privacy.

Virtual Storage Areas

Program modules and data are located within an address space according to characteristics such as whether:

- They can be shared among all address spaces

- They can be paged or must always be backed by real storage (fixed)

- They must reside below the 16-megabyte line

The mapping of an MVS/XA address space in Figure 3-2 shows the various areas of an address space. It appears as it does because of the need to maintain compatibility with MVS/370. Almost every area exists below the 16-megabyte line and has an extended area above the line. As much as possible, MVS/XA treats each area of virtual storage below the line and its extended portion above 16 megabytes as one logical area. For example, if you request a report (dump) of the contents of the common service area (CSA), the system dumps both the CSA below 16 megabytes and the extended CSA. The sections that follow describe the areas of the virtual storage map.

# Prefixed Save Area

1

The PSA contains critical information about both the MVS/XA operating system and the processor. It includes fixed storage locations for such things as the data items that become the contents of the current PSW when an interruption occurs, register save areas for system routines, and pointers to important control blocks. It is always fixed in real storage and never paged out.

For a uniprocessor, the PSA occupies the first 4K, the first page, of virtual and real storage. Each processor in a multiprocessing system running MVS/XA also addresses its own PSA as though the PSA were fixed in the first 4K of storage. MVS/XA uses the **prefix register** and a technique called **prefixing** to distinguish the PSA of one processor from the PSA of another.

With **prefixing**, the processors do not use absolute locations 0-4095. Rather, each processor has its own separate PSA and its own prefix register. When a processor is brought on line, the real starting address of its PSA is stored in its prefix register. Whenever the processor uses an address between 0 and 4095, the hardware adds the the contents of the prefix register to the address and uses the result. With prefixing, the address that normally would be the absolute address of the information in the first page of storage becomes an offset from the start of the real PSA. Because each processor's prefix register contains a different address, each processor can address locations 0 to 4095 and reference its own data.

# The Private Area and Extended Private Area

The private area contains modules and data not shared by other address spaces. It consists of five sections:

- 1. System region

- 2. User region/extended user region

- 3. Authorized user key (AUK)/extended AUK

- 4. Scheduler work area (SWA)/extended SWA

- 5. Local system queue area (LSQA)/extended LSQA

The last three areas (AUK, SWA, and LSQA) are intermixed in the private area virtual addresses and are separate from the system region and the user/extended user regions.

#### System Region

The system region is the only section of the private area that does not have a counterpart above the 16M line. It is used by system functions performing work for an address space. These system functions run under the **region control task** (**RCT**). The region control task is the highest level task in each address space; it plays a key role when an address space must be swapped in or out. The system region consists of four virtual pages (locations 4K to 20K) allocated from the bottom of the private area.

#### **User Region/Extended User Region**

The user region is the section of the private area in which user programs run. MVS/XA programmers try to use the extended user region as much as possible because it is vastly larger than the user region below the 16-megabyte line.

There are two types of user regions: virtual (V=V) and real (V=R). The two types are mutually exclusive; that is, a user region can be V=V or V=R, but it cannot be both.

A virtual (V=V) user region can be any size up to the size of the private area minus the size of LSQA, SWA, AUK, and the system region. Its size can be limited by the REGION parameter on the user's JOB or EXEC statement or by installation-written program exits.

V=V user regions are pageable and swappable. Only enough real storage frames are allocated at any particular time to hold the recently accessed parts of the user program.

Real (V=R) regions occur only below the 16 megabyte line. Each virtual address in the region always corresponds to the same real address. Figure 3-3 illustrates V=R storage mapping. Real storage for the entire region is allocated and fixed when the real region is created. Thus, a V=R job is non-pageable and non-swappable.

The installation must reserve sufficient real storage for all V=R regions that might exist at any one time. During system generation, the REAL= parameter of the CTRLPROG macro reserves real storage; during system initialization, the REAL= system parameter establishes real region storage limits. The system uses storage in the V=R area for normal paging activity if the V=R storage is not being currently used for V=R jobs. Particularly when system activity is high, a V=R job might not be started immediately; it must wait until the system can free the storage the V=R job requires.

|                  |                            | Virtual Storage      | 7 4                  |                      |

|------------------|----------------------------|----------------------|----------------------|----------------------|

|                  |                            | Common Area          | -                    |                      |

|                  | Real Storage               |                      |                      |                      |

|                  |                            | LSQA, SWA and<br>AUK | LSQA, SWA and<br>AUK | LSQA, SWA and<br>AUK |

| ر                | Pageable Area              |                      |                      |                      |

| *V=R Limit       |                            |                      |                      |                      |

|                  |                            |                      |                      |                      |

|                  |                            |                      |                      |                      |

|                  | V=R JOB3                   |                      |                      | V=R JOB3             |

|                  | V=R JOB2                   |                      | V=R JOB2             |                      |

|                  | V=R JOB1                   | V=R JOB1             |                      |                      |

|                  |                            | System Region        | System Region        | System Region        |

|                  | PSA                        | PSA                  |                      |                      |

| *Limit of storag | e available for running V= | R jobs               |                      |                      |

#### Figure 3-3. V=R Storage Mapping

ſ

Real regions should be used only for jobs with time-dependent functions (that is, jobs that cannot wait for paging activity to take place) or for jobs that cannot run in the virtual environment, such as jobs with channel programs that use the program control interruption (PCI) to modify themselves dynamically. See, "Satisfying I/O Requests," later in this book for more information about channel programs.

The default V=R region size is controlled by the VRREGN parameter in the IEASYSxx member of SYS1.PARMLIB. It can be overridden by the REGION parameter in a user JOB or EXEC statement.

#### Authorized User Key (AUK)/Extended AUK

The authorized user key (AUK) area of the private region contains system data relating to a specific user. Protected user resources, such as the data extent block (DEB) that describes a user data set, reside in this area.

This area is also identified as subpools 229 and 230. Subpools 229 and 230 are both protected by the user's storage key, that is, by the key in the PSW that is associated with the program using the storage. In addition, subpool 229 is fetch-protected, which means that its contents cannot even be read unless the key in storage matches the key in the PSW.

The AUK also contains data for the LNKLST lookaside (LLA) directory of modules in the system's LNKLST libraries. Because this directory is always in storage, it provides fast access to system modules and reduces I/O operations that consume time and channel paths.

#### Scheduler Work Area (SWA)/Extended SWA

The scheduler work area (SWA) contains the control blocks that exist from job step initiation to job step termination. These contain the internal form of the job control language (JCL) statements that accompany a job. The information in SWA is created when a job is interpreted and used during job initiation and execution. (Chapter 8, "Entering and Scheduling Work," describes how MVS/XA processes a job.) The SWA is pageable.and swappable.

#### Local System Queue Area (LSQA)/Extended LSQA

The local system queue area (LSQA) contains tables and queues that are unique to a particular address space. For example, LSQA includes the user's segment table and private area page tables. LSQA also contains all the control blocks that the region control task (RCT) requires. LSQA is swappable but not pageable. That is, the LSQA for each address space that is swapped-in is fixed in real storage frames.

## The Common Area and Extended Common Area

)

The common area holds system information, such as program code, control blocks, tables, and data areas. It is common to all address spaces in the sense that any type of data or code in this area has the same virtual addresses in all address spaces. The common area includes:

- 1. Common service area (CSA) and extended CSA

- 2. Pageable link pack area (PLPA) and extended PLPA

- 3. Fixed link pack area (FLPA) and extended FLPA

- 4. Modified link pack area (MLPA) and extended MLPA

- 5. System queue area (SQA) and extended SQA

- 6. Nucleus and extended nucleus

#### Common Service Area (CSA)/Extended CSA

í

The common service area is addressable by all active programs and is shared by all swapped-in users. Data associated with an individual address space can be isolated by a storage protect key, but the primary advantage of CSA is to enable inter-address space communication.

CSA contains some fixed and some pageable system and user data areas; pageable areas are paged in and out of real storage as required. The total amount of storage for CSA is specified during system initialization and is allocated in 4K pages.

## Pageable Link Pack Area (PLPA)/Extended PLPA

The pageable link pack area contains MVS/XA control program functions (SVC routines), access methods, other read-only system programs, and selected user programs. Because these modules are heavily used, and loading the PLPA is a lengthy process, MVS/XA normally saves its contents from one start-up to another.

As its name implies, PLPA is pageable; however, no physical page-outs are performed. PLPA pages that have not recently been used, however, might be stolen.

PLPA space is allocated in 4K pages. The size of PLPA is determined by the number of modules included, and, once the size is set, PLPA does not expand dynamically.

#### Fixed Link Pack Area (FLPA)/Extended FLPA

FLPA pages are fixed in real storage. They contain modules that could be in PLPA but require the extremely fast response that comes from having fixed pages.

<u>.</u>

Because FLPA is fixed, it reduces the amount of real storage available for other uses, such as running installation programs. Thus, the modules selected for FLPA are chosen with care. The MVS/XA paging routines normally keep a heavily-used PLPA module in real storage. Therefore, the most likely candidates for FLPA are modules that are infrequently used (those whose pages would be stolen) but require rapid response when they are used. An installation determines the size and contents of the fixed link pack area each time the MVS/XA system is started.

#### Modified Link Pack Area (MLPA)/Extended MLPA

The modified link pack area can be used for reentrant modules from selected system or user libraries; it acts as an extension to PLPA, but exists only for the duration of the current MVS/XA session. The system does not save the contents of the MLPA from one MVS/XA start-up to another as it does for the PLPA.

MLPA modules are normally read-only. Because MVS/XA searches the MLPA before it searches the PLPA, installations often use the MLPA to test modules before adding them to the PLPA.

#### System Queue Area (SQA)/Extended SQA

The system queue area (SQA) contains tables and queues that relate to the entire system. For example, the page tables that define the system area and the common area reside in SQA. The contents of SQA depend on an installation's configuration and job requirements.

The installation specifies the amount of storage for SQA when the system is initialized. If MVS/XA needs more storage for SQA, it uses CSA storage. If the system then runs out of CSA, it stops creating address spaces. The SQA is always fixed in real storage.

#### Nucleus/Extended Nucleus

1

The nucleus and the extended nucleus hold the resident part of the MVS/XA control program. Aside from the control program load module, the nucleus and extended nucleus contain the page frame table entries (PFTEs), data extent blocks (DEBs) for the system libraries, recovery management support routines, and unit control blocks (UCBs) for the I/O devices. The nucleus and extended nucleus surround the 16-megabyte line in virtual storage. They actually comprise what is known as the **DAT-on nucleus**. The hardware DAT feature translates their addresses to real addresses.