SY26-3823-1 File No. S370-30

# Systems

-

# **OS/VS2 I/O Supervisor Logic**

VS2 Release 1

## Second Edition (March 1973)

This edition replaces the previous edition (numbered SY26-3823-0) and makes that edition obsolete.

This edition applies to Release 1.6 of OS/VS2 and to all subsequent releases of that system unless otherwise indicated in new editions or technical newsletters.

Significant technical and editorial changes made in this edition are outlined in "Summary of Amendments" following the list of figures. Each technical change is marked by a vertical line to the left of the change.

Information in this publication is subject to significant change. Any such changes will be published in new editions or technical newsletters. Before using the publication, consult the latest *IBM System/360 and System/370 Bibliography*, GA22-6822, and the latest *IBM System/370 Advanced Function Bibliography*, GC20-1763, and the technical newsletters that amend those bibliographies, to learn which editions and technical newsletters are applicable and current.

Requests for copies of IBM publications should be made to the IBM branch office that serves you.

Forms for readers' comments are provided at the back of this publication. If the forms have been removed, comments may be addressed to IBM Corporation, Programming Center—Publishing, Department D58, Monterey and Cottle Roads, San Jose, California 95193. All comments become the property of IBM.

© Copyright International Business Machines Corporation 1972, 1973

# PREFACE

This publication, when used with the program listings, enables you to understand the internal operation of the I/O supervisor and to makes changes to it when necessary.

This publication does not replace the program listings; it supplements them and makes the information in them more accessible. This publication has the following sections:

- "Introduction," which contains information about the I/O supervisor's services and overall operation.

- "Method of Operation," which contains diagrams that describe the operation of the I/O supervisor. The diagrams are high-level and are designed to guide you to a particular area of the program listing.

- "Program Organization." which contains a functional organization chart for each of the main functions of the I/O supervisor, and describes what each routine does.

- "Directories," which contains cross-reference lists that include a data area directory, module directory, and routine directory.

- "Data Areas," which contains descriptions of the interrelationship and content of data areas and control blocks that are used primarily by the I/O supervisor.

- "Diagnostic Aids," which contains information to help you interpret the program listings and diagnose program failures.

- "Appendix A: Supporting SVC Routines," which contains information about supporting SVC routines.

- "Appendix B: Alternate Path Retry," which contains information about the alternate path selective retry option and its relationship to the I/O supervisor.

- "Appendix C: Direct-Access Volume Verification," which contains information about the direct-access volume verification option and its relationship to the I/O supervisor.

- "Appendix D: Dynamic Device Reconfiguration," which contains information about the dynamic device reconfiguration option and its relationship to the I/O supervisor.

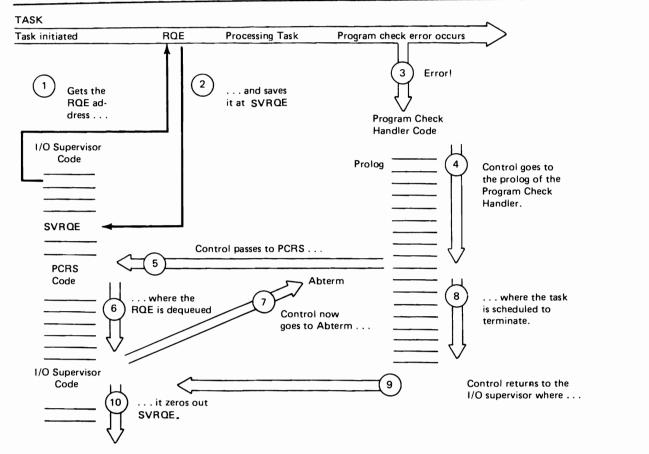

- "Appendix E: Program Check Recovery Subroutine," which contains information about the program check recovery subroutine.

- "Appendix F: Shared Direct-Access Storage Device," which contains information about the shared direct-access storage device option and its relationship to the I/O supervisor.

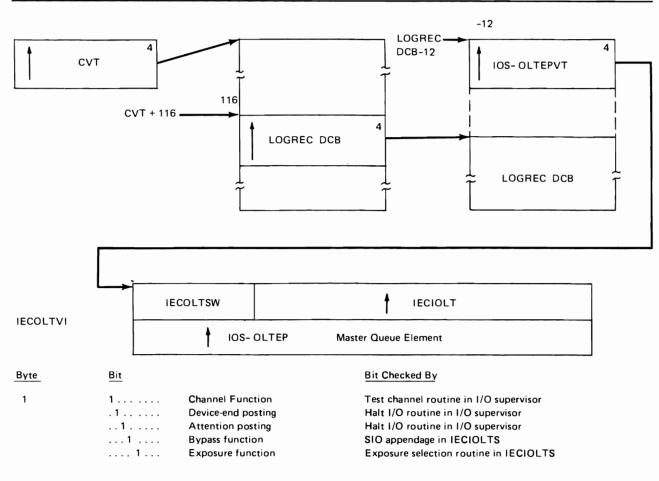

- "Appendix G: I/O Supervisor—OLTEP Synchronizing Module (IECIOCTS)," which contains the requirements of the Online Test Executive Program for the I/O supervisor.

- "Appendix H: Device-Dependent Error Routines," which describes device-dependent error routines and contains information about writing error recovery messages to the operator.

- "Glossary of Terms, Acronyms, and Abbreviations," which contains definitions of terms used in this publication along with the meanings of the acronyms and abbreviations used.

## How to Use This Publication

Before using this publication, read the "Introduction" to establish perspective, and then at least scan the remainder of the publication to familiarize yourself with its content. This publication is primarily a reference manual because each section contains a specific type of information. You will be better able to service the program when you can refer quickly to the section containing the type of information you need.

The "Method of Operation" section contains diagrams, each consisting of two pages. The first page (left or upper) is the actual diagram. The second page (right or lower) consists of expanded text and references to other diagrams and flowcharts. The diagrams are at a high level; therefore, some of the I/O supervisor functions are not shown. The routine directory (see "Directories" can be used to find entry points into the routines that are not included in the diagrams.

### **Referenced System and Data Management Publications**

The following publications (listed in order-number order) are referenced throughout this publication:

- OS/VS Recovery Management Logic, GC27-7239

- OS/VS2 Planning and Use Guide, GC28-0600

- OS/VS Data Management for System Programmers, GC28-0631

- OS/VS2 Debugging Guide, GC28-0632

- OS/VS Service Aids, GC28-0633

- OS/VS Utilities, GC35-0005

- OS/VS Message Library: VS2 System Messages, GC38-1002

- OS/VS Message Library: VS2 System Codes, GC38-1008

- OS/VS2 Supervisor Logic, SY27-7244

- OS/VS2 System Data Areas, SY28-0606

- OS/VS OLTEP Logic, SY28-0637

- OS/VS SYS1.LOGREC Error Recording Logic, SY28-0639

Other OS/VS publications are listed in the IBM System/360 and System/370 Bibliography, GA22-6822.

# CONTENTS

### Page

### iii Preface

- iv How to Use This Publication

- iv Referenced System and Data Management Publications

#### vii Figures

### ix Summary of Amendments

- ix Release 1.6

- ix CCW Translation Header BEBLK

- ix IOS Support of 3333 Disk Storage and Control

#### 1 Introduction

- 1 The User and the I/O Supervisor

- 3 The Page Supervisor and VS Subsystems

- 3 The I/O Supervisor and the Control Program

- 6 The I/O Supervisor

- 8 Concept of Logical Channels

#### 11 Method of Operation

### 47 Program Organization

- 47 Description of Routines

- 53 Directories

- 53 Data Area Directory

- 57 Module Directory

- 63 Routine Directory

### 65 Data Areas

- 67 Data Area Layouts

- 67 Alternate Path Table

- 68 Appendage Vector Table

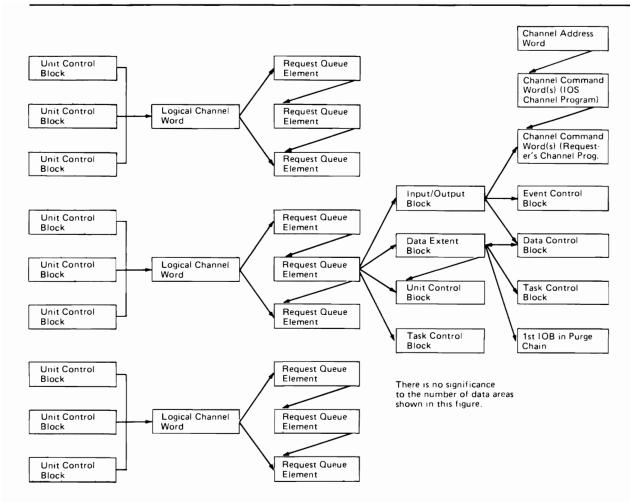

- 68 BEBLK (Beginning-End-Block)

- 69 Channel Address Word

- 70 Channel Command Word

- 71 CCW Translation Header BEBLK

- 73 Channel Error Block Table

- 74 Channel Status Word

- 75 Channel Table

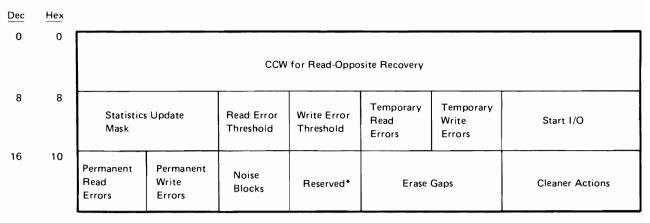

- 76 Device Statistics Table

- 79 Device Table

5

- 80 Indirect Address List

- 81 Logical Channel Word

- 83 Page Fix List

- 84 Program Controlled Interrupt Modify Parameter List

- 84 Program Status Word

- 86 Request Queue Element

- 88 Start Input/Output Extend Parameter List

- 88 Volume Statistics Table

### Page

- 91 Diagnostic Aids

- 91 General Register Assignments

- 91 System Completion Codes

- 93 Problem Determination Area

- 94 Patch Area at IECINT

- 94 Generalized Trace Facility

### 97 Appendix A: Supporting SVC Routines

- 97 Purge Routine (SVC 16)

- 99 Removing Elements From Logical Channel Queues

- 99 Removing Elements From the Supervisor's Request Block Queues

- 99 Removing Elements From the Supervisor's Asynchronous Exit Queues

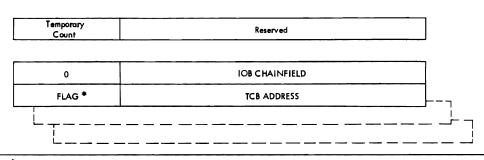

- 100 The IOB Chain

- 101 The Quiesce Option

- 102 Purging A Virtual I/O Request

- 102 Restore Routine (SVC 17)

- 102 DEVTYPE Routine (SVC 24)

- 103 IOHALT Routine (SVC 33)

- 103 VOLSTAT Routine (SVC 91)

- 104 TCB EXCP (SVC 92) (TSO only)

- 104 Extended SVC Routine (SVC 109)

#### 105 Appendix B: Alternate Path Retry

- 105 The Selective Retry Function

- 105 The Vary Path Functions

- 107 Appendix C: Direct-Access Volume Verification

- 109 Appendix D: Dynamic Device Reconfiguration

- 111 Appendix E: Program Check Recovery Subroutine

- 113 Appendix F: Shared Direct-Access Storage Device

- 115 Appendix G: I/O Supervisor-OLTEP Synchronizing Module (IECIOLTS)

- 117 Appendix H: Device-Dependent Error Routines

- 117 Writing Error Recovery Messages to the Operator

- 118 Individual Routines

- 119 1052 Error Routine

- 121 1287 and 1288 Error Routines

- 124 1403 and 1443 Error Routines

- 126 1419 and 1275 Error Routines

- 129 2501 and 2520 Error Routines

- 131 2250 Error Routine

- 133 2260 and 1053 Error Routines

- 135 2305, 2314, 2319, 3330, and 3333 Error Routines

- 139 2400 and 3400 Tape Series Error Routines

- 146 2495 Error Routine

- 148 2540 Error Routine

- 150 3211 Error Routine

- 153 3505 and 3525 Error Routines

- 157 Glossary of Terms, Acronyms, and Abbreviations

- 161 Index

٤

C

Page

| 0  |        |            |                                                      |

|----|--------|------------|------------------------------------------------------|

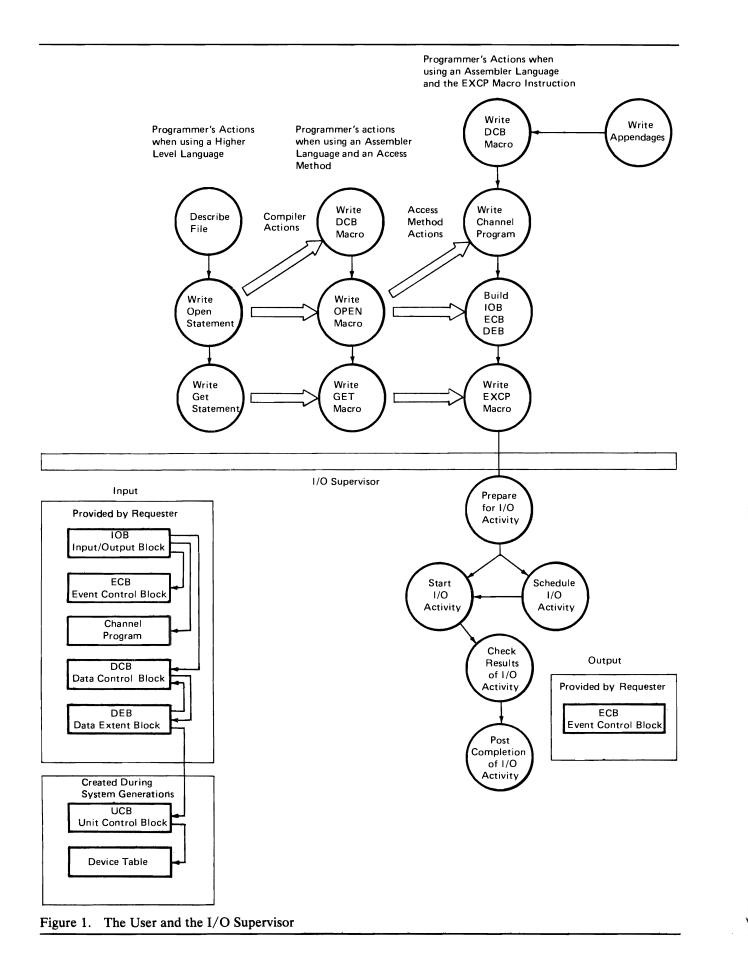

| 2  | Figure | 1.         | The User and the I/O Supervisor                      |

| 4  | Figure | 2.         | Characteristics of I/O Requesters                    |

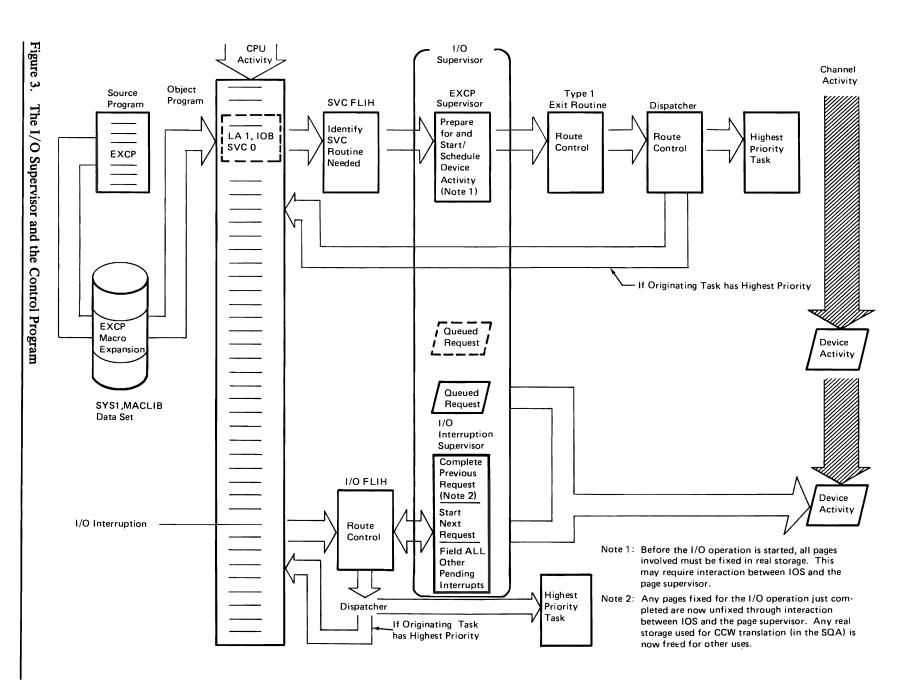

| 5  | Figure | 3.         | The I/O Supervisor and the Control Program           |

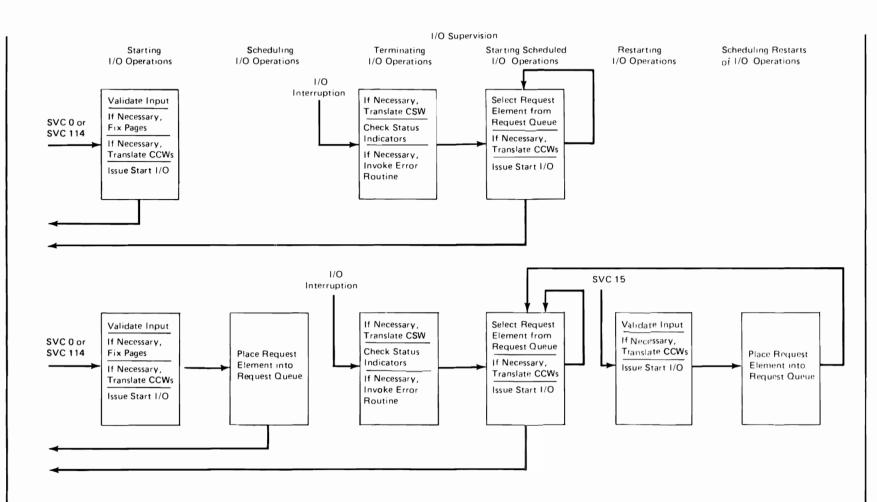

| 6  | Figure | 4.         | I/O Supervision                                      |

| 7  | Figure | 5.         | I/O Supervisor Functions                             |

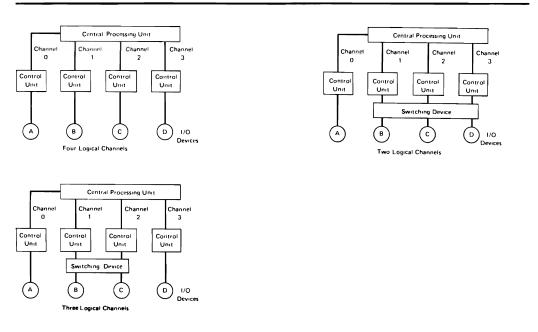

| 8  | Figure | 6.         | Logical Channel-Physical Channel Relationships       |

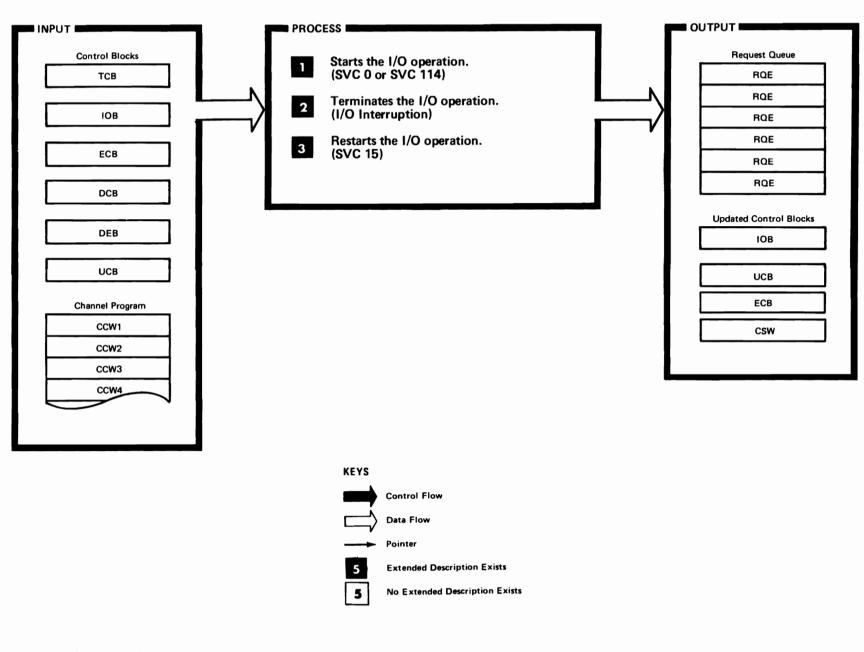

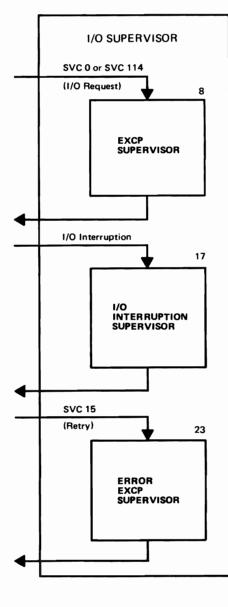

| 12 | Figure | 7.         | I/O Supervisor                                       |

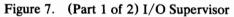

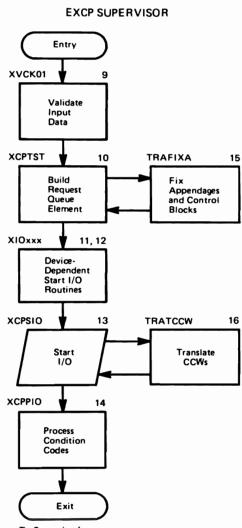

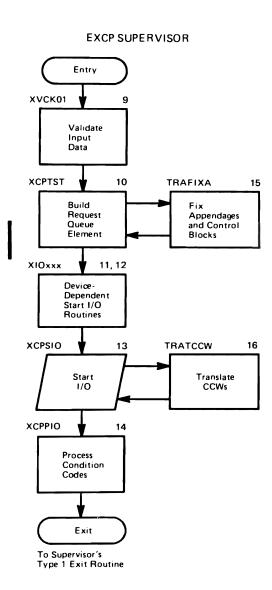

| 14 | Figure | 8.         | EXCP Supervisor                                      |

| 16 | Figure | 9.         | Validity Check Routine                               |

| 18 | Figure | 10.        | Get Request Element Routine                          |

| 20 | Figure | 11.        | Start I/O Routine for Tape                           |

| 20 | Figure | 12.        | Start I/O Routine for DASD                           |

|    | -      | 12.        | SIO Subroutine                                       |

| 24 | Figure | 13.<br>14. | Post Start I/O Routine                               |

| 26 | Figure |            |                                                      |

| 28 | Figure | 15.        | Page Fix Routine<br>CCW Translator                   |

| 30 | Figure | 16.        |                                                      |

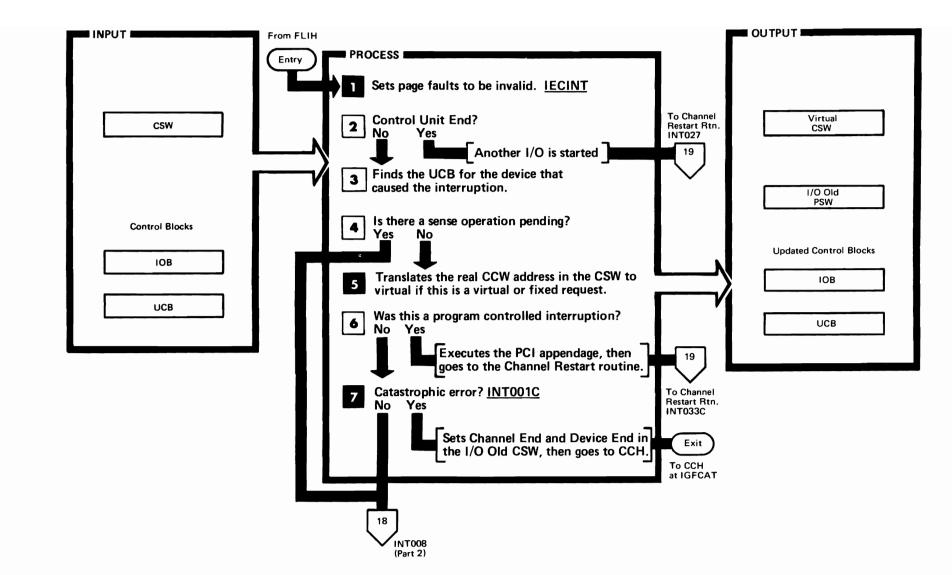

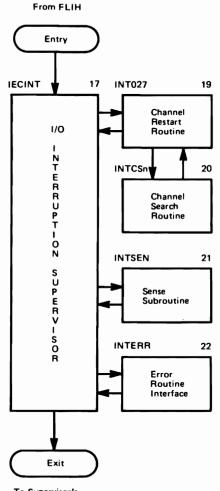

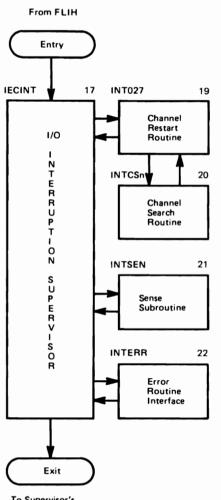

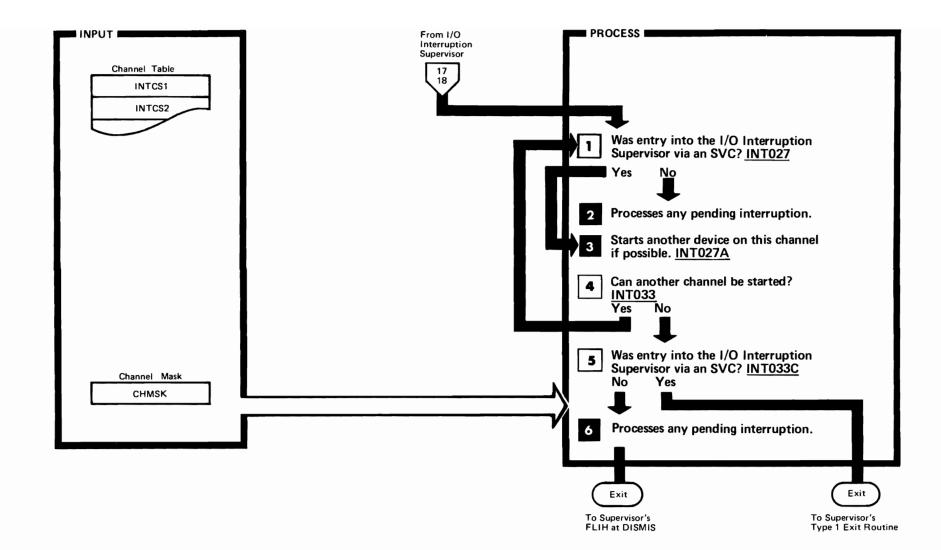

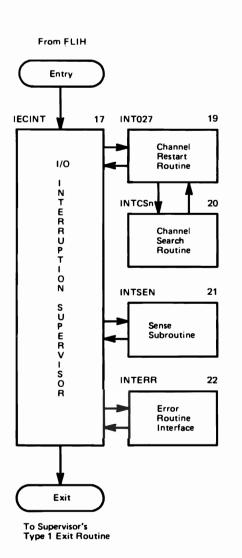

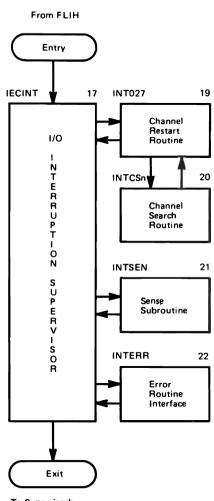

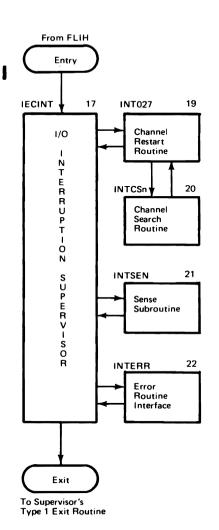

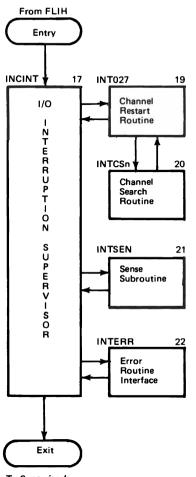

| 32 | Figure | 17.        | I/O Interruption Supervisor (Part 1)                 |

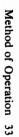

| 34 | Figure | 18.        | I/O Interruption Supervisor (Part 2)                 |

| 36 | Figure | 19.        | Channel Restart Routine                              |

| 38 | Figure | 20.        | Channel Search Routine                               |

| 40 | Figure | 21.        | Sense Subroutine                                     |

| 42 | Figure | 22.        | Error Routine Interface                              |

| 44 | Figure | 23.        | Error EXCP Routine                                   |

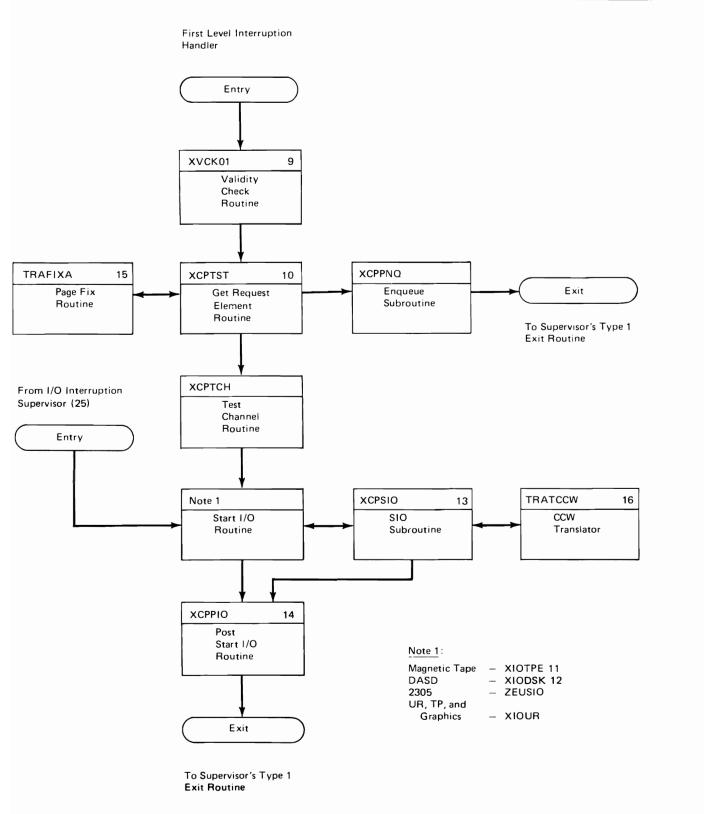

| 48 | Figure | 24.        | Functional Organization, EXCP Supervisor             |

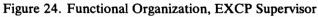

| 49 | Figure | 25.        | Functional Organization, I/O Interruption Supervisor |

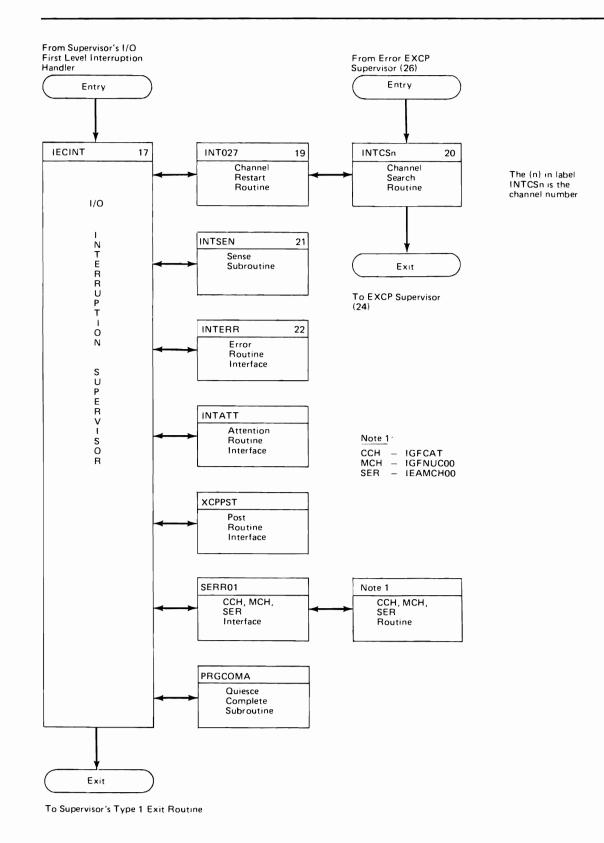

| 50 | Figure | 26.        | Functional Organization, Error EXCP Supervisor       |

| 54 | Figure | 27.        | Data Area Directory                                  |

| 58 | Figure | 28.        | Module Directory                                     |

| 63 | Figure | 29.        | Routine Directory                                    |

| 66 | Figure | 30.        | Data Area Relationships                              |

| 67 | Figure | 31.        | Alternate Path Table                                 |

| 68 | Figure | 32.        | Appendage Vector Table                               |

| 69 | Figure | 33.        | Beginning-End-Block                                  |

| 70 | Figure | 34.        | Channel Address Word                                 |

| 70 | Figure | 35.        | Channel Command Word                                 |

| 72 | Figure | 36.        | CCW Translation Header BEBLK                         |

| 73 | Figure | 37.        | Translation Control Blocks                           |

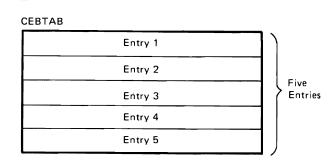

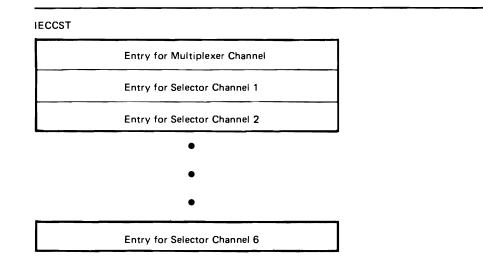

| 74 | Figure | 38.        | Channel Error Block Table                            |

| 74 | Figure | 39.        | Channel Error Block Table Entry                      |

| 75 | Figure | 40.        | Channel Status Word                                  |

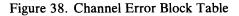

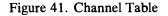

| 76 | Figure | 41.        | Channel Table                                        |

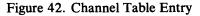

| 76 | Figure | 42.        | Channel Table Entry                                  |

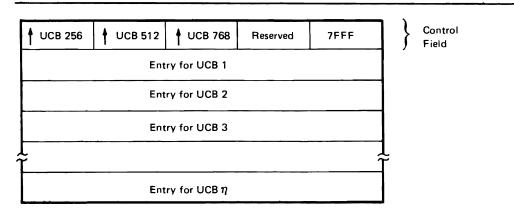

| 77 | -      | 43.        |                                                      |

| 78 | Figure | 44.        | Device Statistics Table Entries                      |

| 79 | Figure | 45.        |                                                      |

| 80 | Figure | 46.        |                                                      |

| 81 | Figure | 47.        | •                                                    |

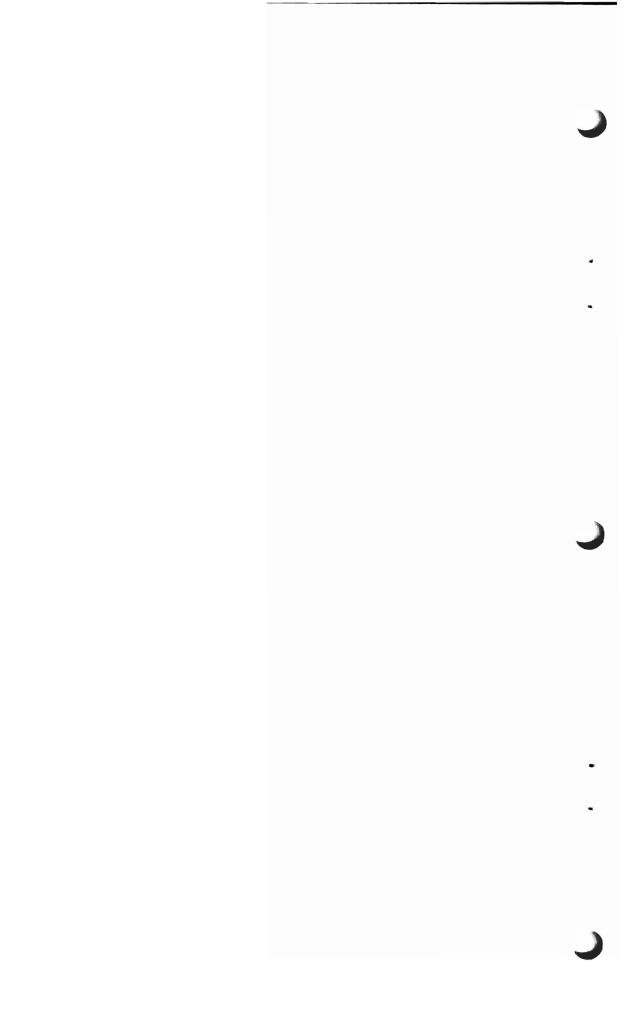

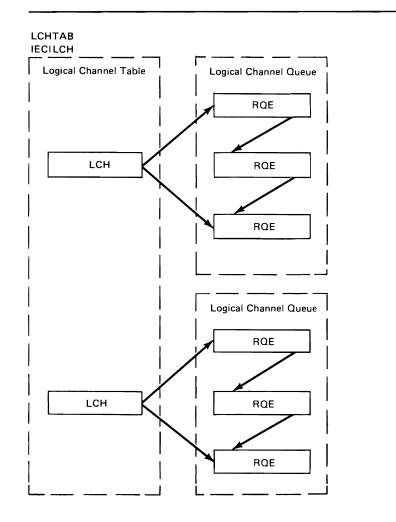

| 82 | Figure | 48.        | Logical Channel Queues                               |

| 82 | Figure | 49.        | Logical Channel Word                                 |

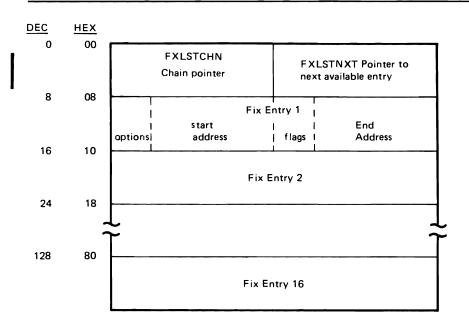

| 83 | Figure | 50.        | Page Fix List                                        |

| 84 | Figure | 51.        | PCI Modify Parameter List Entry                      |

|    | 0      |            |                                                      |

- 85 Figure 52. Program Status Word87 Figure 53. Request Queue Element

### Page

| 88   | Figure     | 54. | SIO Extend Parameter List                                                  |

|------|------------|-----|----------------------------------------------------------------------------|

| 89   | Figure     | 55. | Volume Statistics Table Entry                                              |

| 91   | Figure     | 56. | General Register Assignments                                               |

| 92   | Figure     | 57. | System Completion Codes for I/O Operations                                 |

| 95   | Figure     | 58. | GTF Interfaces                                                             |

| 96   | Figure     | 59. | Purge Routine Parameter List                                               |

| 99   | Figure     | 60. | Quiesce I/O Parameter List                                                 |

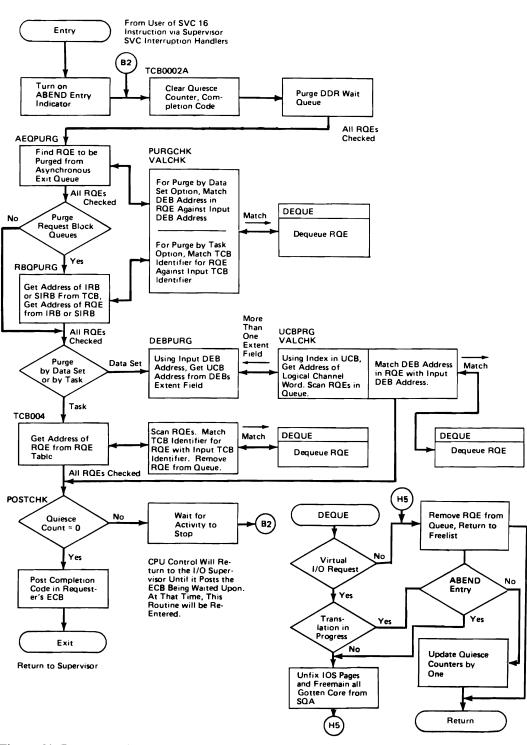

| 100  | Figure     | 61. | Purge Routine                                                              |

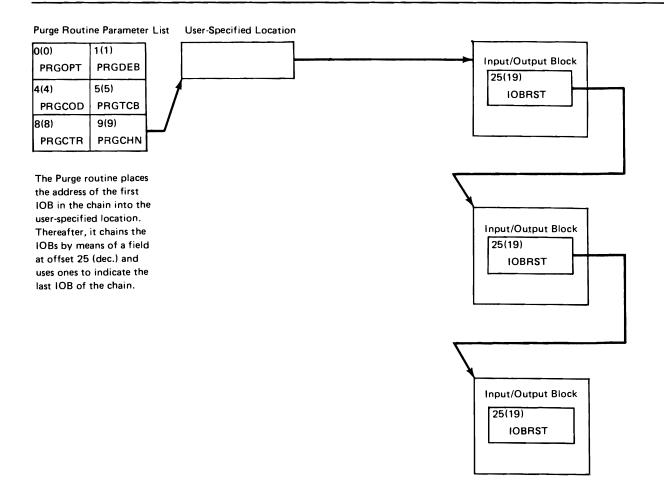

| 101  | Figure     | 62. | Purge Routine IOB Chain                                                    |

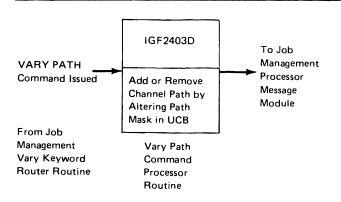

| 105  | Figure     | 63. | Vary Path Command Processing                                               |

| 111  | Figure     | 64. | Operation of PCRS During a Program Check                                   |

| 116  | Figure     | 65. | IECIOLTS Addressing Scheme and Bit Settings                                |

| 120  | Figure     | 66. | 1052 Error Analysis Sequence (Module IGE0000D)                             |

| 120  | Figure     | 67. | 1052 Sense Bits, IOB Flags, and IOB Error Counts                           |

| 122  | Figure     | 68. | 1287 and 1288 Error Analysis Sequence                                      |

| 123  | Figure     | 69. | 1287 and 1288 Sense Bits, IOB Flags, and IOB Error Counts                  |

| 124  | Figure     | 70. | 1403 and 1443 Error Analysis Sequence (Module IGE0000G)                    |

| 125  | Figure     | 71. | 1403 and 1443 Sense Bits, IOB Flags, and IOB Error Counts                  |

| 127  | Figure     | 72. | 1419/1275 Error Analysis Sequence (Module IGE0011E)                        |

| 128  | Figure     | 73. | 1419/1275 Sense Bits, IOB Flags, and IOB Error Counts                      |

| 130  | Figure     | 74. | 2501, and 2520 Error Analysis Sequence (Module IGE0000E)                   |

| 131  | Figure     | 75. | 2501 and 2520 Sense Bits, IOB Flags, and IOB Error Counts                  |

| 132  | Figure     | 76. | 2250 Error Analysis Sequence (Module IGE0010A)                             |

| 133  | Figure     | 77. | 2250 Sense Bits, IOB Flags, and IOB Error Counts                           |

| 134  | Figure     | 78. | 2260 and 1053 Error Analysis Sequence (Load 1–IGE0010B or Load 2–IGE0100B) |

| 135  | Figure     | 79. | 2260 and 1053 Sense Bits, IOB Flags, and IOB Error Counts                  |

| 137  | Figure     | 80. | 2314 and 2319 Error Analysis Sequence (Module IEC23XXF)                    |

| 138  | Figure     | 81. | 2305, 3330, and 3333 Error Analysis Sequence (Module IEC23XXF)             |

| 140  | Figure     | 82. | 2305, 2314, 2319, 3330, and 3333 Sense Bits, IOB Flags, and IOB            |

|      | U          |     | Error Counts                                                               |

| 141  | Figure     | 83. | 2400/3400 Error Analysis Sequence (Load 1-IGE00001, Load                   |

|      | -          |     | 2-IGE0100I, Load 3-IGE0200I, Load 4-IGE0300I, Load                         |

|      |            |     | 5-IGE0400I, or Load 6-IGE0900I)                                            |

| 142  | Figure     | 84. | 2400/3400 Sense Bits, IOB Flags, and IOB Error Counts                      |

| 147  | Figure     | 85. | 2495 Error Analysis Sequence (Module IGE0011A)                             |

| 147  | Figure     | 86. | 2495 Sense Bits, IOB Flags, and IOB Error Counts                           |

| 149  | Figure     | 87. | 2540 Error Analysis Sequence (Load 1–IGE0001C or Load                      |

| 1.50 | <b>D</b> : | 0.0 | 2–IGE0101C)                                                                |

| 150  | Figure     | 88. | 2540 Sense Bits, IOB Flags, and IOB Error Counts                           |

| 151  | Figure     | 89. | 3211 Sense Bits, IOB Flags, and IOB Error Counts                           |

| 153  | Figure     | 91. | 3505/3525 Error Analysis Sequence (Module IGE0001A)                        |

| 154  | Figure     | 92. | 3505/3525 Sense Bits, IOB Flags, and IOB Error Counts                      |

# SUMMARY OF AMENDMENTS

# Release 1.6

## **CCW Translation Header BEBLK**

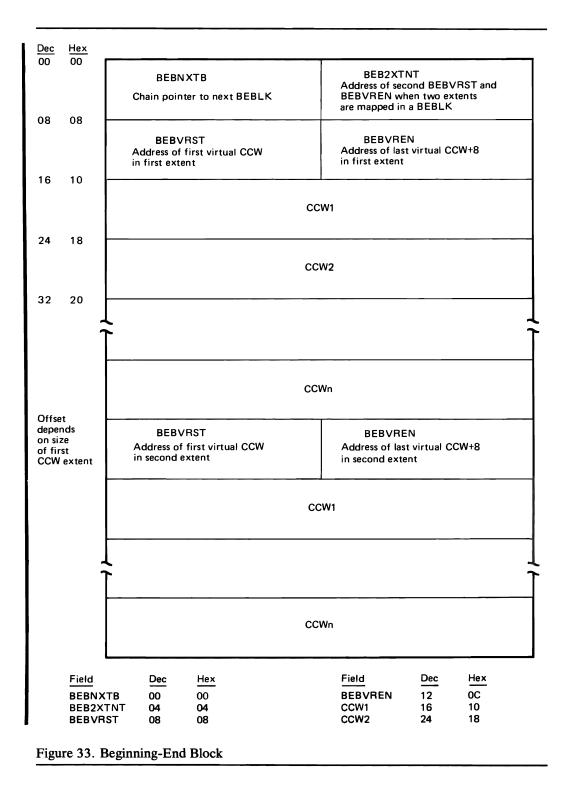

The CCW translation header block has been deleted and a new data area, the CCW translation header BEBLK, has been added. The CCW translation header BEBLK combines the functions of the old data areas, the CCW translation header block and the BEBLK. (Note that the addresses of the real CCWs have been deleted from the BEBLK.) If the channel program requires a second BEBLK (other than the header BEBLK), the format of the BEBLK will be the same as that described in the "Data Areas" section under BEBLK (Beginning-End Block).

The TSTHDR field of the RQE now points to the page fix list before translation, and to the CCW translation header BEBLK during and after translation.

### IOS Support of the IBM 3333 Disk Storage and Control

IOS now fully supports the IBM 3333 Disk Storage and Control. The 3333 is functionally equivalent to the 3330 Disk Storage. All references to the 3330 also apply to the 3333.

•

# **INTRODUCTION**

Following execution of the statements or instructions written by programmers to cause I/O activity, a sequence of events begins in which the I/O supervisor plays a major role. This section defines that role and describes the environment in which it is performed.

An I/O operation can be described as the sequence of events beginning with the execution of the statement or instruction a programmer writes to cause data to be written on or read from an I/O device, and ending when all related activity is completed. Although the I/O supervisor plays a major role in an I/O operation, it is not the only control program element involved. This section establishes the scope and objectives of the I/O supervisor.

# The User and the I/O Supervisor

Three methods a programmer can use to request an I/O operation are shown in Figure 1. The actions taken by the I/O supervisor in satisfying the request are shown below the horizontal line that divides the figure. Specific input data must always be provided to the I/O supervisor, but the extent to which the programmer must define that input data depends upon how he requests the I/O operation.

The user of a higher-level language (PL/I, for example) describes files and writes OPEN and GET statements. When his program is executed, one PL/I subroutine uses a DCB macro instruction to build a data control block (DCB), and an OPEN macro instruction to cause data management routines to build a channel program, and input/output block (IOB), a data extent block (DEB), and an event control block (ECB). Another PL/I subroutine uses a GET macro instruction, and a data management routine executes an EXCP macro instruction that causes entry to the I/O supervisor.

Adjacent to the steps taken by a programmer who uses a higher-level language are shown the steps a programmer must take when he is using an assembler language and chooses to use an access method. With an access method, a programmer must essentially do what the PL/I compiler did; that is, he must himself write all needed DCB, OPEN, and GET macro instructions.

The user of an EXCP macro instruction must provide directly all of the input that is required by the I/O supervisor. He may use the DCB and OPEN macro instructions, and he may use the I/O appendages—user-written routines that receive control at appropriate exits in the I/O supervisor code—but he must write his own channel program, and he must build his own IQB and ECB. To request any kind of I/O activity, he must use the EXCP macro instruction.

The EXCP user has the option, at OPEN time, to specify the use of I/O appendages during the progress of I/O operations associated with his data set. These appendages gain control at specific points in the I/O supervisor. They gain control:

- During page fixing

- During extent checking, if an out-of-extent condition is detected

- Prior to issuing the SIO instruction

- If a PCI interruption is received

- If a normal channel end interruption is detected

- If any abnormal condition is detected with a primary interruption

I/O appendages give the EXCP user a means of extending and altering I/O operations. For further information about I/O appendages, see OS/VS Data Management for System Programmers.

2 OS/VS2 I/O Supervisor Logic

Note from Figure 1 how a higher-level language compiler uses access method routines, and note also the similarity between what access method routines do and what a programmer must do when he uses the EXCP macro instruction.

### The Page Supervisor and VS Subsystems

The page supervisor and VS subsystems uses the EXCPVR macro instruction to request I/O services from the I/O supervisor. (The EXCPVR macro instruction is not available to other users of the I/O supervisor.) The EXCPVR macro instruction generates a calling sequence to the I/O supervisor that creates linkages and issues an SVC 114. The basic difference between an SVC 114 request and SVC 0 request is that an SVC 114 request needs little or no translation service and thus can be processed faster than an SVC 0 request.

VS subsystems prepare channel programs (CCW chains) in fixed virtual address space using real data addresses. Subsystems also fix pages for their own control blocks, I/O appendages, and data areas.

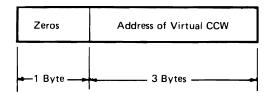

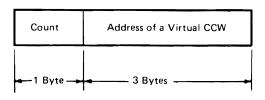

Consequently, the I/O supervisor does not fix pages for subsystems'control blocks, I/O appendages, channel programs, or data areas, and does not translate the CCW data addresses to real addresses. However, the I/O supervisor does translate the CCW start address to *real* at EXCPVR time, and also translates the address of the last CCW+8 in the CSW to *virtual* when an I/O interruption occurs.

The page supervisor prepares CCWs and control blocks in nonpageable storage, so page fixing or address translation operations are not performed by the I/O supervisor.

## The I/O Supervisor and the Control Program

Many control program elements are involved in I/O operations besides the I/O supervisor. Their functions are supporting functions needed to coordinate the actions of the I/O supervisor with other system actions. The general system environment of the I/O supervisor is shown in Figure 1.

When an EXCP macro instruction is encountered during assembly of a processing program, the assembler obtains the corresponding macro expansion from the SYS1.MACLIB data set and inserts it into the object program. The last instruction in the EXCP macro expansion is an SVC 0 instruction.

During execution of the processing program, the SVC 0 instruction causes an SVC interruption and immediate entry to the supervisor's SVC first level interruption handler (SVC FLIH). The SVC FLIH is always given control after SVC interruptions. It refers to a list of SVC numbers (called an SVC table) to determine 1) what SVC routine is to service the request and 2) whether or not the needed SVC routine is of the type that is contained in *real* storage. In the case of SVC 0, the routine to be given control is always the first of the two major I/O supervisor routines; the EXCP supervisor and the I/O interruption supervisor.

In giving control to the EXCP supervisor, the SVC FLIH passes the address of the input/output block (IOB), the key item of input data, to the I/O supervisor, and identifies the requester type. See Figure 2 for the characteristics of I/O requesters.

Because channels cannot translate virtual storage addresses, IOS tranlates any virtual addresses used in the channel program. Figure 3 shows the interface between the I/O supervisor and control program.

IOS also ensures that the pages pertaining to the requested I/O operation are fixed in real storage. For virtual requesters, IOS passes control to the page supervisor to fix pages for:

| Type of<br>Requester             | CCW Chain<br>Location  | CCW Translation<br>Requirements                         | Page Fixing<br>Requirements                                                 | SVC Generated                            |

|----------------------------------|------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------|

| Virtual                          | Pageable<br>storage    | IOS must<br>translate<br>CCW chains.                    | Control blocks<br>and appendages<br>must be fixed.                          | EXCP macro<br>generates an<br>SVC 0.     |

| Fixed (VS<br>subsystems<br>only) | Pageable<br>storage    | CCW chains have<br>been translated<br>by the requester. | Control blocks<br>and appendages<br>have been<br>fixed by the<br>requester. | EXCPVR macro<br>generates an<br>SVC 114. |

| Nonpageable                      | Nonpageable<br>Storage | None                                                    | None                                                                        | EXCP macro<br>generates an<br>SVC 0.     |

| Page<br>Supervisor               | Nonpageable<br>Storage | None                                                    | None                                                                        | EXCPVR macro<br>generates an<br>SVC 114. |

### Figure 2. Characteristics of I/O Requesters

- I/O areas specified in the channel program

- Control blocks (IOB, DCB, DEB, ECB/DECB and AVT)

- I/O appendages

Using input data it obtains from addresses in the IOB, the EXCP supervisor either starts the I/O device or, if the needed device is unavailable, schedules the I/O request by placing an element representing the request into a queue.

For virtual requesters, starting the I/O device involves building a real channel program equivalent to the requester's virtual channel program and then having the channel begin executing the real channel program. The real channel program is built in the system queue area (SQA) of real storage.

The EXCP supervisor then gives control to the supervisor's type 1 Exit routine. All type 1 SVC routines (except those abnormally terminated) pass control to the type 1 Exit routine.

If the routine in which the request for the I/O operation was made is still the highest-priority task in the system, the type 1 Exit routine restores the environment that existed at the time of the interruption and returns control to the dispatcher routine. The dispatcher routine either returns control to the requesting routine or to a routine of a new task with a higher priority.

The next event occurs asynchronously. When the device has completed its part of the I/O operation, it causes an I/O interruption. Following I/O interruptions, control is given to the supervisor's I/O first-level interruption handler (I/O FLIH). The I/O FLIH saves a record of the interrupted environment and gives control to the second of the two major I/O supervisor routines, the I/O interruption supervisor.

For virtual and fixed requesters, the I/O interruption supervisor must retranslate the address of the "last CCW+8" in the CSW to the corresponding virtual address; it must also interface with the page supervisor to unfix any pages that were fixed specifically for the I/O operation just completed. In addition, it now frees the real storage area used for translating the CCWs of virtual requesters.

The I/O interruption supervisor signals the requester that the I/O operation is completed (the task supervisor's post routine posts the requester's event control block), and starts other devices on the channel in response to any requests that were queued while the device, data set, or channel was busy with the request just completed.

While the I/O interruption handler processes on interruption, one or more other interruptions may occur. Because I/O interruptions are disabled, they are stacked (saved

Introduction

S

by the hardware), thus creating a pending interruption. After an interruption is processed and the user is posted, the I/O supervisor enables the system for the I/O interruptions. At this time, one of the stacked interruptions is fielded and processed. This process continues until all pending interruptions have been fielded and all queued I/O requests that can be started have been started. The I/O supervisor enables the system for I/O interruptions one last time to check whether there are any more interruptions to be processed. If there are none, the I/O supervisor exits to the I/O FLIH.

When the I/O interruption supervisor returns control to the I/O FLIH, control via the dispatcher, is routed either to the requesting routine or to a routine of a higher-priority task.

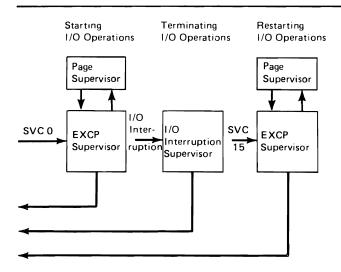

# The I/O Supervisor

The overall objective of the I/O supervisor is to make sure that a requested I/O operation is performed. To achieve its objective, the I/O supervisor performs three major functions: starting I/O operations, terminating I/O operations, and restarting I/O operations (for error-correction purposes). These functions, the two major I/O supervisor routines, and the general control flow to and from the routines, are shown in Figure 4.

Note: The EXCP supervisor and error EXCP supervisor share most of the same routines. However, since their functions are separate and distinct, they are treated separately throughout this manual.

Figure 4. I/O Supervision

The basic control flow to and from the EXCP supervisor and the I/O interruption supervisor has already been shown in Figure 1. However, for restarting I/O operations, an SVC 15 instruction (rather than an SVC 0 instruction) causes entry to the EXCP supervisor for retry of an error condition.

In Figure 5 the major functions are expressed in more detail. The three coordinative functions have been added: scheduling I/O operations, starting scheduled I/O operations, and scheduling restarts of I/O operations.

The first flow diagram in Figure 5 shows the flow for a straightforward I/O operation where the Start I/O instruction is accepted and there is no need to schedule I/O device activity. This flow is shown separately to illustrate how the request queue is checked following completion of every I/O operation. The queue is checked repeatedly until no pending requests remain. If after terminating an I/O operation, the status indicators

Figure 5. I/O Supervisor Functions

show an error condition to exist, the I/O interruption supervisor invokes a user-written or IBM-supplied error correction routine. Error routines can request a retry by issuing an SVC 15 instruction, which will result in entry to the error EXCP supervisor for the retry.

The second flow diagram in Figure 5 shows the flow for an I/O operation that could not be started immediately. Note that the request queue is examined after a restart of the I/O operation is scheduled, just as it is when an I/O operation is terminated.

# **Concept of Logical Channels**

The queues into which request elements are placed when I/O activity cannot be started immediately do not always correspond one-for-one with the physical channels attached to a system. Rather, they correspond to logical channels. A logical channel is the set of all physical channels by which a device can be reached.

Queuing in logical queues makes possible path-device groups in which a common set of paths can be tried for each device of a group. The result is simplified alternate-path logic.

Unless a switching device or a two-channel switch is installed, providing multiple-path capability, every physical channel is also a logical channel and there is a one-for-one correspondence. With switching devices, however, the relationship between physical and logical channels varies, depending upon both the number of switches and their placement.

A system without two-channel switches is shown symbolically at the top of Figure 6. Because each device can only be reached via one path, each physical channel is also a logical channel.

### Figure 6. Logical Channel—Physical Channel Relationships

Also shown in Figure 6 is a system in which a switching device connects two control units. Devices B and C can then be reached via channel 1 or channel 2. Devices B and C are both in the logical channel comprising physical channels 1 and 2.

Another configuration with a switching device is shown at the right in Figure 6. This time, devices B, C, and D may be reached via channels 1, 2, and 3; devices B, C, and D are all in the same logical channel.

Except for the 2870 Multiplexor Channel, all devices attached via the same multiplexor channel will always be in the same logical channel. The devices attached via a 2870 Multiplexor Channel may be contained in more than one logical channel, however, because each of the four optional selector subchannels is considered separately.

• :

, , ,

· . . .. .

₹4

.

# **METHOD OF OPERATION**

This section contains diagrams that are designed to give you a general knowledge of the I/O supervisor's operation and to guide you through the program listing. To do this effectively, the diagrams must be kept at a high level. Therefore, there are some functions of the I/O supervisor that are not shown. Use the I/O supervisor routine directory (Figure 27) to find entry points into the listing for routines that are not included in this section.

Each diagram consists of two pages. The (upper) first is the actual diagram. The second (lower) page consists of expanded text, references to other diagrams, and flowcharts, and a program organization chart that highlights a particular function of the I/O supervisor.

۰

.

,

\*

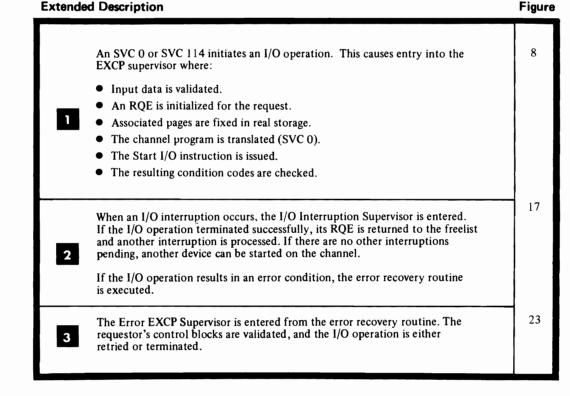

**Extended Description**

Figure 7. (Part 2 of 2) I/O Supervisor

Method of Operation 13

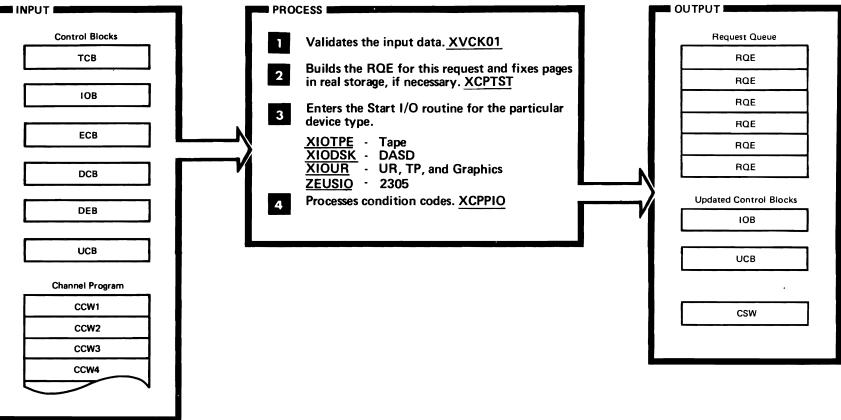

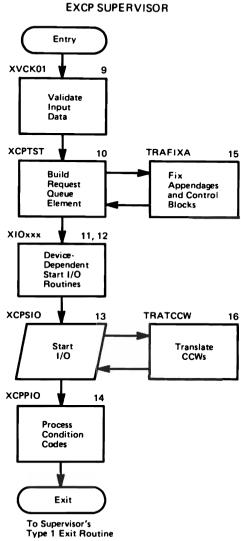

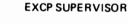

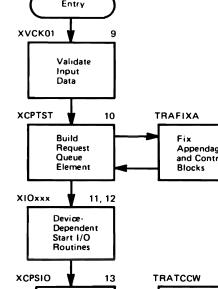

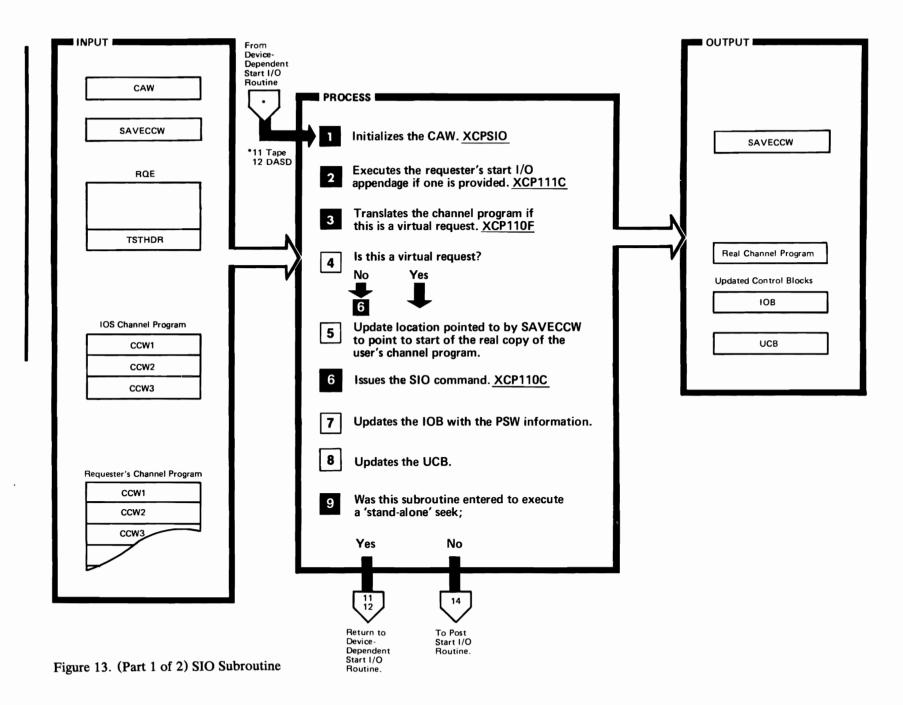

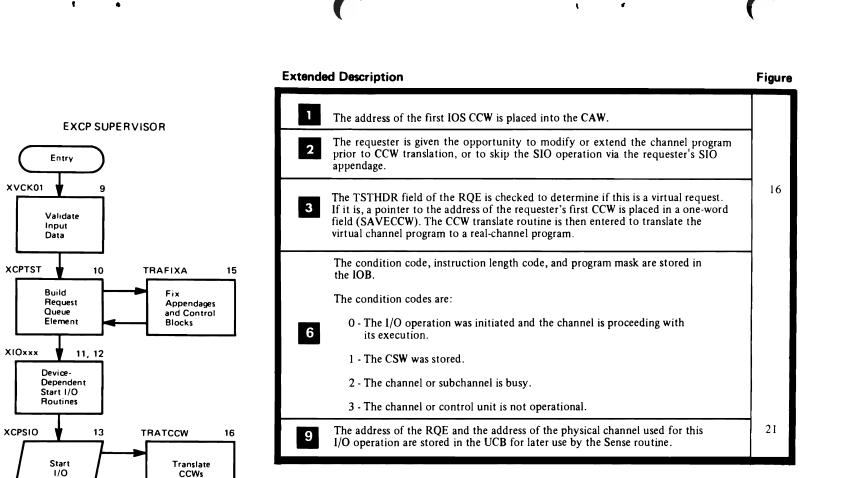

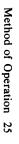

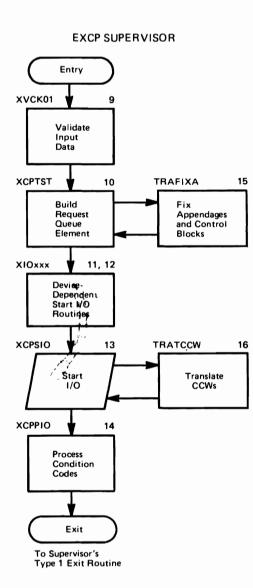

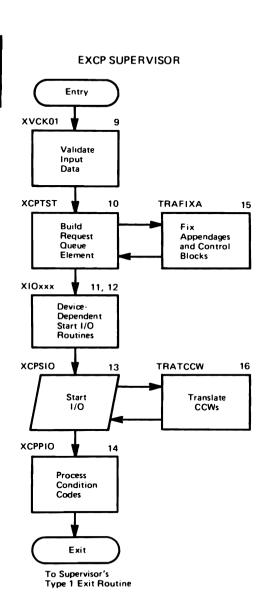

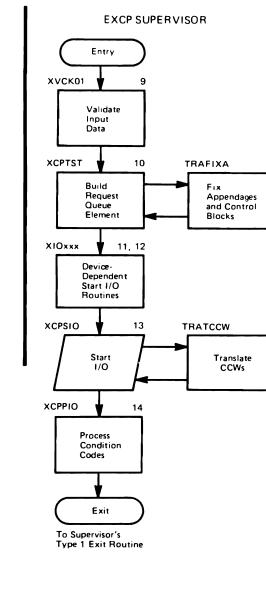

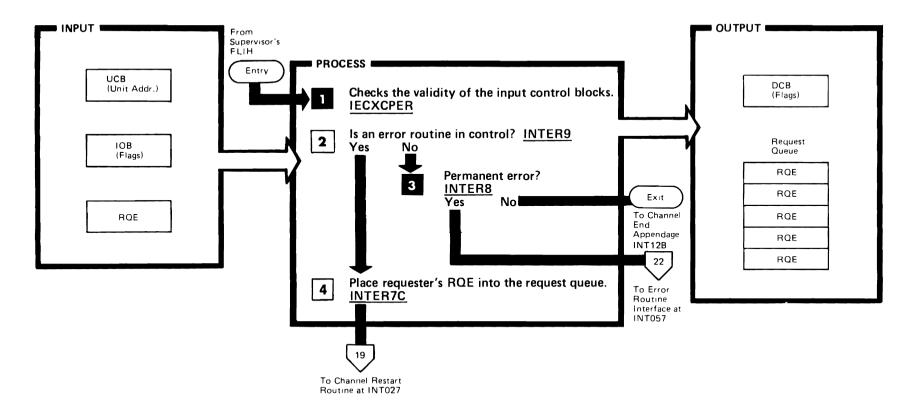

Figure 8. (Part 1 of 2) EXCP Supervisor

.

æ

### Exte

.

.

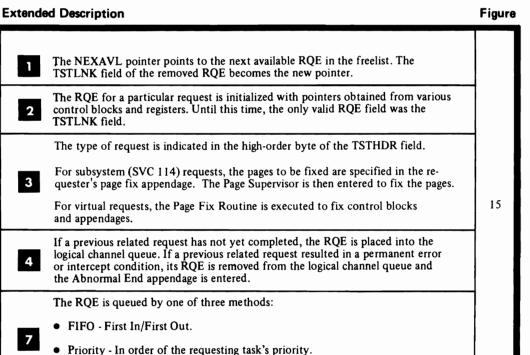

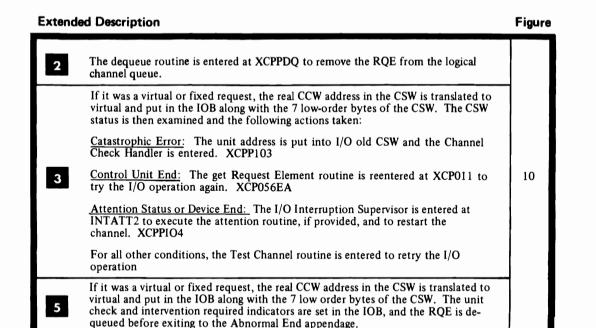

| tendeo | tended Description                                                                                                                                                                                                                                                                                                                                                             |        |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|

| ١      | Various fields within the control blocks are checked to prevent vital system data from being destroyed.                                                                                                                                                                                                                                                                        | 9      |  |

| 2      | An RQE is built for each I/O request. If the request cannot be immediately satisfied, the RQE is placed in the logical channel request queue for that device. For virtual and fixed requestors, the pages involved in the requested I/O operation are fixed in real storage. This prevents the pages from being moved into auxiliary storage through normal paging operations. | 10     |  |

| 3      | The Start I/O module builds any device-dependent prefix CCW chains needed.<br>The SIO subroutine is entered to translate the virtual channel program and<br>execute the SIO instruction.                                                                                                                                                                                       | 11, 12 |  |

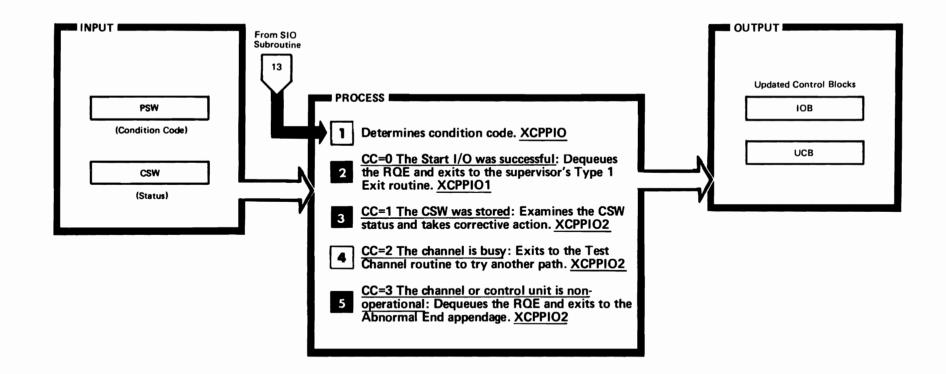

| 4      | The Post Start I/O routine processes the condition codes that resulted from the Start I/O and translates the CCW address in the CSW back to virtual. The IOB and UCB are updated and the RQE is dequeded before exiting to the supervisor's Type 1 exit routine.                                                                                                               | 14     |  |

.

.

# Figure 8. (Part 2 of 2) EXCP Supervisor

.

,

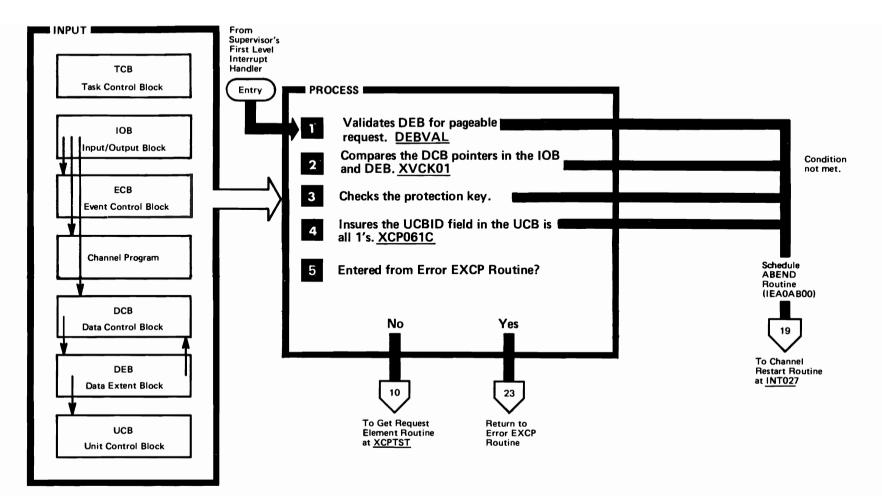

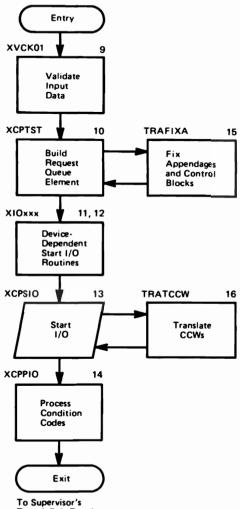

Figure 9. (Part 1 of 2) Validity Check Routine

.

٠

2 The IOB's pointer to the DCB must be the same as the DEB's pointer to the DCB. If not, the ABEND routine is entered. Figure

10

23

If the system has the protection feature, a non-supervisor requester's key must equal the storage key in the DEB. The ABEND routine is entered if the keys do not match.

The UCB is invalid if the UCBID field is not all 1's.

3

4

5 If this routine is entered from the supervisor's SVC First Level Interruption Handler, the Get Request Element routine is entered to build an RQE for this request.

If this routine is entered from the Error EXCP routine, the address of the logical channel word is calculated and placed in a register. The Error EXCP routine is then reentered.

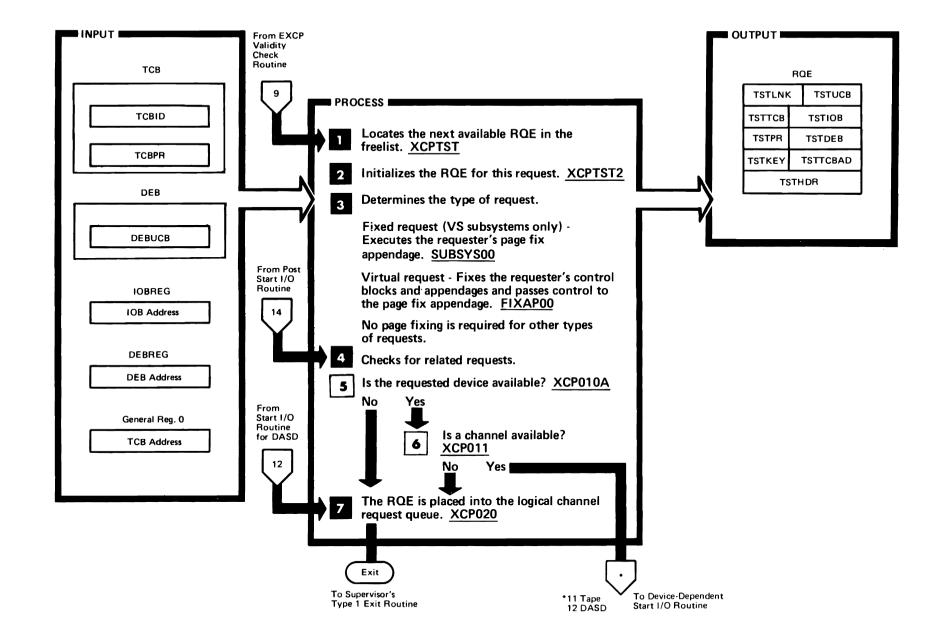

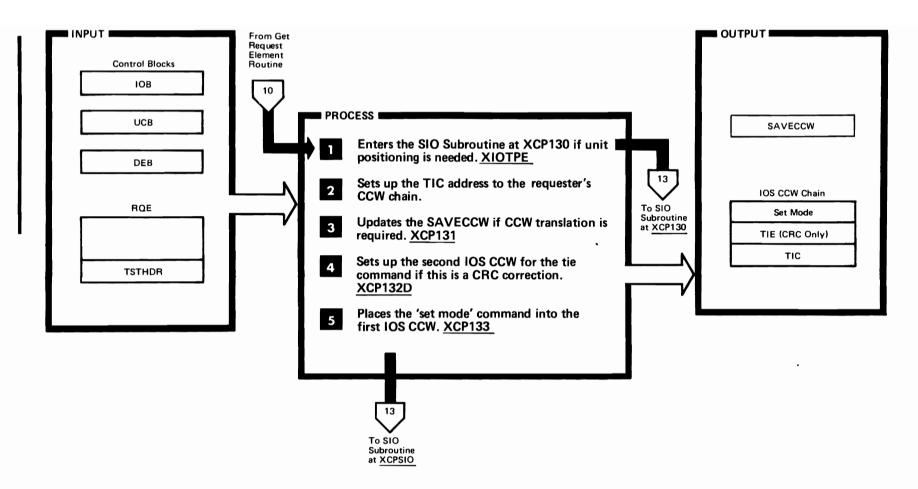

Figure 10. (Part 1 of 2) Get Request Element Routine

. #

To Supervisor's Type 1 Exit Routine

• Ordered Seek - In order of the cylinder address of the requested DASD.

Figure 10. (Part 2 of 2) Get Request Element Routine

ĸ.

.

Figure 11. (Part 1 of 2) Start I/O Routine for Tape

٠

٠

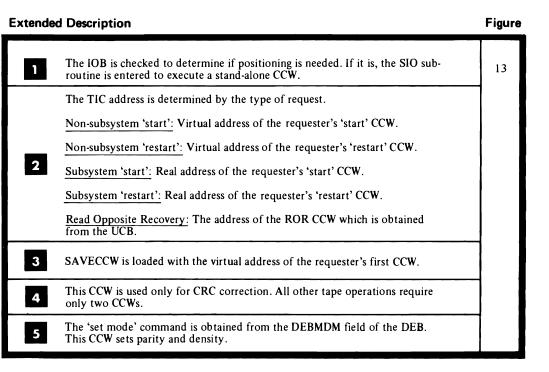

### Figure 11. (Part 2 of 2) Start I/O Routine for Tape.

Method of Operation 21

5

4

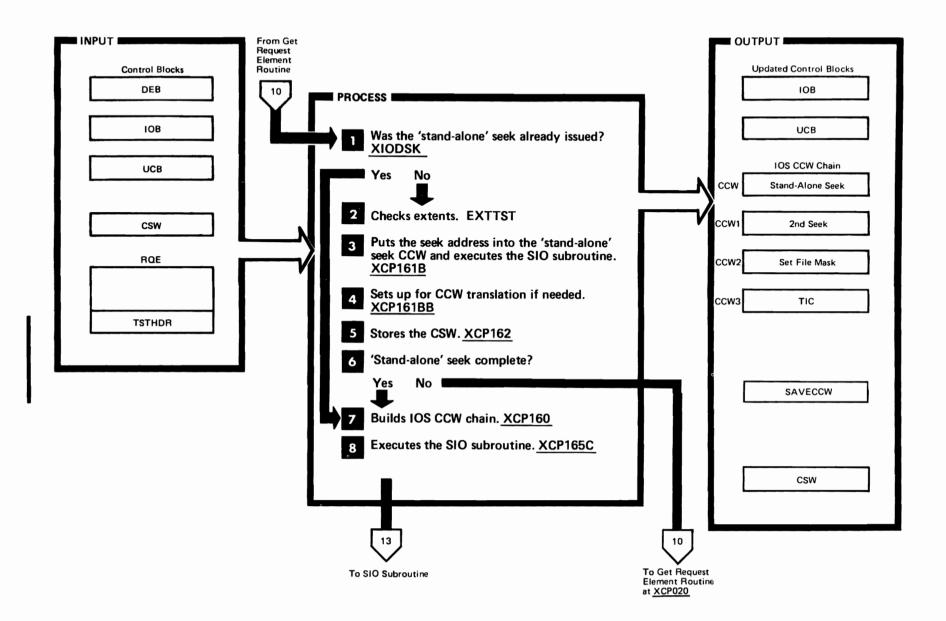

Figure 12. (Part 1 of 2) Start I/O Routine for DASD

.

٠

Exit To Supervisor's Type 1 Exit Routine

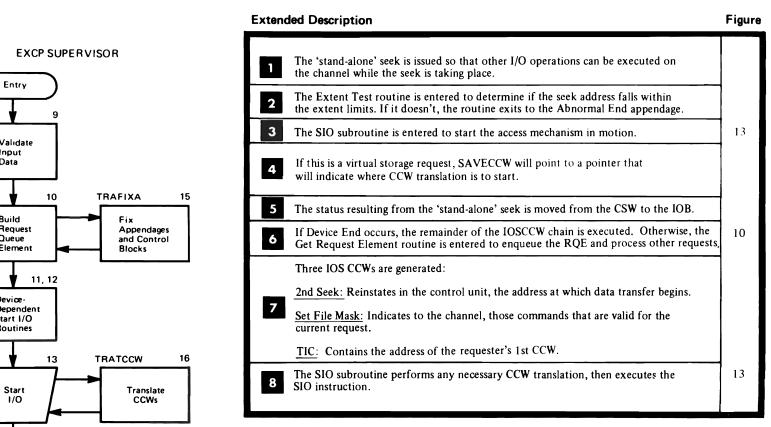

Figure 12. (Part 2 of 2) Start I/O Routine for DASD

Ł

.

24 OS/VS2 I/O Supervisor Logic

ŧ

14

XCPPIO

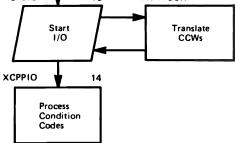

Process Condition Codes

Exit

To Supervisor's Type 1 Exit Routine

đ

.

Figure 14. (Part 1 of 2) Post Start I/O Routine

٤

#### Figure 14. (Part 2 of 2) Post Start I/O Routine

•

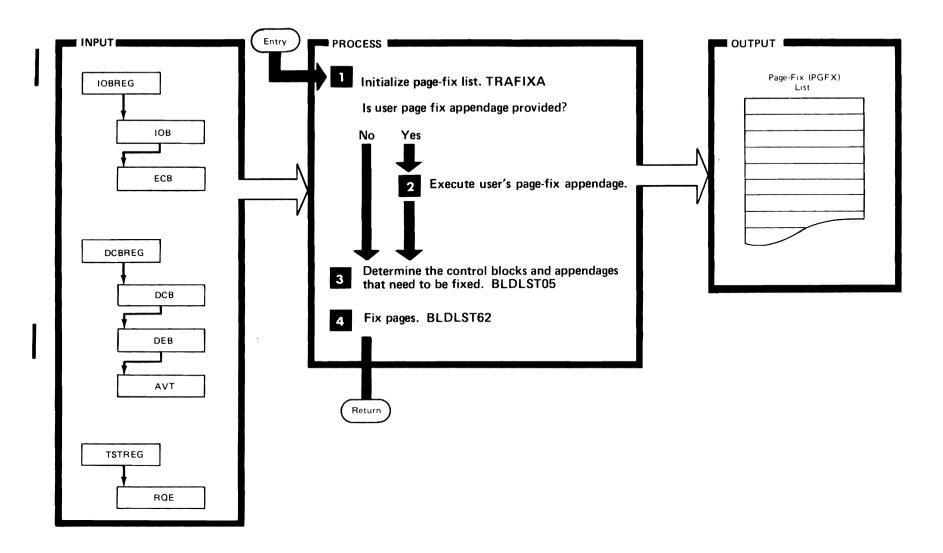

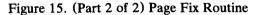

Figure 15. (Part 1 of 2) Page Fix Routine

.

**Extended Description**

1

2

3

4

#### Figure

A block to be used as a page-fix list is acquired from the SQA space owned by IOS. The TSTHDR field of the RQE points to the page-fix list until translation time.

The user can make entries in the page-fix list for I/O appendages and other data. A maximum of seven entries are permitted. Ten entries may be specified with a special return vector (+4). The user must also include entries for his DCB, DECB, and IOB.

Pages for the IOB, ECB, DCB, AVT, and IOS appendages must all be fixed in real storage. Those that are not already fixed are added to the page-fix list.

The Page Supervisor fixes all of the pages that are specified by the page-fix list. If the page is not already in real storage, an I/O operation (page-in) is requested.

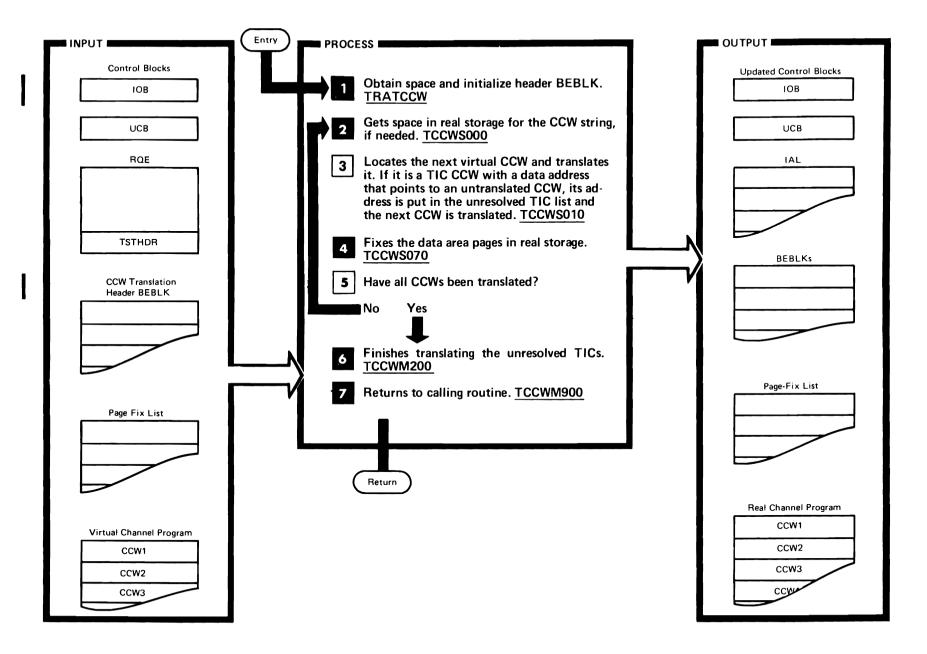

Figure 16. (Part 1 of 2) CCW Translator

Figure Space is obtained from the IOS owned SOA for a CCW translation header BEBLK. The TSTHDR field of the RQE is updated to point to the header BEBLK. The page-1 fix list obtained earlier is now pointed to by the HDRPGLK field of the header BEBLK. If the channel program exceeds the capacity of the header BEBLK, additional space is required to complete the translation and subroutine TCCWM300 is entered. This 2 routine acquires SQA space for a new BEBLK. The new BEBLK is initialized and a TIC CCW is placed in the previous channel program segment. This TIC CCW contains a pointer to the first CCW slot in the new BEBLK. CCW translation continues. 15 If the data area specified by the CCW crosses a page boundary, the page fix list is checked to ensure the page is fixed, and an IAL is generated. The IAL address is placed into the CCW's data address field. When the channel program is executed, 4 data transfer begins with the first address of the IAL and continues until a 2K boundary is reached. It then continues data transfer from the next address in the IAL. This is repeated until the count in the CCW expires. Translation of the unresolved TICs can be completed by referencing the BEBLKs. The virtual addresses in the BEBLKs are scanned until a match is made with the TIC's 6 virtual data address. The corresponding real address is then stored in the TIC command. 16 The starting address of the real channel program is put into the HDRTICL field of 7 the header BEBLK for use by the SIO routine.

**Extended** Description

### Method of Operation 3

Figure 17. (Part 1 of 2) I/O Interruption Supervisor (Part 1)

.

To Supervisor's Type 1 Exit Routine

Extended Description

5

7

#### Figure

The CSW Translator is entered at TRATCSW. If it was a virtual or fixed request, the real CCW address in the CSW is replaced by the corresponding virtual CCW address found in the BEBLK.

Catastrophic errors are:

- Channel Control Check

- Interface Control Check

- Channel Data Check

Figure 17. (Part 2 of 2) I/O Interruption Supervisor (Part 1)

Figure 18. (Part 1 of 2) I/O Interruption Supervisor (Part 2)

t

#### Extended Description

Figure

L

.

To Supervisor's Type 1 Exit Routine

## 8 The seven low-order bytes of the CSW are placed into the IOB. 13 The Unfix/Free routine of the CCW Translator is entered at TRAUFRE. Pages used for control blocks and appendages are unfixed, and space in the SQA that was used for the page-fix list and translation header record is freed.

.

Figure 18. (Part 2 of 2) I/O Interruption Supervisor (Part 2)

.

.

\*

.

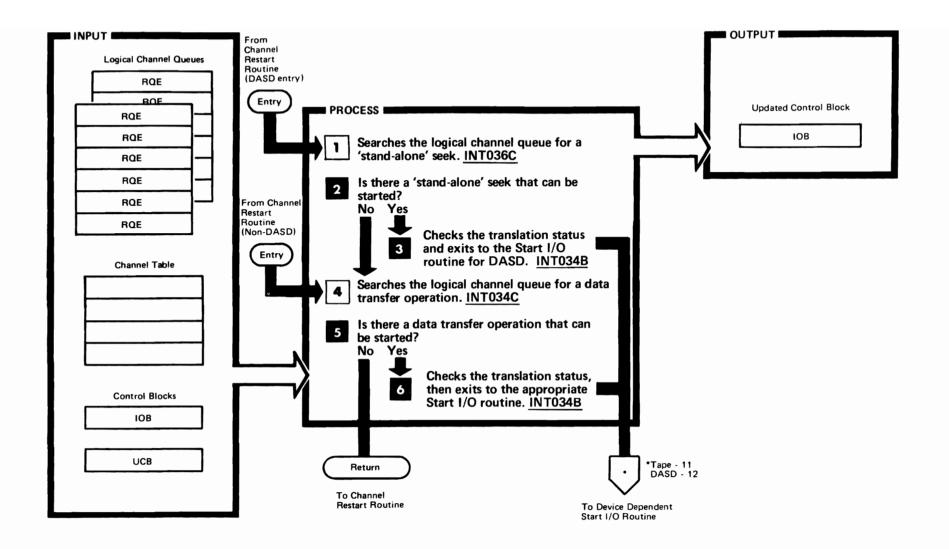

Figure 19. (Part 1 of 2) Channel Restart Routine

#### **Extended Description**

| xtende | ed Description                                                                                                                                                                                                            | Figure |  |  |  |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|--|

| 2      | If there is an interruption pending, the I/O Interruption Supervisor is reentered at IECINT.                                                                                                                              | 17     |  |  |  |  |  |

| 3      | The Channel Search routine is entered at INTCSn to determine if another I/O operation can be started on this logical channel. The channel table contains the Channel Search routine entry point for each logical channel. |        |  |  |  |  |  |

| 6      | Same as 2                                                                                                                                                                                                                 |        |  |  |  |  |  |

#### Figure 19. (Part 2 of 2) Channel Restart Routine

ŧ

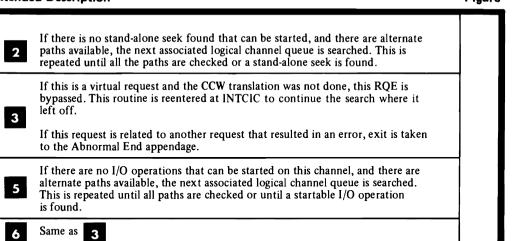

Figure 20. (Part 1 of 2) Channel Search Routine

ŧ

#### **Extended Description**

#### Figure

.

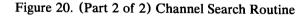

Figure 21. (Part 1 of 2) Sense Subroutine

٠

Extended Description

Figure 21. (Part 2 of 2) Sense Subroutine

ť

.

To Supervisor's Type 1 Exit Routine

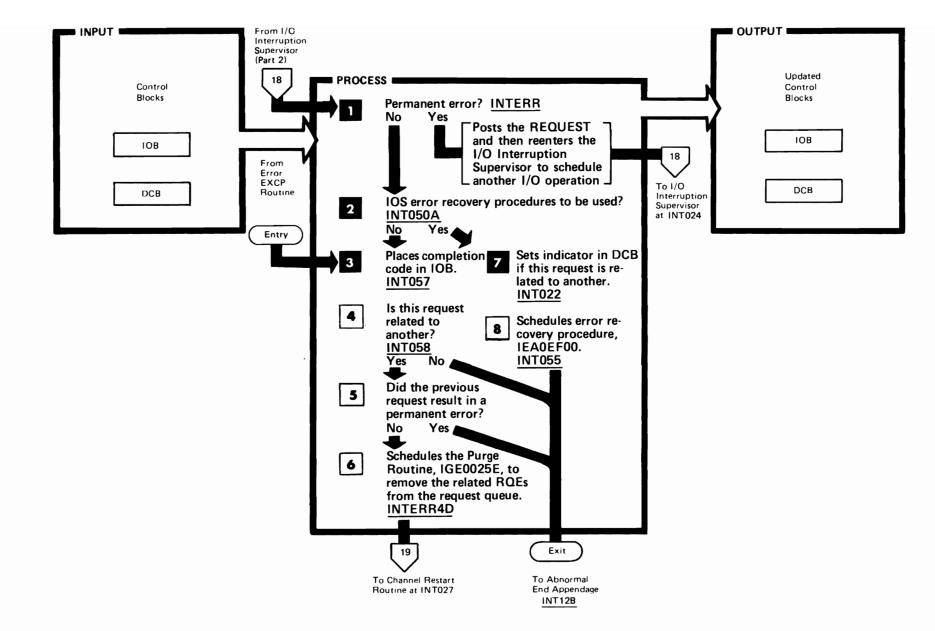

Figure 22. (Part 2 of 2) Error Routine Interface

#### Extended Description

1

2

3

7

#### Figure

An X'41' in the completion code byte of the IOB, IOBCD, indicates a permanent error. An X'OC' in the DCBFL byte of the DCB indicates IOS ERPs are to be used. The completion code, IOBCOD, is set to: <u>X'44' (Intercepted Request)</u> if this request is an intercepted I/O request. <u>X'41' (Permanent Error) if</u> this request is not related to a previous request that resulted in a permanent error.

.

Unchanged if this request is related to a previous request that resulted in a permanent error.

An X'40' is placed into the DCBFL byte to indicate error correction is in progress.

¥

.

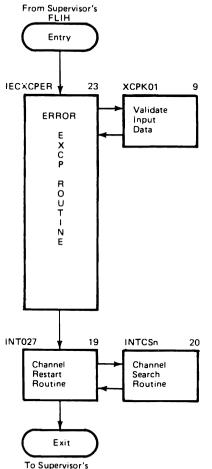

Figure 23. (Part 1 of 2) Error EXCP Routine

\*

# SOR Extended Description Figure iOR I The Validity Check routine is executed to ensure various fields within the control blocks are valid. If any of the tests are not satisfied, the ABEND routine, IEA0AB00, is entered. 9 I If this is not a permanent error, the 'I/O Error Routine in Control' flag in the DCB is turned off before exiting to the Channel End Appendage. 9

.

FLIH at DISMIS

Figure 23. (Part 2 of 2) Error EXCP Routine

#### **PROGRAM ORGANIZATION**

This section contains functional organization charts and a description of the individual routines. There is a functional organization chart for each of the three functions of the I/O supervisor.

#### **Description of Routines**

In Figure 24, 25, and 26 the major I/O supervisor routines are grouped according to the functions that they perform. Brief descriptions of the routines and optional user-written appendage routines follow.

Abnormal end appendage: Optional user-written appendage to which the I/O interruption supervisor exits when there is an error associated with the processing of I/O.

Attention Routine Interface: Determines the address of the appropriate Attention routine; invokes the Attention routine.

Channel Command Word Translator routine: Converts the virtual channel program to a real channel program.

**Channel Check Handler routine:** Builds error recovery procedure interface block to indicate cause of channel failure; builds inboard record to describe environment at time of failure.

**Channel Check Handler Routine Interface:** Places a code into register 15 that indicates which IOS routine intercepted the channel failure and branches to the Channel Check Handler routine.

**Channel end appendage:** Optional user-written appendage to which the I/O interruption supervisor exits after a channel end interruption before indicating to the user how his I/O request ended. Also entered when channel end interruption is accompanied by either a wrong length indicator or a unit exception, or by both conditions.

**Channel Restart routine:** Scans logical channel queues. Selects RQEs representing requests for I/O activity that can be started. Starts the I/O activity. For direct-access devices, first starts all seeks, then starts the data transfer.

Channel Search routines: One for every physical channel. "Driver" type routines consisting mostly of branch instructions. Direct the search of logical channel queues and the starting of I/O activity.

Channel Status Word Translator routine: Converts the real CSW address to a virtual address for virtual requesters.

**Dequeue subroutine:** Locates an RQE in a logical channel queue, removes it from the queue, and returns it to the freelist.

**End-of-extent appendage:** Optional user-written appendage to which the EXCP supervisor exits when the execution of I/O request will violate the extent limits of a direct-access device.

Enqueue subroutine: Places an RQE into a logical channel queue. Normally queues by order of arrival. Optionally queues by requestor's priority or by seek address.

**Error Recovery routine:** Determines if I/O activity can be retried. Supervises retry attempts.

Error Routine Interface: Prepares for and invokes, or schedules the execution of, an error recovery routine.

To I/O Interruption Supervisor (25)

#### Figure 26. Functional Organization, Error EXCP Supervisor

**EXCP Validity Check routine:** Does most of the housekeeping for the EXCP supervisor. Checks for a valid DCB, DEB, IOB, and UCB. With Protection feature uses Validity Check subroutine to check storage keys of input data areas.

Get Request Element routine: Obtains an RQE from the freelist and initializes it. If device is unavailable, causes the RQE to be queued in logical channel request queue.

Page Fix Routine: Fixes pages in real storage for control blocks and appendages.

**Program-controlled interrupt appendage:** Optional user-written appendage to which I/O interruption supervisor exits when program-controlled interruption (PCI) is indicated. Returns control to I/O interruption supervisor where the modified CCW is translated, if a virtual request and normal processing continues.

**Post Routine Interface:** Invokes the supervisor's Post routine, passing to it an event completion code and the address of the requester's ECB. The Post routine posts the requester's ECB.

**Post Start I/O routine:** Routes control, depending upon resulting condition codes of the Start I/O instruction and status bits in the CSW (if the CSW was stored).

Quiesce Complete subroutine: Invokes the supervisor's Post routine, passing to it an event completion code and the address of the purge parameter list. The Post routine posts the Purge routine ECB.

Sense subroutine: Issues a Start I/O instruction to cause a Sense command to be executed. Places the first two bytes of sense data in the requester's IOB.

1

1

System Environment Recording Routine Interface: Places an error code into the machine check new PSW. Uses a Load PSW instruction to invoke the SER0 or SER1 routine.

Start I/O appendage: Optional user-written routine to which the EXCP supervisor exits before the execution of the Start I/O (SIO) instruction for a requested I/O operation.

**Start I/O routine for direct-access devices:** Prepares an I/O supervisor channel program consisting of three CCWs: a Seek command, a Set File Mask command, and a Transfer-in-Channel command. The 2314 direct-access device uses the Start I/O subroutine twice, once to perform a stand-alone seek and once to perform the data transfer.

Start I/O routine for magnetic-tape devices: Prepares an I/O supervisor channel program that may consist of two CCWs (normal start, restart, or opposite direction recovery), or three CCWs (operations following a cyclic redundancy check condition). The last CCW contains a Transfer-in-Channel command containing the address of the requester's first CCW. Uses the Start I/O subroutine.

Start I/O routine for unit record and communications devices: Initializes a register with the address of the requester's first CCW. Uses the Start I/O subroutine.

Start I/O subroutine: Prepares the CAW and issues a Start I/O instruction. Does some checking of resulting condition codes.

**Test Channel routine:** For selector channels, issues a Test Channel instruction. Causes the RQE to be queued if the channel is unavailable. Tries all channels of multiple-path arrangements. Does not issue a Test Channel instruction for byte-multiplexor channels.

**Trap routines:** One for each device class. Perform device-dependent functions following channel-end and device-end interruptions.

Validity Check subroutine: Checks storage keys of areas containing IOB, DCB, and ECB against the requester's protection key; checks that DEB storage key is 0.

#### DIRECTORIES

This section contains cross-reference lists that include a data area directory, module directory and a routine directory.

#### **Data Area Directory**

Figure 27 contains a summary of information about the major data areas used by the I/O supervisor. The column headings and their meanings are:

Data Area Name: The name of the data area and its abbreviation, if there is one.

**Beginning Symbol:** Meaningful only for data areas contained in the nucleus. This symbol identifies the beginning of the data area, and can be used to locate the data area in the program listings.

Creation: Contains some indication as to the origin of the data area.

Permanent Storage Assignment means that the area is part of the hardware and always occupies the real-storage location shown in the "Storage Area" column.

Requester means that creation and maintenance of the data area is the responsibility of the requester of the I/O activity. All requesters do not have to explicitly create the needed data areas. (See Figure 1 and its accompanying text.)

System Generation means that the data area is created during system generation. (This means that space is set aside for the area during system generation.)

Supervisor means that the area is created and maintained by the supervisor portion of the control program.

**Storage Area:** Indicates where the data area can be found in real storage. Where "Requester's" appears in this column, the data area is obtained by the requester when it is needed; consequently, its location is not fixed.

Size: The size of the data area.

Means of Access: The most commonly used way of referring to the data area or one of its entries.

| Data Area Name                 | Beginning<br>Symbol | Creation                                                                               | Storage Area           | Size                                                                          | Means of Access                                                                                                                                                                                                                 |

|--------------------------------|---------------------|----------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Alternate Path<br>Table        | SCPCHnB             | System<br>Generation                                                                   | Nucleus                | Three to Five<br>Fullwords,<br>Depending Upon<br>No. of Paths to<br>a Device  | Beginning symbol.                                                                                                                                                                                                               |

| Beginning-End<br>Block (BEBLK) | BEBNXTB             | I/O Supervisor                                                                         | SQA                    | 136 Bytes                                                                     | TSTHDR field of the RQE.                                                                                                                                                                                                        |

| Channel Address<br>Word (CAW)  | CAWLOC              | Permanent<br>Storage<br>Assignment                                                     | 72(48)                 | Word                                                                          | Beginning symbol.                                                                                                                                                                                                               |

| Channel Command<br>Word (CCW)  |                     | By Requester<br>when Needed.<br>IOS CCWs are<br>Created<br>during System<br>Generation | Requester's<br>Nucleus | Doubleword                                                                    | Address at requester's first CCW<br>is contained at off-sets IOBST<br>(start) or IOBSRS (restart) fields<br>of IOB.<br>Access to IOS CCWs varies<br>with device type and                                                        |

| Channel Error                  | СЕВТАВ              | System                                                                                 | Nucleus                | 24 Bytes                                                                      | circumstances.<br>Beginning Symbol.                                                                                                                                                                                             |

| Block Table                    |                     | Generation                                                                             |                        |                                                                               |                                                                                                                                                                                                                                 |

| Channel Status<br>Word (CSW)   | CSWLOC              | Permanent<br>Storage<br>Assignment                                                     | 64(40)                 | Doubleword                                                                    | Beginning symbol.                                                                                                                                                                                                               |

| Channel Table                  | IECCST              | System<br>Generation                                                                   | Nucleus                | One-Word<br>Entry for<br>Each Physical<br>Channel                             | To locate entry for specific<br>channel, channel number is<br>multiplied by four and added to<br>beginning address of table.                                                                                                    |

| Data Control<br>Block (DCB)    |                     | By Requester                                                                           | Requester's            | Varies with<br>Access Method                                                  | Symbolic names equated to offsets of files.                                                                                                                                                                                     |

| Data Extent<br>Block (DEB)     |                     | By Requester                                                                           | Requester's            | Varies with<br>Devices and<br>Access method                                   | Symbolic names equated to offsets of fields.                                                                                                                                                                                    |

| Device Statistics<br>Fable     | IECSTB              | System<br>Generation                                                                   | Nucleus                | One 10-Byte<br>Entry for Each<br>Device, plus<br>One 10 Byte<br>Control Field | Normally, the address of an entry<br>for a device is obtained by<br>multiplying the statistics table<br>index in the device's UCB by 10<br>and adding the result to the<br>beginning address of the device<br>statistics table: |

|                                |                     |                                                                                        |                        |                                                                               | STATAB x 10 + Beginning Address                                                                                                                                                                                                 |

|                                |                     |                                                                                        |                        |                                                                               | When there are more than 256 devices, however, the following method is used:                                                                                                                                                    |

|                                |                     |                                                                                        |                        |                                                                               | (STATAB) + 256) x 10 + Beginning<br>Address                                                                                                                                                                                     |

|                                |                     | Area Directory                                                                         |                        |                                                                               | 1 1001 000                                                                                                                                                                                                                      |

2

Figure 27. (Part 1 of 3) Data Area Directory

| Data Area Name                 | Beginning<br>Symbol | Creation                           | Storage Area | Size                                                                               | Means of Access                                                                                                                                                                                                                  |

|--------------------------------|---------------------|------------------------------------|--------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |                     |                                    |              |                                                                                    | In the above, n is the number one<br>or two to indicate the second and<br>third 256-entry group in the device<br>statistics table. The UCB addresses<br>in the control field of the table are<br>used to determine the number n. |

|                                |                     |                                    |              |                                                                                    | For the 2314 Direct-Access Storage<br>Facility, the low-order four bits of<br>the fifth sense byte are added to the<br>statistics table index before the<br>index is used.                                                       |

| Device Table                   | DEVTAB              | System<br>Generation               | Nucleus      | One 6-Byte<br>Entry for Each<br>Queuing Option<br>Selected for Each<br>Device Type | Desired entry located by adding device<br>table index from UCB to beginning<br>address of table. A specific field<br>within the entry is then located by<br>adding the field's offset to the<br>above sum.                       |

| Event Control<br>Block (ECB)   |                     | By Requester                       | Requester's  | Word                                                                               | Via address contained at offset 5 of the IOB.                                                                                                                                                                                    |

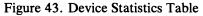

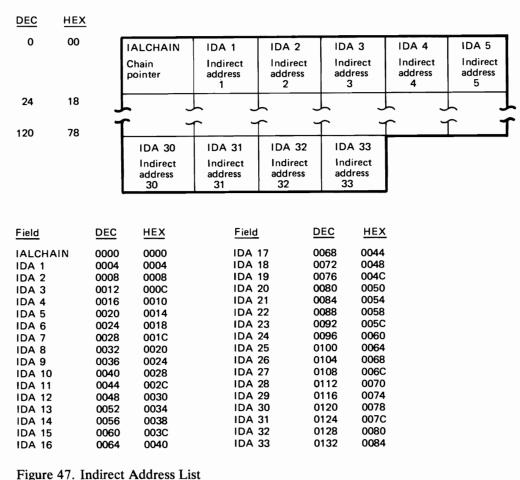

| Indirect Address<br>List (IAL) | IALCHAIN            | I/O Supervisor                     | SQA          | 136 Bytes                                                                          | HDRINDL field of the CCW translation header BEBLK.                                                                                                                                                                               |

| Input/Output<br>Block (IOB)    |                     | By Requester                       | Requester's  | 32 Bytes, plus a<br>Variable Amount<br>that Depends Upon<br>the Access Method      | Initially, address is provided<br>in register 1 by requester. It<br>is moved to and maintained in<br>register 2 (IOBREG).                                                                                                        |

| Logical Channel<br>Table (LCH) | LCHTAB<br>IECILCH   | System<br>Generation               | Nucleus      | One Doubleword<br>Logical Channel<br>Word for Each<br>Logical                      | To locate a needed logical<br>channel word, the logical<br>channel index in the UCB is<br>multiplied by 8 and added to the<br>beginning address of the<br>logical channel table.                                                 |

| Page Fix List<br>(PGFX)        | FXLSTCHN            | NI/O Supervisor                    | SQA          | 136 Bytes                                                                          | Before CCW translation, the<br>TSTHDR field of RQE.<br>HDRPGLK field of the translation<br>header BEBLK.                                                                                                                         |

| Program Status<br>Word (PSW)   |                     | Permanent<br>Storage<br>Assignment |              |                                                                                    |                                                                                                                                                                                                                                  |

| SVC Old PSW<br>I/O Old PSW     | SVCOPSW<br>IOPSWO   |                                    |              | 32(20)<br>56(38)                                                                   | Beginning symbol.<br>Beginning symbol.                                                                                                                                                                                           |

ŀ

t

Ð

1

A .....

| |-

| I | Data Area Name                 | Beginning<br>Symbol | Creation             | Storage Area | Size                                                                                                                                                                          | Means of Access                                                                                                                                                                                                                                                                   |

|---|--------------------------------|---------------------|----------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Request Queue<br>Element (RQE) | TSTAR<br>TECIOQET   | System<br>Generation | Nucleus      | 20 Bytes<br>20 Bytes                                                                                                                                                          | Varies depending upon status of request:                                                                                                                                                                                                                                          |

|   |                                |                     |                      |              |                                                                                                                                                                               | Address of RQE available for<br>assignment is contained in location<br>NEXAVL.                                                                                                                                                                                                    |

|   |                                |                     |                      |              |                                                                                                                                                                               | Address of assigned (but not queued) RQE is contained in requester 1 (TSTREG).                                                                                                                                                                                                    |

|   |                                |                     |                      |              |                                                                                                                                                                               | Address of the first RQE in a logical<br>channel queue is contained in the<br>LCHFTS field of the logical channel<br>word for that queue.                                                                                                                                         |

|   | Fask Control<br>Block (TCB)    |                     | By Supervisor        | Nucleus      | 171 Bytes                                                                                                                                                                     | Symbolic names equated to offsets of fields.                                                                                                                                                                                                                                      |

|   | Franslation<br>Header BEBLK    | BEBNXTB             | I/O Supervisor       | SQA          | 136 Bytes                                                                                                                                                                     | TSTHDR field of the RQE.                                                                                                                                                                                                                                                          |

|   | Unit Control<br>Block (UCB)    |                     | System<br>Generation | Nucleus      | Variable from 24<br>10 288 Bytes.<br>one UCB for Each<br>Device Address<br>Defined for the<br>System.                                                                         | Initially, via address<br>contained in the UCB address<br>field of DEB. The address is<br>moved to the request queue<br>element. Following<br>interruptions, the address of<br>the UCB for the device that<br>caused the interruption is<br>obtained via the UCB lookup<br>table. |

| ι | UCB Lookup Table               | UCGTAB<br>IECILKI   | System<br>Generation | Nucleus      | Variable, depending<br>upon Number and<br>Addresses of Devices,<br>Control Units, and<br>Channels, and Number<br>of Zero Entries<br>Eliminated by Table-<br>Building Routine. | Beginning symbol.<br>r                                                                                                                                                                                                                                                            |

|   | Volume Statistics<br>Fable     |                     | System               | Nucleus      | 24 Bytes for Each<br>Entry                                                                                                                                                    | Via address contained in field<br>at offset 49 of the UCB<br>containing the volume. Each<br>entry is effectively an<br>extension to a UCB.                                                                                                                                        |

#### Module Directory

Figure 28 contains information about the physical structure of the I/O supervisor. The column headings and their meanings are:

Symbolic Name: The symbolic name of a table, routine, object module, or control section.

Description: The type of item to which the symbolic name applies.

**Object Module Name:** The name of the object module containing the item. The microfiche cards containing program listings are ordered by object module name.

Control Section Name: The name of the control section containing the item.

**Publication References:** Places in this publication where more information about the item can be found.

Library: The data set normally containing the item.

| Code | Data Set     |

|------|--------------|

| NUC  | SYS1.NUCLEUS |

| SVC  | SYS1.LPALIB  |

If SVC Routine: Information about I/O supervisor SVC routines. There are four types of SVC routines.

Type 1 SVC routines are part of the nucleus and are disabled (masked) for all interruptions except machine check interruptions.

Type 2 SVC routines are part of the nucleus but may be enabled (interruptable) for part of their operation.

Type 3 SVC routines are nonresident and may be enabled.

Type 4 SVC routines are nonresident and may be enabled.

Name: The name of the item being described.

When the control section name for an item is not the same as the object module name, the item will have two entries in the table—one filed by control section name and the other filed by object module name. Therefore, it is unnecessary to check beyond the first column when looking for a symbolic name.

The three major groups of routines that make up the I/O supervisor—the EXCP supervisor, the I/O interruption supervisor, and the error EXCP supervisor—are contained in the control program nucleus. As a result, there are no CSECT names or load module names in these three major groups of routines. Linkage parameter lists, usually associated with multi-load routines, are also unnecessary. Therefore entry points are not of the formal one-or-two-entries-only type (due to stringent parameter list requirements), but rather are ordinary symbolic labels, undistinguishable from other symbolic labels.

|                  |                    | Object   | Control         |                          |             | Macro    |            | If SVC Routine                                         |

|------------------|--------------------|----------|-----------------|--------------------------|-------------|----------|------------|--------------------------------------------------------|

| Symbolic<br>Name | Description        | Module   | Section<br>Name | Publication<br>Reference | Library Typ | Instruc- | SVC<br>No. | Name                                                   |

| CAWLOC           | Table              | *        | *               | Data Areas               |             |          |            | Channel Address Word                                   |

| CSWLOC           | Table              | *        | *               | Data Areas               |             |          |            | Channel Status Word                                    |

| DEVTAB           | Table              | *        | *               | Data Areas               | NUC         |          |            | Device Table                                           |