Maintenance Library

•

**Processing Unit** Microinstructions

. . .

•

1

SY33-1058-1

3125 MLM. Microinstructions

#### Third Edition (October 1973)

This manual obsoletes SY33-1058-0. Changes are continually made to the information in this manual; any such changes will be reported in subsequent revisions or Technical Newsletters.

· · ·

-

,

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

Forms for reader's comments are provided at the back of the manual. If the forms have been removed, comments may be addressed to 3M Laboratories, Product Publications, Dept 3179, 703 Boeblingen/Wuertt., P.O. Box 210, Germany. Comments become the property of IBM.

© Copyright International Business Machir / s Corporation 1973

.

ii

# Preface

This manual provides information on the IBM 3125 Processing Unit's instruction processing unit (IPU), input/output processor (IOP), and service processor (SVP) microprogram codes. Its main purpose is to explain the functions of:

- Each microinstruction group,

- Each microinstruction and

- Each microinstruction bit.

It also enables the reader to determine the mnemonic by analyzing the bit pattern of a given instruction word.

The reader should have a basic knowledge of the IPU, IOP and SVP data flow of the IBM System/370 Model 125.

# Prerequisite Reading

*3125 Processing Unit, General System Information,* Maintenance Library Manual, Order No. SY33-1059.

### Associated Publications

#### System Library Manuals

*IBM System/370 Principles of Operation,* Order No. GA22-6821. *IBM System/370 Model 125 Functional Characteristics,* Order No. GA33-1506.

#### Maintenance Library Manuals

IBM 3125 Processing Unit, Power Supplies, Order No. SY33-1060. IBM 3125 Processing Unit, Main Storage Controller, Order No. SY33-1061. IBM 3125 Processing Unit, Instruction Processing Unit, Order No. SY33-1062. IBM 3125 Processing Unit, Input/Output Processor, Order No. SY33-1063. IBM 3125 Processing Unit, Magnetic Tape Adapter, Order No. SY33-1064. IBM 3125 Processing Unit, Service Processor Subsystem, Order No. SY33-1065. IBM 3125 Processing Unit, Main Storage, Order No. SY33-1066. IBM 3125 Processing Unit, Multiplexer Channel, Order No. SY33-1067. IBM 3125 Processing Unit, 2560 Attachment, Front End, Order No. SY33-1068. IBM 3125 Processing Unit, 5425 Attachment, Front End, Order No. SY33-1069. IBM 3125 Processing Unit, 3525 Attachment, Front End, Order No. SY33-1070. IBM 3125 Processing Unit, 3504 Attachment, Front End, Order No. SY33-1071. IBM 3125 Processing Unit, 1403 Attachment, Front End, Order No. SY33-1072. IBM 3125 Processing Unit, Direct Disk Attachment, Order No. SY33-1073. IBM 3125 Processing Unit, Integrated Console Printer Attachment, Order No. SY33-1074.

*IBM 3125 Processing Unit, Integrated Communications Adapter,* Part B/M 1876075.

*IBM 3125 Processing Unit, Installation Instructions,* Part 4014001. *IBM 3125 Central Test Manual.* Contains pages appropriate to the individual 3125 Processing Unit.

IBM 3125 Processing Unit, Parts Catalog, Order No. S135-1000.

# Contents

| Section 1: IPU Microprogram Codes                                |  |  |  |  |  |  |  |

|------------------------------------------------------------------|--|--|--|--|--|--|--|

| IPU MICROINSTRUCTION GROUP DETERMINATION                         |  |  |  |  |  |  |  |

| IPU MICROINSTRUCTIONS BY GROUP                                   |  |  |  |  |  |  |  |

| Group 1                                                          |  |  |  |  |  |  |  |

| Group 2                                                          |  |  |  |  |  |  |  |

| Group 3                                                          |  |  |  |  |  |  |  |

| Group 4                                                          |  |  |  |  |  |  |  |

| Group 5                                                          |  |  |  |  |  |  |  |

| Group 6                                                          |  |  |  |  |  |  |  |

| Group 7                                                          |  |  |  |  |  |  |  |

| Group 8                                                          |  |  |  |  |  |  |  |

| Group 9                                                          |  |  |  |  |  |  |  |

| Group 10                                                         |  |  |  |  |  |  |  |

| Group 11                                                         |  |  |  |  |  |  |  |

| Group 12                                                         |  |  |  |  |  |  |  |

| Group 13                                                         |  |  |  |  |  |  |  |

| LISTING OF IPU MNEMONICS                                         |  |  |  |  |  |  |  |

| EXPLANATION OF IPU MICROINSTRUCTION GROUPS 7                     |  |  |  |  |  |  |  |

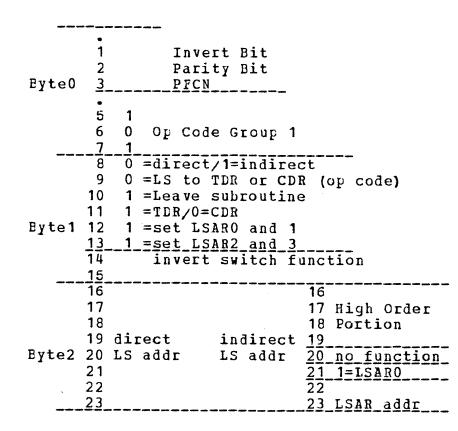

| Group 1: Halfword from Local Store to TDR or CDR                 |  |  |  |  |  |  |  |

| Primary Function                                                 |  |  |  |  |  |  |  |

| Secondary Functions                                              |  |  |  |  |  |  |  |

| Common Layout of Group 1 Instructions                            |  |  |  |  |  |  |  |

| Bit Function Description                                         |  |  |  |  |  |  |  |

| Valid Parameters for Group 1 Instructions                        |  |  |  |  |  |  |  |

| Group 2: Immediate Data to TDR or CDR                            |  |  |  |  |  |  |  |

| Primary Function                                                 |  |  |  |  |  |  |  |

| Secondary Functions                                              |  |  |  |  |  |  |  |

| Common Layout of Group 2 Instructions                            |  |  |  |  |  |  |  |

| Bit Function Description                                         |  |  |  |  |  |  |  |

| Valid Parameters for Group 2 Instructions                        |  |  |  |  |  |  |  |

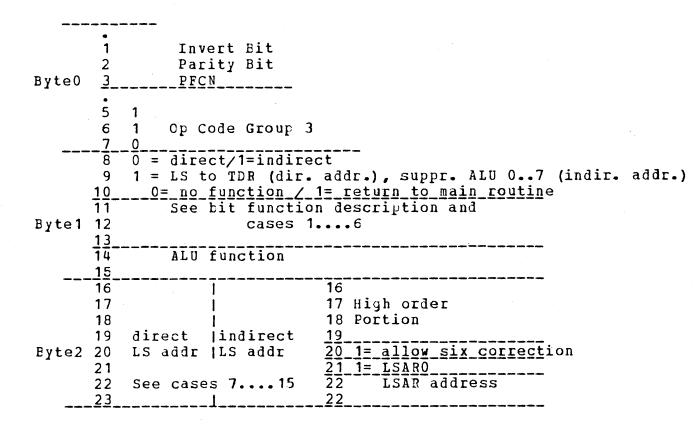

| Group 3: Arithmetic/Logic Operations to Local Storage 9          |  |  |  |  |  |  |  |

| Primary Function                                                 |  |  |  |  |  |  |  |

| Secondary Functions                                              |  |  |  |  |  |  |  |

| Common Layout of Group 3 Instructions                            |  |  |  |  |  |  |  |

| Bit Function Description                                         |  |  |  |  |  |  |  |

| Valid Parameters of Group 3 Instructions                         |  |  |  |  |  |  |  |

| Group 4: Arithmetic/Logic Operations to Main Storage             |  |  |  |  |  |  |  |

| Primary Function                                                 |  |  |  |  |  |  |  |

| Secondary Functions                                              |  |  |  |  |  |  |  |

| Common Layout of Group 4 Instructions                            |  |  |  |  |  |  |  |

| Bit Function Description                                         |  |  |  |  |  |  |  |

| Valid Parameters of Group 4 Instructions                         |  |  |  |  |  |  |  |

| XMSC = Exclusive OR to Main Storage, Read from Main Storage into |  |  |  |  |  |  |  |

| CDR                                                              |  |  |  |  |  |  |  |

| XMSCR = Exclusive OR to Main Storage, Read from Main Storage     |  |  |  |  |  |  |  |

| into CDR, then Return                                            |  |  |  |  |  |  |  |

| Layout of XMSC/XMSCR                                             |  |  |  |  |  |  |  |

|                                                                  |  |  |  |  |  |  |  |

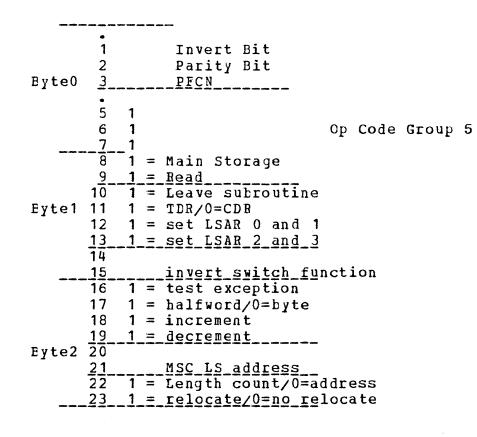

| Group 5: Read from Main Storage into TDR or CDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Primary Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Secondary Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Common Layout of Group 5 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Bit Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Group 6: Read from MSC Local Storage or Key Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Primary Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Secondary Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Common Layout of Group 6 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Bit Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Immediate Control Operation Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

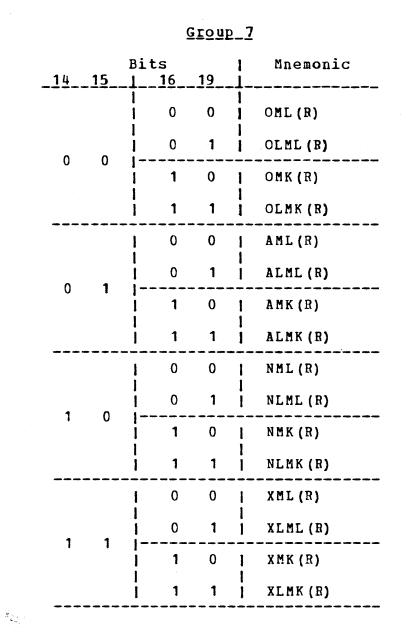

| Group 7: Arithmetic/Logic Operations to MSC Local Storage or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Key Storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Primary Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Secondary Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Common Layout of Group 7 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Bit Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

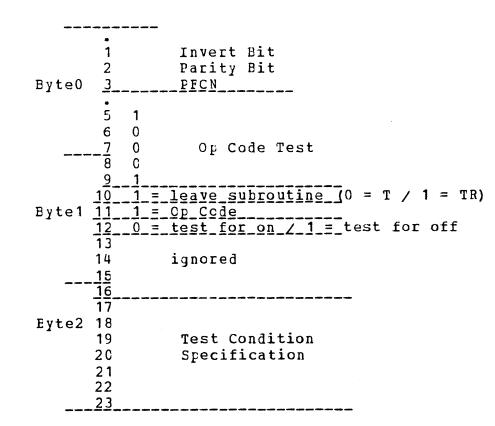

| Group 8: Test Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Primary Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Secondary Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Layout of Test Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Bit Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Table of Test Condition Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

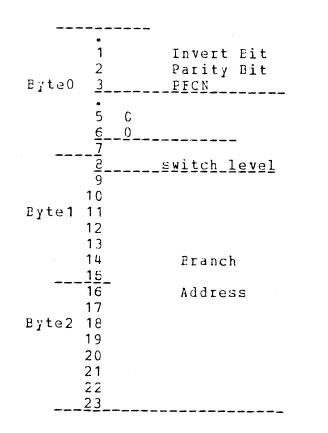

| Group 9: Branch on Test Instructions (Branch Type 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Group 9: Branch on Test Instructions (Branch Type 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Group 9: Branch on Test Instructions (Branch Type 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Secondary Functions26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

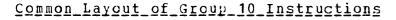

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Common Layout of Group 10 Instructions26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Bit Function Description26Bit Functions26Bit Functions26Bit Functions26Secondary Functions26Bit Function Description26Bit Function Description26Bit Function Description26Bit Function Description26Bit Function Description26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

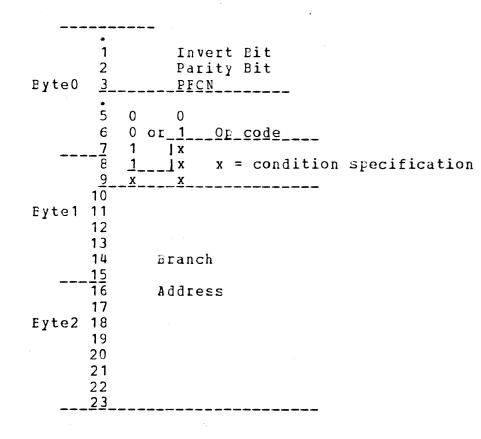

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Bit Function Description26Group 10: Conditional Branch Instructions26Bit Functions26Secondary Functions26Group 10 Instructions26Bit Function Description26Group 11: Shift Instructions27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Bit Function Description26Group 10: Conditional Branch Instructions26Bit Functions26Group 11: Shift Instructions26Group 11: Shift Instructions27Primary Function27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Bit Function Description26Group 10: Conditional Branch Instructions26Secondary Functions26Group 11: Shift Instructions27Primary Function27Secondary Functions27Secondary Functions27Secondary Functions27Secondary Functions27Secondary Functions27Secondary Functions27Secondary Functions27                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Group 10: Conditional Branch Instructions26Group 10: Conditional Branch Instructions26Group 10: Conditional Branch Instructions26Group 11: Shift Instructions26Group 11: Shift Instructions27Primary Function27Secondary Functions27Common Layout of Shift Instructions27Common Layout of Shift Instructions27Secondary Functions27Secondary Functions27Secondary Functions27Secondary Functions27Secondary Functions27Secondary Functions27Secondary Functions27Secondary Functions27Secondary Functions27Secondary Functions27                                                                                                                                                                                                                         |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Group 10: Conditional Branch Instructions26Group 11: Conditional Branch Instructions26Group 11: Shift Instructions26Group 11: Shift Instructions27Primary Function27Secondary Functions27Bit Function Description27Secondary Functions27Bit Function27Secondary Function27Bit Function27Secondary Function27Secondary Function27Bit Function Description27Secondary Function27Bit Function Description27Secondary Functions27Secondary Function27Secondary Function27 </td <td></td> |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Group 10: Conditional Branch Instructions26Bit Function Description26Group 10: Conditional Branch Instructions26Group 11: Source Functions26Group 11: Shift Instructions27Primary Function27Secondary Functions27Secondary Functions27Secondary Functions27Secondary Function27Secondary Function27Secondary Function27Secondary Function27Group 12: Sense and Control Instructions28                                                                                                                                                                                                                                                                                                                                                                    |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Group 10: Conditional Branch Instructions26Group 11: Conditional Branch Instructions26Group 11: Shift Instructions26Group 11: Shift Instructions27Primary Function27Secondary Functions27Bit Function Description27Secondary Functions27Bit Function27Secondary Function27Bit Function27Secondary Function27Secondary Function27Bit Function Description27Secondary Function27Bit Function Description27Secondary Functions27Secondary Function27Secondary Function27 </td <td></td> |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Secondary Functions26Ormon Layout of Group 10 Instructions26Secondary Functions26Group 11: Shift Instructions27Primary Function27Secondary Functions27Secondary Functions27Secondary Functions27Group 11: Shift Instructions27Secondary Functions27Secondary Functions27Group 12: Sense and Control Instructions28Control28                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Secondary Functions26Secondary Functions26Group 10: Conditional Branch Instructions26Bit Function Description26Group 11: Shift Instructions27Primary Function27Secondary Functions27Secondary Functions27Group 11: Shift Instructions27Secondary Function27Secondary Function27Group 12: Sense and Control Instructions28Control28Common Layout of Sense and Control Instructions28Common Layout of Sense and Control Instructions28Common Layout of Sense and Control Instructions28                                                                                                                                                                                                                                                                    |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Secondary Functions26Group 10: Conditional Branch Instructions26Secondary Functions26Secondary Functions26Group 11: Shift Instructions26Group 11: Shift Instructions27Primary Function27Secondary Functions27Secondary Functions27Group 12: Sense and Control Instructions28Common Layout of Sense and Control Instructions28Secondary Functions28Secondary Functions29             |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Secondary Functions26Group 10: Conditional Branch Instructions26Secondary Functions26Secondary Functions26Group 11: Shift Instructions26Group 11: Shift Instructions27Primary Function27Secondary Functions27Secondary Functions27Group 12: Sense and Control Instructions28Common Layout of Sense and Control Instructions28Secondary Functions28Secondary Functions29                                                       |  |

| Group 9: Branch on Test Instructions (Branch Type 1)25Primary Function25Secondary Functions25Common Layout of Branch on Test Instructions25Bit Function Description25Group 10: Conditional Branch Instructions26Primary Functions26Secondary Functions26Secondary Functions26Secondary Functions26Secondary Functions26Group 10: Conditional Branch Instructions26Secondary Functions26Secondary Functions26Group 11: Shift Instructions27Primary Function27Secondary Functions27Secondary Functions27Group 11: Shift Instructions27Secondary Function27Secondary Functions27Group 12: Sense and Control Instructions28Control28Control28Control29Bit Function Description29                                                                                                                                                                                                                                                                                                                                     |  |

.

Contents

1

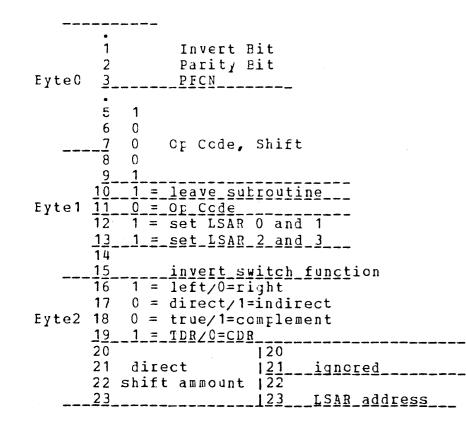

| Group 13: Table Look Up (Translate and Branch) Instruction |       | •    | •   | •     | •  | 31 |

|------------------------------------------------------------|-------|------|-----|-------|----|----|

| Function                                                   | •     | •    | •   | •     | •  | 31 |

| Layout of TRB Instruction                                  | ۰.    | •    | •   | •     | •  | 31 |

| Bit Function Description                                   | •     | •    | •   | •     | •  | 31 |

| Section 2: IOP Microprogram Codes                          |       |      |     |       |    | 33 |

| IOP INSTRUCTION GROUP DETERMINATION                        |       |      |     |       |    | 34 |

| IOP MICROINSTRUCTIONS BY MNEMONICS                         |       |      |     |       |    | 35 |

| EXPLANATION OF IOP MICROINSTRUCTION GROUPS                 |       |      |     |       |    | 37 |

| Group 1: IOP Branch Instructions                           |       |      |     |       |    | 37 |

| Primary Function                                           |       |      |     |       |    | 37 |

| Secondary Functions                                        |       |      |     |       |    | 37 |

| Layout of Group 1 Instructions                             |       | •    | •   | •     | •  | 37 |

| Table of Parameters used with mnemonics BC (U) and BC      | R (   | U)   | •   |       | •  | 38 |

| Bit Function Description                                   |       | •    | •   | •     | •  | 38 |

| Group 2: IOP Data Storage Instructions                     | •     | •    | •   | •     | •  | 38 |

| Primary Function                                           | •     | •    | •   | •     | •  | 38 |

| Secondary Functions                                        | •     | •    | •   | •     | •  | 38 |

| Layout of IOP Group 2 Instructions                         | •     | •    | •   | •     | •  | 38 |

| Bit Function Description                                   | •     | •    | •   | •     | •  | 38 |

| Group 3: IOP Move Instructions                             | •     | •    | •   | •     | •  | 39 |

| Primary Function                                           | •     | •    | •   | •     | •  | 39 |

| Secondary Functions                                        | •     | •    | •   | •     | •  | 39 |

| Layout of IOP Group 3 Instructions                         | •     | •    | •   | •     | •  | 39 |

| Bit Function Description                                   | •     | •    | •   | •     | •  | 39 |

| Group 4: Logical IOP Instructions                          | •     | •    | •   | •     | •  | 41 |

| Primary Function                                           | •     | •    | •   | •     | •  | 41 |

| Secondary Functions                                        | •     | •    | •   | •     | •  | 41 |

| Layout of IOP Group 4 Instructions                         | •     | •    | •   | •     | ٠  | 41 |

| Bit Function Description                                   | •     | •    | •   | •     | •  | 42 |

| Section 3: SVP Microprogram Codes                          | •     | •    |     | •     | •  | 43 |

| SVP OP CODES BY BIT PATTERN                                |       |      | •   |       |    | 44 |

| SUMMARY OF SVP MNEMONICS                                   | •     |      | •   |       |    | 44 |

| ADD = Add LS-Reg plus Accu into Accu                       |       | •    | •   |       | •  | 45 |

| ADDI = Add Accu plus Immediate data byte into Accu .       | •     | •    | •   | •     | •  | 45 |

| AND = AND LS-Reg with Accu into Accu                       | •     | •    | •   | •     | •  | 45 |

| ANDI = AND Accu with Immediate data byte into Accu         | •     | •    | •   | •     | •  | 45 |

| B = Branch unconditionally                                 | •     | •    | •   | •     | •  | 45 |

| BR = Branch unconditionally to address contained in regis  | ter   | •    | •   | •     | •  | 46 |

| BZ = Branch if ALU zero                                    | •     | •    | •   | •     | •  | 46 |

| BZR = Branch to address contained in register if ALU zero  | )     | •    | •   | •     | •  | 46 |

| CHECK = Op code check                                      | •     | •    | •   | •     | •  | 46 |

| BNZ = Branch if (Not) ALU zero                             | •     | •    | •   | •     | •  | 47 |

| CTB = Count, test for zero and branch                      | •     | •    | •   | •     | •  | 47 |

| FR = Fetch one byte from LS-Reg into Accu                  | •     | •    | •   | •     | •  | 47 |

| LBAP = Load Bus and Parity bit from LS-Reg into BAR (S     | ة) (د | or E | SDF | { (\$ | 5) | 47 |

|                                                                | 48 |

|----------------------------------------------------------------|----|

| LBR = Load Accu into Bus Register                              | 48 |

| LDAC = Load immediate data byte into Accu                      | 48 |

| NOP = No operation                                             | 48 |

| OR = Logically OR LS-Reg with Accu into Accu                   | 48 |

| ORI = Logically OR Accu with Immediate data byte into Accu     | 49 |

| SF = Fetch one byte from storage into Accu                     | 49 |

| SLS = Switch Local Storage Zone                                | 49 |

| SST = Store one byte from Accu into storage                    | 50 |

| STBA = Sense, AND with mask into Accu, Branch if ALU zero      | 50 |

| STBX = Sense, exclusively OR with mask into Accu, Branch if    |    |

| ALU zero                                                       | 50 |

| STOP = Halt Service Processor                                  | 51 |

| STR = Store one byte from Accu into LS-Register                | 51 |

| STROB = Sense from Bus 0 and/or 1 into Accu, or activate 'CTRL |    |

| Strobe Bus 0 and/or 1'                                         | 51 |

| XOR = Exclusively OR Ls-Reg with Accu into Accu                | 51 |

| XORI = Exclusively OR Accu with Immediate data byte into Accu  |    |

.

>

.

Contents (continued)

V

.

# Section 1: IPU Microprogram Codes

.

# IPU Microinstruction Group Determination

|   |             |        |        |                |        | Bits<br>]_ <u>11</u> |                  |

|---|-------------|--------|--------|----------------|--------|----------------------|------------------|

|   | 0           | 0<br>0 | 0<br>x | <br>  X<br>  0 | X<br>X | I X<br>I X           | <br>  9<br>  9   |

|   | 0           | 0<br>1 | 1<br>x | <br>  1<br>  X | x<br>x | <br>  X<br>  X       | <br>  10<br>  10 |

|   | 1           | 0      | 0      | <br>  0        | 0      | <br>  X              | <br>  13         |

| 1 | <br>  1     | 0      | 0      | <br>  0        | 1      | 0                    | 1 11             |

| 1 | <br>  _1    | 0      | 0      | <br>  0        | 1      | 1                    | 8                |

| l | 1           | 0      | 0      | <br>  1        | 0      | x                    | 12               |

| 1 | 1           | 0      | 1      | <br>  X        | 0      | x                    | 1                |

|   | 1           | 0      | 1      | <br>  X        | 1      | <br>  x              | 2                |

| 1 | <br>  1     | 1      | 0      | <br>  X        | X      | <br>  X              | 3                |

|   | 1           | 1      | 1      | 0              | 0      | x                    | 7                |

|   | <br>  1     | 1      | 1      |                | 1      | x                    | 6                |

| ] | <br>  1<br> | 1      | 1      | 1              | 0      | <br>  X              | 4                |

|   | <br>  1     | 1      | 1      | 1              | 1      | x I                  | l<br>l . 5       |

|   | 1           |        |        | ł              |        | 1                    | I                |

IPU Microinstructions by Group

| <u>(</u> | irou | <u>p_1</u> |

|----------|------|------------|

| Bit 1    | 11   | Mnemonic   |

| 0        |      | LC(R)      |

| 1        |      | LT(R)      |

|   | <u>Group_2</u> |    |          |  |  |  |  |  |  |

|---|----------------|----|----------|--|--|--|--|--|--|

| 8 | Bits<br>11     | 13 | Mnemonic |  |  |  |  |  |  |

| 0 | 0              | 0  | IRC(R)   |  |  |  |  |  |  |

| 0 | 0              | 1  | ILC (R)  |  |  |  |  |  |  |

| 0 | 1              | 0  | IRT(R)   |  |  |  |  |  |  |

| 0 | 1              | 1  | ILT (R)  |  |  |  |  |  |  |

| 1 | 0              | 0  | ZIRC (R) |  |  |  |  |  |  |

| 1 | 0              | 1  | ZILC(R)  |  |  |  |  |  |  |

| 1 | 1              | 0  | ZIRT(R)  |  |  |  |  |  |  |

| 1 | 1              | 1  | ZILT (R) |  |  |  |  |  |  |

<u>Group 3</u>

| <u>Group</u> | 4 |

|--------------|---|

|--------------|---|

| E<br>14151 | 8its           | 9_         | <u>12</u>         | 20     | Mnemonic           |                     | _14            |           | its<br><u>  16_22_</u> ] | Mnemonic |

|------------|----------------|------------|-------------------|--------|--------------------|---------------------|----------------|-----------|--------------------------|----------|

|            | 0              | 0          | x                 | x      | OL (R)             |                     |                | •         | 0 0                      | OMS(R)   |

| l          | 0              | 1          | 0                 | x      | LTOL (R)           | direct addressing   | C              | 0         | 1 0                      | OSMS(R)  |

|            | 0              | 1          | 1                 | x      | LTCOL (R)          |                     |                |           | 0 0                      | AMS(R)   |

| 0 0        | 1              | <br>0<br>0 | <br>x<br>x        | 0      | OL (R)<br>OSL (R)  |                     | (              |           | <b>1 1 0</b>             | ASMS (R) |

|            |                | 1          |                   | 0      | OBL(R)             | indirect addressing | 1              | 1 0       | 0 0                      | NMS(R)   |

|            | 1              | 1          | x<br>x<br>        | 1      | OSBL (R)           |                     |                |           | 1 0                      | NSMS(R)  |

| 1          | 0              | 0          | x                 | x      | AL (R)             |                     |                |           | 0 0                      | XMS(R)   |

|            | 0              | 1          | 0                 | x      | LTAL (R)           | direct addressing   |                | I 1       | 1 0                      | XSMS(R)  |

| 0 1        | 0              | 1          | 1                 | x      | LTCAL (R)          |                     |                |           | 0 1                      | XMSC (R) |

|            | 1<br>  1       | 0<br>0     | x<br>x            | 0<br>1 | AL (R)<br>ASL (R)  |                     |                |           |                          |          |

|            | 1              | 1          | x                 | 0      | ABL(R)             | indirect addressing | <u>Group 5</u> |           |                          |          |

|            |                |            | х<br>             | ]<br>  | ASBL (R)           | Bits<br>11 16       |                | Mnemon    | Mnemonic                 |          |

|            | 0<br> <br>  0  | 0          | х<br>0            | x<br>x | NL (R)<br>LTNL (R) | direct addressing   | 0              | 0         | MSC (                    | (R)      |

|            | 0              | 1          | 1                 | x      | LTCNL (R)          |                     | 1              | 0         | MST                      | (R)      |

| 10         | <br>  1<br>  1 | 0<br>0     | x<br>x            | 0<br>1 | NL (R)<br>NSL (R)  |                     | 1              | 1         | MSTI                     | IX (R)   |

|            | <br>  1<br>  1 |            |                   | 0<br>1 |                    |                     |                | •         | <u>Group_6</u>           |          |

|            | 0              | 0          | x                 | x      | XL (R)             |                     |                | its<br>16 | Mnemo<br>17              | DNIC     |

|            | 0 1 0 x 1      | LTXL (R)   | direct addressing | 0      | 0                  | 0 MLC               | (B)            |           |                          |          |

| 1 1        | 0              | 1          | 1                 | x      | LTCXL (R)          |                     | 0              | 1         | 0 MKC                    | (R)      |

| 11         | 1<br>  1       |            |                   | 0.1    |                    | 1 0                 | 0              | 0 MLT     |                          |          |

|            | <br>  1        | 1          |                   | 0      | XBL (R)            | indirect addressing | 1              | 0         | 1 MSCI                   | 7L (R)   |

|            | i 1            | 1          |                   | 1      |                    |                     | 1              | 1         | 0 MKT                    | (R)      |

.

3

.

Group\_8

The mnemonic is 'T' or 'TR', depending on the status of bit 10.

<u>Group 9</u> (Branch type I)

| Bi | ts | Mnemonic |

|----|----|----------|

| 7  | 8  |          |

|    |    |          |

| 0  | 0  | BT       |

| •  | •  |          |

| 0  | 1  | BTS      |

| 1  | 0  | BTM      |

| •  | U  | DIU      |

#### Group 10

The mnemonic is 'BC' (Branch conditional).

| G | r | 0 | u | p | 1 | 1 |

|---|---|---|---|---|---|---|

| _ | _ | - |   | - |   | - |

|           | Bit       | s  | Mnemonic          |

|-----------|-----------|----|-------------------|

| <u>16</u> | <u>18</u> | 19 | <b></b>           |

| 0         | 0         | 0  | SRC(R), OF NOP(R) |

| 0         | 0         | 1  | SRT (R)           |

| 0         | 1         | 0  | SRCN (R)          |

| 0         | 1         | 1  | SRTN(R)           |

| 1         | 0         | 0  | SLC (R)           |

| 1         | 0         | 1  | <br>  SLT (R)     |

| 1         | 1         | 0  | SLCN(R)           |

| 1         | 1         | 1  | SLTN (R)          |

|           |           |    | l · · · · ·       |

### <u>Group 12</u>

| <u>11</u> | Bit:<br>13 | s<br>_ <u>16</u> | Mnemonic    |

|-----------|------------|------------------|-------------|

| 0         | 0          | 0                | I SNSCR (R) |

| 0         | 1          | 0                | SNSCL(R)    |

| 1         | 0          | 0                | SNSTR (R)   |

| 1         | 1          | 0                | SNSTL(R)    |

| X<br>     | x          | 1                | CTL(R)      |

|           |            |                  | 4           |

# <u>Group 13</u>

The mnemonic is; TRB = Translate and branch (Bit 10 = off), or TRBR = Translate, branch and return (Bit 10 = on).

if bits 16...23 = all zeros

# Listing of IPU Mnemonics

| <u>Mnemonic</u> | Description                                                                           | Group       |

|-----------------|---------------------------------------------------------------------------------------|-------------|

| ABL (R)         | Add to IPU local storage, suppress ALU Bits 07, (then return).                        | <br>  3<br> |

| AL(R)           | Add to IPU local storage, (then return).                                              | 3           |

| ALMK (R)        | Add to IPU local storage and key storage, (return).                                   | 1 7         |

| ALML (R)        | Add to IPU local storage and MSC local storage,<br>(then return).                     | 7           |

| AMK(R)          | Add to MSC key storage, (then return).                                                | 7           |

| AML (R)         | Add to MSC local storage, (then return).                                              | 7           |

| AMS(R)          | Add to main storage, (return).                                                        | 4           |

| ASBL (R)        | Add with Six correction to IPU local storage,<br>suppress ALU Bits 07, (then return). | 3           |

| ASL (R)         | Add with Six correction to IPU local storage,<br>(then return).                       | <br>  3<br> |

| ASMS(R)         | Add with Six correction to MSC main storage,<br>(then return).                        | 4<br>  4    |

| BC              | Branch Conditional.                                                                   | 10          |

| BT              | Branch on Test (no level switching).                                                  | 9           |

| BTM             | Branch on Test to Main routine.                                                       | 9           |

| BTS             | Branch on Test to Sub routine.                                                        | 9           |

| CTL (R)         | Control, (then return).                                                               | 12          |

| ILC(R)          | Immediate data Left adjusted to CDR, (then return).                                   | 2           |

| ILT (R)         | Immediate data Left adjusted to TDR, (then return).                                   | 2           |

| IRC (R)         | Immediate data Right adjusted to CDR, (then return).                                  | 2           |

| IRT (R)         | Immediate data Right adjusted to TDR, (then return),                                  | 2           |

| LC(R)           | Load CDR, (then return).                                                              | 1 1         |

| <b>LT (</b> R)  | Load TDR, (then return).                                                              | 1 1         |

| LTAL (R)        | IPU Local storage to TDR, Add with CDR into<br>IPU Local storage, (then return).      | 3           |

LTCAL(R) | IPU Local storage to TDR a IPU Local storage, (then LTCNL(R) | IPU Local storage to TDR a into IPU Local storage, LTCOL(R) | IPU Local storage to TDR a into IPU Local storage, LTCXL(R) | IPU Local storage to TDR a into IPU Local storage, LTNL (R) IPU Local storage to TDR, IPU Local storage, (then LTOL (R) | IPU Local storage to TDR, IPU Local storage, (then LTXL(R) IPU Local storage to TDR, 1 IPU Local storage, (then MKC(R) Read from MSC Key storage MKT(R) Read from MSC Key storage MLC(R) Read from MSC Local store MLT(R) Read from MSC Local store MSC(R) Read from Main storage into MSCTL(R) | Main Storage Control. MST (R) Read from Main Storage int MSTIX(R) Read from Main Storage int exception, (then return) NBL(R) AND to IPU Local storage, (then return). NL(R) AND to IPU Local storage, NLMK (R) AND to IPU Local storage a (then return). NLML(R) AND to IPU Local storage a (then return).

NMK (R)

NML (R)

NMS (R)

3125 MLM. Microinstructions

| :)  <br> <br>  | IPU Local storage to TDR and CDR, Add both into<br>IPU Local storage, (then return).       | 3 |

|----------------|--------------------------------------------------------------------------------------------|---|

| <br> <br> <br> | IPU Local storage to TDR and CDR, logically AND<br>into IPU Local storage, (then return).  | 3 |

| <br> <br> <br> | IPU Local storage to TDR and CDR, logically OR<br>into IPU Local storage, (then return).   | 3 |

| <br> <br> <br> | IPU Local storage to TDR and CDR, exclusively OR<br>into IPU Local storage, (then return). | 3 |

| 1              | IPU Local storage to TDR, logically AND into<br>IPU Local storage, (then return).          | 3 |

| 1              | IPU Local storage to TDR, logically OB into<br>IPU Local storage, (then return).           | 3 |

|                | IPU Local storage to TDR, exclusively OR into<br>IPU Local storage, (then return).         | 3 |

| i              | Read from MSC Key storage into CDR, (then return).                                         | 6 |

|                | Read from MSC Key storage into TDR, (then return).                                         | 6 |

|                | Read from MSC Local store into CDR, (then return).                                         | 6 |

| 1              | Read from MSC Local store into TDR, (then return).                                         | 6 |

|                | Read from Main storage into CDR, (then return).                                            | 5 |

| )              | Main Storage Control.                                                                      | 6 |

|                | Read from Main Storage into TDR, (then return).                                            | 5 |

| <br>  (:<br>   | Read from Main Storage into TDR, test for I-Phase exception, (then return).                | 5 |

|                | AND to IPU Local storage, suppress ALU Bit 07,<br>(then return).                           | 3 |

|                | AND to IPU Local storage, (then return).                                                   | 3 |

|                | AND to IPU Local storage and MSC Key storage,<br>(then return).                            | 7 |

|                | AND to IPU Local storage and MSC Local storage,<br>(then return).                          | 7 |

|                | AND to MSC Key storage, (then return).                                                     | 7 |

|                | AND to MSC Local storage, (then return).                                                   | 7 |

| 1              | AND to Main storage, (then return).                                                        | 4 |

5

tructions

| NOP (R)   | No operation (then return).                                                          | 1 11         | SRCN(R)         | Shift Right into CDR, using                                            |

|-----------|--------------------------------------------------------------------------------------|--------------|-----------------|------------------------------------------------------------------------|

| NSBL (R)  | AND with Six correction to IPU Local storage,<br>suppress ALU Bit 07, (then return). | 3            | SRT (R)         | (then return).<br>  Shift Right into TDR, (the)<br>                    |

| NSL (R)   | AND with Six correction to IPU Local storage,<br>(then return).                      | 3            | SRTN(R)         | Shift Right into TDR, using<br>  (then return).<br>                    |

| NSMS (R)  | Add with Six correction to Main storage, (return).                                   | 1            | T (R)           | Test, (then return).                                                   |

| OBL (R)   | <br>  OR to IPU Local storage, suppress ALU Bit 07,                                  | 1 3          | TRB (R)         | Translate and Branch, (the                                             |

|           | (then return).                                                                       |              | XBL (R)         | Exclusive OR to IPU Local s<br>Bit 07, (then return)                   |

| OL(R)     | OR to IPU Local storage, (then return).                                              | 3            | XL(R)           | Exclusive OR to IPU Local s                                            |

| OLMK (R)  | OR to IPU Local storage and MSC Key storage,<br>(then return).                       | 7            | XLMK (R)        | Exclusive OR to IPU Local :                                            |

| OLML (R)  | <br>  OR to IPU Local storage and MSC Local storage,                                 |              | A LINK (N)      | storage, (then return).                                                |

|           | (then return).                                                                       |              | XLML(R)         | Exclusive OR to IPU Local s                                            |

| OMK (R)   | OR to MSC Key storage, (then return).                                                | 1 7          | 11 14 15 4 75 5 | storage, (then return).                                                |

| OML (R)   | OR to MSC Local storage, (then return).                                              | 17           | XMK(R)          | Exclusive OR to MSC Key sto                                            |