#

# **Maintenance Library**

SY33-1063-1

Second Edition (November, 1973)

This manual is a major revision of, and makes obsolete SY33-1063-0. The information in the manual has been completely revised, and the manual must be read in its entirety. Changes are continually made to the information; any such changes will be reported in subsequent revisions or Technical Newsletters.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

Forms for readers' comments are provided at the back of the manual. If the forms have been removed, comments may be addressed to IBM Laboratories, Product Publications, Dept. 3179, 703 Boeblingen/Wuertt, P.O. Box 210, Germany. Comments become the property of IBM.

© Copyright International Business Machines Corporation 1973.

## Preface

This manual describes the theory of operation of the input/output processor (IOP) and provides maintenance information for the IOP. Readers of the manual should have a basic understanding of IBM system concepts. The manual supplements the System/370 Model 125 CE course and serves also as a recall aid; it is not intended for self-education.

The manual is divided into seven chapters.

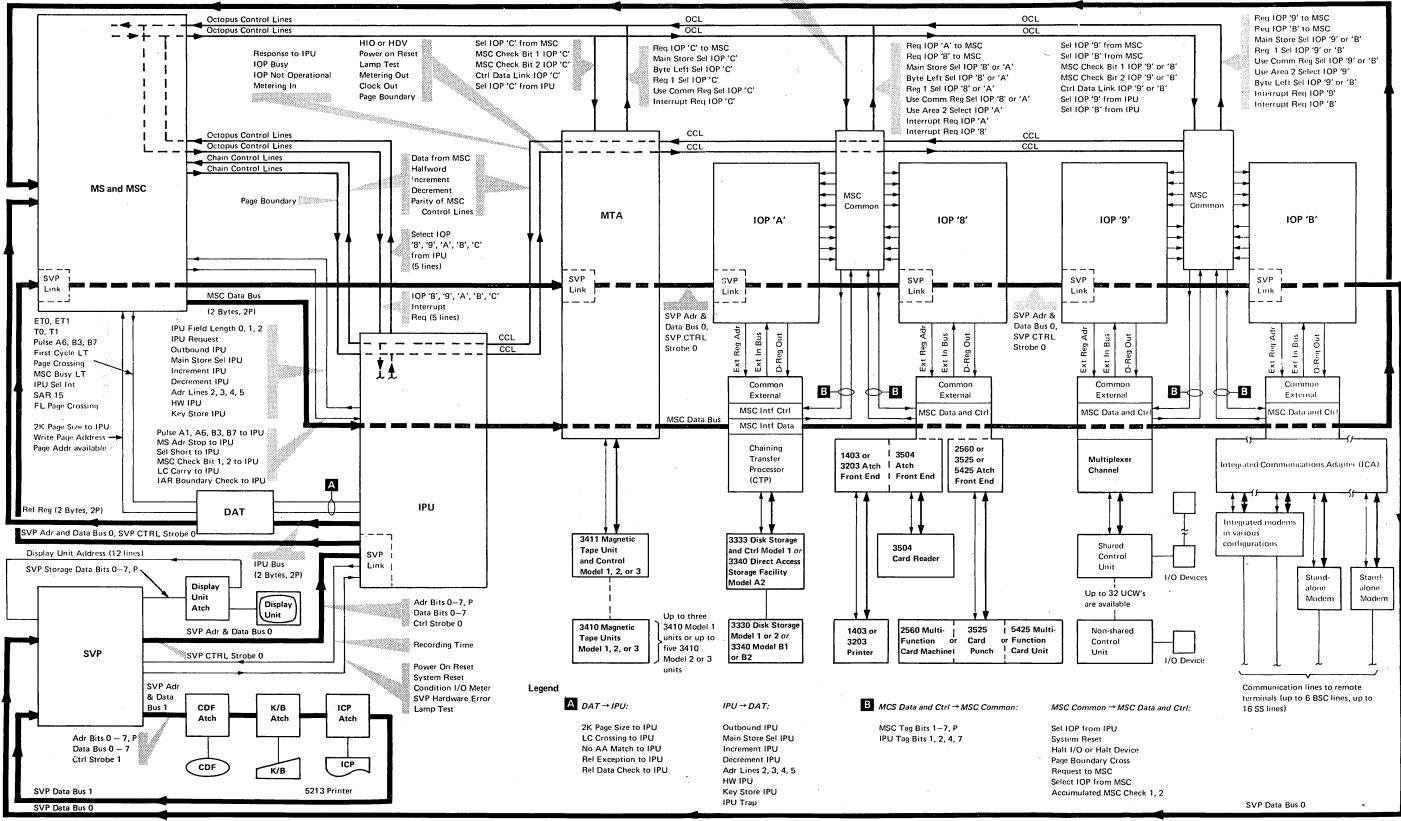

*Chapter 1* contains general information, and an overall data flow of the IBM System/370 Model 125.

Chapter 2 contains operational principles, and IOP-MSC communication.

*Chapter 3* contains operational details, and IOP-SVP communication.

Chapter 4 contains a description of the functional units.

Chapter 5 contains error conditions and their handling.

Chapter 6 contains maintenance information.

Chapter 7 contains reference information.

An appendix contains particular IOP '8' microprogram information.

Common abbreviations for the system and an explanation of the symbols used are given in *IBM 3125 Processing Unit, General System Information,* Maintenance Library Manual, Order No. SY33-1059.

IBM is grateful to the American National Standards Institute (ANSI) for permission to reprint its definitions from the American National Standard Vocabulary for Information Processing (Copyright © 1970 by American National Standards Institute, Incorporated), which was prepared by Subcommittee X3.5 on Terminology and Glossary of American National Standard Committee X3.

### Prerequisite Reading

#### Maintenance Library Manuals

IBM 3125 Processing Unit, Microinstructions, Order No. SY33-1058. IBM 3125 Processing Unit, General System Information, Order No. SY33-1059. IBM 3125 Processing Unit, Main Storage Controller, Order No. SY33-1061. IBM 3125 Processing Unit, Instruction Processing Unit, Order No. SY33-1062. *IBM 3125 Processing Unit, Service Processor Subsystem,* Order No. SY33-1065. Section 1: Service Processor (SVP). Section 2: Console Disk File.

Section 3: Display Unit and Keyboard.

### Associated Publications

System Library Manuals

IBM System/360 Principles of Operation, Order No. GA22-6821. IBM System/370 Principles of Operation, Order No. GA22-7000.

#### Maintenance Library Manuals

IBM 3125 Processing Unit, Power Supplies, Order No. SY33-1060.

IBM 3125 Processing Unit, Magnetic Tape Adapter, Order No. SY33-1064.

IBM 3125 Processing Unit, Main Storage, Order No. SY33-1066.

IBM 3125 Processing Unit, Multiplexer Channel, Order No. SY33-1067.

IBM 3125 Processing Unit, 2560 Attachment, Front End, Order No. SY33-1068.

IBM 3125 Processing Unit, 3525 Attachment, Front End, Order No. SY33-1070.

IBM 3125 Processing Unit, 3504 Attachment, Front End, Order No. SY33-1071.

IBM 3125 Processing Unit, 1403 Attachment, Front End, Order No. SY33-1072.

IBM 3125 Processing Unit, 3330 Direct Disk Attachment, Order No. SY33-1073.

IBM 3125 Processing Unit, Integrated Console Printer Attachment, Order No. SY33-1074.

*IBM 3125 Processing Unit, Integrated Communications Adapter,* Part B/M 1876075.

IBM 3125 Processing Unit, Installation Instructions, Part 4014001.

*IBM 3125 Central Test Manual*, contains pages appropriate to the individual 3125 Processing Unit.

IBM 3125 Processing Unit, Parts Catalog, Order No. S135-1000.

### Preface III

## Contents

|   | Chapter 1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-010 |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|   | Data and Control Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-010 |

|   | General Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

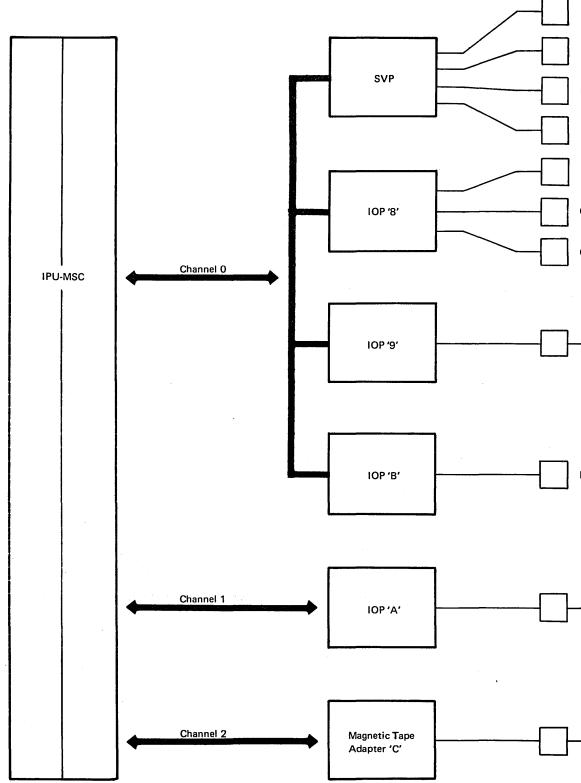

|   | System Internal Buses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-020 |

|   | Channel Concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|   | Principle of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

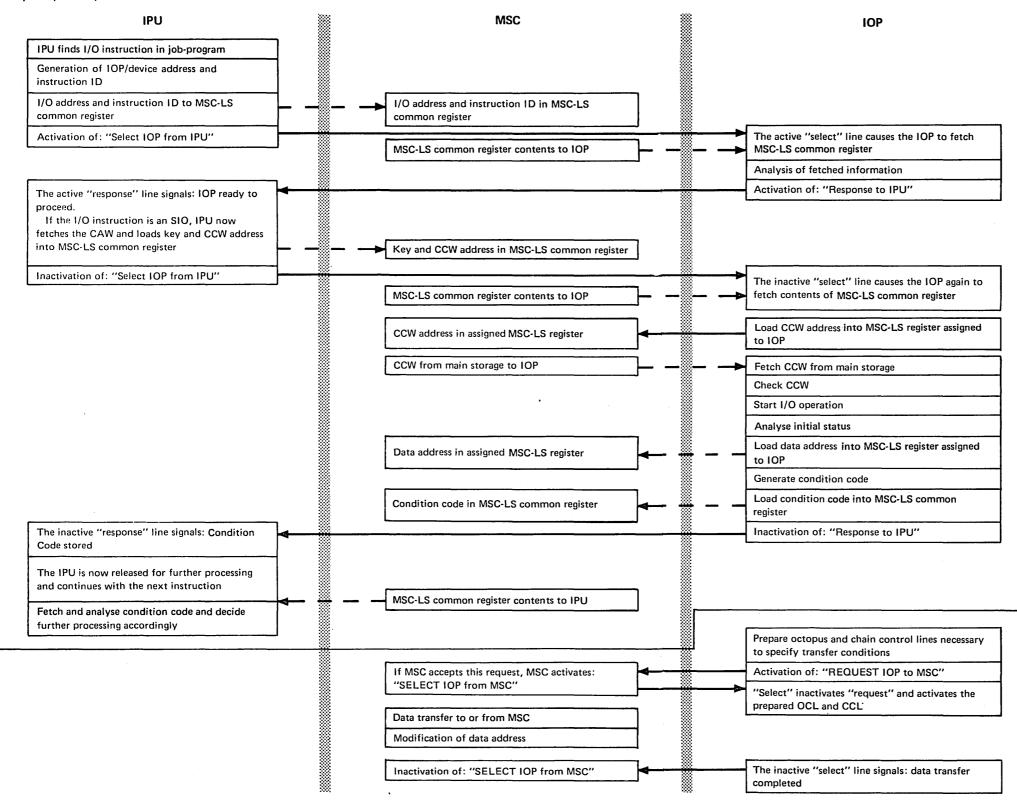

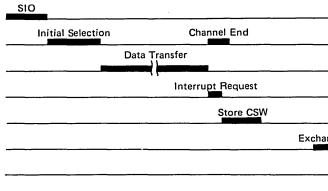

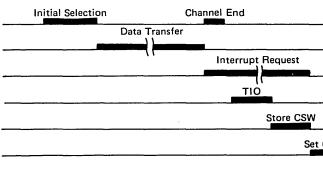

|   | Initiation of an I/O Instruction Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

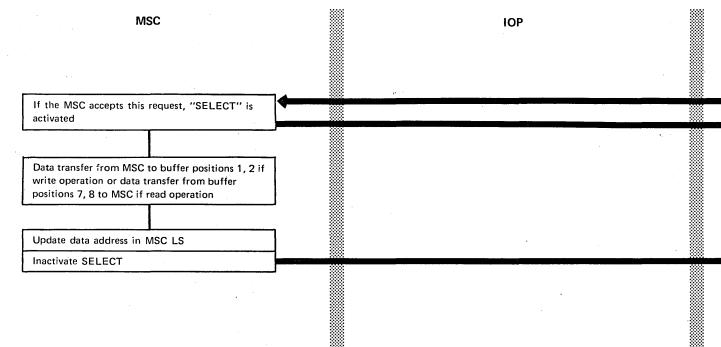

|   | Interrupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

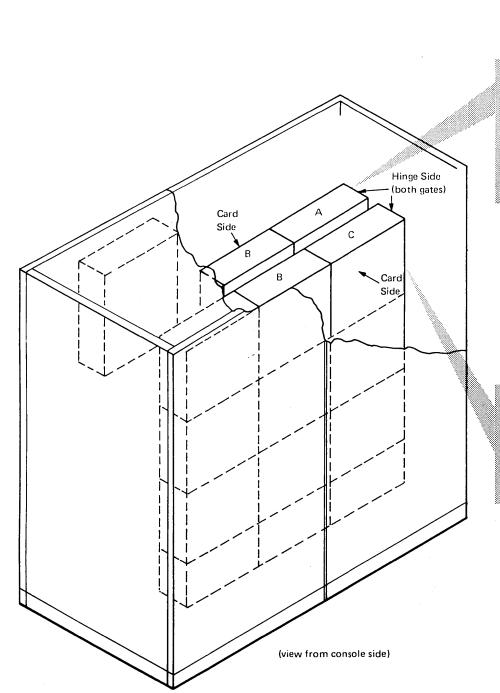

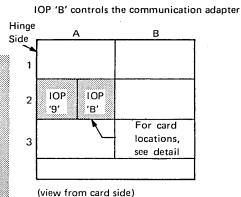

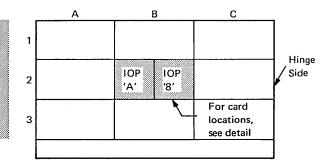

|   | Physical Locations (seen from card side)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-030 |

|   | IOP Board Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

|   | IOP Card Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

|   | Signal Interface Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

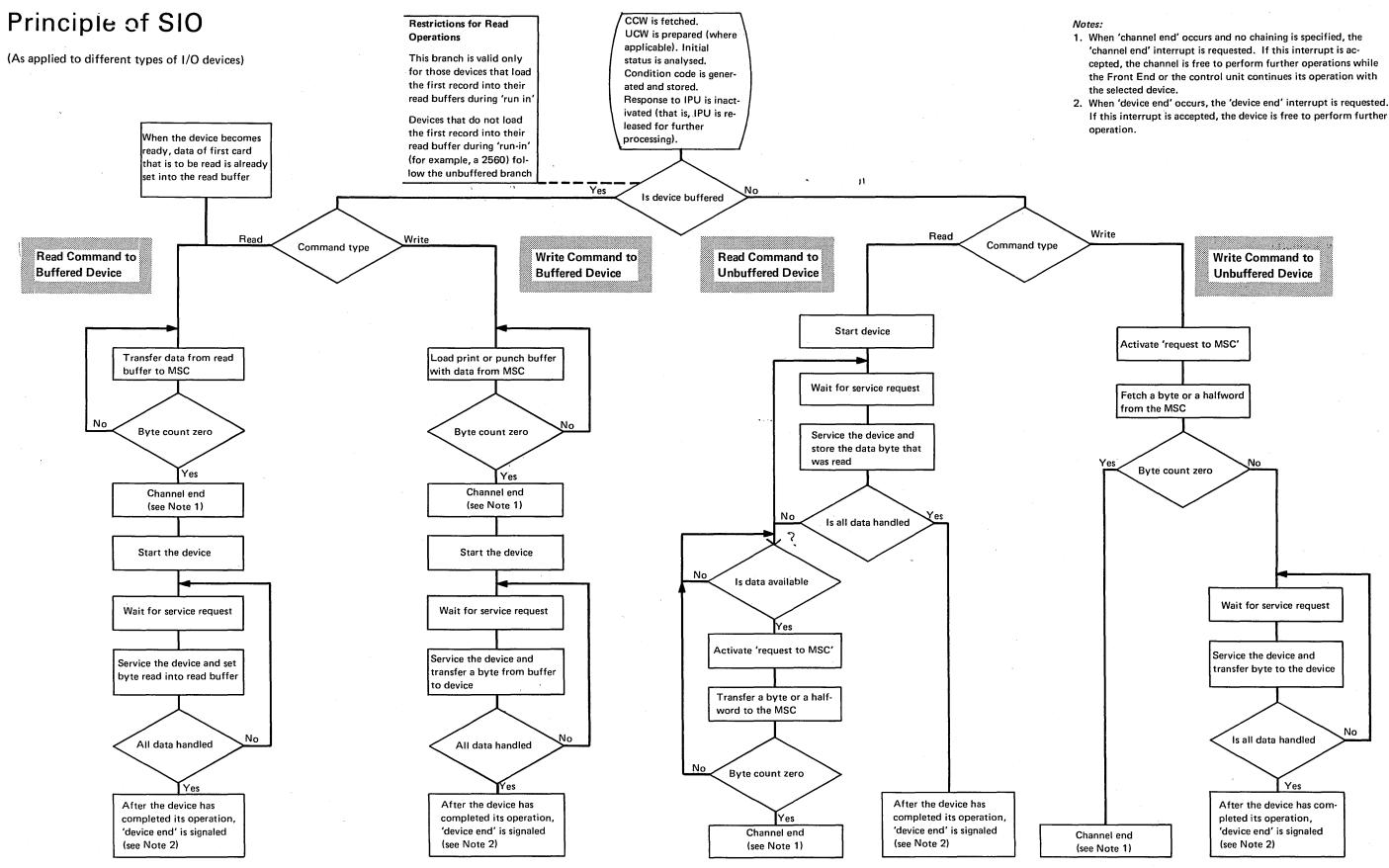

|   | Chapter 2. Principle of Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-010 |

|   | General Data Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

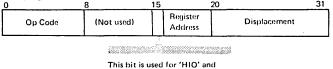

|   | Instructions and Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.015 |

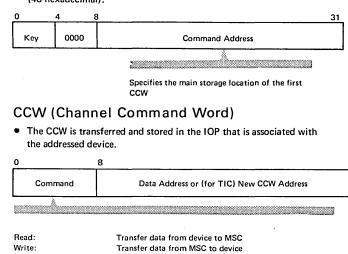

|   | Control Word Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

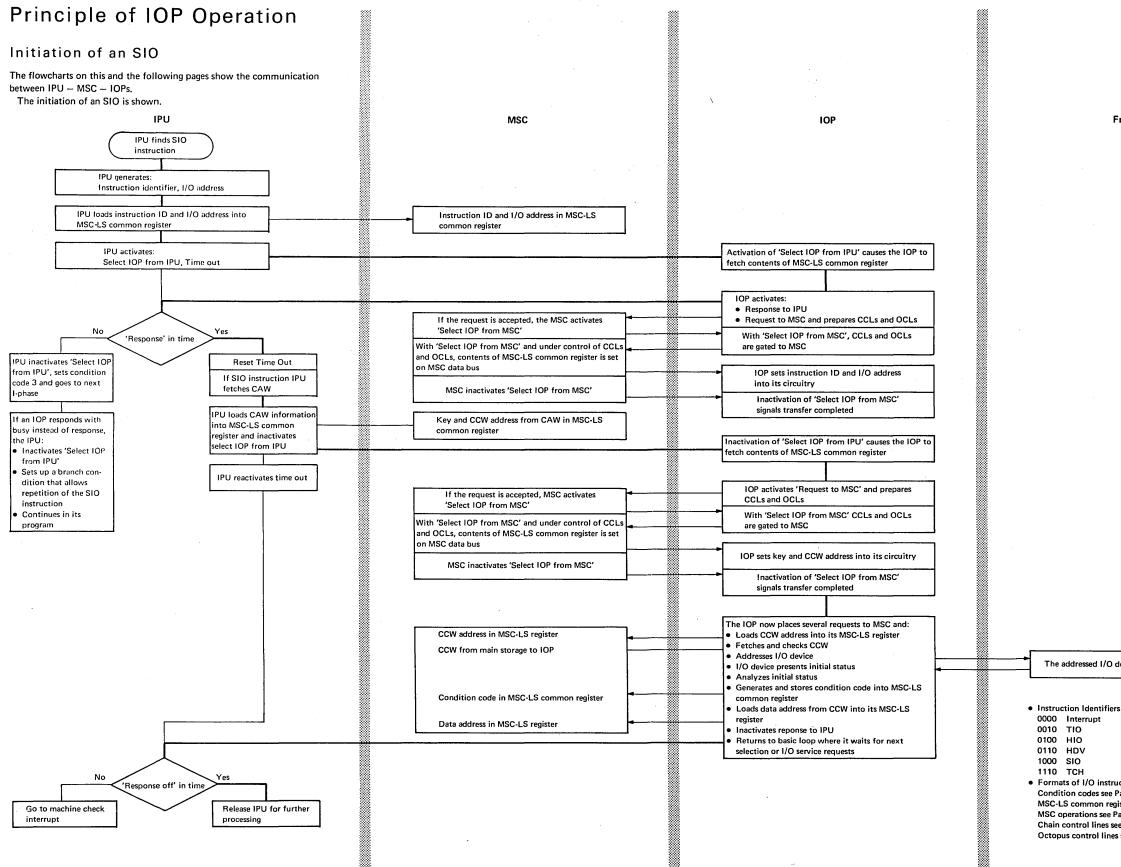

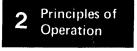

|   | Principle of IOP Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

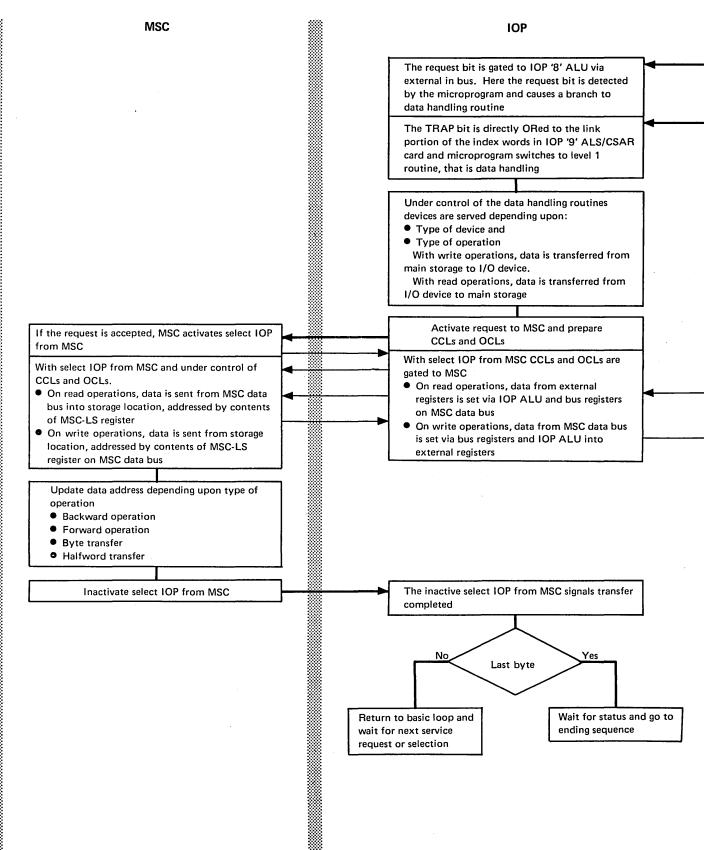

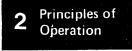

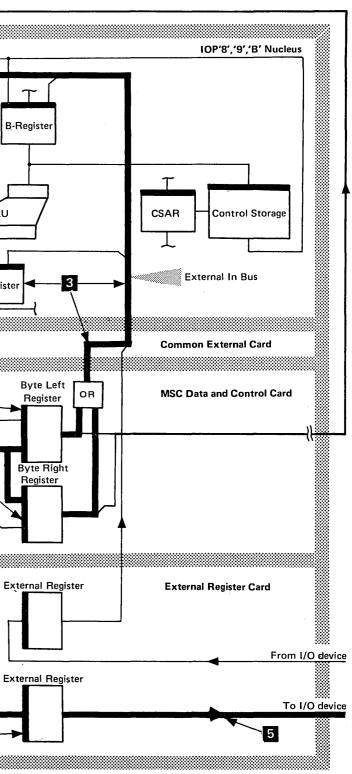

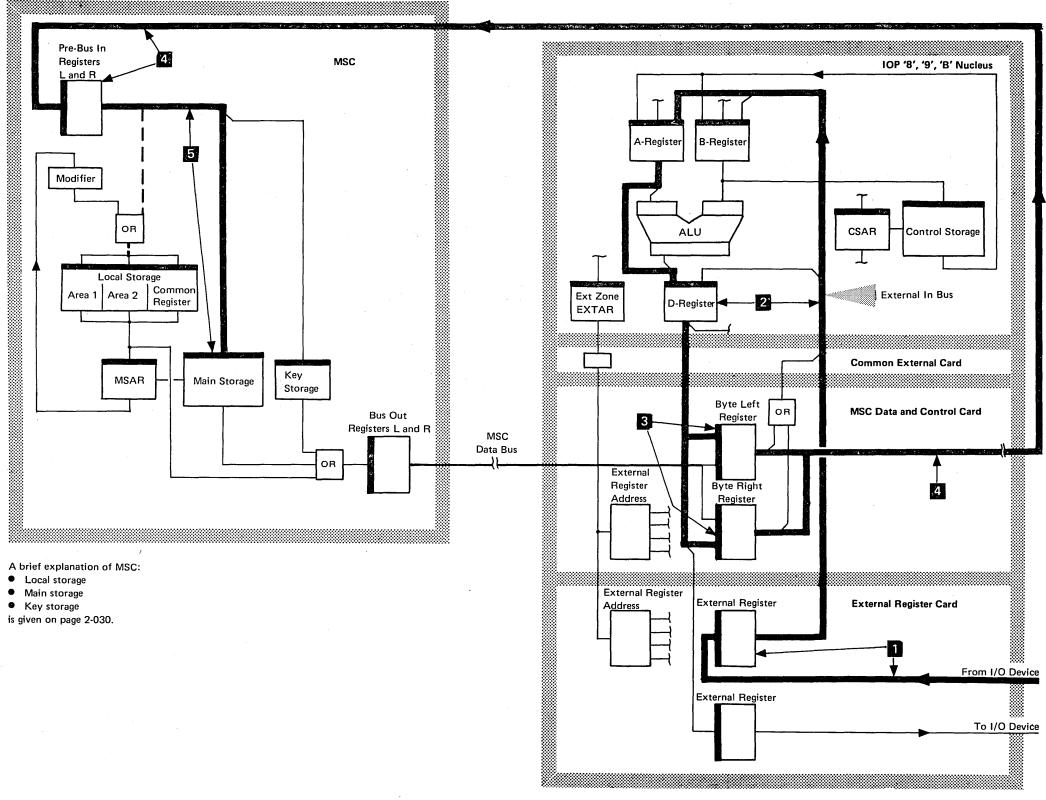

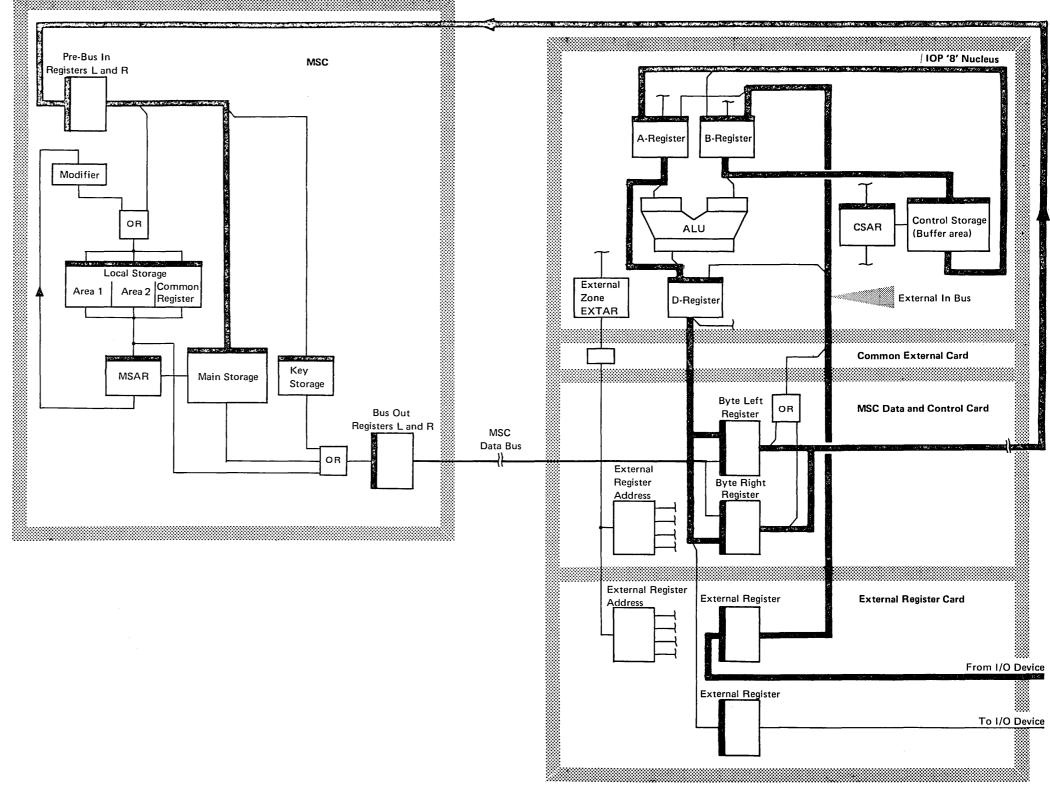

|   | Data Transfer for IOPs '8', '9', 'B'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-020 |

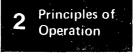

|   | Data Transfer IOP 'A'         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .          .         |       |

| 2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|   | Principle of SIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

|   | IOP Write Operations         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . |       |

|   | Data Transfer IOPs *'8', '9', 'B' Write Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

|   | Data Transfer IOP' 8' Write Operation (to those I/O devices that                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-030 |

|   | have a data buffer in IOP control storage)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 025 |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

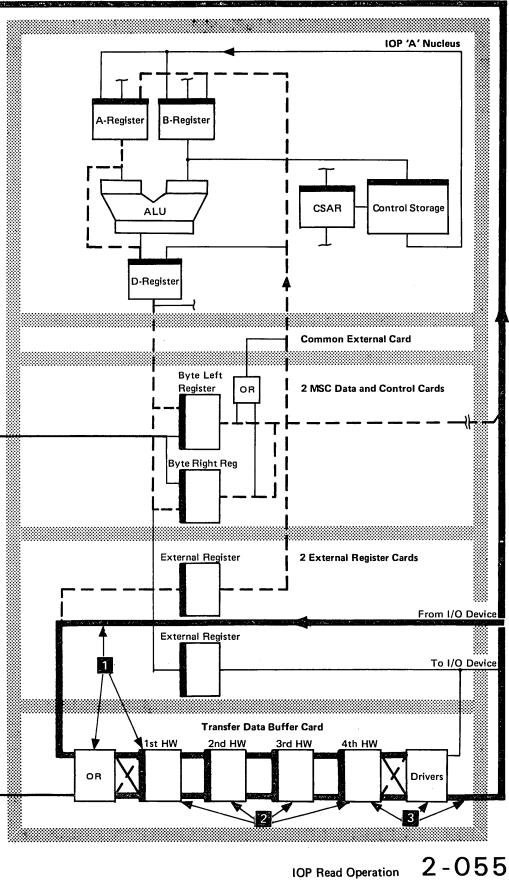

|   | IOP Read Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-040 |

|   | Data Transfer IOP '8' Read Operation (from those I/O devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.045 |

|   | that have a data buffer in IOP control storage)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|   | IOP Write Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

|   | Data Transfer IOP 'A' Write Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

|   | IOP Read Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

|   | Data Transfer IOP 'A' Read Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

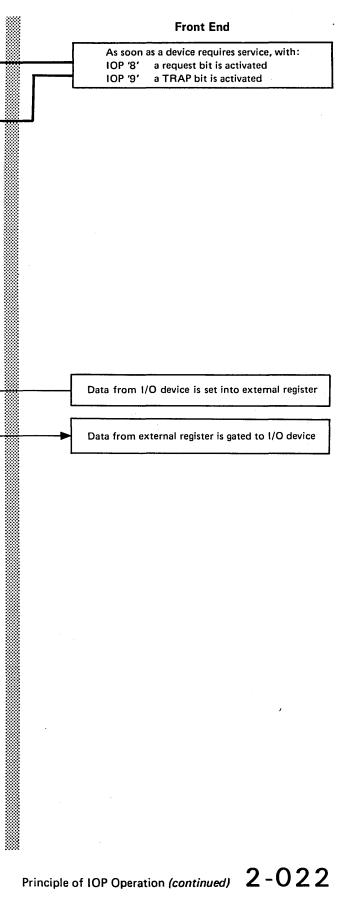

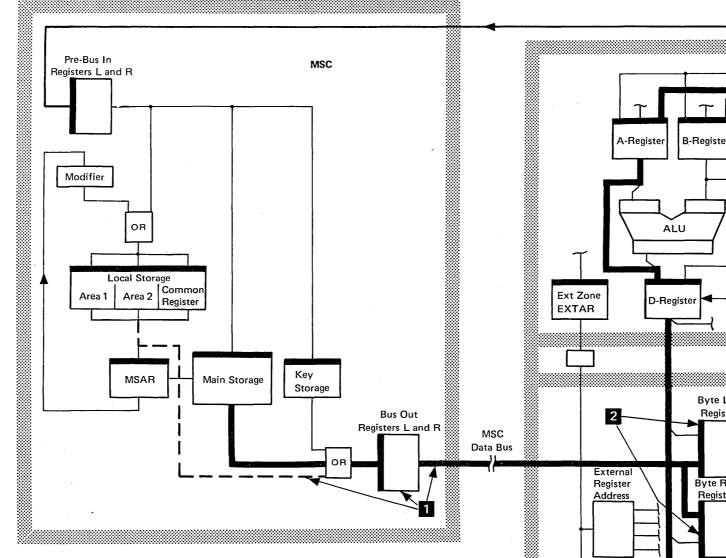

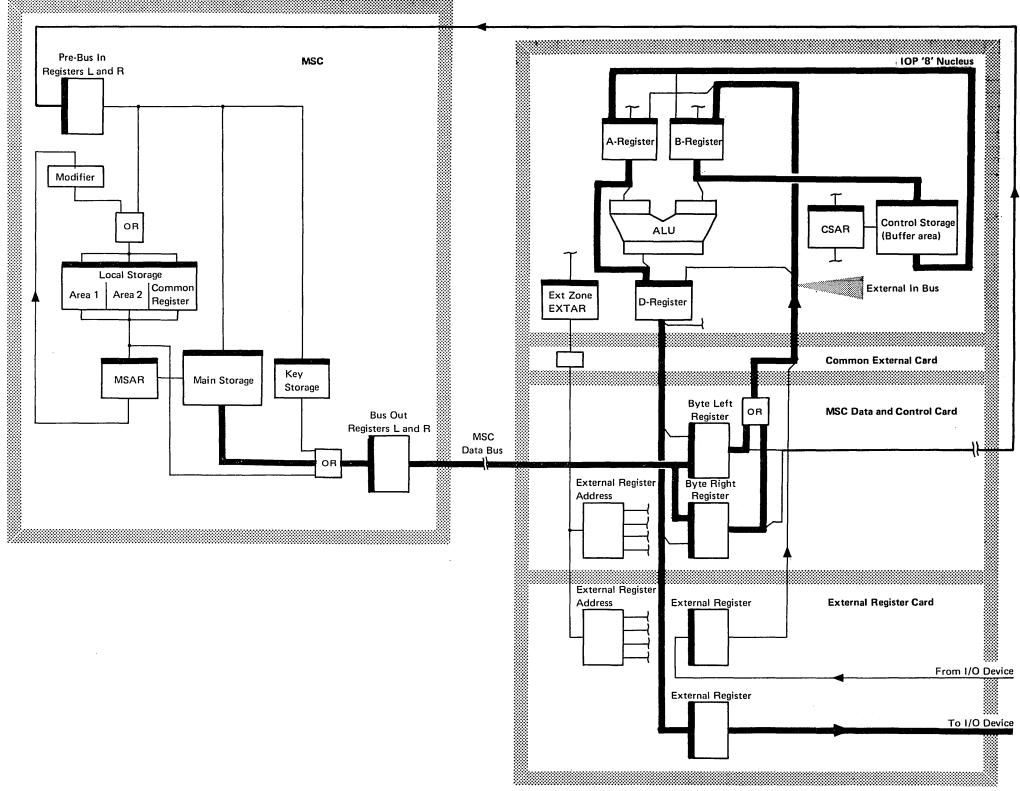

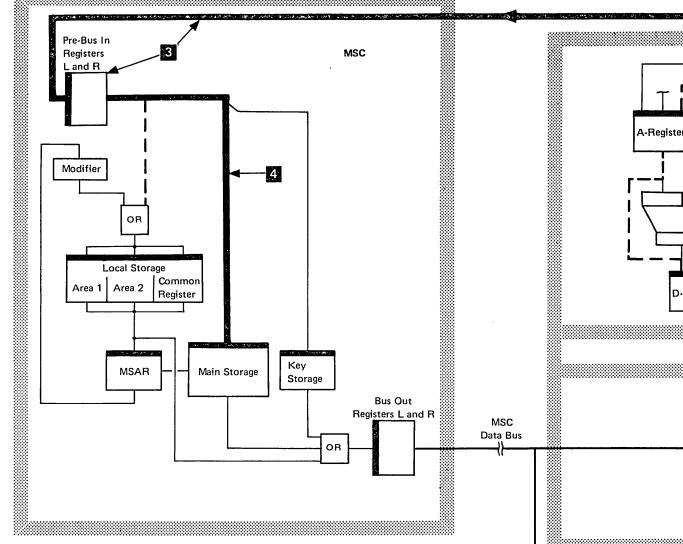

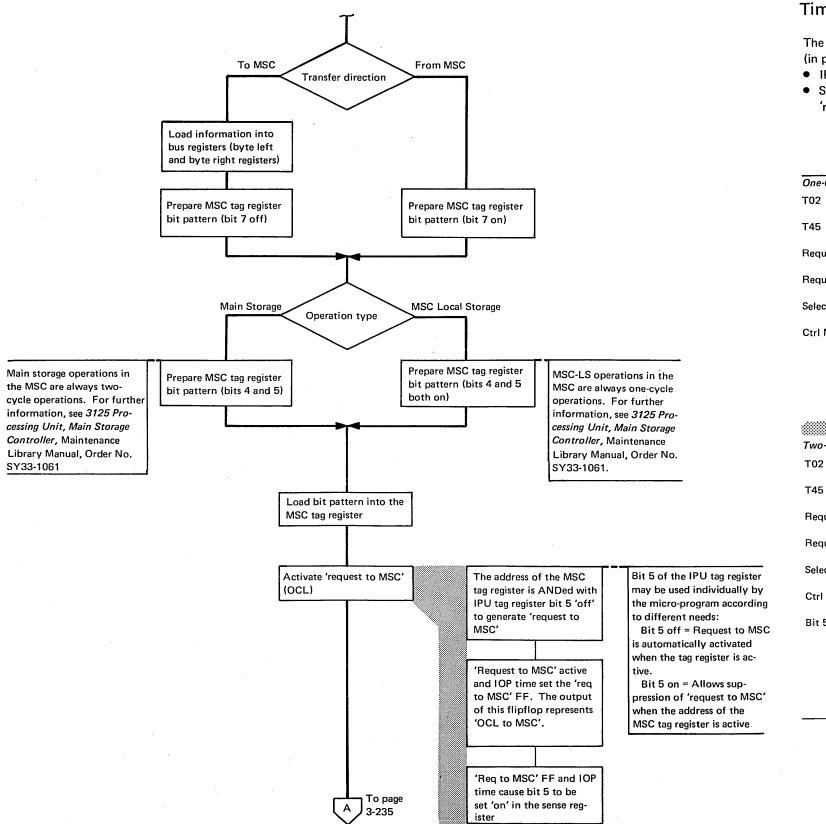

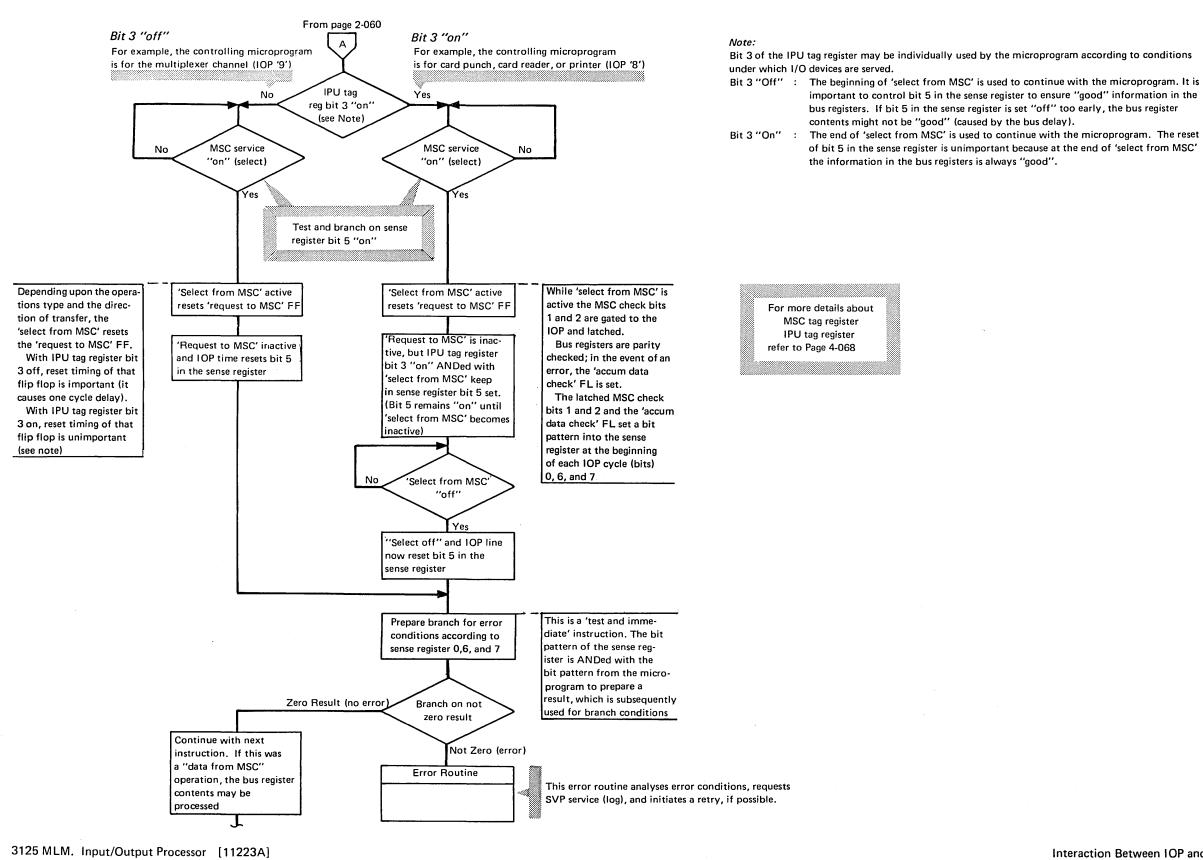

|   | Interaction Between IOP and MSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|   | Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-060 |

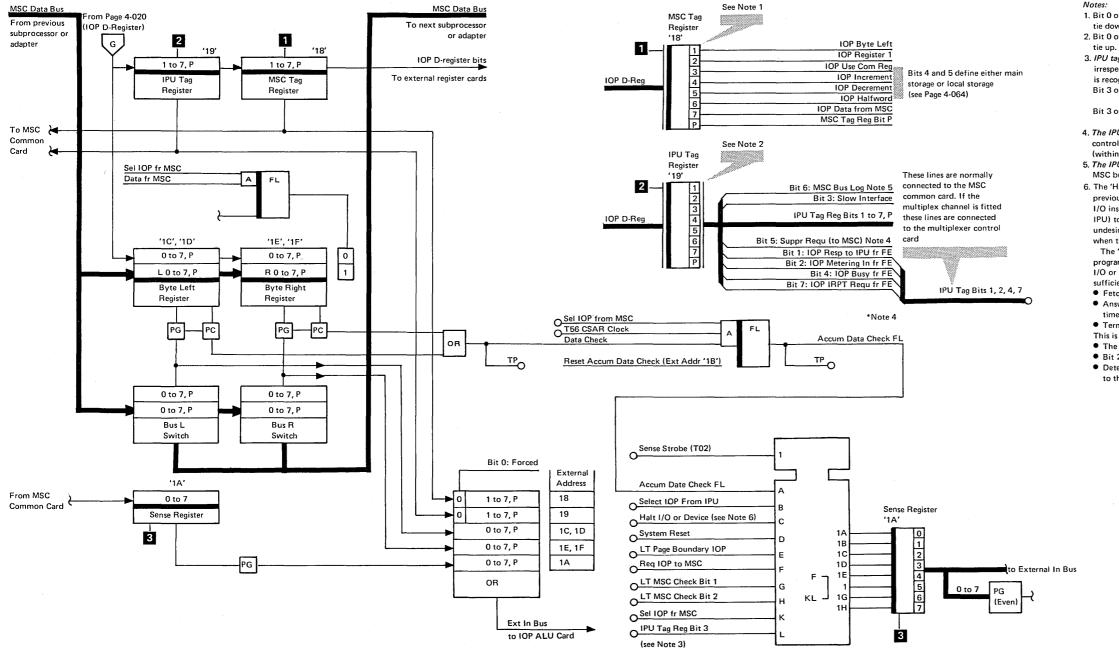

|   | External Register Assignment and Layout – MSC Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

|   | and Control Cards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-070 |

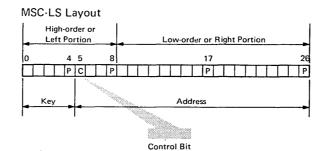

|   | IOP and MSC Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-100 |

|   | Local Storage Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-100 |

|   | Main Storage Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-110 |

|   | Chain Control Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-120 |

|   | Octopus Control Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-130 |

|   | Supplementary Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-150 |

|   | MSC – LS Common Register Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-150 |

|   | MSC – LS Common Register Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-150 |

|   | I/O Condition Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-155 |

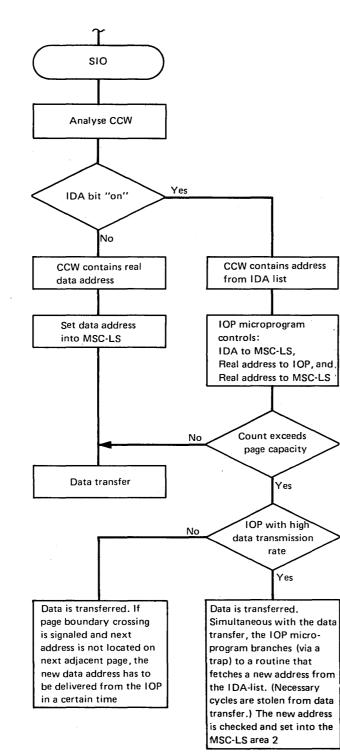

|   | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-155 |

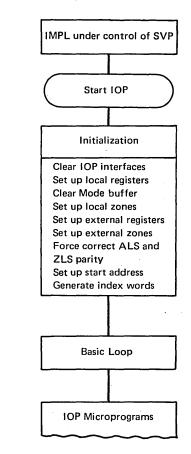

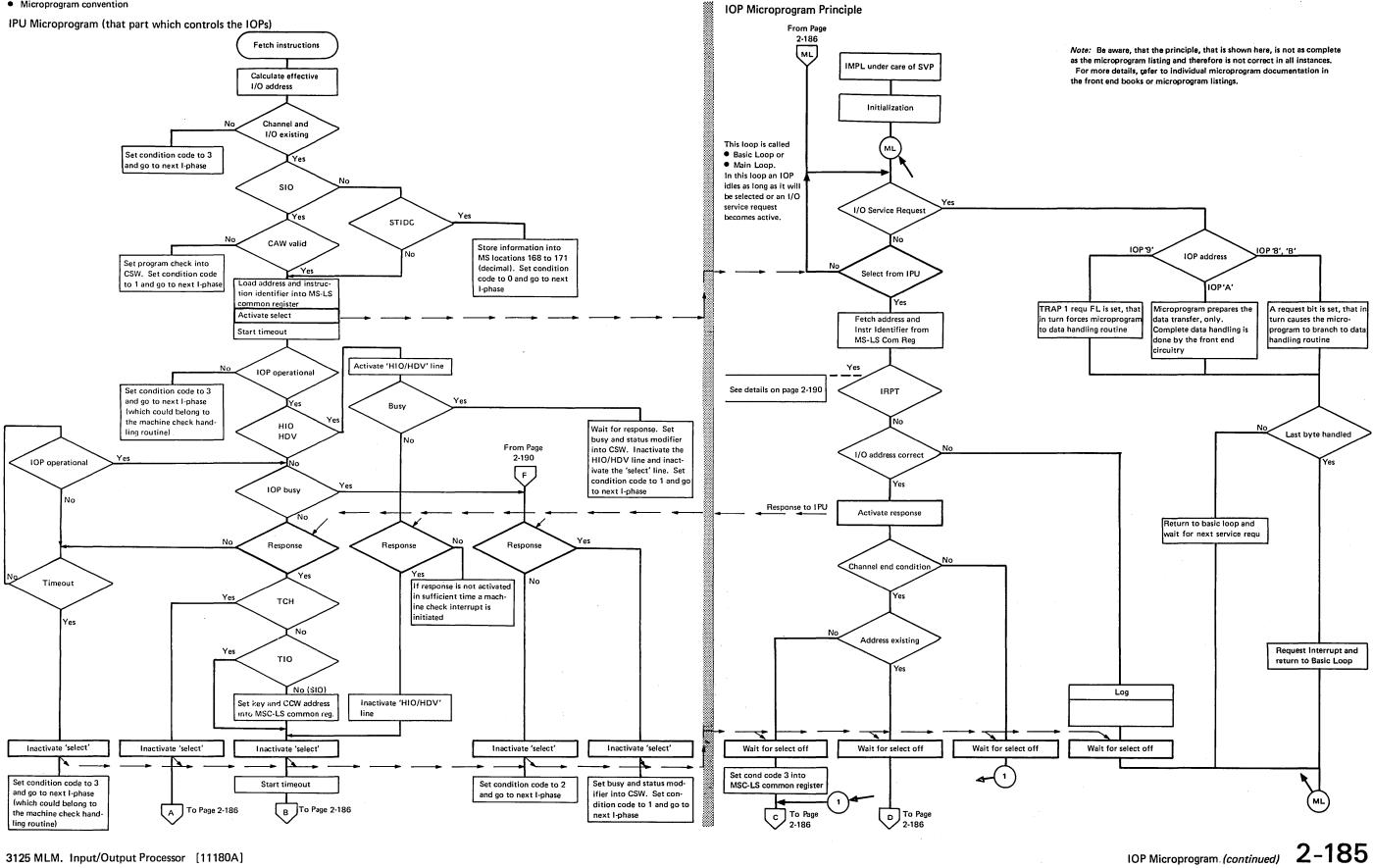

| IOP Microprogram2-180Task and Operation of IOPs2-180                             |  |

|----------------------------------------------------------------------------------|--|

|                                                                                  |  |

| IPU/IOP Communication                                                            |  |

| Indirect Data Addressing                                                         |  |

| Chaining                                                                         |  |

| 'IOP Busy' Line                                                                  |  |

|                                                                                  |  |

|                                                                                  |  |

| Chapter 3. Operational Details                                                   |  |

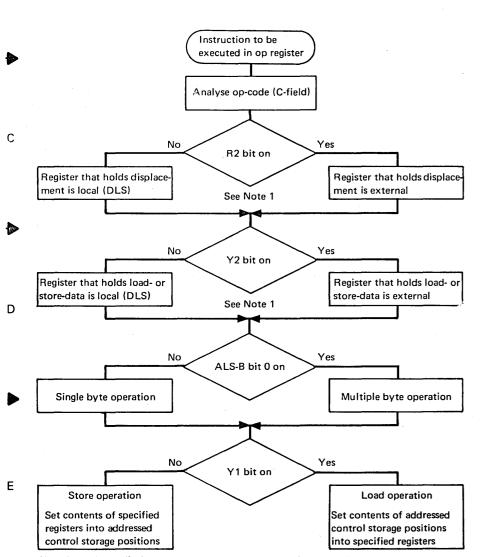

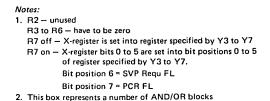

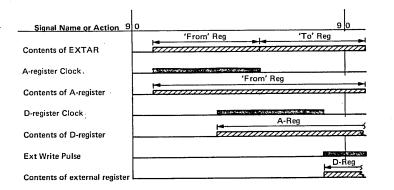

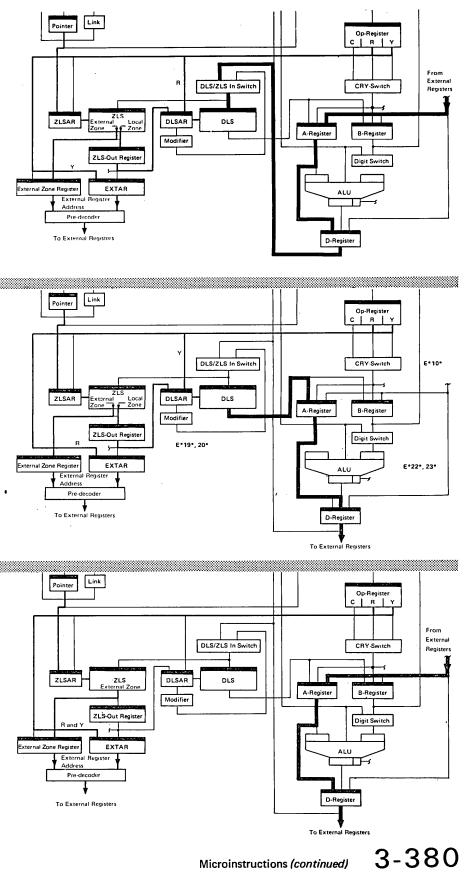

| Microinstructions                                                                |  |

| Visual Index of Groups                                                           |  |

| Groups 1 and 2                                                                   |  |

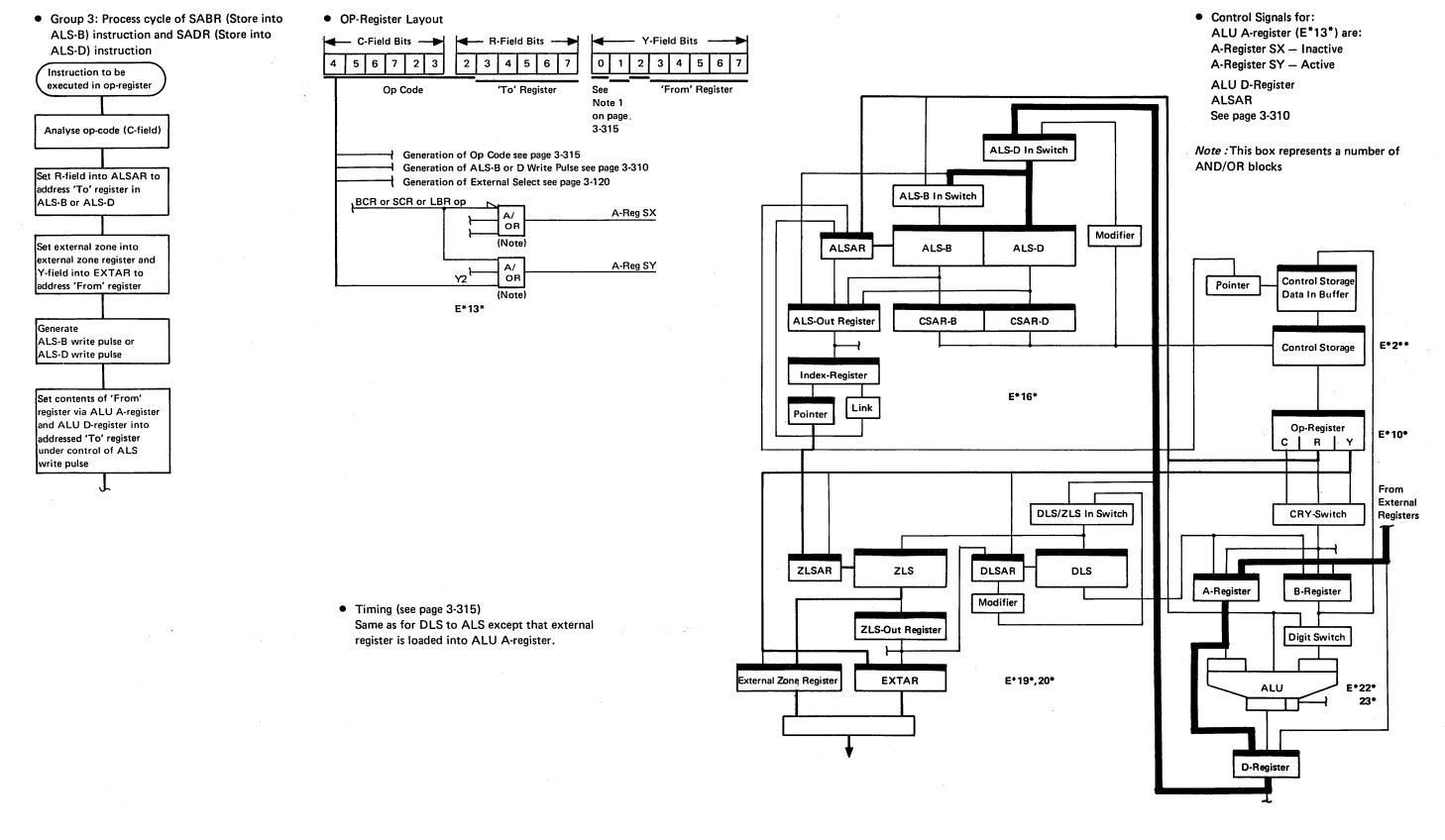

| Groups 3 and 4                                                                   |  |

| Decoding of Microinstructions 3-030                                              |  |

| 'Suffix U' Microinstructions                                                     |  |

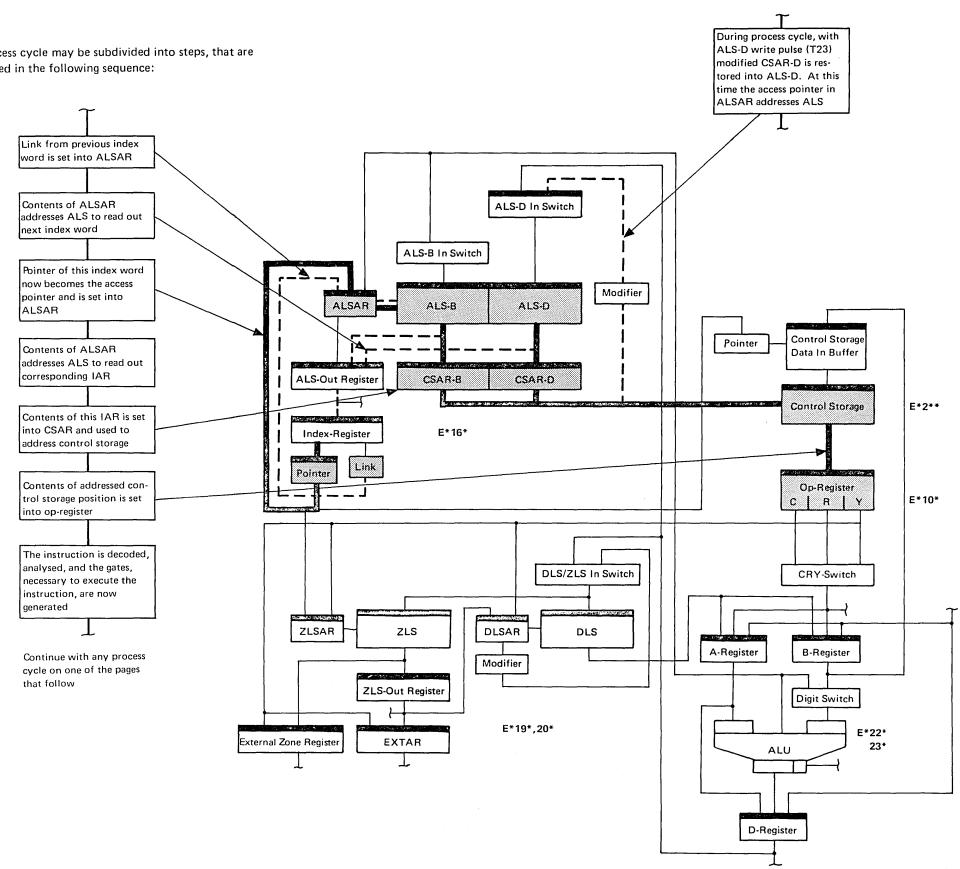

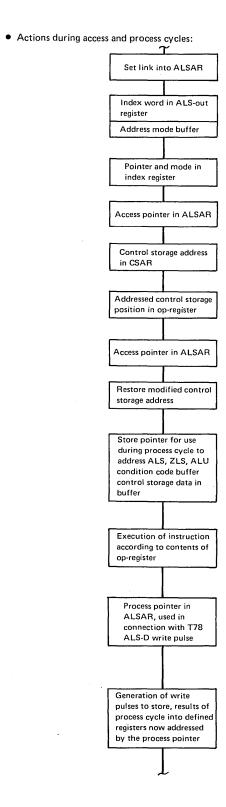

| Access Cycle for all instructions                                                |  |

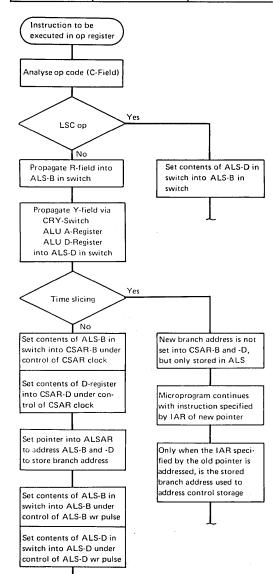

| Access and Process Cycle                                                         |  |

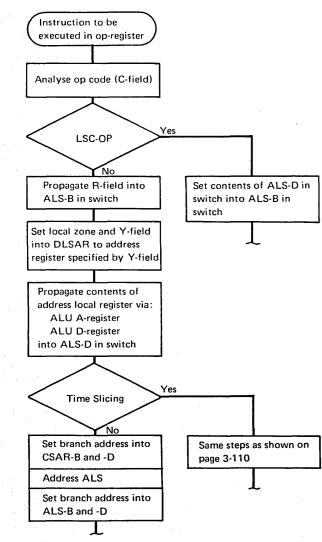

| BNZ, BCY, BCN, BZ, BNC, BZN Process Cycle                                        |  |

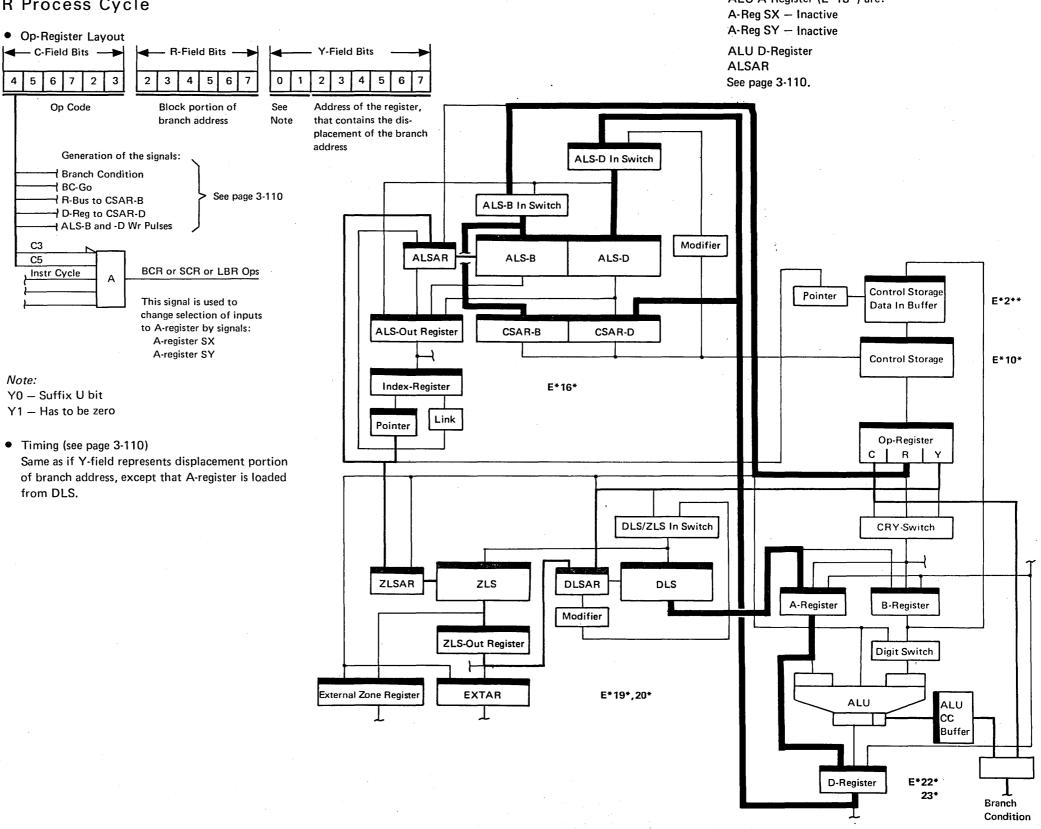

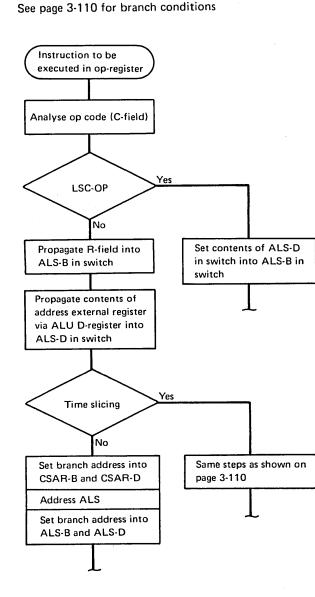

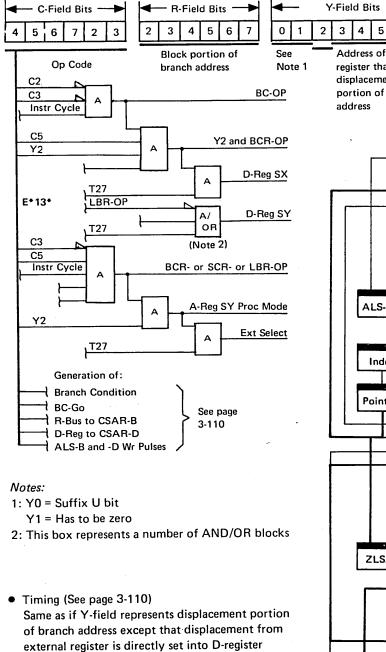

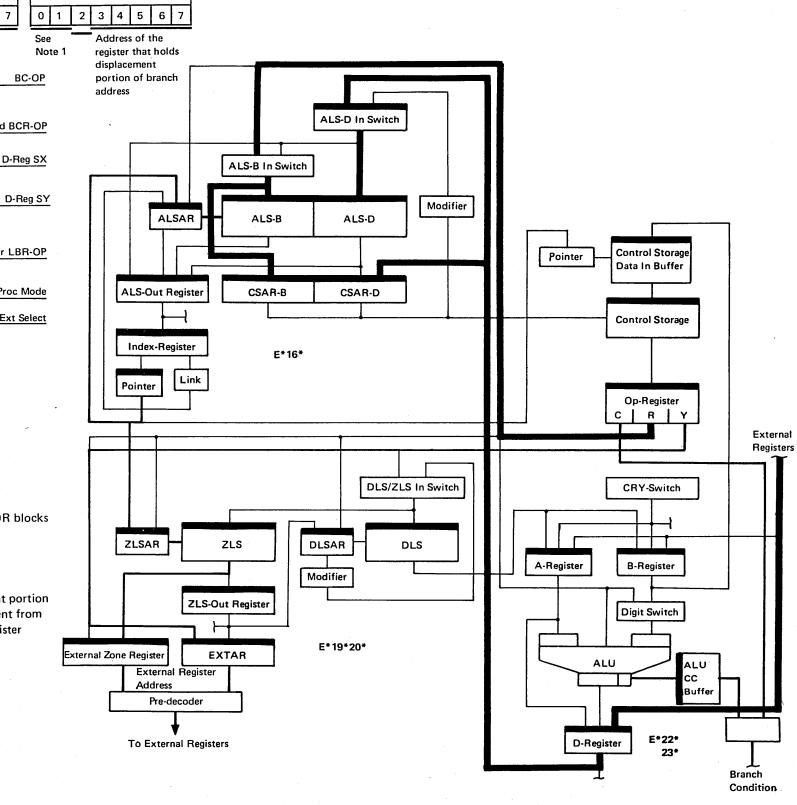

| BNZR, BCYR, BCNR, BZR, BNCR, BZNR Process Cycle                                  |  |

| BNZR, BCYR, BCNR, BZR, BNCR, BZNR Process Cycle                                  |  |

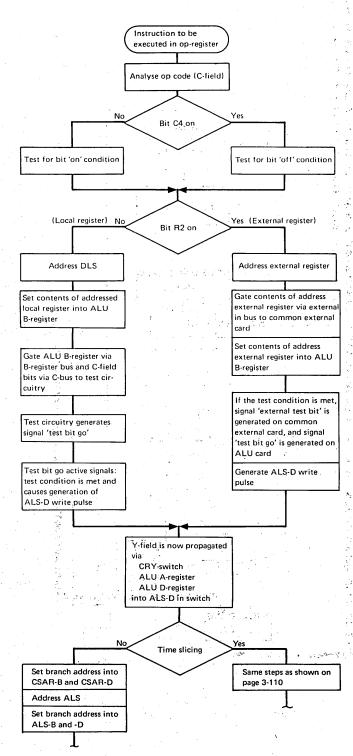

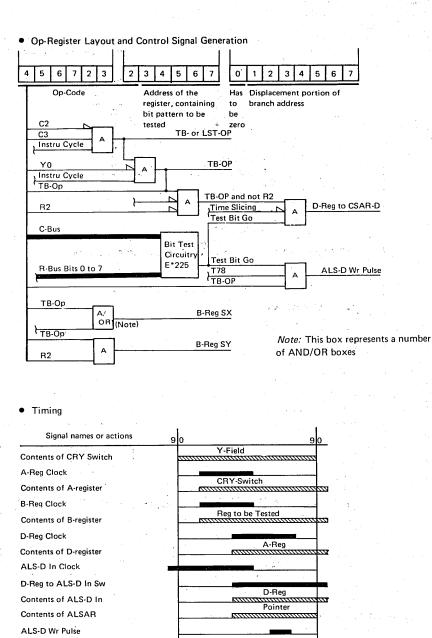

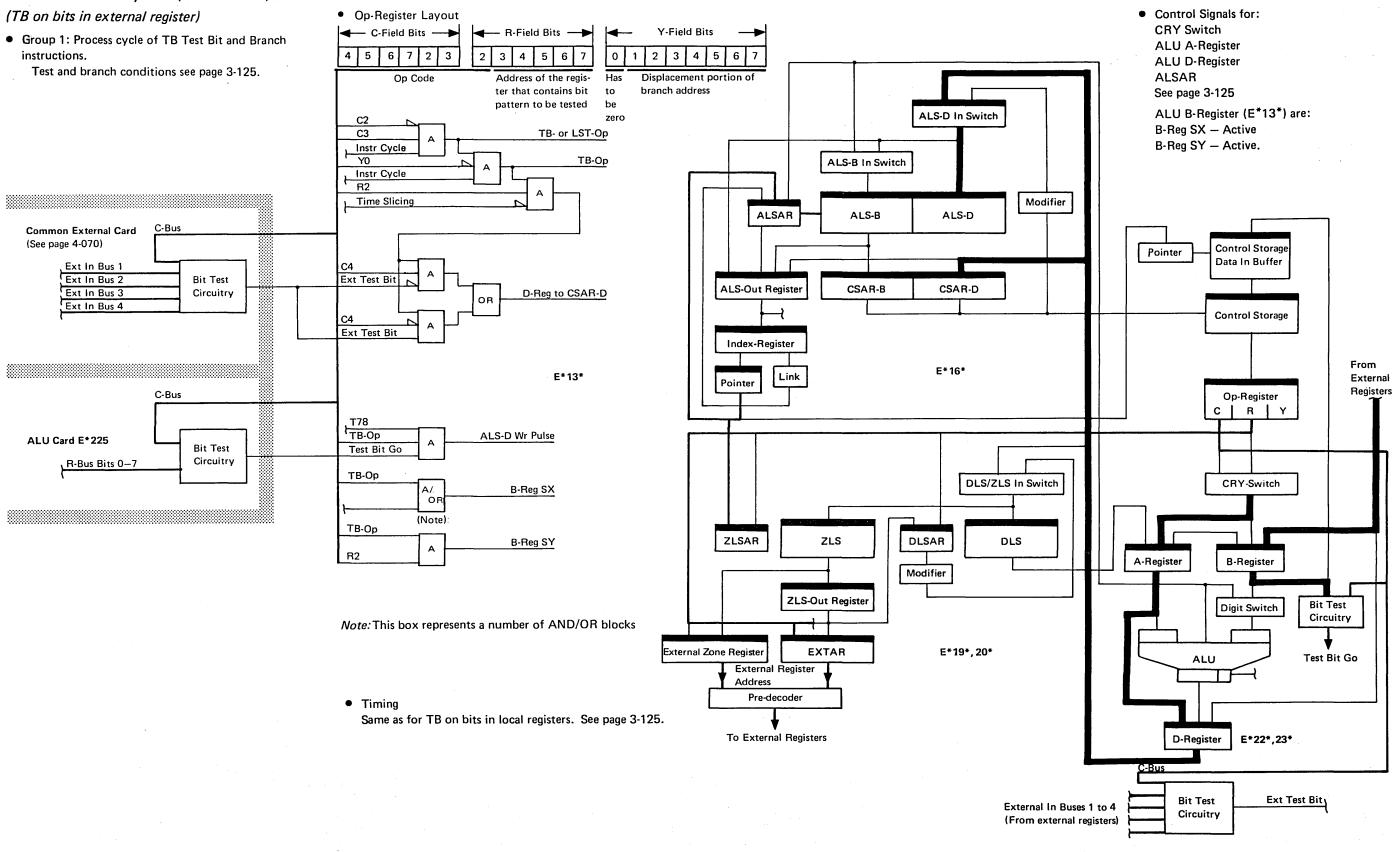

| TB Process Cycle         3-120           TB 200         3-125                    |  |

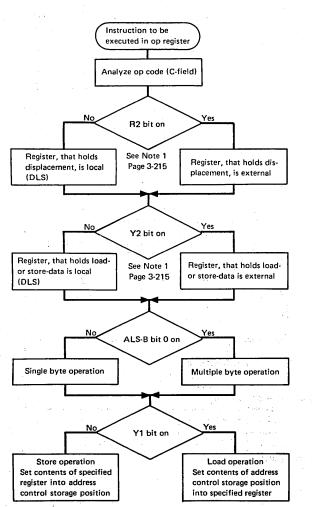

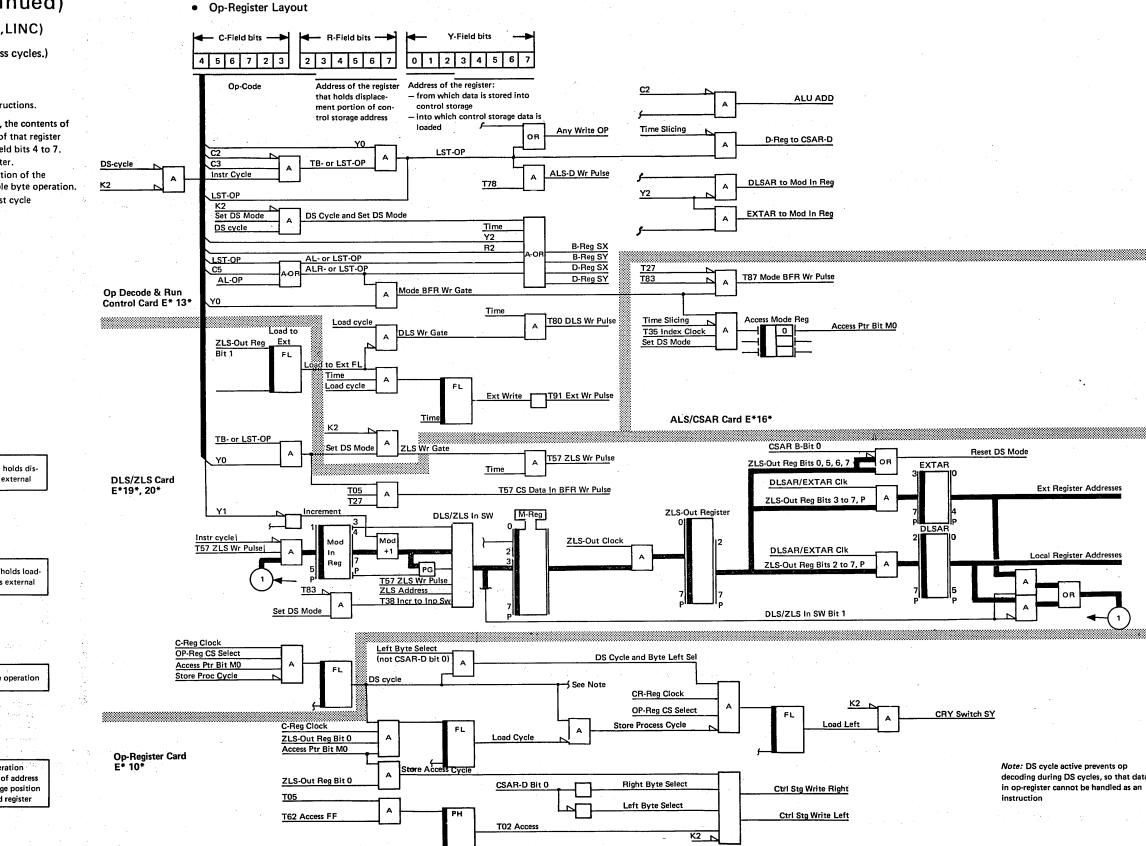

| Store (SDEC, SINC), Load (LDEC, LINC)                                            |  |

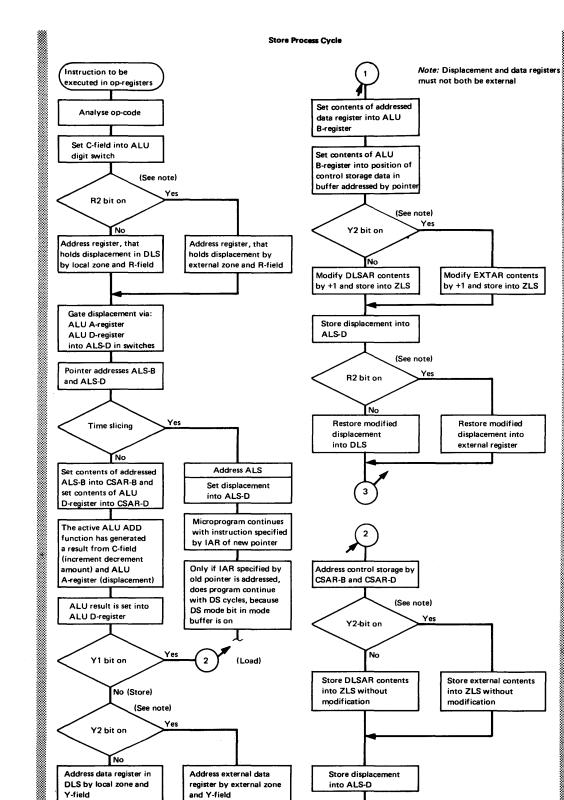

| Store Load Process Cycles                                                        |  |

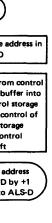

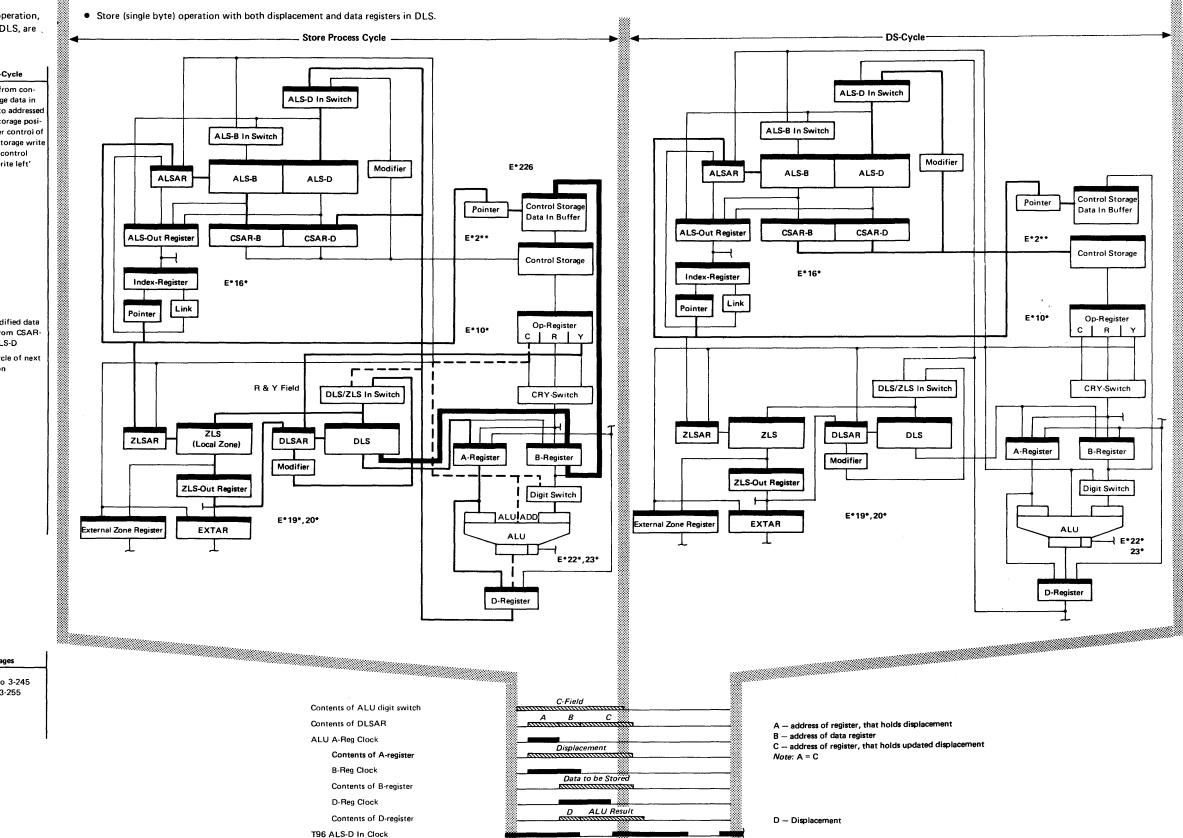

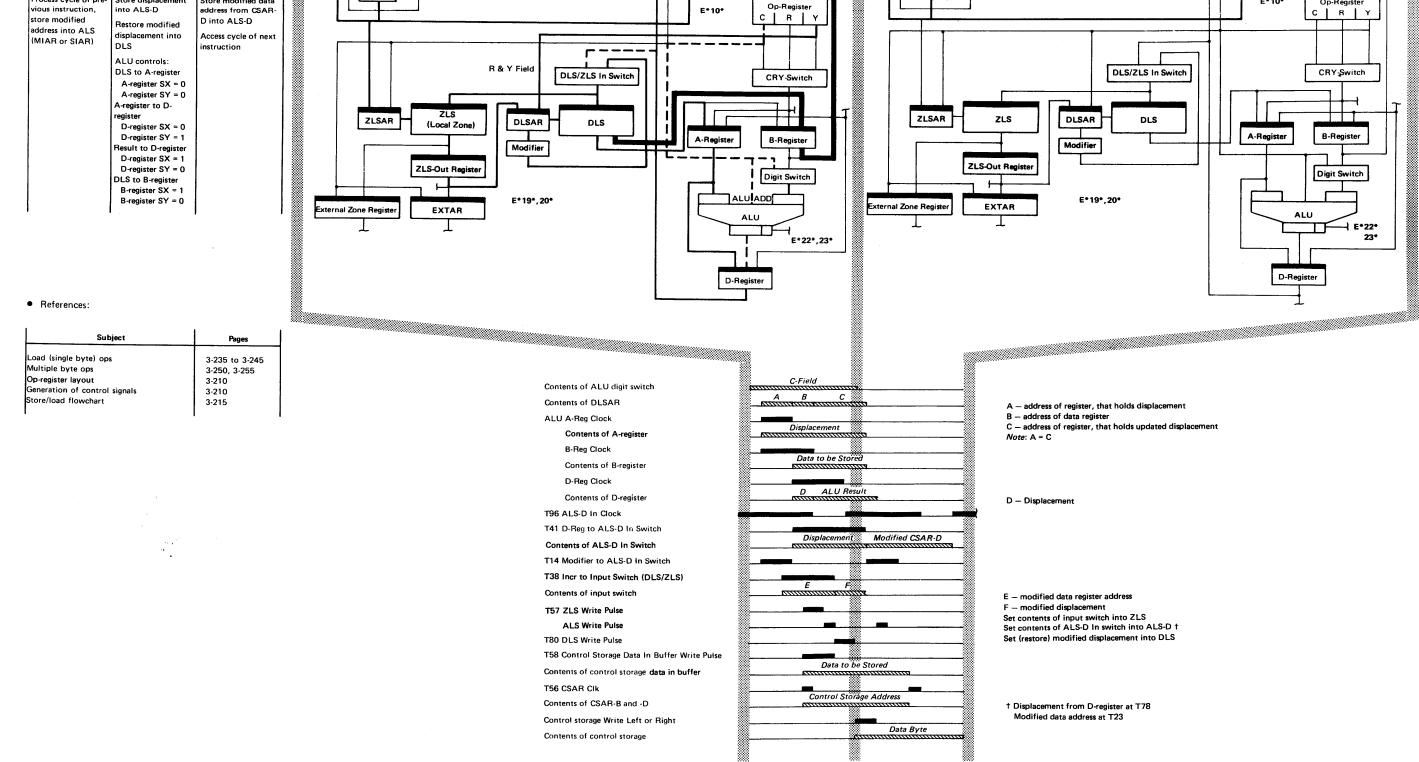

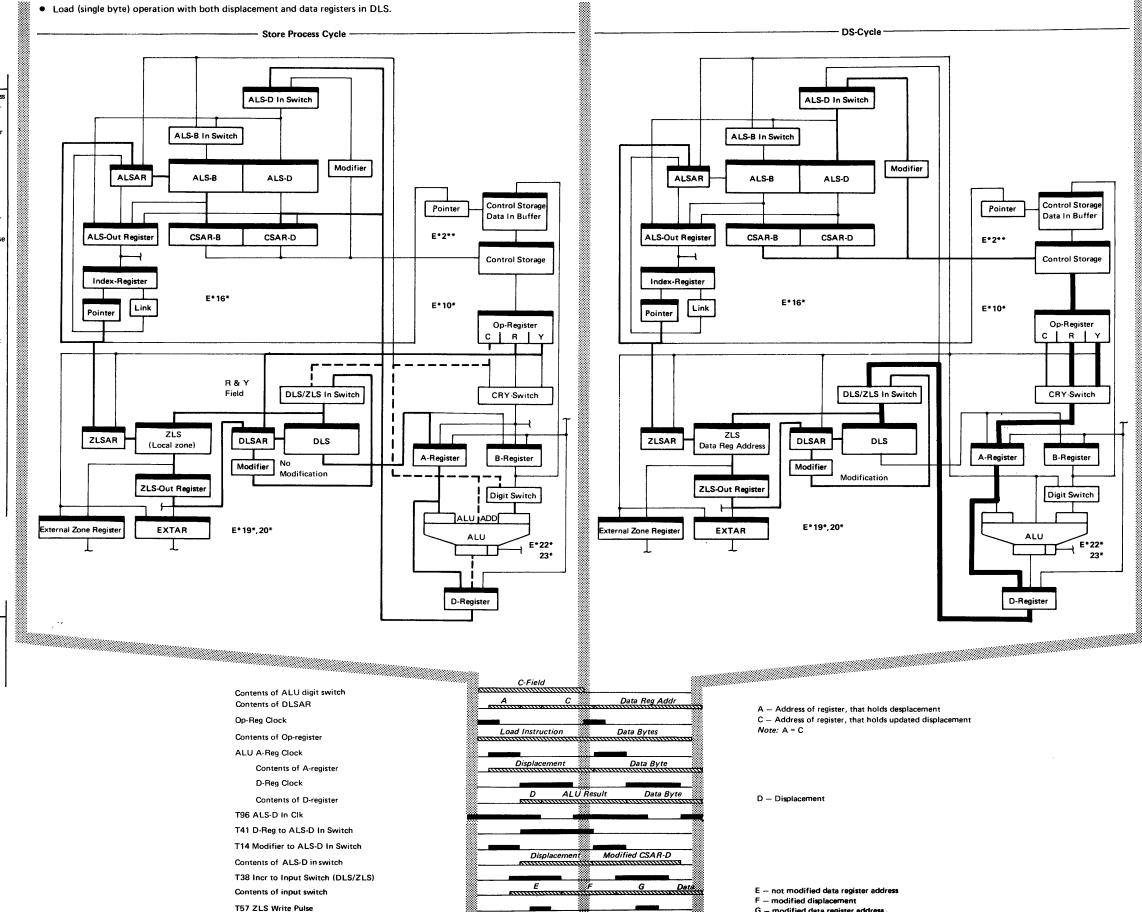

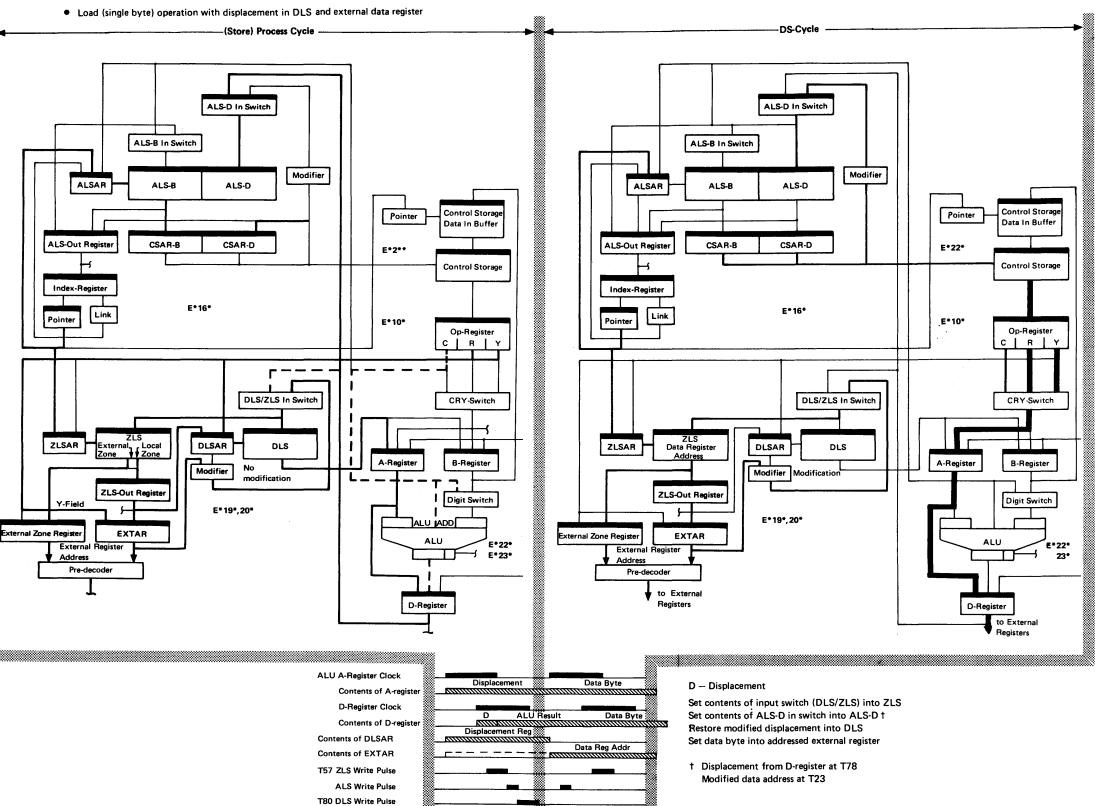

| Store (single byte, with both registers in DLS)                                  |  |

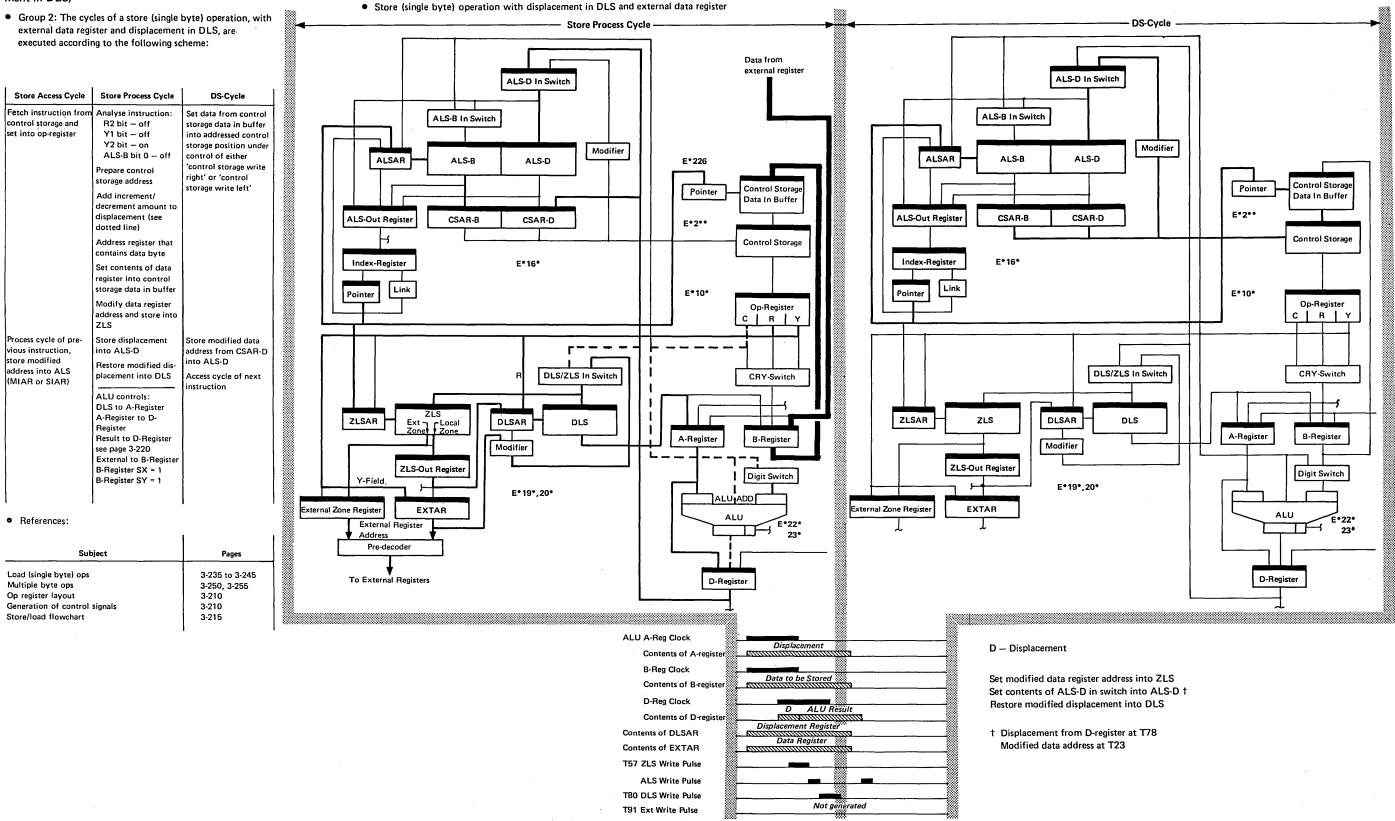

| Store (single byte with external data register and displacement in DLS) 3-225    |  |

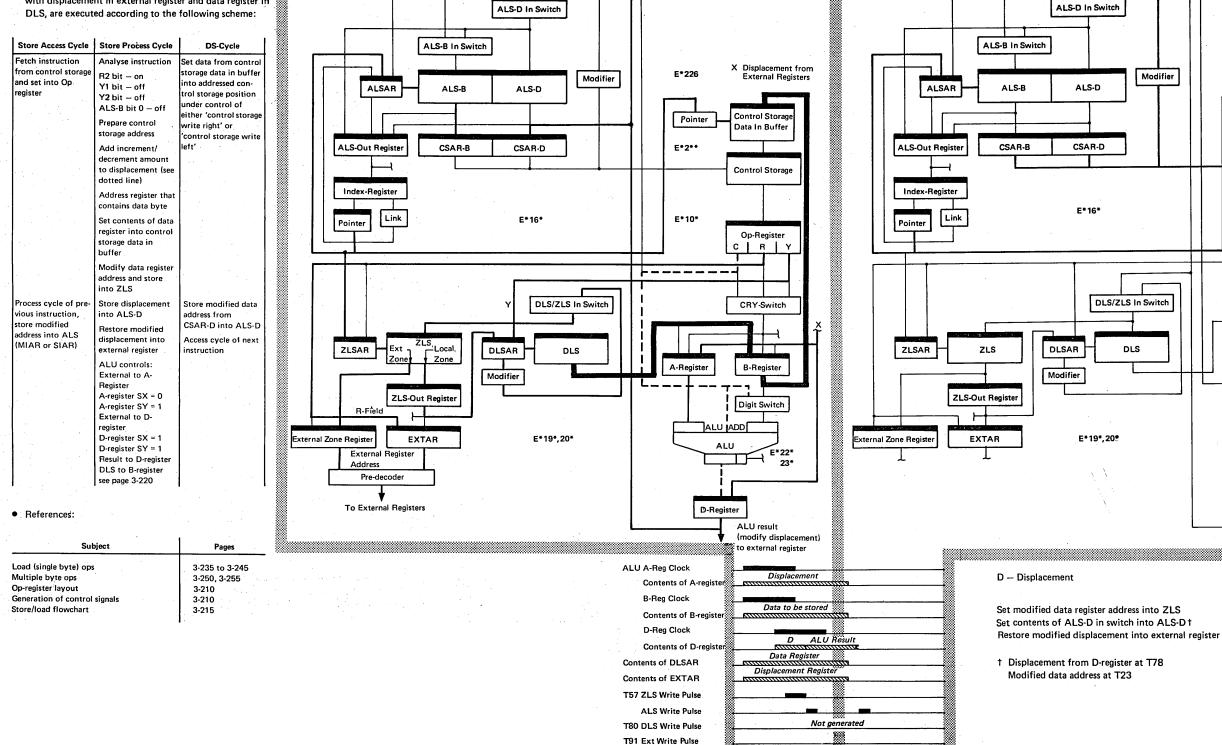

| Store (single byte with data register in DLS and displacement in                 |  |

| external register)                                                               |  |

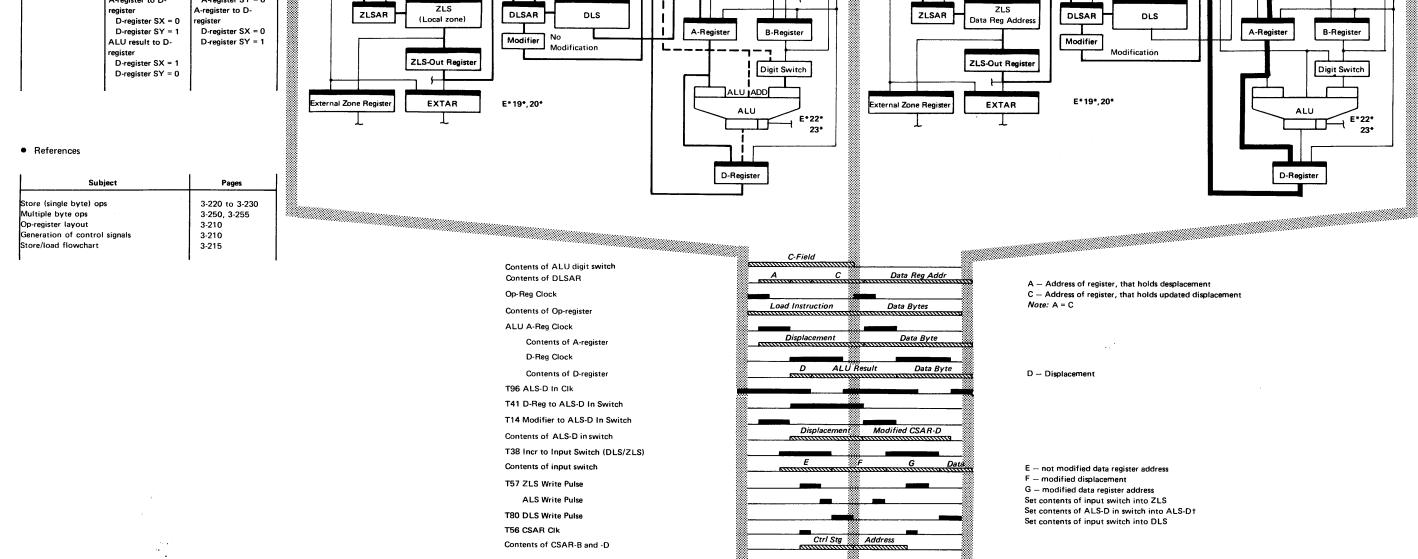

| Load (single byte with both registers in DLS)                                    |  |

| Load (single byte with data register external and displacement in DLS) 3-240     |  |

| Load (single byte with data register in DLS and displacement in                  |  |

| external register)                                                               |  |

| Load, Store (multiple byte) Operations                                           |  |

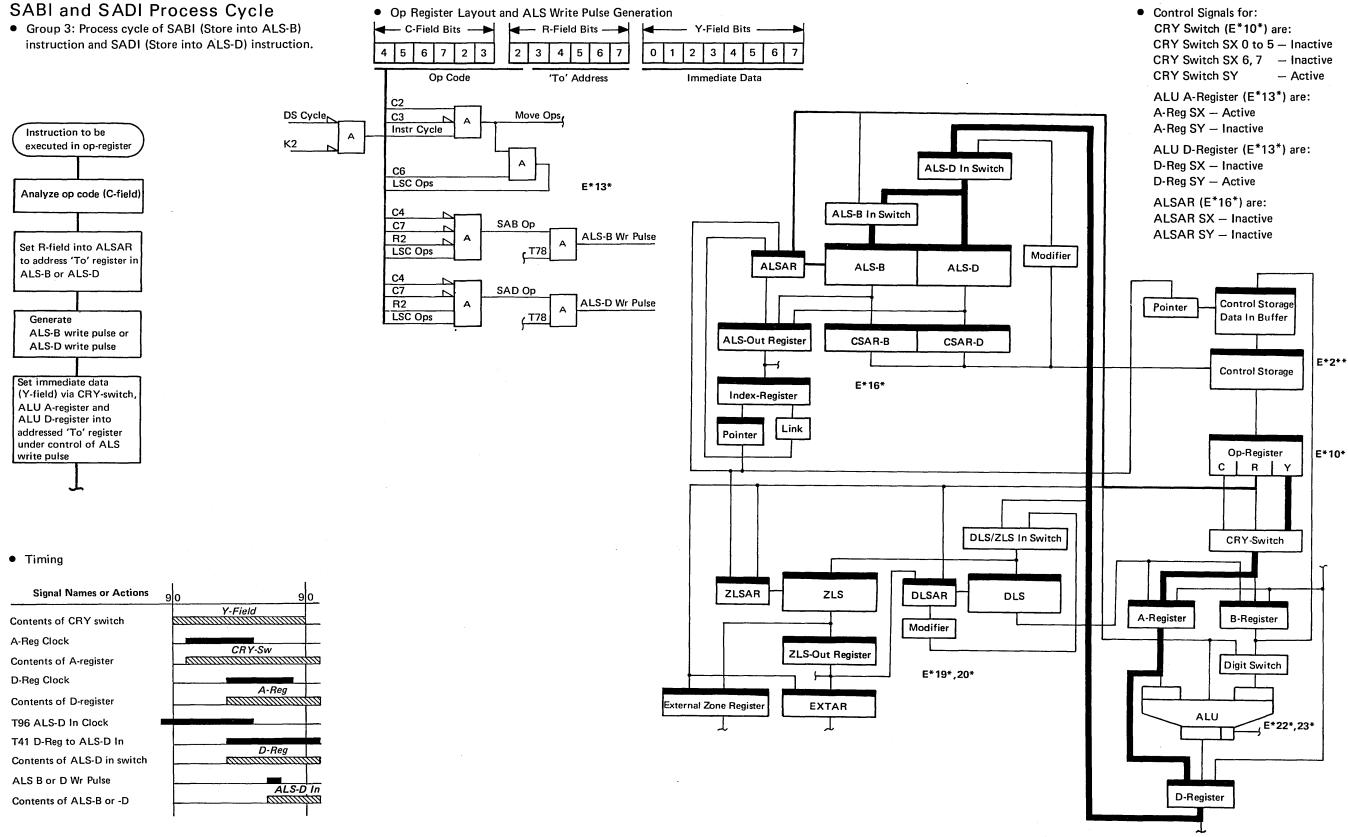

| SABI and SADI Process Cycle                                                      |  |

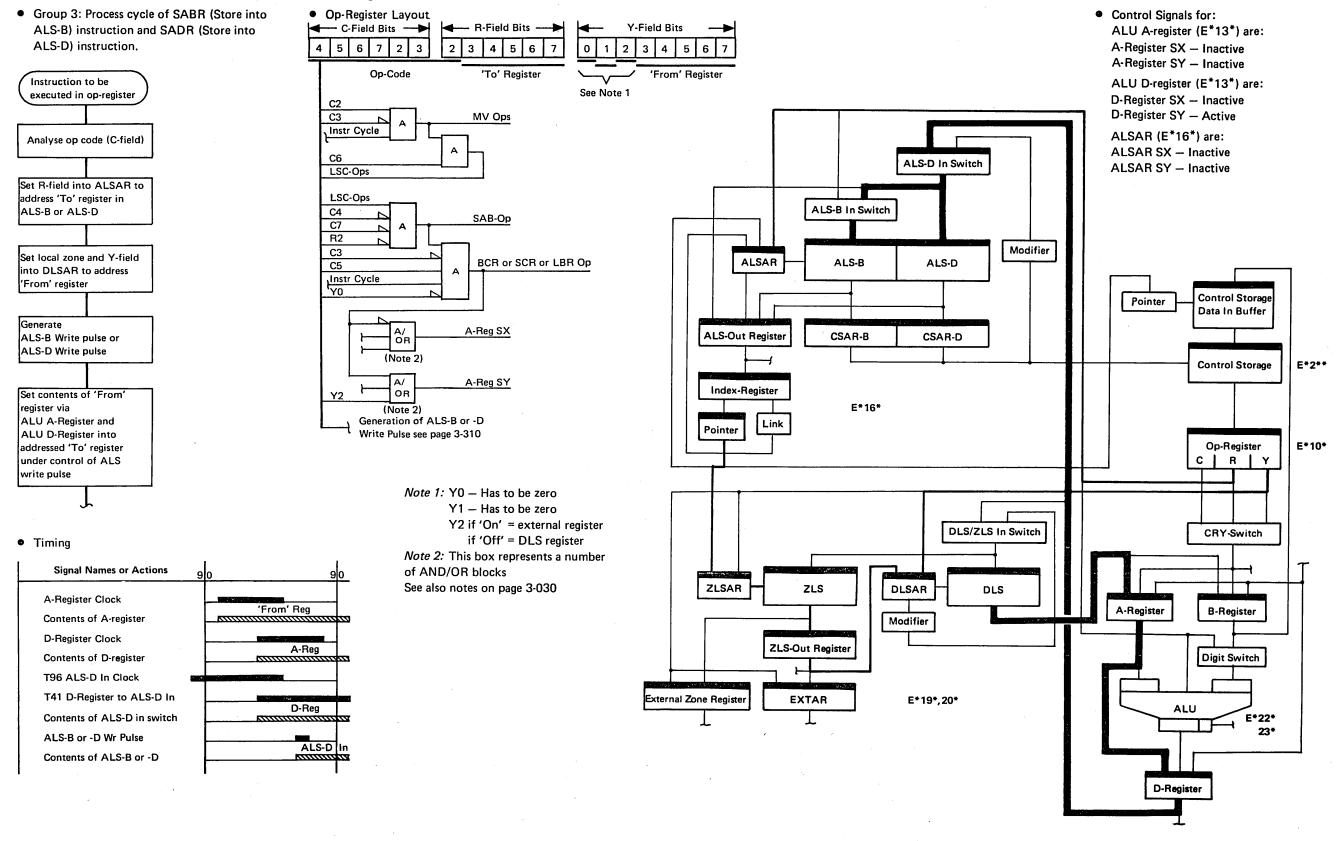

| SABR and SADR Process Cycle (DLS register to ALS)                                |  |

| SABR and SADR Process Cycle (external register to ALS)                           |  |

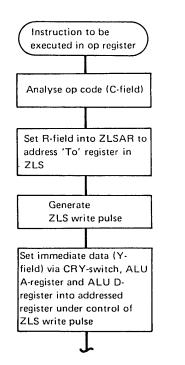

| SZI Process Cycle                                                                |  |

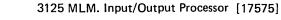

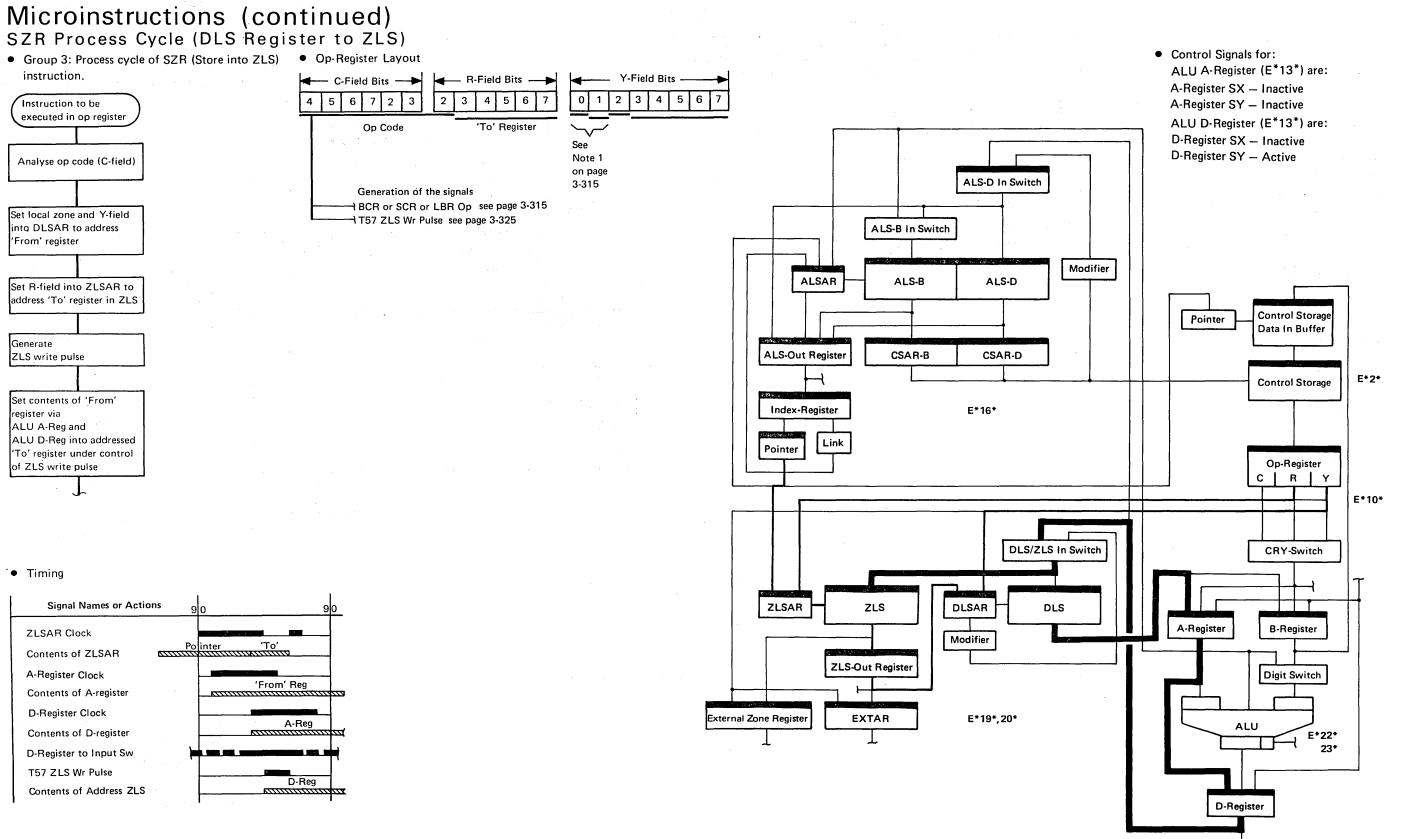

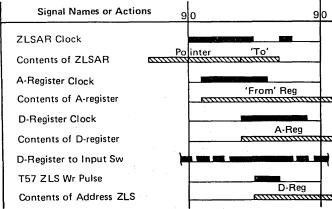

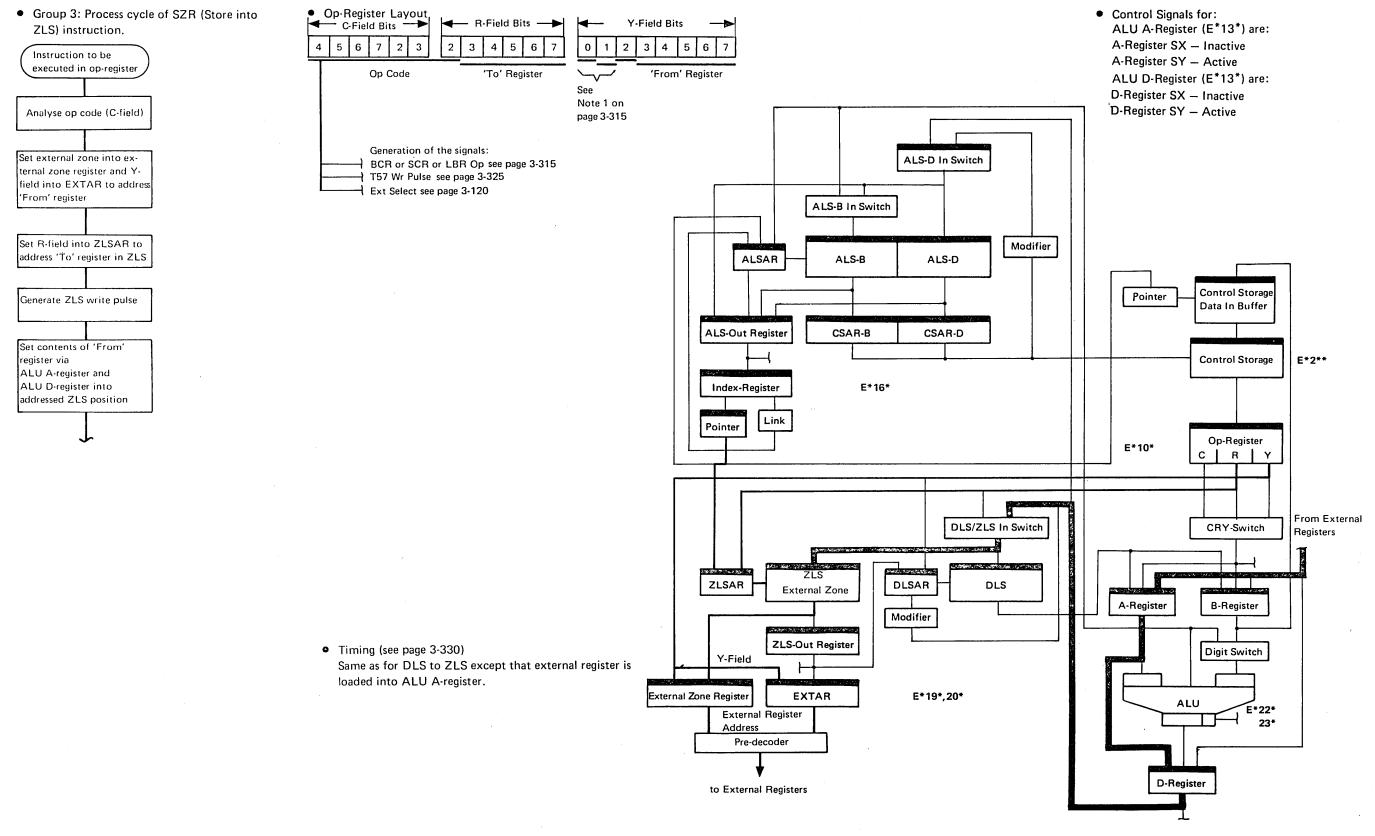

| SZR Process Cycle (DLS register to ZLS)                                          |  |

| SZR Process Cycle (external register to ZLS)                                     |  |

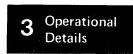

| SLKI Process Cycle                                                               |  |

| SLKR Process Cycle (DLS register to X-register)                                  |  |

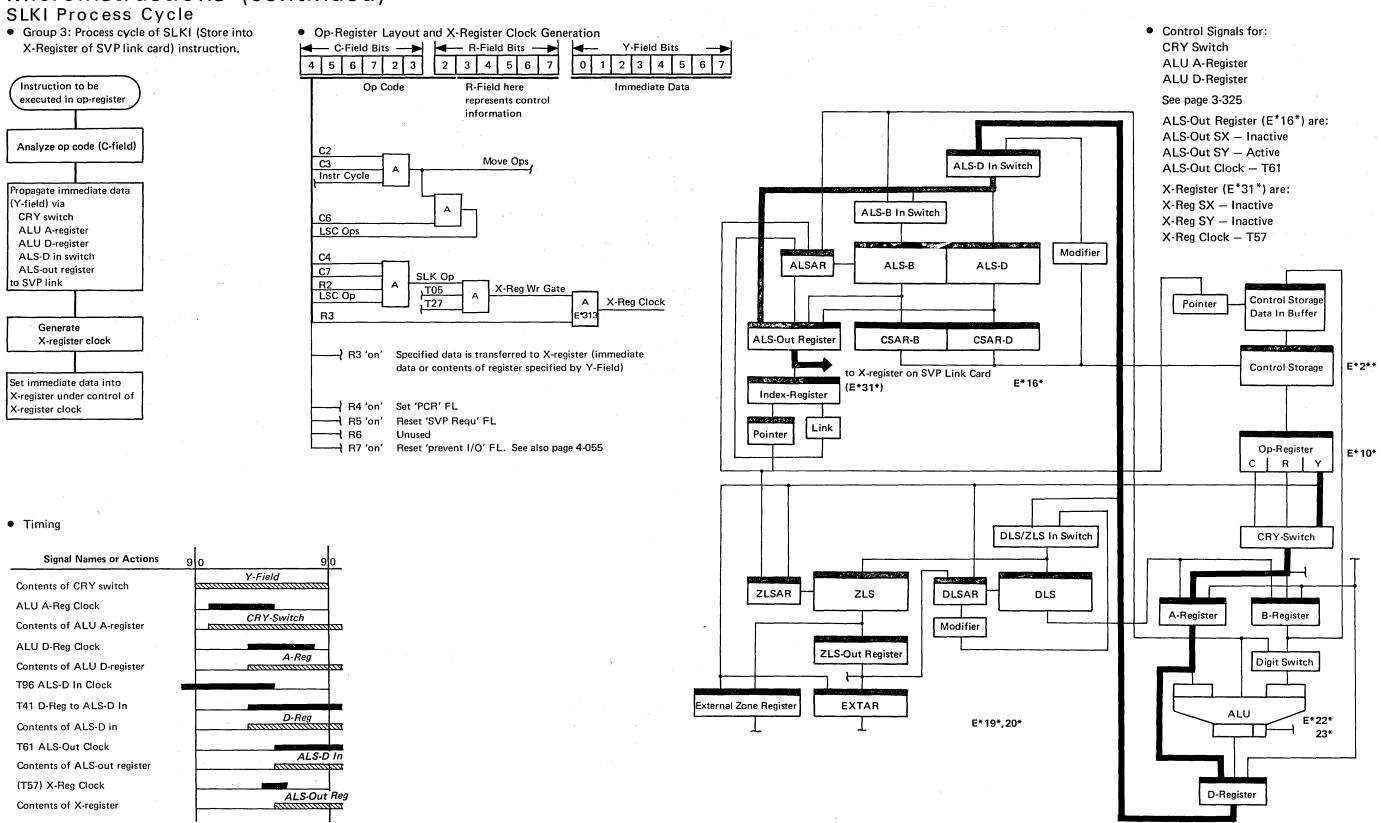

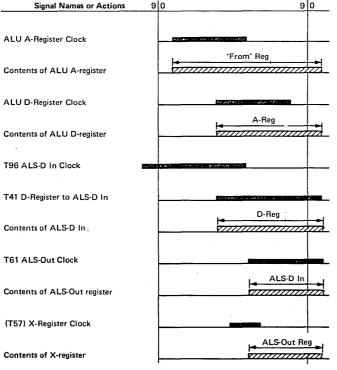

| SLKR Process Cycle (external register to X-register)                             |  |

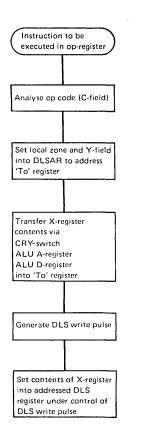

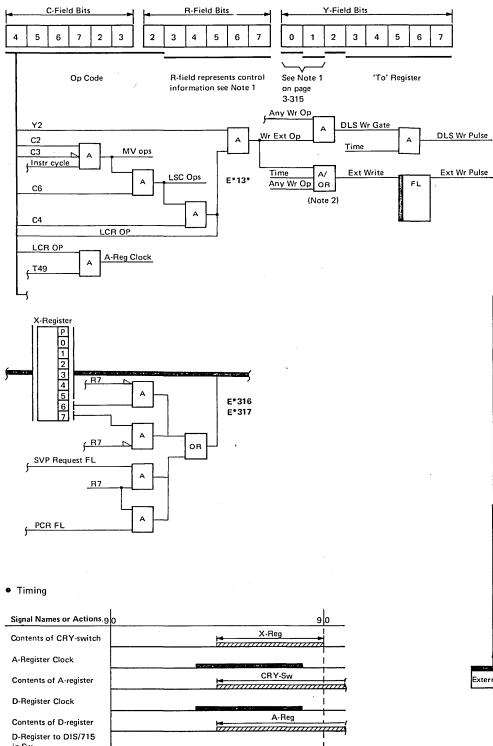

| LLKR Process Cycle (X-register to DLS)                                           |  |

| LLKR Process Cycle (X-register to external register)                             |  |

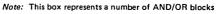

| LBI to DLS Register Process Cycle                                                |  |

| LBI to External Register Process Cycle                                           |  |

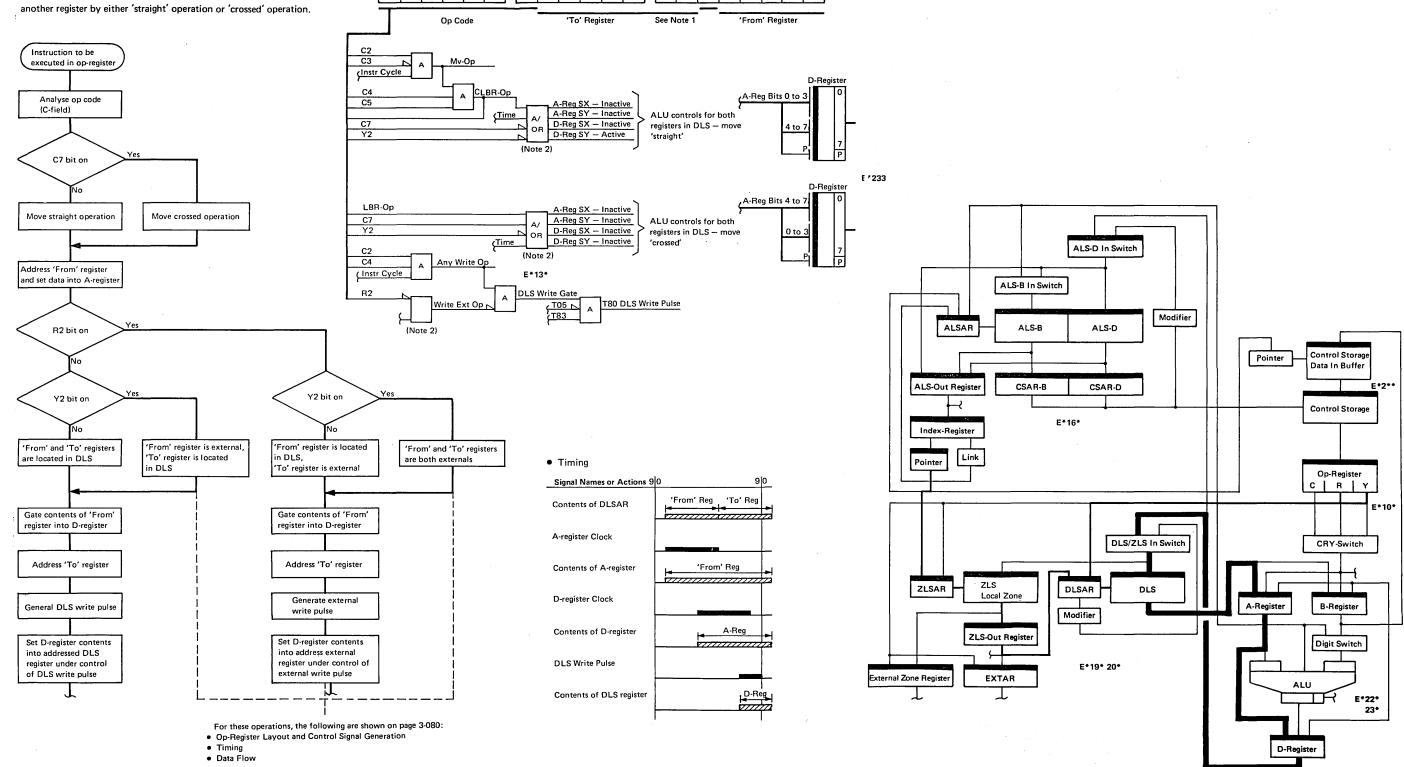

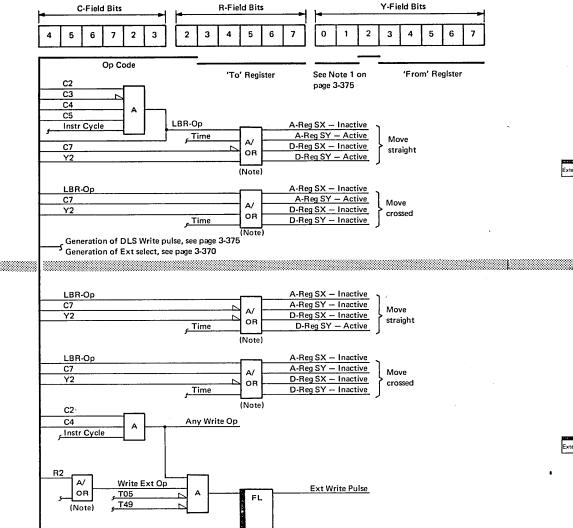

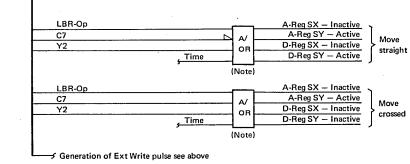

| MV, MVX Process Cycle (both registers in DLS)                                    |  |

| MV, MVX Process Cycle (external register to DLS register), (DLS                  |  |

| register to external register), (external register to external register) . 3-380 |  |

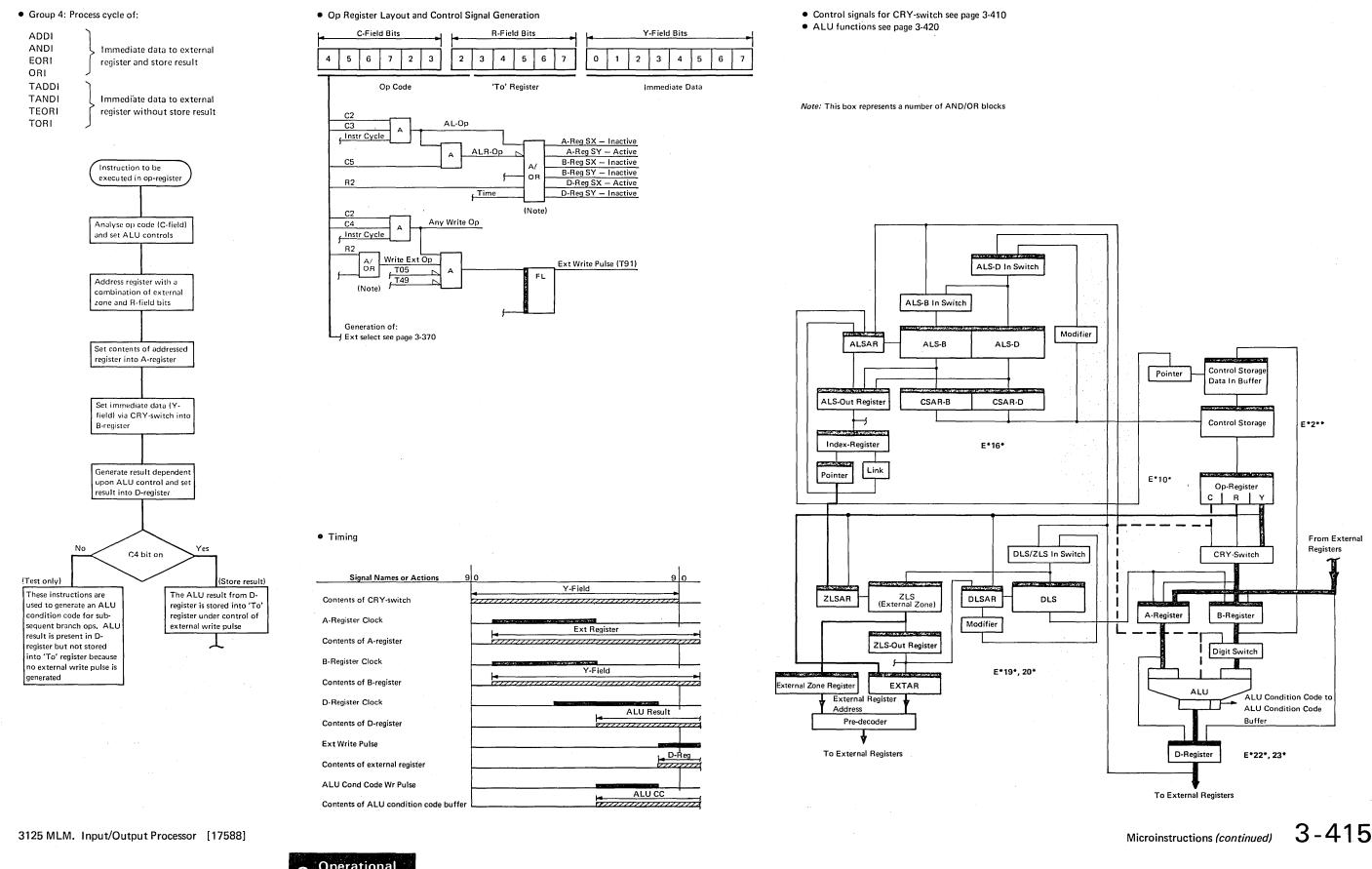

| ADDI, ANDI, EORI, ORI, TADDI, TANDI, TEORI, TORI Process                         |  |

| Cycles                                                                           |  |

| ADDI ANDI EORI ORI TADDI TANDI TEORI TORI Brasses          |       |

|------------------------------------------------------------|-------|

| ADDI, ANDI, EORI, ORI, TADDI, TANDI, TEORI, TORI Process   | 2 415 |

| Cycles                                                     | 3-415 |

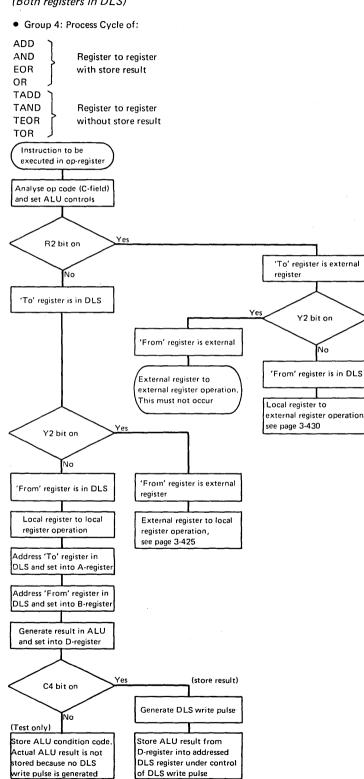

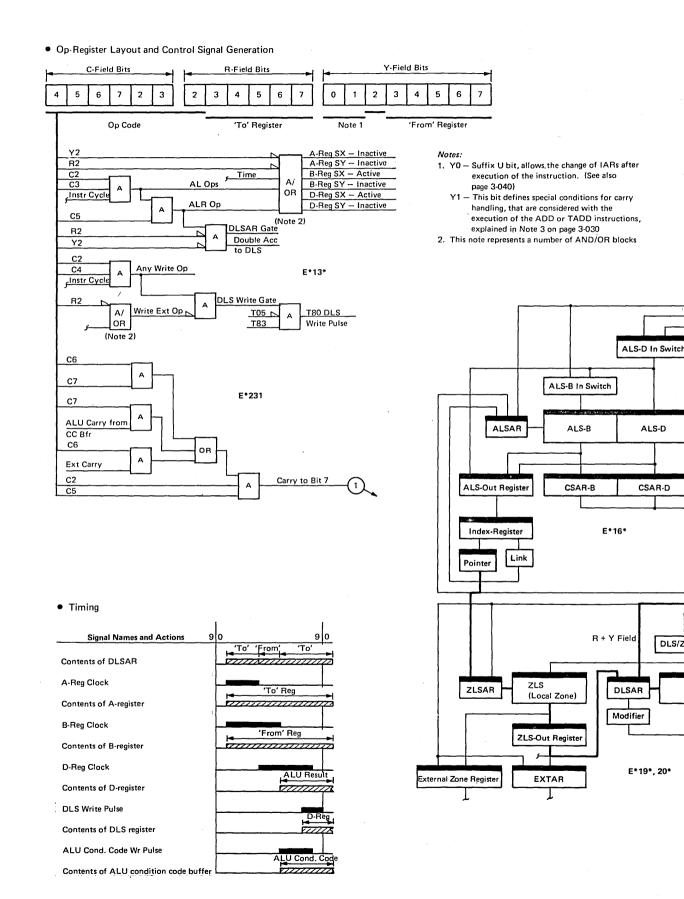

| Cycles (both registers in DLS)                             | 3-420 |

|                                                            | 3-420 |

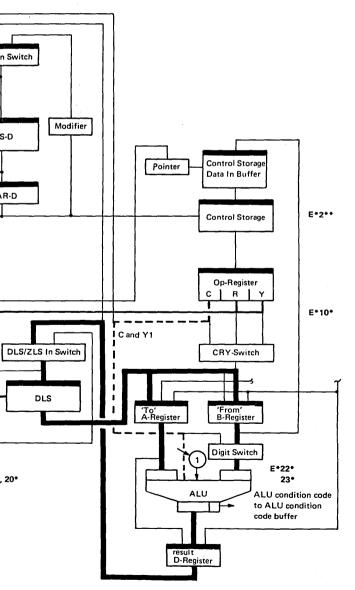

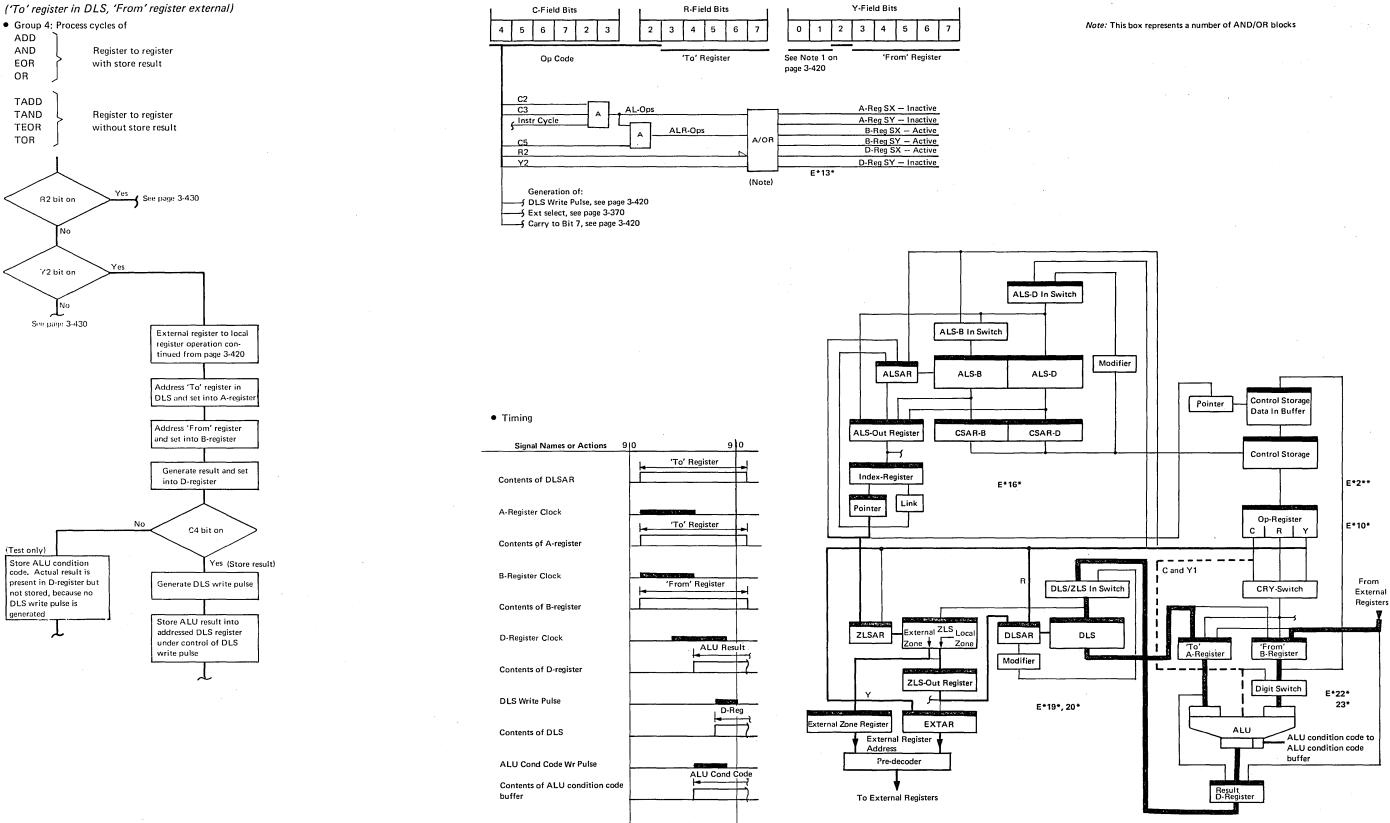

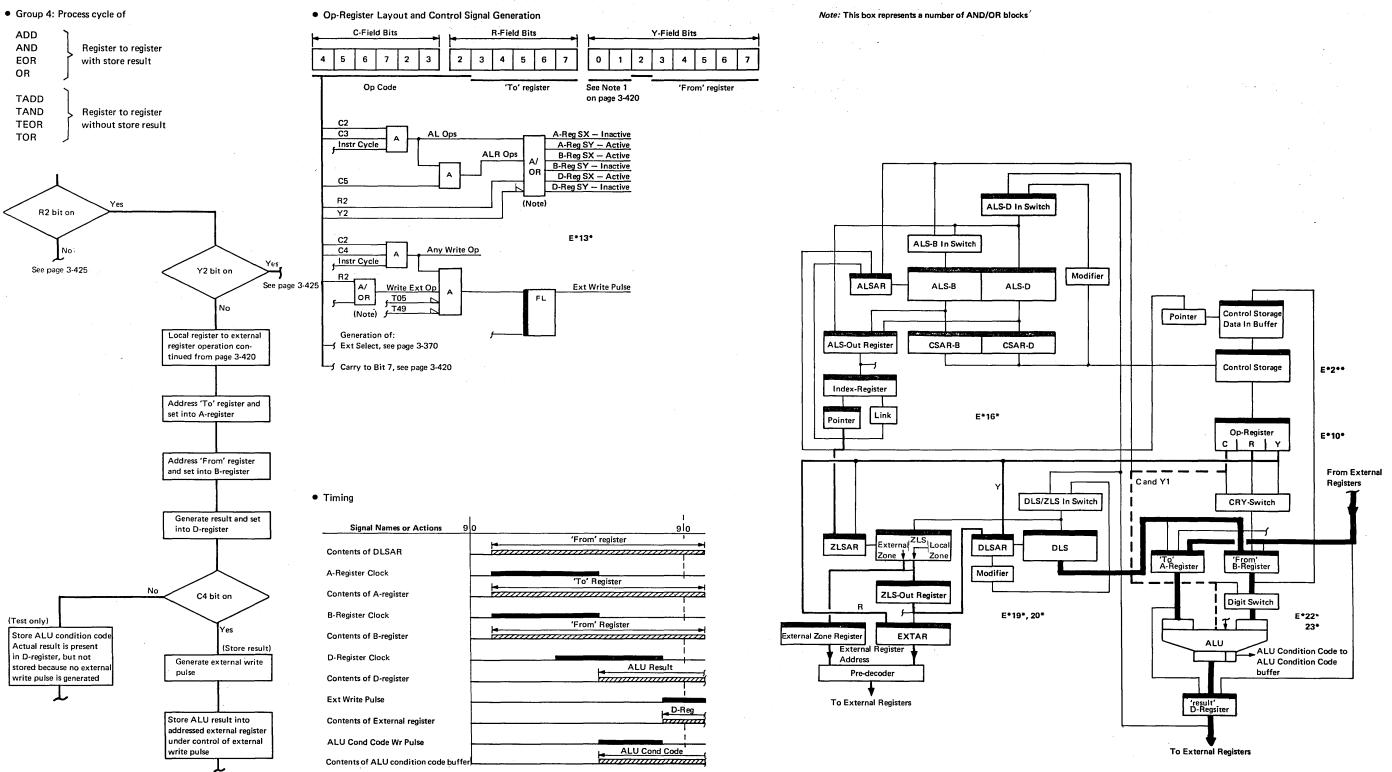

| ADD, AND, EOR, OR, TADD, TAND, TEOR, TOR, Process          |       |

| Cycles ('To' register in DLS, 'From' register external)    | 3-425 |

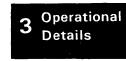

| ADD, AND, EOR, OR, TADD, TAND, TEOR, TOR, Process          |       |

| Cycles ('To' register is external, 'From' register in DLS) |       |

| Microprogram Control                                       |       |

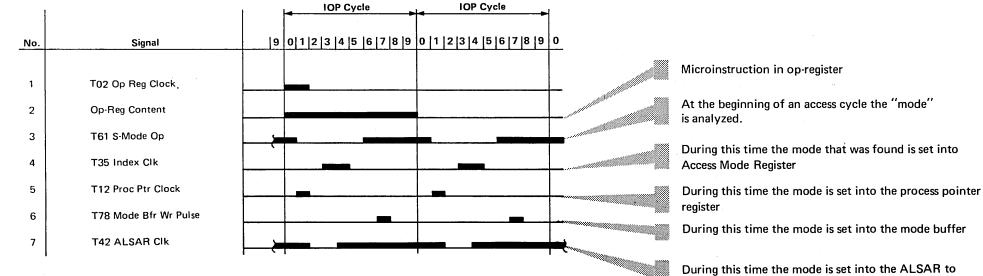

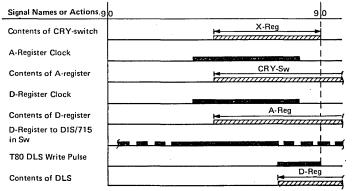

| Cycle Timing and Arrangement                               |       |

| Cycle Timing                                               |       |

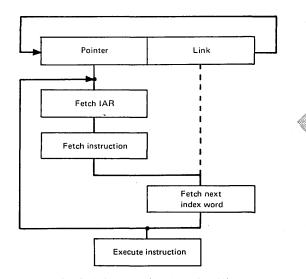

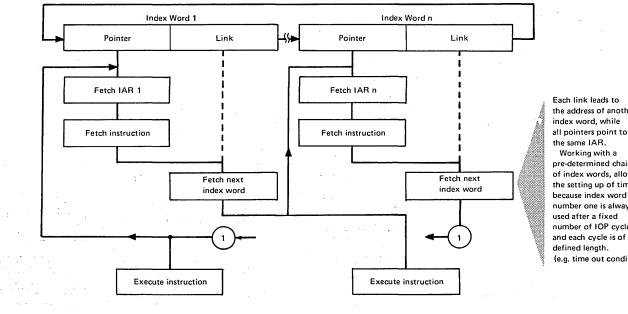

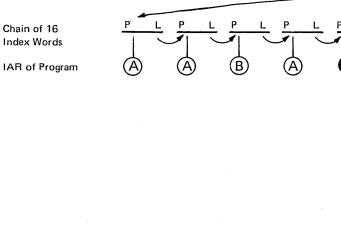

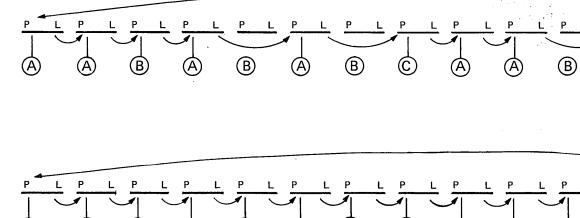

| Execution of IOP Microprograms                             | 3-510 |

|                                                            |       |

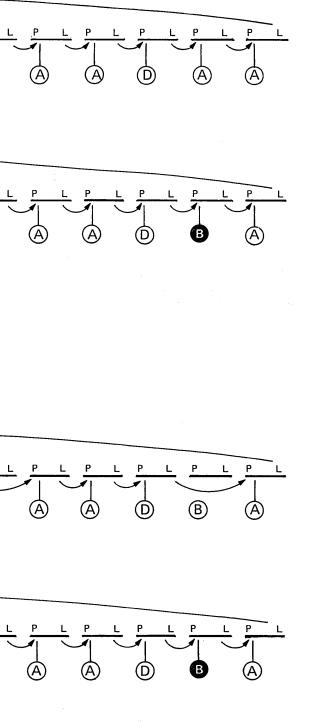

| Versions of Time Slicing                                   |       |

|                                                            |       |

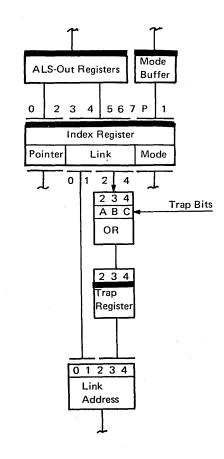

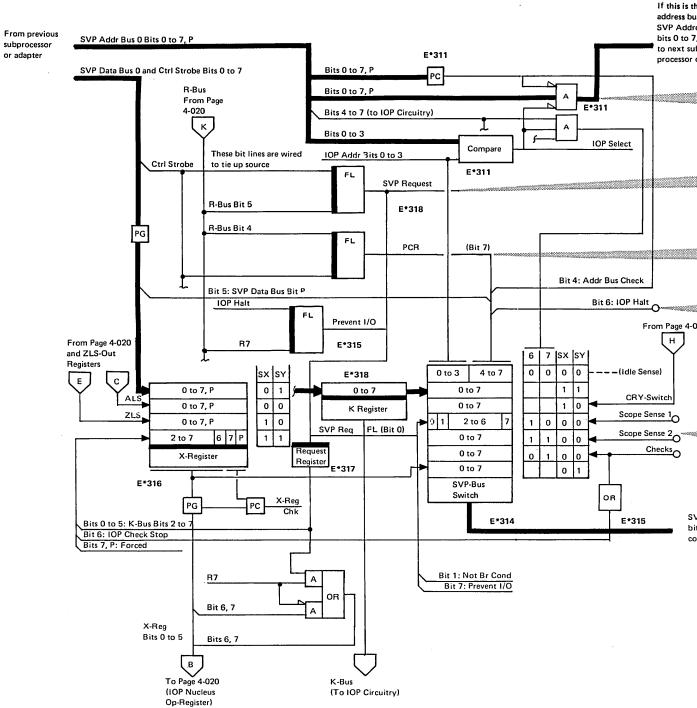

| IOP, SVP Communication                                     |       |

| SENS, CTRL Operations                                      |       |

| SVP SENS Operation                                         |       |

| SVP CTRL Operation                                         |       |

| SVP SENS Table                                             |       |

| SVP CTRL Table                                             | 3-940 |

|                                                            |       |

| Chapter 4. Functional Units                                |       |

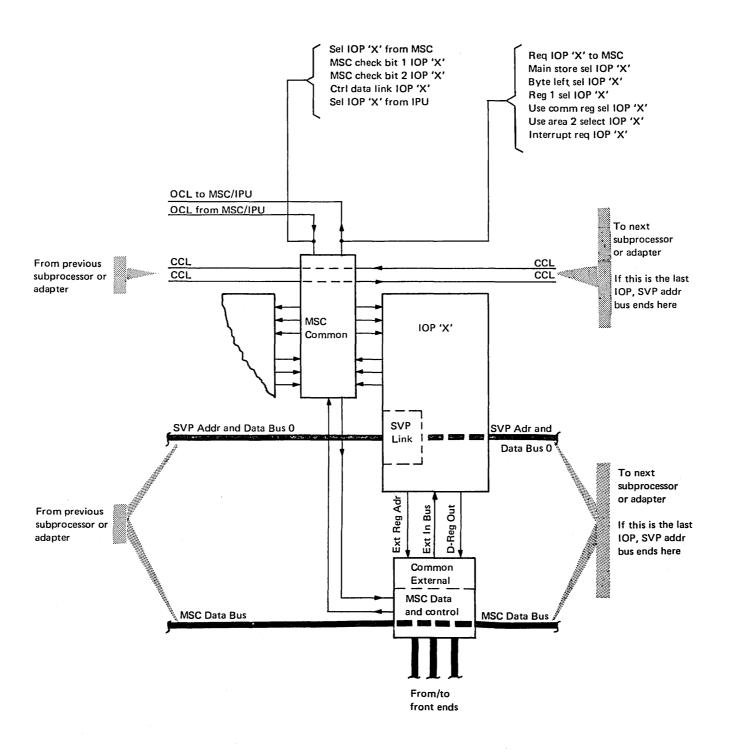

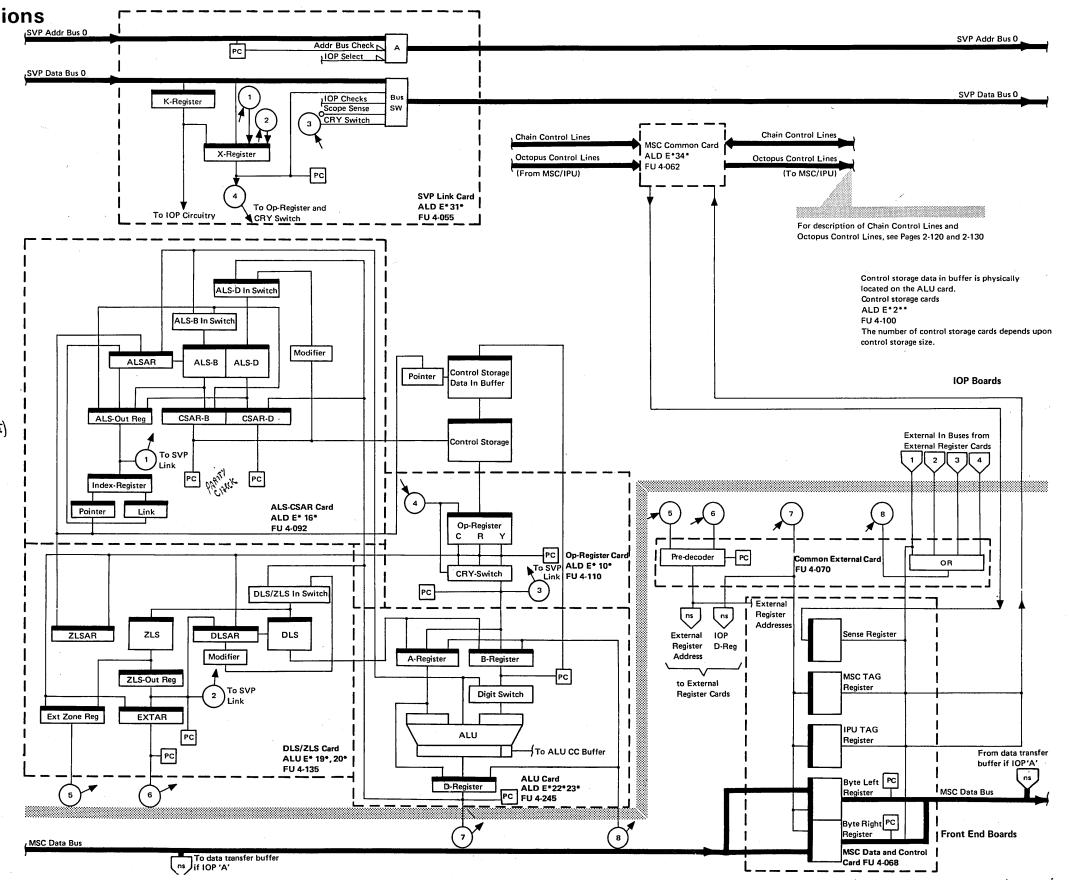

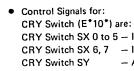

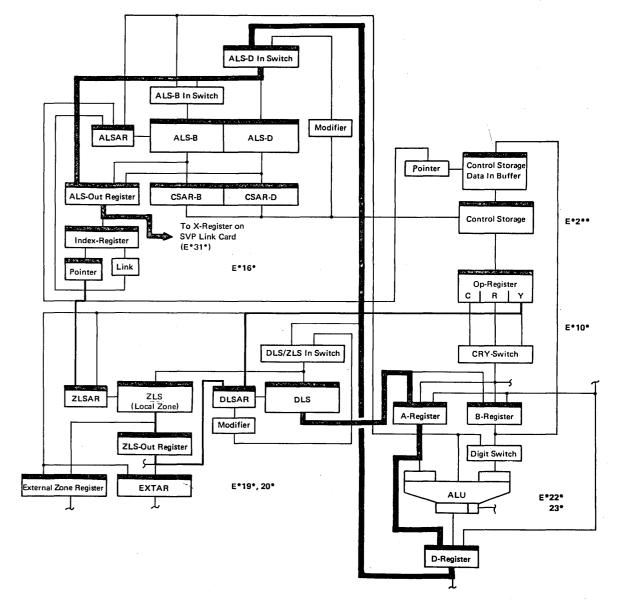

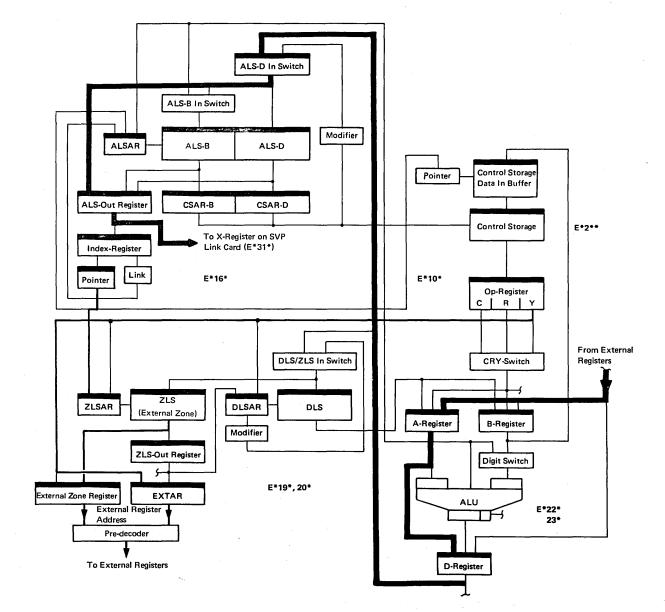

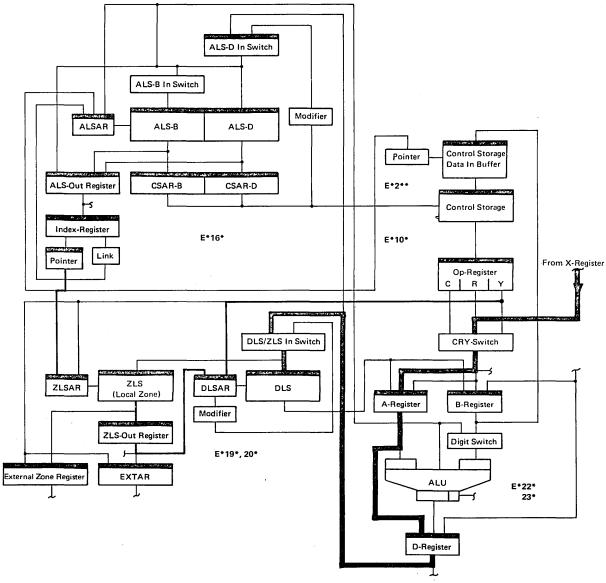

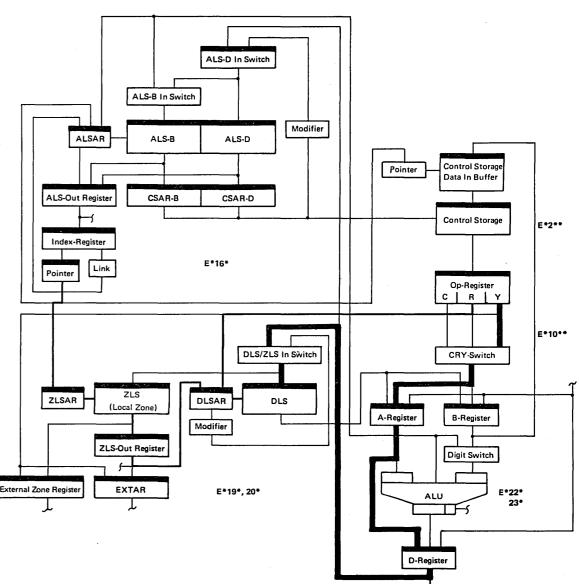

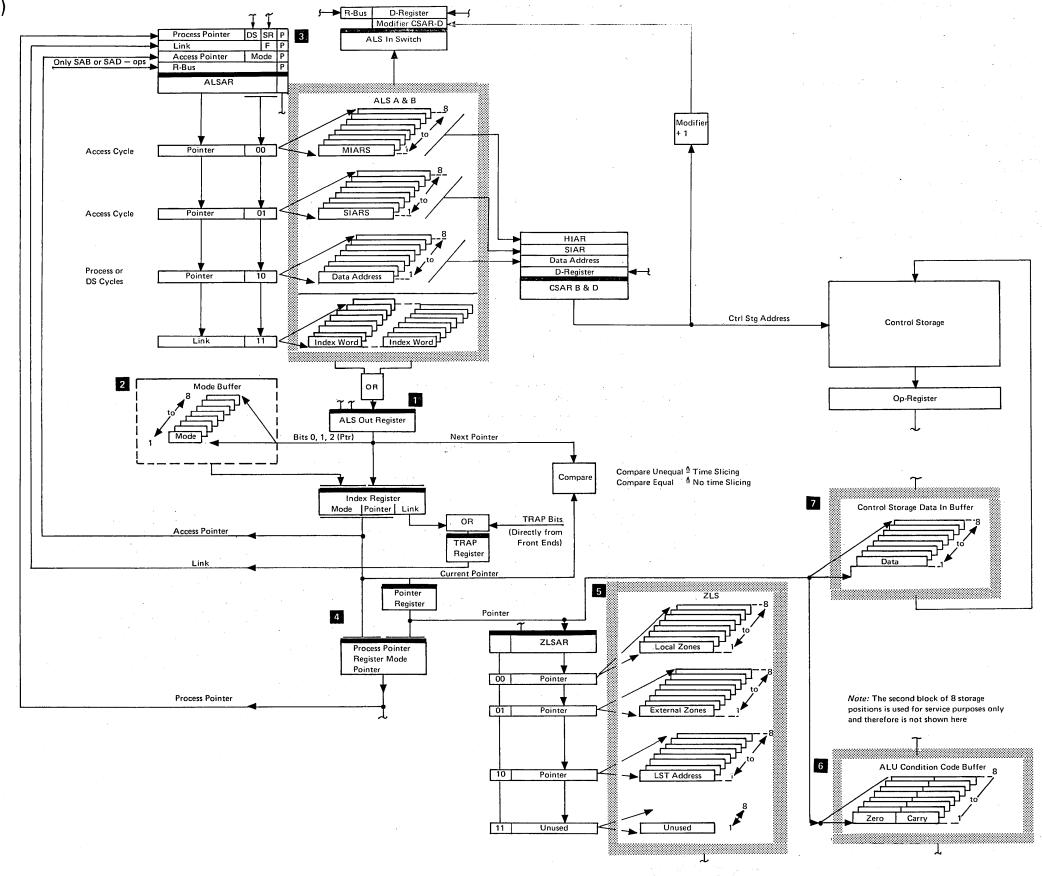

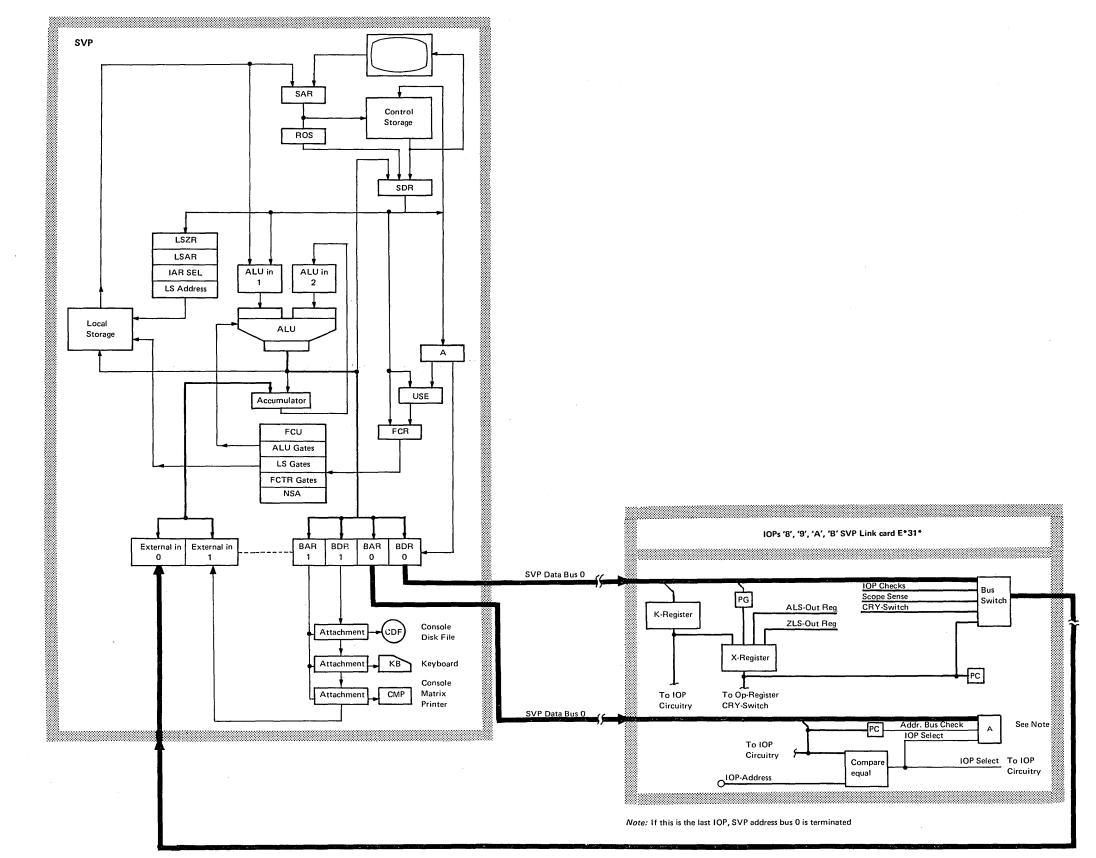

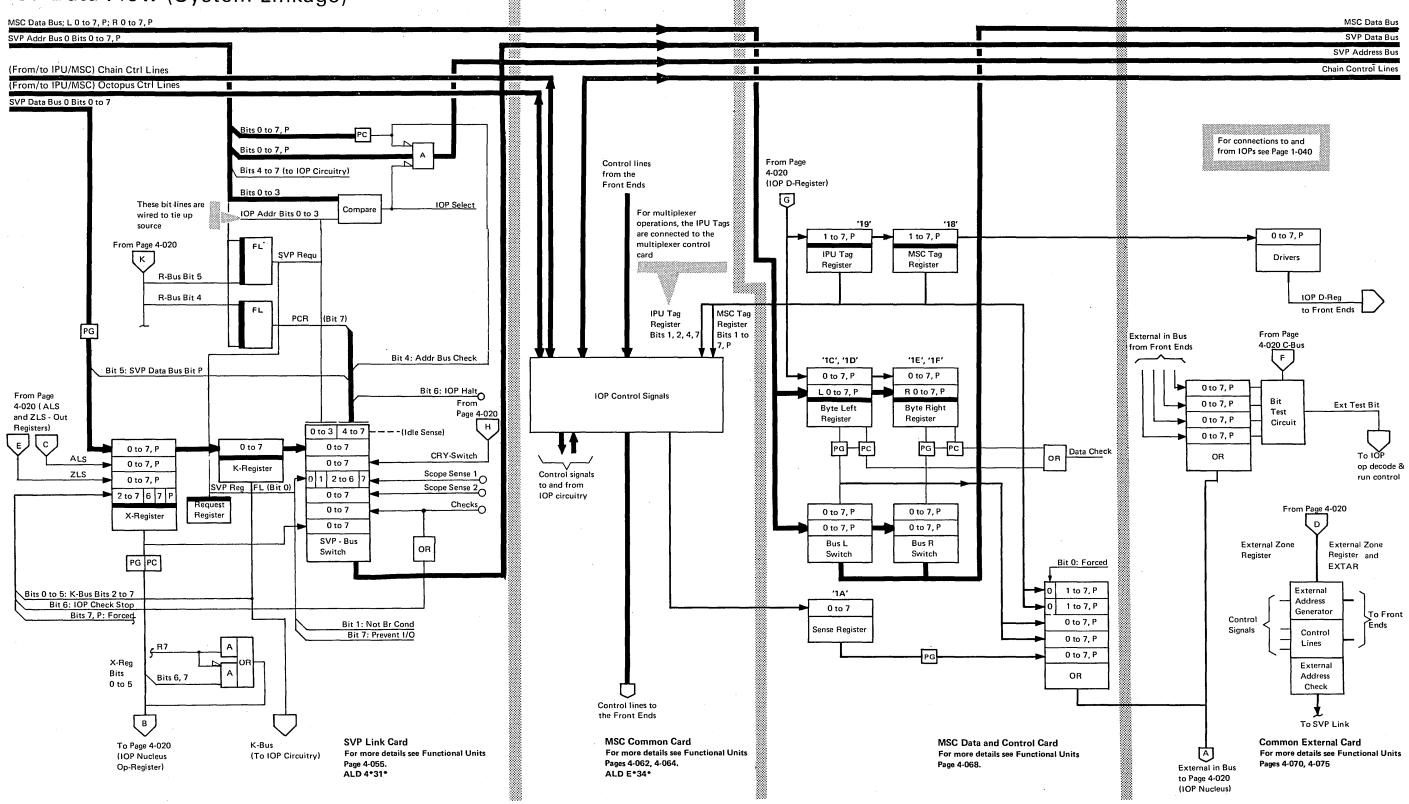

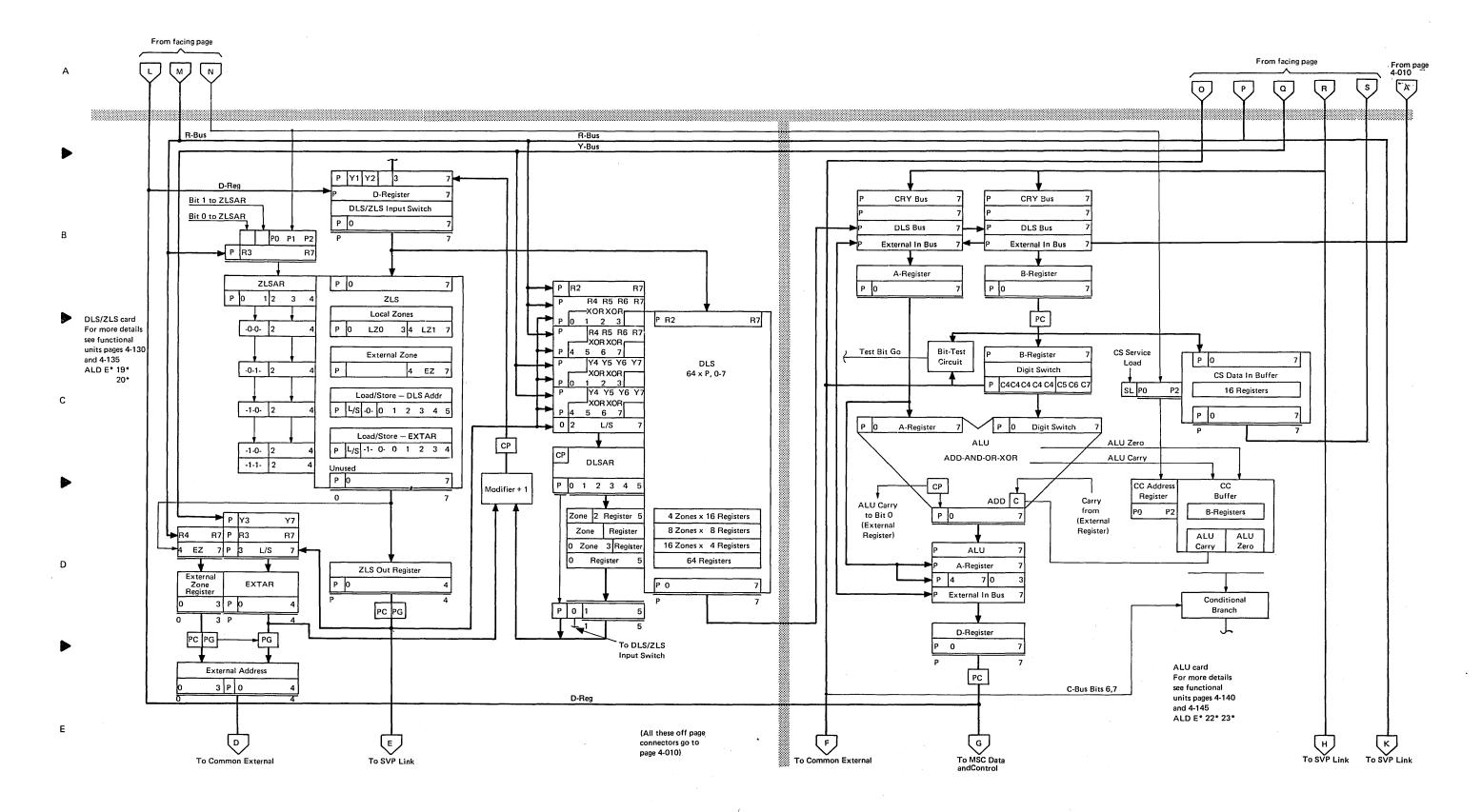

| IOP Data Flow (System Linkage)                             |       |

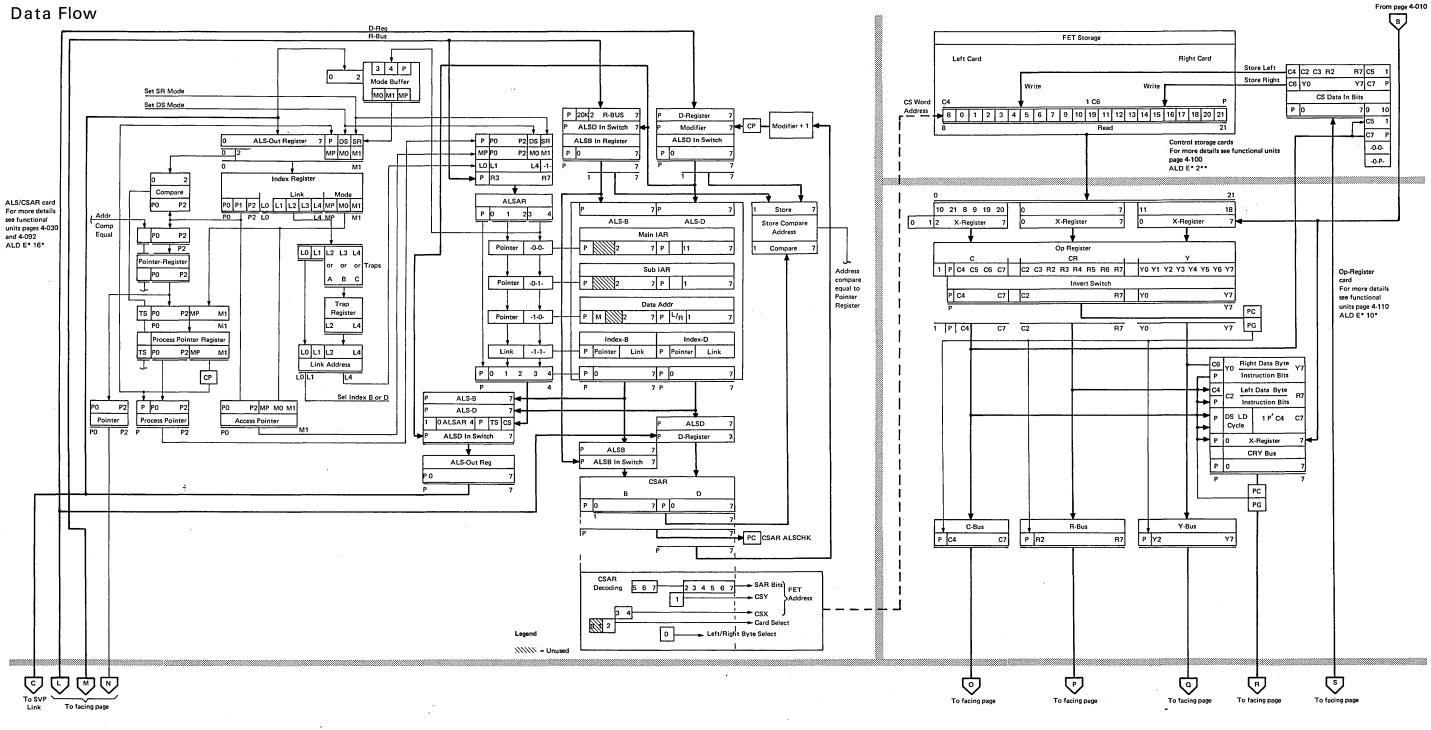

| Data Flow                                                  |       |

| Link to System                                             |       |

| General                                                    | 4-050 |

| IMPL (Initial Microprogram Load)                           |       |

| Link to SVP                                                |       |

| SVP Link Card                                              |       |

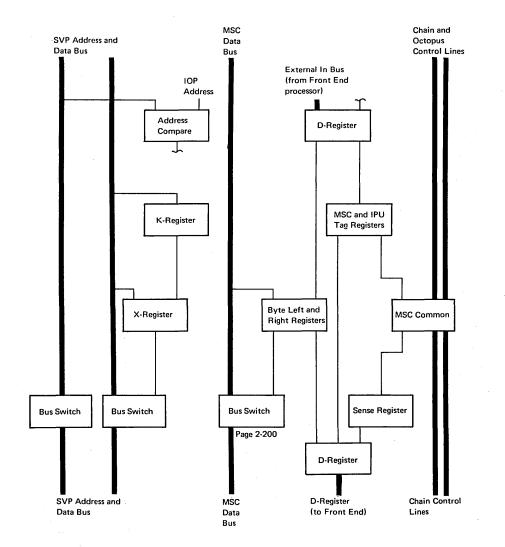

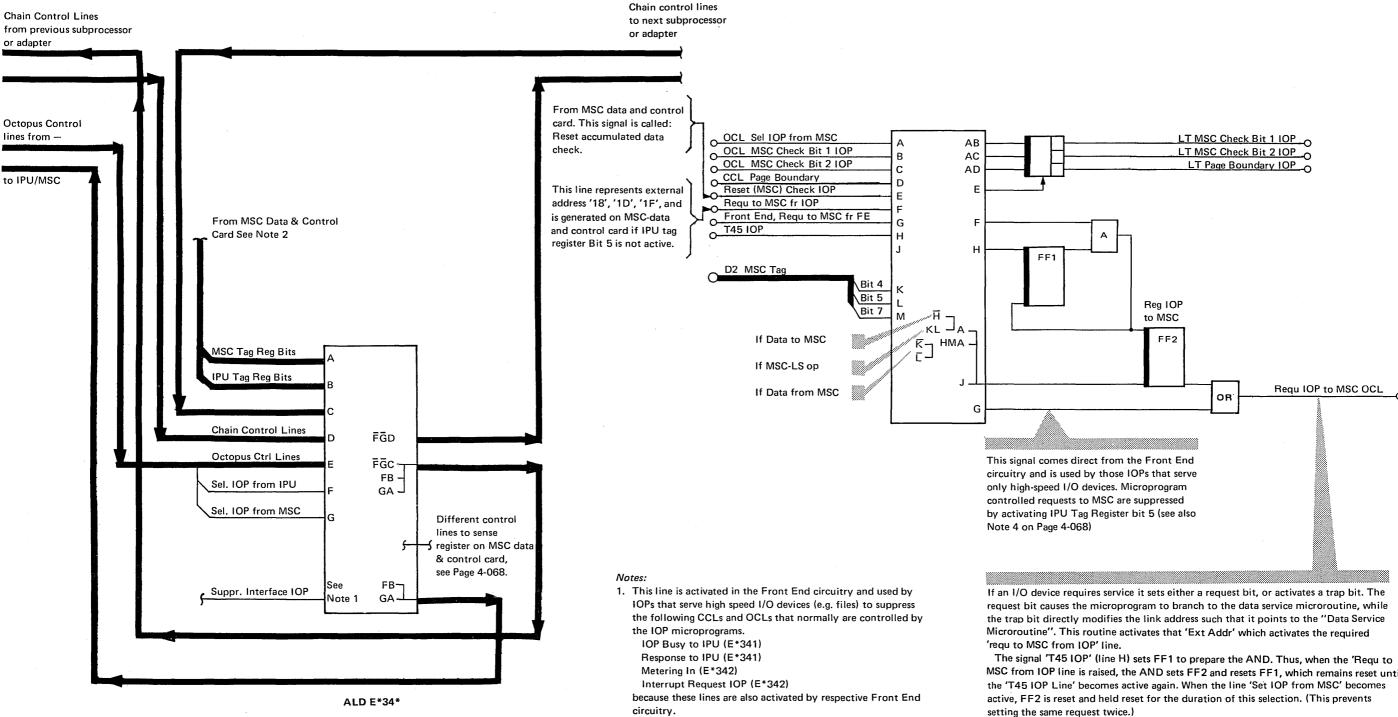

| Link to IPU/MSC                                            |       |

| MSC Common Card                                            |       |

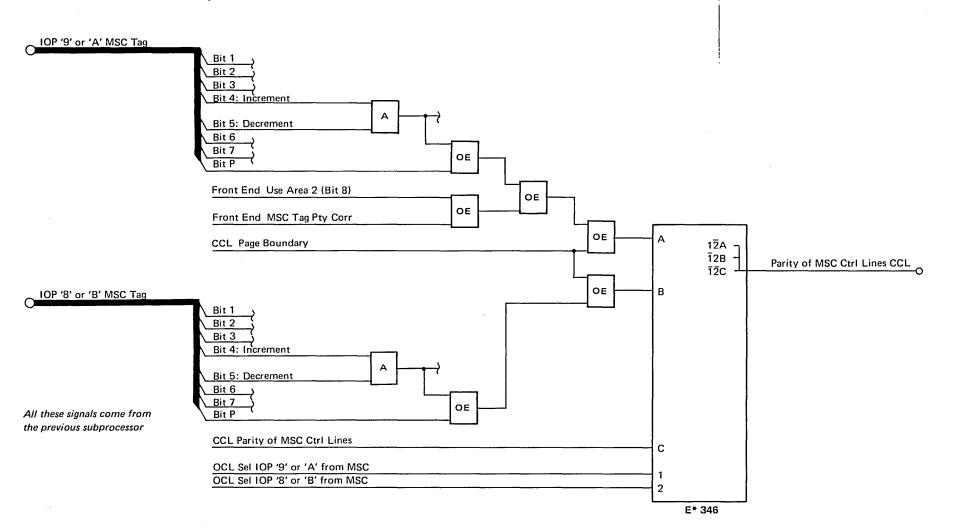

| Generation of 'Parity of MSC Ctrl Lines'                   |       |

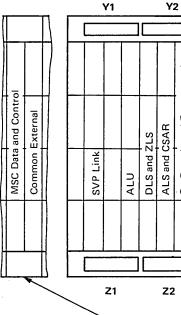

| MSC Data and Control                                       |       |

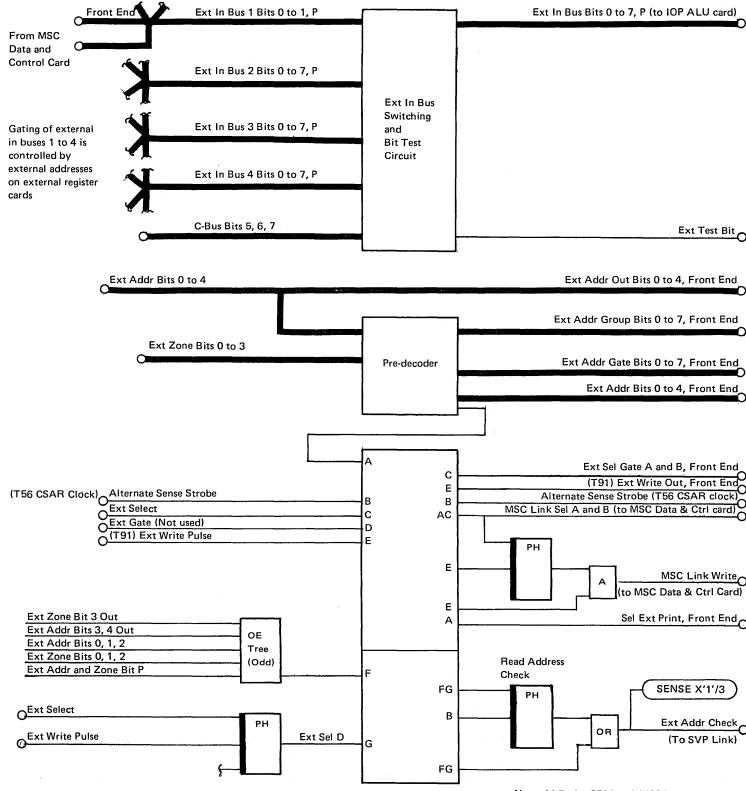

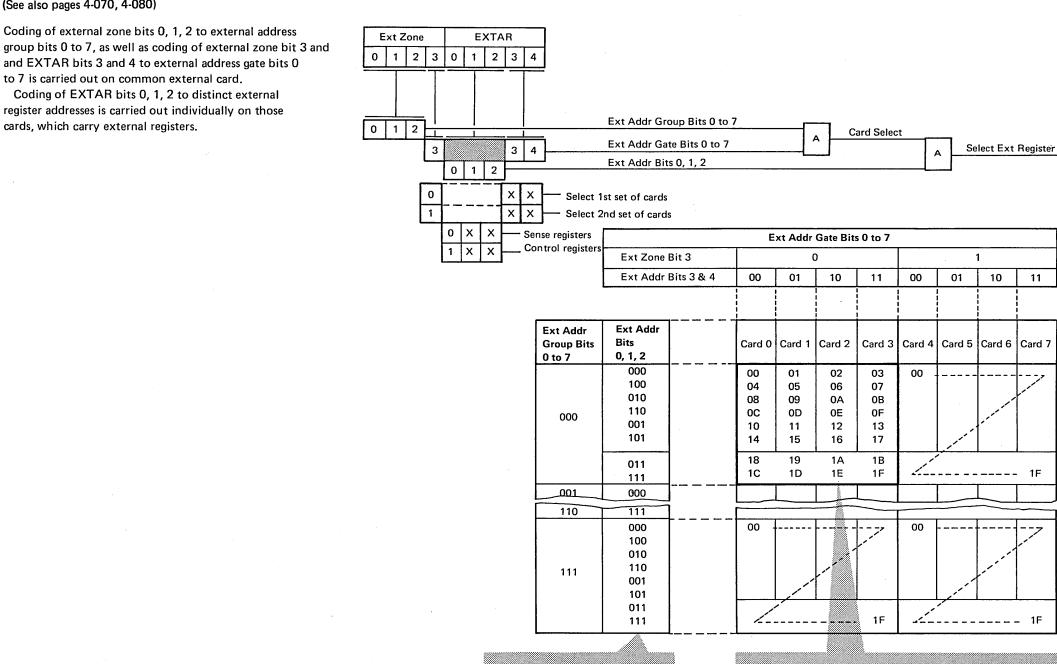

| Link to Front Ends (common external card)                  | 4-070 |

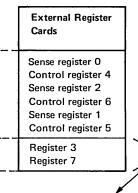

| External Registers                                         |       |

| Typical External Register Addressing and Arrangement for   |       |

| Model 125                                                  | 4-080 |

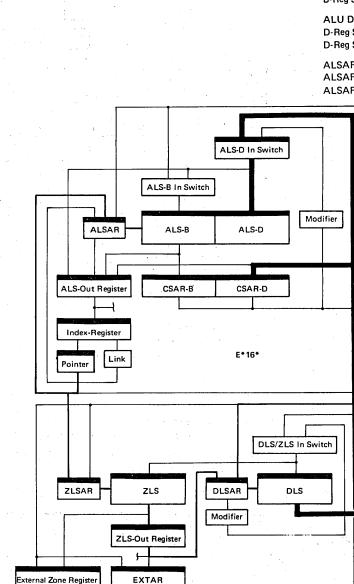

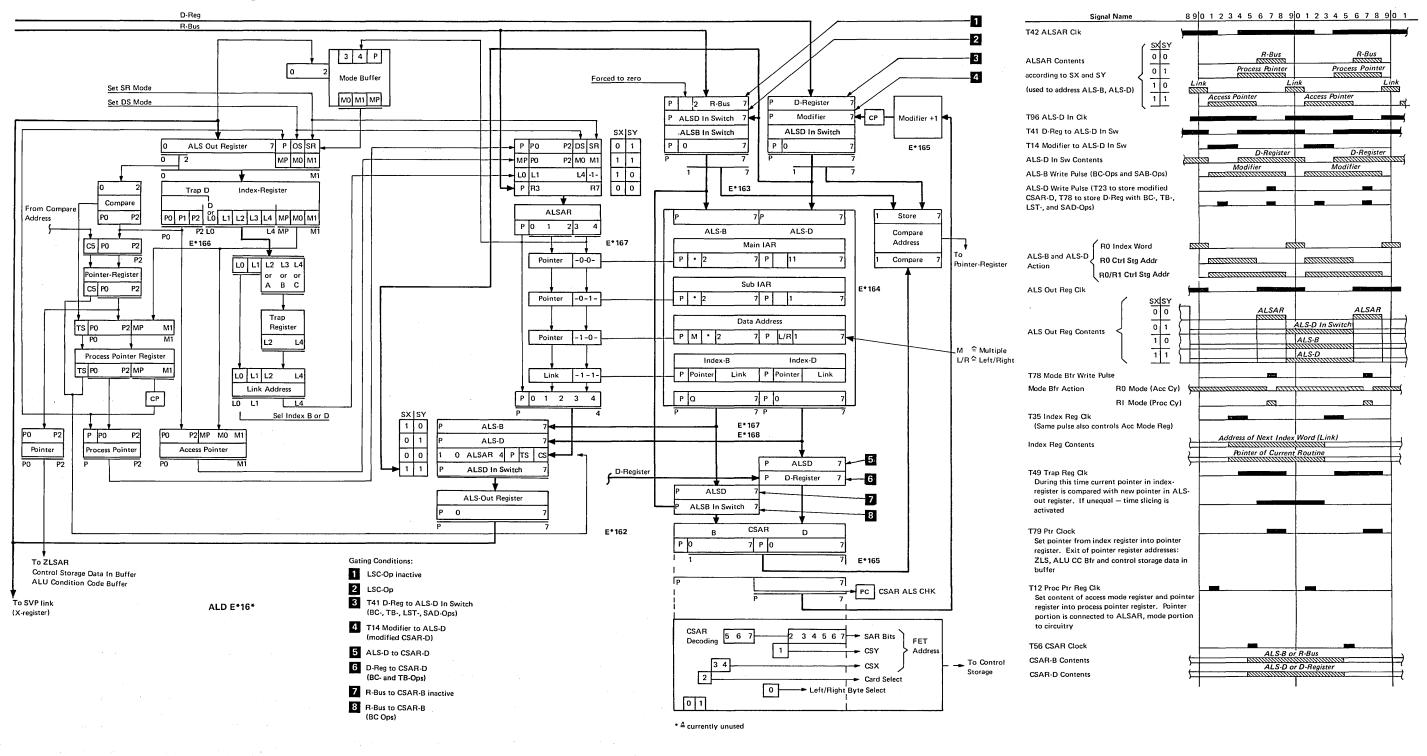

| ALS/CSAR                                                   | 4-090 |

| ALS (Address Local Storage)                                | 4-090 |

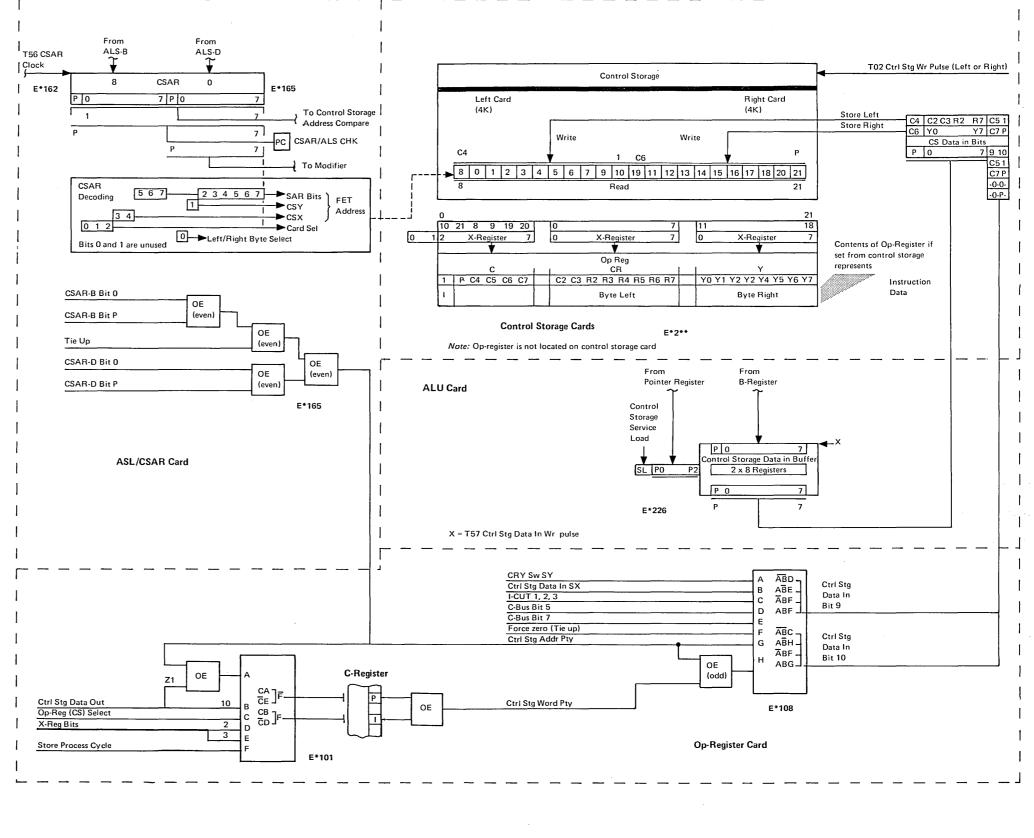

| CSAR (Control Storage Address Register)                    | 4-090 |

| Data and Control Flow, and Timing                          | 4-092 |

| External Register Arrangement and Addressing Scheme        | 4-096 |

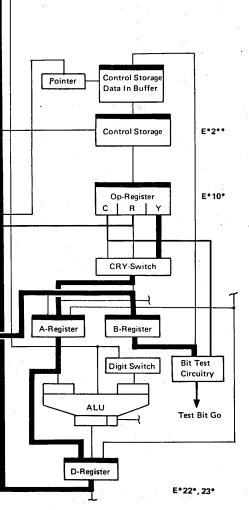

| Control Storage                                            | 4-100 |

| Treatment of Invalid Addresses                             | 4-100 |

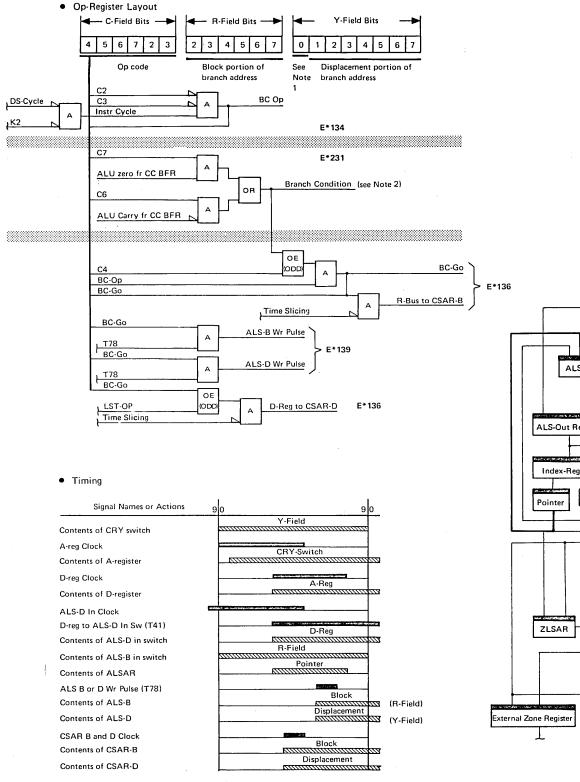

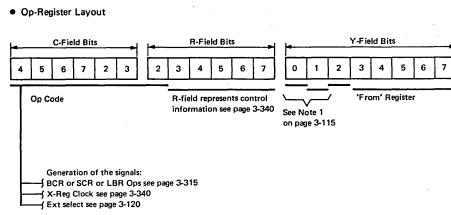

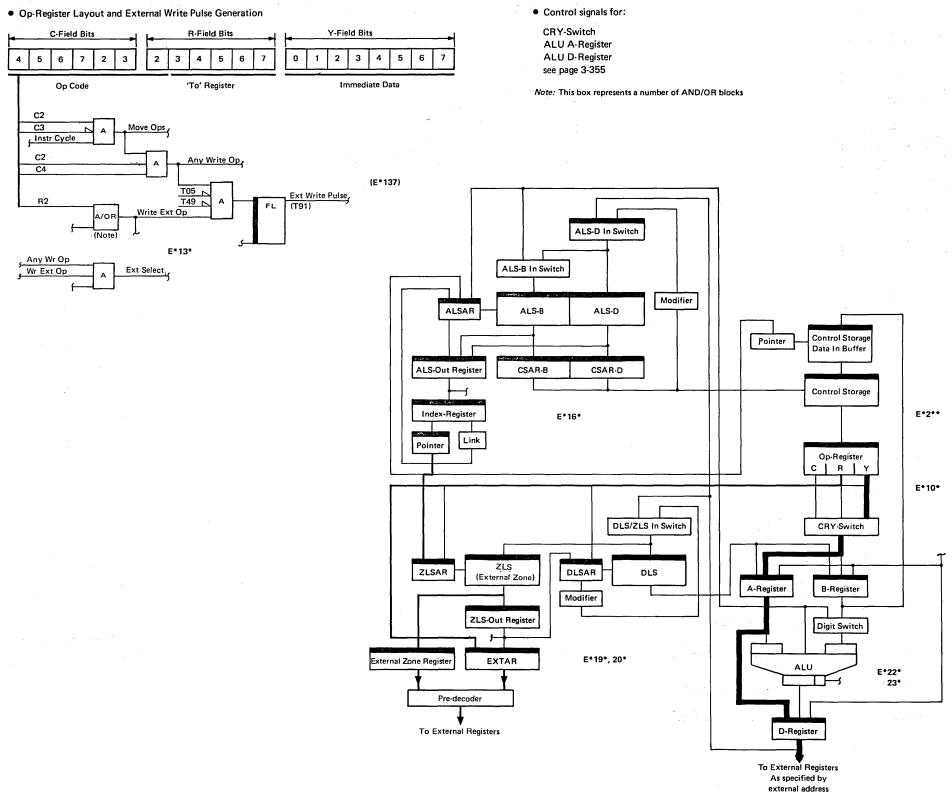

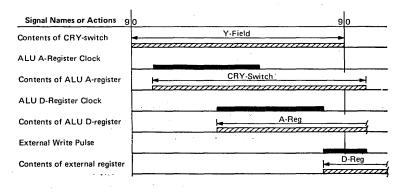

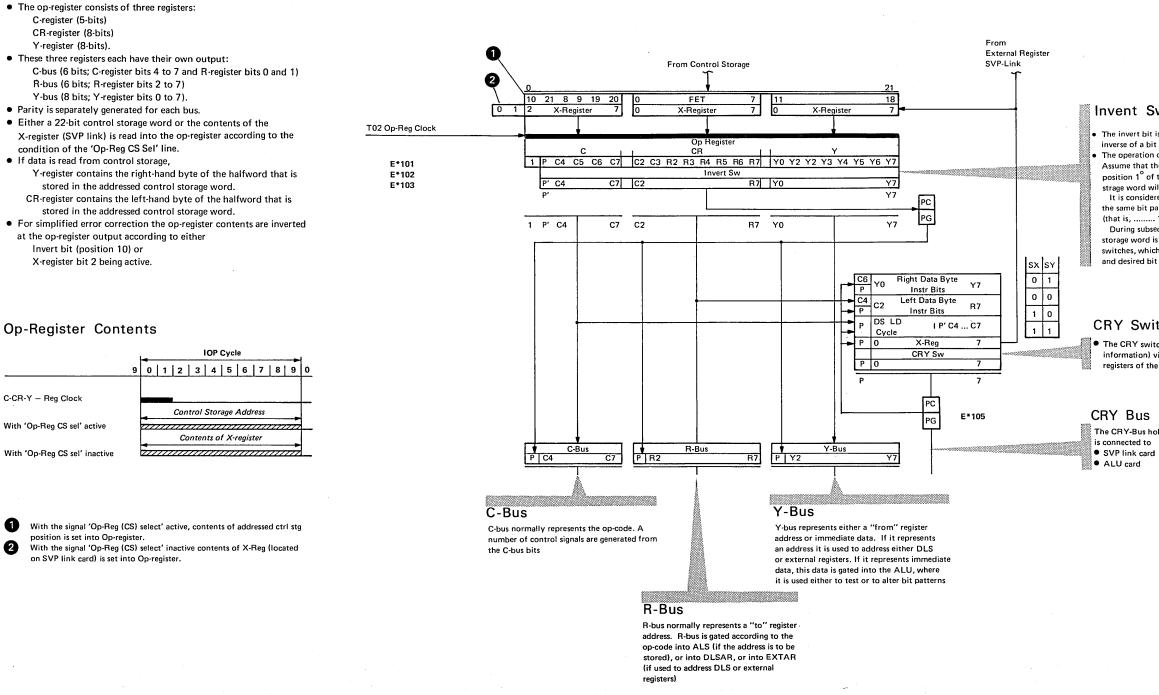

| Op-Register                                                | 4-110 |

| Op-Register Contents                                       | 4-110 |

| Invert Switch                                              | 4-110 |

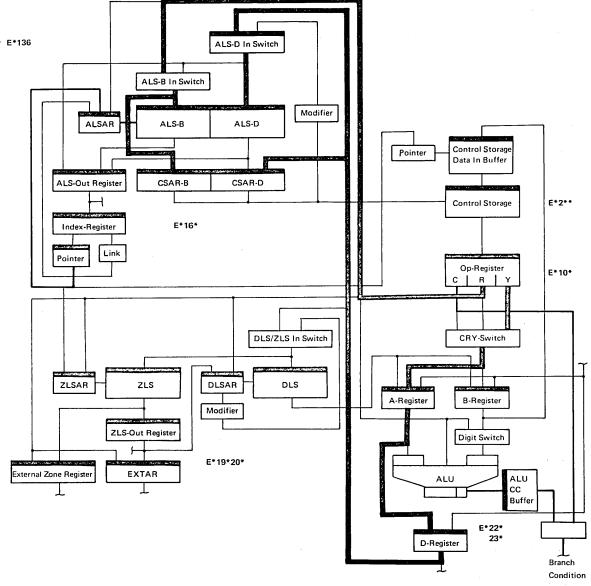

| CRY Switch                                                 |       |

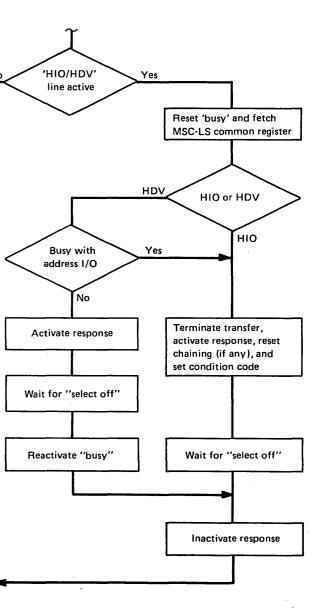

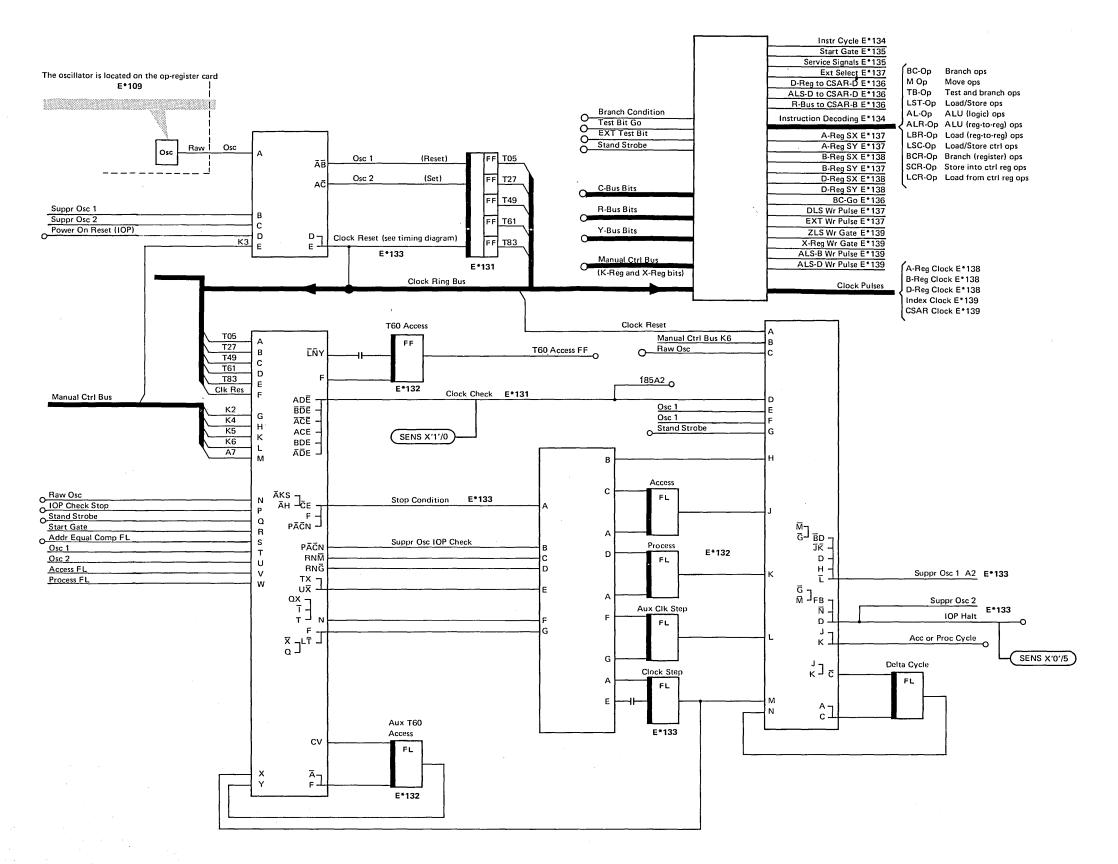

| Op-Decode and Run Control                                  |       |

|                                                            |       |

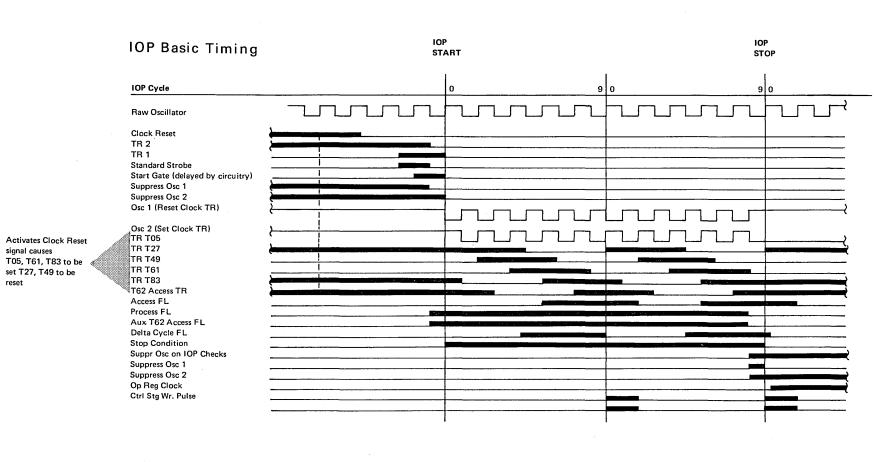

| Basic Timing                          |      |         |          |     |       |          |      |     |    |   |     | 4-125<br>4-125 |

|---------------------------------------|------|---------|----------|-----|-------|----------|------|-----|----|---|-----|----------------|

|                                       |      |         |          |     |       |          |      |     |    |   |     | 4-125          |

| IOP Basic Timing                      |      |         |          |     |       |          |      |     | :  |   |     | 4-125          |

| Miscellaneous IOP Signals             |      |         |          |     | •     |          |      |     | •  |   |     | 4-120          |

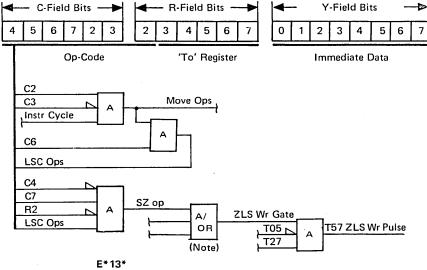

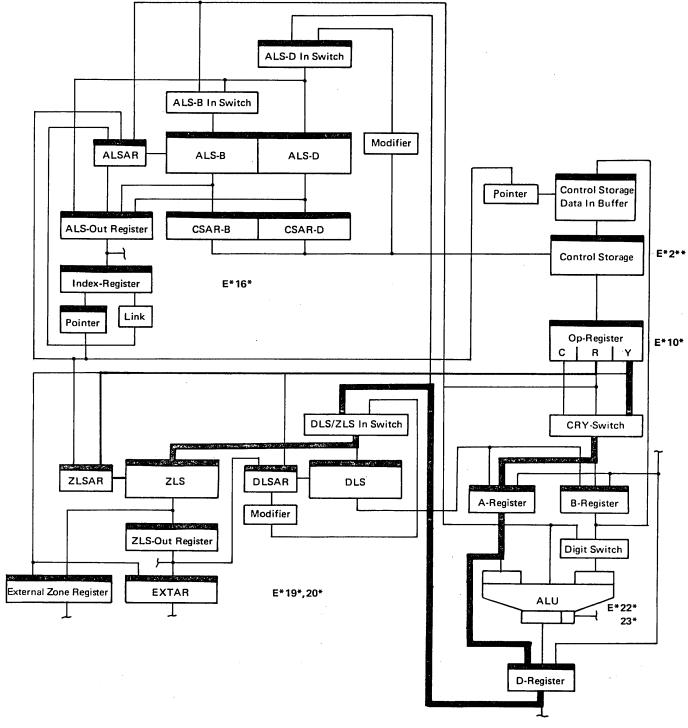

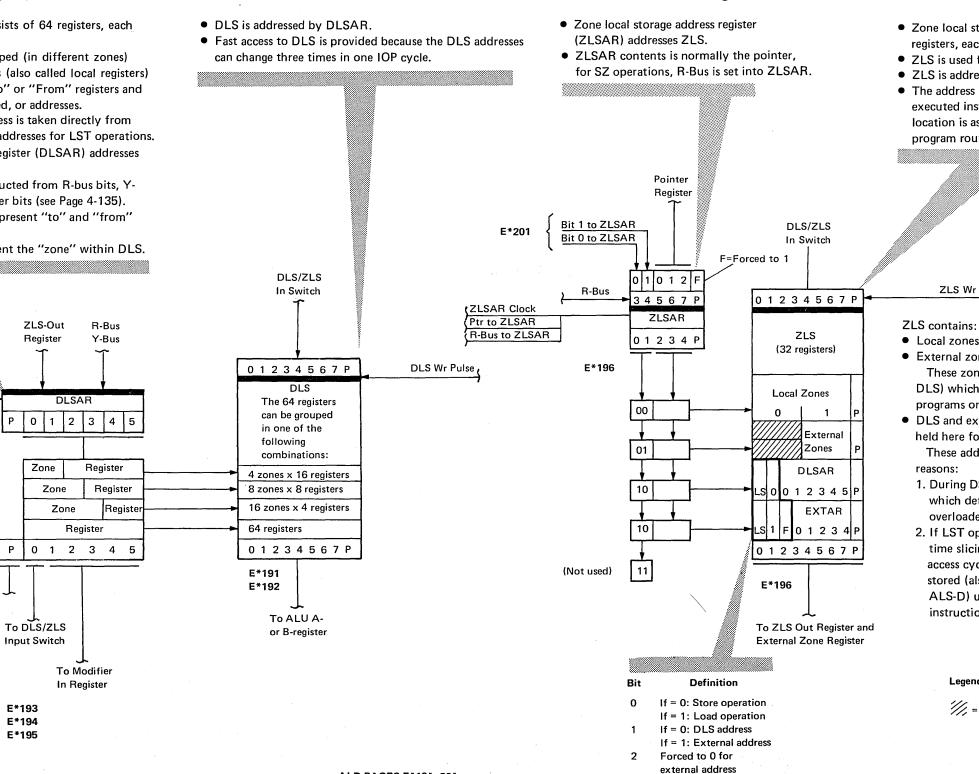

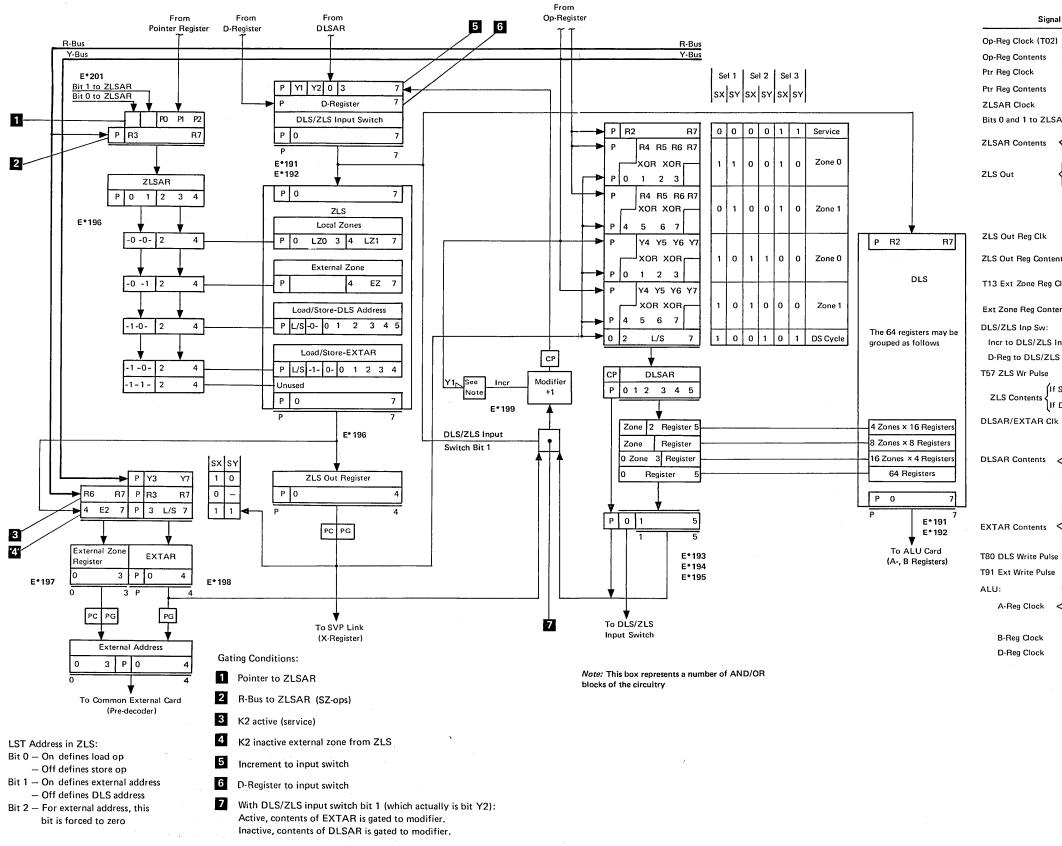

| DLS/ZLS                               |      |         |          |     |       |          |      |     | •  |   |     | 4-130          |

| Zone Local Storage (DLS)              |      |         |          |     |       |          |      |     |    |   |     | 4-130          |

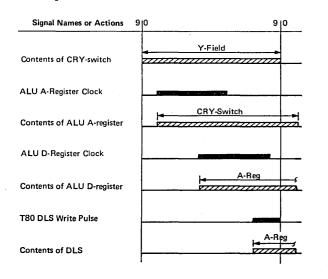

| Data and Control Flow, and Timing     |      |         |          |     |       |          |      |     |    |   |     | 4-135          |

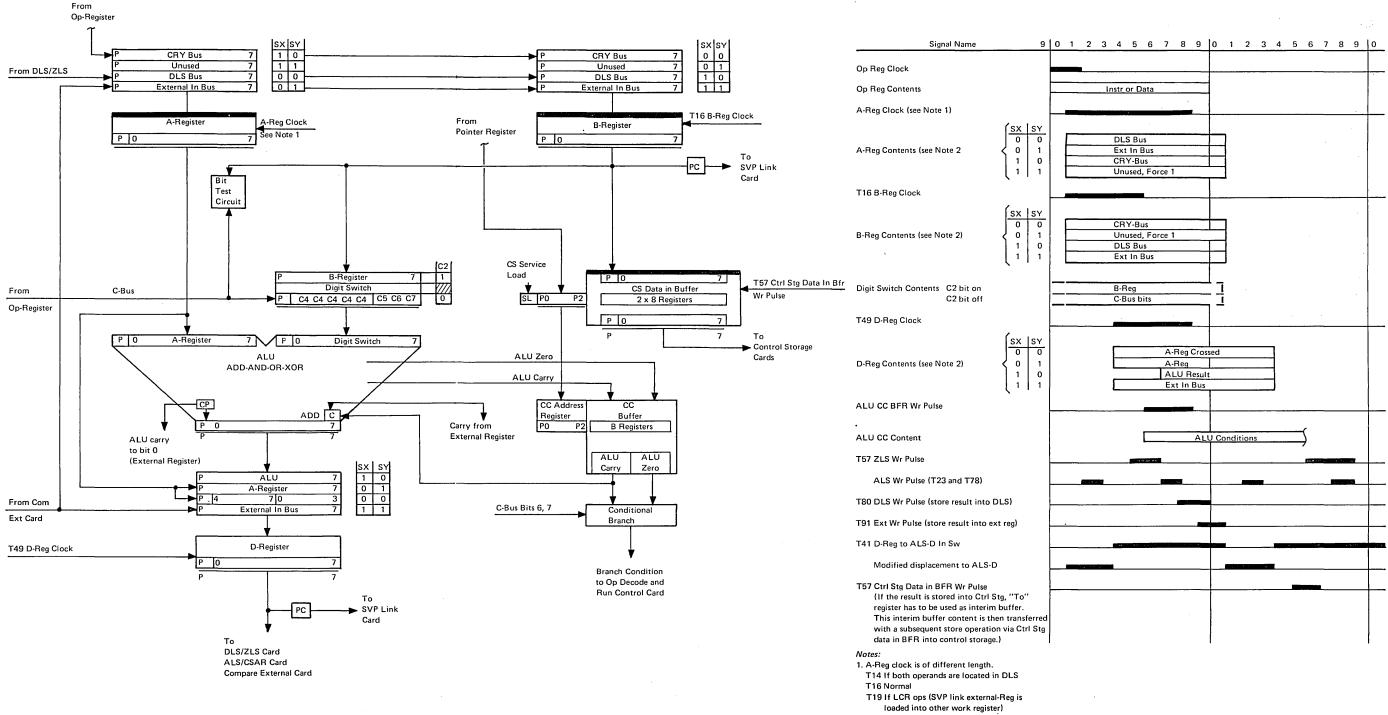

| Arithmetic and Logic Unit (ALU) .     |      |         |          |     |       |          |      |     |    |   |     | 4-140          |

| ALU Operation – Examples              |      |         |          |     |       |          |      |     |    |   |     | 4-140          |

| Specific ALU Signals                  |      |         |          |     |       |          |      |     |    |   |     |                |

| Data and Control Flow, and Timing     |      |         |          |     |       |          |      |     |    |   |     | 4-145          |

|                                       | • •  | •       | •        | •   | •     | •        | •    | •   | •  | • | •   |                |

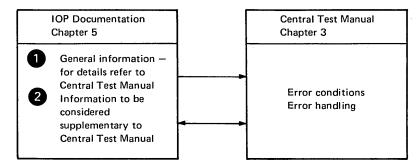

| Chapter 5. Error Conditions           | • •  |         |          |     |       | •        |      |     | •  | • |     | 5-000          |

| Reference to Central Test Manual (CTM | N) : |         |          |     |       |          |      |     |    |   |     | 5-000          |

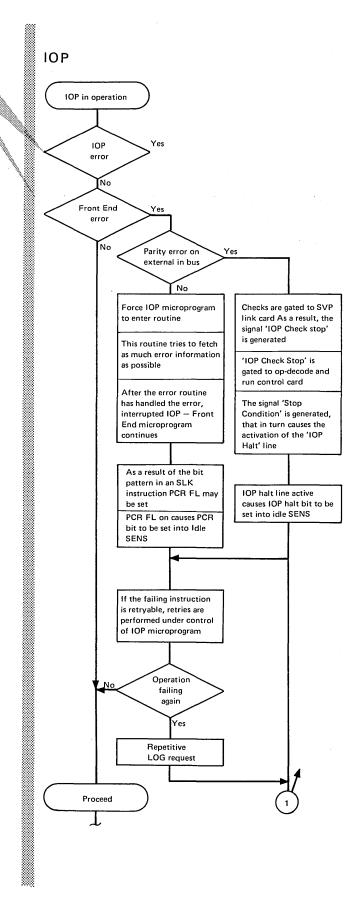

| Unusual or Exceptional Conditions .   |      |         |          |     |       |          |      |     |    |   |     | 5-010          |

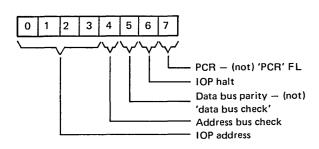

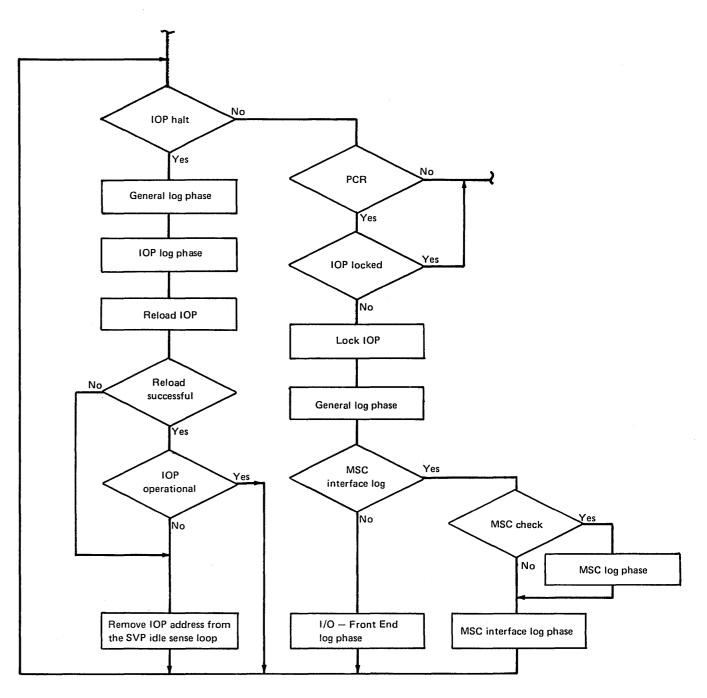

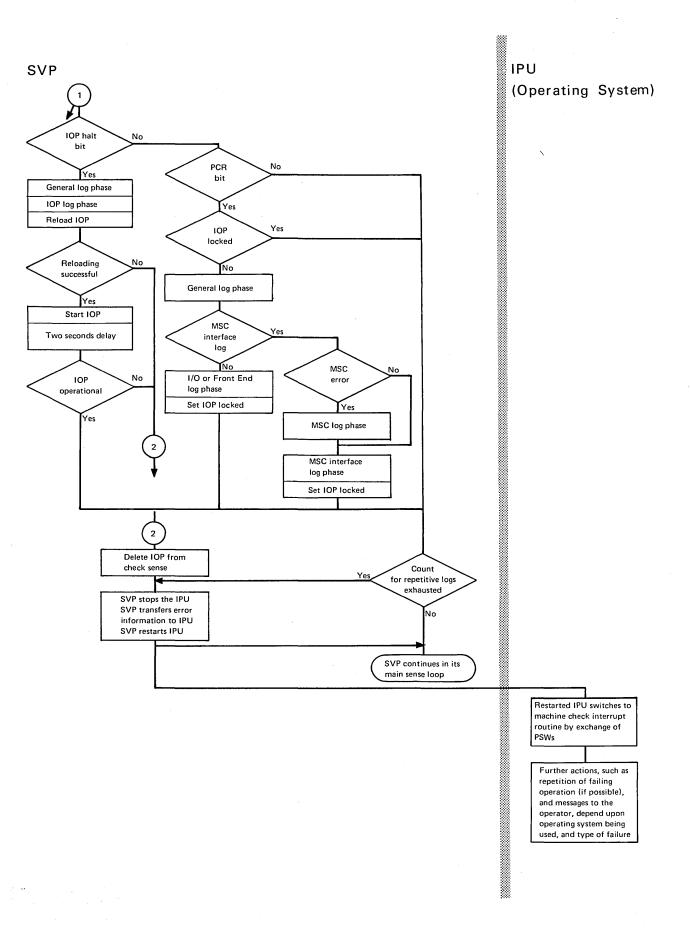

| Error Handling                        |      |         |          |     |       |          |      |     |    |   | • · | 5-020          |

|                                       |      |         |          |     |       |          |      |     |    |   |     | 5-020          |

| SVP                                   |      |         | •        |     |       | •        |      |     |    |   |     | 5-020          |

|                                       |      |         |          |     |       |          |      |     | •  |   |     | 5-020          |

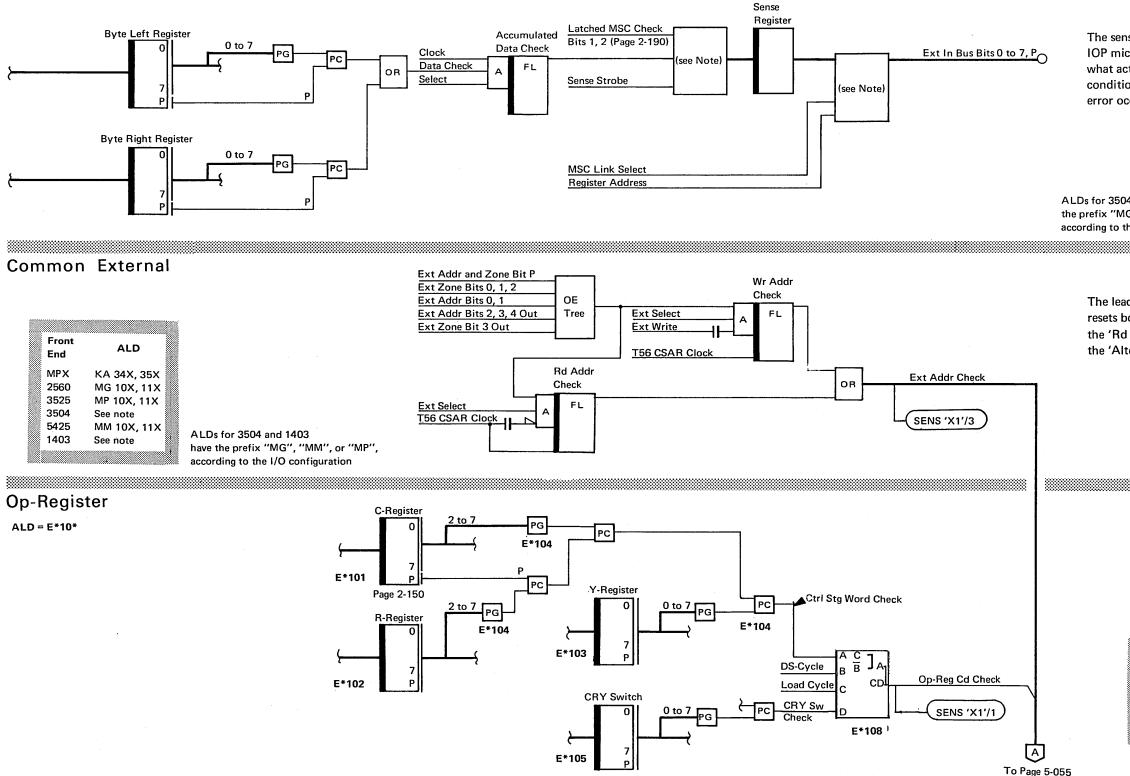

| IOP Error Circuits                    |      |         |          |     |       |          |      |     |    |   |     | 5-050          |

| MSC Data and Control                  |      |         |          |     |       |          |      |     |    |   |     | 5-050          |

| Common External                       |      |         |          |     |       |          |      |     |    |   |     | 5-050          |

| Op-Register                           |      |         |          |     |       |          |      |     |    |   |     | 5-050          |

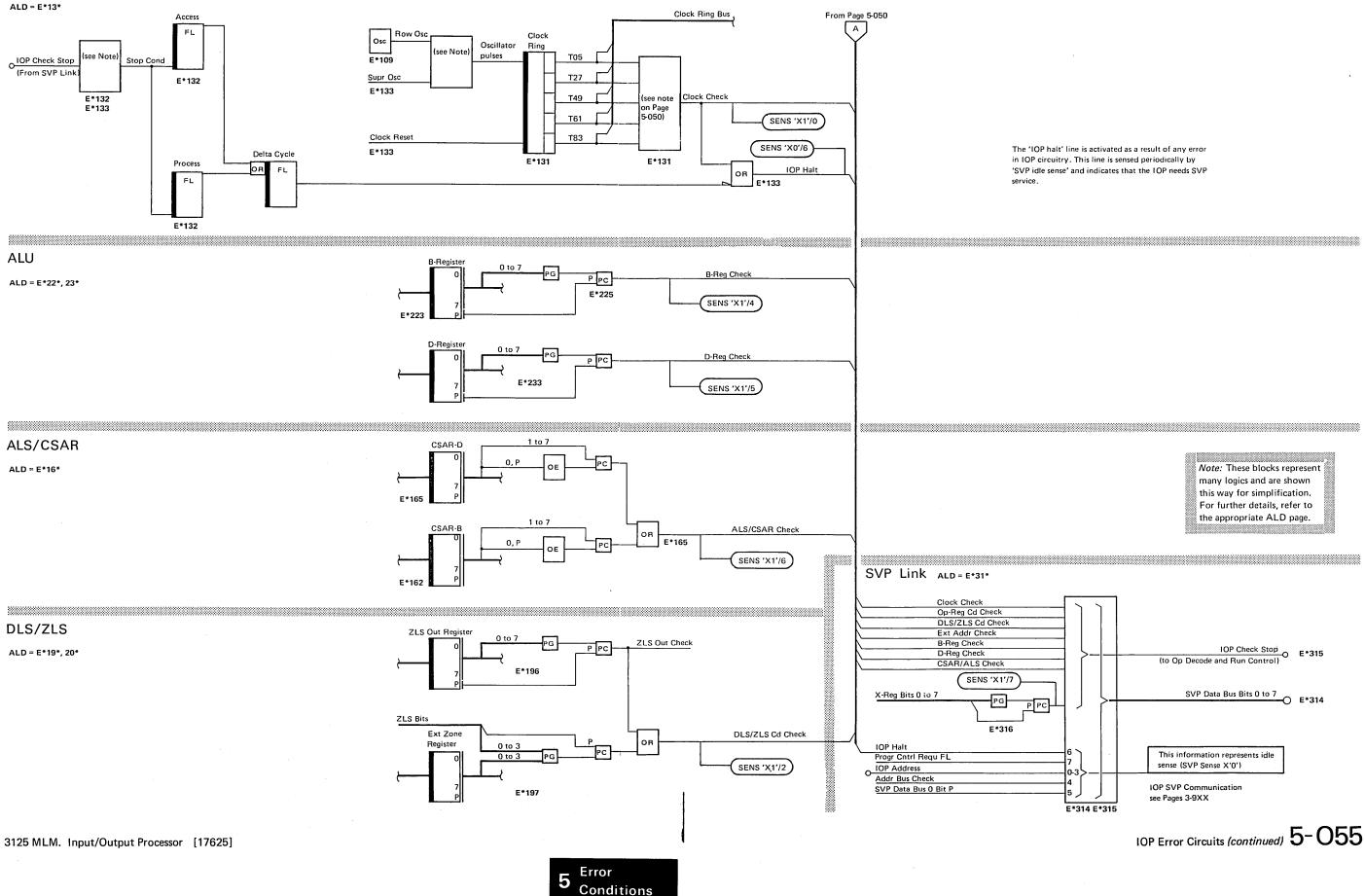

|                                       |      |         |          |     |       |          |      |     |    |   |     | 5-055          |

| ALU                                   |      |         |          |     |       |          |      |     |    |   |     | 5-055          |

| ALS/CSAR                              |      |         |          |     |       |          |      |     |    |   |     | 5-055          |

| DLS/ZLS                               |      |         |          |     |       |          |      |     |    |   |     | 5-055          |

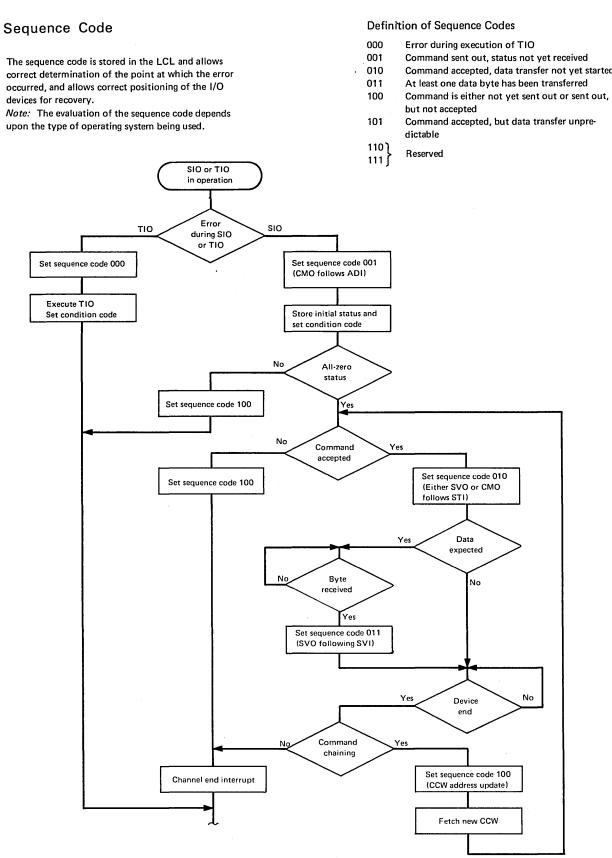

| LCL Layout and Sequence Codes .       |      |         |          |     |       |          |      |     |    |   |     | 5-080          |

| LCL (or ECSW) Layout                  |      |         |          |     |       |          |      |     |    |   |     | 5-080          |

| Sequence Code                         |      |         |          |     |       |          |      |     | •  |   |     | 5-080          |

|                                       |      |         |          |     |       |          |      |     |    |   |     |                |

| Chapter 6. Maintenance Information    |      |         | •        | •   | •     | •        | •    | •   | •  | • | •   | 6-000          |

| Reference to Central Test Manual (CTM | •    |         |          | •   |       | •        | •    | •   | •  | • | •   | 6-000          |

| Maintenance Concept                   |      |         |          |     |       |          | •    | •   | •  | • | •   | 6-010          |

| Diagnostic Techniques                 |      |         |          |     |       | •        | •    | •   | •  | • | •   | 6-010          |

| Manual Operations                     | •    |         | •        | •   | •     | •        | •    | •   | •  | • | •   | 6-010          |

| Scope Sense                           | •    |         | •        | •   | •     | •        | •    | •   | •  | • | •   | 6-010          |

| Matrix                                | •    | •••     | •        | •   | •     | •        | •    | •   | •  | • | •   | 6-010          |

|                                       |      |         |          |     |       |          |      |     |    |   |     | 7 010          |

| Chapter 7. Reference Information .    | •    | •••     | •        | •   | •     | •        | •    | •   | •  | • | •   | 7-010          |

| Abbreviations and Glossary            | •    | • •     | •        | •   | •     | •        | •    | •   | •  | • | •   | 7-010          |

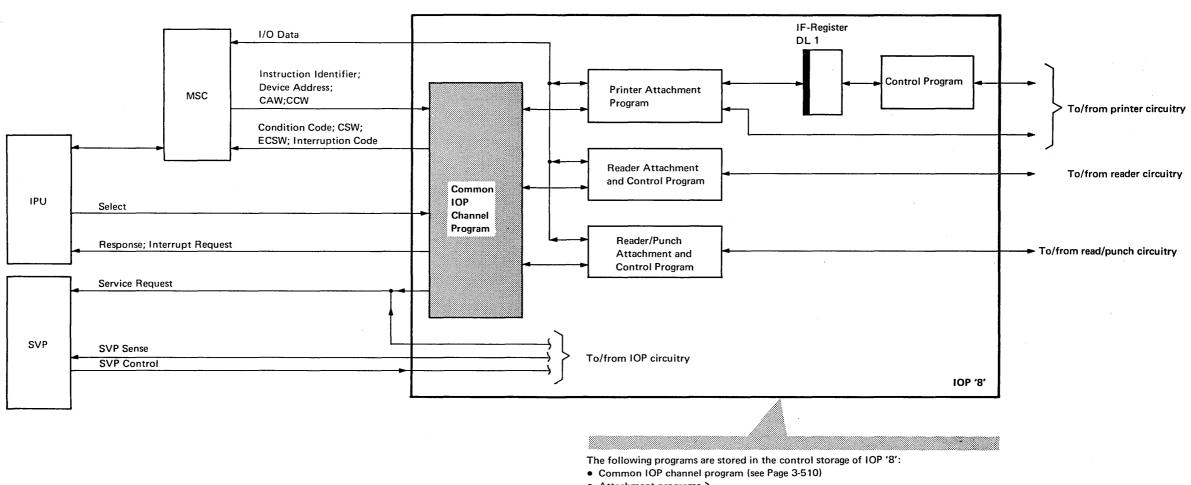

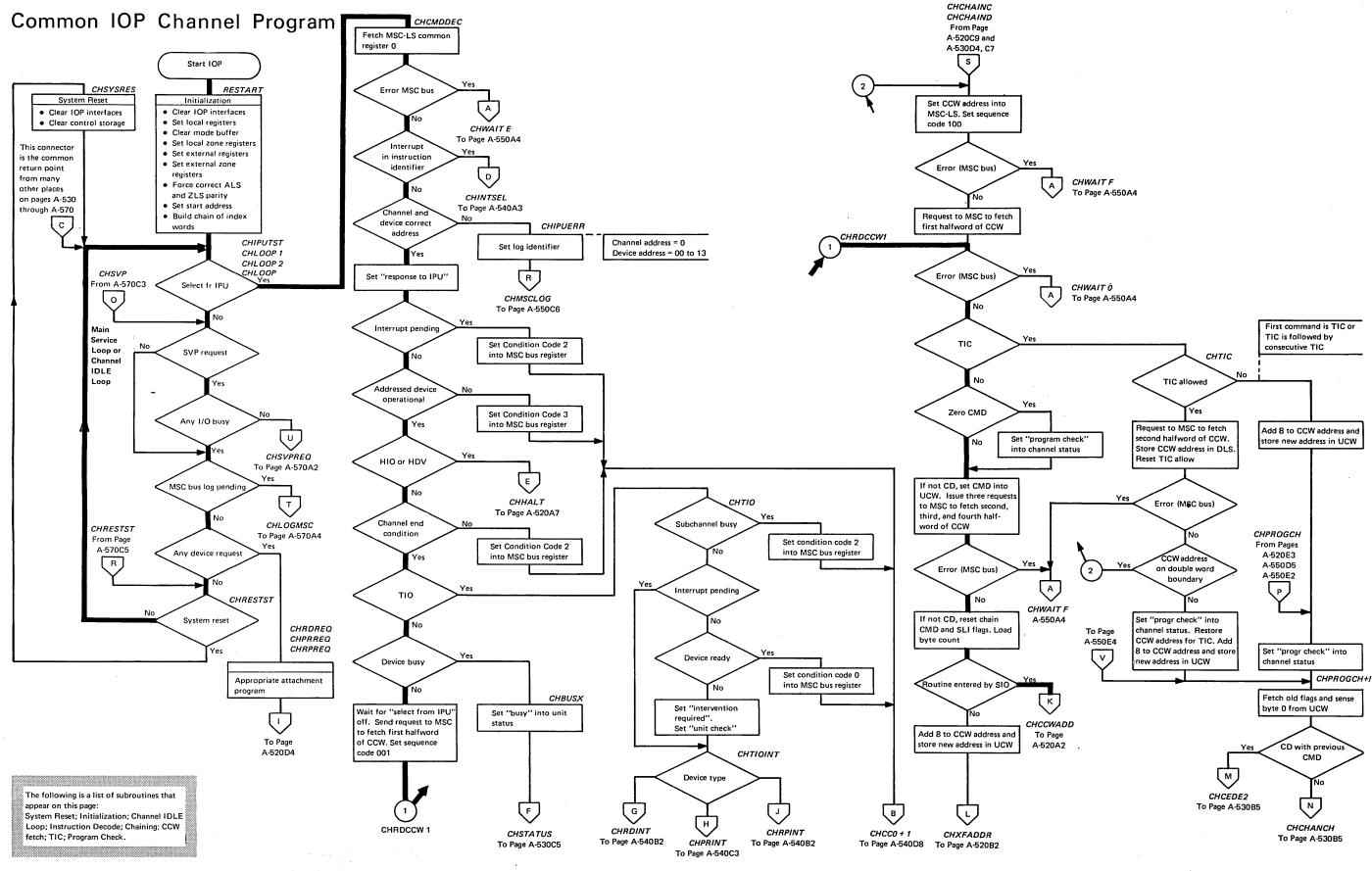

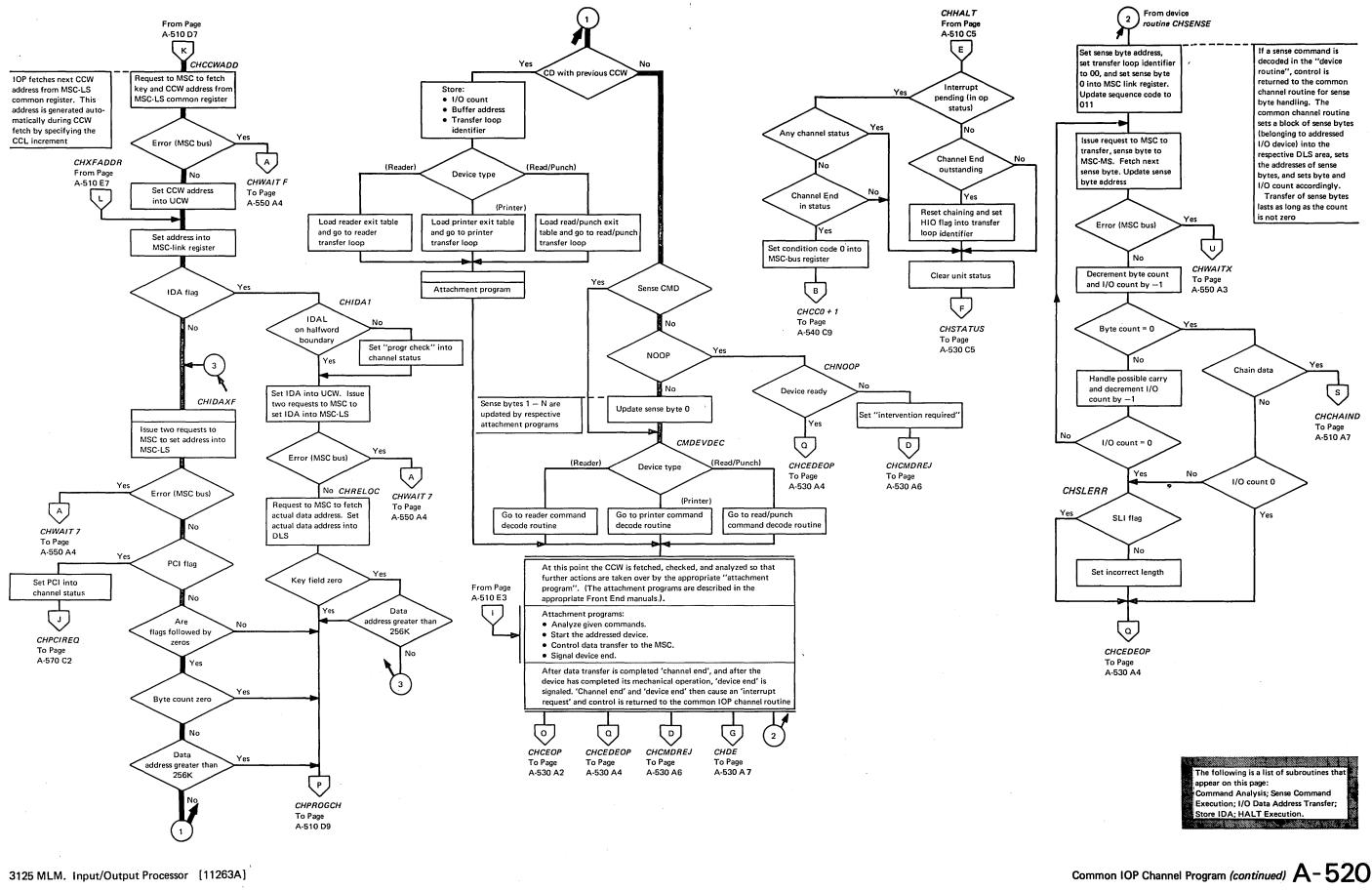

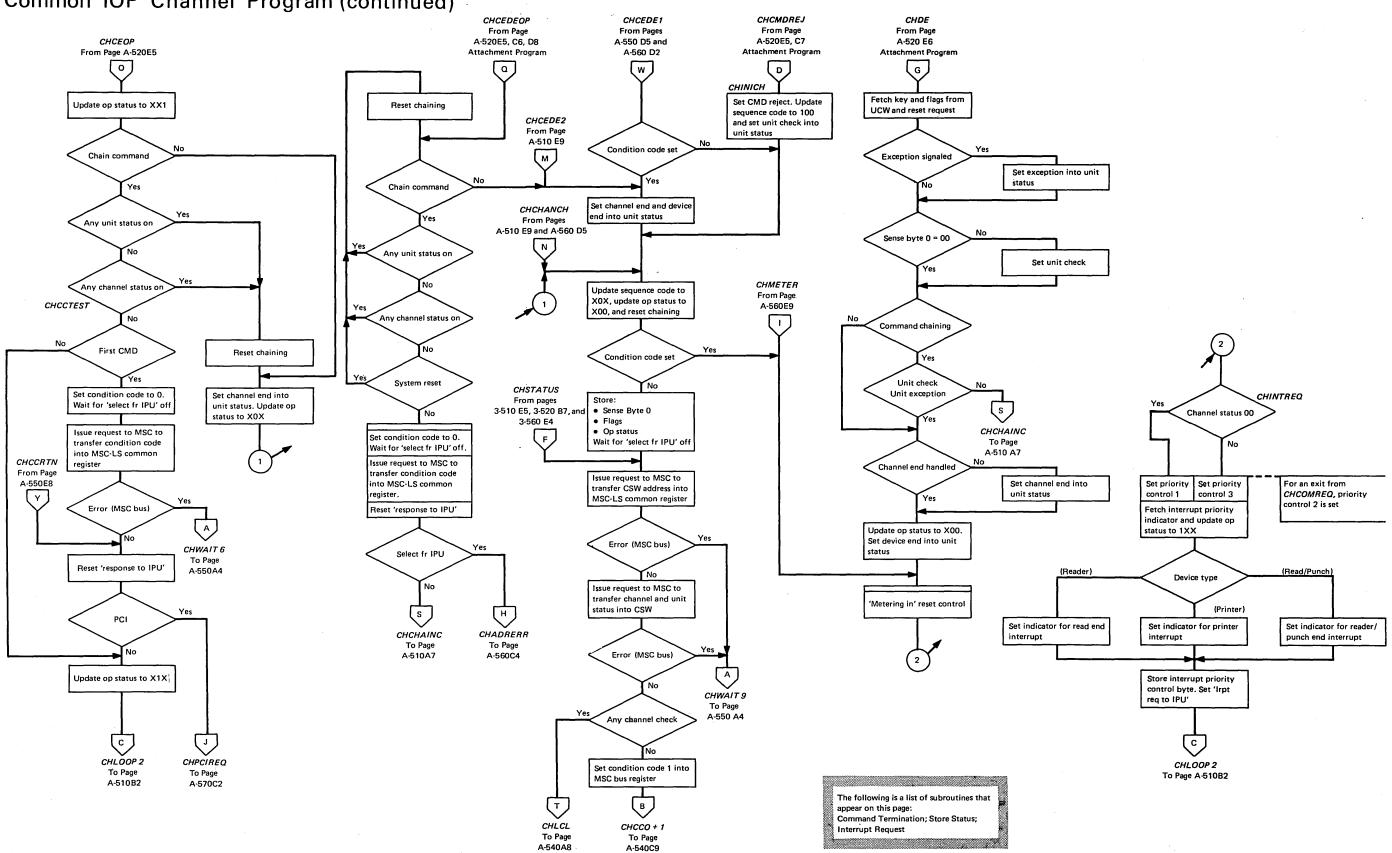

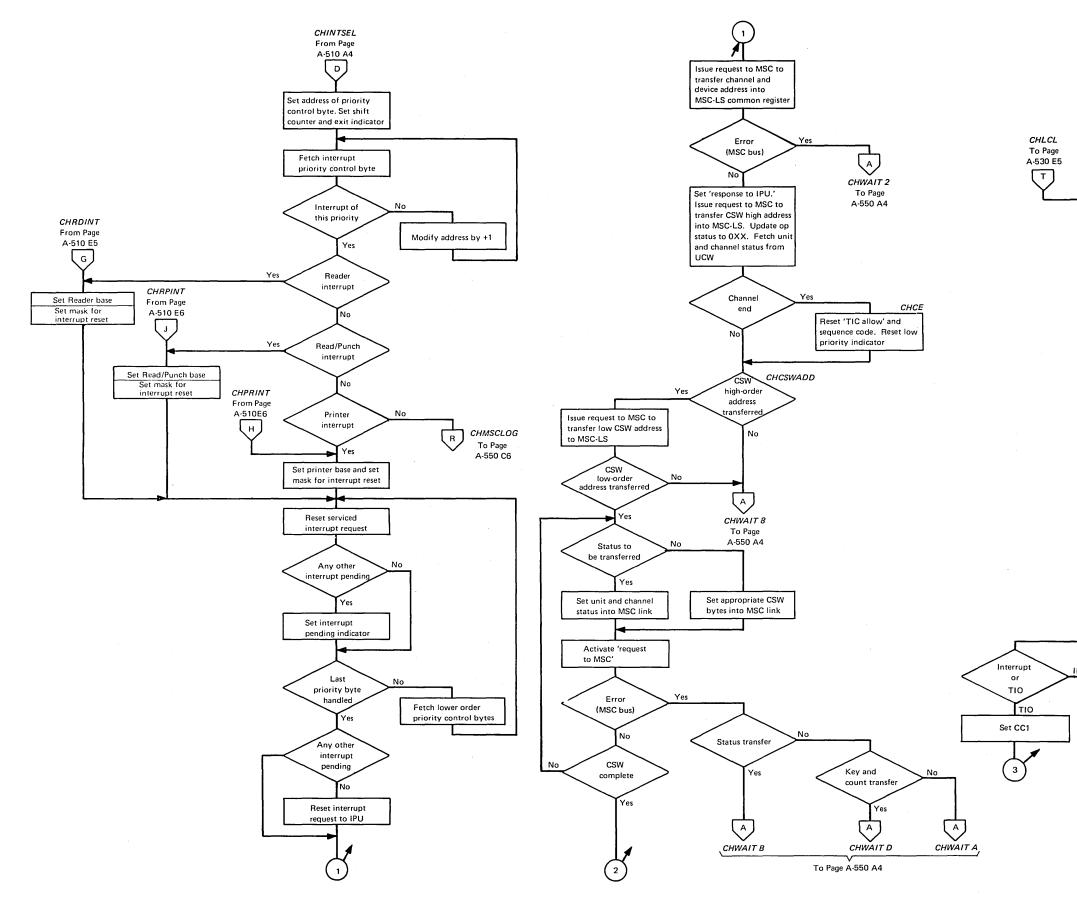

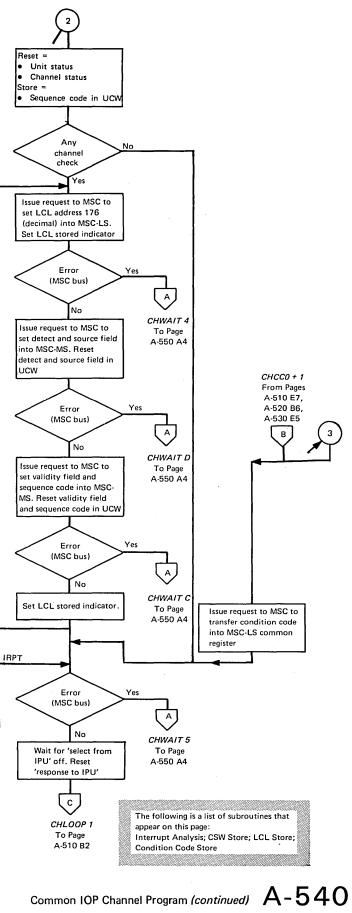

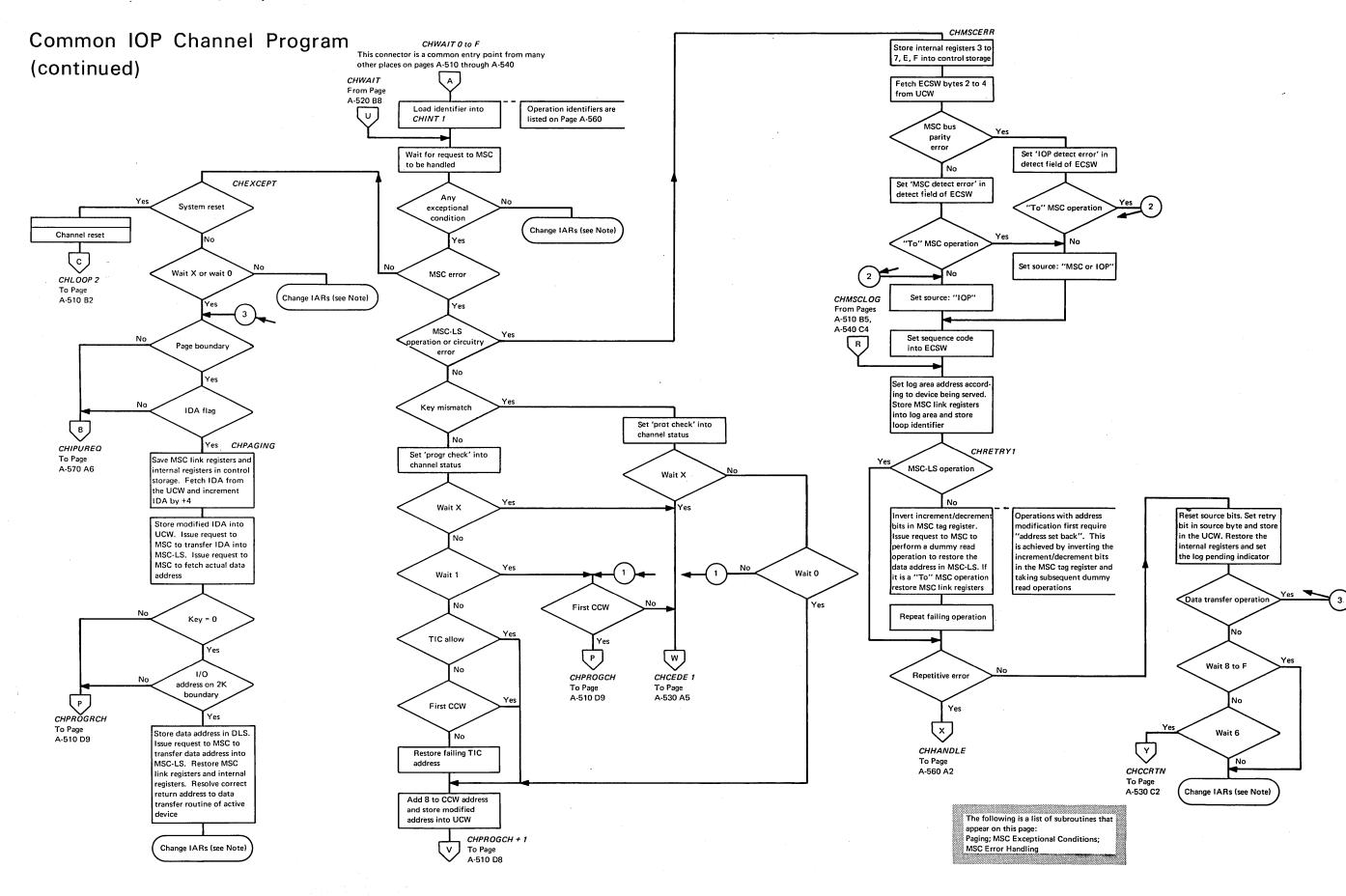

| Appendix A. Information Particular to | o IC | )P '8'  | · .      |     |       |          |      |     |    |   |     | A-500          |

| Common IOP Channel Program Link to    |      |         |          | SI  | VP    | an       | Ы    |     |    |   |     |                |

| Attachment Programs                   | 5 11 | 5, 10   |          | , 0 | * 1 / | , ui     |      |     |    |   |     | A-500          |

| -                                     | •    | •••     | •        | •   | •     | •        | •    | •   | •  | • | :   |                |

|                                       | -    | •••     | •        | •   | •     | •        | •    | •   | •  | • | •   | A-510          |

| Internal Register Assignments – Comn  |      | <br>Cha | •<br>nne | P   | roa   | •<br>ran | n () | DI: | S) | • | •   | A-590          |

| milemai negister Assignments – Comm   |      | ona     |          |     | . 09  |          |      |     | -1 | • | ·   |                |

| Index                                 |      |         |          |     | •     | •        |      |     |    | • | •   | X-001          |

2 Principles of Operation 1 Introduction

**3** Operational Details

**4** Functional Units

### Contents (continued)

V

## Safety

## **Personal Safety**

Personal safety cannot be over-emphasized; it is a vital part of customer engineering. To ensure your safety and that of co-workers, always observe the safety precautions given during your safety training and adhere to the following:

### **General Safety Practices**

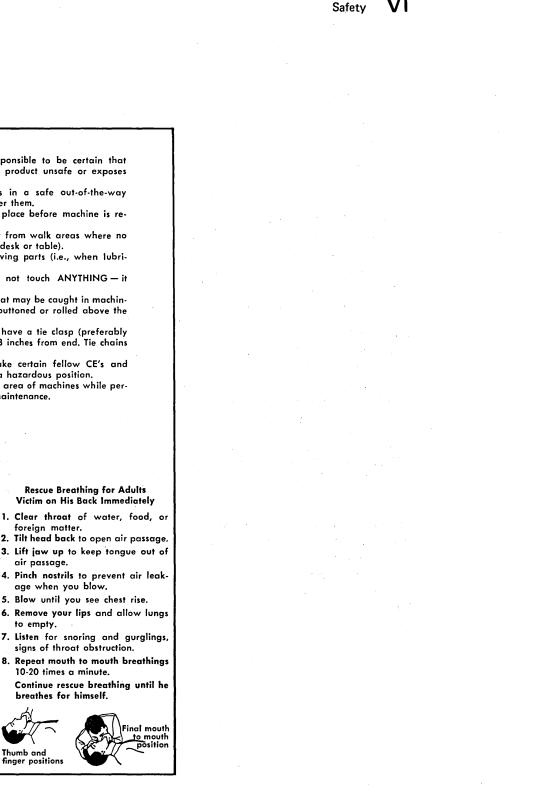

Observe the general safety practices and the procedure for performing artificial respiration that are outlined in CE Safety Practices card, order no. S229-1264 (shown here).

### Grounding

Ground current may reach dangerous levels. Never operate the system with the grounding conductor removed.

### Line-Powered Equipment

Ground all line-powered test equipment through the third-wire grounding conductor in the power cord of the machine being tested.

### Machine Warning Labels

Heed the warning labels placed in hazardous areas of the machines.

### **CE SAFETY PRACTICES**

All Customer Engineers are expected to take every safety precaution possible and observe the following safety practices while maintaining IBM equipment:

- 1. You should not work alone under hazardous conditions or around equipment with dangerous voltage. Always advise your manager if you MUST work alone.

- 2. Remove all power AC and DC when removing or assembling major components, working in immediate area of power supplies, performing mechanical inspection of power supplies and installing changes in machine circuitry.

- 3. Wall box power switch when turned off should be locked or tagged in off position. "Do not Operate" tags, form 229-1266, affixed when applicable. Pull power supply cord whenever possible.

- 4. When it is absolutely necessary to work on equipment having exposed operating mechanical parts or exposed live electrical circuitry anywhere in the machine, the following precautions must be followed:

- a. Another person familiar with power off controls must be in immediate vicinity.

- b. Rings, wrist watches, chains, bracelets, metal cuff links, shall not be worn.

- c. Only insulated pliers and screwdrivers shall be used.

- d. Keep one hand in pocket.

- e. When using test instruments be certain controls are set correctly and proper capacity, insulated probes are used.

- f. Avoid contacting ground potential (metal floor strips, machine frames, etc. - use suitable rubber mats purchased locally if necessary).

- 5. Safety Glasses must be worn when: a. Using a hammer to drive pins, riveting, staking, etc.