Processing Unit Multiplexer Channel

# Maintenance Library

SY33-1067-1

#### Third Edition (August, 1973)

This manual is a major revision of, and makes obsolete, SY33-1067-0; it also obsoletes the preliminary manual ZZ33-1067 (IBM Confidential). Changes are continually made to the information in this manual; any such changes will be reported in subsequent revisions or Technical Newsletters.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

Forms for readers' comments are provided at the back of the manual. If the forms have been removed, comments may be addressed to IBM Laboratories, Product Publications, Dept. 3179, 703 Boeblingen/Wuertt, P.O. Box 210, Germany. Comments become the property of IBM.

© Copyright International Business Machines Corporation 1973.

# Preface

This manual describes the theory of operation of the multiplexer channel and provides maintenance information for the multiplexer channel. Readers of the manual should have a basic understanding of IBM system concepts. The manual supplements the System/370 Model 125 CE course and serves also as a recall aid; it is not intended for self-education.

The manual is divided into seven chapters. *Chapter 1* contains a general introduction to channel operations, together with the overall data flow of System/370 Model 125 and physical locations. *Chapter 2* describes the principles of operation of the multiplexer channel. *Chapter 3* describes the operation of the multiplexer channel in detail. Flowcharts of the MPX microprogram show the major objectives of the operations and instructions. *Chapter 4* describes the major units of the multiplexer channel. Maintenance information is given in *Chapters 5 and 6. Chapter 7* contains a combined abbreviations list and glossary of terms. Common abbreviations for the system and an explanation of the symbols used are given in *IBM 3125 Processing Unit, General System Information,* Maintenance Library Manual, Order No. SY33-1059.

## **Prerequisite Reading**

*IBM 3125 Processing Unit, Microinstructions,* Maintenance Library Manual, Order No. SY33-1058.

*IBM 3125 Processing Unit, General System Information, Maintenance Library Manual, Order No. SY33-1059.*

*IBM 3125 Processing Unit, Input/Output Processor,* Maintenance Library Manual, Order No. SY33-1063.

IBM System/360 and System/370 I/O Interface Channel to Control Unit,

Original Equipment Manufacturers Information Manual, Order No. GA22-6974.

## **Associated Publications**

*IBM System/360 Principles of Operation,* Systems Library Manual, Order No. GA22-6821.

*IBM System/370 Principles of Operation,* Systems Library Manual, Order No. GA22-7000.

*IBM 3125 Processing Unit, Power Supplies,* Maintenance Library Manual, Order No. SY33-1060.

*IBM 3125 Processing Unit, Main Storage Controller,* Maintenance Library Manual, Order No. SY33-1061.

*IBM 3125 Processing Unit, Instruction Processing Unit,* Maintenance Library Manual, Order No. SY33-1062.

*IBM 3125 Processing Unit, Magnetic Tape Adapter,* Maintenance Library Manual, Order No. SY33-1064.

*IBM 3125 Processing Unit, Service Processor Subsystem,* Maintenance Library Manual, Order No. SY33-1065.

Section 1: Service Processor (SVP).

Section 2: Console Disk File.

Section.3: Display Unit and Keyboard.

*IBM 3125 Processing Unit, Main Storage,* Maintenance Library Manual, Order No. SY33-1066.

*IBM 3125 Processing Unit, 2560 Attachment, Front End,* Maintenance Library Manual, Order No. SY33-1068.

*IBM 3125 Processing Unit, 3525 Attachment, Front End,* Maintenance Library Manual, Order No. SY33-1070.

*IBM 3125 Processing Unit, 3504 Attachment, Front End,* Maintenance Library Manual, Order No. SY33-1071.

*IBM 3125 Processing Unit, 1403 Attachment, Front End,* Maintenance Library Manual, Order No. SY33-1072.

*IBM 3125 Processing Unit, 3330 Direct Disk Attachment,* Maintenance Library Manual, Order No. SY33-1073.

*IBM 3125 Processing Unit, Integrated Console Matrix Printer Attachment,* Maintenance Library Manual, Order No. SY33-1074. *IBM 3125 Processing Unit, Integrated* Library Manual, Part B/M1876075. *IBM 3125 Processing Unit, Installatio* Manual, Part 4014001. *IBM 3125 Central Test Manual,* Main appropriate to the individual 3125 F *IBM 3125 Processing Unit, Parts Cata* No. S135-1000.

*IBM 3125 Processing Unit, Integrated Communications Adapter, Maintenance Library Manual, Part B/M1876075. IBM 3125 Processing Unit, Installation Instructions, Maintenance Library*

*IBM 3125 Central Test Manual*, Maintenance Library Manual. Contains pages appropriate to the individual 3125 Processing Unit. *IBM 3125 Processing Unit, Parts Catalog*, Maintenance Library Manual, Order

#### Preface

III

# Contents

| Chapter 1. Introduction               | 1-010 |

|---------------------------------------|-------|

| System Data and Control Flow          | 1-010 |

| General Information                   | 1-020 |

| System Internal Buses                 | 1-020 |

| Standard Interface                    | 1-020 |

| Channel Operation                     | 1-025 |

|                                       | 1-025 |

| Data Transfers                        | 1-026 |

|                                       | 1-030 |

|                                       | 1-030 |

|                                       | 1-030 |

|                                       | 1-040 |

| Signal Interface                      | 1-040 |

| Chapter 2. Principles of Operation    | 2-020 |

|                                       | 2-020 |

| Data Handling                         | 2-020 |

| Termination                           | 2-020 |

|                                       | 2-025 |

|                                       | 2-025 |

|                                       | 2-025 |

|                                       | 2-025 |

|                                       | 2-025 |

|                                       | 2-025 |

|                                       | 2-025 |

|                                       | 2-025 |

| Start I/O Fast Release (SIOF)         |       |

| Formats                               | 2-025 |

|                                       | 2-025 |

| Channel Address Word (CAW)            | 2-025 |

| Channel Command Word (CCW)            | 2-025 |

| Channel Status Word (CSW)             | 2-025 |

| Unit Control Word (UCW)               | 2-026 |

| Write Type Operation                  | 2-030 |

| Read Type Operation                   | 2-040 |

| Data Transfer Conditions              | 2-040 |

| Modes of Operation                    | 2-050 |

| Byte Mode                             | 2-050 |

| Multiple Byte Mode                    | 2-050 |

| Burst Mode                            | 2-050 |

| Example of Byte Mode Operation        | 2-055 |

| General Information                   | 2-060 |

| Microprogram                          | 2-060 |

| Interrupts                            | 2-060 |

| Chaining                              | 2-065 |

| Unusual or Exceptional Conditions     | 2-065 |

| Status Bytes.                         | 2-065 |

| Sense Bytes                           | 2-065 |

| Indirect Data Addressing              | 2-065 |

| Subchannel Arrangement and Addressing | 2.070 |

| Shared Subchannel Addressing.         |       |

| Non-Shared Subchannel Addressing                                 |   |   | 2-070 |

|------------------------------------------------------------------|---|---|-------|

| Device Address Assignments                                       |   |   | 2-070 |

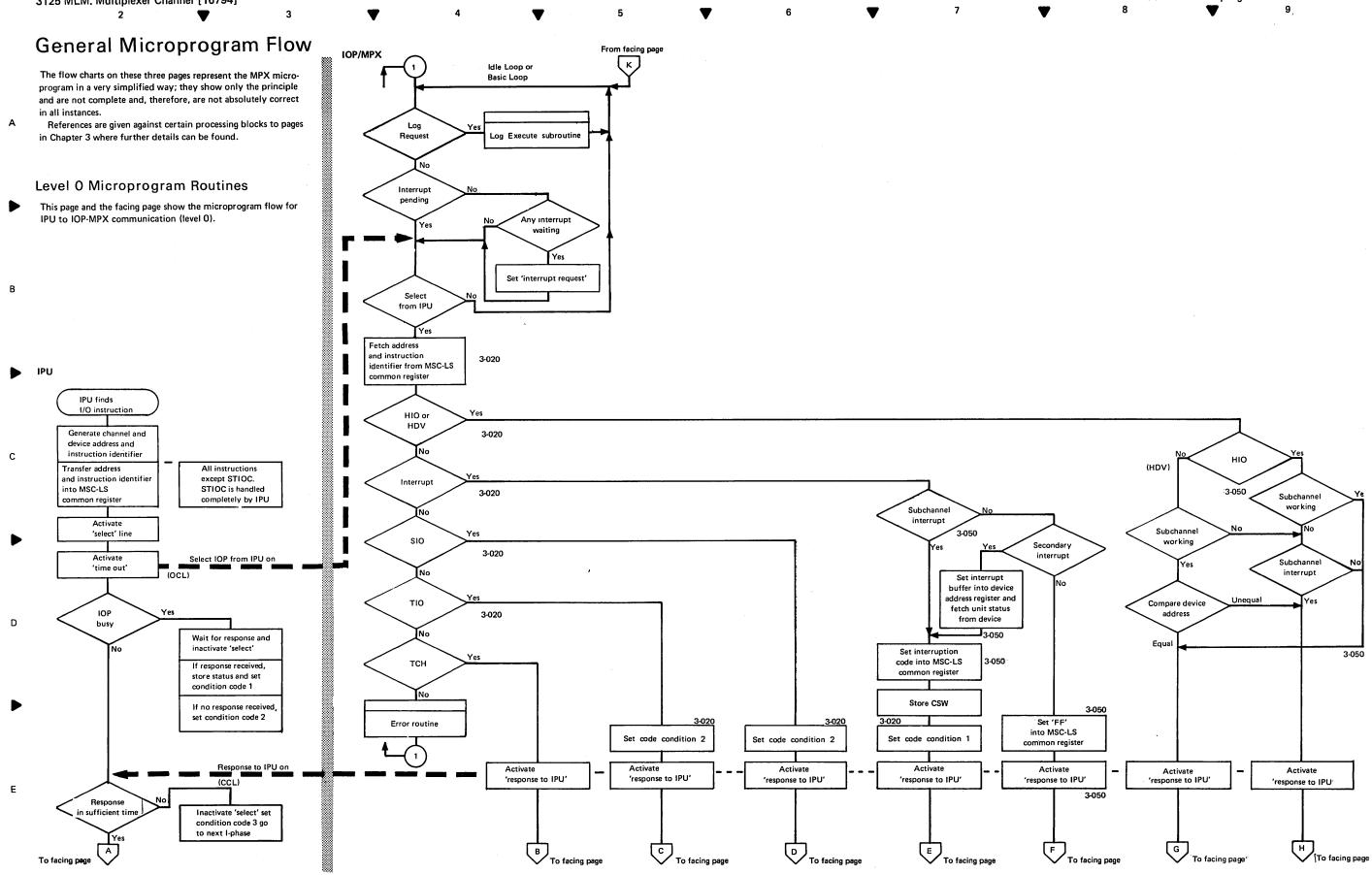

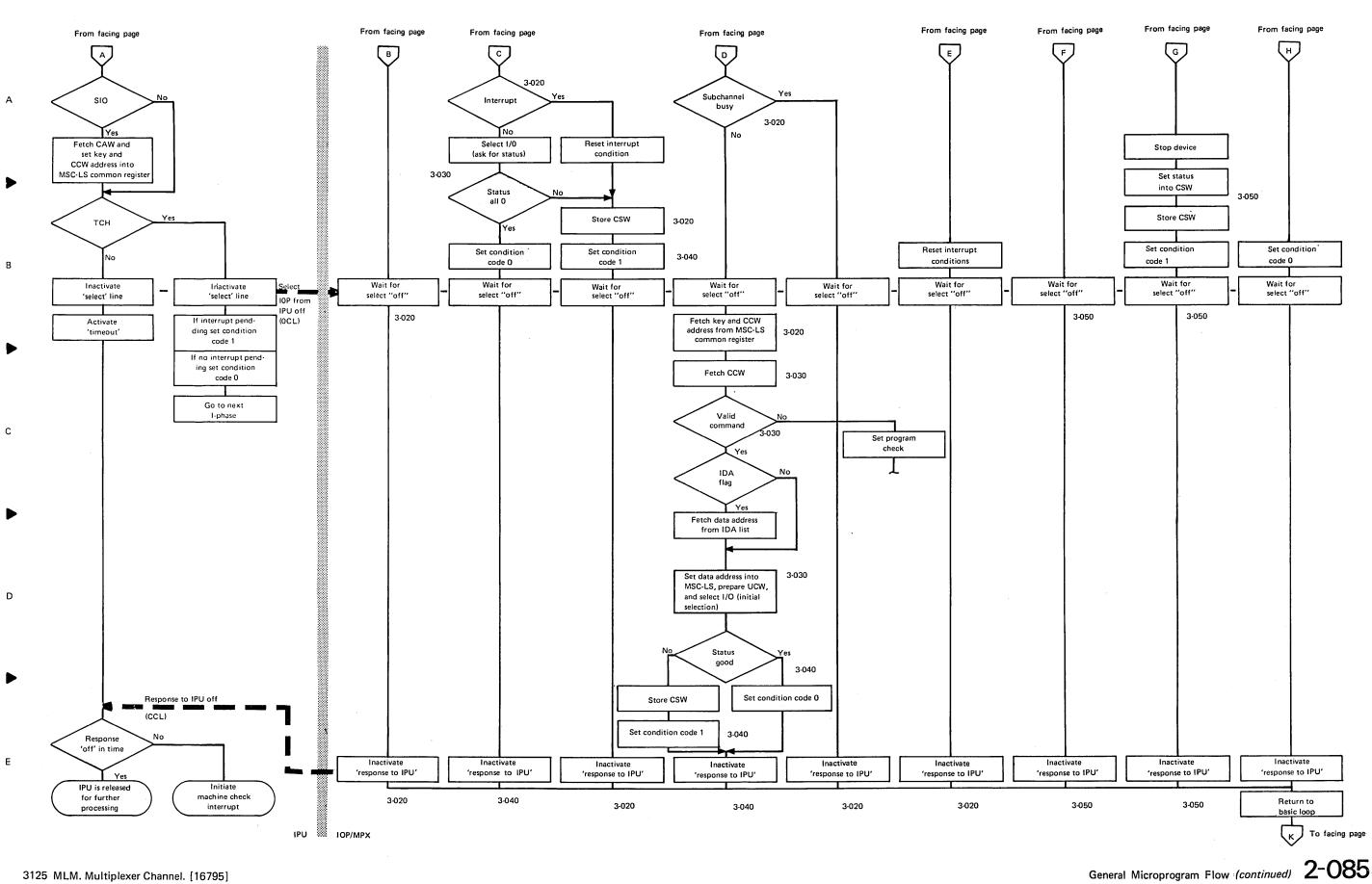

| General Microprogram Flow                                        |   |   | 2-080 |

| Level O Microprogram Routines                                    |   |   | 2-080 |

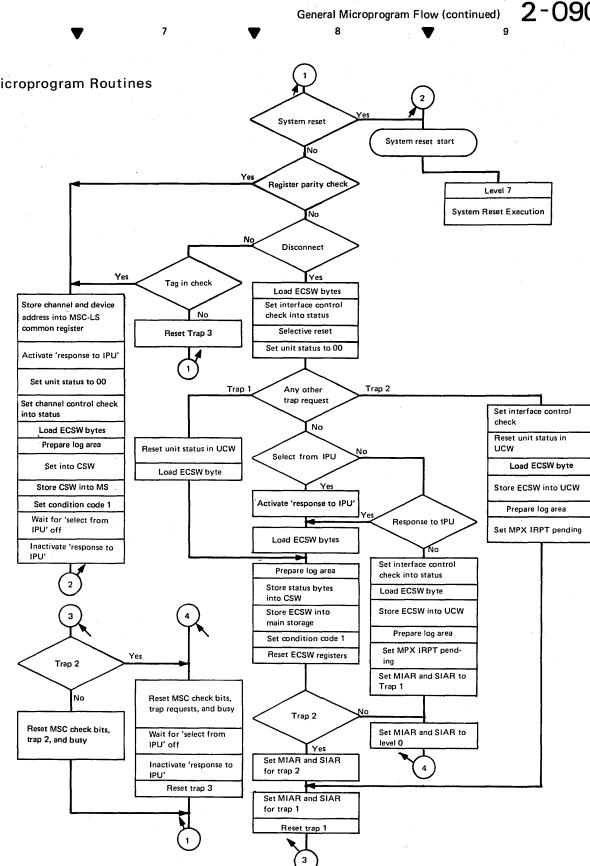

| Level 1 Microprogram Routines                                    |   |   | 2-090 |

| Level 2 Microprogram Routines                                    |   |   | 2-090 |

| Level 3 Microprogram Routines                                    |   |   | 2-090 |

|                                                                  |   |   |       |

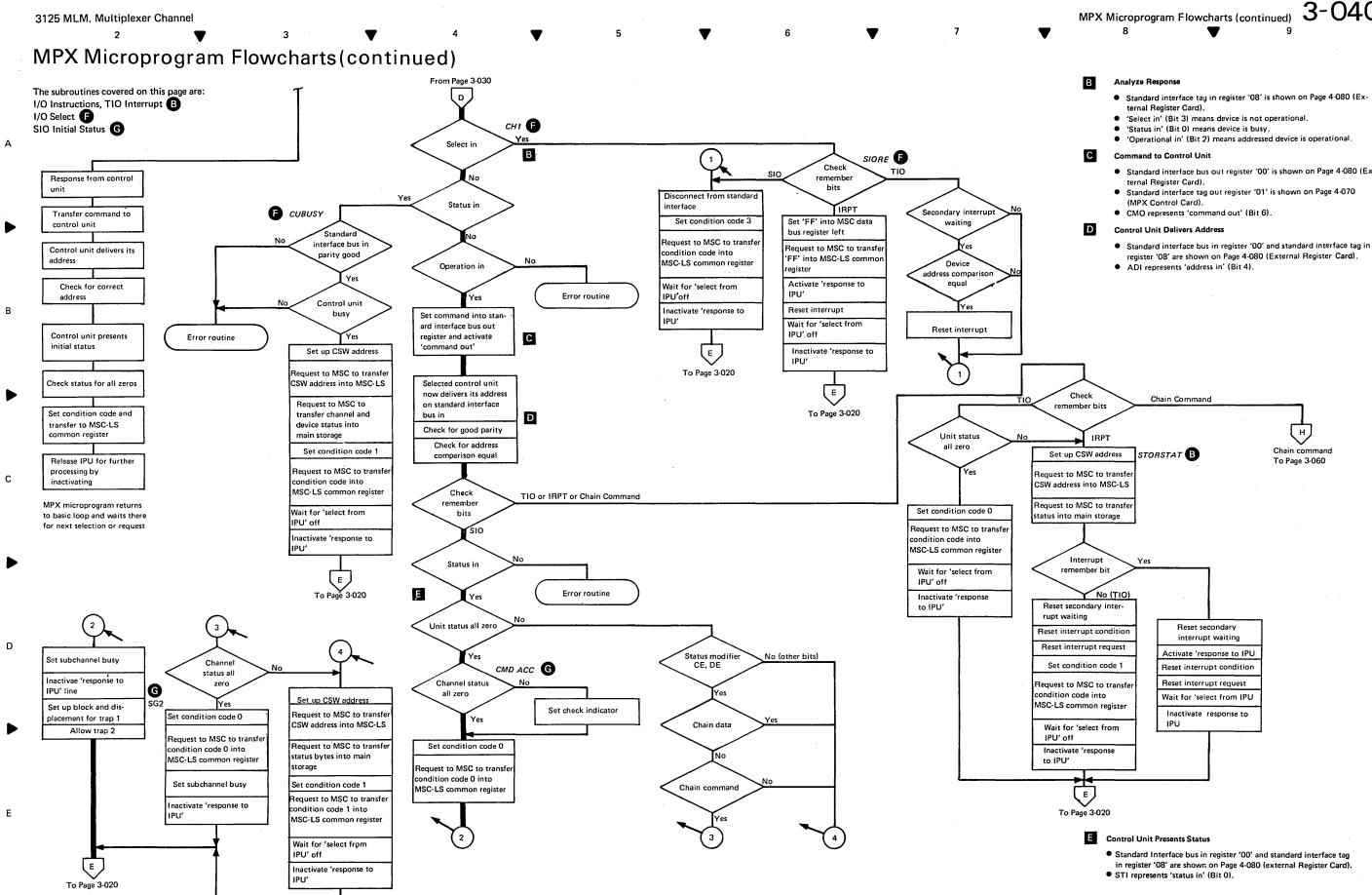

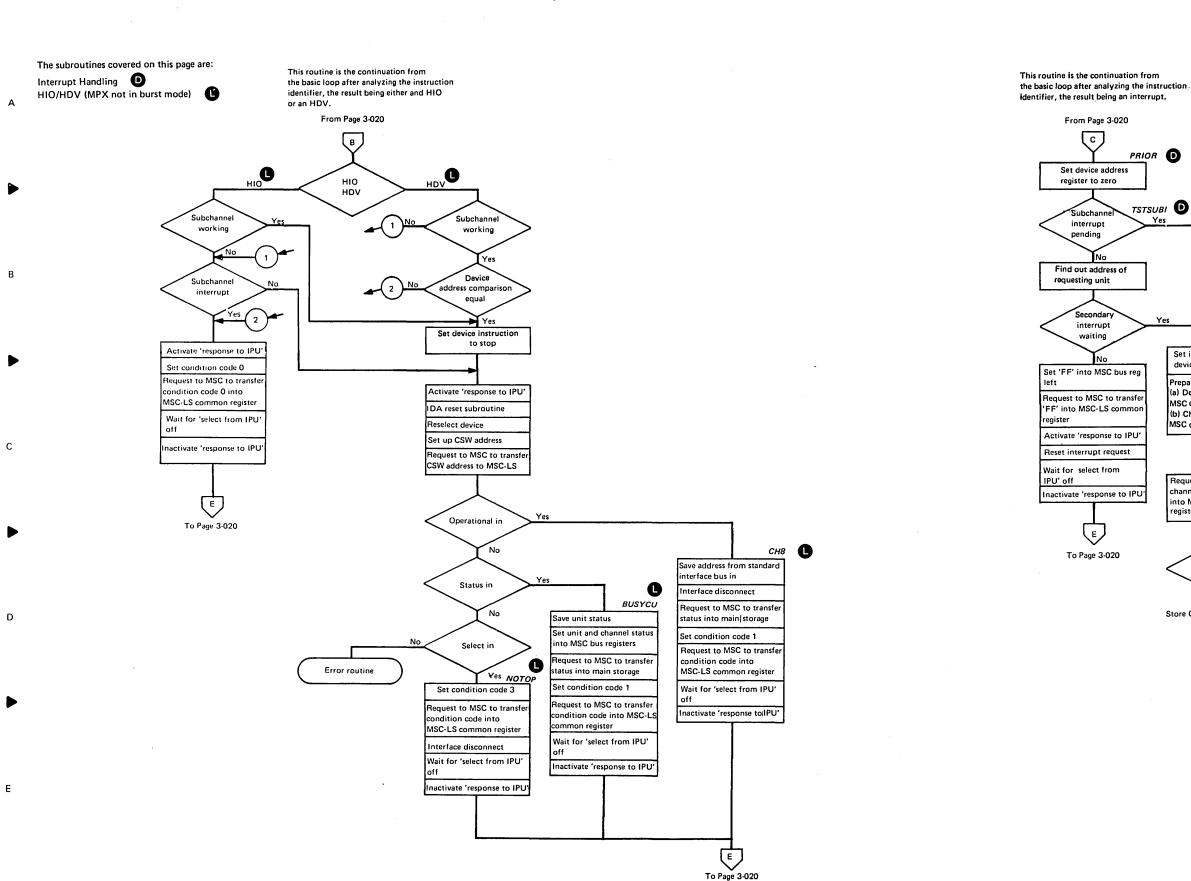

| Chapter 3. Operational Details                                   | • | • |       |

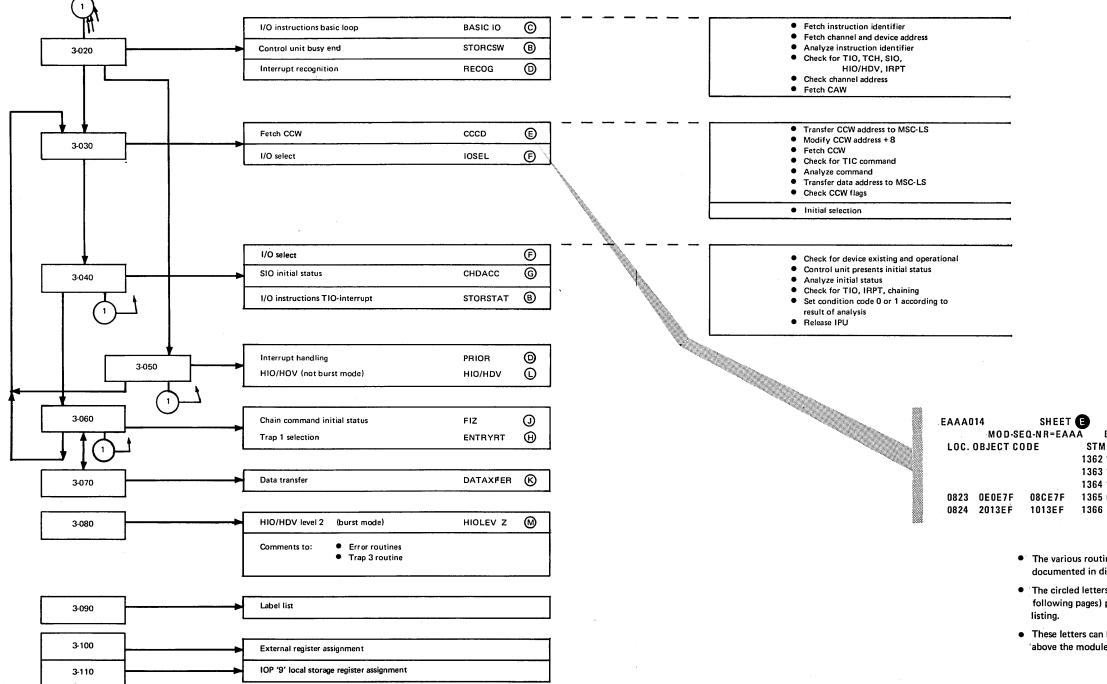

| Visual Index for MPX Microprogram                                | • | • | 3-010 |

| Arrangement of MPX Microprogram Listing                          | • |   |       |

| MPX Microprogram Flowcharts                                      | • | • |       |

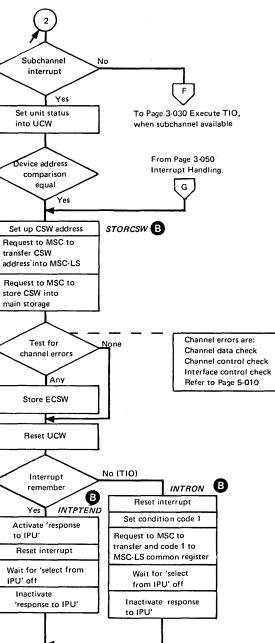

| Control Unit Busy End                                            |   |   | 3-020 |

| I/O Instruction Basic Loop                                       | • |   | 3-020 |

| Interrupt Recognition                                            |   |   | 3-020 |

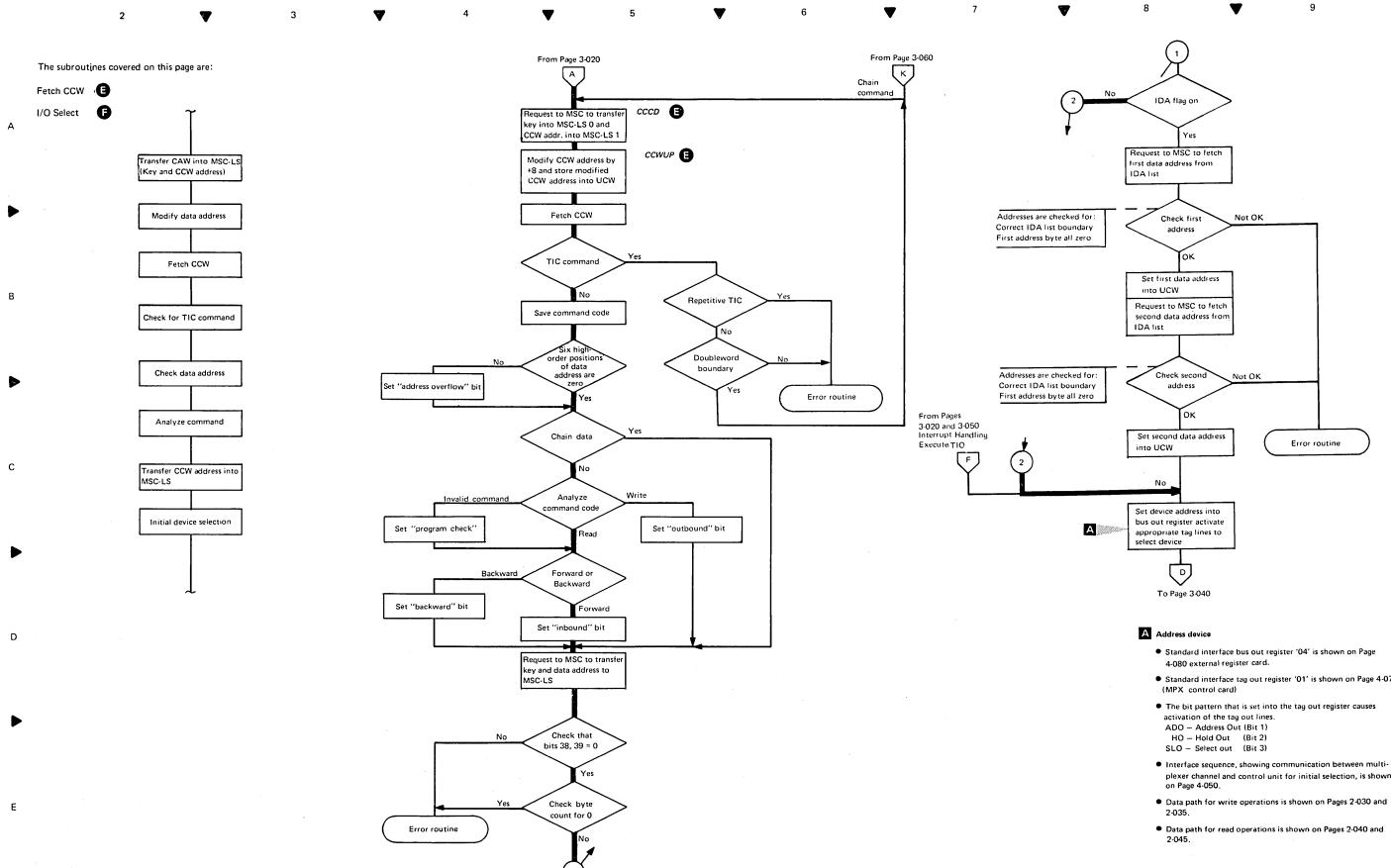

| Fetch CCW                                                        |   |   | 3-030 |

| I/O Select                                                       |   |   | 3-030 |

| TIO Interrupt                                                    |   |   | 3-040 |

| SIO Initial Status                                               |   |   | 3-040 |

| Interrupt Handling                                               |   |   | 3-050 |

| HIO/HDV (MPX not in burst mode)                                  |   |   | 3-050 |

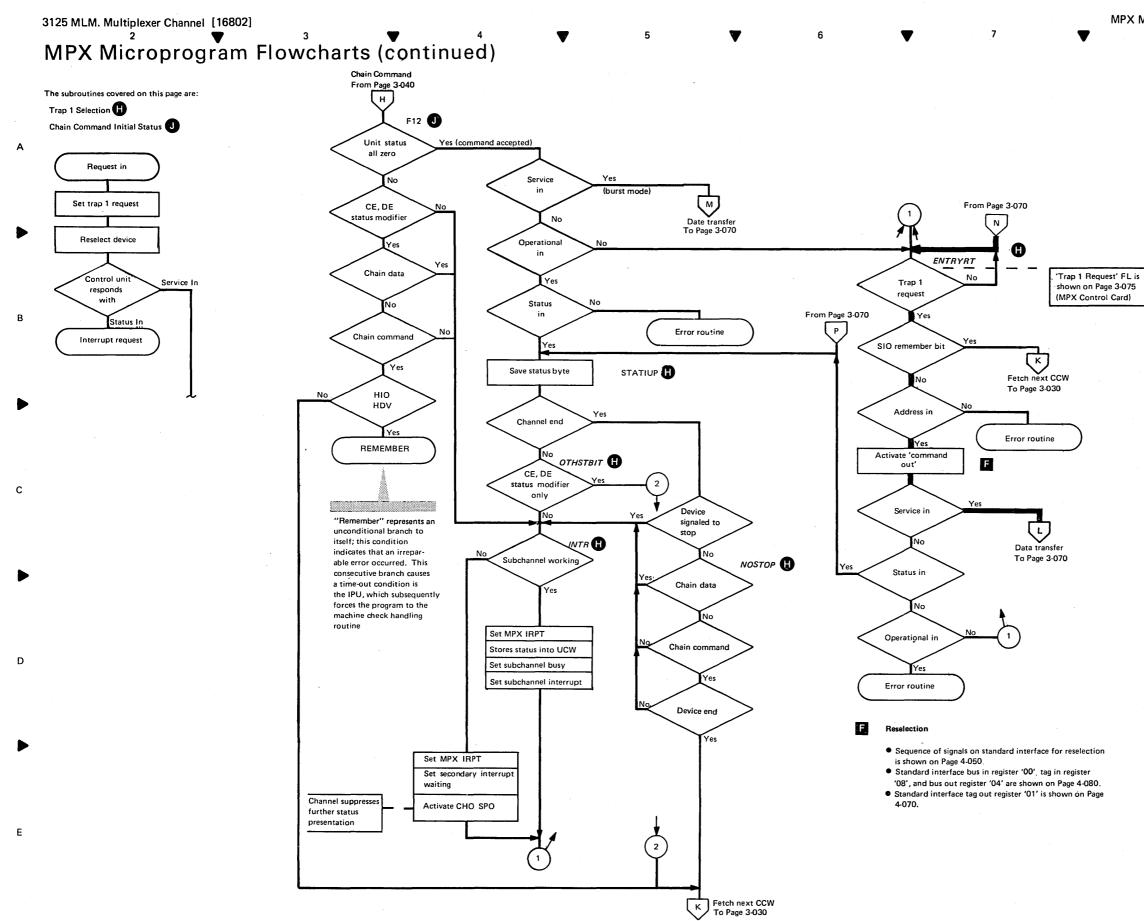

| Trap 1 Selection                                                 |   |   | 3-060 |

| Chain Command Initial Status                                     |   |   | 3-060 |

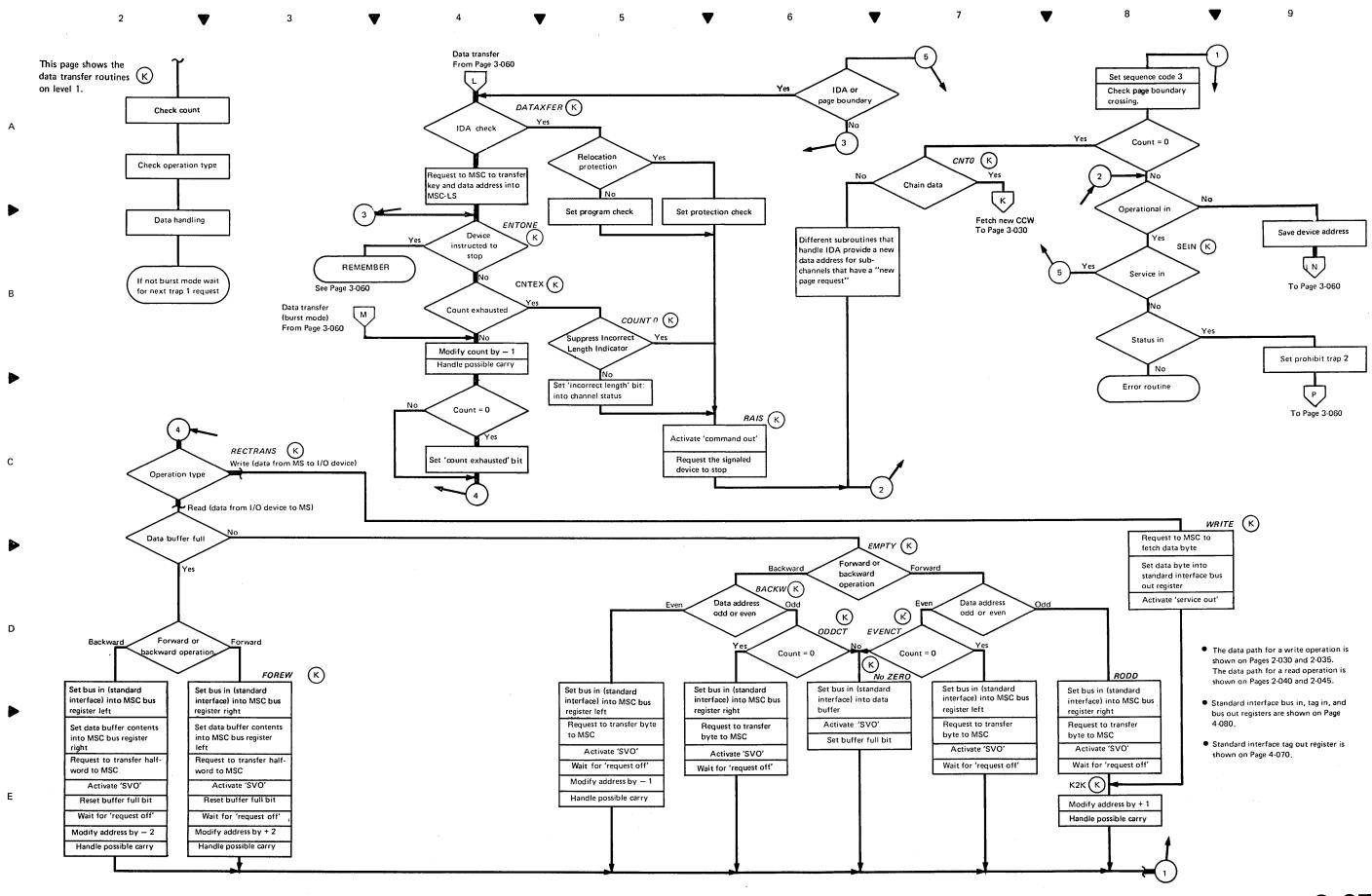

| Data Transfer (level 1)                                          |   |   | 3-070 |

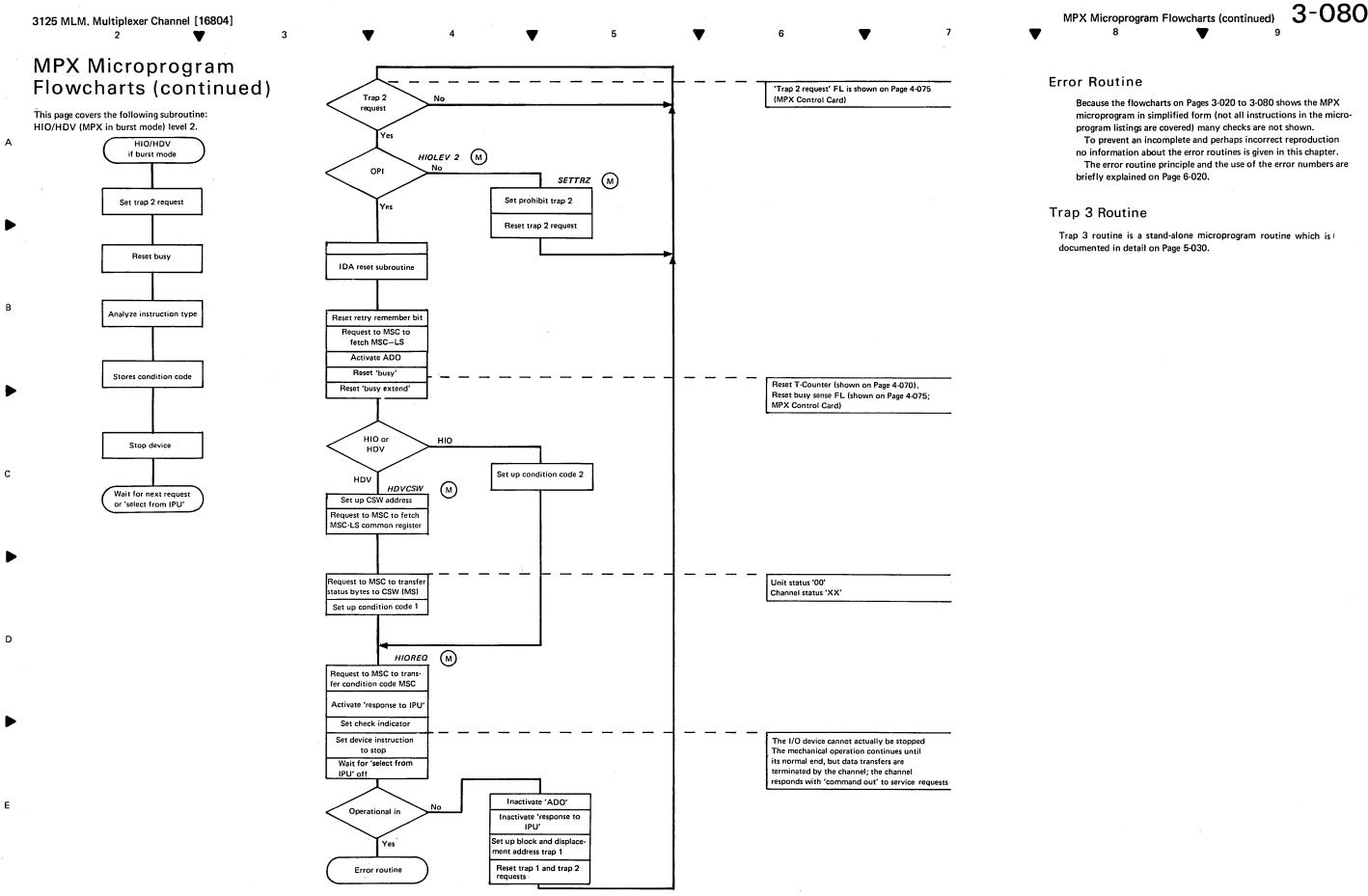

| HIO/HDV (MPX in burst mode)                                      |   |   | 3-080 |

| Error Routine                                                    |   |   | 3-080 |

| Trap 3 Routine                                                   |   |   | 3-080 |

| MPX Microprogram Label List                                      |   |   | 3-090 |

| External Register Assignments                                    |   |   | 3-100 |

| IOP '9' Local Storage Register Assignments                       |   |   |       |

|                                                                  |   |   |       |

| Chapter 4. Functional Units                                      |   |   | 4-010 |

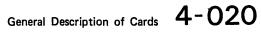

| Interconnections                                                 |   |   | 4-010 |

| General Description of Cards                                     |   |   |       |

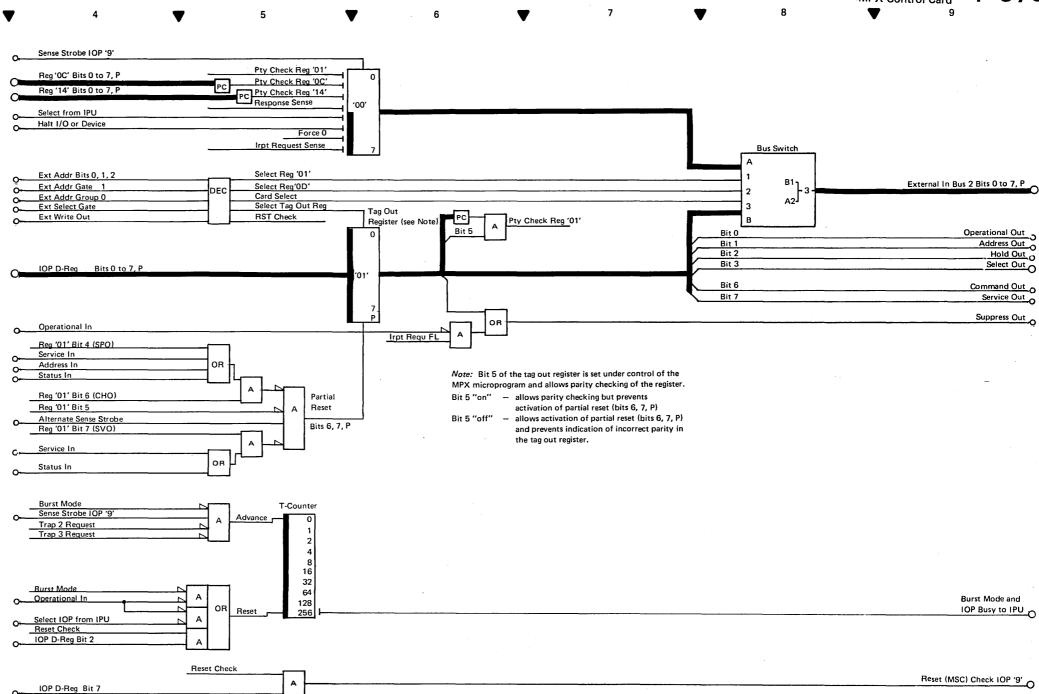

| MPX Control Card (01BAIF)                                        |   |   | 4-020 |

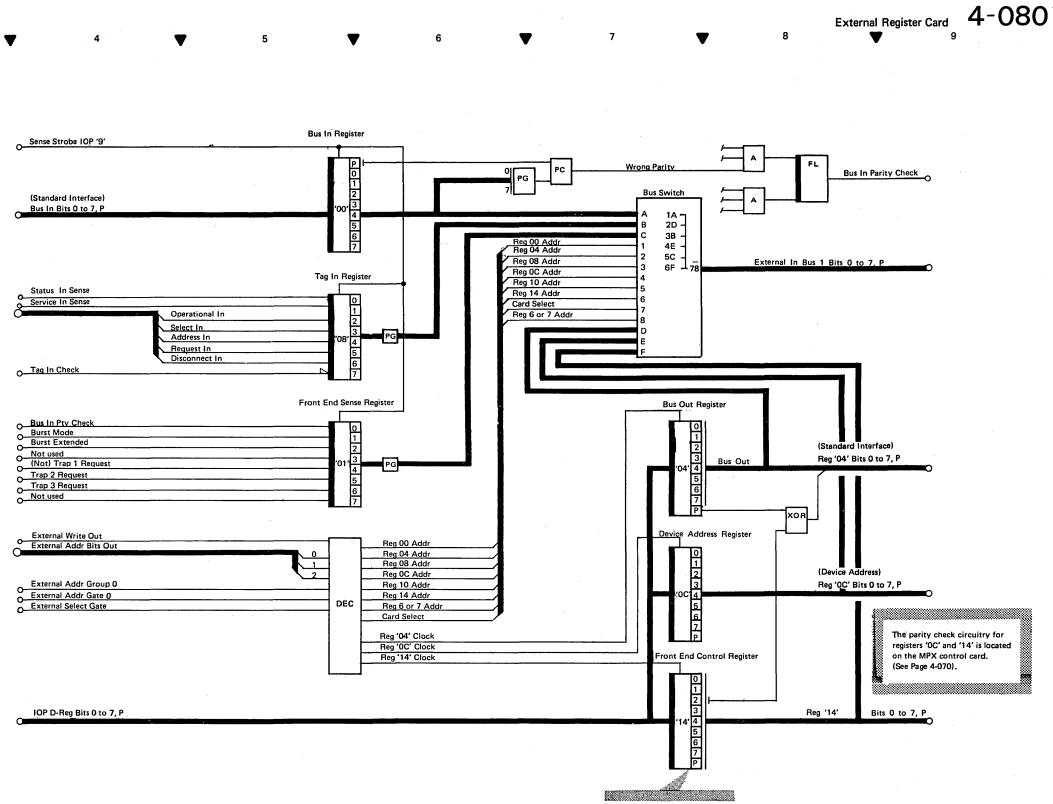

| External Register Card (01BAID)                                  |   |   | 4-020 |

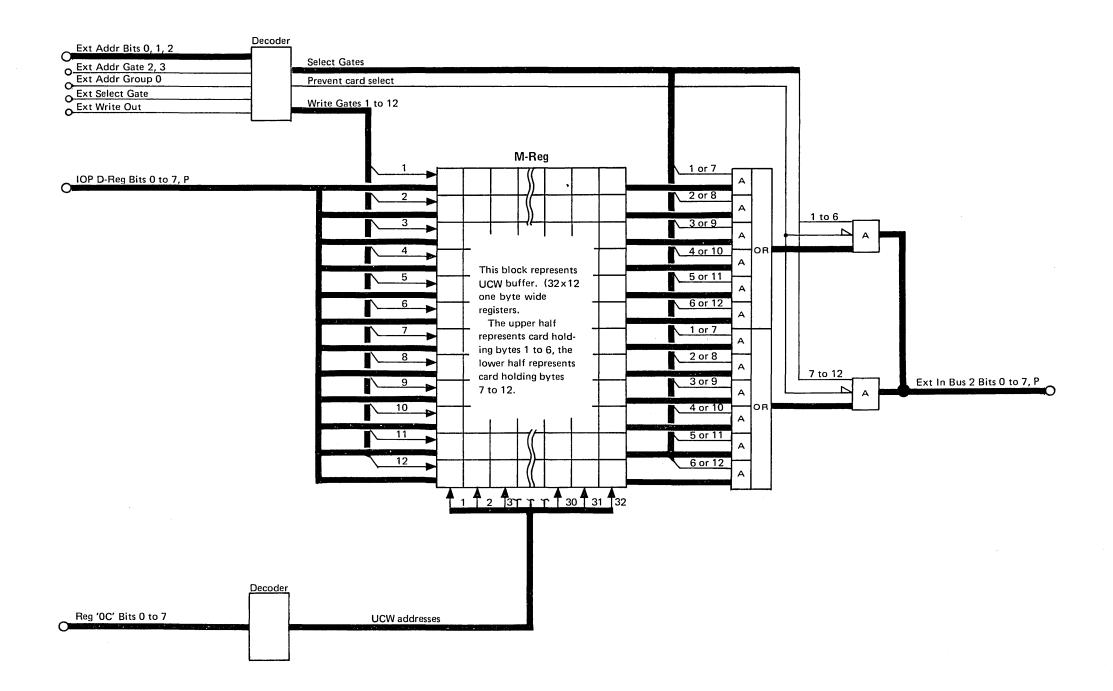

| UCW Buffer Cards (01BAIG&H)                                      |   |   |       |

| MPX Front End Data Flow                                          |   |   | 4-025 |

| Lines from IOP '9' to Multiplexer Channel Front End.             |   |   | 4-030 |

| Lines from Multiplexer Channel Front End to IOP '9'.             |   |   | 4-030 |

| Lines from Standard Interface to Multiplexer Channel Front End . |   |   | 4-040 |

| Lines from Multiplexer Channel Front End to Standard Interface . |   |   | 4-040 |

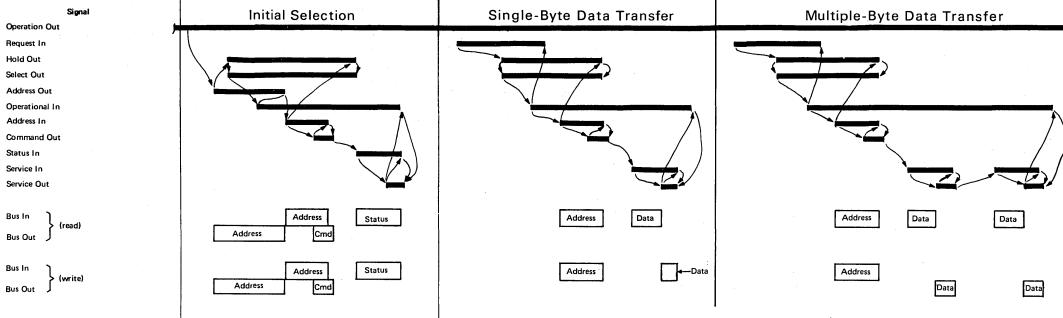

| Sequence of Tag Lines on Standard Interface                      |   |   | 4-050 |

|                                                                  |   |   | 4-050 |

| Single-Byte Data Transfer                                        |   | - | 4-050 |

| Multiple-Byte Data Transfer                                      |   | • | 4-050 |

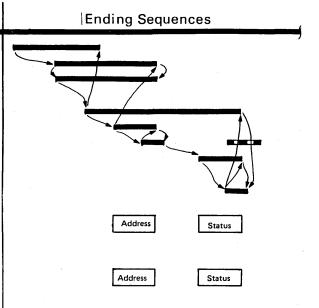

| Ending Sequences                                                 |   | - | 4-050 |

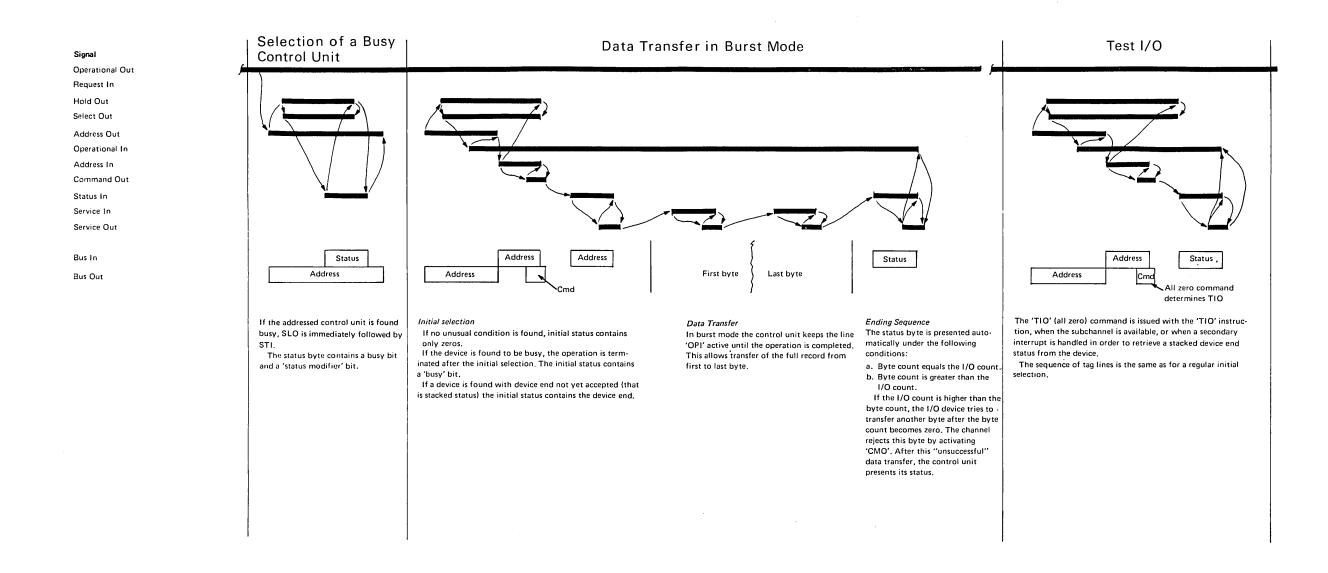

| Selection of a Busy Control Unit                                 |   | • | 4-060 |

| Data Transfer in Burst Mode                                      |   | • | 4-060 |

|                                                                  | • | • |       |

Test I/O . . . . . MPX Control Card . . External In Buses . . . Tag Out Register . T-Counter . . . Trap Request FLs . External Register Card External In Bus. . Suppression of Extern UCW Buffer Cards .

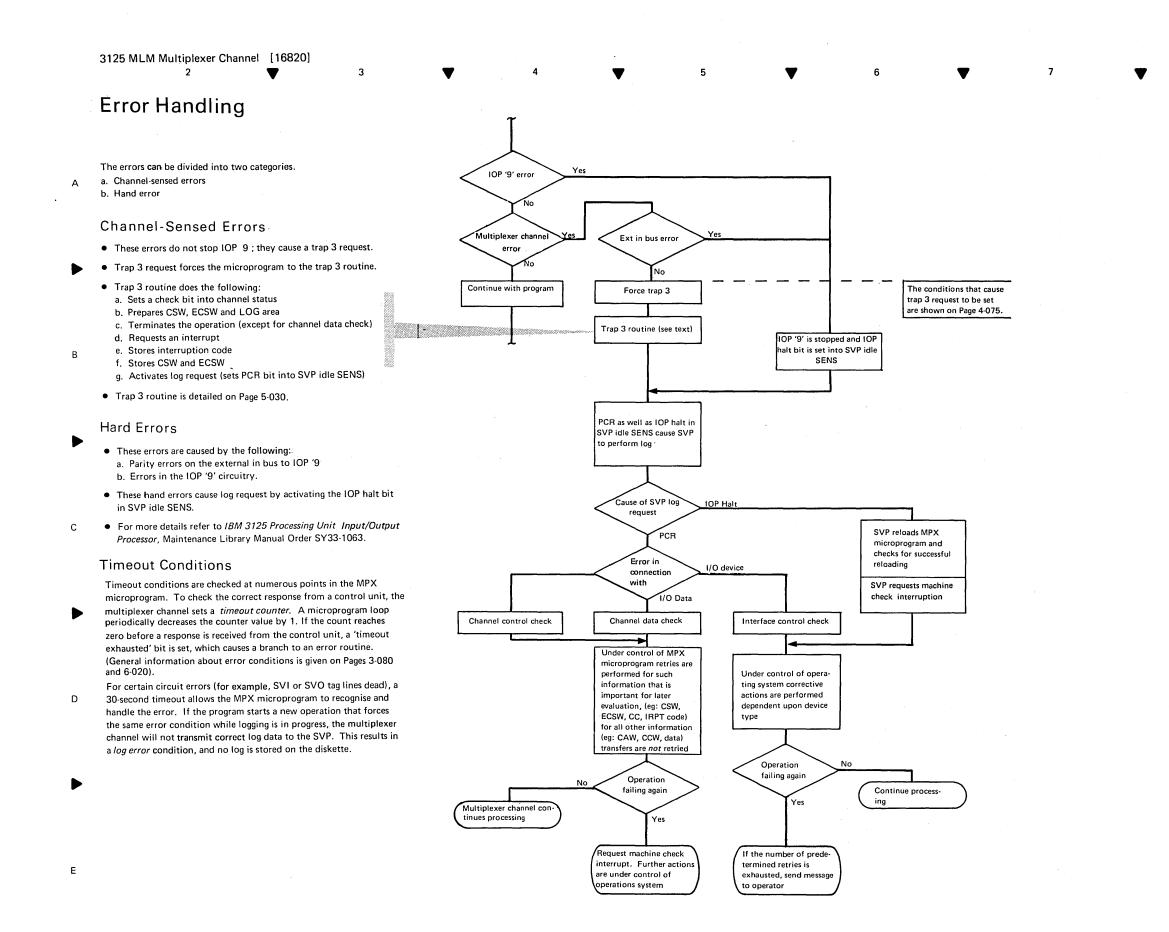

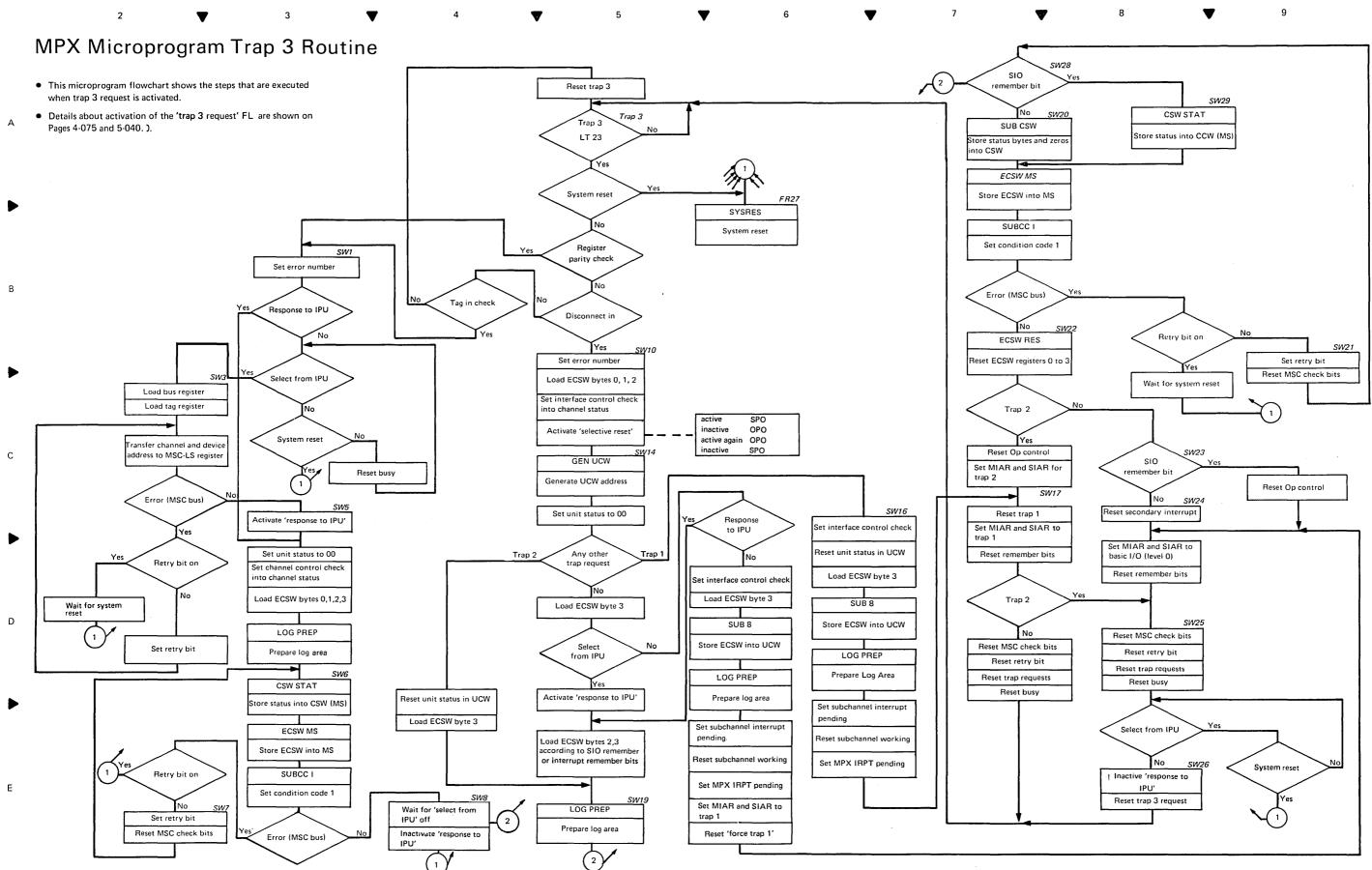

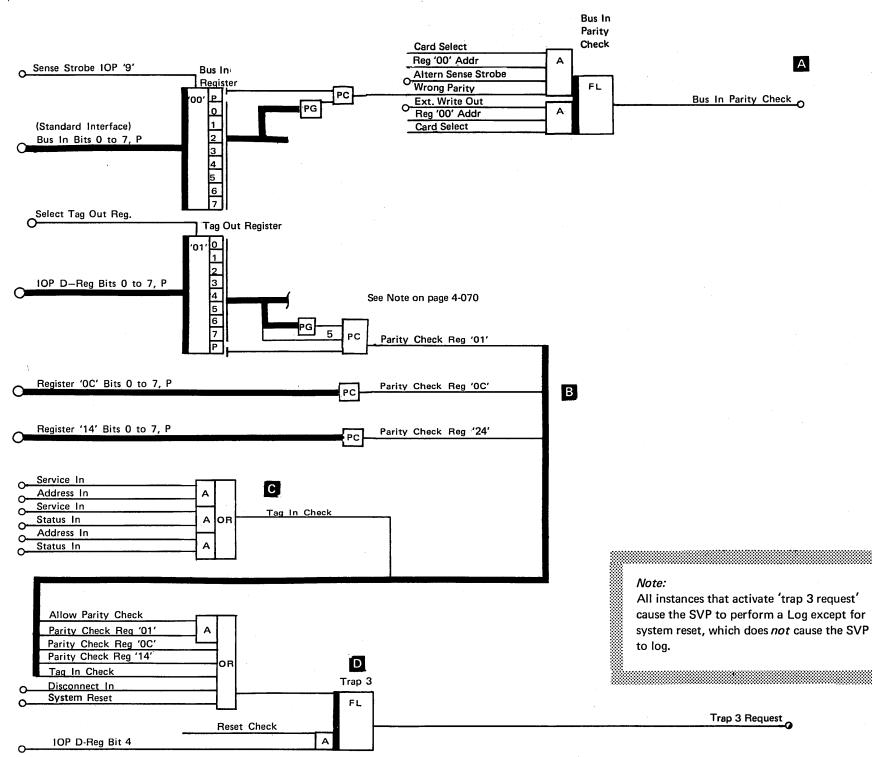

Chapter 5. Error Condit Introduction . . . Unusual or Exceptional Error Handling . . Channel-Sensed Errors Hard Errors . . . **Timeout Conditions** Logging . . . . MPX Microprogram Traj Error Circuits . . . External Register Carc MPX Control Card.

| Chapter | 6.    | M   | ain | ten  | and | e  |

|---------|-------|-----|-----|------|-----|----|

| Introdu | ctic  | n   |     |      |     |    |

| Mainter | nand  | e ( | Con | icep | ot  |    |

| Diagn   | osti  | c 7 | [ec | hni  | que | es |

| Scope S | Sens  | e   |     |      |     |    |

| Matrix  |       |     |     |      |     |    |

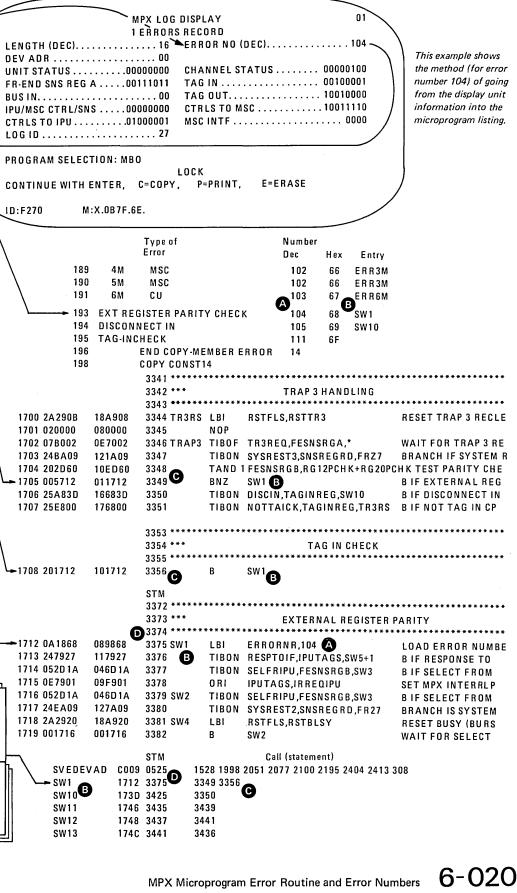

| MPX M   | icro  | pro | ogr | am   | Er  | ro |

| MPX M   | icro  | pr  | ogr | am   | Er  | ro |

|         |       |     |     |      |     |    |

| Chapte  | r 7.  | R   | efe | ren  | ce  | In |

| Abbrev  | iatio | ons | an  | d C  | Slo | SS |

|         |       |     |     |      |     |    |

| Index   | •     | •   | •   | •    | •   | •  |

|         |       |     |     |      |     |    |

|         |       |     |     |      |     |    |

|         |       |     |     |      |     |    |

|         |       |     |     |      |     |    |

3125 MLM. Multiplexer Channel

Maintenance Information

6

7 Reference

Information

|    |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   |     |   | 4-060 |

|----|------|-----|-----|------|-----|---|----|---|---|---|----|---|---|---|---|-----|---|-------|

|    |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   |     | • | 4-070 |

| •  |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   |     |   | 4-070 |

|    |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   |     |   | 4-070 |

|    |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   |     |   | 4-070 |

|    |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   | •   |   | 4-075 |

| d  |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   | • · |   | 4-080 |

|    |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   |     | • | 4-080 |

| er | nal  | In  | Bu  | IS   |     |   |    | • |   |   |    |   | • |   |   | •   | • | 4-080 |

|    |      |     |     |      |     |   |    |   | • | • |    | • | • | • | • | •   | • | 4-090 |

|    |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   |     |   |       |

| ۱d | itio | ns  |     |      | •   | • |    |   |   | • |    | • | • | • | • | •   | • | 5-000 |

|    |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   |     |   | 5-000 |

|    | l Co |     |     | ons  | s., |   |    |   |   |   |    |   |   |   |   | •   |   | 5-010 |

|    |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   | •   |   | 5-020 |

|    | rs   |     |     |      |     |   |    |   |   |   |    |   |   |   |   | •   | • | 5-020 |

|    |      |     |     |      |     |   |    |   |   |   |    |   |   | • |   |     | • | 5-020 |

|    |      |     |     |      |     |   |    |   |   |   |    | • | • |   | • |     | • | 5-020 |

|    |      |     |     |      |     |   |    |   | • |   |    |   | • |   |   | •   | • | 5-020 |

| ٢r | ap ( | 3 R | lou | tin  | e   | • |    |   |   | • | •  | • | • | • | • | •   | • | 5-030 |

|    |      |     |     |      |     |   |    | • | • | • | •  | • | • | • | • | •   | • | 5-040 |

| aı | rd   |     |     |      |     | • |    |   | • | • | •  | • | • | • | • | •   | • | 5-040 |

|    |      |     |     | •    |     |   | •  | • | • | • | •  | • | • | • | • | •   | • | 5-040 |

|    |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   |     |   |       |

| n  | e l  | nfo | orm | nati | ion | • | •  | • | • | • | •  | • | • | • | • | •   | • | 6-000 |

|    |      |     |     |      |     |   |    | • |   | • |    |   | • | • | • | •   | • | 6-000 |

| t  |      |     |     |      |     |   |    |   |   | • | •  | • | • | • | • | •   | • | 6-010 |

| ļu | es a | nd  | Τe  | ests | з.  |   |    |   |   |   | •  | • | • | • | • | •   | • | 6-010 |

|    |      |     |     |      |     |   |    |   |   |   | ۰. | • | • | • | • | •   | • | 6-010 |

|    |      |     |     |      |     |   | •  |   |   | • | •  | • | • | • | • | •   | • | 6-010 |

| Er | ror  | Ro  | out | ine  | es. |   |    |   |   | • |    | • | • | • | • | •   | • | 6-020 |

| Er | ror  | Νı  | ١m  | ber  | s.  | • |    | • |   | • | •  | • | • | • | • | •   | • | 6-020 |

|    |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   |     |   |       |

| e  | Inf  | orn | nat | tior | ı.  |   | •• | • | • | • | •  | • | • | • | • | •   | • | 7-010 |

| lo | ssar | ·у  |     |      |     |   |    |   |   |   |    |   |   |   |   | •   |   | 7-010 |

|    |      | -   |     |      |     |   |    |   |   |   |    |   |   |   |   |     |   |       |

| •  | •    |     |     |      |     | • |    |   |   | • | •  | • | • | • | • | •   | • | X-1   |

|    |      |     |     |      |     |   |    |   |   |   |    |   |   |   |   |     |   |       |

# Safety

# **Personal Safety**

Personal safety cannot be over-emphasized; it is a vital part of customer engineering. To ensure your safety and that of co-workers, always observe the safety precautions given during your safety training and adhere to the following:

# **General Safety Practices**

Observe the general safety practices and the procedure for performing artificial respiration that are outlined in CE Safety Practices card, order no. S229-1264 (shown here).

## Grounding

Ground current may reach dangerous levels. Never operate the system with the grounding conductor removed.

## **Line-Powered Equipment**

Ground all line-powered test equipment through the third-wire grounding conductor in the power cord of the machine being tested.

## Machine Warning Labels

Heed the warning labels placed in hazardous areas of the machines.

## **CE SAFETY PRACTICES**

All Customer Engineers are expected to take every safety precaution possible and observe the following safety practices while maintaining IBM equipment: 1. You should not work alone under hazardous conditions or

- around equipment with dangerous voltage. Always advise your manager if you MUST work alone.

- 2. Remove all power AC and DC when removing or assembling major components, working in immediate area of power supplies, performing mechanical inspection of power supplies and installing changes in machine circuitry.

- 3. Wall box power switch when turned off should be locked or tagged in off position. "Do not Operate" tags, form 229-1266, affixed when applicable. Pull power supply cord whenever possible.

- 4. When it is absolutely necessary to work on equipment have ing exposed operating mechanical parts or exposed live electrical circuitry anywhere in the machine, the following precautions must be followed:

- a. Another person familiar with power off controls must be in immediate vicinity. b. Rings, wrist watches, chains, bracelets, metal cuff links,

- shall not be worn. c. Only insulated pliers and screwdrivers shall be used.

- d. Keep one hand in pocket.

- e. When using test instruments be certain controls are set correctly and proper capacity, insulated probes are used.

- f. Avoid contacting ground potential (metal floor strips, machine frames, etc. — use suitable rubber mats pur-

- chased locally if necessary). 5. Safety Glasses must be worn when:

- a. Using a hammer to drive pins, riveting, staking, etc. b. Power hand drilling, reaming, grinding, etc.

- c. Using spring hooks, attaching springs.

- d. Soldering, wire cutting, removing steel bands.

- e. Parts cleaning, using solvents, sprays, cleaners, chemicals,

- f. All other conditions that may be hazardous to your eyes. REMEMBER, THEY ARE YOUR EYES.

- 6. Special safety instructions such as handling Cathode Ray Tubes and extreme high voltages, must be followed as outlined in CEM's and Safety Section of the Maintenance Manuals.

- 7. Do not use solvents, chemicals, greases or oils that have not been approved by IBM.

- 8. Avoid using tools or test equipment that have not been approved by IBM.

- 9. Replace worn or broken tools and test equipment. 10. The maximum load to be lifted is that which in the opinion

- of you and management does not jeopardize your own health or well-being or that of other employees.

- 11. All safety devices such as guards, shields, signs, ground wires, etc. shall be restored after maintenance

KNOWING SAFETY RULES IS NOT ENOUGH AN UNSAFE ACT WILL INEVITABLY LEAD TO AN ACCIDENT

USE GOOD JUDGMENT - ELIMINATE UNSAFE ACTS

11/71 S229-1264-2

- warm the victim or apply stimulants.

- tongue forward.

- Take care of these items after vic-

- 4. Remain in Position

- 5. Call a Doctor

- aid. 6. Don't Give Up

- is certainly dead.

12. Each Customer Engineer is responsible to be certain that no action on his part renders product unsafe or exposes hazards to customer personnel.

13. Place removed machine covers in a safe out-of-the-way place where no one can trip over them.

14. All machine covers must be in place before machine is returned to customer.

15. Always place CE tool kit away from walk areas where no one can trip over it (i.e., under desk or table).

16. Avoid touching mechanical moving parts (i.e., when lubricating, checking for play, etc.).

17. When using stroboscope - do not touch ANYTHING - it may be movina.

18. Avoid wearing loose clothing that may be caught in machinery. Shirt sleeves must be left buttoned or rolled above the elbow.

19. Ties must be tucked in shirt or have a tie clasp (preferably nonconductive) approximately 3 inches from end. Tie chains are not recommended.

20. Before starting equipment, make certain fellow CE's and customer personnel are not in a hazardous position. 21. Maintain good housekeeping in area of machines while per-

forming and after completing maintenance.

#### **Artificial Respiration** GENERAL CONSIDERATIONS

1. Start Immediately, Seconds Count Do not move victim unless absolutely necessary to remove from danger. Do not wait or look for help or stop to loosen clothing,

2. Check Mouth for Obstructions

Remove foreign objects - Pull

3. Loosen Clothing -- Keep Warm

tim is breathing by himself or when help is available

After victim revives, be ready to resume respiration if necessary.

Have someone summon medical

Continue without interruption until victim is breathing without help or

Reprint Courtesy Mine Safety Appliances Co.

#### **Rescue Breathing for Adults** Victim on His Back Immediately

- Clear throat of water, food, or foreign matter.

- 2. Tilt head back to open air passage.

- 3. Lift jaw up to keep tongue out of air passage.

- 4. Pinch nostrils to prevent air leakage when you blow.

- 5. Blow until you see chest rise.

- 6. Remove your lips and allow lungs to empty.

- 7. Listen for snoring and gurglings, signs of throat obstruction.

- B. Repeat mouth to mouth breathings 10-20 times a minute.

- Continue rescue breathing until he breathes for himself.

# Safety VII

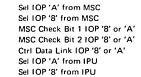

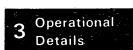

# **Chapter 1. Introduction** System Data and Control Flow

System Data and Control Flow

1-010

# **General Information**

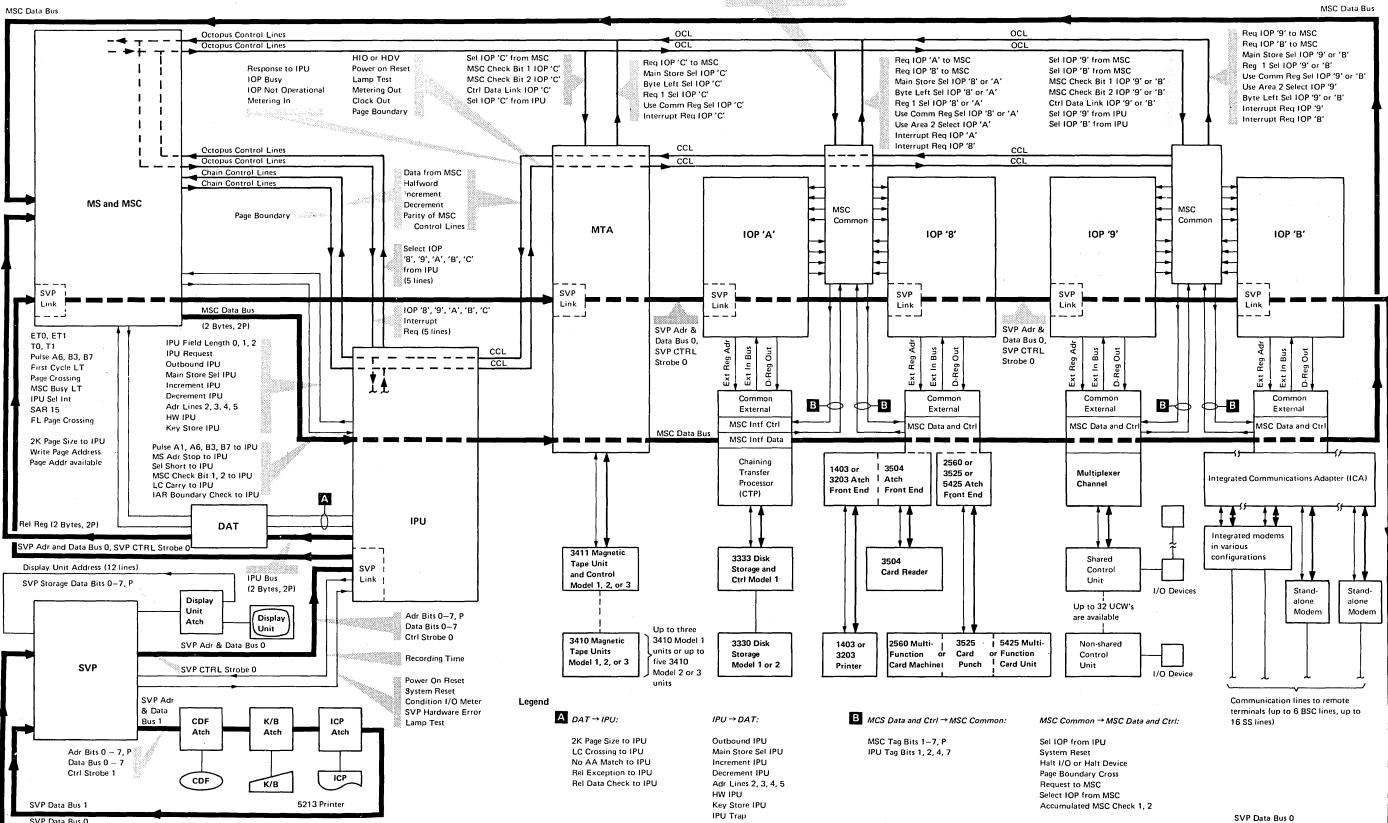

- The multiplexer channel is a specific Front End that is connected to IOP '9'.

- The functions of the multiplexer channel are as follows:

Analyzes the I/O instruction. Initiates the operation of the I/O device. Controls data transfers between I/O devices and MSC. Requests interrupts.

- The multiplexer channel normally serves I/O devices that have relatively low data transmission rates.

- The multiplexer channel can operate in two different modes:

- 1. Byte mode (25 kilobytes per second).

- 2. Burst mode (29 kilobytes per second).

- All multiplexer functions, except interrupt requests, are initiated by the I/O instructions(refer to Page 2-020) and are under microprogram control.

- The microprogram is stored in the control storage of IOP '9'.

- The microprogram principle is shown on Pages 2-080 and 2-090. Detailed microprogram flowcharts are given on Pages 3-020 to 3-080 and 5-030.

- Multiplexer modes are defined by the control units that are connected to the standard interface. (For more details, refer to Pages 2-050 and 2-055.),

# System Internal Buses

- Interconnection between multiplexer channel and the system is made via IOP '9' and the system internal buses.

- The system internal buses are:

- A 12-line bus (see Note) containing octopus control lines (OCL)

- B 16-line bus containing chain control lines (CCL)

- C 17-bit SVP Address and Data Bus (Address Bus is 9 bits); Data Bus is 8 bits)

- D 18-bit MSC Data Bus.

Note: These 12 lines are used by one IOP.

For detailed information refer to IBM 3125 Processing Unit Input /Output Processor, Maintenance Library Manual, order number SY33-1063.

# Standard Interface

- I/O devices with their control units are connected to the multiplexer channel via a standard interface.

- The standard interface consists of four groups of lines:

- One-byte Bus In One-byte Bus Out 7 Tag in lines (6 part of standard interface part of IBM System 370 interface extension) 7 Tag Out lines fall part of the

- standard interface)

Ε

- The standard interface cables are connected to the multiplexer channel by: Bus "serpent" connectors, and Tag "serpent" connectors

- For the explanation of the standard interface Tag lines, refer to Page 4-040.

General Information, Internal Buses, and Standard Interface 1-020

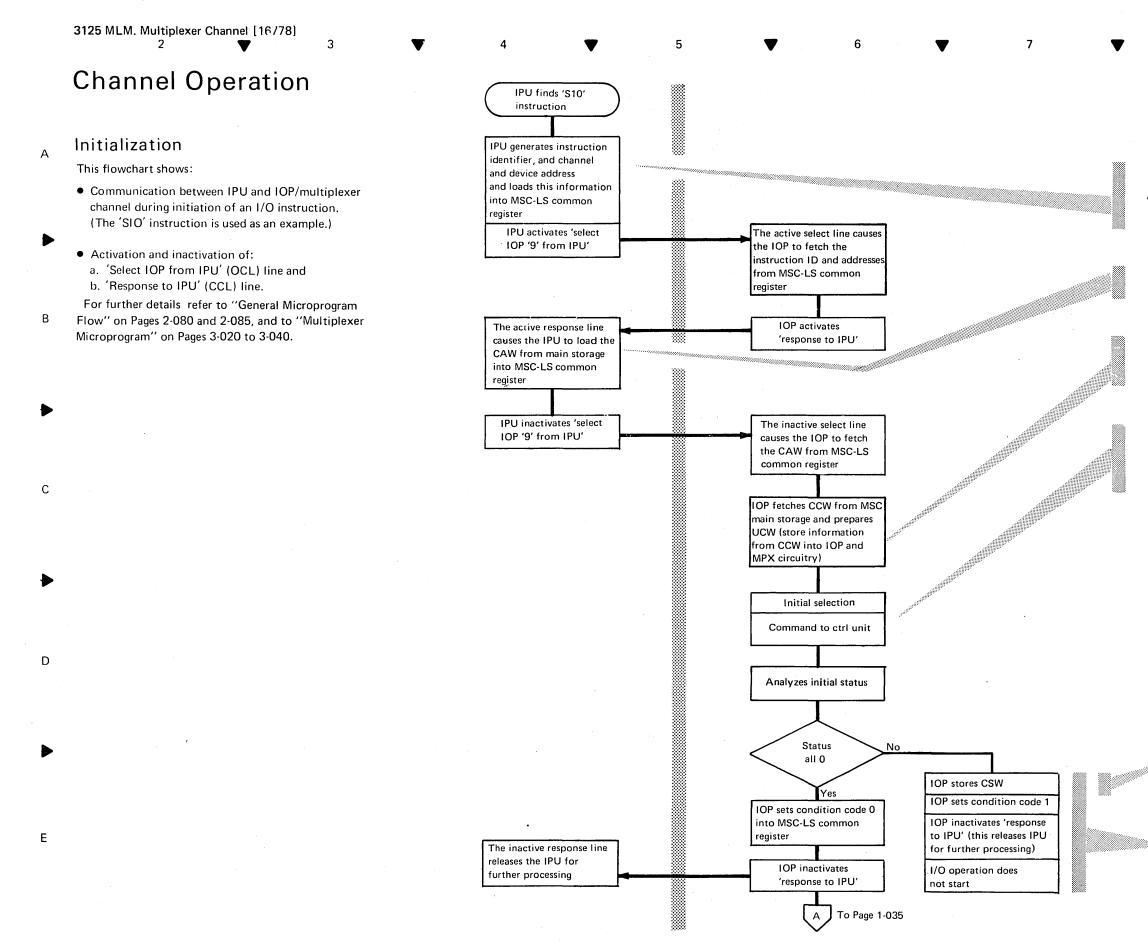

Channel Operation-Initialization

8

1 - 025

For details about instruction identifier and MSC-LS common register layout, refer to *IBM 3125 Processing Unit, Input/Output Processor,* Maintenance Library Manual, Order SY33-1063.

Address range of device addresses are shown on Page 2-070.

CAW layout and location in main storage are shown on Page 2-020.

All necessary device individual information that is required to control an I/O operation is held in the UCW that is assigned to the device. (UCWs are also called subchannel). UCW layout is shown on Page 2-025. UCW addressing is shown on Page 2-070.

Before the operation is started the control unit of the device is selected (initial selection) and the control unit presents an initial status. This status shows whether the I/O device is able to perform the operation, or whether any unusual conditions exist which would prevent the operation from starting.

CSW layout and location in main storage are shown on Page 2-020.

For more details, refer to the "ending sequence" shown on Page 4-050. Refer also to the microprogram flowcharts on Page 3-040.

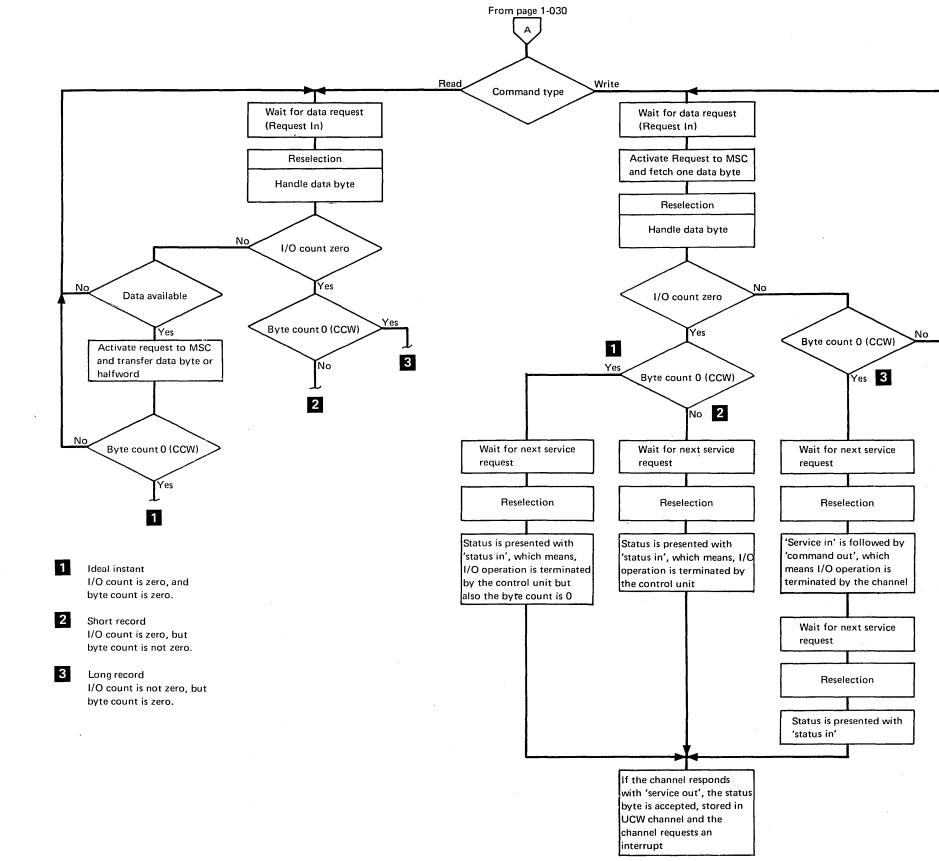

# Data Transfers

2

Two operation types can be performed with the MPX

- Read type operation

- Write type operation.

- The flow chart on this page shows:

- Data transfers for a read type operation (from control unit to MPX and from MPX to main storage)

3

5

6

- Data transfers for a write type operation (from main storage to MPX and from MPX to control unit)

- Channel End and

Α

В

С

D

E

- Device End presentation.

- Data transfers between main storage and IOP/MPX take place for a

- Read type operation: as soon as data byte or halfword is available in MPX

- Write type operation: as soon as data byte is required in MPX. Transfer conditions to MSC are specified by chain- and octopuscontrol lines.

Refer also to microprogram flow charts on pages 3-040 to 3-070. Data transfers between IOP/MPX and I/O devices are always

• byte transfers.

- Transfer conditions are specified by TAG IN- or TAG OUT-lines.

- Channel end is generated by the control unit, as soon as the data transfer between channel and control unit is terminated. Either with channel end alone or with channel and device end together

- (designated as primary status) the channel requests an interrupt. Status byte is held in the UCW which keeps the channel free for further

- operations, while the subchannel remains with a pending interrupt until the interrupt request is accepted by the IPU.

- Device end is generated by the control unit, as soon as the I/O device has completed its mechanical operation. This means, generation of device end very much depends upon the type of I/O device.

- Device end condition (designated as secondary status) is rejected by the channel ('status in' is followed by 'command out') and stacked in the control unit. Further status presentation is suppressed by the channel (by activating 'suppress out').

The channel requests an interrupt and the I/O device remains with a waiting interrupt until this interrupt request is accepted by the IPU and the channel has fetched the status byte.

7

Channel Operation, (Data Transfers and Ending)

1 - 026

T

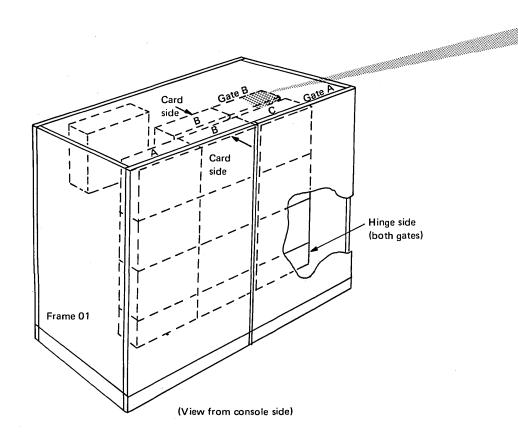

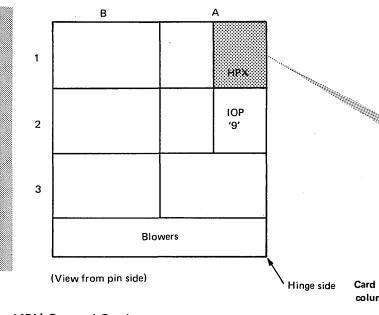

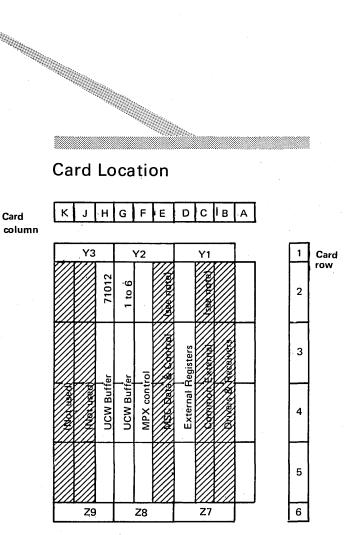

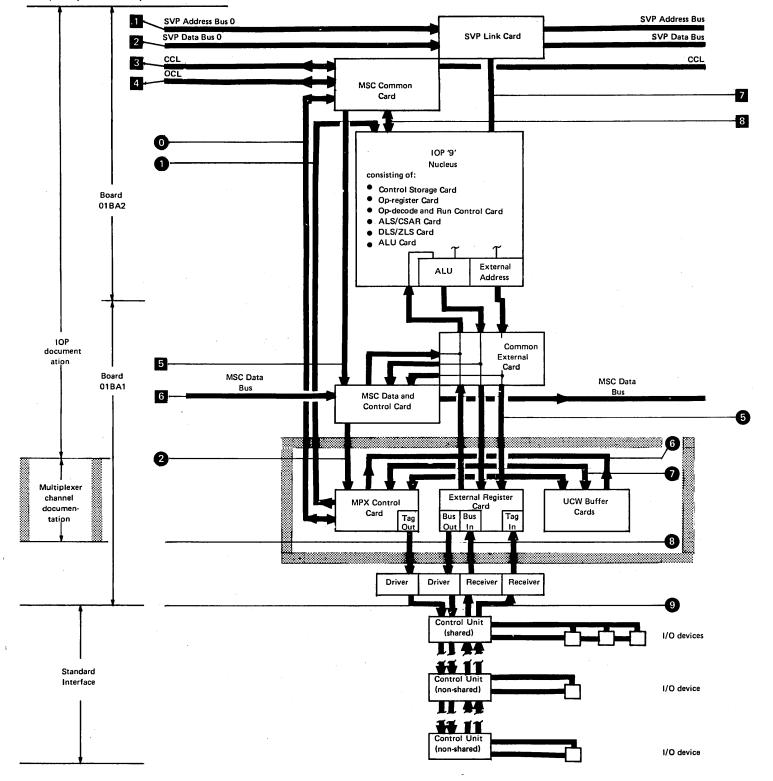

# **Physical Locations**

- This page shows the physical location of the multiplexer channel cards.

- The actual location is

# **Board Location**

- MPX Control Card

- See Pages 4-070 and 4-075.

- ALD Pages are KA 22X.

## External Register Card

- See Page 4-080.

- ALD Pages are KA 28X.

UCW Buffer Cards

- See Page 4-090.

- ALD Pages are KA 10X and KA 16X.

- Note: The common external card and the MSC data and control card are described in IBM 3125 Processing Unit, Input/Output Processor, Maintenance Library Manual order SY33-1063.

Physical Locations 1-030

#### (View from pin side)

Not described in this manual.

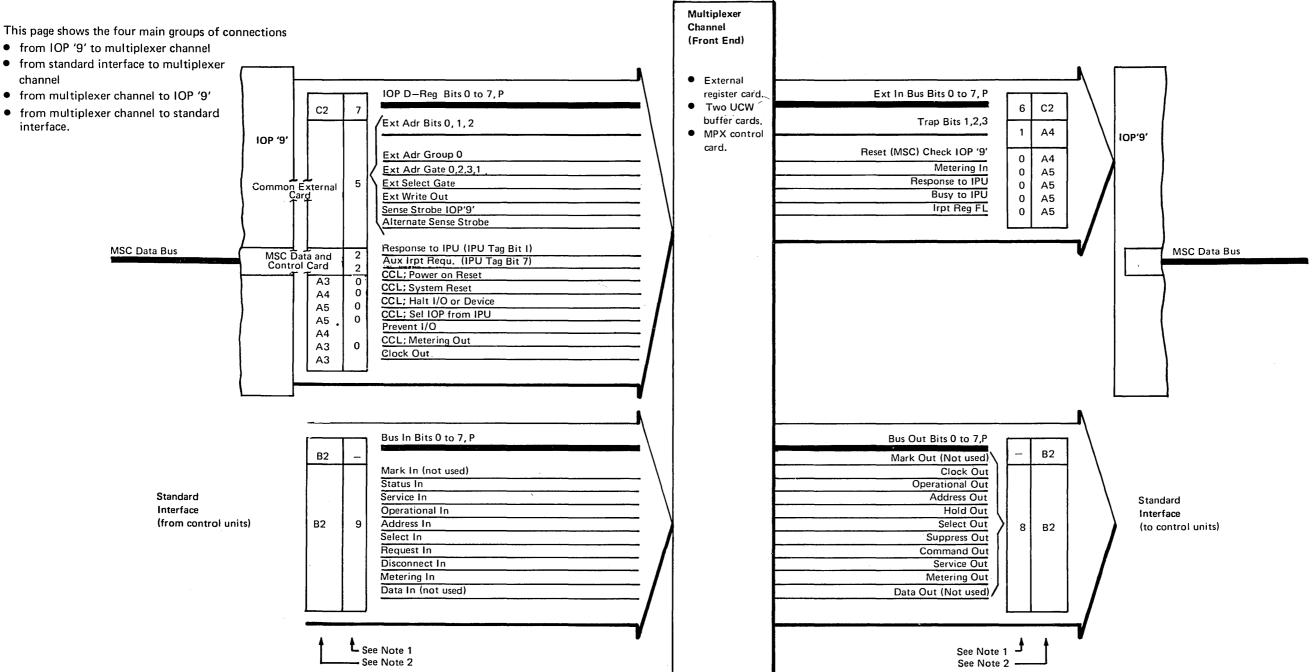

# Signal Interface

Note 1: The numbers in these columns define the line groups as they are shown on Page 4-010 and described on Pages 4-030 and 4-040. Note 2: These letter/number combinations define the plug locations of the cables on multiplexer channel board.

3125 MLM. Multiplexer Channel [16781]

## 3125 MLM, Multiplexer Channel

۰.

1

This page is intentionally left blank

. .

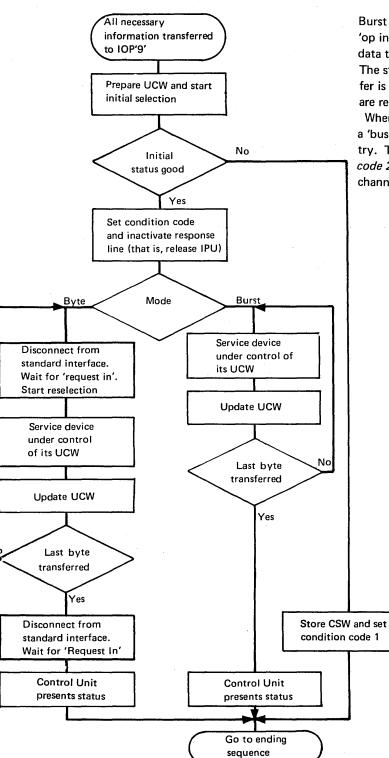

# Chapter 2. Principles of Operation

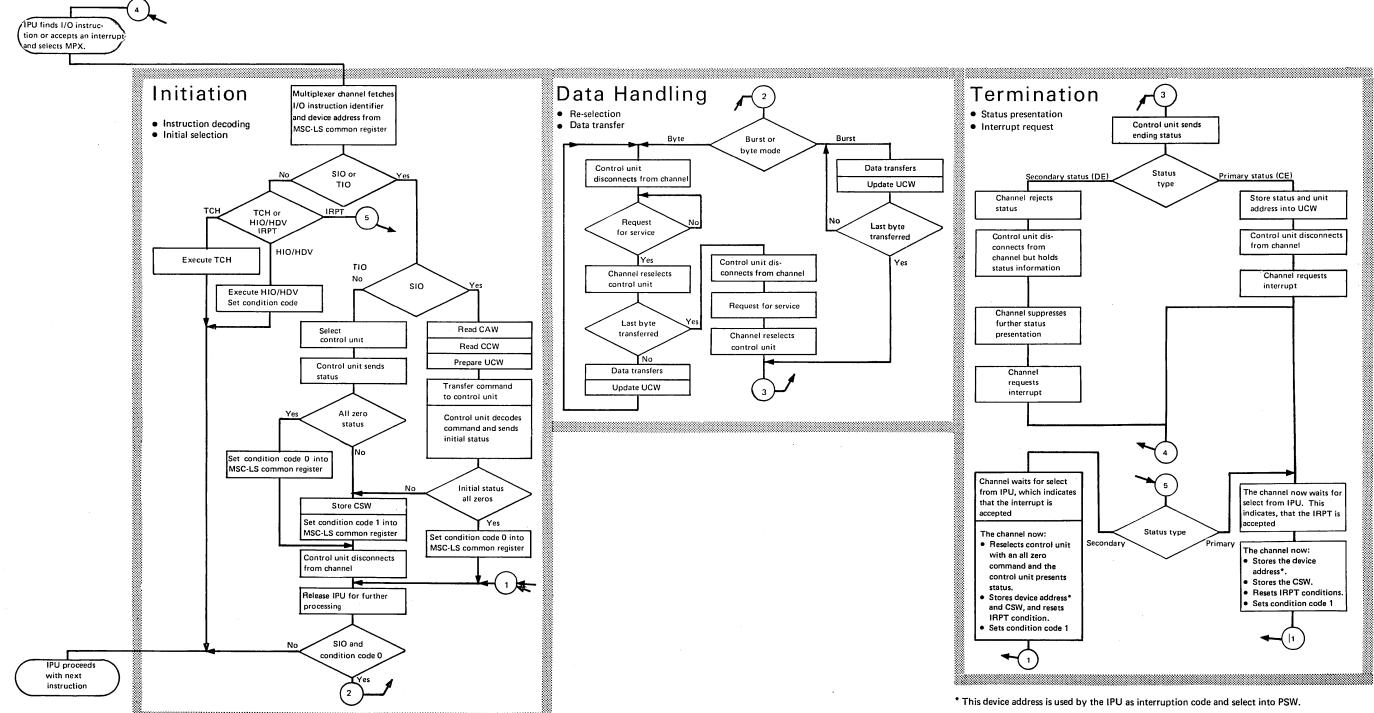

Any channel operation can be dividied into three major portions:

Initiation

Data Handling

Termination.

These three functions are described on this page. For further details, refer to the "Multiplexer Microprogram" on Pages 3-020 to 3-080.

3125 MLM. Multiplexer Channel [16782]

With this flowchart it is assumed, that in all cases the I/O device is available. I/O instructions to devices, that are busy or not operational, are not included here.

For more details refer to pages 2-080, 2-085, 2-090, 3-020 through 3-080.

Principles of Operation 2-020

# I/O Instructions

The following instructions are used with the multiplexer channel: Start I/O (SIO) Halt I/O (HIO) Halt device (HDV) Test I/O (TIO) Test channel (TCH) Store channel identifier (STIDC) Start I/O fast release (SIOF)

## Start I/O (SIO)

Initiates an I/O operation. The address part specifies channel and device. The actual I/O operation is specified by the command in the CCW.

### Halt I/O (HIO)

Terminates an operation that was started by an 'SIO' instruction. The termination is performed in the electronic circuitry while the mechanical operation of the device runs until its normal end. Assume that two devices A and B are connected to a channel.

- 1. If both devices are working in multiplex mode, the addressed device is asked to stop without affecting the other device.

- 2. If device A is currently not working, but device B is working in burst mode, an 'HIO' to device A would stop device B.

#### Halt Device (HDV)

Terminates an operation that was started by an 'SIO' instruction. The termination is performed in the electronic circuitry while the mechanical operation of the device runs to its normal end.

The addressed device is asked to stop. As long as one device operates in burst mode, an 'HDV' to another device is not performed until the burst operation of the first device is completed.

### Test I/O (TIO)

Set a condition code into the PSW to indicate the status of the addressed channel, subchannel and device. A CSW may be stored. This instruction may also be used to clear interrupts.

#### Test Channel (TCH)

Sets a condition code into the PSW to indicate the status of the addressed channel.

#### Store Channel Identifier (STIDC)

This instruction is completely handled by the IPU and sets four bytes of information into main storage at location 168 (decimal); see "Formats".

#### Start I/O Fast Release (SIOF)

This instruction is handled like an 'SIO' instruction.

# Formats

|             | 78             | 14 19 | 16 19               | 20            |                      | 31 |

|-------------|----------------|-------|---------------------|---------------|----------------------|----|

| Op-Code     | Ignored        | *     | Register<br>Address |               | Displacement         |    |

| mat after p | rocessing in I | PU)   | ► for               | 'HDV' only    |                      |    |

|             |                |       |                     |               |                      | _  |

| 3 4         |                | 15    | 16                  | 23            | 24                   | 31 |

|             | used)          | 15    |                     | 23<br>address | 24<br>Device address | 31 |

Command Address

#### Channel Address Word (CAW)

#### • Located in MSC main storage position 72 decimal (48 hexadecimal)

#### 3 4 7 8 Zeros Key

# Channel Command Word (CCW)

| 0             | 7 8 31                                                                                               | 32 |          | 37     |        | 40                     | 48                         | 63 |

|---------------|------------------------------------------------------------------------------------------------------|----|----------|--------|--------|------------------------|----------------------------|----|

| Command       | Data Address or, if TIC, New CCW Address                                                             |    | Flags    |        | Zero   | Ignored                | Length Count or Byte Count |    |

| Commands are: |                                                                                                      | F  | lags are | :      |        |                        |                            |    |

| read          | (transfers data from device to MSC)                                                                  | 3  | 2 = CD   | ) (cha | in dat | a). (only with read c  | ommands)                   |    |

| write         | (transfers data from MSC to device)                                                                  | 3  | 3 = CC   | (cha   | in con | nmand)                 |                            |    |

| read backward | (read, but in reverse order)                                                                         | 3  | 4 = SI   | LI (su | ppres  | s incorrect length ind | ication)                   |    |

| sense (SNS)   | (device information to MSC)                                                                          | 3  | 5 = Sk   | ip (al | lows s | uppression of transfe  | r of zero bytes)           |    |

| control (CTL) | (set up conditions in addressed device)                                                              | 3  | 6 = PC   | (allo  | ws pr  | ogram controlled inte  | errupts)                   |    |

| TIC           | (transfer in channel); allows branching in strings of CCWs and does not initiate any I/O operation). |    |          |        |        | data addressing is spe |                            |    |

command fetches the sense by tes from a selected control unit and device. The 'control' command sets control information into a selected control unit and device.

### Channel Status Word (CSW)

| <ul> <li>Located in MSC main stor</li> </ul> | age position 64 decimal (40 hexadecimal) |    |                                                                  |       |                   |    |    |                                 |                                       |

|----------------------------------------------|------------------------------------------|----|------------------------------------------------------------------|-------|-------------------|----|----|---------------------------------|---------------------------------------|

| 0 3 4 7 8                                    |                                          | 31 | 32                                                               | 3914  | 40                | 47 | 48 |                                 | 63                                    |

| Key Zeros                                    | Command address                          |    | Unit or Device<br>Status                                         | l     | Channel<br>Status |    |    | Residual Count                  |                                       |

| Command Address = Last CC                    | W address +8                             |    | 32 = Attention<br>33 = Status mo<br>34 = Control un<br>35 = Busy | difie |                   |    |    | Residual Count = Numb<br>not be | er of bytes that h<br>een transferred |

# Layout of the four bytes stored (by the IPU) with

After successful generation of fetched channel and

device address the CAW is fetched.

STIDC

The command address of the CAW specifies the location of the first CCW in the main storage

|  | not been |

|--|----------|

|  |          |

36 = Channel end 37 = Device end

38 = Unit check

39 = Unit exception

40 = PCI (program - controlled interrupt)

41 = Incorrect length

42 = Program check

43 = Protection check 44 = Channel data check

45 = Channel control check

46 = Interface control check

47 = Chaining check

All I/O instructions use this format. The displacement is added to the contents of a specified register; the result then represents the channel and device address. From the Op-code an instruction identifier is generated.

The device address and instruction identifier are then transfered, via MSC-LS common register, to the multiplexer channel.

CCWs have to be located on double word boundaries in main storage. After a CCW is transferred to the multiplexer channel and the command does not contain a TIC, the specified command is initiated.

If IDA flag is set, data are addressed indirect via IDA List, whose address is specified in CCW.

Data transfer ends when either the byte count or the I/O count reaches zero. 3 ending conditions are normal

CCW count 0, I/O count 0

CCW count 0, I/O count not 0

• CCW count not 0, I/O count 0.

After the last byte is transferred, the MPX requests an Interrupt. If accepted, interruption code (dev. as is set into PSW and either stator, complete CSW is stored according to conditions during the I/O operation.

# Formats (continued)

# Unit Control Word (UCW)

The multiplexer channel allows simultaneous operation of several I/O devices. Normal mode for the multiplexer channel is, therefore, byte mode.

Because a data transfer of one device may be followed by a data transfer of another device, the conditions of the progress in these data transfers must be individually stored for each I/O device. This is done in the UCW, which is also called a subchannel.

Each UCW is 24 bytes wide. One group of 12 bytes contains:

- Next IDA word address

- Next command address

- ECSW bytes

- Device address

- Unit status.

This group is stored in control storage of IOP '9'.

- $\land$  Another group of 12 bytes contains:

- Flags and operation control

- Key and actual data address

- Byte count

- Buffer byte

- Next data address

- Channel status.

This group is stored in a separate UCW storage area located on the multiplexer channel board.

For a description of the UCW buffer card, refer to page 4-090.

#### UCW portion, stored in control storage of IOP '9'

| 0 to 7, P | 0 to 7, P      | 0 to 7, P | 0 to 7, P | 0 to 7, P | 0 to 7, P      | 0 to 7, P | 0 to 7,P | 0 to 7, P       | 0 to 7, P | 0 to 7, P         | 0 to 7, P                                                                            |

|-----------|----------------|-----------|-----------|-----------|----------------|-----------|----------|-----------------|-----------|-------------------|--------------------------------------------------------------------------------------|

| Ne        | xt Command Add | lress     | 1         | ECS       | W Bytes<br>  3 | 4         | l<br>N   | ext IDA Word Ad | ddress    | Device<br>Address | Unit<br>Status<br>(A definition of<br>bits is given on<br>Pages 2-020 and<br>5-010). |

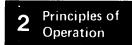

#### UCW portion, stored in UCW buffer of MPX Front End

| 1 | 02                                                         | 03        | 06        | 07       | 0A        | 1 0 | в    | 0E                  | OF        | 1:                                |

|---|------------------------------------------------------------|-----------|-----------|----------|-----------|-----|------|---------------------|-----------|-----------------------------------|

| Γ | 0 to 7, P                                                  | 0 to 7, P | 0 to 7, P | 0 to 7,P | 0 to 7, P | 0–3 | 4–7P | 0 to 7, P           | 0 to 7, P | 0 to                              |

|   | Flags and Operation Control.<br>The meaning of each bit is |           | Byte (    | Count .  | Buffer    | Кеу |      | Actual Data Address |           | Cha                               |

|   | shown on Pa                                                | age 3-100 |           |          |           |     |      |                     |           | (A defin<br>bits is g<br>Pages 2- |

5-010.)

Unit status Contains detect field, here the unit that detected the error is identified.

2 Contains source field, here the unit that probably caused the error is identified.

ECSW

Bytes

1

4

- 3 Contains validity flags to indicate validity of the information stored in designated fields.

- Contains type of termination and sequence code.

- indicates conditions, detected by the I/O device or control unit. These conditions are indicated to the channel via standard I/O interface. The channel does not modify the status bit pattern and stores the status byte into CSW as it was received from the control unit. Channel status - indicates conditions detected by the

- channel, except those that are caused by equipment mal-function during execution of an I/O operation.

3125 MLM. Multiplexer Channel [16784]

different information during an I/O operation. Its main use is to hold one I/O data byte for preparing halfword transfers to main storage with read operations.

2 - 026

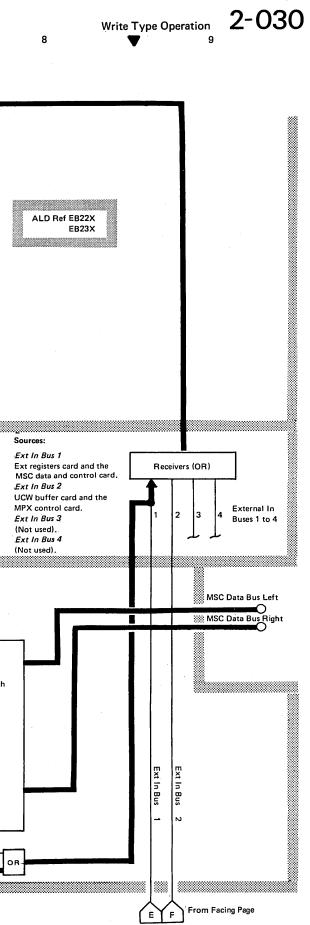

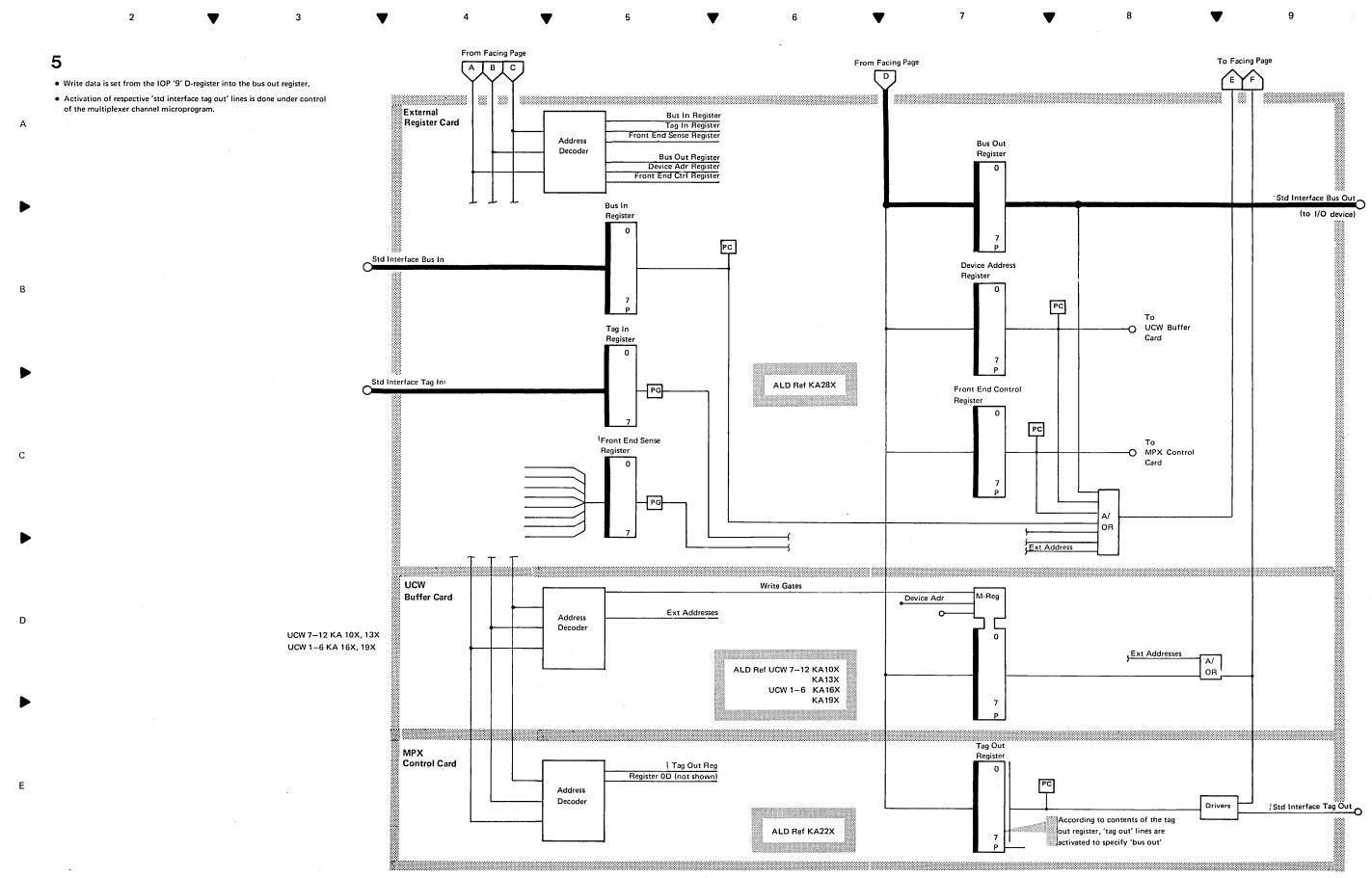

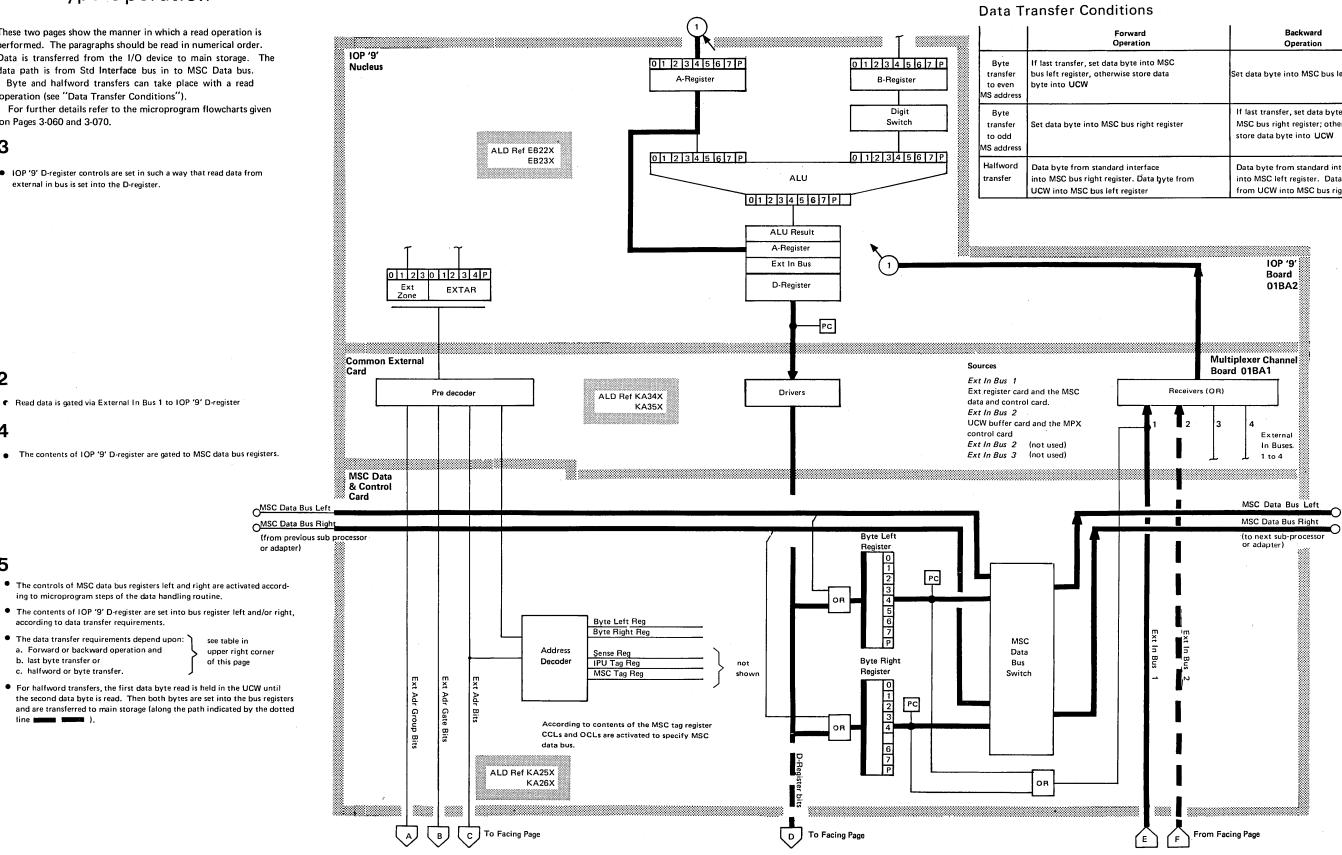

3125 MLM. Multiplexer Channel [16785] T 7 2  $\mathbf{T}$ 3 ▼ 4 ▼ 5 ¥ 6 ¥ Write Type Operation These two pages show the manner in which a write operation is performed. The paragraphs should be read in numerical order. IOP '9' Data is transferred from main storage to the I/O device. The data 1 1 2 3 4 5 6 7 P 01234567P Nucleus path is from MSC Data Bus to Std Interface Bus Out. **B-Register** A-Register А For further details refer to the microprogram flowcharts shown on Pages 3-060 and 3-070. Digit Switch 01234567P 0 1 2 3 4 5 6 7 P 3 ALU 01234567P • IOP '9' D-register controls are set in such a way, that write data from the 'external in bus 1' is set into the IOP '9' D-register. ALU Result A-Register В Ext In Bus D-Register 012 12340 Ext Zone EXTAR -PC IOP '9' 2 Board 01BA2 Multiplexer • Write data is gated via 'external in bus 1' to IOP '9' D-register. Common External Channel Card Drivers Board Predecoder 01BA1 4 ALD Ref KA34X С KA35X • The contents of IOP '9' D-register are gated to the external register card. MSC Data Bus Left MSC Data Bus Right • As soon as a device requires service, this device causes activation of 'Trap 1 O request', which forces the multiplexer channel microprogram to its data Byte Left (from previous handling routine. sub processor Register • The data handling routine controls data path between MSC data bus or adapter) registers and bus out register. MSC Controls of MSC data bus registers are activated according to the micro-D Data Byte Left Register program steps of the data handling routine. Bus Byte Right Register • With write operations, only byte transfers and forward operations take Address Switch place. Thus, a data byte is set into the byte right register and gated via Decoder Sense Register IPU Tag Register MSC Tag Register 'external in bus 1' into the IOP D-register. (The contents of the byte left not register are ignored.) Ext Adr Group Bits Ext Adr Gate Bit shown Byte Right Register According to contents of MSC Tag register, CCLs and OCLs are activated to specify MSC data bus РС ALD Ref KA25X Е KA26X MSC Data & Control Card **D-Register Bits**

A B C To Facing Page

D To Facing Page

3125 MLM. Multiplexer Channel [16786]

Write Type Operation (continued)

#### 3125 MLM. Multiplexer Channel [16787]

# **Read Type Operation**

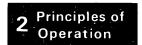

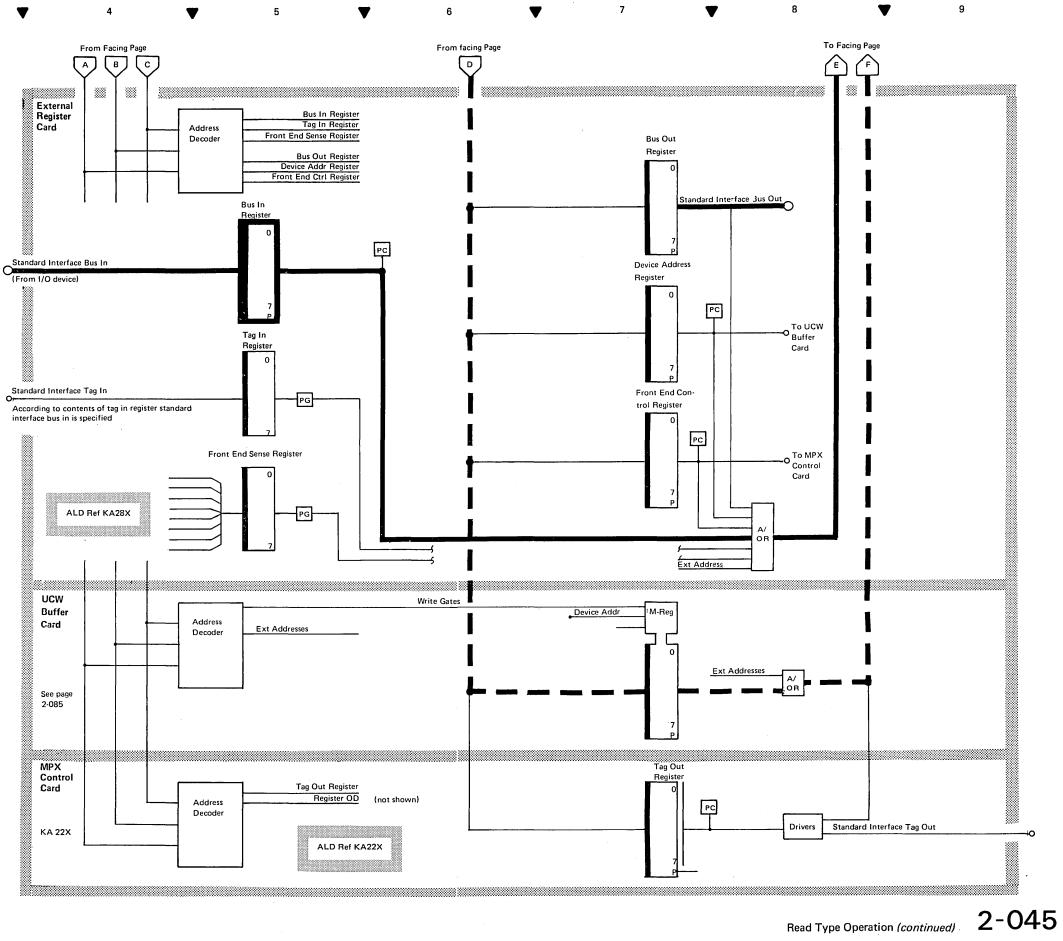

These two pages show the manner in which a read operation is performed. The paragraphs should be read in numerical order. Data is transferred from the I/O device to main storage. The data path is from Std Interface bus in to MSC Data bus. Byte and halfword transfers can take place with a read operation (see "Data Transfer Conditions").

For further details refer to the microprogram flowcharts given on Pages 3-060 and 3-070.

## 3

• IOP '9' D-register controls are set in such a way that read data from external in bus is set into the D-register.

€ Read data is gated via External In Bus 1 to IOP '9' D-register

4

5

• The contents of IOP '9' D-register are gated to MSC data bus registers.

• The contents of IOP '9' D-register are set into bus register left and/or right, according to data transfer requirements. • The data transfer requirements depend upon: ` a. Forward or backward operation and b. last byte transfer or c. halfword or byte transfer.

ing to microprogram steps of the data handling routine.

• For halfword transfers, the first data byte read is held in the UCW until the second data byte is read. Then both bytes are set into the bus registers and are transferred to main storage (along the path indicated by the dotted line ( ).

see table in

of this page

upper right corner

Read Type Operation 2-040

| Forward                                                          | Backward                                                                                              |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Operation                                                        | Operation                                                                                             |

| fer, set data byte into MSC<br>ister, otherwise store data<br>CW | Set data byte into MSC bus left register                                                              |

| te into MSC bus right register                                   | If last transfer, set data byte into<br>MSC bus right register; otherwise<br>store data byte into UCW |

| rom standard interface                                           | Data byte from standard interface                                                                     |

| us right register. Data yyte from                                | into MSC left register. Data byte                                                                     |

| ASC bus left register                                            | from UCW into MSC bus right register                                                                  |

## 1

Α

В

С

• As soon as a device requires service this device causes activation of 'trap 1 request', which forces the multiplexer channel microprogram to its data handling routine.

7

3

2

- The data handling routine controls the data path from the bus in register to the MSC data bus.

- At service In time data from standard interface is set in to Bus In register.

- Contents of Bus In register then are gated via External In Bus 1 to 10P '9' D-register.

- D

- Е

3125 MLM. Multiplexer Channel [16788]

3125 MLM. Multiplexer Channel [16789]

# Modes of Operation Byte Mode

MPX can serve more than one device at a time in "Byte Mode".

Here one byte of one device is handled during one IOP cycle and one byte of another device is handled during a subsequent IOP cycle.

Because after a byte transfer the device disconnects from channel, one UCW is required per device in order to store control in formation of each device.

Each data transfer is initiated by a request from one device. The request is followed by a reselection of the device. After the data transfer is completed the device again disconnects from the channel and the channel waits for the next request. This procedure is repeated until the last byte of a record is handled or the byte circuit reaches zero.

With the next request following a data transfer, the status is presented to the channel. According to type of status this status will be accepted or stacked.

If accepted, the channel stores status information into the unit status byte (which is part of the UCW) and activates its 'interrupt request' line to the IPU.

If stacked the channel status is held in the control unit and has to be presented later.

## Multiple Byte Mode

In principle *multiple byte mode* is the same type of operation as byte mode, but with the exception that a predetermined number of bytes is transferred.

Multiple byte mode and the number of bytes to be transferred are specified by the control unit by holding up 'op in' for as long as it is required.

## Burst Mode

Burst mode is specified by the control unit by holding up 'op in'. The initial selection is directly followed by the data transfer of the complete record (first to last byte). The status is also directly presented after the data transfer is completed. (No separate request and re-selection are required.)

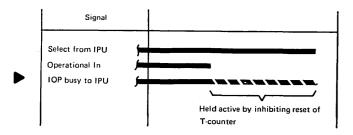

When the multiplexer channel is working in burst mode a 'busy to IPU' line is generated by the channel circuittry. This signal causes the IPU to generate *condition* code 2 (busy) whenever the IPU selects the multiplexer channel.

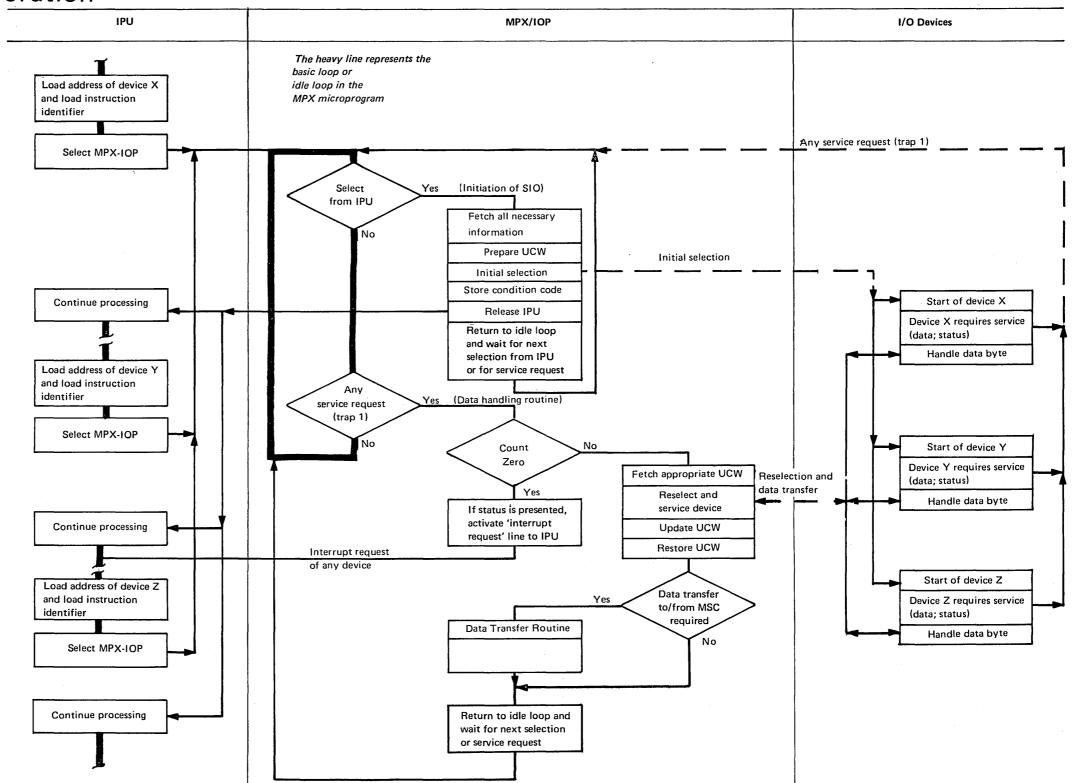

# **Example of Byte Mode Operation**

The IPU, when processing the customer program finds an 'SIO' instruction for device X in the stream of instructions.

- The following actions now take place:

- 1. Select multiplexer channel

- 2. Transfer of necessary data to multiplexer channel

- 3. Prepare UCW

- 4. Start device

- 5. Release IPU for further processing.

The MPX microprogram returns to its idle loop and waits for the next selection from IPU, or for service request.

The IPU now continues executing the customer program and finds the next 'SIO' instruction in the instruction stream. The same actions (listed above) take place.

The IPU again continues executing the customer program and finds a third 'SIO' instruction in the instruction stream. The same actions listed above for first 'SIO' instruction take place and the IPU is again released for further processing. The MPX microprogram returns to its idle loop.

As soon as one of the devices requires service 'Trap 1 request' is activated, which causes the trap bit 1 to be gated to IOP '9' nucleus. This trap bit 1 forces the MPX microprogram to its data handling routine. The following actions now take place:

1. Load UCW of requesting device into work area

- 2. Reselect device

- 3. Handle data byte

- 4. Update and restore UCW

The MPX microprogram returns to its idle loop and waits for the next selection or service request.

Starting more than one device (byte mode) gives the impression that these devices are operated simultaneously. Actually, the mechanical operations of the started devices *are* running simultaneously, but only one device can be serviced at a time. This is because all the devices use the same circuitry and the same microprogram.

3125 MLM. Multiplexer Channel [ 16790]

#### Example of Byte Mode Operation

2-055

# General Information Microprogram

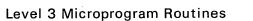

The multiplexer channel is completely controlled by microprogram. After successful loading of the MPX microprogram into the control storage of IOP '9', the microprogram idles in its basic loop and waits either for selection from IPU or for service requests from the I/O devices.

Five program levels exist (levels 0, 1, 2, 3, and 7) within the MPX microprogram. Switching from one level to another is achieved by an internal trapping system. Different jobs within the MPX microprogram are programmed at different program levels (also called trap levels). These trap levels also classify a priority sequence.

The following list shows the trap or program levels (from lowest to highest priority) and the jobs programmed at each level:

| 1 | Ptr | Progm or TRAP<br>Level | Priority | Job                                                             |

|---|-----|------------------------|----------|-----------------------------------------------------------------|

|   | 0   | 0                      | Lowest   | Communication with IPU                                          |

|   | 1   | 1                      |          | <ul> <li>Data Transfer</li> <li>Interrupt Request</li> </ul>    |

|   | 2   | 2                      |          | • HIO/HDV in worst mode                                         |

|   | 3   | 3                      |          | <ul> <li>Error handling</li> <li>System reset, start</li> </ul> |

|   |     | 7                      | Highest  | • System reset, execution                                       |

If a request for a specific job to be done becomes active, trap bits are generated in the multiplexer channel. These trap bits are gated to IOP '9' where they are ORed with the link portions of index words. (The trap register is located on the ALS/CSAR card).

Alteration of the link portion of an index word (comparable with a branch operation) causes a change of the chain of index words. This, in turn, causes the use of other IARs.

### Level 0

In byte mode a new I/O operation can be started after all higher trap requests are serviced.

In burst mode the multiplexer channel does not accept a second SIO. The IPU terminates this second SIO as a result of the active 'IOP busy' line and sets condition code 2.

#### Level 1

Requests for data transfers are handled as soon as an I/O device requires service and all higher trap requests are serviced.

Requests for interrupts are placed after termination of an I/O operation by activating the line interrupt request. (Interrupt requests are the result of the status presentation.)

#### Level 2

I/O operations can be interrupted if the IPU issues an HIO or HDV to the multiplexer channel.

#### Level 3

If parity errors in distinct Front End registers are found or the 'system reset' line becomes active, or a standard interface 'tag in check' is detected, trap 3 is generated.

Trap bit 3 forces the microprogram to the error handling routine that prepares information.

#### Level 7

Level 7 is forced by microprogram and represents system reset routine, which is executed after it was started in level 3.

## Interrupts

#### Channel End

Channel End indicates the completion of that part of an I/O operation that involves:

#### Transfer of I/O data

Transfer of sense information

Transfer of control information between multiplexer channel and main storage and between multiplexer channel and control unit.

Channel end is accepted for all devices and is stored in the corresponding UCW (subchannel). The 'interrupt request' line then signals the waiting interrupts.

When the IPU is ready to process interrupts, level 0 routine selects one waiting interrupt and stores an interruption code (device address) into MSC-LS common register. Subsequently, the multiplexer channel stores a CSW, resets the interrupt condition, and releases the IPU for further processing.

This means, the subchannel appears with a pending interrupt to subsequent SIO instructions until its interrupt request has been accepted.

The instant (within an I/O operation) that channel end is generated depends upon the operation and the type of device. Operations that do not cause any data to be transferred can provide channel end condition already with presentation of the initial status.

When chaining takes place only the channel end of the last operation of the chain is made available to the program.

General Information 2-060

#### Device End

Device end indicates:

- (a) The completion of an I/O operation at the I/O device.

- (b) A manual change of the device from the "not ready" to the "ready" state.

- Device end is stacked by the channel.

Device end status remains stacked in the control unit until the channel is free to handle them either by an interrupt or TIO.

When chaining is specified receipt of device end condition (and no unusual condition) causes the channel to initiate the next operation. Only the device end of the last operation of the chain is made available to the program.

Dependent upon I/O device type, device end condition is generated either simultaneously with the channel end condition or later

## Chaining

Two types of chaining are possible

Data chaining (DC)

Command chaining (CC).

Chaining which is specified by the CCW flags, is detected and performed by microprogram.

When chaining is specified, the microprogram branches to a chaining routine. This chaining routine tests the chaining conditions and performs the following:

1. Fetching of new CCW

2. Testing for TIC

3. Testing for IDA

4. Loading of new CCW information into UCW. Data chaining means that the command code of the

previous CCW remains valid for the new CCW.

Command chaining means that the new CCW completely replaces the previous one.

## Unusual or Exceptional Conditions

Unusual or exceptional conditions that occurred during execution of an I/O instruction are indicated in the status bytes. These unusual or exceptional conditions are handled by the operating system being used.

For arrangement of the status bytes in the CSW, see Page 2-020. For status bit definitions, see Page 5-010.

# Status Bytes

Status bytes are presented at the beginning (*initial status*) and end (*ending status*) of an I/O operation.

Initial status indicates whether an I/O device is ready to execute a given command.

Ending status indicates whether an I/O operation was successful.

For arrangement of the status bytes in the CSW, see Page 2-020. For status bit definitions, see Page 5-010.

## Sense Bytes

Simultaneously with the execution of an I/O operation sense bytes are generated and updated in the control unit. If a status byte indicates a unit check, these sense bytes provide additional, device specific, information about the cause of that malfunction.

Sense byte 0 is common for all I/O devices. The number and the content of all other sense bytes depend upon device type and the requirements of the device.

Sense bytes are fetched with a 'sense' command in the CCW of a 'SIO' instruction and are analyzed by the operating system being used.

For more information about sense bytes, refer to the respective control unit and/or I/O device documentation. A brief explanation of sense byte 0 is given on Page 5-010.

3125 MLM. Multiplexer Channel [16792]

## Indirect Data Addressing

If indirect data addressing is used the CCW contains an indirect data address (indicated by a flag bit; see CCW Format given on Page 2-020).

This IDA flag bit 'on' causes the MPX microprogram to fetch the actual data address from the IDA list in main storage (see microprogram flowchart on Page 3-030).

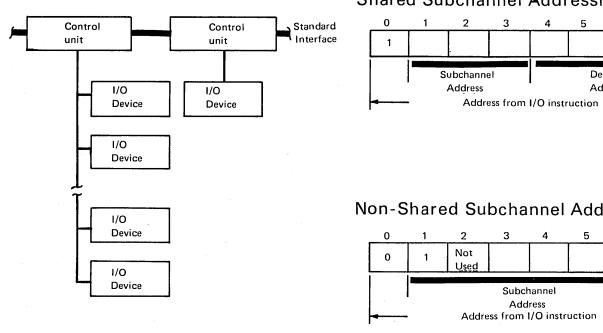

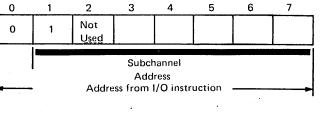

# Subchannel Arrangement and Addressing

UCWs may be shared or non-shared. A shared UCW means that this UCW serves a group of I/O devices that are connected to one control unit, but only serviced one at a time. A non-shared UCW means that this UCW serves only one I/O device.

Out of the 32 UCWs, the first eight alternatively can operate as shared UCWs. Each control unit associated with a shared UCW may have up to 16 I/O devices attached.

When a subchannel is addressed by an I/O address, bit 0 of the address byte defines whether the subchannel is shared (bit 0 = 1) or non-shared (bit 0 = 0). Bit 0, therefore, is not part of the actual address.

# Shared Subchannel Addressing

5

Device

Address

Device Addresses: 80 to FF (hex) (see table on the right)

# Non-Shared Subchannel Addressing

Device Addresses: 40 to 7F (hex) (see table on the right)

Shared

Non-shared

Because shared subchannels 0 to 7 use the same UCW as the non-shared subchannels 0 to 7, addresses of shared subchannels must be chosen in such as way that they do not conflict with addresses of non-shared subchannels.

2 - 070

# **Device Address Assignments**

Certain restrictions apply to address assignment. In any one row of the following table, only one of three address assignments can be chosen for devices which are to operate simultaneously. Taking the first row, for instance, if address 40 (hex) is assigned, addresses 60 (hex) and 80 through 8F (hex) should not be assigned.

| Nonshared<br>Subchannels |    | Shared<br>Subchannels |  |

|--------------------------|----|-----------------------|--|

| (hexadecimal)            |    | (hexadecimal)         |  |

| 40                       | 60 | 80 to 8F              |  |

| 41                       | 61 | 90 to 9F              |  |

| 42                       | 62 | A0 to AF              |  |

| 43                       | 63 | B0 to BF              |  |

| 44                       | 64 | C0 to CF              |  |

| 45                       | 65 | D0 to DF              |  |

| 46                       | 66 | E0 to EF              |  |

| 47                       | 67 | F0 to FF              |  |

| 48                       | 68 |                       |  |

| 49                       | 69 |                       |  |

| 4A                       | 6A | :                     |  |

| 4B                       | 6B |                       |  |

| 4C                       | 6C |                       |  |

| 4D                       | 6D |                       |  |

| 4E                       | 6E |                       |  |

| 4F                       | 6F |                       |  |

| 50                       | 70 |                       |  |

| 51                       | 71 |                       |  |

| 52                       | 72 |                       |  |

| 53                       | 73 |                       |  |

| 54                       | 74 |                       |  |

| 55                       | 75 |                       |  |

| 56                       | 76 |                       |  |

| 57                       | 77 |                       |  |

| 58                       | 78 |                       |  |

| 59                       | 79 |                       |  |

| 5A                       | 7A |                       |  |

| 5B                       | 7B |                       |  |

| 5C                       | 7C |                       |  |

| 5D                       | 7D |                       |  |

| 5E                       | 7E |                       |  |

| 5F                       | 7F | r i                   |  |

3125 MLM. Multiplexer Channel

This page is intentionally left blank.

▼

6

3

2

4

▼

▼

5

▼

7

▼

V

# General Microprogram Flow (continued)

3

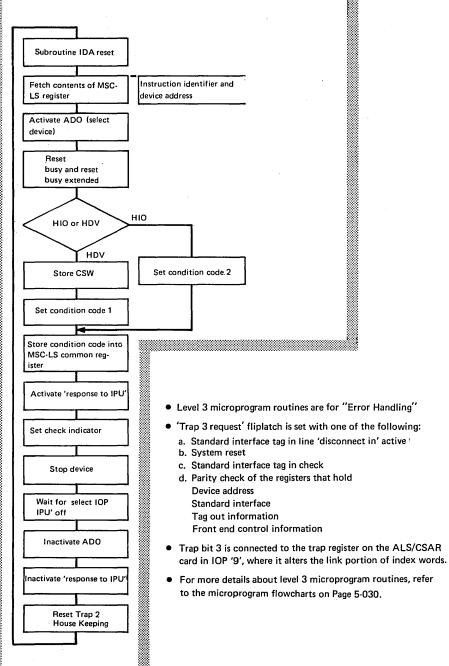

## Level 1 Microprogram Routines

Level 1 microprogram routines are for: "Data Handling" and

2

- "Status Handling"

- 'Trap 1 request' fliplatch is set with the standard interface "tag in" lines: Α Request in Operational in

- Trap bit 1 is connected to the trap register on the ALS/CSAR card in IOP '9', where it alters the link portion of index words.

- For more details about Level 1 microprogram routines, refer to the

- microprogram flowcharts on Pages 3-060 and 3-070.

Е

"HIO" and "HDV" when the multiplexer channel is working in burst mode.

4

• Level 2 microprogram routines are for:

Level 2 Microprogram Routines

• 'Trap 2 request' fliplatch is set with burst mode and the 'HIO/HDV' line from IOP.

T

5

T

- Trap bit 2 is connected to the trap register on the ALS/CSAR card in IOP '9', where it alters the link portion of index words.

- For more details about level 2 microprogram routines, refer to the microprogram flowcharts on Page 3-080.

6

-090

3125 MLM. Multiplexer Channel

This page is intentionally left blank.

# **Chapter 3. Operational Details** Visual Index for MPX Microprogram

• Represents a summary of the MPX microprogram.

• Provides a guide to the microprogram flow.

- Relates various routines to pages within this chapter.

- Provides cross-references to the microprogram listing.

Visual Index for MPX Microprogram

,

3-010

- The various routines of the MPX microprogram are documented in different sections of the microprogram listing.

- The circled letters after the labels (in the flowcharts on the following pages) point to these sections of the microprogram listing.

- These letters can be found in the microprogram listing header above the module sequence number.

# Arrangement of MPX Microprogram Listing

This page represents a "table of contents" of the microprogram listing per section (or sheet) as defined by the circled letters.

> **Error Description** Declares and Equates of External and Local registers System Reset **Start Routine**

I/O Instructions – TIO-Interrupt CU busy end Interrupt Normal status CU busy

B

0

Ø

B

Ø

G

I/O Instructions – Basic Loop

Interrupt Handling Interrupt priorities Interrupt recognition

Fetch CCW CCW address to MSC-LS 1 CCW update Store CCW address +8 Save CCW address +8 CCW update CCW address to MSC-LS 1 Execute TIC Indirect Data Addressing

I/O Select

Control unit busy SIO Set up CSW address Store 2 status bytes Reset UCW Withdraw stacked status

**SIO Initial Status**

Execute command chaining Indicate command chaining I/O operation ANDed, no chaining Set up CCW address Store 2 status bytes Condition code 1 Reset UCW Command accepted

8 0

**TRAP I/O Selection**

**CC Initial Status** Indicate chaining Execute chaining Command accepted, I/O started

3125 MLM. Multiplexer Channel

K Data Transfer M HIO/HDV – Level 2 Set up CSW address Prepare New Page for Indirect Data Addressing Subroutine store condition code 0 Subroutine prepare for Trap 1 when 'request in' 0 HIO/HDV – Not Burst Set up CSW address Reset Time Out counter **Common Error Routines for SIO** Common Error Routines for CC **Common Error Routines for TIO** Subroutine Time Out **Common Subroutines** Subroutine information for SVP Subroutine generate UCW address Set up CSW address +4 and store 2 status bytes Subroutine prepare system reset from Trap 3 Subroutine Address and Store CSW Subroutine NOP Subroutine Address and Store ECSW Subroutine Store Condition Code 1 Entry of routine IPU end Entry of routine channel handling 1 +2 Subroutine Channel Handling 3 Subroutine Interface Disconnect with Selective Reset Subroutine Reset Prefetched IDA Word Subroutine Prepare and Store ECSW into Data Store Subroutine Prepare Log Area Trap 3 Handling Tag In Check System Reset from Trap 3 **External Register Parity Check Disconnect In MPX System Reset** Subroutine Log Execute for Level 0, 1, 2, and 3 Error Routines for Sections (or Sheets) B, C, D, E, F, G, H, J, K, M **UCW Area Definition**

**Cross References**

This is an alphabetical listing of all labels used in that microprogram listing. In connection with all labels:

- their storage location and statement number

- all statement numbers that use the label as symbolic "branch to" address are shown.

**3** Operations

Arrangement of MPX Microprogram Listing

3-012

3125 MLM. Multiplexer Channel [16798] 7 T 6 ▼ ▼ V 4 5 -3 T 2 **MPX Microprogram Flowcharts** From Pages 3-040 and 3-050 E T This page and the following pages up to page 3-080 show the MPX BASICIO C Basic Loop (or Idle Loop) microprogram in a simplified way. Because these flowcharts are not as detailed as the microprogram listings the flowcharts are Α After a successful IMPL, the MPX Log not correct in all details. If detailed information is needed refer microprogram branches to the basic Request to the microprogram listings. (or idle) loop, where the MPX micro-Log Execute program waits for 'select from IPU' The various routines covered on this page are: subroutine and log requests. Control unit busy end B into UCW I/O instructions basic loop C Interrupt recognition D MPX interrupt Analyze type of pending interrupt This flowchart is a sim-Yes plification of the main Set MPX IRPT flowcharts and represents pending the steps for an 'SIO' instruction. В SC4 C transfer CSW Select IOP '9' from IPU IPU selects store CSW into Yes main storage multiplexer channel Request to MSC (3 (4 The thick line Multiplexer channel fetche to fetch MSC-LS through these contents of MSC-LS common register flowcharts shows ommon register, which Set condition code 2 the flow for an now contains the instruc-Request to MSC SIO instruction. ion identifier, and channe to transfer condition and device address For all other HIO or code into MSC-LS instructions HDV common register С and operations. Ô B Activate 'response Multiplexer channel check Activate 'response follow the thin No SELUP to IPU' line to IPU' line for HIO/HDV or lines, Set device address To Page 3-050 interrupt into ext OC Execute HIO-HDV Check channel Yes Subchannel SCH BUSY C address busy Reset SIO remembe S10 Yes (SIO) Multiplexer channel check bit remember for instruction type Instruction Wait for 'select bit TIO, SIO, TCH identifier defines Wait for 'select from IPU' off to IPU' interrup from IPU' off No (TIO) [c, Inactivate 'response Multiplexer channel Request to MSC to to IPU' activates its 'response To Page 3-050 fetch CAW from to IPU' line Interrupt Handling MSC-LS Common Registe IPU' off D (2) Inactivate Multiplexer channel No Channel  $\bigcirc$ waits for 'select address = 0 from IPU' off Error 1 To Page 3-030 routine Yes Multiplexer channel fetches SC7 C contents of MSC-LS Other Instruction common register, which type now contains CAW

sio

Set SIO remember

bit

тсн

4

Yes

Error Routine

L

Е

MPX Microprogram Flowcharts 3-020 8  $\mathbf{T}$

- Standard interface tag out register '01' is shown on Page 4-070

- The bit pattern that is set into the tag out register causes

- plexer channel and control unit for initial selection, is shown on Page 4-050.

- Data path for write operations is shown on Pages 2-030 and

MPX Microprogram Flowcharts (continued)

- Standard interface tag in register '08' is shown on Page 4-080 (Ex-

- Standard interface bus out register '00' is shown on Page 4-080 (Ex-

- Standard Interface bus in register '00' and standard interface tag

▼

6

3125 MLM. Multiplexer Channel [16801]

2

V

3

▼

4

V

5

▼

7

▼

PRIOR D тรтรบві D Yes Generate UCW address BUF TO E12 Set interrupt buffer into device address register Prepare interruption code: (a) Device address into MSC data bus register right (b) Channel address into MSC data bus register left. Request to MSC to transfer channel and device addres into MSC-LS common register Subchannel ALC: interrupt Yes Set device F with an all Store CSW G zero command To Page 3-020 To Page 3-030

MPX Microprogram Flowcharts (continued) 3-050

V

| MPX Microprogram | Flowcharts | (continued) |   |

|------------------|------------|-------------|---|

| 8                | ▼          |             | 9 |

3-060

3125 MLM. Multiplexer Channel [16803]

MPX Microprogram Flowcharts (continued)

3-070

## MPX Microprogram Label List

| =                 | -              |          |                      |

|-------------------|----------------|----------|----------------------|

| В                 |                |          | 0                    |

| - •               | 0.070          | 20       | _                    |

| BACKW<br>BASIC IO | 3-070<br>3-020 | D6<br>A5 | ODD CT<br>OTH ST BIT |

| BUF TO E 12       | 3-050          | C8       | omarbit              |

| BUSYCU            | 3.050          | D5       | Р                    |

|                   |                |          |                      |

| C                 |                |          | PRIOR                |

| •                 |                |          |                      |

| CCCD              | 3-030          | A5       | R                    |

| CCW UP            | 3-030          | A5       | RAIS                 |

| CH 1              | 3-040          | A5       | RECOG                |

| CH 8<br>CMDACC    | 3-050<br>3-040 | C6<br>D4 | RECTRANS             |

| CNTEX             | 3.040          | B4       | REMEMBER             |

| CNT 0             | 3.070          | A7       | RODD                 |

| COUNT 0           | 3.070          | B5       |                      |

| CU BUSY           | 3-040          | A3       | S                    |

|                   |                |          |                      |

| D                 |                |          | SC 4<br>SC 7         |

|                   |                |          | SCH BUSY             |

| DATAXFER          | 3-070          | A4       | SE IN                |

|                   |                |          | SEL UP               |

| E                 |                |          | SETTR 2              |

|                   | 0.070          | 53       | SG 2                 |

| EMPTY<br>ENTONE   | 3∙070<br>3∙070 | D7       | SIO RE               |

| ENTRYRT           | 3.070          | B4<br>B8 | STATI UP             |

| EVENCT            | 3.070          | D7       | STORCSW              |

|                   |                |          | STOR STAT<br>SW 1    |

|                   |                |          | SW 3                 |

| F                 |                |          | SW 5                 |

| FOREW             | 3-070          | D3       | SW 7                 |

| F 12              | 3-060          | A4       | SW 8                 |

|                   |                |          | SW 10                |

| H                 |                |          | SW 14                |

| —                 |                |          | SW 15<br>SW 16       |

| HDV               | 3-050          | A4       | SW 10<br>SW 17       |

| HIO<br>HIO LEV 2  | 3-050<br>3-080 | A3       | SW 18                |

| HDV CSW           | 3-080          | A4<br>C4 | SW 20                |

| HIO RER           | 3-080          | D4       | SW 21                |

|                   |                |          | SW 22                |

| 0                 |                |          | SW 23                |

| 1                 |                |          | SW 24                |

| INTRON            | 3-020          | E8       | SW 25                |

| IOSEL             | 3-030          | D7       | SW 28<br>SW 29       |

| INTR              | 3-060          | C5       | 511 25               |

| INTRTEND          | 3-020          | E7       | _                    |

| K                 |                |          |                      |

| —                 |                |          | TRAP 3               |

| К2К               | 3-070          | E8       | TSTSUBI              |

| Ν                 |                |          | W                    |

| ΝΟ ΤΟΡ            | 3-050          | D4       |                      |

| NO STOP           | 3-060          | C6       | WRITE                |

|                   |                |          |                      |

3125 MLM. Multiplexer Channel [16805]

Operational Details 3

3-070 D6 3-060 C5

3-050 A8

3-070

C6

3-020

B6

3-070