Maintenance Library

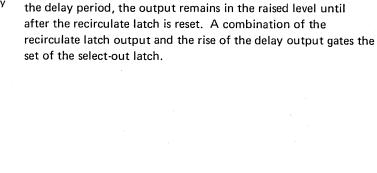

3145

Processing Unit Theory — Maintenance

# Maintenance Library

**7145**

Processing Unit Theory — Maintenance

### **PREFACE**

This manual is for readers who understand the basic concepts of computers and system programming. Introductory information that describes data formats, instruction formats, status switching, and program interrupts is in *IBM System/360 Principles of Operation*, GA22-6821; and *IBM System/370 Principles of Operation*, GA22-7000.

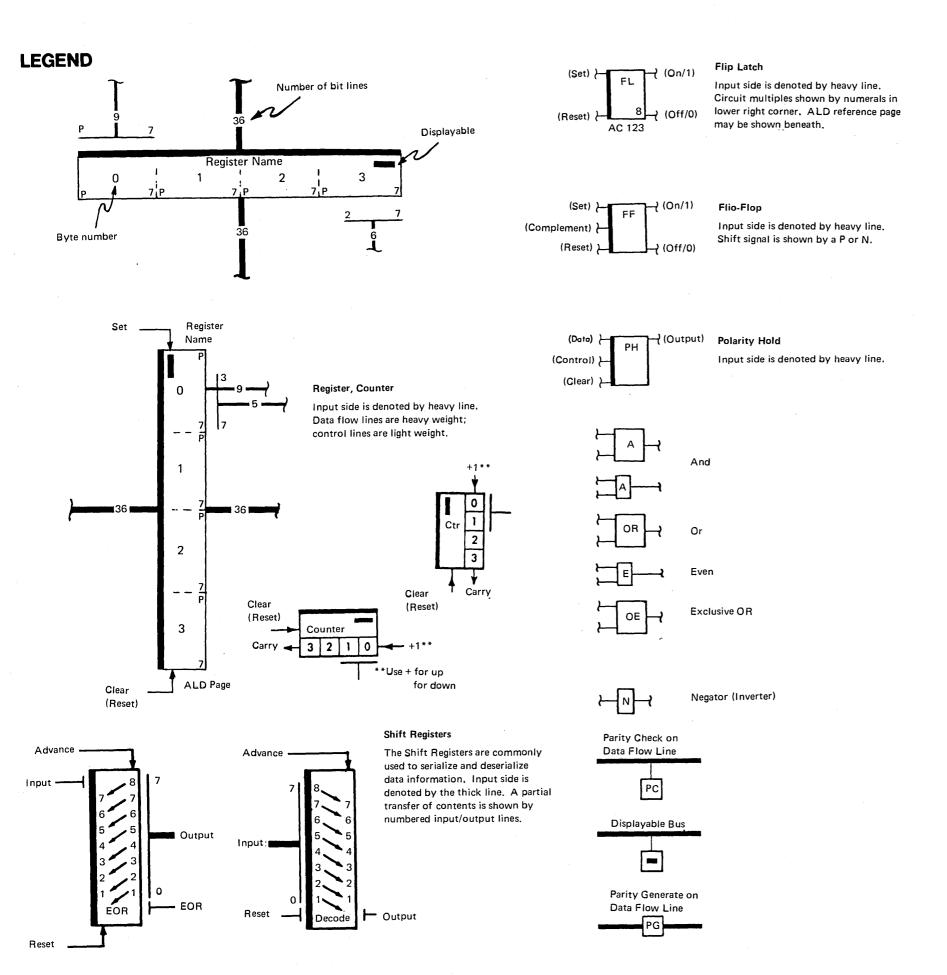

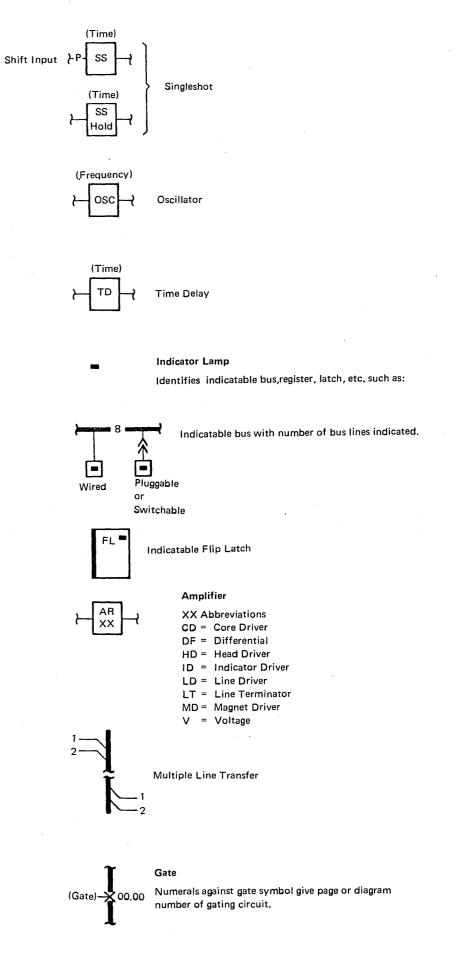

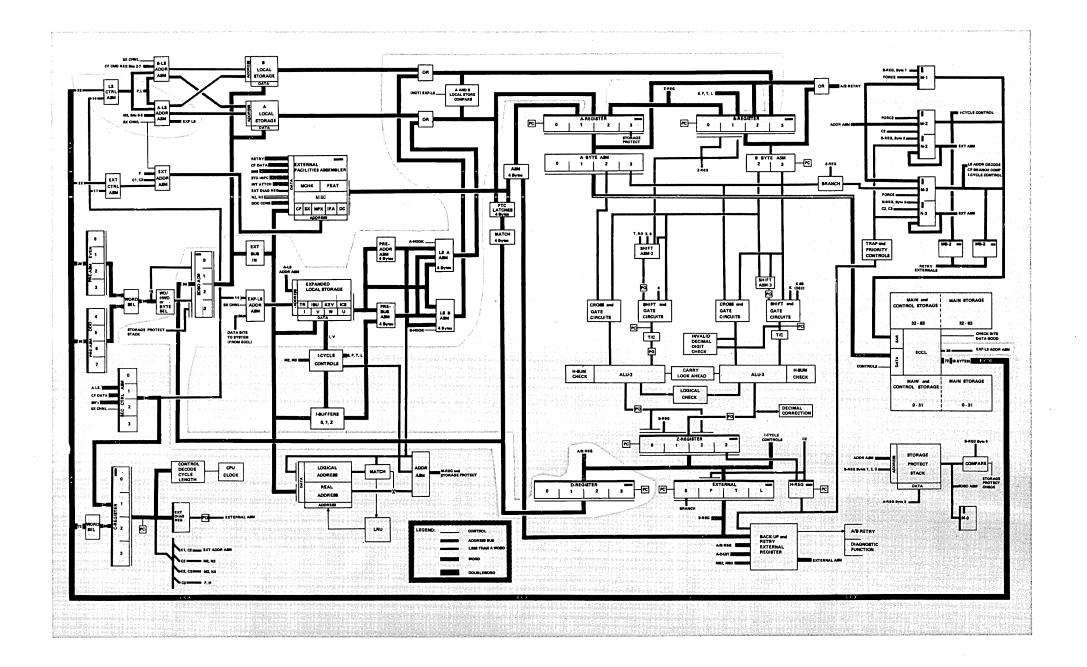

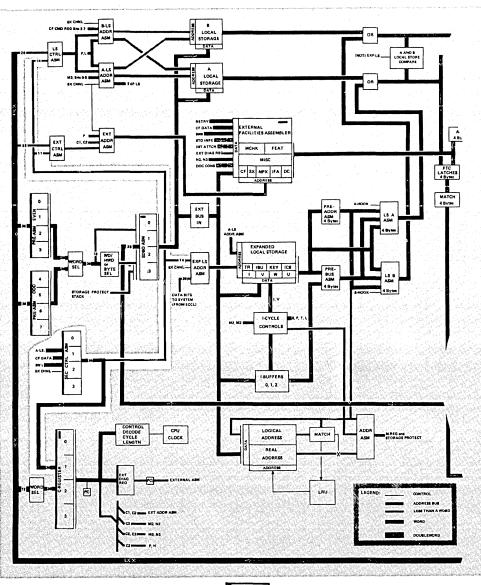

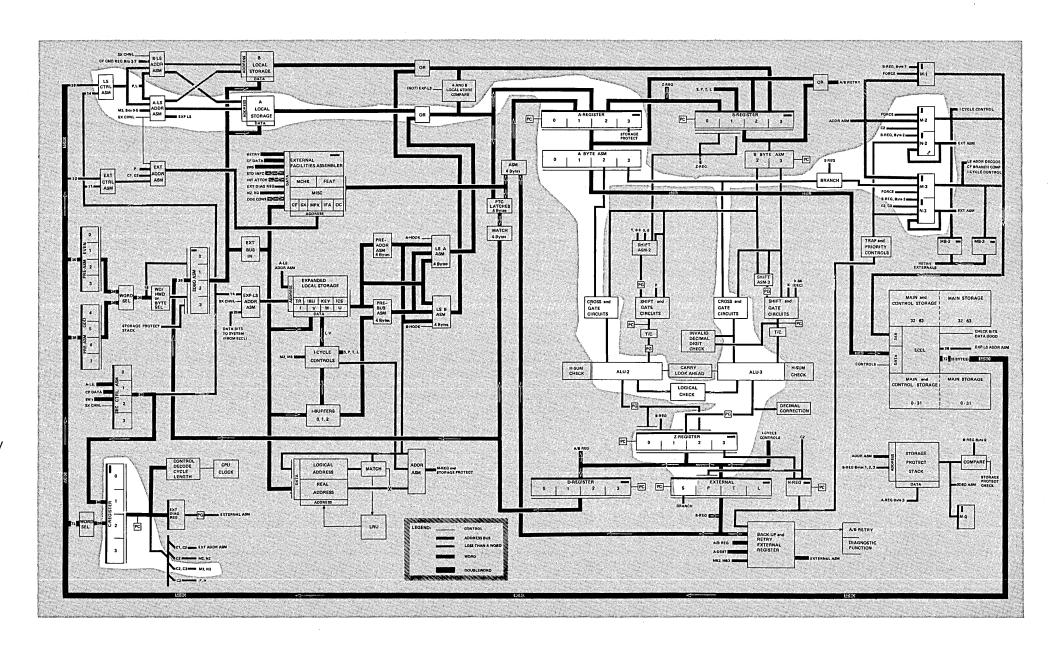

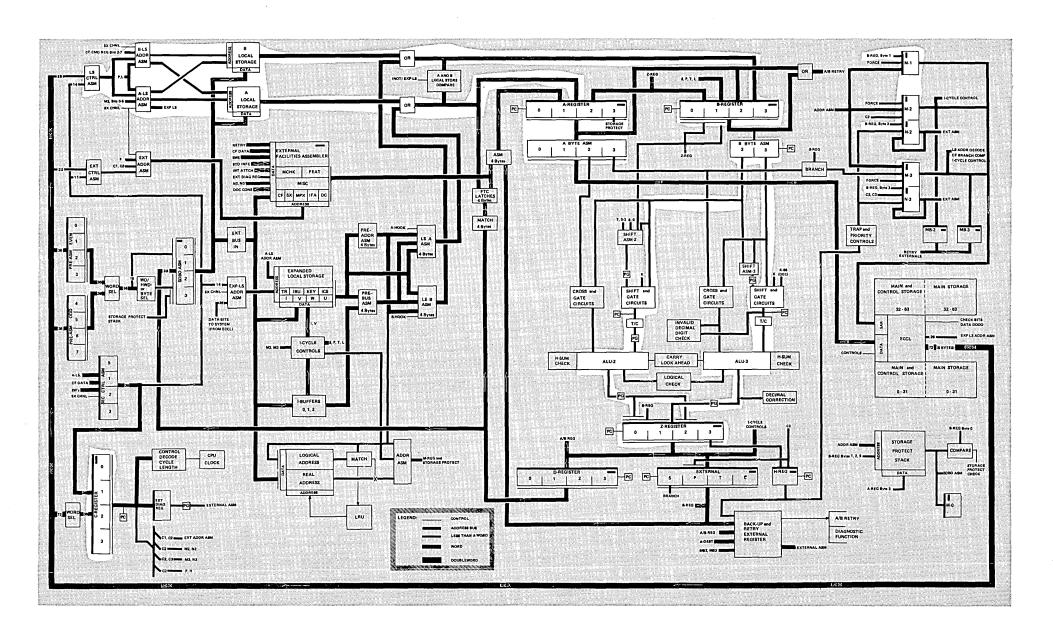

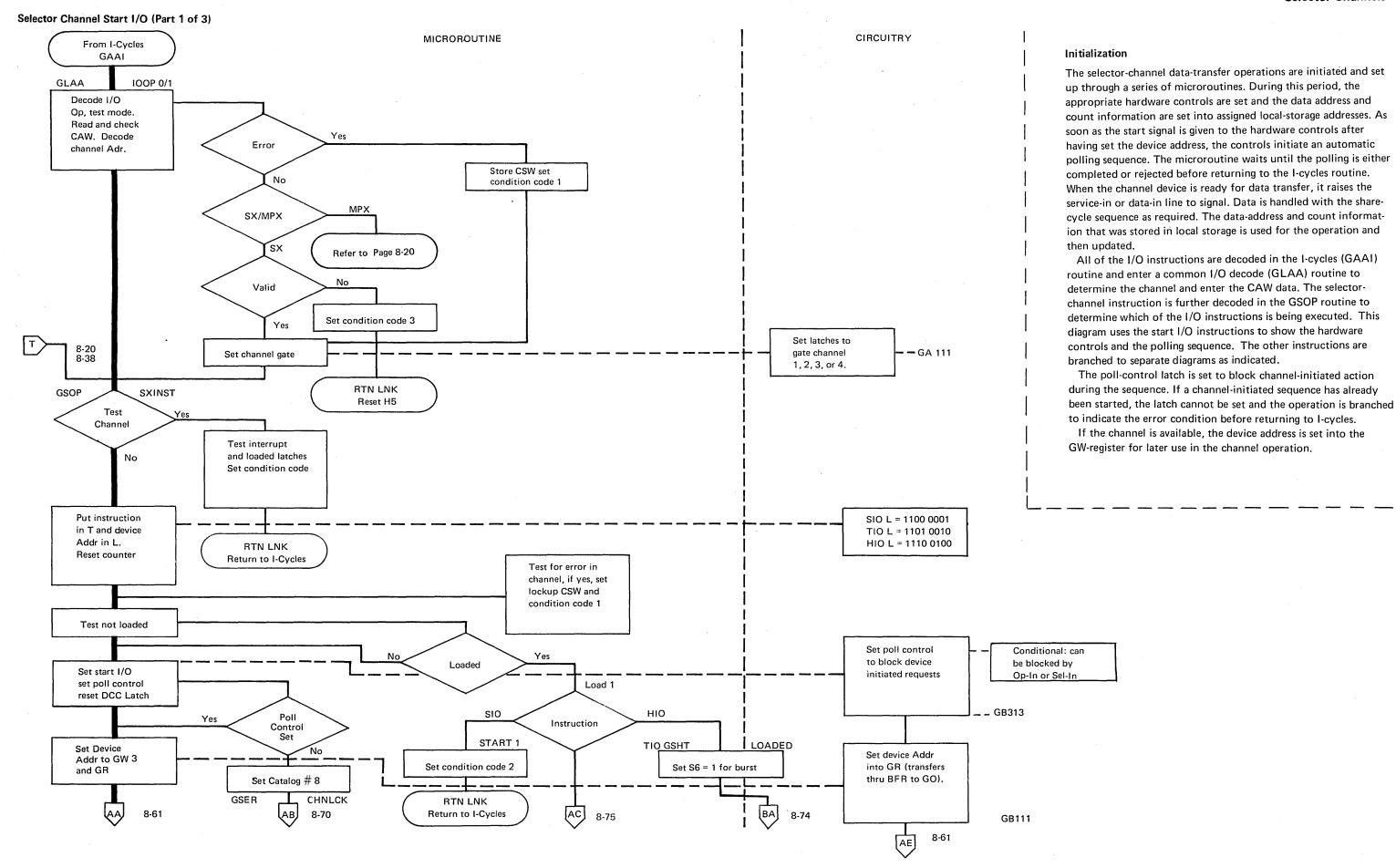

Integrated graphic techniques are used where practical to provide standalone diagrams and modular units of information.

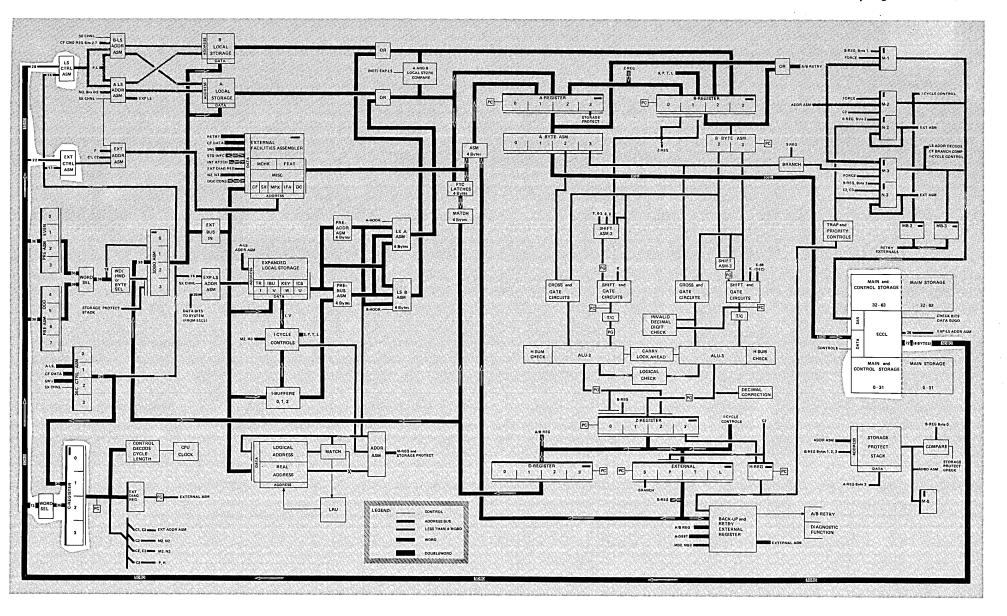

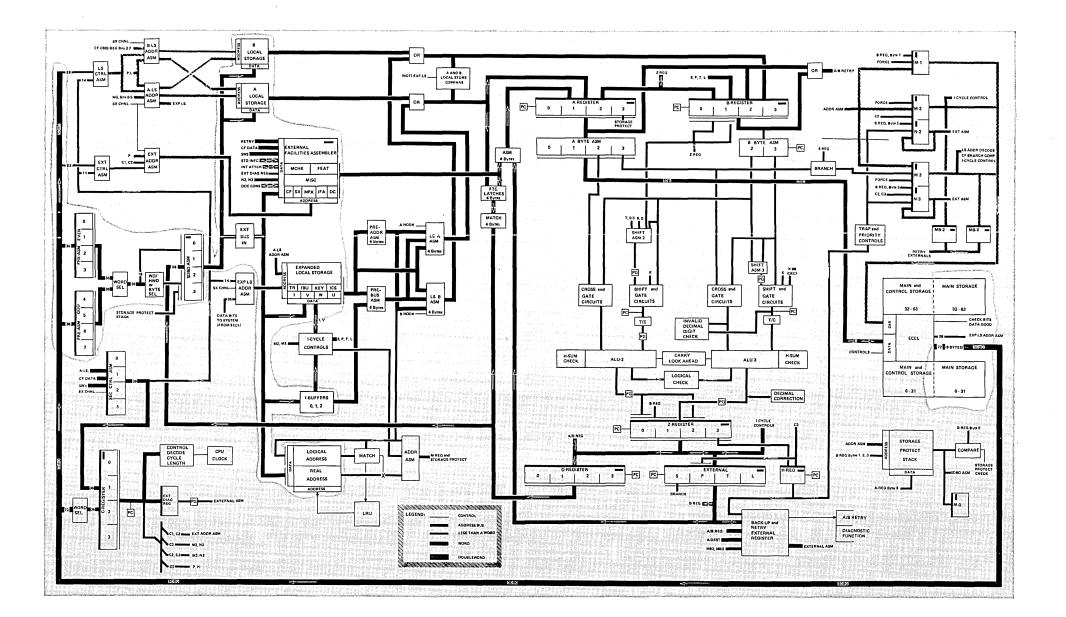

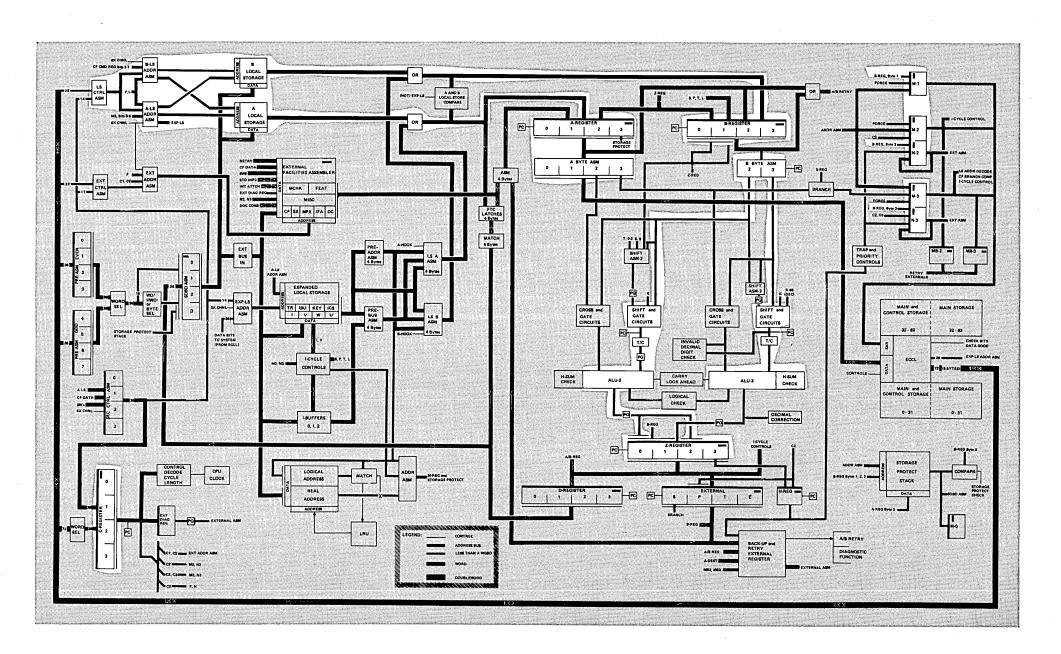

The information ranges from basic system concepts, contained in Chapter 1, to the detailed operations of a functional unit or area contained in Chapters 2-13. Each chapter contains a modular segment of information about a major functional area of the system, such as CPU, storage and console.

This manual also contains information to be used in maintaining or repairing the 3145. It also includes CPU reference data; channel reference data; maintenance techniques; checks, adjustments, and removal procedures, power and cooling maintenance procedures; physical locations; description of panel indicators.

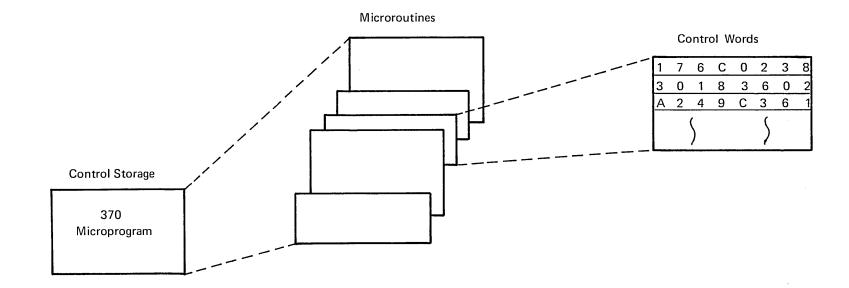

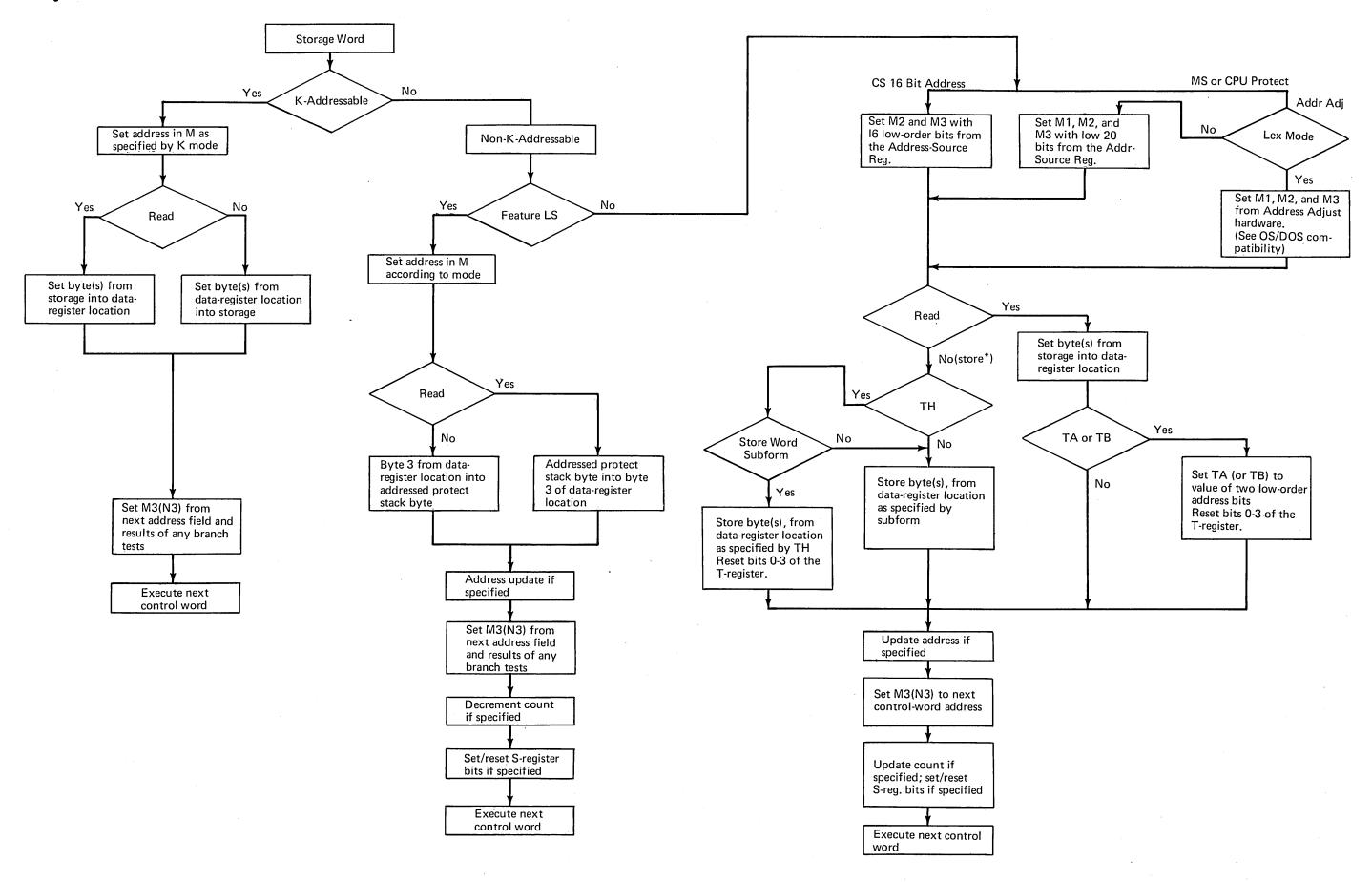

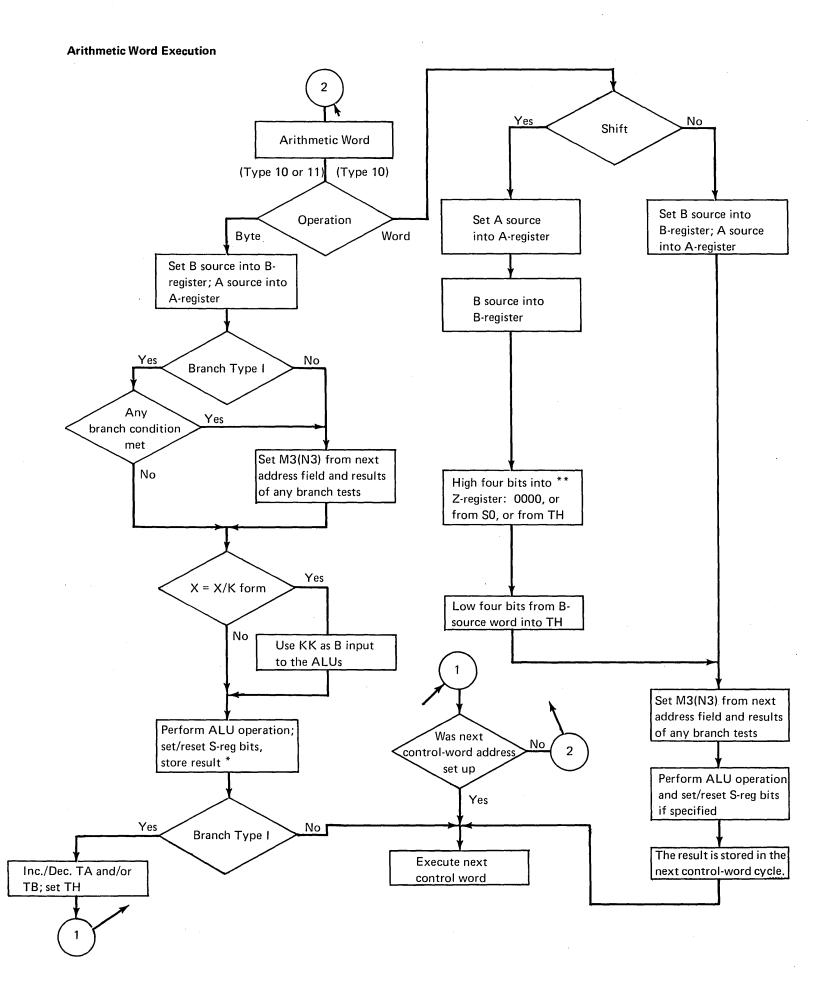

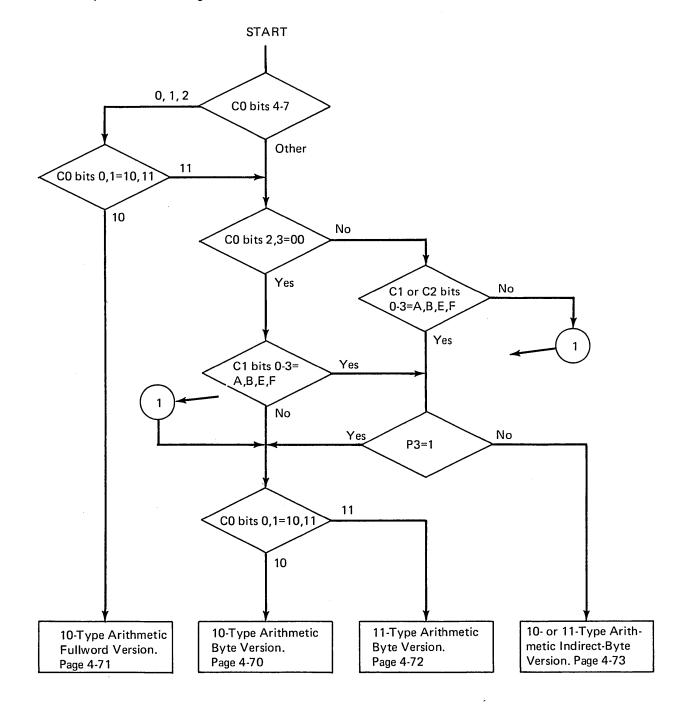

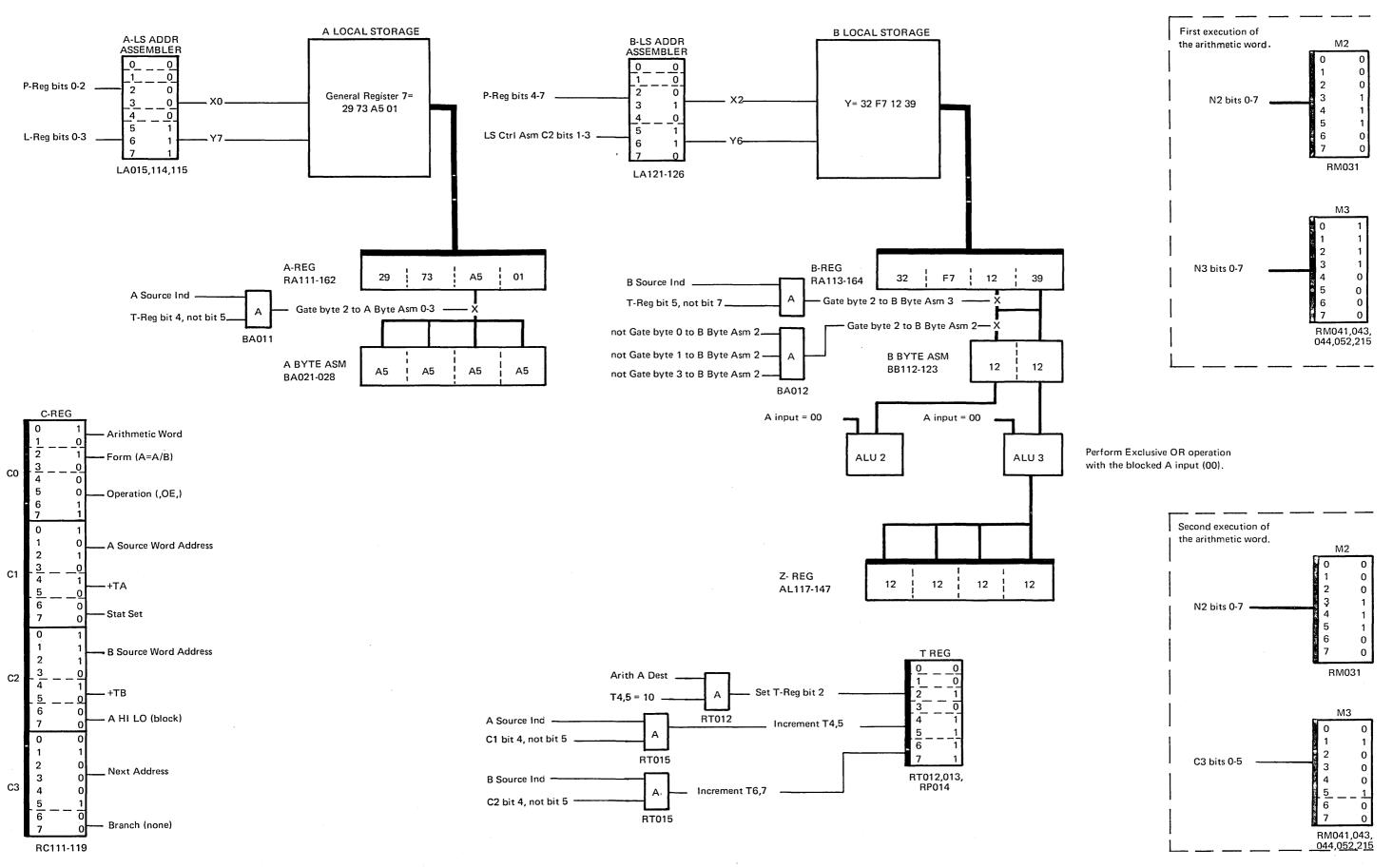

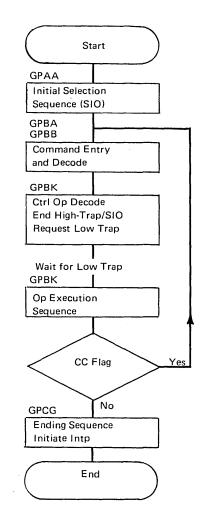

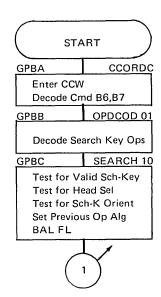

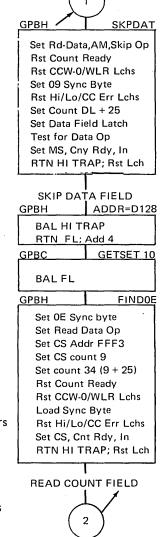

The 370 Microprogram Listing contains the microinstruction sequences required to execute any program instruction. Therefore, the execution of only some of the program instructions is described in this manual. Instead, certain representative examples are described, using flow charts and example operands. The examples show microprogram sequences and data paths required to execute the instruction.

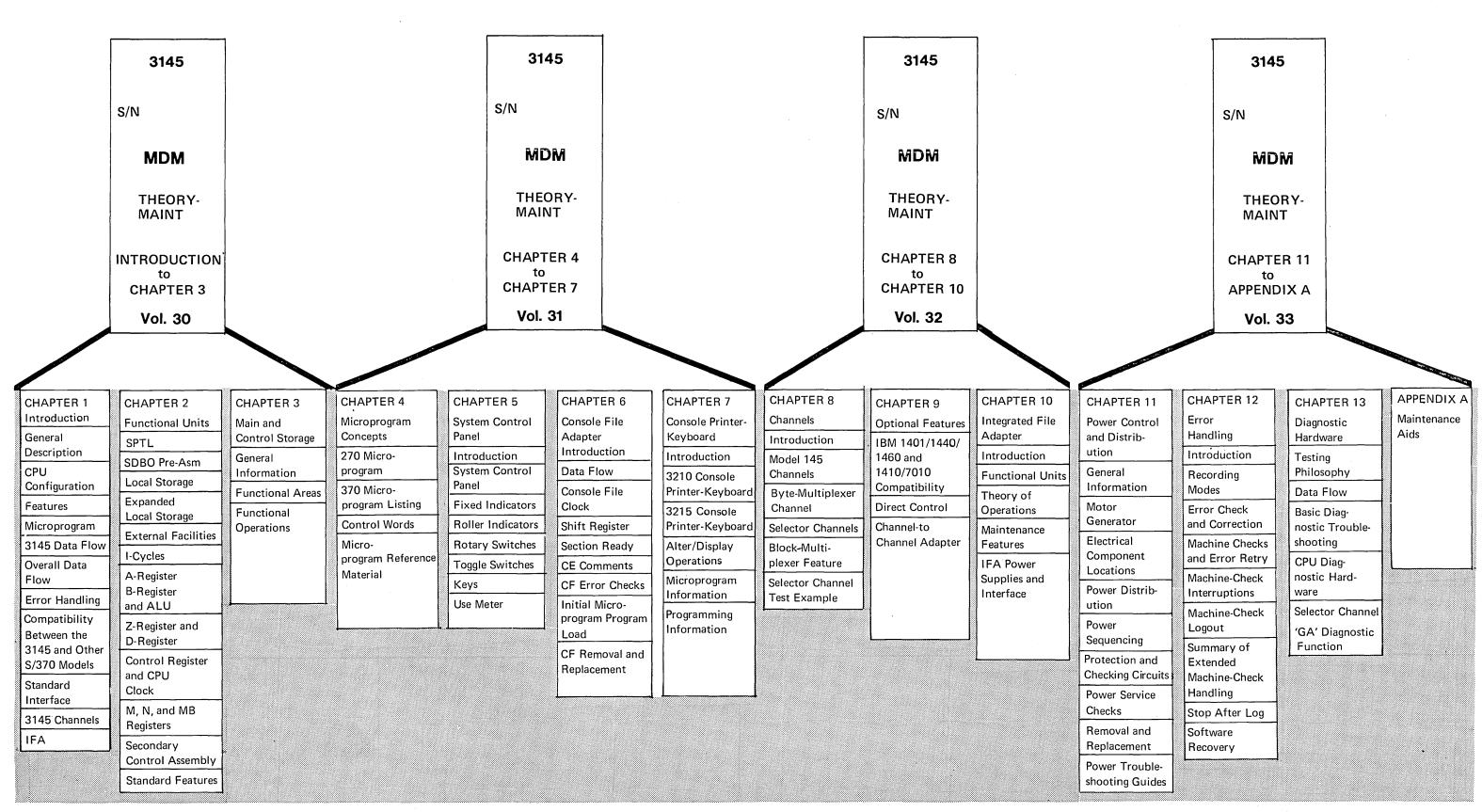

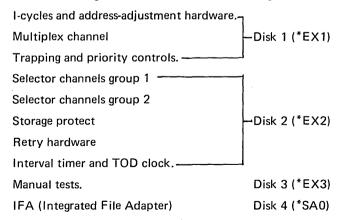

The 3145 Theory-Maintenance manual shipped as part of the maintenance package for the system is contained in four volumes

(30 through 33). The contents of each volume is identified on the accompanying red MDM tab.

Because this manual is split into four parts, the index is in the front of the manual. The index which effectively points to the places where information exists, follows the chart showing the major areas of each chapter. Each chapter contains its own contents. This makes it unnecessary to refer back to Volume 30 whenever you are looking for specific information within a particular chapter.

This manual references diagrams in the 3145 Processing Unit Maintenance Diagrams, SY24-3580.

Other related manuals are:

IBM System/370 Model 145 Functional Characteristics, GA24-3557

IBM System/370 Model 145 Operating Procedures, C38-0015 IBM System/370 Model 145 Channel Characteristics, GA24-3573

IBM System/370 Model 145 Installation Information-Physical Planning, GA22-6976

IBM System/370 System Summary, GA22-7001

IBM FE Theory of Operation, Component Circuits, SLT SLD, ASLT, MST, SY22-2798

IBM FE Theory of Operation, Power Supplies, SLT, SLD, ASLT, MST, SY22-2799

IBM FE Theory of Operation, Monolithic System Technology Packaging Tools, Wiring Change Procedures, SY22-6739

Second Edition (October 1971)

This edition (SY24-3581-1) is a major revision of, and obsoletes SY24-3581-0. This publication has been revised completely with major additions, deletions, and reformatting of existing material. For this reason, the reader should review this edition in its entirety.

Significant changes and additions to the information contained in this publication are continually being made: any such changes will be in subsequent revisions or Technical Newsletters.

Request for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

This manual has been prepared by the IBM Systems Development Division, Product Publications, Dept. K10, P.O. Box 6, Endicott, N.Y. 13760. To help us evaluate this manual, you are encouraged to use the Reader's Comment Form in the back of this manual. Your comments will help to provide better documentation in both this manual and future manuals. If the form has been removed, comments may be sent to the above address. Comments become the property of IBM.

© Copyright International Business Machines Corporation 1971

| ified on                          |   |  |  |   | •                                       |  |

|-----------------------------------|---|--|--|---|-----------------------------------------|--|

| ts in the ts to showing s its own |   |  |  |   | * · · · · · · · · · · · · · · · · · · · |  |

| olume 30<br>nin a                 |   |  |  |   |                                         |  |

| ing Unit,                         |   |  |  |   |                                         |  |

| es,                               |   |  |  |   |                                         |  |

| 88-0015                           |   |  |  |   |                                         |  |

| Physical                          |   |  |  |   |                                         |  |

| <i>T</i> ,                        |   |  |  |   |                                         |  |

| SLD,                              |   |  |  |   |                                         |  |

| chnology,<br>6739                 |   |  |  |   |                                         |  |

|                                   |   |  |  |   |                                         |  |

|                                   |   |  |  |   |                                         |  |

|                                   |   |  |  |   |                                         |  |

|                                   |   |  |  |   |                                         |  |

|                                   |   |  |  | · |                                         |  |

|                                   |   |  |  |   |                                         |  |

|                                   |   |  |  |   |                                         |  |

|                                   |   |  |  |   |                                         |  |

|                                   | · |  |  |   |                                         |  |

|                                   |   |  |  |   |                                         |  |

### 3145 Processing Unit Theory - Maintenance

### REMEMBER

Each chapter has its own table of contents.

### **ABBREVIATIONS**

| A         |                                  | C       |                                        |             |                                     |              |                                              |

|-----------|----------------------------------|---------|----------------------------------------|-------------|-------------------------------------|--------------|----------------------------------------------|

| Α         | and                              | С       | count                                  | CUB         | control unit busy                   | ED           | external damage                              |

| AAR       | A-address register               | CA      | control address                        | CUE         | control unit end                    | EDBI         | external data bus-in                         |

| ABRTY     | A and B retry register           | CAR     | cylinder address register              | cyc         | cycle                               | EDBO         | external data bus-out                        |

| AC        | alternating current              | CAW     | channel address word                   | cyl         | cylinder                            | EM           | external damage report mask                  |

| ACB       | address check boundary           | СВ      | circuit breaker                        |             |                                     | env          | envelope                                     |

| ACBR      | address check boundary register  | CC      | condition code, chain command,         |             |                                     | EOF          | end of file                                  |

| ACR       | automatic carrier return         |         | cyclic code                            | D.          |                                     | EPO          | emergency power off                          |

| ADDR      | address                          | CCC     | channel control check                  | D           | data                                | eq           | equal                                        |

| adj       | adjust                           | CCH     | channel check handler                  | DA          | data address                        | ERDS         | environmental recording data set             |

| Adr-I     | address-in                       | CCW     | channel command word                   | DASD        | direct access storage device        | EREP         | environment recording edit and               |

| Adr-O     | address-out                      | CD .    | chain data time of day clock           | dbl         | double                              |              | print program                                |

| adv       | advance                          | CDC     | channel data check                     | DC          | direct control                      | ERP          | error recovery procedure                     |

| ALD       | automated logic diagram          | CE      | channel end                            | DC          | direct current                      | err          | error                                        |

| ALS       | A-local storage                  | CF      | console file                           | DCBI        | direct control bus-in               | EXCA         | external control assembler                   |

| alt       | alter                            | CFC     | console file checking                  | DCBO        | direct control bus-out              | EXE CPL      | T execute complete                           |

| ALU       | arithmetic logic unit            | CFDA    | console file disk address              | DCC         | disconnect command chaining         | exp          | expanded                                     |

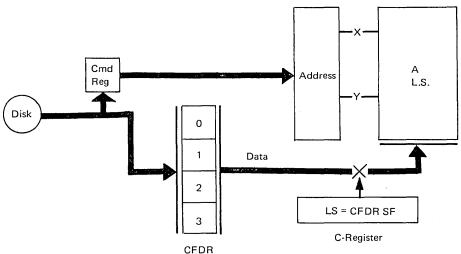

| AM        | address mark .                   | CFDR    | console file data register             | DCHI        | direct control hold-in              | EXPLS        | expanded local storage                       |

| amp       | amplifier, ampere                | chan    | channel                                | DDR         | dynamic device reconfiguration      | ext          | external                                     |

| ANUM      | add numeric                      | char    | character                              | DE          | device end                          | ext asm      | external assembler                           |

| appndg    | appendage                        | chk     | check                                  | dec         | decode, decimal, decrement          | ext dst      | external register destination                |

| APR       | alternate path retry             | chng    | change                                 | DED         | double error detect                 | extint       | external interrupt                           |

| ASCII     | american standard code II        | chnl    | channel                                | dest        | destination                         |              |                                              |

| ASCP      | automatic system control program | CKD     | count, key, and data                   | det         | detect                              | 22           | •                                            |

| asm       | assembler                        | clk     | clock                                  | DF          | disk file                           |              |                                              |

| AT        | attention (file)                 | CM      | current module                         | diag        | diagnostic                          | FBAK         | file backup external word                    |

| ATTN      | attention                        | cmd     | command                                | diff        | difference                          | FBO          | file bus-out                                 |

| avl       | available                        | Cmd-O   | command out                            | DIL         | do interpretive loop                | FCH          | file count register high                     |

|           |                                  | cmnd    | command                                | Dir-In      | direct control bus-in               | FCL          | file count register low                      |

| D         |                                  | cncl    | cancel                                 | Dir-Out     | direct control bus-out              | FCND         | file conditions external word                |

| В         |                                  | cnd     | condition                              | Disc-I      | disconnect in                       | fdbck        | feed back                                    |

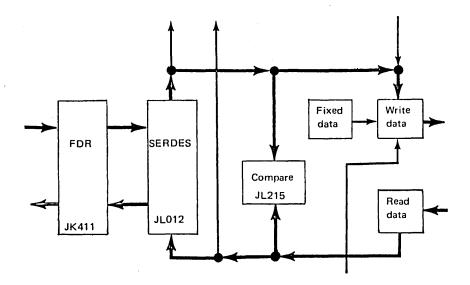

| BAL       | branch and link                  | cnsl    | console                                | dist        | distribution                        | FDR          | file data register                           |

| BAR       | B-address register               | cnt     | count                                  | DL          | data length                         | FERR         | file error external word                     |

| BBE       | branch on bit equal              | cntr    | counter                                | dly         | delay                               | FM           | file mask                                    |

| BC ·      | basic control                    | coax    | coaxial cable                          | D-Mod       | D-modifier                          | FOP          | file operation register                      |

| BCA       | bit count appendage              | comp    | compare                                | Doc         | documentary console                 | F Stat       | file status external word                    |

| BCA       | basic channel adapter            | con-con | contingent connection                  | DOS         | disk operating system               | FTAG         | file tags external word                      |

| BCAI      | basic channel adapter interface  | cond    | condition                              | dply        | display                             | FTC          | flush through checking                       |

| BCD       | binary coded decimal             | corr    | correction                             | dsbld       | disabled                            | fwd          | forward                                      |

| BCE       | branch on character equal        | CP      | circuit protector                      | dup         | duplicate                           |              |                                              |

| BDIL      | branch and do interpretive loop  | cpmt    | complement                             |             |                                     |              |                                              |

| bfr       | buffer                           | CPU     | central processing unit                | 13          |                                     |              |                                              |

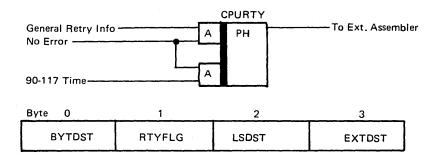

| BI FLAG   | branch on invalid flag           | CPURTY  | central processing unit retry register |             |                                     | G            |                                              |

| B LS      | B-local storage                  | CR      | control register                       | EBCDIC      | extended binary coded decimal       | GBS          | and and the second building about the second |

| BMF       | block multiplexer feature        | C-Reg   | control register                       | <b>5</b> 0. | interchange code                    | GBS          | selector channel buffer status external      |

| BR        | bit ring                         | CS      | control storage                        | EBI         | external bus- in                    | GBUF         | word                                         |

| BR<br>brd | branch<br>board                  | CSW     | channel status word                    | EBO         | external bus-out                    | GBUF         | selector channel buffer external             |

| BS        | byte source                      | CTCA    | channel to channel adapter             | EC          | external control                    |              | word                                         |

| BSM       | basic storage module             | CTCAX   | channel to channel adapter X system    | ECC         | error checking and correction       | gen          | generate                                     |

| bwd       | backward                         | CTCAY   | channel to channel adapter Y system    | ECCL        | error checking and correction logic | GM           | group mark                                   |

| BWF       | branch if wordmark or zone equal | Ctrl    | control                                | ECM         | extended control mode               | gnd          | ground                                       |

| BYTDST    | byte destination                 | CU      | control unit                           | ECNT        | error count register                | grp<br>GSTAT | group                                        |

| 5.1501    | by to doutination                | CUA     | control unit address                   | ECSW        | extended channel status word        | GSTAT        | selector channel status external word        |

|              |                                      |             |                                                         | N           |                                                 |              |                                                |

|--------------|--------------------------------------|-------------|---------------------------------------------------------|-------------|-------------------------------------------------|--------------|------------------------------------------------|

|              |                                      |             | low made                                                |             | many and disease                                | rdu          | ready                                          |

| HA           | home address                         | LC          | length                                                  | . NA<br>NOP | next address                                    | rdy<br>recal | recalibrate                                    |

| HDV          | halt device<br>hardware              | LD          | lower case<br>line driver                               |             | no operation                                    | ref          | reference                                      |

| hdwr<br>h:   | nardware<br>high                     | LEX         | local execute mode                                      | norm<br>NPL | normal                                          |              | regulator, register                            |

| hi           | •                                    |             |                                                         |             | new product language                            | reg          | request                                        |

| HIO<br>HMRTY | halt input/output                    | LO          | low                                                     | ns          | nanoseconds                                     | req<br>reqd  | required                                       |

|              | H and M retry registers              | Logl        | logical                                                 |             |                                                 | Reg-I        | request-in                                     |

| HS           | hard stop                            | LH          | L register high half                                    | 0           |                                                 | rev          | reverse                                        |

| hz           | hertz                                | LHM         | left hand margin                                        | OBR         | outboard recorder                               | RHM          | right-hand margin                              |

|              |                                      | LL          | L-register low                                          |             |                                                 | RM           | record mark                                    |

|              |                                      | LR          | line receiver                                           | oc<br>OE    | overcurrent                                     | RM           |                                                |

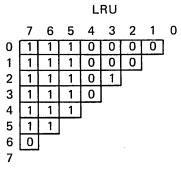

|              |                                      | LRU         | least recently used                                     | OP          | exclusive OR                                    | RMS          | recovery report                                |

| IAR          | instruction address register         | LS          | local storage                                           | OP-I        | operation                                       | RR           | recovery management system                     |

| IB           | interrupt buffer                     | LSCA        | local storage control assembler                         |             | operational in                                  |              | record ready                                   |

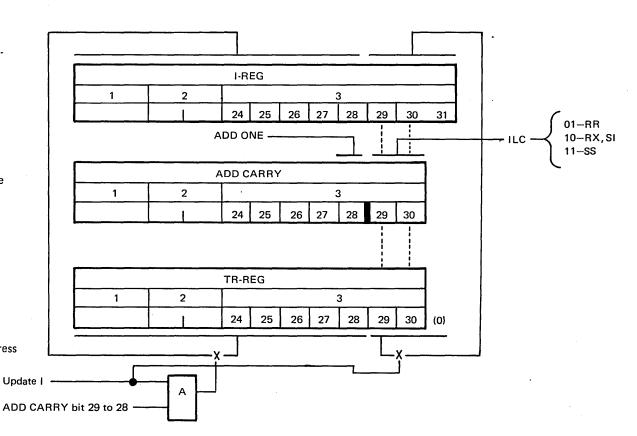

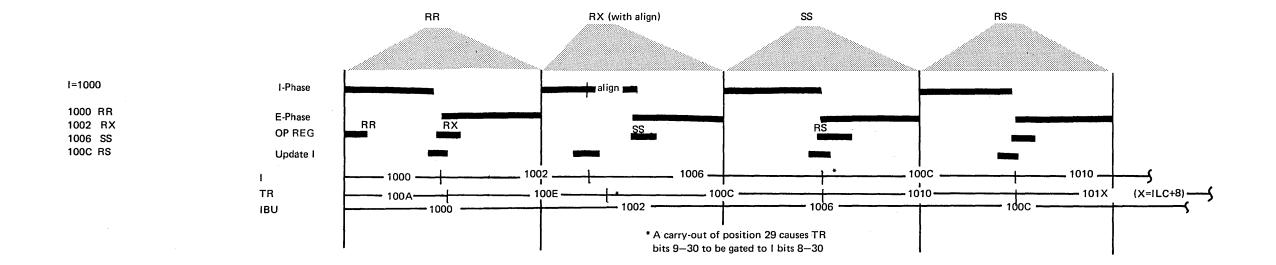

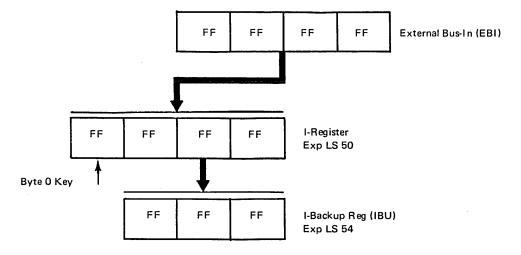

| IBU          | I-register backup                    | LSCS        | local storage control storage                           | OPL<br>OP-O | operational                                     | Rst          | reset, restart                                 |

| IC           | instruction counter                  | LSDST       | local store destination                                 |             | operational-out                                 | rtn          | return                                         |

| ICC          | interface control check              | Ith         | latch                                                   | OS          | operating system                                | rty          | retry                                          |

| icplt        | incomplete                           |             |                                                         | osc         | oscillator                                      | rty flg      | retry flag                                     |

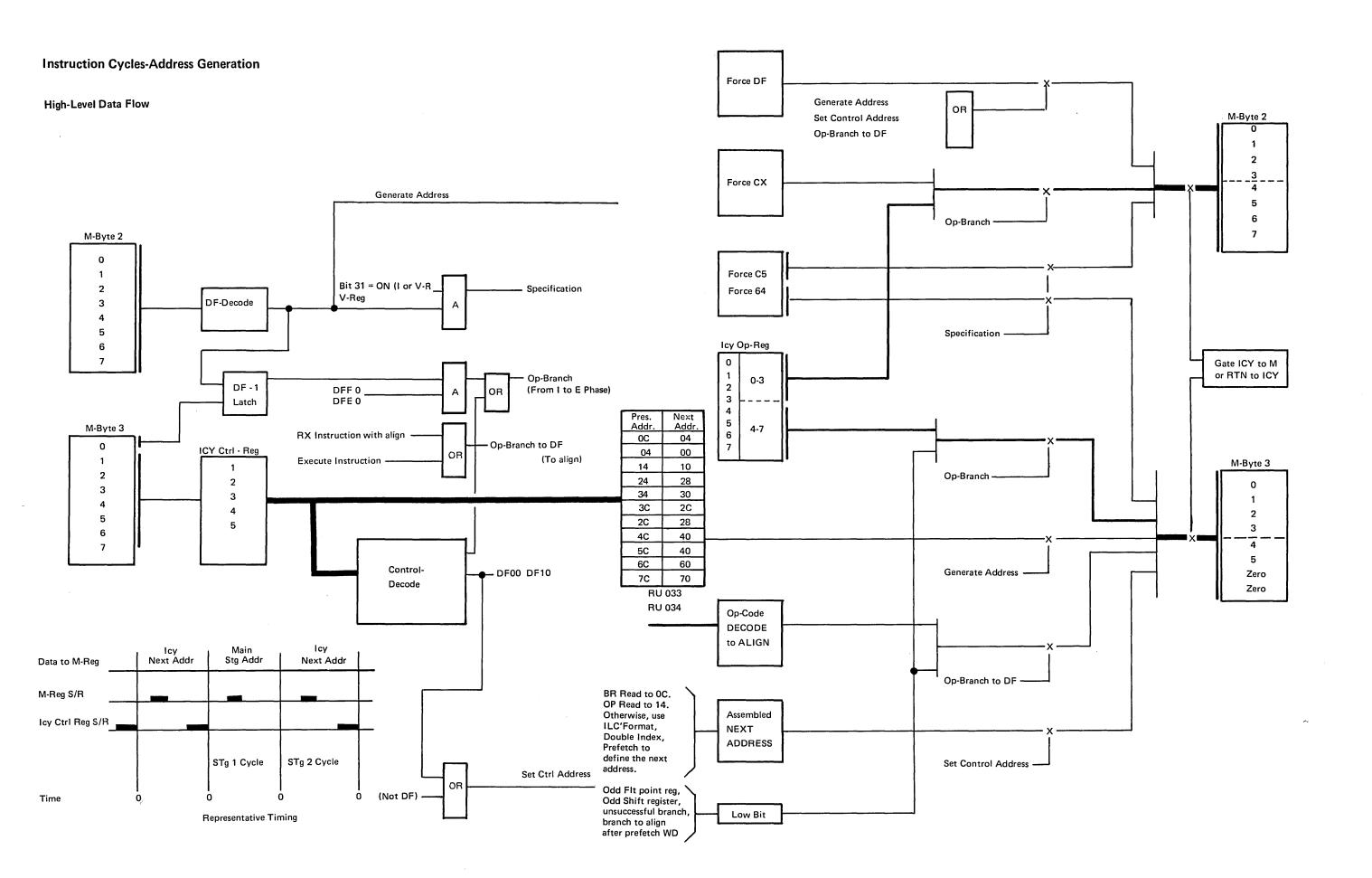

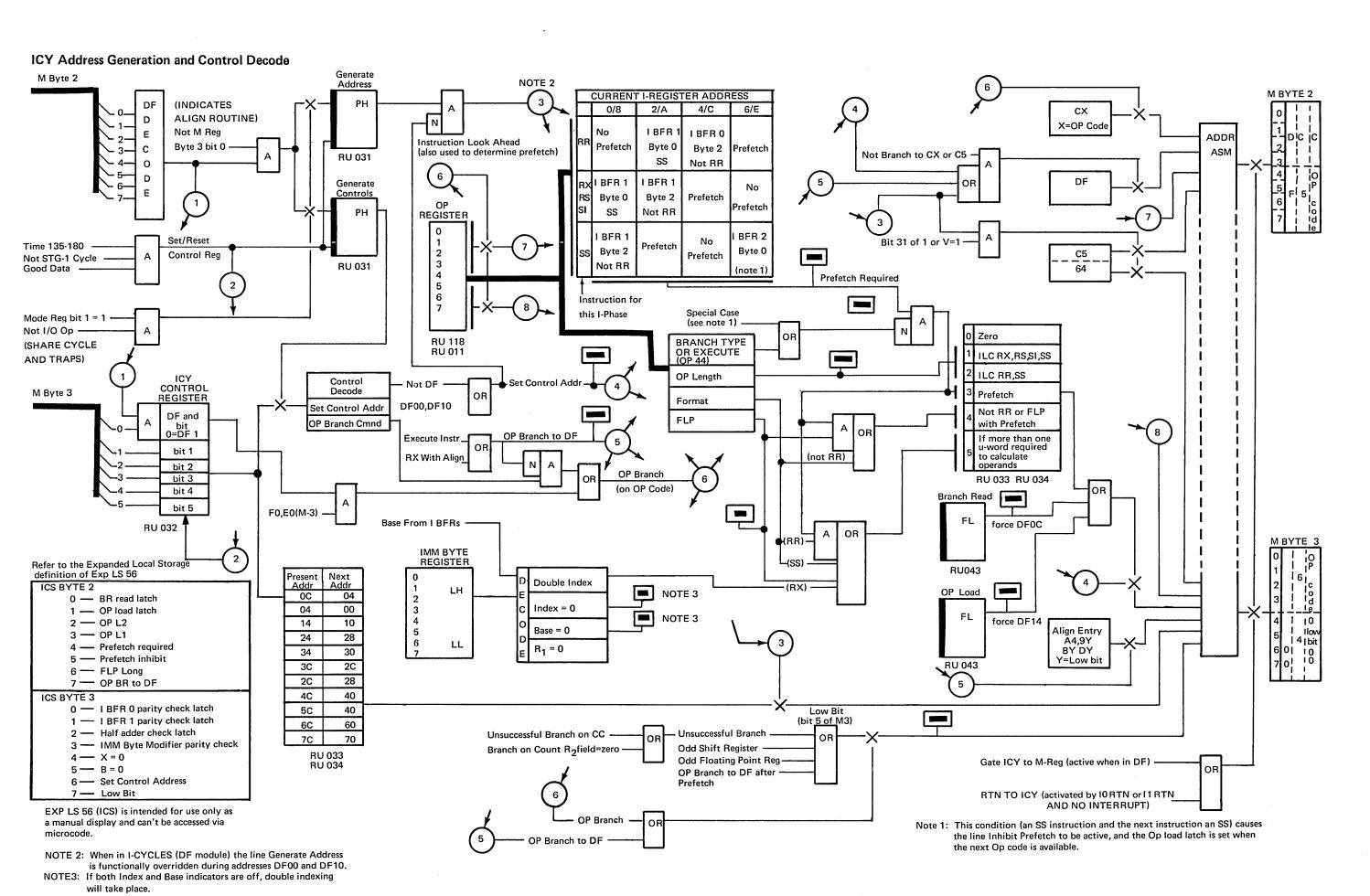

| I-cy         | instruction cycle                    | M           | •                                                       | OV          | over voltage                                    |              |                                                |

| id           | identifier                           | М           |                                                         |             |                                                 | S            |                                                |

| IFA          | integrated file attachment           | mach        | machine                                                 | Р           |                                                 | SAR          | storage address register                       |

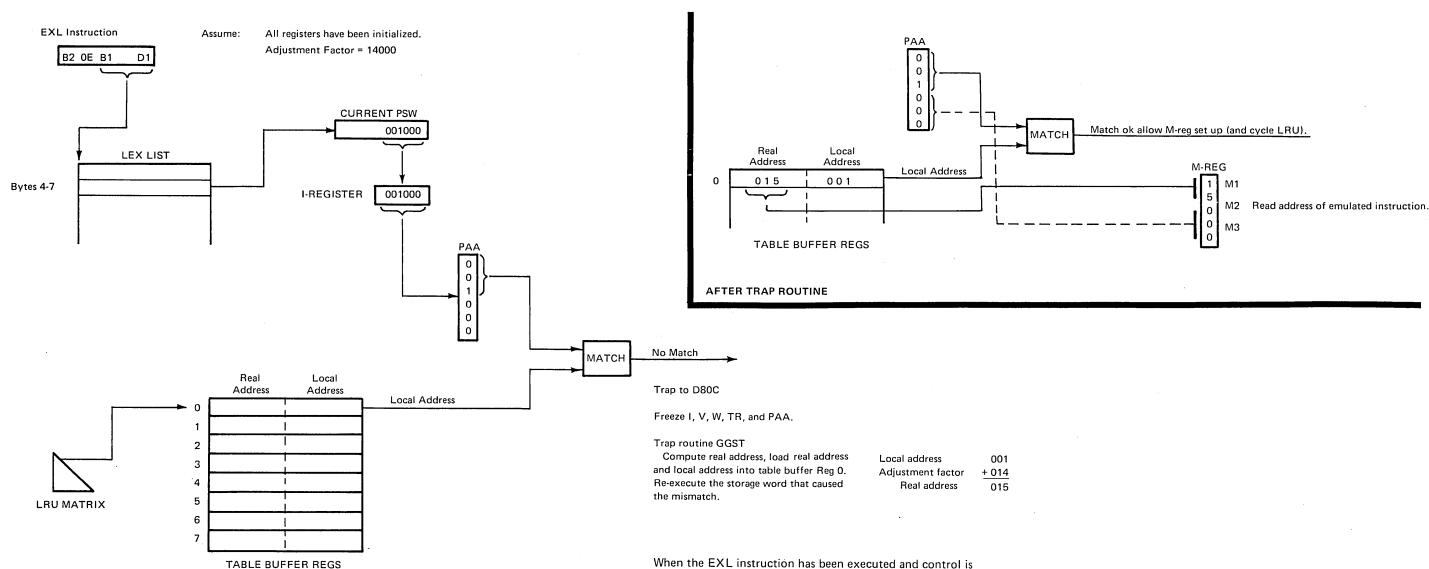

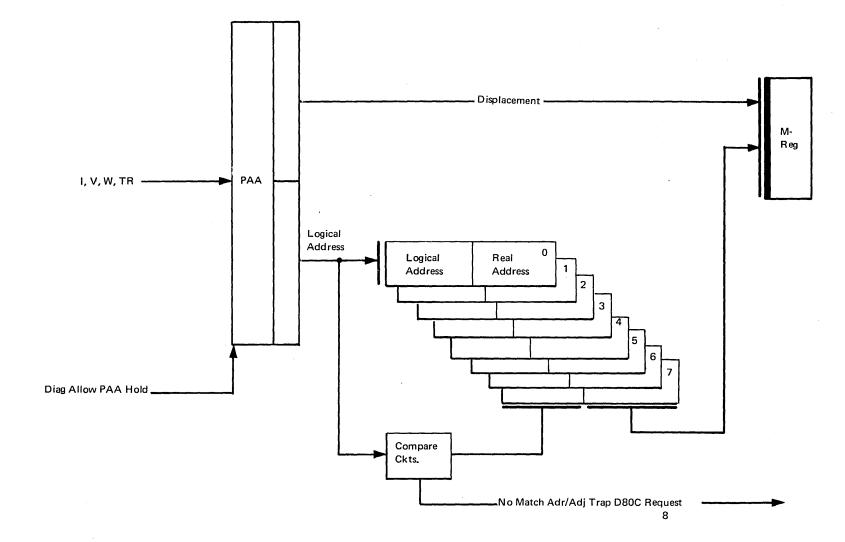

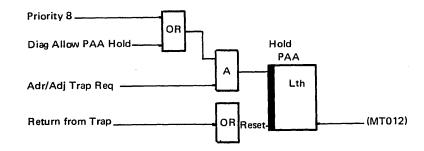

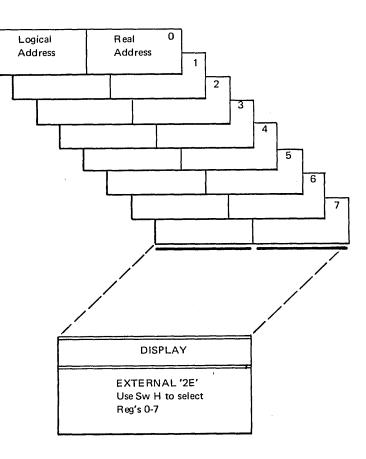

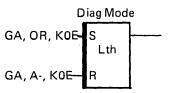

| IFCC         | interface control check              | MB          | M-register back up                                      | PAA         | pre-address assembler                           | sch          | search                                         |

| IFCU         | integrated file control unit         | MBO         | multiplexer bus-out                                     | PCI         | program-controlled interrupt                    | SCR          | silicon controlled rectifier                   |

| IL<br>U.O    | incorrect length                     | MC          | machine check                                           | PD          | instruction processing damage                   | SD           | system damage                                  |

| ILC          | instruction length code              | MCAR        | machine check analysis and recording                    | PDAR        | program damage assessment and repair            | SDBI         | storage data bus-in                            |

| ·IM          | input/output extended logout mask    | MCEL        | machine-check extended logout                           | PE          | print emitter                                   | SDBO         | storage data bus-out                           |

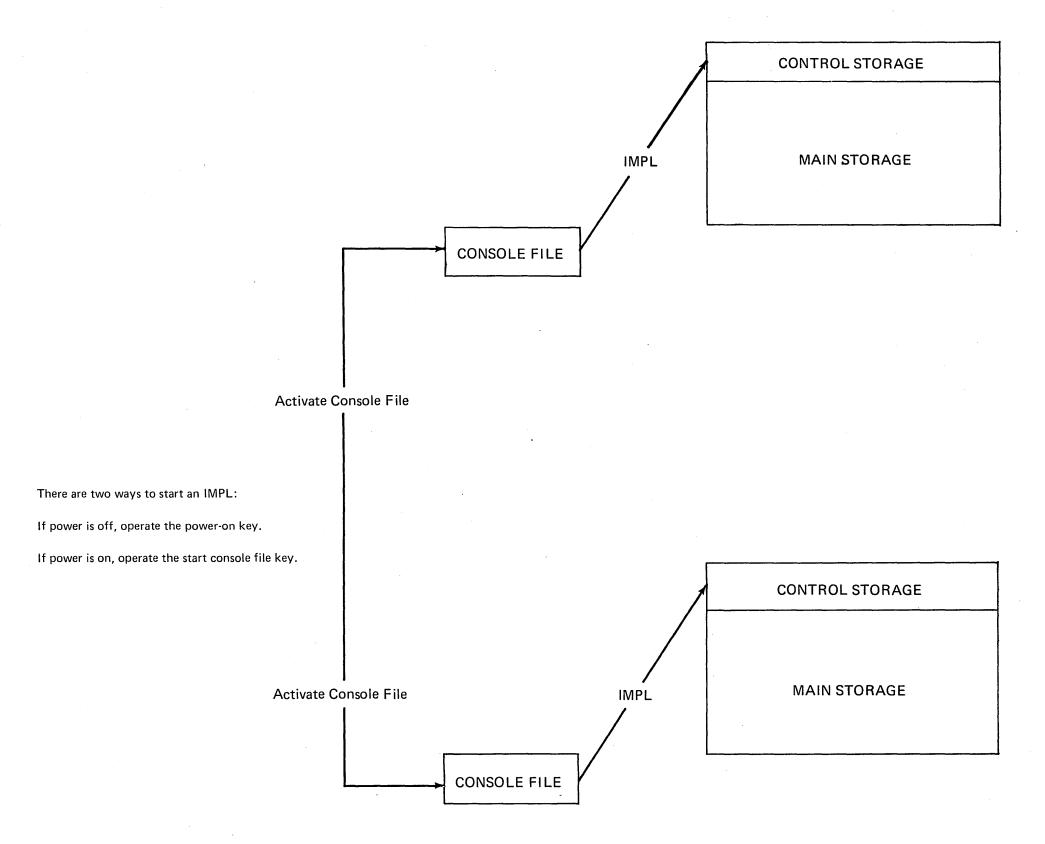

| IMPL<br>·    | initial microprogram program loading | MCH         | machine-check handler                                   | PF          | power frame                                     | SDC          | suppress data check                            |

| inc          | increment                            | MCIC        | machine check interruption code                         | PGA         | power frame                                     | SDK          | set diagnostic key                             |

| ind          | indicator                            | MCKA        | machine-check A register                                | PGB         | power gate B                                    | SDR          | storage data register                          |

| inh<br>· ·   | inhibit                              | MCPU        | move data in CPU                                        | PI DEC      | priority interrupt extended control             | SDR          | statistical data recorder                      |

| inst         | instruction                          | MCRR<br>MFT | machine check recovery recorder<br>multiple fixed tasks | PIR         | priority interrupt extended control             | sec          | secondary                                      |

| intf         | interface                            | MG          | motor generator                                         | PIRM        | priority interrupt register mask                | sect         | sector                                         |

| intlk        | interlock                            | Mid-Pac     | middle power package regulator                          | POH         | power on hours                                  | sel          | select                                         |

| intr         | interrupt                            | MIO         | move data for I/O                                       | pos         | position                                        | seld         | selected                                       |

| intv         | interval                             | misc        | miscellaneous                                           | PR-KB       | printer keyboard                                | Sel-I        | select-in                                      |

| intvn        | intervention                         | MLC         | machine level control                                   |             | •                                               | Sel-O        | select-out                                     |

| invld        | invalid                              | MLS         | micro listings                                          | proc        | process                                         | selr         | selector                                       |

| 1/0          | input or output                      | mod         | module                                                  | prog        | program                                         | seq          | sequence                                       |

| IOCA         | input/output communications area     |             | monolithic                                              | prot<br>PSW | protect program status word                     | ser des      | serializer/deserializer                        |

| IOEL         | input/output extended logout         | mono<br>MOP | mini operation register                                 |             |                                                 | SEREP        | system error recording edited printout         |

| IPL          | initial program load                 | MPF         | main power frame                                        | pry         | parity                                          | Serv-I       | service-in                                     |

| IPM          | in process register                  | MPX         | multiplexer                                             | pwr         | power                                           | Serv-O       | service-out                                    |

| ISK          | insert storage key                   | MRTY        | M retry register                                        |             |                                                 | SI .         | system incidents                               |

|              |                                      |             | millisecond                                             | R           |                                                 | SIO          | start input/output                             |

| J            |                                      | ms          | microsecond                                             | R0          | rooped zoro                                     | SIOF         | start I/O fast release                         |

| JCL          | job control language                 | us.<br>MS   |                                                         | R1          | record zero record 1                            | SLI          | suppress length indication                     |

| 001          | , a =                                | MSF         | main storage                                            | RAC         |                                                 | SM           | suppress length indication<br>synchronous mask |

|              |                                      | MST         | main-storage frame                                      | RAS         | remote analysis center                          |              | single                                         |

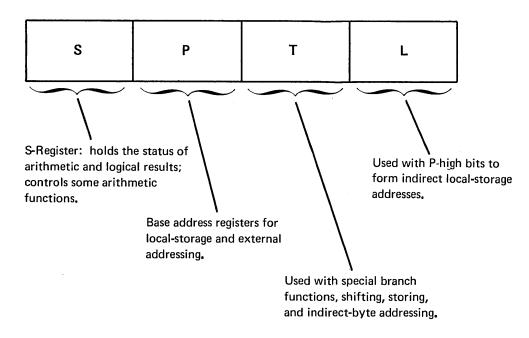

| K            |                                      | MTO         | monolithic systems technology                           | RCNT        | reliability and serviceability                  | sng<br>SPTL  | S, P, T and L registers                        |

| K            | key                                  | MTI         | multiplexer tags-out                                    | RCS         | retry count register reloadable control storage | SPTLB        | SPTL back-up word for SPTL                     |

| KD           | key and data                         | MUA         | multiplexer tags-in                                     | RD          | reioadable control storage                      | SFILD        | registers                                      |

| KL           | key length                           | MVT         | multiple unit address                                   | RDK         | reset diagnostic key                            | SR           | system recovery                                |

|              |                                      | IVIVI       | multiple variable task                                  | אטוו        | reset diagnostic key                            |              | System recovery                                |

S/R set or reset

SS singleshot

SSK set storage key

Stat-I status-in

std standard

stg storage

STI status-in

STIDC store identificat

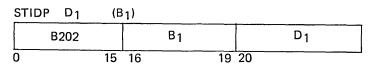

STIDC store identification channel STIDP store identification processor

stkd stacked stor storage stp stop

SUA single unit address supp suppress

Sup-O suppress-out

SUT system unavailable time

SVC supervisor call SVI service-in sw switch

SX selector/block multiplexer channel

sync synchronize sys system

T

terminal block TB TCH test channel TD timer damage transformer tfrm ΤH T-register high therm thermal threshold thld thru through

TIC transfer in channel

TIO test input/output

TOD

TOD time of day

TODH time of day high word

TODL time of day low word

T/R tilt or rotate, transformer/rectifier

tgr trigge

TSBO timing signal bus-out

U

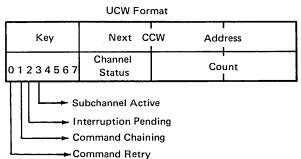

UCW unit control word

V

vac volts alternating current

val validate

vdc volts direct current

VFO variable frequency oscillator VOM volt/ohm meter

W

wd word

WLR wrong length record

WM word mark Wr write

WS word separator, word source

X

XFer transfer X-Late translate

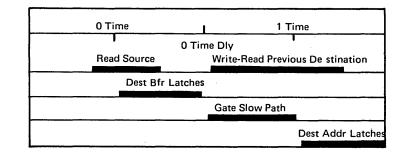

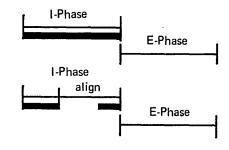

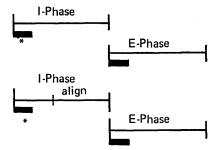

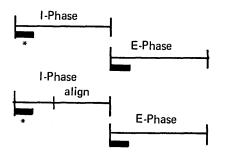

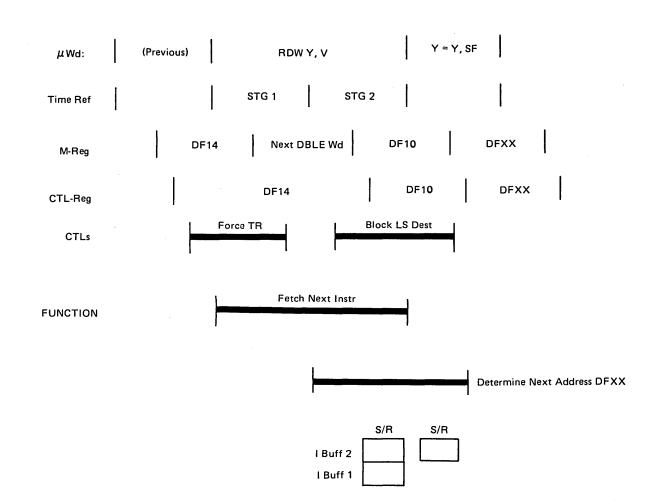

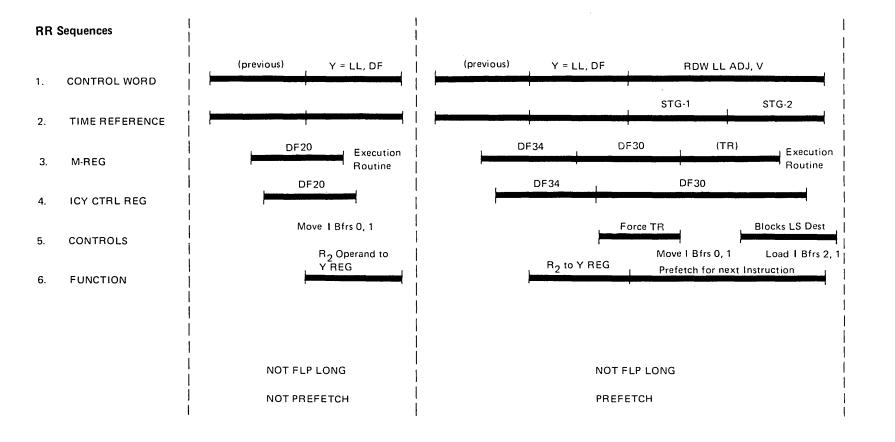

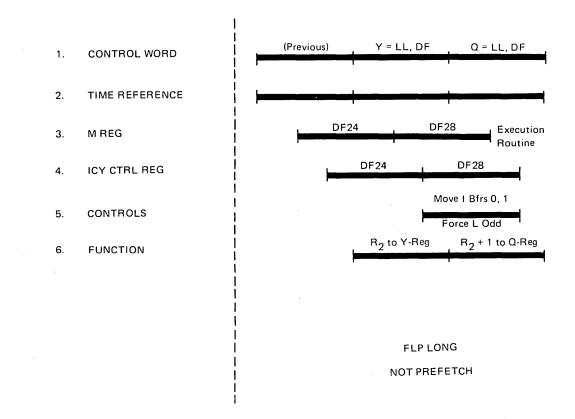

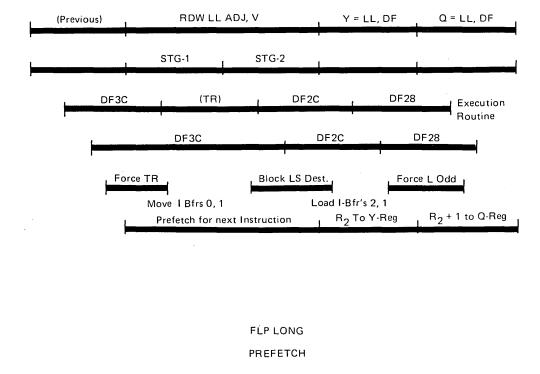

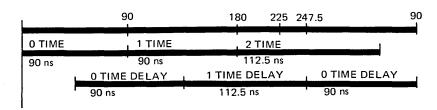

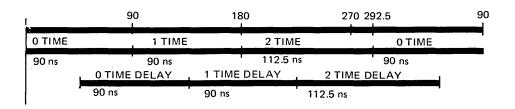

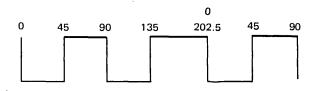

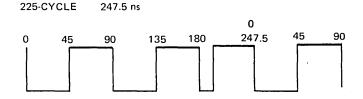

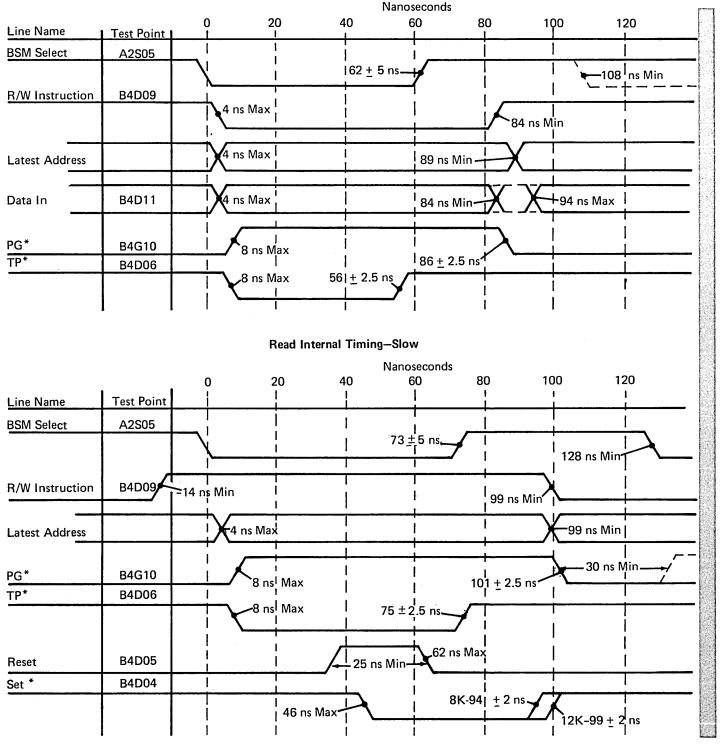

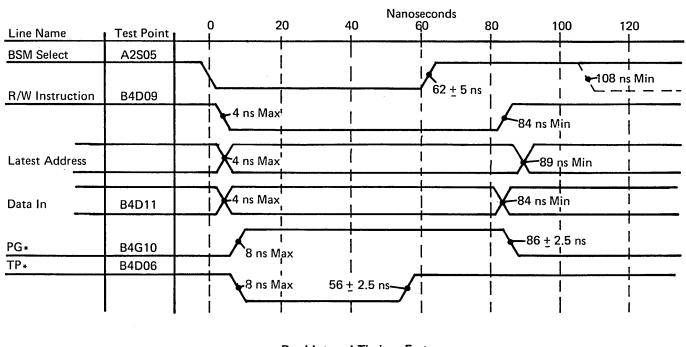

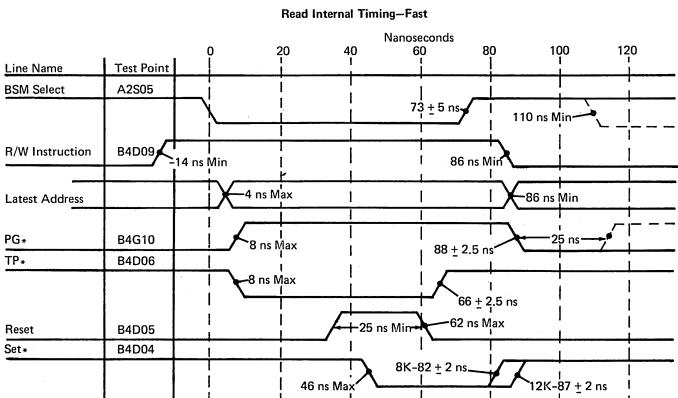

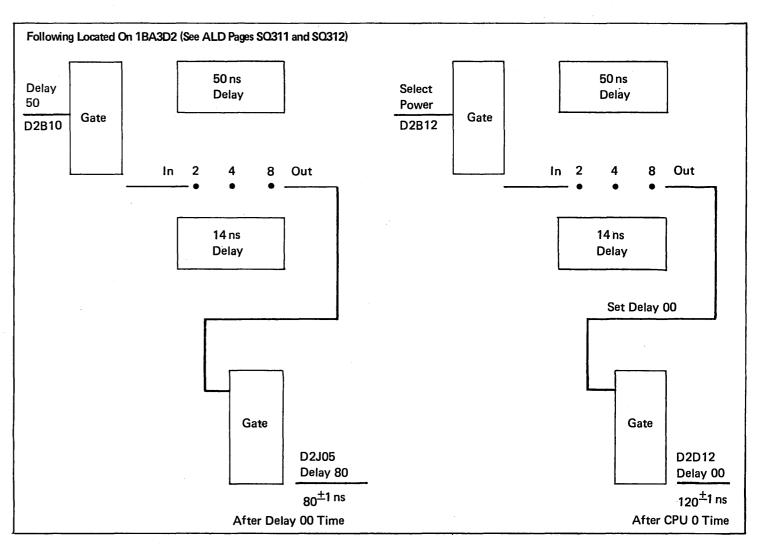

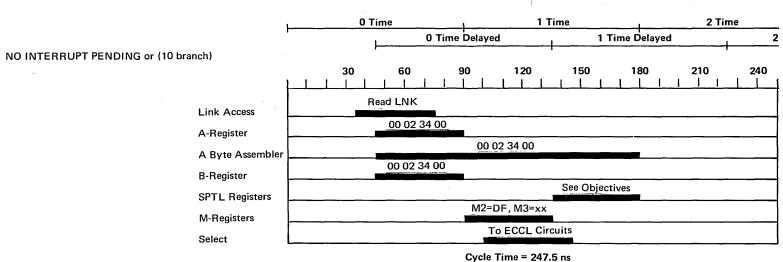

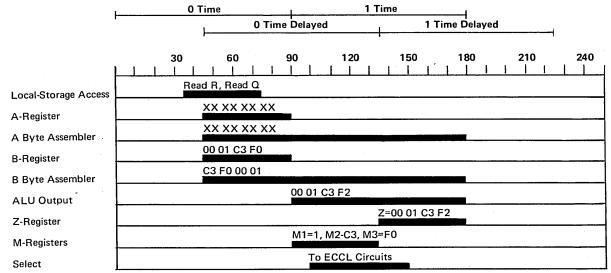

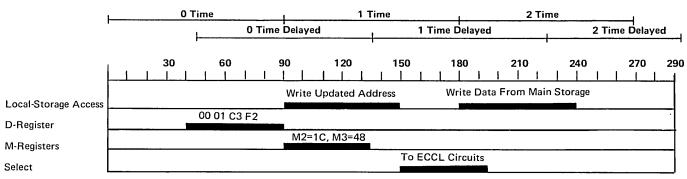

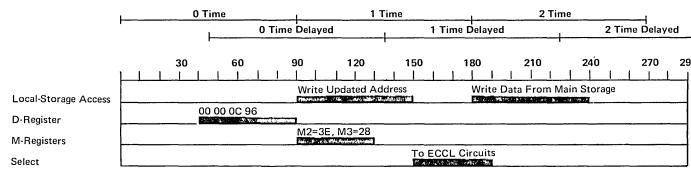

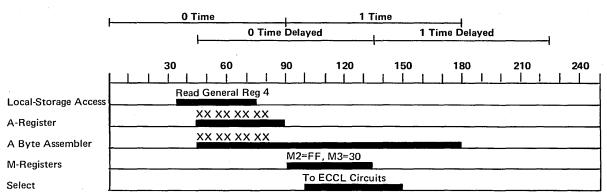

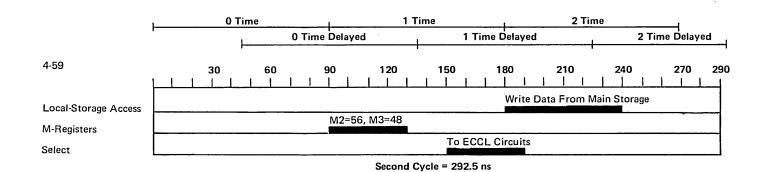

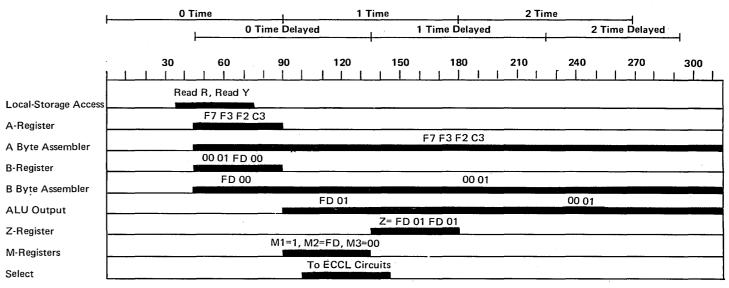

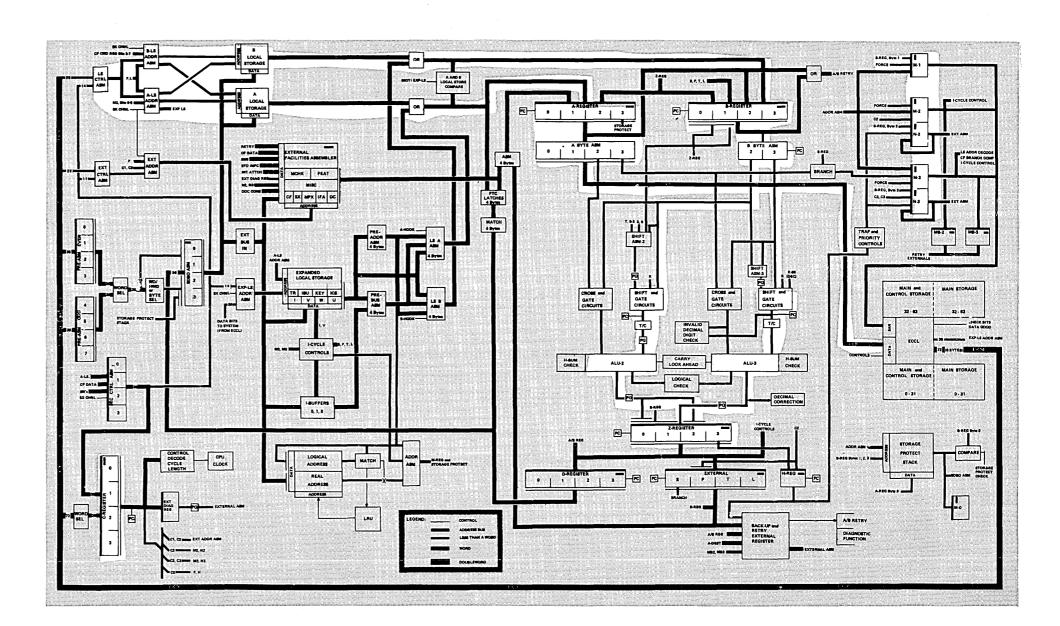

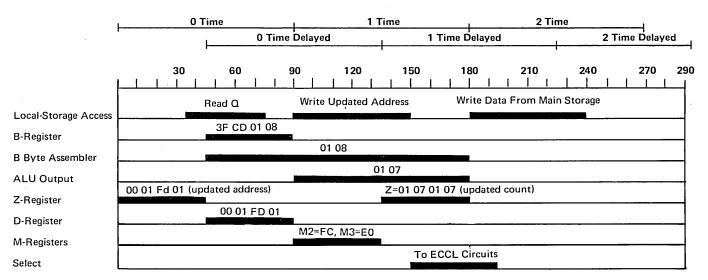

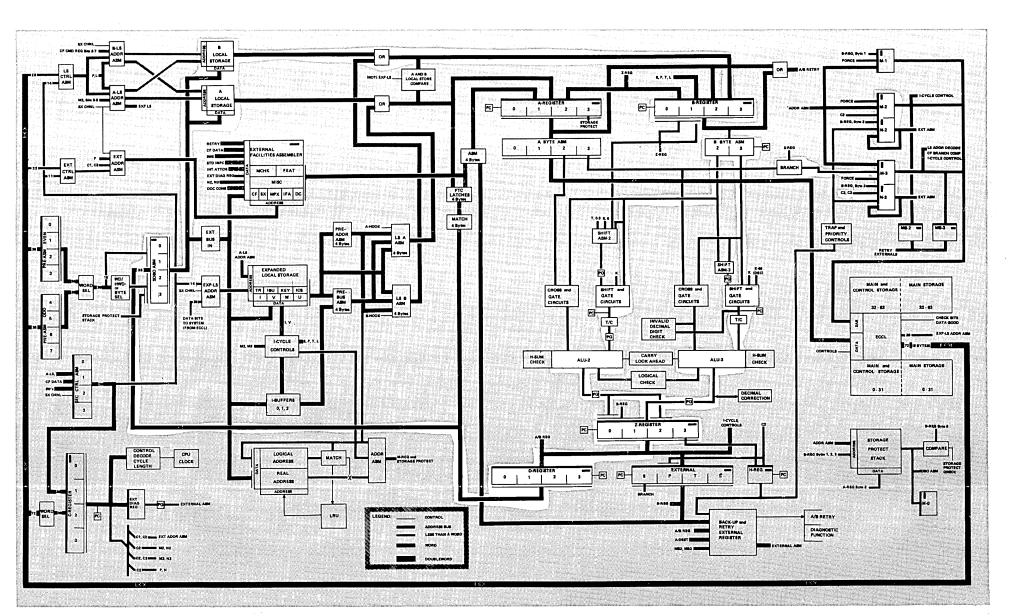

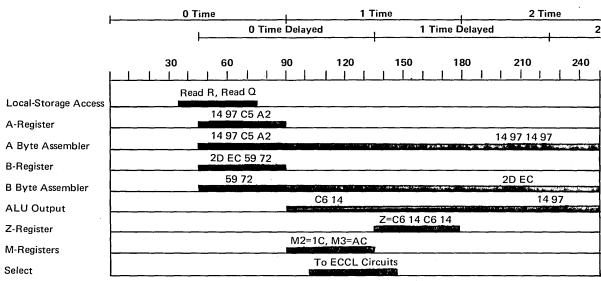

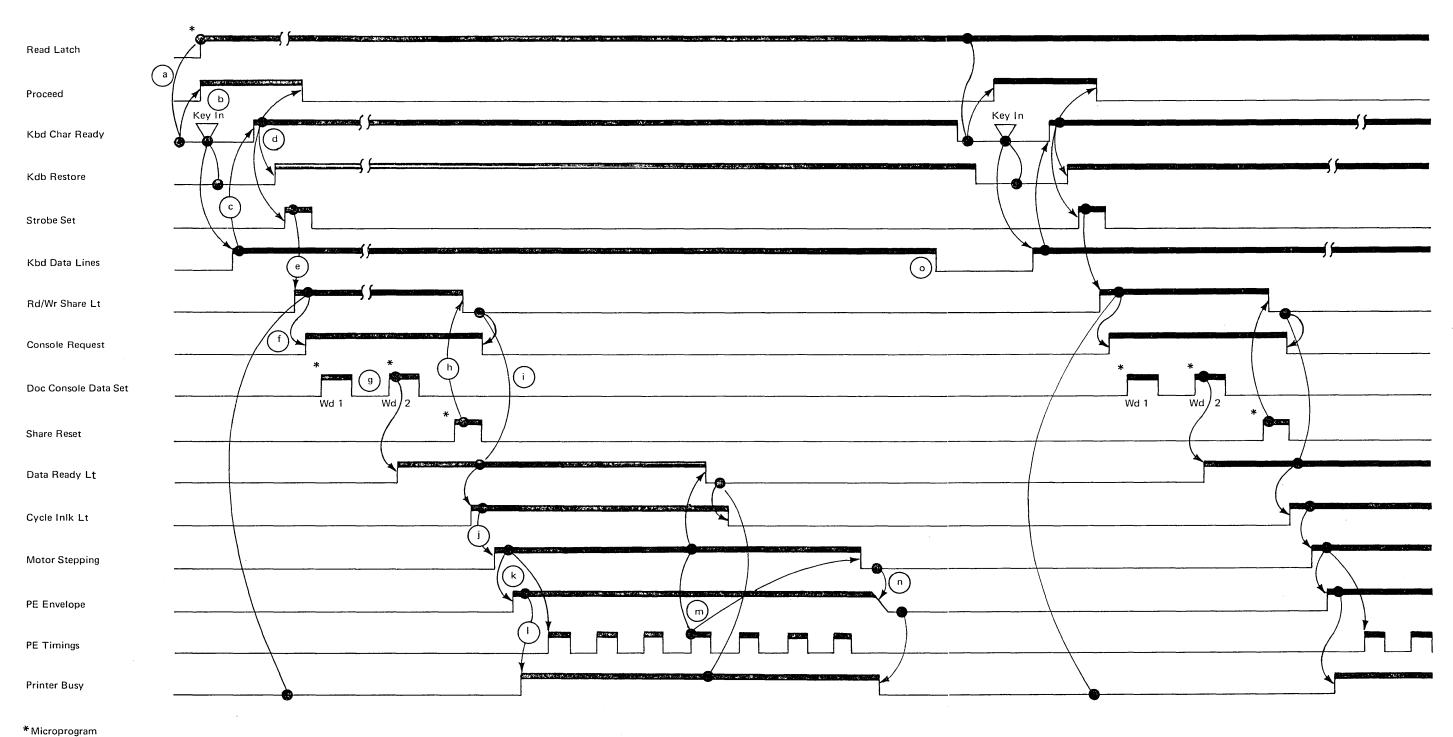

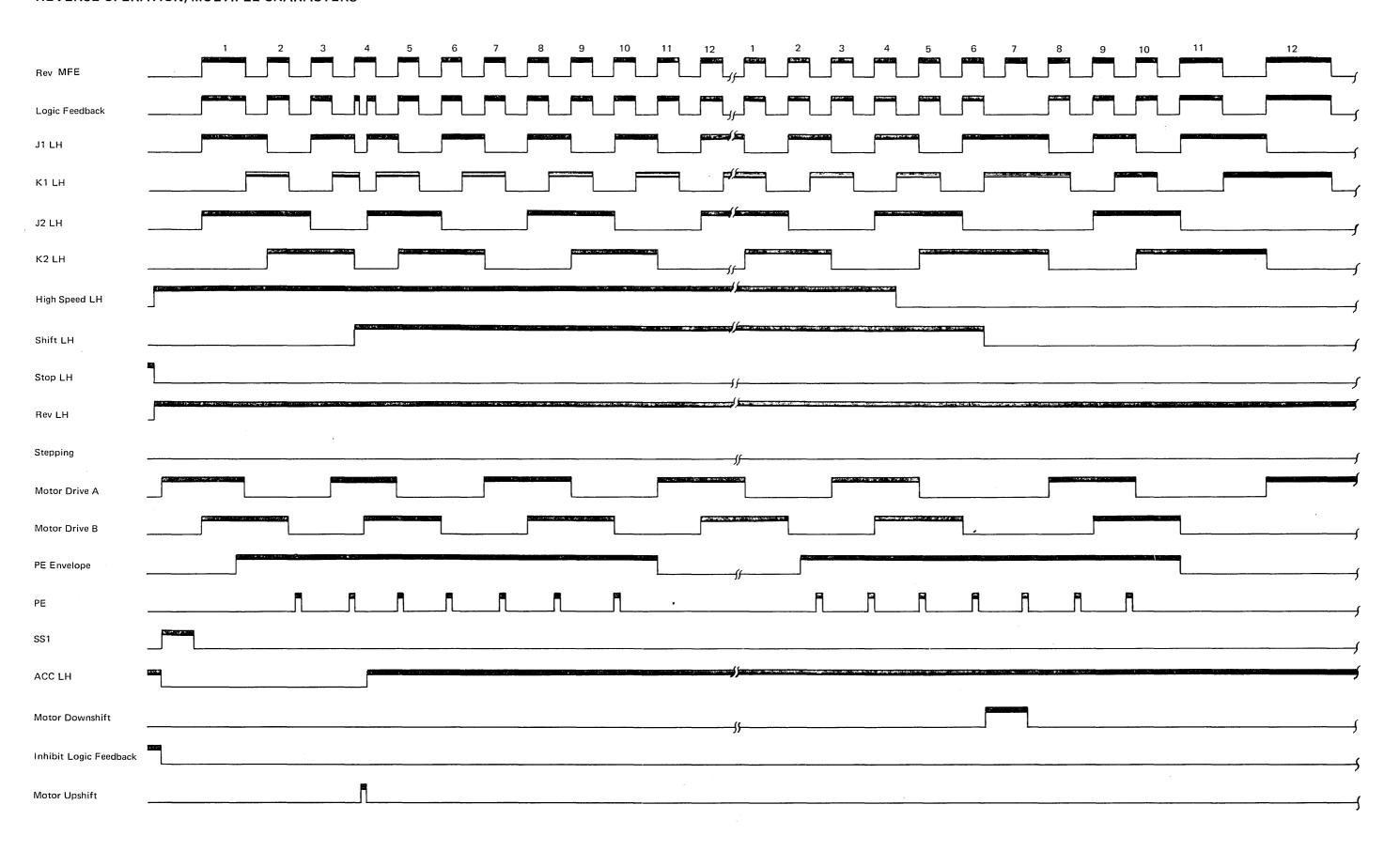

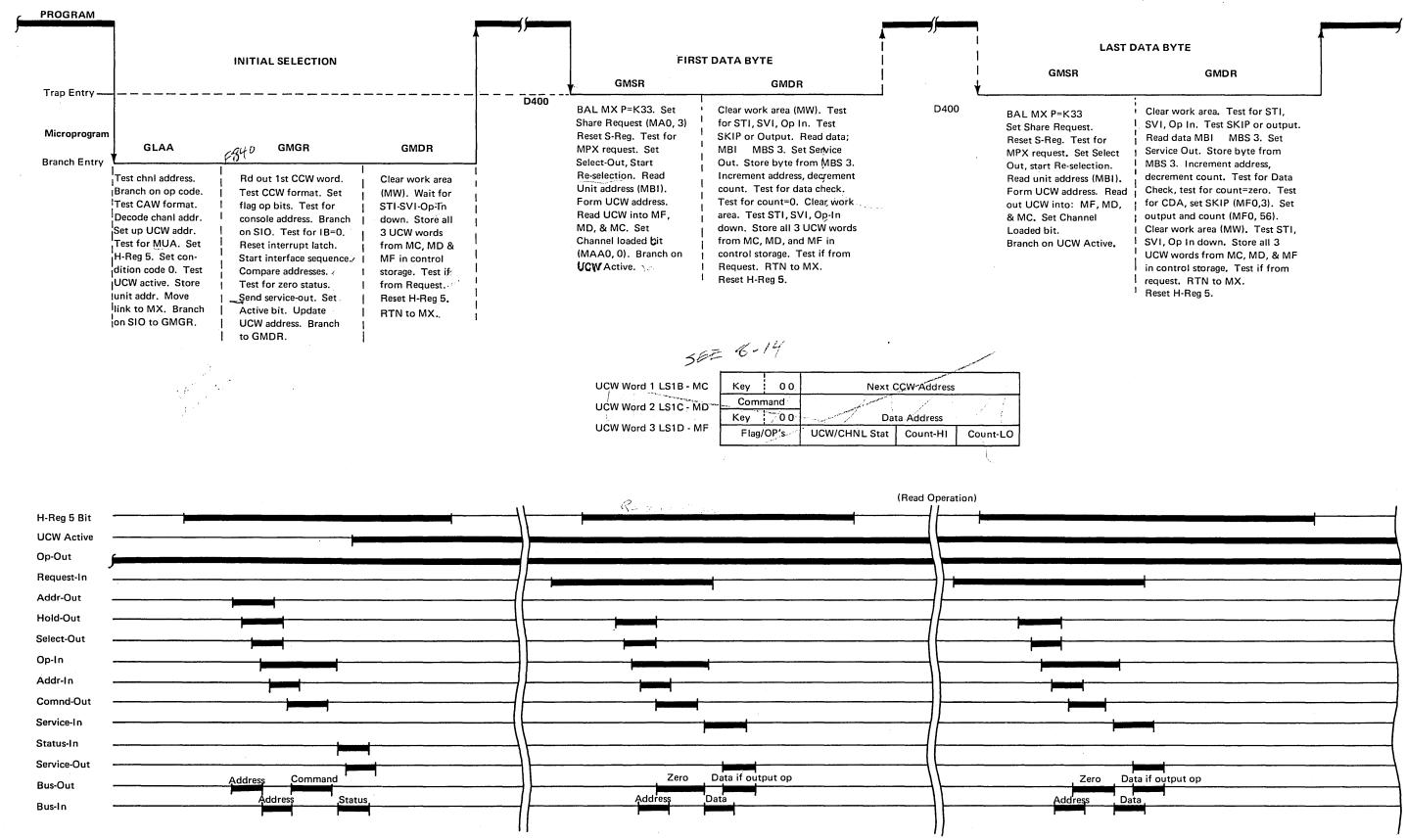

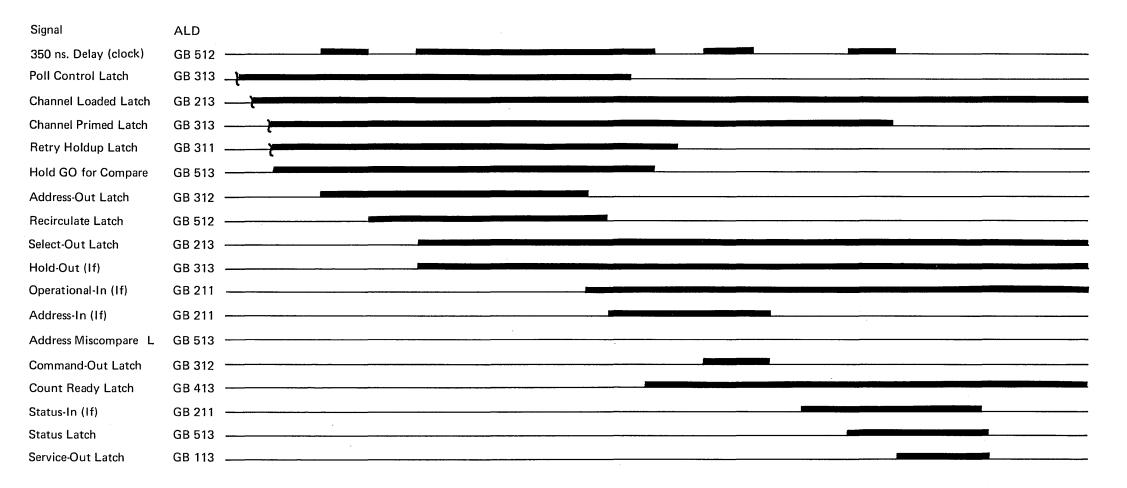

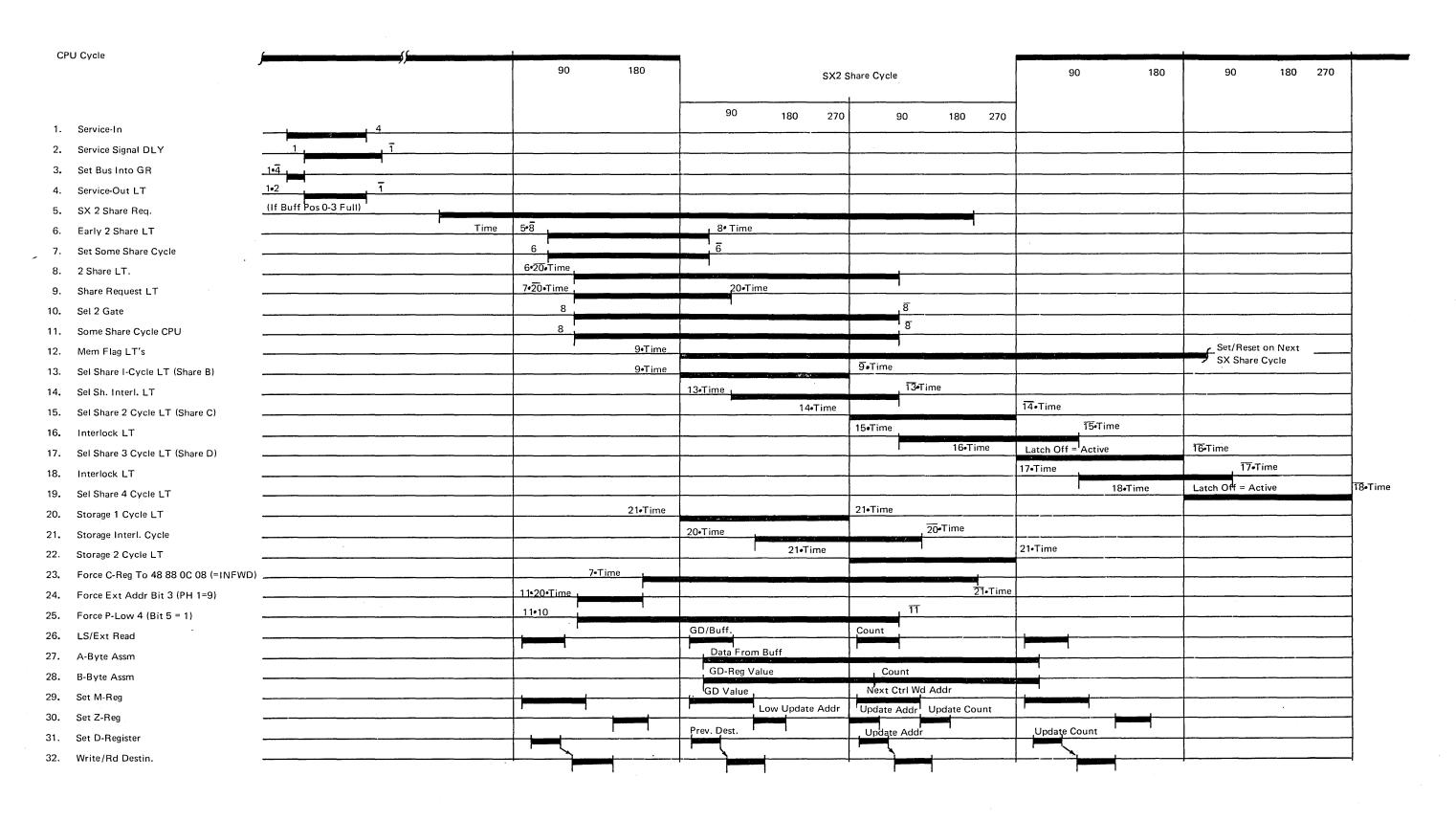

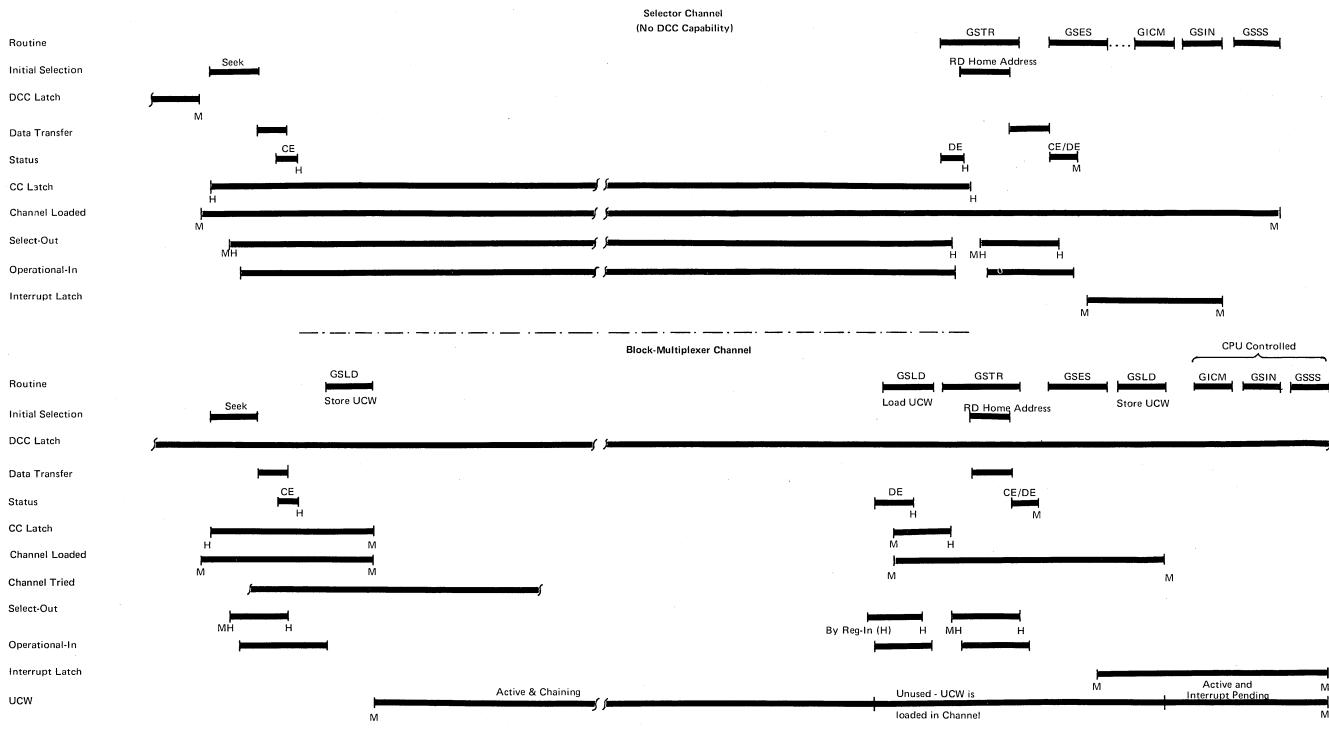

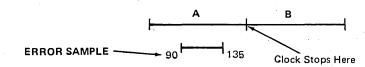

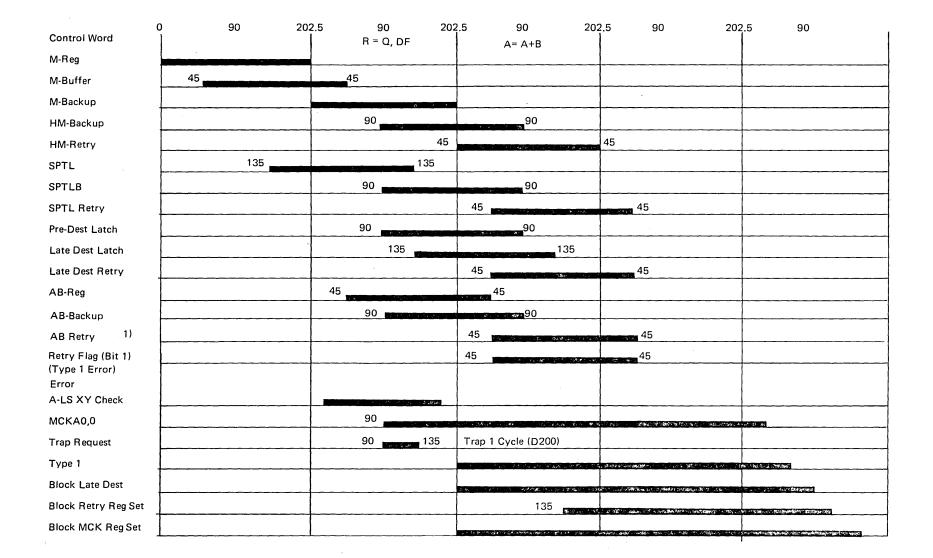

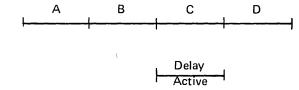

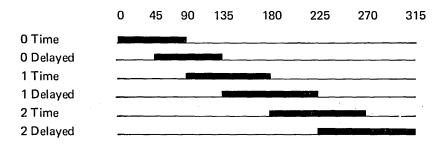

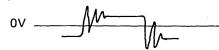

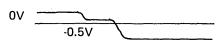

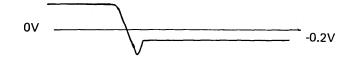

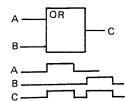

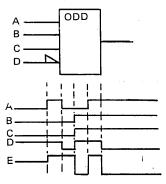

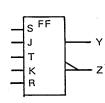

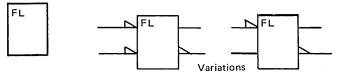

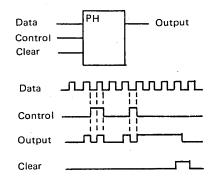

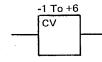

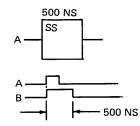

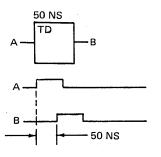

### TIMING CHARTS

#### **Active State**

Numerals at beginning and end of the bar identify the signal(s) on the same chart that activate and deactivate this line. "(Not)" with the number indicates that lock of the signal conditions the line.

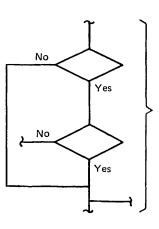

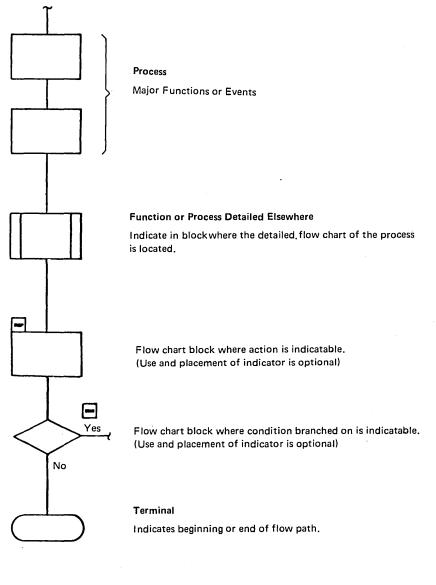

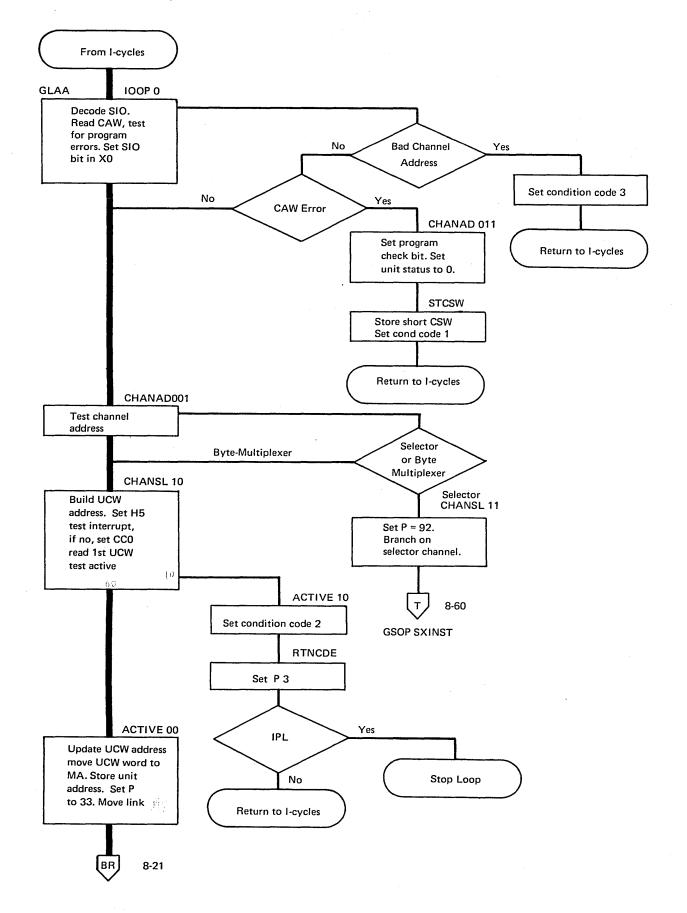

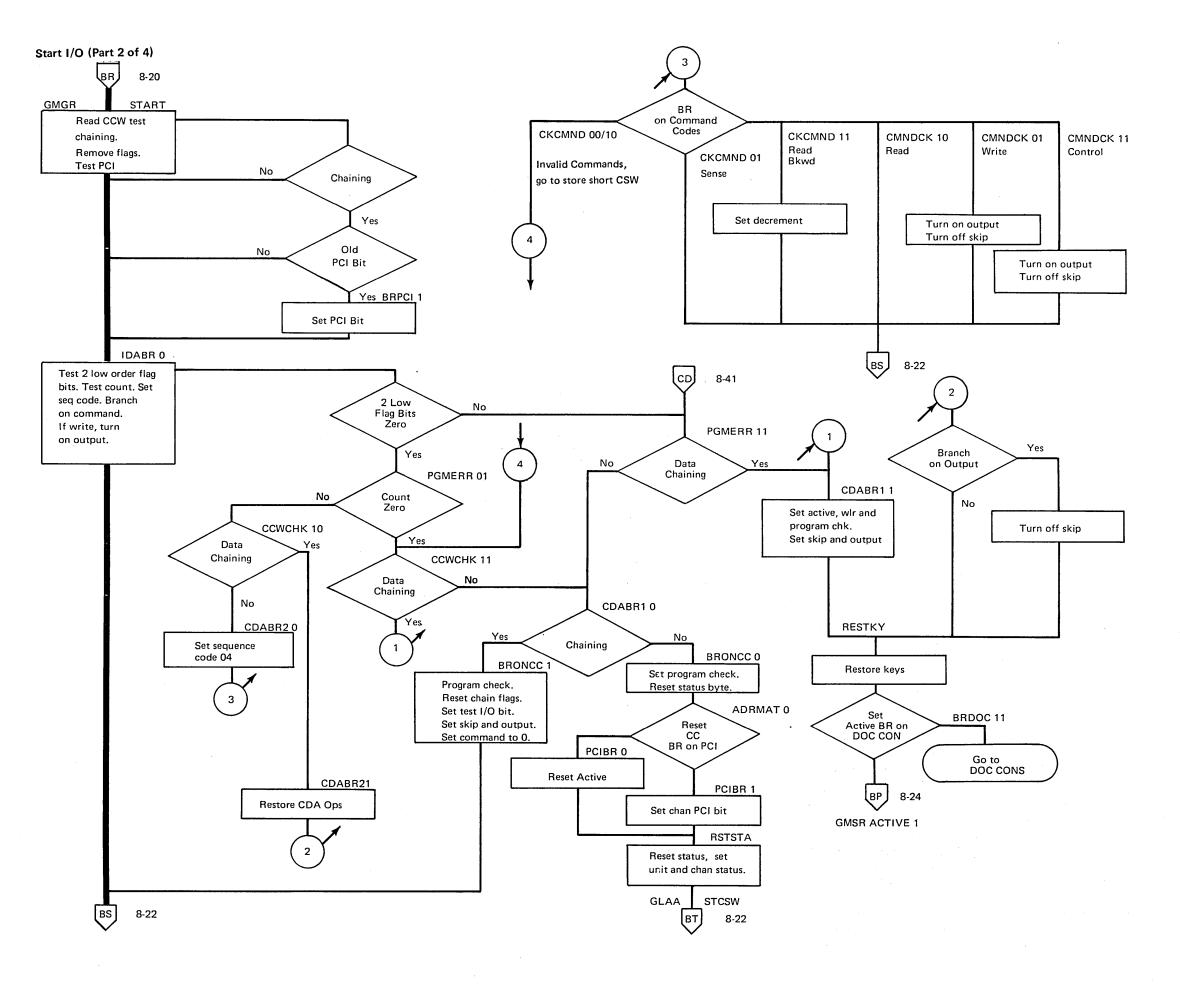

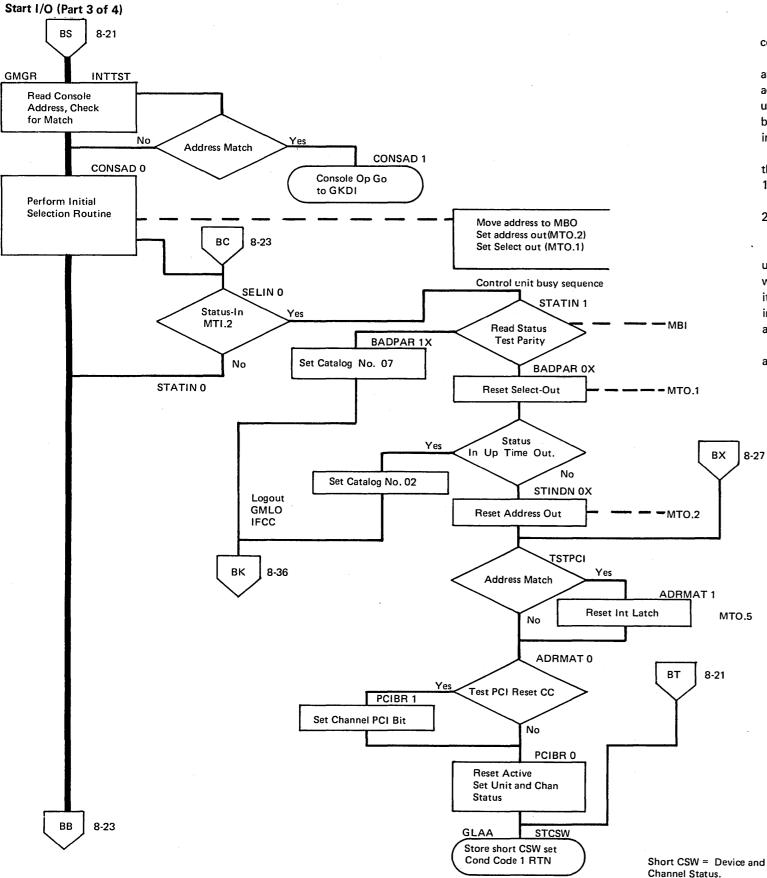

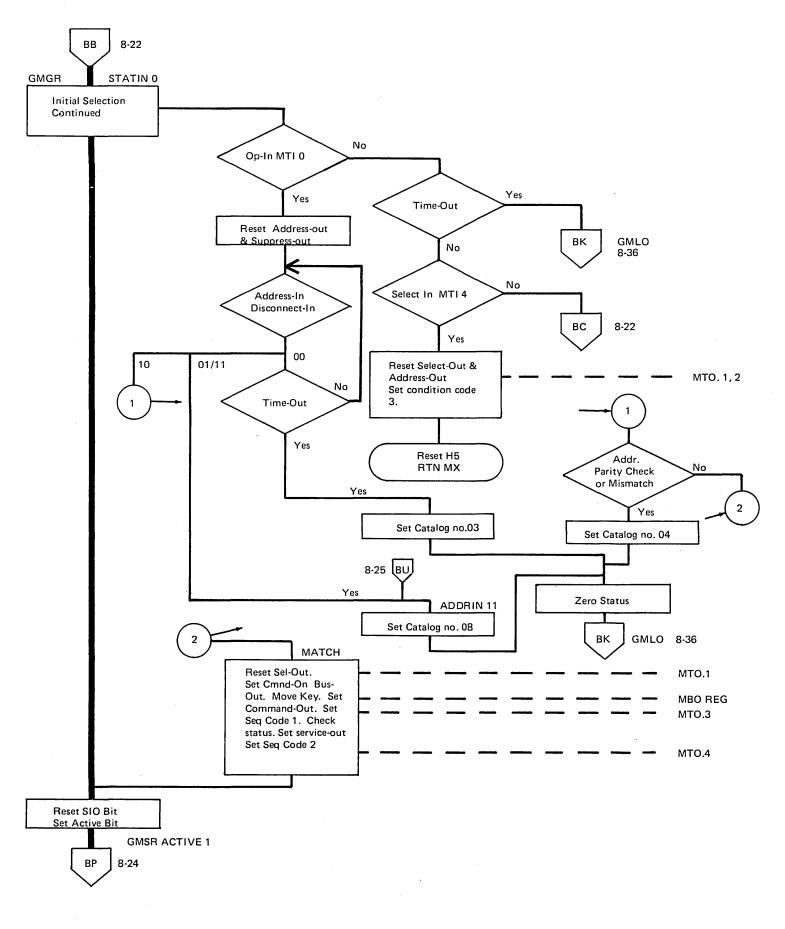

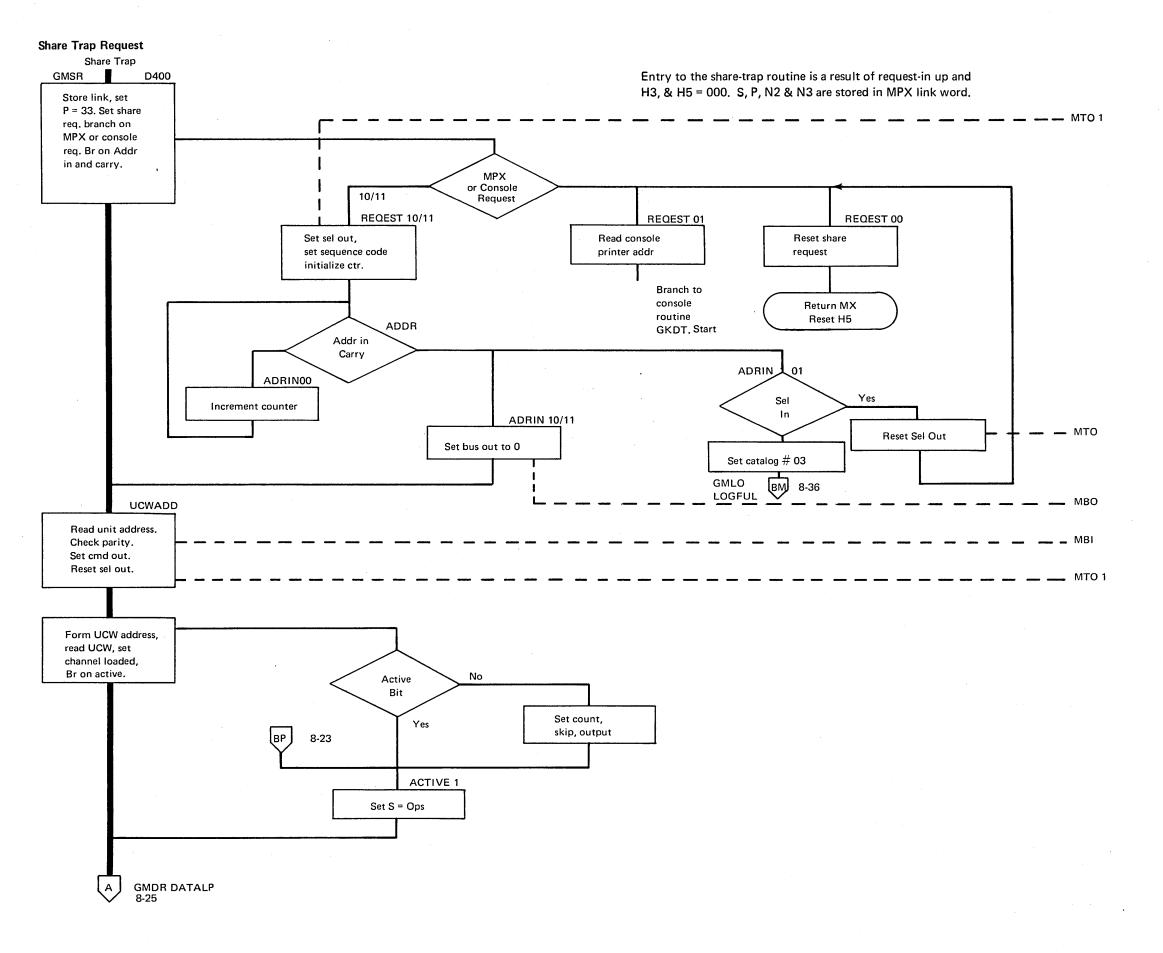

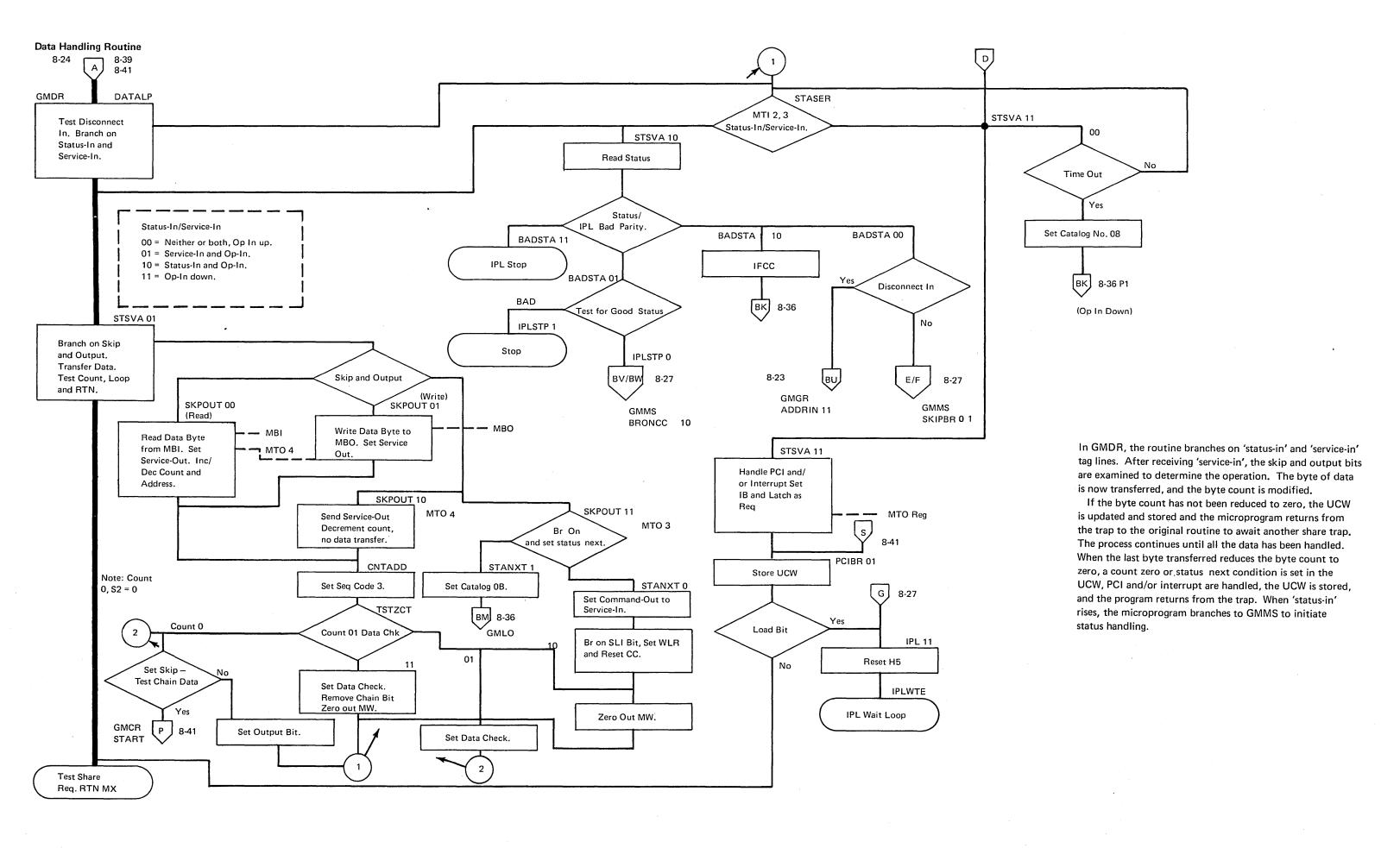

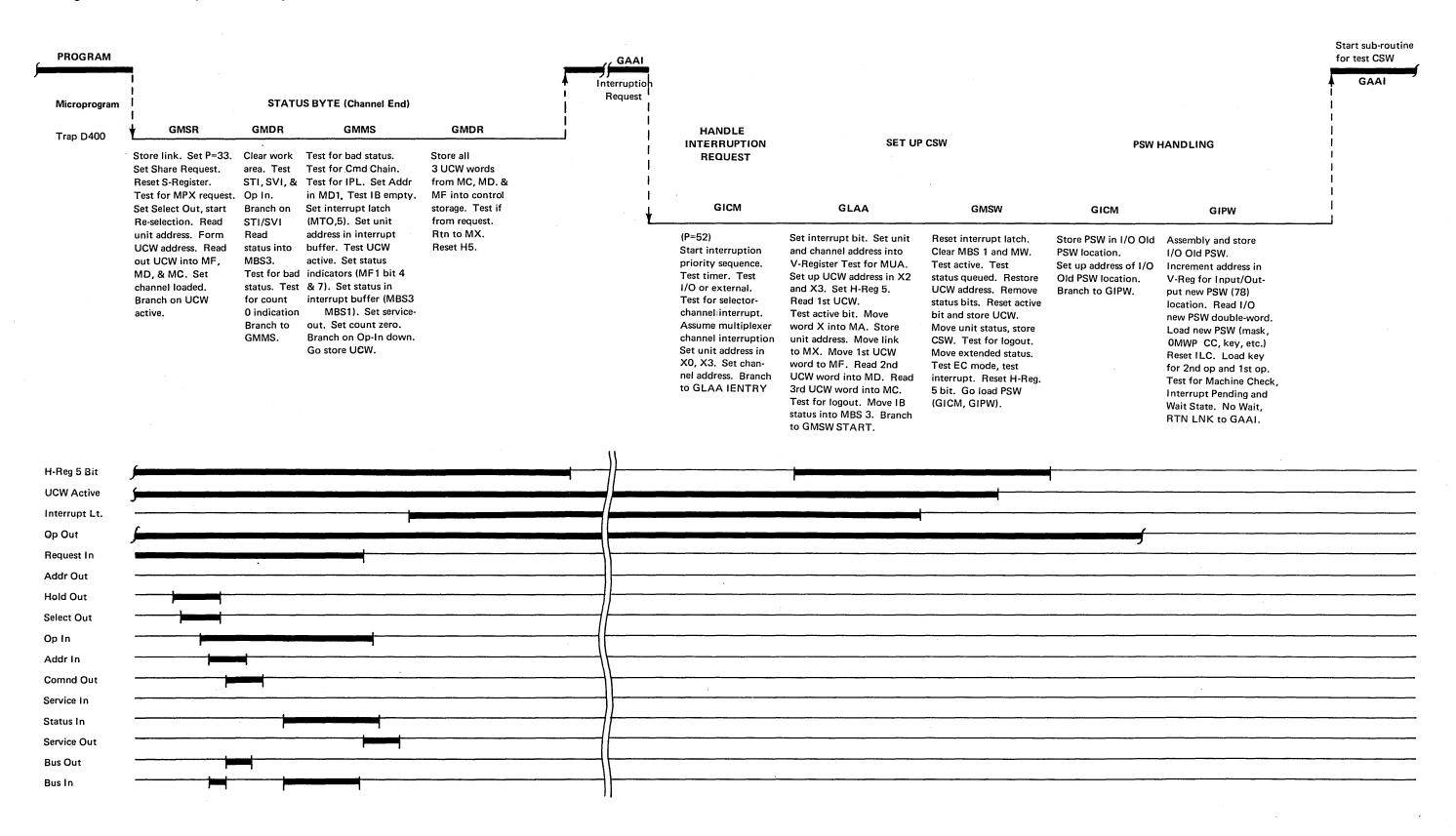

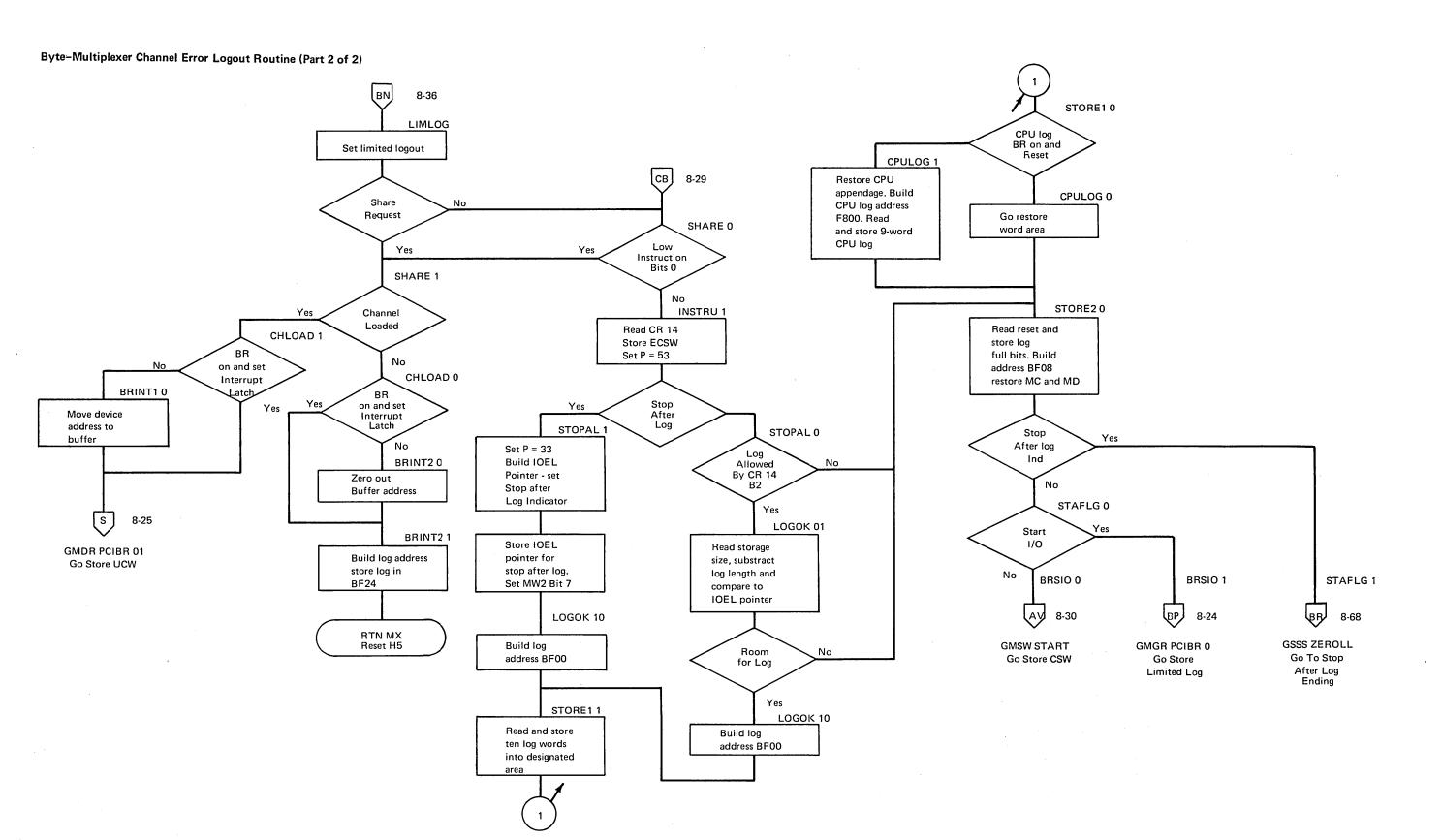

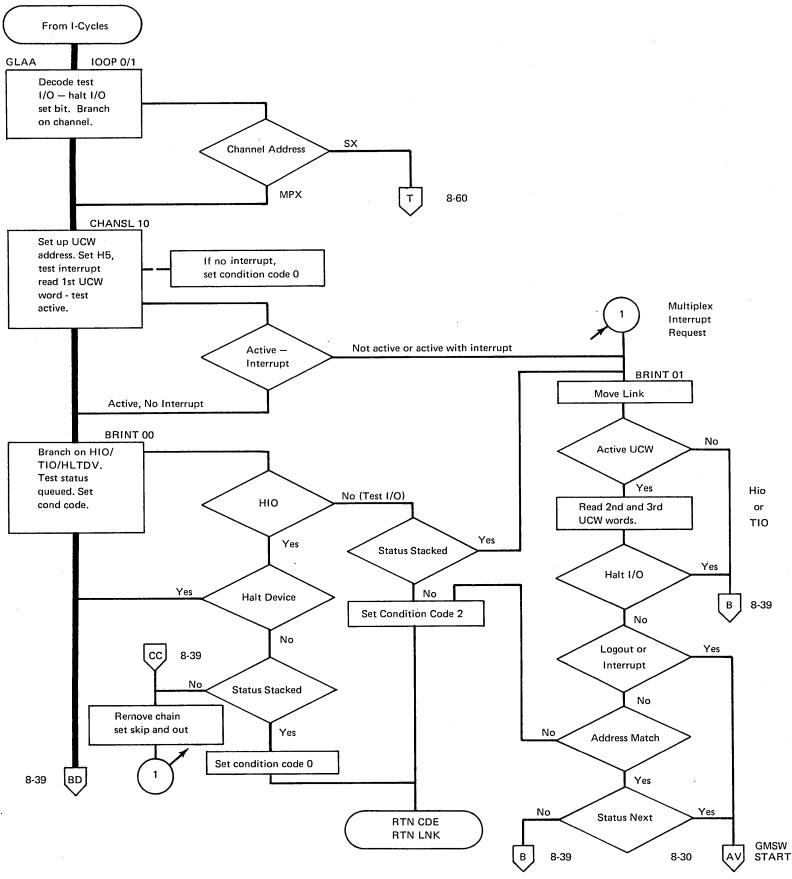

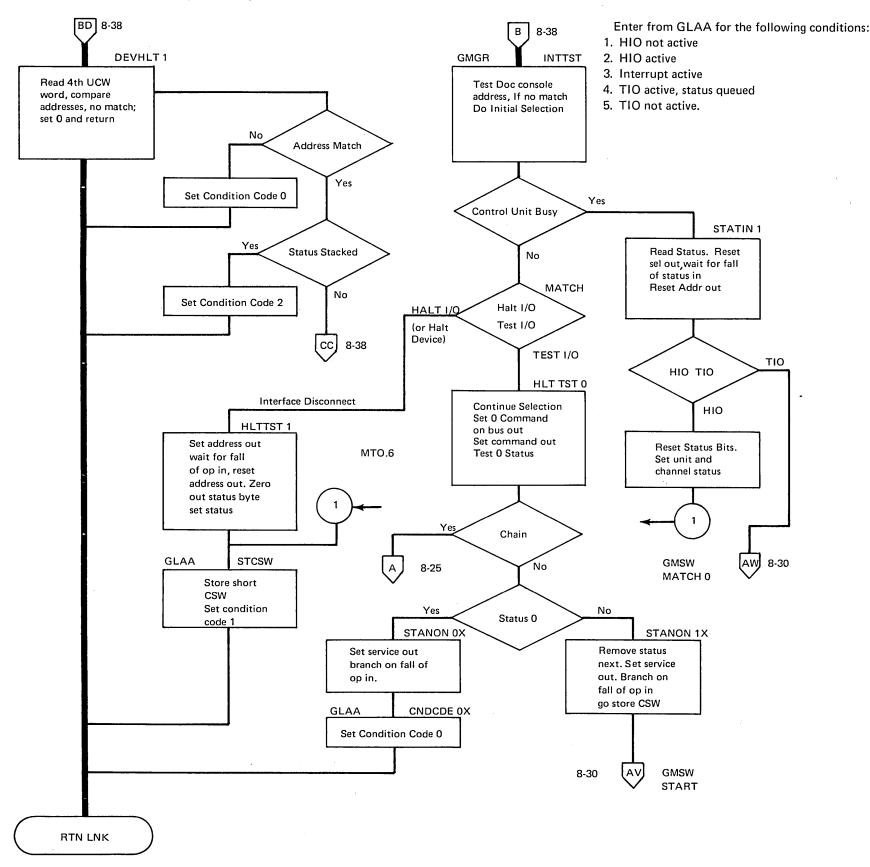

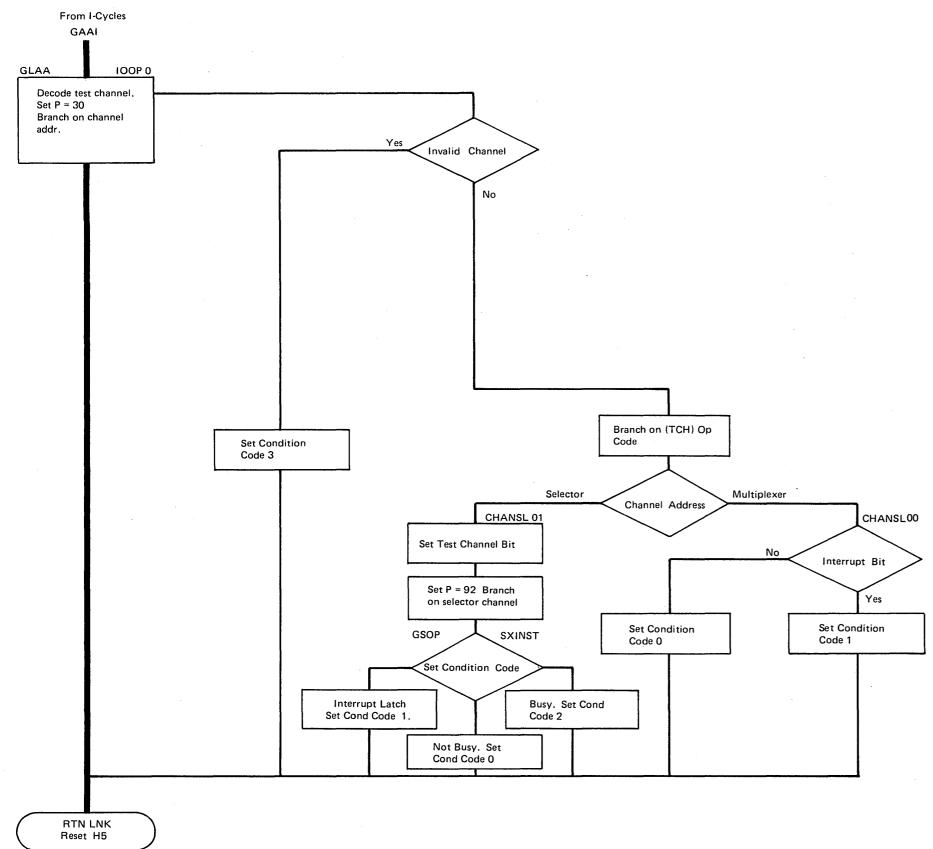

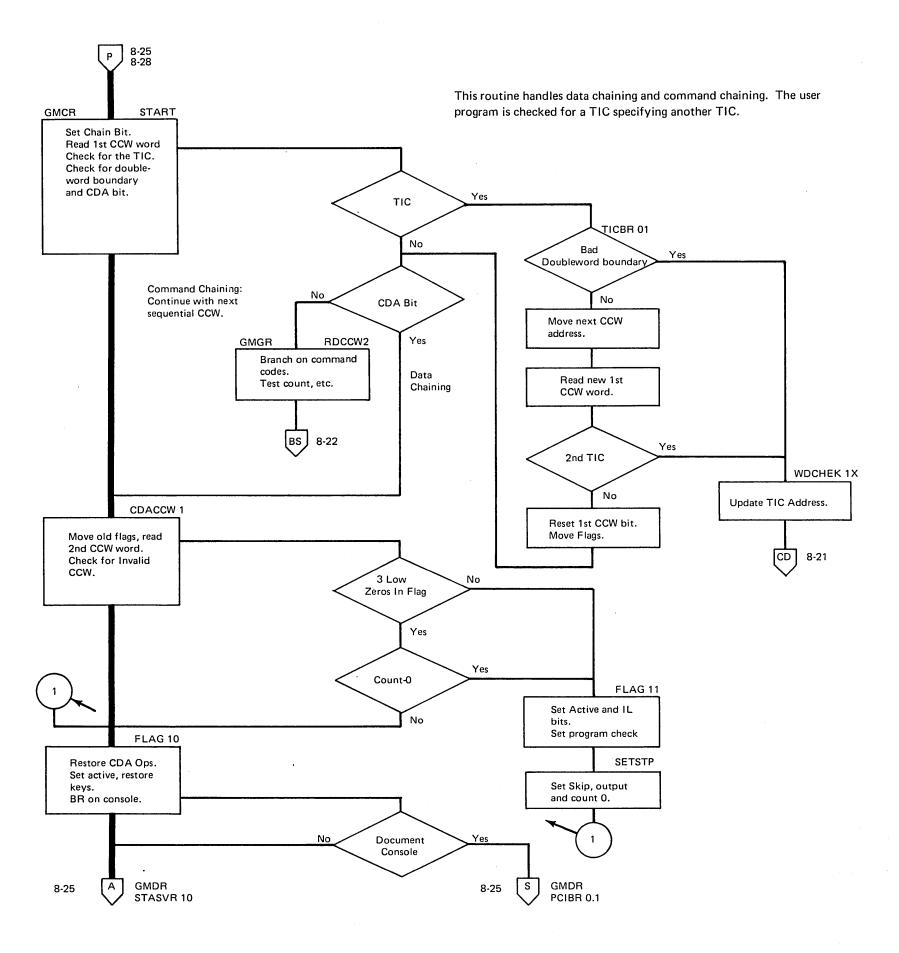

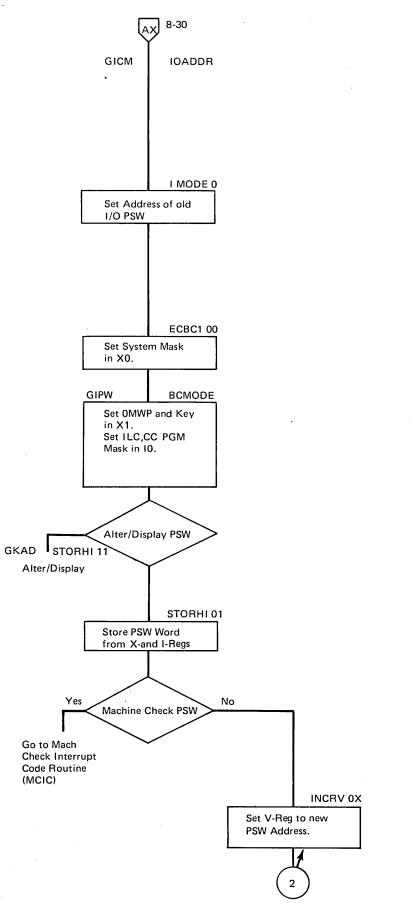

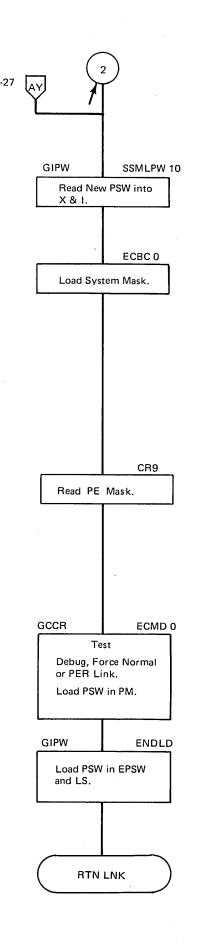

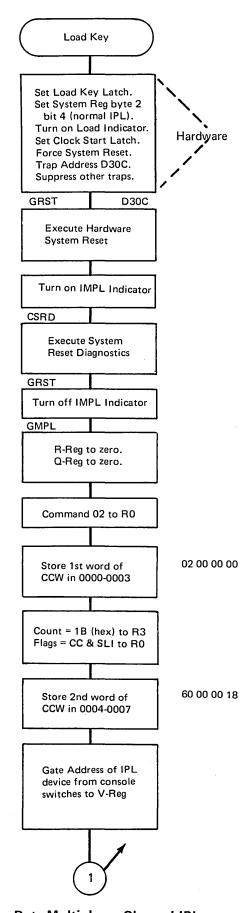

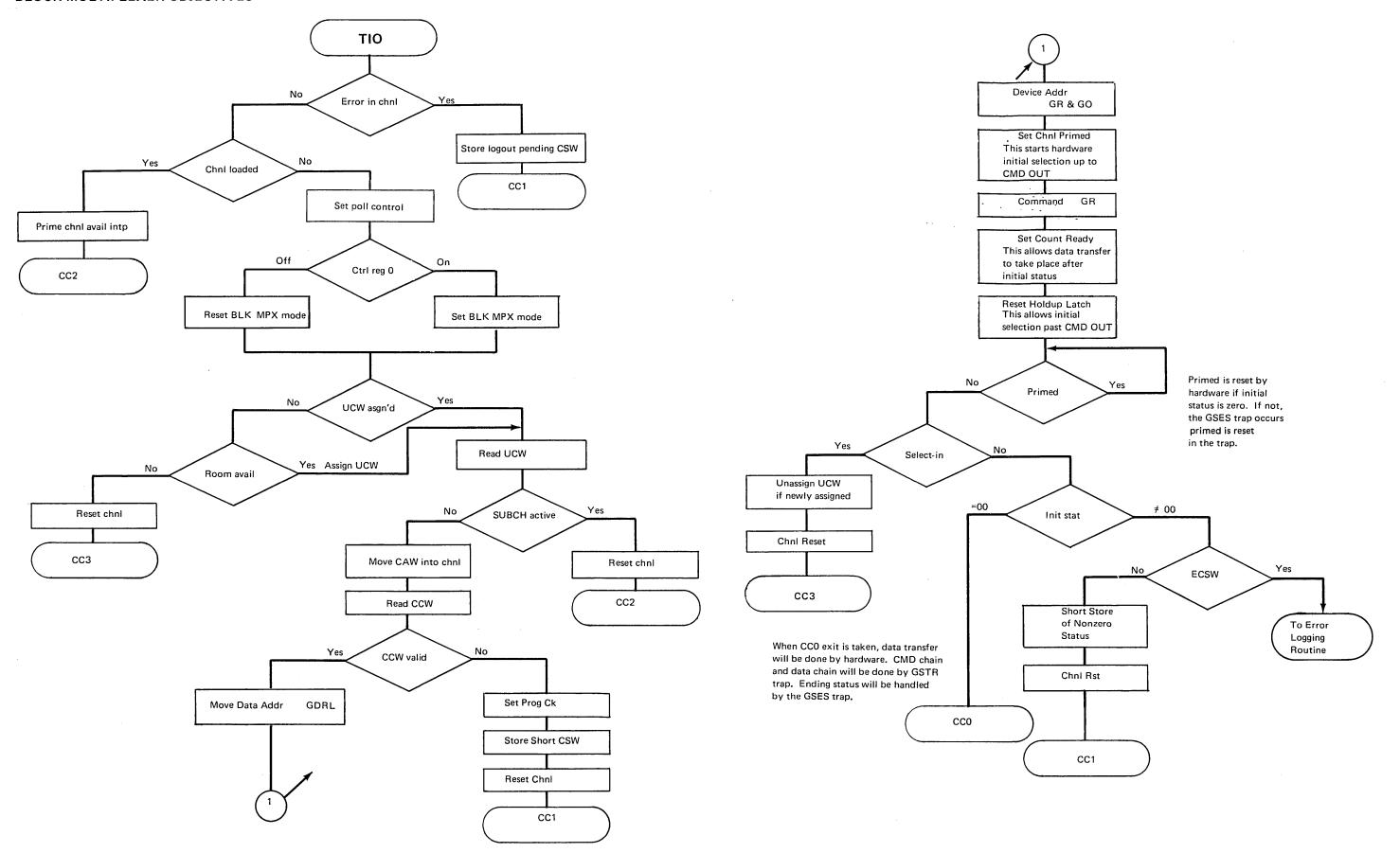

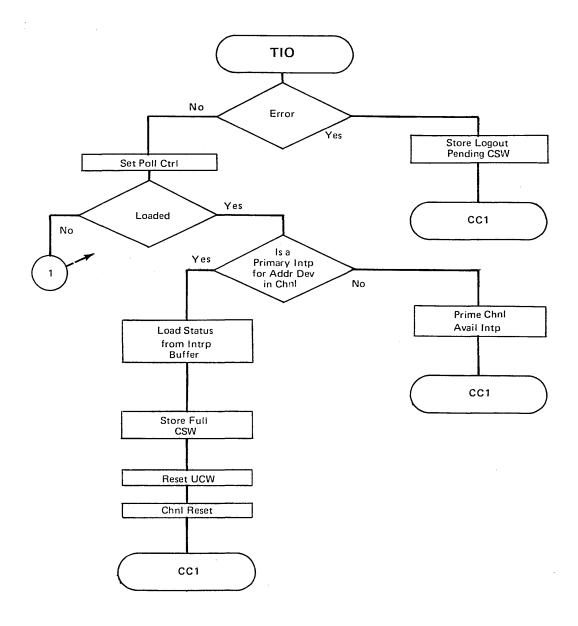

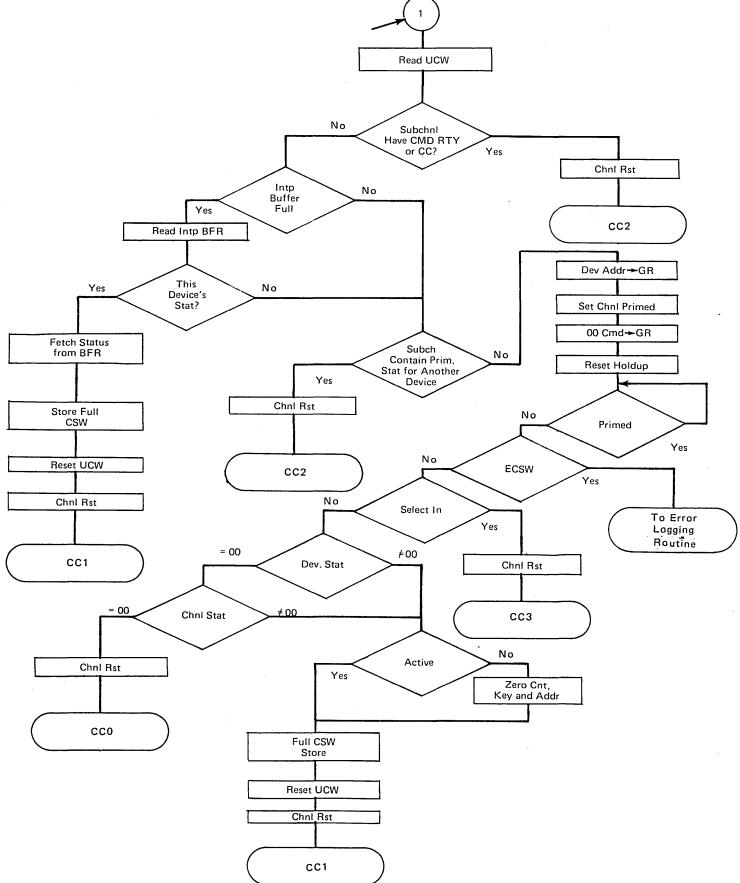

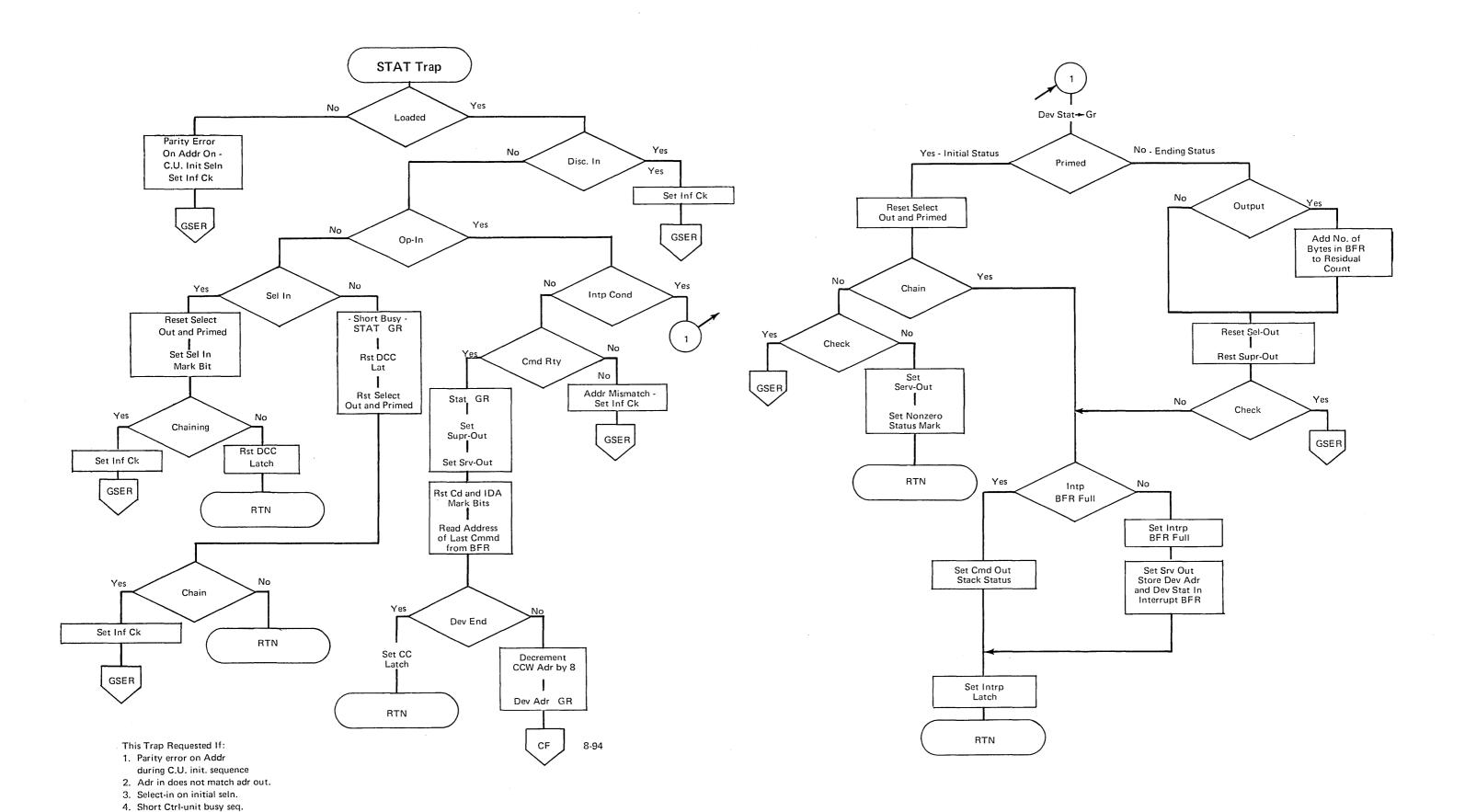

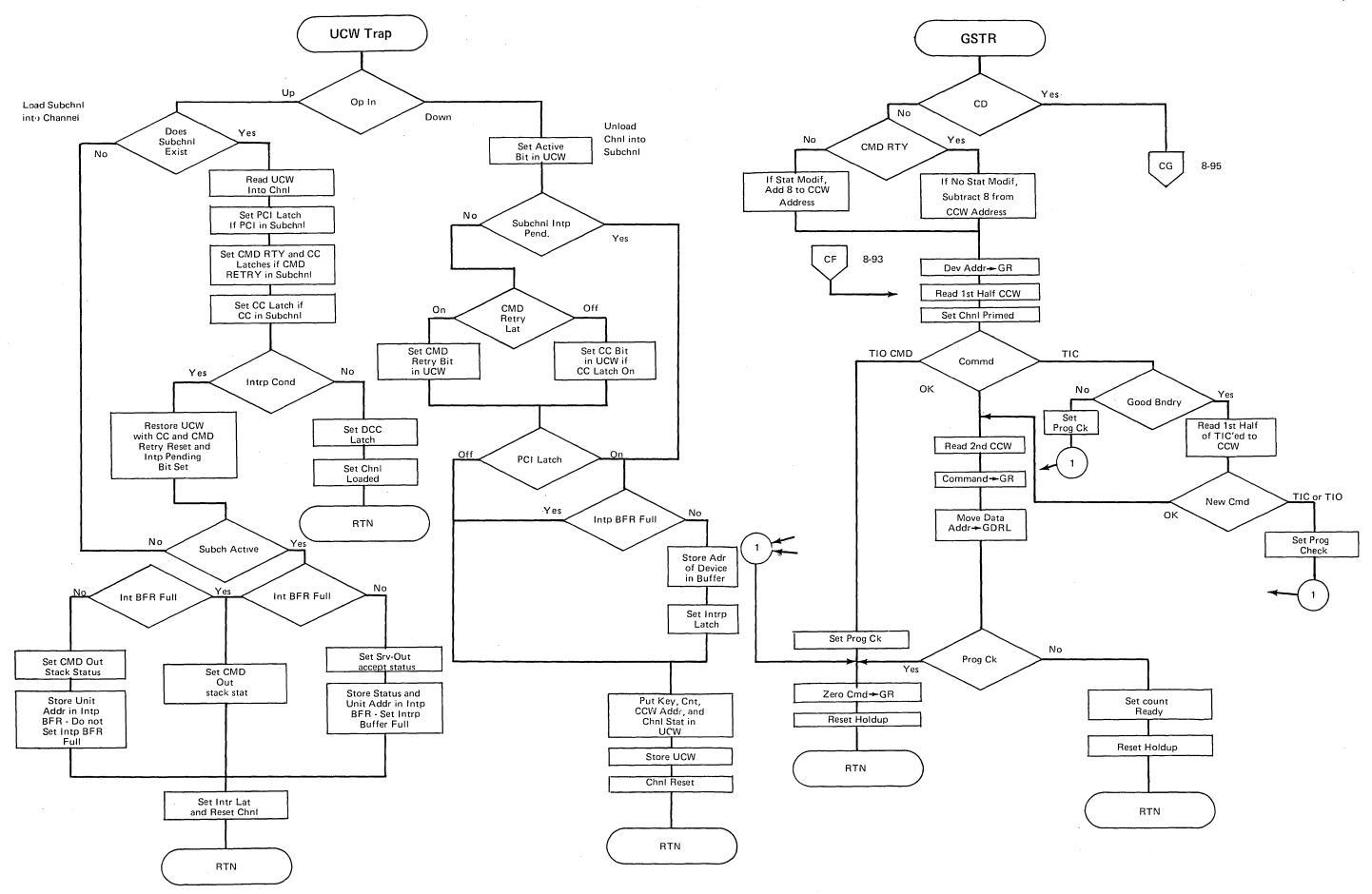

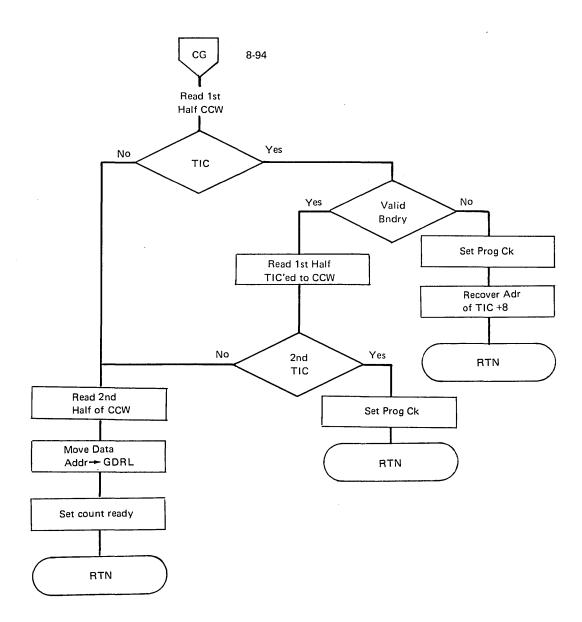

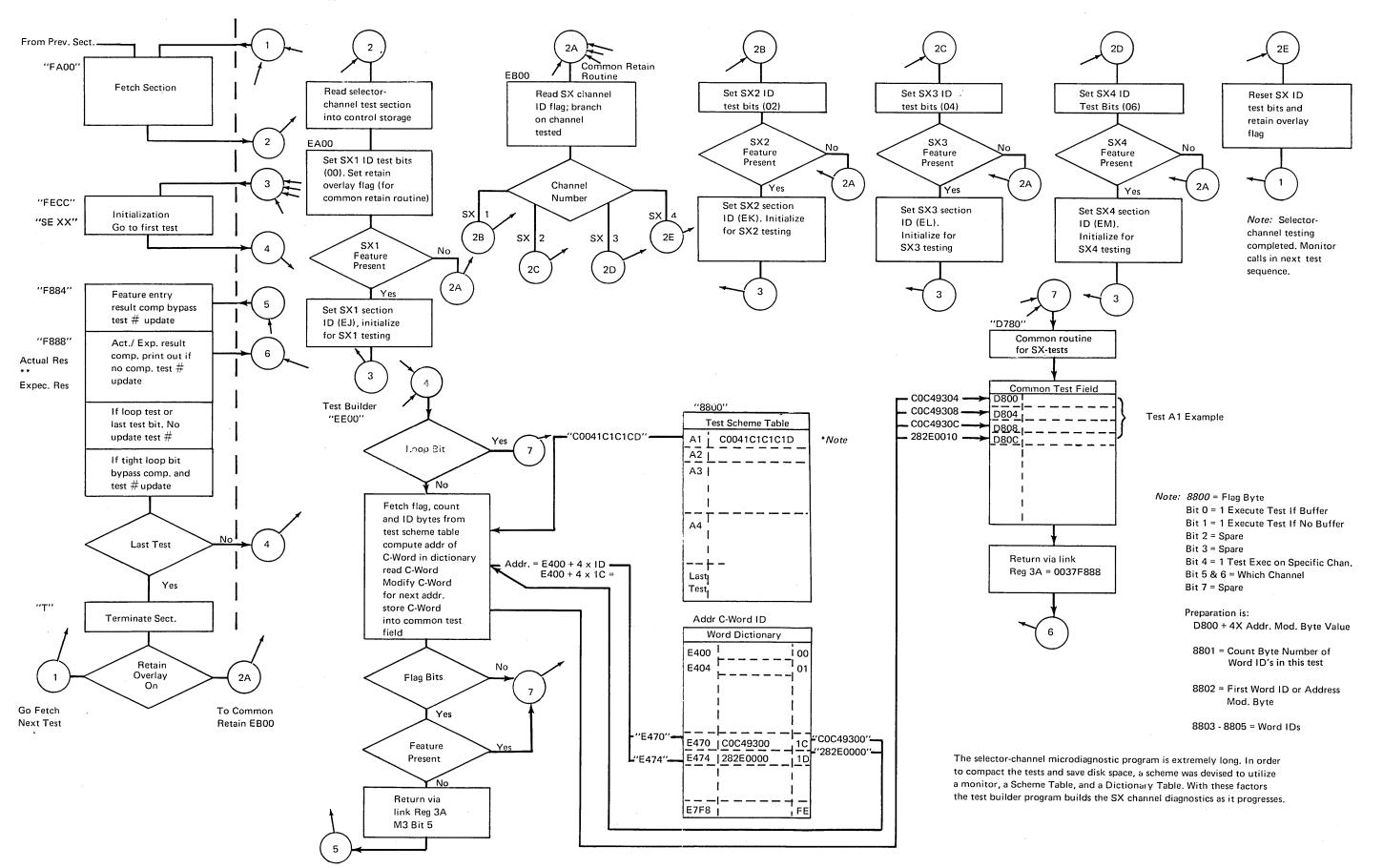

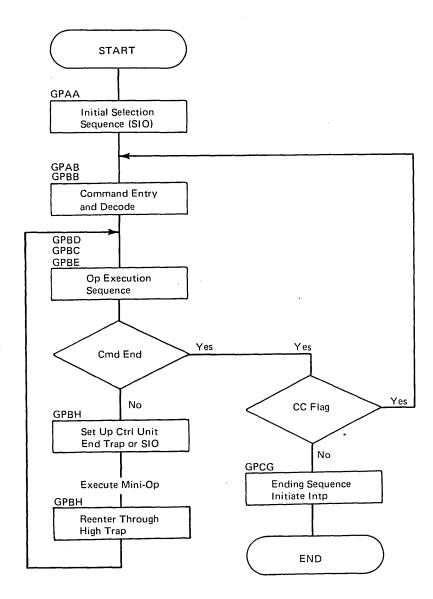

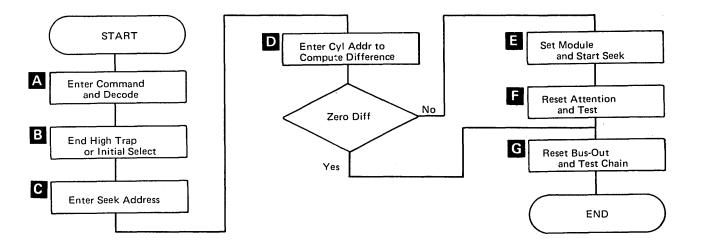

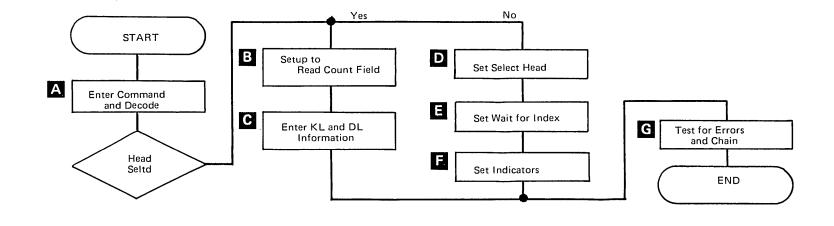

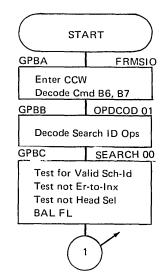

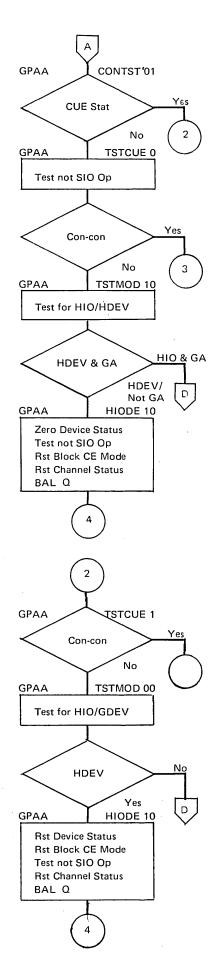

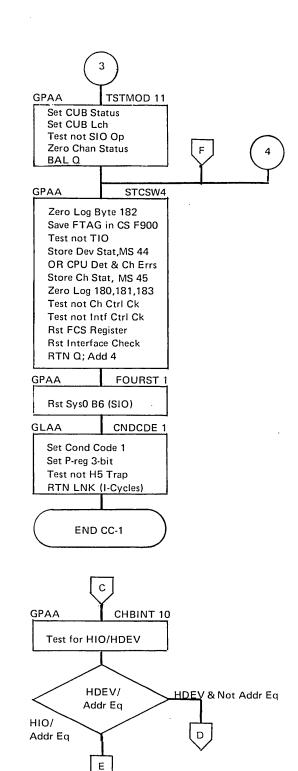

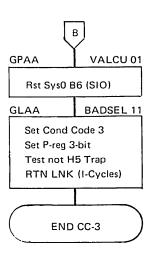

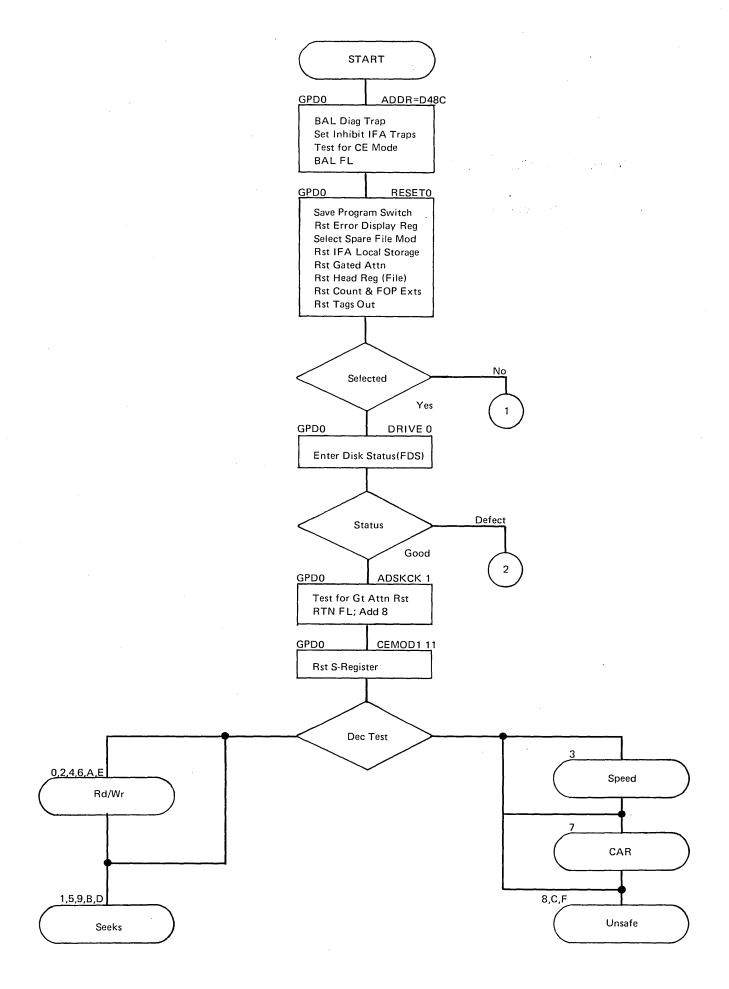

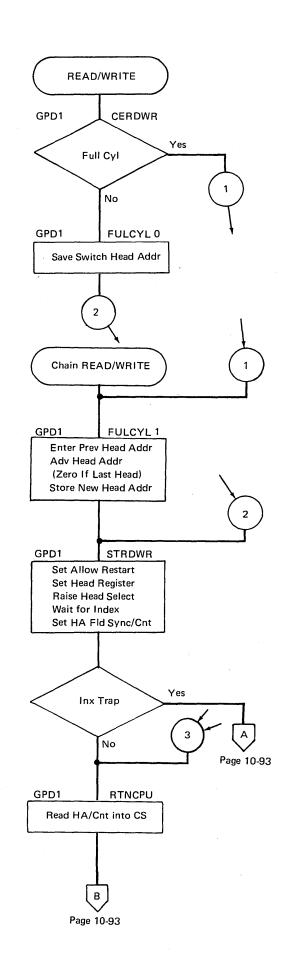

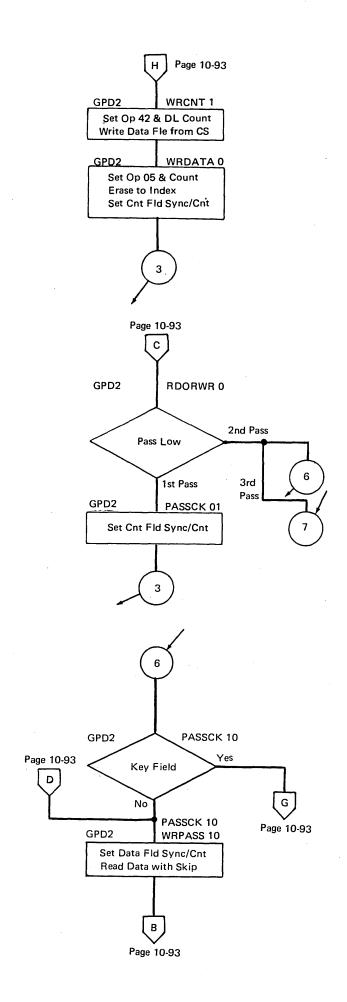

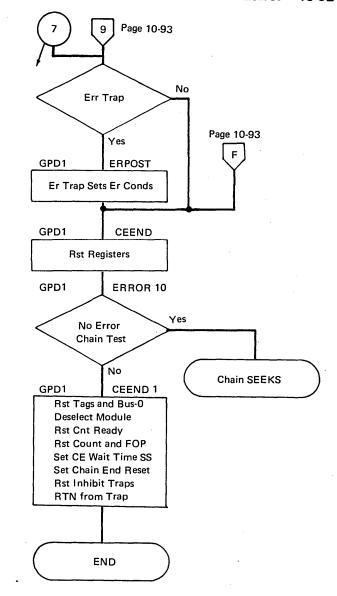

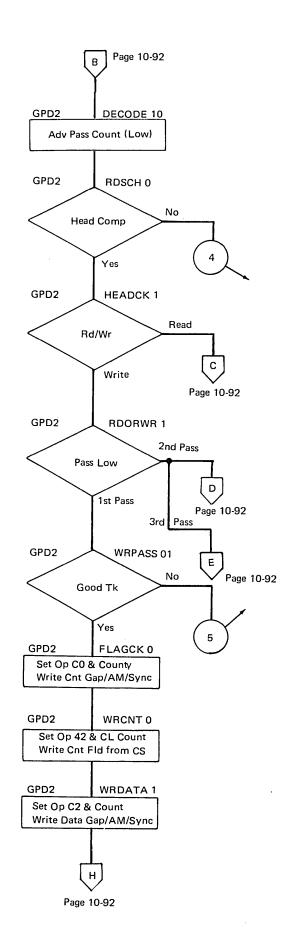

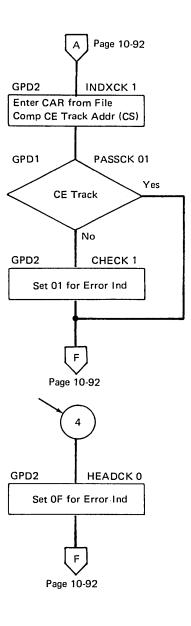

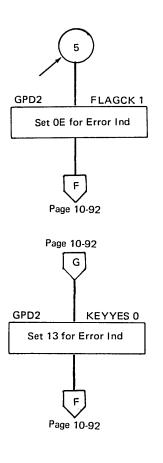

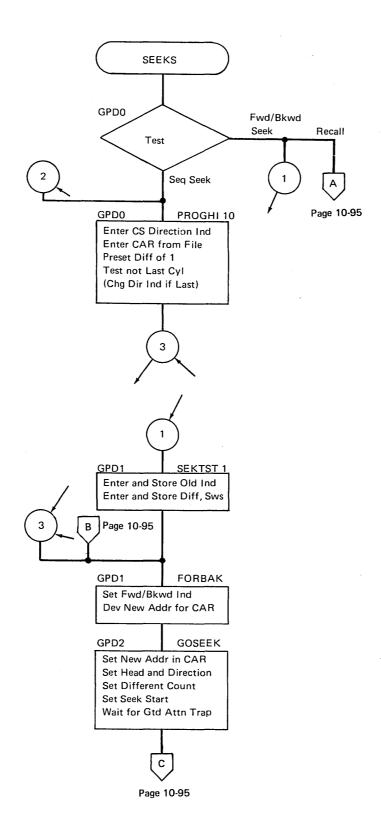

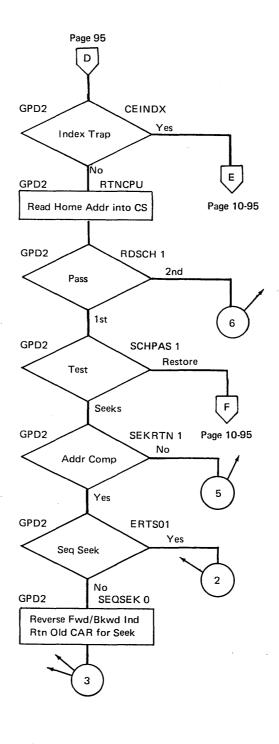

# Flowcharts

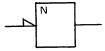

#### Decision

Indicates a point in a flow chart where a branch to alternate paths is possible.

Annotation, comment block.

Gives descriptive comment or explanatory note.

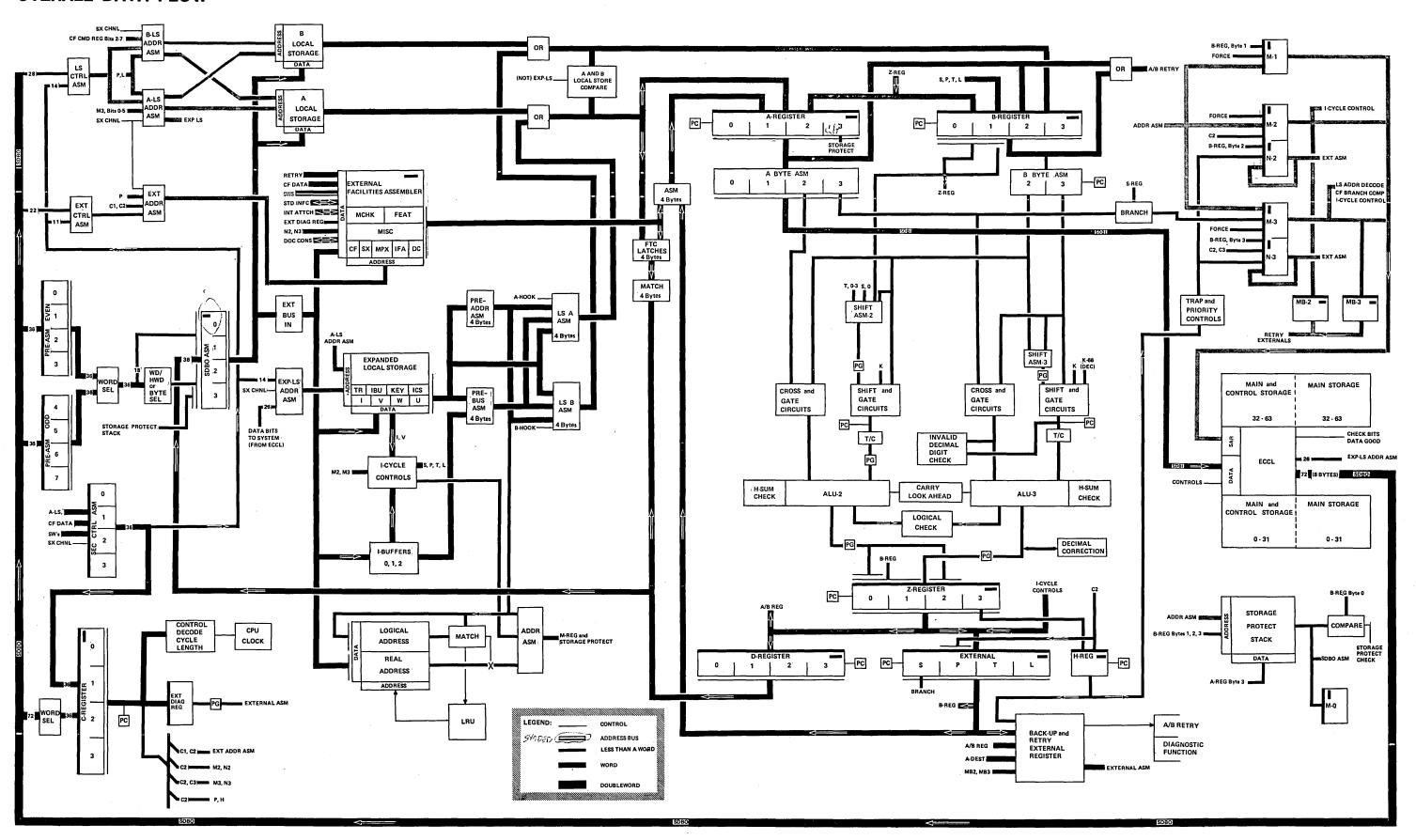

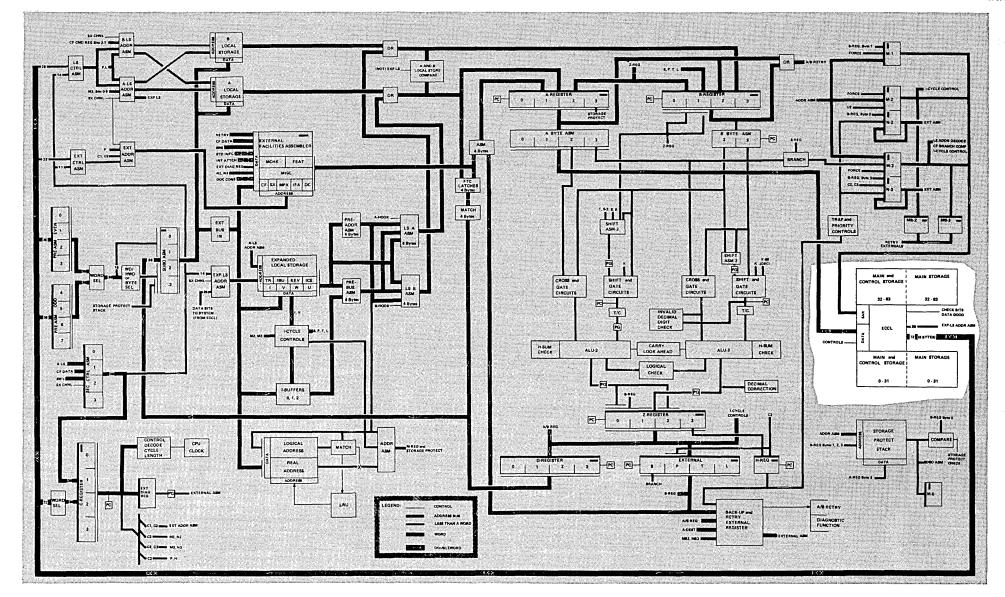

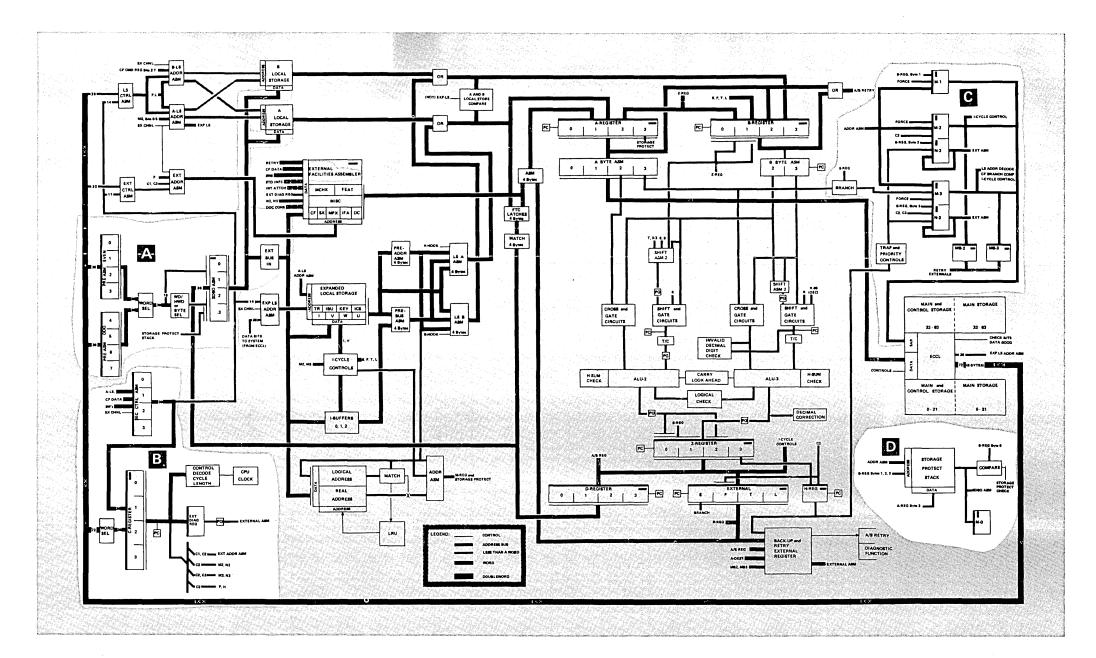

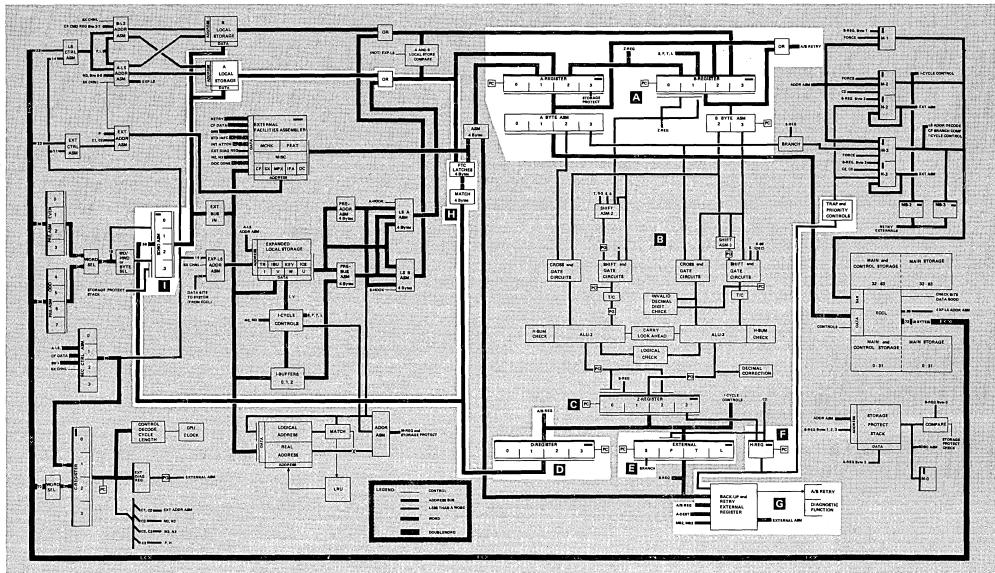

### GENERAL

Diag 1-2

### On-Page Connector

Indicates connection between two parts of the same diagram. Arrow leaving symbol points (line-of-sight) to correspondingly numbered symbol.

### On-Page Connector

Indicates connection between two parts of the same diagram. Alphameric grid coordinate of complementary connector shown beneath,

### Off-Page Connector

Indicates connection between diagrams located on separate pages. Location of correspondingly - lettered symbol shown adjacent. Alphameric grid coordinate may be included.

### INDEX

| A                                                  | ALU shift gating 2-96                                 | block multiplexer selector channel 1-17       | byte-multiplexer channel (continued) |

|----------------------------------------------------|-------------------------------------------------------|-----------------------------------------------|--------------------------------------|

| A-and B-registers 1-9, 1-12                        | AM (asynchronous machine check logout mask) 12-17     | blowers, removal and replacement 11-38, 11-39 | start I/O 8-20                       |

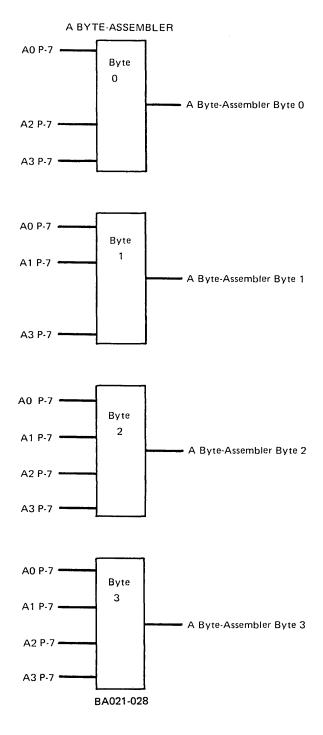

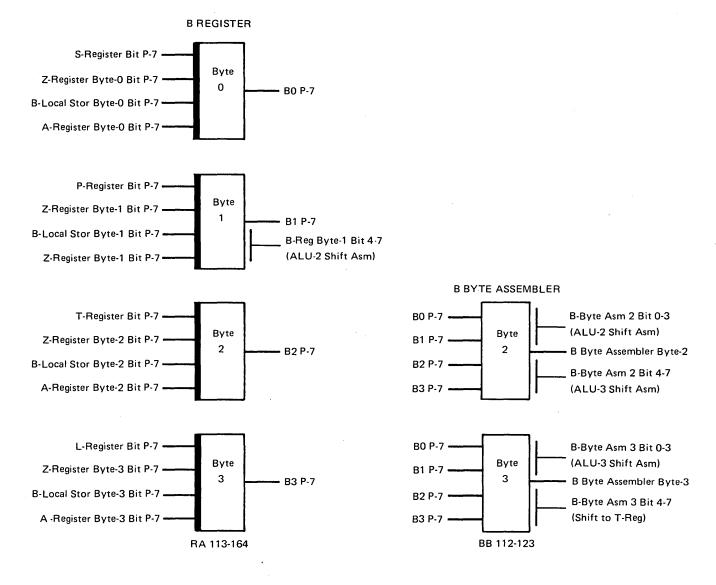

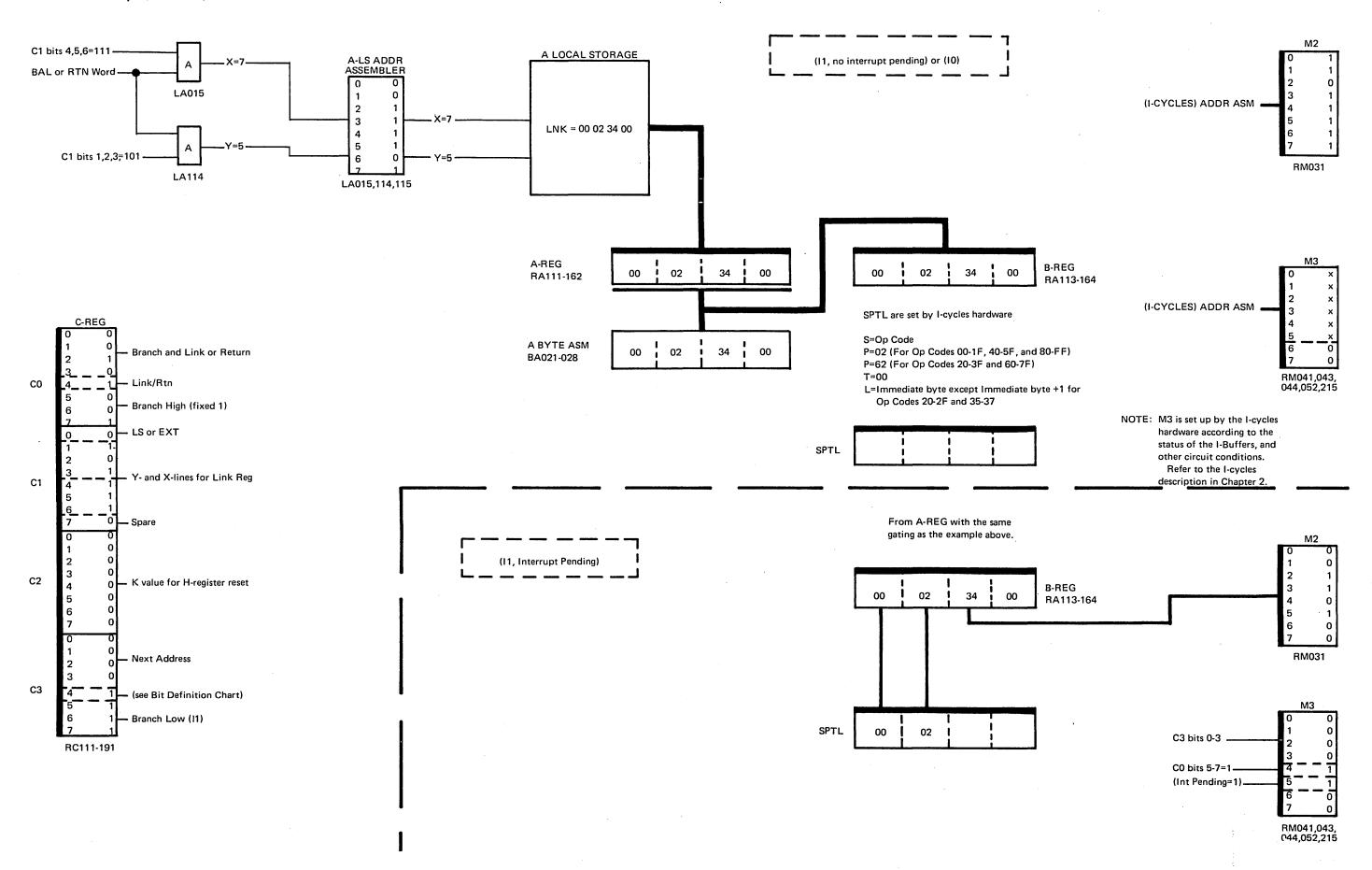

| A byte assembler 2-93                              | AM bytes, IFA 10-17                                   | branch and link control word                  | status interpret 8-27                |

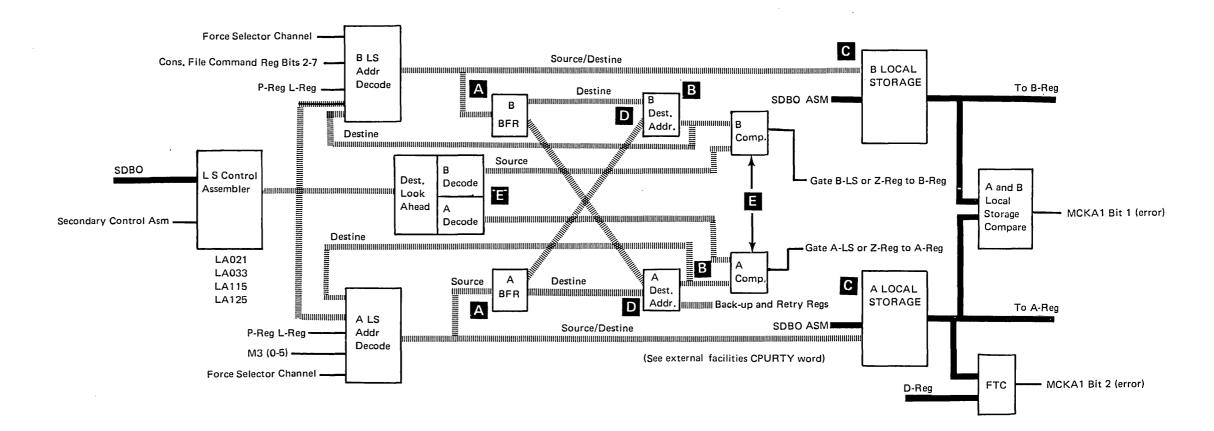

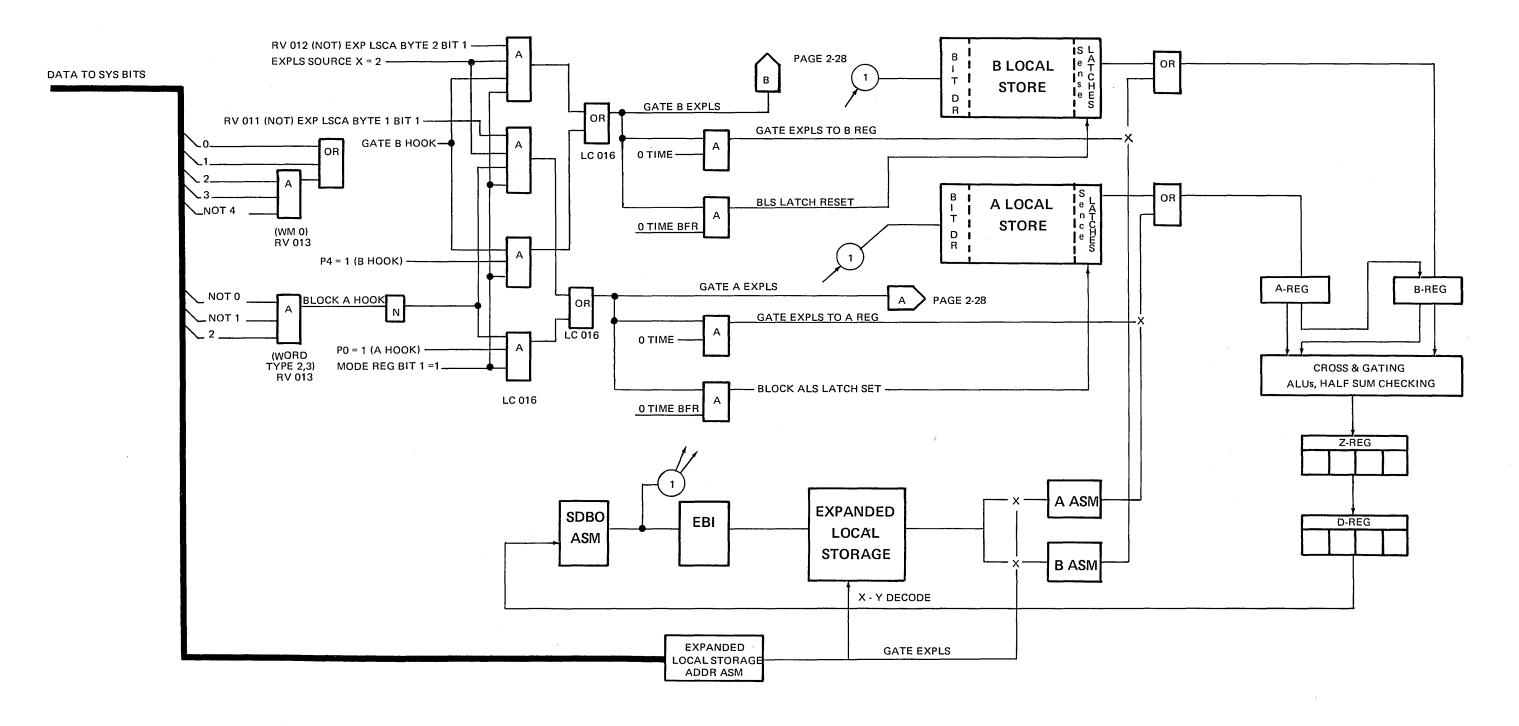

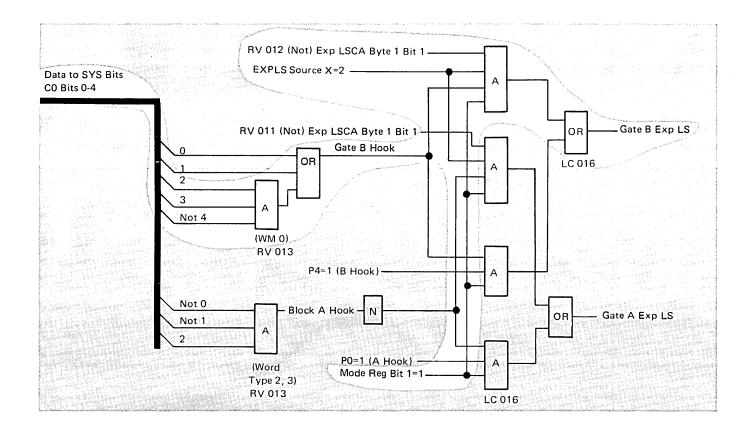

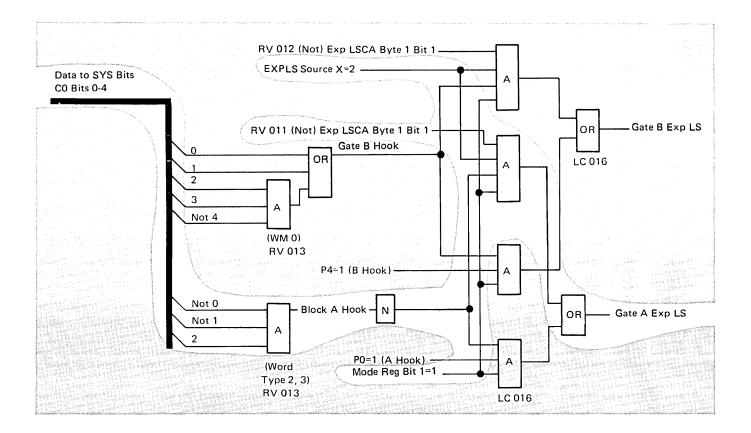

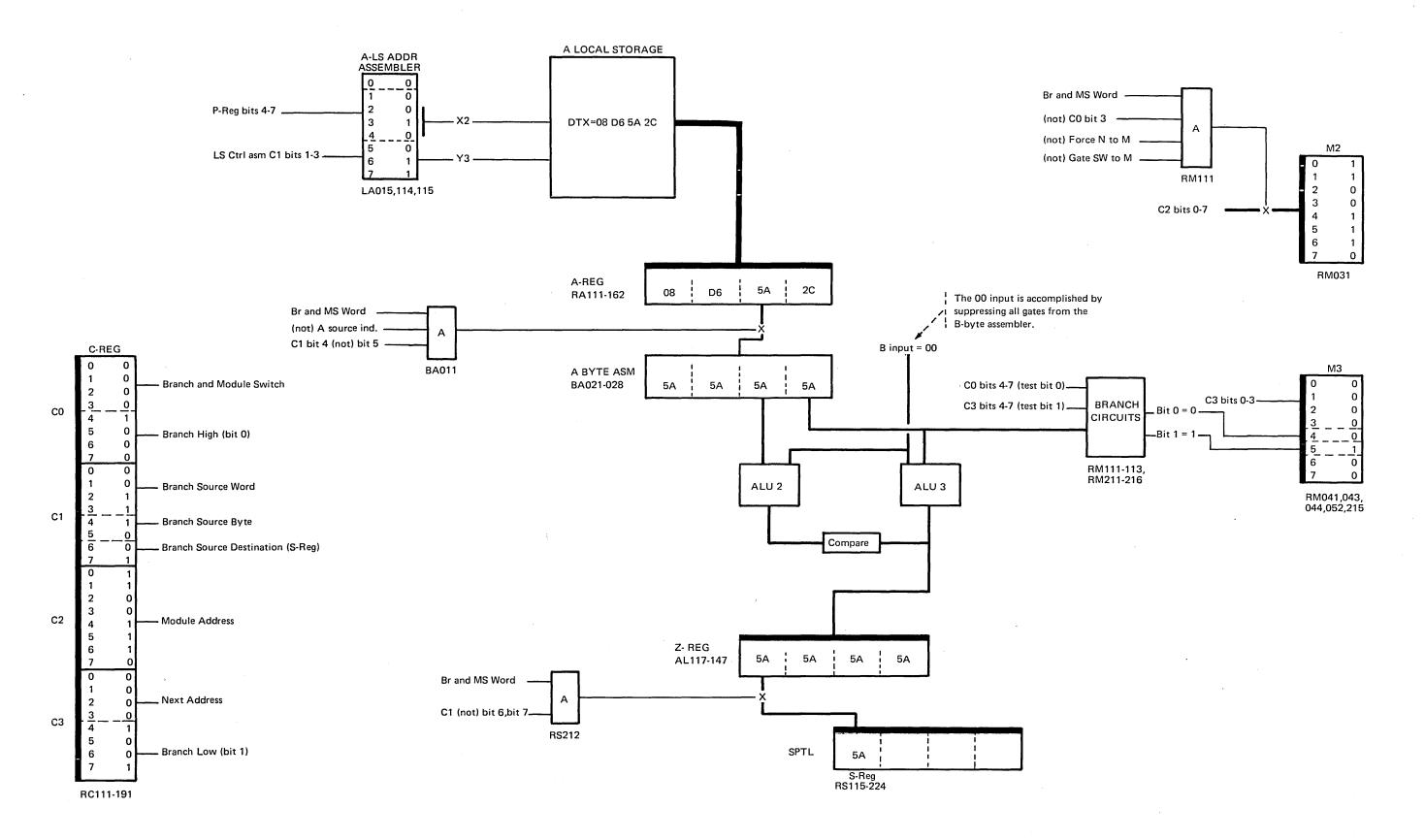

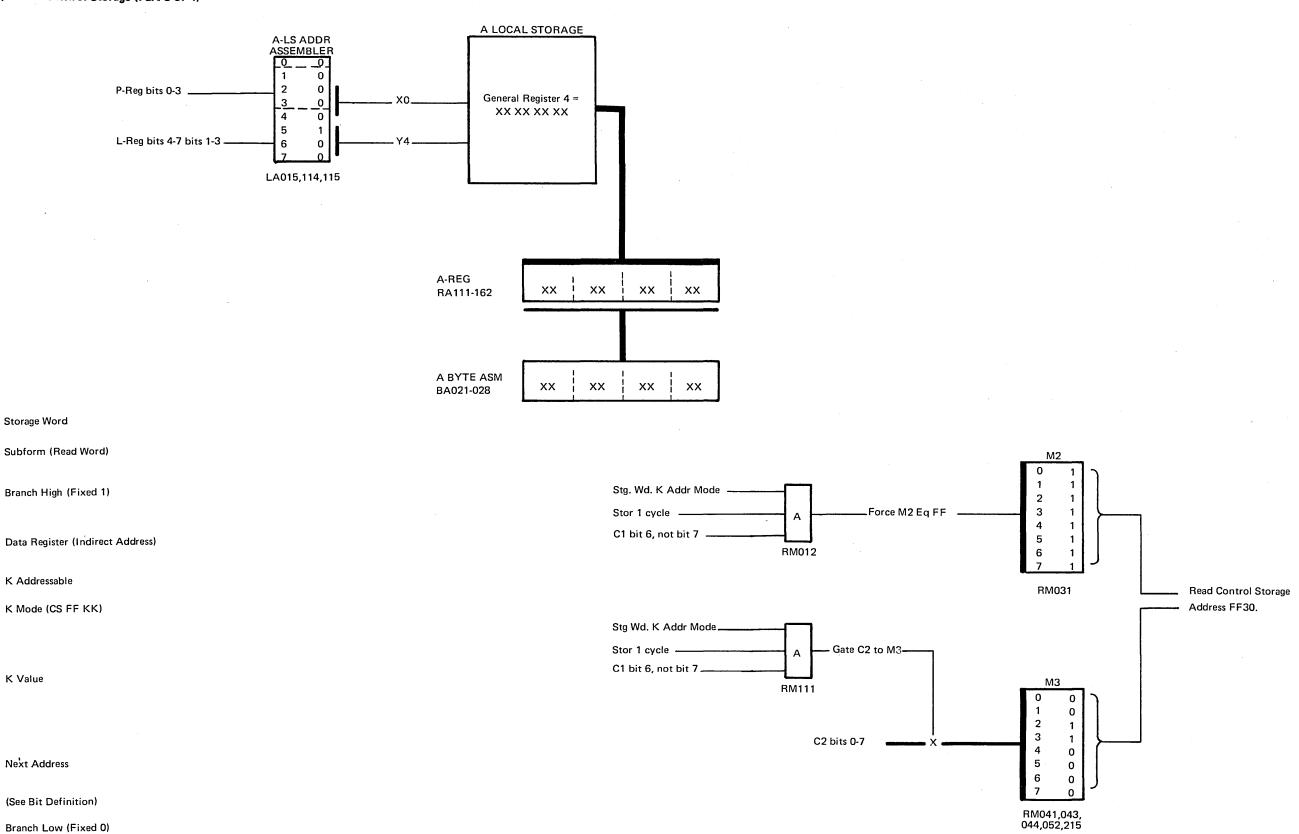

| A-local storage, data flow 2-12                    | analysis, machine check 12-24                         | example 4-34, 4-35                            | stop after log 8-34                  |

| A-register and A byte assembler 2-93               | arithmetic and logic unit (ALU) 1-12, 2-97            | branch and link or return word                | store and load PSW 8-42              |

| A-register, B-register and ALU 2-92                | arithmetic control word                               | bit definition 4-19                           | test channel 8-40                    |

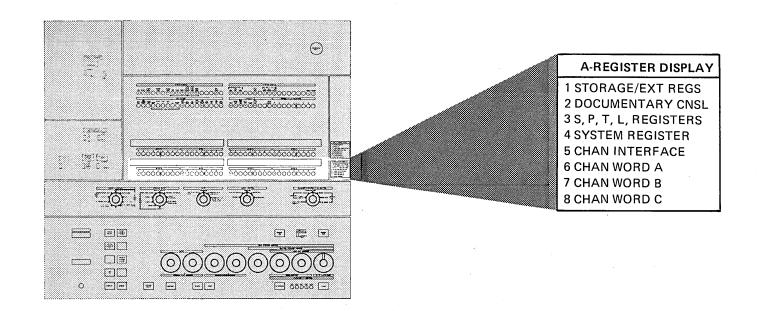

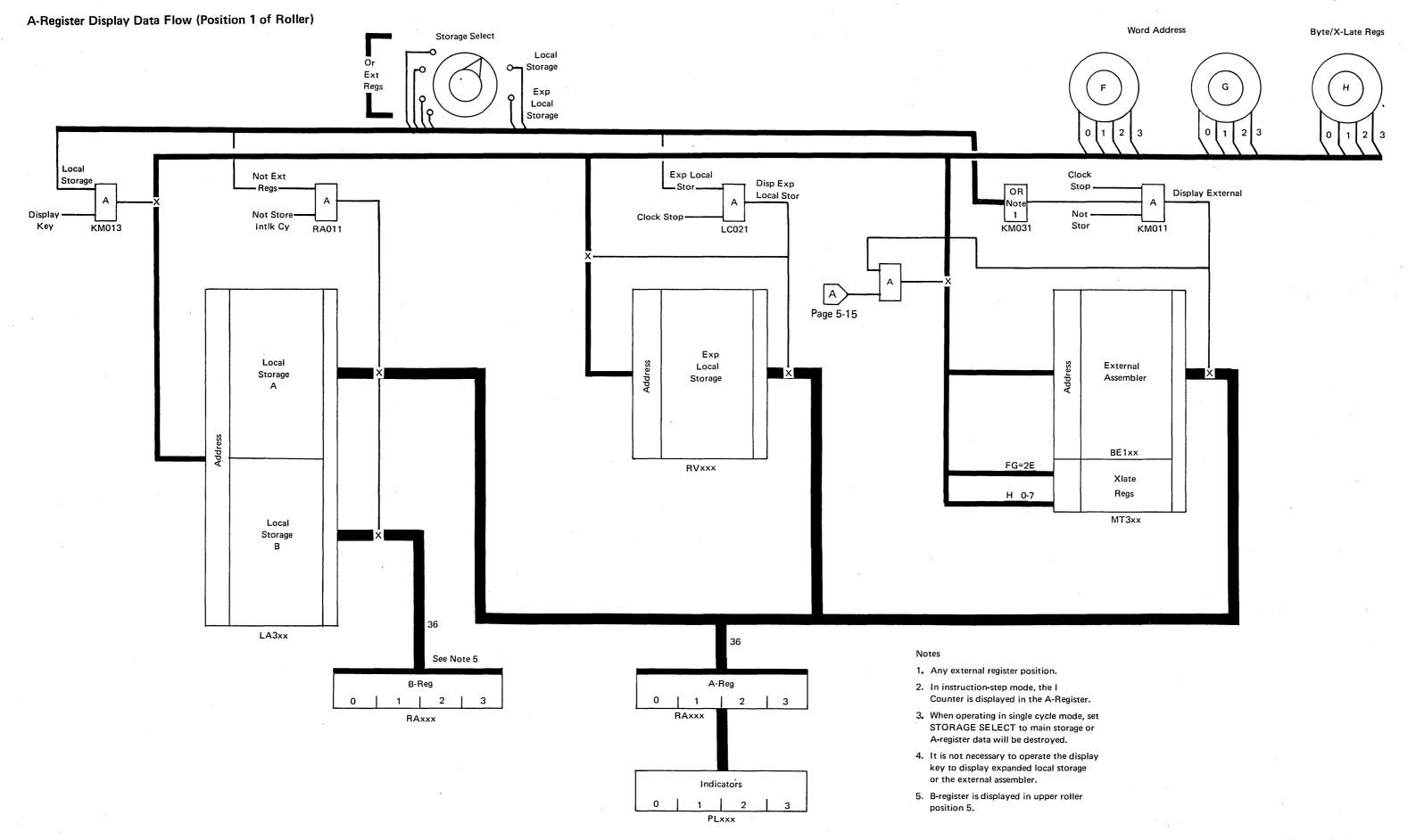

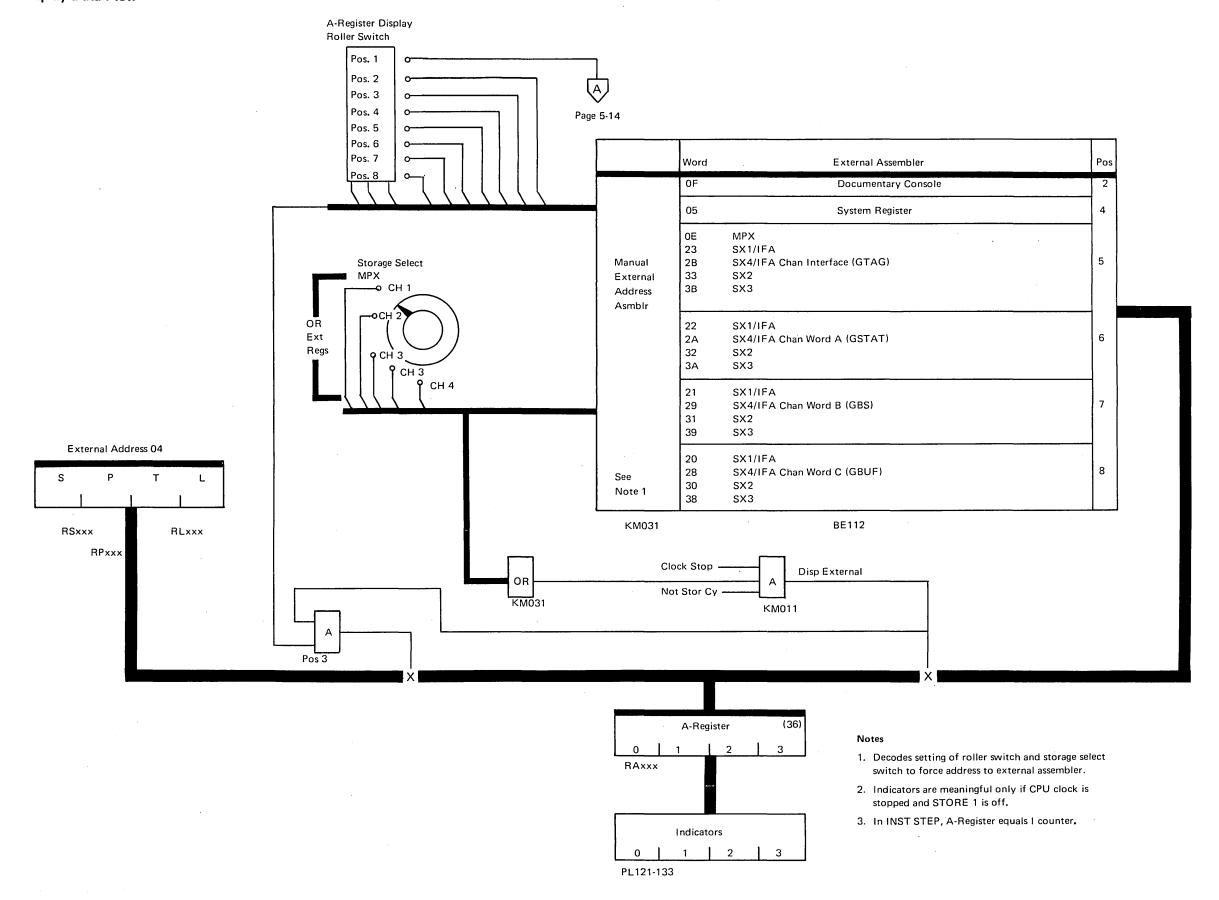

| A-register display, data flow 5-14, 5-15           |                                                       | operation 4-30, 4-31                          | test I/O-halt, I/O-halt device 8-38  |

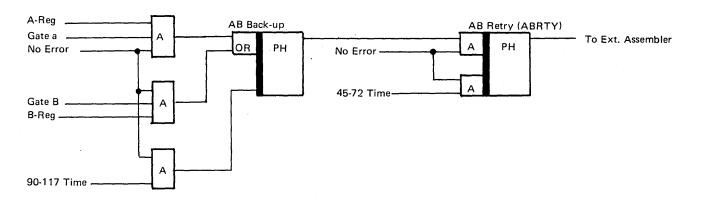

| AB backup 12-10                                    | fullword (bit definition) 4-70                        | branch and module switch                      | unit control word format 8-14        |

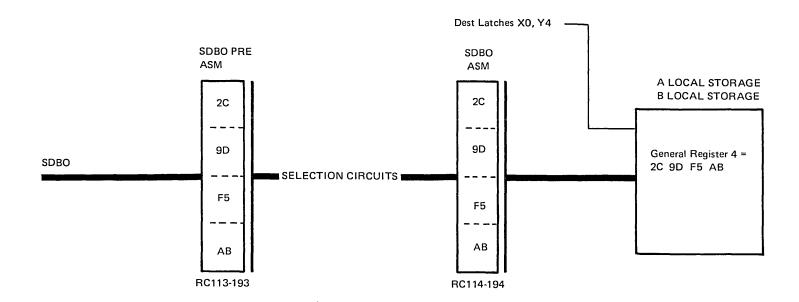

| AB retry 12-10                                     | type 10 byte (bit definition) 4-70                    | bit definition 4-19                           | byte selection (SDB0) 2-8            |

| ABRTY 12-10                                        | type 11 (bit definition) 4-72                         | control-word operation 4-18                   | 5) 11 5011011011 (BBB6)              |

| AC (automatic configuration) 12-18                 | arithmetic indirect byte                              | example 4-20                                  |                                      |

| AC cable, IFA/2319 10-98                           | control word example 4-75                             | branch control word                           |                                      |

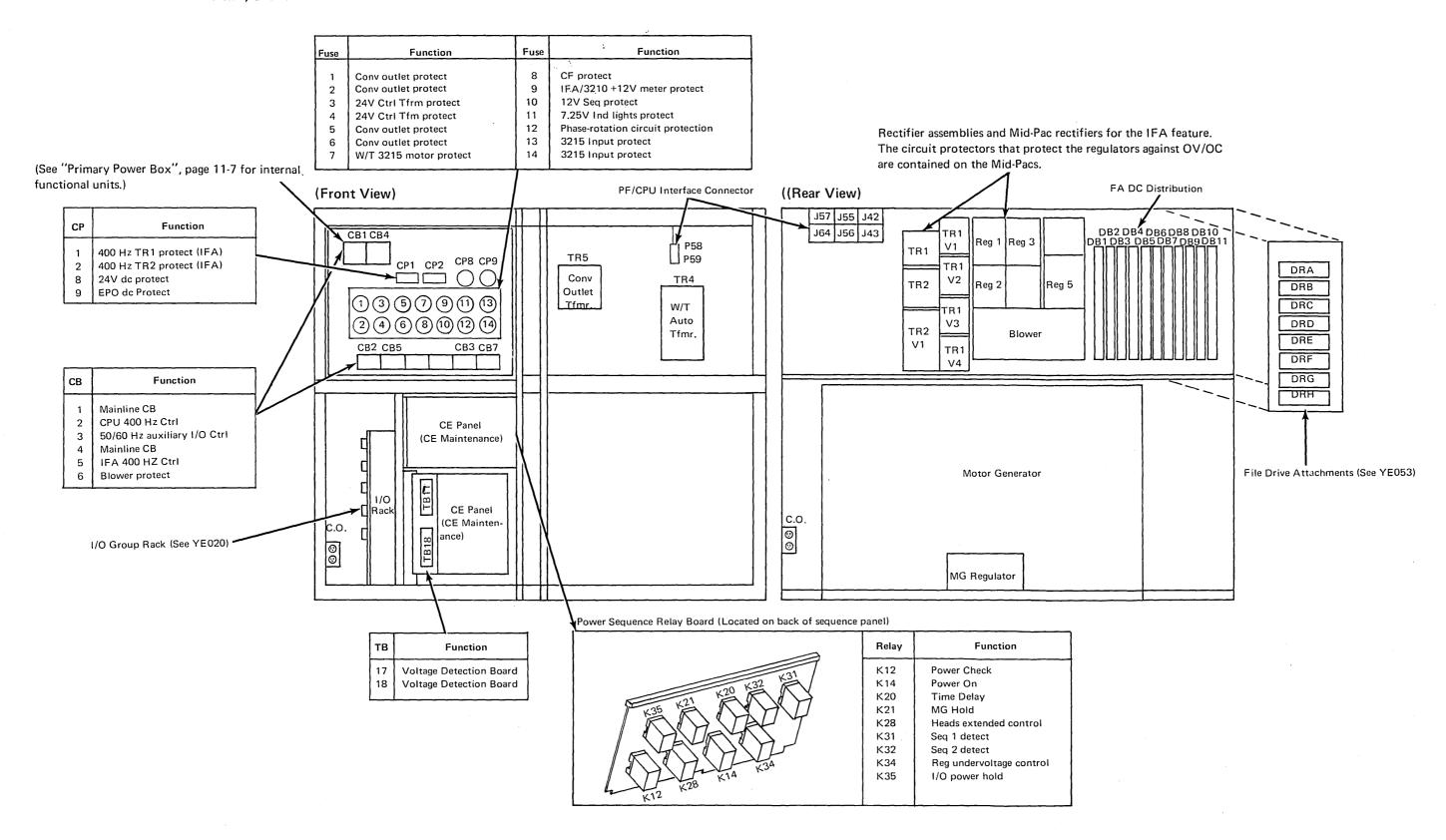

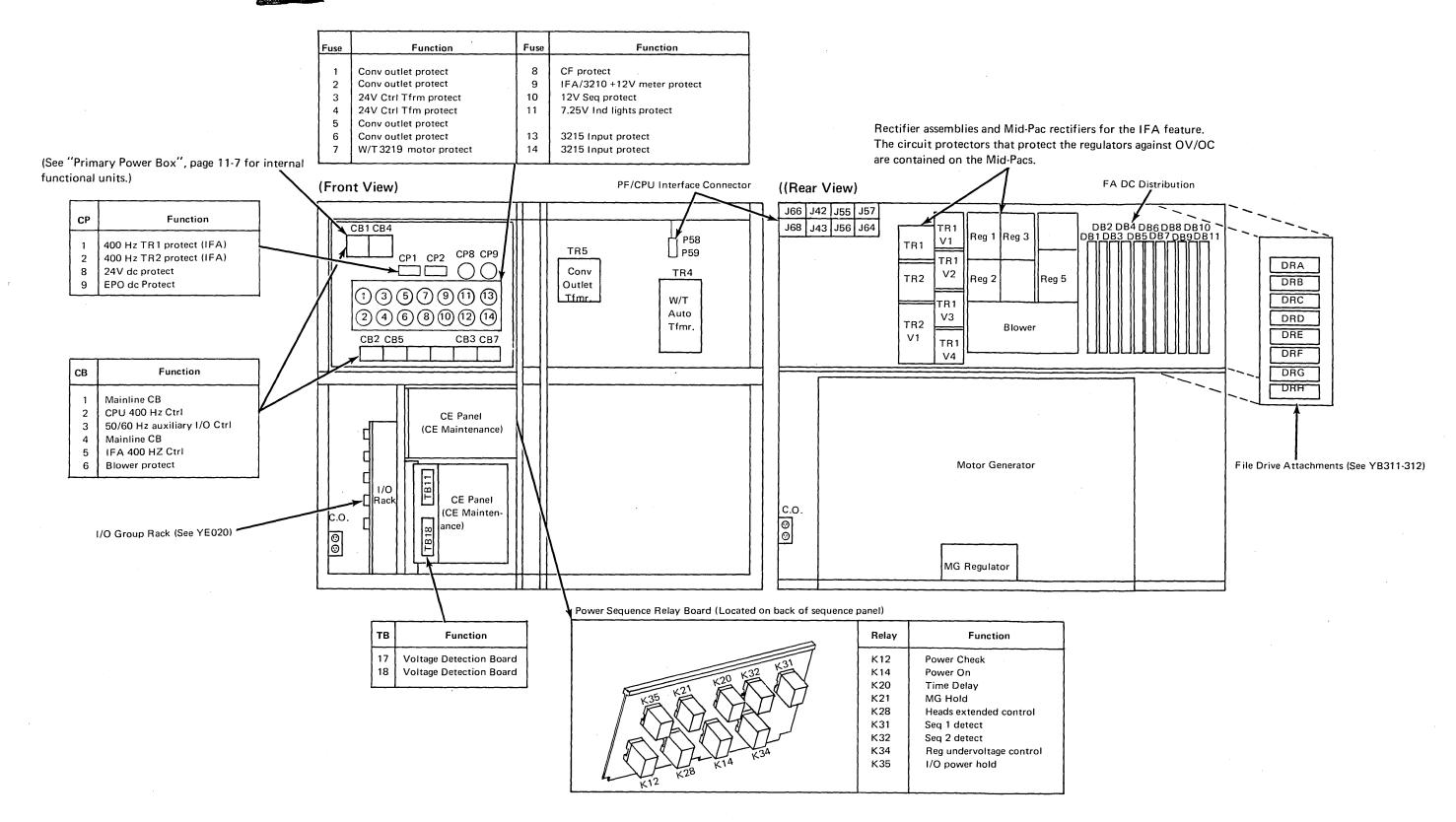

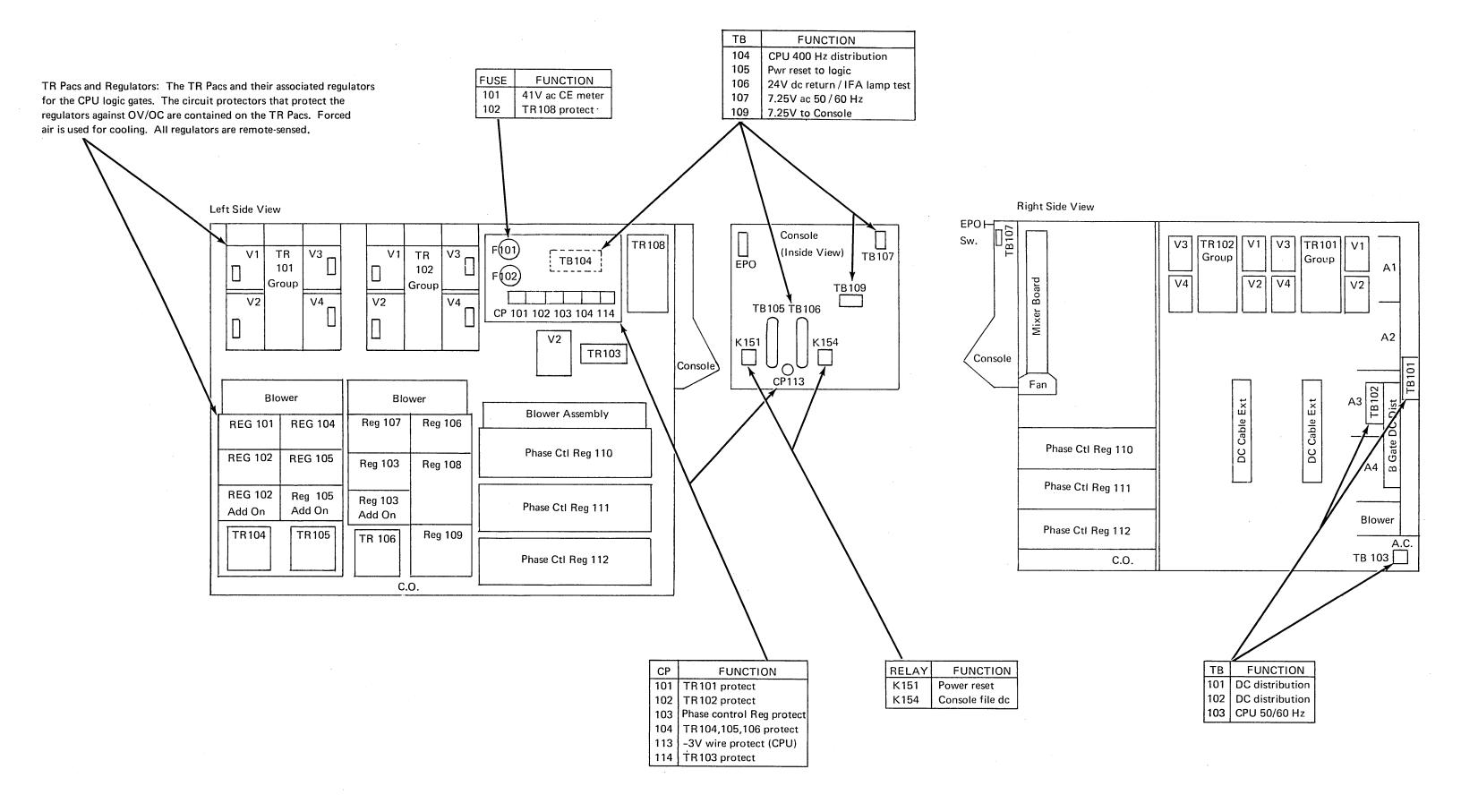

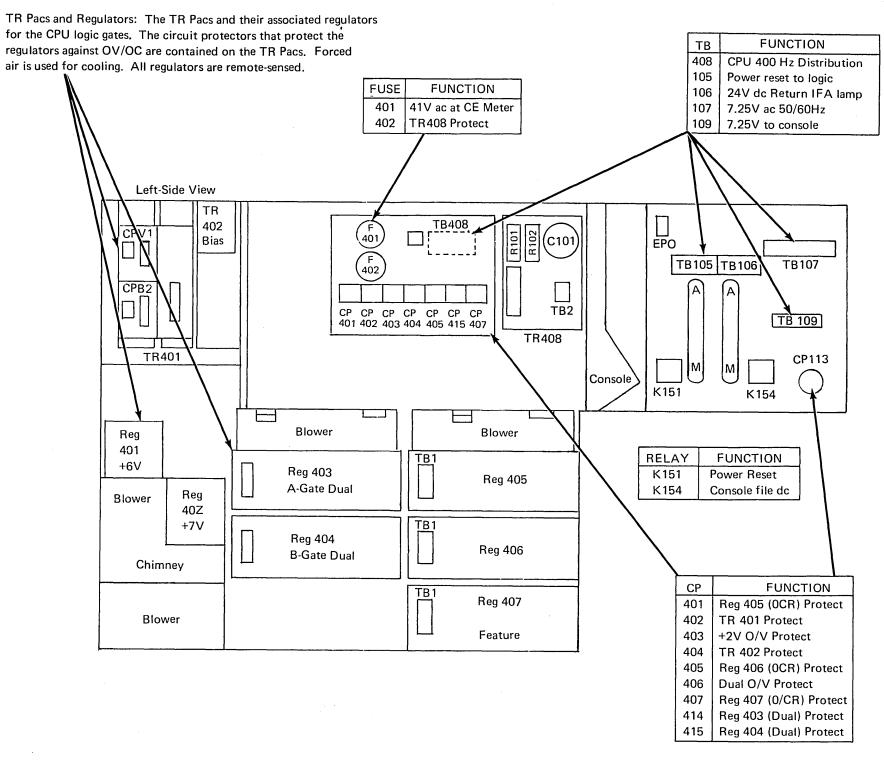

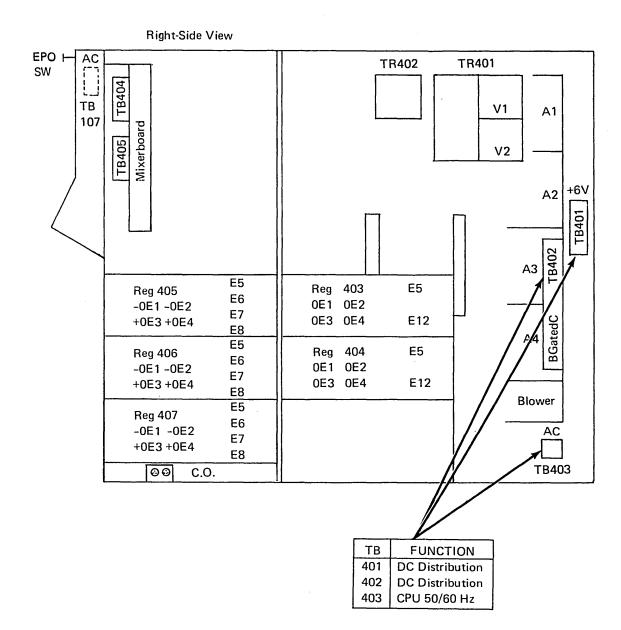

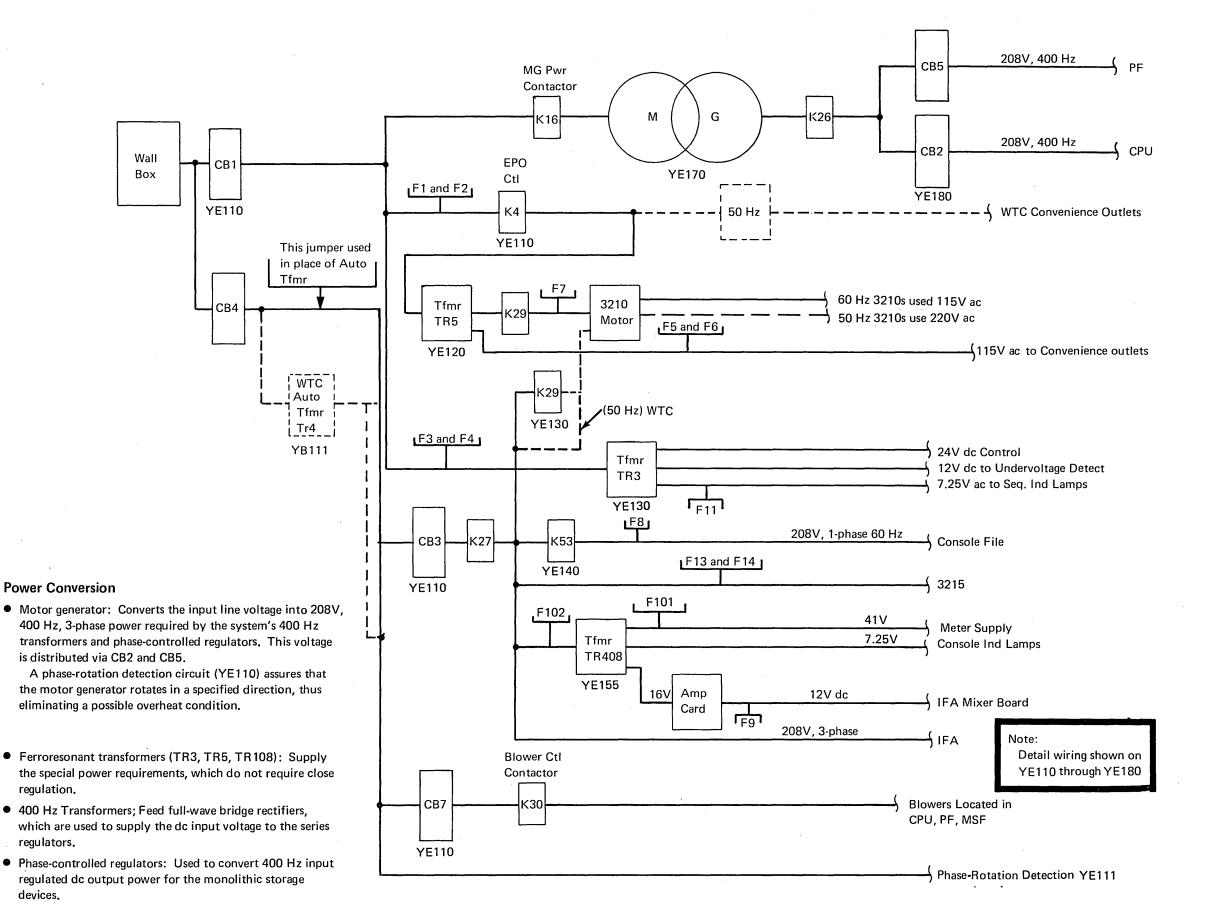

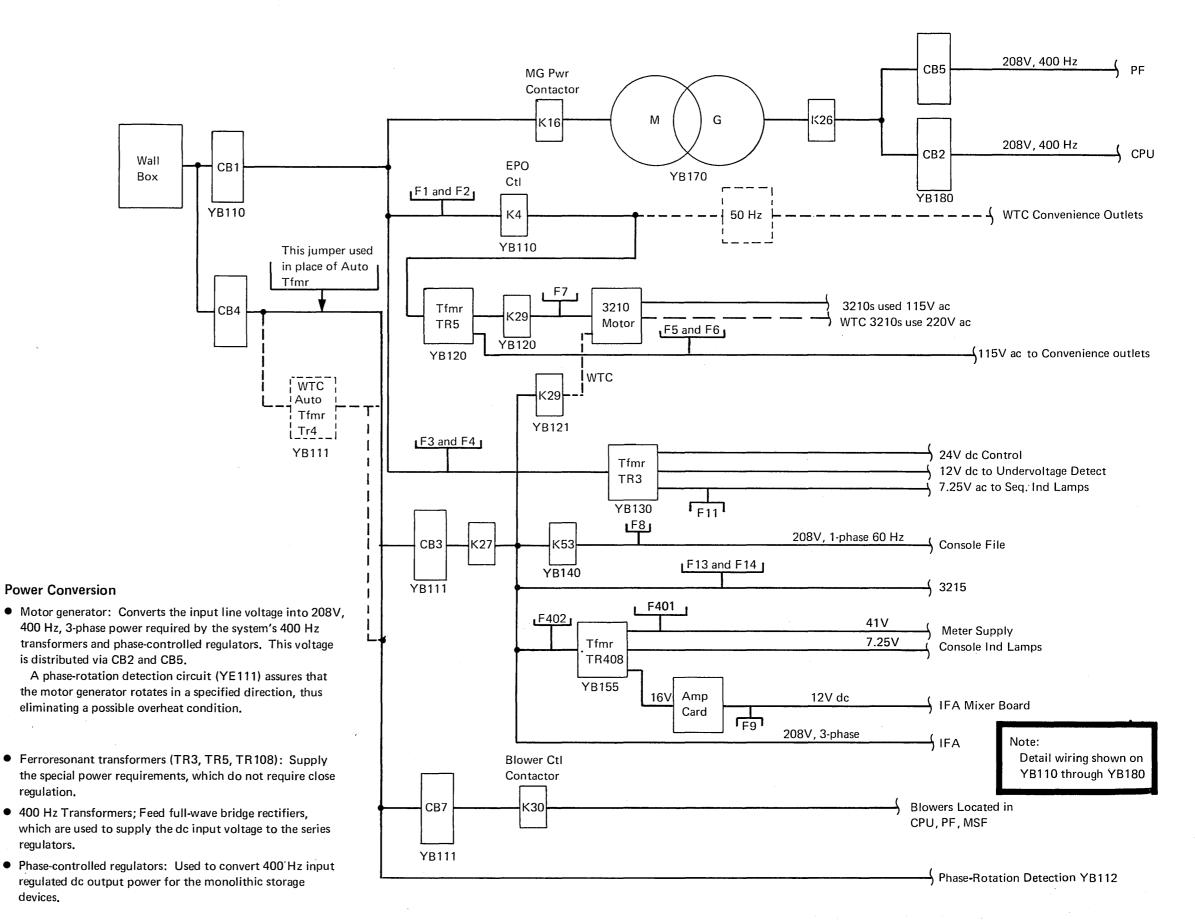

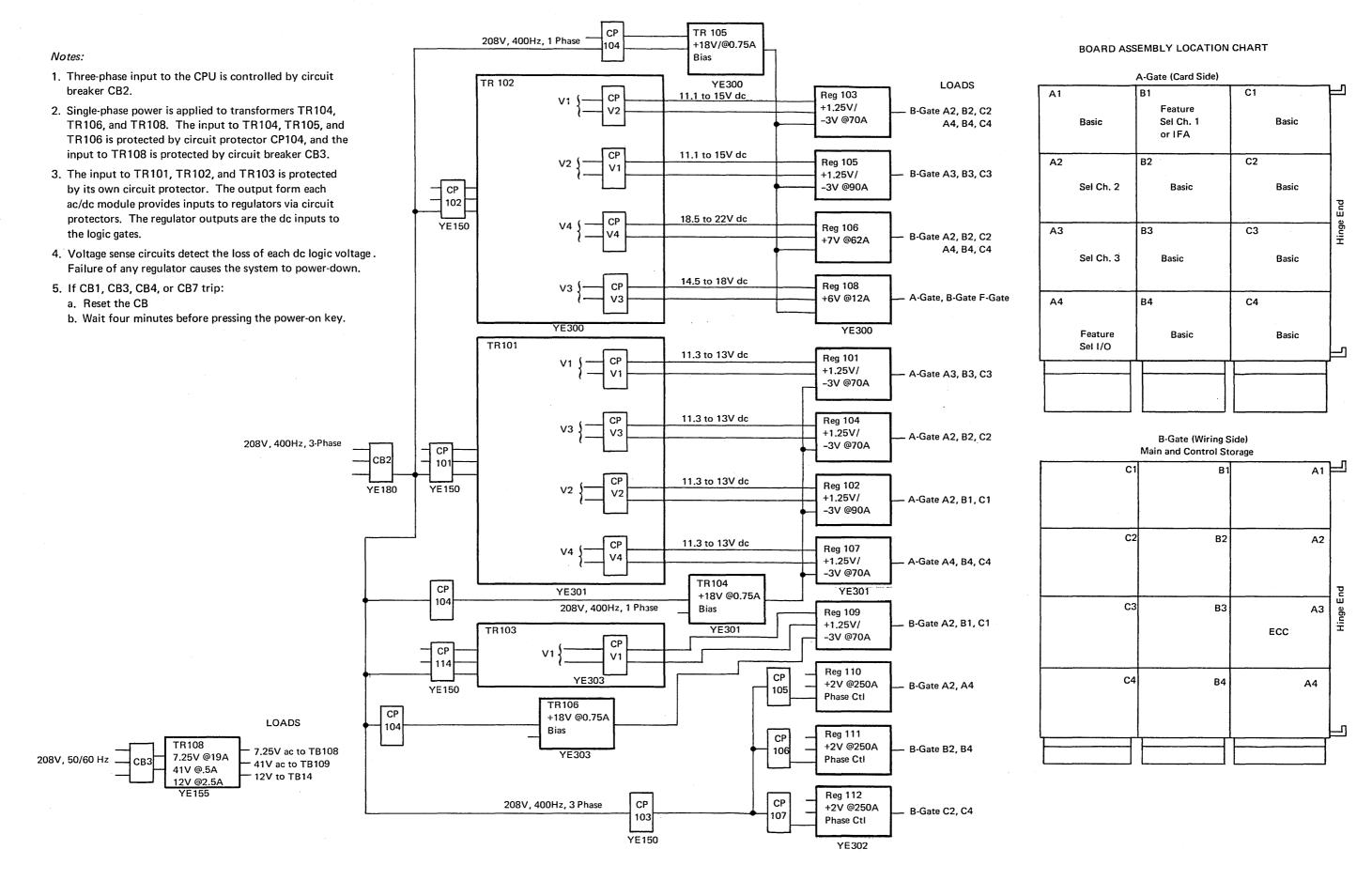

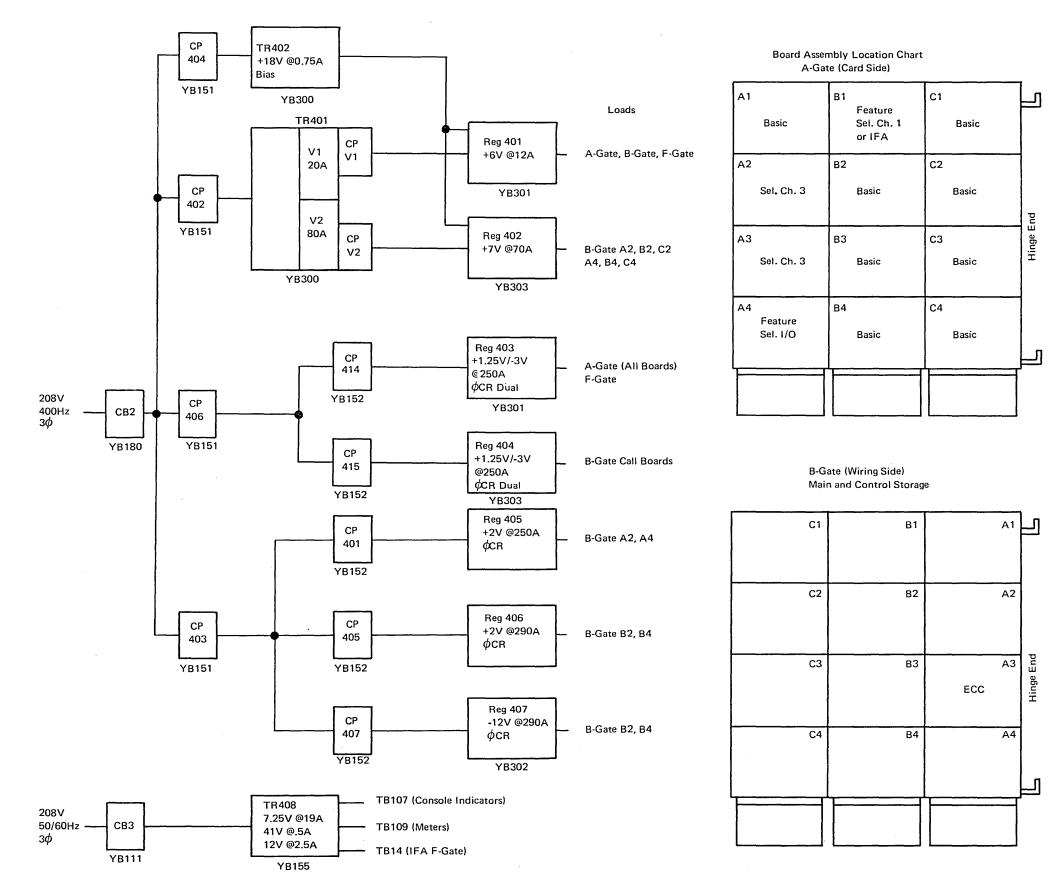

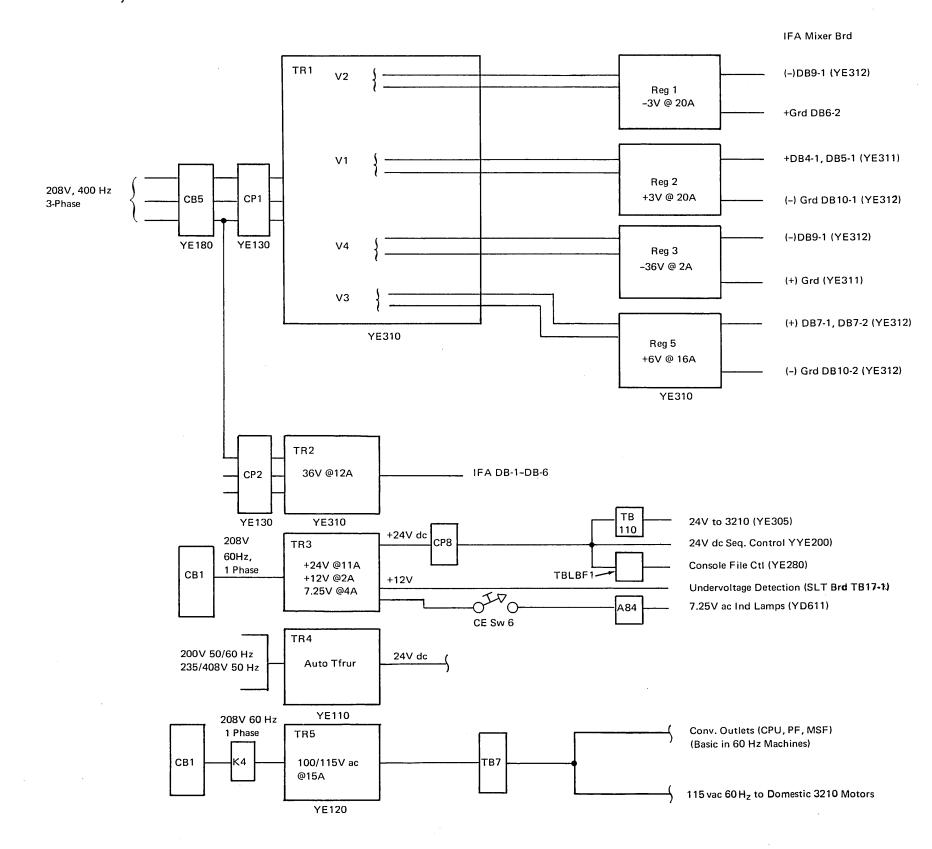

| AC power distribution 11-10                        | type 10 or 11 (bit definition) 4-73                   | bit definition 4-24,                          | C                                    |

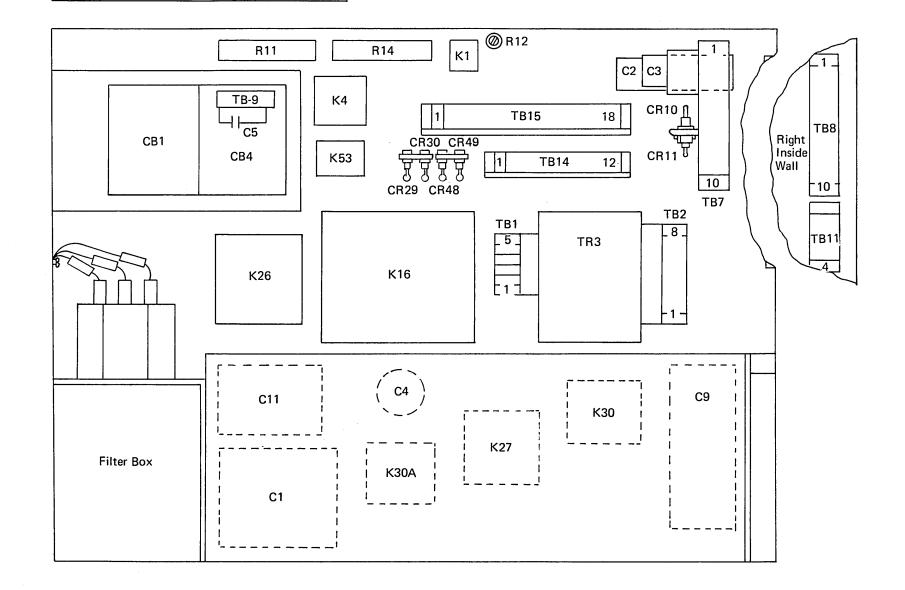

| AC to DC conversion and distribution 11-12 - 11-15 | arithmetic word 4-68                                  |                                               | C-register 1-11, 2-102               |

|                                                    | arithmetic word example                               | example 4-26                                  |                                      |

| ACB control ckts 2-37                              | byte operation 4-76, 4-77                             | operation 4-22                                | C-register force, IFA 10-30          |

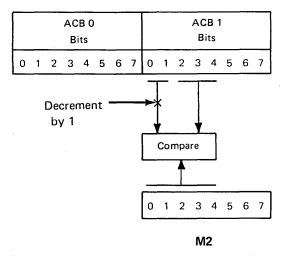

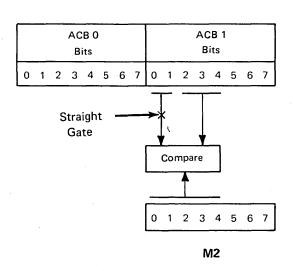

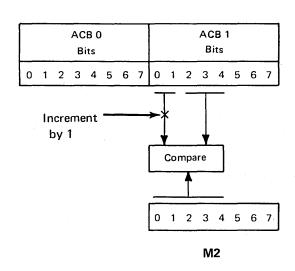

| ACB examples 2-36                                  | fullword operation 4-80, 4-81                         | branch symbols, control word 4-89             | CCW entry and decode, IFA 10-45      |

| ACB-register 2-35                                  | indirect-byte operation 4-78, 4-79                    | branching ckts (microprogram) 2-108           | CD (time of day clock damage) 12-18  |

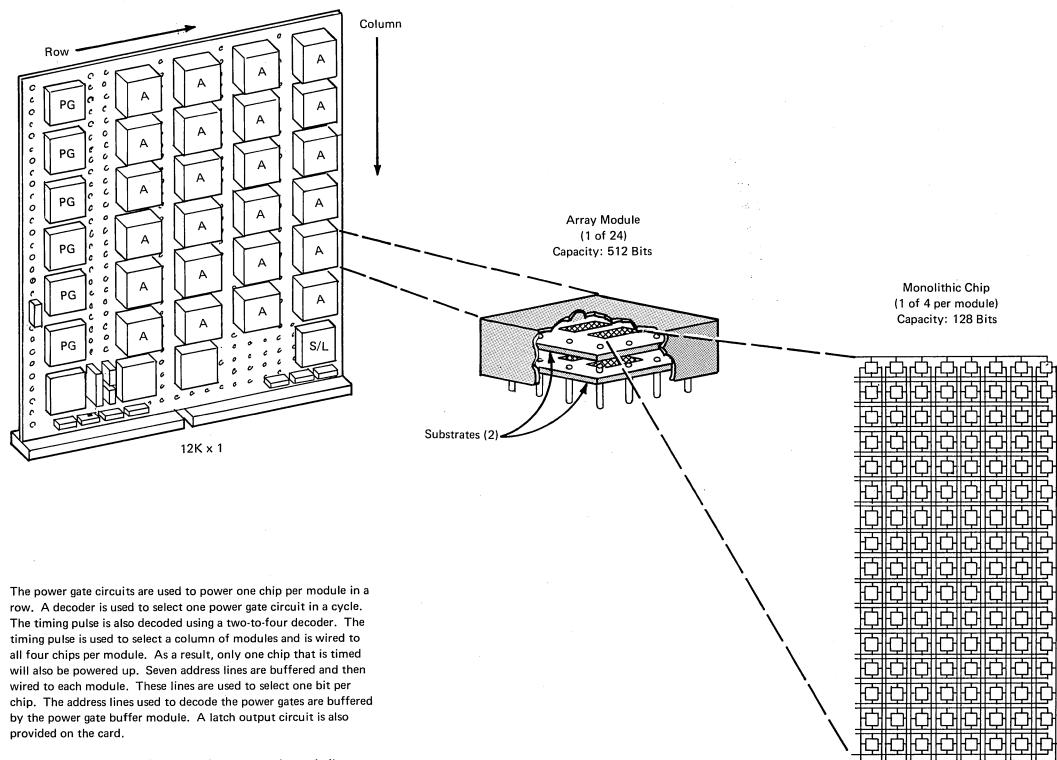

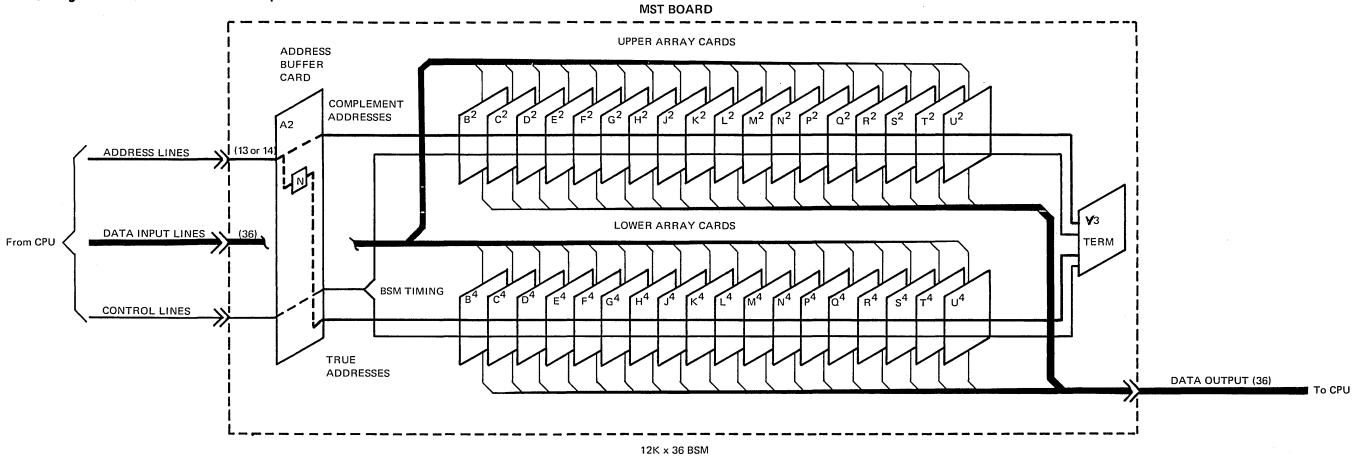

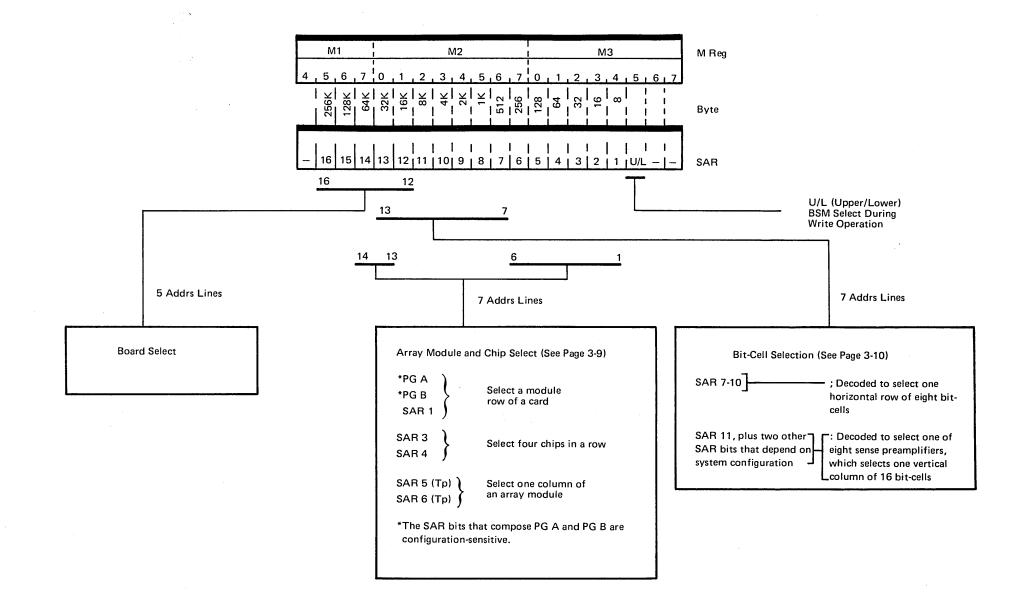

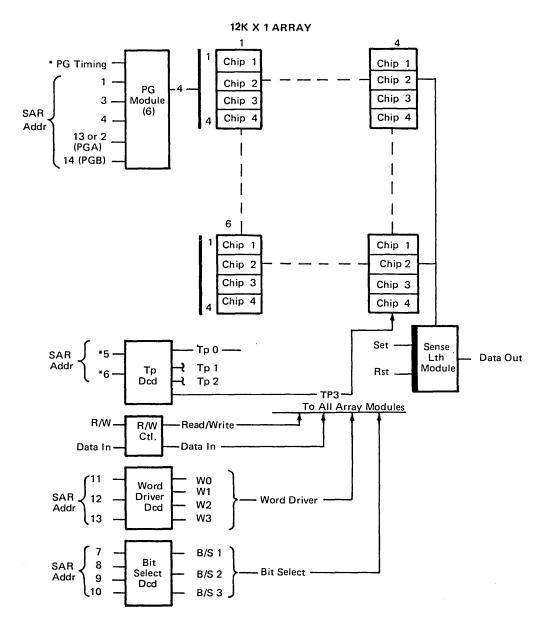

| ACB settings 2-35                                  | shift operation 4-82, 4-83                            | BSM board layout 3-7                          | CE error light, IFA 10-86            |

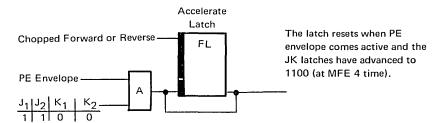

| accelerate latch 7-45                              | assembler instructions 4-10, 4-11                     | BSM configurations 3-4                        | CE mode light, IFA 10-86             |

| ac/dc module, removal and replacement 11-38        | attachment                                            | BSM sizes 3-5                                 | CE panel, IFA/2319 10-86             |

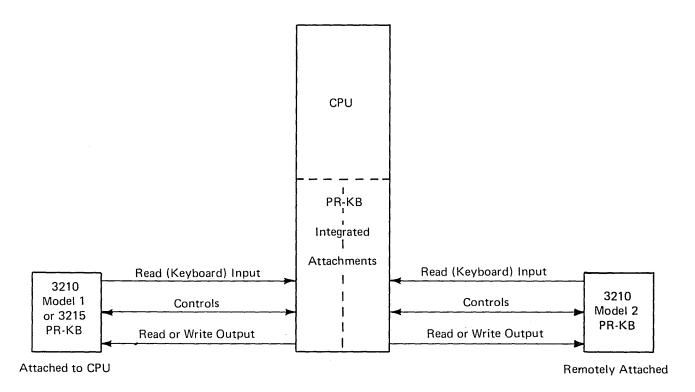

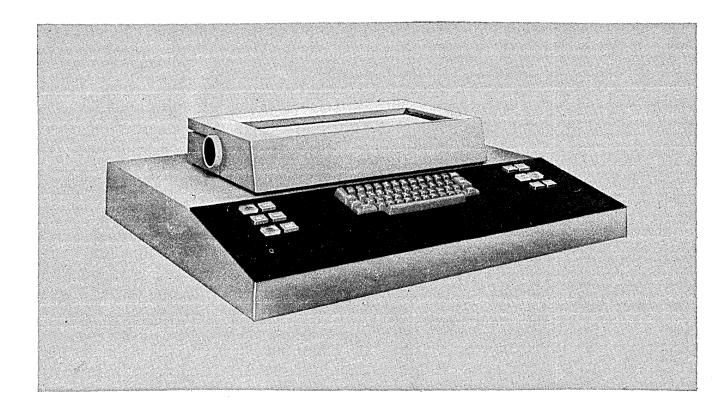

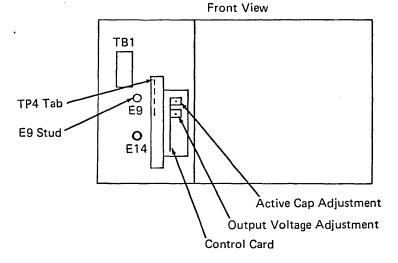

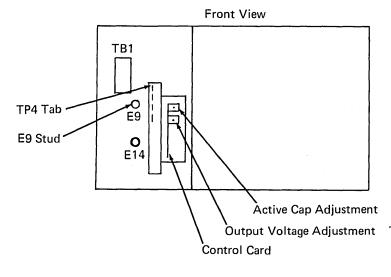

| active-cap adjustment 11-35                        | 3210 PR-KB 7-14                                       | buffer register (MB) 2-107                    | CE power panel 11-16, 11-18          |

| addr X-late mode, indicator 5-6                    | 3215 PR-KB 7-33                                       | bus-out check 7-62                            | CF pwr on, indicator 5-6             |

| address adjust (see OS DOS comaptibility)          | attention (status bit 0) 7-61                         | busy (status bit 3) 7-61                      | CFDAR register 2-34                  |

| address adjust, introduction 1-13                  |                                                       | BYTDST 12-10                                  | chaining check 7-61                  |

| address adjust (see OS DOS compatibility)          |                                                       | byte assembler, A 2-93                        | channel                              |

| address 1 check boundary (ACB) 2-35                |                                                       | byte assembler, B 2-94                        | address word (CAW) 8-4               |

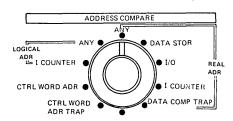

| address 2 compare control switch 5-26              | В                                                     | byte cntr, indicator 5-7                      | available interruption 8-83          |

| address compare switch, logic diagram 5-18         |                                                       | byte count logic, IFA 10-22                   | burst mode, defined 8-3              |

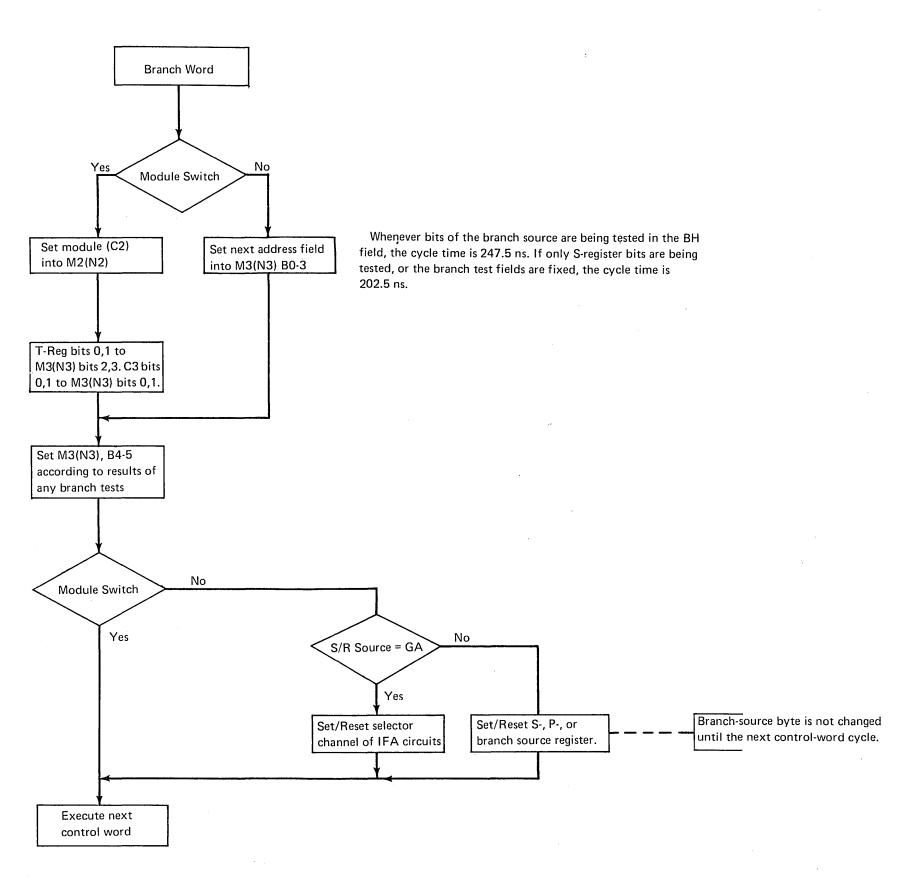

| address formation, next control word 4-16          | B (backup) 12-18                                      | byte counter, IFA 10-22                       | burst mode, operation 8-9            |

| address mark                                       | B-byte assembler 2-94                                 | byte mark register, storage 3-30              | bus-in 8-5                           |

| AM bytes 10-17                                     | B-local storage, data flow 2-14                       | byte-multiplexer channel                      | bus-out 8-5                          |

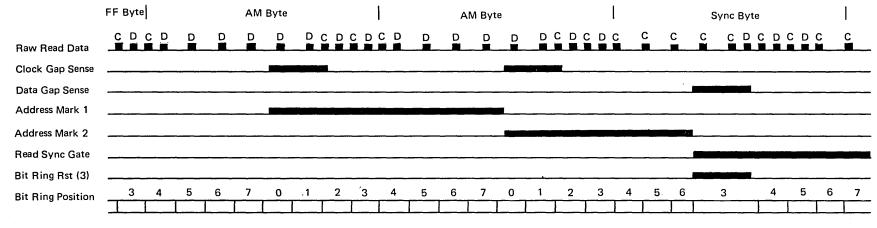

| detect logic 10-17                                 | B-L/S source direct address 2-15                      | catalog numbers 8-35                          | byte-mode operation 8-9              |

| detect timing 10-17                                | backup and retry registers 1-12                       | channel-control check 8-32                    | byte-multiplexer data flow 8-10      |

| detection 10-16                                    | backup registers 12-10                                |                                               | check handler 12-23, 12-24           |

| restart 10-17                                      | backward seek test, IFA 10-94                         | command chaining 8-41                         | command word (CCW), defined 8-4      |

| sync byte 10-17                                    | basic ctrl cmd execution, IFA 10-40                   | CSW store 8-30                                | commands for PR-KB 7-60              |

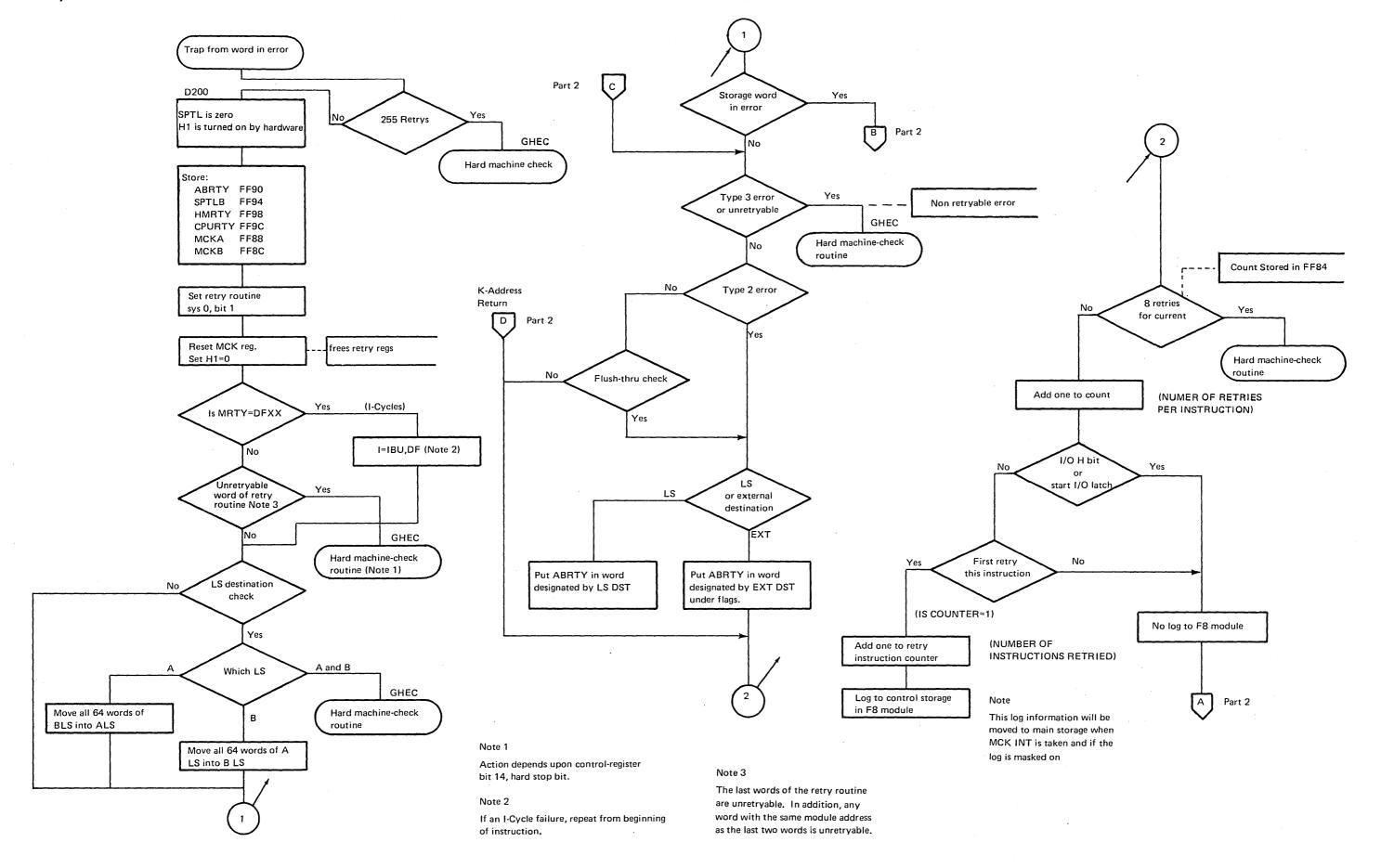

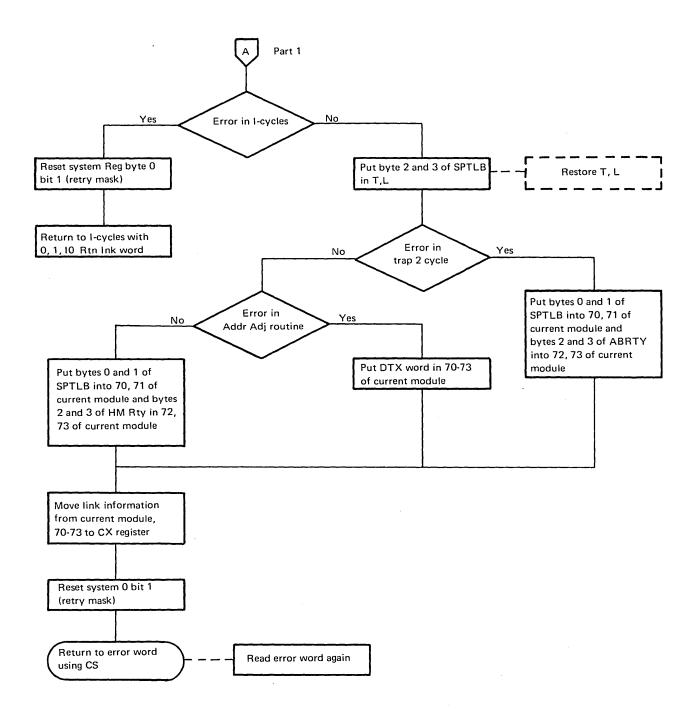

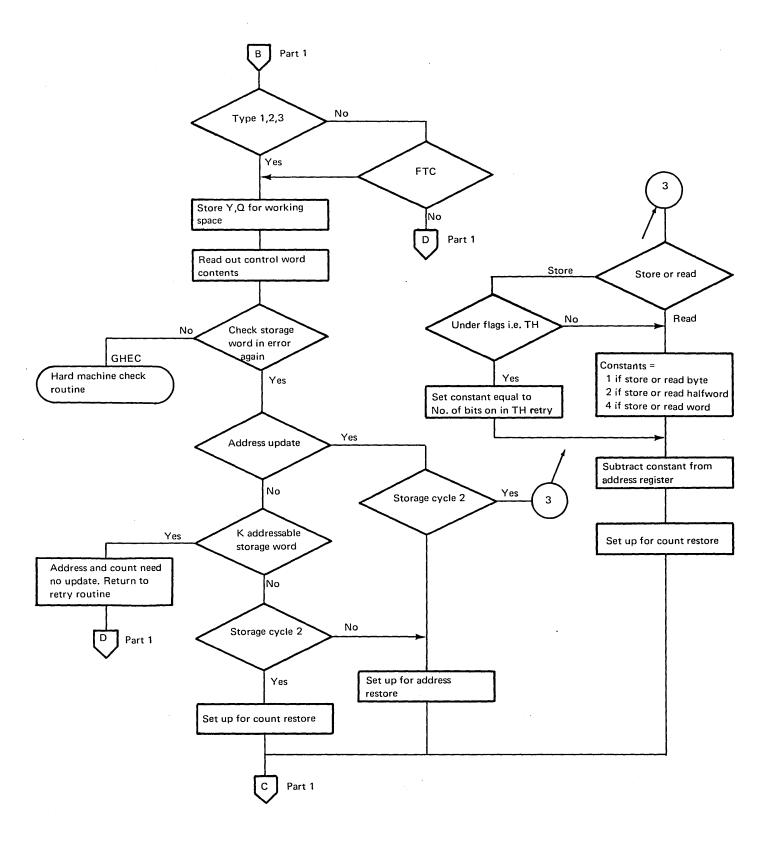

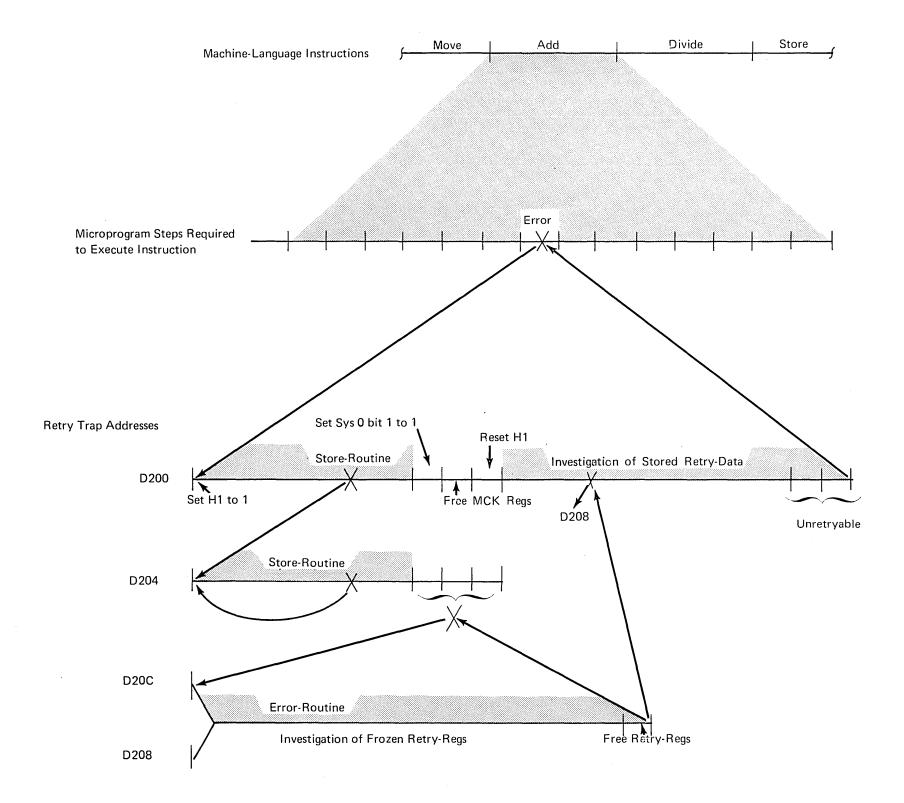

| addresses, trap (retry) 12-15                      | basic data cmd execution, IFA 10-41                   | data chaining 8-41                            | commands, IFA 10-8                   |

| addressing, local storage, scoping procedure 2-17  | basic IFA operations 10-35                            | ending procedure 8-27                         |                                      |

| adjustments                                        | BCA indicator byte, IFA 10-24                         | ending status and interruption handling 8-26  | configurations 8-2                   |

| data separator, IFA 10-15                          | bit assignments, IFA externals 10-11                  | error handling and logout 8-35                | control check 7-61                   |

| delay line, IFA 10-15                              | bit count appendage, IFA 10-24                        | error logout 8-36                             | control words 8-4                    |

| error detector, IFA 10-15                          | bit count, IFA BCA 10-24                              | external facilities 8-15                      | data check 7-61                      |

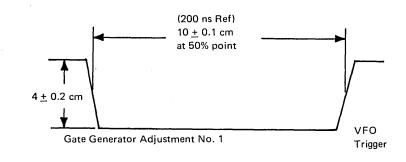

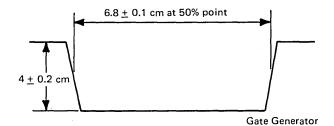

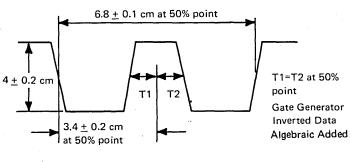

| gate generator, IFA 10-15                          | bit definition charts, control words 4-85, 4-86, 4-87 | functional units 8-14                         | data rates 1-16                      |

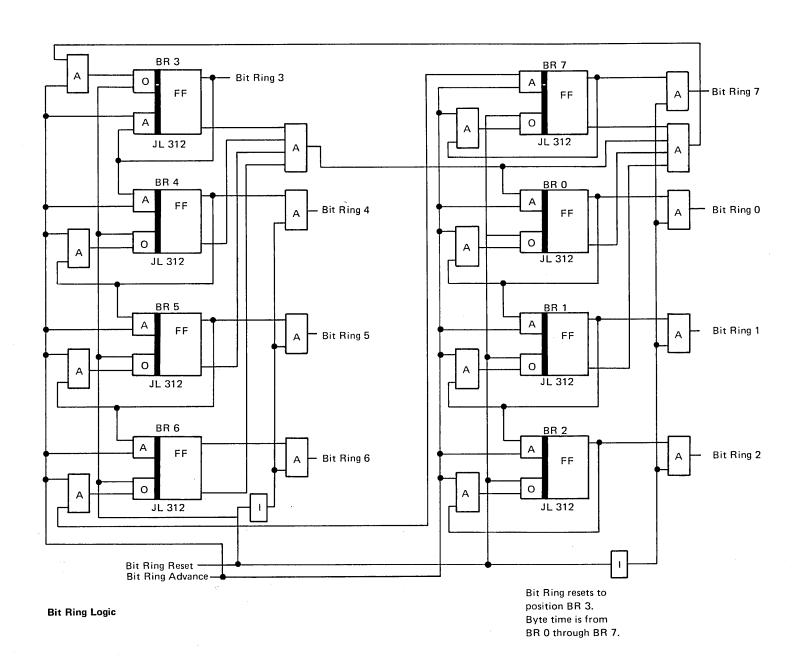

|                                                    | bit ring, IFA 10-19                                   | initial selection routine 8-22                | dependent logout 12-20               |

| IFA power supplies 10-97                           | bit ring logic, IFA 10-19                             | interface control check 8-22                  | end (status bit 4) 7-6               |

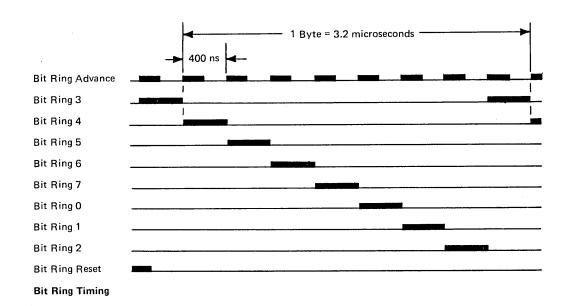

| ramp generator 10-15                               | bit ring timing, IFA 10-19                            | interruptions                                 | general description                  |

| singleshot, IFA VFO 10-15                          | block-multiplexer channels                            | conditions 8-32                               | byte multiplexer 1-16                |

| zero detector, IFA 10-15                           | charts, objectives 8-91                               | normal primary ending status 8-28             | block multiplexer feature 1-17       |

| adr comp match, indicator 5-6                      | operations 8-83                                       | normal secondary ending status 8-29           | data rates 1-16                      |

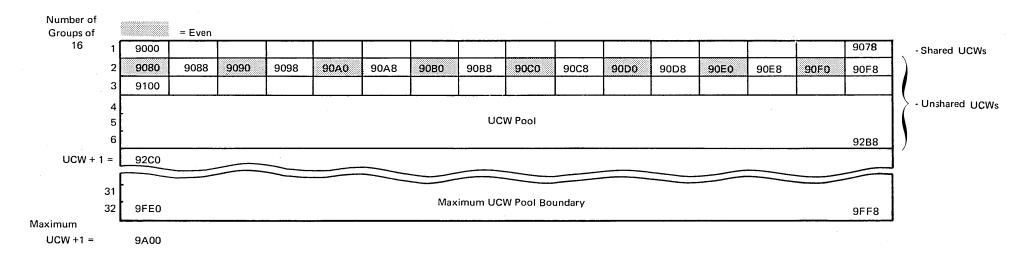

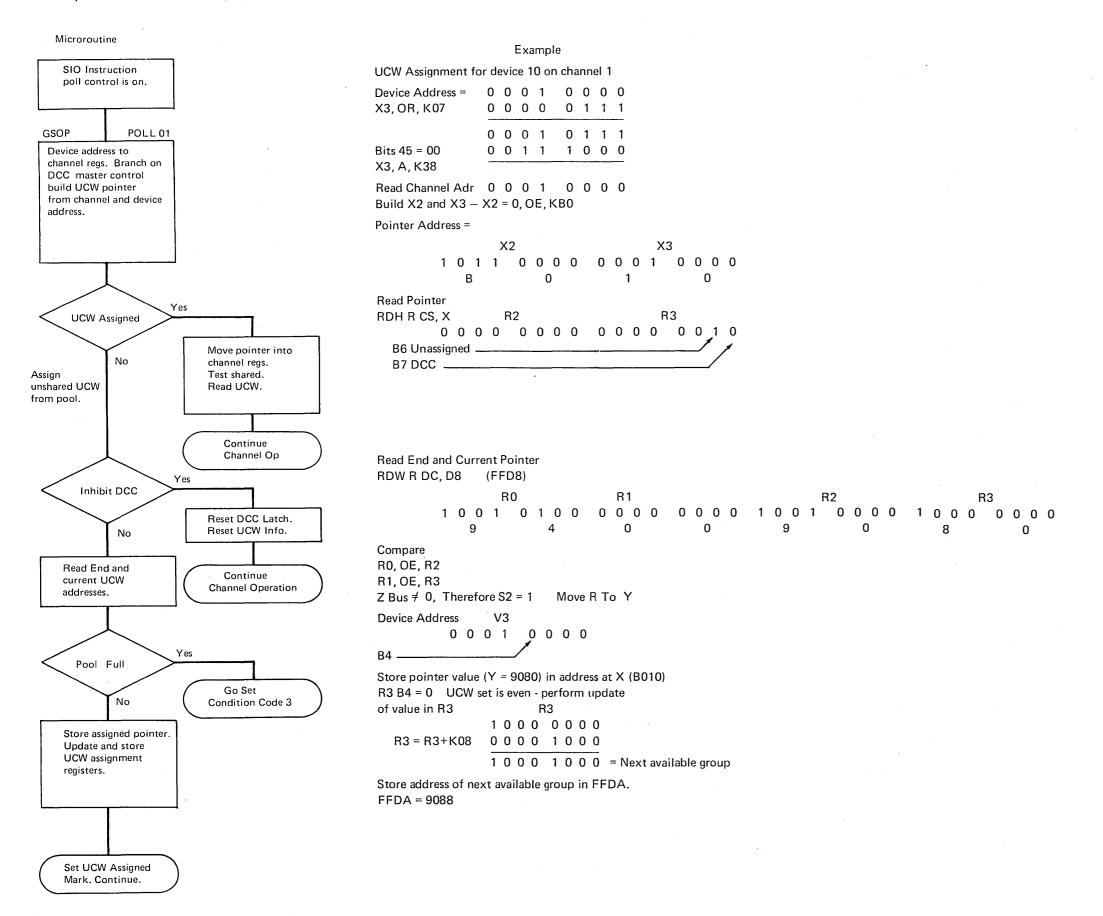

| adr X-late LRU inval, indicator 5-5                | semidynamic UCW address assignment 8-86               | program-controlled interruption (PCI) 8-31    | integrated file adapter 1-17         |

| adr X-late mult match, indicator 5-5               | shared UCW assignment 8-85                            | IPL (initial program load) 8-43               | selector 1-16                        |

| adr X-late no match, indicator 5-5                 | store/load UCW traps 8-89                             | local storage 8-18                            | ID 8-34                              |

| advance head trap 10-77                            | UCW address pointer tables 8-86                       | MBI (multiplexer bus-in) 8-15                 | ID, IFA 10-4                         |

| advanced checkpoint/restart 12-26                  | UCW assignment 8-85                                   | MBO (multiplexer bus-out) 8-15                | identification 12-19                 |

| A-H, rotary switch functions 5-25                  | UCW assignment registers 8-86                         | MTI (multiplexer tags-in) 8-15                | initial selection sequence 8-8       |

| alarm (audible) 7-61                               |                                                       | MTO (multiplexer tags-out) 8-15               |                                      |

| allow CE mode switch, IFA 10-86                    | UCW pool 8-87                                         | operations 8-19                               | instructions 8-3                     |

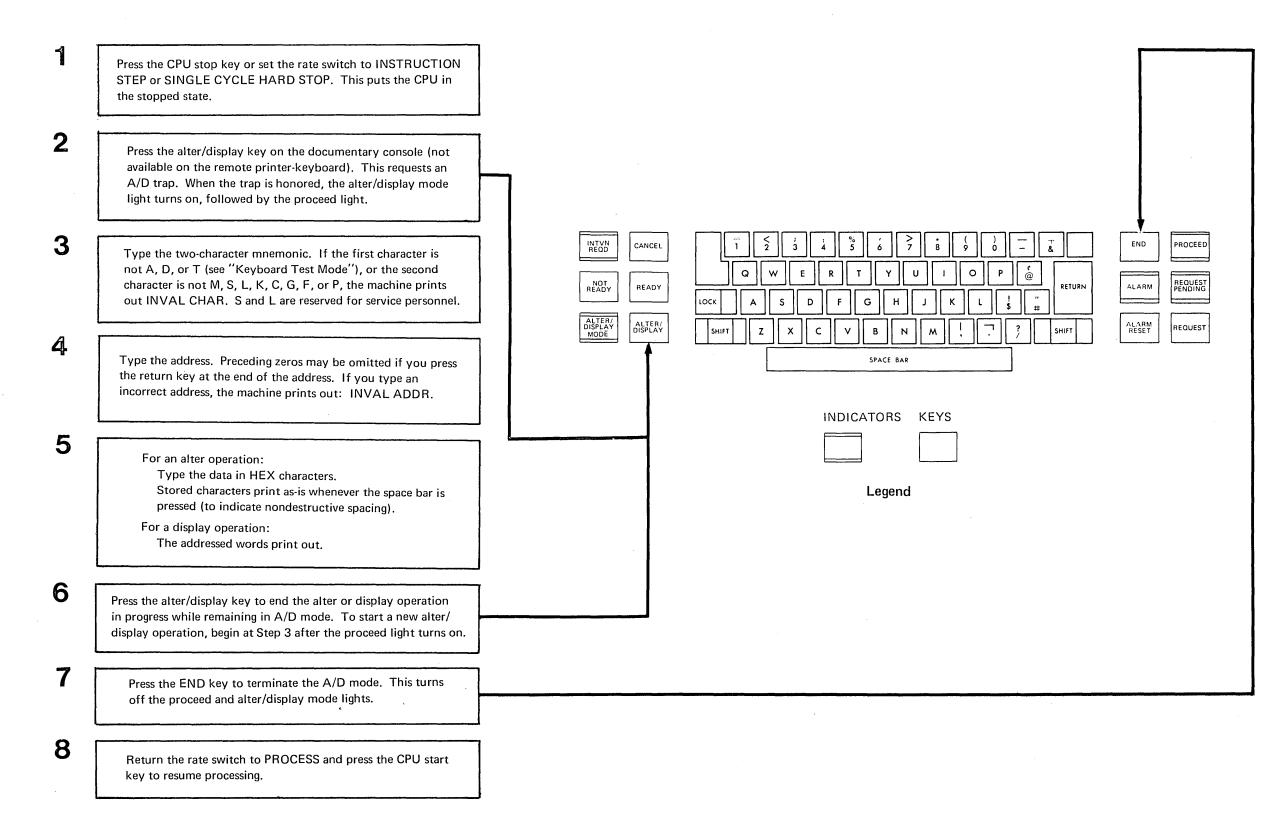

| alter/display operations 7-54                      | block multiplexer selector channel 1-17               | second level diagram 8-16                     | interruption, available 8-83         |

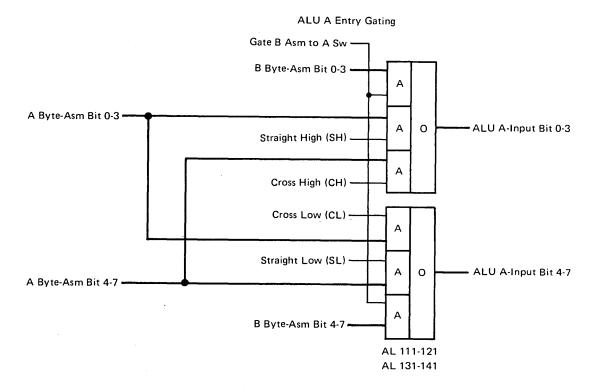

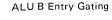

| ALU gating (A/B) 2-95                              | bit definition 4-32                                   | share trap-data handling 8-24                 | introduction 8-2                     |

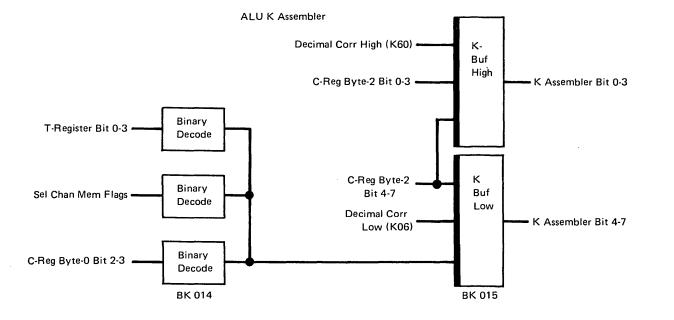

| ALU K assembler 2-96                               | operation 4-30, 4-31                                  | Share trap data handling 0-27                 | logout 8-34                          |

| channel (continued)                             | clock (continued)                             | console file (continued)                                         | control word (continued)                     |

|-------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------|----------------------------------------------|

| mark 0 in 8-5                                   | time of day (see to TOD clock)                | CPU clock start 6-13                                             | branch and link or return word 4-32          |

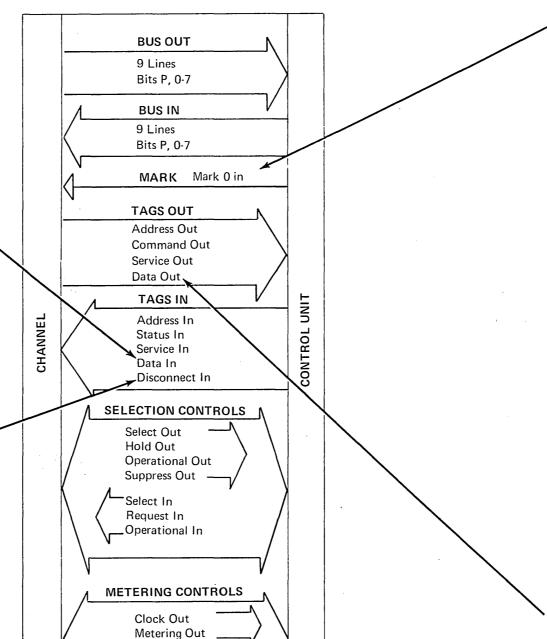

| metering controls 8-7                           | CM (configuration report mask) 12-17          | data and clock bit timing 6-3                                    | branch and module switch 4-19                |

| multiplexer mode 8-3                            | cmnd reg. indicator 5-7                       | data byte 6-3                                                    | branch word 4-24, 4-25                       |

|                                                 | entr match, indicator 5-7                     | data checks 6-12                                                 | storage word (K addressable) 4-50            |

| retry 1-14, 12-9                                | codes                                         | data flow 6-4                                                    | storage word (non K addressable) 4-48, 4-49  |

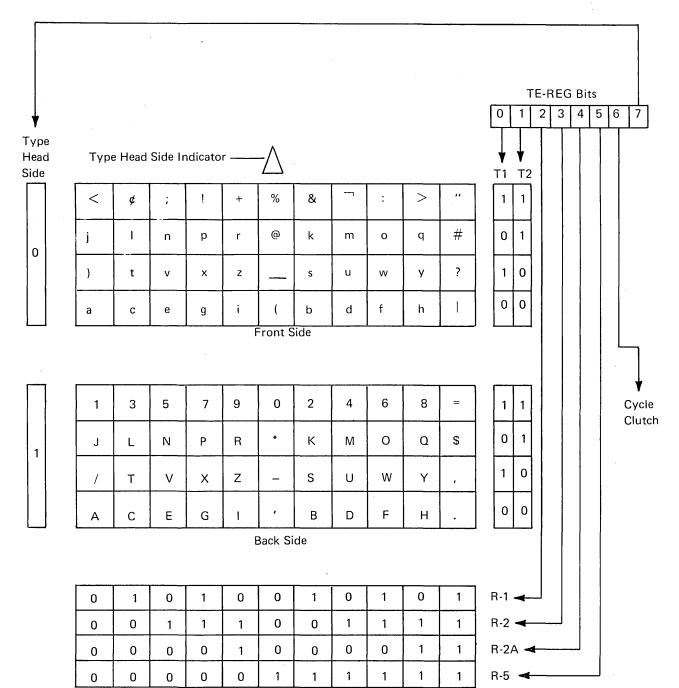

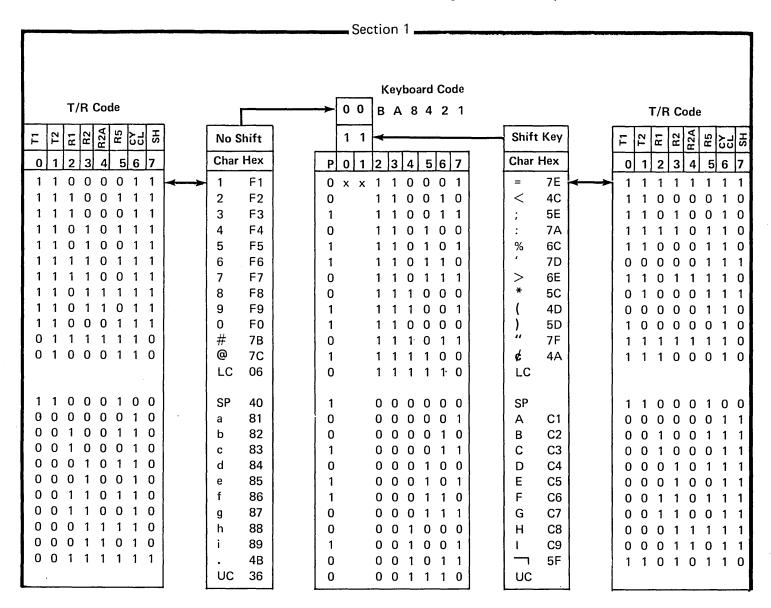

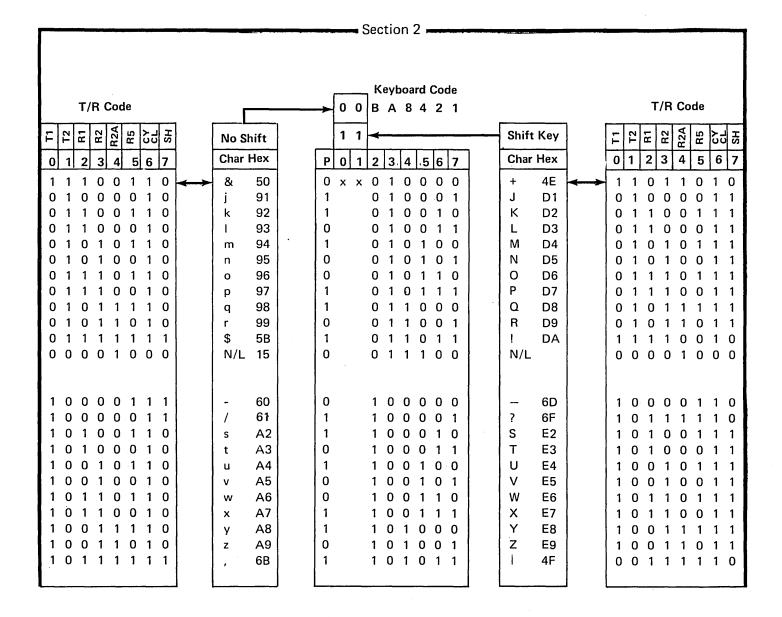

| selection controls 8-6                          | printer tile/rotate 7-8                       | disk-address register 6-13                                       | word-move word 4-40                          |

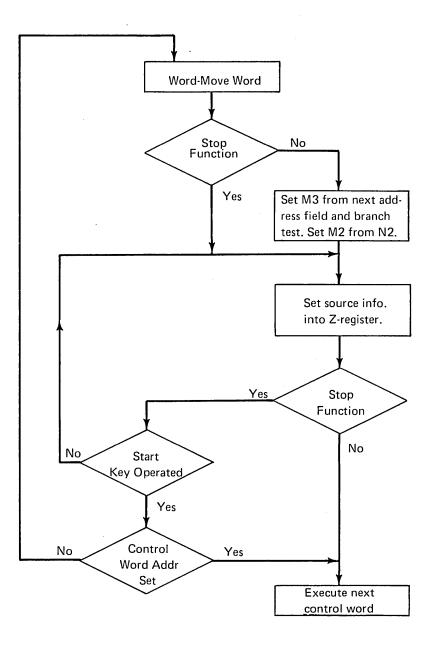

| sequence codes 8-34, 8-69                       | T/R and keyboard, table 7-9                   | disk format 6-3                                                  | branch 4-22, 4-23                            |

| short CSW 8-22                                  |                                               | error checks 6-12                                                | branch and link or return word 4-30, 4-31    |

| status byte for PR-KB 7-61                      | translation, 3210 PR-KB 7-10                  | even-odd check 6-12                                              | branch and module switch 4-18                |

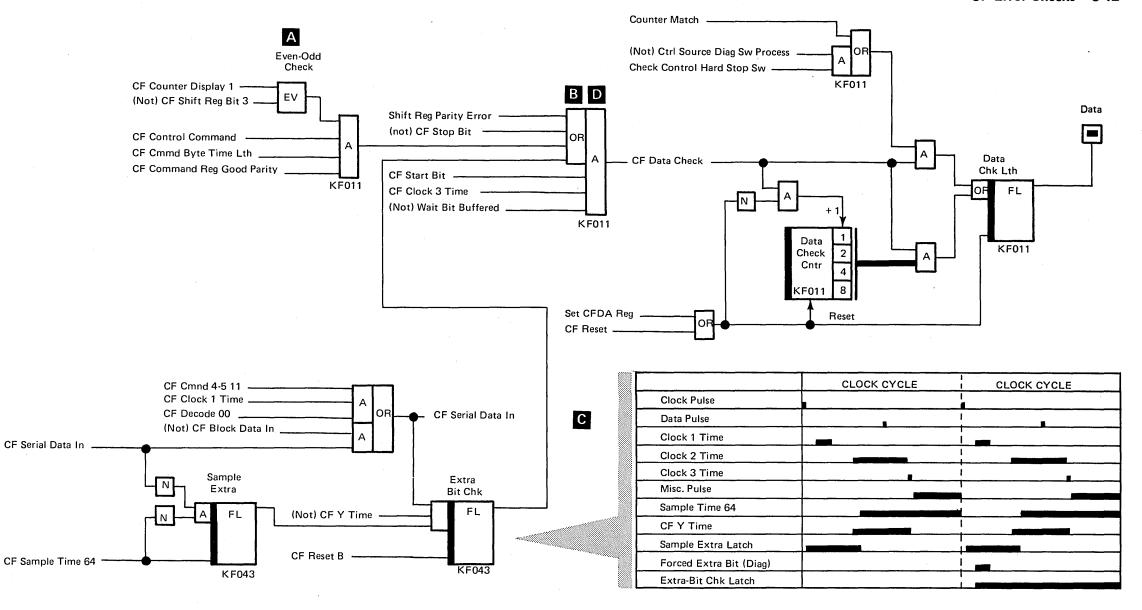

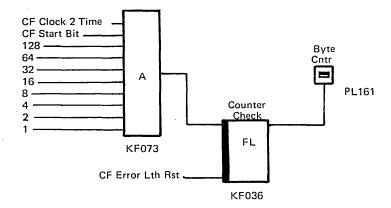

| status bytes, IFA 10-74                         | 3210 keyboard 7-7                             | extra bit check 6-12                                             | branch symbols 4-12, 4-84                    |

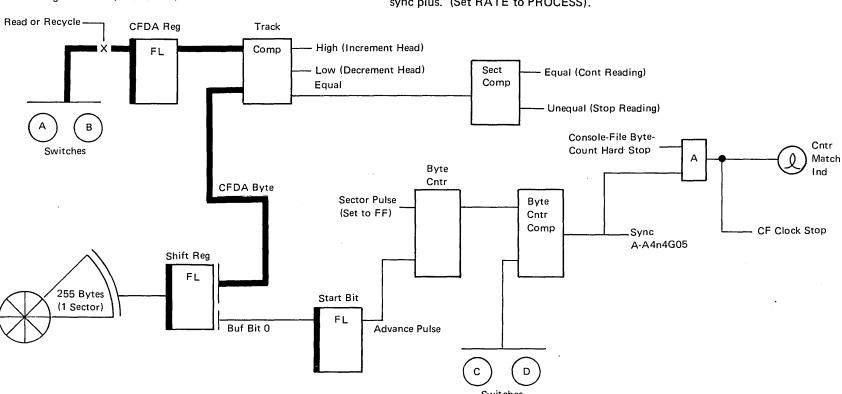

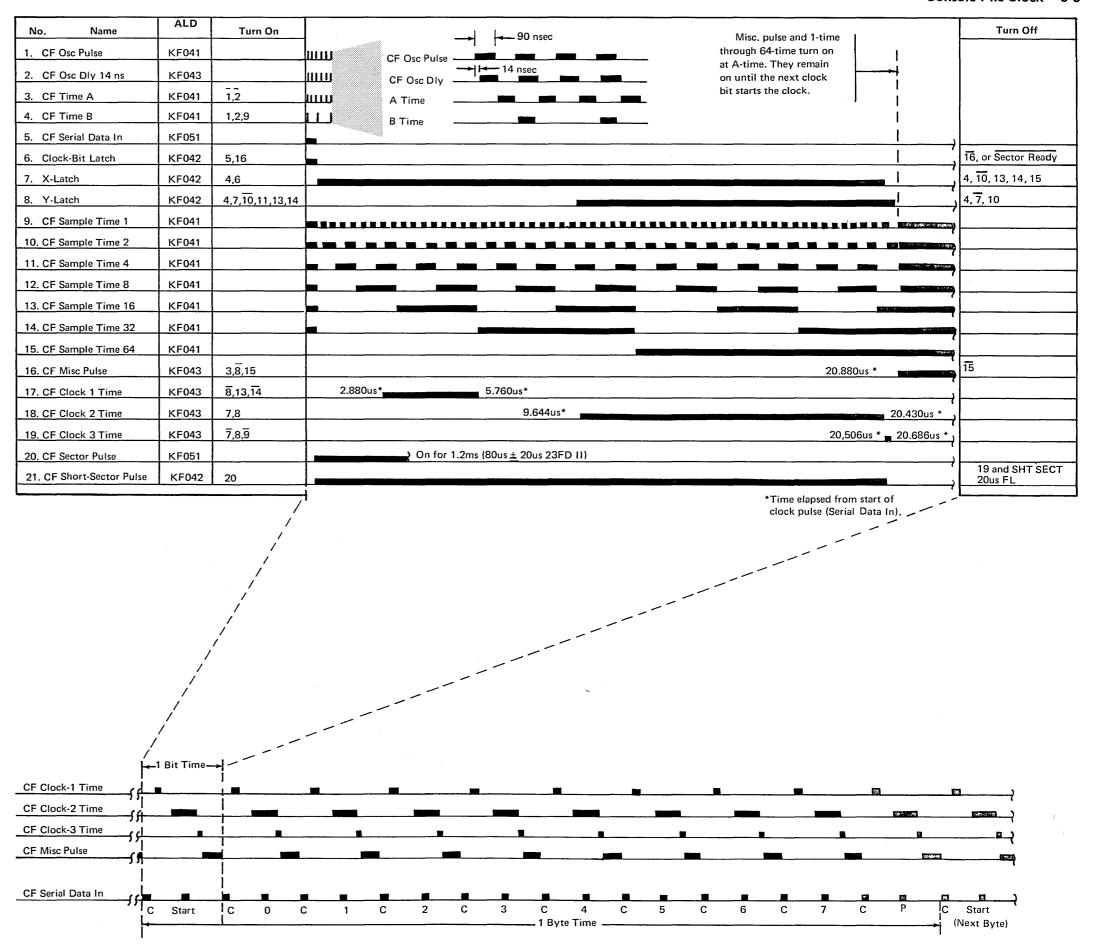

| status word (CSW), defined 8-4                  | 3210 transmission 7-9                         | head control and track accessing 6-5                             | examples                                     |

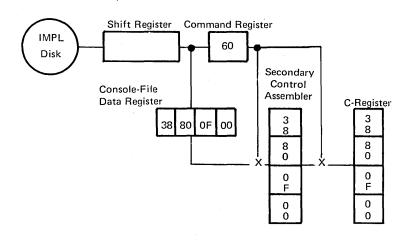

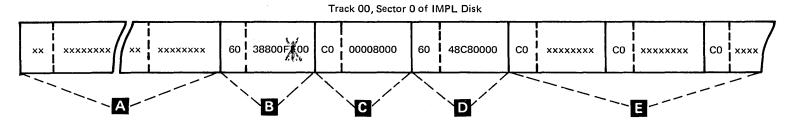

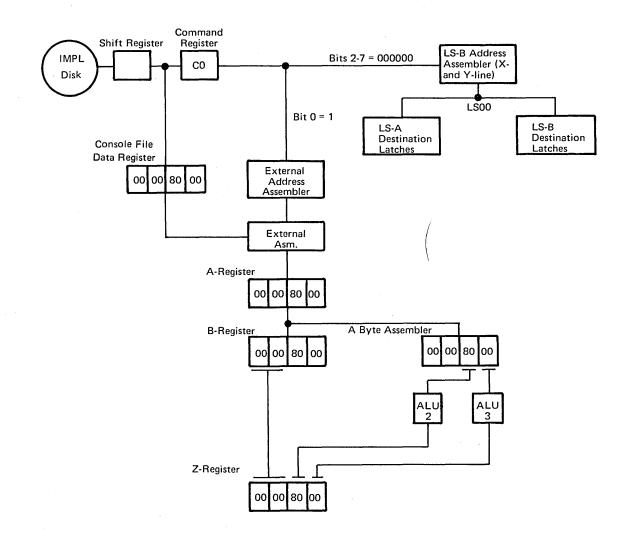

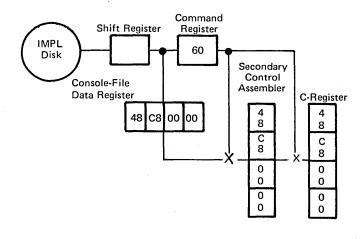

| tags-in 8-5                                     | colon                                         | IMPL example 6-15                                                | •                                            |

| tags-out 8-5                                    | printing the punctuation character, 3210 7-11 | <u>•</u>                                                         | arithmetic, byte operation 4-76, 4-77        |

| channel-to-channel adapter feature              | printing the punctuation character, 3215 7-31 | introduction 6-2                                                 | arithmetic fullword 4-80, 4-81               |

| address compare and data flow X 9-32            | command chart, console file 6-10              | operation commands 6-9                                           | arithmetic indirect byte 4-75                |

| control command 9-24                            | command execution                             | out of sync/missing bit check 6-12                               | arithmetic, indirect-byte operation 4-78     |

| data flow 9-24                                  | IFA control cmd 10-40                         | pause 6-13                                                       | arithmetic, shift operation 4-82, 4-83       |

| description 9-24                                | IFA data cmd 10-41                            | removal and replacement 6-17                                     | branch and link 4-34, 4-35                   |

| disability and compatibility 9-33               | command reject 7-62                           | sector format 6-3                                                | branch and module switch 4-20, 4-21          |

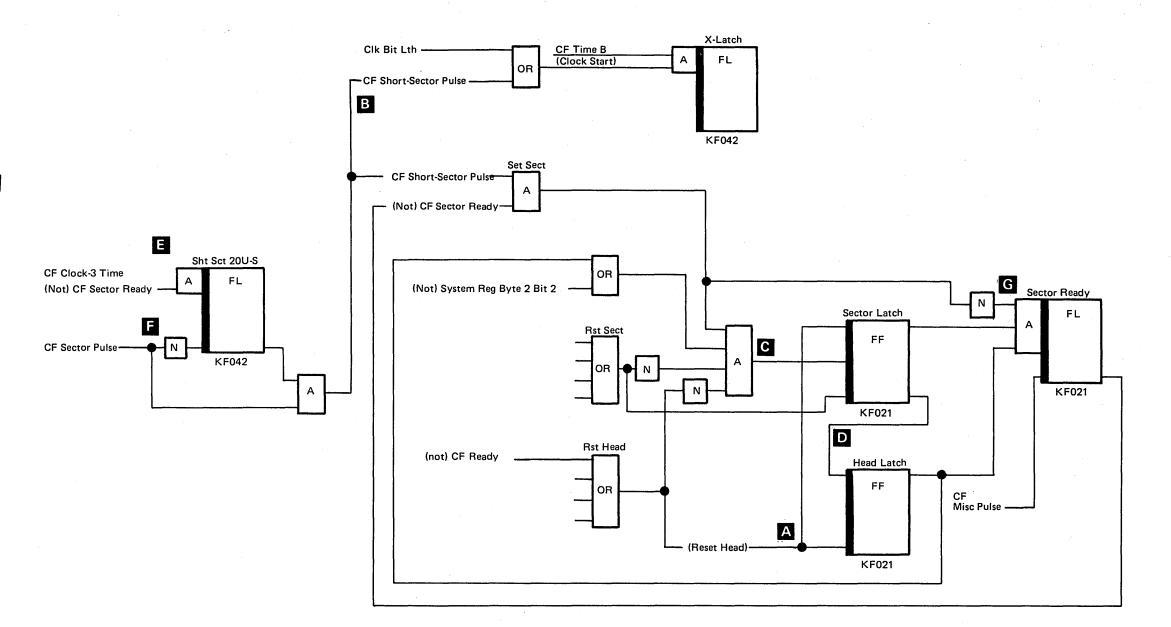

| functional units 9-32                           | command retry                                 | sector ready latch 6-8                                           | branch words 4-26, 4-27, 4-28, 4-29          |

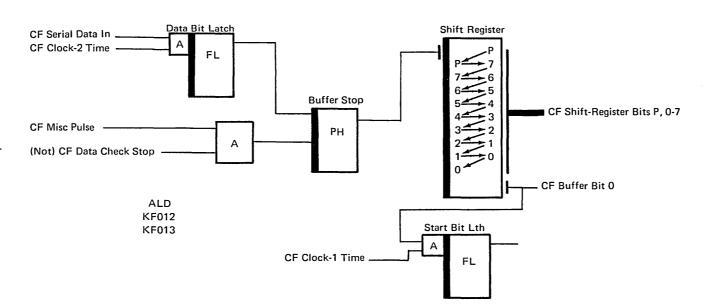

| halt I/O 9-28                                   | I/O interface sequence 8-72                   | shift register 6-5, 6-7                                          | return word 4-36                             |

| I/O interface isolation 9-30                    | introduction 1-14                             | shift register parity error 6-12                                 | storage read halfword 4-52                   |

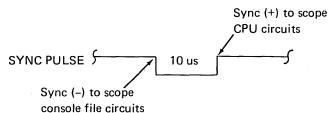

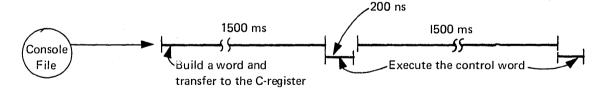

| no operation 9-27                               | operation 12-9                                | timing chart, shift register 6-7                                 | storage word, direct control 4-60            |

| on-line off-line modes 9-29                     | common region, 1400 compatibility 9-4         | voltages 11-33                                                   | storage word, store under mask and decrement |

| operational characteristics 9-24                | compare circuits, IFA 10-26                   | console-file adapter 6-2                                         | count 4-64, 4-65, 4-66, 4-67                 |

| programming notes 9-31                          | compatibility exceptions 1-14                 | console-file disk address (CFDA) byte 6-3                        | storage word, TB function 4-56               |

| · · ·                                           | compatibility feature, 1400/1410              | console-file indicators 5.7                                      | word-move word 4-42, 4-43                    |

| read or read backward 9-26                      | ANUM instruction 9-12                         | console-file register display switch 5-26                        | functions 1-7                                |

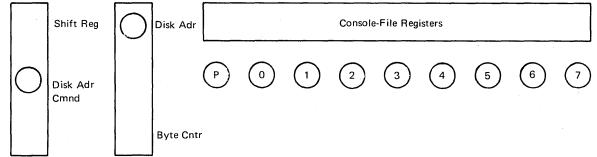

| select priority, mode selection and bypass 9-33 | BIFLAG instruction 9-15                       | console-file registers, indicators 5-7                           | next address generation 4-12                 |

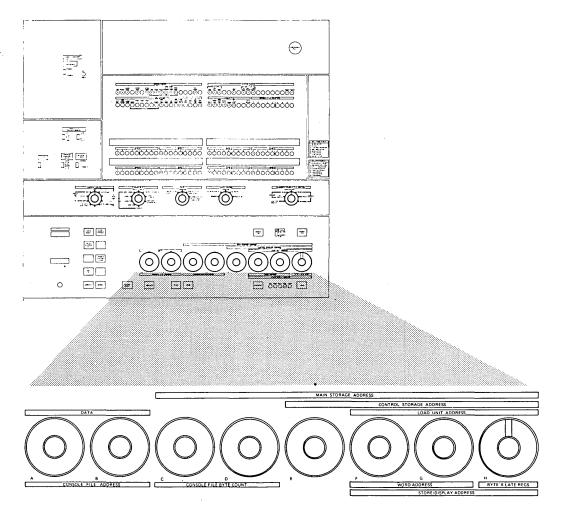

| selection and reset X 9-32                      | common region 9-4                             | console layout 5-2                                               | stat set symbols 4-84                        |

| sense adapter status 9-26                       | COMP instruction 9-12                         | continuing scan commands, IFA 10-70                              | storage word 4-44, 4-45                      |

| sense command byte 9-26                         | control byte chart 9-11                       | control address set, key 5-27                                    | storage word forms 4-46, 4-47                |

| sequence and control X 9-32                     | control storage assignment 9-3                | control and data flow                                            | types 4-15                                   |

| status, sense, and input B bus-in X 9-33        | DIL and BDIL instruction 9-10                 | 3210 7-15                                                        | word-move word 4-38, 4-39                    |

| system or selective reset 9-28                  | instruction 'EA' 9-10                         | 3215 7-34                                                        | conversion, emitter pulse 7-40               |

| test I/O 9-27                                   | local storage assignment 9-3                  | control commands, IFA 10-50                                      | corr cycle, indicator 5-6                    |

| write 9-27                                      | main storage assignment 9-2                   | control Cmd execution, IFA 10-40                                 | count controls, IFA 10-22                    |

| write end of file 9-27                          | MCPU instruction 9-13                         | control, data-transfer 7-49                                      | count externals, IFA 10-22                   |

| check                                           | MIO instruction 9-14                          | control keys (switches) PR-KB 7-6                                | count field, IFA 10-6                        |

| chaining 7-61                                   | op code chart, 1401/1460 9-9                  | control, new line, 3210 7-23                                     | counter decode, IFA 10-22                    |

| channel control 7-61                            | op code chart, 1410/7010 9-8                  | control, read/write cycle, 3210 7-22                             | counter logic, IFA 10-22                     |

| channel data 7-61                               | op codes, 1440 9-9                            | control register                                                 | counts                                       |

| control, rotary switch 5-21                     | program debugging information 9-16            | decode, I-cycles 2-64                                            | PE timing pulse 7-41                         |

| data parity 7-43                                | compatibility feature, 1401/1440/1460 9-2     | machine check 12-17                                              | print emitter timing 7-41                    |

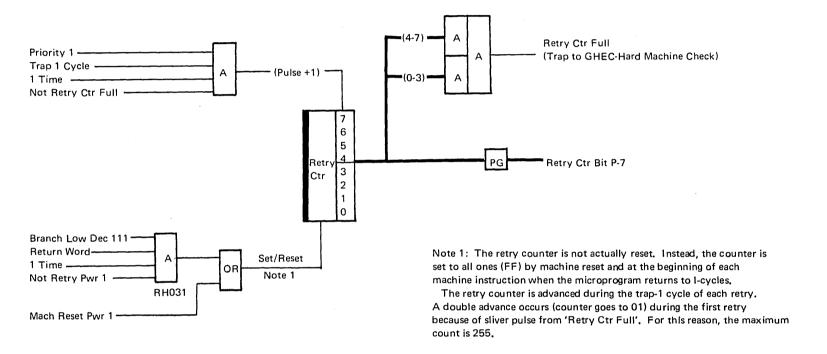

| interface control 7-61                          | compatibility feature, 1410/7010 9-2          | valid 12-18                                                      | retry 12-11                                  |

| print emitter sync 7-43                         | condensed data flow, 3215 7-33                | 14 12-17                                                         | CPU                                          |

| program 7-61                                    | condition code validity 12-18                 | 15 12-17                                                         | configuration 1-3                            |

| protection 7-61                                 | configurations, PR-KB 7-3                     | 3210 7-15                                                        | cycle times (see CPU clock)                  |

| reset, key 5-27                                 | console file                                  | 3215 7-33                                                        | dependent logout 12-19                       |

| checkpoint/restart 12-26                        |                                               | control, stepper motor 7-44                                      | external word 2-34                           |

| checks, machine 12-8                            | byte control 6-5                              | control, stepper motor 7-44<br>control storage assign, IFA 10-12 | frame, electrical components 11-8            |

| chopped forward or reverse singleshot 7-45      | byte counter 6-5, 6-13                        | control storage map 4-13                                         | high priority 2-43                           |

| elock                                           | byte format 6-3                               | control trap, IFA 10-74                                          | identication 12-19                           |

| CPU (see CPU clock)                             | CF data register (CFDR) 6-5                   |                                                                  | independent logout 12-18                     |

| damage 12-18                                    | CFDA register 6-5                             | control-unit end (status bit 2) 7-61                             | indicator 5-5                                |

| IFA 10-18                                       | CFDA track/sector table 6-3                   | control word                                                     | status, indicators 5-6                       |

| logic 10-16                                     | clock 6-6                                     | access 4-4                                                       | CPU clock                                    |

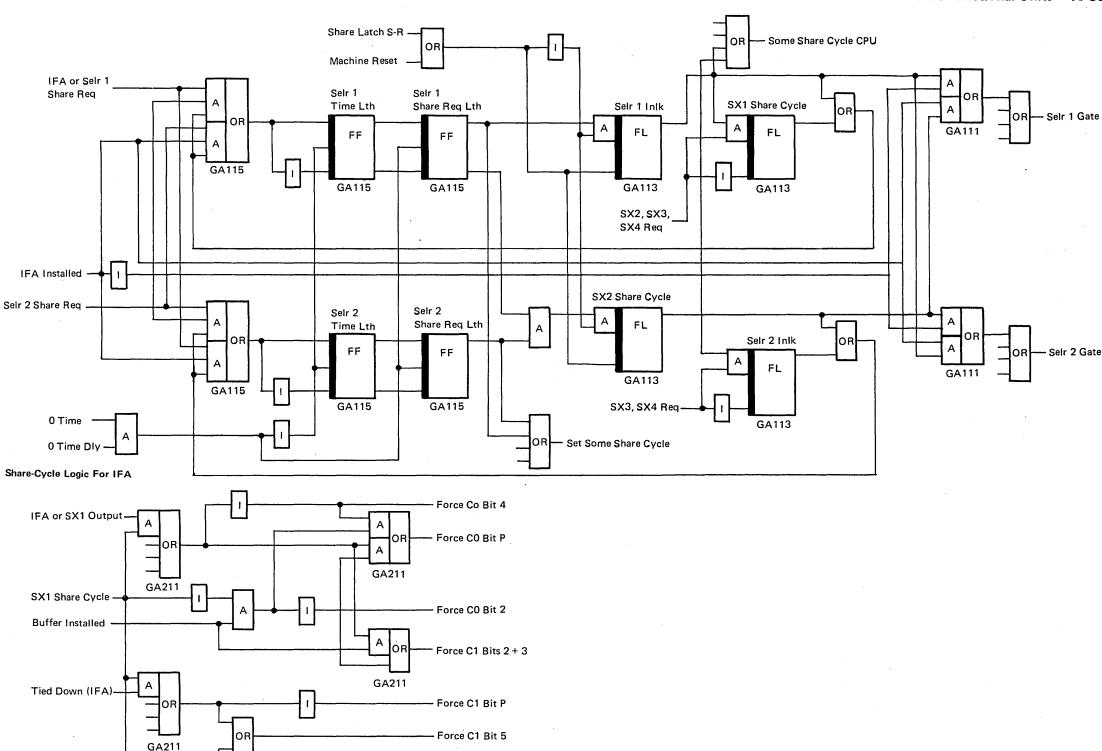

| share cycle logic 10-31                         | command 6-9                                   | arithmetic 4-68, 4-69                                            |                                              |

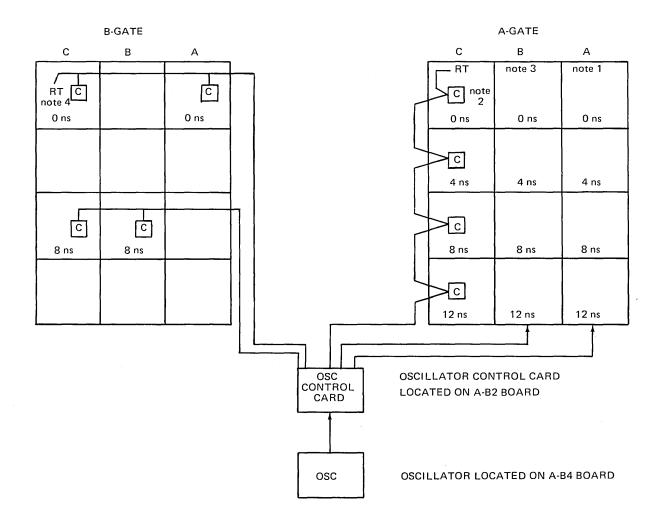

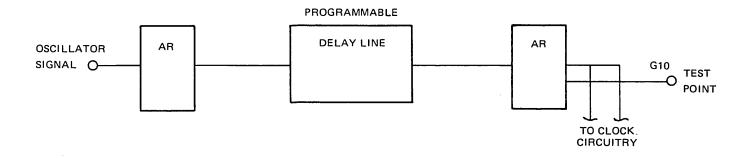

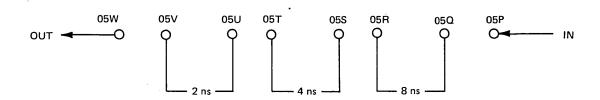

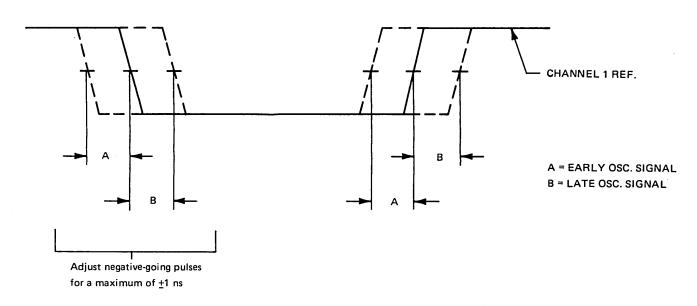

| timing 10-18                                    | command byte 6-3                              | bit definition                                                   | card locations 2-104                         |

| logic diagram, storage 3-19                     | command chart 6-10                            | arithmetic indirect byte type 10 or 11 4-73                      | checks and adjustments 2-104                 |

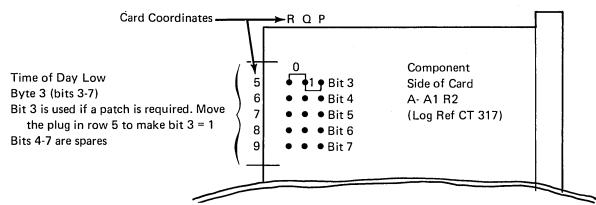

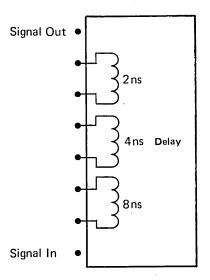

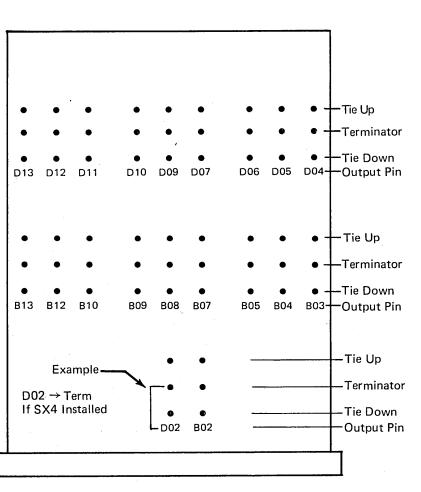

| stop indicator 5-6                              | command register 6-5, 6-13                    | arithmetic type 10 byte 4-70                                     | delay card plugging 2-105                    |

| storage 3-23                                    | compare circuits 6-5                          | arithmetic type 10 fullword 4-71                                 | start, indicator 5-7                         |

| sync, indicator 5-5                             | control commands 6-9                          | arithmetic type 11 4-72                                          | CPURTY 12-10                                 |

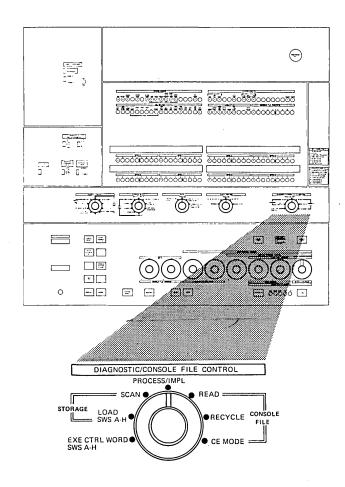

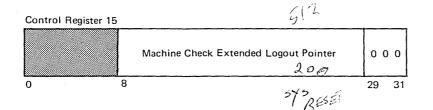

| CR (control registers valid) 12-18     | diagnostic/console file controls rotary switch 5-23, 5-24 | ECC                                                                | extended logout                                       |

|----------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------|

| CS adr, indicator 5-6                  | diagnostic hardware                                       | board to CPU timing diagram 3-22                                   | IFA 10-75                                             |

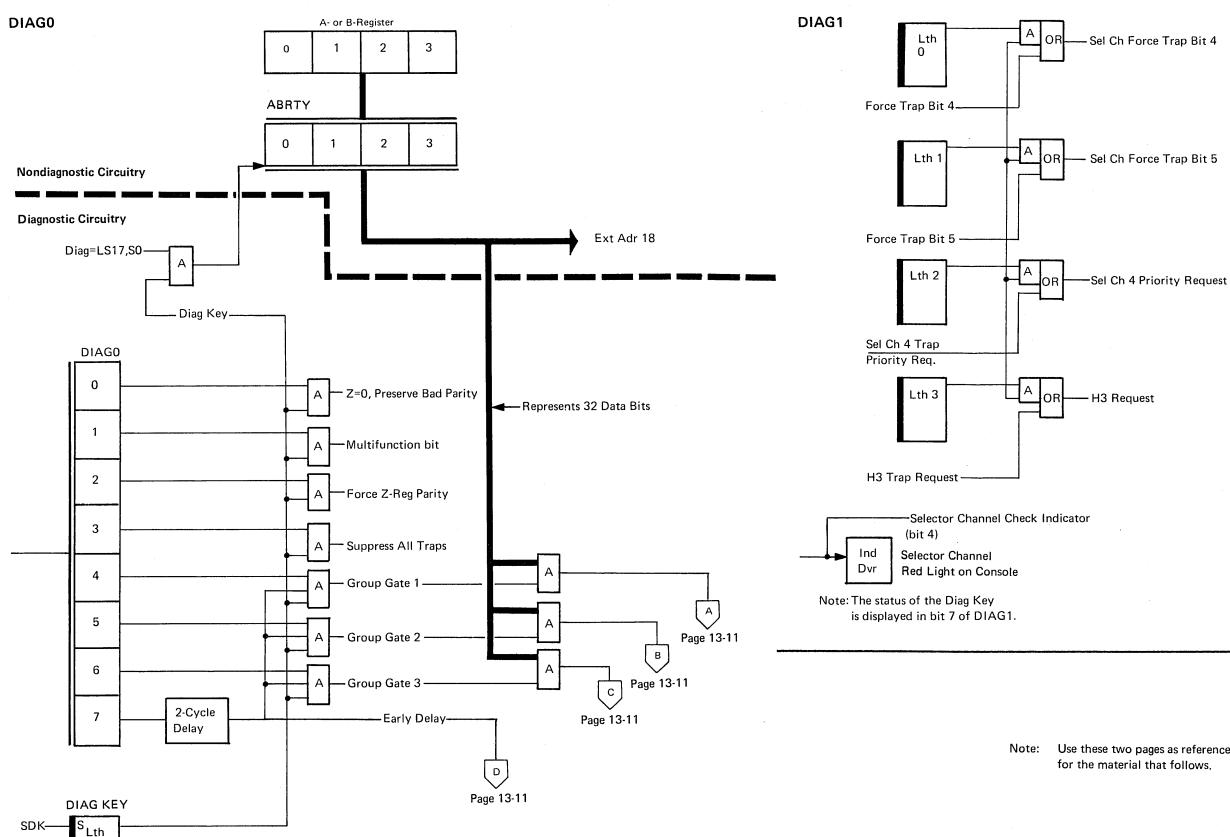

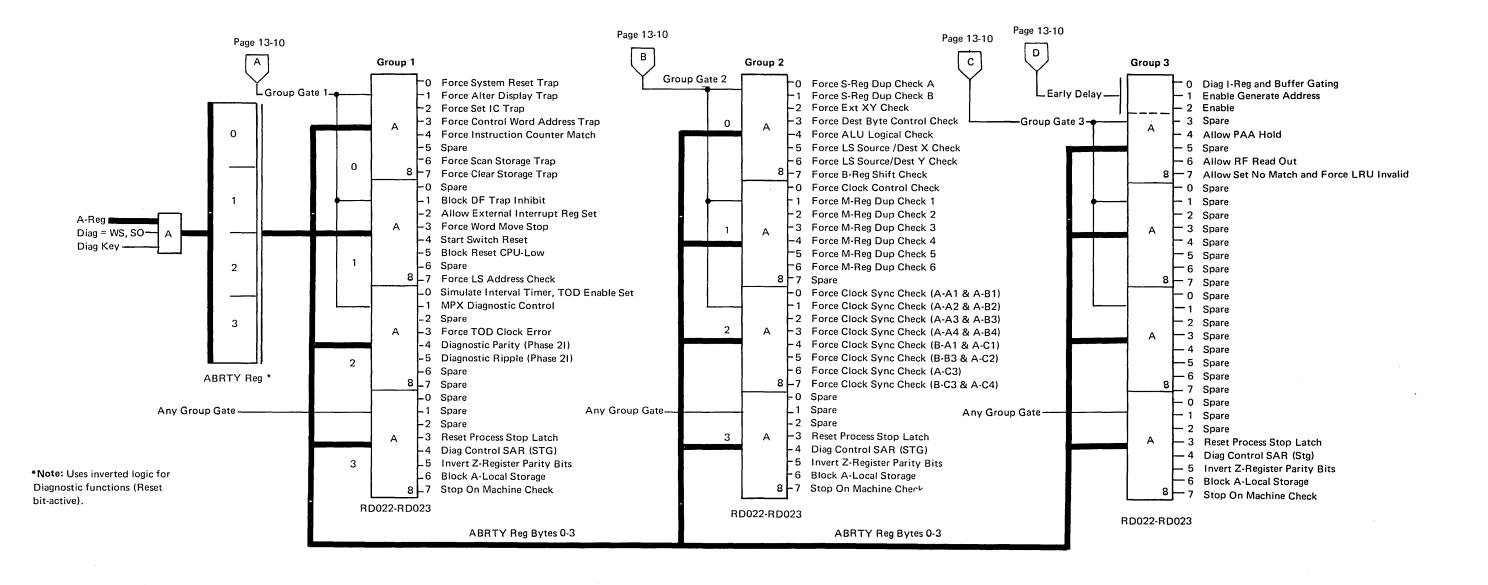

| cycle control, 3210 read/write 7-22    | ABRTY group 1 13-17                                       | busy, indicator 5-5                                                | length 12-18                                          |

| cyclic check, IFA 10-25                | ABRTY group 2 13-26                                       | DBL bit, indicator 5-5                                             | mask 12-17                                            |

| controls 10-24                         | ABRTY group 3 13-32                                       | decode chart 3-34                                                  | pointer 12-17                                         |

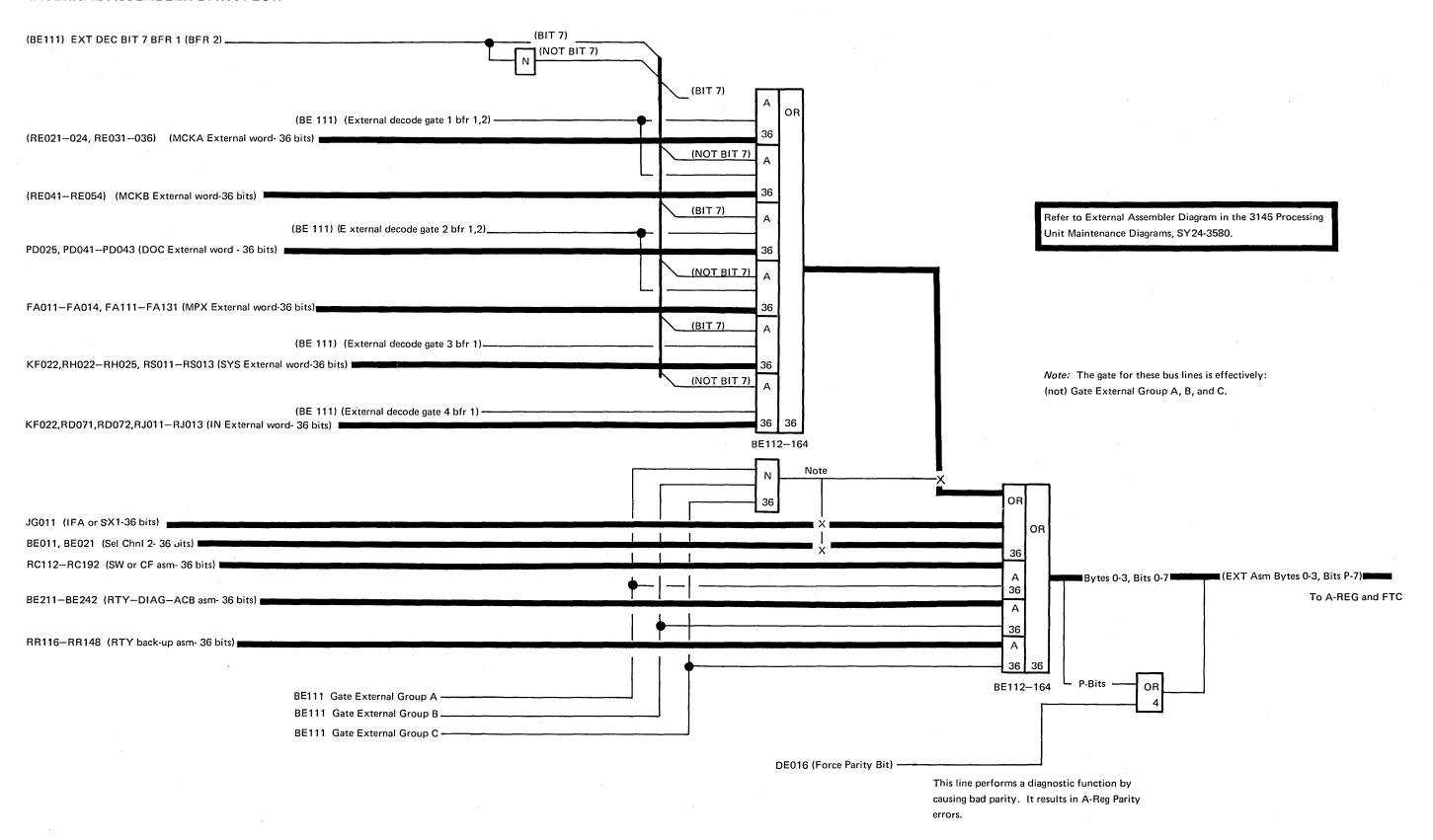

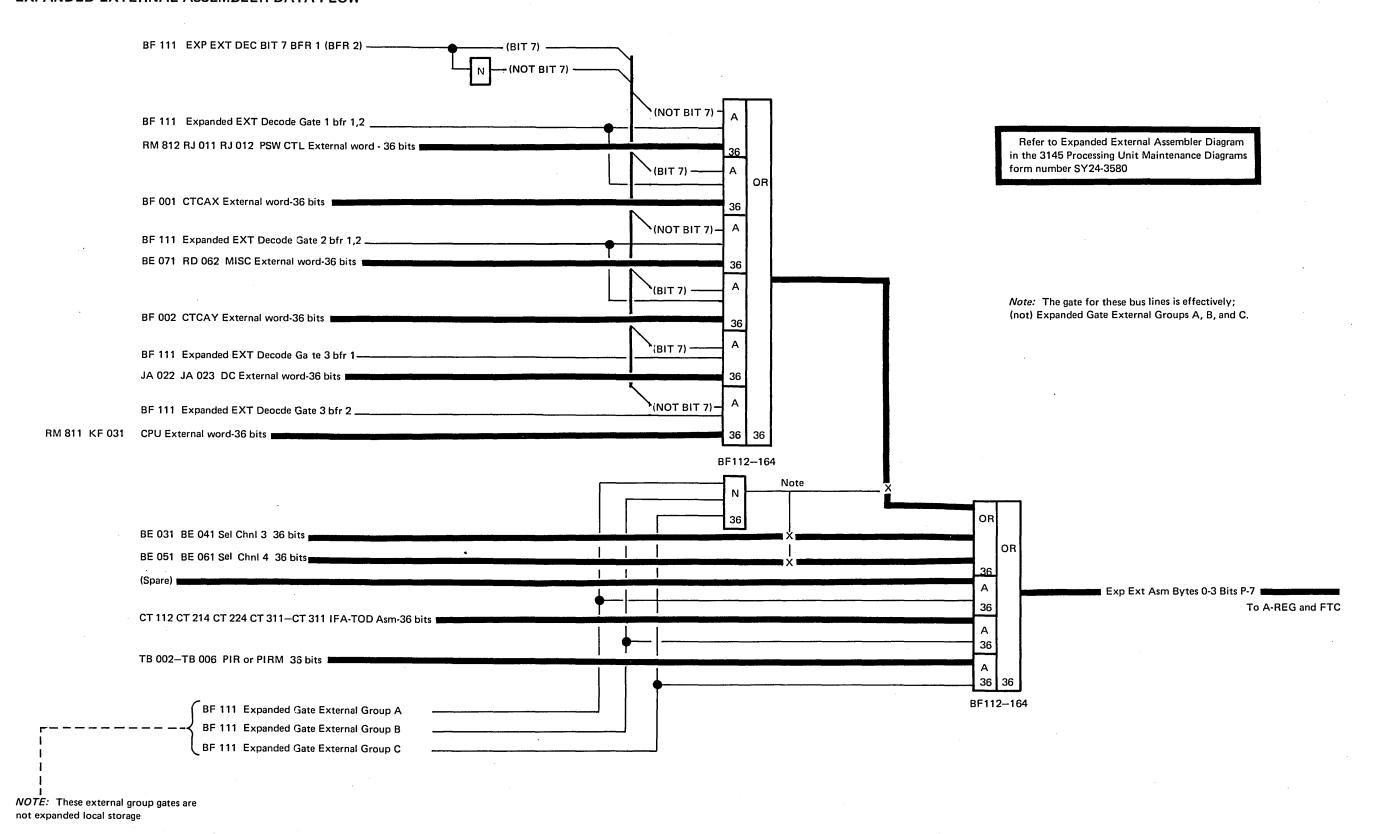

| logic 10-24                            | diagnostic parity 13-20                                   | description 3-32                                                   | external assembler diagram 2-30                       |

| cyclic-code hardware register 10-25    | diagnostic ripple 13-21                                   | hdw, indicator 5-5                                                 | external facilities                                   |

| cyclic-code register, IFA 10-24        | early delay function 13-32                                | logic 12-6                                                         | assignment and index 2-32, 2-33                       |

| cylinder addr reg test, IFA 10-29      | general information 13-1, 13-10                           | logic diagram 3-33                                                 | general information 1-13                              |

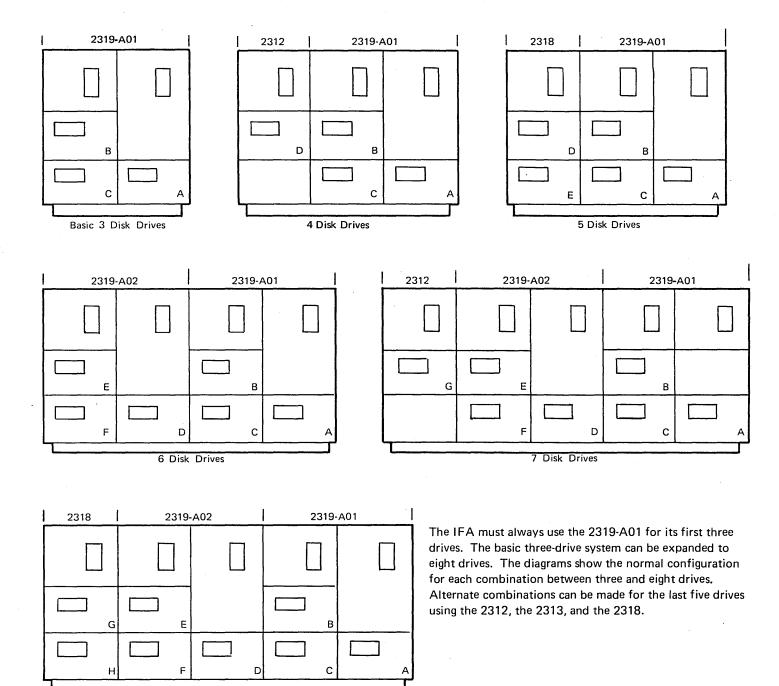

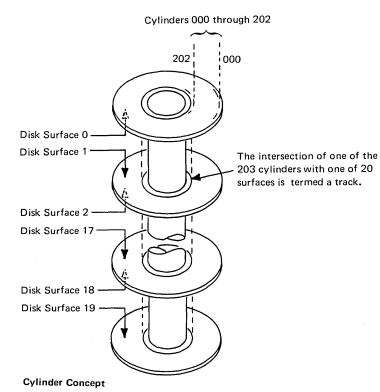

| cylinder concept 10-4                  | MPX diagnostic control 13-20                              | ECCL                                                               | description 2-29                                      |

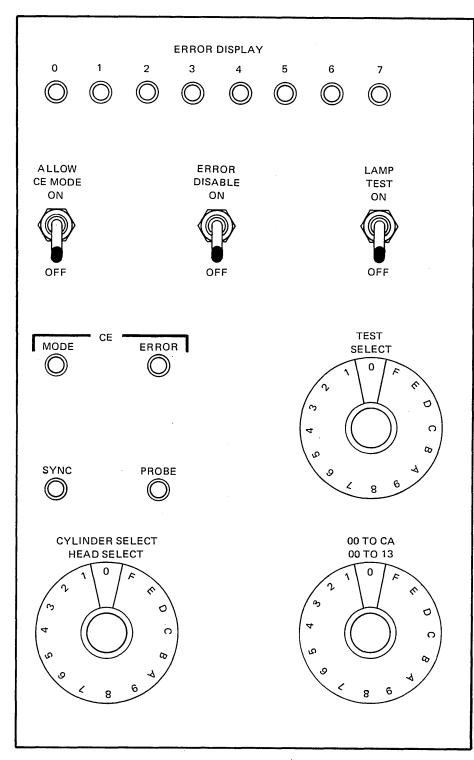

| cylinder select switch, IFA 10-86      | diagnostic indicators, IFA 10-11                          | board layout 3-17                                                  | external words                                        |

|                                        | diagnostic key 13-12                                      | delay line clock 3-23                                              | ACB 2-35                                              |

|                                        | diagnostic local storage assignment 13-43                 | ED (external damage) 12-18                                         | CPU 2-34                                              |

| <b>D</b>                               | diagnostic registers 13-12                                | ED (external damage) 12-18  EM (external damage report mask) 12-17 | diag 2-34                                             |

|                                        | diagnostic service signal - GA, A-, K0D 13-39             |                                                                    | IN (interrupt) 2-34                                   |

| D-register 1-12, 2-99                  | diagnostic strobe 7-17                                    | emergency power off 11-24 emitter pulse conversion 7-40            | misc 2-34                                             |

| damage                                 | diagnostic tests                                          | enable system clear, key 5-27                                      | NOREG 2-34                                            |

| external 12-18                         | BAB5 13-4                                                 | ending an alter/display operation 7-54                             | PSWCTL 2-34                                           |

| instruction processing 12-18           | BEA6 13-6                                                 | ending operation, IFA 10-74                                        | SW 2-34                                               |

| interval timer 12-16                   | EDA9 13-35                                                | ending sequence, IFA 10-74                                         | SYS (system register) 2-38                            |

| report 12-8                            | EGE7 13-9                                                 | environment recording edit and print program 12-26                 | externals, IFA 10-11                                  |

| report mask 12-17                      | EJD5 13-40                                                |                                                                    | externals, map 2-32, 2-33                             |

| system 12-16, 12-18                    | diagnostics, IFA inline                                   | EPO 11-24                                                          |                                                       |

| time of day clock 12-16, 12-18         | indications 10-87                                         | EPSWA external 2-34                                                | <b>a</b>                                              |

| timer 12-18                            | test decode 10-88                                         | equipment check 7-62                                               |                                                       |

| data and control registers, 3210 7-15  | trap 10-74                                                | erase command, IFA 10-57                                           | FA (failing storage address valid) 12-18              |

| data command execution, IFA 10-41      | unsafe condition test 10-91                               | erase gate, IFA 10-27                                              | FCH-register, IFA 10-22                               |

| data field, IFA 10-6                   | diagram legend, IFA 10-34                                 | EREP 12-26                                                         | FCL-register, IFA 10-22                               |

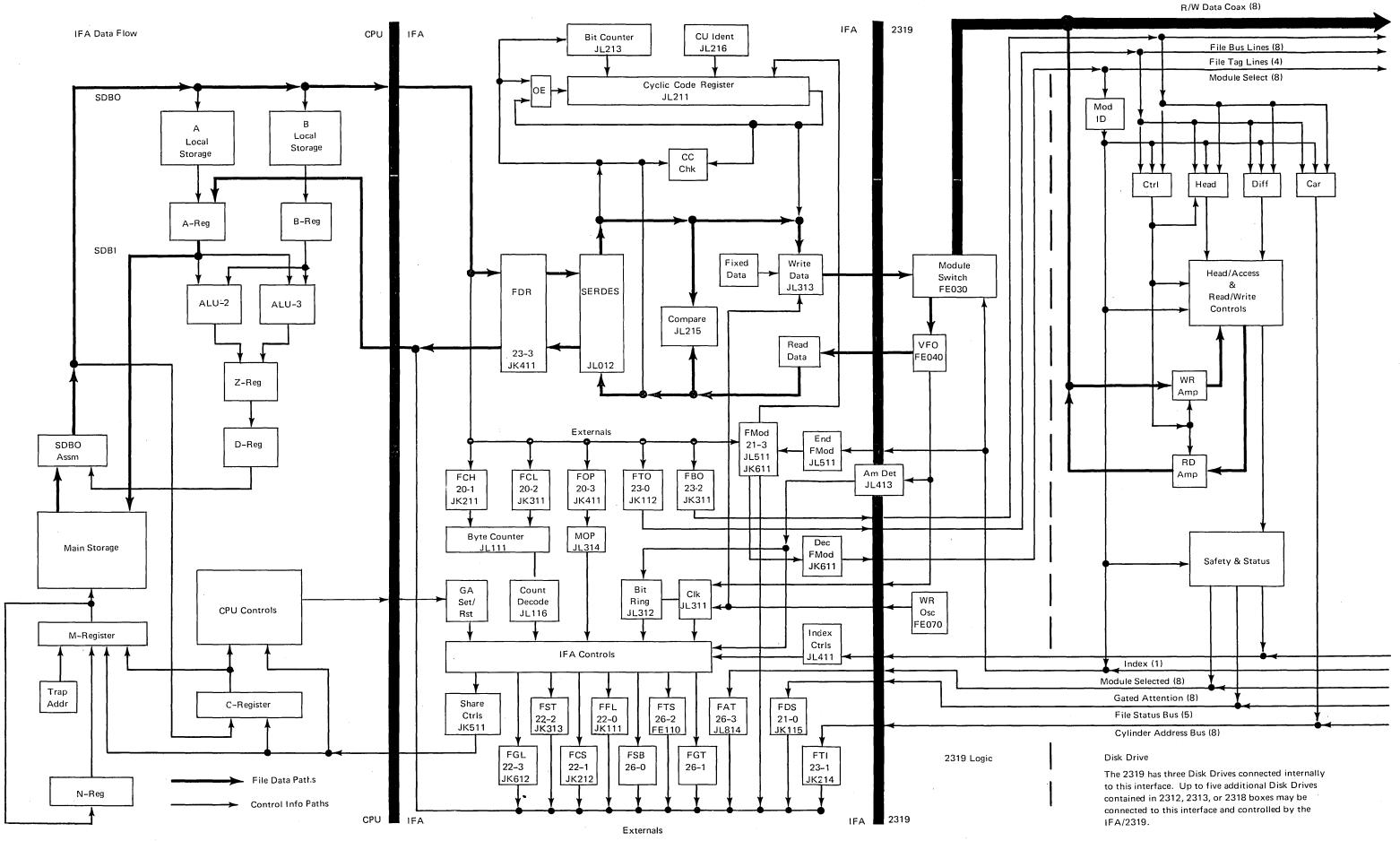

| data flow, IFA 10-4                    | direct control feature                                    |                                                                    | FDR-register, IFA 10-23                               |

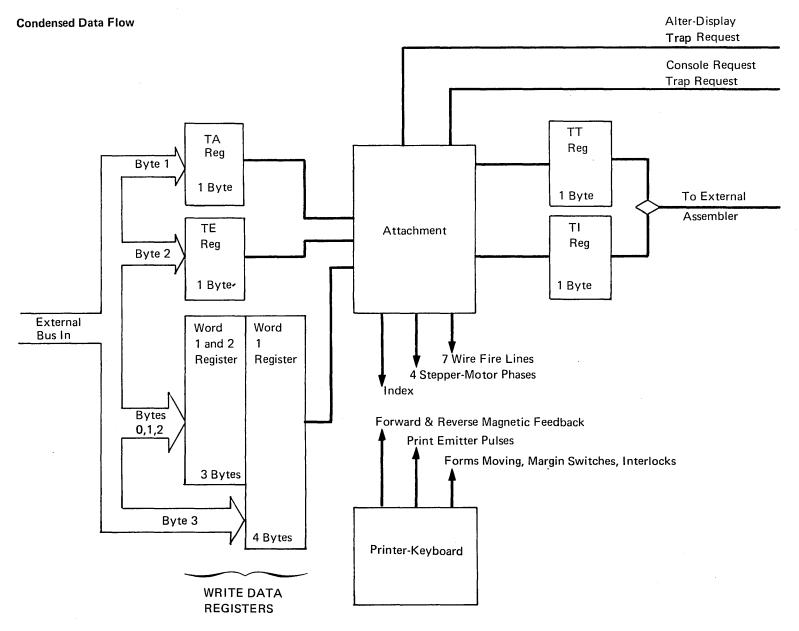

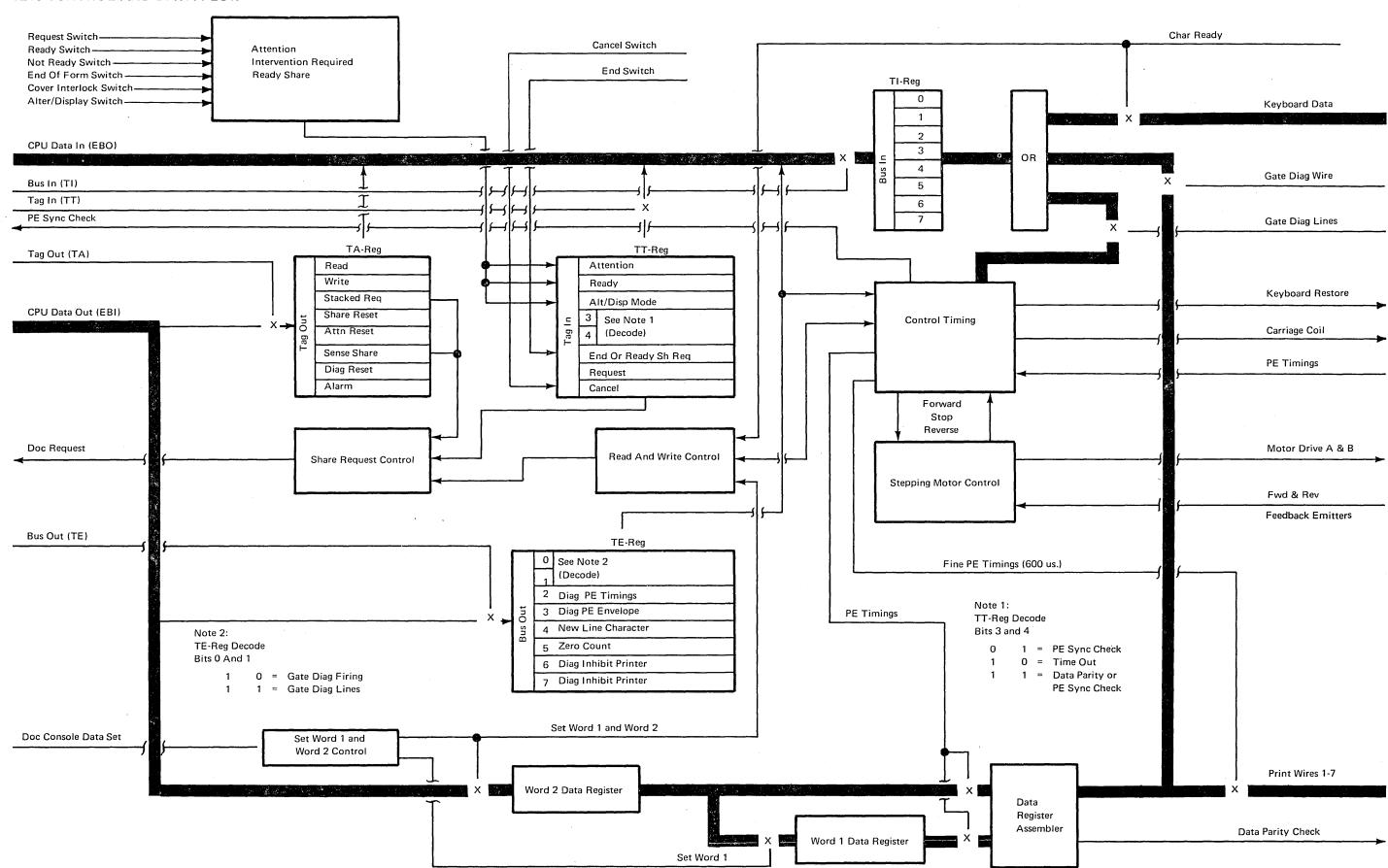

| condensed, 3215, 7-33                  | data flow and controls 9-21                               | error check and correction 12-6                                    | features 1-4                                          |

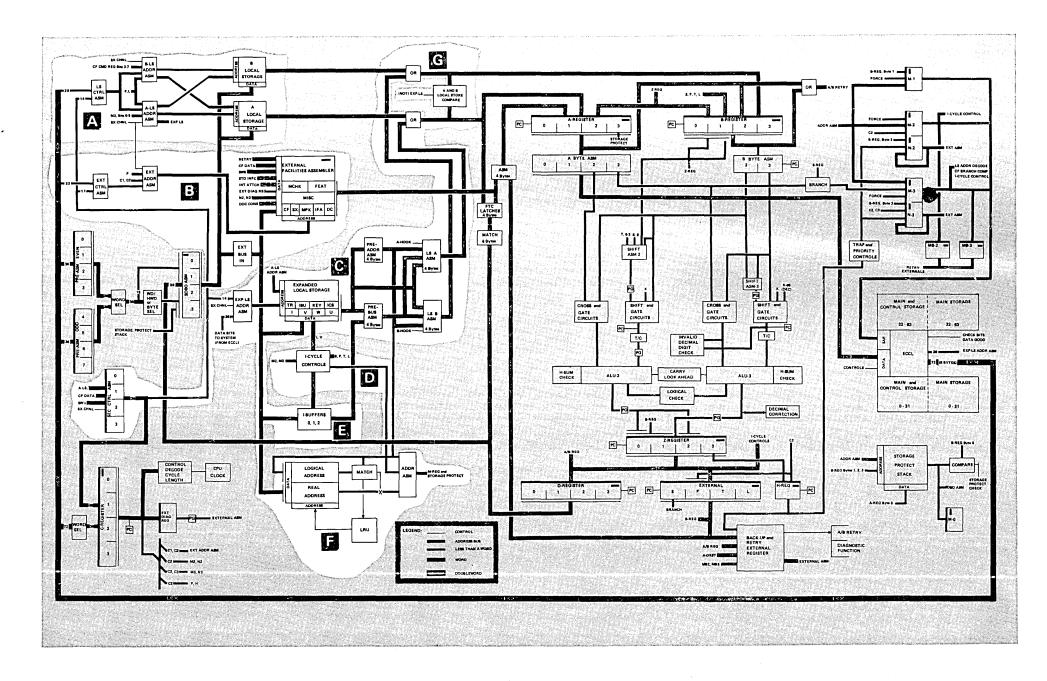

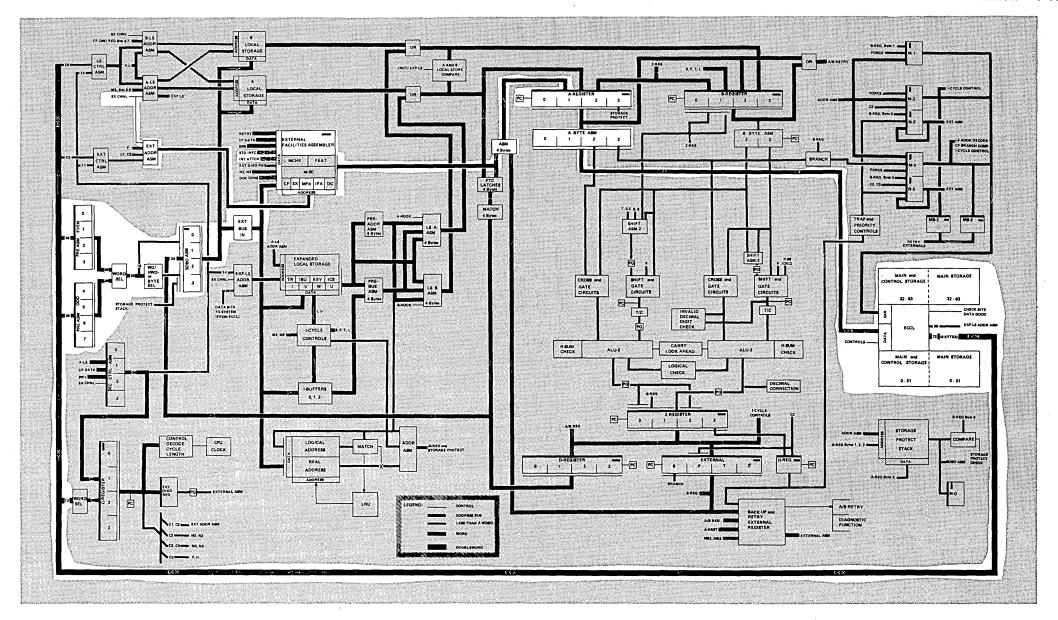

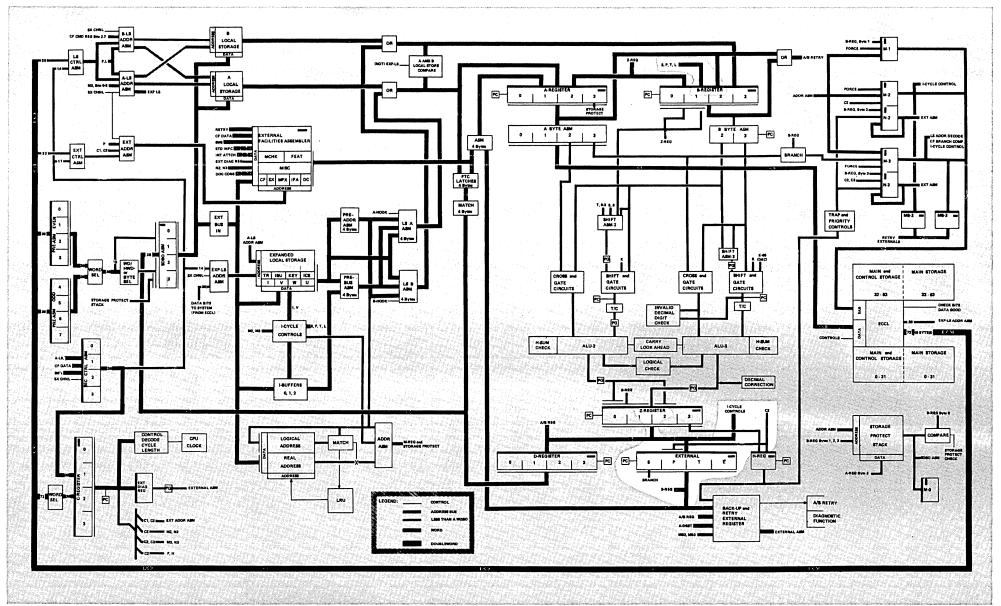

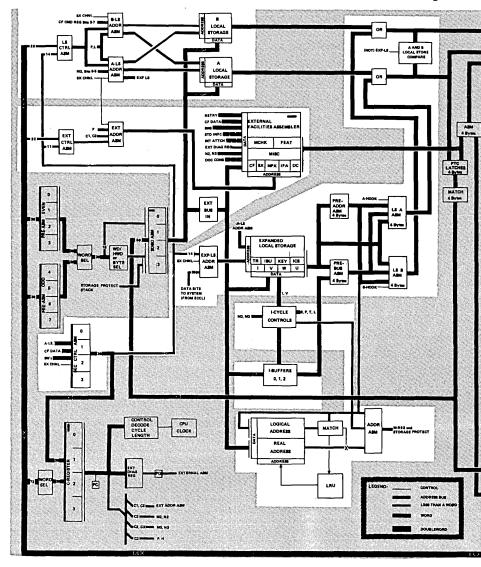

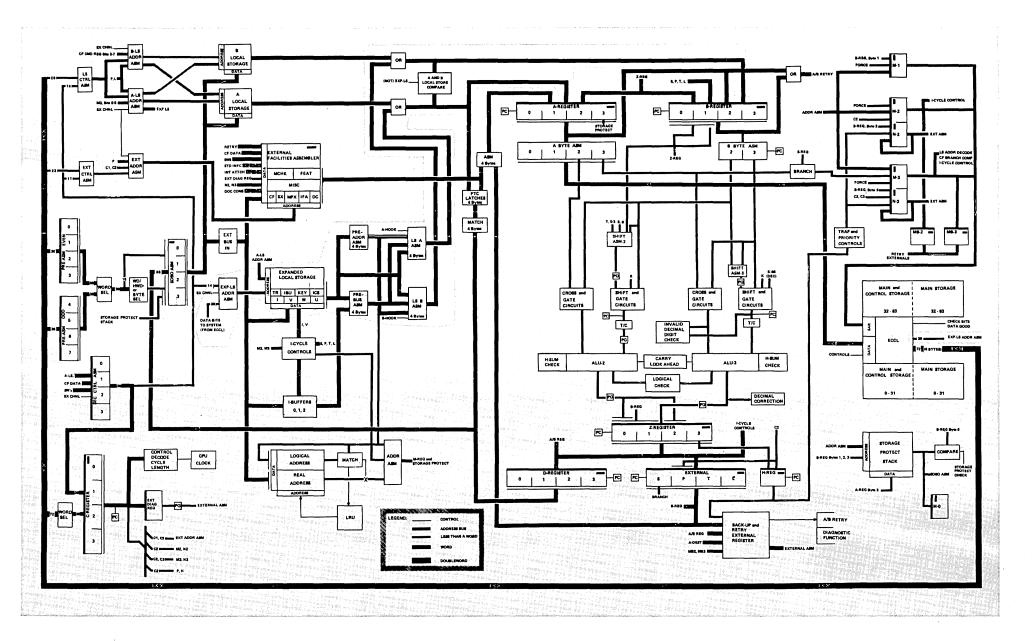

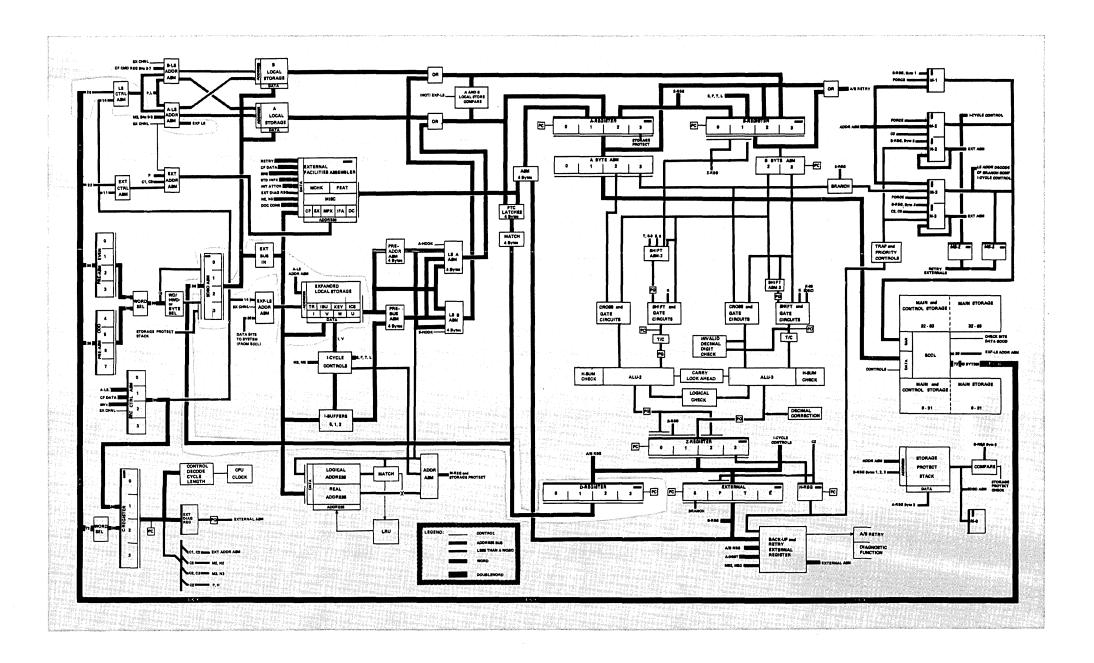

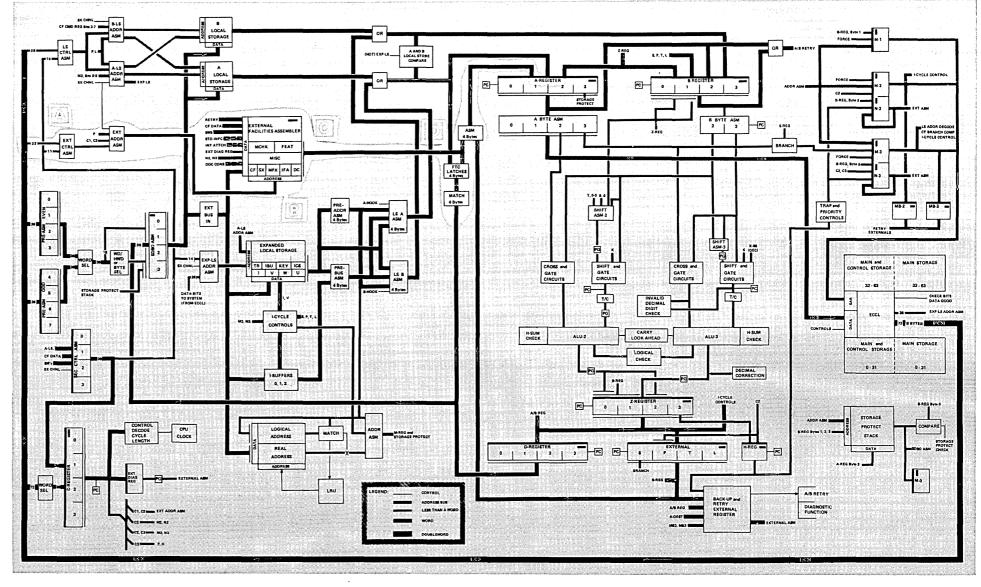

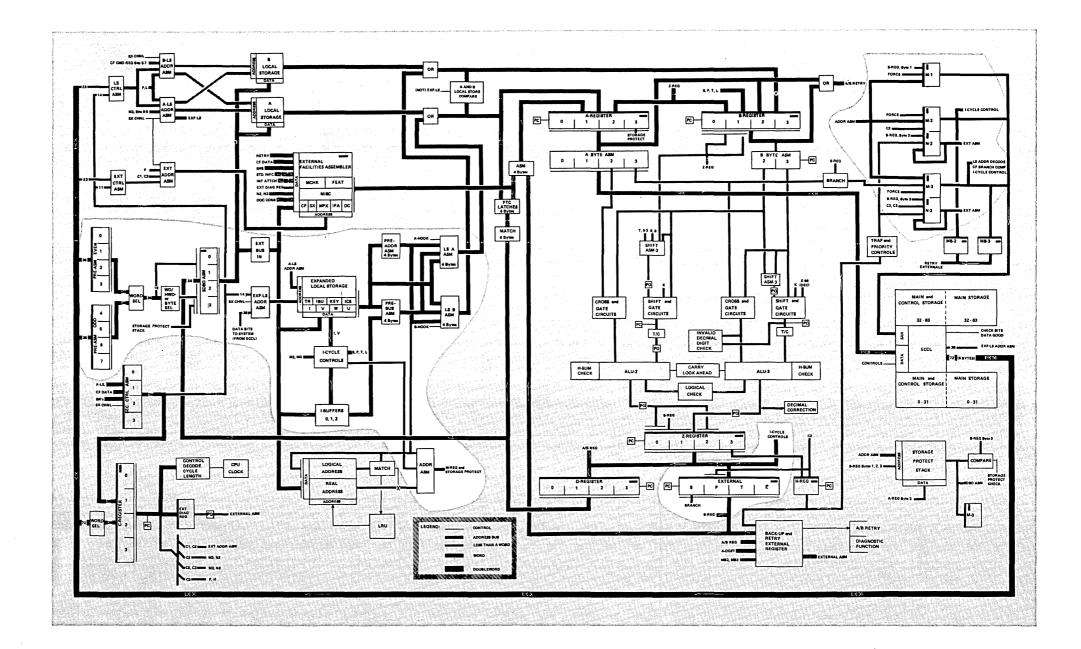

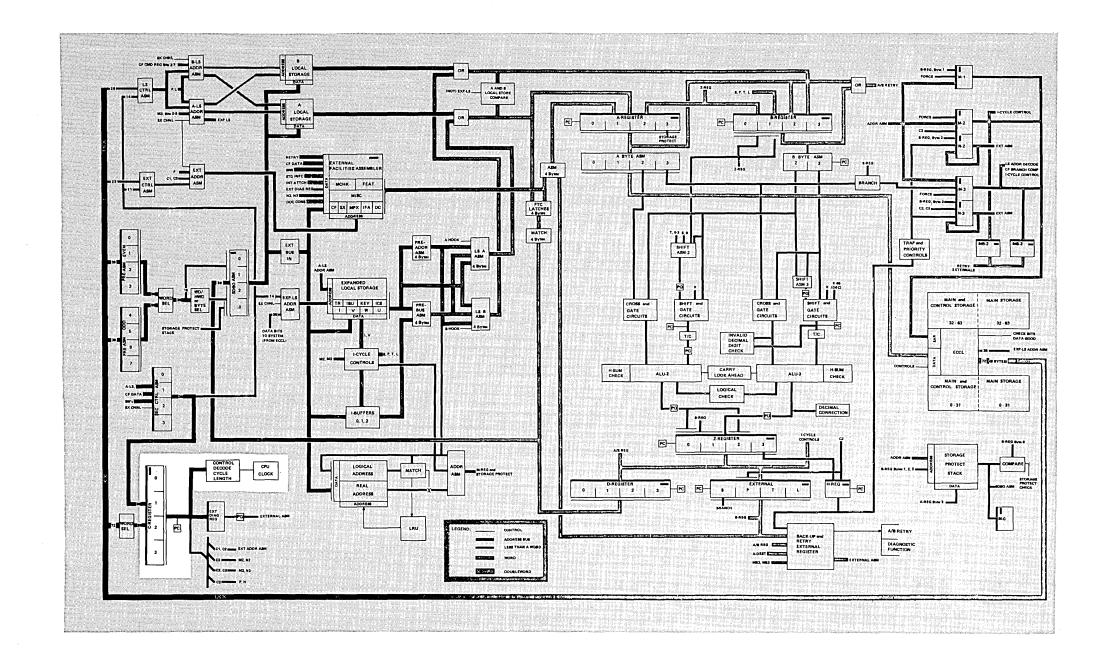

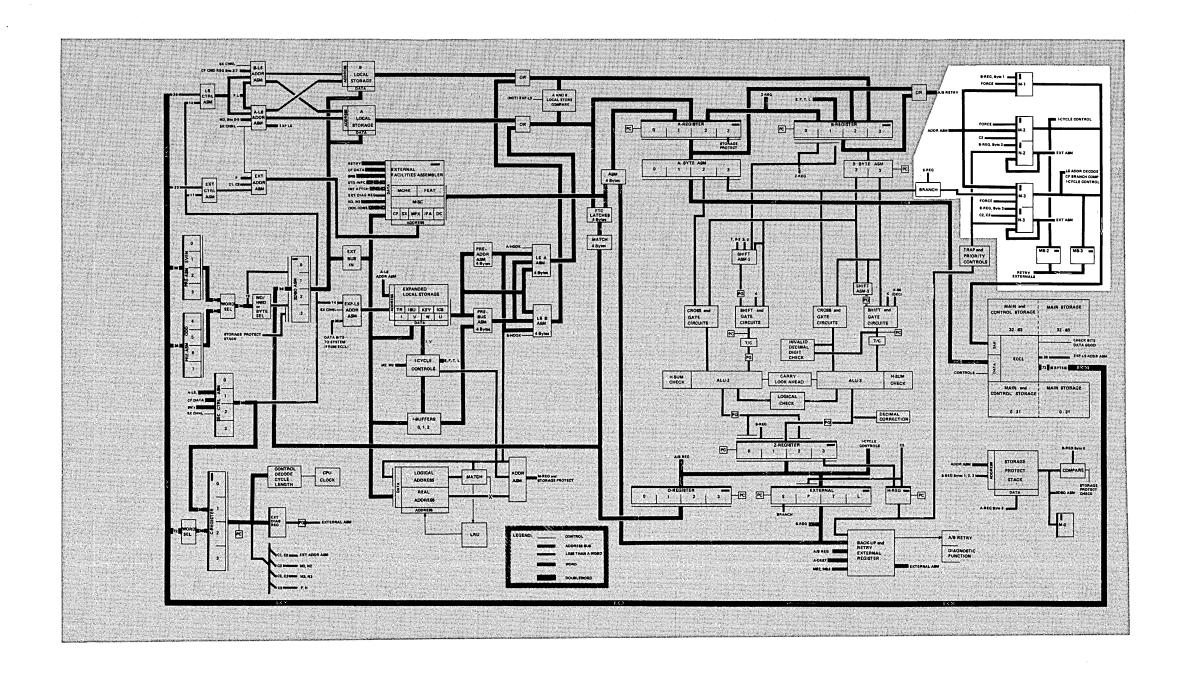

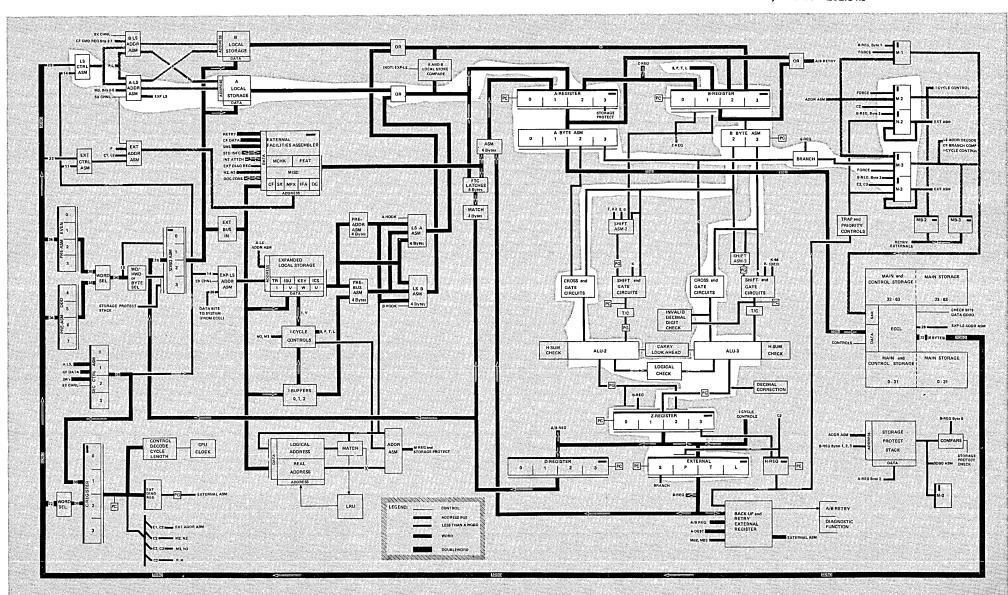

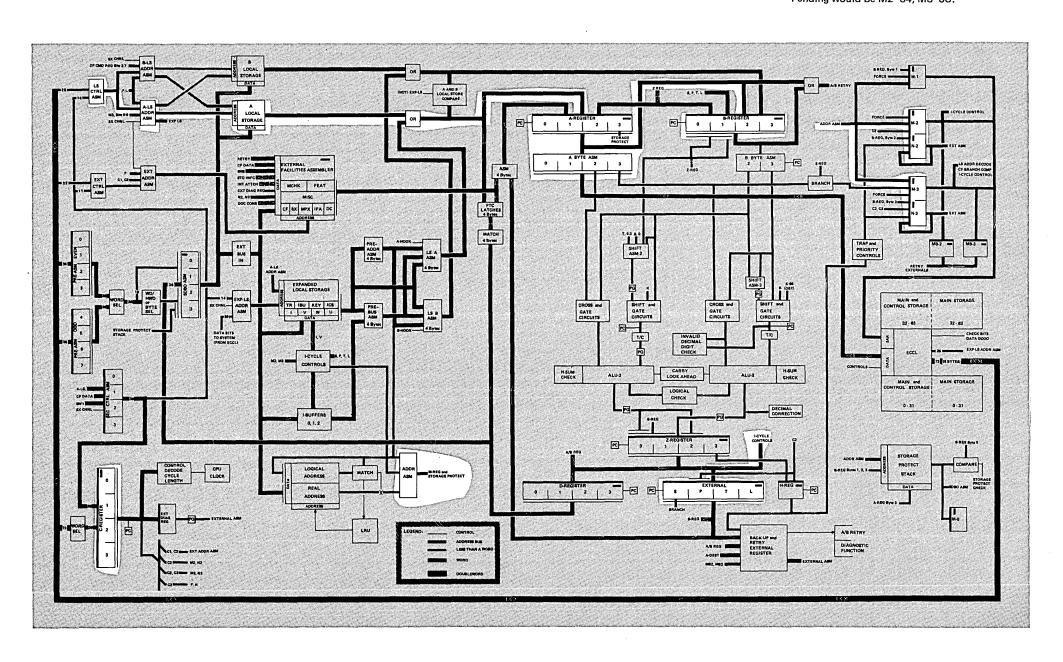

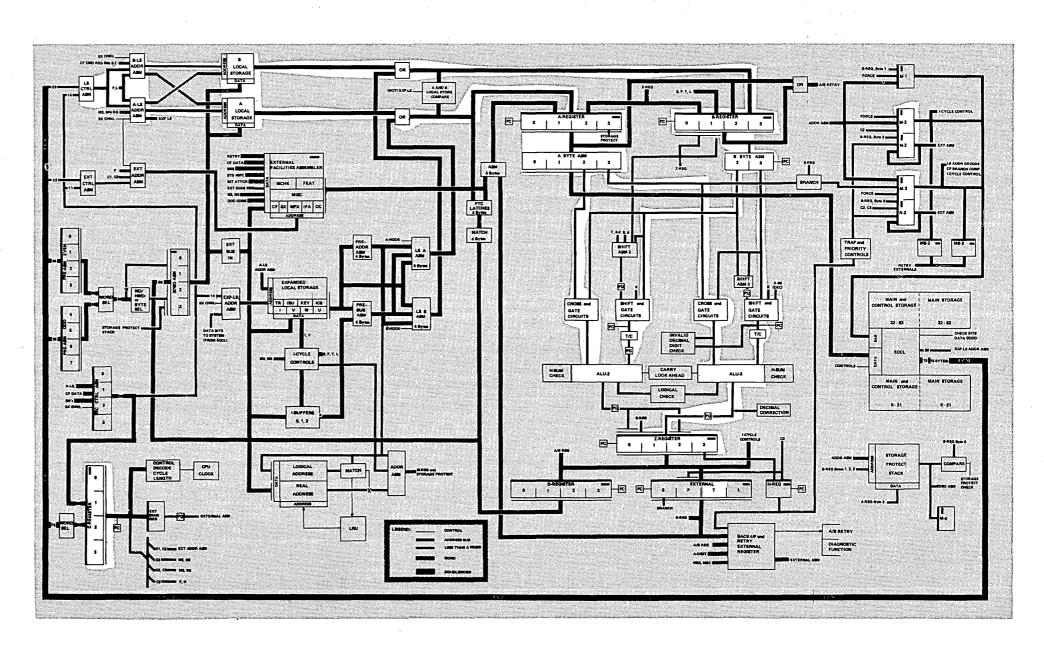

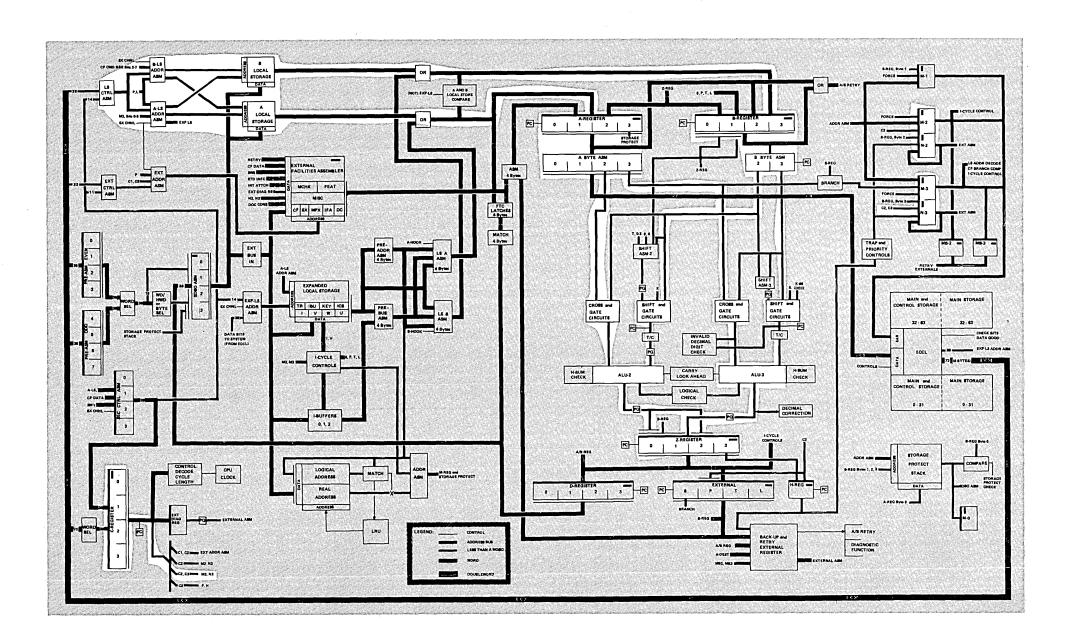

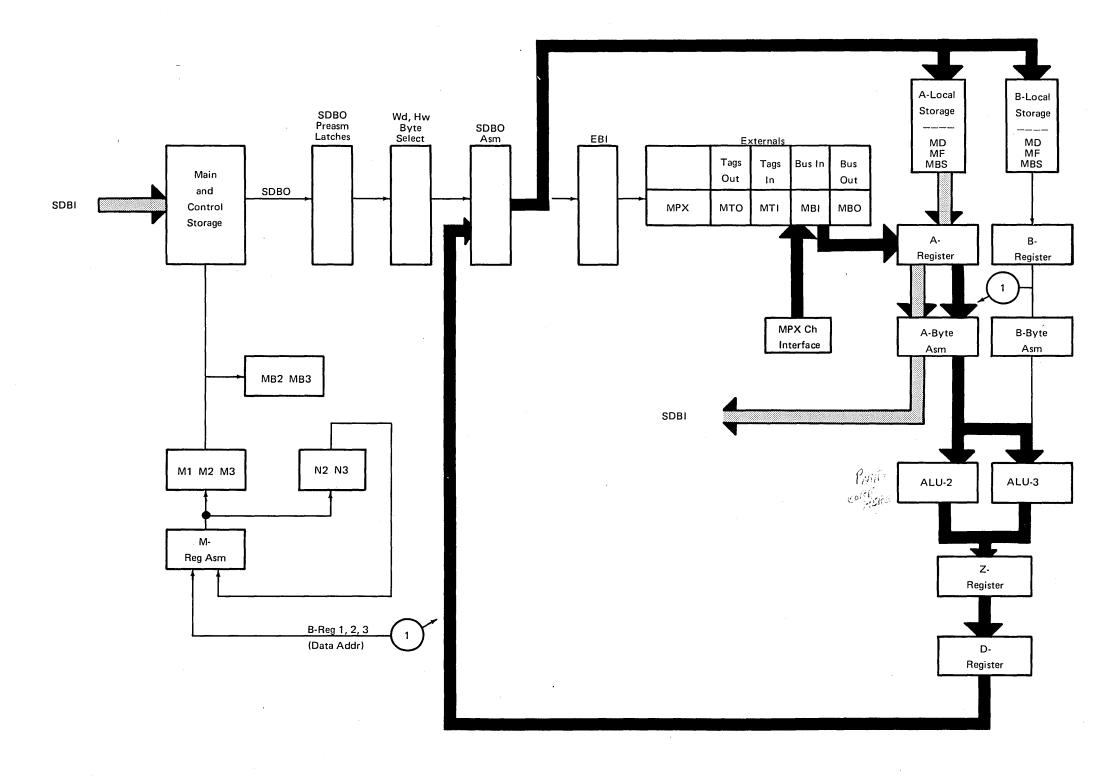

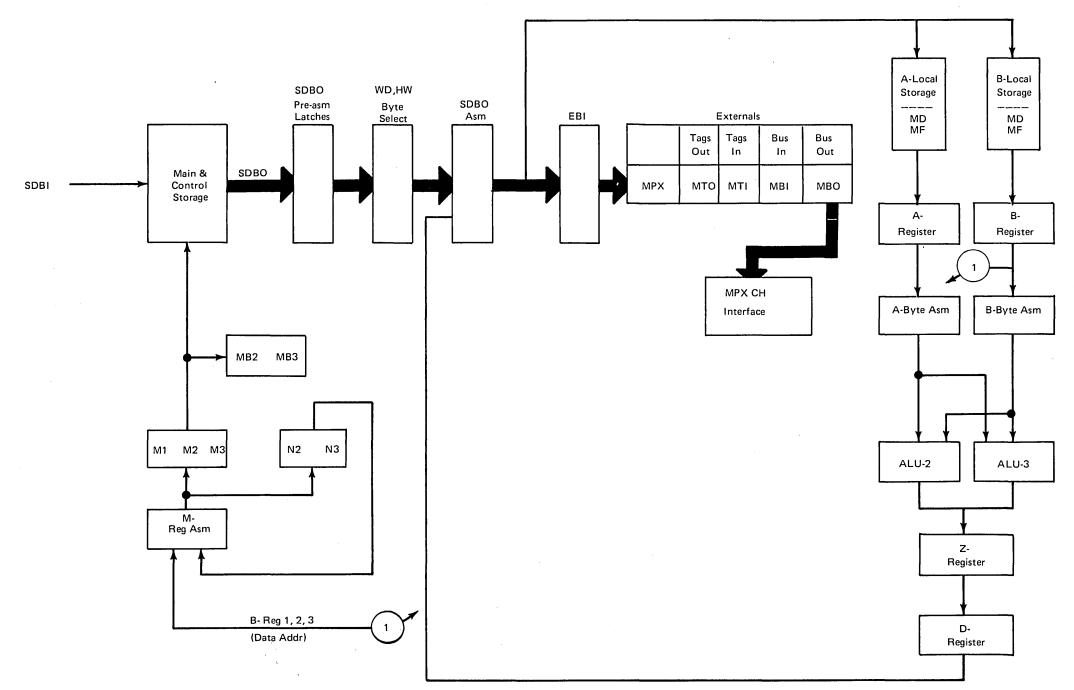

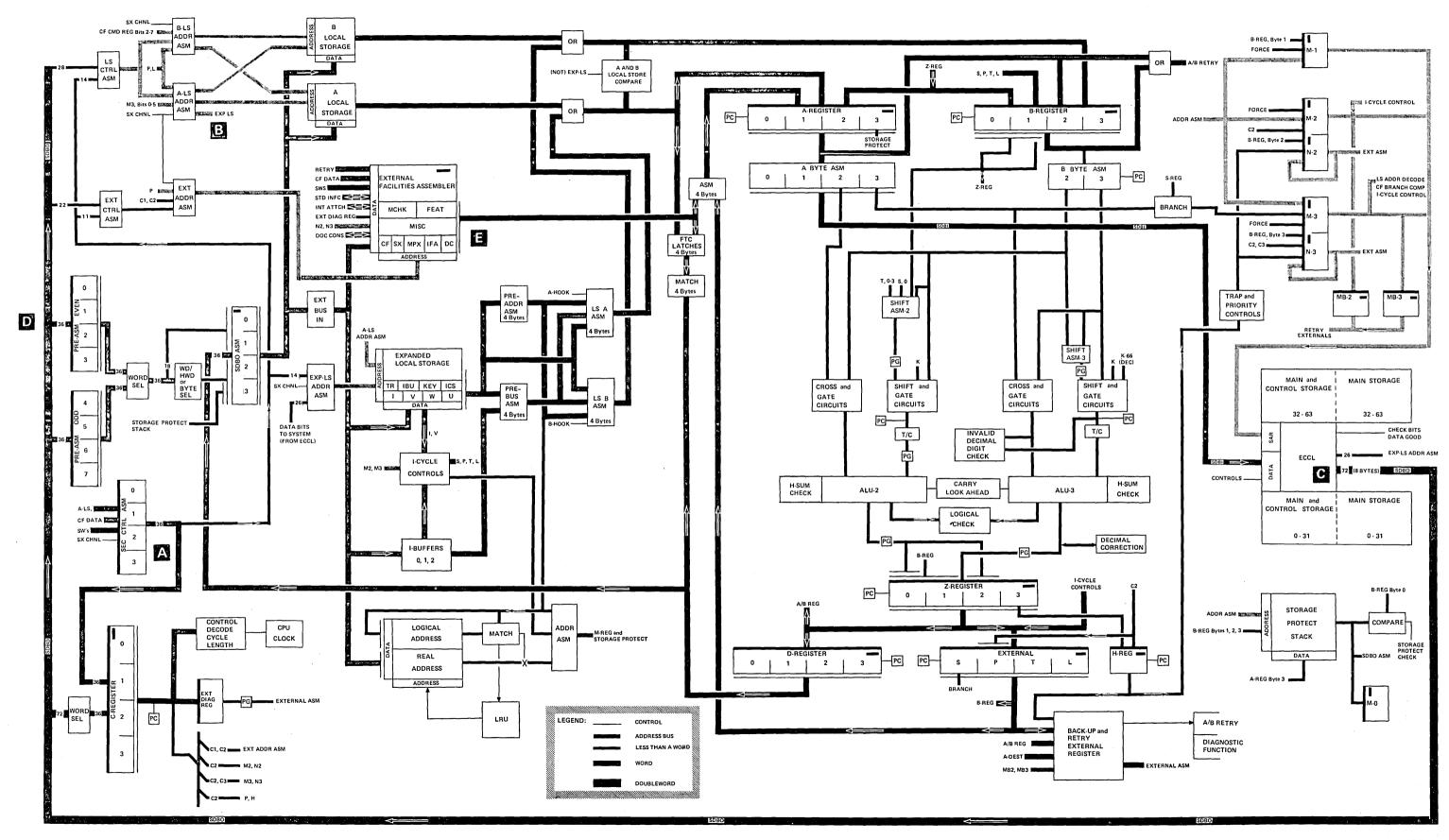

| 3145 1-8                               | flow chart, write & read direct 9-22                      | error checking and correction (ECC)                                | field-count controls, IFA 10-22                       |

| data flow and control                  | general information 9-18                                  | introduction 1-14<br>storage 3-32                                  | file data coax, IFA 10-33                             |

| 3210 7-15                              | interface lines 9-19                                      | error detector, IFA VFO 10-14                                      | file-data register, IFA 10-23                         |

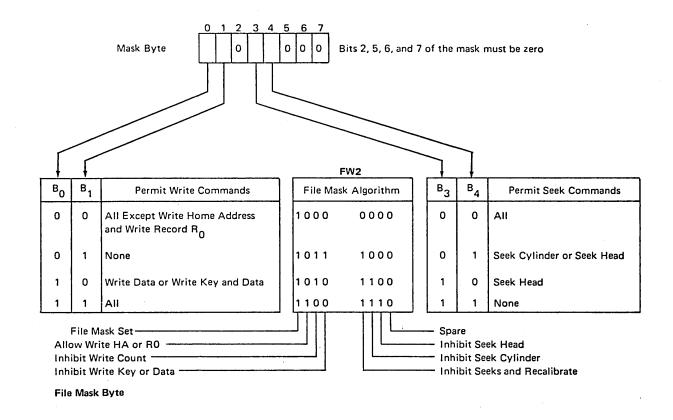

| 3215 7-34                              | read direct instruction 9-18                              | error disable switch, IFA 10-86                                    | file-mask algorithm, IFA 10-50                        |

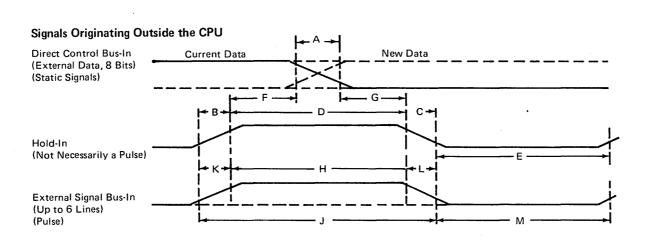

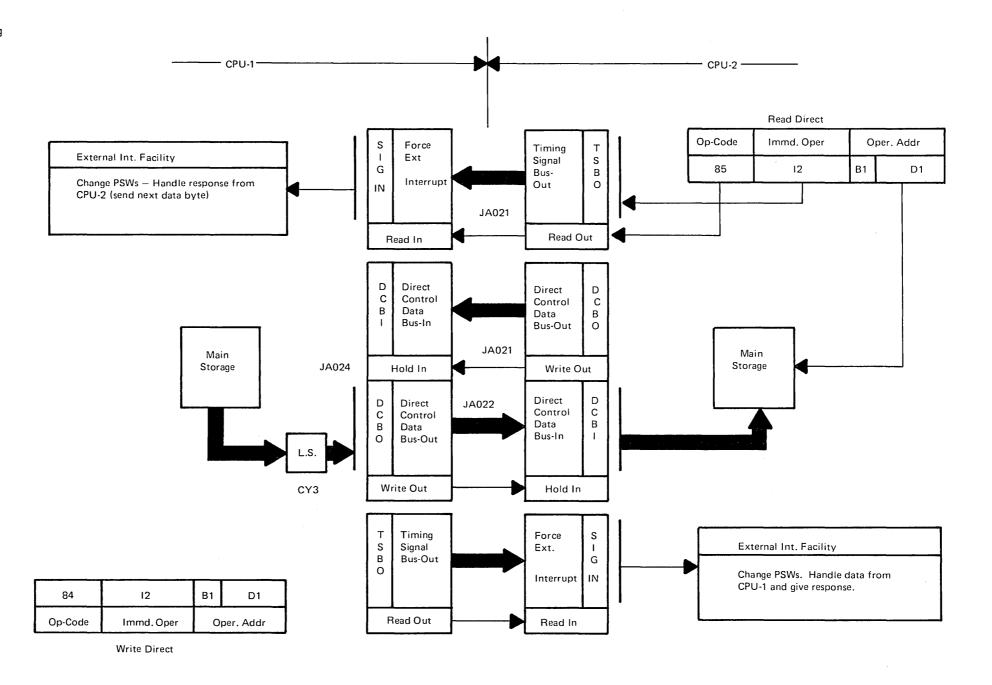

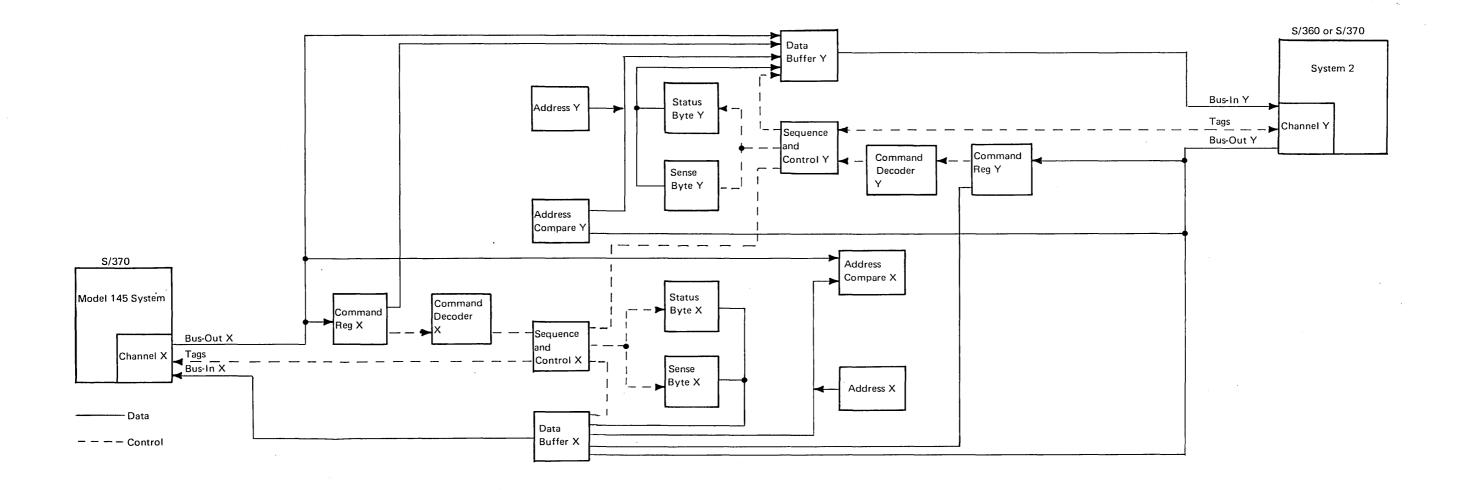

| data-in (interface line) 1-15          | signals originating outside the CPU 9-20                  | error display, IFA/2319 10-86                                      | file-mask bit assignment, IFA 10-12                   |

| data, indicator 5-7                    | signals originating within the CPU 9-19                   | error handling                                                     | Filterslocation, removal and replacement 11-38, 11-39 |

| data, late 7-47                        | timings 9-22                                              | channel retry 1-14                                                 | firing circuits, 3215 print magnet 7-42               |

| data length (DL), IFA 10-6             | write direct instruction 9-18                             | command retry 1-14                                                 | floating-point registers valid 12-18                  |

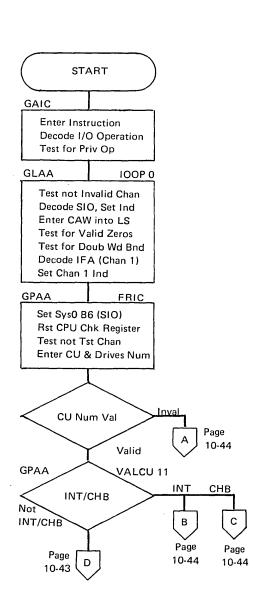

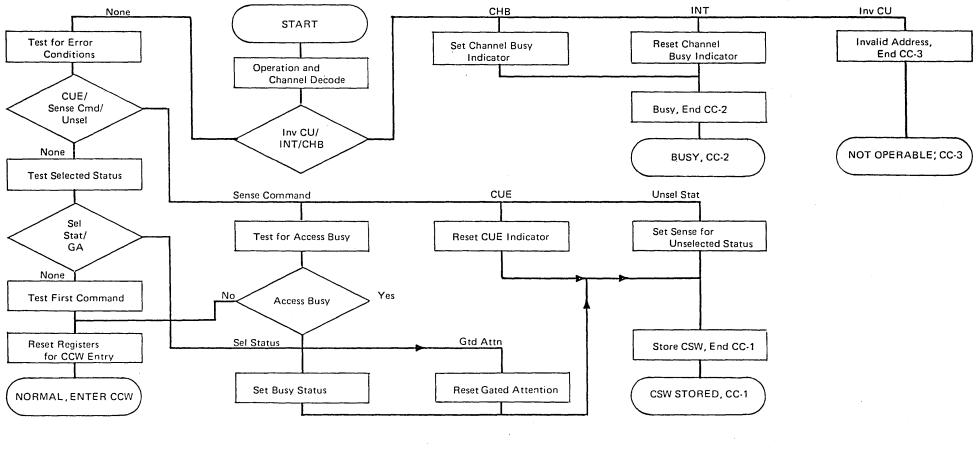

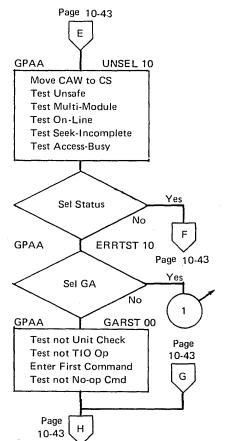

| data-out (interface line) 1-15         | disconnect in (interface line) 1-15                       | error checking and correction (ECC) 1-14                           | flow charts, IFA                                      |

| data parity check 7-43                 | disk adr reg, indicator 5-7                               | introduction 12-2                                                  | CCW entry 10-45                                       |

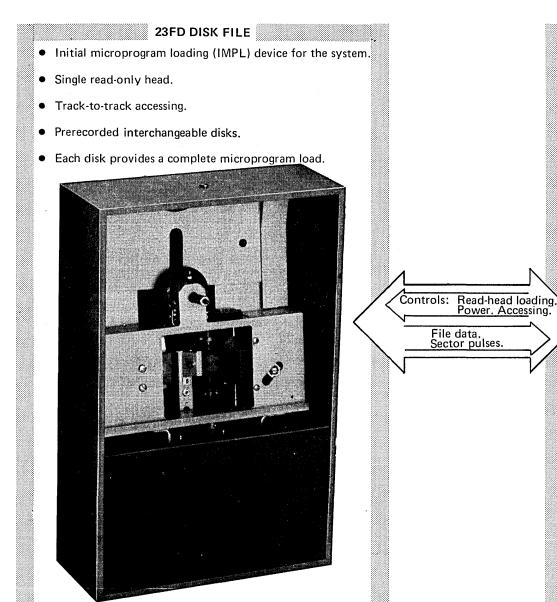

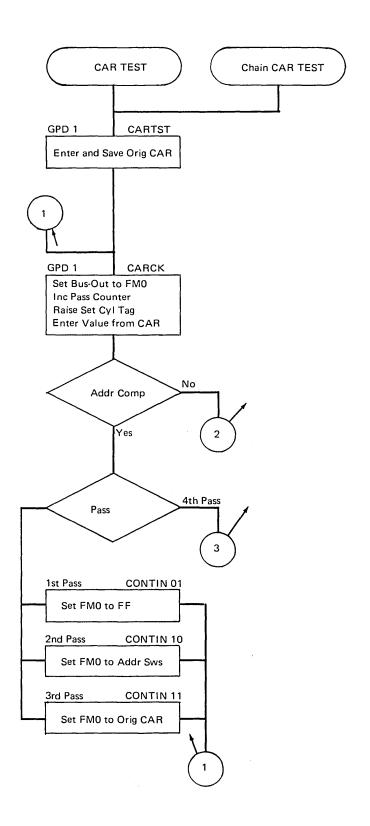

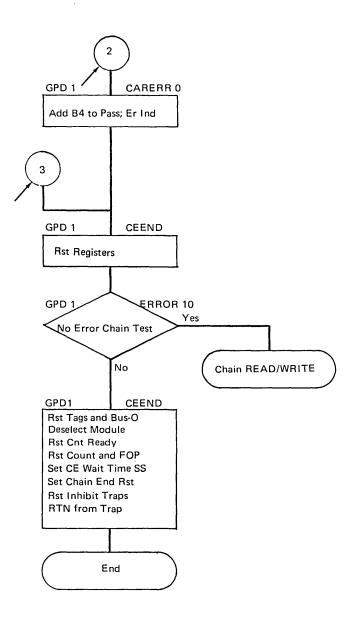

| data parity control, IFA 10-23         | disk drive, 23FD 6-2                                      | microprogram instruction retry 1-14                                | cylinder addr reg test 10-89                          |

| data rates channels 1-16               | disk pack, IFA/2319 10-4                                  | error indications, IFA/2319 10-87                                  | diag error trap 10-96                                 |

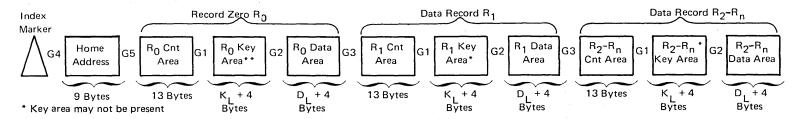

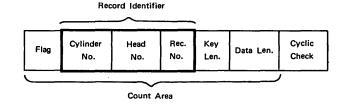

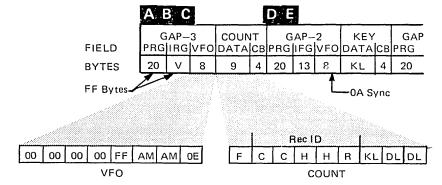

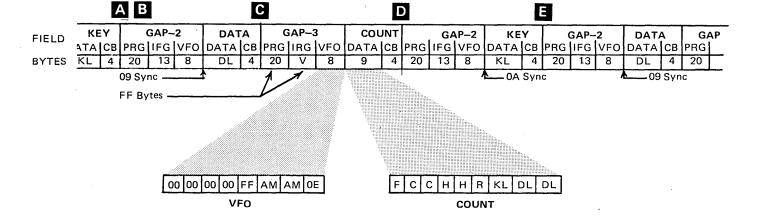

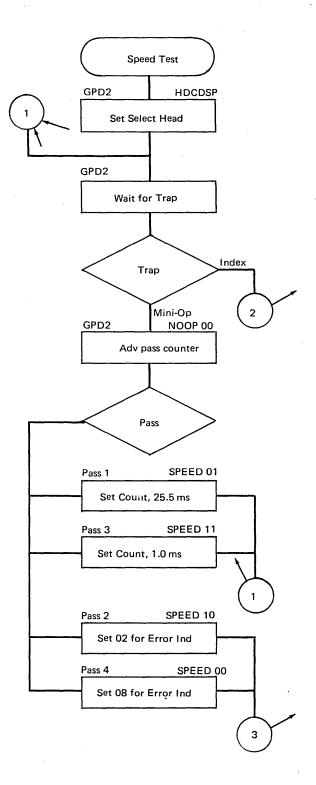

| data records, IFA 10-7                 | disk speed diag test 10-90                                | · ·                                                                | diag test decode 10-88                                |

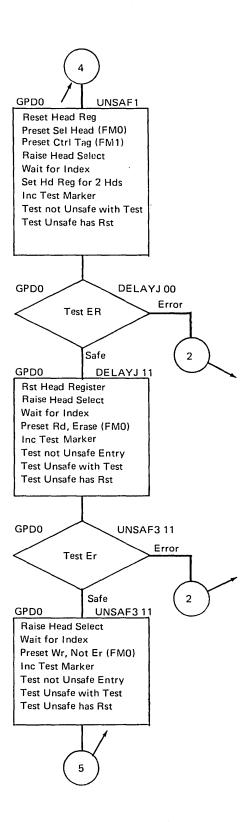

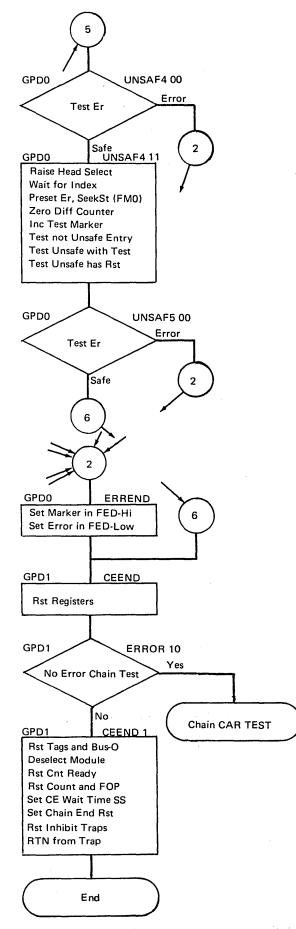

| data registers, 3215 7-33              | disk storage select logic 10-33                           | error messages 7-54                                                | diag unsafe test 10-91                                |

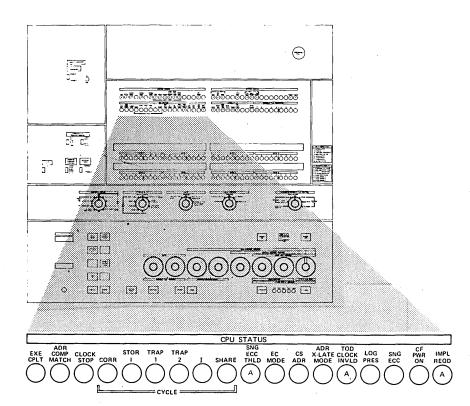

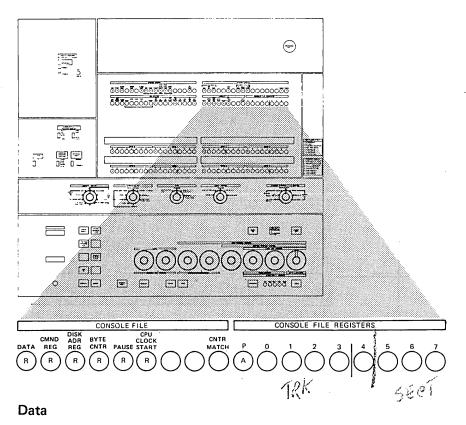

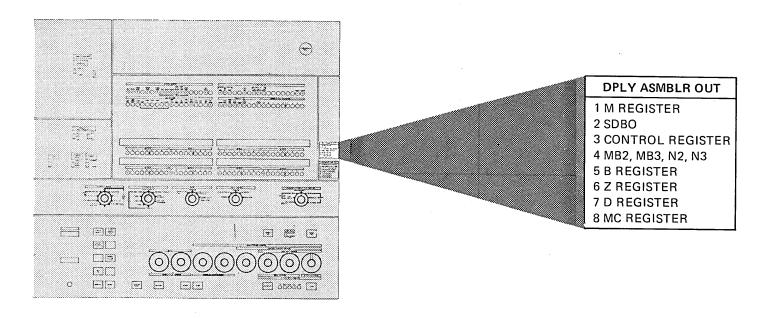

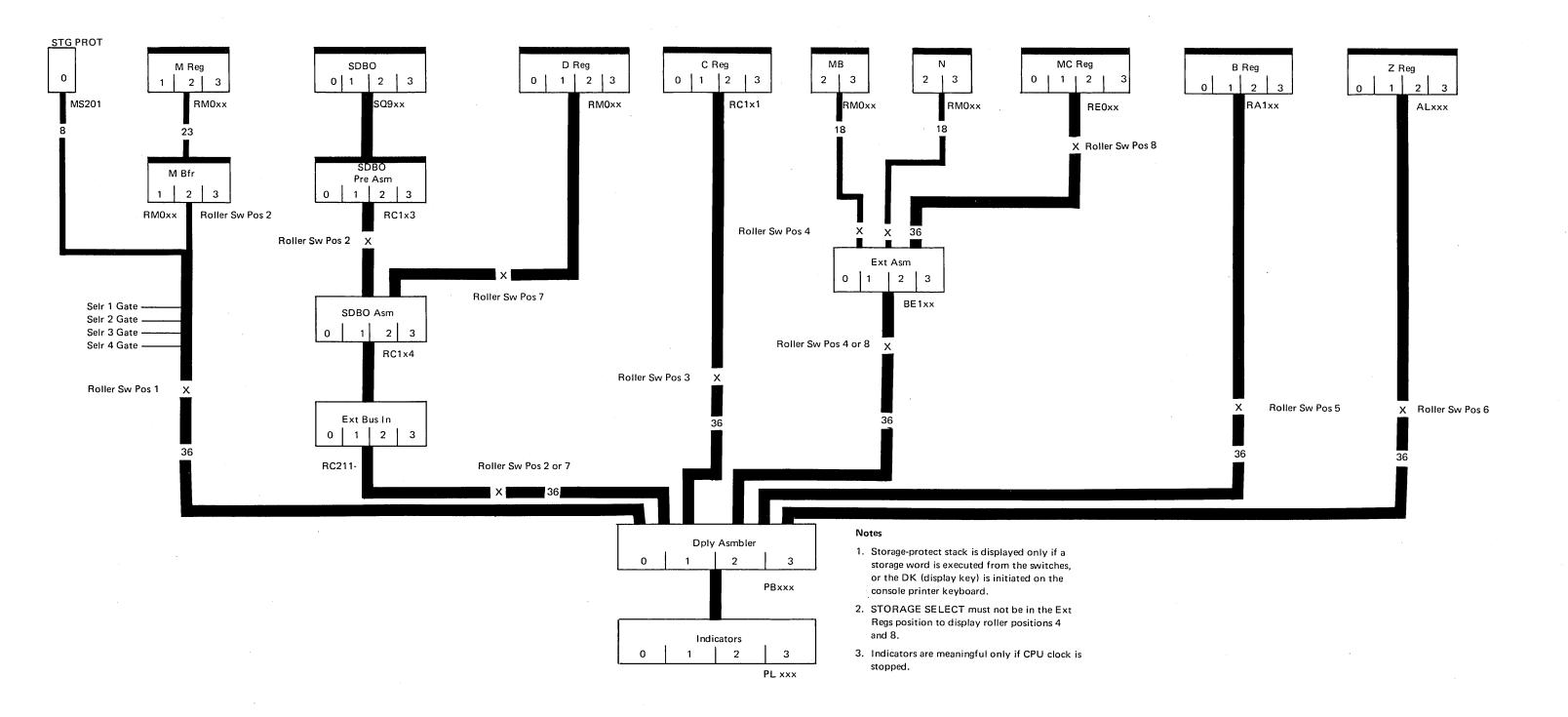

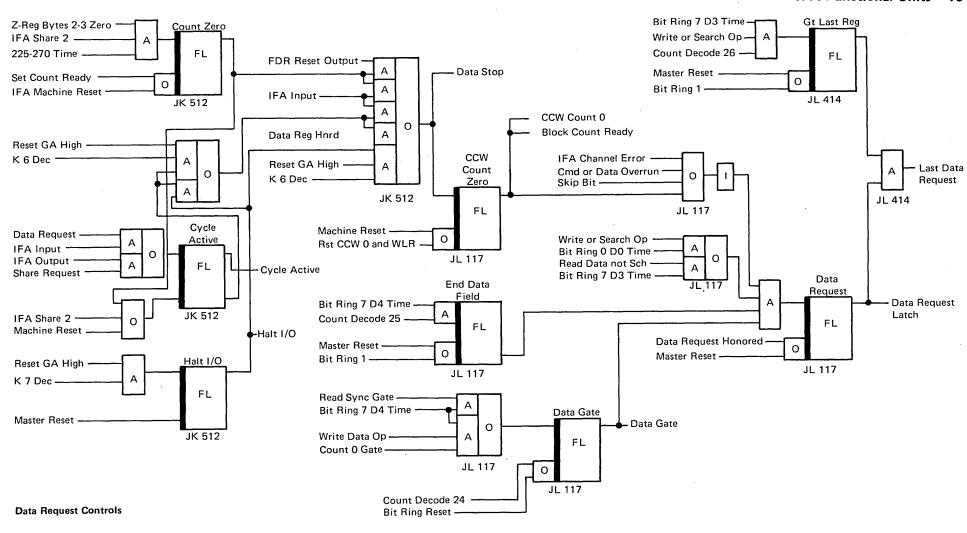

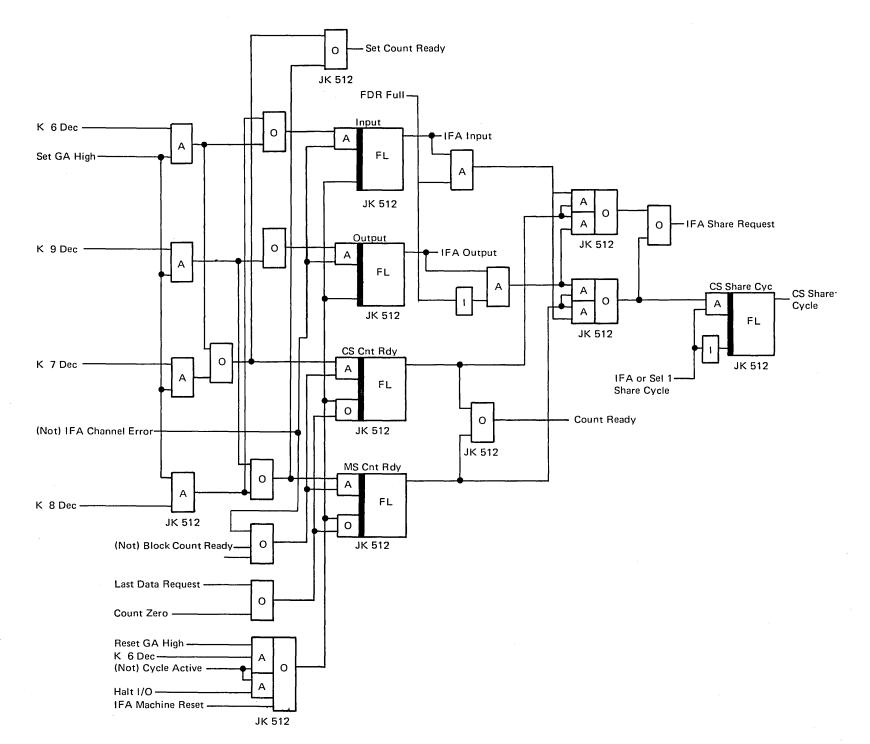

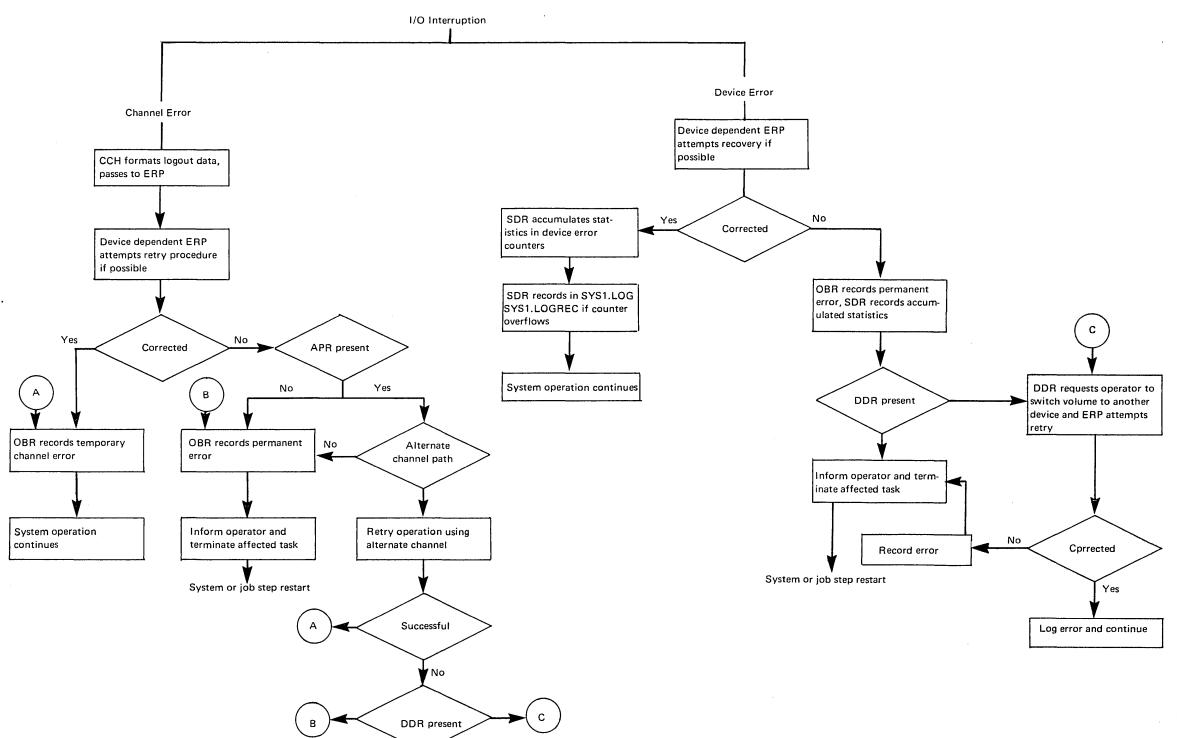

| data request controls, IFA 10-28       | display assembler out data flow 5-10                      | error-recovery procedures 12-25                                    | disk speed test 10-90                                 |

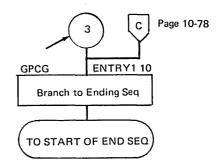

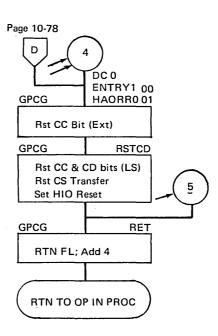

| data storage 10-4                      | display, key 5-27                                         | error retry 12-8, 12-15 error trap sequence, IFA 10-78             | ending sequence 10-76                                 |

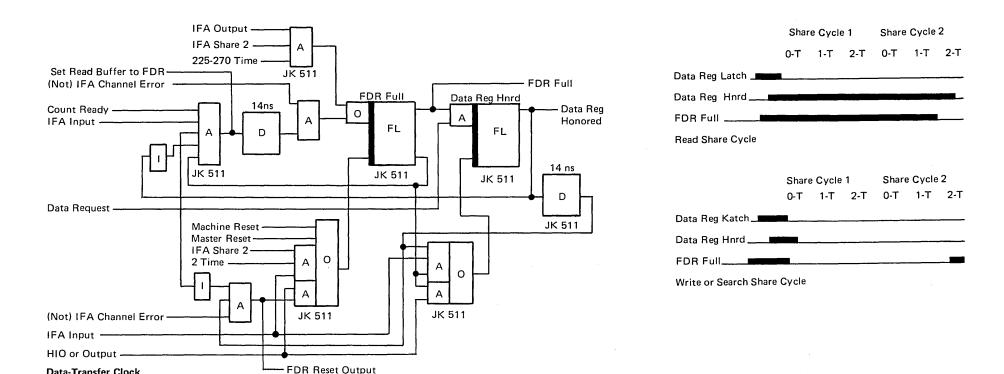

| data transfer clock, IFA 10-26         | display operations 7-54                                   | error trap test, IFA 10-76                                         | error trap 10-78                                      |

| data-transfer control 7-49             | DK-register (expls-7C) 2-22                               | exe cplt, indicator 5-6                                            | halt I/O 10-84                                        |

| data transfer controls, IFA 10-23      | DOS 12.25                                                 | expanded external assembler diagram 2-31                           | index trap 10-77                                      |

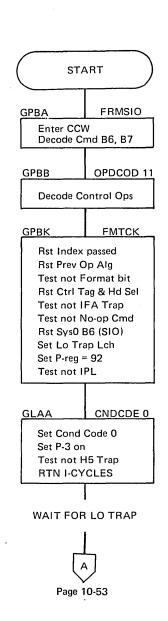

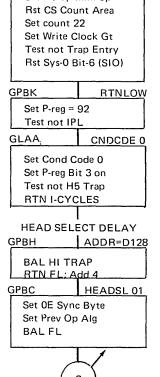

| DC distribution 11-12 - 11-15          | error-recovery procedures 12-25                           | expanded local storage                                             | initial selection 10-42                               |

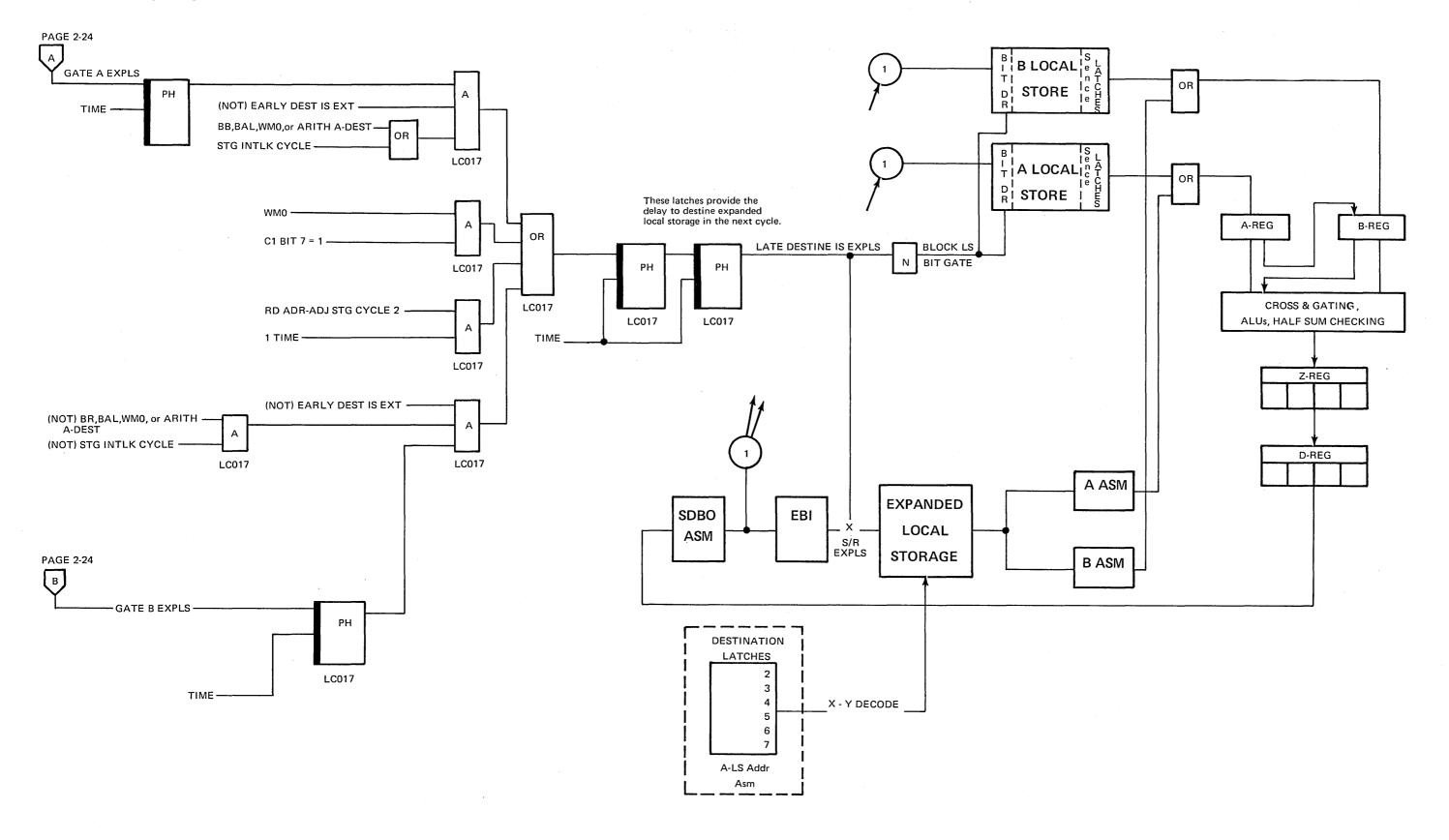

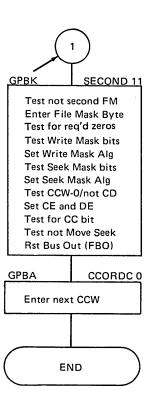

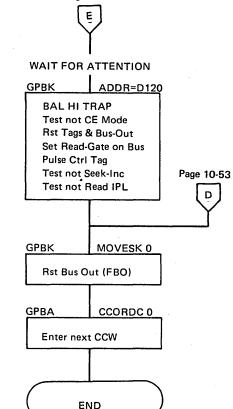

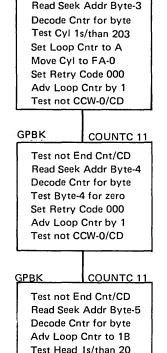

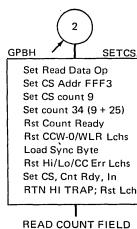

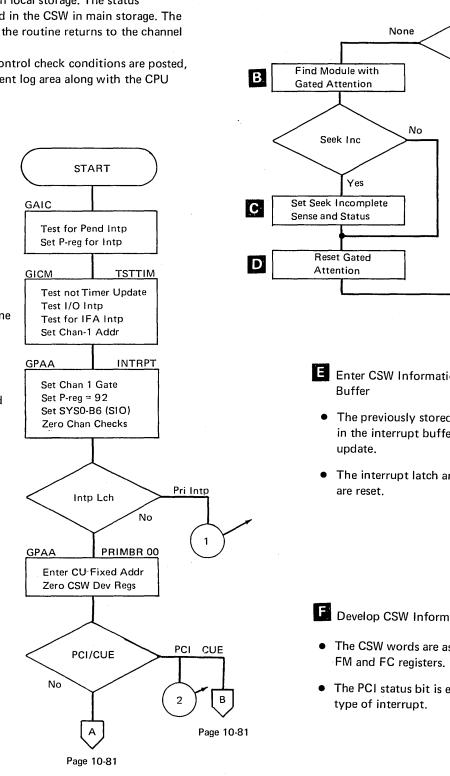

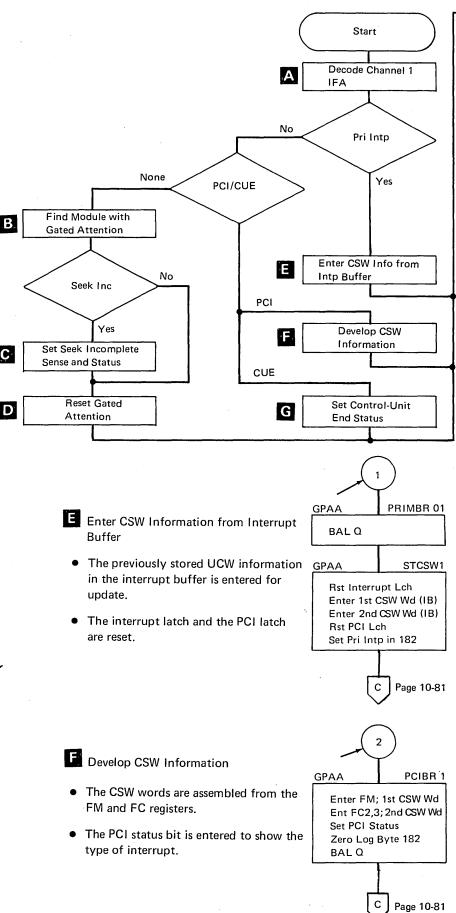

| decode CCW entry, IFA 10-45            | recovery management support 12-24                         | destination control diagram 2-28                                   | interrupt 10-80                                       |

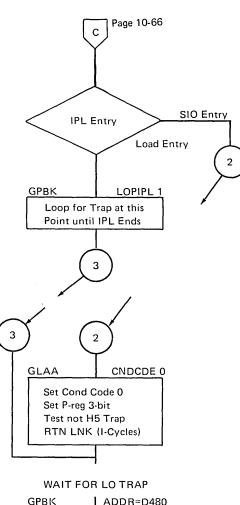

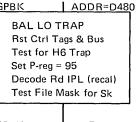

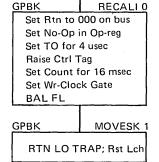

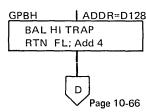

| delta 200 ns index, IFA 10-32          | restart facilities 12-26                                  | destination control diagram 2 20<br>destinations 2-27              | load IPL 10-66                                        |

| dependent logout 12-19                 | RMS 12-24                                                 | gating 2-20                                                        | read data 10-65                                       |

| destination addressing (L/S) 2-11      | DOS-checkpoint/restart 12-26                              | general information 1-13, 2-19                                     | read HA 10-64                                         |

| destination control diagram EXPLS 2-28 | DOS-emulator (ref to OS DOS compatibility)                | map 2-21                                                           | read/write diagnostic 10-92                           |

| destination look ahead (L/S) 2-11      | downshift, (stepper) motor 7-46                           | source gating 2-23                                                 | recalibrate 10-54                                     |

| device end (status bit 5) 7-62         | <b>13</b>                                                 | source gating 2.23                                                 | scan 10-73                                            |

| diag, external word 2-34               |                                                           | source gating examples 2-25, 2-26                                  | search ID 10-71                                       |

| diag stop, indicator 5-5               | EBCDIC                                                    | 20 m. v - Daniel                                                   | search KD 10-73                                       |

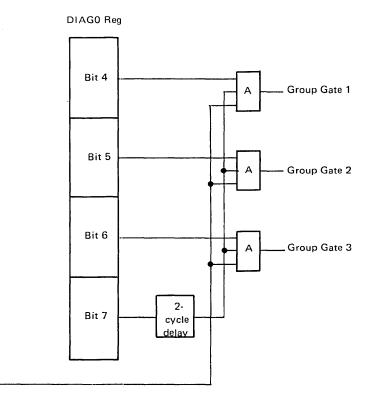

| liag 0 register 13-12                  | for 3210 graphics 7-10                                    | EXPLS 2-19                                                         | search key 10-72                                      |

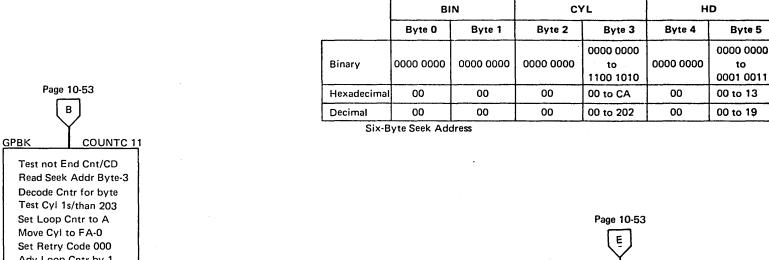

| liag 1 register 13-16                  | matrix code translation 7-29                              | EXTDST 12-10                                                       | seek commands 10-52                                   |

| diagnostic control SAR 13-24           | tilt/rotate location table 7-11                           | extended interruption information 12-19                            | seek tests 10-94                                      |

|                                        |                                                           |                                                                    | sense 10-48                                           |

| flow charts, IFA (continued) .               | H-register (continued)                            | I-cycles (continued)                            | incorrect length (IL) 7-61                  |

|----------------------------------------------|---------------------------------------------------|-------------------------------------------------|---------------------------------------------|

|                                              |                                                   | key register 2-61                               | independent logout 12-18                    |

| set file mask 10-51                          | halt device, IFA 10-84                            | microcode                                       | index control logic, IFA 10-32              |

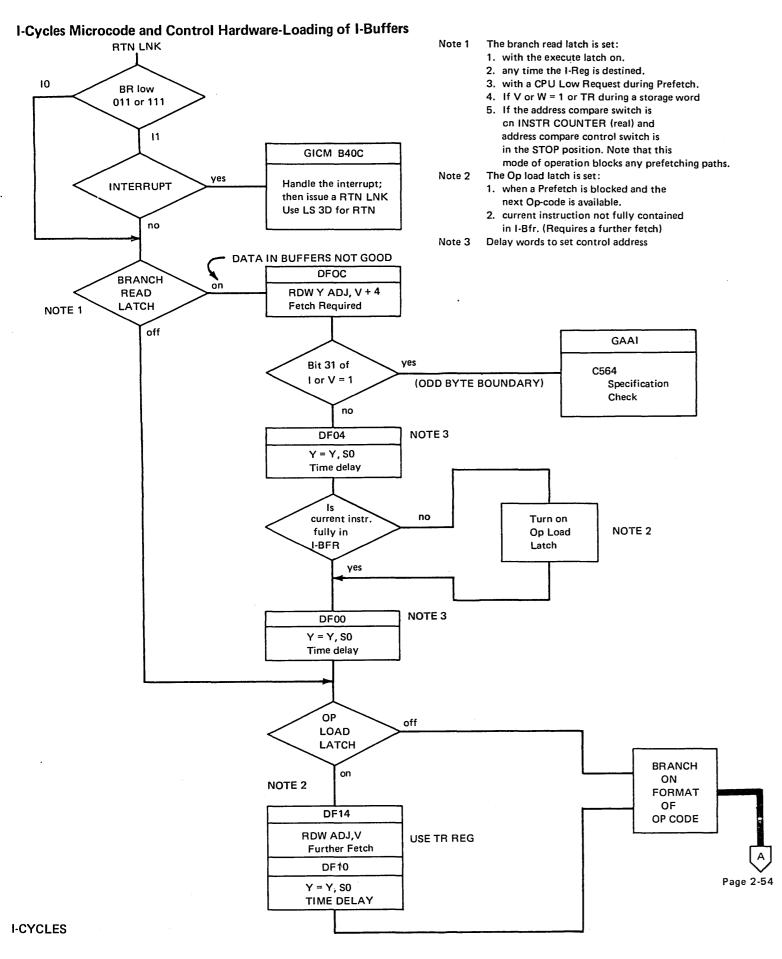

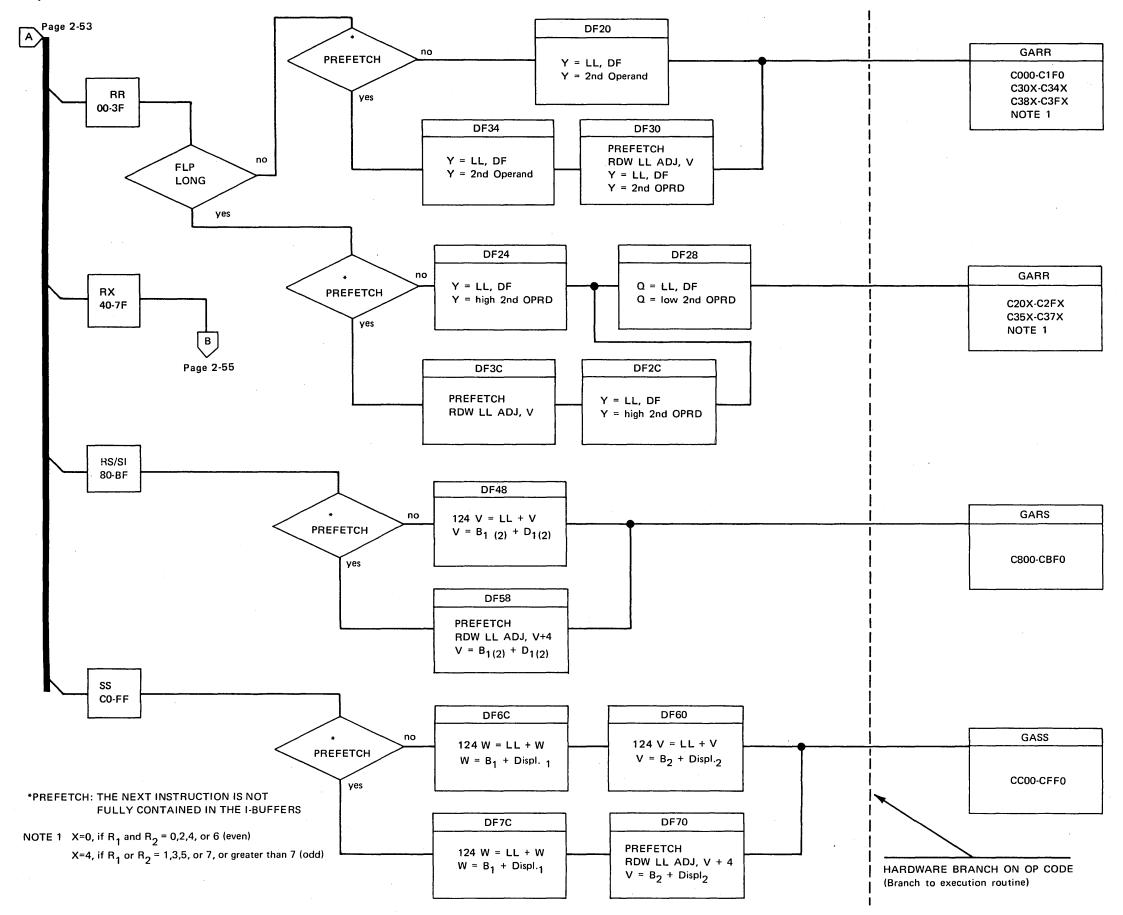

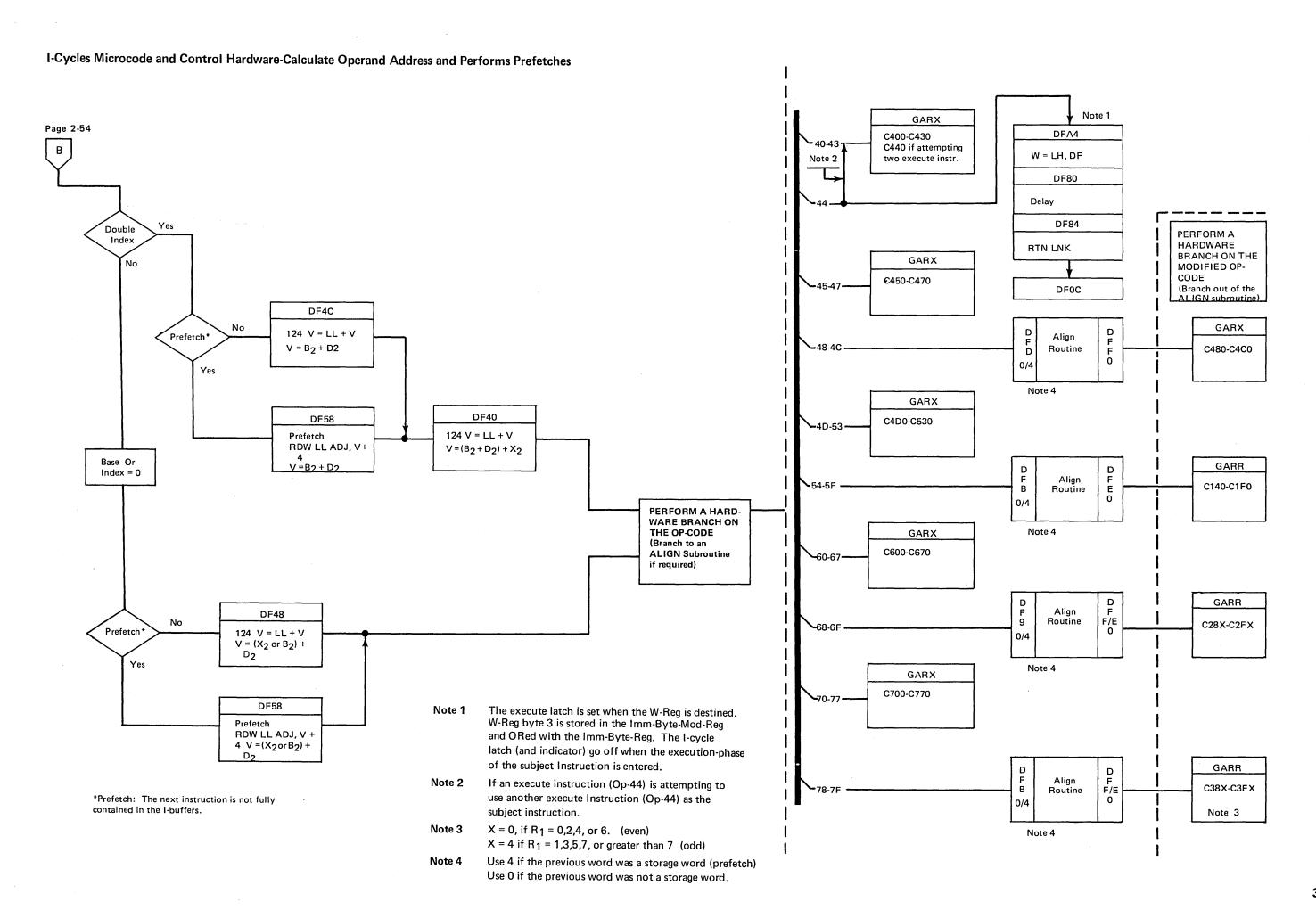

| space count 10-55                            | halt I/O operation, IFA 10-84                     | control hardware loading of I-buffers 2-53      | index controls, IFA 10-32                   |

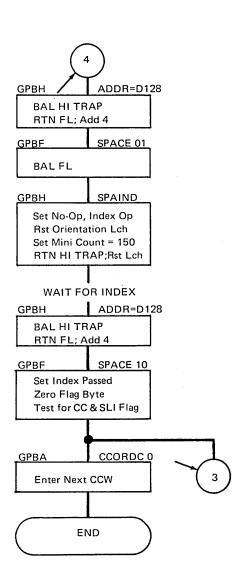

| test I/O 10-82                               | halt word selection (SDBO) 2-8                    | flow charts 2-53, 2-54, 2-55                    | index trap, IFA 10-77, 10-74                |

| write CKD 10-60                              | hand machine checks 12-23, 12-16                  | hardware functions 2-50, 2-51                   | indicator byte, IFA 10-24                   |

| write data 10-59                             | hardware functions, I-cycle 2-49                  | micro module assignment 2-52                    | indicators                                  |

| write HA 10-58                               | hardware recovery logic 12-3                      | op-register 2-60                                | adr comp match 5-6                          |

| lush-through check 1-12                      | head-select switch, IFA 10-86                     | perform prefetches 2-54, 2-55                   | adr X-late LRU inval 5-5                    |

| M (asynchronous fixed logout mask) 12-17     | high trap, IFA 10-74                              | prefetching (example) 2-69                      | adr-X-late mult match 5-5                   |

| MOD register, IFA 10-33                      | HM backup 12-10                                   | program modification 2-78                       | adr X-late no match 5-5                     |

| OP-register, IFA 10-21                       | HM retry 12-10                                    | RR instruction sequence 2-71                    | addr X-late mode 5-6                        |

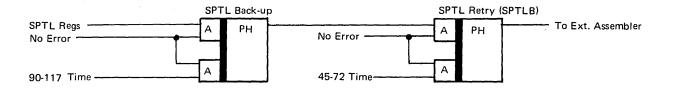

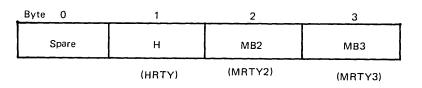

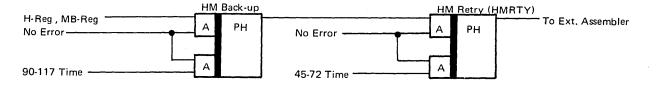

| orce count (odd) register L/S 2-15           | . HMRTY 12-10                                     | RX instruction sequence 2-72                    | byte cntr 5-7                               |