# Systems

# IBM System/370 Model 155 Functional Characteristics

This publication describes the organization, functional characteristics, and features of the IBM System/370 Model 155. System components are described, and consideration is given to the central processing unit, main storage, input/output channels, and the operator control and operator intervention portions of the system control panel.

This publication is intended for users and potential users of the Model 155. The reader is assumed to have a background knowledge of data processing systems.

# Preface

This is the Model 155 machine reference manual, providing information about system and component functions and addressing an audience made up primarily of system analysts, programmers, and operators. Assumed is a background knowledge of data processing systems and of the System/370 and System/360, as provided in *IBM System/* 370 Principles of Operation, GA22-7000, and *IBM System/* 360 Principles of Operation, GA22-6821.

The manual first looks at the system and its features in general, then at the processing unit and its functions. Channel characteristics are discussed in some detail, including channel control and implementation, subchannel and unit control word definitions, and subchannel addressing. This is followed by a description of system control panel functions and commonly used indicators, switches, and keys, then by information about the console I/O unit characteristics and the alter/display feature.

Detailed information about channel loading characteristics is in a separate manual: *IBM System/370 Model 155 Channel Characteristics*, GA22-6962.

#### Second Edition (January 1971)

This is a major revision of, and obsoletes, GA22-6942-0. Changes to the text are indicated by a vertical line to the left of the change; changed illustrations are denoted by the symbol  $\bullet$  to the left of the caption. Changes are continually made to the specifications herein; before using this publication in connection with the installation and operation of IBM equipment, refer to the latest System/360 and System/370 SRL Newsletter, GN20-0360, for editions that are applicable and current.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

This manual has been prepared by the IBM Systems Development Division, Product Publications, Dept. B98, PO Box 390, Poughkeepsie, N.Y. 12602. A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be sent to the above address.

©Copyright International Business Machines Corporation 1970, 1971

# Contents

| System Description                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Components                                                                                                                                                                                                                               |

| Standard Features                                                                                                                                                                                                                               |

| Optional Features                                                                                                                                                                                                                               |

| 3155 Processing Unit                                                                                                                                                                                                                            |

| CPU Data Flow 9                                                                                                                                                                                                                                 |

| Resets                                                                                                                                                                                                                                          |

| Error Checking                                                                                                                                                                                                                                  |

| CPU Instruction Retry11                                                                                                                                                                                                                         |

| Read-only Storage (ROS)11                                                                                                                                                                                                                       |

| Local Storage                                                                                                                                                                                                                                   |

| Buffer Control Unit                                                                                                                                                                                                                             |

| Machine Check Interruptions                                                                                                                                                                                                                     |

| Channel Characteristics                                                                                                                                                                                                                         |

| Channel Control                                                                                                                                                                                                                                 |

| Channel Implementation                                                                                                                                                                                                                          |

| Subchannels and Unit Control Words                                                                                                                                                                                                              |

| Channel Priority                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                 |

| System Control Panel.20System Control Functions20System Reset20Store and Display20Initial Program Loading21System Control Panel Controls22Operator Controls22Operator Intervention Controls26Customer Engineer Controls (Key Switch20           |

| System Control Functions20System Reset20Store and Display20Initial Program Loading21System Control Panel Controls22Operator Controls22Operator Intervention Controls26Customer Engineer Controls (Key Switch<br>and Meters)29Console I/O Unit30 |

| System Control Functions20System Reset20Store and Display20Initial Program Loading21System Control Panel Controls22Operator Controls22Operator Intervention Controls26Customer Engineer Controls (Key Switch<br>and Meters)29                   |

| 3215 Console Printer-Keyboard                |

|----------------------------------------------|

| Printer Functions                            |

| Forms Carriage                               |

| Keyboard                                     |

| EBCDIC Graphic Set                           |

| Operation                                    |

| Addressing                                   |

| Commands                                     |

| Sense Byte                                   |

| Status Byte                                  |

| Operator Controls                            |

| Attachment                                   |

| Alter/Display Feature                        |

| Selection                                    |

| Addressing                                   |

| Alter Operation                              |

| Display Operation                            |

| Test Mode                                    |

| Alter/Display Termination                    |

| Alter/Display Sense and Status Information   |

| Editing                                      |

| Alter/Display Manual Controls and Indicators |

| 3210 Console Printer-Keyboard Model 2        |

| Operation                                    |

| Addressing                                   |

| Commands                                     |

| Sense Byte                                   |

| Status Byte                                  |

| Operator Controls                            |

| Attachment                                   |

|                                              |

| Index . |  |  |  |  |  |  |  |  |  |  | • |  | • |  | • |  |  |  |  |  |  |  |  | • |  |  |  |  |  |  |  | • |  | 3 | 9 |

|---------|--|--|--|--|--|--|--|--|--|--|---|--|---|--|---|--|--|--|--|--|--|--|--|---|--|--|--|--|--|--|--|---|--|---|---|

|---------|--|--|--|--|--|--|--|--|--|--|---|--|---|--|---|--|--|--|--|--|--|--|--|---|--|--|--|--|--|--|--|---|--|---|---|

IBM System/370 Model 155

The IBM System/370 Model 155 is a high-performance data processing system that provides the reliability, availability, and convenience demanded by business and scientific users, as well as by users with applications in communications or control.

The Model 155 includes the advantages, characteristics, and functions pioneered by the IBM System/360, plus others defined for the System/370 in *IBM System/370 Principles of Operation*, GA22-7000. The high performance of the Model 155 can be attributed to:

- 1. Access to 16 main-storage bytes in parallel.

- 2. Local storage used for CPU (general and floating-point registers) and I/O applications.

- 3. High-speed buffer storage that stores currently used sections of main storage for faster accessing during processing.

- 4. Read-only storage (ROS); this control storage contains the microprograms (ROS control words) that control CPU and I/O operations.

- 5. Overlap, where possible, of the instruction and execution portions of CPU operations.

- 6. Overlap, where possible, of CPU and I/O operations.

- 7. Retry facilities at the CPU, channel, and control unit level.

- 8. An optional alter/display feature that provides an easy method to store small program loops or to make changes to programs already in storage.

Programming support for the System/370 Model 155 is provided by System/360 Operating System (OS), MFT and MVT, as well as System/360 Disk Operating System (DOS). The Model 155 is planned to take advantage of the gains possible because of this support.

The Model 155 has a major machine cycle time of 115 nanoseconds. Main-storage data flow is 16 bytes (one quadword). Main-storage cycle time is 2.07 microseconds. However, the high-speed buffer storage operates to make the *effective* system storage cycle time one-third to one-quarter of the actual main-storage cycle time.

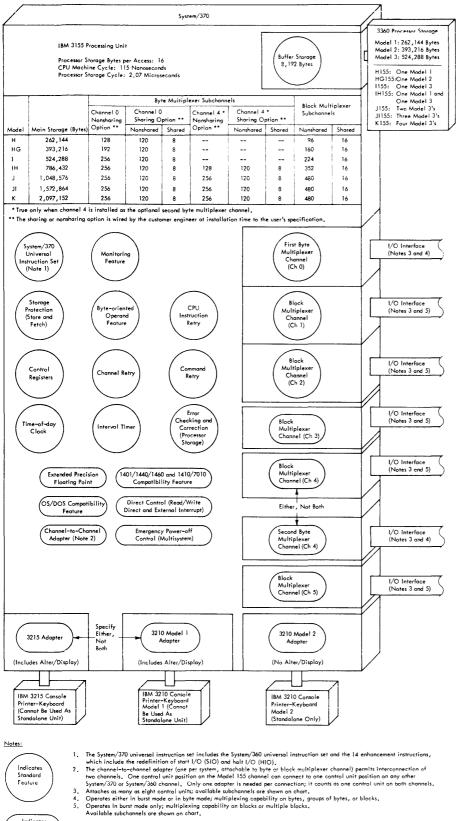

Seven capacities of main storage are available, with error checking and correction (ECC) implemented for the processor storage units; see Figure 1.

For input/output operations, the system may have one byte multiplexer channel and as many as five block multiplexer channels, or two byte multiplexer channels and as many as four block multiplexer channels. See Figure 1.

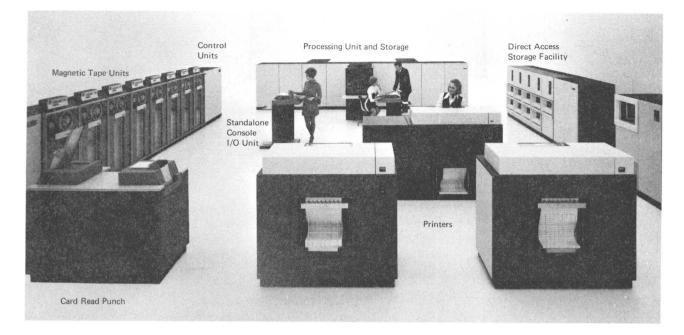

### SYSTEM COMPONENTS

The major components in a System/370 Model 155 are the 3155 Processing Unit, which contains arithmetic and logical circuits, read-only storage, local storage, and at least three

input/output channels; and 3360 Processor Storage. Input/output devices are attached to the channels by control units.

### Standard Features

1

The standard features for any IBM 3155 Processing Unit include:

System/370 Universal Instruction Set Monitoring Feature Storage Protection (Store and Fetch) Byte-oriented Operand Feature High-speed Buffer Storage Error Checking and Correction (Processor Storage) Time-of-day Clock Interval Timer Instruction Retry Channel Retry Command Retry First Byte Multiplexer Channel (Ch 0) Block Multiplexer Channel (Ch 1) Block Multiplexer Channel (Ch 2)

### System/370 Universal Instruction Set

The System/370 universal instruction set includes the System/360 universal instruction set and 14 enhancement instructions. Two instructions, halt device (HDV) and modified halt I/O (HIO), are explained in *IBM System/360 Principles of Operation*, GA22-6821. The following enhancement instructions are discussed in *IBM System/370 Principles of Operation*, GA22-7000:

Compare Logical Characters under Mask (CLM) Compare Logical Long (CLCL) Insert Characters under Mask (ICM) Load Control (LCTL) Move Long (MVCL) Set Clock (SCK) Shift and Round Decimal (SRP) Start I/O Fast Release (SIOF); executed as start I/O on the Model 155 Store Channel ID (STIDC) Store Characters under Mask (STCM) Store Clock (STCK) Store CPU ID (STIDP) Store Control (STCTL)

#### Storage Protection (Store and Fetch)

Storage protection, both store and fetch, is standard for the Model 155. The store and fetch protection features make it possible to protect the contents of main storage from destruction or misuse. The store protection feature is described in *IBM System/360 Principles of Operation*, GA22-6821.

• Figure 1. System/370 Model 155 Configurator

Indicates Optional Feature

# Monitoring Feature

The monitoring feature, with its associated instruction monitor call (MC), provides a means of selectively recording designated events in the execution of a program. See *IBM System/370 Principles of Operation*, GA22-7000.

### Byte-oriented Operand Feature

The byte-oriented operand feature allows the main-storage operands of unprivileged instructions to appear on any byte boundary without causing a specification exception and a program interruption. This feature does not apply to alignment of instructions or channel command words (CCW's). The operation performed when the byte-oriented operand feature is used is called boundary alignment. Boundary alignment causes instruction processing to proceed at less than optimal speed; severe performance degradation may result when operand boundaries are unaligned. For details, see *IBM System/360 Principles of Operation*, GA22-6821.

# Error Checking and Correction (Processor Storage)

Error checking and correction circuitry for the processor storage elements automatically corrects single-bit errors (by doubleword) and automatically detects all double-bit errors (by doubleword) on data in main storage.

### Time-of-day Clock

A binary 52-position time-of-day (calendar) clock is provided for use as a time stamp for error data records, job accounting, teleprocessing, and other functions. The clock is set by the set clock instruction, which causes the current clock value to be replaced by the operand designated by the instruction. The security switch on the control panel is provided to prevent inadvertent changing of the clock value. The store clock instruction is used to inspect the clock. The total clock cycle is approximately 142 years. For detailed information, see *IBM System/370 Principles of Operation*, GA22-7000.

### Interval Timer

The interval timer is functionally equivalent to the timer described in *IBM System/360 Principles of Operation*, GA22-6821, except that the Model 155 timer resolution is 3.3 milliseconds. Bit position 23 is updated every 1/300th of a second by internal timing circuits, rather than by line-frequency power. A complete cycle of the Model 155 timer requires approximately 15.5 hours.

### Instruction Retry

Intermittent failures reduce the effective reliability of data processing systems. The ability to recover from intermittent failures is provided through retry techniques. CPU retry is done by microprogram routines that save the source data before it is altered during an operation. When an error is detected, a microprogram routine returns the CPU to the beginning of the operation or to a point in the operation that was correctly executed, and the operation continues from there. The ROS routines are supplemented in operation by additional machine logic.

### Channel Retry

Channel error retry is done with machine-logic CPU retry procedures plus program-logic recovery action. Where possible, channel instructions are retried using the existing CPU retry machine logic, provided that the error occurs before the I/O command is issued to the I/O device. When the device receives the command, the channel presents an extended channel status word (ECSW) to the program if an error occurs. The ECSW contains information for retry of the channel instruction by programs using modified error recovery procedures. When a channel-only or channel-CPU error occurs, the entire CPU and all channels perform a logout and CPU retry is entered. Channels affected by the error provide a channel status word (CSW) and extended channel status word (ECSW) via an interruption or a condition code 1 CSW store operation.

### Command Retry

Command retry is a control-unit initiated procedure between the channel and the control unit. No I/O interruption is required. The number of retries is device-dependent.

#### First Byte and Block Multiplexer Channels

Channels 0-2, the first byte multiplexer channel and the first two block multiplexer channels, are provided with the basic Model 155.

#### **Optional Features**

The optional features for the 3155 Processing Unit include:

**Extended Precision Floating Point**

Direct Control

OS/DOS Compatibility

- 1401/1440/1460 and 1410/7010 Compatibility Feature

- Channel-to-Channel Adapter

- Emergency Power-off Control (Multisystem)

- Block Multiplexer Channel (Ch 3)

- Block Multiplexer Channel (Ch 4) or Second Byte Multiplexer Channel (Ch 4)

- Block Multiplexer Channel (Ch 5)

- 3210 Model 1 Adapter (for 3210 Console Printer-Keyboard Model 1) or 3215 Adapter (for 3215 Console Printer-Keyboard); one must be specified

- 3210 Model 2 Adapter (for standalone 3210 Console Printer-Keyboard Model 2); the 3215 Console Printer-Keyboard is not available as a standalone console I/O unit

### Extended-precision Floating-point Feature

The extended-precision floating-point feature includes instructions designed to handle extended-precision (28-hexdigit) floating-point operands. Extended-precision operands may also be rounded to long-precision format, and longprecision operands may be rounded to short-precision format. For additional details, see *IBM System/360 Principles of Operation*, GA22-6821.

# Direct Control

The direct control feature provides two instructions, read direct and write direct, and six external interruption lines. The read and write instructions provide for the transfer of a single byte of information between an external device and the main storage of the system. Each of the six external signal lines, when active, sets up the conditions for an external interruption. Additional details are in *IBM System/360 Direct Control and External Interrupt Features, OEMI*, GA22-6845.

# **OS/DOS Compatibility Feature**

The OS/DOS compatibility feature allows the user to run System/360 Disk Operating System (DOS) control programs (including multiprogramming) under control of the System/360 Operating System (OS) in a multiprogramming environment. Refer to *IBM System/360 Operating System: DOS Emulator Planning Guide*, GC24-5076.

# 1401/1440/1460 and 1410/7010 Compatibility Feature

The 1401/1440/1460 and 1410/7010 compatibility feature, in conjunction with either of two integrated emulator programs under OS or two integrated emulator programs under DOS, allows the Model 155 to execute programs and programming systems originally written for other systems. The compatibility feature adds special instructions and internal logic to the Model 155. Either of the two integrated emulator programs uses these facilities and the available instruction sets to execute 14XX-type instructions in a multiprogramming environment. Unlike standalone emulators, integrated emulators must share the CPU and I/O devices with the operating system. In a system with multiprogramming capability, however, the time lost waiting for a shared resource is much less (on the average) than the time lost by a standalone emulator waiting for its I/O operations to be completed. This reduction in system wait time increases total system throughput.

# Channel-to-Channel Adapter

The channel-to-channel adapter feature allows the establishment of a loosely coupled multisystem via one control-unit position on the respective channels of the individual systems. Only one adapter may be installed on the Model 155; the attachment may be on either the byte or the block multiplexer channel.

The Model 155 channel-to-channel adapter provides features in addition to those offered on the System/360 adapter. Under program control, the channel-to-channel adapter can operate as two independent control units with five additional commands available to the programmer. Expanded checking facilities are also provided. Programs written for the System/360 adapter may be run if the additional features are not enabled.

# Emergency Power-off Control (Multisystem)

Emergency power-off control is required on only one of the processing units, normally the largest, in any installation composed of more than one cable-connected processing unit and/or cable-connected units that can be operated off-line. The emergency power-off feature interconnects EPO switches to provide, in effect, a single EPO switch in a room or area.

# Byte and Block Multiplexer Channels

The byte and block multiplexer channels are described in detail under "Channel Characteristics."

# Console I/O Units

The console I/O units are described under "Console I/O Unit" and "3210 Console Printer-Keyboard Model 2." Programming information is also included.

# **3155 PROCESSING UNIT**

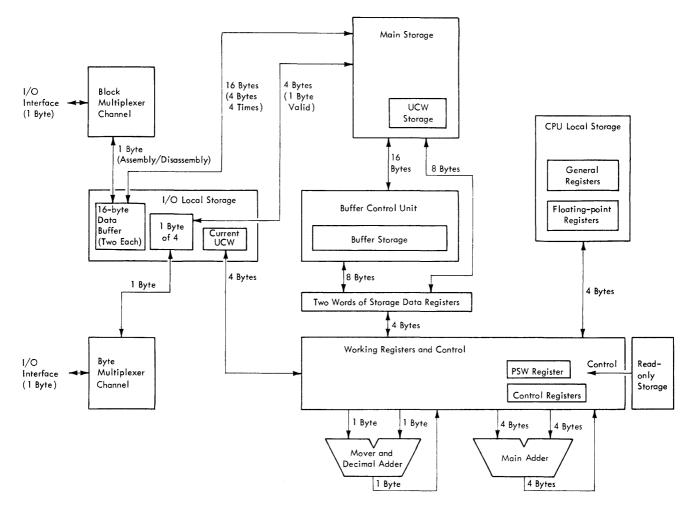

The CPU contains the elements required to decode and execute the instructions and emulator programs featured on the system. Included are the data gates and buses, working registers, adder, one-bit shifter, four-bit shifter, mover, byte counters, CPU and I/O local storage, and I-fetch logic. The CPU machine cycle is 115 nanoseconds.

The general and floating-point registers are in the 64-word CPU local storage; another 64 words of this storage are used for certain channel control words. A second local storage (I/O local storage) is used by the channels for additional control words and for block multiplexer channel data buffering.

In the I-fetch area, three 1-word instruction buffers enable the majority of I-fetches to overlap the execution time of the previous instructions.

Most operations in the basic system are retriable. A machine check error during I-fetch causes the I-fetch to be retried. The manner in which the instruction is retried depends on the instruction. Some instructions do not change the original data in the registers until the last cycle of execution; these instructions are retried from the

beginning. Other instructions change source data in the registers and are retried from a checkpoint, using the intermediate results.

All CPU functions and data gates are controlled by a ROS control word; that is, they are under microprogram control.

### **CPU Data Flow**

The CPU contains three basic data paths: a four-byte path, a one-byte path, and a path for instruction data in the I-fetch logic. In addition, certain other registers or counters attached to the data flow paths are used to retain status or control information. See Figure 2.

# Four-byte Data Flow

The four-byte data path in the CPU enables the processing of the fixed-point and floating-point instructions as well as the enhancement instructions. This data path includes the external switch, working registers, adder and shifters, CPU and I/O<sup>1</sup>local storage, and adder output bus.

The external switch is a four-byte gate through which data enters the CPU. The A-, B-, C-, and D-working registers

are capable of storing four bytes of operand data used during instruction execution or a 24-bit storage address for such functions as instruction counter updating.

The main adder is a four-byte binary adder capable of performing arithmetic or logical functions or one-bit shifts. Fixed data may be inserted by the microprogram. The main adder can accept two 4-byte input operands from the working registers or local storage and can produce a four-byte result on the adder output bus. The adder also can do a three-byte operation simultaneously with, but independently of, a one-byte operation.

The CPU contains a one-bit shifter and a four-bit shifter. The one-bit shifter is attached to the left input of the adder. A four-byte operand may be shifted one bit left or right, or remain unaltered, as it enters the adder. The four-bit shifter provides a four-byte data path parallel to the adder. An operand gated to the four-bit shifter may be shifted right or left one digit, or it may be passed unaltered to the adder output bus. The adder output bus provides a path from the adder or from the four-bit shifter to the working registers, the status logic, and the local storage in

the CPU; it also provides an exit path for data from the CPU to the local storage or to the console.

The local storage address register (LSAR) retains the CPU local storage address when CPU or channel references are made to data in CPU local storage; the second LSAR is used when the channel references its section of CPU local storage.

The CPU contains two storage address registers (SAR's) to easily transfer control from CPU mode to I/O mode of operation. The 36-bit CPU SAR accepts the three-byte CPU storage address and the protection key when an operand is fetched or stored, or during I-fetches. The 36-bit I/O SAR accepts the three-byte I/O main-storage address and the I/O storage protection key when a channel request to main storage is made.

# One-byte Data Flow

The one-byte data paths in the CPU provide the capability of processing variable-field-length instructions, performing certain emulations, and implementing other functions that require the handling of one byte or one digit of data at one time. The basic one-byte data paths include byte ingates and outgates to the A- and C-registers, certain buses, and the mover. Additionally, the arithmetical-logical unit (ALU) function register and the byte counters are used to provide function and byte gate controls. Operations that use the one-byte data flow area are controlled by ROS microprograms.

The mover is a one-byte binary adder with two 1-byte inputs and one 1-byte output. The mover may be used as a one-byte data path, or it may perform logical (such as ANDing), decimal arithmetic, or binary arithmetic functions.

# I-fetch Data Flow

The CPU contains instruction fetch components and controls that provide the capability of prefetching instruction data from main storage during I-fetch operations. The CPU can also overlap I-fetch sequences with the CPU processing time of previous instructions. I-fetch components include instruction buffers, instruction counters, incrementer, and backup registers. I-fetch sequences may overlap CPU operations if main storage is not busy when the fetch sequence starts. CPU and I/O operations overlap after a channel is started and until a breakin occurs. Because I/O operations share CPU data paths to and from storage, CPU operations are suspended when an I/O storage request occurs.

Three 1-word instruction buffer registers (IB1, IB2, and IB3) are used to buffer instruction data in the CPU. During an I-fetch, instruction words from main storage are set into IB2 and IB3. The instructions are later sent to IB1 and are decoded from there. Backup registers provide the capability

of saving the op code and instruction data from IB1 for instruction retries.

Two instruction counter registers (IC1 and IC2) retain the storage address of the instruction words in IB1 and IB2. As the instruction words move from IB2 to IB1, the associated storage addresses move from IC2 to IC1. The storage address for the next I-fetch is supplied by IC1 and the incrementer. The instruction counter backup register saves and restores the contents of IC1 during an instruction retry. The incrementer updates (increments) the current instruction address in IC1 for the next I-fetch; the storage address is incremented +4 or +0, depending on whether the next sequential instruction or a refetch of the same instruction is required.

# PSW Register

The two-byte PSW register is used to retain bytes 0 and 1 of the current PSW. These bytes contain the system mask and the XWMP bits used to control current CPU functions. The remainder of the current PSW is retained in CPU local storage except for the condition code, the instruction length code, the instruction address, and the protection key. The condition code bits are in two CPU status triggers, the instruction length code is in the I-fetch status register, the instruction address is in IC1, and the protection key is in CPU SAR0-7. When an interruption occurs, the old PSW is assembled from the various areas of the CPU and is stored in main storage. The new PSW is fetched from main storage, disassembled, and distributed to the various CPU areas.

# Resets

# System Reset

System reset is either generated by each power-on sequence or by pressing the system reset key on the system control panel. System reset initiates a microprogram routine that resets the CPU system, including the CPU and I/O local storage. Reset validates (places good parity in) all the registers in the data flow. It also validates the buffer storage and index array by setting the buffer contents, row addresses, and valid bits to 0's, and by setting the OK bits to 1's. The 64 words of CPU local storage are validated by reading the local storage words, correcting parity on them (if necessary), and storing those words back into CPU local storage. The machine is set to process instructions normally; that is, with no pending exceptions or retry conditions present.

If (and only if) the enable system clear key is held in while the system reset key is pressed, a microprogram routine clears main storage and the storage protection key storage to 0's with good parity. This is an additional function; the system reset function remains unaltered.

### Hardware Reset

Hardware reset is either generated by the system reset function or by pressing the hardware reset key on the system control panel. This function is the same as for system reset, except that no validation is done.

Holding in the enable system clear key while the hardware reset key is pressed has no effect on the hardware reset function.

### Check Reset

This function resets the error registers in the CPU and the channels. Check reset is either generated by the hardware reset function or by pressing the check reset key on the system control panel.

### **Error Checking**

Every data path in the CPU is parity-checked by byte, either directly or indirectly. The adder is parity-checked in three levels: halfsum, carry, and fullsum checks. Every data path between the CPU and main storage is also paritychecked. In the BCU, input data and control information is parity-checked as it enters and again before it leaves. Error correction codes apply to data stored in and fetched from main storage; single- and double-bit error detection and single-bit error correction are performed.

### **CPU Instruction Retry**

Intermittent failures reduce the effective reliability of data processing systems. The ability to recover from intermittent failures and thereby increase the effective reliability of the Model 155 is provided through retry techniques. Instruction retry is accomplished by microprogram routines that save source data before it is altered during an operation. When an error is detected, the Model 155 enters a microprogram routine that returns the CPU to the beginning of the operation or to a point in the operation that was correctly executed; the operation proceeds from there. The retry procedures use additional system logic as well as the retry microprograms.

Instruction retry operates on all but four instructions: diagnose, test and set, read direct, and write direct. If an error occurs during the execution of an I/O instruction, the execution is checked to determine whether the retry threshhold has been passed. If the instruction execution has not passed predetermined points, the instruction is retried automatically without program assistance. A machine check interruption is taken at the completion of a successful retry for recording purposes. If the instruction execution has progressed too far to be retried, an I/O interruption is taken or the condition code is set to indicate that a CSW and an ECSW have been stored because the I/O operation was not started. The appropriate device-dependent error recovery routine can be scheduled to take the required recovery action. Generally, if an error in the execution of the start I/O instruction occurs before the I/O device becomes involved on the I/O interface, instruction retry is still possible.

### Read-only Storage (ROS)

All channel and CPU operations are under microprogram control. During each CPU cycle, microorders decoded from the ROS control word provide data gates and function controls to the CPU or the channels. A new ROS control word is used on each CPU cycle.

The CPU and channels share read-only storage; controls are the same in the CPU or I/O mode. The CPU and each channel operate within their own microprograms and share CPU logic by switching control at specified points in the microprograms. The change of control is called breakin. When a breakin occurs, the current microprogram is temporarily halted while another microprogram is given control.

### Local Storage

The CPU contains two local storages: one for exclusive use by the channels and one shared by the CPU and channels.

CPU local storage contains the 16 general registers and the 4 floating-point registers, as well as control areas and certain UCW storage.

I/O local storage contains storage areas for data buffering on the block multiplexer channels, as well as working areas for the byte multiplexer channels.

### **Buffer Control Unit**

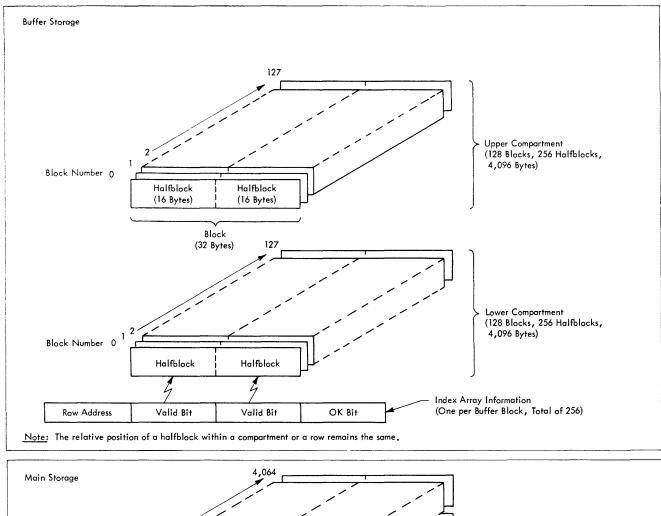

The buffer control unit (BCU) provides the interface between CPU or channels and main storage. The BCU contains an 8,192-byte high-speed buffer storage to provide high-speed access on CPU fetch operations. BCU functions include loading areas of main storage currently being used by the CPU into buffer storage, maintaining address references to the buffer data in the index array, and determining which buffer storage locations to make available for new data when the buffer storage is full.

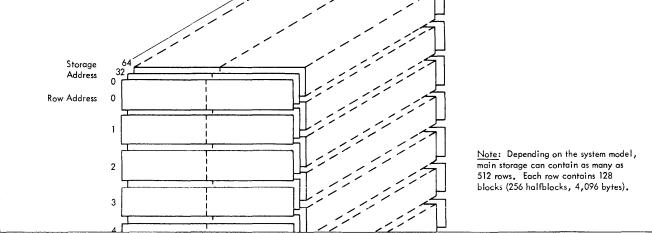

Main storage is divided into 4,096-byte rows for BCU addressing purposes. Each row contains 128 thirty-two-byte blocks; each block contains two halfblocks with 16 bytes each. One halfblock (16 bytes) is read during each main-storage access. Depending on the model, main storage includes from 32 rows to as many as 512 rows. See Figure 3.

### Buffer Storage

Buffer storage contains an upper and a lower 4,096-byte compartment. Each buffer compartment is divided into blocks and halfblocks, just as the main-storage rows. The

Figure 3. Buffer Storage Layout

buffer storage access width is one halfblock (16 bytes). Space in the buffer is reserved on a block basis but is loaded one halfblock at a time. A buffer block is assigned when either halfblock of a block in main storage is fetched by the CPU and is set into the buffer. The remaining halfblock is set into the buffer only if it is referenced by the CPU. Buffer assignment of a block is independent of the row number from which it came.

Channels neither fetch data from nor store data into the buffer storage.

# Index Array

The index array provides a reference to the main-storage addresses of data contained in the buffer storage. The array may contain any or all of the 128 block addresses in a specific row, or as many as 128 block addresses of any combination of rows. Two entries are provided for each of the 128 possible block addresses, one entry for each compartment of the buffer. Each entry consists of a row address, two valid bits (one for each halfblock of the block), and one OK bit. The OK bit indicates that the corresponding block in the buffer storage and in the index array is functioning correctly. The valid bit indicates that its associated halfblock is set in the buffer storage.

The index array is interrogated during each CPU storage reference to determine if the referenced data is in the buffer. A comparison is made between the two entries (one per compartment of the buffer) and the row and halfblock referenced in main storage. An equal comparison of one of the entries determines which, if either, of the compartments contains the wanted data.

Both system reset and IPL set the index array row addresses to 0's, turn off all halfblock valid bits, and turn on all OK bits.

The system can continue to operate even when a component in the buffer fails. When a failure is detected, the OK bit for that block is turned off by the BCU and all subsequent fetches for that block are made directly from main storage. A machine check occurs when a block in the buffer is deleted for error recording purposes.

### Buffer Storage Assignment

Assignment of main-storage data to the upper or lower buffer compartments follows relatively simple rules:

- 1. If neither compartment has valid data in the referenced block, the main-storage data called for will be placed in the compartment other than the one fetched from last.

- 2. If one compartment has valid data in the referenced block but from a row other than the one addressed, and the other compartment does not have valid data in either halfblock of the referenced block, the mainstorage data will be placed in the compartment with the nonvalid block.

3. Finally, if both compartments have valid data in their respective blocks but from rows other than the one addressed, the main-storage data will be placed in the compartment other than the one fetched from last.

### Storage Protection Storage

The storage protection storage and controls are in the BCU. When a protection violation occurs on a store request, the request to main storage is canceled. When a protection violation occurs on a fetch request, the data from the buffer or from main storage is blocked in the BCU.

The storage protection (SP) storage is not validated automatically during system reset or IPL. If incorrect parity is present, it is retained until:

- 1. Enable system clear key is held in and system reset key is pressed; the SP storage is cleared to 0's with good parity during the system reset.

- 2. Enable system clear key is held in and load key is pressed; the SP storage is cleared to 0's with good parity as part of the IPL sequence.

- 3. The set key instruction is executed to replace the invalid key.

### **Channel Operations**

Channels use CPU data paths for control updating and for byte assembly and disassembly into and out of I/O local storage. As many as 16 bytes of data may be transferred to or from the main-storage data register on each storage reference. Internally, however, the data path to or from the storage data register is four bytes wide.

The channels access main storage directly; no channel data reaches the buffer storage. When a channel stores data in main storage, however, the index array is interrogated; if the data corresponding to that main-storage address is in the buffer storage, the valid bits for that block are turned off so that the next access from the CPU to that block must go to main storage.

Unit control words (UCW's) for the byte multiplexer and block multiplexer subchannels are transferred to and from the processor storage units via the BCU. UCW's are neither set into nor taken from buffer storage.

# **CPU** Operations

On a CPU fetch operation, the BCU interrogates the index array to see if the data requested is in the buffer storage. If either entry read out of the index array matches the row address of the requested halfblock, a block for that halfblock is already assigned in the buffer. When the row and halfblock numbers of the requested data match those of the index array, the requested data is in the buffer. The data is sent directly to the CPU and no request is made to main storage. If the requested data is not in the buffer, a fetch must be made from main storage. The block being referenced is assigned in the buffer, if required. The data halfblock is fetched from main storage, stored in the buffer, and sent simultaneously to the CPU. Index array information is updated.

All CPU store operations update (store into) main storage under individual-byte control. Additionally, the index array is interrogated to see if the data location being stored into is also represented in the buffer. When the referenced data is also in the buffer, the buffer is updated at the same time that main storage is updated.

Instruction fetch requests cause eight bytes of the instruction stream to be fetched in the CPU if two of the three instruction buffers are empty and certain other conditions (such as storage not busy) are met. On an instruction fetch, the index array is checked to see if the requested instruction is in the buffer; if the instruction is in the buffer, it is fetched from the buffer. If the instruction is not in the buffer, a main-storage fetch is made to get the instruction and send it to both the buffer storage and to the CPU.

#### **Machine Check Interruptions**

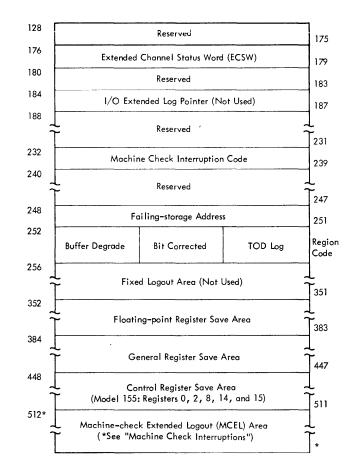

The definitions and implementations of machine check handling are in *IBM System/370 Principles of Operation*, GA22-7000. Further definition for the Model 155 includes the use of control registers 0, 2, 8, 14, and 15, and the fact that the I/O extended log pointer and fixed logout areas are not used. The store channel ID (STIDC) instruction executed on the Model 155 will always indicate the length of the longest I/O extended logout area as 0.

The starting location of the Model 155 machine-check extended logout (MCEL) area is variable. The starting location is recorded in the three low-order bytes of control register 15; it is set to 512 (decimal) after a system reset operation, but it can be changed by the user. The length of the MCEL area for the Model 155 can be found by using the store CPU ID (STIDP) instruction, which stores the length value in an accessible area of main storage. The length value will not exceed 992 bytes.

Fixed-storage locations for the Model 155 are shown in Figure 4.

#### CHANNEL CHARACTERISTICS

IBM System/370 channels transfer data between main storage and I/O devices under control of a channel program executed independently of the CPU program. The Model 155 CPU is free to resume the CPU program after initiating an I/O operation.

Model 155 channels may run concurrently, within the data transfer rate and channel programming conventions specified in *IBM System/370 Model 155 Channel Characteristics*, GA22-6962.

• Figure 4. Model 155 Permanently Allocated Storage Locations

A major feature of the channels is their common I/O interface connection to all System/370 input/output control units. The I/O interface provides for attachment of a variety of I/O devices to a channel.

At the end of an I/O operation, the channel signals an I/O interruption request to the CPU. If not disallowed, an I/O interruption occurs that places the CPU under control of the I/O new PSW. When I/O interruptions are disallowed, interruption requests are queued. Until honored, an I/O interruption condition is called a pending I/O interruption.

At the end of an I/O operation, a channel has information concerning the success of the operation, or has detailed information about any lack of success. This information is available to the CPU program.

Each System/370 channel has facilities for performing the following functions:

Accepting an I/O instruction from the CPU

Addressing the device specified by an I/O instruction

Fetching the channel program from main storage

Decoding the channel command words (CCW's) that make up the channel program

Testing each CCW for validity

Executing CCW functions

Placing control signals on the I/O interface

Accepting control-response signals from the I/O interface

Transferring data between an I/O device and main storage

Checking parity of bytes transferred

Counting the number of bytes transferred Accepting status information from I/O devices

Maintaining channel-status information

Signaling interruption requests to the CPU

Sequencing interruption requests from I/O devices

Sending status information to location 64 (decimal) when an interruption occurs

Sending status information to location 64 (decimal) upon CPU request

### **Channel Control**

IBM System/370 channels provide a common input/output interface to all System/370 and System/360 control units.

All control units are governed by six basic channel commands and a common set of six CPU instructions.

The instructions are: Start I/O Start I/O Fast Release Test Channel Test I/O

Halt I/O Halt Device

All I/O instructions set the PSW condition code; and, under certain conditions, all instructions except test channel may cause a channel status word (CSW) to be stored. A test channel instruction elicits information about the addressed channel; a test I/O instruction elicits information about a channel and a particular I/O device. Halt I/O terminates any operation on the addressed channel, sub-

channel, and I/O device. Halt device terminates only operations associated with the addressed I/O device. Only

SIO and SIOF use channel command words (CCW's).

A start I/O instruction initiates execution of one or more I/O operations. It specifies a channel, a subchannel, a control unit, and an I/O device. It causes the channel to fetch the channel address word (CAW) from location 72. The CAW contains the protection key and the address of the first channel command word (CCW) for the operation. The channel fetches and executes one or more CCW's, beginning with the first CCW specified by the CAW. Note that the Model 155 executes start I/O fast release as start I/O.

Six channel commands are used: Read Write Read Backward Control Sense Transfer in Channel

The first three are self-explanatory. Control commands specify such operations as set tape density, rewind tape, advance paper in a printer, or sound an audible alarm. A sense command brings information from a control unit into main storage concerning unusual conditions detected during the last I/O operation and detailed status about the device.

A transfer in channel (TIC) command specifies the location in main storage from which the next CCW in the channel program is to be fetched. A TIC may not specify another TIC. Also, the CAW may not address a TIC.

Each CCW specifies the channel operation to be performed; and, for data transfer operations, specifies contiguous locations in main storage to be used. One or more CCW's make up a channel program that directs a channel operation.

Command retry is a channel-control unit procedure that can cause a command to be retried without requiring an I/O interruption. Retry is initiated by the control unit. When the command being executed encounters a retriable error, the control unit presents retry status to the channel. If conditions permit, a normal device reselection occurs to reissue the previous command; if retry is not possible, any chaining is terminated and an I/O interruption follows.

#### Channels and Subchannels

System/370 channels maintain the following channel control information for each I/O device selected:

Protection key Data address Identity of operation specified by command code CCW flags Byte count Channel status Address of next CCW

On both byte and block multiplexer channels, the listed information must be maintained for each subchannel in operation. Storage for this information is provided by special channel storage that is not directly addressable. Each subchannel has provision in channel storage for unit control word (UCW) information. When a particular subchannel is selected by a start I/O instruction and a channel program is initiated, the UCW locations for the subchannel are loaded with the information necessary for operation of the subchannel.

At each cessation of activity in a subchannel, its UCW contains updated information, and the channel is available for operation of another subchannel.

#### Chaining

A single CCW may specify contiguous locations in main storage for a data transfer operation, or successive CCW's may be chained together to specify a set of noncontiguous storage areas. Chaining to the next CCW is caused by the presence of a flag bit in a CCW.

In data chaining, the address and count information in a new CCW is used; the command code field is ignored.

Entire CCW's, including their command code fields, may also be chained together for use in a sequence of channel operations. Such coupling is called command chaining, and it is specified by a different flag bit in a CCW.

Data chaining has no effect on a device, as long as the channel has sufficient time to perform both data chaining and data transfer for the device.

In this manual, when a device is said to data chain, it means that the channel program for the device specifies data chaining.

### Fetching Channel Command Words

The channel must fetch a new CCW when a CCW specifies data chaining, command chaining, or transfer in channel (TIC). The extra control activity caused by these operations takes time and diminishes the capability of the channel to do other work.

A data chaining fetch operation usually occurs while a channel also has a data transfer load from the same device. The time required to fetch the new CCW necessarily limits the interval of time available for successive data transfers through the channel. An absence of data chaining ordinarily permits a channel to operate with a faster I/O device.

#### Data Chaining in Gaps

For direct access storage devices such as an IBM 3330 Disk Storage facility or an IBM 2305 Fixed Head Storage Facility Model 2, formatting write commands causes the the control unit to create gaps between count, key, and data fields on the recording track. Read and write commands that address more than one of the fields may specify data chaining to define separate areas in main storage for the fields.

The gaps on a track have significance to channel programming considerations for direct access storage devices. The channel does not transfer data during the time a gap is created or passes under the read/write head, and this time is sufficient for a Model 155 to perform a command chaining or data chaining operation.

Command chaining ordinarily occurs only during gap time, but data chaining may occur during gap time or while data is being transferred. A data chaining operation occuring during gap time has a lesser impact on channel facilities than when data transfers also occur. If a channel program for a direct access storage device calls for data chaining only during gap time, the overall load of the device on channel facilities is significantly less.

When a direct access device is said to data chain in a gap, the reference is to a gap other than a gap following a data field. The latter gap causes a device end indication and command chaining is used in such a gap if the transfer of more information is desired. A device end condition occurring in the absence of a CCW specifying command chaining results in termination of the operation. When command chaining continues the operation, the status information available at the end of the operation relates to the last operation in the chain.

During a read operation, an attempt to data chain in a gap following a data field causes an incorrect-length indication in the channel status byte.

### Late Command Chaining

Operation of direct access devices, such as disk storage, requires the use of command chaining. Between certain operations, such as searching for a record identification key and reading a data field on a direct access storage device, the control unit has a fixed time interval during which it must receive and execute a new command. If activity on other channel(s) causes too much delay in initiation of the operation specified by the new command, the channel program is terminated and an I/O interruption condition occurs. Certain I/O devices can cause a command retry operation without requiring an I/O interruption.

#### Storage Addressing

During a data chaining operation, the beginning and ending byte addresses and the minimum number of bytes transferred are factors in the maximum data rates that different System/370 and System/360 channels can sustain. If the storage width of larger models and the possibility of using faster I/O devices are kept in mind when writing channel programs for smaller models, better performance will be obtained when the programs are run on larger models or with faster I/O devices.

For example, a tape operation at a 30 kb/s (kilobytes per second) data rate may data chain with a byte count of 1 on a System/360 Model 30 with one selector channel, but the same tape operation cannot be performed at 90 kb/s on a Model 155. In this instance, the use of a larger count for data chaining would permit the Model 155 to execute the channel program at 90 kb/s.

Similarly, better performance can be obtained on the Model 155 when data chained blocks (records) begin on fullword, doubleword, or quadword boundaries.

#### **Channel Implementation**

The Model 155 has two types of channels. The byte multiplexer channel and two block multiplexer channels are standard; as many as three block multiplexer channels and a second byte multiplexer channel (which takes the place of one block multiplexer channel) are optional. All channels on the Model 155 are integrated with the 3155 Processing Unit and share part of the CPU facilities. Each channel may attach as many as eight control units and can address as many as 256 I/O devices. Control units are connected to all channels through a standardized I/O interface.

### Block Multiplexer Channel

Each block multiplexer channel provides a path for moving data between storage and a selected I/O device. It has storage for control information and data buffering for multiple subchannels. Data moves to or from an I/O device one byte at a time, but it is buffered to a width of 16 bytes for communication with storage. Block multiplexer channels can operate concurrently with each other and with the CPU.

*Burst Mode* is defined as operation over the I/O interface in which the device and the channel remain connected for a relatively long period of time in terms of system operation.

Byte Mode is defined as byte-interleaved operation over the I/O interface in which the channel and any one device remain connected for a relatively short period of time, typically long enough to transfer one byte or a small number of bytes.

*Multiplexing* refers to the channel and device capability of disconnecting and reconnecting during an operation over the I/O interface. The block multiplexer channel operates in burst mode and has multiplexing capability between blocks of data; the byte multiplexer channel operates either in burst mode or in byte mode with multiplexing capability between bytes, groups of bytes, or blocks.

#### Byte Multiplexer Channel

A byte multiplexer channel has a single data path that may be monopolized by one I/O device (burst mode) or shared by many I/O devices (byte mode). The design of a control unit predetermines whether its operation on the byte multiplexer channel is in burst or byte mode. In either case, data transfer between storage and an I/O device is controlled one byte at a time. Byte multiplexer channel operation may overlap block multiplexer channel and CPU operations.

When multiple I/O devices concurrently share byte multiplexer channel facilities, the operations are in byte mode. Each device in operation is selected, one at a time, for transfer of a byte or a group of bytes to or from main storage. Bytes from multiple devices are interleaved and routed to or from the desired locations in main storage. Therefore, the byte multiplexer channel data path is used by one device for transfer of one or a group of bytes, and then another device uses the same path. The sharing of the data path makes each device appear to the programmer as if it has a data path of its own. This leads to calling a device's share of the data path a subchannel.

### **Subchannels and Unit Control Words**

The channel facilities required to sustain a single I/O operation are termed a subchannel. Subchannels may be either nonshared or shared. A nonshared subchannel has the

facilities to operate only one I/O device; a shared subchannel provides facilities to operate one of an attached set of I/O devices.

The initiation of multiple I/O operations with logiccontrolled channel multiprogramming requires that the subchannels be provided channel storage to record the addresses, count, and status and control information associated with the I/O operation. In the Model 155, the storage for a single set of such information is called a unit control word (UCW). The UCW storage is provided as a normally unaddressable area in the processor storage, making the number of available UCW's model dependent. One half of the UCW's is reserved for the byte multiplexer channels; the other half is reserved for the block multiplexer channels.

#### Byte Multiplexer Channel UCW Assignment

Each byte multiplexer channel has its own set of device addresses and its own set of subchannel numbers. At installation time, the customer engineer may independently wire the first byte multiplexer channel (channel 0) and the second byte multiplexer channel (if installed) either to allow or to inhibit the use of shared subchannels.

When the channel is wired to allow sharing, each device whose eight-bit address has a 1 in the high-order bit position is assigned to a shared subchannel. Each shared subchannel is associated with a block of 16 contiguous device addresses of the form X0 through XF. This arrangement provides eight shared subchannels. The shared subchannels use the same UCW's as the first eight nonshared subchannels. Because no more than one control unit should be used with a shared subchannel, the following device addresses are usually mutually exclusive:

80-8F and 00 90-9F and 01 A0-AF and 02 B0-BF and 03 C0-CF and 04 E0-EF and 06 F0-FF and 07

As an example of an exception, the IBM 2848 Model 2 or 22 with the IBM 1053 Printer Model 4 attached requires 17 device addresses, all of which share one UCW.

When the channel is wired to inhibit sharing (nonsharing option), each device is assigned to a unique subchannel. The subchannel number in this case is the same as the device address. The assignment of more than one subchannel to one UCW is called folding. Folding of nonshared subchannels can occur when the number of subchannels exceeds the number of UCW's available. A byte multiplexer channel wired for the nonsharing option has as many as 256 subchannels, numbered 00 through FF. Each device is assigned to a subchannel number that is the same as the

device address. The subchannels that fold on the byte multiplexer channels are:

| System<br>Model               | Channel 0                                                                            | Channel 4 (When installed as the second byte multiplexer channel) |

|-------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| H<br>HG<br>I<br>IH<br>J, JI,K | 80-FF fold on 00-7F<br>C0-FF fold on 40-7F<br>No folding<br>No folding<br>No folding | -<br>-<br>80-FF fold on 00-7F<br>No folding                       |

Subchannel numbers (device addresses) that fold into each other should be mutually exclusive. See Figure 5 for available subchannels.

### Block Multiplexer Channel UCW Assignment

On the Model 155, block multiplexer channels assign devices to UCW's as needed. Sixteen of the UCW's available to the block multiplexer channels are reserved for shared subchannels; the remaining UCW's are used for nonshared subchannels. Sixteen plugboards are provided to assign the channel number and the device address set of up to 16 shared subchannels. The customer engineer wires these plugcards at installation time. Each shared subchannel refers to a block of 16 contiguous device addresses of the form X0 through XF and no more than one control unit should be attached to each shared subchannel.

During execution of a start I/O addressed to a device not specified on one of the plugcards, a block multiplexer channel in block multiplex mode checks to see if a UCW is already assigned. If a UCW is not assigned and the device is successfully selected, the channel assigns nonshared UCW's to a block of eight contiguous device addresses of the form X0 through X7 and X8 through XF. These UCW's remain assigned until a system reset occurs. For example, the assignment of a nonshared UCW to device 1A3 (channel 1, device A3) causes the assignment of UCW's to I/O addresses 1A0 through 1A7. When a nonshared subchannel operation is initiated after all available UCW's are assigned, the block multiplexer channel's active registers are dedicated to that operation; multiprogramming on the channel is suppressed from the start I/O initiation until the CSW is stored for the operation. In effect, the block multiplexer channel acts as a selector channel.

The block multiplexer channel has three modes of operation:

- 1. When operating in block multiplex mode with a nonshared subchannel that has a UCW assigned, the channel follows all block multiplex rules. (These rules are in *IBM System/360 Principles of Operation*, GA22-6821.)

- 2. When operating in block multiplex mode with a shared subchannel, the channel follows block multiplex rules but does not disconnect during command chaining. However, when terminating status is presented and the CPU is not enabled for interruptions from this channel, the channel disconnects until the status for the shared subchannel operation can be presented.

- 3. When not operating in block multiplex mode or when operating with a nonshared subchannel for which a UCW cannot be assigned (because the UCW pool is exhausted), the block multiplexer channel acts as a selector channel.

Block multiplexer channel UCW availability is shown in Figure 5.

### **Channel Priority**

Priority for allocation of Model 155 CPU facilities is in the following order, for normal operation:

Machine check interruption handling Block multiplexer channel data transfer Block multiplexer channel data chaining

|       |                      |                         |                         | • 1     |                           |                         |        |                                  |        |  |

|-------|----------------------|-------------------------|-------------------------|---------|---------------------------|-------------------------|--------|----------------------------------|--------|--|

|       |                      | Channel 0<br>Nonsharing | Channel 0<br>Sharing Op | tion ** | Channel 4 *<br>Nonsharing | Channel 4<br>Sharing Op |        | Block Multiplexer<br>Subchannels |        |  |

| Model | Main Storage (Bytes) | Option **               | n ** Nonshared          |         | Option **                 | Nonshared               | Shared | Nonshared                        | Shared |  |

| н     | 262,144              | 128                     | 120                     | 8       |                           |                         |        | 96                               | 16     |  |

| HG    | 393,216              | 192                     | 120                     | 8       |                           |                         |        | 160                              | 16     |  |

| 1     | 524,288              | 256                     | 120                     | 8       |                           |                         |        | 224                              | 16     |  |

| IH    | 786,432              | 256                     | 120                     | 8       | 128                       | 120                     | 8      | 352                              | 16     |  |

| J     | 1,048,576            | 256                     | 120                     | 8       | 256                       | 120                     | 8      | 480                              | 16     |  |

| ١L    | 1,572,864            | 256                     | 120                     | 8       | 256                       | 120                     | 8      | 480                              | 16     |  |

| κ     | 2,097,152            | 256                     | 120                     | 8       | 256                       | 120                     | 8      | 480                              | 16     |  |

\* True only when channel 4 is installed as the optional second byte multiplexer channel.

\*\* The sharing or nonsharing option is wired by the customer engineer at installation time to the user's specification.

Figure 5. Available Subchannels by System Model

Block multiplexer channel command chaining Byte multiplexer channel operations Second byte multiplexer channel operations (if implemented) CPU operations

Block multiplexer channels receive data handling priority in numeric order, with highest priority for channel 1.

I/O interruption priority is in order of channel number, with the highest priority for channel 0 and the lowest for channel 5. This priority is unchanged whether channel 4 is a byte multiplexer or a block multiplexer channel.

### Channel Available Interruption

The Model 155 implements the channel available interruption on block multiplexer channels 1 through 5. The channel available interruption is not implemented on byte multiplexer channel 0, or on the second byte multiplexer channel (channel 4), if installed.

# System Control Panel

The system control panel contains the switches and indicators necessary to operate, display, and control the system. The system consists of the CPU, storage, channels, on-line control units, and I/O devices, and the supervisory program. Off-line control units and I/O devices, although a part of the system environment, are not considered part of the system proper.

System controls are logically divided into three classes: operator controls, operator intervention controls, and customer engineer controls (key switch and meters).

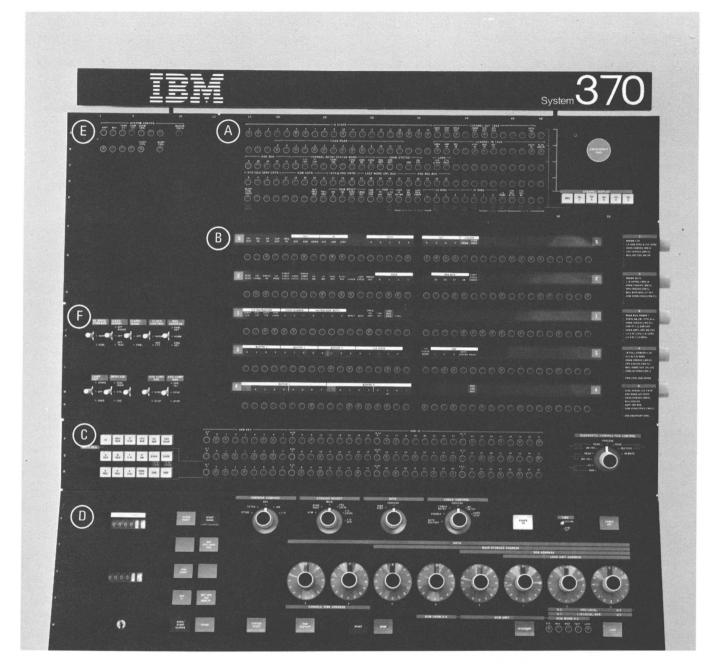

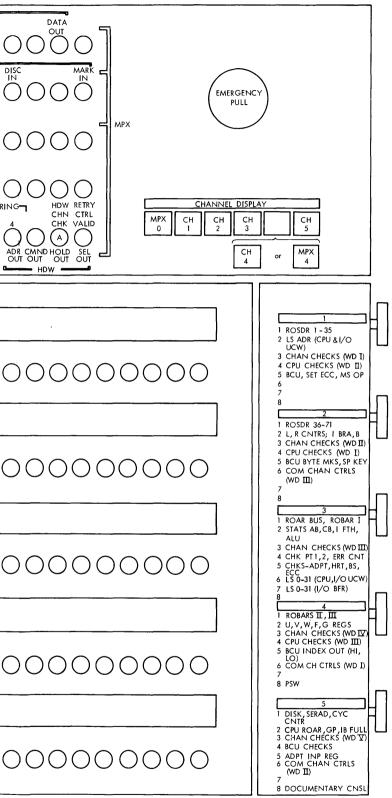

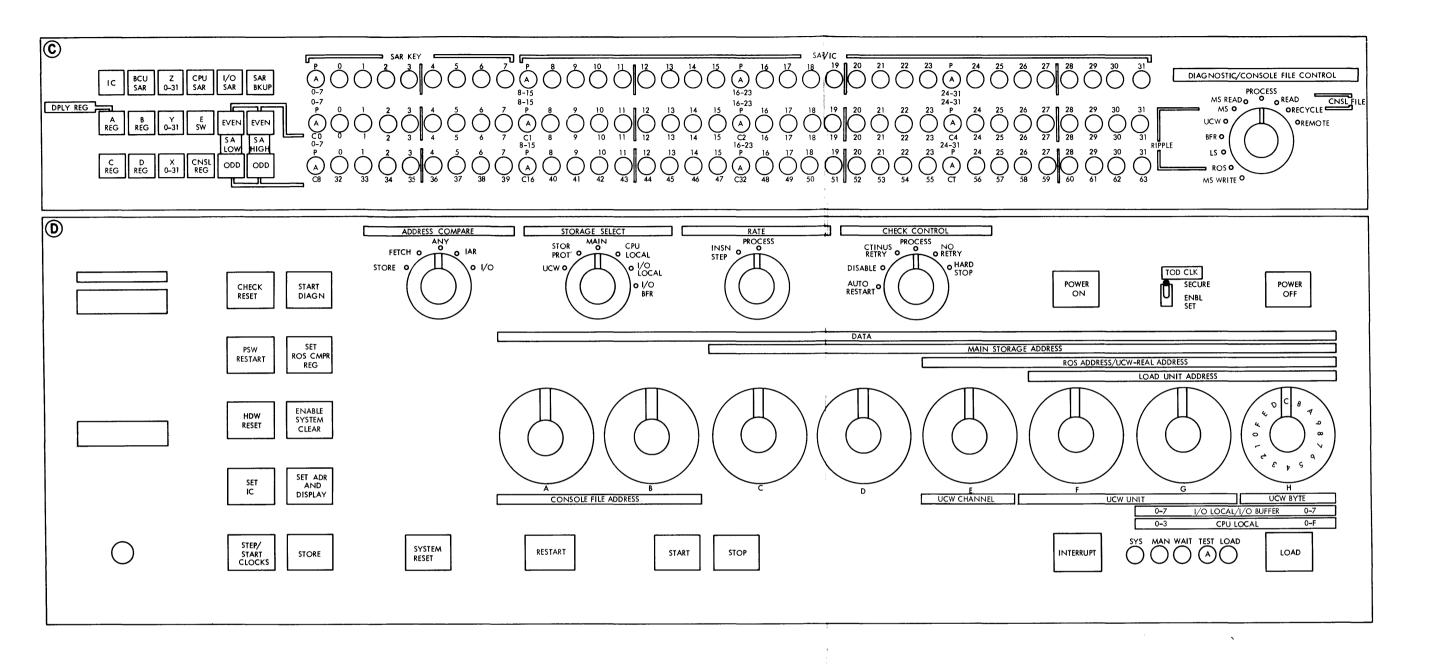

Location of indicators and controls is specified by a coordinate system on the panel: numbers from left to right across the panel, and letters from top to bottom. Subpanels are referenced A through F, although the letters do not physically appear on the subpanels. See Figure 6. System manual control and indicator panels are mounted on the CPU frame above the reading board. Below the reading board is a special disk unit and space for storing diagnostic disks. A console I/O unit is attached to either the left-hand or right-hand reading board extension.

This section of the manual describes the system control functions provided by the system control panel as well as the purpose and use of the switches and indicators on the panel. Generally, the manual controls initiate CPU functions via microprogram action.

# SYSTEM CONTROL FUNCTIONS

Using the control panel, the operator can perform the following system control functions:

- 1. Reset the system.

- 2. Store and display information in storage and registers.

- 3. Load initial program information.

### System Reset

The system reset function resets the CPU, channels, and on-line nonshared control units and I/O devices.

The CPU is placed in the stopped state and all pending interruptions are eliminated. The parity of the general and floating-point registers is corrected and the current PSW is set to 0's with good parity. All error-status indicators are reset to 0's.

The reset state for a control unit or an I/O device is described in the appropriate Systems Reference Library (SRL) publication. A system reset signal from a CPU resets only the functions in a shared control unit or an I/O device belonging to that CPU. Any function pertaining to another CPU remains undisturbed.

The system reset function is performed when the system reset key is pressed, when initial program loading is initiated, when a **PSW** restart is performed, or when a power-on sequence is performed.

### **Programming Notes**

If a system reset occurs in the middle of an operation, the contents of the result registers or storage locations are unpredictable. If the CPU is stopped or in the wait state when the system reset is performed, and no I/O operation is in progress, this uncertainty is eliminated.

A system reset does not correct parity in storage but does correct parity in the registers. Because a machine check occurs when information with incorrect parity is used, the incorrect information should be replaced by loading new information. The enable system clear key is provided to allow clearing main storage and protection key storage to 0's with good parity. The enable system clear key is used in conjunction with the system reset or load key, at the user's option.

#### Store and Display

The store and display function permits manual intervention during the progress of a program. The storing and/or displaying of data may be provided by a supervisor program in conjunction with proper I/O equipment and the interrupt key.

The controls on the operator intervention portion of the panel allow direct storing and displaying of data. This is done by placing the CPU in the stopped state, and subsequently storing and/or displaying information in main storage, in general and floating-point registers, and in the instruction address part of the PSW. The stopped state is achieved at the end of the current instruction when the stop key is pressed, when a single instruction execution is specified, or when a preset address is reached. The store and display function is then achieved through the store and display keys, the data rotary address switches, the data switches, and the storage select switch. When the desired intervention is completed, the CPU can be started again.

Display of the machine registers and triggers is provided by roller charts and fixed indicators. The roller charts are similar to those used on System/360 Model 50.

Figure 6. Model 155 System Control Panel

The stopping and starting of the CPU, in itself, does not cause any alteration in program execution other than in the time element necessary for the transition from operating to stopped state.

Machine checks occurring during store and display functions do not log immediately, but they create a pending log condition that can be removed by a system reset or check reset. The error condition, when not disallowed, forces a logout and a subsequent machine check interruption when the CPU is returned to the operating state.

### **Initial Program Loading**

Initial program loading (IPL) is provided for the initiation of processing when the contents of storage or the PSW are not suitable for further processing. Initial program loading is initiated manually by selecting an input device with the data rotary load-unit switches and by pressing the load key.

Pressing the load key causes a system reset, turns on the load light, turns off the manual light, and initiates a read operation from the selected input device. When the read operation is completed satisfactorily, the IPL-PSW is obtained, the CPU starts operating, and the load light turns off.

System reset suspends all instruction processing, interruptions, and timer updating and also resets all channels, on-line nonshared (not shared with another system) control units, and I/O devices. The contents of the general and floating-point registers remain unchanged. If the enable system clear key is held in when the load key is pressed, the system reset function includes clearing main storage and protection key storage to 0's with good parity.

When IPL is initiated, the selected input device starts transferring data. The first 24 bytes read are placed in storage locations 0-23. Store protection, program-controlled interruption, and a possible incorrect-length indication are ignored. Control of the loading operation is then assumed by the doubleword just read into storage location 8, which is used as the next channel command word (CCW). The remainder of the program to be loaded may, therefore, be located in any desired section of storage. When chaining is specified in this CCW, the doubleword in storage location 16 may also be used as a CCW to provide additional control.

After the input operation is completed, the I/O address is stored in bits 21-31 of the first word in storage. Bits 16-20 are made 0; bits 0-15 remain unchanged.

The CPU then fetches the doubleword in storage location 0 as a new PSW and proceeds as in a normal operation. The load light turns off. When the I/O operations and the PSW loading are not completed satisfactorily, the CPU idles and the load light remains on.

# Programming Notes

Initial program loading (IPL) resembles a start I/O that specifies the I/O device selected in the data rotary switches and a zero protection key. The CCW for this start I/O is simulated by CPU logic, and the CCW contains: read command, zero data address, byte count of 24, chain command flag on, suppress-length-indication flag on, programcontrolled-interruption flag off, chain-data flag off, and skip flag off.

Initial program loading reads new information into the first six words of storage. The remainder of the IPL program may be placed in any desired section of storage.

If the selected input device is a disk, the IPL information is read from track 0. The selected input device may be a channel-to-channel adapter connecting the channels of two CPU's. After a system reset is performed and a read command is issued to the adapter by the requesting CPU, the adapter sends an attention signal to the addressed CPU. That CPU then should issue the write command necessary to load a program into main storage of the requesting CPU.

22

When the PSW in location 0 has bit 14 set to 1, the CPU is in the wait state after the IPL procedure (the manual, the system, and the load lights are off, and the wait light is on). Interruptions that become pending during IPL are taken before instruction execution.

### SYSTEM CONTROL PANEL CONTROLS

System controls are divided into three logical groups: operator controls, operator intervention controls, and customer engineer controls. Figures 7 and 8 show the operator controls and operator intervention controls on the system control panel. The customer engineer will use all controls but some are intended primarily for customer engineer use.

### **Operator Controls**

The main functions provided by the operator controls are: control and indication of power, indication of system status, operator-to-machine communication, and initial program loading. This section is located on subpanel D, except for the emergency pull switch which is on subpanel A.

Note that no remote operator control panel is provided for the Model 155.

The following table lists (alphabetically) all operator controls and indicators and their implementation. All keys and the TOD clock (security) switch have momentary action. The TOD clock switch is normally in the secure position.

| Name           | Implementation                   |

|----------------|----------------------------------|

| Clock Security | Lever Switch                     |

| Emergency Pull | Pull Switch                      |

| Interrupt      | Key                              |

| Load           | Key                              |

| Load           | Light                            |

| Load Unit      | Data Rotary Switches F, G, and H |

| Manual         | Light                            |

| Power Off      | Key                              |

| Power On       | Key, Backlighted                 |

| System         | Light                            |

| Test           | Light                            |

| Wait           | Light                            |

# Clock Security (TOD Clock)