GA22-7010-4 File No. S/370-01

# IBM System/370 Model 168 Functional Characteristics

# Systems

# Preface

This manual describes the functional characteristics and features of the IBM System/370 Model 168. The purpose of this manual is to provide management, programmers, and operations personnel with a fundamental understanding of this System/370 model.

Details concerning the use of programming and peripheral equipment are not given in this manual; however, a partial list of relevant manuals is given in "Appendix A, Bibliography," and programming is outlined in "Programming."

This manual is divided into these sections:

- "Introduction," giving an overall picture of the system.

- "Basic System Description," giving configuration, facilities, features, and system highlights of the Model 168.

- "Central Processing Unit," describing the processing unit (the processor storage control function, processor storage, instruction unit, and execution unit), and including virtual storage and dynamic address translation.

- "Channel Description," describing the selector, byte multiplexer, and block multiplexer channels, and data rate considerations.

- "Functions," describing usage metering, modeldependent functions, the system console, and the operator's console.

- The Appendixes, which provide useful supplementary tables as well as information about the multiprocessing feature, the integrated storage control feature, the power warning feature, the attached processor feature, and the deviations from the Model 168 functional characteristics.

The reader is assumed to have an understanding of data processing systems including fundamental knowledge of IBM System/370 as defined in *IBM System/370 Principles* of Operation, GA22-7000.

#### Fifth Edition (January 1976)

This is a major revision of GA22-7010-3 and all previous editions, including Technical Newsletters GN22-0477, GN22-0485, and GN22-0491, making them obsolete. A new section, Appendix G, describes the IBM 3062 Attached Processing Unit (APU) Model 1. Changes have been made throughout this manual to describe the integration of that unit into the system to create the Model 168 Attached Processor System. A technical change to the text or to an illustration is indicated by a vertical line to the left of the change.

Changes are periodically made to the information herein; before using this publication in connection with the operation of the System/370, consult the *IBM System/370 Bibliography*, GC20-0001, for editions that are applicable and current.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

This manual has been prepared by the IBM System Products Division, Product Publications, Dept. B98, PO Box 390, Poughkeepsie, N.Y. 12602. A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be sent to the above address. Comments become the property of IBM.

©Copyright International Business Machines Corporation 1972, 1973, 1976

# Contents

|   | Introduction                                              |      |      |     |      |      |    |   | • : |    | 5        |

|---|-----------------------------------------------------------|------|------|-----|------|------|----|---|-----|----|----------|

|   | Attachable Input/Output Dev                               | vice | s    |     |      |      |    |   | •   | •  | 5        |

|   | Programming                                               |      |      |     |      |      |    |   |     |    |          |

|   | Programming Compatibility b                               | bety | veen | Thi | s Sy | vste | m. |   |     |    | -        |

|   | Other System/370 Models, a                                | nđ   | Svet | em/ | 360  |      |    |   |     |    | 5        |

|   |                                                           |      | ~,   | ,   |      |      | •  | • | •   |    | •        |

|   | Posis System Description                                  |      |      |     |      |      |    |   |     |    | ~        |

|   | Basic System Description .                                | •    | ·    |     |      |      |    |   |     | •  | 6        |

|   | System Configuration                                      |      |      |     |      |      | •  |   |     | •  | 6        |

|   | Optional Features                                         | •    | •    |     | ·    | •    | •  |   | ·   | ·  | 6        |

|   | Standard Facilities<br>System Timing Facilities .         | ٠    | ·    | ·   | •    | ·    |    | · |     | •  | 8        |

|   | System Liming Facilities .                                | ·    | •    | ·   | •    | •    | •  | · |     | ٠  | 9        |

|   | System Highlights                                         |      |      |     |      | •    | •  |   |     | •  | 10       |

|   | General Data                                              | ٠    | •    | ·   | •    | •    |    |   |     | ٠  | 10       |

|   | Data Storage                                              | •    | •    | •   | •    | •    | •  | • | ·   | ·  | 10       |

|   |                                                           |      |      |     |      |      |    |   |     |    |          |

|   | Central Processing Unit                                   |      |      |     |      |      |    |   |     |    | 11       |

|   | Processor Storage                                         |      |      |     |      |      |    |   |     |    | 11       |

|   | Models                                                    |      |      |     |      |      |    |   |     |    | 11       |

|   | Models                                                    | nt   |      |     |      |      |    |   |     | •  | 12       |

|   | Interleaving                                              |      |      |     |      |      |    |   |     |    | 12       |

|   | Interleaving                                              | •    | •    | ·   | •    |      |    | : |     |    | 12       |

|   | Processor Storage Control Funct                           | ion  | •    | ·   | •    |      |    |   |     |    | 13       |

|   | Buffer Storage Control                                    |      |      |     |      |      |    |   | :   |    | 13       |

|   | High-speed Buffer                                         | •    | •    | •   | •    |      |    | : | •   | .• | 13       |

|   | Translator                                                |      |      |     |      | :    |    | : | :   | •  | 14       |

|   | Translation Lookaside Buffer                              | • (Т | I B) | •   | •    | :    | :  | : |     | •  | 14       |

|   | TLB Operation                                             |      |      |     |      |      |    | : |     |    | 14       |

|   |                                                           |      |      |     |      |      |    |   |     |    | 15       |

|   | I/O Channel Controls (I/O Bu                              |      |      |     |      | ·    |    | · |     | •  | 16       |

|   | Processor Storage Controls                                |      |      |     | •    | •    |    | • | •   | •  | 16       |

|   | Instruction Unit (I-unit)                                 |      |      |     |      | ·    |    | • | •   |    |          |

|   | Execution Unit (E-unit)                                   |      |      |     |      | ·    |    | • |     |    | 16       |

|   | Local Storage                                             | ٠    |      |     |      | •    |    | • |     |    |          |

|   | Writable Control Storage .                                | ٠    | ·    | •   |      |      |    |   |     |    | 16       |

|   | Extended Control                                          | ·    | •    | •   | •    | •    | •  | · | ·   | ·  | 16       |

|   | Dynamic Address Translation                               |      |      |     |      |      |    |   |     |    | 16       |

| I | Service Processor (SVP)                                   | ٠    | ·    | ·   | •    | ·    | •  | • | ٠   | ٠  | 16       |

|   |                                                           |      |      |     |      |      |    |   |     |    |          |

|   | Channel Description                                       |      |      |     |      |      |    |   |     | •  | 17       |

|   | Channels                                                  |      |      |     |      |      |    |   |     |    | 17.      |

|   | Channel Attachment                                        |      |      |     |      |      |    |   |     |    | 17       |

|   | Indirect Data Addressing .                                |      |      |     |      |      |    |   |     | •  | 18       |

|   | 2860 Selector Channel                                     |      |      |     |      |      |    |   |     |    | 18       |

|   | 2860 Selector Channel<br>2870 Byte Multiplexer Chan       | nel  |      |     |      |      |    |   |     |    | 19       |

|   | 2880 Block Multiplexer Char                               | nne  | 1.   | •   |      |      |    |   |     |    | 20       |

|   | · · · · · · · · · · · · · · · · · · ·                     |      | -    |     |      |      |    |   |     |    | -        |

|   | Functions                                                 |      |      |     |      |      |    |   |     |    | 21       |

|   | Usage Metering                                            | •    | •    | •   | •    | ·    | •  | • | •   | ·  | 21       |

|   | Model-dependent Functions .                               | •    | •    | •   | •    | •    | •  | • | •   | •  | 21       |

|   |                                                           | ·    | •    | •   | •    | ·    | •  | • | •   | •  | 22       |

|   | Logout                                                    | •    | •    | ·   | •    | •    | •  | • | •   | •  | 22       |

|   | Hardware Retry                                            | •    | •    | •   | •    | ·    | ·  | · | ·   | ·  | 22       |

|   | Software Retry                                            | •    | •    | •   | •    | •    | •  | · | •   | ·  | 22       |

|   |                                                           | •    | •    | •   | •    | •    | ·  | • | •   | ·  | 22       |

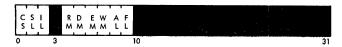

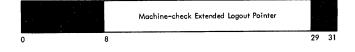

|   | Details of Machine Checks .<br>Machine-check Condition Ma |      |      | •   | ·    | •    | ·  | · | •   | ·  | 24<br>24 |

|   | Machine-check Condition Ma                                |      |      | •   | ·    | •    | •  | · | •   | ·  | 24<br>24 |

|   |                                                           |      |      |     | ·    | •    | •  | · | ·   | ·  | 24<br>24 |

|   | Allocation of Control Regist                              |      |      | 5   | •    | ·    | •  | • | •   | ·  | 24<br>26 |

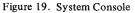

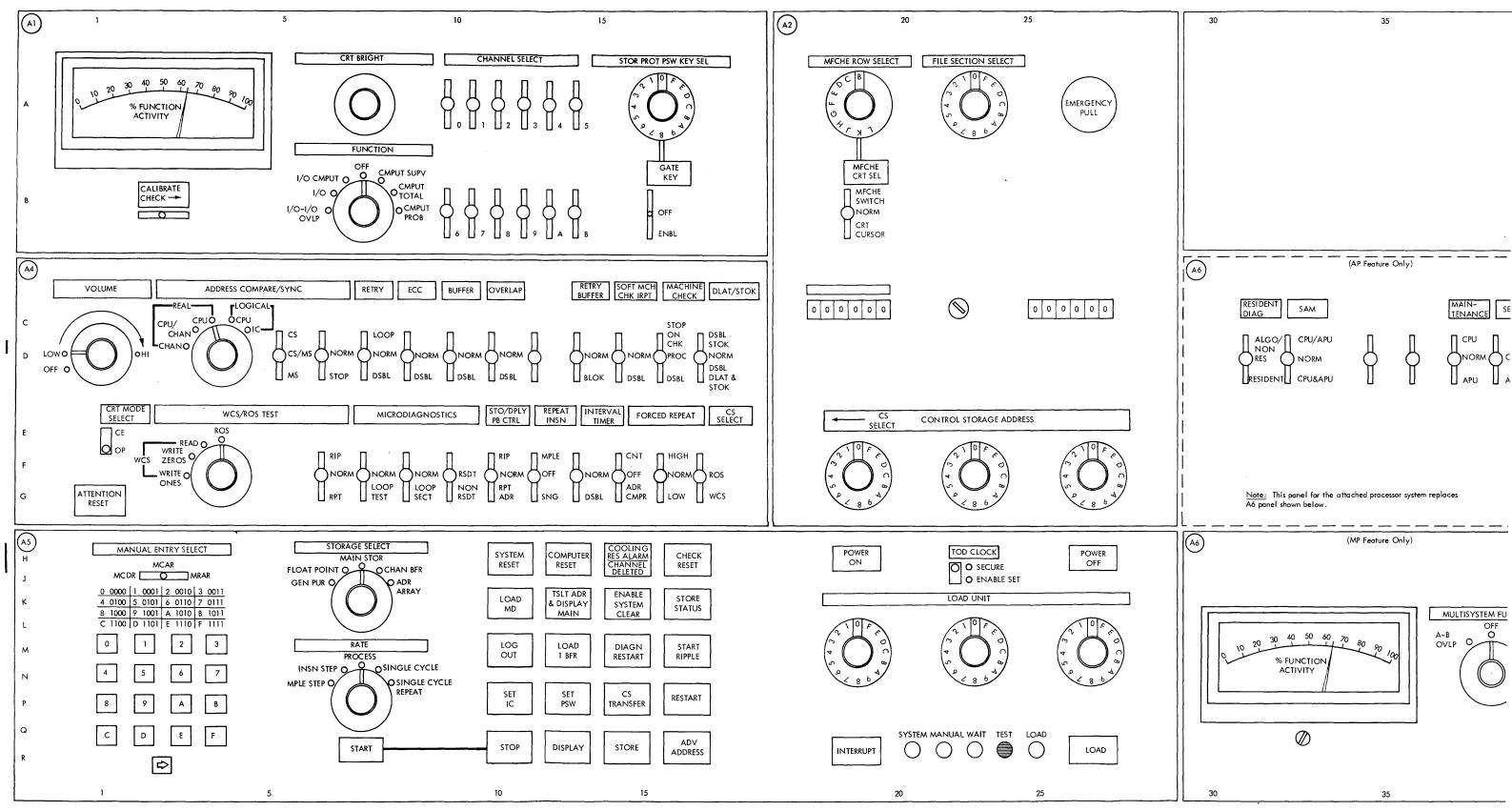

|   | System Console with CRT Displ                             |      | •    | •   | •    | •    | •  | · | ·   | •  | 26<br>27 |

|   | Operator's Console                                        | •    | •    | ·   | ·    | ·    | •  | · | •   | •  |          |

|   | Operations                                                | •    | •    | •   | •    | ·    | ·  | • | •   | •  | 27<br>28 |

|   | Indicators                                                | •    | ٠    | ·   | •    | •    | ·  | · | •   | ٠  | -        |

|   | Status Byte                                               | •    | •    | ٠   | ·    | •    | ·  | · | •   | ·  | 29       |

|   | Sense Byte                                                | :    | ·    | ·   | •    | ·    | ·  | • | •   | ·  | 29       |

|   | Synchronous Checks                                |     |   |   | 29  |

|---|---------------------------------------------------|-----|---|---|-----|

|   |                                                   | •   |   | • | 29  |

|   | -                                                 |     | • | • |     |

|   | Interruptions                                     | •   | • | • | 29  |

|   |                                                   |     |   |   |     |

|   | Appendix A. Bibliography                          | •   | • |   | 31  |

|   | General                                           | •   |   |   | 31  |

|   | IBM Operating System (OS/VS)                      |     |   |   | 31  |

|   | Representative I/O Devices                        |     | • |   | 31  |

|   |                                                   |     |   |   |     |

|   | Appendix B. Controls and Indicators               |     |   | _ | 32  |

|   | •••                                               |     |   |   |     |

|   | Appendix C. Glossary and Abbreviations            |     |   |   | 39  |

|   |                                                   |     |   |   |     |

|   | Appendix D. Integrated Storage Control Featur     | A   |   |   | 41  |

|   | Facilities                                        | •   |   | • | 41  |

|   | Statistical Usage/Error Recording                 | •   | • | • | 42  |

|   |                                                   | •   | • | • | 43  |

|   | Storage Control Diagnostic Tests                  | •   | · | • |     |

|   |                                                   | •   | • | · | 43  |

| I | Interface Time-out Considerations                 | •   | • | • | 43  |

|   | Input/Output Operations                           | •   | • | • | 43  |

|   |                                                   |     |   |   |     |

|   |                                                   | •   |   | • | 45  |

|   |                                                   |     |   |   | 45  |

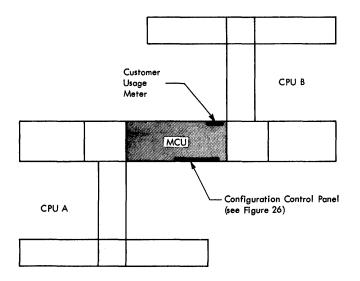

|   | Multisystem Activity Monitor (MSAM)               |     |   |   | 45  |

|   | Prefixing                                         |     |   |   | 45  |

|   |                                                   | •   |   |   | 46  |

|   |                                                   | •   | • | • | 46  |

|   |                                                   | •   | · | • | 46  |

|   | 6                                                 | •   | · | • |     |

|   |                                                   | •   | ٠ | • | 46  |

|   |                                                   | •   | • | · | 46  |

|   |                                                   | •   | • | · | 46  |

|   |                                                   |     |   |   | 46  |

|   | MCU Power Control                                 |     |   |   | 47  |

|   | Resets                                            |     |   |   | 47  |

|   |                                                   |     |   |   | 48  |

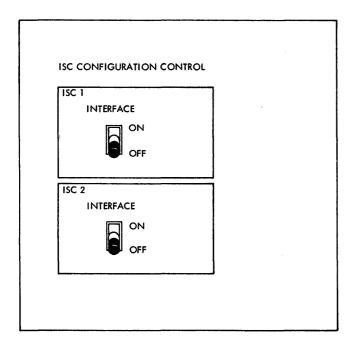

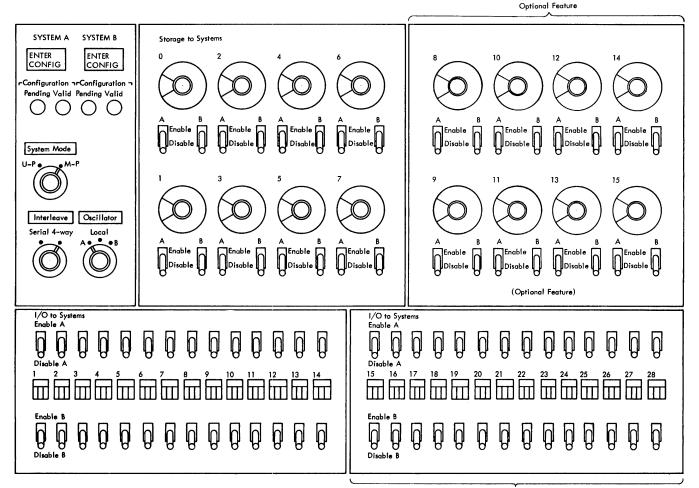

|   | Configuration Control                             |     |   |   | 48  |

|   | Configuration Control                             |     |   | : | 48  |

|   |                                                   | •   | · | • |     |

|   | Appendix F. Power Warning Feature                 |     |   |   | 51  |

|   | Appendix F. Fower Warning Feature                 | •   | • | • | 51  |

|   | Appendix G. Attached Processor Feature            |     |   |   | 52  |

|   |                                                   | •   | • | • | 52  |

|   |                                                   | •   | · | • |     |

|   |                                                   | •   | · | • | 52  |

|   |                                                   | •   | · |   |     |

|   | CPU Signaling and Response                        | •   | ٠ | • |     |

|   | Processor Addresses                               | •   | • | • | 53  |

|   | Storage Control                                   | •   |   | • | 53  |

|   | Malfunction Alert                                 |     |   |   | 53  |

|   | Time-of-day (TOD) Clock                           |     |   |   | 53  |

|   |                                                   | •   |   |   | 53  |

|   |                                                   |     |   |   |     |

|   | Appendix H. Deviations from the IBM System/       | 27  | 2 |   |     |

|   |                                                   | 57  | v |   | E 4 |

|   | Model 168 Functional Characteristics              | •   | • | · | 54  |

|   |                                                   | •   | ٠ | · | 54  |

|   | Interruptions When the Processor Leaves the       |     |   |   |     |

|   | Stopped State                                     | •   | · | • | 54  |

|   | Data Exception during Execution of a Divide Decin | nal |   |   |     |

|   | Instruction                                       | •   | • | • | 54  |

|   | Check-stop Control                                |     |   | - | 54  |

|   | Serialization for a Write Direct Instruction      |     |   | • | 54  |

|   | Enable System Clear Pushbutton                    |     |   |   | 54  |

|   | - · · ·                                           |     |   |   |     |

|   | Index                                             |     |   |   | 55  |

|   |                                                   | •   | • | • | 55  |

Representative Installation Using the IBM System/370 Model 168 Uniprocessing System with Typical I/O Units

Representative Installation Using the IBM System/370 Model 168 Attached Processor System with Typical I/O Units

#### Introduction

The IBM System/370 Model 168 (Frontispiece) is an upward-compatible information processing system, designed for high-speed, large-scale scientific and business applications. The improved speed and power result primarily from the monolithic processor storage, high-speed logic circuitry, dynamic address translation (providing an address space of up to 16,777,216 bytes), concurrency of operations, and use of efficient algorithms. This model can serve as a compatible growth system for installed System/ 360 and System/370 models.

Contributing significantly to the increased efficiency are the processor (real) storage capacities, which range from 1,048,576 bytes (1,024K) to 8,388,608 bytes (8,192K), and a high-speed buffer that holds currently used sections of processor storage, making data available in less time. Speed is further increased by the use of interleaved processor storage elements.

For input/output operations, the system (with the extended channels feature) may connect a maximum of 12 channels: one or two byte multiplexer channels, as many as six selector channels, or up to 11 block multiplexer channels. These channels use dedicated channel data buffers in the CPU to achieve increased aggregate data rates through the effective use of the four-way interleaved processor storage. A further increase in aggregate data rates and external cabling flexibility is achieved with the channel dual-bus facility.

The performance of a Model 168 may be further enhanced by the addition of an instruction processor, the IBM 3062 Attached Processing Unit Model 1. The attached processing unit shares the storage of its host CPU, and programs may be executed simultaneously on both units.

Multiprocessing (MP) is available as an option. With MP installed on two Model 168 systems, programs may be executed simultaneously in each CPU and may share system resources (CPUs, I/O devices, storage, and data). System availability is improved through versatile utilization of these resources. Secondary benefits derived from MP include operational efficiency and flexibility.

#### **Attachable Input/Output Devices**

The I/O devices that can be attached to Model 168 are listed in the *IBM System/370 Input/Output Configurator*, GA22-7002.

#### PROGRAMMING

Programming support for this model includes Operating System/Virtual Storage (OS/VS). This system uses dynamic address translation and the new control functions to provide the virtual storage capability.

In addition to OS/VS, Operating System (OS) provides basic System/370 support (basic control mode) without

invoking the extended control functions. In order to provide recovery support, these control programs must be at the proper level.

Programming support for the APU is provided by an update to the latest level of OS/VS2 Release 3.

Programming support for multiprocessing is provided by OS/VS2 Release 2.

# Programming Compatibility between This System, Other System/370 Models, and System/360

Given the storage capacity, the internal and input/output channel processing rates, and the types of attachable input/output devices, compatibility can be maintained with other System/370 and System/360 models. These are the exceptions:

- 1. Programs using machine-dependent data (for example, machine logouts).

- 2. Programs using the ASCII bit (PSW bit 12).

- 3. Programs that depend upon features or I/O devices that are not implemented on this system (such as special instructions for the System/360 Model 44).

- 4. Programs that depend upon validity of data after the system power has been turned off and restored.

Programs written for other System/370 or System/360 models that contain the following conditions or requirements should be evaluated on an individual basis to ensure proper operation:

- 1. Time-dependent programs.

- 2. Programs written to cause deliberate program checks.

- 3. Programs that depend upon model-dependent features of other System/370 and System/360 models.

- 4. Programs that use storage locations between addresses

- 128 (decimal) and 1927 (decimal) after a diagnostic logout into program storage. *However*, these programs may be executed:

- a. If MACHINE CHECK is set to STOP ON CHK. In this case, no diagnostic logout into program storage takes place.

- b. If program-storage locations that are overlaid by the diagnostic logout are restored with the program requirements before an IPL and program restart.

Any attempt to continue processing after a diagnostic logout to program storage *without* restoring your program information to the logout area will have unpredictable results.

- 5. Programs whose CCW chains are dynamically modified may not run in the virtual address space. To run such programs under OS/VS, the "virtual = real" option may have to be used.

- 1 The 1,416 bytes (between locations 512 and 1927) of the machine-check extended logout (MCEL) area can be moved into another program-storage area. The technique used to accomplish this relocation depends upon your application.

# **Basic System Description**

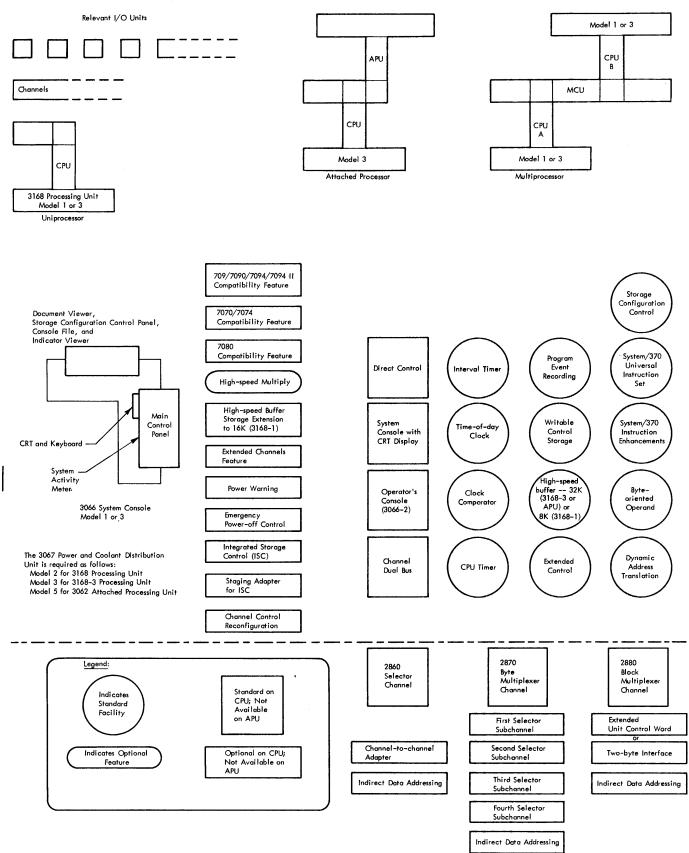

# SYSTEM CONFIGURATION (FIGURE 1)

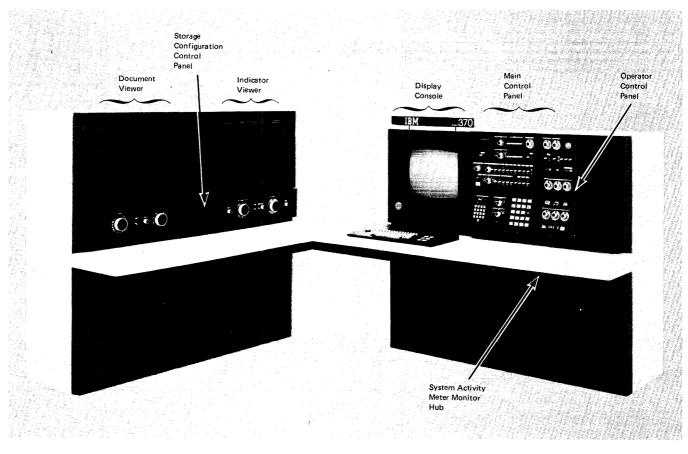

The IBM System/370 Model 168 Data Processing System includes:

- 3066 System Console Model 2 or 3

- An L-shaped grouping which includes the operator's console, main control panel, document and indicator console, main control panel, document and indicator viewers, storage configuration control panel, and console file (see "Functions").

- 3168 Processing Unit Model 1 or 3 This CPU contains the processor storage control function (PSCF), processor storage, instruction unit, and execution unit (see "Central Processing Unit").

- 3067 Power and Coolant Distribution Unit Model 2, 3, or 5.

- Channels (see "Channel Description").

- Relevant I/O Units (see IBM System/370 Input/Output Configurator, GA22-7002).

- Optional Operating System (see "Programming").

# **OPTIONAL FEATURES**

IBM System/370 Model 168 optional features include:

# 709/7090/7094/7094 II Compatibility

This optional feature, in conjunction with its integrated emulator program, allows the Model 168 CPU to execute programs and programming systems originally written for other systems. See IBM System/370 Special Feature Description-709/7090/7094/7094 II Compatibility Feature for IBM System/370 Models 165, 165 II, and 168. GA22-6955.

# 7070/7074 Compatibility

This optional feature, in conjunction with its integrated emulator program, allows the Model 168 CPU to execute programs and programming systems originally written for other systems. See *IBM System/370 Special Feature Description-7080 Compatibility Feature for IBM System/ 370 Models 165, 165 II, and 168, GA22-6963.*

# 7080 Compatibility

This optional feature, in conjunction with its integrated emulator program, allows the Model 168 CPU to execute programs and programming systems originally written for other systems. See *IBM System/370 Special Feature Description-7080 Compatibility Feature for IBM System/370 Models 165, 165 II, and 168, GA22-6963.*

# High-speed Multiply

The use of the high-speed multiply feature allows both fixed-point and floating-point multiply instructions to be performed faster. The basic floating-point long-precision multiply takes about 1,870 nanoseconds and a fixed-point multiply takes about 780 nanoseconds. With the high-speed multiply feature installed, the times required for the two operations are 610 and 420 nanoseconds, respectively. When an attached processing unit is installed on the IBM 3168-3 Processing Unit, the high-speed multiply feature is available on either processing unit or both the APU and the CPU.

# Emergency Power-off (EPO) Control

This feature provides EPO control for two or more System/370 CPUs. By interconnecting the EPO switches on each CPU, the feature provides, in effect, a single EPO switch for the installation.

# Other Optional Features

The high-speed buffer storage extension is described under "High-speed Buffer," the integrated storage controls in Appendix D, the extended channels feature under "2880 Block Multiplexer Channel," and power warning in Appendix F.

*Multiprocessing*: The MP feature, available for 3168 Model 1 and 3 CPUs, enables two Model 168s and an IBM 3068 Multisystem Communication Unit (MCU) to operate as a tightly coupled Model 168 MP. See Appendix E for a description of multiprocessing on the Model 168.

Attached Processing Unit: An IBM 3062 Attached Processing Unit (APU) Model 1 may be added to the IBM 3168-3 Processing Unit. The APU enhances the Model 168 by adding a second instruction processor to the host CPU. The attached processor feature is described in Appendix G.

The term instruction processor, when it is used in this document, refers to both the CPU and APU processor and is equivalent to the term used in the *IBM System/370 Principles of Operation*, GA22-7000, to describe the logical CPU. When no confusion will result, CPU and APU are sometimes used to denote, respectively, the CPU instruction processor and the APU instruction processor.

#### Page of GA22-7010-4 Revised June 18, 1976 By TNL: GN22-0514

Figure 1. System Configuration

# **STANDARD FACILITIES**

Complete descriptions of these facilities are in IBM System/ 370 Principles of Operation, GA22-7000.

# System/370 Universal Instruction Set

The general organization of System/370 instructions is shown in Figure 2. For details, see *IBM System/370 Principles of Operation*, GA22-7000.

# Direct Control

This facility permits the CPU instruction processor to accept external signals from special external devices, which might include another CPU. For details, see *IBM System/360 and System/370 Direct Control and External Interruption Feature*, *OEMI*, GA22-6845.

| System/370<br>Universal<br>Instruction<br>Set | System/370<br>Standard<br>Instruction<br>Set | System/360 Decimal Instructions, and Shift and<br>Round Decimal (SRP) (Decimal Shifting)<br>Instruction<br>System/360 Standard Instruction Set, and the<br>following instructions:<br>Compare Logical Characters Under Mask (CLM)<br>Compare Logical Long (CLCL)<br>Halt Device (HDV) - Halt I/O (HIO) *<br>Insert Characters Under Mask (ICM)<br>Insert Storage Key (ISK) *<br>Load Control (LCTL) *<br>Monitor Call (MC)<br>Move Characters Long (MVCL)<br>Set Clock (SCK) *<br>Set Storage Key (SSK) *<br>Start I/O Fast Release (SIOF) *<br>Store Channel ID (STIDC) *<br>Store Channel ID (STIDC) *<br>Store Control (STCTL) *<br>Store CPU ID (STIDP) * |                                                | ystem/370<br>Commercial<br>Instruction<br>Set |

|-----------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------|

|                                               |                                              | System/360 Floating-point Arithmetic Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Floating-point<br>Facility                     | -                                             |

|                                               |                                              | Read Direct (RDD) *<br>Write Direct (WRD) *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Direct Contro<br>Facility                      | L                                             |

|                                               |                                              | Add Normalized (Extended) (AXR)<br>Load Rounded (Extended to Long) (LRDR)<br>Load Rounded (Long to Short) (LRER)<br>Multiply (Extended) (MXR)<br>Multiply (Long/Extended) (RR) (MXDR)<br>Multiply (Long/Extended) (RX) (MXD)<br>Subtract Normalized (Extended) (SXR)                                                                                                                                                                                                                                                                                                                                                                                          | Extended-precisi<br>Floating-point<br>Facility | ion                                           |

|                                               |                                              | Clear 1/O (CLRIO)*<br>Compare and Swap (CS)<br>Compare Double and Swap (CDS)<br>Insert PSW Key (IPK)*<br>Load Real Address (LRA)*<br>Purge TLB (PTLB)*<br>Reset Reference Bit (RRB)*<br>Set Clock Comparator (SCKC)*<br>Set CPU Timer (SPT)*<br>Set Prefix (SPX)**<br>Set PSW Key from Address (SPKA)*<br>Signal Processor (SIGP)**<br>Store Clock Comparator (STCKC)*<br>Store CPU Address (STAP)**<br>Store CPU Timer (STPT)*<br>Store Prefix (STPX)**<br>Store then AND System Mask (STNSM)*<br>Store then OR System Mask (STOSM)*                                                                                                                         | System/370<br>Instruction<br>Enhancemen        | Facility<br>Instructions                      |

Figure 2. System/370 Instruction Set

#### System/370 Instruction Enhancements

This facility includes new instructions, shown at the lower part of Figure 2. For details, see *IBM System/370 Principles* of Operation, GA22-7000.

#### Byte-oriented Operand

This facility allows the user to ignore, in part, the restriction that all operands in processor storage be aligned on integral boundaries (for example, halfword operands on halfword boundaries). Considerable programming time is saved by this facility; however, performance is degraded when excessive use is made of this capability.

#### **System Timing Facilities**

Timing facilities for the Model 168 include: the interval timer, the CPU timer, the time-of-day (TOD) clock, and the clock comparator.

#### Interval Timer

The interval timer is a 32-bit binary counter with a cycle time of 15.5 hours and a resolution of 3.33 milliseconds. The decrement of the counter to a negative value causes a program interruption. Each instruction processor has an interval timer.

# CPU Timer

The CPU timer measures elapsed instruction processor time, causing an external interruption when a prespecified interval of time has elapsed. Unlike the TOD clock, the CPU timer does not run when the instruction processor is in the stopped state; thus, a more accurate measurement of instruction processor elapsed time is indicated. The APU also contains a timer to measure elapsed instruction processor time. In the APU, the set CPU timer and store CPU timer instructions refer to the APU timer.

#### Time-of-day Clock

The TOD clock is a 64-bit binary counter that is updated every microsecond by adding 1 to bit position 51. With power on, operation is continuous so that the clock is suitable for use, for example, as a function time stamp. Each instruction processor has a TOD clock.

#### Clock Comparator

The clock comparator causes an external interruption when the time-of-day clock reaches a value specified by the user. Each instruction processor has a clock comparator.

# Program Event Recording

This facility, active only in the EC mode, allows for program interruptions (under control of mask bits) in case of: successful branch, alteration of a selected general register, instruction fetching from a selected processor storage area, and alteration of a selected processor storage area.

*Note*: Instruction processor performance is severely degraded when monitoring for successful branch, alteration of a selected general register, or alteration of a selected processor storage area.

# SYSTEM HIGHLIGHTS

Nominal machine specifications are shown in Figure 3. Times given are for single operations, assuming no interference.

#### **General Data**

Parity is checked on all data transfers (except direct control), arithmetic, and logical operations. Odd parity is checked for and maintained on each byte in an instruction processor. I-unit and E-unit operations are overlapped for increased speed.

*Channels:* On the base system, a total of seven channels can be installed. With the extended channels feature, up to 12 channels can be installed. Various combinations are possible according to the installation requirements (see Figure 4).

Dynamic Address Translation (DAT): With the operating system, DAT employs three levels of storage: high-speed buffer storage, processor storage, and some other large capacity storage device such as disk or drum storage.

### Data Storage

L

Storage is four-way interleaved (can be made serial for diagnostic use). All processor storage references are to a doubleword (eight bytes). High-speed buffer storage fetches are for 32-byte blocks. Buffer storage capacity is: 32K in a 3168-3 and APU; 8K (expandable to 16K) in a 3168-1. Virtual storage capacity (regardless of model) is 16,384K. I/O buffers in the PSCF permit optimum use of interleaved processor storage.

|              | Maximum |                              |                       |  |  |  |  |

|--------------|---------|------------------------------|-----------------------|--|--|--|--|

| Channels     | Base    | Extended Channels<br>Feature | Channels per<br>Frame |  |  |  |  |

| Total Number | 7       | 12                           | -                     |  |  |  |  |

| 2860/2870    | 7       | 7                            | -                     |  |  |  |  |

| 2860         | 6       | 6                            | 3                     |  |  |  |  |

| 2870         | 2       | 2                            | 1                     |  |  |  |  |

| 2880         | 6       | 11                           | 2                     |  |  |  |  |

| Total Frames | 7       | 7                            | -                     |  |  |  |  |

| Figure | 4. | Channel | Options |

|--------|----|---------|---------|

|        |    |         |         |

| Element                        | Data Width<br>(Bytes) | Performance                                                                      | Comments                      |

|--------------------------------|-----------------------|----------------------------------------------------------------------------------|-------------------------------|

| Basic machine cycle            | -                     | 80 nanoseconds                                                                   |                               |

| General registers              | 4                     | Once per machine cycle                                                           | 16 general registers          |

| -loating-point registers       | 8                     | Once per machine cycle                                                           | Four floating-point registers |

| Addressing adder               | 3                     | Once per machine cycle                                                           |                               |

| Parallel adder                 | 8                     | Once per machine cycle                                                           |                               |

| Serial adder                   | 1                     | Once per machine cycle                                                           |                               |

| 2860 Selector Channel          | 1                     | 1.3 million bytes per second                                                     | Eight bytes to storage        |

| 2870 Byte Multiplexer Channel  | 1                     | 110 kilobytes to 670 kilobytes<br>(aggregate)<br>(kilobyte = 1,000 bytes/second) | Eight bytes to storage        |

| Burst mode                     | 1                     | 110 kilobytes (Note 1)                                                           |                               |

| Multiplexer mode               | 1                     | 110 kilobytes (Note 1)                                                           |                               |

| Selector subchannels 1–3       | 1                     | 180 or 200 kilobytes each                                                        | Note 3                        |

| Selector subchannel 4          | 1                     | 0 or 100 kilobytes                                                               | Note 3                        |

| 2880 Block Multiplexer Channel | 1                     | 1.5 million bytes/second (Note 2)                                                | Eight bytes to storage        |

Notes:

1. Aggregate 192-subchannel rate for first or second 2870 reduced by concurrent selector subchannel operation.

2. Three million bytes per second when optional two-byte interface is used.

3. Refer to the data rate table in "2870 Byte Multiplexer Channel."

Figure 3. System Highlights

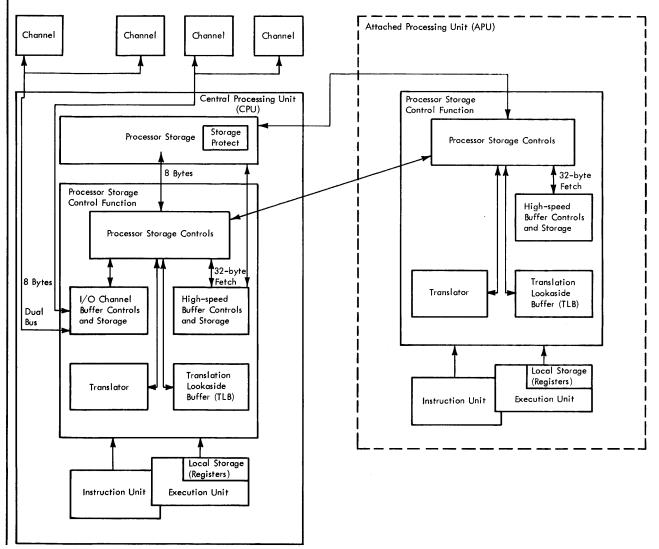

The central processing unit (CPU) includes the processor storage, processor storage control function (PSCF), instruction unit, and execution unit. This integrated complex (Figure 5), the 3168 Processing Unit, has several versions, identified by:

- Processor storage capacity

- Function (uniprocessing, attached processing, or multiprocessing)

- Version (Model 1 or 3)

The Model 3 is an advanced version of the Model 1, offering better performance through improvements such as instruction and interruption enhancements, and buffer expansion. Conversion of the Model 1 to the Model 3 is available. Information in this manual applies to both Models 1 and 3 unless stated otherwise.

# PROCESSOR STORAGE

# Models

The 3168 is available in eight processor-storage capacities, all four-way interleaved:

| Capacity           | 168 Model Designation |                  |  |  |  |

|--------------------|-----------------------|------------------|--|--|--|

| (Bytes)            | If 3168 Used          | If 3168-3 Used   |  |  |  |

| 1,048,576 (1,024K) | J or MP1              | U31, A31, or M31 |  |  |  |

| 2,097,152 (2,048K) | K or MP2              | U32, A32, or M32 |  |  |  |

| 3,145,728 (3,072K) | KJ or MP3             | U33, A33, or M33 |  |  |  |

| 4,194,304 (4,096K) | L or MP4              | U34, A34, or M34 |  |  |  |

| 5,242,880 (5,120K) | LJ or MP5             | U35, A35, or M35 |  |  |  |

| 6,291,456 (6,144K) | LK or MP6             | U36, A36, or M36 |  |  |  |

| 7,340,032 (7,168K) | LKJ or MP7            | U37, A37, or M37 |  |  |  |

| 8,388,608 (8,192K) | M or MP8              | U38, A38, or M38 |  |  |  |

Figure 5. Model 168 Organization

#### Permanent Storage Assignment

In the Model 168, processor storage addressing begins at location 0 and continues upward through the highest storage byte location. All the processor storage is available for programming functions, except the permanent storage assignment areas, which may be found in an abbreviated list in "Model-dependent Functions" and in detail in *IBM System/370 Principles of Operation*, GA22-7000.

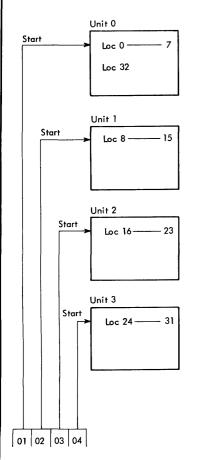

#### Interleaving

Interleaving allows processor storage units to operate independently in an overlapped manner for effective reduction of the storage-cycle time (Figure 6).

In four-way interleaving, four functionally independent storage units (each providing eight bytes per storage access) make up processor storage. Assume that the four units are 0, 1, 2, and 3. Storage locations 0-7 are in unit 0, locations 8-15 are in unit 1, locations 16-23 are in unit 2, and locations 24-31 are in unit 3. Storage locations 32-39 are in unit 0, and the address-distribution sequence continues through all available storage locations. An attempt to reference a processor storage location (unit) may be made during any cycle. Actually, a storage reference is accepted on any cycle during which the functionally independent storage unit containing the requested location is not busy. (A storage unit is defined as busy when it has not completed a storage cycle after being selected.) Once the storage unit is selected for a storage reference, it cannot be referenced again until the total storage-cycle time passes.

#### **Configuration Capability**

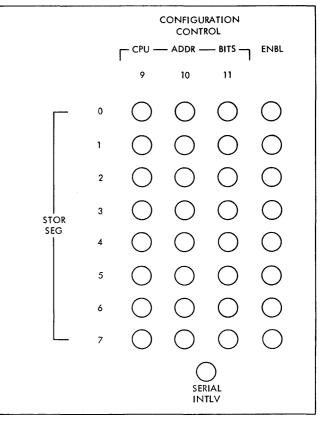

The basic configuration unit is defined as a storage segment (STOR SEG, Figure 7), which represents 1,048,576 bytes (1,024K) of storage. Processor storage contains up to eight segments, designated 0 through 7. The configuration control panel assigns an address range to each segment. Inserting a plug into the interleave socket on the configuration panel causes the system to operate processor storage in a serial fashion. The default (not plugged) mode of operation is four-way interleaved. Depending on processor storage size, any 1,024K address range (starting with byte 0) can be assigned to any physical 1,024K of storage. For a detailed description of the storage configuration control, see *IBM System/370 Model 168 Operating Procedures*, GC38-0030.

Figure 6. Interleaving

Figure 7. Configuration Panel

# PROCESSOR STORAGE CONTROL FUNCTION

All storage accesses from the instruction processor and channels are controlled by the processor storage control function (PSCF). Each access transfers one doubleword (eight bytes). Five different logical areas make up the PSCF:

- 1. High-speed buffer storage and control.

- 2. Translator.

- 3. Translation lookaside buffer (TLB).

- 4. I/O channel control (I/O buffer).

- 5. Processor storage controls.

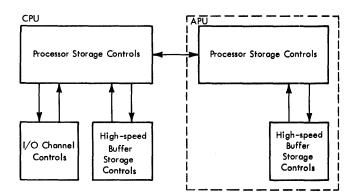

*Note*: The PSCF of the attached processing unit has all the logical areas except the I/O channel buffers. The processor storage controls in the APU are interleaved with the host CPU and are described in Appendix G.

#### **Buffer Storage Control**

The buffer storage control handles all storage requests from the instruction processor for data stores or fetches. It also monitors all channel store operations so that the high-speed buffer storage can be invalidated, if necessary.

#### **High-speed Buffer**

Buffer storage provides high-speed access to instructions and data. A fetch from the buffer takes less than one-fourth of the time required for the same fetch from processor storage. Buffer action is automatic. Although it holds only a portion of processor storage contents, the objective of the buffer is to contain that area that the program is currently using.

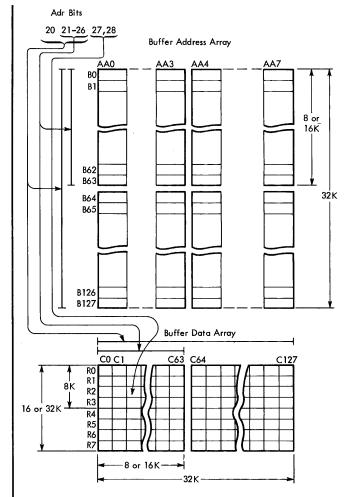

The high-speed buffer holds recently accessed storage data and is constantly being updated. The buffer's standard capacity is 8K in the 3168-1, and 32K in the 3168-3 and APU. Buffer storage is distributed in 32-byte blocks, each block consisting of four doublewords. The 32K buffer of the 3168-3 or APU is partitioned into eight blocks per column, with 128 columns, for a total of 1,024 blocks (Figure 8). In the 3168-1, the 8K buffer has four blocks per column, with 64 columns, for a total of 256 blocks. If the buffer of the 3168 is expanded to 16K, it is then partitioned into eight blocks per column and 64 columns, for a total of 512 blocks. Correspondingly, processor storage also is conceptually divided into 64 or 128 columns, the number of blocks per column varying with the size of processor storage.

During operation, a correspondence is set up that relates each block in buffer storage to a block in the corresponding column of processor storage. Each time the instruction processor makes a fetch, buffer storage control determines whether there is an assigned buffer block corresponding to the addressed processor storage block. If none is found, one of the buffer blocks is automatically assigned to the block that was addressed, the block address is placed in the buffer

Figure 8. High-speed Buffer Operation

block's address array, and a buffer storage block load is called for. While the block is being executed, the address is made invalid until the fetch is complete.

When an instruction processor fetch dictates a block load, four 8-byte (overlapped) accesses to processor storage are required. The first processor storage location selected is the one containing the data addressed. When the location is available, the data is sent directly to the instruction processor and is also loaded into buffer storage. The three remaining (overlapped) processor storage fetches needed to complete the block load are made one at a time on each succeeding cycle, if the required processor storage units are not busy.

For a channel store operation, a check is made to determine whether the referenced data is in the applicable buffer storage; if it is, the buffer storage data is invalidated and processor storage data is updated. If the referenced data is not in the applicable buffer storage, only processor storage is updated. Channel fetch requests are made only to processor storage.

Because buffer storages can contain only a portion of processor storage data at one time, any buffer block can be reassigned to any other block of the corresponding column in processor storage. Priority of reassignment is based on usage. Each time data within a buffer block is referenced by an instruction processor fetch, that block is logically moved to the top of a logic-controlled activity list. Intervening blocks are logically moved down one position to fill the vacated slot. Note, however, that the logical movement of a block within the list involves no data transfer. When all four (eight in the case of a 16K or 32K buffer) buffer blocks within a column are assigned and the instruction processor makes a fetch request to a corresponding storage location not yet in buffer storage, the buffer block lowest on the activity list is cleared and reassigned to the referenced processor storage block. (The buffer block at the bottom of a particular activity list is the one in that column that has gone the longest without being referenced by an instruction processor fetch.)

Store-type operations always update processor storage, but buffer storage is not updated unless the referenced processor storage block has a corresponding buffer storage block assigned. In summary, store operations do not cause reassignment, loading of a buffer storage block, or changing of the buffer storage block activity list.

The 32K buffer is designed for use by the 3168-3 and APU in either basic control mode or extended control mode. When used in extended control mode, 4K paging is required. If a user's system control program requires 2K paging, the buffer defaults to 16K capacity. The buffer is automatically reset to 32K when the system reverts to 4K paging, or it can be reset manually.

# Translator

This unit translates logical addresses to real addresses when the system is in DAT mode and during the execution of an LRA instruction. The translator also holds addresses for TLB searches and updates.

# Translation Lookaside Buffer (TLB)

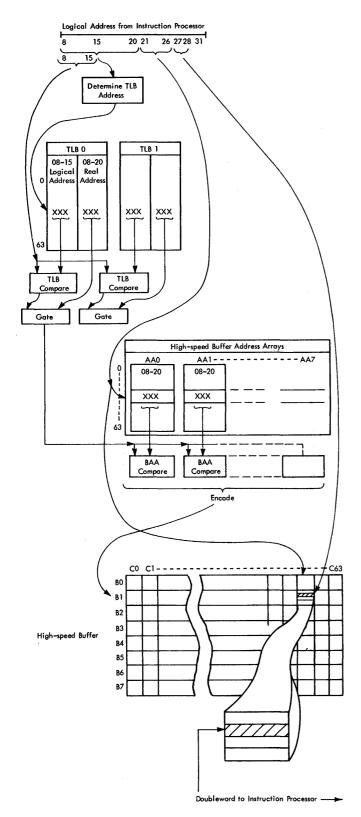

In order to reduce the logical-to-real address translation time, once a translation is completed, the real address of a referenced page is stored in a group of registers called the TLB. Each real address stored in the TLB is identified as belonging to a particular logical address by:

- 1. The position in the TLB into which it is stored.

- 2. Storing bits 8-15 of the logical address into the TLB entry.

Thus, the TLB contains up to 128 logical-real address pairs. Subsequent translations for the same addresses, and their multiple processor storage references, are avoided because the real address required is available immediately from the TLB.

# **TLB** Operation

Each logical address supplied by the program causes access to both the high-speed buffer (to examine address of data contained), and the TLB (to determine if real address and protect key are resident).

If the real address is available from TLB, it is compared with addresses read out of the high-speed buffer-address array to determine if the data field required is there (Figure 9). The real address is also used to access processor storage if the operation requires it. If the real address is not available from the TLB, the logical address is translated and the TLB is updated with the newly translated address.

The TLB can be purged with the program by issuing a purge TLB instruction; it can be partially purged by loading control registers 0 and 1, or by issuing a load PSW instruction. The TLB may also be purged by using manual controls such as COMPUTER or SYSTEM RESET. For a description of these instructions, see *IBM System/370 Principles of Operation*, GA22-7000.

# Possibilities for Final Resolution:

- 1. The logical address has been previously translated, and its real address now resides in the TLB. It is possible for the address to be resolved in one machine cycle, and to have the data available on the following cycle.

- 2. The logical address has not been previously translated, or has been previously translated, but does not currently reside in the TLB; thus, a full translation must take place. Assuming no I/O interference, from 8 to 26 machine cycles are required, depending on the locations of the segment and page table entries required for the translation.

TLB Operation Example: Assume a given logical address is requested by the instruction processor (see Figure 9). Logical address bits 8-20 select the entry line in the TLB. Logical address bits 8-15 are compared against the entry from the TLB. If the TLB compare is unsuccessful, a full translation is performed. Before going to processor storage to do the full translation, a determination is made to see if the required translation entries (or any part of them) are in the buffer. If they are, the translation is made, using the buffer entries. If only part (or none) of the entries is in the buffer, then part (or all) of the translation is made, using processor storage.

If the TLB compare is successful, no translation is required and the real address is transferred from the TLB to the buffer address array to find if the entry is in the buffer. This ultimately determines whether the fetch is made from the buffer or from processor storage.

Figure 9. TLB Operation

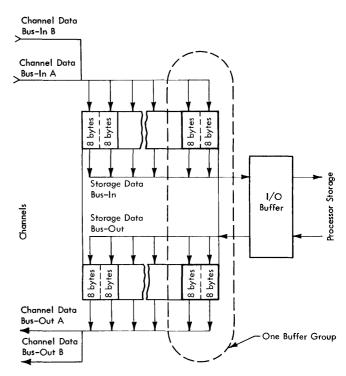

# I/O Channel Controls (I/O Buffer)

The I/O channel controls (Figure 10) receive and process channel storage requests. Each channel attached to the CPU has a fixed amount of channel control buffer (a buffer group) dedicated to its use. This buffering results in attaining higher channel data rates through maximum utilization of the four-way interleaved processor storage.

A channel buffer group provides two sections, each with control ability and data capaoity for one doubleword inbound and one doubleword outbound. To transmit information to processor storage during an I/O read operation, the channels place data and control signals on a channel in-bus to the channel buffers in the I/O channel control. Channel buffer priority determines which buffer section may use storage and transmit data via the storage in-bus at any given time. Priority is established at installation time: highest storage priority is assigned to buffer group 1, second highest priority to buffer group 2, etc. The resultant channel-to-channel buffer relationship may be seen on the indicator viewer. As each channel buffer is loaded, it requests use of one of the four interleaved units of processor storage. If the channel is performing a store operation, the high-speed buffer address array is accessed, and if the affected address is resident there, that buffer block is invalidated.

The loading of a channel buffer section frees the channel in-bus for use by other channels vying for its use. Simultaneous multichannel data transfers are increased by use of the channel dual bus function.

Figure 10. I/O Channel Controls

### **Processor Storage Controls**

The processor storage controls (Figure 11) handle the storage requests made by the high-speed buffer storage controls and by the I/O channel controls.

Both store and fetch operations are modified by the error checking and correction logic in the storage units. Single-bit parity errors are detected and corrected, and double-bit parity errors are detected.

Figure 11. Processor Storage Controls

# **INSTRUCTION UNIT (I-UNIT)**

This unit fetches, decodes, and buffers instructions, calculates addresses, fetches required operands, and issues instructions to the execution unit. In addition, the instruction unit controls those portions of the execution unit required for establishing the initial conditions for instruction execution (such as those used for prefetched operands and decoded operation codes). This unit can prepare several instructions concurrently, and its operation is overlapped with the execution unit.

# **EXECUTION UNIT (E-UNIT)**

This unit, controlled by microprograms can execute (in best case conditions) a new instruction during every cycle. Where data results determine the execution sequence, nonmicroprogram control is used.

#### Local Storage

This unit contains the 16 general registers and four floating-point registers.

#### Writable Control Storage

This facility (in the execution unit) provides basic control as well as microdiagnostic capability. The control storage consists of a combination of read-only storage (ROS) and writable control storage (WCS), plus associated logic. Internal transfers are parity-checked; a parity error causes a machine check. Control storage stores control information that is used to define the state of the execution unit at any given time.

# **EXTENDED CONTROL**

Extended control (EC) mode provides expanded control for the System/370 facilities, including dynamic address translation and program event recording.

EC mode is implemented with a modified PSW format and with extended permanently assigned areas of processor storage. For the format of the EC PSW, see *IBM System/* 370 Principles of Operation, GA22-7000.

#### **Dynamic Address Translation**

Dynamic address translation (DAT) puts a logical address space (expanded processor storage) of up to 16,384K at the user's disposal, regardless of the actual processor storage size. This logical address space is referred to as "virtual storage." For details, see *IBM System/370 Principles of Operation*, GA22-7000.

# **SERVICE PROCESSOR (SVP)**

The 3168-3 service processor (a standard feature) is a functionally separate realtime monitor that provides improved serviceability and availability. Operating under control of the stored-program-controlled processor, the SVP continuously records the most recent 32 cycles of 199 bits of processor control information. When a hardware failure (either recoverable or unrecoverable) occurs, the control information and machine logout data are stored on an internal disk file containing as many as 16 trace data records.

The capture of this intermittent and hard error data permits better online error analysis. The potential for long outages may be further reduced by the use of a remote service facility. This is a customer option that allows service personnel to link the processor to a remote maintenance facility.

The SVP features include:

- Local and remote communications through an interface.

- Optional display of data on the 3168-3 console or on a system printer, using a standalone or online test diagnostic program.

- Optional attachment of an IBM 3213 Console Printer to record SVP data. The 3213 integrated printer attachment feature is required.

- Channel interface connection that can be used to route diagnostic data to the host or other processor for recording.

- Internal disk file that can store as many as 16 events (for example, hardware failures).

#### **CHANNELS**

The IBM 2860 Selector Channel, the IBM 2870 Byte Multiplexer Channel, and the IBM 2880 Block Multiplexer Channel provide for attachment of I/O devices to the Model 168 system (Figure 13). The channel relieves the instruction processor of communication directly with I/O devices and permits data processing to proceed concurrently with I/O operations.

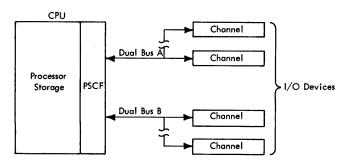

Two buses (A and B) (see Figure 12) are provided to attach the channels. On the standard system, up to three logical channels or three channel frames may attach to bus A and four to bus B. This dual bus facility provides independent priority logic registers and gating for each bus thereby allowing simultaneous data transfer on the two buses.

A standard, single channel-to-control unit interface provides a uniform method of attaching control units to channels. Data is transferred one byte at a time between the I/O device and the channel. An optional two-byte-wide interface on the 2880 channel provides for attachment of devices with very high data rates. Data transfers between the channel and the PSCF are eight bytes (one doubleword) in parallel for both selector and multiplexer channels.

The extended channels feature permits attachment of up to 12 channels to the Model 168. (See Figure 13; also see "Extended I/O Masking" in *IBM System/370 Principles of Operation*, GA22-7000.)

# **Channel Attachment**

The system attaches a minimum of one 2860 or one 2870 with the optional selector subchannel feature installed, or one 2880 Block Multiplexer Channel.

Frame and channel attachment statistics are conveniently tabulated in Figure 13.

Figure 12. Channel Data Flow

|              | Maximum |                              |                       |  |  |  |  |

|--------------|---------|------------------------------|-----------------------|--|--|--|--|

| Channels     | Base    | Extended Channels<br>Feature | Channels per<br>Frame |  |  |  |  |

| Total Number | 7       | 12                           | -                     |  |  |  |  |

| 2860/2870    | 7       | 7                            | -                     |  |  |  |  |

| 2860         | 6       | 6                            | . 3                   |  |  |  |  |

| 2870         | 2       | 2                            | 1                     |  |  |  |  |

| 2880         | 6       | 11                           | 2                     |  |  |  |  |

| Total Frames | 7       | 7                            | -                     |  |  |  |  |

Figure 13. Channel Options

#### **Channel Frame Positions**

- Channels assigned priorities 1, 2, 3, 9, A, and B must be attached to bus A.

- Channels assigned priorities 4, 5, 6, 7, C, and D must be attached to bus B.

- Channels within the same channel frame must be attached to the same bus.

- Channels with the highest speed devices attached should be positioned closest to the instruction processor on the bus to which they are attached.

#### Data Rate Considerations

An 8.5 Mb/sec aggregate data rate can be maintained on each bus providing a total aggregate capability of approximately 17 Mb/sec. Given this capability, Figure 14 illustrates what device data rates can be sustained at various channel priority positions. Generally, the device type noted in each example implies that any other device type with similar characteristics and the same or slower data rate may also be attached.

| Mb/sec<br>3.0 | Device Type     | T            | 2 | 6            | -            |              |   | _ |              |   |   |   |   |

|---------------|-----------------|--------------|---|--------------|--------------|--------------|---|---|--------------|---|---|---|---|

| 3.0           |                 |              | 4 | 3            | 4            | 5            | 6 | 7 | 9            | А | В | С | D |

|               | 2305-1 *        | 1            | 1 |              | $\checkmark$ | 1            |   |   |              |   |   |   |   |

| 1.5           | 2305-2*         | $\checkmark$ | V | 1            | V            | 1            | V |   |              |   |   |   |   |

| 1.25          | 3420-8 (3803-2) | $\checkmark$ | V | $\checkmark$ | 1            | 1            | V | 1 | 1            | * |   |   |   |

| 0.8           | 3330, 3340*     | $\checkmark$ | √ | 1            | 1            | $\checkmark$ | 1 | < | $\checkmark$ | V | V |   |   |

| 0.8           | 3420-6 (3803-2) | $\checkmark$ | V | $\checkmark$ | 1            | ✓            | 1 | 1 | 1            | 1 | 1 | 1 | ~ |

position . \* = attachable via 2880 channel only.

Figure 14. Device Data Rates

Twelve priority positions are designated: 1, 2, 3, 4, 5, 6, 7, 9, A, B, C, and D. Priority is established by plugging jumpers on matrix cards in the PSCF. Devices with higher data rates should be attached to the higher priority channels.

Negligible or no overrun exposure will exist if these guidelines are followed.

The 2870 channels with 0, 1, or 2 selector subchannels may be attached to any priority position, but generally should be positioned as high as possible. The 2870 channels with more than two selector subchannels should be assigned priority position 1, 2, 3, or 4.

### Indirect Data Addressing

In the implementation of dynamic address translation, CCWs in virtual storage must be translated by the control program before execution. To allow the designation of noncontiguous areas of real storage for contiguous areas of virtual storage, the indirect data addressing (optional feature) is used. For details, see *IBM System/370 Principles of Operation*, GA22-7000.

#### 2860 Selector Channel

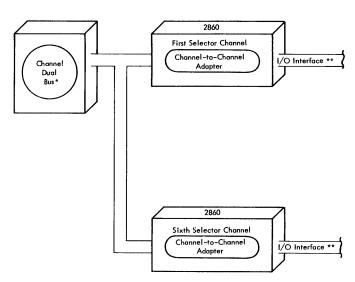

The 2860 Selector Channel provides for attachment and control of I/O control units and associated devices (Figure 15). The 2860 is available in three models:

- Model 1-Provides one selector channel.

- Model 2-Provides two selector channels.

- Model 3-Provides three selector channels.

The 2860 Selector Channel permits data rates of up to 1.3 million bytes a second. I/O operations are overlapped with processing and, depending on the data rates and channel programming considerations, all selector channels can operate concurrently. A set of channel control and buffer registers in the CPU permits each channel to operate with a minimum of interference.

Eight control units can be attached to each selector channel. Each control unit may have more than one I/O device connected, but only one device per channel may transfer data at any given time. A selector channel operates only in burst mode, and may be assigned channel addresses 1 through 6 only. Each selector channel addresses up to 256 I/O devices, one at a time. Operation is in burst mode with overlapped processing.

\* Up to six selector channels can be attached to the Model 168.

\*\* Up to eight control units may be attached. Input/output control units and devices are shown in IBM System/370 Input/Output Configurator, GA22-7002.

Figure 15. 2860 Selector Channel

#### Channel-to-Channel Adapter Feature

A channel-to-channel adapter is available as an optional feature on the 2860. The adapter provides a path for operations to take place between two channels, and synchronizes those operations. It may be used in multiple-processor or single-processor systems; in a multisystem, to achieve rapid communications between the channels of two System/370 models, or between a System/360 and a System/370, or in a single System/370 to move blocks of data from one processor storage area to another.

The adapter uses one control unit position on each of the two channels, but only one of the two connected channels requires the feature. In the Model 168, one adapter may be installed per 2860 Selector Channel.

When a 2870 or 2880 channel is connected to a 2860 channel, the channel-to-channel adapter is installed on the 2860 channel (not on the 2870 or 2880).

For restrictions on channel attachments for another system model used with the Model 168, refer to the Systems Library (SL) functional characteristics publication for that model. See *IBM System/370 Special Feature Description Channel-to-Channel Adapter*, GA22-6983, and *IBM System/360 and System/370 I/O Interface Channelto-Control Unit OEMI*, GA22-6974.

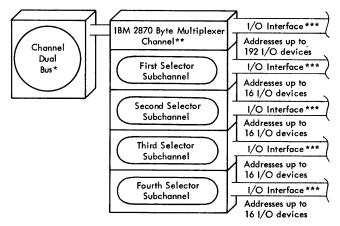

# 2870 Byte Multiplexer Channel

The 2870 Byte Multiplexer Channel provides for attachment of a wide range of low- to medium-speed I/O control units and associated devices (Figure 16). The basic 2870 Byte Multiplexer Channel (with 192 subchannels) can attach eight control units and address 192 I/O devices, using unit addresses up to BF (hexadecimal). The basic byte multiplexer channel can operate several byte multiplexmode I/O devices concurrently or a single burst-mode device.

Two 2870's can be attached to the Model 168: each one provides 192 subchannels, plus four optional selector subchannels. The address of the first 2870 must be 0; the second 2870 may be assigned any address from 1 through 6.

A selector subchannel can (1) operate one I/O device concurrently with the basic byte multiplexer channel, and (2) permit attachment of eight control units for certain devices having a data rate not exceeding 200 kilobytes (kb) a second. Regardless of the number of control units attached, a maximum of 16 I/O devices can be attached to a selector subchannel.

\*Up to two 2870s may be attached to the Model 168.

\*\*A system with the first 2870 may attach up to six selector channels; a system with the first and second 2870 may attach up to five selector channels.

\*\*\*Up to eight control units may be attached. Input/output control units and devices are shown in the <u>IBM System/370 Input/Output Configurator</u>, GA22-7002.

Figure 16. 2870 Byte Multiplexer Channel

The maximum aggregate data rate for the byte multiplexer channel ranges from 110 kb to 670 kb, depending on the number of subchannels in operation and the rates of the attached I/O devices. When four selector subchannels are installed in the 2870, the first three may operate at a maximum of 180 kb and the fourth at 100 kb (maximum). When three selector subchannels are installed, all three may operate at 200 kb (maximum). Note that when four subchannels are installed and the first three are operating at 200 kb, the fourth subchannel cannot be operated.

Each selector subchannel in operation diminishes the basic byte multiplexer channel's maximum data rate of 110 kb; the maximum data rates for concurrent selector subchannel operations are:

| Basic Byte<br>Multiplexer | Data R      | ates for Sei<br>(Kilob) | lector Subch<br>tes) | annel        |  |  |  |

|---------------------------|-------------|-------------------------|----------------------|--------------|--|--|--|

| Channel                   | 1st or 2n   | nd 2870                 | 1st 2870 Only        |              |  |  |  |

| (Kilobytes)               | 1 st        | 2nd                     | 3rd                  | 4th          |  |  |  |

| 110                       | _           | _                       | _                    | _            |  |  |  |

| 88                        | 180         | -                       | -                    | -            |  |  |  |

| 66                        | 180         | 180                     |                      | -            |  |  |  |

| 44                        | 180         | 180                     | 180                  |              |  |  |  |

| 30                        | 180         | 180                     | 180                  | 100          |  |  |  |

| For 200-kb selec          | tor subchan | nel operati             | on, these ra         | tes prevail: |  |  |  |

| 110                       | _           | _                       | -                    | _            |  |  |  |

| 80                        | 200         | -                       | -                    | _            |  |  |  |

| 55                        | 200         | 200                     | _                    | _            |  |  |  |

| 30                        | 200         | 200                     | 200                  | —            |  |  |  |

*Note:* The maximum data rate for 2870 Selector Subchannels pertains to attachment of magnetic tape devices; timing factors other than data rates may preclude attachment of direct-access storage devices that have lesser data rates. Also, note that when other channels in addition to the 2870 are in operation, the total system I/O data rate must be analyzed.

The maximum data rate for selector subchannels and for the basic byte multiplexer channel is a function of the channel buffer priority assigned to that 2870. (See "Data Rate Considerations" for priority assignment.)

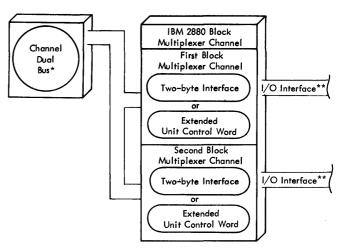

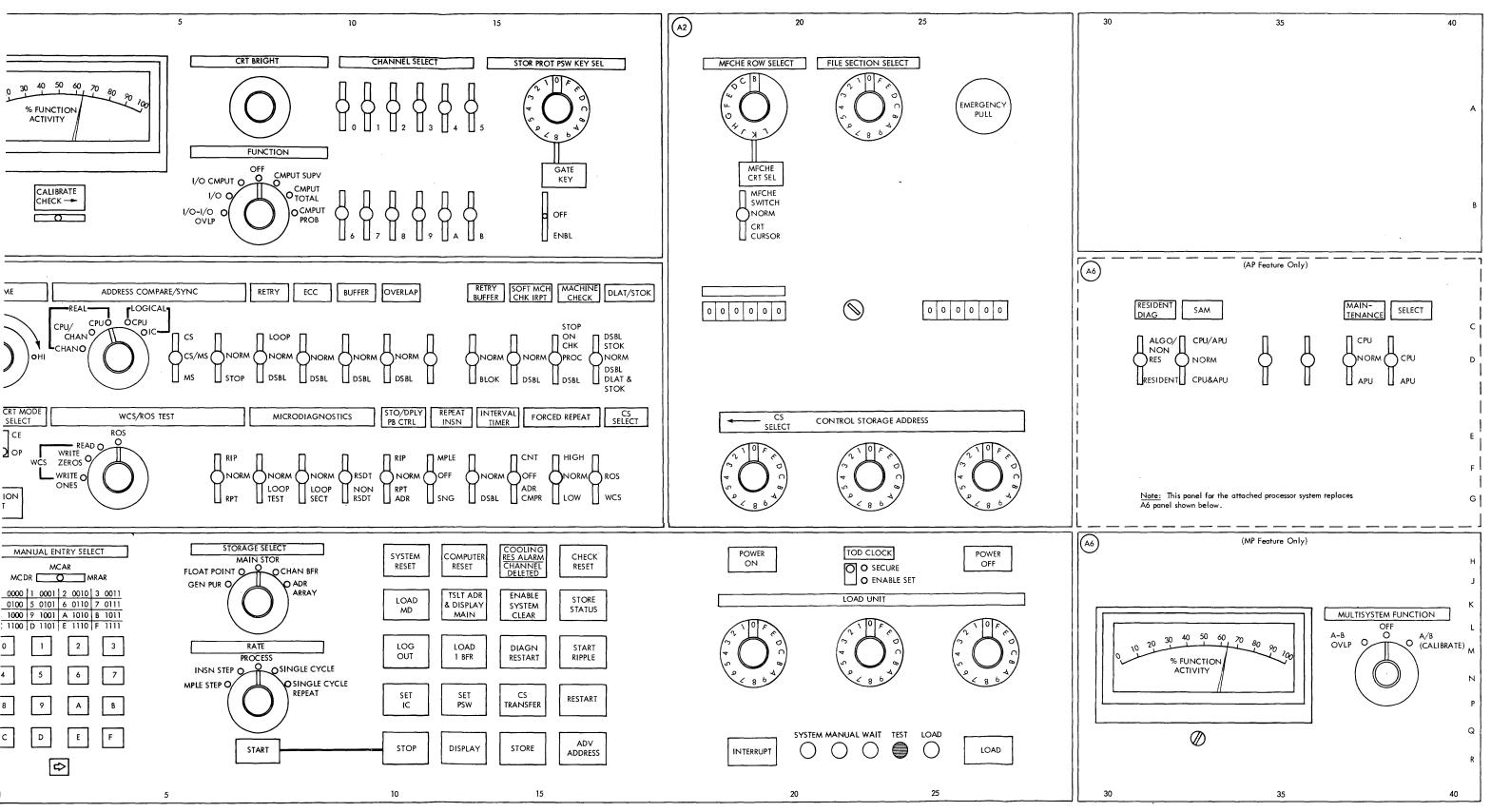

#### 2880 Block Multiplexer Channel

The functional use of the 2880 Block Multiplexer Channel (Figure 17) closely parallels that of the 2860 Selector Channel; devices that attach to the Model 168 through a 2860 may also attach through a 2880 assigned one of the addresses 1 through 6. However, the 2880 is capable of higher data rates than the 2860 and also offers a block multiplexing capability. Unlike the 2860 and 2870 channels, the 2880 performs a channel logout on occurrence of a channel data check condition. The logout occurs at the completion of the current command, and into locations starting at the input/output channel area (IOCA) pointer (in bytes 173-175).

The 2880 always transfers data in burst mode, and may be assigned any address from 1 through 11. Two models of the 2880 Block Multiplexer Channel are available:

Model 1-Provides one channel.

Model 2-Provides two channels.

The standard features of the 2880 are the high-speed data transfer mode (which allows transfer of up to 1.5 million bytes per second) and block-multiplexing capability (which permits concurrent operation of up to 57 devices-56 nonshared, one shared).

The 2880 can have either of two optional features—the extended unit control word (UCW) feature or the two-byte interface. The *extended UCW* feature allows the attachment and concurrent operation of up to 256 I/O devices on each block multiplexer channel, thereby permitting the user to extend the capacity of his channels rather than install additional ones. The *two-byte interface* feature provides for a data transfer rate of up to three million bytes per second.

The basic 2880 Block Multiplexer Channel provides the standard one-byte I/O interface.

Eight control units can be attached to each 2880 Block Multiplexer Channel. Each control unit may have more than one I/O device connected to it, but only one device per channel may transfer data at any given time. However, as many as 256 channel programs (using the extended UCW feature) may be in concurrent execution in each 2880 channel through use of the block multiplexing function.

Of the eight control units, seven may be block multiplexed, permitting a wide variety of attached devices. At least one shared (nonblock multiplexer mode operation) subchannel has all addresses not assigned to the nonshared subchannels.

To facilitate conversion, the 2880 also operates in selector channel mode. The selector or block multiplexer mode is program selectable. (See "Block Multiplexing Control" in *IBM System/370 Principles of Operation*, GA22-7000.)

This channel provides up to 256 nonshared (block multiplexer mode operation) subchannels per block multiplexer channel, allowing up to 256 block multiplexer devices to operate concurrently on the single data path of the channel. Under certain circumstances, 64 nonshared

\*Up to six block multiplexer channels (11 with the extended channels feature) may be attached.

\*\*Up to eight control units may be attached. Input/output control units and devices are shown on the <u>IBM System/370 Input/Output</u> <u>Configurator</u>, GA22-7002.

Figure 17. 2880 Block Multiplexer Channel

subchannels are available without the use of the extended UCW feature, allowing concurrent operation of 64 non-shared devices. The conditions to be met are:

- 1. Addresses 00 to 07 must be used.

- 2. Any control unit capable of attaching more than eight devices must use contiguous address groups.

- 3. All addresses recognized by a control unit must be assigned nonshared subchannels even if the device does not physically exist. That is, an eight-device control unit must have a full complement of eight nonshared subchannels assigned; a 16-device control unit (for example, the 3830-2 or integrated storage control) must have two full contiguous groups of nonshared subchannels assigned.

- 4. No shared subchannel may exist and no shared control units may be attached. If the channel should receive an interruption associated with an address that is not one of the 64 assigned nonshared addresses, a channel control check occurs.

The addresses for the nonshared subchannels are set by the service personnel during installation. Command retry is available on the 2880 Block Multiplexer Channel only.

All block multiplexer devices must be assigned to nonshared subchannels; all nonblock multiplexer devices must be assigned to the shared subchannel. (*Exception:* The 2821 and 3811 control units may be attached to either type of subchannel, but nonshared subchannel attachment is recommended.)

Limitations: Maximum data rates with data-chaining operation can be maintained only if the chaining takes place in "gap time" of the device. In addition, the use of the indirect data addressing (IDA) flag has an effect on data rates similar to data-chaining. Operations combining datachaining and IDA greatly increase the possibility of I/O overrun conditions.

#### Functions

#### **USAGE METERING**

Usage meters appear on the following units of the Model 168: the 3066 System Console, the 2860 Selector Channel, the 2870 Byte Multiplexer Channel, the 2880 Block Multiplexer Channel, and the 3068 Multisystem Communication Unit (Model 168 MP). Meters also appear on individual I/O units.

For the 3168 Processing Unit, the customer usage meter and the CE meter are on the main control panel. The CE key switch controls which of these meters is to be run while the system is in operation; that is, initiating, executing, or completing instructions, including I/O and assignable unit operations. The system light indicates when the system is in operation. The test light may indicate when the key switch is in the CE meter position.

The 2860 Selector Channel Models 1-3, the 2870 Byte Multiplexer Channel, and the 2880 Block Multiplexer Channel each have one usage meter mounted on their respective power control panels.

When each meter runs depends on the general function performed by the unit to which it is attached. The function of those units, by category, and the conditions under which the meter runs, are described in Figure 18. (Also see "Usage Meter" under "Multiprocessing Feature" and "Attached Processor Feature.")

#### System Activity Meter