# **Systems**

# A Guide to the IBM System/370 Model 165

# **Systems**

# A Guide to the IBM System/370 Model 165

This guide presents hardware, programming systems, and other pertinent information about the IBM System/370 Model 165 that describes its significant new features and advantages. Its contents are intended to acquaint the reader with the Model 165 and to be of benefit in planning for its installation.

#### First Edition (June 1970)

This guide is intended for planning purposes only. It will be updated from time to time to reflect system changes; however, the reader should remember that the authoritative sources of system information are the Systems Reference Library (SRL) publications for the Model 165, its associated components and its programming support. These publications will first reflect such changes.

Copies of this and other IBM publications can be obtained through IBM branch offices.

A form has been provided at the back of this publication for readers' comments. If this form has been removed, address comments to: IBM Corporation, Technical Publications Department, 112 East Post Road, White Plains, New York 10601.

© Copyright International Business Machines Corporation 1970

It is assumed that the reader of this document is familiar with System/360. The reader should have a general knowledge of System/360 architecture, channels, I/O devices, and programming systems support. This guide highlights only those Model 165 hardware, I/O, and programming systems features that are different from those of System/360 models and discusses their significance. Additional, more detailed information regarding System/370 Model 165 hardware and programming systems support can be found in the following SRL publications:

IBM System/370 Model 165 Functional Characteristics (GA22-6935)

IBM System/370 Principles of Operation (GA22-7000)

IBM System/370 System Summary (GA22-7001)

IBM System/370 I/O Configurator (GA22-7002)

Component Summary: 3830 Storage Control, 3330 Disk Storage (GA26-1592)

IBM System/360 Component Description: 2835 Storage Control and 2305 Fixed Head Storage Module (GA26-1589)

3211 Printer and 3811 Control Unit Component Description (GA24-3543)

IBM Component Description: 3803/3420 Magnetic Tape Subsystem (GA32-0020)

Form-Design Considerations - System Printers (GA24-3488)

Emulating the 7070/7074 on the IBM System/370 Model 165 using OS/360 (GC27-6948)

Emulating the 709, 7090, 7094, 7094II on the IBM System/370 Model 165 using OS/360 (GC27-6951)

Emulating the 7080 on the IBM System/370 Model 165 using OS/360 (GC27-6952)

IBM System/360 Operating System:

Planning for the IBM 3211 Printer, Data Management Macro Instructions and Services (GC21-5008)

CONTENTS

| Section | 01: System Highlights 1                                                                                                          |

|---------|----------------------------------------------------------------------------------------------------------------------------------|

| Section | 10: Architecture and System Components 6                                                                                         |

| 10:05   | Architecture Design 6                                                                                                            |

| 10:10   |                                                                                                                                  |

|         | Central Processing Unit                                                                                                          |

|         | Instruction and Execution Units 8                                                                                                |

|         | Local Storage and Control Storage 8                                                                                              |

|         | Program States and System Interrupts                                                                                             |

|         | CPU Features                                                                                                                     |

|         | $CPU Cooling. \dots \dots$ |

|         |                                                                                                                                  |

|         | Motor Generator Set                                                                                                              |

|         | System Console                                                                                                                   |

| 10:15   | Storage                                                                                                                          |

|         | Processor (Main) Storage                                                                                                         |

|         | Processor Storage Reconfiguration                                                                                                |

|         | Storage Ripples                                                                                                                  |

|         | High-Speed Buffer Storage                                                                                                        |

| 10:20   | Channels                                                                                                                         |

|         | General Description                                                                                                              |

|         | The 2880 Block Multiplexer Channel                                                                                               |

| 10:25   | Block Multiplexing Operations with Rotational Position                                                                           |

| 10:25   | Block Multiplexing operations with Rotational Position                                                                           |

|         | Sensing Devices                                                                                                                  |

|         | Summary of Block Multiplexing Operations with I/O                                                                                |

|         | Devices                                                                                                                          |

| 10:30   | Standard and Optional System Features                                                                                            |

|         | Standard Features                                                                                                                |

|         | Optional Features                                                                                                                |

|         | -                                                                                                                                |

| Section | 20: I/O Devices                                                                                                                  |

| 20:05   |                                                                                                                                  |

| 20:10   | 3330 Disk Storage and 3830 Storage Control                                                                                       |

| 20:10   | The 2305 Fixed Head Storage Module and 2835 Storage                                                                              |

| 20:13   | The 2505 Fixed head Storage Module and 2655 Storage                                                                              |

|         | Control Models 1 and 2                                                                                                           |

|         | Data Recording on the Model 2                                                                                                    |

|         | Data Recording on the Model 1                                                                                                    |

|         | Effective Capacity of 2305 Facilities 45                                                                                         |

|         | Rotational Position Sensing and Multiple Requesting 47                                                                           |

| 20:20   | The 3211 Printer                                                                                                                 |

| 20:25   | The 3803/3420 Magnetic Tape Subsystem                                                                                            |

|         |                                                                                                                                  |

| Section | 30: Programming Systems Support                                                                                                  |

| 30:05   |                                                                                                                                  |

|         | OS Support                                                                                                                       |

| 30.10   |                                                                                                                                  |

| Section |                                                                                                                                  |

|         |                                                                                                                                  |

| 40:05   |                                                                                                                                  |

| 40:10   |                                                                                                                                  |

| 40:15   |                                                                                                                                  |

| 40:20   | 7080 Emulator Program                                                                                                            |

|         |                                                                                                                                  |

| Section | 50: Reliability, Availability, and Serviceability (RAS)                                                                          |

|         | Features                                                                                                                         |

| 50:05   | Introduction                                                                                                                     |

| 50:10   | Recovery Features                                                                                                                |

|         | Automatic CPU Retry                                                                                                              |

|         | ECC Validity Checking on Processor Storage                                                                                       |

|         |                                                                                                                                  |

|         | I/O Operation Retry                                                                                                              |

|         | Expanded Machine Check Interrupt Facilities                                                                                      |

|         | Recovery Management Support (RMS) - OS MFT and MVT 79                                                                            |

|         | MCH and CCH Routines                                                                                                             |

|         | Error Recovery Procedures (ERP's)                                                                                                |

|         | Statistical Data Recorder (SDR) and Outboard           |       |

|---------|--------------------------------------------------------|-------|

|         | Recorder (OBR)                                         | . 82  |

|         | Environment Recording, Edit, and Print Program (EREP). | . 82  |

|         | I/O RMS (APR and DDR)                                  |       |

|         | Advanced Checkpoint/Restart and Warm Start Facilities. | . 83  |

| 50:15   |                                                        |       |

|         | OLTEP and OLT'S                                        |       |

|         | Processor Logout Analysis Program                      |       |

|         | System Test, Channel Test, CPU Test, and Storage Test  |       |

|         | Programs                                               |       |

|         | Microdiagnostics                                       |       |

| 50:20   | RAS Summary                                            |       |

|         |                                                        |       |

| Section | 60: Programming Systems Preinstallation Planning       | . 87  |

| 60:05   | OS MFT and MVT Transition                              | . 87  |

|         | Existing Processing Programs and Job Control           | . 88  |

|         | Conversion to 3330 and 2305 Facilities                 | . 88  |

|         | Conversion to the 3803/3420 Magnetic Tape Subsystem    |       |

| 60:10   |                                                        |       |

|         | Multiplexer Channels and RPS Devices                   | . 90  |

|         | System Configuration and Generation                    |       |

|         | Job Scheduling                                         |       |

|         | Data Management Parameters                             |       |

| 60:15   |                                                        |       |

| 60:20   |                                                        |       |

|         | ······································                 |       |

| Section | 70: Comparison Table of Hardware and OS Features for   |       |

|         | System/360 Model 65 and System/370 Model 165           | . 97  |

|         | · · · · · · · · · · · · · · · · · · ·                  | - • • |

| Index . |                                                        | .105  |

| Index . |                                                        | .105  |

# FIGURES

| 10.05.1 | System/370 Model 165 system elements 7                      |

|---------|-------------------------------------------------------------|

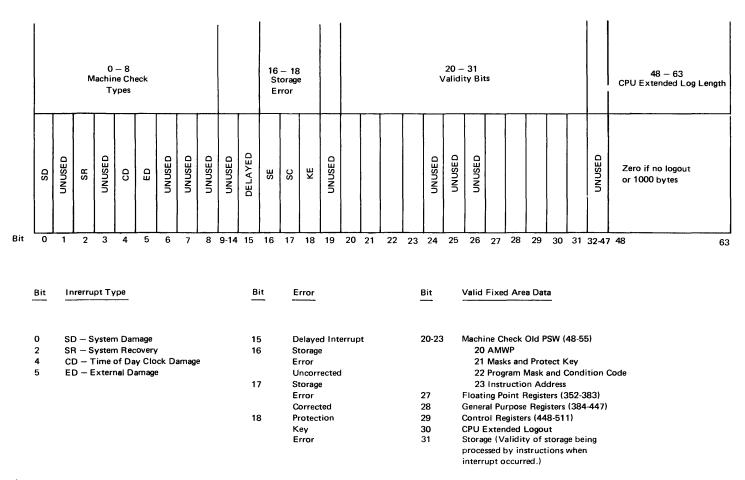

| 10.10.1 | Conceptual flow of the water cooling system in the          |

|         | Model 165                                                   |

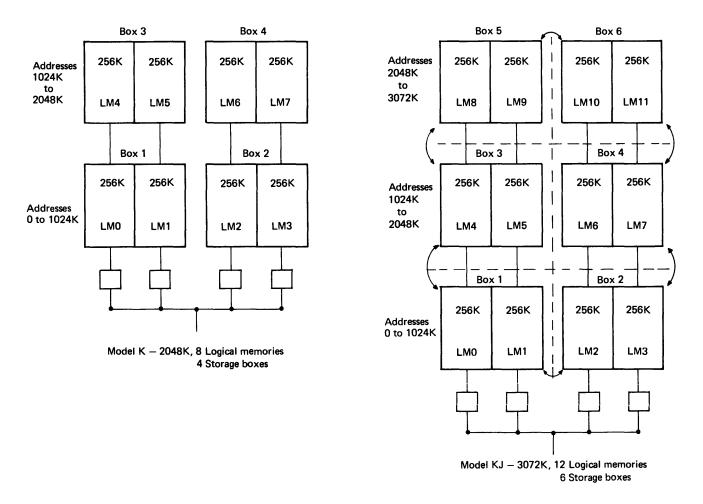

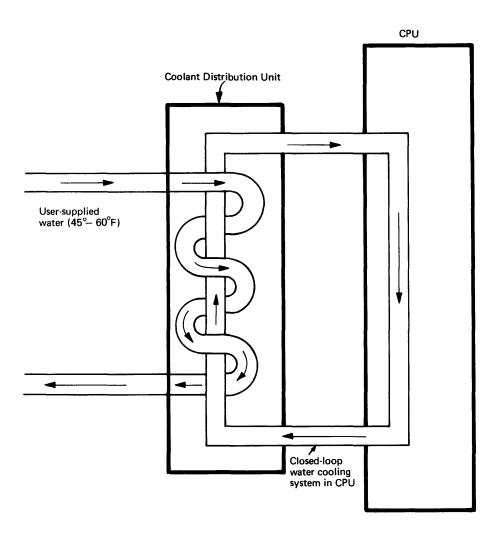

| 10.15.1 | Model 165 processor storage configurations 16               |

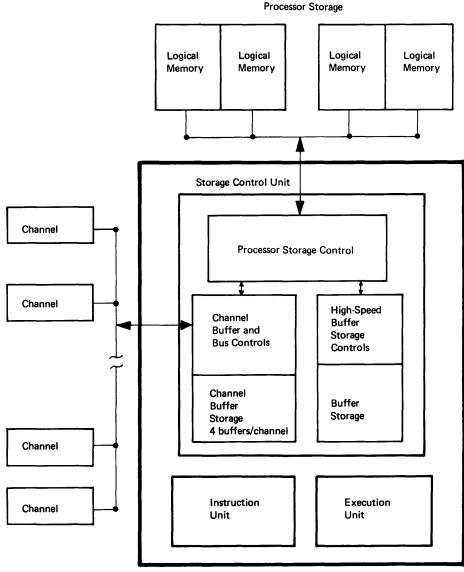

| 10.15.2 | Model 165 storage components and controls                   |

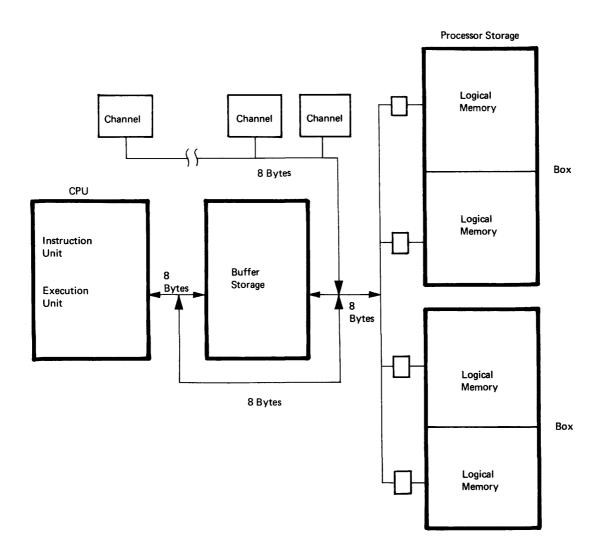

| 10.15.3 | Conceptual data flow in the Model 165                       |

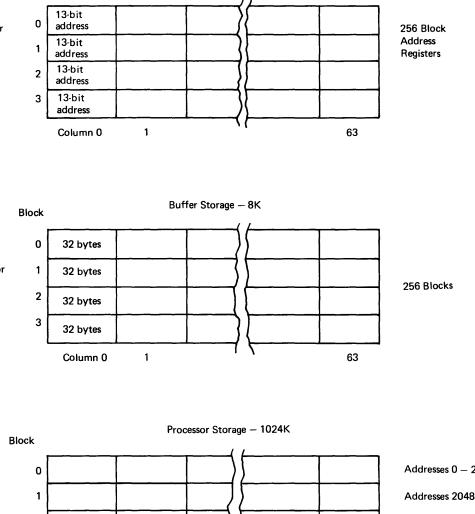

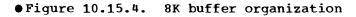

| 10.15.4 | 8K Buffer organization                                      |

| 10.15.5 | Processor storage address format for buffer reference 23    |

| 10.15.6 | Buffer address format                                       |

| 20.10.1 | The 3330 facility                                           |

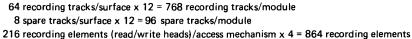

| 20.15.1 | Top view of a 2305 Model 2 disk surface                     |

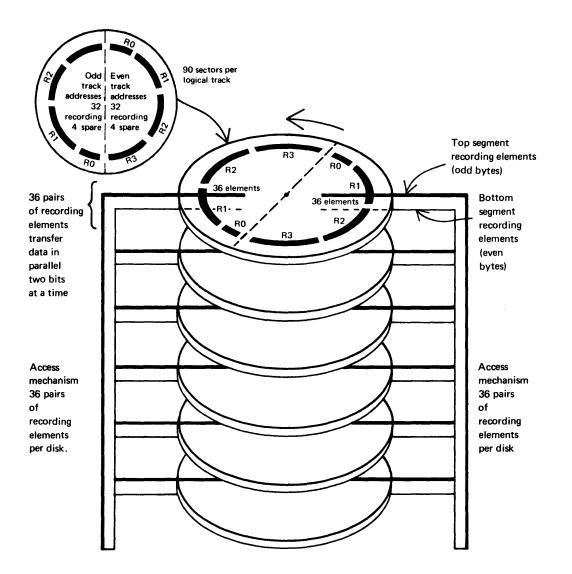

| 20.15.2 | 2305 Model 1 module                                         |

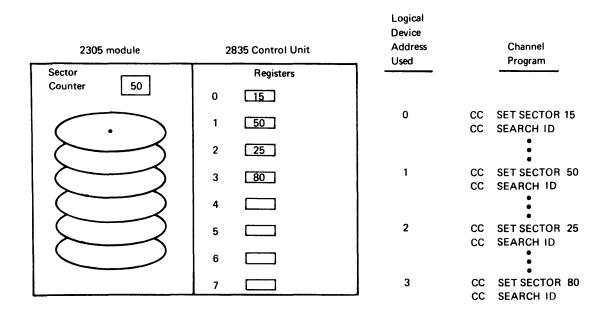

| 20.15.3 | Multiple requesting on the 2305 facility                    |

| 20.13.3 | Tape switching configurations for the 3803/3420             |

| 20.23.1 | Magnetic Tape Subsystem                                     |

| 40.05.1 | Partition or region layout for a 7000-series emulator       |

| 40.03.1 |                                                             |

| E0 10 1 | program job step                                            |

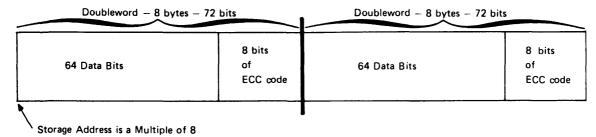

| 50.10.1 | Data representation used in Model 165 processor storage. 72 |

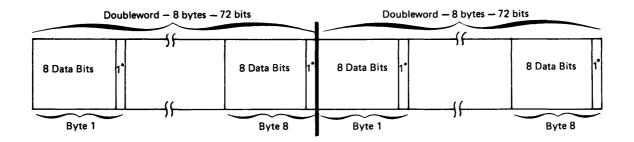

| 50.10.2 | Data representation used in Models 65 and 75 and in the     |

| 50 40 0 | Model 165 in other than processor storage                   |

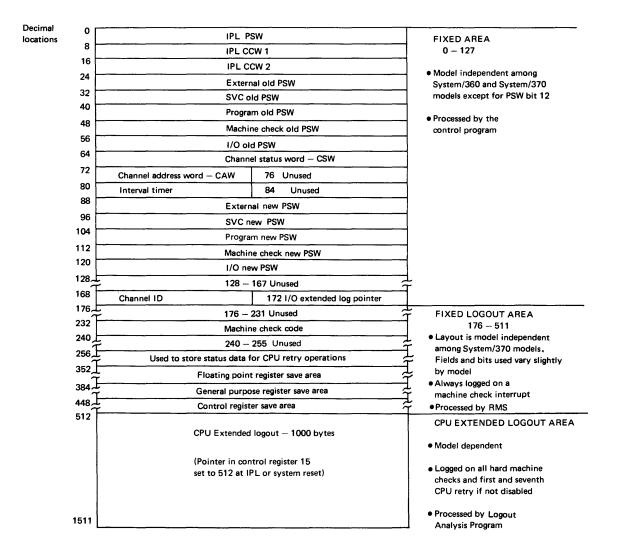

| 50.10.3 | Model 165 fixed storage locations                           |

| 50.10.4 | Machine check code - Model 165                              |

TABLES

| 20.10.1   | Capacity and timing characteristics of the 3330 and 2314 |      |

|-----------|----------------------------------------------------------|------|

|           | facilities and the 2321 Data Cell Drive                  | 38   |

| 20.10.2   | 3336 and 2316 Disk Pack characteristics                  |      |

| 20.10.3   | Hardware features of 3330 and 2314 facilities            |      |

| 20.15.1   | Effective capacity of the 2305 Model 2, the 2305 Model 1 |      |

|           | and the 2301 for various block sizes with a 25-byte key. | 46   |

| 20.15.2   | Effective capacity of the 2305 Model 2, the 2305 Model 1 | 40.  |

| 2001302   | and the 2301 for various block sizes when records are    |      |

|           | written without a key                                    | 16   |

| 20.15.3   | 2305 facilities and 2301 Drum Storage characteristics.   |      |

| 20.25.1   |                                                          | 49   |

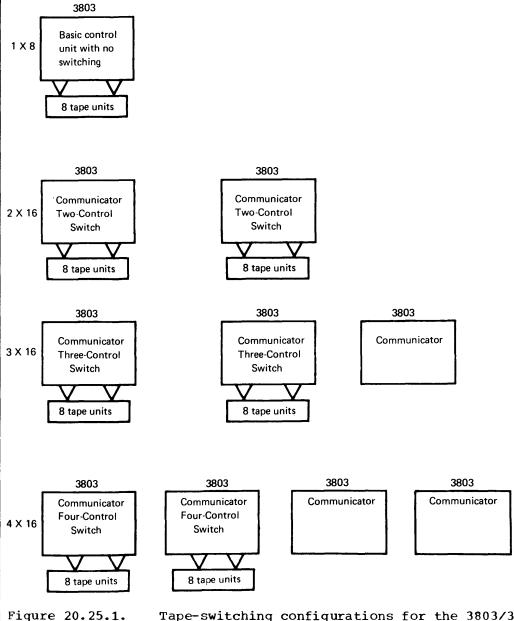

| 20.23.1   | 3803 control unit configurations and capabilities        |      |

| 20. 25. 2 | with Dual Density and Seven-Track features               | 51.5 |

| 20.25.2   | 3420, 2420 and 2401 Magnetic Tape Unit                   |      |

|           | characteristics.                                         | 51.9 |

| 40.10.1   | 7074 hardware and I/O devices supported by the Model 165 |      |

|           | 7074 Emulator Program                                    | 61   |

| 40.10.2   | 7074 I/O devices and features not supported by the       |      |

|           | 7074 Emulator program for the Model 165                  | 62   |

| 40.15.1   | 7094 hardware and I/O devices supported by the 7094      |      |

|           | Emulator program for the Model 165                       | 64   |

| 40.15.2   | 7094 I/O devices and features not supported by the 7094  |      |

|           | Emulator program for the Model 165                       | 65   |

| 40.20.1   | 7080 hardware and I/O devices supported by the 7080      |      |

|           | Emulator program for the Model 165                       | 67   |

| 40.20.2   | 7080 I/O devices and features not supported by the 7080  |      |

|           | Emulator program for the Model 165                       | 67   |

| 50.10.1   | Model 165 machine check interrupts                       |      |

|           | L                                                        | -    |

The System/370 Model 165 is designed to enhance, extend, and broaden the successful concepts of System/360 architecture. It is a highspeed, large-scale growth system for System/360 Model 65 and 75 users that provides significant price performance improvement without the necessity of major reprogramming. The Model 165 is a general purpose system and offers high performance for both commercial and scientific applications. It is compatible with the System/370 Model 155.

Transition from System/360 models to the System/370 Model 165 can be accomplished with a minimum of effort because most current System/360 user programs, I/O devices, and programming systems are upward compatible with the new system. Upward transition from a Model 165 to a Model 195 can also be accomplished. Additional capabilities will be added to OS to support new features of the Model 165, thereby providing proven operating system performance as well as continuity.

Transition with little or no reprogramming is also provided for 7051/11/111/7080, 7070/7074, and 709/7090/7094/709411 users who are presently emulating on System/360. Emulators that operate under OS control on the Model 165 are provided for these systems.

Highlights of the Model 165 are as follows.

- Upward compatibility with most System/360 architecture and programming has been maintained.

- Internal performance is approximately two to five times that of the Model 65.

- CPU features of the System/370 Model 165 are as follows:

The Model 165 standard instruction set includes new general purpose instructions in addition to the powerful System/360 instruction set. These instructions enhance decimal arithmetic performance, eliminate the need for multiple move or compare instructions or move subroutines, and facilitate record blocking and deblocking, field padding, and storage clearing.

Extended precision floating point is a standard feature to provide precision of up to 28 hexadecimal digits, equal to approximately 34 decimal digits.

A high-speed multiply feature is available to provide faster execution of binary and floating-point arithmetic operations. Execution speed increases by a factor of 2 to 3.

An interval timer of 3.33 ms resolution to improve job accounting accuracy is standard. A 16.6 ms resolution timer is standard on the Model 65.

A time of day clock is included to provide more accurate time of day values than the interval timer. It has a 1 microsecond resolution.

Separate instruction and execution units are implemented that provide overlap of instruction fetching, instruction decoding, operand fetching, and instruction execution to increase internal performance. CPU retry of most failing CPU hardware operations is handled automatically by the hardware without programming assistance.

Writable control storage (WCS) is included in addition to readonly storage (ROS) to contain new Model 165 instructions, emulator microcode, and CPU diagnostics.

- Relocatable emulators are provided that operate under OS control. Concurrent execution of System/370 programs with 7000-series programs is supported. A 7080, a 7070/7074, and a 709/7090/7094/7094II emulator are available on a mutually exclusive basis.

- A free-standing 3066 System Console is required. Its features are:

A buffered cathode ray tube and an alphameric keyboard for rapid operator/system communication

An indicator viewer to display system status

A system activity monitor to provide, via the system activity meter, visual display of average system activity

A microfiche document viewer for CE use

A processor storage configuration plugboard

A device for loading WCS and diagnostic routines

• Channel features of the Model 165 are as follows:

2870 Multiplexer Channels, 2860 Selector Channels, and the new 2880 Block Multiplexer Channels can be attached - for a total of seven addressable channels. A single 2880 channel can operate at a 3 MB rate with attachment of an optional feature.

The Extended Channels feature permits a Model 165 to have up to twelve addressable channels, which can support an aggregate channel data rate in excess of nine megabytes per second.

The 2880 Block Multiplexer Channel is a superset of the 2860 Selector Channel. When used in conjunction with rotational position sensing devices, it can increase total system throughput by permitting more data to enter and leave the system in a given time period than can the 2860. A single 2880 channel can support interleaved, concurrent execution of multiple high-speed I/O operations.

Channel retry data is provided after channel errors so that error recovery routines can retry I/O operations.

• Storage features offered by the Model 165 are as follows:

A two-level memory system, consisting of fast, large-size processor (main) storage used as backing storage for a smaller, very highspeed buffer storage, is implemented. The CPU works mostly with the buffer so that the effective access time for data is reduced to a fraction of the processor storage cycle time.

8K or 16K bytes of 80-nanosecond monolithic buffer storage is available (8K is standard). The CPU can initiate a request for eight bytes from the buffer every 80 nanoseconds.

3

512K to 3072K of four-way, doubleword interleaved, twomicrosecond processor storage is available - three times the maximum available on the Model 65.

Byte boundary alignment is permitted for the operands of nonprivileged instructions to eliminate the necessity of adding padding bytes within records or to blocked records for the purpose of aligning fixed or floating-point data.

Error checking and correction (ECC) hardware that automatically corrects all single-bit processor storage errors and detects all double-bit and most multiple-bit errors is standard.

• I/O devices for the Model 165 are as follows:

Most currently announced I/O devices for System/360 Models 65 and above can be attached.

The new 3330 facility is available for attachment to 2880 channels. It offers significantly faster seeks and more than twice the data rate of the 2314 facility, more than three times the capacity of the 2314, and automatic error correction features. The new rotational position sensing and multiple requesting capabilities announced for the 2305 facility are standard.

The 3330 has an 806 KB data transfer rate, average seek time of 30 ms, and full rotation time of 16.7 ms. Up to 800 million bytes can be contained on an eight drive facility.

The 2305 facility Models 1 and 2 can be connected to 2880 channels to provide significantly faster data transfer operations.

The Model 1 has a 3 megabyte data rate, a maximum module capacity of 5.4 million bytes, and average access time of 2.5 ms.

The Model 2 has a 1.5 megabyte data rate, a maximum module capacity of 11.2 million bytes, and average access time of 5 ms.

The new high-speed 3211 Printer with a tapeless carriage and an alphameric print speed of 2000 lines per minute is available. The tapeless carriage decreases operator intervention by eliminating carriage tape loading and unloading.

The new 3803/3420 Magnetic Tape Subsystem is attachable. Models 3, 5, and 7 of the 3420 Magnetic Tape Unit, with data rates of 120 KB, 200 KB, and 320 KB, respectively, at 1600-BPI recording density, are provided. Phase-encoded recording, which automatically corrects all single-bit read errors in-flight, is used. This new tape subsystem offers improved price performance; Dual Density and Seven-Track features for compatibility with, and conversion of, 2400-series tape volumes; greatly reduced operator handling through implementation of such features as automatic tape threading and cartridge loading; lower cost tape switching than is currently provided; and enhanced reliability, availability, and serviceability features.

- Extensive hardware and programming systems error recovery and repair features are provided to improve system reliability, availability, and serviceability.

- Compact physical design reduces Model 165 CPU and processor storage space requirements. The Model 165 CPU has three times the number of circuits as a Model 65, in excess of 75,000 versus 25,000, yet a 512K or 1024K Model 165 requires the same amount of space as a 512K Model 65.

As the highlights indicate, Model 65 and 75 users have a broader range of Model 165 configurations to choose from than before when tailoring a growth system with improved throughput and expanded capabilities. Specifically, the Model 165 offers the following advantages over Models 65 and 75:

# Larger Processor (Main) Storage Sizes

Storage sizes of 512K, 1024K, 1536K, 2048K, and 3072K are provided. The Model 65 offers a maximum of 1024K. Larger Model 165 storage sizes are available at smaller cost increments, and additional storage can contribute significantly to system performance and capabilities.

The addition of more processor storage provides the Model 165 user with the ability to:

- Execute more jobs concurrently, including new application and integrated 7000-series emulator jobs

- Add and expand applications, such as graphics, teleprocessing, time sharing, remote job entry, and data based, that require large amounts of storage

- Use higher level language translators and linkage editors that provide more functions and execute faster

- Execute larger processing programs without the necessity of overlay structures

- Allocate more processor storage to language translators and sorts to improve their execution speed

- Use more and larger I/O buffers to speed up input/output operations and optimize use of direct access storage space

- Include system generation options that improve control program performance and support additional functions

# Expanded Channel Capabilities

The fast internal performance of the Model 165, together with expanded use of multiprogramming, requires that more data be available faster.

The Model 165 offers more and faster channels than the Model 65, twelve instead of seven, and 1.5 MB and 3.0 MB data rates on the 2880 in addition to a 1.3 MB rate on the 2860.

The channel features of the Model 165 provide:

- A significantly higher attainable aggregate data rate than provided by the Model 65 to balance the high performance capabilities of the Model 165 CPU. A twelve-channel Model 165 system can support I/O configurations with an aggregate data rate in excess of 9 MB.

- Attachment of high-speed direct access devices, such as 3330 and 2305 facilities, that will increase I/O throughput

- Channel throughput increase capabilities via use of block multiplexing with rotational position sensing to improve effective data transfer rates

#### Faster I/O Devices with Increased Data Capacity

The 3330 and the 2305 facilities offer significantly faster data access than the 2314 facility and 2301 Drum Storage because of higher data transfer rates, faster rotation, and new features. Rotational position sensing and multiple requesting used with block multiplexing can improve I/O throughput by making more efficient use of channel time. These direct access facilities also offer higher availability through use of advanced hardware-only and program-assisted error correction features.

The 3330 facility provides high capacity and fast access for less cost per bit. It is a growth device for the 2314 facility and the 2321 Data Cell Drive that offers increased price performance. The 3330 facility is designed to be used in every area in which direct access storage is needed, for example:

- As a system residence device and for program library storage

- In teleprocessing applications for message queuing and residence of online applications data

- In online, data-based applications, such as management information systems, airline reservations, etc.

- In time-sharing (or interactive) environments as a swap device and for online work storage (for program and data residence)

- As high-speed work storage for sorting, assembling, and link editing

- For residence of data indexes, such as for ISAM data sets

The 2305 facilities offer larger capacity and faster access than the 2301 drum. For Model 165 users, the 2305 facilities can contribute significantly to system throughput improvements when used:

- As system residence devices

- In time-sharing environments, as a swap device and for program and data residence

- As high-speed work storage and for residence of data indexes

# SUMMARY

The combination of new and improved hardware and input/output facilities, enhanced operating systems support, integrated emulation, and increased system availability provided by the Model 165 offers Model 65 and 75 users expanded computing capabilities without the necessity of a large conversion effort. Little or no time need be spent modifying operational System/360 code or 7000-series programs currently being emulated. Existing CPU-bound programs can execute faster because of the increased internal performance of the Model 165, while I/O-bound programs can benefit from the use of more storage, more channels, faster I/O devices, and block multiplexing.

The increased power and new functions of the Model 165 provide the base for expanded applications growth and penetration of previously marginal application areas. The increased price performance of the Model 165 offers the user the opportunity to widen his data processing base for comparatively less cost and the Model 165 can be an integral part of a growth plan to the higher performance Model 195.

#### SECTION 10: ARCHITECTURE AND SYSTEM COMPONENTS

#### 10:05 ARCHITECTURE DESIGN

The basic design objectives embodied in System/370 Model 165 architecture provide System/360 Model 65 and 75 users and 7000-series emulator users with a growth system that incorporates improvements and additions to System/360 architecture. The Model 165 provides new system capabilities, performance improvements, and features to increase system reliability, availability, and serviceability. This has been achieved under the following conditions:

- System/370 Model 165 architecture is upward compatible with that of System/360 models so that most user programs written for System/360 will run efficiently on the Model 165 without modification.

- Programming systems support for the Model 165 is based on that provided for System/360 models, namely on OS MFT and MVT.

- Most currently announced System/360 I/O devices will operate on the Model 165. (See Section 20:05 for a list of the I/O devices that cannot be included in a Model 165 configuration.)

- The open-ended design characteristic of System/360 has been preserved and extended in System/370.

As a result of the architecture design criteria used for this new system, all programs written for System/360 (Models 25 and up) will operate on a System/370 Model 165 with a comparable hardware configuration, with the following exceptions:

- 1. Time-dependent programs

- 2. Programs using machine-dependent data such as that which is logged in the machine-dependent logout area. (OS SER and MCH and DOS MCRR error-logging routines for System/360 models will not execute correctly.)

- 3. Programs that use the ASCII mode bit in the PSW

- 4. Programs that depend on the nonusable lower processor storage area being smaller than 1512 bytes. This area can be reduced to 512 bytes by moving the CPU logout area. (See Section 50.)

- 5. Programs deliberately written to cause certain program checks

- Programs that depend on devices or architecture not implemented in the Model 165, for example, the native file of the Model 44, relocation implemented in the Model 67, etc.

- Programs that use model-dependent operations of the System/370 Model 165 that are not necessarily compatible with the same operations on System/360 models

Note that these are the same types of restrictions that exist for compatibility among System/360 models.

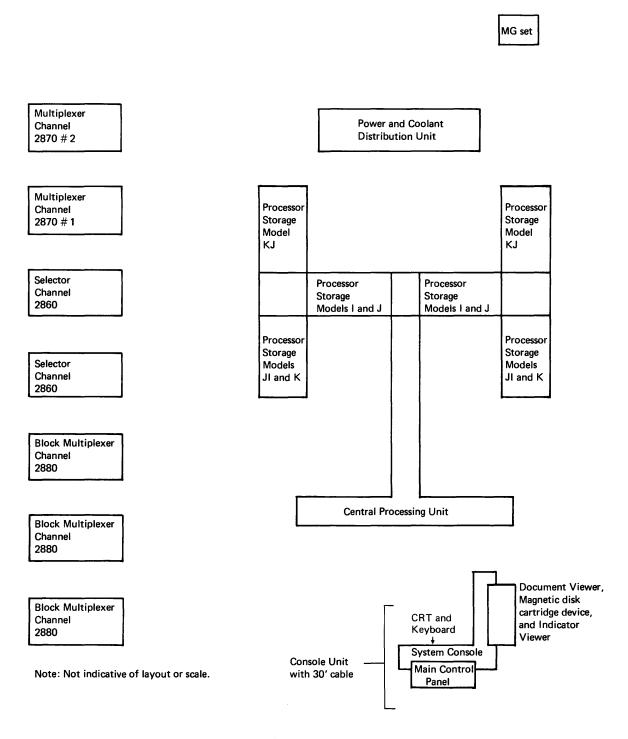

The major elements of the Model 165 computing system are illustrated in Figure 10.05.1. Each component and its new features are discussed in the subsections that follow. Programming systems support of these features is covered in Section 30. Reliability, availability, and serviceability (RAS) hardware features are mentioned only briefly. A full discussion of both hardware and programming systems RAS facilities is contained in Section 50.

Figure 10.05.1. System/370 Model 165 system elements

#### 10:10 THE CENTRAL PROCESSING UNIT (CPU) AND THE SYSTEM CONSOLE

# CENTRAL PROCESSING UNIT

The CPU contains all the elements necessary to decode and execute the instructions in the System/370 Model 165 instruction set and, optionally, those in the hardware compatibility feature required by one of the three 7000-series emulator programs.

The CPU has an 80-nanosecond cycle time and an 8-byte-wide data path. Extensive parity checking is performed in the CPU to insure the validity of the data being used. All data transfer, logical, and arithmetic operations are checked. Automatic hardware retry of most failing CPU operations, without programming assistance, is provided as an availability feature and is discussed in the RAS section.

Among the major elements in the CPU are the instruction unit, the execution unit, local storage, and control storage.

## Instruction and Execution Units

The faster internal performance of the Model 165 is due in part to the use of more concurrence in CPU operations than is implemented in the Model 65. The Model 165 CPU contains an instruction unit and an execution unit that overlap instruction fetching and preparation with instruction execution. The Model 165 instruction unit is controlled by logic circuits and can process several instructions concurrently while the execution unit is executing a single instruction.

The instruction unit prefetches instructions (maintaining them in sequence), decodes instructions, calculates addresses, prefetches instruction operands, and makes estimates of the success of conditional branches. When a conditional branch is encountered, the instructions immediately following the branch and those located at the branch address are prefetched and placed in separate instruction buffers within the instruction unit. Two 16-byte instruction buffers are used. This insures the availability of prefetched instructions whether the branch is taken or not.

The execution unit is microprogram controlled and can execute one instruction at a time. It has the capability of processing a new instruction every cycle. Emphasis is placed on optimizing fixed binary and floating-point arithmetic operations. A 64-bit parallel adder is used to perform binary and floating-point arithmetic, while an 8bit serial adder is used in the execution of packed decimal arithmetic.

An imprecise interrupt occurs on a Model 165 only if an attempt is made to store data at an invalid storage address or at a storageprotected location.

#### Local Storage and Control Storage

Local storage contains the general purpose and floating-point registers and has a read or write cycle time of 80 nanoseconds. It can be accessed by four sources and written into from one source simultaneously.

Model 165 control storage consists of a capacitor read-only storage (ROS) and a monolithic writable control storage (WCS), both of which have an 80-nanosecond cycle time. ROS and WCS contain all required microcode for a specific system configuration. ROS contains the microcode necessary to execute the majority of the Model 165 instructions and some specialized routines. WCS contains the microprogramming required to handle the balance of the instruction set for the Model 165 and other optional features, such as a 7000series compatibility feature.

WCS is also used to house diagnostic routines. The use of some writable control storage in the Model 165 in addition to ROS allows nonresident diagnostics to overlay each other. Thus more extensive diagnostics can be provided without the necessity of adding more control storage.

During a power-on sequence, WCS is automatically loaded with system microcode from a removable magnetic disk cartridge contained on a device in the console unit. The magnetic disk cartridges sent to an installation will be tailored to include the microcode required by the optional features included in the system configuration.

#### Program States and System Interrupts

The program states in which the Model 165 is operating are reflected in the current program status word (PSW) and in new CPU status indicators, called <u>control registers</u>, located in the CPU. Up to 16 control registers, 0-15, can be addressed; however, only 4 are implemented in the Model 165. They are program addressable when the CPU is in the supervisor state. A control register can be set with the new LOAD CONTROL instruction, and its contents can be placed in processor storage with the STORE CONTROL instruction. Additional status indicators contained in control registers are required in order to support new system functions.

The contents, layout, and function of fixed locations 0-127 in System/370 models are identical to these locations in System/360 models with one exception. Bit 12 in the PSW, which sets EBCDIC or ASCII mode in System/360 models, is not used for this purpose in the Model 165. (It must be set to zero.) ASCII mode is not implemented in the Model 165, nor was the mode bit supported by IBM programming systems for System/360 models, since the expectation that System/360 ASCII-8 would become the ASCII standard has not been borne out.

The implementation of the machine check level of interruption in the Model 165 has been altered considerably from its implementation in Models 65 and 75 in order to enhance system availability (see Section 50). However, the other four interrupt levels operate in the same manner on the Model 165 as on Models 65 and 75.

# **CPU** Features

Significant features of the Model 165 CPU are the following:

#### Expanded Instruction Set

The standard instruction set for the System/370 Model 165 is a superset of that provided for System/360 Models 65 and 75. It consists of the System/360 instruction set plus new instructions that support System/370 architecture and provide additional functions. The Model 165 standard instruction set includes all general purpose and I/O instructions and all binary, decimal, floating-point, and extended precision floating-point arithmetic instructions. Storage protect and time of day clock instructions are also standard. The new STORE CPU ID instruction permits a program to determine the model upon which it is operating and provides the system serial number. The new STORE CHANNEL ID instruction can be used to identify the types of channels present in the system. Other new standard instructions are: • Extended Precision Floating Point

Precision of up to 28 hexadecimal digits, approximately equal to 34 decimal digits, is provided by the extended precision data format. Extended precision is achieved by using two doublewords (16 bytes) to represent an extended precision floating-point number instead of using one doubleword as is done in long form representation. Fourteen hexadecimal digits, or up to 17 decimal digits, of precision is provided by the long floating-point format.

Seven floating-point instructions are included in the extended precision feature. They provide addition, subtraction, and multiplication operations for extended precision data, using a pair of floating-point registers, and the ability to round from long to short form or from extended to long form.

• General Purpose Instructions

Six general purpose instructions, which will be of benefit to both control and processing program performance, have been added to the Model 165 standard instruction set.

SHIFT AND ROUND DECIMAL, using a single instruction, provides right or left shifting of packed decimal data. This instruction can save 6 to 18 bytes of instruction storage and instruction execution time for each decimal shift and round operation performed in commercial processing.

MOVE LONG provides for the movement of up to 16 million bytes from one location in storage to another with a single instruction, thereby removing the current limitation of 256 bytes per move. This instruction can eliminate the necessity of multiple move instructions or the inclusion of move subroutines. The format and operation of MOVE LONG facilitates efficient record blocking and deblocking, field padding, and storage clearing, operations frequently performed in commercial processing.

COMPARE LOGICAL LONG can be used to compare logically two fields of up to 16 million bytes in length, thus removing the current 256-byte limit on byte compares. In addition, when an unequal compare occurs, the two characters that caused the inequality are identified.

The MOVE LONG and COMPARE LOGICAL LONG instructions are interruptable. Thus, when an I/O operation terminates during their execution, the interrupt can be taken, and the channel is not held up awaiting termination of what might be a lengthy move or compare.

COMPARE LOGICAL, STORE, and INSERT CHARACTERS UNDER MASK instructions provide byte addressability within the general purpose registers and permit nonword-size data that is not on a word boundary to be compared to data in a register, loaded into a register, and stored from a register. These three instructions can be of most benefit to control program programmers, to compiler writers, and to others who must manipulate processor storage addresses.

High-Speed Multiply Feature (Optional)

This feature substantially increases the internal performance of fixed- and floating-point multiply operations. With use of this feature a long precision floating-point multiply operation improves from 1.81 to .61 microseconds. A fixed-point multiply operation improves from .78 to .42 microseconds.

#### Architecture Implementation Alterations

Two alterations have been made to the system action taken on a Model 165 during the execution of certain instructions common to both System/370 and System/360 models. The first involves all instructions that check the validity of operands involved in packed decimal operations. On the Model 165, an invalid sign in an operand causes the instruction to be suppressed (never executed) rather than terminated during execution as is done on System/360 models. Suppression, rather than termination, of an instruction when an invalid sign occurs insures that the data fields involved remain unchanged. Therefore, when a program check occurs, a routine can be executed that inspects the field that has the invalid sign.

For example, when an invalid sign results from packing an entirely blank field, the sign can be corrected by programming, and transaction deletion or program termination is avoided.

The second alteration concerns the recognition of a storage protection exception during the execution of an EDIT or an EDIT AND MARK instruction. On a Model 165 a protection exception always occurs when a pattern character is fetched from a location protected for storing but remains unchanged during the edit operation. This change eliminates unpredictable system operation during editing on a Model 165. The occurrence of a protection exception for the situation described is model-dependent for System/360 models.

#### Interval Timer (Standard)

The interval timer in decimal location 80 in fixed processor storage of a Model 165 has a resolution of 3.33 ms instead of the 16.6 ms resolution (with 60-cycle power) implemented for the standard timer on the Model 65. Its maximum time period remains 15.5 hours. The higher resolution of this interval timer will eliminate many of the problems encountered in accounting routine accuracy caused by task execution durations that are less than the 16.6 ms resolution.

Time of Day Clock (Standard)

This new clock is a binary counter of 52 bits with a cycle of approximately 142 years. It is updated every microsecond. Two new instructions (SET CLOCK and STORE CLOCK) are provided to set the time and to request that the current time be stored in a specified doubleword of processor storage. The time can be set only when the CPU is in supervisor state and only when the clock security switch on the system console panel is in the enable set position.

The time of day clock can be used for more accurate time stamping than the interval timer. Accurate time of day can be maintained because during normal operations the clock stops only when CPU power is turned off. The interval timer cannot be as accurate as the clock for time of day maintenance because it is not updated when the system is in the stopped state, and its updating may be omitted under certain conditions of excessive system activity. The 15.5-hour cycle time of the interval timer is also a restriction. The time of day clock better answers the timing needs of teleprocessing and real-time applications.

# CPU Cooling

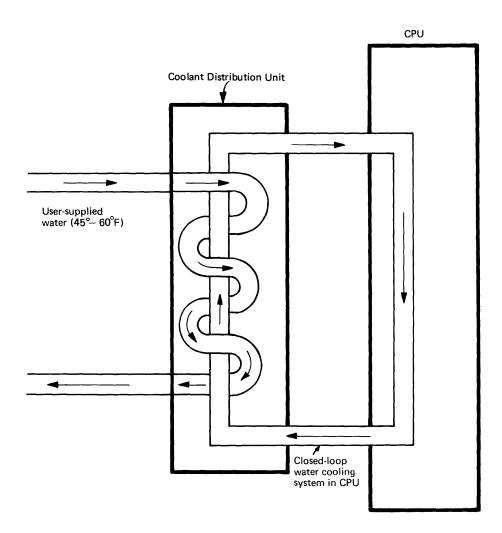

The heat generated by the logic boards in the Model 165 CPU and its associated power frames is removed by forced air and a closed-loop water circulation system. Use of a liquid coolant in addition to air is required because of the amount of heat generated by the densely packed circuits in the CPU. The user must supply 30 gallons of cooled water per minute (45° to 60° F.) to the coolant distribution unit (CDU), which is housed in a stand-alone frame that also contains power and the power distribution unit. Water is supplied to the CDU in pipes under the raised floor. The chilled water entering the CDU is used to control the temperature of the internal water that passes through the CPU. That is, the user-supplied water does not enter the closed-loop system of the CPU. (See Figure 10.10.1.) The CDU houses the necessary controls to maintain the proper temperature in the closed-loop system. The user must supply the controls to maintain the temperature of the chilled water supplied to the CDU.

Figure 10.10.1. Conceptual flow of the water cooling system in the Model 165

The use of water as the cooling liquid offers several advantages. First, it is readily available. The chilled water normally supplied for air conditioning is acceptable. Second, water offers safety features. Low pressure is required and the cooling system can operate at room temperature, thereby eliminating problems with condensation. Last, a simplified circulation system suffices, with relatively few moving parts and less exposure to leaks. Pipe components within the CPU are separated easily, and the valved connections close off automatically to prevent water from escaping. Physical planning for Model 165 installation should insure that arrangements are made to provide the required water. (See <u>System/370</u> <u>Installation Information</u>, <u>Physical Planning</u>, GA22-6971 for more details.)

# Motor Generator Set

The motor generator (MG) set is the converter unit that provides the power required by the Model 165 CPU. It takes 60 Hz (cycle) power from the building electrical distribution system, converts it to 415 Hz power, and supplies it to the CPU.

Unlike the MG sets provided for the 7000-series, which were small enough to be housed within the covers of the system itself, the MG set (including the required starter) for the Model 165 is a stand-alone unit approximately six feet long, weighing 3000 lbs. (See <u>System/370</u> <u>Installation Information, Physical Planning</u> for more details concerning MG set size and installation requirements.)

The MG set should be ordered at the same time as the Model 165, with delivery up to two months prior to system installation. While IBM does not manufacture MG sets, a procedure is established for ordering the required MG set through IBM.

#### 3066 SYSTEM CONSOLE

A stand-alone system console unit, which can be located up to approximately 25 feet away from the CPU, is required for the Model 165. This unit contains the system control panel (buttons, switches, lights, etc., required for system operation), as well as standard advanced console features: a cathode ray tube and keyboard, a microfiche indicator viewer, a microfiche document viewer, a processor storage configuration plugboard, a system activity monitor, and a device for loading microcode and diagnostics. Certain of these features are included to enable the customer engineer to detect CPU malfunctions more rapidly than would otherwise be possible.

Installation of the optional Remote Operator Console Panel Attachment feature on a Model 165 permits duplication of the operator control panel section of the system console unit on a 2150 Console or a 2250 Display Unit Model 1.

The <u>cathode</u> ray <u>tube</u> (CRT) unit provided contains a 4K buffer. In normal mode, the CRT and alphameric keyboard are designed to be used as the operating system operator's console to provide the rapid message display required by large systems like the Model 165. Two operator warning indicators are provided. A switch setting determines whether a visual indicator or an audible alarm with volume control is used. In CE mode, the CRT and a set of 16 data keys can be used to display and manually alter processor storage, the general purpose and floating-point registers, the channel buffers, or the CPU buffer address array. Data is entered in hexadecimal by means of the data keys, each of which represents a hexadecimal digit.

The <u>microfiche indicator viewer</u> is included in the console unit for display of status and control indications. The display utilizes a "framing" concept: the customer engineer uses a "frame selection switch" to select any one of ten images. Each image consists of up to 240 indicators, the current value of which is then displayed in incandescent lights along with the appropriate microfiche image that labels the lights. In this way up to 2400 status and control triggers may be displayed, yet the console requires only 240 incandescent lights. A <u>microfiche</u> <u>document</u> <u>viewer</u> is included in the console unit for display of customer engineer reference materials. It is expected that more than half of all Model 165 CE reference materials will be supplied in microfiche form.

The processor storage configuration plugboard permits automatic generation of the required processor storage configuration (units available to the operating system, their addressing, interleaving, etc.) when power is brought up or upon depression of an "enter configuration" push-button. (See Section 10:15 for further information.) The exact processor storage configuration in effect at any given time can be verified by displaying the appropriate image on the indicator viewer.

The <u>system activity monitor</u> is capable of displaying the average activity of the CPU and the channels via the system activity meter located in the main control panel in the system console. The activity to be displayed is selected via a set of switches. The following can be displayed, one measurement at a time.

- 1. Percentage of compute time relative to the:

- a. Total time CPU is active

- b. Time CPU is active in supervisor state

- c. Time CPU is active in problem state

- 2. Percentage of time the CPU and one or more of the selected channels are concurrently active (to determine CPU and channel activity overlap)

- 3. Percentage of time when all of the selected channels are busy concurrently (to determine channel activity overlap)

- Percentage of time when a single selected channel or one or more of the selected channels are busy (to determine channel activity)

- 5. Percentage of time any of the selected channels and the CPU are busy accessing the selected storage protect key area of processor storage

A device that provides read-only storage for WCS microcode and system diagnostics is contained in the system console unit between the indicator viewer and the document viewer. This device reads interchangeable magnetic disk cartridges. As already indicated, this device is used for WCS loading. It is also a debugging tool for the customer engineer who will load diagnostics from it.

#### 10:15 STORAGE

The Model 165 has a two-level memory system - a very high-speed buffer storage backed by a large processor (main) storage. Prior to this time, such a concept was implemented only in very large-scale, high-internal-performance systems, such as System/360 Models 85 and 195. The Model 165 has four-way doubleword interleaved processor storage with a two-microsecond cycle time, buffered by 8K or 16K of high-speed monolithic buffer storage with an 80-nanosecond cycle time.

The use of interleaving and a two-level memory system drastically reduces the effective storage cycle of the Model 165 and greatly contributes to the fact that the internal performance of the Model 165 is approximately two to five times that of the Model 65.

#### PROCESSOR (MAIN) STORAGE

Processor storage is available in the following increments:

| <u>Model</u> | Capacity |

|--------------|----------|

| I            | 512K     |

| J            | 1024K    |

| JI           | 1536K    |

| K            | 2048K    |

| KJ           | 3072K    |

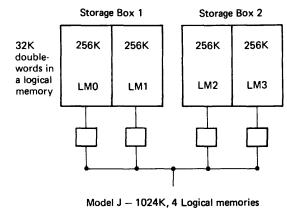

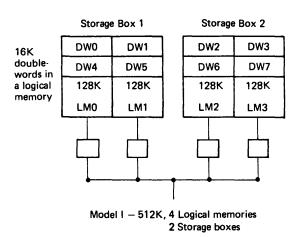

In order to achieve interleaving in the Model 165, the processor storage present in the system is divided into <u>logical memories</u> within storage boxes. A logical memory is defined as that portion of storage that can operate independently from all other storage. A logical memory in the Model 165 is 128K or 256K and there are two per storage box.

Depending on the storage size, the total number of logical memories present is 4 in two boxes for Models I and J, 8 in four boxes for Models K and JI, or 12 in six boxes for Model KJ, as shown in Figure 10.15.1. (Model JI, not shown, consists of four 128K and four 256K logical memories in two boxes.) However, only four logical memories can be active at one time, thus achieving four-way interleaving. As illustrated in Figure 10.15.1, for a 512K system, four consecutively addressed doublewords are spread across logical memories so that 32 consecutive bytes can be accessed concurrently (one doubleword from each of four logical memories, requested one 80-nanosecond cycle apart). That is, processor storage location 0 is in logical memory 0, location 8 is in logical memory 1, location 16 is in logical memory 2, and location 24 is in logical memory 3. Processor storage location 32 is in logical memory 0, and the address distribution sequence continues through all available storage locations.

Figure 10.15.1. Model 165 processor storage configurations

Processor storage can be accessed concurrently by any combination of one or more channels and the CPU for a total of four unique logical memory requests. Contention arises when two or more components attempt to access the same logical memory simultaneously. In addition, requests made to a busy logical memory are delayed until the memory becomes free. The storage control unit (SCU), illustrated in Figure 10.15.2, controls all storage references by components and schedules requests according to a priority scheme. The channels have priority over the CPU for simultaneous requests and there is a definable priority among channel positions. Thus, the SCU ensures that an effective storage access of 32 bytes in two microseconds is achieved for the system whenever possible.

Storage access times stated in this guide are obtainable, assuming the four logical memories required are free when requested and accessed concurrently with no interference from other components.

Central Processing Unit (CPU)

Figure 10.15.2. Model 165 storage components and controls

17

Error checking and correction (ECC) hardware provides automatic detection and correction of all single-bit processor storage errors and detection, but not correction, of all double-bit and most multiplebit errors. The ECC feature is discussed fully in the RAS section.

The Model 165 also supports a byte boundary alignment facility for processor storage. The presence of the byte-oriented operand function allows the storage operands of unprivileged instructions (RX and RS formats) to appear on any byte boundary without causing a specification program interrupt. Without this facility, operands must be aligned on integral boundaries, that is, on storage addresses that are integral multiples of operand lengths. Byte orientation is standard and does not apply to alignment of instructions or channel command words (CCW's).

Use of byte alignment in a program degrades instruction execution performance. However, byte orientation can be used effectively in commercial processing to eliminate the padding bytes added within records and to blocked records to insure binary and floating-point field alignment. The smaller physical record that results from the elimination of padding bytes requires less external storage and increases effective I/O data rates. I/O-bound commercial programs, in which throughput is in almost direct proportion to the I/O data rate, can achieve performance improvement by using byte alignment for binary and floating-point data.

A program written to use byte boundary alignment will not necessarily run on a System/360 model that does not have the feature. Therefore, programs that are to run on both the Model 165 and on System/360 models without byte orientation should be written to adhere to integral boundary rules.

# Processor Storage Reconfiguration

If a processor storage box develops a malfunction, it can be configured out of the system by use of the storage configuration plugboard in the system console. Then the operating system can be re-IPLed and the system can continue operating with reduced available storage. The configuration indicated by the plugboard is established during a power-on sequence or a system reset operation.

The user has the ability to remove one or more storage boxes from the operative system and reconfigure the addressing of the remaining boxes to achieve consecutive storage addressing. Interleaving is reduced from four-way to two-way if the configuration consists of an odd number of boxes. Therefore, four-way interleaving can be maintained in systems with four or six processor storage boxes by removing a pair of boxes instead of the malfunctioning box only. A pair must be removed in a 3072K (six-box) system as a 2560K configuration is not supported. Serial operation is possible also and will be used primarily by customer engineers.

The configuration panel is relatively simple to use. The operator inserts plugs into the appropriate holes in the panel to describe the processor storage configuration: number of boxes (one to six) using up to three plugs, box addressing sequence (box reversals) using up to two plugs, and interleaving (four-way, two-way, or serial) using up to two plugs.

With the few reversal combinations defined, any box can be placed in the first or last box addressing position. Assume box 2 in a sixbox configuration is to be configured out of the operational system. (Refer to Figure 10.15.1, in which box numbers also indicate the sequential positioning of consecutive processor storage box addressing.) Boxes 1 and 2 would be vertically reversed in position with boxes 3 and 4, respectively, and then with boxes 5 and 6, respectively. Box 2 is then in the last (or highest) addressing position and an inline ripple (discussed below) can be performed on it. If box 1 is the malfunctioning box, a horizontal reversal of boxes 3, 5, and 1 with boxes 4, 6, and 2, respectively, puts box 1 in the highest addressing position. (The ascending addressing sequence of the boxes is then 4-3, 6-5, 2-1.)

#### Storage Ripples

Five storage ripple functions are implemented in Model 165 hardware as maintenance aids for use by customer engineers. (A ripple is a nonprogrammed read or write of ones or zeros through every available storage address for the purpose of locating a malfunction.) A ripple is provided for ROS, WCS, local storage, and processor storage that requires dedication of the system to the ripple function. However, an <u>inline</u> processor storage ripple also is implemented. It can be executed on a malfunctioning storage box that has been configured out of the operational system while processing continues. (The processor storage box must be in the highest addressing position.) An inline ripple is not provided for the Model 65, which therefore requires total system unavailability during processor storage rippling. In addition, there is no reconfiguration capability for main storage boxes in uniprocessor Model 65 systems.

## HIGH-SPEED BUFFER STORAGE

The increase in the internal performance of the Model 165 is achieved largely by the inclusion of a high-speed buffer storage unit. The 8K buffer is a standard feature and provides high-speed data access for CPU fetches. Installation of the optional Buffer Expansion feature permits inclusion of an additional 8K of buffer storage.

The buffer has an 80-nanosecond cycle. The CPU can obtain eight bytes from the buffer in two cycles, or 160 nanoseconds, and a request can be initiated every cycle. This compares with 1.44 microseconds (or 18 cycles) required to obtain eight bytes of data directly from processor storage. The conceptual data flow in the Model 165 is pictured in Figure 10.15.3.

Buffer storage control and use is handled entirely by hardware and is transparent to the programmer, who need not adhere to any particular program structure in order to obtain close to optimum use of the buffer. The buffer algorithm implemented in the Model 165 is very similar to that used in the System/360 Model 195. Sample job step executions have shown that in a Model 165 the data accessed by the CPU is in the buffer 95% of the time on the average.

CPU fetch from buffer - 160 nanoseconds for 8 bytes (2 cycles) CPU fetch from processor storage - 1.44 microseconds for 8 bytes (18 cycles) Buffer fetch from processor storage - 1.44 microseconds for 32 bytes (18 cycles) Channels to and from processor storage - 32 bytes in a 2 microsecond cycle

Figure 10.15.3. Conceptual data flow in the Model 165. Times given assume no interference.

The storage control unit (SCU) contains the high-speed buffer and controls all buffer and processor storage references made by the CPU, the channels, and manual controls. The buffer storage control portion of the SCU handles CPU to processor storage references, both fetches and stores. Parity checking is used for data verification in the buffer.

When a data fetch request is made by the CPU, buffer storage control determines whether or not the requested data is in the high-speed buffer by interrogating its address array of the buffer's contents. If the data requested is present in the buffer, it is sent directly to the CPU without a processor storage reference. If the requested data is not currently in the buffer, a processor storage fetch is made. The data obtained is sent to the CPU. The data is also assigned a buffer location and stored in the buffer. When data is stored by the CPU, both the buffer and processor storage are updated if the processor storage location being altered is one whose contents are currently being maintained in the buffer.

The channels never access the buffer directly. They read into and write from processor storage only. When a channel stores data in processor storage, the address array is interrogated. If data from the affected processor storage address is being maintained in the buffer, the data is placed in the buffer as well as in processor storage.

The entire buffer can be disabled manually by a system console switch or via execution of a DIAGNOSE instruction. When the buffer is disabled, all CPU fetches are made directly to processor storage and effective system execution speed is reduced.

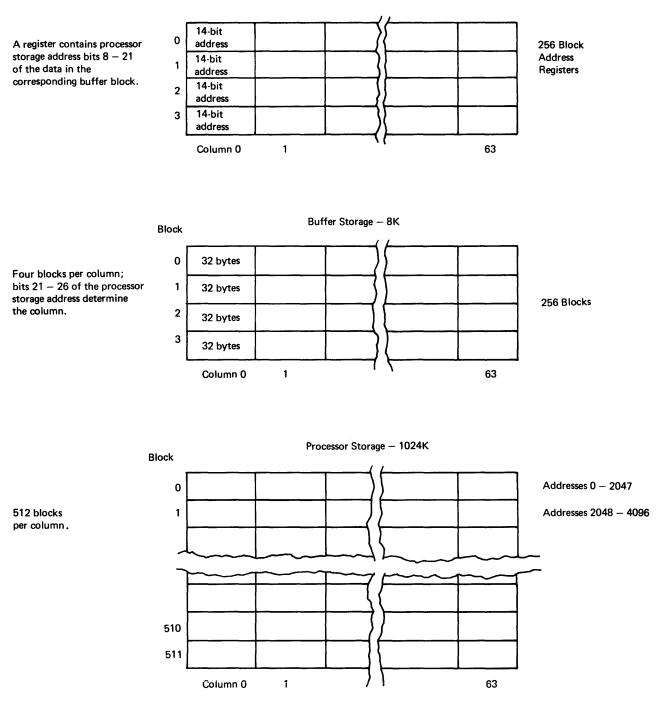

The 8K buffer is shown in Figure 10.15.4. It contains 64 columns of 128 bytes each. Every buffer column is subdivided into four blocks. A block is 32 bytes and can contain 32 consecutive bytes from processor storage that are on a 32-byte boundary. The 8K buffer can contain a maximum of 256 different blocks of processor storage data (4 blocks per column times 64 columns). A valid trigger is associated with each buffer block and is set to indicate whether or not the block contains | valid data. All valid triggers are set off during system reset or IPL.

Processor storage is logically divided into the same number of columns as buffer storage: 64 or 128. While there are always four blocks in a buffer column, the number of blocks in a processor storage column varies with the size of processor storage. For example, when an 8K buffer is present, bits 21-26 of the processor storage address determine which of the 64 columns to use. As shown in Figure 10.15.4, a processor storage column consists of 512 blocks in a system with 1024K. Any of the 512 blocks in a given processor storage column can be placed in any of the four blocks in the corresponding buffer column. Figures 10.15.5 and 10.15.6 show the formats used for processor and buffer storage addressing.

The larger the processor storage size, the greater the number of storage blocks that contend for the four blocks in the same buffer column. If a 16K buffer is used instead of an 8K, the number of buffer columns is doubled from 64 to 128; the number of processor storage blocks contending for the blocks in each buffer column is thereby halved if processor storage size remains the same. (A 1024K processor storage divided into 128 columns has 256 blocks per column.)

The 16K buffer is provided for users with larger Model 165 processor storage configurations that have applications such that increased system throughput results from an increase in internal performance.

A register contains processor storage address bits 8-20 of the data in the corresponding buffer block.

Four blocks per column; bits 21 - 26 of the processor storage address determine the column.

Processor Storage Address Bits

|   | 8  | 9               | 10  | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23           | 24 | 25  | 26 | 27 | 28 | 29 | 30 | 31 |

|---|----|-----------------|-----|----|----|----|----|----|----|----|----|----|----|----|----|--------------|----|-----|----|----|----|----|----|----|

| I | == | <u>ts</u><br>-1 | 9,2 | 20 |    |    |    |    |    |    |    | -  |    | •  | •  | 3K b<br>Lumr |    | er) | I  |    |    |    |    |    |

21-26 Used to reference 8K buffer columns

27-28 Used to reference doubleword within a block

29-31 Used to reference byte within doubleword

Figure 10.15.5. Processor storage address format for buffer reference

# Buffer Reference Bits

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 |  |

|---|---|---|---|---|---|---|---|---|---|----|--|

|---|---|---|---|---|---|---|---|---|---|----|--|

Bits

| 0-1  | Generated as result of address compare; this two-bit encoded<br>field represents block in buffer column containing desired<br>data |

|------|------------------------------------------------------------------------------------------------------------------------------------|

| 2-8  | Used to reference column for 16K buffer (processor storage address bits 20-26)                                                     |

| 3-8  | Used to reference column for 8K buffer (processor storage<br>address bits 21-26)                                                   |

| 8-10 | Used to reference doubleword within a block (processor storage address bits 27-28)                                                 |

Figure 10.15.6. Buffer address format

Buffer contents and buffer block assignment are controlled by an <u>address</u> <u>array</u>, shown in Figure 10.15.4, and a special <u>replacement</u> <u>array</u>. The address array, like the 8K buffer, is divided into 64 columns consisting of four block address registers each such that there is a one-for-one correspondence between address array registers and blocks in the buffer. An address array block register contains the 13-bit processor storage block address from bits 8-20 of the processor storage address of the data contained in its corresponding buffer block. When a CPU to processor storage reference is made, the four appropriate address array column registers (13-bit block addresses) are interrogated to determine whether the requested data is currently in the buffer.

The replacement array is used to maintain knowledge of the activity of the data blocks within each of the buffer columns. When an 8K buffer is present, the array consists of 64 logic-controlled activity lists, one list for each column in the buffer. A list contains four entries, one for each buffer block in its column. A block's entry is placed at the top of the list for its column when the buffer block is referenced during a CPU fetch operation. This approach insures that the block used longest ago within a given column is at the bottom of the list. When a block within a buffer column has to be assigned and loaded, because the data requested by the CPU is not in the buffer, the buffer block at the bottom of a column activity list is allocated. Thus, the more active data is maintained in the buffer.

The 8K buffer operates as follows. When the CPU requests data, bits 21-26 of the data's processor storage address are used to obtain a buffer column address. The 13 high-order bits of the processor storage address are then compared to the address in each of the four block address registers in that buffer column in the address array. Page of GC20-1730-0 Revised 7/14/70 By TNL GN20-2227

If an equal compare occurs for an address in one of the registers in the address array and the valid trigger for that block is on in the buffer, the appropriate doubleword from the buffer block is sent to the CPU as determined by bits 27 and 28 of the processor storage address. A processor storage reference is not made. The referenced buffer block is put at the top of its column activity list in the replacement array.

If the desired data block is not in the buffer column interrogated, the requested data must be fetched from processor storage, sent to the CPU, and stored in the buffer. The replacement array entry for the column involved is inspected and the buffer block at the bottom of the activity list is assigned to receive the requested data from processor storage. Four processor storage references, one cycle apart, are made to obtain the 32 consecutive bytes and place them in the assigned buffer block. The valid trigger for the buffer block is set on and the 13 high-order processor storage address bits are placed in the appropriate column within the address array. The first doubleword fetched from processor storage is the one containing the data required by the CPU. It is sent to the CPU as well as to the buffer so that processing can continue as soon as possible.

Assuming no channel interference, a 32-byte buffer block can be filled from processor storage in 1.44 microseconds (or 18 cycles) with four-way interleaving utilized. One buffer block can be loaded every 2 microseconds (25 cycles), assuming no interference.

#### 10:20 CHANNELS

#### GENERAL DESCRIPTION

The channels available on a System/370 Model 165 are functionally compatible with those of System/360 models. Combinations of 2870 Multiplexer, 2860 Selector, and 2880 Block Multiplexer channels can be attached to a Model 165. If the Extended Channels special feature is installed, up to twelve channels can be connected to a single Model 165 to provide an aggregate channel data rate in excess of nine megabytes, twice the rate possible on a Model 65.

The 2870 and 2860 channels that attach to the Model 165 are the same as those used on a Model 65 but have minor hardware changes (as is true when these channels are attached to System/360 Models 75 and up). When a Model 165 replaces a Model 65 or 75, the 2870/Model 165 and 2860/Model 165 features can be field installed on the existing 2870 and 2860 channels, respectively, so that the latter can be attached to the Model 165.

The standard number of addressable channels permitted on a Model 165 is seven. Any combination of one or two 2870 Multiplexer, up to six 2860 Selector, and up to six 2880 Block Multiplexer channels can be attached up to the limit of seven channels. If the optional Extended Channels feature is installed, the maximum number of each type of channel that can be included in the twelve channels permitted is:

- 2870 Multiplexer two. (The first must have address 0, the second can be assigned an address from 1 to 6.)

- 2860 Selector six. (Addresses 1 through 6 can be assigned.)

- 2880 Block Multiplexer eleven. (Addresses 1 through 11 can be assigned.)

Model 165 channels are not integrated with the CPU. Channels compete with each other and the CPU only for processor storage accesses and, therefore, cause a minimum of CPU interference. A 2870, 2860, or 2880 channel contains the hardware required to control its I/O operations (channel registers, local storage, control functions, buffers, etc.). A channel interferes with the Model 165 CPU if the CPU accesses a logical memory that is busy because of a channel operation. Contention between channels and the CPU for processor storage is reduced drastically by the use of high-speed buffer storage, which eliminates CPU to processor storage fetches for approximately 95% of the fetches required.

The standard instruction set also includes a new I/O instruction called HALT DEVICE. This instruction is specifically designed to stop an I/O operation on a particular device on a multiplexer channel without interfering with other I/O operations in progress on the channel. HALT DEVICE should always be used instead of HALT I/O to stop an I/O operation on a 2880 Block Multiplexer channel.

The 2870 Multiplexer can control concurrent execution of 192 slowspeed to medium-speed devices, one with each of its 192 subchannels. Depending on the channel priority assigned, the 2870 can support a data rate of up to 110 KB. The maximum aggregate byte data rate of the 2870 Multiplexer subchannels is reduced by the inclusion of one or more selector subchannels, each of which can have up to 16 I/O devices attached. Each of the first three selector subchannels included can operate at a 180 KB rate, can handle one burst operation at a time, and reduces the aggregate byte rate of the multiplexer interface by 10 KB to 25 KB depending on the priority of the 2870 and the total I/O configuration. The fourth selector subchannel can operate at a rate of 100 KB and further reduces the maximum aggregate rate of the multiplexer subchannels by 14 KB. If two 2870 Multiplexer Channels are installed, the second 2870 can have only two selector subchannels.