Maintenance Library

$\overline{3705} = \overline{30}$  Communications Controller

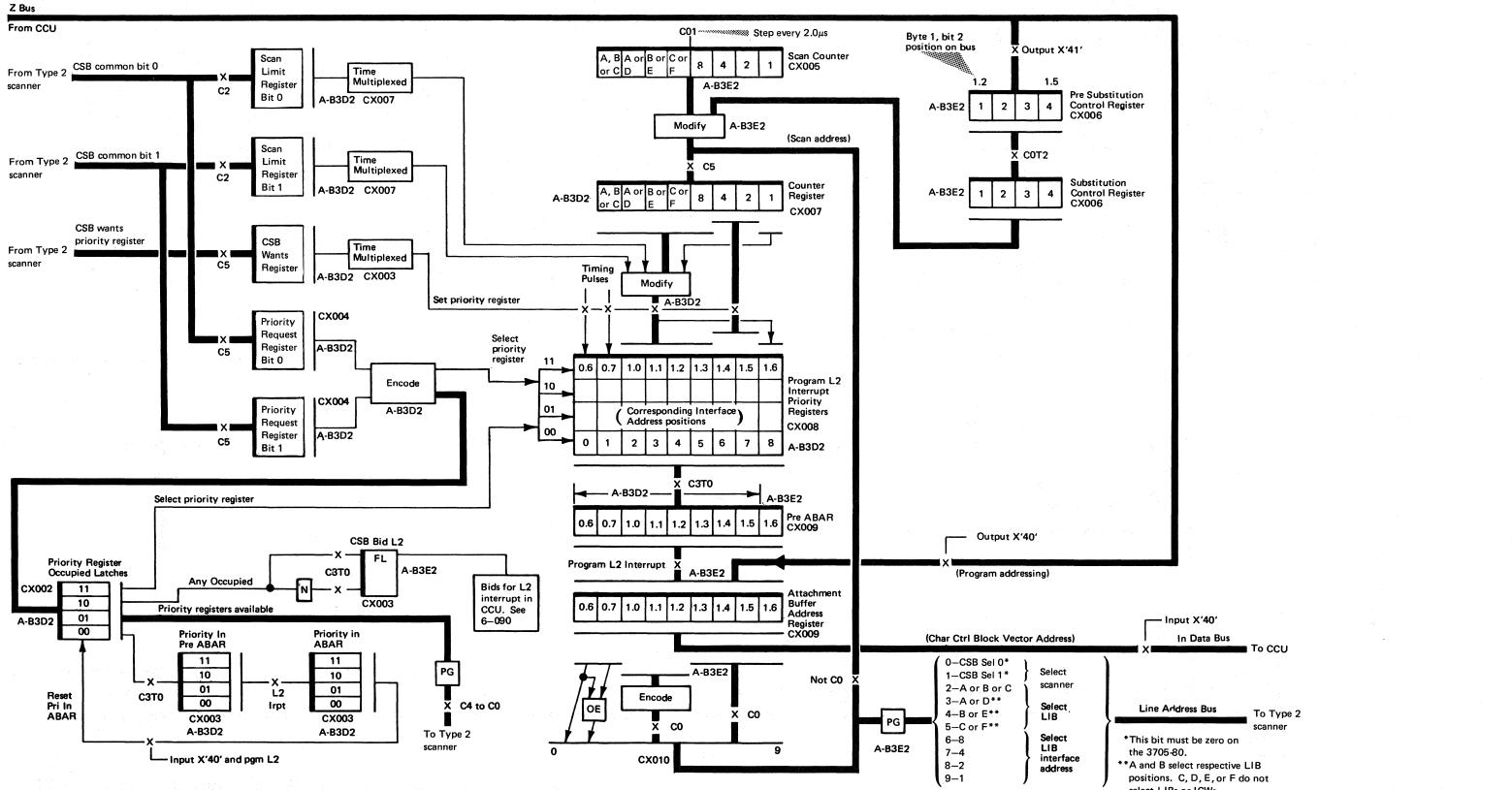

Theory-Maintenance Volume III

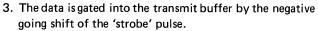

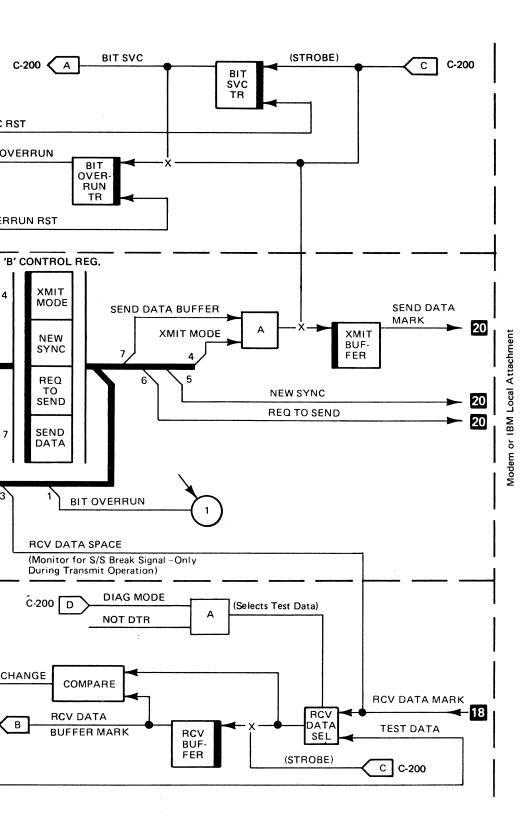

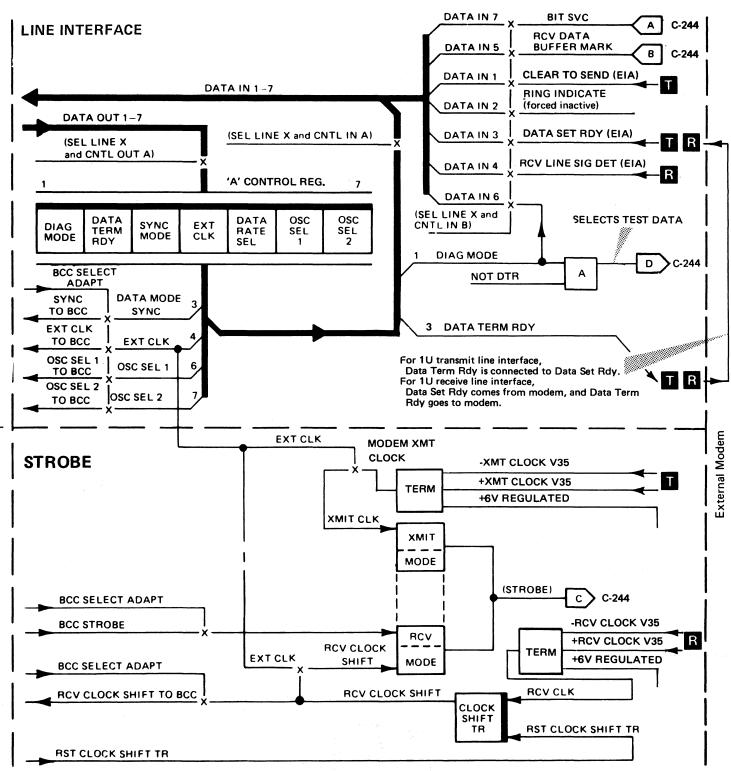

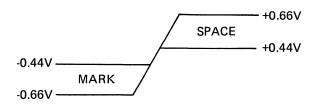

SY27-0209-1

#### Abbreviations

| А        | And circuit or ampere                    | ck     | check                                    | ESC      | emulation subchannel                             |

|----------|------------------------------------------|--------|------------------------------------------|----------|--------------------------------------------------|

| AA       | automatic answering                      | clk    | clock                                    | EXT      | external                                         |

| ABAR     | attachment buffer address register       | cm     | centimeter                               | FCS      | final control sequence                           |

| ABO      | adapter bus out (register)               | CMDR   | channel adapter command register         | FET      | field effect transistor modem card               |

| ac       | alternating current                      | CMND   | command                                  | FETOM    | Field Engineering Theory of Operation Manual     |

| ACO      | automatic call originate                 | com    | common                                   | FF       | flip flop                                        |

| ACF/NCP/ | Advanced Communications Function for     | COS    | Call Originate Status                    | FL       | flip latch                                       |

| VS       | Network Control Program/Virtual Storage  | CP     | circuit protector                        | FRU      | field replaceable unit                           |

| ACR      | abandm call and retry                    | CPU    | central processing unit                  | GB       | ground bus                                       |

| ACU      | automatic calling unit                   | CR     | compare register (instruction)           | gnd      | ground                                           |

| adr      | address                                  | CRC    | cyclic redundancy check                  | grp      | group                                            |

| AEQ      | automatic equalizer                      | CRI    | compare register immediate (instruction) | hex      | hexadecimal                                      |

| AHR      | add halfword register (instruction)      | CRQ    | Call Request                             | Hlfwd    | halfword                                         |

| ALD      | automated logic diagram                  | CS     | cycle steal                              | horz     | horizontal                                       |

| ALU      | arithmetic logic unit                    | CSAR   | cycle steal address register             | HS       | heat sink                                        |

| AMP      | amplifier                                | CSB    | communication scanner base               | Hz       | Hertz                                            |

| APAR     | authorized program analysis report       | CSCD   | clear to send, carrier detect            | 1        | instruction (cycle)                              |

| AR       | add register (instruction)               | CSMC   | cycle steal message counter              | IAR      | instruction address register                     |

| ARI      | add register immediate (instruction)     | ctrl   | control                                  | IC       | insert character (instruction)                   |

| В        | branch (instruction)                     | CTS    | Clear To Send                            | ICS      | initial control sequence                         |

| BAL      | branch and link (instruction)            | CUE    | Control Unit End (status)                | ICT      | insert character and count (instruction)         |

| BALR     | branch and link register (instruction)   | CW     | control word                             | ICW      | interface control word                           |

| BAR      | buffer address register                  | CWAR   | control word address register            | IFT      | internal functional test                         |

| BB       | branch on bit (instruction)              | CWCNTR | control word byte count register         | IN       | input (instruction)                              |

| BC       | bit clock                                | DAA    | data access arrangement                  | INCWAR   | inbound control word address register            |

| BCB      | bit control block                        | DA     | data modem ready                         | Init     | initial                                          |

| BCC      | bit clock control                        | dB     | decibel                                  | int      | internal                                         |

| BCL      | branch on C latch (instruction)          | DBAR   | diagnostic buffer address register       | intf     | interface                                        |

| BCT      | branch on count (instruction)            | dc     | direct current                           | 1/0      | input/output                                     |

| BO       | bus out                                  | DCE    | data circuit-terminating equipment       | IPL      | initial program load                             |

| BP       | break point                              | DCM    | diagnostic control monitor               | IR       | interrupt remember                               |

| bps      | bit per second                           | DCR    | data channel ready                       | irpt     | interrupt                                        |

| BSC      | binary synchronous communication         | DE     | Device End (status)                      | ISACR    | initial selection address and command register   |

| BSM      | bridge storage module                    | DET    | detector                                 | 1        | load (instruction)                               |

| BZL      | branch on Z latch (instruction)          | diag   | diagnostic                               | LA       | load address (instruction)                       |

| CA       | channel adapter                          | dist   | distance                                 | LAR      | lagging address register                         |

| CACHKR   | channel adapter check register           | DLO    | data line occupied                       | LCD      | line code definer                                |

| CACR     | channel adapter control register         | DOS    | Disk Operating System                    | LCOR     | load character with offset register              |

| CADB     | channel adapter data buffer              | DPR    | digit present                            |          | (instruction)                                    |

| CAMR     | channel adapter mode register            | DR     | display register or                      | LCR      | load character register (instruction)            |

| CASNSR   | channel adapter sense register           |        | data ring (modem)                        | LED      | light emitting diode                             |

| CASTR    | channel adapter status register          | DCS    | distant station connect (ACO only)       | LGF      | leading graphics flag                            |

| СВ       | circuit breaker                          | DSR    | data set ready                           | LH       | load halfword (instruction)                      |

| CBAR     | CSB buffer address register              | DT     | data tip (modem)                         | LHOR     | load halfword with offset register (instruction) |

| CCB      | character control block                  | DTE    | data terminal equipment                  | LHR      | load halfword register (instruction)             |

| CCR      | compare character register (instruction) | DTR    | data terminal ready                      | LIB      | line interface base                              |

| ССТ      | coupler cut through (modem)              | EC     | edge connector                           | lim      | limiter                                          |

| CCU      | central control unit                     | EB     | extended buffer                          | LOR      | load with offset register (instruction)          |

| CD       | carrier detect                           | ECP    | emulation control program                | LOSC     | last oscillator sample condition                 |

| CDS      | configuration data set                   | EIA    | Electronic Industries Association        | LR       | load register (instruction)                      |

| CE       | Channel End (status)                     | enbl   | enable                                   | LRI      | load register immediate (instruction)            |

| chan     | channel                                  | EON    | end of number (ACO only)                 | LS or Is | local store                                      |

| char     | character                                | EPO    | emergency power off                      | lt       | latch                                            |

| CHR      | compare halfword register (instruction)  |        |                                          | L1       | level 1                                          |

|          |                                          |        |                                          |          |                                                  |

L2 level 2 L3 level 3 L4 level 4 L5 level 5 mΑ milliampere Mem TB memory terminal board modem modulator/demodulator ms/divn milliseconds per division MST monolithic system technology mν millivolt NB Digit Signal N/C normally closed NCP network control program NCR and character register (instruction) NHR and halfword register (instruction) N/O normally open NR and register (instruction) NRI and register immediate (instruction) NRZI non-return-to-zero inverted ns nanoseconds NSC native subchannel OBR outboard recorder O/C overcurrent OCR or character register (instruction) OE exclusive or ОН off hook (modem) OHR or halfword register (instruction) OLT on line test OLTEP on line test executive program OLTLIB on line test library OLTSEP on line test standalone executive program operation ор operation register op reg OR or register (instruction) ORI or register immediate (instruction) OS **Operating System** OSC oscillator OUT output (instruction) OUTCWAR outbound control word address register OVRN overrun 0/V overvoltage Ρ parity PC parity check PCF primary control field PCI program controlled interrupt PDF parallel data field PEP partitioned emulation programming PG parity generation program pgm PH polarity hold PND Present Next Digit P/N part number

| DOCO  |                                               |

|-------|-----------------------------------------------|

| POSC  | present oscillator sample condition           |

| pot   | potentiometer                                 |

| P-P   | post processor modem card                     |

| PPB   | prime power box                               |

| PUT   | programmable unijunction transistor           |

| PWI   | power indicator                               |

| R     | resistance or resistor                        |

| rcv   | receive                                       |

| rd    | read                                          |

| rdy   | ready                                         |

| RE    | register and external register (instructions) |

| ref   | reference                                     |

| reg   | register                                      |

| regen | regenerative                                  |

| req   | request                                       |

| RI    | register immediate (instruction) or           |

|       | ring indicator (modem)                        |

| RLSD  | receive line signal detector                  |

| RMS   | root mean square                              |

| ROS   | read-only storage                             |

| RPL   | remote program loader                         |

| RR    | register to register (instructions)           |

| RS    | register to storage (instructions)            |

| RSA   | register and storage with addition            |

|       | (instructions)                                |

| RT    | register branch or register and branch        |

|       | (instructions)                                |

| RTS   | Request To Send                               |

| rly   | relay                                         |

| SAR   | storage address register                      |

| SCF   | secondary control field                       |

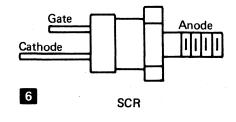

| SCR   | silicon controlled rectifier or               |

| 0011  | subtract character register (instruction)     |

| SCRID | silicon controlled rectifier indicator driver |

| SDF   | serial data field                             |

| SDLC  | synchronous data link control                 |

| SDR   | · · · ·                                       |

|       | storage data register                         |

| sec   | second                                        |

| sel   | selection (A CO as ha)                        |

| SEP   | separator (ACO only)                          |

| seq   | sequence                                      |

| SG    | signal ground                                 |

| SH    | switch hook (modem)                           |

| SHR   | subtract halfword register (instruction)      |

| SIG   | signal                                        |

| SIO   | start I/O                                     |

| SMS   | standard modular system                       |

| SR    | subtract register (instruction)               |

| SRI   | subtract register immediate (instruction)     |

| SRL   | Systems Reference Library                     |

| S/S   | start/stop                                    |

| ST    | store (instruction)                           |

| STC   | store character (instruction)                 |

| STCT  | store character and count (instruction)       |

|       |                                               |

| STH    | store halfword (instruction)                  |

|--------|-----------------------------------------------|

| stk    | stacked                                       |

| SVC    | service                                       |

| sw     | switch                                        |

| SYN    | synchronous idle                              |

| sync   | synchronization or synchronous                |

| TAR    | temporary address register                    |

| ТВ     | terminal board                                |

| TIC    | Transfer In Channel                           |

| tr     | trigger                                       |

| TRM    | test register under mask (instruction)        |

| TSL    | Technical Service Letter                      |

| Т2     | test 2                                        |

| Т3     | test 3                                        |

| Т4     | test 4                                        |

| UC     | Unit Check (status)                           |

| UE     | Unit Exception (status)                       |

| V      | volts                                         |

| V/divn | volts per division                            |

| wd     | word                                          |

| wr     | write                                         |

| XCR    | exclusive-or character register (instruction) |

| xfer   | transfer                                      |

| xfmr   | transformer                                   |

| XHR    | exclusive-or halfword register (instruction)  |

| xmt    | transmit                                      |

| XR     | exclusive-or register (instruction)           |

| XRI    | exclusive-or register immediate (instruction) |

| 2W     | two-wire line connection (implies             |

|        | half-duplex)                                  |

| 4W     | four-wire line connection (implies duplex,    |

|        | but actual duplex depends on the line set     |

|        |                                               |

type and telephone company equipment).

iv

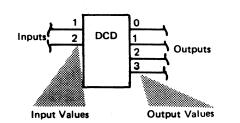

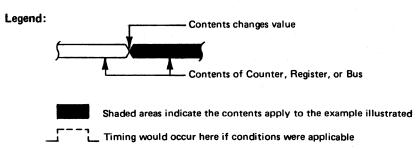

#### Legend (Part 1 of 2)

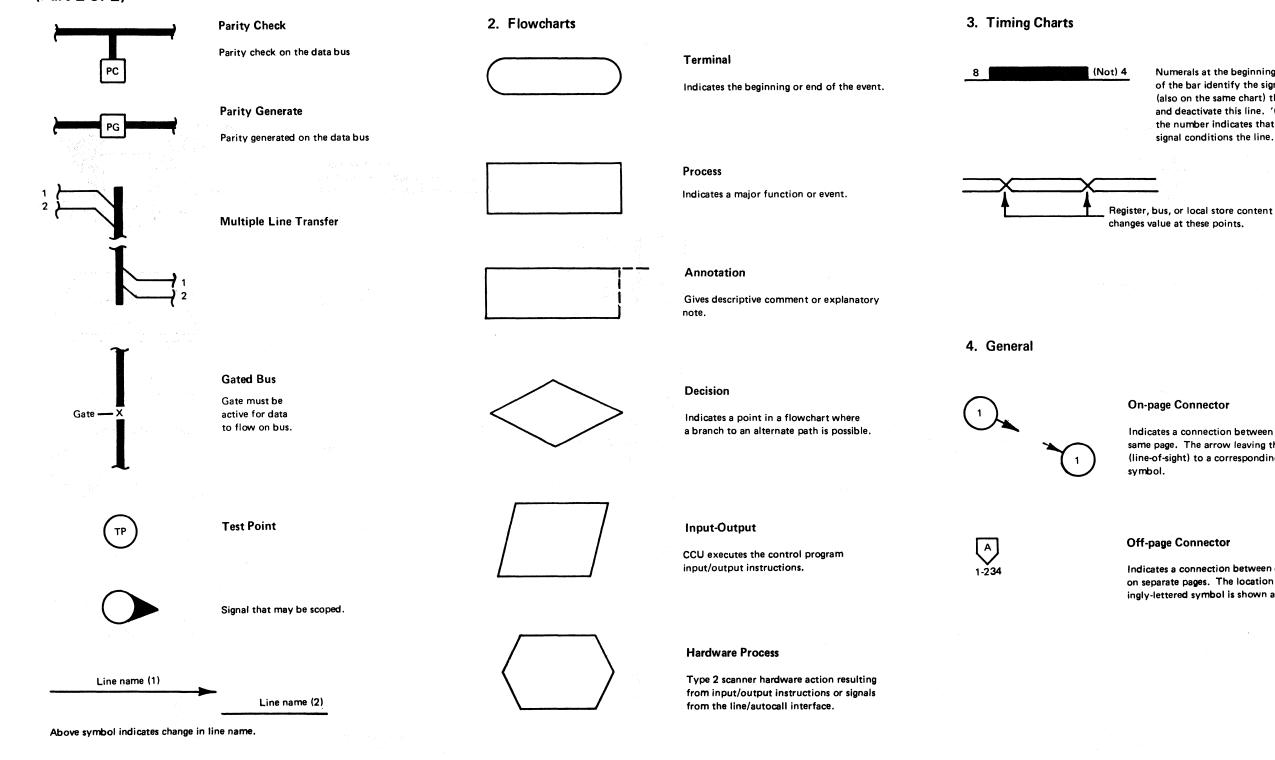

1. Logic Diagrams

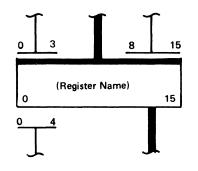

#### Register

The input side is denoted by a thick line. A partial transfer of contents is shown by numbered input and/or output lines.

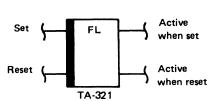

#### Flip Latch

Input side is denoted by a thick line. ALD reference page may be shown beneath.

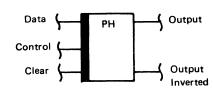

#### **Polarity Hold**

The 'output' of the polarity hold block is at the indicated polarity when both the 'data' and the 'control' lines go to their indicated polarity. When the 'control' line goes to the polarity opposite to that indicated, the 'output' line holds at the polarity it is at. When the 'clear' line goes to its indicated polarity, the 'output' line goes to the polarity opposite to that indicated.

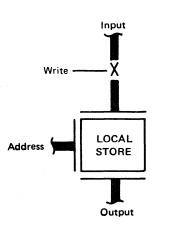

#### Local Store

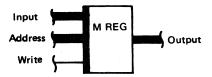

**M REG**

See Local Store

Read---Output from the local store addressed. Contents of local store is not destroyed. Write---Input contents stored in the local store addressed when 'write' is active.

OE

A-CD

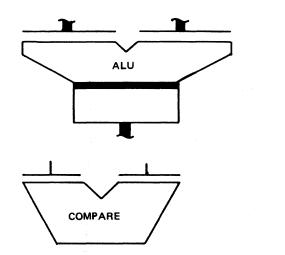

Compare

ALU

The active output is the output whese output value equals the sum of the active input values.

# -f AND --f OR -----f AND Current Driver

-{ Exclusive OR

Amplifier

Negator (Inverter)

Time Delay

An input pulse starts the time delay. Each output pulse has the same duration as the input pulse but is delayed by the specified amount.

> LEGEND (PART 1 OF 2)

V

Legend (Part 2 of 2)

#

LEGEND (PART 2 OF 2)

Numerals at the beginning and end of the bar identify the signal(s) (also on the same chart) that activate and deactivate this line. '(Not)' with the number indicates that lack of the signal conditions the line.

Indicates a connection between two parts of the same page. The arrow leaving the symbol points (line-of-sight) to a correspondingly-numbered

Indicates a connection between diagrams located on separate pages. The location of the correspondingly-lettered symbol is shown adjacent the symbol.

## **CONTENTS-VOLUME 3**

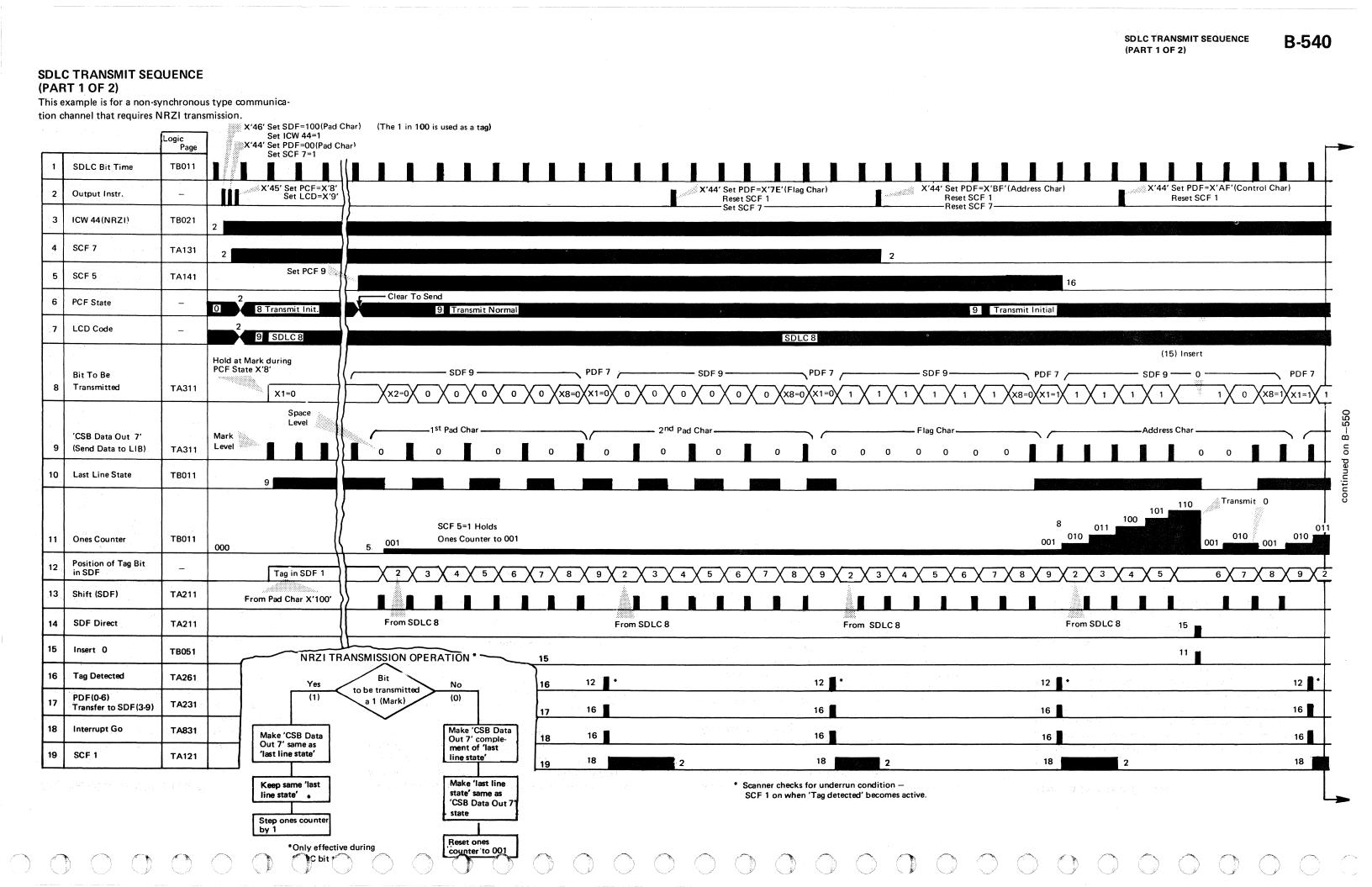

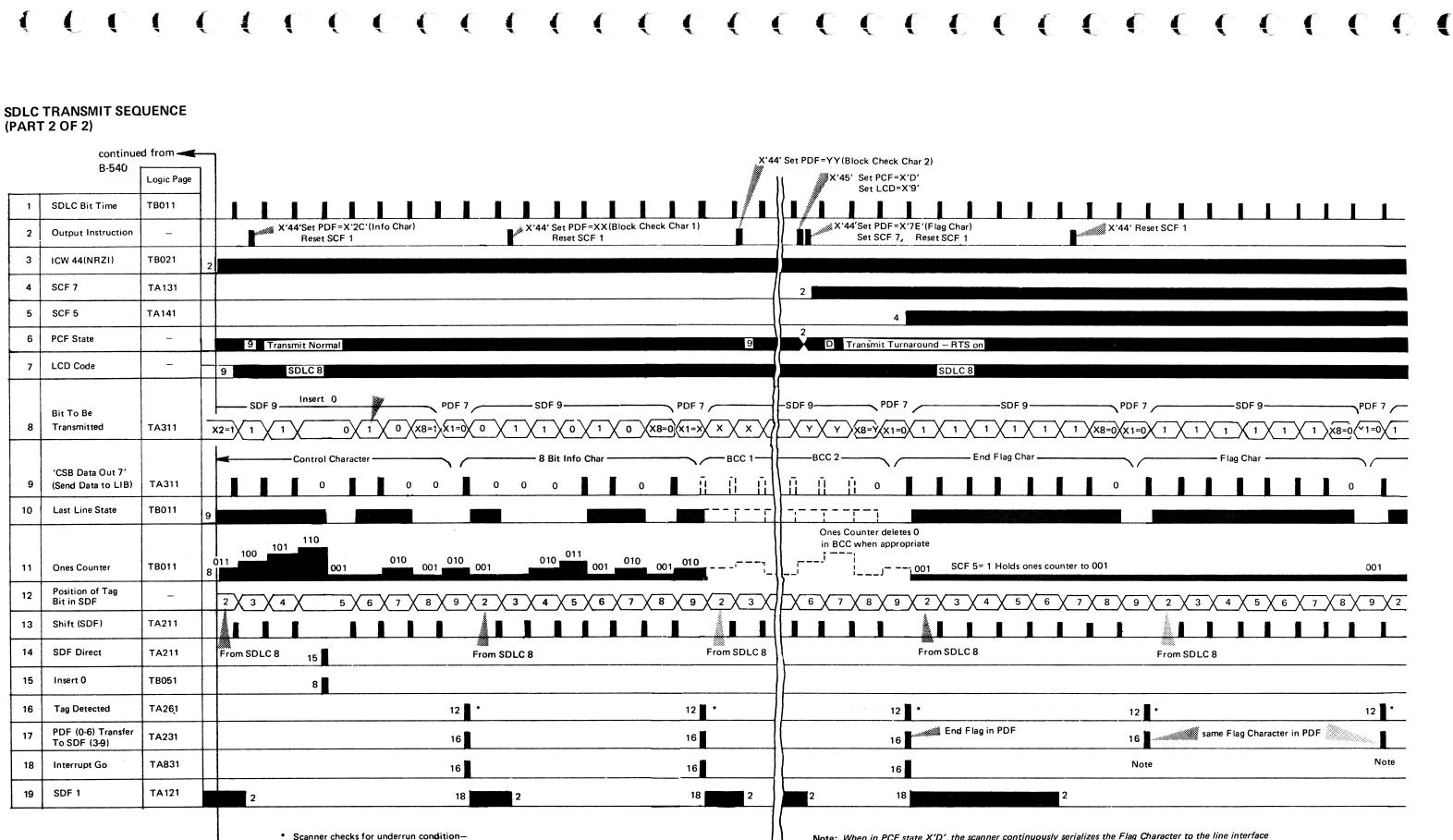

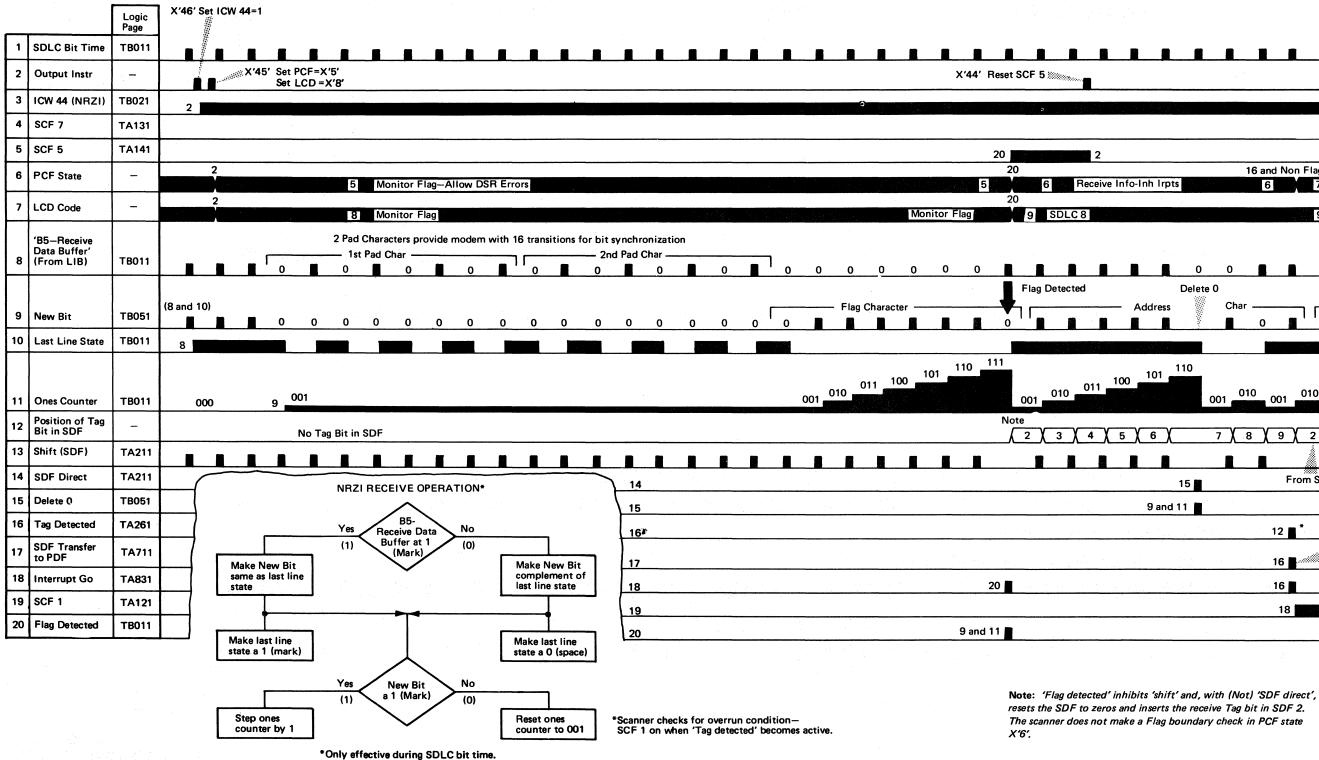

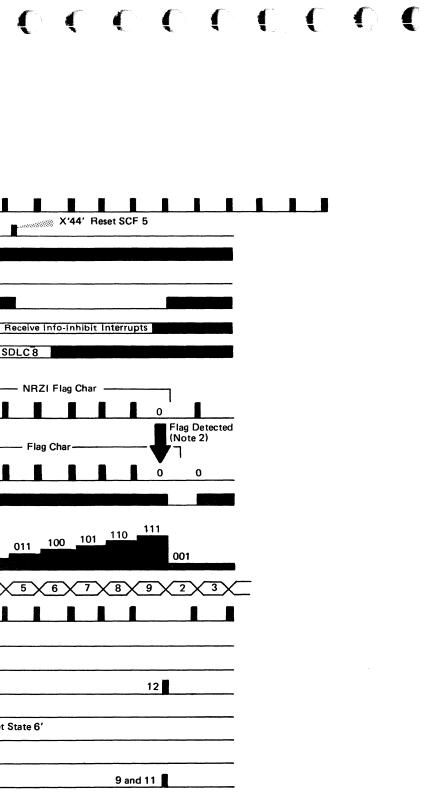

| TYPE 1 CHANNEL ADAPTER                                                    |                                                                                                                  | ICW - LCD Field                 | B-062          | SDLC TRANSMIT SEQUENCE                   | B-540          | MISCELLANEOUS                                             |        |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------|------------------------------------------|----------------|-----------------------------------------------------------|--------|

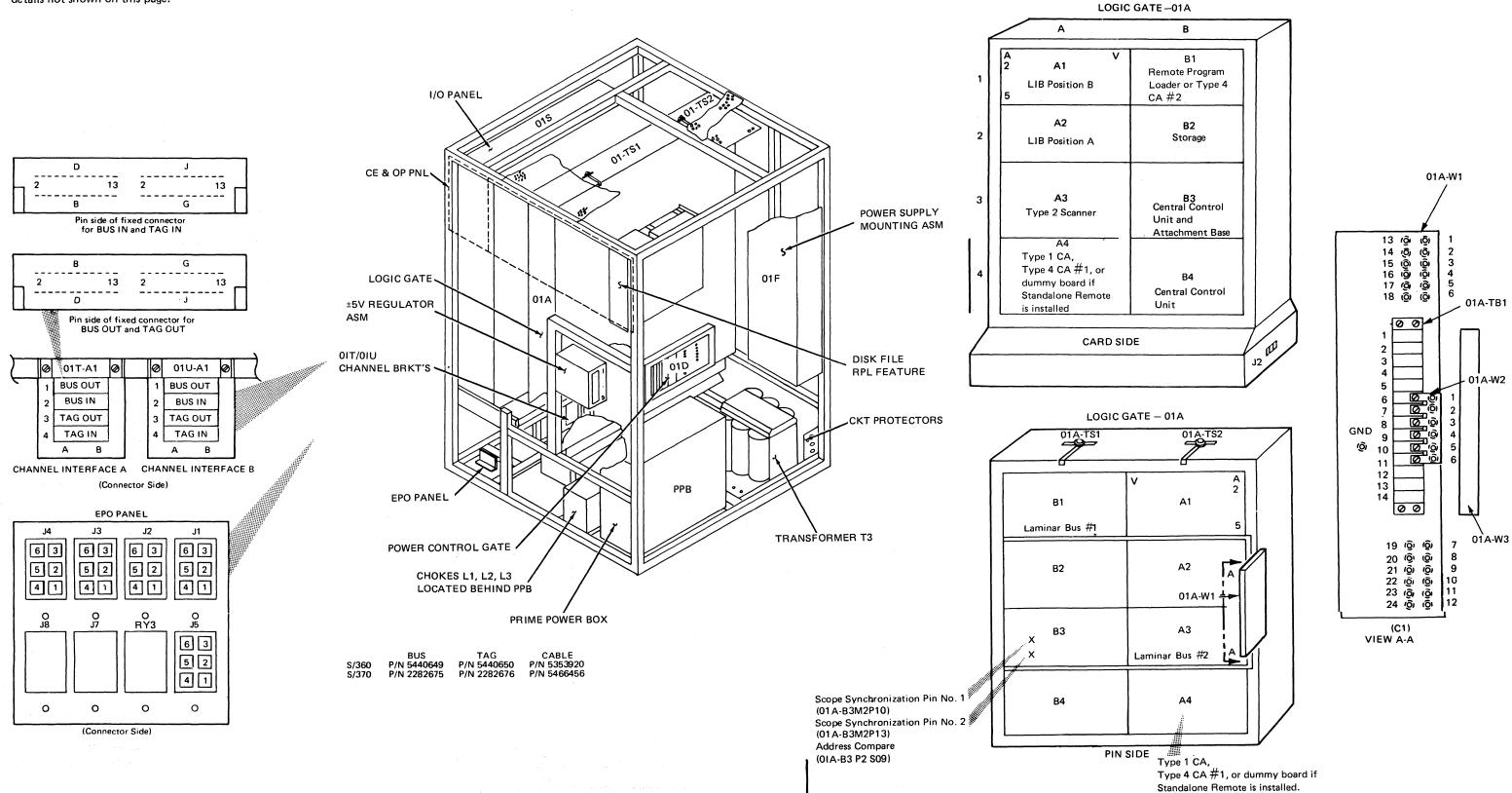

| INTRODUCTION                                                              | 8-000                                                                                                            | ICW - SDF Field                 | B-070          | SDLC RECEIVE SEQUENCE                    | B-560          | 3705-80 PHYSICAL LOCATIONS                                | E-     |

| TYPE 1 CHANNEL ADAPTER                                                    |                                                                                                                  | ICW - Primary Control Field     | B-080          |                                          |                | TOOLS AND TEST EQUIPMENT                                  | E-     |

|                                                                           | 8-010                                                                                                            | ICW Bits 34-37 and 44 (SDLC)    | B-081          | LIB'S AND LINE SETS                      |                | PREVENTIVE MAINTENANCE                                    | E٠     |

| CARD FUNCTIONS AND                                                        |                                                                                                                  | ICW - Autocall Interface        | B-090          | LIB'S AND LINE SETS                      |                |                                                           |        |

|                                                                           | 8-030                                                                                                            | Access of ICW by Input/Output   |                | INTRODUCTION                             | C-000          | REMOTE PROGRAM LOADER                                     |        |

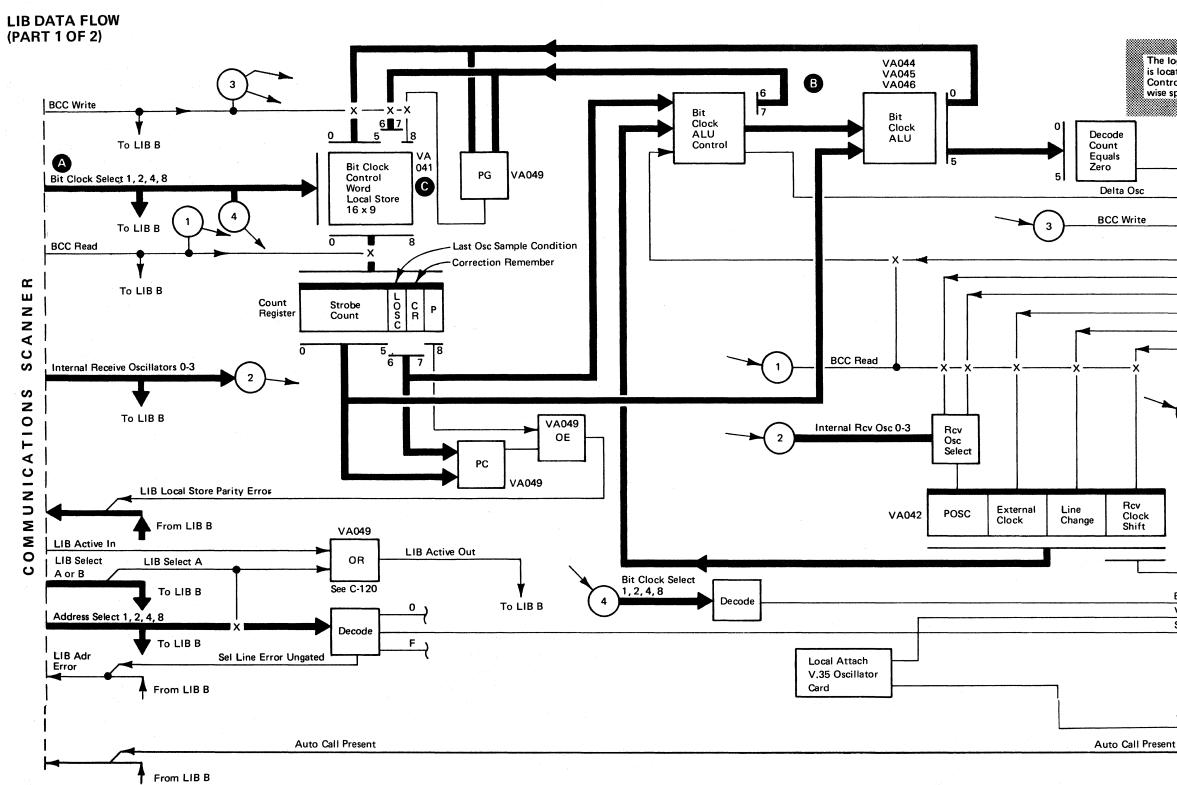

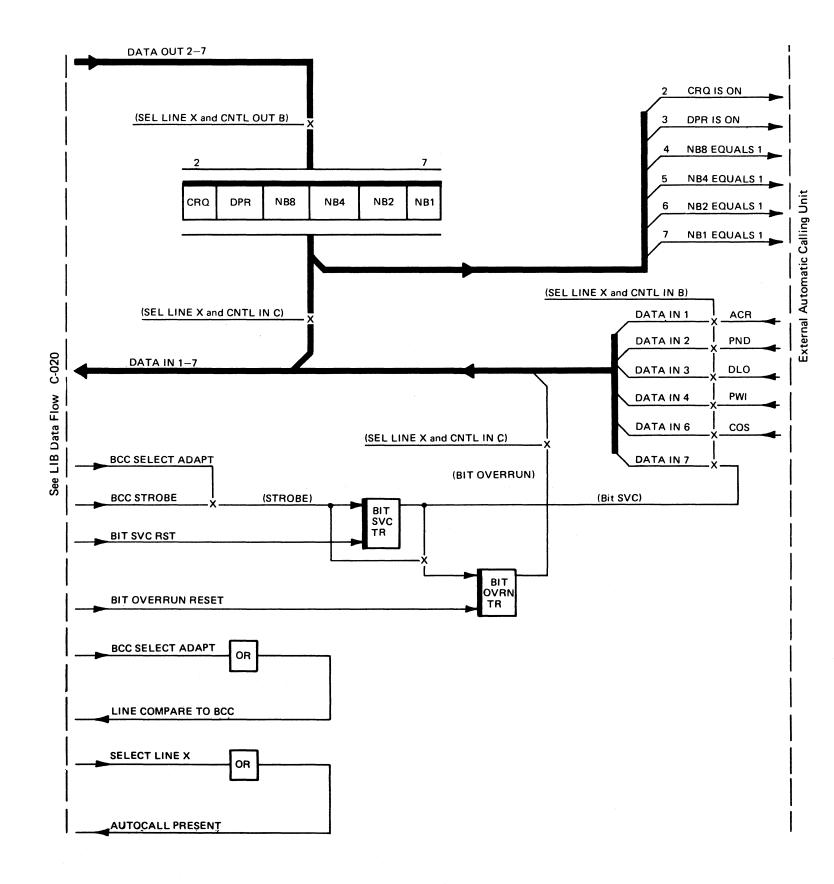

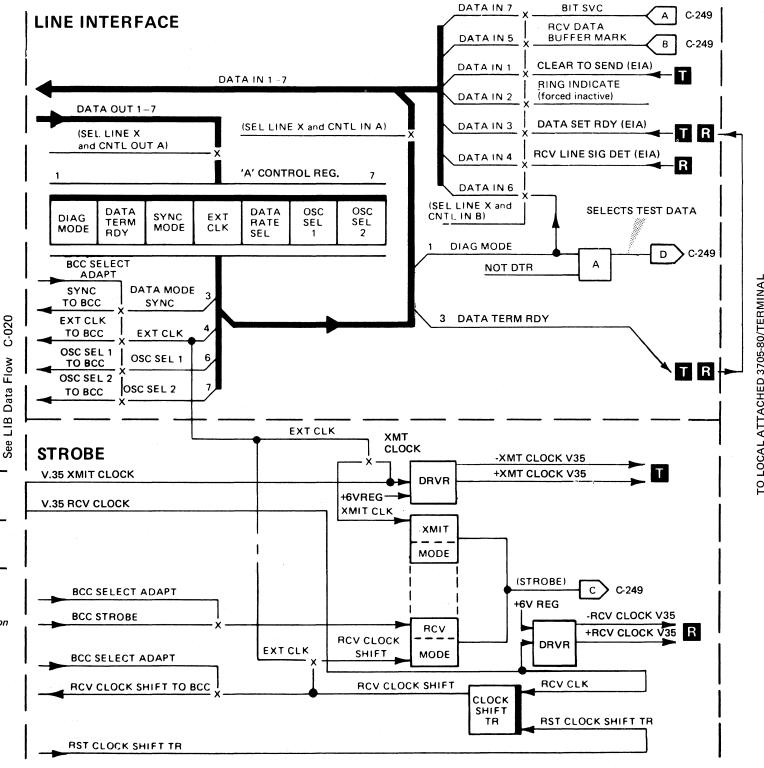

| INPUT AND OUTPUT                                                          | 0.000                                                                                                            | Instructions                    | B-100          | LIB DATA FLOW                            | C-020          |                                                           | -      |

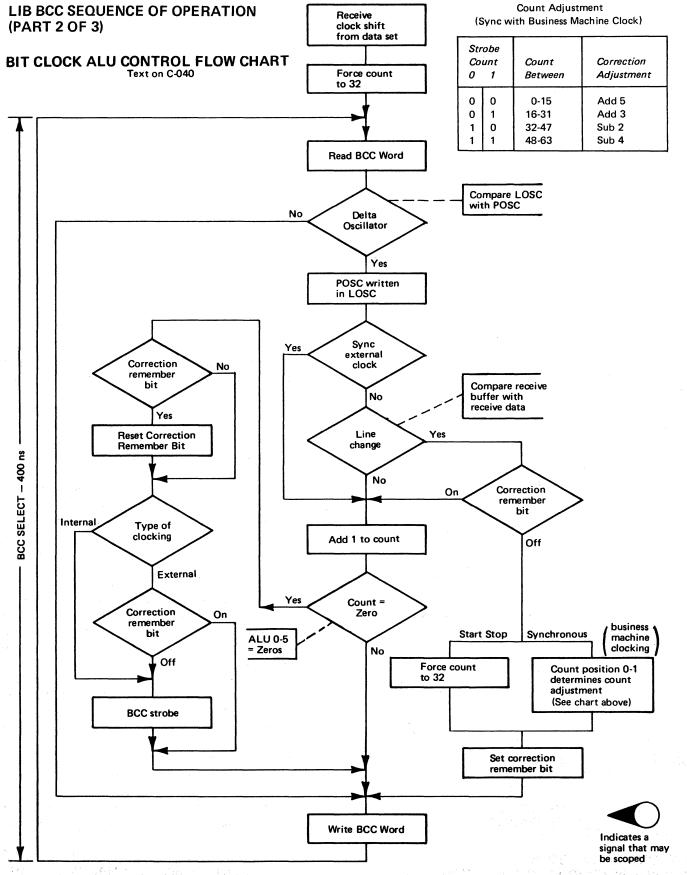

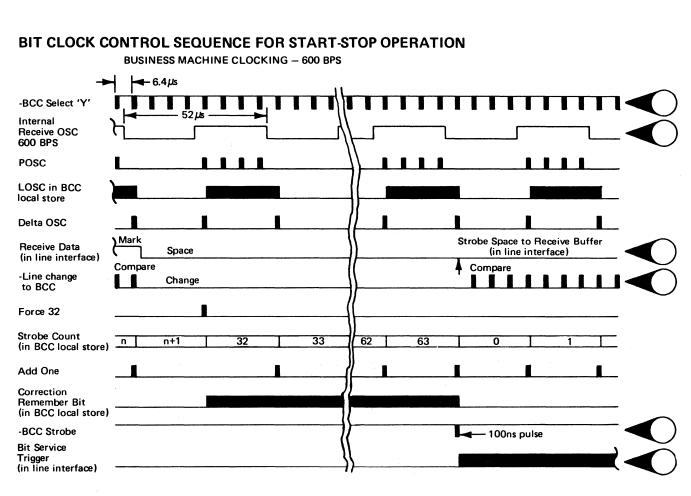

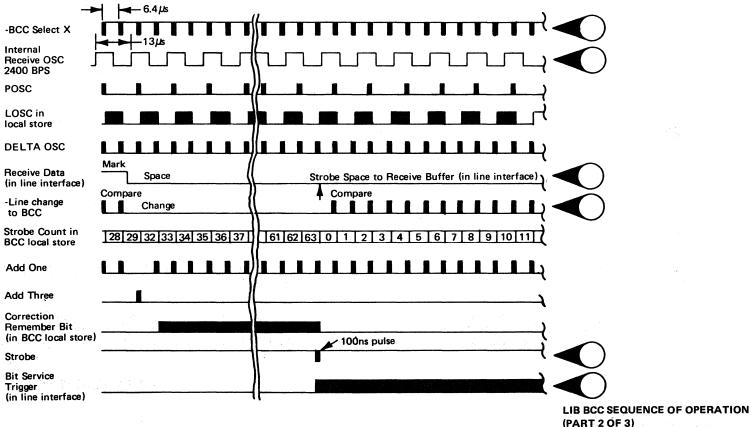

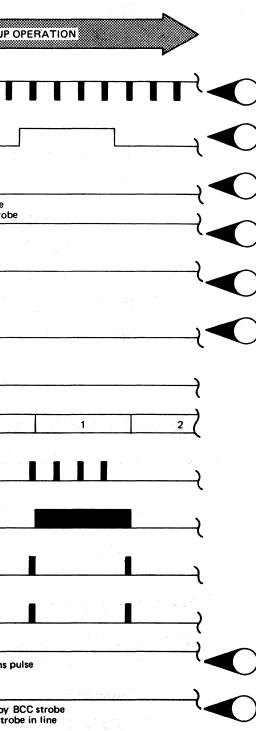

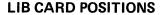

|                                                                           | 8-060                                                                                                            | INPUT AND OUTPUT                |                | LIB BCC SEQ. OF OPERATION                | C-040          | INTRODUCTION                                              | F٠     |

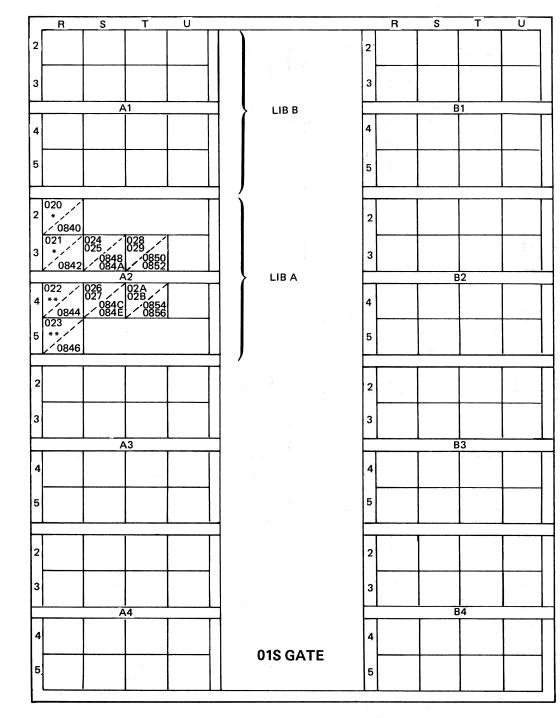

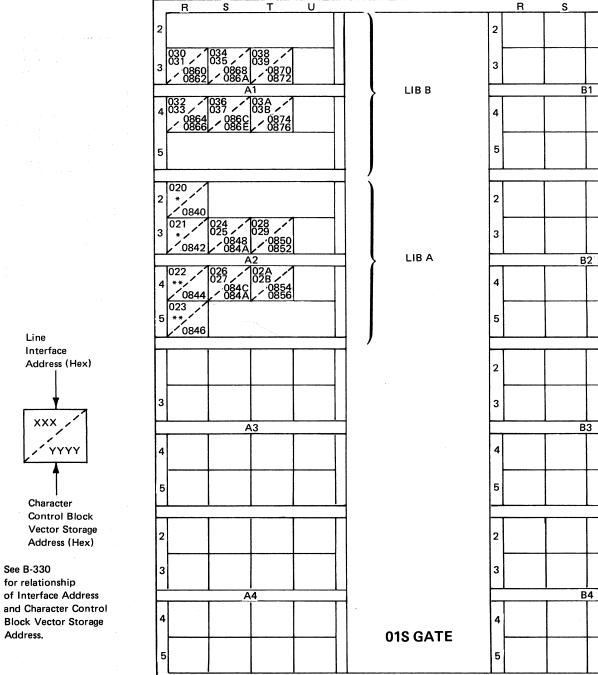

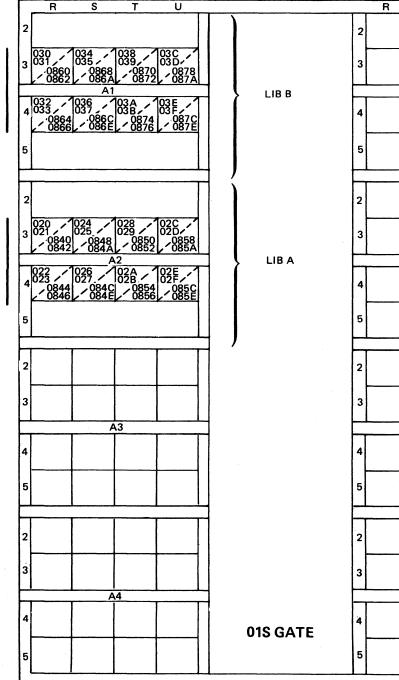

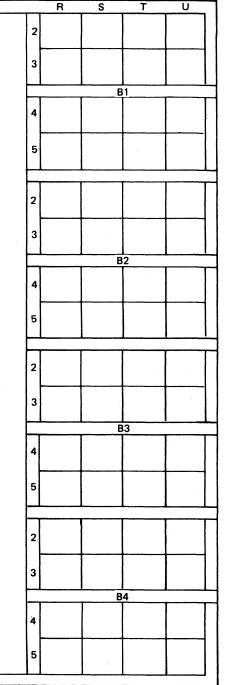

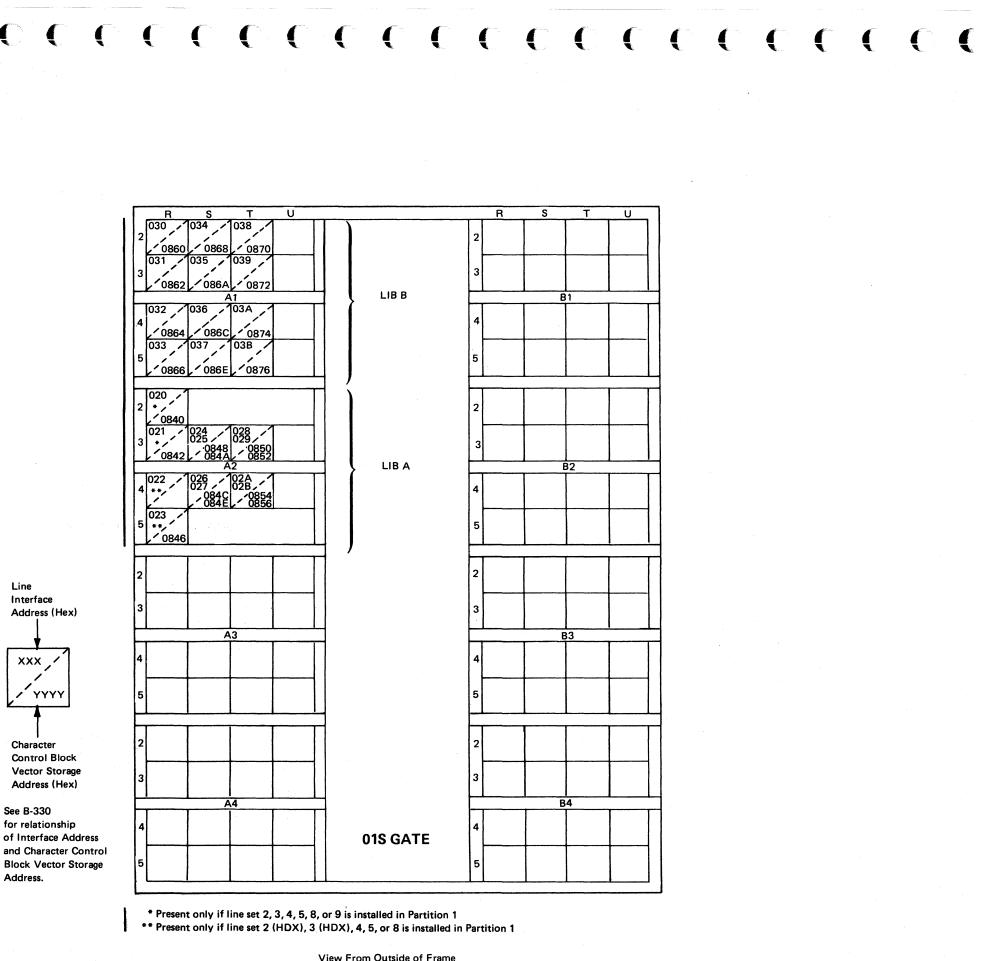

|                                                                           | 8-070                                                                                                            | INSTRUCTIONS                    | B-110          | CARD POSITIONS                           | C-070          | CONTROL PROGRAM LOAD                                      | _      |

|                                                                           | 8-070                                                                                                            | Input X'40' (Interface Address) | B-120          | LIB CABLING                              | C-110          | DATA FLOW                                                 | F٠     |

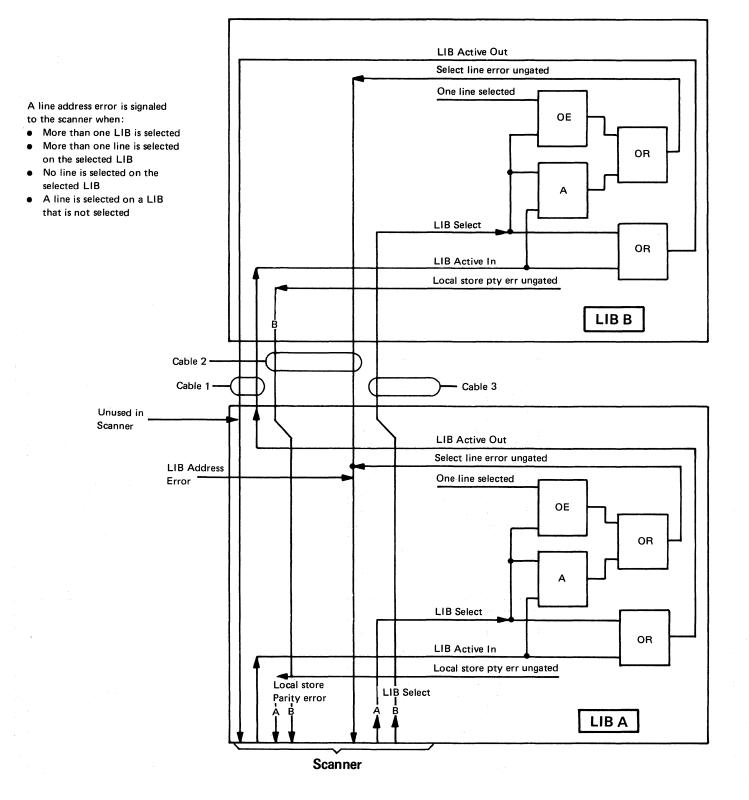

|                                                                           | 8-080                                                                                                            | Input X'43' (Check Register)    | B-130          | LIB ADDRESS ERROR AND                    | 0-110          | DATA TRANSFER BETWEEN                                     |        |

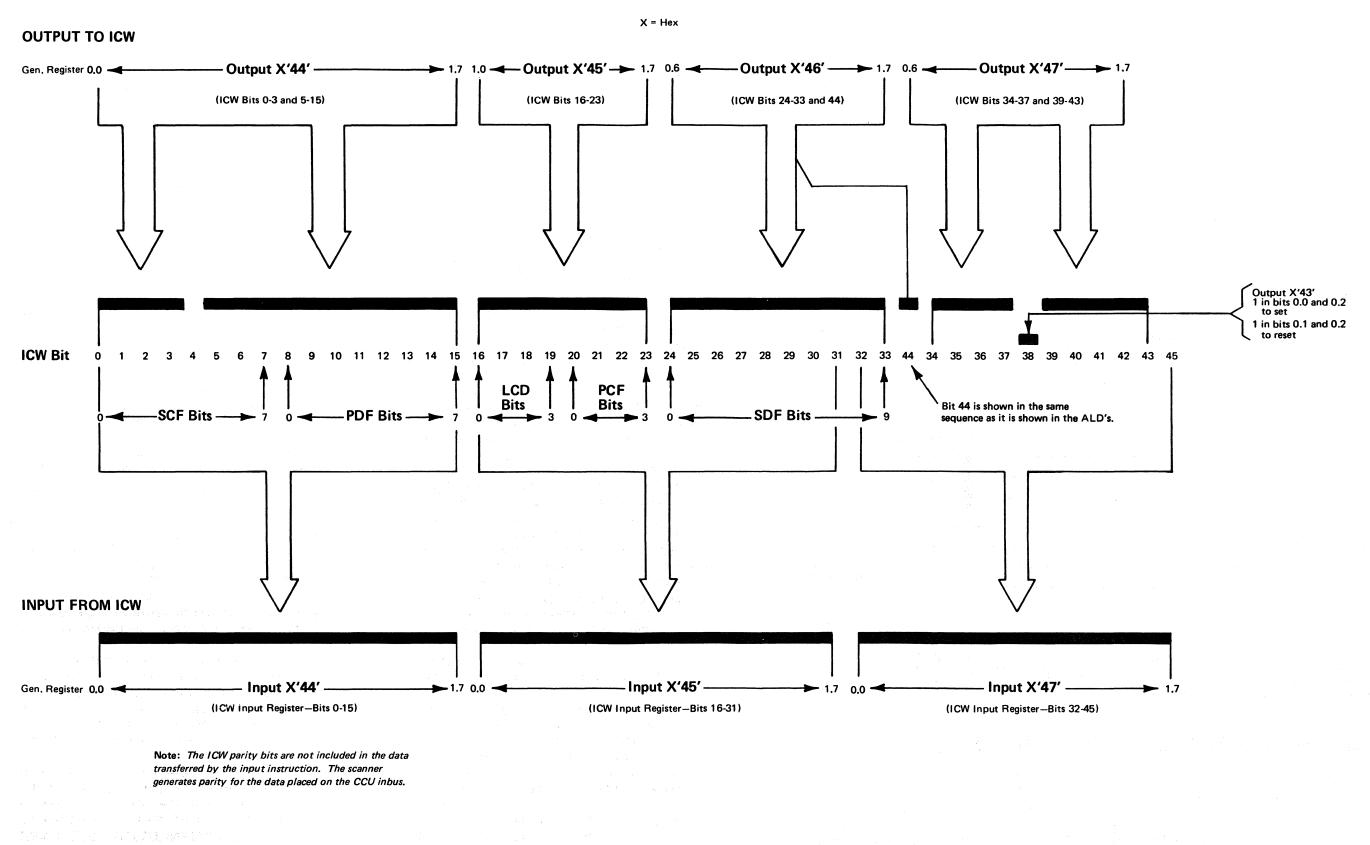

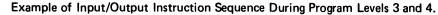

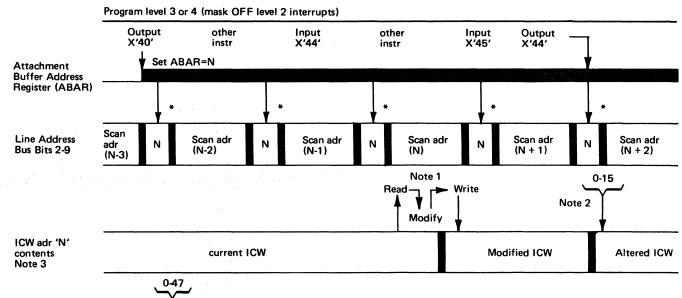

|                                                                           | 8-090                                                                                                            | Input X'44', X'45', and X'47'   | B-140          | LOCAL STORE PARITY ERROR                 | C-120          | HOST PROCESSOR AND REMOTE                                 |        |

| Output and Input X'63'                                                    | 0-090                                                                                                            | Input X'46' (Display Register)  | B-150          | I/O GATE-INTERFACE                       | 0-120          | STATION USING A LOCAL AND                                 |        |

|                                                                           | 8-100                                                                                                            | Output X'40' and X'41'          | B-160          | CONNECTOR POSITIONS                      |                | REMOTE CONTROLLER                                         | F٠     |

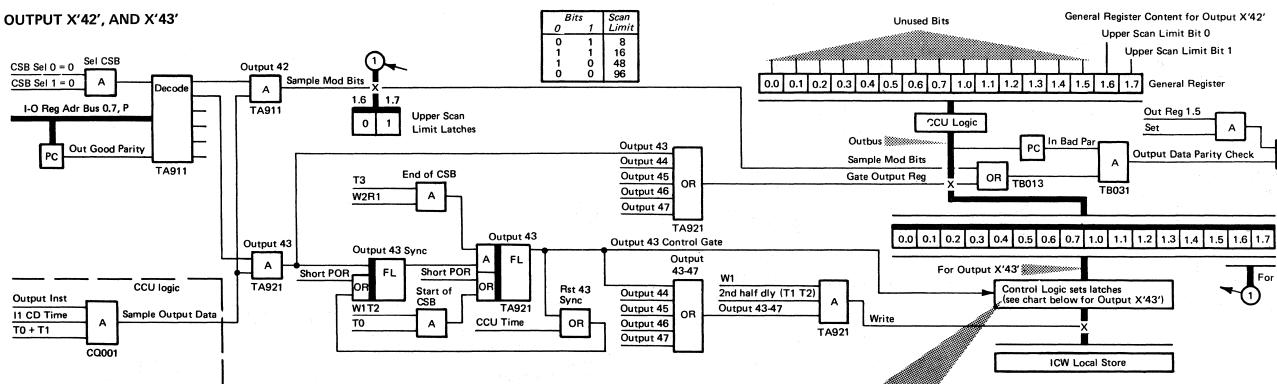

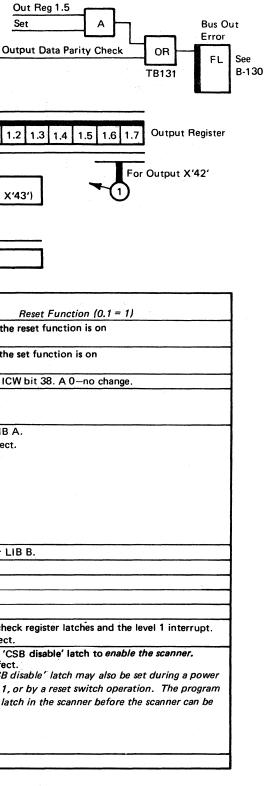

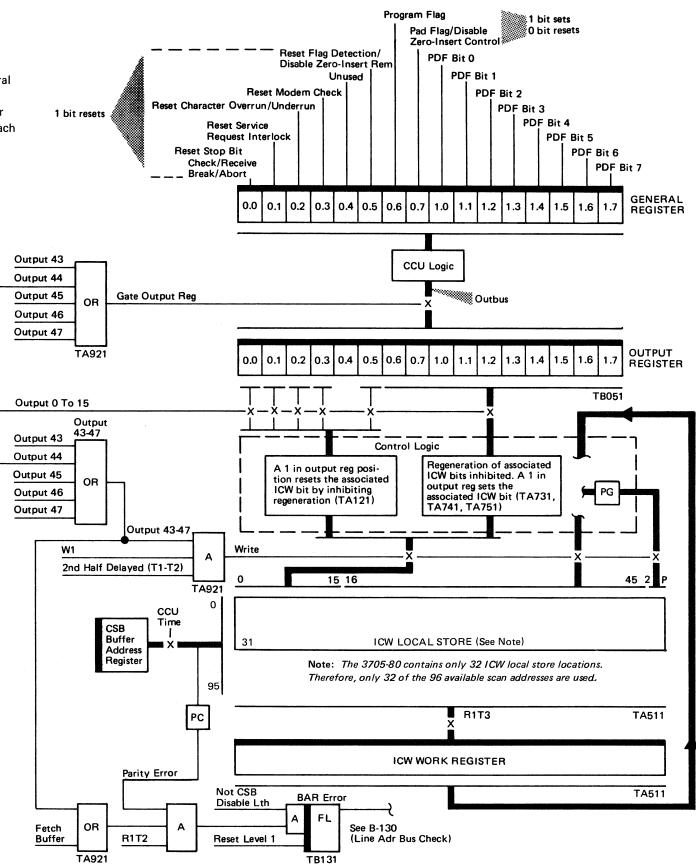

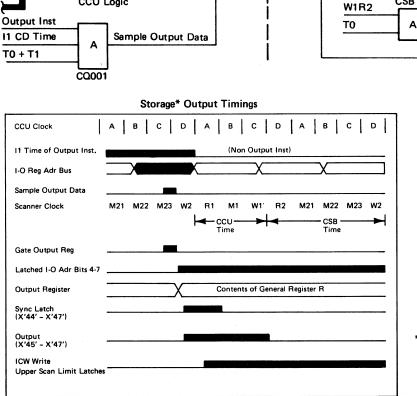

| Output and Input X'64'                                                    | 0-100                                                                                                            | Output X'42' and X'43'          | B-170          | Type 2 Scanners 1-2                      | C-140          | REMOTE 3705-80 CONTROL                                    |        |

|                                                                           | 0 1 1 0                                                                                                          | Output X'44' (ICW 0-3, 5-15)    | B-180          |                                          | C-140<br>C-150 | PANEL                                                     | F٠     |

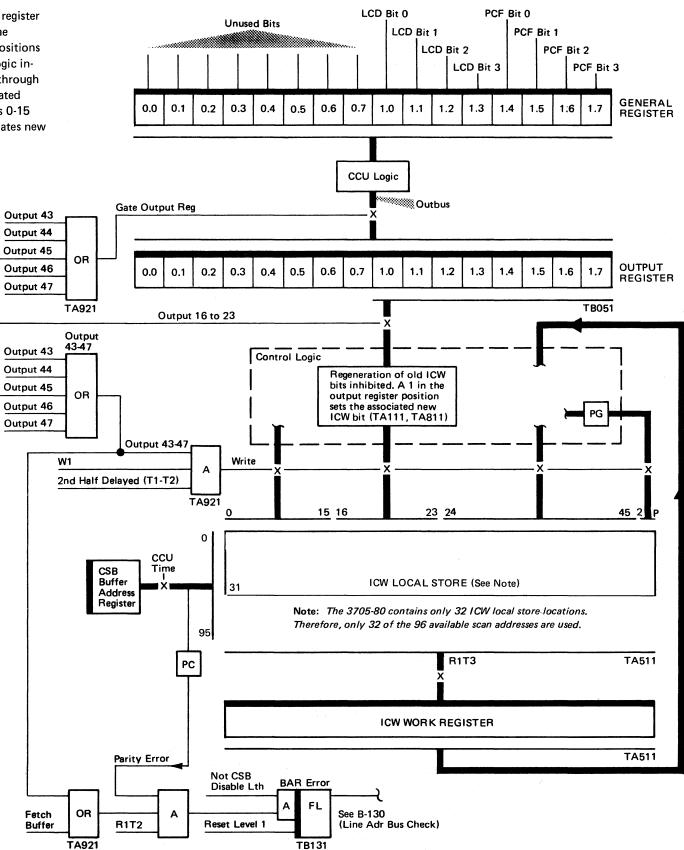

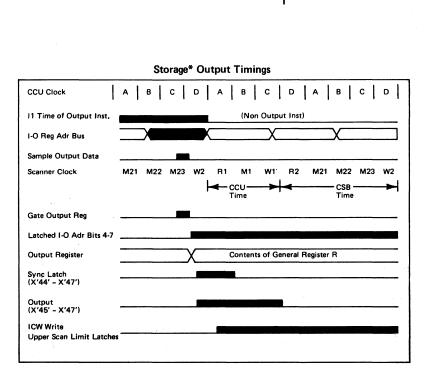

|                                                                           | 8-110                                                                                                            | Output X'45' (ICW 16-23)        | B-190          | Type 2 Scanners 3-4                      |                | REMOTE IPL SEQUENCE                                       | F      |

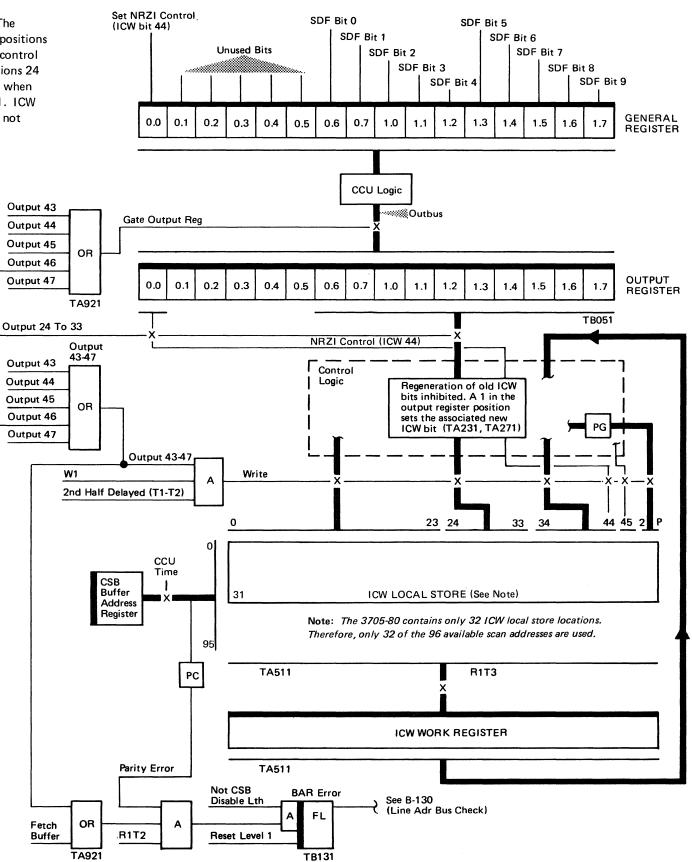

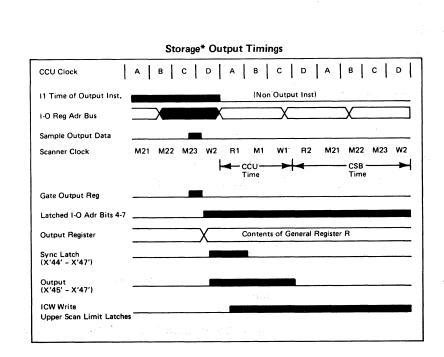

| Output and Input X'65'                                                    | 0 1 1 0                                                                                                          | Output X'46' (ICW 24-33)        | B-200          |                                          | C-160          | RPL ROS SELECTION                                         | F      |

|                                                                           | 8-110                                                                                                            | STORAGE TIMING                  |                | LINE SET LS1-START/STOP                  | C-170          | DISKETTE CONTROLLER DATA                                  |        |

| •                                                                         | 8-120                                                                                                            | Output X'44', X'45', X'46', and |                | LINE SET LS1-LOCAL                       | 0.400          | FLOW                                                      | F      |

| •                                                                         | 8-120                                                                                                            | X'47                            | B-201          | ATTACHMENT INTERFACE                     | C-190          | 3705-80 DISKETTE CONTROLLER                               |        |

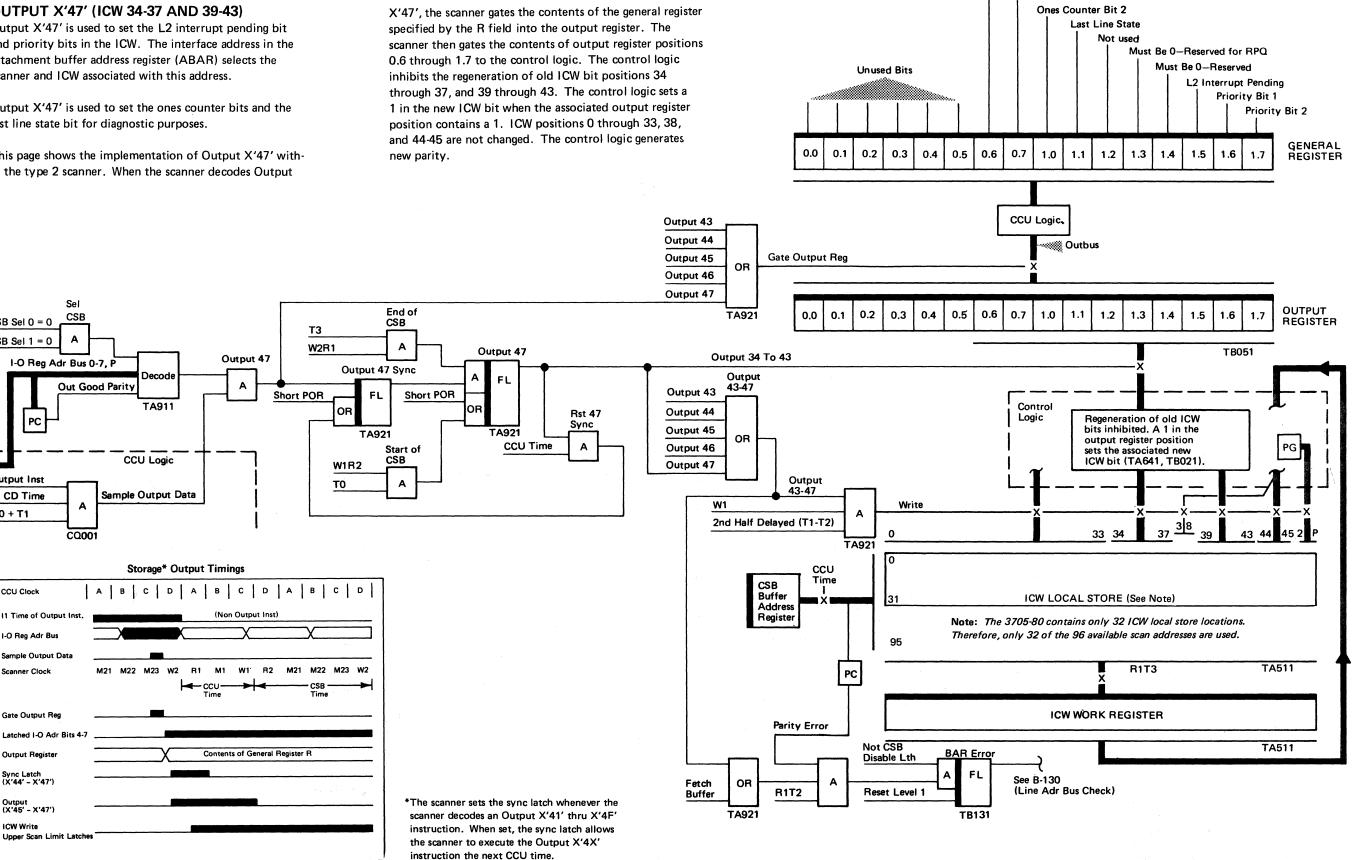

| Output and Input X'67'                                                    |                                                                                                                  | Output X'47' (ICW 34-37 and     | 5-201          | LINE SET LS1-SYNCHRONOUS                 | C-200          | CARD LOCATIONS AND                                        |        |

|                                                                           | 8-130                                                                                                            | 39-43)                          | B-210          | LINE SET LS2-HALF-DUPLEX/                |                | FUNCTIONS                                                 | F      |

| CHANNEL ADAPTER                                                           |                                                                                                                  |                                 |                | DUPLEX                                   | C-220          | DISKETTE FORMAT                                           | F      |

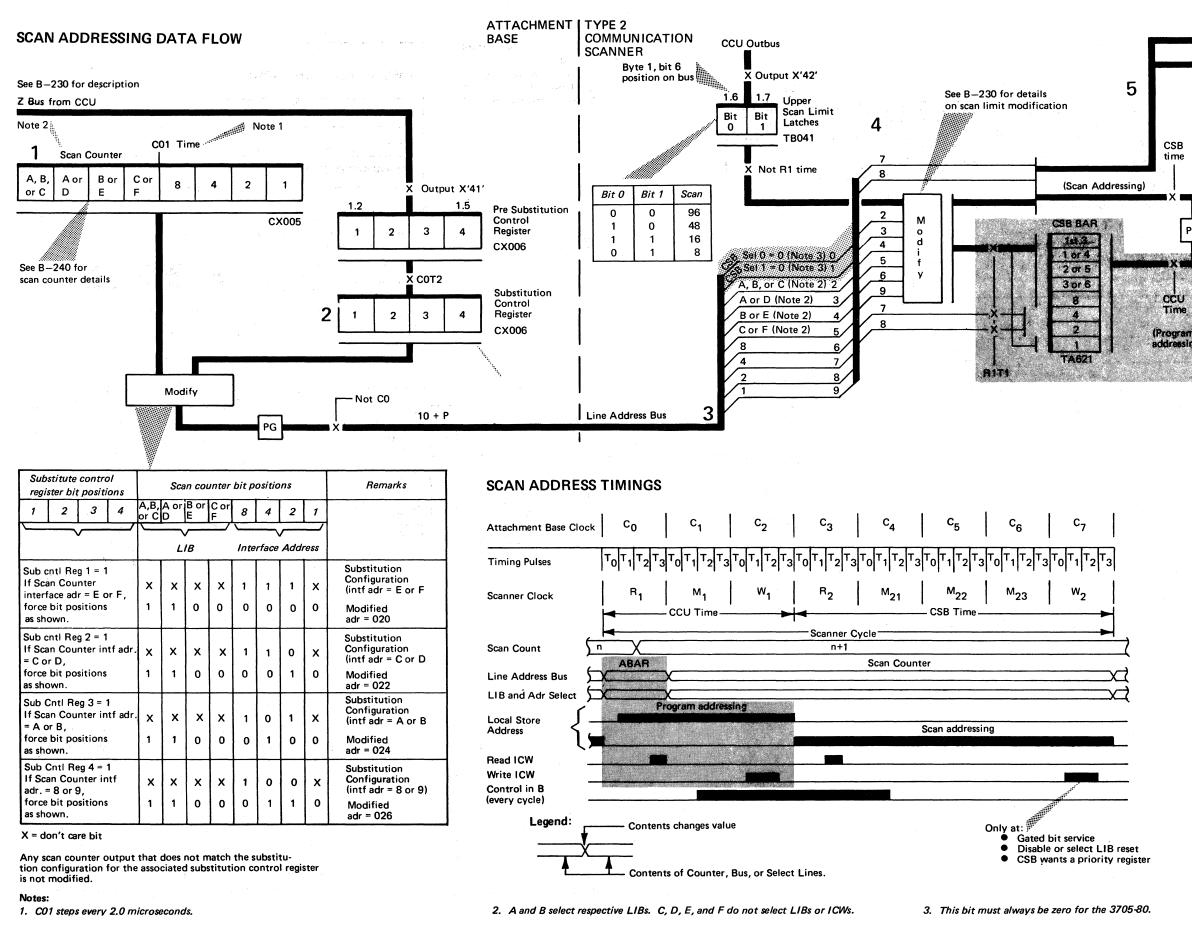

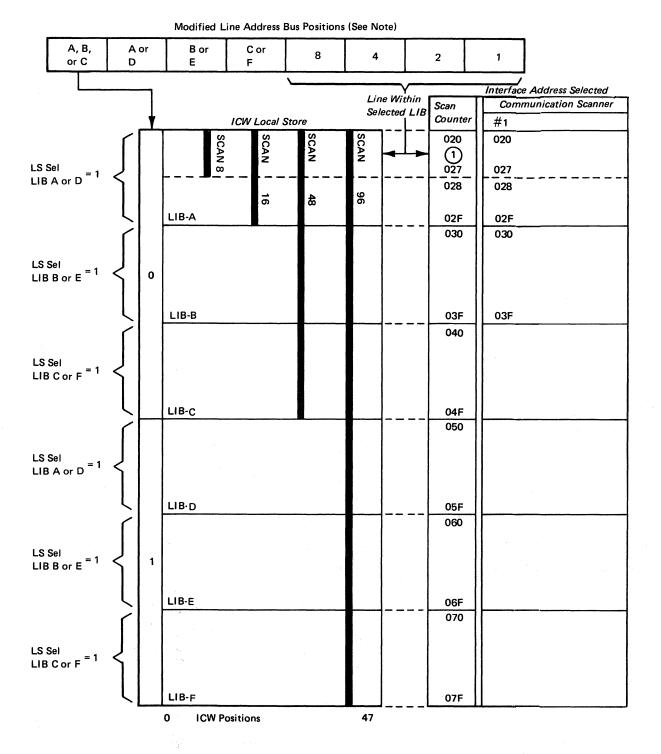

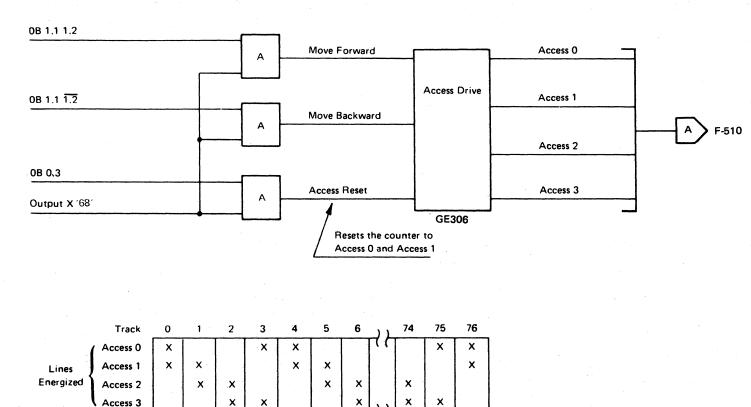

|                                                                           | 8-140                                                                                                            | SCAN ADDRESSING DATA FLOW       | B-220          | LINE SET LS3–DIGITAL                     |                | ACCESS DRIVE                                              | F      |

| EXPECTED CPU RESPONSE TO                                                  |                                                                                                                  | SCAN ADDRESSING                 | B-230          | SYNCHRONOUS HIGH SPEED                   |                | VARIABLE FREQUENCY                                        |        |

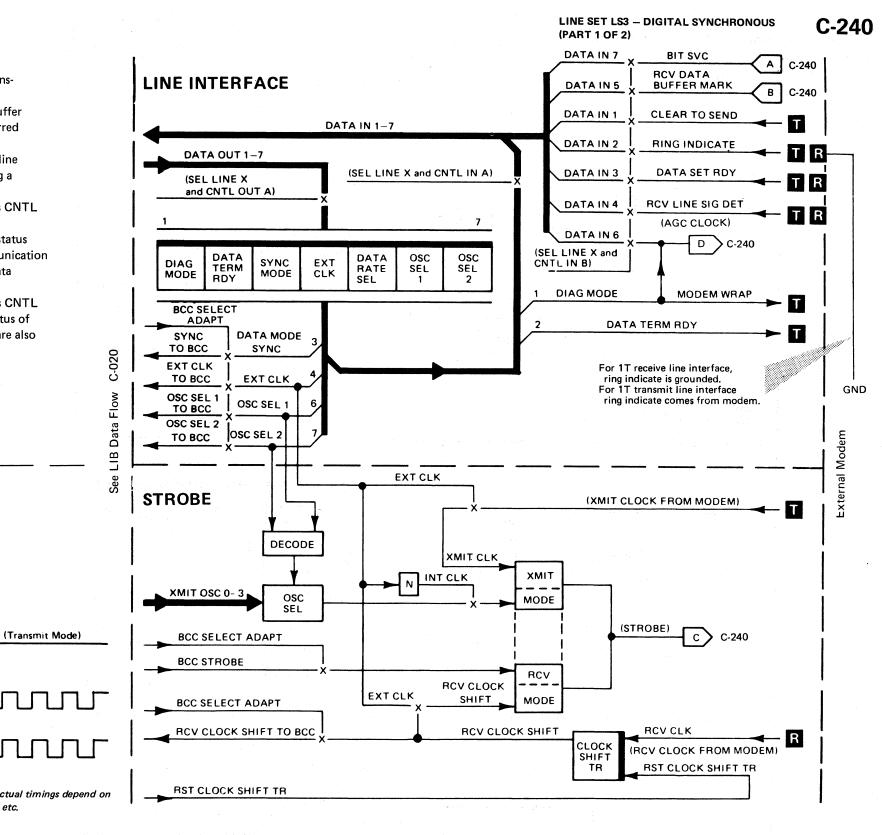

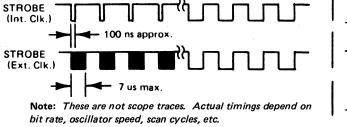

|                                                                           | 8-160                                                                                                            | SCAN COUNTER                    | B-240          | DUPLEX EXTERNAL MODEM                    | C-240          | OSCILLATOR OPERATION AND                                  |        |

|                                                                           | 8-170                                                                                                            | SCAN ADDRESSING EXAMPLES        | B-250          | LINE SET LS4-AUTOCALL                    |                | TIMING                                                    | F      |

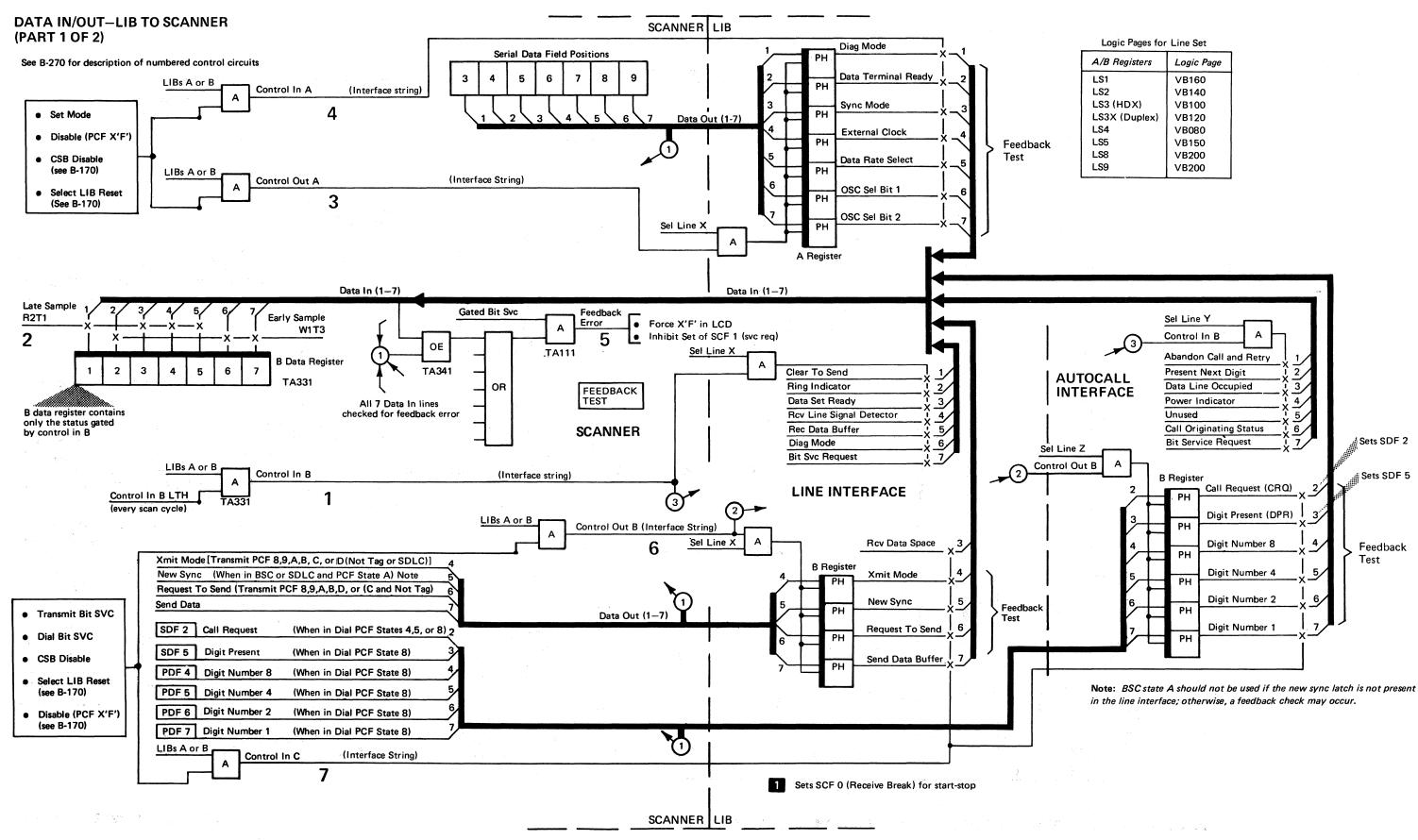

|                                                                           | 8-180                                                                                                            | DATA IN/OUT-LIB TO SCANNER      | B-260          | INTERFACE                                | C-260          | INPUT AND OUTPUT                                          |        |

| CA DECODES A CHANNEL                                                      |                                                                                                                  | PROGRAM ADDRESSING              |                | LINE SET LS5-HIGH SPEED                  |                | INSTRUCTIONS                                              | F      |

| COMMAND                                                                   |                                                                                                                  | DATA FLOW                       | B-280          | DUPLEX (CCITT V.35                       |                | Input X'68' (Level 1 Status)                              | F      |

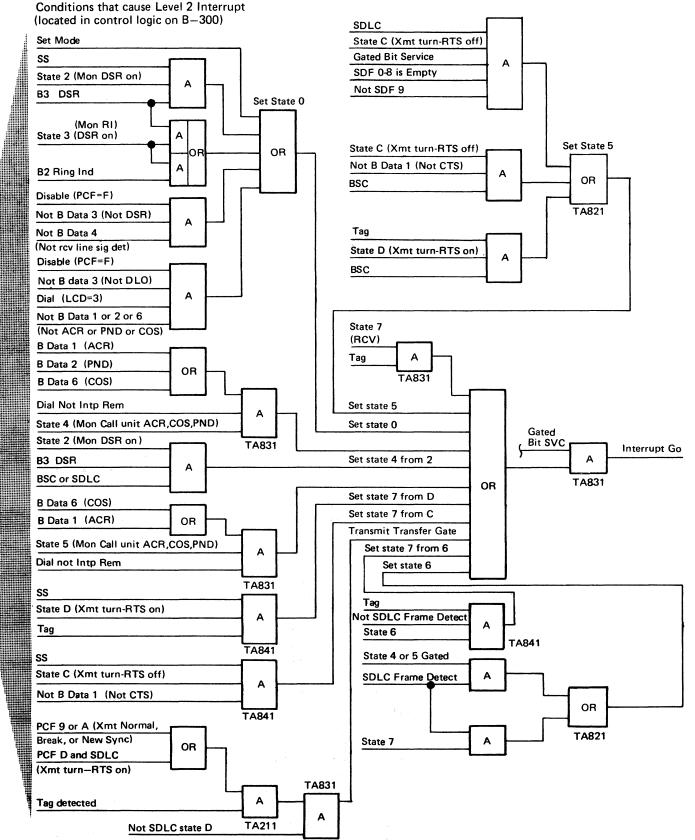

| •                                                                         | 8-210                                                                                                            | PROGRAM LEVEL 2 INTERRUPT       |                | INTERFACE)                               | C-270          | Output X'68' (Control)                                    | F      |

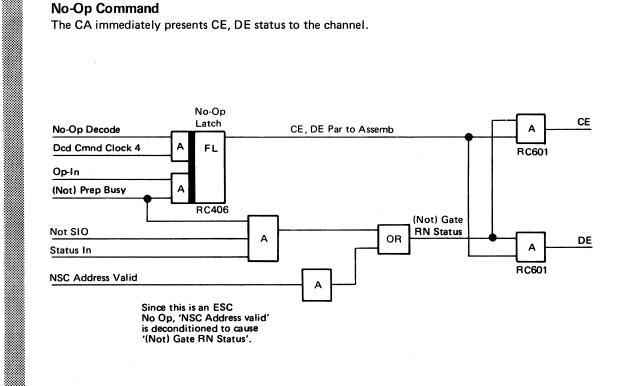

| ESC No-Op                                                                 | 8-210                                                                                                            | DATA FLOW                       | B-300          | LINE SET LS8 OR LS9-DUPLEX O             | R              | Use of I/O Instructions During                            | •      |

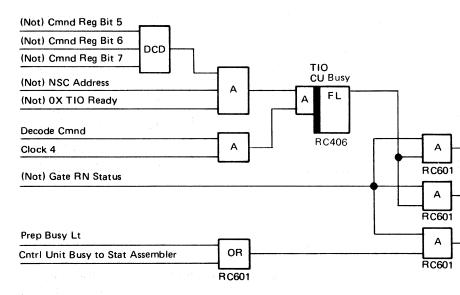

| NSC Test I/O                                                              | 8-220                                                                                                            | CHARACTER CONTROL BLOCK         |                | HALF-DUPLEX-NON-SWITCHED                 |                | Interrupts                                                | F      |

| ESC Test I/O                                                              | 8-220                                                                                                            | VECTOR ADDRESS                  | B-330          | (CCITT X.21 INTERFACE)                   | C-290          | Input X'69' (Level 3 Status)                              | F      |

|                                                                           | 8-250                                                                                                            | PROGRAM LEVEL 2                 |                | LINE SET LS8 OR LS9-DUPLEX-              |                | Output X'69' (Read/Write)                                 | F      |

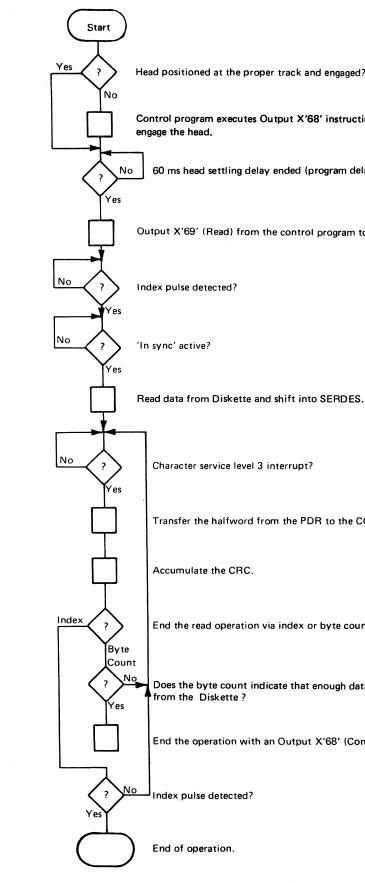

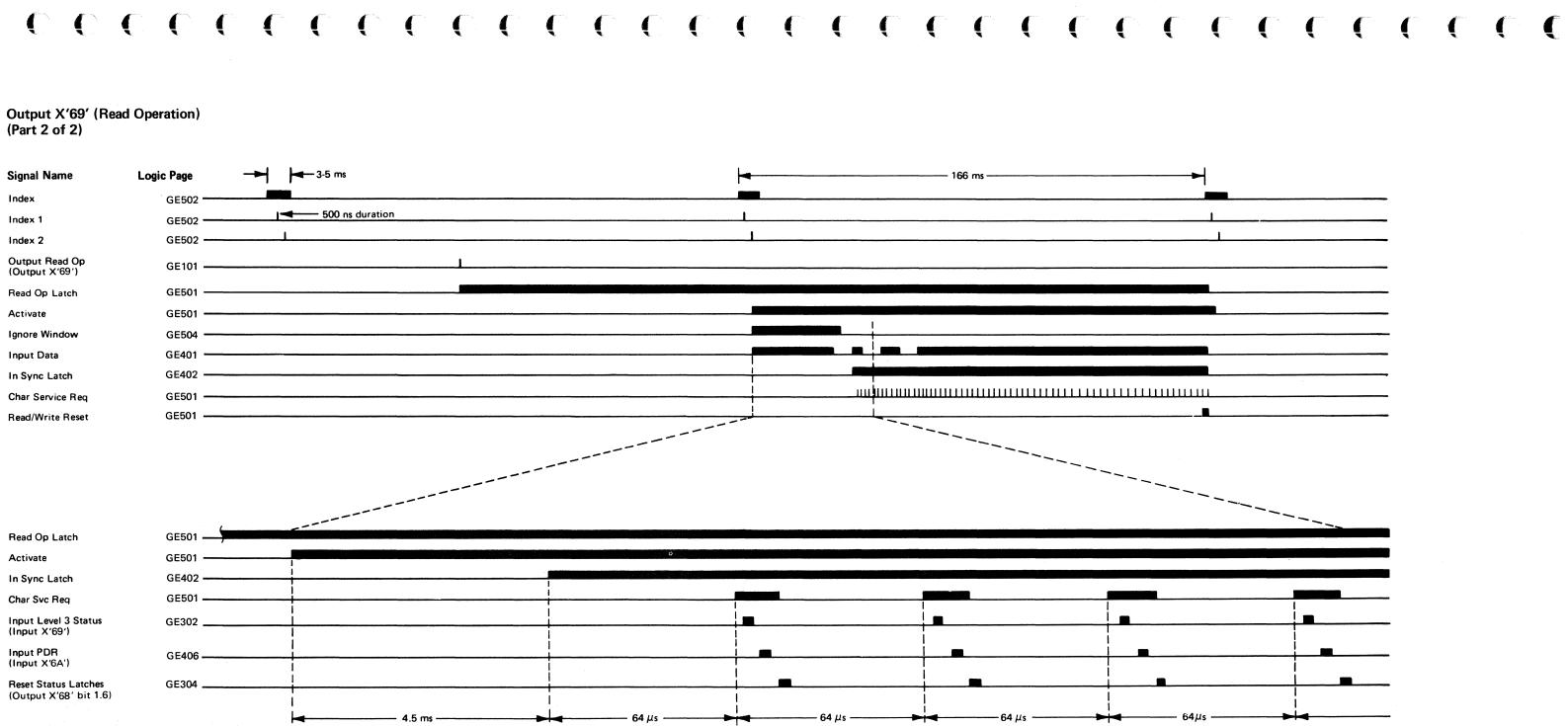

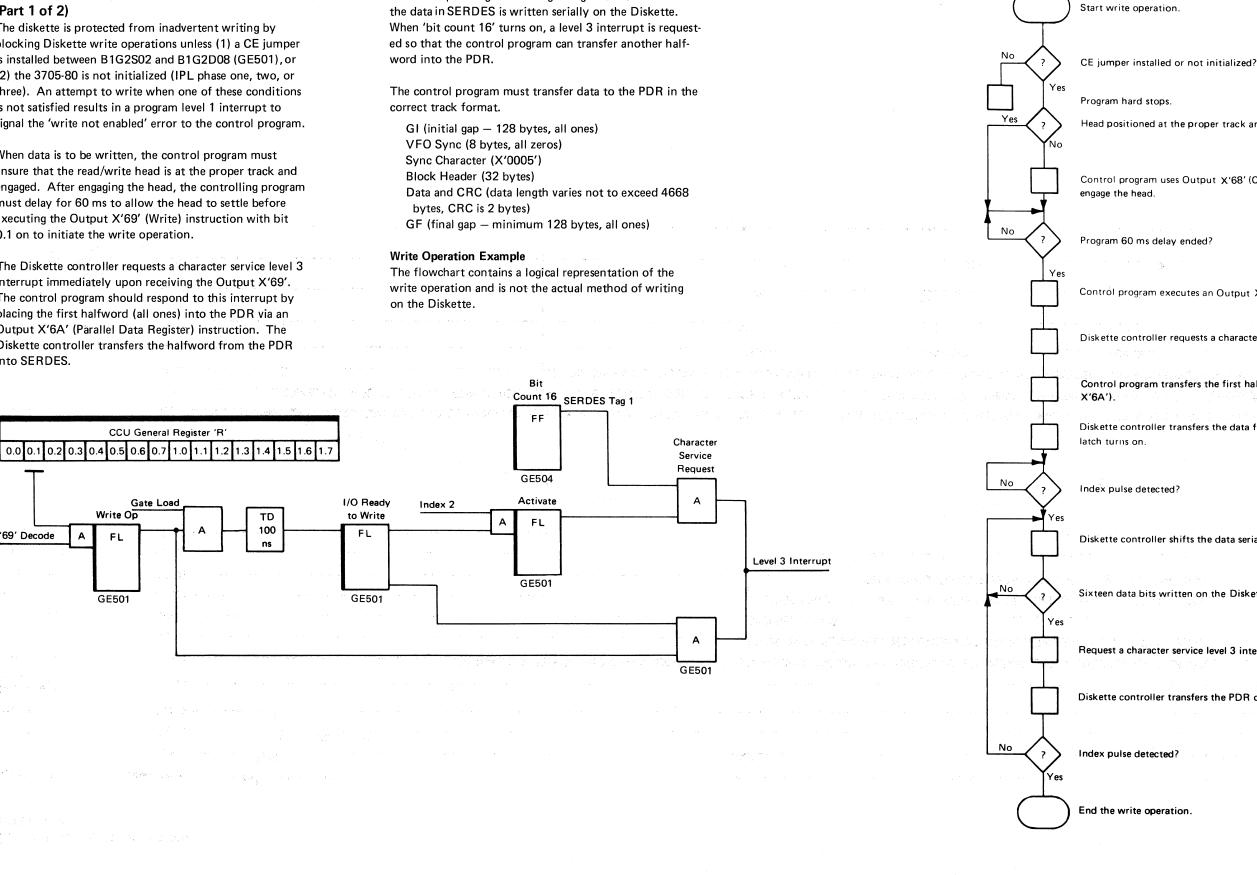

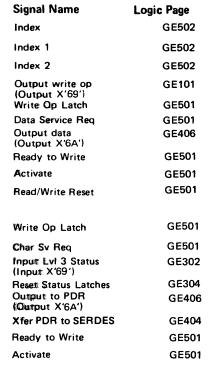

| ENDING SEQUENCE, STATUS                                                   |                                                                                                                  | INTERRUPT TIMINGS               | B-340          | SWITCHED (CCITT X.21                     |                | Output X 69 (Read/Write)<br>Output X'69' (Read Operation) | г<br>с |

|                                                                           | 8-301                                                                                                            | PROGRAM LEVEL 2 INTERRUPT       |                | INTERFACE)                               | C-310          |                                                           | г      |

|                                                                           | 8-310                                                                                                            | EXAMPLES                        | B-360          |                                          |                | Output X'69' (Diskette Write                              | -      |

|                                                                           | 8-360                                                                                                            | BI-SYNC TERMINAL                | _ 000          | 3705-80 POWER SUPPLY                     |                | Operation                                                 | F      |

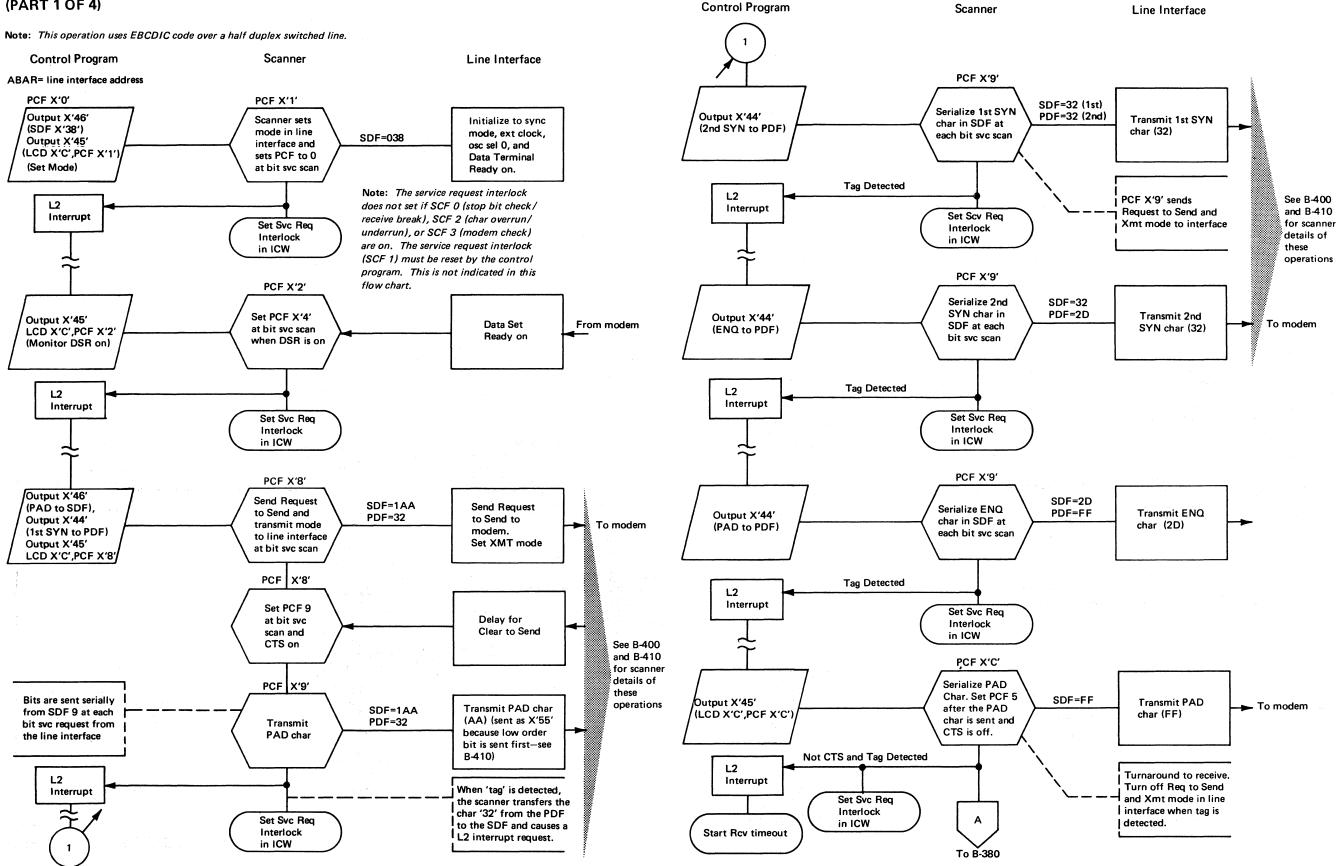

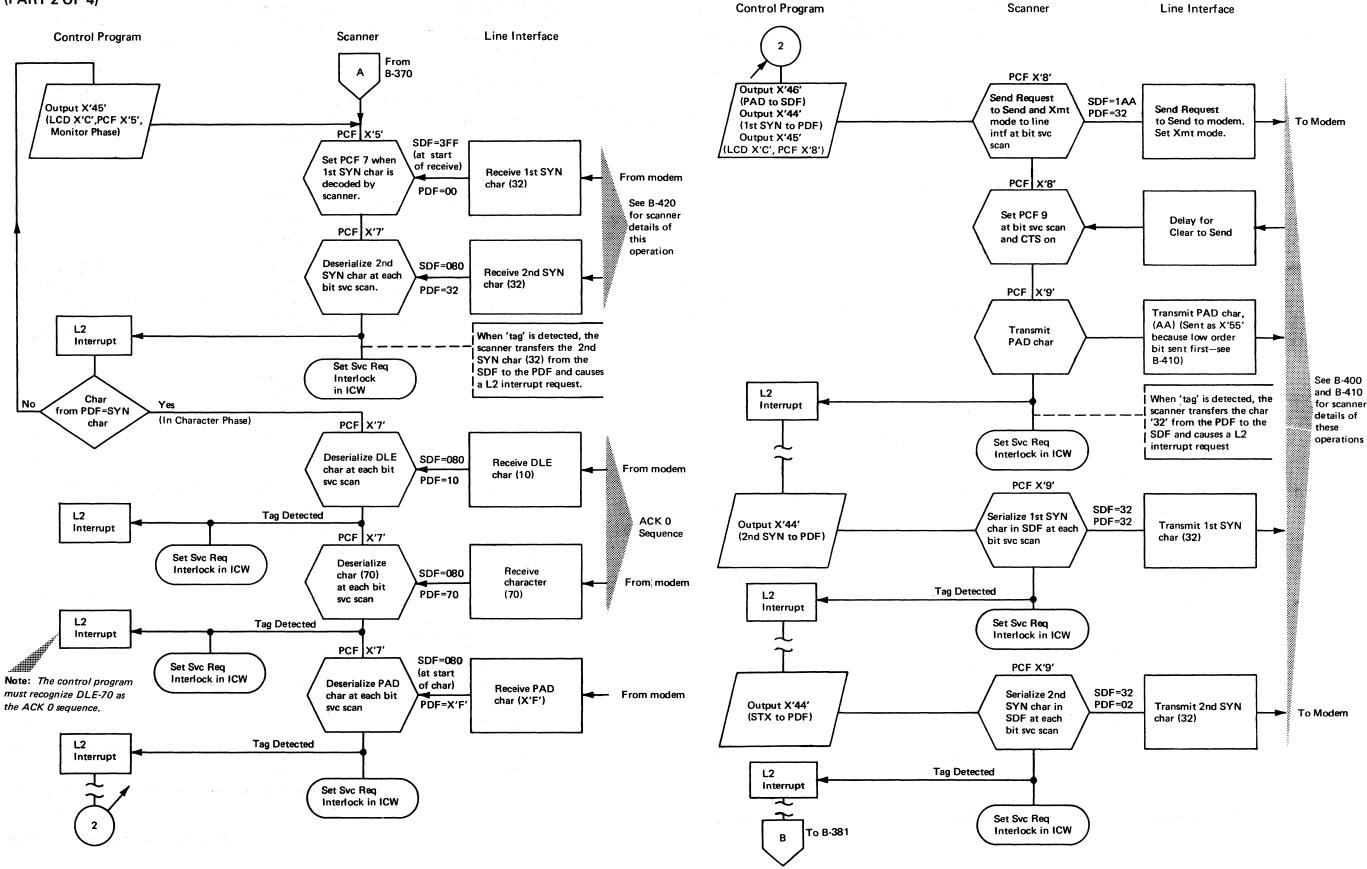

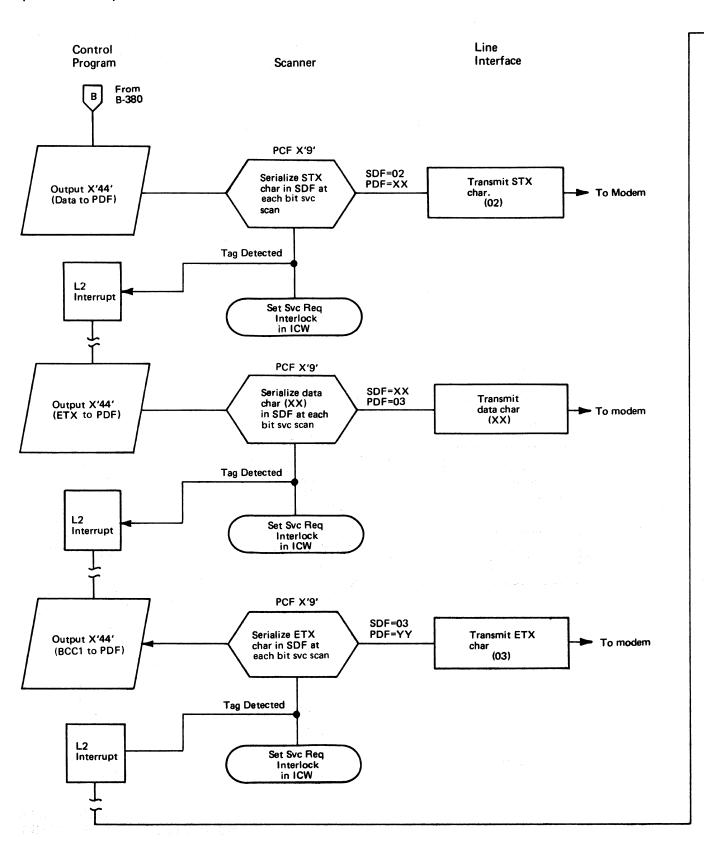

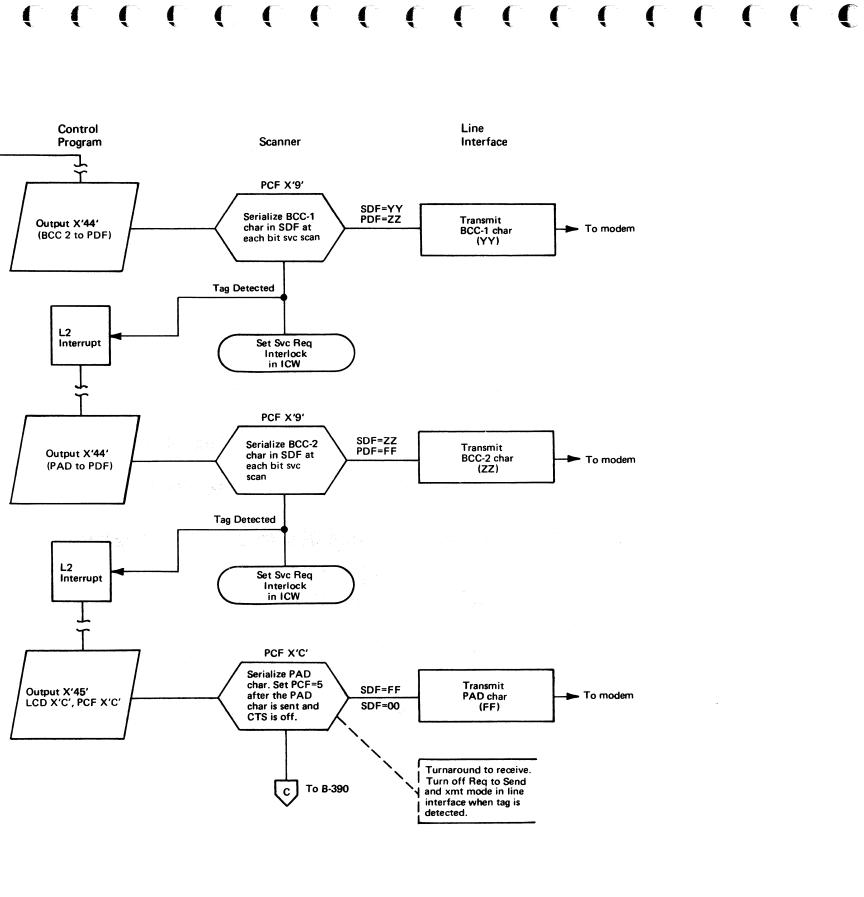

|                                                                           | 8-370                                                                                                            | OPERATION                       | B-370          |                                          | D 500          | Input X'6A' (Parallel Data                                | -      |

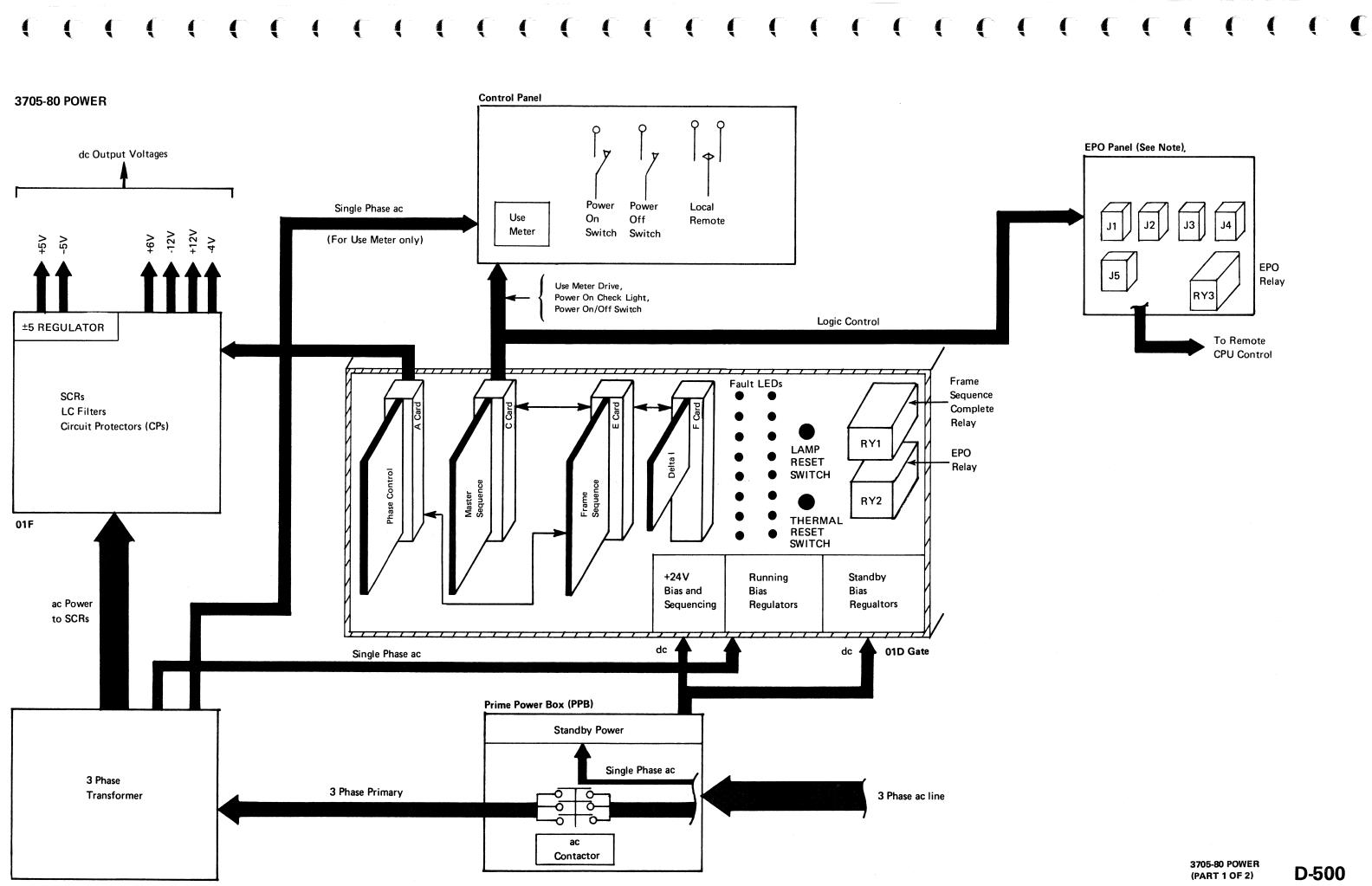

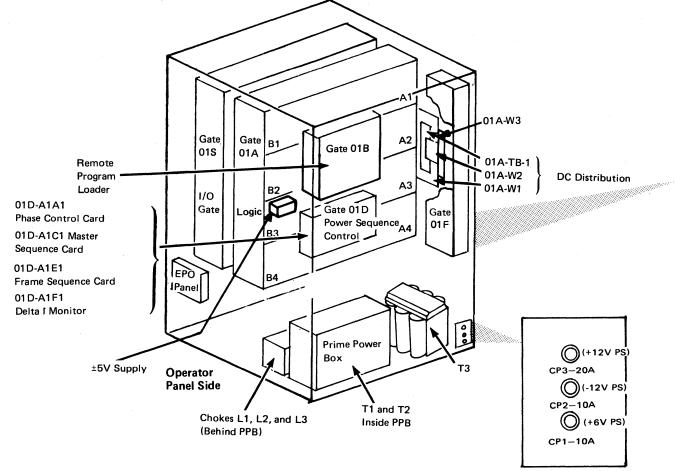

| CHANNEL INTERFACE                                                         |                                                                                                                  | BSC Transmit Sequence           | B-400          | 3705-80 POWER                            | D-500          | Register)                                                 | F      |

|                                                                           | 8-380                                                                                                            | BSC Transmit Details            | B-400<br>B-410 | Component Locations                      | D-505          | Output X'6A' (Parallel Data                               | _      |

|                                                                           | 0-000                                                                                                            | BSC Receive Details             | B-410<br>B-420 | 3705-80 POWER CHECK                      | D-510          | Register)                                                 | F      |

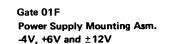

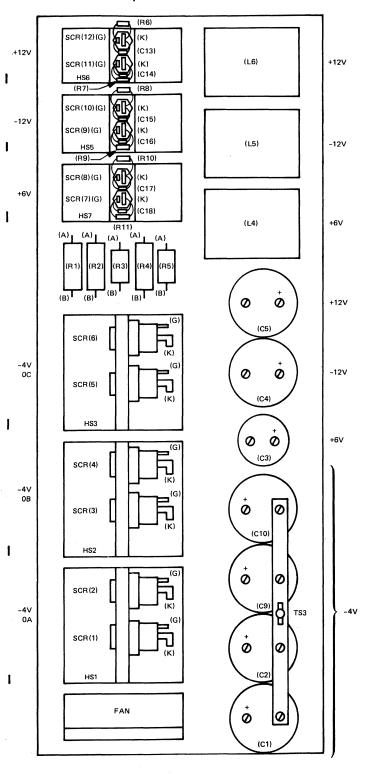

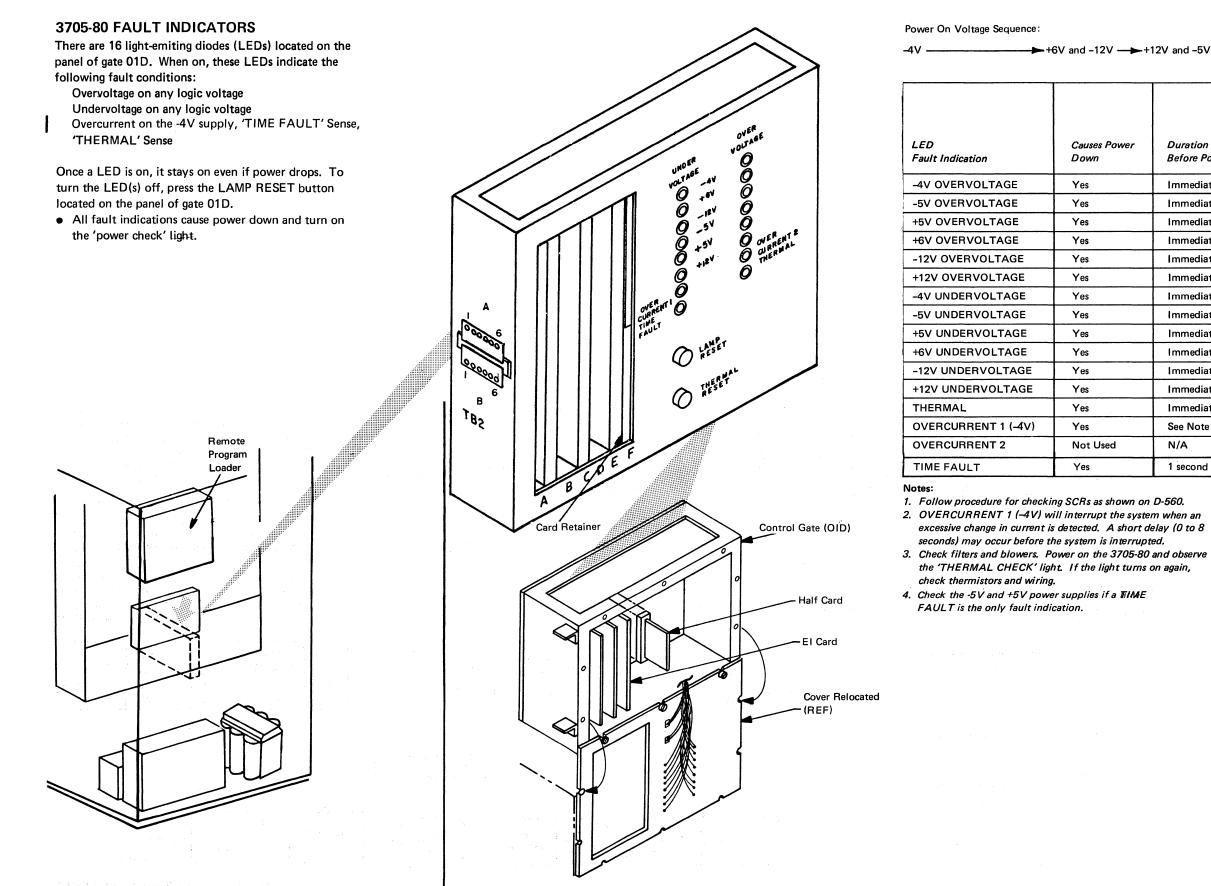

|                                                                           | D                                                                                                                |                                 | D-420          | 3705-80 FAULT INDICATORS                 | D-520          | Output X'6B' (Input/Output                                |        |

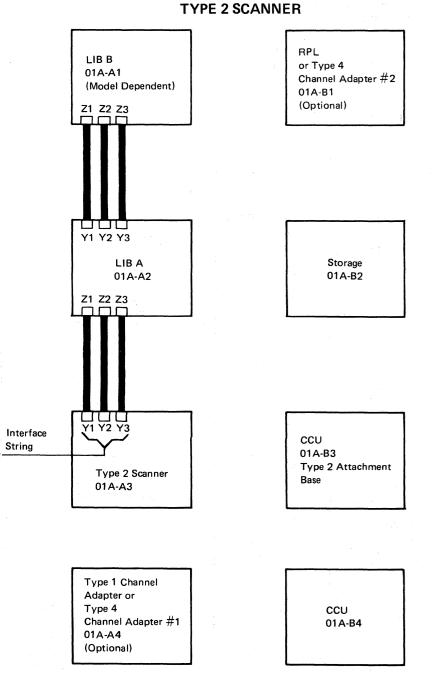

| TYPE 2 COMMUNICATION SCANNE                                               |                                                                                                                  |                                 | P 420          | 3705-80 POWER DISTRIBUTION               | D-530          | Register)                                                 | F      |

| INTRODUCTION                                                              | B-000                                                                                                            |                                 | B-430          | 3705-80 POWER-ON SEQUENCE                | D-540          | Input X'68' (Input/Output                                 |        |

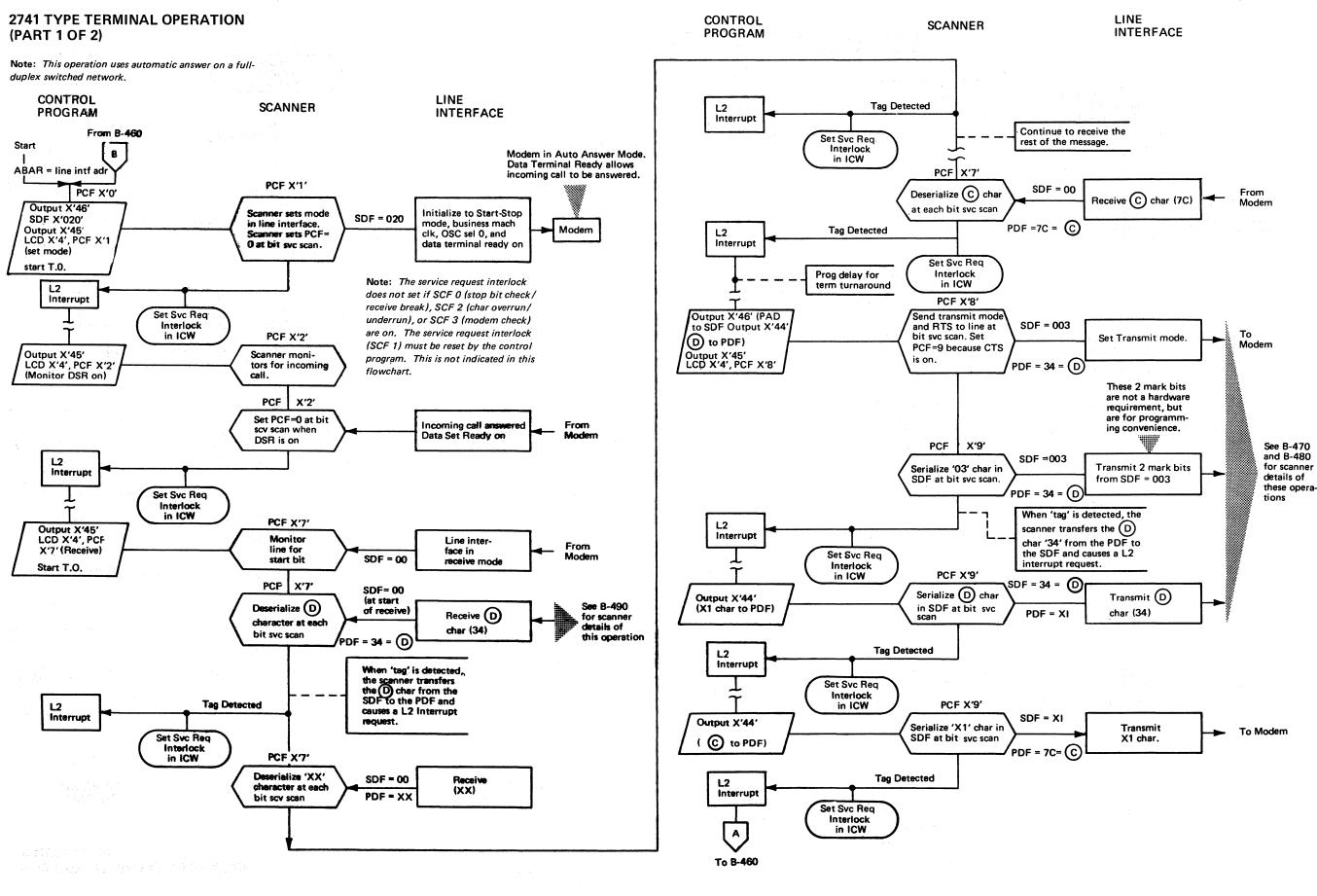

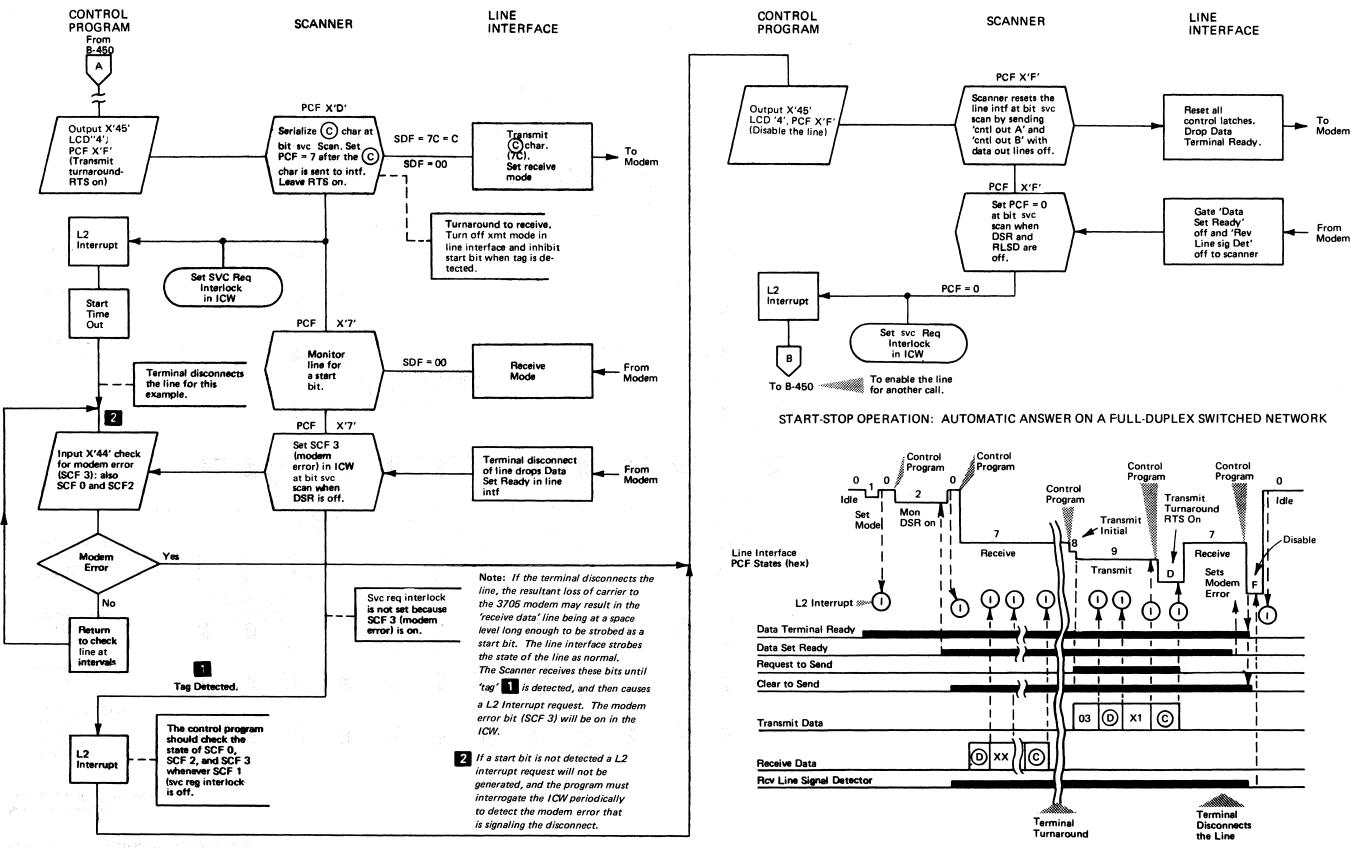

| ATTACHMENT BASE AND                                                       |                                                                                                                  | 2741 TYPE TERMINAL              | D 450          | 3705-80 DC VOLTAGE                       |                | Register)                                                 | F      |

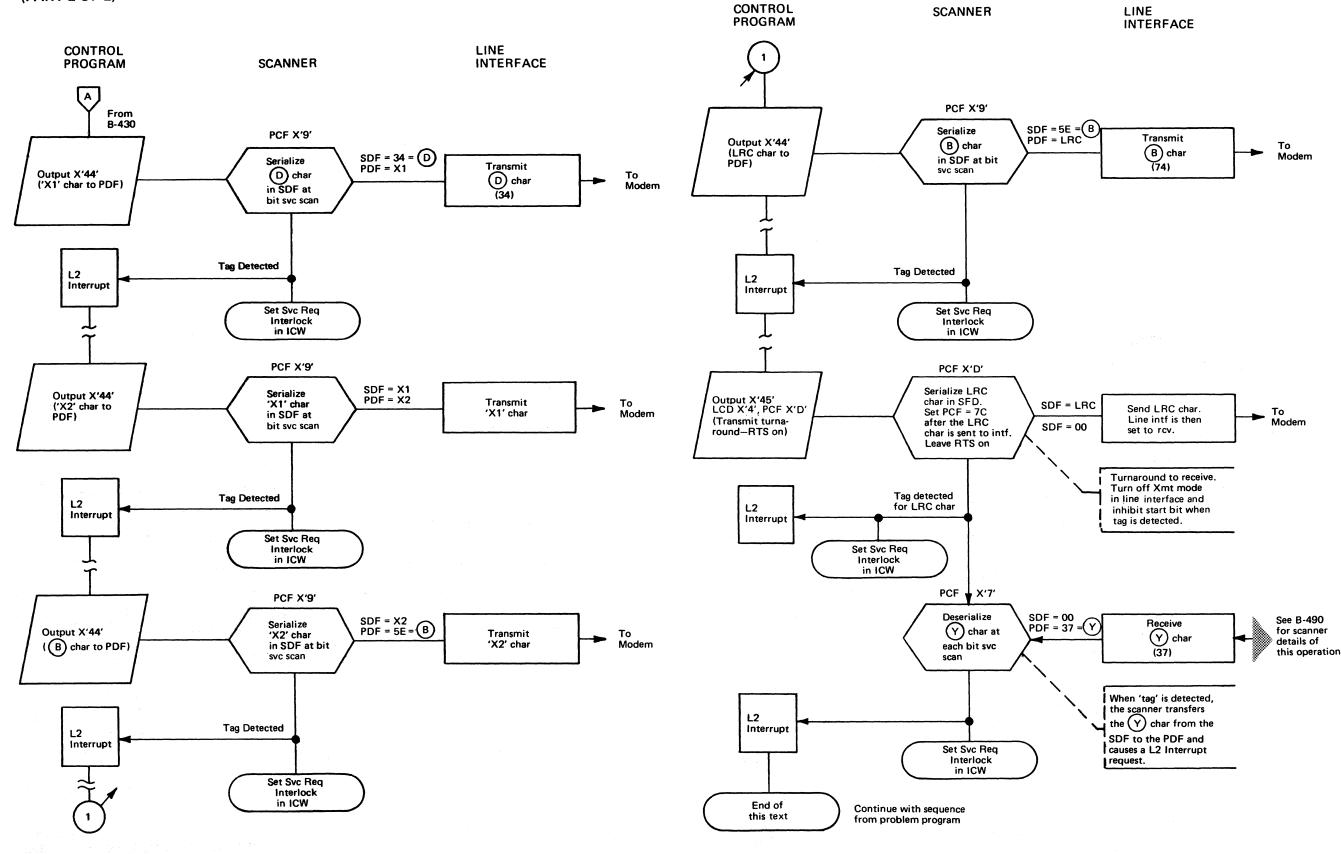

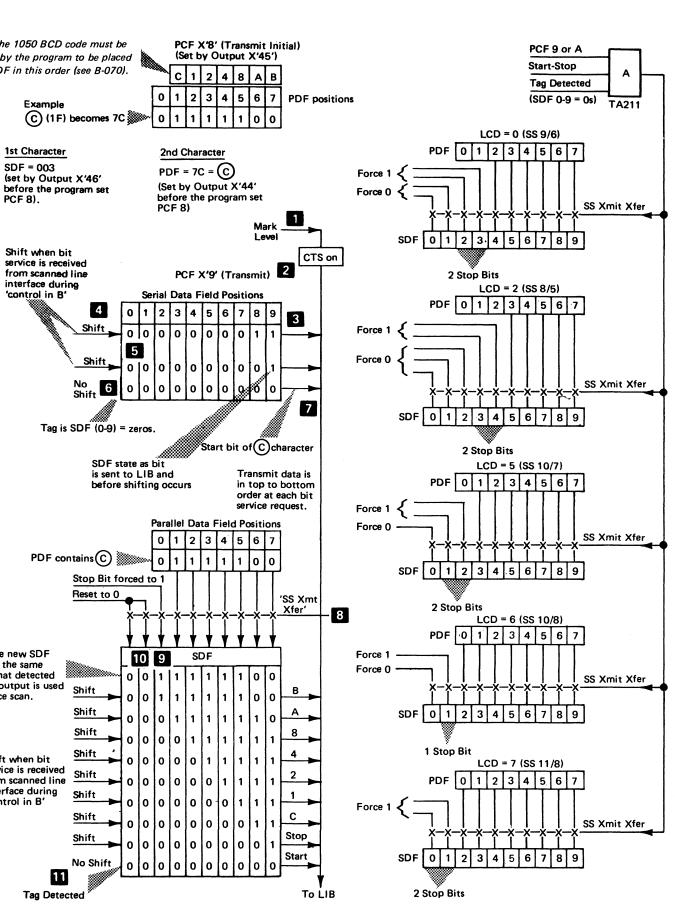

| COMMUNICATION SCANNER                                                     |                                                                                                                  | OPERATION                       | B-450          | DISTRIBUTION                             | D-550          | DISKETTE CONTROLLER                                       |        |

| DATA FLOW                                                                 | B-020                                                                                                            | Start-Stop Transmit Sequence    | B-470          | CHECKING +6V, ±12V, AND                  |                | DIAGNOSTIC APPROACH FOR                                   |        |

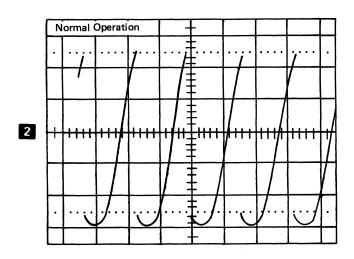

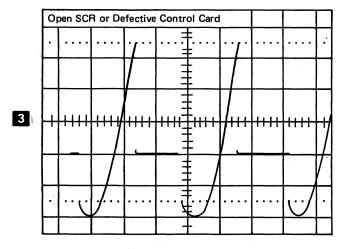

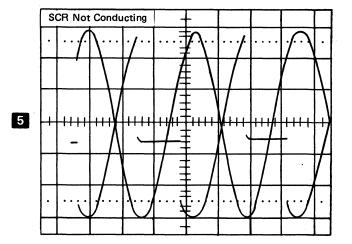

| ATTACHMENT BASE DATA FLOW                                                 | B-030                                                                                                            | Start-Stop Transmit Details     | B-480          | -4V SCRs                                 | D-560          | READ FAILURES                                             | F      |

| TYPE 2 COMMUNICATION                                                      |                                                                                                                  | Start-Stop Receive Details      | B-490          | INDICATOR LIGHTS-SUPPLY/                 |                | DISKETTE DRIVE                                            |        |

|                                                                           | B-040                                                                                                            | DIAL OPERATION                  | B-500          | CONTROL                                  | D-570          | Components                                                | F      |

|                                                                           | and the second | DIAGNOSTIC WRAP                 | B-511          | INDICATOR LIGHTS-CHARTS                  |                | Operating Sequence                                        | F      |

| SCANNER BOARD LAYOUT                                                      | B-051                                                                                                            |                                 |                |                                          |                |                                                           | -      |

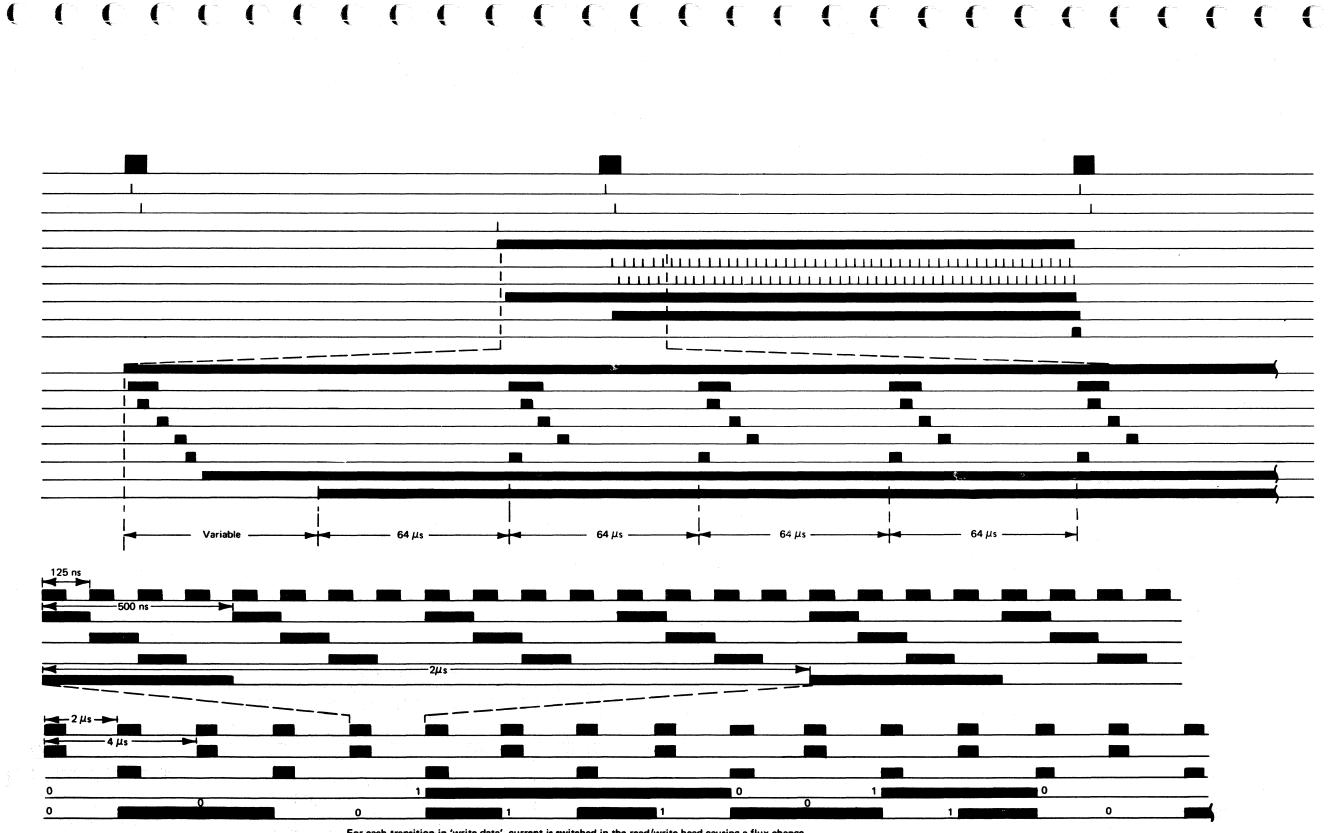

| SCANNER BOARD LAYOUT<br>CLOCK AND TIMINGS-STORAGE                         | B-051                                                                                                            | SDLC TRANSMISSION FRAME         |                |                                          | D-575          |                                                           | F      |

| SCANNER BOARD LAYOUT<br>CLOCK AND TIMINGS-STORAGE<br>ICW CONTROL AND DATA | B-051<br>B-060                                                                                                   |                                 | B-520<br>B-530 | AND PROCEDURES<br>DC VOLTAGE MEASUREMENT | D-575<br>D-580 | Read/Write Circuit Principles<br>Diskette                 | F      |

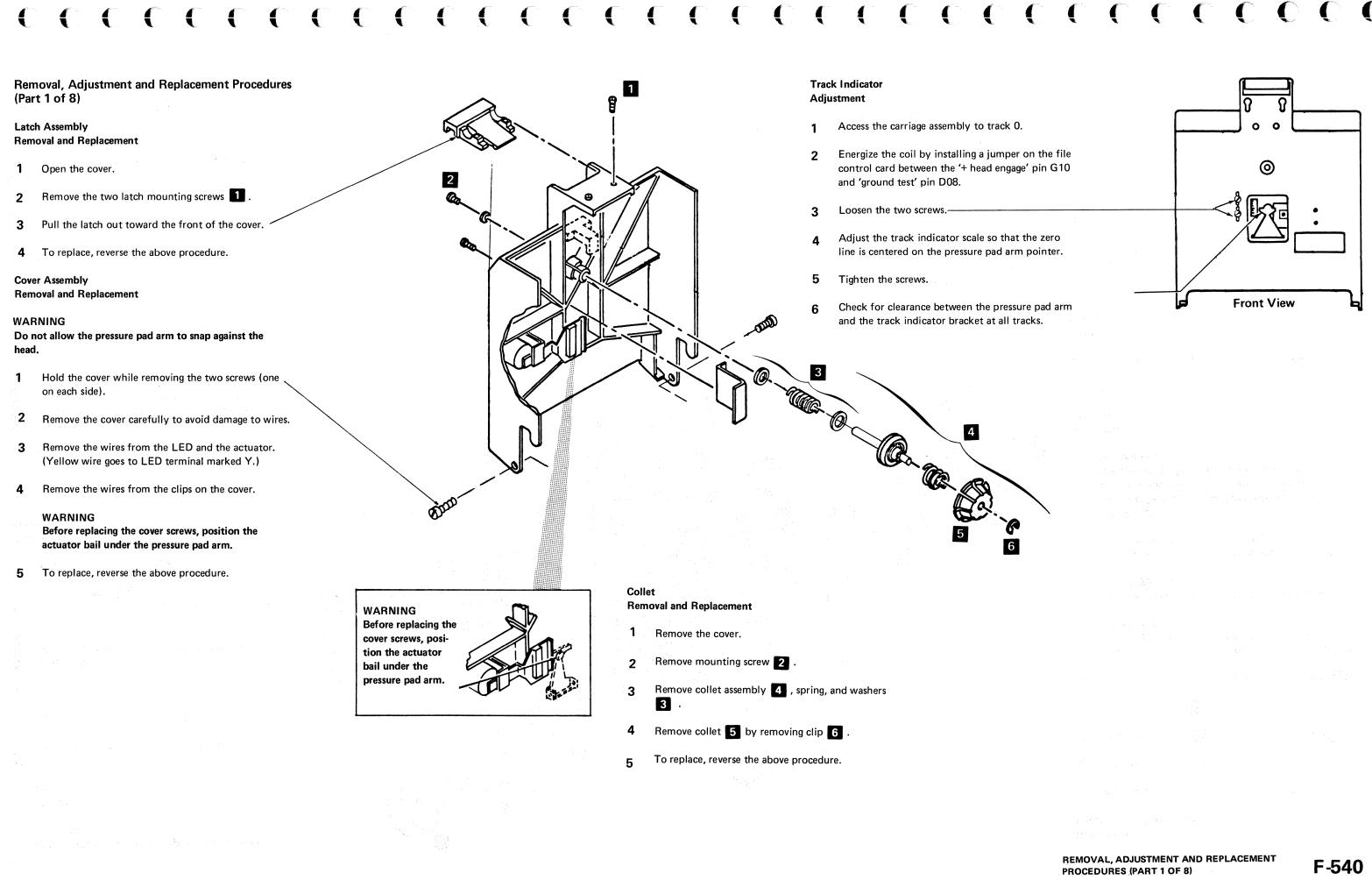

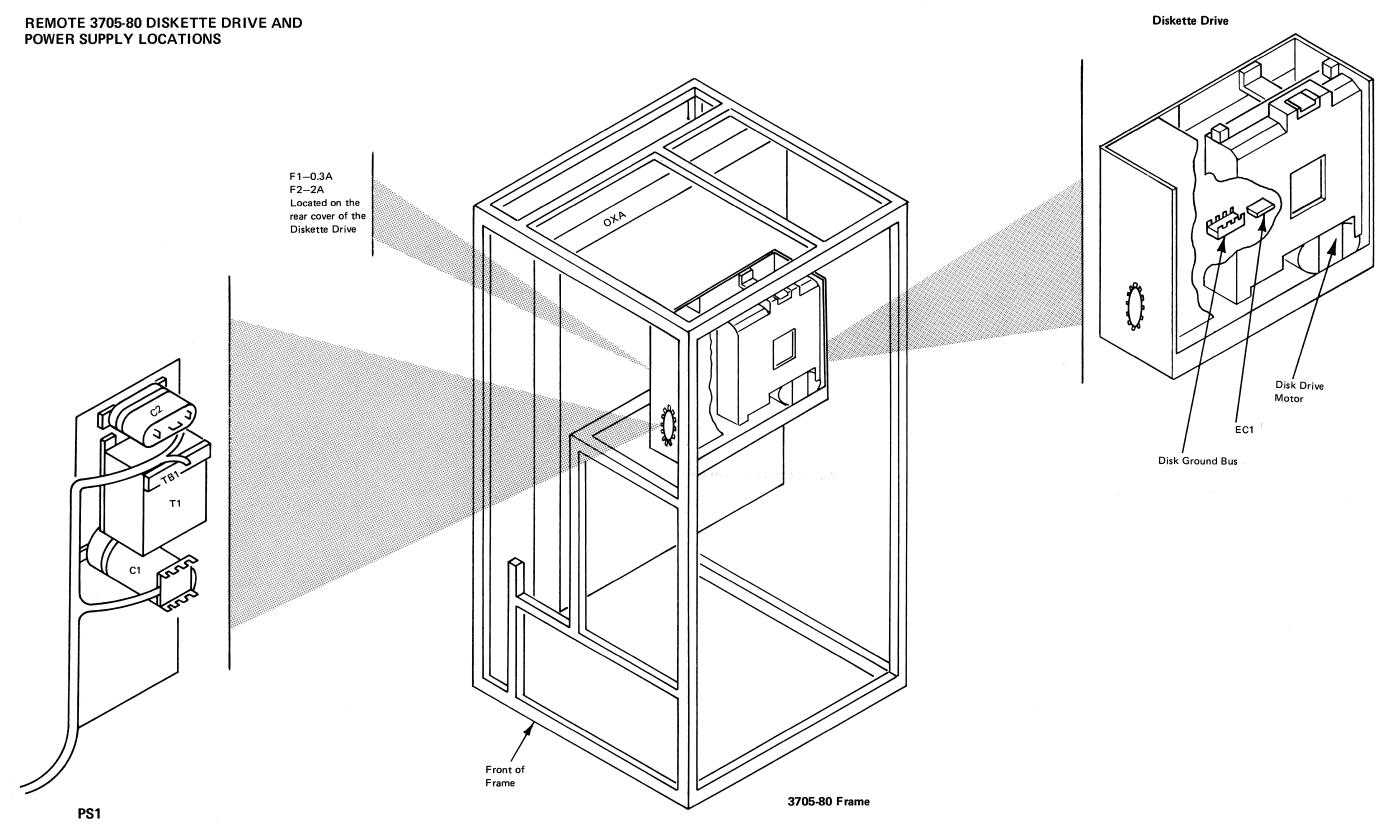

| Replacement Procedure<br>REMOTE 3705-80 DISKETTE                                                                                                                                                                                         | F-540                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| DRIVE AND POWER SUPPLY<br>LOCATIONS<br>REMOTE 3705-80 DISKETTE<br>DRIVE POWER SUPPLY                                                                                                                                                     | F-600                                                                                                    |

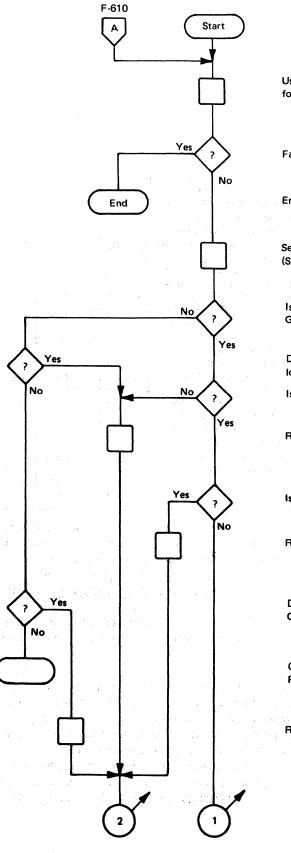

| MAINTENANCE PROCEDURE<br>TOOLS AND TEST EQUIPMENT<br>PREVENTIVE MAINTENANCE<br>CE SERVICE HINTS                                                                                                                                          | F-610<br>F-620<br>F-620<br>F-620                                                                         |

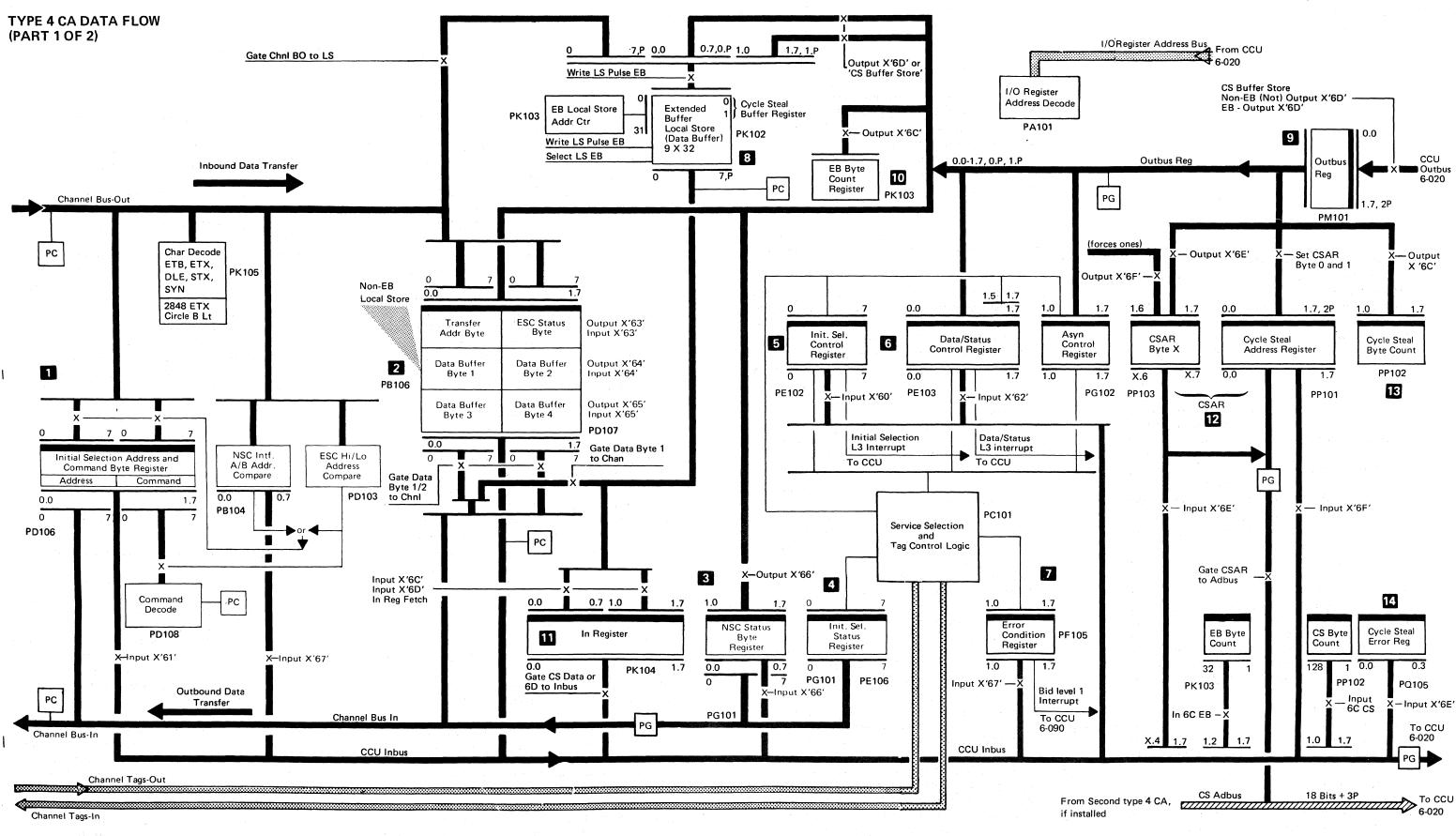

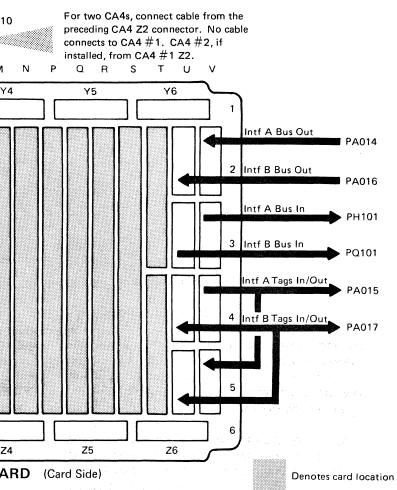

| TYPE 4 CHANNEL ADAPTER                                                                                                                                                                                                                   |                                                                                                          |

| INTRODUCTION<br>TYPE 4 CA DATA FLOW<br>CARD FUNCTIONS AND                                                                                                                                                                                | H-000<br>H-010                                                                                           |

| LOCATIONS<br>INPUT AND OUTPUT                                                                                                                                                                                                            | H-030                                                                                                    |

| INFOT AND COTTONS<br>INPUT X'60', X'61'<br>Output X'62'<br>Input X'62'<br>Output and Input X'63'<br>Output and Input X'64', X'65'<br>Output and Input X'66'<br>Input X'67'<br>Output X'67'<br>Input X'6C'<br>Output X'6C'<br>Input X'6D' | H-040<br>H-050<br>H-060<br>H-070<br>H-080<br>H-090<br>H-100<br>H-110<br>H-120<br>H-130<br>H-140<br>H-150 |

| Output X'6D'                                                                                                                                                                                                                             | H-160                                                                                                    |

| Input X'6E', X'6F'<br>Output X'6E', X'6F'<br>OUTBOUND DATA TRANSFERS–                                                                                                                                                                    | H-170<br>H-180                                                                                           |

| EB MODE<br>INBOUND DATA TRANSFERS—                                                                                                                                                                                                       | H-190                                                                                                    |

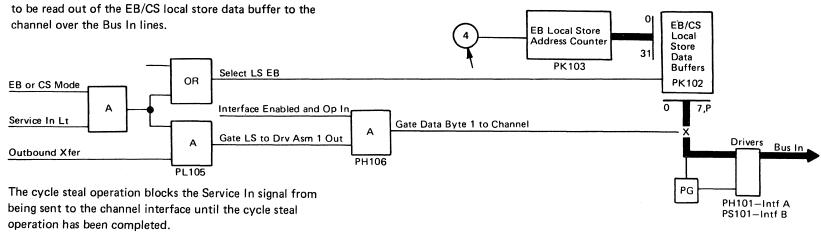

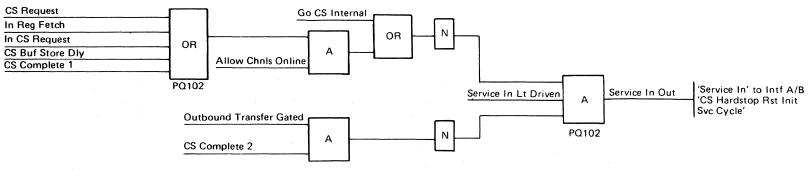

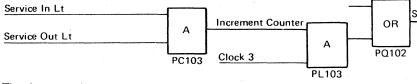

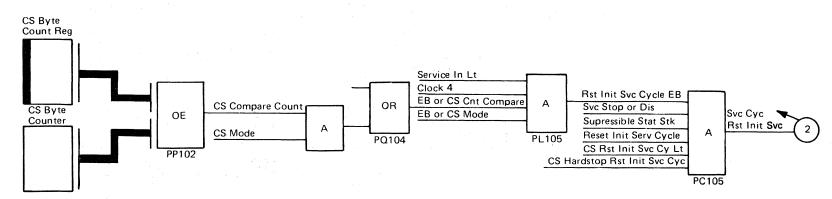

| EB MODE<br>CYCLE STEAL OPERATION-                                                                                                                                                                                                        | H-250                                                                                                    |

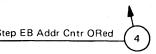

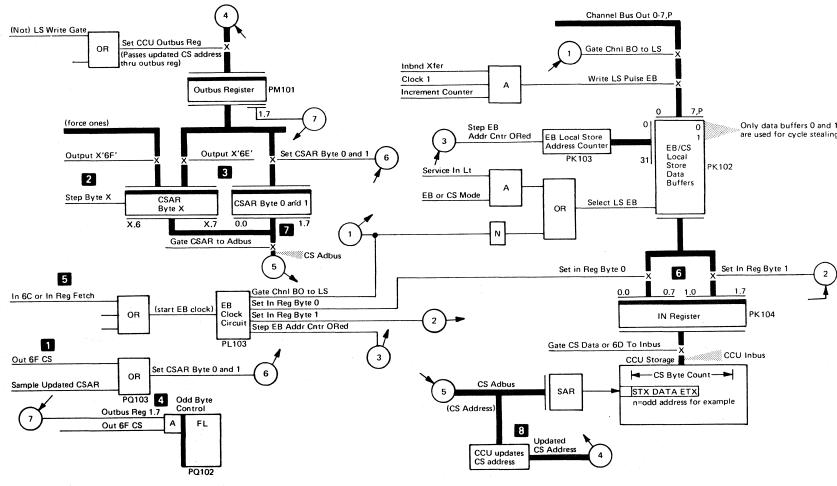

| OUTBOUND DATA TRANSFERS<br>CYCLE STEAL OPERATION-                                                                                                                                                                                        | H-300                                                                                                    |

| INBOUND DATA TRANSFERS<br>CA4 INTERRUPTS<br>INITIAL SELECTIVE RESET<br>INITIAL INTERFACE<br>DISCONNECT AND SERVICE<br>SELECTIVE RESET—<br>SELECTOR CHANNEL                                                                               | H-340<br>H-380                                                                                           |

| CONTROLS<br>DISCONNECT IN-SELECTOR                                                                                                                                                                                                       | H-390                                                                                                    |

| CHANNEL                                                                                                                                                                                                                                  | H-400                                                                                                    |

E-000

E-010

E-010

F-000

F-010

F-020

F-040

F-050

F-080

F-100

F-200

F-300 F-310

F-320

F-400

F-400

F-410

F-420

F-430

F-440

F-450

F-460

F-470

F-470

F-480

F-480

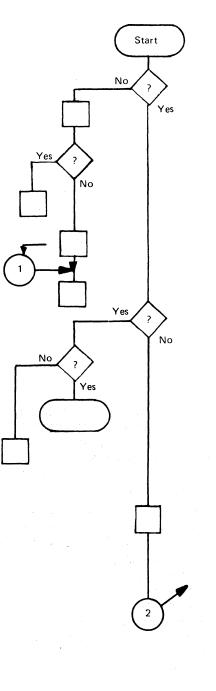

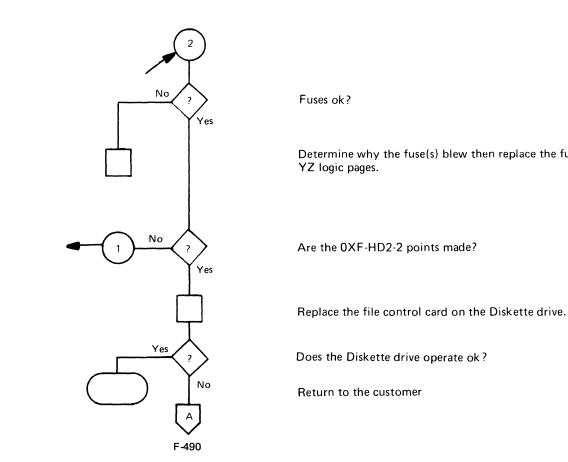

F-490

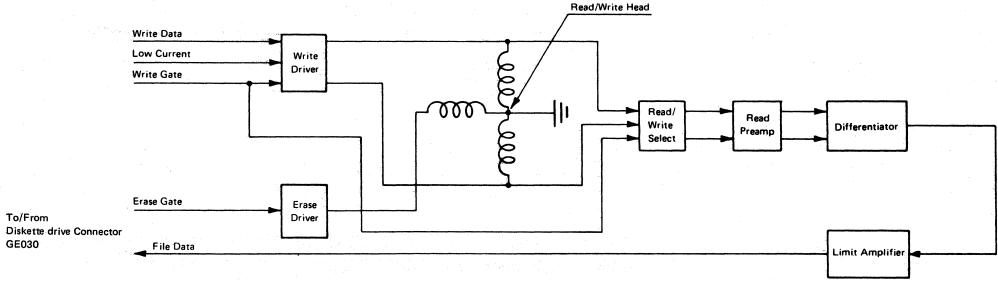

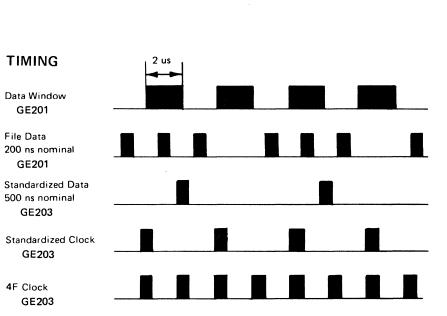

F-500 F-510

F-520 F-530

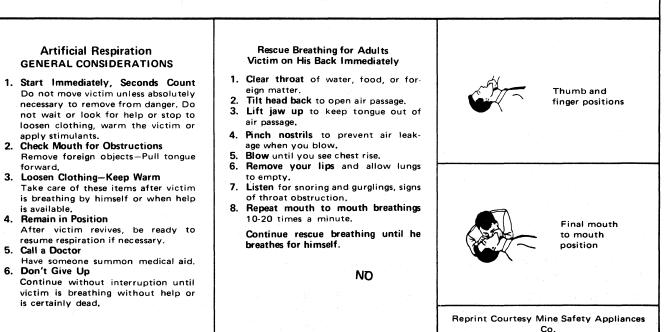

#### **CE SAFETY PRACTICES**

All Customer Engineers are expected to take every safety precaution possible and observe the following safety practices while maintaining IBM equipment:

- 1. You should not work alone under hazardous conditions or around equipment with dangerous voltage. Always advise your manager if you MUST work alone.

- 2. Remove all power AC and DC when removing or assembling major components, working in immediate area of power supplies, performing mechanical inspection of power supplies and installing changes in machine circuity.

- 3. Wall box power switch when turned off should be locked or tagged in off position. "Do not Operate" tags, form 229-1266, affixed when applicable. Pull power supply cord whenever possible.

- 4. When it is absolutely necessary to work on equipment having exposed operating mechanical parts or exposed live electrical circuity anywhere in the machine, the following precautions must be followed.

- a. Another person familiar with power off controls must be in immediate vicinity.

- b. Rings, wrist watches, chains, bracelets, metal cuff links, shall not be worn.

- c. Only insulated pliers and screwdrivers shall be used. d. Keep one hand in pocket.

- e. When using test instruments be certain controls are set correctly and proper capacity, insulated probes are

- used. f. Avoid contacting ground potential (metal floor strips,

- machine frames, etc. use suitable rubber mats purchased locally if necessary).

- 5. Safety Glasses must be worn when:

- a. Using a hammer to drive pins, riveting, staking, etc. b. Power hand drilling, reaming, grinding, etc.

- c. Using spring hooks, attaching springs.

- d. Soldering, wire cutting, removing steel bands.

- e. Parts cleaning, using solvents, sprays, cleaners, chemicals etc. f. All other conditions that may be hazardous to your

- eyes. REMEMBER, THEY ARE YOUR EYES.

- 6. Special safety instructions such as handling Cathode Ray Tubes and extreme high voltages, must be followed as outlined in CEM's and Safety Section of the Maintenance Manuals.

- 7. Do not use solvents, chemicals, greases or oils that have not been approved by IBM.

- 8, Avoid using tools or test equipment that have not been approved by IBM.

- 9. Replace worn or broken tools and test equipment.

- 10. Lift by standing or pushing up with stronger leg muscles-this takes strain off back muscles. Do not lift any equipment or parts weighing over 60 pounds,

- 11. All safety devices such as guards, shields, signs, ground wires, etc. shall be restored after maintenance.

- 12. Each Customer Engineer is responsible to be certain that no action on his part renders product unsafe or exposes hazards to customer personnel.

- 13. Place removed machine covers in a safe out-of-the-way place where no one can trip over them.

- 14. All machine covers must be in place before machine is returned to customer.

- 15. Always place CE tool kit away from walk areas where no one can trip over it (i.e., under desk or table).

- 16. Avoid touching mechanical moving parts (i.e., when lubricating, checking for play, etc.).

- 17. When using stroboscope-do not touch ANYTHINGit may be moving.

- 18. Avoid wearing loose clothing that may be caught in machinery. Shirt sleeves must be left buttoned or rolled above the elbow.

- 19. Ties must be tucked in shirt or have a tie clasp (preferably nonconductive) approximately 3 inches from end. Tie chains are not recommended.

- 20. Before starting equipment, make certain fellow CE's and customer personnel are not in a hazardous posi-

- tion. 21. Maintain good housekeeping in area of machine while performing and after completing maintenance.

#### KNOWING SAFETY RULES IS NOT ENOUGH AN UNSAFE ACT WILL INEVITABLY LEAD TO AN ACCIDENT USE GOOD JUDGMENT – ELIMINATE UNSAFE ACTS

#### LOCATION OF LOGIC PAGES BY VOLUME NUMBER

| Volume                                                           | Logic Pages                                                                         |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| 41<br>42<br>A42<br>43<br>44<br>45<br>46<br>47<br>48<br>A48<br>49 | YZ<br>AA-CV<br>CW-CZ<br>DF-DZ<br>MM<br>TA-TB<br>VA<br>VB<br>RA-RS<br>PA-PS<br>GA-GC |

|                                                                  |                                                                                     |

229-1264-1

forward

CE SAFETY PRACTICES

## VIII

Contents

Power supply-installation instruction CCU ROS-Type 2 attachment base-CCU CCU Storage Type 2 scanner LIB-reference material LIB-line sets 1, 2, 3, 4, 5, 8, and 9 Type 1 channel adapter Type 4 channel adapter Remote Program Loader Diskette Controller

### Type 1 Channel Adapter

#### INTRODUCTION

The type 1 channel adapter (CA) handles data transfers between the 3705-80 and the channel with the CCU interrupt facilities. This adapter accepts a range of subchannel addresses and commands consistent with the IBM 2701, IBM 2702, and IBM 2703 transmission control units. However, the 3705-80 must be assigned a single subchannel address to be used when the 3705-80 is not emulating one of the other transmission control units.

The range of subchannel addresses and commands enables the 3705-80 to emulate the other IBM control units under program control.

The type 1 channel adapter does not cycle steal data into storage. This adapter requires control program intervention for each inbound and outbound data transfer.

Data transfers between the channel and the channel adapter are controlled by the data-status control register. Up to four bytes can be transferred (byte count in status control register) before the control program intervenes in the operation. However, each 4 byte transfer requires control program intervention before and after the transfer.

#### **Channel Adapter Modes of Operation**

The type 1 channel adapter operates in either native subchannel (NSC) or emulation subchannel (ESC) mode. The 3705-80 control program selects the mode with an Output X'67' instruction (see 8-130). NSC mode uses a single channel address for each channel interface installed, and must be used in the initial program load. The 3705-80 control program handles line control and message assembly while operating in this mode.

ESC mode uses a range of addresses assigned to each communication line attached to the 3705-80. The host processor is responsible for line control while operating in this mode. ESC mode is used when IBM 2701, 2702, or 2703 operation is emulated.

#### Address Assignment

During initial selection, the channel adapter must be able to recognize the I/O device address presented on the channel bus-out if the channel interface is enabled. Since the type 1 CA can have a NSC address and a range of ESC addresses, alternate means of assigning the addresses are provided.

The NSC address is assigned on the plug card at Y4P2, RC104. The NSC address can be any address from 0 to 255. If the Two Channel Switch feature is installed, NSC addresses for interface A and B are assigned by different plug cards (A on Y4P2, B on Y4R2, RF106, Y4P2 is an address source for the control program). The 2 NSC addresses need not be identical.

ESC addresses are assigned on the plug card at Y4M2, RC302-305, and are a contiguous group of addresses. The lowest address in the group can be 0 or any multiple of 16 from 0 to 240. The highest address that can be assigned must be greater than the lowest address and 1 less than an even multiple of 4 from 3 to 255. The range of addresses can be set to include a minimum of 4 and a maximum of 256 addresses. The range of addresses must be the same for both interfaces if the Two Channel Switch feature is installed.

Refer to FEALD YZ000 pages 10-13 for I/O channel address jumpering.

#### WARNING

The hard stop latch disables the channel interface without extinguishing the interface enabled light. The channel adapter does not recognize its address and trap select out if the hard stop latch is set.

#### **Channel Commands**

The type 1 channel adapter initially accepts as a valid command any configuration from X'00' to X'FF'. The only limitation is that the command byte must be in parity on the channel. The channel adapter presents an initial status of X'00' if the parity is correct and the command is not a No-Op, an ESC Test I/O, or a Start I/O clearing NSC stacked status. The CA then requests an initial selection level 3 interrupt so that the control program can further determine if the command is valid for the subchannel address the command was issued to. If the command is not valid for that address (determined by the control program), the CA presents CE, DE, and UC status to the channel under program control.

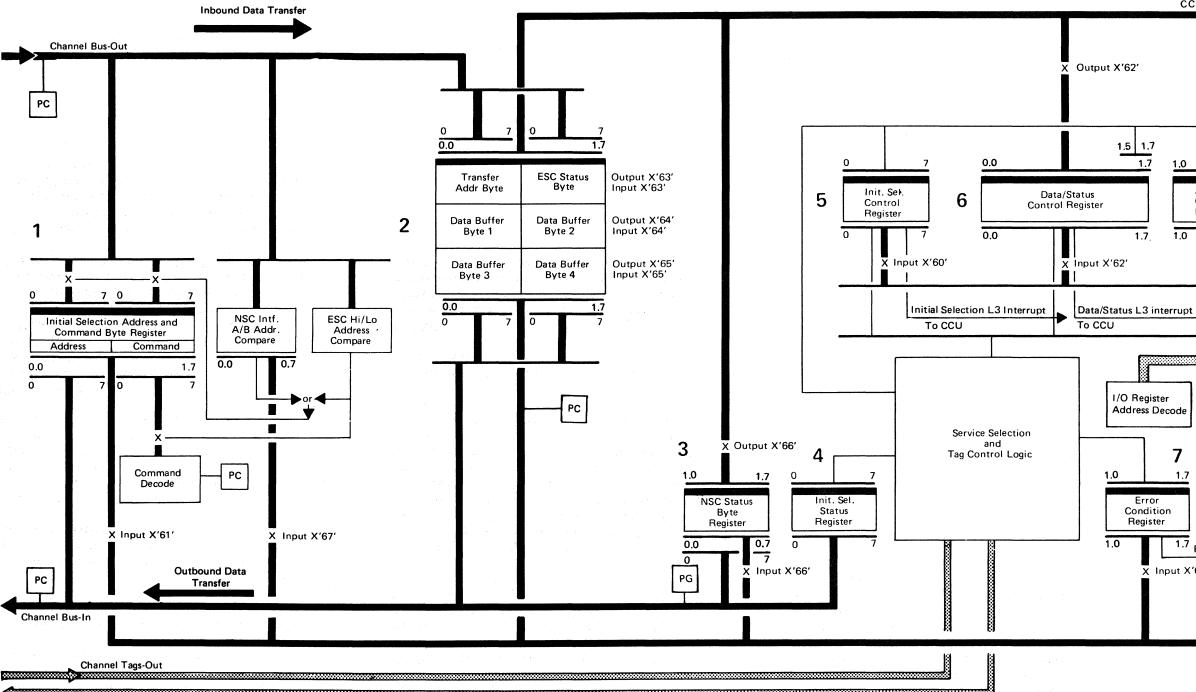

#### TYPE 1 CA DATA FLOW (PART 1 OF 2)

Channel Tags-In

化氯 医内部性外的 整洁的 建筑

TYPE 1 CA DATA FLOW (PART 1 OF 2) 8-010

6-020 CCU Out Bus PC X Output X'67' 1.7 1.0 Asyn Control Register 1.0 1.7 1/0 Register Address Bus 7 1.7 1.7 Program level 1 Interrupt To CCU 6-090 X Input X'67' PG CCU In Bus

6--020

#### TYPE 1 CA DATA FLOW (PART 2 OF 2)

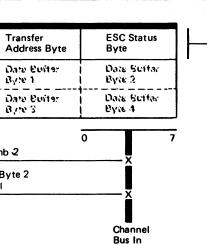

## 1 Initial Selection Address and Command Register

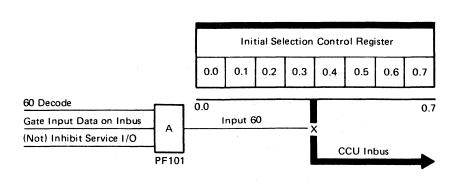

This register contains the I/O device address byte and command byte presented to the channel adapter during initial selection. The register can be accessed by Input X'61' which should be executed only if the type 1 channel adapter initial or data/status level 3 interrupt request is set. See 8-070 for Input X'61' description. This register is referred to as the SIO register in the ALD's.

#### 2 Local Store

The local store provides buffering for the I/O address byte used in all data and status transfer sequences initiated by the 3705-80. Buffering for up to four bytes of data for inbound and outbound data transfers is provided here also.

The control program loads or accesses the I/O device address and the emulation status byte with Output X'63' and Input X'63' respectively. The data bytes are transferred with X'64' or X'65' instructions, see chart below.

| Data | Data Ti | ransfer        |  |

|------|---------|----------------|--|

| Byte | Out     | In             |  |

| 1    | X'64′   | X'64'          |  |

| 2    | X'64′   | X <i>'</i> 64' |  |

| . 3  | X'65'   | X'65'          |  |

| 4    | X'65′   | X'65'          |  |

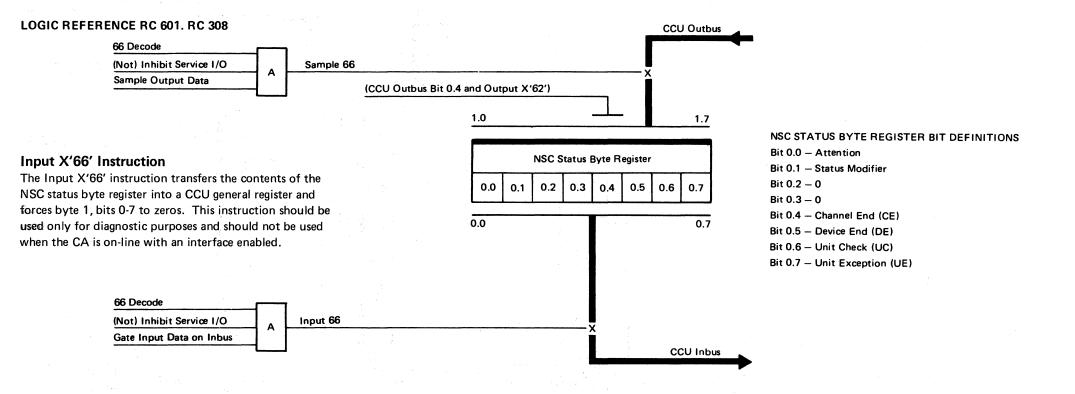

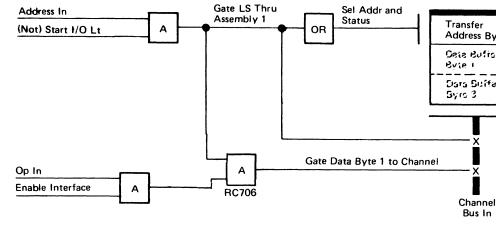

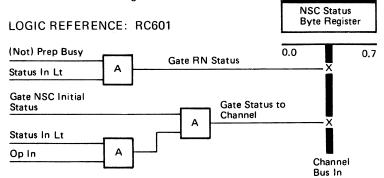

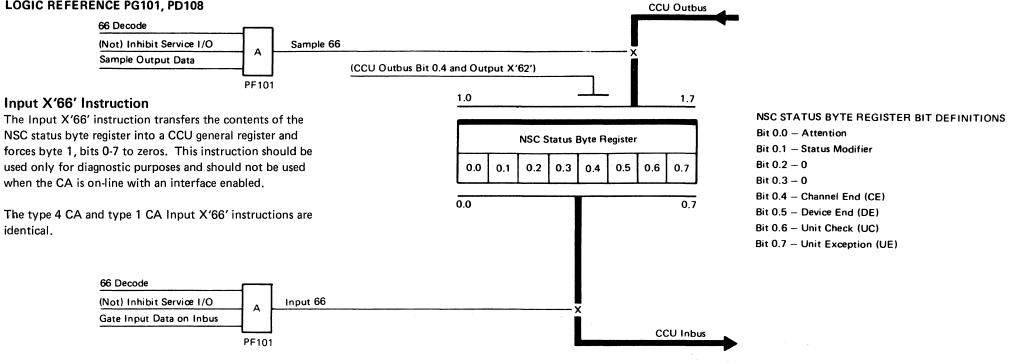

### **3** NSC Status Byte Register

The current status of the NSC is maintained in this register and gated over the channel interface during NSC status transfer sequences. The control program should set the NSC status by executing an Output X'66' instruction. The control program has access to this register with the Input X'66' instruction.

#### 4 Initial Selection Status Register

The status byte is generated and presented to the channel from this register during initial selection sequences except under the following conditions.

- An initial selection sequence occurs for the native mode subchannel before the NSC status byte provided by the control program has been accepted. The NSC status byte from the NSC status register is presented instead of the hardware generated status.

- An initial selection sequence occurs for an emulation address when the control program has signaled that an ESC status transfer sequence is required and has signaled that ESC Test I/O status is available. The ESC status byte provided by the program is presented instead of hardware generated status.

#### 5 Initial Selection Control Register

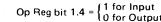

The information in this register identifies the event causing the type 1 channel adapter initial level 3 interrupt request to be set. The register can be accessed by Input X'60', which should be executed only if the interrupt request is set.

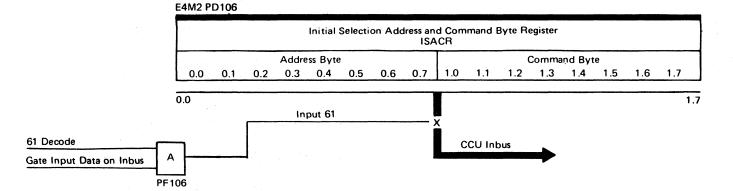

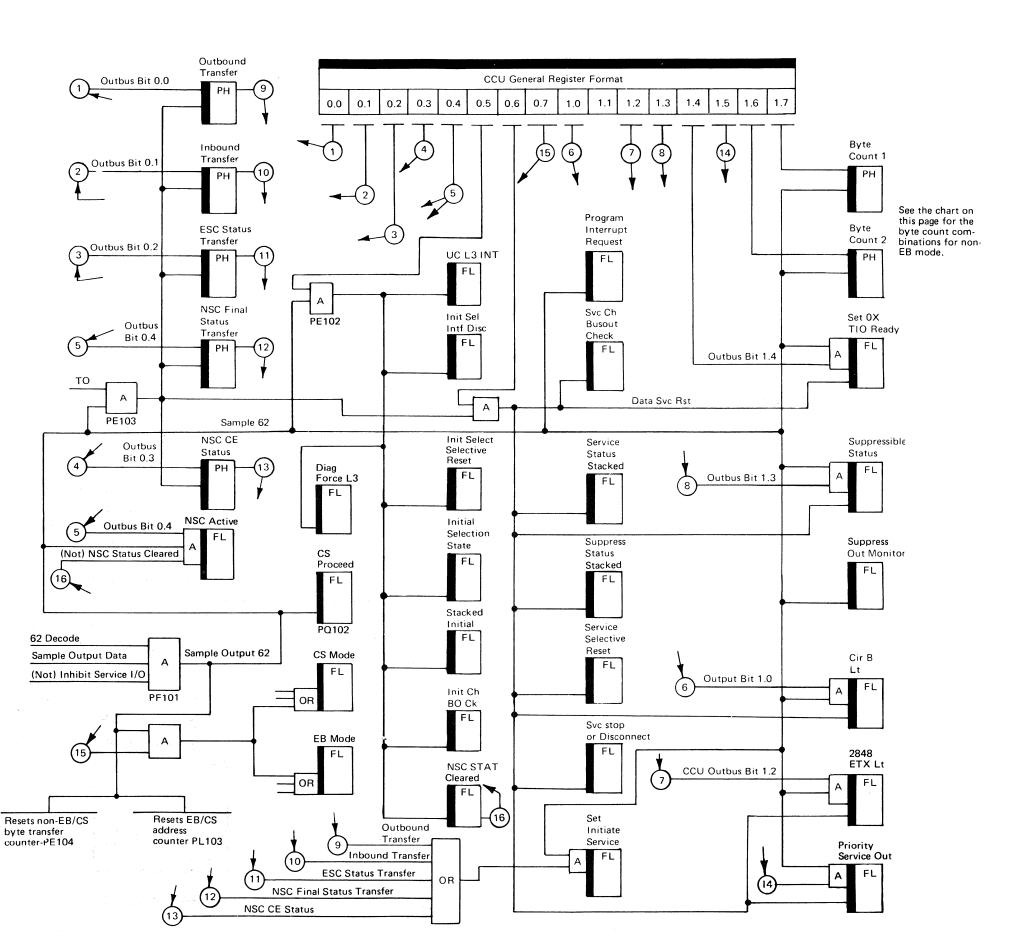

### 6 Data/Status Control Register

The information in this register controls and identifies events that cause the type 1 channel adapter data/status level 3 interrupt request to be set. The register can be accessed by Input X'62', which should be executed only if the interrupt request is set. The control program can perform various control functions by setting or resetting bits in this register with an Output X'62' instruction. The instruction should be executed only when the control program is servicing a type 1 CA level 3 interrupt request.

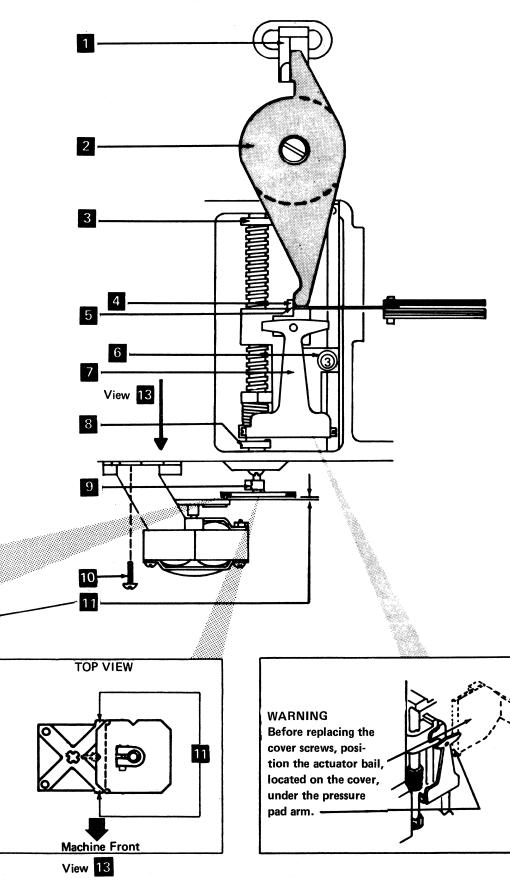

## 7 Error/Condition Register

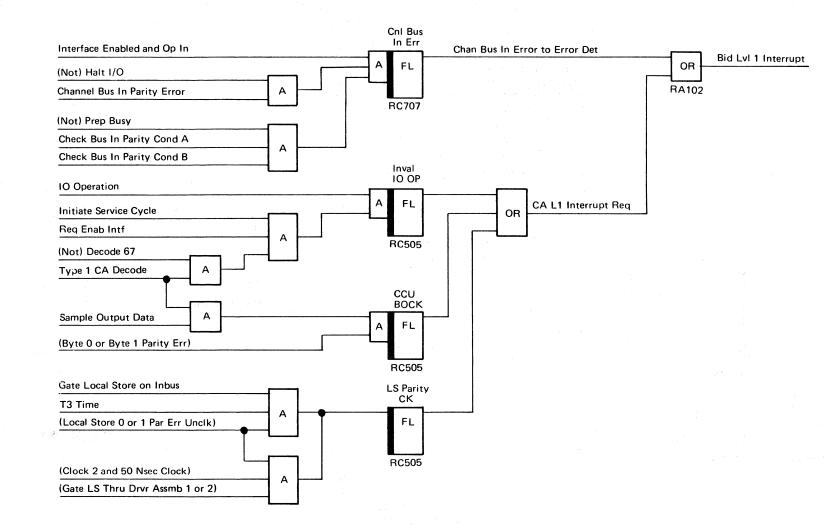

The error/condition register is a collection of latches that are set when the CA detects an error or an occurrence of specific asynchronous conditions. The 3705-80 control program has access to this register with an Input X'67' instruction, (see page 8-140). The errors indicated by the error/condition register cause type 1 CA error interrupts (see page 8-360).

> TYPE 1 CA DATA FLOW (PART 2 OF 2)

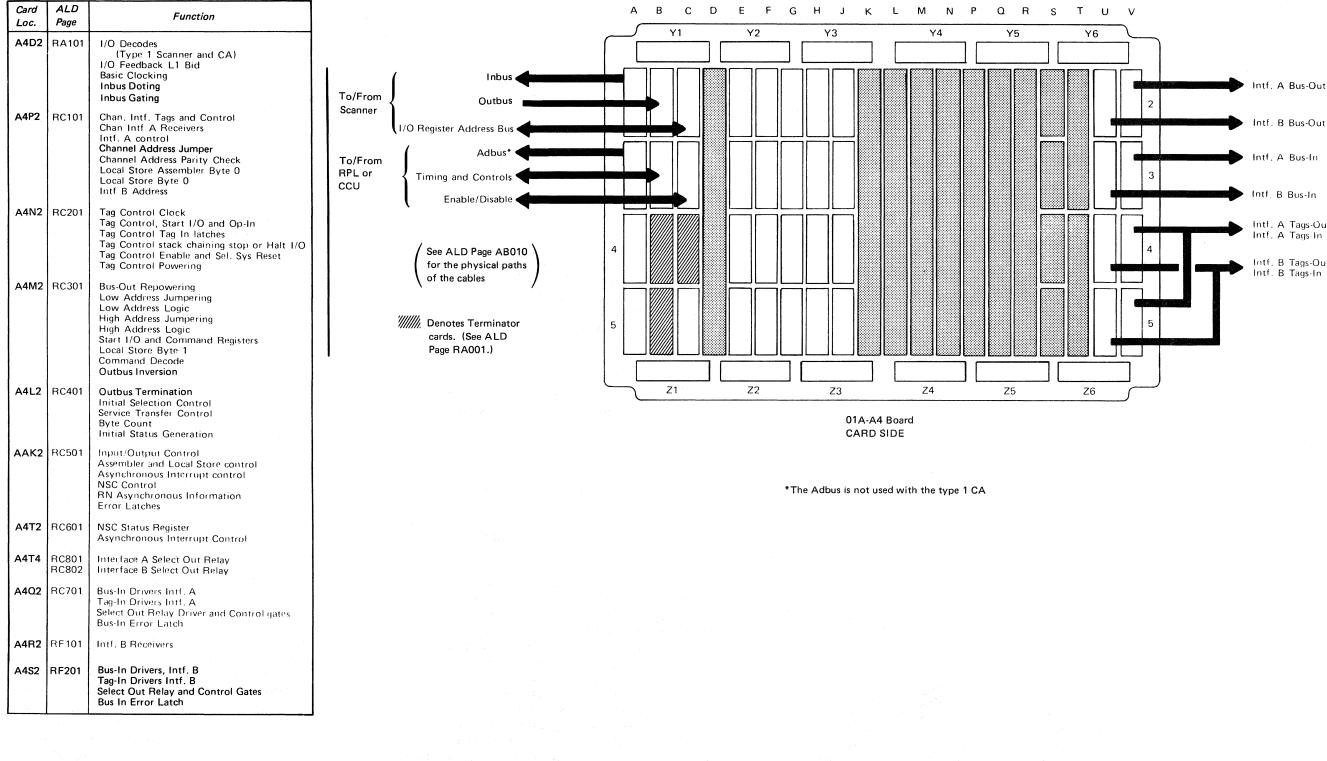

#### CARD FUNCTIONS AND LOCATIONS

CARD FUNCTIONS AND LOCATIONS

8-030

Intf. B Bus-Out Intf. A Bus-In Intf. B Bus-In Intf. A Tags-Out Intf. A Tags In Intf. B Tags-Out Intf. B Tags-In-

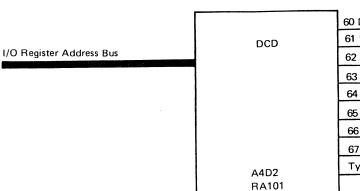

#### INPUT AND OUTPUT INSTRUCTIONS

The type 1 channel adapter relies on the 3705-80 control program to use input and output instructions to control data transfers. The control program initiates channel data and status transfers, and transfers data between the CA and the CCU with input and output instructions.

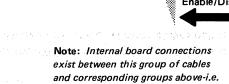

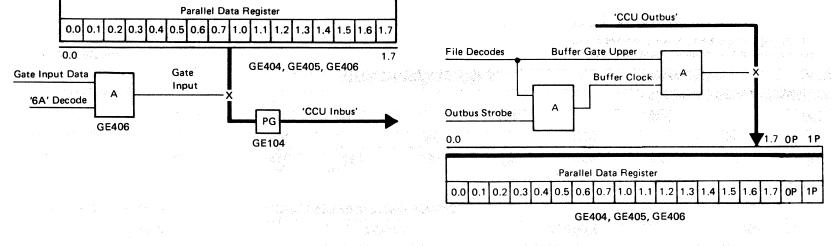

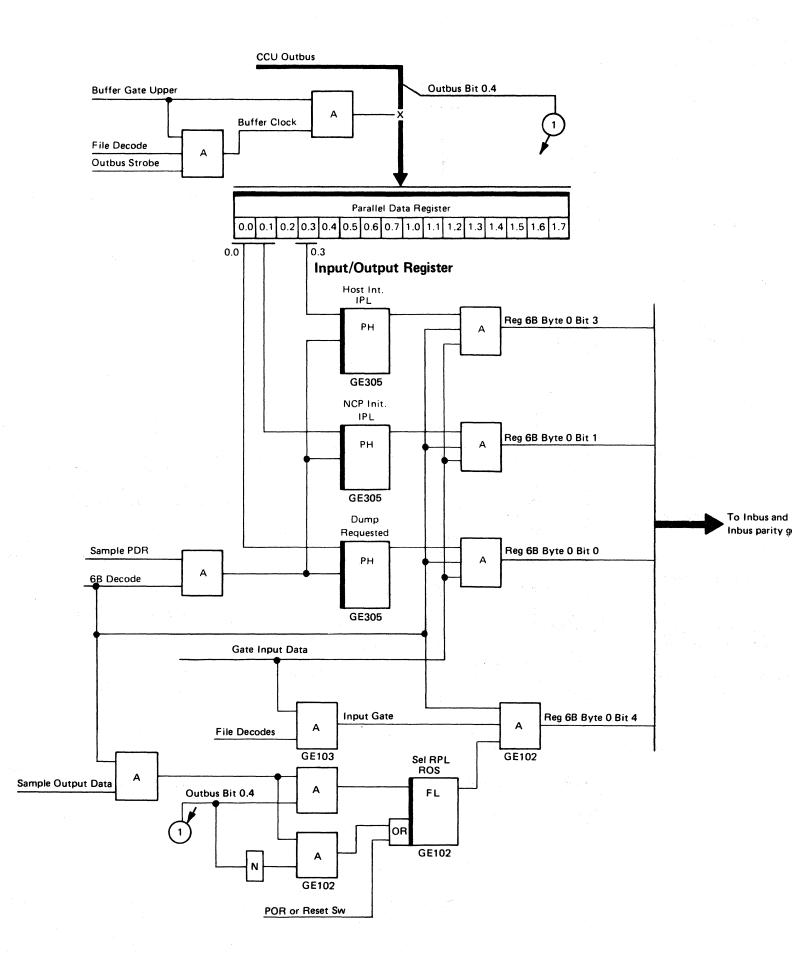

Each input or output instruction addresses an external register. The input instructions gate the external register to CCU general registers via the CCU Inbus. Output instructions gate CCU general registers to CA registers via the CCU Outbus. The 'I/O register address bus' is decoded in the type 1 attachment base.

Executing an Input or Output X'60', X'61', X'62', X'63', X'64', X'65', or X'66' when the CA is actively handling a data or status transfer sequence causes an in/out check to occur; see 8-360.

#### **Control Panel Access to CA Registers**

Type 1 CA registers X'60' through X'66' should be accessed from the control panel with Input or Output instructions only when either of the type 1 CA level 3 interrupts are pending.

To ensure that this interrupt remains pending, the 3705-80 should be in either Program Stop or Hard Stop mode before these instructions are executed from the control panel.

If these conditions are not met, the following occurs:

- If the type 1 CA is in the process of a data or status transfer sequence and an Input or Output X'60' through X'66' is initiated from the control panel, the type 1 CA hardware:

- a. Causes a type 1 CA level 1 interrupt request.

- b. Sets the type 1 CA In/Out instruction accept latch.c. Gates X'0000' onto the CCU Inbus to be displayed in

- display B if the instruction is an Input.

- d. Does not recognize Output instructions.

- 2. If the type 1 CA is not transferring data or status and a type 1 CA level 3 interrupt request is not pending, one of the following occurs:

- a. For Input X'60', X'61', or X'66' instructions, either the instruction is executed without error or, if at the same time the instruction is being executed, the CA is being selected by the host processor channel, the CCU may sample invalid data from the type 1 CA. The data in display B should be considered invalid.

- b. For Output X'66' instructions, either the instruction is executed without error or, if at the same time the instruction is being executed, the type 1 CA is being selected by the host processor channel, a type 1 CA channel bus in check and a type 1 CA level 1 interrupt request may be set or a processor data check may be detected at the host processor.

- If the type 1 CA is in the process of presenting ESC status to a Test I/O issued to an ESC address, and an Input X'60' through X'66' or an Output X'62' through X'66' is executed, one of the following occur:

- a. The instruction executes without error.

- b. If at the same time any of these instructions are being executed, the type 1 CA is being selected by the host processor channel, either a type 1 channel bus in check, a type 1 CA local store, a level 1 interrupt request, or a processor data check may occur.

Input and Output X'67' can be executed from the 3705-80 control panel without causing an error.

| 60 Decode         |  |  |  |  |  |

|-------------------|--|--|--|--|--|

| 61 Decode         |  |  |  |  |  |

| 62 Decode         |  |  |  |  |  |

| 63 Decode         |  |  |  |  |  |

| 64 Decode         |  |  |  |  |  |

| 65 Decode         |  |  |  |  |  |

| 66 Decode         |  |  |  |  |  |

| 67 Decode         |  |  |  |  |  |

| Type 1 CA Decodes |  |  |  |  |  |

|   | 1/0 |   |   |   |   |   |        |

|---|-----|---|---|---|---|---|--------|

| 1 | 2   | 3 | 4 | 5 | 6 | 7 | Decode |

| 1 | 1   | 0 | 0 | 0 | 0 | 0 | 60     |

| 1 | 1   | 0 | 0 | 0 | 0 | 1 | 61     |

| 1 | 1   | 0 | 0 | 0 | 1 | 0 | 62     |

| 1 | 1   | 0 | 0 | 0 | 1 | 1 | 63     |

| 1 | 1   | 0 | 0 | 1 | 0 | 0 | 64     |

| 1 | 1   | 0 | 0 | 1 | 0 | 1 | 65     |

| 1 | 1   | 0 | 0 | 1 | 1 | 0 | 66     |

| 1 | 1   | 0 | 0 | 1 | 1 | 1 | 67     |

INPUT AND OUTPUT INSTRUCTIONS

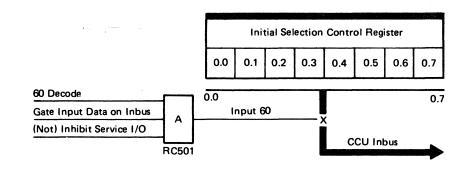

#### Input X'60' Instruction

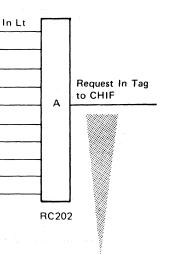

Input X'60' transfers the contents of the initial selection control register into a CCU general register. The 3705-80 control program uses this instruction to determine the exact cause of a type 1 CA initial selection level 3 interrupt.

An Output X'60' resets the initial selection control register and the L3 interrupt request resulting from the initial selection.

| Bit                                                  | Logic<br>Page                                               | Function                                                                                                                                                                                                     |

|------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.0<br>0.1<br>0.2<br>0.3<br>0.4<br>0.5<br>0.6<br>0.7 | RC402<br>RC205<br>RC205<br>RC402<br>RC402<br>RC505<br>RC205 | Input Initial Selection State*<br>Input Initial Interface Disconnect<br>Input Initial Selective Reset<br>Input Initial Bus Out Check<br>O<br>Input Stack Initial<br>NSC Status Cleared<br>Input System Reset |

\*Normal Initial Selective

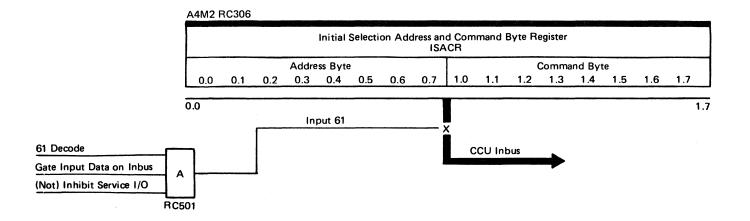

#### Input X'61' Instruction

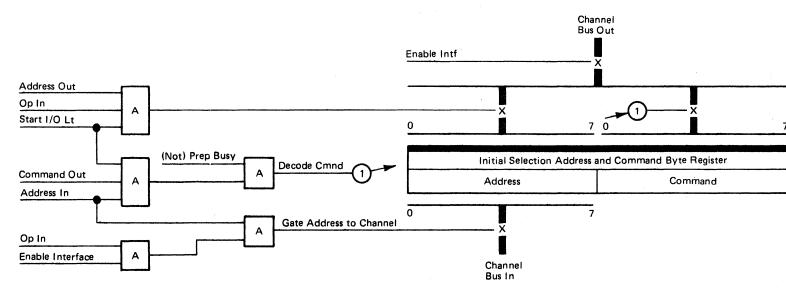

Input X'61' transfers the contents of the initial selection address and command byte register into a CCU general register. During an initial selection sequence, a type 1 CA initial selection level 3 interrupt is requested, and the 3705-80 control program must investigate the subchannel address and command causing the interrupt. Byte 0 is the address to which the command in byte 1 was issued.

The 3705-80 control program must store the address and command because the host processor can send the CA a new command before the 3705-80 control program has completed the previous one when in ESC mode. The 3705-80 control program must also control the CA action for each command.

An Output X'61' instruction has no effect on the channel adapter.

#### INPUT X'60' INSTRUCTION INPUT X'61' INSTRUCTION

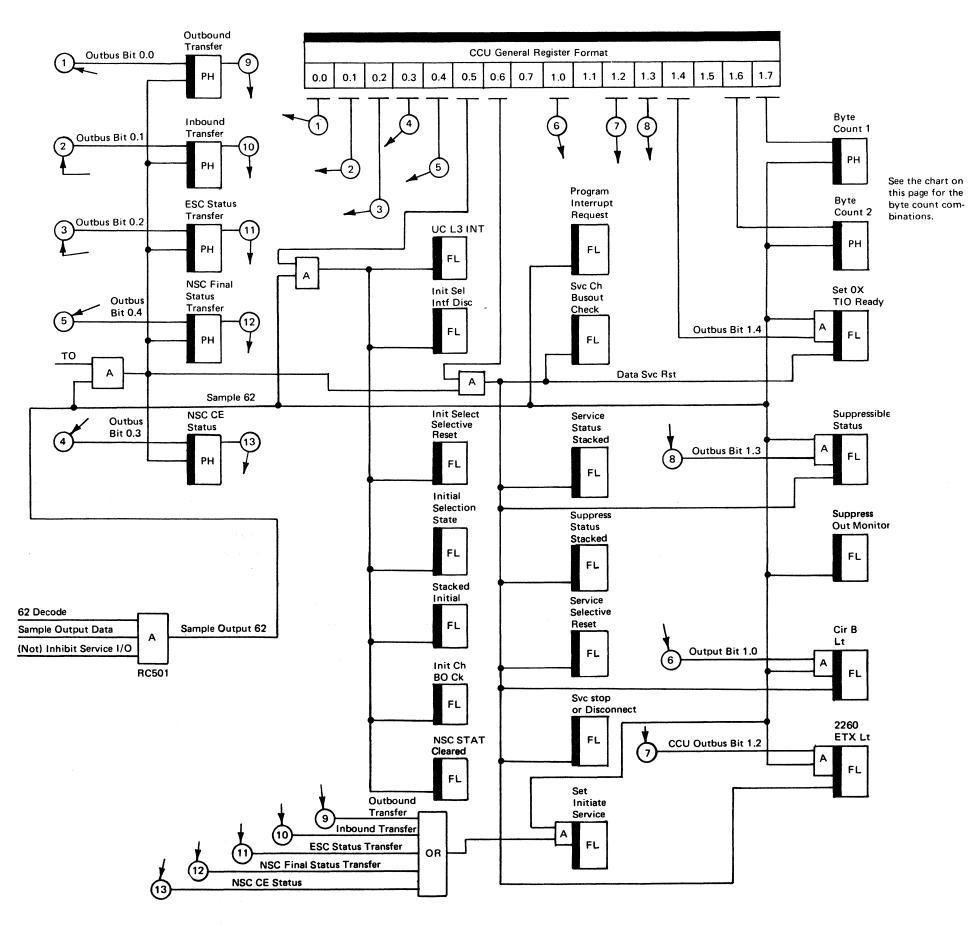

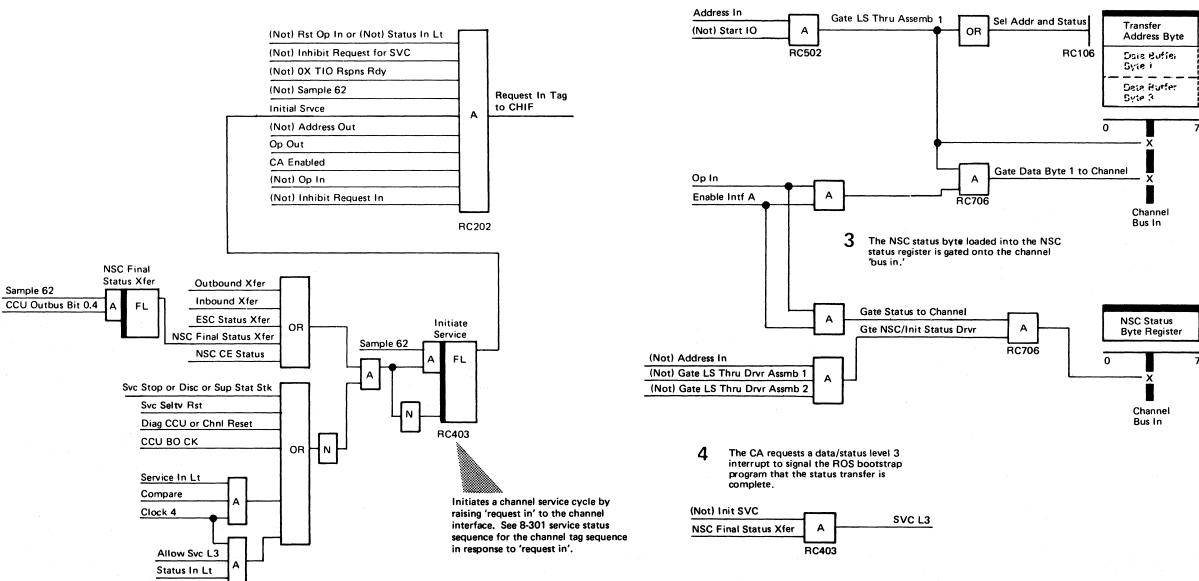

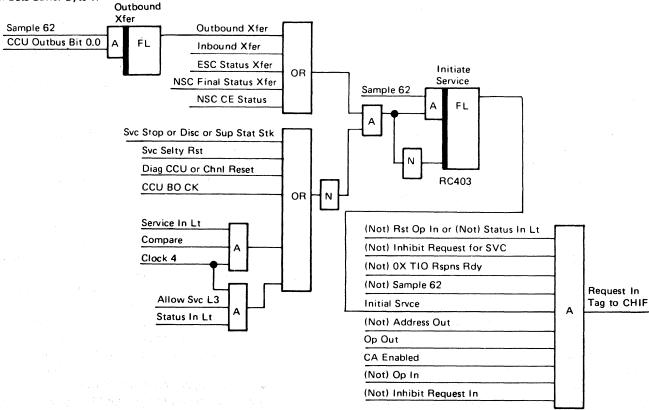

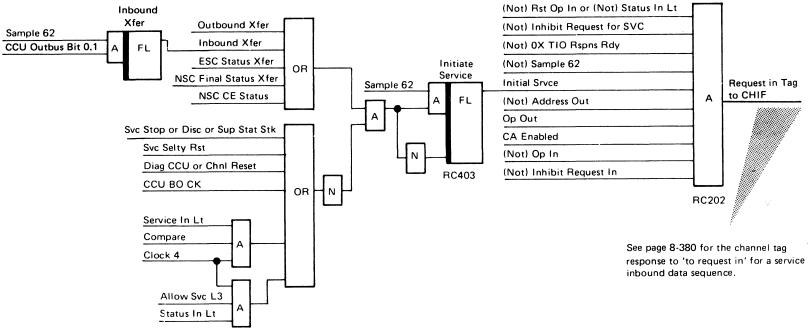

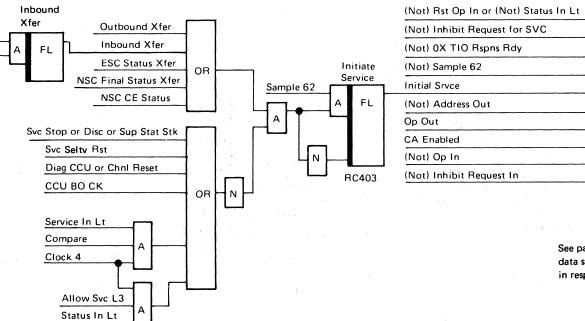

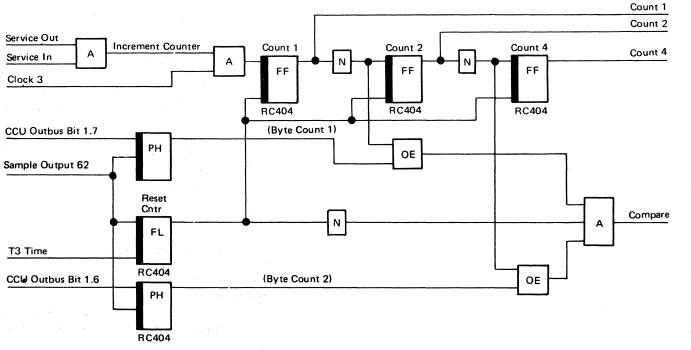

#### **Output X'62' Instruction**

This instruction initiates inbound and outbound data transfers and status presentations. The 3705-80 control program uses this instruction to control CA action and to specify the number of bytes of data to transfer across the channel interface on a channel data transfer.

| Byte  |     | Bits |     |

|-------|-----|------|-----|

| Count | 1.5 | 1.6  | 1.7 |

| 1     | 0   | 0    | 1   |

| 2     | 0   | 1    | 0   |

| 3     | 0   | 1    | 1   |

| 4     | х   | 0    | 0   |

#### X This bit may be on or off for a byte count of four.

#### Summary of Output X'62' bit definitions and ALD locations

| Bit  | Card     | ALD   | Function                                     |

|------|----------|-------|----------------------------------------------|

|      | Location | Page  | · · · · · · · · · · · · · · · · · · ·        |

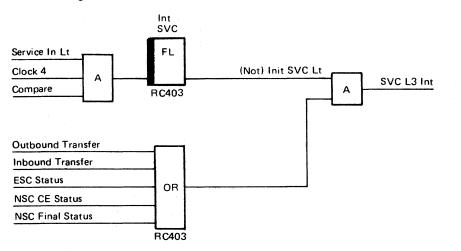

| 0.0* | A4L2     | RC403 | 1 = set; 0 = rst outbound transfer           |

| 0.1* | A4L2     | RC403 | 1 = set; 0 = rst inbound transfer            |

| 0.2* | A4L2     | RC403 | 1 = set; 0 = rst ESC status transfer         |

| 0.3* | A4L2     | RC403 | 1 = set; 0 = rst NSC channel end status      |

| 0.4* | A4L2     | RC403 | 1 = set; 0 = rst NSC final status transfer   |

| 0.5  | A4K2     | RC503 | Reset NSC status cleared                     |

|      | A4L2     | RC402 | Reset initial channel bus out check          |

|      | A4L2     | RC402 | Reset stacked initial                        |

|      | A4L2     | RC402 | Reset initial selection state                |

|      | A4L2     | RC402 | Reset Unit Check L3 interrupt                |

|      | A4N2     | RC205 | Reset initial selection interface disconnect |

|      | A4N2     | RC205 | Reset initial selection selective reset      |

| 0.6  | A4K2     | RC504 | Reset monitor for 2260 ETX                   |

|      | A4K2     | RC504 | Reset monitor for circle B                   |

|      | A4L2     | RC406 | Reset 0X TIO ready                           |

|      | A4L2     | RC405 | Reset service channel bus-out check          |

|      | A4L2     | RC405 | Reset service status stack                   |

|      | A4N2     | RC204 | Reset suppressible status                    |

|      | A4N2     | RC205 | Reset service selective reset                |

|      | A4N2     | RC205 | Reset svc stop or disconnect                 |

|      | A4N2     | RC204 | Reset suppress status stack                  |

| 0.7  |          |       | This bit ignored                             |

| 1.0  | A4K2     | RC504 | Set monitor for circle B                     |

| 1.1  |          |       | This bit ignored                             |

| 1.2  | A4K2     | RC504 | Set Monitor for 2260 ETX                     |

| 1.3  | A4N2     | RC204 | Set suppressible status                      |

| 1.4  | A4L2     | RC406 | Set 0X TIO ready                             |

| 1.5  | A4K2     | RC504 | This bit ignored                             |

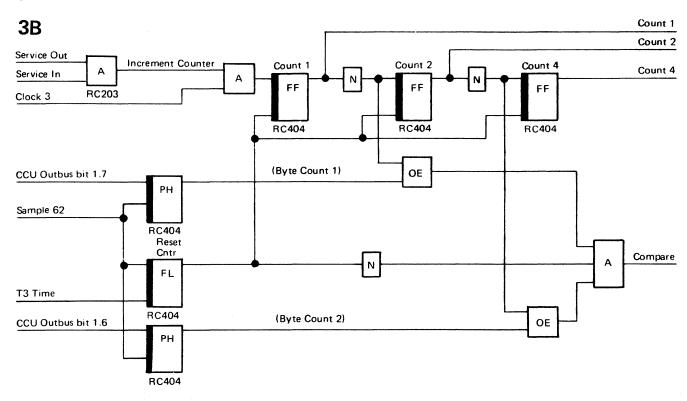

| 1.6  | A4L2     | RC404 | Byte count 2                                 |

| 1.7  | A4L2     | RC404 | Byte count 1                                 |

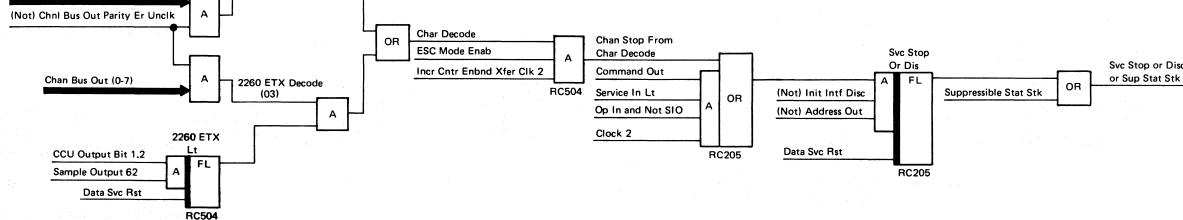

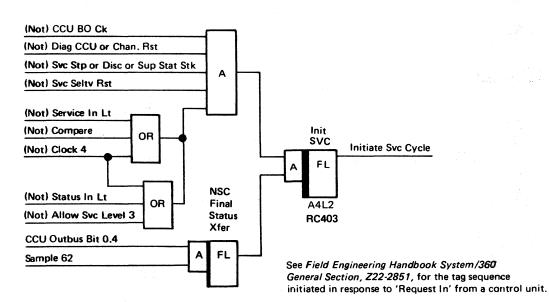

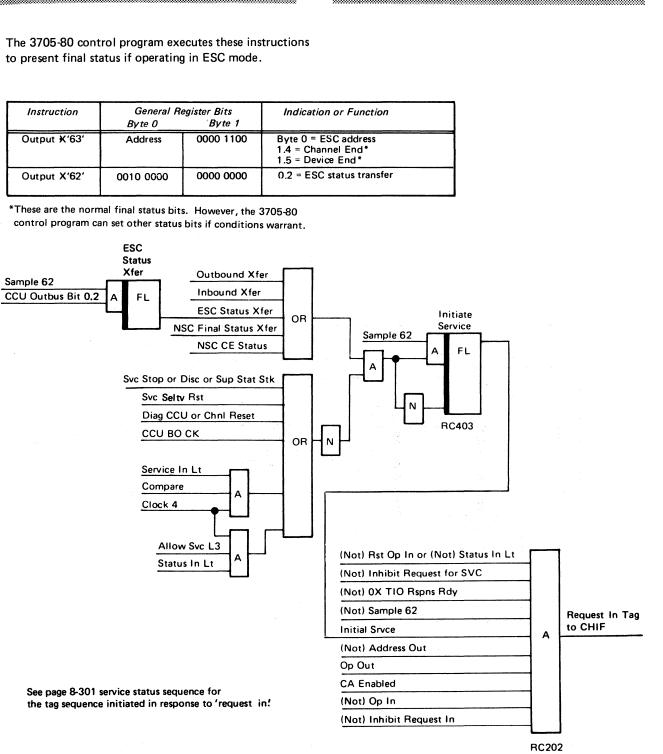

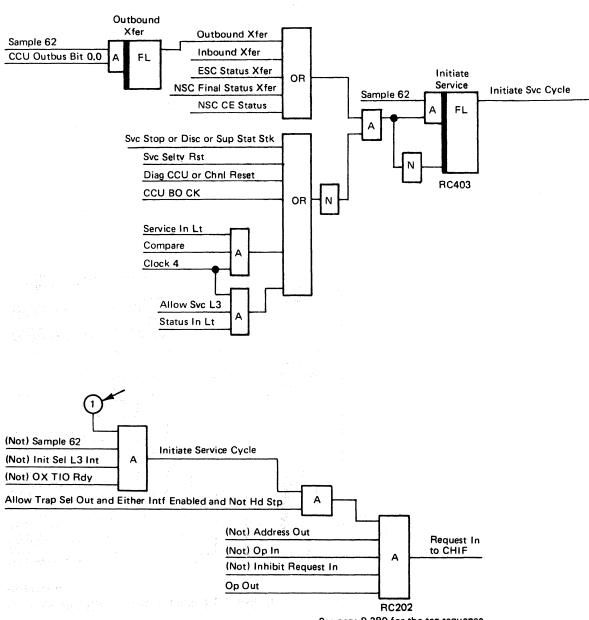

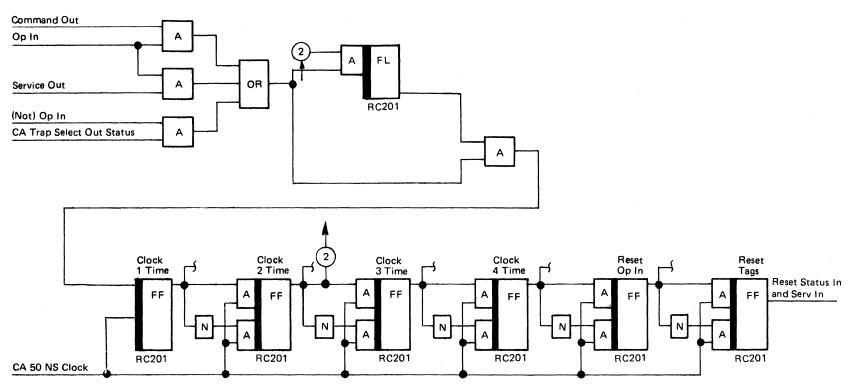

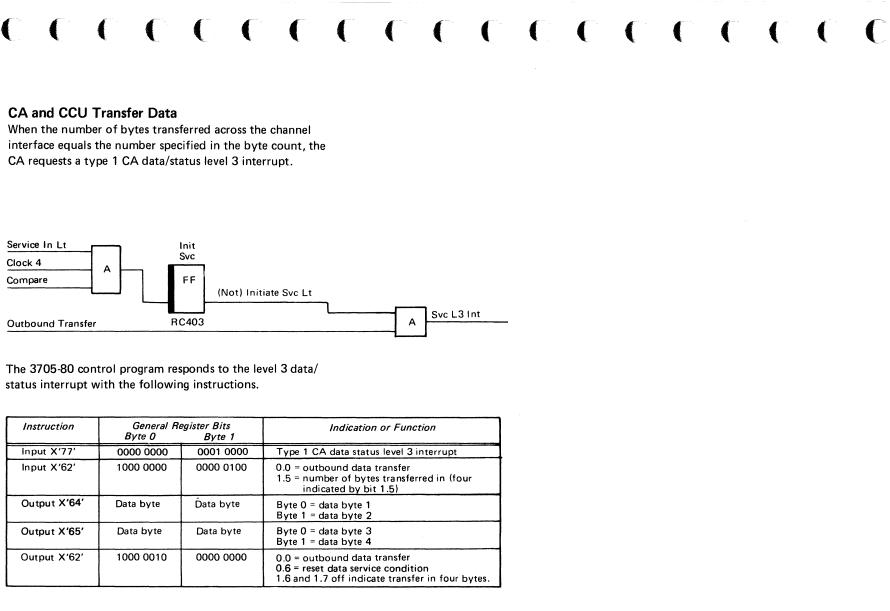

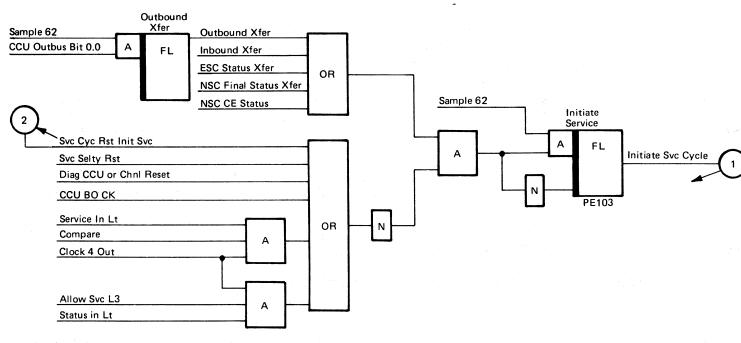

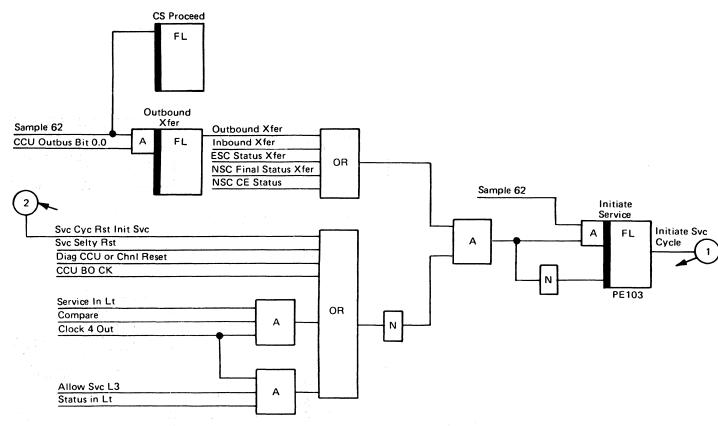

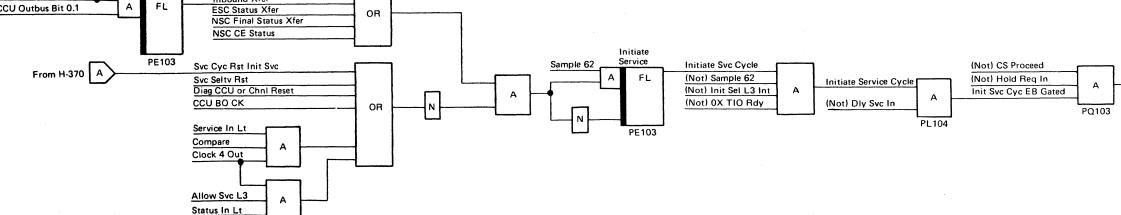

\*Any of these bits with 'Sample 62' set Initiate Service, A4L2, RC404

#### **OUTPUT X'62' INSTRUCTION**

(

8-080

C

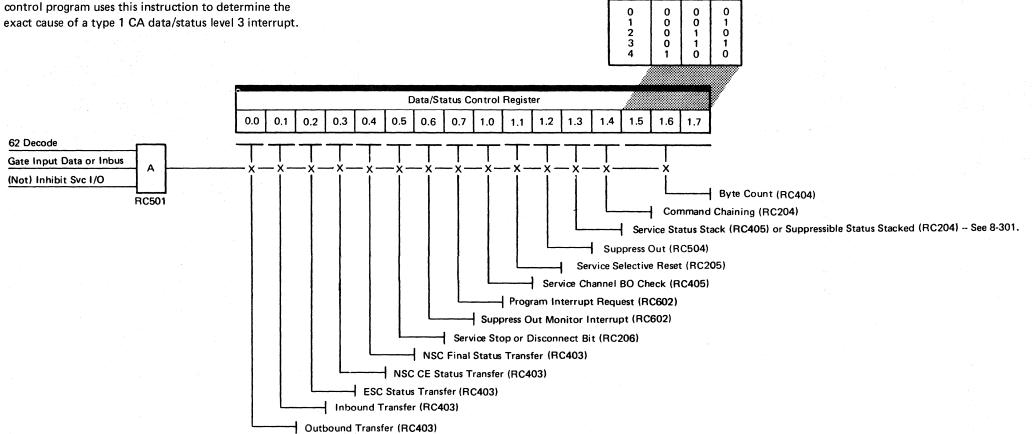

#### Input X'62' Instruction

This instruction transfers the contents of the data/status control register into a CCU general register. The 3705-80 control program uses this instruction to determine the exact cause of a type 1 CA data/status level 3 interrupt.

Count transferred to the CCU

Count

Bits

1.5 1.6 1.7

#### INPUT X'62' INSTRUCTION

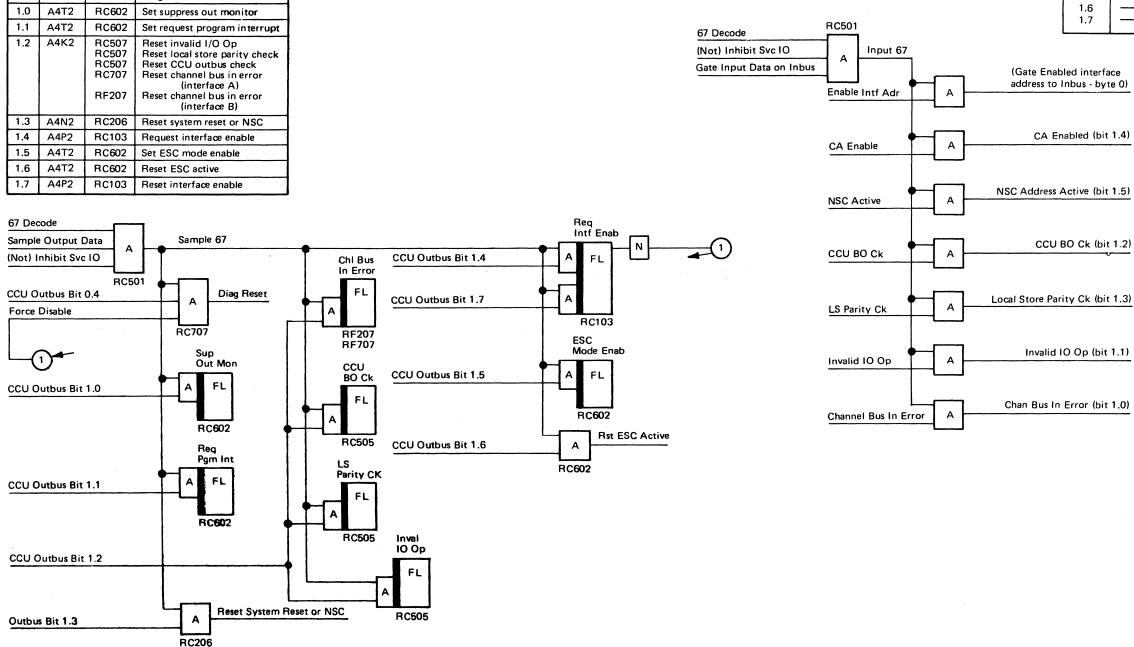

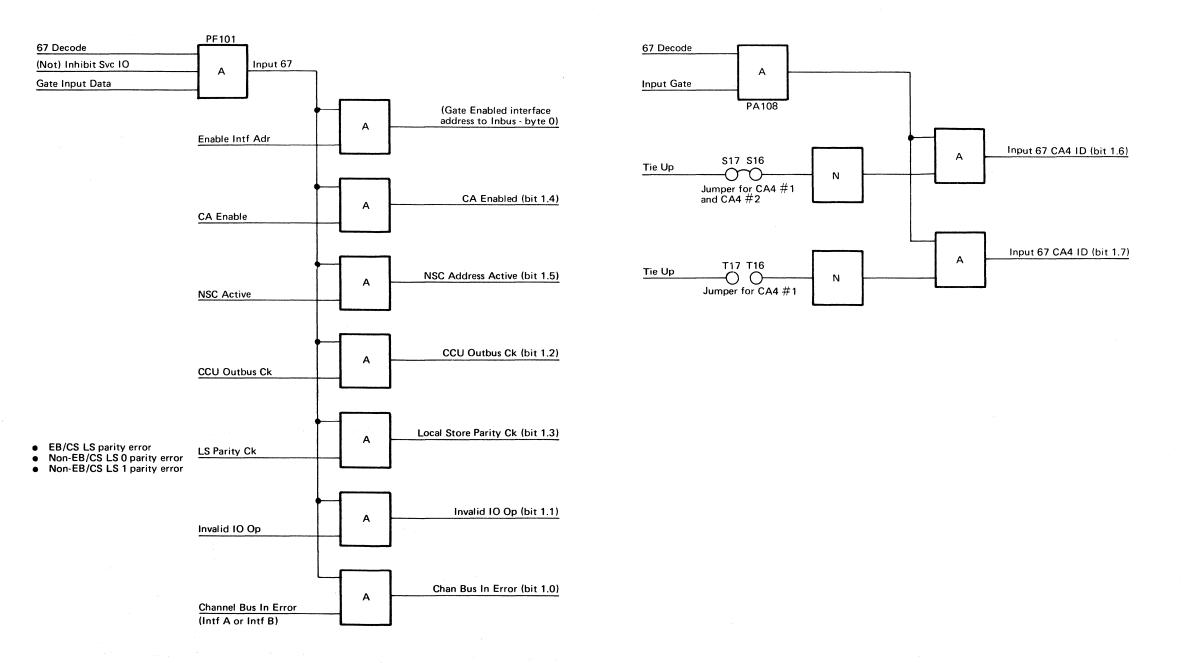

#### Output and Input X'67' Instruction

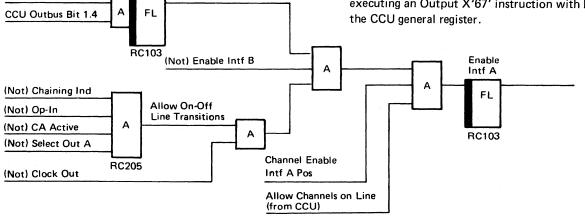

The Output X'67' instruction sets or resets the various control latches. The 3705-80 control program must execute an Output X'67' instruction to enable the CA interface before the CA can transfer data to or from the channel.

#### Summary of Outbus bits during Output X'67'

| Bit | Card | ALD                                       | Function                                                                                                                                                                       |

|-----|------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Loc. | Page                                      |                                                                                                                                                                                |

| 0.4 | A4Q2 | RC707                                     | Diagnostic reset                                                                                                                                                               |

| 1.0 | A4T2 | RC602                                     | Set suppress out monitor                                                                                                                                                       |

| 1.1 | A4T2 | RC602                                     | Set request program in terrupt                                                                                                                                                 |

| 1.2 | A4K2 | RC507<br>RC507<br>RC507<br>RC707<br>RC707 | Reset invalid I/O Op<br>Reset local store parity check<br>Reset CCU outbus check<br>Reset channel bus in error<br>(interface A)<br>Reset channel bus in error<br>(interface B) |

| 1.3 | A4N2 | RC206                                     | Reset system reset or NSC                                                                                                                                                      |

| 1.4 | A4P2 | RC103                                     | Request interface enable                                                                                                                                                       |

| 1.5 | A4T2 | RC602                                     | Set ESC mode enable                                                                                                                                                            |

| 1.6 | A4T2 | RC602                                     | Reset ESC active                                                                                                                                                               |

| 1.7 | A4P2 | RC103                                     | Reset interface enable                                                                                                                                                         |

The Input X'67' transfers the error condition register and the hardware address of the NSC channel interface address to the CCU.

| Bit        | Card<br>Loc. | Logic<br>Page | Function                    |

|------------|--------------|---------------|-----------------------------|

| 0.0-0.7    | A4P2         | RC104         | NSC hardware address intf A |

| 0.0-0.7    | A4P2         | RC107         | NSC hardware address intf B |

| 1.0        | A4Q2         | RC707         | Chan bus in error           |

| 1.1        | A4K2         | RC507         | Invalid I/O Op              |

| 1.2        | A4K2         | RC507         | CCU outbus check            |

| 1.3        | A4K2         | RC507         | Local store parity check    |

| 1.4        | A4K2         | RC504         | CA enabled                  |

| 1.5        | A4K2         | RC504         | NSC address active          |

| 1.6<br>1.7 |              | _             | 0<br>0                      |

#### OUTPUT AND INPUT X'67' INSTRUCTIONS

8-130

Summary of Inbus bits during Input X'67':

#### **Output X'66' Instruction**

The Output X'66' instruction loads the final status byte to be presented to the channel into the NSC Status Byte Register.

#### OUTPUT X'66' INSTRUCTION INPUT X'66' INSTRUCTION

8-120

$\bigcirc$

$\bigcirc$

$\bigcirc \bigcirc \bigcirc \bigcirc$

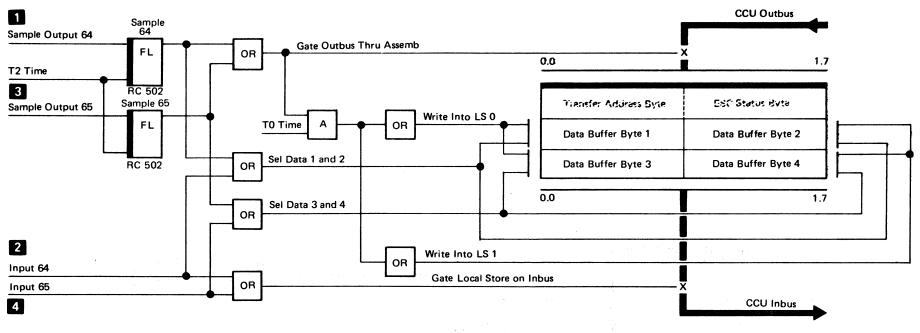

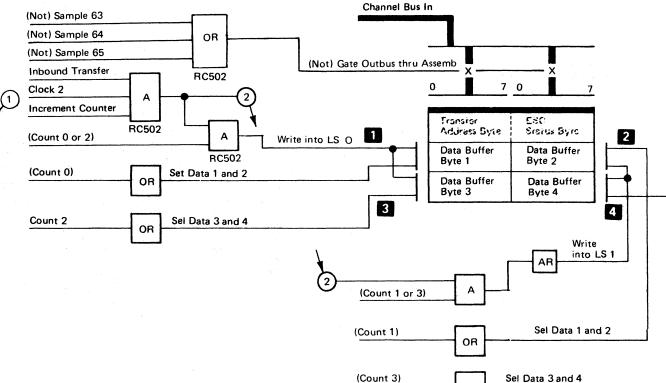

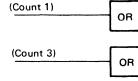

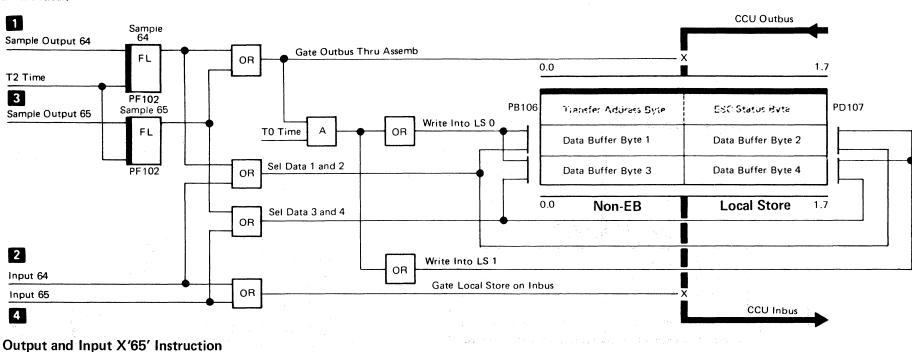

#### Output and Input X'64' Instruction

## 1

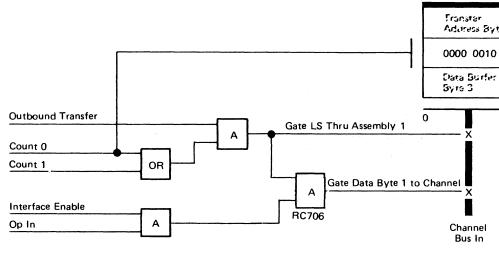

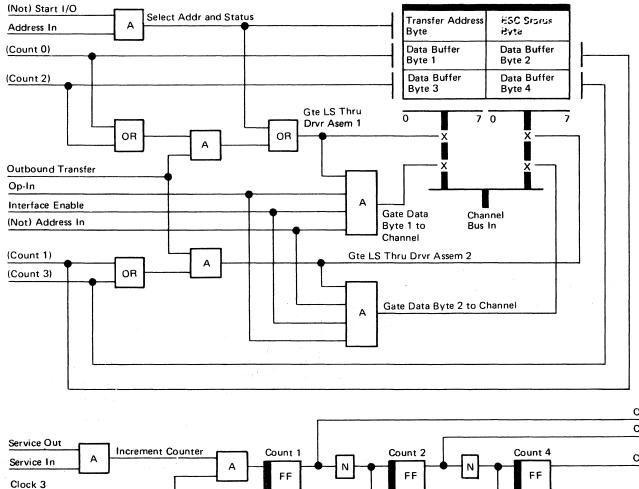

Output X'64' instruction loads data buffer byte 1 and data buffer byte 2 with the first two data bytes to be transferred across the channel to the host processor. These two data bytes are transferred to the host processor one byte at a time during an outbound data transfer.

## 2

Input X'64' transfers into a CCU general register the two data bytes that were received from the channel and stored in data buffer byte 1 and data buffer byte 2.

#### Output and Input X'65' Instruction

## 3

Output X'65' instruction loads data buffer byte 3 and data buffer byte 4 with the second two bytes to be transferred across the channel to the host processor. These two data bytes are transferred to the host processor one byte at a time during an outbound data transfer.

## 4

Input X'65' transfers into a CCU general register the two data bytes that were received from the channel and stored in data buffer byte 3 and data buffer byte 4. OUTPUT AND INPUT X'64' INSTRUCTIONS OUTPUT AND INPUT X'65' INSTRUCTIONS

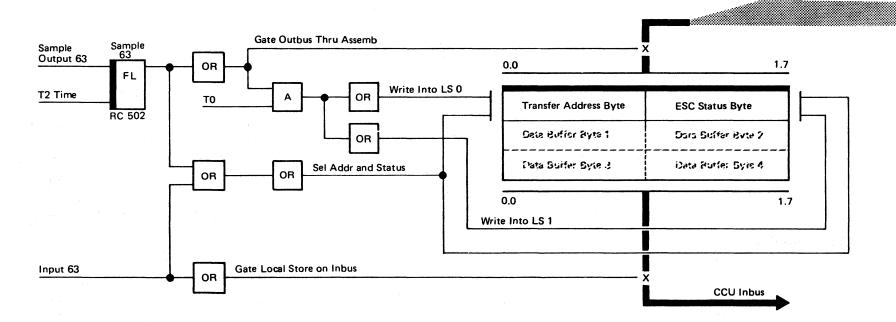

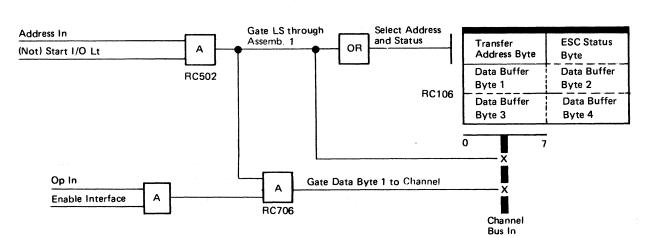

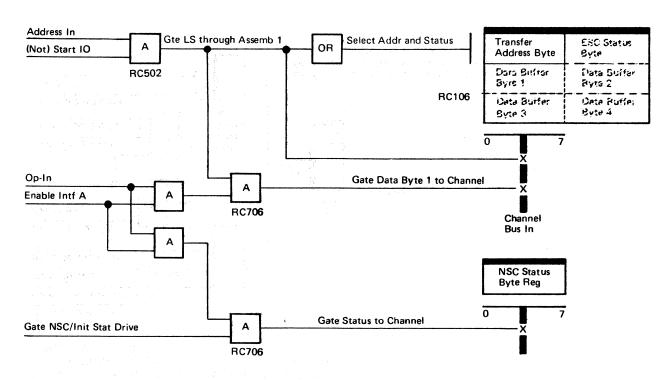

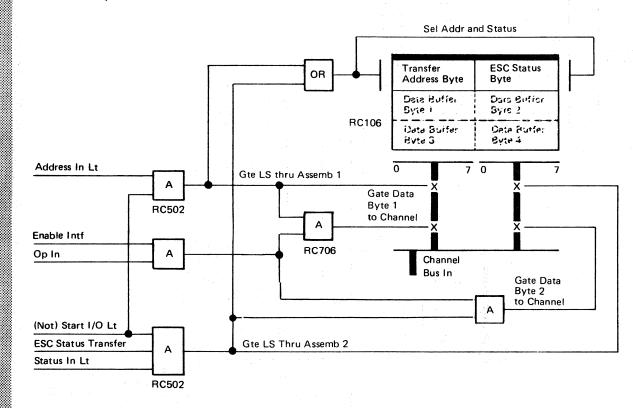

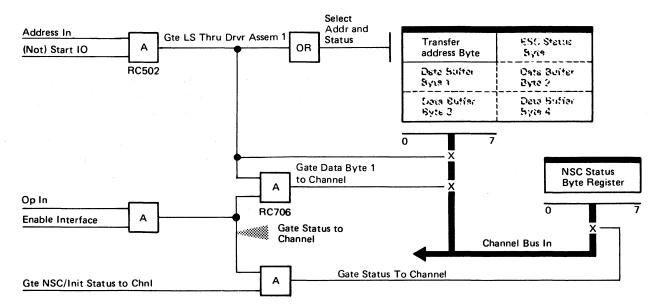

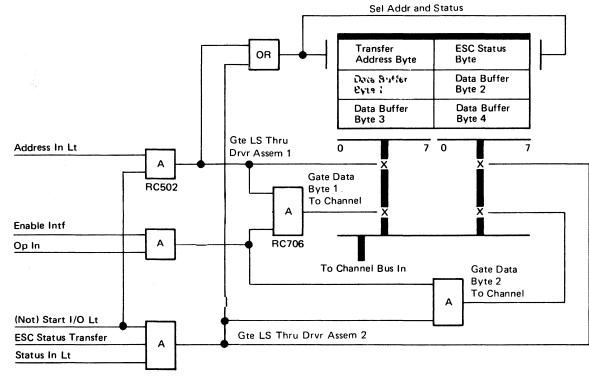

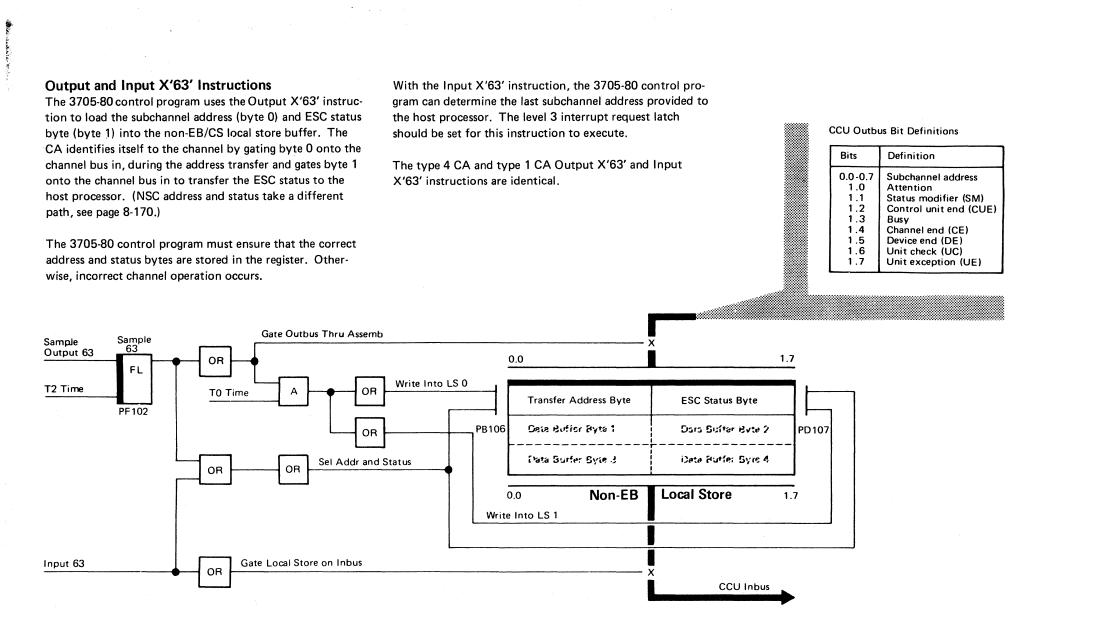

#### Output and Input X'63' Instructions

The 3705-80 control program uses the Output X'63' instruction to load the subchannel address (byte 0) and ESC status byte (byte 1) into the local store buffer. The CA identifies itself to the channel by gating byte 0 onto the channel bus-in, during the data transfer and gates byte 1 onto the channel bus-in to transfer the ESC status to the host processor. (NSC address and status take a different path, see page 8-170.) The 3705-80 control program must ensure that the correct address and status bytes are stored in the register. Otherwise, incorrect channel operation occurs.

With the Input X'63' instruction, the 3705-80 control program can determine the last subchannel address provided to the host processor. The level 3 interrupt request latch should be set for this instruction to execute.

#### CCU Outbus Bit Definitions

| Bits                                                            |

|-----------------------------------------------------------------|

| 0.0-0.7<br>1.0<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7 |

i ev

OUTPUT AND INPUT X'63' INSTRUCTIONS

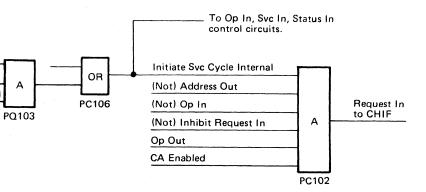

## CHANNEL ADAPTER INITIALIZATION (IPL) (PART 1 OF 2)

Channel adapter initialization involves enabling the CA to a channel interface and requesting a Write IPL command from the host processor.

The type 1 CA is not affected by the reset performed in IPL phase 1 unless the IPL sequence is started by a power on sequence. Therefore, the ROS bootstrap program must handle the following situations:

1. Channel interface disabled.

Sample 67

- 2. Channel interface enabled without a channel command in progress.

- 3. Channel interface enabled with a channel command in progress.

Req Intf Enab The CA can be enabled to one of two channel interfaces. The second channel interface is optional and allows the CA to be attached to two different host processors. The CA can also be attached to the same channel through the interfaces. However, only one interface can be enabled at a time.

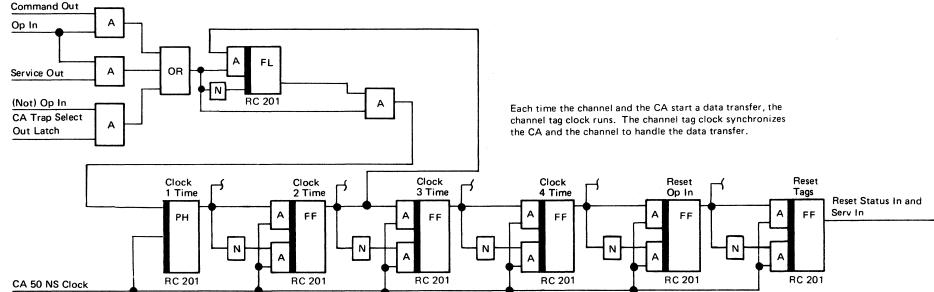

The channel interface must be enabled for the channel and CA to communicate. The manual procedure to enable a channel interface is described on page 1-050. The bootstrap program must execute an Output X'67' instruction with bit 1.4 on in the general register. This bit allows the channel interface to be enabled. The ROS bootstrap program checks for the interface to become enabled with an Input X'67' instruction. When the Input X'67' transfers bit 1.4 to the CCU general register, the ROS bootstrap program requests a CA data/status level 3 interrupt by executing an Output X'67' instruction with bit 1.1 on in the CCU general register.

If no channel command is in progress, the program signals the CA to send an asynchronous status of Device End (DE) Unit Check (UC) to the channel. The bootstrap program must execute the following instructions to present the asynchronous attention.

| Instruction  | General F<br>Byte 0 | Register Bits<br>Byte 1 | Indication or Fund                                                                                              |