**Maintenance Library**

Volume 1

PLAN MLM LAYOUT

START MSG SYSTEM MESSAGES

**PANEL**

MICRO DIAGNOSTICS

Volume 2

OLTDIAG

SENSE DATA

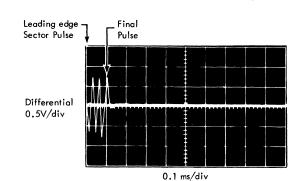

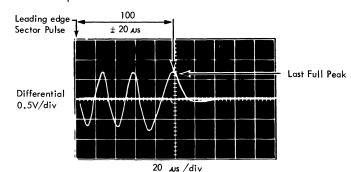

CTRL CONTROL MPL 23FD

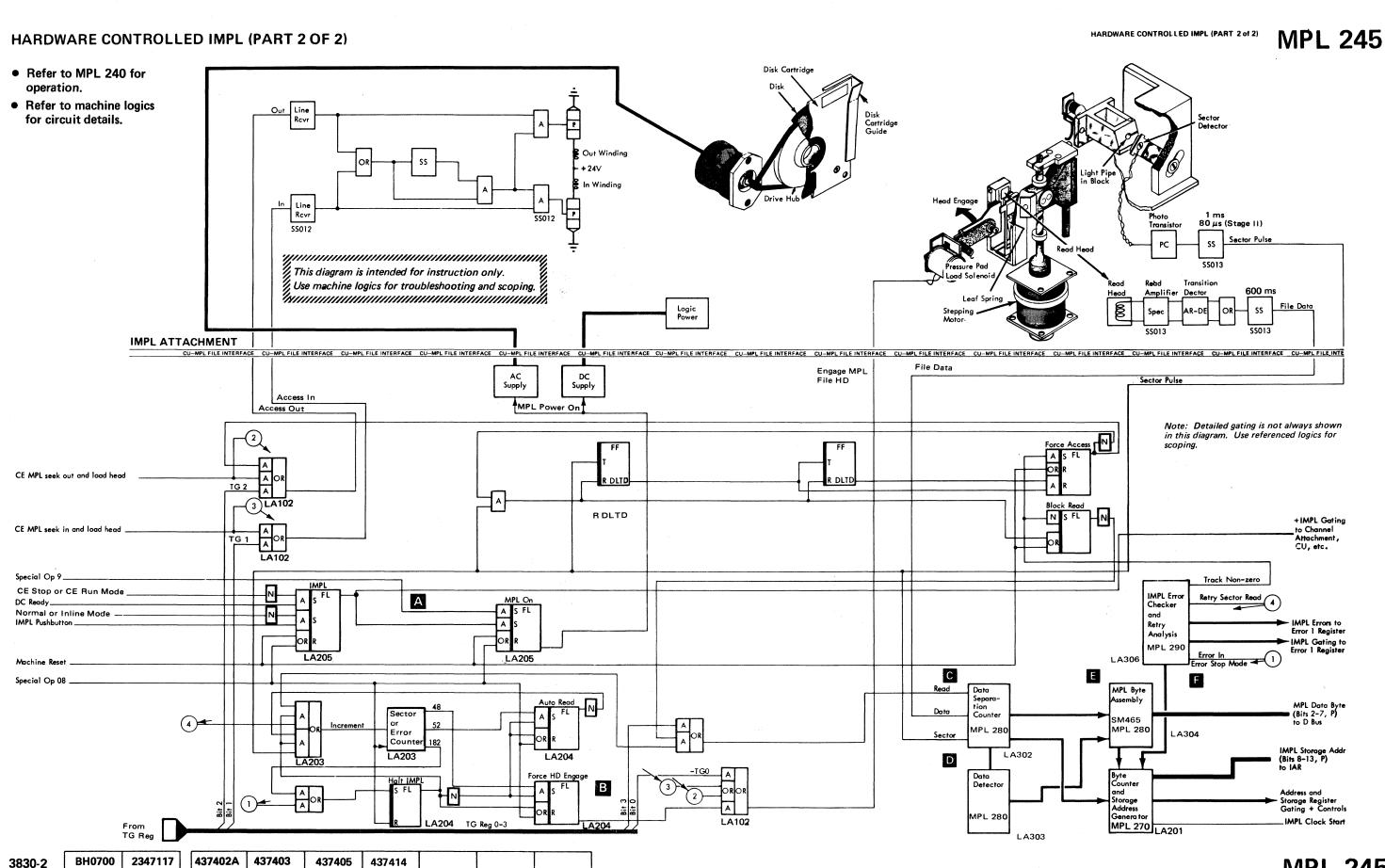

MPL ATTACHMENT

CHL-I CHANNEL INTERFACE

CTL-I CONTROL INDEX

Volume 3

PWR POWER

INTR ODUCTION

**CMD** COMMANDS

MIC ROPROGRAM

MICFL DIAG FLOW LOC ATIONS

INSTALLATION

Storage Control, Model 2

437405 437408

437414

CE-MLM Feedback forms are provided at the front of Volume R01 for reader comments. If the forms have been removed, send your comments to the address below.

This manual was prepared by the IBM General Products Division, Product Publications, Department G24, San Jose, California 95193.

SAFETY

Be constantly aware of hazardous situations when working on the 3830-2 Storage Control. Take time to review the CE safety practices listed below which have been reprinted from the pocket-size card available from Mechanicsburg (Order No. S229-1264).

## **CE SAFETY PRACTICES**

All Customer Engineers are expected to take every safety precaution possible and observe the following safety practices while maintaining IBM equipment:

- You should not work alone under hazardous conditions or around equipment with dangerous voltage. Always advise your manager if you MUST work alone.

- Remove all power, ac and dc, when removing or assembling major components, working in immediate areas of power supplies, performing mechanical inspection of power supplies, or installing changes in machine circuitry.

- After turning off wall box power switch, lock it in the Off position or tag it with a "Do Not Operate" tag, Form 229-1266. Pull power supply cord whenever possible.

- 4. When it is absolutely necessary to work on equipment having exposed operating mechanical parts or exposed live electrical circuitry anywhere in the machine, observe the following precautions:

- a. Another person familiar with power off controls must be in immediate vicinity.

- b. Do not wear rings, wrist watches, chains, bracelets, or metal cuff links.

- c. Use only insulated pliers and screwdrivers.

- d. Keep one hand in pocket.

- e. When using test instruments, be certain that controls are set correctly and that insulated probes of proper capacity are used.

- f. Avoid contacting ground potential (metal floor strips, machine frames, etc.). Use suitable rubber mats, purchased locally if necessary.

- 5. Wear safety glasses when:

- a. Using a hammer to drive pins, riveting, staking, etc.

- b. Power or hand drilling, reaming, grinding, etc.

- c. Using spring hooks, attaching springs.

- d. Soldering, wire cutting, removing steel bands.

- e. Cleaning parts with solvents, sprays, cleaners, chemicals, etc.

- f. Performing any other work that may be hazardous to your eyes. REMEMBER THEY ARE YOUR EYES.

- Follow special safety instructions when performing specialized tasks, such as handling cathode ray tubes and extremely high voltages. These instructions are outlined in CEMs and the safety portion of the maintenance manuals.

- Do not use solvents, chemicals, greases, or oils that have not been approved by IBM.

- Avoid using tools or test equipment that have not been approved by IBM.

- 9. Replace worn or broken tools and test equipment.

- Lift by standing or pushing up with stronger leg muscles this takes strain off back muscles. Do not lift any equipment or parts weighing over 60 pounds.

- After maintenance, restore all safety devices, such as guards, shields, signs, and grounding wires.

- 12. Each Customer Engineer is responsible to be certain that no action on his part renders products unsafe or exposes customer personnel to hazards.

- 13. Place removed machine covers in a safe out-of-the-way place where no one can trip over them.

- Ensure that all machine covers are in place before returning machine to customer.

- Always place CE tool kit away from walk areas where no one can trip over it; for example, under desk or table.

- Avoid touching moving mechanical parts when lubricating, checking for play, etc.

- When using stroboscope, do not touch ANYTHING it may be moving.

- Avoid wearing loose clothing that may be caught in machinery. Shirt sleeves must be left buttoned or rolled above the elbow.

- Ties must be tucked in shirt or have a tie clasp (preferably nonconductive) approximately 3 inches from end. Tie chains are not recommended

- 20. Before starting equipment, make certain fellow CEs and customer personnel are not in a hazardous position.

- 21. Maintain good housekeeping in area of machine while performing and after completing maintenance.

Knowing safety rules is not enough.

An unsafe act will inevitably lead to an accident.

Use good judgment - eliminate unsafe acts.

#### **ARTIFICIAL RESPIRATION**

#### **General Considerations**

- Start Immediately Seconds Count

Do not move victim unless absolutely necessary to remove from danger. Do not wait or look for help or stop to loosen clothing, warm the victim, or apply stimulants.

- 2. Check Mouth for Obstructions

Remove foreign objects. Pull tongue forward.

- Loosen Clothing Keep Victim Warm

Take care of these items after victim is breathing by himself or when help is available.

- Remain in Position

After victim revives, be ready to resume respiration if necessary.

- 5. Call a Doctor

Have someone summon medical aid.

- Don't Give Up

Continue without interruption until victim is breathing without help or is certainly dead.

#### **Rescue Breathing for Adults**

- 1. Place victim on his back immediately.

- 2. Clear throat of water, food, or foreign matter.

- 3. Tilt head back to open air passage.

- 4. Lift jaw up to keep tongue out of air passage.

- 5. Pinch nostrils to prevent air leakage when you blow,

- 6. Blow until you see chest rise

- 7. Remove your lips and allow lungs to empty.

- 8. Listen for snoring and gurglings signs of throat obstruc-

- Repeat mouth to mouth breathing 10-20 times a minute.

Continue rescue breathing until victim breathes for himself.

Final mouth-tomouth position

3830-2

AX0050 2347443 Seq 2 of 2 Part Number 437405 437408 437414 15 Aug 72 16 Oct 72 4 Jun 73

© Copyright IBM Corporation 1972, 1973

SAFFTY

SAFETY

# **CONTENTS**

# OLT

| Online Tests - Running Refre            | sher  | •   | •   |     | •   |   | • | OLT | 10  |

|-----------------------------------------|-------|-----|-----|-----|-----|---|---|-----|-----|

| OLTSEP                                  |       |     |     |     |     |   |   |     |     |

| Preparation                             |       |     |     |     |     |   |   |     |     |

| Starting OLTSEP                         |       |     |     |     |     |   |   |     |     |

| Making a Run Request                    |       |     |     |     |     |   |   |     |     |

| Options OLTCER                          |       |     |     |     |     |   |   |     |     |

| Halting OLTSEP                          |       |     |     |     |     |   |   |     |     |

| OS-OLTEP<br>Preparation                 |       |     |     |     |     |   |   |     |     |

| • • • • • • • • • • • • • • • • • • • • |       |     |     |     |     |   |   |     |     |

| Starting OS-OLTEP                       |       |     |     |     |     |   |   |     |     |

| Making a Run Request Options            |       |     |     |     |     |   |   |     |     |

| •                                       |       |     |     |     |     |   |   |     |     |

| Halting OS-OLTEP DOS OLTEP              |       |     |     |     |     |   |   | OLT | 15  |

| Preparation                             | •     | •   | •   | •   | •   | • | • | OL. |     |

| Starting DOS-OLTEP                      |       |     |     |     |     |   |   |     |     |

| Making A Run Request                    |       |     |     |     |     |   |   |     |     |

| Option Field Entries                    |       |     |     |     |     |   |   |     |     |

| Halting DOS-OLTEP                       |       |     |     |     |     |   |   |     |     |

| Traiting DOS-OLTER                      |       |     |     |     |     |   |   |     |     |

| OLT Prerequisites                       |       |     |     |     |     |   |   | OLT | 20  |

| Program Requirements                    |       |     |     | -   | -   | - | - |     |     |

| Equipment Requirements                  |       |     |     |     |     |   |   |     |     |

| Device Configuration Data Se            | et Ei | ntr | v   |     |     |   |   |     |     |

| 3830 CU Configuration Data              |       |     |     | v   |     |   |   |     |     |

| Standalone/Online Support F             |       |     |     | •   |     |   |   |     |     |

| ••                                      | Ī     |     |     |     |     |   |   |     |     |

| Online Test Description .               |       |     |     |     |     |   |   | OLT | 25  |

| Section ID T3830AAA                     |       |     |     |     |     |   |   |     |     |

| Initialization                          |       |     |     |     |     |   |   |     |     |

| Routines                                |       |     |     |     |     |   |   |     |     |

| Running                                 |       |     |     |     |     |   |   |     |     |

| Section ID T3830AAB                     |       |     | •   |     | •   |   |   | OLT | 30  |

| Routine                                 |       |     |     |     |     |   |   |     |     |

| Running                                 |       |     |     |     |     |   |   |     |     |

|                                         |       |     |     |     |     |   |   |     |     |

| Online Tests - Error Messages           |       |     |     | •   |     |   |   | OLT | 50  |

| CU Channel Interface Test (7            |       |     | ٩A  | A)  |     |   |   |     |     |

| Format for Error Codes L                |       |     |     |     |     |   |   |     |     |

| Error Codes Displayed in                |       | /PI | ו כ | Lan | nps |   |   |     |     |

| Control Storage Location                |       |     |     |     |     |   |   |     |     |

| OLTEP/OLTSEP Error Mess                 | anae  |     |     |     |     |   |   | OLT | 80  |

| OLILI/OLIGEI EIIOI Wess                 | ages  | •   | •   | •   | •   | • | ٠ | OL. | 00  |

| T3830AAA Error Messages                 |       |     |     |     |     |   |   | OLT | 100 |

|                                         |       |     |     |     |     |   |   |     |     |

| T3830AAB Error Messages                 | •     | •   | •   | •   | ٠   | • | ٠ | OLT | 200 |

| Standard Error Numbers .                |       |     |     |     |     |   |   | OLT | 300 |

|                                         |       |     |     |     |     |   |   |     |     |

3830-2

| AX0200 2347064           | 437402A   | 437403    | 437404    | 437405    | 437408    | 437413   | 437414   |

|--------------------------|-----------|-----------|-----------|-----------|-----------|----------|----------|

| Seq. 1 of 2 Part No. ( ) | 15 Mar 72 | 21 Apr 72 | 23 Jun 72 | 15 Aug 72 | 16 Oct 72 | 5 Mar 73 | 4 Jun 73 |

# Refer to OLT 25 for detailed running procedure.

OLTSEP

| Prepa | arati | on |

|-------|-------|----|

Mount OLTSEP pack or tape and IPL.

# Starting OLTSEP

OLTSEP will print:

04 SEP188D ENTER DATE (AND TIME) 'MM/DD/YY,HH/MM/SS'

Your reply is:

r 04, 'xx/xx/xx, hh/mm/ss'

### OLTSEP will print:

04 SEP102I OLTS RUNNING

04 SEP107I OPTIONS ARE NTL, NEL, EP, CP, NPP, PR, FE, NMI, SI

01 SEP105D ENTER DEV/TEST/OPT

To run OLTS from card decks, the RDR (reader) device must be varied from its default of disk or tape to card. To do this, reply:

r 01, 'VARY RDR=00C'

'00C' is the address of the card reader. Modify the address to conform to your system. OLTSEP will print:

01 SEP219I VARY COMPLETE

01 SEP105D ENTER DEV/TEST/OPT

If the RDR device is to remain on the disk or tape, do not reply with the Vary command.

# Making a Run Request

Make a run request to select the test you want to run.

Note: OLTs 3830 AAA and AAB must be selected. You cannot enter /3830//.

Your reply is:

r 01,'160/3830AAA//'

This reply will begin testing on device 160. Run OLT test AAA and use the default options. To select some other sequence of testing, enter a reply of:

r 01,'160/3830AAA,7/MI,NFE'/'

This will run only routine 7 of the control unit online tests, and will cause all the default options to be selected except the option FE (first error communications), which will be altered to NFE and NMI (no manual intervention), which will be altered to MI.

Note: See OS-OLTEP paragraph "Make a Run Request" for additional examples.

| OLTSEP (Continu |     |         |

|-----------------|-----|---------|

| Yes             | No  | Default |

| TL (Value)      | NTL | NTL     |

|   | Option              | 1 62       | NO  | Delaui |

|---|---------------------|------------|-----|--------|

|   | Test Loop           | TL (Value) | NTL | NTL    |

|   | Error Loop          | EL         |     |        |

|   |                     | EL (I)     |     |        |

|   | ·                   | EL (Value) | NEL | NEL    |

|   | Error Print         | EΡ         | NEP | EP     |

| ı | Control Print       | CP         | NCP | CP     |

|   | Parallel Print      | PP (Value) | NPP | NPP    |

|   | Print               | PR         | NPR | PR     |

| i | First Error Comm.   | FE         | NFE | FE     |

|   | Manual Intervention | MI         | NMI | NMI    |

|   | Spurious Interrupt  | SI         | NSI | SI     |

|   | Data Entry Field    | EXT=(Data) |     |        |

|   | Remote FE Control   | RF         | NRF | NRE    |

The RE option is only recognized if the RETAIN interface has been activated. ('REI' was entered in response to the SEP105D message.)

## Halting OLTSEP

Options

Ontion

To halt OLTSEP at any time, press Request key on the console. **OLTSEP** will print:

04 SEP 107I OPTIONS ARE -----01 SEP105D ENTER DEV/TEST/OPT

#### Your reply is:

r Ol, '(new device)/(new test)/ (new options)/' New instructions to OLTSEP

or:

(EOB) To continue

r 01,'//' To continue or restart the section under test.

or:

r 01, 'cancel' To terminate the section under test.

Note: See OLTSEP Guide (D99-SEPDT) for detail,

#### OS-OLTEP

#### Preparation

Units to be tested must be varied offline. This is accomplished through the console by using the Vary command. Examples:

V 160.OFFLINE (will vary unit 160 offline) V (160,161,162), OFFLINE (will vary units 160, 161, and 162 offline. The system will reply 160 OFFLINE when the vary is completed.)

Note: SYSRES cannot be varied offline.

It is important that you vary the units to be used offline prior to starting OS-OLTEP. If you decide to test another unit after OS-OLTEP has started, type in the Vary Offline command;

- 1. If running under MVT, type in S INIT, and after the initiator is started, type in P INIT. This causes an initiator to start and stop and varies the unit offline.

- 2. If running under MFT, type in C OLTEP. After OS-OLTEP is cancelled, type in S OLTEP. PX. This cancels and restarts OS-OLTEP and varies the unit offline.

# Starting OS—OLTEP

S - causes a job to be started if a reader procedure is incorporated in your system. Examples:

SOLTEP S OLTEP. PX (for an MVT system)

(for an MFT system — where X is the partition number OLTEP is to run in.

If in doubt, ask an operator which

partition to use.)

OR - (Use JCL on cards to execute

program IFDOLT.)

Once OS-OLTEP is running, it generates various messages. These can be found in the Messages and Completion Codes SRL. Here are a few examples:

IFD102I OLTS RUNNING (To inform you that OS-OLTEP is running.)

00 IFD104E TO FORCE COMMUNICATION

WITH OLTEP EXECUTIVE. ENTER ANY CHARACTER

(A reply of any character will cause the test to stop at this point. Message IFD105D will then be presented.

# OS—OLTEP (Continued)

# Making a Run Request

OS-OLTEP will wait for a reply after issuing this message:

Ol IFD105D ENTER-DEV/TEST/ OPT/

Example of DEV/TEST/OPT/reply:

r 01,'160/3830AAA//'

#### Options

Use the Options chart from OLTSEP paragraph.

# Halting OS—OLTEP

Reply to message '00' with any character to force communications. OS-OLTEP will print:

01 IFD105D ENTER -- DEV/ TEST/OPT/

You will reply:

r 01, 'cancel' (This will cancel OS-OLTEP.)

Or press Request on the console, then enter:

C OLTEP This will also cancel OLTEP.

Note: See OS/OLTEP SRL (Order No. GC28-6650) for details and procedures.

3830-2

2347064 AX0200 Seq 2 of 2 Part Number

© Copyright IBM Corporation 1972, 1973

437402A

15 Mar 72

437403 437404 21 Apr 72 23 Jun 72

437405 15 Aug 72

437408 16 Oct 72

437413

437414

ONLINE TESTS - RUNNING REFRESHER (Part 1 of 2)

**OLT 10**

# ONLINE TESTS — RUNNING REFRESHER (Part 2 of 2)

ONLINE TESTS - RUNNING REFRESHER (Part 2 of 2)

## DOS-OLTEP

#### Preparation

Units to be tested must not be assigned to either of the foreground programs. The background program must be available for CE use.

### Starting DOS—OLTEP

You may put job control cards in the reader or you may enter JCL commands from the system console. The example shown is for the console. Underlined characters are entered by the CE.

- AR START BG

- BG // JOB TEST 3830 MOD2

- BG // ASSGN SYS014, X'160'

- BG // EXEC IJZADOLT

- BG E102I OLTS RUNNING

- BG E107I OPTIONS ARE-NTL, NEL, NPP, FE, NMI, EP, CP, PR, NRE, NTR

- BG 01E105D ENTER--DEV/TEST/OPT/

Note: This will be printed after the first error, after pressing the interrupt key, or at job completion.

# Making a Run Request (Reply to E005D)

BG r 01, '160/3830AAA//' (Test 160 with 3830AAA)

BG E158I S T3830AAA \$ UNIT 0160 (Testing

#### **Option Field Entries**

Use the Options chart from OLTSEP paragraph on OLT 10.

# Halting DOS—OLTEP

To halt DOS-OLTEP at any time, press the CPU/ INTERRUPT button. DOS-OLTEP will print:

BG 01E105D ENTER--DEV/TEST/OPT/ BG r 01, 'cancel'

DOS-OLTEP will be cancelled and the background program will again be available to the customer.

Note: See DOS/OLTEP SRL (Order No. GC24-5086) for details.

© Copyright IBM Corporation 1972, 1973, 1974, 1975, 1976

#### 3830-2

| AX0300    |              | See        | 437416    | 447460    | 447461    |  |  |

|-----------|--------------|------------|-----------|-----------|-----------|--|--|

| Seq. 1 of | Part No. (8) | EC History | 11 Jan 74 | 19 Dec 75 | 12 Mar 76 |  |  |

The 3830-2 online tests verify that:

- CPU can communicate with the control unit (CU).

- All tag and bus lines between the CU and channel are operational.

- Channel interface logic in the CU is operational.

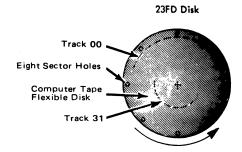

- Identity of 23FD disk is correct.

Complete test descriptions are found on OLT 25, 30.

## **PROGRAM REQUIREMENTS**

All documentation in this OLT section applies only to OLTs 3830AAA and 3830AAB at Version 2, Level 0 (PID release 5.0). These OLTs require a 3830-2 CU diagnostic disk at EC 437418 or higher. The control program used must be at the level specified below:

**OLTSEP 8.0** or higher OS/OLTEP 21.7 or higher DOS/OLTEP 29.0 or higher VS1/OLTEP 2.6 or higher VS2/OLTEP 2.0 or higher

OLTEP requires a system or private library containing: Configuration data set (CDS) OLT sections T3830AAA and AAB

OLTSEP requires a load tape or disk load file containing:

IPL loader

**OLTSEP** nucleus

**OLTSEP** transient modules

SOSP

Configuration data set

OLT sections T3830AAA and AAB

# **EQUIPMENT REQUIREMENTS**

3830-2 Storage Control

Integrated Storage Control (ISC) for 3145, 3158, or

3830 Diagnostic 23FD disk

# **DEVICE CONFIGURATION DATA SET ENTRY**

Configuration data must be correctly supplied for the unit addresses to be entered at dev/test/opt time as follows (one card per unit address plus one card per 3830 control unit).

| Card<br>Column | Enter                                     |

|----------------|-------------------------------------------|

| 1              | Blank                                     |

| 2-4            | CDS                                       |

| 5-9            | Blank                                     |

| 10-17          | Device address (example: 00000160)        |

| 18-19          | Model code (02)                           |

| 20-21          | Feature code (02)                         |

| 22–23          | Class (20)                                |

| 24-25          | Type 09 - 3333/3330 Mod 1, 2*             |

|                | Type 0A — 3340/3344                       |

|                | Type 0B - 3350*                           |

|                | Type 0D - 3333 Mod 11/3330 Mod 11*        |

| 26-29          | Blank                                     |

| 30-31          | 04 = Two Channel Switch or Two Chan-      |

| 00 0.          | nel Switch, Additional                    |

| flags          | 40 = Shared (either by string or channel) |

| , iugs         | 44 = Both of above                        |

| 32-35          | Blank                                     |

| 36-37          | Suffix to identify control unit CDS.      |

|                | This field must match card columns 42     |

|                | and 43 in the CU 3830 CDS card that       |

|                | defines the control unit through which    |

|                | this unit address is accessed.            |

| 38             | Enter a slash (/) to indicate end of CDS  |

|                | entry                                     |

<sup>\*</sup>If in compatability mode, punch card for compatability type. For example, for 3330-11 compatability, punch 0D.

CDS must include entries for each device on your system. (See CDS Guide, D99-CDSGA.) Devices accessible via Two-Channel Switch, Two Channel Switch Additional, or String Switch will have more than one CDS entry per device.

# 3830 CU CONFIGURATION DATA SET ENTRY

When T3830AAA is running, control unit CDS information is used to:

1. Tell the CE which unit addresses must be made unusable to the system; e.g., vary offline (OS), unassign (DOS).

2. Test the CU device address register.

| Card<br>Column | Enter                                                                                                                                                                                                              |  |  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 5-29           | Unused – leave blank                                                                                                                                                                                               |  |  |  |  |

| 30             | Flags code — 4 if control unit is shared                                                                                                                                                                           |  |  |  |  |

|                | with another system, otherwise leave blank.                                                                                                                                                                        |  |  |  |  |

| 31             | Flags code ('8') — indicates symbolic CDS                                                                                                                                                                          |  |  |  |  |

| 31             | name in card columns 36–43                                                                                                                                                                                         |  |  |  |  |

| 32-35          | Blank                                                                                                                                                                                                              |  |  |  |  |

| 36-41          |                                                                                                                                                                                                                    |  |  |  |  |

| 42-43          | Symbolic CDS name prefix — CU3830                                                                                                                                                                                  |  |  |  |  |

| 42-43          | Symbolic CDS name prefix — this field                                                                                                                                                                              |  |  |  |  |

|                | must match card columns 36–37 in all                                                                                                                                                                               |  |  |  |  |

| ·              | device CDS cards that define unit addresses                                                                                                                                                                        |  |  |  |  |

|                | that are accessible through the control                                                                                                                                                                            |  |  |  |  |

| 44-71          | unit described by this card.                                                                                                                                                                                       |  |  |  |  |

| 1 -7-71        | Unit address extent blocks. These describe                                                                                                                                                                         |  |  |  |  |

|                | unit addresses accessible through this control unit. Unit addresses for each                                                                                                                                       |  |  |  |  |

|                | channel interface on this system must be                                                                                                                                                                           |  |  |  |  |

| ·              | provided. Use device addresses accessible                                                                                                                                                                          |  |  |  |  |

| -              | by only one system. DO NOT use device                                                                                                                                                                              |  |  |  |  |

| 1              | addresses of systems sharing this CU or                                                                                                                                                                            |  |  |  |  |

|                | controller.                                                                                                                                                                                                        |  |  |  |  |

| ]              | Format (repeated for each set of con-                                                                                                                                                                              |  |  |  |  |

|                | tiguous unit addresses):                                                                                                                                                                                           |  |  |  |  |

|                | a. An even number of blank card columns (e.g., 2, 4, 6) may be used to separate blocks.                                                                                                                            |  |  |  |  |

|                | b. Two card columns that indicate, in                                                                                                                                                                              |  |  |  |  |

|                | hexadecimal, the number of contiguous unit addresses (01 through 20) defined by this block.                                                                                                                        |  |  |  |  |

|                | c. Four card columns containing the                                                                                                                                                                                |  |  |  |  |

|                | lowest unit address defined by this block (right-justified).                                                                                                                                                       |  |  |  |  |

|                | Examples: 040130 (defines 130, 131, 132 and 133)                                                                                                                                                                   |  |  |  |  |

|                | 020120 020130 (defines<br>120, 121, 130 and<br>131)                                                                                                                                                                |  |  |  |  |

|                | 020120 020320 (defines                                                                                                                                                                                             |  |  |  |  |

|                | 120, 121, 320 and 321)                                                                                                                                                                                             |  |  |  |  |

| 72             | Continuation character when continuation card is required. Refer to Section 3 of CDS Guide, D99-CDSGA, for continuation card layout. Slash (/) must appear after all unit address extent blocks have been defined. |  |  |  |  |

# STANDALONE/ONLINE SUPPORT PROGRAM

The standalone/online support program (SOSP) is used to build CDS, add or update OLTs, etc. See SOSP Operators Guide (D99-SOSPB).

3830-2

AX0300 2347065 Seq. 2 of 2 Part No. (8)

**EC** History

437416 11 Jan 74

447460 19 Dec 75

447461

12 Mar 76

© Copyright IBM Corporation 1972, 1973, 1974, 1975, 1976

**OLT PREREQUISITES**

- a floor gilboy for Selected to drap. If Selected finds California de mode la compania CAM de cambra anadicama de la compania del compania del compania de la compania del la compania de la compania

# **ONLINE TEST DESCRIPTION (Part 2 of 2)**

ONLINE TEST DESCRIPTION (Part 2 of 2)

**OLT 30**

# **SECTION ID T3830AAA** (Continued)

#### Running (Continued)

- 7. Place the Operation Mode switch in Forced Logging position. Other positions will result in false check-1

- Place the Enter/Display switch in Program Data Entry position.

- Select OLT T3830AAA 'xxx/3830AA/ /', where xxx can be any unit normally addressable by the channel/CU path under test. With 32 Drive Expansion feature, use only base (even) CU path.

Note: The OLTSEP Device Address cannot be used in the device field (xxx).

- 10. When OLT(S)EP indicates "DEVICE NOT OPERA-TIONAL CC=3," enable the CU/channel interface to be tested and reply "p" to cause the OLT to proceed.

- 11. If an error occurs, the error code should be displayed in the CU CE panel Address/Check/Program Display lamps. See OLT 50 for error display codes and related control storage locations.

- 12. Upon successful completion, perform IMPL of the functional microprogram disk and restore the 3830(s) and the drives to normal operation.

#### **SECTION ID T3830AAB**

#### Routine

Allows identification of any 23FD disk by:

Date

Device controlled

Feature

Part number

E/C number

### Running

- 1. Insert 23FD disk to be verified into 23FD file for the control unit.

- Select OLT 3830AAB, 'xxx/3830AAB/NFE/', where xxx can be any device address. No reading or writing will be performed on this device.

- When OLT terminates, see identification information on output device.

3830-2

# SECTION ID T3830AAC (Tracer Dumper Formatter)

**Note:** Before running this OLT, the Tracer Dumper micro (routine 90) must be run.

#### **Run Instructions**

- 1. Vary a device on the controller that is running the trace offline.

- 2. Select OLT T3830AAC:

R01,'XXX/3830AAC/NFE/'

(Where XXX is the device varied offline.) See

OLT 10 for additional run instructions.

- 3. If any console error messages are printed, see OLT 250 for the message description.

- 4. The formatted trace is printed on the printer.

# **Formatted Output**

### FORMATTED TRACE

See OLT 42 for a description and example of the formatted trace.

#### DISPLACEMENT TABLE

Use the reference pages in Figure 1 to correlate the displacement to the microcode storage dump area for all functional microcode disks except for disks with P/Ns 4168811 and 4168816. For disk P/N 4168811, see microfiche page QA032, P/N 4168831; and for disk P/N 4168816, see microfiche page QA032, P/N 4168836.

# ZERO BOUNDARY WORDS

Use the reference pages in Figure 1 for all functional microcode disks except for disks with P/Ns 4168811 and 4168816. For disk P/N 4168811, see microfiche page QA032, P/N 4168831; and for disk P/N 4168816, see microfiche page QA032, P/N 4168836.

3830-2

AX0450 4290607 Seq. 2 of 2 Part No. (8) **447462** 5 Nov 76

© Copyright IBM Corporation 1976

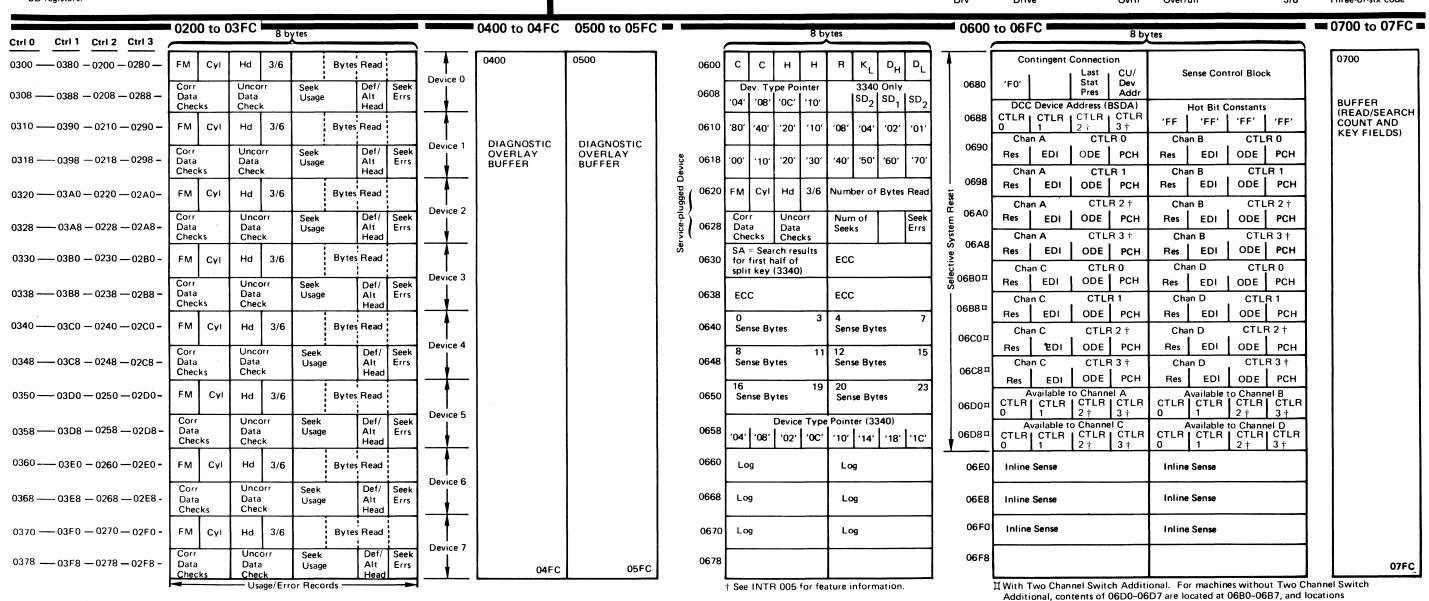

Figure 1. Dump Data Storage Area

| Displacement<br>(Hex) | Number of<br>Bytes | Control Storage<br>Addresses | Contents               | Page<br>Reference |  |

|-----------------------|--------------------|------------------------------|------------------------|-------------------|--|

| 0000                  | 256                | 0200-02FF                    | Usage/error            | CTLR 650          |  |

| 0100                  | 256                | 0300-03FF                    | records                |                   |  |

| 0200                  | 256                | 0400-04FF                    | CHL-I Trace            | OLT 42            |  |

| 0300                  | 256                | 0500-05FF                    | CTL-I Trace            |                   |  |

| 0400                  | 256                | 0600-06FF                    | Working Storage        | CTLR 650          |  |

| 0500                  | 256                | 0000xx003F0C                 | Zero Boundary<br>words | CTLR 652          |  |

Upon entering the dumper (3C3C), the contents of the storage control unit registers are saved in control storage as follows:

| Displacement<br>(Hex) | Register | Displacement<br>(Hex) | Register | Displacement<br>(Hex) | Register |

|-----------------------|----------|-----------------------|----------|-----------------------|----------|

| 04E0                  | ND       | 04E9                  | TA       | 04F3                  | TG       |

| 04E1                  | NC       | 04EA                  | TD       | 05F0                  | SA       |

| 04E2                  | NB ·     | 04EB                  | MA       | 05F1                  | SB       |

| 04E3                  | TC       | 04EC                  | MD       | 05F2                  | SC       |

| 04E4                  | GB       | 04ED                  | GC       | 05F3                  | SD       |

| 04E5                  | GA       | 04EE                  | BR       | 05F4                  | GE       |

| 04E6                  | ТВ       | 04EF                  | MC       | 05F5                  | NE       |

| 04E7                  | NA       | 04F1                  | ST       | 05F6                  | TE       |

| 04E8                  | MB       | 04F2                  | GD       | 05F7                  | ME       |

# **ONLINE TEST DESCRIPTION**

ON LINE TEST DESCRIPTION

**OLT 42**

## FORMATTED TRACE OUTPUT

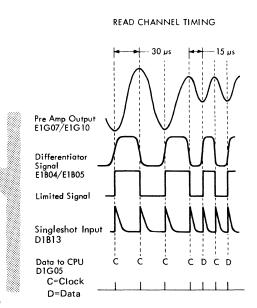

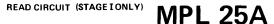

# Channel Interface Tracer

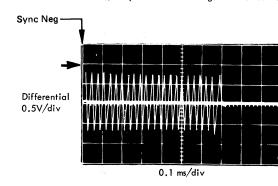

The channel interface tracer stores a word in the channel trace table every time the storage control unit attempts to present status to the channel, except for zero initial status.

Each entry contains:

Channel the trace is being run on.

3 Address of the controller and device.

Bits 3-4 Logical controller address

Bits 5—7 Logical device address

4 Channel Command is the last channel command before status is presented to the channel. Test I/O commands do not update this byte.

5 Unit Status presented to the channel. This does not indicate that the status was accepted by the channel.

6 ST—Register is a microcode register.

# **7** Controller Interface Tracer

The controller interface tracer stores a word in the controller trace table every time the storage control unit issues a tag to a controller or drive, except for the poll tag (82) in the idle wait loop.

8 Normally many control interface tags are expected for each channel interface trace entry. Due to the greater number of tag responses on the controller interface trace, in respect to the channel interface trace and the trace storage limitations to 64 lines for each trace, the earlier tag entrys from the controller interface are overlayed.

Each entry contains:

9 TD Register contents, CTL-I Bus Out

10 TA Register contents, CTL-I Tag Bus

11 Return address for the DCI Tag

12 13 The operations on the channel interface, such as in line 61 of the trace, correspond to the operations on the controller interface lines 61.01, 61.02, etc.

|                    | OLTSEP DATE=0 | 0/00/00   | PAGE 0011 | REL=9A         |          |                |          |         | 7       |              |

|--------------------|---------------|-----------|-----------|----------------|----------|----------------|----------|---------|---------|--------------|

| First Trace Entry  | LINE #        | CHANNEL 2 | ADDR      | CMD            | STATUS   | ST-REG         | LINE #   | TAG(TD) | BUS(TA) | RETURN       |

| First Hace Lifting | 01.00         | A         | <b>3</b>  | <b>4</b><br>00 | <b>5</b> | <b>6</b><br>47 | <u>I</u> | 9       | 10      | , LL         |

|                    | 02.00         | А         | 00        | 00             | 00       | 47             | 8        |         |         |              |

|                    | 03.00         | А         | 00        | 00             | 00       | 47             |          |         |         |              |

| İ                  | 60.00         | А         | 00        | 04             | ОС       | 05             |          |         |         |              |

|                    |               |           |           |                |          |                | 60.01    | 84      | 01      | 2A84         |

|                    |               |           |           |                |          |                | 60.02    | 8F      | 00      | 2ABC         |

|                    |               |           |           |                |          |                | 60.03    | 84      | 01      | 2A80         |

|                    |               |           |           |                |          |                | 60.13    | 04      | 10      | 2518         |

|                    | 12 61.00      | Α         | 00        | 44             | 00       | 05             |          |         |         |              |

|                    |               |           |           |                |          |                | 61.01    | 84      | 01      | 2A84         |

|                    |               |           |           |                |          |                | 13 61.02 | 8F      | 00      | 2ABC         |

| S                  |               |           |           |                |          |                | (61.03   | 84      | 01      | 2A80         |

|                    |               |           |           |                |          |                |          |         |         |              |

| Last Trace Entry   | 64.00         | А         | 00        | 04             | OC       | 05             |          |         |         |              |

|                    |               |           |           |                |          |                | 64.01    | 84      | 01      | 2A84         |

|                    |               |           |           |                |          |                | 64.02    | 8F      | 00      | 2ABC         |

|                    |               |           |           |                |          |                | 64.03    | 84      | 01      | 2A80         |

|                    |               |           |           |                |          |                | 64.04    | 06      | 40      | <b>252</b> C |

|                    |               |           |           |                |          |                | 64.05    | 07      | 50      | 2AE0         |

3830-2 AX0460 4290608 Seq. 1 of 1 Part No. (8) 5 Nov 76

# **ONLINE TESTS — ERROR MESSAGES**

# **CU CHANNEL INTERFACE TEST (T3830AAA)**

Note: CE panel Enter/Display switch must be in Program Data Entry/Display position. Read error message code in Address/Check/Program Display (A/C/PD) lamps.

# Format for Error Codes Listed

|                                | A/C/PI                                                                                                                                                                | D Bits                         | s 0-7                                                                                                                                  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| with A/C/PD bit                | 8 off                                                                                                                                                                 | ١                              | with A/C/PD bit 8 on                                                                                                                   |  |

| Bit                            |                                                                                                                                                                       | Bit                            |                                                                                                                                        |  |

| 0 Command dec                  | ode                                                                                                                                                                   | 0                              | Channel buffer parity check                                                                                                            |  |

| 1 Not used                     |                                                                                                                                                                       | 1                              | Interface check                                                                                                                        |  |

| 2 (00 channel A                |                                                                                                                                                                       | 2                              | Interface check                                                                                                                        |  |

| and 01 channel B               |                                                                                                                                                                       | 3                              | Channel transfer check                                                                                                                 |  |

| 11 channel D                   |                                                                                                                                                                       | 4<br>5                         | CTL-I check CTL-I load S register                                                                                                      |  |

| 4-7 Device address             |                                                                                                                                                                       | 6<br>7                         | check<br>Compare assist check<br>Not used                                                                                              |  |

| A/C/PD Bits 8-15               | ered wit<br>0-7 cont<br>(NA reg<br>'1000' b                                                                                                                           | th the tain the ister), byte 3 | a check 2 was encount-<br>error, and A/C/PD bits<br>e channel error byte<br>and storage position<br>contains the CTL-I<br>D register). |  |

| A/C/PD Lamps<br>Ripple         | If A/C/PD lamps ripple, turn off Multitag switch. If lamps continue to ripple, the Multitag switch is failing to disconnect.                                          |                                |                                                                                                                                        |  |

| A/C/PD Lamps<br>Fail to Ripple | If the command decode is enabled, the A/C/PD lamps should ripple as long as the Multitag switch is on. If the Multitag switch is off, the lamps should stop rippling. |                                |                                                                                                                                        |  |

# Error Codes Displayed in A/C/PD Lamps

| A/C/PD<br>Bits 8-15 | Meaning                                                                                                  |

|---------------------|----------------------------------------------------------------------------------------------------------|

| ×000 0000           | Address Out placed bad parity on bus out. CU storage location '1201' contains the address byte received. |

| x000 0100           | SELTD was detected, then ADDRO was tested and found down. It should be up.                               |

| A/C/PD<br>Bits 8-15 | Meaning                                                                                                                                                                                                                   |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| x000 0110           | COMMO or HLTIO failed to come up.                                                                                                                                                                                         |

| ×000 1000           | Command Out placed bad parity on bus out (BOPAR). CU storage location '1203' contains the command byte received.                                                                                                          |

| x000 1010           | COMMO failed to drop after address in was dropped.                                                                                                                                                                        |

| ×000 1110           | A command, other than the special OLT command set, has been issued.                                                                                                                                                       |

| ×000 1111           | Neither SER VO nor COMMO was received in response to Status In.                                                                                                                                                           |

| x001 0000           | Received both SERVO and COMMO responses to Status In.                                                                                                                                                                     |

| x001 0010           | Request In was raised. This should raise SELTD. SELTD failed to raise.                                                                                                                                                    |

| x001 0100           | Request In was raised. The CU selected and raised Op In and Address In with its CU address on bus in. The channel should have responded with Command Out but Command Out was not received.                                |

| x001 0110           | XFER was checked and found up when it should be down. The channel transfer hardware is in neither Read nor Write mode.                                                                                                    |

| x001 1000           | BFRDY was checked and found up when it should be down. The channel transfer hardware is in neither Read nor Write mode.                                                                                                   |

| ×001 1010           | During a Write data transfer, XFER failed to come up.                                                                                                                                                                     |

| ×001 1100           | During a Write data transfer, BFRDY failed to come up.                                                                                                                                                                    |

| x001 1110           | During a Write data transfer, a bus out parity error (BOPAR) was detected. CU storage locations '1400' and '1401' contain the received data bytes.  ('1400' = first byte of 2-byte XFER; '1401' = second or single byte.) |

| x010 0000           | At the start of a Read operation, XFER should be up. When tested, it was found to be down.                                                                                                                                |

| x010 0010           | At the start of a Read operation, BFRDY should be up. When tested, it was found to be down.                                                                                                                               |

| A/C/PD<br>Bits 8-15 | Meaning                                                                                                                                                                                               |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| x010 0100           | During a 2-byte Read data transfer, XFER failed to come up after the first byte was transferred.                                                                                                      |

| ×010 0110           | During a Read operation, BFRDY failed to come up after all read data was transferred.                                                                                                                 |

| x010 1000           | During a 256-byte Write data transfer,<br>an unexpected Command Out was<br>detected.                                                                                                                  |

| x010 1010           | During a 256-byte transfer Read or Write, XFER failed to come up.                                                                                                                                     |

| x010 1100           | During a 256-byte Write, a bus out parity error (BOPAR) was detected. CU storage location '1400' contains the data byte expected and location '1401' contains the data byte received.                 |

| x010 1110           | During a 256-byte Write data transfer, the data expected did not compare to the data received. CU storage location '1400' contains the byte expected, and location '1401' contains the byte received. |

| x011 0000           | During a 256-byte Read operation,<br>BFRDY should come up. When<br>checked, it was found down.                                                                                                        |

| x011 0010           | During a Sense command, BFRDY failed to come up after the data was transferred.                                                                                                                       |

| x011 1011           | Busy was not detected during the test for busy.                                                                                                                                                       |

## **Control Storage Location**

## CONTROL STORAGE LOCATION '1000' CONTAINS:

#### Byte 0 Bit

| 0 | Diagnostic command decoded |

|---|----------------------------|

| 1 | Not used                   |

| •   | NOT useu       |

|-----|----------------|

| 2-3 | 00 channel A   |

|     | 01 channel B   |

|     | 10 channel C   |

|     | 11 channel D   |

| 1-7 | Device address |

Byte 1 Error code

# ONLINE TESTS - ERROR MESSAGES

# **OLT 50**

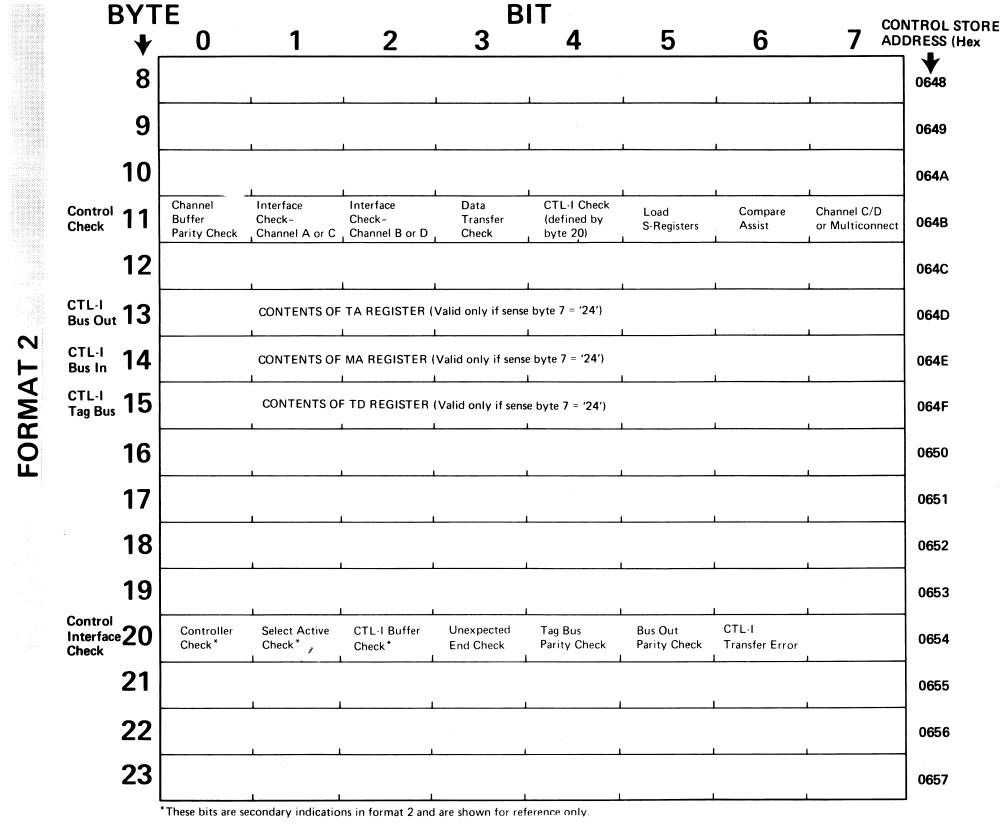

|   | Byte 2<br>Bit    |                                                    |

|---|------------------|----------------------------------------------------|

|   | 0                | Channel buffer parity check                        |

|   | 1                | Interface check channel A/C                        |

|   | 2                | Interface check channel B/D                        |

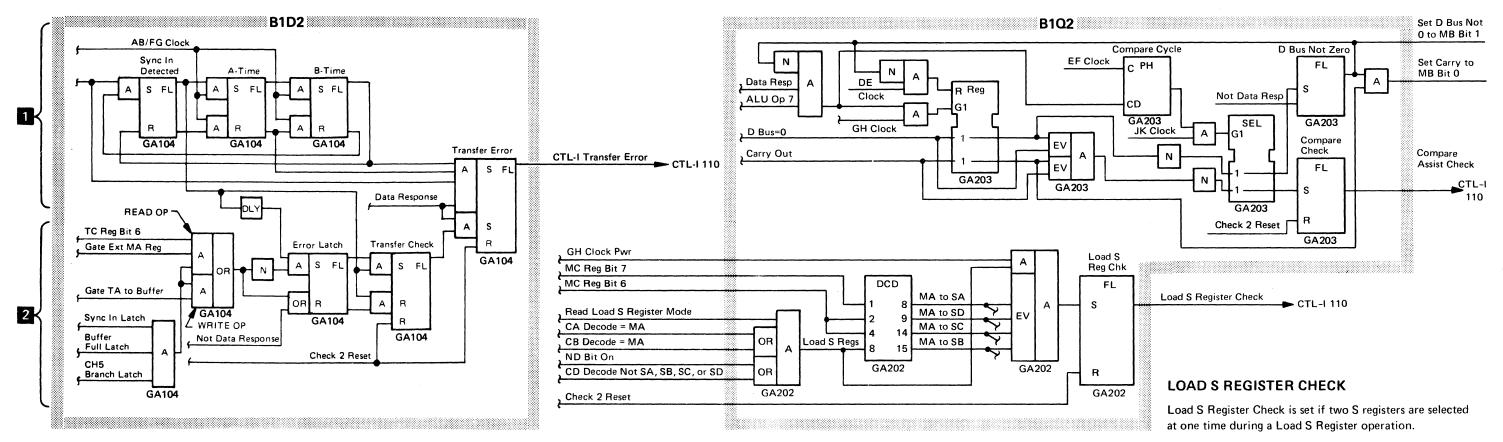

|   | 3                | Channel transfer check                             |

|   | 4                | CTL-I check                                        |

|   | 5                | CTL-I load S register check                        |

|   | 6                | Compare assist check                               |

|   | 7                | Interface check C/D or multiconnect                |

|   |                  | error                                              |

|   | Byte 3<br>Bit    |                                                    |

| ļ | 0                | Controller check                                   |

|   | 1                | Select active or select check                      |

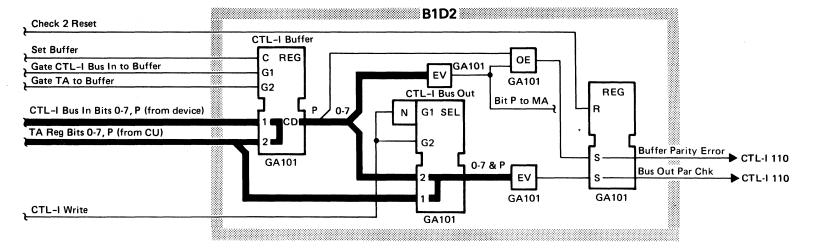

|   | 2                | CTL-I buffer (CTL-I bus in) parity check           |

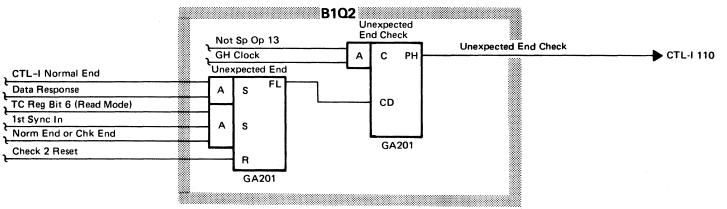

|   | 3                | Unexpected end check                               |

|   | 4                | CTL-I tag bus parity check                         |

|   | 5                | CTL-I bus out parity check                         |

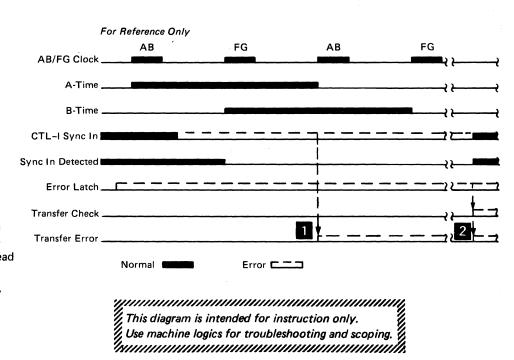

|   | 6                | CTL-I transfer error                               |

|   | 7                | Unused                                             |

|   |                  |                                                    |

|   | CONTR            | OL STORAGE LOCATION '1200' CONTAINS:               |

|   | Byte 0<br>Byte 1 | Error code at Address Out time<br>Received address |

# CONTROL STORAGE LOCATION '1400' CONTAINS:

Byte 2 Error code at Command Out time

Byte 3 Received command

- Byte 0 The first byte from a 2-byte write transfer or the expected data during a 256-byte write operation

- Byte 1 The second byte from a 2-byte write transfer, the received data from a single byte write, or the last received data byte from a 256-byte write operation

# Byte 2 Used to store:

- The data byte ('D9' or 'DA') for use in routine 0B (Mark In test). 'DA' indicates CU retry successful.

- The data byte ('00' or 'D5') for use in routine 7 (CU busy). 'D5' indicates CU (short) busy occurred.

Byte 3 Not used

3830-2

| AX0500      | 2347067     |  |

|-------------|-------------|--|

| Seq. 1 of 2 | Part No. () |  |

437402A

437403

437404

437405

437408

437414

15 Mar 72

21 Apr 72

23 Jun 72

15 Aug 72

16 Oct 72

4 Jun 73

© Copyright IBM Corporation 1972, 1973

# **OLTEP/OLTSEP ERROR MESSAGES**

| Sect. ID    | REFNUM             | Error Messages and Console Communications                                                      | Diagnostic Information                                                                                                                                                                                                                                                                                                   | CE Action                                           |

|-------------|--------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| OLTSEP      | 1                  | UNREADABLE LABEL ON xxxx CSW xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx                              | These messages are presented by OLT(S)EP when IMPL of the CU diagnostic disk is successfully completed prior to starting 3830AAA. This message will occur because the commands used by OLT(S)EP are not recognized by the microdiagnostic.  OLTSEP may wait for approximately 30 seconds before presenting this message. | Reply p to start 3830AAA.                           |

| OS<br>OLTEP | IFD1251            | UNREADABLE LABEL ON XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                        |                                                                                                                                                                                                                                                                                                                          |                                                     |

| OLTSEP      | SEP138I<br>SEP139D | DEV xxxx NOT OPERATIONAL, CC=3 REPLY B TO BYPASS, R TO RETRY, P TO PROCEED                     | If the CU channel interface switch is disabled when starting 3830AAA, this message will be presented.                                                                                                                                                                                                                    | Enable the CU channel interface switch and reply p. |

|             |                    |                                                                                                | •                                                                                                                                                                                                                                                                                                                        |                                                     |

| OS<br>OLTEP | IFD138I<br>IFD139D | DEVICE xxx NOT OPERATIONAL CC=3 REPLY B TO BYPASS, R TO RETRY, P TO PROCEED (MAY DESTROY DATA) |                                                                                                                                                                                                                                                                                                                          |                                                     |

|             |                    |                                                                                                |                                                                                                                                                                                                                                                                                                                          |                                                     |

|             |                    |                                                                                                |                                                                                                                                                                                                                                                                                                                          |                                                     |

|             |                    |                                                                                                |                                                                                                                                                                                                                                                                                                                          |                                                     |

|             |                    |                                                                                                |                                                                                                                                                                                                                                                                                                                          |                                                     |

|             |                    |                                                                                                |                                                                                                                                                                                                                                                                                                                          |                                                     |

|             |                    |                                                                                                |                                                                                                                                                                                                                                                                                                                          |                                                     |

|             |                    |                                                                                                |                                                                                                                                                                                                                                                                                                                          |                                                     |

2020 2

AX0500 2347067 437402A 437403 437404 437405 437408 437414 Seq. 2 of 2 Part No. ( ) 15 Mar 72 21 Apr 72 23 Jun 72 15 Aug 72 16 Oct 72 4 Jun 73

© Copyright IBM Corporation 1972, 1973

OLTEP/OLTSEP ERROR MESSAGES

# T3830AAA ERROR MESSAGES (Part 1 of 14)

T3830AAA ERROR MESSAGES (Part 1 of 14)

**OLT 100**

# **CU CHANNEL INTERFACE TEST**

| Sect. ID | REFNUM                   | Error Messages and Console Communications                                                                             | Diagnostic Information                                                                                                                                                                                                                             | CE Action                                                                                                                                                |

|----------|--------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3830AAA  | Any                      | ERROR CODE IS-xx                                                                                                      | An unexpected error occurred, resulting in a Unit Check. A Sense ('C4') command successfully read the error code.                                                                                                                                  | Refer to OLT 50 for definition of the error code.                                                                                                        |

| 3830AAA  | Any<br>Any<br>Any<br>Any | * ATTEMPT TO SENSE ERROR CODE FAILED  XPTD CC-0 XPTD STATUS-0C00  RCVD CC-x • • • •  CHECK CU CE PANEL FOR ERROR CODE | An unexpected Unit Check previously occurred. When the OLT tried to sense the error code, the Sense command failed.                                                                                                                                | Refer to OLT 50 for information on obtaining the error code (for the sense error) from the CU CE panel.                                                  |

| 3830AAA  | Any                      | CHECK CU CE PANEL FOR ERROR CODE                                                                                      | An unexpected error occurred, resulting in a Unit Check. No attempt was made to sense the error code because data transfer had not yet been tested.                                                                                                | Refer to OLT 50 for information on obtaining the error code from the CU CE panel.                                                                        |

| 3830AAA  | Any                      | RUN THE CHANNEL WRAP DIAGNOSTIC                                                                                       | This message is presented to direct the user to run the channel wrap diagnostic from the CU CE panel.  This message is presented only if an error occurs.                                                                                          | Refer to MICRO 200 and perform the indicated task.                                                                                                       |

| 3830AAA  | 000                      | T3830AAA CANNOT RUN ON UNIT-xxxx. UNSUPPORTED DEV TYPE-tt                                                             | Unit address xxxx, entered at the OLT(S)EP "ENTER-DEV/TEST/OPT/" communications interval, is assigned to type code tt. Supported device types include the following:  Type Device  09 3330 or 3333 0A 3340/3344 0B 3350 0D 3330 Mod 11/3333 Mod 11 | 1. Ensure that the specified unit address is correct. 2. If the right unit address was used, correct the CDS entry for that unit xxxx.  Refer to OLT 20. |

| AX0600      | 2347373      | 437  |

|-------------|--------------|------|

| Sea. 1 of 2 | Part No. (8) | 23 J |

# **CU CHANNEL INTERFACE TEST**

| Sect. ID | REFNUM            | Error Messages and Console Communications                                                                                                                                                                                                                                                                                                                                                                                    | Diagnostic Information                                                                                                                                                                       | CE Action                                                                                                                                                                                                                                |

|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3830AAA  | 001<br>001<br>001 | * WAIT TIMEOUT  CONTROL UNIT=aacd ROUTINE-rr PASS-pp  XPTD CC-x • • •                                                                                                                                                                                                                                                                                                                                                        | Ending status was not received within 1 second from the time an I/O operation was started.                                                                                                   | Check subsequent messages for additional details.     For information about these messages, refer to OLT 100.     Run the channel wrap diagnostic. Refer to MICRO 200.     If channel wrap runs error free, run all channel diagnostics. |

|          |                   | aacd = Unit address entered at OLT(S)EP DEV/TEST/OPT/ communications interval.  aa = channel c = control unit d = device (not addressed)                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                              |                                                                                                                                                                                                                                          |

|          |                   | rr = OLT routine number.  00 = OLT initialization FF = OLT termination or cleanup See routine description on OLT 25.  pp = Routines 01-OC are each exercised 255 times unless the EXT=option is used. This count is intended to indicate if a failure may be solid (PASS-01) or if it is intermittent. The pass count is not presented if the error did not occur in routines 01-OC, or if the EXT=I or N options were used. |                                                                                                                                                                                              |                                                                                                                                                                                                                                          |

| 3830AAA  | 002               | * CU CDS SUFFIX NOT IN CDS ENTRY FOR UNIT-xxxx                                                                                                                                                                                                                                                                                                                                                                               | The CDS (configuration data set) entry for unit xxxx does not contain any information in card columns 36-37.                                                                                 | Correct the CDS entry for unit xxx. Refer to OLT 20.                                                                                                                                                                                     |

| 3830AAA  | 003               | * UNIT ADDRESSES NOT IN CDS ENTRY CU3830xx                                                                                                                                                                                                                                                                                                                                                                                   | The 3830 CDS (configuraiton data set) entry does not contain required unit address information.                                                                                              | Correct the CU3830xx CDS entry. Refer to OLT 20.                                                                                                                                                                                         |

| 3830AAA  | 004               | * TOO MANY UNIT ADDRESSES IN CDS ENTRY CU3830xx                                                                                                                                                                                                                                                                                                                                                                              | One of the following conditions has been detected:  1. More than 32 unit addresses were specified in a unit address block.  2. More than 128 unit addresses were specified in the CDS entry. |                                                                                                                                                                                                                                          |

437404 437405 437408 23 Jun 72 15 Aug 72 16 Oct 72 **437414** 4 Jun 73 **437416** 11 Jan 74 **447461** 12 Mar 76 AX0600 2347373 23 Jun 72 Seq. 2 of 2 Part No. (8)

© Copyright IBM Corporation 1972, 1973, 1974, 1976

T3830AAA ERROR MESSAGES (Part 2 of 14)

# T3830AAA ERROR MESSAGES (Part 3 of 14)

T3830AAA ERROR MESSAGES (Part 3 of 14)

**OLT 110**

**CU CHANNEL INTERFACE TEST**