|                                                                                     |     | R R                                        | Ma                      |

|-------------------------------------------------------------------------------------|-----|--------------------------------------------|-------------------------|

| MIM                                                                                 |     | PCM                                        | MDM                     |

| INTRO<br>LGND<br>GLOS                                                               |     | PARTS<br>CATALOG                           | CARD<br>PLUG<br>CHARTS  |

| START<br>MLX<br>PROG                                                                |     |                                            | POWER<br>DIAGRAM        |

| LOC<br>PWR<br>CARR<br>INST<br>INSP<br>INDEX                                         |     |                                            | VOLTAGE<br>PIN<br>LISTS |

| VOL.R10                                                                             |     | VOL.R20                                    | VOL.R30                 |

|                                                                                     |     | •                                          |                         |

| ECM                                                                                 | ] [ | MSM                                        | LRM                     |

| INTRO<br>ECI<br>CTL-I<br>MNT-C<br>DBFR<br>CTRL<br>CHL-I<br>DD<br>PORT<br>STOR<br>DC |     | INTRO<br>SENSE<br>OPER<br>PDA<br>REF<br>MD | LOGIC<br>REFER<br>ENCE  |

| VOL.R45                                                                             |     | VOL.R60                                    | VOL.R70                 |

|      |            |            |           |           | · * . |  |

|------|------------|------------|-----------|-----------|-------|--|

| 3880 |            | PN 6315755 | 881216    | A15621    |       |  |

| MSM  | Seq JA0010 | 1 of 2     | 15 Aug 84 | 01 Apr 85 |       |  |

© Copyright IBM Corp. 1984, 1985

# laintenance Library

## Preface

### Preface

The drawings and specifications contained herein shall not be reproduced in whole or in part without written permission.

IBM has prepared this maintenance manual for the use of IBM customer engineers in the installation, maintenance, and repair of the specific machines indicated. IBM makes no representation that it is suitable for any other purpose.

Information contained in this manual is subject to change from time to time. Any such change will be reported in subsequent revisions.

It is possible that this material may contain reference to, or information about IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office servicing your locality.

A form for reader's comments is provided at the back of this publication. If the form has been removed comments may be addressed to:

International Business Machines Corporation Department 61C/313 Tucson, Arizona, U.S.A. 85744

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever. You may, of course, continue to use the information you supply.

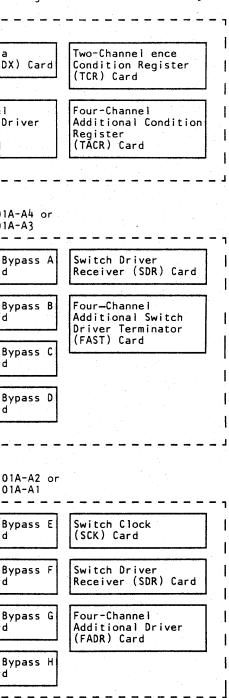

### **Maintenance Manual Ordering Procedure** (IBM Internal)

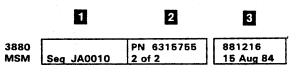

Individual pages of the 3880 Maintenance manual can be ordered from the Tucson plant by using the Wiring Diagram/Logic Page Request, Z150-0130 (U/M 015). In the logic page columns, enter the page identifier information: sequence number and side number 1, part number 2, and engineering change (EC) number 3.

Copyright IBM Corp. 1984

Groups of pages can be ordered by including a description (section, volume) and the machine serial number.

### **Related Publications**

A list of related publications can be found in the Maintenance Support Manual, REF section.

| 3880<br>MSM | Seq JA0010 | PN 6315755<br>2 of 2 | 881216<br>15 Aug 84 | A15621<br>01 Apr 85 |  |

|-------------|------------|----------------------|---------------------|---------------------|--|

© Copyright IBM Corp. 1984, 1985

Preface PRE 5

Preface PRE 5

# Introduction

# **Contents of This Section**

| 3880 |            | PN 6315724 |           | A15621    |  |  |

|------|------------|------------|-----------|-----------|--|--|

| MSM  | Seg JC0001 | 1 of 2     | 15 Aug 84 | 01 Apr 85 |  |  |

|      |            |            |           |           |  |  |

<sup>©</sup> Copyright IBM Corp. 1984, 1985

# Contents INTRO 1

# Contents INTRO 1

# **Description By Section**

Intro-

duction

and content of the manual sections.

SENSE Sense Data

INTRO

of the sense data.

OPER

The 3880 Maintenance Support Manual (MSM) is divided into sections identified by tabs.

The following is a description of the tab labels and the section content.

The Introduction section defines the organization of the manual

The Sense section contains a summary and detailed description

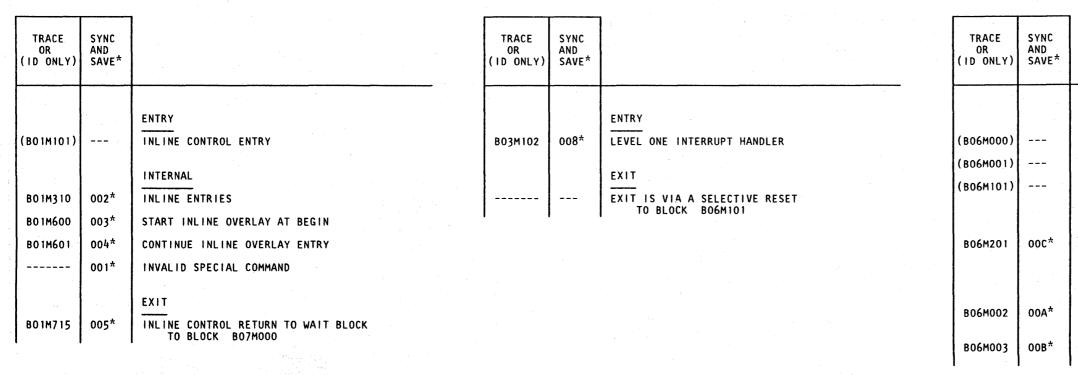

The Problem Determination Aids section describes the use, selection, and interpretation of the following topics:

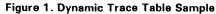

- Trace program

- Dynamic trace tables ٠

- Sync and save tables ٠

- State save tables ٠

- ٠ Maintenance connection trace tables

- Abnormal maintenance connection conditions ٠

- Unusual operating conditions ٠

- Unusual maintenance conditions ٠

- Generalized trace facility .

- Channel monitor .

- ٠ Logic analyzer

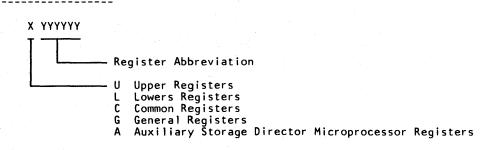

The Reference section contains tables and descriptions of the external, general, common, and upper and lower port registers.

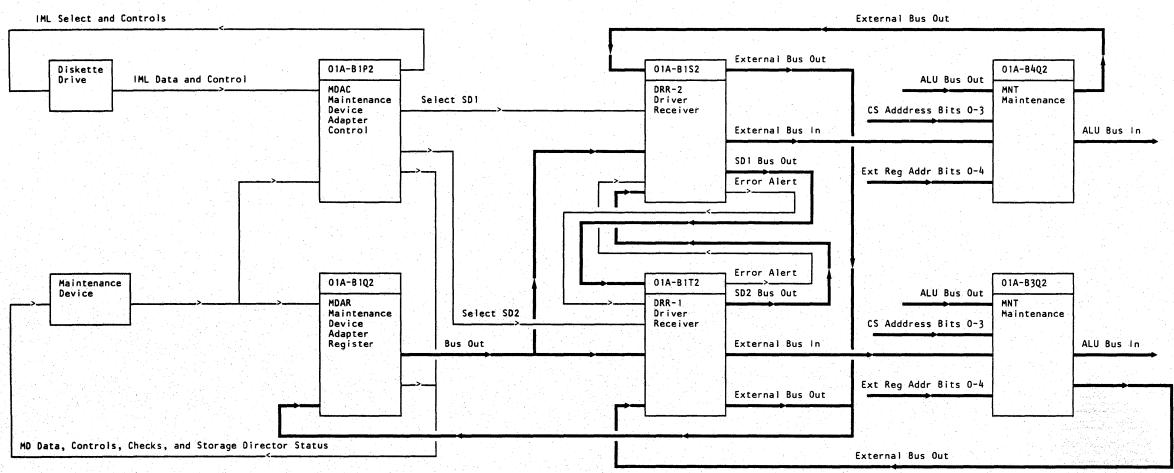

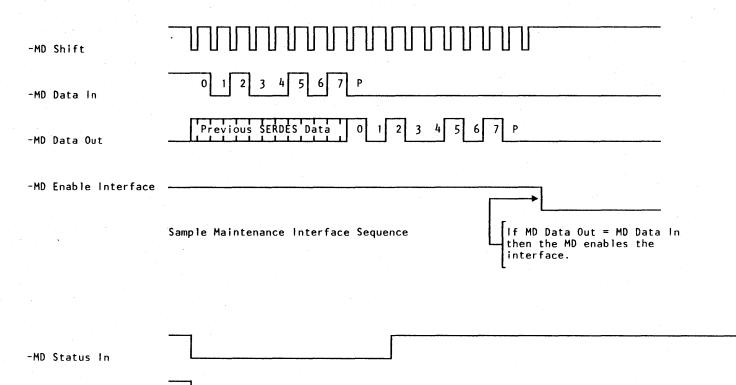

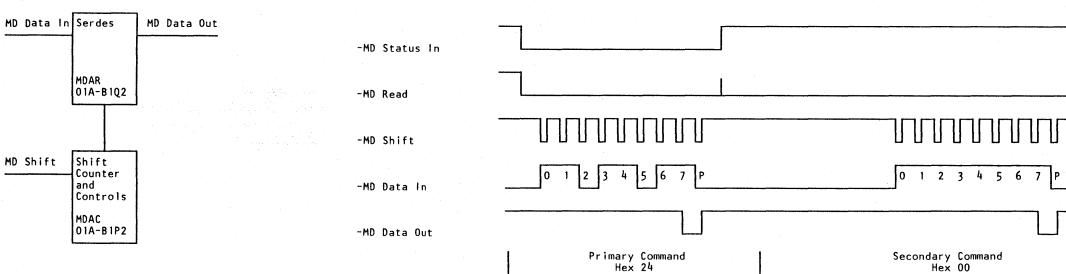

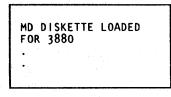

The Maintenance Device section describes the interaction of the maintenance device with a storage director that is actively attached to a processor channel.

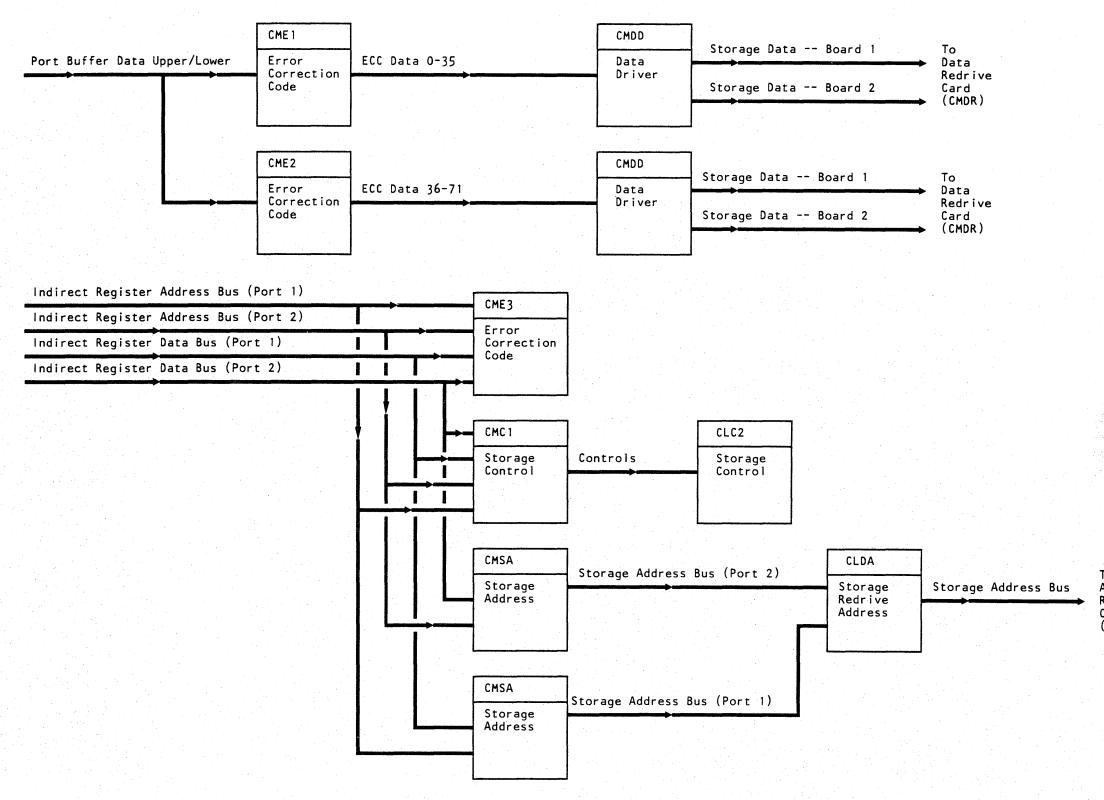

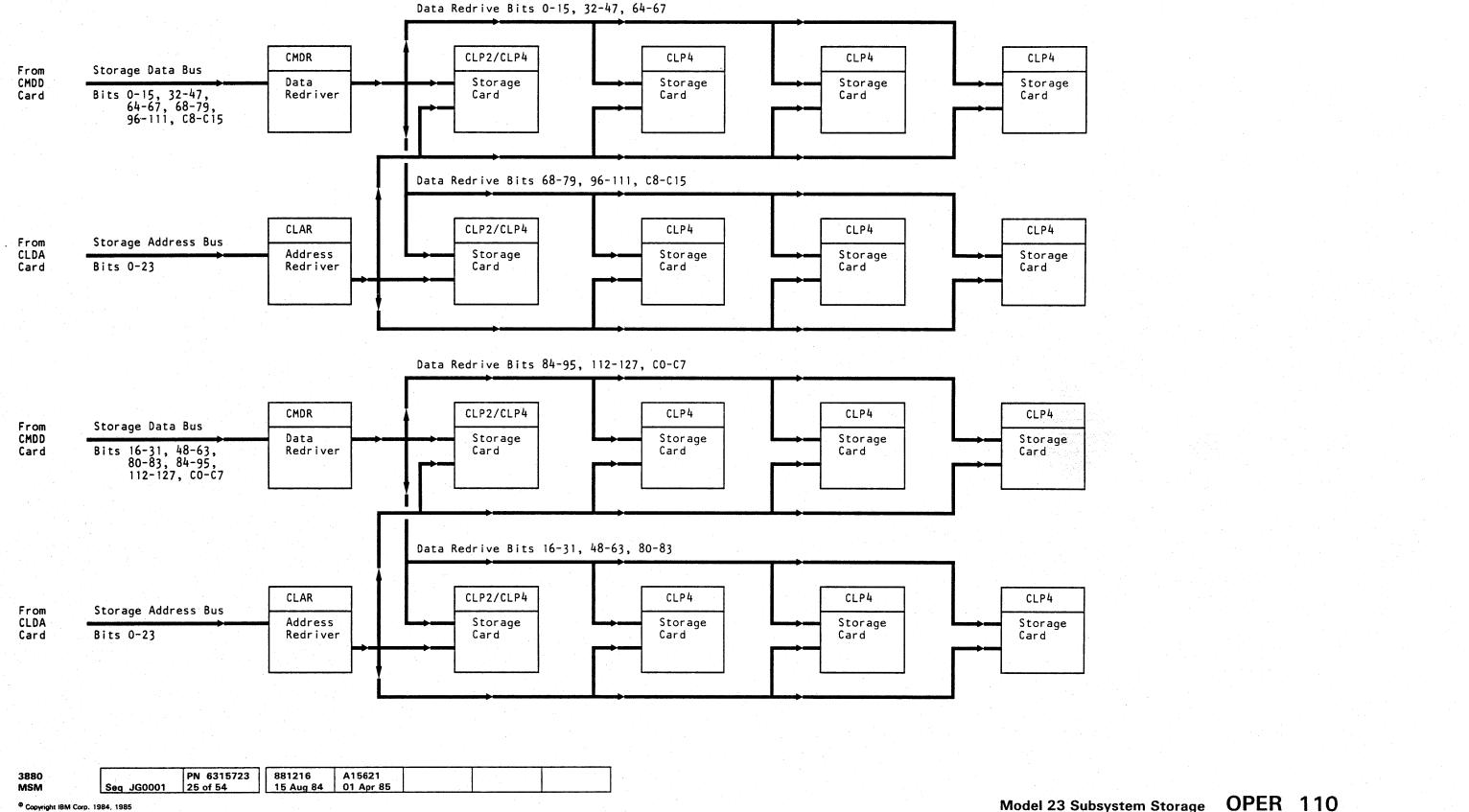

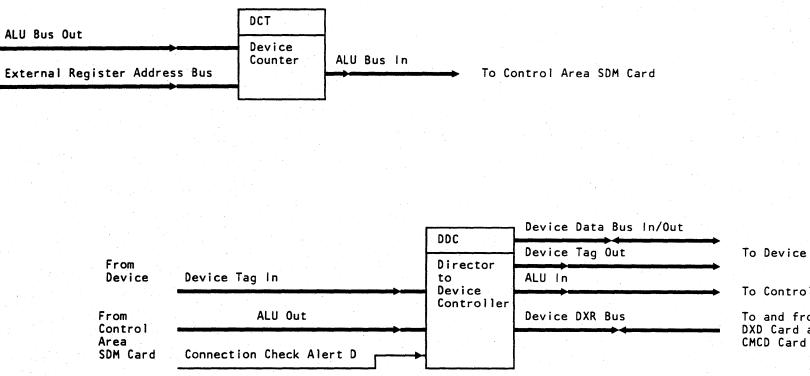

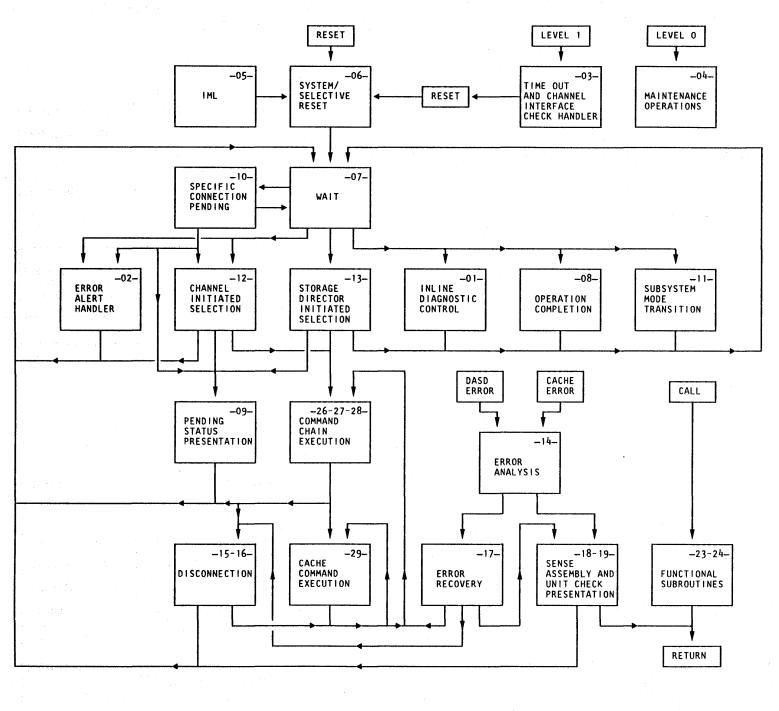

The Operations section contains data and control flow diagrams

and descriptions of the product. Included are description on the:

Subsystem **Functional Areas** Logic cards

Operations

Commands Initial Microcode Load **Storage Director Communications**

| 3880 |            | PN 6315724 | 881143    | 881216    | A15621    |  |

|------|------------|------------|-----------|-----------|-----------|--|

| MSM  | Seg JC0001 | 2 of 2     | 13 Jan 84 | 15 Aug 84 | 01 Apr 85 |  |

<sup>©</sup> Copyright IBM Corp. 1984, 1985

Description By Section INTRO 10

# Sense

### **Contents of This Section**

| Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5555555   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Sense Bytes 0-7 Summary         11           Sense Byte 0         11           Sense Byte 1         20           Sense Byte 2         21           Sense Byte 3 - 5         30           Sense Byte 6         33           Sense Byte 7         34           Format Identifier         34           Message Identifier         34           Sense Byte 8 through 23         34                                                                                                                                                                                                                                                                                                   | 50502555  |

| Format 0 - Program or System Checks for Model 21 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5         |

| Format 0 - Program or System Checks for Model 23       50         Format 0 Messages       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -         |

| Format 2 - Storage Director Equipment Checks       55 - 10         Format 2 Messages       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |

| Format 3 - Storage Director Clock Stopped Check 1         110 - 12           Format 3 Messages for Clock Stopped Check 1         16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

| Format 3 – Storage Director Channel Check 1         125 - 16           Format 3 Messages for Channel Check 1         16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |

| Format 6 - Usage, Overrun, and Error Statistics170 - 18For 3350 Machines170For 3380 Machines175Format 6 Messages18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | )<br>5    |

| Format F Sense Data       190 - 24         Message Descriptions For Format F       190         Format F Message Summary       190         Format F Messages       190         Format F Messages       190         Format F Messages       190         Message 2 - Subsystem Storage Equipment Check       200 - 233         Message 3 - Subsystem Storage Availability Threshold Crossed       235         Message 4 - Subsystem Storage is Unusable       231         Message 5 - Subsystem Storage must be Initialized       240         Message 7 - Track Format not Supported for Paging       240         Message 8 - Storage Director Communication Failed       245 - 248 | 005785700 |

# **References to Other Sections**

See the REF section for a description of the external and indirect registers.

|             |            |                       |                     |                     |                     |   | 1 |  |

|-------------|------------|-----------------------|---------------------|---------------------|---------------------|---|---|--|

| 3880<br>MSM | Seg JE0001 | PN 6315725<br>1 of 70 | 881144<br>13 Jan 84 | 881216<br>15 Aug 84 | A15621<br>01 Apr 85 | - |   |  |

|             |            |                       |                     |                     |                     |   |   |  |

Contents SENSE 1

# Contents SENSE 1

## Introduction to the Sense Section

### Formats

The 3880 gives 24 bytes of sense information arranged into error formats. These formats are used to class errors because of where they come from and are reported. The errors can be found in the channel, storage control, subsystem storage, or the device.

#### The formats are:

#### **Format Condition**

- 0 Program or system checks

- 1 **Device equipment checks**

- 2 Storage director equipment checks

- 3 Storage director control checks

- 4 Uncorrectable data checks

- 5 Correctable data checks

- Usage, overrun, and error statistics 6

- Controller check 1 (Model 23 only) 7

- Controller check 2 and device check 1 (Model 23 only) 8

- F Subsystem storage errors.

Of these formats, only formats 0, 2, 3, 6 and F are used by the 3880, and only these formats are described in this SENSE section. The remaining formats (1, 4, 5, 7, and 8) describe errors detected and reported by the devices and are described in the device documentation.

#### Format 0 – Program or System Checks

Format 0 is all program or system check errors. These checks occur in the channel or the channel side of the channel interface, but are detected by a storage director. Examples are a not correctly programmed channel routine, a malfunction in the channel causing a not valid tag sequence, or a parity check.

### Format 2 – Storage Director Equipment Checks

Format 2 is all check 2 errors and is generated after the microcode detects a storage director error condition. The storage director sets and sends a unit check signal to the channel at the end of the operation.

### Format 3 – Storage Director Control Checks

Format 3 is all check 1 errors. These errors prevent error reporting to the connected channel because of a not operating channel interface or a control error that destroys the integrity of the microcode. Format 3 is divided into two parts: storage director clock stopped check 1 and storage director channel check 1.

#### Storage Director Clock Stopped Check 1

With a storage director clock stopped check 1, the microcode does not run. When a check is detected that affects the integrity of the microcode, the clock is stopped to stop instruction execution. For more details on a clock stopped check 1 operation, see Sense 110-120.

#### **Storage Director Channel Check 1**

The second part of Format 3 checks consists of errors that do not affect the integrity of the microcode, but inhibit communication to the connected channel. The microcode in the failing storage director passes the sense information to the alternate storage director. The alternate storage director reports the information to the first channel that generates a Start I/O command. The resulting selective reset is kept until the sense information is reported. For more details on a channel check 1 operation, see SENSE 125-165.

### Format 6 – Usage, Overrun, and Error Statistics

Format 6 is different from format 0, 2, and 3 and does not result directly from a fault or check condition. Format 6 sense information is generated after the channel issues a Read and Reset Buffered Log Command. The channel requests format 6 information to prepare a report on device and channel usage, or to flag an unusually high number of overruns or intermittent failures. A storage director can request the channel to read the log, because a counter is full.

### Format F – Subsystem Storage Errors

Format F is divided into small formats (subformats) based on the message in byte 7. Sense byte 7 equals X'Fx'; where x equals the message number as follows:

- 0 = Operation Terminated (Model 23 only)

- 1 = Subsystem Processing Error

- 2 = Subsystem storage equipment check

- 3 = Availability threshold crossed

- 4 = Subsystem storage unusable

- 5 = Subsystem storage initialization required (Model 21 only)

- 6 = Not used

- 7 = Track format not supported for paging (Model 21 only)

- 8 = Storage director communication failure.

- 9 = Caching Reinitiated

- A-F = Not used

| 3880 | [          | PN 6315725 | 881144    | 881216    | A15621    |  |

|------|------------|------------|-----------|-----------|-----------|--|

| MSM  | Seg JE0001 | 2 of 70    | 13 Jan 84 | 15 Aug 84 | 01 Apr 85 |  |

Copyright IBM Corp. 1984, 1985

Introduction to the Sense Section SENSE 5

# Sense Bytes 0-7 Summary

|      |                                        |                                        |                                                                                       | SENSE BYTE                             | SUMMARY                                 |                                     |                    |                                                      |

|------|----------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|-------------------------------------|--------------------|------------------------------------------------------|

| BYTE | BIT O                                  | BIT 1                                  | BIT 2                                                                                 | BIT 3                                  | BIT 4                                   | BIT 5                               | BIT 6              | BIT 7                                                |

| 0    | Command<br>Reject                      | Intervention<br>Required               | Channel Bus Out<br>Parity Check                                                       | Equipment<br>Check                     | Data Check                              | Overrun                             | Not Used           | Not Used                                             |

| 1    | Permanent Error<br>(see device lib.)   | Invalid Track<br>Format                | End of<br>Cylinder                                                                    | Message to<br>Operator                 | No Record<br>Found                      | File<br>Protected                   | Write<br>Inhibited | Operation<br>Incomplete<br>(not used in<br>Model 23) |

| 2    | Not Used                               | Correctable                            | Alternate Con-<br>troller Select-<br>ed in Model 21<br>First Error Log<br>in Model 23 | Environmental<br>Data Present          | Intent Violation<br>(Model 23 only)     | Imprecise Ending<br>(Model 23 only) | Write<br>Operation | 3880 Model 21<br>or 23 sense<br>data                 |

| 3    | Restart command i                      | n Model 21; Contr                      | oller Identificati                                                                    | on/Residual Record                     | Count in Model 23                       | <b>.</b>                            |                    |                                                      |

| 4    | Device Identifica<br>(See SENSE 30 for | tion<br>more information               | )                                                                                     |                                        | 1                                       |                                     |                    |                                                      |

| 5    | Instruction Addre<br>(See SENSE 30 for | ess Register, High<br>more information | o Order Byte; or Di                                                                   | skette Checks; or                      | Cylinder Address, Lo                    | w Order Byte                        |                    |                                                      |

| 6    | Head Address and<br>or Subsystem Stor  | Cylinder Address,<br>age Identifier    | , High Order Byte;<br>(See SENSE 32 for )                                             | or Instruction Ad<br>more information) | dress Register, Low O                   | rder Byte; or Stora                 | age Director Ide   | ntification;                                         |

| 7    | Bits 0 - 3 = Form<br>(See SENSE 35 for | nat Identifier<br>more information     | ,)                                                                                    |                                        | Bits 4 - 7 = Messa<br>(See SENSE 35 for | ge Identifier<br>more information)  |                    |                                                      |

The table on this page gives a summary of bytes 0 through 7 of the sense information. More detailed information on each byte is given in the following pages of this SENSE section.

### Sense Bytes 0-23

.

Sense bytes 0 through 6 do not change their contents because of the format and message identified by byte 7. Byte 7 identifies the format and message of the sense information. Bytes 8 through 23 are variable and depend on the format and message identified in byte 7. Bytes 8 through 23 are described under each format description.

| 2000        |            | DNL COLEZOF           | 881144                                                                                                          | 881216                                                                                                         | A15001              |  |

|-------------|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------|--|

| 3880<br>MSM | Seq JE0001 | PN 6315725<br>3 of 70 | 13 Jan 84                                                                                                       |                                                                                                                | A15621<br>01 Apr 85 |  |

|             |            |                       | The second se | the second s | A                   |  |

# Sense Bytes 0-7 Summary SENSE 10

Sense Bytes 0-7 Summary SENSE 10

# Sense Bytes 0—2

Sense bytes 0 through 2 are generated when a unit check occurs. Bytes 0 through 2 describe the error condition in general terms and identify the specific action to recover from the error.

### Sense Byte 0

### Bit 0 – Command Reject

Bit 0 indicates a command has been rejected. Sense byte 7 identifies the error condition in more specific terms. Any one of the following conditions causes bit 0 to be set:

- A not valid command is received from the channel when the command code is either:

- ---not known

- acceptable only for some devices \_\_\_\_

- not acceptable when some features are installed.

- A command that is not valid in paging mode is received on a paging address (Model 21 only).

- A command that is not valid in direct mode is received on a base address (Model 21 only).

- A not valid sequence of commands is detected.

- A not valid or not complete argument has been transferred for a control command.

- A write command has been received that violates the file mask.

- A track accessed by a command has a not correct alternate or defective track pointer. The RO count area of a defective track points to itself instead of an alternate track.

- A write command is received on a direct address and the Write Inhibit switch is in the read only position. Write inhibited (byte 1, bit 6) is also on (Model 21 only).

- A format write command other than Write Home Address or Write Record Zero is received while accessing a defective track.

- In the domain of a Locate Record command, a command code is decoded that conflicts with the Locate Record parameters (Model 23 only).

- A diagnostic command has been received that violates the file mask (Model 23 only).

- Not valid or not complete home address data has been transferred by a Write Home Address or Diagnostic Home Address command (Model 23 only).

### Bit 1 – Intervention Required

Bit 1 indicates that the addressed device is:

- Not physically attached to the system

- Not ready

- For Model 21 only not available because a subsystem storage to DASD transfer cannot complete because the device is not installed or is not ready. Environmental data present (byte 2, bit 3) is also on.

### Bit 2 – Channel Bus Out Parity Check

Bit 2 indicates that a data parity error has been detected in data transferred from the channel. A parity error detected during command transfer is a bus out parity check and not a command reject.

### Bit 3 – Equipment Check

Bit 3 indicates that an unusual hardware condition originated in the channel, either storage director, the subsystem storage, the subsystem communication link, or the device.

Note: The subsystem communication link is used in the Model 21 only. The Model 23 storage directors communicate through an area in the dynamic path selection feature in the shared DASD controllers.

The conditions of bit 3 are described in sense bytes 7 through 23.

### Bit 4 – Data Check

Bit 4 is set on when the storage director detects a data error in the information received from the device. If correctable (byte 2, bit 1) is also set, the data error is correctable and bytes 15 through 22 in Model 21 or bytes 20 through 23 in Model 23 give the correction information. If the data error is uncorrectable, sense byte 7 defines the specific condition.

#### Bit 5 – Overrun

A service overrun condition occurs when a response to a request for data was not received by the storage director in the permitted time.

The following conditions cause this bit to be set:

- The storage director receives a data byte from the device or subsystem storage before the previous byte is accepted by the channel.

- During a write operation, a data byte is received too late from the channel.

The storage director posts an overrun error only if it occurs:

- More than 10 times for a single command

- During a format write operation

- During execution of a Read Multiple CKD command.

The detection of an overrun stops data transmission. When writing, the remaining part of the record is padded with '0's. Except in the three conditions given above, the storage director attempts to recover the data overruns by trying the channel command again. If the attempt is not successful, ending status includes unit check (overrun).

Permanent error (byte 1, bit 0) is never presented with overrun (byte 0, bit 5).

Command overrun errors are also detected. They are tried again by the storage director.

### Bits 6 and 7

Bits 6 and 7 are not used.

|        |            |            | ·····     |           |           | <br> |

|--------|------------|------------|-----------|-----------|-----------|------|

| 3880   |            | PN 6315725 | 881144    | 881216    | A15621    |      |

| MSM    | Sea JE0001 | 4 of 70    | 13 Jan 84 | 15 Aug 84 | 01 Apr 85 |      |

| inom . | 004 020001 | + 01 70    |           |           |           | <br> |

Copyright IBM Corp. 1984, 1985

# Sense Byte 0 SENSE 15

# Sense Bytes 0—2 (Continued)

### Sense Byte 1

### Bit 0 – Permanent Error

The storage director sets this bit on, in combination with one or more additional sense bits, to indicate that internal error recovery has been attempted and failed or that it is not desired.

If environmental data present (byte 2, bit 3) is also on, the sense data is associated with an internal operation (such as a subsystem storage to DASD transfer) rather than with the current command chain. The system should try the operation again that received the unit check.

If environmental data present (byte 2, bit 3) is off, system error recovery procedures should not be attempted.

### Bit 1 – Invalid Track Format

Bit 1 is set when:

- During a format write operation, an attempt is made to write data for more than the track will hold

- An index point is detected in the gap that precedes a key or data field.

The Invalid Track Format bit is set when a previous operation attempted to write data for more than the track will hold; this operation results in a record written into index. This record was met while attempting to execute a read, search, or write command. As long as this record remains on the track, invalid track format can be posted while attempting to locate a record successfully written on the track. However, search ID-type commands will execute on any count field successfully written on the track without posting invalid track format.

In the Model 21 only, the storage director sets this bit in paging mode when data is transferred between cache and DASD and the data format is not supported in paging mode. The following formats are not valid:

- Key length other than zero

- Data length other than 4096

- Record is a part of an overflow record .

- The track has been formatted without a Home Address

- The Record O count field of a defective track points to itself instead of the alternate track.

If the failed operation is a paging mode read miss, only this bit is set. If the failed operation is a subsystem storage to DASD write, message to operator (byte 1, bit 3) and environmental data present (byte 2, bit 3) are also on.

#### Bit 2 – End of Cylinder

This bit is set when:

- An attempt is made to continue a multitrack operation across a cylinder boundary.

- Model 21 only An attempt is made to continue a read or write operation for an overflow record across a cylinder boundary.

### Bit 3 – Message to Operator

Bit 3 indicates that a message, defined by byte 7, is to be sent to the operator console.

For Model 21, the operator console messages are as follows:

#### Byte 7 Console Message

- ddd REPORTS DISABLED INTERFACE ON (nn) FAULT Зx CODE = cccc

- SUBSYSTEM PROCESSING ERROR FAULT CODE = F1 cccc - cuu

- F2 SUBSYSTEM STORAGE EQUIPMENT CHECK - FAULT CODE = cccc -cuu

- F3 SUBSYSTEM STORAGE AVAILABILITY THRESHOLD CROSSED - cuu

- F4 SUBSYSTEM STORAGE UNUSABLE - FAULT CODE = cccc - cuu

- F5 SUBSYSTEM STORAGE MUST BE INITIALIZED - FAULT CODE = cccc - cuu

- TRACK FORMAT NOT SUPPORTED FOR PAGING -F7 DEVICE ddd - cuu

- FR STORAGE DIRECTOR COMMUNICATION FAILED -FAULT CODE = cccc - cuu

- For Model 23, the operator console messages are as follows:

### Byte 7 Console Message

- ddd REPORTS DISABLED INTERFACE (nn) FAULT Зx CODE = cccc

- F1 SUBSYSTEM PROCESSING ERROR - FAULT CODE = cccc - ss-XX-XX

- CODE = cccc ss-XX-XX

- SUBSYSTEM STORAGE EQUIPMENT CHECK FAULT F2

dd device = Physical identifier of the 55

CUU.

nn

cc

F3

F4

F8

F9

LEGEND:

reporting storage director

SUBSYSTEM STORAGE AVAILABILITY THRESHOLD

STORAGE DIRECTOR COMMUNICATION FAILED -

SUBSYSTEM STORAGE IS UNUSABLE - FAULT CODE =

CROSSED - ss-XX-XX

FAULT CODE = cccc - ss-XX-XX

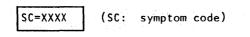

cccc = Fault symptom code from sense

= Address of the reporting path

= Physical identifier of the

= Physical identifier of the

bytes 22 and 23

= Installation number

ddd = Device address

controller

CACHING REINITIALIZED - ss-XX-XX

cccc - ss-XX-XX

| 3880 |            | PN 6315725 | 881144    | 881216    | A15621    |   |  |

|------|------------|------------|-----------|-----------|-----------|---|--|

| MSM  | Seg JE0001 | 5 of 70    | 13 Jan 84 | 15 Aug 84 | 01 Apr 85 | I |  |

Copyright IBM Corp. 1984, 1985

# Sense Byte 1 SENSE 20

# Sense Byte 1 SENSE 20

# Sense Bytes 0—2 (Continued)

### Sense Byte 1 (Continued)

### Bit 4 – No Record Found

In the Model 21, the following conditions cause this bit to be set:

- During execution of a direct mode channel program, two index marks have been detected in the same CCW chain without an intermediate read operation in a home address or data area, or without an intermediate control, write, or sense command. The storage director always verifies that the accessor is placed correctly before reporting this condition.

- · While executing a Read Data command in paging mode, the storage director can not locate a record whose logical block identifier was communicated by the preceding Search ID Equal command.

- While attempting to perform an asynchronous operation that required transferring data from the subsystem storage to the 3350, the storage director can not locate a record whose logical block identifier is taken from the subsystem storage directory. Message to operator (byte 1, bit 3) and environmental data present (byte 2, bit 3) are also on.

In the Model 23, this bit is set by the storage director when index has been detected twice (or its cache equal) in the same CCW chain without an intermediate read operation on a data field or home address, or without an intermediate control, write, or sense command. For operations direct to the device, the storage director verifies that the access mechanism is placed correctly before reporting this condition.

### Bit 5 – File Protected

Bit 5 indicates one of the following conditions:

- A seek command has violated the file mask.

- A read multitrack or search multitrack operation has violated the file mask.

- In the Model 21, a read or write operation that accesses an overflow record violates the file mask. Operation incomplete (byte 1, bit 7) is also on.

- In the Model 23, a Locate Record operation attempts to go over the boundaries of the Define Extent command.

### Bit 6 – Write Inhibited

In the Model 21 only, this bit is on when:

- A write command is received on a base address and the device write inhibit switch is in the read only position. Command reject (byte 0, bit 0) is also on.

- A subsystem storage to DASD write is attempted and the device write inhibit switch is in the read only position. Environmental data present (byte 2, bit 3) is also on.

In the Model 23 only, this bit is turned on when a write command or a Locate Record command specifying a write-type operation is received on a channel that is 'write inhibited' by a Diagnostic Control command. Equipment Check (byte 0, bit 3) is also on.

### Bit 7 – Operation Incomplete

This bit is used by the Model 21 only.

This bit is on when:

- Accessing of a segment other than the first requires a switch to a track that is protected by the file mask. File protected (byte 1, bit 5) is also on.

- Accessing of a segment other than the first requires a switch beyond the end of the cylinder. End of cylinder (byte 1, bit 2) is also on.

- A correctable data check is met in a segment other than the last. Data check (byte 0, bit 4) and correctable (byte 2, bit 1) are also on.

- . An uncorrectable data check is met in a segment other than the first. Data check (byte 0, bit 4) is also on.

- Accessing of a segment other than the first segment requires a switch to a track that is defective or from an assigned alternate track.

- A seek error is detected while attempting to access a • segment other than the first segment.

| 2000        |            |                       | 001144              | 001010              | A15001              | İ |  |

|-------------|------------|-----------------------|---------------------|---------------------|---------------------|---|--|

| 3880<br>MSM | Seg JE0001 | PN 6315725<br>6 of 70 | 881144<br>13 Jan 84 | 881216<br>15 Aug 84 | A15621<br>01 Apr 85 |   |  |

|             |            |                       |                     |                     |                     |   |  |

Copyright IBM Corp. 1984, 1985

# Sense Byte 1 (Cont.) SENSE 22

Sense Byte 1 (Cont.) SENSE 22

# Sense Bytes 0—2 (Continued)

### Sense Byte 2

Bit 0

Bit 0 is not used.

### Bit 1 - Correctable

This bit is on when the data error indicated by data check (byte 0, bit 4) is correctable. Bytes 18-22 of format 5 give information to permit correction.

In the Model 21, the following conditions cause this bit to be set:

- A correctable data error is detected in information received from the device during a direct mode read or search operation. Correctable (byte 2, bit 1) is also on, and bytes 15-22 of format 5 give information to permit correction.

- A correctable data check is met in a segment other than the last. Data check (byte 0, bit 4) and operation incomplete (byte 1, bit 7) are also on.

In the Model 23, the following condition causes this bit to be set:

PCI fetch mode is active when a data error is detected in • data transferred to the channel from the device and the data is transmitted correctly on channel command retry. Data check (byte 0, bit 4) is also on and the ECC displacement and pattern are zero.

### Bit 2 – Alternate Controller Selected or First Error Log

This bit in the Model 21 is named Alternate Controller Selected. This bit in the Model 23 is named First Error Log.

In the Model 21, this bit indicates that the controller in the 3350 C2 unit is selected. This bit gives aid in fault isolation between controllers when the dual control option is installed.

In the Model 23, this bit indicates that the 3380 or subsystem storage entered soft error logging mode. Environmental data present (byte 2, bit 3) is also on.

### Bit 3 – Environmental Data Present

Bit 3 indicates that sense bytes 8 through 23 give either usage and error statistics or error log information. Byte 7 indicates the formats for bytes 8 through 23.

Bit 3 is set by any of the following:

- A usage counter or error counter overflow.

- An internal error recovery procedure has either failed or completed correctly and the forced error logging mode or soft error logging mode is in effect.

- An error has occurred during a subsystem storage to DASD transfer.

- During a subsystem storage to DASD write, the record or track being updated is found to be a format that is not valid for paging mode (Model 21 only).

- A subsystem storage to DASD write is attempted and the write inhibit switch is in the read-only position.

- The amount of space available for subsystem storage is ٠ below one of the reporting thresholds.

- A subsystem processing error is detected that is not associated with the current command chain.

- An attempted communication with the other storage director fails or is not permitted because of the subsystem storage mode switch setting and the attempted communication is not associated with the current command chain.

### Bit 4 – Intent Violation

This bit is used by the Model 23 only.

This bit indicates that an update write operation in the domain of a Locate Record command has met a conflict between the Define Extent or Locate Record command parameters and the recorded track format. This condition is reported in the following instances.

- A Write Data command is chained from a Locate Record command with the Write Data subcommand specified and the block size value from the preceding Define Extent command or the Transfer Length Factor value from the Locate Record command, (if specified), is not equal to the actual data length of the record to be updated.

- · A Write Update Data command is received in the domain of a Locate Record command with the Write Data subcommand specified and the block size value from the preceding Define Extent command or the Transfer Length Factor value from the Locate Record command, (if specified), is not equal to the actual data length of the record to be updated.

- A Write Key and Data command is chained from a Locate Record command and the block size value from the preceding Define Extent command or the Transfer Length Factor value from the Locate Record command, (if specified), is not equal to the total of the key and data lengths of the record to be updated.

- A Write Update Key and Data command is received in the domain of a Locate Record command and the block size value from the preceding Define Extent command or the Transfer Length Factor value from the Locate Record command, (if specified), is not equal to the total of the key and data lengths of the record to be updated.

- ٠ A Write Update Data or Write Update Key and Data command has been received and after orienting to index following a head switch, the expected number of records (Home Address, a record to pass over and a record for update) are not identified on the track.

- A Write Update Data or Write Update Key and Data command has been received and after orienting to index following a head switch, the expected record following home address (record 0) is not identified on the track.

- The RO data field length is not equal to 8 during a Write Track operation.

- Home Address or Record 0 is not found following a head-switch during a Write Count, Key, and Data Next Track command execution.

### Imprecise Ending (Byte 2, Bit 5)

This bit is used by the Model 23 only.

This bit is set to one when an abnormal channel program termination occurs and the exception status is for a preceding completed CCW (i.e., the search function of a Locate Record command). This bit indicates that the CSW command address is not synchronized with the transfer of data by the Model 23 to the device.

### Bit 6 – Write Operation

Bit 6 is set to indicate that the error occurred during the execution of a write command.

### Bit 7 – 3880 Model 21 or 23 Storage Control Unit

When this bit is on, it indicates that the sense record was made by the 3880 Model 21 or 23.

| 3880<br>MSM | Seg JE0001 | PN 6315725<br>7 of 70 | 881144<br>13 Jan 84 | 881216<br>15 Aug 84 | A15621<br>01 Apr 85 |  |

|-------------|------------|-----------------------|---------------------|---------------------|---------------------|--|

|             |            |                       |                     |                     |                     |  |

Copyright IBM Corp. 1984, 1985

# Sense Byte 2 SENSE 25

# Sense Byte 2 SENSE 25

### Sense Bytes 3—5

### Sense Byte 3 – Restart Command or Controller Identification/Residual Record Count

In Model 21 this byte is named the restart command. In Model 23 this byte is named the controller identification/residual record count byte.

#### Model 21:

In Model 21, this byte is set when operation incomplete (byte 1, bit 7) is on. Bits 5-7 identify the type of operation in progress when the unit check occurred. If the bits are set to 0000 0110, a read operation was in progress; if they are set 0000 0101, a write operation was in progress.

#### Model 23:

In Model 23 for sense formats 1, 2, 6, 7, and 8 this byte identifies the controller for which the sense data is reported. For sense formats 0, 3, 4, 5 and F:

- With Imprecise ending (byte 2, bit 5) set OFF, this byte is zero

- With Imprecise ending set ON, this byte indicates the number of records that remain to be processed in the domain of the Locate Record command.

### Sense Byte 4 – Device Identification

Bits 0 through 7 identify the device associated with the sense information.

#### Model 21:

When the sense data is presented on a direct address or when sense formats 1, 2, 4, 5, or message 7 of format F are presented on a paging address, the byte description is as follows:

- Bit 0 = Device 0 Bit 1 = Device 1 Bit 2 = Device 2 Bit 3 = Device 3 Bit 4 = Not used Bit 5 = Not used

- Bit 6 = Not used

- Bit 7 = Not used

When sense formats 0, 3, and messages 0 through 5 and 8 of format F are presented on a paging address, this byte contains all zeros.

### Model 23:

When the sense data has been collected as a result of errors detected in the subsystem storage, this byte identifies the device addressed by the command chain.

When this bit is on it is defined as follows:

- Bit 0 DPS feature installed

- Bit 1 Reserved, always zero

- Bit 2 Reserved, always zero except in format 7 where this • bit indicates a permanent path error.

- Bit 3 Reserved, always zero

- Bit 4 Spindle address 4

- Bit 5 Spindle address 2 •

- Bit 6 Spindle address 1

- Bit 7 If 0, left actuator: if 1, right actuator

### Sense Byte 5 for Model 21

This byte contains different types of information depending on the format being reported in sense byte 7. The following formats are possible:

- When format 3 is identified and not with message 8, the error reported by sense byte 5 reports an Instruction Address Register-High Order Byte error.

- When format 6 is identified, sense byte 5 reports a Diskette . Check error.

- When formats 0, 1, 2, 4, 5, or F is identified or has the value X'38', sense byte 5 reports a Cylinder Address-Low Order Byte error.

A description of each of the conditions of sense byte 5 follows.

Instruction Address Register - High Order Byte

If sense byte 7 indicates format 3 and not message 8, this byte contains the High-Order Byte of the instruction address register at the time of the error.

#### Diskette checks

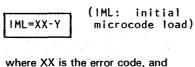

If sense byte 7 indicates format 6, this byte contains the number of recoverable diskette checks after an initial microcode load (IML), or whether or not a storage director-to-storage director communication failure occurred during the most recent IML as follows:

- Bit 0 Communication failure during an IML

- Bit 1 Not used

- Bits 2-4 Number of diskette seek errors

- Bits 5-7 Number of diskette read errors

- Cylinder Address Low Order Byte

If sense byte 7 indicates formats 0, 1, 2, 4, 5, F or has the value X'38' this byte contains the most recent seek argument from the channel as follows:

Bit 0 = Cylinder 128 Bit 1 = Cylinder 64 Bit 2 = Cylinder 32 Bit 3 = Cylinder 16 Bit 4 = Cylinder 8 Bit 5 = Cylinder 4 Bit 6 = Cylinder 2Bit 7 = Cylinder 1

### Sense Byte 5 for Model 23

This byte contains different types of information depending on the format being reported in sense byte 7. The following formats are possible:

- When format 3 is identified and not with message 8, the error reported by sense byte 5 reports an Instruction Address Register-High Order Byte error.

- When format 6 is identified, sense byte 5 reports a Diskette Check error.

- When formats 0, 1, 2, 4, 5, 7, 8, or F is identified or has the value X'38', sense byte 5 reports a Cylinder Address Low Order Byte error.

A description of each of the conditions of sense byte 5 follows.

Instruction Address Register - High Order Byte

If sense byte 7 indicates format 3 and not message 8, this byte contains the High-Order Byte of the instruction address register at the time of the error.

|      |            | ·          |           |           |           |  |

|------|------------|------------|-----------|-----------|-----------|--|

| 3880 |            | PN 6315725 | 881144    | 881216    | A15621    |  |

| MSM  | Seg JE0001 | 8 of 70    | 13 Jan 84 | 15 Aug 84 | 01 Apr 85 |  |

<sup>©</sup> Copyright IBM Corp. 1984, 1985

Sense Bytes 3—5 SENSE 30

• Diskette checks

If sense byte 7 indicates format 6, this byte contains the number of recoverable diskette checks after an initial microcode load (IML), or whether or not a storage director-to-storage director communication failure occurred during the most recent IML as follows:

Bit 0 - Communication failure during an IML Bit 1 - Not used Bits 2-4 - Number of diskette seek errors Bits 5-7 - Number of diskette read errors

Cylinder Address - Low Order Byte

If sense byte 7 indicates formats 0, 1, 2, 4, 5, 7, 8, or F, or has the value X'38' this byte contains the most recent seek argument from the channel as follows:

Bit 0 = Cylinder 128 Bit 1 = Cylinder 64 Bit 2 = Cylinder 32 Bit 3 = Cylinder 16 Bit 4 = Cylinder 8 Bit 5 = Cylinder 4 Bit 6 = Cylinder 2 Bit 7 = Cylinder 1

# Sense Bytes 3—5 SENSE 30

## Sense Byte 6

### Sense Byte 6 for Model 21

This byte contains different types of information depending on the format being reported in sense byte 7. The following formats are possible:

- When formats 0, 1, 2, 4, 5, or F is identified or has the value X'38', sense byte 6 reports a Head Address and Cylinder Address-High Order Byte error.

- When format 3 is identified and not with message 8, sense byte 6 reports an Instruction Address Register-Low Order Byte error.

- When format 6 is identified, sense byte 6 reports the Storage Director Identification.

- When format F is identified with messages 3 or 4, sense byte 6 reports the Subsystem Storage Identifier.

A description of each of the conditions of byte 6 follows.

- Head Address and Cylinder Address High Order Byte

- If sense byte 7 indicates format 0, 1, 2, 4, 5, F or is equal to X'38', this byte gives the High-Order Cylinder address of the most recent seek argument received from the channel and the head address resulting from the most recent head switch (seek or multitrack operation).

If an alternate track condition is detected while processing an overflow record and operation incomplete (byte 1, bit 7) is on, the head address is that of the defective track +1. The ERPs use this byte to make the seek argument to continue the operation.

In direct mode, the head address and High-Order Cylinder address values of rejected seek commands are not given in this byte. In paging mode, they are given.

Operations that include head switching update the head address bits (bits 3-7) of this byte.

This byte is formatted as follows:

Bit 0 = CE cylinder Bit 1 = Cylinder 512 Bit 2 = Cylinder 256 Bits 3 to 7 = Head address

Instruction Address Register - Low Order Byte

If sense byte 7 identifies format 3 and not with message 8. this byte is used to indicate the low order byte of the instruction address register at the time the error occurred.

Storage Director Identification

If sense byte 7 identifies the data as format 6, this byte contains the storage director identification.

Subsystem Storage Identifier

If sense byte 7 identifies Format F and messages 3 or 4, this byte contains the subsystem storage identifier.

### Sense Byte 6 for Model 23

This byte contains different types of information depending on the format being reported in sense byte 7. The following formats are possible:

- When formats 0, 1, 2, 4, 5, 7, 8, or F is identified or has the value X'38', sense byte 6 reports a Head Address and Cylinder Address-High Order Byte error.

- When format 3 is identified and not with message 8, sense byte 6 reports an Instruction Address Register-Low Order Byte error.

- When format 6 is identified, sense byte 6 reports the ٠ Storage Director Identification.

A description of each of the conditions of byte 6 follows.

Head Address and Cylinder Address - High Order Byte

If sense byte 7 indicates format 0, 1, 2, 4, 5, 7, 8, or F, or is equal to X'38', this byte gives the High-Order Cylinder address of the most recent seek argument received from the channel and the head address resulting from the most recent head switch (seek or multitrack operation).

If an alternate track condition is detected while processing an overflow record and operation incomplete (byte 1, bit 7) is on, the head address is that of the defective track +1. The ERPs use this byte to make the seek argument to continue the operation.

Operations that include head switching update the head address bits (bits 4-7) of this byte.

This byte is formatted as follows:

- Bit 0 = Not used

- Bit 1 = Equal to bit 5 of the High-Order Cylinder Byte Bit 2 = Equal to bit 6 of the High-Order Cylinder Byte Bit 3 = Equal to bit 7 of the High-Order Cylinder Byte Bits 4 to 7 = Head address

Instruction Address Register - Low Order Byte

If sense byte 7 identifies format 3 and not with message 8, this byte is used to indicate the low order byte of the instruction address register at the time the error occurred.

Storage Director Identification

If sense byte 7 identifies the data as format 6, this byte contains the storage director identification.

|      | <br>       |            | · · · · · · · · · · · · · · · · · · · |           |           |  |

|------|------------|------------|---------------------------------------|-----------|-----------|--|

| 3880 |            | PN 6315725 | 881144                                | 881216    | A15621    |  |

| MSM  | Seg JE0001 | 9 of 70    | 13 Jan 84                             | 15 Aug 84 | 01 Apr 85 |  |

|      |            |            |                                       |           |           |  |

Copyright IBM Corp. 1984, 1985

# Sense Byte 6 SENSE 32

# Sense Byte 6 SENSE 32

# Sense Bytes 7—23

### Sense Byte 7

This sense byte consists of two fields, the format identifier in bits 0 through 3 and the message identifier in bits 4 through 7.

| Sense Byte 7:        |       |      |           |   |

|----------------------|-------|------|-----------|---|

| 0 1 2 3              | <br>4 | 5    | 6         | 7 |

| Format<br>Identifier | Mes   | ssag | e<br>fier |   |

### Format Identifier

For formats 0 to 6 (except format 3), these bits identify the specific format of sense bytes 5-6 and 8-23. For formats 3 and F, these bits plus the message identifier identify the specific format of sense bytes 5-6 and 8-23. The possible values are defined in the sections that describe the corresponding formats of bytes 8-23.

Formats 0, 2, and 3 pertain to storage control errors. Format 0 is generated when an error or unusual condition is specified by sense bytes 0 through 7. Format 2 is generated after the microcode detects a storage director error condition. Format 3 is generated after an error condition occurs in the channel interface or the control and results in a disconnect-in sequence to the channel.

Formats 1, 4, and 5 pertain to device errors and are described in the device maintenance library.

Format 6 contains usage, overrun and error statistics information that is described in both this Maintenance Support Manual (MSM) and the device MIM.

### Message Identifier

These bits give a message that describes the error.

| CODE | MEANING                                             |

|------|-----------------------------------------------------|

| 0000 | Format 0 - Program or system checks                 |

| 0001 | Format 1 - Device equipment checks                  |

| 0010 | Format 2 - Storage director<br>equipment checks     |

| 0011 | Format 3 - Storage director control<br>checks       |

| 0100 | Format 4 - Uncorrectable data checks                |

| 0101 | Format 5 - Correctable data checks                  |

| 0110 | Format 6 - Usage, overrun, and<br>error statistics  |

| 0111 | Format 7 - Controller check 1                       |

| 1000 | Format 8 - Controller check 2<br>and device check 1 |

| 1111 | Format F - Subsystem storage errors                 |

Note: Format 5 can also be presented on device errors which are not ECC correctable but which need restart displacement information.

### Byte 1, Bit 3 - Message to Operator

Byte 1, bit 3 indicates that a message, defined by byte 7, is to be sent to the operator console.

For Model 21, the operator console messages are as follows:

### Byte 7 Console Message

- ddd REPORTS DISABLED INTERFACE ON (nn) FAULT CODE = cccc 3x

- F1 SUBSYSTEM PROCESSING ERROR - FAULT CODE = cccc - cuu

- F2 SUBSYSTEM STORAGE EQUIPMENT CHECK - FAULT CODE = cccc -cuu

- SUBSYSTEM STORAGE AVAILABILITY THRESHOLD CROSSED cuu F3

- SUBSYSTEM STORAGE UNUSABLE FAULT CODE = cccc cuu F4

- F5 SUBSYSTEM STORAGE MUST BE INITIALIZED - FAULT CODE = cccc - cuu

- TRACK FORMAT NOT SUPPORTED FOR PAGING DEVICE ddd cuu F7

- F8 STORAGE DIRECTOR COMMUNICATION FAILED - FAULT CODE = cccc - cuu

| •     |                                     |

|-------|-------------------------------------|

| F1    | SUBSYSTEM PRO                       |

| F2    | SUBSYSTEM STO                       |

| F3    | SUBSYSTEM STO                       |

| F4    | SUBSYSTEM STO                       |

| F8    | STORAGE DIRECT<br>ss-XX-XX          |

| F9    | CACHING REINITI                     |

| LEGEN | 1D :                                |

| cccc  | = Fault symptom c<br>bytes 22 and 2 |

|       | = Address of the                    |

|       | = Device address                    |

|       | = Installation nu                   |

| cc    | = Physical identi                   |

controller hh

device 55

### Sense Bytes 8 through 23

The content of sense bytes 8 through 23 changes depending on the value specified in byte 7. See the following descriptions of sense formats for more information.

881144 PN 6315725 A15621 3880 881216 MSM Seg JE0001 10 of 70 13 Jan 84 15 Aug 84 01 Apr 85

<sup>©</sup> Copyright IBM Corp. 1984, 1985

Зx

Byte 7 Console Message

# Sense Bytes 7—23 SENSE 35

For Model 23, the operator console messages are as follows:

ddd REPORTS DISABLED INTERFACE (nn) - FAULT CODE = cccc CESSING ERROR - FAULT CODE = cccc - ss-XX-XX RAGE EQUIPMENT CHECK - FAULT CODE = cccc - ss-XX-XX RAGE AVAILABILITY THRESHOLD CROSSED - ss-XX-XX RAGE IS UNUSABLE - FAULT CODE = cccc - ss-XX-XX FOR COMMUNICATION FAILED - FAULT CODE = cccc -

ALIZED - ss-XX-XX

code from sense reporting path umber ifier of the = Physical identifier of the Physical identifier of the reporting storage director

# Sense Bytes 7—23 SENSE 35

# Format 0—Program or System Checks for Model 21

Format 0 is used when sense bytes 0 through 7 completely describe the error or unusual condition caused by a program or system error.

Bytes 8 to 23 contain the following data:

Bytes 8 through 17 are not used and are set to zero.

Byte 18 through 23 - Skip Displacement

If a Sense command is chained from a correct Read Home Address command and no contingent allegiance exists, bytes 18 through 23 contain the skip displacement bytes on the track.

If a Sense command is not chained from a Read Home Address and a contingent allegiance exists, bytes 8 to 20 contain zeros, byte 21 contains the storage director identification, and bytes 22 and 23 contain the symptom code.

If not, bytes 18 through 23 are set to zero.

Messages for format 0 are described below.

### Format 0 Messages

### Message 0 – No Message

No additional information required.

### Message 1 – Invalid Command

A not valid command was sent to the device that is not in the device command set or the command pertains to a feature that is not installed.

### Message 2 – Invalid Command Sequence

A not valid sequence of commands has occurred. Included are the following:

- A read, search, Seek Head, Space Count, or Diagnostic Write Home Address command is received without being preceded by a Seek, Seek Cylinder, Locate Record, Read IPL, or Recalibrate command in the same chain.

- A Read Initial Program Load (IPL), Device Reserve, or Device Release, Set File Mask or Define Extent command was preceded by a Set File Mask or Define Extent command in the same chain.

- A write command has violated the write part of a preceding Set File Mask command.

- A write command has not satisfied the prerequisites.

- A Write, Read IPL, Set File Mask, Define Extent, Device Reserve, or Device Release command was sent in the same chain following a Space Count command.

- An Unconditional Reserve command is preceded by a channel command word (CCW) in the same chain.

- A Space Count command is chained from a formatting write command.

- A write command is received while the SA cylinder is accessed.

- A Locate Record command which specifies a subcommand of Write Data is received and the file mask inhibits all write operations.

- A Locate Record command which specifies a subcommand of Format Write or Write Track is received and the file mask inhibits all write or format write operations.

- A Locate Record command is received without being preceded by a Define Extent command or a Read IPL command in the same command chain.

- Any control, search, or sense command is received in the domain of a Locate Record command.

- Any of the following commands is received in the domain of a Locate Record command: Read Multiple Count, Key, and Data, Read Sector, Diagnostic Read Home Address, and Diagnostic Write Home Address.

- Any of the following commands is received in the domain of a Locate Record command which has a subcommand other than Read Data: Read Home Address, Read Record Zero, Read Count, Read Data, Read Key and Data, or Read Count, Key and Data.

- A Set Path Group Identifier, Sense Path Group Identifier, Set Subsystem Mode, or Sense Subsystem Status command is chained from any command or any command command is chained from one of these commands.

### Message 3 - CCW Count Less Than Required

The CCW count of a command is less than required. Included are the following:

- Any seek command with a CCW count of less than six

- A Set Paging Parameters command with a count less than ten

- A Discard Block command with a count of from two to 322

- A Set Subsystem Mode command with a count less than two

- A Search ID Equal command (paging mode only) with a count less than five

- A Write Home Address command with a CCW count of less than seven.

### Message 4 – Invalid Argument

The data argument is invalid. Included are the following:

- A Seek, Seek Cylinder, or Seek Head command that seeks a not valid address

- A Set Sector command argument that seeks a not valid sector number

- A Set File Mask command argument that does not have bits 2 and 6 set to zero.

### Message 5 – Diagnostic Write Command Not Permitted By File Mask

A Diagnostic Write command is sent that violates bit 5 of the file mask.

### Message 6 – Channel Discontinued Retry Operation

The channel does not indicate chaining when retry status is activated. See the MD section of the Maintenance Support Manual (MSM) for the maintenance device (MD), option 5, to perform a check out procedure.

### Message 7 – Channel Returned With Incorrect Retry CCW

This message is generated when the command returned after a command retry sequence does not match the command for which the channel command retry status was presented.

### Message 8 – IML Device Not Ready

During a Diagnostic Load command, message 8 is activated if the initial microcode load (IML) device is not ready.

### Message 9 – IML Device Permanent Seek Check

During a Diagnostic Load command, message 9 is activated if the operation cannot be completed because of an IML device permanent seek check.

| 3880 PN 6315725 88114 | 1 881216 A15621        |

|-----------------------|------------------------|

|                       | 84 15 Aug 84 01 Apr 85 |

|                       |                        |

© Copyright IBM Corp. 1984, 1985

# Format 0 for Model 21 SENSE 45

### Message A – IML Device Permanent Read Check

During a Diagnostic Load command, message A is activated if the operation cannot be completed because of an IML device permanent read check.

### Message B – Defective Or Alternate Track Pointer Points to Itself

An alternate track pointer in the record 0 (R0) count field of a defective track equals the track address of the defective track.

### Message C – Unconditional Reserve

The microcode was unable to get access to the string switch with the use of of the Unconditional Reserve command.

### Message C Through Message F

Message C through message F are not used.

# Format 0 for Model 21 SENSE 45

# Format 0—Program or System Checks for Model 23

Format 0 is used when sense bytes 0 through 7 completely describe the error or unusual condition caused by a program or system error.

Bytes 8 to 23 contain the following data:

Bytes 8 through 19 are not used and are set to zero.

Byte 20 - Controller Physical Identifier

If Message to operator (byte 1, bit 3) and Environmental data present (byte 2, bit 3) are on, byte 20 contains the controller physical identifier. Otherwise, it is zero.

Byte 21 - Storage Director Identification

Bytes 22 and 23 contain the fault symptom code.

Messages for format 0 are described below.

### Format 0 Messages

When Message to Operator (byte 1, bit 3) is off; the messages for Format 0 are as follows:

Note: When Message to Operator (byte 1, bit 3) is off, use Format 0 messages described on this page. If Message to Operator is on, use Format 0 messages described on SENSE 52.

### Message 0 – No Message

No additional information required.

### Message 1 – Invalid Command

This message indicates the device received a command that is not in the device command set. A not valid command can also pertain to a feature that is not installed.

### Message 2 – Invalid Command Sequence

This message indicates an invalid sequence of commands has occurred. Included are the following:

- A Read, Search, Seek Head, Space Count, or Diagnostic Write Home Address command is received without being preceded by a Seek or a Seek Cylinder, Locate Record, Read IPL, or Recalibrate command in the same command chain.

- A Read Initial Program Load (IPL), Device Reserve, Device Release, Set File Mask, or Define Extent command is preceded by a Set File Mask or Define Extent command in the same command chain.

- A Write command has not satisfied the prerequisites of the ٠ file mask.

- A Write command is not chained from a stated prerequisite command.

- A write command is received while the surface analysis cylinder is accessed.

- A Write, Read IPL, Set File Mask, Define Extent, Device Reserve, or Device Release command is received in the same chain following a Space Count command.

- A Space Count command is chained from a formatting Write command.

- An Unconditional Reserve command is received as other than the first command in a chain.

- A Locate Record command which specifies a subcommand of Write Data, Format Write, or Write Track is received and the file mask inhibits all write operations.

- A Locate Record command is received without being preceded by a Define Extent or Read IPL command in the same command chain.

- A command received in the domain of a Locate Record command is not correct for the domain.

- A Set Path Group Identifier, Sense Path Identifier, Set Subsystem Mode, or Sense Subsystem Status command is chained from any command or any command is chained from one of these commands.

### **MESSAGE 3 - CCW COUNT LESS THAN** REQUIRED

The CCW count of a command is less than required. The following commands are subject to this condition:

- Any seek command with a CCW count of less than 6.

- A Space Count command with a CCW count of less than 3.

- A Set Path Group Identifier command with a CCW count of less than 12.

- A Define Extent command with a CCW count of less than 16

- A Locate Record command with a CCW count of less than 16.

- A Diagnostic Control command with a CCW count of less than 4.

- A Write Home Address command with a CCW count of less than 5.

- A Diagnostic Write Home Address command with a CCW count of less than 28.

• A Set Subsystem Mode command with a CCW count of less than 2.

### Message 4 – Invalid Data Argument

The data argument is not valid. Included are these general conditions:

- · A Seek command argument that is not a valid seek address

- A Set Sector command argument that is not valid

- A Set File Mask command argument that does not have bits 2 and 6 set to zero

- A Write HA or Diagnostic Write HA fails specified parameter checking

- A Set Path Group ID argument is not valid.

- A Diagnostic Control command is received with one of the following:

- Byte 0 is other than X'02' or X'08'.

- Byte 0 is X'02' and byte 1 is other than X'80', X'40', or X'20'.

- Byte 0 is X'08' and byte 1 is other than X'00'.

- Bytes 2 and 3 are other than zeros

### Message 5 - Diagnostic Read or Write Command Not Permitted By File Mask

A Diagnostic Control, Diagnostic Read Home Address, or Diagnostic Write Home Address command is sent that violates bit 5 of the file mask.

### Message 6 – Retry Status Presented and Channel Did Not Indicate Chaining

The channel does not indicate chaining when retry status is activated. Select maintenance device (MD) option 5 in the maintenance mode and perform a machine check out.

### Message 7 – Channel Returned With Incorrect Retry CCW

The channel retry commands are out of sequence. Perform a machine checkout by selecting maintenance device (MD) option 5 in the maintenance mode.

|         |            |                |           |           |           | T |  |

|---------|------------|----------------|-----------|-----------|-----------|---|--|

| 3880    |            | PN 6315725     | 001144    | 881216    | A15621    |   |  |

| 3000    |            | jriv 0319729 j | 001144    | 001210    | AISOZI    |   |  |

| MSM     | Sea JE0001 | 12 of 70       | 13 Jan 84 | 1 04      | 01 4 95   |   |  |

| 1412141 | Seq JE0001 | 12 01 70       | 13 Jan 64 | 15 Aug 04 | UT Apr 85 |   |  |

|         |            |                |           |           |           |   |  |

Copyright IBM Corp. 1984, 1985

Format 0 for Model 23 SENSE 50

# Format 0—Program or System Checks for Model 23(Continued)

### Messages 8 through A

Messages 8 through A are not used.

### Message B – Defective or Alternate Track Pointer Points to Itself

The alternate track pointer in record zero (RO) count field of a defective track equals the track address of the defective track or the alternate track equals the track address of the alternate track.

### Message C – Dynamic Path Selection Installation Configuration Check

Message C indicates that either: (1), the cables to the controllers attached to a storage director are not correct for the dynamic path selection feature, or (2), the dynamic path selection feature is not installed or operating in one of the controllers.

### Messages D through F

Messages D through F are not used.

### Format 0 Messages

When Message to Operator (byte 1, bit 3) is on, the messages for Format 0 are as follows:

Note: When Message to Operator (byte 1, bit 3) is on, use Format 0 messages described on this page. If Message to Operator is off, use Format 0 messages described on SENSE 50.

### Message 0 - No Message

No additional information required.

### Message 1 - Soft Error Logging Complete for Device

This message is generated when soft error logging has been completed for one of the attached devices. The code, SS-CC-DD, is shown on the operator console as follows:

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SS | The storage director<br>physical ID is found in<br>sense byte 21            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CC | The controller physical<br>ID is found in byte 20                           |

| and the second se | DD | The failing device<br>physical ID as shown in<br>bits 4 through 7 of byte 4 |

#### 881144 3880 PN 6315725 881216 A15621 MSM Seq JE0001 13 of 70 13 Jan 84 15 Aug 84 01 Apr 85

<sup>©</sup> Copyright IBM Corp. 1984, 1985

### Message 2 - Soft Error Logging Complete for Controller

This message is generated when soft error logging has been completed for one of the attached controllers. The code. SS-CC-DD, is shown on the operator console as follows:

| \$\$ | The storage director<br>physical ID is found in<br>sense byte 21                                                        |

|------|-------------------------------------------------------------------------------------------------------------------------|

| CC   | The failing controller<br>physical ID is found<br>in byte 20                                                            |

| DD   | The failing device<br>physical ID, connected to<br>the failing controller,<br>as shown in bits 4<br>through 7 of byte 4 |

### Message F - Soft Error Logging Complete for Subsystem Storage

This message is generated when soft error logging has been completed for the subsystem storage. See the EREP reports for the error which caused the storage director to go into logging mode.

Format 0 for Model 23 (cont.) SENSE 52

# Format 2—Storage Director Equipment Checks

# Format 2—Storage Director Equipment Checks SENSE 55

The table below gives a summary of bytes 8 through 23 for format 2. The following pages give more detailed information on format 2.

|                                       |       | BITS                                            |                                                               |                                                                  |                                                                                          |                                                                                                     |                                                  |                                                          |                                     |