GA22-7070-0 File No. 4300-01

# IBM 4300 Processors Principles of Operation for ECPS:VSE Mode

Systems

· Charles - Stores

| 1 - Peter | - 1000 - 1000 - 10 |  |

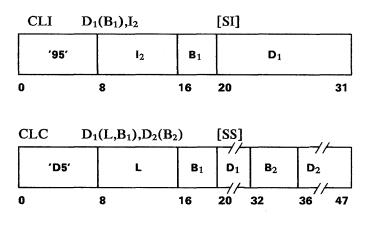

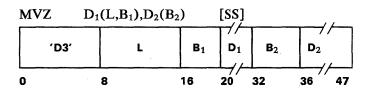

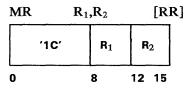

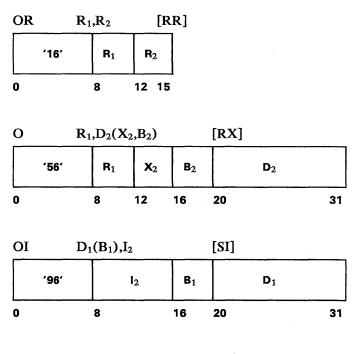

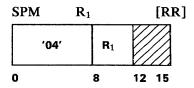

|-----------|--------------------|--|

|           |                    |  |

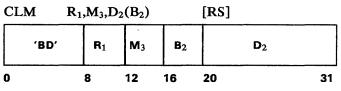

|           |                    |  |

GA22-7070-0 File No. 4300-01

IBM 4300 Processors Principles of Operation for ECPS:VSE Mode

# **Systems**

#### First Edition (January 1979)

Changes are continually made to the information herein; any such changes will be reported in subsequent revisions or Technical Newsletters.

Publications are not stocked at the address given below; requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for reader's comments is provided at the back of this publication. If the form has been removed, comments may be addressed to IBM Corporation, Product Publications, Department B98, PO Box 390, Poughkeepsie, NY, U.S.A. 12602. IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever. You may, of course, continue to use the information you supply.

© Copyright International Business Machines Corporation 1979

# Preface

This publication provides, for reference purposes, a detailed definition of the architecture of IBM 4300 Processors when operating in the Extended Control Program Support: Virtual Storage Extended (ECPS:VSE) mode.

The publication describes each function of the architecture to the level of detail that must be understood in order to prepare an assembler-language program that relies on that function. It does not, however, describe the notation and conventions that must be employed in preparing such a program.

The information in this publication is provided principally for use by assembler-language programmers, although anyone concerned with the functional details of the IBM 4300 Processors will find it useful.

This publication is written as a reference document and should not be considered an introduction or a textbook.

All facilities discussed in this publication are not necessarily available on every processor. Furthermore, in some instances the definitions have been structured to allow for some degree of extensibility, and therefore certain capabilities may be described or implied that are not offered on any model. An example of such capabilities is the provision for the number of channel-mask bits in the control register. The allowance for this type of extensibility should not be construed as implying any intention by IBM to provide such capabilities. For information about the characteristics and availability of features on a specific processor, use the functional characteristics manual for that processor. The availability of features on processors is summarized in the *IBM*  4300 Processors Summary and Input/Output & Data Communications Configurator, GA33-1523.

This publication applies only to the ECPS:VSE mode of operation. The *IBM System/370 Principles* of Operation, GA22-7000, should be consulted regarding the functions of the architecture which apply when the processor operates in the System/370 mode.

#### Size Notation

The letters K, M, and G denote the multipliers  $2^{10}$ ,  $2^{20}$ , and  $2^{30}$ , respectively. It should be noted that although the letters are borrowed from the decimal system and stand for kilo (10<sup>3</sup>), mega (10<sup>6</sup>), and giga (10<sup>9</sup>), they do not have the decimal meaning, but instead represent the power of 2 closest to the corresponding power of 10. Their meaning in this publication is as follows:

Symbol Value

| K (kilo) | $1,024 = 2^{10}$         |

|----------|--------------------------|

| M (mega) | $1,048,576 = 2^{20}$     |

| G (giga) | $1,073,741,824 = 2^{30}$ |

The following are some examples of the use of K, M, and G:

2,048 is expressed as 2K.

4,096 is expressed as 4K.

65,536 is expressed as 64K (not 65K).

$2^{24}$  is expressed as 16M.

When the words "thousand," "million," and "billion" are used, no special power-of-2 meaning is assigned to them. This page left blank intentionally.

# **Contents**

Chapter 1. Introduction 1-1 The IBM 4300 Processors 1-1 Compatibility 1-2 **Compatibility Among 4300 Processors** 1-2 **Compatibility Between 4300 Processors** and System/370 1-2 Control-Program Compatibility 1-2 Problem-State Compatibility 1-2 Chapter 2. Organization 2 - 1Main Storage 2-1 Central Processing Unit 2-1 General Registers 2-2 Floating-Point Registers 2 - 2Control Registers 2-3 Input and Output 2-3 Channels 2-4 Input/Output Devices and Control Units 2-4 **Operator Facilities** 2-4 Chapter 3. Storage 3-1 Information Formats and Addressing 3-1 Information Formats 3-1 Storage Addressing 3-2 **Integral Boundaries** 3-2 **One-Level Addressing** 3-2 Storage Size 3-3 Pages 3-3 **Page Frames** 3-3 Page Description 3-3 Storage Key 3-3 Page Bits 3-4 Page States 3-4 Frame Index 3-5 Page and Frame Control 3-5 Capacity Counts 3-5 Storage-Control Instructions 3-6 Key-Controlled Protection 3-6 Protection Action 3-6 Accesses Protected 3-7 **Reference and Change Recording** 3-7 Assigned Storage Locations 3-8 Storage While CPU Is in Operating State 3-8 Storage While CPU Is in Load State 3-10 Chapter 4. Control 4-1 **CPU States** 4-1 Wait State 4-2 Supervisor and Problem States 4-2 Stopped, Operating, Load, and Check-Stop States EC and BC Modes 4-3 Program-Status Word 4-4

Program-Status-Word Format in EC Mode 4-4

Program-Status-Word Format in BC Mode 4-6 **Control Registers** 4-7 Monitoring 4-8 Program-Event Recording 4-9 Control-Register Allocation 4-9 Operation 4-10 Identification of Cause 4-10 Priority of Indication 4-11 Storage-Area Designation 4 - 11PER Events 4-12 Successful Branching 4-12 Instruction Fetching 4-12 Storage Alteration 4-12 General-Register Alteration 4-12 Indication of Events Concurrently with Other Interruption Conditions 4-13 Timing 4-15 Time-of-Day Clock 4-15 Format 4-15 States 4-16 Setting and Inspecting the Value 4-16 Clock Comparator 4-18 CPU Timer 4-18 Interval Timer 4-19 **Externally Initiated Functions** 4-20 Resets 4-20 Program Reset 4-21 **Initial Program Reset** 4-23 Clear Reset 4-23 Power-On Reset 4-23 Initial Program Loading 4-24

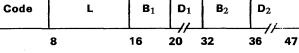

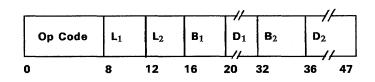

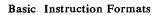

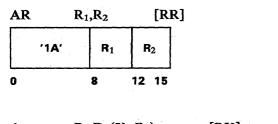

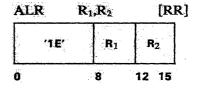

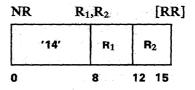

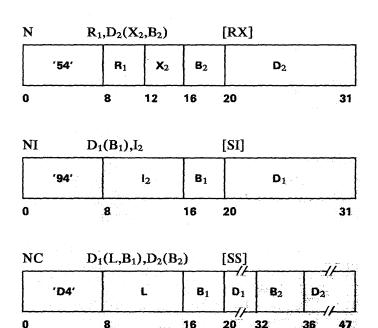

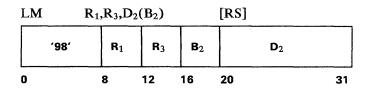

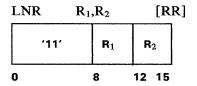

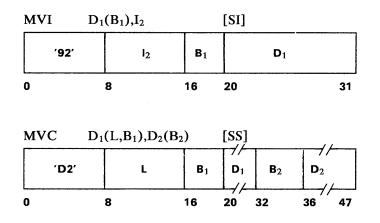

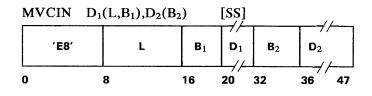

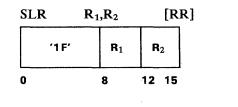

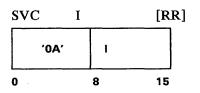

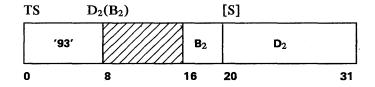

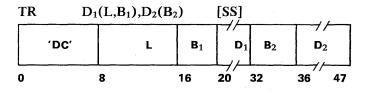

Chapter 5. Program Execution 5-1 Instructions 5-1 Operands 5-1 Instruction Format 5-2 Register Operands 5-3 Immediate Operands 5-3 Storage Operands 5-3 **Operand-Address** Generation 5-4 Instruction Execution 5-4 Sequential Instruction Execution 5-4 Branching 5-4 Interruptions 5-5 Sequence of Storage References 5-5 Instruction Fetch 5-6 **Page-Description Accesses** 5-6 Storage-Operand References 5-7 Storage-Operand Fetch References 5-7 Storage-Operand Store References 5-7 Storage-Operand Update References 5-7 Storage-Operand Consistency 5-8

Machine Save 4-25

4-2

**Relation Between Operand Accesses** 5-8 Other Storage References 5-9 Serialization 5-9 **CPU** Serialization 5-9 Channel Serialization 5-10 Chapter 6. Interruptions 6-1 Interruption Action 6-1 Source Identification 6-2 Enabling and Disabling 6-4 Instruction-Length Code 6-4 Zero ILC 6-5 **ILC on Instruction-Fetch Exceptions** 6-5 Exceptions Associated with the PSW 6-6 Early Exception Recognition 6-6 Late Exception Recognition 6-6 Types of Instruction Ending 6-6 Interruptible Instructions 6-7 Point of Interruption 6-7 **Ending of Interruptible Instructions** 6-7 Machine-Check Interruption 6-8 Supervisor-Call Interruption 6-8 Program Interruption 6-8 **Program-Interruption Conditions** 6-9 Addressing Exception 6-9 Data Exception 6-9 Decimal-Divide Exception 6-10 Decimal-Overflow Exception 6-10 Execute Exception 6-10 Exponent-Overflow Exception 6-10 6-10 Exponent-Underflow Exception 6-10 Fixed-Point-Divide Exception Fixed-Point-Overflow Exception 6-11 Floating-Point-Divide Exception 6-11 Monitor Event 6-11 **Operation Exception** 6-11 Page-Access Exception 6-11 Page-State Exception 6-12 **Page-Transition Exception** 6-12 PER Event 6-12 Privileged-Operation Exception 6-12 Protection Exception 6-12 Significance Exception 6-13 Special-Operation Exception 6-13 Specification Exception 6-13 **Recognition of Access Exceptions** 6-13 Nontransparent Nullification 6-16 **Multiple Program-Interruption Conditions** 6-17 External Interruption 6-19 Clock Comparator 6-19 CPU Timer 6-19 6-20 External Signal Interrupt Key 6-20 Interval Timer 6-20

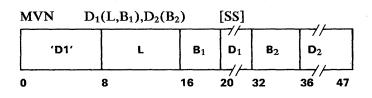

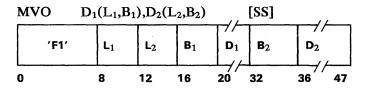

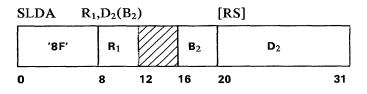

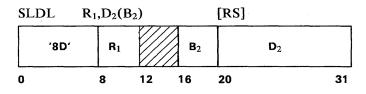

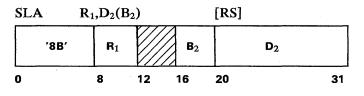

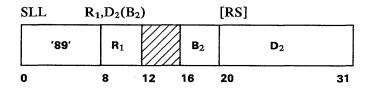

Input/Output Interruption 6-20 Restart Interruption 6-21 Priority of Interruptions 6-21 Chapter 7. General Instructions 7-1 Data Format 7-1 7-2 Binary-Integer Representation Signed and Unsigned Binary Arithmetic 7-3 Signed and Logical Comparison 7-3 Instructions 7-4 ADD 7-7 ADD HALFWORD 7-7 ADD LOGICAL 7-7 AND 7-7 **BRANCH AND LINK** 7-8 **BRANCH ON CONDITION** 7-9 BRANCH ON COUNT 7-10 BRANCH ON INDEX HIGH 7-10 BRANCH ON INDEX LOW OR EOUAL 7-10 COMPARE 7-11 COMPARE AND SWAP 7-11 COMPARE DOUBLE AND SWAP 7-11 COMPARE HALFWORD 7-13 COMPARE LOGICAL 7-13 **COMPARE LOGICAL CHARACTERS** UNDER MASK 7-13 COMPARE LOGICAL LONG 7-14 CONVERT TO BINARY 7-15 CONVERT TO DECIMAL 7-16 DIVIDE 7-16 EXCLUSIVE OR 7-17 EXECUTE 7-17 **INSERT CHARACTER** 7-18 **INSERT CHARACTERS UNDER MASK** 7-18 LOAD 7-19 LOAD ADDRESS 7-19 LOAD AND TEST 7-19 LOAD COMPLEMENT 7-20 LOAD HALFWORD 7-20 LOAD MULTIPLE 7-20 LOAD NEGATIVE 7-21 7-21 LOAD POSITIVE MONITOR CALL 7-21 MOVE 7-22 MOVE INVERSE 7-22 MOVE LONG 7-23 MOVE NUMERICS 7-25 MOVE WITH OFFSET 7-25 MOVE ZONES 7-26 MULTIPLY 7-26 MULTIPLY HALFWORD 7-27 OR 7-27 PACK 7-28 SET PROGRAM MASK 7-28 SHIFT LEFT DOUBLE 7-29

SHIFT LEFT DOUBLE LOGICAL 7-29 SHIFT LEFT SINGLE 7-30 SHIFT LEFT SINGLE LOGICAL 7-30 SHIFT RIGHT DOUBLE 7-30 SHIFT RIGHT DOUBLE LOGICAL 7-31 SHIFT RIGHT SINGLE 7-31 SHIFT RIGHT SINGLE LOGICAL 7-32 **STORE** 7-32 STORE CHARACTER 7-32 STORE CHARACTERS UNDER MASK 7-32 STORE CLOCK 7-33 STORE HALFWORD 7-33 STORE MULTIPLE 7-33 7-34 SUBTRACT SUBTRACT HALFWORD 7-34 SUBTRACT LOGICAL 7-34 SUPERVISOR CALL 7-35 TEST AND SET 7-35 TEST UNDER MASK 7-36 TRANSLATE 7-36 TRANSLATE AND TEST 7-37 UNPACK 7-38

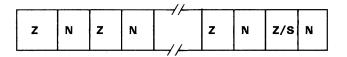

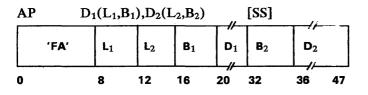

**Chapter 8. Decimal Instructions** 8-1 Data Format 8-1 Zoned Format 8-1 Packed Format 8-1 Number Representation 8-2 Instructions 8-2 ADD DECIMAL 8-3 COMPARE DECIMAL 8-4 DIVIDE DECIMAL 8-4 EDIT 8-5 EDIT AND MARK 8-8 MULTIPLY DECIMAL 8-8 SHIFT AND ROUND DECIMAL 8-8 SUBTRACT DECIMAL 8-10 ZERO AND ADD 8-10

Chapter 9. Floating-Point Instructions 9-1 Data Format 9-1 Guard Digit 9-2 9-3 Number Representation Normalization 9-3 Instructions 9-4 ADD NORMALIZED 9-6 ADD UNNORMALIZED 9-7 COMPARE 9-8 DIVIDE 9-8 HALVE 9-9 LOAD 9-10 LOAD AND TEST 9-10 LOAD COMPLEMENT 9-11 LOAD NEGATIVE 9-11 9-11 LOAD POSITIVE

LOAD ROUNDED 9-12 MULTIPLY 9-12 **STORE 9-14** SUBTRACT NORMALIZED 9-14 SUBTRACT UNNORMALIZED 9-15 Chapter 10. Control Instructions 10-1 CLEAR PAGE 10-3 CONNECT PAGE 10-3 DECONFIGURE PAGE 10-4 DIAGNOSE 10-4 DISCONNECT PAGE 10-5 INSERT PAGE BITS 10-5 **INSERT PSW KEY** 10-5 **INSERT STORAGE KEY** 10-6 LOAD CONTROL 10-6 LOAD FRAME INDEX 10-6 LOAD PSW 10-7 MAKE ADDRESSABLE 10-7 MAKE UNADDRESSABLE 10-8 RESET REFERENCE BIT 10-8 **RETRIEVE STATUS AND PAGE** 10-8 SET CLOCK 10-9 SET CLOCK COMPARATOR 10-9 SET CPU TIMER 10-10 SET PAGE BITS 10-10 SET PSW KEY FROM ADDRESS 10-10 SET STORAGE KEY 10-11 SET SYSTEM MASK 10-11 STORE CAPACITY COUNTS 10-11 STORE CLOCK COMPARATOR 10-12 STORE CONTROL 10-12 STORE CPU ID 10-12 STORE CPU TIMER 10-13 STORE THEN AND SYSTEM MASK 10-13 STORE THEN OR SYSTEM MASK 10-14 Chapter 11. Machine-Check Handling 11-1 Machine-Check Detection 11-1 **Correction of Machine Malfunctions** 11-1 Handling of Machine Checks 11-2

Invalid CBC in Storage 11-2 Invalid CBC in Page Descriptions 11-2 Invalid CBC in Registers 11-3 Usage of Validation 11-3 11-3 Check-Stop State Machine-Check Interruption 11-4 Exigent Conditions 11-4 Repressible Conditions 11-4 Interruption Action 11-4 Point of Interruption 11-5 Machine-Check-Interruption Code 11-6 Subclass 11-7 Auxiliary Bits 11-8 Machine-Check Interruption-Code Validity Bits 11-8 Machine-Check Extended Interruption Information 11-9 Register-Save Areas 11-9 Failing-Storage Address 11-9 Machine-Check Masking 11-9

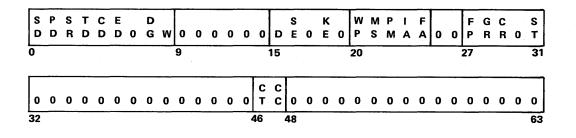

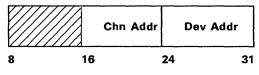

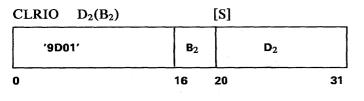

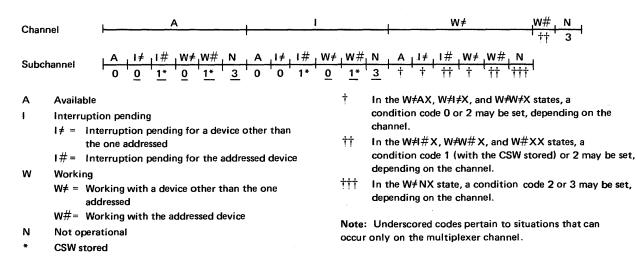

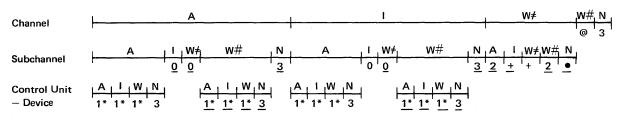

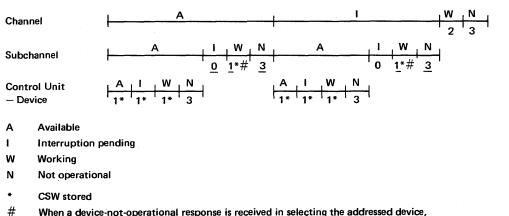

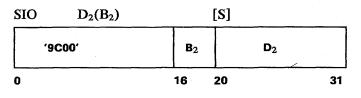

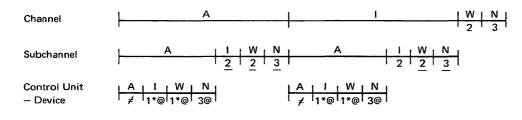

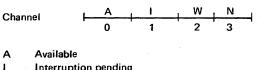

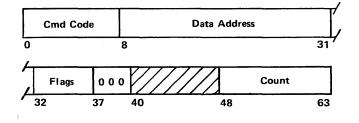

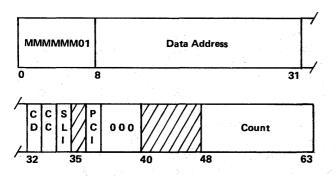

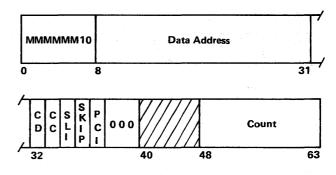

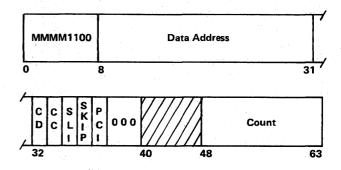

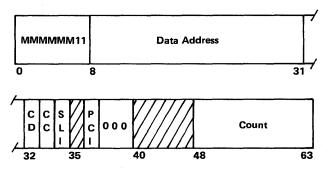

Chapter 12. Input/Output Operations 12 - 1Attachment of Input/Output Devices 12-2 Input/Output Devices 12-2 Control Units 12-2 Channels 12-3 Modes of Operation 12-3 **Types of Channels** 12-4 I/O-System Operation 12-5 Compatibility of Operation 12-7 Control of Input/Output Devices 12-7 Input/Output Device Addressing 12-7 States of the Input/Output System 12-8 Resetting of the Input/Output System 12-11 I/O System Reset 12-11 I/O Selective Reset 12-11 Effect of Reset on a Working Device 12-11 Reset Upon Malfunction 12-12 Condition Code 12-12 Instruction Formats 12-14 Instructions 12-15 CLEAR I/O 12-16 HALT DEVICE 12-18 HALT I/O 12-21 START I/O 12-23 **START I/O FAST RELEASE** 12-23 STORE CHANNEL ID 12-26 TEST CHANNEL 12-27 TEST I/O 12-27 Input/Output-Instruction-Exception Handling 12-30 Execution of Input/Output Operations 12-30 **Blocking of Data** 12-30 Channel-Address Word 12-30 Channel-Command Word 12-31 Command Code 12-32 Designation of Storage Area 12-32 Chaining 12-33 **Data** Chaining 12-35 Command Chaining 12-36 Skipping 12-36 **Program-Controlled Interruption** 12-36 Commands 12-37 Write 12-39 Read 12-39 **Read Backward** 12-39 Control 12-40 Sense 12-40 Transfer in Channel 12-42 12-42 Command Retry Conclusion of Input/Output Operations 12-43 Types of Conclusion 12-43

Conclusion at Operation Initiation 12-43 Immediate Operations 12-44 Conclusion of Data Transfer 12-44 Termination by HALT I/O or HALT DEVICE 12-45 Termination by CLEAR I/O 12-46 Termination Due to Equipment Malfunction 12-47 Input/Output Interruptions 12-47 Interruption Conditions 12-47 Channel-Available Interruption 12-48 Priority of Interruptions 12-48 Interruption Action 12-49 Channel-Status Word 12-49 Unit Status 12-50 12-50 Attention Status Modifier 12-50 Control-Unit End 12-51 12-51 Busy Channel End 12-53 Device End 12-53 Unit Check 12-53 Unit Exception 12-54 **Channel Status** 12-55 **Program-Controlled Interruption** 12-55 12-55 Incorrect Length Program Check 12-55 Protection Check 12-56 Channel-Data Check 12-56 Channel-Control Check 12-56 Interface-Control Check 12-57 Chaining Check 12-57 Contents Of Channel-Status Word 12-57 Information Provided by Channel-Status Word 12-57 Subchannel Key 12-58 CCW Address 12-58 Count 12-59 Status 12-60 12-63 Channel Logout I/O Communications Area 12-63 Chapter 13. Operator Facilities 13-1 **Basic Operator Facilities** 13-1 Address-Compare Controls 13-1 Alter-and-Display Controls 13-2 Check Control 13-2 Check-Stop Indicator 13-2 **IML** Controls 13-2 Interrupt Key 13-2 Interval-Timer Control 13-3 Load Indicator 13-3

Load-Clear Key

Load-Normal Key

Machine-Save Key

Manual Indicator

Load-Unit-Address Controls

13-3

13-3

13-3

13-3

13-3

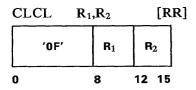

Mode Indicator **Power Controls** 13-4 Rate Control 13-4 Restart Key 13-4 Save Indicator 13-4 13-4 Start Key Stop Key 13-4 Storage-Size Control 13-4 System Indicator 13-5 System-Reset-Clear Key 13-5 System-Reset-Normal Key 13-5 Test Indicator 13-5 TOD-Clock Control 13-5 13-5 Wait Indicator Appendix A. Number Representation and Instruction-Use Examples A-1 Number Representation A-2 **Binary Integers** A-2 Signed Binary Integers A-2 **Unsigned Binary Integers** A-3 **Decimal Integers** A-3 **Floating-Point Numbers** A-4 **Conversion Example** A-5 Instruction-Use Examples A-5 **Machine Format** A-5 Assembler-Language Format A-5 **General Instructions** A-6 ADD HALFWORD (AH) A-6 AND (N, NR, NI, NC) A-6 AND (NI) A-6 **BRANCH AND LINK (BAL, BALR)** A-7 **BRANCH ON CONDITION (BC, BCR)** A-7 **BRANCH ON COUNT (BCT, BCTR)** A-8 **BRANCH ON INDEX HIGH (BXH)** A-8 BRANCH ON INDEX LOW OR EQUAL (BXLE) A-9 COMPARE HALFWORD (CH) A-9 COMPARE LOGICAL (CL, CLR, CLI, CLC) A-9 Compare Logical (CLR) A-9 A-9 Compare Logical (CLI) Compare Logical (CLC) A-10 COMPARE LOGICAL CHARACTERS UNDER MASK (CLM) A-10 **COMPARE LOGICAL LONG (CLCL)** A-11 CONVERT TO BINARY (CVB) A-12 CONVERT TO DECIMAL (CVD) A-12 DIVIDE (D,DR) A-13 EXCLUSIVE OR (X, XR, XI, XC) A-13 Exclusive OR (XI) A-13 Exclusive OR (XC) A-13 EXECUTE (EX) A-14 **INSERT CHARACTERS UNDER** MASK (ICM) A-15 LOAD (L, LR) A-16 LOAD ADDRESS (LA) A-16

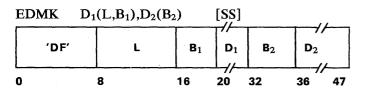

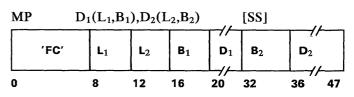

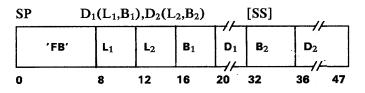

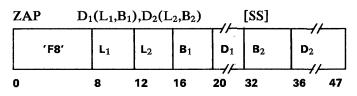

13-3

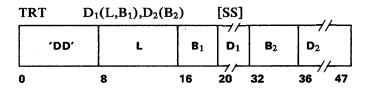

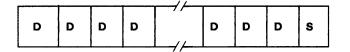

LOAD HALFWORD (LH) A-16 MOVE (MVI) A-17 MOVE (MVC) A-17 MOVE LONG (MVCL) A-18 **MOVE NUMERICS (MVN)** A-18 MOVE WITH OFFSET (MVO) A-19 MOVE ZONES (MVZ) A-19 MULTIPLY (M, MR) A-20 MULTIPLY HALFWORD (MH) A-20 OR (O, OR, OI, OC) A-21 OR (OI) A-21 PACK (PACK) A-21 SHIFT LEFT DOUBLE (SLDA) A-21 SHIFT LEFT SINGLE (SLA) A-22 STORE CHARACTERS UNDER MASK (STCM) A-22 STORE MULTIPLE (STM) A-23 **TEST UNDER MASK (TM)** A-23 TRANSLATE (TR) A-23 TRANSLATE AND TEST (TRT) A-24 **UNPACK (UNPK)** A-25 **Decimal Instructions** A-25 A-26 ADD DECIMAL (AP) COMPARE DECIMAL (CP) A-26 **DIVIDE DECIMAL (DP)** A-26 EDIT (ED) A-27 EDIT AND MARK (EDMK) A-28 **MULTIPLY DECIMAL (MP)** A-28 SHIFT AND ROUND DECIMAL (SRP) A-29 Decimal Left Shift A-29 **Decimal Right Shift** A-29 Decimal Right Shift and Round A-29 Multiplying by a Variable Power of 10 A-30 ZERO AND ADD (ZAP) A-30 **Floating-Point Instructions** A-30 ADD NORMALIZED (AE, AER, AD, ADR) A-30 ADD UNNORMALIZED (AU, AUR, AW, AWR) A-31 COMPARE (CE, CER, CD, CDR) A-31 Multiprogramming and Multiprocessing Examples A-32 Example of a Program Failure Using **OR** Immediate A-32 COMPARE AND SWAP (CS, CDS) A-32 Setting a Single Bit A-33 **Updating Counters** A-33 Appendix B. Lists of Instructions B-1 Appendix C. Condition-Code Settings C-1 Appendix D. Table of Powers of 2 **D-1** Appendix E. Hexadecimal Tables E-1 Index X-1

# Contents

The IBM 4300 Processors 1-1 Compatibility 1-2 Compatibility Among 4300 Processors 1-2 Compatibility Between 4300 Processors and System/370 1-2 Control-Program Compatibility 1-2 Problem-State Compatibility 1-2

# The IBM 4300 Processors

The IBM 4300 Processors are small and moderately sized processors that have evolved from System/370. They may be used in one of two architectural modes of operation. When operating in the Extended Control Program Support: Virtual Storage Extended (ECPS:VSE) mode, a processor provides new facilities that are designed specifically to enhance the DOS/VSE control program. To run control programs such as VM/370 and OS/VS1, which do not use these facilities, a processor is placed in the System/370 mode. This publication describes the architecture of the 4300 Processors when operating in the ECPS:VSE mode.

The architecture of a machine defines its attributes as seen by the programmer, that is, the conceptual structure and functional behavior of the machine, as distinct from the organization of the data flow, the logical design, the physical design, and the performance of any particular implementation. Several dissimilar machine implementations may conform to a single architecture. When programs running on different machine implementations produce the results that are defined by a single architecture, the implementations are considered to be compatible.

The ECPS:VSE mode includes a new storagecontrol facility, called one-level addressing, for creating a single virtual storage of up to 16,777,216 bytes, which both the CPU and the channels address directly using one uniform set of virtual addresses. Mapping the virtual storage onto the real storage is performed internal to the machine.

The one-level-addressing facility provides new instructions and interruptions which the control

program uses to determine which parts of virtual storage currently are mapped onto real storage and thereby are made addressable. These instructions and interruptions, and the associated internal address-mapping functions, take the place of dynamic address translation (DAT) and channel indirect data addressing in System/370.

The ECPS:VSE mode also includes a new statussaving function, called machine save, which preserves the entire CPU state and the first 2,048 (2K) bytes of storage. The operator uses machine save in preparation for a complete storage dump. Machine save replaces the store-status function of System/370, which necessarily alters some of the storage to be dumped.

If multiple virtual storages are not required, the ECPS:VSE mode affords the following advantages when compared to System/370:

- Simpler storage-mapping function, with more of the function performed automatically by the machine

- Improved control-program performance, because the control program need not translate the virtual addresses of channel programs

Programming of the machine has been simplified, relative to System/370, by omitting the following functions:

- Multiprocessing and associated instructions

- Machine-check logout and full channel logout These model-dependent logouts are replaced by internal facilities for diagnosing machine malfunctions. This removes model-dependent errorhandling procedures from the control program and improves serviceability.

# Compatibility

# **Compatibility Among 4300 Processors**

Although models of the 4300 Processors differ in implementation and physical capabilities, logically they are upward and downward compatible. Compatibility provides for simplicity in education, availability of system backup, and ease in system growth. Specifically, any program will give identical results on any model, provided that it:

- 1. Is not time-dependent.

- 2. Does not depend on system facilities (such as storage capacity, I/O equipment, or optional features) being present when the facilities are not included in the configuration.

- 3. Does not depend on system facilities being absent when the facilities are included in the configuration. For example, the program should not depend on interruptions caused by the use of operation codes or command codes that in some models are not assigned or not installed. Also, it must not use or depend on fields associated with uninstalled facilities. For example, data should not be placed in an area used by another model for logout. Similarly, the program must not use or depend on unassigned fields in machine formats (control registers, instruction formats, etc.) that are not explicitly made available for program use.

- 4. Does not depend on results or functions that are defined in this publication to be unpredictable or model-dependent, or on special-purpose functions (such as emulators and assists) that are not described in this publication. This includes the requirement that the program should not depend on the assignment of I/O addresses.

- 5. Does not depend on results or functions that are defined in the functional-characteristics publication for a particular model to be deviations from this publication.

# Compatibility Between 4300 Processors and System/370

## **Control-Program Compatibility**

If the preceding compatibility restrictions are observed, a program written for the 4300 Processors or System/370 will run on the other system. However, because of the compatibility restrictions, control programs cannot be transferred between these systems if they take advantage of facilities that are available on one system but not the other. In particular, the 4300 Processors do not offer the System/370 dynamic-address-translation facility in the ECPS:VSE mode and, hence, cannot execute programs which rely on this particular facility.

To provide full control-program compatibility between System/370 and the 4300 Processors, the 4300 Processors offer an alternate microprogram that causes the machine to assume the characteristics of a System/370 model. When the machine is in this mode, the operation of the machine is as described in the *IBM System/370 Principles of Operation*, GA22-7000.

## **Problem-State Compatibility**

A high degree of compatibility exists at the problemstate level between 4300 Processors operating in the ECPS:VSE mode and System/370. Because the majority of a user's applications are written for the problem state, this problem-state compatibility is useful in many installations.

A program written to run in the problem state on 4300 Processors or System/370 will run on the other system, provided that it:

- 1. Observes the limitations described in the section "Compatibility Among 4300 Processors."

- 2. Is not dependent on results defined in this publication or in the *IBM System/370 Principles* of Operation, as appropriate, to be unpredictable or model-dependent (an extension of the fourth rule in the section "Compatibility Among 4300 Processors").

- 3. Is not dependent on control-program facilities which are unavailable on the system.

To allow the problem programmer to guard against the effects of facilities that are available on System/370 but not on 4300 Processors, this publication in several places describes the results of such effects. For example, when a program is written which shares storage in a multiprogramming environment on a single-CPU configuration, precautions should be taken to allow such a program to run correctly on a multiple-CPU (multiprocessing) configuration.

Specifically, COMPARE AND SWAP, COMPARE DOUBLE AND SWAP, and TEST AND SET are the only instructions which should be used to create interlocks between concurrent programs. These are the only instructions that do not, between fetching and storing of the storage operand, permit another CPU to access the operand location. The instructions AND (NI or NC), EXCLUSIVE OR (XI or XC), and OR (OI or OC) should not be used for such interlocks.

Serialization of CPU operations, which is performed by all interruptions and by the execution of certain instructions, affects the sequence of events as observed by other CPUs in a multiprocessing configuration as well as by channels. (See the section "Serialization" in Chapter 5, "Program Execution.")

#### **Programming Note**

This publication assigns meanings to various operation codes, to bit positions in instructions, channelcommand words, registers, and table entries, and to fixed locations in the low 512 bytes of storage (addresses 0-511). Other operation codes, bit positions, and low-storage locations are specifically noted as being available for programming use. The remaining ones are unassigned and reserved for future assignment to new facilities and other extensions of the architecture.

To ensure that existing programs run if and when such new facilities are installed, programs should not depend on an indication of an exception as a result of invalid values that are currently defined as being checked. If a value must be placed in unassigned positions that are not checked, the program should enter zeros. When the machine provides a code or field, the program should take into account that new codes and bits may be assigned in the future. The program should not use unassigned low-storage locations for keeping information since these locations may be assigned in the future in such a way that the machine causes this location to be changed.

# Chapter 2. Organization

# Contents

Main Storage 2-1 Central Processing Unit 2-1 **General Registers** 2-2 **Floating-Point Registers** 2-2 Control Registers 2-3 Input and Output 2-3 Channels 2-4 Input/Output Devices and Control Units 2-4 **Operator Facilities** 2-4

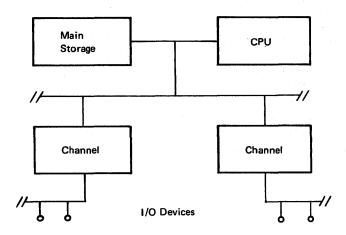

Logically, IBM 4300 Processors consist of main storage, a central processing unit (CPU), operator facilities, and channels. The channels allow input/output (I/O) devices to be attached, usually through control units (see the figure "Logical Structure").

Specific processors may differ in their internal characteristics, the number and types of channels, the size of main storage, and the representation of the operator facilities. The differences in internal characteristics are apparent to the observer only as differences in machine performance.

Logical Structure

# **Main Storage**

The 4300 Processors provide fast-access main storage and storage-control functions to permit high-speed processing of data by the CPU and channels. The storage-control functions permit main storage to be controlled at two levels: real storage and virtual storage.

Real storage is the storage where data and instructions actually reside at the time they are accessed by the CPU and channels, but neither CPU programs nor channel programs can address real storage directly. The size of real storage depends on the model.

Virtual storage allows both CPU programs and channel programs to address an apparent main storage of up to 16,777,216 (16M) bytes. Virtual storage may be larger than the underlying real storage. If the virtual storage is larger than the real storage, a supervisory control program using the storage-control functions of the machine is required for controlling which parts of virtual storage are currently mapped onto real storage. This control is dynamic and transparent to the other programs except for the time delay.

## **Central Processing Unit**

The central processing unit (CPU) is the controlling center of the machine. It contains the sequencing and processing facilities for instruction execution, interruption action, timing functions, initial program loading, and other machine-related functions.

The physical makeup of the CPU in the various models of the machine may be different, but the

logical function remains the same. The result of executing a valid instruction is the same for each model.

The CPU, in executing instructions, can process binary integers and floating-point numbers of fixed length, decimal integers of variable length, and logical information of either fixed or variable length. Processing may be in parallel or in series; the width of the processing elements, the multiplicity of the shifting paths, and the degree of simultaneity in performing the different types of arithmetic differ from one CPU to another without affecting the logical results.

Instructions which the CPU executes fall into five classes: general, decimal, floating-point, control, and input/output instructions. The general instructions are used in performing fixed-point arithmetic operations and logical, branching, and other nonarithmetic operations. The decimal instructions operate on data in the decimal format, and the floating-point instructions on data in the floating-point format. The control instructions and the input/output instructions are privileged instructions that can be executed only when the CPU is in the supervisor state.

To perform its functions, the CPU may use a certain amount of internal storage. Examples of such functions include the mapping of virtual storage to real storage and the arithmetic and logical functions. This internal storage is not considered part of main storage and is not addressable by programs.

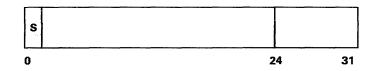

The CPU provides registers which are available to programs but do not have addressable representations in main storage. They include the current programstatus word (PSW), the general registers, the floating-point registers, the control registers, and registers associated with the timing facilities. The current PSW contains information used to control instruction sequencing and to hold and indicate the states of the machine in relation to the program currently being executed. Registers associated with the timing facilities are the time-of-day (TOD) clock, the clock comparator, and the CPU timer.

Some models may use the same physical storage for both addressable main storage and unaddressable internal storage, and internal storage may actually contain the CPU registers. Such internal storage is not considered to be part of main storage, because the program cannot access the contents of internal storage by means of storage addresses.

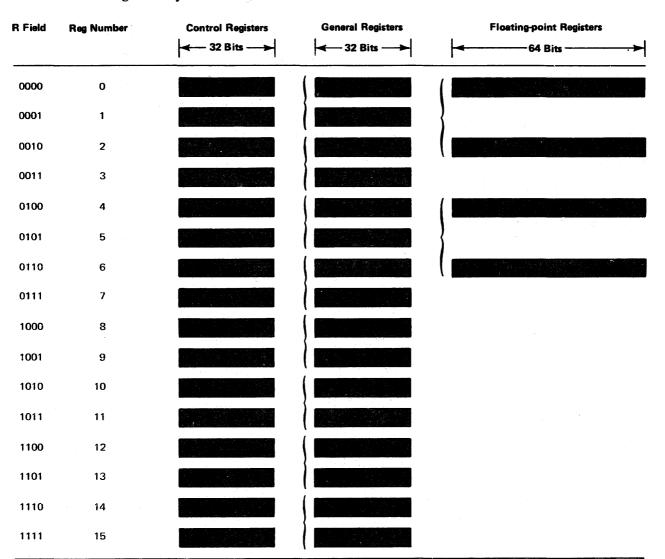

The general, floating-point, and control registers are discussed separately in the following sections. (See also the figure "General, Floating-Point, and Control Registers.") The instruction operation code determines which type of register is to be used in an operation.

## **General Registers**

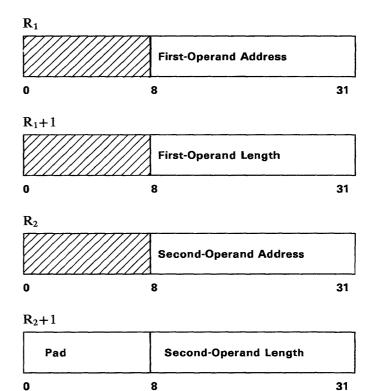

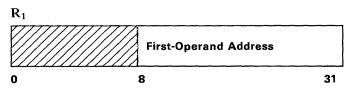

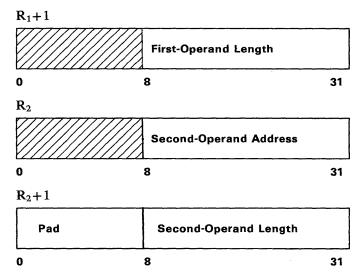

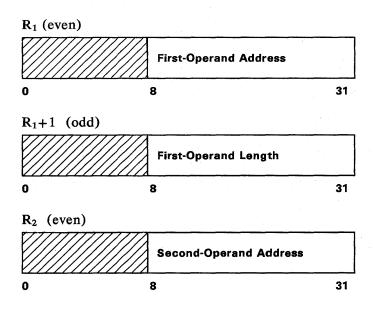

Instructions may designate information in one or more of 16 general registers. The general registers may be used as base-address registers and index registers in address arithmetic and as accumulators in general arithmetic and logical operations. Each register contains 32 bits. The general registers are identified by the numbers 0-15 and are designated by a four-bit R field in an instruction. Some instructions provide for addressing multiple general registers by having several R fields.

For some operations, two adjacent general registers are coupled, providing a 64-bit format. In these operations, the program must designate an evennumbered register, which contains the leftmost (high-order) 32 bits. The next higher-numbered register contains the rightmost (low-order) 32 bits.

In addition to their use as accumulators in general arithmetic and logical operations, 15 of the 16 general registers are also used as base-address and index registers in address generation. In these cases, the registers are designated by a four-bit B field or X field in an instruction. A value of zero in the B or X field specifies no base or index is to be applied, and, thus, general register 0 cannot be designated as containing a base address or index.

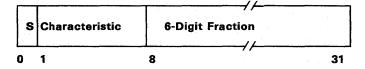

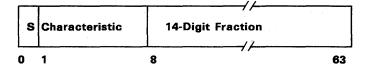

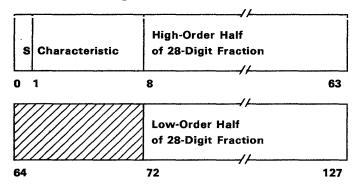

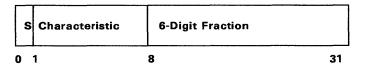

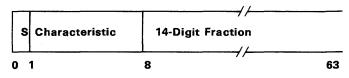

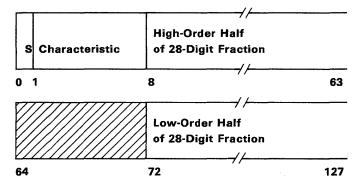

## Floating-Point Registers

Four floating-point registers are available for floating-point operations. They are identified by the numbers 0, 2, 4, and 6. Each floating-point register is 64 bits long and can contain either a short (32-bit) or a long (64-bit) floating-point operand. A short operand occupies the leftmost bit positions of a floating-point register. The rightmost portion of the register is ignored and remains unchanged in arithmetic operations that call for short operands. Two pairs of adjacent floating-point registers can be used for extended operands: registers 0 and 2, and registers 4 and 6. Each of these pairs provides a 128-bit format.

## **Control Registers**

The CPU has provisions for 16 control registers, each having 32 bit positions. The bit positions in the registers are assigned to particular facilities in the system, such as program-event recording, and are used either to specify that an operation can take place or to furnish special information required by the facility.

The control registers are identified by the numbers 0-15 and are designated by four-bit R fields in the

instructions LOAD CONTROL and STORE CONTROL. Multiple control registers can be addressed by these instructions.

# Input and Output

Input/output (I/O) operations involve the transfer of information between main storage and an I/O device. I/O devices attach to channels, which control this data transfer.

Note: The braces indicate that the two registers may be coupled as a double-register pair, designated by specifying the lowernumbered register in the R field. For example, the general-register pair 0 and 1 is designated in the R field by the number 0.

General, Floating-Point, and Control Registers

## Channels

A channel relieves the CPU of the burden of communicating directly with I/O devices and permits data processing to proceed concurrently with I/O operations. A channel connects with the CPU, with main storage, and with control units.

A channel may be an independent unit, complete with the necessary logical and internal-storage capabilities, or it may time-share CPU facilities and be physically integrated with the CPU. In either case, channel functions are identical. Channels may be implemented, however, to have different maximum data-transfer capabilities.

There are three types of channels: byte-multiplexer, block-multiplexer, and selector channels.

## Input/Output Devices and Control Units

Input/output devices include such equipment as card readers and punches, magnetic-tape units, directaccess storage, displays, keyboards, printers, teleprocessing devices, and sensor-based equipment. Many I/O devices function with an external medium, such as punched cards or magnetic tape. Some I/O devices handle only electrical signals, such as those found in sensor-based networks. In either case, I/O-device operation is regulated by a control unit. The control-unit function may be housed with the I/O device or in the CPU, or a separate control unit may be used. In all cases, the control-unit function provides the logical and buffering capabilities necessary to operate the associated I/O device. From the programming point of view, most control-unit functions merge with I/O-device functions.

# **Operator Facilities**

The operator facilities provide the functions necessary for operator control of the machine. It may have an associated operator-console device which may also be used as an I/O device for communicating with the control program and problem programs.

The main functions provided by the operator facilities are system reset, clearing, initial program loading, start, stop, alter, and display.

# Chapter 3. Storage

## Contents

Information Formats and Addressing 3-1 **Information Formats** 3-1 Storage Addressing 3-2 **Integral Boundaries** 3-2 **One-Level Addressing** 3-2 Storage Size 3-3 Pages 3-3 **Page Frames** 3-3 Page Description 3-3 Storage Key 3-3 Page Bits 3-4 Page States 3-4

This chapter discusses the representation of information in storage, how information is addressed, and the one-level-addressing facility for controlling virtual and real storage. The chapter also contains a list of permanently assigned storage locations.

The term "main storage" is used generically to describe both virtual and real storage, in order to distinguish this fast-access storage from auxiliary storage, such as direct-access storage devices. Because, in this publication, most references to main storage apply to virtual storage, the abbreviated term "storage" is generally used in place of "virtual storage" when the meaning is clear.

All addresses of storage locations are virtual addresses, because they always refer to virtual storage. Hence, when applied to main storage, address means virtual address in this publication.

# **Information Formats and Addressing**

#### Information Formats

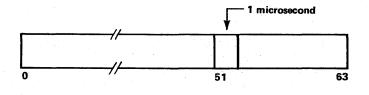

Information is transmitted between storage and the CPU or a channel in units of eight bits, or a multiple of eight bits, at a time. Each eight-bit unit of information is called a byte, the basic building block of all formats. The bits in a byte are numbered 0 through 7, from left to right.

The bits in an address, which is 24 bits long, are numbered 8 through 31. Within any other fixed-length format of multiple bytes, the bits making up the format are consecutively numbered from left to right, starting with the number 0. Leftmost bits

Frame Index 3-5 Page and Frame Control 3-5 **Capacity Counts** 3-5 Storage-Control Instructions 3-6 **Key-Controlled Protection** 3-6 **Protection Action** 3-6 Accesses Protected 3-7 **Reference and Change Recording** 3-7 Assigned Storage Locations 3-8 Storage While CPU Is in Operating State 3-8 Storage While CPU Is in Load State 3-10

are sometimes referred to as the "high-order" bits and rightmost bits as the "low-order" bits.

For purposes of error detection, and in some models for correction, one or more check bits may be transmitted with each byte or with a group of bytes. Such check bits are generated automatically by the machine and cannot be directly controlled by the program. References in this manual to the length of data fields and registers exclude mention of the associated check bits. All storage capacities are expressed in number of bytes.

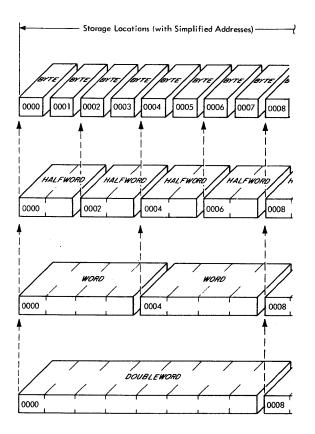

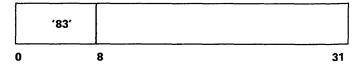

Bytes may be handled separately or grouped together in fields. A halfword is a group of two consecutive bytes and is the basic building block of instructions. A word or fullword is a group of four consecutive bytes; a doubleword is a group of eight bytes. The location of any field or group of bytes is specified by the address of its leftmost byte.

The length of fields is either implied by the operation to be performed or stated explicitly as part of the instruction. When the length is implied, the information is said to have a fixed length, which can be one, two, four, or eight bytes.

When the length of a field is not implied by the operation code, but is stated explicitly, the information is said to have variable field length. Variable-length operands are variable in length by increments of one byte.

When information is placed in storage, the contents of only those byte locations are replaced that are included in the designated field, even though the width of the physical path to storage may be greater than the length of the field being stored.

## Storage Addressing

Byte locations in storage are consecutively numbered, left to right, starting with 0; each number is considered the address of the corresponding byte. A group of bytes in storage is addressed by the leftmost byte of the group. The number of bytes in the group is either implied or explicitly defined by the operation. Addresses are 24-bit binary numbers, which provide 16,777,216 (2<sup>24</sup> or 16M) byte addresses.

Storage addressing wraps around from the maximum byte address, 16,777,215, to address 0. In a 16M-byte storage, information may be located partially in the last and partially in the first locations of storage and is processed without any special indication of crossing the maximum-address boundary.

## **Integral Boundaries**

Certain units of information must be located in storage on an integral boundary. A boundary is called integral for a unit of information when its storage address is a multiple of the length of the unit in bytes. Special names are given to fields of two, four, and eight bytes when they are located on an integral boundary. A halfword is a group of two consecutive bytes on a two-byte boundary and is the basic building block of instructions. A word is a group of four consecutive bytes on a four-byte boundary. A doubleword is a group of eight consecutive bytes on an eight-byte boundary.

Thus, a word is on an integral boundary when it is located in storage so that its address (that is, the address of the leftmost of the four bytes) is a multiple of the number 4. Similarly, a halfword is on an integral boundary when it has an address that is a multiple of the number 2, and a doubleword is on an integral boundary when it has an address that is a multiple of the number 8. (See the figure "Integral Boundaries for Halfwords, Words, and Doublewords.")

When storage addresses designate halfwords, words, and doublewords on integral boundaries, the binary representation of the address contains one, two, or three low-order zero bits, respectively.

Instructions must appear on halfword integral boundaries, and channel-command words and the storage operands of certain instructions must appear on other integral boundaries. The storage operands of most instructions do not have boundary-alignment requirements.

Integral Boundaries for Halfwords, Words, and Doublewords

#### **Programming Note**

Significant performance degradation is possible when storage operands are not positioned at addresses that are integral multiples of the operand length. To improve performance, frequently used storage operands should be aligned on integral boundaries.

## **One-Level Addressing**

The one-level-addressing facility may be used by the control program to create virtual storage that is larger than the actual capacity of the underlying real storage. Other programs and channels address this virtual storage directly as if all data and instructions actually resided in virtual storage.

Main storage is volatile; that is, the contents are not preserved when power is off.

## Storage Size

The storage size is the number of addressable byte locations provided in virtual storage. A model may allow one or more storage sizes. If more than one storage size is provided, the current storage size is determined by the manual storage-size control during an initial microprogram loading (IML) operation. The storage size cannot be changed by programming.

The storage size is always a multiple of 2,048 (2K) bytes, up to a maximum of 16,777,216 (16M) bytes.

When the storage size exceeds the size of real storage, the parts of virtual storage which are currently not directly accessible may be kept on auxiliary storage, such as direct-access storage devices (DASD). The transfer of the contents of virtual storage to and from auxiliary storage may be controlled by a supervisory control program using I/O instructions in such a way that the remaining CPU programs and channel programs can address any part of virtual storage as if it were all directly accessible.

Storage addresses range from zero to one less than the storage size. If the CPU attempts to refer to a storage location that is not provided or to the corresponding page description (see below), that attempt is indicated by an addressing exception or, in the case of the LOAD FRAME INDEX instruction, by the condition code. If an I/O operation attempts to access a storage location that is not provided, the operation is terminated by a channel program check.

Normally, the indication that a location is not provided is given only when the information associated with that location is actually required, and not when the operation can be completed without that information.

When the storage size is set to the maximum of 16M bytes, all storage locations are provided; addressing exceptions or channel program checks for CCW or data locations cannot occur.

#### Pages

Virtual storage is divided into pages, each page consisting of 2,048 (2<sup>11</sup>) consecutive bytes on a 2,048-byte address boundary. Virtual storage has up to 8,192 (2<sup>13</sup>) pages of storage. The size of virtual storage and, hence, the number of pages provided depend on the model and on the setting of the manual storage-size control, if one is provided.

Storage-control instructions, except for INSERT STORAGE KEY and SET STORAGE KEY, refer to a page by the address of any byte in that page. The low-order 11 bits of an operand address referring to a whole page are ignored. The INSERT STORAGE KEY and SET STORAGE KEY instructions also use a page address, but the low-order four bits of their operand address must be zeros.

## Page Frames

Real storage is divided into page frames, each capable of containing the data for one page of virtual storage. The size of real storage and, hence, the number of page frames present in the machine depend on the model. Real storage is not explicitly addressable by CPU programs and channel programs.

A virtual-storage page, to be accessible to CPU programs and channel programs, must be associated with a real-storage page frame. An instruction is provided which assigns to a page a free page frame selected by the machine. This instruction is said to connect the page to its assigned frame. Thereafter, the page frame is referred to by the address of the corresponding page. When any previous contents of the page have been retrieved from external storage and the page is ready for accessing by a CPU program, another instruction is used to make the page addressable.

As the supply of free page frames diminishes, the control program may make a page not addressable and, if any bytes in the page have been changed, write the contents of the page on auxiliary storage. An instruction may then be issued to disconnect the page, thus freeing its frame.

A page frame cannot be assigned to more than one page at a time.

#### Page Description

Associated with each virtual-storage page which is provided are a seven-bit storage key, three programmable page bits, a page state, and the frame index of the page frame currently assigned to the page, if any. This information, called the page description, is maintained in internal storage.

#### Storage Key

A control field, called storage key, is associated with each page that is provided.

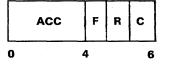

The bit positions in the storage key are allocated as follows:

Access-Control Bits (ACC): The four access-control bits, bits 0-3, are matched with the four-bit access key whenever information is stored, or whenever information is fetched from a location that is protected against fetching.

**Fetch-Protection Bit (F):** The fetch-protection bit, bit 4, controls whether protection applies to fetch-type references: a zero indicates that only store-type references are monitored and that fetching with any access key is permitted; a one indicates that protection applies both to fetching and storing. No distinction is made between the fetching of instructions and of operands.

**Reference Bit (R):** The reference bit, bit 5, normally is set to one each time a location in the corresponding page is referred to either for storing or for fetching of information.

**Change Bit (C):** The change bit, bit 6, is set to one each time information is stored at a location in the corresponding page.

The entire storage key is set by SET STORAGE KEY and inspected by INSERT STORAGE KEY. The reference and change bits are also set by SET PAGE BITS and inspected by INSERT PAGE BITS. Additionally, the instruction RESET REFERENCE BIT provides a means of inspecting the reference and change bits and of setting the reference bit to zero.

#### **Page Bits**

The three programmable page bits associated with each page may be set by the instruction SET PAGE BITS and inspected by INSERT PAGE BITS. The page bits are disregarded by the machine during other operations.

#### **Programming Note**

The page bits may be used by the program to assist in managing pages on auxiliary page storage. For example, one of the bits may indicate whether a version of the corresponding page exists on auxiliary storage.

#### **Page States**

- A page may be in one of three states:

- Disconnected

- Connected

- Addressable

If disconnected, the page does not have a page frame assigned to it. Any attempt by the CPU to access a disconnected page causes a page-access exception or, when a CLEAR PAGE instruction is being executed, a page-state exception. Any attempt by a channel to access a disconnected page, in order to fetch a CCW or to access a data area designated during the execution of a CCW, creates an I/O-interruption condition indicating protection check. However, if a CCW is prefetched, a protection check is not indicated until the CCW is due to be executed.

If connected, the page has a page frame assigned to it. A connected page may be accessed, if the protection mechanism permits:

- 1. By I/O channels

- 2. By the CPU as the operand of a CLEAR PAGE instruction

Except when executing CLEAR PAGE, an attempt by the CPU to access a connected page causes a page-access exception.

If addressable, the page has a page frame assigned to it, and the CPU and I/O channels may access the page if the protection mechanism permits.

Although the addressable state implies that the page is also connected, the term "connected state" refers specifically to the state of a page that is neither addressable nor disconnected.

The page state is checked for all storage accesses to locations that are explicitly or implicitly accessed by the CPU or by a channel.

The page state is changed by instructions, which may make the transition from the disconnected to the connected state and from the connected to the addressable state, or vice versa. The instructions are CONNECT PAGE, DECONFIGURE PAGE, DISCONNECT PAGE, MAKE ADDRESSABLE, and MAKE UNADDRESSABLE. Most of these instructions may also be applied to pages which are already in the desired state. An attempt to change directly from disconnected to addressable, or vice versa, causes a page-transition exception. A page-transition exception is also caused by DECONFIGURE PAGE when applied to a disconnected page. The first page, page 0, containing byte locations 0 to 2047, is always addressable. It cannot be placed in the connected or disconnected state.

The clear-reset function causes a number of consecutive pages, starting with page 0, to be assigned to page frames, cleared, and placed in the addressable state. (See the section "Clear Reset" in Chapter 4, "Control.")

#### **Programming Notes**

- The three page states permit programs to distinguish pages in the disconnected state, which cannot be accessed at all, from pages in the connected state, which are undergoing I/O operations to or from external page storage, and from pages in the addressable state, which are ready for normal storage access.

- 2. The storage-control instructions other than CLEAR PAGE operate on page descriptions, not pages. Instructions which operate on page descriptions do not make storage accesses and do not cause page-access or protection exceptions.

- 3. All channel accesses to storage appear as if they referred to pages and not to the associated page frames. If a page that is being accessed by a channel becomes disconnected and another channel access is attempted, protection check is indicated, and the I/O operation terminates. If the page becomes disconnected and then becomes reconnected before protection check is indicated, protection check may be indicated subsequently, or accesses may continue using the newly assigned page frame.

#### **Frame Index**

A unique 16-bit binary integer is assigned to each page frame existing in the machine. This integer is the frame index of the page frame. The value of the frame index ranges from zero up to, but not including, the existing-frame-capacity count (EFCC) (see the section "Capacity Counts" in this chapter).

When a CONNECT PAGE instruction connects a page to a frame, the frame index of the connected frame is returned by the instruction. The frame index remains associated with that page until the page is disconnected. When the same page is connected again, the new frame index is, in general, different and unpredictable unless there was only one free frame remaining.

The frame index for an already connected or addressable page may be displayed by LOAD FRAME INDEX. When DECONFIGURE PAGE makes a page frame unavailable, the frame index of that frame will not recur until a clear-reset operation is performed.

The frame index currently associated with a page is part of its page description. A disconnected page has no frame index, and LOAD FRAME INDEX returns no frame-index value for a disconnected page.

#### **Programming Notes**

- 1. The frame index assists the control program in maintaining compact tables of connected or addressable pages. The frame index is not, and should not be interpreted as, the address of a frame in real storage. The algorithm for assigning a frame index to a page frame is implementation-dependent. Programming should not depend on a particular algorithm.

- 2. The set of frame indexes is dense if the EFCC equals the AFCC, that is, if there are no unavailable page frames. It becomes nondense to the extent that frames are made unavailable by DECONFIGURE PAGE or by maintenance intervention.

- 3. DECONFIGURE PAGE removes a page frame from contention for connection when a machine check has indicated damage to a page. This can be done only while the frame is connected to a page, because a frame cannot be addressed directly.

#### **Page and Frame Control**

#### **Capacity Counts**

Four internally maintained counts are defined to assist the program in managing pages and page frames. Each count is a 16-bit unsigned binary integer. The counts are set or updated by the machine. They are displayed by the STORE CAPACITY COUNTS instruction, which stores each count as a 32-bit integer with 16 high-order zero bits.

The page-capacity count (PCC) is the number of virtual-storage pages provided by the machine. The pages have page addresses from 0 to PCC minus one. The value of the PCC is equal to the storage size divided by 2,048; it is set during clear reset according to the current setting of the manual storage-size control, if one is provided.

The existing-frame-capacity count (EFCC) is the number of page frames existing in a particular implementation of the machine. The EFCC reflects the total capacity of real storage. The value of the EFCC is set during clear reset. The available-frame-capacity count (AFCC) is the number of page frames connected or available for connection to pages. The value of AFCC may be equal to or less than the EFCC. During CPU operation, the AFCC may be decreased by the instruction DECONFIGURE PAGE. The clear-reset function initializes the AFCC to the value of the EFCC less the number of frames that are kept unavailable for connection by maintenance intervention.

The free-frame-capacity count (FFCC) is the number of available page frames that are currently not connected to pages. The value of the FFCC may range from zero to the AFCC minus one. During CPU operation, the value of the FFCC may be changed by the instructions CONNECT PAGE and DISCONNECT PAGE. The clear-reset operation initializes the FFCC to zero or to the value of AFCC minus PCC, depending on whether the AFCC is less than the PCC or not.

Since page 0 must always be addressable, the frame connected to page 0 is considered available but not free. Hence, the minimum value of the AFCC is one, and the maximum value of the FFCC is the AFCC minus one.

#### **Storage-Control Instructions**

CONNECT PAGE is used to change a page from the disconnected to the connected state. MAKE ADDRESSABLE changes a page from connected to addressable. MAKE UNADDRESSABLE changes the page state from addressable to connected. DISCONNECT PAGE changes the page state from connected to disconnected. DECONFIGURE PAGE disconnects a connected page and makes the corresponding page frame and its frame index unavailable. LOAD FRAME INDEX tests the page state of a page and displays its frame index, if any. These six instructions do not change or check the storage key of the specified pages.

CLEAR PAGE sets the contents of a page to zero and validates the page.

SET STORAGE KEY replaces the storage key of a page. INSERT STORAGE KEY retrieves the storage key of a page except, in the BC mode, for the reference and change bits. RESET REFERENCE BIT tests the reference and change bits and resets the reference bit to zero.

SET PAGE BITS tests the reference and change bits of a page and then explicitly sets them along with the three programmable page bits of that page. INSERT PAGE BITS retrieves the values of the three page bits, the reference bit, and the change bit of a page.

All storage-control instructions are privileged.

# **Key-Controlled Protection**

Key-controlled protection is provided to protect the contents of storage from destruction or misuse caused by erroneous or unauthorized storing or fetching by the program. It affords protection against improper storing or against both improper storing and fetching, but not against improper fetching alone.

## **Protection** Action

When key-controlled protection applies to a storage access, a store is permitted only when the storage key matches the access key associated with the request for storage access; a fetch is permitted when the keys match or when the fetch-protection bit of the storage key is zero.

The keys are said to match when the four access-control bits of the storage key are equal to the access key or when the access key is zero.

The protection action is summarized in the figure "Summary of Protection Action."

| Conditions            |              | Is access to storage permitted? |       |

|-----------------------|--------------|---------------------------------|-------|

| Fetch-Protection      |              |                                 |       |

| Bit of Storage<br>Key | Key Relation | Fetch                           | Store |

| 0                     | Match        | Yes                             | Yes   |

| 0                     | Mismatch     | Yes                             | No    |

| 1                     | Match        | Yes                             | Yes   |

| 1                     | Mismatch     | No                              | No    |

Explanation:

Match The four access-control bits of the storage key are equal to the access key, or the access key is zero.

Yes Access is permitted.

No Access is not permitted. On fetching, the information is not made available to the program; on storing, the contents of the storage location are not changed.

Summary of Protection Action

When the access to storage is initiated by the CPU, and protection applies, the PSW key is the access key which is used as the comparand. The PSW key occupies bit positions 8-11 of the current PSW.

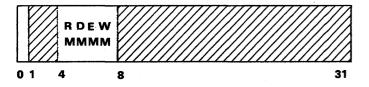

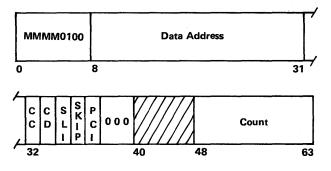

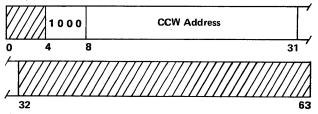

When the reference is made by a channel, and protection applies, the subchannel key associated with the I/O operation is the access key which is used as the comparand. The subchannel key is specified for

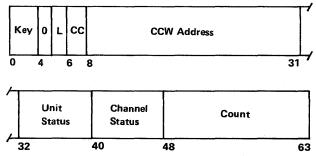

an I/O operation in bit positions 0-3 of the channel-address word (CAW); the subchannel key is later placed in bit positions 0-3 of the channel-status word (CSW) that is stored as a result of the I/O operation.

When a CPU access is prohibited because of protection, the operation is suppressed or terminated, and a program interruption for a protection exception takes place. When a channel access is prohibited, protection check is indicated in the CSW stored as a result of the operation.

When a store access is prohibited because of protection, the contents of the protected location remain unchanged. When a fetch access is prohibited, the protected information is not loaded into a register, moved to another storage location, or provided to an I/O device.

Key-controlled protection is always active, regardless of whether the CPU is in the problem or supervisor state, and regardless of the type of CPU instruction or channel-command word being executed.

#### Accesses Protected

All accesses to storage locations that are explicitly designated by the program and that are used by the CPU to store or fetch information are subject to protection.

All storage accesses by a channel to fetch a CCW or to access a data area designated during the execution of a CCW are subject to protection. However, if a CCW or output data is prefetched, a protection check is not indicated until the CCW is due to be executed or the data is due to be written.

Protection is not applied to accesses that are implicitly made by the CPU or channel for such sequences as:

- Interruptions,

- Updating the interval timer,

- Fetching the CAW during the execution of an I/O instruction,

- Storing the CSW by an I/O instruction or interruption,

- Storing channel identification during the execution of STORE CHANNEL ID,

- Limited channel logout, or

- Initial program loading

Similarly, protection does not apply to accesses initiated via the operator facilities for altering or displaying information. However, when the program explicitly designates these locations, they are subject to protection.

# **Reference and Change Recording**

Reference recording provides information for use in selecting pages for replacement. Change recording provides information as to which pages have to have their contents saved when their connected page frames are to be reused.

The reference bit normally is set to one each time a location in the corresponding page is referred to either for storing or fetching of information. The change bit is set to one each time information is stored in the corresponding page.

Reference and change recording takes place for any storage access and applies to accesses made by the CPU, as well as accesses due to I/O operations. References to a storage location associated with interruptions and I/O instructions, such as references to the CAW, CSW, or PSW locations, are included. It is unpredictable whether updating of the interval timer causes the reference and change bits for location 80 to be set to ones.

References to the page operand of the following instructions do not cause storage access and do not cause reference and change bits to be set to ones implicitly:

#### CONNECT PAGE

DECONFIGURE PAGE (both bits are set to zeros) DISCONNECT PAGE (both bits are set to zeros) INSERT PAGE BITS INSERT STORAGE KEY LOAD FRAME INDEX MAKE ADDRESSABLE MAKE UNADDRESSABLE RESET REFERENCE BIT (reference bit is set to zero) SET PAGE BITS (both bits are set explicitly) SET STORAGE KEY (both bits are set explicitly)

The change bit is not set to one for an attempt to store if the storage reference is not permitted, regardless of whether the CPU instruction responsible for the reference is suppressed or terminated. In particular, a CPU reference causing a protection or page-access exception, and an I/O reference causing a protection check, do not cause the change bit to be set to one.

The instructions SET PAGE BITS and SET STORAGE KEY may be used to set the reference and change bits explicitly to either zero or one. SET PAGE BITS also sets the condition code to indicate the previous state of the reference and change bits. The instruction RESET REFERENCE BIT tests both the reference and change bits and sets the condition code; it also sets the reference bit to zero. The instructions DECONFIGURE PAGE and DISCONNECT PAGE set both the reference and change bits to zeros.

The record of references provided by the reference bit is substantially accurate. The reference bit may be set to one by fetching data or instructions that are neither designated nor used by the program, and, under certain conditions, a reference may be made without the reference bit being set to one. Under certain unusual conditions, a reference bit may be set to zero by other than explicit program action.

The record of changes provided by the change bit is also substantially accurate. Under certain conditions, the change bit may be set to one when storing is permitted but no storing has actually taken place. However, the change bit is always set to one when storing occurs and is never set to zero without explicit program action.

## **Programming Note**

The accuracy of reference and change recording is sufficient to allow effective operation of page-replacement algorithms.

# **Assigned Storage Locations**

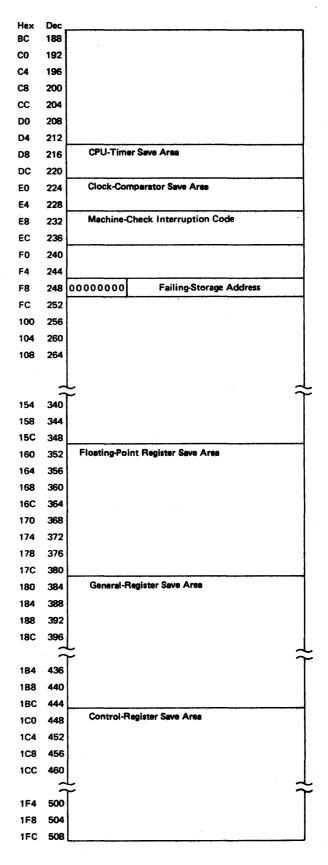

Assigned locations in storage have different uses when the CPU is in the operating state or in the load state. This section is summarized in the figure "Assigned Storage Locations."

## **Programming Note**

In the BC mode, there is no implicit storing in locations 128 and above if all of the following conditions are met:

- 1. The manual check control is set to stop.

- 2. The MONITOR CALL and STORE CHANNEL ID instructions are not issued.

- 3. The page-capacity count is equal to or less than the available-frame-capacity count and all pages are addressable.

## Storage While CPU Is in Operating State

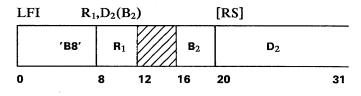

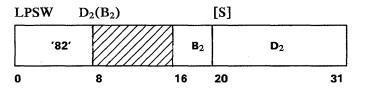

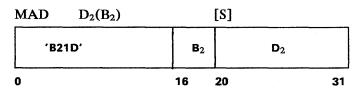

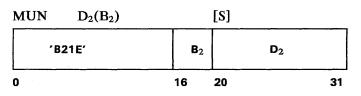

This section shows the format and extent of the assigned storage locations while the CPU is in the operating state. Unless specifically noted, the usage applies to both the EC and BC modes.

0-7 *Restart New PSW*: The new PSW is fetched from locations 0-7 during a restart interruption.

- 8-15 *Restart Old PSW*: The current PSW is stored as the old PSW at locations 8-15 during a restart interruption.

- 24-31 *External Old PSW:* The current PSW is stored as the old PSW at locations 24-31 during an external interruption.

- 32-39 Supervisor-Call Old PSW: The current PSW is stored as the old PSW at locations 32-39 during a supervisor-call interruption.

- 40-47 *Program Old PSW:* The current PSW is stored as the old PSW at locations 40-47 during a program interruption.

- 48-55 *Machine-Check Old PSW:* The current PSW is stored as the old PSW at locations 48-55 during a machine-check interruption.

- 56-63 Input/Output Old PSW: The current PSW is stored as the old PSW at locations 56-63 during an I/O interruption.

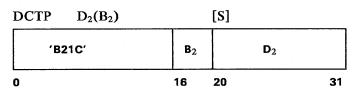

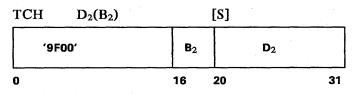

- 64-71 CSW: The channel-status word (CSW) is stored at locations 64-71 during an I/O interruption. It, or a portion thereof, may be stored during the execution of START I/O, START I/O FAST RELEASE, TEST I/O, CLEAR I/O, HALT I/O, or HALT DEVICE, in which case condition code 1 is set.

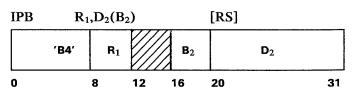

- 72-75 CAW: The channel-address word (CAW) is fetched from locations 72-75 during the execution of START I/O and START I/O FAST RELEASE.

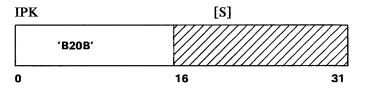

- 80-83 *Interval Timer:* Locations 80-83 contain the interval timer. The interval timer is updated whenever the CPU is in the operating state and the manual intervaltimer control is set to enable.

- 88-95 *External New PSW:* The new PSW is fetched from locations 88-95 during an external interruption.

- 96-103 Supervisor-Call New PSW: The new PSW is fetched from locations 96-103 during a supervisor-call interruption.

- 104-111 *Program New PSW:* The new PSW is fetched from locations 104-111 during a program interruption.

- 112-119 Machine-Check New PSW: The new PSW is fetched from locations 112-119 during a machine-check interruption.

- 120-127 Input/Output New PSW: The new PSW is fetched from locations 120-127 during an I/O interruption.

- 132-135 External-Interruption Code: During an external interruption in the EC mode, the interruption code is stored at locations 134-135, and zeros are stored at locations 132-133.

- 136-139 Supervisor-Call-Interruption Identification: During a supervisor-call interruption in the EC mode, the instruction-length code is stored in bit positions 5 and 6 of location 137, and the interruption code is stored at locations 138-139. Zeros are stored at location 136 and in the remaining bit positions of 137.

- 140-143 Program-Interruption Identification: During a program interruption in the EC mode, the instruction-length code is stored in bit positions 5 and 6 of location 141, and the interruption code is stored at locations 142-143. Zeros are stored at location 140 and in the remaining bit positions of 141.

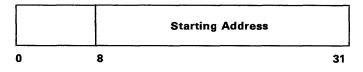

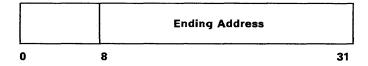

- 144-147 Access-Exception Address: During a program interruption due to a page-access exception, the address for which the exception is being indicated is stored at locations 145-147, and zeros are stored at location 144.

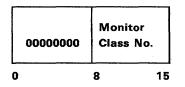

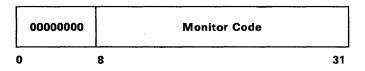

- 148-149 *Monitor-Class Number:* During a program interruption due to a monitor event, the monitor-class number is stored at location 149, and zeros are stored at 148.

- 150-151 *PER Code:* During a program interruption due to a program event, the programevent-recording (PER) code is stored in bit positions 0-3 of location 150, and zeros are stored in bit positions 4-7 and at location 151. This field can be stored only when the instruction causing the PER condition was executed under the control of a PSW specifying the EC mode.

- 152-155 *PER Address:* During a program interruption due to a program event, the program-event-recording (PER) address is stored at locations 153-155, and zeros are stored at location 152. This field can be stored only when the instruction causing the PER condition was executed under the control of a PSW specifying the EC mode.

- 156-159 *Monitor Code:* During a program interruption due to a monitor event, the monitor code is stored at locations 157-159, and zeros are stored at location 156.

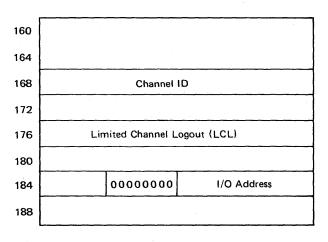

- 168-171 *Channel ID:* The four-byte channelidentification information is stored at locations 168-171 during the execution of STORE CHANNEL ID.

- 176-179 Limited Channel Logout: The limitedchannel-logout information is stored at locations 176-179. This field may be stored only when the CSW or a portion of the CSW is stored.

- 185-187 *I/O Address:* During an I/O interruption in the EC mode, the two-byte I/O address is stored at locations 186-187, and zeros are stored at location 185.

- 216-223 CPU-Timer Save Area: During a machine-check interruption, the contents of the CPU timer are stored at locations 216-223.

- 224-231 Clock-Comparator Save Area: During a machine-check interruption, the contents of the clock comparator are stored at **locations** 224-231.

- 232-239 Machine-Check-Interruption Code: During a machine-check interruption, the machine-check-interruption code is stored at locations 232-239.

- 248-251 Failing-Storage Address: During a machine-check interruption, a failingstorage address, if any, is stored at locations 249-251, and zeros are stored at location 248.

- 352-383 Floating-Point-Register Save Area: During a machine-check interruption, the contents of the floating-point registers are stored at locations 352-383.

- 384-447 General-Register Save Area: During a machine-check interruption, the contents of the general registers are stored at locations 384-447.

- 448-511 Control-Register Save Area: During a machine-check interruption, the contents of the control registers are stored at locations 448-511.

## Storage While CPU Is in Load State

- 0-7 *IPL PSW:* The first eight bytes read during the IPL initial read operation are stored at locations 0-7. The contents of these locations are used as the new PSW at the completion of the IPL operation. These locations may also be used for temporary storage at the initiation of the IPL operation.

- 8-15 *IPL CCW1:* Bytes 8-15 read during the IPL initial-read operation are stored at

locations 8-15. The contents of these locations are ordinarily used as the next CCW in an IPL CCW chain after completion of the IPL initial-read operation.

16-23 *IPL CCW2:* Bytes 16-23 read during the IPL initial-read operation are stored at locations 16-23. The contents of these locations may be used as another CCW in the IPL CCW chain to follow IPL CCW1.

| Hex      | Dec        |                                        |

|----------|------------|----------------------------------------|

| 0        | 0          | Restart New PSW                        |

| 4        | 4          |                                        |

| 8        | 8          | Restart Old PSW                        |

| С        | 12         |                                        |

| 10       | 16         |                                        |

| 14       | 20         |                                        |

| 18       | 24         | External Old PSW                       |

| 1C       | 28         |                                        |

| 20       | 32         | Supervisor-Call Old PSW                |

| 24       | 36         |                                        |

| 28       | 40         | Program Old PSW                        |

| 2C       | 44         |                                        |

| 30       | 48         | Machine-Check Old PSW                  |

| 34       | 52         |                                        |

| 38       | 56         | Input/Qutput Old PSW                   |

| 3C       | 60         |                                        |

| 40       | 64         | Channel Status Word                    |

| 44       | 68         |                                        |

| 48       | 72         | Channel Address Word                   |

| 4C       | 76         |                                        |

| 50       | 80         | Interval Timer                         |

| 54       | 84         | ·                                      |

| 58       | 88         | External New PSW                       |

| 5C       | 92         |                                        |

| 60       | 96         | Supervisor-Call New PSW                |

| 64       | 100        |                                        |

| 68       |            | Program New PSW                        |

| 6C       | 108        | · · · · · · · · · · · · · · · · · · ·  |

| 70       | 112        |                                        |

| 74<br>79 | 116        |                                        |

| 78<br>7C | 120<br>124 | Input output New York                  |

| 7C<br>80 | 124        |                                        |

| 80<br>84 |            | 00000000000000000000000000000000000000 |

| 88       |            | 00000000000000000000000000000000000000 |

| 8C       |            | 00000000000000000000000000000000000000 |

| 90       |            | 0000000 Access-Exception Address       |

| 94       |            | 00000000 Access-Exception Address      |

| 98       |            |                                        |

| 9C       |            |                                        |

| A0       | 160        |                                        |

| A4       | 164        |                                        |

| A8       | 168        |                                        |

| AC       | 172        |                                        |

| BO       | 176        |                                        |

| B4       | 180        |                                        |

| B8       | 184        |                                        |

|          |            |                                        |

**Assigned Storage Locations**

# **Chapter 4.** Control

# Contents

CPU States 4-1 Wait State 4-2 Supervisor and Problem States 4-2 Stopped, Operating, Load, and Check-Stop States 4-2 EC and BC Modes 4-3 Program-Status Word 4-4 Program-Status-Word Format in EC Mode 4-4 Program-Status-Word Format in BC Mode 4-6 Control Registers 4-7 Monitoring 4-8 **Program-Event Recording** Control-Register Allocation 4-9 Operation 4-10 Identification of Cause 4-10 **Priority of Indication** 4-11 Storage-Area Designation 4 - 11PER Events 4-12 Successful Branching 4-12 Instruction Fetching 4-12 Storage Alteration 4-12

This chapter describes in detail a number of facilities for:

- Changing and interrogating the state of the CPU

- Measuring time

- Initiating certain operations externally

- In general, enhancing the efficiency, utility, and programmability of the machine

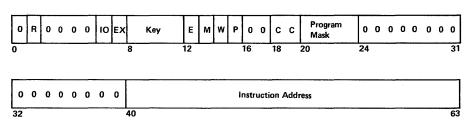

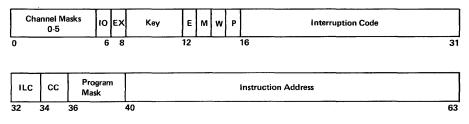

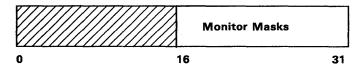

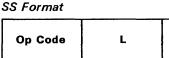

The information determining the state and controlling the operation of the CPU resides in the program-status word (PSW) and in control registers. Additional status and control information appears in permanently assigned storage locations which are listed in Chapter 3, "Storage." Supervisor state and a set of instructions that are valid only in supervisor state provide a means for avoiding unauthorized or inadvertent change of the machine state.

There are four facilities for measuring time:

- The time-of-day clock permits indication of calendar time.