# Nitrided gate oxides for 3.3-V logic application: Reliability and device design considerations

by T. B. Hook J. S. Burnham R. J. Bolam

Device characteristics and reliability in a 3.3-V logic CMOS technology with various gate oxidation and nitridation processes are described. The technology was designed to extend 3.3-V devices to the ultimate dielectric reliability limit while maintaining strict manufacturing cost control. A nitrided gate oxide provided the means to maintain hotelectron reliability at the level of the previous iteration, but at higher performance and lower processing cost. Conventional furnace processes in nitrous and nitric oxide, highpressure oxidation in oxygen and nitrous oxide, and rapid-thermal processes using nitrous and nitric oxide were investigated. We found that the concomitant variations in fixed charge and thermal budget have a significant influence on both n-FET and p-FET device parameters such as threshold voltage, carrier mobility, and inverse short-channel effect (ISCE). Reliability effects, such as charge to breakdown ( $Q_{BD}$ ), hot-electron degradation,

and negative-bias temperature instability (NBTI) were examined and correlated with the nitrogen profile in the gate dielectric. Secondary ion mass spectroscopy (SIMS) profiles were used to characterize the oxidation techniques and to correlate gate dielectric composition to the parametric and reliability parameters.

# Introduction

The formation of the gate dielectric is central to the CMOS process and device design. The conditions under which the dielectric is grown or deposited play a significant role in establishing the dopant profile in the silicon under the gate. For thermally grown oxide as a gate dielectric, this process probably represents the single largest diffusion step to which the well dopants will be subjected; in addition to the temperature excursion, the injection of vacancy point defects during the oxidation enhances the diffusivity of the dopants in the silicon [1–4]. The shape of the dopant profile is an important aspect of

Copyright 1999 by International Business Machines Corporation. Copying in printed form for private use is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the Journal reference and IBM copyright notice are included on the first page. The title and abstract, but no other portions, of this paper may be copied or distributed royalty free without further permission by computer-based and other information-service systems. Permission to republish any other portion of this paper must be obtained from the Editor.

0018-8646/99/\$5.00 © 1999 IBM

the design of the device. A flat dopant profile, or a profile in which the dopant decreases at greater depth, produces a device with relatively poor short-channel behavior but relatively good body effect. That is, the threshold voltage of such a device decreases rapidly at short channel lengths, thereby limiting the minimum usable length (the short-channel effect), but the threshold voltage does not increase very rapidly when the source potential is larger than the bulk potential, thereby improving the available dynamic range (the body effect). A retrograde doping profile, or one in which the dopant increases at a depth below the gate dielectric-silicon interface, produces a device in which the body effect is relatively poor, but the reduction in threshold voltage with decreasing channel length is suppressed. The precise shape of the well-doping profile is therefore critical in determining the device characteristics, and the role of gate dielectric processing that modifies the profile is important.

The final composition of the dielectric can also determine the performance and reliability of the FETs. The integrity of the silicon-silicon dioxide interface is key to the device behavior; fixed charge and unpassivated electronic states degrade the carrier mobility [5–8]. It is also important for long-term stability of the devices that the interface be able to retain its integrity under the influence of applied voltage and current flow encountered in product operation. The benefits to be gained by introducing small amounts of other elements in the silicon-silicon dioxide system have been extensively investigated [9-14]. Chlorine is often used in oxidation to keep the tools clean of sodium and other metallic contamination. Chlorine may be introduced into the process in a number of ways, such as adding HCl or TCA (trichloroacetone) to the oxidizing ambient [12]. The intended result (aside from the benefit in reducing mobile sodium) is to improve the reliability of the oxide [10]. Hot-electron immunity and carrier mobility have been shown to depend on the incorporation of trace amounts of fluorine in the gate oxide [13-17]. Adding nitrogen to the oxide has received much focus in research [18-35] and has recently been used in mainstream production [36-40]. The advantages in hot-electron immunity have been known for several years [18-20], and the benefits of suppressing boron penetration of gate oxide have been well documented [22, 23]. The incorporation of nitrogen also degrades low-field electron mobility [8], increases high-field electron mobility [30], improves charge to breakdown [24–27, 35], and increases fixed positive charge [28, 29].

Less extensively discussed in the literature are the ramifications of the nitrided gate process for FET device design. The use of a nitrided oxide introduces design parameters different from those typically considered for FET design with a conventional gate oxide. First, the well dopings must be designed to achieve the desired threshold

voltage with the fixed positive charge that results from nitridation. Depending on the method of nitridation, there may be additional thermal budget to redistribute the well dopants, limiting the steepness of the well that may be achieved and modifying the short-channel effect. Finally, the improvement in hot-electron immunity may be utilized in a variety of ways. In principle, a larger electric field may be allowed with the same level of hot-electron reliability in a device with a nitrided oxide than with a conventional oxide. To take advantage of this, faster devices might be fabricated by using shorter channel lengths. In our case, we avoid the addition of a lightly doped drain (LDD) implant to grade the junction and reduce the electric field. This reduces processing cost and complexity and improves the short-channel behavior of the device. Although the resultant electric field is higher, the nitridized oxide has greater immunity to damage, and the same hot-electron reliability is achieved as for a device with an LDD and a conventional oxide.

Although the effect of nitridation on  $Q_{\rm BD}$  has been addressed in the literature [24–27, 35], NBTI has not been widely discussed, even though this phenomenon is clearly related to oxide and interfacial quality. The creation of fixed positive charge and interface traps in p-FET devices through temperature- and field-accelerated stress is well known, and variations in oxidation conditions have been shown to affect NBTI [41–43].

In this paper we present data (such as threshold voltage, hot-electron reliability, NBTI, electron and hole mobility, and dopant and nitrogen profiles) that illustrate the effects of various nitridation schemes with nitrous and nitric oxide on device parameters and oxide reliability. A large variation in oxidation was performed with the same basic process while holding parameters such as implant dose and energy, oxide thickness, and gate photolithography relatively constant. Data comparing conventional furnace oxidation with nitridation in nitrous and nitric oxide are given. Atmospheric furnace processes were further contrasted with high-pressure oxidations (with and without nitridation) and with rapid thermal oxidation (with and without nitridation). High-pressure oxidation and rapid-thermal processing offer greater flexibility in device design because of the lower thermal cycle employed, but all methods of introducing nitrogen do not provide the same device and reliability characteristics.

A cost-effective and simple nitridation scheme was adopted that provided adequate hot-electron reliability without unduly compromising device performance. The simplest conventional furnace process met the goals for this technology. However, the data taken from the other processes provide valuable information as to the nature of the nitrogen in the oxide. Physical and chemical explanations for the observed behavior are beyond the

**Table 1** Description of the various oxidation experiments. The labels are used in Figures 1–3, 5–10, 14.

| Description   | Label  | Oxidation conditions                                                             | Post-polysilicon anneal                      |

|---------------|--------|----------------------------------------------------------------------------------|----------------------------------------------|

| Standard      | Е-Н, с | 800°C O <sub>2</sub> /H <sub>2</sub> O/950°C 20% N <sub>2</sub> O/N <sub>2</sub> | none                                         |

| No nitrogen   | В      | $800^{\circ}\text{C O}_2/\text{H}_2\text{O}$                                     | none                                         |

| Undiluted     | K, L   | 800°C O <sub>2</sub> /H <sub>2</sub> O/950°C 100% N <sub>2</sub> O               | none                                         |

| Post-anneal   | I      | 800°C O <sub>2</sub> /H <sub>2</sub> O/950°C 100% N <sub>2</sub> O               | $1050^{\circ}\mathrm{C~N}_{2}~60~\mathrm{s}$ |

|               | J      | 800°C $O_2/H_2O/950$ °C 100% $N_2O$                                              | $1100^{\circ}\mathrm{C~N}_{2}$ 30 s          |

| Furnace, NO   | M      | NO 900°C                                                                         | none                                         |

|               | N      | NO 950°C                                                                         | none                                         |

| High pressure | A      | ${ m O_2~800^{\circ}C~15~atm}$                                                   | none                                         |

|               | С      | $N_2O~800^{\circ}C~20~atm$                                                       | none                                         |

|               | D      | $N_2O~800^{\circ}C~15~atm$                                                       | none                                         |

| RTO           | a      | ${\rm O_2~1050^{\circ}C~60~s}$                                                   | none                                         |

|               | b      | $N_2O/O_2$ 1050°C 104 s                                                          | none                                         |

|               | d      | $N_2O~1050^{\circ}C~260~s$                                                       | none                                         |

|               | e      | $\rm O_2~1050^{\circ}C~56s/NO~1000^{\circ}C~20~s$                                | none                                         |

|               | f      | ${\rm O_2~1050^{\circ}C~51s/NO~1000^{\circ}C~120~s}$                             | none                                         |

scope of this work, but it is hoped that these observations offer practical guidelines to technology integration.

# **Device processing and oxidation experiments**

The technology described below is for 3.3-V device applications in the 0.35- $\mu m$  design rule generation; shallow-trench isolation and aluminum wire/tungsten stud planar metallization are used. The nominal channel lengths of the devices were 0.31 and 0.27  $\mu$ m respectively for the n-FET and the p-FET. A shallow boron implant determines the threshold voltage and the short-channel effect for the n-FET. A deeper boron implant is included to reduce substrate resistivity and improve latch-up immunity, but has no direct impact on the n-FET device characteristics. An antimony implant determines the nearsurface n-well doping, while a deep phosphorus implant defines the n-well isolation and lateral sheet resistance. The standard gate-oxidation process is a 7.0-nm nitrided oxide, grown by conventional oxidation in O2 and H2O at 800°C and then further oxidized in a furnace in diluted nitrous oxide at 950°C. Both n-FET and p-FET devices have a single sidewall spacer and only one implant to define the source/drain junction. Both FETs are surfacechannel devices; the polysilicon gate doping is provided simultaneously with the source/drain implant. Adequate n-FET hot-electron immunity is achieved by using nitrided gate oxide, despite the lack of a graded n-FET LDD implant [36]. A single rapid-thermal anneal (RTA) at

approximately 1000°C drives and activates both source/drains. Self-aligned titanium disilicide is formed over all gates and source/drain regions. With the exception of the gate oxidation, all processing during the experiments was held constant. Implant doses and energies were nominally identical, and in every case the oxide thickness was near 7.0 nm. Shallow-trench isolation processing and metallization were nominally identical for all wafers.

As described above, the standard gate oxidation is an 800°C wet/dry oxidation, followed by further oxidation in diluted N<sub>2</sub>O at 950°C. The various oxidation processes are briefly summarized in Table 1. The furnace processes were run in an ASM Model 300 vertical-tube furnace capable of running 100-wafer batches. The samples oxidized at elevated pressure were run in a GaSonics International Vertical High Pressure (VHP) system. The system is capable of pressures up to 25 atm (367 psi) and temperatures up to 1100°C in batch sizes of 63 wafers with rapid pressure and temperature ramp capability. For these experiments the gas flows, process pressure, and temperature ramps were established to optimize the oxide uniformity and nitrogen incorporation. The rapid thermal oxidation (RTO) wafers were processed in an Applied Materials RTP Centura<sup>™</sup> system consisting of a vacuum load-lock, an N<sub>2</sub> purge chamber, and an isolated process chamber. For controllability and uniformity the wafer is spun at 90 rpm in the process chamber. The tool

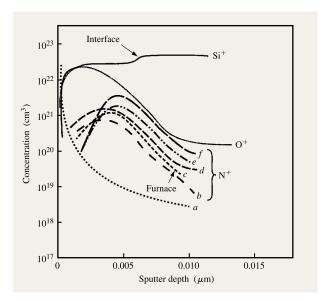

SIMS profiles of nitrogen, oxygen, and silicon concentration for some of the wafers in Table 1. The detected species are  $^{133}$ Cs  $X^+$ , where X is Si, O, or N, and are designated in the figure as Si $^+$ , O $^+$ , and N $^+$ . The integrated nitrogen concentration and the peak nitrogen concentration are tabulated from these data in Table 2. The labels on the curves correspond to the entries in Table 2. The N $_2$ O-nitridized samples (curves b-d) have a larger relative bulk incorporation than the NO-nitridized wafers (curves e, f).

conditions were individually optimized for controllability and uniformity for each experimental cell.

Secondary ion mass spectrometry (SIMS) was performed with a Cameca IMS4F spectrometer. The boron profiles were acquired with 8-keV O<sub>2</sub><sup>+</sup> primary ions and B<sup>+</sup> secondary ions. To obtain good depth resolution across the 7.0-nm oxide and minimize SIMS matrix effects in the nitrogen analysis, 3-keV Cs<sup>+</sup> primary ions were used and CsN<sup>+</sup> secondary ions were detected. After the electrical measurements were completed, a wafer from each of the experimental variations was stripped by extended immersion in hydrofluoric acid. This process removes all of the metallurgy and insulators, leaving only the gate polysilicon over the gate oxide on the wafer. The remaining polysilicon is quite rough, having been partially consumed by the formation of titanium silicide during the fabrication of the wafers. The roughness reduces the depth resolution that may be obtained from SIMS analysis, but using fully processed wafers has the advantage of correlating SIMS data on the very same wafers from which the electrical measurements were obtained. Figure 1 shows the SIMS profiles for the various permutations of the RTO processing, as well as for the standard furnace process. Two parameters were extracted from each of

these plots. The total integrated nitrogen concentration (in cm<sup>-2</sup>) was obtained by integrating the SIMS signal from the surface to the bulk. The peak concentration (in cm<sup>-3</sup>) was also abstracted from the data and summarized in **Table 2**.

The amount and location of nitrogen incorporated in the oxide is a function of the oxidation sequence, the processing temperature, and the gas species used. Oxidation in nitrogen-rich gases not only incorporates nitrogen into the film as it grows, but also removes nitrogen from the bulk of the oxide [32, 33]. The standard furnace process and RTO variations e and f have an initial oxide grown in oxygen, followed by a nitridation step. This results in a peak nitrogen concentration at or near the silicon-silicon dioxide interface, with relatively little nitrogen in the bulk. The furnace N<sub>2</sub>O-nitridized sample (curve c) has more nitrogen in the bulk of the oxide than the RTO NO-nitridized sample (curves e and f). Process variations b and d were completely oxidized in nitrous oxide. Although the peak nitrogen concentration still occurs near the interface, there is more incorporation in the bulk of the oxide than in the sample with an initial oxide. The sample run without any nitrogen is shown in curve a; the apparent presence of nitrogen near the top surface in this sample is an artifact of the SIMS measurement.

In the following sections, changes to the device characteristics and reliability for these various oxidation processes are examined. Device design considerations (fixed charge, dopant distribution, and carrier mobility) for n-FETs and p-FETs are first described. The effect on reliability parameters (hot-electron shift,  $Q_{\rm BD}$ , and NBTI) is then discussed. Generally, the data points presented in the figures represent an average value obtained from 15 to 20 individual chips on each of two to three similarly processed wafers.

# **Device design**

• Threshold voltage  $(V_t)$  and short-channel effects It is known that nitridation introduces fixed positive charge into the oxide [28, 29]. The effect of the nitridation-induced fixed positive charge is readily observed in the p-FET. Although the nitridation schemes listed in Table 1 have varying thermal cycles, they have little effect on the antimony profile; therefore, the threshold voltage is only a function of the nitridation-induced fixed charge [28]. On the other hand, the boron profile in the n-FET is significantly altered by the heat applied during the nitridation; thus, the threshold voltage is a function of both the fixed charge and dopant redistribution.

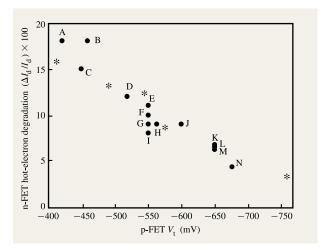

We have observed that the p-FET threshold voltage varies with the amount of nitrogen in the oxide across all of the process variations investigated. Previously [28], we reported a one-to-one correlation between p-FET threshold voltage and n-FET hot-electron immunity; in this work we extend this correlation to additional process variations and also introduce SIMS data to directly relate nitrogen concentration in the gate oxide to the p-FET threshold voltage. **Figure 2** shows data from [28] with additional data points (asterisks). The new data points reinforce the correlation and extend the data to a wider range of p-FET threshold voltage variation. Reading from left to right, the new data points are RTO processing variations a, b, d-f, as indicated in Table 1.

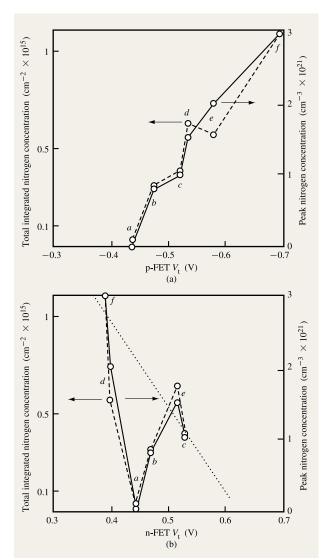

Using the data presented in Table 2, we have correlated the p-FET threshold voltage directly with the measured nitrogen in the oxide. Figure 3(a) shows p-FET threshold voltage as a function of the interfacial and the integrated nitrogen concentration. The p-FET  $V_{t}$  is clearly related to the nitrogen content of the oxide as measured by SIMS. Figure 3(b) shows the n-FET threshold voltage on the same wafers as a function of the integrated and peak nitrogen concentrations. In this case, factors other than fixed positive charge must contribute to establishing the threshold voltage. The n-FET threshold voltage is a more complex function of the dopant redistribution, the fixed charge, and the interface trap density. If the same fixed positive charge were present in the n-FET as in the p-FET, the threshold voltage would follow the slope of the dotted-line curve superimposed on the data in Figure 3(b). The threshold voltage is always lower than expected, even for points a and b, which have less nitrogen and fixed charge than point c. This behavior may be explained by considering the boron doping profile beneath the dielectric. As described above, the n-FET well in this technology is retrograde; that is, the center of the dopant implant is located far beneath the surface. Boron diffuses to the surface to establish the threshold voltage, leaving a substantial concentration beneath the surface to arrest

# Figure 2

n-FET hot-electron shift (percentage of drain current degradation, normalized for substrate current) as a function of p-FET threshold voltage (normalized for oxide thickness). Process conditions associated with each of the points are given in Table 1. (Adapted with permission from [28]; © 1997 IEEE.)

the short-channel effect. For larger thermal cycles there is more dopant spreading and the surface dopant concentration grows, increasing the threshold voltage. Conversely, for a reduced thermal cycle, there is little diffusion of the boron toward the surface, reducing the threshold voltage. Points a and b have lower threshold voltage than point c because the dopant diffusion during the RTO step is less than that of the standard 950°C  $\rm N_2O$  oxidation, and therefore the surface doping is less. The same effect has been observed with other variants to the oxidation process with lower-temperature processing than the standard process, even with similar nitrogen incorporation. By increasing the pressure during oxidation in nitrous oxide, nitrogen may be readily incorporated in the dielectric, even at only  $800^{\circ}\rm C$  (high-pressure variants C

Table 2 Summary of SIMS data for RTO experiments. The labels appear in Figures 1, 3, 6, 8–14.

| Process          | Label | Oxidation conditions                               | Integrated nitrogen<br>concentration<br>(cm <sup>-2</sup> ) | Peak nitrogen<br>concentration<br>(cm <sup>-3</sup> ) |

|------------------|-------|----------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------|

| RTO              | а     | O <sub>2</sub> 1050°C 60 s                         | $<3 \times 10^{13}$                                         | 0                                                     |

|                  | b     | $N_2O/O_2$ 1050°C 104 s                            | $3.1 \times 10^{14}$                                        | $8.0 \times 10^{20}$                                  |

|                  | d     | $N_2O~1050^{\circ}C~260~s$                         | $6.3 \times 10^{14}$                                        | $1.5 \times 10^{21}$                                  |

|                  | e     | $\mathrm{O_2~1050^{\circ}C~56~s}$ + NO 1000°C 20 s | $5.7 \times 10^{14}$                                        | $2.0 \times 10^{21}$                                  |

|                  | f     | $O_2$ 1050°C 51 s + NO 1000°C 120 s                | $1.1 \times 10^{15}$                                        | $3.0 \times 10^{21}$                                  |

| Standard furnace | c     | $O_2/H_2O$ 800°C + $N_2O/N_2$ 950°C                | $3.9 \times 10^{14}$                                        | $1.0 \times 10^{21}$                                  |

(a) p-FET threshold voltage plotted against both the peak and integrated nitrogen concentration as obtained from SIMS profiles in Figure 2 and tabulated in Table 2. The solid line refers to the interfacial nitrogen concentration and the dashed line to the total integrated concentration. The labels  $a\!-\!f$  are identified with the corresponding nitridation experiment in Table 2. (b) n-FET threshold voltage plotted against both the peak and integrated concentration of nitrogen as obtained from SIMS profiles. The dashed line refers to the total integrated nitrogen concentration, and the solid line to the interfacial concentration. The process conditions associated with the data at points  $a\!-\!f$  are specified in Table 2. The dotted line is the curve that would be expected if the n-FET behavior were determined only by fixed positive charge.

and D from Table 1). Data for p-FET  $V_{\rm t}$  fall on the "universal" curve in Figure 2, but the n-FET  $V_{\rm t}$  does not correlate directly with the fixed charge. All high-pressure-oxidation wafers have a lower threshold voltage by

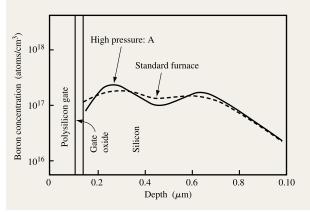

#### Figure 4

SIMS profiles of boron well doping for two different oxidation conditions. The boron is more evenly distributed in the standard furnace process because of the higher thermal cycle and the accompanying dopant diffusion. The concentration of boron is higher at the surface in that process, and therefore the threshold voltage is larger.

100–150 mV compared to other wafers processed in the same lot. For these wafers, the change in the n-FET threshold voltage is dominated by the difference in thermal budget between the standard furnace process and that used at elevated pressure. SIMS profiles of the boron well for two of the processes are shown in **Figure 4**. The standard process spreads the dopant significantly, particularly during the 950°C nitridation step. The high-pressure oxidation, although incorporating a similar amount of nitrogen, results in a much steeper doping profile, both in the near-surface implant and in the deep implant. It is apparent from the figure that the doping at the surface is lower; this results in a lower threshold voltage.

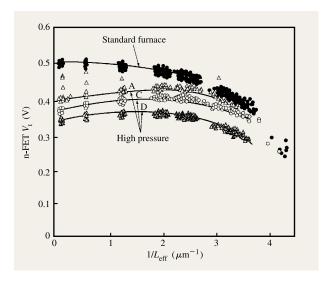

Another effect of reduced dopant spreading is evident in the inverse short-channel effect (ISCE); **Figure 5** shows the n-FET saturated threshold voltage as a function of inverse channel length for the standard furnace process and high-pressure variants as described in Table 1. All of the high-pressure oxidation wafers show an increase of threshold voltage at shorter channels (ISCE) before the threshold decreases owing to the short-channel effect (SCE). The threshold voltage for the standard furnace process decreases monotonically as the channel becomes shorter. ISCE is found in devices designed with a halo, or pocket, implant [44–47]. The additional p-type doping surrounding the drain region becomes more significant for shorter channels, causing the threshold to increase before it decreases at even shorter channels. There is no halo

implant in these devices; therefore, the ISCE is caused by flattening of the dopant profile near the source/drain regions, increasing the threshold voltage in a manner similar to that described above for increased processing temperatures. Flattening of the well profile near the source/drain is possible only if it is not already flattened by diffusion during gate oxidation. Therefore, the more retrograde the well profile, the greater the degree of ISCE. In accordance with expectation, wafers with steeper doping gradient, as in Figure 4, show greater ISCE, as in Figure 5.

Although the p-FET polysilicon gate is doped with boron, penetration of boron through the oxide does not affect the p-FET threshold voltage. The only major thermal cycle following the introduction of boron into the polysilicon gate is a single 1000°C (average) RTA. In an experiment in which the temperature of this anneal was altered, little change in the p-FET threshold voltage was found. Table 3 presents these results. The change for the n-FET threshold voltage was almost identical to that of the p-FET, and may be attributed to the elimination of fixed charge associated with post-oxidation annealing [22]. If boron penetration were important in determining the p-FET threshold voltage, a higher-temperature anneal would drive more boron through the oxide and alter the threshold voltage of the p-FET independently of the n-FET. The results given in Table 3 show little dependence of the threshold voltage on the anneal, and equivalent behavior of the p-FET and the n-FET.

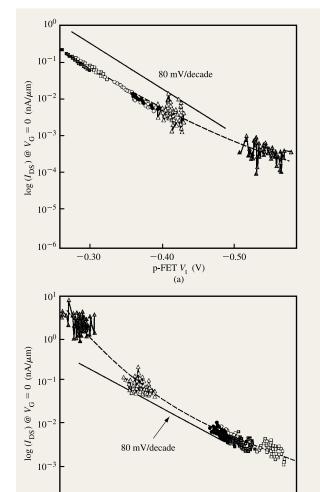

The quality of the silicon-silicon dioxide also contributes to the threshold voltage. As it is known that nitridized oxides can have a higher interface trap density than conventional oxide, the contribution of this component should be determined [31]. In the presence of interface traps, the threshold voltage is increased in magnitude to reflect the density of charge required to populate the traps. Another manifestation of the interface trap density is in the subthreshold slope, which is the gatevoltage dependence of the drain-source current when the gate voltage is below threshold. A typical value of this parameter at room temperature is 80-85 mV/decade; that is, the drain-source current is reduced by a factor of 10 for every 80-85 mV change in gate voltage. A larger subthreshold slope is indicative of a larger interface trap density. Therefore, a larger drain-source current for a given voltage less than the threshold voltage is a direct measure of the subthreshold slope, and therefore the interface trap density. The vertical axis of Figure 6(a) is the drain-source current for a short-channel p-FET device with the gate-source voltage at zero, the abscissa is the measured threshold voltage, and the slope of the curve is the subthreshold slope. A line at 80 mV/decade is drawn on the plot as a guide to the eye. Each point represents an individual chip, and the various symbols correspond to

#### Fiaure 5

n-FET saturated threshold voltage as a function of the inverse of the effective channel length for various methods of oxidation. The various processes are described in Table 1. Solid circles: standard furnace process; open triangles: high pressure (A); open circles: high pressure (C); solid triangles: high pressure (D).

**Table 3** Threshold voltage results of dopant activation annealing experiment (p-FET dopant: B; n-FET dopant: P).

| Annealing temperature (peak) | $V_{\rm t}$ |       |  |

|------------------------------|-------------|-------|--|

| (°C)                         | p-FET       | n-FET |  |

| 1068                         | -538        | 527   |  |

| 1075                         | -534        | 532   |  |

| 1085                         | -532        | 536   |  |

| 1092                         | -528        | 541   |  |

the RTO variations from Table 2. The wafers with the highest nitrogen concentration (those to the right-hand side of the plot) show degraded subthreshold characteristics, indicative of additional interface trap density in the lower half of the silicon bandgap.

A correlation of nitrogen content to interface trap concentration has been reported elsewhere [31]. However, the threshold voltage is relatively unaffected for all but the wafers with the highest nitrogen concentration. If it were not for the increased interface trap density, the threshold voltage of these wafers would have been slightly more positive. The threshold voltage at point *f* in Figure 3(a) would have been less negative if it were not for the additional interface trap density.

**Figure 6(b)** shows the subthreshold slope of the n-FET; this is entirely analogous to Figure 6(a) for the p-FET.

0.30

0.35

n-FET  $V_{\rm t}$  (V)

(b)

0.40

0.45

10

Drain–source current for zero gate–source voltage plotted as a function of saturated threshold voltage: (a) p-FET ( $V_{\rm DS}=-3.3~\rm V$ ) and (b) n-FET ( $V_{\rm DS}=3.3~\rm V$ ). A device with an ideal siliconsilicon dioxide interface would follow a curve of 80–85 mV/decade, which is indicated in the figure. The various symbols relate to the oxidations specified in Table 2. Solid triangles: RTO in nitric oxide (f); open squares: RTO in nitric oxide (e); open triangles: RTO in nitrous oxide (d), open circles: RTO in dilute nitrous oxide (b); solid circles: standard furnace nitridation (c); solid squares: RTO in oxygen (a).

Wafers with a perfect interface are expected to see an increase in current of one decade for every 80–85 mV of threshold reduction. As with the p-FET, a marked deviation from the ideal subthreshold slope is evident in the wafers with the highest nitrogen concentration. The

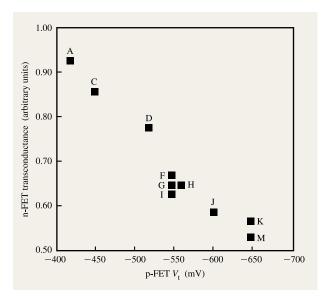

# Figure 7

n-FET linear transconductance (normalized for oxide thickness) plotted against p-FET threshold voltage for various oxidation methods. Most of the variations specified in Table 1 and Figure 1 are included.

increased interface trap density increases the threshold voltage; the threshold voltage for the wafers of point f in Figure 3(b) would have been smaller in the absence of the additional interface traps.

To summarize, the p-FET threshold voltage is a relatively straightforward function of the fixed positive charge and, at the highest nitrogen concentration, the interface trap density. The n-FET threshold voltage is a function of the fixed charge, the interface trap density, the total thermal budget applied, and the resulting dopant distribution. In addition, changes in the dopant profile also alter the dependence of the threshold voltage on the channel length, modifying the ISCE.

# Mobility effects

It is well established that nitridation affects the carrier mobilities in the inversion layer [6–8]. Figure 7 shows the n-FET linear transconductance for the various nitridation processing as a function of the p-FET threshold voltage. The p-FET threshold voltage is used here because it is the most direct measure of the charge in the oxide. Clearly, there is a direct relationship of the fixed positive charge in the p-FET and the electron mobility in the inversion layer of the n-FET. The effective mobility is nearly halved at the very highest nitrogen concentration relative to the base value. Surprisingly [22], no perturbation to the hole mobility was observed.

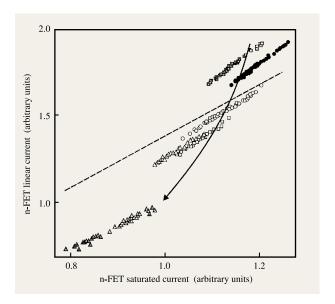

Overall, the performance of devices with high nitrogen content is not as degraded as the low-field electron mobility degradation might imply. Figure 8 shows the linear drain current versus the saturated drain current for each of the gate oxidation variations in Table 2. The linear drain current is measured with a gate-source voltage of 3.3 V and a drain voltage of 100 mV. In saturated conditions, the gate-source voltage is 3.3 V, and the drain-source voltage is also 3.3 V. A straight line sketched in the figure represents equal fractional change in the linear and saturated currents. This relationship is approximately followed by chips with the same gate-oxide process, but for wafers of varying nitrogen concentration, the change in saturated current is less than that of the linear current. This is because the low-field mobility is degraded, while the high-field mobility degrades less or even increases with increasing nitrogen concentration [30]. Therefore, although the linear current is halved by the addition of a large amount of nitrogen, the saturated current is degraded by a much smaller fraction. Because the performance of many circuits is dominated by saturated current, the overall circuit degradation for nitrided oxide is much less than would be expected from the linear transconductance alone.

To summarize the device design considerations, we have found that the primary effect of nitridized oxide in the p-FET is on the threshold voltage, and that this is effectively predicted from the fixed charge alone. No significant change in dopant profile was found. For the p-FET, antimony is implanted as the well-dopant species; different effects may be found with arsenic or phosphorus. We have found no effect on the hole mobility, so the only degradation to the device performance is in the accommodation that must be made in the well doping to achieve the proper threshold voltage. With a nitrided oxide, less doping must be used to achieve a given threshold voltage, and this may limit the ability of the device to achieve very short channels. When boron is used as the well dopant for the n-FET, the dopant redistribution during the gate oxidation/nitridation step must be taken into account to predict the threshold voltage. The fixed charge and the interface trap density also play a role, but the dopant diffusion dominates the device behavior. As the profile is changed by the dielectric process, the short-channel effect is also changed. A lowthermal-budget process with a steeply retrograde well profile will have threshold roll-up, or ISCE. For the n-FET, boron is used for the well doping; different effects might be found for indium. There is a substantial decrease in transconductance with heavy nitridation, but there is less degradation in saturated current than in linear current.

# Figure 8

n-FET linear current vs. n-FET saturated current for various oxidation methods incorporating varying amounts of nitrogen. The various symbols relate to the oxidations specified in Table 2. Solid triangles: RTO in nitric oxygen (f); open squares: RTO in nitric oxide (e); open triangles: RTO in nitrous oxide (d); open circles: RTO in dilute nitrous oxide (b); solid circles: standard furnace nitridation (c); solid squares in oxygen (a). The dotted line represents equal fractional change of current on both axes, and the solid line schematically indicates wafers of increasing nitrogen content. Linear current is measured at large gate—source potential but at small drain bias. Saturated current is measured at large drain—source potential as well as large gate—source voltage. For convenience, the data have been normalized to an arbitrary value.

# Reliability

# • n-FET hot-electron shift

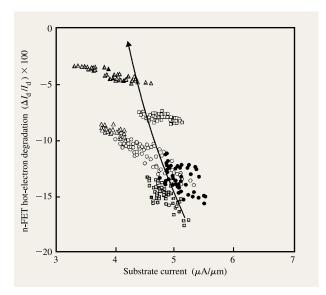

The hot-electron shift for the n-FET device is illustrated in Figure 2 for all of the experimental wafers. The percentage of degradation in drain current after a short stress at maximum substrate current is plotted as the ordinate. The response to hot-electron stress is a monotonic function of the amount of nitrogen at the silicon-silicon dioxide interface, regardless of the method by which the nitrogen was introduced. For further illustrative purposes, the hot-electron shift (percentage of drain-current change) is shown as a function of the substrate current for the various RTO variants in Figure 9. The substrate current is generally well correlated with the hot-electron shift [48]. The substrate current increases for shorter channels and for devices with higher electric field at the drain. The substrate current is the result of the production of electron-hole pairs at the drain from

n-FET hot-carrier-induced drain current degradation (%) as a function of substrate current for various oxidation processes as described in Table 2. Solid triangles: RTO in nitric oxide (f); open squares: RTO in nitric oxide (e); open triangles: RTO in nitrous oxide (d); open circles: RTO in dilute nitrous oxide (b); solid circles: standard furnace nitridation (c); solid squares: RTO in oxygen (a). The solid line schematically indicates wafers of increasing nitrogen content.

energetic electrons heated in the drain field. In addition to the created holes that appear as part of the substrate current, the hot electrons also affect the silicon-silicon dioxide interface. The hot electrons may become trapped or may damage the interface by creating interface traps that shift the threshold voltage and degrade the electron mobility. The incorporation of nitrogen in the dielectric makes the interface more robust with respect to damage [18-20]. In Figure 9 it is apparent that for the same substrate current, the wafers with more nitrogen have less hot-electron shift; and Figure 2 suggests that the hotelectron improvement is directly tied to the interfacial nitrogen and hence to the p-FET threshold voltage. From a device design perspective, the improved immunity to hot-electron degradation may be utilized in one of several ways: The channel length of the device may be shortened, keeping the same shift; the drain may be engineered for a higher electric field while maintaining the same shift; or a superior reliability may be offered to relieve circuit design restrictions.

# • p-FET hot-electron shift

The shift in drain current and threshold voltage in n-FETs under hot-electron stress is caused by the creation of

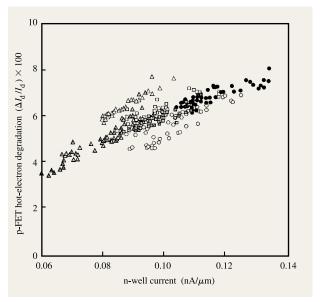

## Figure 10

p-FET hot-carrier-induced drain current degradation (%) as a function of well current for various oxidation processes, as described in Table 2. Solid triangles: RTO in nitric oxide (f); open squares: RTO in nitric oxide (e); open triangles: RTO in nitrous oxide (d); open circles: RTO in dilute nitrous oxide (b); solid circles: standard furnace nitridation (c); solid squares: RTO in oxygen (a).

interface traps and trapping of electrons in the oxide bulk [48]. It is possible for both of these mechanisms to occur in p-FETs as well [49, 50]. Under peak gate-current bias conditions, the shift in these devices is dominated by electron trapping in the oxide. A large drain-source voltage is applied, and only a moderate gate-source voltage. Under these conditions the gate potential is negative enough for a large drain-source current, but still more positive than the drain, so as to not repel electrons from traversing the gate oxide. Figure 10 shows the percentage of shift in drain current for p-FETs. The shift is plotted against the n-well current, since, as in the n-FET and its substrate current, a higher well current indicates a larger shift, simply by virtue of indicating a larger generation of hot carriers. In Figure 10 all RTO wafers have virtually the same shift; the furnace-oxidized cell is slightly inferior to the RTO group, and of these, the N<sub>2</sub>O is marginally superior. Essentially, hot-electron shift dependence on the nitrogen incorporation is not observed for the p-FET.

# • Charge to breakdown

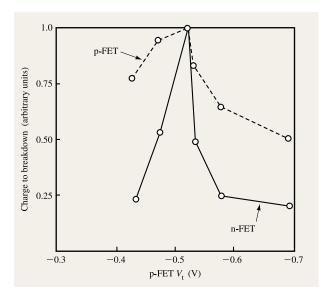

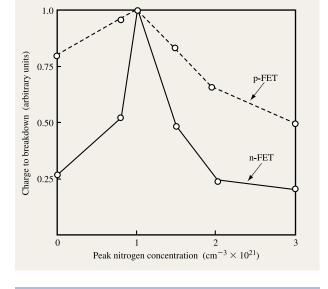

The intrinsic dielectric reliability of the oxides described in Table 2 was determined by applying an elevated voltage

Charge to breakdown (p-FET + n-FET) as a function of p-FET threshold voltage. The data points correspond to the entries in Table 2, ranging in nitrogen concentration from left to right.

## Figure 12

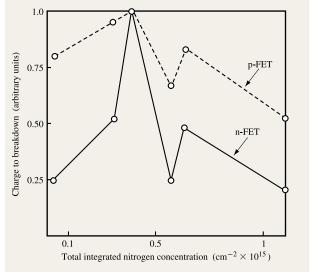

Charge to breakdown (p-FET + n-FET) as a function of total integrated nitrogen concentration. The data correspond to the entries in Table 2.

at an elevated temperature to capacitor structures until dielectric failure was noted. All stressing was performed with the silicon surface in inversion, and both p-FETs and n-FETs were measured. Constant voltage stressing was performed, and the current was measured during the stress. At the completion of the stress (it typically took 20-200 seconds for the capacitors to fail at 9-9.5 V), the total charge that had flowed was calculated and tabulated. The charge for which 50% of the capacitors failed is presented here as  $Q_{\rm BD}$ . Figure 11 shows the  $Q_{\rm BD}$  for both n-FET and p-FET as a function of the p-FET threshold voltage, which is used because it is a measure of the oxide charge. In Figure 12 we have used the SIMS data from Table 2, and plotted the same data points as a function of the integrated nitrogen concentration. In Figure 13 the same  $Q_{\rm BD}$  data are plotted against the peak nitrogen concentration from Table 2. The  $Q_{BD}$  is improved by adding some nitrogen, but further nitridation caused the charge to breakdown to degrade in both n-FETs and p-FETs. A peak nitrogen concentration in excess of  $1.0 \times 10^{21}$  cm<sup>-2</sup> degrades the charge to breakdown. In these devices the poorest  $Q_{\mathrm{BD}}$  is obtained from wafers processed with nitric oxide. The best wafers were processed with nitrous oxide.

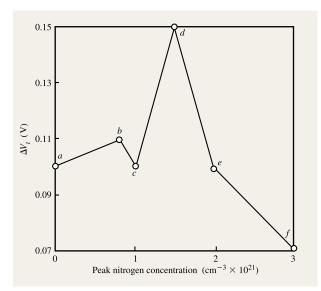

# • NBTI

Negative-bias temperature stressing was performed at elevated temperature and voltage. In this type of stressing, a negative bias of the order of 5 V is applied to the gate

#### Figure 13

Charge-to-breakdown (p-FET + n-FET) as a function of peak nitrogen concentration. The points correspond to the entries in Table 2.

of a p-FET while holding the drain, source, and well at ground potential. Devices are stressed for 2–5 hr

Shift in threshold voltage after NBTI stress as a function of peak nitrogen concentration. The points correspond to the entries in Table 2.

under these conditions. Stressing in this mode induces a threshold-voltage shift through the creation of fixed positive charge and interface traps [41-43]. Figure 14 plots the threshold-voltage shift (normalized for  $t_{av}$ ) against the nitrogen concentration as derived from the SIMS analysis. The NBTI shift is largest at an intermediate nitrogen concentration. The degraded NBTI behavior of point d in Figure 14 is consistent with another experiment in which the NBTI shift in undiluted nitrous oxide-oxidized samples (points K and L from Table 1 and Figure 2) was measured to be one and one-half times as large as standard diluted N<sub>2</sub>O samples (points E-H from Table 1 and Figure 2). It is unfortunate that the best  $Q_{\rm RD}$ (as in Figure 13) is found at an intermediate nitrogen concentration, for which the NBTI threshold shift was the largest.

To summarize the reliability data, we have found that the improvement in n-FET hot-electron shift is directly related to the interfacial nitrogen concentration. Since the p-FET hot-electron shift is nearly unchanged by the oxidation/nitridation experiments, there appears to be no change in the trapping of electrons in the bulk oxide. The intrinsic charge to breakdown is significantly altered by the experiments, with the best  $Q_{\rm BD}$  found at intermediate nitrogen concentration. In contrast, the NBTI threshold voltage shift is found to be worst in the wafers with intermediate nitrogen concentration.

## **Summary**

We have examined the effects of nitrogen in the gate dielectric and various methods of its introduction on the reliability and device characteristics for a particular device design. The effects across a large range of nitrogen incorporation (from 0 to 10% of the interfacial bonds) have been studied. Data on device design and reliability across this wide range of nitrogen incorporation have been presented.

Some effects are common to all means of nitridation. Nitrogen increases the surface charge, so the well dopants must be modified to readjust the threshold voltage and maintain useful currents. The n-FET is affected by the different heat cycles that may be used to introduce the nitrogen. The optimum degree and method of nitridation will vary for different technologies, depending on the specific design goals. For instance, a steeply retrograde well design requires a low-thermal-budget process such as high-pressure oxidation or RTO, while a device design that is best satisfied by a flat well profile may utilize the simpler conventional furnace process.

The n-FET hot-electron reliability is very much improved by the interfacial nitrogen, but the p-FET electron trapping is unaffected. The dielectric integrity is improved by adding nitrogen to the interface, but not too much. The NBTI is degraded by the initial addition of nitrogen, but then improves as more is added.

A practical compromise to the trade-offs involved in a nitrided-gate oxide has been given. The standard process as described in Table 1 achieves the desired design goals of adequate hot-electron reliability with minimal cost and complexity. In addition, we have tried to show some fundamental aspects of nitrided oxides and their relationship with the device design. Improvements in hot-electron immunity appear to be invariably accompanied by increased fixed charge and degraded mobility. Data have also been presented that indicate a complex interaction of nitrogen in the classic oxide degradation mechanisms of time-dependent dielectric breakdown and NBTI.

# **Acknowledgments**

This work could not have been completed without the contributions of many individuals. R. Ganesh, S. Berg, and J. Blouse of GaSonics were instrumental in oxidizing some of the samples at high pressure at the GaSonics facility at San Jose, California. J. Piccirillo and G. Xing did the RTO processing on our samples at Applied Materials Corporation in Santa Clara, California. A. Ray of IBM in East Fishkill, New York, provided the furnace nitric oxide samples, and the standard furnace samples were produced through the efforts of D. Martin and E. Ward of IBM in Essex Junction, Vermont. General wafer-processing support was provided by J. Ramsey of IBM in Essex Junction, and the authors are further indebted to D. Cook

and D. Brochu of IBM in Essex Junction for much of the testing and stressing. A critical reading of the manuscript by D. Buchanan of IBM in Yorktown Heights, New York, and E. Nowak of IBM in Essex Junction is greatly appreciated.

#### References

- S. Hu, "Vacancies and Self Interstitials in Silicon," Proceedings of the Second Symposium on Defects in Silicon, 1991, pp. 211–236.

- S. Hu, "General Theory of Impurity Diffusion in Semiconductors Via the Vacancy Mechanism," *Phys. Rev.* 183, No. 3, 773 (1969).

- 3. P. Packan and J. Plummer, "Temperature and Time Dependence of B and P Diffusion in Si During Surface Oxidation," *J. Appl. Phys.* **68**, No. 8, 4327 (1990).

- A. Lin, D. Antoniadis, and R. Dutton, "The Growth of Oxidation Stacking Faults and the Point Defect Generation at the Si-SiO, Interface During Thermal Oxidation of Silicon," J. Electrochem. Soc. 128, No. 5, 1131 (1981).

- T. Matsuoka, S. Taguchi, Q. Khosru, and K. Taniguchi, "Degradation of Inversion Layer Mobility Due to Interface Traps in Metal Oxide Semiconductor Transistors," J. Appl. Phys. 78, No. 5, 3252–3257 (1995).

- L. Perron, A. Lacaita, A. Pacelli, and R. Bez, "Electron Mobility in ULSI MOSFETs: Effect of Interface Traps and Oxide Nitridation," *IEEE Electron Device Lett.* 18, No. 5, 235–237 (1997).

- F. Gamiz, J. Lopez Villaneuva, J. Banqueri, J. Carceller, and P. Cartujo, "Universality of Electron Mobility Curves in MOSFETs: A Monte Carlo Study," *IEEE Trans. Electron Devices* 42, No. 2, 258–265 (1995).

- 8. M. Schmidt, F. Terry, B. Malthur, and S. Senturia, "Inversion Layer Mobility of MOSFET's with Nitrided Oxide Gate Dielectrics," *IEEE Trans. Electron Devices* **35**, 1627 (1988)

- 9. P. W. Mertens, M. McGeary, M. Schaekers, H. Sprey, B. Vermeire, M. Depas, M. Meuris, and M. Heyns, "Effect of Cl in Gate Oxidation," *Proceedings of the Symposium on the Science and Technology of Semiconductor Surface Preparation*, 1997, pp. 89–100.

- Y. Kim, C. Jun, and S. Chung, "Effects of Chlorine Based Gettering on the Electrical Properties of Rapid Thermal Oxidation/Nitridation Dielectric Films," *J. Vac. Sci. Technol. A* 11, No. 4, pt. 1, 1039–1043 (1993).

- G. Hames, S. Beck, A. Gilicinski, W. Henson, and J. Wortman, "Influence of HCl on Rapid Thermal Oxides," Proceedings of the Symposium on Rapid Thermal and Integrated Processing V, 1996, pp. 219–224.

- B. Vermeire, P. Mertens, M. McGeary, K. Kenis,

M. Heyns, M. Schaekers, and A. Lubbers, "Effect of Different Chlorine Sources During Gate Oxidation," Proceedings of the Second International Symposium on Ultra Clean Processing of Silicon Surfaces, 1994, pp. 143–146.

E. da Silva, Y. Nishioka, Y. Wang, and T. Ma, "Dramatic

- E. da Silva, Y. Nishioka, Y. Wang, and T. Ma, "Dramatic Improvement of Hot-Carrier-Induced Interface Degradation in MOS Structures Containing F or Cl in SiO<sub>2</sub>," *IEEE Electron Device Lett.* 9, No. 1, 38–40 (1988).

T. Nakanishi, T. Kawamoto, and K. Takasaki, "Instability

- T. Nakanishi, T. Kawamoto, and K. Takasaki, "Instability of SiO<sub>2</sub> Film Caused by Fluorine and Chlorine Inclusion," *Jpn. J. Appl. Phys. 1* 37, No. 8, 4316–4320 (1998).

- A. Balasinski, M. Tsai, L. Vishnubhotla, T. Ma, H. Tseng, and P. Tobin, "Interface Properties in Fluorinated (100) and (111) Si/SiO<sub>2</sub> MOSFETs," *Microelectron. Eng.* 22, No. 1–4, 97–100 (1993).

- T. Ma, "Metal–Oxide–Semiconductor Gate Oxide Reliability and the Role of Fluorine," *J. Vac. Sci. Technol.* A 10, No. 4, 469–471 (1992).

- T. Lo, W. Ting, D. Kwong, J. Kuehne, and C. Magee, "MOS Characteristics of Fluorinated Gate Dielectrics Grown by Rapid Thermal Processing in O<sub>2</sub> with Diluted NF<sub>3</sub>," *IEEE Electron Device Lett.* 11, No. 11, 511–513 (1990).

- T. Matsuoka, S. Taguchi, H. Ohtsuka, K. Taniguchi, C. Hamaguchi, S. Kakimoto, and K. Uda, "Hot-Carrier-Induced Degradation of N<sub>2</sub>O-Oxynitrided Gate Oxide NMOSFET's," *IEEE Trans. Electron Devices* 43, 1364–1373 (1996).

- A. Uchiyama, H. Fukuda, and T. Hayashi, "Dual-Gate CMOSFET with N<sub>2</sub>O-Nitrided Gate SiO<sub>2</sub> Film," *OKI Tech. Rev.* 58, 53–58 (1991).

- C. Papadas, G. Ghibaudo, F. Pio, C. Monserie, G. Pananakakis, P. Mortini, and C. Riva, "On the Charge Build-Up Mechanisms in Gate Dielectrics," *Solid-State Electron.* 37, No. 3, 495–505 (1994).

- 21. J. Hu, J. Keuhne, T. Grider, M. Rodder, and I. Chen, "A Comparative pMOS Study of 33Å Nitrided Oxides Prepared by Either N<sub>2</sub>O or Nitrogen Implant Before Gate Oxidation for 0.18-0.13 mm CMOS Technologies," Proceedings of the Symposium on VLSI Technology, Systems, and Applications, 1997, pp. 167-171.

- H. Fang, K. S. Krisch, B. J. Gross, C. Sodini, J. Chung, and D. Antoniadis, "Low Temperature Furnace-Grown Deoxidized Nitrided Oxide Gate Dielectrics as a Barrier to Boron Penetration," *IEEE Electron Device Lett.* 13, 217–219 (1992).

- L. Han, D. Wristers, M. Bhat, and D. Kwong, "Highly Suppressed Boron Penetration in NO-Nitrided SiO<sub>2</sub> for p+ Polysilicon Gated MOS Device Applications," *IEEE Electron Device Lett.* 16, 319–321 (1995).

- D. Lin, J. Cable, and J. Woo, "Temperature and Electric Field Characteristics of Time-Dependent Dielectric Breakdown for Silicon Dioxide and Reoxidized-Nitrided Oxide," *IEEE Trans. Electron Devices* 42, 1329–1332 (1995).

- Y. Wu and J. Hwu, "Characterization of Metal-Oxide-Semiconductor Capacitors with Improved Gate Oxide by Repeated Thermal Annealings in N<sub>2</sub>O," J. Vac. Sci. Technol. B 12, No. 4, 2400-2404 (1994).

- J. Ahn, A. Joshi, G. Lo, and D. Kwong, "Time-Dependent Dielectric Breakdown Characteristics of N<sub>2</sub>O Oxide Under Dynamic Stressing," *IEEE Electron Device Lett.* 13, No. 18, 513–515 (1992).

- 27. M. Bhat, J. Kim, J. Yan, G. Yoon, L. Han, and D. Kwong, "MOS Characteristics of Ultrathin NO-Grown Oxynitrides," *IEEE Electron Device Lett.* **15**, No. 10, 421–423 (1994).

- 28. T. Hook, K. Watson, E. Lee, D. Martin, R. Ganesh, S. Kim, and A. Ray, "Correlation Between Fixed Positive Charge and Hot-Electron Immunity for Nitrided Oxides," *IEEE Electron Device Lett.* 18, No. 10, 471–473 (1997).

- A. Philipossian, B. Doyle, and K. Van Wormer, "Nitrogen Incorporation in Gate Dielectrics: A Correlation Between Auger Electron Spectroscopy and Surface Charge Analysis Techniques," *J. Electrochem. Soc.* 142, No. 10, L171–L172 (1995).

- Z. Ma, Z. Liu, Y. Cheng, P. Ko, and C. Hu, "New Insight into High-Field Mobility Enhancement of Nitrided-Oxide N-MOSFET's Based on Noise Measurements," *IEEE Trans. Electron Devices* 41, No. 11, 2205–2209 (1994).

- 31. K. Hirabayashi, "Interface States in Nitrogen Incorporated Gate Oxides," *Appl. Phys. Lett.* **68**, No. 14, 1978–1980 (1996).

- 32. N. Saks, D. Ma, and W. Fowler, "Nitrogen Depletion During Oxidation in N<sub>2</sub>O," *Appl. Phys. Lett.* **67**, No. 3, 374–376 (1995).

- E. Carr, K. Ellis, and R. Buhrman, "N Depth Profiles in Thin SiO<sub>2</sub> Grown or Processed in N<sub>2</sub>O: The Role of Atomic Oxygen," Appl, Phys. Lett. 66, No. 12, 1492–1494 (1995).

- T. Arakawa, R. Matsumoto, and A. Kita, "Effect of Nitrogen Profile on Tunnel Oxynitride Degradation with Charge Injection Polarity," *Jpn. J. Appl. Phys* 35, pt. 1, No. 2B, 1491–1495 (1996).

- 35. Y. Okada, P. Tobin, V. Lakhotia, W. Feil, S. Ajuria, and R. Hegde, "Relationship Between Growth Conditions, Nitrogen Profile, and Charge to Breakdown of Gate Oxynitrides Grown from Pure N<sub>2</sub>O," *Appl. Phys. Lett.* 63, No. 2, 194–196 (1993).

- 36. T. Hook, J. Piccirillo, K. Watson, and E. Nowak, "A CMOS Technology for a Sub-5-ns 3.3-V LVTTL 1 Mbit SRAM," Proceedings of the European Solid-State Device Research Conference, 1995, pp. 531–534.

- 37. D. Grider, S. Hattangady, R. Kraft, P. Nicollian, J. Keuhne, G. Brown, S. Au, R. Eklund, M. Pas, W. Hunter, and M. Douglas, "A 0.18 μm CMOS Process Using Nitrogen Profile Engineered Gate Dielectrics," *Proceedings of the Symposium on VLSI Technology*, 1997, pp. 47–48.

- J. Hayden, T. McNelly, A. Perera, J. Pfiester, C. Subramanian, and M. Thompson, "A High Performance 0.25 μm CMOS Technology for Fast SRAMs," *Proc. SPIE* 2875, 148–163 (1996).

- 39. M. Luo, P. Tsui, W. Chen, P. Gilbert, B. Maiti, A. Sitaram, and S. Sun, "A 0.25 μm CMOS Technology with 45Å Nitrided Oxide," *Proceedings of the International Electron Devices Meeting*, 1995, pp. 691–694.

- G. Yoon and Y. Epstein, "Cycle Time Improvement in Manufacturing Nitrided Gate Oxides for ULSI CMOS Applications," Proceedings of the Advanced Semiconductor Manufacturing Conference, 1996, pp. 186–191.

- G. La Rose, F. Guarin, S. Rauch, A. Acovic, J. Lukaitis, and E. Crabbe, "NBTI Channel Hot Carrier Effects in PMOSFETs in Advanced CMOS Technologies," Proceedings of the 1997 IEEE International Reliability Physics Symposium, 1997, pp. 282–286.

S. Ogawa, M. Shimaya, and N. Shiono, "Interface-Trap

- S. Ogawa, M. Shimaya, and N. Shiono, "Interface-Trap Generation at Ultrathin SiO<sub>2</sub> (4-6 nm)-Si Interfaces During Negative-Bias Temperature Aging," *J. Appl. Phys.* 77, No. 3, 1137-1148 (1995).

- E. Poindexter, "Point Defects and Charge Traps in the Si/SiO<sub>2</sub> System and Related Structures," Semiconductor Interfaces, Microstructures and Devices: Properties and Applications, Institute of Physics Publishing, Philadelphia, 1993, pp. 229–256.

- 44. J. Chun, E. Nowak, L. Ding, and Y. Loh, "Optimization of Boron Pocket Implantation for Deep Submicron NMOSFET Process," Proceedings of the Fourth International Conference on Solid State and IC Technology, 1995, pp. 224–226.

- 45. A. Das, H. De, V. Misra, S. Venkatesan, S. Veeraraghavan, and M. Foisy, "Effects of Halo Implant on Hot Carrier Reliability of Sub-Quarter-Micron MOSFETs," *Proceedings of the 1998 IEEE International Reliability Physics Symposium*, 1998, pp. 189–193.

- J. Lutze and S. Venkatesan, "Techniques for Reducing the Reverse Short Channel Effect in Sub 0.5 mm CMOS," *IEEE Electron Device Lett.* 16, No. 9, 373–375 (1995).

- 47. S. Chaudhrya, C. Rafferty, W. Nagy, Y. Chyan, M. Carroll, A. Chen, and K. Lee, "Suppression of Reverse Short Channel Effect by High Energy Implantation," *Proceedings of the International Electron Devices Meeting*, 1997, pp. 679–682.

- 48. C. Hu, S. Tam, F. Hsu, P. Ko, T. Chan, and K. Terrill, "Hot-Electron-Induced MOSFET Degradation—Model, Monitor, and Improvement," *IEEE Trans. Electron Devices* ED-32, No. 2, 375–385 (1985).

- R. Wojlter, G. Paulzen, H. Pomp, H. Lifka, and P. Woerlee, "Three Hot Carrier Degradation Mechanisms in Deep Submicron PMOSFET's," *IEEE Trans. Electron Devices* 42, No. 1, 109–115 (1995).

S. Jang, T. Tang, Y. Chen, and C. Sheu, "Modeling of Hot Carrier Stressed Characteristics of Submicrometer pMOSFETs," *Solid State Electron.* 39, No. 7, 1043–1049 (1996).

Received January 8, 1998; accepted for publication March 3, 1999

**Terence B. Hook** *IBM Microelectronics Division, Burlington facility, Essex Junction, Vermont 05452 (tbhook@us.ibm.com)*. Dr. Hook received an Sc.B. degree in electrical engineering from Brown University in 1980, and the Ph.D. degree from Yale University in 1986. His thesis, under Prof. T. P Ma, addressed Fowler–Nordheim tunneling currents and reliability in MOS structures. Since joining IBM in 1980, he has worked on device design, reliability, and process integration on CMOS, BiCMOS, and bipolar technologies. Dr. Hook is a Senior Engineer in the Semiconductor Research and Development Center; he divides his time between Essex Junction, Vermont, and East Fishkill, New York, working on 0.18-μm generation device design and process-induced charging issues,

Jay S. Burnham IBM Microelectronics Division, Burlington facility, Essex Junction, Vermont 05452 (burnhamj@us.ibm.com). Dr. Burnham joined the IBM Microelectronics Division in Essex Junction, Vermont, in 1995. He currently works in the Surface and Materials Analysis Laboratory as a Staff Engineer/Scientist and is responsible for leading the SIMS team. He received the B.A. degree in chemistry from the State University of New York at Potsdam in 1987 and the Ph.D. degree in physical chemistry from Pennsylvania State University in 1995 for studies in the fundamentals of ion beam/solid interactions. He also spent an additional year at Penn State for postdoctoral studies concerning real-time characterization of plasma-deposited films. Dr. Burnham has authored many technical publications and is a member of the American Chemical Society and the American Vacuum Society.

Ronald J. Bolam IBM Microelectronics Division, Burlington facility, Essex Junction, Vermont 05452 (A093271@us.ibm.com). Mr. Bolam is a Staff Engineer in the Technology Reliability Development group, currently responsible for MOSFET, BJT, and SOI device reliability, including gate wear-out, channel hot-electron effects, and bias temperature stability. Mr. Bolam joined IBM in 1981 after receiving an Associate degree in electrical engineering from the Electronics Institute of Pittsburgh. He received a B.S. degree in physics and an M.S. degree in materials science, specializing in silicon device fabrication, from the University of Vermont in 1986 and 1992, respectively.