# Technical Reference Options and Adapters Volume 2

5

**IBM Industrial Computer**

Technical Reference Options and Adapters Volume 2

**IBM Industrial Computer**

# IBM Monochrome Display and Printer Adapter

# Contents

| Monochrome Display Adapter Function | 1 |

|-------------------------------------|---|

| Printer Adapter Function            | 8 |

| Logic Diagrams                      | 3 |

# IBM Monochrome Display and Printer Adapter

#### **Monochrome Display Adapter Function**

The IBM Monochrome Display and Printer Adapter has two functions. The first is to provide an interface to the IBM Monochrome Display. The second is to provide a parallel interface for the IBM Printers. We will discuss this adapter by function.

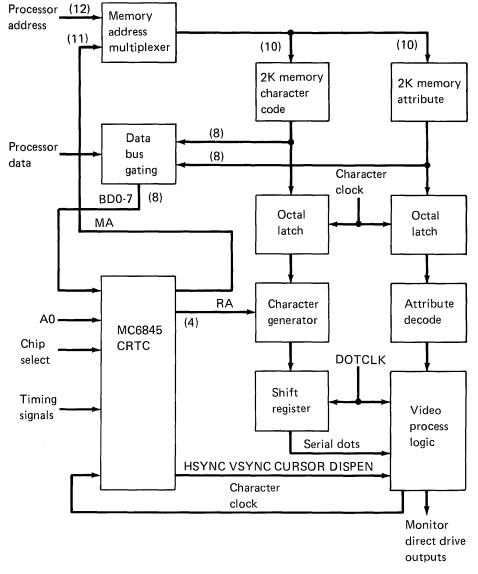

The IBM Monochrome Display and Printer Adapter is designed around the Motorola 6845 CRT Controller module. There are 4K bytes of RAM on the adapter that are used for the display buffer. This buffer has two ports to which the system-unit microprocessor has direct access. No parity is provided on the display buffer.

Two bytes are fetched from the display buffer in 553 ns, providing a data rate of 1.8M-bytes/second.

The adapter supports 256 different character codes. An 8K-byte character generator contains the fonts for the character codes. The characters, values, and screen characteristics are given in "Of Characters, Keystrokes, and Colors" in your *Technical Reference* system manual.

# Monochrome Display Adapter Function (continued)

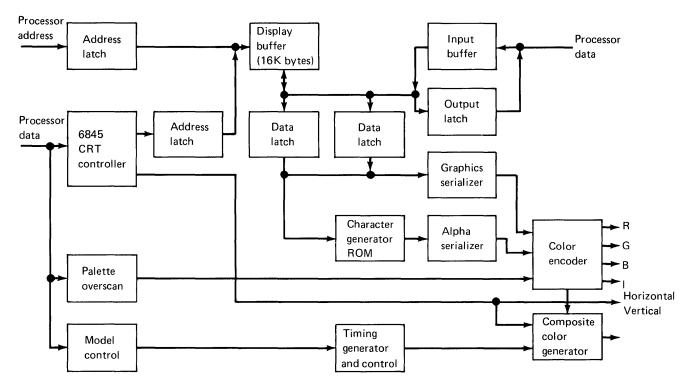

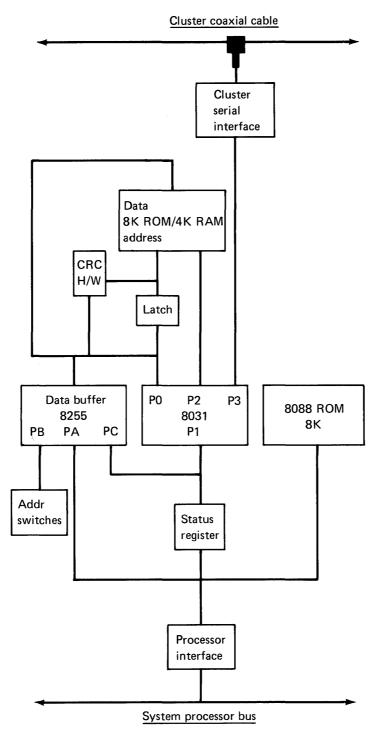

The following is a block diagram of the monochrome display adapter portion of the IBM Monochrome Display and Printer Adapter.

IBM monochrome display adapter block diagram

#### Monochrome Display Adapter Function (continued)

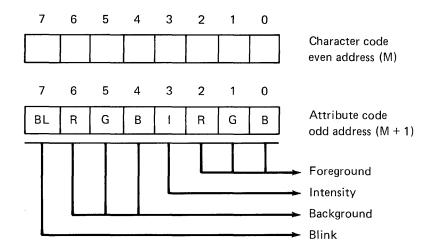

The adapter decodes the character attribute byte as defined above. The blink and intensity bits may be combined with the foreground and background bits to further enhance the character attribute functions listed below:

| Bac | ckgrou | ınd | Fo | regrou | ind | Function                         |

|-----|--------|-----|----|--------|-----|----------------------------------|

| R   | G      | B   | R  | G      | B   |                                  |

| 0   | 0      | 0   | 0  | 0      | 0   | Non-display                      |

| 0   | 0      | 0   |    | 0      | 1   | Underline                        |

| 0   | 0      | 0   | 1  | 1      | 1   | White character/black background |

| 1   | 1      | 1   | 0  | 0      | 0   | Reverse video                    |

The 4K display buffer supports one screen of the 25 rows of 80 characters, plus a character attribute for each display character. The starting address of the buffer is hex B0000. The display buffer can be read using direct memory access (DMA); however, at least one wait state will be inserted by the system-unit microprocessor. The duration of the wait state will vary, because the microprocessor/monitor access is synchronized with the character clock on this adapter.

Interrupt level 7 is used on the parallel interface. Interrupts can be enabled or disabled through the printer control port. The interrupt is a high-level active signal.

# Monochrome Display Adapter Function (continued)

| Bit<br>number | Function            |

|---------------|---------------------|

| 0             | + Horizontal drive  |

| 1             | Reserved            |

| 2             | Reserved            |

| 3             | + Black/white video |

6845 CRT status port (Hex 3BA)

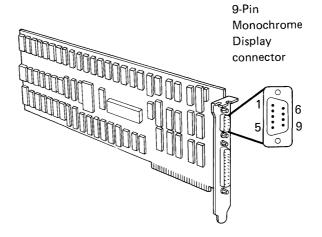

#### **Connector Specifications**

|            | Ground       |          | 1 |             |

|------------|--------------|----------|---|-------------|

|            | Ground       |          | 2 |             |

|            |              | Not used | 3 |             |

|            |              | Not used | 4 | IBM         |

| IBM        |              | Not used | 5 | Monochrome  |

| Monochrome | + Intensity  | ł        | 6 | Display     |

| Display    | + Video      |          | 7 | and Printer |

|            | + Horizontal |          | 8 | Adapter     |

|            | – Vertical   |          | 9 | ]           |

| F          | •            |          |   |             |

**Note:** Signal voltages are 0.0 to 0.6 Vdc at down level and +2.4 to 3.5 Vdc at high level.

#### **Connector specifications**

# Printer Adapter Function (continued)

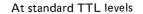

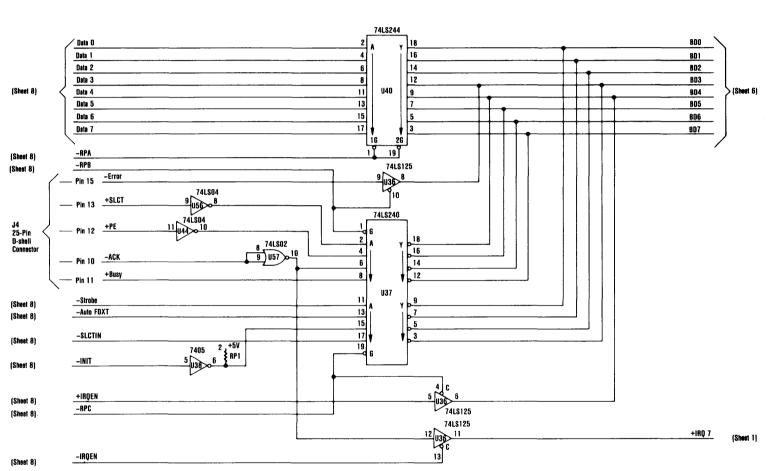

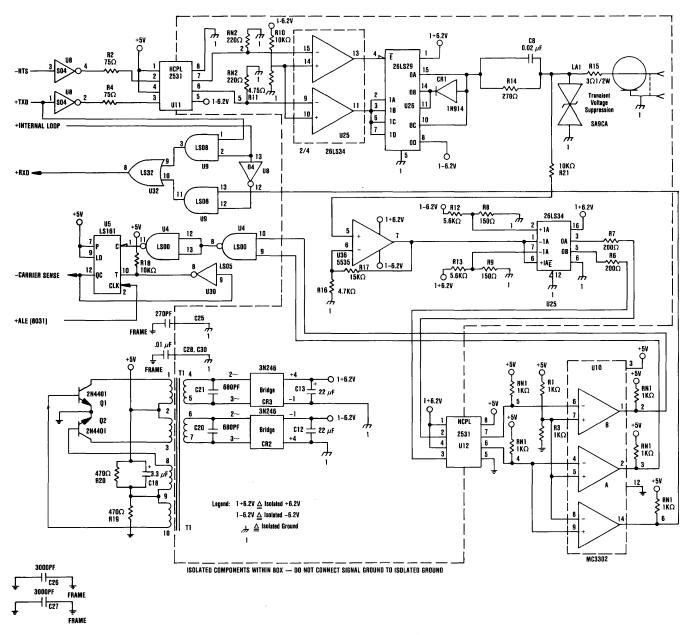

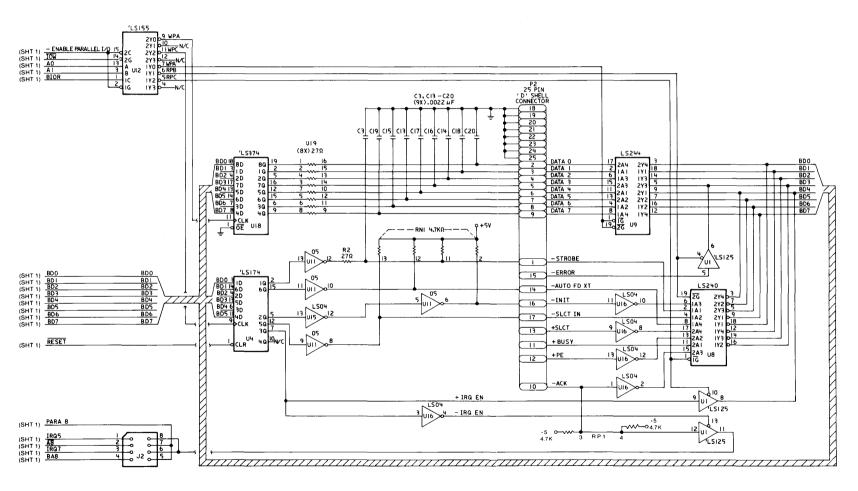

The following is a block diagram of the printer adapter portion of the Monochrome Display and Printer Adapter.

Printer adapter block diagram

## Printer Adapter Function (continued)

| IBM monochrome display and |  |

|----------------------------|--|

| printer adapter            |  |

Input from address hex 3BC

This instruction presents the system-unit microprocessor with data present on the pins associated with the output to hex 3BC. This should normally reflect the exact value that was last written to hex 3BC. If an external device should be driving data on these pins at the time of an input (in violation of usage ground rules), this data will be ORed with the latch contents.

| IBM monochrome display and printer adapter |

|--------------------------------------------|

| Input from address hex 3BD                 |

This instruction presents the realtime status to the system-unit microprocessor from the pins as follows.

| Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|--------|--------|--------|-------|-------|-------|

| Pin 11 | Pin 10 | Pin 12 | Pin 13 | Pin 15 | —     | _     | -     |

| IBM monochrome display and printer adapter |

|--------------------------------------------|

| Input from address hex 3BE                 |

This instruction causes the data present on pins 1, 14, 16, 17, and the IRQ bit to be read by the system-unit microprocessor. In the absence of external drive applied to these pins, data read by the system-unit microprocessor will match data last written to hex 3BE in the same bit positions. Notice that data bits 0-2 are not included. If external drivers are dotted to these pins, that data will be ORed with data applied to the pins by the hex 3BE latch.

| Bit 7 | Bit 6 | Bit 5 | Bit 4         | Bit 3   | Bit 2   | Bit 1   | Bit O   |

|-------|-------|-------|---------------|---------|---------|---------|---------|

|       |       |       | IRQ<br>Enable | Pin 17  | Pin 16  | Pin 14  | Pin 1   |

|       |       |       | Por = 0       | Por = 1 | Por = 0 | Por = 1 | Por = 1 |

These pins assume the states shown after a reset from the system-unit microprocessor.

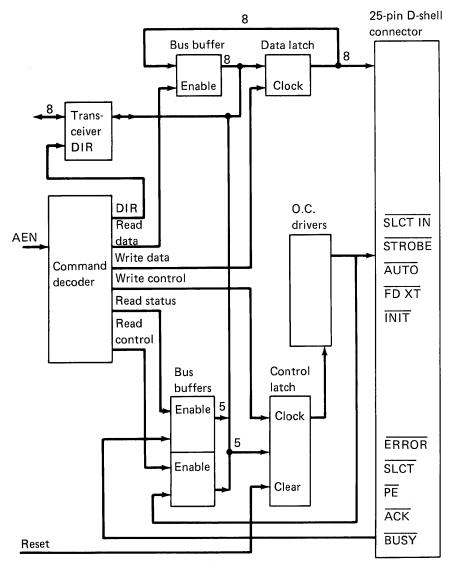

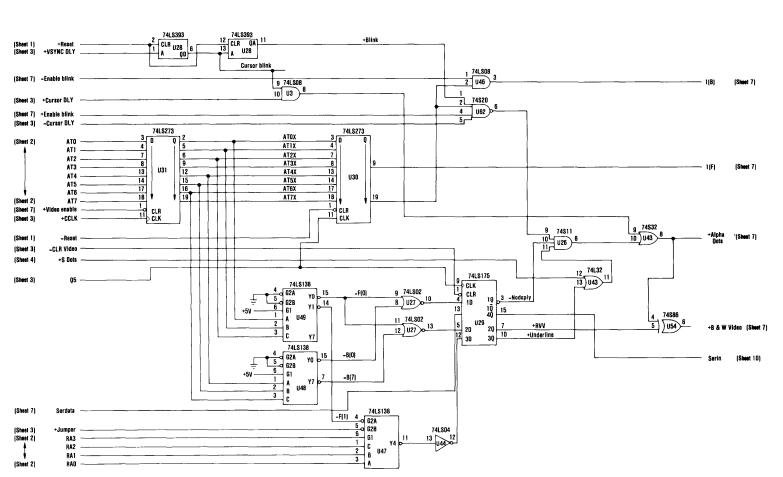

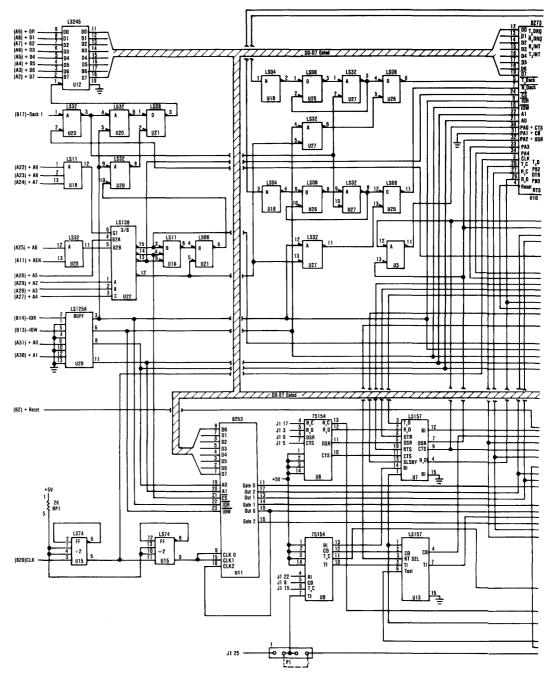

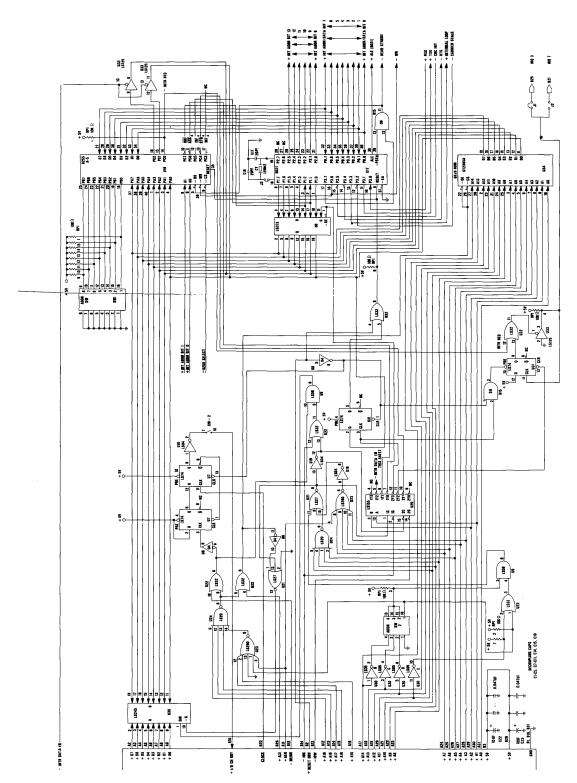

Monochrome display adapter (Part 1 of 10)

Monochrome display adapter (Part 3 of 10)

Monochrome display adapter (Part 5 of 10)

Monochrome display adapter (Part 7 of 10)

Monochrome display adapter (Part 9 of 10)

# IBM Color/Graphics Monitor Adapter

# Contents

| Descri | ption     |         |        | • • | • |       |   | <br>••  | • | <br>• | • • |  |     | • |   |     |   | • |     |   |   |     |       |         | 1  |

|--------|-----------|---------|--------|-----|---|-------|---|---------|---|-------|-----|--|-----|---|---|-----|---|---|-----|---|---|-----|-------|---------|----|

| Progra | amming Co | onsider | ations | ι.  |   |       | • | <br>    |   | <br>• | •   |  |     | • |   |     | • | • |     |   | • | • • | <br>• | <br>. 1 | 13 |

| Specif | ications  |         |        |     |   |       | • | <br>    |   |       | •   |  |     | • |   |     |   | • |     |   |   |     | <br>• | <br>. 2 | 21 |

| Logic  | Diagrams  |         |        | •   |   | <br>• | • | <br>• • |   | <br>• | •   |  | • • | • | • | • • | • | • | • • | • | • | • • |       | <br>2   | 23 |

# IBM Color/Graphics Monitor Adapter

#### Description

The IBM Color/Graphics Monitor Adapter is designed to attach to the IBM 5532 Industrial Color Display, or to a variety of television-frequency monitors.

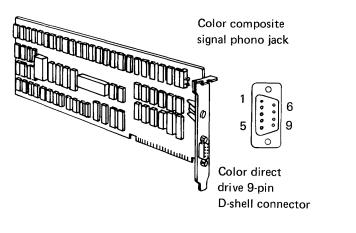

The adapter is capable of operating in black-and-white or color. It provides three video interfaces: a composite-video port, a direct-drive port, and a connection interface for driving a user-supplied RF modulator. A light pen interface is also provided.

The adapter has two basic modes of operation: alphanumeric (A/N) and all-points-addressable (APA) graphics. Additional modes are available within the A/N or APA graphics modes. In the A/N mode, the display can be operated in either a 40-column by 25-row mode for a low-resolution monitor, or in an 80-column by 25-row mode for high-resolution monitors. In both modes, characters are defined in an 8-wide by 8-high character box and are 7-wide by 7-high, double dotted characters with one descender. Both uppercase and lowercase characters are supported in all modes.

The character attributes of reverse video, blinking, and highlighting are available in the black-and-white mode. In the color mode, 16 foreground and 8 background colors are available for each character. In addition, blinking on a per-character basis is available.

Color/graphics monitor adapter block diagram

#### **Character Generator**

A ROS character generator is used with 8K bytes of storage that cannot be read from or written to under program control. This is a general-purpose ROS character generator with three character fonts. Two character fonts are used on the Color/Graphics Monitor Adapter: a 7-high by 7-wide double-dot font and a 7-high by 5-wide single-dot font. The font is selected by a jumper (P3). The single-dot font is selected by inserting the jumper; the double-dot font is selected by removing the jumper.

#### **Timing Generator**

This generator produces the timing signals used by the 6845 CRT Controller and by the dynamic memory. It also solves the processor/graphic controller contentions for access to the display buffer.

#### **Composite Color Generator**

This generator produces base-band-video color information.

#### **Alphanumeric Mode**

Every display character position in the alphanumeric mode is defined by two bytes in the regen buffer (a part of the monitor adapter), not the system memory. Both the Color/Graphics Monitor Adapter and the Monochrome Display and Printer Adapter use the following 2-byte character-attribute format.

|   |   | Di | splay-o | harac | ter co | de byt | e |   |   |   | A | ttribu | te byte | е |   |   |

|---|---|----|---------|-------|--------|--------|---|---|---|---|---|--------|---------|---|---|---|

| Γ | 7 | 6  | 5       | 4     | 3      | 2      | 1 | 0 | 7 | 6 | 5 | 4      | 3       | 2 | 1 | 0 |

The low-resolution alphanumeric mode:

- Supports home color televisions or low-resolution monitors

- Displays up to 25 rows of 40 characters each

- Has a ROS character generator that contains dot patterns for a maximum of 256 different characters

- Requires 2,000 bytes of read/write memory (on the adapter)

- Has an 8-high by 8-wide character box

- Has two jumper-controlled character fonts available: a 7-high by 5-wide single-dot character font with one descender, and a 7-high by 7-wide double-dotted character font with one descender

- Has one character attribute for each character.

The high-resolution alphanumeric mode:

- Supports the IBM Color Display or other color monitor with direct-drive capability

- Supports a black-and-white composite-video monitor

- Displays up to 25 rows of 80 characters each

- Has a ROS display generator that contains dot patterns for a maximum of 256 characters

- Requires 4,000 bytes of read/write memory (on the adapter)

- Has an 8-high by 8-wide character box

- Has two jumper-controlled character fonts available: a 7-high by 5-wide single-dot character font with one descender, and a 7-high by 7-wide double-dot character font with one descender

- Has one character attribute for each character.

#### Low-Resolution Color/Graphics Mode

The low-resolution mode supports home televisions or color monitors. This mode is not supported in ROM. The low-resolution mode:

- Contains a maximum of 160 PELs by 100 rows, with each PEL being 2-high by 2-wide

- Specifies one of 16 colors for each PEL by the I, R, G, and B bits

- Requires 16,000 bytes of read/write memory on the adapter

- Uses memory-mapped graphics.

#### Medium-Resolution Color/Graphics Mode

The medium-resolution mode supports home televisions or color monitors. The medium-resolution mode:

- Contains a maximum of 320 PELs by 200 rows, with each PEL being 1-high by 1-wide

- Preselects one of four colors for each PEL

- Requires 16,000 bytes of read/write memory on the adapter

- Uses memory-mapped graphics

- Formats four PELs per byte in the following manner:

| 7               | 6      | 5               | 4            | 3               | 2      | 1             | 0            |

|-----------------|--------|-----------------|--------------|-----------------|--------|---------------|--------------|

| C1              | CO     | C1              | C0           | C1              | C0     | C1            | CO           |

| First<br>Displa | ay PEL | Secor<br>Displa | nd<br>ay PEL | Third<br>Displa | ay PEL | Four<br>Displ | th<br>ay PEL |

#### **High-Resolution Black-and-White Graphics Mode**

The high-resolution mode supports color monitors. This mode:

- Contains a maximum of 640 PELs by 200 rows, with each PEL being 1-high by 1-wide.

- Supports black-and-white only.

- Requires 16,000 bytes of read/write memory on the adapter.

- Addressing and mapping procedures are the same as medium-resolution color/graphics, but the data format is different. In this mode, each bit in memory is mapped to a PEL on the screen.

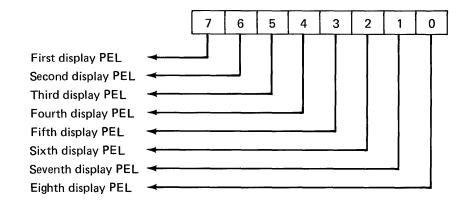

- Formats eight PELs per byte in the following manner:

# **Programming Considerations**

| Hex<br>address | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Function of register       |

|----------------|----|----|----|----|----|----|----|----|----|----|----------------------------|

| 3D8            | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | Mode control register (D0) |

| 3D9            | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 1  | Color select register (D0) |

| 3DA            | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | Status register (D1)       |

| 3DB            | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | Clear light pen latch      |

| 3DC            | .1 | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 0  | Preset light pen latch     |

| 3D4            | 1  | 1  | 1  | 1  | 0  | 1  | 0  | Z  | Z  | 0  | 6845 index register        |

| 3D5            | 1  | 1  | 1  | 1  | 0  | 1  | 0  | Z  | Z  | 1  | 6845 data register         |

#### Programming the Mode Control and Status Register

The following I/O devices are defined on the Color/Graphics Monitor Adapter:

#### Programming the 6845 CRT Controller

The controller has 19 internal accessible registers, which are used to define and control a raster-scan CRT display. One of these registers, the index register, is used as a pointer to the the other 18 registers. It is a write-only register, which is loaded from the processor by executing an "out" instruction to I/O address hex 3D4. The five least-significant bits of the I/O bus are loaded into the index register.

In order to load any of the other 18 registers, the index register is first loaded with the necessary pointer, then the data register is loaded with the information to be placed in the selected register. The data register is loaded from the processor by executing an "out" instruction to I/O address hex 3D5.

# Programming Considerations (continued)

#### **Color-Select Register**

The color-select register is a 6-bit output-only register. Its I/O address is hex 3D9, and it can be written to using a processor "out" command. The following are the bit definitions for this register.

- Bit 0 Selects blue border color in 40-by-25 alphanumeric mode. Selects blue background color (C0-C1) in 320-by-200 graphics mode. Selects blue foreground color in 640-by-200 graphics mode.

- Bit 1 Selects green border color in 40-by-25 alphanumeric mode. Selects green background color (C0-C1) in 320-by-200 graphics mode. Selects green foreground color in 640-by-200 graphics mode.

- **Bit 2** Selects red border color in 40-by-25 alphanumeric mode. Selects red background color (C0-C1) in 320-by-200 graphics mode. Selects red foreground color in 640-by-200 graphics mode.

- **Bit 3** Selects intensified border color in 40-by-25 alphanumeric mode. Selects intensified background color (C0-C1) in 320-by-200 graphics mode. Selects intensified foreground color in 640-by-200 graphics mode.

- **Bit 4** Selects alternate, intensified set of colors in the graphics mode. Selects background colors in the alphanumeric mode.

## Programming Considerations (continued)

#### **Mode-Control Register**

The mode-control register is a 6-bit output-only register. Its I/O address is hex 3D8, and it can be written to using a processor "out" command. The following are bit definitions for this register.

- Bit 0 A 1 selects 80-by-25 alphanumeric mode. A 0 selects 40-by-25 alphanumeric mode.

- Bit 1 A 1 selects 320-by-200 graphics mode. A 0 selects alphanumeric mode.

- Bit 2 A 1 selects black-and-white mode. A 0 selects color mode.

- Bit 3 A 1 enables the video signal. The video signal is disabled when changing modes.

- **Bit 4** A 1 selects the high-resolution (640-by-200) black-and-white graphics mode. One of eight colors can be selected on direct-drive monitors in this mode by using register hex 3D9.

- **Bit 5** A 1 will change the character background intensity to the blinking attribute function for alphanumeric modes. When the high-order attribute is not selected, 16 background colors or intensified colors are available. This bit is set to 1 to allow the blinking function.

## Programming Considerations (continued)

#### **Status Register**

The status register is a 4-bit read-only register. Its I/O address is hex 3DA, and it can be read using the processor "in" instruction. The following are bit definitions for this register.

- **Bit 0** A 1 indicates that a regen-buffer memory access can be made without interfering with the display.

- **Bit 1** A 1 indicates that a positive-going edge from the light pen has set the light pen's trigger. This trigger is reset when power is turned on and may also be cleared by a processor "out" command to hex address 3DB. No specific data setting is required; the action is address-activated.

- **Bit 2** The light pen switch is reflected in this bit. The switch is not latched or debounced. A 0 indicates that the switch is on.

- **Bit 3** A 1 indicates that the raster is in a vertical retrace mode. Screen-buffer updating can be performed at this time.

# **Specifications**

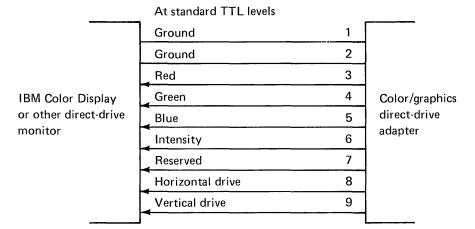

Connector specifications (Part 1 of 2)

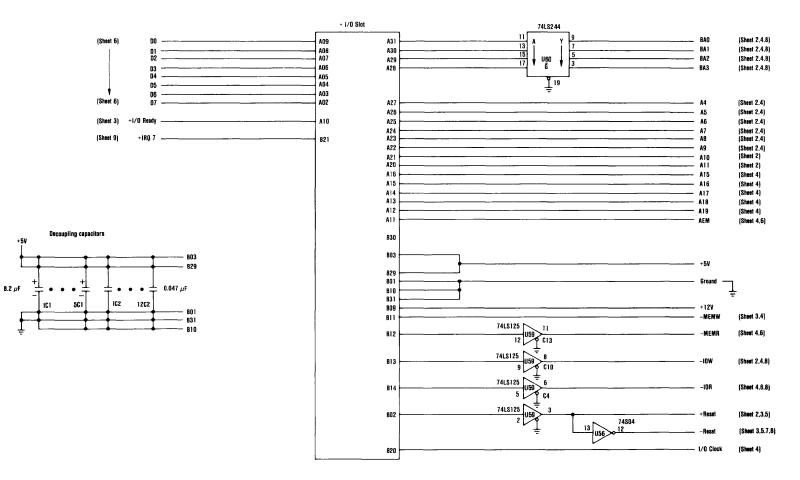

# **Logic Diagrams**

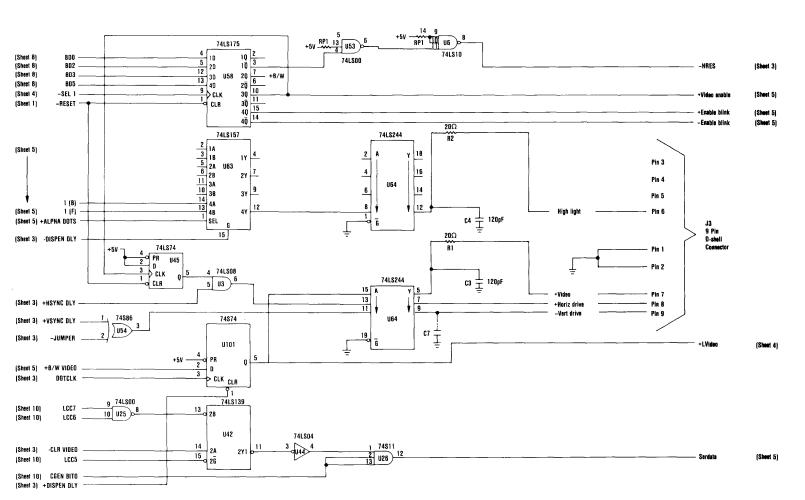

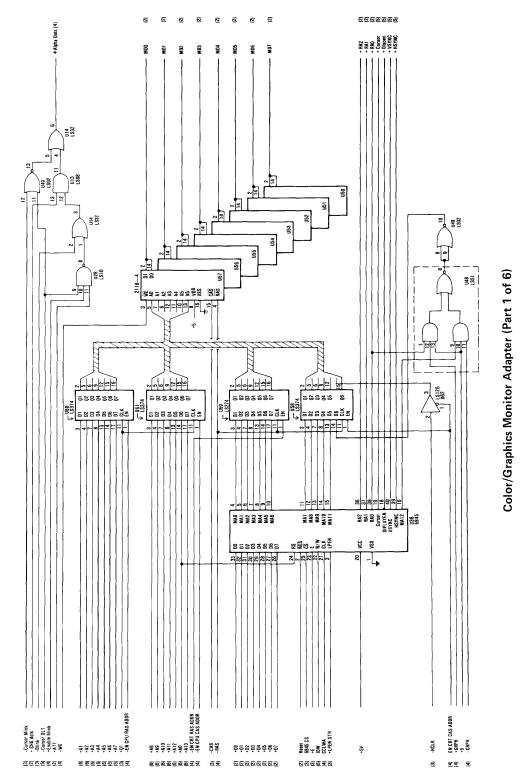

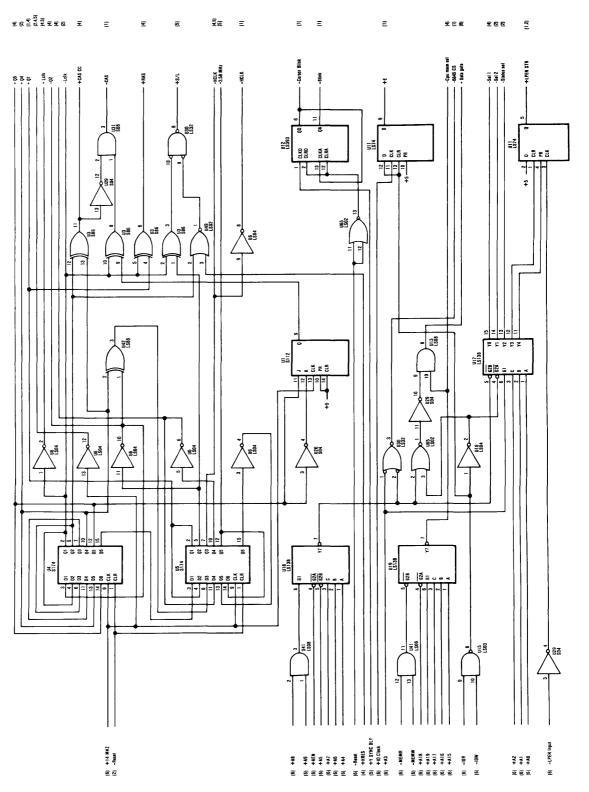

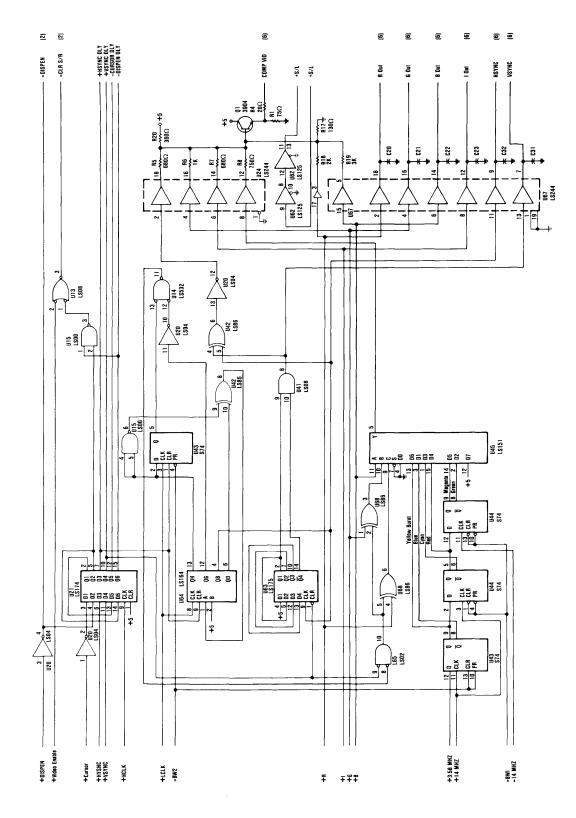

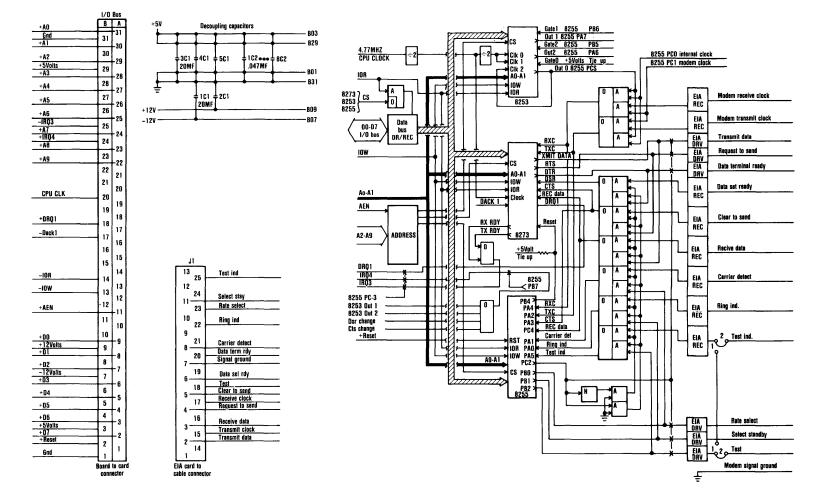

The following pages contain the logic diagrams for the IBM Color/Graphics Monitor Adapter.

Logic Diagrams (continued)

Color/Graphics Monitor Adapter (Part 3 of 6)

# **IBM Printer Adapter**

# Contents

| Description                | 1 |

|----------------------------|---|

| Programming Considerations | 3 |

| Specifications             | 5 |

| Logic Diagrams             | 6 |

# **IBM Printer Adapter**

#### **Description**

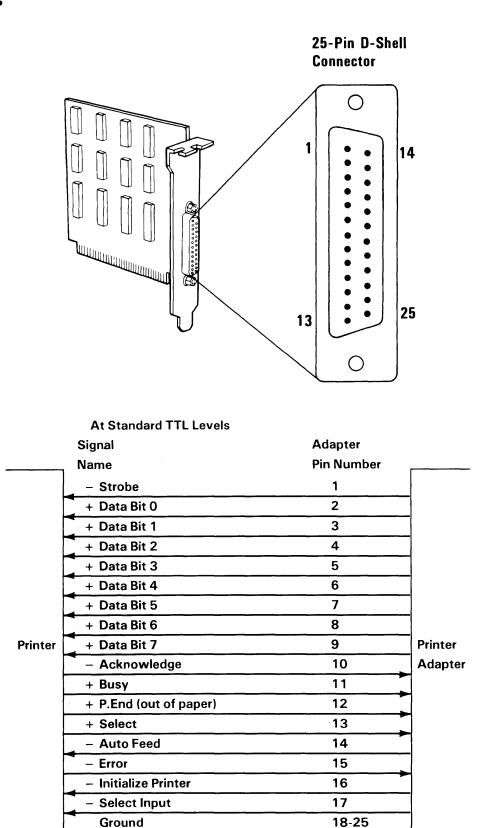

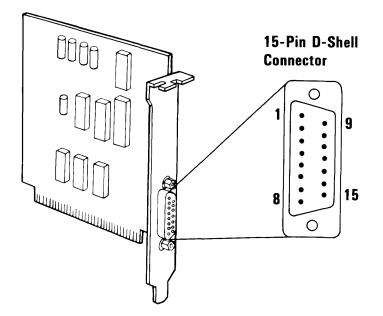

The IBM Printer Adapter is specifically designed to attach printers with a parallel port-interface, but it can be used as a general input/output port for any device or application that matches its input/output capabilities. It has 12 TTL-buffer output points, which are latched and can be written and read under program control using the microprocessor In or Out instruction. The adapter also has five steady-state input points that may be read using the microprocessor's In instructions.

In addition, one input can also be used to create a microprocessor interrupt. This interrupt can be enabled and disabled under program control. A reset from the power-on circuit is also ORed with a program output point, allowing a device to receive a "power-on reset" when the system unit's microprocessor is reset.

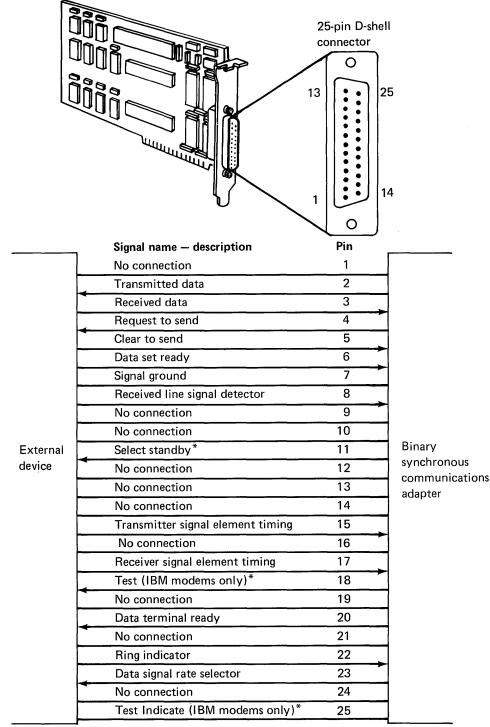

The input/output signals are made available at the back of the adapter through a right-angle, printed-circuit-board-mounted, 25-pin, D-shell connector. This connector protrudes through the rear panel of the system unit or expansion unit, where a cable may be attached.

When this adapter is used to attach a printer, data or printer commands are loaded into an 8-bit, latched, output port, and the strobe line is activated, writing data to the printer. The program then may read the input ports for printer status indicating when the next character can be written, or it may use the interrupt line to indicate "not busy" to the software.

The output ports may also be read at the card's interface for diagnostic loop functions. This allows faults to be isolated to the adapter or the attaching device.

This same function is also part of the IBM Monochrome Display and Printer Adapter.

## **Programming Considerations**

The Printer Adapter responds to five I/O instructions; two output and three input. The output instructions transfer data into two latches whose outputs are presented on pins of a 25-pin D-shell connector.

Two of the three input instructions allow the system unit's microprocessor to read back the contents of the two latches. The third allows the system unit's microprocessor to read the real-time status from a group of pins on the connector.

A description of each instruction follows.

|       | Printer /    | Adapter     |       |

|-------|--------------|-------------|-------|

| Οι    | utput to add | lress hex 3 | 78    |

| Bit 3 | Bit 2        | Bit 1       | Bit O |

| Pin 5 | Pin 4        | Pin 3       | Pin 2 |

The instruction captures data from the data bus and is present on the respective pins. Each of these pins is capable of sourcing 2.6 mA and sinking 24 mA.

It is essential that the external device does not try to pull these lines to ground.

| Printer Adapter           |        |        |       |  |  |

|---------------------------|--------|--------|-------|--|--|

| Output to address hex 37A |        |        |       |  |  |

| Bit 3                     | Bit 2  | Bit 1  | Bit O |  |  |

| Pin 17                    | Pin 16 | Pin 14 | Pin 1 |  |  |

|                           |        |        |       |  |  |

This instruction causes the latch to capture the five least significant bits of the data bus. The four least significant bits present their outputs, or inverted versions of their outputs, to the respective pins as shown in the previous figure. If bit 4 is written as a 1, the card will interrupt the system unit's microprocessor on the condition that pin 10 changes from high to low.

# **Specifications**

**Connector Specifications**

# IBM 5-1/4 Inch Diskette Drive Adapter

# Contents

| scription               | . 1  |

|-------------------------|------|

| gramming Considerations | . 3  |

| erface                  | . 18 |

| nnector Specifications  | . 22 |

| gic Diagrams            | . 24 |

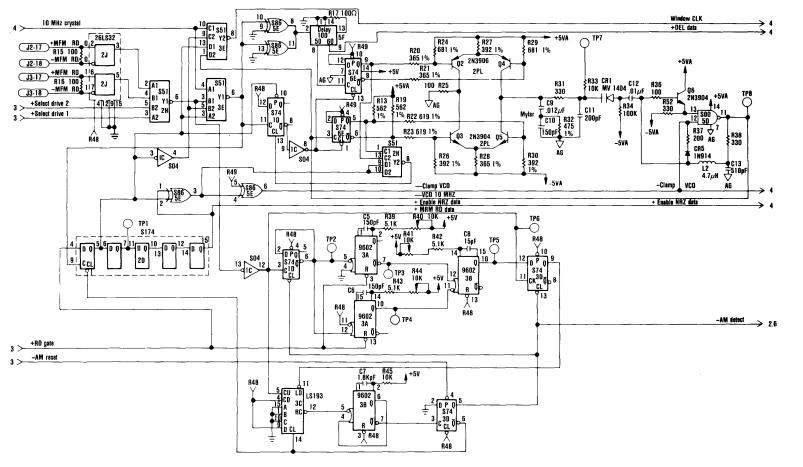

# IBM 5-1/4 Inch Diskette Drive Adapter

#### Description

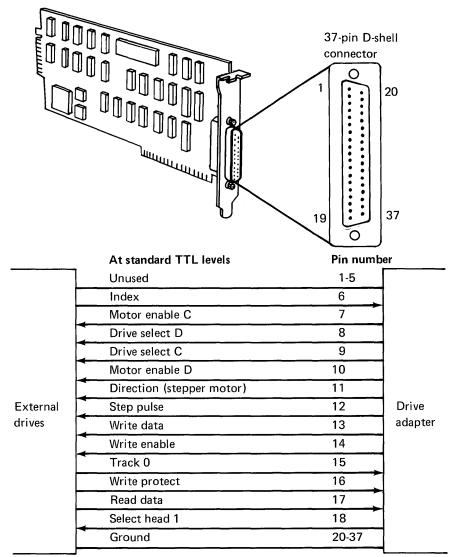

The IBM 5-1/4 inch Diskette Drive Adapter fits into one of the expansion slots in the system unit. It is connected to one or two diskette drives through an internal, daisy-chained flat cable. The adapter has a connector at the other end that extends through the rear panel of the system unit. This connector has signals for two additional external diskette drives; thus, the 5-1/4 inch diskette drive adapter can attach four 5-1/4 inch drives — two internal and two external.

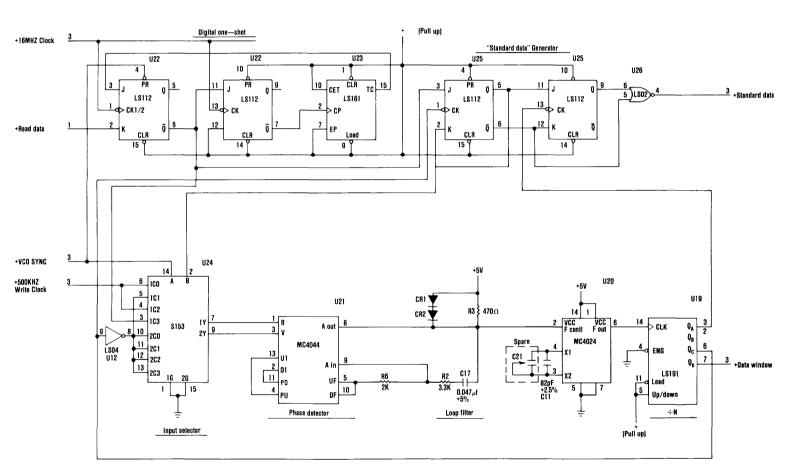

The adapter is designed for double-density, MFM-coded, diskette drives and uses write precompensation with an analog phase-lock loop for clock and data recovery. The adapter is a general-purpose device using the NEC PD765 or equivalent controller. Therefore, the diskette drive parameters are programmable. In addition, the attachment supports the diskette drive's write-protect feature. The adapter is buffered on the I/O bus and uses the system board's direct memory access (DMA) for record data transfers. An interrupt level also is used to indicate when an operation is complete and that a status condition requires microprocessor attention.

In general, the 5-1/4 inch diskette drive adapter presents a high-level command interface to software I/O drivers.

## **Programming Considerations**

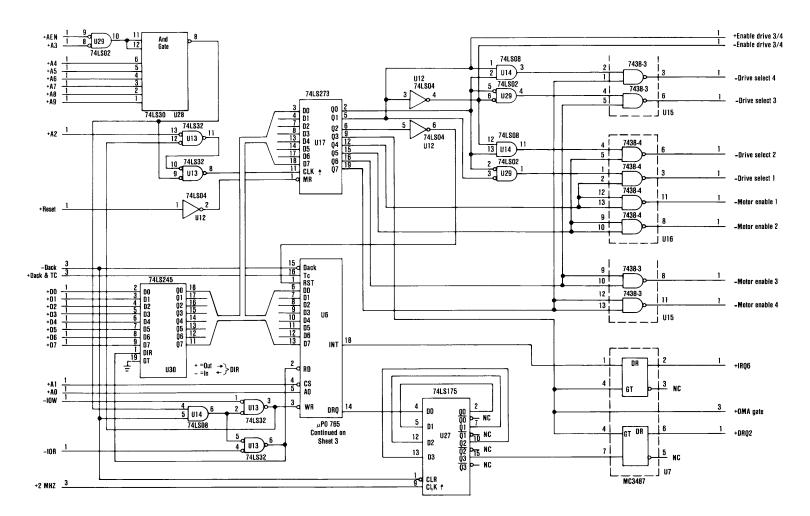

This attachment consists of an 8-bit digital output register in parallel with a NEC PD765 or equivalent floppy disk controller (FDC).

In the following description, drive numbers 0, 1, 2, and 3 are equivalent to drives A, B, C, and D.

#### **Digital-Output Register**

The Digital-Output register (DOR) is an output-only register used to control drive motors, drive selection, and feature enable. All bits are cleared by the I/O interface "reset" line. The bits have the following functions:

| Bits 0 and 1        | These bits are decoded by the hardware to select one drive if its motor is on:                                                                                                       |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 1 0             | Drive                                                                                                                                                                                |

| 0 0                 | 0 (A)                                                                                                                                                                                |

| 01                  | 1 (B)                                                                                                                                                                                |

| 10                  | 2 (C)                                                                                                                                                                                |

| 11                  | 3 (D)                                                                                                                                                                                |

| Bit 2               | The FDC is held reset when this bit is clear. It must be set by the program to enable the FDC.                                                                                       |

| Bit 3               | This bit allows the FDC interrupt and DMA requests to be gated onto the $I/O$ interface. If this bit is cleared, the interrupt and DMA request $I/O$ interface drivers are disabled. |

| Bits 4, 5, 6, and 7 | These bits control, respectively, the motors of drives 0, 1, 2 (A, B, C), and 3 (D). If a bit is clear, the associated motor is off, and the drive cannot be selected.               |

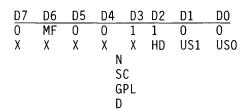

#### **Floppy Disk Controller**

The floppy disk controller (FDC) contains two registers that may be accessed by the system-unit microprocessor: a status register and a data register. The 8-bit main status register contains the status information of the FDC and may be accessed at any time. The 8-bit data register (actually consisting of several registers in a stack with only one register presented to the data bus at a time) stores data, commands, parameters, and provides floppy disk drive (FDD) status information. Data bytes are read from or written to the data register in order to program or obtain results after a particular command. The main status register can only be read and is used to facilitate the transfer of data between the system-unit microprocessor and FDC.

| Symbol                       | Name                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A0                           | Address line 0                               | A0 controls selection of main status register (A0 = 0) or data register (A0 = 1).                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| С                            | Cylinder number                              | C stands for the current/selected cylinder (track) number of the medium.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| D                            | Data                                         | D stands for the data pattern that is going to be written into a sector.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| D7-D0                        | Data bus                                     | 8-bit data bus, where D7 stands for a most significant bit, and D0 stands for a least significant bit.                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| DTL                          | Data length                                  | When N is defined as 00, DTL stands for the data length that users are going to read from or write to the sector.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| EOT                          | End of track                                 | EOT stands for the final sector number on a cylinder.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| GPL                          | Gap length                                   | GPL stands for the length of gap 3 (spacing between sectors excluding VCO sync field).                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Н                            | Head address                                 | H stands for head number 0 or 1, as specified in ID field.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| HD                           | Head                                         | HD stands for a selected head number 0 or 1. (H - HD in all command words).                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| HLT                          | Head load time                               | HLT stands for the head load time in the FDD (4 to 512 ms in 4-ms increments).                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| НՍТ                          | Head unload time                             | HUT stands for the head unload time after a read or write operation has occurre (0 to 480 ms in 32-ms increments).                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| MF                           | FM or MFM mode                               | If MF is low, FM mode is selected; if it is high, MFM mode is selected only if MFM is implemented.                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| МТ                           | Multi-track                                  | If MT is high, a multi-track operation is to be performed. (A cylinder under both HD0 and HD1 will be read or written.)                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| N                            | Number                                       | N stands for the number of data bytes written in a sector.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| NCN                          | New cylinder<br>number                       | NCN stands for a new cylinder number, which is going to be reached as a result of the seek operation. (Desired position of the head.)                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| ND                           | Non-DMA mode                                 | ND stands for operation in the non-DMA mode.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| PCN                          | Present cylinder<br>number                   | PCN stands for cylinder number at the completion of sense-interrupt-status command indicating the position of the head at present time.                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| R                            | Record                                       | R stands for the sector number, which will be read or written.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| R/W                          | Read/write                                   | R/W stands for either read (R) or write (W) signal.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| SC                           | Sector                                       | SC indicates the number of sectors per cylinder.                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| SK                           | Skip                                         | SK stands for skip deleted-data address mark.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| SRT                          | Step rate time                               | SRT stands for the stepping rate for the FDD (2 to 32 ms in 2-ms increments.                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| ST 0<br>ST 1<br>ST 2<br>ST 3 | Status 0<br>Status 1<br>Status 2<br>Status 3 | STO-3 stand for one of four registers that store the status information after a command has been executed. This information is available during the result phase after command execution. These registers should not be confused with the main status register (selected by $A0 = 0$ ). ST 0-3 may be read only after a command has been executed and contain information relevant to that particular command. |  |  |  |  |  |

Symbol Descriptions (Part 1 of 2)

#### **Command Summary**

In the following table, 0 indicates "logical 0" for that bit, 1 means "logical 1," and X means "don't care."

| <b></b>   | Data bus |    |      |    |            |        |     |     |                          |                           |

|-----------|----------|----|------|----|------------|--------|-----|-----|--------------------------|---------------------------|

| Phase     | R/W      | D7 | D6   | D5 | Data<br>D4 | D3     | D2  | D1  | D0                       | Remarks                   |

|           |          |    |      |    | Read       | data   |     |     |                          |                           |

| Command   | w        | мт | MF   | SK | 0          | 0      | 1   | 1   | 0                        | Command Codes             |

|           | Ŵ        | X  | X    | X  | x          | x      | HD  |     | USO                      |                           |

|           | w        |    |      |    | Ċ          | 2      |     |     |                          | Sector ID information     |

|           | w        |    |      |    | H          | -      |     |     |                          | prior to command          |

|           | w        |    |      |    | F          | 7      |     |     |                          | execution.                |

|           | W        |    |      |    | ſ          | J      |     |     |                          |                           |

|           | w        |    |      |    | EC         |        |     |     |                          |                           |

|           | W        |    |      |    | GF         |        |     |     |                          |                           |

|           | W        |    |      |    | D1         | ٢L     |     |     |                          |                           |

| Execution |          |    |      |    |            |        |     |     |                          | Data transfer between the |

|           |          |    |      |    | 07         |        |     |     |                          | FDD and main system.      |

| Result    | R<br>R   |    |      |    | ST         |        |     |     |                          | Status information        |

|           | R        |    |      |    | ST<br>ST   | -      |     |     |                          | after command execution.  |

|           | R        |    |      |    | 31         | -      |     |     |                          | Sector ID information     |

|           | R        |    |      |    | L<br>L     |        |     |     |                          | after command             |

|           | R        |    |      |    |            | २      |     |     |                          | execution.                |

|           | R        |    |      |    | N          |        |     |     |                          |                           |

|           |          |    |      | Re | ad del     | eted d | ata |     |                          |                           |

| Command   | W        | МТ | MF   | SK | 0          | 1      | 1   | 0   | 0                        | Command Codes             |

|           | W        | X  | Х    | Х  | Х          | Х      | HD  | US1 | US0                      |                           |

|           | W        |    |      |    | C          | ;      |     |     |                          | Sector ID information     |

|           | W        |    |      |    | H          |        |     |     |                          | prior to command          |

|           | W        |    |      |    | F          |        |     |     |                          | execution.                |

|           | W        |    |      |    | Ν          |        |     |     |                          |                           |

|           | W        |    |      |    | EC         |        |     |     |                          |                           |

|           | W<br>W   |    |      |    | GF<br>D1   |        |     |     |                          |                           |

| Execution | vv       |    |      |    | U          | i L    |     |     |                          | Data transfer between the |

|           |          |    |      |    |            |        |     |     |                          | FDD and main system.      |

| Result    | R        |    | ST 0 |    |            |        |     |     |                          | Status information        |

|           | R        |    | ST 0 |    |            |        |     |     | after command execution. |                           |

|           | R        |    | ST 2 |    |            |        |     |     |                          |                           |

|           | R        |    | C    |    |            |        |     |     |                          | Sector ID information     |

|           | R        |    |      |    | ۲          | ł      |     |     |                          | after command             |

|           | R        |    |      |    | F          |        |     |     |                          | execution.                |

|           | R        |    |      |    | <u>۱</u>   | 1      |     |     |                          |                           |

|           |     |                                                  |    |    | Data    | bus            |                                                                                    |                                                                                                                         |     |                          |

|-----------|-----|--------------------------------------------------|----|----|---------|----------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|--------------------------|

| Phase     | R/W | D7                                               | D6 | D5 | D4      | D3             | D2                                                                                 | D1                                                                                                                      | D0  | Remarks                  |

|           |     |                                                  |    | R  | ead a T | <b>Frack</b>   |                                                                                    |                                                                                                                         |     |                          |

| Command   | w   | 0                                                | MF | SK | 0       | 0              | 0                                                                                  | 1                                                                                                                       | 0   | Command Codes            |

|           | w   | X                                                | Х  | Х  | Х       | Х              | HD                                                                                 | US1                                                                                                                     | US0 |                          |

|           | , w |                                                  |    |    | C       | )              |                                                                                    |                                                                                                                         |     | Sector ID information    |

|           | W   |                                                  |    |    | H       | 1              |                                                                                    |                                                                                                                         |     | prior to command         |

|           | w   |                                                  |    |    | F       | 3              |                                                                                    |                                                                                                                         |     | execution.               |

|           | w   |                                                  |    |    | N       | J              |                                                                                    |                                                                                                                         |     |                          |

|           | W   |                                                  |    |    | EC      | DT             |                                                                                    |                                                                                                                         |     |                          |

|           | W   |                                                  |    |    | GF      | ۲Ľ             |                                                                                    |                                                                                                                         |     |                          |

|           | W   |                                                  |    |    | DT      | ΓL             |                                                                                    |                                                                                                                         |     |                          |

| Execution |     |                                                  |    |    |         |                |                                                                                    | Data transfer between the<br>FDD and main system.<br>FDC reads all of cylinder's<br>contents from index hole<br>to EOT. |     |                          |

| Result    | R   |                                                  |    |    | ST      | 0              |                                                                                    |                                                                                                                         |     | Status information after |

|           | R   |                                                  |    |    | ST      | <sup>-</sup> 1 |                                                                                    |                                                                                                                         |     | command execution.       |

|           | R   |                                                  |    |    | ST      | 2              |                                                                                    |                                                                                                                         |     |                          |

|           | R   |                                                  |    |    | C       | )              |                                                                                    |                                                                                                                         |     | Sector ID information    |

|           | R   | ł                                                |    |    | ŀ       | 4              |                                                                                    |                                                                                                                         |     | after command            |

|           | R   |                                                  |    |    | F       | F              |                                                                                    |                                                                                                                         |     | execution.               |

|           | R   |                                                  |    |    | Ν       | J              |                                                                                    |                                                                                                                         |     |                          |

|           |     |                                                  |    |    | Read    | ID             |                                                                                    |                                                                                                                         |     |                          |

| Command   | w   | 0                                                | MF | 0  | 0       | 1              | 0                                                                                  | 1                                                                                                                       | 0   | Command Codes            |

|           | w   | X                                                | Х  | Х  | Х       | Х              | HD                                                                                 | US1                                                                                                                     | US0 |                          |

| Execution |     | The first correct ID information on the cylinder |    |    |         |                | The first correct ID<br>information on the cylinder<br>is stored in data register. |                                                                                                                         |     |                          |

| Result    | R   |                                                  |    |    | ST      | 0              |                                                                                    |                                                                                                                         |     | Status information after |

|           | R   |                                                  |    |    | ST      | 1              |                                                                                    |                                                                                                                         |     | command execution.       |

|           | R   | ST 2                                             |    |    |         |                |                                                                                    |                                                                                                                         |     |                          |

|           | R   | C                                                |    |    |         |                |                                                                                    | Sector ID information                                                                                                   |     |                          |

|           | R   |                                                  |    |    |         |                |                                                                                    | during execution                                                                                                        |     |                          |

|           | R   |                                                  |    |    | F       | 3              |                                                                                    |                                                                                                                         |     | phase.                   |

|           | R   |                                                  |    |    | Ν       | J              |                                                                                    |                                                                                                                         |     |                          |

|           | R   |                                                  |    |    | ۱<br>   | ۷              |                                                                                    |                                                                                                                         |     |                          |

|           |     | <u> </u> |              |      | Data   | bus    |         |     |     |                                                |

|-----------|-----|----------|--------------|------|--------|--------|---------|-----|-----|------------------------------------------------|

| Phase     | R/W | D7       |              |      |        |        | Remarks |     |     |                                                |

|           |     |          |              | Scan | low o  | r equ  | al      |     |     |                                                |

| Command   | w   | MT       | MF           | SK   | 1      | 1      | 0       | 0   | 1   | Command Codes                                  |

|           | W   | X        | Х            | Х    | Х      | Х      | HD      | US1 | US0 |                                                |

|           | W   |          |              |      | C      | ;      |         |     |     | Sector ID information                          |

|           | W   |          |              |      | ŀ      | ł      |         |     |     | prior to command                               |

|           | W   |          |              |      | F      |        |         |     |     | execution.                                     |

|           | W   |          |              |      | Ν      |        |         |     |     |                                                |

|           | W   |          |              |      | EC     |        |         |     |     |                                                |

|           | W   |          |              |      | GF     |        |         |     |     |                                                |

|           | W   |          |              |      | ST     | P      |         |     |     |                                                |

| Execution |     |          |              |      |        |        |         |     |     | Data compared between                          |

|           |     | ľ        |              |      |        |        |         |     |     | the FDD and main system.                       |

| Result    | R   |          |              |      | ST     | -      |         |     |     | Status information                             |

|           | R   |          |              |      | ST     |        |         |     |     | after command execution.                       |

|           | R   |          |              |      | ST     | _      |         |     |     |                                                |

|           | R   | [        |              |      | C      |        |         |     |     | Sector ID information                          |

|           | R   |          |              |      | -      | 1      |         |     |     | after command                                  |

|           | R   |          |              |      | F      |        |         |     |     | execution.                                     |

|           | R   | <b>_</b> |              |      | ۱<br>  |        |         |     |     |                                                |

|           |     |          |              |      | high   | -      |         |     |     |                                                |

| Command   | W   | MT       | MF           | SK   | 1      | 1      | 1       | 0   | 1   | Command Codes                                  |

|           | W   | X        | Х            | Х    | Х      | Х      | HD      | US1 | US0 |                                                |

|           | W   |          |              |      | C      |        |         |     |     | Sector ID information                          |

|           | W   |          |              |      |        | 1      |         |     |     | prior to command                               |

|           | W   |          |              |      | F      |        |         |     |     | execution.                                     |

| 1         | W   |          |              |      | N      |        |         |     |     |                                                |

|           | W   |          | EOT<br>GPL   |      |        |        |         |     |     |                                                |

|           | W   |          |              |      |        |        |         |     |     |                                                |

| Execution | W   |          |              |      | ST     | ٢      |         |     |     | Data compared between                          |

| Execution |     |          |              |      |        |        |         |     |     | Data compared between the FDD and main system. |

| Result    | R   |          |              |      | ст     | - n    |         |     |     | Status information                             |

| nesur     | R   |          | ST 0         |      |        |        |         |     |     | after command execution.                       |

|           | R   |          | ST 1<br>ST 2 |      |        |        |         |     |     |                                                |

|           | R   |          | C SI 2       |      |        |        |         |     |     | Sector ID information                          |

|           | R   |          |              |      |        | ,<br>1 |         |     |     | after command                                  |

|           | R   |          |              |      |        | י<br>ז |         |     |     | execution.                                     |

|           | R   |          |              |      | י<br>ז |        |         |     |     | oxeeu con.                                     |

|           | l   |          |              |      |        | -      |         |     |     |                                                |

|          | Bit                            |              |                                                                                                                                                                                                                                                                                                                                                                |

|----------|--------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.      | Name                           | Symbol       | Description                                                                                                                                                                                                                                                                                                                                                    |

| D7       | Interrupt<br>Code              | IC           | D7 = 0 and D6 = 0<br>Normal termination of command (NT).<br>Command was completed and properly executed.                                                                                                                                                                                                                                                       |

| D6       |                                |              | D7 = 0 and D6 = 1<br>Abnormal termination of command (AT). Execution of command was started,<br>but was not successfully completed.<br>D7 = 1 and D6 = 0<br>Invalid command issue (IC). Command that was issued was never started.<br>D7 = 1 and D6 = 1<br>Abnormal termination because, during command execution, the ready<br>signal from FDD changed state. |

| D5       | Seek End                       | SE           | When the FDC completes the seek command, this flag is set to 1 (high).                                                                                                                                                                                                                                                                                         |

| D4       | Equipment<br>Check             | EC           | If a fault signal is received from the FDD, or if the track 0 signal fails to occur after 77 step pulses (recalibrate command), then this flag is set.                                                                                                                                                                                                         |

| D3       | Not Ready                      | NR           | When the FDD is in the not-ready state and a read or write command is issued, this flag is set. If a read or write command is issued to side 1 of a single-sided drive, then this flag is set.                                                                                                                                                                 |

| D2       | Head Address                   | HD           | This flag is used to indicate the state of the head at interrupt.                                                                                                                                                                                                                                                                                              |

| D1<br>D0 | Unit Select 1<br>Unit Select 0 | US 1<br>US 0 | These flags are used to indicate a drive unit number at interrupt.                                                                                                                                                                                                                                                                                             |

Command status register 0

|     | Bit                                      |        |                                                                                                                                                                                    |

|-----|------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Name                                     | Symbol | Description                                                                                                                                                                        |

| D7  | _                                        | _      | Not used. This bit is always 0 (low).                                                                                                                                              |

| D6  | Control Mark                             | СМ     | During execution of the read data or scan command, if the FDC encounters a sector that contains a deleted data address mark, this flag is set.                                     |

| D5  | Data Error in<br>Data Field              | DD     | If the FDC detects a CRC error in the data, then this flag is set.                                                                                                                 |

| D4  | Wrong<br>Cylinder                        | WC     | This bit is related to the ND bit, and when the contents of C on the medium are different from that stored in the ID register, this flag is set.                                   |

| D3  | Scan Equal<br>Hit                        | SH     | During execution of the scan command, if the condition of "equal" is satisfied, this flag is set.                                                                                  |

| D2  | Scan Not<br>Satisfied                    | SN     | During execution of the scan command, if the FDC cannot find a sector on the cylinder that meets the condition, then this flag is set.                                             |

| D1  | Bad Cylinder                             | BC     | This bit is related to the ND bit, and when the contents of C on the medium are different from that stored in the ID register, and the contents of C is FF, then this flag is set. |

| D0  | Missing<br>Address Mark<br>in Data Field | MD     | When data is read from the medium, if the FDC cannot find a data address mark<br>or deleted data address mark, then this flag is set.                                              |

Command status register 2

| Bit |                    |        |                                                                    |

|-----|--------------------|--------|--------------------------------------------------------------------|

| No. | Name               | Symbol | Description                                                        |

| D7  | Fault              | FT     | This bit is the status of the fault signal from the FDD.           |

| D6  | Write<br>Protected | WP     | This bit is the status of the write-protected signal from the FDD. |

| D5  | Ready              | RY     | This bit is the status of the ready signal from the FDD.           |

| D4  | Track 0            | то     | This bit is the status of the track 0 signal from the FDD.         |

| D3  | Two Side           | TS     | This bit is the status of the two-side signal from the FDD.        |

| D2  | Head Address       | HD     | This bit is the status of the side-select signal from the FDD.     |

| D1  | Unit Select 1      | US 1   | This bit is the status of the unit-select-1 signal from the FDD.   |

| D0  | Unit Select 0      | US 0   | This bit is the status of the unit-select-0 signal from the FDD.   |

Command status register 3

#### **Drive Constants**

| Head load   | 35 ms  |

|-------------|--------|

| Head settle | 15 ms  |

| Motor start | 250 ms |

#### Comments

- Head loads with drive select, wait HD load time before R/W.

- Following access, wait HD settle time before R/W.

- Drive motors should be off when not in use. Only A or B and C or D may run simultaneously. Wait motor start time before R/W.

- Motor must be on for drive to be selected.

- Data errors can occur while using a home television as the system display. Placing the TV too close to the diskette area can cause this to occur. To correct the problem, move the TV away from, or to the opposite side of the system unit.

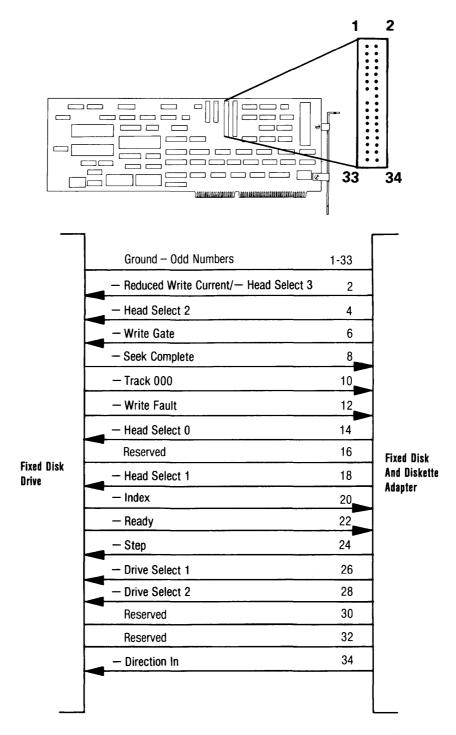

### Interface (continued)

+IRQ6 (Adapter output, driver: 74LS 3-state): This line is made active when the FDC has completed an operation. It results in an interrupt to a routine that should examine the FDC result bytes to reset the line and determine the ending condition.

### Interface (continued)

#### Adapter Outputs

|                | Drive Select A and B | (Driver: 7438): These two lines are used by drives A and B to degate all drivers to the adapter and receivers from the attachment (except "motor enable") when the line associated with a drive is inactive. |

|----------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Motor Enable A and B | (Driver: 7438): The drive associated with each of these lines must control its spindle motor such that it starts when the line becomes active and stops when the line becomes inactive.                      |

|                | Step                 | (Driver: 7438): The selected drive moves the read/write head one cylinder in or out per the direction line for each pulse present on this line.                                                              |

|                | Direction            | (Driver: 7438): For each recognized pulse of the "step" line, the read/write head moves one cylinder toward the spindle if this line is active, and away from the spindle if inactive.                       |

|                | Head Select          | (Driver: 7438): Head 1 (upper head) will be selected when this line is active (low).                                                                                                                         |

|                | Write Data           | (Driver: 7438): For each inactive-to-active transition of this line<br>while "write enable" is active, the selected drive causes a flux<br>change to be stored on the diskette.                              |

|                | Write Enable         | (Driver: 7348): The drive disables write current in the head unless this line is active.                                                                                                                     |

| Adapter Inputs |                      |                                                                                                                                                                                                              |

|                | Index                | The selected drive must supply one pulse per diskette revolution on this line.                                                                                                                               |

|                | Write Protect        | The selected drive must make this line active if a write-protected diskette is in the drive.                                                                                                                 |

|                | Track 0              | The selected drive must make this line active if the read/write head is over track $0$ .                                                                                                                     |

|                | Read Data            | The selected drive supplies a pulse on this line for each flux change encountered on the diskette.                                                                                                           |

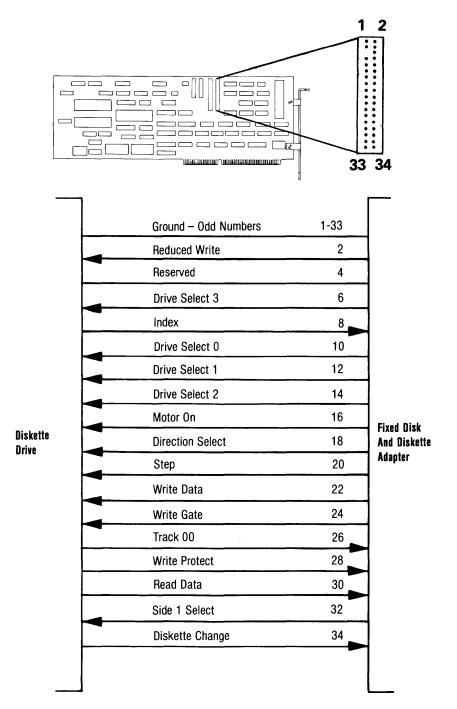

### **Connector Specifications (continued)**

Connector specifications (Part 2 of 2)

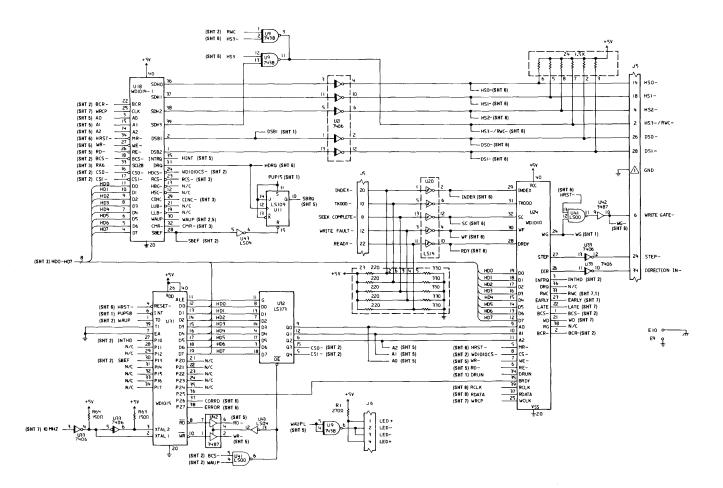

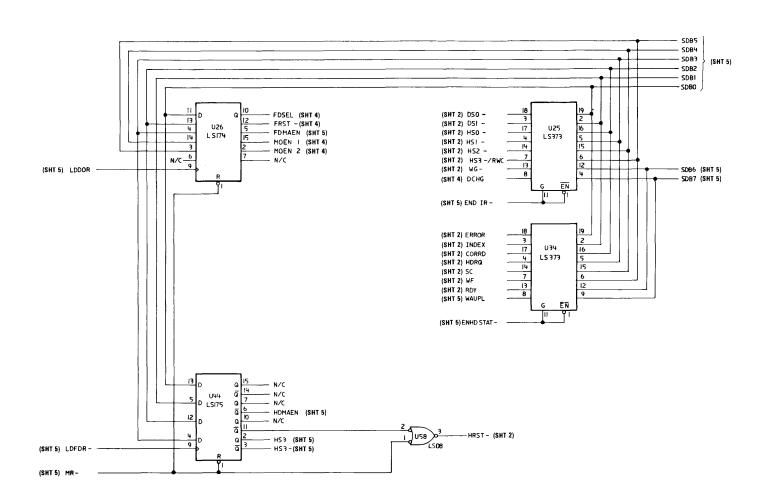

5-1/4 inch diskette drive adapter (Part 2 of 4)

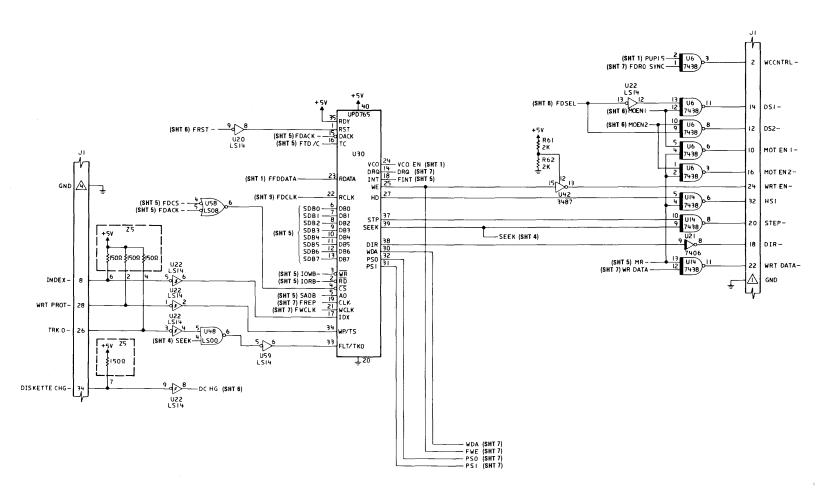

5-1/4 inch diskette drive adapter (Part 4 of 4)

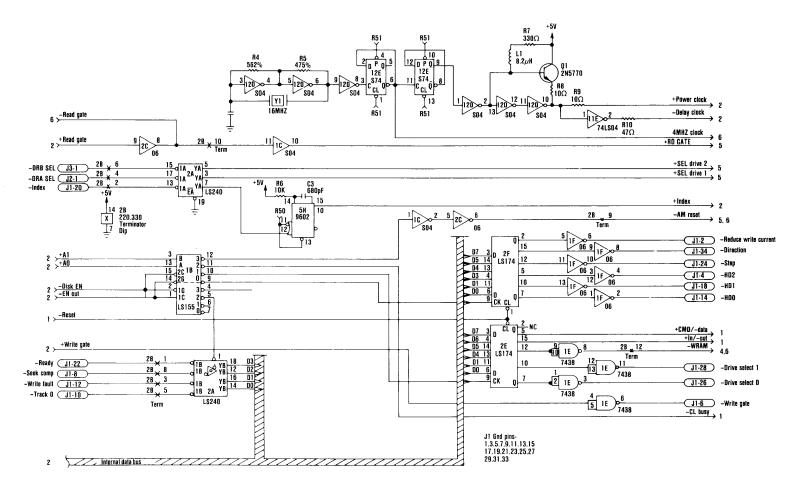

# **IBM Fixed Disk Adapter**

### Contents

| scription                | 1  |

|--------------------------|----|

| ogramming Considerations | 3  |

| erface                   | 15 |

| ecifications             | 16 |

| gic Diagrams             | 17 |

| OS Listing               | 23 |

|                          |    |

### **IBM Fixed Disk Adapter**

#### Description

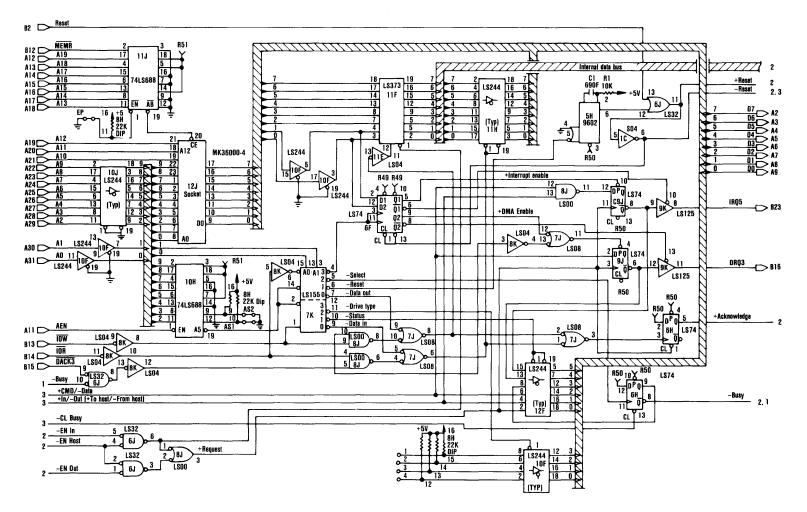

The Fixed Disk Adapter attaches to one or two fixed disk drive units through an internal, daisy-chained, flat cable (data/control cable). Each system supports a maximum of one Fixed Disk Adapter and one fixed disk drive.

The adapter is buffered on the I/O bus and uses the system board's direct memory access (DMA) for record data transfers. An interrupt level also is used to indicate operation completion and status conditions that require microprocessor attention.

The Fixed Disk Adapter provides automatic 11-bit burst error detection and correction in the form of 32-bit error checking and correction (ECC).

The device level control for the Fixed Disk Adapter is contained on a ROM module on the adapter. A listing of this device level control can be found in "BIOS Listing" of this section.

Warning: The last cylinder on the fixed disk drive is reserved for diagnostic use. The diagnostic write test will destroy any data on this cylinder.

#### **Fixed Disk Controller**

The disk controller has two registers that may be accessed by the system-unit microprocessor: a status register and a data register. The 8-bit status register contains the status information of the disk controller, and can be accessed at any time. The 8-bit data register (actually consisting of several registers in a stack with only one register presented to the data bus) stores data, commands, and parameters, and provides the disk controller's status information. Data bytes are read from, or written to the data register in order to program or obtain the results after a particular command. The status register is a read-only register that is used to help the transfer of data between the system-unit microprocessor and the disk controller. The controller-select pulse is generated by writing to port address hex 322.

#### **Programming Considerations**

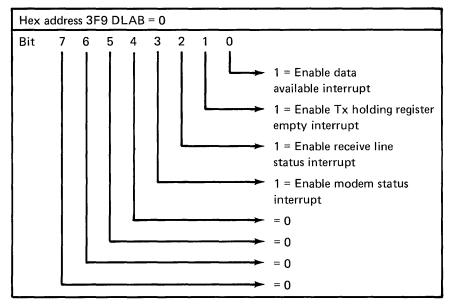

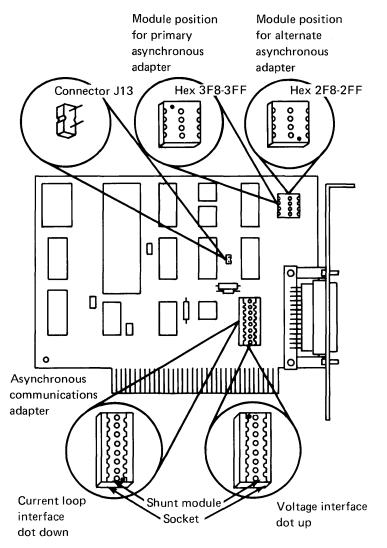

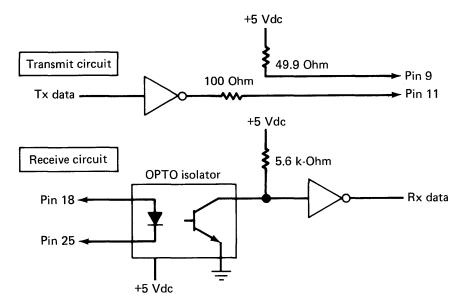

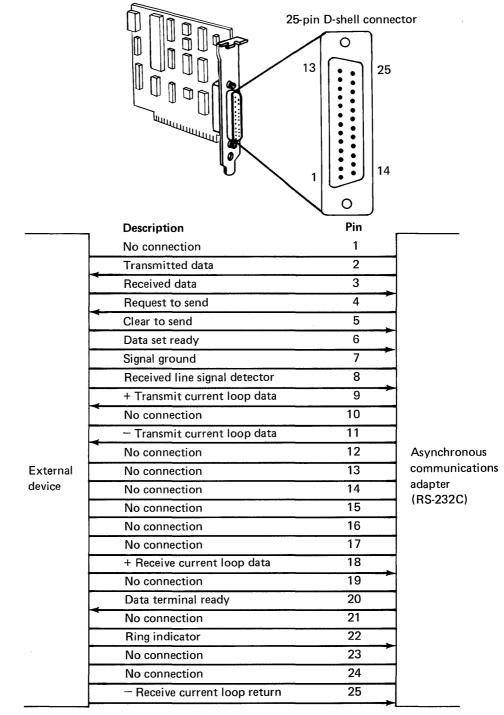

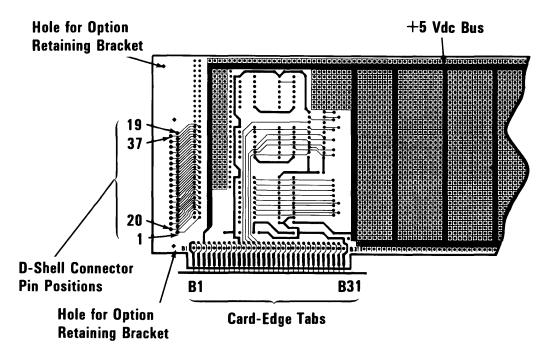

#### **Status Register**