Personal Computer Hardware Reference Library

# IBM RT PC Hardware Technical Reference

Volume II

Personal Computer Hardware Reference Library

# IBM RT PC Hardware Technical Reference

Volume II

#### Second Edition (September 1986)

Changes are made periodically to the information herein; these changes will be incorporated in new editions of this publication.

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM program product in this publication is not intended to state or imply that only IBM's program product may be used. Any functionally equivalent program may be used instead.

International Business Machines Corporation provides this manual "as is," without warranty of any kind, either express or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this manual at any time.

Products are not stocked at the address given below. Requests for copies of this product and for technical information about the system should be made to your authorized IBM RT PC dealer.

A reader's comment form is provided at the back of this publication. If the form has been removed, address comments to IBM Corporation, Department 997, 11400 Burnet Road, Austin, Texas 78758. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

© Copyright International Business Machines Corporation 1986

# **About This Book**

## Purpose

The options and adapters manual is the second part of the IBM RT PC Hardware Technical Reference manual. It is to be used in conjunction with the IBM RT PC Hardware Technical Reference, Volume 1.

# Audience

The information in this manual is for reference. It is intended for hardware and program designers, programmers, engineers, and anyone else who needs to understand the design and operation of the options and adapters in the IBM RT PC Product Family.

# How to Use This Book

This manual is modular in format, with each module providing information about a specific option or adapter available for the IBM RT PC family of products. Modules having a large amount of text contain indexes.

The modules are grouped by type of device. To find a specific module:

- 1. Locate the full length hard tab with the type of device (Displays, Printers, Storage Devices, etc.) printed on it that decribes the option or adapter you need information about.

- 2. Open the manual to that section.

- 3. Leaf through that section to find the proper module.

**COMMUNICATION ADAPTERS**

| _ | _ | _ | _ |

|---|---|---|---|

|   |   |   |   |

| - |   |   |   |

| - |   | _ |   |

|   |   |   |   |

| _ | _ |   |   |

|   |   |   |   |

| - |   | _ |   |

|   |   |   |   |

Personal Computer Hardware Reference Library

# 4-Port Asynchronous Adapter RS232C

ii RS232C Adapter

# Contents

| Description                                            |

|--------------------------------------------------------|

| 4 Port Asynchronous RS232C Adapter Switch Settings     |

| Modes of Operation                                     |

| Interrupts $$                                          |

| Serial Data Format                                     |

| External Interface Description                         |

| Asynchronous Communications Element Pin Description 10 |

| Programming Considerations                             |

| Connector Specifications                               |

| Logic Diagrams                                         |

# Description

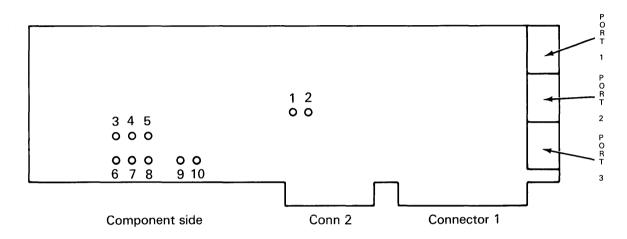

The 4 Port Asynchronous RS232C Adapter provides four serial output ports on a 4.25- by 13.12-inch board that plugs into one I/O position. The adapter system control signals and voltage requirements are provided through a 2- by 31-position and a 2- by 18-position tab on the bottom of the adapter.

Up to four adapters may be used in one RT PC system. A DIP switch on the adapter is used to assign the adapter's I/O address range. The port I/O address assignments are contained in the adapter's I/O address range.

The adapter is fully programmable and supports asynchronous communications only. It will add and remove start bits, stop bits, and parity bits. A programmable baud-rate generator allows operation from 50 bps to 19200 bps. Five-, 6-, 7- or 8-bit characters with 1, 1-1/2, or 2 stop bits are supported. A priority interrupt system controls transmit, receive, error, line status, and data set interrupts.

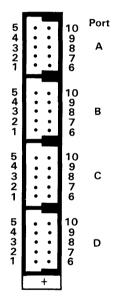

Four 10-pin male connectors on the adapter provide external access to the four ports.

The heart of the adapter is an NS16450 LSI chip or a functional equivalent. Features in addition to those listed above include:

Note: The NS16450 is functionally equivalent to all INS8250.

- Full double buffering that eliminates the need for precise synchronization

- Independent receiver clock input

- Modem control functions: clear to send (CTS), request to send (RTS), data set ready (DSR), data terminal ready (DTR), ring indicator (RI), and received line signal detect (RLSD), which is also known as data carrier detect (DCD) or carrier detect (CD)

- False start bit detection

- Line-break generation and detection.

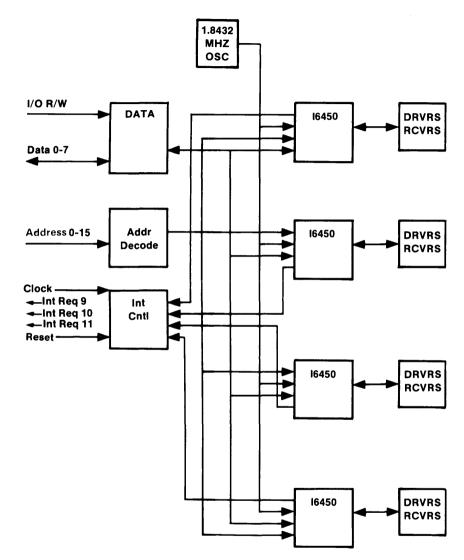

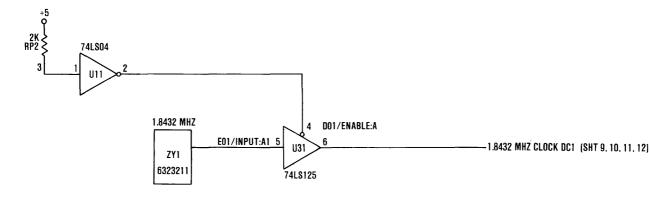

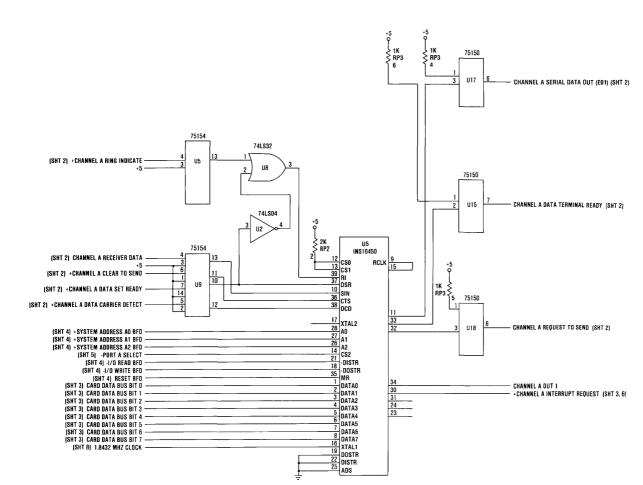

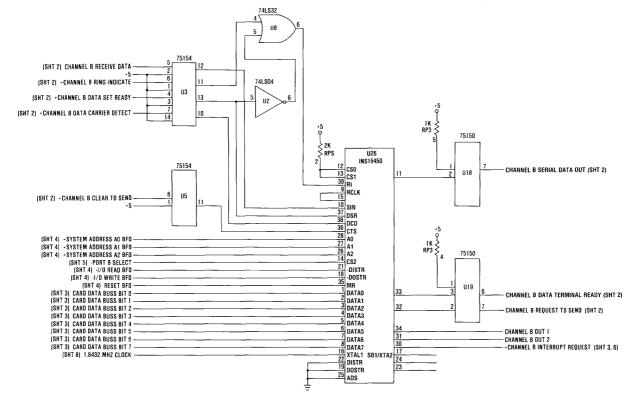

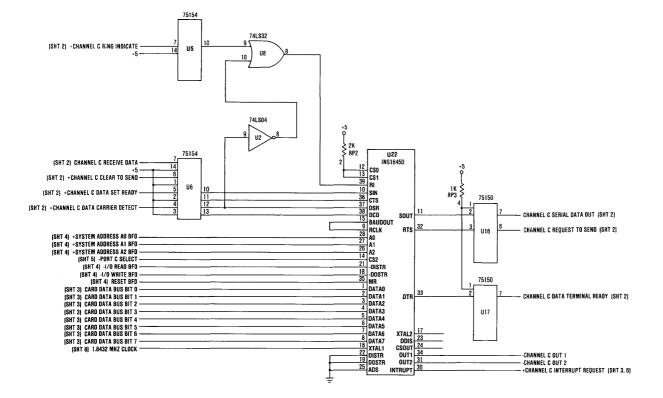

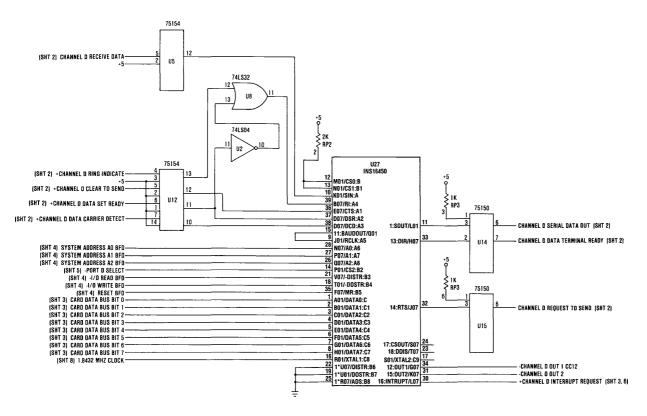

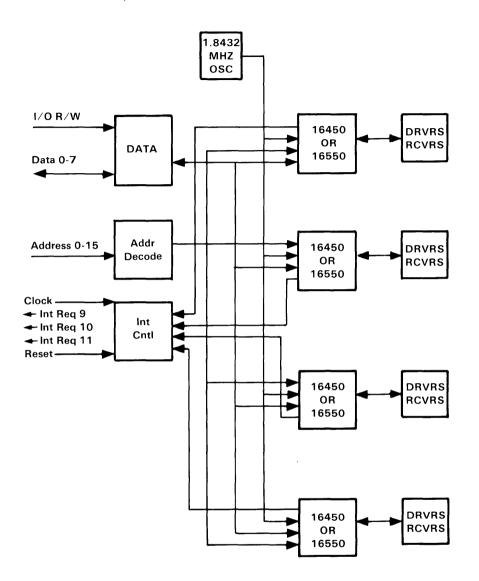

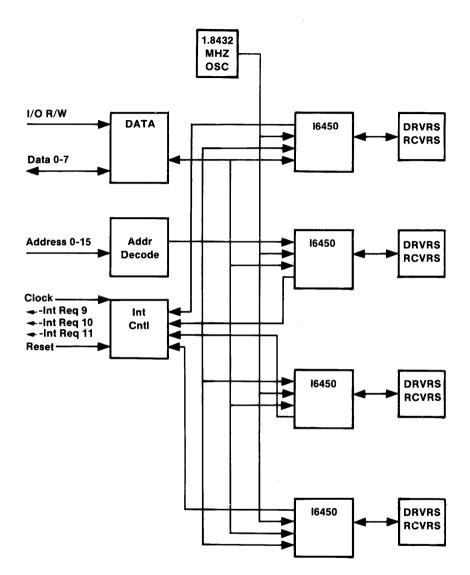

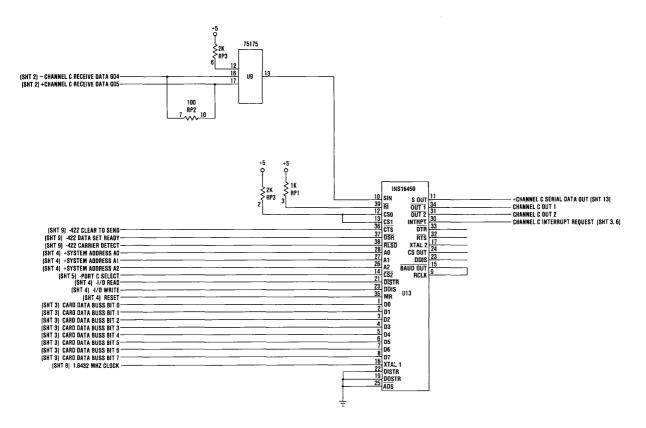

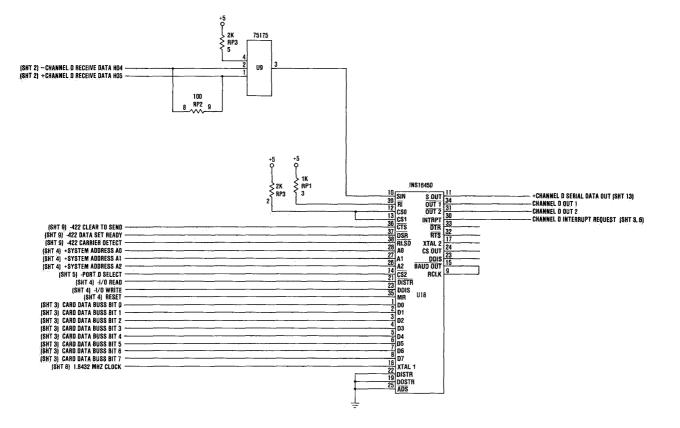

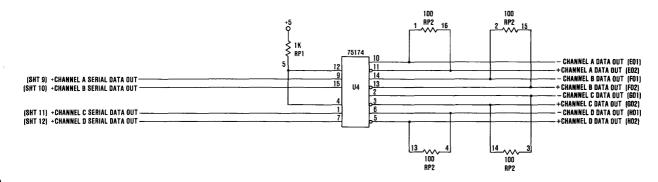

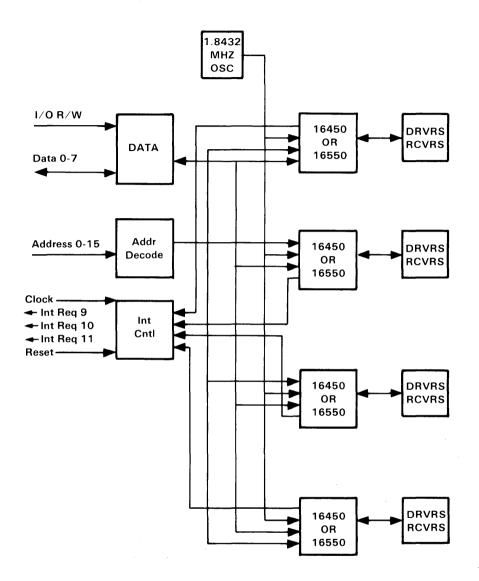

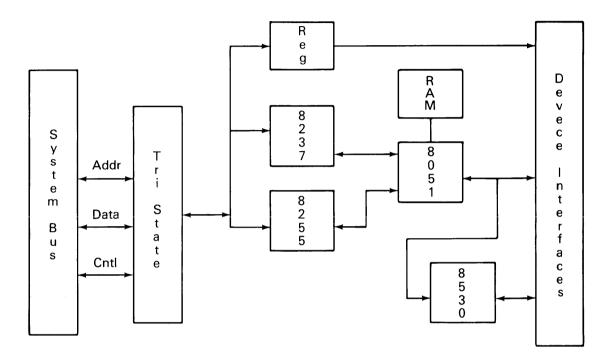

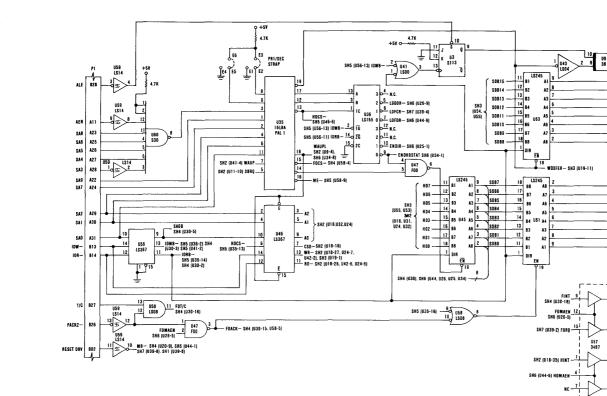

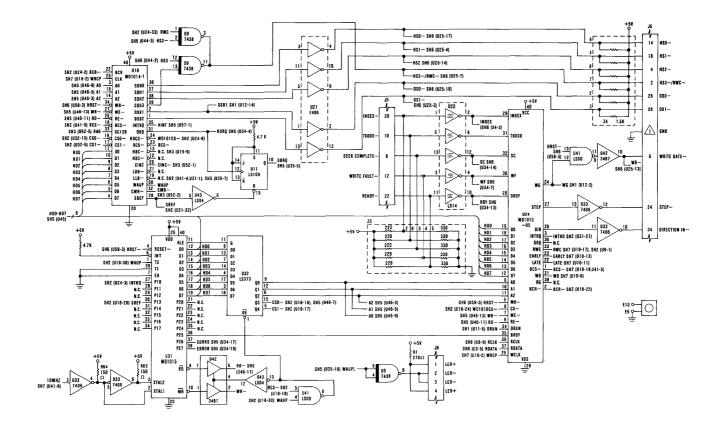

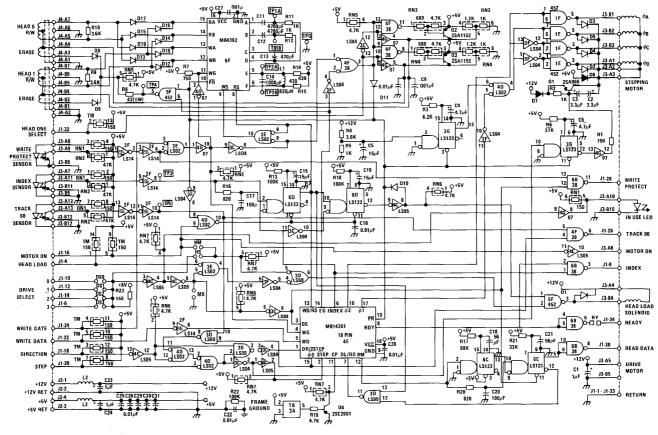

All communications protocol is a function of the system microcode that must be loaded before the adapter is operational. All pacing of the interface and control signal status must be handled by the system software. Figure 1 on page 2 is a block diagram of the 4 Port Asynchronous RS232C Adapter.

Figure 1. 4 Port Asynchronous RS232C Adapter Block Diagram

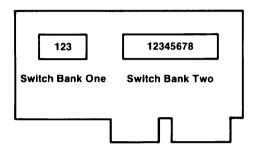

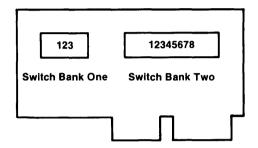

# 4 Port Asynchronous RS232C Adapter Switch Settings

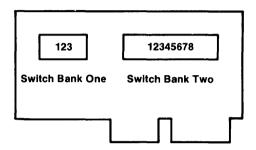

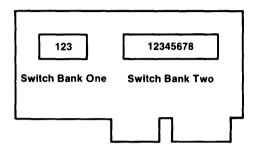

The 4 Port Asynchronous RS232C Adapter switch settings select the interrupt level and the address range of adapters installed.

Figure 2. 4 Port Asynchronous RS232C Adapter Switches

| Interrupt<br>Level  | Switch Bank One Setting |           |            |  |  |  |  |

|---------------------|-------------------------|-----------|------------|--|--|--|--|

| Selected            | Switch 1                | Switch 2  | Switch 3   |  |  |  |  |

| Level 9<br>Level 10 | On<br>Off               | Off<br>On | Off<br>Off |  |  |  |  |

| Level 11            | Off                     | Off       | On         |  |  |  |  |

Figure 3. Switch Bank One Settings

,

| Address<br>Range of                              | Switch Bank Two Setting |                         |                         |                         |  |  |  |

|--------------------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--|--|--|

| Adapters                                         | Switch 1                | Switch 2                | Switch 3                | Switch 4                |  |  |  |

| 1230-124F<br>2230-224F<br>3230-324F<br>4230-424F | On<br>Off<br>Off<br>Off | Off<br>On<br>Off<br>Off | Off<br>Off<br>On<br>Off | Off<br>Off<br>Off<br>On |  |  |  |

Figure 4. Switch Bank Two Settings

Note: Switches 5 through 8 are not used.

# **Modes of Operation**

The different modes of operation are selected by programming the NS16450 asynchronous communications element. This is done by selecting the I/O address and writing data out to the I/O address. Address bits A0, A1, and A2 select the different registers that define the modes of operation. Also, the divisor latch access bit (bit 7) of the line control register is used to select certain registers.

The address range for this adapter is Hex 1230 through Hex 424F. Figure 5 and Figure 6 on page 5 depict a value of n which represents a variable determined by the setting of switch bank two. Switches 1, 2, 3, and 4 of switch bank two allow the card to operate and select the appropriate address range.

| I/O Decou<br>Port B | le (In Hex)<br>Port A | Register Selected         | DLAB State     |

|---------------------|-----------------------|---------------------------|----------------|

| n238                | n230                  | TX Buffer                 | DLAB=0 (Write) |

| n238                | n230                  | RX Buffer                 | DLAB=0 (Read)  |

| n238                | n230                  | Divisor Latch LSB         | DLAB=1         |

| n239                | n231                  | Divisor Latch MSB         | DLAB=1         |

| n239                | n231                  | Interrupt Enable Register | DLAB=0         |

| n23A                | n232                  | Interrupt Identification  |                |

|                     |                       | Register                  |                |

| n23B                | n233                  | Line Control Register     |                |

| n23C                | n234                  | Modem Control Register    |                |

| n23D                | n235                  | Line Status Register      |                |

| n23E                | n236                  | Modem Status Register     |                |

### Figure 5. I/O Decodes, Port A and Port B

### Notes:

- 1. n is equal to the first digit of the adapter address range

- 2. DLAB means Divisor Latch Access Bit.

| I/O Deco | le (In Hex) |                           |                |

|----------|-------------|---------------------------|----------------|

| Port D   | Port C      | Register Selected         | DLAB State     |

| n248     | n240        | TX Buffer                 | DLAB=0 (Write) |

| n248     | n240        | RX Buffer                 | DLAB=0 (Read)  |

| n248     | n240        | Divisor Latch LSB         | DLAB=1         |

| n249     | n241        | Divisor Latch MSB         | DLAB=1         |

| n249     | n241        | Interrupt Enable Register | DLAB=0         |

| n24A     | n242        | Interrupt Identification  |                |

|          |             | Register                  |                |

| n24B     | n243        | Line Control Register     |                |

| n24C     | n244        | Modem Control Register    |                |

| n24D     | n245        | Line Status Register      |                |

| n24E     | n246        | Modem Status Register     |                |

Figure 6. I/O Decodes, Port C and Port D

### Notes:

- 1. n is equal to the first digit of the adapter address range

- 2. DLAB means Divisor Latch Access Bit.

| A9—>A3<br>Decode | A2 | A1 | A0 | DLAB | Register                                                    |

|------------------|----|----|----|------|-------------------------------------------------------------|

| See              | х  | x  | x  |      |                                                             |

| Note 1           | 0  | 0  | 0  | 0    | Receive Buffer Reg. (read)<br>Transmit Holding Reg. (write) |

|                  | 0  | 0  | 1  | 0    | Interrupt Enable                                            |

|                  | 0  | 1  | 0  | x    | Interrupt Identification                                    |

|                  | 0  | 1  | 1  | x    | Line Control                                                |

|                  | 1  | 0  | 0  | x    | Modem Control                                               |

|                  | 1  | 0  | 1  | x    | Line Status                                                 |

|                  | 1  | 1  | 0  | x    | Modem Status                                                |

|                  | 1  | 1  | 1  | x    | Scratch (See note 3)                                        |

|                  | 0  | 0  | 0  | 1    | Divisor Latch (LSB)                                         |

|                  | 0  | 0  | 1  | 1    | Divisor Latch (MSB)                                         |

#### Figure 7. Address Bits

#### Notes:

- 1. Bits A9 through A3 are used to select specific adapter and serial port.

- 2. A2, A1, and A0 bits are "don't cares" and are used to select the different registers of the NS16450 chip.

- 3. The Scratch Register of the NS16450 module should be initialized to all zeros and never be written to with any data afterwards. This would cause indeterminate data when Read address X237 (see "Interrupts") is executed.

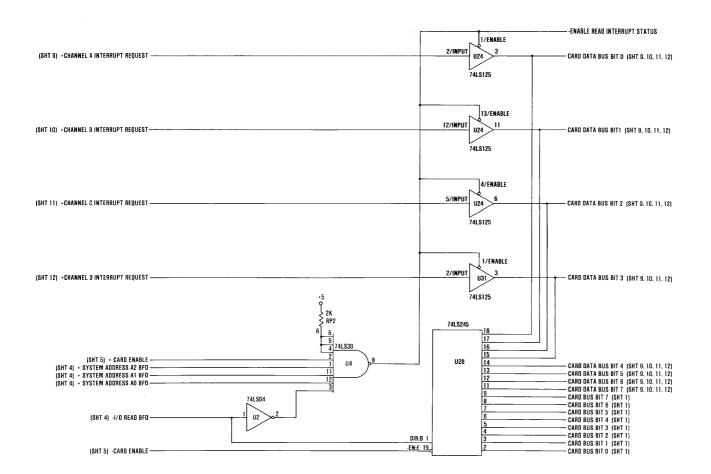

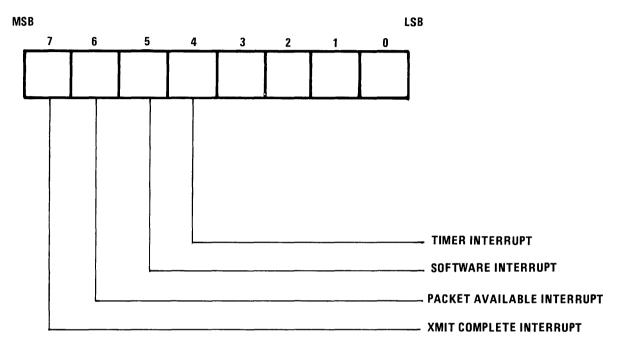

# Interrupts

Three interrupts lines are provided to the system. The interrupt level (9, 10, or 11) is selected by placing the appropriate switch on switch bank one to the on position. An interrupt register (read adr n237, where n is the first digit of address range) is provided to store pending port interrupts. Interrupt register bit assignment as shown in Figure 8.

|       | Hex Addres | ss n237 |       |        |        |        |        |

|-------|------------|---------|-------|--------|--------|--------|--------|

| Bit 7 | Bit 6      | Bit 5   | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

| 1     | 1          | 1       | 1     | Port 4 | Port 3 | Port 2 | Port 1 |

#### Figure 8. Interrupt Register Read Format

The reset or enable for interrupt level 9 is hex address 02F2.

The reset or enable for interrupt level 10 is hex address 06F2.

The reset or enable for interrupt level 11 is hex address 06F3.

# **Serial Data Format**

The data format is as follows:

| Transmit<br>Data<br>Marking | Start<br>Bit | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | Parity<br>Bit | Stop<br>Bit |  |

|-----------------------------|--------------|----|----|----|----|----|----|----|----|---------------|-------------|--|

|-----------------------------|--------------|----|----|----|----|----|----|----|----|---------------|-------------|--|

Data bit 0 is the first bit to be transmitted or received. The adapter automatically inserts the start bit, the correct parity bit (if programmed to do so), and the stop bit (1, 1-1/2, or 2 depending on the command in the line control register).

# **External Interface Description**

The adapter provides an EIA 4 Port Asynchronous RS232C Adapter-like interface.

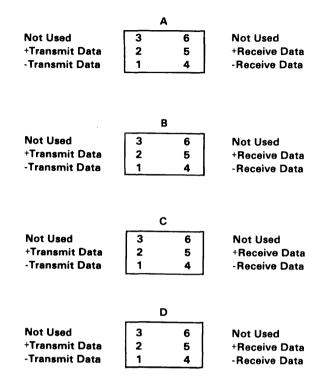

The pin functions for the 10-pin connector are shown in Figure 9 on page 8.

|                     |   | <u>A</u> |                     |

|---------------------|---|----------|---------------------|

| Unassigned          | 5 | 10 5     | Ground              |

| Ring Indicate       | 4 | 9        | Data Carrier        |

| Request to Send     | 3 | 8        | Clear to Send       |

| Data Terminal Ready | 2 | 7        | Data Set Ready      |

| Transmit Data       | 1 | لے 6     | Receive Data        |

|                     | L |          |                     |

|                     |   | B        |                     |

| Unassigned          | 5 | 10 5     | Ground              |

| Ring Indicate       | 4 | 9        | Data Carrier        |

| Request to Send     | 3 | 8        | Clear to Send       |

| Data Terminal Ready | 2 | 7        | Data Set Ready      |

| Transmit Data       | 1 | لے 6     | <b>Receive Data</b> |

|                     | L |          |                     |

|                     |   | С        |                     |

| Unassigned          | 5 | 10 7     | Ground              |

| Ring Indicate       | 4 | 9        | Data Carrier        |

| Request to Send     | 3 | 8        | Clear to Send       |

| Data Terminal Ready | 2 | 7        | Data Set Ready      |

| Transmit Data       | 1 | 6        | <b>Receive Data</b> |

|                     | L |          |                     |

|                     |   | D        |                     |

| Unassigned          | 5 | 10 4     | Ground              |

| Ring Indicate       | 4 | 9        | Data Carrier        |

| Request to Send     | 3 | 8        | Clear to Send       |

| Data Terminal Ready | 2 | 7        | Data Set Ready      |

| Transmit Data       | 1 | لے 6     | Receive Data        |

|                     |   |          |                     |

Figure 9. 10 Pin Interface Signals Connector (viewed from rear of adapter)

The adapter converts the interface signals from TTL levels to EIA 4 Port Asynchronous RS232C Adapter voltage levels, and vice versa. These signals are sampled or generated by the communications control chip. These signals can then be sensed by the system software to determine the state of the interface or peripheral device. The drivers and receivers used on the adapter are the inverting type; therefore, a 0 EIA level on the line is received or transmitted as a 0 TTL level, and a 1 EIA level is received or transmitted as a 1 TTL level.

# **Voltage Interchange Information**

The signal will be considered in the marking condition when the voltage on the interchange circuit, measured at the interface point, is more negative than -3 Vdc with respect to signal ground. The signal will be considered in the spacing condition when the voltage is more positive than +3 Vdc with respect to signal ground. The region between +3 Vdc and -3 Vdc is defined as the transition region and is considered an invalid level. The voltage that is more negative than -15 Vdc or more positive than +15 Vdc is also considered an invalid level.

During the transmission of data, the marking condition denotes the binary state 1 and the spacing condition denotes the binary state 0.

For interface control circuits, the function is on when the voltage is more positive than +3 Vdc with respect to signal ground and is off when the voltage is more negative than -3 Vdc with respect to signal ground.

| Interchange<br>Voltage | Binary<br>State | Signal<br>Condition | Interface<br>Control<br>Function |

|------------------------|-----------------|---------------------|----------------------------------|

| Positive Voltage       | Binary 0        | Spacing             | = On                             |

| Negative Voltage       | Binary 1        | Marking             | = Off                            |

Figure 10. 4 Port Asynchronous RS232C Adapter. Signal Levels

# **Asynchronous Communications Element Pin Description**

The following describes the function of all NS16450 input/output pins. Some of these descriptions reference internal circuits. The use of each signal as implemented on the multiport adapter is described.

Note: In the following descriptions, a low represents a logic 0 (0 Vdc nominal) and a high represents a logic 1 (+2.4 Vdc nominal).

## **Input Signals**

**Chip Select (CS0, CS1, -CS2), Pins 12-14:** When CS0 and CS1 are high and -CS2 is low, the chip is selected. Chip selection is complete when the decoded chip select signal is latched with an active (low) address strobe (-ADS) input. This enables communications between the NS16450 and the processor.

**Data Input Strobe (DISTR, -DISTR), Pins 22 and 21:** When DISTR is high or -DISTR is low while the chip is selected, the processor can read status information or data from a selected register of the NS16450.

**Note:** Only an active DISTR or -DISTR input is required to transfer data from the NS16450 during a read operation. Therefore, tie either the DISTR input permanently low or the -DISTR line permanently high, if not used.

**Data Output Strobe (DOSTR, -DOSTR), Pins 19 and 18:** When DOSTR is high or -DOSTR is low while the chip is selected, the processor can write data or control words into a selected register of the NS16450.

**Note:** Only an active DOSTR or -DOSTR input is required to transfer data to the NS16450 during a write operation. Therefore, tie either the DOSTR input permanently low or the -DOSTR input permanently high, if not used.

-Address Strobe (-ADS), Pin 25: When low, this signal provides latching for the register select (A0, A1, A2) and chip select (CS0, CS1, -CS2) signals.

**Note:** An active -ADS input is required when the register select (A0, A1, A2) signals are not stable for the duration of a read or write operation. If not required, tie the -ADS input permanently low.

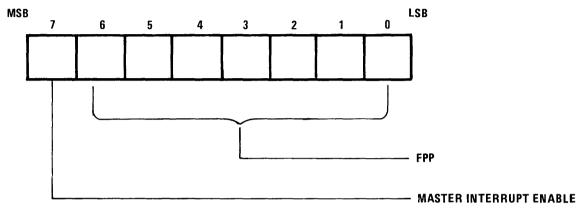

**Register Select (A0, A1, A2), Pins 26-28:** These three inputs are used during a read or write operation to select an NS16450 register to read from or write into as indicated in Figure 11. Note that the state of the divisor latch access bit (DLAB), which is the most significant bit of the line control register, affects the selection of certain NS16450 registers. The DLAB must be set high by the system software to access the baud-generator divisor latches.

| DLAB | A2 | A1 | AO | Register                                                       |

|------|----|----|----|----------------------------------------------------------------|

| 0    | 0  | 0  | 0  | Receiver Buffer (Read)<br>Transmitter Holding Register (Write) |

| 0    | 0  | 0  | 1  | Interrupt Enable                                               |

| x    | 0  | 1  | 0  | Interrupt Identification (Read Only)                           |

| х    | 0  | 1  | 1  | Line Control                                                   |

| x    | 1  | 0  | 0  | Modem Control                                                  |

| x    | 1  | 0  | 1  | Line Status                                                    |

| x    | 1  | 1  | 0  | Modem Status                                                   |

| x    | 1  | 1  | 1  | Scratch                                                        |

| 1    | 0  | 0  | 0  | Divisor Latch (Least Significant Byte)                         |

| 1    | 0  | 0  | 1  | Divisor Latch (Most Significant Byte)                          |

Figure 11. NS16450 Register Selection

**Master Reset (MR), Pin 35:** When high, this signal clears all the registers (except the receive buffer, transmitter holding, and divisor latches), and the control logic of the NS16450. Also, the state of various output signals (SOUT, INTRPT, -OUT 1, -OUT 2, -RTS, -DTR) is affected by an active MR input. Refer to the table in Figure 12 on page 12 for reset functions.

| Register/Signal                                                    | Reset Control                                                | Reset State                                                                    |  |

|--------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| Interrupt Enable<br>Register                                       | Master Reset                                                 | All Bits Low 0-3<br>Forced and 4-7<br>Permanent                                |  |

| Interrupt<br>Identification Register                               | Master Reset                                                 | Bit 0 is High, Bits 1<br>and 2 are Low, and<br>Bits 3-7 are<br>Permanently Low |  |

| Line Control Register                                              | Master Reset                                                 | All Bits Low                                                                   |  |

| Modem Control<br>Register                                          | Master Reset                                                 | All Bits Low                                                                   |  |

| Line Status Register                                               | Master Reset                                                 | All Bits Low, except<br>Bits 5 and 6 are High                                  |  |

| Modem Status<br>Register                                           | Master Reset                                                 | Bits 0-3 are Low<br>Bits 4-7 = Input Signal                                    |  |

| SOUT                                                               | Master Reset                                                 | High                                                                           |  |

| INTRPT (RCVR<br>Errors)                                            | Read LSR/MR                                                  | Low                                                                            |  |

| INTRPT (RCVR<br>Data Ready)                                        | Read RBR/MR                                                  | Low                                                                            |  |

| INTRP (THRE)                                                       | Read IIR/<br>Write THR/MR                                    | Low                                                                            |  |

| INTRPT (Modem<br>Status Changes)                                   | Read MSR/MR                                                  | Low                                                                            |  |

| <ul> <li>OUT 2</li> <li>RTS</li> <li>DTR</li> <li>OUT 1</li> </ul> | Master Reset<br>Master Reset<br>Master Reset<br>Master Reset | High<br>High<br>High<br>High                                                   |  |

Figure 12. NS16450 Reset Functions

**Receiver Clock (RCLK), Pin 9:** This input is the 16x baud-rate clock for the receiver section of the chip.

Serial Input (SIN), Pin 10: Serial data input from the communications link (peripheral device, modem, or data set).

-Clear to Send (-CTS), Pin 36: The -CTS signal is a modem control function input whose condition can be tested by the processor by reading bit 4 (CTS) of the modem status register. Bit 0 (DCTS) of the modem status register indicates whether the -CTS input has changed state since the previous reading of the modem status register.

**Note:** Whenever the CTS bit of the modem status register changes state, an interrupt is generated if the modem status interrupt is enabled.

-Data Set Ready (-DSR), Pin 37: The -DSR signal is a modem control function input whose condition can be tested by the processor by reading bit 5 (DSR) of the modem status register. When low, this signal indicates that the modem or data set is ready to establish the communications link and transfer data with the NS16450. Bit 1 (DDSR) of the modem status register indicates whether the -DSR input has changed since the previous reading of the modem status register.

**Note:** Whenever the DSR bit of the modem status register changes state, an interrupt is generated if the modem status interrupt is enabled.

-Received Line Signal Detect (-RLSD), Pin 38: The -RLSD signal is a modem control function input whose condition the processor can test by reading bit 7 (RLSD) of the modem status register. When low, this signal indicates that the data carrier had been detected by the modem or data set. Bit 3 (DRLSD) of the modem status register indicates whether the -RLSD not input has changed state since the previous reading of the modem status register.

#### Notes:

- 1. Whenever the RLSD bit of the modem status register changes state, an interrupt is generated if the modem status interrupt is enabled.

- 2. Received Line Signal Detect is also called Data Carrier Detect (DCD), or Carrier Detect (CD).

-Ring Indicator (-RI), Pin 39: The -RI signal is a modem control function input whose condition the processor can test by reading bit 6 (RI) of the modem status register. When low, this signal indicates that a telephone ringing signal has been received by the modem or data set. Bit 2 (TERI) of the modem status register indicates whether the -RI input has changed from a low to high state since the previous reading of the modem status register.

**Note:** Whenever the RI bit of the modem status register changes from a high to a low state, an interrupt is generated if the modem status interrupt is enabled.

VCC, Pin 40: +5 Vdc supply.

VSS, Pin 20: Ground (0 Vdc) reference.

## **Output Signals**

**-Data Terminal Ready (-DTR), Pin 33:** When low, this signal informs the modem or data set that the NS16450 is ready to communicate. The -DTR output signal can be set to an active low by programming bit 0 (DTR) of the modem control register to a high level. The -DTR signal is set high by a master reset operation. The -DTR signal is set high during loop mode operation.

-Request to Send (-RTS), Pin 32: When low, this signal informs the modem or data set that the NS16450 is ready to transmit data. The -RTS output signal can be set to an active low by programming bit 1 (RTS) of the modem control register. The -RTS signal is set high by a master reset operation. The -RTS signal is set high during loop mode operation.

-Output 1 (-OUT 1), Pin 34: With this signal, user-designated output can be set to an active low by programming bit 2 (-OUT 1) of the modem control register to a high level. The -OUT 1 signal is set high by a master reset operation. The -OUT 1 signal is set high during the loop mode operation.

-Output 2 (-OUT 2), Pin 31: With this signal, user-designated output can be set to an active low by programming bit 3 (-OUT 2) of the modem control register to a high level. The -OUT 2 signal is set high by a master reset operation. The -OUT 2 signal is set high during the loop mode operation.

Chip Select Out (CSOUT), Pin 24: When high, this signal indicates that the chip has been selected by active CS0, CS1, and -CS2 inputs. No data transfer can be initiated until the CSOUT signal is a logic 1.

**Driver Disable (DDIS), Pin 23:** This signal goes low whenever the processor is reading data from the NS16450. A high-level DDIS output can be used to disable an external transceiver (if used between the processor and NS16450 on the D7-D0 data bus) at all times, except when the processor is reading data.

-Baudout (-BAUDOUT), Pin 15: This signal is a 16x clock signal for the transmitter section of the NS16450. The clock rate is equal to the main reference oscillator frequency divided by the specified divisor in the baud-generator division latches. The -Baudout may also be used for the receiver section by tying this output to the RCLK input of the chip.

**Interrupt (INTRPT), Pin 30:** This signal goes high whenever any one of the following interrupt types has an active high condition and is enabled through the IER: receiver error flag, received data available, transmitter holding register empty, or modem status. The Intrpt signal is reset low upon the appropriate interrupt service or a master reset operation.

Serial Output (SOUT), Pin 11: Composite serial data output to the communications link (peripheral, modem or data set). The SOUT signal is set to the marking (logic 1) state upon a master reset operation.

## Input/Output Signals

**Data Bus (D7-D0), Pins 1-8:** This bus comprises eight tri-state input/output lines. The bus provides bidirectional communications between the NS16450 and the processor. Data, control words, and status information are transferred through the D7-D0 data bus.

External Clock Input/Output (XTAL1, XTAL2), Pins 16 and 17: These two pins connect the main timing reference (crystal or signal clock) to the NS16450.

# **Programming Considerations**

The NS16450 has a number of accessible registers. The system programmer may access or control any of the NS16450 registers through the processor. These registers are used to control NS16450 operations and to transmit and receive data.

Note: The n in address is the card number (1-4).

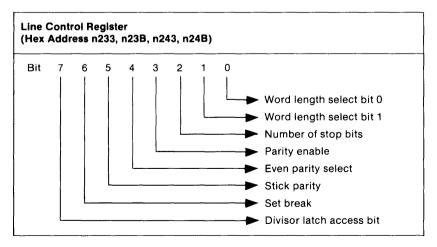

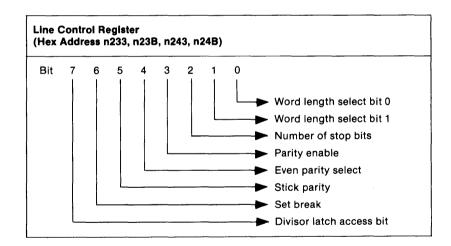

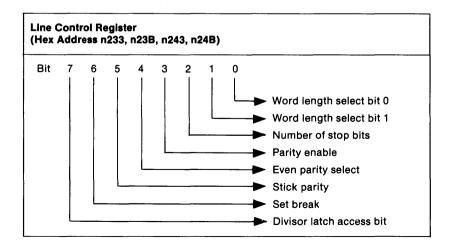

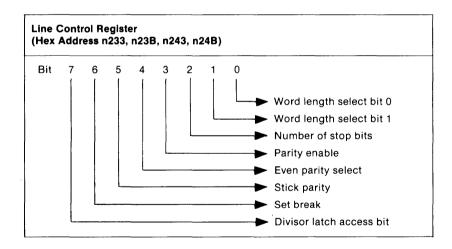

## Line Control Register

The system programmer specifies the format of the asynchronous data communications exchange through the line control register. In addition to controlling the format, the programmer may retrieve the contents of the line control register for inspection. This feature simplifies system programming and eliminates the need for separate storage of the line characteristics in system memory. The contents of the line control register are described below:

**Bits 0, 1** These two bits specify the number of bits in each transmitted or received serial character. The encoding of bits 0 and 1 is as follows:

| Bit 1 | Bit 0 | Word Length |

|-------|-------|-------------|

| 0     | 0     | 5 bits      |

| 0     | 1     | 6 bits      |

| 1     | 0     | 7 bits      |

| 1     | 1     | 8 bits      |

- **Bit 2** This bit specifies the number of stop bits in each transmitted or received serial character. If bit 2 is a logical 0, one stop bit is generated or checked in the transmit or receive data, respectively. If bit 2 is a logical 1 when a 5-bit word length is selected through bits 0 and 1, 1-1/2 stop bits are generated or checked. If bit 2 is a logical 1 when either a 6-, 7-, or 8-bit word length is selected, two stop bits are generated or checked.

- **Bit 3** This bit is the parity enable bit. When bit 3 is a logical 1, a parity bit is generated (transmit data) or checked (receive data) between the last data word bit and stop bit of the serial data. (The parity bit is used to produce an even or odd number of 1's when the data word bits and the parity bit are summed.)

- **Bit 4** This bit is the even parity select bit. When bit 3 is a logical 1 and bit 4 is a logical 0, an odd number of logical 1's are transmitted or checked in the data word bits and parity bit. When bit 3 is a logical 1 and bit 4 is a logical 1, an even number of bits are transmitted or checked.

- **Bit 5** This bit is the stick parity bit. When bit 3 is a logical 1 and bit 5 is a logical 1, the parity bit is transmitted and then detected by the receiver as a logical 0 (space parity) if bit 4 is a logical 1, or as a logical 1 (mark parity) if bit 4 is a logical 0.

- **Bit 6** This bit is the set break control bit. When bit 6 is a logical 1, the serial output (SOUT) is forced to the spacing (logical 0) state and remains there regardless of other transmitter activity. The set break is disabled by setting bit 6 to a logical 0. This feature enables the processor to alert a terminal in a computer communications system.

- **Bit 7** This bit is the divisor latch access bit (DLAB). It must be set high (logical 1) to access the divisor latches of the baud-rate generator during a read or write operation. It must be set low (logical 0) to access the receiver buffer, the transmitter holding register, or the interrupt enable register.

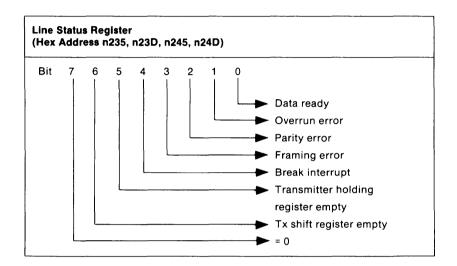

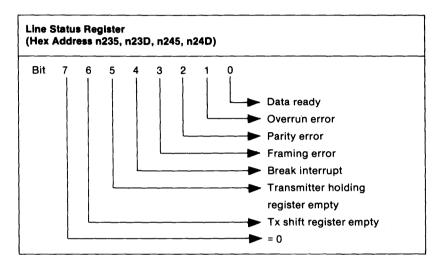

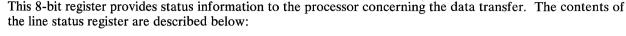

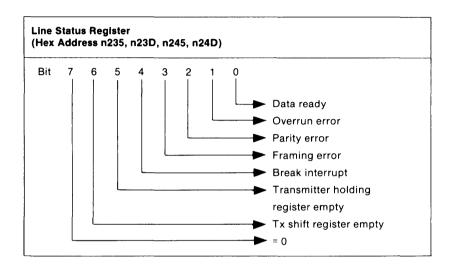

# Line Status Register

This 8-bit register provides status information to the processor concerning the data transfer. The contents of the line status register are described below:

- **Bit 0** This bit is the receiver data ready (DR) indicator. Bit 0 is set to a logical 1 whenever a complete incoming character has been received and transferred into the receiver buffer register. Bit 0 may be reset to a logical 0 either by the processor reading the data in the receiver buffer or by writing a logical 0 into it from the processor.

- **Bit 1** This bit is the overrun error (OE) indicator. Bit 1 indicates that data in the receiver buffer register was not read by the processor before the next character was transferred into the receiver buffer register, and thereby destroyed the previous character. The OE indicator is reset whenever the processor reads the contents of the line status register.

- **Bit 2** This bit is the parity error (PE) indicator. Bit 2 indicates that the received data character does not have the correct even or odd parity as selected by the even parity select bit. The PE bit is set to a logical 1 whenever a parity error is detected and is reset to a logical 0 whenever the processor reads the contents of the line status register.

- **Bit 3** This bit is the framing error (FE) indicator. Bit 3 indicates that the received character does not have a valid stop bit. Bit 3 is set to a logical 1 whenever the stop bit following the last data bit or parity is detected as a zero bit (spacing level).

- **Bit 4** This bit is the break interrupt (BI) indicator. Bit 4 is set to a logical 1 whenever the received data input is held in the spacing (logical 0) state for longer than a full word transmission time (that is, the total time of start bit + data bits + parity + stop bits).

|       | <b>Note:</b> Bits 1 through 4 are the error conditions that produce a receiver line status interrupt whenever any of the corresponding conditions are detected.                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit 5 | This bit is the transmitter holding register empty (THRE) indicator. Bit 5 indicates that the NS16450 is ready to accept a new character for transmission. In addition, this bit causes the NS16450 to issue an interrupt to the processor when the THRE interrup enable is set high. The THRE bit is set to a logical 1 when a character is transferred from the transmitter holding register into the transmitter shift register. The bit is reset to logical 0 concurrently with the loading of the transmitter holding register by the processor. |  |

| Bit 6 | This bit is the transmitter empty (TEMT) indicator. Bit 6 is set to a logical 1 whenever the transmitter holding register (THR) and the transmitter shift register (TSR) are both empty. It is reset to a logical 0 whenever either the THR or TSR contain a data character. Bit 6 is a read-only bit.                                                                                                                                                                                                                                                |  |

| Bit 7 | This bit is permanently set to logical 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

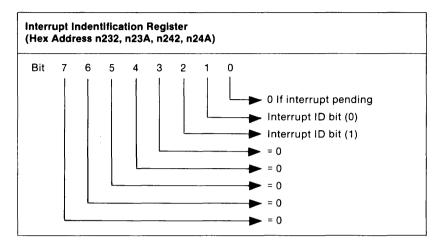

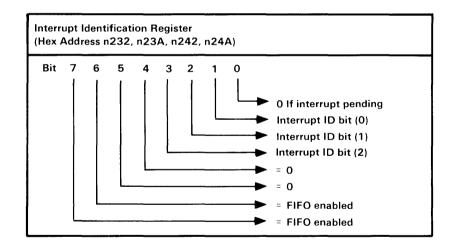

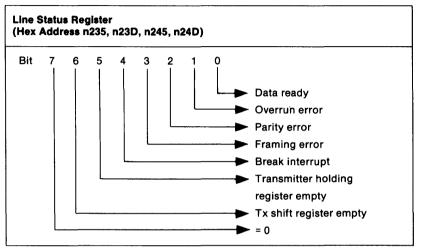

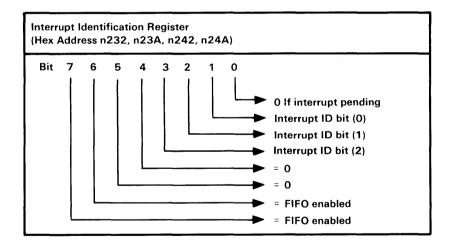

# **Interrupt Identification Register**

The NS16450 has an on-chip interrupt capability that allows for complete flexibility in interfacing to microprocessors. In order to provide minimum software overhead during data character transfers, the NS16450 prioritizes interrupts into four levels:

- Receiver line status (priority 1)

- Received data ready (priority 2)

- Transmitter holding register empty (priority 3)

- Modem status (priority 4).

Information indicating that a priority interrupt is pending and information on the type of interrupt is stored in the interrupt identification register. Refer to the "Interrupt Control Functions" table in Figure 13 on page 20. The interrupt identification register (IIR), when addressed during chip-select time, freezes the highest priority interrupt pending, and no other interrupts are acknowledged until that particular interrupt is serviced by the processor. The contents of the IIR are described below.

- **Bit 0** This bit can be used in hardwired, priority, or polled environment to indicate whether an interrupt is pending. When bit 0 is a logical 0, an interrupt is pending and the IIR contents may be used as a pointer to the appropriate interrupt service routine. When bit 0 is a logical 1, no interrupt is pending and polling (if used) is continued.

- **Bits 1, 2** These two bits of the IIR are used to identify the highest priority interrupt pending as indicated in Figure 13 on page 20.

- **Bits 3-7** These five bits of the IIR are always logical 0.

| Interrupt<br>ID<br>Register |          | Interrupt Set and Reset Functions |                   |                                             |                                                                                           |                                                                                    |

|-----------------------------|----------|-----------------------------------|-------------------|---------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Bit<br>2                    | Bit<br>1 | Bit<br>0                          | Priority<br>Level | Interrupt<br>Type                           | Interrupt<br>Source                                                                       | Interrupt<br>Reset Control                                                         |

| 0                           | 0        | 1                                 |                   | None                                        | None                                                                                      | _                                                                                  |

| 1                           | 1        | 0                                 | Highest           | Receiver<br>Line<br>Status                  | Overrun Error or<br>Parity Error or<br>Framing Error or<br>Break Intrpt.                  | Reading the Line<br>Status Register                                                |

| 1                           | 0        | 0                                 | Second            | Received<br>Data<br>Available               | Receiver Data<br>Available                                                                | Reading the Receiver<br>Buffer Register                                            |

| 0                           | 1        | 0                                 | Third             | Transmitter<br>Holding<br>Register<br>Empty | Transmitter Holding<br>Register Empty                                                     | Reading the IIR<br>Register or Writing<br>into the Transmitter<br>Holding Register |

| 0                           | 0        | 0                                 | Fourth            | Modem<br>Status                             | Clear to Send or Data<br>Set Ready or Ring<br>Indicator or Received<br>Line Signal Detect | Reading the Modem<br>Status Register                                               |

Figure 13. Interrupt Control Functions

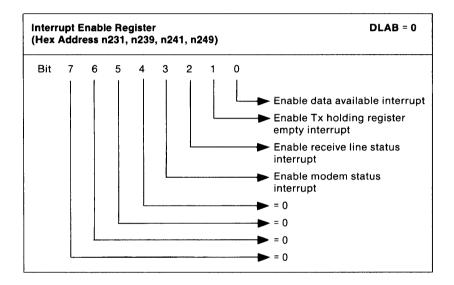

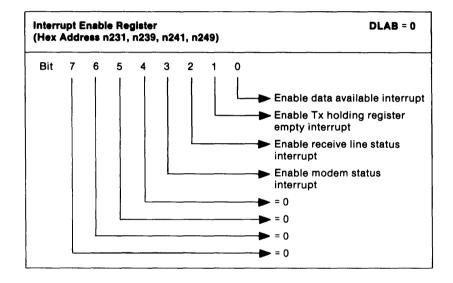

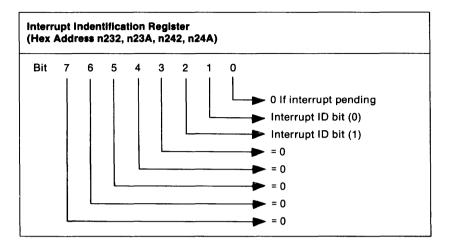

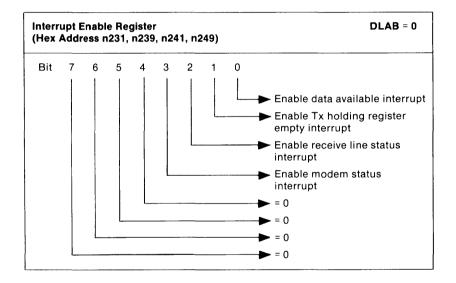

## **Interrupt Enable Register**

This 8-bit register enables the four types of interrupts of the NS16450 to separately activate the chip interrupt (INTRPT) output signal. The interrupt system can be totally disabled by resetting bits 0 through 3 of the interrupt enable register. Similarly, by setting the appropriate bits of this register to a logical 1, selected interrupts can be enabled. Disabling the interrupt system inhibits the interrupt identification register and the active (high) INTRPT output from the chip. All other system functions operate in their normal manner, including the setting of the line status and modem status registers. The contents of the interrupt enable register are described below:

- **Bit 0** This bit enables the received data available interrupt when set to logical 1.

- **Bit 1** This bit enables the transmitter holding register empty interrupt when set to logical 1.

- **Bit 2** This bit enables the receiver line status interrupt when set to logical 1.

- **Bit 3** This bit enables the modem status interrupt when set to logical 1.

- **Bits 4-7** These four bits are always logical 0.

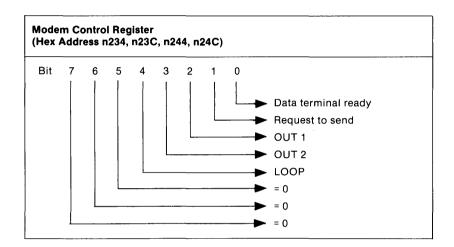

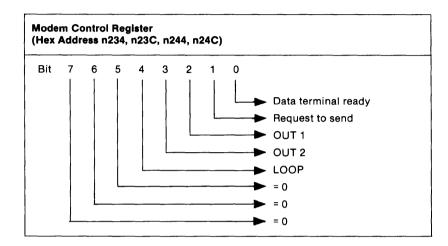

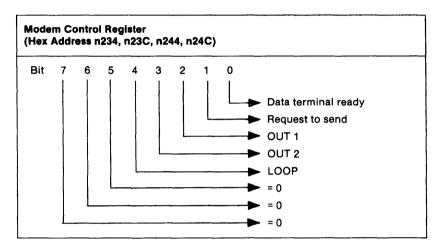

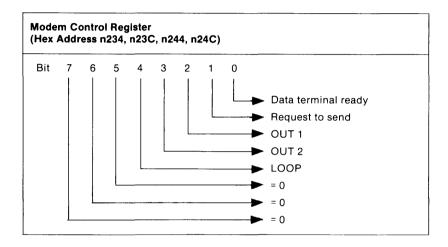

# **Modem Control Register**

This 8-bit register controls the interface with the modem or data set (or other peripheral device). The contents of the modem control register are described below:

**Bit 0** This bit controls the data terminal ready (-DTR) output. When bit 0 is set to a logical 1, the -DTR output is forced to a logical 0. When bit 0 is reset to a logical 0, the -DTR output is forced to a logical 1.

**Note:** The -DTR output of the NS16450 may be applied to an EIA inverting line driver to obtain the proper polarity input at the modem or data set.

**Bit 1** This bit controls the request to send (-RTS) output. Bit 1 affects the -RTS output in a manner identical to that described above for bit 0.

**Note:** The -RTS output of the NS16450 may be applied to an EIA-inverting line driver to obtain the proper polarity input at the modem or data set.

**Bit 2** This bit controls the output 1 (-OUT 1) signal, which is an auxiliary user-designated output. Bit 2 affects the -OUT 1 output in a manner identical to that described above for bit 0.

**Note:** The -OUT 1 output of the NS16450 may be applied to an EIA inverting line driver to obtain the proper polarity input at the modem or data set.

**Bit 3** This bit controls the output 2 (-OUT 2) signal, which is an auxiliary user-designated output. Bit 3 affects the -OUT 2 output in a manner identical to that described above for bit 0.

**Note:** The -OUT 2 output of the NS16450 may be applied to an EIA inverting line driver to obtain the proper polarity input at the modem or data set.

**Bit 4** This bit provides a loopback feature for diagnostic testing of the NS16450. When bit 4 is set to logical 1, the following occurs:

The transmitter serial output (SOUT) is set to the marking (logical 1) state.

The receiver serial input (SIN) is disconnected.

The output of the transmitter shift register is "looped back" into the receiver shift register input.

The four modem control inputs (-CTS, -DSR, -RLSD, and -RI) are disconnected.

The four modem control outputs (-DTR, -RTS, -OUT 1, and -OUT 2) are internally connected to the four modem control inputs, and the modem control output pins are forced high.

In the the diagnostic mode the receiver and transmitter interrupts are fully operational. The modem control interrupts are also operational, but the sources of the interrupts are now the lower 4 bits of the modem control register instead of the 4 modem control inputs. The interrupts are still controlled by the interrupt enable register.

The NS16450 interrupt system can be tested by writing into the lower 6 bits of the line status register and into the lower 4 bits of the modem status register. Setting any of these bits to a logical 1 generates the appropriate interrupt (if enabled). The resetting of these interrupts is the same as in normal NS16450 operation. To return to normal operation, the registers must be reprogrammed for normal operation and then bit 4 of the modem control register must be reset to logical 0. The transmitter should be idle when this bit changes state.

**Bits 5-7** These bits are permanently set to logical 0.

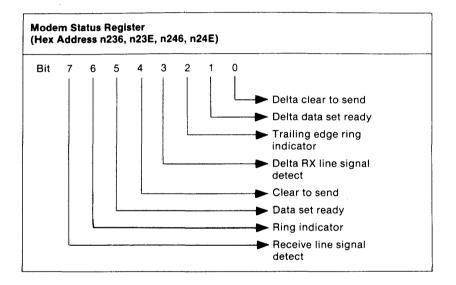

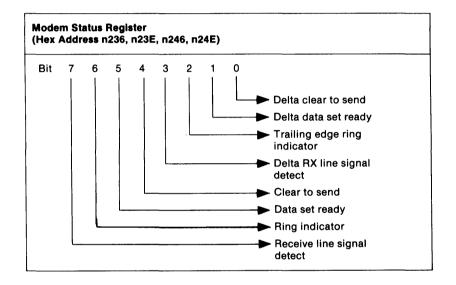

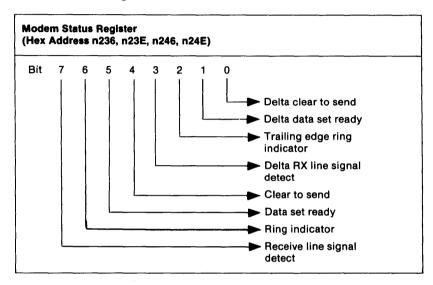

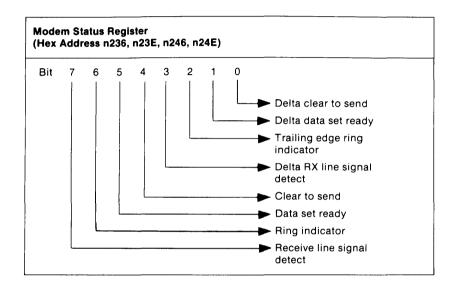

## **Modem Status Register**

This 8-bit register provides the current state of the control lines from the modem (or peripheral device) to the processor. In addition to this current-state information, four bits of the modem status register provide change information. These bits are set to a logical 1 whenever a control input from the modem changes state. They are reset to logical 0 whenever the processor reads the modem status register.

The contents of the modem status register are described below:

- **Bit 0** This bit is the delta clear-to-send (DCTS) indicator. Bit 0 indicates that the -CTS input to the chip has changed state since the last time it was read by the processor.

- **Bit 1** This bit is the delta data set ready (DDSR) indicator. Bit 1 indicates that the -DSR input to the chip has changed state since the last time it was read by the processor.

- **Bit 2** This bit is the trailing edge of the ring indicator (TERI) detector. Bit 2 indicates that the -RI input to the chip has changed from an ON (logical 1) to an OFF (logical 0) condition.

- **Bit 3** This bit is the delta received line signal detector (DRLSD) indicator. Bit 3 indicates that the -RLSD input to the chip has changed state since the last time it was read by the processor.

**Note:** Whenever bit 0, 1, 2, or 3 is set to a logical 1, a modem status interrupt is generated, if the appropriate interrupt enable bit is set in the IER.

| Bit 4 | This bit is the complement of the clear to send (-CTS) input. Setting bit 4 (loop) of the MCR to a logical 1, is equivalent to RTS in the MCR.                              |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit 5 | This bit is the complement of the data set ready (-DSR) input. If bit 4 (loop) of the MCR is set to a logical 1, this bit is equivalent to DTR in the MCR.                  |  |  |  |

| Bit 6 | This bit is the complement of the ring indicator (-RI) input. If bit 4 (loop) of the MCR is set to a logical 1, this bit is equivalent to -OUT 1 in the MCR.                |  |  |  |

| Bit 7 | This bit is the complement of the received line signal detect (-RLSD) input. If bit 4 (loop) of the MCR is set to a logical 1, this bit is equivalent to -OUT 2 of the MCR. |  |  |  |

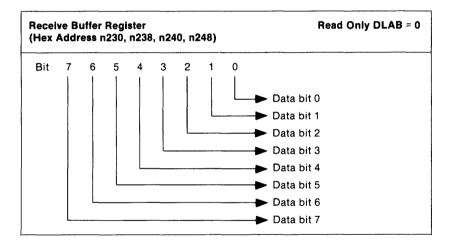

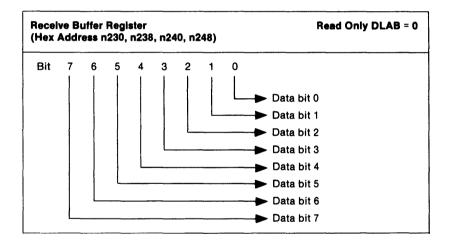

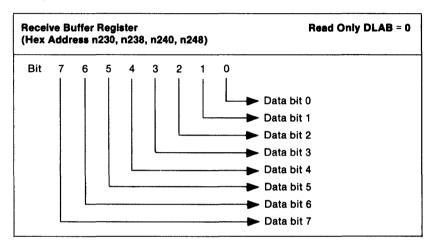

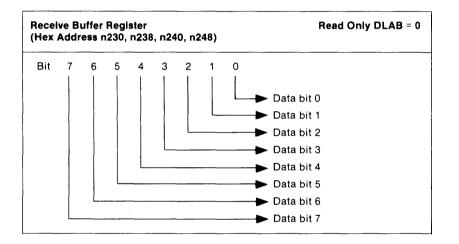

# **Receiver Buffer Register**

The receiver buffer register contains the received character as defined below:

Bit 0 is the least significant bit and is the first bit serially received.

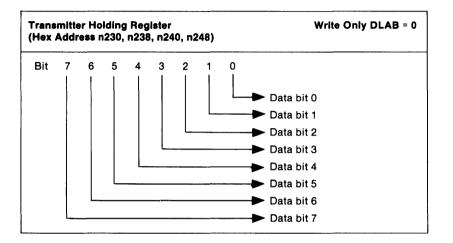

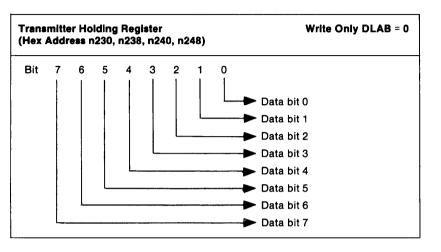

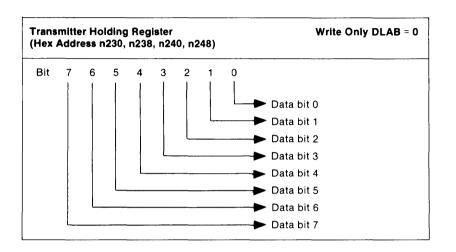

# **Transmitter Holding Register**

**Transmitter Holding Register** Write Only DLAB = 0 (Hex Address n230, n238, n240, n248) Bit 7 6 5 4 3 2 ٥ 1 Data bit 0 Data bit 1 Data bit 2 Data bit 3 Data bit 4 Data bit 5 Data bit 6 Data bit 7

The transmitter holding register contains the character to be serially transmitted and is defined below:

Bit 0 is the least significant bit and is the first bit serially transmitted.

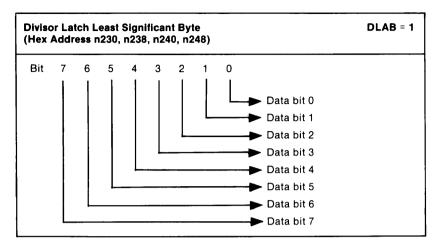

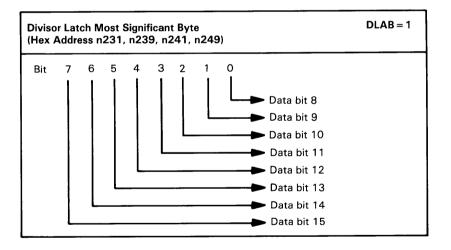

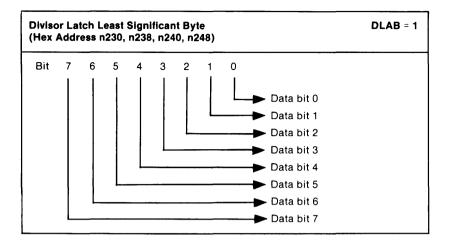

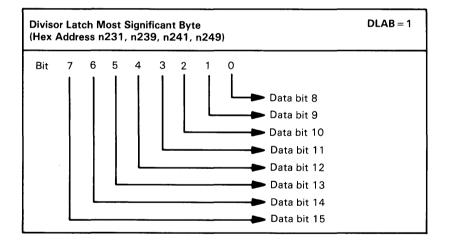

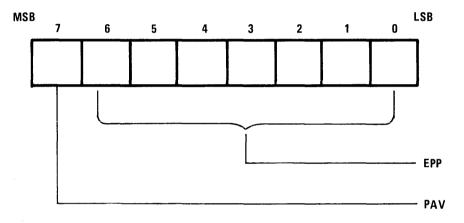

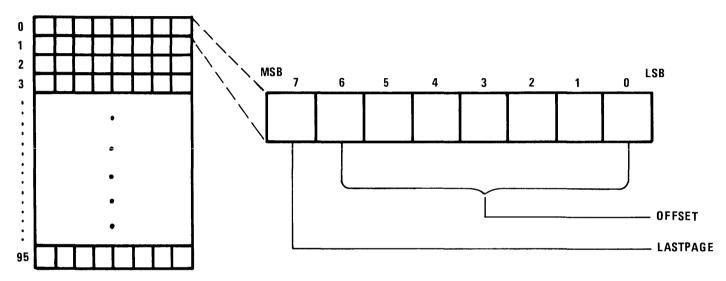

## **Programmable Baud-Rate Generator**

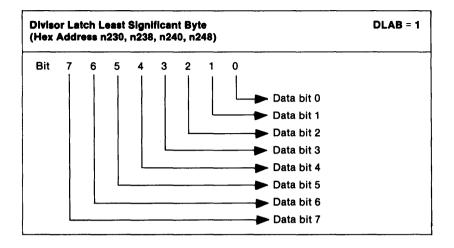

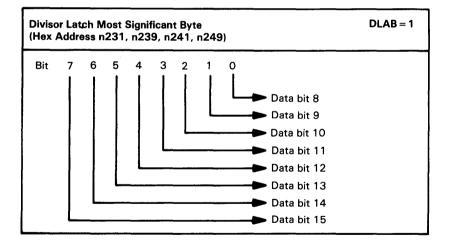

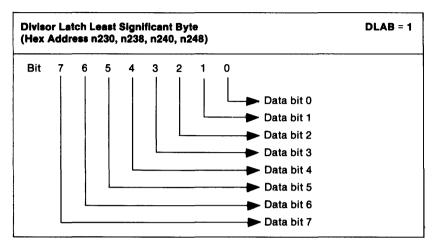

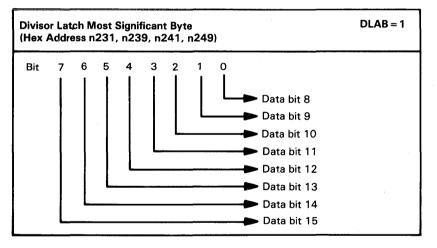

The NS16450 contains a programmable baud-rate generator that can divide the clock input (1.8432 MHz) by any divisor from 1 to 655,535 or 2<sup>16</sup>-1. The output frequency of the baud-rate generator is the baud rate multiplied by 16. Two 8-bit latches store the divisor in a 16-bit binary format. These divisor latches must be loaded during initialization in order to insure desired operation of the baud-rate generator. Upon loading either of the divisor latches, a 16-bit baud counter is immediately loaded. This prevents long counts on initial load. The contents of the divisor latches are indicated below:

Figure 14. Divisor Latch Least Significant Byte

Figure 15. Divisor Latch Most Significant Byte

Figure 16 illustrates the use of the baud-rate generator with a frequency of 1.8432 MHz. For baud rates of 19,200 and below, the error obtained is minimal.

**Note:** The maximum operating frequency of the baud generator is 3.1 MHz. In no case should the data rate be greater than 19,200 baud.

| Desired<br>Baud | Divisor Used<br>16x Clo |       | Percent Error<br>Difference Between |

|-----------------|-------------------------|-------|-------------------------------------|

| Rate            | (Decimal)               | (Hex) | Desired and Actual                  |

| 50              | 2304                    | 900   |                                     |

| 75              | 1536                    | 600   |                                     |

| 110             | 1047                    | 417   | 0.026                               |

| 134.5           | 857                     | 359   | 0.058                               |

| 150             | 786                     | 300   |                                     |

| 300             | 384                     | 180   |                                     |

| 600             | 192                     | CO    |                                     |

| 1200            | 96                      | 60    |                                     |

| 1800            | 64                      | 40    |                                     |

| 2000            | 58                      | 3A    | 0.69                                |

| 2400            | 48                      | 30    | _                                   |

| 3600            | 32                      | 20    | —                                   |

| 4800            | 24                      | 18    | —                                   |

| 7200            | 16                      | 10    |                                     |

| 9600            | 12                      | С     |                                     |

| 19200           | 6                       | 6     |                                     |

Figure 16. Baud Rates at 1.8432 MHz

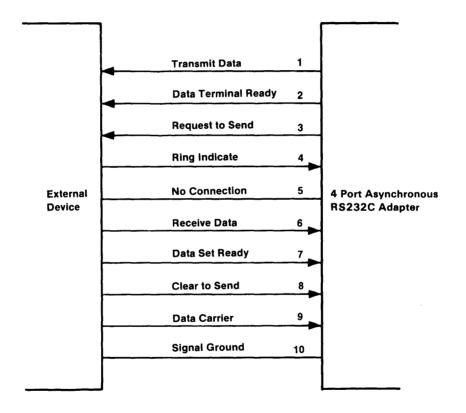

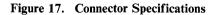

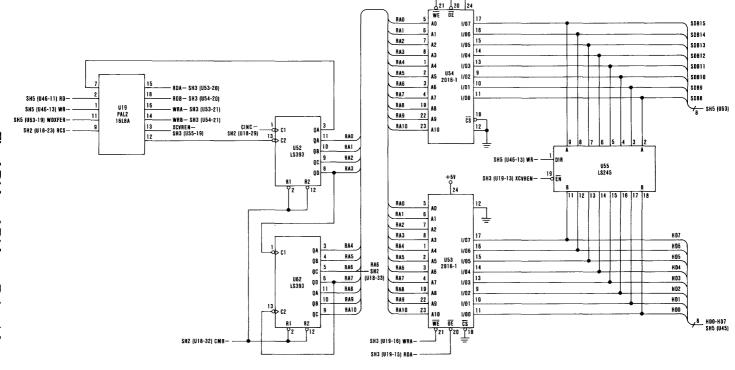

## **Connector Specifications**

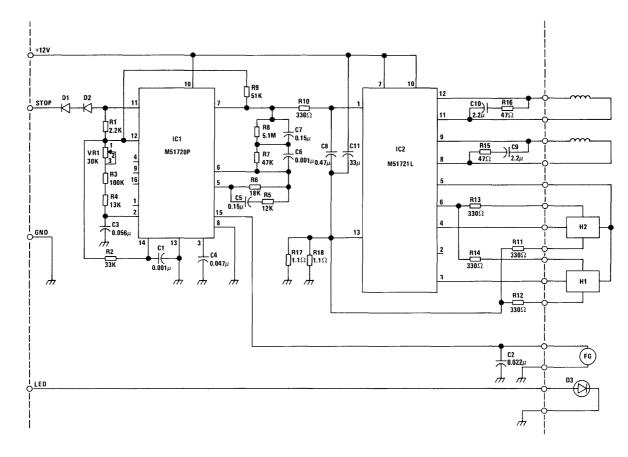

The adapter has a 10-pin connector at the rear of the adapter. The following figure shows the signals and their pin assignments.

Figure 17. Connector Specifications

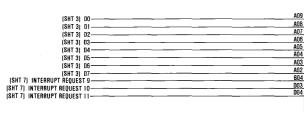

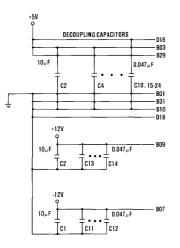

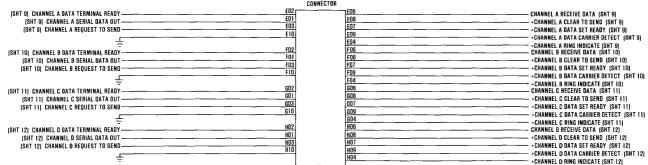

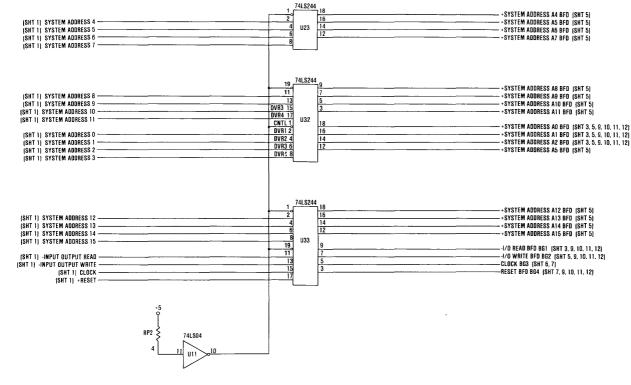

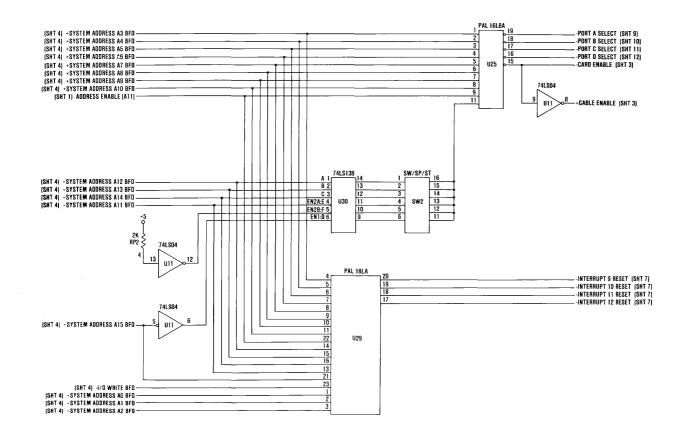

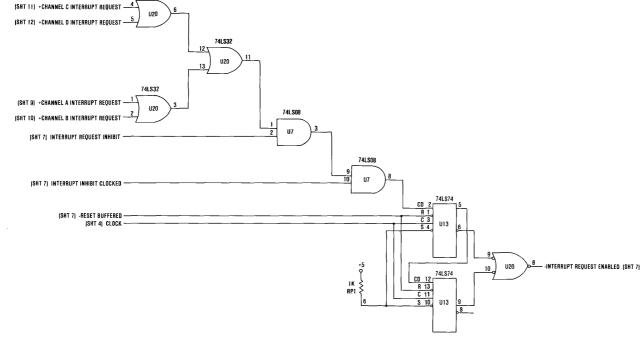

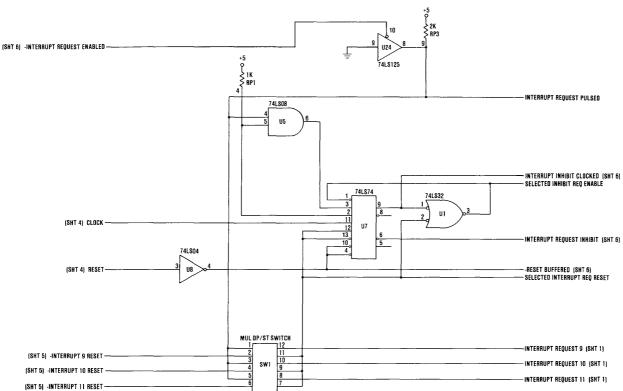

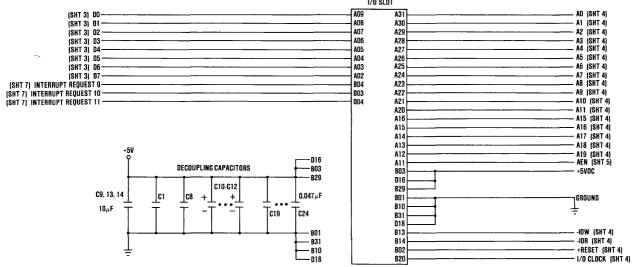

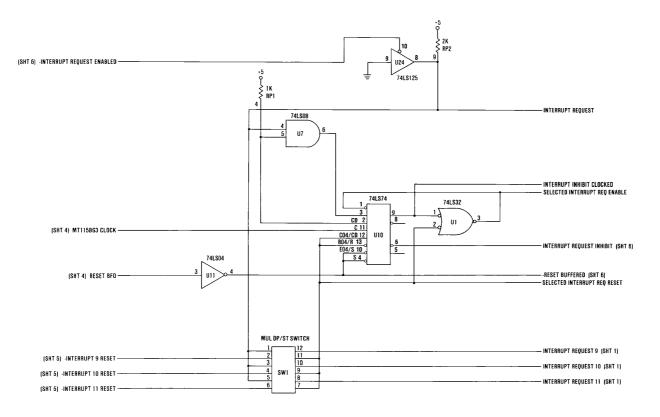

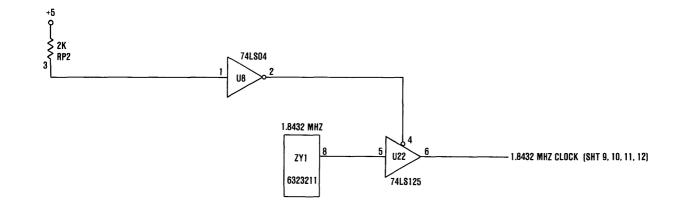

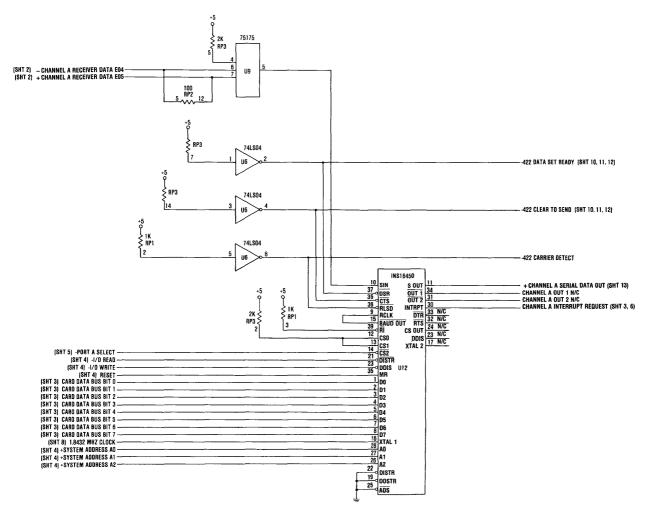

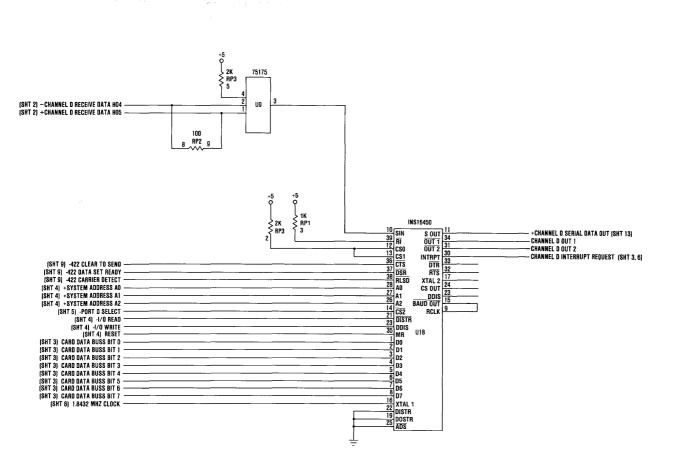

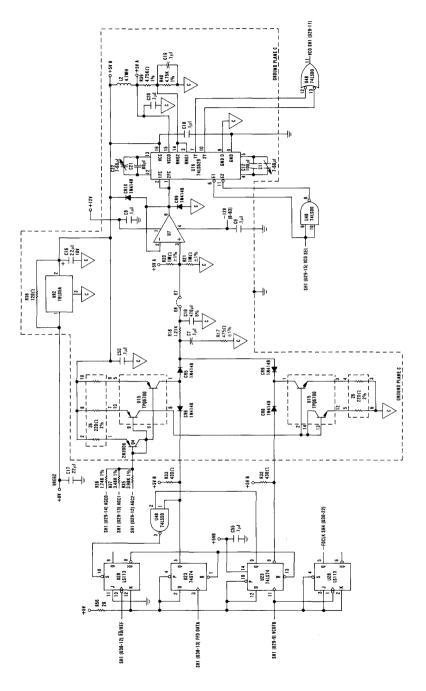

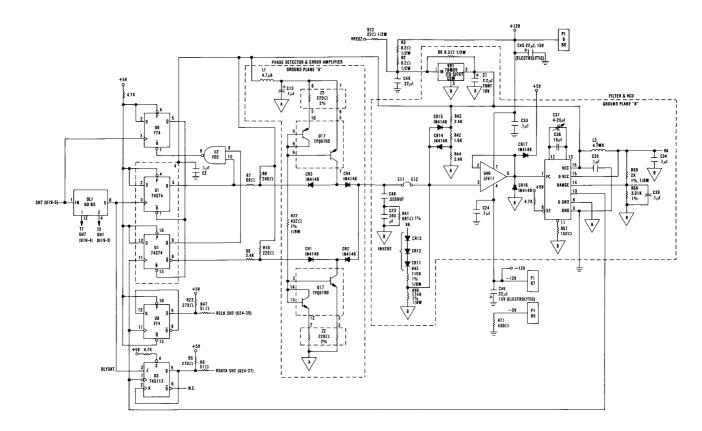

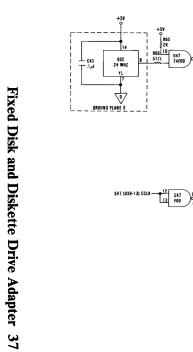

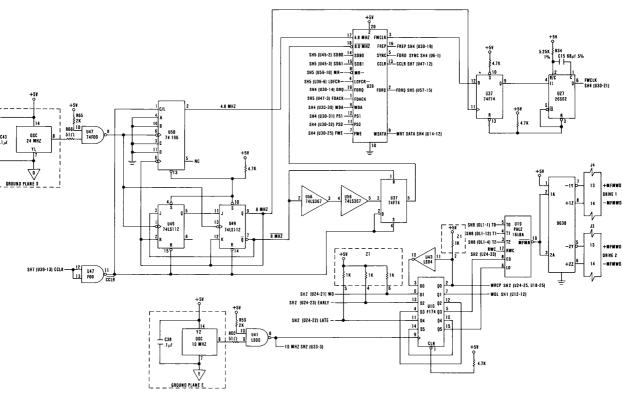

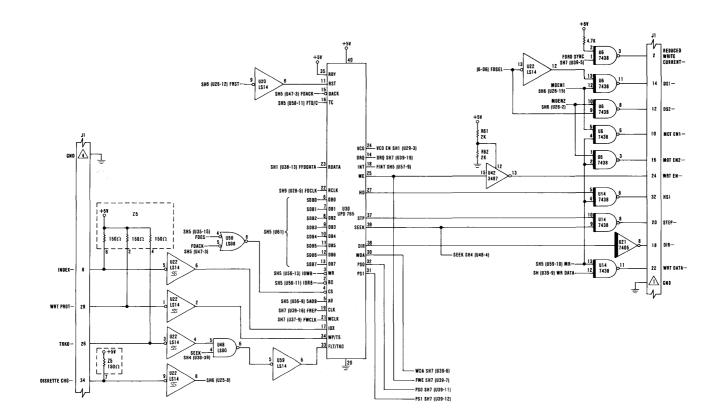

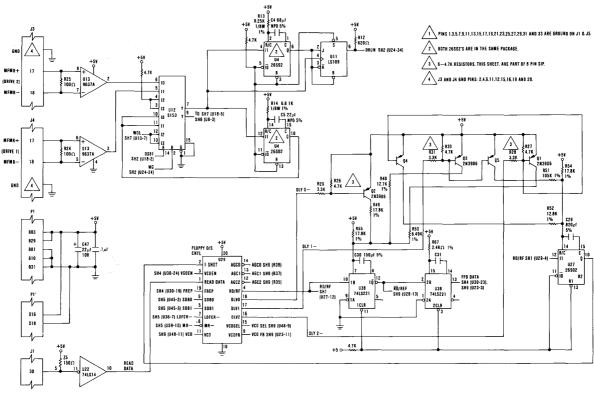

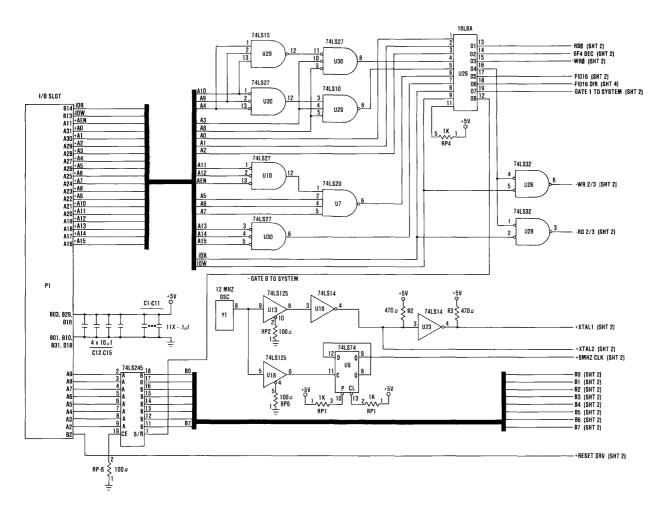

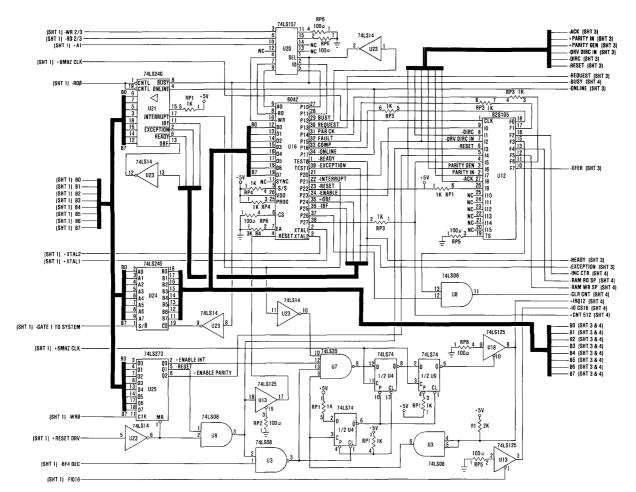

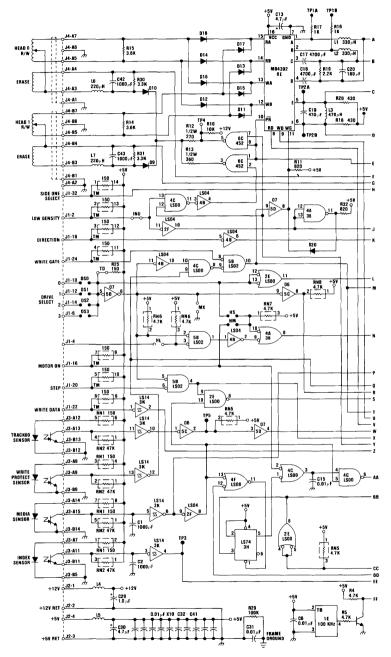

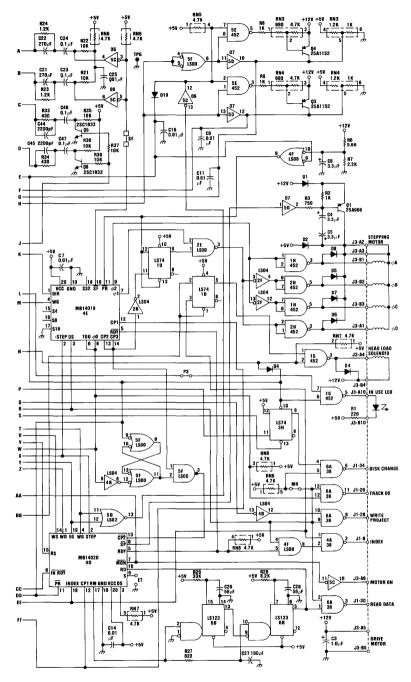

# Logic Diagrams Sheet 1 of 12

| 1/0.01/                                                       | 7   |                          |

|---------------------------------------------------------------|-----|--------------------------|

| 1/0 SL                                                        | A31 | A0 (SHT 4)               |

| 3<br>3<br>7<br>5<br>5<br>4<br>4<br>3<br>2<br>4<br>4<br>4<br>4 | A30 | AU (SHT 4)               |

| 7                                                             | A29 | A2 (SHT 4)               |

| 6                                                             | A28 | A2 (SHT 4)<br>A3 (SHT 4) |

| 5                                                             | A27 | A3 (SHT 4)               |

| 4                                                             | A26 |                          |

| 3                                                             | A25 |                          |

| 2                                                             | A24 | A6 (SHT 4)               |

| 4                                                             | A23 | A7 (SHT 4)               |

| 31                                                            | A22 | A8 (SHT 4)               |

| 4                                                             | A21 | A9 (SHT 4)               |

| 1                                                             | A20 | A10 (SHT 4)              |

|                                                               | A16 | A11 (SHT 4)              |

|                                                               | A15 | A15 (SHT 4)              |

| 1                                                             | A14 | A16 (SHT 4)              |

|                                                               | A13 | A17 (SHT 4)              |

|                                                               | A12 | A18 (SHT 4)              |

|                                                               | A11 | A19 (SHT 4)              |

|                                                               | B03 | AEN (SHT 5)              |

|                                                               | D16 | +5 DC                    |

| [                                                             | B29 |                          |

|                                                               | 801 |                          |

|                                                               | B10 | GROUND                   |

|                                                               | B31 | ÷                        |

|                                                               | 018 |                          |

| 1                                                             | 809 |                          |

|                                                               | B07 | +12V DC                  |

|                                                               | 813 |                          |

|                                                               | B14 |                          |

|                                                               | B02 |                          |

| 1                                                             | 820 | +RESET (SHT 4)           |

| L                                                             |     | I/O CLOCK 4              |

74L\$32

42 RS232C Adapter

Personal Computer Hardware Reference Library

# 4-Port Asynchronous Adapter RS232C

#### TNL SN20-9844 (March 1987) to 75X0235

# Contents

| Description                                           |

|-------------------------------------------------------|

| 4-Port Asynchronous RS-232C Adapter Switch Settings   |

| Modes of Operation                                    |

| Interrupts                                            |

| Serial Data Format                                    |

| External Interface Description                        |

| Asynchronous Communications Element Pin Description 1 |

| Programming Considerations 1                          |

| Connector Specifications                              |

#### TNL SN20-9844 (March 1987) to 75X0235

## Description

The 4-Port Asynchronous RS-232C Adapter provides four serial output ports on a 4.25- by 13.12-inch board that plugs into one I/O position. The adapter system control signals and voltage requirements are provided through a 2- by 31-position and a 2- by 18-position tab on the bottom of the adapter.

Up to four adapters may be used in one &sailboat. system. A DIP switch on the adapter is used to assign the adapter's I/O address range. The port I/O address assignments are contained in the adapter's I/O address range.

The adapter is fully programmable and supports asynchronous communications only. It will add and remove start bits, stop bits, and parity bits. A programmable baud-rate generator allows operation from 50 bps to 19200 bps. Five-, 6-, 7- or 8-bit characters with 1, 1-1/2, or 2 stop bits are supported. A priority interrupt system controls transmit, receive, error, line status, and data set interrupts.

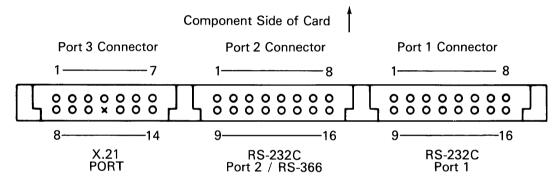

Four 10-pin male AMPMODU connectors on the adapter provide external access to the four ports.

There are two versions of this adapter, one uses the NS16450 LSI chip and the other uses the NS16550. Features in addition to those listed above include:

- Independent receiver clock input.

- Modem control functions: clear to send (CTS), request to send (RTS), data set ready (DSR), data terminal ready (DTR), ring indicator (RI), and received line signal detect (RLSD), which is also known as data carrier detect (DCD) or carrier detect (CD).

- False start bit detection.

- Line-break generation and detection.

- The NS16450 version has full double buffering that reduces the need for precise synchronization.

- The NS16550 is capable of running all existing NS16450 software in its character mode, and in its FIFO mode has a built-in 16 byte buffer for both receive and transmit operations for improved performance.

Note: The NS16550 (Buffered) adapter can be identified by a plus (+) sign stamped at the bottom of the 10-pin interface signals connector. See Figure 9 on page 9.

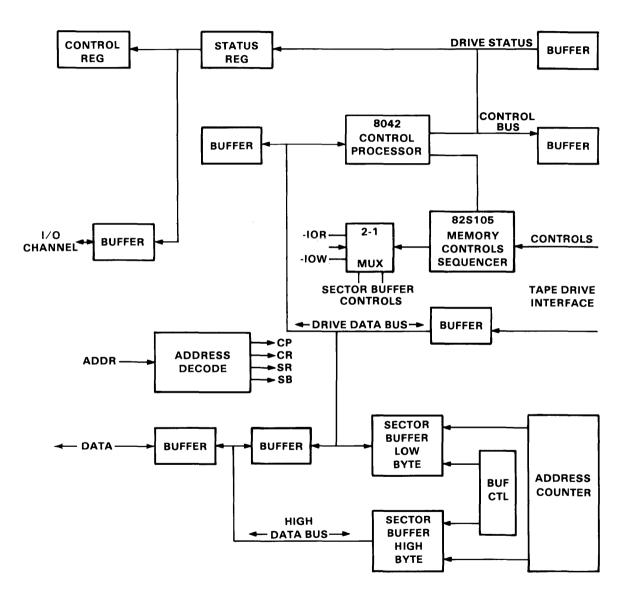

All pacing of the interface and control signal status must be handled by the system software. Figure 1 on page 2 is a block diagram of the 4-Port Asynchronous RS-232C Adapter.

Figure 1. 4-Port Asynchronous RS-232C Adapter Block Diagram

## 4-Port Asynchronous RS-232C Adapter Switch Settings

The 4-Port Asynchronous RS-232C Adapter switch settings select the interrupt level and the address range of adapters installed.

Figure 2. 4-Port Asynchronous RS-232C Adapter Switches

| Interrupt<br>Level              | Switch Bank One Setting |                  |                  |  |  |  |  |

|---------------------------------|-------------------------|------------------|------------------|--|--|--|--|

| Selected                        | Switch 1                | Switch 2         | Switch 3         |  |  |  |  |

| Level 9<br>Level 10<br>Level 11 | On<br>Off<br>Off        | Off<br>On<br>Off | Off<br>Off<br>On |  |  |  |  |

Figure 3. Switch Bank One Settings

#### TNL SN20-9844 (March 1987) to 75X0235

| Address<br>Range of                              | Switch Bank Two Setting |                         |                         |                         |  |  |  |

|--------------------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--|--|--|

| Adapters                                         | Switch 1                | Switch 2                | Switch 3                | Switch 4                |  |  |  |

| 1230-124F<br>2230-224F<br>3230-324F<br>4230-424F | On<br>Off<br>Off<br>Off | Off<br>On<br>Off<br>Off | Off<br>Off<br>On<br>Off | Off<br>Off<br>Off<br>On |  |  |  |

(

Figure 4. Switch Bank Two Settings

Note: Switches 5 through 8 are not used.

#### **Modes of Operation**

The different modes of operation are selected by programming the NS16450/NS16550 asynchronous communications element. Address bits A0, A1, and A2 select the different registers that define the modes of operation. Also, the divisor latch access bit (bit 7) of the line control register is used to select certain registers.

The address range for this adapter is Hex 1230 through Hex 424F. Figure 5 and Figure 6 on page 6 depict a value of n which represents a variable determined by the setting of switch bank two. Switches 1, 2, 3, and 4 of switch bank two allow the adapter to operate and select the appropriate address range.

| I/O Deco<br>Port B | de (In Hex)<br>Port A | Register Selected                                                  | DLAB State       |

|--------------------|-----------------------|--------------------------------------------------------------------|------------------|

| n238               | n230                  | TX Buffer                                                          | DLAB = 0 (Write) |

| n238               | n230                  | RX Buffer                                                          | DLAB = 0 (Read)  |

| n238               | n230                  | Divisor Latch LSB                                                  | DLAB = 1         |

| n239               | n231                  | Divisor Latch MSB                                                  | DLAB = 1         |

| n239               | n231                  | Interrupt Enable Register                                          | DLAB = 0         |

| n23A               | n232                  | Interrupt Identification                                           |                  |

| n23A               | n232                  | Register (Read)<br>FIFO Control Register<br>(Write - NS16550 Only) |                  |

| n23B               | n233                  | Line Control Register                                              |                  |

| n23C               | n234                  | Modem Control Register                                             |                  |

| n23D               | n235                  | Line Status Register                                               |                  |

| n23E               | n236                  | Modem Status Register                                              |                  |

Figure 5. I/O Decodes, Port A and Port B

#### Notes:

1

- 1. n is equal to the first digit of the adapter address range

- 2. DLAB means Divisor Latch Access Bit.

| I/O Deco<br>Port D | de (In Hex)<br>Port C | Register Selected                                                  | DLAB State       |

|--------------------|-----------------------|--------------------------------------------------------------------|------------------|

| n248               | n240                  | TX Buffer                                                          | DLAB = 0 (Write) |

| n248               | n240                  | RX Buffer                                                          | DLAB = 0 (Read)  |

| n248               | n240                  | Divisor Latch LSB                                                  | DLAB = 1         |

| n249               | n241                  | Divisor Latch MSB                                                  | DLAB = 1         |

| n249               | n241                  | Interrupt Enable Register                                          | DLAB = 0         |

| n24A               | n242                  | Interrupt Identification                                           |                  |

| n24A               | n242                  | Register (Read)<br>FIFO Control Register<br>(Write - NS16550 Only) |                  |

| n24B               | n243                  | Line Control Register                                              |                  |

| n24C               | n244                  | Modem Control Register                                             |                  |

| n24D               | n245                  | Line Status Register                                               |                  |

| n24E               | n246                  | Modem Status Register                                              |                  |

Figure 6. I/O Decodes, Port C and Port D

Notes:

- 1. n is equal to the first digit of the adapter address range

- 2. DLAB means Divisor Latch Access Bit.

| A9—>A3<br>Decode | A2 | A1 | AO | DLAB | Register                                                    |

|------------------|----|----|----|------|-------------------------------------------------------------|

| See              | х  | X  | x  |      |                                                             |

| Note 1           | 0  | 0  | 0  | 0    | Receive Buffer Reg. (Read)<br>Transmit Holding Reg. (Write) |

|                  | 0  | 0  | 1  | 0    | Interrupt Enable                                            |

|                  | 0  | 1  | 0  | X    | Interrupt Identification (Read Only)                        |

|                  | 0  | 1  | 0  | x    | FIFO Control (Write - NS16550 Only)                         |

|                  | 0  | 1  | 1  | x    | Line Control                                                |

|                  | 1  | 0  | 0  | X    | Modem Control                                               |

|                  | 1  | 0  | 1  | x    | Line Status                                                 |

|                  | 1  | 1  | 0  | x    | Modem Status                                                |

|                  | 1  | 1  | 1  | x    | Scratch (See note 3)                                        |

|                  | 0  | 0  | 0  | 1    | Divisor Latch (LSB)                                         |

|                  | 0  | 0  | 1  | 1    | Divisor Latch (MSB)                                         |

#### Figure 7. Address Bits

Notes:

- 1. Bits A9 through A3 are used to select specific adapter and serial port.

- 2. A2, A1, and A0 bits are *don't cares* and are used to select the different registers of the NS16450/NS16550 chip.

- 3. The Scratch Register of the NS16450/NS16550 module should be initialized to all ones and never be written to with any data afterwards. This would cause indeterminate data when Read address n237 (see "Interrupts" on page 8) is executed.

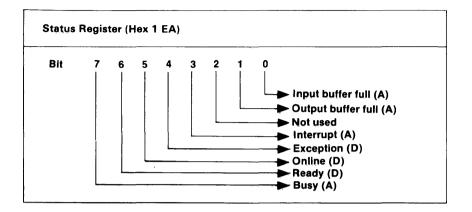

#### Interrupts

Three interrupt lines are provided to the system. The interrupt level (9, 10, or 11) is selected by placing the appropriate switch on switch bank one to the on position. An interrupt register (read adr n237, where n is first digit of the address range) is provided for storage of pending port interrupts. Interrupt register bit assignments are shown in Figure 8.

|       | Hex Addres | ss n237 |       |        |        |        |        |

|-------|------------|---------|-------|--------|--------|--------|--------|

| Bit 7 | Bit 6      | Bit 5   | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

| 1     | 1          | 1       | 1     | Port 4 | Port 3 | Port 2 | Port 1 |

#### Figure 8. Interrupt Register Read Format

Before the 4-Port Asynchronous RS-232C Adapter can generate an interrupt to the processor, it must be enabled by writing any data byte to the interrupt enable address. This address corresponds to the interrupt level that the adapter is jumpered for.

The enable for interrupt level 9 is hex address 02F2.

The enable for interrupt level 10 is hex address 06F2.

The enable for interrupt level 11 is hex address 06F3.

After the adapter generates an interrupt, it must be reset by writing any data byte to the interrupt enable address for that interrupt.

#### Serial Data Format

The data format is as follows:

| Transmit<br>Data<br>Marking | Start<br>Bit | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | Parity<br>Bit | Stop<br>Bit |  |

|-----------------------------|--------------|----|----|----|----|----|----|----|----|---------------|-------------|--|

|-----------------------------|--------------|----|----|----|----|----|----|----|----|---------------|-------------|--|

Data bit 0 is the first bit to be transmitted or received. The adapter automatically inserts the start bit, the correct parity bit (if programmed to do so), and the stop bit (1, 1-1/2, or 2 depending on the command in the line control register).

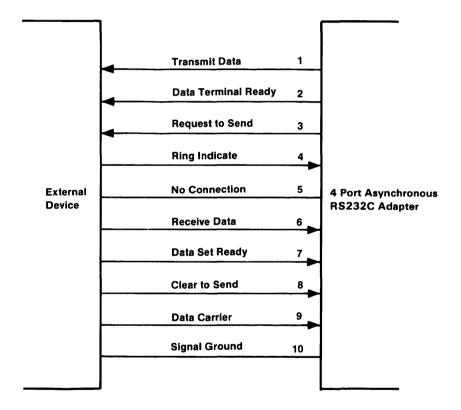

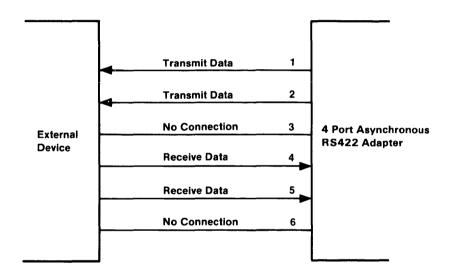

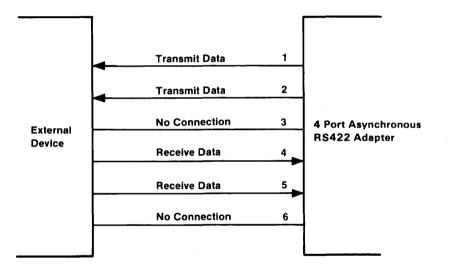

#### **External Interface Description**

The adapter provides an EIA 4-Port Asynchronous RS-232C Adapter-like interface. The pin functions for the 10-pin male connector are shown in Figure 9.

| Pin | Signal              |

|-----|---------------------|

| 1   | Transmit Data       |

| 2   | Data Terminal Ready |

| 3   | Request to Send     |

| 4   | Ring Indicate       |

| 5   | No Connection       |

| 6   | Receive Data        |

| 7   | Data Set Ready      |

| 8   | Clear to Send       |

| 9   | Data Carrier        |

| 10  | Signal Ground       |

Figure 9. 10-Pin Interface Signals Connector (viewed from rear of adapter)

The adapter converts the interface signals from TTL levels to EIA 4-Port Asynchronous RS-232C Adapter voltage levels, and vice versa. These signals are sampled or generated by the communications control chip. These signals can then be sensed by the system software to determine the state of the interface or peripheral device. The drivers and receivers used on the adapter are the inverting type; therefore, a 0 EIA level on the line is received or transmitted as a 0 TTL level, and a 1 EIA level is received or transmitted as a 1 TTL level.

#### **Voltage Interchange Information**

The signal will be considered in the marking condition when the voltage on the interchange circuit, measured at the interface point, is more negative than -3 Vdc with respect to signal ground. The signal will be considered in the spacing condition when the voltage is more positive than +3 Vdc with respect to signal ground. The region between +3 Vdc and -3 Vdc is defined as the transition region and is considered an invalid level. The voltage that is more negative than -15 Vdc or more positive than +15 Vdc is also considered an invalid level.

During the transmission of data, the marking condition denotes the binary state 1 and the spacing condition denotes the binary state 0.

For interface control circuits, the function is on when the voltage is more positive than +3 Vdc with respect to signal ground and is off when the voltage is more negative than -3 Vdc with respect to signal ground.

| Interchange<br>Voltage | Binary<br>State | Signal<br>Condition | Interface<br>Control<br>Function |

|------------------------|-----------------|---------------------|----------------------------------|

| Positive Voltage       | Binary 0        | Spacing             | = On                             |

| Negative Voltage       | Binary 1        | Marking             | = Off                            |

Figure 10. 4-Port Asynchronous RS-232C Adapter Signal Levels

#### **Asynchronous Communications Element Pin Description**

The following describes the function of all NS16450/NS16550 input/output pins. Some of these descriptions reference internal circuits. The use of each signal as implemented on the multiport adapter is described.

Note: In the following descriptions, a low represents a logic 0 (0 Vdc nominal) and a high represents a logic 1 (+2.4 Vdc nominal).

#### **Input Signals**

Chip Select (CS0, CS1, -CS2), Pins 12-14: When CS0 and CS1 are high and -CS2 is low, the chip is selected. Chip selection is complete when the decoded chip select signal is latched with an active (low) address strobe (-ADS) input. This enables communications between the NS16450/NS16550 and the processor.

**Data Input Strobe (DISTR, -DISTR), Pins 22 and 21:** When DISTR is high or -DISTR is low while the chip is selected, the processor can read status information or data from a selected register of the NS16450/NS16550.

**Note:** Only one active DISTR or -DISTR input is required to transfer data from the NS16450/ NS16550 during a read operation. Therefore, the DISTR input has been permanently tied low and the -DISTR line is used.

**Data Output Strobe (DOSTR, -DOSTR), Pins 19 and 18:** When DOSTR is high or -DOSTR is low while the chip is selected, the processor can write data or control words into a selected register of the NS16450/NS16550.

**Note:** Only one active DOSTR or -DOSTR input is required to transfer data to the NS16450/ NS16550 during a write operation. Therefore, the DOSTR input has been permanently tied low and the -DOSTR input is used.

-Address Strobe (-ADS), Pin 25: When low, this signal provides latching for the register select (A0, A1, A2) and chip select (CS0, CS1, -CS2) signals.

**Note:** The -ADS input has been tied low because the register select (A0, A1, A2) signals are stable for the duration of read and write operations.

**Register Select (A0, A1, A2), Pins 26-28:** These three inputs are used during a read or write operation to select an NS16450/NS16550 register to read from or write into as indicated in Figure 11. Note that the state of the divisor latch access bit (DLAB), which is the most significant bit of the line control register, affects the selection of certain NS16450/NS16550 registers. The DLAB must be set high by the system software to access the baud-generator divisor latches.

#### TNL SN20-9844 (March 1987) to 75X0235

| DLAB | A2 | A1 | A0 | Register                               |

|------|----|----|----|----------------------------------------|

| 0    | 0  | 0  | 0  | Receiver Buffer (Read)                 |

| 0    | 0  | 0  | 0  | Transmitter Holding Register (Write)   |

| 0    | 0  | 0  | 1  | Interrupt Enable                       |

| x    | 0  | 1  | 0  | Interrupt Identification (Read Only)   |

| х    | 0  | 1  | 0  | FIFO Control (Write - NS16550 Only)    |

| х    | 0  | 1  | 1  | Line Control                           |

| х    | 1  | 0  | 0  | Modem Control                          |

| х    | 1  | 0  | 1  | Line Status                            |

| х    | 1  | 1  | 0  | Modem Status                           |

| x    | 1  | 1  | 1  | Scratch                                |

| 1    | 0  | 0  | 0  | Divisor Latch (Least Significant Byte) |

| 1    | 0  | 0  | 0  | Divisor Latch (Most Significant Byte)  |

(

Figure 11. NS16450/NS16550 Register Selection

| Register/Signal                      | <b>Reset Control</b>          | Reset State                                                              |

|--------------------------------------|-------------------------------|--------------------------------------------------------------------------|

| Interrupt Enable<br>Register         | Master Reset                  | All Bits Low, 0-3<br>Forced and 4-7<br>Permanent                         |

| Interrupt<br>Identification Register | Master Reset                  | Bit 0 is High, Bits 1<br>and 2 are Low, and<br>Bits 3-7 are<br>Permanent |

| Line Control Register                | Master Reset                  | All Bits Low                                                             |

| Modem Control<br>Register            | Master Reset                  | All Bits Low                                                             |

| Line Status Register                 | Master Reset                  | All Bits Low, except<br>Bits 5 and 6 are High                            |

| Modem Status<br>Register             | Master Reset                  | Bits 0-3 are Low, Bits $4-7 =$ Input Signal                              |

| SOUT                                 | Master Reset                  | High                                                                     |

| INTRPT (RCVR<br>Errors)              | Read LSR/MR                   | Low                                                                      |