Personal Computer Hardware Reference Library

# RT PC Technical Reference Token-Ring Network Adapter

Personal Computer Hardware Reference Library

# RT PC Technical Reference Token-Ring Network Adapter

#### Second Edition (February 1987)

Changes are made periodically to the information herein; these changes will be incorporated in new editions of this publication.

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM program product in this publication is not intended to state or imply that only IBM's program product may be used. Any functionally equivalent program may be used instead.

International Business Machines Corporation provides this manual "as is," without warranty of any kind, either express or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purposes. IBM may make improvement and/or changes in the product(s) and/or the program(s) described in this manual at any time.

Products are not stocked at the address given below. Requests for copies of this product and for technical information about the system should be made to your IBM representative or to the IBM branch office serving your locality.

Address comments on this publication to IBM Corporation, Department EO2, PO. Box 12195, Research Triangle Park, North Carolina 27709. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

©Copyright International Business Machines Corporation 1986, 1987

#### Federal Communications Commission (FCC) Statement

Warning: This equipment generates, uses and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

iv Token-Ring Network Adapter

# **About This Book**

# Purpose

This manual describes the operating characteristics of the IBM Token-Ring Network RT PC Adapter.

# Audience

The information in this publication is for reference, and is intended for hardware and program designers, programmers, engineers, and anyone else who needs to understand the design and operation of the IBM Token-Ring Network RT PC Adapter.

# How to Use This Book

The manual consists of four chapters: Chapter 1 is an introduction to the function and features of the IBM Token-Ring Network RT PC Adapter, Chapter 2 describes the hardware and its operation, Chapter 3 describes the software required to utilize the Adapter, Chapter 4 provides the environmental requirements to ensure proper operation. Appendix A is provided for example software.

# **Related Publications**

Refer to the following IBM publications for additional information:

- A Building Planning Guide for Communication Wiring G230-8059

- IBM Cabling System Planning and Installation Guide, GA27-3361

- Using the IBM Cabling System with Communication Products, GA27-3677.

# **Prerequisite Publications**

Information from the following publications is necessary for use of this manual.

- IBM Token-Ring Network Architecture Reference

- IEEE Standards for Token-Ring Networks: Logical Link Control, ANSI/IEEE Std 802.2 1985

# Contents

| Chapter 1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -3  |

| Chapter 2. Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -1  |

| Architecture 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-3 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-5 |

| Adapter Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41  |

| Chapter 3. Software Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -1  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-3 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-4 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-5 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13  |

| 2 mB up 2 mBroomes that the second seco                                                                                                                                                                                                                                             | 15  |

| i aup of initialization of the test of | 23  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 78  |

| Chapter 4. Environmental Requirements 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-3 |

| Appendix A. Software Example A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -1  |

viii Token-Ring Network Adapter

# Figures

| 1-1.  | Token Format                                                                      | 1-5  |

|-------|-----------------------------------------------------------------------------------|------|

| 1-2.  | Frame Format                                                                      | 1-6  |

| 2-1.  | Token-Ring Adapter Architecture                                                   | 2-3  |

| 2-2.  | Adapter Bus Memory Map                                                            | 2-11 |

| 2-3.  | Differential Manchester Code                                                      | 2-14 |

| 2-4A. | Token-Ring Adapter Logic Diagram (card assembly 56X2295 or 69X8139)               | 2-17 |

|       | Token-Ring Adapter Logic Diagram (card assemblies other than 56X2295 and 69X8139) | 2-29 |

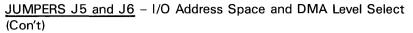

| 2-5A. | Jumper Diagrams (card assembly 56X2295 or 69X8139)                                | 2-42 |

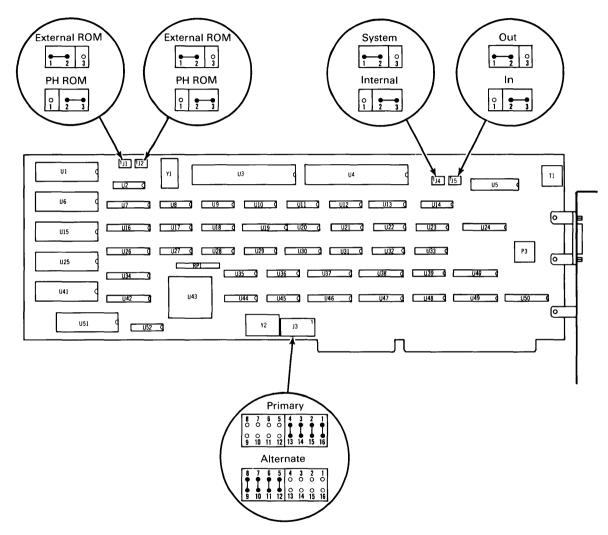

| 2-5B. | Jumper Diagrams (card assemblies other than 56X2295 and 69X8139)                  | 2-43 |

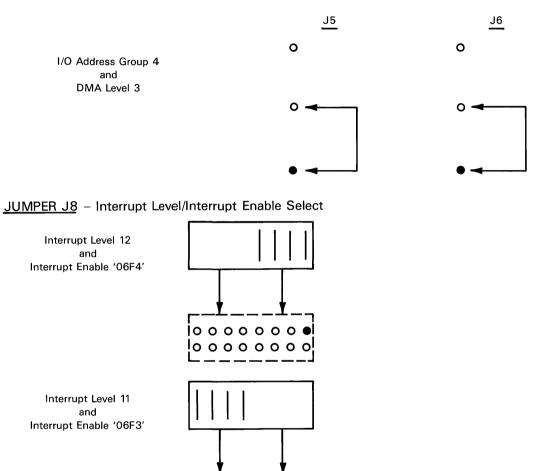

| 2-6A. | Token-Ring Adapter Card (card assemblies 56X2295 and 69X8139)                     | 2-47 |

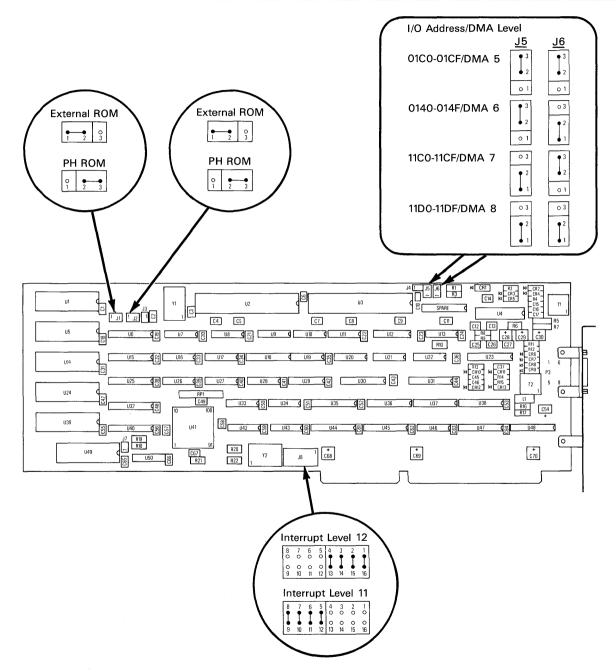

| 2-6B. | Token-Ring Adapter Card (card assemblies other than 56X2295 or 69X8139)           | 2-48 |

| 3-1.  | CMD/STS Register Write Bit Assignments                                            |      |

| 3-2.  | CMD/STS Register Read Bit Assignments                                             |      |

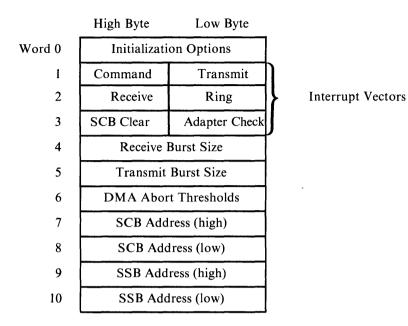

| 3-3.  | Parameter Initialization Block                                                    | 3-16 |

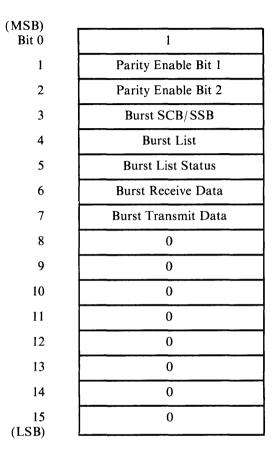

| 3-4.  | Initialization Options Bit Assignments                                            | 3-17 |

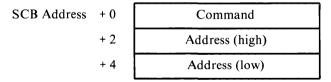

| 3-5.  | System Command Block Format                                                       | 3-23 |

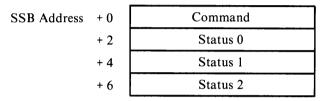

| 3-6.  | System Status Block Format                                                        | 3-25 |

| 3-7.  | RING STATUS SSB Format                                                            | 3-26 |

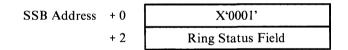

| 3-8.  | RING STATUS Field Bit Assignments                                                 | 3-27 |

| 3-9.  | COMMAND REJECT SSB Format                                                         | 3-29 |

|       | Reject Reason Field Bit Assignment                                                | 3-30 |

|       | Adapter Check Status Format                                                       | 3-31 |

|       | Adapter Check Field Bit Assignments                                               | 3-32 |

|       | OPEN Command SCB                                                                  | 3-36 |

|       | OPEN Parameter List                                                               | 3-37 |

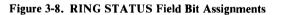

|       | OPEN Command SSB                                                                  | 3-41 |

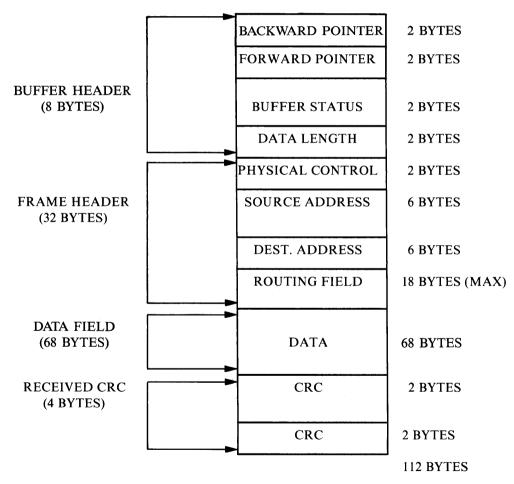

|       | Example Adapter Internal Frame Format                                             | 3-44 |

|       | Attached System Frame Logical Format                                              | 3-46 |

|       | TRANSMIT SCB                                                                      | 3-49 |

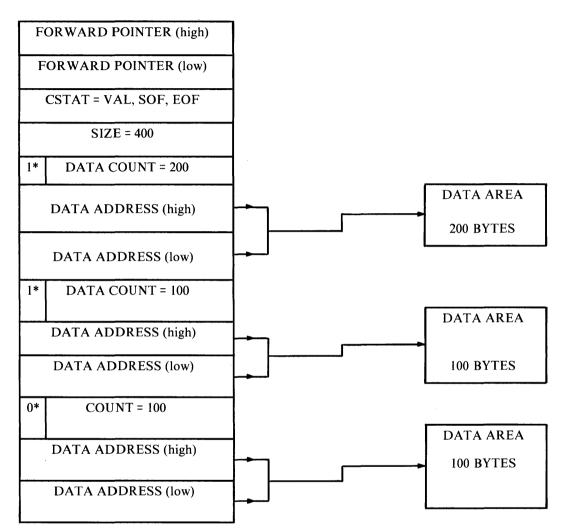

|       | TRANSMIT Parameter List shown with three Data Counts                              | 3-50 |

|       | TRANSMIT SSB                                                                      | 3-54 |

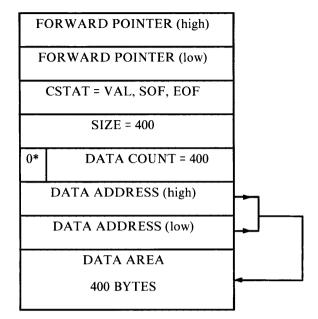

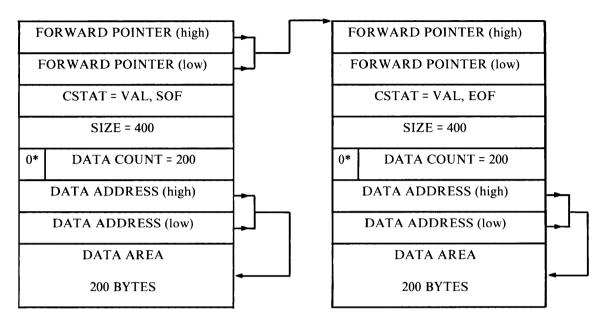

|       | Transmit List Format: Example 1                                                   | 3-58 |

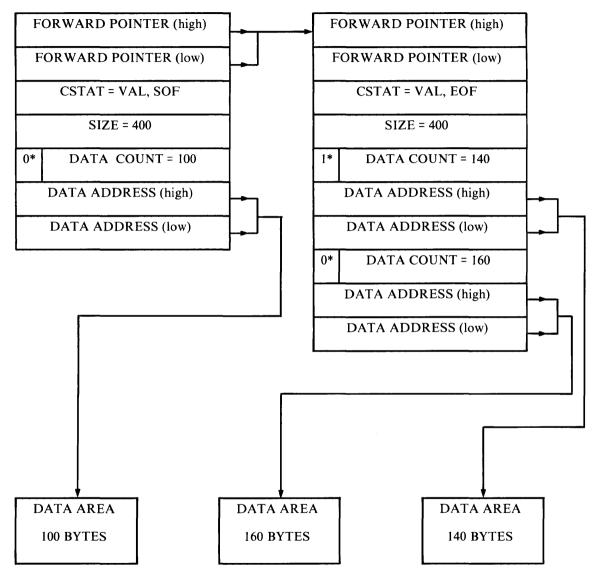

|       | Transmit List Format: Example 2                                                   | 3-59 |

|       | Transmit List Format: Example 3                                                   | 3-60 |

|       | Transmit List Format: Example 4                                                   | 3-61 |

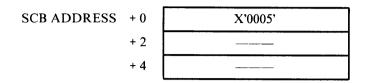

|       | TRANSMIT HALT Command SCB                                                         | 3-62 |

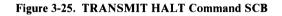

|       | RECEIVE Command SCB                                                               | 3-63 |

| 3-27. | RECEIVE Parameter List Shown with three Data Counts                               | 3-63 |

| 3-28. RECEIVE Command SSB                | 3-67 |

|------------------------------------------|------|

| 3-29. CLOSE Command SCB                  | 3-69 |

| 3-30. CLOSE Command SSB                  | 3-70 |

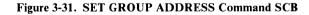

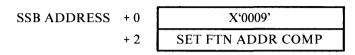

| 3-31. SET GROUP ADDRESS Command SCB      | 3-70 |

| 3-32. SET GROUP ADDRESS Command SSB      | 3-71 |

| 3-33. SET FUNCTIONAL ADDRESS Command SCB | 3-71 |

| 3-34. SET FUNCTIONAL ADDRESS Command SSB | 3-72 |

| 3-35. READ ERROR LOG Command SCB         | 3-72 |

| 3-36. Error Log Table                    | 3-73 |

| 3-37. READ ERROR LOG Command SSB         | 3-73 |

| 3-38. READ ADAPTER BUFFER Command SCB    | 3-74 |

| 3-39. READ ADAPTER System Buffer Space   | 3-75 |

| 3-40. READ ADAPTER BUFFER Command SSB    | 3-77 |

# Tables

| 2-1.  | DIO Register Addresses                                               | 2-5  |

|-------|----------------------------------------------------------------------|------|

| 2-2.  | Adapter I/O Addresses                                                | 2-10 |

| 2-3.  | Ring Connector Pin Assignment                                        | 2-13 |

| 2-4.  | Default Jumper Configuration                                         | 2-31 |

| 2-4A  | . Default Jumper Configuration (card assemblies 56X2295 and 69X8139) | 2-46 |

| 2-4B. | Default Jumper Configuration (other card assemblies )                | 2-46 |

| 3-1.  | CMD/STS Register Write Bit Functions                                 | 3-7  |

| 3-2.  | CMD/STS Register Read Bit Functions                                  | 3-9  |

| 3-3.  | Bring-up Diagnostics Error Codes                                     | 3-14 |

| 3-4.  | Initialization Options Field Bit Functions                           | 3-18 |

| 3-5.  | Adapter Initialization Errors                                        | 3-22 |

| 3-6.  | RING STATUS Field Bit Functions                                      | 3-28 |

| 3-7.  | Reject Reason Field Bit Functions                                    | 3-31 |

| 3-8.  | Adapter Check Bit Definitions                                        | 3-33 |

| 3-9.  | Adapter Command Summary                                              | 3-35 |

| 3-10. | OPEN Parameter Functions                                             | 3-38 |

| 3-11. | OPEN Status Bit Definitions                                          | 3-41 |

|       | OPEN Phases and OPEN Error Codes                                     | 3-42 |

| 3-13. | OPEN Error Code                                                      | 3-43 |

| 3-14. | Attached System Frame Fields                                         | 3-47 |

| 3-15. | TRANSMIT Parameter List Fields                                       | 3-51 |

|       | Transmit Complete Field Bit Definitions                              | 3-55 |

| 3-17. | RECEIVE Parameter List Field Definitions                             | 3-64 |

|       | RECEIVE COMPLETE Field Bit Definitions                               | 3-67 |

| 3-19. | CLOSE COMPLETION Field Bit Definitions                               | 3-70 |

| 3-20. | SET GROUP ADDRESS Completion Field Bit Definitions                   | 3-71 |

| 3-21. | SET FUNCTIONAL ADDRESS Completion Field Bit Definitions              | 3-72 |

| 3-22. | READ ERROR LOG COMPLETION Field Bit Definitions                      | 3-74 |

|       | Adapter Internal Pointers                                            | 3-76 |

|       | READ ADAPTER BUFFER Completion Field Bit Definitions                 | 3-77 |

# Chapter 1. Overview

Overview 1-1

# CONTENTS

| Description                                 |     |

|---------------------------------------------|-----|

| Components of the IBM Token-Ring Network    | 1-3 |

| Communicating on the IBM Token-Ring Network |     |

| Adapter Communication on the Network        | 1-4 |

| Token Format                                | 1-5 |

| Frames                                      | 1-5 |

# Description

The IBM Token-Ring Network, a token-ring, star-wired network, can accomodate up to 260 attaching devices (printers, processors, controllers). These work stations, within a moderate-sized geographic area, can be connected to one another via a series of cable, multistation access units, and special adapter cards installed in the attaching devices. Application programs running in each work station (such as an IBM RT Personal Computer) can direct the adapter to become a part of the ring.

### **Components of the IBM Token-Ring Network**

Cable connects work areas to wiring closets and wiring closets to one another.

Access units, such as IBM 8228 Multistation Access Units, are connected to the ring with patch cables. You may connect up to eight attaching devices, such as IBM RT Personal Computers, to each 8228 Access Unit.

Adapter cards, such as the IBM Token-Ring Network RT PC Adapters, are installed in each attaching device to enable the devices to communicate to one another on the network.

### Communicating on the IBM Token-Ring Network

The IBM Token-Ring Network uses a protocol to control data flow, monitor ring conditions, and encapsulate and route data for devices attached to the physical ring. The Token, Frame and Medium Access Control (MAC) are involved in this LAN protocol. This protocol is not totally explained in this manual. See *IBM Token-Ring Network Architecture Reference* for more detail about this protocol.

# Adapter Communication on the Network

An IBM RT PC is ready to become part of the network when:

- An IBM Token-Ring Network RT PC Adapter has been installed.

- The IBM Token-Ring Network RT PC Adapter is connected to the IBM Cabling System using an attachment cable to a multistation access unit. (The Token-Ring Adapter can also be attached to telephone twisted-pair media by using the Type 3 Media Filter. Reference the *IBM Token-Ring Network Telephone Twisted-Pair Media Guide*, GA27-3714.)

- A program to support the IBM Token-Ring Network RT PC Adapter has been loaded into the RT PC.

To communicate on the network a device adapter obtains a token and changes the token to a frame containing control information and data. The frame is then passed around the ring, and each device on the ring monitors the frame and retransmits it. When the frame reaches the device to which it is addressed, the device copies the frame while retransmitting it and indicates in the frame that the data has been received. The frame continues in the same direction around the ring until it returns to the device that sent the frame. The sending device removes the frame from the ring replacing it with a token.

#### Transmission of Data on the Network

When the RT Personal Computer is powered on, the Token-Ring Network Adapter goes through a series of operational diagnostics before attempting to attach to the network. The adapter card verifies:

- The correct operation of the adapter card.

- That a cable between the attaching device and the 8228 Access Unit exists.

- That a test message sent along the lobe cable (the cable between the attaching device and the 8228 Access Unit) can pass through the cable and return unchanged.

The **ADAPTER.OPEN** command tells the adapter to send a direct current to the 8228 Access Unit to which it is attached. This causes the attaching device to become an active part of the ring, receiving, monitoring, and retransmitting ring traffic.

The device places data on the ring by changing a token into a frame that will pass around the ring in place of the token.

# **Token Format**

A token is a unique sequence of bits in 3 bytes transmitted on the ring. The sequence is a start delimiter followed by an access control field of one byte and ending with an end delimiter byte. Each byte is eight bits in length without parity. Both the start delimiter (SD) and the end delimiter (ED) are unique bit arrangements recognized by all adapters compatible with an IBM Token-Ring Network. The access control (AC) field controls access to the ring. Refer to Figure 1-1.

| SD     | AC     | ED     |

|--------|--------|--------|

| 1 Byte | 1 Byte | 1 Byte |

|        |        |        |

#### Figure 1-1. Token Format

The same three bytes are included in a frame. However, the token indicator bit is set to 1 in the AC byte to indicate a frame rather than a token. Additional information bytes are included between the AC byte and the ED byte.

#### Frames

A frame consists of a physical header followed by information bytes and a physical trailer. Refer to figure 1-2.

The physical header consists of the starting delimiter (SD) byte, the access control (AC) byte with the token indicator bit set to 1, the frame control (FC) byte, 6 bytes of destination address, 6 bytes of source address, and from zero to 18 bytes of routing information. This is followed by the information field which contains the user-provided data. At the end of the frame is the physical trailer which consists of a 4 byte frame check sequence (FCS), the ending delimiter (ED) byte, and the frame status (FS) byte. The data contained in the frame may be of two types:

- MAC frames

- Non-MAC frames

Medium Access Control (MAC) frames contain information about the status of an adapter or the ring itself. Non-MAC frames contain data and messages that users transmit to one another. The 2 most significant bits of the FC byte define the frame type. The types are :

B'00'= MAC frame B'01'= LLC frame B'10'= reserved B'11'= reserved

Frames are described in detail in the IBM Token-Ring Network Architecture Reference.

| SD     | AC     | FC     | Dest.<br>Addr. | Source<br>Addr. | ROUTING       | Info<br>Field | FCS     | ED     | FS     |

|--------|--------|--------|----------------|-----------------|---------------|---------------|---------|--------|--------|

| 1 byte | 1 byte | l byte | 6 bytes        | 6 bytes         | 0-18<br>bytes | bytes         | 4 bytes | 1 byte | 1 byte |

Figure 1-2. Frame Format

# Chapter 2. Description

# CONTENTS

| Architecture                            |     |

|-----------------------------------------|-----|

| Features                                | 2-4 |

| System Interface Description            | 2-5 |

| Signal Levels                           | 2-5 |

| IBM RT PC Bus Connector Pin Description | 2-5 |

| Adapter Bus Interface                   |     |

| Adapter Bus Memory Map 2-               | -11 |

| Ring Interface 2-                       | -12 |

| Hardware Description                    | -12 |

| Physical Signaling                      | -14 |

| Schematic Diagrams 2-                   |     |

| Physical Description                    | -41 |

| Jumper Descriptions                     | -41 |

| Card Layout 2-                          | -46 |

# Architecture

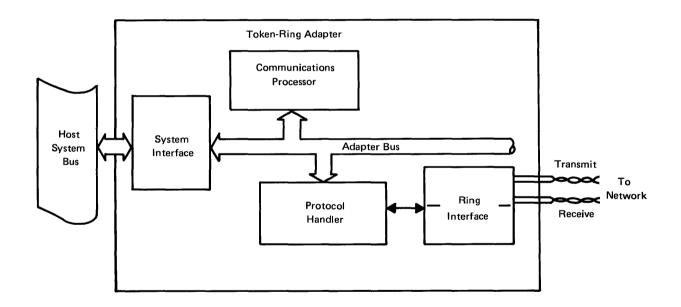

The Adapter hardware can be conceptualized as three different interfaces: the Host System Interface, the Adapter Bus interface which provides the internal communication link of the adapter, and the Ring Interface which provides the communications interface to the IBM Token-Ring Network. See figure 2-1. The information which follows is presented in this manner with a hardware description of the Host System Interface, the Adapter Bus, and the Ring Interface. Schematic diagrams for the Adapter Card and some physical characteristics of the Adapter Card are also provided.

Figure 2-1. Token-Ring Adapter Architecture

# Features

The RT PC Token-Ring Network Adapter is designed to provide a communications interface between an IBM Token-Ring Network and an Intel 80286-type interface such as the IBM RT Personal Computer. A summary of the Adapter's features are listed below:

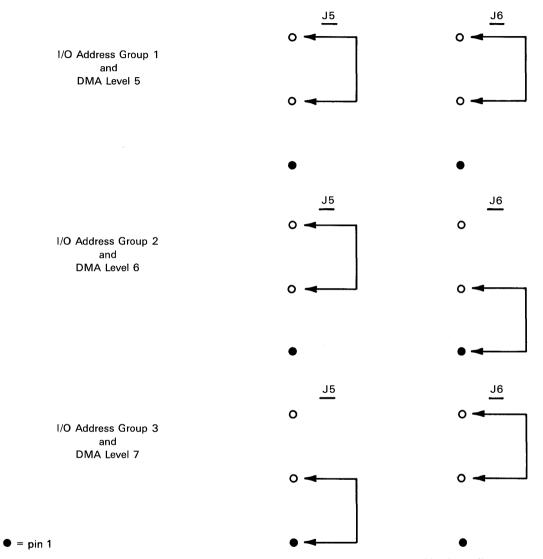

- IEEE 802.5 Token-Ring LAN Compatible

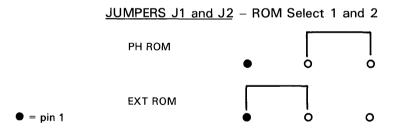

- Jumper selectable DMA levels and I/O address space

- Microcode Update Capability -EPROM Sockets for Microcode Instructions (Jumper Selectable)

- 16K Bytes Data Buffer

- DMA Bus Master

- Direct I/O Addressing

- Interrupt sharing

- Jumper selectable\* interrupt levels

- \* Not applicable to card assembly 56X2295 or 69X8139

# System Interface Description

This interface provides for read/writes between the Token-Ring Network Adapter (hereafter referred to as Adapter) and the IBM RT PC, termed a Direct Input/Output (DIO), and Direct Memory Access (DMA) in which the Adapter is bus owner and controls read/writes to the Host System Bus. The interface also features a sharable interrupt on interrupt levels 11\* and 12.

\* Not applicable to card assembly 56X2295 or 69X8139.

### **Signal Levels**

Signals are active high except when the signal name is preceded by the symbol "-", which indicates that the signal is active low.

## **IBM RT PC Bus Connector Pin Description**

#### System Address Bus (SA0 - SA19, LA17 - LA23)

This tri-state bus consists of 27 latched address lines. This bus is driven by the Adapter when it is Bus Owner. During DIO cycles, address bits SA16 and LA17 - LA23 are all 0. LA23 is the most significant bit and SA0 is the least significant bit.

Address bits SA1 and SA2 are wired to bits SRS1 and SRS0, respectively, on the system interface of the Adapter Card. The state of SRS1 and SRS0 selects one of four halfword registers through the DIO interface. A summary of the register addresses is provided in the following table.

| SA2<br>(SRS0) | SA1<br>(SRS1) | BHE | Register Accessed    |

|---------------|---------------|-----|----------------------|

| 0             | 0             | 0   | SIFD MSB and LSB     |

| 0             | 1             | 0   | SIFD/INC MSB and LSB |

| 1             | 0             | 0   | SIFADR MSB and LSB   |

| 1             | 1             | 0   | SIFCMD and SIFSTS    |

#### Table 2-1. DIO Register Addresses

**Note:** When -BHE is 0, both bytes of the halfword register are accessed together; when -BHE is 1, the LSB of the halfword register is accessed.

#### System Bus High Enable (-SBHE)

This is a tri-state bidirectional line that is driven during a DMA operation and is an input during a DIO operation. It is placed in the high impedance state at all other times. The signal is active when the high byte is to be enabled on the output bus. As an input, the signal selects the most significant byte of the DIO register.

#### **Address Enable (AEN)**

Address enable is used in the address decode of the Adapter to ensure proper device selection during a DIO cycle. AEN low and a valid address properly selects the Adapter.

#### System Data Bus (SD0 - SD15)

This tri-state bidirectional bus consists of sixteen data lines which are used to transfer data between the Adapter and system memory. The Adapter sends data on write cycles and the memory sends data on read cycles. SD15 is the most significant bit and SD0 is the least significant bit.

#### Memory Read (-MEMR)

The Memory Read Command is a tri-state signal driven by the Adapter card during DMA operations. It instructs the selected device in the memory space to drive data onto the data bus.

#### **Memory Write (-MEMW)**

The Memory Write Command is a tri-state signal driven by the Adapter card during DMA operations. It instructs the selected device in the memory space to store the data present on the data bus.

#### I/O Read (-IOR)

The I/O Read command is a tri-state signal driven by the System Bus which instructs the Adapter card to drive data onto the data bus during DIO operations. This data is held on the bus for as long as -IOR is active.

#### I/O Write (-IOW)

The I/O Write command is a tri-state signal driven by the System Bus which instructs the Adapter card to store the data presently on the data bus during DIO operations.

#### I/O Channel Ready (I/OCHRDY)

I/O Channel Ready is a normally high, open collector signal that is used by the Adapter to lengthen a current cycle. During a DIO, when the Adapter is a controlled device, I/OCHRDY is driven low after a valid select is detected and held low until the Adapter is able to complete the cycle. During a DMA, when the Adapter controls the bus, the current cycle may be lengthened by the Host System Bus driving I/OCHRDY low.

#### I/O Card Select 16-Bit (-I/OCS16)

This signal is driven active by the Adapter card after decoding a valid address.

#### DMA Request (DRQ3\*, DRQ5, DRQ6, DRQ7\*)

The DMA Request line (DRQx, jumper selectable) is driven high by the Adapter to request DMA service or control of the system bus. DRQx is held high by the Adapter card throughout the bus operation. DRQ3 has the highest priority and DRQ7 has the lowest priority. The DRQ is tri-stated by the assertion of a System Reset. In the case of a soft reset, a DIO to the Adapter Reset address, the DRQ will be tri-stated and this may cause the DMA controller to erroneously detect a DMA request. To avert this problem the DMA controller should be disabled before a soft reset is asserted.

\* Not applicable to card assembly 56X2295 or 69X8139.

#### DMA Acknowledge (-DACK3\*, -DACK5, -DACK6, -DACK7\*)

The DMA Acknowledge signal is driven active by the System Bus in response to the corresponding DMA request. The -DACKx signal indicates that the Adapter will be granted use of the bus following proper activation of the -MASTER control signal.

\* Not applicable to card assembly 56X2295 or 69X8139.

#### **Bus Master (-MASTER)**

This signal is used by the Adapter to gain control of the I/O Bus after receiving a DMA Acknowledge. After receiving the -DACK the Adapter drives the -MASTER line low, then after a delay the Adapter drives the address and data lines. When releasing the bus all address, data, and control lines are tri-stated before driving -MASTER high (inactive).

#### Interrupt Request (IRQ11\*, IRQ12)

The interrupt request line is used to signal the System processor that the Adapter card requires attention. An interrupt request is generated by pulsing the IRQxx line. This pulse is formed by a transition from high-to-low and held low for two clock cycles before transitioning high. The low-to-high transition of the pulse signals an interrupt to the Using Product System. A 2-kilohm pullup resistor is included on the output of the IRQxx tri-state driver to accommodate interrupt sharing. This driver has an enable/disable function which is programmable by the Using Product system software and an interrupt is disabled by a system reset.

\* Not applicable to card assembly 56X2295 or 69X8139.

#### **Reset Driver (RESET DRV)**

Reset Driver is an input to the Adapter used to set internal devices to a known state.

# I/O Pin Assignments

| SIGNAL<br>NAME | I/O<br>PIN |  | SIGNAL<br>NAME   | I/O<br>PIN |

|----------------|------------|--|------------------|------------|

| SA0            | A31        |  | -IOW             | B13        |

| SA1            | A30        |  | GND              | B10        |

| SA2            | A29        |  | +5               | B03        |

| SA3            | A28        |  | <b>RESET DRV</b> | B02        |

| SA4            | A27        |  | GND              | B01        |

| SA5            | A26        |  | SD15             | C18        |

| SA6            | A25        |  | SD14             | C17        |

| SA7            | A24        |  | SD13             | C16        |

| SA8            | A23        |  | SD12             | C15        |

| SA9            | A22        |  | SD11             | C14        |

| SA10           | A21        |  | SD10             | C13        |

| SA11           | A20        |  | SD9              | C12        |

| SA12           | A19        |  | SD8              | C11        |

| SA13           | A18        |  | -MEMW            | C10        |

| SA14           | A17        |  | -MEMR            | C09        |

| SA15           | A16        |  | LA17             | C08        |

| SA16           | A15        |  | LA18             | C07        |

| SA17           | A14        |  | LA19             | C06        |

| SA18           | A13        |  | LA20             | C05        |

| SA19           | A12        |  | LA21             | C04        |

| AEN            | A11        |  | LA22             | C03        |

| I/O CHRDY      | A10        |  | LA23             | C02        |

| SD0            | A09        |  | -SBHE            | C01        |

| SD1            | A08        |  | GND              | D18        |

| SD2            | A07        |  | -MASTER          | D17        |

| SD3            | A06        |  | +5               | D16        |

| SD4            | A05        |  | DRQ7*            | D15        |

| SD5            | A04        |  | -DACK7*          | D14        |

| SD6            | A03        |  | DRQ6             | D13        |

| SD7            | A02        |  | -DACK6           | D12        |

| GND            | B31        |  | DRQ5             | D11        |

| +5             | B29        |  | -DACK5           | D10        |

| DRQ3*          | B16        |  | IRQ12            | D05        |

| -DACK3*        | B15        |  | IRQ11 *          | D04        |

| -IOR           | B14        |  | -I/OCS16         | D02        |

\* Not applicable to card assembly 56X2295 or 69X8139

# Adapter I/O Addresses

| Table 2-2. | Adapter | I/0 | Addresses |

|------------|---------|-----|-----------|

|------------|---------|-----|-----------|

| Primary<br>(Hex Address) | Alternate<br>(Hex Address) | Register                               |

|--------------------------|----------------------------|----------------------------------------|

| 01C0                     | 0140                       | SIF Data                               |

| 01C2                     | 0142                       | SIF Data INC                           |

| 01C4                     | 0144                       | SIF Address                            |

| 01C6                     | 0146                       | Command/Status                         |

| 01C8                     | 0148                       | Enable Interrupts                      |

| 01CC                     | 014C                       | Disable Interrupts                     |

| 01CE                     | 014E                       | Adapter Reset                          |

| 06F4                     | 06F4                       | Interrupt Level Enable (ILE), Level 12 |

# **Adapter Bus Interface**

The Adapter Bus Interface is internal to the Adapter Card. It interfaces to the Communications Processor, the Protocol Handler, the System Interface, as well as the Adapter RAM and sockets for the Microcode Update EPROMs.

### **Adapter Bus Memory Map**

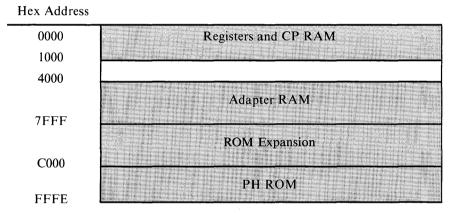

The memory map for the Adapter is shown in Figure 2-2. This memory map illustrates a memory space of 64 K bytes.

Figure 2-2. Adapter Bus Memory Map

#### Microcode Update EPROMs

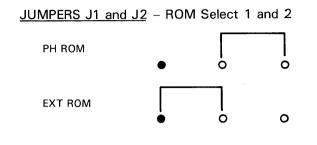

The Adapter's control program currently resides in ROM within the Protocol Handler. The adapter features sockets for three EPROMs which allow for microcode updates.

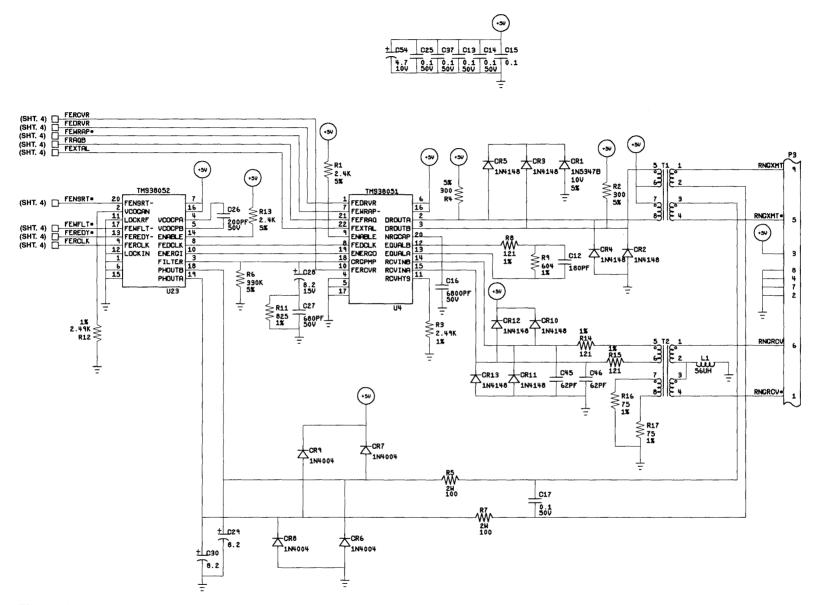

# **Ring Interface**

### Hardware Description

The interface of the Adapter to the IBM Token-Ring Network is via the Ring Interface circuit, containing two bipolar MSI circuits and several discrete components. The two bipolar MSI chips are an anolog chip set which provide the IEEE 802.5 compatible interface functions between the Adapter's Protocol Handler (PH), and the IBM Token-Ring Network. These chips are referred to as the Adapter's Ring Transceiver and Ring Controller. The Transceiver provides the transmit and receive functions while the Controller provides ring interface control functions. Included in the schematic shown in Schematic Diagrams, are all the necessary passive components in addition to an Adapter Address and a Processor Activity Timer which are discussed in further detail below.

#### **Adapter Address**

The 1024x4 PROM and the 74LS164 in the schematic in Chapter 2, implement the Adapter Address feature of the Adapter. This feature provides the Adapter with a 48-bit node address if a node address is not passed during the **OPEN** command. Whenever the Adapter is initialized, the Communication Processor will fetch the Adapter Address from the address module. If the node address passed to the Adapter during the **OPEN** command is zero, the Adapter Address will be used as the Adapter's Ring Station Address. The Adapter software tests for the presence of the address module circuitry during initialization. The Adapter reads the PROM and checks the integrity of the data in the address PROM, but does not check for valid addresses. An error in the address PROM will cause the **OPEN** command to terminate with a node address error.

#### Notes:

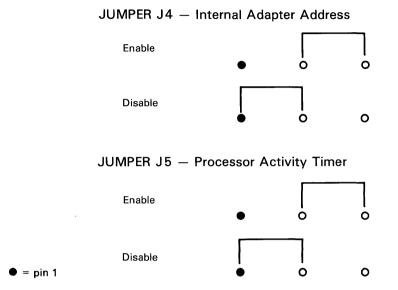

- 1. On card assemblies 56X2295 and 69X8139, the Adapter Address feature is selectable through the use of Jumper J4. The jumper is set in either the internal or system position with the internal address as the default position.

- 2. On other card assemblies, the internal address is always selected (no jumper).

#### **Processor Activity Timer**

The Processor Activity Timer (PAT) feature includes a one-shot which is configured to provide a 20 millisecond pulse when a negative transition occurs on signal -PHNSRT. The inverted Q output of the one-shot serves as the active-low signal causing the Adapter to physically insert onto the ring. The Adapter's program code toggles the -PHNSRT line every 10 milliseconds whenever the Adapter is inserted on the ring. The failure of the Adapter to toggle the -PHNSRT causes the one-shot to time out and the Adapter is physically de-inserted from the ring.

#### Notes:

- 1. On card assemblies 56X2295 and 69X8139, this timer may be disabled with Jumper J5. The default position of Jumper J5 is enabled.

- 2. On other card assemblies, this timer is always enabled (no jumper).

#### **Ring Connector Interface**

| Pin Number | Pin Name            |  |

|------------|---------------------|--|

| POS 1      | Ring In 1 (Green)   |  |

| POS 2      | DC Common           |  |

| POS 3      | + 5 Volts           |  |

| POS 4      | DC Common           |  |

| POS 5      | Ring Out 2 (Black)  |  |

| POS 6      | Ring In 2 (Red)     |  |

| POS 7      | DC Common           |  |

| POS 8      | DC Common           |  |

| POS 9      | Ring Out 1 (Orange) |  |

Table 2-3. Ring Connector Pin Assignment

## **Physical Signaling**

#### **Differential Manchester Code**

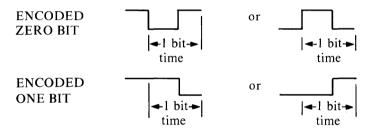

The Token-Ring Protocol calls for a ring signaling format called Differential Manchester Code. This signaling scheme follows these rules:

- 1. A signal transition always occurs in the center of the bit time.

- 2. A zero bit has a transition at the beginning of the bit time. A one bit has no transition during this time.

Figure 2-3 illustrates this coding scheme. The signaling transitions are symmetric around the zero volt level, thus providing an average zero volt DC level. This facilitates transformer coupling of the Adapter's transmitter and receiver to the ring.

Figure 2-3. Differential Manchester Code

#### **Ring Clocking**

An Adapter, randomly designated via a claim-token process, provides master clocking to the ring by deriving its timebase from a crystal oscillator. This Adapter is called the Active Monitor. Any Adapter on the ring may assume the role of Active Monitor.

The remaining ring stations on the ring derive their timebase by phase synchronizing a voltage controlled oscillator to the incoming bit stream. This Phase Locked Loop (PLL) derived clock provides the necessary timebase from which the bit stream is received and transmitted by the Adapter.

For more information about the IBM Token-Ring Network operations see the *IBM Token-Ring* Network Architecture Reference.

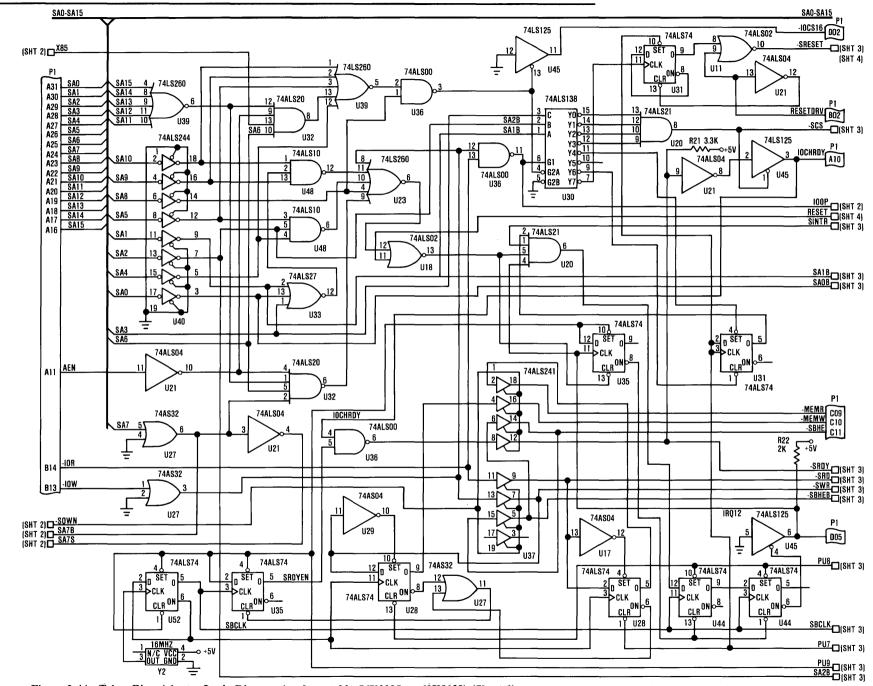

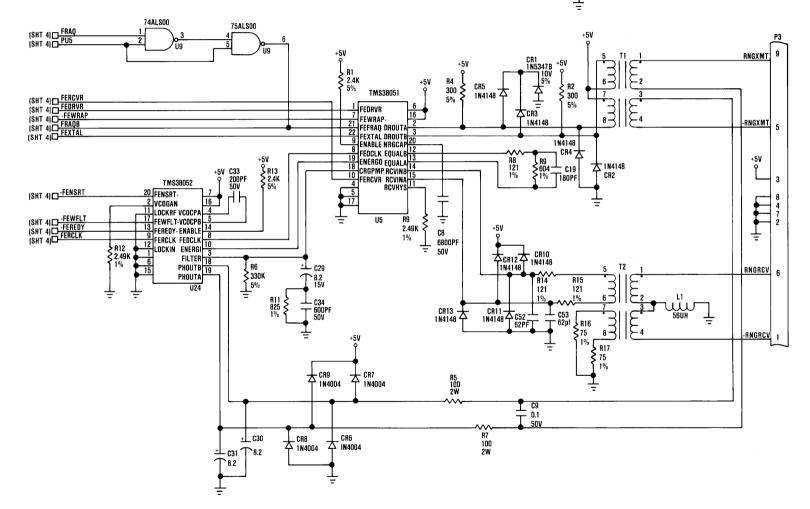

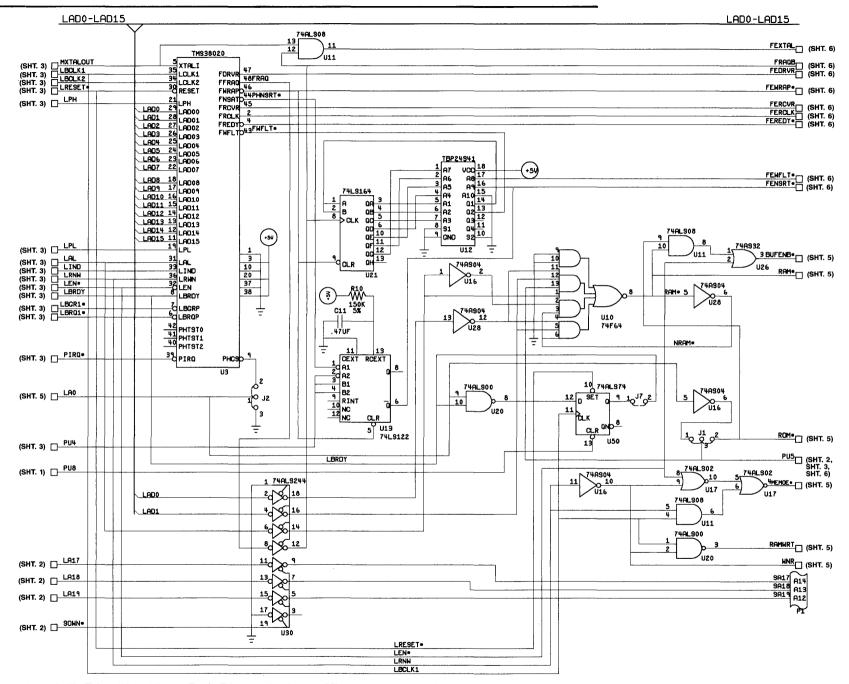

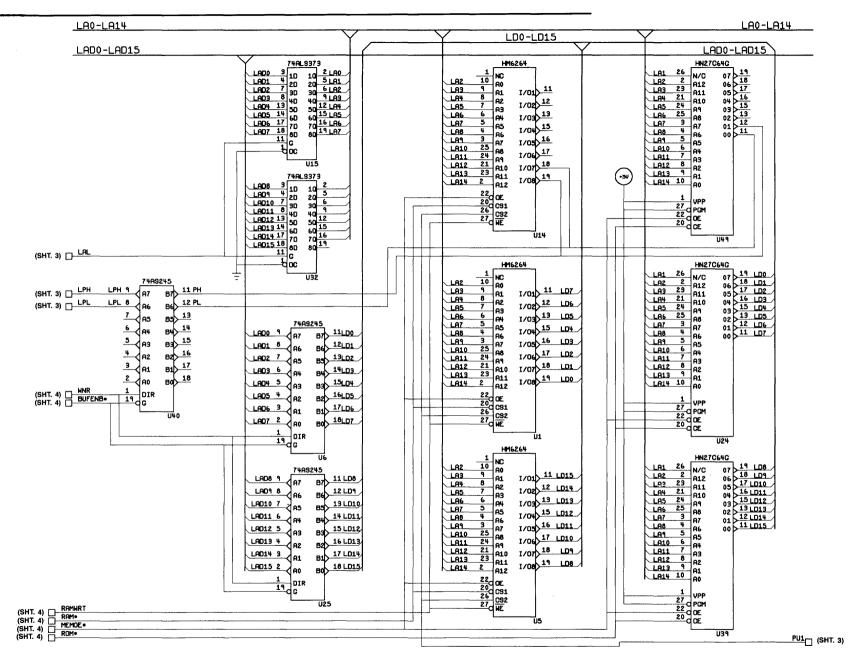

# Schematic Diagrams

The following section displays the logic diagrams for the RT PC Token-Ring Network Adapter.

2-16 Token-Ring Network Adapter

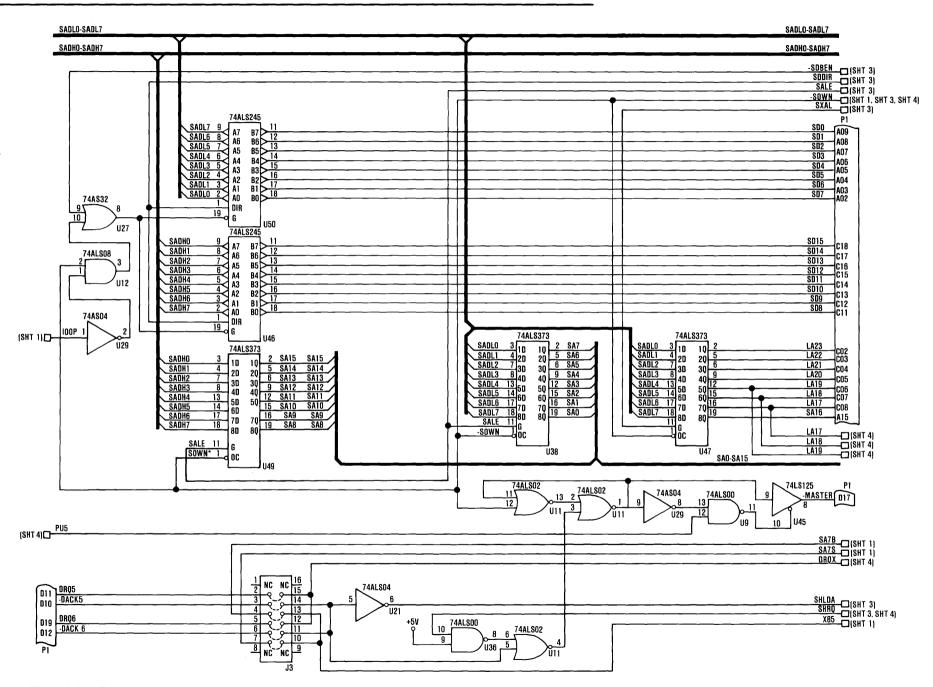

Figure 2-4A. Token-Ring Adapter Logic Diagram (card assembly 56X2295 or 69X8139) (Sheet 1)

#### 2-18 Token-Ring Network Adapter

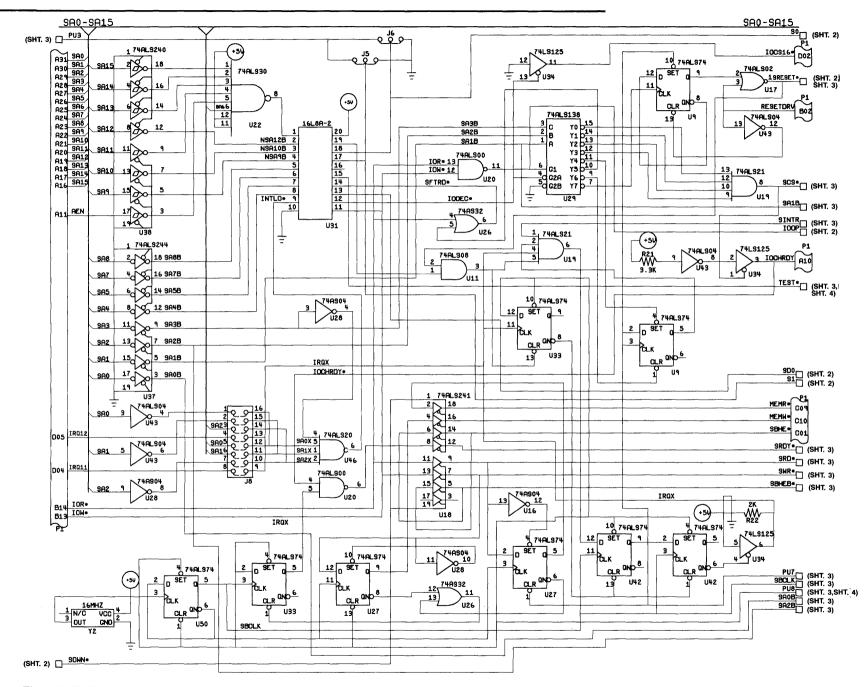

Figure 2-4A. Token-Ring Adapter Logic Diagram (card assembly 56X2295 or 69X8139) (Sheet 2)

2-20 Token-Ring Network Adapter

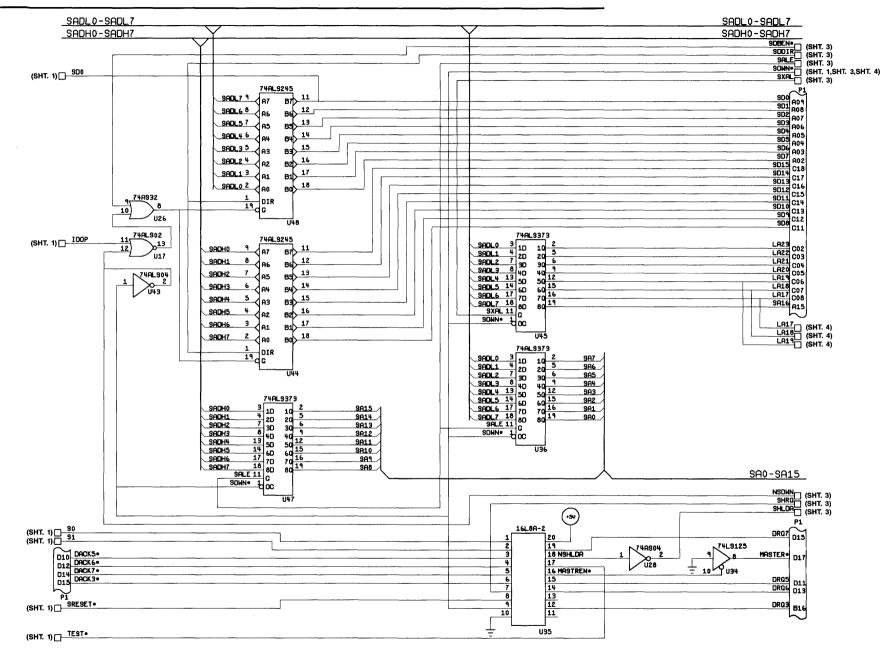

Figure 2-4A. Token-Ring Adapter Logic Diagram (card assembly 56X2295 or 69X8139) (Sheet 3)

2-22 Token-Ring Network Adapter

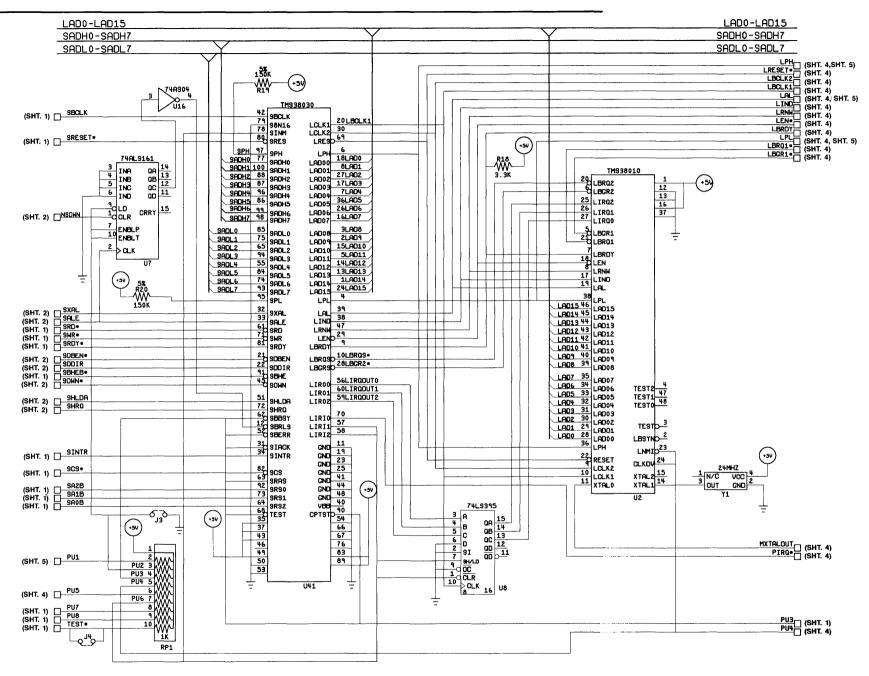

Figure 2-4A. Token-Ring Adapter Logic Diagram (card assembly 56X2295 or 69X8139) (Sheet 4)

2-24 Token-Ring Network Adapter

`~

Figure 2-4A. Token-Ring Adapter Logic Diagram (card assembly 56X2295 or 69X8139) (Sheet 5)

2-26 Token-Ring Network Adapter

Figure 2-4A. Token-Ring Adapter Logic Diagram (card assembly 56X2295 or 69X8139) (Sheet 6)

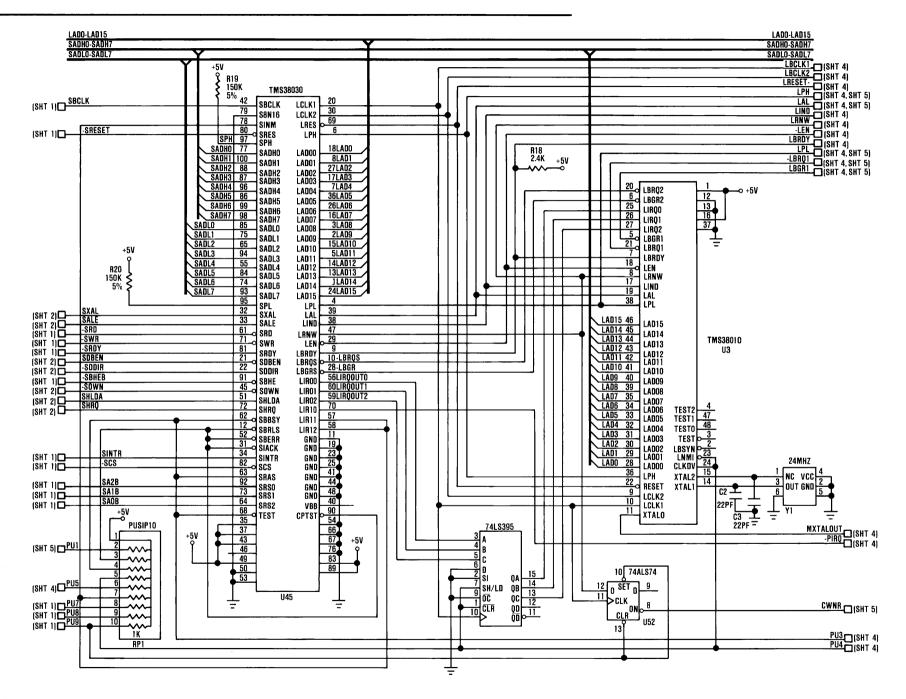

Figure 2-4B. Token-Ring Adapter Logic Diagram (card assemblies other than 56X2295 and 69X8139) (Sheet 1)

2-30 Token-Ring Network Adapter

Figure 2-4B. Token-Ring Adapter Logic Diagram (card assemblies other than 56X2295 and 69X8139) (Sheet 2)

#### 2-32 Token-Ring Network Adapter

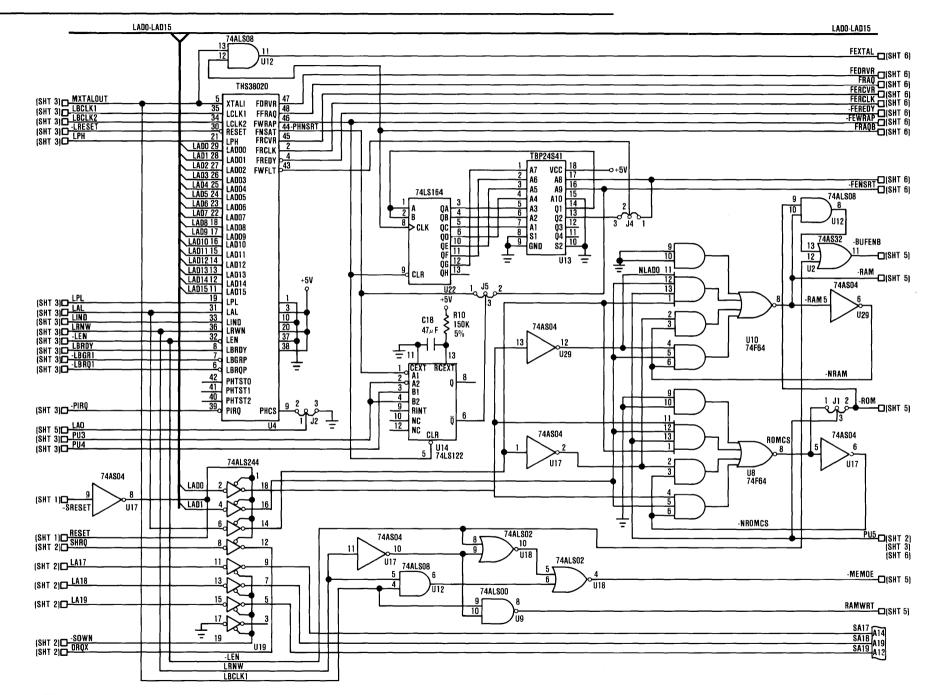

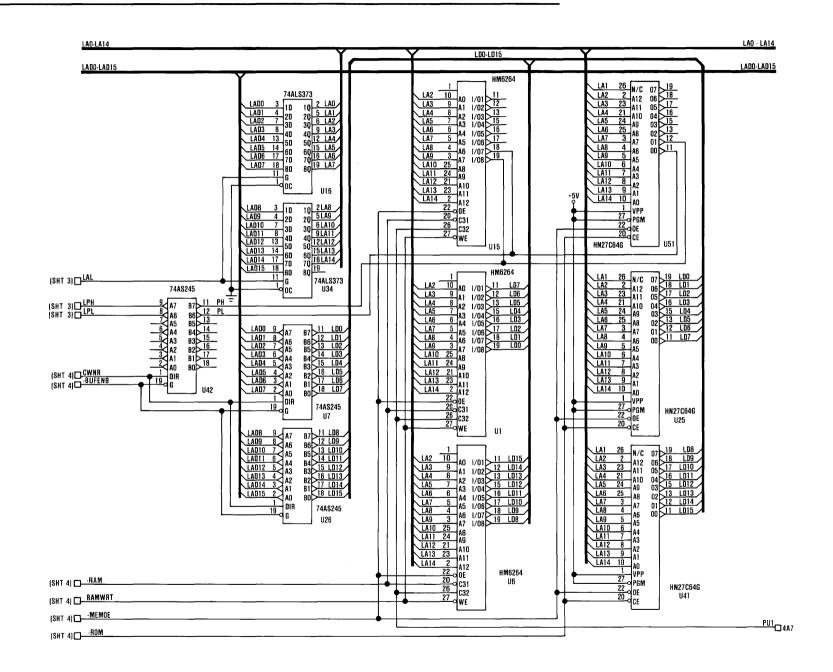

Figure 2-4B. Token-Ring Adapter Logic Diagram (card assemblies other than 56X2295 and 69X8139) (Sheet 3)

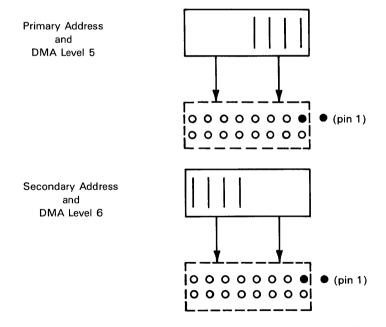

2-34 Token-Ring Network Adapter