## PowerPC<sup>™</sup> 604 SMP Reference Design Technical Specification

Release 3.0

This document provides a detailed technical description of the PowerPC 604 SMP Reference Design. It is intended as a first source of information for both hardware and software designers. Where appropriate, other documents are referenced.

Document Number: MPRZAPTSU-03 December 1995

© International Business Machines Corporation, 1995. Printed in the United States of America 12/95. All Rights reserved.

IBM Microelectronics, PowerPC, PowerPC 603e, PowerPC 604, RISCWatch, and AIX are trademarks of the IBM corporation. IBM and the IBM logo are registered trademarks of the IBM corporation. Other company names and product identifiers are trademarks of the respective companies.

This document contains information which is subject to change by IBM without notice. IBM assumes no responsibility or liability for any use of the information contained herein. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. The products described in this document are not intended for use in implantation or other direct life-support applications where malfunction may result in physical harm or injury to persons. NO WARRANTIES OF ANY KIND, INCLUDING BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, ARE OFFERED IN THIS DOCUMENT.

## Contacts

IBM Microelectronics Division 1580 Route 52, Bldg. 504 Hopewell Junction, NY 12533-6531 Tel: (800) PowerPC Fax: (800) PowerFax

http://www.chips.ibm.com http://www.ibm.com ftp://ftp.austin.ibm.com/pub/PPC\_support

## **ESD** Warning

The motherboard, CPU, and memory cards contain CMOS devices which are very susceptible to ElectroStatic Discharge (ESD). DO NOT remove them from the antistatic bags until you have connected yourself to an acceptable ESD grounding strap. Work in a static free environment and be sure any person or equipment coming into contact with the cards does not have a static charge. The cards are particularly susceptible until they are placed in a properly designed enclosure. Bench work should be done by persons connected to ESD grounding straps.

#### IBM POWERPC 604™ SMP REFERENCE DESIGN AGREEMENT

BEFORE READING THE REST OF THE DOCUMENT, YOU SHOULD CAREFULLY READ THE FOLLOWING TERMS AND CONDITIONS. OPENING THE PACKAGE INDICATES YOUR ACCEPTANCE OF THESE TERMS AND CONDI-TIONS. IF YOU DO NOT AGREE WITH THEM, YOU SHOULD PROMPTLY RETURN THE PACKAGE UNOPENED TO YOUR IBM SALES OFFICE.

International Business Machines Corporation ("IBM") agrees to provide you a PowerPC 604 SMP Reference Design (Reference Design) in return for your promise to use reasonable efforts to develop a system based on the technology in the Reference Design. The Reference Design contains documentation and software listed below:

#### Documentation

PowerPC 604 SMP Reference Design Technical Specification PowerPC 604 RISC Microprocessor Hardware Specification IBM PowerPC 604 SMP Reference Board Design Files (on 8mm tape) IBM PowerPC 604 SMP Reference Board Mfg. Data Files (in Gerber format) IBM1104360B Data Sheet IBM11D4360B Data Sheet Selected data sheets from other manufacturers (included with their permission).

#### LICENSE TO SOFTWARE

The software is licensed not sold. IBM, or the applicable IBM country organization, grants you a license for the software only in the country where you received the software. Title to the physical software and documentation (not the information contained in such documentation) transfers to you upon your acceptance of these terms and conditions. The term "software" means the original and all whole or partial copies of it, including modified copies or portions merged into other programs. IBM retains title to the software. IBM owns, or has licensed from the owner, copyrights to the software provided under this agreement. The terms of this Agreement apply to all of the hardware, software and documentation provided to you as part of the Reference Design.

With regard to the software provided hereunder, it is understood and agreed that you intend to use the software solely for the purpose of designing PowerPC<sup>TM</sup> compatible products, testing your designs, and making your own independent determination of whether you wish to eventually manufacture PowerPC compatible products commercially. In accordance with this understanding, IBM hereby grants you the rights to: a) use, run, and copy the software, but only make such number of copies and run on such number of machines as are reasonably necessary for the purpose of designing PowerPC compatible products and testing such designs; and b) copy the software for the purpose of making one archival or backup copy.

With regard to any copy made in accordance with the foregoing license, you must reproduce any copyright notice appearing thereon. With regard to the software provided hereunder, you may not: a) use, copy, modify or merge the software, except as provided in this license; b) reverse assemble or reverse compile it; or c) sell, sublicense, rent. lease, assign or otherwise transfer it. In the event that you no longer wish to use the software, you will return it to IBM.

#### LICENSE TO DESIGN DOCUMENTATION

With regard to the design documentation provided hereunder, it is understood that you intend to use such documentation solely for the purpose of designing your own PowerPC compatible products, testing your designs, and making your own independent determination of whether you wish to eventually manufacture PowerPC compatible products commercially. In accordance with this understanding, IBM hereby grants you the right to: a) use the design documentation for the purpose of designing PowerPC compatible products and testing such designs; b) make derivative works of the design documentation for the purpose of designing PowerPC compatible products, and testing such designs; and c) make copies of the design documentation and any such derivative works, but only such numbers as are reasonably necessary for designing PowerPC compatible products and testing such designs.

With regard to any copy made in accordance with the forgoing license, you must reproduce any copyright notice appearing thereon. With regard to the design documentation provided hereunder, you may not: a) copy, modify, or merge the design documentation as provided in this license; or b) sell, sublicense, rent, lease, assign, or otherwise transfer it.

In the event you no longer wish to use the design documentation or any derivative versions thereof, you must return them to IBM.

#### **DISCLAIMER OF WARRANTY**

IBM does not represent or warrant that the Reference Design (which may contain prototype items): a) meets any particular requirements; b) operates uninterrupted; c) is error free; or d) is non-infringing of any patent, copyright, or other intellectual property right of any third party. IBM makes no representation or warranty regarding the performance or compatibility that may be obtained from the use of the Reference Design or that the Reference Design is adequate for any use. The Reference Design may contain errors and may not provide the level of completeness, functionality, support, performance, reliability, or ease of use available with other products, whether or not similar to the Reference Design. IBM does not represent or warrant that errors or other defects will be identified or corrected.

THE REFERENCE DESIGN IS PROVIDED "AS IS" WITH ALL FAULTS, WITHOUT WARRANTY OF ANY KIND, EX-PRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE REFERENCE DESIGN IS WITH YOU.

Some jurisdictions do not allow exclusion of implied warranties, so the above exclusions may not apply to you.

#### LIMITATION OF REMEDIES

IBM's entire cumulative liability and your exclusive remedy for damages for all causes, claims or actions wherever and whenever asserted relating in any way to the subject matter of this agreement including the contents of the Reference Design and any components thereof, is limited to twenty five thousand dollars (\$25,000.00) or its equivalent in your local currency and is without regard to the number of items in the Reference Design that caused the damage. This limitation will apply, except as otherwise stated in this Section, regardless of the form of the action, including negligence. This limitation will not apply to claims by you for bodily injury or damages to real property or tangible personal property. In no event will IBM be liable for any lost profits, lost savings, or any incidental damages or economic consequential damages, even if IBM has been advised of the possibility of such damages, or for any damages caused by your failure to perform your responsibilities. In addition, IBM will not be liable for any damages claimed by you based on any third party claim. Some jurisdictions do not allow these limitations or exclusions, so they may not apply to you.

#### **RISK OF LOSS**

You are responsible for all risk of loss or damage to the Reference Design upon its delivery to you.

#### **IBM TRADEMARKS AND TRADE NAMES**

This Agreement does not give you any rights to use any of IBM's trade names or trademarks. You agree that should IBM determine that any of your advertising, promotional, or other materials are inaccurate or misleading with respect to IBM trademarks or trade names, that you will, upon written notice from IBM, change or correct such materials at your expense.

#### NO IMPLIED LICENSE TO IBM INTELLECTUAL PROPERTY

Notwithstanding the fact that IBM is hereby providing design information for your convenience, you expressly understand and agree that, except for the rights granted under the sections above, no right or license of any type is granted, expressly or impliedly, under any patents, copyrights, trade secrets, trademarks, or other intellectual property rights of IBM. Moreover, you understand and agree that in the event you wish to be granted any license beyond the scope of the expressly stated herein, you will contact IBM's Intellectual Property Licensing and Services Office (currently located at 500 Columbus Avenue, Thornwood, N.Y.), or such other IBM offices responsible for the licensing of IBM intellectual property, when you seek the license.

#### YOUR ASSUMPTION OF RISK

You shall be solely responsible for your success in designing, developing, manufacturing, distributing, and marketing any product(s), or portion(s), where use of all or any part of the Reference Design is involved. You are solely responsible for any claims, warranties, representations, indemnities and liabilities you undertake with your customers, distributors, resellers or others, concerning any product(s) or portion(s) of product(s) where use of all or any part of the Reference Design is involved. You assume the risk that IBM may introduce other Reference Designs that are somehow better than the Reference Design which is the subject of this Agreement. Furthermore, you accept sole responsibility for your decision to select and use the Reference Design; for attainment or non-attainment of any schedule, performance, cost, reliability, maintainability, quality, manufacturability or the like, requirements, or goals, self-imposed by you or accepted by you from others, concerning any product(s) of product(s), or for any part of the any part of the Reference Design; for attainment or non-attainment or accepted by you from the like, resulting from such non-attainment, where use of all or any part of the Reference Design is involved.

#### GENERAL

In the event there is a conflict between the terms of this Agreement and the terms printed or stamped on any item or any ambiguities with respect thereto, including documentation, contained in the Reference Design, the terms of this Agreement control to the extent IBM is afforded greater protection thereby. IBM may terminate this Agreement if you fail to comply with the terms and conditions of this Agreement. Upon termination of this Agreement, you must destroy all copies of the software and documentation. You are responsible for payment of anytaxes, including personal property taxes, resulting from this Agreement. Neither party may bring an action hereunder, regardless of form, more than one (1) year after the cause of the action arose. If you acquired the Reference Design in the United States, this Agreement is governed by the laws of the State of New York. In the event of litigations, trial shall be in New York without a jury. If you acquired the Reference Design in Canada, this Agreement is governed by the laws of the Contry in which you acquired the Reference Design. All obligations and duties which, by their nature, survive termination or expiration of this Agreement, shall remain in effect beyond termination or expiration of this Agreement, and shall bind IBM, you and your successors and assigns. If any section or paragraph of this Agreement is found by competent authority to be invalid, illegal or unenforceable in any respectfor any reason, the validity, legality, and enforceability of any such section or paragraph in every other respect, and the remainder of this Agreement shall continue in effect so long as it still expresses the intent of the parties. If the intent of the parties cannot be preserved, the parties will attempt to renegotiat this Agreement in any way. No failure by IBM in exercising any right, power or remedy under this Agreement shall serve as a waiver of any such right, power or remedy. Neither this Agreement than or she splanning information to you. You agree to comply with lage gove

## **Table of Contents**

| Section | 1 Introduction                                  | 23 |

|---------|-------------------------------------------------|----|

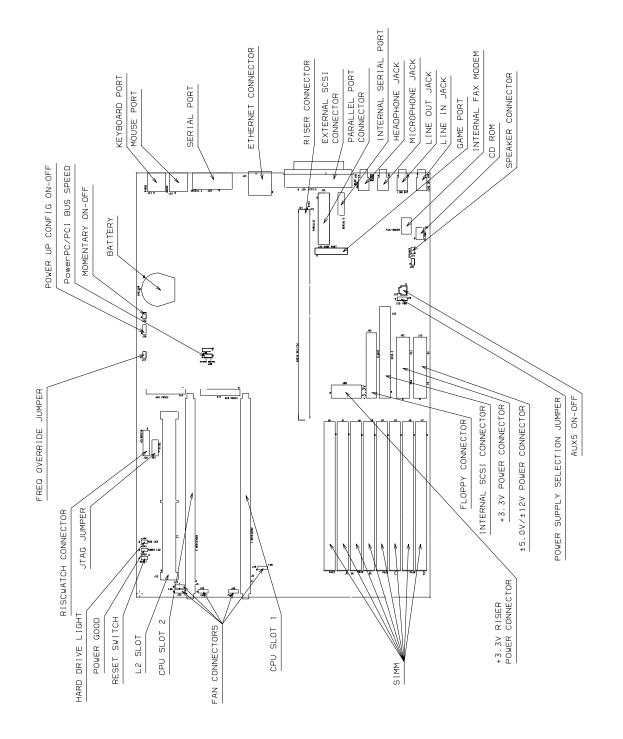

| 1.1     | IBM Reference Products                          | 23 |

| 1.1.1   | Reference Design                                | 23 |

| 1.1.2   | Reference Boards and Systems                    | 2  |

| 1.1.3   | Reference Firmware                              | 2  |

| 1.2     | Purpose                                         | 2  |

| 1.3     | Differences Between Release 1.0 and Release 3.0 | 2  |

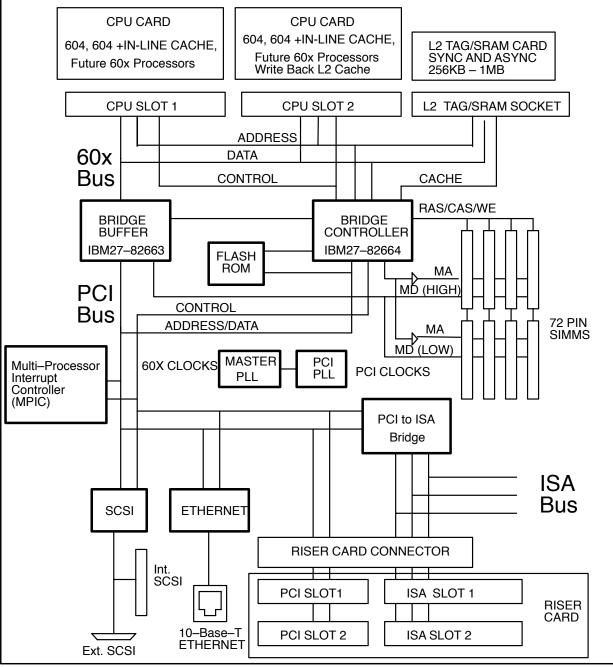

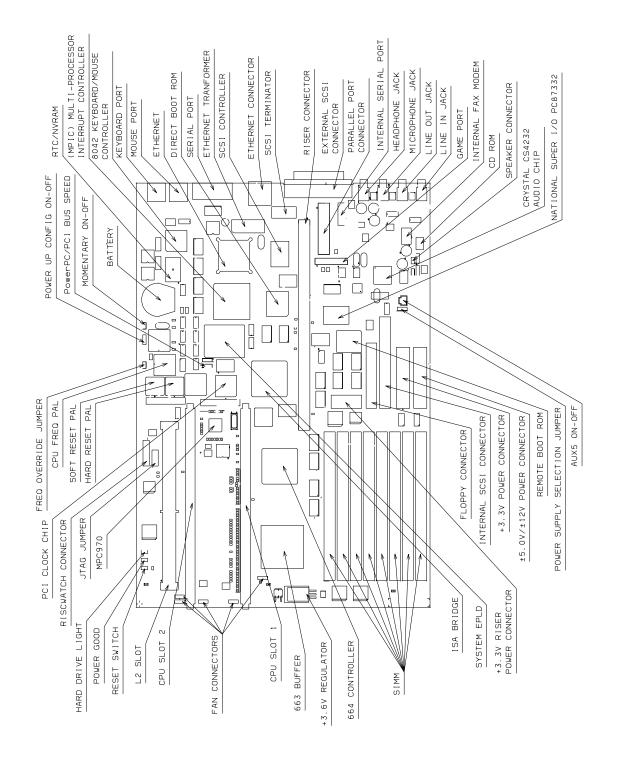

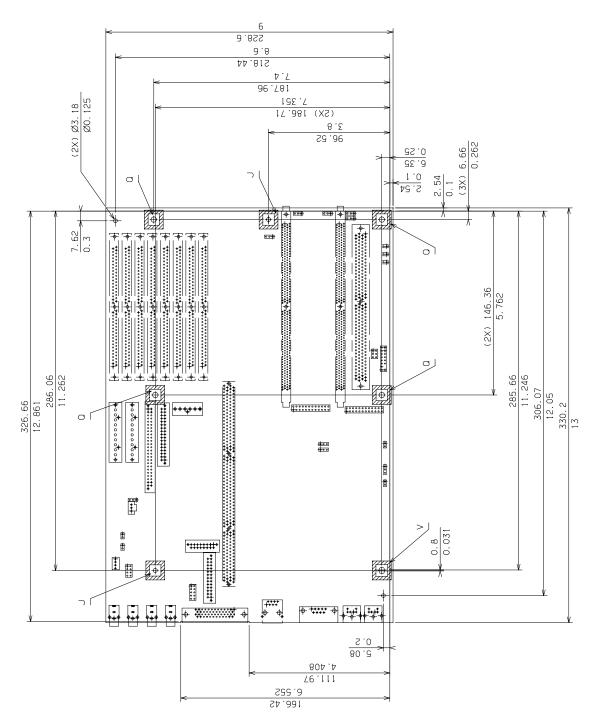

| 1.4     | Reference Design Overview                       | 2  |

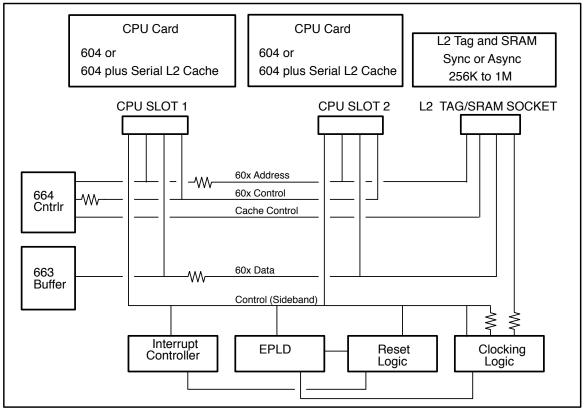

| 1.4.1   | Processor Cards                                 | 2  |

| 1.4.2   | Other CEC Functions                             | 2  |

| 1.4.3   | IBM27-82660 Bridge                              | 2  |

| 1.4.4   | L2 Cache                                        | 2  |

| 1.4.5   | System Memory                                   | 2  |

| 1.4.6   | PCI Bus                                         | 2  |

| 1.4.7   | SCSI Controller                                 | 2  |

| 1.4.8   | Network Support AMD AM79C970A (Ethernet)        | 2  |

| 1.4.9   | Multi-Processor Interrupt Controller (MPIC)     | 2  |

| 1.4.10  |                                                 | 2  |

| 1.4.11  |                                                 | 2  |

| 1.4.12  |                                                 | 2  |

| 1.4.13  |                                                 | 3  |

| 1.4.14  | •                                               | 3  |

| 1.4.15  |                                                 | 3  |

| 1.4.16  | •                                               | 3  |

| 1.4.17  |                                                 | 3  |

| 1.4.18  | •                                               | 3  |

| 1.5     | Quickstart Peripheral List                      | 3  |

| Section | 2 CPU Bus                                       | 3  |

| 2.1     | CPU Busmasters                                  | 3  |

| 2.1.1   | CPU Bus Arbitration                             | 3  |

| 2.1.2   | Fast L2/Data Streaming Mode (No-DRTRY#)         | 3  |

| 2.1.3   | CPU Bus Frequency                               | 3  |

| 2.1.4   | Bi-Endian Mode Operation                        | 3  |

| 2.2     | System Response by CPU Bus Transfer Type        | 3  |

| 2.3     | System Response by CPU Bus Address Range        | 3  |

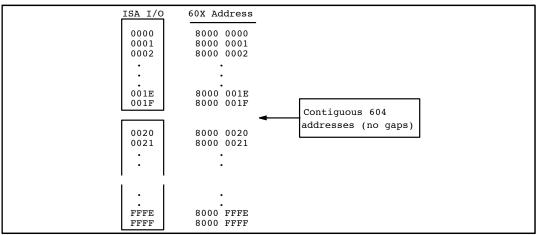

| 2.3.1   | Address Mapping for Contiguous I/O              | 3  |

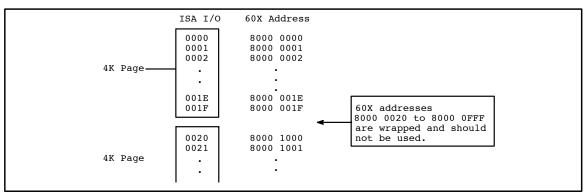

| 2.3.2   | Address Mapping for Non-Contiguous I/O          | Э  |

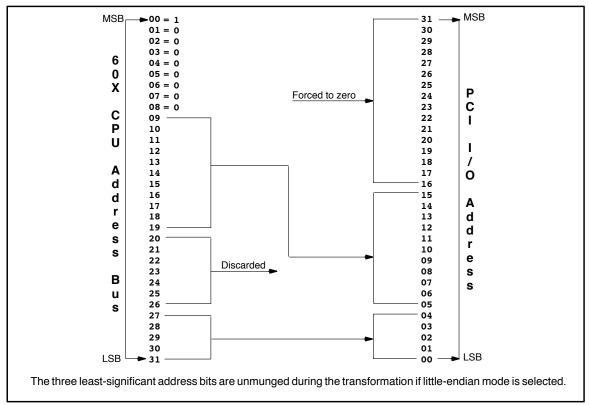

| 2.3.3   | PCI Final Address Formation                     | З  |

| 2.4     | CPU to Memory Transfers                         | З  |

| 2.4.1   | LE Mode                                         | 3  |

| 2.5     | CPU to PCI Transactions               | 39       |

|---------|---------------------------------------|----------|

| 2.5.1   |                                       | 40       |

| 2.5.2   |                                       | 40<br>40 |

| 2.5.2   |                                       | 40<br>40 |

| 2.5.2   |                                       | 40<br>40 |

| 2.5.4   |                                       | 40<br>40 |

| 2.5.4   |                                       | 40<br>40 |

| 2.5.5   | 5                                     | 40<br>41 |

| 2.5.0   |                                       | 41<br>41 |

| -       |                                       | 41<br>41 |

| 2.6     |                                       |          |

| 2.6.1   |                                       | 42       |

| 2.6.2   |                                       | 42       |

| 2.6.2.  |                                       | 42       |

| 2.6.3   |                                       | 43       |

| 2.7     |                                       | 43       |

| 2.7.1   |                                       | 44       |

| 2.7.2   |                                       | 56       |

| 2.7.3   | 5                                     | 56       |

| 2.7.4   |                                       | 57       |

| 2.7.5   |                                       | 57       |

| 2.7.6   |                                       | 58       |

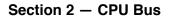

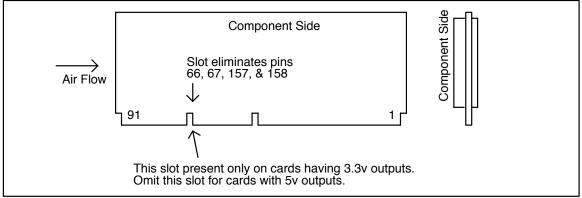

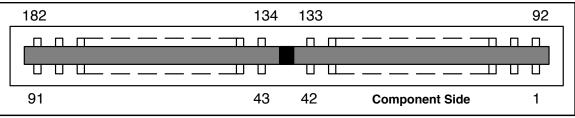

| 2.7.7   | Auxiliary CPU Slot Connectors         | 63       |

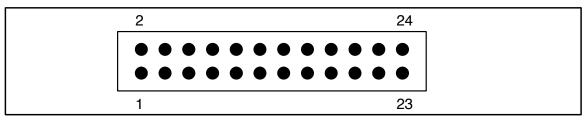

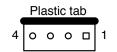

| 2.8     | L2 Tag/SRAM Interface (L2 Slot)       | 64       |

| 2.8.1   |                                       | 64       |

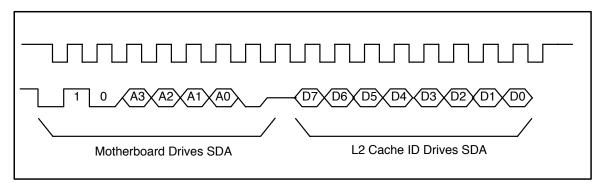

| 2.8.1.  | 1 L2 Cache ID ROM Signaling Interface | 66       |

| 2.8.2   |                                       | 67       |

| 2.8.3   | L2 Slot DC Characteristics            | 71       |

| 2.8.4   |                                       | 72       |

| 2.8.5   | L2 Slot Power Supplies                | 72       |

| 2.8.6   |                                       | 73       |

| 2.8.7   |                                       | 73       |

| 2.8.8   | 5 1 5                                 | 74       |

| 2.8.9   |                                       | 75       |

| 2.9     | 6                                     | 78       |

| -       |                                       | 79       |

| 2.10.1  |                                       | 79       |

| 2.10.2  |                                       | 80       |

| 2.10.2  |                                       | 80       |

| 2.10.4  |                                       | 80       |

| 2.10.5  |                                       | 80       |

| 2.10.0  | •                                     | 81       |

| 2.10.0  | 6 Model Building                      | 5 I      |

| Section | 3 Endian Mode Considerations          | 83       |

| 3.1     |                                       | 84       |

| 3.1.1   |                                       | 84       |

| 5       |                                       |          |

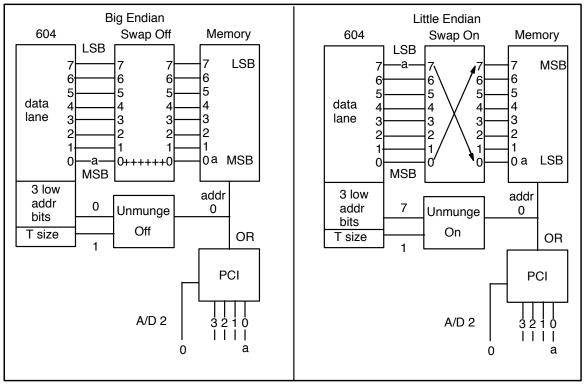

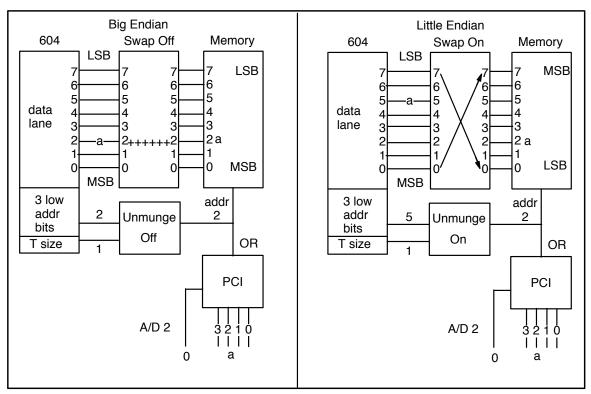

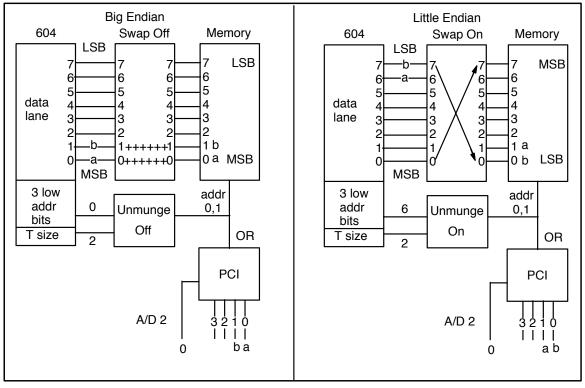

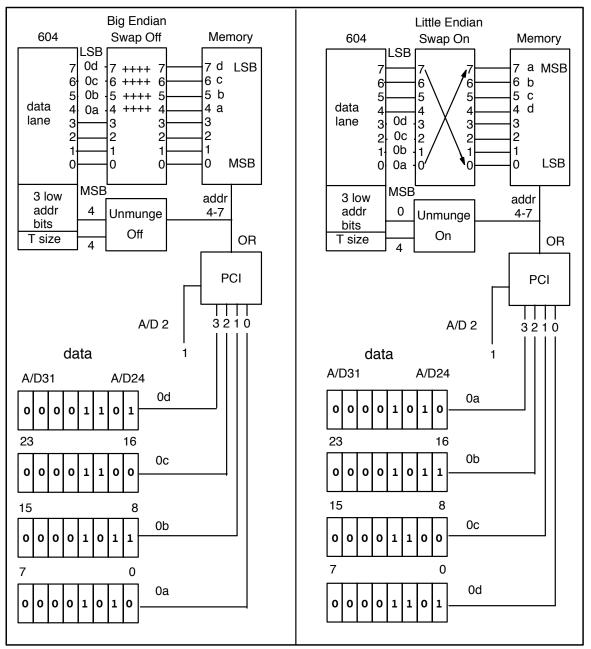

| 3.1.2   | The 604 Data Shift                       | 84  |

|---------|------------------------------------------|-----|

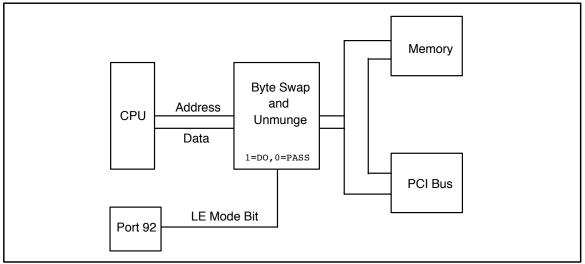

| 3.2     | What the 660 Bridge Does                 | 84  |

| 3.2.1   | The 660 Bridge Address Unmunge           | 84  |

| 3.2.2   | The 660 Bridge Data Swapper              | 84  |

| 3.3     | Bit Ordering Within Bytes                | 86  |

| 3.4     | Byte Swap Instructions                   | 87  |

| 3.5     | 604 CPU Alignment Exceptions In LE Mode  | 87  |

| 3.6     | Single-Byte Transfers                    | 88  |

| 3.7     | Two-Byte Transfers                       | 92  |

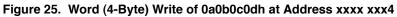

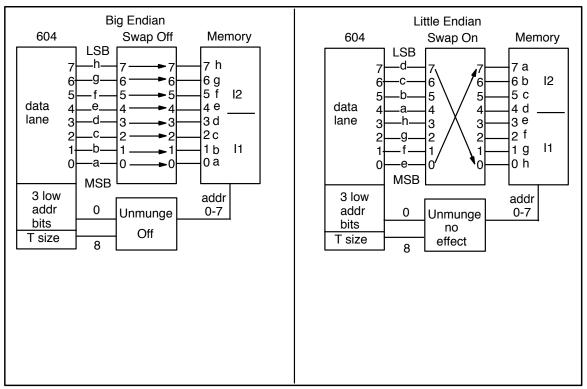

| 3.8     | Four-Byte Transfers                      | 94  |

| 3.9     | Three byte Transfers                     | 96  |

| 3.10    | Instruction Fetches and Endian Modes     | 97  |

| 3.11    | Changing BE/LE Mode                      | 98  |

| 3.12    | Summary of Bi-Endian Operation and Notes | 100 |

| Section | 4 CPU Card                               | 101 |

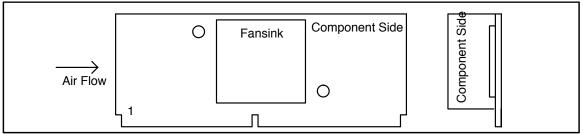

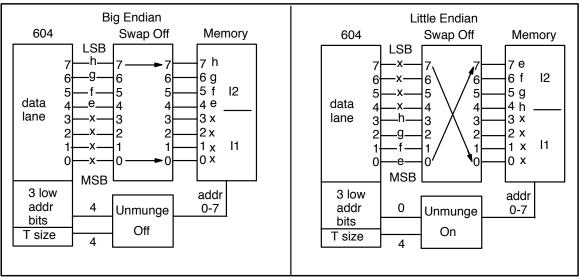

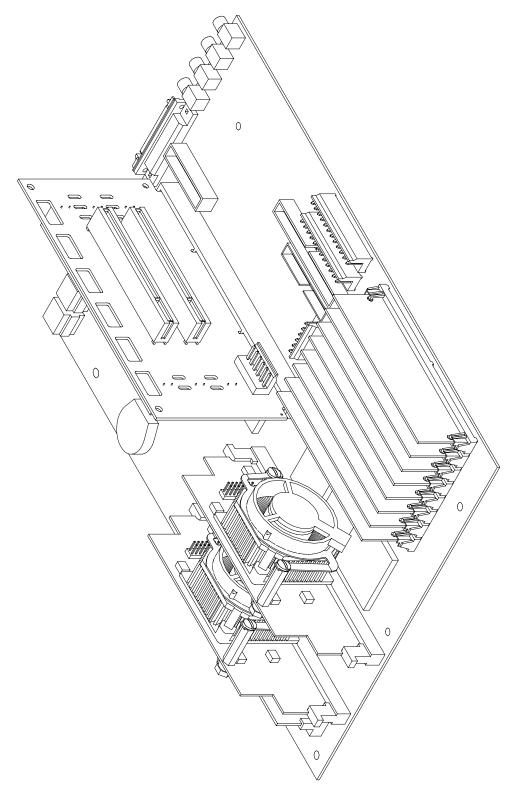

| 4.1     | Major Components                         | 102 |

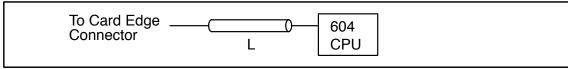

| 4.1.1   | PowerPC 604 Processor                    | 102 |

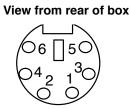

| 4.1.2   | JTAG/RISCWatch Interface                 | 102 |

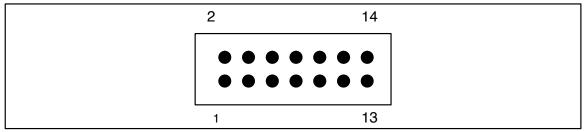

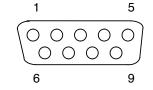

| 4.1.3   | J2 Auxiliary Test Connector              | 102 |

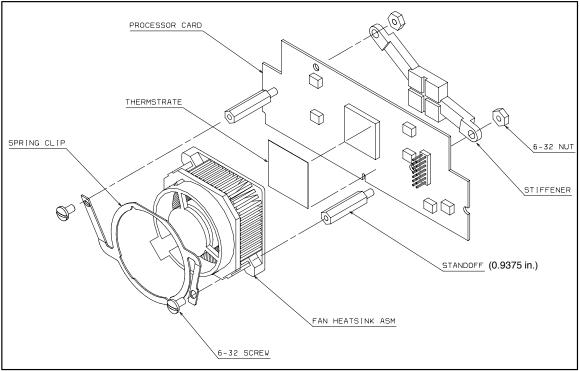

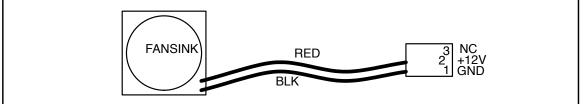

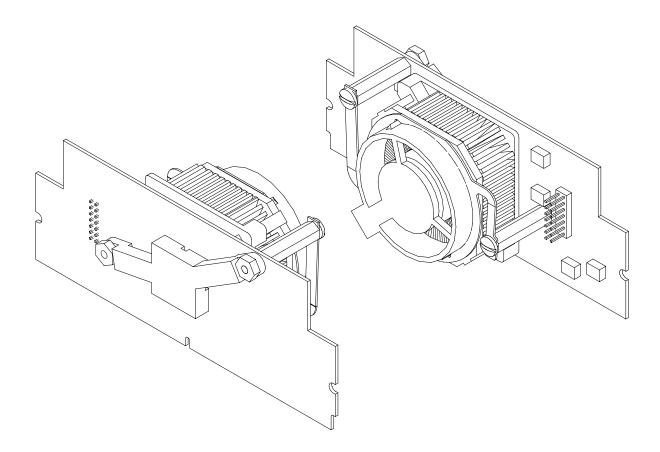

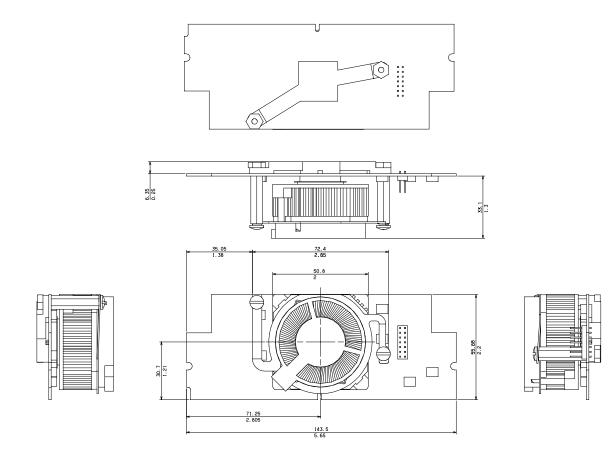

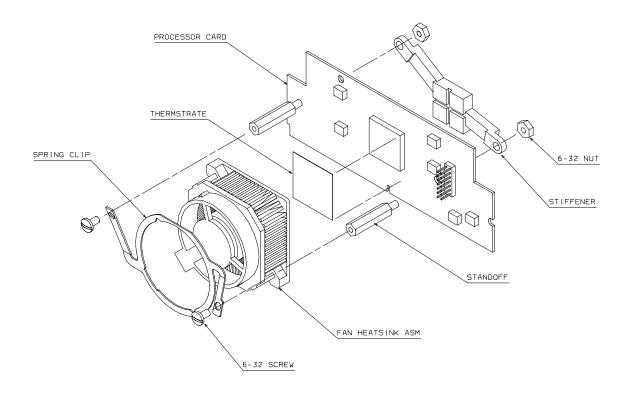

| 4.1.4   | Fansink                                  | 102 |

| 4.2     | Configuration Options                    | 104 |

| 4.2.1   | Bus Clock Skew Circuit                   | 104 |

| 4.2.2   | 2.5v Power Supply                        | 104 |

| 4.2.3   | Presence Detect Bits                     | 104 |

| 4.2.4   | DRVMOD Bits                              | 104 |

| 4.2.5   | Additional Bits                          | 104 |

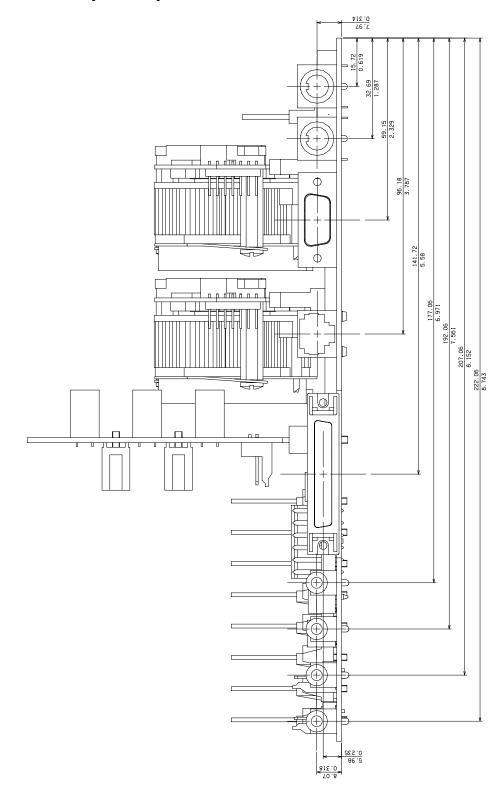

| 4.3     | Electrical and Thermal Requirements      | 105 |

| 4.3.1   | Absolute Maximum Ratings                 | 105 |

| 4.3.2   | DC Specifications                        | 105 |

| 4.3.3   | Thermal                                  | 106 |

| 4.3.4   | AC Timing Requirements                   | 106 |

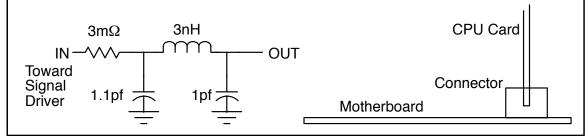

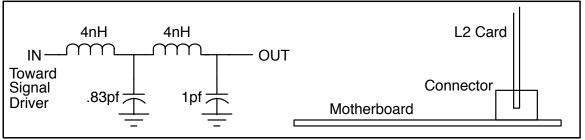

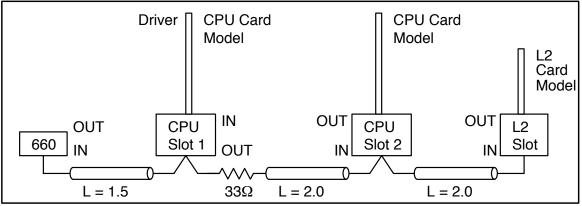

| 4.4     | Electrical Model of Major Signal Groups  | 107 |

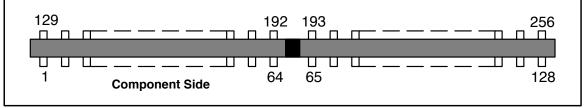

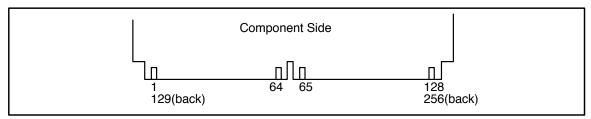

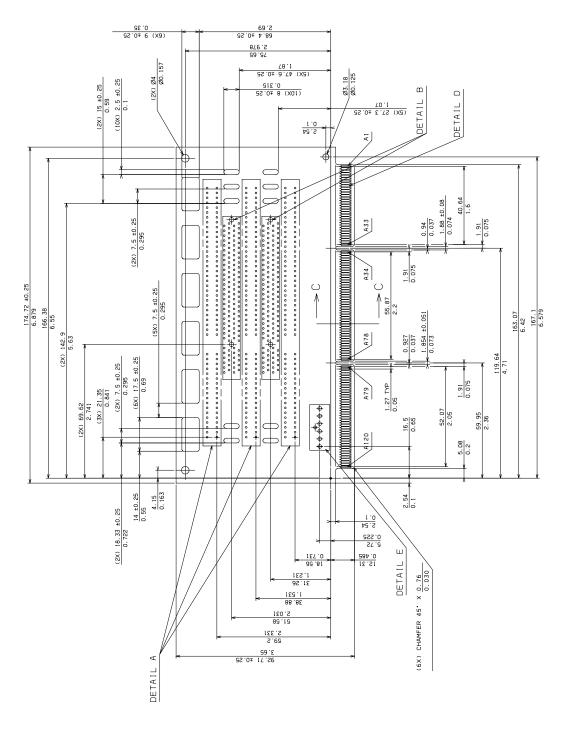

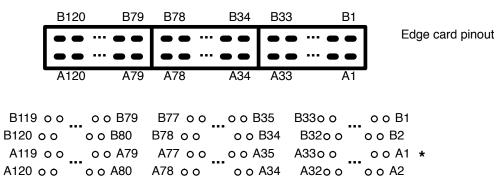

| 4.5     | CPU Card Slot Connector                  | 108 |

| 4.5.1   | Pin Definitions                          | 108 |

| -       |                                          |     |

|         | 5 DRAM and ROM                           | 113 |

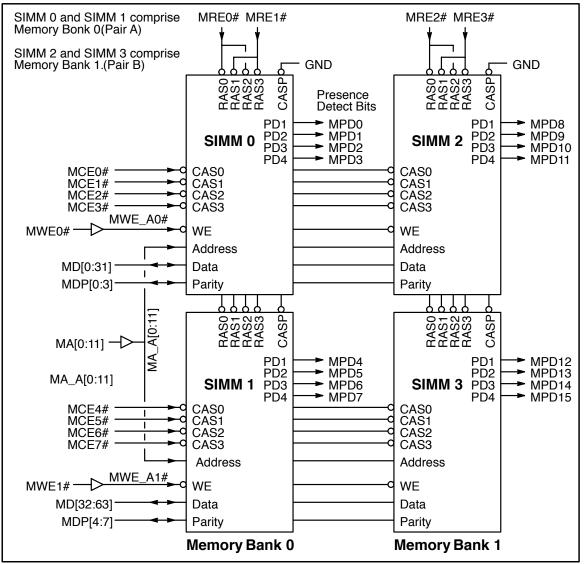

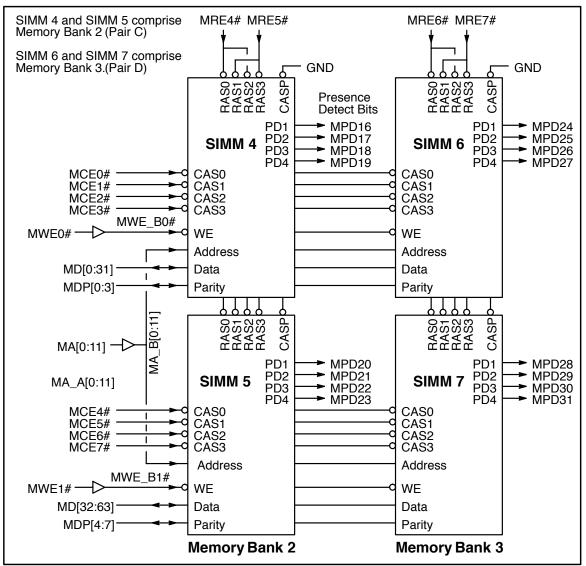

| 5.1     | DRAM                                     | 113 |

| 5.1.1   | Memory Controller (DRAM)                 | 113 |

| 5.1.2   | Organization                             | 114 |

| 5.1.3   | Refresh                                  | 115 |

| 5.1.4   | DRAM Presence Detection                  | 115 |

| 5.1.5   | DRAM Bank Rules                          | 116 |

| 5.2     | ROM                                      | 116 |

| 5.2.1   | PCI Bus ROM                              | 116 |

|    | 5.2.2      | Remote ROM                                      | 116 |

|----|------------|-------------------------------------------------|-----|

|    | 5.2.3      | ROM Read, Write, and Write Protect              | 116 |

| Se | ection 6 F | Exceptions                                      | 117 |

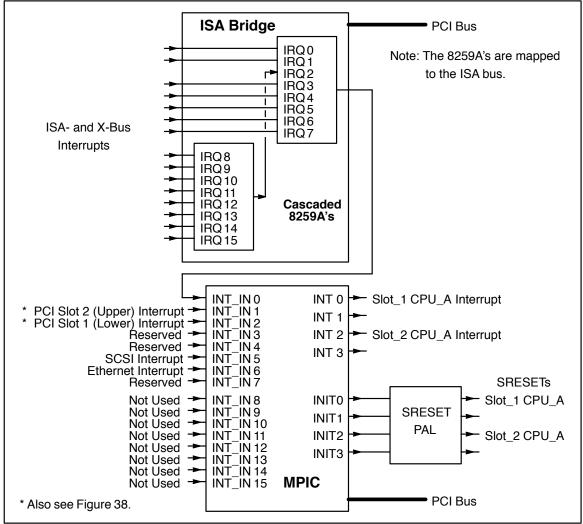

|    |            | terrupts                                        | 117 |

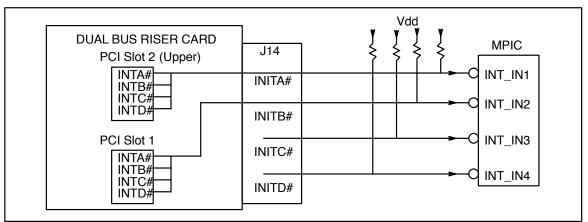

|    | 6.1.1      | PCI interrupt handling                          | 118 |

|    | 6.1.2      | ISA interrupt handling                          | 118 |

|    | 6.1.3      | CPU to CPU Interrupt Handling                   | 119 |

|    | 6.1.4      | PCI Interrupt Assignments                       | 119 |

|    | 6.1.5      | ISA Interrupt Assignments                       | 120 |

|    | 6.1.5.1    | Scatter/Gather (SG) Interrupts                  | 121 |

|    | 6.1.6      | SCSI Bus Interrupts                             | 121 |

|    | 6.1.7      | MCP# Considerations                             | 121 |

|    | 6.1.8      | SMI# Considerations                             | 121 |

|    | 6.2 Re     | esets                                           | 122 |

|    | 6.2.1      | HRESET# Logic                                   | 122 |

|    | 6.2.1.1    | JTAG Interface Hard Resets                      | 122 |

|    | 6.2.1.2    | HRESET PAL Equations                            | 123 |

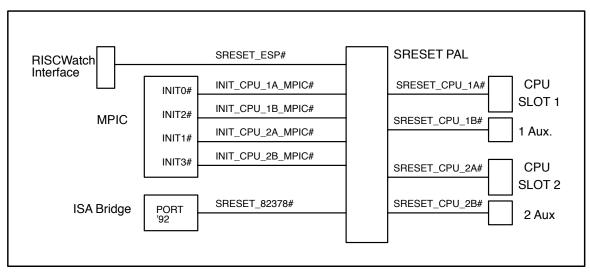

|    | 6.2.2      | SRESET Logic                                    | 125 |

|    | 6.2.3      | SRESET PAL equations                            | 126 |

|    |            | MP Reset Considerations                         | 128 |

|    | 6.3.1      | Hard Reset                                      | 129 |

|    | 6.3.1.1    | Hard Reset Phase 1                              | 129 |

|    | 6.3.1.2    | Hard Reset Phase 2                              | 130 |

|    | 6.3.1.3    | Hard Reset Phase 3                              | 130 |

|    | 6.3.2      | Soft Reset                                      | 131 |

|    |            | rror Handling                                   | 132 |

|    | 6.4.1      | Data Error Checking                             | 132 |

|    | 6.4.1.1    | CPU to Memory Writes                            | 132 |

|    | 6.4.1.2    | CPU to Memory Reads                             | 132 |

|    | 6.4.1.3    | PCI to Memory Parity Errors                     | 132 |

|    | 6.4.1.4    | CPU to PCI Transaction Data Parity Errors       | 133 |

|    | 6.4.2      |                                                 | 133 |

|    | 6.4.3      | SERR, I/O Channel Check, and NMI Logic          | 133 |

|    | 6.4.4      | Out of Bounds PCI Memory Accesses               | 133 |

|    | 6.4.5      | No Response on CPU to PCI Cycles — Master Abort | 133 |

|    | 6.4.6      | CPU to PCI Cycles That Are Target Aborted       | 134 |

|    | 6.4.7      | Error Status Registers                          | 134 |

|    | 6.4.8      | Reporting Error Addresses                       | 134 |

|    | 6.4.9      | Errant Masters                                  | 134 |

|    | 6.4.10     | Special Events Not Reported as Errors           | 135 |

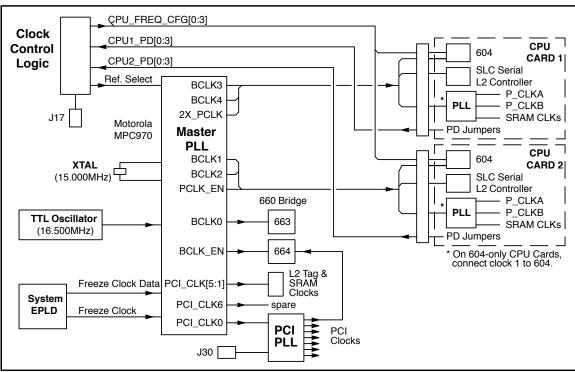

| Se | ection 7 ( | Clocks                                          | 137 |

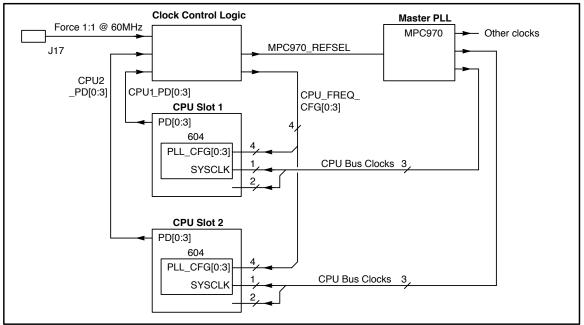

|    |            | PU Clocks                                       | 137 |

|    | 7.1.1      | CPU Card Clock Repeater                         | 138 |

|    |            |                                                 |     |

|          | 7.1.2<br>7.2<br>7.2.1<br>7.2.1.<br>7.2.1.<br>7.2.1.<br>7.2.1.<br>7.2.1.<br>7.2.2 | <ul> <li>CPU Clock Control Logic</li></ul>         | 138<br>139<br>140<br>140<br>140<br>140<br>140<br>142 |

|----------|----------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------|

|          | 7.2.3                                                                            | Clock Freezing                                     | 143                                                  |

|          | 7.3                                                                              | PCI Clocks                                         | 144                                                  |

|          | 7.3.1                                                                            | PCI Bus speed Selection                            | 144                                                  |

|          | 7.4                                                                              | ISA Bus Clock                                      | 144                                                  |

|          | 7.5                                                                              | Oscillators, Crystals, and Clocks                  | 144                                                  |

| <u> </u> | ation                                                                            |                                                    | 145                                                  |

| 36       | 8.1                                                                              | 8 PCI Bus<br>PCI Transaction Decoding              | <b>145</b><br>146                                    |

|          | 8.1.1                                                                            | PCI Transaction Decoding By Bus Command            | 140                                                  |

|          | 8.1.2                                                                            | •                                                  | 140                                                  |

|          | 8.1.3                                                                            | PCI I/O Transaction Decoding                       | 148                                                  |

|          | 8.1.4                                                                            | ISA Master Considerations                          | 148                                                  |

|          | 8.2                                                                              | PCI Transaction Details                            | 149                                                  |

|          | 8.2.1                                                                            | Bus Snooping on PCI to Memory Cycles               | 149                                                  |

|          | 8.2.2                                                                            | PCI Peer to PCI Peer Transactions                  | 149                                                  |

|          | 8.2.3                                                                            | PCI to System Memory Transactions                  | 149                                                  |

|          | 8.3                                                                              | Bus Arbitration Logic                              | 151                                                  |

|          | 8.4                                                                              | PCI Configuration Transactions                     | 151                                                  |

|          | 8.4.1                                                                            | 650 Bridge Compatible Method                       | 151                                                  |

|          | 8.5                                                                              | PCI Bus Loading                                    | 151                                                  |

| _        |                                                                                  |                                                    | 4 5 0                                                |

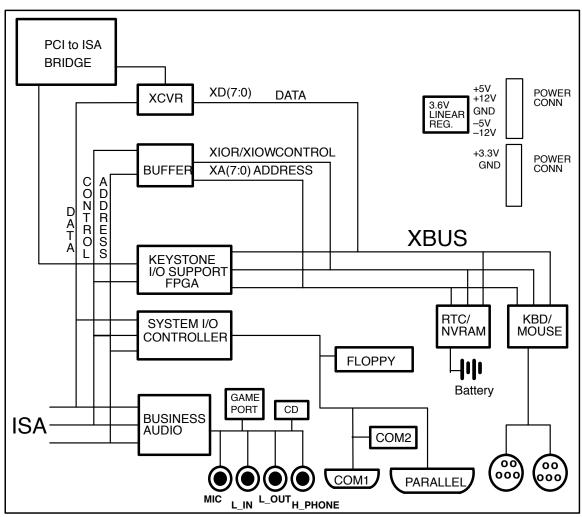

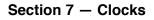

| Se       |                                                                                  | 9 ISA and X-Bus                                    | 153                                                  |

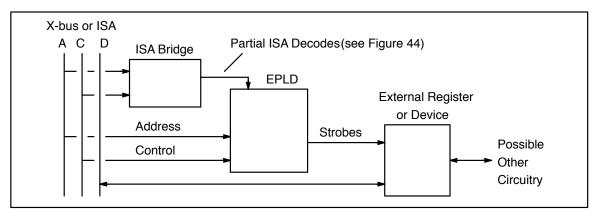

|          | 9.1                                                                              | The ISA Bridge                                     | 154                                                  |

|          | 9.2<br>9.3                                                                       | Address Ranges                                     | 154<br>155                                           |

|          | 9.3<br>9.4                                                                       | ISA Bus ConcurrencyISA Busmasters and IGN_PCI_AD31 | 155                                                  |

|          | 9.4<br>9.5                                                                       |                                                    | 155                                                  |

|          | 9.5.1                                                                            | Supported DMA Paths                                | 157                                                  |

|          | 9.5.2                                                                            | DMA Timing                                         | 157                                                  |

|          | 9.5.3                                                                            | Scatter-Gather                                     | 157                                                  |

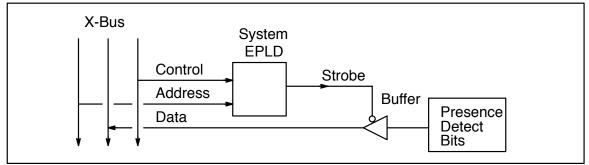

|          | 9.6                                                                              | X-Bus                                              | 158                                                  |

|          | 9.7                                                                              | Keyboard/Mouse Controller                          | 159                                                  |

|          | 9.7.1                                                                            | Keyboard/Mouse Control Registers                   | 159                                                  |

|          | 9.8                                                                              | Real Time Clock (RTC)                              | 160                                                  |

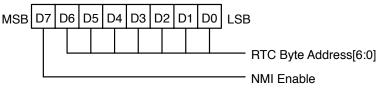

|          | 9.8.1                                                                            | RTC Address and NMI Enable Register                | 160                                                  |

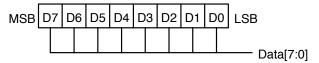

|          | 9.8.2                                                                            | RTC Data Register                                  | 160                                                  |

|          | 9.9                                                                              | Non-Volatile RAM (NVRAM)                           | 161                                                  |

|          |                                                                                  |                                                    |                                                      |

|    | 9.9.1     | NVRAM Address Register Low                              |

|----|-----------|---------------------------------------------------------|

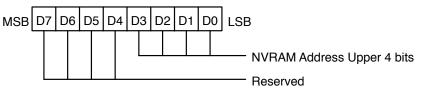

|    |           | NVRAM Address Register High                             |

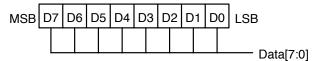

|    |           | NVRAM Data Register                                     |

|    |           | therboard Presence Detect Registers                     |

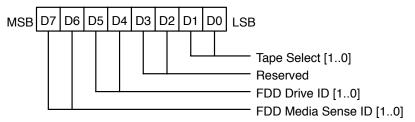

|    | 9.10.1    | Floppy Media Sense ID                                   |

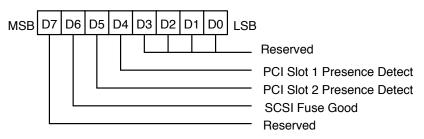

|    | 9.10.2    | Equipment Presence Register                             |

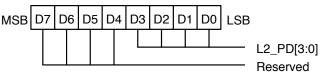

|    |           | L2 ID Register                                          |

|    |           | Motherboard ID Register                                 |

|    |           | CPU ID Registers                                        |

|    | 9.10.6    | DRAM ID Registers                                       |

| Se | ection 10 | System EPLD                                             |

|    |           | ternal Registers                                        |

|    |           | ernal Registers                                         |

|    |           | Storage Light Register                                  |

|    |           | System Control Register 081C                            |

|    |           | Power Management Control Registers                      |

|    |           | Power Management Control Register 1                     |

|    |           | Power Management Control Register 2                     |

|    | 10.2.6    | IRQ13 Interrupt Request Active Register (Not Supported) |

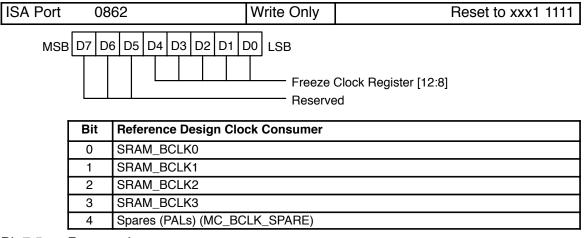

|    | 10.2.7    | Freeze Clock Registers                                  |

|    |           | Freeze Clock Register (FCR) Low                         |

|    | 10.2.7.2  | Freeze Clock Register (FCR) High                        |

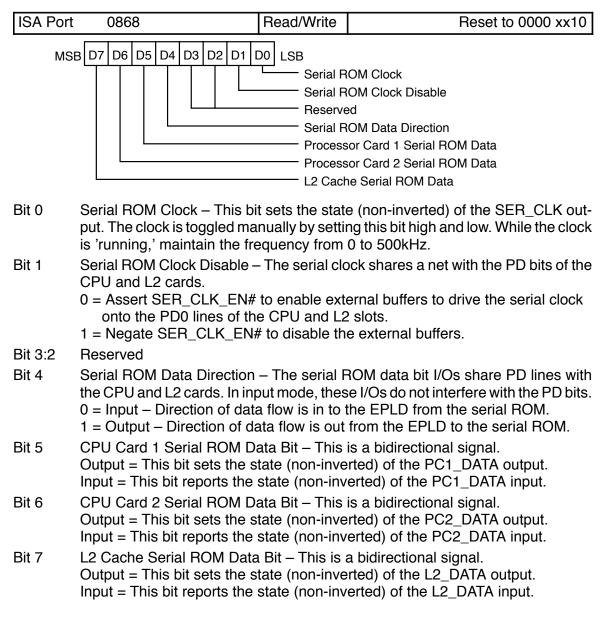

|    | 10.2.8    | Serial ROM Control Register                             |

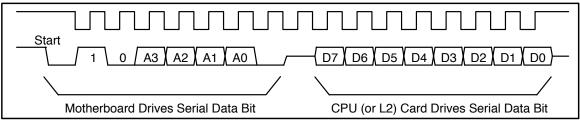

|    | 10.2.8.1  | Serial ROM Communications Protocol                      |

|    | 10.2.8.2  | Serial ROM vs. PD bits                                  |

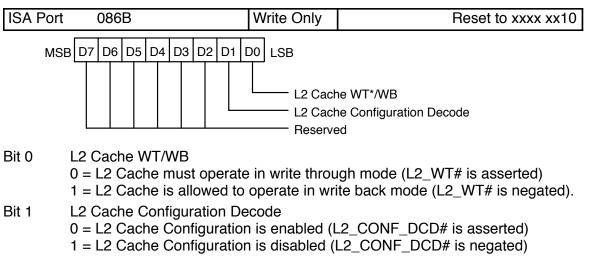

|    | 10.2.9    | L2 Control Register                                     |

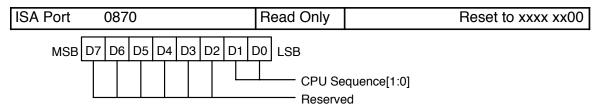

|    |           | CPU Sequence Register                                   |

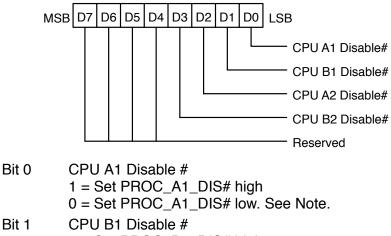

|    | 10.2.11   | CPU Enable Register                                     |

|    | 10.2.11.1 | External Hardware Reset                                 |

|    |           | nal Descriptions                                        |

|    | 10.4 EP   | LD Design Equations                                     |

|    |           | LD Pinout                                               |

| Se | ection 11 | /O Subsystems                                           |

| -  |           | nernet Subsystem                                        |

|    |           | Ethernet Physical and Electrical Design Guidelines      |

|    | 11.1.1.1  |                                                         |

|    |           | Ethernet 10BASE-T Layout Guidelines                     |

|    | 11.1.1.3  | Ethernet Oscillator Guidelines                          |

|    | _         | Ethernet Sleep Mode                                     |

|    |           | SI Subsystem                                            |

|    |           | SCSI Physical and Electrical Design Guidelines          |

|    | 11.2.1.1  | SCSI Component Location                                 |

|    | 11.2.1.2  | SCSI Bus Routing                                        |

|    | —         | 5                                                       |

| 11.2.1.3 SCSI Decoupling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 207                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 11.2.1.4 SCSI Impedance Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 207                                                                                                                               |

| 11.2.1.5 SCSI EMC Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 207                                                                                                                               |

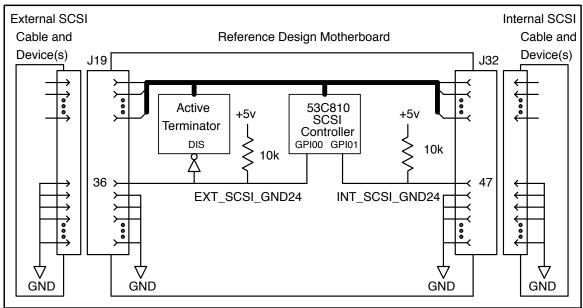

| 11.2.2 SCSI Termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 208                                                                                                                               |

| 11.2.3 Cable/Device Presence Detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 209                                                                                                                               |

| 11.2.4 SCSI Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 209                                                                                                                               |

| 11.3 Native I/O Subsystems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 210                                                                                                                               |

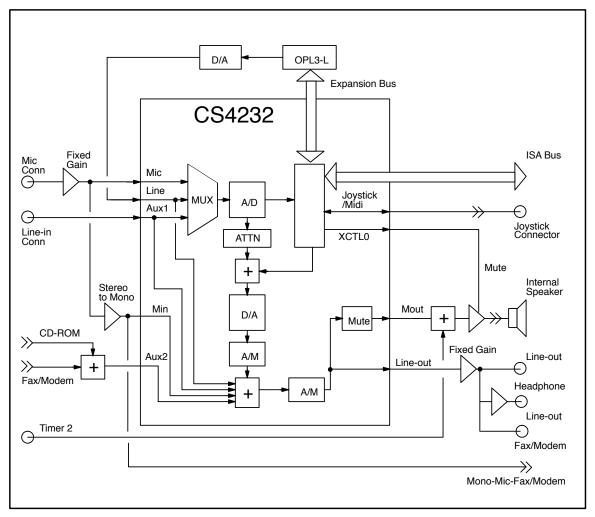

| 11.4 Business Audio Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 210                                                                                                                               |

| 11.4.1 Audio Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 212                                                                                                                               |

| 11.4.2 Audio Connector Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 213                                                                                                                               |

| 11.4.3 Audio Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 214                                                                                                                               |

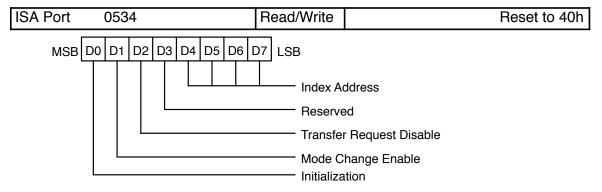

| 11.4.3.1 Audio Index Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 214                                                                                                                               |

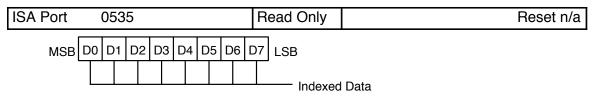

| 11.4.3.2 Audio Index negister                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 214                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 214                                                                                                                               |

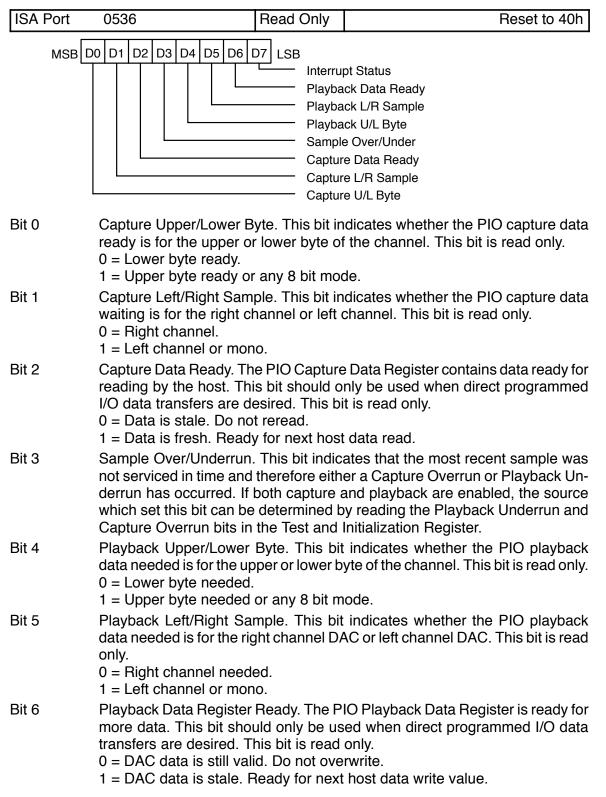

| 11.4.4       Audio Status Register         11.4.5       Audio PIO Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 215                                                                                                                               |

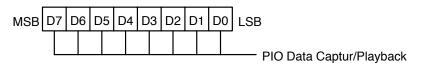

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 210                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 217                                                                                                                               |

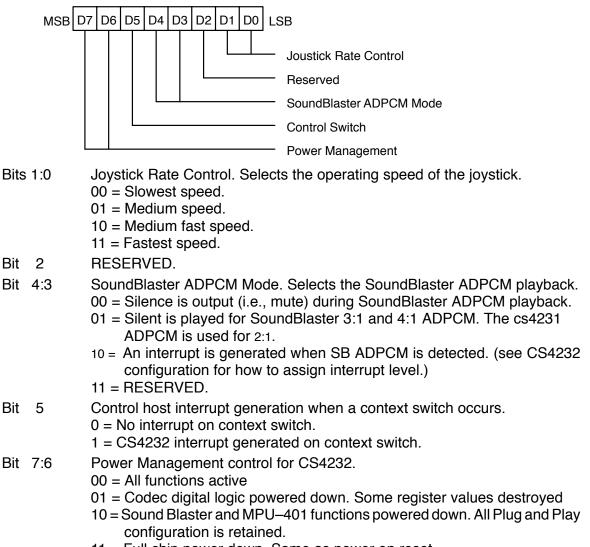

| 11.4.7 Control Register 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   |

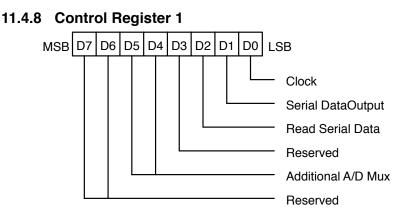

| 11.4.8 Control Register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 218                                                                                                                               |

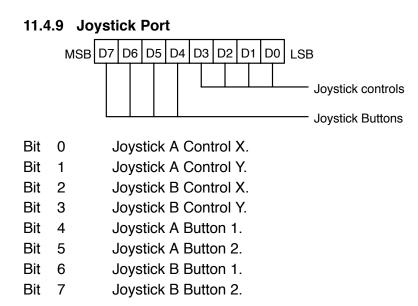

| 11.4.9 Joystick Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 218                                                                                                                               |

| 11.4.10 SoundBlaster Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 219                                                                                                                               |

| 11.4.11 MPU–401 MIDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 221                                                                                                                               |

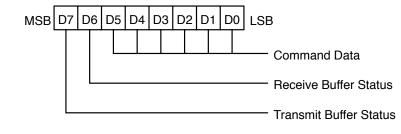

| 11.4.11.1 MIDI Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 221                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                   |

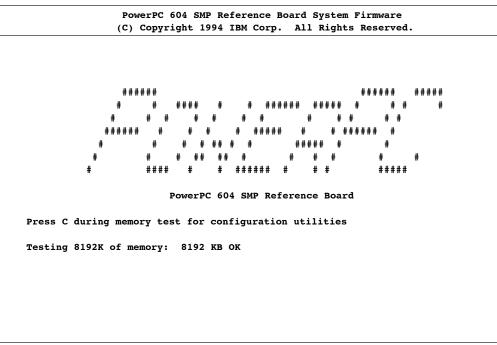

| Section 12 System Firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 223                                                                                                                               |

| Section 12 System Firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>223</b><br>223                                                                                                                 |

| 12.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 223                                                                                                                               |

| 12.1       Introduction         12.2       Power On System Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 223<br>223                                                                                                                        |

| <ul><li>12.1 Introduction</li><li>12.2 Power On System Test</li><li>12.3 Boot Record Format</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 223<br>223<br>223                                                                                                                 |

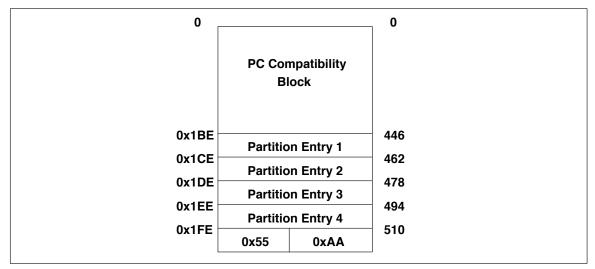

| 12.1 Introduction12.2 Power On System Test12.3 Boot Record Format12.3.1 Boot Record                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 223<br>223<br>223<br>223                                                                                                          |

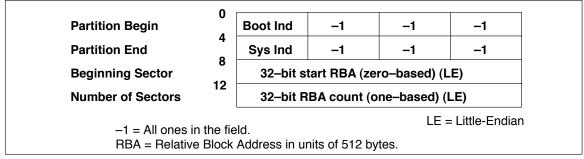

| 12.1 Introduction12.2 Power On System Test12.3 Boot Record Format12.3.1 Boot Record12.3.1.1 PC Partition Table Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 223<br>223<br>223<br>223<br>223<br>224                                                                                            |

| <ul> <li>12.1 Introduction</li> <li>12.2 Power On System Test</li> <li>12.3 Boot Record Format</li> <li>12.3.1 Boot Record</li> <li>12.3.1.1 PC Partition Table Entry</li> <li>12.3.1.2 Extended DOS Partition</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                           | 223<br>223<br>223<br>223<br>223<br>224<br>225                                                                                     |

| <ul> <li>12.1 Introduction</li> <li>12.2 Power On System Test</li> <li>12.3 Boot Record Format</li> <li>12.3.1 Boot Record</li> <li>12.3.1.1 PC Partition Table Entry</li> <li>12.3.1.2 Extended DOS Partition</li> <li>12.3.1.3 PowerPC Reference Platform Partition Table Entry</li> </ul>                                                                                                                                                                                                                                                                                                                                        | 223<br>223<br>223<br>223<br>224<br>225<br>226                                                                                     |

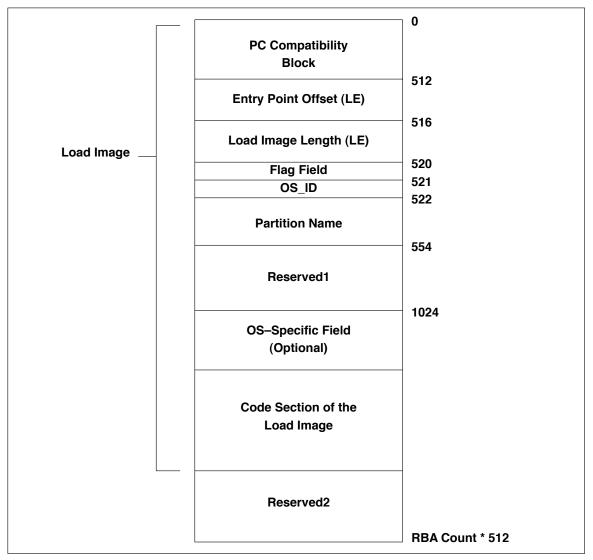

| <ul> <li>12.1 Introduction</li> <li>12.2 Power On System Test</li> <li>12.3 Boot Record Format</li> <li>12.3.1 Boot Record</li> <li>12.3.1.1 PC Partition Table Entry</li> <li>12.3.1.2 Extended DOS Partition</li> <li>12.3.1.3 PowerPC Reference Platform Partition Table Entry</li> <li>12.3.2 Loading the Load Image</li> </ul>                                                                                                                                                                                                                                                                                                 | 223<br>223<br>223<br>223<br>224<br>225<br>226<br>227                                                                              |

| <ul> <li>12.1 Introduction</li> <li>12.2 Power On System Test</li> <li>12.3 Boot Record Format</li> <li>12.3.1 Boot Record</li> <li>12.3.1.1 PC Partition Table Entry</li> <li>12.3.1.2 Extended DOS Partition</li> <li>12.3.1.3 PowerPC Reference Platform Partition Table Entry</li> <li>12.3.2 Loading the Load Image</li> <li>12.4 System Configuration</li> </ul>                                                                                                                                                                                                                                                              | 223<br>223<br>223<br>223<br>224<br>225<br>226<br>227<br>229                                                                       |

| <ul> <li>12.1 Introduction</li> <li>12.2 Power On System Test</li> <li>12.3 Boot Record Format</li> <li>12.3.1 Boot Record</li> <li>12.3.1.1 PC Partition Table Entry</li> <li>12.3.1.2 Extended DOS Partition</li> <li>12.3.1.3 PowerPC Reference Platform Partition Table Entry</li> <li>12.3.2 Loading the Load Image</li> <li>12.4 System Configuration</li> <li>12.4.1 System Console</li> </ul>                                                                                                                                                                                                                               | 223<br>223<br>223<br>224<br>225<br>226<br>227<br>229<br>229                                                                       |

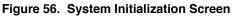

| <ul> <li>12.1 Introduction</li> <li>12.2 Power On System Test</li> <li>12.3 Boot Record Format</li> <li>12.3.1 Boot Record</li> <li>12.3.1.1 PC Partition Table Entry</li> <li>12.3.1.2 Extended DOS Partition</li> <li>12.3.1.3 PowerPC Reference Platform Partition Table Entry</li> <li>12.3.2 Loading the Load Image</li> <li>12.4 System Configuration</li> <li>12.4.1 System Console</li> <li>12.4.2 System Initialization</li> </ul>                                                                                                                                                                                         | 223<br>223<br>223<br>224<br>225<br>226<br>227<br>229<br>229<br>229                                                                |

| <ul> <li>12.1 Introduction</li> <li>12.2 Power On System Test</li> <li>12.3 Boot Record Format</li> <li>12.3.1 Boot Record</li> <li>12.3.1.1 PC Partition Table Entry</li> <li>12.3.1.2 Extended DOS Partition</li> <li>12.3.1.3 PowerPC Reference Platform Partition Table Entry</li> <li>12.3.2 Loading the Load Image</li> <li>12.4 System Configuration</li> <li>12.4.1 System Console</li> <li>12.4.2 System Initialization</li> <li>12.4.3 Main Menu</li> </ul>                                                                                                                                                               | 223<br>223<br>223<br>224<br>225<br>226<br>227<br>229<br>229<br>229<br>229<br>230                                                  |

| 12.1Introduction12.2Power On System Test12.3Boot Record Format12.3.1Boot Record12.3.1.1PC Partition Table Entry12.3.1.2Extended DOS Partition12.3.1.3PowerPC Reference Platform Partition Table Entry12.3.2Loading the Load Image12.4System Configuration12.4.1System Console12.4.2System Initialization12.4.3Main Menu12.4.1System Configuration Menu                                                                                                                                                                                                                                                                              | 223<br>223<br>223<br>224<br>225<br>226<br>227<br>229<br>229<br>229<br>229<br>230<br>231                                           |

| 12.1Introduction12.2Power On System Test12.3Boot Record Format12.3.1Boot Record12.3.1.1PC Partition Table Entry12.3.1.2Extended DOS Partition12.3.1.3PowerPC Reference Platform Partition Table Entry12.3.2Loading the Load Image12.4System Configuration12.4.1System Console12.4.2System Initialization12.4.3Main Menu12.4.3.1System Configuration Menu12.4.3.2Run a Program                                                                                                                                                                                                                                                       | 223<br>223<br>223<br>224<br>225<br>226<br>227<br>229<br>229<br>229<br>229<br>229<br>230<br>231<br>237                             |

| <ul> <li>12.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 223<br>223<br>223<br>224<br>225<br>226<br>227<br>229<br>229<br>229<br>229<br>229<br>230<br>231<br>237<br>238                      |

| 12.1Introduction12.2Power On System Test12.3Boot Record Format12.3.1Boot Record12.3.1.1PC Partition Table Entry12.3.1.2Extended DOS Partition12.3.1.3PowerPC Reference Platform Partition Table Entry12.3.2Loading the Load Image12.4System Configuration12.4.1System Console12.4.2System Initialization12.4.3Main Menu12.4.3.1System Configuration Menu12.4.3.2Run a Program12.4.3.3Reprogram Flash Memory12.4.3.4Exit Options                                                                                                                                                                                                     | 223<br>223<br>223<br>224<br>225<br>226<br>227<br>229<br>229<br>229<br>229<br>230<br>231<br>237<br>238<br>239                      |

| <ul> <li>12.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 223<br>223<br>223<br>224<br>225<br>226<br>227<br>229<br>229<br>229<br>229<br>229<br>230<br>231<br>237<br>238                      |

| <ul> <li>12.1 Introduction</li> <li>12.2 Power On System Test</li> <li>12.3 Boot Record Format</li> <li>12.3.1 Boot Record</li> <li>12.3.1.1 PC Partition Table Entry</li> <li>12.3.1.2 Extended DOS Partition</li> <li>12.3.1.3 PowerPC Reference Platform Partition Table Entry</li> <li>12.3.2 Loading the Load Image</li> <li>12.4 System Configuration</li> <li>12.4.1 System Console</li> <li>12.4.2 System Initialization</li> <li>12.4.3 Main Menu</li> <li>12.4.3.1 System Configuration Menu</li> <li>12.4.3 Run a Program</li> <li>12.4.3 Reprogram Flash Memory</li> <li>12.4.4 Default Configuration Values</li> </ul> | 223<br>223<br>223<br>224<br>225<br>226<br>227<br>229<br>229<br>229<br>229<br>230<br>231<br>237<br>238<br>239<br>239               |

| 12.1Introduction12.2Power On System Test12.3Boot Record Format12.3.1Boot Record12.3.1.1PC Partition Table Entry12.3.1.2Extended DOS Partition12.3.1.3PowerPC Reference Platform Partition Table Entry12.3.2Loading the Load Image12.4System Configuration12.4.1System Console12.4.2System Initialization12.4.3Main Menu12.4.3System Configuration Menu12.4.3Reprogram12.4.3Reprogram Flash Memory12.4.4Default Configuration ValuesSection 13 Registers and System Setup                                                                                                                                                            | 223<br>223<br>223<br>224<br>225<br>226<br>227<br>229<br>229<br>229<br>229<br>230<br>231<br>237<br>238<br>239<br>239<br>239<br>239 |

| <ul> <li>12.1 Introduction</li> <li>12.2 Power On System Test</li> <li>12.3 Boot Record Format</li> <li>12.3.1 Boot Record</li> <li>12.3.1.1 PC Partition Table Entry</li> <li>12.3.1.2 Extended DOS Partition</li> <li>12.3.1.3 PowerPC Reference Platform Partition Table Entry</li> <li>12.3.2 Loading the Load Image</li> <li>12.4 System Configuration</li> <li>12.4.1 System Console</li> <li>12.4.2 System Initialization</li> <li>12.4.3 Main Menu</li> <li>12.4.3.1 System Configuration Menu</li> <li>12.4.3 Run a Program</li> <li>12.4.3 Reprogram Flash Memory</li> <li>12.4.4 Default Configuration Values</li> </ul> | 223<br>223<br>223<br>224<br>225<br>226<br>227<br>229<br>229<br>229<br>229<br>230<br>231<br>237<br>238<br>239<br>239               |

| 13.2.1       CPU to PCI Configuration Transactions       242         13.2.1.1       Preferred Method of Generating PCI Configuration Transactions       243         13.2.1.2       650 Bridge Compatible Method       243         13.2.2       PCI Configuration Scan       243         13.2.2.1       Multi-Function Adaptors       243         13.2.2.2       PCI to PCI Bridges       243         13.2.3       660 Bridge Indexed BCR Summary       243         13.3       ISA Bridge (SIO) Initialization       247         13.3.1       ISA Bridge PCI Configuration Registers       250         13.4       MPIC PCI Configuration Registers       251         13.4.2       MPIC PCI //O Registers       251         13.4.2.1       MPIC PCI Configuration Registers (PCI I/O)       253         13.4.2.2       MPIC PCI Processor Registers (PCI I/O)       253         13.4.2.3       MPIC PCI Configuration Registers       255         13.5.1       Ethernet Initialization       255         13.5.2       Ethernet PCI Configuration Registers       255         13.5.3       Ethernet PCI I/O Registers       255         13.5.4       Ethernet PCI I/O Registers       256         13.5.3       Ethernet PCI I/O Registers       256       | 13.2 660 Bridge Initialization        | 242 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|

| 13.2.1.1       Preferred Method of Generating PCI Configuration Transactions       242         13.2.1.2       650 Bridge Compatible Method       243         13.2.2       PCI Configuration Scan       243         13.2.2.1       Multi-Function Adaptors       243         13.2.2.2       PCI to PCI Bridges       243         13.2.3       660 Bridge Indexed BCR Summary       243         13.3       ISA Bridge (SIO) Initialization       247         13.3.1       ISA Bridge PCI Configuration Registers       250         13.4       IMPIC Initialization       251         13.4.1       MPIC PCI I/O Registers (PCI I/O)       251         13.4.2       MPIC Colodiguration Registers (PCI I/O)       251         13.4.2       MPIC Global Registers (PCI I/O)       253         13.4.2.3       MPIC PCI I/O Registers (PCI I/O)       253         13.4.2.3       MPIC Per Processor Registers (PCI I/O)       254         13.5       Ethernet Initialization       255         13.5.1       Ethernet PCI Configuration Registers       255         13.5.2       Ethernet PCI I/O Registers       255         13.5.4       Ethernet EEPROM Interface       258         13.6       SCSI PCI I/O Registers       260                             |                                       | 242 |

| 13.2.1.2       650 Bridge Compatible Method       243         13.2.2       PCI Configuration Scan       243         13.2.2.1       Multi-Function Adaptors       243         13.2.2.2       PCI to PCI Bridges       243         13.2.3       660 Bridge Indexed BCR Summary       243         13.3       ISA Bridge PCI Configuration Registers       250         13.4       MPIC PCI Configuration Registers       251         13.4.1       MPIC PCI Configuration Registers       251         13.4.2       MPIC PCI I/O Registers       251         13.4.2       MPIC PCI I/O Registers       251         13.4.2.1       MPIC PCI Configuration Registers (PCI I/O)       253         13.4.2.3       MPIC Per Processor Registers (PCI I/O)       253         13.4.2.4       MPIC Per Processor Registers       255         13.5.1       Ethernet Initialization       255         13.5.2       Ethernet PCI I/O Registers       255         13.5.3       Ethernet PCI I/O Registers       256         13.5.4       Ethernet EEPROM Interface       258         13.6.2       SCSI PCI I/O Registers       260         13.6.2       SCSI PCI I/O Registers       260         13.6.2       SCSI PCI Configuration                                     |                                       | 242 |