POWERstation and POWERserver

# Hardware Technical Information General Architectures

# Fourth Edition (October 1993)

This edition notice applies to the POWERstation and POWERserver Hardware Technical Information-General Architectures. This edition obsoletes all previous editions.

The following paragraph does not apply to the United Kingdom or any country where such provisions are inconsistent with local law: THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions; therefore, this statement may not apply to you.

This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication.

It is possible that this publication may contain reference to, or information about, products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that such products, programming, or services intend to be announced in your country. Any reference to a licensed program in this publication is not intended to state or imply that you can use only the licensed program mentioned. You can use any functionally equivalent program instead.

Micro Channel is a registered trademark of International Business Machines Corporation.

POWER2 is a trademark of International Business Machines Corporation.

©Copyright International Business Machines Corporation, 1992. All rights reserved.

Note to U.S. Government Users – Documentation and programs related to restricted nghts – Use, duplication, or disclosure is subject to the restrictions set forth in GSA ADP Schedule Contract.

# Table of Contents

| About This Book                                | v             |

|------------------------------------------------|---------------|

| Chapter 1. System Processors                   | 1-1           |

| Description                                    | 1-5           |

| Central Electronics Complex                    | 1-5           |

| Document Conventions                           | 1-10          |

| Systems Overview                               | 1-11          |

| Instruction Formats                            | 1-12          |

| Memory Addressing                              | 1-19          |

| Branch Processor                               | 1-21          |

| Fixed-Point Processor Registers                | 1-25          |

| Floating-Point Processor Overview              | 1-27          |

| Floating-Point Data Representation             | 1-33          |

| Floating-Point Exceptions                      | 1-39          |

| Floating-Point Resource Management             | 1-45          |

| Floating-Point Execution Models                | 1-45          |

| Interrupts                                     | 1-48          |

| Storage Control                                | 1-69          |

| Timer Facilities                               | 1-82          |

| Floating-Point Round to Single Model           | 1-87          |

| Floating-Point Integer Convert Model           | 1-92          |

| VO Space Rules                                 | 1-94          |

| Serializing Semantics of Various Instructions  | 1 <b>-9</b> 5 |

| Chapter 2. System I/O Structure                | 2-1           |

| Description                                    | 2-3           |

| Bit and Byte Numbering Conventions             | 2-7           |

| VO Bus Protocols                               | 2-13          |

| Programming Model                              | 2-21          |

| Special Facilities                             | 2-72          |

| System I/O and Standard I/O                    | 2-84          |

| Exception Reporting and Handling               | <b>2-8</b> 5  |

| Implementation Details                         | 2-86          |

| Chapter 3. Vital Product Data                  | 3-1           |

| Description                                    | 3-3           |

| Keyword Descriptor Summary                     | 3-5           |

| Hardware VPD Descriptor Summary                | 3-13          |

| Micro Channel Adapter Requirements             | 3-16          |

| Sample Layout of the Micro Channel Adapter VPD | 3-20          |

| Chapter 4. Initial Program Load (IPL) ROM | 4-1  |

|-------------------------------------------|------|

| Description                               | 4-3  |

| IPL ROM Components                        | 4-6  |

| IPL ROM Functional Characteristics        | 4-13 |

| Error Codes                               | 4-16 |

| Index                                     | X-1  |

# **About This Book**

This manual describes architecture features that are common to the system family.

Note: The information in this book can also be found in the CD-ROM Hypertext Information Base Library. This online documentation is designed for use with the InfoExplorer hypertext retrieval system.

#### Who Should Use This Book

This book is an overview of the operation of the system. It is intended for programmers and engineers who understand computer architecture and programming concepts and who develop hardware and software products for the system family.

### How to Use This Book

#### **Overview of Contents**

This book contains the following chapters:

- Chapter 1, "Processors," describes the central electronics complex, the document conventions, a general systems overview, instruction formats, and memory addressing.

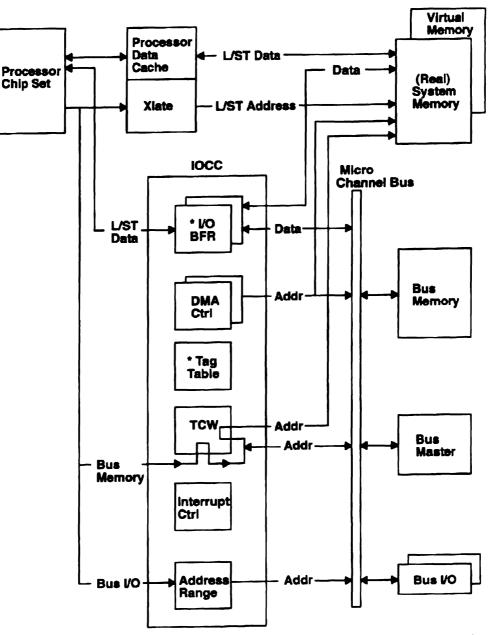

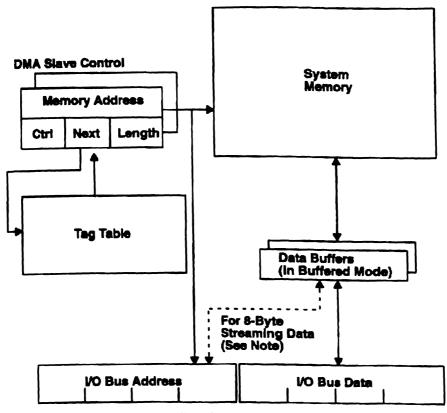

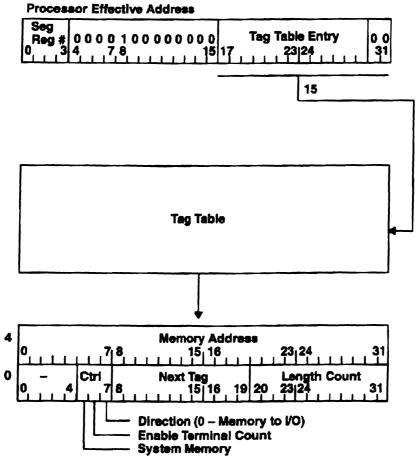

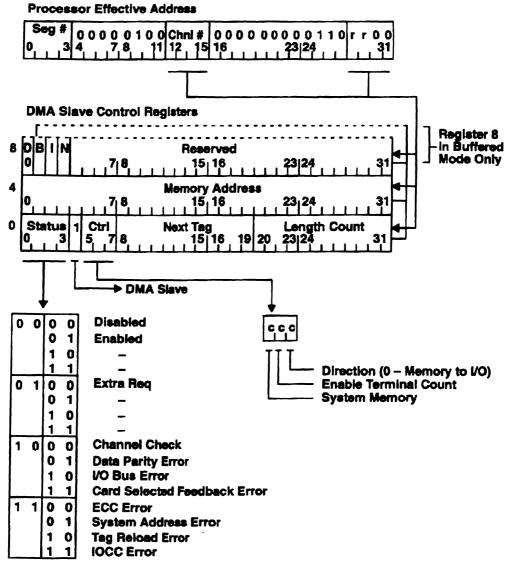

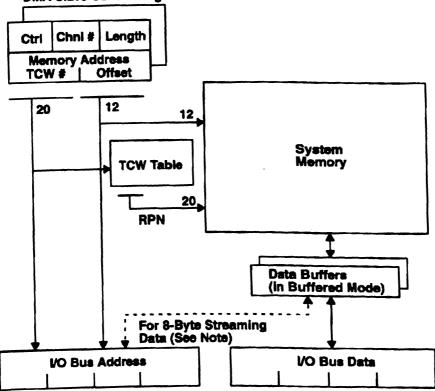

- Chapter 2, "System I/O Structure," describes bit and byte numbering conventions, I/O bus protocols, the programming model, load and store instructions, the translation, protection, and TCW table, the bus master, the DMA slave, IOCC Commands, Buffer Flush commands, I/O interrupts, special facilities, the system I/O and standard I/O, exception reporting and handling, and implementation details.

- Chapter 3, "Vital Product Data," contains the keyword descriptor summary, the hardware VPD descriptor summary, the Micro Channel adapter requirements, and a sample layout of the Micro Channel adapter VPD.

- Chapter 4, "Initial Program Load (IPL) ROM," describes IPL ROM components, IPL ROM functional characteristics, and error codes.

#### **Overview of Reference Library Contents**

This general information manual, is one part of the hardware technical information library. This manual describes features that are common to the system family. Since the last edition, new products have evolved that feature economy of cost and size. Check the front of each chapter in this manual for a note specifying which models are covered in the chapter. The *General Architectures* manual should be used in conjunction with the following hardware technical information manuals:

- POWERstation and POWERserver Hardware Technical Information-Options and Devices (SA23-2646)

- 7011 POWERstation and POWERserver Hardware Technical Information (SA23-2666)

- 7012 POWERstation and POWERserver Models 34x, 35x, 36x, and 37x Hardware Technical Information (SA23-2680)

- 7013 POWERstation and POWERserver Models 550L, 57x, 58x, 58H, and 590 Hardware Technical Information (SA23-2684)

- 7015 POWERserver Models 97x, 98x, and 99x Hardware Technical Information (SA23-2686).

#### Highlighting

The following highlighting conventions are used in this book:

- Bold Identifies commands, keywords, files, directories, and other items whose names are predefined by the system.

- Italics Identifies parameters whose actual names or values are to be supplied by the user.

Monospace Identifies examples of specific data values, examples of text similar to what you might see displayed, examples of portions of program code similar to what you might write as a programmer, messages from the system, or information you should actually type.

#### **Related Publications**

The following is a list of related publications. For information on ordering these publications, contact your authorized dealer or marketing representative.

- IBM RISC System/6000 System Overview (GC23-2408)

- Personal System/2 Hardware Interface Technical Reference: Architectures (S84F-9808)

- AIX Version 3.2 Assembler Language Reference (SC23-2197)

- AIX Version 3.2 Kernel Extensions and Device Support Programming Concepts (SC23-2207)

- AIX Version 3.2 Problem Solving Guide and Reference (SC23-2204).

#### **Ordering Publications**

You can order IBM publications from your IBM sales representative or, in the U.S., from IBM Customer Publications Support at 1 800 879-2755. If you believe you are entitled to publications that were not shipped with your RISC System/6000 or AIX purchases, contact your IBM sales representative or Customer Publications Support for assistance.

To order additional copies of this book, use Order Number SA23-2643.

# Chapter 1. System Processors

# **Chapter Contents**

| Description                                | 1-5  |

|--------------------------------------------|------|

| Central Electronics Complex                | 1-5  |

| Document Conventions                       | 1-10 |

| Systems Overview                           | 1-11 |

| Instruction Formats                        | 1-12 |

| Forms                                      | 1-12 |

| D Form                                     | 1-12 |

| DS Form                                    | 1-12 |

| B Form                                     | 1-12 |

| I Form                                     | 1-12 |

| SC Form                                    | 1-13 |

| X Form                                     | 1-13 |

| XL Form                                    | 1-13 |

| XFX Form                                   | 1-13 |

| XFL Form                                   | 1-13 |

| XO Form                                    | 1-13 |

| A Form                                     | 1-14 |

| M Form                                     | 1-14 |

| Instruction Fields                         | 1-14 |

| Memory Addressing                          | 1-19 |

| Branch Processor                           | 1-21 |

| Fixed-Point Processor Registers            | 1-25 |

| General Purpose Registers                  | 1-25 |

| Fixed-Point Exception Register             | 1-26 |

| Multiply Quotient Register                 | 1-26 |

| Floating-Point Processor Overview          | 1-27 |

| Floating-Point Registers                   | 1-28 |

| Floating-Point Status and Control Register | 1-29 |

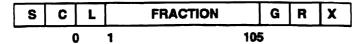

| Floating-Point Data Representation         | 1-33 |

| Data Format                                | 1-33 |

| Value Representation                       | 1-34 |

| Binary Floating-Point Numbers              | 1-34 |

| Normalized Numbers (+NOR)                  | 1-35 |

| Zero Values (+0)                           | 1-35 |

| Denormalized Numbers (+DEN)                | 1-35 |

| Infinities (+INF)                          | 1-35 |

| Not a Numbers (NaNs)                       | 1-36 |

| Normalization and Denormalization          | 1-36 |

| Precision                                  | 1-37 |

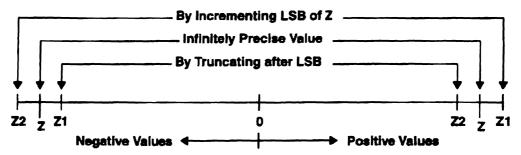

| Rounding                                   | 1-37 |

| Data Handling                              | 1-38 |

| Floating-Point Exceptions                          | 1-39         |

|----------------------------------------------------|--------------|

| Invalid Operation Exception                        | 1-40         |

| Zero Divide Exception                              | 1-41         |

| Overflow Exception                                 | 1-42         |

| Underflow Exception                                | 1-44         |

| Inexact Exception                                  | 1-44         |

| Floating-Point Resource Management                 | 1-45         |

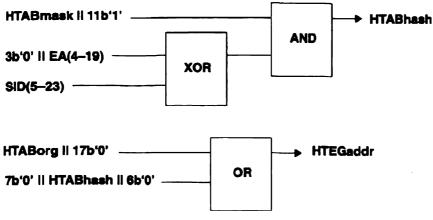

| Floating-Point Execution Models                    | 1-45         |

| Execution Model for IEEE Operations                | 1-45         |

| Execution Model for Multiply-Add Type Instructions | 1-47         |

| Interrupts                                         | 1-48         |

| Interrupt Definitions                              | 1-50         |

| System Reset Interrupt                             | 1-50         |

| Machine Check Interrupt                            | 1-50         |

| Data Storage Interrupt                             | 1-51         |

| Instruction Storage Interrupt                      | 1-53         |

| Alignment Interrupt                                | 1-54         |

| Program Interrupt                                  | 1-56         |

| External Interrupt                                 | 1-57         |

| Floating-Point Unavailable Interrupt               | 1-58         |

| Trace Interrupt (POWER2 Only)                      | 1-58         |

| Floating-Point Imprecise Interrupt (POWER2 only)   | 1-59         |

| Supervisor Call Interrupt                          | 1-60         |

| Interrupt Priorities                               | 1-60         |

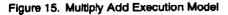

| External Interrupt Mechanism for POWER             | 1-62         |

| External Interrupt Enable                          | 1-63         |

| External Interrupt Control Registers               | 1-64         |

| Functions                                          | 1-64         |

| Addressing the EICRs                               | 1-64         |

| Accessing the EICRs                                | 1-65         |

| Reading from the EICRs                             | 1-65         |

| Writing to the EICRs                               | 1-66         |

| External Interrupt Sources                         | 1-66         |

| Submitting Interrupts                              | 1-66         |

| EICR Mapping                                       | 1-66         |

| External Interrupt Mechanism for POWER2            | 1-00<br>1-67 |

| Interrupt Level Control Registers                  | 1-67         |

| MFSPR RT, ILCR                                     | 1-67         |

| MTSPR ILCR, RS                                     | 1-68         |

|                                                    | 1-68         |

| EISBID Registers                                   | 1-69         |

| PEIS Registers                                     |              |

| Storage Control Registern                          | 1-69<br>1-70 |

| Storage Control Registers                          |              |

| Segment Registers                                  | 1-70<br>1-71 |

| Storage Description Register for POWER             | 1-71<br>1-72 |

|                                                    | 1-12         |

| Virtual Address Translation                                          | 1-72 |

|----------------------------------------------------------------------|------|

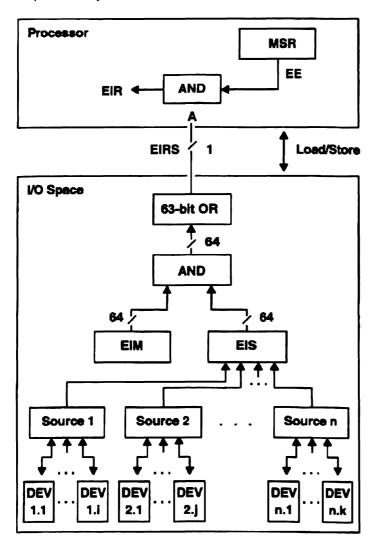

| Inverted Page Table (POWER Only)                                     | 1-73 |

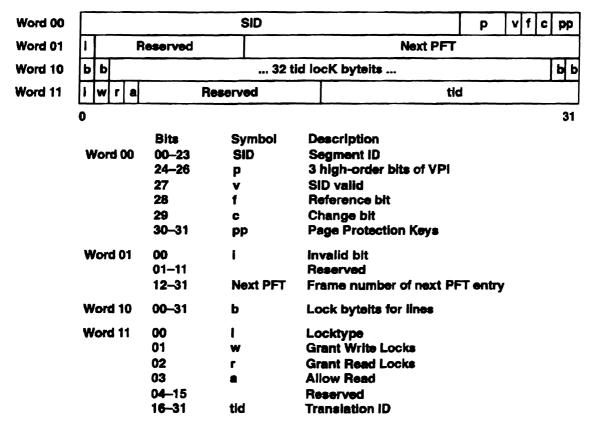

| Hashed Page Table (POWER2 Only)                                      | 1-76 |

| Address Aliasing                                                     | 1-80 |

| Storage Access Recording Mechanism                                   | 1-81 |

| Storage Protection Mechanism                                         | 1-81 |

| Page Protection                                                      | 1-81 |

| Timer Facilities                                                     | 1-82 |

| Real-Time Clock                                                      | 1-82 |

| RTCL Description                                                     | 1-83 |

| RTCU Description                                                     | 1-84 |

| Setting and Reading the RTC                                          | 1-84 |

| Decrementer                                                          | 1-85 |

| Decrementer Interrupts                                               | 1-86 |

| Decrementer Usage                                                    | 1-86 |

| Floating-Point Round to Single Model                                 | 1-87 |

| Floating-Point Round to Single Model                                 | 1-87 |

| Disabled Exponent Underflow                                          | 1-87 |

| Enabled Exponent Underflow                                           | 1-88 |

| Disabled Exponent Overflow                                           | 1-89 |

| Enabled Exponent Overflow                                            | 1-90 |

| Infinity Operand                                                     | 1-90 |

| QNaN Operand                                                         | 1-90 |

| SNaN Operand                                                         | 1-90 |

| Normal Operand                                                       | 1-91 |

| Round Single (sign, exp, frac, G, R, X)                              | 1-91 |

| Floating-Point Integer Convert Model                                 | 1-92 |

| Floating-Point Integer Conversion                                    | 1-92 |

| Round Integer (sign, frac, gbit, rbit, xbit, round_mode)             | 1-92 |

| Infinity Operand                                                     | 1-93 |

| SNaN Operand                                                         | 1-94 |

| QNaN Operand                                                         | 1-94 |

|                                                                      | 1-94 |

| I/O Space Rules                                                      | 1-94 |

| Serializing Semantics of Various Instructions                        | 1-95 |

| Some Serialization Cases                                             | 1-95 |

| Instruction Cache Synchronize and Data Cache Synchronize Definitions | 1-96 |

| ics Instruction                                                      | 1-96 |

| dcs Instruction                                                      | 1-97 |

| Other Instructions Possibly Requiring Serialization                  | 1-97 |

# Description

This section describes the central electronics complex (CEC) for the POWER2 and POWER implementations of the RISC System/6000, the document conventions, a general systems overview, instruction formats, and memory addressing.

A POWER processor is used in this system family. Like earlier processors, the POWER processor employs a simple register-oriented instruction set that is completely hardwired, and features a pipelined implementation and an efficient storage hierarchy. This enables the processor chip set to run an instruction almost every cycle. Unlike earlier processors, however, this unit employs several advanced architectural and implementation features including separate instruction and data caches, zero-cycle branches, multiple instruction dispatch, simultaneous running of fixed- and floating-point operations, and overlapped running of register-register (RR) operations and load and store commands. As such, the unit combines the simplicity of an instruction set with sophisticated hardware design techniques to achieve a short cycle time and a low cycles-per-instruction (CPI) ratio.

In the POWER2 implementation, six instructions can be executed in a single cycle: a branch, two fixed-point, two floating-point, and a Condition register logical instruction. Counting the floating-point multiply-add instruction as two operations, this yields a peak run rate of eight operations per cycle. In the POWER implementation, four instructions can be executed in a single cycle: a branch, a fixed-point, a floating-point, and a Condition register logical instruction. Counting the floating-point multiply-add instructions, this yields a peak run rate of eight operations per cycle.

Note: This chapter provides information for system models 32x, 34x, 35x, 36x, 37x, 52x, 53x, 540, 55x, 56x, 57x, 58x, 58H, 59x, 730, 930, 95x, 97x, 98x, and 99x. Information for other system models can be found in the product-specific technical information manual for those models.

The processor chip sets described in this chapter are representative of the chip sets used in the models mentioned in the preceding paragraph. The megahertz number of the processor chip set varies depending on the system model.

# **Central Electronics Complex**

The POWER and POWER2 processor chip sets form the central electronics complex (CEC) and have up to eleven semi-custom chips: a fixed-point unit (FXU), a floating-point unit (FPU), an instruction cache and branch processing unit (ICU), four data cache units (DCU), a memory control unit (MCU), an Input/Output (I/O) Channel controller a Serial Optical Channel converter, and a clock chip (CLK). Every memory board contains two data multiplexing modules and one control module for interfeaving.

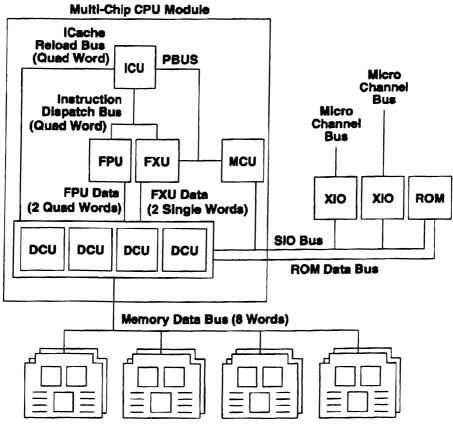

There are four basic processor chip sets in this family of system units. The first chip set shown in Figure 1 on page 1-6 is the POWER2 implementation having the following characteristics:

- · Fixed-point unit with two execution units

- · Floating-point unit with two multiply add units

- 32K-byte instruction cache

- 256K-byte data cache.

This implementation supports configurations with two, four, or eight memory boards. A two memory board configuration supports a 128K-byte data cache and a 128-bit memory interface. A four or eight board configuration supports a 256K-byte data cache and a 256-bit memory interface. The eight chips (ICU, FXU, FPU, 4X DCU, and MCU) are packaged on a multichip carrier. The I/O subsystem can contain up to two extended input/output (XIO) modules.

Note: Some systems have only two memory boards. Some systems have only one XIO module.

POWER2 System Configuration, 8 Word Memory Bus

Figure 1. First Processor Chip Set

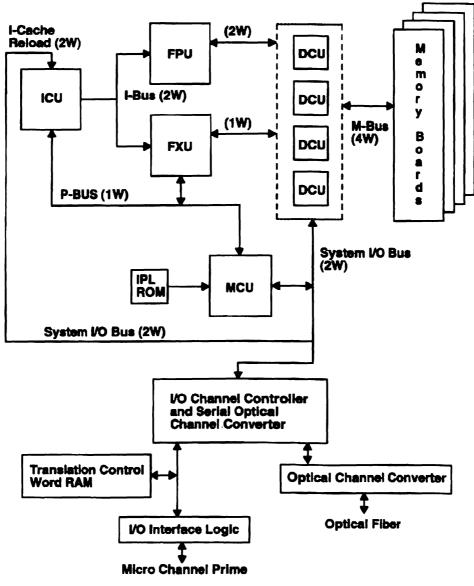

The second chip set has two data cache units and a system memory interface that is 64 bits wide.

The third chip set uses the same modules, but has four data cache units and a 128-bit bus to system memory.

The second and third chip sets a have an instruction cache unit with 8K bytes. It has an input and output unit (IOU) that combines the I/O channel controller (for Micro Channel bus) and the serial link logic. Figure 2 shows the chip sets described previously with four data cache units like the second chip set.

Figure 2. Second and Third Processor Chip Sets

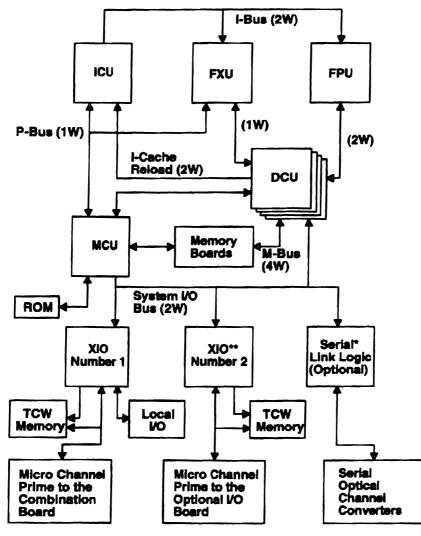

The fourth chip set is shown in Figure 3. This chip set has an instruction cache unit with 32K bytes of chip memory. The I/O subsystem can contain up to two XIO modules and a serial link logic for system serial optical channels. The XIO module, contains the I/O channel control unit that generates the Micro Channel interface.

\*The serial link logic is optional on some models. \*The XIO Number 2 is only available on some models.

Figure 3. Fourth Processor Chip Set

The POWER2 and POWER implementations have an ICU that contains a two-way set-associative instruction cache. It runs branch instructions and Condition register logical instructions, and supports interrupts. In many cases, branches cost zero cycles because the ICU looks ahead in the instruction stream and removes branches from the stream. In a given cycle, the ICU in the POWER implementation can dispatch two instructions (two to the FXU, or two to the FPU, or one to the FXU and one to the FPU) by way of the I-bus shown in Figure 1 on page 1-6. The ICU in the POWER2 implementation can dispatch four instructions. The floating-point unit contains a full 64-bit double-precision floating-point data flow and conforms to the IEEE 754 binary floating-point instructions for maximum performance. The FXU contains the general purpose registers and the arithmetic logic units, and runs all fixed-point instructions. The FXU includes an address translation and data protection unit that makes precise interrupts easier to implement with minimal performance penalty. The FXU also provides the directories and control for the data cache, and controls the running of fixed-point load, floating-point load, and store instructions.

In the POWER2 implementation four DCUs provide a four-way set-associative data cache. The DCUs form an eight-word (four or eight memory boards) and a four-word (two memory boards) interface to memory, two four-word (4W) interfaces to FPU, and two single-word (1W) interfaces to FXU. In the POWER implementation four DCUs provide a four-way set-associative data cache. The DCUs form a four-word (4W) interface to memory, a two-word (2W) interface to FPU, and a single-word (1W) interface to FXU. DCUs contain error checking and correction (ECC) and bit steering logic. They provide the data path for Direct Memory Accesses (DMA), and supply the path for instruction cache (I-cache) reloads. The MCU contains the controls and configuration registers for system memory. The MCU provides the data path between I/O and processor chip set for I/O load and store instructions. The MCU also interfaces to the ROM that contains the system initialization code for the processor chip set, also referred to as the initial program load read-only memory (IPL ROM).

The processor bus (P-bus) shown in Figure 1 on page 1-6 is used to send the address to the MCU for D-cache (data cache) reloads (by FXU) and for I-cache reloads (by ICU). It is used for I-cache translation look-aside buffer (TLB) reloads (by FXU), and for I/O loads and stores (by FXU). The P-bus is also used for moves to and from special registers (for example, Segment registers, Link register, and Machine State register) between FXU and ICU. The system I/O bus is used to transfer the DMA data between the IOU and system memory by way of the DCU, and provides a path for I/O load and store operations between the FXU and the IOU by way of the MCU.

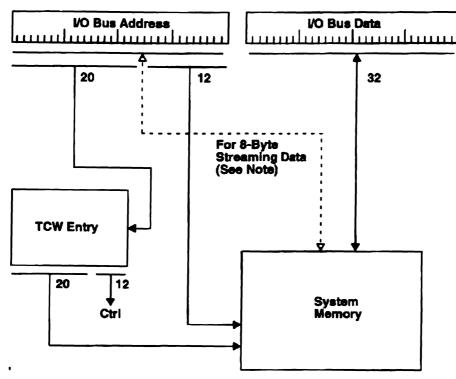

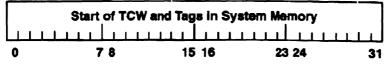

The I/O unit contains an I/O channel control unit that generates the Micro Channel Interface. The I/O channel control unit uses the data stored in translation control word (TCW) and tag tables for address translation and data protection during I/O operations.

# **Document Conventions**

The following conventions are used throughout this document:

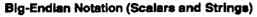

- Quadwords are 128 bits, doublewords are 64 bits, words are 32 bits, halfwords are 16 bits, bytes are 8 bits.

- All numbers are decimal unless specified in some special way.

- · b'nnn' means a number expressed in binary format.

- x'nnn' means a number expressed in hexadecimal format.

- n x b'0' means n zeros.

- n x b'1' means n ones.

- (RAI0) means the contents of register RA if the RA field has the value 1 through 31, or the value 0 if the RA field is 0.

- (Rx) means the contents of register Rx.

- (FRx) means the contents of register FRx.

- X(p) means bit p of register or field X.

- X sub p means bit p of register or field X.

- X(p-q) means bits p through q of register or field X.

- X(p..q) means bits p through q of register or field X.

- X sub p-q means bits p through q of register or field X.

- ¬(RA) means the ones complement of the contents of register RA.

- /, //, ///, ... means a field that is ignored by the hardware.

- The symbol II is used to describe two fields that are appended or concatenated to each other. For example, 010II111 is the same as 010111.

- All bits in registers that are reserved are 0 on read and can be either 0 or 1 on write.

- 2\*\*\* means 2 raised to the n\*\* \* power.

- Field i refers to bits 4 x i to (4 x i) + 3 of a register.

- Positive means greater than 0.

- Negative means less than 0.

- Instructions are assumed to be nonprivileged unless stated otherwise in the instruction description.

# **Systems Overview**

The processor or processor unit contains the sequencing and processing controls for instruction fetch, instruction execution, and interrupt action. The following classes of instructions can be executed by the processing unit:

- Branch processor instructions

- Fixed-point processor instructions

- Floating-point processor instructions.

Refer to AIX Version 3.2 Assembler Language Reference for information on a specific instruction.

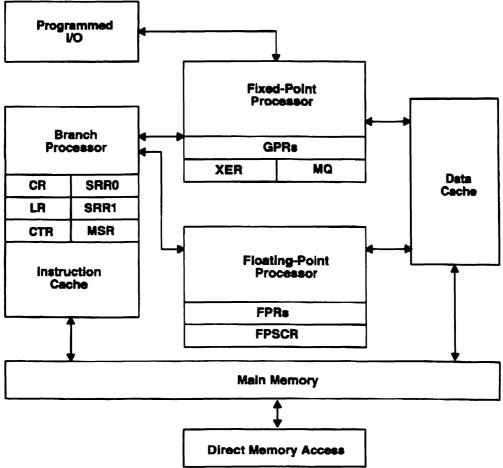

See Figure 4 for a representation of the logical partitioning provided by the system architecture. The processing unit is a word-oriented fixed-point processor and in a doubleword-oriented floating-point processor. The system architecture uses 32-bit word-aligned instructions and provides for byte, halfword, word, and doubleword operand fetches and stores between system memory and a set of 32 general purpose registers (GPRs), and between system memory and a set of 32 floating-point registers (FPRs).

Figure 4. System Architecture View

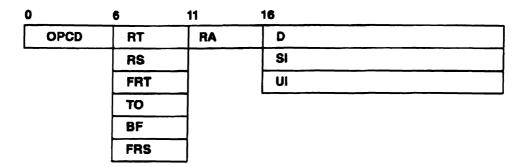

# **Instruction Formats**

All instructions are 4 bytes long and are located on word boundaries. Thus, whenever instruction addresses are presented to the processing unit (as in branch instructions) the two low-order bits are ignored. Similarly, whenever the processing unit develops an instruction address, its two low-order bits are 0.

Bits 0 through 5 always specify the opcode. For XO-form instructions, an extended opcode is specified in bits 22 through 30. For all other X-form instructions, an extended opcode is specified in bits 21 through 30. For A-form instructions, an extended opcode is specified in bits 26 through 30.

The remaining bits contain one or more alternative fields for the different instruction formats.

#### Forms

#### D Form

#### **DS Form**

| 0    | 6  | 11 | 16 | 30 |

|------|----|----|----|----|

| OPCD | RT | RA | DS | XO |

|      | RS | RA |    |    |

#### **B** Form

| 0    | 6  | 11 | 16 | 30 | 31 |

|------|----|----|----|----|----|

| OPCD | BO | BI | BD | ** | LK |

#### I Form

| 0    | 8 | 30 | 31 |

|------|---|----|----|

| OPCD | L | *  | LK |

### SC Form

| 0    | 6 | 11 | 16  | 20  | 27  | 30 | 31 |

|------|---|----|-----|-----|-----|----|----|

| OPCD |   |    | FL1 | LEV | FL2 | SA | LK |

|      |   |    | SV  |     |     |    |    |

# X Form

| 0    | 6   | 11  | 16                                     | 21 | 31 |

|------|-----|-----|----------------------------------------|----|----|

| OPCD | RT  | RA  | RB                                     | EO | Rc |

|      | FRT | FRA | FRB                                    |    |    |

|      | BF  | BFA | SH                                     |    |    |

|      | RS  | SPR | NB                                     |    |    |

|      | FRS |     | 1                                      | _  |    |

|      | то  |     | •••••••••••••••••••••••••••••••••••••• |    |    |

|      | ВТ  |     |                                        |    |    |

### XL Form

|   | 0    | 6  | 11 | 16 | 21 | 31 |

|---|------|----|----|----|----|----|

| [ | OPCD | BT | BA | BB | EO | LK |

| • |      | BO | BI |    |    |    |

### **XFX** Form

| 0    | 6  | 11  | 21 | 31 |

|------|----|-----|----|----|

| OPCD | RT | FXM | EO | Rc |

# XFL Form

| 0    | 6   | 16  | 21 | 31 |

|------|-----|-----|----|----|

| OPCD | FLM | FRB | EO | Rc |

### **XO** Form

| 0    | 6  | 11 | 16 | 21 22  | 31 |

|------|----|----|----|--------|----|

| OPCD | RT | RA | RB | OE EO' | Rc |

#### A Form

**M** Form

A-form instructions are used for four operand instructions. The operands, all floating-point registers, are specified by the FRT, FRA, FRB, and FRC fields. The short extended opcode, XO, is in bits 26 through 30.

| 0    | 6       | 11       | 1 <b>6</b> | 21  | 26       | 31       |

|------|---------|----------|------------|-----|----------|----------|

| OPCD | FRT     | FRA      | FRB        | FRC | xo       | Rc       |

|      |         |          |            |     |          |          |

| D    | 6       | 11       | 16         | 21  | 26       | 31       |

| OPCD | 6<br>RS | 11<br>RA | 16<br>RB   |     | 26<br>ME | 31<br>Rc |

### **Instruction Fields**

The following instruction fields are defined for the various instruction formats:

| Fields             |                                                                                                                                                                                        | Instruction fields are defined for the various instruction formats:<br>Description                                                                                                                                                                                                                                                                                                                     |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AA (30)            | Following is the description of the Absolute Address bit.                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| ()                 | Bit                                                                                                                                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                    | 0                                                                                                                                                                                      | The immediate field represents an address relative to the current instruction address. For I-form branches, the effective address of the branch is the sum of the LI field sign extended to 32 bits and the address of the branch instruction. For B-form branches, the effective address of the branch is the sum of the BD field sign extended to 32 bits and the address of the branch instruction. |  |  |

|                    | 1                                                                                                                                                                                      | The immediate field represents an absolute address. For<br>I-form branches, the effective address of the branch is the<br>LI field sign extended to 32 bits. For B-form branches, the<br>effective address of the branch is the BD field sign<br>extended to 32 bits.                                                                                                                                  |  |  |

| BA (11-15)         | Field used to s source.                                                                                                                                                                | pecify a bit in the Condition register (CR) to be used as a                                                                                                                                                                                                                                                                                                                                            |  |  |

| BB (16-20)         | Field used to s                                                                                                                                                                        | pecify a bit in the CR to be used as a source.                                                                                                                                                                                                                                                                                                                                                         |  |  |

| BD (16–29)         |                                                                                                                                                                                        | d specifying a 14-bit signed twos complement branch<br>which is concatenated on the right with b'00' and sign<br>bits.                                                                                                                                                                                                                                                                                 |  |  |

| BF (68)            | Field used to specify one of the CR compare result fields or one of the FPSCR fields as a target. If $i = BF(6-8)$ , then field i refers to bits i x 4 to (i x 4) + 3 of the register. |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| <b>BFA</b> (11–13) | FPSCR fields,                                                                                                                                                                          | pecify one of the CR compare result fields, one of the or one of the XER fields as a source. If $j = BFA(11-13)$ , then bits $j \ge 4$ to $(j \ge 4) + 3$ of the register.                                                                                                                                                                                                                             |  |  |

| BI (11–15)         | Field used to s<br>branch.                                                                                                                                                             | pecify the bit in the CR to be used as the condition of the                                                                                                                                                                                                                                                                                                                                            |  |  |

| Fields      | Description                                                                                                                             |                                                                                         |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| BO (6-10)   | Field used to specify different options that can be used in conditional brain instructions. Following is the encoding for the BO field: |                                                                                         |  |

|             | во                                                                                                                                      | Description                                                                             |  |

|             | 0000x                                                                                                                                   | Decrement the CTR, then branch if the decremented CTR $\neq$ 0 and condition is false.  |  |

|             | 0001x                                                                                                                                   | Decrement the CTR, then branch if the decremented $CTR = 0$ and condition is false.     |  |

|             | 001xx                                                                                                                                   | Branch if condition is false.                                                           |  |

|             | 0100x                                                                                                                                   | Decrement the CTR, then branch if the decremented CTR $\neq$ 0 and condition is true.   |  |

|             | 0101x                                                                                                                                   | Decrement the CTR, then branch if the decremented $CTR = 0$ and condition is true.      |  |

|             | 011xx                                                                                                                                   | Branch if condition is true.                                                            |  |

|             | 1x00x                                                                                                                                   | Decrement the CTR, then branch if the decremented CTR $\neq$ 0.                         |  |

|             | 1 <b>x01</b> x                                                                                                                          | Decrement the CTR, then branch if the decremented $CTR = 0.$                            |  |

|             | 1x1xx                                                                                                                                   | Branch always.                                                                          |  |

| BT (6–10)   | Field used to s<br>instruction.                                                                                                         | pecify a bit in the CR as the target of the result of an                                |  |

| D (16–31)   | Immediate field<br>extended to 32                                                                                                       | d specifying a 16-bit signed twos complement integer sign<br>t bits.                    |  |

| DS (16–29)  |                                                                                                                                         | d specifying a 14-bit signed twos complement integer to<br>s concatenated on the right. |  |

| EO (21-30)  | A 10-bit extend                                                                                                                         | led opcode used in X-form instructions.                                                 |  |

| EO' (22–30) | A 9-bit extende                                                                                                                         | ed opcode used in XO-form instructions.                                                 |  |

| FL1 (16–19) | A 4-bit field in 1                                                                                                                      | the Supervisor Call (SVC) instruction.                                                  |  |

| FL2 (27-29) | A 3-bit field in 1                                                                                                                      | the SVC instruction.                                                                    |  |

| FXM (12-19) | Field mask, ide                                                                                                                         | antifies which CR field is to be updated.                                               |  |

|             | Blt                                                                                                                                     | Description                                                                             |  |

|             | 12                                                                                                                                      | CR Field 0 (bits 00–03)                                                                 |  |

|             | 13                                                                                                                                      | CR Field 1 (bits 04–07)                                                                 |  |

|             | 14                                                                                                                                      | CR Field 2 (bits 08–11)                                                                 |  |

|             | 15                                                                                                                                      | CR Field 3 (bits 12–15)                                                                 |  |

|             | 16                                                                                                                                      | CR Field 4 (bits 16–19)                                                                 |  |

|             | 17                                                                                                                                      | CR Field 5 (bits 20–23)                                                                 |  |

|             | 18                                                                                                                                      | CR Field 6 (bits 24–27)                                                                 |  |

|             | 19                                                                                                                                      | CR Field 7 (bits 28–31).                                                                |  |

| Fields      | Description                                                                                                                                                                                                                                                                              |                                                                                                                     |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| FLM (7-14)  | Field mask, identifies which FPSCR field is to be updated.                                                                                                                                                                                                                               |                                                                                                                     |  |

|             | Bit                                                                                                                                                                                                                                                                                      | Description                                                                                                         |  |

|             | 7                                                                                                                                                                                                                                                                                        | FPSCR Field 0 (bits 00-03)                                                                                          |  |

|             | 8                                                                                                                                                                                                                                                                                        | FPSCR Field 1 (bits 04–07)                                                                                          |  |

|             | 9                                                                                                                                                                                                                                                                                        | FPSCR Field 2 (bits 08-11)                                                                                          |  |

|             | 10                                                                                                                                                                                                                                                                                       | FPSCR Field 3 (bits 12-15)                                                                                          |  |

|             | 11                                                                                                                                                                                                                                                                                       | FPSCR Field 4 (bits 16–19)                                                                                          |  |

|             | 12                                                                                                                                                                                                                                                                                       | FPSCR Field 5 (bits 20-23)                                                                                          |  |

|             | 13                                                                                                                                                                                                                                                                                       | FPSCR Field 6 (bits 24-27)                                                                                          |  |

|             | 14                                                                                                                                                                                                                                                                                       | FPSCR Field 7 (bits 28-31).                                                                                         |  |

| FRA (11-15) | Field used to s                                                                                                                                                                                                                                                                          | pecify an FPR as a source of an operation.                                                                          |  |

| FRB (16-20) | Field used to s                                                                                                                                                                                                                                                                          | pecify an FPR as a source of an operation.                                                                          |  |

| FRC (21-25) | Field used to s                                                                                                                                                                                                                                                                          | pecify an FPR as a source of an operation.                                                                          |  |

| FRS (6-10)  | Field used to s                                                                                                                                                                                                                                                                          | pecify an FPR as a source of an operation.                                                                          |  |

| FRT (6-10)  | Field used to sp                                                                                                                                                                                                                                                                         | pecify an FPR as the target of an operation.                                                                        |  |

| l (16–19)   | Immediate field                                                                                                                                                                                                                                                                          | used as the data to be placed into a field in the FPSCR.                                                            |  |

| LEV (20-26) |                                                                                                                                                                                                                                                                                          | in the SVC instruction that addresses the SVC routine by $00000^{\circ}$ if SA = 0.                                 |  |

| LI (6–29    |                                                                                                                                                                                                                                                                                          | specifying a 24-bit signed two's complement integer that is<br>n the right with b'00' and sign extended to 32 bits. |  |

| LK (31)     | Following is the                                                                                                                                                                                                                                                                         | description of the Link bit.                                                                                        |  |

|             | Bit                                                                                                                                                                                                                                                                                      | Description                                                                                                         |  |

|             | 0                                                                                                                                                                                                                                                                                        | Do not set the Link register.                                                                                       |  |

|             | 1 Set the Link register. If the instruction is a branch, the<br>address of the instruction following the branch instruction<br>placed into the Link register. If the instruction is an SVC<br>address of the instruction following the SVC instruction<br>placed into the Link register. |                                                                                                                     |  |

#### Fields Description

MB (21-25) & ME (26-30)

Fields used to specify a 32-bit string, consisting of either a substring of ones surrounded by zeros or a substring of zeros surrounded by ones. The encoding is as follows:

| Fields     | Description                                                                                                           |

|------------|-----------------------------------------------------------------------------------------------------------------------|

| MB (21-25) | Index to start bit of substring of ones.                                                                              |

| ME (2630)  | Index to stop bit of substring of ones.                                                                               |

|            | Let mstart = MB and mstop = ME.                                                                                       |

|            | If <i>mstart &lt; mstop</i> + 1<br>then mask ( <i>mstartmstop</i> ) = ones<br>mask (all other) = zeroes.              |

|            | If <i>mstart</i> = <i>mstop</i> + 1 then<br>mask (0–31) = ones.                                                       |

|            | If <i>mstart &gt; mstop</i> + 1 then<br>mask ( <i>mstop</i> + 1 <i>mstart</i> -1) = zeros<br>mask (all other) = ones. |

|            |                                                                                                                       |

- NB (16-20) Field used to specify the number of bytes to move in a load or store string immediate.

- OPCD (0-5) The basic opcode field of the instruction.

- OE (21) Used for extended arithmetic to inhibit the setting of OV and SO in XER.

- RA (11-15) Field used to specify a GPR to be used as a source or as a target.

- **RB (16-20)** Field used to specify a GPR to be used as a source.

- Rc (31) Following is the description of the Record bit.

#### Setting Description

- 0 Do not set the Condition register (CR).

- 1 Set the Condition register to reflect the result of the operation.

For fixed-point instructions, CR bits (0 to 3) are set to reflect the result as a signed quantity. The result as an unsigned quantity or a bit string can be deduced from the EQ bit.

For floating-point instructions, CR bits (4 to 7) are set to reflect Floating-Point Exception, Floating-Point Enabled Exception, Floating-Point Invalid Operation Exception, and Floating-Point Overflow Exception.

- RS (6-10) Field used to specify a GPR to be used as a source.

- RT (6-10) Field used to specify a GPR to be used as a target.

| Fields                 | Description                               |                                                       |  |  |

|------------------------|-------------------------------------------|-------------------------------------------------------|--|--|

| SA (30)                | The following describes the SVC Absolute. |                                                       |  |  |

|                        | Setting                                   | Description                                           |  |  |

|                        | 0                                         | SVC routine at address '1' II LEV II b'00000'.        |  |  |

|                        | 1                                         | SVC routine at address X'1FE0'.                       |  |  |

| SH (16-20)             | Field used to a                           | specify a shift amount.                               |  |  |

| Si (16-31)             | Immediate fiel                            | d used to specify a 16-bit signed integer.            |  |  |

| SPR (11-15)            | Special Purpo                             | se register.                                          |  |  |

|                        | SPR                                       | Special Purpose Register                              |  |  |

|                        | 00000 (00)                                | MQ                                                    |  |  |

|                        | 00001 (01)                                | XER                                                   |  |  |

|                        | 00100 (04)                                | from RTCU                                             |  |  |

|                        | 00101 (05)                                | from RTCL                                             |  |  |

|                        | 00110 (06)                                | from DEC                                              |  |  |

|                        | 01000 (08)                                | LR                                                    |  |  |

|                        | 01001 (09)                                | CTR                                                   |  |  |

|                        | 10100 (20)                                | to RTCU                                               |  |  |

|                        | 10101 (21)                                | to RTCL                                               |  |  |

|                        | 10110 (22)                                | to DEC                                                |  |  |

|                        | 11010 (26)                                | SRR 0                                                 |  |  |

|                        | 11011 (27)                                | SRR 1.                                                |  |  |

| TO ( <del>6</del> –10) | TO bit ANDed                              | with condition.                                       |  |  |

|                        | TO bit                                    | ANDed with Condition                                  |  |  |

|                        | 6                                         | Compares less than.                                   |  |  |

|                        | 7                                         | Compares greater than.                                |  |  |

|                        | 8                                         | Compares equal.                                       |  |  |

|                        | 9                                         | Compares logically less than.                         |  |  |

|                        | 10                                        | Compares logically greater than.                      |  |  |

| UI (16–31)             |                                           | used to specify a 16-bit unsigned integer.            |  |  |

| XO (26–30)             |                                           | ons contain a 5-bit extended opcode.                  |  |  |

| XO (30, 31)            | DS-form instruc                           | DS-form instructions contain a 2-bit extended opcode. |  |  |

.

# **Memory Addressing**

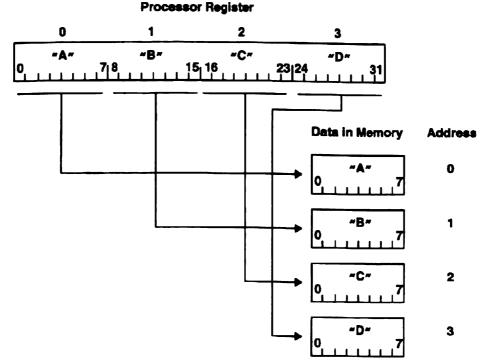

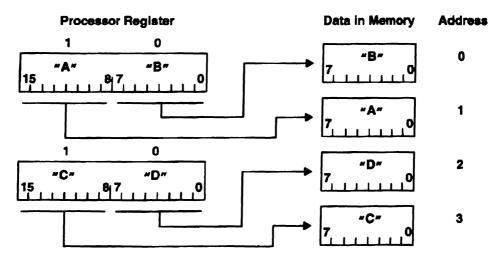

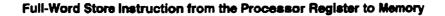

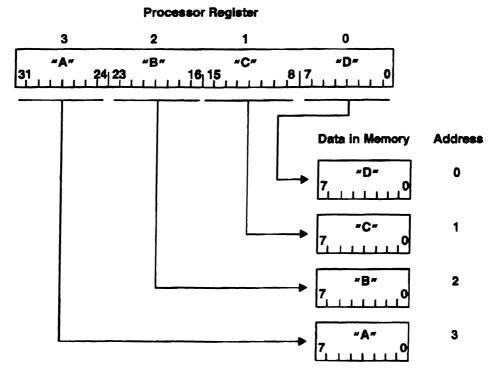

Within the context of a program executing on the processing unit (PU), system memory is organized into doublewords, words, halfwords, and bytes, which are constrained to lie on boundaries that are multiples of their sizes. See Figure 5 for an example of byte, halfword, word, doubleword, and quadword memory addressing.

| Bits   | Addresses |          |      |            |          |

|--------|-----------|----------|------|------------|----------|

|        | Byte      | Halfword | Word | Doubleword | Quadword |

|        | 0000      | 0000     |      |            |          |

| 0-31   | 0001      | 0000     |      |            | 0000     |

| 0-31   | 0010      | 0010     | 0000 |            |          |

|        | 0011      | 0010     |      | 0000       |          |

|        | 0100      | 0100     |      | 0000       |          |

| 31-63  | 0101      | 000      | 0100 |            |          |

| 31-03  | 0110      | 0110     |      |            |          |

|        | 0111      |          |      |            |          |

|        | 1000      | 1000     | 1000 | 1000       |          |

| 32-63  | 1001      |          |      |            |          |

| 32-03  | 1010      | 1010     |      |            |          |

|        | 1011      | 1010     |      |            |          |

|        | 1100      | 1100     | 1100 |            |          |

| 64-127 | 1101      | 1100     |      |            |          |

| 04-127 | 1110      | 1110     |      |            |          |

|        | 1111      |          |      |            |          |

Figure 5. Memory Organization

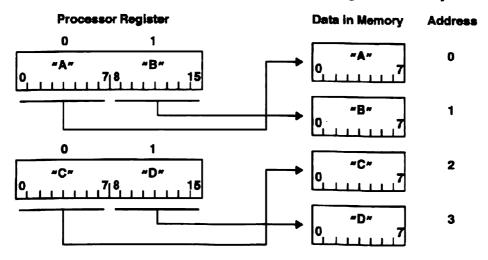

Bytes in system memory are consecutively numbered starting with 0. Each number is the address of the corresponding byte. The 32-bit addresses computed for system memory access are termed *effective addresses* and specify a byte in memory. System memory address arithmetic wraps around from the maximum byte address,  $2^{32} - 1$ , to address 0.

System memory can be accessed by quadword, doubleword, word, halfword, or byte. The required number of bytes are fetched from a property aligned area of memory. The rules when the operands are not properly aligned are controlled by a mode bit, MSR(AL). See "Machine State Register" on page 1-22.

The mapping to *real memory* addresses is controlled by relocate (address translation) facilities. When the relocate facility is active, effective addresses generated by program execution are first transformed to 52-bit *virtual address*, which in turn are mapped to real memory.

In general, the terms *memory* and *address* are used within the context of the effective addresses generated by the PU.

All processor computations are performed in registers in the processing unit (PU). There are no instructions, for instance, to add two numbers, one of which is in memory.

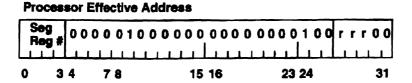

### **Effective Address Calculation**

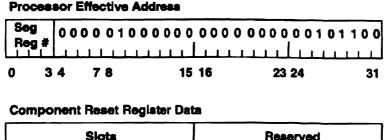

Effective addresses (EAs) are generated by instructions that reference data in system memory and by taken branch instructions. Address calculations use 32-bit two's complement binary arithmetic. A carry from bit 0 is ignored.

A value of 0 in the RA field indicates the absence of the corresponding address component. For the absent component, a 0 value is used in forming the address. This is shown in the instruction descriptions as (RAI0).

X-form instructions are used for data references. Address computation adds the GPR contents designated by the RA field or the value 0 if RA equals a value of 0 with the GPR contents designated by the RB field. The computation is shown as (RAIO) + (RB).

With D-form instructions, the 16-bit D field is sign extended to form a 32-bit address component. In computing the effective address of a data element, this address component is added to the GPR contents designated by the RA field or the value 0 if RA equals a value of 0.

With DS-form instructions, the 2-bits of zeros are added to the 14-bit DS field which is then sign extended to form a 32-bit address component. In computing the effective address of a data element, this address component is added to the GPR contents designated by the RA field or the value 0 if RA equals a value of 0.

With I-form branch instructions, the 24-bit LI field is concatenated on the right with b'00' and sign extended to form a 32-bit address. When AA equals a value of 0, this address is added to the address of the branch instruction to form the effective address. If AA equals a value of 1, this 32-bit value is the effective address.

With B-form branch instructions, the 14-bit BD field is concatenated on the right with b'00' and sign extended to form a 32-bit value. If AA equals a value of 0, this 32-bit value is added to the address of the branch instruction to form the effective address. If AA equals a value of 1, this 32-bit value is the effective address.

With XL-form branch instructions, bits 0 to 29 of the Link register or the Count register are concatenated on the right with b'00' to form the effective address.

# **Branch Processor**

This section describes the registers and instructions that make up the branch processor facilities.

### **Branch Processor Registers**

This section describes the branch processor registers and their bit definitions.

#### **Condition Register**

The Condition register (CR) is a 32-bit register that reflects the result of certain operations and provides a mechanism for testing (and branching).

| 0     |             | 31 |

|-------|-------------|----|

|       | CR          |    |

| Bits  | Name        |    |

| 0003  | CR Field 0  |    |

| 0407  | CR Field 1  |    |

| 06-11 | CR Field 2  |    |

| 12-15 | CR Field 3  |    |

| 16-19 | CR Field 4  |    |

| 20-23 | CR Field 5  |    |

| 24-27 | CR Field 6  |    |

| 28-31 | CR Field 7. |    |

The Condition register bits are grouped into eight 4-bit fields, named CR Field 0 through CR Field 7, which are set in one of the following ways:

- A load or copy operation into a specific CR field.

- CR Field 0 can be set as the implicit result of a fixed-point operation.

- CR Field 1 can be set as the implicit result of a floating-point operation.

- . As the result of either a fixed or floating-point compare operation into a specified CR field.

Instructions are provided to test these bits singly and in combination.

When the record bit (Rc) is set to 1 in most fixed-point instructions, the first three bits of CR Field 0 are set by a comparison of the result, which is interpreted as a signed integer, to a value of 0. The fourth bit of CR Field 0 is copied from the SO field of the XER. Add Immediate, Add Immediate Lower, and Add Immediate Upper instructions set these four bits implicitly. These bits are interpreted as shown in the following list:

#### Description Bit Compares Less Than, Negative (LT). For arithmetic operations, the result is 0 negative or less than a value of 0. For compare operations, (RA) < SI, UI, or (RB). Compares Greater Than, Positive (RB). For arithmetic operations, the result 1 is positive or greater than a value of 0. For compare operations, (RA) > SI, UI. or (RB). Compares Equal, Zero (EQ). For arithmetic operations, the result is a value 2 of 0 or equal to a value of 0. For compare operations, (RA) = SI, UI, or (RB). Summary Overflow (SO). This is a copy of the final state of XER(SO) at the 3 completion of the instruction.

When the Rc bit equals a value of 1 in all floating-point instructions except the Floating-Point Compare instruction, CR Field 1 (Condition register bits 4 to 7) is set to the floating-point exceptions status. These bits are interpreted as shown in the following list:

| Bit | Description                                                                                                                           |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|

| 4   | Floating-Point Exception (FX). This is a copy of the final state of FPSCR(FX) at the completion of the instruction.                   |

| 5   | Floating-Point Enable Exception (FEX). This is a copy of the final state of FPSCR(FEX) at the completion of the instruction.          |

| 6   | Floating-Point Invalid Operation Exception (VX). This is a copy of the final state of FPSCR(VX) at the completion of the instruction. |

7 Floating-Point Overflow Exception (OX). This is a copy of the final state of FPSCR(OX) at the completion of the instruction.

Condition register bits 4 to 7 are copies of bits 0 to 3 in the Floating-Point Status and Control register.

#### Link Register

The Link register (LR) is a 32-bit register. The Link register provides the branch target address for the Branch Conditional Register instruction and holds the return address (link address) for branch and link type instructions and SVC instructions.

| 0 3 | 1 |

|-----|---|

| LR  | ] |

#### **Count Register**

The Count register (CTR) is a 32-bit register. The Count register contains a loop count and is automatically decremented during execution of the branch and count instructions, wrapping from X'00000000' around through X'FFFFFFF'. The Count register also provides the branch target address for the Branch to Count Register instruction. The Count register contains a copy of bits 16 to 31 of MSR and bits 16 to 31 of the SVC instruction after execution of that SVC instruction. Both registers can be copied to and from any GPR.

| 0 | 31  |

|---|-----|

|   |     |

|   | CTR |

#### Machine State Register

The Machine State register (MSR) is a 32-bit register that defines the modal state of the processor. When the RFI instruction is executed, bits 16 to 31 of SRR 1 are placed into bits 16 to 31 of the MSR. The MSR can also be modified by the Move to Machine State Register instruction.

| 0     |      |                           | 31 |

|-------|------|---------------------------|----|

|       |      | MSR                       |    |

| Bit   | Name | Description               |    |

| 00-15 |      | Reserved                  |    |

| 16    | EE   | External Interrupt Enable |    |

| 17    | PR   | Problem State             |    |

| 18    | FP   | FP Available              |    |

| 19    | ME   | Machine Check Enable      |    |

| 20    | FE   | FP Exception Enable       |    |

| 21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30–31 | SE<br>BE<br>FE<br>IP<br>IR<br>DR<br>PM |                  | Single-Step Enable<br>Branch and Trap Enable<br>FP Imprecise Enable<br>Alignment Check<br>Interrupt Prefix<br>Instruction Relocate<br>Data Relocate<br>Reserved<br>Performance Monitor Control<br>Reserved. |

|-------------------------------------------------------------|----------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The follow                                                  | ving a                                 |                  | State register bit definitions and settings:                                                                                                                                                                |

| Bits                                                        |                                        | Description      |                                                                                                                                                                                                             |

| 0–15                                                        |                                        | Reserved         |                                                                                                                                                                                                             |

| 16                                                          |                                        | External Interru | • • •                                                                                                                                                                                                       |

|                                                             |                                        | Setting          | Description                                                                                                                                                                                                 |

|                                                             |                                        | 0                | The processor is disabled against external interrupts.                                                                                                                                                      |

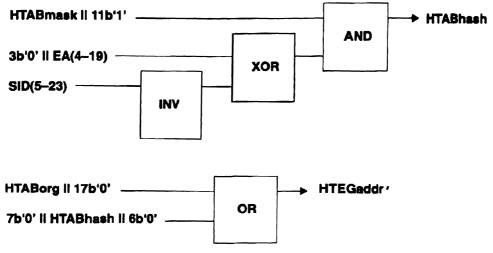

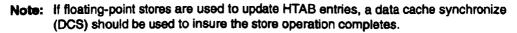

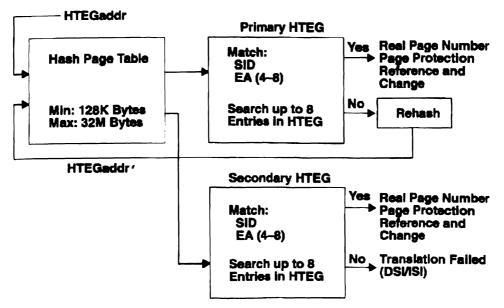

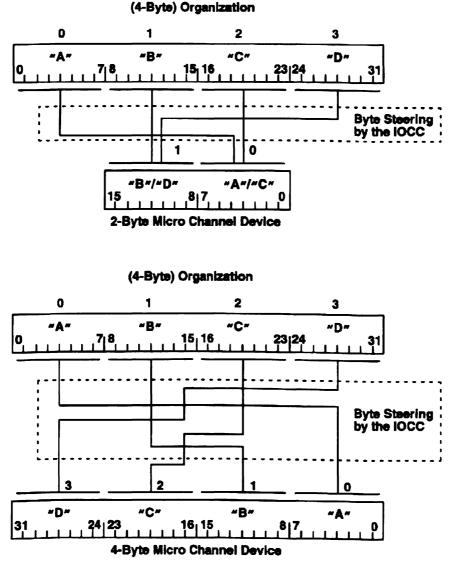

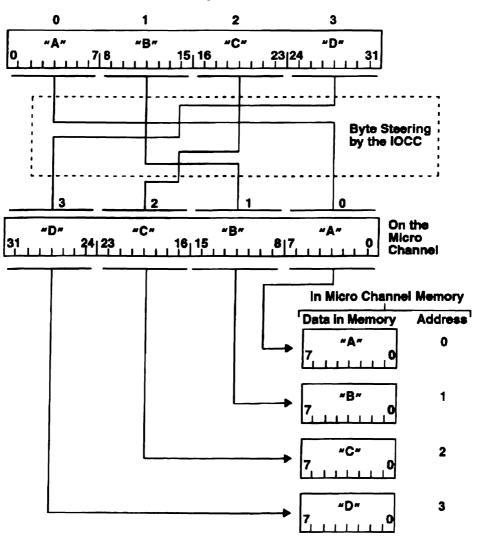

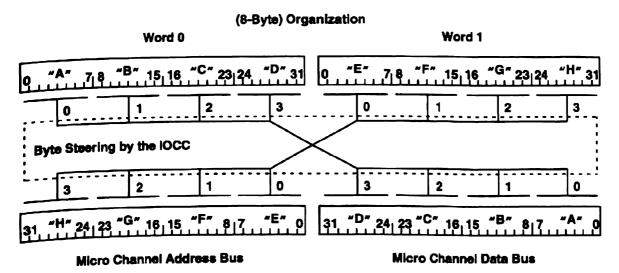

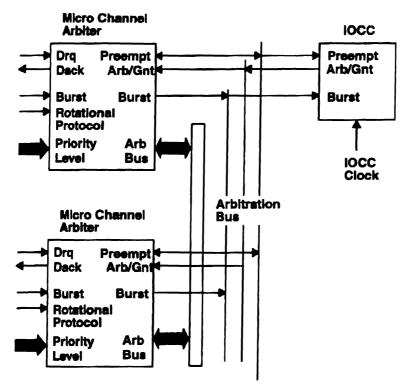

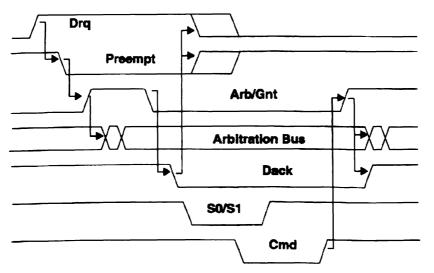

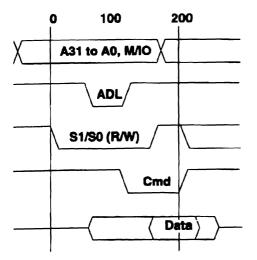

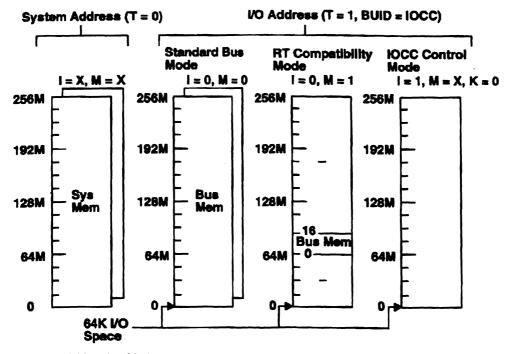

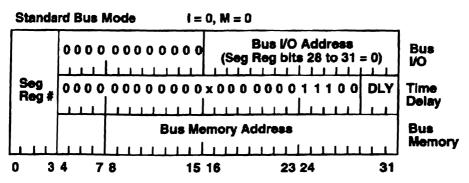

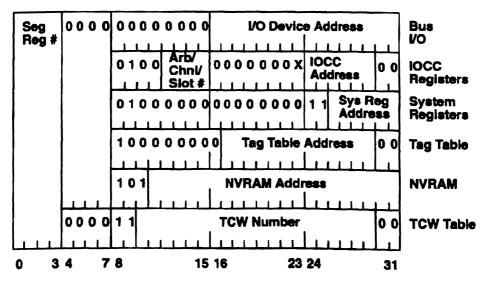

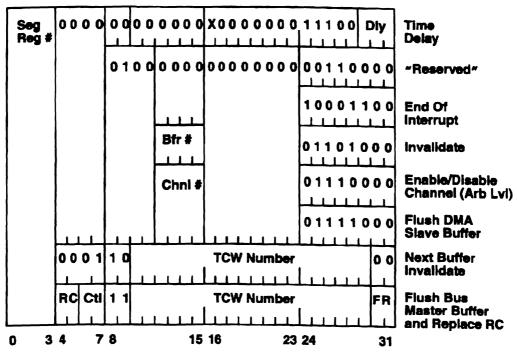

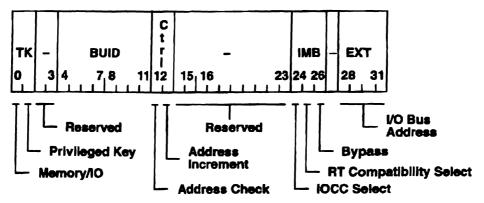

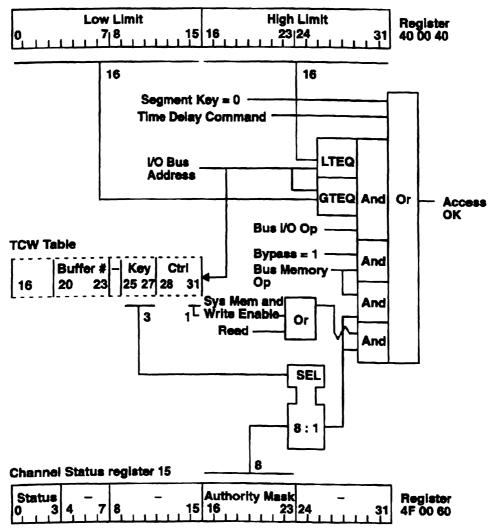

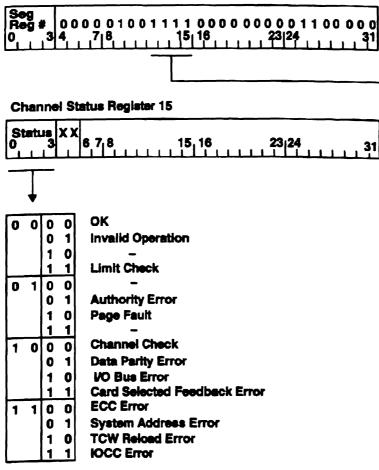

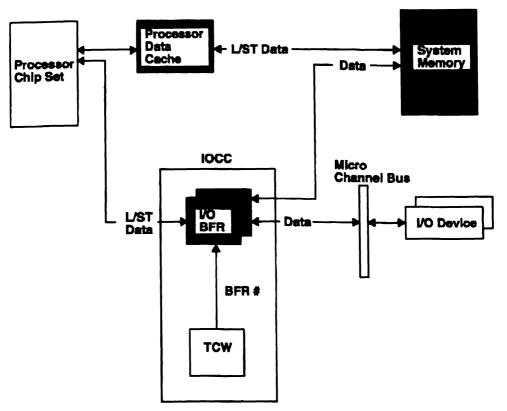

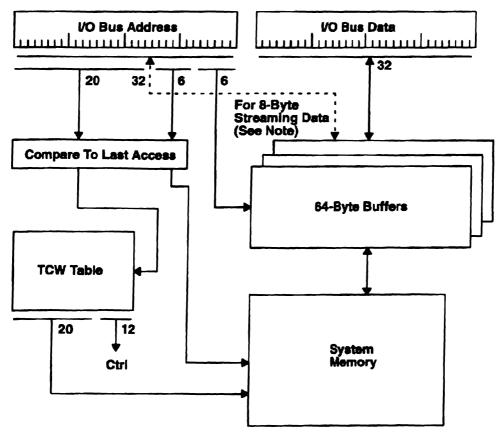

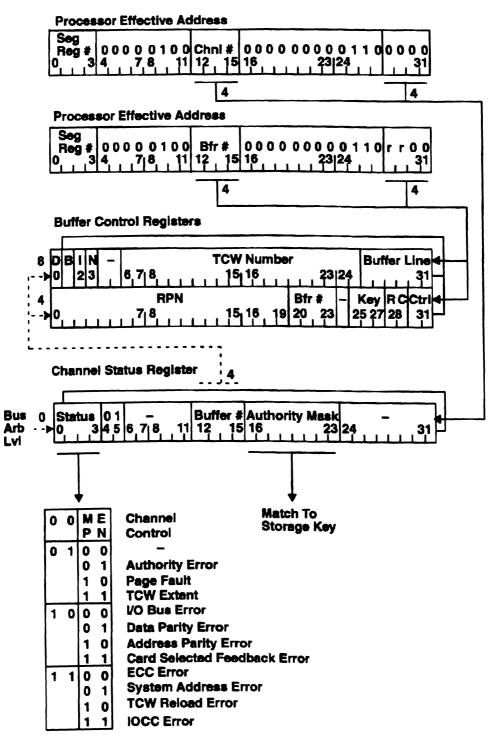

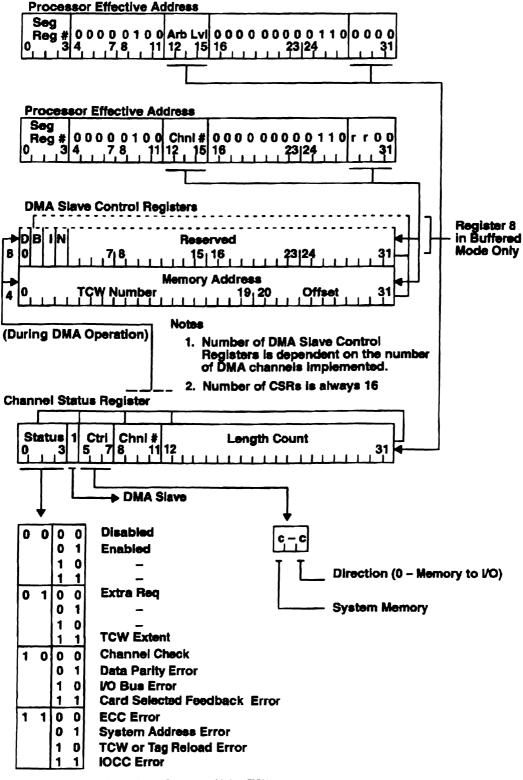

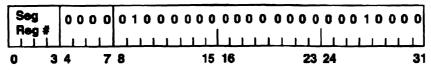

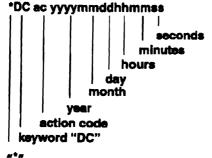

|                                                             |                                        | 1                | The processor is enabled to take external interrupts.                                                                                                                                                       |