STUDENT TEXT ABR30533-1

C696-416L-ST

**Computer Systems Department**

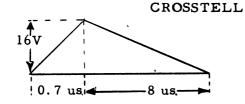

### CROSSTELL INPUT SYSTEM

April 1967

Keesler Technical Training Center Keesler Air Force Base, Mississippi

- Designed For ATC Course Use -

-

#### NOTICE

The text and illustrations included in this publication have been prepared for teaching purposes and as an aid for learning. All material was prepared from information at a given engineering level. Engineering changes may alter timings, logic, and so on; therefore, do not use this information alone as a reference manual or in diagnosing equipment malfunctions. Computer Systems Department KTTC, Mississippi

# Student Text for AN/FSO - 7 & 8

## **Crosstell Inputs**

### FE 0-203-2

This Student Text provides student study material in support of Type II and Type III computer maintenance courses relating to WS 416L.

> This document contains information of a proprietary nature. Any use or reproduction of this document for other than government purposes is subject to the prior consent of International Business Machines Corporation.

This student study material has been reproduced intact from materials printed by IBM corporation, Kingston, New York.

Computer Systems Department KTTC, Mississippi

TABLE OF CONTENTS

|    |     | TITLE                                                                | PAGE # |

|----|-----|----------------------------------------------------------------------|--------|

| 1. | INT | RODUCTION                                                            | 0010   |

|    | A.  | Function of XTL Input Element                                        | 0010   |

|    | в.  | Definition of Terms                                                  | 0010   |

|    | c.  | Relationship of the XTL Elements to Data Sources<br>and destination. | 0010   |

|    | D.  | XTL Data Flow                                                        | 0010   |

|    | E.  | Message Layout                                                       | . 0040 |

|    | F.  | XTL-Physical Characteristics                                         | 0070   |

|    | G., | Channel Equipment and Common Block Diagram                           | 0070   |

|    | н.  | Simplex Maintenance Console XTL Control Panels                       | 0080   |

|    | I.  | Summary Questions                                                    | 0110   |

| п. | ļnf | PUT PHONE LINE SWITCHING                       | 0130 |

|----|-----|------------------------------------------------|------|

|    | А.  | Function                                       | 013Q |

|    | в.  | General                                        | 0130 |

|    | c.  | Digital Data Receiver Switching                | 0150 |

|    | D.  | Input Switching for Channels 13 thru 24        | 0160 |

|    | E.  | Input Data Switching                           | 0180 |

|    | F.  | Spare Channel Switching                        | 0180 |

|    | G.  | Switching Basic Telephone Terminal Indications | 0210 |

|    | н.  | Summary Questions                              | 0220 |

```

Crosstell

```

### TABLE OF CONTENTS (CONT'D)

|     |    | TITLE                                                 | PAGE #       |

|-----|----|-------------------------------------------------------|--------------|

| ш.  | хт | L CHANNEL INPUT SECTION                               | 0230         |

|     | Α. | Introduction                                          | 0230         |

|     | в. | Data Converter and Synchronizer                       | 0310         |

|     | c. | Data Distributor                                      | 0340         |

|     | D. | Core Shift Pulse Generator and Fast Shift Generator . | 0380         |

|     | E. | Twenty-Five Counter                                   | 0420         |

|     | F. | Buffer Storage                                        | 0450         |

|     | G. | Main Storage                                          | 0480         |

|     | н. | Main Storage Shift Control                            | 0530         |

|     | Ι. | Message Address Check                                 | 0540         |

|     | J. | Good Message Check                                    | 0640         |

|     | к. | Readout of Main Storage                               | 0650         |

|     | L. | Summary Questions                                     | 0760         |

|     |    |                                                       |              |

| IV. | DU | PLEX SWITCHING                                        | 0790         |

|     | Ά. | General                                               | 0790         |

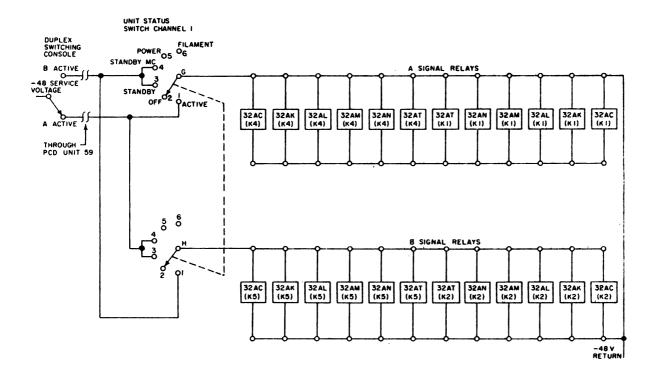

|     | в. | Driving of A and B Signal Relays                      | 0790         |

|     | c. | Core Data Switching Circuit                           | 0840         |

|     | D. | Write Level Switching                                 | 0840         |

|     | E. | Site Neon Indication Switching                        | <b>08</b> 60 |

|     | F. | Good Message Level and Readout Alarm Switching        | 0860         |

ii

## TABLE OF CONTENTS (CONT'D)

|    |            | TITLE                                  | PAGE # |

|----|------------|----------------------------------------|--------|

|    | G.         | Status Indication Switching            | 0870   |

|    | н.         | Drum Demand Switching                  | 0880   |

|    | I.         | DD, XTL Pulses and XTL Level Switching | 0900   |

|    | J.         | SummaryQuestions                       | 0900   |

|    |            |                                        |        |

| v. | XT         | L DRUM INPUT (COMMON)                  | 0920   |

|    | A.         | Common Inputs                          | 0920   |

|    | в.         | Common Outputs                         | 0920   |

|    | c.         | Function of Commons                    | 0920   |

|    | D.         | Discussion of Block Diagram            | 0930   |

|    | E.         | Circuit Analysis                       | 0970   |

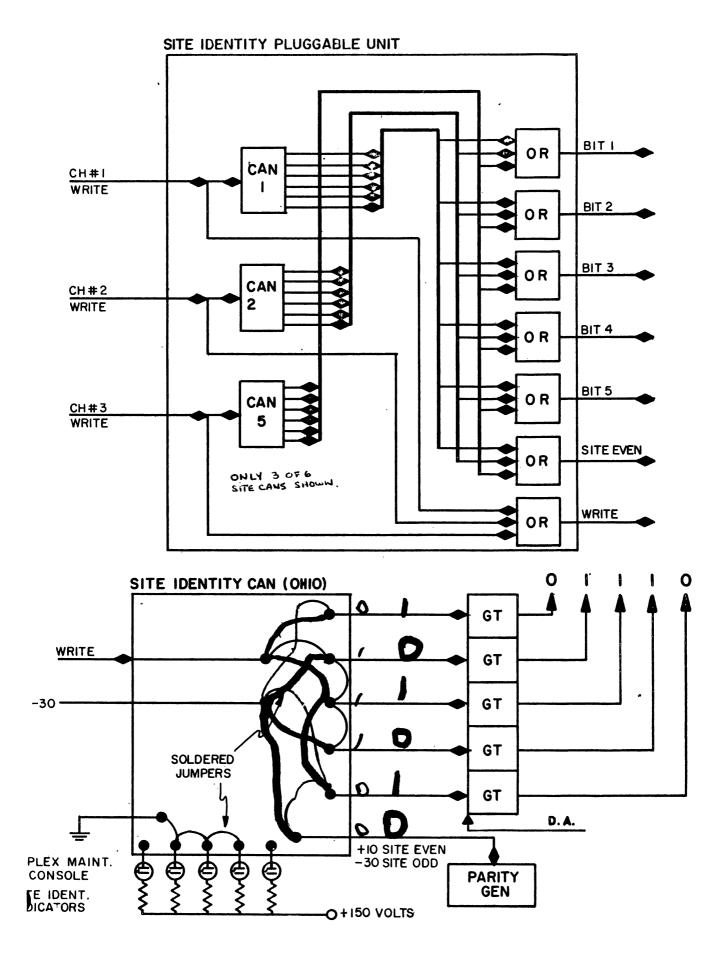

|    | F.         | Function of Site Identity              | 0980   |

|    | G.         | Generation of Site Identity            | 0980   |

|    | н.         | Channel Write Level Switching          | 1000   |

|    | Ι.         | Phone Line Indication Switching        | 1000   |

|    | J.         | Drum Field Selection                   | 1000   |

|    | к.         | Circuit Analysis                       | 1000   |

|    | L.         | XTL Clock and Associated Circuitry     | 1060   |

|    | м.         | Site Identity Generator Analysis       | 1140   |

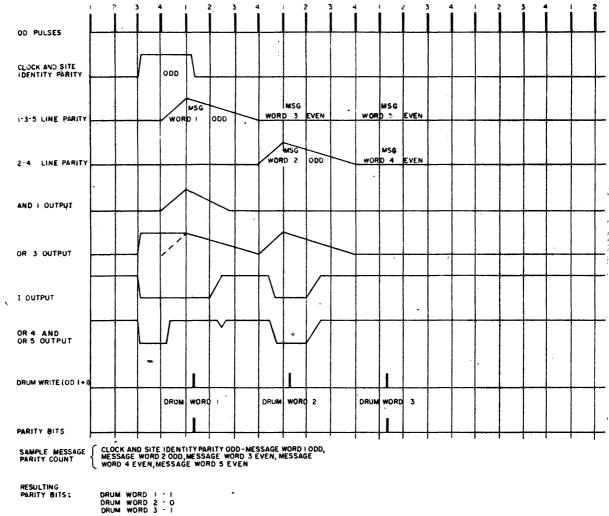

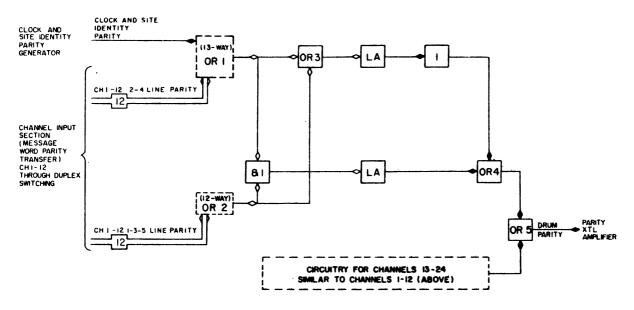

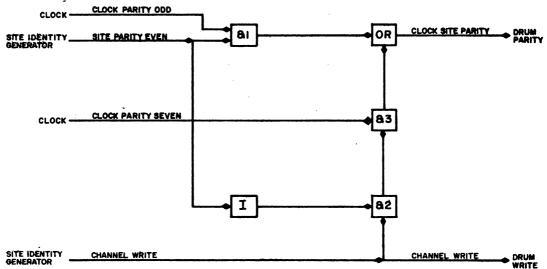

|    | N.         | Clock and Site Identity Parity         | 1150   |

|    | <b>0</b> . | Drum Parity                            | 1180   |

|    | P.         | Summary Parity Generation              | 1200   |

### TABLE OF CONTENTS (CONT'D)

|      |     | TITLE                                       | PAGE # |

|------|-----|---------------------------------------------|--------|

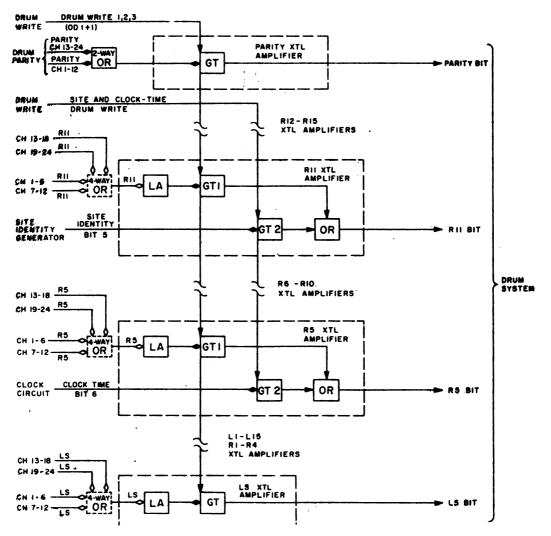

|      | Q.  | Message Amplifiers                          | 1210   |

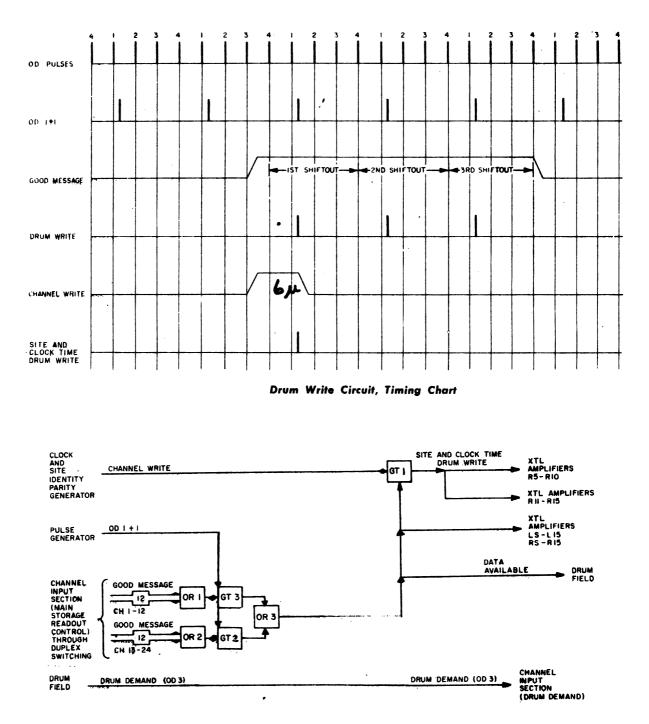

|      | R.  | Drum Write                                  | 1250   |

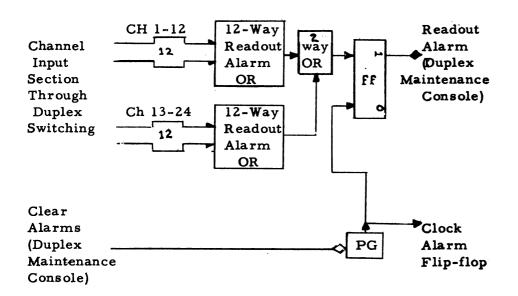

|      | s.  | Readout Alarm                               | 1270   |

|      | т.  | Summary Questions                           | 1280   |

| VI.  | SIN | APLEX AND DUPLEX MAINTENANCE CONSOLE        | 1300   |

|      | А.  | Unit Status Switch                          | 1300   |

|      | в.  | Source Switch                               | 1310   |

|      | c.  | Data Circuit Switch                         | 1310   |

|      | D.  | Parity Diable Switch                        | 1310   |

| /    | E.  | Spare Selector Switch (ON Chan. #6)         | 1330   |

| 1    | F.  | Channel Indicators                          | 1330   |

|      | G.  | Common Indicators                           | 1330   |

|      | н.  | Summary Questions                           | 1330   |

|      | I.  | Answers to Summary Questions                | 1340   |

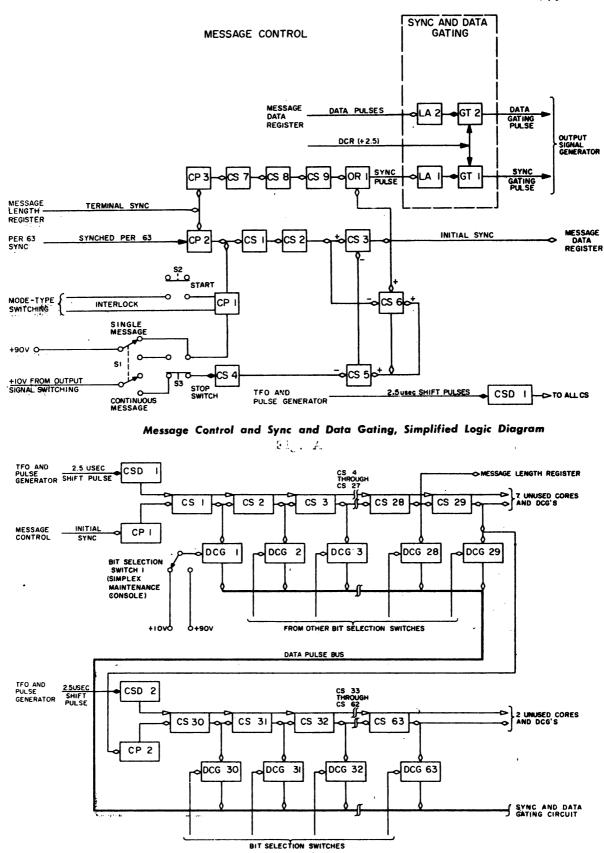

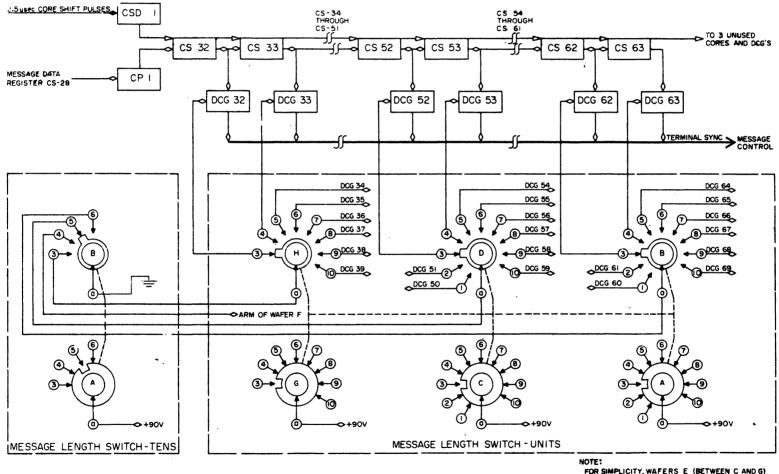

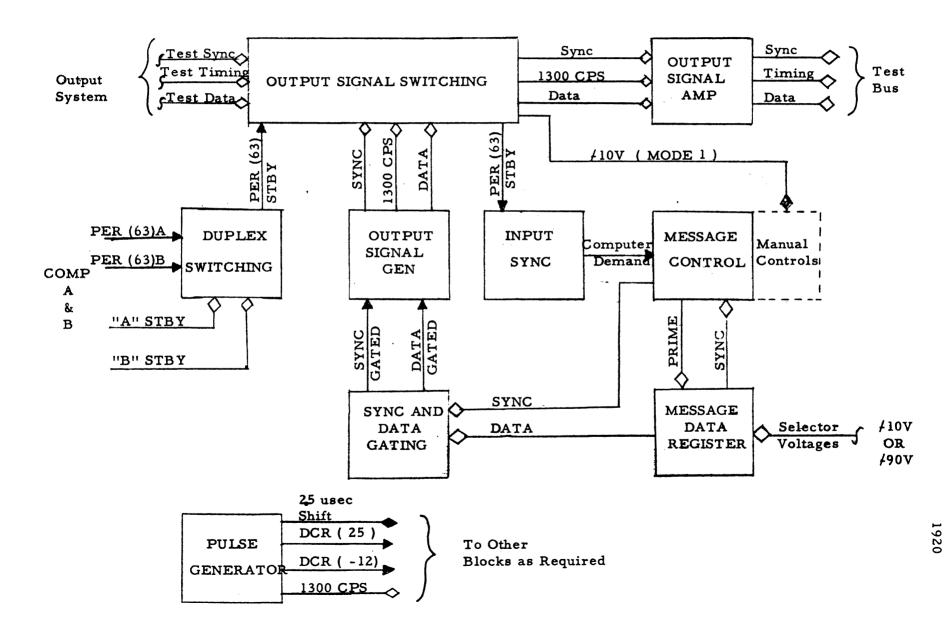

| VII. | TE  | ST PATTERN GENERATOR                        | 1350   |

|      | Α.  | Introduction to LRI TPG                     | 1350   |

|      | в.  | Basic Differences between LRI and XTL TPG's | 1900   |

|      | с.  | XTL TPG. Summary                            | 1930   |

|      | D,  | Summary Questions                           | 2010   |

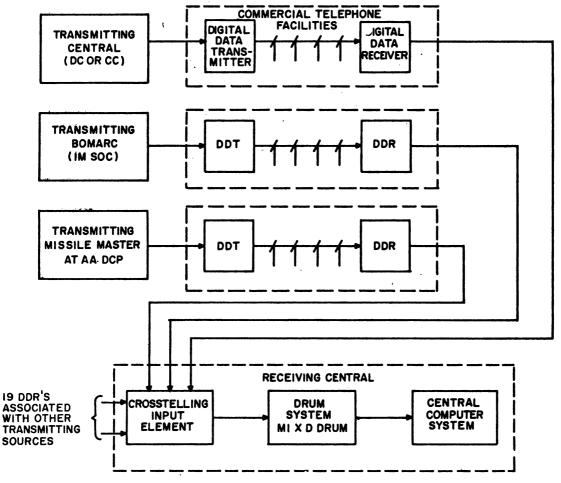

#### 1. INTRODUCTION

Note: Crosstell is abbreviated XTL.

- A. Function of the XTL Input Element:

- The function of the XTL element is to receive, serially and at a relatively slow speed, information originating at other Direction Centrals, Combat Centrals, Missile Master and Bomarc Control Centers. The information is processed, temporarily stored and when drum space is available on the MIXD drum, it is transferred to the Drum System at relatively high speed, in parallel form.

- B. Definition of Terms.

- 1. Crosstelling refers to the system of exchanging information between external sources and AN/FSQ-7 Direction Centrals and/or AN/FSQ-8 Combat Centrals. In this exchange of information, the XTL element functions as the informationprocessing element at the receiving Central. The exchange of information from one Central to a Central of higher echelon is termed Forwardtell. The exchange of information from a Central of higher echelon to a Central of lower echelon is termed Backtell. Information exchanged between Centrals of common echelon is termed Lateraltell.

- C. Relationship of the XTL elements to data sources or destination.

Page 0020

- D. Crosstell Data Flow

- 1. Purpose of XTL

- a. Receive data from other Centrals, Missile Master or Bomarc Centers.

- b. Process data and write it on magnetic drum.

- c. Data will consist of track information principally.

#### 0010

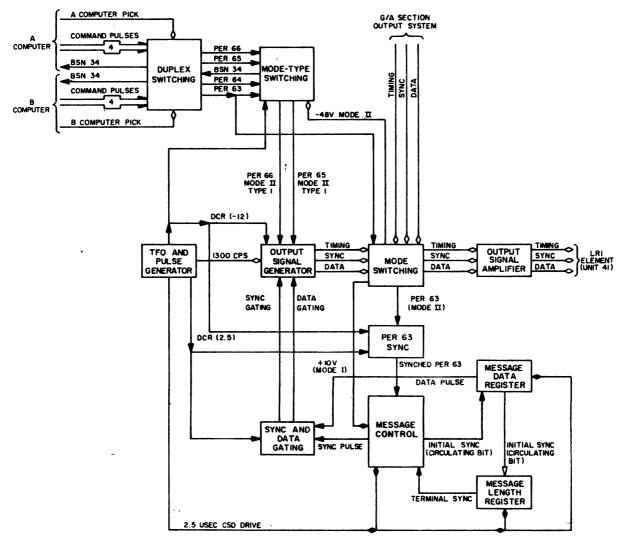

FIG. A

BLOCK DIAGRAM OF CROSSTELL INPUT ELEMENT

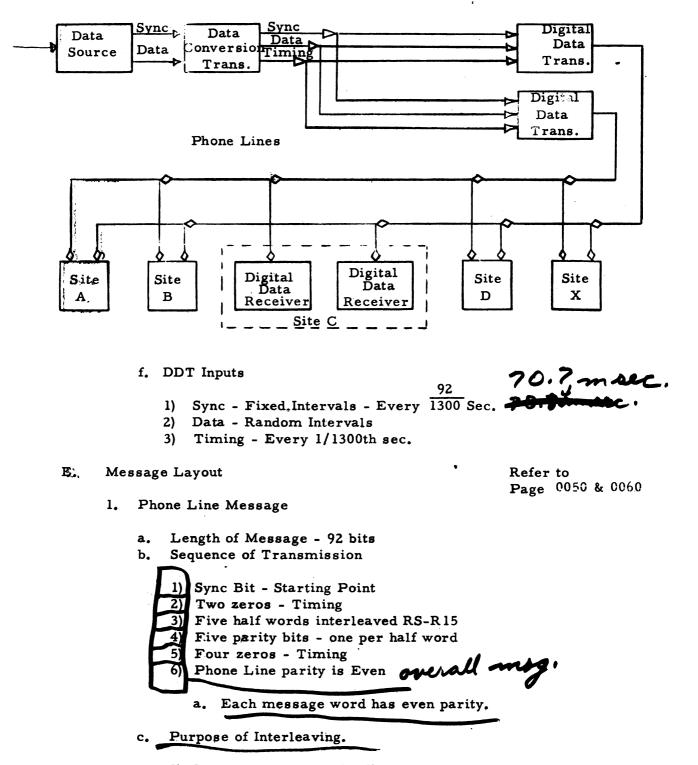

- 2. Data Flow

- a. Five word message is generated at an external source.

- b. The message is sent out to the DDT in serial interleaved form.

- 1) Data is condensed to five half words.

- 2) Pulses converted to sine waves.

- 3) Frequency of 1300 cycles per second.

- c. Digital Data Transmitter (DDT) used to amplitude modulate a telephone line carrier frequency.

- d. Digital Data Receiver (DDR) is used to demodulate the carrier.

- e. Data enters a Crosstell Input Channel in serial interleaved form and is stored pending the writing process of data on the Crosstell drum field.

- f. A Crosstell Drum Demand results in five half words being written as three computer words, on the MIXD Drum.

- g. The computer reads the Crosstell drum field to obtain the message information.

- 3. Data Transmission

- a. Data is transmitted on a pair of phone lines.

- b. Data is sent to several sites.

- c. Carrier frequency is amplitude modulated.

- 1) A "O" has relative amplitude of 1/3 total amplitude.

- 2) A "1" has relative amplitude of 2/3 total amplitude.

- 3) A "Sync" has relative amplitude of 3/3 total amp.

- a) Determines start of a message.

- b) Transmitted periodically.

- d. Only one pulse transmitted at a time highest amplitude has precedence.

e. Block Diagram

- 1) Improve parity check efficiency.

- a) Each word's parity is checked separately.

- b) By having bits interleaved the probability of noise interferring with 2 bits and appearing as correct parity is held to a minimum.

- c) An error in any of the 5 parity checks will rejec t the message.

- d. Message Address Bits

- Since data is sent to several sites at once, the "Message Address" controls which site will receive the message.

- 2) Bits 59, 64, 69, and 74 Bits R11, R12, R13 and R14 of the 4th message word.

- a) Bit 74 is the least significant message address bit.

- 3) If all the sites on the line are to receive the message Bit 79 will be a "1". This corresponds to bit R15 of word 4 being a "1".

- a) This bit is the "All Parties" bit.

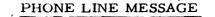

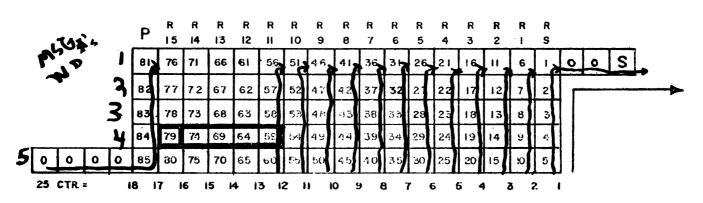

- e. Interleaved XTL Message  $\rho$   $\psi$

- 1) See message layout

- 2. Drum Message

Page 0600

- 1. A complete message is composed of 92 Timing Bits.

- 2. A "Sync" and Two "0" Bits preceeds the First data Bit.

- 3. The Incoming Information is contained in 86 Data Bits plus one Parity Bit for each word.

- 4. There are Four "0" Bits following the Parity Bits before the receipt of the Sync. of the next message.

- 5. Bits R11, R12, R13, R14 of Word 4 are address Bits.

- 6. Bit R15 of Word 4 is the "All Partys" Bit.

- 7. Bits 81, 82, 84, 85 are the Parity Bits for each word.

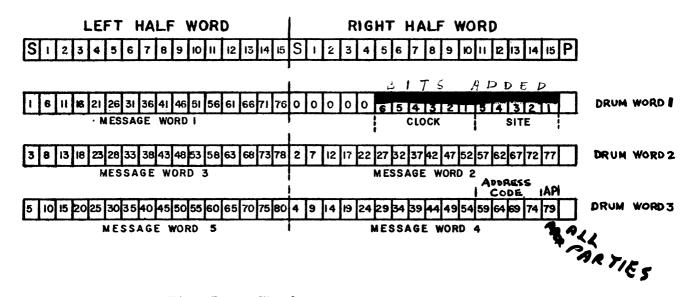

- a. First Drum Word

- 1) Left Half 1st of 5 half words in

- 2) Right Half

- a) Clock Relative time data written on drum.

- b) Site Indicates source of message

- b. Second Drum Word

- 1) Left Half 3rd of 5 half words in.

- 2) Right Half 2nd of 5 half words in.

- c. Third Drum Word

- 1) Left Half 5th of 5 half words from phone line.

- 2) Right Half 4th of 5 half words from phone line.

- a) Message Word 4 R11 thru R15 is the Address Code.

|        | (1)        | R15 is the All Party Bit. If R15 = 1, message accepted regardless of R11 thru R14.                    |

|--------|------------|-------------------------------------------------------------------------------------------------------|

|        | (2)        | No XTL channel has a message address of 0000.                                                         |

| F. XTI | L - Physic | al Characteristics                                                                                    |

| 1.     | 24 channe  | s available                                                                                           |

|        | b. 6 & 13  | els No. 1 thru 24<br>are spares<br>pare for 1-12<br>pare for 14-24.                                   |

|        | C. Norma   | NNEL from any site<br>I complement is 12 channels.                                                    |

| , m (  | c          | a site needs more than 12 <b>Lotol</b><br>hannels, extra section may be<br>dded 3 channels at a time. |

| 7      |            | nnel per Module.<br>2 - XTL channels.                                                                 |

|        | 1-1-1      |                                                                                                       |

| AA      | BB                | cc | DD | EE | FF | A | в | с | D | E | F                          | G                     | н | J                 | к | L | м | N | P  | R  | S  | Т                           | U  | v  | w  | x  | Y  |

|---------|-------------------|----|----|----|----|---|---|---|---|---|----------------------------|-----------------------|---|-------------------|---|---|---|---|----|----|----|-----------------------------|----|----|----|----|----|

| 24<br>} | <b>23</b><br>C 44 | 22 | 21 | 20 | 19 | 1 | 2 | 3 | 4 | 5 | 6<br>S<br>P<br>A<br>R<br>E | С<br>О<br>М<br>О<br>N | - | C O M<br>M<br>O N | B | 7 | 8 | 9 | 10 | 11 | 12 | 13<br>S<br>P<br>A<br>R<br>E | 14 | 15 | 16 | 17 | 18 |

----Indicates Channel Modules that can be added. 3 Module Sections.

- f. Common Equipment

- 1. Common "A" in Modules G and H. Output to Crosstell "A" Field.

- 2. Common "B" in Modules J and K. Output to Crosstell "B" Field.

- 3. Two Modules for each common.

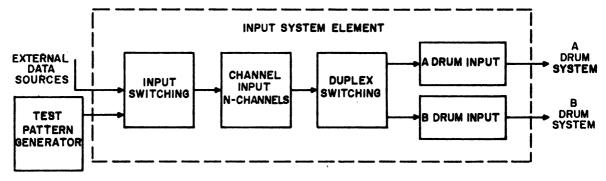

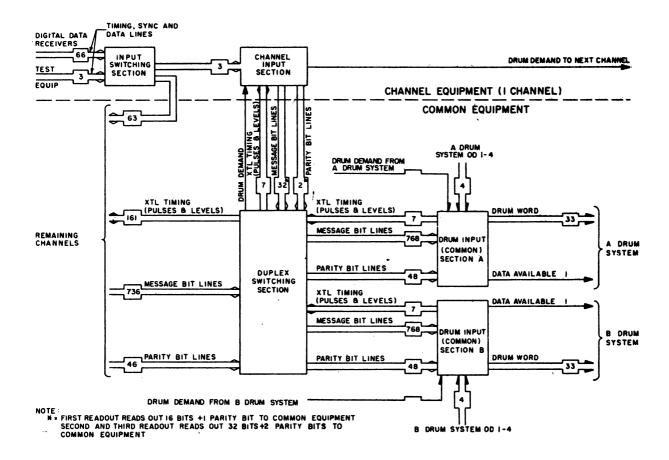

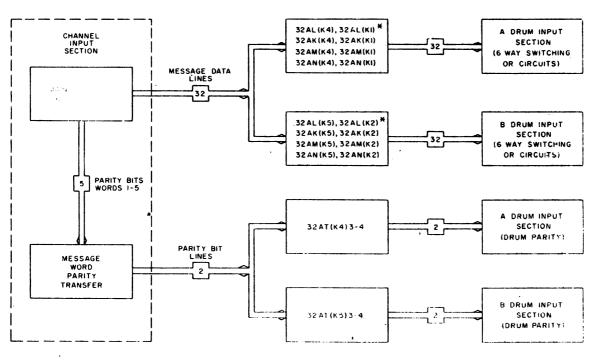

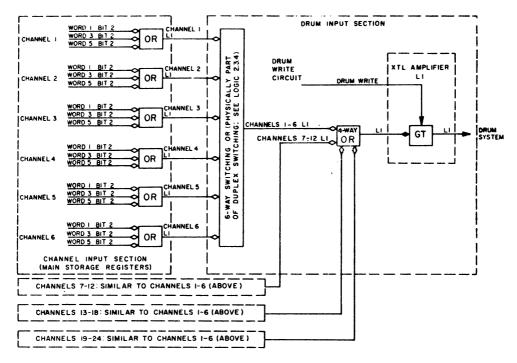

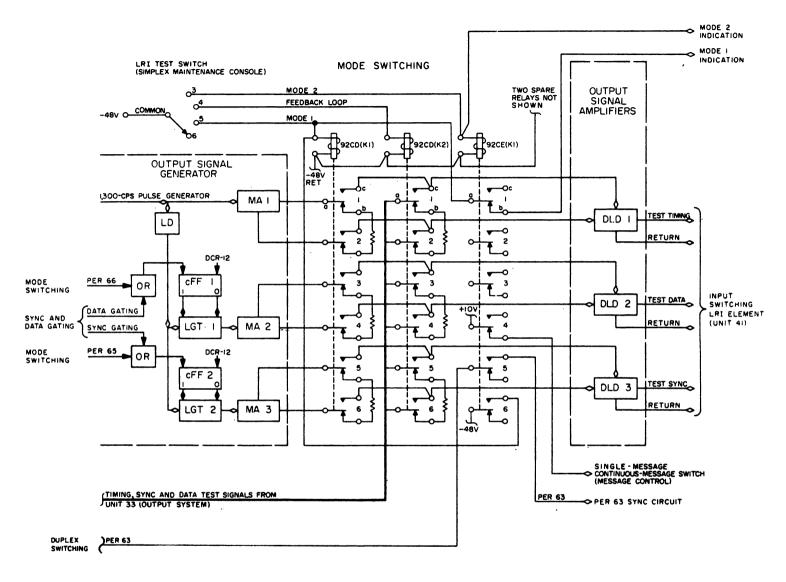

- G. Channel Equipment and Common Block Diagram

- 1. Channel Timing pulses come from the drum that is to receive data from that channel.

· - -

Page 0090

<sup>^</sup>0070

- 2. Input switching determines whether phone data is sent to the channel.

- 3. Input switching also determines which channel is replaced by the spare.

- 4. Duplex Switching routes the data to common "A" or common "B".

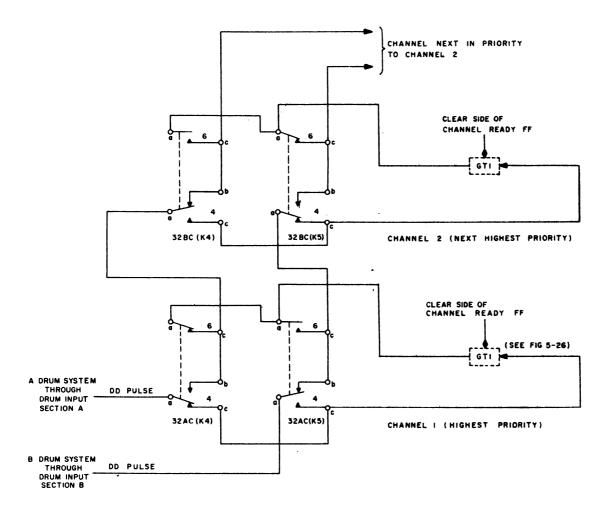

- 5. The drum demand pulse will check each channel sequentially, i.e., channels 1, 2, 3, etc. until it finds a channel with a good message and causes it to be readout to drums via common.

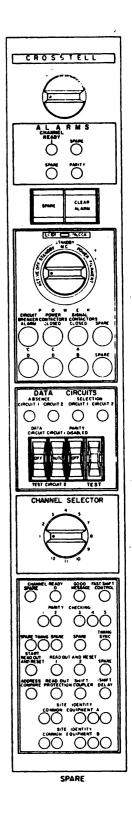

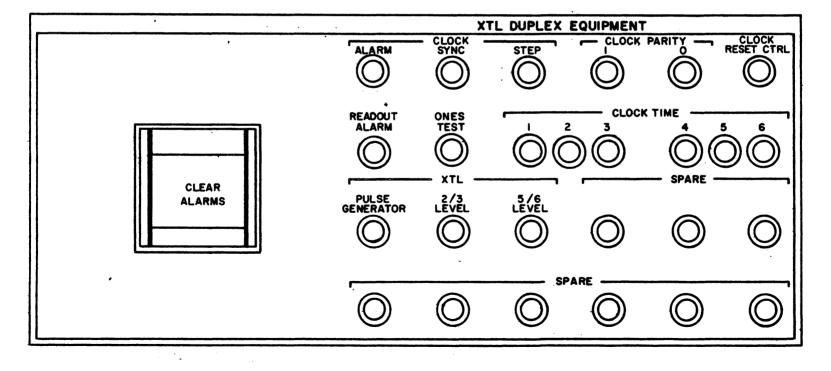

- H. Simplex Maintenance Console Unit 47 XTL Control Panels

- 1. General

There are 24 XTL, control panels located in the upper sections of modules A, B. C, and D of the simplex maintenance console & unit 47). Each panel is made up of alarm, power control, data circuit, and neon indicators sections. Two of the panels (corresponding to channels 6 and 13) are spares and contain a channel selector section in addition to sections common to all panels. Only the switches on the panels are discussed as related to input switching.

2. Function of XTL Control Panel Switches.

The unit status switch in the power control section of each XTL control panel determines the status (active or standby) of the channel. With the switch set to ACTIVE, the related channel is connected to the active computer. Only phone line data can be processed when the switch is set to the ACTIVE position. In the STANDBY (or STANDBY MC) position, the channel is connected to the standby computer; in this position, either phone line data or test data may be processed.

There are three switches, in the data circuit section of the panel, concerned with data flow: Pa the data source switch, the data circuit switch, and the parity disabled switch. In conjunction

Page 0100

Page 0100

####

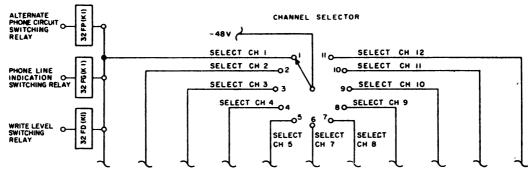

The CHANNEL SELECTOR switch, which appears only on the panels corresponding to channel 6 and 13, is used to electrically substitute the spare channel for any of the channels within a group. Spare channel 6 can be substituted for channels 1 through 5 or 7 through 12. Channel 13 can be substituted for channels 14 through 24.

0N 5 М  $\overline{\phantom{a}}$

with the unit status switch, the data source switch selects the source from which data is to be received. With the switch set to DATA CIRCUIT, the channel receives data on phone line circuits from other Centrals. In the off position, the channel is inactive, and data is not received or processed. In the TEST position, data is received from the test pattern generator (TPG) to permit testing of channel operations in maintenance procedures. 3. Parity Disabled = To prevent test data from entering the active computer, the test position of the switch functions only when the unit status switch (power control section) is set to the STANDBY or STANDBY MC position. The data circuit switch is used to select one of two phone line circuits which feed data to the XTL channel, With the switch set to AUTO, telephone company equipment automatically selects the proper circuit. Either circuit can be manually selected by setting the switch to the CIRCUIT 1 or CIRCUIT 2 position. The parity disable switch has two positions: off and PARITY DISABLED. In the off position, channel operation is normal - a message with incorrect parity is discarded. In the PARITY DISABLED position, test messages can be processed without regard to message parity.

#### I. SUMMARY QUESTIONS

- 1. Crosstell inputs provides for communication between Sage Sectors. (True or False).

- 2. The maximum number of XTL channels provided for is channels.

- 3. A XTL message on the phone line consists of bits.

- 4. Each XTL message received by a XTL channel includes \_\_\_\_\_ parity bits.

- 5. The parity of the overall XTL message on the phone lines is \_\_\_\_\_.

1. Note: In the Data Circuits Section, the Switches are:

- 1. Data Source = Left

- 2. Data Circuit Selection = 2nd from left

- 3rd from Left

- 4. Test = 4th from Left. The "TEST" Switch is used to simulate open filaments for Ghannel Ready FF.

- The relative amplitude of the sync and data pulses as compared to Timing pulse, while on the phone line is \_\_\_\_\_&\_\_\_.

- 7. The spare channel for channel 1 thru 12 is channel\_\_\_\_\_.

- 8. The 5 message words of a XTL message are written on the \_\_\_\_\_\_ drum as \_\_\_\_\_\_ drum words.

- 9. If the "All Parities" bit is a "1", what does this indicate?

- 10. The XTL element consists of the following basic blocks.

- a. Input Switching

- b. A & B common

- c. Duplex Switching

- d. XTL channel

Draw the blocks and use arrows to connect them showing data flow.

#### INPUT AND PHONE LINE SWITCHING

#### A. Function

- 1. The input switching section contains the controls, relays, indicators, and associated circuitry necessary to perform the following functions:

- a. Establish the status (active or standby) of each channel.

- b. Apply incoming phone line data to active channels and test data to standby channels when desired.

- c. Substitute a spare channel for another channel within a group.

- d. Provide indications at the simplex maintenance console to monitor the above functions.

#### B. General

A Central may contain a maximum of 24 XTL channels. However, it can receive information from a maximum of 22 other sources, since two of the channels are spares. A total of six telephone input line pairs are provided for each channel normally in use. These lines are divided into two circuit groups, designated circuit l and circuit 2, each group being made up of timing, sync, and data line pairs.

The XTL message for each channel is carried by both circuits. One circuit, selected by the data circuit switch on the XTL control panel, is connected to the channel input section; the alternate circuit is then available to the spare channel. For example, when the data circuit selector switch on the Channel 1 control panel is set to CIRCUIT 1, circuit 1 is connected to channel 1 and circuit 2 is available for use by the spare channel. When the switch is in the AUTO position, phone company equipment, not part of the XTL Element, determines whether circuit 1 or 2 will be made available to the channel input section.

#### NOTE

In a Combat Control Central at a combined site (Combat Control Central adjacent to a Combat Direction Central), only one phone line is provided for channel 5. Consequently, the data circuits selector switch is not employed. The data circuit selector switch on the spare channels is non-operative since its data circuit is selected on the channel, for which it is inserted.

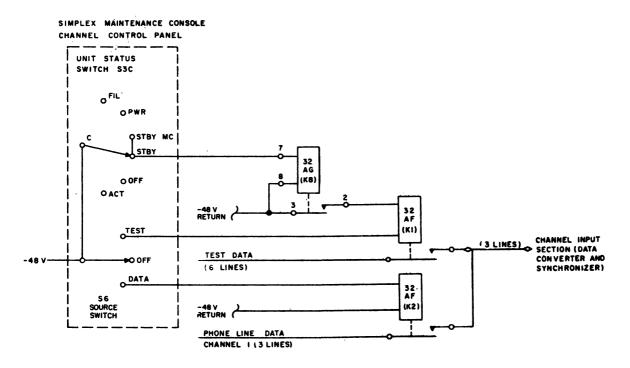

2. In addition to the phone line circuits, a test circuit is available to each channel input section. The test circuit consists of three line pairs (timing, sync, and data) connected to the TPG through a test bus for each pair. When the source switch on the XTL channel control panel is set to TEST (and the channel is in the standby status), the output of the TPG is applied to the channel input section. When the switch is in the DATA CIRCUIT position, phone line inputs are available (from either circuit 1 or 2) to the channel input section.

The switching functions discussed above are performed by the input switching section which also provides suitable monitoring indications at the channel control panels. The input switching section may be regarded as the connecting of two interrelated subsections: input data switching and spare channel switching. The input data switching circuit selects phoneline or test data as the input to the individual channels.

3. The spare-channel switching circuits perform the various operations required to substitute a spare channel for one of the other 11 channels. In subsequent spare channel considerations, although only channel 6 is discussed as a spare for channels 1 through 5 and 7 through 12, the discussion applies equally for channel 13, as a spare for channels 14 through 24, except for references to specific contact designations, relays, terminals, etc.

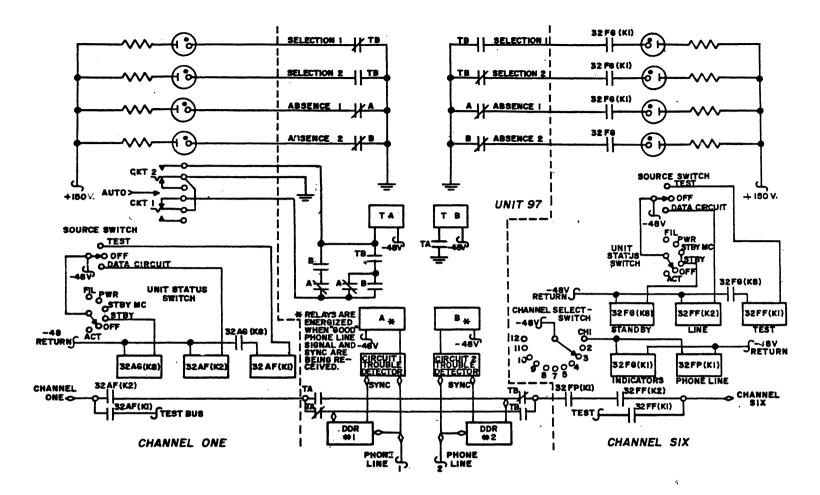

- C. Digital Data Receiver Switching

- 1. Relays TA and TB control circuit 1 and circuit 2 distribution.

- 2. With TA and TB dropped Circuit 1 to Channel 1 and Circuit 2 to Channel 6.

- 3. With TA & TB picked Circuit 2 to Channel 1 and Circuit 1 to Channel 6.

- 4. Relay A & Relay B are energized if good data is being received.

- 5. When in "Auto" Position the telephone company equipment will switch from a faulty circuit to a good one only. 1 to 2 or 2 to 1.

- 6. Absence indicators signify data not valid on circuit specified.

- 7. Select indicators signify which circuit sends data to channel.

- 8. Channel one operation

- a. Selection of Test Data

- 1) Source Switch TEST

- 2) Energize 32AF (K1)

- 3) Unit Status Switch STANDBY or STANDBY - MC

- b. Selection of Line Data

- 1) Source Switch DATA Circuit

- 2) Energize 32AF (K2)

- 3) Circuit Switch Circuit 1 or Circuit 2 or Auto as desired.

.

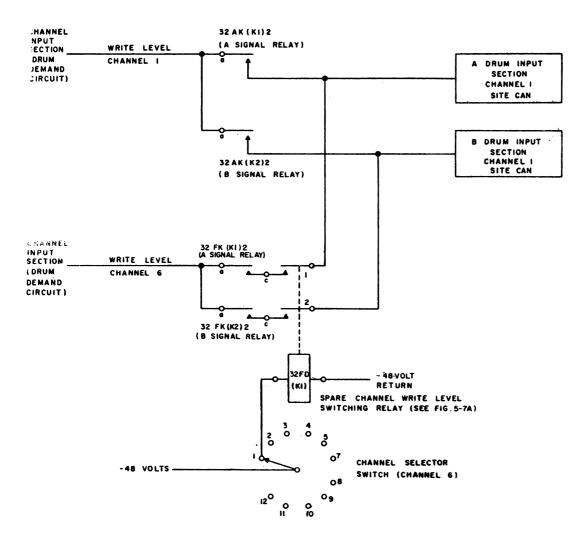

- 9. Channel Six Operation

- a. Selection of Test Data

- 1) Source Switch TEST Position

- 2) Energize 32FF (K1)

- 3) Unit Status Switch STAND BY or STANDBY MC

- b. Selection of Channel 1 Data

- 1) Spare Selector On 1

- 2) Energize 32FP (K1); FG(K1); FD(K1).

- 3) Source Switch Data Position

- 4) Energize 32FF (K2)

- D. Input Switching for Channels 13 24.

- 1. Channel 14 Operation.

- a. Selection of Test Data.

- 1) Source Switch to Test position to pick 32UF (K1).

- 2) Unit Status Switch to STANDBY or STANDBY-MC to pick 32UG (K8). (Enables 32UF (K1) to pick.)

- b. Selection of Line Data

- 1) Energize 32UF (K2)

- 2) Source Switch in Data Circuit position.

- 3) Unit Status Switch to any position desired.

- 2. Channel 13 Operation. (Spare Channel)

- a. Selection of Test Data

- 1) Energize 32TF (K1)

- 2) Source Switch to Test position.

- 3) Unit Status Switch to STANDBY or STANDBY-MC.

CROSSTELL PHONE LINE SWITCHING (CHANNEL ONE)

- b. Selection of Channel 14 Data.

- 1) Energize 32TP (K1); TG (K1); TD (K1)

- 2) Spare Selector Switch on 1.

- 3) Energize 32TF (K2).

- 4) Source Switch in Data Circuit position.

- E. Input Data Switching

- 1. The relationship of the unit status switch and source switch for channel 1 is shown on page 0190. The circuit applies to all other channels except channels 6 and 13, the spare channels.

- 2. Placing the source switch in the DATA CIRCUIT position causes 32AF (K2) to be energized regardless of the position of the unit status switch. Phone line data is thereby applied to the channel input section. (The phone line data will be carried on circuit 1 or 2, depending on the position of the data circuit selector switch and associated phone line circuitry.)

- 3. When the unit status switch is placed in the STANDBY or STANDBY - MC position, 32AG (K8) is energized, providing a -48V return for 32AF(K1). When the source switch is placed in the TEST position, 32AF (K1) is energized, applying test signals (from the XTL TPG) to the channel input section. The purpose of this interlock is to prevent test signals from being applied to an active channel and thus transferred into the Central Computer.

- F. Spare Channel Switching

- Spare channel switching is the operation of electrically substituting a spare channel, channel 6 or channel 13, for one of the 11 other channels. It is accomplished by setting the CHANNEL SELECTOR switch (on the spare channel control panel, simplex maintenance console) to the number of the channel to be replaced:

Page 6200

Input Data Switching

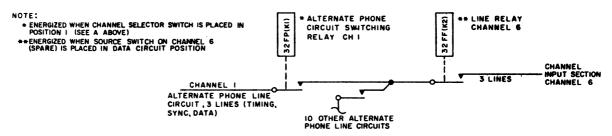

C. PHONE LINE INDICATION SWITCHING

**Spare Channel Switching**

Three functions are thereby performed:

- a. The alternate telephone circuit for the replaced channel is connected to the spare channel Input Switching Relay.

- b. The telephone-terminal-equipment indicators of the spare channel are substituted for these indicators on the replaced channel.

- c. A write level, generated in the spare channel, is applied to the site can of the replaced channel.

(The write level causes readout of site identity, via the site can, to associate the source of a message with the message data. In spare channel operations, it is necessary to associate the site identity of the replaced channel with the information processed by the spare channel.)

- NOTE: In the discussion of a and b, it is assumed that spare channel 6 has been substituted for channel 1.

- G. Switching Basic Telephone-Terminal Indications.

- Telephone line and terminal facilities are not part of the AN/FSQ-7 or -8 but are monitored to ensure proper operation of the Central. Each XTL control panel mounts indicators to show which phone line circuit is connected to the channel input section (SELECTION, CIRCUIT 1, and CIRCUIT 2) and whether there has been a loss of data on a circuit (ABSENCE, CIRCUIT 1 and CIRCUIT 2). When the spare channel is substituted for another channel, the indicators on the spare channel are also substituted, as described below, for the indicators on the replaced channel.

2. Placing the CHANNEL SELECTOR switch in position 1 causes relay 32FG (K1) to be energized. Four lines from unit 97 (telephone terminal equipment) are thereby connected to appropriate indicators on the spare channel control panel: the channel 1, circuit 1 indication line to the SELECTION CIRCUIT light; the channel 1, circuit 2 indication line to the SELECTION CIRCUIT 1, absence circuit 1 line to the ABSENCE CIRCUIT 1 light; and the channel 1, absence circuit 2 light.

#### H. SUMMARY QUESTIONS

- 1. Each XTL channels, including the spares, has a source switch. (T or F).

- 2. The source switch is a Two position switch, i.e. "Test", or "Data Circuit," positions. (T of F)

- 3. In a 24 channel installation, the two spare channels are 6 & 13. (T of F).

- Each XTL channel (except the spares) has two phone lines available, i. e. circuit l or circuit 2. (T or F).

- Each XTL channel has test data available. Test data is directed through any channel simply by placing the Source Switch in the Test position. (T of F).

- When a XTL channel is replaced by a spare channel, the neon indicators for circuit 1 or circuit 2 and the absence circuits 1 or 2 will be indicated not on the spare panel but on the channel being replaced. (T of F).

#### III. XTL CHANNEL INPUT SECTION

#### A. Introduction

- 1. Function

- a. The function of the channel input section in the XTL input element is to receive, in interleaved serial form, the XTL message from the DDR, to unscramble the received data, reforming it into the five original message words, and to transfer these message words to the drum input (common) section. During these operations, the message is checked for the correct address (included as part of incoming message) and is also checked for parity (to detect any errors introduced during transmission).

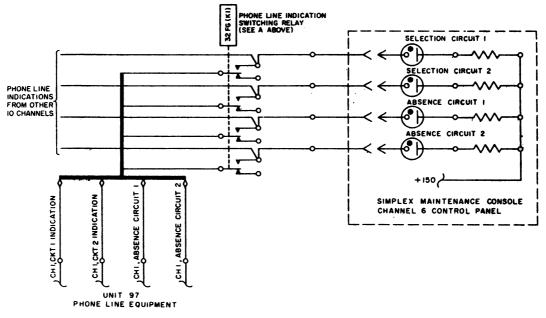

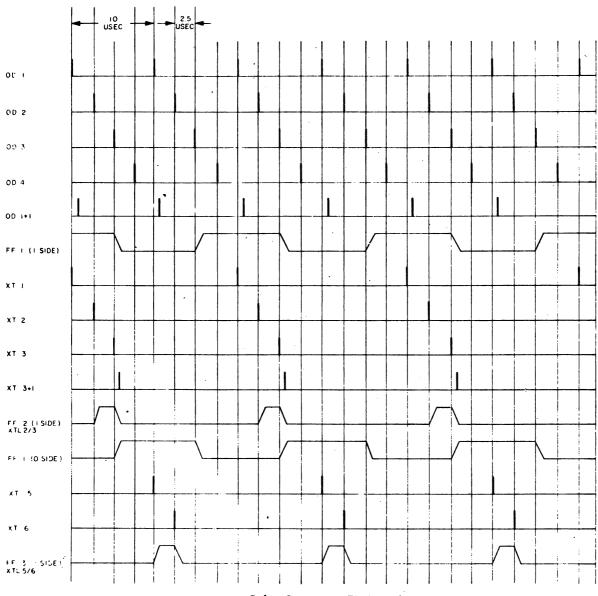

- 2. XTL Timing Pulses

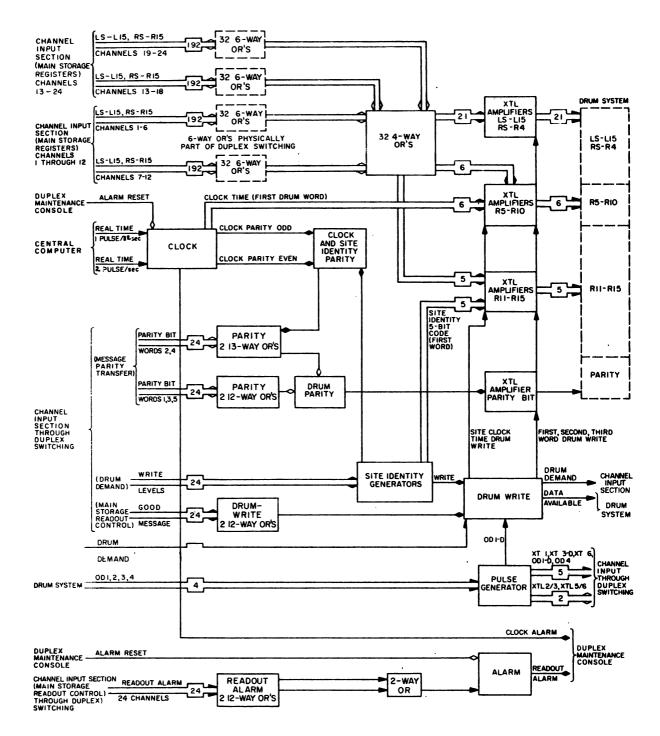

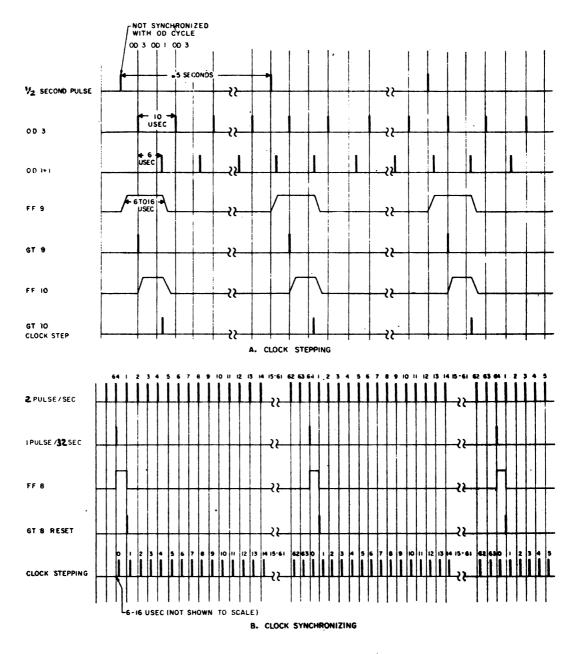

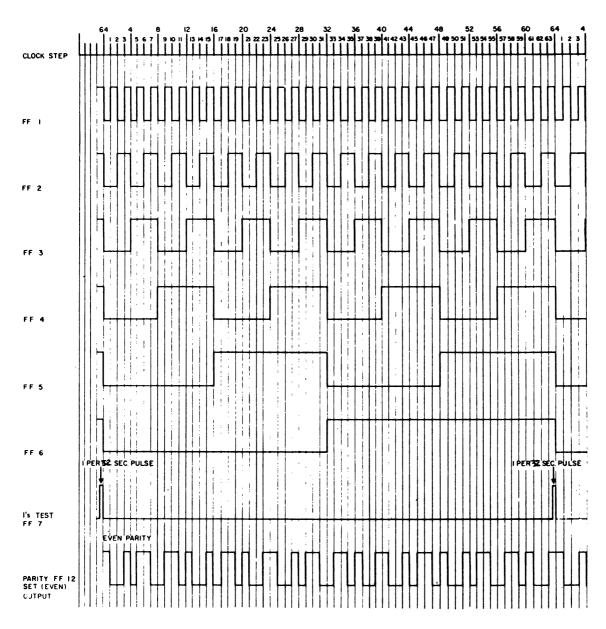

- The operation of the channel input section a. is synchronized by OD pulses and by pulses and levels developed from OD pulses, specifically for the use of the XTL element. The OD drum timing pulses are a series of four standard pulses, OD 1, OD 2, OD 3, and OD 4, equally spaced at 2.5 usec. Recycling takes place without delay so that OD 1 occurs 2.5 usec after OD 4. The OD pulse repetition rate of 10 usec is too fast for some of the circuits in the channel input section. Therefore, the XTL common section develops, in synchronism with the OD pulses, a group of timing pulses having a repetition rate of 20 usec; these pulses are designated XT 1, XT 3, XT 6, etc. The common equipment also generates standard level outputs of a fixed duration; these outputs are designated XTL 2/3 and XTL 5/6. The XTL 2/3 level is a standard  $\neq 10V$  level started by the ΧТ 2 pulse and terminating with the XT 3 pulse. Similarly, the XTL 5/6 level is bounded by the XT 5 and 6 pulses. The generation of these pulses and levels is discussed in connection with the drum input section. The following pulses and levels are furnished by the drum input section to the channel input section through duplex switching:

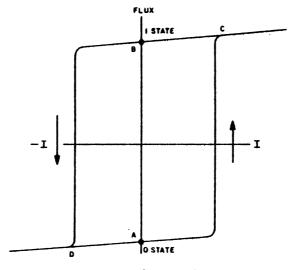

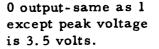

Page 0240 Logic A2. 3.5 - Vol 232 B 2. 3.5

\* THROUGH DUPLEX SWITCHING

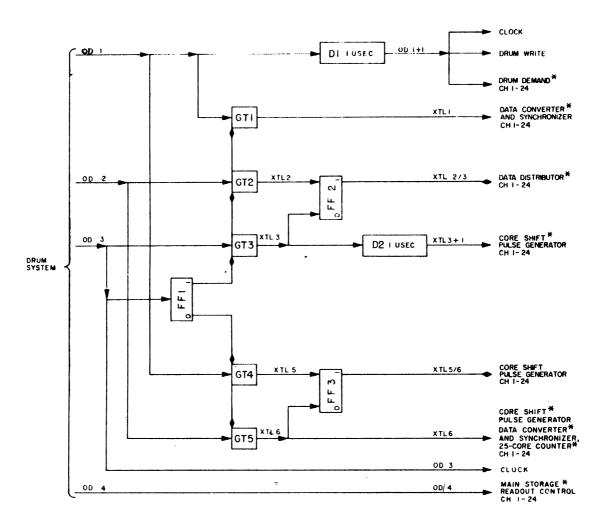

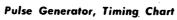

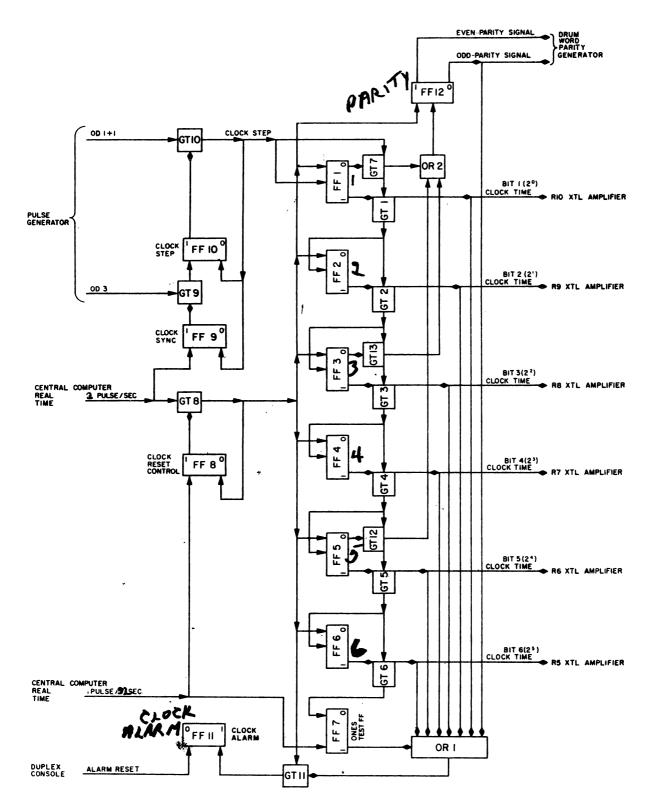

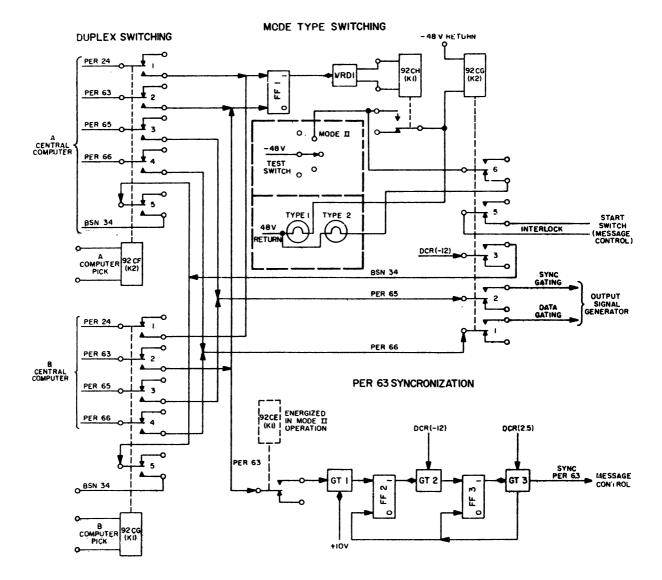

Figure 5-48. Pulse Generator, Simplified Logic Diagram

|       |             | ABPRATION | AF BUUCE | OFLIFS ATOS |

|-------|-------------|-----------|----------|-------------|

| IABLE | <b>30</b> . | OPERATION | OF PULSE | GENERATOR   |

|       |             |           |          |             |

| INCOMING<br>PULSE | EFFECT IN CIRCUIT                            | OUTPUT   | WHERE USED                                                                                                        |

|-------------------|----------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------|

| First OD 1        | a. Delayed 1 μsec in delay circuit D 1       | OD 1 + 1 | Clock circuit, drum write circuit<br>of drum input section; drum de-<br>mand circuit of channel input<br>section. |

|                   | b. Strobes conditioned GT 1                  | XTL 1    | Data converter and synchronizer,<br>channel input section                                                         |

|                   | c. Strobes deconditioned GT 4                | None     | -                                                                                                                 |

| First OD 2        | a. Strobes conditioned GT 2, setting<br>FF 2 | _        | _                                                                                                                 |

|                   | b. Strobes deconditioned GT 5                | None     |                                                                                                                   |

| INCOMING<br>PULSE | EFFECT IN CIRCUIT                                                                                                                                                                                | OUTPUT                 | WHERE USED                                                                                                       |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------|

| First OD 3        | a. None                                                                                                                                                                                          | OD 3                   | Clock circuit, drum input section                                                                                |

|                   | b. Strobes conditioned GT 3, clear-<br>ing FF 2; FF 2 is therefore set<br>from first OD 2 to first OD 3<br>pulse.                                                                                | XTL 2/3                | Data distributor, channel input sec-<br>tion                                                                     |

|                   | c. Output of GT 3 delayed 1 µsec in<br>D2                                                                                                                                                        | $\mathbf{XTL} \ 3 + 1$ | Core shift pulse generator, channel<br>Input section                                                             |

|                   | d. Clears FF 1 through complement<br>input; GT 1, GT 2, GT 3 are<br>deconditioned. GT 4 and GT 5<br>are conditioned. However, be-<br>cause of time delay, GT 3 has<br>already passed OD 3 pulse. | _                      |                                                                                                                  |

| First OD 4        | None                                                                                                                                                                                             | OD 4                   | Main storage readout control,<br>channel input section                                                           |

| Second OD 1       | a. Delayed 1 µsec in delay circuit D 1                                                                                                                                                           | OD 1 + 1               | Same as first OD 1 + 1                                                                                           |

|                   | b. Strobes GT 1, now deconditioned                                                                                                                                                               | None                   | -                                                                                                                |

| Second OD 2       | a. Strobes GT 2, now deconditioned                                                                                                                                                               | None                   | -                                                                                                                |

|                   | b. Strobes GT 5, now conditioned                                                                                                                                                                 | XTL 6                  | Data converter and synchronizer,<br>core shift pulse generator, 25-<br>core counter, channel input sec-<br>tion. |

|                   | c. Output of GT 5 clears FF 3. This<br>flip-flop is therefore set between<br>second OD 1 pulse and second<br>OD 2 pulse.                                                                         | XTL 5/6                | Core shift pulse generator                                                                                       |

| Second OD 3       | a. None                                                                                                                                                                                          | OD 3                   | Clock circuit, drum input section                                                                                |

|                   | b. Strobes GT 3, still deconditioned.                                                                                                                                                            | None                   | -                                                                                                                |

|                   | c. Sets FF 1 through complement in-<br>put. GT 1, GT 2, GT 3 are con-<br>ditioned; GT 4, GT 5 are decon-<br>ditioned.                                                                            |                        |                                                                                                                  |

| Second OD 4       | None                                                                                                                                                                                             | 0D 4                   | Same as first OD 4                                                                                               |

#### TABLE 5-6. OPERATION OF PULSE GENERATOR (cont'd)

Note: All outputs to channel input section pass through duplex switching (Cb 4).

....

- 1) OD 1 delayed (OD 1 *4* 1)

- 2) OD 4

- 3) XT 1

- 4) XT 3 delayed (XT  $3 \neq 1$ )

- 5) XT 6

- 6) XTL 2/3

- 7) XTL 5/6

- NOTE: Timing Circuitry covered in detail in common section.

- b. Inputs

- Logic 2.3.5

- OD1, 2, 3 & 4 pulses from A or B drum systems respectively.

- c. Outputs

- 1) 100 KC rate pulses (Called OD)

- a) OD1-D (OD1 / 1-D)

- b) OD4

- c) OD3 To clock circuit only.

- 2) 50 KC rate pulses (Called XT).

- 1) XT1 Alternate OD1's

- 2) XT3 D (OD3 / 1-D) Alternate OD3's.

- 3) XT6 Alternate OD2's.

- 3) 50 KC rate shift pulses

- a) XT 2/3

- b) XT 5/6

- NOTE: The OD pulses are sent from "A" or "B" drums to common where they are converted to XT pulses in the common section. From common through Duplex switching to the channel. Thus, the incoming data is synchronized with Drum Timing Pulses before being transferred to Drums.

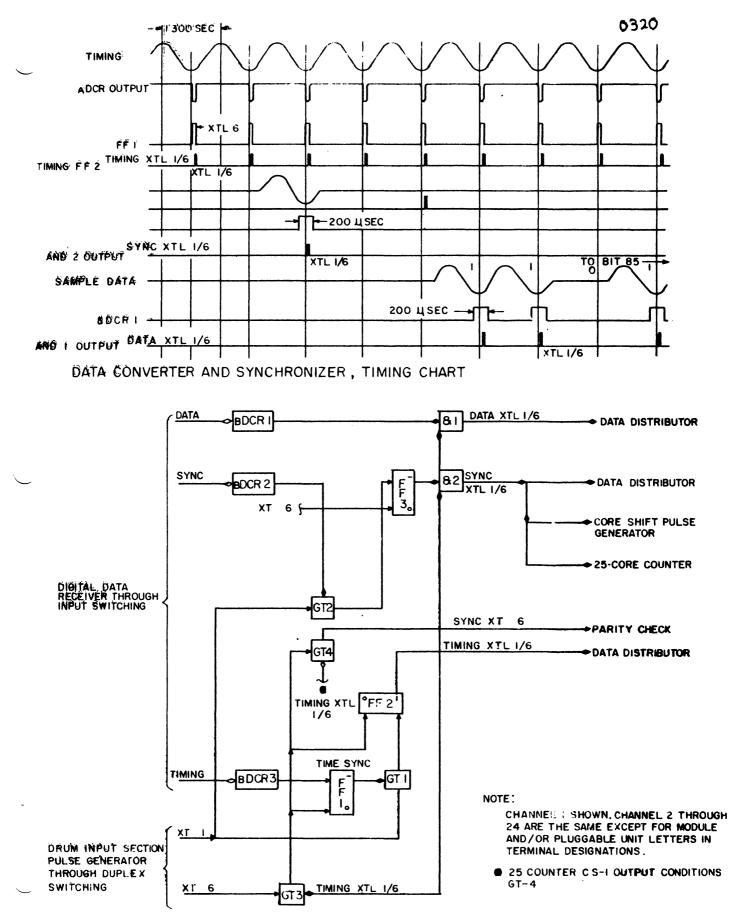

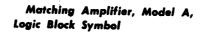

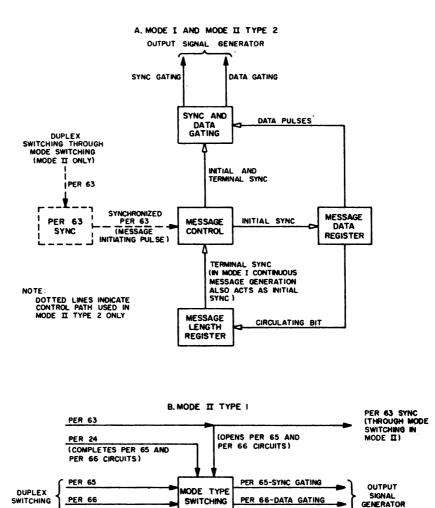

3. XTL Channel Input Section, Simplified Block Diagram.

Page 0290 Logic S 2.3.2

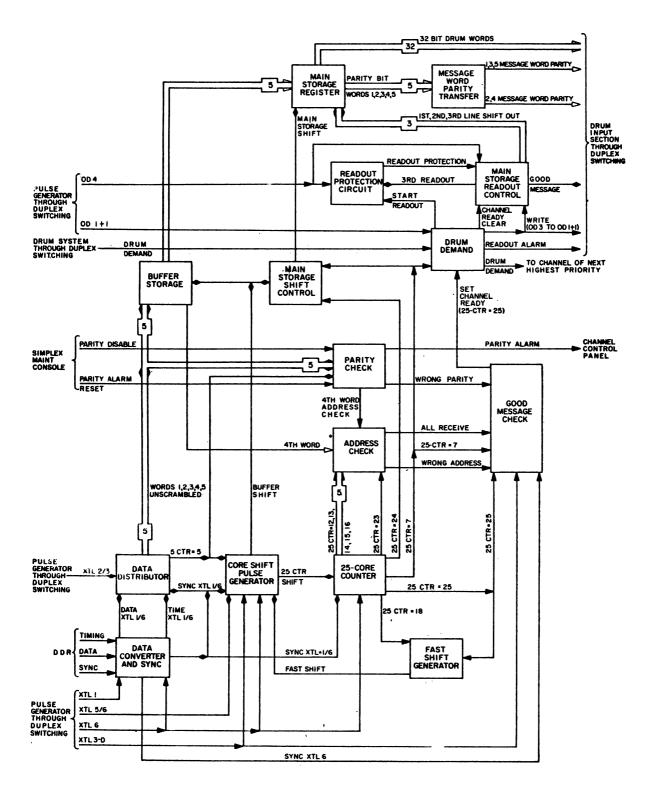

- The timing, sync, and data inputs that make a. up a XTL message are sent to the data converter and synchronizer circuit which converts these sinusoidal inputs into standard levels synchronized with OD and XTL timing pulses. The timing input is a continuous 1,300-cps sine wave signal and is converted into a single timing XTL 1/6 level for each cycle of the input sine wave. The sync input is a single cycle of a 1,300-cps sine wave signal which is converted into a single sync XTL 1/6 level. The data input is a single cycle of a 1,300-cps sine wave signal for each 1 data bit and no signal for each 0 data bit; it is converted into a single XTL 1/6data level for each 1 data bit and no output for each 0 data bit. The three separate outputs (timing, sync, and data) are sent to the data distributor. The sync XTL 1/6 level is also sent to the 25-core counter to indicate the start of a message.

- b. The five XTL message words are transmitted to the channel in interleaved form; the first data bit of each of the five words is received, followed by the second data bit of each word, etc. The successive data bits of the same word are five bits apart as the data bits are received.

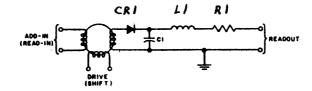

The data distributor circuit re-forms the five original XTL message words by producing five separate outputs, each of which is the data of a particular XTL message word. The five separate outputs of the data distributor are designated word 1 through word 5 data. They are inserted into separate buffer storage registers for each word and are also sent to the parity check circuit where the parity of each word is checked.

**Crosstell Channel Input Section, Simplified Block Diagram**

0290

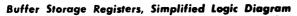

- The buffer storage registers are five 7 core c. shift (CS) registers, with the output of each last core connected to the main storage registers. The latter are five 17-CS registers. Each main storage register is capable of storing a complete XTL message word (17 data bits); the entire XTL message is eventually stored here to await transfer to the Drum System. The reason for sending the unscrambled data bits to the buffer storage registers before transfer to the main storage registers is to enable the channel to receive and store the first 35 data bits (seven bits in each buffer storage register) of an incoming message before destroying the words of a previous message stored in the main storage registers. This time delay gives the Drum System ample time to locate an empty drum slot and to transfer the previous message from the main storage registers to the Drum System.

- d. The rest of the circuits contained in the channel do not process data and are related only with the shifting readout, and checking of the message. These circuits are described in detail in the logic discussions of each. The following is only a brief functional description.

- The CS pulse generator produces a buffer-shift e. pulse after every five data bits (one from each message word) have been inserted into their proper buffer storage registers. The buffershift pulses are also used to shift the 25-core counter which keeps track of the position of the first group of data bits as they are transferred through the buffer and main storage registers. After seven buffer shifts, the first group of data bits is contained in the last core of each buffer storage register. The 25-counter then sends a 25-counter-equals-7 pulse to the main storage shift control circuit, causing the buffer-shift pulses to be simultaneously applied to the main storage registers. After the complete XTL message has been received by the channel and stored (seven bits of each word in the buffer storage registers and 10 bits of each word in

the main storage registers), a 25 counterequals-18 pulse is applied, through the fast-shift generator, to the CS pulse generator. The latter then produces buffer-shift pulses at a 20-usec rate (fast shift), rapidly transferring the last \_\_\_\_\_\_\_\_\_ bits of each word from the buffer storage registers to the main storage registers.

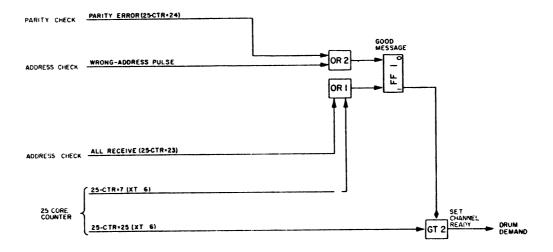

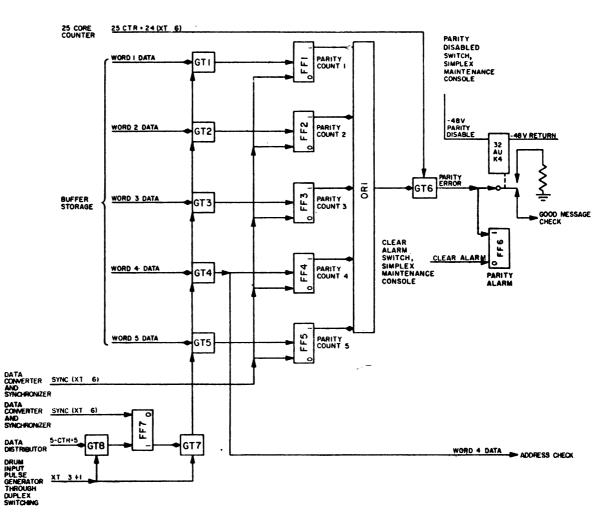

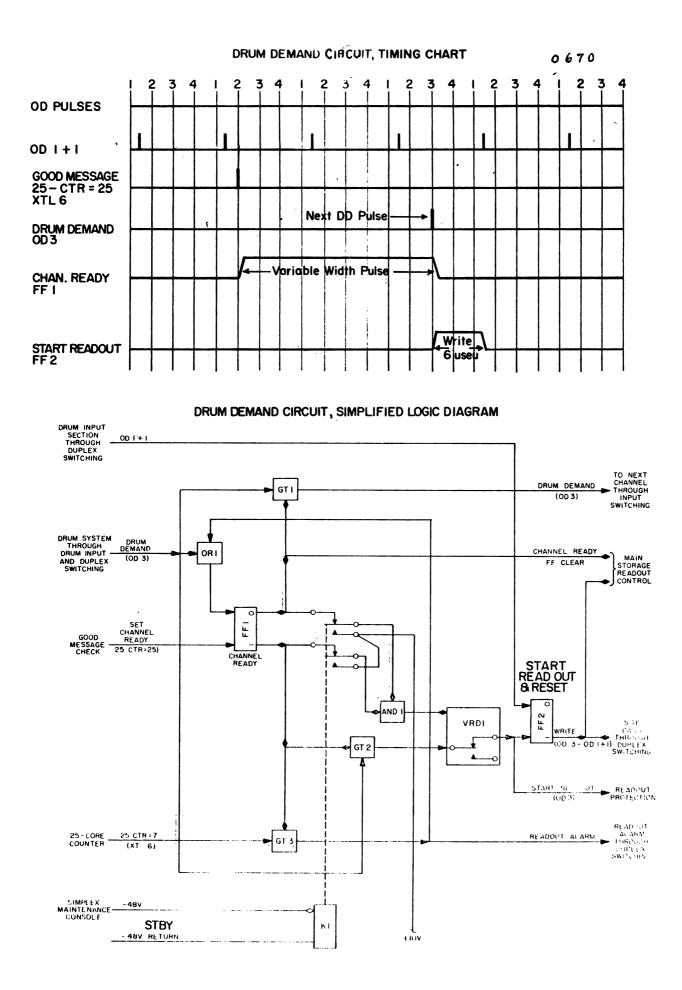

f. The parity check circuits receive the data bits of the five message words from the data distributor and check the parity of each message word. The address check circuit receives data from word 4 only. In the event of an incorrect parity count, the parity check circuit produces a wrong-parity signal. In the event of an incorrect address, the address check circuit generates a wrong-address signal. In the absence of a wrong-parity or a wrong-address signal, the good message check circuit produces a set-channel-ready (25 counter-equals-25) signal when a message has been received and stored in the main registers. The drum demand circuit is informed of the reception and storage of a message by the set-channelready pulse and the 25-counter-equals-25 pulse.

The drum demand circuit then produces a write signal when an empty drum slot is available. The write signal is applied to the main storage readout control circuit which then produces three readout signals, causing the parallel readout of the message words from the main storage registers to the drum input section (Common equipment).

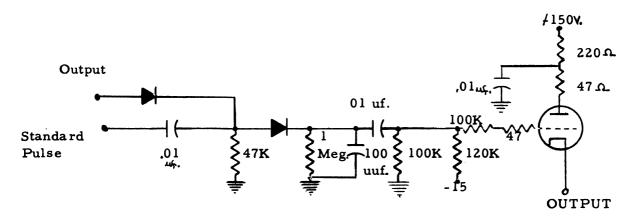

- B. Data Converter and Synchronizer

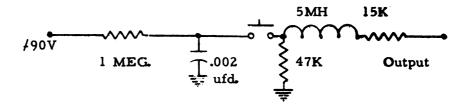

- The data converter and synchronizer converts timing, sync, and data sinusoidal inputs into Pag standard levels of fixed duration synchronized Log with XTL timing pulses. The synchronized timing, sync, and data levels are used in other circuits of the XTL channel input section.

Page 0320 Logic S 2.3.2

DATA CONVERTER AND SYNCHRONIZER, SIMPLIFIED LOGIC DIAGRAM

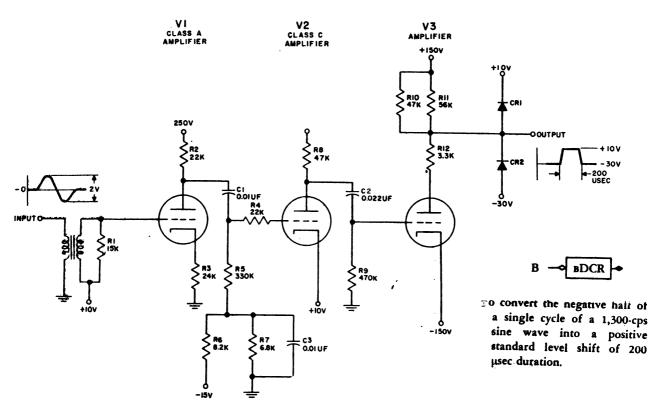

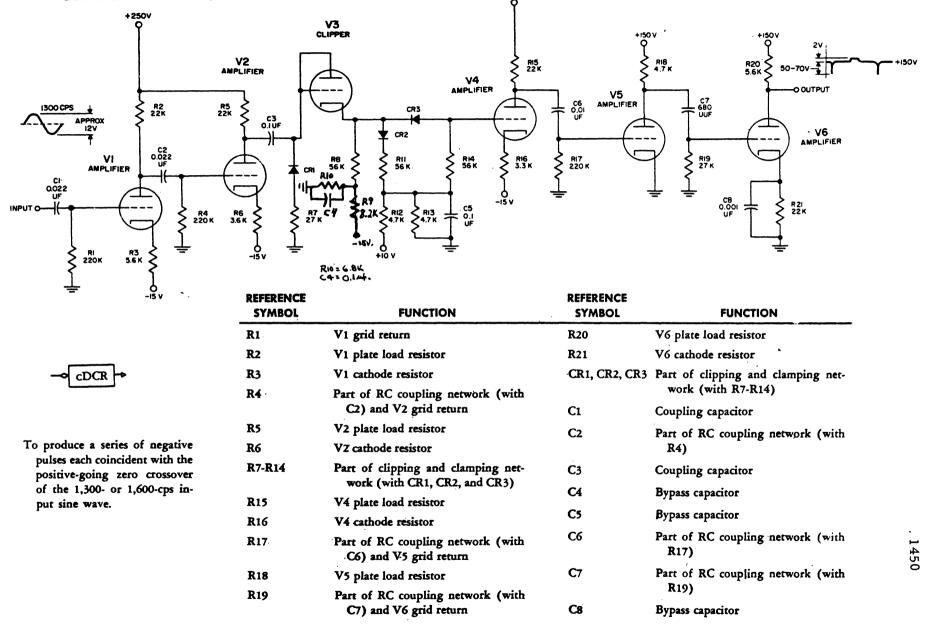

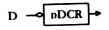

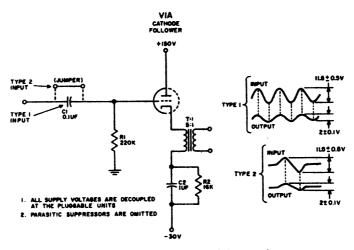

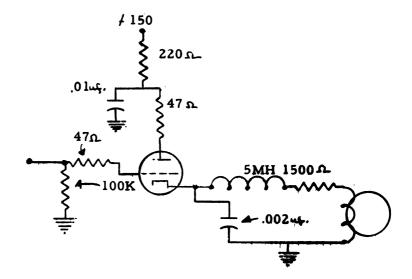

2. The timing, sync, and data (sinusoidal) inputs are sent to the XTL input channel on separate lines. Each of the three input signals is applied to a data conversion receiver (DCR).

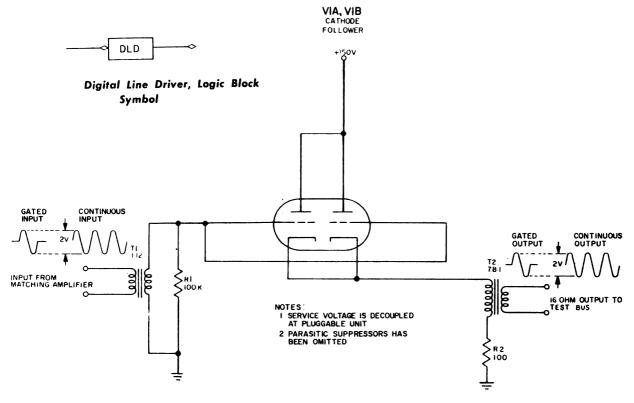

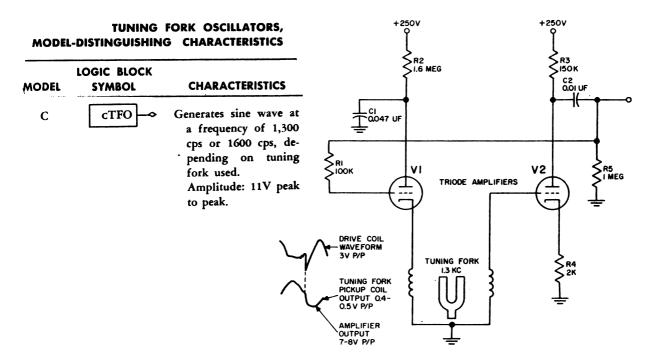

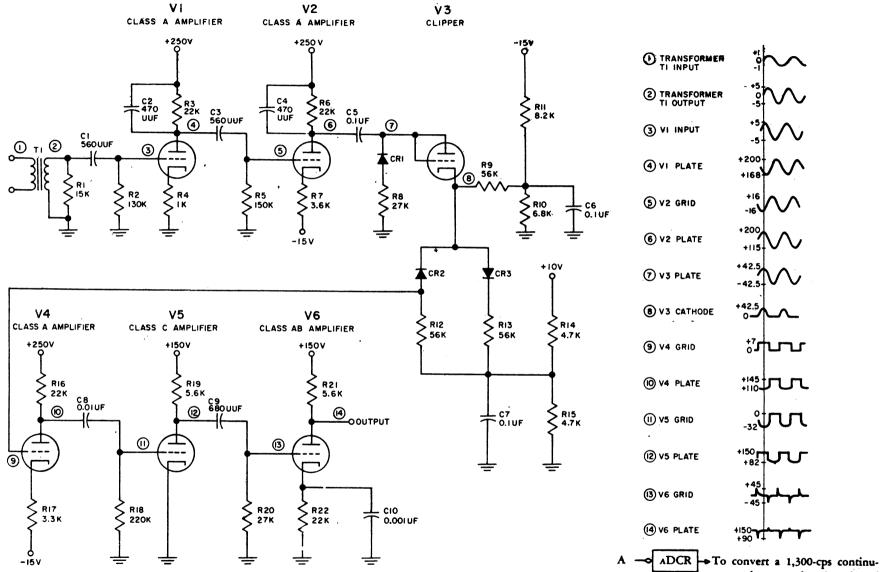

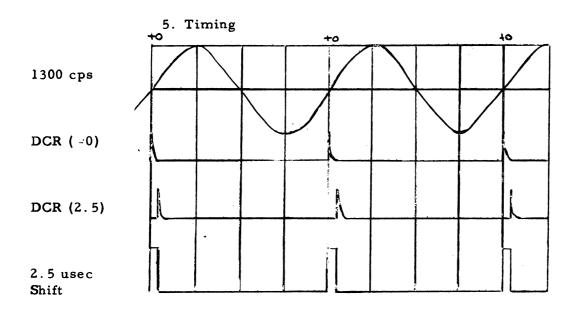

The timing input, a continuous 1,300-cps sine wave, is applied to a model ADCR, which produces a negative nonstandard pulse for each negative peak of the timing sinusoidal input. This negative pulse is used to set flip-flop (FF) 1. The 1 output level of FF 1 conditions gate tube (GT) 1, permitting an XT 1 pulse to pass and set FF 2. The 1 output level of FF 2 conditions GT 3, allowing an XT 6 pulse to pass. The XT 6 clears FF's 1 and 2. Since FF 2 was set by an XT) 1 pulse and cleared by the following XT 6 pulse, it produces a set output level for the time between XT 1 and XT 6, designated timing XTL 1/6, with a duration of 12.5 usec. Timing XTL 1/6 levels are sent to the data distributor, to AND 1, AND 2, and GT 3.

- 3. The sync pulse consists of a single cycle (1300 cps) sine wave, indicating the start of a message which is applied to BDCR-2. The DCR-2 output is a standard level 200 usecs duration for each negative peak input. The level is applied to GT-2. XT 1 pulses will get thru GT-2 during this 200 usec. period, every 10 usecs, to set FF-3. FF-3 is cleared by a XT 6 pulse, thus the output of "and-2" is a sync XTL 1/6 (12.5 us) level. The 25 counter CS-1 output which occurs after the two 0 intervals following the sync have past. Then a XT 6 pulse will get thru GT-3 and GT-4 to clear parity check FF's so the two zero's following the sync bit are not included in the parity check count.

- 4. The data input consists of a single cycle of a 1,300-cps since wave signal for each 1 data bit and no signal for each 0 data bit. This input is applied to BDCR 1, which produces a 200-usec standard level output for each 1 data bit. The BDCR1 output is applied to AND 1. AND 1 passes an XTL 1/6 level whenever a 1 data bit appears and has no output for 0 data bits. These data XTL 1/6 levels are sent to the data distributor.

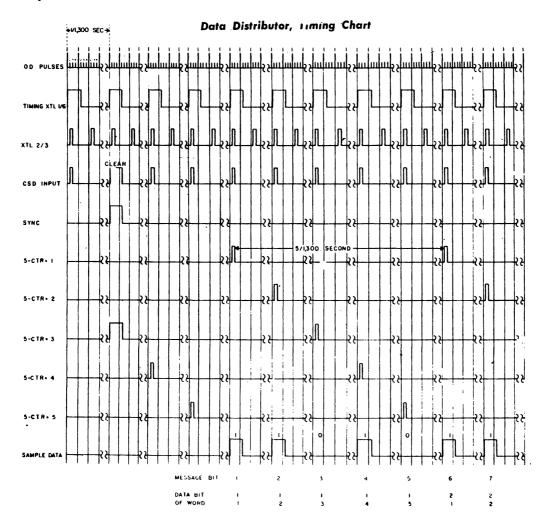

| c. | Data | a Dis | D 0460                                                       |                                                                                                                   |                  |  |  |  |  |  |  |  |  |  |

|----|------|-------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|--|--|--|--|--|--|

|    | 1.   | Fun   | ction                                                        | <b>Page 0</b> 360                                                                                                 |                  |  |  |  |  |  |  |  |  |  |

|    |      | a.    | The d<br>XTL v<br>of an<br>words<br>word<br>also s<br>the pa |                                                                                                                   |                  |  |  |  |  |  |  |  |  |  |

|    |      | ь.    | A 5 cc                                                       |                                                                                                                   |                  |  |  |  |  |  |  |  |  |  |

|    |      |       | Logic S 2.3.2                                                |                                                                                                                   |                  |  |  |  |  |  |  |  |  |  |

|    |      | с.    |                                                              |                                                                                                                   |                  |  |  |  |  |  |  |  |  |  |

|    |      |       | ata                                                          |                                                                                                                   |                  |  |  |  |  |  |  |  |  |  |

|    |      |       |                                                              | will be associated with word 1, core 2 with word 2 etc.                                                           |                  |  |  |  |  |  |  |  |  |  |

|    |      | d.    | Output Pulses                                                |                                                                                                                   |                  |  |  |  |  |  |  |  |  |  |

|    |      |       | 1. L<br>2. 5<br>b<br>3. O                                    |                                                                                                                   |                  |  |  |  |  |  |  |  |  |  |

|    |      | e.    | Circui                                                       |                                                                                                                   |                  |  |  |  |  |  |  |  |  |  |

|    |      |       | levels                                                       | ata distributor, receives data XTL 1/6, timing XTL 1/6 levels, and a sync<br>/6 level from the data converter and | <b>Page</b> 03ú0 |  |  |  |  |  |  |  |  |  |

synchronizer. The data bits ( a single XTL

0340

1/6 level for each 1 data bit and a 0 level for each 0 data bit) are applied simultaneously to AND circuits 1, 2, 3, 4, and 5. Each of the AND circuits also receives a single output signal from the 5-core ring counter. The 5-core ring counter outputs are 5-counterequals - 1, -2, -3, -4, and -5 and are applied to AND circuits 1, 2, 3, 4, and 5, respectively. The 5-counter is primed and shifted so that, when the first incoming data bit is present, only the 5-counter-equals-1 pulse appears. If the first data bit is a 1, AND 1 passes the 5-counter-equals-1 pulse. The 5-counterequals-2 pulse appears when the incoming data bit is applied and passes through AND 2 if the second data bit is a 1. In the same manner, AND 3 passes a 5-counter-equals-3 pulse if the third data bit is a 1; AND 4 passes a 5-counter-equals-4 pulse if the fourth data bit is a 1; and AND 5 passes a 5-counter-equals-5 pulse if the fifth data bit is a 1. The 5-counter then recycles, with AND 1 passing a 5-counterequals-1 pulse if the sixth data bit is a 1, etc. Each AND circuit passes every fifth data bit if it is a 1 and produces no output for each 0 data bit, thereby accomplishing the unscrambling of the interleaved data and re-forming the original 5 words.

At the start of a message, a sync XTL 1/6level is applied through an OR circuit to the core shift driver (CSD), producing a longduration-shift signal (12.5 usec) that clears the five core shifts to 0. The same sync XTL 1/6 level is also applied to the input winding of CS 4 through a delay network in the CS circuit. The delay circuit enables the sync XTL 1/6 level to prime the CS after the clearing shift XTL 1/6 signal has terminated. Thus, a single 1 is stored in CS 4, and the other core shifts store a 0 at the beginning of a message.

0360

|             |      |    |    |    |    |    |    |    |    |    |    |      |    |     |    |    | IDLIN | 0370       |

|-------------|------|----|----|----|----|----|----|----|----|----|----|------|----|-----|----|----|-------|------------|

|             | Sync | :  |    |    |    |    |    |    |    |    |    |      |    |     |    |    |       |            |

|             | 0    |    |    |    |    |    |    |    |    |    |    |      |    |     |    |    |       |            |

| Output of   | 0    |    |    |    |    |    |    |    |    |    |    |      |    |     |    |    |       |            |

| AND 1       | 1    | 6  | 11 | 16 | 21 | 26 | 31 | 36 | 41 | 46 | 51 | 56   | 61 | 66  | 71 | 76 | 81    | XTL word 1 |

|             | MB   |    |    |    |    |    |    |    |    |    |    |      |    |     |    | MB | PAR   |            |

| AND 2       | 2    | 7  | 12 | 17 | 22 | 27 | 32 | 37 | 42 | 47 | 52 | 57   | 62 | 67  | 72 | 77 | 82    | XTL word 2 |

|             | MB   |    |    |    |    |    |    |    |    |    |    |      |    |     |    | MB | PAR   |            |

| AND 3       | 3    | 8  | 13 | 18 | 23 | 28 | 33 | 38 | 43 | 48 | 53 | 58   | 63 | 68  | 73 | 78 | 83    | XTL word 3 |

|             | MB   |    |    |    |    |    |    |    |    |    |    |      |    |     |    | MB | PAR   |            |

| AND 4       | 4    | 9  | 14 | 19 | 24 | 29 | 34 | 39 | 44 | 49 | 54 | 59   | 64 | 69  | 74 | 79 | 84    | XTL word 4 |

|             | MB   |    |    |    |    |    |    |    |    |    | AD | ) A1 | DA | D.A | ١D | AP | PAR   |            |

| AND 5       | 5    | 10 | 15 | 20 | 25 | 30 | 35 | 40 | 45 | 50 | 55 | 60   | 65 | 70  | 75 | 80 | 85    | XTL word 5 |

|             | MB   |    |    |    |    |    |    |    |    |    |    |      |    |     |    |    | PAR   |            |

| Word bits · | 1    | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12   | 13 | 14  | 15 | 16 | 17    |            |

DATA DISTRIBUTOR, DATA BIT DISTRIBUTION - UNSCRAMBLING 0.370

MB = Incoming message bit

PAR = Parity bit

AD = Address bit

AP = All-parties bit

Timing XTL 1/6 levels are applied to AND 6 which then passes XTL 2/3 levels from the drum input section. AND 6 passes a single XTL 2/3 level whenever a timing XTL 1/6level is present. This timing XTL 2/3 level is applied through the OR circuit to the CSD, producing a shift pulse output (2.5 usec) to the five CS's. The shift pulse transfers the contents of each CS to the adjacent CS. The first timing XTL 2/3 level transfers the 1 in CS 4 to CS 5. The second timing XTL 2/3 level transfers the 1 from CS 5 to CS 1. The next timing XTL 2/3 level which occurs simultaneously with the first incoming data bit (sync is followed by two 0's before the first incoming data bit), moves the 1 from CS 1 to CS 2. The output line connected between CS 1 and CS 2 is activated by the transfer. This nonstandard output is applied to a level setter (LA) which produces a standard level output designated 5-counterequals-1. The next timing pulse (which occurs simultaneously with data bit 2) transfers the 1 from CS 2 to CS 3, producing a 5-counter-equals-2 pulse. The 5 counterequals-3, -4, and -5 pulses occur simultaneously with data bits 3, 4, and 5, respectively. Since the 5-CS register is connected as a ring (CS 5 drives CS 1), the 5-counter-equals-1 pulse occurs again when the sixth data bit is present, etc. In this manner, the output of AND 1 is data bits 1, 6, 11, 16, 21, etc., which is the unscrambled word 1 data. The AND 2, 3, 4, and 5 outputs are unscrambled word 2, 3, 4, and 5 data respectively.

The 5-counter-equals-5 pulse is also sent to the CS pulse generator circuit.

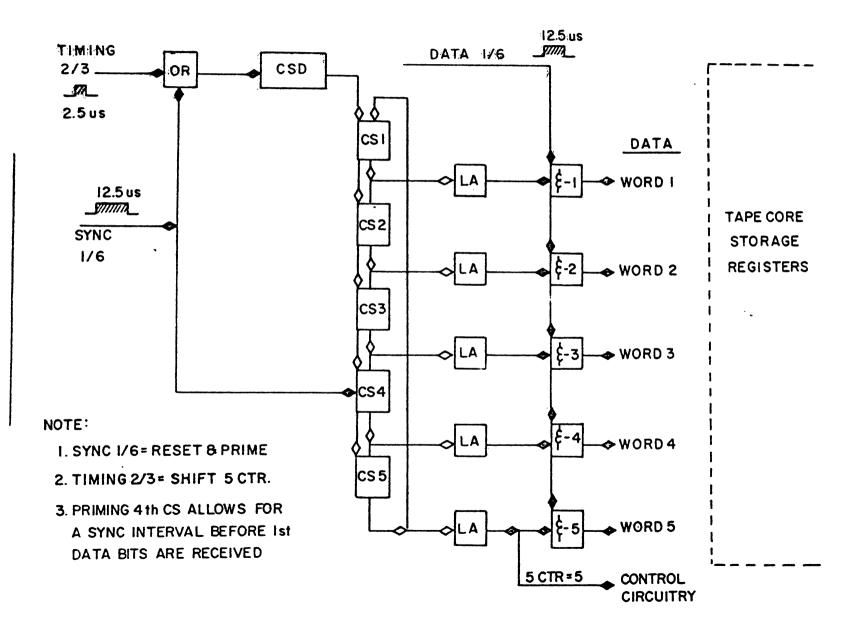

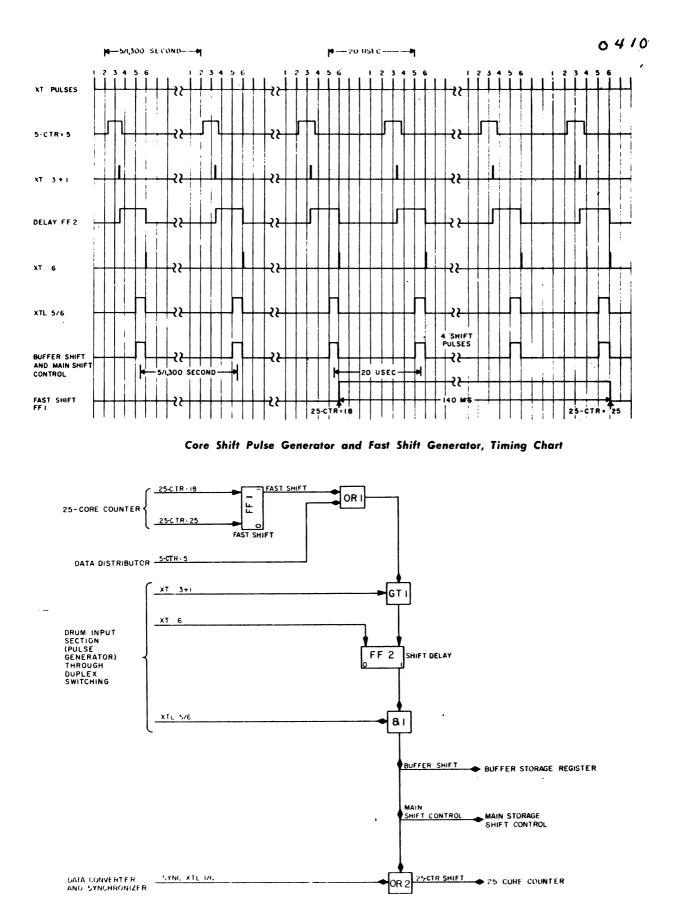

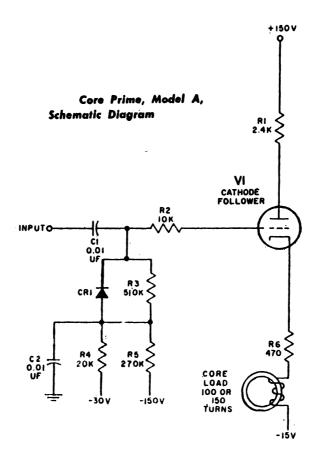

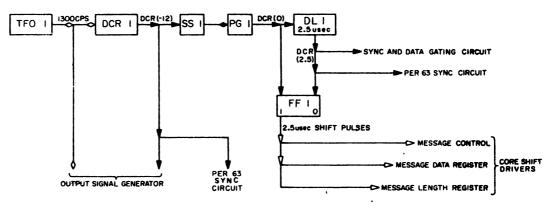

# D. Core Shift Pulse Generator and Fast Shift Generator Page 0410

1. The CS Pulse generator produces the pulses used to shift the buffer storage registers. The buffershift pulses are also applied to the main storage shift control circuit and to the 25-core counter.

The CS pulse generator, is suppled with the 5-counter-equals-5 level from the data distributor. This level appears after a data bit has been inserted in each of the five buffer registers. (Also occurs after S and two"O's at the time 5 CTR = 5 and 25 CTR = 1). The latter must now be shifted so that the next data bit of each word may be inserted in its respective register. The CS pulse generator produces an XTL 5/6 buffer shift level after each 5-counter-equals-5 level has appeared. After 17 buffer-shift pulses have been generated, the complete XTL message will have been received and stored in the channel equipment (11 bits of each word in the main storage registers and six bits of each word in the buffer storage registers). The fast shift is then turned on, permitting a buffershift pulse to occur every 20 usec. This transfers the six bits in each buffer register to the associated main storage register at a rapid rate.

OR circuit 1 receives either the 5-counterequals-5 level or the fast-shift level from FF 1. The 5-counter-equals-5 pulse, passing through OR 1, conditions GT 1. Gate 1 passes on XT 3 / 1 pulse which sets FF 2. The set output of FF 2 is applied to AND 1 which then passes an XTL 5/6 level. The output of AND 1 is used to drive the CSD of each buffer register. Flip-flop 2 is cleared by an XT 6 level, deconditioning AND 1 after it has passed the single XTL 5/6 shift level. The XTL 5/6 shift level is also sent to the main storage shift control circuit where it is used to shift the main storage registers at the appropriate time.

The fast shift (mentioned above) is controlled by FF 1 which, in turn, is controlled by the 25-core counter. The 25-counter counts the number of buffer-shift levels. The 18th buffer shift causes the 25-counter-equals-18 (XT  $\pm$  6)

pulse to appear, setting FF 1. The output of FF 1 (fast-shift signal) is applied through OR 1 and conditions GT 1. Gate 1 passes each XT  $3 \neq 1$  pulse that occurs while the fast shift is on. These XT 3 / 1 pulses set FF 2. The set output of FF 2 is applied to AND 1 which then passes each XTL 5/6 level, producing a shift pulse every 20 usec (the pulse repetition time of XTL 5/6 levels). These XTL 5/6 levels are used to shift the buffer storage registers, main storage registers, and 25-counter. After six shift levels at the fast-shift rate, the complete message is in the main storage registers, and the 25-counter-equals-24 pulse turns off the shift coupler FF. The 25-counterequals-25 (XT 6) pulse clears FF 1, turning the fast shift off. The main storage registers now hold the complete XTL message (five words of 17 bits each) until it is transferred to the drum input section (common equipment).

- 2. Timing Summary

- a. Buffer Storage

- 1) Normal Shift

- a) When 5 ctr = 5 shift delay set for 6.5 usec.

- b) One XTL5/6 pulse shift

- (1) 25 counter

- (2) buffer storage

- (3) attempts to shift main storage

- 2) Fast Shift

- a) "Fast Shift" set when 25 ctr = 18 (Entire message received)

- b) Ends with 25 ctr = 25 (Message cycle completed).

- b. Main Storage

- 1) Shifted same as buffer storage

Core Shift Pulse Generator and Fast Shift Generator, Simplified Logic Diagram

- a) Starting when 25 ctr = 7

- b) Ending when 25 ctr = 24

- NOTE: By disconnecting Main Storage when 25 counter = 24, the 5 phone line parity bits and the 5 message words are now in the Main Storage Reg. Then, the 25 counter = 25 will allow a check for good message.

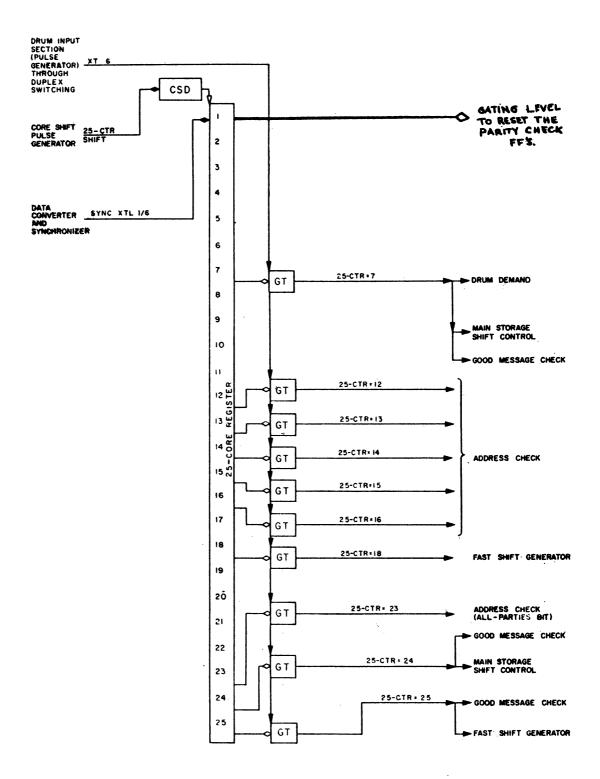

- E. Twenty Five Counter

- 1. Function

Page 0440

- a. Controls timing and sequence of operation as data is received from phone line.

- b. Twenty-five core shift register.

- 1) Contains a single "one"

- 2) Shifted from core to core.

- 2. Control of Counter

- a. Reset 12.5 usec pulse at sync. time.

- b. Prime core 1 12.5 usec pulse at sync time.

- 1) Same pulse that resets will prime

- 2) Reset 50 turns.

- 3) Prime 100 turns.

- c. Shift 2.5 usec. pulse

- 1) Every 5th timing pulse or (3850 usec.)

- 2) During fast shift (20 usec.)

- 3. Circuit Analysis

The 25-core counter reflects the progress of the message through the buffer and main storage registers by counting the 5 ctr = 5 levels (applied by the CS pulse generator). At various counts, the 25-core counter supplies pulses which initiate and terminate the operation of other circuits.

0420

The 25-core counter circuit, consists of a 25-CS register, 10 GT's and a CSD. At the start of a message, the CS pulse generator provides a pulse, derived from a sync XTL 1/6 level, on its 25counter output line. This pulse is applied to a CSD, the output of which clears the cores in the 25-core register. The sync XTL 1/6 level, fed from the data converter and synchronizer primes the first CS of the 25-counter. The 25-counter now counts 5 Ctr. = 5 levels. The first buffer-shift level causes the 1 in the first CS of the 25-counter to be shifted to the second CS. After the first group of five data bits has been inserted into the buffer storage registers, the second buffer-shift level shifts the buffer storage registers and the 25-core counter, moving the 1 in CS 2 to CS 3. The process continues, with the single 1 in the 25-CS register moving one CS each time the buffer storage registers are shifted. In this manner, the position of the 1 in the 25-counter indicates the progress of the first group of data bits through the buffer and then through the main storage reigsters. When the first group of data bits is transferred to the seventh core of each buffer storage register, the 1 in the 25-core counter moves from CS 7 to CS 8, producing an output on the line connected between these two CS's. This output conditions a gate, permitting an XT<sup>°</sup> 6 pulse to pass as the 25-counter-equals-7 pulse. The 25-counterequals-7 pulse (indicating that the first group of data bits is in the seventh core of the buffer storage registers) is sent to the main storage shift control circuits where it is used to initiate the generation of shift pulses to the main storage registers. (It is necessary to start shifting the main storage registers at 25-counter-equals-7 time since the next buffershift pulse will transfer the first group of data bits to the main storage register). The 25-counter-equals 7 pulse is also sent to the good message check circuit and to the channel ready.

When the 25-counter-equals-12 line is pulsed, the first group of data bits has been shifted 11 times and the 12th data bit of each XTL word is about to be inserted into the buffer storage registers. The 25-counter equals -12, -13, -14, -15, and-16 pulses are sent to the address check circuit because address data is contained in the 12th, 13th, 14th, and 15th bit of the

Twenty-Five Core Counter, Simplified Logic Diagram

#### CROSSTÉLL

fourth word. The 25-counter-equals-18 pulse appears after the 17th data bit of each word has been entered into the buffer storage registers. The complete XTL message has now been received (17 bits per word). The 25counter-equals-18 pulse is sent to the fastshift generator to initiate the fast-shift signal.

The 16th bit of the fourth word leaves the word 4 buffer storage register when the 25-counter-equals 23 pulse appears. Since the 16th bit of the fourth word is the all-parties bit, the 25-counter-equals -23 pulse is sent to the address check circuit where it permits the all parties bit (when present) to pass.

The 25-counter-equals-18 pulse appears after the 17th data bit of each word has been entered into the buffer storage registers. The complete XTL message has now been received (17 bits per word). The 25-counter-equals-18 pulse is sent to the fast shift generator to initiate the fast-shift signal.

The 16th bit of the fourth word leaves the word 4 buffer storage register when the 25-counterequals 23 pulse appears. Since the 16th bit of the fourth word is the all-parties bit, the 25-counterequals-23 pulse is sent to the address check circuit where it permits the all parties bit (when present) to pass.

The 25-counter-equals-24 pulse is sent to the good message check circuit where it is passed if a parity error is present, and to the main storage shift control circuit, where it terminates the generation of main-storage-shift pulses. The 25-counter-equals 25 pulse is sent to the fast-shift generator to terminate the fast-shift signal and to the good message check circuit to provide a set-channel-ready pulse thus condition in the drum demand circuit when a good message has been stored in the main storage registers.

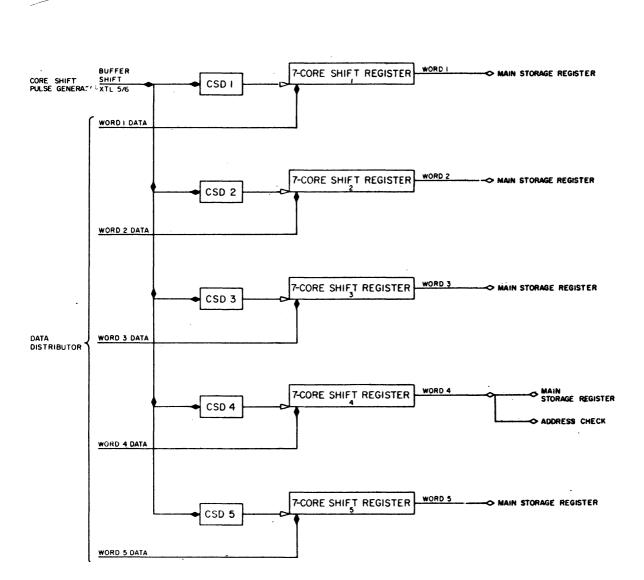

## F. Buffer Storage

3

### 1. Function

a. Isolate incoming data from main storage to allow adequate time for previous message to be written on drum.

- 1) Seven core shift registers.

- 2) One for each of the 5 message words.

- 2. Reset shifted clear during fast shift.

- 3. Prime coincidence of pulses. A correct 5 counter output.

- a. Correct 5 counter output

- b. Receipt of data ("1" bit).

- 4. Parity FF's are complemented by each "1" bit in each word.

- a. Five FF's one per word.

- b. FF's cleared initially during 3rd timing pulse. Even No. of "1" bits in each word should leave the FF's cleared.

- 5. Shift 2.5 usec signal

- a. Every 5th timing pulse (5 counter = 5).

- b. During fast shift 50 kilocycle rate.

- 6. Circuit Analysis

The five buffer storage registers are filled serially by the data bits of the five XTL words from the data distributor. Their function is to delay the transfer of data to the main storage register sufficiently to permit the drum to demand and to accept a previous message from the main storage registers.

They achieve this delay by receiving and storing the first 30 bits of an incoming message. A time lapse of 30/1, 300 second is thereby provided in which the drum section can locate an available drum slot and receive the previous message from the main storage circuit.

The buffer storage circuit, consists of five 7-CS registers. The first core of each of these buffer storage registers is primed by the word data bits from the data distributor. Page 0470 Logic 5-2.3.2

Buffer storage registers 1 through 5 receive the data of words 1 through 5, respectively. After the first group of five data bits has been inserted into the first core of each buffer storage register, a shift XTL 5/6 level from the CS pulse generator circuit is applied to the CSD of each buffer storage register. This shift level transfers the contents of each core to the adjacent core. The five data bits of the next group are then inserted into their respective buffer storage registers, and a second shift level is applied. The shift level is applied after the insertion of every five data bits, producing a shift rate of 5/1, 300 second. (3.846 MS)

After the buffer storage registers have received the first 30 data bits, they are full (six bits in each word register). At this time the main storage shift control circuit permits the main storage registers to shift. The data bits of each word are then transferred from the last: core of each buffer storage register to the first core of each main storage register. After an additional 55 data bits have been received, the entire message (85 data bits) will have been received and stored (six bits in each buffer storage register and 11 bits in each main storage register). The CS pulse generator now produces shift levels at a fast-shift rate (50,000 pps), transferring the last six bits of each word from the buffer storage registers to the main storage registers.

The main storage registers then contain the complete message (17 bits per word). The fourth word buffer storage register output is also sent to the address check circuit, since the All Parties Bit is contained in the 16th bit of the fourth XTL message word.

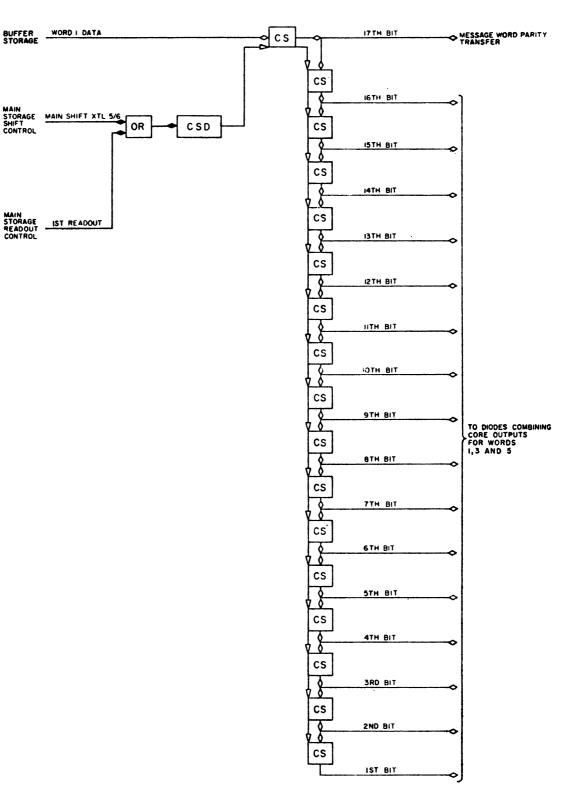

## G. Main Storage

| 1. | Function - stores incoming message until | <b>Page</b> 0500 |

|----|------------------------------------------|------------------|

|    | transferred to drums.                    | Logic S-2.3.2    |

- a. Seventeen core shift register.

- b. One for each of five words.

- Reset readout of data to drum is a 10 usec. pulse that leaves register cleared. If not Readout prior to 25 CTR = 7 the register is shifted clear as new data is shifted in.

- 3. Prime Transfer in from the buffer register.

- 4. Shift 2.5 usec pulses.

- Every 5th timing pulses following the buffer storage being full (25 ctr = 7).

- b. Fast shift (50 KC) after last parity bit is received until the message is entirely in main storage.

- 5. Circuit Analysis

- a. The main storage circuit serially receives the data bits of each of the five words constituting the XTL message, temporarily stores the words, and when an XTL drum slot becomes available, transfers the words in the required order to the XTL drum input section.

- b. Word Storage

The data bits from the five buffer storage registers are each fed to the corresponding 17-CS main storage register. Like data bits for each word are received simultaneously by the main storage registers. For example, the first bit of words 1 thru 5 is transferred into its respective main storage register at the same time. A shift pulse from the main storage shift is then applied through each OR circuit to each CS driver, shifting all five registers. The second bit of each word is then received by the five main storage registers. This process continues until the five registers are full, containing the entire XTL message. The shifting pulse from the main storage shift then stops.

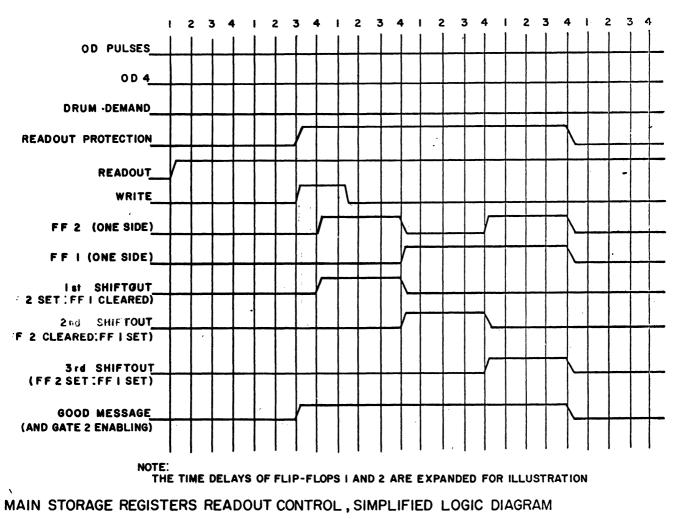

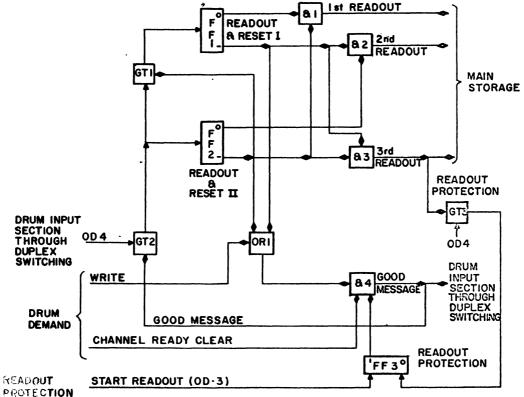

MAIN STORAGE READOUT CONTROL

Main Storage Register Word, Simplified Logic Diagram

Main Storage Registers, Simplified Logic Diagram

The main storage shift does not occur at the same rate continuously. During the input of the first 11 bits of each word, the mainstorage-shift pulse occurs every 5/1,300 second. After the 10th bit of each word is inserted in the main storage registers, the entire message of 17 bits per word is stored in the channel input; i.e., 10 bits of each word in the main storage registers and seven bits of each word in the buffer storage registers. At 5/1, 300 second after this time, the main-storage- register and bufferstorage-register-shift pulses are applied every 20 usec, and the six bits for each word that are stored in the buffer enter the main storage at this rate (fast shift).

c. Word Readout

The 25-counter-equals-25 pulse now indirectly informs the drum demand -channel ready circuit (through the good message circuit) that the entire XTL message is in the main storage circuit awaiting transfer to the drum field. The next drum-demand pulse, indicating an empty slot on the drum initiates the readout process during where the drum input section. This readout is controlled by the main storage readout control circuit which generates three readout levels.

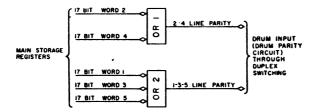

The first readout level is applied to the CSD for register 1 through an OR circuit. This shift level causes each core to shift and to prode an output on each of the 17 lines connected to the output of each of the 17 cores. Thus, the readout to the drum input is done in a parallel manner: all 16 data bits and parity are transferred at once. The main storage registers containing words 2 and 3 transfer their data in the same manner when the second readout level is applied. The third readout level transfers words 4 and 5 to the drum input secion. The parity bit, which is the 17th bit of each word, is sent to the message word parity transfer circuit. d. Diode Isolating Circuits

The purpose of the diodes is to function as an OR circuit and to isolate the main storage regs. of one channel from those of another. A total of 32 diodes are provided which accomodate all core output lines except the word parity cores. Sixteen diodes are for message words 1, 3 and 5. These message words become the left half drum words. 16 diodes are for message words 2 and 4. These message words become the right half drum words.

H. Main Storage Shift Control

## Page 0540

The Main storage shift control circuit controls the flow of shift pulses to the main storage registers. The circuit contains a flip - flop set by the 25 - counter - equals - 7 pulse and cleared by the 25 - counter - equals - 24 pulse. The set output of the flip - flop conditions on AND circuit, allowing XTL 5/6 shift levels from the CS pulse generator to pass. The XTL 5/6 shift levels drive the CSD in the main storage registers circuit.

From the 25 - counter - equals - 1 time to 25counter - equals - 7 time, the buffer storage circuit receives the first 30 data bits of the XTL message. During this time, the main storage registers are not shifted. At 25 - counter - equals -7 time, the first group of data bits is inserted into the last core of each buffer storage register and will be transferred to the main storage registers by the next shift level. Thereafter, the shift levels are supplied to the CSD in the main and buffer storage registers. After the 25 - equals -24 time, the complete message is stored in the main storage registers and further shifting would destroy the message. Therefore, the 25 - counter equals - 24 pulse clears the flip - flop, preventing any additional shift XTL 5/6 levels from shifting the main storage registers.

Core Shift Shift XTL 5/6 Generator 25-Ctr = 7(XTL 6) Core Shifter 25-Ctr = 24 (XTL 6) Shift Coupler

# Main Storage Register Shift Control, Simplified Logic Diagram

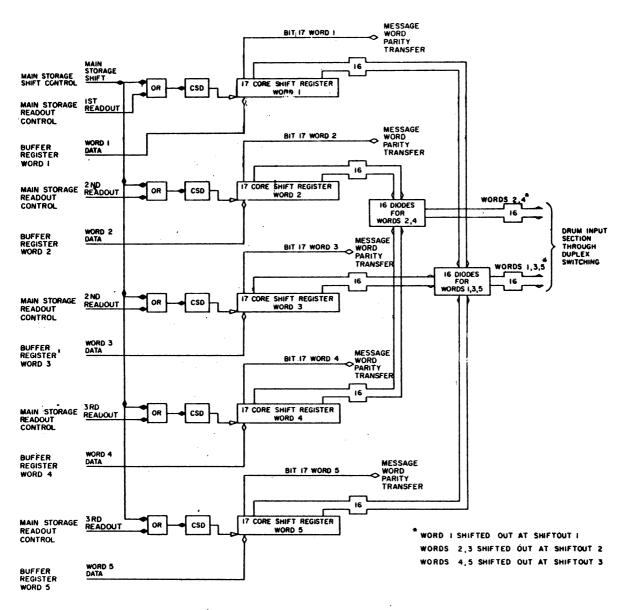

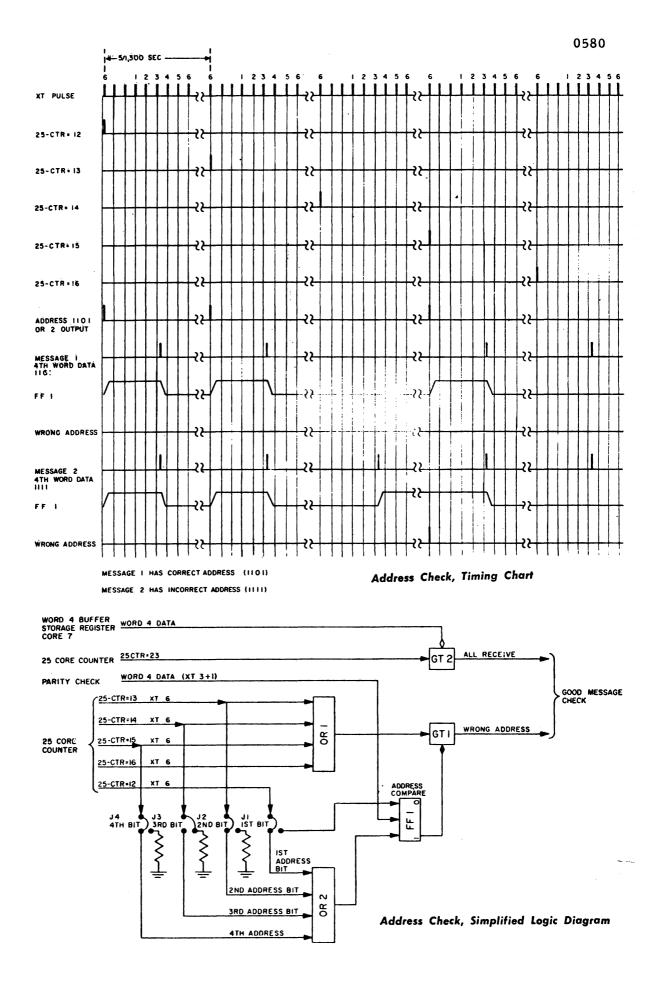

# I. Message Address Check

- 1. Function

- a. Determines which messages are addressed to us and allows message to be accepted if so addressed.

- b. Prevents lack of messages (all 0's) from being treated as a message.

- c. Message address 0000 will never be used.

- d. Each channel must be wired for its proper coded message address all 12 wired the same will vary from site to site.

- 2. Operation

a. Address Compare FF

Logic 2.3.2 - Vol. 232

- Controls GT 9 a pulse thru GT 9 indicates wrong address.

- 2) Complemented with every "1" associated with wor'd 4 (all address bits in word 4)

- 3) Clearing and setting determined by message address of channel and 25 counter.

- b. Twenty-five counter

- 1) 25 ctr = 12 precedes first address bit.

- a) Should clear "Address Compare" if first bit of address is a O.

- b) Should set "Address Compare" if first bit of address is a 1.

- 2) 25 ctr = 13 follows first address bit.

- a) Checks for wrong address

- b) Should set "Address Compare" if second bit of address is a 1.

- 3) 25 ctr = 14 follows second address bit.

- a) Checks for wrong address

- b) Should set "Address Compare" if third bit of address is a 1.

- 4) 25 ctr = 15 follows third address bit.

- a) Checks for wrong address

- b) Should set "Address Compare" if 4th bit of address is a "1".

- 5) 25 ctr = 16 follows fourth address bit

- a) Checks for wrong address.

NOTE: The channels have one address which has to be plugged with jumper wires on channel back panel. (Logic S 2.3.2)

- 3. Circuit Analysis

- a. The address check circuit serially receives the data bits of the fourth word (from the parity check circuit), checks the address contained in the word, and produces a wrong address pulse if the pulse is incorrect. The address check circuit also produces an all receive pulse if the all-parties bit (16th bit, word 4) is a 1.

The operation of the address check circuit consists of checking the address bits to determine whether the message is to be accepted and further processed.

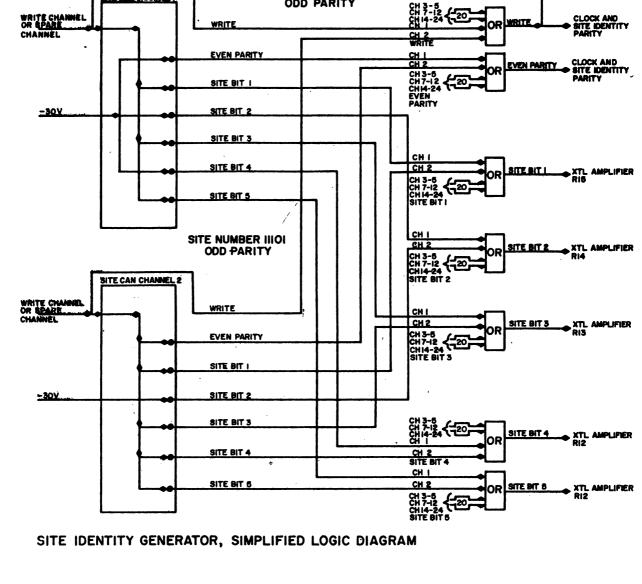

- b. In address checking, jumpers are connected to conform with the address of the receiving Central. The 25-counterequals-12 line is connected to OR 2 (through J1) if the first bit of the receiving Central Address is a 1 or is connected to the clear input of the flip-flop if the first bit of the receiving Central address is 0. The 25counter-equals-13 line is jumpered (j2) to OR 2 if the second bit of the receiving Central address is a 1; the 25-counterequals-14 line is jumpered (J3) to OR 2 if the third bit is a 1; and the 25-counterequals-15 line is jumpered (J4) to OR 2 if the fourth bit is a 1. In figure 5-21, the proper connections for an address of 1101 are shown; i.e., Jl, J2, and J4 are connected to OR 2.

- c. If a 25-counter-12, -13, -14, or -15 pulse (XT<sup>\*</sup> 6) is passed by the jumper connector to OR 2, it sets FF 1 which conditions GT 1. When the incoming word 4 data contains the correct address, address compare FF 1 is cleared each time by XT<sup>\*</sup> (3 / 1) pulses applied to the complement input, and GT 1 is deconditioned.

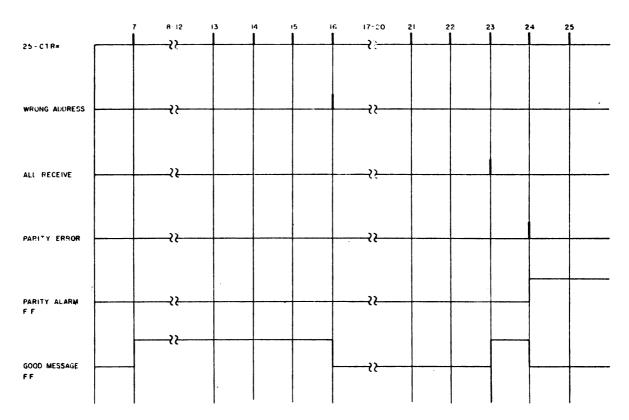

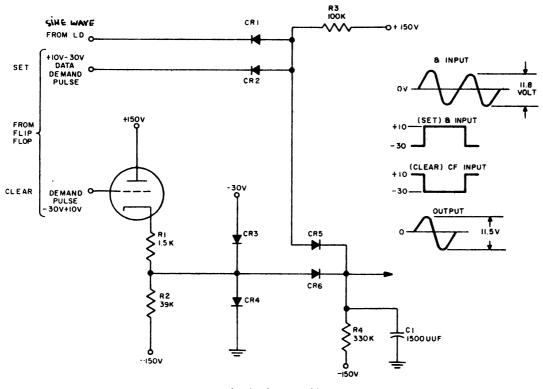

When the incoming word 4 data contains the wrong address, one of two conditions results either of which causes a wrong-address output pulse: