Series/1

GA34-0241-0 File No. S1-09

**IBM Series/1**

Synchronous Communication Single-Line Control Attachment Feature Description

GA34-0241-0 File No. S1-09

IBM Series/1

Synchronous Communication Single-Line Control Attachment Feature Description

#### Federal Communications Commission (FCC) Notice

Warning: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

#### First Edition (May 1983)

Use this publication only for the purpose stated in the Preface.

Changes are periodically made to the information herein; any such changes will be reported in subsequent revisions or Technical Newsletters.

It is possible that this material may contain reference to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country.

Publications are not stocked at the address given below. Requests for copies of IBM publications should be made to your IBM representative or the IBM branch office serving your locality.

This publication could contain technical inaccuracies or typographical errors. A form for readers' comments is provided at the back of this publication. If the form has been removed, address your comments to IBM Corporation, Information Development, Department 27T, P. O. Box 1328, Boca Raton, Florida 33432. IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever. You may, of course, continue to use the information you supply.

© Copyright International Business Machines Corporation 1983

This book describes the Series 1/Synchronous Communications Single-Line Control (SCSLC) attachment feature. The information in this publication is intended for assembler language programmers who need to create or modify programs written for the SCSLC. The reader should understand data processing terminology and stored-program concepts. The subject matter is presented in eight chapters: Chapter 1, "Introduction," describes the SCSLC. • Chapter 2, "Synchronous Communication Single Line Control," describes the attachment feature card data flow, device addressing, and jumper options. Chapter 3, "Device Commands," describes the set of attachment commands. Chapter 4, "Status," presents the status information available to the user. Chapter 5, "Synchronous Data Link Control (SDLC/HDLC)," presents the commands and formats used in SDLC/HDLC operation. Chapter 6, "Binary Synchronous Communication (BSC)," presents the commands, format, and modes used in BSC operation.

- Chapter 7, "Communications Indicator Panel," describes the communications indicator panel and associated lights and switches.

- Chapter 8, "Error Recovery," describes the error conditions and recommended recovery technique.

**Prerequisite Publications**

- IBM Series/1 Principles of Operation, GA34-0152

- For processor information, refer to the applicable processor and processor feature description manual.

#### **Related Publications**

- IBM Series/1 Installation Manual—Physical Planning, GA34-0029

- IBM Series/1 Operator's Guide, GA34-0039

- IBM Series/1 Customer Site Preparation Manual, GA34-0050

- IBM Synchronous Data Link Control, General Information, GA27-3093

- General Information-Binary Synchronous Communications, GA27-3004

- IBM Implementation of X.21 Interface, General Information Manual, GA27-3287

ounie your e Trais pole

1951

readers of removed be begarting of any of the following obligation

Preface iii<sup>r ) ©</sup>

(

# Contents

•

| Chapter 1. Int | roduction                                   |

|----------------|---------------------------------------------|

| Interfaces     |                                             |

| Data Links .   |                                             |

| Point-to-P     | oint Nonswitched (Leased) 1-2               |

| Point-to-Pe    | oint Switched                               |

|                | Nonswitched                                 |

| •              | th (SCSLC)                                  |

|                | ntrols (DLC)                                |

|                | on Codes                                    |

|                |                                             |

|                | nchronous Communication Single-Line Control |

|                |                                             |

|                |                                             |

|                | ssing                                       |

| Jumperable O   | ptions                                      |

| Chanten 2 De   | vice Commands                               |

|                |                                             |

| -              |                                             |

| Ų              | tic 1                                       |

| -              | tic 2                                       |

| Local Attac    |                                             |

|                | 2 3-6                                       |

| Local Attac    | 2 Multipoint                                |

| Read ID        |                                             |

| Halt I/O       |                                             |

| Device Reset   |                                             |

| Start Control  | (Leased Lines)                              |

|                | (X.21 Switched)                             |

|                |                                             |

|                | ovided Information (NPI)                    |

| Auto-Answ      |                                             |

|                | n Incoming Call                             |

| -              |                                             |

|                | tion                                        |

|                |                                             |

|                | 3-22                                        |

| start Cycle-St | eal Status                                  |

| Chapter 4. Sta | tus                                         |

| -              | rmation Byte (IIB)                          |

|                | us Byte (ISB)                               |

| -              | Lesets                                      |

|                | Reset                                       |

|                | des                                         |

| condition co   | 165                                         |

| Chapter 5. Syr | nchronous Data Link Control (SDLC/HDLC)     |

| Operating Mo   | des                                         |

|                | ode                                         |

|                |                                             |

|                | ode                                         |

|                | ode                                         |

|                | n Load (IPL)                                |

| -              | LC IPL                                      |

| •              | ine IPL                                     |

| Switched Li    | ане иг                                      |

,

| Transmission Codes                                        |            |

|-----------------------------------------------------------|------------|

| Control Characters                                        |            |

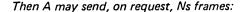

| Frame Format                                              |            |

| Flag                                                      |            |

| Primary/Secondary Station Addressing                      |            |

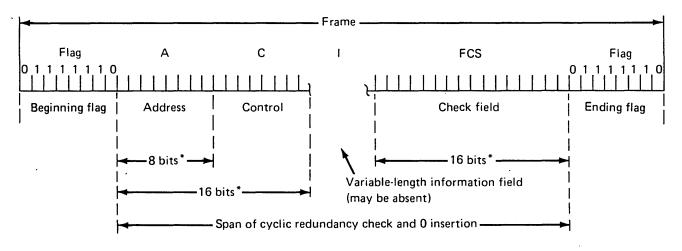

| 0-Insertion                                               | 5-9        |

| Active Stations                                           | 5-11       |

| Address Field                                             | 5-11       |

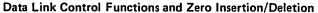

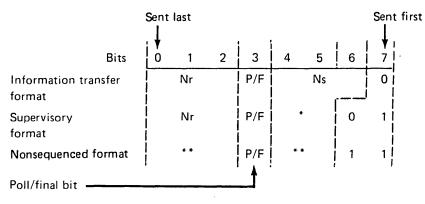

| Control Field and Poll/Final (P/F) Bit                    | 5-12       |

| Information Transfer Format                               | 5-14       |

| Supervisory Format                                        | 5-14       |

| Nonsequenced Format                                       |            |

| Information Field (I-Field)                               |            |

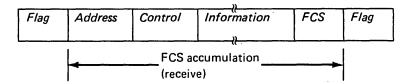

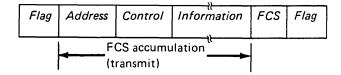

| Frame Check Sequence Field                                |            |

| Synchronization                                           |            |

| SDLC/HDLC Timers                                          |            |

| Timer 1                                                   |            |

| Timer 2                                                   |            |

| SDLC/HDLC Commands                                        |            |

| Start                                                     |            |

| Start Cycle-Steal Status                                  |            |

| Start Cycle-Steal Status                                  | 5-21       |

| Charter ( Binom Sunchronous Communication (BSC)           | 6 1        |

| Chapter 6. Binary Synchronous Communication (BSC)         | <u> </u>   |

| Text Mode                                                 |            |

|                                                           |            |

| Transparent Text Mode                                     |            |

| Control Mode                                              |            |

| Selected Mode                                             |            |

| Passive Mode                                              |            |

| Initial Program Load (IPL) Mode                           |            |

| Transmit Mode                                             |            |

| Receive Mode                                              |            |

| Transmission Codes                                        |            |

| Control Characters                                        |            |

| Line Error Checking                                       |            |

| Synchronization And Timing                                |            |

| Transmit Synchronization                                  |            |

| Receive Synchronization                                   | 6-10       |

| Time-Outs                                                 | 6-10       |

| BSC Commands                                              | 6-11       |

| Start                                                     | 6-11       |

| Start Cycle-Steal Status (SCSS)                           | 6-17       |

| BSC Timer Usage                                           |            |

| 0                                                         |            |

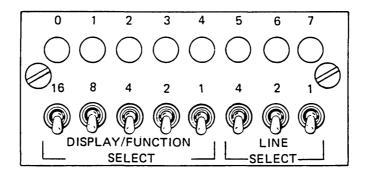

| Chapter 7. Communications Indicator Panel                 | 7-1        |

| LINE SELECT Switches                                      |            |

| DISPLAY/FUNCTION SELECT Switches                          |            |

|                                                           | . –        |

| Chapter 8. Error Recovery                                 | 8-1        |

|                                                           | 0-1        |

| Appendix A. Attachment Initialization                     | Δ_1        |

| Appendix A. Attachment mitianzation                       | <b>A-1</b> |

| Appendix B. Communications Operator's Self-Test Procedure | B-1        |

|                                                           | <b>.</b> . |

| Appendix C. CCITT State Conditions                        | C-1        |

.

.

1

(

•

•

| Glossary | ••••• | ••••• | • • • • • • • • • • • • • • | <br>. X-1 |

|----------|-------|-------|-----------------------------|-----------|

| Index    |       | ••••• | •••••                       | <br>. X-3 |

.

.

. .

. .

## **Chapter 1. Introduction**

The synchronous communication single line control (SCSLC) feature provides bisynchronous communications (BSC) or synchronous data link control/high level data link control (SDLC/HDLC) protocols. It supports bit rates up to 56000 bits-per-second (V.35) and 48000 bits-per-second (X.21). Operation may be point-to-point or multipoint. IPL capability is supported for switched or leased lines.

The SCSLC communication feature provides several line speeds, line configurations, clocking sources, line protocols, and data transmission codes to choose from.

### Interfaces

The SCSLC feature provides a CCITT<sup>1</sup> X.21 (switched and leased) or V.35 (leased) interface. It also has local attachment capabilities through an EIA<sup>2</sup> RS-422A interface using customer supplied cabling.

<sup>1</sup> The International Telegraph and Telephone Consultative Committee

<sup>&</sup>lt;sup>2</sup> Electronic Industries Association

### **Data Links**

The SCSLC attachment can operate with any one of the following types of data links:

- Point-to-point nonswitched

- Point-to-point switched

- Multipoint nonswitched

- Local attach (direct connect)

#### **Point-to-Point** Nonswitched (Leased)

.

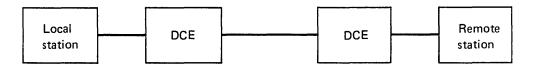

A point-to-point nonswitched data link consists of a local station connected to a single remote station using a CCITT V.35 or CCITT X.21 interface. The line is called *nonswitched* because of the permanent connection between the local station and the remote station through their data circuit-terminating equipment (DCEs).

I

.

A *point-to-point switched* data link consists of a local station connected to one of several remote stations (using CCITT X.21 interface) after establishing a link between the local station and the remote station. The connection remains only for the duration of the communication.

### Multipoint Nonswitched

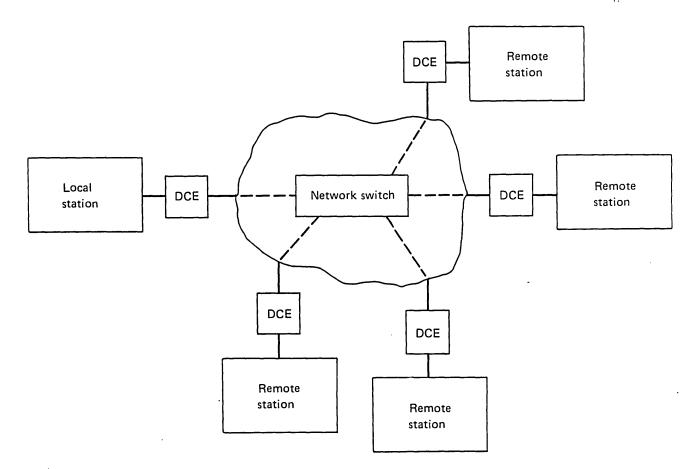

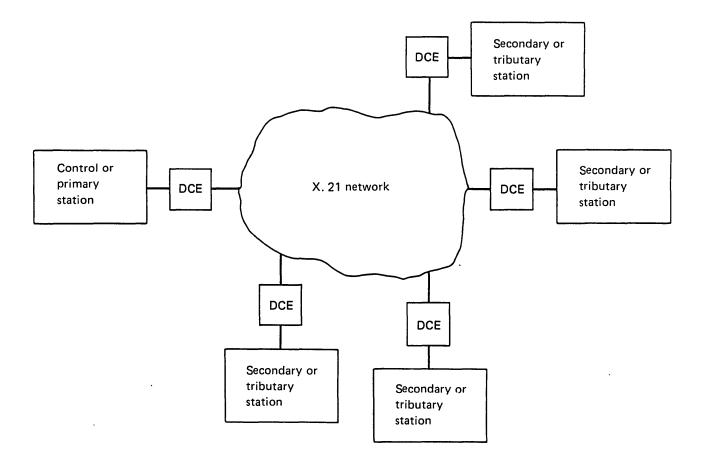

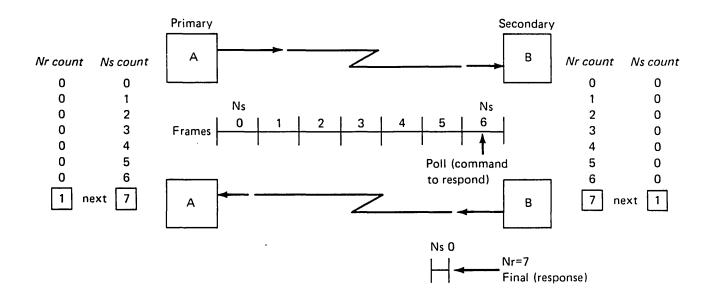

A multipoint nonswitched data link consists of a primary/control station connected to several secondary/tributary stations through their DCEs. The primary/control station polls the secondary or tributary stations using unique station addresses. Only the addressed station can respond to the poll.

Local attach (direct connect) capabilities are available in several modes using the EIA RS-422A interface.

### Data Link Controls (DLC)

The SCSLC communication feature provides the following data link controls:

- BSC

- SDLC/HDLC

### Transmission Codes

BSC

The BSC feature uses:

- American Standard Code for Information Interchange (ASCII)—nontransparent only

- Extended binary-coded decimal interchange code (EBCDIC)—transparency is available

#### SDLC/HDLC

The SDLC/HDLC feature allows any 8-bit code, including:

- ASCII

- EBCDIC

Transparency is standard in all SDLC/HDLC procedures.

•

• •

.

•

.

.

•

(

## **Chapter 2. Synchronous Communication Single-Line Control**

#### Introduction

The synchronous communication single-line control (SCSLC) attachment provides one International Telegraph and Telephone Consultative Committee (CCITT) X.21 interface that allows the interchange of data between the Series/1 processor and a remote terminal that uses the synchronous mode of data transmission. The terminal must comply with the electrical and functional requirements of CCITT recommendation X.21. Interconnection between the Series/1 and the remote terminal may be made by using public or private leased data networks, as well as switched lines. In addition, terminals can be locally connected at distances up to 1220 meters (4000 feet).

The attachment supports synchronous data link control/high level data link control (SDLC/HDLC) or binary synchronous communication (BSC) protocol. When operating with SDLC/HDLC protocol, it can be operated in duplex mode. Duplex mode allows data to be concurrently transmitted and received between the Series/1 and the terminal. The communicating bit rate is normally controlled by clocking signals supplied by the data circuit-terminating equipment (DCE), except when using the local attach option, which provides clocking by the attachment. The attachment provides clocking for data rates of 9,600 or 48,000 bits per second (bps) when the local attach option is used.

For further information about the X.21 interface, refer to *IBM Implementation of* X.21 Interface - General Information Manual, GA27-3287. In case of a conflict with the CCITT X.21 recommendation, use the IBM documentation.

**Note:** The local attach option allows the connection of remote terminals without DCEs by using the EIA RS-422A interface for distances up to 1220 meters (4000 feet).

The attachment also provides one CCITT V.35 interface and supports both the SDLC/HDLC and BSC protocols with a maximum rate of 56,000 bps.

Note: Sustained throughput at 48,000 and 56,000 bps when using BSC protocol is considerably less than the clocking rate. Refer to the chapter on BSC protocol. Two basic connection methods exist for the local attach options:

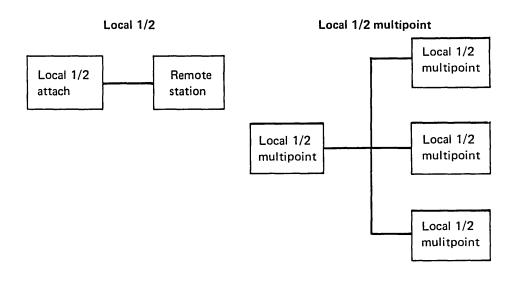

- Local Attach 1: Internal clocking occurs at a data rate of 9,600 bps with the remote device capable of deriving the clocking information from the data stream. This mode of operation allows connecting the remote terminal up to a distance of 1220 meters (4000 feet), using an EIA RS-422A interface. This clocking method supports only the SDLC/HDLC half-duplex operation. When operating in local 1 mode, the attachment transmits and receives in NRZI mode (bits 9 and 12 of the control word are ignored on transmit and bit 9 is ignored on receive). The attachment automatically transmits leading pads at the beginning of each frame sequence.

- Local Attach 2: The attachment provides a 48,000 bps clocking signal to an EIA RS-422A interface. This allows the remote device to use the clock as if a data circuit-terminating equipment (DCE) were present. If using this method of operation, the remote terminal must be connected at a distance up to 305 meters (1000 feet). Both the SDLC/HDLC (half-duplex and duplex) and bisynchronous (BSC) half-duplex protocols are supported in this mode.

Note: Multidrop configuration is allowed when using local attach 1 or 2.

Control of up to 10 remote stations may be achieved by attaching them in a multidrop configuration (stub length not exceeding 15 meters (45 feet)).

Note: For cable information, refer to the maintenance logic diagrams and the *Customer Site Preparation Manual*, GA34-0050.

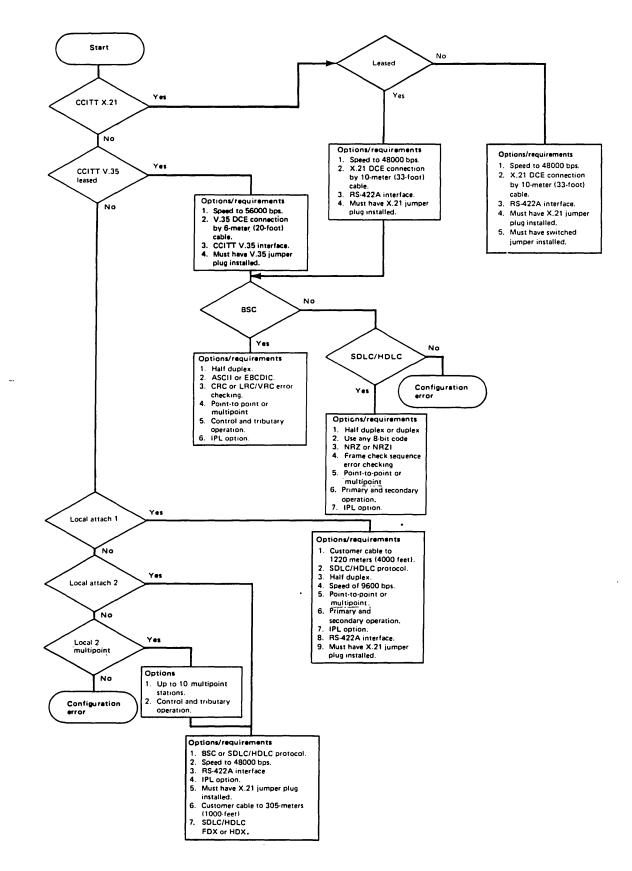

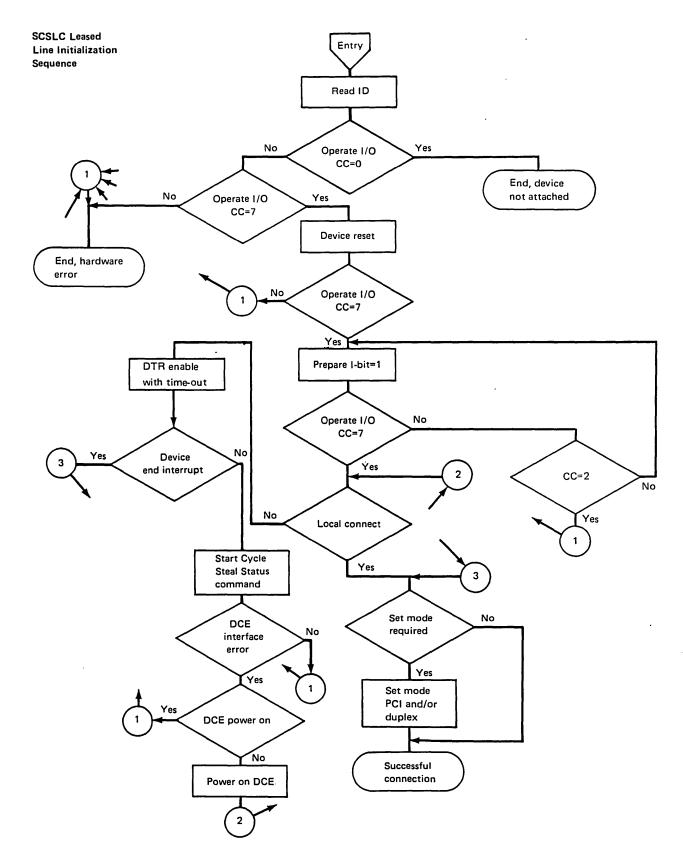

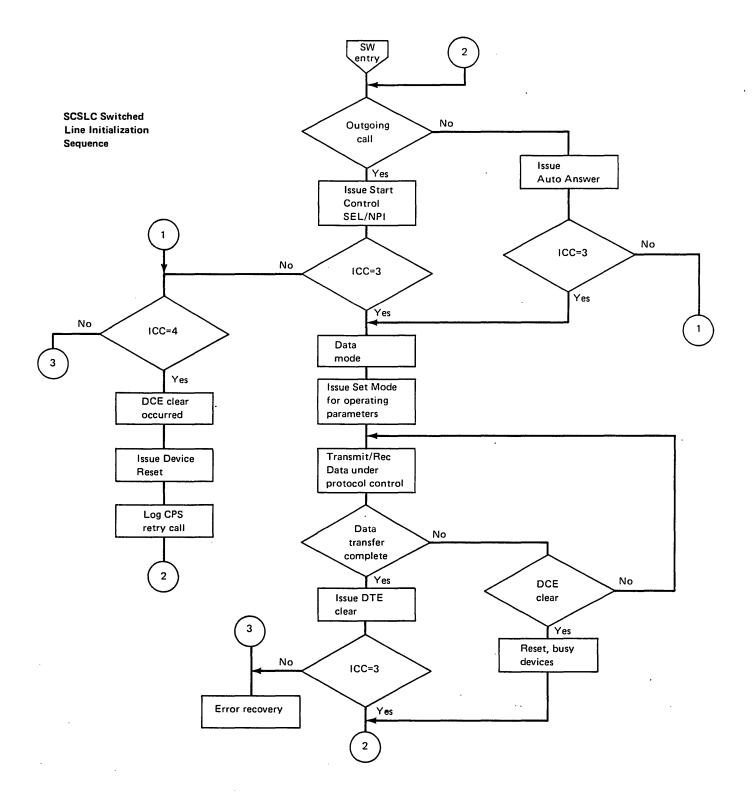

Refer to the flowchart (Figure 2-1) for a graphic representation of installation considerations and available options.

Figure 2-1. Installation considerations and options

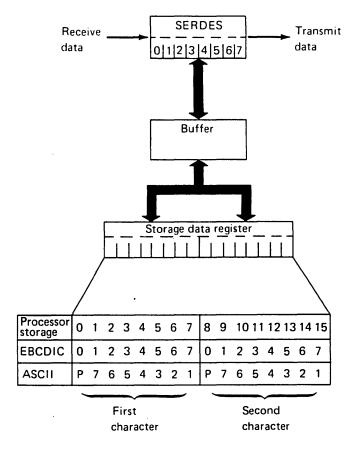

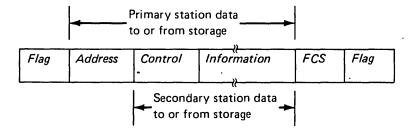

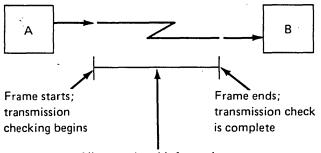

Data transmission and reception protocol may be either SDLC/HDLC or BSC. Two characters at a time are fetched from processor storage during transmission. Bits 0–7 hold the first character transmitted and bits 8–15 hold the next. However, if the first character is located at an odd data address or the last character is located at an even data address, only one data character is fetched and transmitted.

On receive, the first bit received is placed in the least-significant bit, the second bit placed in the next higher bit position, and so on, until a character is assembled. The first character received is placed in bits 0–7 and the second character is placed into bits 8–15. Again, however, if the first character has an odd data address or the last character has an even data address, only one character is assembled and placed into processor storage.

See Figure 2-2 for an example of data flow for both transmit and receive operations.

Figure 2-2. Data flow

## **Device Addressing**

.

The attachment can respond to Operate I/O commands for two unique device addresses. The addresses are contiguous, beginning with an even address. The attachment card jumper positions are for the assignment of the base device address which is always even.

Note: This attachment always uses two device addresses.

When in half-duplex mode, device 0 is the even address. The following table shows the device commands, addresses, and mode of operation.

|                          | Half Du | uplex | Duplex |       |  |

|--------------------------|---------|-------|--------|-------|--|

| Command                  | Dev 0   | Dev 1 | Dev 0  | Dev 1 |  |

| Start                    | X       |       | x      |       |  |

| Enable*                  | X       |       | x      |       |  |

| Disable*                 | x       |       | x      |       |  |

| Transmit*                | x       |       | x      |       |  |

| Receive*                 | X       |       |        | х     |  |

| Timer*                   | X       |       | x      | Х     |  |

| Start Control**          | X       |       | x      |       |  |

| Start Cycle Steal Status | X       | x     | x      | х     |  |

| Start Diag 1             | X       | x     | x      | Х     |  |

| Start Diag 2**           | X       |       | x      |       |  |

| Read ID                  | X       | x     | x      | Х     |  |

| Halt I/O .               | X       | x     | x      | х     |  |

| Device Reset             | X       | Х     | X      | Х     |  |

| Prepare                  | X       | x     | x      | Х     |  |

| Start Modification**     | X       |       | х      |       |  |

Note: Any command directed to device 0 or device 1,

other than the ones indicated above, will cause an exception interrupt.

\*DCB specification check reported

\*\*Delayed command reject reported

#### **Jumperable Options**

The following attachment options can be enabled by installation of a card jumper:

Allow IPL: This jumper causes the attachment to monitor for a BSC or SDLC/HDLC IPL sequence.

**Bi-Sync Mode:** This jumper sets the attachment to BSC mode. Absence of this jumper indicates SDLC/HDLC mode to the attachment.

*Local Attach 1:* This jumper is installed in the local attach 1 cable. The attachment provides clocking in the SDLC/HDLC mode at a speed of 9,600 bps.

Note: The X.21 jumper plug must be installed.

*Local Attach 2:* This jumper is installed in the local attach 2 cable. The attachment provides clocking at a speed of 48,000 bps.

Note: The X.21 jumper plug must be installed.

Secondary Station Address/Multipoint Address: These jumpers are used to assign the secondary station address in SDLC/HDLC mode, or to assign the multipoint address in BSC mode.

Note: In BSC mode the attachment is a multipoint tributary if the multipoint address is not 0. Therefore, 0 is not a valid multipoint address.

**Signal to Protective Ground:** If this jumper is installed, signal ground is connected to protective ground. Installation of this jumper is to meet local code requirements when attaching to X.21 data circuit terminating equipment (DCE).

**X.21 Jumper:** If this jumper plug is installed, the attachment operates with the X.21 interface.

**V.35 Jumper:** If this jumper plug is installed, the attachment operates with the V.35 interface.

Note: Refer to the maintenance logic diagrams for jumper locations and cable information.

(

## **Chapter 3. Device Commands**

The attachment has several device commands:

- Prepare

- Start Diagnostic 1

- Start Diagnostic 2

- Read ID

- Halt I/O

- Device Reset

- Start Control

- Start Modification

- Start

- Start Cycle-Steal Status

#### Prepare

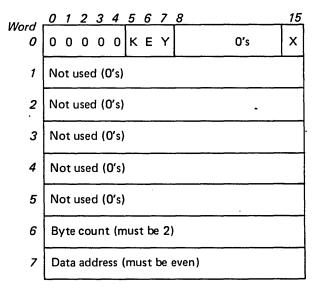

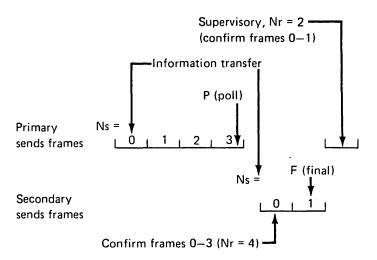

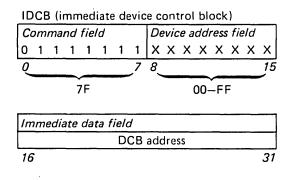

The Prepare command controls the interrupt parameters of the addressed device. The immediate data field (bits 16-31) contains the level and I-bit. The attachment accepts and executes a Prepare command, even if it is busy or has an interrupt request pending from a previous command. The IDCB for the Prepare command has the following format:

IDCB (immediate device control block)

| Command field |     |      |     |     |     | De   | vic | e a | ddi | ress | ;    |   |   |   |             |

|---------------|-----|------|-----|-----|-----|------|-----|-----|-----|------|------|---|---|---|-------------|

| 0             | 1   | 1    | 0   | 0   | 0   | 0    | 0   | X   | Х   | Х    | Х    | Х | Х | Х | Х           |

| Q             |     |      |     |     |     |      | 7   | 8   |     |      | _    |   |   |   | <i>,</i> 15 |

| 60            |     |      |     |     |     |      |     |     | 00  | —F   | F۰   |   |   |   |             |

| In            | nme | edia | əte | dat | a f | ielc | 1   |     |     |      |      |   |   |   |             |

| 0's           |     |      |     |     |     |      |     |     | Γ   | Le   | evel |   | 1 |   |             |

|               |     |      |     |     |     |      |     |     |     |      |      |   |   |   |             |

*Level - bits 27-30:* This 4-bit field specifies the priority interrupt level assigned to the device. The binary value of bits 27-30 indicates priority levels of 0-3.

| Bits 27-30 | Level |

|------------|-------|

| 0000       | 0     |

| 0001       | 1     |

| 0010       | 2     |

| 0011       | 3     |

**I-Bit - bit 31:** This bit determines if the device can present interrupt requests. An I-bit set to 1 means that the device can request an interrupt; a 0 means that the device cannot interrupt.

Each time the attachment presents an interrupt request, it stores the level data and presents it to the processor. Either a system reset or a power-on reset resets the prepare information (level and I-bit).

The Prepare command causes an interrupt request only when the attachment is not prepared (I-bit set to 0) and has an interrupt pending upon receipt of a Prepare command with the I-bit set to 1.

A successful Prepare command always causes the attachment to respond with a condition code 7 (satisfactory).

#### Start Diagnostic 1

The IDCB for the Start Diagnostic 1 command is:

IDCB (immediate device control block)

| Immediate data field |     |

|----------------------|-----|

| DCB addr             | ess |

| 16                   | 31  |

This command causes two types of tests to occur in the attachment. The results of the tests are placed in processor storage, beginning at the address specified in word 7 (data address) of the DCB. The byte count for this operation must be equal to 11, and the data address must be even. Otherwise, an exception interrupt occurs with bit 3 (DCB specification check) set in the interrupt status byte.

A DCB specification check occurs if the DCB control word has any bit set to 1 other than bit 2, 5, 6, or 7.

The DCB format is as follows:

The first diagnostic test is an attachment storage test that consists of writing/reading 1's and 0's through all the attachment storage locations. If the test is successful, a hex FF is written into data word 5, high-order byte. If the test fails, a hex 00 is written into data word 5, bits 0-7.

(

Note: During initial power-on sequencing, the attachment storage patch (PATCH) area is tested. The diagnostic command does not test the PATCH area.

The next test computes a checksum for the two read only storage (ROS) modules used by the attachment. The result, along with a checksum that was written into the ROS modules at the time the modules were fabricated, are placed in data words 1, 2, 3, and 4 in the following manner:

| Data word 1 | Stored checksum ROS 1                                                                                                                                                                                       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data word 2 | Computed checksum ROS 1 (complemented)                                                                                                                                                                      |

| Data word 3 | Stored checksum ROS 2                                                                                                                                                                                       |

| Data word 4 | Computed checksum ROS 2 (complemented)                                                                                                                                                                      |

| Data word 5 | Bits 0-7 (FF good storage test)                                                                                                                                                                             |

|             | Bits 0-7 (00 storage test failure)                                                                                                                                                                          |

|             | Bits 8-15 (Secondary station or MP tributary address)                                                                                                                                                       |

| Data word 6 | Bits 0-7<br>Bit 0 Not used<br>Bit 1 BSC jumper<br>Bit 2 X.21 switched jumper<br>Bit 3 Local attach 2 jumper<br>Bit 4 Local attach 1 jumper<br>Bit 5 Allow IPL jumper<br>Bit 6 V.35 jumper<br>Bit 7 Not used |

|             | Bits &15 refer to text                                                                                                                                                                                      |

The attachment reports the secondary station/multipoint tributary address jumpers in data word 5, bits 8–15. The attachment also reports the configuration jumpers in data word 6, bits 0–7. Bits 8–15 of the data storage register are set to a hex AA to test the byte mode of data transfer to storage. If byte mode fails, a hex AA appears in data word 6, bits 8–15, otherwise, the value stored in data word 6, bits 8–15, is dependent upon the processor storage initialization.

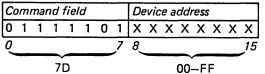

Following is the IDCB for the Start Diagnostic 2 command:

| 10          | IDCB (immediate device control block) |     |     |    |     |      |    |     |     |    |      |    |   |   |    |

|-------------|---------------------------------------|-----|-----|----|-----|------|----|-----|-----|----|------|----|---|---|----|

| Co          | Command field                         |     |     |    |     |      | De | vic | e a | dd | ress | S  |   |   |    |

| 0           | 1                                     | 1   | 1   | 1  | 1   | 1    | 0  | X   | Х   | Х  | Х    | Х  | Х | Х | Х  |

| 0           |                                       |     |     |    |     |      | 7  | 8   |     |    |      |    |   |   | 15 |

|             |                                       |     | 7   | Έ  |     |      | -  |     |     |    | 00-  | -F | F |   | -  |

| In          | nm                                    | edi | ate | da | tai | fiel | d  |     |     |    |      |    |   |   |    |

| DCB address |                                       |     |     |    |     |      |    |     |     |    |      |    |   |   |    |

| 16          |                                       |     |     |    |     |      |    |     |     |    |      |    |   |   | 31 |

This command causes a wrap test to occur in the attachment. The results are placed in processor storage, beginning at the address specified in word 7 (data address) of the DCB. The byte count for this operation must be equal to 2 and the data address must be even. Otherwise, an exception interrupt occurs with bit 3 (DCB specification check) set in the interrupt status byte (ISB).

A DCB specification check occurs if the DCB control word has any bit set to one other than bit 2, 5, 6, 7, or 15. The DCB for the Start Diagnostic 2 command is:

DCB word 0, bit 15, indicates the following:

- Bit 15 = 1, signal timing provided

- Bit 15 = 0, signal timing not provided

Note: Signal timing provided indicates that data circuit terminating equipment (X.21 or V.35) is attached and is supplying the signal timing during the wrap test.

With the X.21 jumper plug installed, the attachment is tested in the X.21 mode in the following sequence:

- 1. Test 1 checks the control, indicate, receive, and transmit lines. If the test is successful, the attachment sets bits 0-3 in data word 1 to 1's.

- 2. Test 2 causes the attachment to monitor the signal timing lines for transitions if bit 15 of DCB word 0 is set to a one. If transitions are detected, the associated bit in data word 1 is set to 1. The byte timing indicator is set to a zero when bit 15 of DCB word 0 is set to 1. If bit 15 of DCB word 0 is set to zero, the attachment drives the signal timing line with a 48,000 bps clocking signal. When the card wrap connector is installed, these transitions are monitored on the byte timing line and if detected, the associated bits for signal timing and byte timing in data word 1 are set to 1.

- 3. Test 3 causes the attachment to perform a BSC wrap test. If the test is successful, the attachment sets bit 6 in data word 1 to a 1.

Note: This test is not performed in local attach 1 mode.

- 4. Test 4 causes the attachment to perform an SDLC wrap test. If the test is successful, the attachment sets bit 7 in data word 1 to a 1.

- 5. Test 5 causes the attachment to read the switches on the indicator panel and report the hexadecimal value in bits 8-15 of data word 1. If the indicator panel is not attached, the attachment reports a hex 00 in bits 8-15 of data word 1.

Bit 15 of the DCB control word must be set to 0. There are no changes to tests one through five.

| Bit  | Definition                     |

|------|--------------------------------|

| 0    | Transmit                       |

| 1    | Receive                        |

| 2    | Indicate                       |

| 3    | Control                        |

| 4    | Signal timing                  |

| 5    | Byte timing                    |

| 6    | BSC wrap                       |

| 7    | SDLC wrap                      |

| 8-15 | Indicator panel switch setting |

Note: Data word 1 has the following bit definitions for X.21:

#### Local Attach 1

The attachment card must have the following jumpers installed:

J1-A16 to J1-B16 J1-A17 to J1-B17 J1-A18 to J1-B18 J1-A19 to J1-B19

Bit 15 of the DCB control word must be set to 0. In test 2, the 'byte timing' line is not examined (Bit 5 of data word 1 is 0). Test 3 is not performed. Bit 6 of data word one is set to 0.

The attachment card must have a jumper from J1-A20 to J1-B20 installed. Bit 15 of the DCB control word must be set to a 0. There are no changes to tests one through five.

### Local Attach 2 Multipoint

The attachment card must have the following jumpers installed:

J1-A19 to J1-B19 J1-A20 to J1-B20

With the V.35 jumper plug installed, the attachment is tested in the V.35 mode.

Note: All tests, with the exception of Tests 1 and 2, function in the same manner as the preceding X.21 tests. Test 2 is not performed in V.35 mode.

Test 1 causes transitions on the 'request-to-send' (RTS) line while monitoring the 'clear-to-send' (CTS) line. If the test is successful, the attachment sets the associated bit in data word 1 to a 1. The attachment also checks for an active level on the 'data-set-ready' line.

Data word 1 has the following bit definitions for V.35:

| Bit  | Definition                     |

|------|--------------------------------|

| 0    | Data-set-ready (DSR)           |

| 1    | Clear-to-send (CTS)            |

| 2    | Request-to-send (RTS)          |

| 3    | Not used (O's)                 |

| 4    | Not used (O's)                 |

| 5    | Not used (O's)                 |

| 6    | BSC wrap                       |

| .7   | SDLC wrap                      |

| 8-15 | Indicator panel switch setting |

Note: The diagnostic 2 results for word 1, bits 0-7 are:

| Configuration   | Result |      |   |

|-----------------|--------|------|---|

| X.21 DCE wrap   | FB     |      |   |

| X.21 cable wrap | FB     | ·. · |   |

| X.21 card wrap  | FF     |      | · |

| Local 1         | F9     |      |   |

| Local 2         | FF     |      |   |

| V.35            | E3     |      |   |

| . ·             | • • •  | <br> |   |

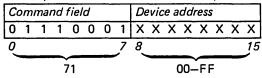

**Read ID**

The Read ID command transfers the attachment's identification word from the device to the data word position of the IDCB.

The attachment's ID is 5042. The IDCB for the Read ID command is:

| IDCB (i | immediate | device | control | block) |

|---------|-----------|--------|---------|--------|

|---------|-----------|--------|---------|--------|

| Command field |   |   |   |    |   |   | Device address |   |   |   |     |     |   |   |    |

|---------------|---|---|---|----|---|---|----------------|---|---|---|-----|-----|---|---|----|

| 0             | 0 | 1 | 0 | 0  | 0 | 0 | 0              | X | Х | Х | Х   | Х   | Х | Х | Х  |

| Q             |   |   |   |    |   |   | 7              | 8 |   |   |     |     |   |   | 15 |

|               |   |   |   | 20 |   |   |                |   |   | ( | -00 | -FI | = | · |    |

| Immediate data field |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

|----------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| 0                    | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0  |

| 16                   | ; |   |   |   |   |   |   |   |   |   |   |   |   |   | 31 |

#### Halt I/O

This command halts all I/O activity on the I/O interface and sets 'DTE ready'. It resets the residual byte count to 0 and clears pending interrupts. It does not reset the I-bit, prepared level or residual address.

IDCB (immediate device control block)

| Са | omi | mai | nd | fiel | d |     |   | Device address |   |   |    |    |   |   |    |

|----|-----|-----|----|------|---|-----|---|----------------|---|---|----|----|---|---|----|

| 1  | 1   | 1   | 1  | 0    | 0 | 0   | 0 | X              | Х | Х | Х  | Х  | Х | Х | Х  |

| Q  |     |     |    |      |   |     | 7 | 8              |   |   |    |    |   |   | 15 |

|    |     |     | F  | 0    |   |     |   |                |   |   | 00 | -F | F |   |    |

| 1- |     | di  |    | da   |   | ial |   |                |   |   |    |    |   |   |    |

| Immediate data field |    |

|----------------------|----|

| 0'                   | S  |

| 16                   | 31 |

The Device Reset command resets the addressed device. Pending interrupt requests (except controller end) are cleared. This command does not reset the prepare level, I-bit, residual address, and interface state. The Device Reset command has the following format:

IDCB (immediate device control block)

| Са | m   | mai  | nd i | fiel | d    |      |         | De | vic | e a | ddi | ress | ;  |                                              |     |

|----|-----|------|------|------|------|------|---------|----|-----|-----|-----|------|----|----------------------------------------------|-----|

| 0  | 1   | 1    | 0    | 1    | 1    | 1    | 1       | X  | Х   | Х   | Х   | Х    | Х  | Х                                            | Х   |

| 0  |     |      |      |      |      |      | 7       | 8  |     |     |     |      |    |                                              | ,15 |

|    |     |      | 6    | F    |      |      |         |    |     | ÷   | 0   | 0—1  | FF |                                              |     |

|    |     |      |      |      |      |      |         |    |     |     |     |      |    |                                              |     |

| Im | nme | dia  | ate  | dat  | ta f | ielo | 1       |    |     |     |     |      |    |                                              |     |

| In | nme | edia | ate  | dat  | a f  | ielo | /<br>0' | s  |     |     |     |      |    | <u>.                                    </u> |     |

A Device Reset command issued to the attachment causes the attachment to become busy after reset while carrying out the reset functions. The length of time that the attachment remains in busy after reset is a function of the microcode program in the attachment. The attachment may present a busy after reset (CC2) to an Operate I/O immediately following a Device Reset.

#### 3-8 GA34-0241

#### **Start Control (Leased Lines)**

To setup operating conditions, use the Start Control command. The IDCB for the Start Control command is:

IDCB (immediate device control block)

| Сс | m | ma | nd | fiel | d |   |   | Device address |   |     |     |     |   |   |    |  |

|----|---|----|----|------|---|---|---|----------------|---|-----|-----|-----|---|---|----|--|

| 0  | 1 | 1  | 1  | 0    | 0 | 0 | 1 | X              | Х | Х   | X   | Х   | Х | Х | X  |  |

| Q  |   |    |    |      |   |   | 7 | 8              |   |     |     |     |   |   | 15 |  |

|    |   |    |    | 11   |   |   | - |                |   | · ( | 20- | -FF | : |   |    |  |

| Immediat | e data field |    |

|----------|--------------|----|

|          | DCB address  |    |

| 16       |              | 31 |

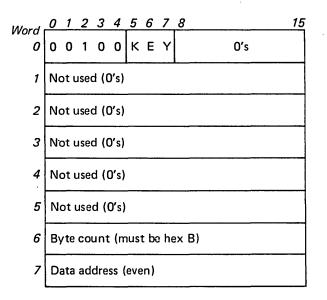

Following is the format for the Start Control (set mode) DCB:

|      | D  | СВ   | (de  | evic | e c  | ont | trol | bl | ock | () |   |   |   |   |   |    |

|------|----|------|------|------|------|-----|------|----|-----|----|---|---|---|---|---|----|

| Word | 0  | 1    | 2    | 3    | 4    | 5   | 6    | 7  | 8   |    |   |   |   |   | _ | 15 |

| 0    | х  | 0    | 0    | 0    | 0    | к   | E    | Y  | 0   | 0  | 0 | 0 | 0 | 0 | 0 | 0  |

| 1    | 0  | 0    | 0    | 0    | 0    | 0   | 0    | 0  | 0   | 0  | 0 | x | x | х | 0 | 0  |

| 2    | N  | stι  | use  | d (( | )'s) |     |      |    |     |    |   |   |   |   |   |    |

| 3    | N  | otι  | Jse  | d (( | )'s) |     |      |    |     |    |   |   |   |   |   |    |

| 4    | N  | ot ι | Jse  | d (( | D's) |     |      |    |     |    |   |   |   |   |   |    |

| 5    | Cł | nair | ning | g ac | dr   | ess |      |    |     |    |   |   |   |   |   |    |

| 6    | N  | ot ι | ıse  | d (( | D's) |     |      |    |     |    |   |   |   |   |   |    |

| . 7  | N  | otι  | use  | d (( | )'s) |     |      |    |     |    |   |   |   |   |   |    |

Word 0: Word 0 has the following format:

Bit 0 - Chaining: This bit, when set to 1, indicates chaining is in effect.

Bits 1-4: These bits are not used and must be set to 0.

Bits 5-7 - Key: These bits represent a 3-bit key. The attachment presents this key to the processor during data transfers to verify that the program has authorization to access processor storage. An invalid address key causes an exception-interrupt request (condition code 2), with bit 6 set to 1 (protect check) in the ISB.

Bits 8-15: These bits are not used and must be set to 0.

Word 1: Word 1 has the following format:

Bits 0-10: These bits are not used and must be 0's.

Bit 11 - Enable PCI: If this bit is a 1, the attachment supports a program controlled interrupt (PCI).

Bit 12 - Mode: If this bit is a 1, the attachment is in duplex mode of operation. If this bit is a 0, the attachment is in half-duplex mode of operation.

Note: When this bit is a 1, the attachment supports only SDLC/HDLC mode.

Bit 13 - Installation Test: If this bit is a 1, the attachment performs internal tests (used for installation measurements).

Bit 14: This bit is not used and must be 0.

Bit 15: This bit is not used and must be 0.

Words 2-4: These words are not used and must be set to 0.

*Word 5 - Chaining Address:* This word contains the address of the next DCB in a chaining operation.

Note: Chaining should not be used on the Start Control (leased) command because the only function that can be performed is set mode.

Words 6-7: These words are not used and must be set to 0.

#### Start Control (X.21 Switched)

To operate in the X.21 switched environment, software must use the Start Control command. This command along with associated DCBs allows the attachment to make a transition through defined X.21 CCITT states that are necessary to establish a switched connection on an X.21 network. This command may also be issued during leased operation (X.21 or V.35) local connect mode, or after the connection is established on a switched network to set the operational mode (Set Mode operation). For example; to setup PCI or duplex modes.

Use this command to perform the following Start Control operations:

- 1. Set mode

- 2. Network provided information

- 3. Auto-answer

- 4. Clear

The IDCB for the X.21 switched mode of operation is the same as for the Start Control command for leased lines and is as follows:

IDCB (immediate device control block)

| Immediate data field |       |

|----------------------|-------|

| DCB add              | dress |

| 16                   | 31    |

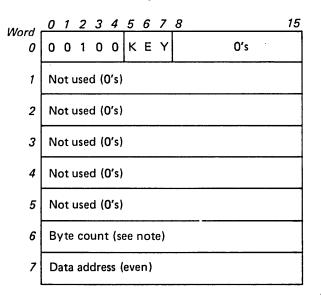

The set mode DCB format is as follows:

| D    | СВ | (de            | evic | e c  | on   | trol | bl | ock | :) |   |   |   |   |   |   |    |

|------|----|----------------|------|------|------|------|----|-----|----|---|---|---|---|---|---|----|

| Word | 0  |                |      |      |      | 5    |    | 7   | 8  |   |   |   |   |   |   | 15 |

| 0    | х  | 0              | 0    | 0    | 0    | к    | E  | Y   | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0  |

| 1    | 0  | 0              | 0    | 0    | 0    | 0    | 0  | 0   | 0  | 0 | х | х | х | х | х | x  |

| 2    | No | otι            | ised | d (C | )′s) |      |    |     |    |   |   |   |   |   |   |    |

| 3    | No | Not used (0's) |      |      |      |      |    |     |    |   |   |   |   |   |   |    |

| 4    | No | ot u           | ised | d (C | )'s) |      |    |     |    |   |   |   |   |   |   |    |

| 5    | Ch | air            | ning | g ac | ldr  | ess  |    | -   |    |   |   |   |   |   |   |    |

| 6    | By | te             | col  | unt  |      |      |    |     |    |   |   |   |   |   |   |    |

| 7    | Da | ata            | ado  | dres | is   |      |    |     |    |   |   |   |   |   |   |    |

#### Word 0

Bit 0 - Chaining: Set this bit to 1 when specifying a chaining operation.

Bits 1-4: These bits are not used and must be 0's.

Bits 5-7 - Key: These bits represent a 3-bit key. The attachment presents this key to the processor during data transfers to verify that the program has authorization to access processor storage. An invalid address key causes an exception-interrupt request (condition code 2), with bit 6 set to 1 (protect check) in the interrupt status byte (ISB).

Bits 8-15: These bits are not used and must be set to 0's.

Word 1

Bits 0-9: These bits are not used and must be set to 0's.

Bit 10 - Auto Answer: Set this bit to 1 when the remote station is configured for auto-answer. When this bit is a 1, the attachment uses 2 seconds as a time-out (T3). When this bit is a 0, the attachment uses 60 seconds as a time-out.

Bit 11 - Enable Program Controlled Interrupt (PCI): If this bit is a 1, the attachment supports PCI.

*Bit 12 - Mode:* If this bit is a 1, the attachment is in duplex mode. If this bit is a 0, the attachment is in half duplex mode.

Note: Duplex mode is only used in SDLC/HDLC mode of operation.

Bit 13 - Test: This bit is used for installation tests.

*Bit 14 - Direct Call:* If this bit is a 1, a direct call is in effect, and no selection or facility registration/cancellation parameters will be transmitted.

Bit 15 - Registration/Cancellation Selection: If this bit is a 1, software provides a selection or facility registration/cancellation code for transmission.

Words 2-4: These words are not used and must be set to 0's.

*Word 5 - Chaining Address:* This word contains the address of the next DCB in a chaining operation.

*Word 6 - Byte Count:* This 16-bit byte count word contains the number of bytes included in the selection sequence or facility registration/cancellation code.

Note: The attachment supports a maximum byte count of 255 bytes. If the byte count specified is greater than 255, an exception interrupt (CC2) is reported with bit 3 (DCB specification check) set in the ISB.

*Word 7 - Data Address:* This word contains the address, in processor storage, of the selection sequence required to establish a connection on the switched X.21 network or facility registration/Cancellation code.

Notes:

- 1. The Data Address and Byte Count of data word 1 are meaningful only when bit 15 is a 1.

- 2. The selection sequence and facility registration/cancellation codes must be coded exactly as required by the network. These are not checked by the attachment prior to transmission to the network DCE.

- 3. If either of the following conditions exist, the attachment reports an exception interrupt with bit 3 (DCB specification check) set to 1 in the ISB.

- The BSC jumper is installed and the Set Mode DCB specifies duplex mode.

- Both bits 14 and 15 are set to 1 in word 1 of the Set Mode DCB.

- 4. The format of the Start Cycle-Steal Status words (CCSW) reported after an interrupt to a Start Control command depends on the BSC jumper. If the jumper is installed, BSC status is reported. If it is not installed, SDLC status is reported.

- 5. The Set Mode DCB specifying either direct call or selection causes the attachment to take the following actions:

- a. The attachment checks for CCITT state 1 and, if not active, presents an exception interrupt (CC2) with bit 0 (device dependent status available) set in the ISB, and BSC bit 2 (DCE interface error) set in cycle-steal status word 1, or SDLC bit 7 (DCE interface error) set in cycle-steal status word 2. If CCITT state 1 is active, the attachment enters CCITT state 2.

- b. If the data circuit terminating equipment (DCE) does not provide CCITT state 3 within 3 seconds (T1), the attachment reports an exception interrupt (CC2) with bit 0 (device dependent status available) set in the interrupt status byte (ISB), BSC bit 15 (T1 time-out) set in cycle-steal status word 4 or in the case of SDLC mode, bit 15 (T1 time-out) is set in cycle-steal status word 5.

- c. After detecting CCITT state 3, the attachment enters CCITT state 4 and transmits the selection or facility registration/cancellation (SFRC) parameters pointed to by the Set Mode DCB. The attachment transmits 2 synchronization (SYN) characters preceding the SFRC parameters.

d. After transmitting the SFRC parameters, the attachment enters CCITT state 5 and reports a device end interrupt (CC3) or initiates a chaining operation if so specified in the control word. If Direct Call is specified, no SFRC is transmitted and the attachment interrupts or initiates a chaining operation after making the transition from CCITT state 3 to CCITT state 5. If a DCE clear occurs during selection, an attention interrupt (CC4) is presented and no NPI DCB is fetched.

3-14 GA34-0241

#### Network Provided Information (NPI)

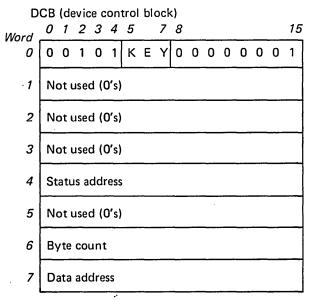

The NPI DCB is an integral part of the connection process and must be issued when an outgoing call is attempted. The format of the NPI DCB is as follows:

#### Word 0 - Control Word:

Bits 0-1: These bits are not used and must be set to 0's.

Bit 2 - Input Flag: When this bit is set to a 1 it allows cycle-steal of data into main storage. This bit is set to 1 along with bit 4 to prevent an exception interrupt (CC2) being reported.

Bit 3: This bit is not used and must be set to 0.

Bit 4 - Suppress Exception: When this bit is set to a 1 it allows residual status reporting. This bit along with bit 2 is set to 1 or an exception interrupt (CC2) is reported, with bit 3 (DCB specification check) set in the ISB.

Bits 5-7 - Key: These bits represent a 3-bit key. The attachment presents this key to the processor during data transfers to verify that the program has authorization to access processor storage. An invalid address key causes an exception-interrupt request (CC2), with bit 6 set to 1 (protect check) in the interrupt status byte (ISB).

Bits 8-14: These bits are not used and must be set to 0's.

Bit 15 - Network Provided Information (NPI): This bit is set to 1 to establish that this is an NPI DCB when issued under a Start Control command.

Words 1-3: These words are not used and all bits must be set to 0's.

**Word 4 - Status Address:** This 16-bit word contains the processor storage address of the residual status block (RSB). The RSB contains two words, the first of which is the residual byte count. The second (word 1) contains the system architecture bits as follows:

Bit 0 - End Of Chain (EOC): This bit is set to 1 to indicate no chaining since chaining from the NPI DCB is not permitted.

Bits 1-14: These bits are not used and must be set to 0's.

Bit 15 - No Exception (NE): This bit is set to 1 to indicate the NPI was received without error. A T2 or T3 timeout or an ILR to an NPI causes the NE bit to be set to 0 because these conditions are reported by an exception interrupt.

**Note:** Use of the set suppress exception (SE) bit and the residual status block (RSB) allows software to determine the number of bytes received in the NPI without issuing a Start Cycle-Steal Status command.

Word 5: This word is not used and all bits must be set to 0's.

Word 6 - Byte Count: This word contains the total byte count allocated for the NPI.

The attachment supports a maximum byte count of 255 bytes. If the byte count specified is greater than 255, an exception interrupt (CC2) is reported, with bit 3 (DCB specification check) set in the ISB.

All network provided information (call progress signals (CPS) and DCE provided information (DPI) are passed into processor storage beginning with CPS (when present). This information is passed to processor storage as coded by the network. The attachment deletes any inserted synchronization (SYN) characters. The input flag (I/F) and suppress exception (SE) bits of the DCB control word must be set to 1; if not, the attachment presents an exception interrupt (CC2) with bit 3 (DCB specification check) set to 1 in the ISB. The selection or facility registration/cancellation sequence or a direct call must have been previously specified by a Set Mode DCB. If the NPI DCB is issued before the Set Mode DCB or on a leased network, the attachment presents an exception interrupt (CC2) with bit 3 (DCB specification check) set in the ISB.

The attachment may be in one of several states when the NPI DCB is fetched. The execution the Set Mode DCB specifying of selection, facility registration/cancellation; or direct call allows the attachment to move to CCITT state 5. The attachment may cause a transition to CCITT state 6, 7, 10, 11, 12, or 19 before fetching the NPI DCB. The CPS and DPI information (up to 255 bytes maximum) are stored on the attachment when not directed by the NPI DCB. The NPI DCB must be issued after an outgoing call by the Set Mode DCB. Chaining from the Set Mode DCB is recommended.

The NPI DCB causes the attachment to take the following actions:

- CCITT state 7, 12, or 19 must be detected within 20 seconds (T2) after entering CCITT state 5. If it is not, the attachment reports an exception interrupt (CC2) with bit 0 (device dependent status available) set in the ISB, BSC bit 14 (T2 time-out) set in cycle-steal status word 4, or SDLC bit 14 (T2 time-out) set in cycle-steal status word 5.

- 2. If the attachment detects CCITT state 12, or 19, it stores the CPS and DPI information into processor storage as directed by the NPI DCB. Once the attachment receives the CPS and DPI signals, it waits (T3) for 2 or 60 seconds for CCITT state 12 or 19 to come active.

- 3. If CCITT state 12 or 19 is not reached, the attachment reports an exception interrupt (CC2) with bit 0 (device dependent status available) set in the interrupt status byte (ISB), BSC bits 14, 15 (T3 time-out) set in cycle-steal status word 4, or SDLC bits 14, 15 (T3 time-out) set in cycle-steal status word 5.

- 4. Once CCITT state 12 or 19 is presented by the DCE, the attachment presents an interrupt (see following note). CCITT State 12 is a transition made by the DCE and therefore receive data may appear at the interface as soon as

CCITT state 12 is established. CCITT State 13 may be entered if the DCE provides receive data to the attachment. The attachment must be directed by a receive DCB conforming to either SDLC/HDLC or BSC format in order to accept the data. If the DCE presents CCITT state 19, the attachment starts a 2-second timer (T6) and then goes through a clearing sequence (CCITT states 19, 20, 21, and 1). If CCITT state 1 is reached, the attachment presents an attention interrupt (CC4) with bit 0 (clear successful) set in the IIB. If CCITT state 1 is not reached, the attachment reports an attention interrupt with bit 7 (clear failure - T6 time-out) set in the IIB.

Note: If the byte count specified in the DCB is equal to or greater than the number of bytes received in the NPI, the attachment presents a device end interrupt (CC3) when state 12 (ready for data) is reached. If the byte count is insufficient to allow for cycle-stealing all of the NPI information into processor storage, the attachment reports an exception interrupt (CC2) with bit 2 (incorrect length record - long record) set in the ISB. If state 19 (DCE clear) is reached, the attachment presents an attention interrupt (CC4) with IIB bit 0 (clear successful) set or with bit 7 (clear failure) set. The attachment remains busy to the NPI or Auto-Answer DCB when terminated with an attention interrupt. Therefore, the software must issue a Device Reset command.

The format for the Auto-Answer DCB is as follows: DCB (device control block)

| U    | CR                     | DCB (device control block) |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

|------|------------------------|----------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| Word | 0                      | 1                          | 2 | 3 | 4 | 5 |   | 7 | 8 |   |   |   |   |   |   | 15 |

| 0    | 0                      | 0                          | 1 | 0 | 1 | к | E | Y | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0  |

| 1    | Timer 1 Not used (0's) |                            |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| 2    | N                      | Not used (O's)             |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| 3    | No                     | Not used (O's)             |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| 4    | Status address         |                            |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| 5    | N                      | Not used (O's)             |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| 6    | Ву                     | Byte count                 |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| 7    | Da                     | Data address               |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| •    |                        |                            |   |   |   |   |   |   |   |   | _ | _ |   | _ | _ |    |

Word 0 - Control

Bits 0-1: These bits are not used and must be set to 0's.

Bit 2 - Input Flag: This bit and bit 4 must be set to 1 or an exception interrupt (CC2) is reported, with bit 3 (DCB specification check) set in the ISB.

Bit 3: This bit is not used and must be set to 0.

*Bit 4 - Suppress Exception:* This bit when set to 1 allows residual status reporting. This bit along with bit 2 must be set to 1 or an exception interrupt (CC2) is reported, with bit 3 (DCB specification check) set in the ISB.

*Bits 5–7 - Key:* These bits represent a 3-bit key. The attachment presents this key to the processor during data transfers to verify that the program can access processor storage. An invalid address key causes an exception-interrupt request (CC2), with bit 6 set to 1 (protect check) in the ISB.

Bits 8-13: These bits are not used and must be set to 0's.

Bit 14 - Auto-Answer: This bit is set to 1 to identify the DCB as an Auto-Answer DCB.

Bit 15: This bit is not used and must be set to 0.

Word 1

Bits 0-7 - Timer 1: Use these bits to limit the time the attachment waits for an incoming call. The time is specified in increments of 106 milliseconds. If a value of 0 is coded, the attachment waits indefinitely.

Bits 8-15: These bits are not used and must be set to 0's.

Words 2-3: These words are not used and all bits must be set to 0's.

#### Word 4 - Status Address

Bit 0 - End Of Chain (EOC): Set this bit to 1 to indicate no chaining; the attachment does not permit chaining from the Auto-Answer DCB.

Bits 1-14: These bits are not used and must be set to 0's.

Bit 15 - No Exception (NE): This bit is set to a 1 to indicate the DPI was received without error. A T4 time-out or an ILR to an Auto-Answer causes the NE bit to be set to 0 since these conditions are reported in an exception interrupt.

Word 5: This word is not used and all bits must be set to 0's.

**Word 6 - Byte Count:** This word indicates the total number of bytes allocated for the DCE provided information (DPI). The attachment supports a maximum byte count of 255 bytes. If the byte count specified is greater than 255, an exception interrupt (CC2) is reported, with bit 3 (DCB specification check) set in the ISB.

*Word 7 - Data Address:* This word contains the address in processor storage of the starting location for the DPI.

#### Notes:

- 1. Use of the SE bit and the RSB allows software to determine the number of bytes received in the DPI without issuing a Start Cycle-Steal Status command.

- 2. The Auto-Answer DCB can be issued before an incoming call is detected or in response to an attention interrupt. If issued before an incoming call, the attachment, on detection of an incoming call:

- Establishes the connection

- Cycle-steals the DPI into processor storage

- Deletes any SYN characters in the DPI

- Presents an interrupt (see the note following this list)

The time that the attachment waits for an incoming call can be limited by specifying a time-out period in word 1 of this DCB. If the timer expires before an incoming call, the attachment presents an exception interrupt (CC2), with bit 0 (device dependent status available) set in the ISB, and BSC bit 1 (time-out) set in cycle-steal status word 1 or SDLC bit 4 (time-out) set in cycle-steal status word 2. A timer value (DCB word 1) of 0 results on no time-out.

3. The Auto-Answer command is valid for switched line opertion only. If issued while in leased line mode, the attachment presents an exception interrupt (CC2) with bit 3 (DCB specification check) set in the ISB.

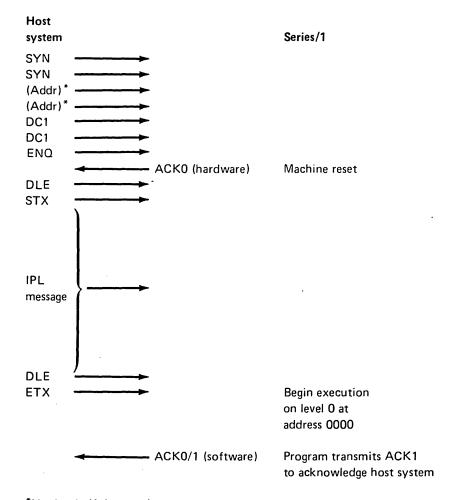

### Handling An Incoming Call

The attachment takes the following actions to handle an incoming call:

- 1. If not in Auto-Answer mode, the attachment recognizes CCITT state 8 and presents an attention interrupt (CC4) with the interrupt information byte equal to 0.

- 2. The attachment must next be directed by the Auto-Answer DCB.

- 3. The attachment must enter CCITT state 9 within 500 milliseconds or the DCE may cancel the call and proceed to the DCE ready state.

- 4. The attachment, once directed by the Auto-Answer DCB, enters CCITT state 9 and starts a 2-second timer (T4).

- 5. When in CCITT state 10, the DCE provides the DPI (if present) to the attachment.

- 6. After recognizing CCITT state 12 or 19, the attachment cycle-steals the DPI into processor storage.

- 7. When CCITT state 12 or 19 is active, the attachment presents an interrupt (see the note following this list)

- 8. CCITT state 13 can be entered if the DCE provides receive data to the attachment. The attachment must be directed by a receive DCB in order to accept the data.

- 9. If the attachment does not reach CCITT state 12 or 19, a 2-second time-out (T4) occurs. The attachment then presents an exception interrupt (CC2) with bit 0 (device dependent status available) set in the ISB, BSC bit 13 (T4 time-out) set in cycle-steal status word 4 or SDLC bit 13 (T4 time-out) set in cycle-steal status word 5.

- 10. CCITT state 8 may be an incoming call from the network indicating information is available (charge information previously requested through selection). In this situation, the DCE ends the call (after the DPI is provided) by entering CCITT state 19.

- 11. The attachment then starts a 2-second timer (T6) and procedes to clear the line.

- 12. An attention interrupt (CC4) is then presented (see the note following this list) for the Auto-Answer DCB with bit 0 (clear successful) set in the IIB.

- 13. If the clearing operation is not successful (CCITT state 1 is not reached), the attachment reports an attention interrupt (CC4) with bit 7 (clear failure T6 time-out) set in the IIB.

- 14. If CCITT state 19 is not entered within 2-seconds, the same condition exists that is present for a normal call when CCITT state 12 is not reached; a T4 time-out occurs.

Note: If the byte count specified in the DCB is equal to or greater than the number of bytes received in the NPI, the attachment presents a device end interrupt (CC3) when state 12 (ready for data) is reached. If the byte count is insufficient to allow for cycle-stealing all of the NPI information into processor storage, the attachment reports an exception interrupt (CC2) with bit 2 (incorrect length record - long record) set in the ISB. If state 19 (DCE clear) is reached, the attachment presents an attention interrupt (CC4) with IIB bit 0 (clear successful) set or with bit 7 (clear failure) set. The attachment remains busy to the NPI or Auto-Answer DCB when ended with an attention interrupt, therefore the software must issue a Device Reset command.

The Clear operation is valid for switched line operation only. If this operation is issued while in leased line mode, the attachment presents an exception interrupt (CC2) with bit 3 (DCB specification check) set in the ISB.

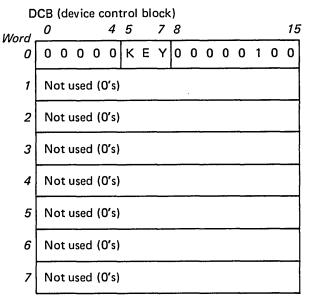

The format of the Clear DCB is as follows:

The attachment executes the line clearing procedure on an X.21 switched network and returns to ready (CCITT state 1). A device end interrupt (CC3) occurs at the completion of the clearing procedure. If an error occurs during the clearing procedure, the attachment presents an exception interrupt (CC2) with bit 0 (device dependent status available) set in the ISB.

When the attachment receives a clear operation, it does the following:

- The attachment enters CCITT state 16 and starts a 2-second (T5) timer.

- When the attachment makes the transition to CCITT state 1, a device end interrupt (CC3) occurs.

- If CCITT state 1 is not reached within 2-seconds, an exception interrupt (CC2) is reported with bit 0 (device dependent status available) set in the ISB, BSC bits 13 and 15 (T5 time-out) set in cycle-steal status word 4 or SDLC bits 13 and 15 (T5 time-out) set in cycle-steal status word 5.

- CCITT state 16 may be entered from any state except state 1.

- If a Clear DCB is issued to the attachment while in CCITT state 1, a device end interrupt (CC3) occurs.

## **Start Modification**

This command is used to modify the attachment microcode. This command initiates a cycle-steal operation for device 0. If issued to device 1, a delayed command reject is reported (information status byte, bit 1 is set on). The IDCB for this command is as follows:

IDCB (immediate device control block)

| Command field |    |      |     |    |      |      |    | Device address field |     |   |     |     |   |   |    |

|---------------|----|------|-----|----|------|------|----|----------------------|-----|---|-----|-----|---|---|----|

| 0             | 1  | 1    | 1   | 0  | 0    | 1    | 0  | X                    | Х   | Х | Х   | Х   | Х | Х | Х  |

| Q             |    |      |     |    |      |      | 7  | 8                    |     |   |     |     |   |   | 15 |

|               |    |      | 7   | 2  |      |      |    |                      |     | ( | 00- | -FI | = |   | -  |

| In            | nm | edia | ate | da | ta f | iele | d  |                      |     |   |     |     |   |   |    |

|               |    |      |     |    | (    | C    | Ba | ddr                  | ess |   |     |     |   |   |    |

| 16            | ;  |      |     |    |      |      |    |                      |     |   |     |     |   |   | 31 |

A description of the DCB for the Start Modification command is:

- 1. Word 0 is used to support KEY (bits 5–7).

- 2. Words 2–5 of the DCB are not used.

- 3. Word 1 of the DCB contains the address of the attachment storage location where the microcode patch begins.

- 4. Word 6 of the DCB contains the byte count of the number of bytes to be allocated in the attachment for the microcode patch.

- 5. Word 7 of the DCB contains the processor storage address where the microcode patch begins.

Note: The attachment does not support chaining for the Start Modification command.

### Start

Information on the Start command is presented in Chapters 5 and 6 of this document.

Start Cycle-Steal Status

Information on the Start Cycle-Steal Status command is presented in Chapters 5 and 6 of this document.

## **Interrupt Information Byte (IIB)**

When the attachment presents an interrupt request to the processor, the IIB is used to record information that cannot be indicated to the program by the condition codes (CCs). The IIB is meaningful only with condition codes 1, 3, or 4.

If the IIB bit 0 is a 1 when condition code 3 is reported, the suppress-exception (SE) bit was equal to 1 for a previous receive operation and a suppressible error occurred.

If condition code 1 (PCI) is reported, the IIB high byte contains the DCB identifier.

An attention interrupt (CC4) and IIB bit 0 set to 1 indicates a successful data circuit terminating equipment (DCE) initiated clear. An attention interrupt (CC4) and IIB bit 7 set to 1 indicates an unsuccessful DCE initiated clear. When interrupt condition code 2 is reported, the IIB has a fixed format called the interrupt status byte (ISB).

## Interrupt Status Byte (ISB)

When the attachment presents an interrupt request to the processor, the ISB is used to record status that cannot be indicated to the program by condition codes. The ISB is meaningful only when interrupt condition code 2 is reported. The processor detects the ISB in bits 0–7 of the interrupt ID word.

Definitions of the ISB bits are as follows:

Bit 0 - Device-Dependent Status Available: If this bit is a 1, additional status is available by using the Start Cycle-Steal Status command. This bit may be a 1 in conjunction with bit 2 (incorrect-length record).

Bit 1 - Delayed Command Reject: This bit is a 1 for the following conditions:

- The command field of the IDCB contains an invalid function or modifier bit combination.

- The IDCB contains an odd DCB address.

- A Start command other than Start Control is issued in response to an attention interrupt caused by an incoming call.

- A Start Modification command is issued to device one.

- A command was issued to the wrong device.

*Bit 2 - Incorrect-Length Record:* This error can occur during both transmit and receive operations. It is caused by any of the following conditions:

- The byte count decremented to 0 because the attachment did not detect a change-of-direction (COD) character, and the chaining flag is off.

- The attachment detected a COD character, and the byte count has not been decremented to 0.

In this case, interrupt status byte bit 0 is also a 1. A Start Cycle-Steal Status command can be used to determine the location of the COD in storage (residual address).

• In X.21 switched mode, if the byte count specified in the DCB is equal to or greater than the number of bytes received in the NPI, the attachment presents a device end interrupt (CC3) when state 12 (ready for data) is reached. If the byte count is not sufficient to allow for cycle-stealing all of the NPI signals into storage, the attachment reports an exception interrupt (CC2) with bit 2 (Incorrect-Length Record) set in the ISB.

*Bit 3 - DCB Specification Check:* This bit is set to a 1 if any of the following conditions exist when the DCB is examined:

- An odd byte chaining address with the chain bit set to a 1 in the control word.

- An odd byte SDLC status address with the SE bit set on in the control word.

- An odd byte data address for a Start Cycle-Steal Status command.

- The SDLC byte count does not equal 8 or 12 for a Start Cycle-Steal Status command.

- There is an odd byte data address for a Start Diagnostic command.

- The byte count is not hexadecimal 11 for a Start Diagnostic 1 command.

- The byte count is not 2 for a Start Diagnostic 2 command.

- The byte count is 0 for a receive operation.

- The byte count is 0 for a transmit operation.

- The input flag (I/F) bit of the control word was not set to 1 for a Start Diagnostic or a Start Cycle-Steal Status command.

- More than one of the following operations was specified in the control word fat the same time: receive, transmit, disable terminal, and enable terminal.

- Bit 3 of the SDLC control word is set to one for a Start command.

- Bit 1 of the SDLC control word is set to one for a Start command without a previous set mode DCB specifying PCI.

- The I/F bit of the control word for a NPI Set Control DCB or Auto-Answer DCB is not set to one.

- A Start command was issued to the wrong device.

- The BSC byte count does not equal 6 or 10 for a Start Cycle-Steal Status command.

- An SDLC receive operation with the SE bit set to 0.

- An Auto-Answer or NPI DCB which specifies a byte count greater than 255.

- A Set Control DCB issued to a leased line with a Clear, NPI, Selection or Direct Call, or Auto-Answer command specified.

- A Set Mode, DCB with direct call and selection or facility registration/cancellation specified.

- A DCB other than a transmit or receive with the program-controlled-interrupt (PCI) bit set to one in the control word was issued.

- A set mode DCB specifying duplex when the BSC jumper is on was issued.

- A set mode DCB specifying installation test (bit 13 set to one in word 1 of the DCB) was set to one while any other bit in word 1 of the DCB is set to one.

- A Set Mode DCB specifying selection (Bit 15 or in word 1 of the DCB) and the byte count (DCB word 6) specified as zero.

- A Start Diagnostic 1 command occurred with any bit set to one in the control word other than bit 2 or bits 5-7. A Start Diagnostic 2 command occurred with any bit set to one in the control word other than 2, 5, 6, 7, or 15.

- In BSC mode, an exit transparent command was issued with the byte count not equal to 2.

- A Start Control command with a DCB specifying Auto-Answer, Clear, or NPI with the chaining bit set to one.

- A Start Control command with a DCB specifying Auto-Answer, or NPI without the set exception (SE) bit set to one.

- A Start Control command with a DCB specifying Auto-Answer or NPI with an odd status address.

- A Start Control command issued specifying Auto-Answer, NPI, or a set mode with selection, or a direct call set to one when the attachment is already connected on a switched line.

Bit 4 - Storage Data Check: This bit is set to 1 during cycle-steal output operations only to indicate that the processor storage location accessed during the current cycle contains incorrect parity. The attachment ends the operation with an exception interrupt request.

Bit 5 - Invalid Storage Address: This bit is set to 1 if the address presented by the attachment for data or DCB access exceeds the storage size of the system. The attachment ends the operation with an exception interrupt request.

*Bit 6 - Protect Check:* This bit is set to 1 if the attachment attempts to access a storage location without the correct cycle-steal key.

Bit 7 - Interface Data Check: This bit is set to 1 if a parity error was detected on an interface cycle-steal data transfer. The condition may be detected by the channel or the attachment. In either case, the attachment ends the operation with an exception interrupt request.

# **Status After Resets**

### **Power-On Reset**

Resets the attachment, performs an attachment storage and attachment read-only storage test, and resets the X.21 interface to DTE ready. The control parameters are reset to no PCI and half-duplex.

### System Reset