## IBM Series/1 IBM

Series/1

## **IBM Series/1**

## The Small Computer Concept

by

James D. Schoeffler

Professor and Chairman Department of Computer and Information Science Cleveland State University Cleveland, Ohio

International Business Machines Corporation General Systems Division Atlanta, Georgia Library of Congress Catalog Card Number: 78-61315

IBM Order Number: SH30-0237

Additional copies of this book can be obtained from local IBM Branch Offices, using the IBM Order Number.

Comments concerning this publication should be addressed to International Business Machines Corporation, General Systems Division, Technical Publications, Dept. 796, P.O. Box 2150, Atlanta, Georgia 30301.

IBM may use and distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever. You may, of course, continue to use the information supplied.

© Copyright International Business Machines Corporation 1978

First edition published August, 1978

Printed in the United States of America

#### Preface

The trend toward small computers and distributed systems for a wide variety of applications has been termed a revolution by some. Although the impressive decrease in the cost of these systems has certainly made this trend feasible, the driving force has been the changing nature of computer use. Applications today tend to be much more interactive and online and less suitable for batch processing. Because such applications are critical to the operation of business or industry, they place stringent demands on system hardware, application and system software, and system maintenance.

Consequently, the choice of a small computer system is not totally determined by its price. Unfortunately, too many small computer systems have been designed to minimize price rather than to meet such critical specifications. Hence, users have often been frustrated in their attempts to utilize the benefits of small computers and distributed applications.

After being exposed to the designers and planners of the Series/1 following its introduction by IBM in November 1976, I was enthusiastic about writing this book. I believe that the Series/1 was expressly designed to meet the kinds of critical applications indicated above. I view it as an "integrated system" in the sense that the hardware, software, and maintenance concepts all were designed from the beginning to work closely together so that critical applications can be realized. Furthermore, the system design is such that non-IBM devices can be included in the system without sacrificing performance, use of system software, reliability, or availability. This aspect of small computer applications is very important to the original equipment manufacturers designing application systems around such a computer.

For the above reasons, I have organized the book around this integrated hardware, software, and maintenance concept. The book is intended for users who wish to critically evaluate the IBM Series/1 for their applications and want to know what it does, how it does it, and why it does it that way. The book is not a handbook or reproduction of the various system reference manuals. It is not an attempt to describe every processor, software product, or device in great detail. Rather, those items which I considered important to the overall integration of the product into successful applications have been included.

Throughout this project, I have been aided by useful suggestions from a variety of IBM people, most of whose names I do not even know. However, three people in particular contributed significantly: Mr. Michael I. Davis, one of the principal architects of the Series/1; Mr. Harry J. Dewhurst of the marketing group; and Mr. Charles E. Snyder, my editor for the book. In my many discussions of the Series/1, its objectives, its realization, and its future, I have been impressed with their knowledge and insight of small computers and grateful for the opportunity of knowing and working with them.

James D. Schoeffler

July, 1978

### Contents

| Chapter 1. Introduction to the Small Computer Concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | • |   | 1        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|----------|

| Small Computer Application Needs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   | 2        |

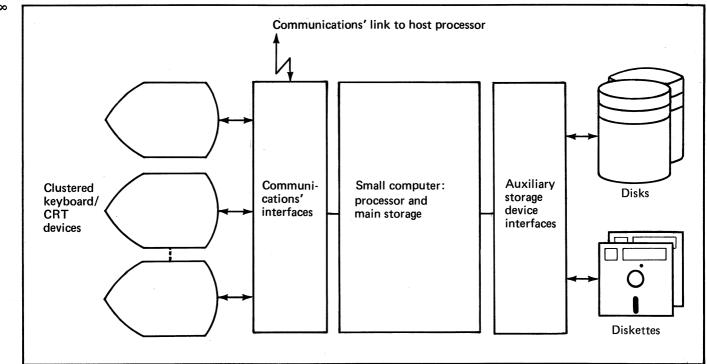

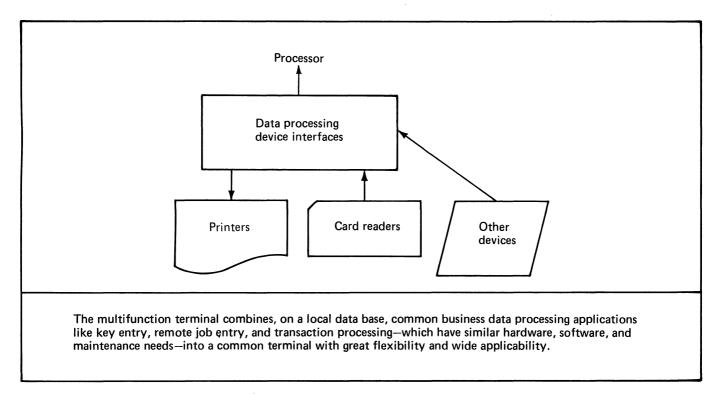

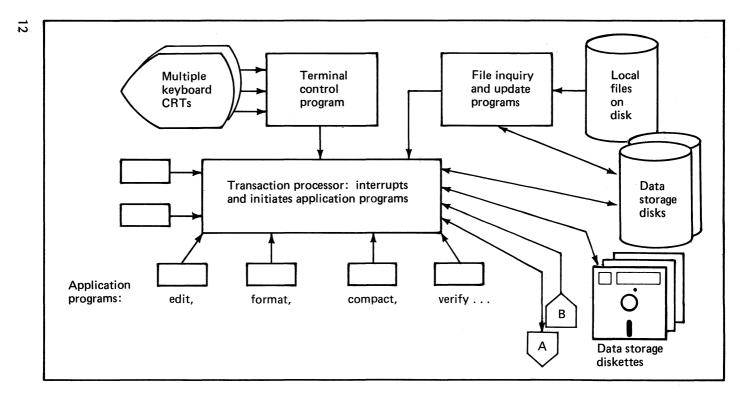

| The Multifunction Terminal Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |   |   | 5        |

| Hardware Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   | 7        |

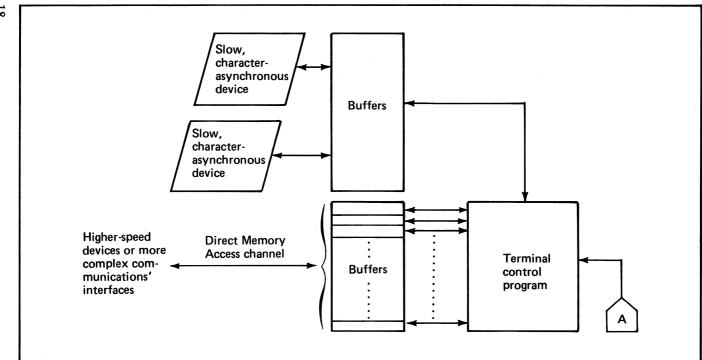

| Software Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   | 10       |

| Support Needs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |   | 11       |

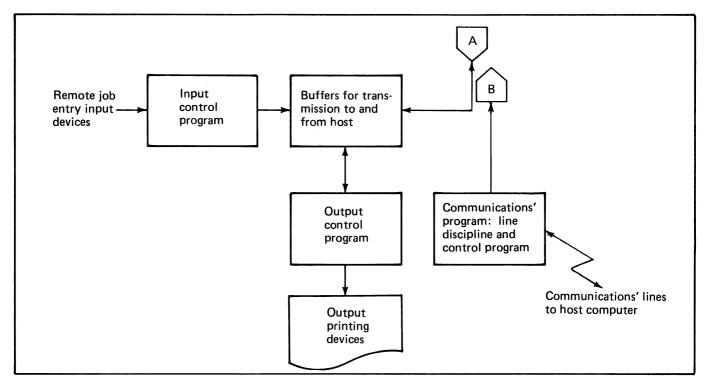

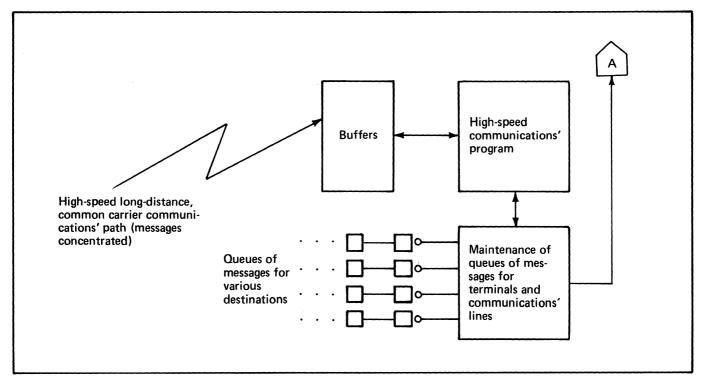

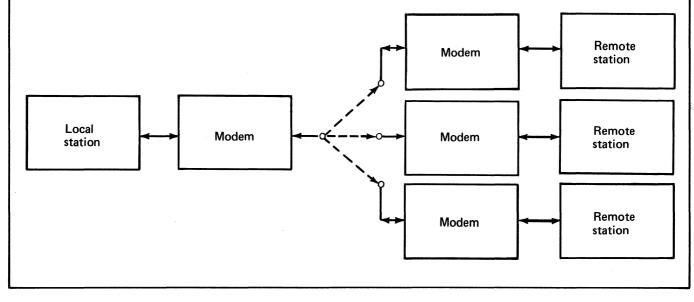

| The Communications' Concentrator Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |   |   | 11       |

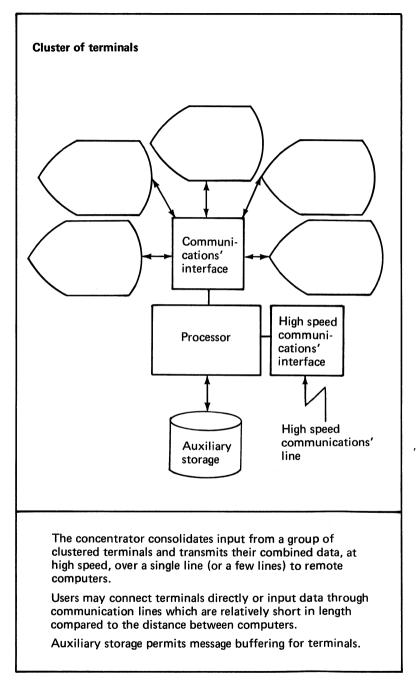

| The Concentrator Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |   |   | 15       |

| Hardware Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   | • | 16       |

| Software Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   | 16       |

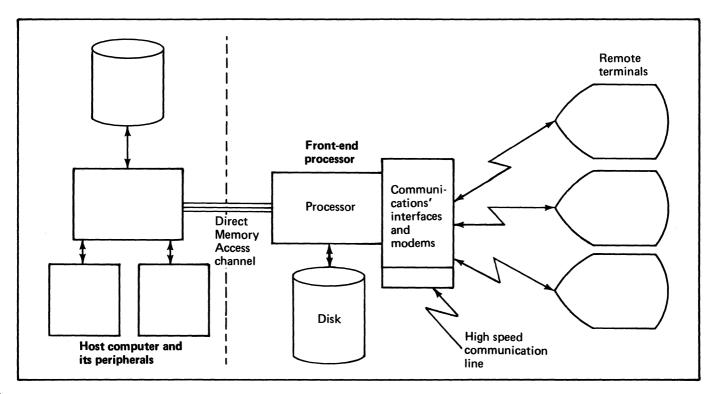

| The Front-End Processor Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |   | • | 22       |

| Hardware and Software Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |   | 22       |

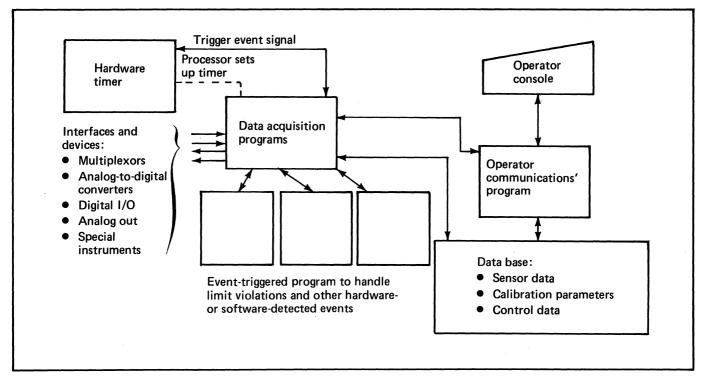

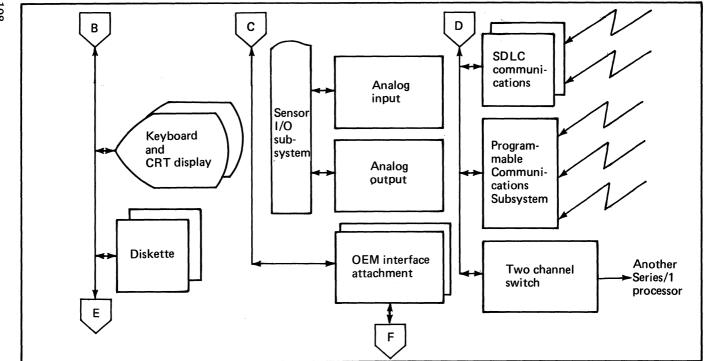

| The Data Acquisition and Control Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |   |   | 25       |

| The Data Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |   | 26       |

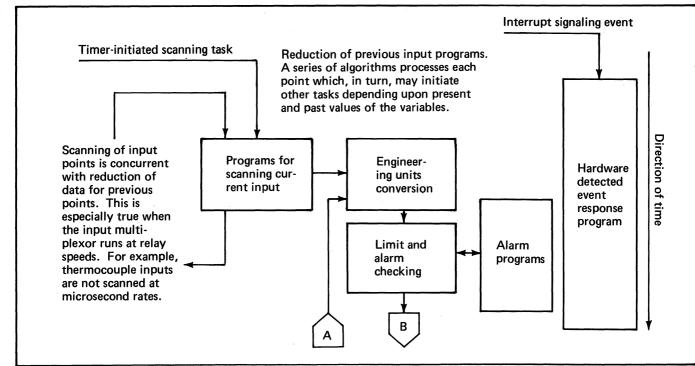

| Response Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |   | 26       |

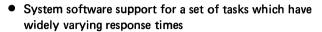

| Hardware and Software Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |   |   | 27       |

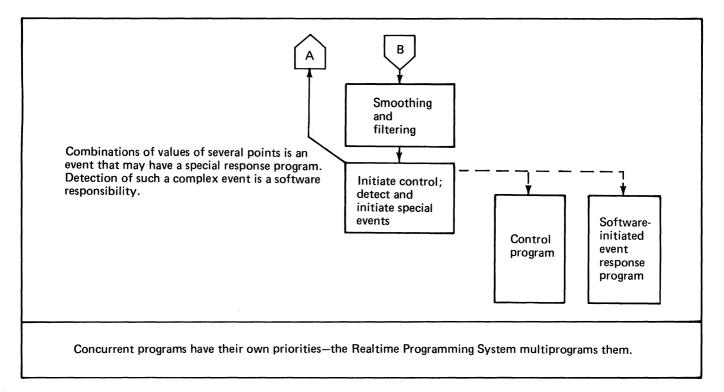

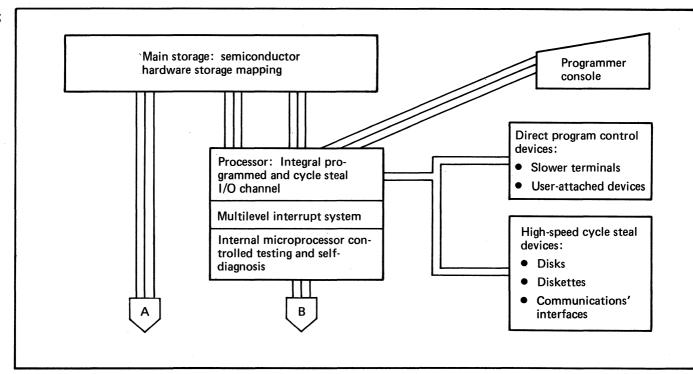

| Software Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   | 30       |

| Summary of Application Needs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |   |   | 34       |

| Chapter 2. Overview of the IBM Series/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |   |   | 38       |

| Series/1 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |   |   | 38       |

| System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • | • | • | 38       |

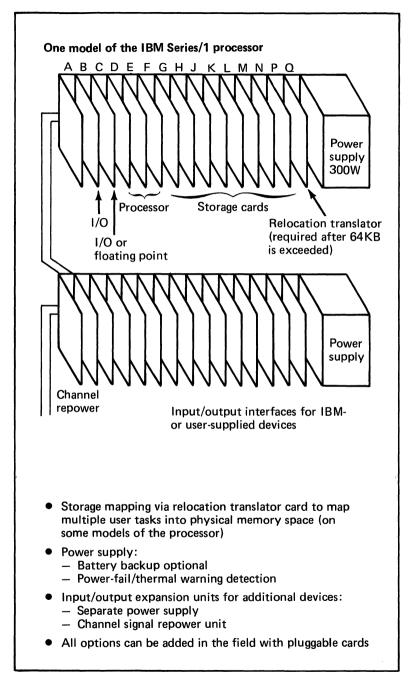

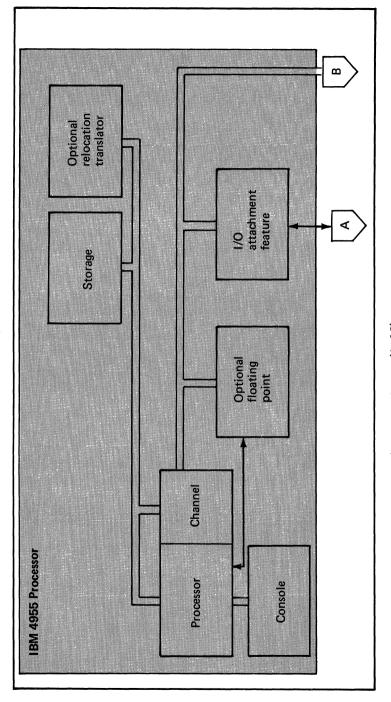

| The Processors         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .                                                        | • | • | · | 39       |

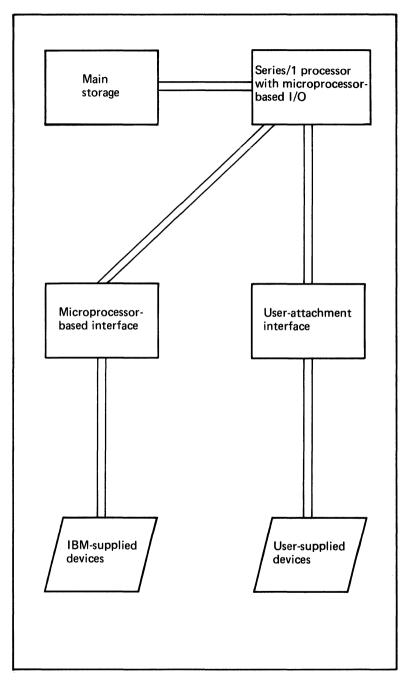

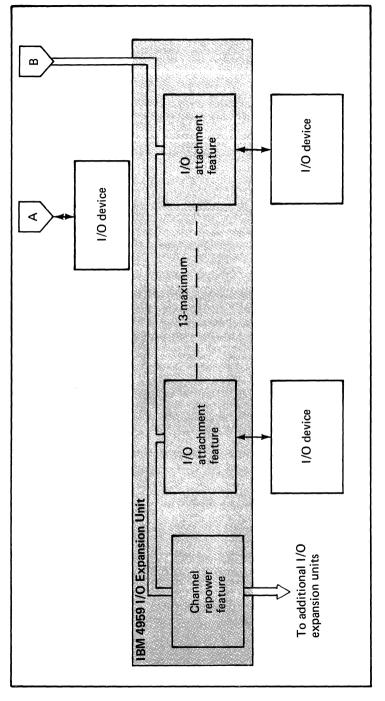

| Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • | • | · | 39       |

| Main Storage         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <t< td=""><td>•</td><td>•</td><td>·</td><td>43</td></t<> | • | • | · | 43       |

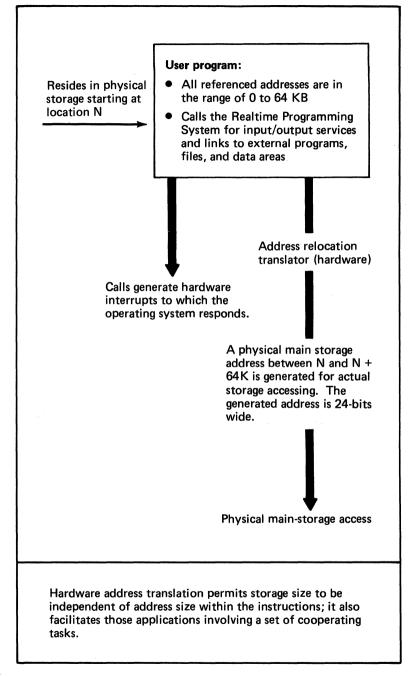

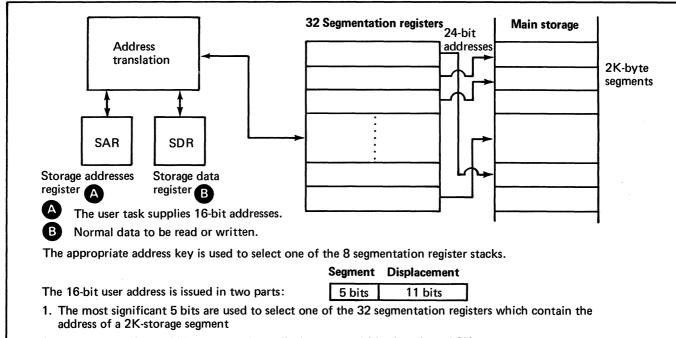

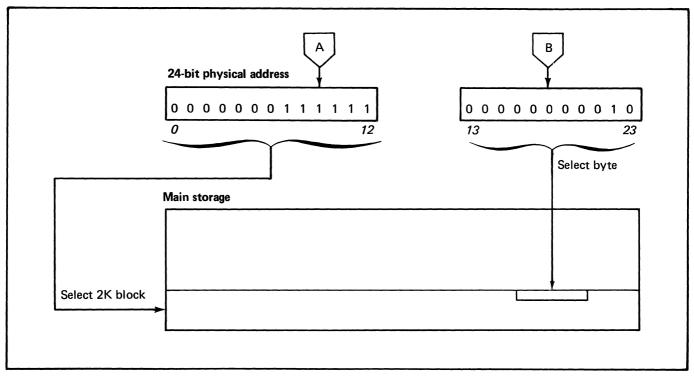

| Address Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • | • | · | 43       |

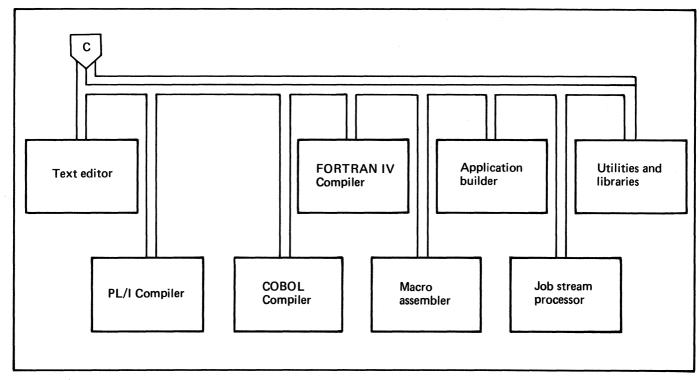

| Software Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • | • | · | 47       |

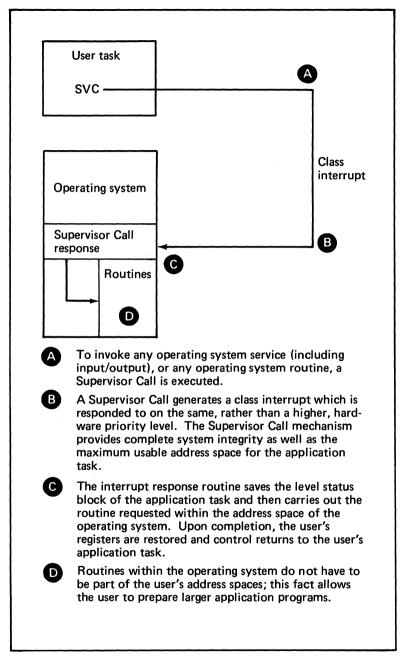

| Control Program Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | · | • | • | 48       |

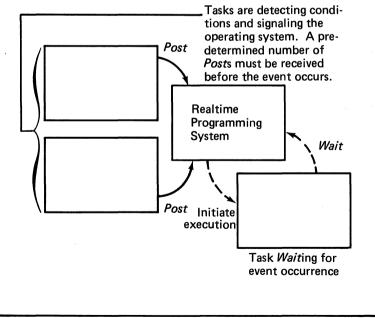

| Event Driven Executive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • | • | • | 48       |

| Higher-Level Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • | • | • | 49       |

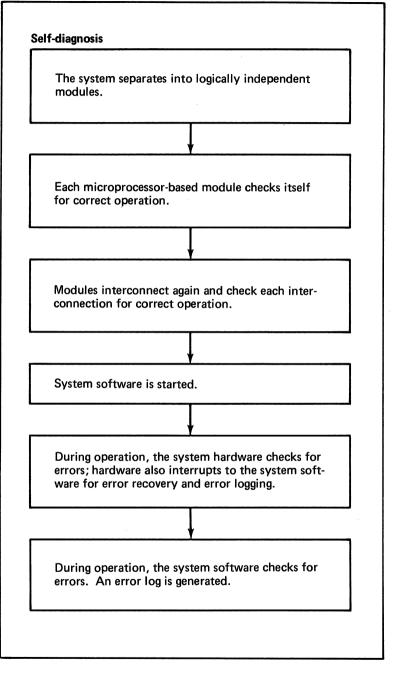

| Self-Diagnosis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | • | • |   | 49       |

| Maintenance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | · | • | 50       |

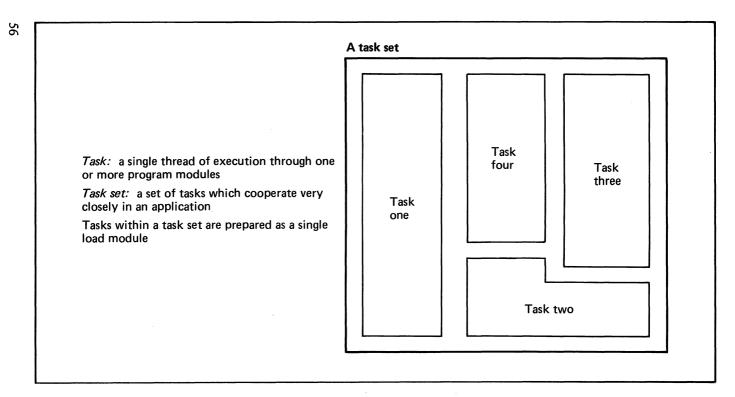

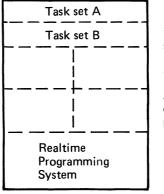

| Hardware and Software Support of Multiple, Cooperating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | • | · | 50       |

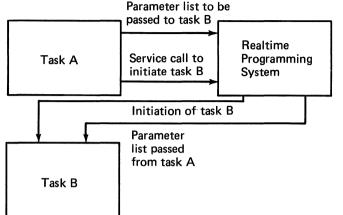

| Application Tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |   | 53       |

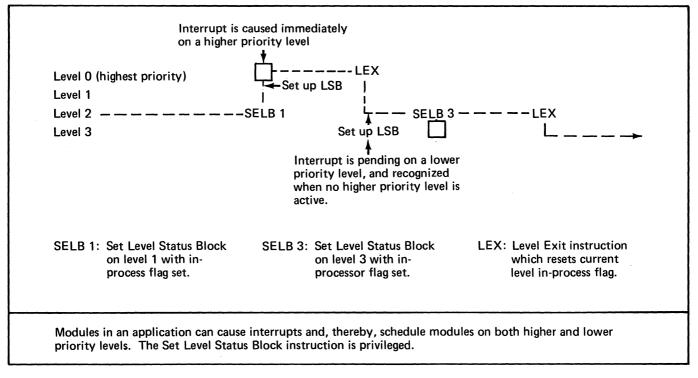

| Interrupt System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | • | · | 55       |

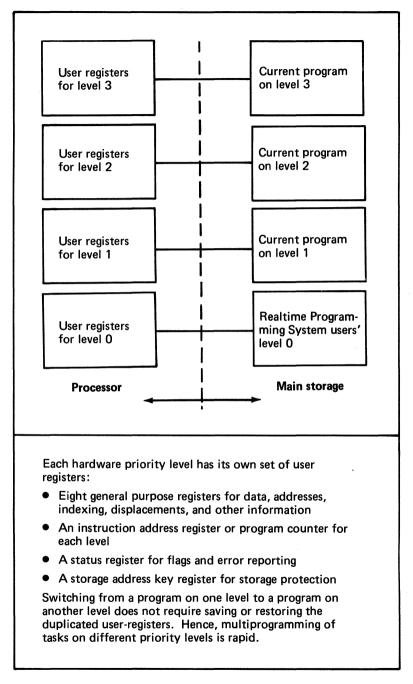

| Multiprogramming and Multitasking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • | • | · | 55       |

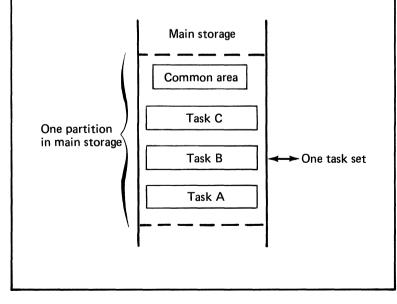

| Storage Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • | • | • | 55       |

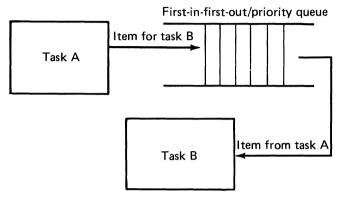

| Intertask Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • | • | • | 59       |

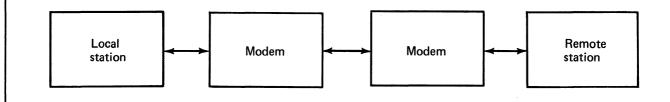

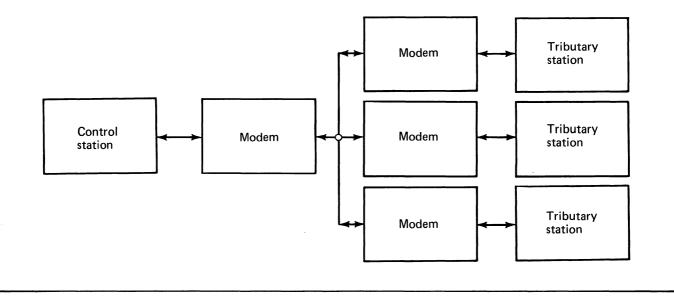

| Communications with Remote Devices and Computers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | • | • | 63       |

| Communications' Protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | • | • |   | 63       |

| Communications' Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • | • | • | 63<br>68 |

| Communications software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • | • | · | 68       |

| Communications to an iDM System/S/U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • | • | • | 00       |

۷

| Auxiliary Storage Devices                      | •••    |       |   |   |   | . 69  |

|------------------------------------------------|--------|-------|---|---|---|-------|

| Disks                                          |        |       |   |   |   | . 69  |

| Diskettes                                      |        |       | • |   |   | . 69  |

| Large-Volume Diskette                          |        |       |   |   |   | . 70  |

| User Attachment Features                       |        |       |   |   |   |       |

| Asynchronous Terminals                         |        |       |   |   |   |       |

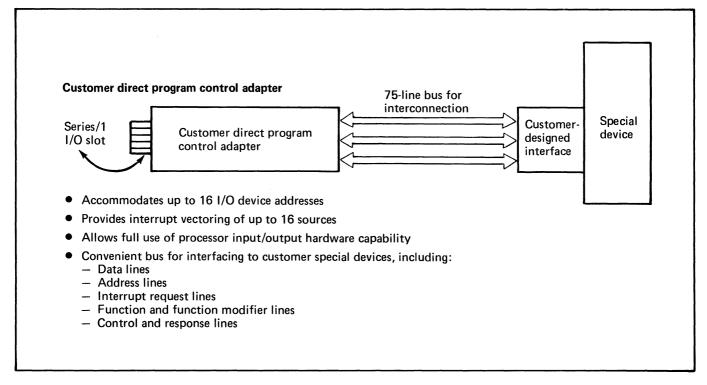

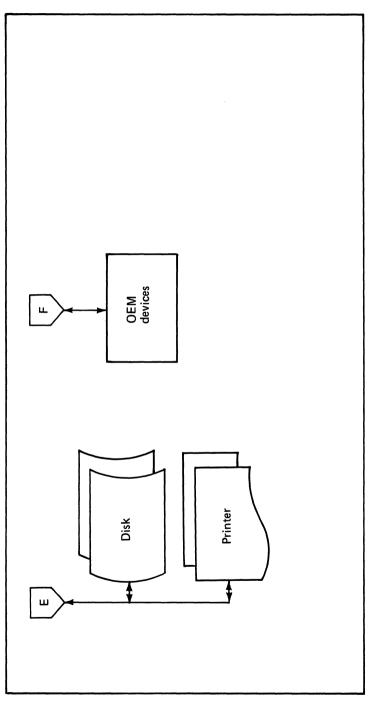

| OEM Devices                                    |        |       |   |   | • | . 76  |

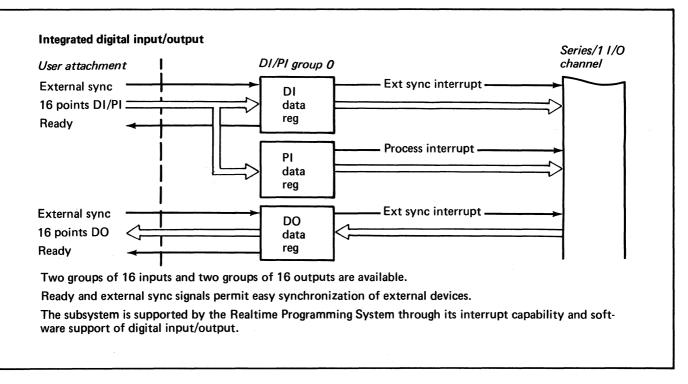

| Sensor-Based Devices                           |        |       |   |   |   |       |

| Multiple Processors and a Shared Input/Outp    |        |       |   |   |   |       |

|                                                |        |       |   |   |   |       |

| Program Preparation Facilities                 | •••    | •••   | • | • | • | . 79  |

| Chapter 3. Processor Organization              |        | •••   |   | • |   | . 81  |

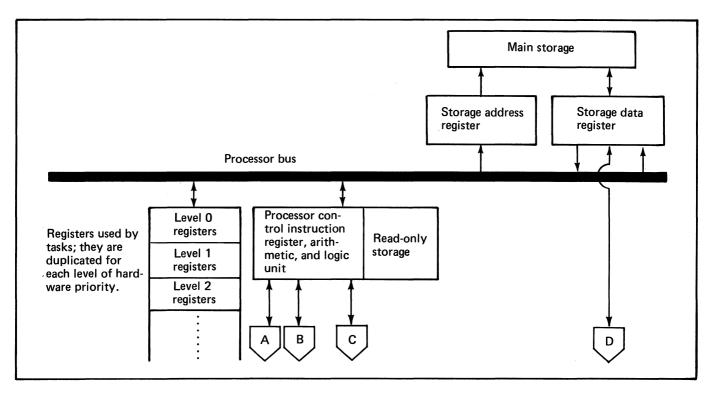

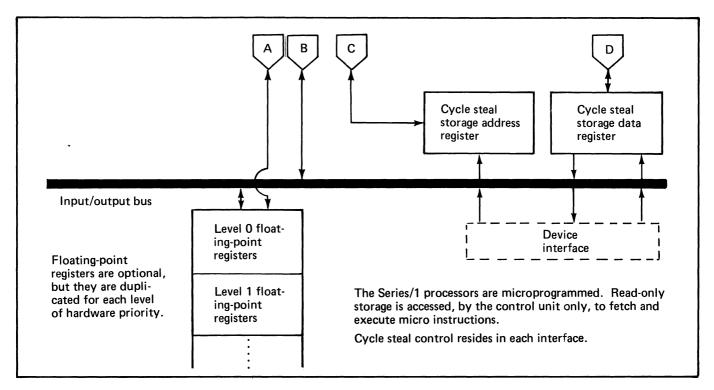

| Overall Flow of Information in the Series/1 P  | roces  | sors  |   |   |   |       |

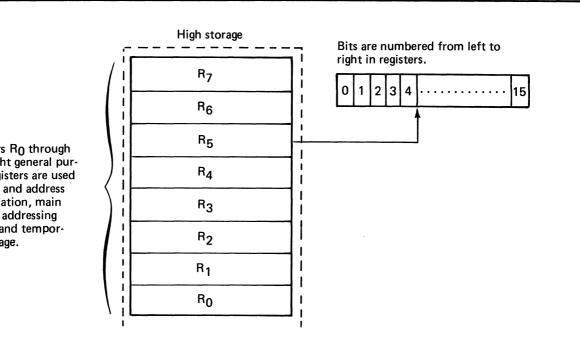

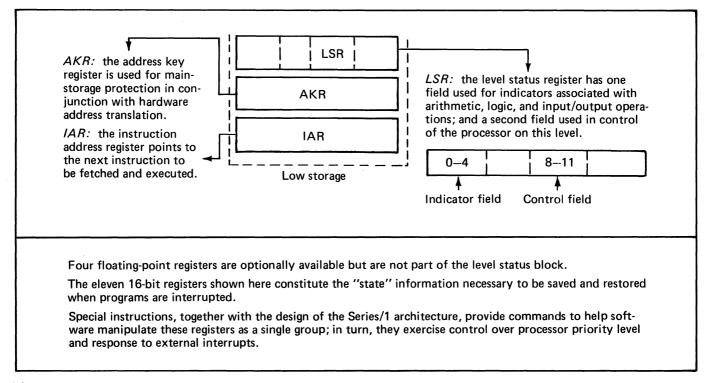

| Registers and Their Use by Tasks               |        | • •   | • |   |   | . 87  |

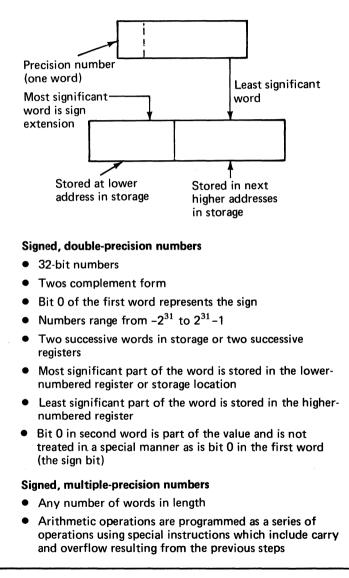

| Storage and Manipulation of Data Types .       |        |       |   |   |   | . 90  |

| Logical or Flag Variables                      |        |       |   |   |   | . 90  |

| Character Variables                            |        |       |   |   |   | . 90  |

| Unsigned and Signed Numbers of Various         | Precis | sions |   |   |   | . 91  |

| Floating-Point Numbers with Two Precisio       | ons    |       |   |   | • | . 91  |

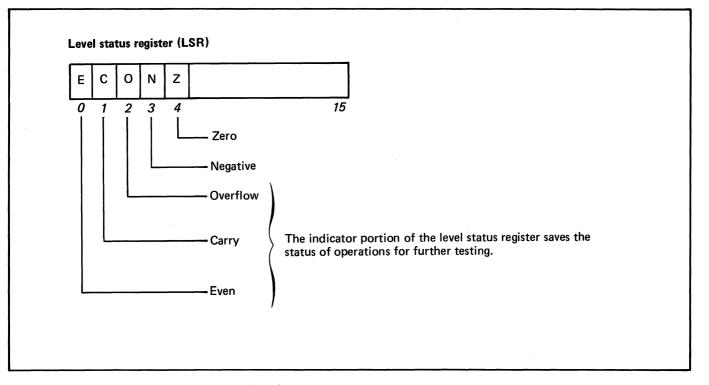

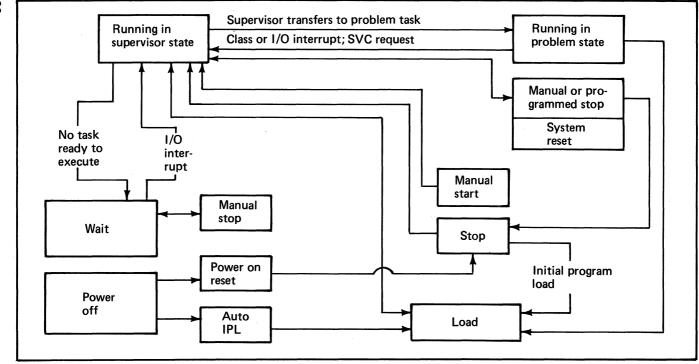

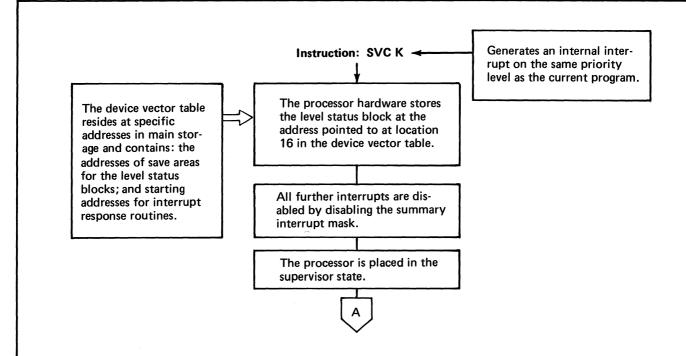

| Processor States and the Interrupt System      |        |       |   |   |   |       |

| Initial Program Load (IPL) State               |        |       |   |   |   | . 99  |

| Stop State                                     |        |       |   |   |   | . 100 |

| Wait State                                     |        |       |   |   |   | . 100 |

| Load State                                     |        |       |   |   |   | . 101 |

| Supervisor and Problem States                  |        |       |   |   |   |       |

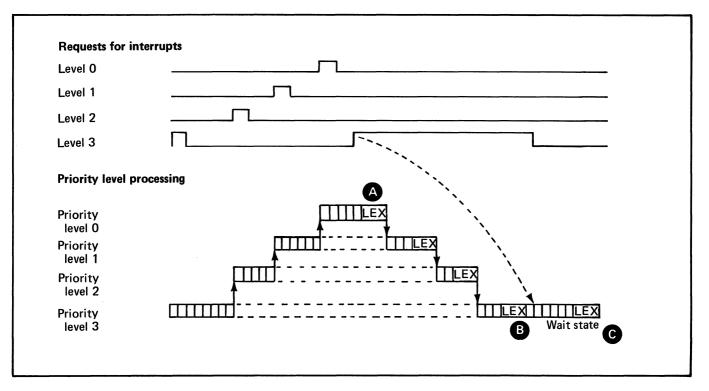

| Effect of Interrupts on the Processor State    |        |       |   |   |   |       |

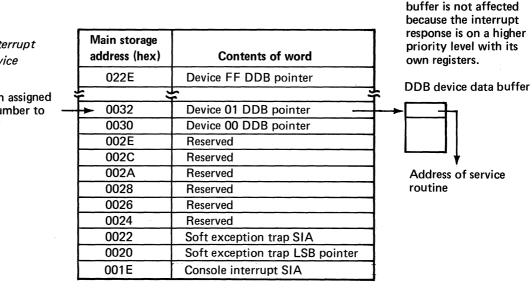

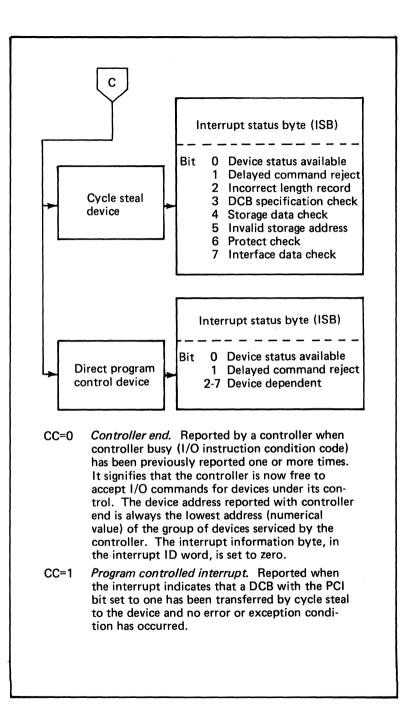

| Input/Output Interrupts                        |        |       |   |   |   | . 102 |

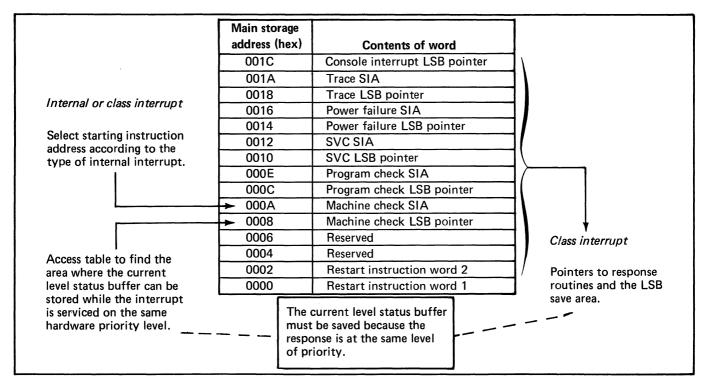

| Internal or Class Interrupts                   |        |       |   |   |   |       |

| Different Responses to the Two Types of        |        |       |   |   |   |       |

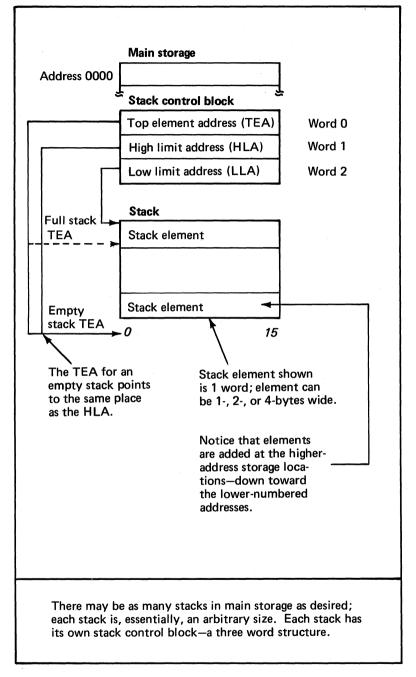

| Class Interrupts in the Use of Stacks          |        |       |   |   |   |       |

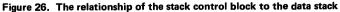

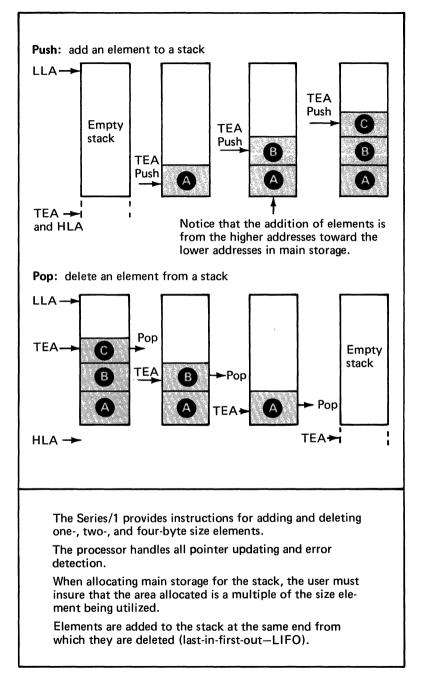

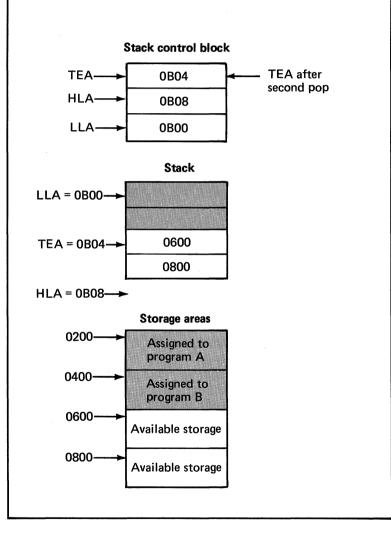

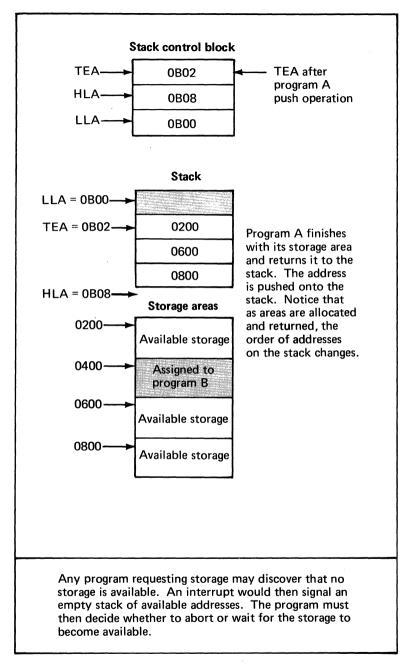

| Data Stacking Description                      |        |       |   |   |   | . 107 |

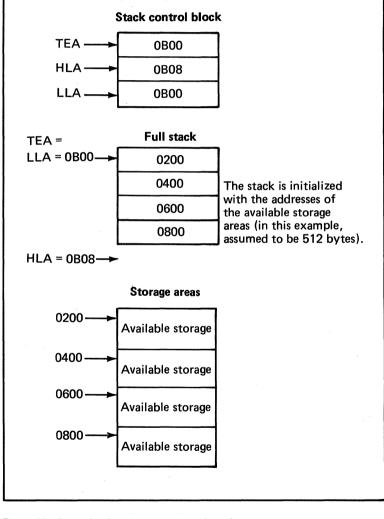

| Data Stacking Example-Allocating Fixed         |        |       |   |   |   |       |

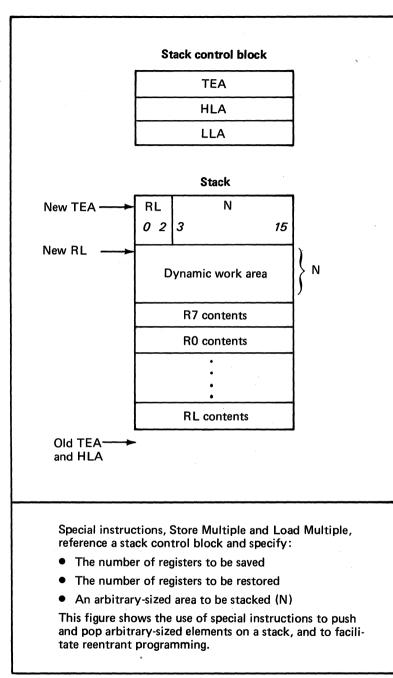

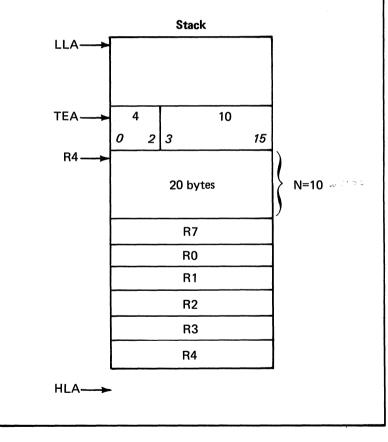

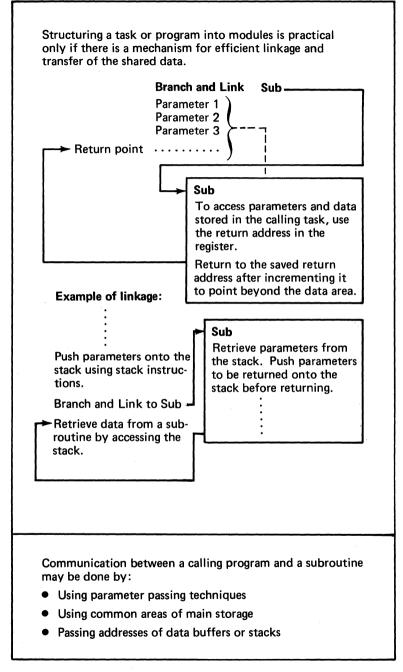

| Linkage Stacking Description                   |        |       |   |   |   |       |

| Linkage Stacking Example-Reentrant Sub         |        |       |   |   |   |       |

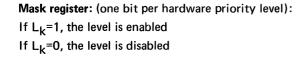

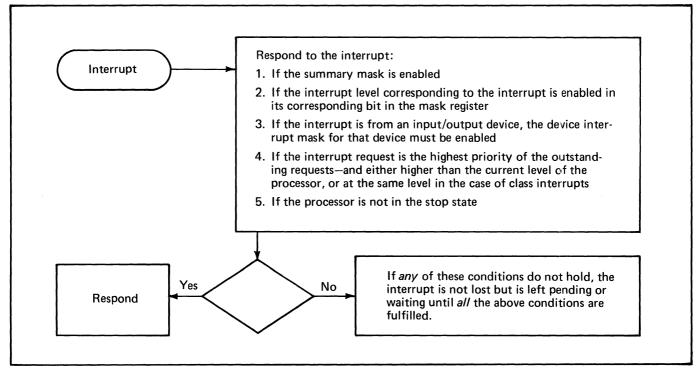

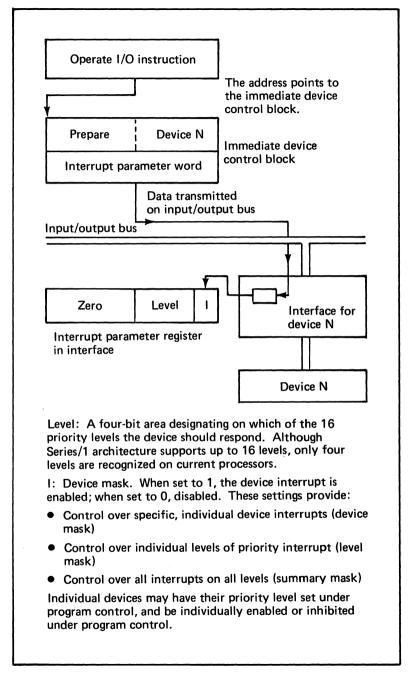

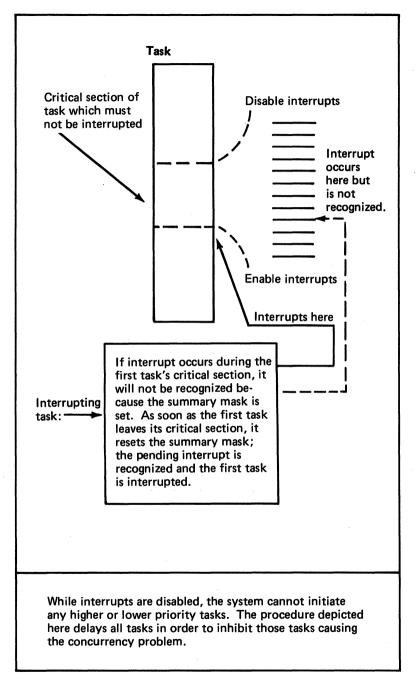

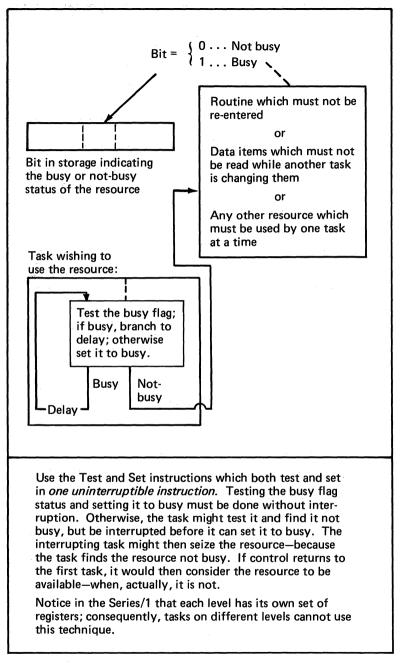

| Interrupt Masking Facilities and the Interrupt |        |       |   |   |   |       |

| Algorithm                                      |        |       |   |   |   | . 125 |

| Summary Mask                                   |        |       |   |   |   |       |

| Disabled (Set to Zero)                         |        |       |   |   |   |       |

| Enabled (Set to One)                           | •••    |       | • | • | • | . 130 |

| Interrupt Level Mask Register                  | •••    | • •   |   |   |   | . 130 |

| Device Mask                                    |        |       |   |   |   |       |

| Chapter 4. Organization and Mar  |       |     |      |     |     |          |    |    |   |   |    |                |

|----------------------------------|-------|-----|------|-----|-----|----------|----|----|---|---|----|----------------|

| User Concerns in Main Storage O  | rga   | niz | ati  | on  |     |          |    |    |   |   |    | . 133          |

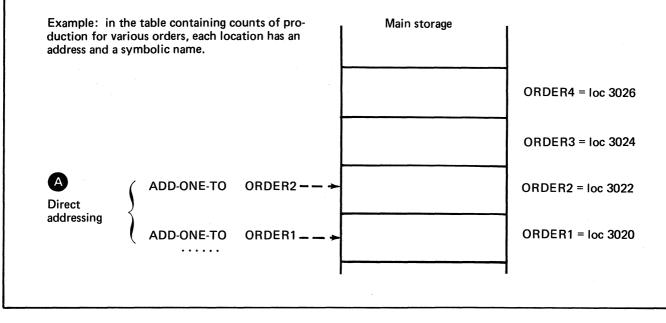

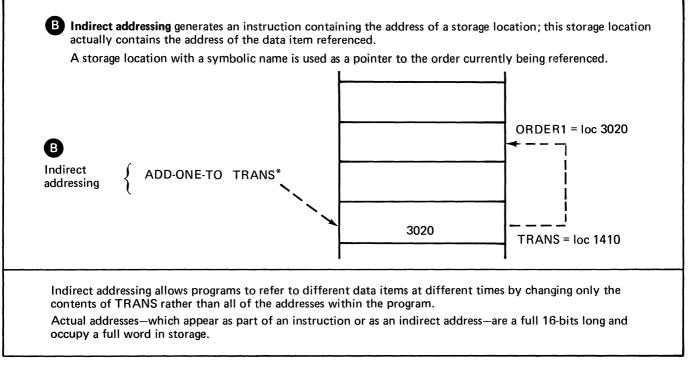

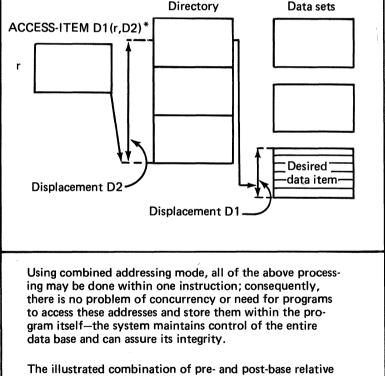

| Main Storage Addressing Mode     |       |     |      |     |     |          |    |    |   |   |    | . 135          |

| Direct and Indirect              | •     |     |      |     |     |          |    | •  |   |   | •  | . 136          |

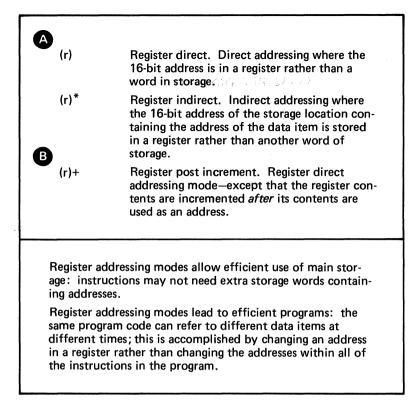

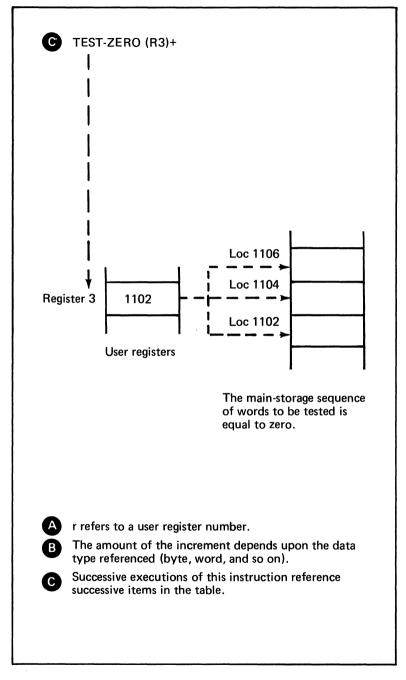

| Register Modes                   |       |     |      |     |     |          |    |    |   |   |    | . 137          |

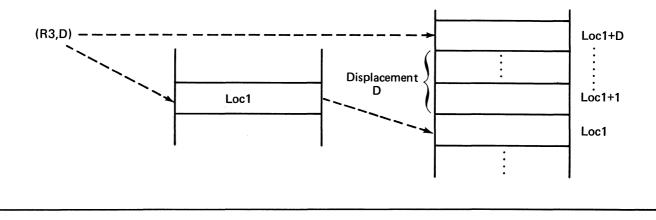

| Based Addressing                 | •     |     |      |     |     |          |    |    |   |   |    | . 141          |

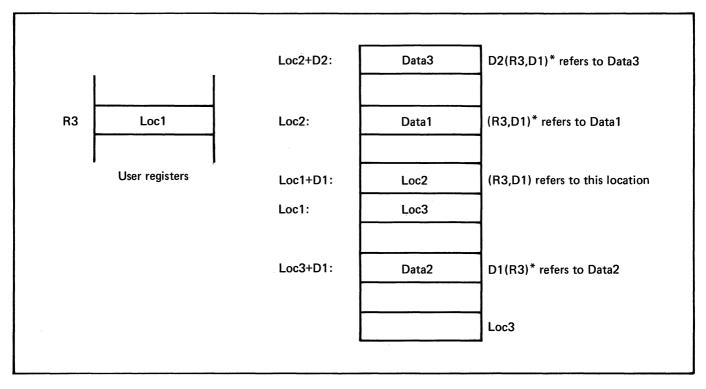

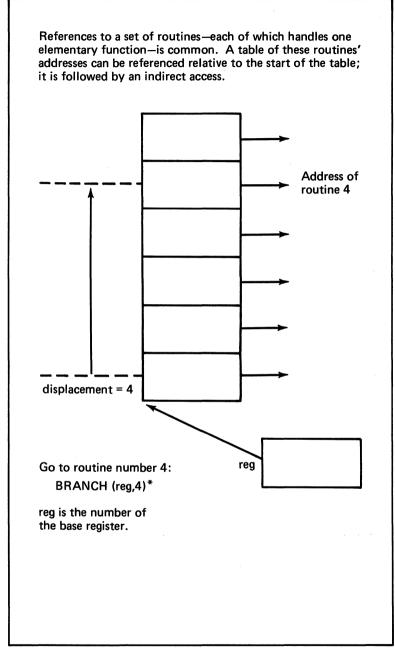

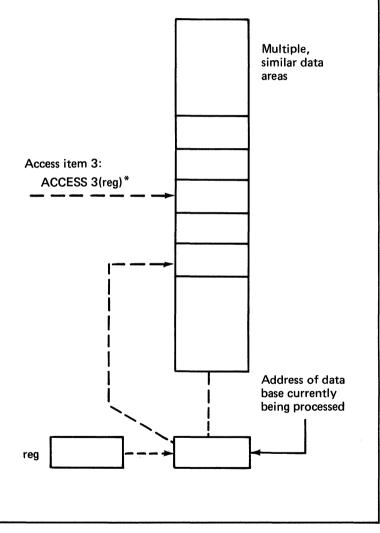

| Indirect and Base Relative .     | •     | •   |      | •   |     | •        |    | •  |   |   | •  | . 142          |

| Excluded Modes                   |       | •   |      |     | •   | •        | •  | •  |   |   | •  | . 151          |

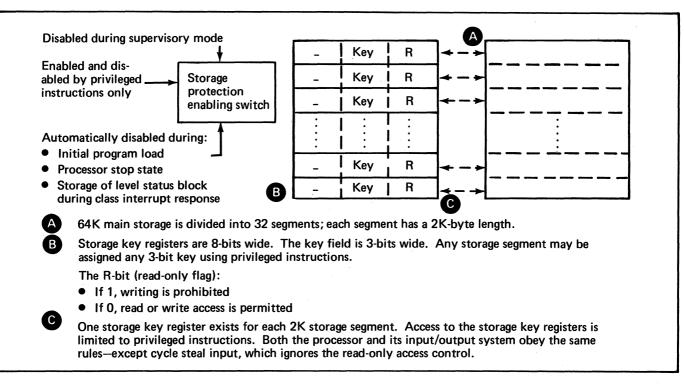

| Main Storage Protection .        | •     |     |      |     | •   |          | •  | •  |   |   |    | . 152          |

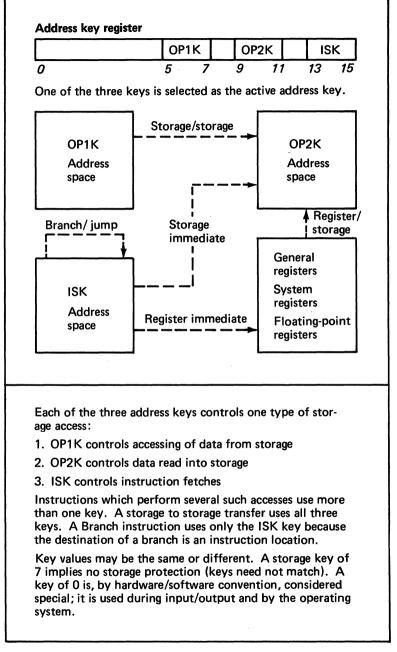

| Address Key Protection .         |       |     |      |     |     | •        | •  | •  |   |   |    | . 152          |

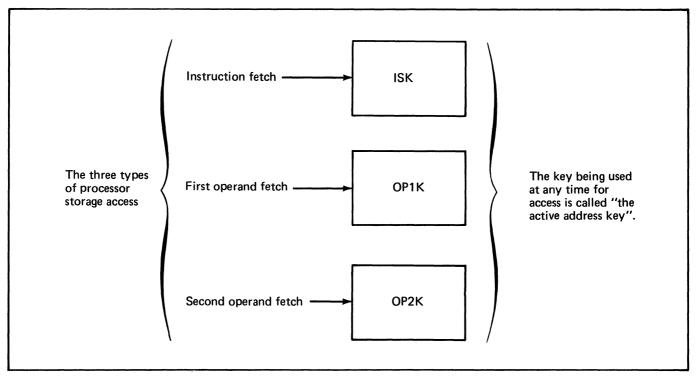

| Storage Access Types             | •     | •   |      |     |     |          |    |    |   |   |    | . 153          |

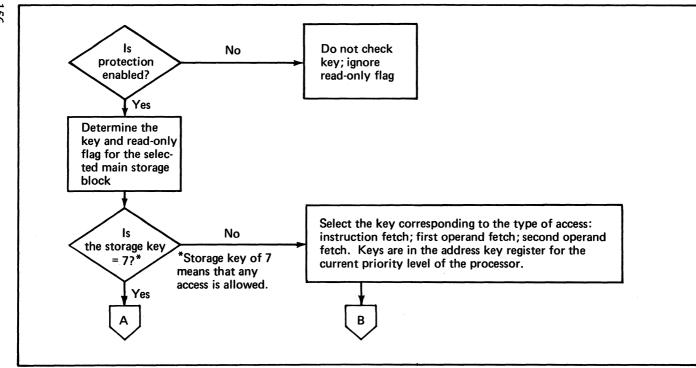

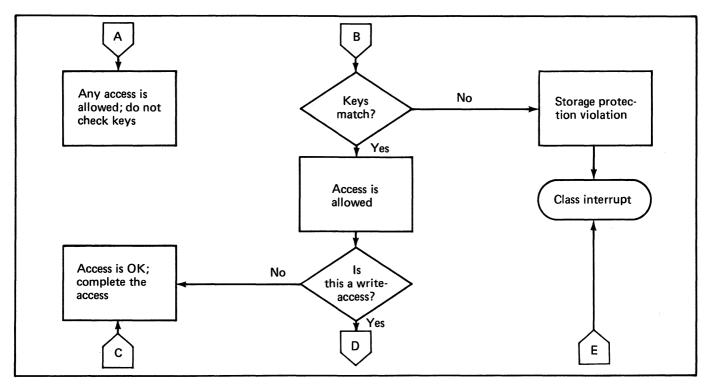

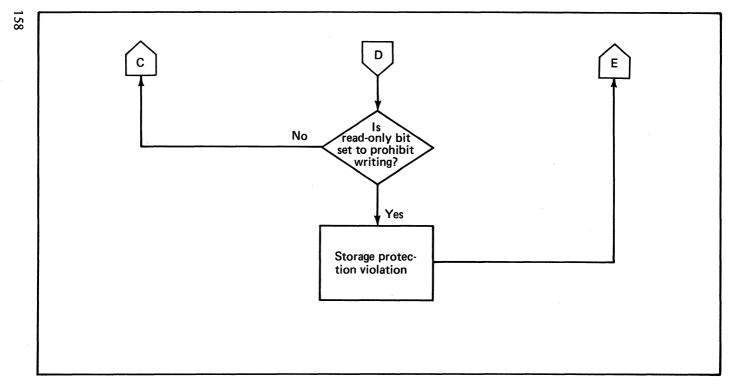

| Storage Access Checking .        |       |     |      |     |     |          |    | •  |   |   | •  | . 153          |

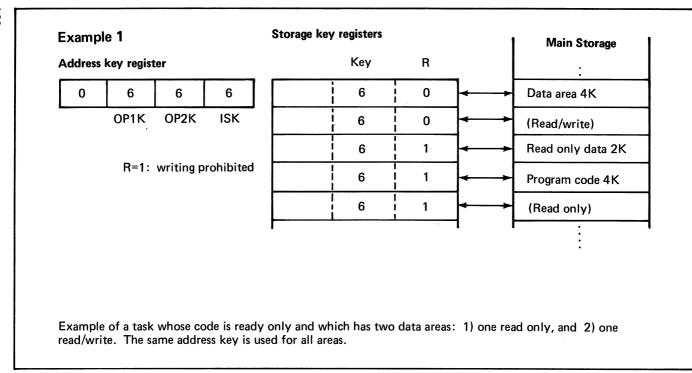

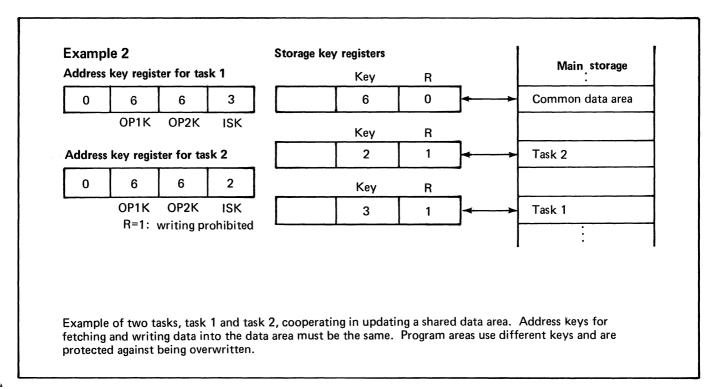

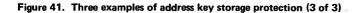

| Multiple Task Protection .       |       | •   |      |     | •   |          |    |    |   |   |    | . 159          |

| Main Storage Mapping System      | IS    | •   |      |     | •   |          |    |    |   |   |    | . 161          |

| Storage Segmentation             |       | •   | •    |     | •   |          |    | •  |   |   |    | . 161          |

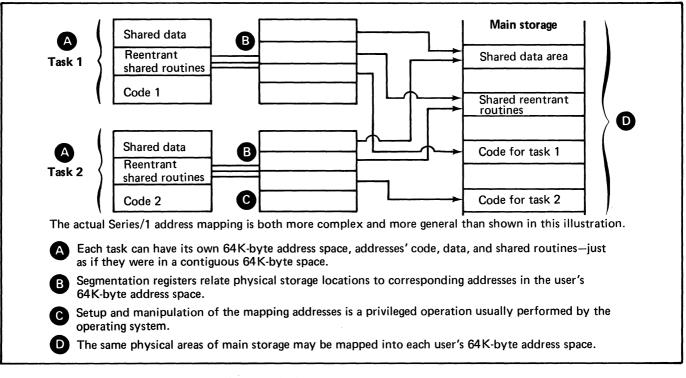

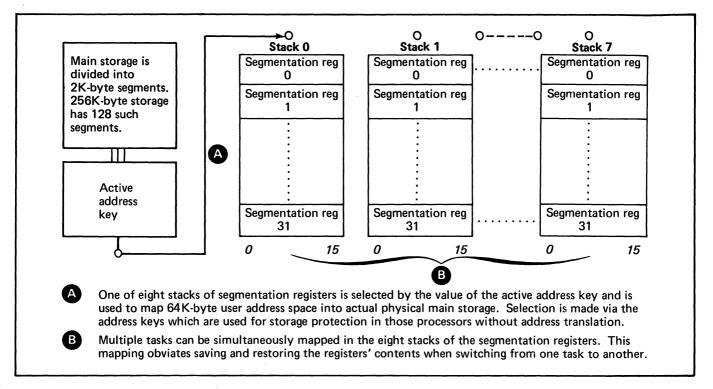

| Mapping Multiple Tasks .         |       |     |      |     |     | •        |    |    |   |   |    | . 165          |

| Mapped Storage Protection        |       |     |      |     |     |          |    |    |   |   |    | . 168          |

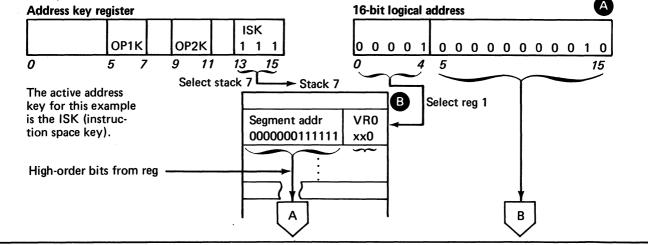

| Segmentation Registers           |       | •   |      |     |     | •        | •  |    |   |   |    |                |

| User Address Spaces              |       |     |      |     |     |          |    |    |   |   |    | . 170          |

| Protection Violations            |       |     |      |     |     |          |    |    |   |   |    |                |

| Intertask Communications .       |       |     |      |     |     |          |    |    |   |   |    | . 171          |

| Tasks and the Operating Syste    | m     |     |      |     | •   |          |    |    |   |   |    | . 175          |

| Tasks and Separate Data .        | •     | •   | •    |     |     |          |    |    |   |   |    | . 175          |

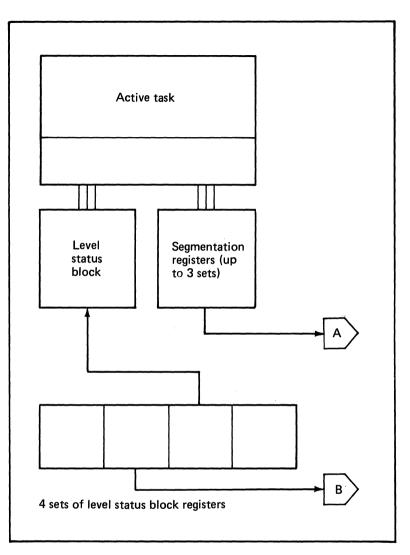

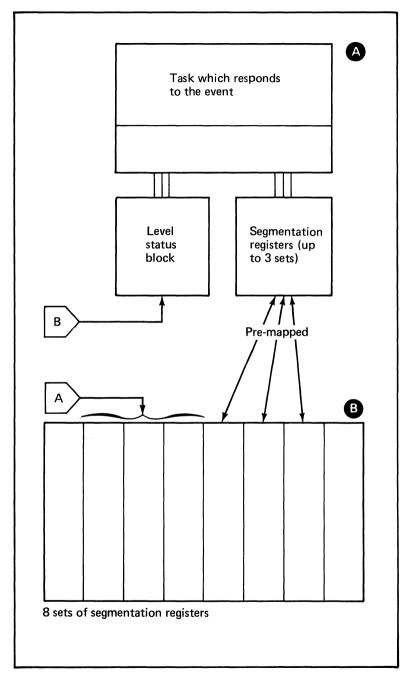

| Task Switching                   |       |     |      |     |     |          |    |    |   |   |    |                |

| Auxiliary Storage Managemen      |       |     |      |     |     |          |    |    |   |   |    | . 179          |

| Storage Overlay Management       |       |     |      |     |     |          |    |    |   |   |    | . 186          |

|                                  |       |     |      |     |     |          |    |    |   |   |    |                |

| Chapter 5. Organization and Mar  |       |     |      |     |     |          |    |    |   |   |    |                |

| Input/Output System              |       |     |      |     |     |          |    |    |   |   |    |                |

| Important Factors in Computer I  |       |     |      |     |     |          |    |    |   |   |    |                |

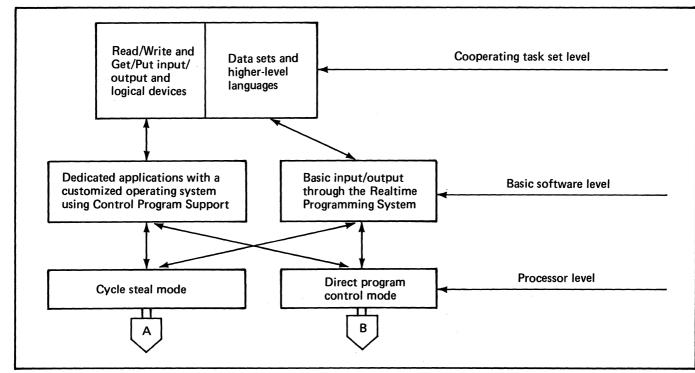

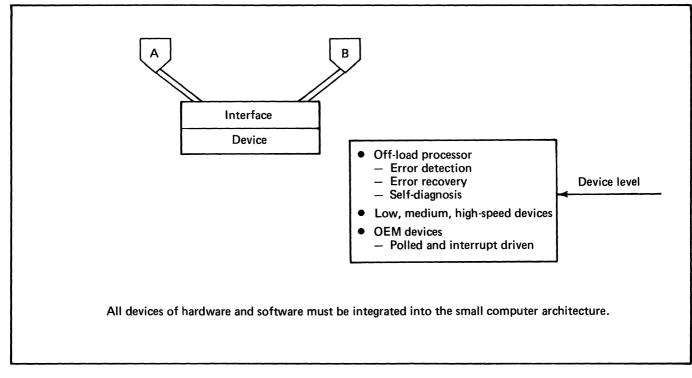

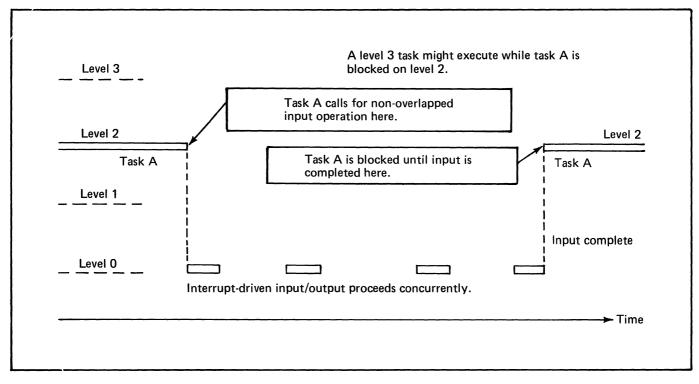

| Processor Level                  | • •   |     | •    | •   | •   | •        | •  | •  | • |   |    |                |

| The Basic Software Level         | • • • |     | •    | •   | •   | •        | •  | •  | • | • | •  | . 191<br>. 194 |

| The Cooperating Task Set Lev     | el    |     | •    | •   | •   | •        | •  | •  | • | • | •  | . 194          |

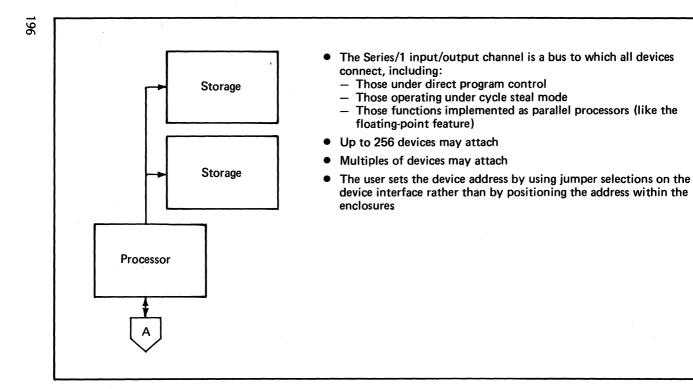

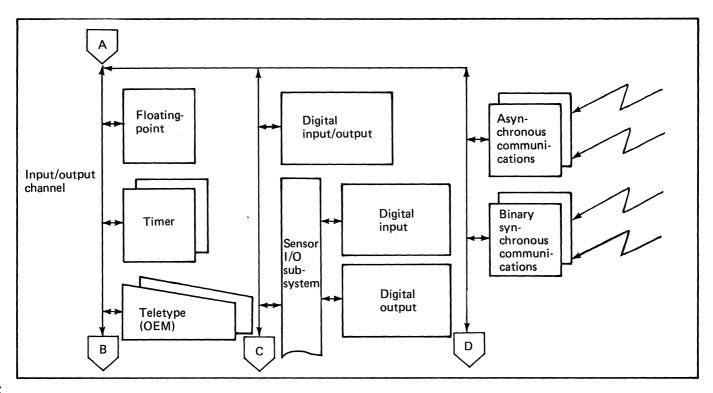

| Overview of the Series/1 Input/O | utp   | ut  | Ch   | anr | nel |          | •  | •  | • | • | •, | . 195          |

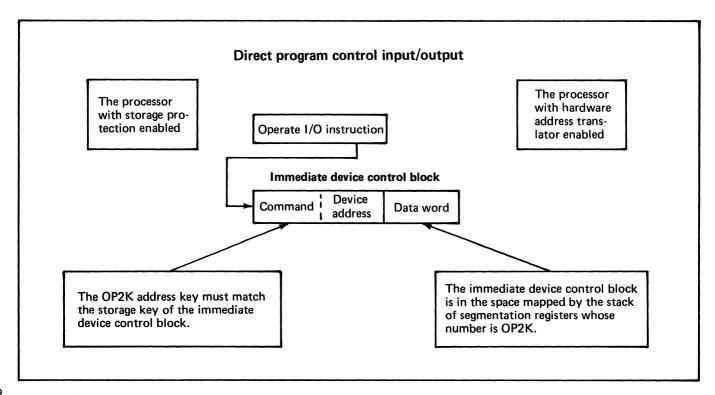

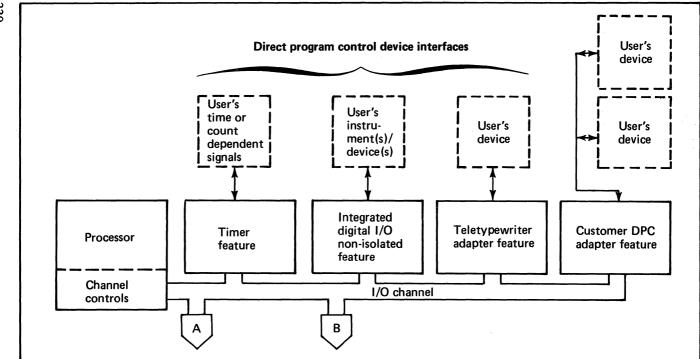

| Input and Output Under Direct P  |       |     |      |     |     |          |    |    |   |   |    |                |

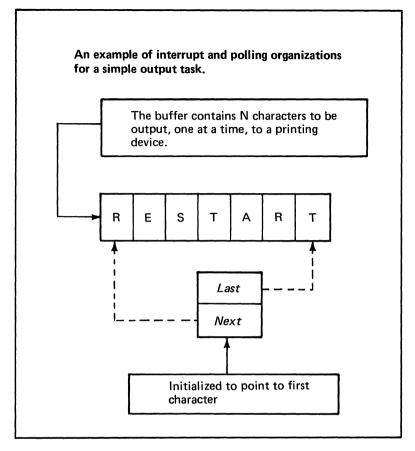

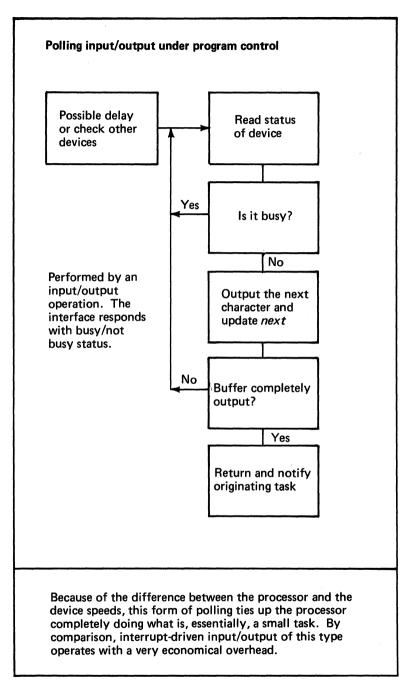

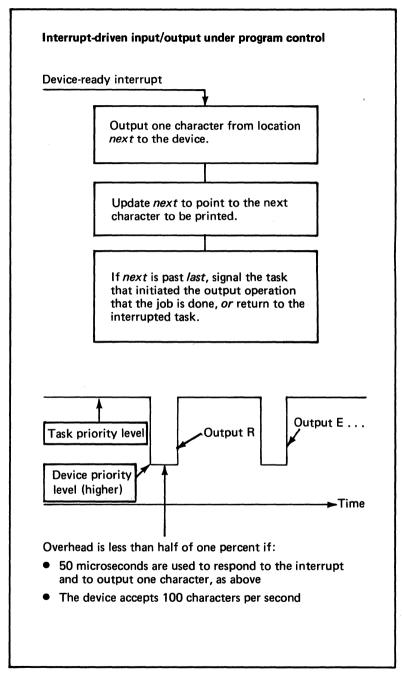

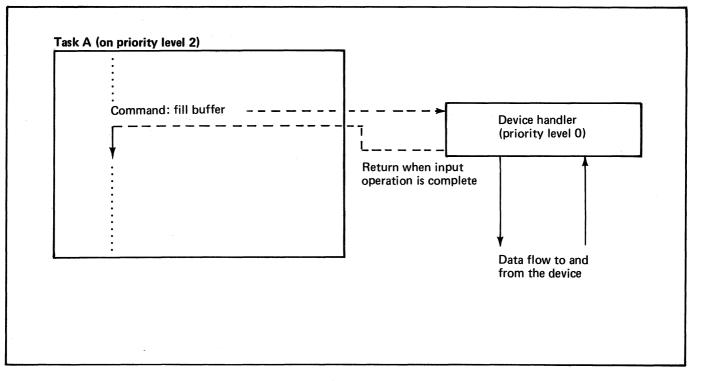

| Polling vs. Interrupt-Driven In  |       |     |      |     |     |          |    |    |   |   |    | . 208          |

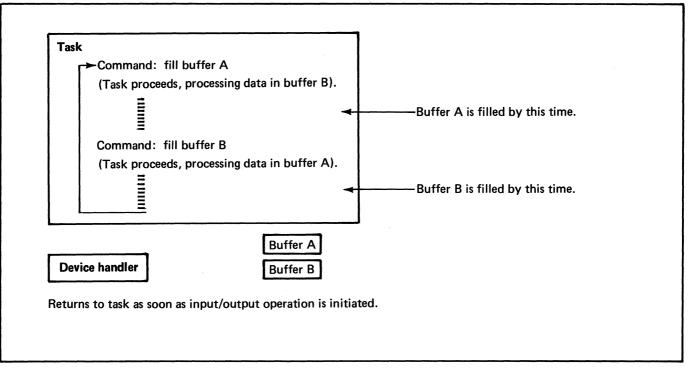

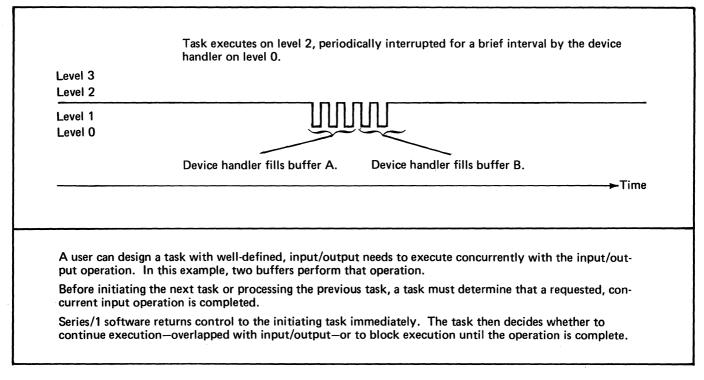

| Effects of Buffering on Task E   |       |     |      |     |     |          |    |    |   |   |    |                |

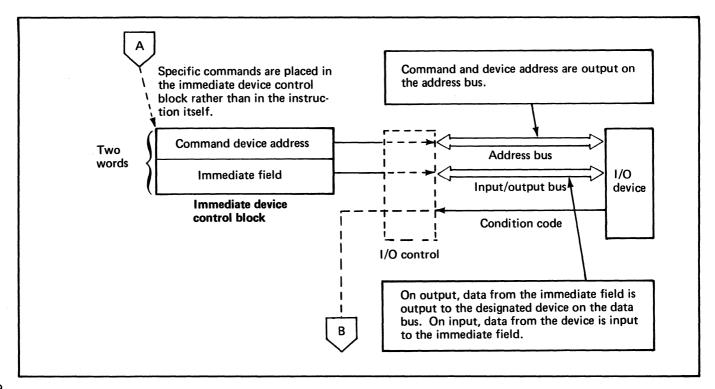

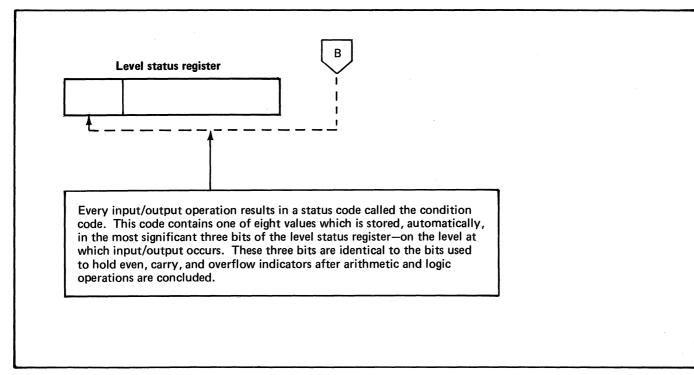

| Direct Program Control Instru    | ctic  | ons |      | •   | •   | •        | •  | •  | • | • | •  | . 216          |

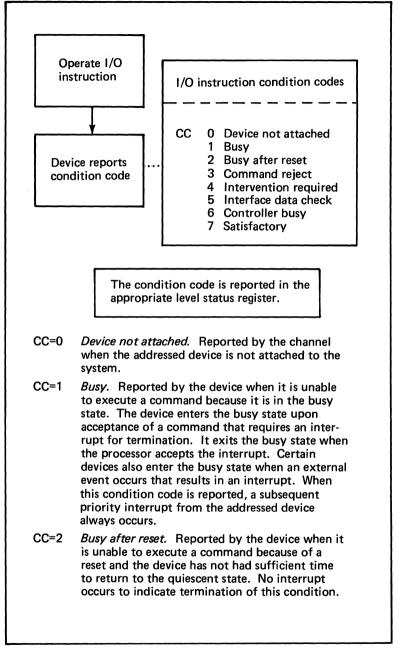

| Error Detection and Reporting    |       |     |      |     |     |          |    |    |   |   |    |                |

| Overall Operation of Direct Pr   |       |     |      |     |     |          |    |    |   |   |    |                |

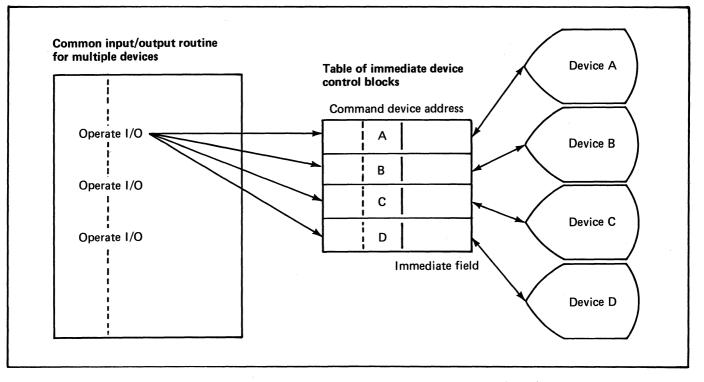

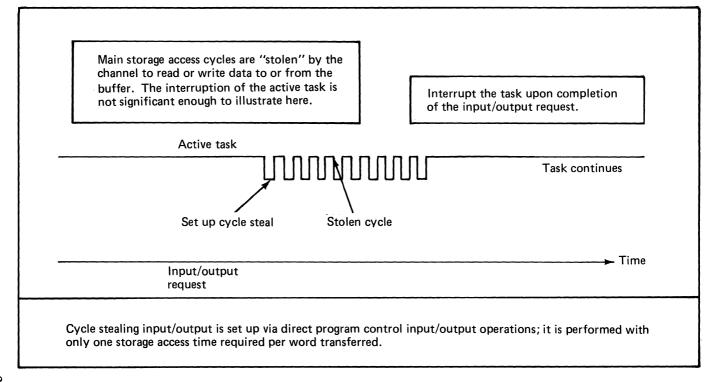

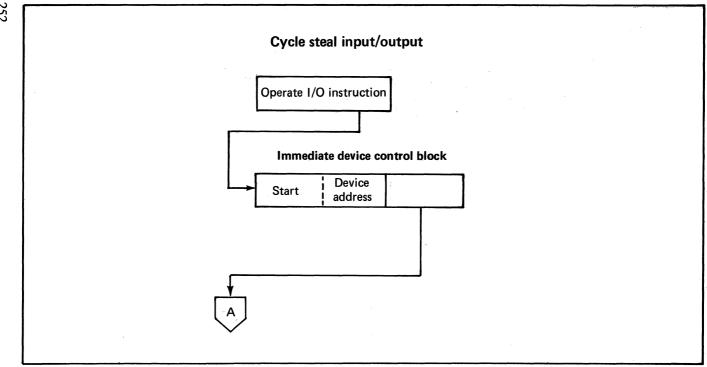

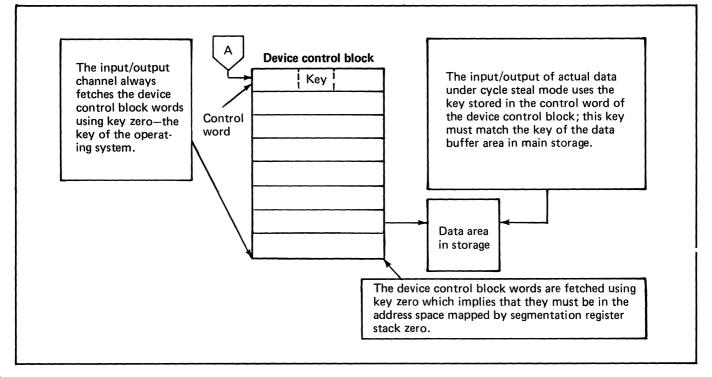

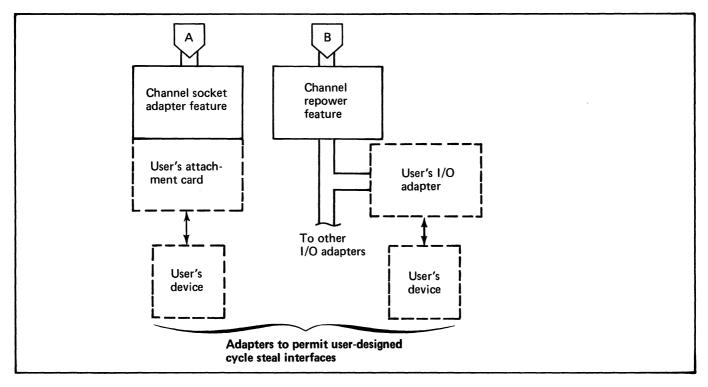

| Input and Output in the Cycle St | eali  | ng  | Mo   | ode |     | •        | •  | •  | • | • | •  | . 233          |

| Use of Microprocessors in Cyc    | le S  | tea | al C | Con | tro | ller     | 'S | •  | • | • | •  | . 238          |

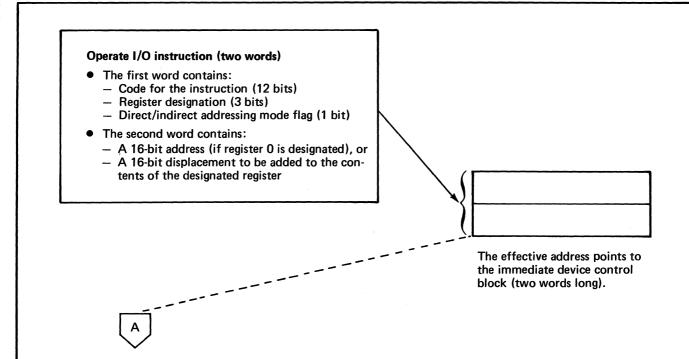

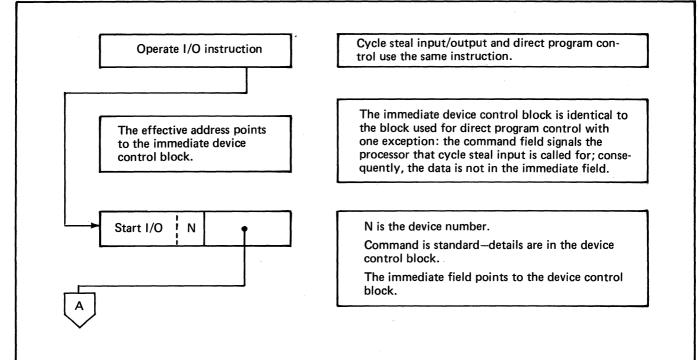

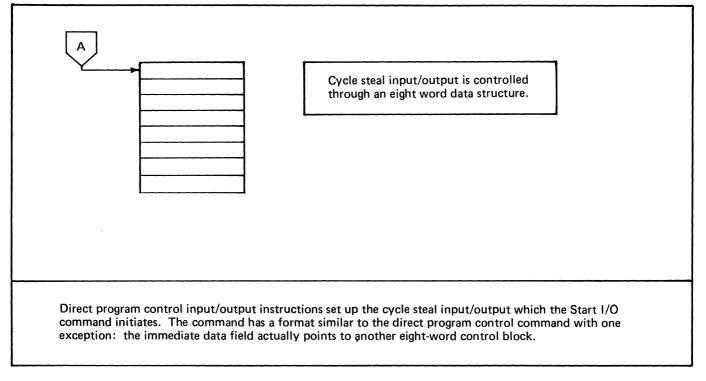

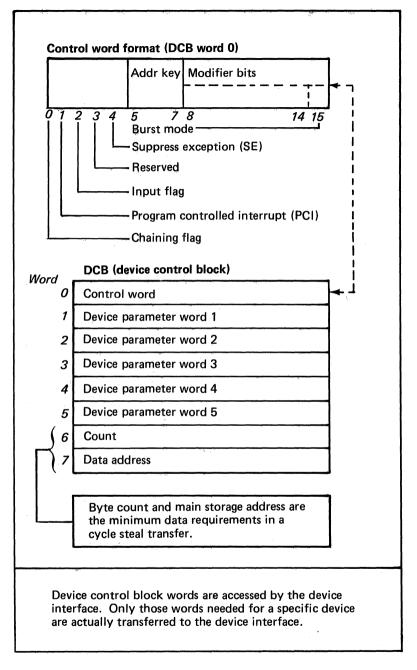

| Cycle Steal Input/Output Inst    | ruc   | tio | ns a | and | Co  | <b>m</b> | ma | nd | 5 | • | •  | . 239          |

| Input/Output Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Storage Protection and Address Translation Effects on      |       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------|

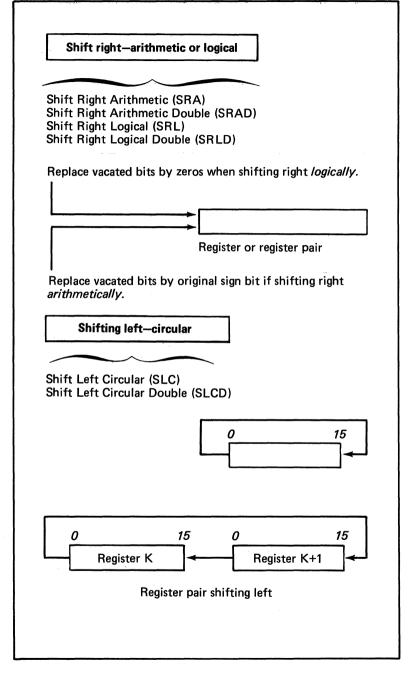

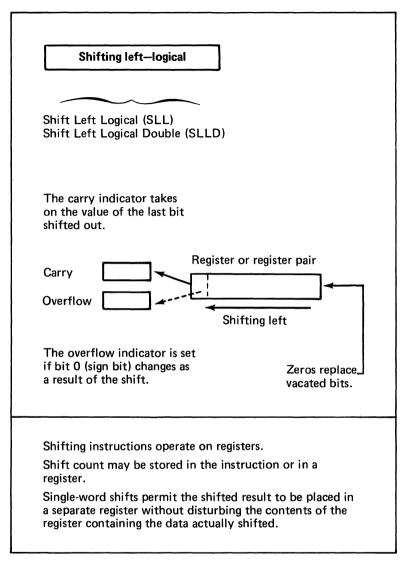

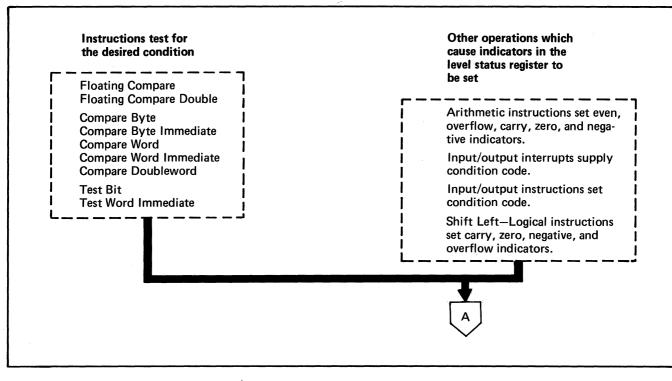

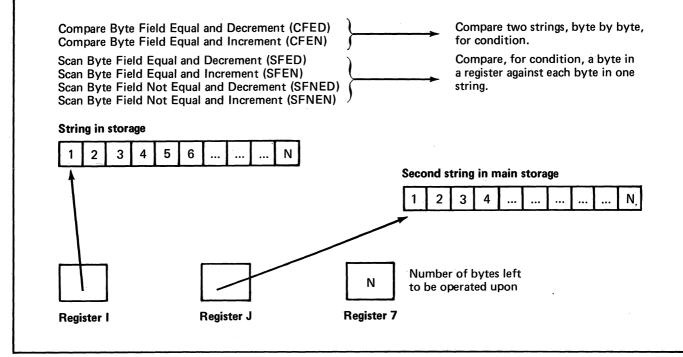

| Storage Protection With Address Translation250Software Use of Input/Output Hardware255Control Program Support of Input/Output255Operating System Support of Input/Output270Chapter 6. The Instruction Set and Its Use278Instruction Formats282Instruction Suged for Data Movement284Basic Data Movement Instructions287Floating-Point Data Movement Instructions287String-Data Movement Instructions290Special Data-Type Movement Instructions291Instructions Used for Arithmetic and Logical Operations291Numeric Data Operations295Logical Data Operations295Shifting Data Operations295Shifting Data Operations302Instructions Associated with Testing Operations' and301Interruptible and Non-Interruptible Testing Instructions303Conditional Transfer Instructions302Bit and Field Testing Instructions302Serializing Resource Usage312Application Software Modularizing312Serializing Resource Usage326Importance of the Processor Input/Output Architecture327Timers and Their Use329Interval Timing336Pulse Rate Measurement336Pulse Rate Measurement336Pulse Rate Measurement336Pulse Rate Measurement342Three Detection344 | Input/Output Operations                                    | . 249 |

| Software Use of Input/Output Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Storage Protection Without Address Translation             | . 249 |

| Software Use of Input/Output Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Storage Protection With Address Translation                | . 250 |

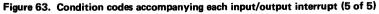

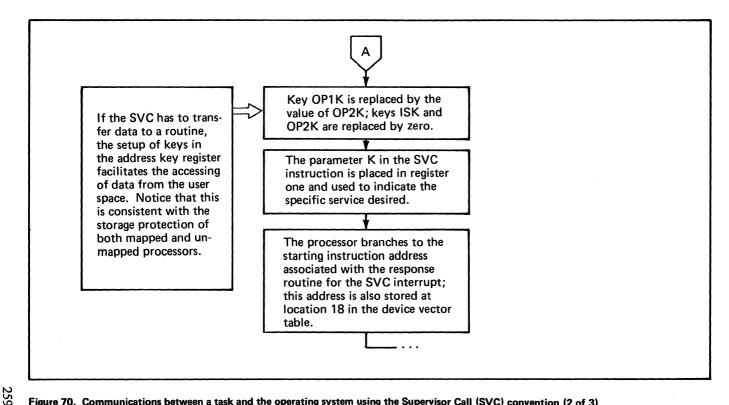

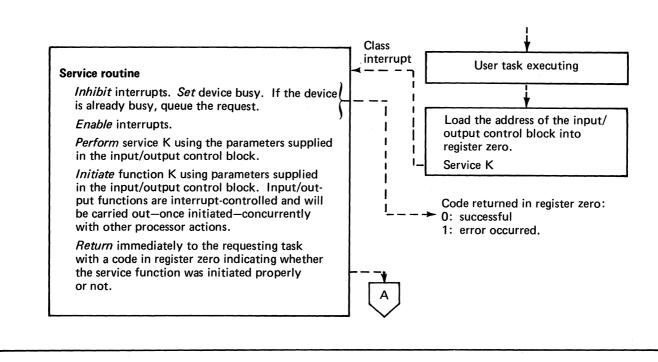

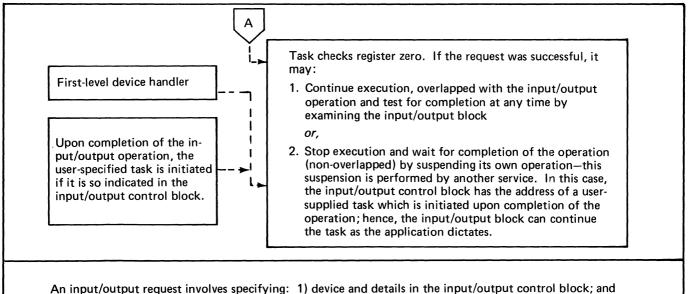

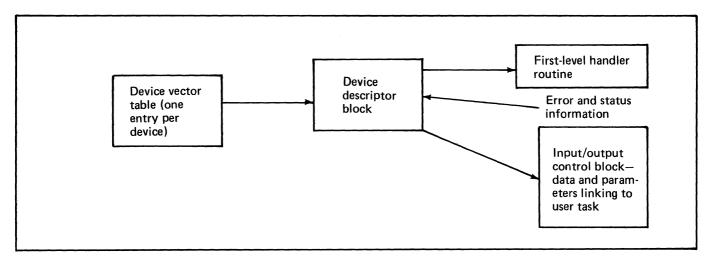

| Operating System Support of Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Software Use of Input/Output Hardware                      | . 255 |

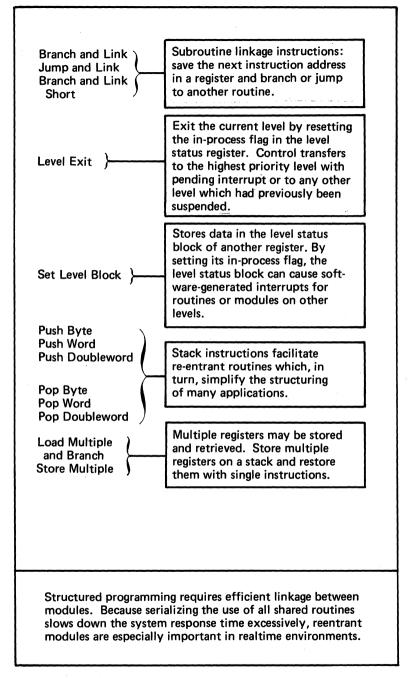

| Chapter 6. The Instruction Set and Its Use278Instruction Formats282Instructions Used for Data Movement284Basic Data Movement Instructions287Floating-Point Data Movement Instructions287String-Data Movement Instructions290Special Data-Type Movement Instructions290Instructions Used for Arithmetic and Logical Operations291Numeric Data Operations294Floating-Point Data Operations295Logical Data Operations295Shifting Data Operations296Instructions Associated with Testing Operations' and296Computations' Status301Interruptible and Non-Interruptible Testing Instructions302Bit and Field Testing Instructions303Conditional Transfer Instructions307Instructions Associated with Structured Programming and312Control of Concurrency312Serializing Resource Usage326Importance of the Processor Input/Output Architecture327Importance of System Software Architecture327Importance of System Software Architecture327Importance of System Software Architecture326Interval Timing336Pulse Duration Measurement342Error Detection342The Teletypewriter Interface343                                                     |                                                            |       |

| Instruction Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Operating System Support of Input/Output                   | . 270 |

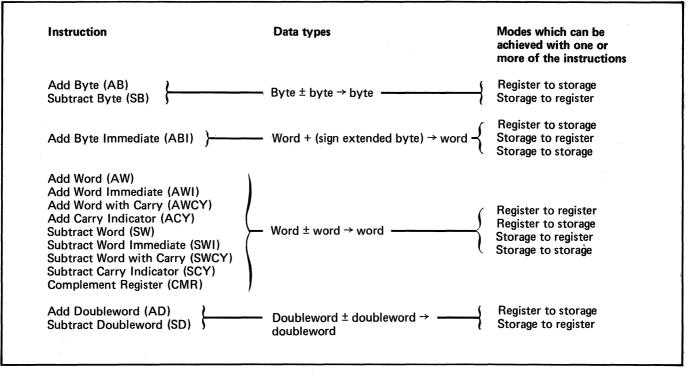

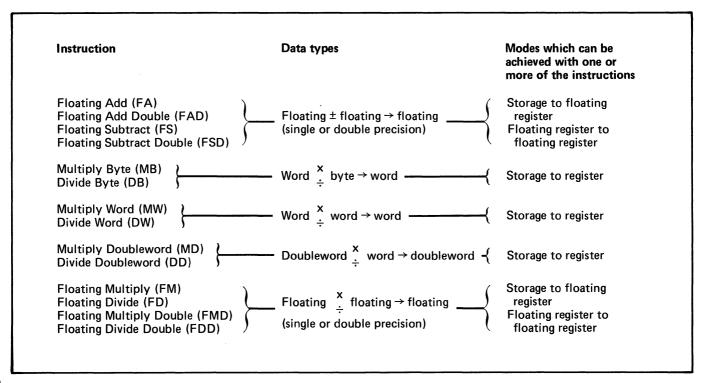

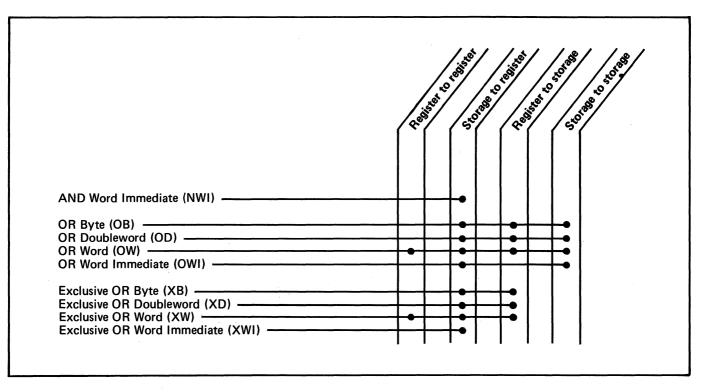

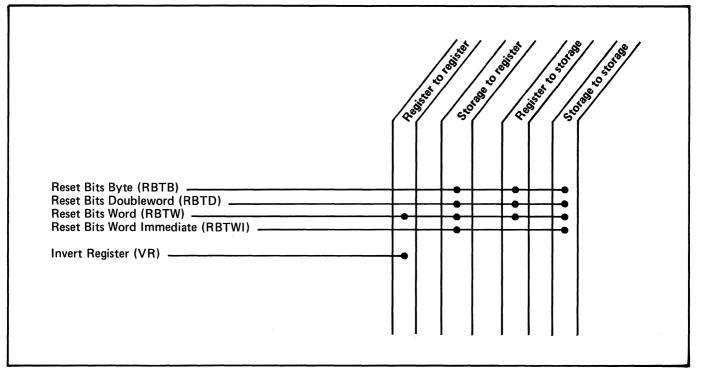

| Instructions Used for Data Movement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chapter 6. The Instruction Set and Its Use                 | . 278 |

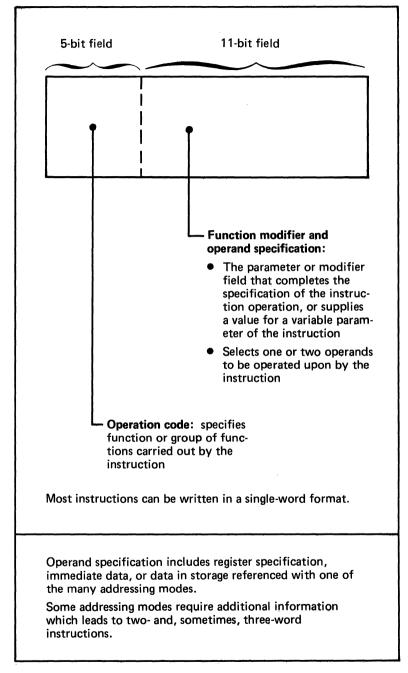

| Instructions Used for Data Movement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Instruction Formats                                        | . 282 |

| Floating-Point Data Movement Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            |       |

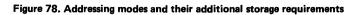

| Floating-Point Data Movement Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Basic Data Movement Instructions                           | . 287 |

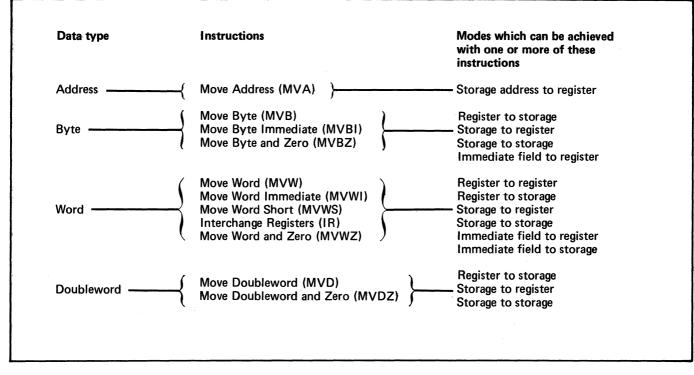

| Special Data-Type Movement Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                            |       |

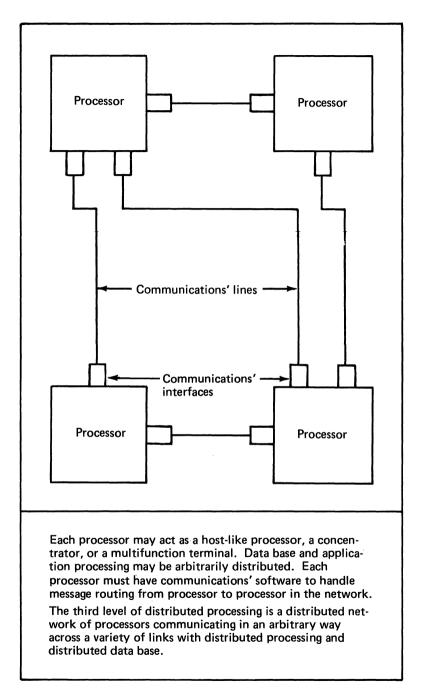

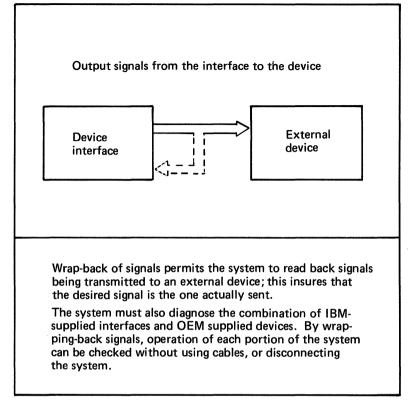

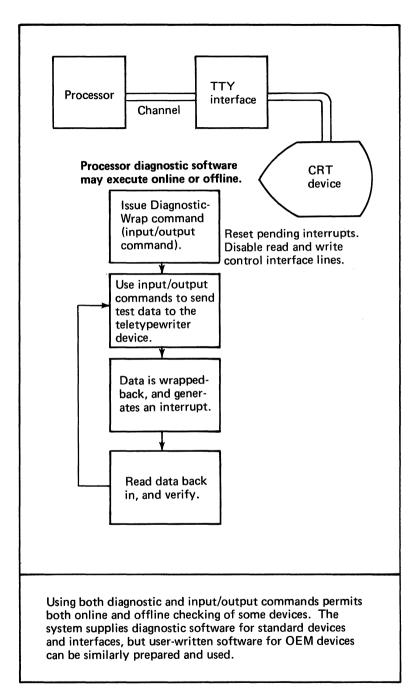

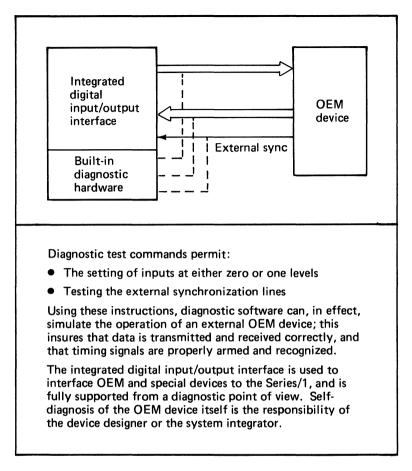

| Special Data-Type Movement Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | String-Data Movement Instructions                          | . 290 |