# IBM

Series/1

GC34-0317-0 File No. S1-21 LICENSED PROGRAM

IBM Series/1 Event Driven Executive Macro Assembler Reference

Program Number 5719-ASA

C

LICENSED PROGRAM

IBM Series/1 Event Driven Executive Macro Assembler Reference

Program Number 5719-ASA

#### First Edition (April 1979)

This edition applies to Version 1 of the IBM Series/1 Event Driven Executive Macro Assembler, Program Number 5719-ASA.

Use this publication only for the purpose stated in the Preface.

Changes are periodically made to the information herein; any such changes will be reported in subsequent revisions or Technical Newsletters.

Publications are not stocked at the address given below. Requests for copies of IBM publications should be made to your IBM representative or the IBM branch office serving your locality.

This publication could contain technical inaccuracies or typographical errors. A form for readers' comments is provided at the back of this publication. If the form has been removed, address your comments to IBM Corporation, Systems Publications, Department 27T, P.O. Box 1328, Boca Raton, Florida 33432. IBM may use and distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever. You may, of course, continue to use the information you supply

© Copyright International Business Machines Corporation 1979

# What This Manual Can Do For You

This publication is a reference for programmers who use the IBM Series/1 assembler language. It gives specific information about assembler language functions and coding specifications.

## How This Manual Is Organized

- Chapter 1 gives a brief introduction to the assembler and its features.

- Chapter 2 discusses the structure of the assembler language. It also explains the coding rules you must follow in coding an assembler-language program.

- Chapter 3 describes the characteristics of the IBM Series/1 processor. It explains register usage, addressing modes, and other information you should understand to effectively use the assembler.

- Chapter 4 describes the machine instructions. It explains the function of each instruction and how to code it. For most instructions, this chapter gives examples to help you better understand how the instructions work.

- Chapter 5 describes the assembler instructions. It explains what they do and how to code them, then gives examples of their use.

- Chapter 6 describes the macro language. Programming in macro language simplifies coding, reduces the chance for making errors, and ensures that standard sequences of instructions are coded.

- Chapter 7 describes assembler options, the program listing produced by the assembler, and the control statements necessary to run an assembly. It also includes invoking the assembler and object module formats.

- The appendixes cover assembler messages, conversion tables, a priority list for assembler instructions, a summary of constants, and a summary of the macro language.

Each chapter of this publication is a separate module. This organization allows you to use the chapters as published or to combine them with information from other sources.

Each chapter has a detailed table of contents. A master index is included at the end of the manual.

## What You Should Know Before You Begin

You should be familiar with the concepts of modular programming, and you should be experienced in assembler-language coding.

#### **Related Publications**

The following publications may be helpful to you.

*IBM Series/1 Event Driven Executive System Guide*, SC34-0312

IBM Series/1 Event Driven Executive Utilities, Operator Commands, and Program Preparation, SC34-0313

IBM Series/1 Event Driven Executive Language Reference, SC34-0314

IBM Series/1 Event Driven Executive Communications Guide, SC34-0316

IBM Series/1 Event Driven Executive Reference Summary, SX34-0101

IBM Series/1 Event Driven Executive Internal Design, LY34-0168

•

# Contents

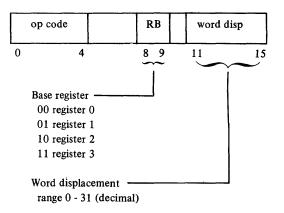

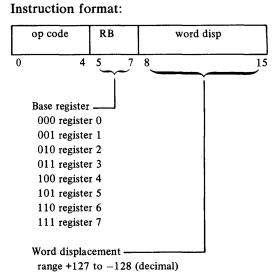

Chapter 1. Introduction 1-1 The Assembler Language 1-3 Machine Instructions 1-3 Assembler Instructions 1-3 Macro Instructions 1-3 The Assembler Program 1-3 Coding Aids 1-5 Symbolic Representation of Program Elements 1-5 Variety of Data Representation 1-5 Relocatability 1-5 Addresses and Addressing 1-5 Register Usage 1-5 Segmenting a Program 1-6 Linkage Between Source Modules 1-7 Program Listing 1-7 Programmer Procedures 1-7 Chapter 2. Coding and Structure of the Assembler Language 2-1 Coding Conventions 2-3 Field Boundaries 2-3 The Statement Field 2-4 The Continuation Indicator Field 2-4 The Identification and Sequence Field 2-4 Field Positions 2-4 Continuation Lines 2-5 Comments Statement Format 2-5 Instruction Statement Format 2-5 Assembler Language Structure 2-7 Character Set 2-7 Terms 2-8 Symbols 2-8 The Symbol Table 2-8 Restrictions on Symbols 2-9 Location Counter Reference 2-11 Symbol Length Attribute Reference 2-12 Other Attribute References 2-14 Self-Defining Terms 2-15 Expressions 2-17 Absolute Expressions 2-17 Register Expressions 2-18 Relocatable Expressions 2-19 Rules for Coding Expressions 2-20 Evaluation of Expressions 2-20 Parentheses in Instruction Operands 2-21 Chapter 3. Functional Characteristics 3-1 Introduction 3-3 Registers 3-3 Registers Fitted on a Per-Level Basis 3-3 Registers Fitted on a Per-System Basis 3-4 Number Representation 3-5 Indicators 3-5 Other Uses of Indicators 3-7 Storage Addressing 3-8 Effective Address Generation 3-8 Base Register, Word Displacement Short 3-9 Base Register, Word Displacement 3-10 Four-Bit Address Argument 3-11 Five-Bit Address Argument 3-13

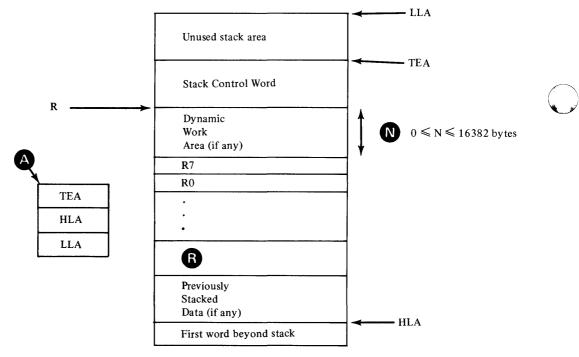

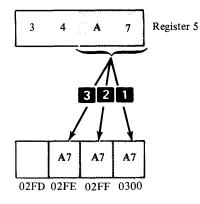

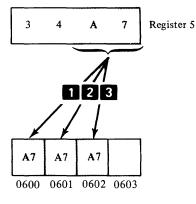

Instruction Length Variations for Address Arguments 3-14 Stack Operations 3-15 Stack Control Block 3-15 Linkage Stacking 3-17 Chapter 4. Machine Instructions 4-1 Coding Notes 4-3 Coding the Assembler Language Instructions 4-3 Data Movement Instructions 4-7 Fill Byte Field and Decrement (FFD) 4-7 Fill Byte Field and Increment (FFN) 4-8 Interchange Registers (IR) 4-9 Move Address (MVA) 4-9 Move Byte (MVB) 4-10 Move Byte and Zero (MVBZ) 4-11 Move Byte Field and Decrement (MVFD) 4-11 Move Byte Field and Increment (MVFN) 4-12 Move Byte Immediate (MVBI) 4-13 Move Doubleword (MVD) 4-14 Move Doubleword and Zero (MVDZ) 4-15 Move Word (MVW) 4-15 Move Word and Zero (MVWZ) 4-16 Move Word Immediate (MVWI) 4-16 Move Word Short (MVWS) 4-17 Arithmetic Instructions 4-18 Add Address (AA) 4-18 Add Byte (AB) 4-18 Add Byte Immediate (ABI) 4-19 Add Carry Indicator (ACY) 4-19 Add Doubleword (AD) 4-20 Add Word (AW) 4-21 Add Word Immediate (AWI) 4-21 Add Word with Carry (AWCY) 4-22 Subtract Address (SA) 4-22 Subtract Byte (SB) 4-23 Subtract Carry Indicator (SCY) 4-24 Subtract Doubleword (SD) 4-24 Subtract Word (SW) 4-25 Subtract Word Immediate (SWI) 4-26 Subtract Word with Carry (SWCY) 4-26 Multiply Byte (MB) 4-27 Multiply Doubleword (MD) 4-27 Multiply Word (MW) 4-28 Divide Byte (DB) 4-29 Divide Doubleword (DD) 4-29 Divide Word (DW) 4-30 Complement Register (CMR) 4-30 Branching Instructions 4-32 Branch (B) 4-32 Branch and Link (BAL) 4-32 Branch and Link External (BALX) 4-32 Branch and Link Short (BALS) 4-33 Branch External (BX) 4-34 Branch if Mixed (BMIX) 4-34 Branch if Not Mixed (BNMIX) 4-35 Branch if Not Off (BNOFF) 4-35 Branch if Not On (BNON) 4-36 Branch if Off (BOFF) 4-37

Base Register, Storage Address 3-14

Branch if On (BON) 4-37 Branch Indexed Short (BXS) 4-38 Branch on Carry (BCY) 4-38 Branch on Condition (BC) 4-38 Branch on Condition Code (BCC) 4-39 Branch on Equal (BE) 4-40 Branch on Error (BER) 4-40 Branch on Even (BEV) 4-40 Branch on Greater Than (BGT) 4-41 Branch on Greater Than or Equal (BGE) 4-41 Branch on Less Than (BLT) 4-42 Branch on Less Than or Equal (BLE) 4-42 Branch on Logically Greater Than (BLGT) 4-43 Branch on Logically Greater Than or Equal (BLGE) 4-43 Branch on Logically Less Than (BLLT) 4-44 Branch on Logically Less Than or Equal (BLLE) 4-44 Branch on Negative (BN) 4-44 Branch on No Carry (BNCY) 4-45 Branch on Not Condition (BNC) 4-45 Branch on Not Condition Code (BNCC) 4-46 Branch on Not Equal (BNE) 4-47 Branch on Not Error (BNER) 4-47 Branch on Not Even (BNEV) 4-47 Branch on Not Negative (BNN) 4-48 Branch on Not Overflow (BNOV) 4-48 Branch on Not Positive (BNP) 4-48 Branch on Not Zero (BNZ) 4-49 Branch on Overflow (BOV) 4-49 Branch on Positive (BP) 4-50 Branch on Zero (BZ) 4-50 No Operation (NOP) 4-50 Coding Jump Instructions 4-51 Jump (J) 4-51 Jump and Link (JAL) 4-51 Jump if Mixed (JMIX) 4-52 Jump if Not Mixed (JNMIX) 4-52 Jump if Not Off (JNOFF) 4-53 Jump if Not On (JNON) 4-53 Jump if Off (JOFF) 4-54 Jump if On (JON) 4-54 Jump on Carry (JCY) 4-55 Jump on Condition (JC) 4-55 Jump on Count (JCT) 4-56 Jump on Equal (JE) 4-57 Jump on Even (JEV) 4-57 Jump on Greater Than (JGT) 4-57 Jump on Greater Than or Equal (JGE) 4-58 Jump on Less Than (JLT) 4-58 Jump on Less Than or Equal (JLE) 4-59 Jump on Logically Greater Than (JLGT) 4-59 Jump on Logically Greater Than or Equal (JLGE) 4-60 Jump on Logically Less Than (JLLT) 4-60 Jump on Logically Less Than or Equal (JLLE) 4-61 Jump on Negative (JN) 4-61 Jump on No Carry (JNCY) 4-61 Jump on Not Condition (JNC) 4-62 Jump on Not Equal (JNE) 4-62 Jump on Not Even (JNEV) 4-63 Jump on Not Negative (JNN) 4-63 Jump on Not Positive (JNP) 4-64 Jump on Not Zero (JNZ) 4-64 Jump on Positive (JP) 4-65 Jump on Zero (JZ) 4-65 Shift Instructions 4-66 Coding Shift Instructions 4-66 Shift Left Circular (SLC) 4-66

Shift Left Circular Double (SLCD) 4-66 Shift Left Logical (SLL) 4-67 Shift Left Logical Double (SLLD) 4-68 Shift Left and Test (SLT) 4-68 Shift Left and Test Double (SLTD) 4-69 Shift Right Arithmetic (SRA) 4-70 Shift Right Arithmetic Double (SRAD) 4-70 Shift Right Logical (SRL) 4-71 Shift Right Logical Double (SRLD) 4-72 Stack Instructions 4-73 Store Multiple (STM) 4-73 Load Multiple and Branch (LMB) 4-73 Coding Pop/Push Instructions 4-74 Pop Byte (PB) 4-74 Pop Doubleword (PD) 4-74 Pop Word (PW) 4-75 Push Byte (PSB) 4-75 Push Doubleword (PSD) 4-76 Push Word (PSW) 4-77 Compare Instructions 4-78 Using Compare Instructions 4-78 Compare Address (CA) 4-78 Compare Byte (CB) 4-79 Compare Byte Field Equal and Decrement (CFED) 4-79 Compare Byte Field Equal and Increment (CFEN) 4-81 Compare Byte Field Not Equal and Decrement (CFNED) 4-82 Compare Byte Field Not Equal and Increment (CFNEN) 4-83 Compare Byte Immediate (CBI) 4-84 Compare Doubleword (CD) 4-84 Compare Word (CW) 4-85 Compare Word Immediate (CWI) 4-85 Scan Byte Field Equal and Decrement (SFED) 4-85 Scan Byte Field Equal and Increment (SFEN) 4-86 Scan Byte Field Not Equal and Decrement (SFNED) 4-87 Scan Byte Field Not Equal and Increment (SFNEN) 4-88 Logical Instructions 4-89 AND Word Immediate (NWI) 4-89 Exclusive OR Byte (XB) 4-89 Exclusive OR Doubleword (XD) 4-90 Exclusive OR Word (XW) 4-90 Exclusive OR Word Immediate (XWI) 4-91 Invert Register (VR) 4-91 OR Byte (OB) 4-92 OR Doubleword (OD) 4-92 OR Word (OW) 4-93 OR Word Immediate (OWI) 4-94 Reset Bits Byte (RBTB) 4-94 Reset Bits Doubleword (RBTD) 4-95 Reset Bits Word (RBTW) 4-95 Reset Bits Word Immediate (RBTWI) 4-96 Set Bits Byte (SBTB) 4-97 Set Bits Doubleword (SBTD) 4-97 Set Bits Word (SBTW) 4-98 Set Bits Word Immediate (SBTWI) 4-98 Test Bit and Invert (TBTV) 4-100 Test Bit and Reset (TBTR) 4-100 Test Bit and Set (TBTS) 4-101 Test Word Immediate (TWI) 4-101 Processor Status Instructions 4-103 Copy Level Status Register (CPLSR) 4-103 Set Indicators (SEIND) 4-103 Stop (STOP) 4-103 Supervisor Call (SVC) 4-104 Privileged Instructions 4-105

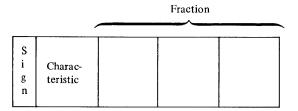

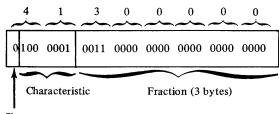

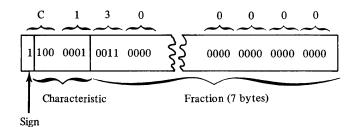

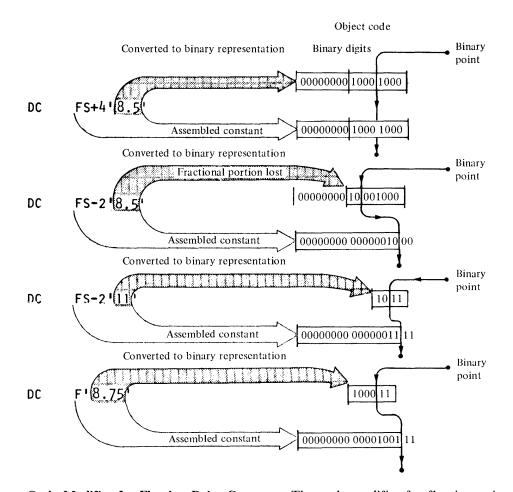

Copy Clock (CPCLK) 4-105 Copy Comparator (CPCMP) 4-105 Copy Console Data Buffer (CPCON) 4-106 Copy Current Level (CPCL) 4-106 Copy In-Process Flags (CPIPF) 4-107 Copy Instruction Space Key (CPISK) (4955 Processor Only) 4-107 Copy Interrupt Mask Register (CPIMR) 4-108 Copy Level Status Block (CPLB) 4-108 Copy Operand1 Key (CPOOK) (4955 Processor Only) 4-109 Copy Operand2 Key (CPOTK) (4955 Processor Only) 4-110 Copy Processor Status and Reset (CPPSR) 4-110 Copy Segmentation Register (CPSR) (4955 Processor Only) 4-111 Copy Storage Key (CPSK) (4955 Processor Only) 4-112 Diagnose (DIAG) 4-112 Disable (DIS) 4-113 Enable (EN) 4-113 Interchange Operand Keys (IOPK) (4955 Processor Only) 4-114 Level Exit (LEX) 4-114 Operate I/O (IO) 4-115 Set Address Key Register (SEAKR) (4955 Processor Only) 4-115 Set Clock (SECLK) 4-116 Set Comparator (SECMP) 4-116 Set Console Data Lights (SECON) 4-116 Set Instruction Space Key (SEISK) (4955 Processor Only) 4-117 Set Interrupt Mask Register (SEIMR) 4-117 Set Level Status Block (SELB) 4-118 Set Operand1 Key (SEOOK) (4955 Processor Only) 4-119 Set Operand2 Key (SEOTK) (4955 Processor Only) 4-119 Set Segmentation Register (SESR) (4955 Processor Only) 4-120 Set Storage Key (SESK) (4955 Processor Only) 4-121 Floating-Point Instructions 4-122 Floating-Point Number Representation 4-122 Floating-Point Registers and Instructions 4-123 Copy Floating Level Block (CPFLB) 4-124 Floating Add (FA) 4-124 Floating Add Double (FAD) 4-125 Floating Compare (FC) 4-125 Floating Compare Double (FCD) 4-126 Floating Divide (FD) 4-126 Floating Divide Double (FDD) 4-127 Floating Move (FMV) 4-128 Floating Move Double (FMVD) 4-128 Floating Move and Convert (FMVC) 4-129 Floating Move and Convert Double (FMVCD) 4-129 Floating Multiply (FM) 4-130 Floating Multiply Double (FMD) 4-131 Floating Subtract (FS) 4-131 Floating Subtract Double (FSD) 4-132 Set Floating Level Block (SEFLB) 4-132 Chapter 5. Assembler Instructions 5-1 Establishing Symbolic Representation 5-3 Assigning Values to Symbols 5-3 Defining Data 5-5 Parameter Reference (PREF) 5-27 Program Sectioning 5-29 Communication Between Program Parts 5-29 The Source Module 5-29 General Information About Control Sections 5-33

Defining a Control Section 5-36 Symbolic Addressing Within Source Modules-Establishing Addressability 5-42 Symbolic Addressing Between Source Modules-Symbolic Linkage 5-49 To Refer to External Data 5-51 To Branch to an External Address 5-52 Controlling the Assembler Program 5-55 Determining Statement Format and Sequence 5-57 Listing Format and Output 5-60 Chapter 6. Macro Language 6-1 Overview of Creating Macros 6-4 Contents of a Macro Definition 6-5 Where to Place a Macro Definition in the Source Module 6-6 Parts of a Macro Definition 6-6 Symbolic Parameters 6-8 Model Statements 6-12 Processing Statements 6-15 Comment Statements in Macro Definitions 6-18 System Variable Symbols 6-19 Using the Calling Macro Instruction 6-23 Macro Instruction Operands 6-24 Sublists in the Macro Instruction Operand 6-28 Values in Macro Instruction Parameters 6-29 Nesting Macro Definitions 6-32 Conditional Assembly Language 6-34 SET Symbols 6-35 Data Attributes 6-37 Sequence Symbols 6-38 Declaring SET Symbols 6-39 Assigning Values to Set Symbols 6-43 Using Expressions in SET Instructions 6-46 Selecting Characters from a String-Substring Notation 6-54 Branching 6-55 Chapter 7. Using the Macro Assembler 7-1 Assembler Options 7-3 Required Files 7-3 Optional Files 7-4 Assembler Program Listing 7-4 External Symbol Dictionary (ESD) 7-4 Source and Object Program 7-5 Relocation Dictionary 7-9 Cross-Reference 7-9 Diagnostics 7-10 Statistics 7-10 Invoking the Assembler (Examples) 7-11 Object Module Formats 7-14 Record Formats 7-14 General Record Format 7-14 Record Types 7-14 External Symbol Dictionary (ESD) Record 7-14 Text (TXT) Record 7-15 Relocation Dictionary (RLD) Record 7-16 End of Module (END) Record 7-16 Appendix A. CPA-Assembler Messages A-1 Message Format A-1 Organization A-1 Message Documentation A-1 Appendix B. Decimal/Binary/Hexadecimal Conversions B-1

Appendix C. American National Standard Code for Information Interchange (ASCII) C-1

- Appendix D. Perforated Tape Transmission Code/Extended Binary Coded Decimal (PTTC/EBCD) D-1

- Appendix E. Priority List for Assembler Instructions E-1

- Appendix F. Summary of Constants F-1

- Appendix G. Macro Language Summary G-1

- Appendix H. Assembler Language Summary H-1

- Appendix J. Macro Language Instruction Summary J-1

- Index X-1

viii GC34-0317

# **Chapter 1. Introduction**

The Assembler Language 1-3 Machine Instructions 1-3 Assembler Instructions 1-3 Macro Instructions 1-3 The Assembler Program 1-3 Coding Aids 1-5 Symbolic Representation of Program Elements 1-5 Variety of Data Representation 1-5 Relocatability 1-5 Addresses and Addressing 1-5 Register Usage 1-5 Segmenting a Program 1-6 Linkage Between Source Modules 1-7 Program Listing 1-7 Programmer Procedures 1-7 This page intentionally left blank.

1-2 GC34-0317

| The Assembler Lan      | Assembler language is a symbolic programming language that resembles machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | language in form and content. It is made up of statements that represent<br>instructions and comments. The instruction statements are the working part of<br>the language and are divided into three groups:                                                                                                                                                                                                                                                                                                                                                                                                            |

|                        | <ul> <li>Machine instructions</li> <li>Assembler instructions</li> <li>Macro instructions</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Machine Instructions   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | A machine instruction is the symbolic representation of a hardware instruction in the Series/1 instruction set. Machine instructions are described in Chapter 4 of this manual.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Assembler Instructions | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | An assembler instruction is a request to the assembler program to perform<br>certain operations during the assembly of a source module; for example,<br>defining data constants, defining the end of the source module, and reserving<br>storage areas. Except for the instructions that define constants, parameter lists,<br>or provide boundary alignment, the assembler does not translate assembler<br>instructions into object code. The assembler instructions are described in<br>Chapter 5 of this manual.                                                                                                     |

| Macro Instructions     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | A macro instruction is a request to the assembler program to process a<br>predefined sequence of code called a <i>macro definition</i> . From this definition, the<br>assembler generates machine and assembler instructions which it then processes<br>as if they were part of the original input in the source module.<br>You can prepare macro definitions, then call them by coding the<br>corresponding macro instructions. A complete description of the macro<br>language, including the macro definition, the macro instruction, and the<br>conditional assembly language is given in Chapter 6 of this manual. |

The assembler program, \$S1ASM also referred to as the *assembler*, processes the machine, assembler, and macro instructions you have coded in the assembler language and produces an object module in machine language.

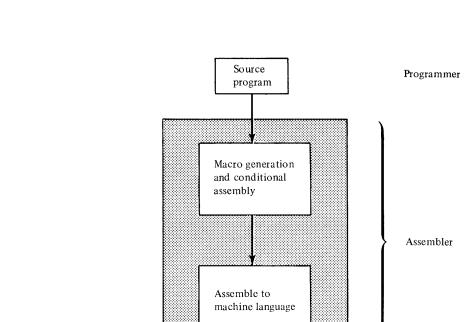

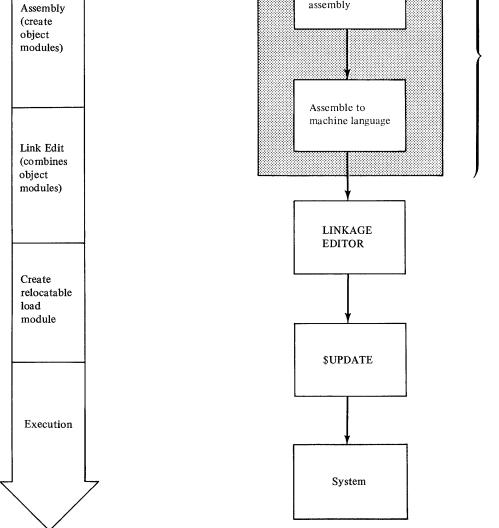

The assembler processes the three types of assembler language instructions at different times during its processing sequence. You should be aware of this processing sequence in order to code your program correctly. The following diagram relates the assembler processing sequence to other times at which your program is processed and executed.

The assembler processes instructions at two distinct times. It processes macro instructions at preassembly time, and it processes machine instructions and assembler instructions at assembly time.

The assembler also produces information for other programs. The linkage editor uses such information to combine two or more input object modules into a single output object module.

Coding

It is normally difficult to write an assembler language program using only machine instructions. The assembler provides some coding aids that make this task easier. They are summarized next.

#### Symbolic Representation of Program Elements

Symbols greatly reduce programming effort and errors. You can define symbols to represent storage addresses, displacements, constants, registers, and other elements that make up the assembler language. These elements include operands, operand subfields, terms, and expressions. Symbols are easier to remember and code than numbers; also, they are listed in a symbolic cross-reference table which is printed in the program listing. Thus, you can easily find a symbol when searching for an error in your code.

#### Variety of Data Representation

You can use decimal, binary, hexadecimal, ASCII or EBCDIC character representation, which the assembler converts for you into the binary equivalents required by the machine instructions.

#### **Relocatability**

The assembler produces an object module that can be relocated from the originally assigned storage area to any other suitable main storage area without affecting program execution. The \$UPDATE utility creates an executable, relocatable load module, and the loader (\$L) does the relocation.

#### Addresses and Addressing

Each byte in main storage is specified by a unique numeric address. When you write a program, you are essentially telling the computer what addresses are involved in the operation you want it to perform. You are usually not concerned with the specific main storage locations, because the assembler keeps track of the location of the statement in your program (relative to the beginning of your program). The assembler assigns the proper address to each assembled machine-language instruction.

To keep track of the locations, the assembler uses a location counter. The counter is set to zero at the beginning of an assembly unless your program specifies otherwise. The counter is then increased by the number of bytes of main storage that each instruction needs. In this way, each statement is assigned an address relative to the beginning of the program. The assembler can then assign the addresses and displacements that are required when it produces the object program. (A displacement is the difference between the counter value of one statement and that of another.)

When your program is loaded, each statement for which storage is allocated takes on a relocated address, which is equal to the beginning main-storage address of the program *plus* the location counter value for that instruction (based on a beginning location counter value of zero).

To locate data, most machine instructions refer to a storage address. The Series/1 uses a variety of methods (called *addressing modes*) to find the data you request in your machine instructions. Addressing modes are described in Chapter 3; how you use them is discussed in Chapter 4.

**Register** Usage

Any one of the eight general-purpose registers can be used to hold a value, an address, or a displacement for manipulating data, maintaining counters, or determining the address of a particular instruction or storage location.

The instruction address register contains the address of the next instruction to

be executed unless a branch or jump instruction breaks the normal sequence. When this occurs, the contents of the instruction address register change because the program transfers control to an instruction not immediately following the current instruction.

### Segmenting a Program

You can code a program in sections and later combine the sections into the executable program. Sections are assembled in any combination, individually or grouped. You arrange the sections in the order required for proper execution of the program during the combining process. The combining process is called *linking* and is performed by the linkage editor.

Dividing a large program into several sections and assemblies has certain advantages:

- More than one programmer can code sections of the program. Each can assemble and debug his sections independently of the others.

- The linking process is much faster, in terms of computer time, than the assembly process. You can assemble a section of the program and link the new section to the already assembled program. This uses less computer time than assembling the entire program.

- Sections that are common to more than one program are assembled only once. You can then link the common sections to the unique sections of each program. You again reduce computer time and also have shorter assembly listings that are easier to debug.

- You can configure a program to various main storage requirements much more easily by linking the sections into different combinations of storage loads or phases. Of course, you must make provisions for these variations in your program logic.

Three types of program sections can be defined in the assembler language-control sections, common sections, and dummy sections. Control sections define the object code, that is, machine instructions and data definitions. A common section defines an area of main storage that can be shared with the program sections in multiple assemblies within a task. A dummy section describes to the assembler the format of data located elsewhere. Dummy sections do not appear in the output module of an assembly. The linking process combines only control and common sections.

The following assembler instructions define the beginning and end of the various sections in your assembly.

- START and CSECT instructions define the beginning of a control section. START is used only to define the first control section in an assembly.

- The COM instruction defines the beginning of a common section.

- The DSECT instruction defines the beginning of a dummy section.

- The end of any type of section is defined when another section is started. The END instruction defines the end of all sections in an assembly.

You can create symbolic linkages between separately assembled source modules. This allows you to refer symbolically from one source module to data defined in another source module. You can also use symbolic addresses to branch between modules.

Combining separately assembled control sections successfully depends on the techniques for symbolic linkages between the control sections. For example, symbols can be defined in one module and referred to in another. The linkage editor then completes the linkage, using the information passed to it by the assembler. Not only is the linkage symbol defined (used as a name), it must also be identified to the assembler by means of an ENTRY assembler instruction unless the symbol is the name of a CSECT or START statement. After a symbol is identified as one that names an entry point, another module can then use that symbol to bring about a branch operation or a data reference.

A module that refers to a linkage symbol defined in another module must identify it as an externally defined symbol used to bring about linkage. The EXTRN or WXTRN assembler instructions identify such symbols.

Symbolic linkage can also be achieved by means of the V-type or W-type address constant, or by means of the BALX or BX machine instruction. Each constant is an external reference since it is created from an externally defined symbol that need not be identified by an EXTRN or WXTRN statement. The V-type or W-type address constant can be used to branch to other modules or to refer to data in those modules.

### **Program** Listing

The assembler produces a listing of your source module, including any generated statements, and the object code assembled from the source module. You can control the content of the listing to a certain extent. The assembler also prints messages about actual errors and warnings about potential errors in your source module. A complete description of the program listing is given in Chapter 7 of this manual.

## **Programmer Procedures**

This book gives you information on the assembler language and on the execution of the assembler. Using Series/1 involves much more. This section gives you an outline of the process required to generate and execute a program. A step by step procedure points you to the library source containing more information.

| Programmer Procedure                                        | Associated System Step           | Publication                                                                                                                                                     |

|-------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. Planning and Design of<br>your Operating System          | None.                            | IBM Series/1 Event<br>Driven Executive System<br>Guide, SC34-0312                                                                                               |

| 2. Building the Event Driven<br>Executive Operating System  | System Generation                | IBM Series/I Event<br>Driven Executive Internal<br>Design, LY34-0168                                                                                            |

| 3. Coding your Programs                                     | None. (Coding sheet)             | IBM Series/I Event<br>Driven Executive Macro<br>Assembler Reference,<br>SC34-0317<br>IBM Series/I Event<br>Driven Executive<br>Language Reference,<br>SC34-0314 |

| 4. Creating Source Modules<br>(On diskette)                 | Text Editor (Note. Or, use 3741) | IBM Series/1 Event<br>Driven Executive                                                                                                                          |

| 5. Creating Object Modules                                  | Assembler                        | - Utilities, Operator Com-<br>mands, and Program                                                                                                                |

| <ol> <li>Combining Object Modules<br/>(optional)</li> </ol> | Linkage Editor                   | <i>Preparation</i> , SC34-0313                                                                                                                                  |

| 7. Building Task Sets                                       | Update Utility                   |                                                                                                                                                                 |

| 8. Executing your Programs                                  | Relocating Loader                |                                                                                                                                                                 |

| 9. Debugging your Programs                                  | DEBUG Utility                    |                                                                                                                                                                 |

# Chapter 2. Coding and Structure of the Assembler Language

Coding Conventions 2-3 Field Boundaries 2-3 The Statement Field 2-4 The Continuation Indicator Field 2-4 The Identification and Sequence Field 2-4 Field Positions 2-4 Continuation Lines 2-5 Comments Statement Format 2-5 Instruction Statement Format 2-5 Assembler Language Structure 2-7 Character Set 2-7 Terms 2-8 Symbols 2-8 The Symbol Table 2-8 Restrictions on Symbols 2-9 Location Counter Reference 2-11 Symbol Length Attribute Reference 2-12 Other Attribute References 2-14 Self-Defining Terms 2-15 Expressions 2-17 Absolute Expressions 2-17 Register Expressions 2-18 Relocatable Expressions 2-19 Rules for Coding Expressions 2-20 Evaluation of Expressions 2-20 Parentheses in Instruction Operands 2-21

This page intentionally left blank.

# **Coding Conventions**

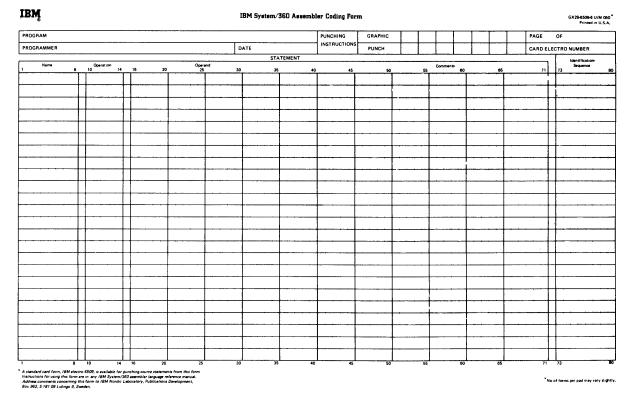

This chapter describes the coding conventions that you must follow in writing assembler language programs. Assembler language statements are usually written on a coding form before they are entered as source statements through some form of input to the system. You can write assembler language statements on the standard coding form (GX28-6509). Columns 1-72 of this form correspond to the positions on a source statement entered at the operator station.

Field Boundaries

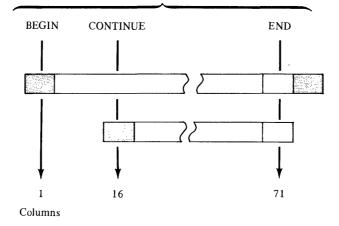

Assembler language statements usually occupy one 80-column line on the standard form. (For statements occupying more than 80 columns, see "Continuation Lines" in this chapter.) Note that any printable character entered at a position in a source statement is reproduced in the listing printed by the assembler. Each line of the coding form is divided into three main fields:

- The statement field

- The continuation indicator field.

- The identification and sequence field

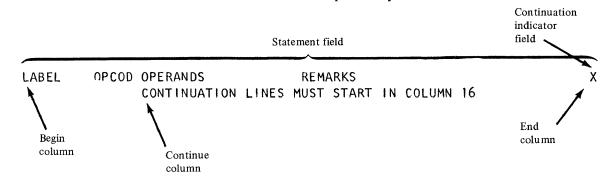

The instructions and comments statements must be written in the statement field. The statement field starts in the "begin" column and ends in the "end" column. Any continuation lines needed must start in the "continue" column and may extend to the "end" column. The assembler assumes the following standard values for these columns:

- The "begin" column is column 1

- The "end" column is column 71

- The "continue" column is column 16.

These standard values can be changed by using the ICTL instruction. However, all references to the "begin", "end", and "continue" columns in this manual refer to the standard values previously described.

# The Continuation Indicator Field

The continuation indicator field occupies the column following the end column. Therefore, the standard position for this field is column 72. A nonblank character in this column indicates that the current statement is continued on the next line. This column must be blank if a statement is completed on the same line; otherwise the assembler will treat the statement that follows on the next line as a continuation line of the current statement.

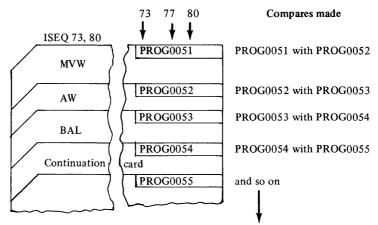

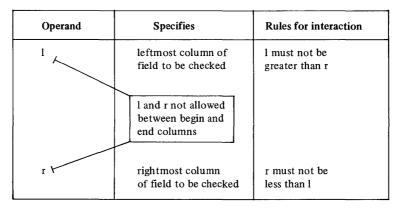

## The Identification and Sequence Field

The identification and sequence field can contain identification characters, or sequence numbers, or both. If you have coded the ISEQ instruction, the assembler will verify whether or not the source statements are in the correct sequence.

*Note.* The ISEQ instruction is used to define the identification and sequence field column boundaries (there are no 'standard' assembler default boundaries for this field). However, column 73 through 80 are set aside for this purpose on the standard coding form, and so are normally used. The single requirement is that this field must not be specified to be within the statement field boundaries.

# Field Positions

The statement field is always coded between the begin and the end columns. The continuation indicator field is always coded in the column after the end column. The identification and sequence field usually is the field after the continuation indicator field. However, the ICTL instruction, by changing the standard begin, end, and continue columns can create a field before the begin column. This field can then contain the identification and sequence field.

## **Continuation Lines**

To continue a statement on another line:

- 1. Enter a nonblank character in the continuation indicator field (column 72). This character is not treated as part of the statement coding. An operand field can be continued by coding it up through column 71, or by terminating it with a comma followed by at least one blank.

- Continue the statement on the next line, starting in the continue column (column 16). The columns prior to the continue column (columns 1-15) must be blank.

Only one continuation line is allowed for a single assembler language statement. However, macro instruction statements and the prototype statement of macro definitions can have as many continuation lines as needed. When more than one continuation line is needed, enter a nonblank character in the continuation indicator field of each line that is to be continued.

#### **Comments Statement Format**

Comments statements are not assembled as part of the object module, but are only printed on the assembly listing. You can write as many comments statements as you need, as long as you follow these rules:

• Comments statements require an asterisk in the begin column.

*Note.* Internal macro definition comments statements require a period in the begin column, followed by an asterisk in the next column (for details, see "Comment Statements in Macro Definitions" in Chapter 6).

- You can use any characters, including blanks and special characters, of the character set.

- Comments statements cannot be continued. Code comments statements in the statement field and do not let them run over into the continuation indicator field.

- Comments statements must not appear between an instruction statement and its continuation lines.

#### **Instruction Statement Format**

The statement field of an instruction statement must include an operation entry and can contain one or more of the following entries:

- A name entry

- An operand entry

- A remarks entry

The standard coding form is divided into fields that provide fixed positions for the name, operation, and operand entries.

- 1. An 8-character name field starting in column 1

- 2. A 5-character operation field starting in column 10

- 3. An operand field that begins in column 16

| LABEL   | MVW | R3,ADCON | REMARKS ENTRY                                                             |

|---------|-----|----------|---------------------------------------------------------------------------|

| SECTDEF |     |          | NAME ENTRY OMITTED<br>OPERAND ENTRY NOT REQUIRED<br>OPERAND ENTRY OMITTED |

Adherence to these field positions is called *fixed format*.

It is not necessary to code the operation and operand entries according to the fixed fields on the standard coding form. Instead, you can write these entries in any position, called *free format*, subject to certain formatting specifications.

Whether you use fixed or free format, the following general rules apply when you code an instruction statement:

- Write the entries in the following order: name, operation, operand, and remarks.

- The entries must be contained in the begin column (1) through the end column (71) of the first line and, if needed, in the continue column (16) through the end column (71) of any continuation lines.

- The entries must be separated from each other by one or more blanks.

- If used, the name entry must start in the begin column (normally column 1).

- The name and operation entries, each followed by at least one blank, must be in the first line of an instruction statement.

- The operation entry must start to the right of the begin column.

| LABEL | MVW      | R3,ADCON     | FIXED FORMAT STATEMENT.                 |   |

|-------|----------|--------------|-----------------------------------------|---|

| LABEL | MVW R3,  | ADCON FREE   | FORMAT STATEMENT.                       |   |

| LABEL | MVW      | R3,ADCON     | ONLY OPERANDS AND REMARKS ALLOWED HERE. | x |

| MVW   | R3,ADCON | NAME ENTRY   | OMITTED, COLUMN I MUST BE BLANK.        |   |

| LABEL | MVW      | R3,<br>Adcon | CONTINUE OPERANDS<br>ON NEXT LINE       | x |

The *name entry* identifies an instruction statement. The following rules apply to the name entry:

- It is usually optional.

- It must be a valid symbol of 1-8 characters at assembly time (after substitution for variable symbols, if specified on model statements within macro definitions).

The *operation entry* is the symbolic operation code that specifies the machine, assembler, or macro instruction to be processed. The following rules apply to the operation entry:

- It is mandatory.

- For machine and assembler instructions it must be a valid symbol at assembly time (after substitution for variable symbols, if specified on model statements within macro definitions). The standard symbolic operation codes are 5 characters or less.

- For macro instructions it can be any valid symbol of 1-8 characters that is not identical to the operation codes for machine and assembler instructions.

The *operand entry* has one or more operands that identify and describe the data used by an instruction. The following rules apply to operands:

- One or more operands are usually required, depending on the instruction.

- Operands must be separated by commas. No blanks are allowed between the operands and the commas that separate them. When an operand entry is being continued on the next line, the last operand on the first line can be terminated with a comma followed by one or more blanks.

• Operands must not contain embedded blanks, because a blank normally indicates the end of the operand entry. However, blanks are allowed if they are included in character strings enclosed in apostrophes (for example, C' JN') or in logical expressions (see "Logical (SETB) Expressions" in Chapter 6).

You can use a *remarks entry* to comment on the current instruction. The following rules apply to the remarks entry:

- It is optional.

- It can contain any of the 256 characters of the character set, including blanks and special characters.

- It can follow any operand entry.

- If an entire operand entry is omitted, remarks are allowed if the absence of the operand entry is indicated by a comma preceded and followed by one or more blanks.

*Note.* Macro prototype statements and macro instructions without operands cannot have a remarks entry, even if a comma is coded as described above.

# **Assembler Language Structure**

This section describes the structure of the assembler language (the various statements allowed in the language and the elements that make up those statements).

A source module is a sequence of instruction and comment statements that make up the input to the assembler. There are 3 types of instruction statements:

- *Machine instructions*—symbolic representation of machine language instructions, which the assembler translates into machine language code

- Assembler instructions—instructions to the assembler program to perform certain operations during assembly of a source module, such as defining data constants and reserving storage areas

- *Macro instructions*—instructions to the assembler program to process predefined sequences of code called *macro definitions* (from which the assembler generates machine and assembler instructions which it then processes as if they were part of the original input source module)

The operand field of machine instructions is composed of *expressions*, which are composed of *terms* and combinations of terms. Remarks on the instruction statements and comments statements are composed of *character strings*. Terms and character strings are both composed of characters. The following paragraphs define these language elements.

## **Character** Set

Terms, expressions, and character strings used to build source statements are written with the following characters:

- Alphameric characters

- Alphabetic characters A through Z

- Special characters \$, #, and @

- Digits 0 through 9

- Special characters

- + , = . \* () ' / & blank

*Note.* Character strings can contain any of the 256 characters of the character set.

• Data or field delimiters • Indicators to the assembler for specific handling A term is the smallest element of the assembler language that represents a distinct and separate value. It can therefore be used alone or in combination with other terms to form expressions. Terms have absolute or relocatable values program origin. The types of terms are: • Self-defining terms—absolute; value is inherent in term **Symbols** values. The advantages of symbolic numeric representation are: programming errors and increasing programming efficiency. or INDEX can name a register to be used for indexing. prints in the program listing. statements in which the symbol is used in the operands. The assembler maintains an internal table called a symbol table. When the

special characters are used as:

• Arithmetic operators in expressions

2-8

Terms

that are assigned by the assembler or are inherent in the terms themselves. A term is absolute if its value does not change upon program relocation and

Normally, strings of alphameric characters are used to represent data, and

is *relocatable* if its value can be modified to compensate for a change in

- Symbols—absolute or relocatable; value is assigned by the assembler

- Location counter reference—relocatable; value is assigned by the assembler

- Symbolic parameter attributes-absolute; value is assigned by the assembler

You can use a symbol to represent storage locations or arbitrary values. You can write a symbol in the name field of an instruction and and then specify this symbol in the operands of other instructions, thus referring to the former instruction symbolically. This symbol represents a relocatable address.

You can also assign an absolute value to a symbol by coding it in the name field of an EQU or EQUR instruction with an operand whose value is absolute. Symbols in the name field of EQUR instructions can be used in other instruction operands to represent registers; symbols in the name field of EQU instructions can be used in other instruction operands as displacements in explicit addresses, immediate data, lengths, and implicit addresses with absolute

- You can remember symbols more easily than numeric values, thus reducing

- You can use meaningful symbols to describe the program elements they represent; for example, INPUT can name a field that is to contain input data,

- You can change the value of one symbol (through an EQU instruction) more easily than you can change several numeric values in many instructions.

- Symbols are entered into a cross-reference table that the assembler optionally

The symbol cross-reference table helps you to find a symbol in a program listing, because it lists (1) the number of the statement in which the symbol is defined (that is, used as the name entry), and (2) the numbers of all the

# The Symbol Table

GC34-0317

assembler processes your source statements for the first time, the assembler assigns an absolute or relocatable value to every symbol that appears in the name field of an instruction. The assembler enters this value, which normally reflects the setting of the location counter, into the symbol table; it also enters the attributes with the data represented by the symbol. The values of the

symbol and its attributes are available later when the assembler finds this symbol used as a term in an operand or expression.

The assembler recognizes three types of symbols:

- Ordinary symbols—used in the name and operand fields of machine and assembler instruction statements; written as an alphabetic character followed by 0–7 alphameric characters (no blanks allowed). For example: BEGIN

- Variable symbols—used only in macro processing conditional assembly instructions; written as an ampersand followed by an alphabetic character followed by 0–6 alphameric characters (no blanks allowed). For example: & PARAM

- Sequence symbols—used only in macro processing conditional assembly instructions; written as a period followed by an alphabetic character followed by 0–6 alphameric characters. For example: .SEQ01

An ordinary symbol is considered defined when it appears as:

- The name entry in a machine or assembler instruction of the assembler language, or

- One of the operands of the following instructions: EXTRN, WXTRN.

Ordinary symbols that appear in instructions generated from model statements at preassembly time are also considered defined.

The assembler assigns a value to the ordinary symbol in the name field as follows.

- According to the address of the leftmost byte of the storage area that contains one of the following:

- Any machine instruction

- A storage area defined by the DS instruction

- Any constant defined by the DC instruction

The address value thus assigned is relocatable, because the object code assembled from these items is relocatable.

- According to the value of the expression specified in the operand of an EQU instruction. This expression can have a relocatable or absolute value, which is then assigned to the ordinary symbol.

- According to the value of the expression specified in the operand of an EQUR instruction. This expression must have an absolute value in the range 0-7, which is then assigned to the register symbol.

The value of an ordinary symbol must be representable in 16 bits.

*Note.* The symbol table can contain a maximum of 57330 entries. In a single assembly, the total number of ordinary symbol entries plus ESD entries cannot exceed this maximum. ESD entries are created for:

- control sections

- dummy sections

- common sections

- unique symbols in EXTRN, WXTRN, and ENTRY statements

- V, W, and N-type address constants

- BALX and BX instructions.

#### **Restrictions on Symbols**

**Predefined Register Symbols**

The following symbols are predefined by the assembler and reserved for use only as register symbols:

- R0 (general-purpose register 0)

- R1 (general-purpose register 1)

- R2 (general-purpose register 2)

- R3 (general-purpose register 3)

- R4 (general-purpose register 4)

- R5 (general-purpose register 5)

- R6 (general-purpose register 6)

- R7 (general-purpose register 7)

- FR0 (floating-point register 0)

- FR1 (floating-point register 1)

- FR2 (floating-point register 2)

- FR3 (floating-point register 3)

These symbols are absolute and used only for register reference in machine and assembler instruction operands. Any other usage causes an error message to be generated. Predefined register symbols appear in the cross-reference listing.

#### **Unique Definition**

A symbol must be defined only once in a source module (even a source module that contains two or more control sections) with the following exceptions:

- You can use a duplicate symbol as the name entry of a CSECT, COM or DSECT instruction. The first use identifies the beginning of the control section, and subsequent uses identify continuations of the control section. A symbol used in the name field of one type of section may not be repeated on another type. For example, a DSECT and a COM statement may not have the same name field. A label appearing on a START statement may be used on a subsequent CSECT statement.

- A symbol can appear more than once in the operands of the following instructions:

- ENTRY

- BALX

- BX

- EXTRN

- WXTRN

- DC for V-, W-, or N-type address constants provided the attributes are not contradictory (that is, the same symbol can be repeated in an EXTRN and BALX instruction but cannot be repeated in a WXTRN and EXTRN).

*Note.* An ordinary symbol that appears in the name field of a TITLE instruction is not a definition of that symbol. It can, therefore, be used in the name field of any other statement in a source module.

The symbols used in the operands of the following instructions must be defined in a previous instruction:

- EQU

- EQUR

- ORG

- DC and DS (in modifier and duplication factor expressions)

The following sample code indicates the ways symbols can be defined and used:

| FIRST        | START<br>EXTRN    | 128<br>READER,PRINTER | FIRST CONTROL SECTION STARTS HERE,<br>SYMBOLS DEFINED IN EXTRN STATEMENT.                                                                               |  |

|--------------|-------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| XR3          | EQUR              | 3                     |                                                                                                                                                         |  |

| INDEX<br>XR4 |                   | XR3<br>4              | 'XR3' IS PREVIOUSLY DEFINED.                                                                                                                            |  |

| ENTRIES      | MVW               | TABLE, XR 3           | SYMBOL USED IN NAME AND OPERAND.                                                                                                                        |  |

| TABLE        | DS                | F                     | SYMBOL IN NAME FIELD OF DS.                                                                                                                             |  |

| SECOND       | CSECT             |                       | SECOND CONTROL SECTION STARTS HERE.                                                                                                                     |  |

|              | MVW<br>:          | XR4,ADCON             | SYMBOL IN OPERAND FIELD.                                                                                                                                |  |

| ADCON        | DC<br>:           | A(READER)             | SYMBOL IN NAME FIELD OF DC.                                                                                                                             |  |

| FIRST        | CSECT<br>:<br>END |                       | RESUME FIRST CONTROL SECTION.                                                                                                                           |  |

|              |                   |                       | The unique symbols, in the order they<br>were defined, are:<br>FIRST<br>READER<br>PRINTER<br>XR3<br>INDEX<br>XR4<br>ENTRIES<br>TABLE<br>SECOND<br>ADCON |  |

## Location Counter Reference

The assembler maintains a location counter to assign storage addresses to your program statements. You can refer to the current value of the location counter at any place in a source module by specifying an asterisk as a term in an operand.

As the instructions and constants of a source module are being assembled, the location counter has a value that indicates a location in storage. The assembler increases the location counter according to the following rules:

• As each instruction or constant is assembled, the location counter increases by the length of the assembled item.

- The location counter always points to the first byte of the instruction being assembled.

- All references to the location counter in the operand field are relative to the first byte of the instruction being assembled.

- If the statement is named by a symbol, the value of the symbol is the value of the location counter.

The assembler maintains a location counter for each control section in the source module. (For complete details about the location counter setting in control sections, see "Program Sectioning" in Chapter 5.) The assembler maintains the internal location counter as a 16-bit value. If you specify addresses greater than 65,535, the assembler issues the error message 'CPA205S LOCATION COUNTER ERROR'.

You refer to the location counter reference by coding an asterisk (\*). Code an asterisk as a relocatable term only in the operands of:

- Machine instructions

- DC and DS instructions

- EQU, ORG, and USING instructions

The value of the location counter reference (\*) is the current value of the location counter when the asterisk is specified as a term. The asterisk has the same value as the address of the first byte of the instruction being assembled. For the value of the asterisk in address constants with duplication factors, see "A-type Address Constant" in Chapter 5.

Coding an asterisk in the operand of an assembler language instruction or a machine instruction (as part of an address) is the same as placing a symbol in the name field of the same statement and then using that symbol in the operand. Be careful how you use this technique; inserting or deleting instructions between an instruction and the location it refers to makes the displacement from the location counter invalid.

| LOCATION | EQU     | *           |                                |

|----------|---------|-------------|--------------------------------|

|          | AWI     | -1,R1       |                                |

|          | :       |             |                                |

|          | B       | LOCATION    | BRANCH TO AWI INSTRUCTION      |

| LOCAD    | :<br>DC | A(LOCATION) | ADDRESS OF AWI INSTRUCTION     |

|          | :       |             |                                |

| LOC2     | DC      | A(*)        | ADDRESS OF LOC2SAME AS CODING: |

| *        |         |             | LOC2 DC A(LOC2)                |

| LOC2     | :       | •           | ADDRESS OF LOC2SAME AS CODI    |

### Symbol Length Attribute Reference

When you reference the length attribute of a symbol, you get the length of the instruction or data referred to by the symbol. You can use this reference as a term in instruction operands to:

- Specify storage area lengths

- Cause the assembler to compute length specifications

- Build expressions to be evaluated by the assembler.

#### **Specifications for Length Attribute References**

You must code a length attribute reference according to the following rules.

- The format must be L' immediately followed by a valid symbol.

- The symbol must be defined in the same source module in which the symbol length attribute reference is specified.

- The symbol length attribute reference can be used in the operand of any instruction that requires an absolute term.

The value of the length attribute is normally the length, in bytes, of the storage area required by an instruction, constant, or field represented by a symbol. The assembler stores the value of the length attribute in the symbol table along with the address value assigned to the symbol. When the assembler encounters a symbol length attribute reference, it substitutes the value of the attribute from the symbol table entry for the symbol specified in the reference.

The assembler assigns the length attribute values to symbols in the name field of instructions as follows:

- For machine instructions, it assigns a value of 2, 4 or 6 depending on the length of the instruction.

- For the DC and DS instructions, it assigns either the length or explicitly specified length of the first operand. The length attribute is not affected by a duplication factor.

- For the EQU instruction, it assigns the length attribute value of the leftmost or only term in the operand.

The length attribute of a self-defining term is always one. The length attribute of another length attribute is always one. See the length specifications for the individual instructions in Chapter 5. Note that the value of the length attribute is available only at assembly time.

| Value of symbol    |

|--------------------|

| length attribute   |

| (at assembly time) |

| МАСНА<br>ЧАСНВ | MVW<br>IR | DISP,R5<br>R1,R3                      | GENERATES A FOUR BYTE INSTRUCTION.<br>GENERATES A TWO BYTE INSTRUCTION. | L'MACHA = 4<br>L'MACHB = 2 |

|----------------|-----------|---------------------------------------|-------------------------------------------------------------------------|----------------------------|

|                | :         |                                       |                                                                         |                            |

|                | :         |                                       |                                                                         |                            |

| DISPO          | DC        | A(OTHER)                              | IMPLICIT LENGTH OF TWO BYTES                                            | L'DISPO = 2                |

| CHAR4          | DC        | C'ABCD'                               | IMPLICIT LENGTH OF FOUR BYTES                                           | L'CHAR4 = 4                |

| DUPLC          | DC        | 3F'200'                               | IMPLICIT LENGTH NOT AFFECTED BY DUP.                                    | L'DUPLC = 2                |

| INPUT          | DS        | CL40                                  | EXPLICIT LENGTH SPECIFIED.                                              | L'INPUT =40                |

| AREAI          | DS        | 0CL 40                                | NOT AFFECTED BY DUPLICATION FACTOR.                                     | L'AREA1 =40                |

| AREA2          | DS        | 40 C                                  | IMPLICIT LENGTH OF ONE BYTE                                             | L'AREA2 = 1                |

| AREA3          | DS        | 4XL2                                  | EXPLICIT LENGTH NOT AFFECTED BY DUP.                                    | L'AREA3 = 2                |

|                | :         | Leftmost or only terr                 | n                                                                       |                            |

|                | :         | · · · · · · · · · · · · · · · · · · · |                                                                         |                            |

| CABCD          | EQU       | CHAR4                                 | SINGLE TERM.                                                            | $L^{CABCD} = 4$            |

| TERM2          | EQU       | CHAR4+2                               | TWO TERMS, LENGTH OF LEFTMOST ONLY.                                     | L'TERM2 = 4                |

| TE RM3         | EQU       | AREA2-AREA1                           | TWO TERMS, LENGTH OF LEFTMOST ONLY.                                     | L'TERM3 = 1                |

| TERM4          | EQU       | TERM3                                 | SINGLE TERM.                                                            | L'TERM4 = 1                |

|                | :         |                                       |                                                                         |                            |

| 00 <b></b>     | :         |                                       | CANOLE OF E DEELNING TEDN                                               |                            |

| SDTMI          | EQU       | 102                                   | SINGLE SELF-DEFINING TERM.                                              | L'SDTM1 = 1                |

| SDTM2          | EQU       | X'FF*+A-B                             | MULTIPLE TERMS, LEFTMOST IS SELF-                                       | 1 (CDT) (2 - 1             |

| *              | 5011      |                                       | DEFINING.                                                               | $L^{\circ}SDTM2 = 1$       |

| SDTM3          | EQU       | C'AB'                                 | CHARACTER SELF-DEFINING TERM.                                           | $L^{\circ}SDTM3 = 1$       |

|                | :         |                                       |                                                                         |                            |

| LOCAT          | :         | *+2                                   | LOCATION COUNTER REFERENCE.                                             | L'LOCAT = 1                |

| LOCAT          | EQU       |                                       |                                                                         | $L^{\prime}LNGH1 = 2$      |

| LNGHI          | DC        | A(L'LNGH1)                            | LENGTH OF CURRENT INSTRUCTION.                                          | 2 200000 2                 |

|                | DC        |                                       | LENGTH OF CURRENT INSTRUCTION.                                          | L'LOADX = 4                |

|                | MVWI      | L'LOADX,R4<br>L'LOADX                 | LENGTH OF A LENGTH ATTRIBUTE.                                           | L'LATTR = 1                |

| LATTR          | EQU       | LILUADA                               | LENGIN OF A LENGIN ALINIDUIE.                                           |                            |

# Other Attribute References

Other attributes describe the characteristics and structure of the data you define in a program (for example, the kind of constant you specify or the number of characters you need to represent a value). These attributes are the type (T), count (K), and number (N) attributes.

You can refer to these attributes only in macro definition statements; for full details, see "Data Attributes" in Chapter 6.

## Self-Defining Terms

A self-defining term lets you specify a value explicitly. With self-defining terms, you can specify decimal, binary, hexadecimal, EBCDIC character data or ASCII character data. These terms have absolute values and can be used as absolute terms in expressions to represent bit configurations, absolute addresses, displacements, length or other modifiers, and duplication factors. Self-defining terms:

- Represent machine language binary values

- Are absolute terms; their values do not change upon program relocation

- Are padded on the left with zeros if less than one word

The assembler maintains the values represented by self-defining terms to 16 bits; self-defining terms are always considered as positive values in the range zero through 65,535.

A decimal self-defining term is an unsigned decimal number. The assembler allows:

• High-order zeros

- A maximum of five decimal digits

- A range of values from zero through 65,535

*Note.* A negative number is specified as an expression. For details, see "Expressions" later in this chapter.

| Decimal self-<br>defining term | Binary<br>value |          |

|--------------------------------|-----------------|----------|

| 003                            | 00000000        | 00000011 |

| 65535                          | 11111111        | 11111111 |

A binary self-defining term must be coded as the letter B followed by 1–16 binary digits enclosed in apostrophes. For example:

| Binary self-<br>defining term | Binary<br>value      |                      |

|-------------------------------|----------------------|----------------------|

| B'1111100'<br>B'100'          | 00000000<br>00000000 | 01111100<br>00000100 |

| B'1'                          | 00000000             | 0000001              |

The assembler assembles each binary digit exactly as specified.

A hexadecimal self-defining term must be coded as the letter X followed by 1–4 hexadecimal digits enclosed in apostrophes. For example:

| Hexadecimal<br>self-defining<br>term | Binary<br>value |          |

|--------------------------------------|-----------------|----------|

| X'FFA0'                              | 11111111        | 10100000 |

| X'F'                                 | 00000000        | 00001111 |

| X'C01'                               | 00001100        | 0000001  |

| X'7FFF'                              | 01111111        | 11111111 |

| X'8000'                              | 10000000        | 0000000  |

| X'0'                                 | 00000000        | 00000000 |

The assembler assembles each hexadecimal digit into its 4-bit binary equivalent as shown above, and allows a range of values from X'0000' through X'FFFF'.

An *EBCDIC character self-defining term* must be coded as the letter C, followed by 1 or 2 characters enclosed in apostrophes. When assembling EBCDIC character constants, the assembler:

- Allows any of the 256 8-bit combinations as input. This includes the printable characters, including blanks and special characters.

- Assembles each character into its 8-bit EBCDIC equivalent.

- Requires that two ampersands or two apostrophes be specified in the character sequence for each ampersand or apostrophe required in the assembled term.

| Character<br>self-defining<br>term | Characters<br>assembled | Hexadecimal<br>value  | Binary<br>value |        |

|------------------------------------|-------------------------|-----------------------|-----------------|--------|

| C'AB'                              | AB                      | X'C1C2'               | 11000001 11     | 000010 |

| C'C'                               | / C                     | X'C3'                 | 0000000 11      | 000011 |

| C'3'                               | 3                       | X'F3'                 | 00000000 11     | 110011 |

| C'D2'                              | D2                      | X'C4F2'               | 11000100 11     | 110010 |

| С''                                | blank                   | X'40'                 | 00000000 01     | 000000 |

| Cʻ#'                               | #                       | Х'7В'                 | 00000000 01     | 111011 |

| C'&&'                              | &                       | X'50'                 | 00000000 01     | 010000 |

| C' · · ·                           | •                       | <b>X'7</b> D <b>'</b> | 00000000 01     | 111101 |

| C'L' ' '                           | L'                      | X'D37D'               | 11010011 01     | 111101 |

| C'5&&'                             | 5&                      | X'F550'               | 11110101 01     | 010000 |

An ASCII character self-defining term must be coded as the letter S, followed by 1 or 2 characters enclosed in apostrophes. When assembling ASCII character constants, the assembler:

- Allows any of the 256 8-bit EBCDIC characters as input. This includes the printable characters, including blanks and special characters.

- Assembles each character into its 8-bit ASCII equivalent (7 bit character code with high-order zero bit). All characters for which there is not ASCII equivalent will assemble as an ASCII blank character code (X'20').

- Requires that two ampersands or two apostrophes be specified in the character sequence for each ampersand or apostrophe required in the assembled term.

#### **Examples:**

| ASCII self-defining<br>term | Characters<br>assembled | Hex value       | Binary value      |

|-----------------------------|-------------------------|-----------------|-------------------|

| S'AB'                       | AB                      | X'4142'         | 01000001 01000010 |

| S'C'                        | C                       | X'43'           | 0000000 01000011  |

| S'3'                        | 3                       | X'33'           | 0000000 00110011  |

| S'R3'                       | R3                      | X'5233'         | 01010010 00110011 |

| S' '                        | blank                   | X'20'           | 0000000 00100000  |

| Sʻ#'                        | #                       | X'23'           | 0000000 00100011  |

| S'&&'                       | &                       | X'26'           | 00000000 00100110 |

| S' ` ` `                    | ۰                       | X'27'           | 0000000 00100111  |

| S'I' ' '                    | I,                      | X'4927'         | 01001001 00100111 |

| S'7&&'                      | 7&                      | <b>'X'3726'</b> | 00110111 00100110 |

The assembler maintains the values represented by self-defining terms as 16 bits. If a term is used as the operand on a byte immediate instruction, the low-order byte of the term is placed in the immediate field. The high-order byte must be zero.

**Expressions**

You can use an expression to code:

- An address

- An absolute value

- An explicit length

- A length modifier

- A duplication factor

- A complete operand

You can write an expression with a simple term or as an arithmetic combination of terms. The assembler reduces multiterm expressions to single values. Thus, you do not have to compute these values. For example, expressions are used in the following instructions as indicated:

| ADDRESS | :<br>MVW | R2,DATA+4       | EVERESSION USED AS AN ADDRESS  |

|---------|----------|-----------------|--------------------------------|

|         |          | •               | EXPRESSION USED AS AN ADDRESS. |

| VALUE   | MVWI     | 5+2,R3          | AS AN ABSOLUTE VALUE,          |

|         | :        |                 | ·                              |

| LENGTH  | DS       | CL (ALPHA-BETA) | AS AN EXPLICIT LENGTH,         |

| FACTOR  | DS       | (ALPHA-BETA+2)C | AS A DUPLICATION FACTOR.       |

|         |          | •               | •                              |

| OPERAND | EQU      | LABEL+1         | OR AS A COMPLETE OPERAND.      |

|         |          |                 |                                |

Expressions have absolute or relocatable values. Whether an expression is absolute or relocatable depends on the attributes of the terms it contains. You can use the absolute or relocatable expressions described in this section in a machine instruction or any assembler instruction other than a conditional assembly instruction. The assembler evaluates relocatable and absolute expressions at assembly time. Throughout this manual, the word "expressions" refers to these types of expressions.

*Note.* The three types of expressions that you can use in conditional assembly instructions are arithmetic, logical, and character. They are evaluated at preassembly time. In this manual they are always referred to by their full names; they are described in detail in Chapter 6.

An expression is *absolute* if its value is not changed by program relocation; it is *relocatable* if its value is changed upon program relocation.

#### Absolute Expressions

The assembler reduces an expression to a single absolute value if the expression:

- Is composed of a symbol with these values, a self-defining term, or any arithmetic combination of absolute terms

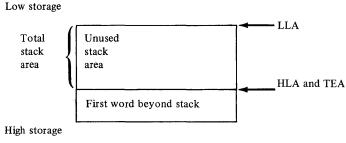

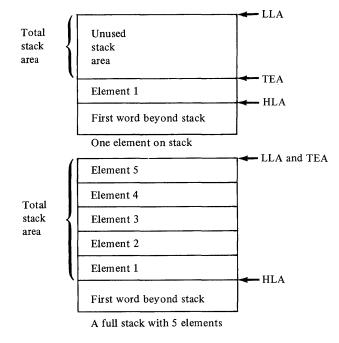

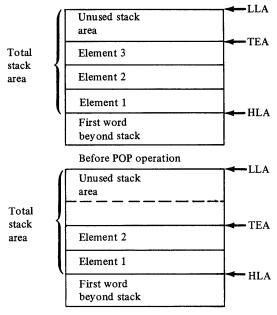

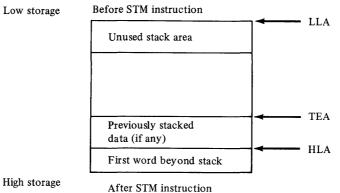

- Contains relocatable terms, alone or in combination with absolute terms, and if all these relocatable terms are paired