System/3 5444 Disk Storage Drive Attachment

Theory-Maintenance

System/3 5444 Disk Storage Drive Attachment

Theory-Maintenance

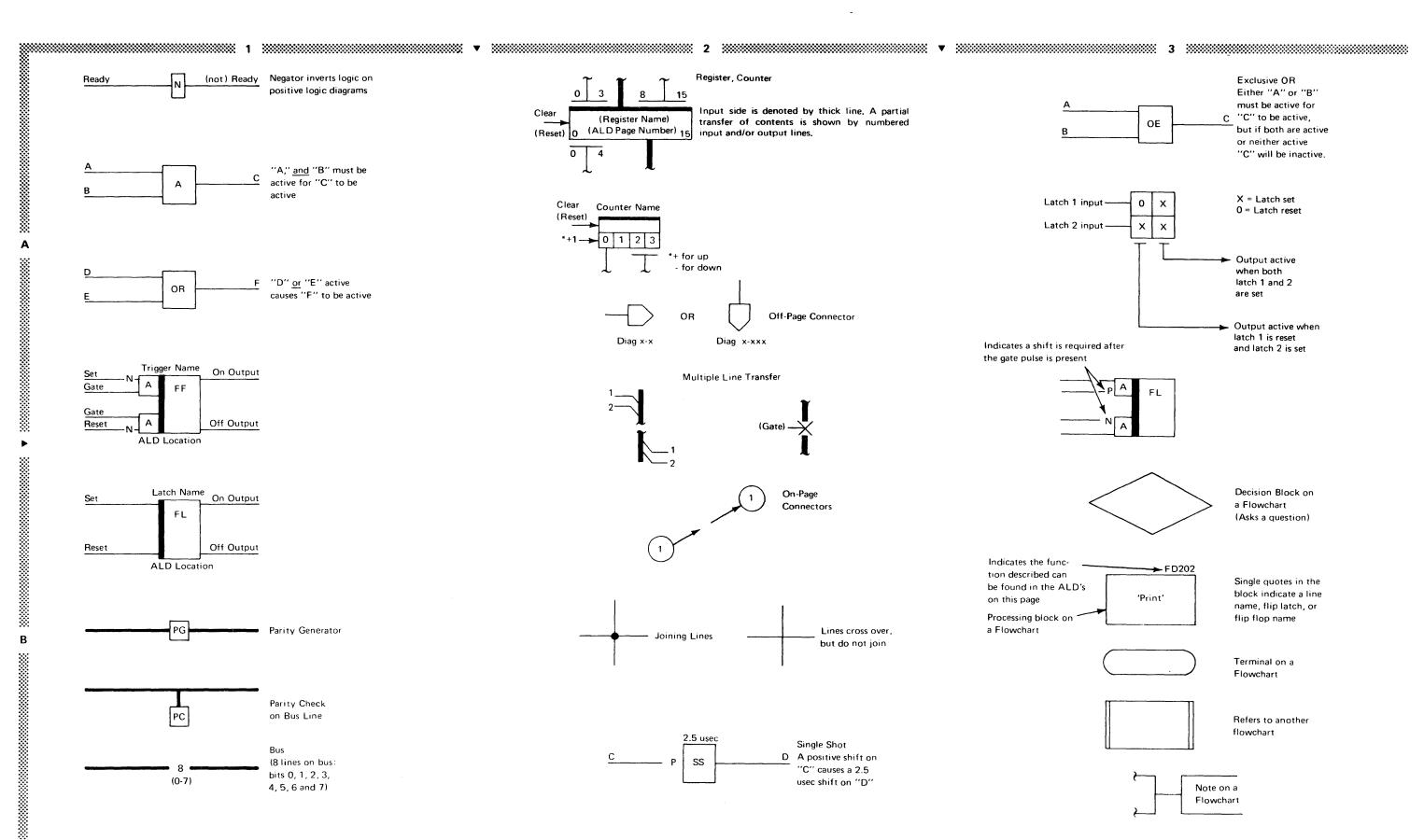

| ▼ X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2 XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | This is a combined theory-diagram manual on the disk attachment for the IBM System/3 Model 10 and System/3 Model 6. There are no other manuals for the disk attachment.<br>This manual is organized into three chapters: introduction, functional units, and operations. Information on how to use each chapter is found on the first page of the chapter.<br>The page numbering system of this manual is as follows:<br>$\frac{8 \text{ XXX}}{1 \text{ Image numbering system of this manual is as follows:}$                                             | ACK<br>ALD<br>ALU<br>AM<br>BCA<br>C<br>CC<br>CCR<br>CPU<br>CSR<br>DBI<br>DBO<br>DCF<br>DFCR |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ol> <li>Section number: applies to the Model 6 FETM. This manual is Section 8.</li> <li>Chapter number: a "1" means chapter 1, a "2" means chapter 2, a "3"</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                    | DFDF<br>F<br>FCU<br>G                                                                       |

| Second Edition (November 1970)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul><li>means chapter 3.</li><li>Page number of chapter: numbered 01 through 99.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | HSA<br>ID<br>I/O                                                                            |

| This is a major revision of, and obsoletes, SY34-0021-0. This edition incorporates use<br>of the disk attachment in the IBM 5406 in addition to its previous use in the IBM<br>5410. Chapter 2 is completely new and now contains second-level diagrams of each<br>eard in the disk attachment. Chapter 3 has been extensively revised by adding more<br>detailed information on disk attachment operations.<br>Changes are periodically made to the information herein; any such changes will be<br>reported in subsequent revisions or Technical Newsletters. | <ul> <li>The diagrams and flowcharts in this manual are at engineering level 571538.<br/>Other manuals needed to understand and service the file attachment are:</li> <li>Field Engineering Theory of Operations Manual. <i>IBM 5410 Central</i><br/><i>Processing Unit</i>, Order No. SY31-0207</li> <li>Field Engineering Maintenance Diagrams Manual. <i>IBM 5410 Central</i><br/><i>Processing Unit</i>, Order SY31-0202</li> <li>Field Engineering Maintenance Manual. <i>IBM 5410 Central Processing</i><br/><i>Unit</i>, Order SY31-0202</li> </ul> | IPL<br>LIO<br>LSR<br>N<br>OE<br>PC<br>PG<br>S<br>SAR                                        |

| Some illustrations in this manual have a code number in the lower corner. This is a publishing control number and is not related to the subject matter.                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>Field Engineering Theory-Maintenance Manual, System/3 Model 6 5406<br/>Processing Unit and Attachments, Order No. SY34-0022</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                            | SERI<br>SIO<br>SLD                                                                          |

| Copies of this and other IBM publications can be obtained through IBM Branch Offices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • Field Engineering Theory of Operations Manual, <i>IBM 5406 Central Process-</i><br>ing Unit, Order No. SY34-0023                                                                                                                                                                                                                                                                                                                                                                                                                                         | SNS<br>TIO                                                                                  |

| A form for readers' comments is provided at the back of this publication. If the form has been removed, send your comments to IBM Corporation, General Systems Division, Systems Publications, Department 707, Boca Raton, Florida 33432, Comments become the property of IBM.                                                                                                                                                                                                                                                                                  | <ul> <li>Field Engineering Theory-Maintenance Manual, <i>IBM 5444 Disk Storage</i><br/><i>Unit</i>, Order No. SY33-0026</li> <li>Field Engineering Theory-Maintenance Manual, <i>IBM 5444 Disk Storage</i><br/><i>Drive (Machines with serial numbers up to 30100)</i>, Order No. SY33-0026</li> </ul>                                                                                                                                                                                                                                                     |                                                                                             |

| ©Copyright International Business Machines Corporation 1970                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • IBM Maintenance Library, 5444 Disk Storage Drive, Theory-Maintenance (Machines with serial numbers above 30100), Order No. SY33-0029                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                             |

# Abbreviations

Acknowledged Automated Logic Diagram Arithmetic and Logic Unit Address Mark Bit Count Appendage Byte containing the binary number that corresponds to the number of the track Cyclic Check Cycle Control Ring Central Processing Unit Cycle Steal Request Data Bus In Data Bus Out Disk Control Field Disk File Control Register Disk File Data Register Flag Byte File Control Unit Gap High Speed Access Identifier Area Input/Output Initial Program Load Load I/O Instruction Local Storage Register Byte in the disk control field Sync Byte Character Parity Check Parity Generator Sector Byte Storage Address Register Serializer-Deserializer Start I/O Instruction Solid Logic Dense Sense I/O Instruction Test I/O Instruction

ŧ

IBM, / Technical Newsletter

System System/3

Base Publ. No. SY34-0021-1

This Newsletter No. SN34-0059

Date August 1971

Previous Newsletter Nos. None

IBM Field Engineering Theory-Maintenance, System/3 5444 Disk Storage Drive Attachment

©IBM Corp. 1970

This Technical Newsletter provides replacement pages for the subject publication. Pages to be inserted and/or removed are:

| Title page, ii      | 8-227, 8-228        |

|---------------------|---------------------|

| iii, iv             | 8-231, 8-232        |

| 8-101 through 8-104 | 8-237 through 8-242 |

| 8-107 through 8-112 | 8-249, 8-250        |

| 8-201 through 8-208 | 8-305, 8-306        |

| 8-211, 8-212        | 8-313, 8-314        |

| 8-213, 8-214        | X-1, X-2            |

| 8-215, 8-216        |                     |

|                     |                     |

A change to the text or to an illustration is indicated by a vertical line to the left of the change.

### Summary of Amendments

- 1. Incorporate information for high speed access

- 2. Technical corrections

Note. Please file this cover letter at the back of the manual to provide a record of changes.

IBM Corporation, Systems Publications, Boca Raton, Florida 33432

©IBM Corp. 1971

PRINTED IN ITALY

Α ► В

Error Detection 8-101 Cycle Steal Requests (CSR) 8-102 Serializer-Deserializer (Serdes) 8-102 High Speed Access Control 8-102 **IBM** 5444 Disk Storage Drive 8-102 Operator Console (Model 10) 8-103 Operator Console (Model 6) 8-103 Data Storage 8-103 Track Format 8-104 Local Storage Registers (LSR) 8-105 File Instructions 8-106 Load I/O (LIO) 8-107 Test I/O / Advance Program Level (TIO/APL) 8-108 Sense I/O (SNS) 8-109 Start I/O (SIO) 8-111 Initial Program Load (IPL) 8-111 Write Operation 8-112 Read Data Operation 8-113

Compare/Scan Operation 8-114

Load I/O and Test I/O Operations 8-115

Sense Operation 8-115

Chapter 1. Introduction

Chapter 2. Functional Units

Chapter 3. Operations

IBM 5444 Disk Storage Drive Attachment 8-101

Introduction to Functional Units 8-201

Introduction to Operations 8-301

Program Instructions 8-101

Enuctional Unit Index. ALD-Card Cross Reference Chart 8-202

Introduction to Operation 8-301

Timing 8-101

Board Layout 8-203

Test I/O Operation 8-304

Local Storage Register Addressing 8-101

Data Flow 8-204

Sense I/O Operation 8-305

Attachment Interface 8-205 Cards C2 and C3 8-206 Card C4 8-207 Cards D3, D4, and E4 (2 Parts) 8-208, 8-209 Card E2 (2 Parts) 8-210, 8-211 Card G2 (4 Parts) 8-212 through 8-215 Card J2 (4 Parts) 8-216 through 8-219 Card K2 (4 Parts) 8-220 through 8-223 Card L2 (4 Parts) 8-224 through 8-227 Card M2 (4 Parts) 8-228 through 8-231 Card N2 (4 Parts) 8-232 through 8-235 Card P2 (3 Parts) 8-236 through 8-239 Card Q2 (3 Parts) 8-240, 8-241, 8-243 Card R2 (3 Parts) 8-244, 8-245, 8-247 Card S2 (3 Parts) 8-248, 8-249, 8-251 Card T2 (3 Parts) 8-252 through 8-254

# Contents

- Initial Program Load (3 Parts) 8-307 through 8-309

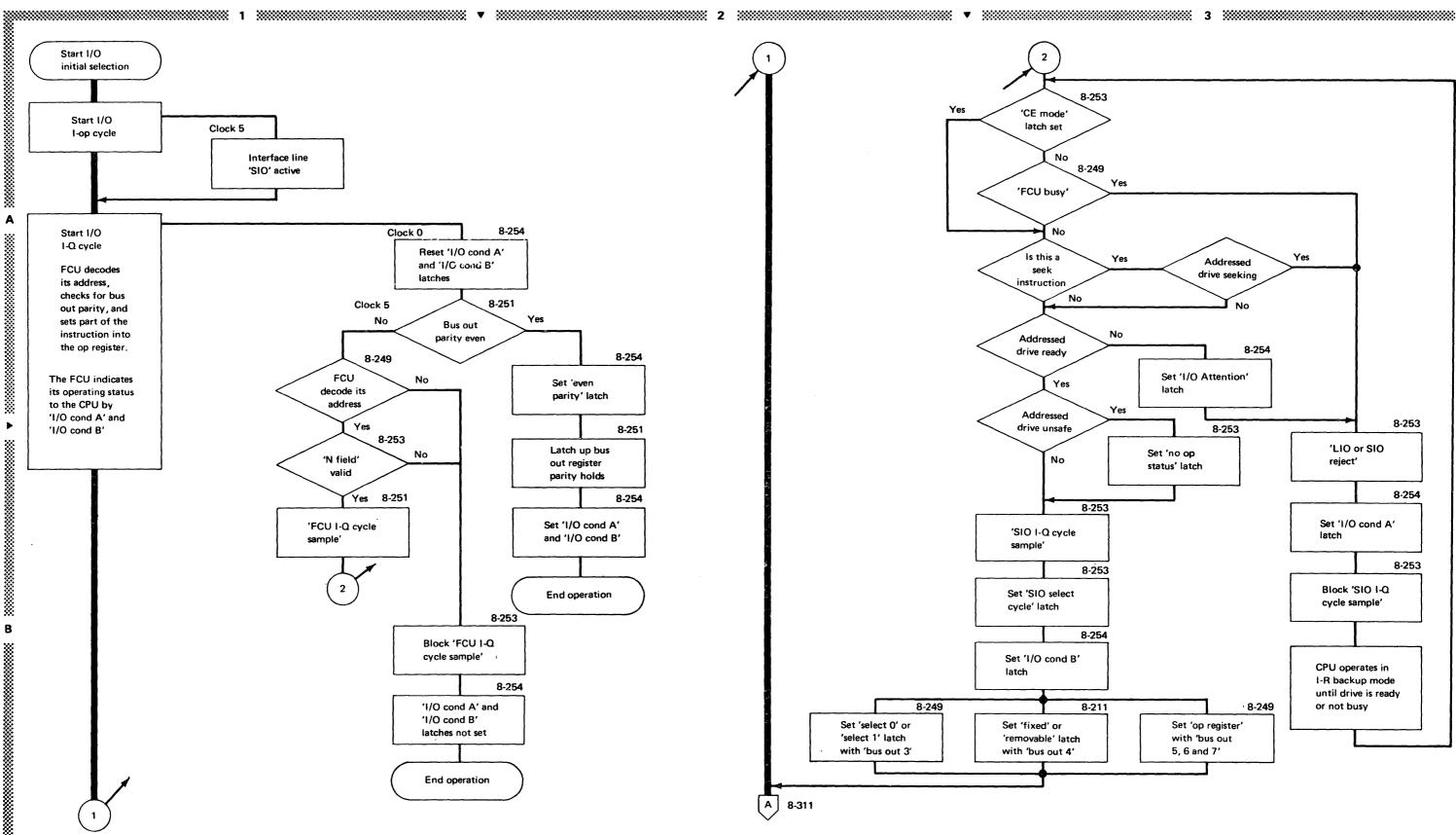

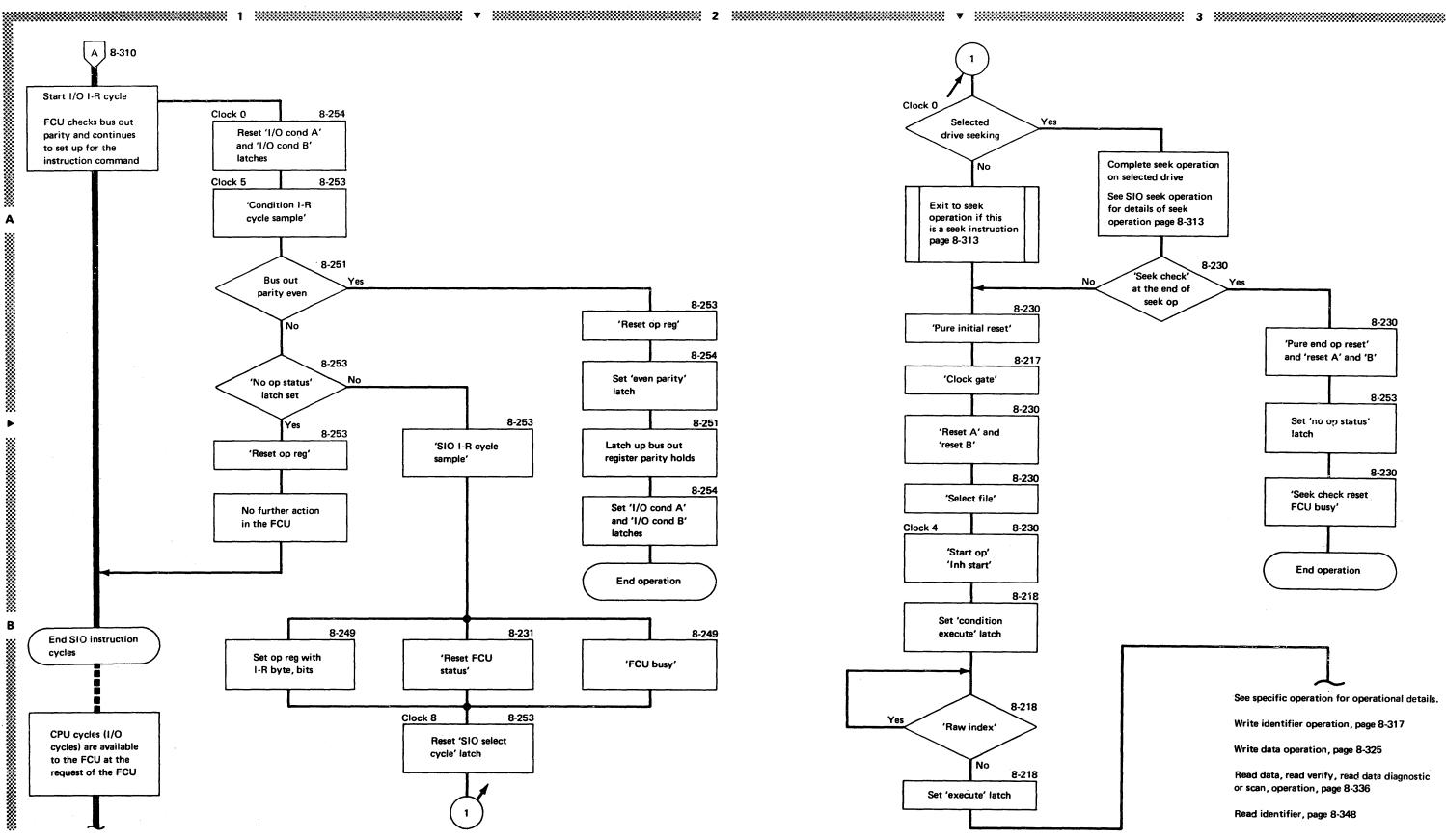

- Start I/O Initial Selection (3 Parts) 8-310 through 8-312

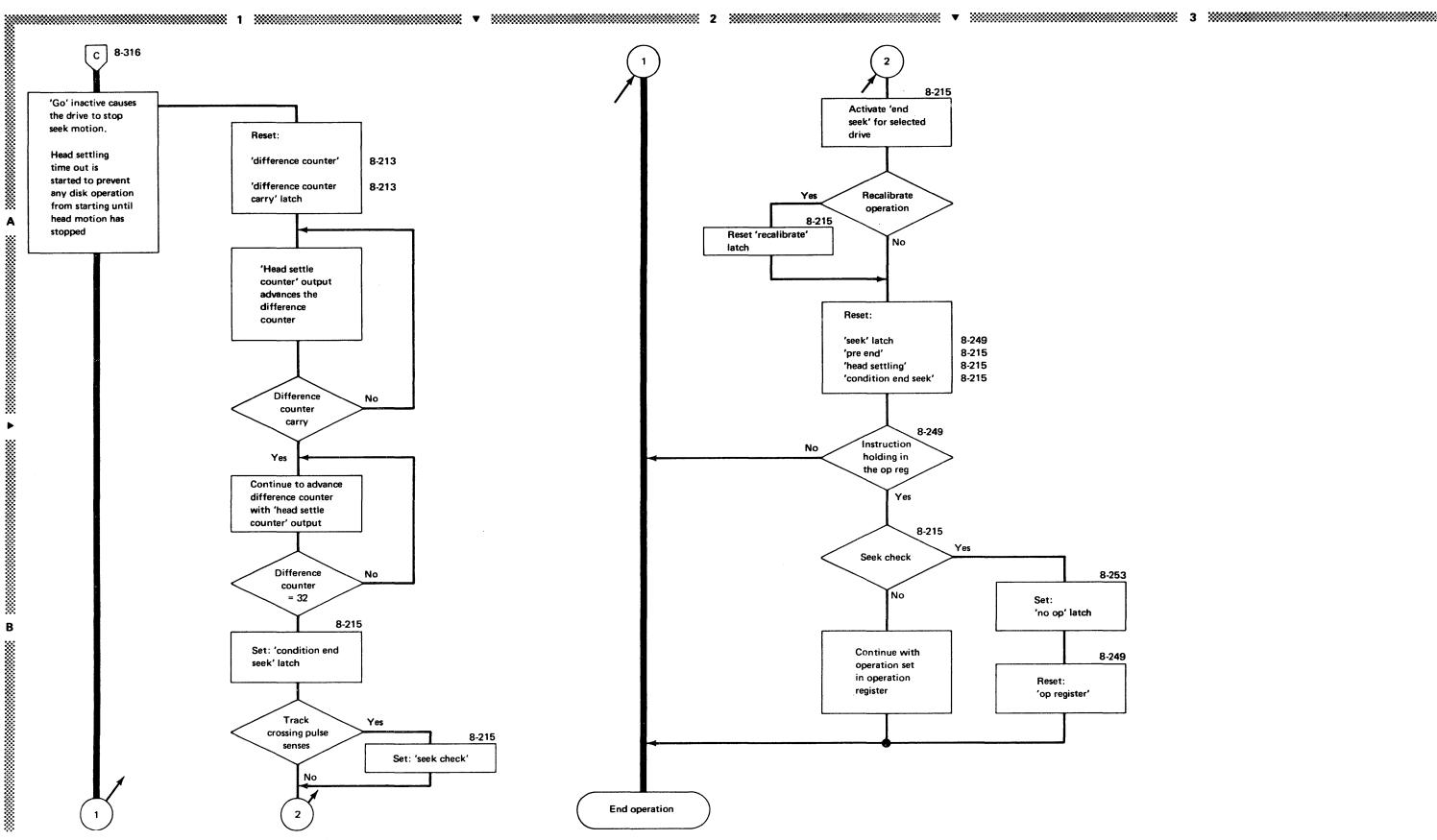

- Seek Operation (4 Parts) 8-313 through 8-316

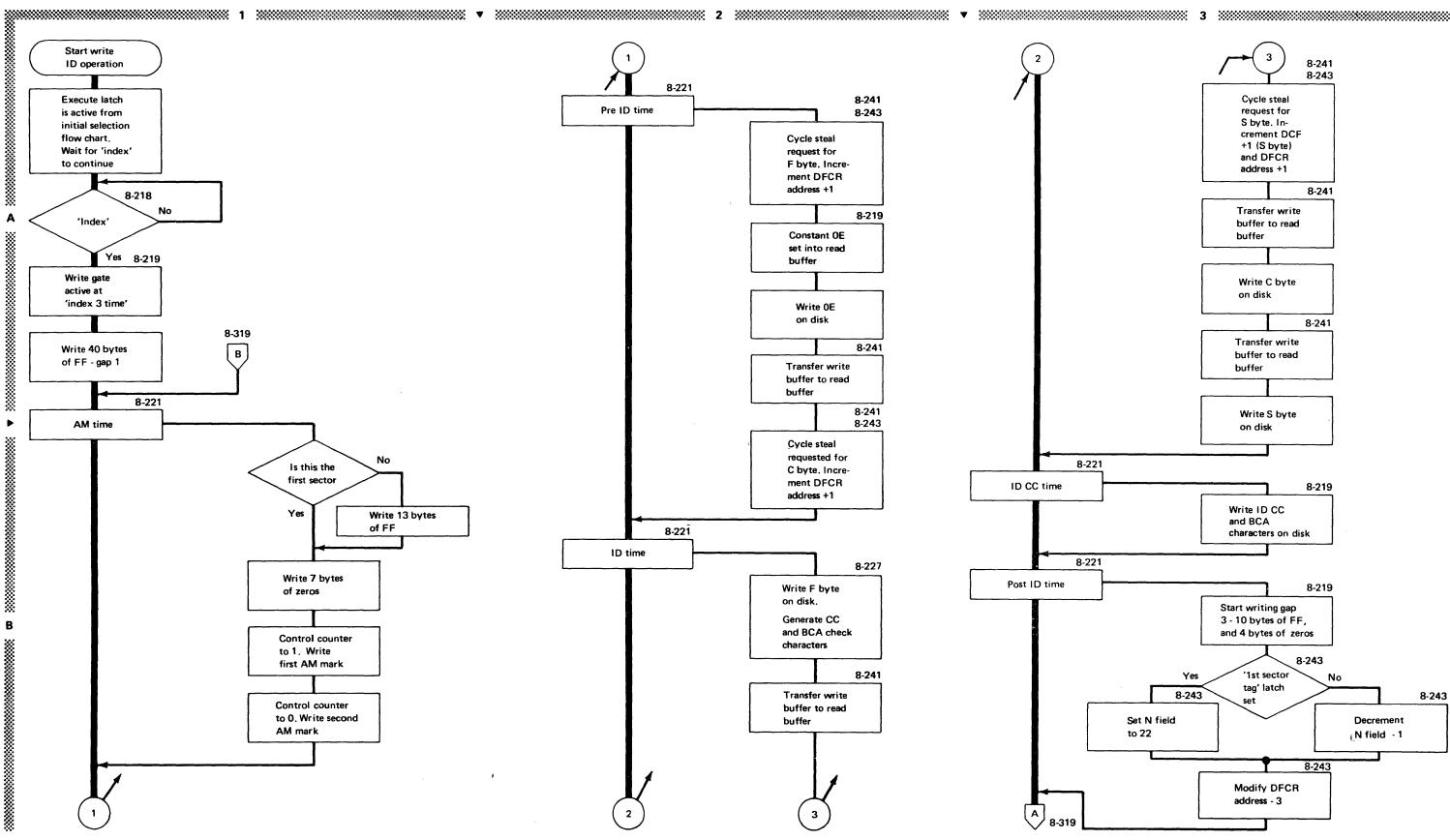

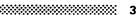

- Write Identifier Operation (9 Parts) 8-317 through 8-325

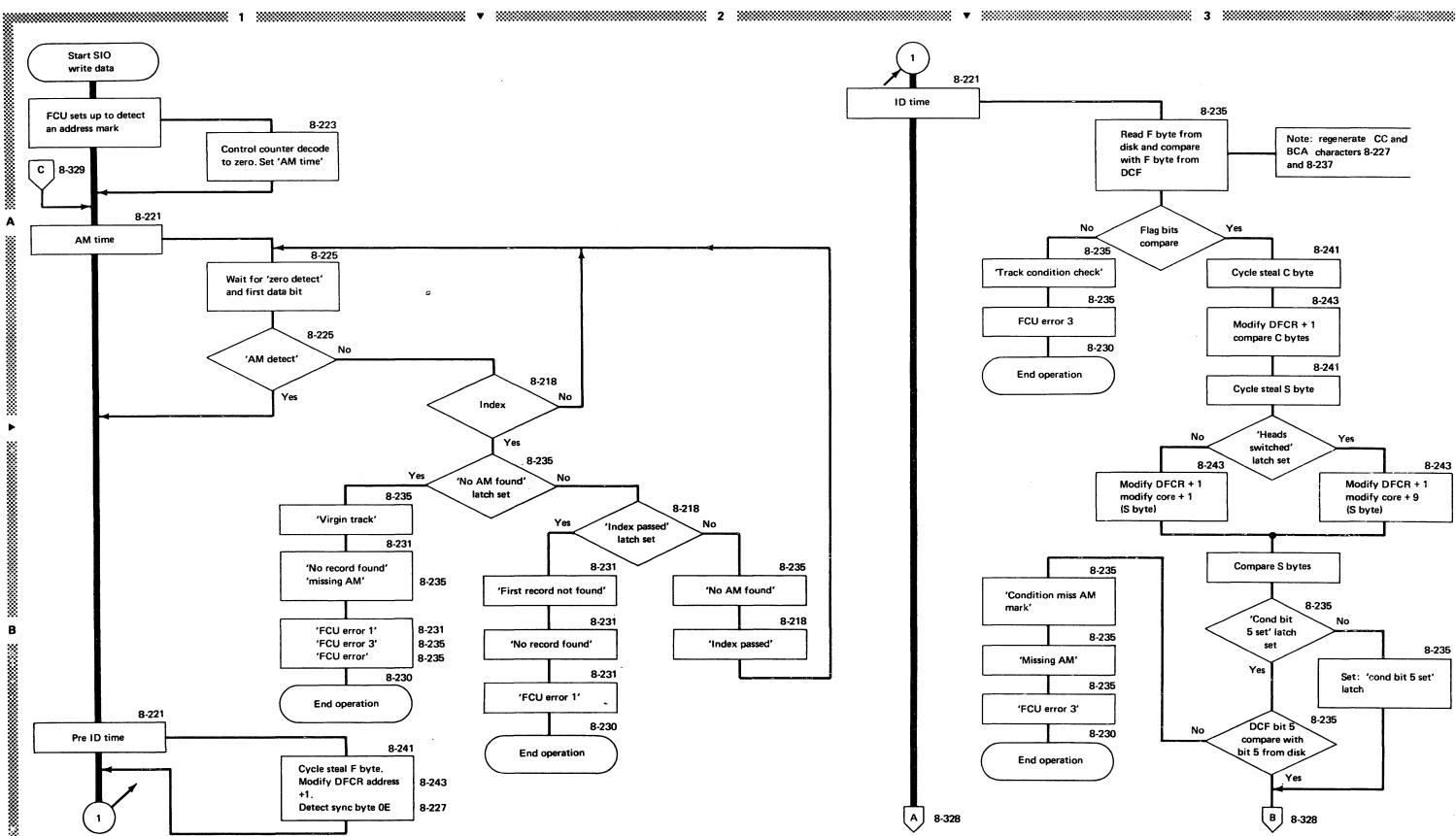

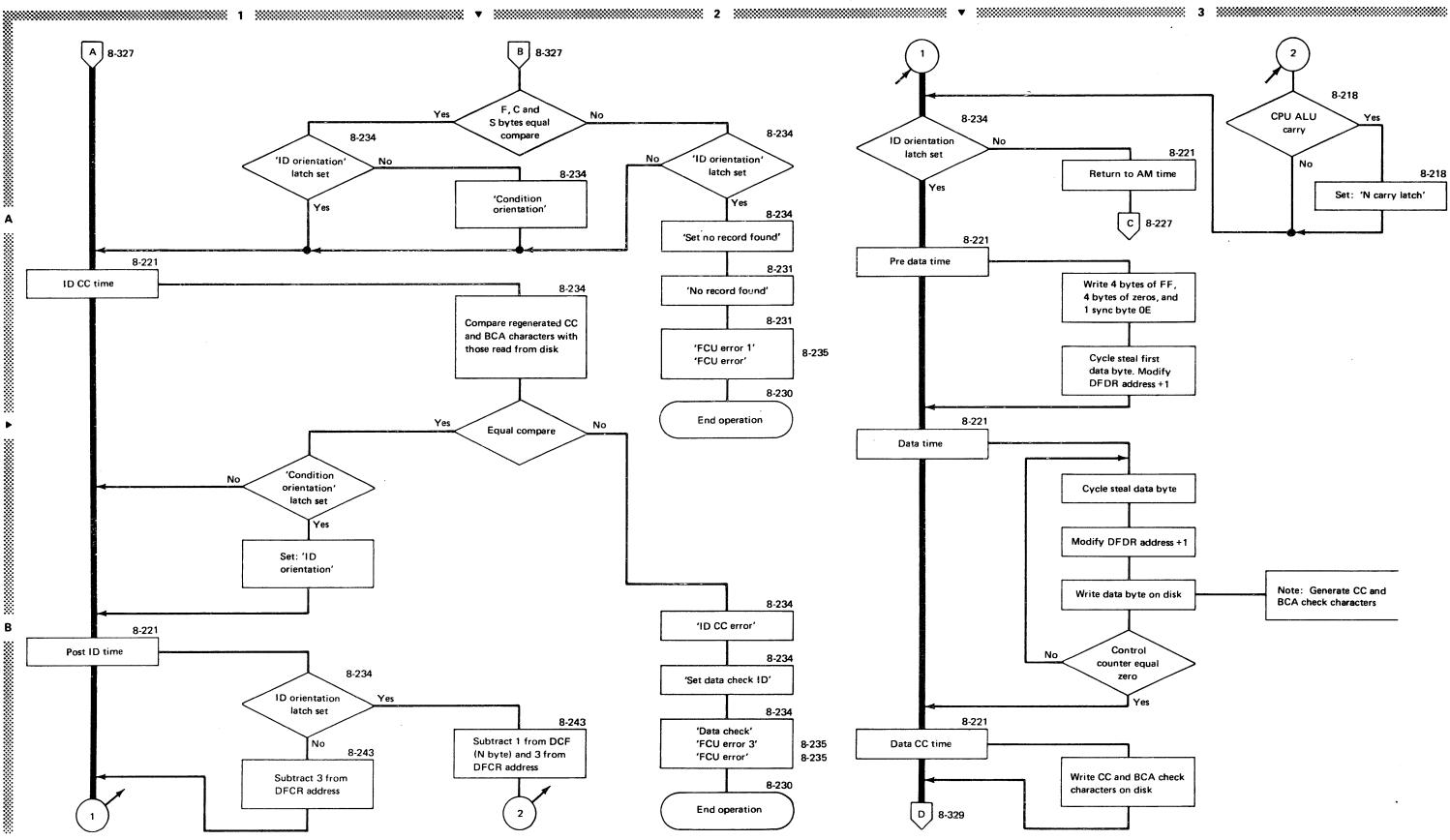

- Write Data Operation (9 Parts) 8-326 through 8-334

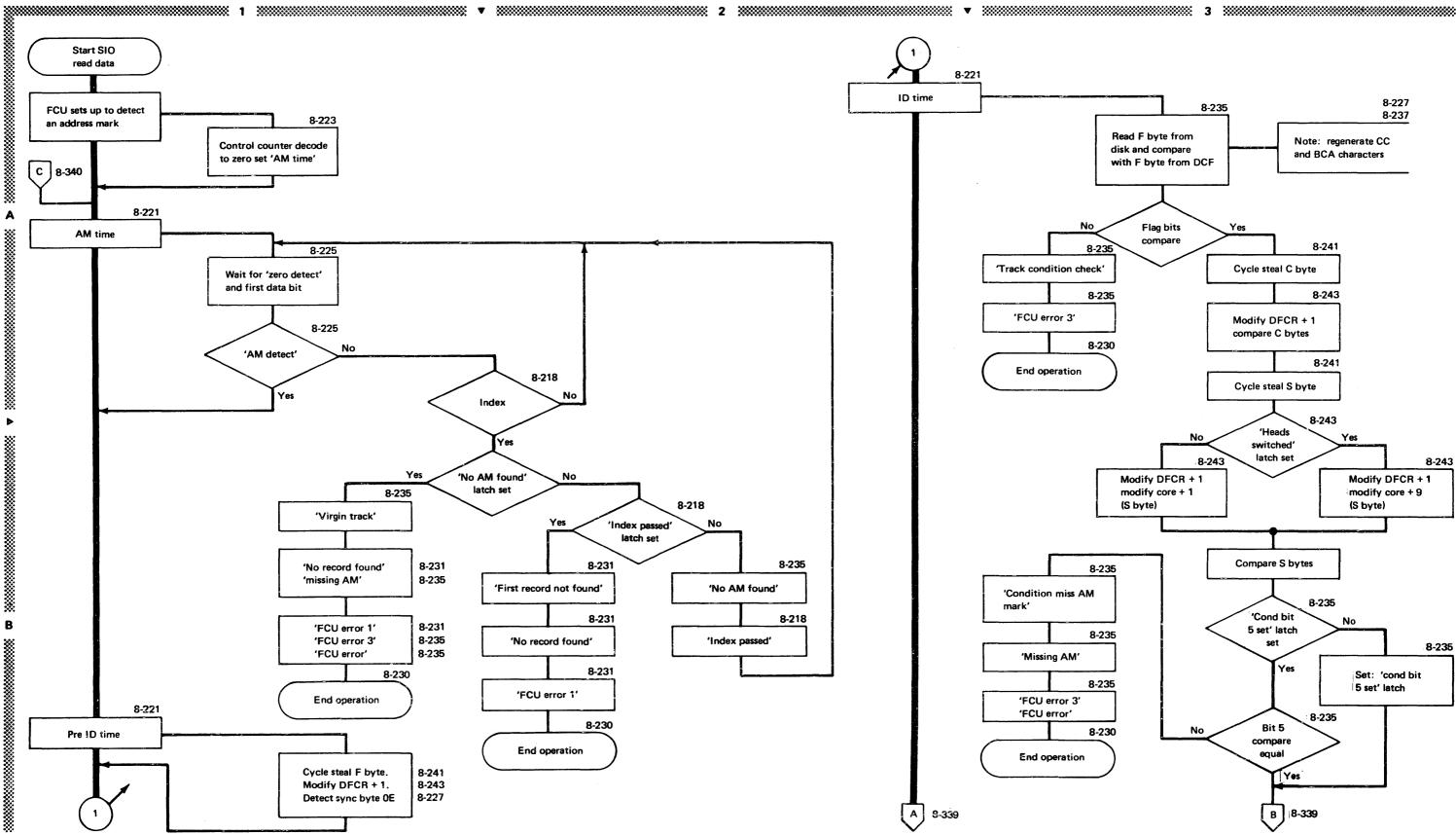

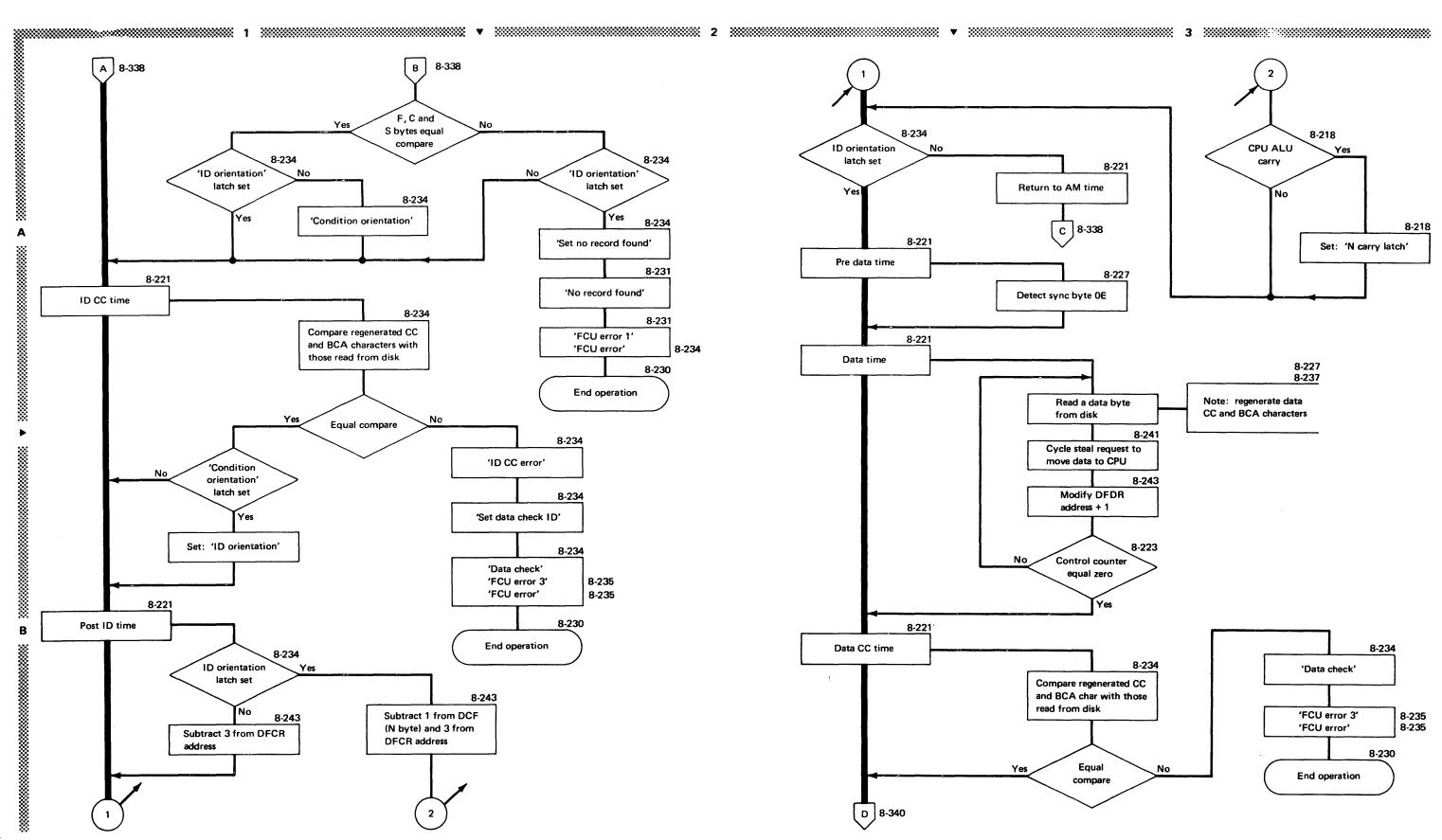

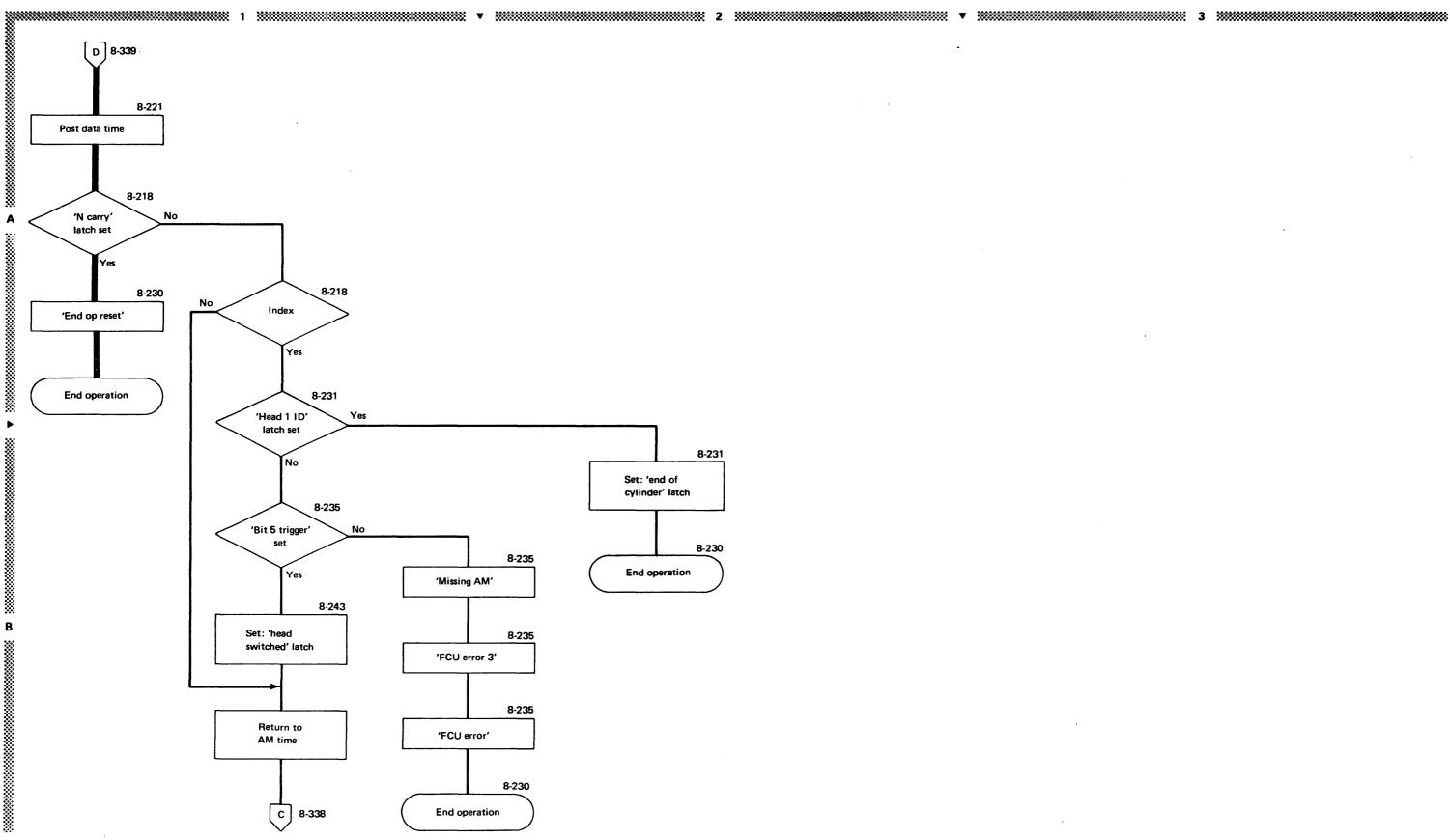

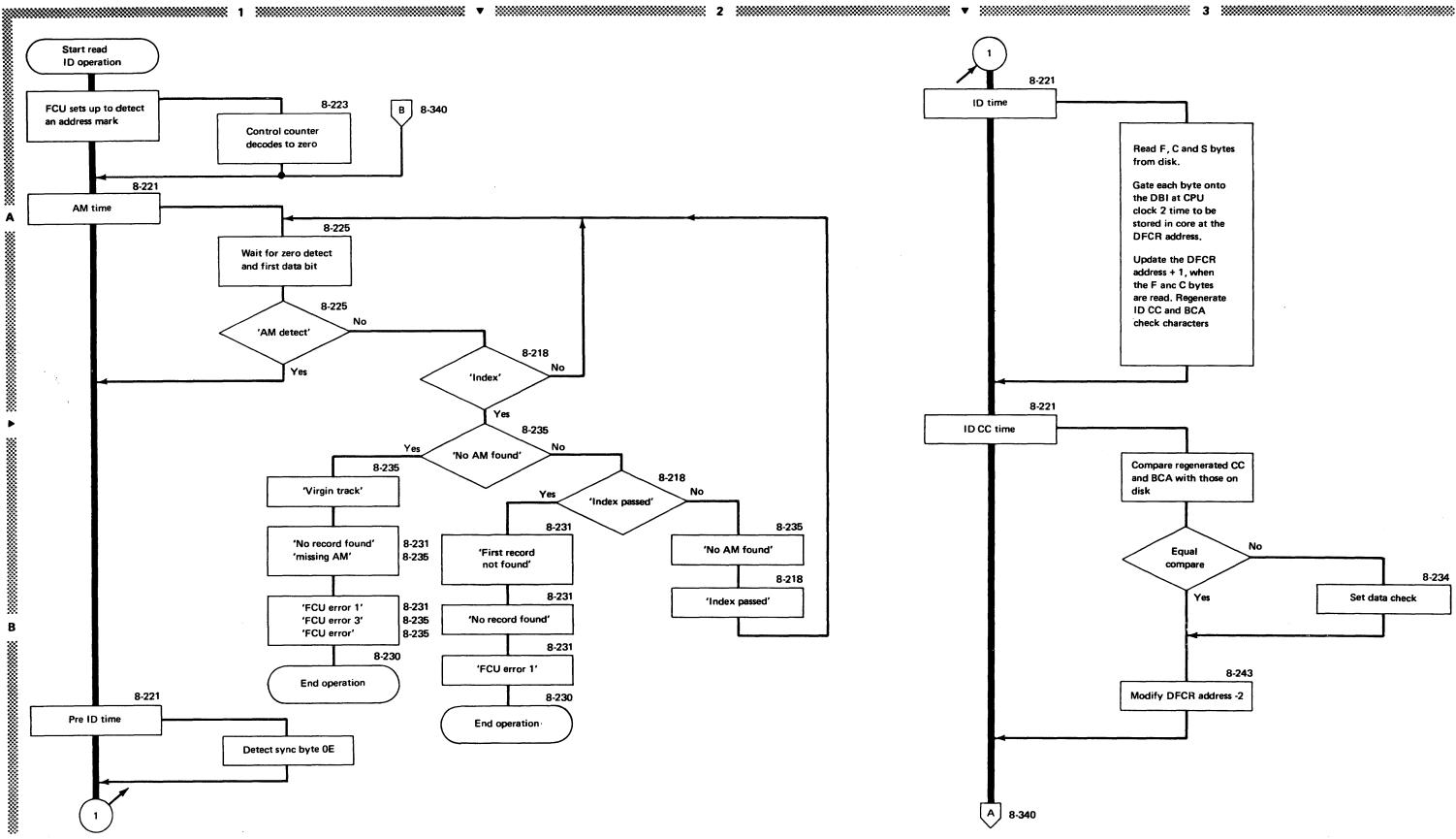

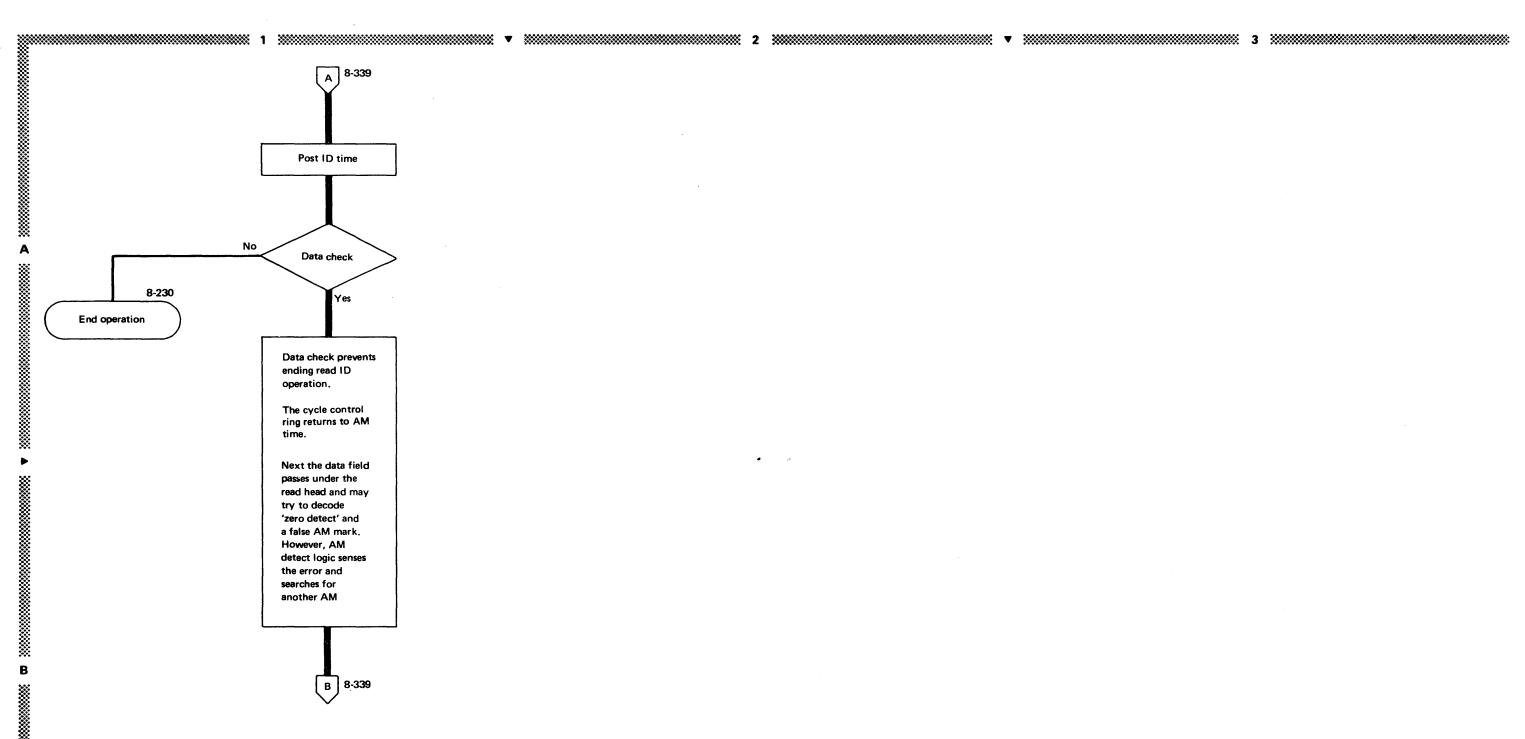

- Read Operations (12 Parts) 8-335, 8-337 through 8-347

- Read Identifier Operation (9 Parts) 8-348 through 8-356

### **IBM 5444 DISK STORAGE DRIVE ATTACHMENT**

Α

В

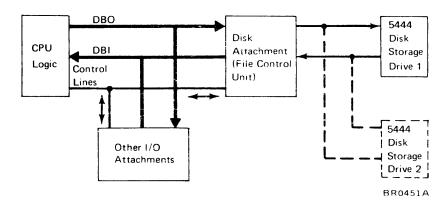

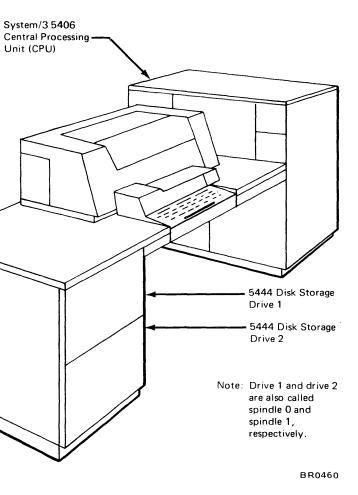

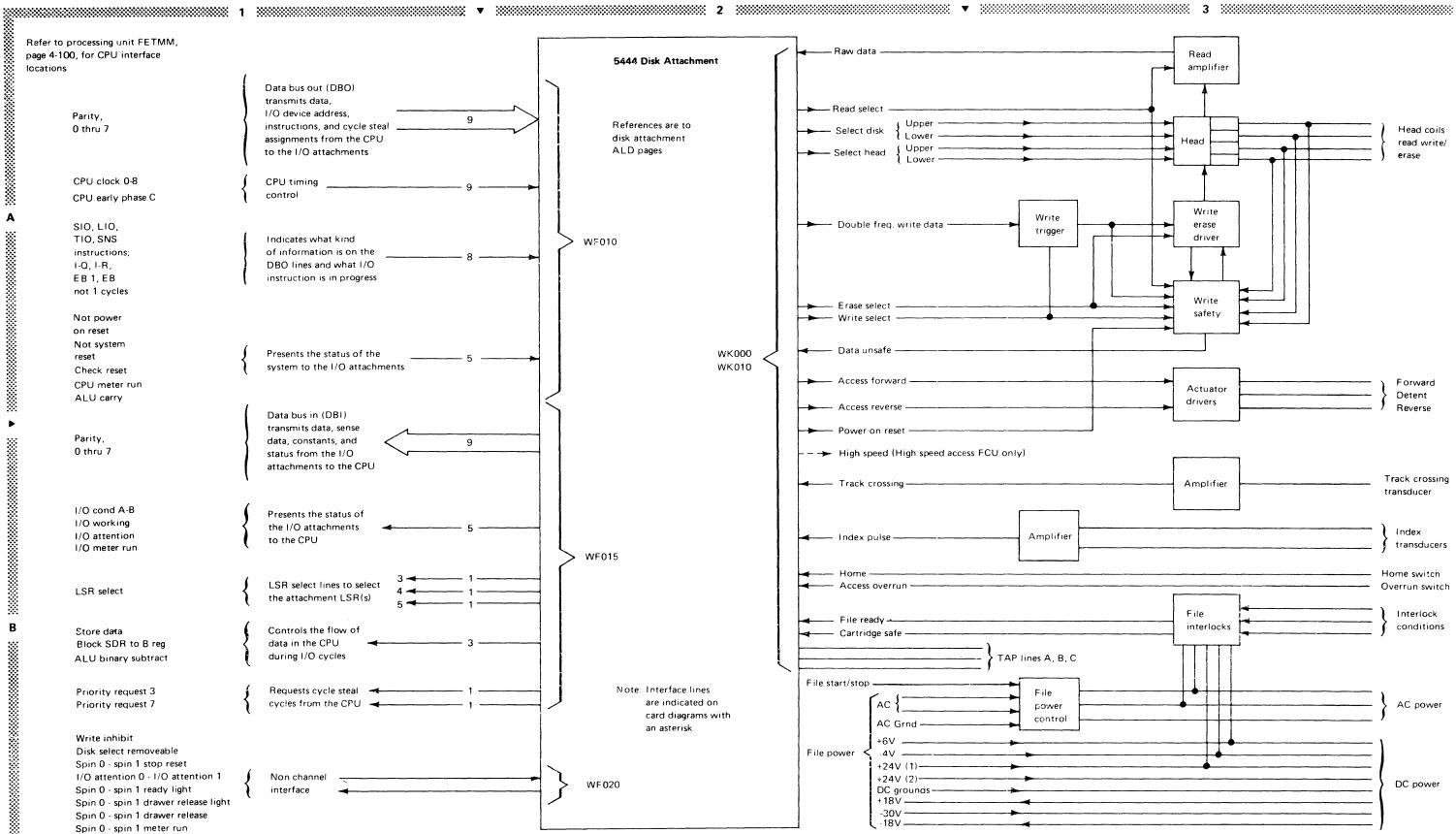

The IBM 5444 Disk Storage Drive Attachment, also called the disk attachment or file control unit (FCU), can attach either one or two 5444 Disk Storage Drives to the IBM System/3 Model 10 or the IBM System/3 Model 6.

The file control unit is the interface between the disk storage drive and the central processing unit (CPU). The file control unit (FCU) provides a way for the disk storage drive to use the facilities of the CPU to communicate with core storage. Communication between the CPU and file control unit (FCU) is via the data bus out (DBO) lines and data bus in (DBI) lines, with additional lines for control signal interchange.

The disk attachment is located in the main gate of the CPU. In the Model 10 it is located in gate 01A-A2; in the Model 6 it is located in gate 01A-A1. A disk attachment may be either *standard* or *high speed*, depending on the model of 5444 Disk Storage Drive attached to the CPU. The difference between a standard and high speed attachment is determined by the type

of logic card plugged into positions G2 and F2 of the attachment board. The standard disk attachment is used in either the Model 6 or Model 10 CPU to attach 5444 Disk Storage Drives with friction drive or stepper motor access mechanisms.

The high speed disk attachment is used only with the Model 10 CPU to attach 5444 Disk Storage Drives with the high-speed access feature installed.

The file control unit contains logic circuits to:

- Decode program instructions into signals to control a disk operation. 1.

- Generate timing signals for data transfer to and from the disk. 2.

- 3. Address the local storage registers assigned to disk operation.

- Detect error conditions. 4.

- Generate the cyclic code (CC) and bit count appendage (BCA) check 5. characters.

- Provide status information about the file control unit and drive(s). 6.

- 7. Generate cycle steal requests.

- 8. Serialize data (change from parallel-by-byte to serial-by-bit) and deserialize data (change from serial-by-bit to parallel-by-byte).

- Control the high-speed access interface line for drives that have the 9. high-speed access feature installed. (Model 10 CPU only.)

#### **Program Instructions**

Four program instructions are used for disk operation:

- Load I/O (LIO) 1

- 2. Test I/O (TIO) / Advance Program Level (APL)

- 3. Sense I/O (SNS)

- Start I/O (SIO) Δ

#### Load I/O (LIO)

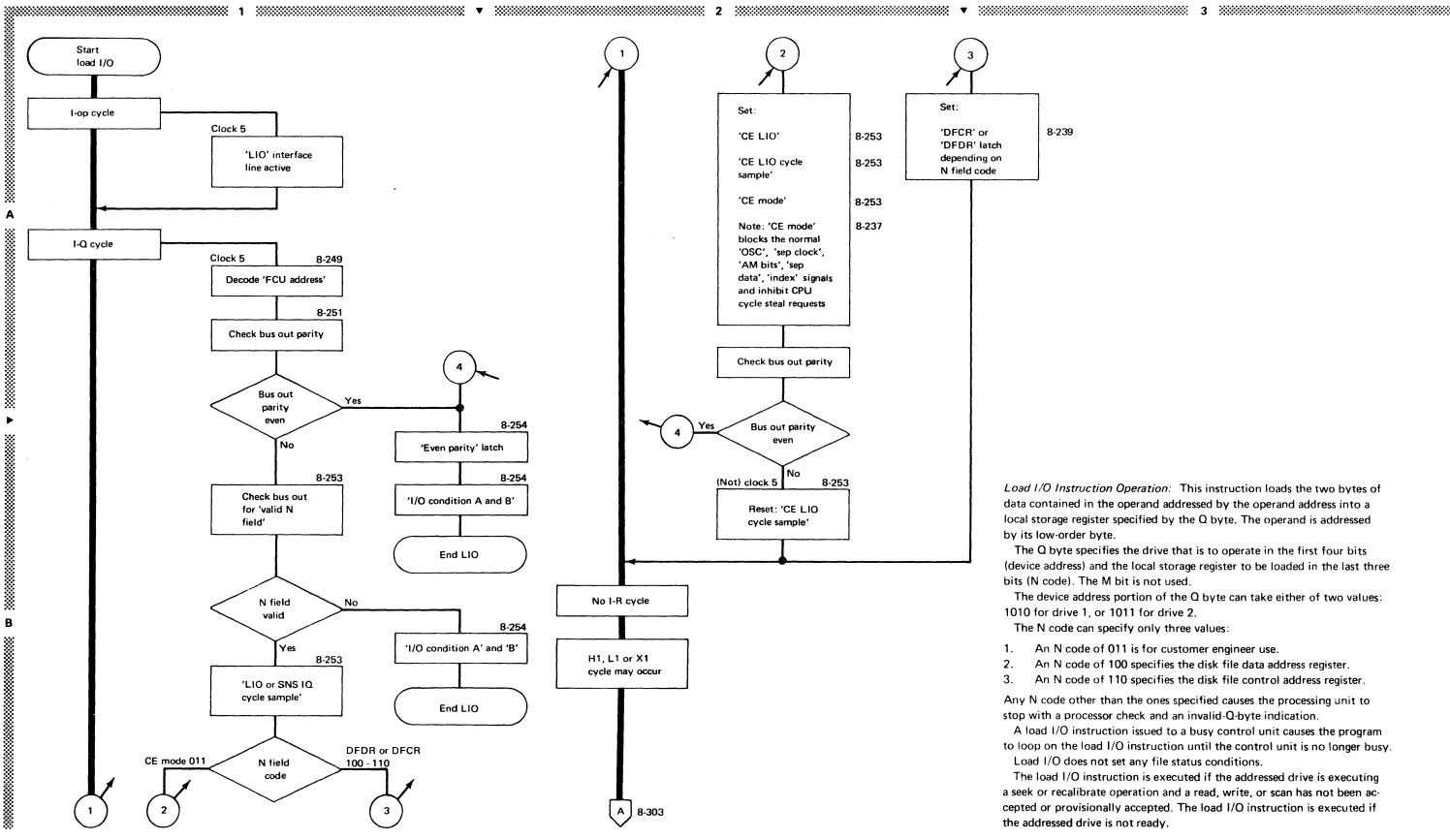

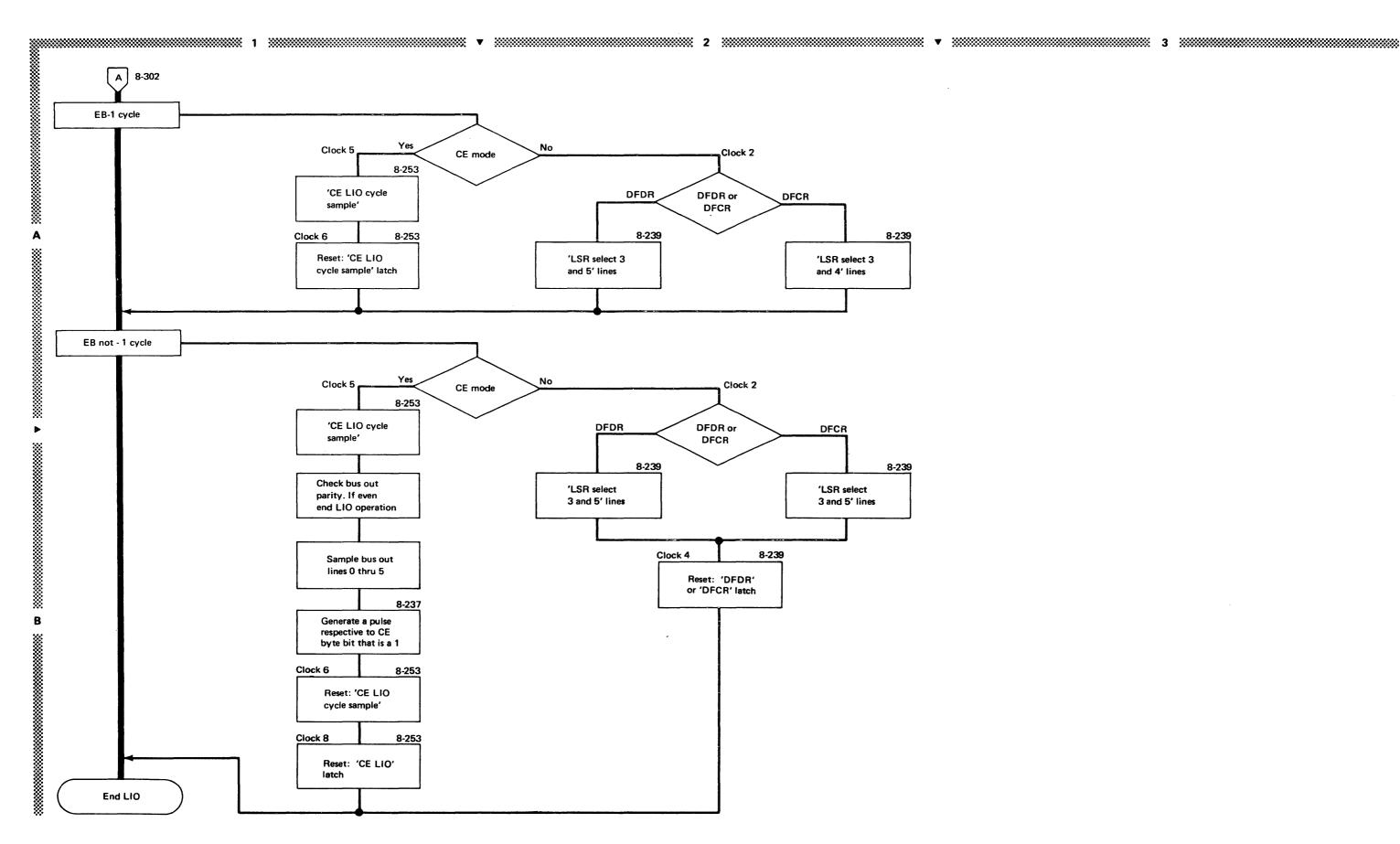

Load I/O transfers two bytes of data from core storage into either of the local storage registers assigned to disk, disk file data register (DFDR) or disk file control register (DFCR). For diagnostic purposes, a CE load I/O (LIO) instruction transfers two bytes from core storage to the file control unit. This information controls logic lines in a manner that duplicates disk drive functions to facilitate diagnostic programs.

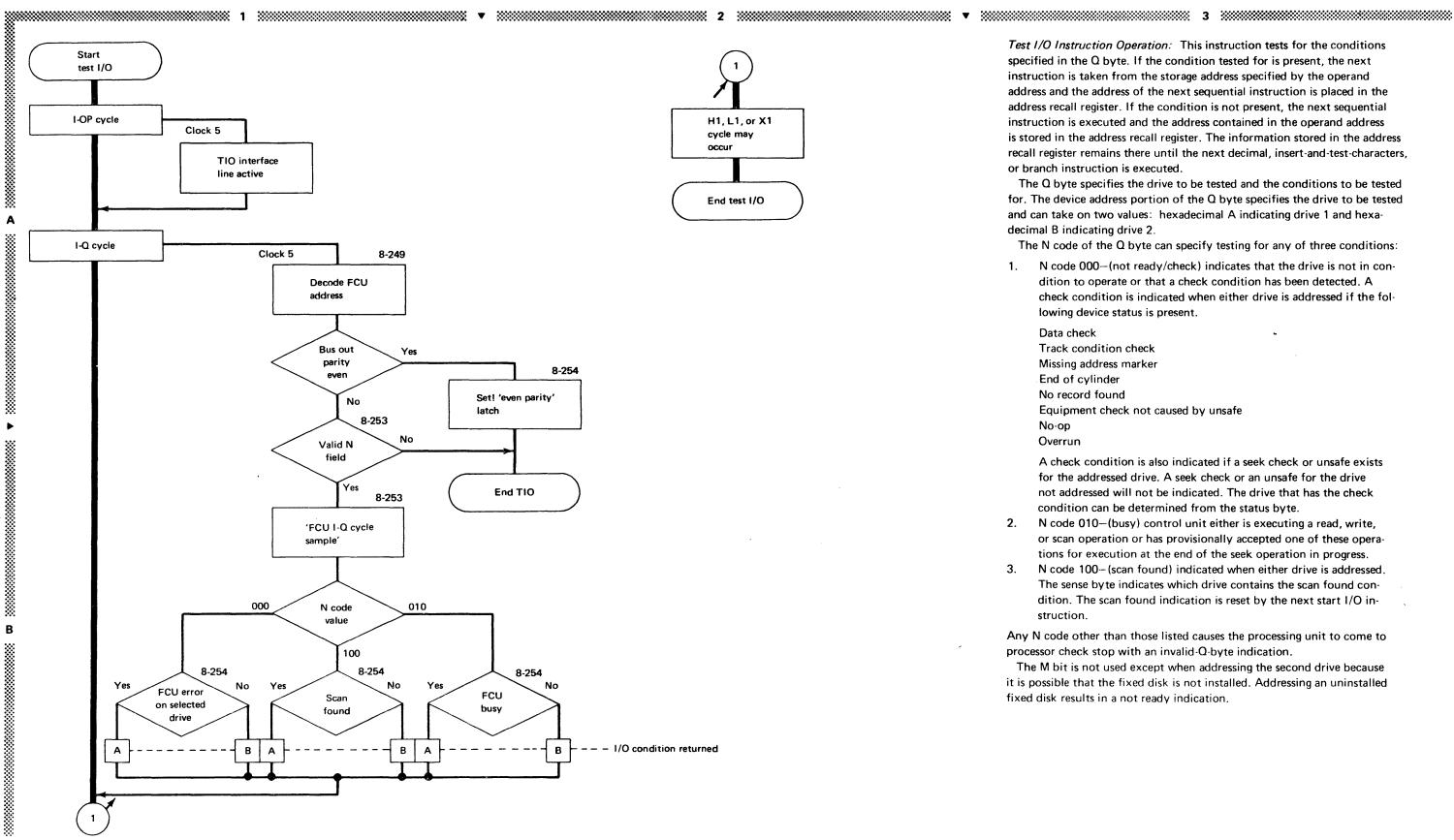

### Test I/O (TIO)

Test I/O / Advance Program Level tests for operating conditions of the drive and attachment. This instruction is used to branch the program into subroutines depending on the results found in the test (condition met or not met). If the system has the dual program feature, the program may branch into another program depending on the conditions found in the test. Without the dual program feature, the program loops on the advance program level (APL) instruction until the condition specified in the test is no longer present.

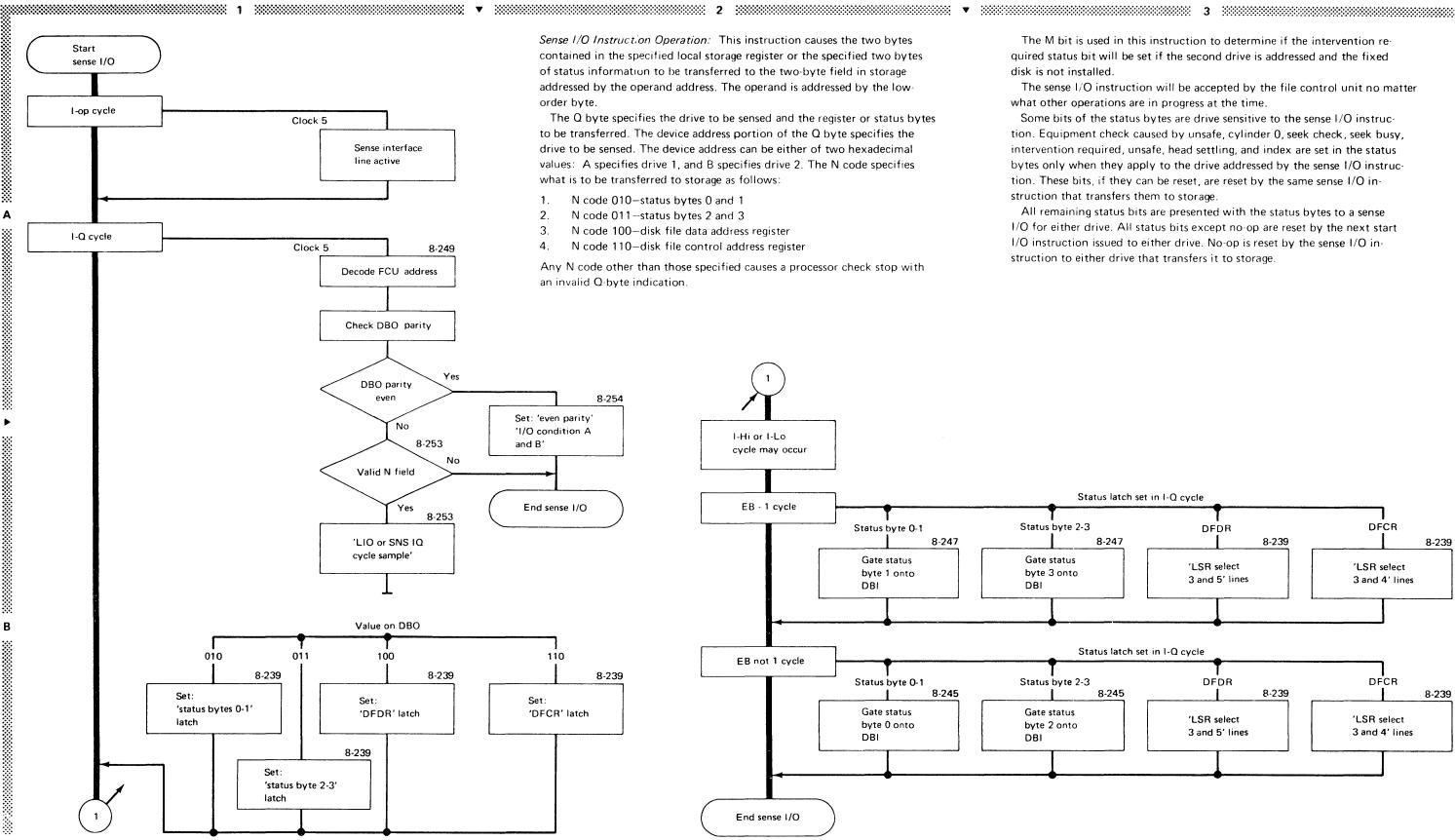

### Sense I/O (SNS)

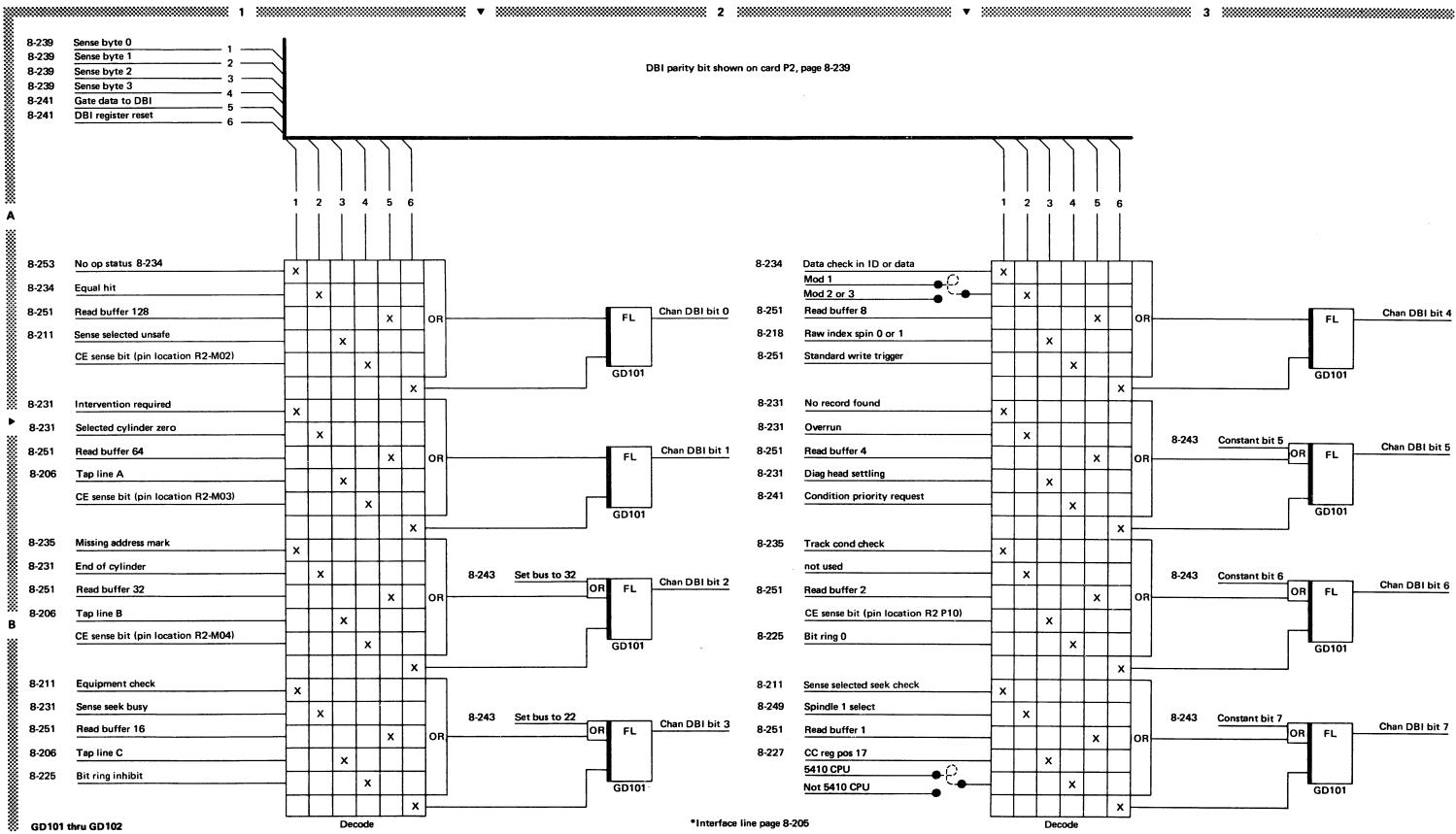

Sense I/O transfers (1) the two bytes in either local storage register (LSR) or (2) two bytes of file control unit status information into core storage. The four status bytes indicate operating conditions about the file control unit and drive(s). Each bit within each byte carries a significance, providing up to 32 indications of the condition of the units.

### Start I/O (SIO)

Start I/O selects the drive an operation is directed to, selects the disk (either fixed or removable), and specifies the command (operation) to be performed. These commands are:

Write-records data on the disk from the data field in core storage.

Read-reads data recorded on the disk and transfers the data to the data field in core storage.

Scan-compares data on disk with a data field in core storage. An equal, low or equal, or high or equal indication can be obtained.

#### Timing

- 1

- 2. 3.

- 4.

### **Error Detection**

1 2

# Chapter 1. Introduction

Seek-positions the read heads in the 5444 to a desired location (cylinder) and selects a read head to be used in the next start I/O instruction operation (read, write, or scan). Head selection determines the upper or lower surface of the disk to be addressed.

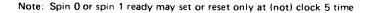

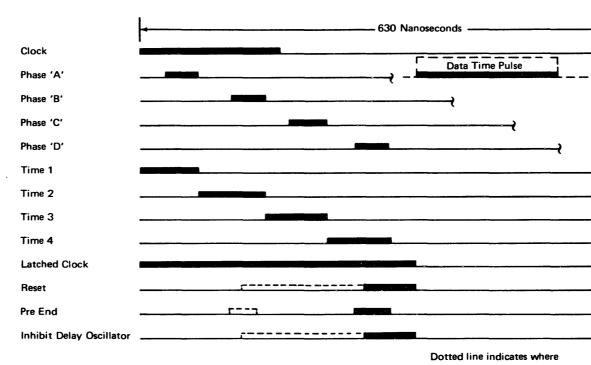

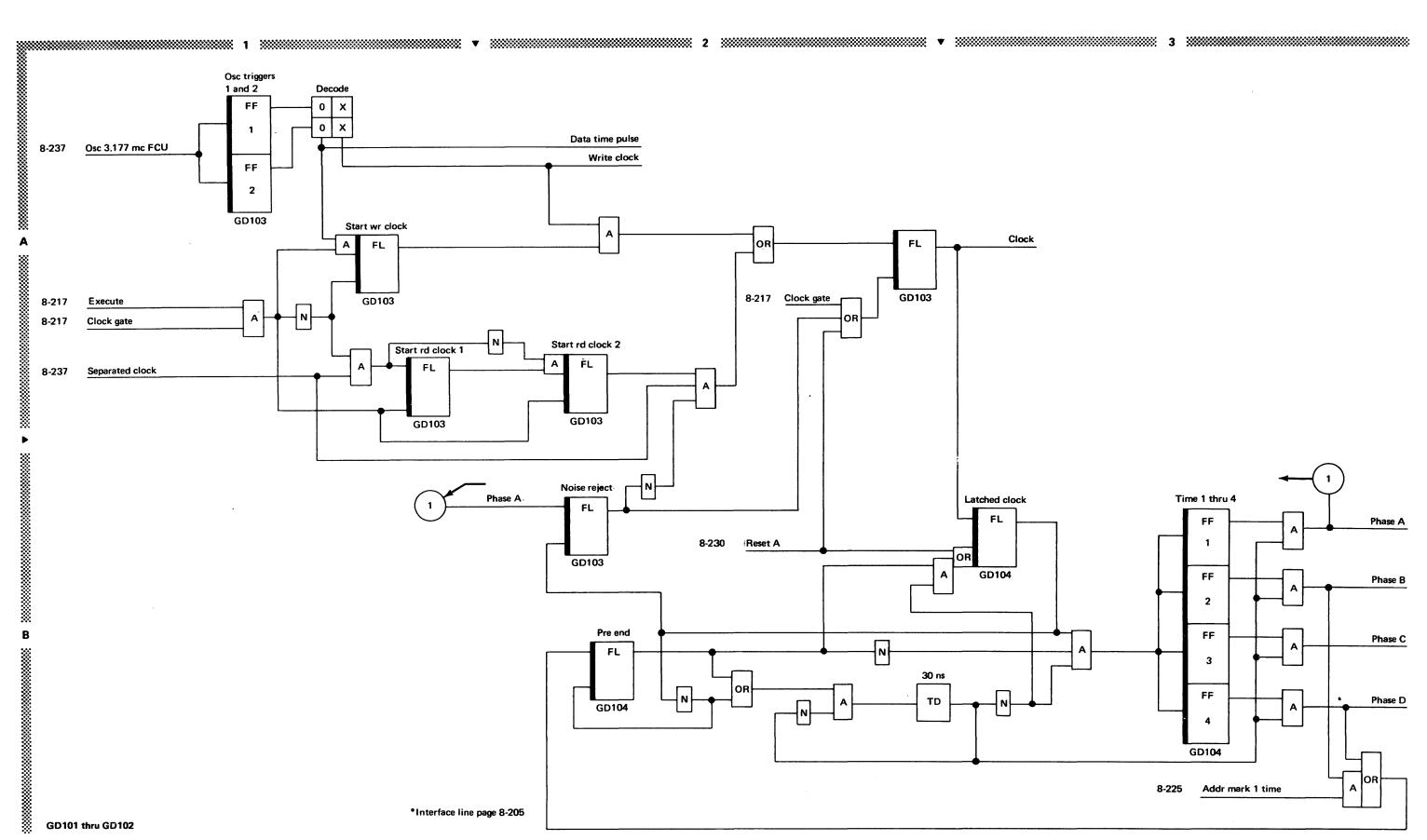

File control unit circuits are controlled by timing (clock) signals. These signals are generated by (1) a crystal oscillator (write clock) or (2) signals produced from the clock signals when data is read from the disk (read clock). Clock signals drive other time-generating logic needed to control the transfer of data through the file control unit and to and from the disk.

### Local Storage Register Addressing

The local storage registers disk file data register and disk file control register are addressed by the file control unit to:

Locate the data field in core storage.

Locate the disk control field in core storage.

Increment or decrement the address in a register.

Load the local storage register with an address.

Errors in the file control unit may be of two types:

Error in data (parity).

Failure of the file control unit to follow the functional objectives of a program instruction.

Α

►

В

#### Parity Errors

The parity of the data is checked as it enters the file control unit. After the data byte is under control of the file control unit, the parity bit is separated from the data byte, but retained and transferred in step with the data through the file control unit. At each transfer point the parity is compared with the separated parity bit. As the data byte leaves the file control unit to be recorded on disk, the odd-even status of the data bits is checked against the separated parity bit to insure that the data was transferred out of the file control unit with the same parity as when it entered the file control unit.

In place of recording parity bits on the disk, the file control unit generates check characters (cyclic code and bit count appendage) from the serialized data bits and records the characters at the end of the identifier area (ID) and data fields on the disk. With a known input (the data byte parity), the parity of the check character can be predicted. The check character generated is therefore compared with the separated parity bit for error in generation.

When data is read from the disk, the check characters are regenerated and compared to the check characters recorded on disk to insure that the data was read correctly. Before the data byte is returned to the CPU, a parity bit generator reinserts the parity bit that was removed from it before the byte was serialized.

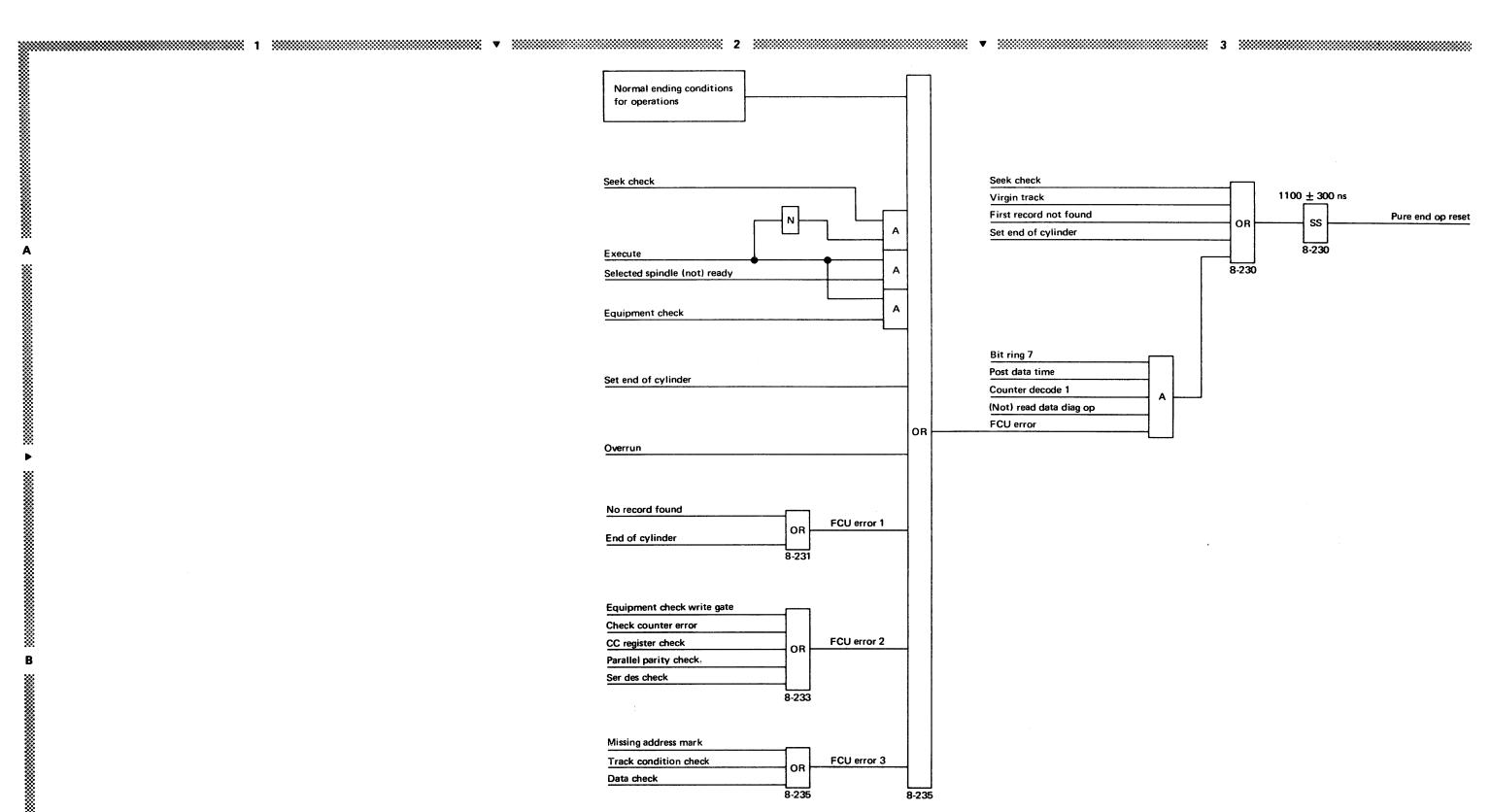

#### Functional Objective Errors

Functional objectives of each program instruction are checked and if the objectives are not met, an error is indicated by setting an error latch. If an error is indicated, the operation in progress is ended, and a status (error) latch is set to indicate the type of error.

#### Cycle Steal Requests (CSR)

A cycle steal request operation permits the file control unit to share processing time with the CPU and other I/O devices. Cycle steal requests for disk data transfer are highest in priority of the cycle steal devices.

The file control unit requests a cycle steal when there is data or control information to transfer to or from the file control unit or when the address of a LSR is to be modified. A LSR is usually addressed during a cycle steal to locate the data field or the disk control field in core storage.

One data byte is buffered (stored) in the file control unit. As a result the file control unit requests a cycle steal one cycle before the data is needed at the file control unit, or one cycle after the data byte is ready to send to the CPU.

#### Serializer-Deserializer (Serdes)

Data is transferred to the file control unit parallel-by-byte but is recorded on the disk serial-by-bit. Data is read from the disk serial-by-bit and transferred to the CPU parallel-by-byte.

Two registers in the file control unit operate in a multifunction manner to change the byte into bits or the bits back into a byte. One register acts as a buffer while the other shifts or vice-versa. These registers are called a serdes (serializer-deserializer).

Note: Drive 1 and drive 2 are also called spindle 0 and spindle 1, respectively. BR0442A

#### High-Speed Access Control

During seek operations on disk drives with the high-speed access feature installed, the disk attachment must monitor the carriage position relative to the desired track. Depending on the length of the seek, the disk attachment deactivates the high-speed access interface line at various numbers of tracks before the end of the seek. This is to allow the carriage to slow to normal speed and stop at the desired track without overtravel.

### IBM 5444 DISK STORAGE DRIVE

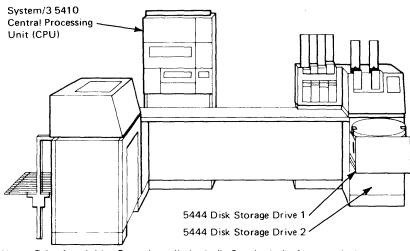

The IBM 5444 Disk Storage Drive is a direct access storage device for the IBM System/3 Model 10 or System/3 Model 6.

A 5444 drive contains two disks mounted on a common spindle. One disk is permanently mounted in an enclosure at the base of the drive spindle. The other disk, which is removable, is housed in a cartridge at the top of the spindle above the fixed disk. When removed from the drive, the cartridge is placed into a base to form a fully sealed enclosure for protected, off-line storage.

5444 Disk Storage Drives use either of two types of access drive mechanism, friction drive or stepper motor. Early drives below serial number 30100 use friction drive, later drives above serial number 30100 use the stepper motor.

A high speed access feature is available for drives above serial number 30100 and is available for use on the Model 10 only. High speed access and normal speed drives can not be installed (mixed) on the same system.

A system can contain one or two drives. The drives are mounted within the system on sliding drawers.

Six models of the 5444 can be used to obtain four different drive configurations as shown in the following tables. The first table lists and describes the available models. The second table shows the drive configurations.

Available Models

Model

A3

1 2 3 A1 A2

### Description

- Single drive. Accesses 104 cylinders on removable cartridge and 104 cylinders on fixed nonremovable disk. Single drive. Accesses 204 cylinders on removable cartridge and 204 cylinders on fixed nonremovable disk. Single drive. Accesses 204 cylinders on removable cartridge only.

- Model A1, A2, and A3, are equivalent to models 1, 2, and 3 except that high speed access is installed. These models are available on the Model 10 only.

| Drive C          | onfiguration                 | ns                        |                                        | Cylinders Ac           | cessed        |

|------------------|------------------------------|---------------------------|----------------------------------------|------------------------|---------------|

| No. of<br>Drives | Normal<br>Speed<br>Model (s) | High<br>Speed<br>Model(s) | Storage<br>Capacity<br>(million bytes) | Removable<br>Cartridge | Fixed<br>Disk |

| 1                | 1                            | A1                        | 2.46                                   | 104                    | 104           |

| 1                | 2                            | A2                        | 4.92                                   | 204                    | 204           |

| 2                | 2&3                          | A2&A3                     | 7.37                                   | 204                    | 204           |

| 2                | 2                            | A2                        | 9.83                                   | 204                    | 204           |

Model 1 is located in the upper drawer; model 3 or a second model 2 is located in a lower drawer.

The disk drive uses solid logic dense (SLD)-100 circuits and SLD-100 line levels between the drive and disk attachment.

For further information about the 5444 disk storage drives, refer to:

FE Theory-Maintenance Manual, IBM 5444 Disk Storage Drive, (Machines with serial numbers up to 30100), Order No. SY33-0026

IBM Maintenance Library, 5444 Disk Storage Drive, Theory-Maintenance, (Machines with serial numbers above 30100), Order No. SY33-0029

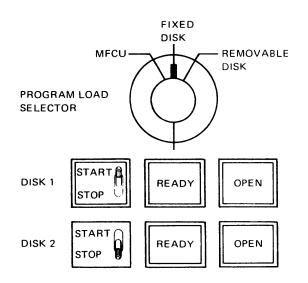

### **Operator Console (Model 10)**

Operator controls for the disk drives are located on the system console.

Program Load Selector

This three-position switch determines what I/O device will be selected for the program load operation:

MFCU position selects the multifunction card unit.

Fixed Disk and Removable Disk select disk drive one and either the fixed (lower) or removable (upper) disk, depending on the switch position.

The START-STOP switch and indicators **READY and OPEN provide individual** control and status for the drives:

Start-Stop switches apply AC power to the respective drive.

Ready indicator on means that the respective drive is ready for operation.

Open indicator on means that the drive drawer may be opened to attend to the drive or to change the remov-

able disk.

BR0443A

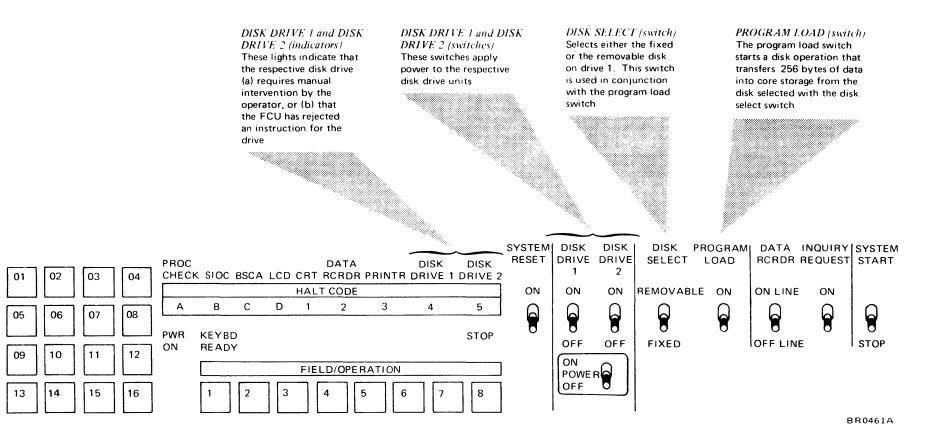

### **Operator Console (Model 6)**

Operator controls for the disk drives are located on the system console.

#### Data Storage

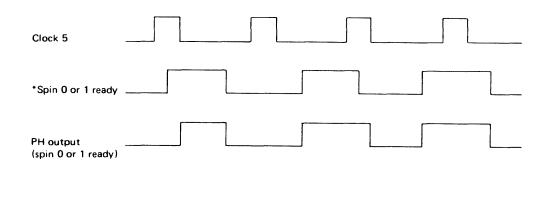

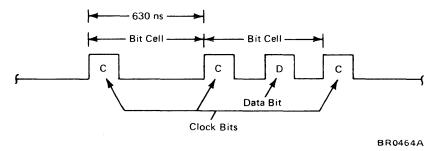

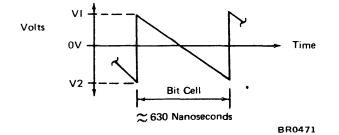

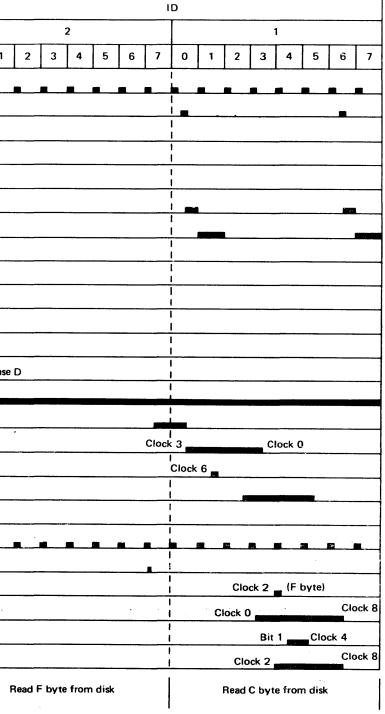

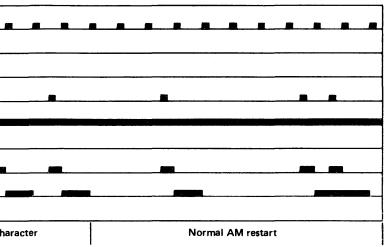

Data is recorded (written) on the disk serially by byte and serially by bit. In addition to data, clock bits are recorded on the disk. Data bits are recorded between the clock bits in a continuous pattern without separation or extra bits as markers. The clock bits provide timing signals when the data is recovered (read) from the disk. This method of recording data is referred to as double-frequency recording. A data byte of hexadecimal FF, for example, is written as all ones-twice the frequency of zeros that are recorded as clock bits only.

Clock Bit Data Bit Zeros BR0444

Data recorded on the disk does not contain a parity bit; it is removed from the data byte before it is recorded on the disk. Instead of a parity bit, check characters are generated from the data bits and recorded at the end of the data field. When data is recovered (read) from the disk, the check characters are regenerated and compared with the check characters recorded on the disk to verify the data.

Data is recovered serially by bit and reassembled into an 8-bit byte. A parity-bit generator reinserts the parity bit removed in the recording process, before the data byte is returned to the system for processing.

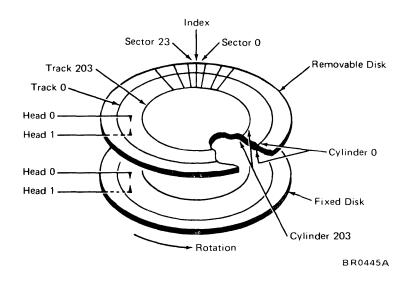

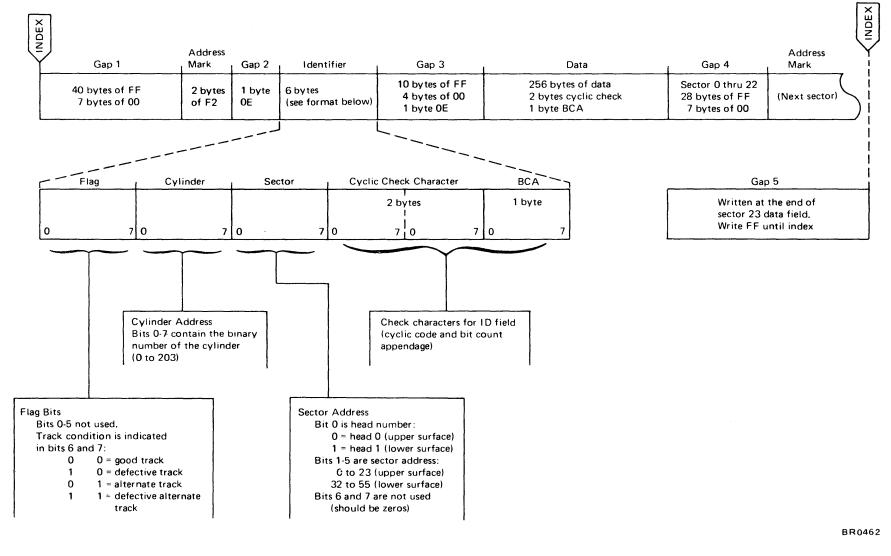

Track Format

The track is the smallest addressable unit to which the drive access mechanism can position its heads. Each track is divided into 24 sectors, each with its own address. A sector may be read or written selectively through programming. A fixed point on the disk, index, is the starting point for all tracks. Each disk surface contains either 104 or 204 tracks. The tracks that are related to each other in the vertical plane on a single disk form a cylinder. On drives with two disks, the corresponding cylinders on both disks have the same cylinder numbers. Depending on the disk drive model, 100 or 200 cylinders are used for data storage. Cylinders 001, 002, and 003 are for alternate tracks and cylinder 103 or 203 is for customer engineer use.

- A mark which is fixed for each disk and provides orientation Index information to the disk attachment. It is the starting point for every track.

- G1 A gap area between index and the first address mark. G1 contains 40 bytes of FF followed by seven bytes of zeros.

- AM Address mark (AM) is a specially written group of bits that indicate the start of a new sector. AM contains two bytes. (See "Data Separator" for additional information on address marks.)

- G2 A gap area between an address mark and the identifier of a sector. G2 contains a one-byte sync character (hexadecimal 0E).

- ID The identifier area (ID) of a sector contains six bytes, one flag byte, two address bytes, and three bytes of check characters.

G3 A gap area between the identifier and the data area of a sector. G3 contains 15 bytes: ten bytes of FF, followed by four bytes of zeros, followed by one sync character (hexadecimal OE).

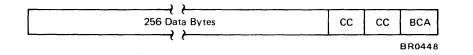

Data The data area contains 256 bytes of data and three bytes of check characters.

| G4 | A gap   |

|----|---------|

|    | the ne  |

|    | of zero |

| G5 | A gap   |

|    | G5 is f |

|    | tional  |

# $\mathbf{v}$

area between the data field and the address mark of ext sector. G4 contains 28 bytes of FF and seven bytes os.

area between the end of the last sector and index. filled with FF (number of ones varies with disk rotaspeed).

The track format for address marks, gaps, identifier fields, and data field is established by the disk attachment while executing a write identifier command. (This command is principally used to prepare a new disk for operation.) Data recorded on the disk during subsequent write data operations is written between gaps three and four. These gaps may vary slightly in length due to disk rotational speed.

Two local storage registers, located in the CPU, are assigned to disk operation. They are the disk file data register and disk file control register.

#### Disk File Data Register (DFDR)

A

В

This register addresses the disk data field in core storage. The data field contains data to be written on the disk or data received from the disk.

At the start of an operation, the disk file data register contains the twobyte address of the first byte in the data field. The disk file data register is updated by one as each byte is read from or written on the disk. At the end of an operation, the address in the disk file data register is one greater than the last address used during the operation. (For read data diagnostic, scan, and write identifier commands, the disk file control register address is equal to the original address.) If there is no data transferred, the contents of the disk file data register remain unchanged.

*Note:* In any of the described operations, the contents of the disk file data register are not predictable if an equipment check occurs.

The data field format is:

Disk File Control Register (DFCR)

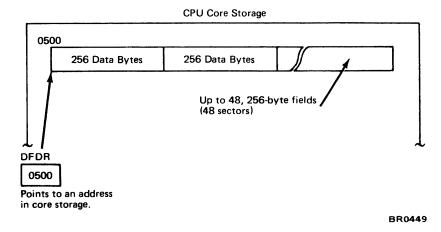

The disk file control register contains the address of a four-byte disk control field (DCF) in core storage. The disk control field contains information regarding (1) track condition, (2) cylinder address, (3) sector address, (4) head selection, (5) number of sectors to process during an operation, (6) number of cylinders to move the access mechanism during a seek instruction, and (7) the direction in which the access mechanism should move for the seek operation.

#

### The disk control field format is:

# CORE STORAGE С S N 0123456 011 2 3 4 5 6 7 0 1 2 3 4 5 6 7 78 15 16 23 24 31 Cylinder Byte Bits 0-7 contain the binary number of the cylinder address (0 to 203) Sector Byte Bit 0 is head selection (See note) 0 = select head 0 1 = select head 1 Bits 1 through 5 are sector address: on disk upper surface address will be 0 to 23, lower surface 32 to 55 Bits 6 and 7 indicate direction of seek: 0 = seek reverse 0 0 1 = seek forward N Byte (Field) Bits 0-7 contain a binary number of the number of cylinders to move in a seek operation, or a number that indicates how many sectors to process. This number is equal to the number of sectors desired, less one (N = 16 will process 17 sectors)

BR0450A

Α

►

B

#### File Instructions

Before a disk operation begins, a load I/O instruction is issued to load the local storage registers, disk file data register and disk file control register, with the address in core storage of the data field and disk control field, respectively.

Next, the availability and operating status of the device should be checked with the test I/O and sense I/O instructions. If the results of the test I/O and sense I/O indicate that the device is ready to accept an instruction, a start I/O instruction is issued.

All devices on the data bus out receive the start I/O instruction; however, only the device that decodes its address from the device address in the Q-byte may accept the instruction. The device that decodes its address must return a signal to the CPU (I/O condition A-I/O condition B) to indicate if the device accepts or rejects the instruction.

After the start I/O instruction cycles (I-op, I-Q, I-R) are complete, the instruction is set up in the disk attachment. The disk attachment will complete the specific operation with only cycle steal requests from the CPU.

If a start I/O instruction read, write, or scan instruction is issued to a drive that is currently in a seek operation, the instruction will be provisionally accepted (held) by the disk attachment for execution at the end of the seek. If a seek check (error) occurred during the seek operation, the provisionally held start I/O instruction will be reset and a status bit set to indicate the result.

The disk instructions and the functional objectives of each are given in the following headings: Load I/O, Test I/O, Sense I/O, and Start I/O.

#### Load I/O General Notes

- 1.

2.

3

- accepted 4.

In diagnostic mode, two bytes, located at the operand 1 address, control the disk operation. The format and description of these two bytes follow.

Bit O-Index. Presence of this bit generates an index pulse in the file control unit. Index stays on until the next load I/O instruction is issued without bit 0 on, or until a CPU system reset occurs.

Bit 1-Write Oscillator. A write oscillator pulse is generated each time a load I/O instruction is issued with bit 1 on.

Bit 2-Separated Clock. A separated clock pulse is generated each time a load I/O instruction is issued with bit 2 on.

Bit 3-AM Indicate. An address mark indicate pulse is generated each time a load I/O instruction is issued with bit 3 on. (This pulse normally is produced when the data separator reads an address mark.)

Bit 4-Separated Data. One separated data pulse is generated when bit 4 is on. When a data bit is desired, it should be used after a separated clock bit is issued. Bits 1-4 operate file control unit lines of the same name and allow program control of these lines.

Bit 5-Inhibit CPU Request. This bit will cause CPU requests made by the attachment, to be inhibited until the next LIO instruction without this bit on or there is a system reset.

If a high speed FCU is installed, this bit also simulates a track crossing pulse from both drives. The track crossing pulse will stay on until the next LIO instruction without this bit or a system reset.

### Bits 6-15. These bits are not used.

A diagnostic load I/O instruction sets the file control unit into a diagnostic mode. In diagnostic mode, the file control unit is not busy to another load I/O instruction or start I/O instruction. Load I/O instructions can be issued during a sense I/O instruction when they would normally not be accepted.

Programming Note: An example of proper instruction sequence after the disk file control register and disk file data register are loaded is:

- LIO (Diagnostic; to set the file control unit into diagnostic mode)

- SIO (Write ID)

- LIO (Diagnostic)

- LIO (Diagnostic)

- LIO (Diagnostic) LIO (Diagnostic)

by the appropriate bit or bits present in the diagnostic control byte.

Operate file control unit interface lines

Diagnostic mode is reset at the end of the start I/O instruction or by a system reset.

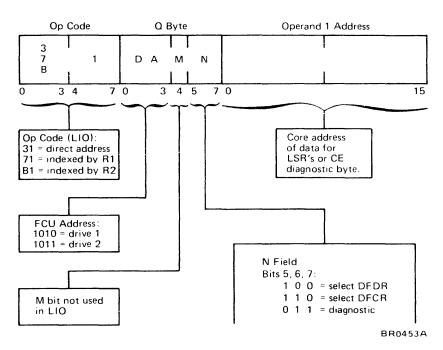

### Load I/O (LIO)

- This instruction loads the local storage registers (disk file data register or disk file control register) with an address used by the file control unit during start I/O instructions.

- Load I/O can be used to set diagnostic CE mode, allowing CE control of a disk operation.

The format of the Load I/O instruction is:

#### DFDR and DFCR (N Field = 100 or 110)

Two bytes located in storage at the address specified by the operand address are loaded into the register designated by the N bits as shown. If any combination of N bits other than shown is used, a processor check stop will occur.

### Diagnostic (N Field = 011)

This combination of N bits is for diagnostic use. The file control unit logic is operated at a reduced rate of speed with no data transfer to and from the disk. The rate of speed is controlled by the diagnostic program. One clock pulse is issued with each diagnostic load I/O instruction. By stopping the CPU after a diagnostic load I/O instruction, the disk operation can be stopped to probe signal levels with a light indicator or a sense I/O instruction command may be issued to sense the status of attachment conditions.

If the file control unit is busy, the load I/O instruction becomes equivalent to an advance-program-level-on-busy operation.

Load I/O does not set any disk status conditions. The M-bit is not used by the file control unit.

Load I/O is executed if the drive is executing a seek or recalibrate instruction, and a read, write, or scan has not been provisionally

If the drive is not ready, a load I/O instruction is executed.

Α

B

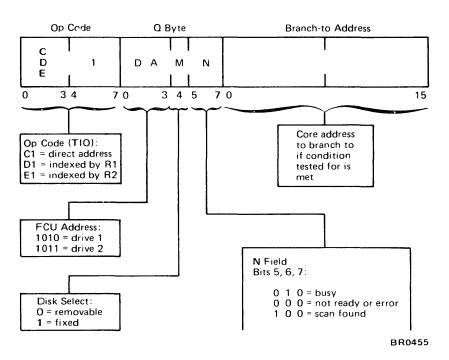

### Test I/O / Advance Program Level (TIO/APL)

• This instruction is used to test for scan-found, error, drive-not-ready, and file control unit busy.

The format of the test I/O instruction is:

### Busy (N Field = 010)

A control-unit-busy condition may be indicated by a test I/O and branch/advance program level instruction or by the rejection of a load I/O or start I/O. The busy condition is indicated to all file I/O instructions except sense I/O while:

- 1. The file is executing any read, write, or scan on any drive.

- 2. The file has provisionally accepted any operation for automatic execution at the conclusion of a seek currently in progress.

#### Not Ready or Error (N Field = 000)

The ready state of the disk drive is indicated to the file control unit by the conditioning of the file ready line. Failures that result in a not-ready state of the disk drive include:

- Failures of drive interlock switches

- Failure of the disk to maintain the rotational speed

- Failures that interrupt the normal head loading sequence or which cause the heads to unload

- A failure of ac power

- The occurrence of an unsafe condition

Unsafe conditions turn on latches located in the file circuitry.

### 1. Write unsafe latch

- a. Write selected and no write transitions detected.

- b. Write selected and multiple heads selected.

- c. Write not selected and write current source on.

- 2. Erase unsafe latch

- a. Write selected and erase current source not on.

- b. Write not selected and erase current source on.

- 3. Read/write selection unsafe latch

- a. Read selected and write selected.

- b. Read selected and erase selected.

- c. File accessing and write selected.

- d. File accessing and erase selected.

A test I/O instruction error is indicated when either drive is addressed if the following device status is present:

Data check Track condition check Missing address mark End of cylinder No record found Equipment check (if not caused by unsafe) No-op Overrun

Note: See "Device Status" for description of the individual device status conditions. An error is indicated if there is a seek check or unsafe for the drive addressed. A seek check or unsafe condition for the unselected drive does not cause an error to be indicated. The drive to which the device status applies may be determined by the device status, status address (byte 1, bits 6-7).

### Scan Found (N Field = 100)

The result of a start I/O scan instruction is determined by a test I/O scan found. The result is indicated if either drive 1 or drive 2 is addressed. The drive that the scan found condition occurred on is determined by a sense I/O instruction in status byte 1, bit 7.

### Test I/O General Notes

1 If any N field other than the three previously shown (010,000, or 100) is used, the operation causes a processor-check stop. The test I/O instruction does not receive a busy indication if a seek is in progress on either or both drives 1 and 2 and no other operation has been provisionally accepted. If another operation (read, write, or scan) has been provisionally accepted or is in progress, busy is indicated when either drive is addressed.

2. File control unit busy rejects (equivalent to advance program level) a start I/O seek when the addressed drive is executing a previous seek instruction. This busy condition is not indicated by test I/O and branch/advance program level but may be checked by sense I/O. A busy condition occurs only when two consecutive seeks are issued to the same drive and the second seek is issued before the first is completed.

If a read, write, or scan is issued to a drive that is currently seeking, the new instruction is provisionally accepted for execution at the end of the seek. The provisionally accepted instruction causes a busy indication to a test I/O instruction. If there is a seek check at the end of the seek, the provisionally accepted read, write, or scan is not executed and no-op is set.

4.

3.

#### Advance Program Level (APL)

however, is different (F1).

Op Code

```

F1

```

The manner in which the CPU executes the advance program level instruction depends on whether the advance program level feature is installed on the CPU.

level.

#### $\bullet$

The scan-found indication is reset by the next start I/O.

An advance program level instruction tests for the same conditions as the test I/O instruction and uses the same N field codes. The OP code,

The format of the advance program level instruction is:

QByte

| <br>DA | T<br> <br> | М | 1 | N | Not Used |

|--------|------------|---|---|---|----------|

|        |            |   |   |   | BR0463   |

*Operation:* This instruction tests for the conditions specified in the Q byte. If the condition tested for is present, a system with the dual programming feature installed activates the inactive program level; a system without the dual programming feature loops on the advance program level instruction until the condition no longer exists. If the condition is not present, systems with and without the dual programming feature take the next sequential instruction in the active program

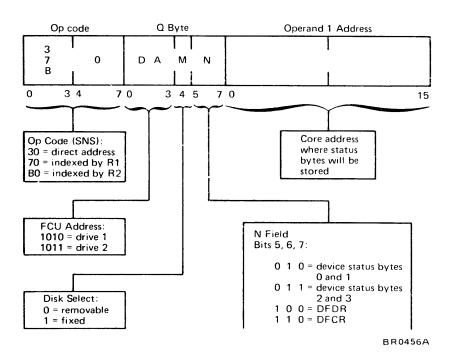

### Sense I/O (SNS)

• This instruction causes the contents (two bytes) of the specified local store register or device status to be stored into core storage at the address specified in the first operand address.

The format of the sense I/O instruction is:

### Device Status (N Field = 010 or 011)

- Device status is four bytes of information assembled by the control unit which provide information about the control unit and the file.

- Device status is made available by use of a sense I/O instruction.

The device status bits are:

|       | Byte 0                    | Byte 1              | Byte 2           | Byte 3                         |

|-------|---------------------------|---------------------|------------------|--------------------------------|

| Bit O | No-op                     | Scan Equal<br>Hit   | Unsafe           | CE sense Bit                   |

| Bit 1 | Intervention<br>Required  | Cylinder<br>Zero    | TAP Line A       | CE sense Bit                   |

| Bit 2 | Missing Address<br>Marker | End of<br>Cylinder  | TAP Line B       | CE sense Bit                   |

| Bit 3 | Equipment<br>Check        | Seek Busy           | TAP Line C       | Not Bit Ring<br>Inhibit        |

| Bit 4 | Data Check                | 100<br>Cylinder     | Index            | Standard Write<br>Trigger      |

| Bit 5 | No Record<br>Found        | Overrun             | Head<br>Settling | Condition Priority<br>Request  |

| Bit 6 | Track Condition<br>Check  | Status<br>Address A | CE sense<br>Bit  | Bit Ring 0                     |

| Bit 7 | Seèk Check                | Status<br>Address B | Model 6          | Not CC-Register<br>Position 17 |

BR0457A

Byte O, Bit O-No Op. This bit indicates that the last issued command was not executed. It is caused by the selected file being unsafe or by a seek check occurring during a seek on the drive that read, write, or scan is provisionally accepted for. The no-op status bit is reset only by (1) a sense I/O command, (2) a CPU check reset, or (3) a general reset.

Byte 0, Bit 1-Intervention Required. This bit indicates that the addressed drive is not ready. The condition may be corrected by making the file ready. An uninstalled second drive causes an intervention required indication in response to a start I/O. A two-drive system with an uninstalled fixed disk on the second drive also causes an intervention required when the fixed disk is addressed.

A seek in reverse of too many cylinders may cause the high speed model files to become not ready if the carriage mechanism approaches cylinder zero at a speed greater than the normal speed files. This can occur from cylinder 4 or greater if a reverse seek beyond cylinder zero is attempted. Recalibration will never cause ready to drop as it is executed in low speed mode. To reinstate ready, the file power must be turned off and back on again.

Byte 0, Bit 2-Missing Address Mark. This bit is set on any multisector operation after identifier area orientation is established when any two following sequential sectors read from the file have identical bits in bit position 5 of the head/sector byte of the identifier. If this condition is detected before ID orientation or on a single sector operation, it is indicated after the control unit has determined that the record cannot be found on the track. This bit is also set if no address mark is found and index has passed twice while looking for address mark. This bit is not set if a data check is detected in one of the two identifier fields.

Byte 0, Bit 3–Equipment Check. This bit indicates that the control unit has detected a hardware failure, such as a CC register check, an equipment check write gate, a check counter error, a parallel parity check, or a serdes check. This status bit will also indicate that the selected drive has detected an unsafe drive condition.

Byte O. Bit 4-Data Check. This status bit indicates that a cyclic check or bit-count appendage check was detected while reading the identifier area or data fields from the file.

Byte 0, Bit 5-No Record Found. This bit indicates that the first identifier called for on a read, write, or scan could not be found on the track; or, after the first hit of a multisector operation, there is a subsequent identifier noncompare. This bit is set with track condition check. The identifier compare takes place on all bits of the identifier.

Byte 0, Bit 6-Track Condition Check. This status bit is an indication that a data operation was attempted, but the track condition bits in the flag byte in main storage did not agree with the track condition bits written on the file.

- 2.

1.

- 3. operation

- 4. 5. time

equal command is issued.

clock.

Bit 6 Status Address

0

0

accepted on either drive.

#

- Byte 0, Bit 7-Seek Check. This status bit indicates that the control unit has detected a seek error caused by one of the following conditions:

- Access overrun on selected drive while go forward is active

- Go forward or go reverse active and drive not ready

- Go reverse active, cylinder zero active and not in a recalibrate

- Go forward or go reverse active for longer than 1 to 2 seconds Track crossing pulse from drive sensed at the end of head settling

- Byte 1, Bit 0-Scan Equal Hit. This status bit indicates that the equal condition was satisfied whenever a scan equal/low, an equal/high, or

- Byte 1, Bit 1-Cylinder Zero. An indication that the selected drive's access mechanism is positioned at cylinder zero.

- Byte 1, Bit 2-End of Cylinder. This status indicates that on a multiple sector data or scan operation one of the following occurred:

- a. An attempt was made to operate beyond the end of the cylinder. (Head 1 of the selected disk).

- b. Head 1 ID's were written on Head 0 (Bit 0=1 of S byte) and an attempt was made to operate beyond the end of the track. This can happen on alternate tracks.

- In both cases, all sectors up to and including the last one on the track were successfully handled.

- Byte 1, Bit 3-Seek Busy. This bit indicates that the drive addressed by the sense I/O is seeking (includes head settling time).

- Byte 1, Bit 4-100 Cylinder. This status bit indicates that the first drive (drive 0) attached to the system has 100 cylinders available to the customer. This indication is generated by the attachment hardware.

- Byte 1, Bit 5-Overrun. This bit is set when a data cycle request is not honored within the time required to maintain data transfer with the file. This condition occurs due to a process-check stop which stops the CPU

- Byte 1, Bits 6 and 7-Status Address A and Status Address B. Status A and Status B indicate the address of the drive that was specified in the last read, write, or scan instruction. They provide the drive number that per tains to the attachment-dependent status bits.

| A | Bit 7<br>Status Address B | Drive |

|---|---------------------------|-------|

|   | 0                         | 1     |

|   | 1                         | 2     |

This address is updated when a start I/O is accepted or provisionally

#

Byte 2, Bit 0-Unsafe. This bit indicates that one of the following errors has been detected by the disk drive:

- 1. Write unsafe

- a. Write selected and no write transitions detected.

- b. Write selected and multiple heads selected.

- c. Write not selected and write current source on.

- 2. Erase unsafe

- a. Write selected and erase current source not on.

- b. Write not selected and erase current on.

- Read/write selection unsafe 3

- a. Read selected and either write or erase selected.

- b. Carriage accessing and either write or erase selected.

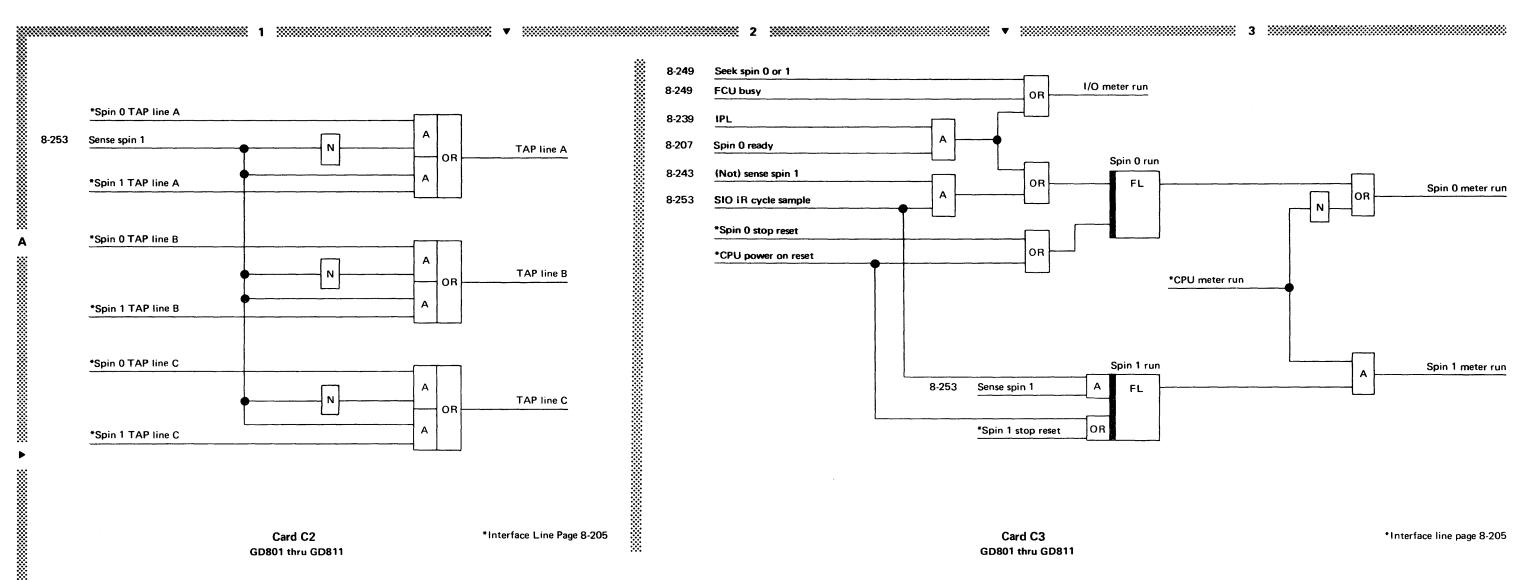

Byte 2, Bit 1-Tap Line A. Used by the timing analysis program (TAP). These lines can be jumpered at the drive to sense signals that normally are not checked. See note 5.

Byte 2, Bit 2-Tap Line B. Same as byte 2, bit 1.

Byte 2, Bit 3-Tap Line C. Same as byte 2, bit 1.

Byte 2, Bit 4-Index. This line is active for about 43 micro seconds starting with each index pulse from the selected drive.

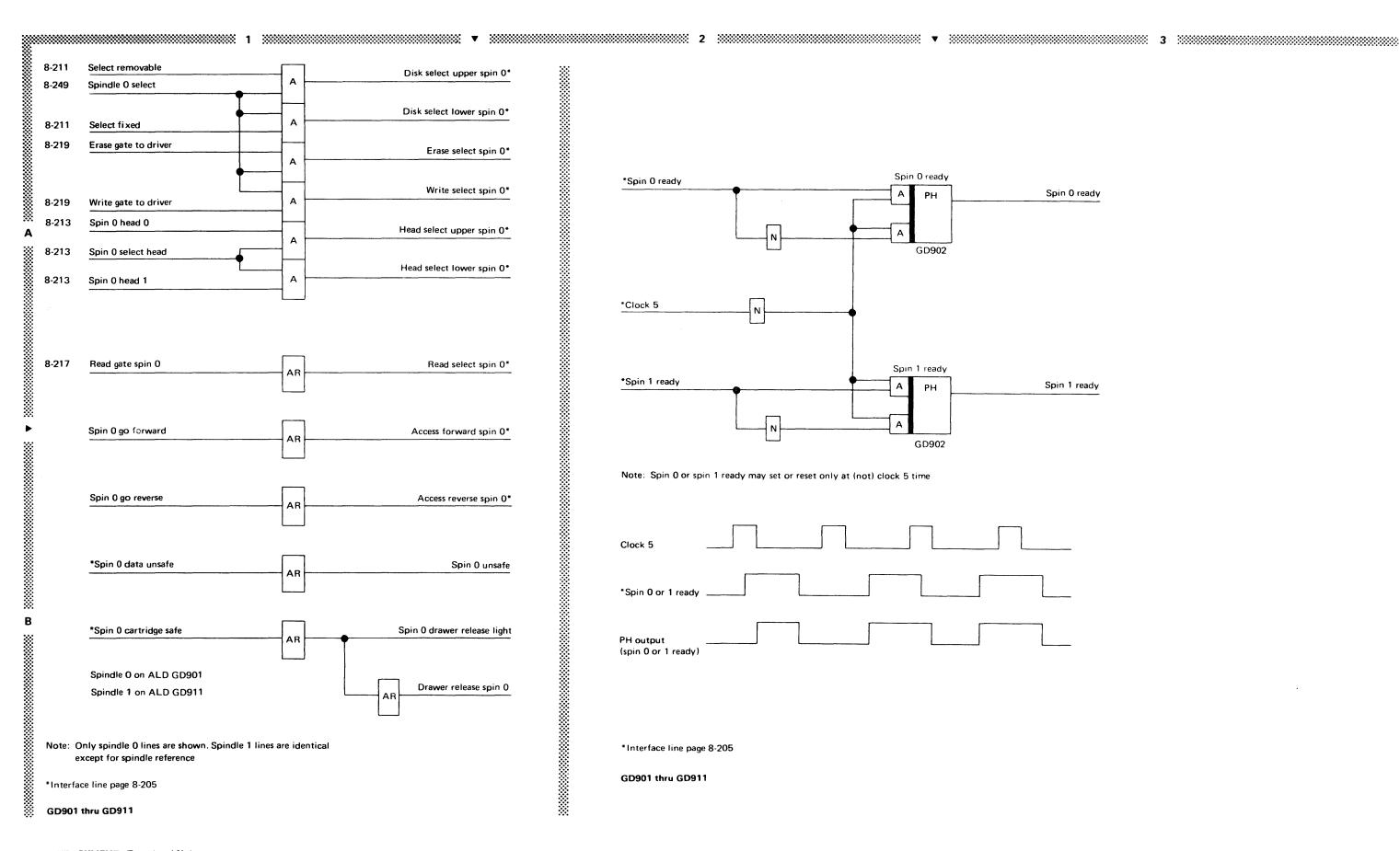

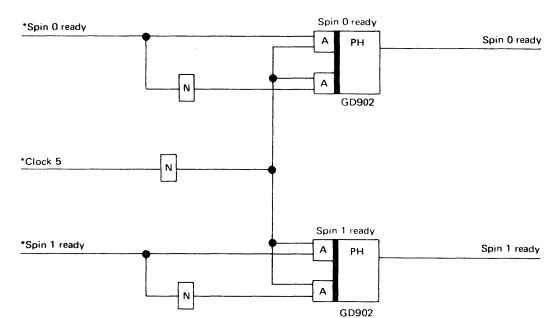

Byte 2, Bit 5-Head Settling. This line turns on at the end of a seek operation to time out head settling. It is on for 24.67 (+3.2, -3.74) milliseconds for the high speed files and about 28 milliseconds for the standard speed drives.

Byte 2. Bit 6-Wireable CE Sense Bit. This sense bit allows the customer engineer to provide the CPU with MST signals which normally are not available for sensing (used for diagnostic programs).

By te 2, Bit 7-Model 6. This bit indicates that the CPU is a 5406.

Byte 3, Bit 0, Bits 1 and 2-Wireable CE Sense Bit. Same as byte 2, bit 6.

Byte 3, Bit 3-Not Bit Ring Inhibit. For CE use in diagnostic programs.

Byte 3, Bit 4-Standard Write Trigger. For CE use in diagnostic programs.

Byte 3, Bit 5–Condition Priority Request. This bit indicates the status of the condition-priority-request latch.

Byte 3, Bit 6-Bit Ring 0. This bit is active at bit ring 0 time.

Byte 3, Bit 7-(Not) Cyclic Check-Register Position 17. This bit indicates the status of position 17 of the cyclic check-register.

### DFDR/DFCR (N Field = 100 or 110)

The local storage register designated in the N field coding is sensed and the address in the local storage register is transferred into core storage at the address specified in the operand one address.

### Sense I/O General Notes

- If any combination of N bits other than the four designated is 1. used, the operation causes a processor-check stop.

- The file attachment is not busy to a sense 1/0. 2.

- 3. Sense I/O does not set any file status conditions.

- The sense bytes are placed in core so that the highest numbered 4 byte is placed at the highest address.

- TAP lines A, B, and C are normally jumpered to the three unsafe 5. latches in the file drive. If these lines (jumpers) are moved to sense other signals as required in diagnostic programs, be sure to reinstall the jumpers to the unsafe latches. (See 5444 ALD FN260 for drives below serial 30100, 5444 ALD FS260 for drives above serial 30100. for normal jumpering of these lines.)

- 6. Device status bits equipment check (due to unsafe condition) cylinder zero, seek check, seek busy, intervention required, unsafe, head settling, and index may vary depending on the drive selected by the sense I/O instruction. These bits are presented only when the drive to which they apply is selected. They are reset when the drive to which they apply is selected if the error condition is no longer present. All remaining bits may be presented when either drive is selected by sense I/O. All remaining bits except no-op are reset when a start I/O is executed on either drive. No-op is reset by the sense I/O instruction that transfers no-op to core storage (N code 010).

# Start I/O (SIO)

• This instruction selects an I/O device and provides the additional information to specify the detailed operation.

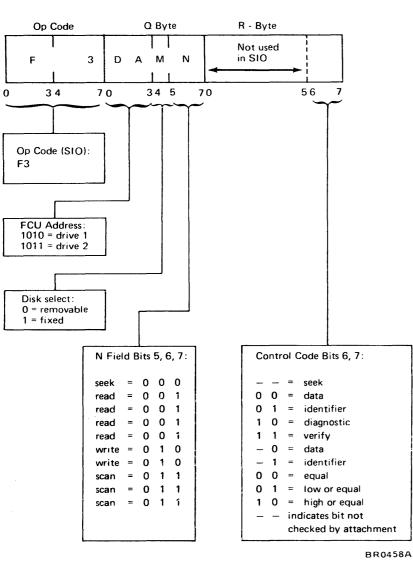

The format of the start I/O instruction is:

There are four basic disk operations: write, read, scan, and seek. These are further defined into twelve specific operations.

| Operation | Definer    |

|-----------|------------|

| Write     | Data       |

|           | Identifier |

| Read      | Data       |

|           | Identifier |

|           | Diagnostic |

|           | Verify     |

|           |            |

| Scan | Equal         |

|------|---------------|

|      | Low or Equal  |

|      | High or Equal |

| Seek | Forward       |

|      | Reverse       |

Recalibrate

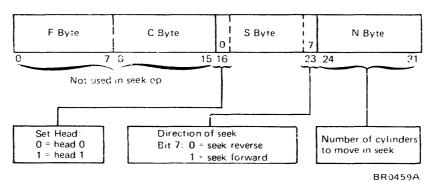

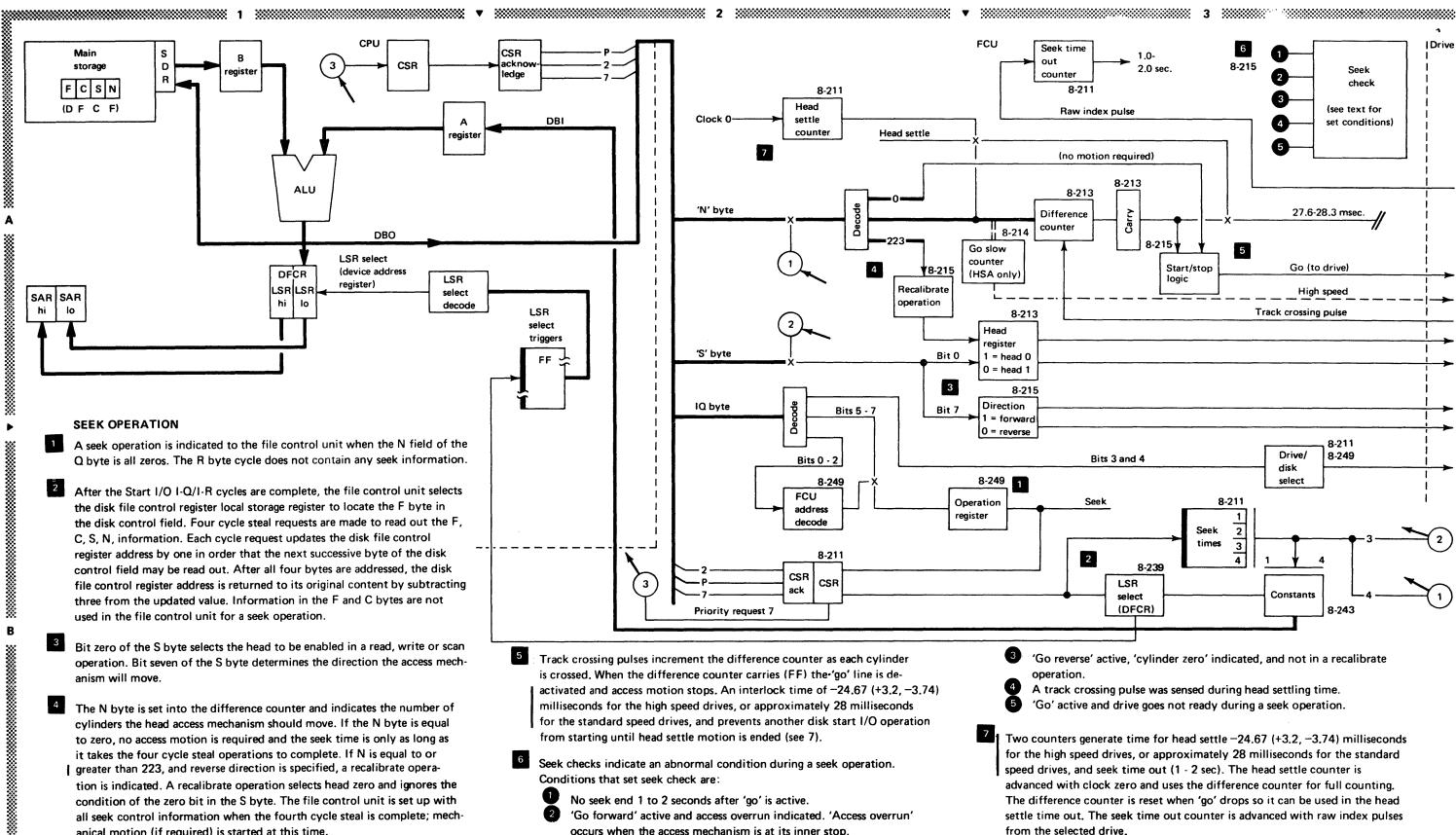

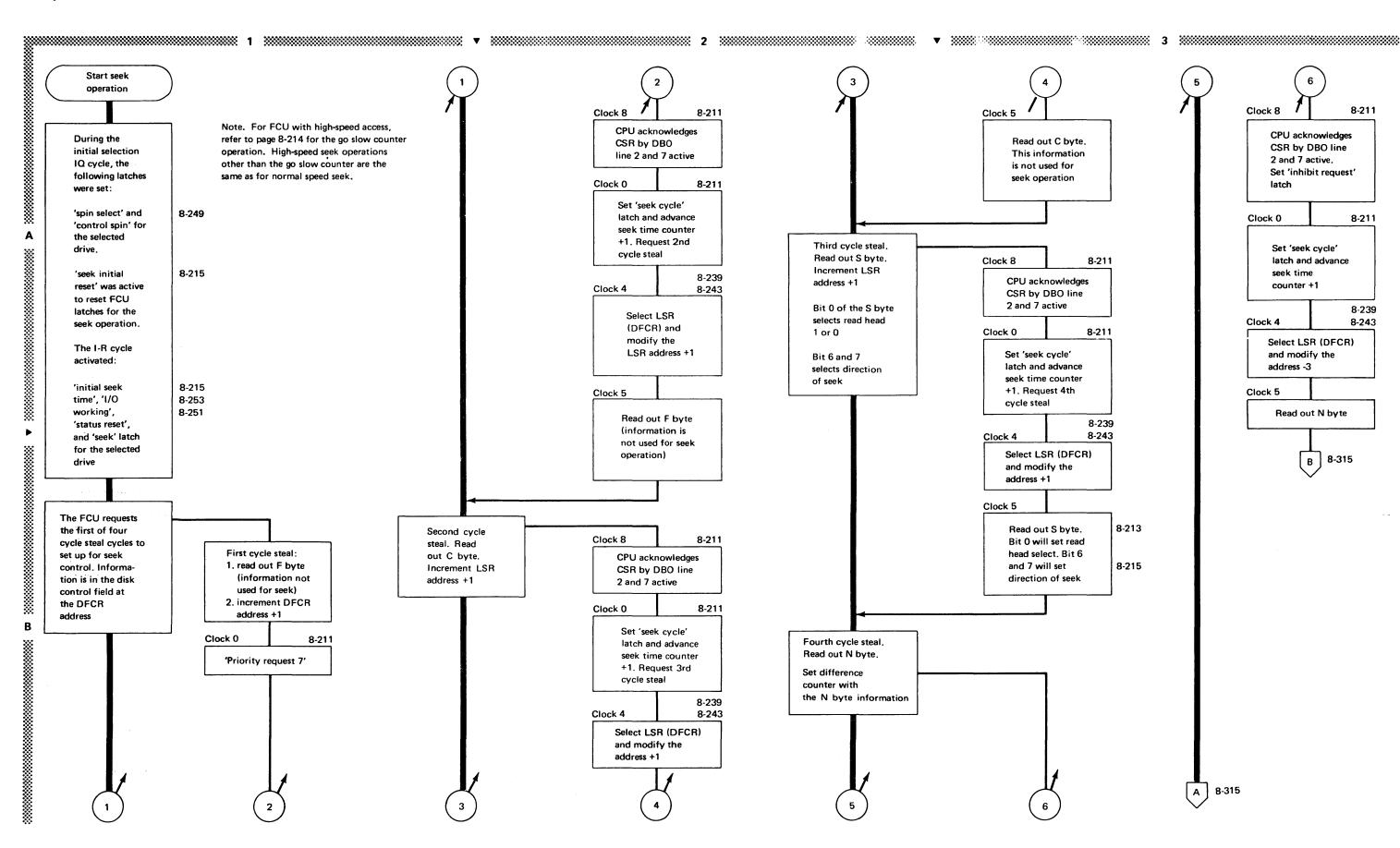

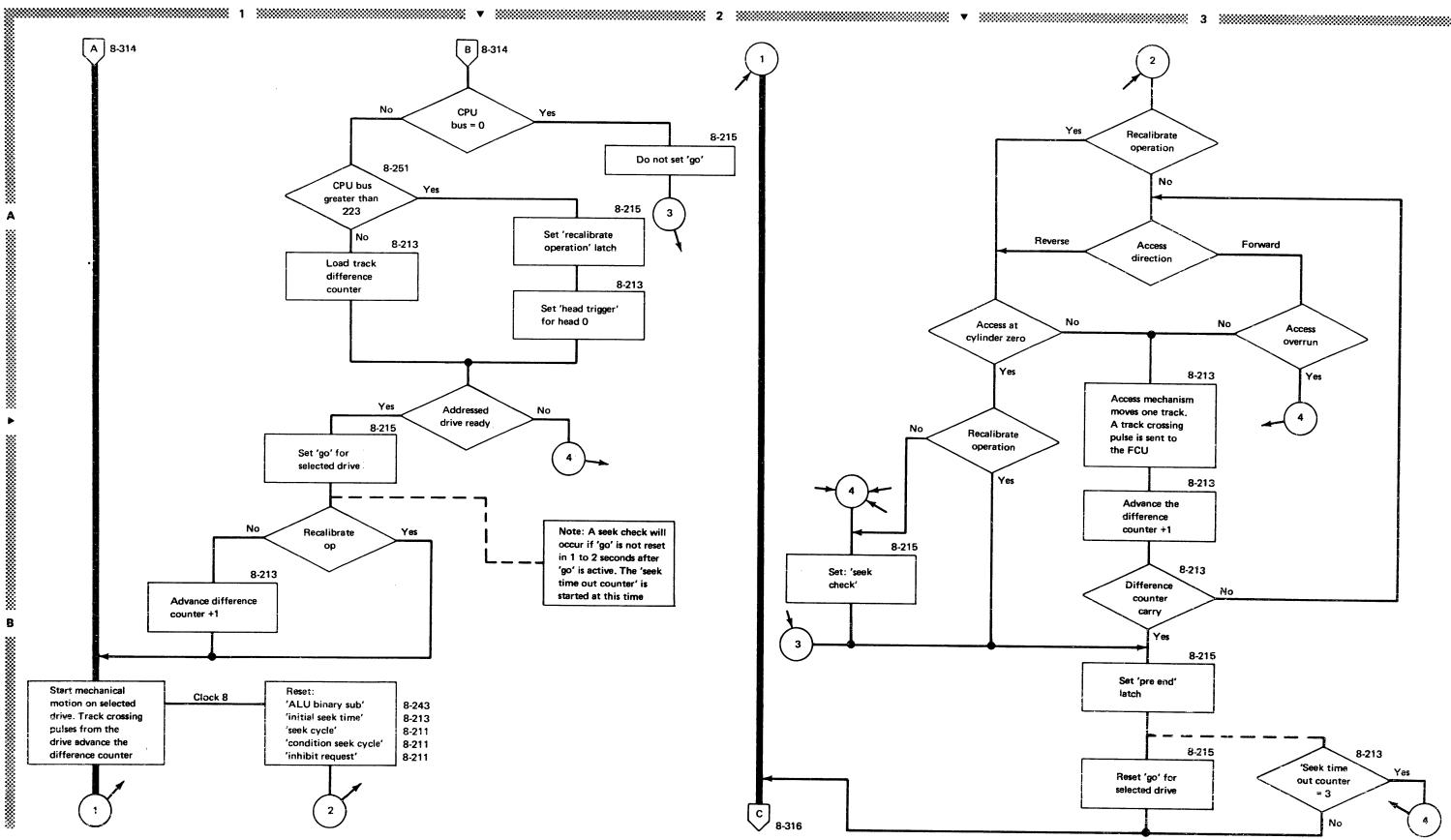

### Seek

The head access of the selected drive is moved a specified number of cylinders, and the specified head number is set for future read, write, or scan operations. Seek uses only two bytes of information from the disk control field: the S and N bytes. The disk file control register address must contain the address of the F byte.

The N byte specifies the number of cylinders the access mechanism will move on the seek. Bit 23 of the S byte specifies the direction of movement. Forward (bit 23 = 1) is from cylinder 0 to 202.

Recalibration is executed by specifying a seek in the reverse direction and a number of cylinders to be moved that is equal to or greater than 223. Head 0 is selected automatically for a recalibration operation.

Seek Forward: Moves the head-access mechanism forward. (Forward direction is from the outer edge of the disk to the inner tracks.)

Seek Reverse: Moves the head-access mechanism from the inner to the outer edge of the disk.

Seek Recalibrate: Moves the nead-access mechanism to cylinder zero. This positions the mechanism to a specific location (cylinder zero) when needed in error recovery routines. On high speed drives, recalibrate operation is always in low (normal) speed.

#### Write Operations

Write Data: Records data on disk from the data field in core storage.

Write Identifier: Records addresses from the disk control field for sectors and cylinders in the identifier area field on disk. Address marks and gaps generated by the file control unit are written by this command. Twentyfour sectors are always written.

#### Read Operations

instruction

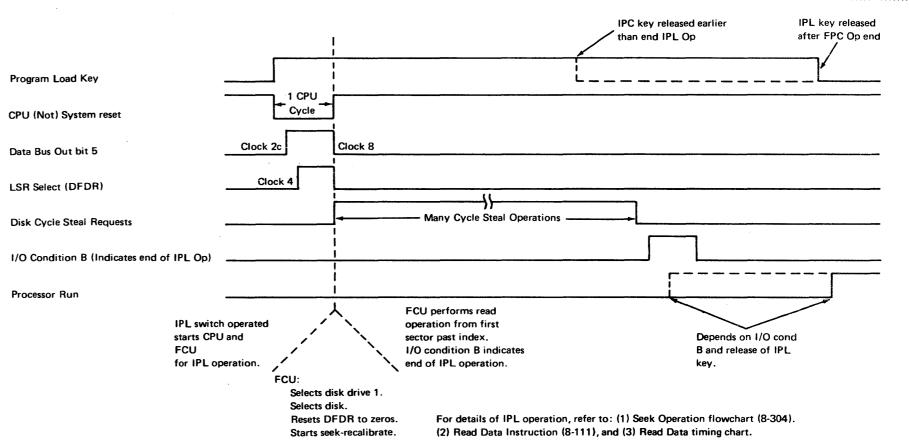

# Initial Program Load (IPL)

from drive 2.

- Read Data: Recovers data recorded on disk and transfers this information to the data field in core storage.

- Read Identifier: Transfers only the identifier area field information on disk into the disk control field.

- Read Diagnostic: The file control unit is operated with reduced requirements for detection of address marks. Otherwise, this operation is very similar to read data.

- Read Verify: Does not transfer any information. Regenerates the cyclic check and bit count appendage check characters and compares them with the check characters recorded on the disk. This command usually follows a write operation and verifies that the data-check characters were written correctly.

- Scan Equal: Compares data on disk with data in core. The result is indicated by a status bit and is available to a sense I/O instruction or test I/O

- Scan Low or Equal and Scan High or Equal: These commands differ from scan equal only in the indication returned about the compare.

- The initial program load operation is not under program control. It is started with the program load switch on the operator console. An initial program load operation reads a 256-byte data field from sector 0, head 0, from either the fixed or removable disk as determined by the program load selector switch on the operator console. Drive 1 is selected by the file control unit. Initial program load cannot be performed

- At the start of an initial program load operation, the disk file data register address is set to 0000 and a seek recalibrate is performed to position the read heads to cylinder 0. Data is read from the first sector past index (sector 0). At the end of the data field, the file control unit signals the central processing unit to start processing at core address 0000. No compare is made on the identifier of the first record: the first record found after the index mark is read and any error conditions are made available for program testing. If no record is found or the wrong record is read, the program will not start correctly. An unsuccessful initial program load operation requires an operator retry

- A test I/O and branch instruction should be performed to test for errors or busy before attempting the first start I/O instruction.

- local storage register addresses.

- drive to be recorded on disk.

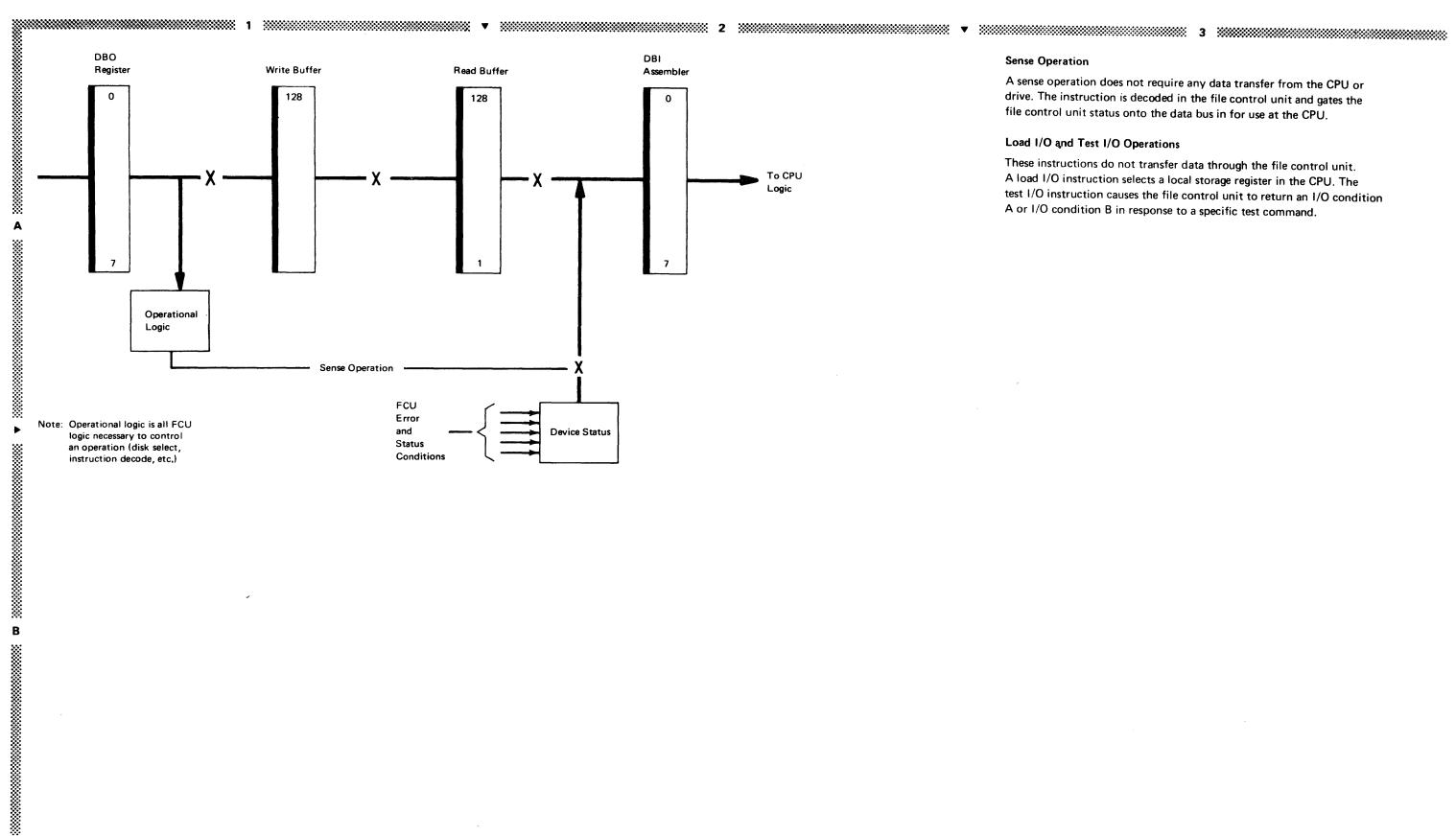

- for use at the CPU.

### 3

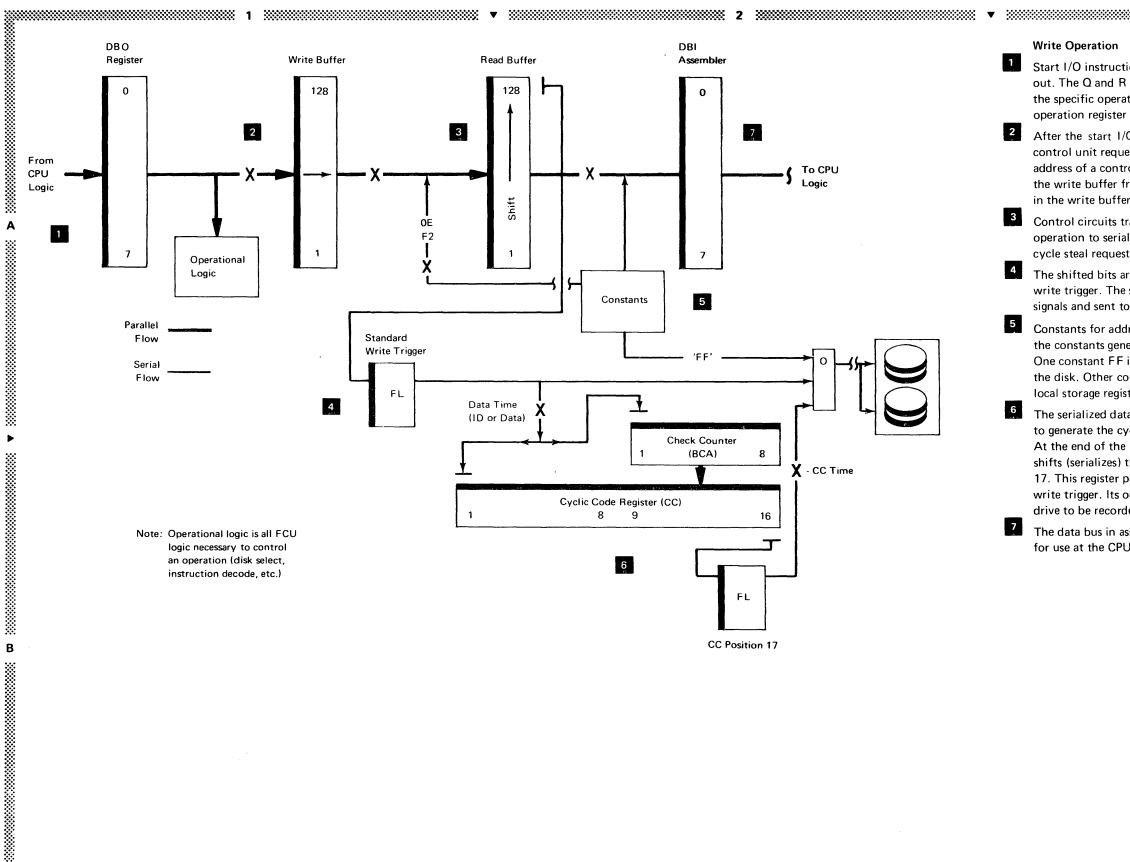

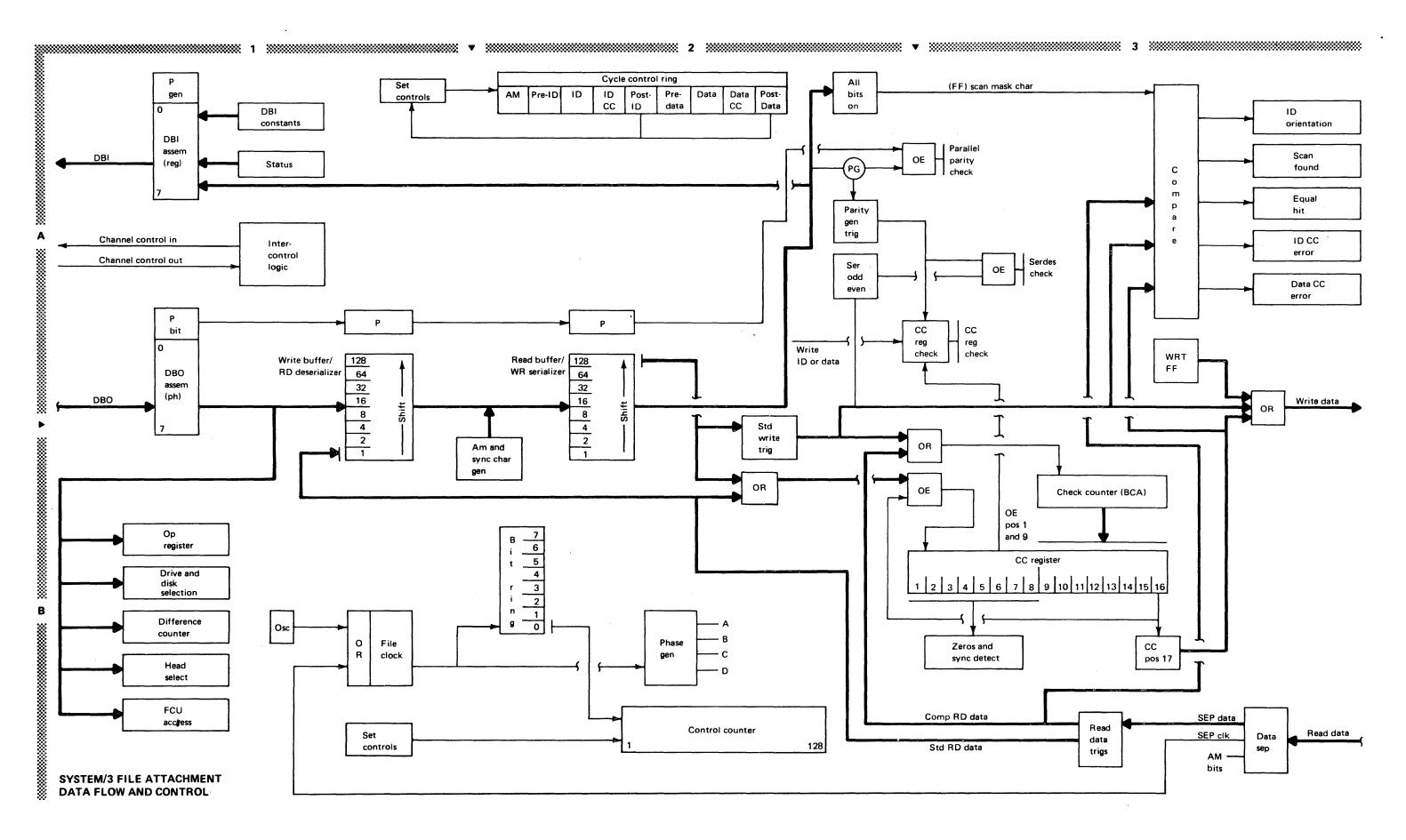

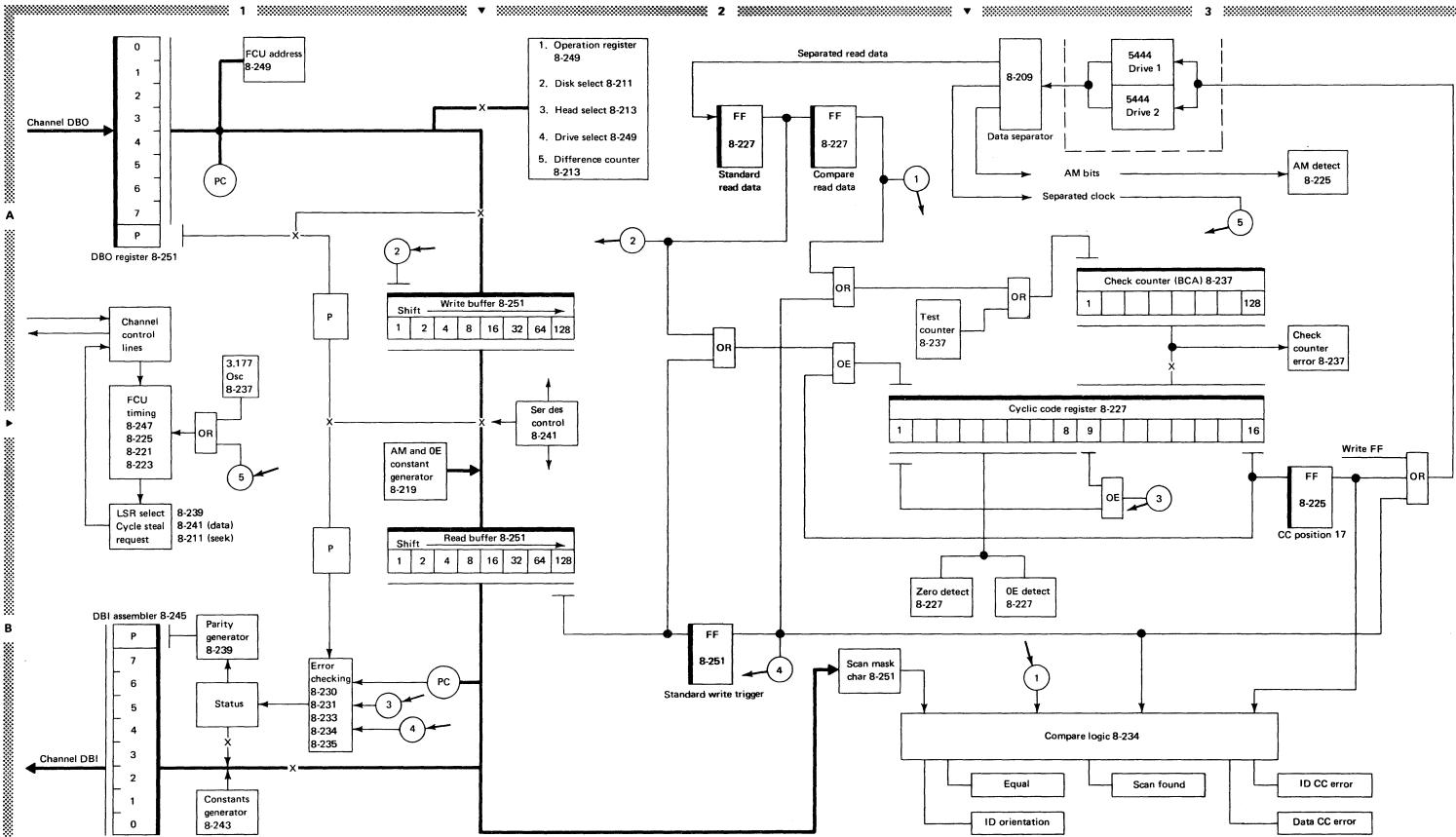

Start I/O instructions and data enter the file control unit via the data bus out. The Q and R bytes are decoded for the file control unit address and the specific operation to be performed. The operation is stored in the operation register within the operational logic.

After the start I/O operation I-Q and I-R cycles are complete, the file control unit requests a cycle steal, selects a local storage register for an address of a control or data field, and receives the data (in parallel) into the write buffer from the data bus out. One data byte is buffered (stored) in the write buffer until it is needed at the read buffer.

Control circuits transfer the write buffer to the read buffer, start a shift operation to serialize the byte, and at the same time generate another cycle steal request to refill the write buffer.

The shifted bits are transferred out of the read buffer into the standard write trigger. The standard write trigger output is combined with clock signals and sent to the drive to be recorded.

5. Constants for address marks (F2) and sync bytes (0E) are generated by the constants generator and gated into the read buffer to be serialized. One constant FF is combined directly with clock bits to write all ones on the disk. Other constants are gated onto the data bus in to modify the

The serialized data bits enter the check counter and cyclic code register to generate the cyclic check and bit count appendage check characters. At the end of the identifier area or data field, the cyclic check register shifts (serializes) the register contents into cyclic check register position 17. This register position functions in the same manner as the standard write trigger. Its output is combined with clock timing and sent to the

The data bus in assembler gates the constants onto the data bus in lines

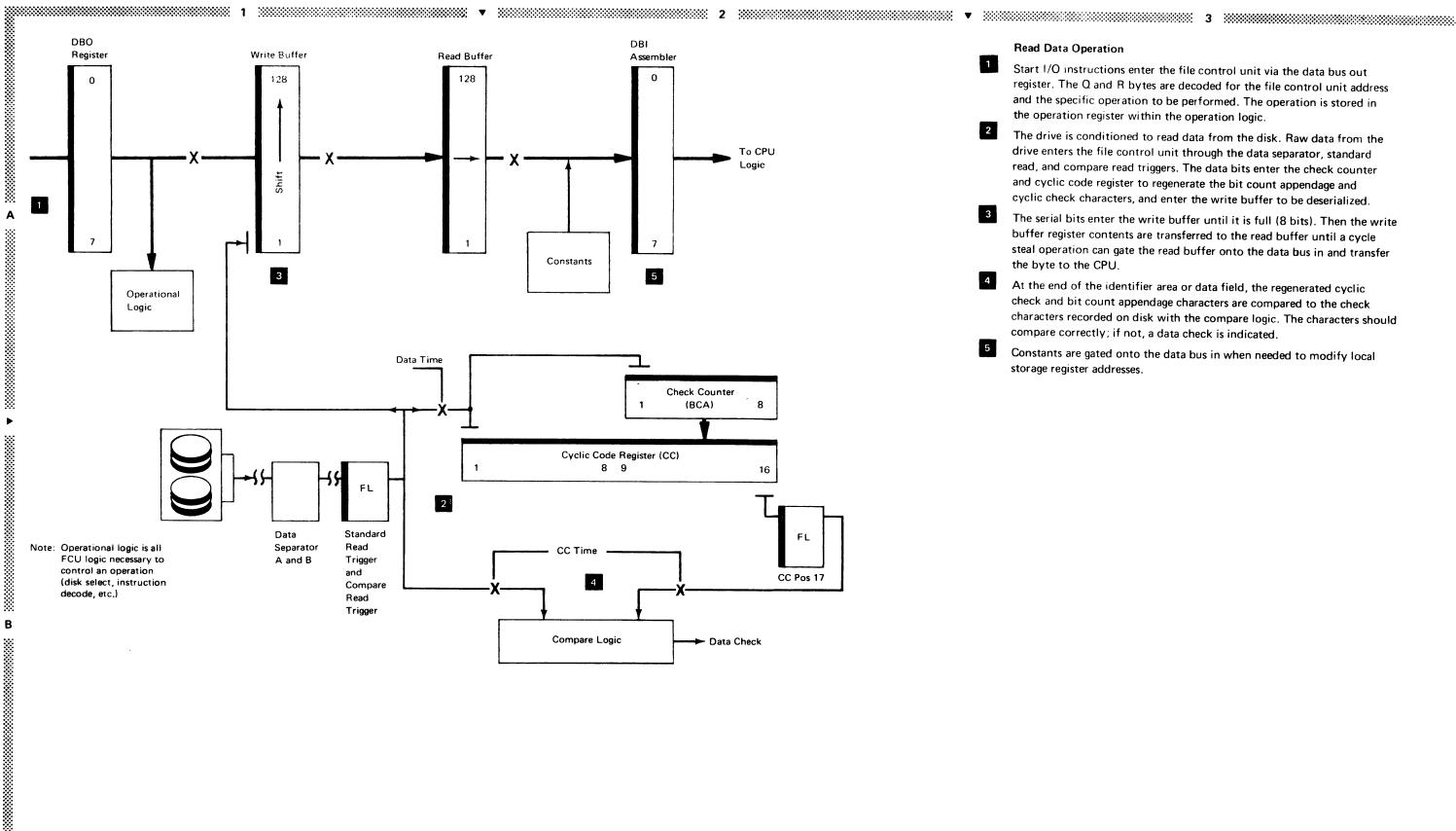

Start I/O instructions enter the file control unit via the data bus out register. The Q and R bytes are decoded for the file control unit address and the specific operation to be performed. The operation is stored in the operation register within the operation logic.

The drive is conditioned to read data from the disk. Raw data from the drive enters the file control unit through the data separator, standard read, and compare read triggers. The data bits enter the check counter and cyclic code register to regenerate the bit count appendage and cyclic check characters, and enter the write buffer to be deserialized.

The serial bits enter the write buffer until it is full (8 bits). Then the write buffer register contents are transferred to the read buffer until a cycle steal operation can gate the read buffer onto the data bus in and transfer

At the end of the identifier area or data field, the regenerated cyclic check and bit count appendage characters are compared to the check characters recorded on disk with the compare logic. The characters should compare correctly; if not, a data check is indicated.

Constants are gated onto the data bus in when needed to modify local

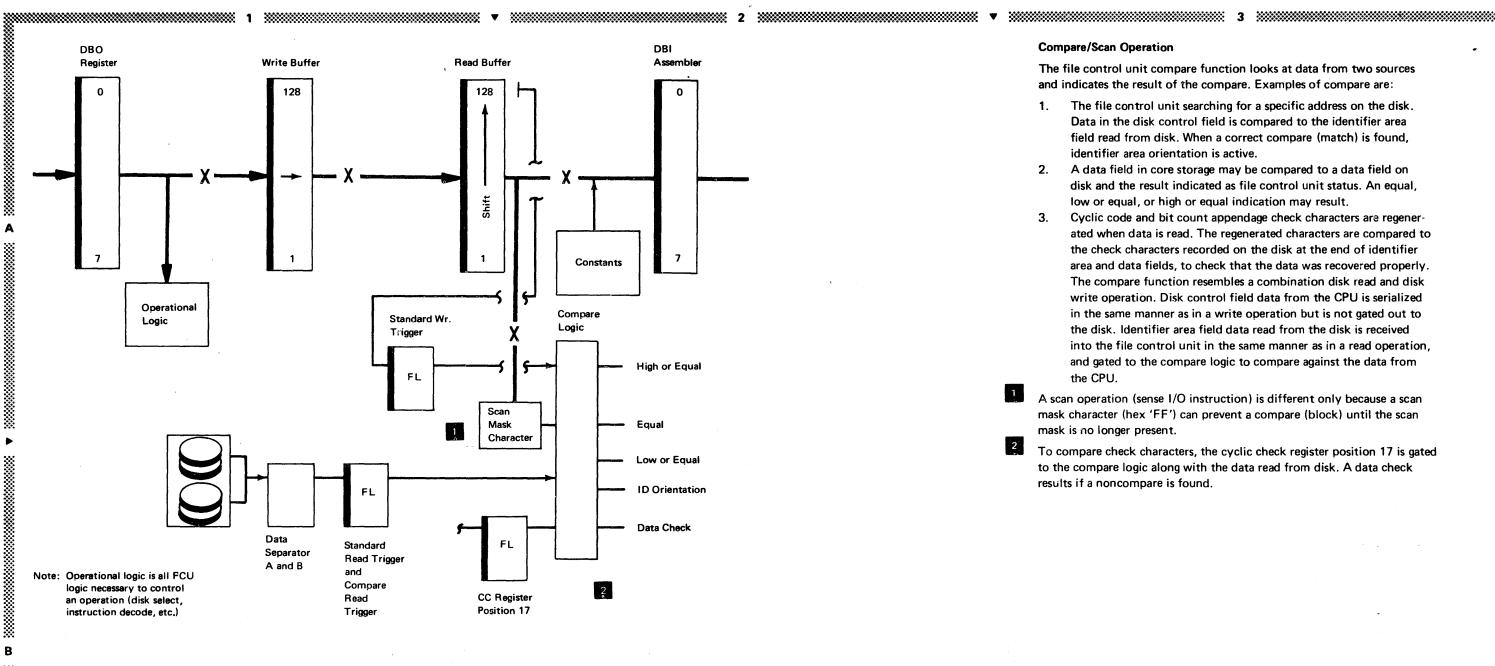

The file control unit compare function looks at data from two sources and indicates the result of the compare. Examples of compare are:

1. The file control unit searching for a specific address on the disk. Data in the disk control field is compared to the identifier area field read from disk. When a correct compare (match) is found, identifier area orientation is active.

A data field in core storage may be compared to a data field on disk and the result indicated as file control unit status. An equal, low or equal, or high or equal indication may result.

Cyclic code and bit count appendage check characters are regenerated when data is read. The regenerated characters are compared to the check characters recorded on the disk at the end of identifier area and data fields, to check that the data was recovered properly. The compare function resembles a combination disk read and disk write operation. Disk control field data from the CPU is serialized in the same manner as in a write operation but is not gated out to the disk. Identifier area field data read from the disk is received into the file control unit in the same manner as in a read operation, and gated to the compare logic to compare against the data from

A scan operation (sense I/O instruction) is different only because a scan mask character (hex 'FF') can prevent a compare (block) until the scan

To compare check characters, the cyclic check register position 17 is gated to the compare logic along with the data read from disk. A data check results if a noncompare is found.

#### INTRODUCTION TO FUNCTIONAL UNITS

This chapter describes the functional units of the disk attachment and contains second-level diagrams. Chapter 2 is divided as follows:

- 1. A functional unit index for the second-level diagrams and a cross reference chart for card locations vs ALDs.

- A layout of the disk attachment board and the major logic functions 2. within each card.

- 3. An overall data flow of the disk attachment.

- A CPU-to-disk attachment and disk-attachment-to-disk-drive interface 4. diagram.

- Second-level diagrams combined with descriptions of the functional 5. units.

Each card location has its own group of second-level diagrams. For most card locations, there is a description of the functional units contained on the card in front of the second-level diagrams.

The 8-XXX references on the second-level diagrams are page numbers to the card second-level diagram that originates the incoming signal line. An asterisk refers to an interface line and is shown on the interface diagram, page 8-205. There are no second-level diagrams for drive 1 seek controls, card F2, because the logic on card F2 is identical to the logic on card G2. Where a drive 1 seek control line is referenced on the second-level diagrams, the reference is to a card G2 diagram. The reference is in parentheses to indicate that it actually originates on card F2:

#### Example

Α

►

В

8-213 refers to drive 0, card G2 (8-213) refers to drive 1, card F2

The GDXXX references below latches and logic blocks within the diagrams refer to disk attachment ALDs. The GDXXX numbers in the lower left corner of each diagram refer to the span of disk attachment ALD pages for that card position.

File control units to attach standard speed access drives, use version 000 ALDs. File control units to attach high speed access drives use version 001 ALDs. Version numbers are printed below the ALD page number.

# Chapter 2. Functional Units

|                                                      | *** 1 ********* |             | ******           |     | ************************ |                    | •          | ***** | 3 3 |  |

|------------------------------------------------------|-----------------|-------------|------------------|-----|--------------------------|--------------------|------------|-------|-----|--|

| tional Unit Index                                    |                 |             |                  |     |                          |                    |            |       |     |  |

| Functional unit                                      | Card location   | Description | Diagram          |     |                          | ss reference chart |            |       |     |  |

| Address mark detect                                  | L2              | 8-224       | 8-225            |     |                          |                    |            |       |     |  |

| Bit ring                                             | L2              | 8-224       | 8-225            | Вус | card location            | By ALD loca        | ation      |       |     |  |

| CE controls                                          | P2              | 8-236       | 8-237            | C2  | GD-811                   | GD-101-104         | R2         |       |     |  |

| Check counter (BCA)                                  | P2              | 8-236       | 8-237            |     |                          |                    |            |       |     |  |

| Clock                                                | R2              | 8-244       | 8-247            | C3  | 801                      | 111-117            | L2         |       |     |  |

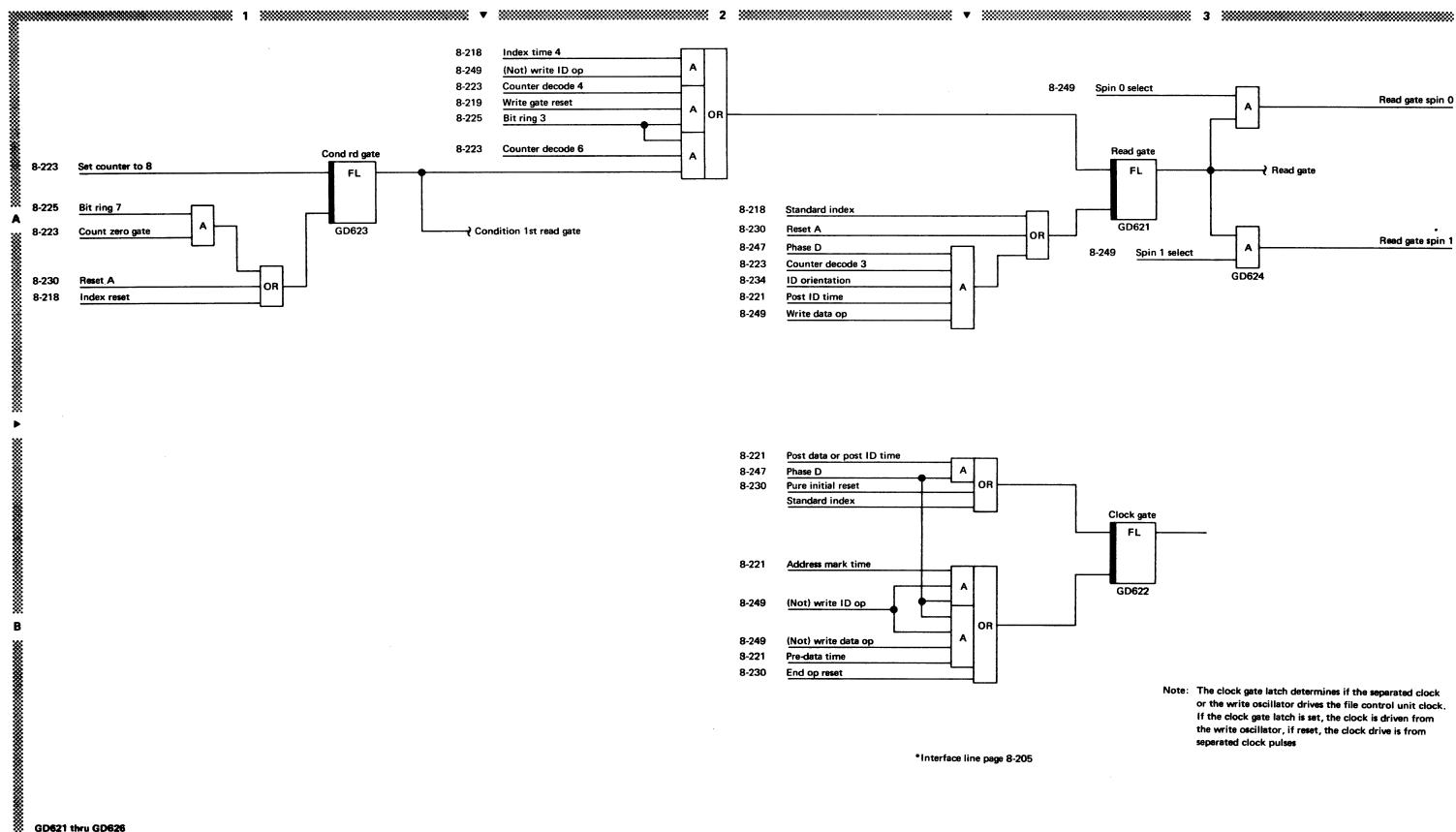

| Clock gate                                           | J2              | 8-216       | 8-217            |     |                          |                    |            |       |     |  |

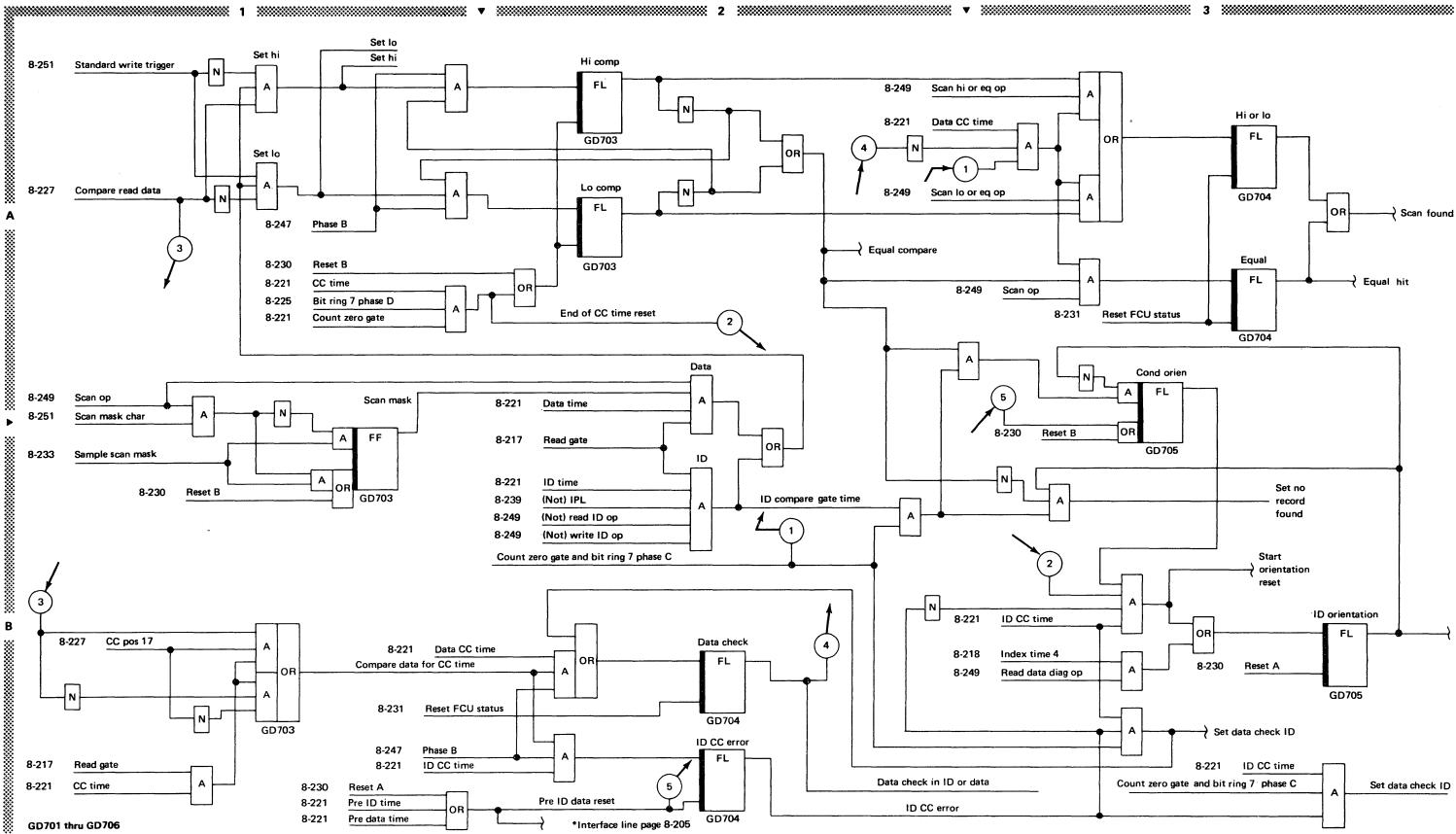

| Compare                                              | N2              | 8-232       | 8-234            | C4  | 901-902                  | 121-125            | К2         |       |     |  |

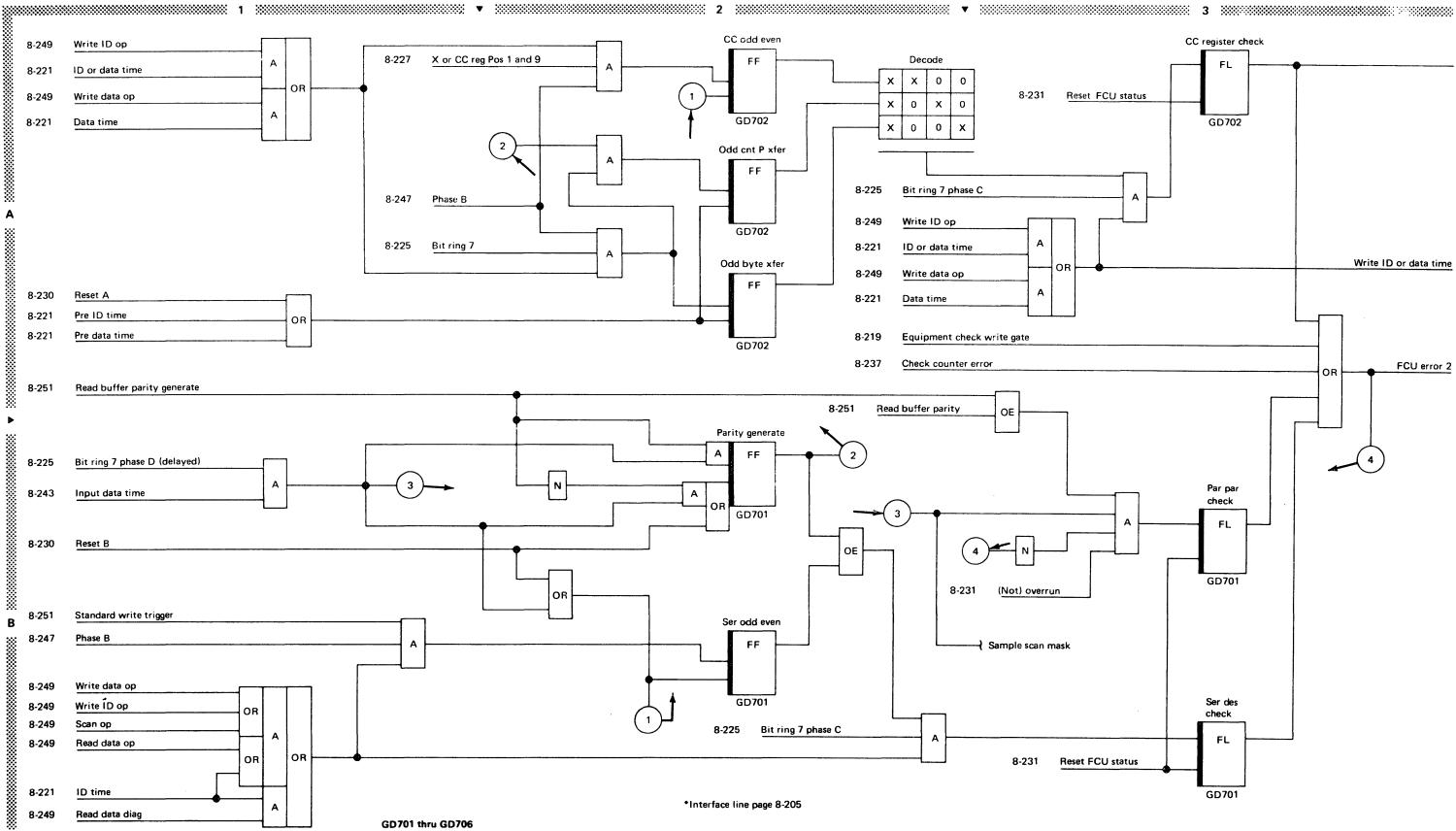

| Compare read data trigger                            | L2              | 8-226       | 8-227            |     |                          |                    | 11         |       |     |  |

| Constants                                            | 02              |             | 8-243            | D2  | 911                      | 201-204            | T2         |       |     |  |

| Control counter                                      | К2              | 8-222       | 8-223            |     |                          | 1                  | <u> </u> ] |       |     |  |

| Cycle control ring                                   | K2              | 8-220       | 8-221            | D3  | 501                      | 211-216            | S2         |       |     |  |

| Cyclic code register                                 | L2              | 8-226       | 8-227            | D4  | 511-512                  | 301-304            | E2         |       |     |  |

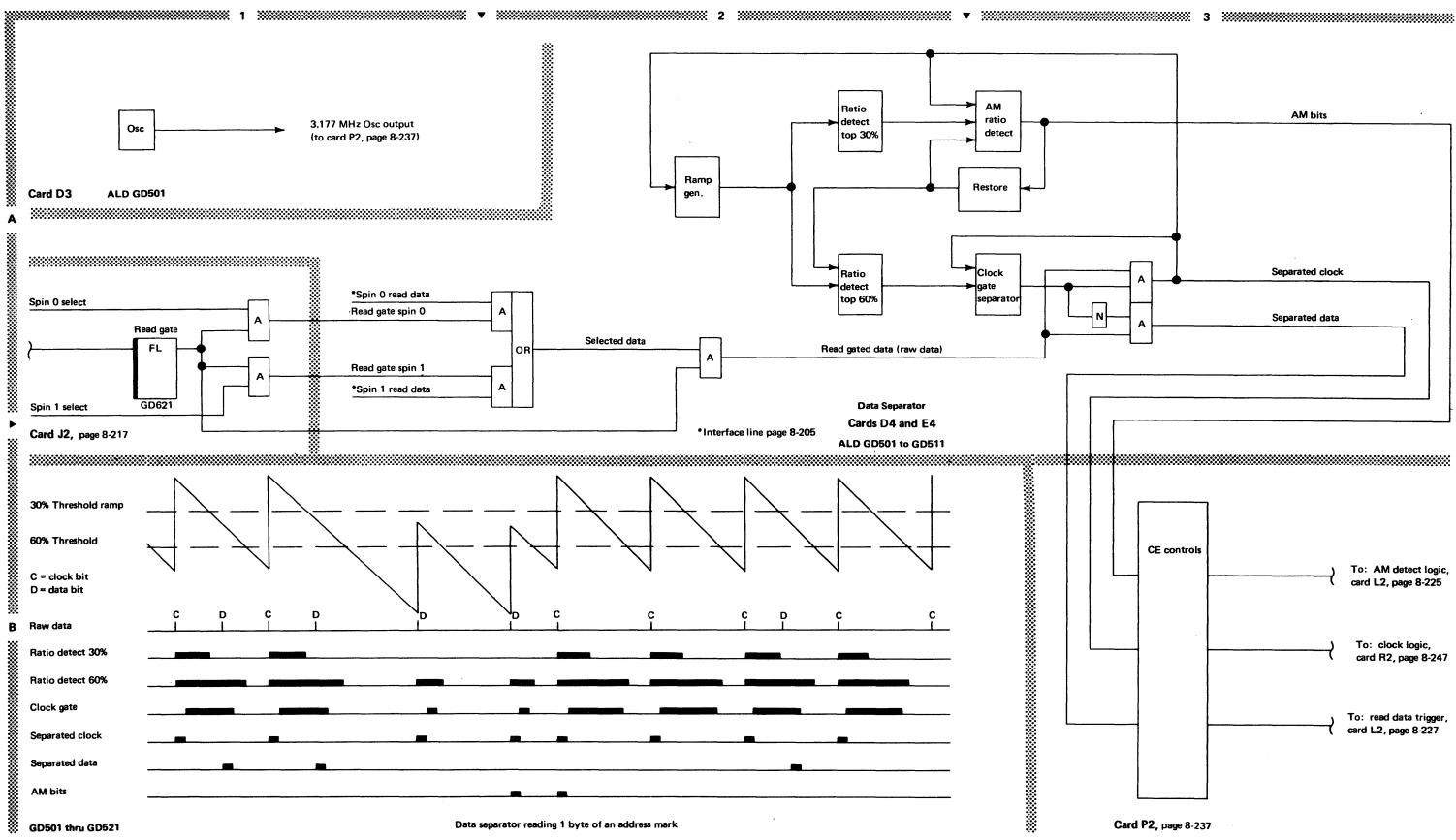

| Data separator                                       | D4-E4           | 8-208       | 8-209            | 50  |                          | 014.043            | 62         |       |     |  |

| Data bus in (DB1)                                    | R2              | 8-244       | 8-245            | E2  | 301-304                  | 311-317            | G2         |       |     |  |

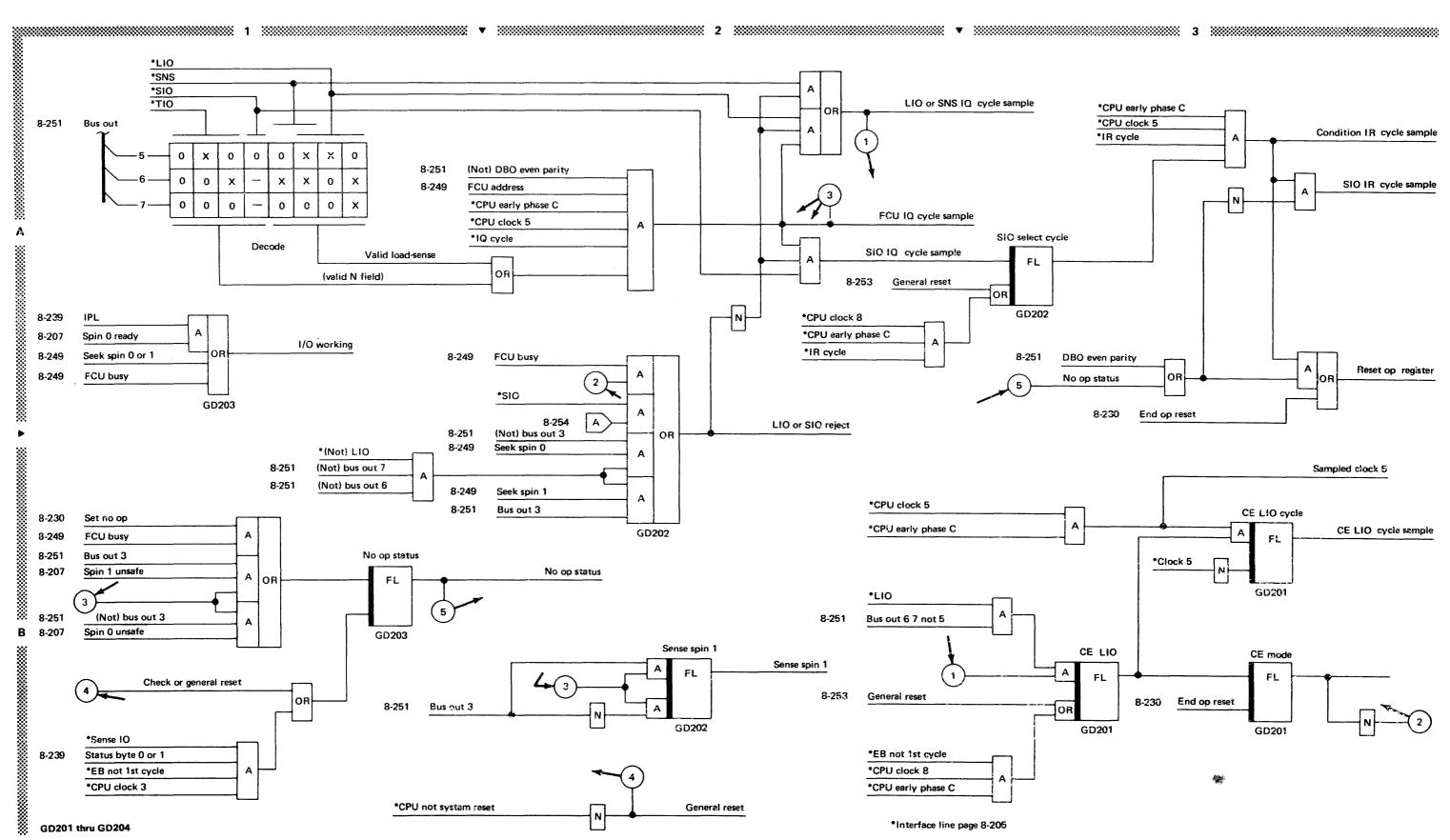

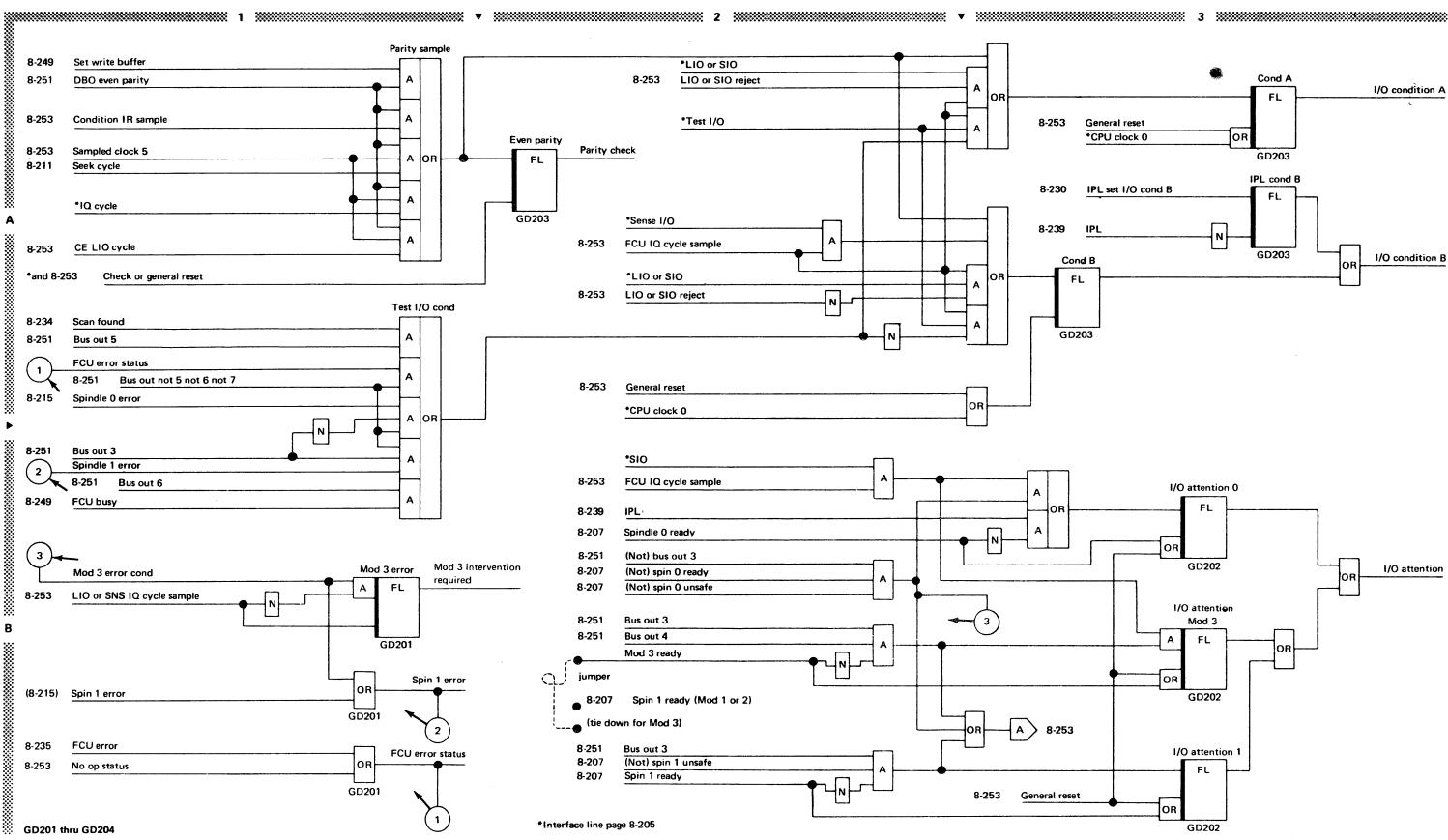

| Data bus out (DBO)                                   | S2              | 8-248       | 8-251            | E4  | 521                      | 321-327            | F2         |       |     |  |

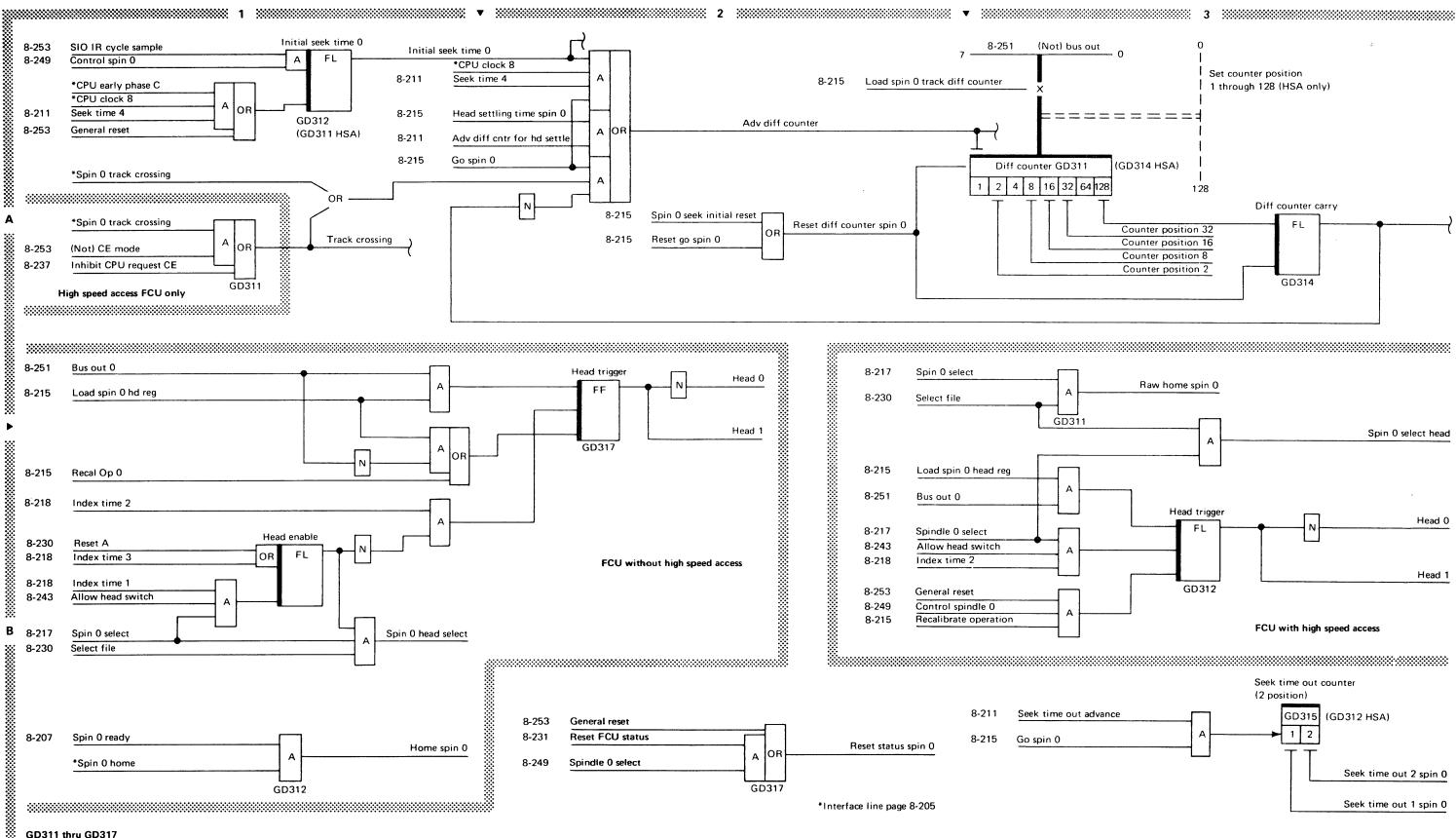

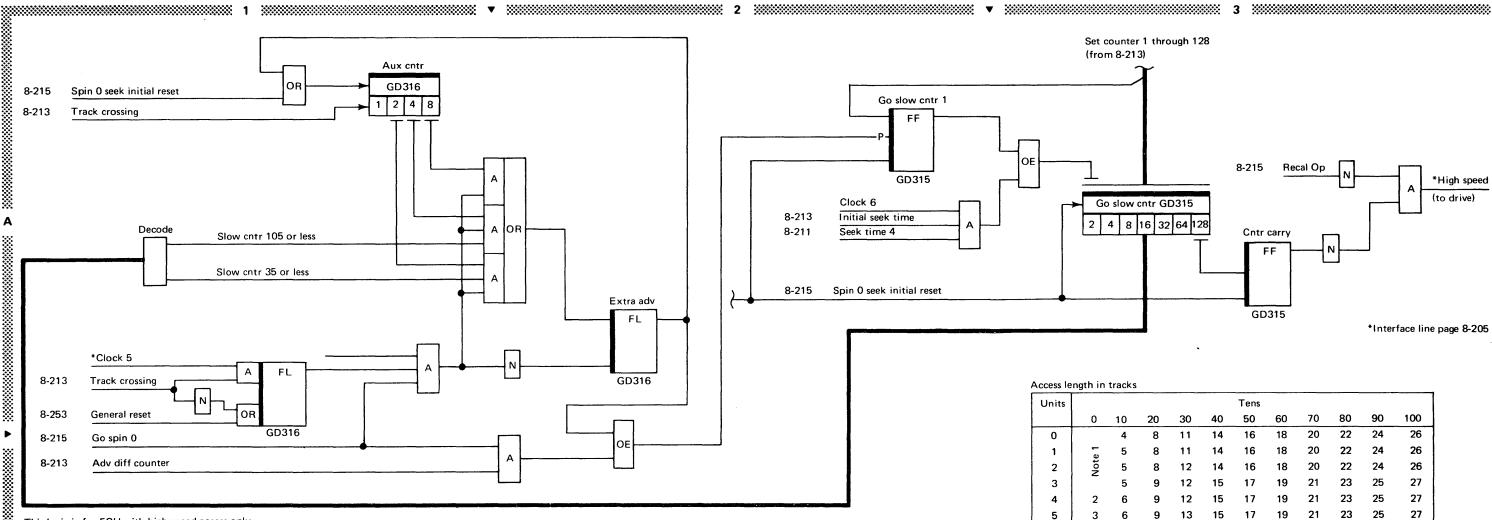

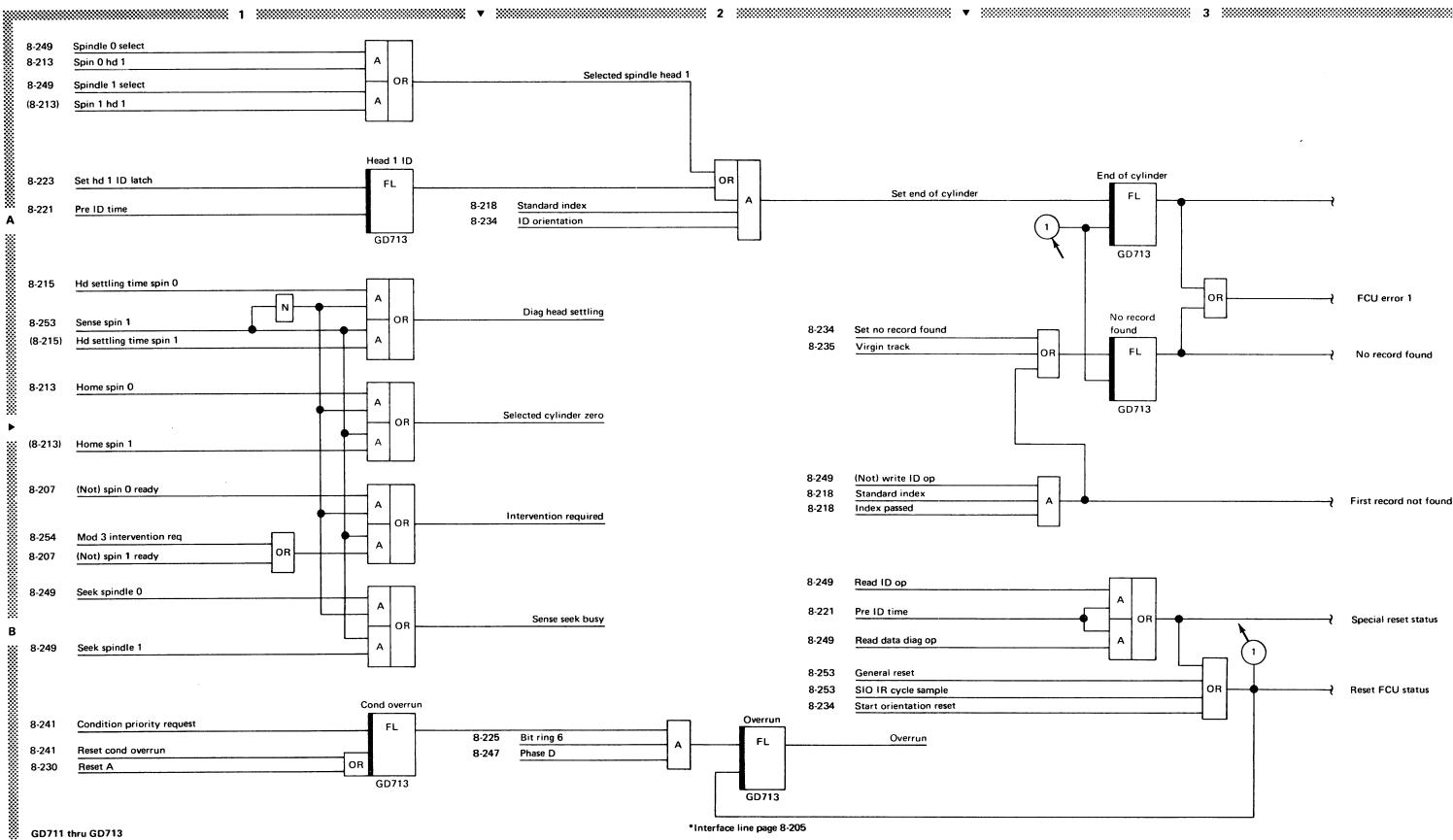

| Difference counter                                   | G2              | 8-212       | 8-213            | E4  | 52 1                     | 521-527            | F2         |       |     |  |

| Erase gate                                           | J2              | 8-216       | 8-219            | F2  | 321-327                  | 501                | D3         |       |     |  |

| Error conditions                                     | M2 - N2         | 8-228       | 8-230 thru 8-235 | G2  | 311-317                  | 511-512            | D4         |       |     |  |

| Go slow counter                                      | G2              | 8-214       | 8-214            | Н2  | not used                 | 521                | E4         |       |     |  |

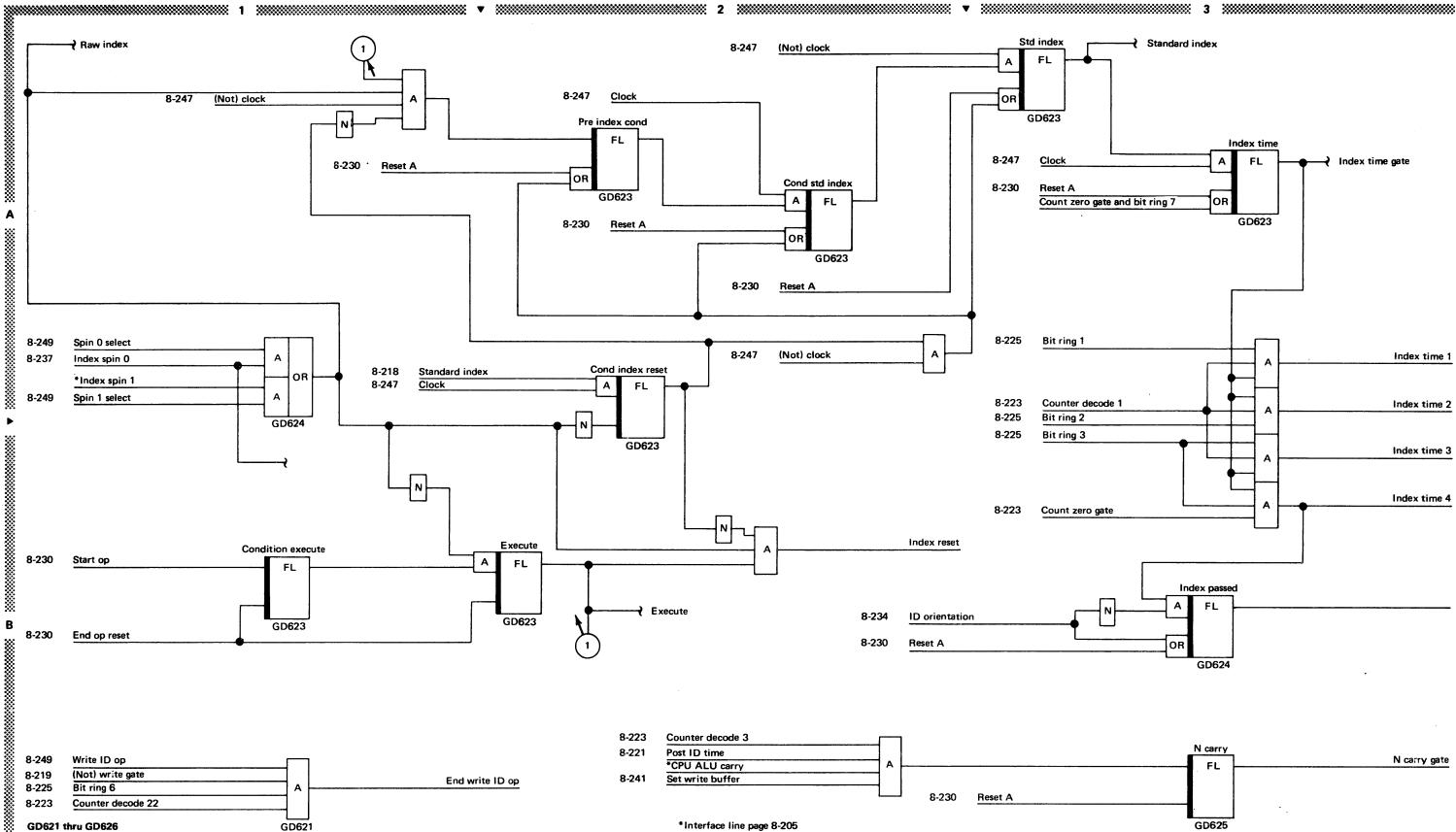

| Index                                                | J2              | 8-216       | 8-218            |     | 621-626                  | 601-606            | P2         |       |     |  |

| Initial selection                                    | Т2              | 8-252       | 8-253, 8-254     | J2  | 621-626                  | 001-000            | FZ         |       |     |  |

| Initial program load (IPL)                           | P2              | 8-236       | 8-239            | К2  | 121-125                  | 611-615            | Q2         |       |     |  |

| LSR selection                                        | P2              | 8-236       | 8-239            | L2  | 111-117                  | 621-626            | J2         |       |     |  |

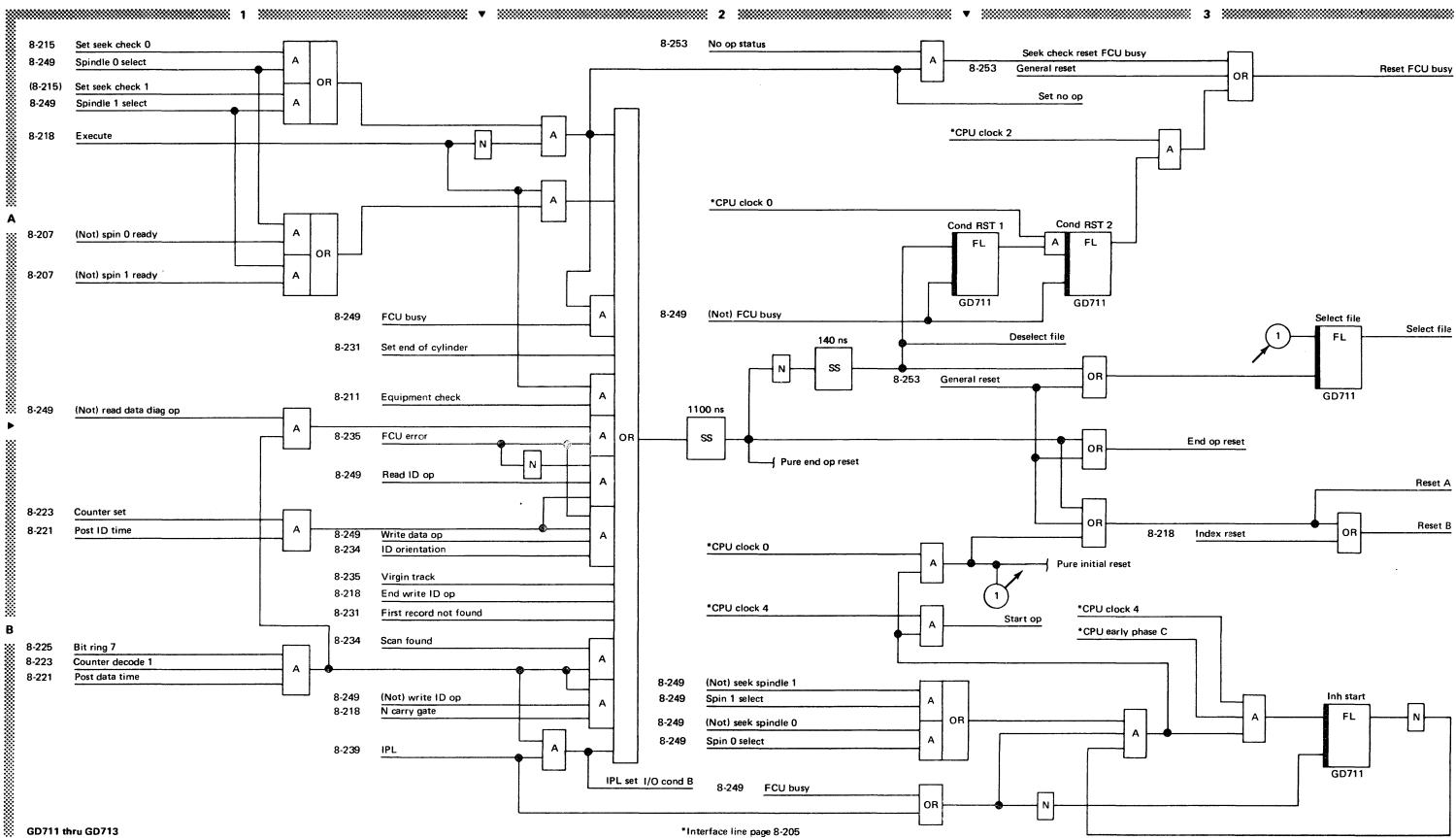

| Operation register                                   | S2              | 8-248       | 8-249            | M2  | 711-713                  | 701-706            | N2         |       |     |  |

| Priority request 3 (data)                            | 02              | 8-240       | 8-241            | N12 | 701 700                  | 711 710            | M2         |       |     |  |

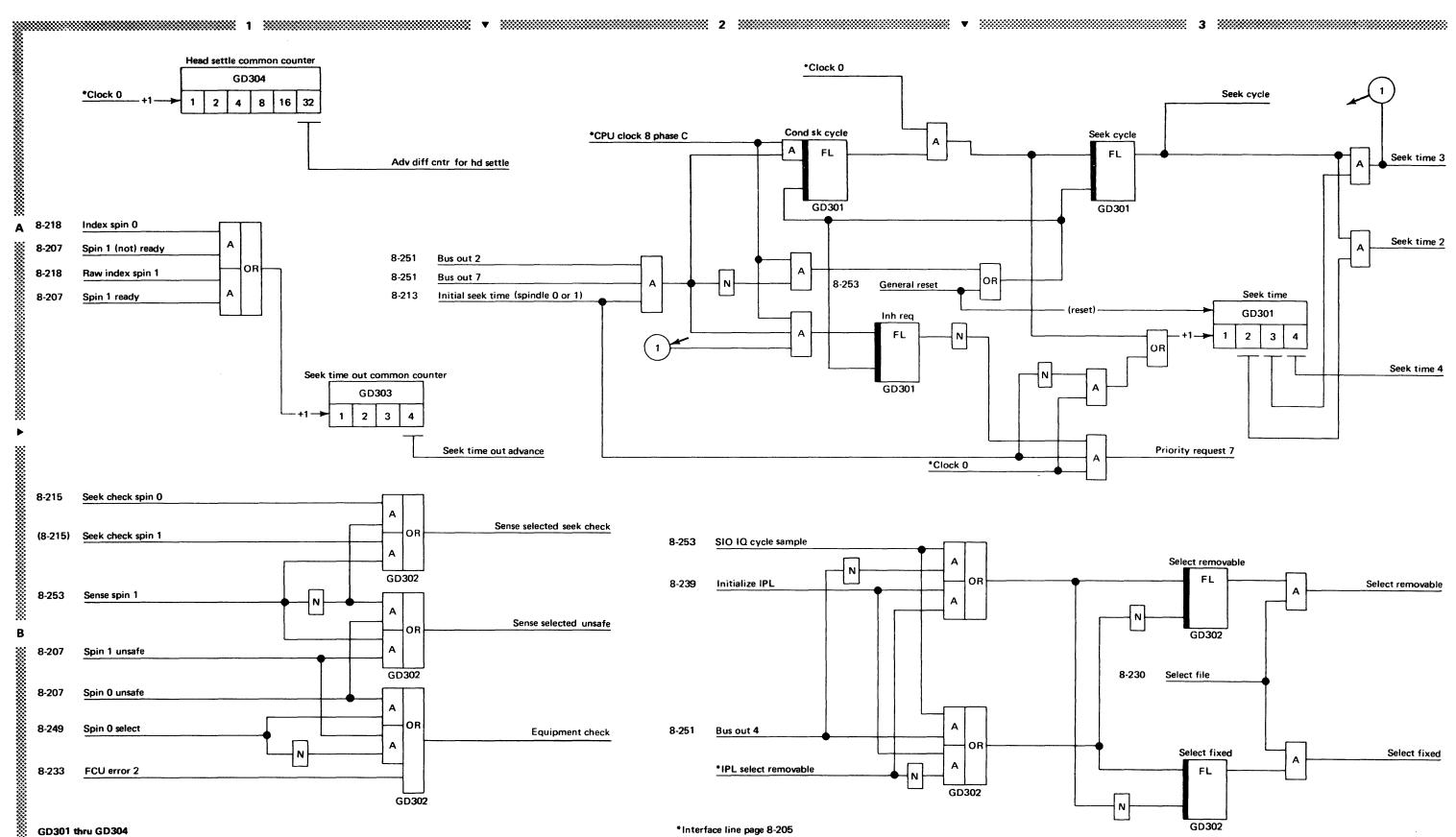

| Priority request 7 (seek)                            | E2              | 8-210       | 8-211            | N2  | 701-706                  | 711-713            | +          |       |     |  |

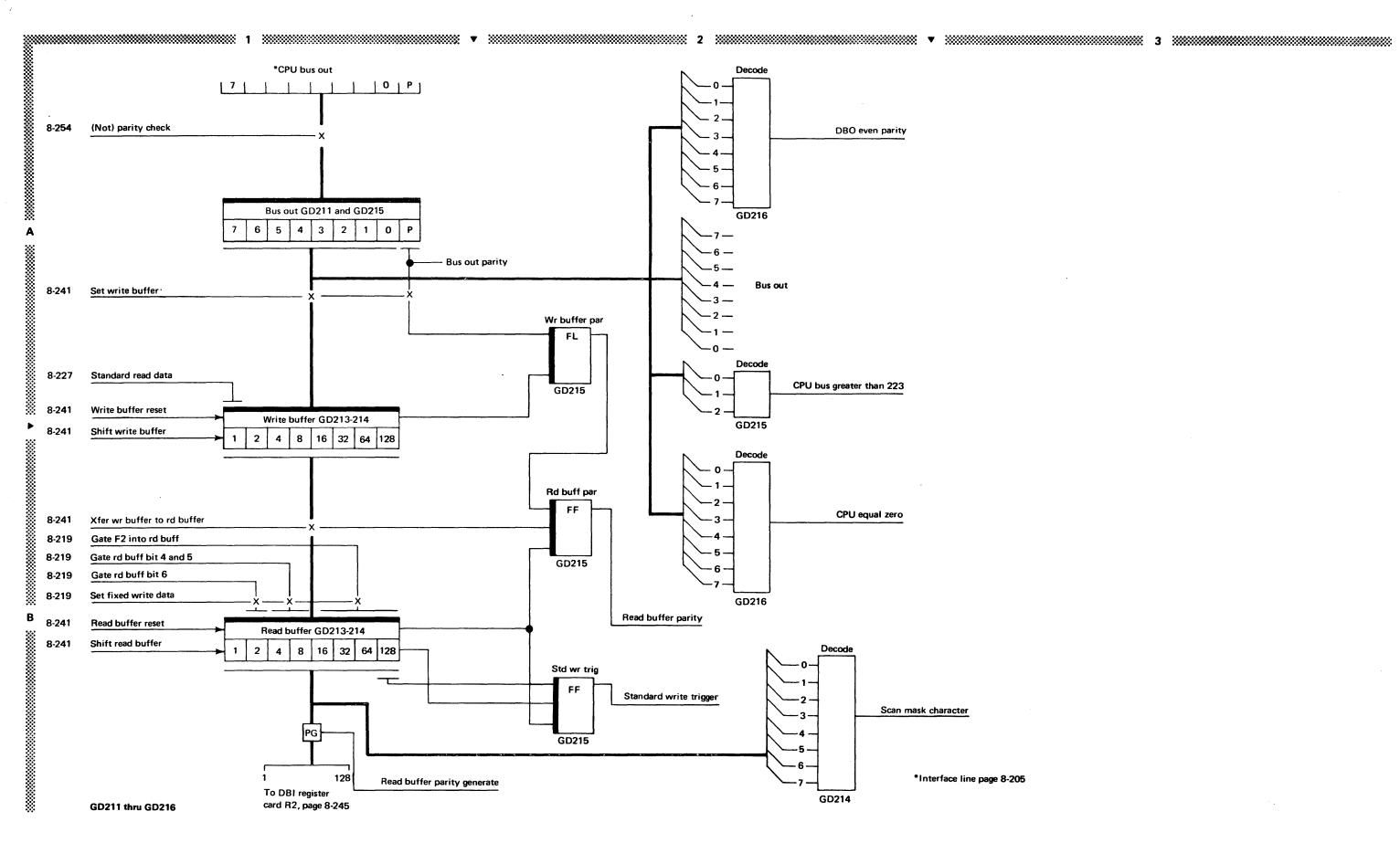

| Read buffer                                          | S2              | 8-248       | 8-251            | P2  | 601-606                  | 801                | C3         |       |     |  |

| Read gate                                            | J2              | 8-216       | 8-217            | Q2  | 611-615                  | 811                | C2         |       |     |  |

| Resets                                               | M2              | 8-228       | 8-230, 8-231     |     |                          |                    |            |       |     |  |

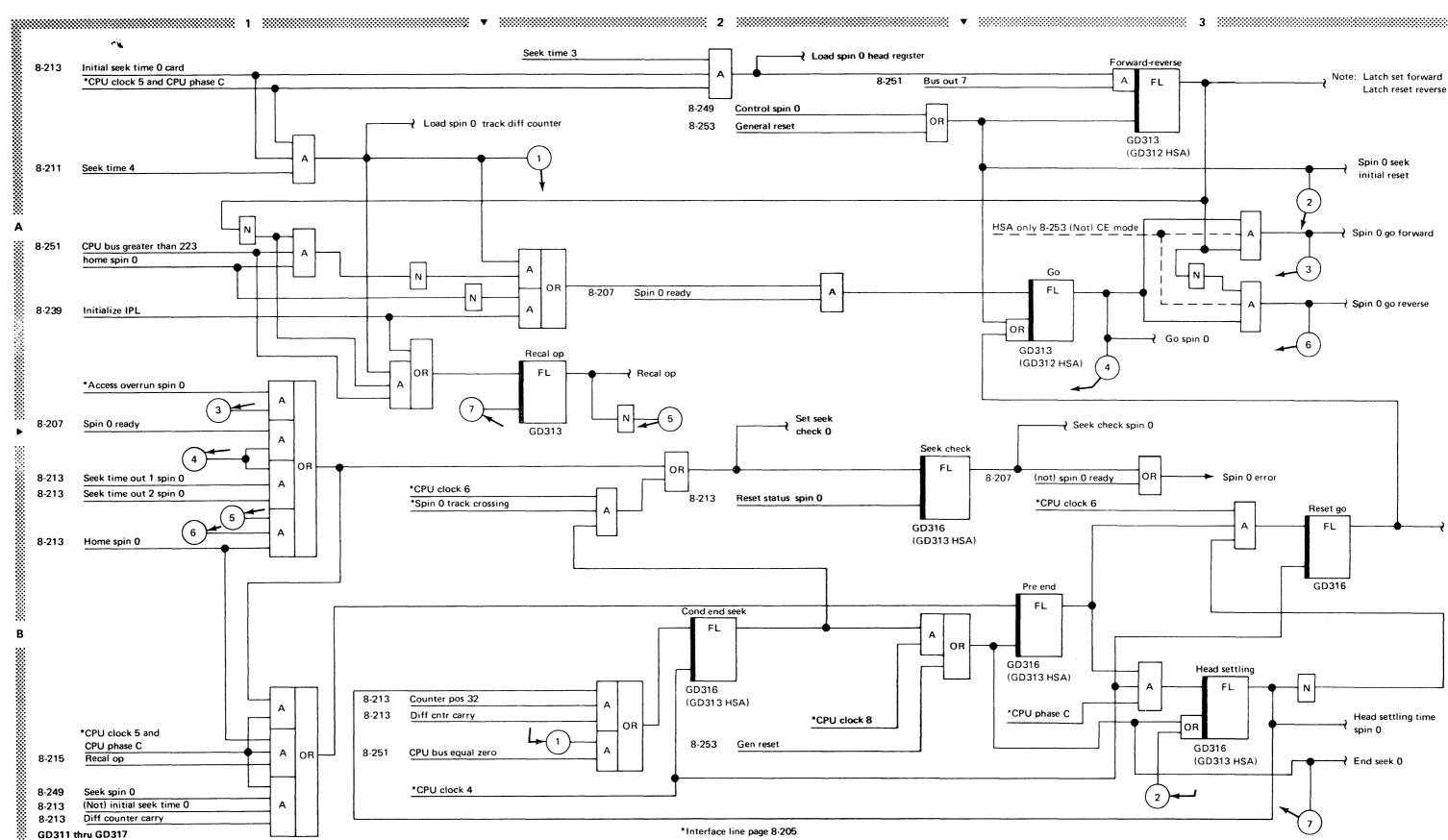

| Seek (common controls)                               | E2              | 8-210       | 8-211            | R2  | 101-104                  | 901-902            | C4         |       |     |  |

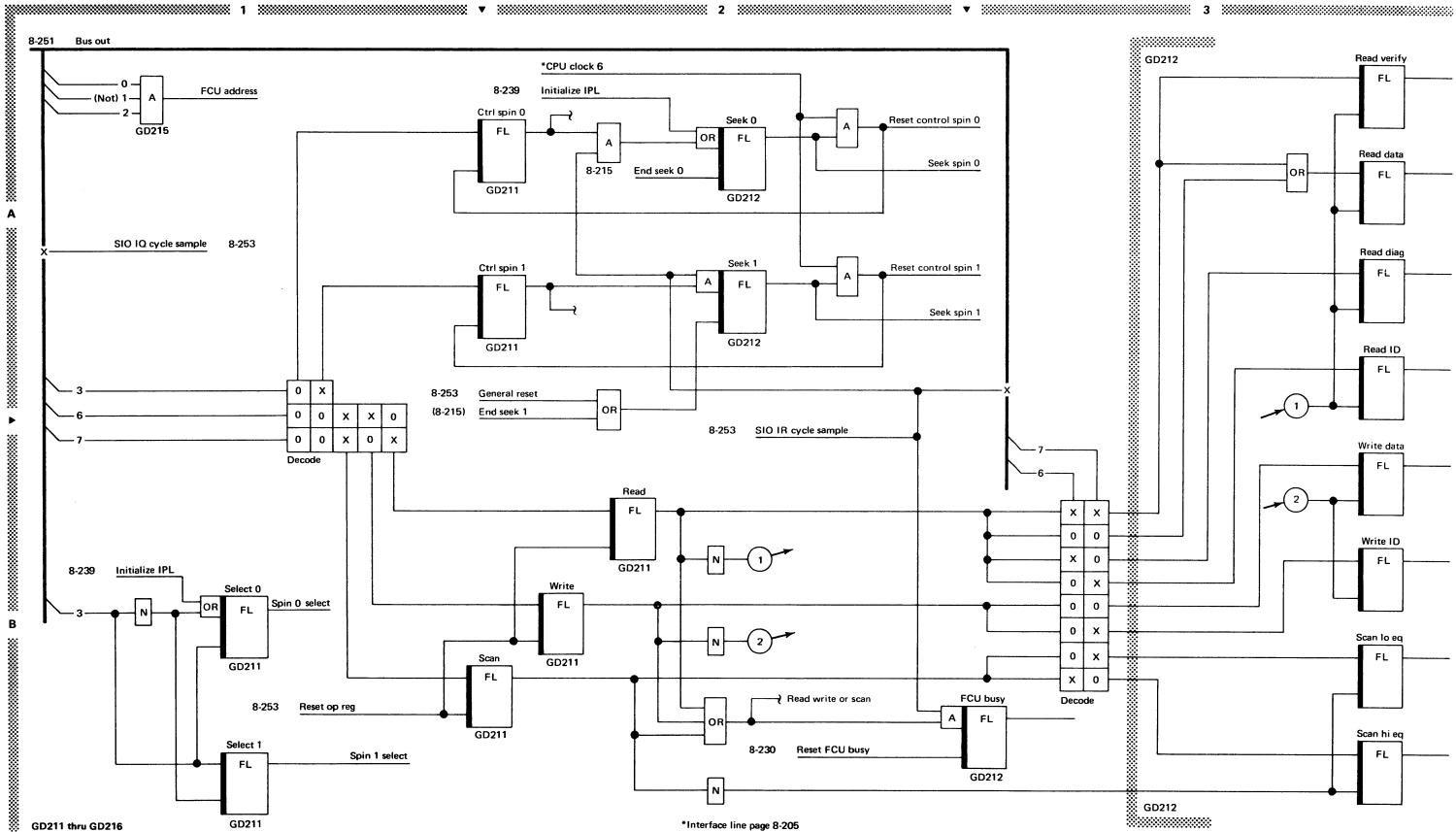

| Seek (individual drive controls)                     | G2              | 8-212       | 8-213, 8-215     | S2  | 211-216                  | 911                | D2         |       |     |  |

| Serdes                                               | S2              | 8-248       | 8-251            | 52  | 211-210                  | 311                | 02         |       |     |  |

| Serdes control                                       | 02              | 8-248       | 8-241            | T2  | 201-204                  |                    |            |       |     |  |

| Standard read data trigger                           | L2              | 8-226       | 8-241            | 12  | 201-204                  |                    | L          |       |     |  |

| Standard read data trigger<br>Standard write trigger | S2              | 8-226       | 8-227<br>8-251   | U2  | not used                 |                    |            |       |     |  |

|                                                      |                 |             |                  | ·   | •                        |                    |            |       |     |  |

| Write buffer                                         | S2<br>J2        | 8-248       | 8-251            |     |                          |                    |            |       |     |  |

|    | CARD ALD cro  | ss reference chart |       |  |  |

|----|---------------|--------------------|-------|--|--|

| Ву | card location | By ALD loca        | ation |  |  |

| C2 | GD-811        | GD-101-104         | R2    |  |  |

| СЗ | 801           | 111-117            | L2    |  |  |

| C4 | 901-902       | 121-125            | К2    |  |  |

| D2 | 911           | 201-204            | T2    |  |  |

| D3 | 501           | 211-216            | S2    |  |  |

| D4 | 511-512       | 301-304            | E2    |  |  |

| E2 | 301-304       | 311-317            | G2    |  |  |

| E4 | 521           | 321-327            | F2    |  |  |

| F2 | 321-327       | 501                | D3    |  |  |

| G2 | 311-317       | 511-512            | D4    |  |  |

| H2 | not used      | 521                | E4    |  |  |

| J2 | 621-626       | 601-606            | P2    |  |  |

| К2 | 121-125       | 611-615            | Q2    |  |  |

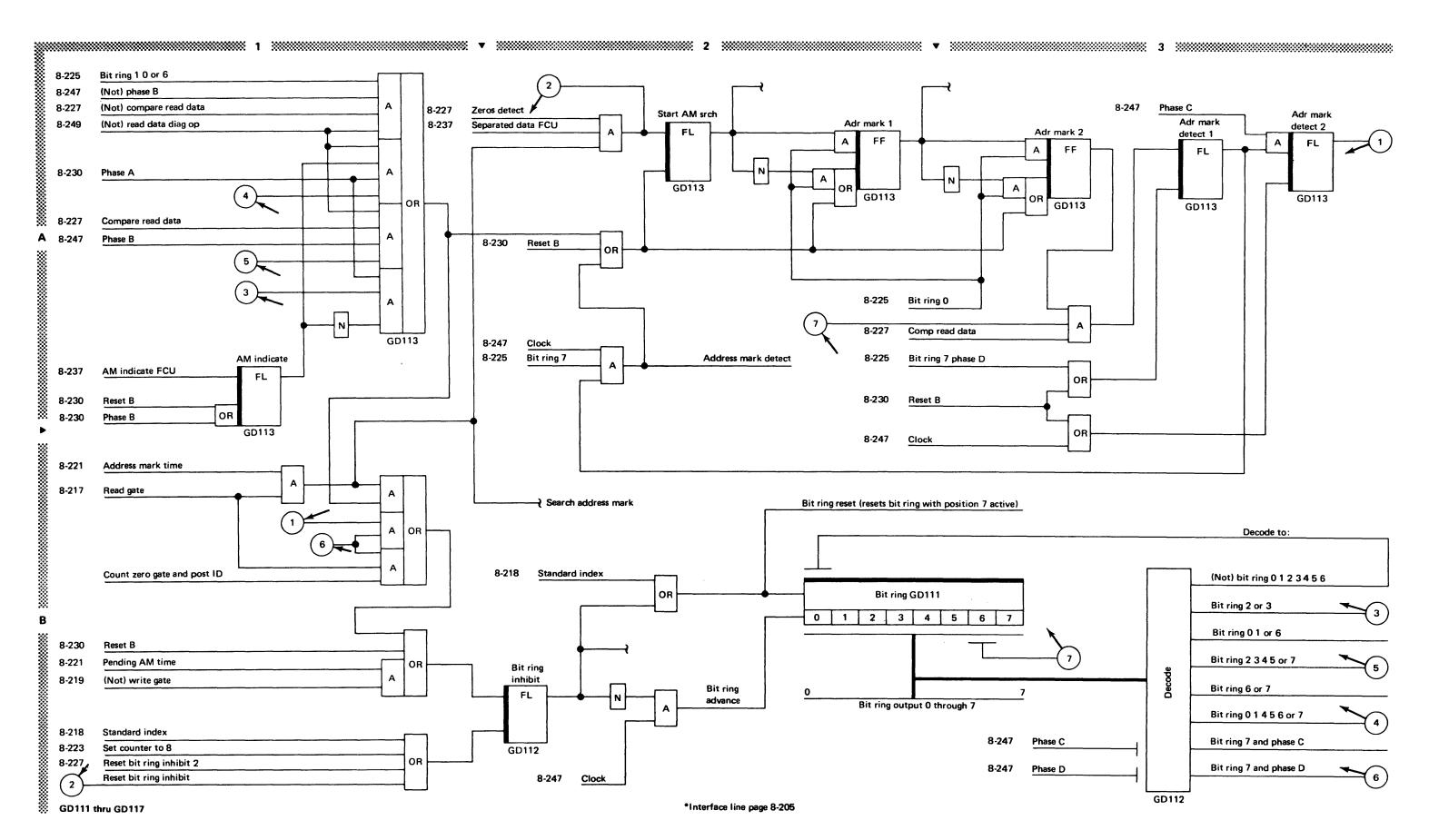

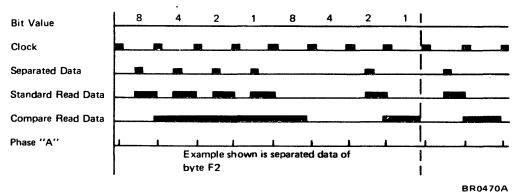

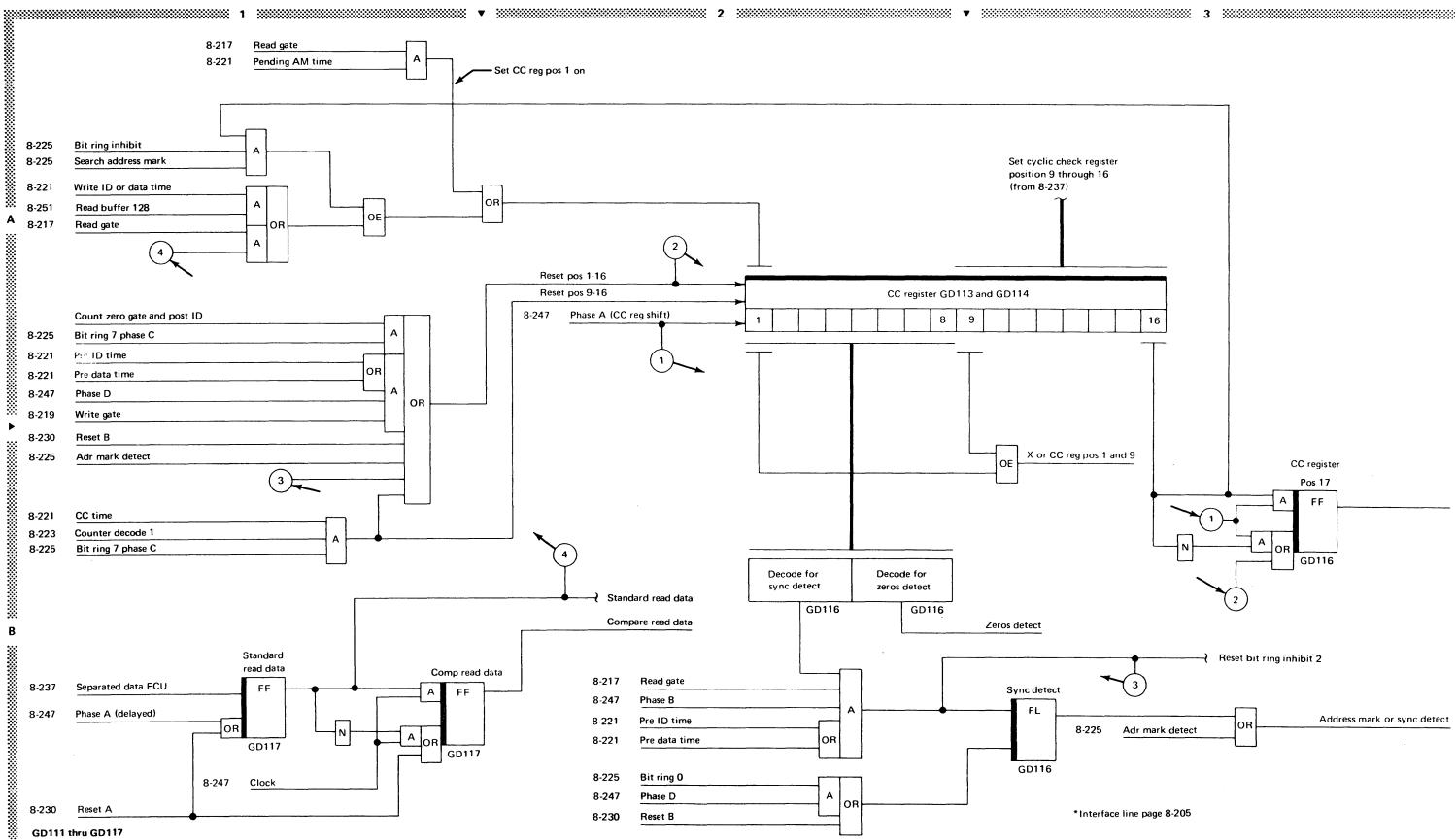

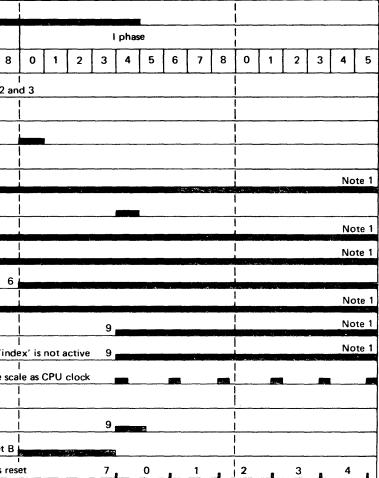

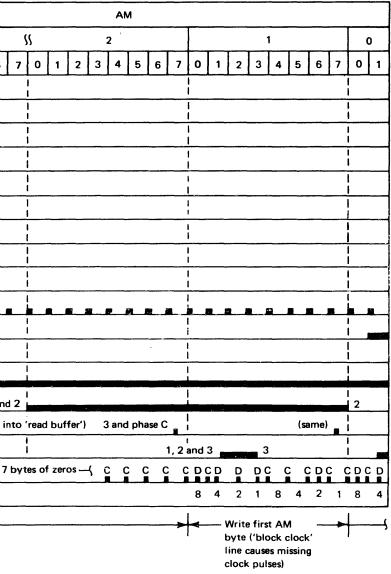

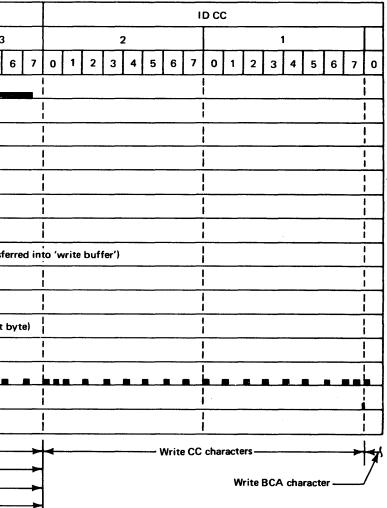

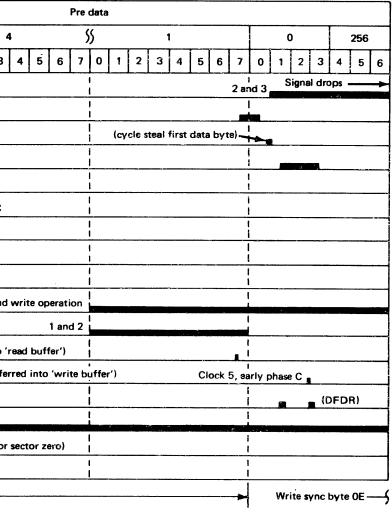

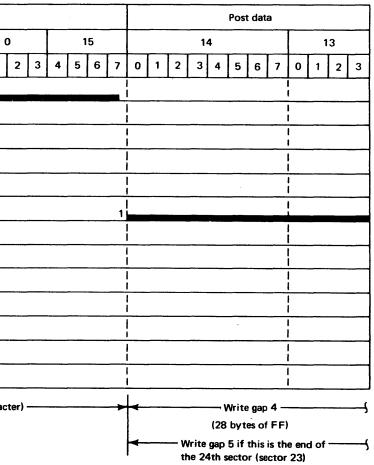

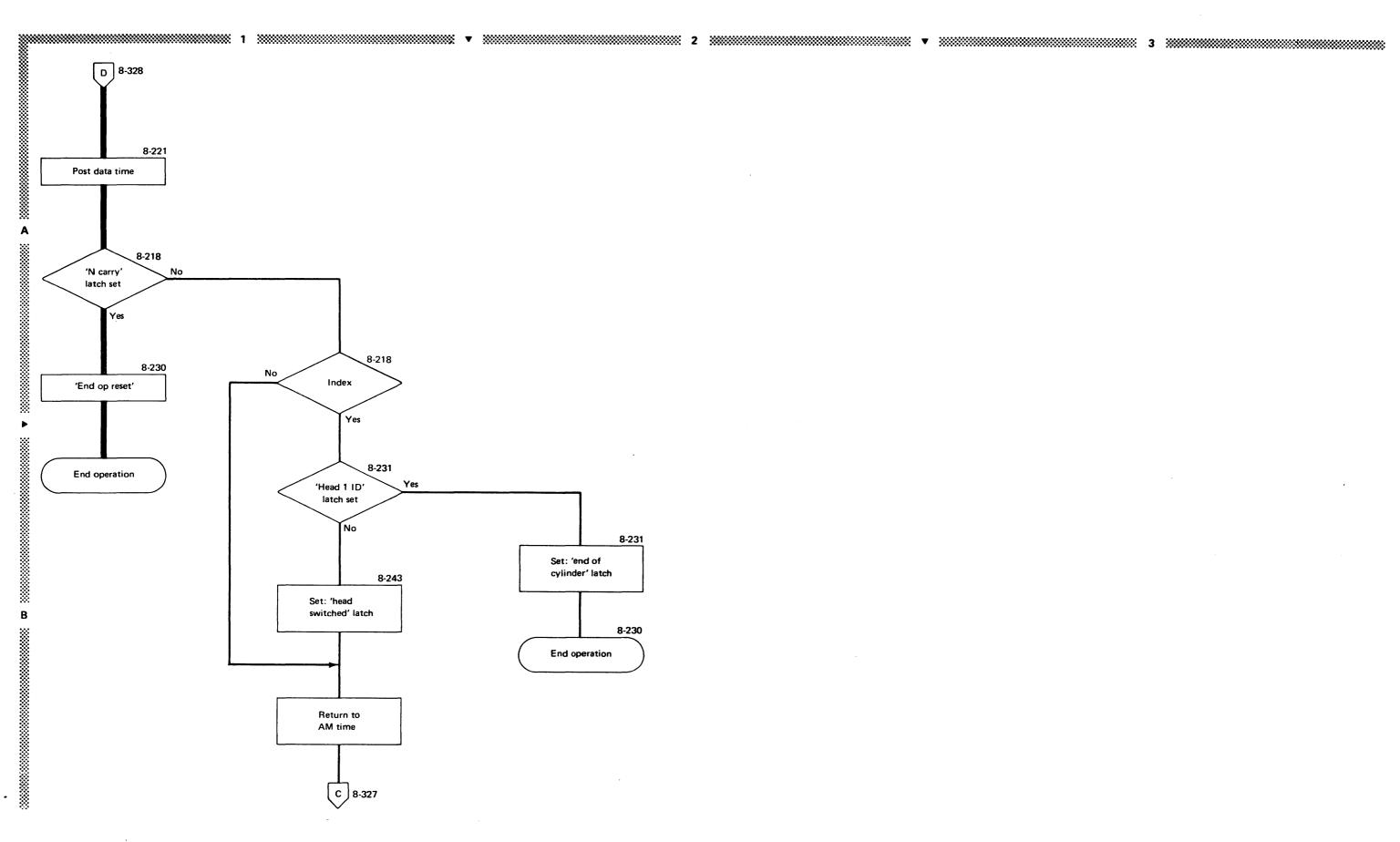

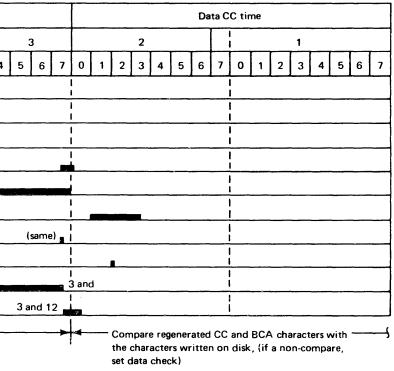

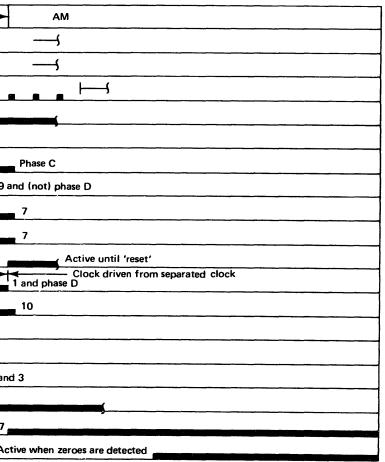

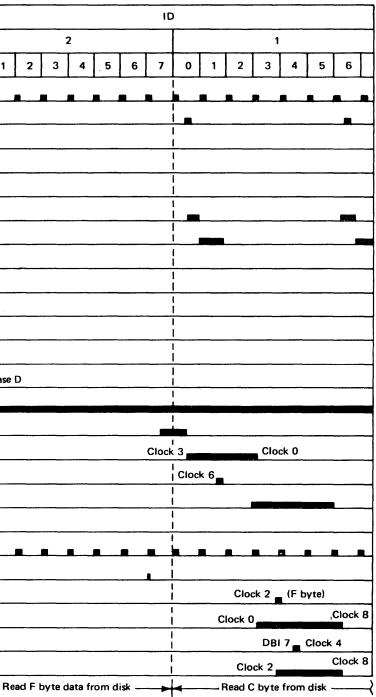

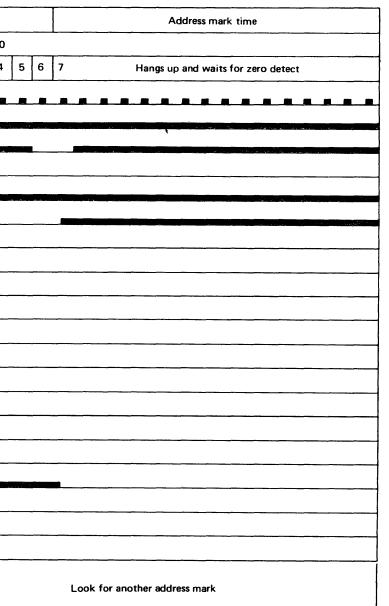

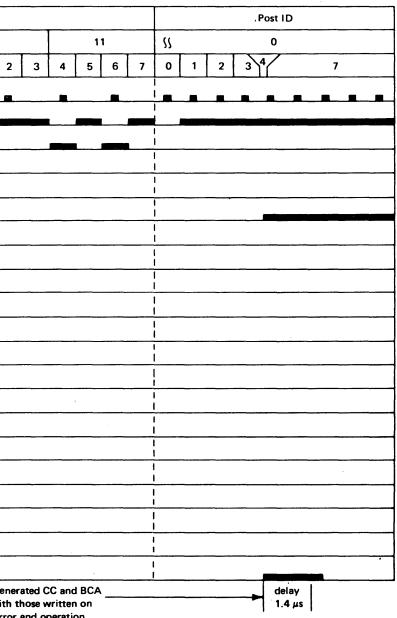

| L2 | 111-117       | 621-626            | J2    |  |  |