# Contents

| 62EH DISK DRIVE AND ATTACHMENT 7-           | -  |

|---------------------------------------------|----|

| INTRODUCTION                                |    |

| 62EH Disk Drive                             |    |

| Subframe                                    |    |

| Grounding                                   |    |

| Disk Enclosure                              |    |

| Disk Spindle                                |    |

| Transducer                                  | 3  |

| Actuator Lock                               | 3  |

| Actuator                                    | 4  |

| Actuator Position Indicator 7-              | 4  |

| Circuit Locations                           | 4  |

| Motor and Brake                             |    |

| Write Safety                                |    |

| Data Unsafe Conditions                      |    |

| File Ready                                  |    |

| Disk Speed                                  |    |

| Power On                                    |    |

| Disk Format                                 |    |

| Data Tracks                                 |    |

| Sector Format                               |    |

| Disk Addressing                             |    |

| Servo Tracks                                |    |

| Landing Zone                                |    |

| Guard Band                                  |    |

| Data Recording                              |    |

| Actuator Movement                           |    |

| Seek                                        |    |

| Recalibrate                                 |    |

| Servo Track Follow                          |    |

| Head Alignment and Disk Description         |    |

| Missing Clock Pulse and Position Pulses 7-1 |    |

| Guard Band                                  |    |

| Behind Home                                 |    |

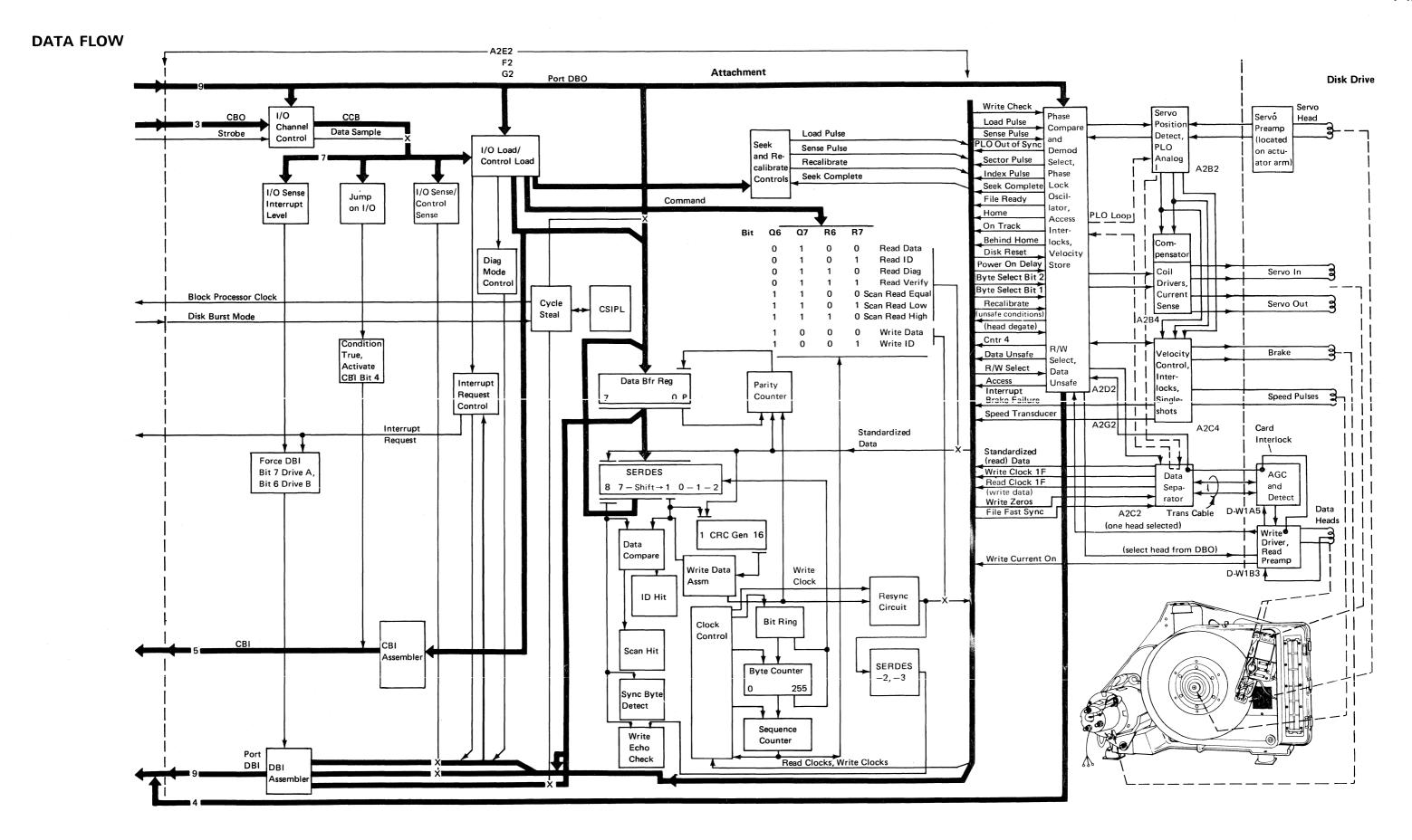

| DATA FLOW                                   |    |

| OPERATIONS                                  |    |

| Write Identification                        |    |

| Read Identification                         |    |

|                                             |    |

|                                             |    |

|                                             |    |

| <b>o</b>                                    |    |

|                                             |    |

| Scan Read Data Equal                        |    |

| Scan Read Data Low or Equal                 |    |

| Scan Read Data High or Equal                |    |

| Write Circuits                              |    |

| Write                                       |    |

| Write Waveshapes                            |    |

| Read Circuits                               |    |

| Read                                        |    |

| Read Waveshapes                             | 17 |

| Track Follow Principles                   |     | 7-30         |

|-------------------------------------------|-----|--------------|

| Track Follow                              |     | 7-30         |

| Track Follow Waveshapes                   |     |              |

| Servo Clock                               |     |              |

| Servo Clock Waveshapes                    |     |              |

| Phase Lock Oscillator                     |     |              |

| Phase Lock Oscillator Synchronization     |     |              |

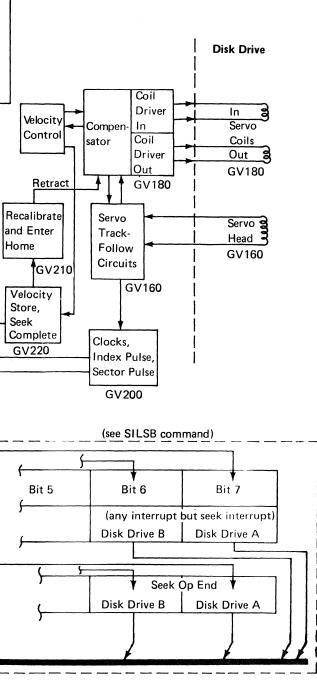

| Recalibrate Operation                     |     | 7-35         |

| Disk Ready                                |     |              |

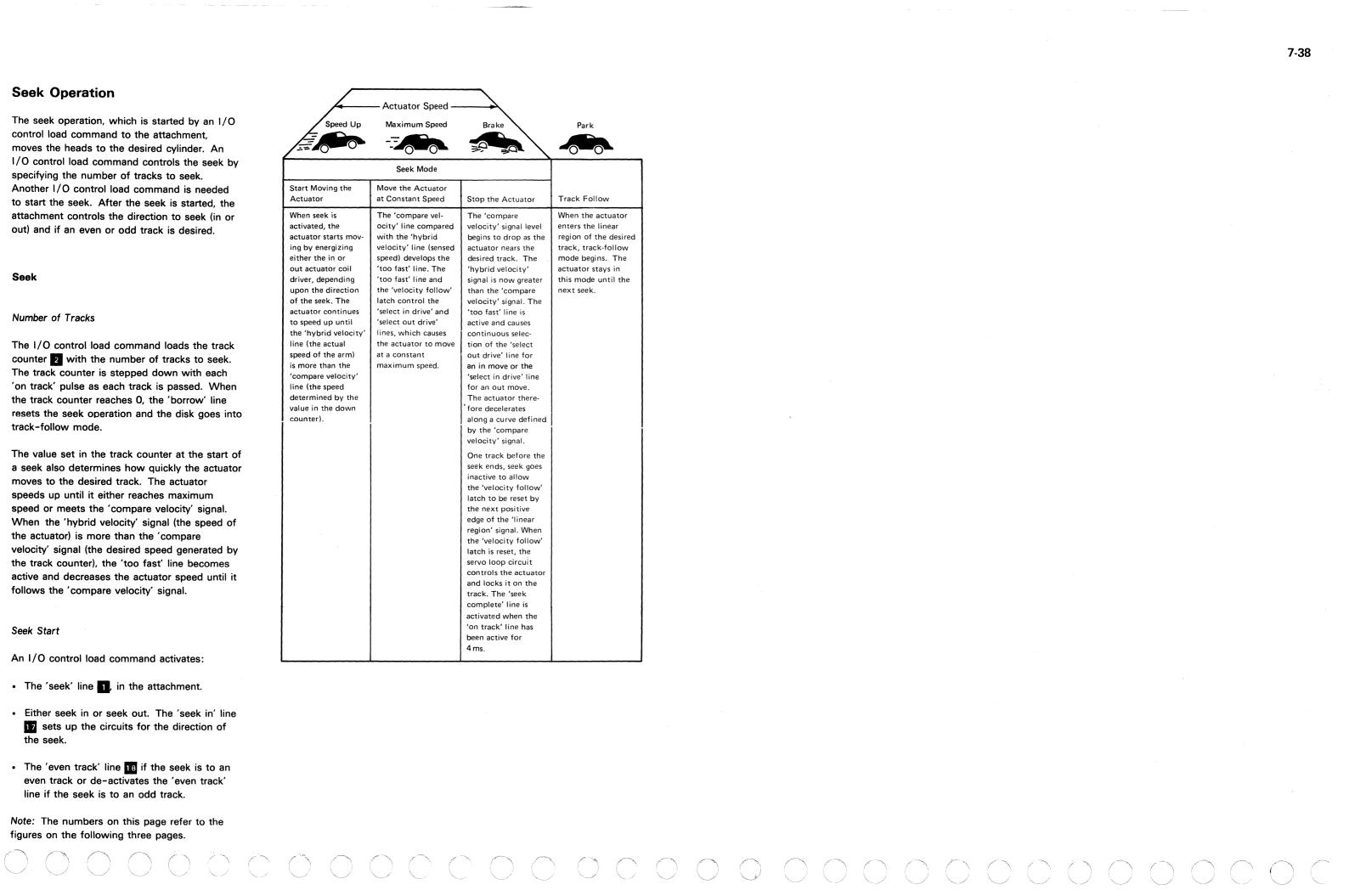

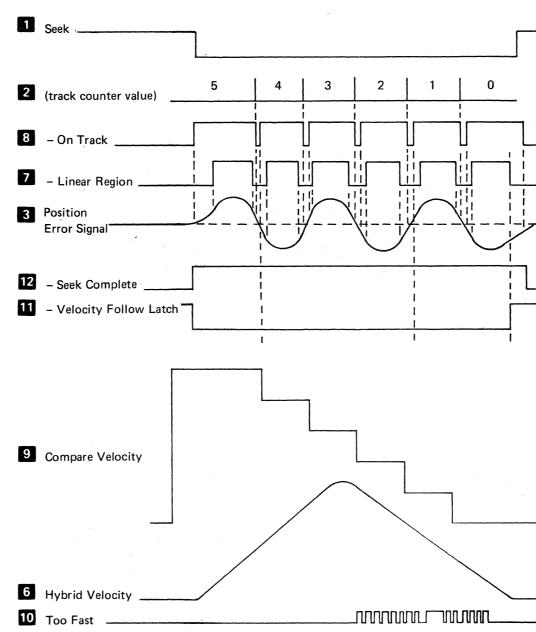

| Seek Operation                            |     |              |

| Seek                                      |     |              |

| Actuator Feedback During Seek             |     |              |

| Seek Waveshapes                           |     |              |

| Power On and Off                          | • • | 7-42         |

| Power On and Seek Home                    |     |              |

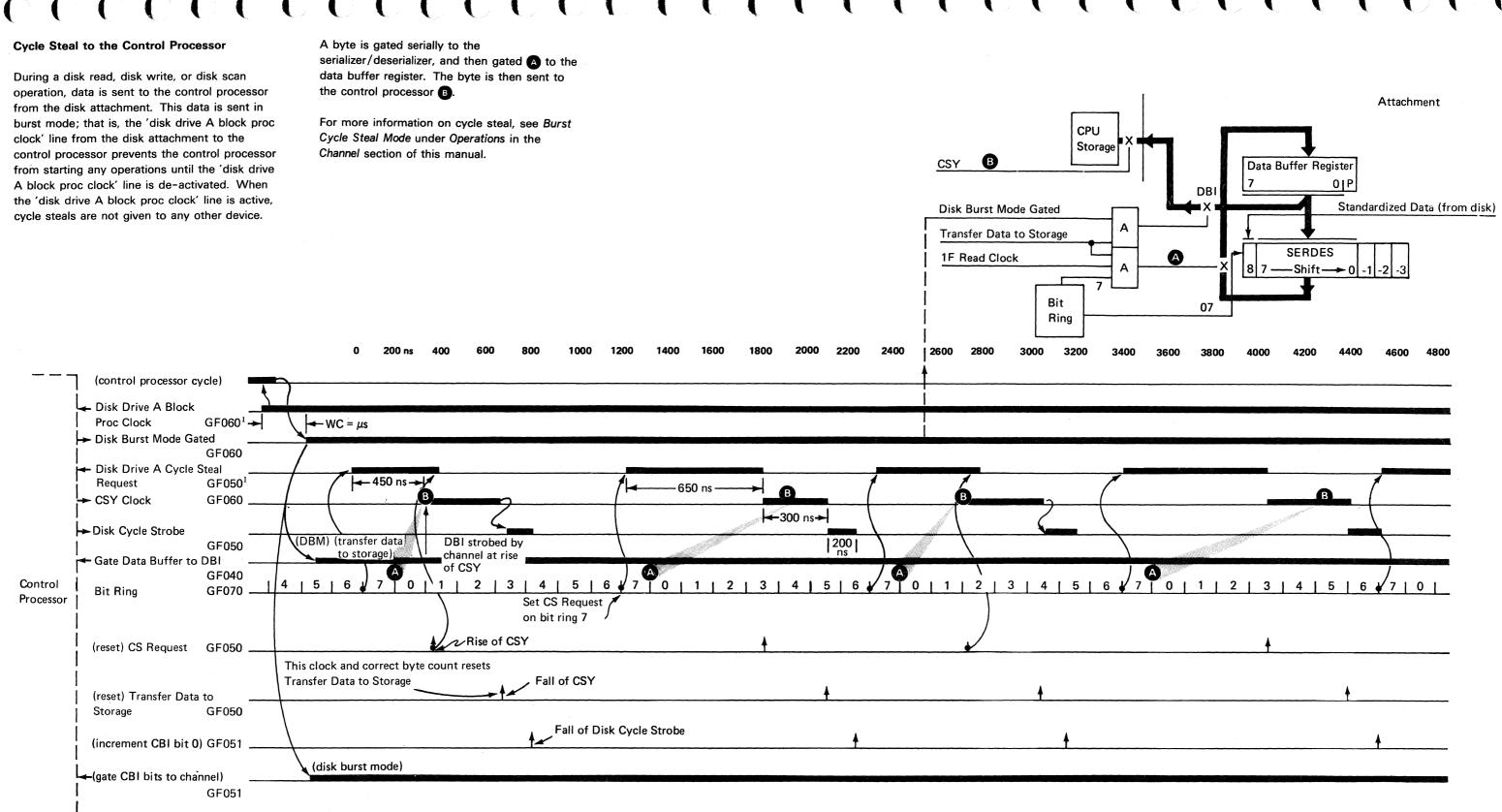

| Cycle Steal                               |     |              |

| Cycle Steal from the Control Processor    |     | 7-44         |

| Cycle Steal for the Control Processor     |     |              |

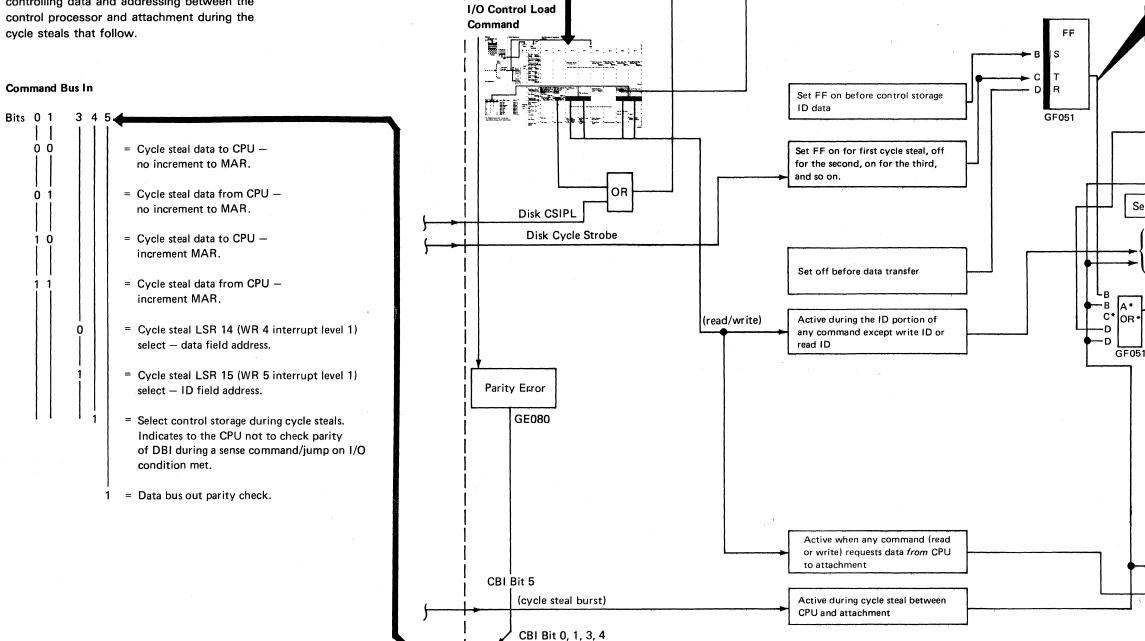

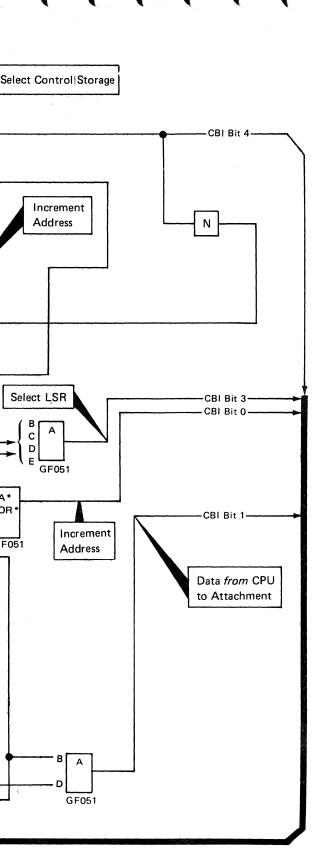

| Control Storage Initial Program Load      |     |              |

|                                           |     |              |

| Command Bus In                            | •   | 7-47<br>7-48 |

|                                           | •   | /-48         |

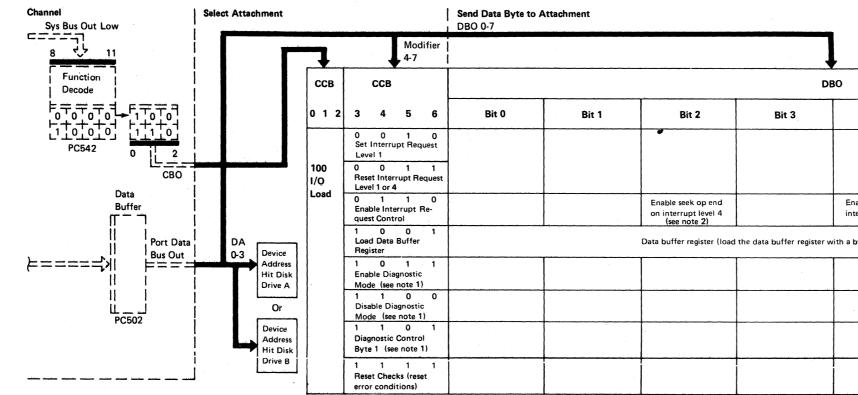

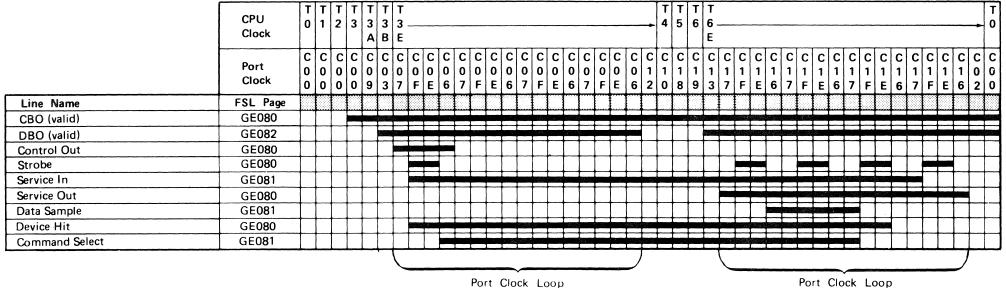

| I/O Load Command–I/O Control Load         |     | 7 40         |

| Command                                   | •   | 7-48         |

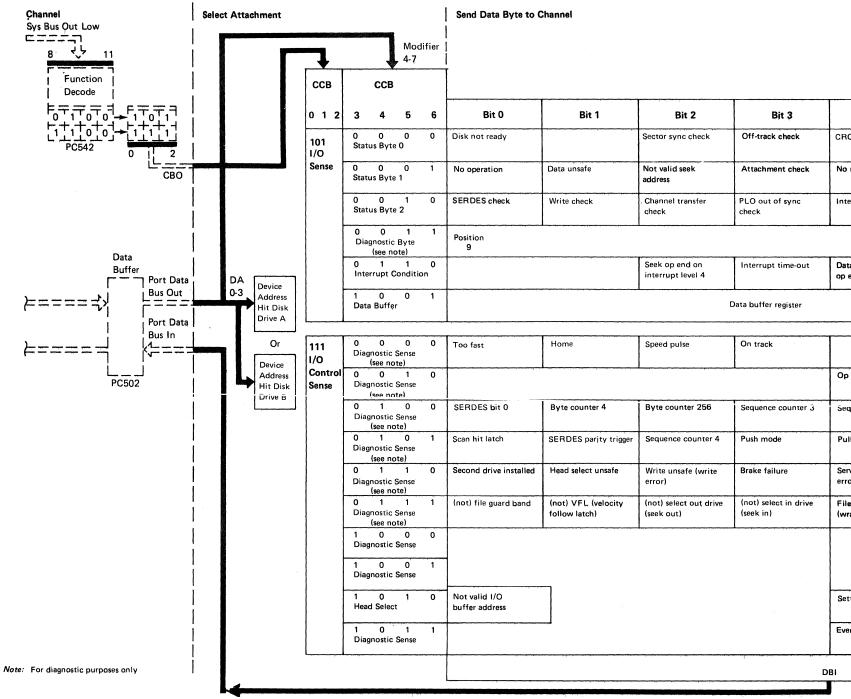

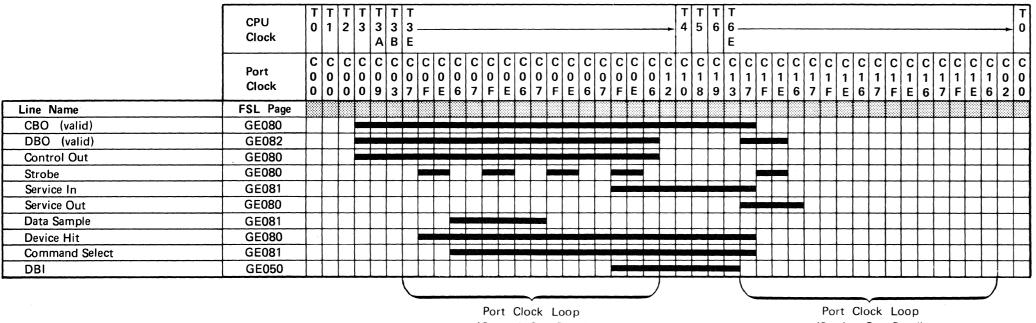

| I/O Sense Command–I/O Control Sense       |     |              |

| Command                                   |     | 7-50         |

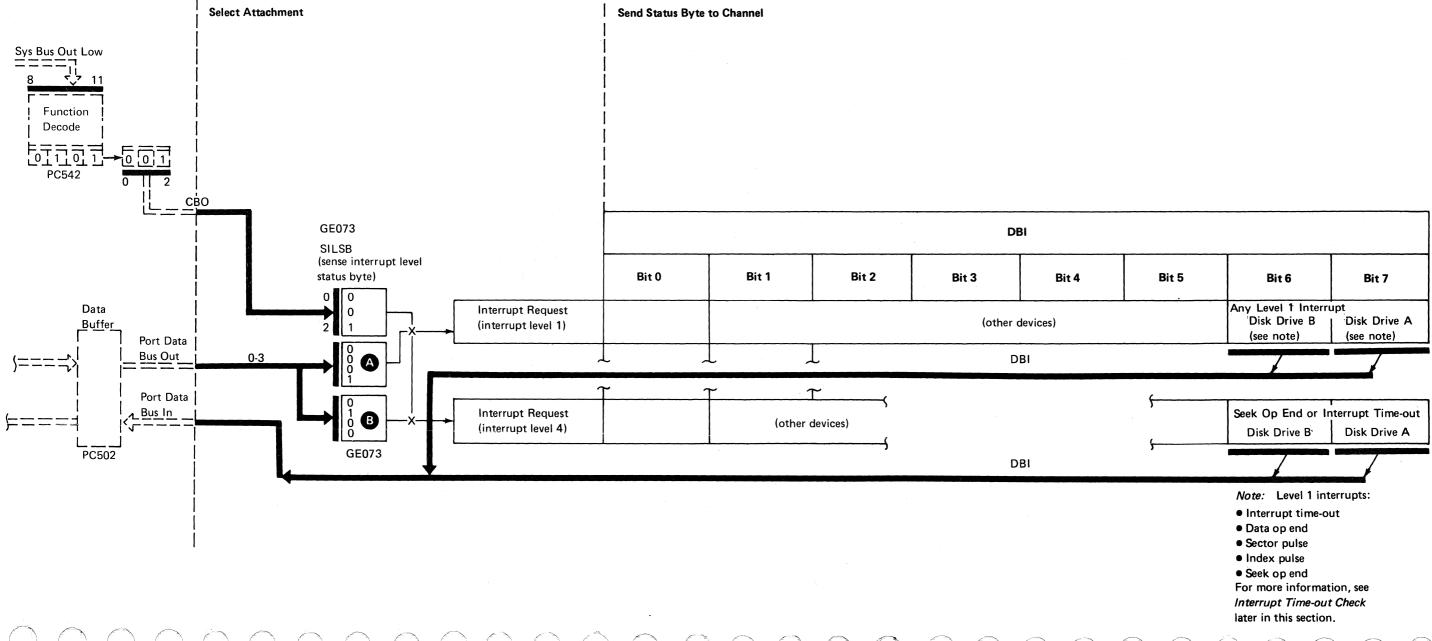

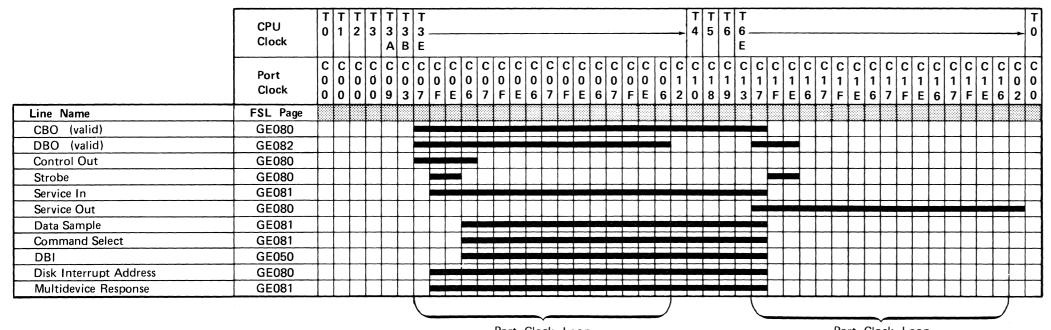

| Sense Interrupt Level Status Byte Command |     |              |

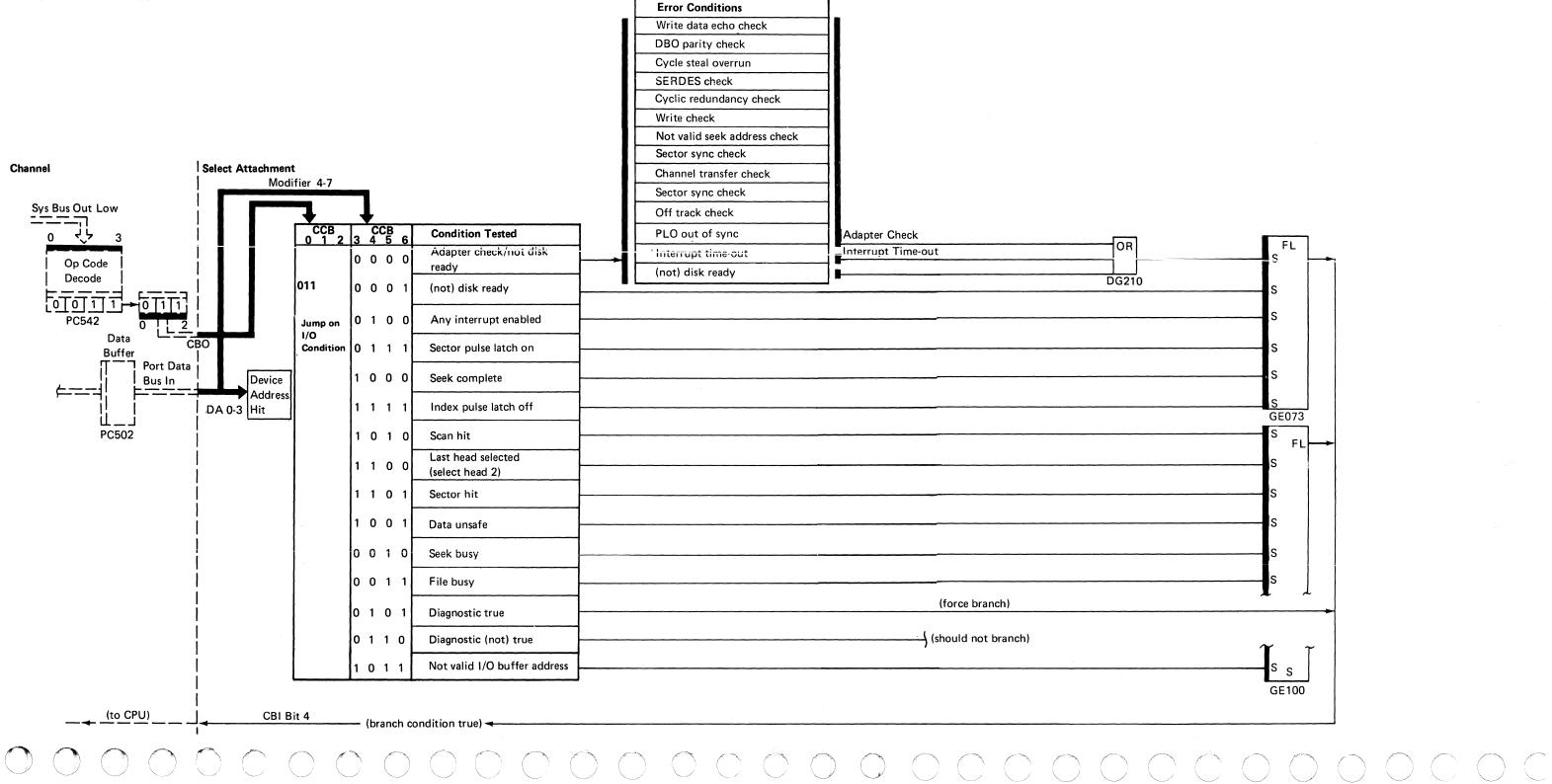

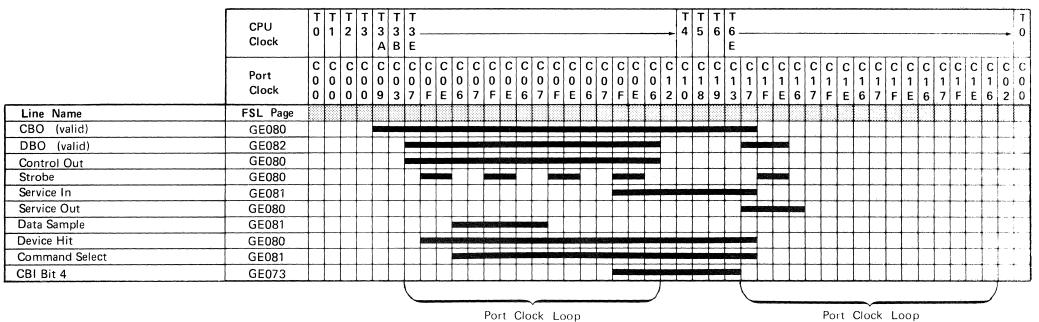

| Jump on I/O Command                       |     |              |

| ERROR CONDITIONS                          |     |              |

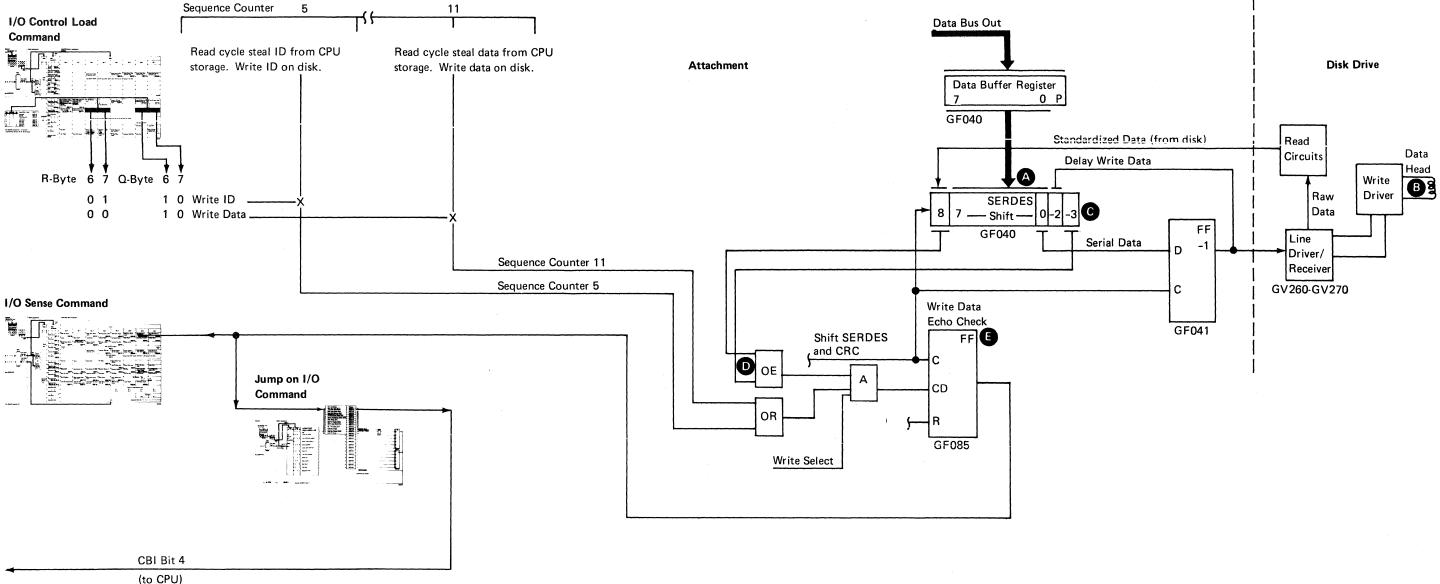

| Write Data Echo Check                     | •   | 7-56         |

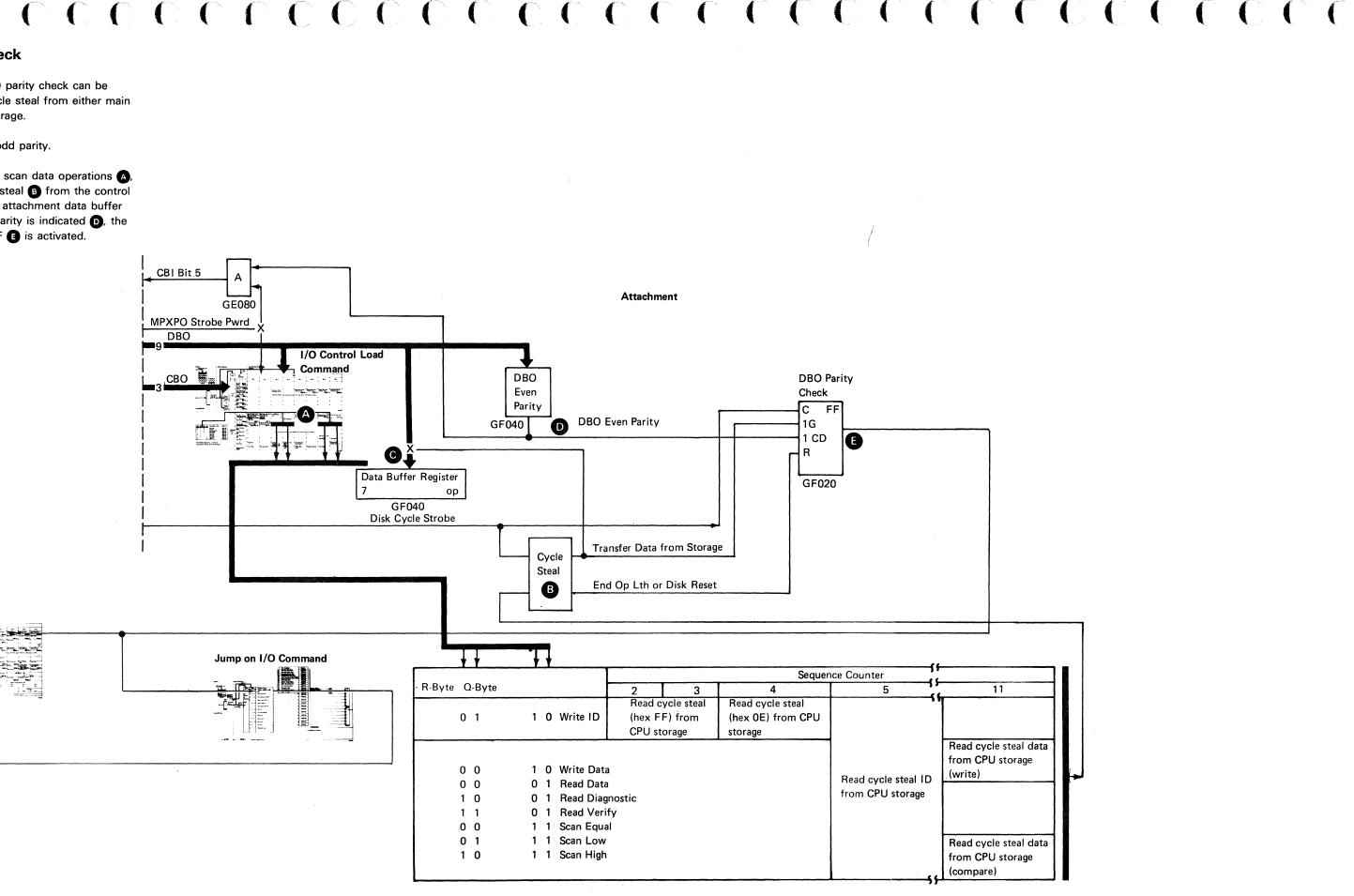

| DBO Parity Check                          |     |              |

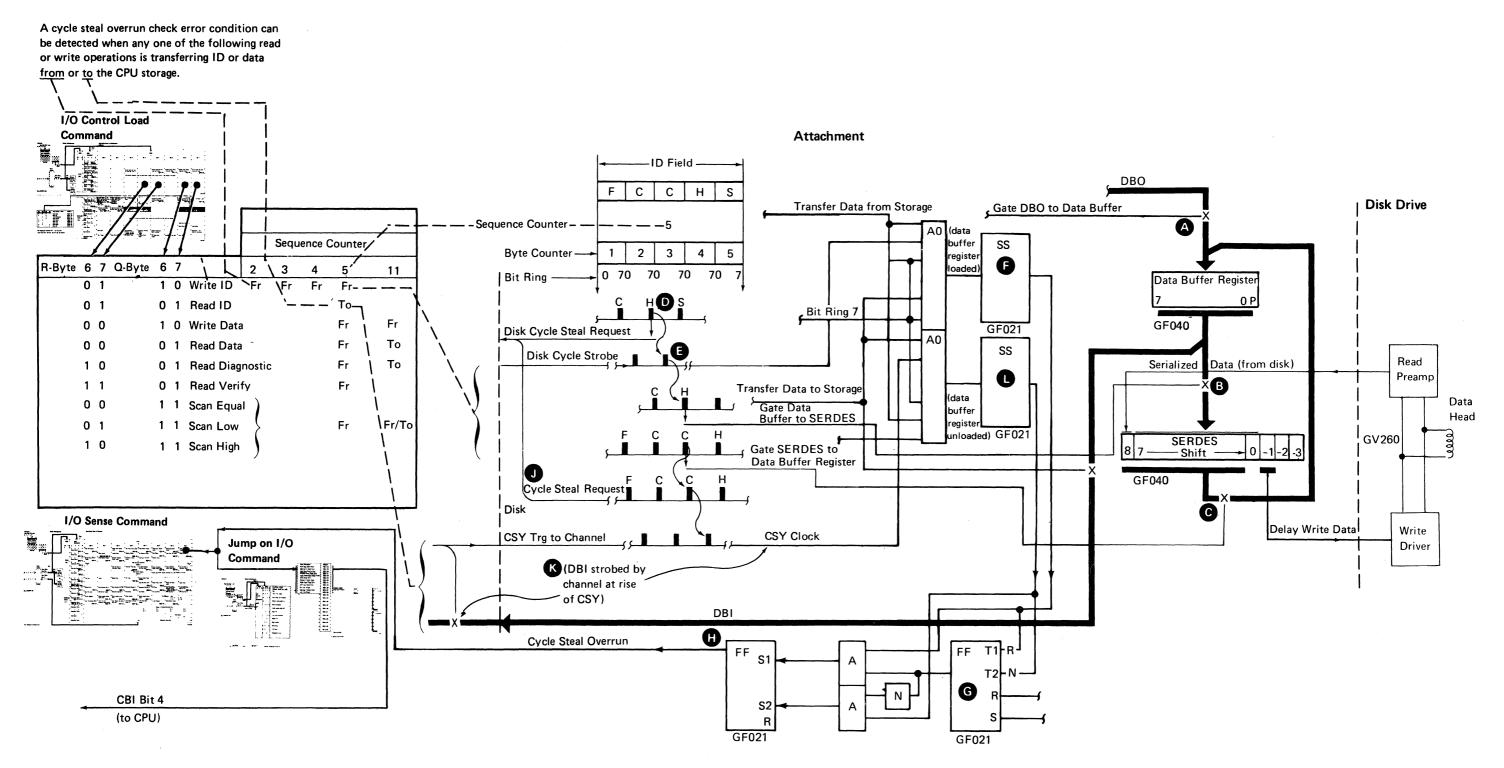

| Cycle Steal Overrun Check                 |     |              |

| Overrun Circuit Description               |     |              |

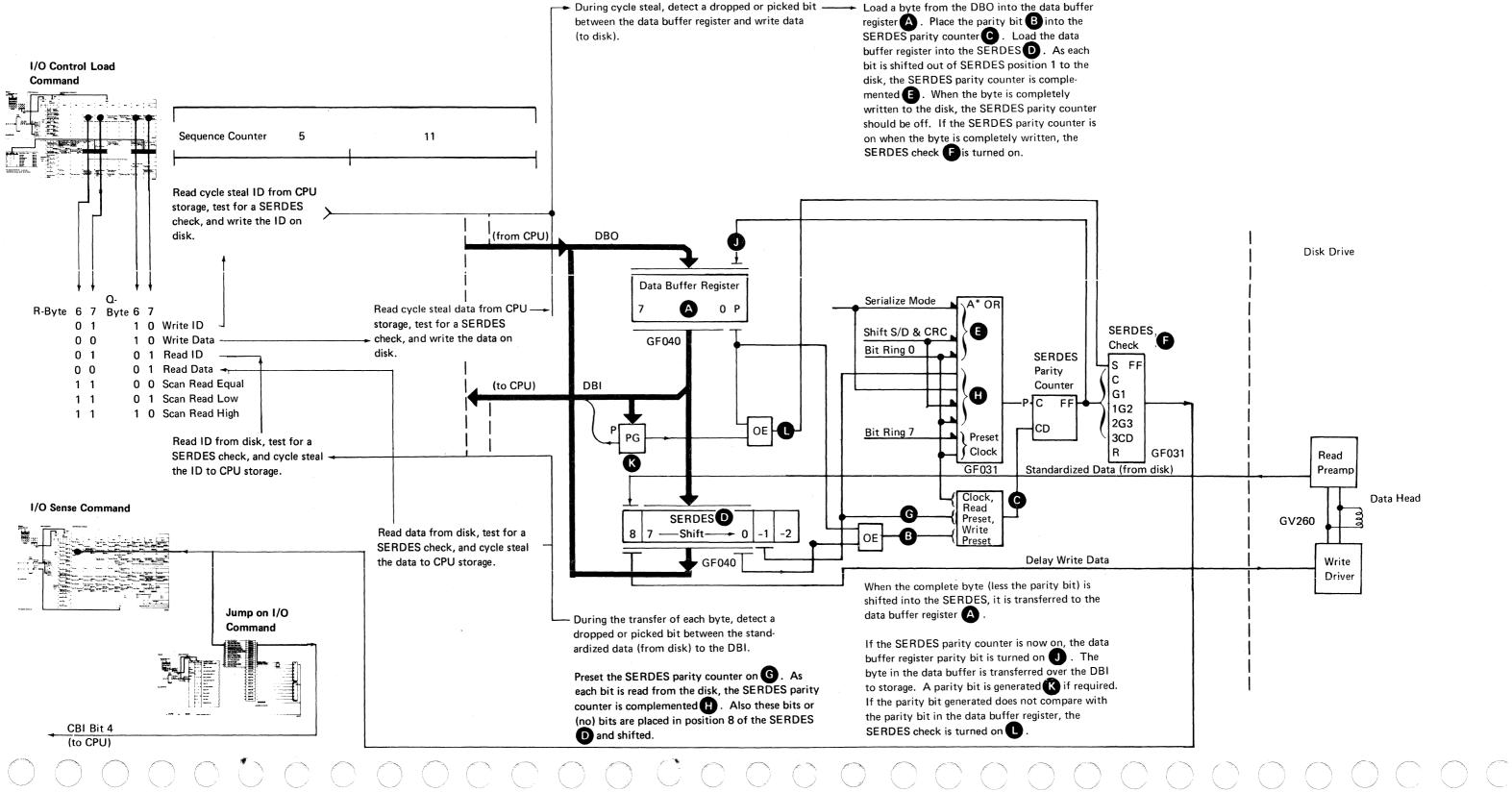

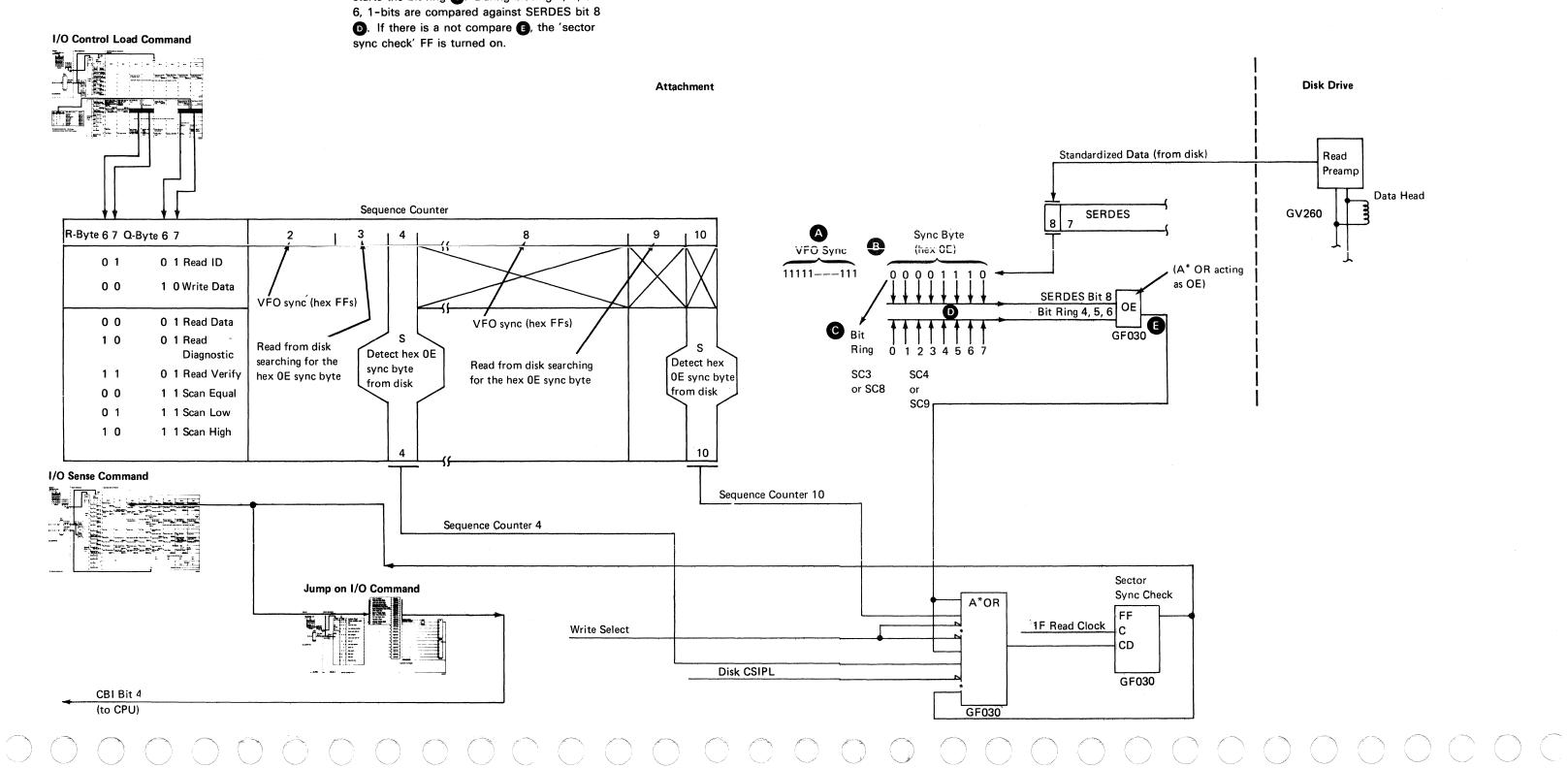

| SERDES Check                              | •   | 7-60         |

| Cyclic Redundancy Check                   | •   | 7-61         |

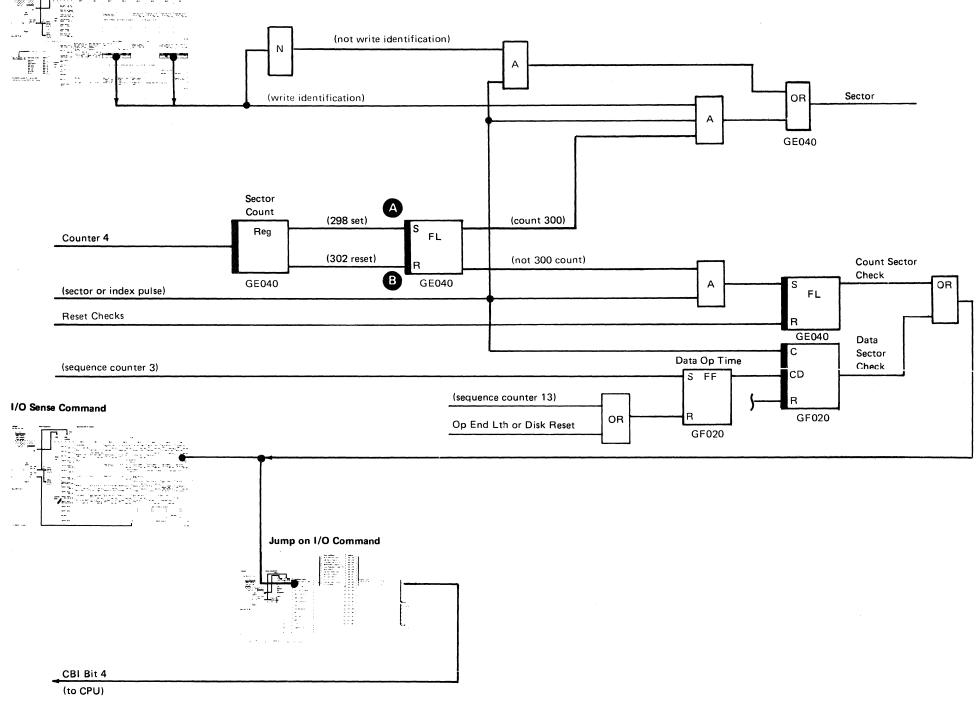

| Sector Check                              | •   | 7-62         |

| Sector Check Circuit Description          |     | 7-62         |

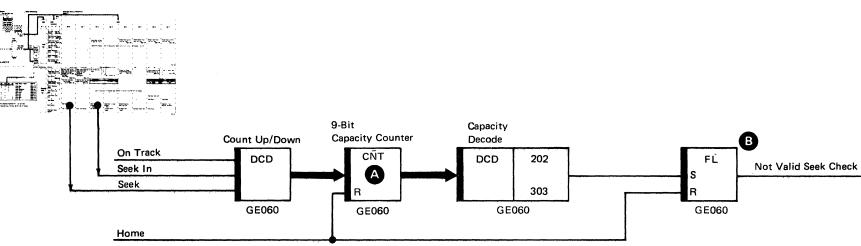

| Not Valid Seek Address                    |     | 7-63         |

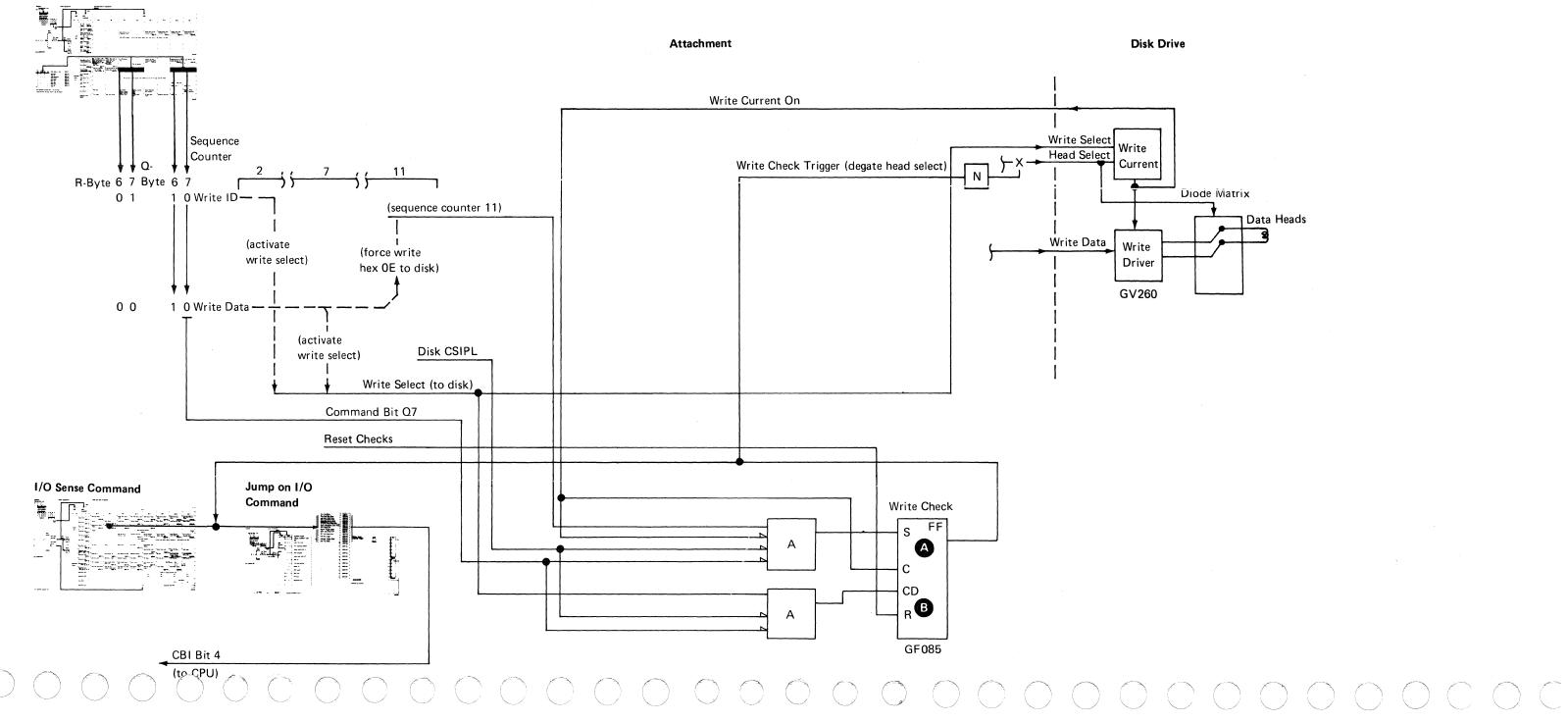

| Write Check                               |     | 7-64         |

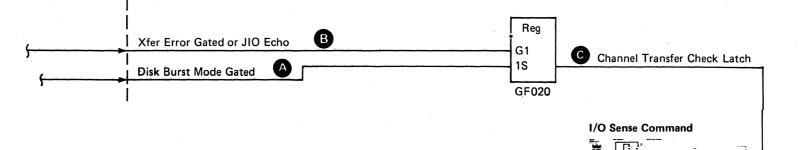

| Channel Transfer Check                    |     | 7-65         |

| Sector Sync Check                         |     | 7-66         |

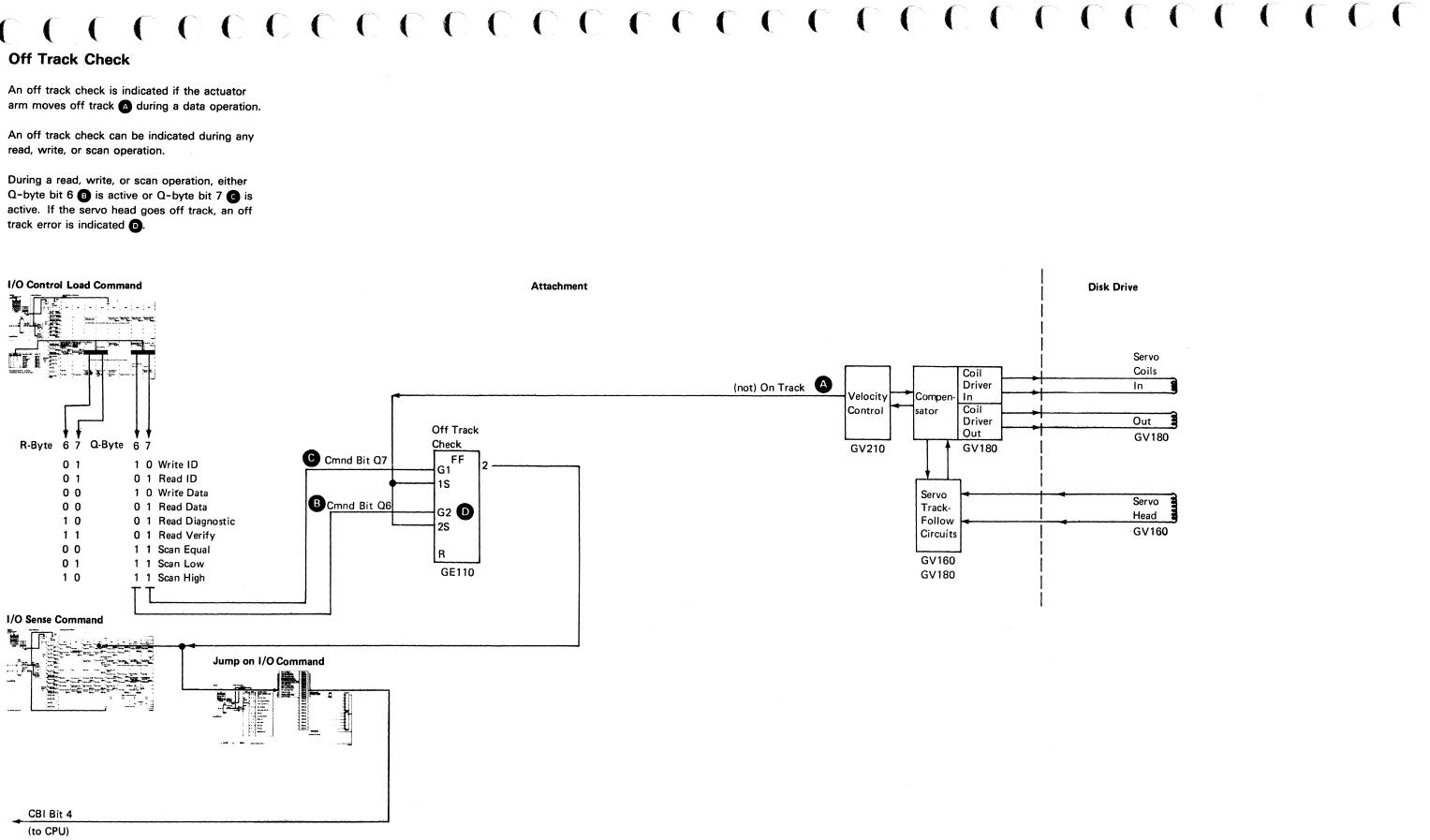

| Off Track Check                           |     | 7-67         |

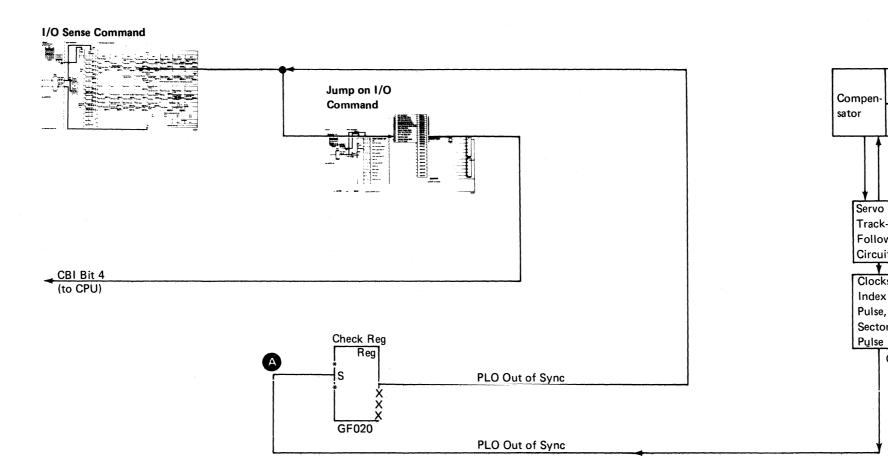

| PLO Out of Sync                           |     | 7-68         |

|                                           |     | 7-69         |

|                                           |     | 7-70         |

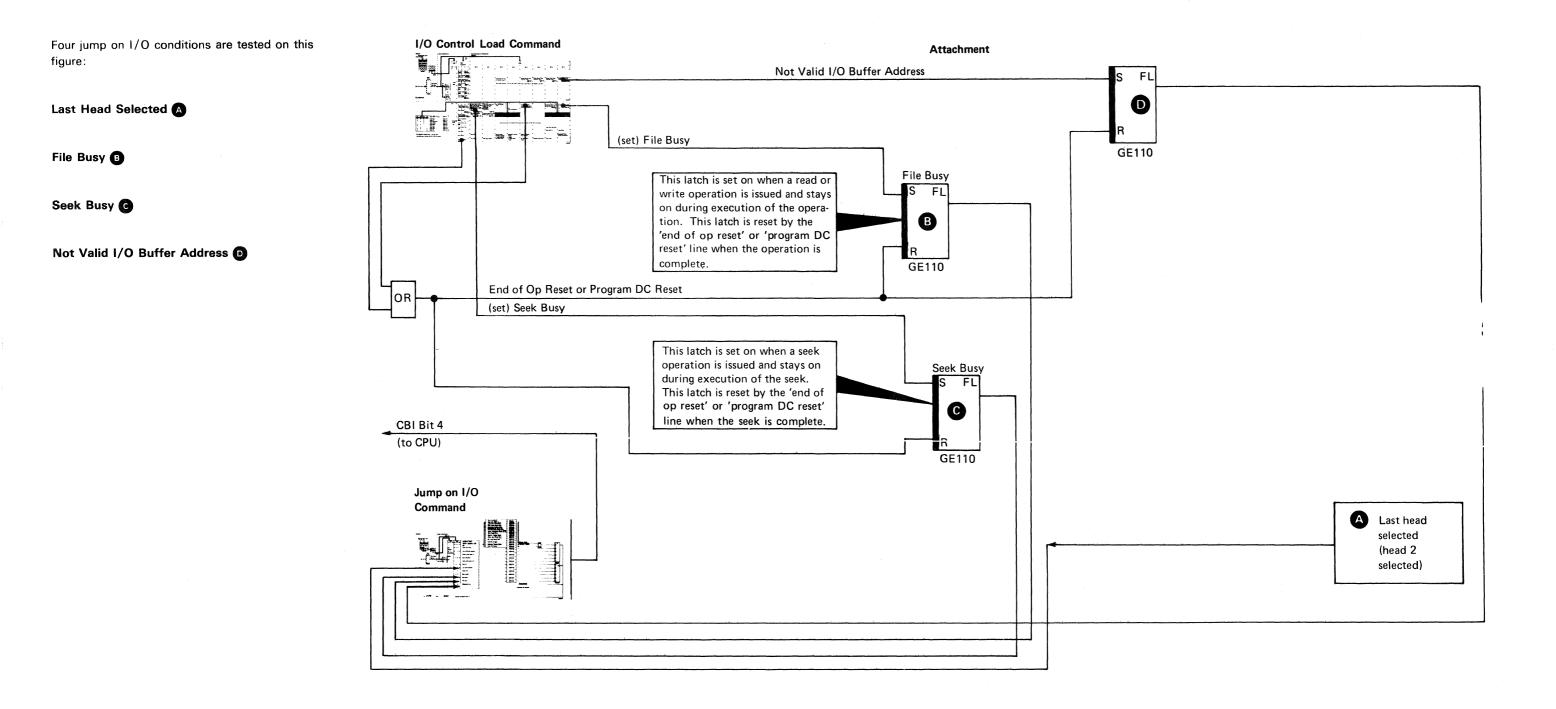

| JUMP ON I/O CONDITIONS                    |     | 7-71         |

| Sector Hit                                |     |              |

| Scan Hit                                  |     |              |

| INPUT/OUTPUT AND SENSE LINES              |     |              |

| Output Bus Lines                          |     |              |

| Input Bus Lines                           |     |              |

| Sense Lines Used with MAPs                |     |              |

|                                           | • • |              |

Contents for 62EH Disk Drive and Attachment

This page intentionally left blank.

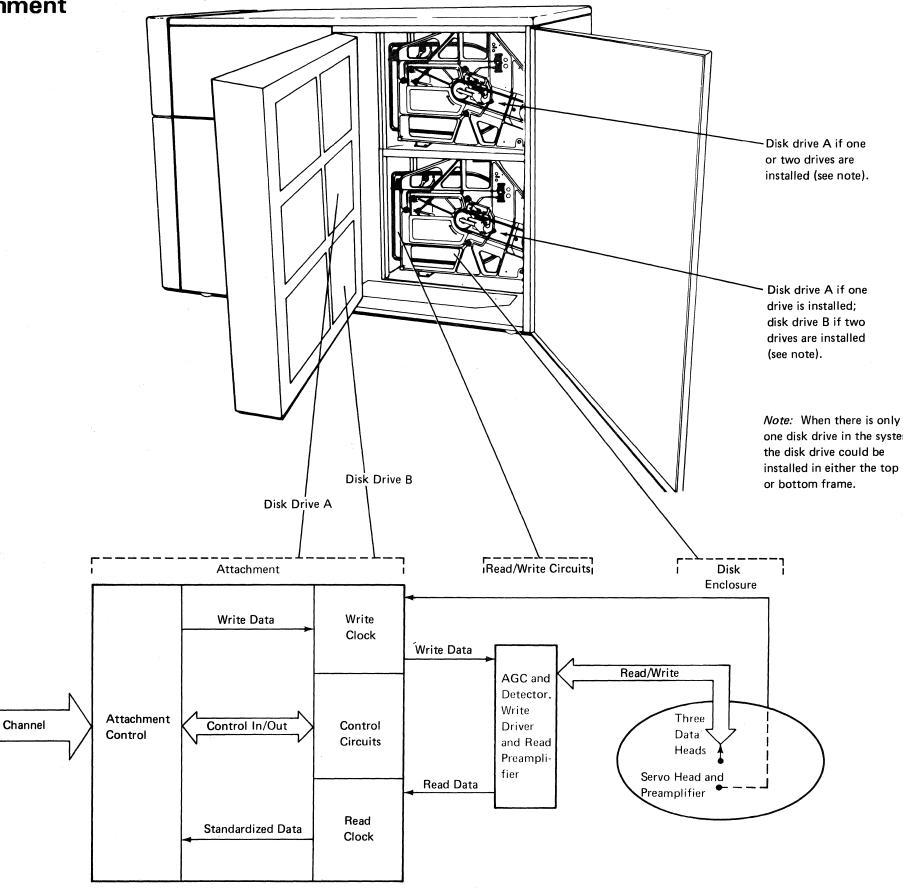

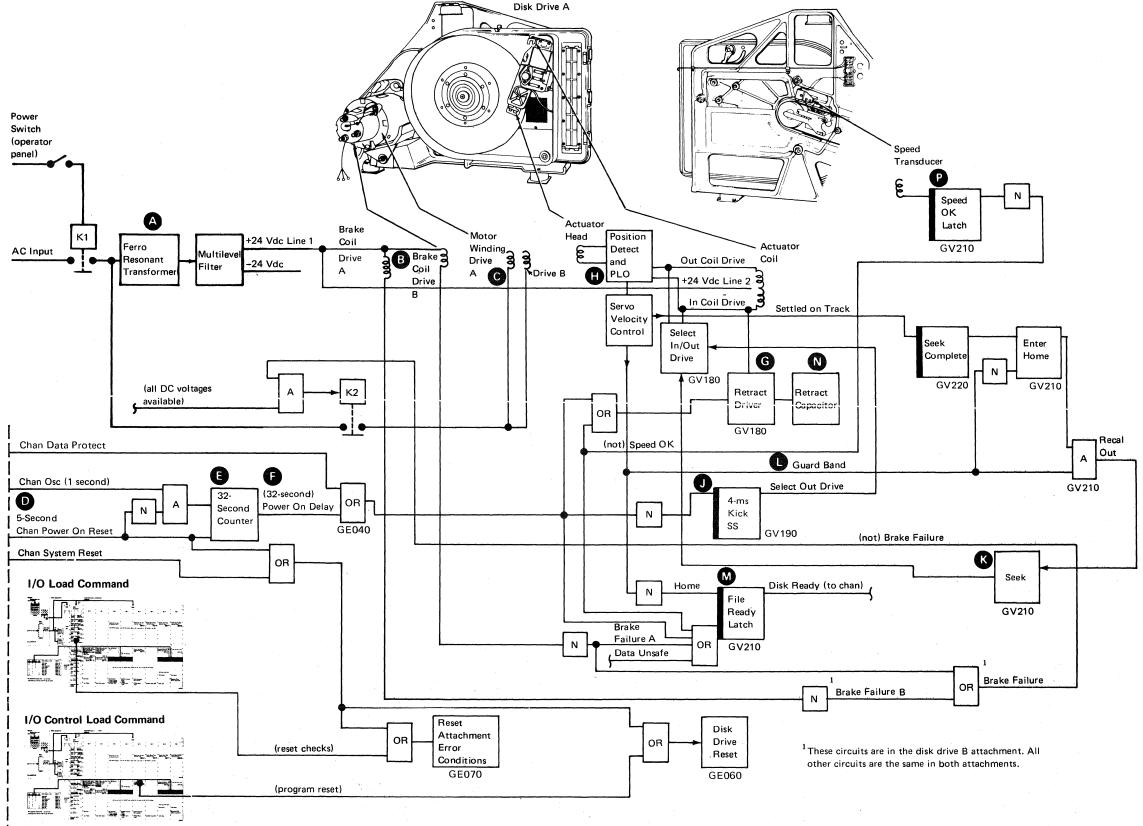

# **62EH Disk Drive and Attachment**

# INTRODUCTION

The circuits for a disk drive are located in three separate areas: on the disk enclosure, inside the disk enclosure, and on the input/output boards.

The attachment circuits on the A-A2 input/output board are for disk drive A, and the attachment circuits on the A-A3 input/output board are for disk drive B. The circuits on both input/output boards are the same. The disk drive A circuits are always located on A-A2 but, depending on your system, disk drive A could be installed in either the top or bottom frame.

# 62EH Disk Drive

The 62EH disk drive has one permanently installed magnetic disk. Data is written to and read from the disk by three data heads attached to an actuator. The disk drive has either 8.6 or 13.2 megabytes of customer storage. A second disk drive can be installed, which would increase total customer storage to 27.1 megabytes.

one disk drive in the system, installed in either the top

62EH Disk Drive and Attachment 7-1

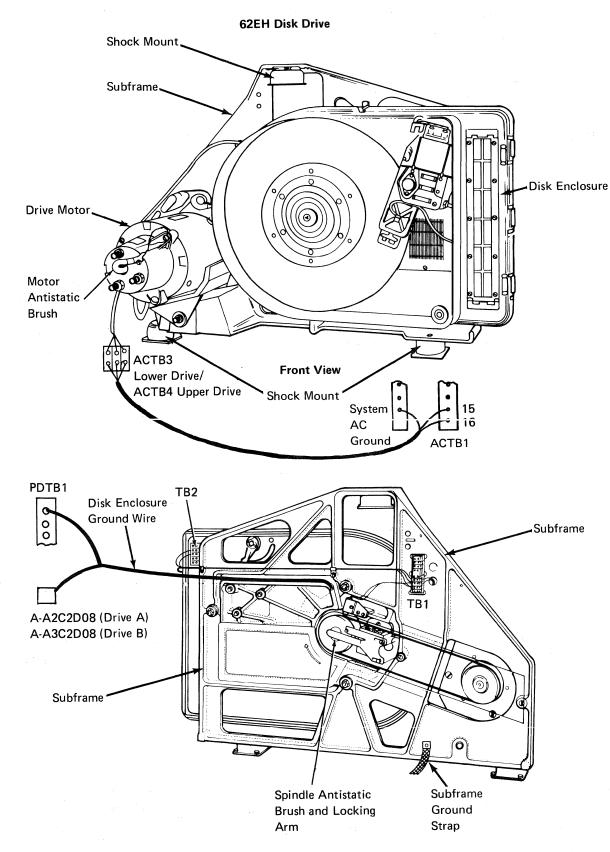

# Subframe

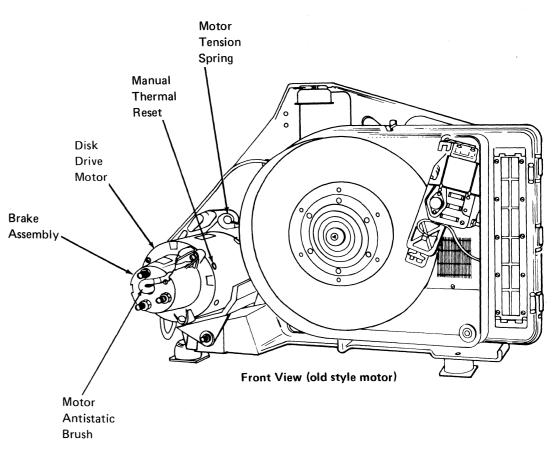

The subframe is installed vertically using three shock mounts. The shock mounts isolate the disk drive from the machine frame. The disk enclosure and the disk drive motor are installed on the subframe.

# Grounding

The subframe is grounded by a ground strap connected to the machine frame. The drive motor is grounded by the system AC ground. The disk enclosure is grounded to the system DC ground. The spindle is grounded to the subframe by the spindle antistatic brush, which is part of the spindle locking arm. The motor armature is grounded by the motor antistatic brush, which is installed on the brake housing.

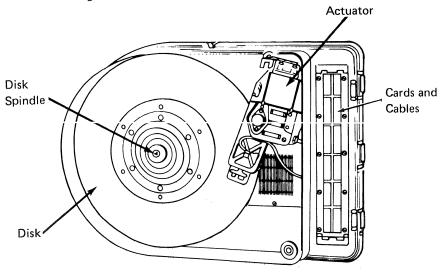

### **Disk Enclosure**

The disk enclosure contains the disk, the disk spindle, and the actuator. These parts are visible through the clear plastic cover, but they are not accessible to the customer or the customer engineer.

Note: The disk enclosure is sealed at the factory and should not be opened in the field.

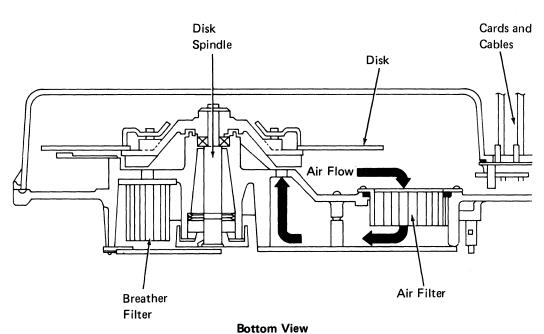

The disk enclosure has a closed-loop, air-moving system that uses blades on the spindle hub to continuously move air through the air filter. The filter lets the air pressure remain equal as the disk is getting up to speed and as the temperature inside the disk enclosure changes.

**Front View**

**Back View**

# Disk Spindle

The disk spindle assembly is installed in a housing in the back of the disk enclosure. The housing is sealed to prevent dirt from getting inside the disk enclosure through the bearings.

The disk is fastened to a hub on the disk spindle. A pulley is installed on the other end of the spindle and is driven by a drive motor installed on the subframe.

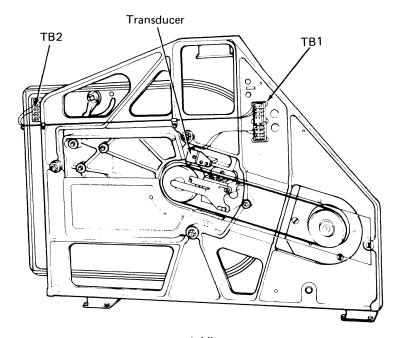

# Transducer

The transducer, which is installed on the disk enclosure, indicates the disk speed by sensing a slot in the spindle pulley.

Back View

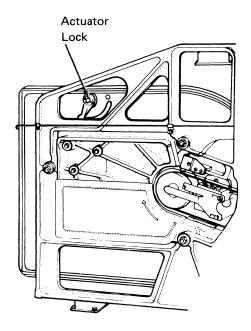

# Actuator Lock

The actuator lock in the On position locks the actuator in the landing zone position. The lock prevents the actuator from moving during shipment, installation, or removal of the disk enclosure.

(

**Back View**

### Actuator

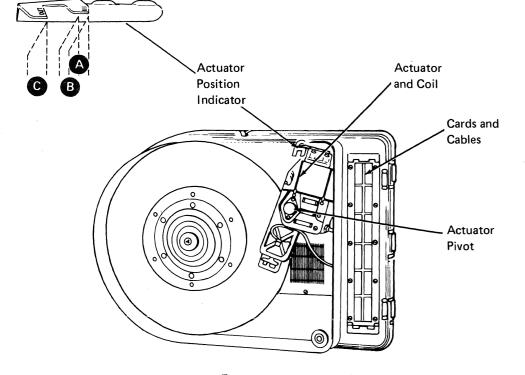

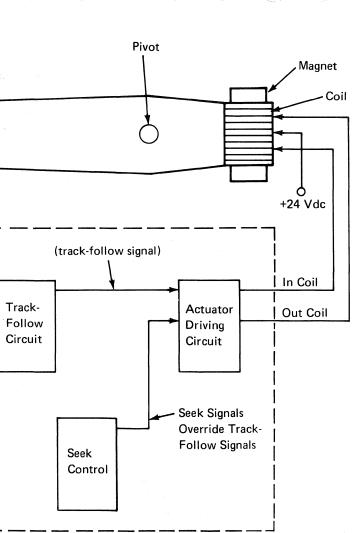

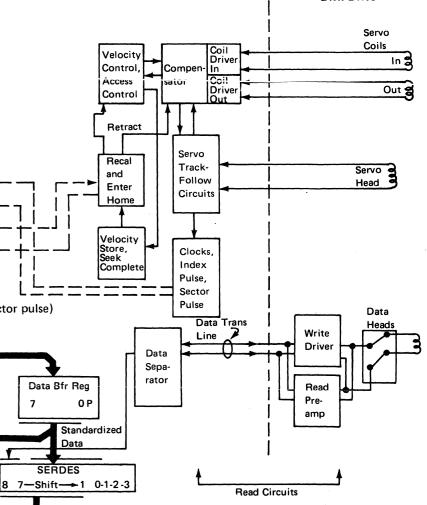

The actuator is inside the disk enclosure on a pivot beside the disk and carries the servo head and the data heads. The servo head and the data heads are attached to one end of the actuator, and a coil is on the other end. The coil, which is located in the field of a permanent magnet, moves when current passes through it. This causes the servo head and the data heads to move across the disk surface.

As the actuator moves across the disk surface, track-follow information is read from the servo tracks by the servo head to position the data heads over a desired data track. The servo head preamplifier is installed on the actuator close to the servo head. During any power-off condition, the actuator is retracted against the inner (spindle) stop and the magnetic catch holds the actuator in the retracted position.

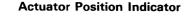

When the edge of the actuator coil is in line with the ln edge of the indicator  $\triangle$ , the actuator is at the inner stop and behind home.

When the edge of the actuator coil is in line with the center of the ln tab (B), the actuator is at home (cylinder 0).

When the edge of the actuator coil is in line with the Out edge of the indicator **C**, the actuator is at the outer stop.

The circuits for a disk drive are installed in three separate locations. The cards and cables for the servo head output preamplifier, the write driver, and the read preamplifier are installed on the disk enclosure. The servo head preamplifier is installed on the actuator inside the disk enclosure. The remainder of the circuits are installed on either the A-A2 input/output board or the A-A3 input/output board.

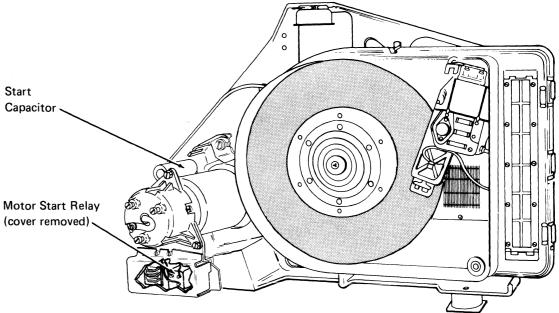

# Motor and Brake

To limit the time that the servo head and the data heads touch the disk as it turns, the drive motor quickly starts the disk and the motor brake quickly stops the disk.

The brake is de-activated when 24 Vdc is present on the brake coil. The brake is activated by a spring when the machine power is off. There are two motor styles; the new style motor has a start capacitor on the top, a motor start relay on the bottom, and is smaller than the old style motor.

The motor has a manual thermal reset switch. A motor tension spring puts tension on the disk drive motor, which keeps tension on the drive belt. The motor antistatic brush is located on the brake assembly.

Front View (new style motor)

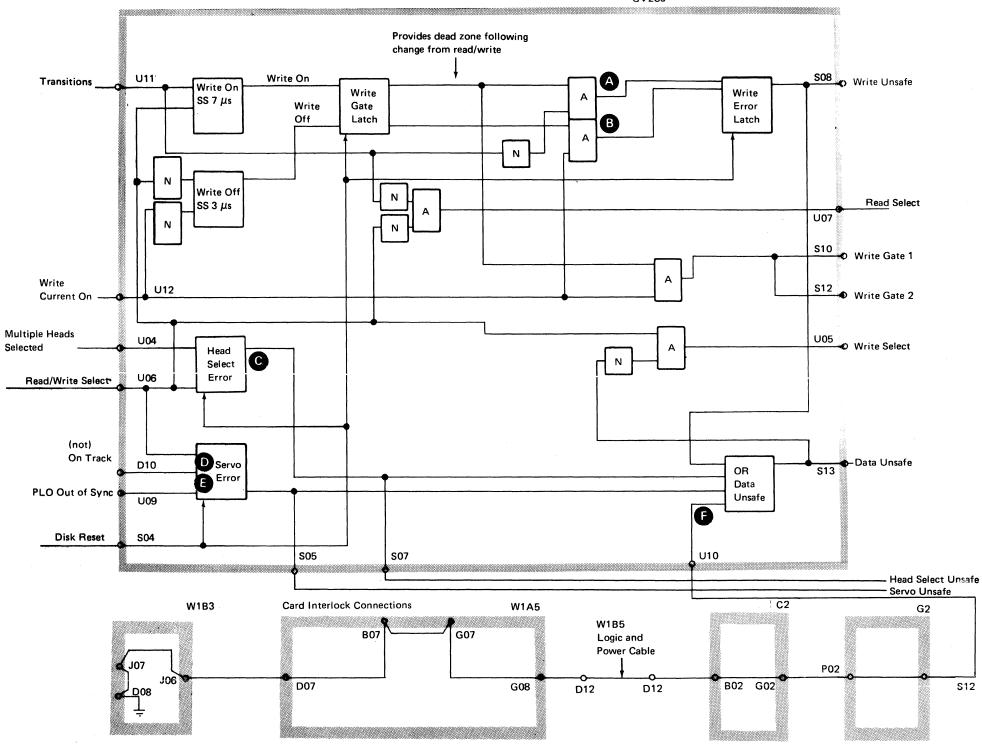

# Write Safety

# **Data Unsafe Conditions**

Circuits protect data from being destroyed during other than normal conditions. The data unsafe conditions that can occur are:

- Write selected and no write current.

- Write current source on but write not selected.

- Write selected and more than one head selected.

- Write selected and off track indicated.

- Write selected and disk not synchronized with attachment.

- · Disk speed not correct.

- Card interlock circuit open, which indicates a loose or missing circuit card or cable.

When any of the data unsafe conditions occur, the 'write current' line is turned off and both the 'disk ready' and 'select head' lines are de-activated. The 'data unsafe' line signals the attachment of the condition. A reset line resets the 'data unsafe' line and a recalibrate-to-home operation sets the file 'ready' latch on.

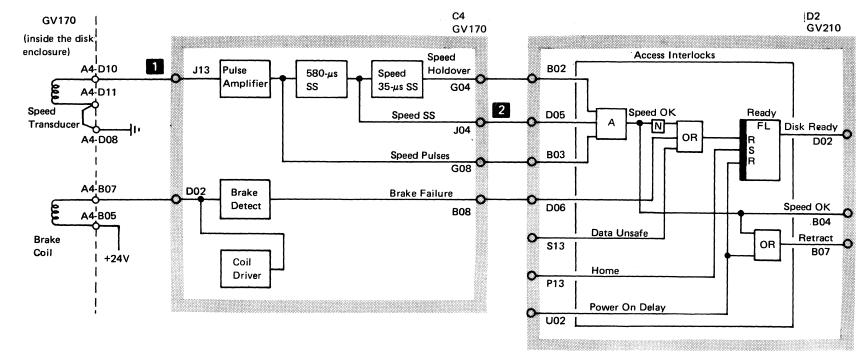

# File Ready

The disk drive becomes not ready for either of the following reasons:

- An electrical failure in the motor brake

- A data unsafe condition

# Disk Speed

If the disk speed falls below 1,100 revolutions per minute, the disk drive becomes not ready and the actuator retracts.

# Power On

During power on, the actuator is held against the inner stop until the disk is up to speed. This ensures that:

- The disk and control circuits can synchronize.

- The servo head and the data heads are off the disk before they move out of the landing zone.

After a 32-second time-out, the actuator seeks to home (cylinder 0) and ready is indicated in the attachment.

# **Disk Format**

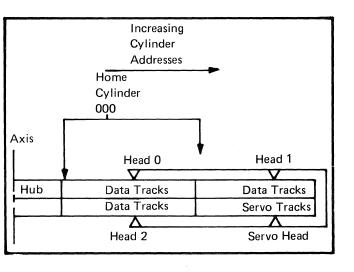

# Data Tracks

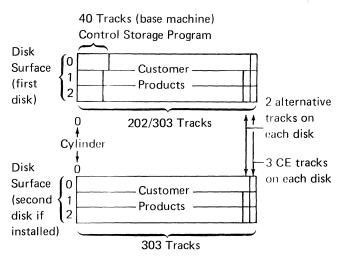

The disk has cylinders, tracks, and sectors. A cylinder is the area that passes under the three data heads in one revolution, and a track is the area that passes under a single data head in one revolution. Each track is divided into 60 sectors. The data stored in one sector is a record. Each record contains 256 bytes. Therefore, there are 15,360 bytes per track and 46,080 bytes per cylinder. Information about the 62EH disk surface is shown in the following charts:

| Number of disk drives installed | 1 2           |  |  |  |  |

|---------------------------------|---------------|--|--|--|--|

| Disk capacity in megabytes      | 8.6 13.2 27.1 |  |  |  |  |

| Number of tracks                | 606 909 181   |  |  |  |  |

| Number of cylinders             | 202 303 606   |  |  |  |  |

| Data heads                      | 3 6           |  |  |  |  |

| Bytes per sector (record)       | 256           |  |  |  |  |

| Sectors (records) per track     | 60            |  |  |  |  |

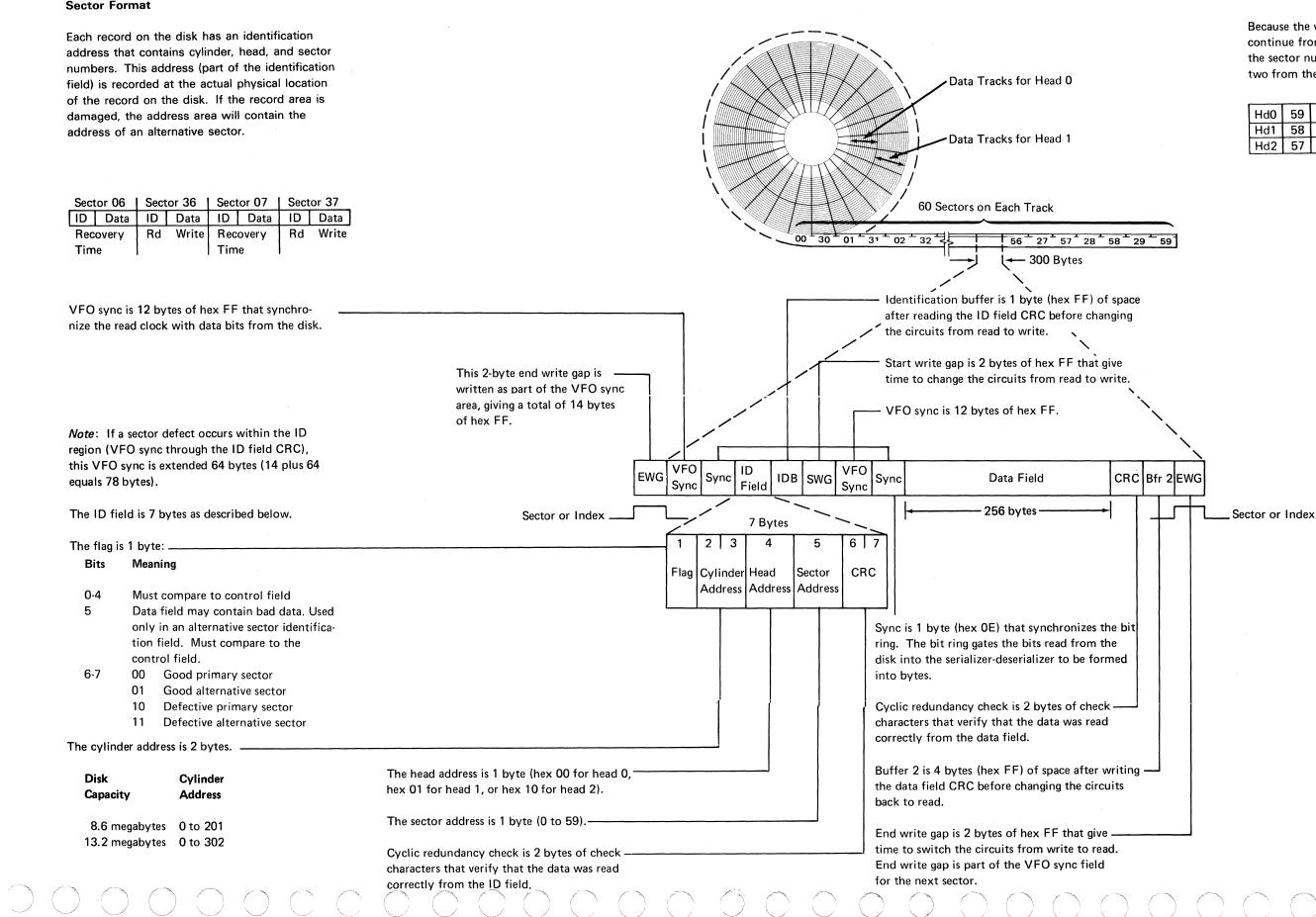

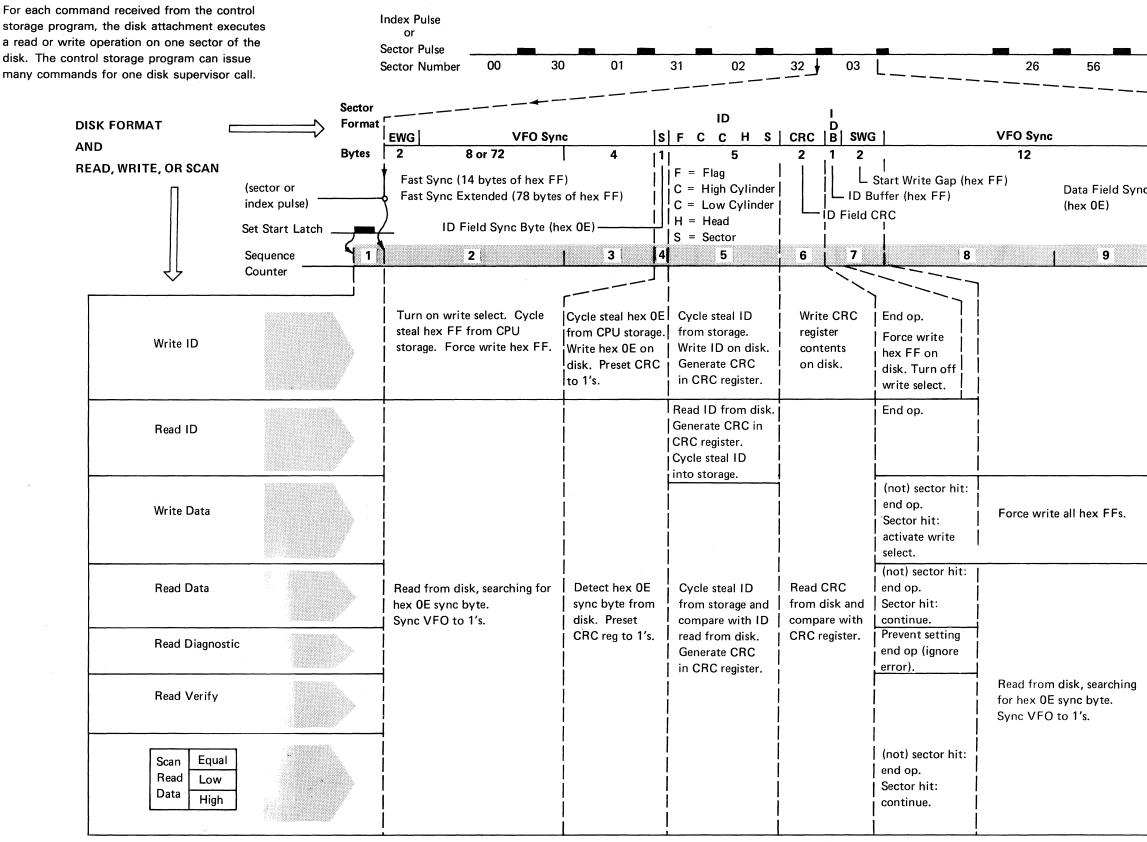

# **Sector Format**

Each record on the disk has an identification address that contains cylinder, head, and sector numbers. This address (part of the identification field) is recorded at the actual physical location of the record on the disk. If the record area is damaged, the address area will contain the address of an alternative sector.

| Sect | or 06 | Sector 36 |       | Sect     | or 07 |    |       |  |

|------|-------|-----------|-------|----------|-------|----|-------|--|

| ID   | Data  | ID        | Data  | ID       | Data  | ID | Data  |  |

| Rec  | overy | Rd        | Write | Recovery |       | Rd | Write |  |

| Tim  | е     |           |       | Tim      | e     |    |       |  |

VFO sync is 12 bytes of hex FF that synchro-

nize the read clock with data bits from the disk.

Note: If a sector defect occurs within the ID region (VFO sync through the ID field CRC), this VFO sync is extended 64 bytes (14 plus 64 equals 78 bytes).

The ID field is 7 bytes as described below.

#### The flag is 1 byte: \_ Bits Meaning

- 0-4 Must compare to control field 5 Data field may contain bad data. Used

- only in an alternative sector identification field. Must compare to the control field. 6-7

- 00 Good primary sector

- Good alternative sector 01

- 10 Defective primary sector

- 11 Defective alternative sector

The cylinder address is 2 bytes.

Disk Cvlinder Capacity Address

8.6 megabytes 0 to 201 13.2 megabytes 0 to 302

Because the write operation may continue from one head to another, the sector numbers are moved by two from the preceding head.

| Hd0 | 59 | Index | 0  | 30 | 01 | 31 | 02 | 32 |

|-----|----|-------|----|----|----|----|----|----|

| Hd1 | 58 | Index | 29 | 59 | 0  | 30 | 01 | 31 |

| Hd2 | 57 | Index | 28 | 58 | 29 | 59 | 0  | 30 |

### Disk Addressing

# Sequential Sector Addressing

The type of addressing used by the main storage program to identify disk data areas is sequential sector addressing. The sequential sector number is a binary number, starting at hexadecimal 000001 (cylinder 0, head 0, sector 0), and is increased by 1 for each sector processed. Sequential sector addressing extends through the last data sector on the first disk and onto the second disk if two disks are installed. (See the *Data Areas Handbook* for more information on disk addressing.)

# Actual Sector Addressing

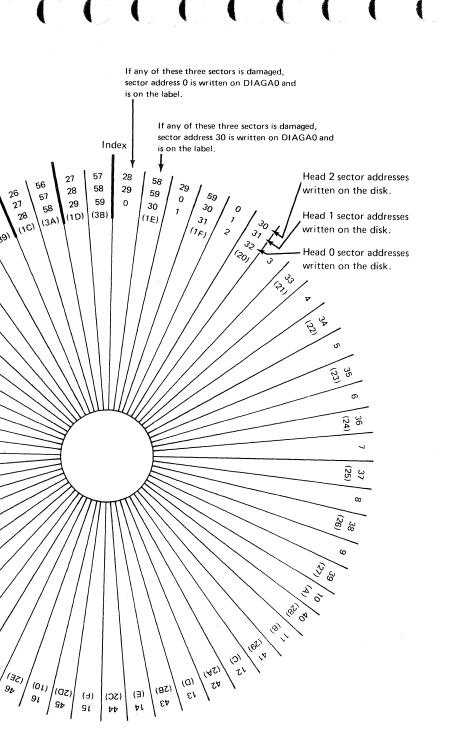

This figure shows how the 62EH disk sectors are assigned. Although there are three separate read and write surfaces, this figure shows the three surfaces as they are to each other in sector address numbering from the index.

Each sector is 300 bytes long. The main fields of a sector are the identification field and the data field.

The time needed to change from a write operation to a read operation is too long to permit writing consecutive sectors because the read amplifiers need time to become operational. A data operation must be started before sensing the index pulse or sector pulse of the sector on which the operation is to be performed. The index pulse or sector pulse starts the operation. Because one data operation cannot be ended and the next one started before the next sector pulse, the sector addresses are alternated on the surface of the disk; that is, between sector 0 and sector 1 is sector 30 (hex 1E). Between sector 1 and sector 2 is sector 31 (hex 1F). This numbering sequence is continued around the surface until sector 59 (hex 3B).

With this numbering sequence, there is time to start a data operation on alternate physical sectors, so that every sector address on the surface can be read (or written) consecutively, in two revolutions of the disk, with the exception that the index pulse or a sector pulse must be skipped between the operation on sector 29 (hex 1D) and the operation on sector 30 (hex 1E). This occurs because sector 59 (hex 3B) and sector 0 are next to each other, and are also between sector 29 (hex 1D) and sector 30 (hex 1E).

Looking from the index in a clockwise direction, you can see that heads 1 and 2 are offset. On the surface for head 1, the sector addresses are offset two physical sectors from the sectors for head 0. On head 2, the sector addresses are offset by four physical sector addresses from the head 0 sector addresses. This means that the sector addresses for head 1 are as follows. starting at the index: sector 29 (hex 1D), sector 59 (hex 3B), sector 0 (hex 00), . . . . sector 57 (hex 39), sector 28 (hex 1C), sector 58 (hex 3A), The sector addresses on head 2 are as follows, starting at the index: sector 28 (hex 1C), sector 58 (hex 3A), sector 29 (hex 1D), . . . . sector 56 (hex 38), sector 27 (hex 1B), sector 57 (hex 39).

The disk file used in System/34 is the same type of disk file that is used in System/32. As the disk drives are assembled, they are initialized for use as System/32 files. That is, sector addresses on all heads are in the same position on the surface relative to the index (the same as head 0 sectors on System/34).

After the disk drives are assembled, they are tested for damaged sectors. The damaged sectors have flag bits set on in the identification field on the disk and are recorded on labels that are attached to the disk drive cover. Because the disk is initialized for use on System/32, it must be initialized again by the System/34 initialization program. All sectors flagged as damaged must be assigned to alternative sectors, or be flagged as damaged alternative sectors so they will not be used for data.

The damaged sector identification fields and the disk drive sequence numbers are recorded on the DIAGAO diskette for use by the program on later initializations. The same damaged sector identification fields appear on the label on the disk drive cover.

During the initialization process, a list of the sector identification fields on the alternative sector tracks is given to the operator. The sector identification fields of the damaged sectors replace the sector identification fields found in sectors on the alternative sector tracks. Any sector identification field recorded on the label on the disk drive cover is shown in this list. However, the damaged sectors for heads 1 and 2 have a different sector address than the one shown on the label(s) and written on the DIAGA0 diskette. Damaged sectors for tracks using head 1, other than sector 0 and sector 30 (hex 1E), are lowered by a count of 1. Sector 0 becomes sector 29 (hex 1E) and sector 30 (hex 1E) becomes sector 59 (hex 3B). Damaged sectors from tracks using head 2, other than sectors 0, 1, 30 (hex 1E), and 31 (hex 1F), are lowered by a count of 2. In this case, sector 0 becomes sector 28 (hex 1C), sector 1 becomes sector 29 (hex 1D), sector 30 (hex 1E) becomes sector 58 (hex 3A), and sector 31 (hex 1F) becomes sector 59 (hex 3B).

53 (35)

23

52 (34)

22 16)

51 (33)

21 (15)

৾৻৻

(1)

# Servo Tracks

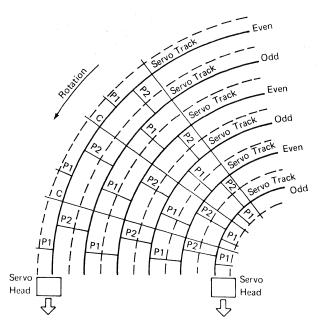

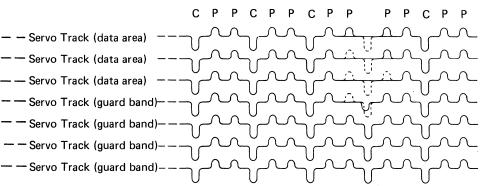

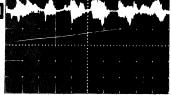

The servo tracks are electrical patterns that are written on the disk at the factory. The servo tracks include clock pulses, missing clock pulses, and position pulses in a specific sequence. The 2.2-microsecond clock pulses generate the 140-nanosecond write clock pulses in the attachment. The position pulses are used by the servo head to keep the data heads over a specified track.

Specific combinations of clock pulses and missing clock pulses generate either the index pulses, the sector pulses, or the sector midpoint pulses. The sector midpoint pulses are used during seek operations to indicate that the actuator is not in the guard band area.

# Landing Zone

The servo head and the data heads are retracted to the landing zone when the disk speed is less than 1,100 revolutions per minute. This prevents the heads from destroying data. The landing zone is indicated by missing sector pulses, index pulses, or sector midpoint pulses, and is about 40 tracks wide.

## Guard Band

The guard band is a servo track area that contains clock pulses and position pulses but does not contain sector pulses, index pulses, or sector midpoint pulses. When the servo head is in the guard band position, the data heads are behind home.

| <b>.</b>     |      |             |      |     |       | Data Head   | i 0   | Data Head 1   |

|--------------|------|-------------|------|-----|-------|-------------|-------|---------------|

| Behind Home  | -    |             |      |     |       | V           |       | V             |

| Data Tracks  | BHLZ | Data Tracks | BHLZ | Hub | LZ BH | Data Tracks | LZ BH | Data Tracks 🕔 |

| Servo Tracks | GBLZ | Data Tracks | BHLZ |     | LZ BH | Data Tracks | LZ GB | Servo Tracks  |

| Guard Band - |      |             |      |     |       | $\Delta$    |       |               |

| Landing Zone |      |             |      | 1   |       | Data Head   | 12    | Servo Head    |

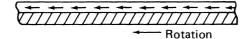

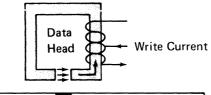

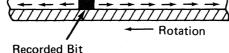

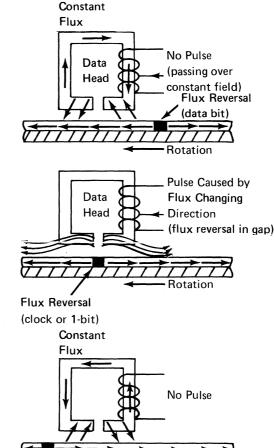

# **Data Recording**

# Read and Write Data

During a write operation, data is recorded by reversing the direction of the current in the coil, which reverses the direction of the magnetic flux in the data head gap. When the flux in the data head gap reverses, there is a magnetic change of direction on the disk surface. Each change of direction on the disk represents a recorded 0-bit or 1-bit.

During a read operation, when the recorded disk surface is in one magnetic direction (no data bit), constant flux flows through the data head and no output pulse is generated. When a data bit, recorded on the disk surface, passes the data head, the magnetic change from the data bit causes a flux change in the data head and an output pulse is generated.

Only data bits are written on the disk drive data tracks. For write operations, the attachment uses clock pulses read from the servo tracks to generate the write clock. On read operations, the read clock is generated from the variable frequency oscillator sync fields and from the data being read.

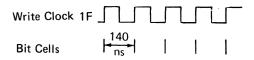

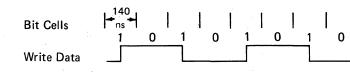

The time during which a data bit may be written is known as a bit cell. A bit cell is 140 nanoseconds long and is generated by the 'write clock 1F' line.

Writing 1-Bits

One-bits are always written in the center of a bit cell.

| Bit Cells  | 1 |   |   |   |   |  |

|------------|---|---|---|---|---|--|

|            |   | 1 | 1 | 1 | 1 |  |

| Write Data |   |   |   |   |   |  |

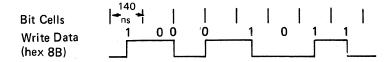

# Writing 0-Bits

With one exception, 0-bits are always written at the start of a bit cell.

The exception is when a 0-bit immediately follows a 1-bit. In this case, no bit is written and the 0-bit is represented by no magnetic change of direction during its bit cell time.

By writing hex 8B, both methods of writing 0-bits and the method of writing 1-bits can be shown.

The data written is transmitted on the data transmission line to the write circuits installed on the disk drive. For each change on the data transmission line, a 0-bit or a 1-bit is written on disk. These changes cause the current in the data head to be switched, which results in a polarity change on the disk track.

# Reading Data Bits

When data is read from the disk drive, the read clock is generated by the variable frequency oscillator. This oscillator is synchronized to the read data by the variable frequency oscillator sync field as it is read from the disk. The phase lock loop then keeps the oscillator in sync with the read data (1's and 0's) so it can be decoded.

1F Read Clock 2F Read Clock 140 ns Bit Cells Read Data (hex 8B)

# **Actuator Movement**

Seek

During the first part of a long seek operation, the seek controls cause the actuator to leave track-follow mode and increase the actuator speed until it reaches a maximum speed. During the last part of a long seek operation, the seek controls slow the actuator to a stop at the desired track. During short seeks, the actuator does not reach maximum speed. The actuator speed is increased for the first part of the seek and decreased for the last part of the seek. For more information, see Seek Operation later in this section.

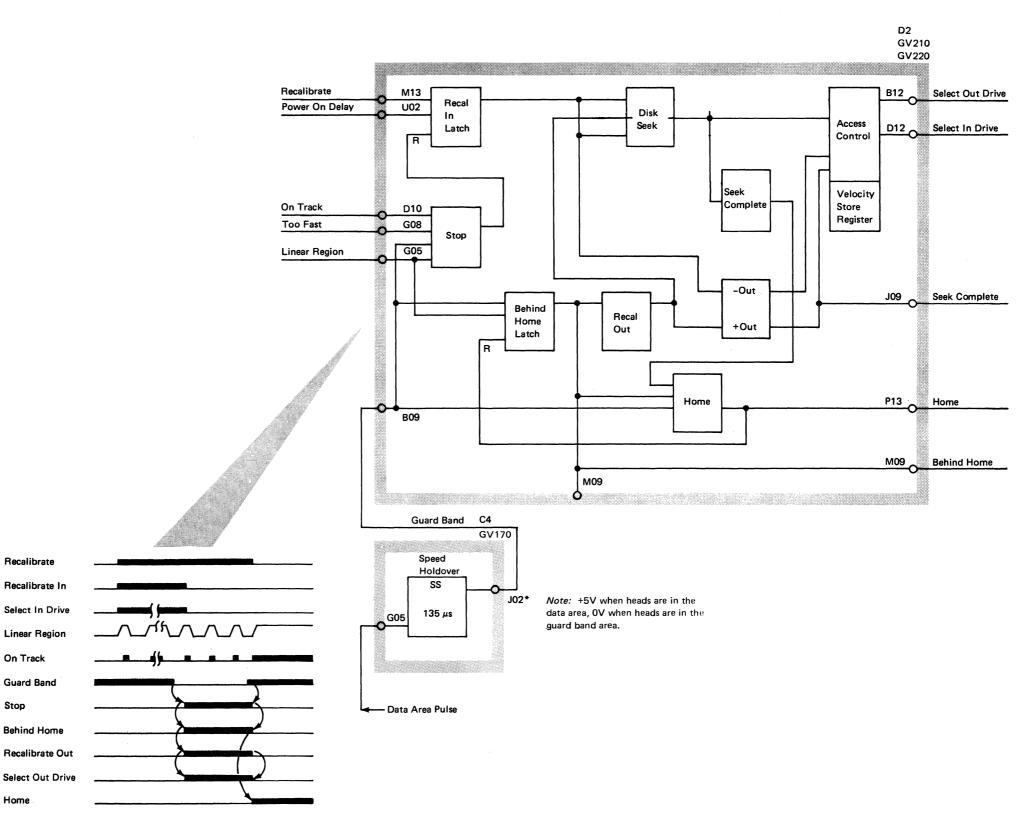

### Recalibrate

A recalibrate operation is executed by activating the actuator driving circuits. The actuator driving circuits move the heads across the tracks into the guard band area and then out to home (cylinder 0). The actuator moves at slow speed during the recalibrate operation.

A recalibrate operation is started during a normal power-on sequence and during error correction.

Actuator

Output

Preamp

Servo

Head

Circuits on A-A2 (I/O board) for disk drive A, on A-A3 for disk drive B.

# Servo Track Follow

# Servo Head Aligned Correctly

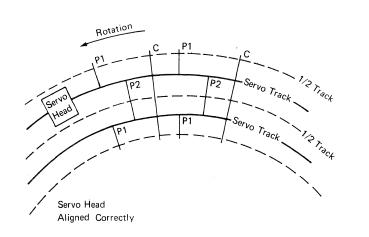

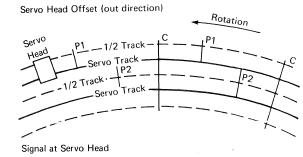

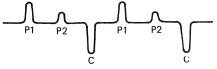

When the servo head is aligned correctly on the servo track, the servo head follows the area between position pulses P1 and P2. The C-patterns are common to all servo tracks and are used to generate the write clock pulses, sector pulses, and index pulses. Position pulses ensure correct alignment of the servo head over the servo track. When there is a seek to an even track, P1 is the inside pulse and P2 is the outside pulse. For a seek to an odd track, P1 is the outside pulse and P2 is the inside pulse. Note that the C-patterns are valid during seeks and are used during seeks.

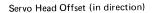

# Servo Head Offset

The servo control follows the tracks by ensuring that the position pulses are received at equal amplitudes. This positions the servo head between two servo tracks.

If the servo head moves off track, one position pulse is received at a low amplitude and the other position pulse is received at a high amplitude.

The servo control drives the servo head in the direction that increases the amplitude of the low amplitude position pulses (P1 and P2). The direction and degree of movement of the heads, to adjust for the error, is determined by the track being odd or even and the difference between the P1 and P2 pulses.

C = Clock Pulse P1 = Position Pulse 1

P2 = Position Pulse 2

Signal at Servo Head When Aligned Correctly

$$\bigvee_{C} \stackrel{1}{\xrightarrow{P_1}} \stackrel{1}{\xrightarrow{P_2}} \stackrel{1}{\xrightarrow{P_1}} \stackrel{1}{\xrightarrow{P_2}} \stackrel{1}{\xrightarrow{P_1}} \stackrel{1}{\xrightarrow{P_2}} \stackrel{1}{\xrightarrow{P_1}} \stackrel{1}{\xrightarrow{P_2}} \stackrel{1}{\xrightarrow{P_2}} \stackrel{1}{\xrightarrow{P_1}} \stackrel{1}{\xrightarrow{P_2}} \stackrel{1}{\xrightarrow{P_2}} \stackrel{1}{\xrightarrow{P_1}} \stackrel{1}{\xrightarrow{P_2}} \stackrel{1}{\xrightarrow{P_1}} \stackrel{1}{\xrightarrow{P_2}} \stackrel{1}{\xrightarrow{P_1}} \stackrel{1}{\xrightarrow{P_2}} \stackrel{1}{\xrightarrow{P_2}} \stackrel{1}{\xrightarrow{P_1}} \stackrel{1}{\xrightarrow{P_2}} \stackrel{1}{\xrightarrow{P_2$$

Even track, servo head offset. Servo head signal.

$P1 \neq P2$  with an even track destination. If P2 > P1, the heads will move out. If P2 < P1, the heads will move in

Odd track, servo head offset. Servo head signal.

P1  $\neq$  P2 with an odd track destination. If P2 > P1, the heads will move in. If P2 < P1, the heads will move out.

<u>/</u>Hub

# Head Alignment and Disk Description

.

One side of the disk is a data surface only (data heads 0 and 1). The other side is the servo surface (for the servo head) and the data surface for data head 2.

**Missing Clock Pulse and Position Pulses**

Servo Head (on track) Data Head 0 Data Head 1 СР LZ BH Data Tracks Data Tracks LZ BH Data Head LZ BH Data Tracks LZ GB Servo Tracks (on track) Data Head 2 Servo Head LZ = Landing Zone BH = Behind Home GB = Guard Band Direction Servo Head Surface and Data Head 2 of Disk Motion Surface This side of the disk has a landing zone, a Data Track 0 guard band used as an aid for locating home Data Track 1 (cylinder 0), and a servo area for the servo Servo Track head. This side of the disk also has one landing zone, one behind home zone, and one data area for data head 2. Data Head 0 and Data Head 1 Surface Servo Tracks Servo Track 0 This side of the disk has two landing zones, two behind home zones, and two data areas Guard (one of each for each head). No data is written -Servo Track -20 Band in the landing zone or behind home. Landing -Servo Track -40 Zone Head 1 Data Tracks Landing Zone Head 0 Data Tracks Data Data Data Track Data Track Track Track \_anding Hub 13.2 Megaby tes ------ 302 0 302 0 Zone 8.6 Megabytes -----> 201 0 201 0

Patterns of missing clock pulses decode into index pulses, sector pulses, or sector midpoint pulses, which activate the data area pulse.

P = Position Pulse

C = Clock Pulse

### **Guard Band**

The guard band is a normal track area that has no index pulse, sector pulse, or sector midpoint pulse. The guard band is indicated at the servo track that has no missing clock pulses, which in turn indicates no data area pulses. Missing data area pulses let a 135-microsecond singleshot time-out, which indicates the guard band.

The guard band indicates that the data heads are behind home.

# **Behind Home**

Behind home is the condition when the data heads are behind cylinder 0.

If the data heads attempt to seek to a cylinder that is farther in than cylinder 0, the seek operation is ended. When the heads stop, the actuator seeks to home (cylinder 0).

# **OPERATIONS**

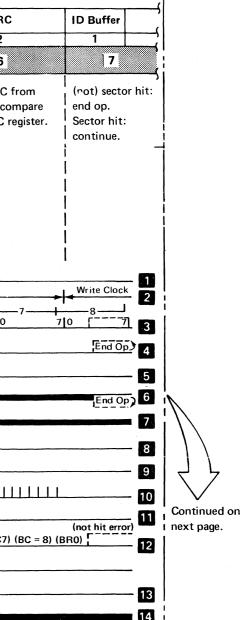

| CC                                                      | C C (                                                                                                                                                                                                                          |                                                   | C C                                              |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------|

| 7 57                                                    | 28 58                                                                                                                                                                                                                          | 29                                                | 59                                               |

|                                                         | Data<br>256<br>Data Field CF                                                                                                                                                                                                   | CRC  <br>2<br>1 ↓  <br>1 ↓ (hex FF)-              | Buffer                                           |

| 10                                                      | 11                                                                                                                                                                                                                             | 12                                                | 13<br> <br> <br>                                 |

|                                                         | Cycle steal data                                                                                                                                                                                                               |                                                   | <br> <br> <br> <br>  Force write                 |

| Force write<br>hex 0E to disk.<br>Preset CRC<br>to 1's. | from storage.                                                                                                                                                                                                                  | Write CRC<br>register<br>contents<br>onto disk.   | hex FFs. Turn<br>off write<br>select.<br>End op. |

|                                                         | Read data from<br>disk. Cycle steal<br>into storage.<br>Generate CRC in<br>CRC register.                                                                                                                                       | <br> <br> <br>  Read CRC                          | Read hex                                         |

| Read hex OE<br>from disk.<br>Preset CRC<br>to 1's.      | Read data from<br>disk. Generate<br>CRC in CRC<br>register.                                                                                                                                                                    | from disk<br>and compare<br>with CRC<br>register. | FFs from<br>disk.<br>End op.                     |

|                                                         | Compare data from<br>storage with data<br>read from disk. At<br>mask FF byte test<br>for scan hit: if hit,<br>read remainder of<br>field into storage; if<br>not hit, set on the<br>'equal hit' latch and<br>restart scanning. |                                                   |                                                  |

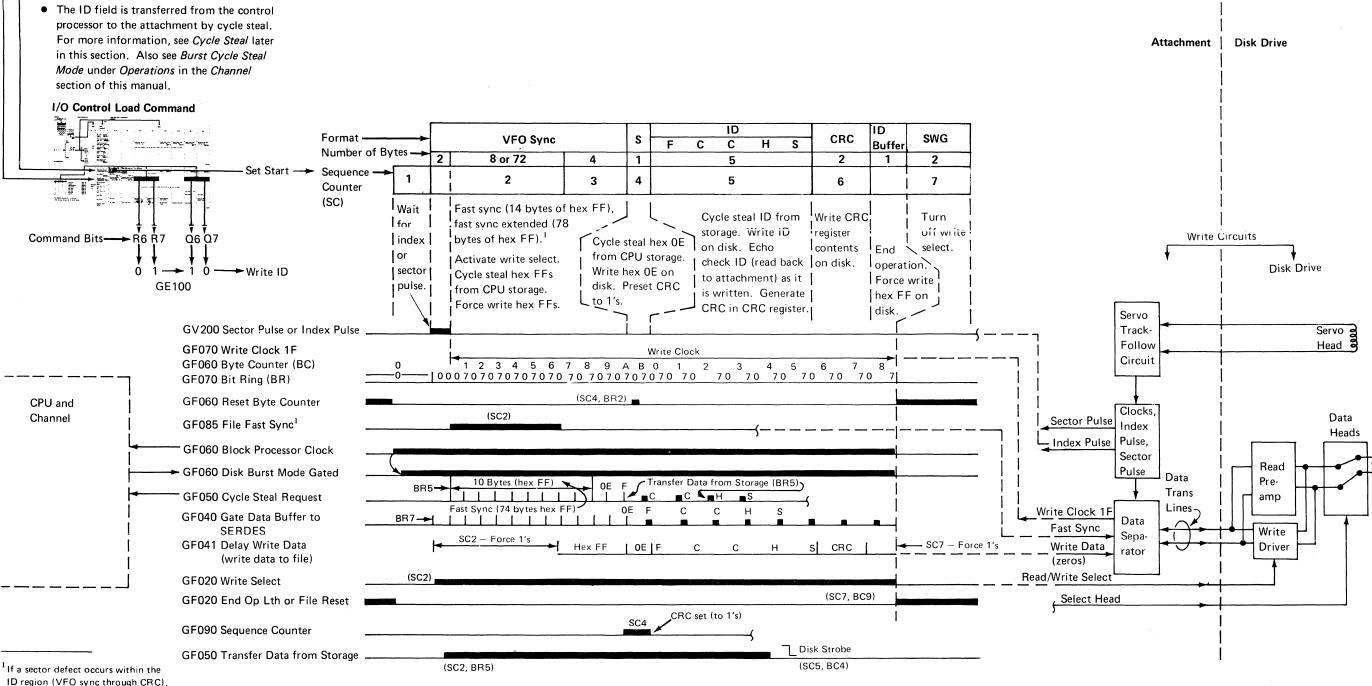

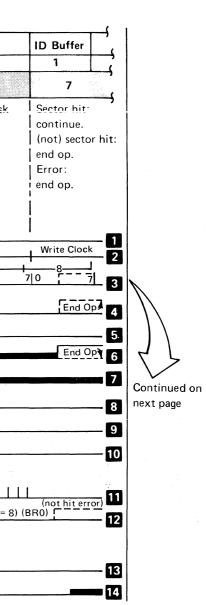

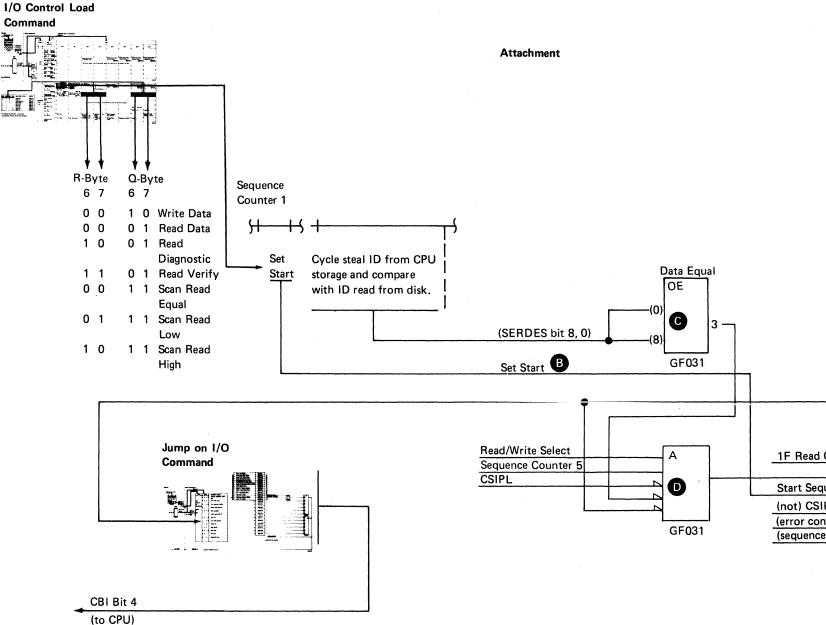

# Write Identification

The primary use of the write identification operation is to write a new identification field when a damaged sector is found. When a

A control load command issues write ID.

- A control load command issues set start, which gates the sequence counter and sets the block processor clock. The next sector or index pulse starts the sequence counter, and write ID is executed.

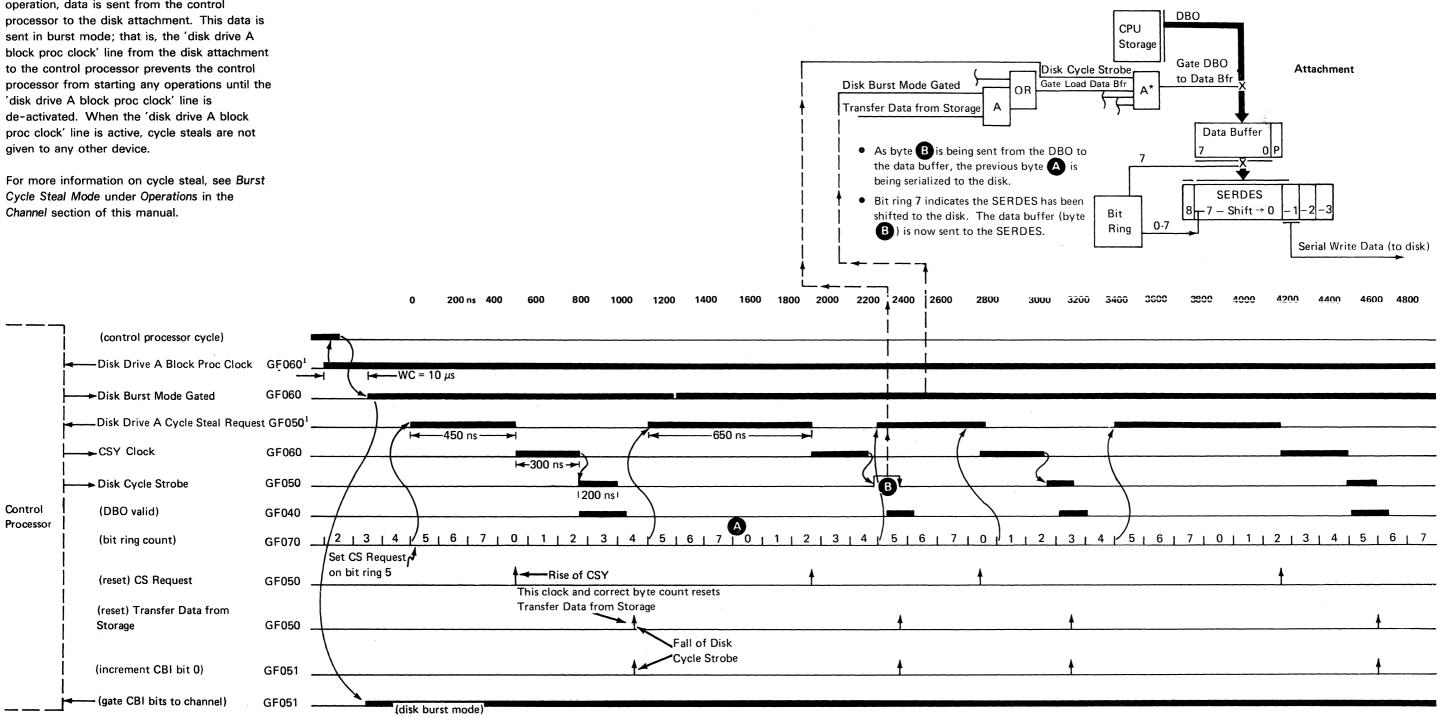

- processor to the attachment by cycle steal. For more information, see Cycle Steal later in this section. Also see Burst Cycle Steal Mode under Operations in the Channel section of this manual.

# ID region (VFO sync through CRC), the VFO fast sync is extended 64 bytes.

$\begin{array}{c} \begin{array}{c} \begin{array}{c} \end{array} \\ \end{array} \end{array}$

permanent error is found in a sector, the sector's identification field must be written again to indicate which alternative track the data has been written on and to flag that sector as being damaged.

7-14

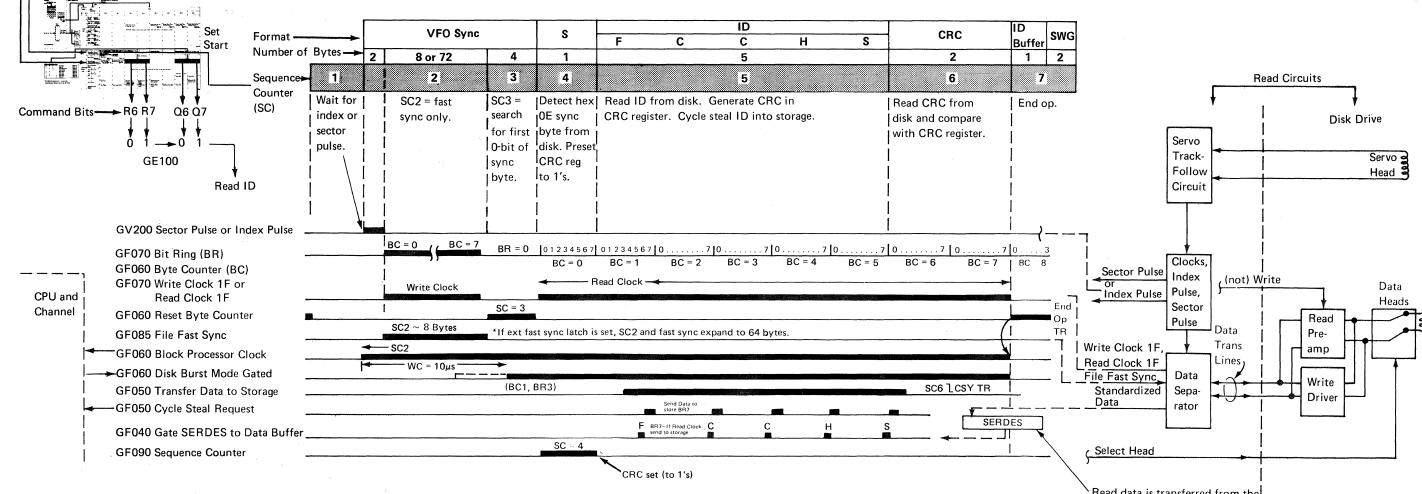

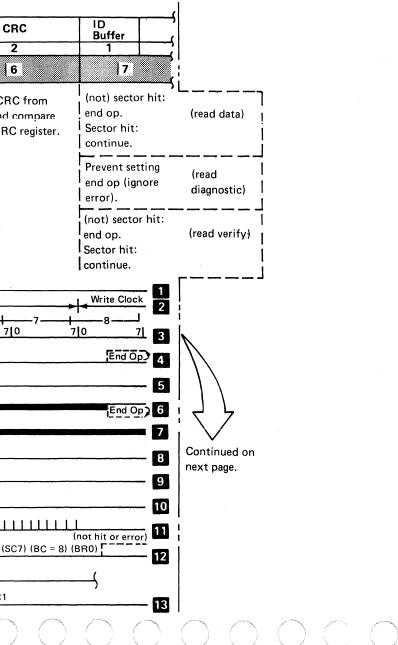

# **Read Identification**

The read identification operation reads the identification field from a sector of the disk and sends the field to the control processor. There, the field is used during error correction to identify damaged sectors and to locate alternative sectors.

- A control load command issues read ID.

- A control load command issues set start, which gates the sequence counter. The next sector or index pulse starts the sequence counter, sets the 'block processor clock' latch, and executes read ID.

- The ID field is transferred from the attachment to the control processor by cycle steal. For more information, see *Cycle Steal* later in this section. Also see *Burst Cycle Steal Mode* under *Operations* in the *Channel* section of this manual.

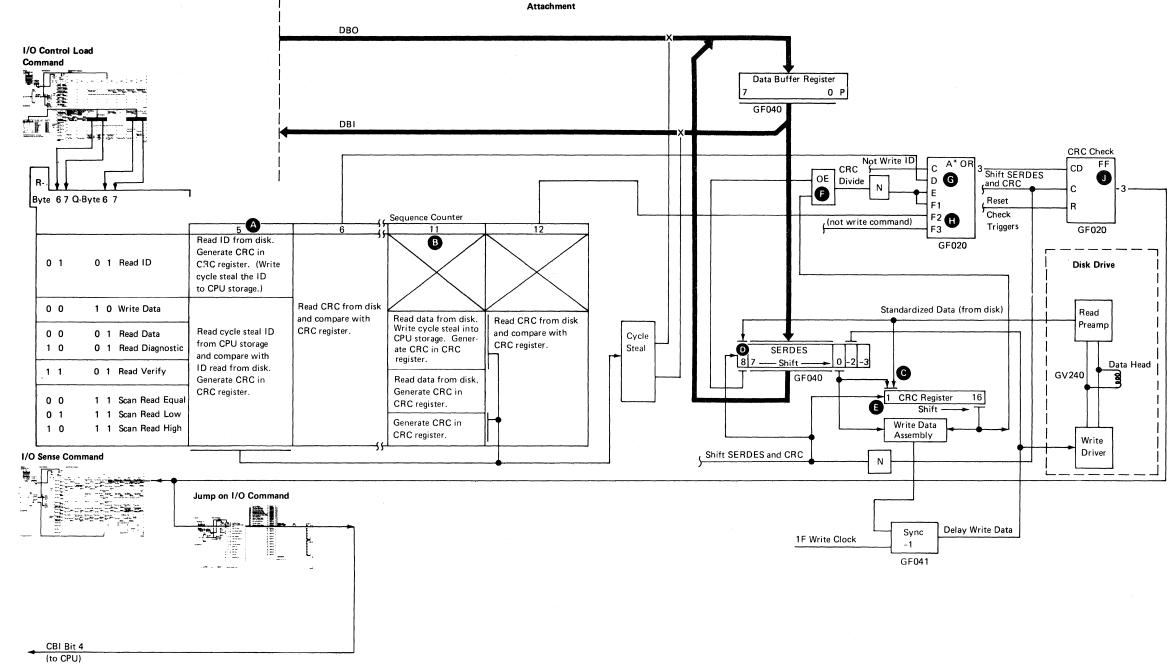

I/O Control Load Command

# Attachment

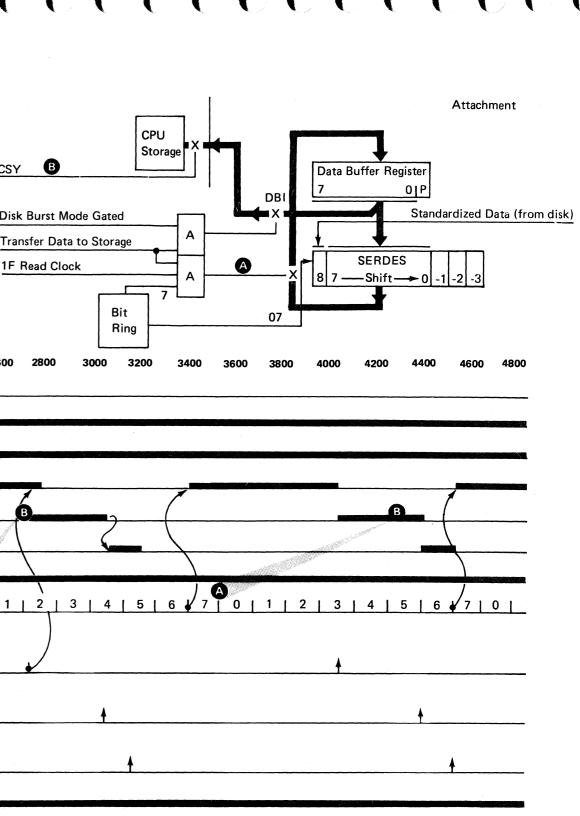

Read data is transferred from the SERDES to the data buffer.

# Write Data

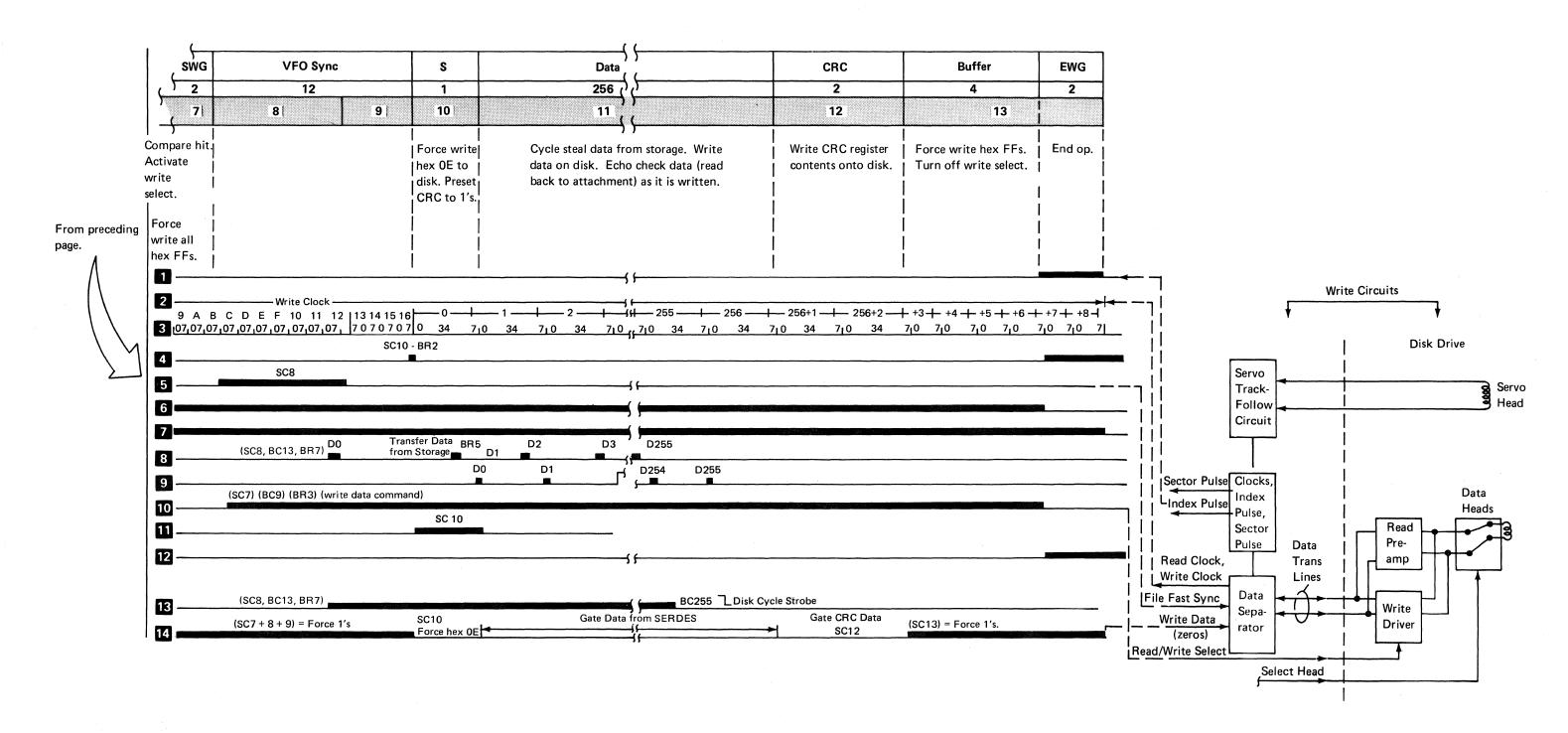

The write data operation sends 256 bytes of data from the control processor to the disk attachment, and the 256 bytes are written into the data field of a sector on the disk.

- A control load command issues write data.

- A control load command issues set start, which gates the sequence counter. The next sector or index pulse starts the sequence counter, sets the 'block processor clock' latch, and executes write data.

- The ID field and the data field are transferred from the control processor to the attachment by cycle steal. For more information, see Cycle Steal later in this section. Also see Burst Cycle Steal Mode under Operations in the Channel section of this manual.

Attachment

| VFO Sync                      | s                                     |                                                                                                                                                                      | ID                                            |                   | CRC                                                     | ID Buffer                                                                     |

|-------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------|---------------------------------------------------------|-------------------------------------------------------------------------------|

| 2 8 4                         |                                       | F C                                                                                                                                                                  | <u> </u>                                      | H S               | 2                                                       | 1                                                                             |

| 2 3                           |                                       |                                                                                                                                                                      | 5                                             |                   | 6                                                       | 7                                                                             |

|                               |                                       |                                                                                                                                                                      | ) from storage and ee<br>k. Generate CRC in   |                   | Read CRC from disk<br>and compare with<br>CRC register. | Sector hit:<br>continue.<br>(not) sector hit:<br>end op.<br>Error:<br>end op. |

| - Write Clock Drives Bit Ring |                                       |                                                                                                                                                                      | Read Cl                                       | ock               | •                                                       | Write Clock                                                                   |

| 8 Bytes ~ SC = 2              | = 3                                   | <u>1</u><br><u>1</u><br><u>1</u><br><u>1</u><br><u>2</u><br><u>2</u><br><u>2</u><br><u>2</u><br><u>2</u><br><u>2</u><br><u>2</u><br><u>2</u><br><u>2</u><br><u>2</u> | <u>-   3 -   </u><br>7 <u> 0</u> 7 <u> </u> 0 | 455               | 6 7 7<br>7 0 7 0                                        | 2<br>7 0 7 7 3<br>1 End Op 4<br>5.<br>End Op 6                                |

| WC ≈ 10µs →                   |                                       |                                                                                                                                                                      |                                               |                   |                                                         | 7                                                                             |

| Set Transfer TR Req           | C<br>Flag BR5<br>BR7                  | с<br>=с                                                                                                                                                              | Head Sector                                   | ∎S                |                                                         | 8                                                                             |

|                               |                                       |                                                                                                                                                                      | ·                                             |                   | ·                                                       | 10                                                                            |

| (SC4) (1                      | 1F) <b>→</b>                          |                                                                                                                                                                      |                                               |                   |                                                         |                                                                               |

|                               | SC = 4                                | CRC set (to 1's)                                                                                                                                                     |                                               | (strobe) SC6 Read | 1F                                                      | (not hit error)                                                               |

|                               | • • • • • • • • • • • • • • • • • • • |                                                                                                                                                                      |                                               |                   | (SC7) (BC = 8)                                          | (BR0) <b>12</b>                                                               |

| ·                             | (SC5) (RD1F)                          |                                                                                                                                                                      |                                               |                   |                                                         |                                                                               |

| ID Compare (SC2, BC8)         |                                       |                                                                                                                                                                      |                                               |                   | obe, SC5, BC4, BR1                                      | 13<br>14                                                                      |

|                               |                                       | Compare (SC2, BC8)                                                                                                                                                   | Compare (SC2, BC8)                            |                   | Compare (SC2, BC8)                                      | compare (SC2, BC8)                                                            |

7-16

$(\bigcirc)$

Attachment

(

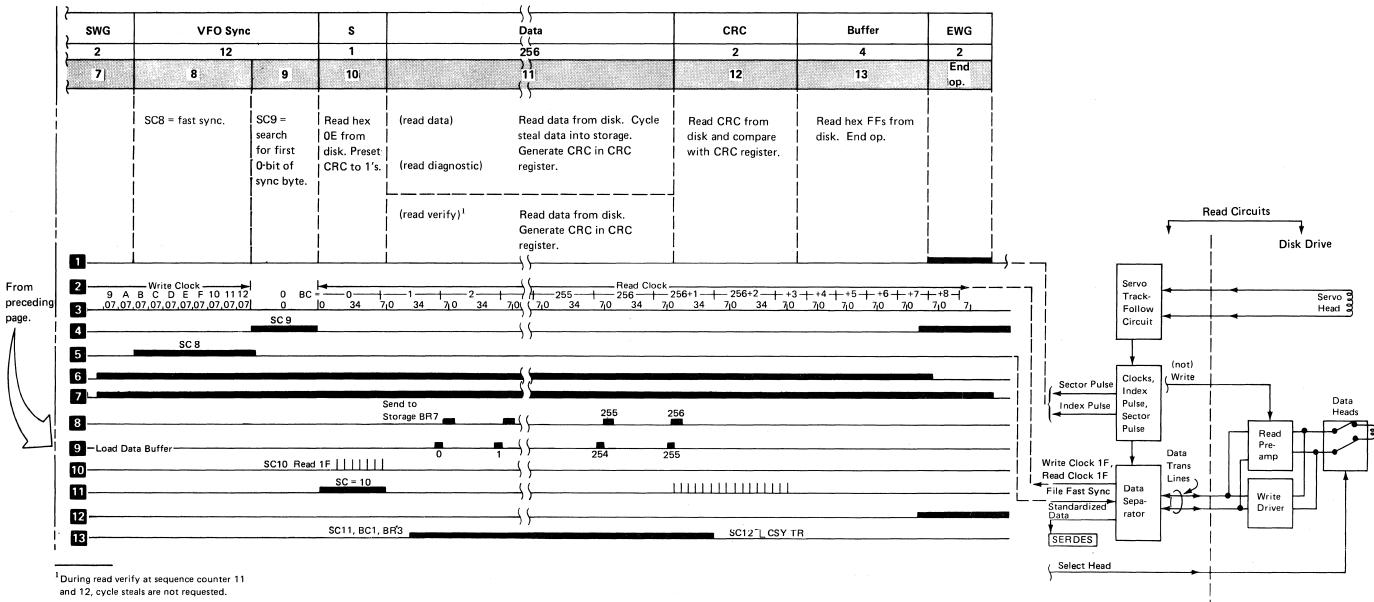

# **Read Data**

The read data operation reads 256 bytes of data from the data field of a sector on the disk and sends the 256 bytes of data through the attachment to the control processor.

A control load command issues read data or read diagnostic or read verify.

A control load command issues set start, which gates the sequence counter. The next sector or index pulse starts the sequence counter, sets the 'block processor clock' latch, and executes read data, read diagnostic, or read verify.

• The ID field and the data field are transferred from the attachment to the control processor by cycle steal. For more information, see *Cycle Steal* later in this section. Also see *Burst Cycle Steal Mode* under *Operations* in the *Channel* section of this manual.

# **Read Diagnostic**

Normally, the data field of a record can be read only if a sector hit condition occurred during the identification search. The sector hit indicates that the desired record has been found. However, if an identification field becomes damaged after the data has been written, it is possible that a sector hit may not occur during the identification search. If that is the case, the program can issue a read diagnostic operation. The read diagnostic operation is a normal read operation, but it does not end the operation if an error occurs during the identification compare. This lets the control processor recover data if the identification field becomes damaged. If an error occurs during the identification compare or if the identification does not compare, the 'sector hit' latch is not on at the end of the operation.

# **Read Verify**

A read verify operation checks the contents of the data field after the field has been written. The read verify operation simulates read data in the attachment, but no data is sent to the control processor. As the record is read, the cyclic redundancy check character is generated to verify that the record can be read.

### Attachment

I/O'Control Load Command ID VFO Sync CRC S Format-----Number of Bytes-2 2 8 4 1 , and and and and 4 1 2 3 5 6 Set Start Sequence Counter SC3 = Wait for SC2 = fast syncDetect hex Cycle steal ID from storage and compare with ID Read CRC from (SC) 0E sync read from disk. Generate CRC in CRC register. disk and compare index or search Read Data sector byte from with CRC register. for first | disk. Preset pulse. 0-bit of **R6 R7** Q6 Q7 sync byte CRC reg to 1's. **Command Bits** Read Diagnostic Ó Read Verify GE100 GV200 Sector Pulse or Index Pulse GF070 Write Clock 1F or Read Clock 1F Read Clock Write Clock GF060 Byte Counter (BC) 000707 78 710 710 710 710 710 GF070 Bit Ring (BR) CPU and SC = 3 Channel GF060 Reset Byte Counter 10 Bytes ~ SC = 2 GF085 File Fast Sync GF060 Block Processor Clock -WC ≈ 10 µs · -GF060 Disk Burst Mode Gated Set Transfer TR Head С С Sector 📕 🖌 Req Flag BR5 GF050 Cycle Steal Request BR5 н BR7 BR7 BR7 GF040 Gate Data Buffer to SERDES (SC4)(1F) → | | | | | | GF030 (strobe the sync byte) Set CRC (to 1's) SC = 4 **GF090 Sequence Counter** GF020 End Op Lth or File Reset (SC5)(RD 1F) GF031 (strobe the sector hit latch) ∼ Disk Strobe, SC5, BC4, BR1 ID Compare SC2, BC8 GF050 Transfer Data from Storage

Attachment

62EH Disk Drive and Attachment 7-19

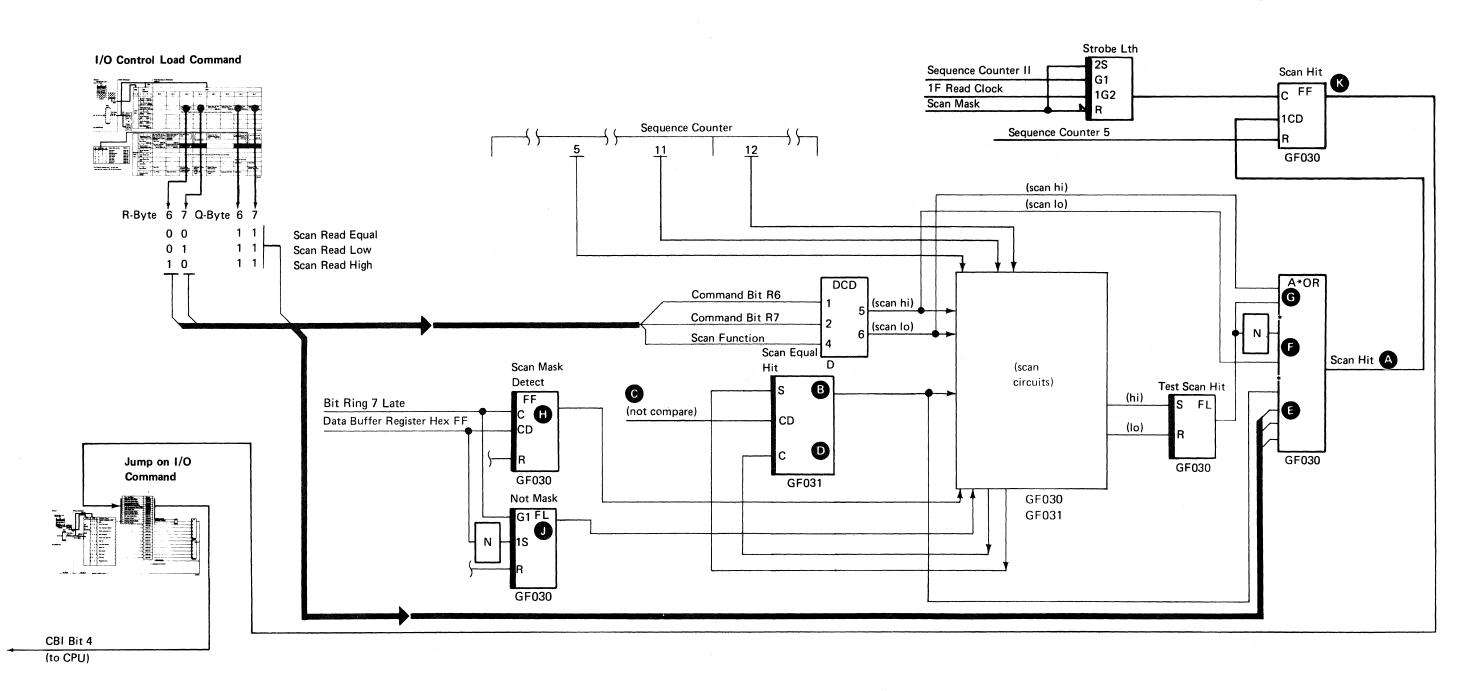

# Scan Read Data Equal

# Scan Read Data High or Equal

Scan Read Data Low or Equal

CPU issues I/O control load, which specifies a scan data operation.

CPU issues an I/O control load-set start. The next sector pulse starts the sequence counter, sets the 'block processor clock' latch, and executes the scan operation.

• The ID field and the data field are transferred from the control processor to the attachment by cycle steal. For more information, see *Cycle Steal* later in this section. Also see *Burst Cycle Steal Mode* under *Operations* in the *Channel* section of this manual.

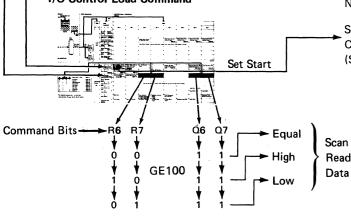

I/O Control Load Command

|         | )<br>  | GV200 Sector Pulse or Index Puls<br>GF070 Write Clock 1F or<br>Read Clock 1F |

|---------|--------|------------------------------------------------------------------------------|

|         | 1      | GF060 Byte Counter (BC)                                                      |

| CPU and | 1      | GF070 Bit Ring (BR)                                                          |

| Channel | 1      | GF060 Reset Byte Counter                                                     |

|         | 1      | GF085 File Fast Sync                                                         |

|         | l      | GF060 Block Processor Clock                                                  |

|         | <br> > | - GF060 Disk Burst Mode Gated                                                |

|         |        | GF050 Cycle Steal Request                                                    |

|         | [      | GF040 Gate Data Buffer to SERD                                               |

|         | l      | GF030 (strobe the sync byte)                                                 |

|         |        | GF090 Sequence Counter                                                       |

|         | 1      | GF020 End Op Lth or File Reset                                               |

|         |        | GF031 (strobe the sector hit latch                                           |

The control processor issues an I/O control load command specifying a scan read data equal, a scan read data low or equal, or a scan read data high or equal operation.

The control processor issues an I/O control load command specifying set start, which starts the sequence counter. Starting at the next sector pulse, the scan operation is executed. The contents of all or part of the data field on the disk are compared to a fixed field in the control processor. Following a hit decision, the data from the disk is read into main storage or control storage moved to the right by 2 bytes. The 2-byte delay is needed to change the direction of the data flow in the channel.

Attachment

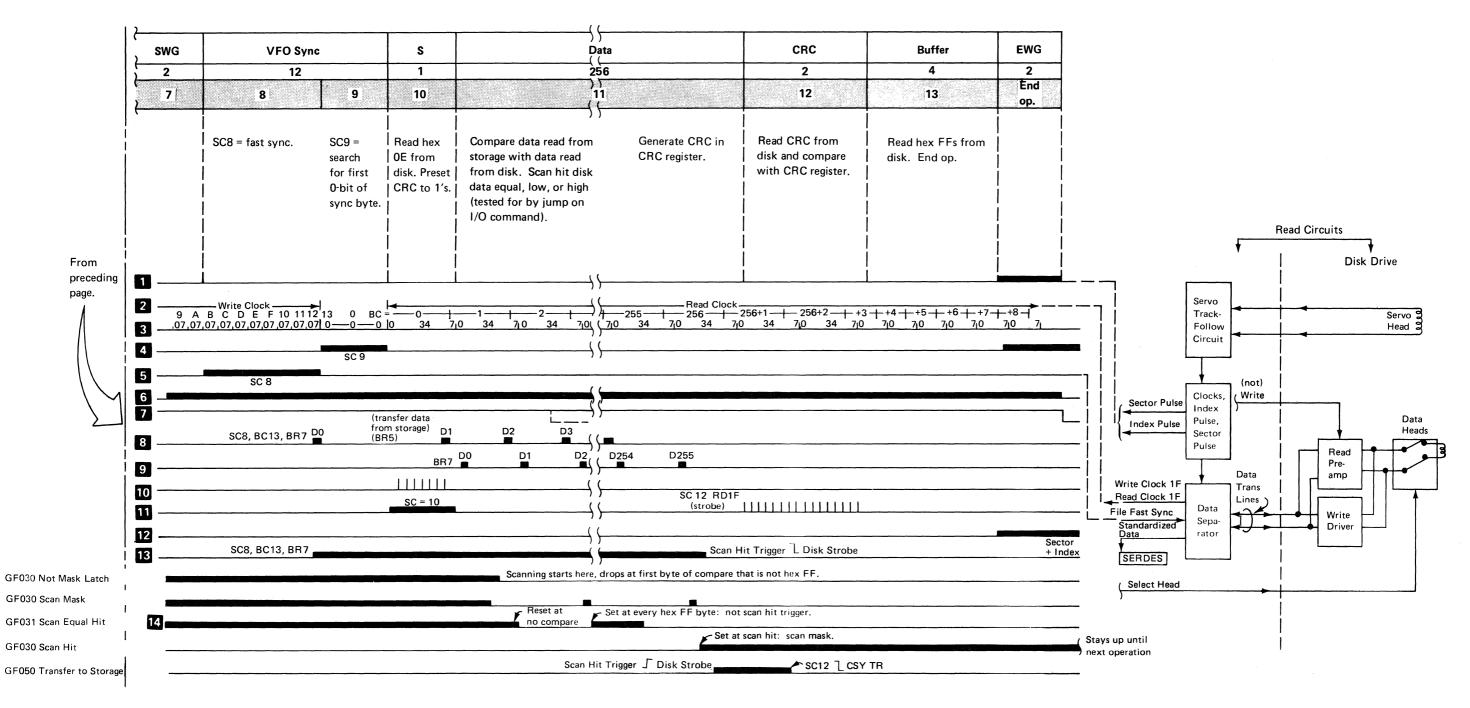

| section of this manual.                               | Format-         |                                          |     | V         | FO Sync    |                      | S                                                                        |                |             |                                     | ID            |                               |                                | CRC                                                     |

|-------------------------------------------------------|-----------------|------------------------------------------|-----|-----------|------------|----------------------|--------------------------------------------------------------------------|----------------|-------------|-------------------------------------|---------------|-------------------------------|--------------------------------|---------------------------------------------------------|

| d                                                     | Number of E     | Bytes                                    | 2   |           | 8          | 4                    | 1                                                                        | F              |             | С                                   | <u>C</u><br>5 | Н                             | S                              | 2                                                       |

| :- =                                                  | Sequence        | 1                                        |     |           | 2          | 3                    | 4                                                                        |                |             |                                     | 5             |                               |                                | 6                                                       |

| Set Start                                             | Counter<br>(SC) | Wait for<br>index or<br>sector<br>pulse. |     | SC2 = fa  | ast sync.  | 1.01.11.01           | Detect hex<br>OE sync<br>byte from<br>disk. Preset<br>CRC reg<br>to 1's. |                |             |                                     |               | compare with<br>RC in CRC rec |                                | Read CRC from<br>disk and compare<br>with CRC register. |

|                                                       | ad              |                                          |     |           |            |                      |                                                                          | <br> <br> <br> |             |                                     |               |                               |                                |                                                         |

| GV200 Sector Pulse or Inde<br>GF070 Write Clock 1F or | ex Pulse        |                                          |     | Write C   | lock       | <u> </u>             |                                                                          | 1              |             |                                     | Read CI       | ock                           |                                |                                                         |

| Read Clock 1F<br>GF060 Byte Counter (BC)              |                 |                                          | • • | 1 2       |            |                      | <b> </b> ←                                                               | 1              |             |                                     | 2 1           | 4                             | с 1                            | c 1 7                                                   |

| GF070 Bit Ring (BR)                                   | _               |                                          |     | 70 7      | 78<br>07   |                      | BC=0 +<br>0 1 2 3 4 5 6 7                                                | 10             | 7 0         | 7 0                                 | 7 0           | 7 0                           | -37                            | 0 7 0                                                   |

| GF060 Reset Byte Counter                              |                 |                                          |     |           |            | SC = 3               |                                                                          |                |             |                                     |               |                               |                                |                                                         |

|                                                       |                 |                                          |     | 8 Bytes   | ~ SC = 2   |                      | Carlie Carl Control Page                                                 |                | -           | - Nga Milak - Kala Anka Mali Manaka |               |                               | an a chairte a chairte an agus |                                                         |

| GF085 File Fast Sync                                  |                 |                                          |     |           |            | L                    |                                                                          |                |             |                                     | -             |                               |                                |                                                         |

| <ul> <li>GF060 Block Processor Clo</li> </ul>         | ock             |                                          | 4   |           | ≈ 10 µs —— |                      |                                                                          |                |             |                                     |               |                               |                                |                                                         |

| ← GF060 Disk Burst Mode Ga                            | ated            |                                          |     |           | •          |                      |                                                                          |                |             |                                     |               |                               |                                |                                                         |

| – GF050 Cycle Steal Request                           |                 |                                          |     |           | Set Tra    | nsfer TR<br>Req Flag | C<br>9 BR5                                                               |                | C           | Head<br>BR5                         | Sector        |                               |                                |                                                         |

| GF040 Gate Data Buffer to                             | SERDES -        |                                          |     |           |            |                      | Ĩ                                                                        | F              | c           | BR7 C                               | н             | S                             |                                |                                                         |

|                                                       |                 |                                          |     |           |            | (SC4)(1F)-           |                                                                          | F              | С           | C                                   | н             |                               | 6 - Read 1 F<br>obe)           |                                                         |

| GF030 (strobe the sync byt                            |                 |                                          |     |           |            |                      | SC = 4                                                                   | CR             | C set (to 1 | l's)                                |               | (3(1                          | 00007                          |                                                         |

| GF090 Sequence Counter                                |                 |                                          |     |           |            |                      |                                                                          |                |             |                                     |               |                               |                                |                                                         |

| GF020 End Op Lth or File                              | Reset           |                                          |     |           |            |                      | ······································                                   |                |             |                                     |               |                               | -                              | (SC7) (BC = 8                                           |

| GF031 (strobe the sector hi                           | it latch)       |                                          |     |           |            |                      | (SC5)(RD 1F)                                                             |                |             |                                     |               |                               |                                |                                                         |

| GF050 Transfer Data from                              | Storage         |                                          |     | ID Compar | e SC2, BC8 |                      |                                                                          |                | -           |                                     |               | Disk Str                      | obe, SC5, BC                   | 24, BR1                                                 |

| GF031 Scan Equal Hit                                  |                 |                                          |     |           |            |                      |                                                                          | SC = 5         |             |                                     |               |                               |                                |                                                         |

|                                                       |                 |                                          |     |           |            |                      |                                                                          |                |             |                                     |               |                               |                                |                                                         |

# Attachment

# 7

(

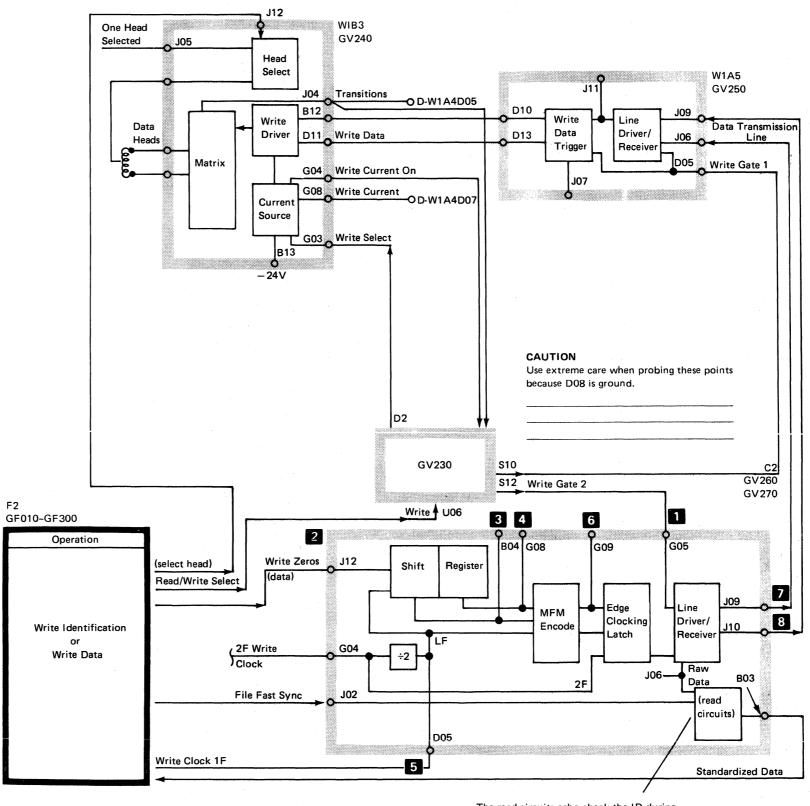

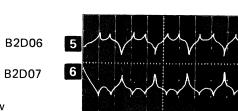

# Write Circuits

# Write

Write data is sent to the disk on the 'write zeros' line. The 'write zeros' line (data bits) is gated to the shift register by the 'write clock 1F' pulse. Data bits are gated through the MFM encode circuit to the 'edge clocking' latch and sent to the line driver/receiver. The 'write gate 1' line sets the write data trigger and the data is sent to the write driver.

The timing chart shows how data (100100) is modified frequency modulation encoded and written.

Write Clock 1F (D05) 5 Write Zeros (J12) 90 ns Shift Reg 1 In Bit O 3 (B04) Out Shift Reg 2 In Bit 1 4 (G08) Out MFM Zeros Ones MFM Encoding 6 (G09)

Note: The numbers on this figure ( 11 through 8 ) refer to the waveshapes on the following two pages.

The read circuits echo check the ID during write ID and the data during write data.

# Write Waveshapes

All of these waveshapes use the 'write gate 2' line as a sync point, with a times-10 grounded probe. There may be a small difference in amplitude of signals from one machine to another.

# Write Identification

The following waveshapes can be seen on an oscilloscope when running the disk exerciser test using the following commands and options:

- Seek to the CE cylinder:

a. Recalibrate.

- b. Seek to the CE cylinder (these waveshapes were taken from a 13.2-megabyte disk). The CE cylinder is hex 00C9 on an 8.6-megabyte disk and hex 012E on a 13.2-megabyte disk.

- c. Select no options.

- d. Execute the command table.

- 2. Set up the command table for write identification:

- a. Write the identification.

- b. Select head 0.

- c. Select sector hex 1E.

- d. Select the option to restore the original control field.

- e. Select the scope loop option.

- f. Execute the command table.

This waveshape shows write gate 2. Write gate 2 is active once during a write ID command.\_\_\_\_\_

Chan 1 Write Gate 2 Sync Internal - Write Gate 2

Voltage: 0.1 V/div Time: 5 µs/div DC Input

Turn the delay time multiplier to 0, then slowly advance the multiplier to get this figure.

$12\mathchar`-\mu s$  delay. Keep the multiplier setting the same for the next waveshape.

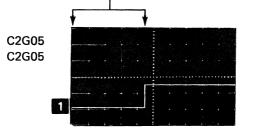

Chan 1Write ZerosC2J12Sync External - Write Gate 2C2G05

Voltage: 0.2 V/div Time: Main Sweep 20 μs/div Delayed Sweep 1 μs/div DC Input

Chan 1 Shift Register Bit 0 C2B04

Chan 1 Shift Register Bit 1 C2G08 Sync External - Write Gate 2 C2G05

Voltage: 0.1 V/div Time: Main Sweep 20 µs/div Delayed Sweep 1 µs/div DC Input

7

62EH Disk Drive and Attachment 7-23

This page intentionally left blank.

# Write Data

The following waveshapes can be seen on an oscilloscope when running the disk exerciser test using the following commands and options:

- 1. Seek to the CE cylinder:

- a. Recalibrate.

- b. Seek to the CE cylinder (these waveshapes were taken from a 13.2-megabyte disk). The CE cylinder is hex 00C9 on an 8.6-megabyte disk and hex 012E on a 13.2-megabyte disk.

- c. Select no options.

- d. Execute the command table.

- 2. Set up the command table for write data:

- a. Select head 0.

- b. Select sector hex 1E.

- c. Select main storage data field 1.

- d. Set data field 1 to hex AAAA by pressing the A key.

- e. Select the scope loop option.

- f. Execute the command table.

This waveshape shows write gate 2. Write gate 2 is active once during a write data command.

Chan 1 Write Gate 2 Sync Internal - Write Gate 2 C2G05

Voltage: 0.1 V/div Time: 50 µs/div DC Input (about 35  $\mu$ s)

Turn the delay time multiplier to 0, then slowly advance the multiplier to get this figure.

Keep the multiplier setting the same for the following waveshapes.

Chan 1 Write Zeros C2J12 Sync External - Write Gate 2 C2G05

Voltage: 0.2 V/div Time: Main Sweep 50 µs/div Delayed Sweep 0.5 µs/div DC Input

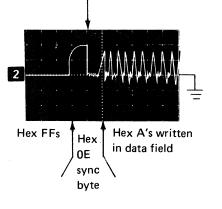

Chan 1 Shift Register Bit O

Chan 1 Shift Register

C2G08

3 \_\_\_\_\_ 4

Bit 1

Sync External - Write Gate 2 C2G05

Voltage: 0.1 V/div Time: Main Sweep 50  $\mu$ s/div Delayed Sweep 0.5 µs/div DC Input

Chan 1 Write Clock 1F

Chan 1 MFM Encoding C2G09 Sync External - Write Gate 2 C2G05

Voltage: 0.1 V/div Time: Main Sweep 50  $\mu$ s/div Delayed Sweep 0.5 µs/div DC Input

Chan 1 Data Transmission C2J09

Line

Chan 1 Data Transmission C2J10 8 mm vvvvvvv Line

Sync External - Write Gate 2 C2G05

Voltage: 0.1 V/div Time: Main Sweep 50  $\mu$ s/div Delayed Sweep 0.5  $\mu$ s/div DC Input

62EH Disk Drive and Attachment 7-25

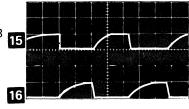

# **Read Circuits**

# Read

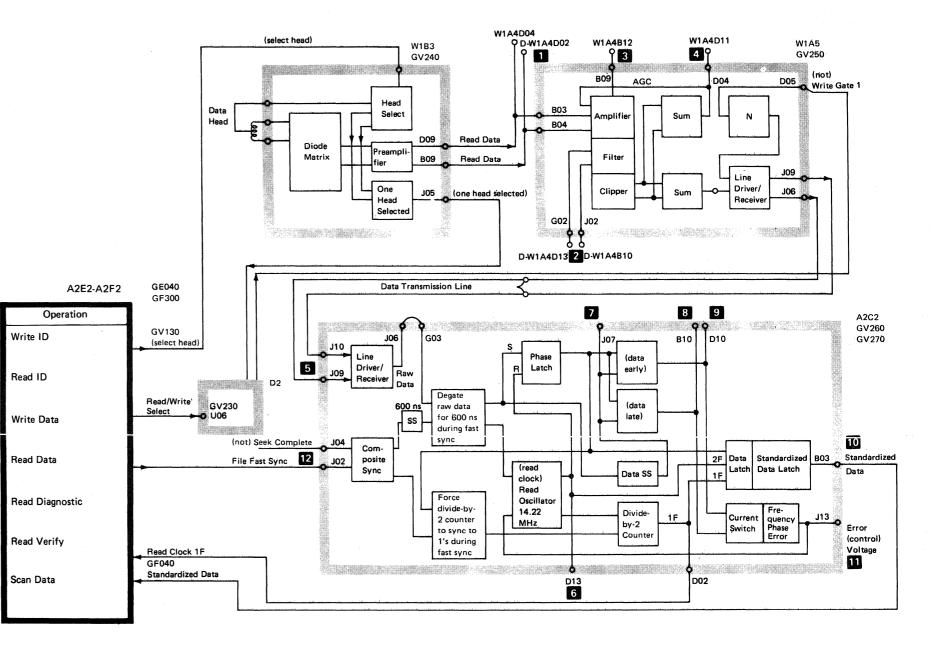

When the 'read select' and 'head select' lines from the attachment are activated, data is read from the disk and preamplified by a variable gain amplifier. Following the preamplifier is a circuit card that filters and shapes the data. This card also has a line driver/receiver that connects the read/write cable (data transmission line) to the logic gate.

## Read Clock and Divide-by-2 Counter

The data separator card receives the data from the read/write cable and generates the read clock and standardized data. The read clock, which runs at 14.2 megahertz, is synchronized to the incoming data (see *File Fast Sync*).

# Read Clock Synchronization Control

To lower the frequency of the clock (that is, delay the phase), the control voltage is lowered. To increase the clock frequency, the control voltage is increased. Therefore, to keep the clock locked to the data, the positive current source is turned on if the clock is behind phase with the data, and the negative current source is turned on if the clock runs in advance of the data.

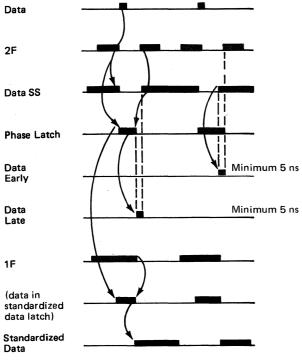

# Read Clock Sync

Current control is obtained from the 'data early' and 'data late' pulses that are generated from the data. The 'data early' and 'data late' pulses control the read clock as follows: each data bit sets the 'data SS' and 'phase' latches. The 'phase' latch output is compared with the 'data SS' latch output, which generates either the 'data early' or 'data late' pulse for use by the read clock '2F' pulse. If data is late, the frequency of the read clock is decreased; if data is early, the frequency of the read clock is increased.

# Data Latch and Standardized Data Latch

Input to the 'data' latch comes from the 2F clock, the 1F clock, and the 'phase' latch. The 'phase' latch activates the 'standardized data' latch. The 'standardized data' latch (read data) is then gated to the serializer/deserializer.

# File Fast Sync

The 'file fast sync' line is activated for all read and write operations. For example, if a read identification operation is started, the variable frequency oscillator field is the first field read from the disk. The 'file fast sync' line is activated during the first 8 bytes of the field, which causes the read clock to sync to these 1's. This occurs because a field of 1's and a field of 0's have the same data pattern. Therefore, by forcing the read clock to synchronize to known 1's, the read clock senses 1's and 0's correctly for the remainder of the field.

# Composite Sync

During a seek operation, the variable frequency oscillator is synchronized to the write clock. This keeps the oscillator near the correct frequency so it can sync to the read data after the seek.

*Note:* The numbers on this figure ( 1 through ) refer to the waveshapes on the following two pages.

# **Read Waveshapes**

All of the read waveshapes were taken using a times-10 grounded probe. A scope hood should be used to view the signals. There may be a small difference in amplitude of signals from one machine to another.

# **Read Identification**

The following waveshapes can be seen on the oscilloscope when running the disk exerciser test using the following commands and options:

- 1. Seek to the CE cylinder:

- a. Recalibrate.

- b. Seek to the CE cylinder (these waveshapes were taken from a 13.2-megabyte disk). The CE cylinder is hex 00C9 on an 8.6-megabyte disk and hex 012E on a 13.2-megabyte disk.

- c. Select no options.

- d. Execute the command table.

- 2. Set up the command table for read identification:

- a. Select head 0.

- b. Select sector hex 1E.

- c. Select the scope loop option.

- d. Execute the command table.

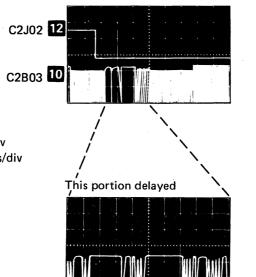

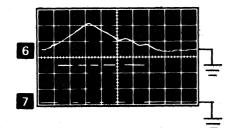

Chan 1 File Fast Sync C2J02 12 Sync + Internal Chan 1

Voltage: 0.2 V/div Time: 5 ms/div AC Input

Chan 1 File Fast Sync C2J02 12 Sync + Internal Chan 1 Chan 2 Standardized C2B03 10 Data

Voltage: 0.2 V/div Time: Main Sweep 5 μs/div Delayed Sweep 1 μs/div

62EH Disk Drive and Attachment 7-27

This page intentionally left blank.

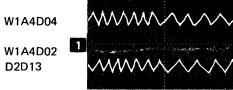

# Read Data

These waveshapes of hexadecimal A's were taken when the disk exerciser test was in a loop and reading from the CE track. Before these waveshapes are scoped, all hexadecimal A's must be written (on the CE track) by using the disk exerciser test.

The following waveshapes can be seen on the oscilloscope when running the disk exerciser test using the following commands and options:

- 1. Seek to the CE cylinder:

- a. Recalibrate.

- b. Seek to the CE cylinder (these waveshapes were taken from a 13.2-megabyte disk). The CE cylinder is hex 00C9 on an 8.6-megabyte disk and hex 012E on a 13.2-megabyte disk.

- c. Select no options.

- d. Execute the command table.

- 2. Set up the command table for read data:

- a. Select head 0.

- b. Select sector hex 1E.

- c. Select the scope loop option.

- d. Execute the command table.

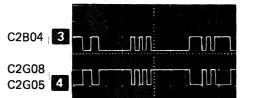

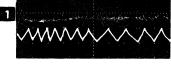

This waveshape shows file fast sync. File fast sync is active twice during a read data command. Chan 1<sup>1</sup> Chan 1 File Fast Sync C2J02 12-Ţ Chan 1<sup>1</sup> Sync + Index Pulse D2D13 Sync + Index Pulse D2D13 Voltage: 0.2 V/div Time: 50  $\mu$ s/div Voltage: 20 mv/div \_\_\_\_J Time: Main Sweep 50  $\mu$ s/div DC Input Last 4  $\mu$ s of second file fast sync pulse shown using delayed sweep. AC Input Chan 1 File Fast Sync C2J02 12 Chan 1<sup>1</sup> D2D13 Sync + Index Pulse 그 Chan 1<sup>1</sup> Voltage: 0.2 V/div Time: Main Sweep 50 µs/div Delayed Sweep 2 µs/div DC Input File fast sync shown in relationship to standardized data.

Sync + Index Pulse D2D13 Voltage: 50 mv/div Time: Main Sweep 50  $\mu$ s/div Delayed Sweep 0.5 µs/div AC Input Chan 1 Error Voltage C2J13 11 Chan 1 Standardized C2B03 Data D2D13 Sync + Index Pulse Voltage: 0.2 V/div Hex A's read Hex FFs Hex OE Hex Time: Main Sweep 50  $\mu$ s/div 0E from data field Delayed Sweep 0.5 µs/div sync DC Input byte

to left before expanding.

Standardized data (expanded). Move hex OE --- -- ---

Delayed Sweep 0.5 µs/div

W1A4D13

W1A4B10

Voltage: 0.1 V/div Time: Main Sweep 50 µs/div Delayed Sweep 0.5 µs/div DC Input

Clock

Chan 1

Voltage: 0.1 V/div Time: Main Sweep 50 µs/div

Chan 1

Sync + Index Pulse

DC Input

Frequency D2D13 9 Sync + Index Pulse

Voltage: 0.1 V/div Time: Main Sweep 50 µs/div Delayed Sweep 0.5 µs/div

**DC Input**

<sup>1</sup>May need a card extender

Data

Time: Main Sweep 50 µs/div

Delayed Sweep 2 µs/div

Sync + Index Pulse

Voltage: 0.2 V/div

Chan 1

DC Input

Standardized C2B03 10

D2D13

Chan 1<sup>1</sup> W1A4D11 Sync + Index Pulse D2D13

Voltage: 5 mv/div Time: Main Sweep 50  $\mu$ s/div Delayed Sweep 0.5 µs/div AC Input

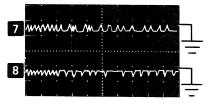

Chan 1<sup>1</sup> A2D2J09

Chan 1<sup>1</sup> A2C2J10 Sync + Index Pulse D2C13

Mun on man within the C2D13 6 \*\*\*\*\* 2F Read Data SS C2J07 D2D13

7 WWWWWWWWWWW

Delayed Sweep 0.5 μs/div Chan 1 Increase VFO C2B10 Frequency 8 Chan 1 Decrease VFO C2D10

Ţ Ţ

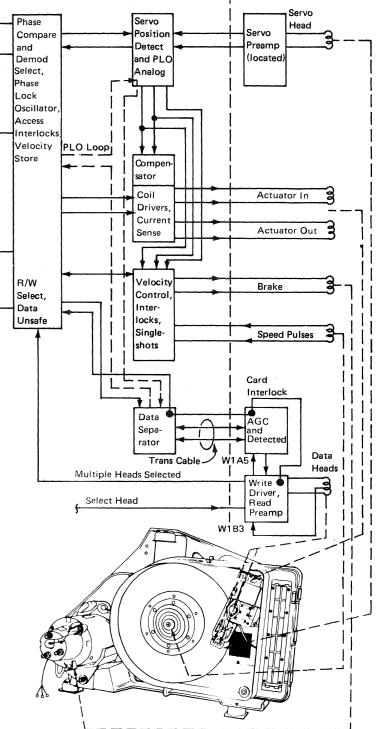

# **Track Follow Principles**

The track follow circuits align the data heads on the track at the end of each seek operation and maintain head-to-track alignment during read and write operations.

The servo head reads a pattern that is aligned with each data track. The pattern is made up of position pulses (P1 and P2) and servo clock pulses (C) that repeat around each servo track.

Sequences of missing clock pulses identify the index pulses, sector pulses, and sector midpoint pulses. For more information, see Servo Clock later in this section.

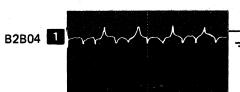

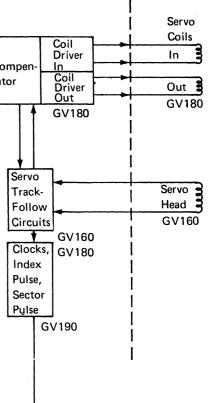

# **Track Follow**

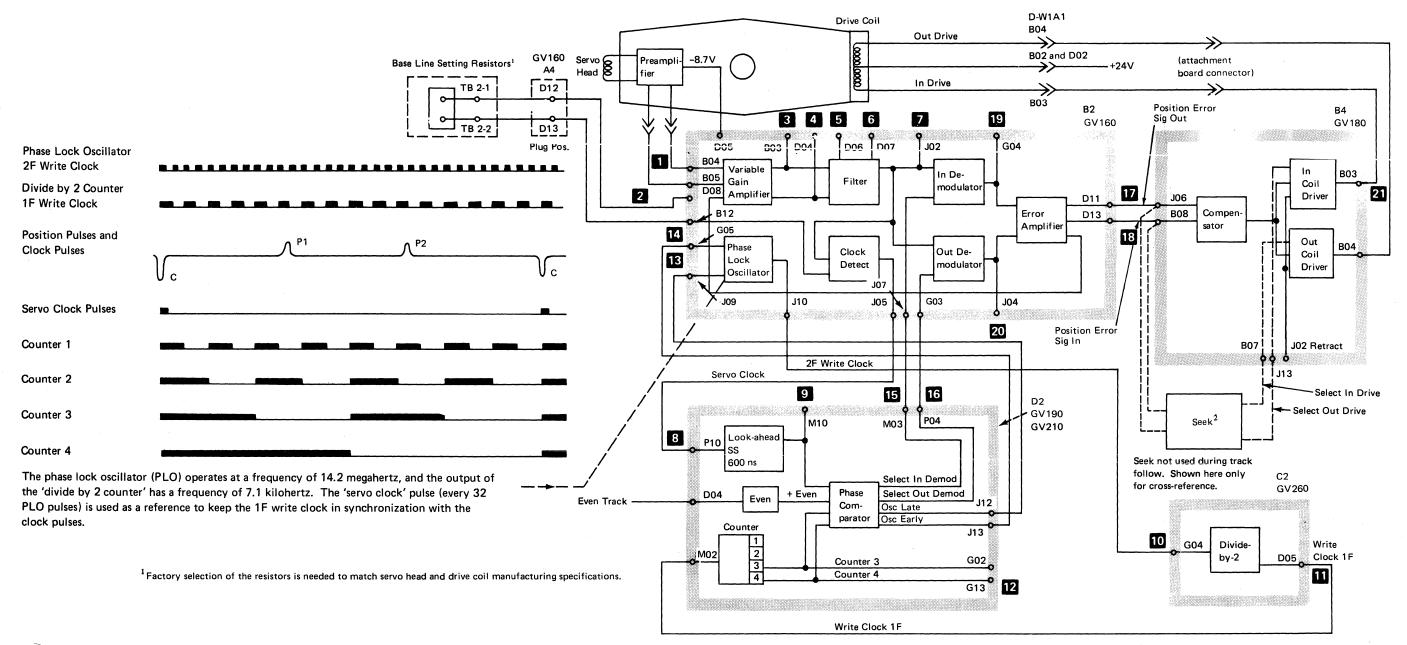

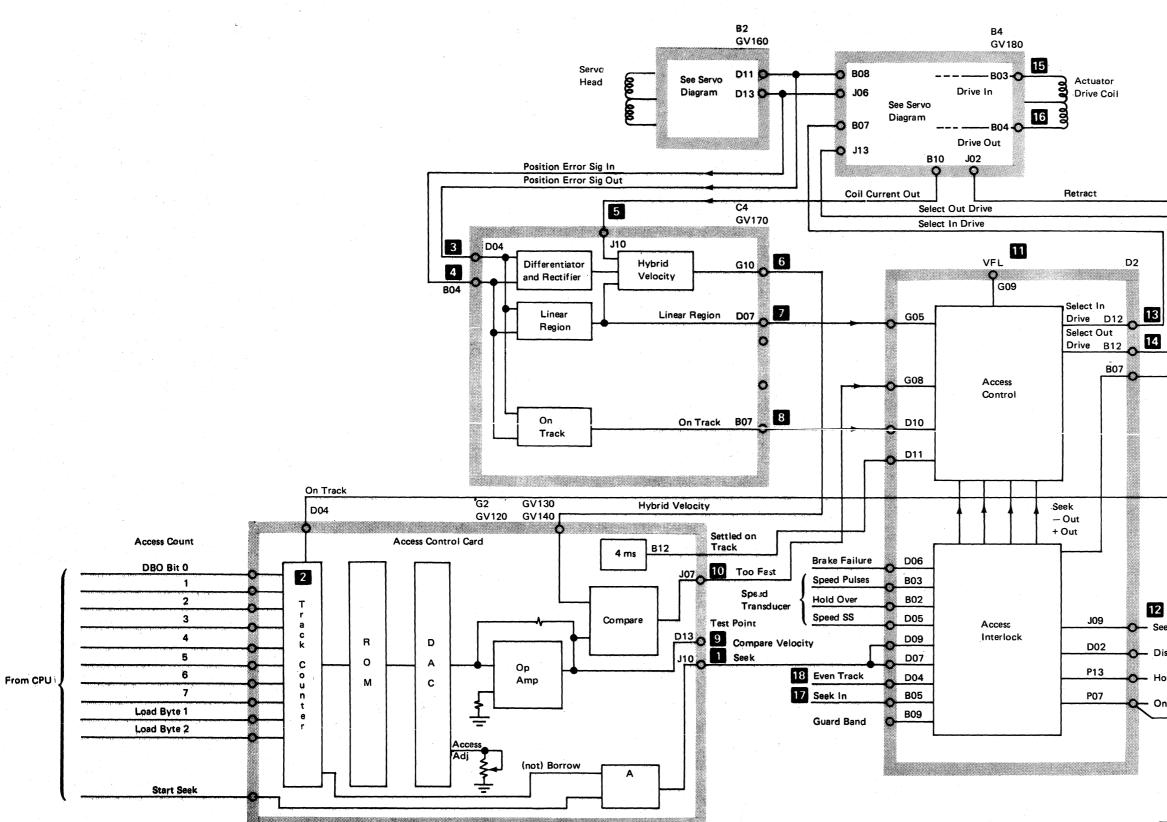

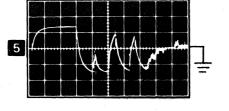

The servo track signal from the servo head is amplified, filtered, and separated into two signals: clock pulses and position pulses. These pulses are generated on the position detection and phase lock oscillator analog card (B2).

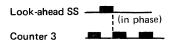

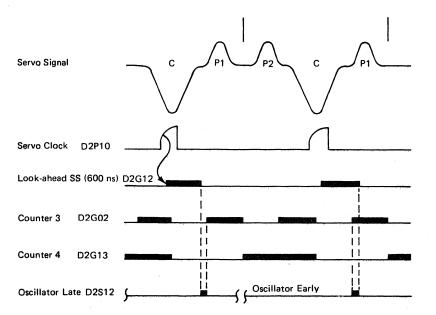

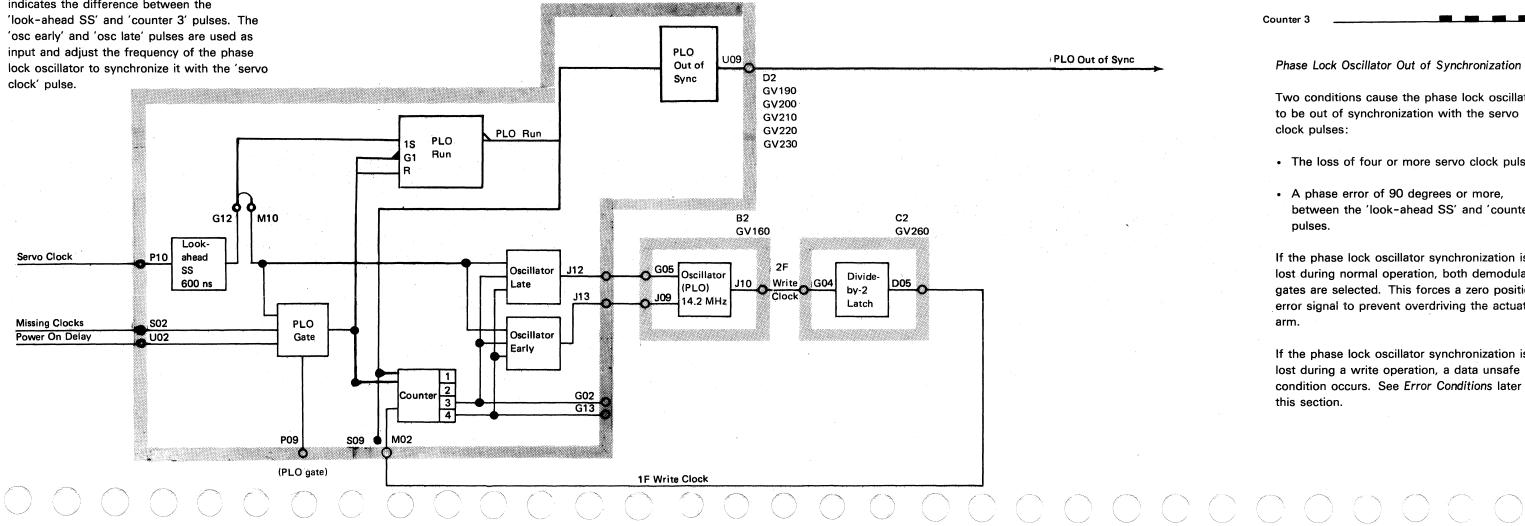

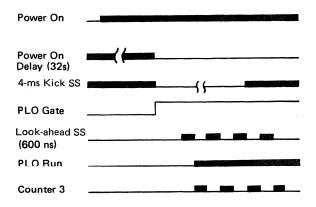

On the control and safety card (D2), each servo clock pulse fires a 600-nanosecond singleshot named the look-ahead singleshot. This singleshot permits a phase compare between the servo clock and the phase lock oscillator. If the servo clock occurs before the phase lock oscillator, a pulse is generated on the 'osc late' line. The width of the pulse is equal to the phase difference. If the servo clock is later than the phase lock oscillator, the pulse occurs on the 'osc early' line. The 'osc early' and 'osc late' signals are combined to form a control voltage to control the frequency of the phase lock oscillator. The phase lock oscillator runs at a frequency that is 32 times the frequency of the servo clock. A group of counters count the frequency down to the servo clock frequency. The 'select in demod' and 'select out demod' signals are synchronized with the servo pattern and switched so that one position pulse is gated to the in demodulator and the other position pulse is gated to the out demodulator. The polarity of even track (up for even and down for odd) indicates which position pulse is gated to which demodulator (select in or select out). This permits the position error signals to be used to keep the head on the desired track.

Drive coil resistance nominal 50 $\Omega$ .

Important coils within 5 $\Omega$  of each other.

The position pulses, which generate the position error signals, are generated on the position detection card.

The position error signals are combined in the compensator to generate the drive signals for the coil drivers. The coil drivers move the actuator in the correct direction to position the servo head over the selected track. For more information, see Servo Track Follow later in this section.

# $\mathbf{O} \mathbf{O} \mathbf{O} \mathbf{O}$

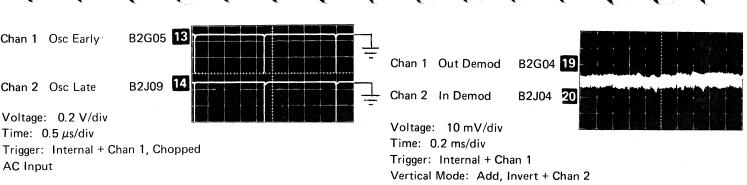

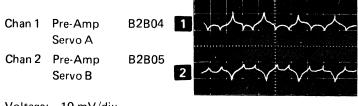

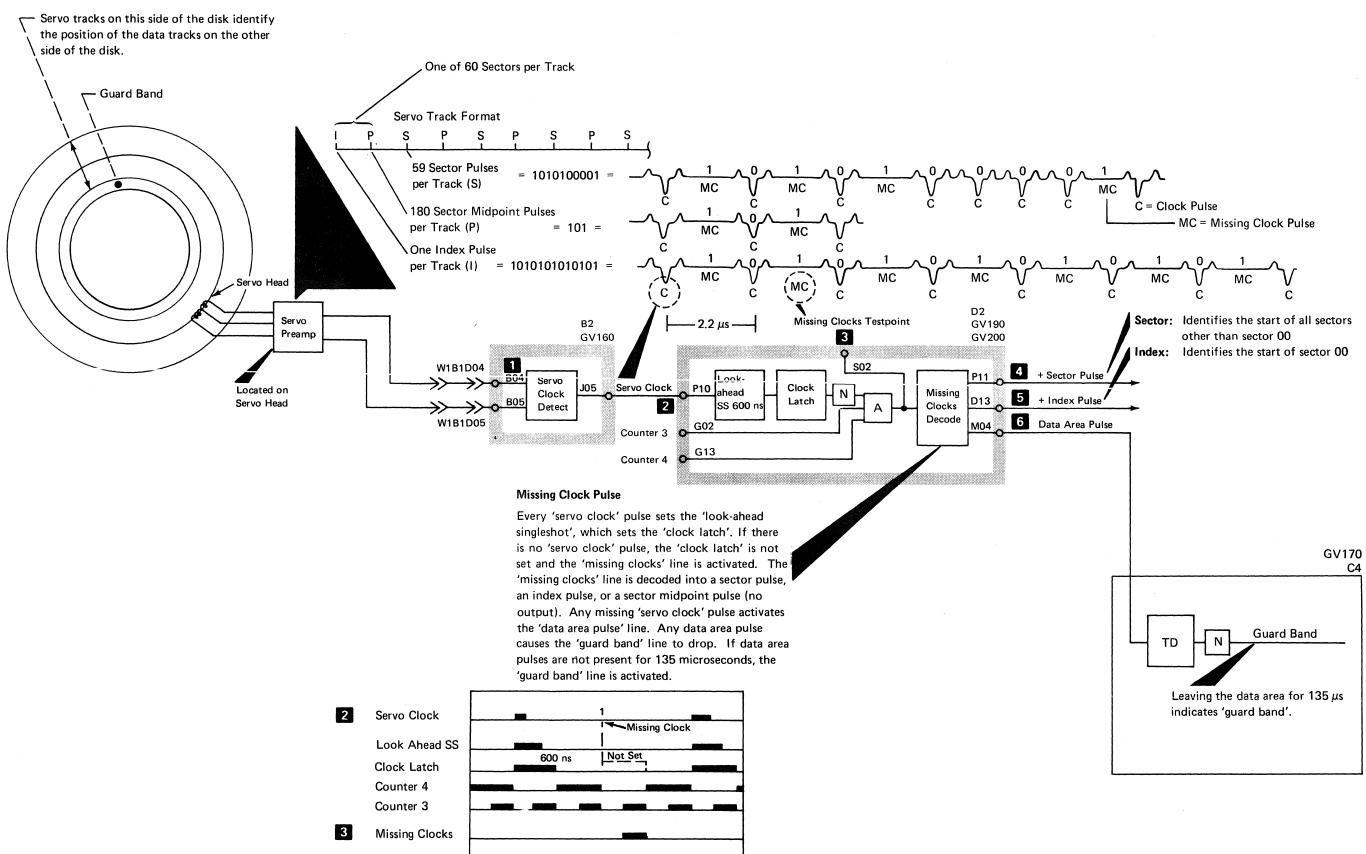

# **Track Follow Waveshapes**

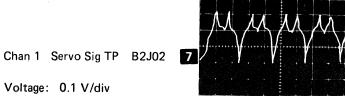

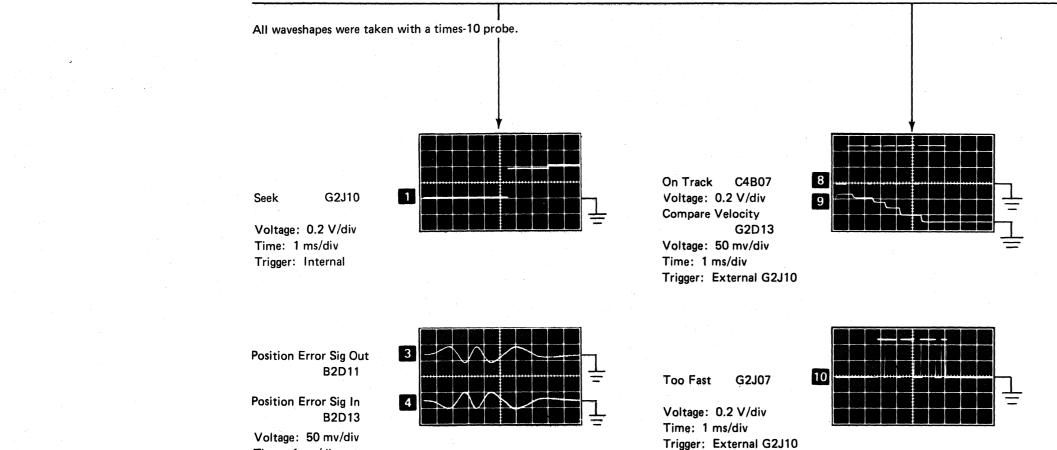

The following waveshapes can be seen on an oscilloscope if the servo operation is working correctly and the servo head is on a servo track. All waveshapes were taken with a times-10 grounded probe.

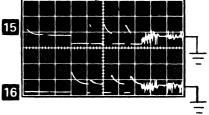

Voltage: 0.1 V/div Time:  $1 \,\mu s/div$ Trigger: External + D2P11, Chopped AC Input

Chan 1 Servo Clock D2P10

| <u> М М А</u> | Chan         |

|---------------|--------------|

| Y V Y         | Chan         |

|               | Volt<br>Time |

Trigger: Internal + Chan 1, Chopped AC Input

3

4

Voltage: 10 mV/div Time:  $1 \mu s/div$ Trigger: External + D2P11 - Sector Pulse AC Input

B2B03

B2D04

Chan 2

Voltage: 10 mV/div Time:  $1 \,\mu s/div$ Trigger: External + D2P11, Chopped AC Input

Chan 1

Chan 2

Voltage: 20 mV/div Time:  $1 \mu s/div$ Trigger: External + D2P11, Chopped AC Input

Chan 2 Look-ahead D2M10 9 SS Voltage: 0.2 V/div Time:  $1 \,\mu s/div$ Trigger: External + D2P11, Chopped DC Input

8

May be distorted at beginning because PLO is syncing in.