IBM System/36 Processing Unit and Channel Maintenance Information Manual Stage 3

Order Number SY31-9035-0

# Section 10

#### First Edition (October 1986)

The drawings and specifications contained herein shall not be reproduced in whole or in part without written permission.

IBM has prepared this maintenance manual for use by hardware service representatives in the maintenance or repair of the specific machines indicated. IBM makes no representations that it is suitable for any other purpose.

Information contained in this manual is subject to change from time to time. Any such change will be reported in subsequent revisions or Technical Newsletters.

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates.

Publications are not stocked at the address given below. Requests for IBM publications should be made to your IBM representative or to your IBM-approved remarketer.

This publication could contain technical inaccuracies or typographical errors. A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be addressed to IBM Corporation, Information Development, Department 245, Rochester, Minnesota, U.S.A. 55901. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

© Copyright International Business Machines Corporation 1986

### Preface

This manual contains the maintenance information necessary to service the System/36 processing unit and channel. This manual includes maintenance procedures, FRU descriptions, interface descriptions, and sequence of events sections to aid in diagnosing machine failures not found by the MAPs.

This manual uses a specific range of words so that the text can be understood by customer engineers in countries where English is not the normal language.

It is assumed that the hardware service representative using this manual has been trained on System/36, as described in the System/36-5360 New Product Planning Technical Service Letter.

#### About This Manual

The service procedures in this manual are numbered.

- The MAPs can send you to a specific procedure in this manual.

- Other System/36 MIMs can send you to a specific procedure in this manual.

- Steps in a procedure in this manual can send you to another procedure in this manual or in other System/36 MIMs.

- The index can send you to procedures where key words can be found.

#### **Related Publications**

#### System/36 Hardware Publications

- General Maintenance Information Manual, SY31-8999

- Data Storage Attachment Maintenance Information Manual, SY31-9001

- 51TD Diskette Drive and Adapter Maintenance Information Manual, SY31-9003

- Work Station Attachment Maintenance Information Manual, SY31-9004

- 10SR Disk Drive and Adapter Maintenance Information Manual, SY31-9005

- 72MD Diskette Magazine Drive and Adapter Maintenance Information Manual, SY31-9006

- Data Communications Attachment Maintenance Information Manual, SY31-9007

- 3262 Printer Attachment Maintenance Information Manual, SY31-9008

- Power Maintenance Information Manual, SY31-9009

- 8809 Tape Adapter Maintenance Information Manual, SY31-9010

- Single-Line Communications Attachment Maintenance Information Manual, SY31-9017

- Eight-Line Communications Attachment Maintenance Information Manual, SY31-9018

- 1255 MCR Attachment Maintenance Information Manual, SY09-1026

- Local Area Network Attachment Maintenance Information Manual, SY31-9021

- 6157 Tape Adapter Maintenance Information Manual, SY31-9037

#### **Other System Publications**

• Control Storage Service Information Manual, LY31-0650

### Safety

### Danger and Caution Notices

In the System/36 maintenance manuals, the word DANGER informs you of conditions that could cause personal injury or death. (The word HAZARDOUS or WARNING may appear on labels on machines and field-supply items.) The word CAUTION informs you of an action that could cause damage to a program, to a device or system, or to data.

There are blank lines below each notice. You can translate these notices and write your own words on the blank lines.

#### **Danger Notices**

A danger notice appears on page vii of this Safety section under "Electrical Accidents-First Aid."

Danger notices also appear in the following procedures:

10-320 Opening Covers 10-325 Control Panel Removal

#### **Caution Notices**

A caution notice appears in the following procedure:

10-325 Control Panel Removal

#### **Rules for Safety**

If you know the safety rules for working with electrical and mechanical equipment and you observe the rules, you can work safely with IBM equipment.

Do not fear electricity, but respect it.

While you are maintaining IBM equipment, observe every safety precaution possible and the following safety rules.

#### **Work Environment**

- Do not work alone in hazardous conditions or near equipment that has dangerous voltage. Always inform your manager if the conditions or voltages are a possible problem.

- Always look for possible hazards in your work environment. Examples of hazards are: moist floors, nongrounded extension cables, power surges, and missing grounds.

- Do not perform any action that makes the product unsafe or that causes hazards for customer personnel.

- Before you start the equipment, ensure that other personnal are not in a hazardous position.

- Do not wear loose clothing that can be trapped in the moving parts of a machine. Ensure that the sleeves of your clothing are fastened or are rolled above the elbow.

- Insert your necktie into your clothing or fasten it with a clip (preferably nonconductive) at approximately 8 centimeters (3 inches) from its end.

- Lift the equipment or parts by standing or pushing up with your stronger leg muscles; this action removes the strain from the muscles in your back. Do not lift any equipment or parts that are too heavy for you.

- Put removed machine covers in a safe place while you are servicing the machine. Reinstall the covers before returning the machine to the customer.

- Always keep your tool kit away from walk areas so that other persons cannot trip over it. For example, keep the kit under a desk or table.

- Observe good housekeeping practices in the area of the machines while you are performing maintenance and after completing it.

- After maintenance, reinstall all safety devices, such as guards, shields, labels, and grounding devices. Exchange safety devices that are worn or defective. Remember, the safety devices protect you from a hazard. You destroy their purpose if you do not reinstall them when you have completed the service call.

#### **Electrical Safety**

• If possible, always disconnect the power-supply cables before you work on a machine. When you switch off power at the wall box, lock the switch in the off position or attach a DO NOT OPERATE tag (Z229-0237) to the switch.

**Note:** A non-IBM attachment to an IBM machine may be powered from another source and may be controlled by a different switch or circuit breaker.

- Switch off all power before:

- Removing or assembling the main units of the equipment

- Working near power supplies

- Inspecting power supplies

- Installing changes in machine circuits

- If you really need to work on equipment that has exposed live electrical circuits, observe the following precautions:

- Ensure that another person who understands the power off controls, is near you. Another person must be there to switch off the power, if necessary.

- Do not wear jewelry, chains, metal-frame eyeglasses, or other personal metal objects.

Remember, if the metal touches the machine, the flow of current increases because the metal is a conductor.

- Use only insulated probe tips or extenders. Remember, worn or cracked insulation is unsafe.

- Use only one hand while you are working on live equipment. Keep the other hand in your pocket or behind your back. Remember, there must be a complete circuit for an electrical shock to occur. This precaution prevents your body from completing the circuit.

- When you use a tester, set its controls correctly and use insulated probes that have the correct electrical specification.

- Do not touch objects that are grounded, such as metal floor strips, machine frames, or other conductors. Use suitable rubber mats obtained locally, if necessary.

- When you are working with machines having voltages more than 30 Vac or 42 Vdc, observe the special safety instructions given in customer engineering memorandums (CEMs).

- Never assume that power has been removed from a circuit. First, ensure that power has been removed.

- Do not touch live circuits with the surface of a plastic dental mirror. Remember, the surface of the dental mirror is conductive and can cause damage or personal injury.

- If an electrical accident occurs:

- Use caution. Do not be a victim yourself.

- Switch off the power.

- Instruct another person to get medical aid.

- If the victim is not breathing, perform mouth-to-mouth rescue breathing. See "Electrical Accidents-First Aid."

#### **Mechanical Safety**

Do not touch moving mechanical parts when you are lubricating a part, checking for play, or doing other similar work.

#### Safety Glasses

Wear safety glasses when:

- Using a hammer to drive pins or other similar parts

- Using a power drill

- Using a spring hook to attach or remove a spring

- Soldering parts

- Cutting wire or removing steel bands

- Using solvents, chemicals, or cleaners to clean parts

- Working in any other conditions that could injure your eyes

#### **Tools, Testers, and Field-Use Materials**

- Do not use tools or testers that have not been approved by IBM. Ensure that electrical hand tools, such as Wire-Wrap<sup>1</sup> tools and power drills, are inspected regularly.

- Exchange worn or broken tools or testers.

- Do not use solvents, cleaners, or lubricants that have not been approved by IBM.

#### Summary

Prevention is the main aid to electrical safety. Always think about electrical safety and use good practice; for example:

- Ensure that the customer's power receptacle matches the IBM equipment specifications.

- Inspect power cables and plugs; check for loose, damaged, or worn parts.

- Review the procedures in the maintenance documents before you remove a part that can hold an electrical charge from the machine. Carefully discharge the necessary parts exactly as instructed by the procedure.

Never assume that a machine or a circuit is safe. No machine is always completely safe. You may not know the exact condition of a machine because, for example:

- The power receptacles could be wrongly wired.

- Safety devices or features could be missing or defective.

- The maintenance or machine level change history could be wrong or not complete.

- The design could have a problem.

- The machine could have been damaged when it was shipped.

- The machine could have an unsafe change or attachment.

- An engineering change or a sales change could be wrongly installed.

- The machine could be deteriorated because it is old, or because it operates in an extreme environment.

- A part could be defective, therefore causing a hazard.

- A part could be wrongly assembled.

These are some of the ways that the condition of the machine could affect safety. Before you start a service call or procedure, have good judgment and use caution.

#### **Electrical Accidents-First Aid**

When performing rescue procedures for an electrical accident, do as follows:

- Use Caution: If the victim is touching the electrical-current source, remove the power. To do this, you may need to operate the room emergency power-off switch or the disconnecting switch. If you cannot find the switch, use a dry wooden rod or other nonconductive object to pull or push the victim away so he or she is not touching the electrical-current source.

- *Work Quickly:* If the victim is unconscious, he or she may need mouth-to-mouth rescue breathing and possibly external cardiac compression if the heart is not beating.

- *Get Medical Aid:* Instruct another person to dial the rescue service (such as the ambulance or the hospital).

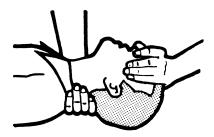

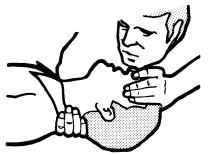

Determine if the victim needs mouth-to-mouth rescue breathing. If he or she does, perform the following steps:

#### DANGER

Use extreme care when you perform rescue breathing for a victim who may have breathed in toxic fumes. Do not breathe in air that the victim has breathed out.

|   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| • | • | • | • | • | • | • | • | • | • |   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |

| • | • |   | • | • | • |   | • |   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |   | • | • |

|   |   | • |   |   |   |   | • |   |   |   |   |   |   | • | • |   |   |   |   |   |   |   |   |   |   |   |   |

1. Prepare for rescue breathing:

- a. Ensure that the victim's airway is open and that it is not obstructed; check the mouth for objects that may be obstructing the airway, such as chewing gum, food, dentures, or the tongue.

- b. Place the victim on his or her back, put one hand behind the victim's neck, and put the other hand on his or her forehead.

- c. Lift the neck with one hand, and tilt the head backward by pressing on the forehead with the other hand.

- 2. Look, listen, and feel to determine if the victim is breathing freely.

- a. Put your cheek near the victim's mouth and nose.

- b. Listen and feel for the breathing out of air. At the same time, look at the victim's chest and upper abdomen to see if they move up and down.

- 3. If the victim is not breathing correctly:

- a. Keep the victim's head tilted backward. Continue to press on the forehead with your hand; at the same time, position the same hand so that you can pinch together the victim's nostrils with your thumb and finger.

b. Open your mouth wide and take a deep breath. Make a tight seal with your mouth around the victim's and blow into the victim's mouth.

c. Remove your mouth to let the victim breathe out, and check that the victim's chest moves down.

d. Repeat steps b and c once every 5 seconds either until the victim breathes for himself or herself, or until medical aid comes.

<sup>&</sup>lt;sup>1</sup> Trademark of the Gardner-Denver Co.

### **Reporting Accidents**

Report, to your field manager, all electrical accidents, possible electrical hazards, and accidents that nearly occurred. Remember, an accident that nearly occurs might be caused by a design problem; your immediate reporting ensures that the problem will be solved quickly.

Also report all small electrical shocks. Remember, a condition that causes a small shock need only differ slightly to cause serious injury.

## Contents

1

| OVERVIEW                                               |        |

|--------------------------------------------------------|--------|

| Introduction                                           | 10 100 |

|                                                        | 10-100 |

| LOCATIONS                                              |        |

|                                                        | 10.000 |

| Processing Unit Cards                                  | 10-200 |

| Top Card Connectors                                    | 10-205 |

| Channel Cables                                         | 10-210 |

| Control Panel FRUs                                     | 10-215 |

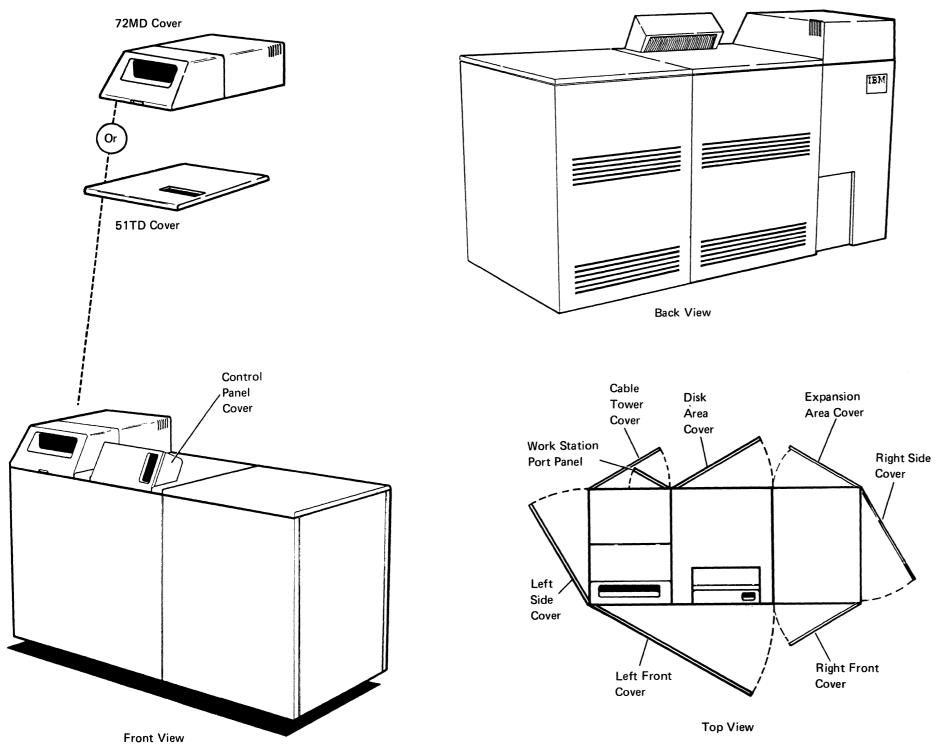

| Covers                                                 | 10-220 |

| Main Storage Card Types                                | 10-230 |

|                                                        |        |

| MAINTENANCE PROCEDURES                                 |        |

| SERVICE CHECKS AND REMOVAL PROCEDURES                  |        |

| Opening Covers                                         | 10-320 |

| Control Panel Removal                                  | 10-325 |

| How to Identify a Failing Main Storage Card            | 10-360 |

| DIAGNOSTIC INFORMATION                                 |        |

| IPL Good Machine Path                                  | 10-400 |

| MSP Test Unit Descriptions                             | 10-420 |

| Identifying MSP Instructions in Hexadecimal Format     | 10-430 |

| Identifying CSP Instructions in Hexadecimal Format     | 10-440 |

| Identifying CSP I/O Instructions in Hexadecimal Format | 10-450 |

| HOW TO INTERPRET ERAP REPORTS                          |        |

| CSP Error History Table                                | 10-500 |

| System Reference Code                                  | 10-502 |

| Processor Condition Register                           | 10-504 |

| Interrupt Level Backup Byte                            | 10-506 |

| Processor Error Byte                                   | 10-508 |

| Channel Error Byte                                     | 10-510 |

| Channel Register                                       | 10-512 |

| Storage Error Byte                                     | 10-514 |

| Microinstruction Address Register                      | 10-516 |

| Microinstruction Address Backup Register               | 10-518 |

| MSP Status Byte 4                                      | 10-520 |

| MSP Status Byte 5                                      | 10-522 |

| Failing 2K Page of Main Storage                        | 10-524 |

| Work Registers 0 through 7                             | 10-526 |

| MSP Error History Table                                | 10-550 |

| System Reference Code                                  | 10-552 |

| MSP Status Byte 0                                      | 10-552 |

| MSP Status Byte 0                                      | 10-556 |

| MSP Status Byte 4                                      | 10-558 |

| MSP Status Byte 5                                      | 10-558 |

| Failing 2K Page of Main Storage                        | 10-562 |

| OP Register                                            | 10-564 |

|                                                        | 10-364 |

| Q-Byte                                                 |        |

| Program Mode Register                                  | 10-568 |

| Instruction Address Register                           | 10-570 |

| Address Recall Register                                | 10-572 |

| XR1                                                    | 10-574 |

| XR2                                                    | 10-576 |

| OP1                                                    | 10-578 |

| OP2                                                    | 10-580 |

| PSREG                                                  | 10-582 |

| ATRS IR                                                | 10-584 |

| ATRS 01                                                | 10-586 |

| ATRS 02                                                | 10-588 |

| Q-Register                                             | 10-590 |

| Backup Mode Register                                   | 10-592 |

| PACT Registers                                         | 10-594 |

|                                                        |        |

#### FRU DESCRIPTIONS

| FRU DESCRIF HUNS                                       |        |

|--------------------------------------------------------|--------|

| Processing Unit FRUs                                   | 10-600 |

| CONTROL STORAGE PROCESSOR                              |        |

| CSP Card                                               | 10-610 |

| Channel                                                | 10-615 |

| Control Storage                                        | 10-620 |

| MAIN STORAGE PROCESSOR                                 | 10 020 |

| MSP Card                                               | 10-650 |

|                                                        |        |

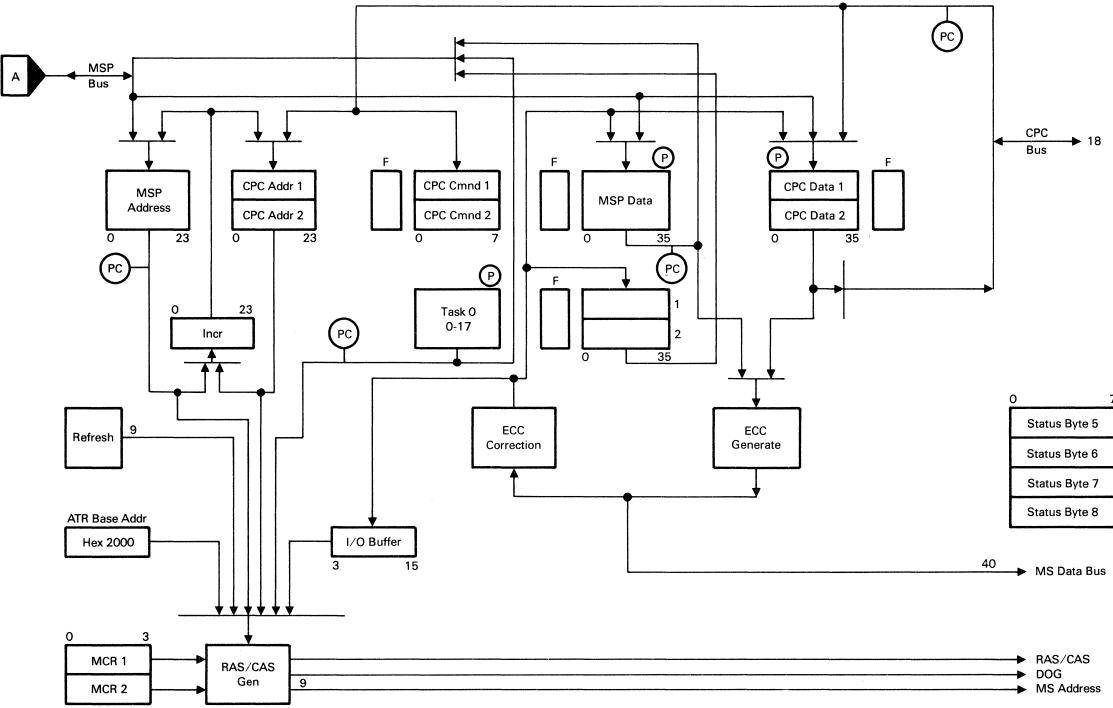

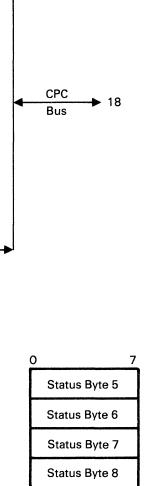

| MSP Use of Addressing                                  | 10-655 |

| Instruction Formats                                    | 10-660 |

| Main Storage Addressing                                | 10-670 |

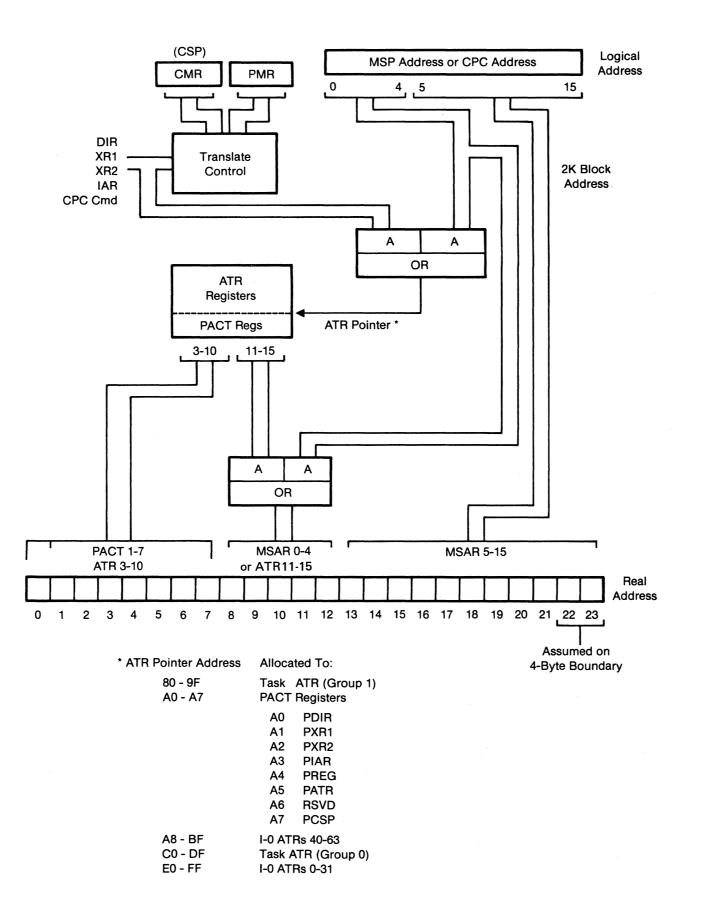

| Main Storage                                           | 10-675 |

| CONTROL PANEL                                          |        |

| Control Panel Interface Card                           | 10-680 |

| Control Panel Driver Board                             | 10-685 |

| Control Panel Display Board                            | 10-690 |

|                                                        |        |

| INTERFACE DESCRIPTIONS                                 |        |

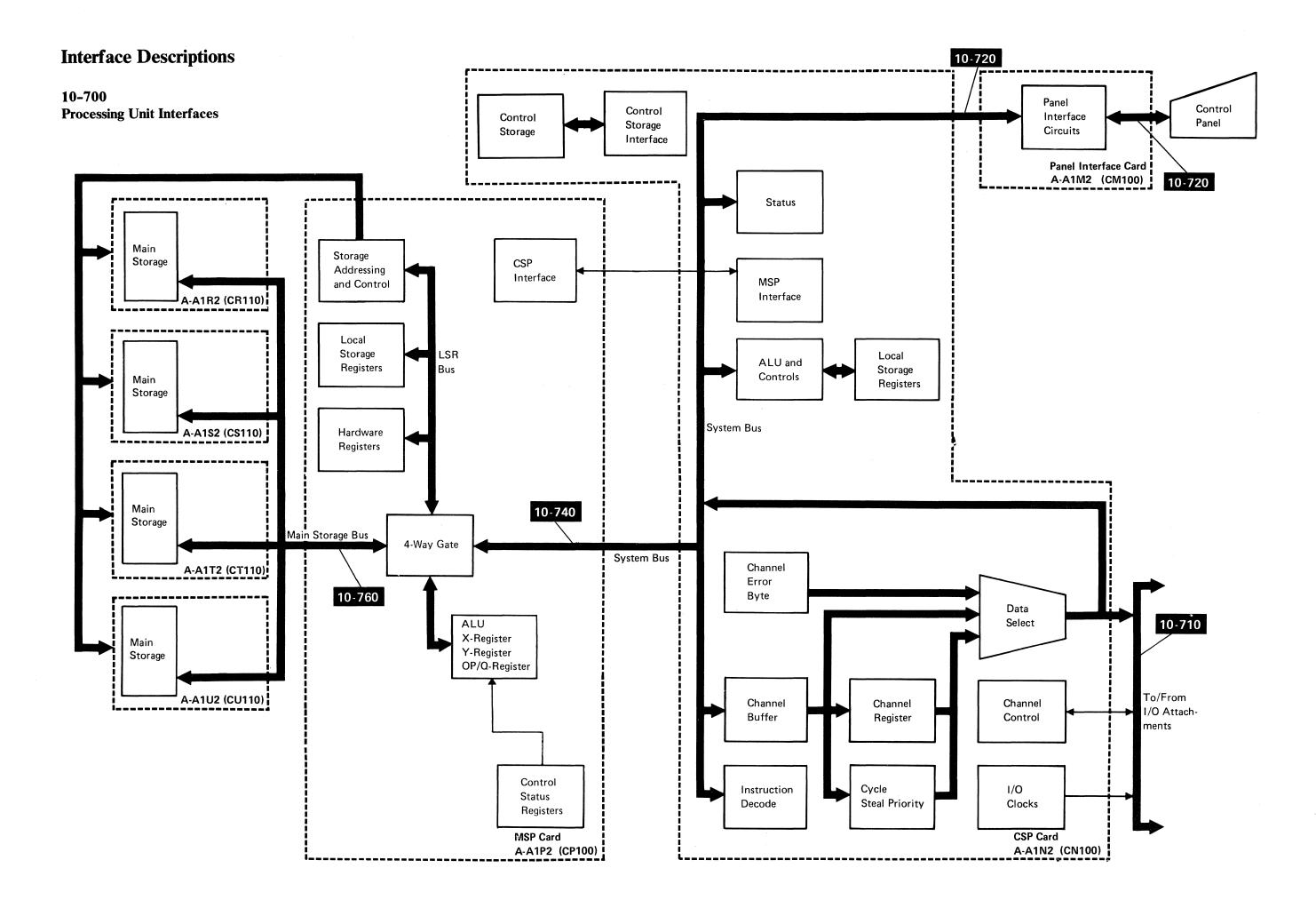

| Processing Unit Interfaces                             | 10-700 |

| Channel                                                | 10-710 |

| CSP to Control Panel                                   | 10-720 |

| CSP to MSP                                             | 10-740 |

| MSP to Main Storage                                    | 10-760 |

|                                                        | 10-700 |

| SEQUENCE OF EVENTS                                     |        |

| Initial Program Load                                   | 10-810 |

| 10SR Attachment IPL                                    | 10-810 |

| 51TD Attachment IPL                                    | 10-811 |

| 72MD Attachment IPL                                    | 10-813 |

|                                                        | 10-814 |

| General I/O Operation                                  |        |

| I/O Instruction Transfer                               | 10-821 |

| Cycle Steal Read from Main Storage                     | 10-822 |

| Cycle Steal Write to Main Storage                      | 10-823 |

| Single Read from Main Storage                          | 10-824 |

| Single Write to Main Storage                           | 10-825 |

| Channel Errors                                         | 10-830 |

| CSP or Cycle Steal Sense of MSP Register               | 10-840 |

| CSP or Cycle Steal Load of MSP Register                | 10-841 |

| Main Storage Read                                      | 10-850 |

| Main Storage Refresh                                   | 10-852 |

| Main Storage Write                                     | 10-853 |

| MSP Instruction Fetch                                  | 10-860 |

| MSP Instruction Operation for Two-Address Instructions | 10-861 |

| MSP Instruction Operation for One-Address Instructions | 10-862 |

| MSP Instruction Operation for Control Instructions     | 10-863 |

| MSP Fast Task Save                                     | 10-865 |

| MSP Fast Task Load                                     | 10-866 |

| MSP Alternate Mode                                     | 10-870 |

|                                                        | 20 010 |

|                                                        |        |

INDEX ...... X-1

Contents ix

### Overview

#### 10-100 Introduction

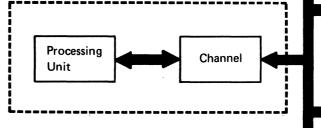

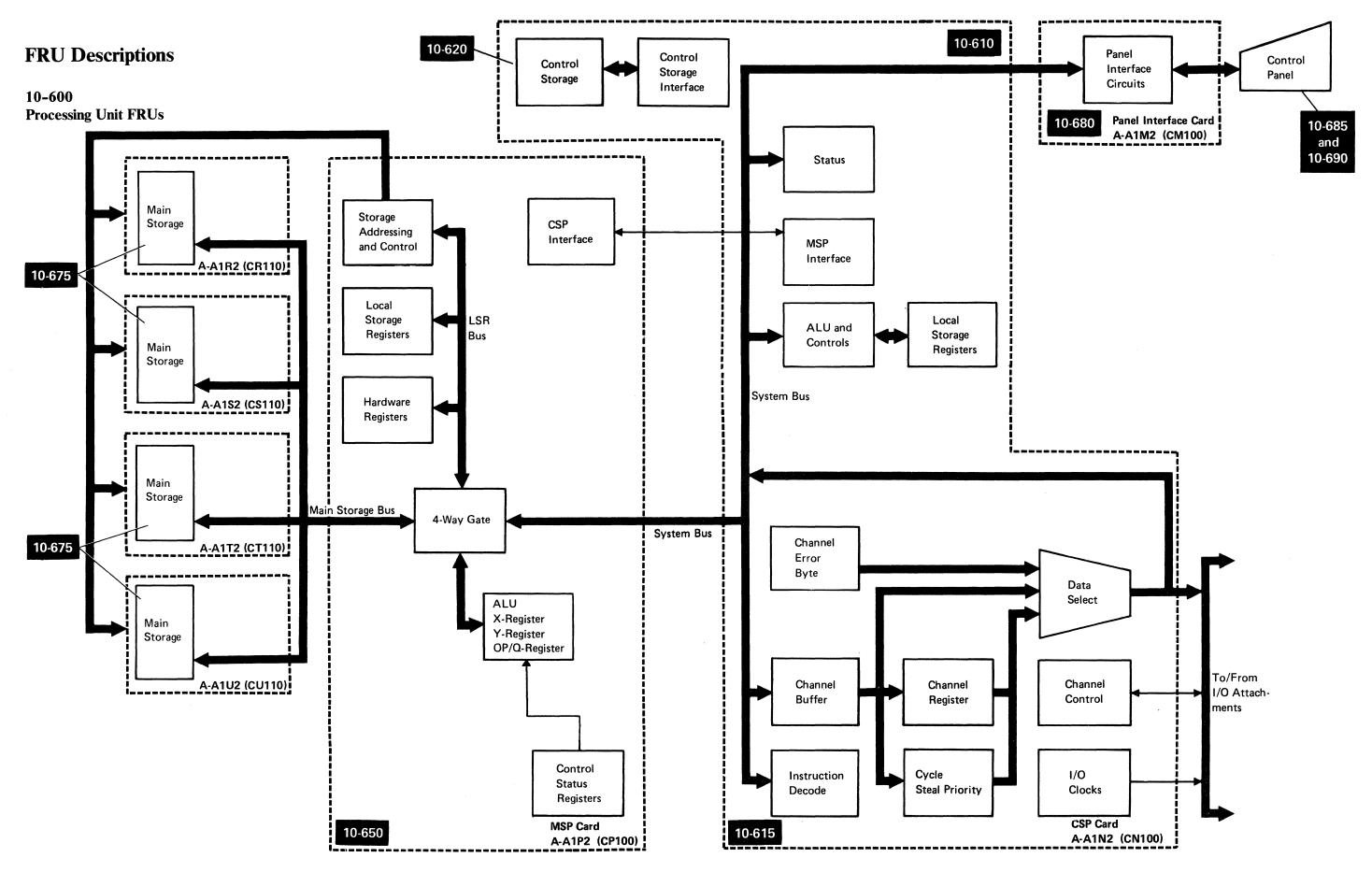

The IBM System/36 is made up of the following parts:

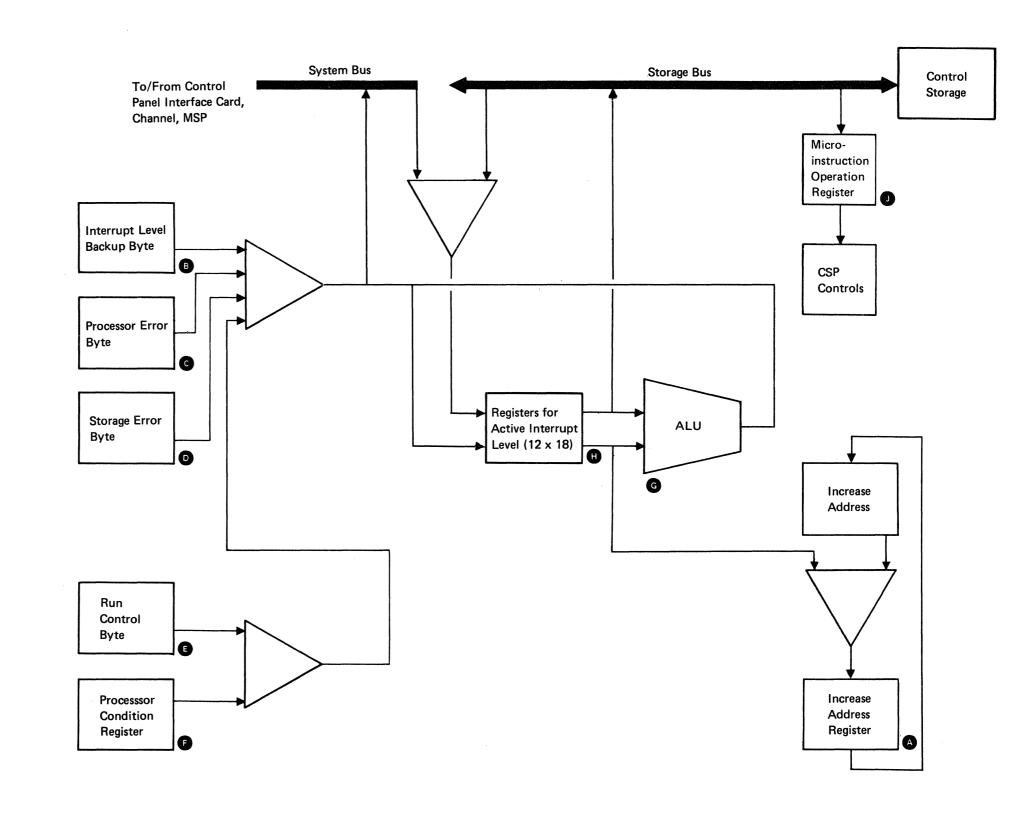

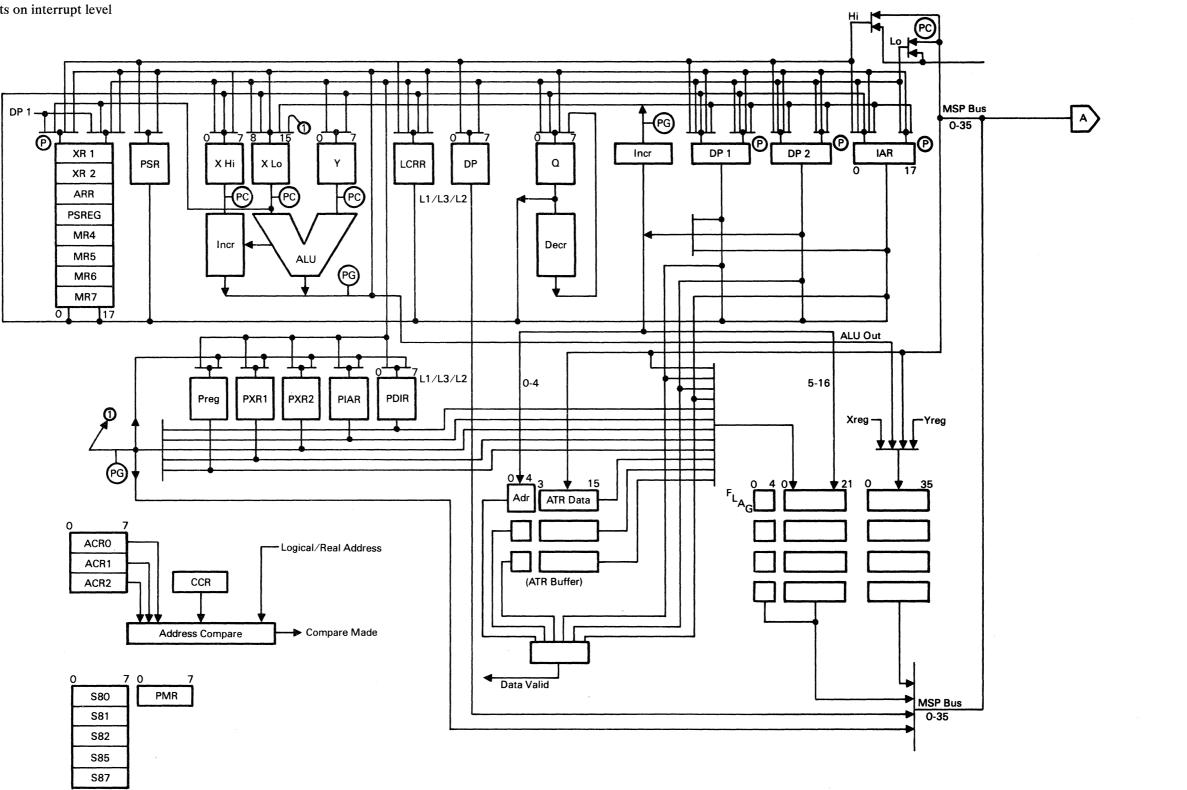

- Processing unit: The processing unit includes:

- The main storage processor (MSP) for user programs

- Main storage

- The control storage processor (CSP) for system control

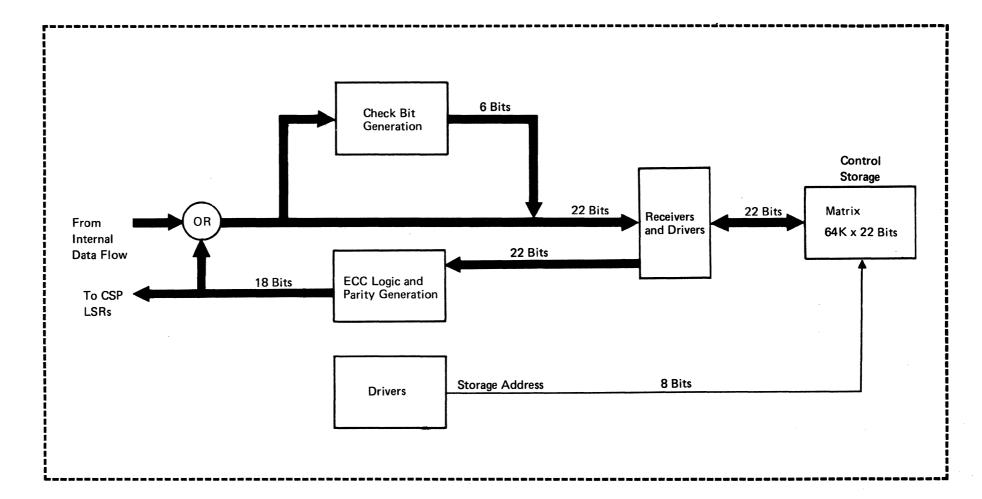

- Control storage

- The control panel

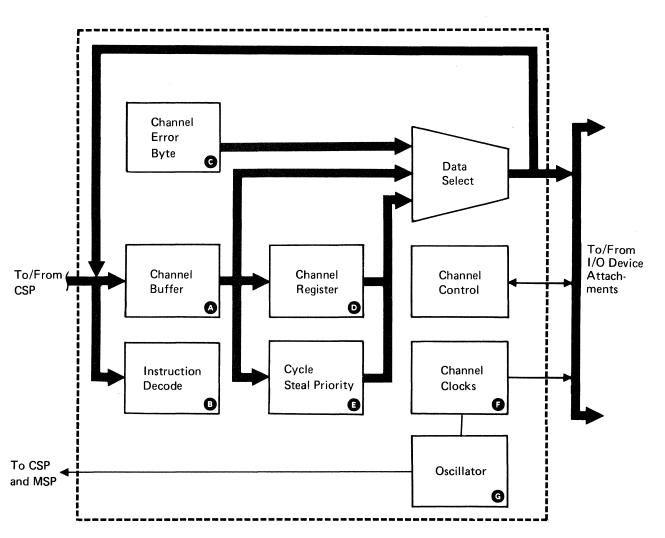

- Channel: The channel is the link between the processing unit and the I/O attachments. It supplies a data path and control circuits to transfer data between the I/O attachments and any part of the processing unit.

- Work station attachment: The work station attachment connects the channel to up to 72 work station devices (display stations or printers). The attachment supplies control circuits for data transfer between the devices and the channel.

- Data communications attachment: The data communications attachment can be a single-line communications attachment (SLCA), a multiline communications attachment (MLCA), or an eight-line communications attachment (ELCA). The SLCA connects one data communications line to the channel; the MLCA connects up to four data communications lines to the channel; the ELCA connects up to eight data communications lines to the channel. Each communications line can be controlled by either binary synchronous communication (BSC) or synchronous data link control (SDLC) line protocols.

- Data storage attachment: The data storage attachment connects the channel to the following:

- Disk drive adapters, for storage of large blocks of data such as user programs, large data files, and the System Support Program Product (SSP).

- A diskette drive adapter (or a diskette magazine drive adapter), for offline storage of data and to save and restore data from the system disk files.

- A tape adapter, for offline storage of data and to save and restore data from the system disk files.

- Printer attachment: The printer attachment connects a system-controlled printer to the channel for printed output.

- 1255 MCR attachment: The 1255 magnetic character reader (MCR) attachment connects the channel to a 1255 MCR for input of data that is read from source documents.

- Local area network attachment: The local area network attachment connects the channel to an IBM PERSONAL COMPUTER AT<sup>®</sup>. The Personal Computer AT connects to the local area network.

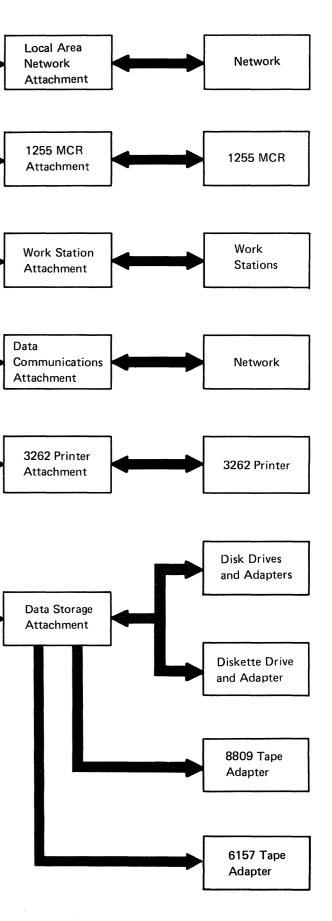

### Locations

<sup>1</sup> If you add or remove any main storage cards, you must reconfigure main storage. A-A1U2 must contain a 1024K-byte main storage card.

<sup>2</sup>A-A1V3 contains this cable only if SLCA is installed.

<sup>3</sup> If the channel crossover cables are IBM part 2595676, they are installed on the pin side only. See the labels for correct installation.

Locations 10-200

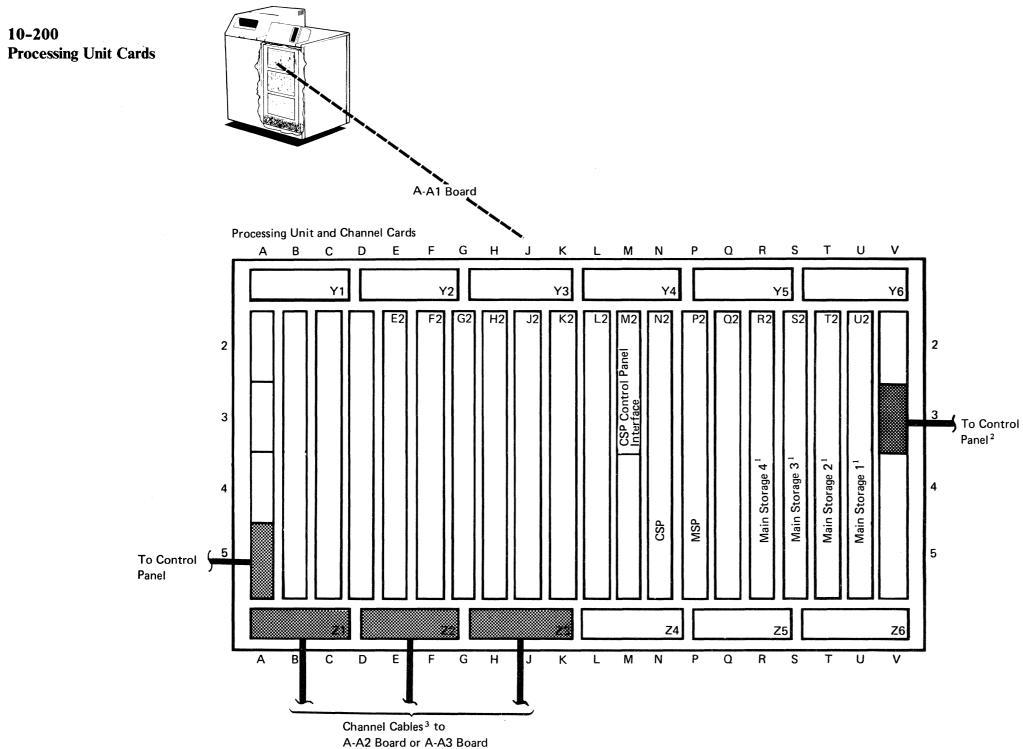

### 10-205 Top Card Connectors

#### Notes:

- 1. Top card connectors W and X:

- Have the same part number (IBM Part 6819205)

- Can be swapped with each other, but not with the top card connectors Y and Z.

- Can be installed only so that the housing of the top card connector matches the pin connectors of the cards.

- 2. Top card connectors Y and Z:

- Have the same part number (IBM Part 6819202)

- Can be swapped with each other, but not with the top card connectors W and X.

- Can be installed only so that the housing of the top card connector matches the pin connectors of the cards.

#### 10-205

á i.

### 10-210 **Channel Cables**

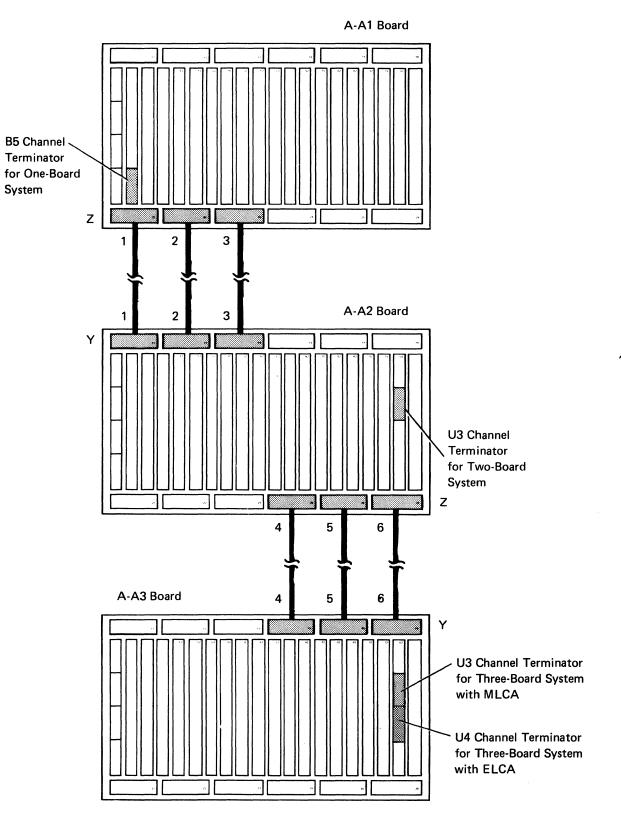

One-Board Systems, or Two- or Three-Board Systems with A2 Board Installed

Note: If the channel crossover cables are IBM part 2595676, they are installed on the pin side only. See the labels for correct installation.

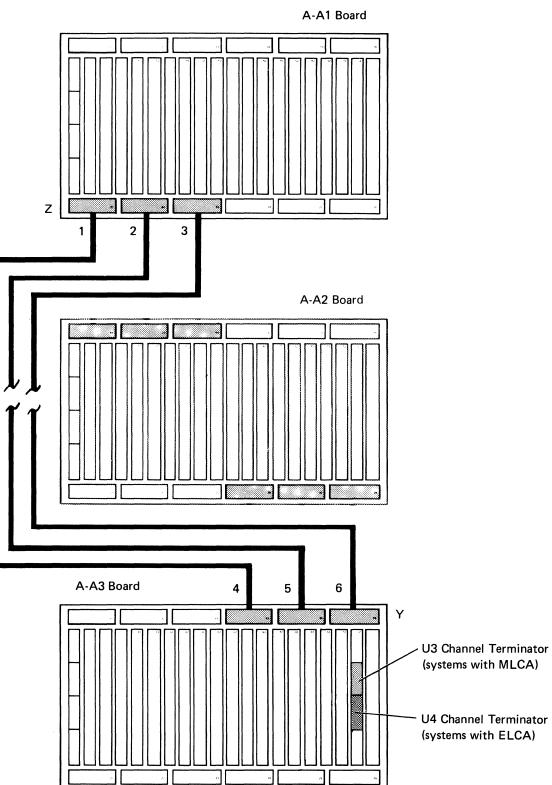

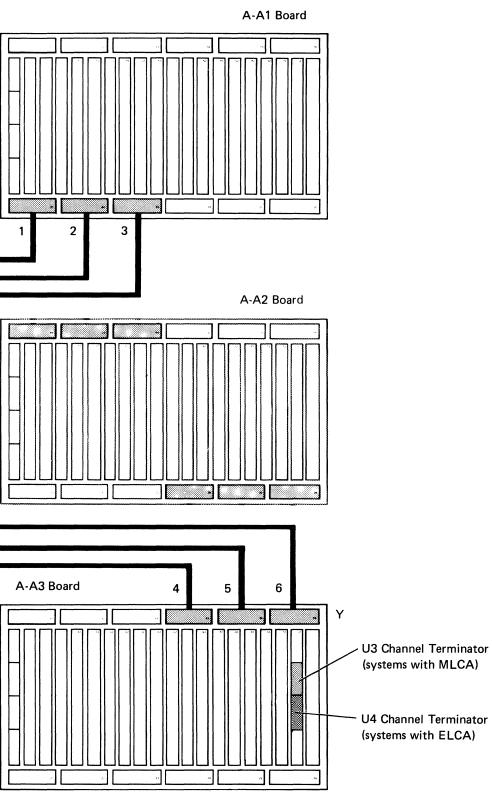

Two-Board Systems without A2 Board Installed

×.

Locations 10-220

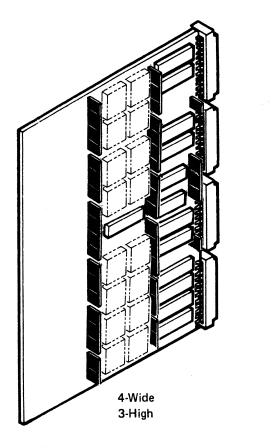

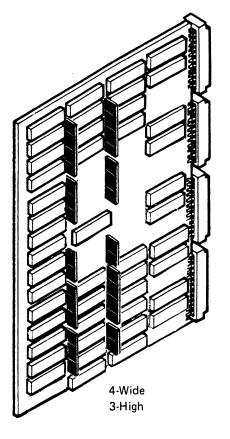

### 10–230 Main Storage Card Types

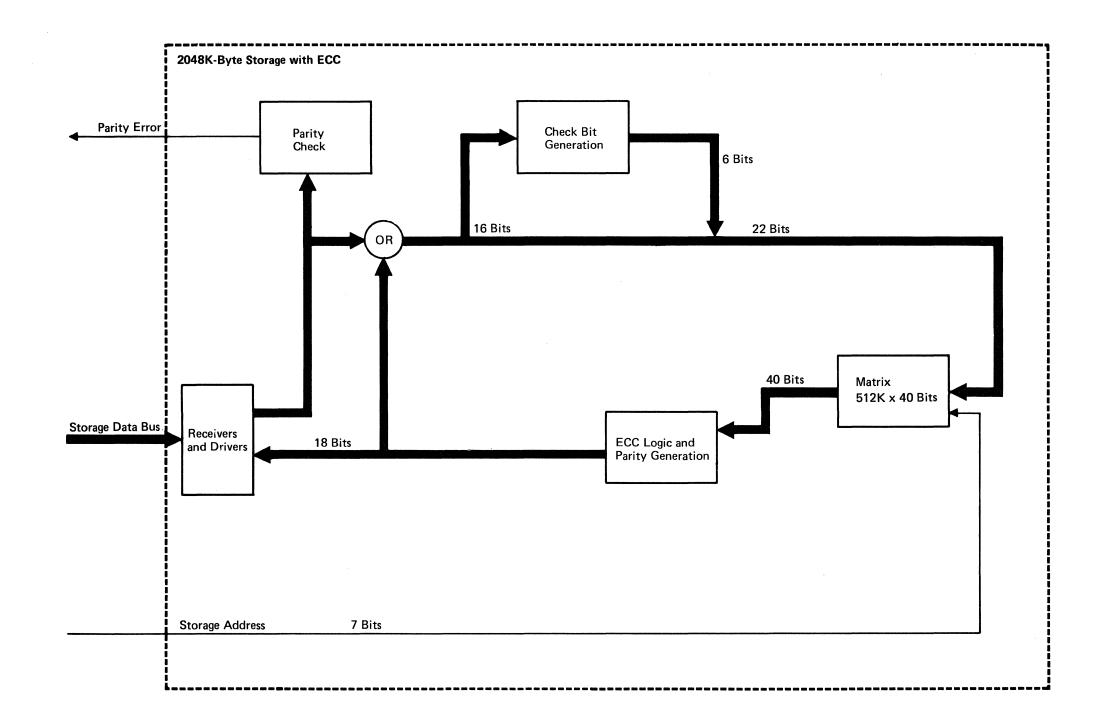

1024K Bytes with ECC

Used for Main Storage (A-A1U2, A-A1T2, A-A1S2, and A-A1R2)

2048K Bytes with ECC

:

Used for Main Storage (A-A1T2, A-A1S2, and A-A1R2)

### **Maintenance Procedures**

# SERVICE CHECKS AND REMOVAL PROCEDURES

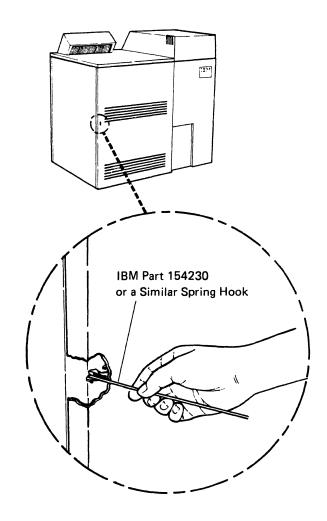

### 10-320 Opening Covers

A latch inside each System/36 cover holds the cover closed. To open the cover:

1. Insert a spring hook (IBM part 154230 or a similar spring hook) into the access slot in the cover.

#### DANGER

You can injure your hand when opening or closing the logic gate.

You can jam your hand between the top of the gate and the frame. Pull on the rear of the gate to open it, and push on the front of the gate to close it.

| • | • | • | • | · | • | • | • | • | • | • | • | • | • | • | • | • | • | ٠ | • | • | • | • | • | • | • |  |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |  |

|   |   | • | • | • | • | • | • | • | • | • | • | • |   |   | • |   |   |   |   | • | • |   | • |   | • |  |

|   |   | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |  |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

2. Pull out on the latch with the spring hook to open the cover.

\_\_\_\_

Maintenance Procedures 10-320

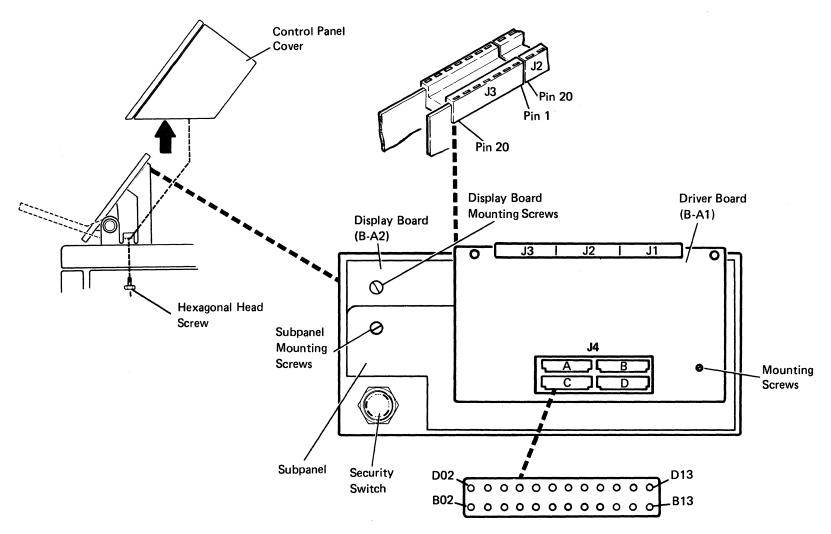

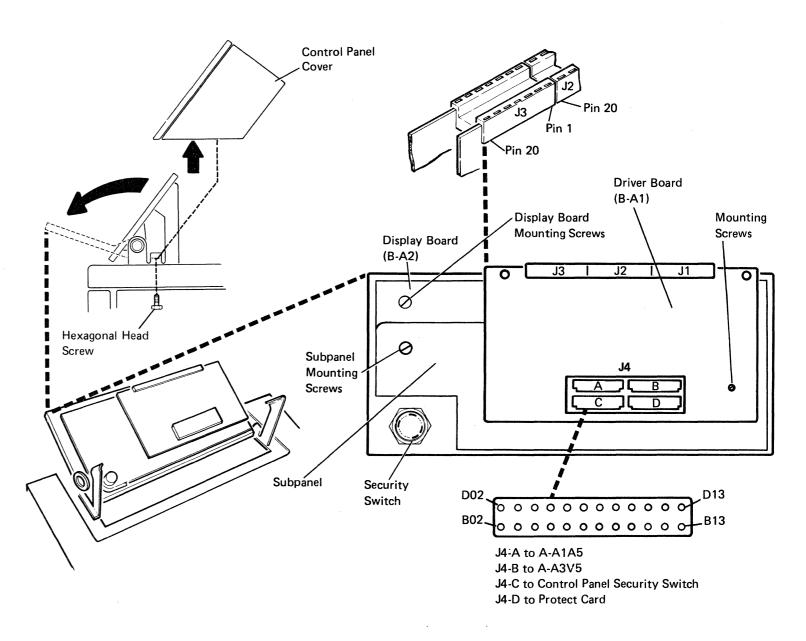

### 10-325 Control Panel Removal

Perform the following steps to remove a control panel FRU:

- 1. Power off (01-115).

- 2. Set CB1 to off.

- 3. Disconnect the line cord.

#### DANGER

You can injure your hand when opening or closing the logic gate.

You can jam your hand between the top of the gate and the frame. Pull on the rear of the gate to open it, and push on the front of the gate to close it.

- 4. Open the front cover and open the logic gate.

- 5. Locate and remove two control panel cover mounting screws (under the control panel).

- 6. Lift the cover off the control panel.

- 7. Tilt the control panel forward to access the rear of the panel.

- 8. Remove and label the cables from connectors J4-A, B, C, and D.

**Note:** In the following steps, keep the panel in a horizontal position to prevent losing small parts.

9. Remove the driver board mounting screws and the driver board.

#### CAUTION

When you remove the two subpanel mounting screws that are behind the communications display, the communications display comes off.

10. While supporting the communications display from the bottom of the panel, remove the subpanel mounting screws, the communications display, and the subpanel.

#### CAUTION

Panel switch keybuttons are pulled loose when you remove the display board. Be careful not to lose or damage them.

11. Remove the display board mounting screws and the display board.

12. Remove the rubber cover from the display board if it is still attached.

Perform the steps in reverse order to assemble. Top connectors must be on the display board before you reinstall the display board.

)

### 10-360 How to Identify a Failing Main Storage Card

If exchanging the card indicated by the system reference code (see MAP 0113, MAP 0114, MAP 0115, and MAP 0116) does not repair a main storage problem, use the following procedure to identify the failing main storage card:

Check the MSP error history table (10-550) to determine if any of the following bits of status byte 4 (10-558) are on:

| Bit(s) | Description                |

|--------|----------------------------|

| 4      | Single-bit storage error   |

| 5      | Multiple-bit storage error |

2. If any of the bits in step 1 are on, use the entry labeled "Fail 2K" in the MSP error history table (10-550) to determine the Fail 2K Value. Find this Fail 2K Value in the first column of the table below. Then, read across to the failing card in the column that matches the largest main storage card installed on the system. See 10-230 to determine card types.

|               | Main Storage Card Types |                            |  |  |  |  |  |

|---------------|-------------------------|----------------------------|--|--|--|--|--|

|               | Only 1024 Kb<br>Cards   | Largest Card<br>is 2048 Kb |  |  |  |  |  |

| Fail 2K Value | Failing Card            | Failing Card               |  |  |  |  |  |

| 0000 to 01FF  | A-A1U2                  | A-A1U2                     |  |  |  |  |  |

| 0200 to 03FF  | A-A1T2                  | A-A1T2                     |  |  |  |  |  |

| 0400 to 05FF  | A-A1S2                  | A-A1S2                     |  |  |  |  |  |

| 0600 to 07FF  | A-A1R2                  | A-A1R2                     |  |  |  |  |  |

| 0800 to 09FF  | -                       | A-A1U2                     |  |  |  |  |  |

| 0A00 to 0BFF  | _                       | A-A1T2                     |  |  |  |  |  |

| 0C00 to 0DFF  | -                       | A-A1S2                     |  |  |  |  |  |

| 0E00 to 0FFF  | -                       | A-A1R2                     |  |  |  |  |  |

Maintenance Procedures 10-360

### **DIAGNOSTIC INFORMATION**

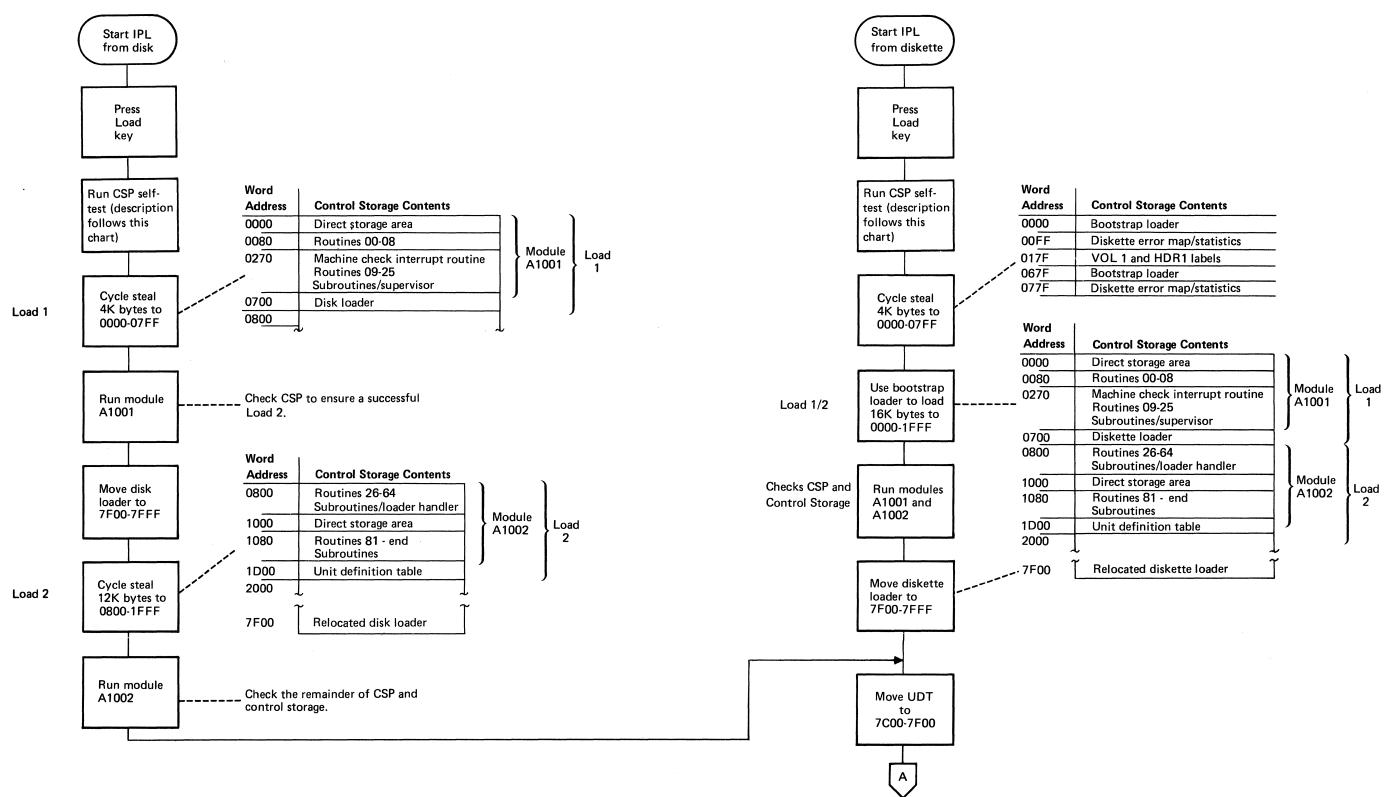

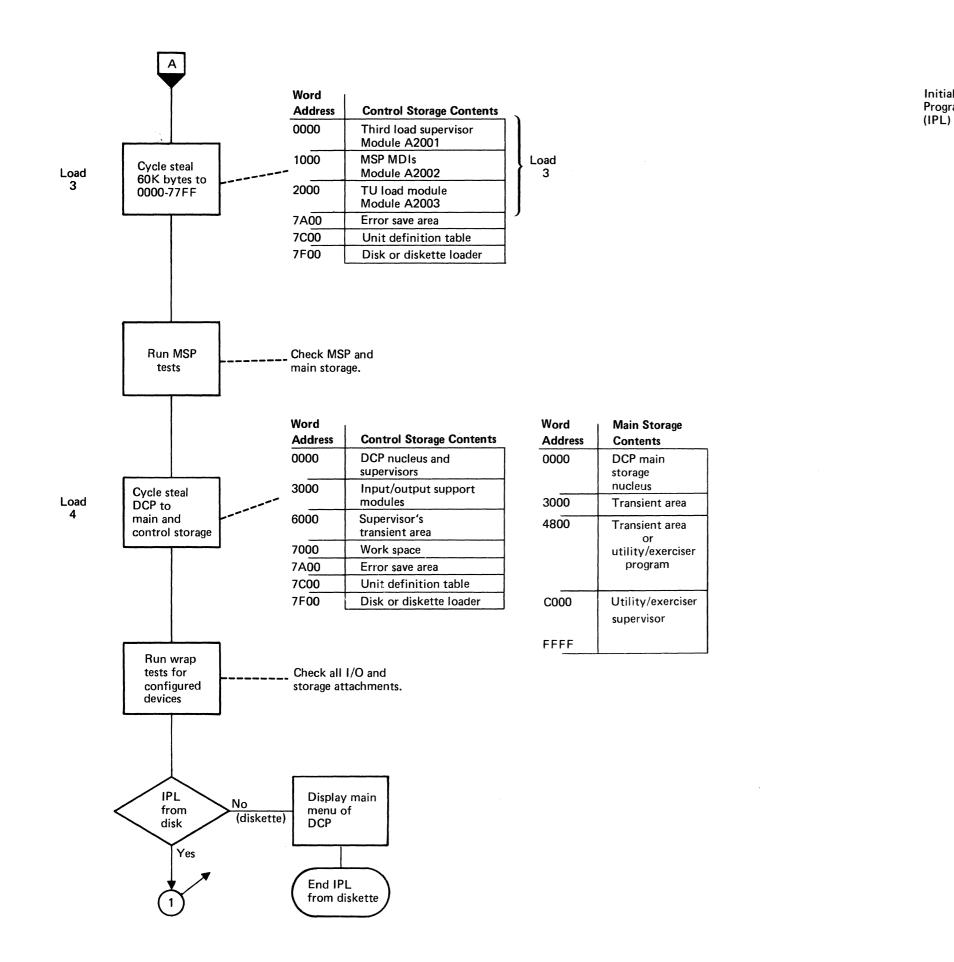

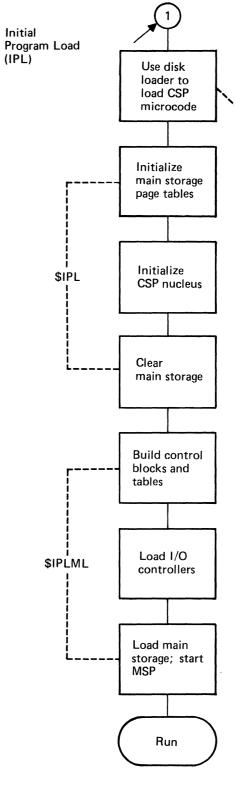

### 10-400 IPL Good Machine Path

When the Load key on the control panel is pressed (01-140), the system automatically runs diagnostic tests that check the operation of the CSP and control storage, the channel, the MSP and main storage, and wrap tests with all configured I/O devices. When these tests complete without error, the System Support Program Product (SSP) can be loaded.

Ó

The IPL diagnostics are stored on the load device (either disk or diskette). The load process is different for each device, as shown in the following charts. However, in each case, the IPL diagnostics run as follows:

- CSP Self-Test: Basic check of CSP and control storage, and partial check of channel

- Load 1: Initial check of CSP, control storage, and channel

- Load 2: Complete check of CSP, control storage, and channel

- Load 3: Complete check of MSP and main storage

- Load 4: I/O wrap tests

Maintenance Procedures 10-400

### 10-400 (continued) **IPL Good Machine Path**

| Word    | Control Stores Contents                                                       |

|---------|-------------------------------------------------------------------------------|

| Address | Control Storage Contents                                                      |

| 0000    | Segment 0: common<br>routines and disk I/O                                    |

| 1000    | Segment 1: nucleus                                                            |

| 2000    | Segment 2: nucleus and work station/printer I/O                               |

| 3000    | Segment 3: nucleus                                                            |

| 4000    | Segment 4: nucleus, tables, and transient area 4C00                           |

| 5000    | Segment 5: diskette I/O,<br>communications I/O,<br>and concurrent maintenance |

| 6000    | Segment 6: IPL code                                                           |

| 7000    | Segment 7: relocatable code<br>and machine check logout                       |

|         |                                                                               |

See *IBM System/36 Control Storage Service Information Manual.*

### 10-400 (continued) IPL Good Machine Path

### CSP Self-Test

The CSP self-test consists of modules 0 through 21. These modules check the basic operation of the CSP and control storage and perform a partial check of the channel. The modules are loaded from the control panel interface card to control storage when the Load key is pressed. CSP self-test modules do not use result bytes. If an error occurs, the system reference code (SRC) appears on the control panel display. The CSP self-test modules run in the following sequence.

| Self-Test<br>Module | Description                                                                             | System<br>Reference<br>Code |

|---------------------|-----------------------------------------------------------------------------------------|-----------------------------|

| 0                   | Initialize the machine check MAB to E880.                                               | FFFF                        |

| 1                   | Test unconditional branching.                                                           | E880                        |

| 2                   | Test conditional branch by setting the PCR.                                             | E881                        |

| 3                   | Test the subroutine linkage.                                                            | E882                        |

| 4                   | Test the test mask instruction.                                                         | E883                        |

| 5                   | Test for the correct selection of bytes in work registers.                              | E884                        |

| 6                   | Test the compare immediate instruction.                                                 | E885                        |

| 7                   | Test the subtract immediate instruction.                                                | E886                        |

| 8                   | Test all 1-byte logical instructions.                                                   | E887                        |

| 9                   | Test all 1-byte arithmetic instructions.                                                | E888                        |

| 10                  | Test all 2-byte logical instructions.                                                   | E889                        |

| 11                  | Test all 2-byte, and 2-byte with 1-byte, arithmetic instructions.                       | E88A                        |

| 12                  | Test all hexadecimal branch instructions.                                               | E88C                        |

| 13                  | Test all hexadecimal move instructions.                                                 | E88E                        |

| 14                  | Initialize the low 32K words of control storage.                                        | E88F                        |

| 15                  | Test storage data and ECC check bits.                                                   | E890<br>E893                |

| 16                  | Test base + displacement instructions.                                                  | E894                        |

| 17                  | Test full-word and half-word load and store instructions. Test load from a direct area. | E895<br>E896<br>E897        |

| Self-Test<br>Module | Description                                                    | System<br>Reference<br>Code |

|---------------------|----------------------------------------------------------------|-----------------------------|

| 18                  | Test the following:                                            |                             |

|                     | 1. Channel register                                            | E898                        |

|                     | 2. Channel DBO and DBI bus                                     | E899                        |

|                     | 3. Set machine check level                                     | E89C                        |

|                     | 4. Sensing a not valid device address                          | E89F                        |

|                     | 5. Sensing a CPC bus parity check                              | E8A0                        |

|                     | 6. Sensing a parity check in OUT1 gate                         | E8A2                        |

|                     | 7. Sensing a channel check                                     | E8A6                        |

|                     | 8. Sensing a parity check in OUT2 gate                         | E8A8                        |

|                     | 9. Channel bits                                                | E8AA                        |

|                     | 10. LSR exception check                                        | E8AD                        |

| 19                  | Test the following:                                            |                             |

|                     | 1. Enable interrupts                                           | E8AE                        |

|                     | 2. Interrupt level 5                                           | E8AF                        |

|                     | -                                                              |                             |

| 20                  | Test the following:                                            |                             |

|                     | 1. Enable and disable interrupts using the 8-millisecond timer | E8B0                        |

|                     | 2. Interrupt levels 1 through 4 using the 8-millisecond timer  | E8B0<br>E8B1                |

|                     |                                                                |                             |

| 21                  | Test load and sense of the run control byte.                   | E8B2                        |

|                     | Update SRC on exit from the self-test.                         | E8B3                        |

|                     |                                                                |                             |

### Load 1 Diagnostic Routines

Load 1 consists of diagnostic routines 00 through 25, the needed supervisor functions for running the routines, and a loader. The routines check the basic operation of the CSP and control storage to ensure that the remaining tests can be loaded. Load 1 routines do not use result bytes. If an error occurs, the system reference code (SRC) appears on the control panel display. Load 1 routines run in the following sequence.

| Routine | Description                                                                                                                                                | System<br>Reference<br>Code |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 00      | Test unconditional branching to some addresses.                                                                                                            | E900                        |

| 01      | Test conditional branching. The CSP must have been reset when the Load key was pressed.                                                                    |                             |

| 02      | Test conditional branching by setting the condition register. This routine uses the SBN, SBF, and load PCR instructions.                                   |                             |

| 03      | Test the test mask instruction. This routine uses SBN, SBF, and<br>branch on condition (BOC) instructions to test mask the low byte of<br>work register 1. |                             |

| 04      | Test the test mask instruction. This routine uses SBN, SBF, and BOC instructions to test mask the high byte of work register 1.                            |                             |

| 05      | Test the load immediate instruction. This routine uses the TM and conditional branch instructions.                                                         |                             |

| 06      | Test the compare immediate instruction. This routine uses the LI and conditional branch instructions.                                                      |                             |

| 07      | Test the branch and link instruction and the return instruction.<br>This routine uses the LI, CI, MVR, and conditional branch instructions.                |                             |

| 08      | Test the sense input register instruction. This routine performs the sense and checks that no error occurs.                                                |                             |

| 09      | Test the subtract 1 from a register instruction (1 byte minus 1). This routine uses the LI, CI, and BOC instructions.                                      | E909                        |

| 10      | Test the add 1 to a register instruction (1 byte plus 1). This routine uses the LI, CI, and BOC instructions.                                              | E910                        |

| Routine | Description                                                                                                                                                                                                                            | System<br>Reference<br>Code |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 11      | Test the subtract 1 from a register instruction (2 bytes minus 1). This routine uses the LI, CI, and BOC instructions.                                                                                                                 | E911                        |

| 12      | Test the add registers instruction (2 bytes plus 1 byte). This routine uses the LI, CI, branch on condition, and MPLF reset carry instructions.                                                                                        | E912                        |

| 13      | Test the add registers instruction (2 bytes plus 2 bytes).<br>This routine uses the LI, CI, branch on condition, and<br>MPLF reset carry instructions.                                                                                 | E913                        |

| 14      | Test the subtract registers instruction (2 bytes minus 2 bytes).<br>This routine uses the LI, CI, branch on condition, and MPLF reset<br>carry instructions.                                                                           | E914                        |

| 15      | Test the load register from a direct area of control storage<br>instruction. This routine uses the LI, CI, and BOC instructions<br>and performs multiple tests of this instruction.                                                    | E915                        |

| 16      | Test the store register to a direct area of control storage<br>instruction. This routine uses the LI, L, CI, and BOC instructions<br>and performs multiple tests of this instruction.                                                  | E916                        |

| 17      | Test the load register from control storage instruction. This routine uses the LI, CI, and BOC instructions and performs multiple tests of this instruction.                                                                           | E917                        |

| 18      | Test the store register to control storage instruction. This routine<br>uses the LI, LC, CI, and BOC instructions and performs multiple<br>tests of this instruction.                                                                  | E918                        |

| 19      | Test the channel. This routine uses I/O immediate instructions to<br>load and sense the channel register and compares the value sensed to<br>the value loaded. The routine also senses the channel error byte and<br>checks its value. | E919                        |

| 20      | Load and sense the processor condition register.                                                                                                                                                                                       | E920                        |

| 21      | Test the subtract immediate instruction.                                                                                                                                                                                               | E921                        |

| 22      | Test the add 1 to a register instruction (2 bytes plus 1). This routine uses the LI, CI, BOC, and reset carry/set equal instructions.                                                                                                  | E922                        |

| 23      | Test the OR registers instruction (1 byte with 1 byte).                                                                                                                                                                                | E923                        |

| 24      | Test the AND registers instruction (1 byte with 1 byte).                                                                                                                                                                               | E924                        |

| 25      | Test the shift left logical instruction. This routine shifts left 1 bit of a selected byte in a register.                                                                                                                              | E925                        |

### 10-400 (continued) IPL Good Machine Path

### Load 2 Diagnostic Routines

Load 2 consists of the remaining diagnostic routines for the CSP and control storage. The routines check the complete operation of the CSP and control storage. Load 2 routines do not use result bytes. If an error occurs, the system reference code (SRC) appears on the control panel display. Load 2 routines run in the following sequence.

•

| Routine | Description                                                                                                 | System<br>Reference<br>Code |

|---------|-------------------------------------------------------------------------------------------------------------|-----------------------------|

|         | Load module A1002.                                                                                          | E990                        |

| 26      | Test the exclusive OR registers instruction (1 byte with 1 byte).                                           | EA26                        |

| 27      | Test the AND complement registers instruction (1 byte with 1 byte).                                         | EA27                        |

| 28      | Test the OR complement registers instruction (1 byte with 1 byte).                                          | EA28                        |

| 29      | Test the add registers instruction (1 byte plus 1 byte).                                                    | EA29                        |

| 30      | Test the subtract registers instruction (1 byte minus 1 byte).                                              | EA30                        |

| 31      | Test the add registers with carry instruction (1 byte plus 1 byte).                                         | EA31                        |

| 32      | Test the subtract registers with borrow instruction (1 byte minus 1 byte).                                  | EA32                        |

| 36      | Test the exclusive OR registers instruction (2 bytes with 2 bytes).                                         | EA36                        |

| 37      | Test the OR registers instruction (2 bytes with 2 bytes).                                                   | EA37                        |

| 38      | Test the AND registers instruction (2 bytes with 2 bytes).                                                  | EA38                        |

| 39      | Test the AND complement registers instruction (2 bytes with 2 bytes).                                       | EA39                        |

| 40      | Test the OR complement registers instruction (2 bytes with 2 bytes).                                        | EA40                        |

| 41      | Test the shift left logical double instruction. This routine shifts left 1 bit of both bytes in a register. | EA41                        |

| 42      | Test the subtract registers instruction (2 bytes minus 1 byte).                                             | EA42                        |

| 43      | Test the subtract registers with borrow instruction (2 bytes minus 2 bytes).                                | EA43                        |

| 44      | Test the add registers with carry instruction (2 bytes plus 2 bytes).                                       | EA44                        |

| 45      | Test the move zone instruction.                                                                             | EA45                        |

| 46      | Test the hexadecimal branch instruction.                                                                    | EA46                        |

| 47      | Test the shift right logical and the shift right logical double instructions.                               | EA47                        |

| 48      | Test the direct storage areas of control storage.                                                           | EA48                        |

| 49      | Test the move register instruction.                                                                         | EA49                        |

| Routine | Description                                                                                                                                     | System<br>Reference<br>Code |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 50      | Test the zero and add registers instruction (1 byte with 1 byte).                                                                               | EA50                        |

| 51      | Test the 'I/O service request' latch.                                                                                                           | EA51                        |

| 53      | Sense the processor control byte and the processor error byte and test<br>the 'flag' latch in the processor condition register.                 | EA53                        |

| 55      | Test the I/O clocks.                                                                                                                            | EA55                        |

| 60      | Force a storage data register parity check, an X-register parity check, and a microinstruction operation register parity check.                 | EA60                        |

| 61      | Force, detect, and reset the following: device address not valid check and system bus parity check.                                             | EA61                        |

| 63      | Perform the control storage block tests.                                                                                                        | EA63                        |

| 64      | Test all control storage locations.                                                                                                             | EA64                        |

| 81      | Test the load high byte of a register from control storage instruction<br>and the store high byte of a register to control storage instruction. | EA81                        |

| 82      | Test the add n to a register instruction $(n = 1 \text{ through 16})$ (1 byte plus n and 2 bytes plus n)                                        | EA82                        |

| 83      | Test the branch extended instruction.                                                                                                           | EA83                        |

| 84      | Test the branch and link instruction.                                                                                                           | EA84                        |

| 85      | Test the compare registers instruction (1 byte with 1 byte and 2 bytes with 2 bytes).                                                           | EA85                        |

| 86      | Test the subtract n from a register instruction $(n = 1 \text{ through 16})$<br>(1 byte minus n and 2 bytes minus n).                           | EA86                        |

| 88      | Test the control storage base-plus-displacement instructions.                                                                                   | EA88                        |

| 89      | Test control storage ECC logic.                                                                                                                 | EA89                        |

| A1      | Test the level 5 interrupt.                                                                                                                     | EAA1                        |

| A2      | Test the fixed-interval timer at interrupt levels 1, 2, 3, and 4.                                                                               | EAA2                        |

| _       | Load MSP diagnostics.                                                                                                                           | EA90                        |

### Load 3 Diagnostic Routines

Load 3 diagnostic routines consist of test units (TUs) that test the complete operation of the MSP and main storage. The TUs run in the following sequence for a good machine path (if test option 0000 is selected). If errors occur, the test may branch to other tests not included here, or a system reference code (SRC) may appear on the control panel display (see MAP 0113, MAP 0114, MAP 0115, and MAP 0116). See 10-420 for a complete list of the MSP test units, a description of each TU, and the result bytes that each TU generates.

| TU<br>Sequence | Area Tested                                                    |

|----------------|----------------------------------------------------------------|

| T20B1          | Check test options                                             |

| T20EE          | PATR and MCR load/sense                                        |

| T20DA          | Task 0 ATR data                                                |

| T20DB          | Task 0 ATR parity check                                        |

| T20E2          | Load and store configuration control register (CCR)            |

| T20EF          | Address compare register 2                                     |

| T20F0          | Address compare register 1                                     |

| T20F1          | Address compare register 0                                     |

| T20E5          | MSP register load/sense                                        |

| T20F2          | CSP read/write MSP register immediate instructions             |

| T20E4          | LSR addressing                                                 |

| T20E3          | Reset MSP, sense status bytes, PSR,<br>OP register, Q-register |

| T207F          | Sense main storage and load MCR                                |

| T2082          | Sense bad main storage bits                                    |

| T20F5          | Auto configure                                                 |

| T20E6          | CCR and storage-not-valid check                                |

| T20E8          | Storage exception generation                                   |

| T20E9          | Single storage cell                                            |

| T20EA          | Single storage cell addressing                                 |

| T20EB          | Single storage cell addressing                                 |

| T20E0          | Main storage refresh                                           |

| T20B5          | Analyze results of main storage tests                          |

| T20EC          | Main storage real and translated addressing                    |

| T20ED          | Main storage real and translated addressing                    |

| T20E1          | 2-byte and base-plus-displacement main storage accesses        |

| T20DF          | Reset interrupt level 5                                        |

| T20E7          | Address translation registers                                  |

| T20DE          | ATR main storage access                                        |

| T20DD          | Main storage card ECC logic test                               |

| TU<br>Sequence | Area Tested                                                                          |

|----------------|--------------------------------------------------------------------------------------|

| T20B6          | Supervisor call instruction using<br>PACT, ATR task group 0, and<br>ATR task group 1 |

| T20BB          | Load register instruction                                                            |

| T20B7          | Branch on condition instruction                                                      |

| T20BC          | Store register instruction                                                           |

| T20C5          | Load address instruction                                                             |

| T20B8          | Jump on condition instruction                                                        |

| T20B9          | Jump backward instruction                                                            |

| T20C6          | Compare logical characters instruction                                               |

| T20BA          | Load program mode register instruction                                               |

| T20BF          | Branch on ARR instruction                                                            |

| T20BD          | Compare logical immediate instruction                                                |

| T20BE          | Move immediate instruction                                                           |

| T20C2          | Add to register instruction                                                          |

| T20CE          | Add logical characters instruction                                                   |

| T20C0          | Set bits on, set bits off instructions                                               |

| T20C1          | Test bits on, test bits off instructions                                             |

| T20C3          | Subtract from register instruction                                                   |

| T20C4          | Subtract logical immediate instruction                                               |

| T20C7          | Zero and add zoned decimal instruction                                               |

| T20C8          | Add zoned decimal instruction                                                        |

| T20C9          | Subtract zoned decimal instruction                                                   |

| T20CA          | Move hexadecimal character instruction                                               |

| T20CB          | Edit instruction                                                                     |

| T20CC          | Insert and test characters instruction                                               |

| T20CD          | Move characters instruction                                                          |

| T20CF          | Subtract logical characters instruction                                              |

| TU<br>Sequence | Area Tested                                                                |

|----------------|----------------------------------------------------------------------------|

| T20D2          | Shift right character instruction                                          |

| T20D4          | Many instructions, using both<br>PACT and ATR address translation<br>modes |

| T20D0          | MSP temporary suspend                                                      |

| T20D6          | MSP instruction step                                                       |

| T20D1          | X-register parity check                                                    |

| T20D5          | MSP soft stop                                                              |

| T20D7          | Address compare stop                                                       |

| T20F3          | Force storage exception on not valid address                               |

| T20F4          | Fast task load function                                                    |

| T20D9          | Fast task save                                                             |

| T20DC          | Storage extend cycle                                                       |

| T20D8          | Not valid operation code                                                   |

| T20B1          | Check for normal IPL                                                       |

| T20B4          | Set up MSP, using system UDT information                                   |

### 10-420 MSP Test Unit Descriptions

In addition to running as part of the IPL testing, the MSP test units (TUs) can be loaded and run separately to check an area of the MSP operation (01-450). For most I/O devices, descriptions of the tests and their result bytes appear on the system console when the test is selected. However, when MSP tests are run, the system console may not be working. For that reason, this section contains a short description of each test and its result bytes to aid in interpreting results from the tests. The tests appear in numeric order by their TU number (T20xx). Some tests included here are not run during the IPL good machine path.

Result byte 1 is in WR7 high; result byte 2 is in WR7 low. See 01-225 to display WR7. Unless indicated differently, a good machine generates a result byte value of 00.

### T207F

#### Main Storage Size Determination and MCR Load

This TU senses each main storage card to determine the number and size of storage cards in the system. This TU then loads the memory configuration register (MCR) with the correct value.

#### **Result Byte 1**

| Bit(s) | Description                                                             |

|--------|-------------------------------------------------------------------------|

| 0      | There is no card in A-A2U2 or there is an empty location between cards. |

| 1      | A machine check interrupt occurred.                                     |

| 2-7    | Not used.                                                               |

#### **Result Byte 2**

Not used.

### T2082 Sense and Replace Bad Main Storage Bit

This TU senses each main storage location and determines if a bad bit is present. If so, this TU replaces the bad bit with the redundant bit in the main storage logic.

#### **Result Byte 1**

| Bit(s) | Description                            |

|--------|----------------------------------------|

| 0      | A machine check interrupt occurred.    |

| 1      | The TU did not find a bad bit.         |

| 2      | The TU failed.                         |

| 3      | The TU did not find a bad ECC bit.     |

| 4      | The TU did not correct an ECC problem. |

| 5      | More than one ECC bit is bad.          |

| 6, 7   | Not used.                              |

#### **Result Byte 2**

Not used.

### T20B1

#### TU Supervisor

This TU checks the action control word bit that records the test options.

#### **Result Byte 1**

| Bit(s) | Description                                           |

|--------|-------------------------------------------------------|

| 0      | Bypass the MSP tests was selected (mode E).           |

| 1      | Bypass the MSP tests was selected (mode 0 or mode F). |

| 2-7    | Not used.                                             |

### T20B2 FF00 Initialization-Mode E

This TU sets the MSP control registers, the LSRs, and main storage to known values. The values are the results of storage accesses to main storage. Values are set for storage with ECC, and 128K bytes of storage are set to FF. The address translation registers are set as if there were no bad pages in main storage.

#### **Result Byte 1**

| Bit(s) | Description                            |

|--------|----------------------------------------|

| 0      | The TU could set main storage to FF.   |

| 1      | The TU could not access MSP registers. |

| 2-7    | Not used.                              |

**Result Byte 2**

Not used.

#### T20B3 FF00 Initialization-Mode 0 or Mode F

This TU sets the MSP control registers, the LSRs, and main storage to known values. The values are from the unit definition table (UDT). The address translation registers are set as if there were no bad pages in main storage.

#### **Result Byte 1**

| Bit(s) | Description                              |

|--------|------------------------------------------|

| 0      | The TU could not set main storage to FF. |

| 1-7    | Not used.                                |

#### **Result Byte 2**

Not used.

#### **Result Byte 2**

Not used.

### T20B4 0000 Initialization

This TU sets the MSP control registers, the LSRs, and main storage to known values. The values are from the unit definition table (UDT). The address translation registers are set using the information in the bad page table area.

#### **Result Byte 1**

| Bit(s) | Description                              |

|--------|------------------------------------------|

| 0      | The TU could not set main storage to FF. |

| 1-7    | Not used.                                |

#### **Result Byte 2**

Not used.

### T20B5 Analysis of Main Storage Bad Page Table

This TU checks the bad page table to determine if there are enough good storage pages to continue with the tests. The TU uses the following rules:

- The number of bad pages cannot be more than a maximum value.

- There can be no bad pages if the FC03 test option was selected.

- The area from 0-16K bytes must have no bad pages.

#### **Result Byte 1**

| Bit(s) | Description                                              |

|--------|----------------------------------------------------------|

| 0      | The number of bad pages is more than the maximum number. |

| 1      | There are bad pages in the first 16K-byte area.          |

| 2      | A machine check interrupt occurred.                      |

| 3-7    | Not used.                                                |

#### **Result Byte 2**

Not used.

### *T20B6* SVC Instruction and ATR Selection Test

This TU tests the SVC instruction. It performs SVC operations in aligned and non-aligned modes.

#### **Result Byte 1**

| Bit(s) | Description                                        |

|--------|----------------------------------------------------|

| 0      | Interrupt level 5 did not occur.                   |

| 1      | A machine check interrupt occurred.                |

| 2      | No SVC occurred.                                   |

| 3      | An MSP check occurred as indicated in SB4 and SB5. |

| 4      | A Q-code error occurred.                           |

| 5-7    | Not used.                                          |

#### **Result Byte 2**

Result byte 2 holds the contents of SB4 if result byte 1, bit 3 is on. If bit 3 is off, result byte 2 is not used.

### T20B7

#### **Branch On Condition Instruction Test**

This TU tests the branch on condition instruction for all valid Q-codes and with many PSR values.

#### **Result Byte 1**

| Bit(s) | Description                                |

|--------|--------------------------------------------|

| 0      | Interrupt level 5 did not occur.           |

| 1      | A machine check interrupt occurred.        |

| 2      | An error SVC was received.                 |

| 3      | An MSP check occurred as indicated in SB2. |

| 4-7    | Not used.                                  |

#### **Result Byte 2**

Result byte 2 holds the contents of SB4 if result byte 1, bit 3 is on. If bit 3 is off, result byte 2 is not used.

### **T20B8** Jump On Condition Instruction Test

This TU tests the jump on condition instruction for all valid Q-codes and with many PSR values.

#### **Result Byte 1**

| Bit(s) | Description                                |

|--------|--------------------------------------------|

| 0      | Interrupt level 5 did not occur.           |

| 1      | A machine check interrupt occurred.        |

| 2      | An error SVC was received.                 |

| 3      | An MSP check occurred as indicated in SB2. |

| 4-7    | Not used.                                  |

#### **Result Byte 2**

Result byte 2 holds the contents of SB4 if result byte 1, bit 3 is on. If bit 3 is off, result byte 2 is not used.

#### T20B9

#### Jump Backward Instruction Test

This TU tests the jump backward instruction.

#### **Result Byte 1**

| Bit(s) | Description                         |

|--------|-------------------------------------|

| 0      | The test results were not correct.  |

| 1      | A machine check interrupt occurred. |

| 2      | Interrupt level 5 did not occur.    |

| 3      | An error SVC was received.          |

| 4-7    | Not used.                           |

#### **Result Byte 2**

Not used.

### **T20BA** Load PMR Instruction Test

This TU tests the load PMR instruction for many valid Q-codes and with many PSR values.

#### **Result Byte 1**

| Bit(s) | Description                                               |

|--------|-----------------------------------------------------------|

| 0      | Interrupt level 5 did not occur.                          |

| 1      | A machine check interrupt occurred.                       |

| 2      | The results of the load PMR instruction were not correct. |

| 3      | No storage exception occurred at the end of the test.     |

| 4      | An MSP check occurred as indicated in SB2.                |

| 5-7    | Not used.                                                 |

#### **Result Byte 2**

Result byte 2 holds the contents of SB4 if result byte 1, bit 3 is on. If bit 3 is off, result byte 2 is not used.

### **T20BB**

#### Load Register Instruction Test

This TU tests the load register instruction.

#### **Result Byte 1**

| Bit(s) | Description                                |

|--------|--------------------------------------------|

| 0      | Interrupt level 5 did not occur.           |

| 1      | A machine check interrupt occurred.        |

| 2      | An error SVC was received.                 |

| 3      | An MSP check occurred as indicated in SB2. |

| 4-7    | Not used.                                  |

#### **Result Byte 2**

Result byte 2 holds the contents of SB4 if result byte 1, bit 3 is on. If bit 3 is off, result byte 2 is not used.

### *T20BC* Store Register Instruction Test

This TU tests the store register instruction.

#### **Result Byte 1**

| Bit(s) | Description                         |

|--------|-------------------------------------|

| 0      | Interrupt level 5 did not occur.    |

| 1      | A machine check interrupt occurred. |

| 2      | An error SVC was received.          |

| 3-7    | Not used.                           |

#### **Result Byte 2**

Not used.

### T<sub>20</sub>BD **Compare Logical Immediate Instruction Test**

This TU tests the compare logical immediate instruction.

#### **Result Byte 1**

| Bit(s) | Description                         |

|--------|-------------------------------------|

| 0      | The test results were not correct.  |

| 1      | A machine check interrupt occurred. |

| 2      | Interrupt level 5 did not occur.    |

| 3      | An error SVC was received.          |

| 4-7    | Not used.                           |

#### **Result Byte 2**

Not used.

### **10-420 (continued)** MSP Test Unit Descriptions

### **T20BE** Move Immediate Instruction Test

This TU tests the move immediate instruction.

#### **Result Byte 1**

| Bit(s) | Description                         |

|--------|-------------------------------------|

| 0      | The test results were not correct.  |

| 1      | A machine check interrupt occurred. |

| 2      | Interrupt level 5 did not occur.    |

| 3      | An error SVC was received.          |

| 4-7    | Not used.                           |

#### Result Byte 2

Not used.

### T20BF Branch on ARR Instruction Test

This TU tests the branch on ARR instruction.

#### **Result Byte 1**

| Bit(s) | Description                                |

|--------|--------------------------------------------|

| 0      | Interrupt level 5 did not occur.           |

| 1      | A machine check interrupt occurred.        |