# **PROCEEDINGS**

OF THE

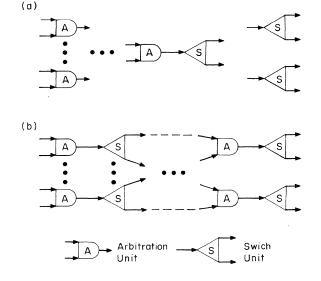

# 1975 SAGAMORE COMPUTER CONFERENCE

ON

# PARALLEL PROCESSING

Syracuse University

# PROCEEDINGS OF THE 1975 SAGAMORE COMPUTER CONFERENCE ON PARALLEL PROCESSING

Papers presented on August 19-22, 1975

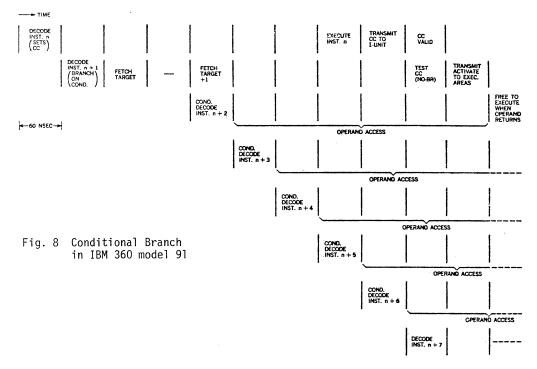

Copyright © 1975

IEEE Computer Society P.O. Box 639

Silver Spring, Maryland 20907

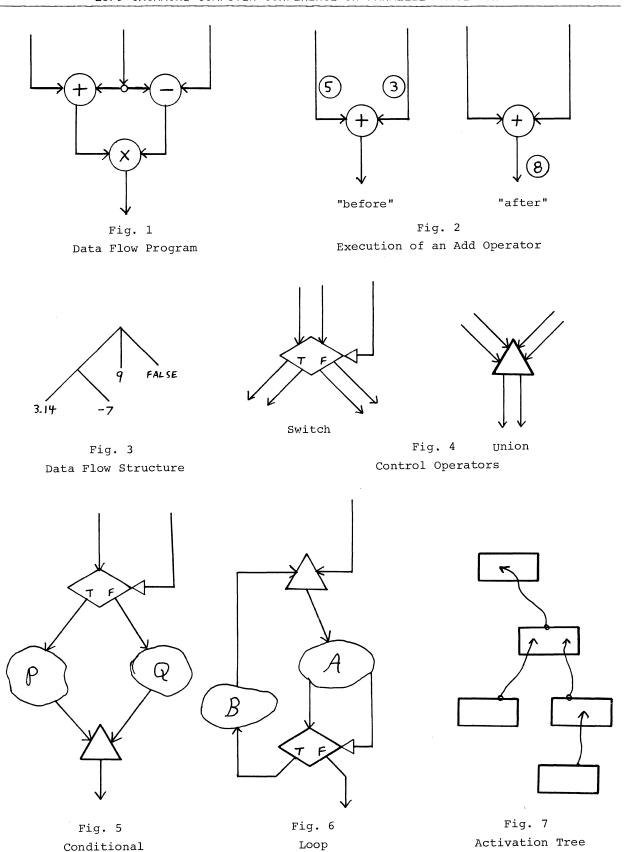

Additional copies are available from: IEEE Computer Society 5855 Naples Plaza, Suite 301 Long Beach, CA 90803

Manufactured in the U.S.A.

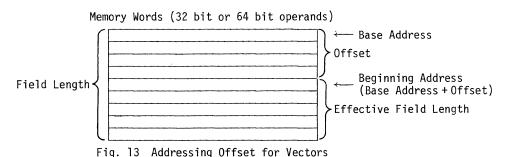

#### **PREFACE**

The Sagamore Computer Conference has been held annually for the past four years at the former Vanderbilt summer estate in the Central Adirondack Mountains. The Conference was originally conceived to provide a secluded environment, a 1300-acre preserve surrounding the private Sagamore Lake, for the participants with excellent opportunities for exchanging ideas and learning each other's research activities. Thus informative discussions may be made not only during the technical sessions but also throughout the various sports and social gatherings provided by the Conference.

The first Sagamore Computer Conference was held on August 23-25, 1972. The subject of that conference was on "RADCAP (Rome Air Development Center Associative Processor) and Its Applications". About 90 invited participants attended the 2-day conference to hear the 17 technical papers presented. The Conference Proceedings were published and distributed by RADC and Syracuse University, co-sponsors of the Conference. In 1973, the Conference broadened its scope to "Parallel Processing" and issued the Call-for-Papers announcement. Among the submitted papers, 34 were accepted and presented on August 22-24, 1973. The 1973 Conference was sponsored by Syracuse University in cooperation with IEEE and ACM. Copies of its Proceedings (IEEE Catalog Number 73 CHO812-8 C) may be available from any one of these institutions. The 1974 Conference was extended to three days (August 20-23, 1974) to provide the participants with more time for individual activities. In addition to a panel discussion, the participants heard the presentation of 35 technical papers. The Conference was again sponsored by Syracuse University, but the Proceedings were published and distributed by Springer-Verlag as Volume 24 in their series of Lecture Notes in Computer Science.

Since 1972, the number of submitted papers and, in particular, the number of requests to attend the Conference have increased significantly and persistently. In 1973 and 1974, the Minnowbrook Conference Center was opened to accommodate the overflow from Sagamore. But this year, even with this added facility, we had to turn down many requests to attend the Conference. Thus, the Conference had grown out of Sagamore (as well as Minnowbrook) accommodations, and, much to our regret, this year's Conference had to be the last one held at Sagamore.

The success of the Sagamore Computer Conference is mostly due to the vigorous support of many individuals. For this year's conference we are grateful to Col. Robert D. Krutz of Rome Air Development Center for his enlightening Keynote Address. Also, at the request of many past Sagamore participants, this year we invited Professors Enslow, Kuck, Ramamoorthy, and Yau to write survey papers on various computer architectures related to Parallel Processing. Their time and effort in this respect are very much appreciated. We appreciate the efforts of the authors who submitted papers for consideration. We are also much indebted to all the reviewers who, in order to meet the stringent review deadlines, put aside their own busy work schedule to carefully evaluate the papers sent for their comments. The success of the Conference is also attributable to the generous help we received from the session chairpersons. In addition, a special acknowledgement is due to Elliott McCulley, Anne Woods, Mary Jo Fairbanks, and Angela Wisniewski for their administrative assistance and typing help.

Tse-yun Feng

Department of Electrical & Computer Engineering

Syracuse University

## TABLE OF CONTENTS

|   |                                                                                                                       | Page |

|---|-----------------------------------------------------------------------------------------------------------------------|------|

|   | KEYNOTE ADDRESS  Parallel Processing: A Dilemma Col. Robert D. Krutz Rome Air Development Center                      |      |

|   | INVITED PAPERS  Associative Processor Architecture - A Survey S. S. Yau, H. S. Fung                                   | 1    |

|   | Parallel Processor Architecture - A Survey D. Kuck                                                                    | 15   |

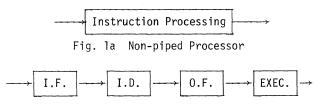

| ٩ | Pipeline Processor Architecture - A Survey C. V. Ramamoorthy, H. F. Li                                                | 40   |

| ļ | Multiprocessor Architecture - A Survey                                                                                | 63   |

|   | SESSION 1 MULTIPROCESSORS Chairperson: Professor 0. Garcia                                                            |      |

| Ĺ | Parallel Processing in Software and Hardware - The MASCOT Approach K. Jackson, C. Moir                                | 71   |

| ~ | Sequencing Control in Multifunctional Pipeline Systems C. V. Ramamoorthy, H. F. Li                                    | 79   |

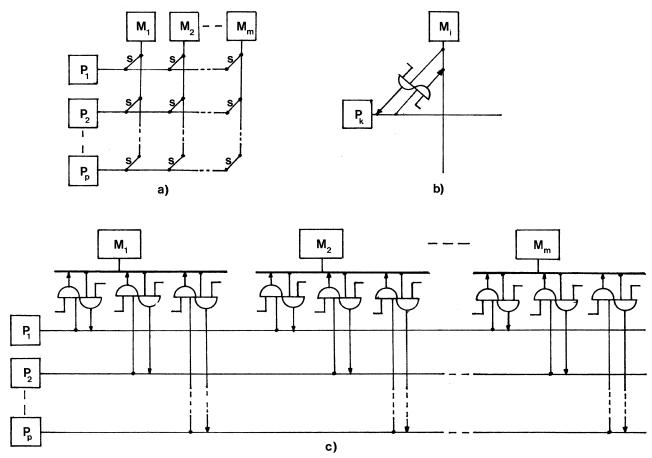

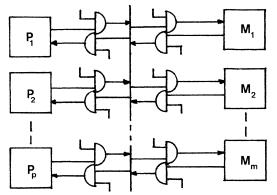

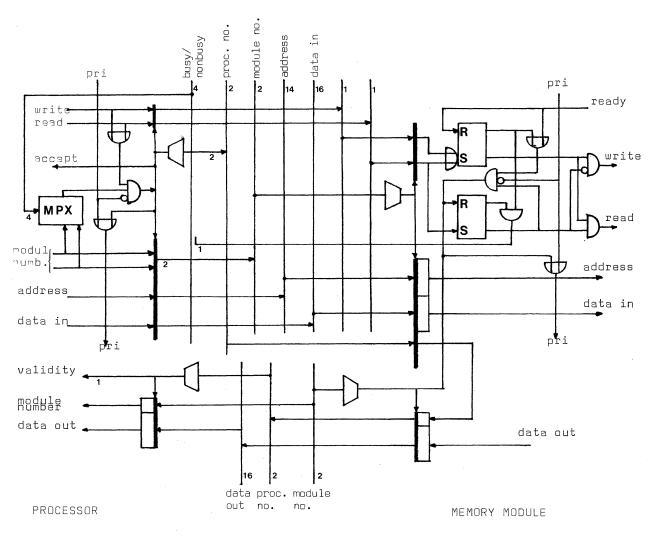

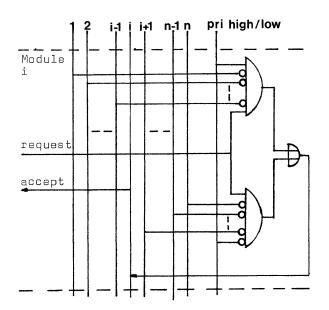

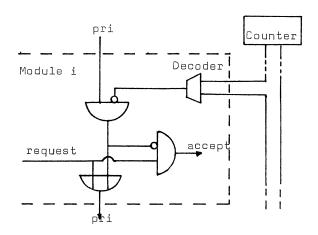

| · | Time-Shared Memory-Processor Interface P-E Danielsson, B. Gudmundsson                                                 | 90   |

| v | Dynamic Tuning in an Asymmetric Multiprocessing Environment H. Nirsberger, S. Vestal                                  | 99   |

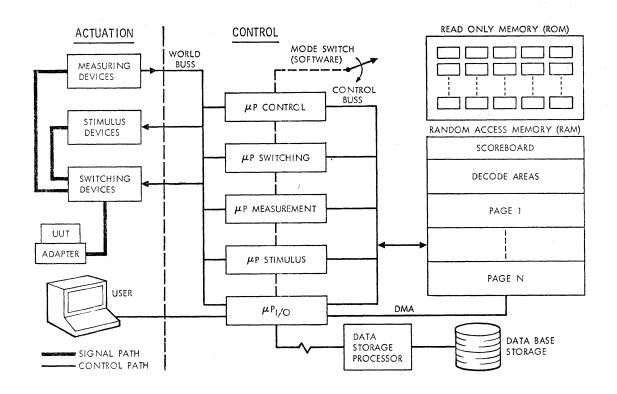

| L | Parallelism in Automatic Testing M. N. Matelan                                                                        | 100  |

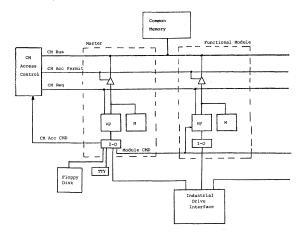

| v | Multi-Microprocessor System for Industrial Control A. C. M. Chen, W. D. Barber                                        | 105  |

|   | SESSION 2: PROCESSOR/MEMORY INTERCONNECTIONS Chairperson: Dr. G. Couranz                                              |      |

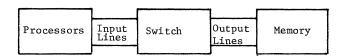

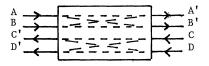

| ٠ | Analysis Techniques for SIMD Machine Interconnection Networks and the Effects of Processor Address Masks H. J. Siegel | 106  |

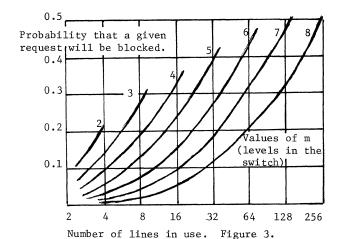

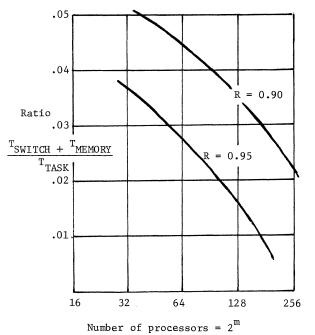

| ί | Design Criteria for a Switch for a Multiprocessor Computing System  I. A. Davidson, J. A. Field                       | 110  |

|   | A Cellular Data Manipulating Array  I-N Chen                                                                          | 114  |

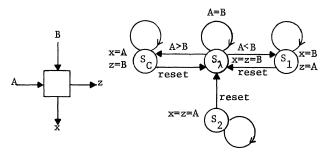

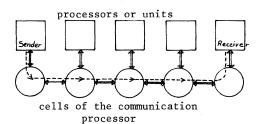

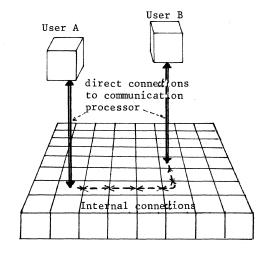

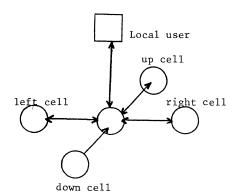

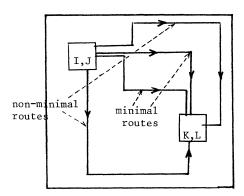

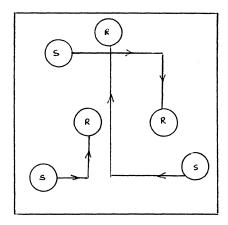

| v | A Two Dimension Pipe-Lined Processor for Communication in a Parallel System                                           | 115  |

## TABLE OF CONTENTS (CONT'D.)

|                                                                                                             | Page |

|-------------------------------------------------------------------------------------------------------------|------|

| SESSION 3: ASSOCIATIVE/PARALLEL PROCESSORS Chairperson: Capt. A. Klayton                                    |      |

| The Design and Implementation of a High/Low Magnitude Search Instruction on PEPE M. C. DiVecchio            | 122  |

| The Associative Linear Array Processor C. A. Finnila                                                        | 123  |

| Programming the Associative Linear Array Processor H. H. Love                                               | 124  |

| Architecture for a Highly Reliable Parallel Computer System W. W. Gaertner                                  | 125  |

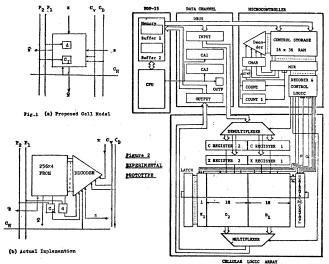

| Parallel Processing in a Cellular Logic Array K. S. Lin, Y. S. Shen, D. R. Smith                            | 126  |

| SESSION 4: PROGRAM DECOMPOSITION AND PETRI NETS Chairperson: Dr. B. Hays                                    |      |

| The Design of Programs for Asynchronous Multiprocessors P. H. Mason                                         | 127  |

| A Criterion for Synchronization Schemes R. C. Chen, J. E. Coffman                                           | 130  |

| A Comparative Analysis of Two Parallel Computation Models S. C. Meyer, J. R. Jump                           | 131  |

| SESSION 5: STARAN Chairperson: Mr. O. Reimann                                                               |      |

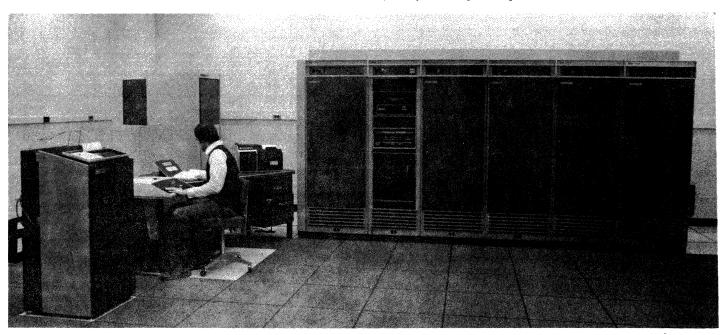

| STARAN Complex-Defense Mapping Agency US Army Engineer Topographic Laboratories L. A. Gambino, R. L. Boulis | 132  |

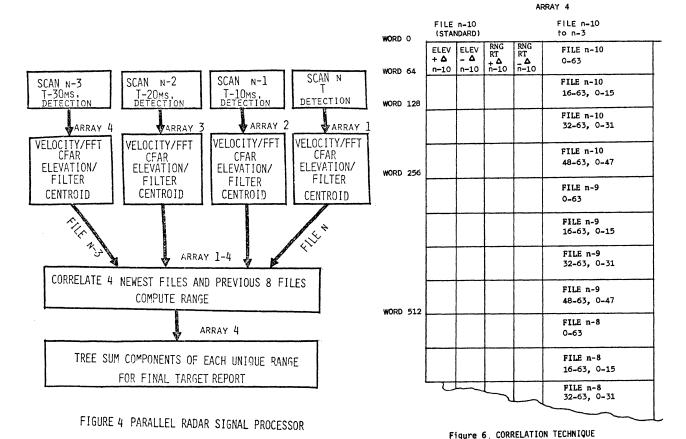

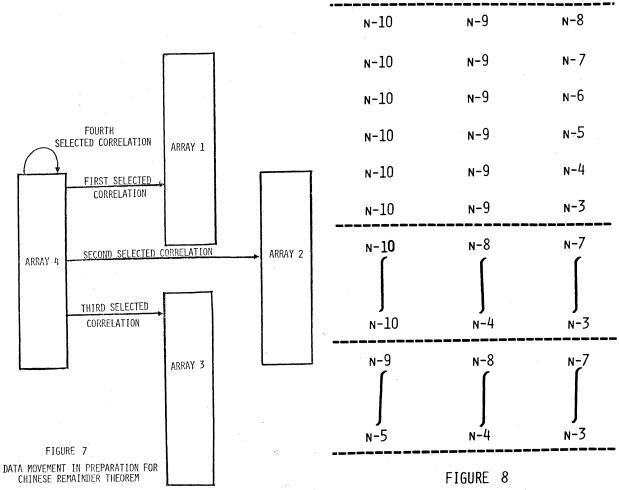

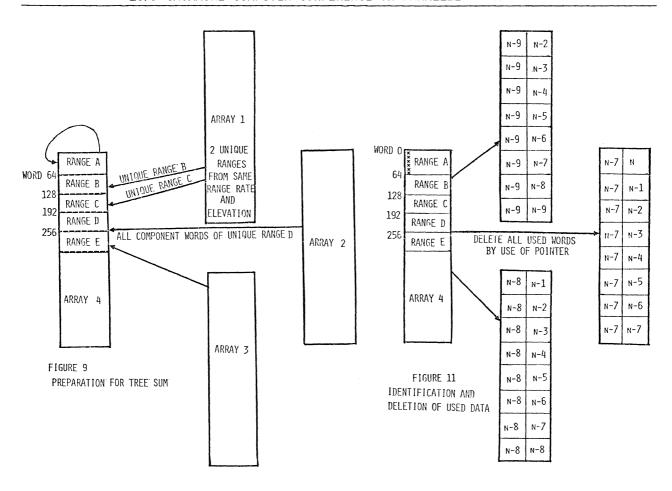

| A Parallel Approach to High PRF Doppler Radar Signal Processing F. E. Schenfele                             | 142  |

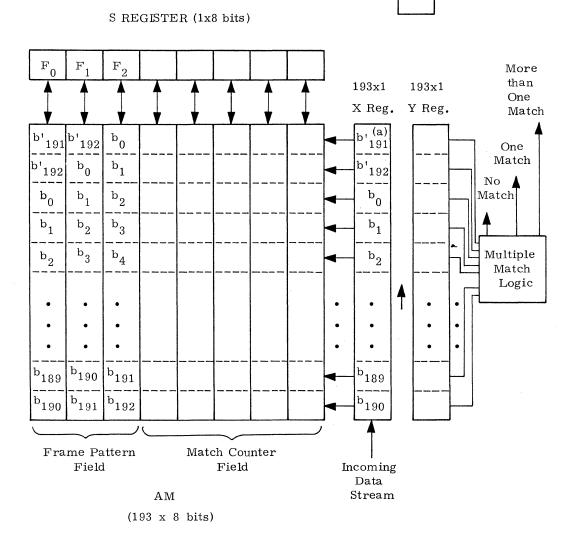

| An Optimal Synchronous Reframing Technique Using an Associative Processor T. L. Saxton, C. C. Huang         | 152  |

| SESSION 6: MEMORY ORGANIZATION Chairperson: Professor T. Feng                                               |      |

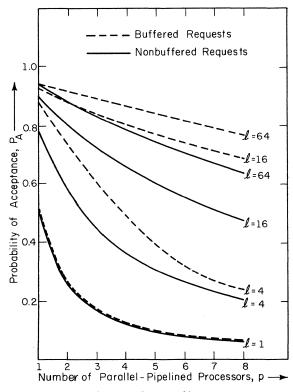

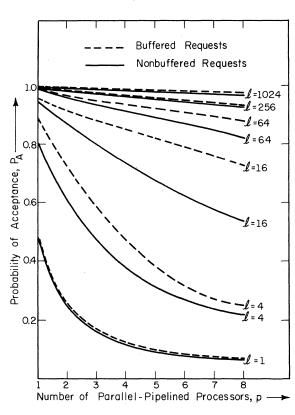

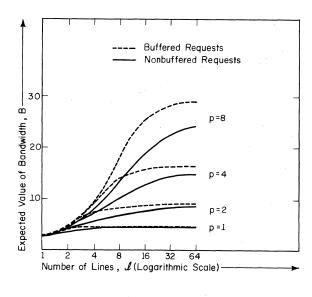

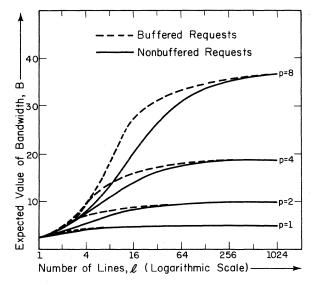

| Organization of Semiconductor Memories for Parallel-Pipelined Processors F. A. Briggs, E. S. Davidson       | 155  |

| Storage Schemes in Parallel Memories H. D. Shapiro                                                          | 159  |

| The Multi-Dimensional Access Memory in STARAN  K. E. Batcher                                                | 167  |

## TABLE OF CONTENTS (CONT'D.)

|                                                                                                                                                                     | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| SESSION 7: LANGUAGES<br>Chairperson: Professor R. J. Zingg                                                                                                          |      |

|                                                                                                                                                                     |      |

| Polyautomaton Design for Recognizing Certain L System Languages by Parallel Computation C. Weiman, J. Rothstein                                                     | 168  |

| SIMPARAG - Simultaneous Parallel Array Grammars P. S-P Wang, W. I. Grosky                                                                                           | 171  |

| Preliminary results of a Comparative Analysis of ILLIAC IV Languages R. L. Milton                                                                                   | 172  |

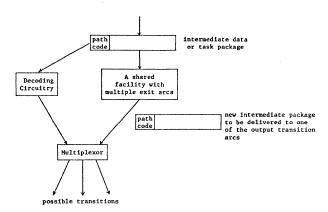

| Systems Design and Documentation Using Path Descriptions A. C. Shaw                                                                                                 | 180  |

| A New Scheme for Analyzing Parallel Processing Systems I. Margaria, A. Meo, M. Zacchi                                                                               | 182  |

| Fortran Extension Design Concepts for Associative Processing E. B. Allen, A. G. Larson                                                                              | 186  |

| SESSION 8: COMPILING TECHNIQUES Chairperson: Professor J. Marzolf                                                                                                   |      |

| Parallel Execution on Array and Vector Computers L. Lamport                                                                                                         | 187  |

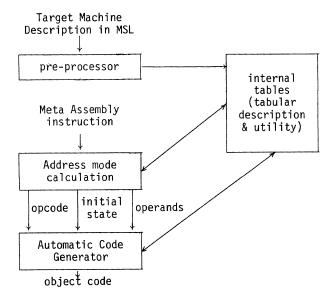

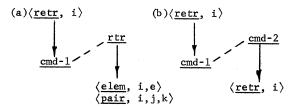

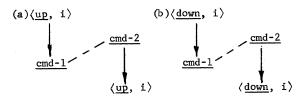

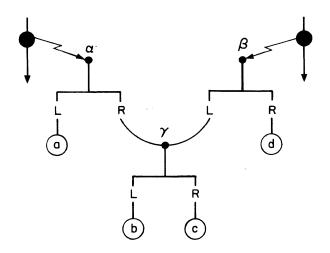

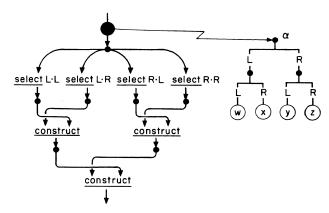

| Formalizing Code Generation in the Multi Mini Computer Compiler C. V. Ramamoorthy, P. Jahanian                                                                      | 192  |

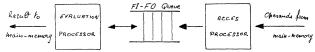

| Evaluation of a Polish Form Expression on a FI-FO Queue: A New Approach Towards the Realization of a High Level "Pipeline" Computer G. G. Baille, J. P. Schoellkopf | 200  |

| SESSION 9: OPERATING SYSTEMS Chairperson: Capt. R. Johnson                                                                                                          |      |

| A Companies of Ammonimatine Calcivities Alexandrian                                                                                                                 |      |

| A Comparison of Approximative Scheduling Algorithms K. Ecker                                                                                                        | 201  |

| A Linear Scheduling Algorithm for a Forest on a Multiprocessor System D. Hennings, S. Schindler, M. Steinacker                                                      | 202  |

| A Graph-Theoretic Characterization of a Class of Synchronizing Primitives P. B. Henderson, Y. Zalcstein                                                             | 203  |

| SESSION 10: IMAGE PROCESSING Chairperson: Ms. A. Krygiel                                                                                                            |      |

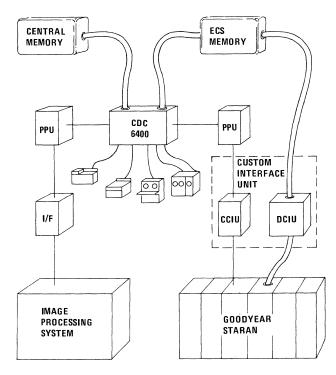

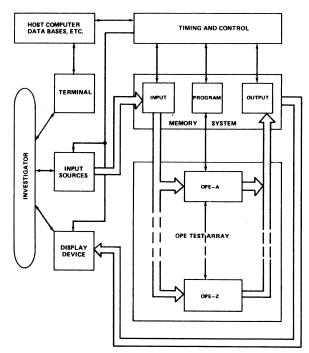

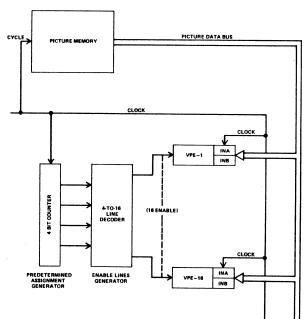

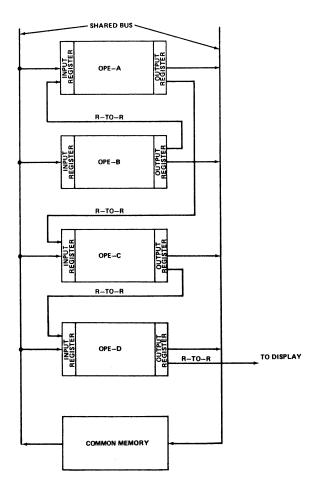

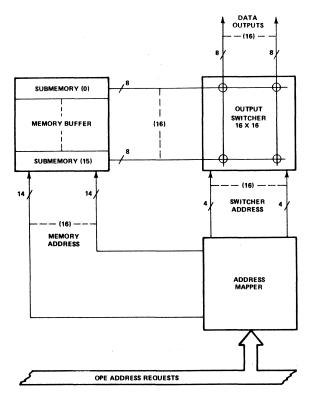

| An Image Array Processor for the Investigation of Architectures and Algorithms R. M. Brown, P. L. Neely                                                             | 204  |

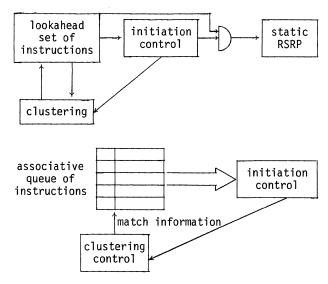

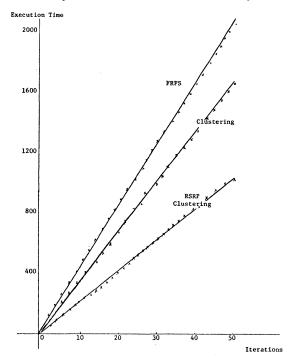

| Parallelism in AI Problem Solving: A Case Study of Hearsay II R. D. Fennell, V. R. Lesser                                                                           | 214  |

## TABLE OF CONTENTS (CONT'D.)

|                                                                                                                                          | Page |

|------------------------------------------------------------------------------------------------------------------------------------------|------|

| CRECTON 11. DAMA DI OLI ADGUTTELIGIUDE                                                                                                   |      |

| SESSION 11: DATA FLOW ARCHITECTURE Chairperson: Professor J. Dennis                                                                      |      |

| Data Flow Languages                                                                                                                      |      |

| J. E. Rumbaugh                                                                                                                           | 217  |

| A Data Flow Multiprocessor J. E. Rumbaugh                                                                                                | 220  |

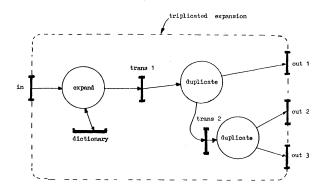

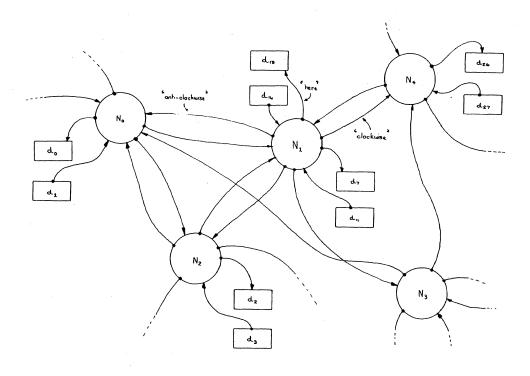

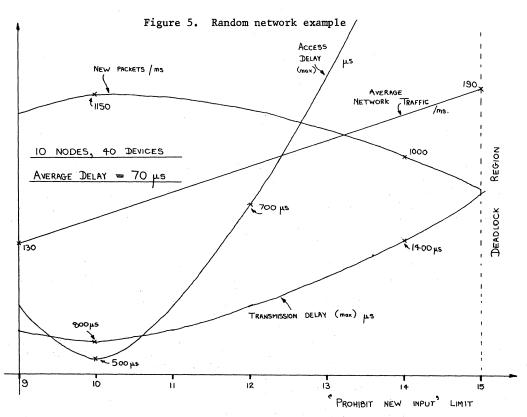

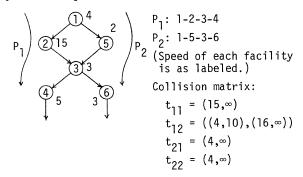

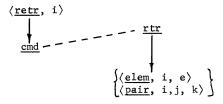

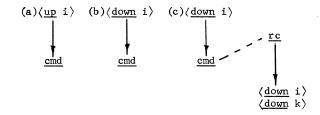

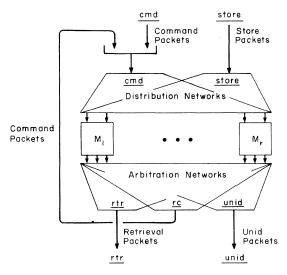

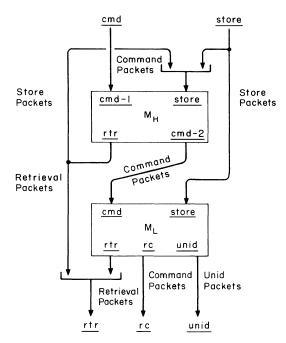

| Packet Communication Architecture J. B. Dennis                                                                                           | 224  |

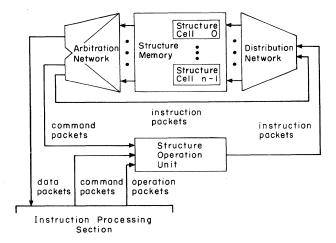

| Structure Processing in a Data-Flow Computer D. P. Misunas                                                                               | 230  |

| SESSION 12: ALGORITHMS AND APPLICATIONS Chairperson: Dr. R. Downs                                                                        |      |

| The Stability of a Parallel Algorithm for the Solution of Tridiagonal Linear Systems M. A. Diamond                                       | 235  |

| Parallel Algorithms for Evaluation of Arithmetic Expressions A. Deb, A. Mukhopadhyay                                                     | 236  |

| On Parallel Triangular System Solvers S. Chen, A. Sameh                                                                                  | 237  |

| Sorting Algorithms for Parallel Processing C. C. Lee, T. Y. Feng                                                                         | 239  |

| Short-Term Weather Prediction on ILLIAC IV J. S. Daley, B. D. Underwood                                                                  | 240  |

| The Feasibility of Using Associative Processors in Change Detection P. B. Berra, A. K. Singhania                                         | 241  |

| Plasma Simulation Using an Associative Processor K. B. Irani, D. S. Lo                                                                   | 242  |

| Some Timing Figures for Inverting Large Matrices Using the STARAN Associative Processor P. B. Berra, A. K. Singhania                     | 243  |

| SESSION 13: PERFORMANCE EVALUATION Chairperson: Professor E. Stabler                                                                     |      |

| An Experimental Comparison of CDC STAR-100 and 7600 Computer Speeds for Explicit Finite-Difference Hydrodynamics Calculations T. E. Rudy | 244  |

|                                                                                                                                          | 444  |

| Evaluation Criteria for Process Synchronization R. J. Lipton, L. Synder, Y. Zalcstein                                                    | 245  |

| Exploiting Vector Mode in an SISD Computer                                                                                               | 251  |

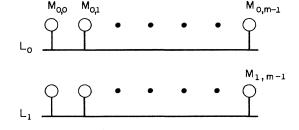

#### ASSOCIATIVE PROCESSOR ARCHITECTURE - A SURVEY

S. S. Yau and H. S. Fung

Departments of Computer Sciences and Electrical Engineering

Northwestern University

Evanston, Illinois 60201 U.S.A.

(Invited Paper)

Abstract -- A survey of associative processor architecture is presented. Based on their architecture, associative processors are classified into four categories, namely fully parallel, bit-serial, word-serial and block-oriented. The fully parallel associative processors are divided into two classes, word-organized and distributed logic. The architecture of each of these categories is described.

#### Introduction

An associative processor can generally be described as a processor which has the following two properties: (1) Stored data items can be retrieved using their content or part of their content (instead of their addresses) and (2) data transformation operations, both arithmetic and logic operations, can be performed over many sets of arguments with a single instruction. Because of these parallel processing characteristics, associative processors have a much faster data processing rate than conventional sequential computers, and hence are more effective in handling many types of information processing problems, such as information storage and retrieval of rapidly changing data bases, fast search of a large data base, arithmetic and logic operations on large sets of data, control and executive functions in large-scale computer systems, radar signal processing and weather computations. However, because of their relatively high implementation cost, associative processors are usually used in conjunction with standard sequential computer systems so that many required high-speed parallel processing tasks which cannot be effectively executed by sequential processors are performed by associative processors. It is anticipated that associative processors will be used more extensively in the future for enhancing the performance of many specialpurpose and general-purpose computer systems.

In this paper, we will present a survey of the architecture of various associative processors. We will first give a general description of associative processor architecture and then classify associative processors on the basis of their architecture. Then we will discuss each of the categories of associative processors in some detail.

#### General Description

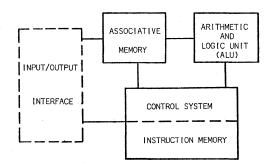

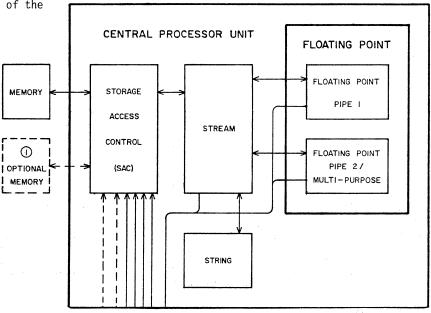

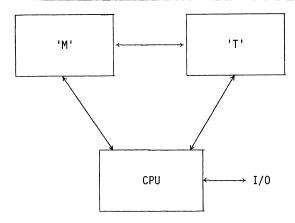

In general, the architecture of an associative processor can be described as shown in Fig. 1, which consists of an associative memory, arithmetic and logic unit (ALU), control system, instruction memory, and an input/output interface. The major difference between an associative processor as shown in Fig. 1 and a standard sequential processor is the use of an associative memory instead of a location-addressed memory. Because of this difference, all the other blocks are also different between an associative processor and a standard sequential processor. Furthermore, the associative memory has a major impact on the architecture of an associative processor, and the associative processor architecture can be classified based on the organization of its associative memory.

An <u>associative memory</u> [1] - [8] can be defined as a memory system with the property that stored data items can be retrieved by their content or part of their content (that is, the first property of an associative processor). An associative memory is also called <u>catalog memory</u> [9], content-addressed memory [10], data-addressed memory [11], parallel search memory [12], search memory [13] - [15], search associative memory [16], content-addressable memory [17], distributed logic memory [18], associative pushdown memory [19], and <u>multi-access associative memory</u> [20].

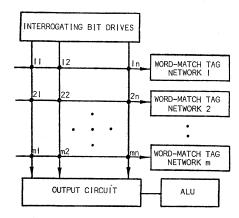

From the hardware point of view, in order to retrieve stored data items by their content or part of their content, it is required that the memory words can be accessed by matching their content or part of their content with the given search key words, instead of by an address as in a location-addressed memory. The basic memory element of the associative memory is called the bit-cell, which has the property that one-bit information can be written in, read out, and compared with interrogating information. The search operations, which consist of masking and comparison, are executed in a fashion that depends on the organization of the associative memory. The search key word can be compared with all the words of the memory through the interrogating bit drives and comparison logic circuitry. The possibility of matching multiple

words to a search key word requires the associative memory to have some method of tagging all the matched words. The tag function and matchedword indication are performed by the so-called word-match tag networks. Those matched words can be accessed with a single instruction [4], [6], [7], [21]. It is noted that a memory can have the associative property by performing either parallel comparison (word-parallel or word-serial) or serial comparison (bit-serial).

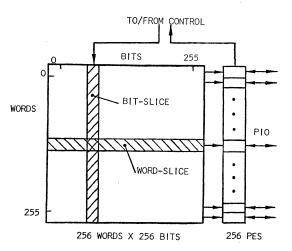

The first associative memory was developed by Slade and McMahon [9] in 1956 using cryotrons. Since then, associative memories have been implemented using tunnel diodes [22], [23], evaporated organic diode arrays [2], magnetic cores [22], [24] - [27], plated wire [22], [28], thin permalloy film on copper wire [22], semiconductors [29], transfluxors [30], biax cores [31], laminated ferrites [32], magnetic films [33], solenoid arrays [34], bicore thin film sandwiches [22], multi-aperture logic elements [35], and large-scale integrated (LSI) circuits [36]. The capacity of these associative memories is limited by factors such as half-select noise which limits the word length and interrogation drive problems which limit the number of words. Because of these limitations and because of high implementation cost, most associative memories in early years had small capacity, say up to 1K words with length up to 100 bits [26]. Recent associative memories have become larger and more flexible due to the development of new architectural concepts and the use of LSI technology. For example, in PEPE (parallel element processing ensemble) [37] - [42] there are a number of processing elements each of which contains a simple  $1K \times 32$ -bit random-access memory, called the element memory, which is shared on a cycle-stealing basis by the arithmetic unit, correlation unit and associative output unit in the processing element to perform associative processing. In each associative array module of STARAN [43] -[46], a so-called multi-dimensional access memory - implemented by a 256  $\times$  256-bit randomaccess memory is used to accommodate both bitslice accesses for associative processing and word-slice accesses for input/output.

An associative memory may perform the following comparison operations:

equal

less than

less than or equal

maximum value

between limits

next higher

not equal greater than greater than or equal minimum value not between limits next lower

An associative processor normally performs other complicated data transformation operations. For instance, the matched words in the associative memory are retrieved serially to the ALU through the output circuit of the associative memory under the control of the control system. The ALU performs the specified data transformation operations and the result is then stored to the associative memory, if necessary.

The first associative processor was developed by Behnke and Rosenberger [47] in 1963 using cryotrons. Since then a number of laboratory models of associative processors have been built using various types of associative memories. However, associative processors have not been put to practical use until the development of PEPE (parallel element processing ensemble) [37] - [42] and STARAN [43]-[46].

The architecture of associative processors can generally be classified into four categories according to the comparison process of their associative memories. The four categories are fully parallel, bit-serial, word-serial, and block-oriented. These are two types of fully parallel associative processors: word-organized and distributed logic. The former has its comparison logic associated with each bit-cell of every word, and the latter has its comparison logic associated with each character-cell (for a fixed number of bits) or a group of charactercells. In a bit-serial associative processor, only one bit-column (bit-slice) of all the words is operated at a time. A word-serial associative processor essentially represents hardware implementation of a simple program loop for search. The important factor which contributes to the relative efficiency of this approach as compared with programmed search in a standard sequential processor is that the instruction decoding time is greatly reduced since the search operation requires only a single instruction in the word-serial associative processor. A block-oriented associative processor can be implemented by using a logic-per-track rotating memory which consists of a head-per-track disk with some logic associated with each track.

In the following sections, we will discuss each of these categories in more detail.

#### Fully Parallel Associative Processors

# $\frac{\text{Fully Parallel Word-Organized Associative}}{\text{Processors}}$

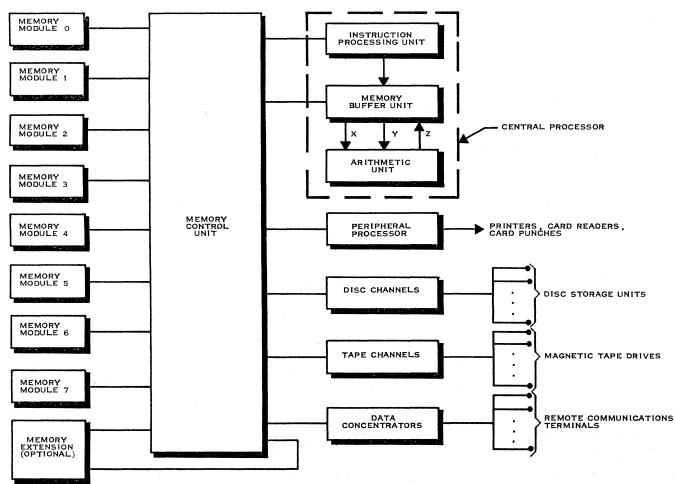

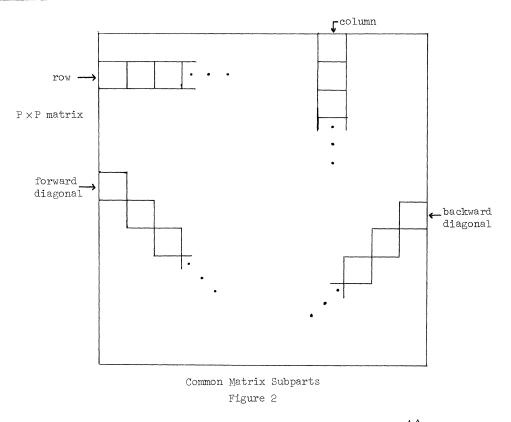

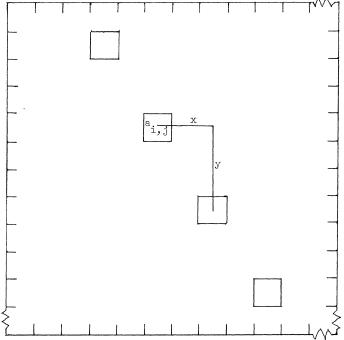

As mentioned before, the major characteristic of a fully parallel word-organized associative processor is that the comparison logic is associated with each bit-cell of every word of its associative memory. Thus, its comparison process is performed in a parallelby-word and parallel-by-bit fashion. The general organization of the associative memory with the ALU in such an associative processor is shown in Fig. 2. In this figure each cross-point represents a bit-cell. Although the operations of a fully parallel word-organized associative processor are simplest and fastest compared to other types of associative processors, its hardware is also the most complicated because each bit-cell has to contain the comparison logic. Because of its hardware complexity, this type of associative processor was developed only during the early stages although many experimental models were developed and their fully

parallel word-organized associative memory systems used cryogenic components [9], [11], [31], [48] - [53], magnetic cores [24], [25] and cutpoint cellular logic [54].

#### <u>Distributed Logic Associative Processors</u>

A distributed logic associative processor is a fully parallel character-oriented associative processor whose memory (usually called distributed logic memory [18]) has its comparison logic associated with each character-cell or each group of character-cells. A number of distributed logic associative processors have been developed [37] - [42], [55] - [62]. The first associative processor of this type was proposed by Lee [55] and a number of its variations were presented later [56] - [61]. The most well-known associative processor system of this type so far developed is the PEPE [37] - [42] by Bell Laboratories for the U.S. Army Advanced Ballistic Missile Defense Agency. In this section, these associative processors will be briefly described.

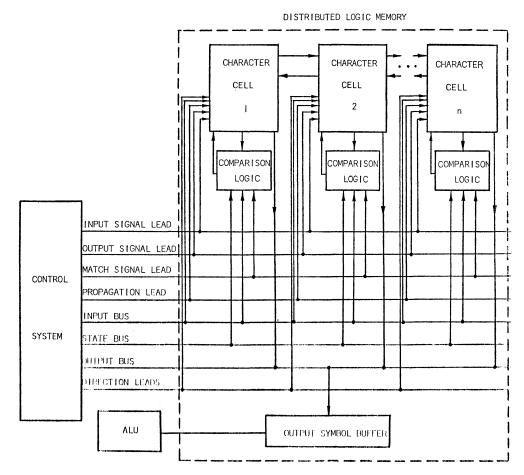

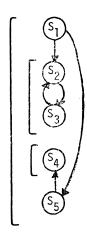

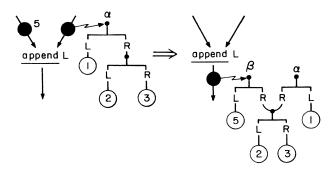

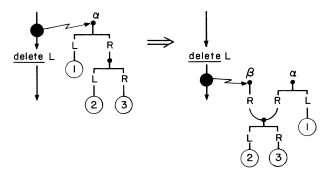

Lee's Distributed Logic Associative Processor and Its Modifications. The distributed logic associative processor proposed by Lee [55] can be represented by the block diagram shown in Fig. 3. Each character-cell has a single cell state element (state part) S which may either be in an active state or in a quiescent state, and each character-cell also has a number of cell symbol elements (symbol part) X1, ..., X depending upon the size of the symbol alphabet. The cell state element or cell symbol element is a bistable device, such as a flip-flop. Each character-cell stores one character symbol of information and can communicate with its two neighboring character-cells as well as the control system. A string of information is therefore stored in a corresponding string of character-cells.

Each data block consists of a name string and an arbitrary number of parameter strings. Every name string is preceded by a tag  $\alpha$ , and every parameter string is preceded by a tag  $\beta$ . When the input search key is a name string, the fully parallel distributed logic memory is expected to output all of the parameter strings associated with the name string. This is the so-called direct retrieval. On the other hand, when the input search key is a parameter string, the fully parallel distributed logic memory is expected to output all of the name strings associated with that parameter string. This is so called crossretrieval. In order to perform direct retrieval and cross retrieval, each character-cell in the fully parallel distributed logic memory must have enough cell logic circuitry so that it can produce a "yes" or "no" answer to a simple question such as whether the symbol of the character-cell is A or not A. If we want to retrieve all of the parameter strings whose name is AB, we will ask each character-cell whether its character symbol is A. If a cell gives us an answer "yes," we also want each character-cell to have enough cell logic circuitry so that it can signal its next character-cell to be ready to determine

whether the symbol of the character-cell is B. The character-cells which finally respond "yes" to the name string AB are now ready to signal all those character-cells storing all the parameter strings associated with the name string AB to output their contents.

Typical operations of a character-cell are changing state, transmitting state information to a neighboring character-cell, accepting data from the input bus, or putting its character symbol on the output bus. When a character-cell is in an active state and when the input signal lead is activated, the symbol which is carried on the input bus is then stored in that character-cell. When a character-cell is in an active state, an output signal causes that charactercell to read out its symbol through the output bus and store its symbol in the output symbol buffer. Comparison operation is controlled by the match signal through the comparison logic of each character-cell. The stored symbol of each character-cell is compared with the symbol carried on the input bus, and a signal from each matched character-cell is transmitted to one of its neighboring character-cells which then becomes active. The directions of transmission of the signals are controlled by the signal on the direction leads. All the character-cells evaluate and act according to the input conditions (given by the input and state buses) independently and simultaneously.

Lee's system has been experimented using cryogenics consisting of 72, 8-bit charactercells [62].

Several modifications of Lee's original system have been proposed. Lee and Paull [18] proposed a distributed logic memory using two cell state elements instead of one for each character-cell, more control bus leads and a threshold circuit. They defined the complex symbol of a character-cell which includes both the two cell state elements and the cell symbol elements of the character-cell. The matching process requires that an entire complex symbol be used for matching. They presented a more complicated design for a character-cell memory and an external control unit in order to have more capabilities to deal with problems such as cross retrieval, erasing, gap closing and preference which appear in information retrieval.

In order to overcome the propagation timing problems, Gaines and Lee [59] proposed to redesign the logic circuitry using two different-purpose cell state elements, called the match flip-flop and control flip-flop, and adding a mark line to simultaneously activate all cells to the right of each active cell up to the first cell whose control flip-flop is set. Due to the control of the propagation of the marking signal, this memory system is capable of performing two new simultaneous operations, shifting and marking strings.

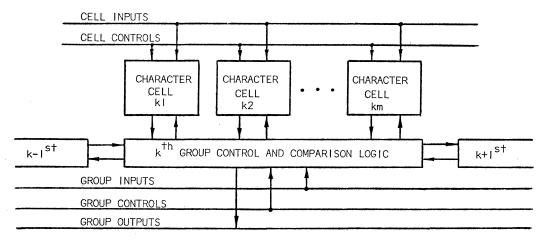

Crane and Githens [60] extended Lee's

system to a two-dimensional distributed logic memory which could be used to perform highly parallel arithmetic operations through the use of a large number of identical processing units on many sets of data simultaneously while retaining content-addressing capability to these data sets. Such an extension can be illustrated by the block diagram shown in Fig. 4.

Parallel Element Processing Ensemble (PEPE). PEPE [37] - [41] is one of the two large-scale associative processors developed to date. Its basic concept was derived from Lee's distributed logic associative processor and was originally developed by Bell Laboratories for the U.S. Army Advanced Ballistic Missile Defense Agency [37] - [39]. A second model of PEPE with both architectural and circuit technology improvements is being developed by the Agency [40] - [42]. The description of PEPE presented in this section is primarily for the current model.

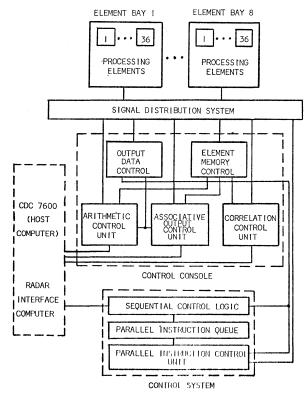

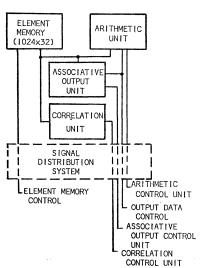

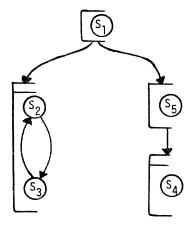

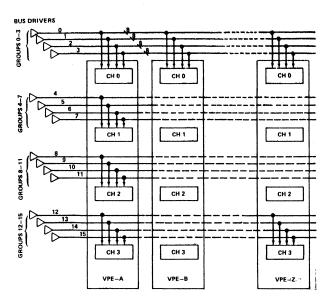

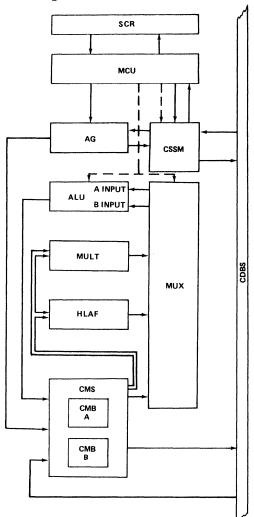

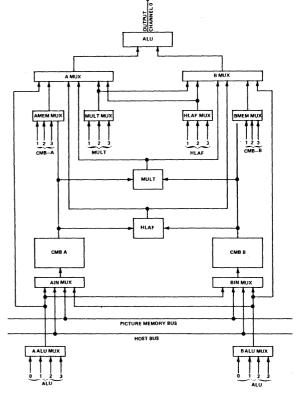

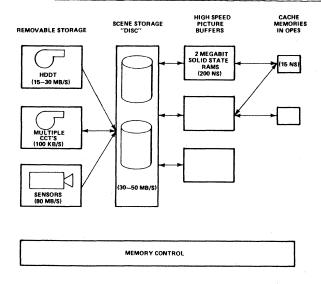

PEPE is composed of the following functional subsystems: an output data control, an element memory control, an arithmetic control unit, a correlation control unit, an associative output control unit, a control system, and a number of processing elements. Each processing element consists of an arithmetic unit, a correlation unit, an associative output unit and a  $1024 \times 32$ bit element memory. In addition, there are primary power and signal distribution subsystems to convert and route power and control and data signals between various functional subsystems. It is noted that the number of processing elements used in the PEPE is variable and may be increased or decreased to meet the requirements of the application. This variability has no impact on PEPE system performance, except that enough processing elements must be available to accommodate the expected number of objects to be tracked. A PEPE with 288 processing elements organized in 8 element bays was presented in [40].

The block diagrams of PEPE and its processing elements are shown in Figs. 5 and 6, respectively. The processing elements are the main computational component of PEPE. Selected portions of the data processing load are loaded from the host computer (a CDC 7600) to the processing elements. The loading selection process is determined by the inherent parallelism of the task and the ability of PEPE's unique architecture to manipulate the task more efficiently than the host computer. Each processing element is delegated the responsibility of an object under observation by the radar system. Each processing element maintains a data file for specific objects within its memory and uses its arithmetic capability to continually update its respective file.

The processing element operation and control are directed by the three global control units as follows: All the processing element arithmetic units, correlation units, and associative output units are controlled simultaneously by the arithmetic control unit, correlation control unit and associative output control unit, respectively.

In applying PEPE to radar data processing, the data for each tracked object are stored in a separate processing element memory. The arithmetic units are used to execute tracking and other programs on all or a selected subset of the tracked objects simultaneously. The control units are used to input new radar data into the correct processing element memories, and radar orders are obtained from the processing element memories by the arithmetic output units for transmission to the radar interface computer, concurrent with the processing in the arithmetic units. Arithmetic programs, correlation programs and output programs can be executed independently and simultaneously.

Each arithmetic unit, correlation unit and arithmetic output unit contains a contentaddressed tag register, and only those arithmetic units, correlation units and arithmetic output units whose tag register contents match the currently specified "activity" tags will be set to perform subsequently issued instructions. All these units have the capability to make less-than, greater-than, and equal to comparisons between their contents and data issued by the respective control unit. This capability provides content-addressed access to object data and is achieved through a set of registers whose contents can be compared with the input data stream. Only data meeting comparative criteria is stored in the processing element memory.

Arithmetic processes such as track updating, track prediction, discrimination, and interceptor guidance are performed in parallel by the arithmetic units. All the activated arithmetic units simultaneously execute instruction signals issued by the arithmetic control unit.

Input of new information to the processing element is handled by the correlation unit under control of the correlation control unit. The correlation processes of the correlation unit consist of comparing newly received object position information (as derived from radar returns) with predicted object position information generated by the processing element arithmetic units and transferred to the respective correlation units. Information on one object at a time is broadcast by the correlation control unit to all correlation units simultaneously, and all or a selected subset of correlation units compare their stored data with the broadcast data. The object information is input to the correlation unit (or correlation units), where correlation occurs, or into the first empty processing element memory in those cases where no correlation occurs.

Output information sent to the radar is handled by the associative output unit under the control of the associative output control unit and control system through the output data control. Allocation of pulses for the radar consists of ordering pulse requests generated by the processing elements as the result of

object file updates calculated by the arithmetic units and stored in the respective element memories for access. The ordered retrieval of the pulse requests on one object at a time are handled by the associative output control unit using a maximum-minimum search for associatively addressing data.

#### Bit-Serial Associative Processors

Because of the expensive logic in each memory bit and the communication problems in fully parallel associative processors, the bitserial word-parallel associative processor using the concept of parallel processing with vertical data (one bit-column of a large number of words is processing at a time) was introduced by Shooman in 1960 [63]. His system is essentially a hypothetical vertical data processing computer (referred to as an orthogonal computer) which embodies both vertical data processing and conventional (referred to as horizontal data processing) techniques. Shooman also gave descriptions and algorithms for several vertical data processing instructions. Since the number of words to be processed is usually larger than the number of bits in each word, this approach represents a compromise between fully parallel and word-serial associative processing.

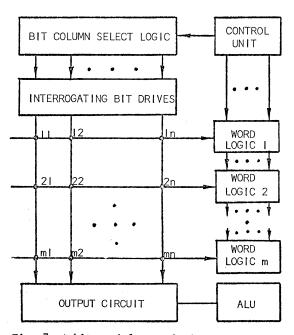

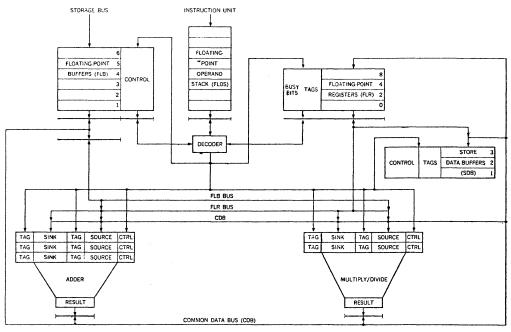

Since then, this concept has resulted in many proposals for associative processors. Kaplan [14] proposed a bit-serial associative memory which he called a search memory; this memory may be used as a subsystem for a generalpurpose computer. The main memory may communicate via a memory register with the search memory subsystem, accumulator, arithmetic unit, control unit and input/output unit. The match logic to execute search operations was placed in the search memory subsystem. Ewing and Davies [28] proposed the design logic of a bit-serial associative processor. The block diagram of a bitserial associative memory with the ALU is shown in Fig. 7. In this memory, storage for one bit is provided at each intersection of a word line and a bit line, and only one bit-column is operated one at a time. The particular bit-column is selected by the bit-column select logic. A pulse on a bit line causes a signal to be emitted by each bit on each word line. The signals are transmitted through the word lines to the sense amplifiers. The word logic associated with each word line gives the ability to perform associative processing. This logic is identical for all words and consists of a sense amplifier, storage flip-flops, a write amplifier and control logic. The storage flip-flop remembers the match state from one interrogating bit to the next. The output of the sense amplifier determines the state of the storage flip-flops in various ways as determined by the control signals from the control unit. The capability of the storage flip-flops to act as a shift register provides the communication link between adjacent words. Such a bit-serial associative processor can be considered as an external logic associative processor, in contrast to a distributed logic associative processor.

Chu [3] proposed the implementation of a bit-serial associative memory which makes use of conventional destructive-readout magnetic memory elements. This memory has two-dimensional read/ write capability, resulting in two word lengths: a short-word length which is the number of bits in a word and a long-word length which is the number of words in a bit-column because the number of bits in a word is usually smaller than the number of words. This memory can read or write in either a horizontal or vertical direction of the array, called the short-word mode or the long-word mode, respectively. The shortword mode is the conventional memory organization. The long-word mode is equivalent to bit-serial associative technique.

Bit-serial associative processing through the use of 2-1/2 D core search memory was reported by many researchers [64], [65]. Fulmer and Meilander [66] presented a modular platedwire implementation of a bit-serial associative processor which has arithmetic capability as well as storage and logic capability at each word of the memory.

Goodyear Associative Processor (GAP), developed by Goodyear Aerospace Corporation [67], uses the processor modules as basic building blocks. Each processor module contains 256 plated-wire processing elements. Each plated-wire processing element consists of one plated-wire, which is a memory device for one 256-bit word, and one response store, whose function is to signal the matching of the word, stored in the plated-wire. The limit on the number of processor modules largely depends on the hardware physical size (a single plated-wire module occupies about 0.5 cubic foot) and the processor's speed requirements.

One of the two large-scale associative processors developed to data is Goodyear Aerospace Corporation's STARAN [43] - [46]. Because of its importance we are going to discuss it in more detail.

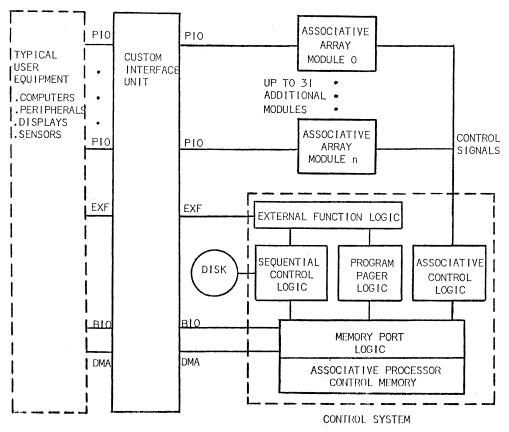

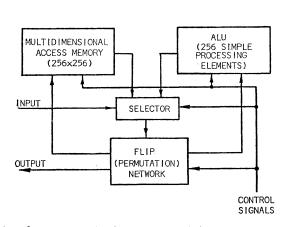

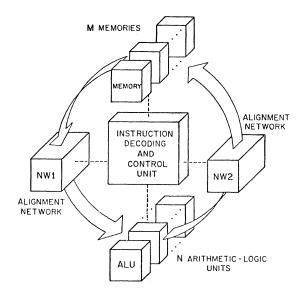

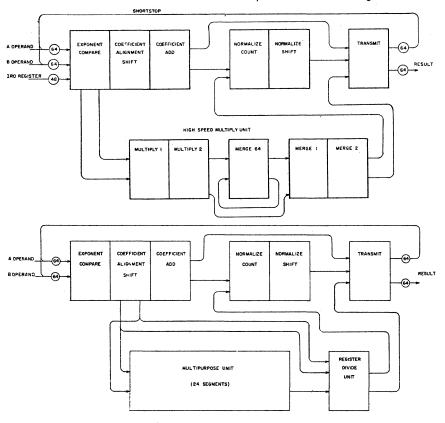

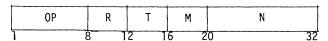

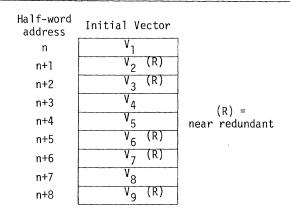

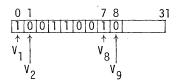

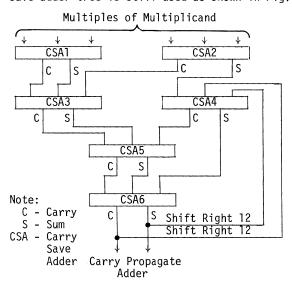

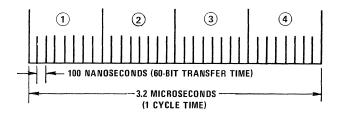

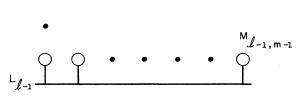

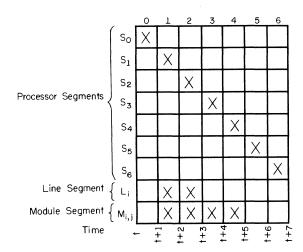

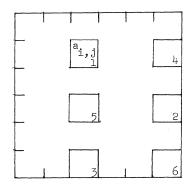

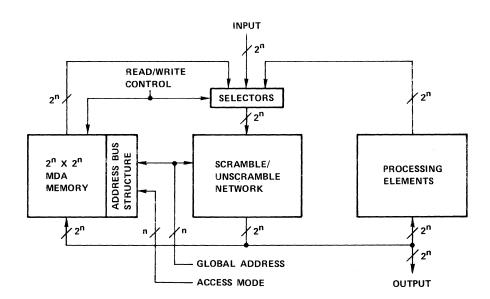

$\underline{\mathtt{STARAN}}.$  The basic structure of STARAN is shown in Fig. 8. It consists of a control system and a number of associative array modules (current system configuration allows up to 32 such modules). Each associative array module contains a 256-word  $\times$  256-bit multi-dimensional access memory, 256 simple processing elements, a flip network (or called permutation network), and a selector as shown in Fig. 9. There is a simple processing element for each of the 256 words of the memory, and each simple processing element operates serially by bit on the data in the memory word. This operational concept is shown in Fig. 10. Using the flip network, the data stored in the multi-dimensional access memory can be accessed through the input/output channel either in the bit direction or the word direction. A flip network (or permutation

network) is also used for shifting and rearranging of data in an associative array module so that parallel search, arithmetic or logical operations can be performed between words of the multi-dimensional access memory. By proper arrangements, the multi-dimensional access memory can be implemented using random access memory chips [45], [68].

To locate a particular data item, STARAN initiates a search by calling for a match against an input data item. All words in the memories of all the modules that satisfy the search criterion are identified by a single instruction. The simple processing elements simultaneously execute operations as specified by the associative control logic. Therefore, in one instruction execution, the data in all selected word in the memories of all the modules are processed simultaneously by the simple processing element at each word.

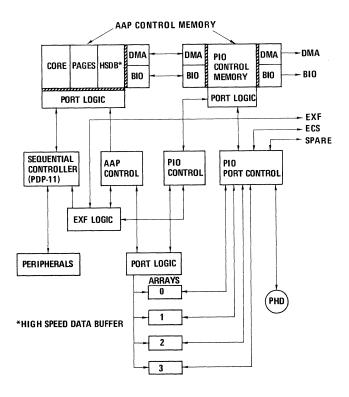

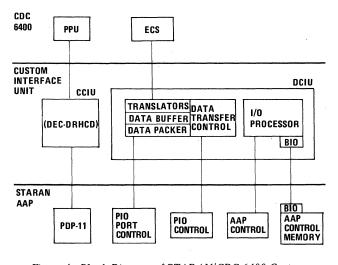

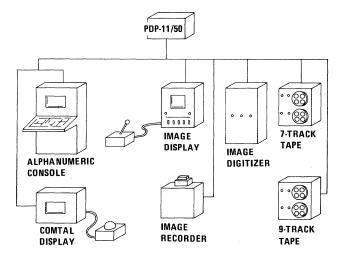

The interface unit involves interface with sensors, conventional computers, a signal processor, interactive displays and mass storage devices. A variety of I/O options are implemented in the custom interface unit, including the direct memory access (DMA), buffered I/O (BIO) channels, external function (EXF) channels and parallel I/O (PIO). Each associative array module can have up to 256 inputs and 256 outputs into the custom interface unit. They can be used to increase speed of inter-array data communication, allow STARAN to communicate with a high-bandwidth I/O device, and allow any device to communicate directly with the associative array modules.

A mass storage device, like a multihead disk, is connected to the associative array modules via the PIO. The information transfer rates obtained with this configuration depend on the cycle time and the number of heads on the disk being used. In requesting data from the disk, STARAN will send the disk one or more external functions specifying a starting sector address, the number of sectors, and the direction of transfer. The disk system may interrupt STARAN when the disk reaches the requested sector to initiate the transfer over PIO lines. The STARAN control instructions that actually read or write the PIO can be synchronized to the disk so that STARAN timing is slaved to the disk timing during the transfer.

In 1973, an operational associative processor facility, called RADCAP, was installed at Rome Air Development Center [69] - [72]. This facility consists of a STARAN and various peripheral devices, all interfaced with a Honeywell Information Systems (HIS) 645 sequential computer which runs under the Multics time-sharing operating system. The objective of the RADCAP facility is to explore various applications of the system to various real-time problems.

Other Bit-Serial Associative Processors. In addition to those presented before, several other

bit-serial associative processors have been developed recently. Sanders Associates [73] developed the OMEN computer in which a conventional serial processor, such as DEC PDP-11, and a bit-serial associative processor both address an orthogonal memory, which has a capacity of 64 words × 16-bits. The associative processor contains 64 identical processors which form the vertical arithmetic unit that has bit-slice access to the orthogonal memory. These 64 processors perform the same operations at the same time under the control of masks.

Hughes Aircraft Co. [74] developed an associative processor which contains 10 bit-serial associative memories and an MOS shift-register bulk memory. The bulk memory consists of a set of MOS shift registers, each having, at least 16,000 bits each. The purpose of this configuration is to achieve efficient operation of an associative memory when the data base is stored in a large inexpensive mass storage device.

Raytheon Co. [36] developed the Raytheon Associative/Array Processor (RAP) which contains a processing element array and a direct array access channel which facilitates bulk data transfer to/from the processing element array. The function of the processing element is to perform search, arithmetic and logic operation on data stored in its own private memory. Each processing element can be thought of as a bit-serial microprocessor with associative capability.

It should be noted that byte-serial associative processors are conceived between bit-serial and fully parallel associative processors. For reasons of efficiency, at a reasonable cost, a byte-serial word-parallel associative processor, called the Associative Processor Computer System (APCS), was proposed by Linde, Gates and Peng [75] at System Development Corporation. APCS contains two associative processing units and a parallel input/output channel. The word logic consists of byte operation logic, instead of bit operation logic as in bit-serial associative processors, and tags.

#### Word-Serial Associative Processors

As mentioned before, a word-serial associative processor essentially represents hardware implementation of a simple program loop for search. The important factor which contributes to the relative efficiency of this approach as compared with programmed search in standard sequential processor is that the instruction decoding time is reduced since the search operation requires a single instruction in the word-serial associative processor.

In 1962 Young [76] proposed to use "circulating" associative memories to allow many memory words to time-share a single set of content-addressing logic. In 1966, Crofut and Sottile [77] presented a word-serial associative processor based on a word-serial associative memory

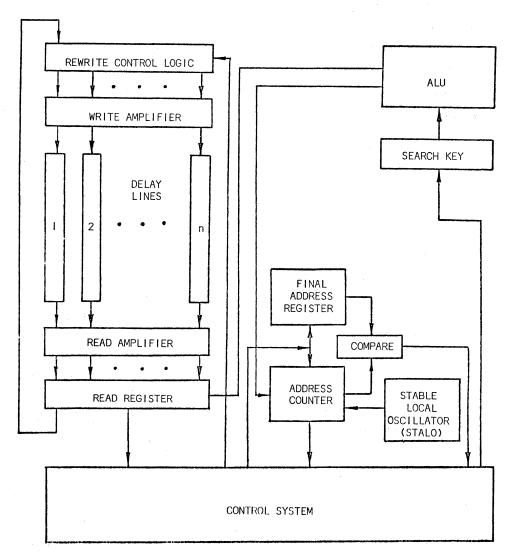

using n ultrasonic digital delay lines operating at 100 MHz with 10  $\mu sec$  delay time, where n is the number of bits of a word. Each delay line stores one bit of the word, and all bits of the stored word propagate down the delay lines synchronously. A stable oscillator (Stalo) was used to generate the synchronizing clock pulses for advancing the address counter. Individual words can be interrogated and updated when they appear at the output of delay lines. The rewrite control logic allows the delay-line system to select either recirculating information or new data inputs. The operational characteristics of such a memory resemble that of a drum or disk. Such a word-serial associative processor is shown in Fig. 11. In 1969, Rux [78] presented a wordserial associative memory with 35 glass delay lines storing 2046 bits per line at 20.48 MHz which was connected to a general purpose mediumspeed sequential computer called NEBULA [79], [80].

Because of the slow speed of word-serial associative memories only experimental models have been developed for word-serial associative processors.

#### Block-Oriented Associative Processors

For applications such as information storage and retrieval where a large storage capacity is required, neither bit-serial nor word-serial associative processors are cost-effective. Bit-serial associative processors become too expensive, while word-serial associative processors require a long processing time. Thus, block-oriented associative processors, which use mass rotating storage devices, such as a disk to provide a limited degree of associative capabilities, have been proposed [81] - [85].

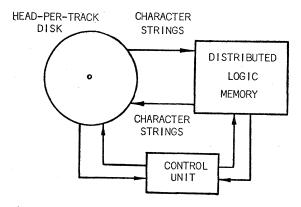

Slotnick [81] and Parker [82] presented the concept of logic-per-track devices which consist of a head-per-track disk memory with some logic associated with each track. Based on this concept and Lee's distributed logic memory for information storage and retrieval applications, Parhami [83] presented a block-oriented associative processor, called RAPID (stands for Rotating Associative Processor for Information Dissemination), which can be shown in Fig. 11. Since the data rates between head-per-track disks and distributed logic memory is high, the RAPID system is suitable for applications requiring a large storage capacity which presently suffer from the high cost of random access memories or from performance degradation due to the frequent transfers between primary and secondary memories.

Minsky [84] proposed the associativity on rotating memories either in the form of drums or disks. He defined the term "partially associative memory" by specifying the primitive structure of information (name part and data part) to be stored on it and the operational characteristics (predicates and instructions). The activity of the memory is supervised by a special

processor, called controller. Instead of spending the time in looking for a given address, he proposed to use the delay time for a search for a content.

Another block-oriented associative processor has been proposed by Healy, Lipovski and Doty [85] based on storage and retrieval from a segmented sequential table data structure utilizing associative addressing.

#### Summary

In this paper, we have reviewed the architecture of various associative processors and classified them into four major categories based on the organization of their associative memories. Among these associative processors, PEPE and STARAN are most well-known. Lloyd and Merwin [86] have made an evaluation of the performance of PEPE, STARAN and others in a realtime environment. In general, fully parallel and bit-serial associative processors are used for high-speed parallel data processing which cannot be carried out effectively in ordinary sequential computers. However, their implementation costs are also higher. For low-cost associative processing which is required in large information storage and retrieval systems, block-oriented associative processors offer a promising architecture.

#### Acknowledgment

The authors would like to thank Professors T. Y. Feng of Wayne State University, M. J. Gonzalez, Jr. of Northwestern University and Dr. Richard E. Merwin of U.S. Army Ballistic Missile Defense Program Office for many helpful discussions. They also would like to thank Capt. A. R. Klayton of U.S. Air Force Rome Air Development Center for providing useful information on the STARAN/RADCAP system.

#### References

- [1] R. R. Seeber, "Cryogenic Associative Memory,"

<u>Proc. Assoc. Computing Machinery Nat. Conf.</u>,

Aug. 1960.

- [2] M. H. Lewin, H. R. Beelitz and J. A. Rajchman, "Fixed Associative Memory Using Evaporated Organic Diode Arrays," <a href="Proc. 1963">Proc. 1963</a>

<a href="Fall Joint Computer Conf">Fall Joint Computer Conf</a>., pp. 101-106.

- [3] Y. H. Chu, "A Destructive-Readout Associative Memory," <u>IEEE Trans. on Electronic Computers</u>, Vol. EC-14 (Aug. 1965), pp. 600-605.

- [4] A. A. Hanlon, "Content-Addressable and Associative Memory Systems: A Survey," <u>IEEE Trans. on Electronic Computers</u>, Vol. EC-15 (Aug. 1966), pp. 509-521.

- [5] A. Weinberger, "The Hybrid Associative Memory Concept," <u>Computer Design</u> (Jan. 1971), pp. 77-85.

- [6] J. Minker, "An Overview of Associative or Content-Addressable Memory Systems and a KWIC Index to the Literature," <u>Computing</u> <u>Reviews</u>, Vol. 12 (Oct. 1971), pp. 453-504.

- [7] B. Parhami, "Associative Memories and Processors: An Overview and Selected Bibliography," <u>Proc. of the IEEE</u>, Vol. 61 (June 1973), pp. 722-730.

- [8] M. Quinones, "An Associative-Capacitive ROM for Reprogrammable Logic Applications," Computer Design (Jan. 1974), pp. 98-101.

- [9] A. Slade and H. O. McMahon, "A Cryotron Catalog Memory System," Proc. 1956 East Joint Computer Conf., pp. 115-120.

- [10] M. H. Lewin, "Retrieval of Ordered Lists from a Content-Addressed Memory," <u>RCA Re-views</u>, Vol. 23 (June 1962), pp. 215-229.

- [11] V. L. Newhouse and R. E. Fruin, "A Cryogenic Data Addressed Memory," Proc. 1962

Spring Joint Computer Conf., pp. 89-99.

- [12] A. D. Falkoff, "Algorithms for Parallel Search Memories," <u>Jour. Assoc. Computing</u> <u>Machinery</u> (Oct. 1962), pp. 488-511.

- [13] E. C. Joseph and A. Kaplan, "Target-Track Correlation with a Search Memory," Proc.

Nat. Conv. on Military Electronics

1962), pp. 255-261.

(June

- [14] A. Kaplan, "A Search Memory Subsystem for a General-Purpose Computer," Proc. 1963

Fall Joint Computer Conf., pp. 193-200.

- [15] R. G. Gall, "A Hardware-Integrated GPC/ Search Memory," <u>Proc. 1964 Fall Joint</u> <u>Computer Conf.</u>, pp. 159-173.

- [16] G. G. Pick, "A Read-Only Multi-Megabit Parallel Search Associative Memory," <u>The</u> 26th Annual Meeting of American Documentation, Oct. 1963.

- [17] A. Estrin and R. Fuller, "Algorithms for Content-Addressable Memories," <u>IEEE Pacific Computer Conf. Proc</u>. (March 1963), pp. 118-128.

- [18] C. Y. Lee and M. C. Paull, "A Content Addressable Distributed Logic Memory with Applications to Information Retrieval,"

<u>Proc. IEEE</u>, Vol. 51 (June 1963), pp. 924-932.

- [19] R. B. Derickson, "A Proposed Associative Pushdown Memory," <u>Computer Design</u> (March 1968), pp. 60-66.

- [20] N. K. Natarajan and P. A. V. Thomas, "A Multiaccess Associative Memory," IEEE Trans. on Computers, Vol. C-18 (May 1969), pp. 424-428.

- [21] Y. H. Chu, <u>Computer Organization and Micro-programming</u>, <u>Prentice-Hall</u>, Inc., 1972.

- [22] R. H. Fuller, "Content-Addressable Memory Systems," <u>Disser. Absts.</u>, Vol. 24 (Nov. 1963), p. 1960, 611 pp.

- [23] S. Nissim, "Organizing the Nanophile Computers," <u>Electronic Design</u>, Vol. 11 (March 1963), pp. 44-53.

- [24] W. L. McDermid and H. E. Peterson, "A Magnetic Associative Memory System," IBM J. Res. and Dev., Vol. 5 (Jan. 1961), pp. 59-62.

- [25] J. R. Kiseda, H. E. Peterson, W. C. Seelback and M. Teig, "A Magnetic Associative Memory," IBM J. Res. and Dev., Vol. 5 (April1961), pp. 106-121.

- [26] R. T. Hunt, D. L. Snider, J. Suprise and H. N. Boyd, "Study of Elastic Switching for Associative Memory Systems," <u>U.S. Gov. Res. Repts.</u>, Vol. 39, p. 188(A), AD432041, May 20, 1964.

- [27] E. L. Younker, C. H. Heckler, D. P. Masher and J. M. Yarbourough, "Design of an Experimental Multiple Instantaneous Reference File," <u>Proc. 1964 Spring Joint Computer</u> <u>Conf.</u>, pp. 515-528.

- [28] R. G. Ewing and P. M. Davies, "An Associative Processor," <u>Proc. 1964 Fall Joint Computer Conf.</u>, pp. 147-158.

- [29] E. S. Lee, "Associative Techniques with Complementing Flip-Flops," Proc. 1963

Spring Joint Computer Conf., pp. 381-394.

- [30] R. R. Lussier and R. P. Schneider, "All Magnetic Content Addressed Memory,"

Electronic Indust., Vol. 22 (March 1963), pp. 92-98.

- [31] J. E. McAteer, J. A. Capobianco and R. L. Koppel, "Associative Memory System Implementation and Characteristics," <u>Proc. 1964</u>

<u>Fall Joint Computer Conf.</u>, pp. 81-92.

- [32] M. F. Wolff, "What's New in Computer Memories," <u>Electronics</u> (Nov. 1963), pp. 35-39.

- [33] J. I. Raffel and T. S. Crowther, "A Proposal for an Associative Memory Using Magnetic Films," IEEE Trans. on Electronic Computers (Short Notes), Vol. EC-13 (Oct. 1964), p. 611.

- [34] G. G. Pick, "A Semipermanent Memory Utilizing Correlation Addressing," <u>Proc. 1964</u>

- Fall Joint Computer Conf., pp. 107-121.

- [35] G. T. Tuttle, "How to Quiz a Whole Memory at Once," <u>Electronics</u> (Nov. 1963), pp. 43-46.

- [36] G. R. Couranz, M. S. Gerhardt and C. J. Young, "Programmable Radar Signal Processing Using the RAP," <u>Proc. of the Sagamore Computer Conference on Parallel Processing</u>

(Aug. 1974), pp. 37-52.

- [37] B. A. Crane, M. J. Gilmartin, J. H. Huttenhoff, P. T. Rux and R. R. Shively, "PEPE Computer Architecture," <u>IEEE COMPCON</u> (1972), pp. 57-60.

- [38] D. E. Wilson, "The PEPE Support Software System," <u>IEEE COMPCON</u> (1972), pp. 61-64.

- [39] J. A. Cornell, "Parallel Processing of Ballistic Missile Defense Radar Data with PEPE," <u>IEEE COMPCON</u> (1972), pp. 69-72.

- [40] A. J. Evensen and J. L. Troy, "Introduction to the Architecture of a 288-Element PEPE,"

Proc. of the 1973 Sagamore Computer Conf.

on Parallel Processing, (Aug. 1973), pp.

162-169.

- [41] J. R. Dingeldine, H. R. Martin and W. M. Patterson, "Operating System and Support Software for PEPE," Proc. of the 1973

Sagamore Computer Conf. on Parallel Processing (Aug. 1973), pp. 170-178.

- [42] C. R. Vick and R. E. Merwin, "An Architecture Description of a Parallel Element Processing Element," <u>Proc. 1973 International Workshop on Computer Architecture</u>.

- [43] J. A. Rudolph, "A Production Implementation of an Associative Array Processor: STARAN,"

Proc. 1972 Fall Joint Computer Conf., pp. 229-241.

- [44] K. E. Batcher, "Flexible Parallel Processing and STARAN," <u>WESCON Tech. Papers</u>, Sept. 1972.

- [45] K. E. Batcher, "STARAN Parallel Processor System Hardware," <u>Proc. 1974 National Computer Conf.</u>, pp. 405-410.

- [46] E. W. Davis, "STARAN Parallel Processor System Software," <u>Proc. 1974 National Computer Conf.</u>, pp. 17-22.

- [47] E. A. Behnke and G. B. Rosenberger, "Cryogenic Associative Processor," <u>IBM Final</u> <u>Report</u>, Sept. 1963.

- [48] A. E. Slade and C. R. Smallman, "Thin Film Cryotron Catalog Memory," <u>Automatic Control</u>, Vol. 13 (Aug. 1960), pp. 48-50.

- [49] R. F. Rosin, "An Organization of an Associative Cryogenic Computer," <u>Proc. 1962 Spring</u>

- Joint Computer Conf., pp. 203-212.

- [50] P. M. Davies, "A Superconductive Associative Memory," <a href="Proc. 1962 Spring Joint Computer Conf">Proc. 1962 Spring Joint Computer Conf</a>, pp. 79-88.

- [51] R. W. Ahrons, "Superconductive Associative Memories," <u>RCA Reviews</u>, Vol. 24 (Sept. 1962), pp. 325-354.

- [52] J. D. Barnard, F. A. Behnke, A. B. Lind-quist and R. R. Seeber, "Structure of a Cryogenic Associative Processor," Proc. IEEE, Vol. 52 (Oct. 1964), pp. 1182-1190.

- [53] S. S. Yau and C. C. Yang, "A Cryogenic Associative Memory System for Information Retrieval," <a href="Proc. National Electronic Conf.">Proc. National Electronic Conf.</a>, vol. 22 (Oct. 1966), pp. 764-769.

- [54] C. C. Yang and S. S. Yau, "A Cutpoint Cellular Associative Memory," <u>IEEE Trans.on Electronic Computers</u>, Vol. EC-15 (Aug. 1966), pp. 522-528.

- [55] C. Y. Lee, "Intercommunicating Cells, Basis for a Distributed Logic Computer," <u>Proc.</u> 1962 Fall Joint Computer Conf., pp. 130-136.

- [56] R. P. Edwards, "Content-Addressable Distributed-Logic Memories," Proc. IEEE, Vol. 52 (Jan. 1964), pp. 83-84.

- [57] E. S. Spiegelthal, "A Content Addressable Distributed Logic Memory with Applications to Information Retrieval," <u>Proc. IEEE</u>, Vol. 52 (Jan. 1964), p. 74.

- [58] C. Y. Lee, "Content-Addressable and Distributed Logic Memories," <u>Applied Automata Theory</u>, J. T. Tou, Ed., New York; Academic Press, 1968.

- [59] R. S. Gains and C. Y. Lee, "An Improved Cell Memory," <u>IEEE Trans. on Electronic Computers</u> (Feb. 1965), pp. 72-75.

- [60] B. A. Crane and J. A. Crithens, "Bulk Processing in Distributed Logic Memory," <u>IEEE Trans. on Electronic Computers</u>, Vol. EC-14 (April 1965), pp. 186-196.

- [61] G. J. Lipovski, "The Architecture of a Large Associative Processor," <u>Proc. 1970</u> <u>Spring Joint Computer Conf.</u>, pp. 385-396.

- [62] B. A. Crane and R. R. Laane, "A Cryoelectronic Distributed Logic Memory," Proc. 1967 Spring Joint Computer Conf., pp. 517-524.

- [63] W. Shooman, "Parallel Computing With Vertical Data," Proc. 1960 East Joint Computer Conf., pp. 111-115.

- [64] P. A. Harding and M. W. Rolund, "A 2-1/2D Core Search Memory," Proc. 1968 Fall Joint Computer Conf., pp. 1213-1218.

- [65] H. S. Stone, "Associative Processing for General Purpose Computers Through the Use of Modified Memories," Proc. 1968 Fall Joint Computer Conf., pp. 949-955.

- [66] L. C. Fulmer and W. C. Meilander, "A Modular Plated Wire Associative Processor,"

IEEE Int. Computer Group Conf. Proc. (June 1970), pp. 325-335.

- [67] J. A. Rudolph, L. C. Fulmer and W. C. Meilander, "The Coming of Age of the Associative Processor," <u>Electronics</u> (Feb. 15, 1971), pp. 91-96.

- [68] K. E. Batcher, "The Multi-Dimensional Access Memory in STARAN," <u>Proc. of the 1975 Saga-</u> more Computer Conf. on Parallel Processing.

- [69] J. D. Feldman and L. C. Fulmer, "RADCAP -An Operational Parallel Processing Facility," Proc. 1974 National Computer Conf., pp. 7-15.

- [70] J. D. Feldman and O. A. Reiman, "RADCAP: An Operational Parallel Processing Facility,"

Proc. of the 1973 Sagamore Computer Conf.

on Parallel Processing (Aug. 1973), pp. 140-146.

- [71] K. E. Batcher, "STARAN/RADCAP Hardware Architecture," Proc. of the 1973 Sagamore Computer Conf. on Parallel Processing (Aug. 1973), pp. 147-152.

- [72] E. W. Davis, "STARAN/RADCAP System Software,"

Proc. of the 1973 Sagamore Computer Conf.

on Parallel Processing, (Aug. 1973), pp.

153-159.

- [73] L. C. Higbie, "The OMEN Computers: Associative Array Processors," <u>IEEE COMPCON</u> (1972), pp. 287-290.

- [74] H. H. Love, Jr., "An Efficient Associative Processor Using Bulk Storage," Proc. of the 1973 Sagamore Computer Conf. on Parallel Processing (Aug. 1973), pp. 103-112.

- [75] R. R. Linde, R. Gates and T. F. Peng, "Associative Processor Applications to Real-Time Data Management," <u>Proc. 1973 National Computer Conf.</u>, pp. 187-195.

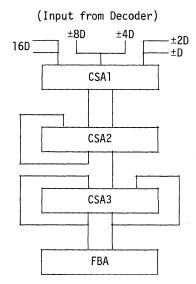

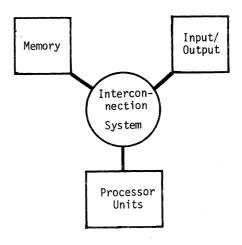

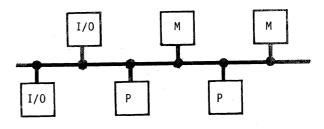

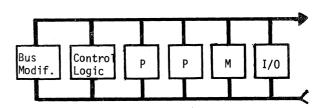

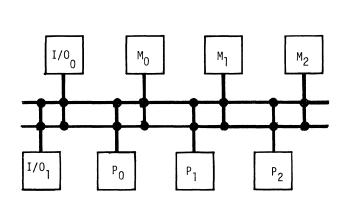

Fig. 1. An associative processor.

- [76] F. H. Young, "Circulating Associative Memories," <u>Dept. of Math. Rept.</u>, Oregon State University, 1962.

- [77] W. A. Crofut and M. R. Sottile, "Design Techniques of a Delay-Line Content-Addressed Memory," <u>IEEE Trans. on Electronic Computers</u> (Aug. 1966), pp. 529-534.

- [78] P. T. Rux, "A Glass Delay Line Contet-Addressable Memory System," <u>IEEE Trans. on</u> <u>Computers</u> (June 1969), pp. 512-520.

- [79] J. A. Boles, P. T. Rux and W. Weingarten, Jr., "NEBULA: A Digital Computer Using a 20 Mc Glass Delay Line Memory," <u>Comm.</u> <u>Assoc. Computing Machinery</u> (July 1966), pp. 503-508.

- [80] W. Weingarten, "On an Associative Memory for the NEBULA Computer," <u>Dept. of Math. Rept.</u>, Oregon State University, 1964.

- [81] D. L. Slotnick, "Logic per Track Devices,"

Advances in Computers, Vol. 10, New York:

Academic Press, 1970, pp. 291-296.

- [82] J. L. Parker, "A Logic Per Track Retrieval System," IFIP Congress, 1971.

- [83] B. Parhami, "A Highly Parallel Computing System for Information Retrieval," <u>Proc.</u> 1972 Fall Joint Computer Conf., pp. 681-690.

- [84] N. Minsky, "Rotating Storage Devices as Partially Associative Memories," <u>Proc. 1972</u> Fall Joint Computer Conf., pp. 587-595.

- [85] L. D. Healy, G. J. Lipovski and K. L. Doty,

"The Architecture of a Context Addressed

Segment-Sequential Storage," Proc. 1972

Fall Joint Computer Conf., pp. 691-701.

- [86] G. R. Lloyd and T. E. Merwin, "Evaluation of Performance of Parallel Processors in a Real-Time Environment," <u>Proc. 1973</u> <u>National Computer Conf.</u>, pp. 101-108.

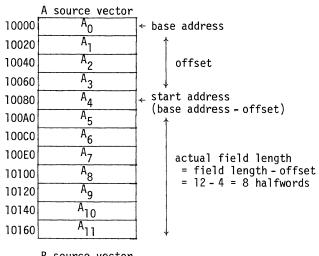

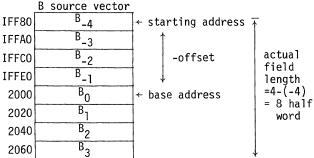

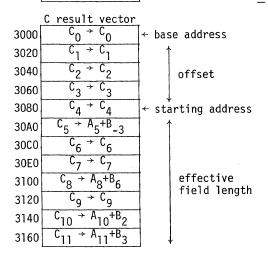

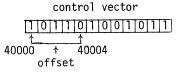

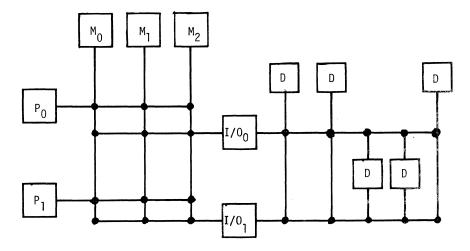

Fig. 2. A fully parallel word-organized associative memory and ALU.

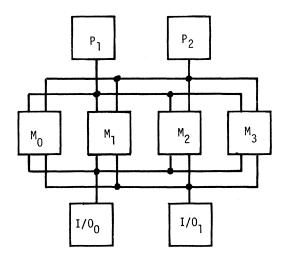

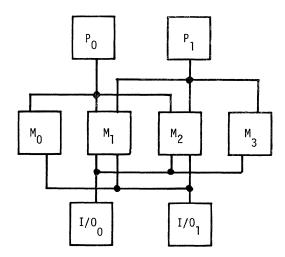

Fig. 3. A fully parallel distributed logic associative processor.

Fig. 4. A fully parallel two-dimensional distributed logic associative memory.

Fig. 5. The parallel element processing ensemble (PEPE) - a modified distributed logic associative processor.

Fig. 6. A processing element of the PEPE.

Fig. 7. A bit-serial associative memory and ALU.

Fig. 8. The STARAN - a bit-serial associative processor.

Fig. 9. An associative array module of the STARAN.

Fig. 10. The operational concept of a STARAN associative array module.

Fig. 11. A word-serial associative processor.

Fig. 12. The block-oriented associative memory used in the RAPID.

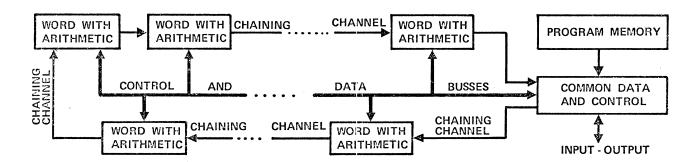

#### PARALLEL PROCESSOR ARCHITECTURE -- A SURVEY\*

David J. Kuck

Department of Computer Science

University of Illinois at Urbana-Champaign

Urbana, Illinois 61801

(Invited Paper)

#### Abstract

This paper is a survey of parallel machine organizations and programming. We define parallelism in a broad sense, which encompasses the bit level, operation level, and algorithm level. A number of abstract and practical questions are discussed.

#### I. Introduction

We will interpret "parallel processor architecture" broadly in this paper. In the strict sense, we could limit our attention to a few machines, some already in operation, some being built, and others being proposed. But this would tend to perpetuate certain bits of folklore about parallel machines which puts them in a zoo somewhere between the chimera and the white elephant.

Indeed, some parallel (and other) computers probably belong there. But recent theoretical developments lead us to the conclusion that a broad interpretation of "parallel processing" is justified here. By taking this point of view, we will show that a number of previously diverse ideas can be unified.

It is certainly true that the term "parallel processing" has been used in many ways since the dawn of computer history. Twenty-five years ago it referred to arithmetic operations on whole words rather than one bit at a time. Now, it refers sometimes to multiple processors, other times to array-type machines (parallel or pipeline), and occasionally to multiprogrammed machines. In this paper we will touch on all of the above. Furthermore, we will not restrict our attention to processing the sense of logic and arithmetic. Memory access and data alignment problems are equally important.

Several theoretical results will be given and discussed. It turns out that by looking at things correctly, a few abstract ideas can be interpreted in several important practical ways. For example, by studying recurrence relations we can develop algorithms to transform sequential logic equations (e.g., for bit serial arithmetic) into combinational circuit diagrams (e.g., for fast carry lookahead arithmetic). Using exactly the same theory, we can develop compiler algorithms to transform standard serial programs (e.g., Fortran) into highly parallel programs (e.g., for array processors).

We will also study tree-height reduction techniques which can be interpreted as logic design or compiler algorithms. As another example, we will present new results about the effective bandwidth of parallel memories. This can be interpreted for multiprocessors, associative processors, parallel or pipeline processors. Also, we will discuss data alignment techniques which have interpretations as bit shifters within one processor, as data alignment networks between several processors, or as merge networks between a secondary and primary memory.

Our approach is to study the structure of programs and the structure of certain machine parts to see how the two can be brought together. Our primary goal is to achieve high speed at low cost. Obviously, there are other very important considerations in machine design. But we choose this goal first, for several reasons. For one, it is widely used in practice and is thus practically important. For another, it has a great deal of theoretical importance as follows.

Computer speeds are determined by two basic limitations. One concerns the physics of the hardware being used, e.g., how fast do gates switch and how many inches of wire must a signal traverse? The other concerns the logic of machine organization and program organization. It is the latter question that we shall study.

Suppose that hardware speeds were fixed. Then, given a set of programs, how fast could they be executed? Theoretical lower bounds can be given on the number of time steps needed to compute certain functions. Once these are known for an algorithm or class of algorithms, then we can attempt to design "perfect" machine organizations for these algorithms. Such machines would execute the algorithms in the fastest possible way at the lowest cost. When we mention cost, logic design questions arise. How many gates or integrated circuits or microprocessors, etc., are needed? Real costs are measured in printed circuit bounds, power supplies, cabinets and so on, so "lowest cost" is difficult to define, but logic component counts tend to reflect overall hardware costs. We will deal at various points with bounds on gate, integrated circuit, processor and memory unit counts.

In this paper we will not give much attention to specific algorithms or to lower bounds. Rather, we will study Fortran-like programming languages to see what elementary set of language constructs may be universal to a large class of algorithms. Assignment statements, recurrences, and conditional statements together with program

<sup>\*</sup>This work was supported in part by NSF Grant DCR73-07980 A02.

graphs will be discussed in detail. Instead of lower bounds, we will give upper bounds on time and components, all of which can be achieved by algorithms which support the bounds. In many cases, these upper bounds are not far from lower bounds obtained by simple fan-in arguments.

Overall, we are attempting to develop a better understanding of the structure of programs and of the relations of programs to machine organizations. By presenting bounds with constructive proofs, logic design automation or compiler algorithms follow. Furthermore, we repeat that a few theoretical ideas can be given a number of useful interpretations which provide insights in several areas. Finally, we will point out that a better understanding of some fundamentals about program and machine organization may lead to better understanding of structured programming and paging in the memory hierarchies of existing computer systems.

This paper is divided into three main parts. In section II, we give some theoretical background. Then, in section III we use this to study the overall structure of programs. We also use the theory in section IV for processor design. Section V discusses data handling; memory access and data alignment are both considered.

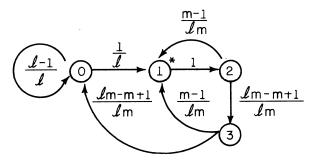

#### II. Theoretical Background

In this section we will be concerned with upper bounds on processing time and the number of processors required to achieve such time bounds. We will ignore for the moment memory activity, data alignment and control unit times, and assume an idealized multioperation machine. We will allow any number of arithmetic processors to be used at once (although we will bound this number). For expression evaluation, any processor may perform any of the arithmetic operations on any time step. This multiple instruction execution (c.f. MIMD [1,2]) is less desirable than having all processors execute the same instruction type (SIMD [ 1]). Our recurrence method requires only one instruction type at a time (SIMD). Clearly, expression evaluation is slowed down by at most a small constant if SIMD instructions are used. Further, we assume that each arithmetic operation takes one unit of time. Later in the paper we will discuss more realistic machine details.

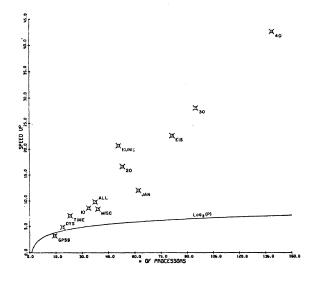

If  $T_p$  is the number of unit time steps required to perform some calculation using  $p \geq 1$  processors, we define the <u>speedup</u> of the p processor calculation over a uniprocessor as

$$\begin{split} S_p &= \frac{T_1}{T_p} \geq 1 \text{ and we define the efficiency of the} \\ \text{calculation as } E_p &= \frac{S_p}{p} \leq 1 \text{ which may be regarded} \\ \text{as actual speedup divided by the maximum possible speedup using p processors. For various computations we will discuss the maximum possible speedup known according to some algorithm and in such cases we use P to denote the minimum number of processors known to achieve this maximum speedup. \end{split}$$

In such cases we will use the notation  $\mathbf{T}_{\mathbf{p}}$ ,  $\mathbf{S}_{\mathbf{p}}$  and  $\mathbf{E}_{\mathbf{p}}$  to denote the corresponding time, speedup and efficiency, respectively.

Time and processor bounds for some computation A will be expressed as  $T_p[A]$  and P[A] in the minimum time cases and  $T_p[A]$  in the restricted processor (p < P) case. When no ambiguity can result, we will write T[A] or just T in place of  $T_p[A]$  and P in place of P[A], for simplicity. We write log x to denote  $\log_2$  x and  $\lceil x \rceil$  for the ceiling of x.

#### Arithmetic Expression Tree-Height Reduction

Now we consider time and processor bounds for arithmetic expression evaluation. We restrict our attention to transforming expressions using associativity, commutativity and distributivity which lead us to speedups of  $0(\frac{n}{\log n})$ . Since this is asymptotic to the best possible speedup, more complex transformations (e.g., factoring, partial fraction expansion seem unnecessary. In section IV, we shall return to this subject in the form of Boolean expression evaluation for combinational logic circuits.

#### Definition 1

An <u>arithmetic expression</u> is any well-formed string composed of the four arithmetic operations (+,-,\*,/), left and right parentheses, and <u>atoms</u> which are constants or variables. We denote an arithmetic expression E of n distinct atoms by E < n > .

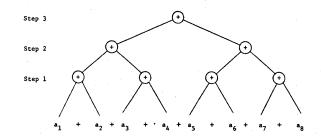

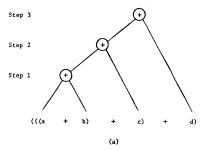

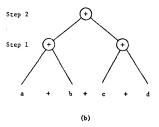

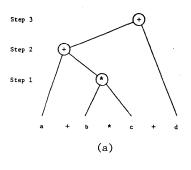

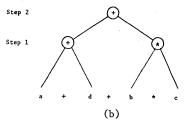

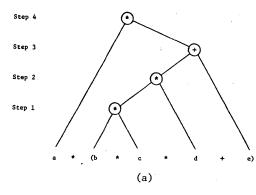

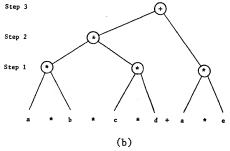

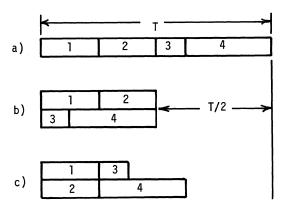

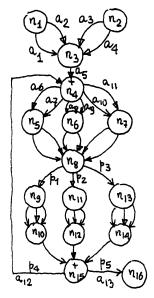

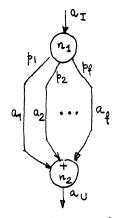

If we use one processor, then the evaluation of an expression containing n operands requires n-1 units of time. But suppose we may use as many processors as we wish. Then it is obvious that some expressions E<n> may be evaluated in  $\log_2 n$  units of time as illustrated in Figure 1.

Figure 1. Expression of 8 Atoms

In fact, we can establish, by a simple fan-in argument, the following lower bound:

<u>Lemma 1</u> Given any arithmetic expression E<n> $T[E<n>] > [log_2n].$

On the other hand, it is easy to construct expressions E< n> whose evaluation appears to require O(n) time units regardless of the number of processors available. Consider the evaluation of a polynomial by Horner's rule:

$$p_n(x) = a_0 + x(a_1 + x(a_2 + \dots + x(a_{n-1} + xa_n) + \dots)).$$

(1)

A strict sequential order is imposed by the parentheses in Eq. 1 and more processors than one are of no use in speeding up this expression's evaluation.

However, we are not restricted to dealing with arithmetic expressions as they are presented to us. For example, the associative, commutative, and distributive laws of arithmetic operations may be used to transform a given expression into a form which is numerically equivalent to the original but which may be evaluated more quickly. We now consider examples of each of these.