## INTEL. MULTIBUS® SPECIFICATION

Order Number: 9800683-04

Copyright © 1978, 1979, 1981, 1982 Intel Corporation Intel Corporation, 3065 Bowers Avenue, Santa Clara, CA 95051

| REV. | <b>REVISION HISTORY</b>         | PRINT<br>DATE |

|------|---------------------------------|---------------|

| -03  | Revised Issue                   | 4/81          |

| -04  | Revised Issue. See change bars. | 6/82          |

|      |                                 |               |

|      |                                 |               |

|      |                                 |               |

|      |                                 |               |

|      |                                 |               |

|      |                                 |               |

|      |                                 |               |

|      |                                 |               |

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

....

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BXP    | Intel        | iSBX            | Multichannel  |

|--------|--------------|-----------------|---------------|

| CREDIT | Intel        | Library Manager | Multimodule   |

| 1      | Intelevision | MCS             | Plug-A-Bubble |

| ICE    | Intellec     | Megachassis     | PROMPT        |

| iCS    | iOSP         | Micromainframe  | RMX/80        |

| ١m     | iRMX         | Mircromap       | System 2000   |

| iMMX   | iSBC         | Multibus        | ÚPI           |

| Insite | iPDS         |                 |               |

|        |              |                 |               |

# CONTENTS

| SECTION 1    | PAC | ЗE  |

|--------------|-----|-----|

| INTRODUCTION |     | 1-1 |

## SECTION 2

#### FUNCTIONAL DESCRIPTION

| Introduction                 |     | . 2-1        |

|------------------------------|-----|--------------|

| MULTIBUS Elements            |     | 2-1          |

| Data Transfer Operation      |     | 2-4          |

| Interrupt Operations         |     | 2 - 11       |

| MULTIBUS Exchange            | • • | $2 \cdot 13$ |

| Power Failure Considerations |     | $2 \cdot 17$ |

#### **SECTION 3**

#### **ELECTRICAL SPECIFICATION**

| Introduction                          | 3-1  |

|---------------------------------------|------|

| General Bus Considerations            | 3-1  |

| Timing                                | 3-4  |

| Electrical Specifications: Receivers, |      |

| Drivers, Terminations                 | 3-11 |

#### **SECTION 4**

#### **MECHANICAL SPECIFICATIONS**

| Introduction                | 4-1 |

|-----------------------------|-----|

| Backplane Considerations    | 4-1 |

| MULTIBUS Board Form Factors | 4-2 |

| SECTION 5             | PAC     | GΕ  |

|-----------------------|---------|-----|

| DESIGN GUIDELINES AND |         |     |

| SYSTEM APPLICATIONS   |         |     |

| Introduction          | • • • • | 5-1 |

| Introduction          | ••••    | 5-1 |

| Master Design Example                    | 5-1 |

|------------------------------------------|-----|

| Slave Design Example 5                   | -11 |

| Bus Exchange Implementation Examples 5   |     |

| Power Failure Backup Methods 5           | -23 |

| Design Recommendation Summary 5          | -24 |

| AC and DC Specification Recommendation 5 | -24 |

| Bus Termination Considerations 5         | -27 |

| Miscellaneous Considerations 5           | -27 |

#### **SECTION 6**

## LEVELS OF COMPLIANCE

| Introduction                    | 6-1 |

|---------------------------------|-----|

| Variable Elements of Capability | 6-1 |

| Masters and Slaves              | 6-1 |

| Compliance Level Notation       | 6-2 |

#### APPENDIX A MULTIBUS CONNECTIONS

## P1 AND P2 SIGNAL DEFINITIONS

APPENDIX B ELECTRICAL SPECIFICATION SUMMARY

## TABLES

| TABL | E TITLE                            | PAGE  |

|------|------------------------------------|-------|

| 2-1  | Notational Summary                 | 2-1   |

| 3-1  | Location of Key Information        |       |

| 3-2  | Bus Power Specifications           | 3-2   |

| 3-3  | Bus Timing Specifications Summary  | y 3-4 |

| 3-4  | Bus Drivers, Receivers, and        |       |

|      | Terminations                       | 3-11  |

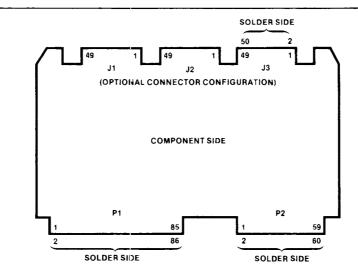

| 4-1  | Pin Assignment of Bus Signals on   |       |

|      | Multibus Board Connector (P1)      | 4-4   |

| 4-2  | P2 Connector PIN Assignment of     |       |

|      | Bus Signals                        |       |

| 4-3  | Compatible Bus Connectors          | 4-6   |

| 4-4  | Vendor Information                 | 4-6   |

| 4-5  | Top Edge Compatible Connector      |       |

|      | Hardware (Recommended)             | 4-9   |

| 5-1  | Location of Key Information        | 5-1   |

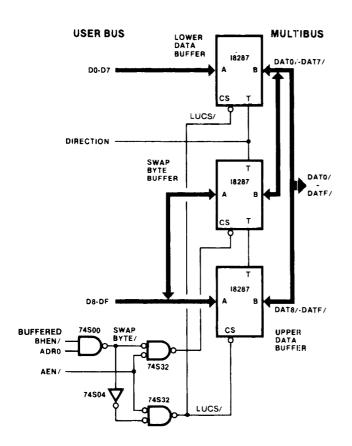

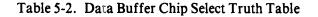

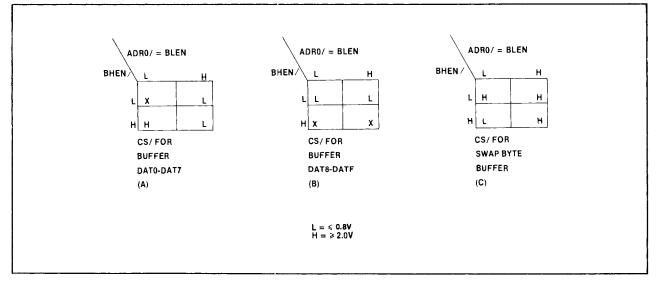

| 5-2  | Data Buffer Chip Select Truth Tabl | e 5-7 |

| 5-3  | Recommended Power Supply           |       |

|      | Specifications                     | 5-26  |

| 5-4  | Bus Module D.C. Mnemonic           |       |

|      | Definitions                        | 5-27  |

| TABL        | E TITLE                           | PAGE        |

|-------------|-----------------------------------|-------------|

| 5-5         | Slave AC Timing Mnemonic          |             |

|             | Definitions                       | 5-27        |

| 5-6         | Master AC Timing Mnemonic         |             |

|             | Definitions                       | 5-28        |

| 5-7         | Bus Termination Resistor Values . | 5-28        |

| A-1         | MULTIBUS Connector (P1) Signal    |             |

|             | Definitions                       | <b>A</b> -1 |

| A-2         | Auxiliary Connector (P2) Signal   |             |

|             | Definitions                       | A-2         |

| <b>A-</b> 3 | Pin Assignment of Bus Signals on  |             |

|             | Multibus Board Connector (P1)     | A-3         |

| A-4         | P2 Connector PIN Assignment of    |             |

|             | Bus Signals                       | A-4         |

| B-1         | Bus Timing Specifications Summary | 7B-1        |

| B-2         | Bus Power Supply Specifications   | B-3         |

| B-3         | Bus Drivers, Receivers, and       |             |

|             | Terminations                      | B-4         |

# **FIGURES**

| FIGU         | RE TITLE                               | PAGE     |

|--------------|----------------------------------------|----------|

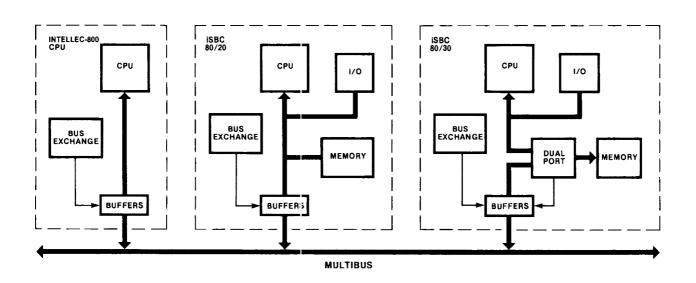

| 2-1          | Types of MULTIBUS Masters              | 2-1      |

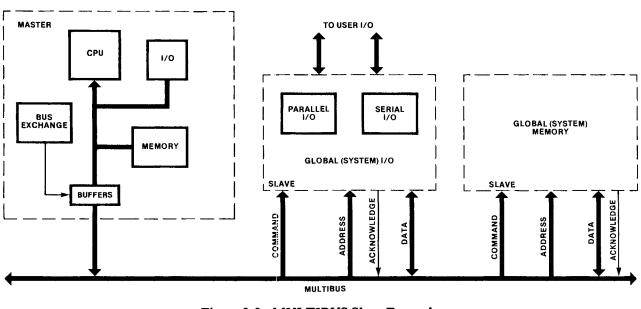

| 2-2          | MULTIBUS Slave Examples                |          |

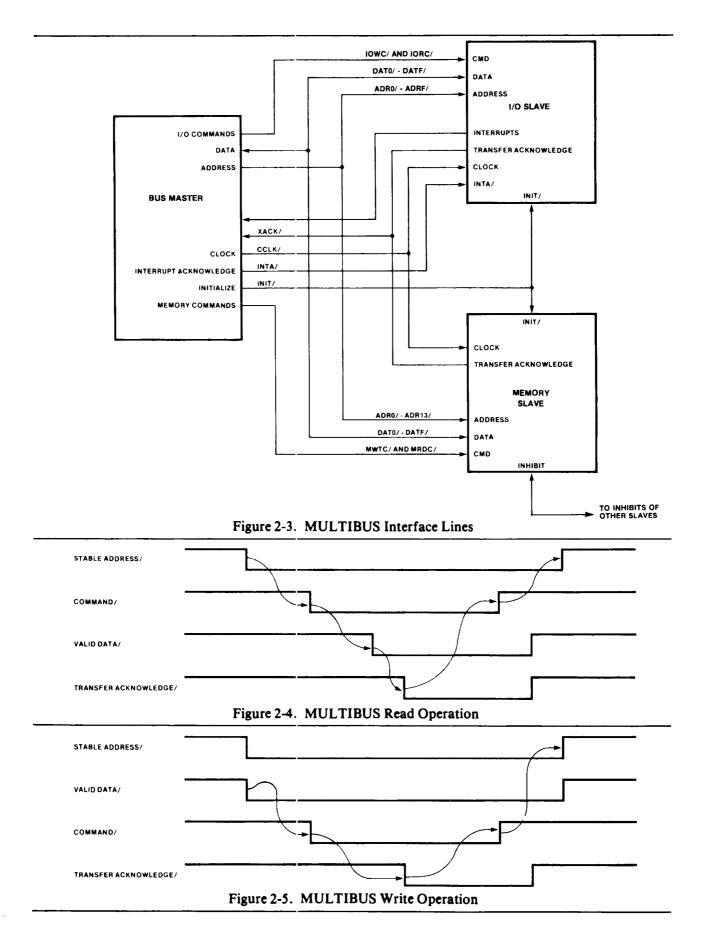

| 2-3          | MULTIBUS Interface Lines               |          |

| 2-4          | MULTIBUS Read Operation                |          |

| 2-5          | MULTIBUS Write Operation               |          |

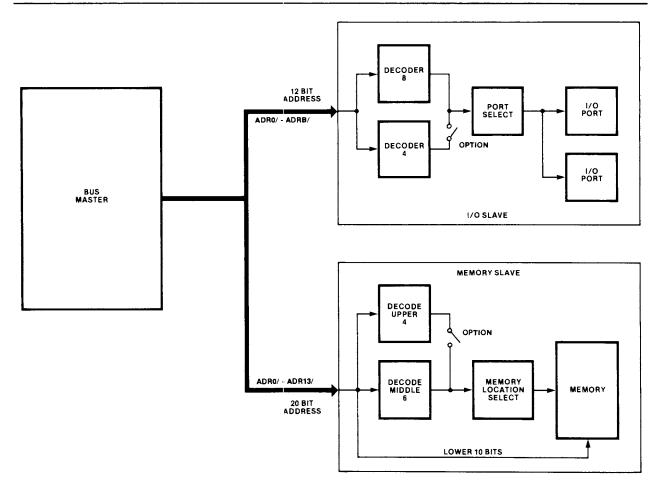

| 2-6          | MULTIBUS Address Line Use              |          |

| 2-7          | MULTIBUS Data Line Use                 |          |

| 2-8          | Memory or I/O Read Timing              |          |

| 2-9          | Memory or I/O Write Timing             |          |

| 2 - 10       | Inhibit Timing                         |          |

| 2-11         | Lock Usage                             |          |

| 2-12         | Lock Timing                            |          |

| 2-13         | Non-Bus Vectored Interrupt Logic .     | 2-12     |

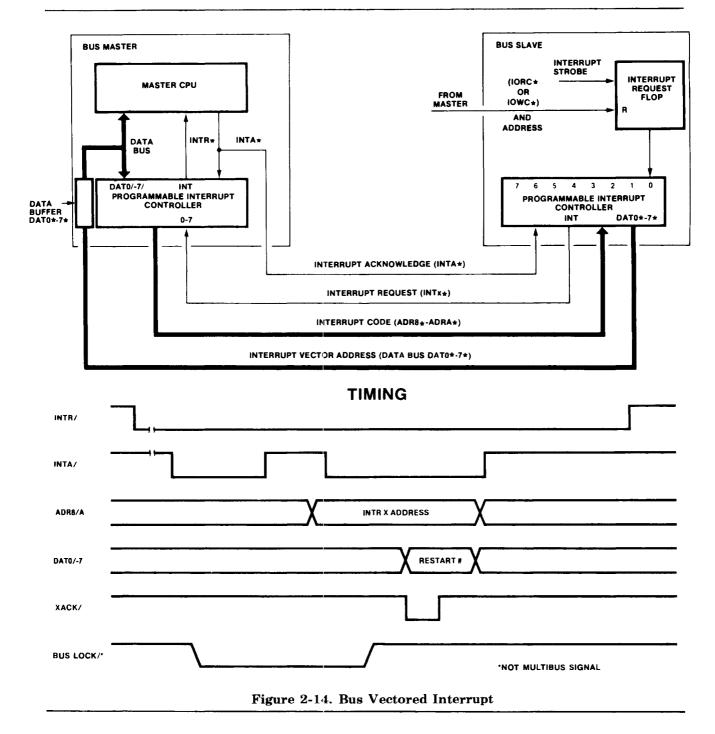

| 2 - 14       | Bus Vectored Interrupt                 |          |

| 2 - 15       | Serial Priority Technique              |          |

| $2 \cdot 16$ | Parallel Priority Technique            |          |

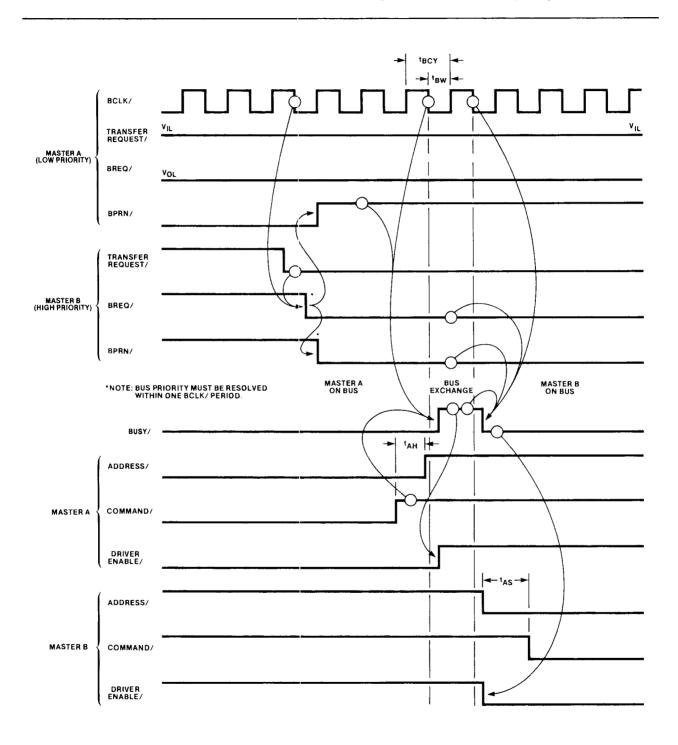

| 2 - 17       | Bus Exchange Timing                    |          |

| 2-18         | Power Fail Timing Sequence             |          |

| 3-1          | Setup, Hold, Timing Summary            | 3-3      |

| 3-2          | Coupling                               | 3-3      |

| 3-3          | Read AC Timing                         | 3-6      |

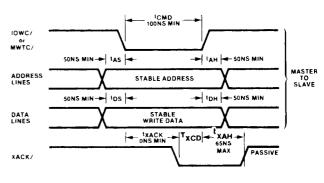

| 3-4          | Write AC Timing                        | 3-6      |

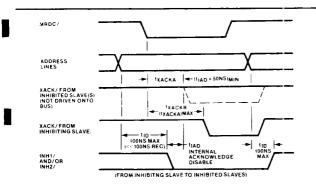

| 3-5          | Inhibit AC Timing                      | 3-7      |

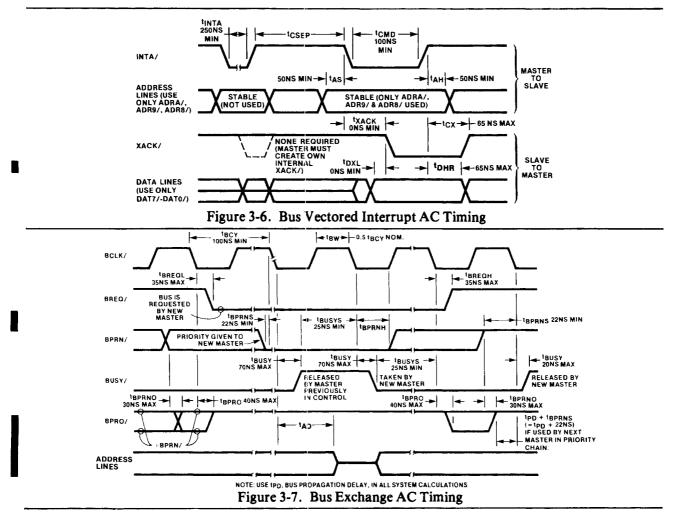

| 3-6          | Bus Vectored Interrupt AC Timing       | 3-8      |

| 3-7          | Bus Exchange AC Timing                 | 3-8      |

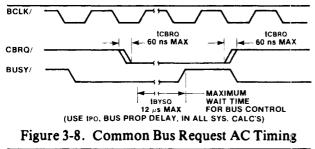

| 3-8          | Common Bus Request AC Timing .         | 3-8      |

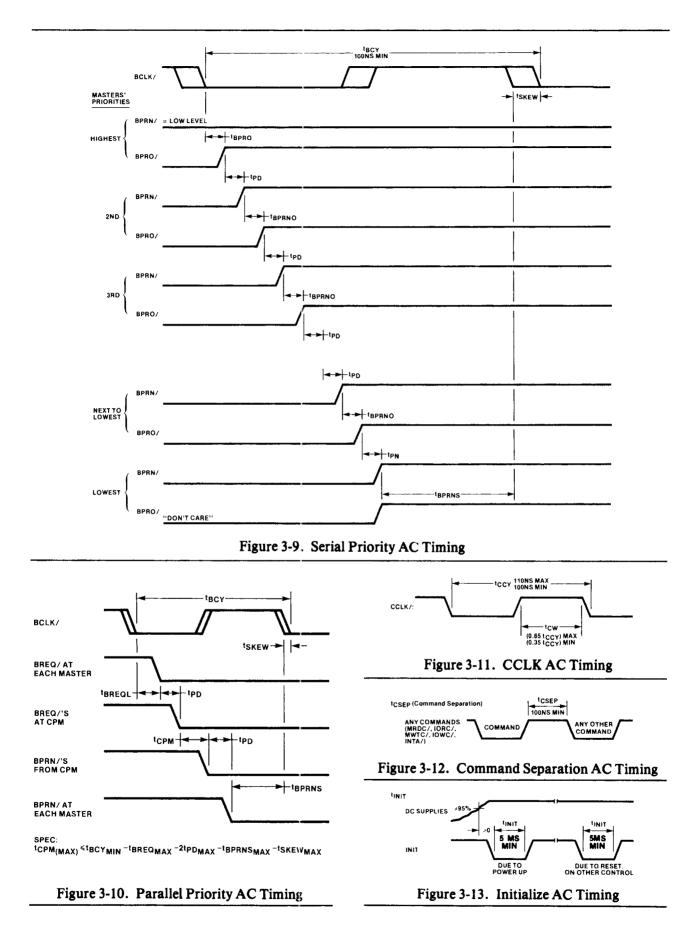

| 3-9          | Serial Priority AC Timing              | 3-9      |

| 3-10         | Parallel Priority AC Timing            | 3-9      |

| 3-11         | CCLK AC Timing                         |          |

| $3 \cdot 12$ | Command Separation AC Timing           | 3-9      |

| 3-13         | Initialize AC Timing                   |          |

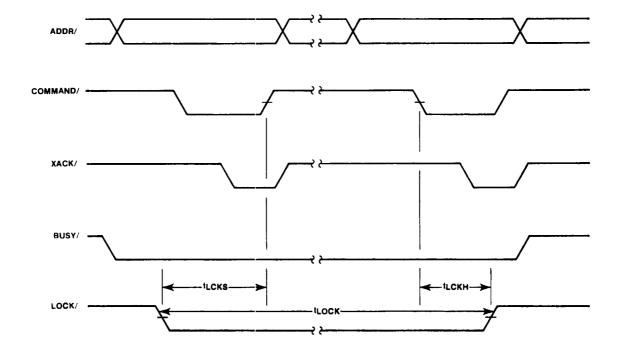

| 3-14         | Lock AC Timing                         | 3-10     |

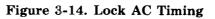

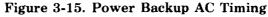

| 3-15         | Power Backup AC Timing                 | 3-11     |

| 4-1          | Multibus Backplane Card to             |          |

|              | Cage Separation                        |          |

| 4-2          | Typical MULTIBUS Backplane             |          |

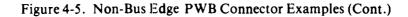

| 4-3          | Connector and Pin Numbering            |          |

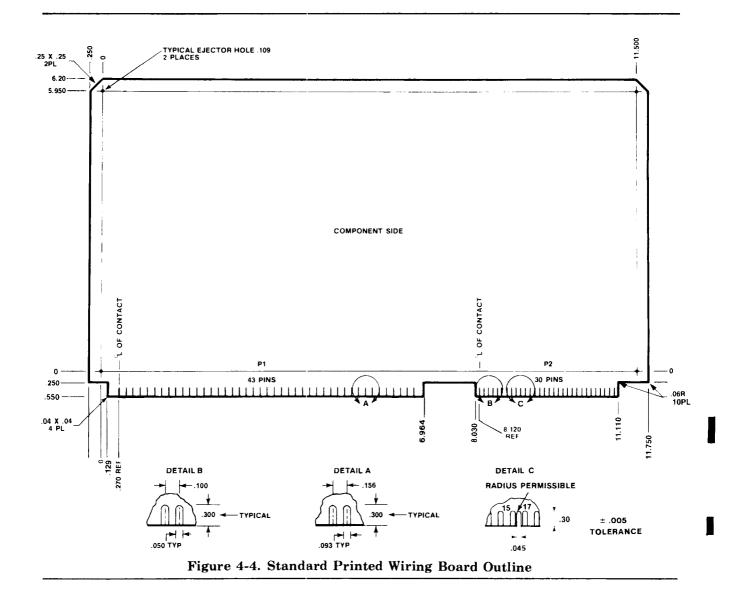

| 4-4          | Standard Printed Wiring Board Out      | line 4-3 |

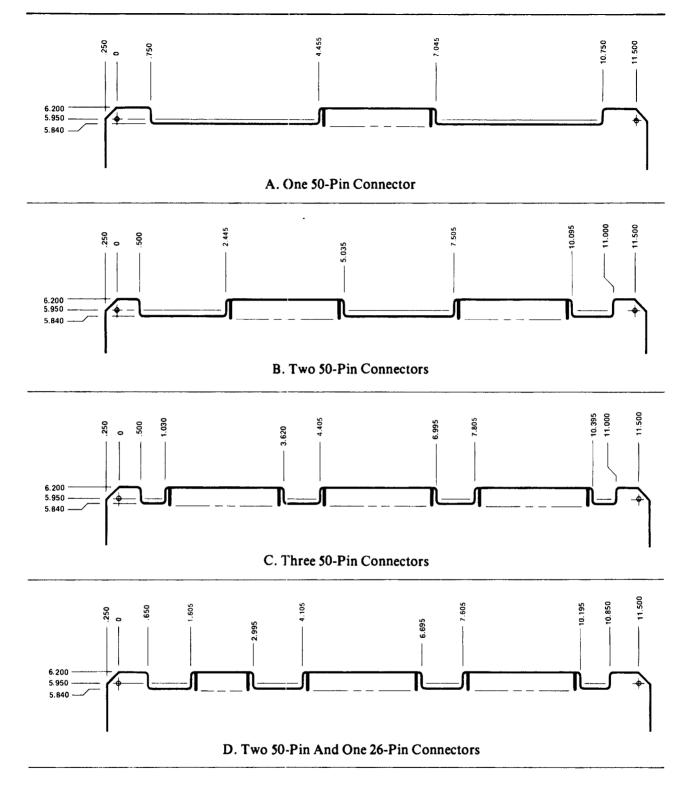

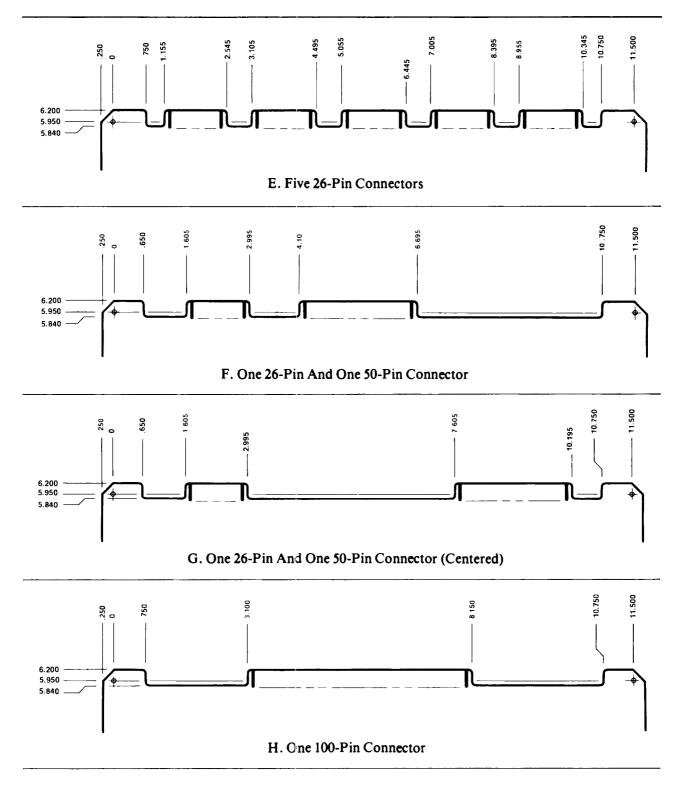

| 4-5          | Non-Bus Edge PWB Connector<br>Examples | 4-7      |

| 4-6          | Auxiliary Connector Key Slot           |          |

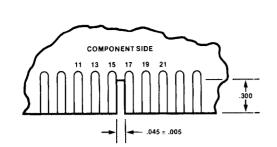

| 4∘0<br>5-1   | Master Multibus Interface              |          |

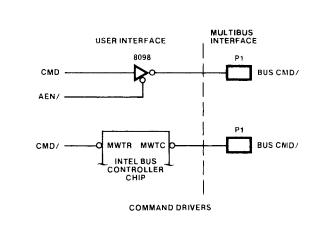

| 5-1<br>5-2   | Command Drivers                        |          |

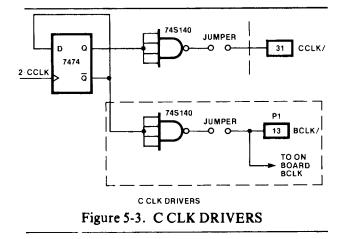

| 5-2<br>5-3   | CCLK Drivers                           |          |

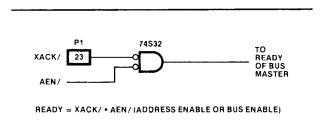

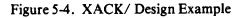

| 5-3<br>5-4   | XACK/ Design Example                   |          |

| 0-4          | Aron, Design Example                   | 0-2      |

| FIGU | RE TITLE                             | PAGE |

|------|--------------------------------------|------|

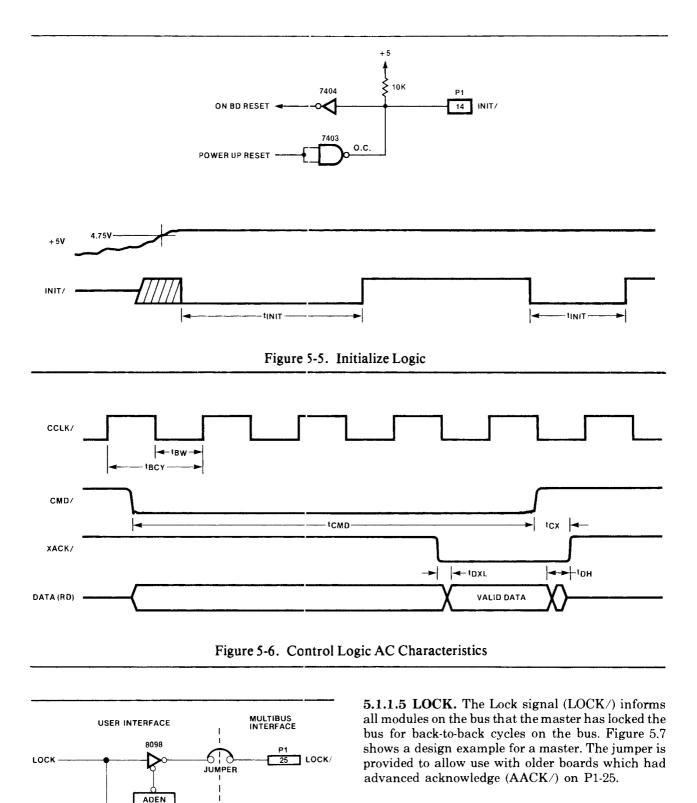

| 5-5  | Initialize Logic                     | 5-3  |

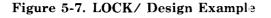

| 5-6  | Control Logic AC Characteristics .   |      |

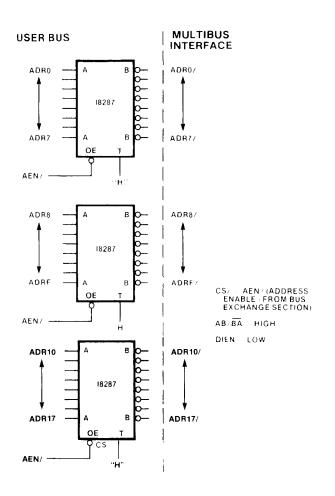

| 5-7  | LOCK/ Design Example                 | 5-3  |

| 5-8  | 24 Bit Uni-Directional               |      |

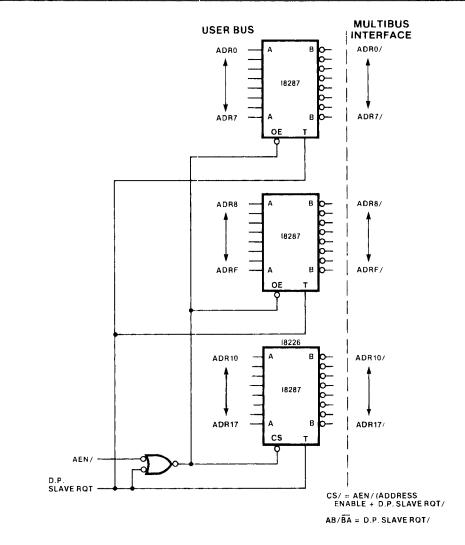

|      | Bus Drivers                          | 5-4  |

| 5-9  | 24 Bit Directional Address           |      |

|      | Bus Drivers                          | 5-5  |

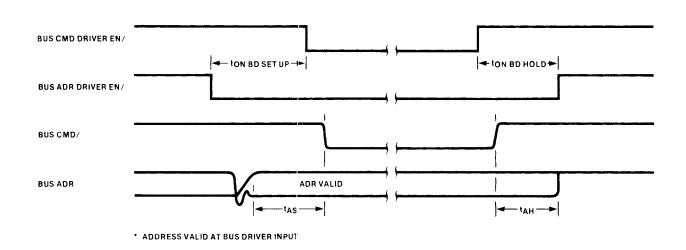

| 5-10 | Address Timing                       | 5-5  |

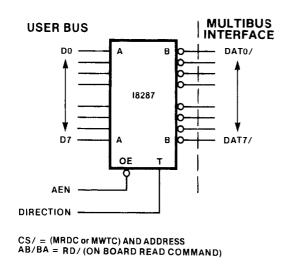

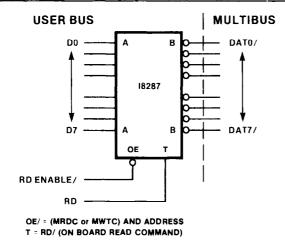

| 5-11 | 8 Bit Data Drivers                   |      |

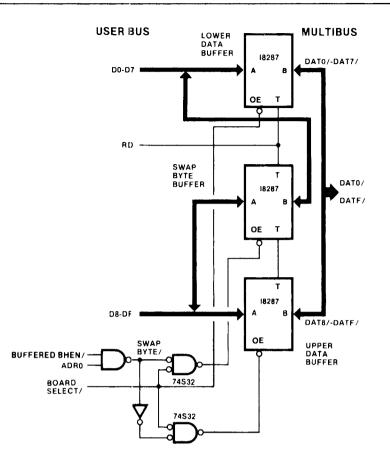

| 5-12 | 16/8 Bit Data Drivers                | 5-6  |

| 5-13 | Memory-Operation (Master)            | 5-7  |

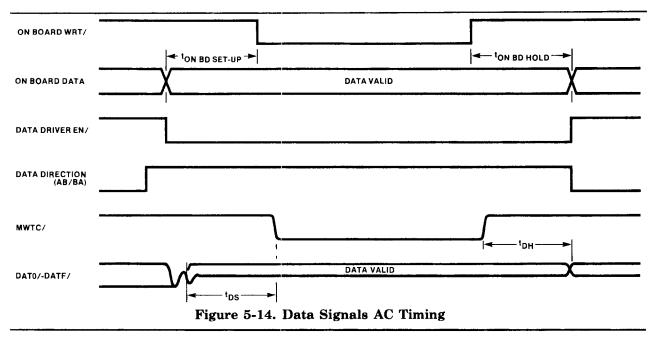

| 5-14 | Data Signals AC Timing               | 5-8  |

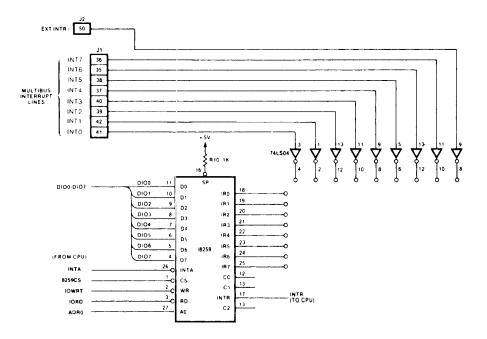

| 5-15 | 8080/8085 Non Bus Vectored           |      |

|      | Interrupt Logic                      | 5-9  |

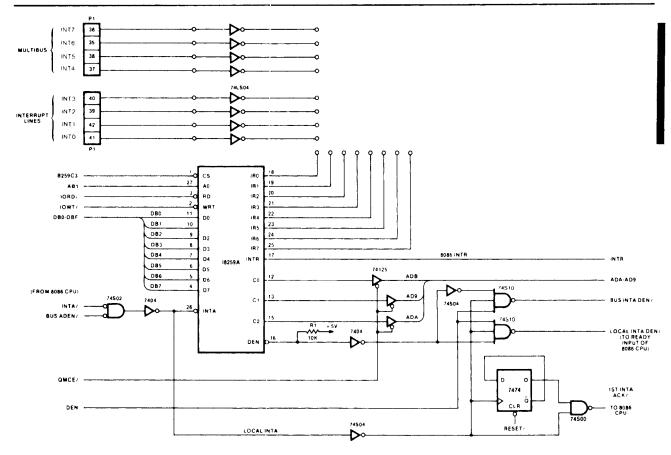

| 5-16 | 8086 Bus Vectored Interrupt Logic    | 5-9  |

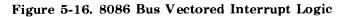

| 5-17 | 2 INTA Bus Vectored Interrupt        |      |

|      | AC Timing                            | 5-10 |

| 5-18 | 3 INTA Bus Vectored Interrupt        |      |

|      | AC Timing                            | 5-11 |

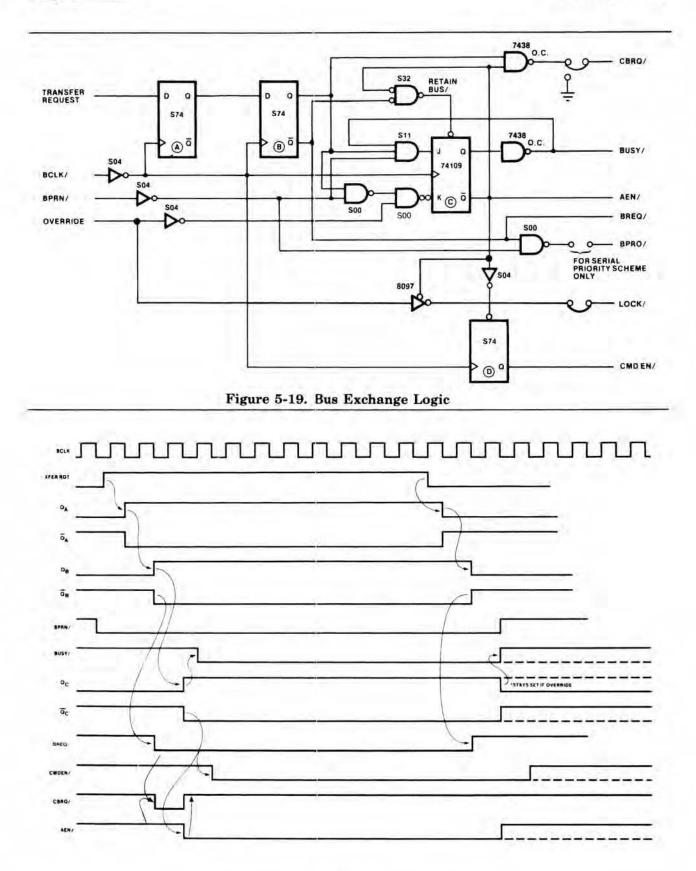

| 5-19 | Bus Exchange Logic                   |      |

| 5-20 | Bus Exchange Timing                  |      |

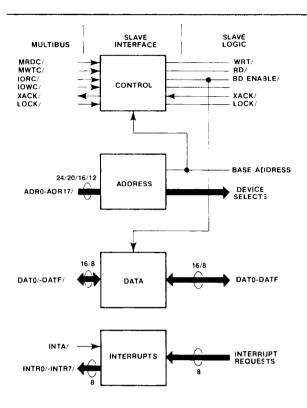

| 5-21 | Slave MULTIBUS Interface             |      |

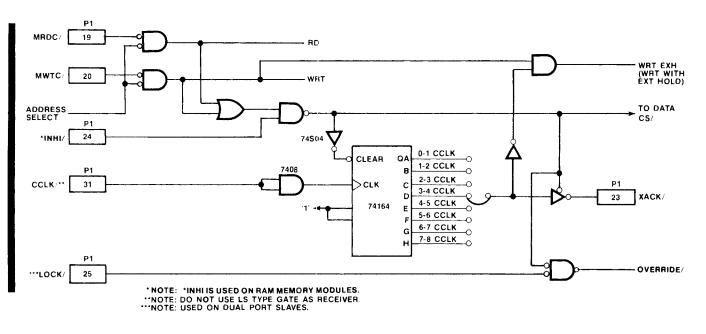

| 5-22 | Slave Control Logic                  | 5-14 |

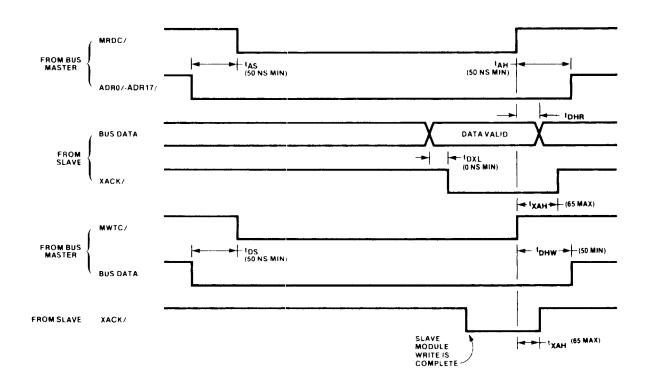

| 5-23 | Slave Logic AC Timing                | 5-14 |

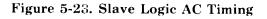

| 5-24 | Two Stage I/O Decoding Scheme .      | 5-15 |

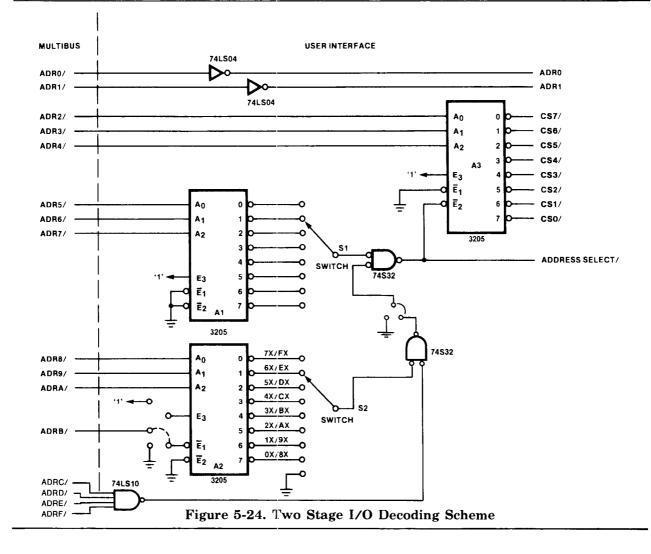

| 5-25 | Memory Decoding Scheme               |      |

| 5-26 | Inhibit AC Timing                    | 5-17 |

| 5-27 | 8 Bit I/O Bidirectional Bus Drivers  | 5-17 |

| 5-28 | 16/8 Bit Data Drivers                | 5-18 |

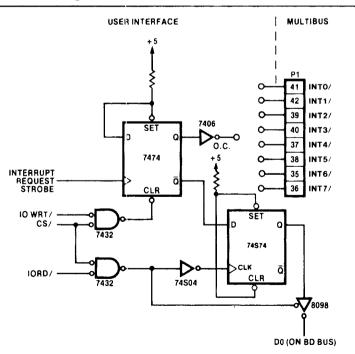

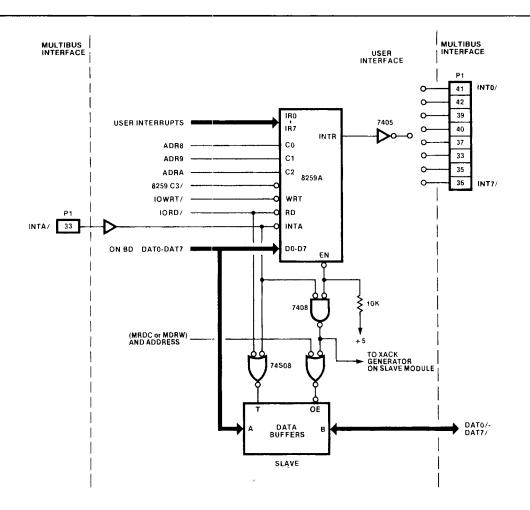

| 5-29 | Slave NBV Interrupt Logic            | 5-18 |

| 5-30 | Slave BV Interrupt Logic             | 5-19 |

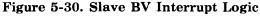

| 5-31 | Parallel Priority Resolution Circuit |      |

|      | for up to 16 Masters                 |      |

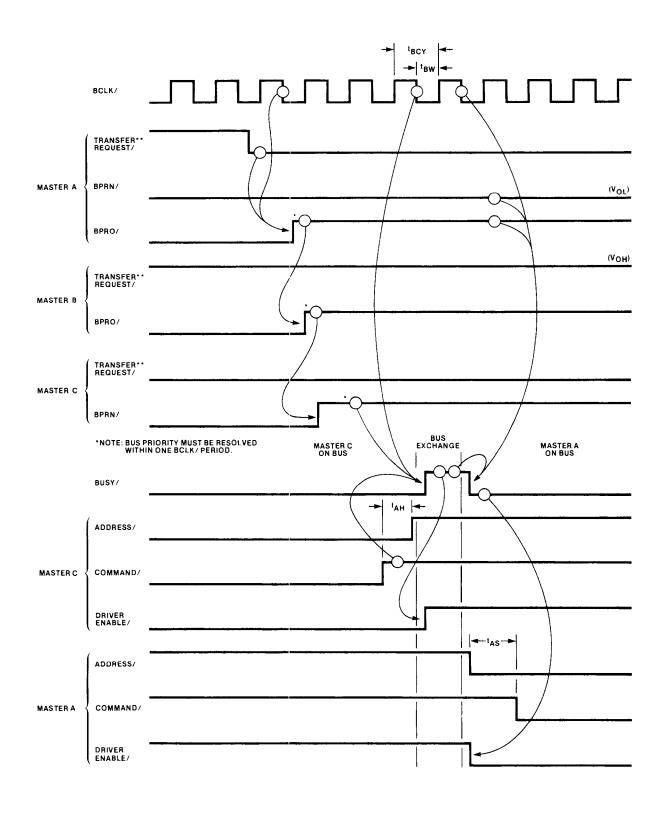

| 5-32 | Bus Control Exchange Operation .     |      |

| 5-33 | Serial Priority Circuit              |      |

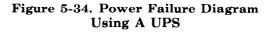

| 5-34 | Power Failure Diagram Using a UF     |      |

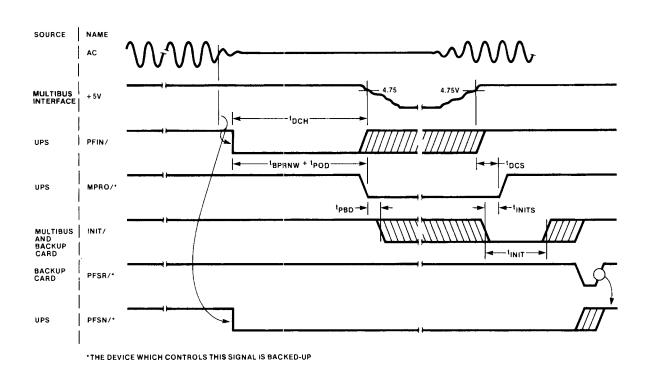

| 5-35 | UPS Control Signals AC Timing        | 5-24 |

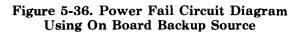

| 5-36 | Power Fail Circuit Diagram Using     |      |

|      | On Board Backup Source               | 5-24 |

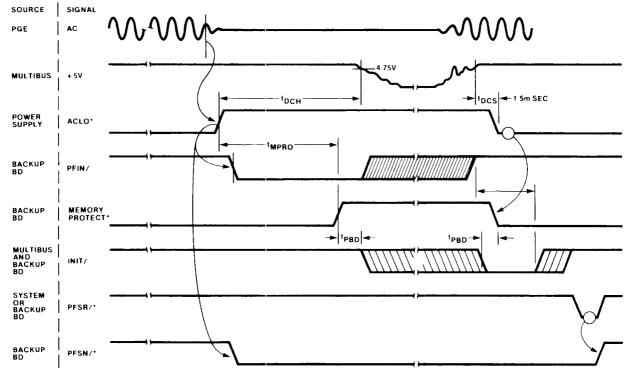

| 5-37 | Power Fail AC Timing With            |      |

|      | On Board Backup Source               | 5-25 |

| 5-38 | Slave AC Timing                      |      |

| 5-39 | Master AC Timing                     |      |

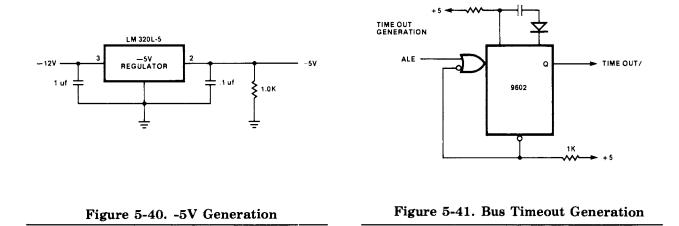

| 5-40 | -5V Generation                       |      |

| 5-41 | Bus Timeout Generation               | 5-32 |

|      |                                      |      |

One of the most important elements in a computer system is the bus structure that holds all the hardware components together. This bus structure contains the necessary signals to allow the various system components to interact with each other, i.e., it allows memory and I/O data transfers, direct memory accesses, generation of interrupts, etc. This document has been written to provide a detailed description of all the Intel MULTIBUS elements and features.

The MULTIBUS interface is the flexible bus structure used to interface the family of Intel's 80/86 products which include 8- and 16-bit single board computer, memory expansion boards, digital and analog I/O boards and peripheral controllers. It supports direct addressability up to 16 megabytes through 24-bit addresses and 8- and 16-bit data transfers.

The bus structure is built upon the master-slave concept where the master device in the system takes control of the MULTIBUS interface and the slave device, upon decoding its address, acts upon the command provided by the master. This handshake between master and slave devices allows modules of different speeds to use the MULTIBUS interface and allows data rates up to five million transfers per second (bytes or words).

Another important MULTIBUS feature is the ability to connect multiple master modules for multiprocessing configurations. The MULTIBUS interface provides control signals for connecting multiple masters either in a daisy-chain priority fashion or in parallel. With this latter arrangement, up to sixteen masters may share MULTIBUS resources.

This document has been prepared for those users who intend to evaluate or design products that will be compatible with the MULTIBUS system bus structure. In addition to the detailed signal definitions, timing, electrical and mechanical specifications, this document also includes many design examples showing the reader how to implement the various control circuits associated with the MULTIBUS interface.

## 2.0 INTRODUCTION

Section 2 will give the reader an overall understanding of how the MULTIBUS functions. The section contains information about the elements which connect to the bus, a description of the signals which provide the interface to the bus, and the different types of operations which are performed on the MULTIBUS interface.

In this section, as well as throughout the specification, a clear and consistent notation for signals has been used. The Memory Write Command (MWTC) will be used to explain this notation. The terms one: zero and true: false can be ambiguous, so their use will be avoided. In their place, we will use the terms electrical High and Low (H and L). A slash following the signal name (MWTC/) indicates that the signal is active low as shown:

# $MWTC = \overline{MWTC} = MWTC - = Asserted at 0$ volts

The signal (MWTC/) driven by a three state driver will be pulled up to Vcc when not asserted. Table 2-1 is used to further explain the notation used in this specification.

#### Table 2-1. Notational Summary

| Function |            |   | Definiti      | on               |

|----------|------------|---|---------------|------------------|

|          | Electrical | L | ogical        | State            |

| мwтс     | н          | 1 | True          | Active, Asserted |

| MWTC/    |            | 0 | False<br>True | Active, Asserted |

| MWTC/    | L<br>H     | 1 | True<br>False | Active, Asserted |

## 2.1 MULTIBUS ELEMENTS

This section will describe the elements that interface to the bus (masters, slaves, and intelligent-slaves), and the MULTIBUS signal lines which make up this interface.

#### 2.1.1 BUS MASTERS

A bus master is any module which has the ability to control the bus. The master exercises this control by acquiring the bus through bus exchange logic and then generating command signals, address signals, and memory addresses. There are many modules which fall into the class of bus master. The most basic type of masters, would include the INTELLEC-800 CPU Module. This module contains a processor and bus exchange logic as shown in figure 2-1. A more complex master would be the iSBC 80/20. This module contains a processor, memory,

Figure 2-1. Types of MULTIBUS Masters

input/output logic, and Bus Exchange logic. A complex master shown in figure 2-1, is the iSBC 80/30. This module contains a CPU, memory, input/output logic, bus exchange logic, and a next generation board architecture.

The MULTIBUS interface can support more than one master on the same system. In order to do this, there must be a means for each master to gain MULTIBUS control. This is done through bus exchange logic which will be explained in detail in Section 2.5. Figure 2-1 depicts a multi-master system, and shows some typical master configurations. This figure is for explanation purposes only.

#### 2.1.2 BUS SLAVES

Another type of module which can use the MULTI-BUS interface is the bus slave. The bus slaves decode the address lines and act upon the command signals from the bus masters. The slaves are not capable of controlling the MULTIBUS interface. Some examples of bus slaves are shown in figure 2-2.

## 2.1.3 INTELLIGENT SLAVE

The third type of module that can use the MULTI-BUS interface is the intelligent slave. The intelligent slave has all the attributes of a slave module in that it decodes addresses and acts upon commands from master modules. However, the intelligent slave contains a micro processor which is programmed with software or firmware. The on-board processor is used to control the on-board memory and I/O and not the MULTIBUS interface. The combination of on-board processor, memory and I/O allows the intelligent slave to complete on-board operations without constant MULTIBUS access. In some cases, the intelligent slave's memory may be available to the system through on-board dual port logic.

#### 2.1.4 MULTIBUS SIGNAL CLASSES

MULTIBUS signals can be grouped into several classes based on the functions which they perform. The classes are:

- A. Control Lines

- B. Address and Inhibit Lines

- C. Data Lines

- D. Interrupt Lines

- E. Bus Exchange Lines

- F. Power Failure Lines (Optional)

The following sub-sections will explain the different classes of MULTIBUS signals.

**2.1.4.1 CONTROL LINES.** The following signals are classified as control lines:

| A. Clocks      | Constant Clock (CCLK/)<br>Bus Clock (BCLK/)                                          |

|----------------|--------------------------------------------------------------------------------------|

| B. Commands    | Memory Write (MWTC/)<br>Memory Read (MRDC/)<br>I/O Write (IOWC/)<br>I/O Read (IORC/) |

| C. Acknowledge | Transfer Acknowledge<br>(XACK/)                                                      |

| D. Initialize  | INIT/                                                                                |

| E. LOCK        | LOCK/                                                                                |

Figure 2-2. MULTIBUS Slave Examples

#### 2.1.4.1.1 CLOCK LINES.

Bus Clock (BCLK/). - This clock signal is used to synchronize the bus contention logic. It may be slowed, stopped, or single stepped. If there is more than one master on the system, one and only one should be used to generate a master clock.

Constant Clock (CCLK/). - CCLK/ is a clock signal of constant frequency which may be used by bus masters or slaves as a master clock. If there is more than one master on the system, one and only one should be used to generate a master clock.

2.1.4.1.2 COMMAND LINES (MWTC/, MRDC/, IOWC/, IORC/). The command lines are the communication links between the bus masters and bus slaves. There are four command lines for memory and I/O reads and writes. An active command line indicates to the slave that the address lines are carrying a valid address, and that the slave should perform the specified operation.

2.1.4.1.3 TRANSFER ACKNOWLEDGE LINE (XACK/). This line is the slave's acknowledgement of the master's command. XACK/ indicates to the master that the requested action is complete, and that data has been placed on or accepted from the data lines.

**2.1.4.1.4 INITIALIZE (INIT/).** The INIT/ signal is generated to reset the entire system to a known internal state. This signal is usually generated prior to starting any operations on the system. INIT?/ may be generated by any or all of the bus masters or by an external source such as a buffered and debounced front panel switch.

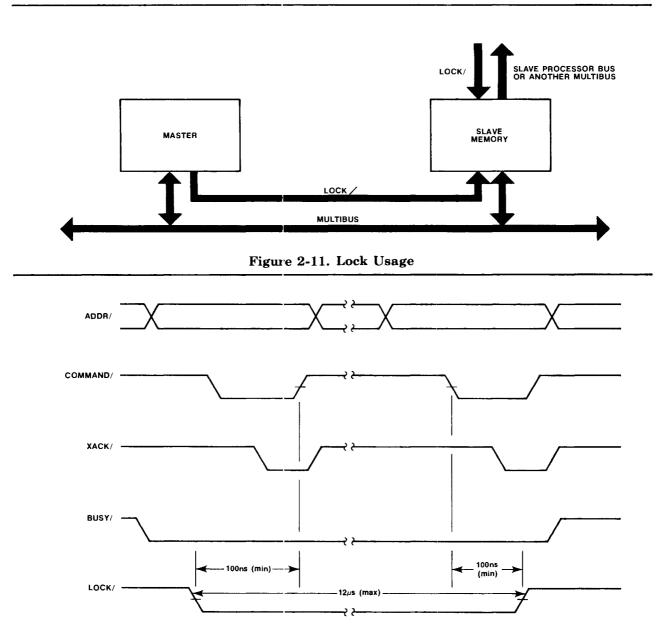

**2.1.4.1.5 LOCK (LOCK/).** The LOCK/ signal is generated by the master in control of the bus to indicate the bus is locked. LOCK/ is used to extend mutual exclusion to multiple-port ram designs.

2.1.4.2 ADDRESS AND INHIBIT LINES. The address and inhibit lines are made up of the following groups of signals:

- A. Address Lines ADR0/ ADR17/ (0-9, A-F, 10-17); in Hex Notation.

- B. Inhibit Lines INH1/ and INH2/

- C. Byte Control BHEN/

**2.1.4.2.1** ADDRESS LINES (24 LINES). ADR0/ - ADRF/ and ADR10/ - ADR17/ carry the address of the memory location or the I/O device that is being referenced. Twenty four address lines allow  $\varepsilon$  maximum of 16 million bytes of memory to be accessed. When addressing an I/O device, sixteen address lines (ADR0/ - ADRF/) are used allowing the addressing of a maximum of 64K devices. There are various class of modules which use a subset of the address lines. These classes are defined in Section 6 of this specification. Design examples showing compatibility with various classes of modules are given in Chapter 5.

For I/O bus cycles, master modules have the option of generating 8 bit or 16 bit addresses. Because of this, all I/O slaves must be capable of being configured to decode 8 address bits (ADR0/ · ADR7/) and ignore the upper address bits or to decode all 16 bits of address (ADR0/ · ADRF/). Note that in a system using 8 bit I/O addresses, the value of the upper 16 bits of address is unknown. A master generating only 8 bit addresses may set the upper 16 address bits to any arbitrary value.

2.1.4.2.2 INHIBIT LINES. Two inhibit lines (INH1/ and INH2/) are provided on the MULTIBUS. INH1/ prevents RAM memory slave modules from responding to the memory address and command on the MULTIBUS. This effectively allows ROM memory modules or memory mapped I/O devices to override RAM memory modules when both are assigned the same memory addresses. INH2/ prevents ROM memory modules from responding to the memory address and command on the MULTIBUS. This effectively allows auxiliary ROM (e.g., a bootstrap program.) to override ROM memory modules when they both are assigned the same memory addresses.

2.1.4.2.3 BYTE CONTROL LINE. The byte control line (BHEN/) is used to select the upper byte (bits 8-F) of a 16 bit word. This signal is used only on systems that incorporate sixteen-bit memory and I/O modules.

2.1.4.3 DATA LINES (DAT0/ - DATF/). Sixteen bidirectional data lines (DAT0/ - DATF/) are used to transmit or receive information to or from a memory location or an I/O port (DAT0/ being the least significant bit). In eight bit systems, only lines DAT0/ - DAT7/ are used.

2.1.4.4 INTERRUPT LINES. The interrupt lines consist of the following signals:

- A. Interrupt Requests INT0/ INT7/

- B. Interrupt Acknowledge INTA/

2.1.4.4.1 INTERRUPT REQUEST LINES. Interrupts are requested by activating one of the eight Interrupt Request Lines (INT0/ - INT7/). INT0/ has the highest priority and INT7/ has the lowest.

2.1.4.4.2 INTERRUPT ACKNOWLEDGE. Interrupt Acknowledge (INTA/) is generated by the bus master in response to an interrupt request to freeze interrupt status and request the placement of the interrupt vector address onto the MULTIBUS data lines. **2.1.4.5. BUS EXCHANGE LINES.** The Bus Exchange lines are made up of the following signals:

- A. Bus Request BREQ/

- B. Bus Priority BPRN/, BPRO/

- C. Bus Busy BUSY/

- D. Common Bus Request CBRQ/

- E. Bus Clock BCLK/

A bus master gains control through the manipulation of these MULTIBUS signals.

2.1.4.5.1 BUS REQUEST. BREQ/ is used by the bus masters in a parallel priority resolution circuit to indicate a request for MULTIBUS control.

**2.1.4.5.2** BUS PRIORITY. Bus Priority In (BPRN/) indicates to a particular master module that no higher priority module is requesting use of the MULTIBUS interface. The Bus Priority Out (BPRO/) signal is used with serial (daisy chain) bus priority resolution schemes. BPRO/ is passed to the BPRN/ input of the master with the next lower bus priority.

**2.1.4.5.3 BUS BUSY.** Bus Busy (BUSY/) is activated by the bus master in control, to indicate that the MULTIBUS interface is in use. This prevents other masters from gaining control of the bus.

**2.1.4.5.4 COMMON BUS REQUEST.** Common Bus Request (CBRQ/) is used to allow a bus master to retain control of the bus without contending for it each processor cycle, as long as no other master is requesting control of the bus. A bus master requesting control of the bus but not currently controlling it asserts CBRQ/. This causes the controlling bus master to relinquish control of the bus.

## 2.2 DATA TRANSFER OPERATION

The primary function of the MULTIBUS interface is to provide a path for the transfer of data between modules. The following sections will describe the different types of data transfers and the means by which they are implemented using the signals previously described in Section 2.1. Figure 2-3 can be referenced during the following discussions. The discussion of the MULTIBUS data transfer operation will be covered in three parts: 1) an overview of the operation, 2) A detailed description of the signals used in the transfer, and 3) A discussion of the specifics pertaining to the different transfers.

It will be assumed that there is only one MULTIBUS master and therefore no MULTIBUS contention exists. The MULTIBUS Exchange logic will be discussed in a later section.

#### 2.2.1 DATA TRANSFER OVERVIEW

A MULTIBUS data transfer is accomplished as follows. First the bus master places the memory or I/O port address on the address bus. If the operation is a write, the data would also be placed on the data bus at this time. The bus master then generates a command (I/O read or write, or memory read or write) which activates the appropriate bus slave. The slave accepts the data if it is a write operation, or places the data on the data bus if it is a read. A transfer acknowledge is then sent to the bus master by the bus slave allowing the bus master to complete its cycle, removing the command from the command line, and then removing the address and data from the MULTIBUS interface. Figures 2-4 and 2-5 show the basic timing for a read and write data transfer operation.

#### 2.2.2 MULTIBUS SIGNAL DESCRIPTION

This section is a detailed description of the Multibus signals used for data transfer operations. It contains timing information, signal origination information, and information pertaining to the specific function that each signal performs in the data transfer operation.

**2.2.2.1 INITIALIZATION (INIT/).** Prior to any MULTIBUS data transfer operations, all the system modules should be reset to a known internal state. This can be accomplished by the INIT/ signal. This signal can be driven from many sources. The following are three examples:

- A. A power-on clear circuit (RC network) which holds INIT/ low until the power supplies reach their specific voltage outputs.

- B. A RESET button, sometimes provided on the system front panel for operator use. Note that this button must be debounced.

- C. A software command which can be implemented to pull down the INIT/ line.

The INIT/ line is driven by open-collector gates.

**2.2.2.2 CONSTANT CLOCK (CCLK/).** The Constant Clock line is driven by only one bus module, and provides a timing source for the MULTIBUS which can be used by any module on the bus. CCLK/ is a symmetrical signal with a frequency of approximately 10 megahertz, driven by a clock driver circuit.

**2.2.2.3 ADDRESS LINES (ADR0/ - ADR17/).** The MULTIBUS Address lines are used to carry the address of the memory location or the I/O device that is being referenced by the command. There are 24 address lines, allowing up to 16 million bytes of memory to be referenced. These lines are driven by three state drivers and are always under control of the bus master which controls the bus.

During an I/O command, only the lower 16 address lines (ADR0/ - ADRF/) are used. This allows a bus master the capability of addressing a maximum of 64K I/O ports. The address bits are decoded to produce a select signal for each specific port. Sections 5 and 6 may be referenced for an explanation of the various classes of modules which use a subset of the address lines. These sections also contain design information pertaining to the compatability of the various module classifications.

See figure 2-6 for an example of MULTIBUS address line use.

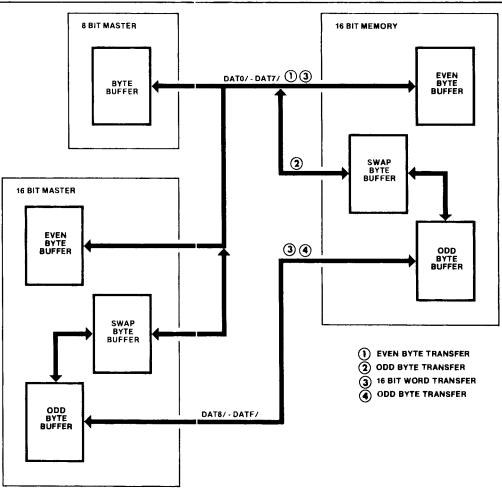

2.2.2.4 DATA LINES (DAT0/ - DATF/). The sixteen bi-directional data lines are used to transmit or receive information to or from a memory location or I/O port. The lines are driven by the bus master on write operations and by the addressed slave (memory or I/O) on read operations. Both sixteen bit and eight bit transfers are supported by the MULTIBUS. Eight bit transfers are accomplished by using lines DAT0/ - DAT7/ (with DAT0/ being the least significant bit) for eight bit or sixteen bit systems which are compatible with eight bit systems.

Figure 2-6. MULTIBUS Address Line Use

across the MULTIBUS:

- 1. Transfer of even byte on DAT0/ DAT7/.

- 2. Transfer of odd byte on DAT0/ DAT7/ (using swap byte buffer).

- 3. Transfer of 16 bit word.

- 4. Transfer of odd byte on DAT8/ DATF/ (sixteen bit system only).

Figure 2-7 shows the MULTIBUS data lines, and the contents of these lines for the four types of transfers mentioned.

Two signals control the data transfers. Byte High Enable (BHEN/) active indicates that the MULTIBUS is operating in sixteen bit mode, and Address Bit 0 (ADR0/) defines an even or odd byte transfer. ADR0/ is inactive indicating the transfer of an even eight bit byte. The transfer takes place across data lines DAT0/ - DAT7/.

On the second type of transfer, BHEN/ is inactive, and ADR0/ is active indicating the transfer of an odd byte. On this type of transfer, the odd byte is transferred through the Swap Byte Buffer to DAT0/ - DAT7/. This makes eight bit and sixteen bit systems compatible.

The third type of transfer is a 16 bit (word) transfer. This is indicated by BHEN/ being active, and ADR0/ being inactive. On this type of transfer, the even byte is transferred on DAT0/ - DAT7/ and the odd byte is transferred on DAT8/ - DATF/.

The last type of transfer is used on systems which only employ sixteen bit modules. On this transfer BHEN/ is active, and ADR0 is active, indicating the transfer of the odd byte on DAT8/ - DATF/. This type of transfer eliminates the need for the Swap Byte Buffer. It should be noted however, that this is

Figure 2-7. MULTIBUS Data Line Use

not a recommended transfer type, because it eliminates the capability of communicating with eight bit modules.

The MULTIBUS data lines are always driven by three state drivers.

2.2.2.5 MULTIBUS COMMANDS. In this section, we will discuss the command lines and how they work in conjunction with the lines explained in the previous sections to accomplish a read or a write operation.

There are four MULTIBUS command lines.

Memory Read Command - MRDC/ I/O Read Command - IORC/ Memory Write Command - MWTC/ I/O Write Command - IOWC/

The command lines, which are driven by three state drivers on the bus master, indicate to the bus slave the action that is being requested.

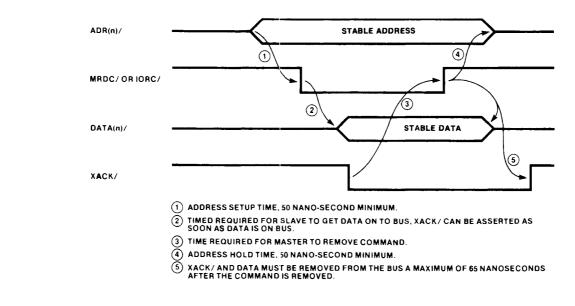

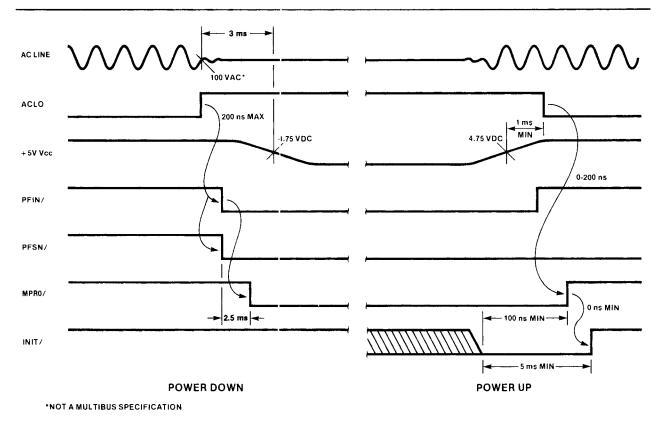

*Read Operations*. The two read commands (MRDC/ and IORC/) initiate the same basic type of operation. The only difference being that MRDC/ indicates that a memory address is valid on the MULTIBUS address lines, and IORC/ indicates that there is an I/O port address on the MULTIBUS address lines. This address (memory or I/O port) must be valid on the bus 50ns prior to the read command being generated. When the read command is

generated, the slave module (memory or I/O port) puts the data on the MULTIBUS data lines and returns a Transfer Acknowledge (XACK/), indicating that the data has been placed on the bus. When the bus master receives the acknowledge, it strobes in the data and removes the command (MRDC/ or IORC/) from the MULTIBUS interface. The slave address (memory or I/O port) is removed from the bus a minimum of 50ns after the read command is removed. XACK/ must be removed from the MULTIBUS interface within 65nsec after the command is removed, to allow for the next bus cycle. Figure 2-8 shows the timing for the Memory Read or I/O Read command.

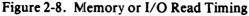

Write Operations. The write commands (MWTC/ and IOWC/) initiate basically the same type of operation. MWTC/ indicates that a memory address is valid on the MULTIBUS address lines, while IOWC/ indicates that there is an I/O port address on the MULTIBUS address lines. The address (memory or I/O) and data must be valid on the bus 50ns prior to the command being generated. This requirement allows data to be latched on either the leading or trailing edge of the command. When the write command (MWTC/ or IOWC/) is asserted, the MULTIBUS data is stable and can be accepted by the slave. The slave indicates acceptance of the data by returning a Transfer Acknowledge (XACK/), allowing the bus master to remove the address command, and data from the MULTIBUS interface. XACK/ must be removed from the MULTIBUS interface within 65nsec to allow for the next bus cycle. Figure 2-9 shows the timing for the Memory Write or I/O Write command.

2.2.2.6 TRANSFER ACKNOWLEDGE LINE (XACK/). The transfer acknowledge (XACK/) is the response of the bus slave (memory or I/O) indicating that the commanded read or write operation is complete and that the data has been placec on or accepted from the MULTIBUS interface. This signal allows the bus master to proceed to the completion of the current bus cycle. If the bus slave does not generate XACK/, the bus master is not able to remove its command from the bus, and will not be able to terminate its bus cycle. The system therefore would be in an indeterminate state, and system operation could not proceed. This situation can be aleviated by providing a Bus Timeout function which will terminate the bus cycle after some fixed period of time (determined by designer) by generating an XACK/. The Bus Timeout function is a separate piece of logic which constantly monitors the MULTI-BUS interface for the above mentioned condition.

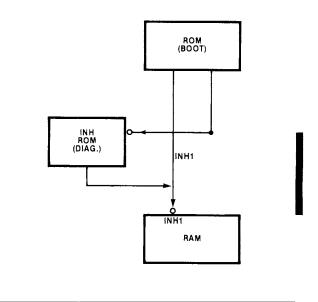

2.2.2.7 INHIBIT OPERATION. The Inhibit Lines (INH1/ and INH2/) give different memory components the ability to occupy the same memory space under certain specified conditions. For example, RAM could occupy the whole memory space but during a bootstrap, ROM could be invoked which would overlay a portion of the memory occupied by RAM. In addition, a ROM card containing diagnostics could be inserted into a system overlaying RAM, but letting the bootstrap ROM overlay it. The following diagram illustrates the Inhibit lines.

The RAM inhibit signal (INH1/) prevents the RAM devices from responding to the address on the MULTIBUS address lines, allowing ROM or memory mapped I/O components with the same addresses to use the RAM's memory area.

The ROM inhibit signal (INH2/) is basically the same except that it allows auxiliary ROM components to overlay ROM devices using the same memory space.

#### NOTE

For bootstrap application both INH1/ and INH2/ must be generated.

The inhibit lines are intended to function only on read operations. During the read of an inhibited memory component, the inhibit signal must disable the acknowledge and data drivers of the component. The effect of an inhibit during a write operation is undefined.

The timing of the inhibit operation is critical. The inhibit signals must be generated within 100nsec after the address is stable. A command is generated 50nsec after the address is stable, therefore the inhibit occurs after the command has already been received by the inhibited component. Since the inhibited module has already started its cycle, it may be necessary for it to complete it to avoid destroying the contents of RAM. For this reason the inhibiting component must generate an acknowledge (XACK/) which encompasses the acknowledge generated by the inhibited device with the longest cycle time. Also, to prevent false acknowledges, the inhibited device must not generate an acknowledge until the inhibit signals have had time to become valid (50 nsec after command).

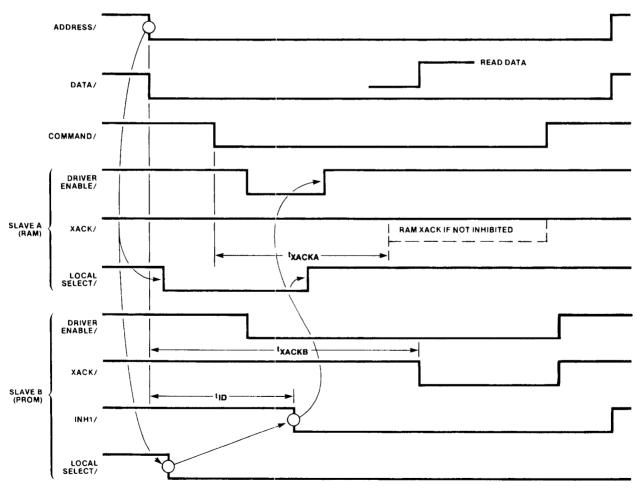

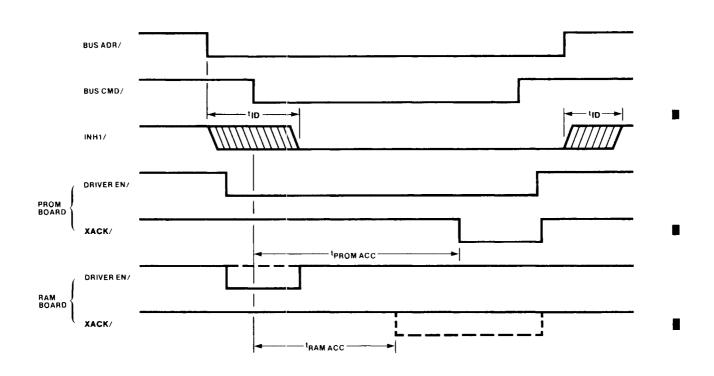

Figure 2-10 shows the timing for an inhibit operation. In this example, both PROM and RAM have the same memory addresses, so the PROM inhibits the RAM.

After the address is stable, local selects are generated for both the PROM and the RAM. The PROM local select produces the INH1 signal which then removes the RAM local select, and driver enable. Because the slave RAM has been inhibited after it had already begun its cycle, the PROM XACK/ must be delayed (tXACKB) until after the latest possible acknowledgement from the RAM (tXACKA). 2.2.2.8 LOCK (LOCK/). The lock line is driven by the master in control of the bus when a locked bus access is required. A locked access is typically required in a read-modify-write semaphore operation to prevent another processor from accessing the memory between the read and the write. The busy line allows for this mutual exclusion on the MULTI-BUS. The Lock line allows mutual exclusion to be extended off of the bus. The Lock signal (LOCK/) must be active 100 nanoseconds prior to the read or write command going away. It must remain active a minimum of 100 nanoseconds after the falling edge of the command signal for the last locked memory cycle. The slave locks its multiple-ported memory to the MULTIBUS when it is addressed and the lock line is asserted. The lock signal must not be asserted for more than 12 microseconds continuously. This assures the processor on the other side of the multiple-ported memory that it will gain access to the memory in a reasonable amount of time. The busy signal (BUSY/) must be active whenever the Lock line is asserted. Figure 2-12 shows the timing for the lock signal.

Figure 2-10. Inhibit Timing

## 2.3 INTERRUPT OPERATIONS

The following sections, will explain the Multibus signal lines used in the interrupt operation, and the two different types of interrupt implementation.

#### 2.3.1 INTERRUPT SIGNAL LINES

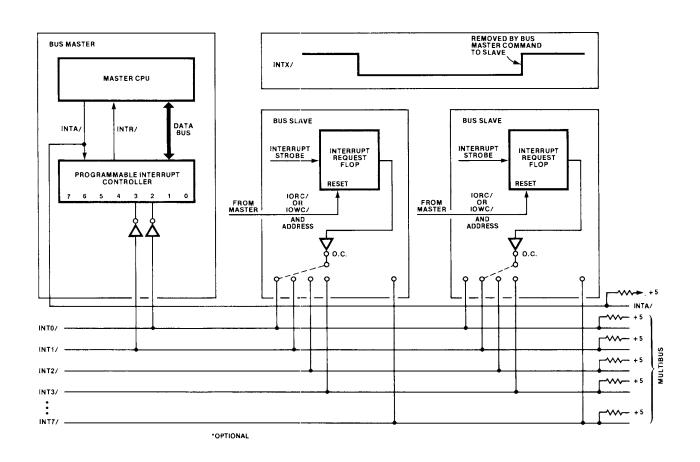

2.3.1.1 INTERRUPT REQUEST LINES (INTO/ - INT7/). A set of MULTIBUS interrupt request lines (INTO/ - INT7/) is provided. An interrupt is generated by activating one of the eight interrupt request lines with an open collector driver. All interrupts are level triggered, rather than edge triggered. Requiring no edge allows several sources to be attached to each line. The interrupt request lines are prioritized, with INTO/ having the highest priority.

**2.3.1.2 INTERRUPT ACKNOWLEDGE** (INTA/). An interrupt acknowledge line (INTA/), driven by the bus master, requests the transfer of interrupt information onto the MULTIBUS interface. The specific information timed onto the bus

Figure 2-12. Lock Timing

depends upon the implementation of the interrupt scheme. In general, the leading edge of INTA/ indicates that the address bus is active while the trailing edge indicates that data is present on the data lines.

#### 2.3.2 CLASSES OF INTERRUPT IMPLEMENTATION

There are two types of interrupt implementation schemes, Non Bus Vectored (NBV) and Bus Vectored (BV). The two schemes are explained in the following sections.

**2.3.2.1 NON BUS VECTORED INTERRUPTS** (NBVI). Non Bus vectored interrupts are those interrupts which are handled on the bus master and do not require the MULTIBUS interface for transfer of the interrupt vector address. The interrupt vector address is generated by the interrupt controller on the master and transferred to the processor over the local bus. The slave modules generating the interrupts can reside on the master module or on

other bus modules, in which case they use the MULTIBUS interrupt request lines (INT0/ - INT7/) to generate their interrupt requests to the bus master. When an interrupt request line is activated, the bus master performs its own interrupt operation and processes the interrupt. Figure 2-11 shows an example of NBV interrupt implementation.

2.3.2.2 BUS VECTORED INTERRUPTS (BVI). Bus vectored interrupts are those interrupts which transfer the interrupt vector address along the MULTIBUS data lines from the slave to the bus master using the INTA/ command signal for synchronization.

When an interrupt request occurs, the interrupt control logic on the bus master interrupts its processor. The processor on the bus master generates an INTA/ command on the system bus, which freezes the state of the interrupt logic on all bus modules for priority resolution. The bus master also locks (retains the bus between bus cycles) the MULTIBUS to allow back to back bus cycles. After the first INTA command,

Figure 2-13. Non-Bus Vectored Interrupt Logic

the bus master's interrupt control logic puts an interrupt code on to the MULTIBUS address lines. The interrupt code is the address of the highest priority active interrupt request line. At this point in the BVI procedure, two different sequences could take place. The difference occurs, because the MULTIBUS can support masters which generate two INTAs or three INTAs.

If the bus master generates two INTAs, one more INTA command would be generated. This second INTA would cause the bus slave interrupt control logic to transmit its interrupt vector address on the MULTIBUS data lines. The address would be used by the bus master to service the interrupt.

If the bus master generates three INTAs, two more INTA commands would be generated. These two INTA commands would allow the bus slave to put its two byte interrupt vector address on to the MULTIBUS data lines (one byte for each INTA). The interrupt vector address would be used by the bus master to service the interrupt.

#### NOTE

The MULTIBUS interface can support only one type of Bus Vectored Interrupt in a given system. However the MULTIBUS interface can support Bus Vectored and Non-Bus Vectored Interrupts at the same time.

Figure 2-12 depicts an example of bus vectored interupt implementation.

## 2.4 MULTIBUS EXCHANGE

The MULTIBUS interface can accommodate several bus masters on the same system, each one taking control of the bus as it needs to affect data transfers. The bus masters request bus control through a bus exchange sequence.

The discussion of the MULTIBUS Exchange will be seperated into three parts. The first part will explain the signals involved, the second part will discuss the Bus Exchange Priority Techniques (seria and parallel), and the third part will explain the implementation of the Exchange Logic.

#### 2.4.1 MULTIBUS EXCHANGE SIGNALS

A set of six signals is used to implement the MULTIBUS exchange operation.

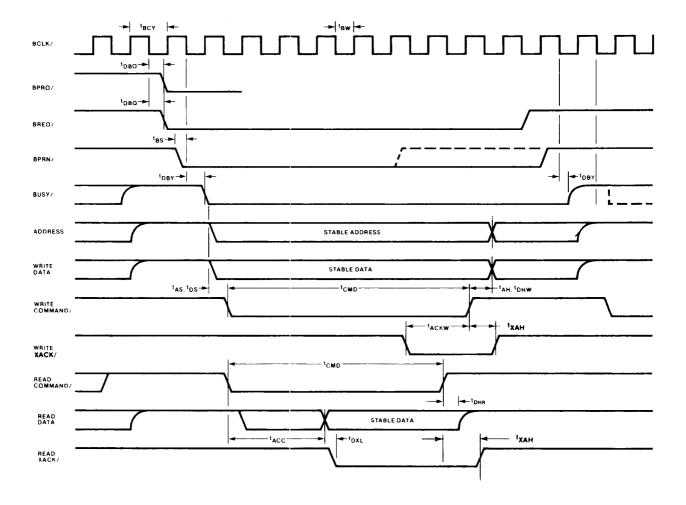

**2.4.1.1 BUS CLOCK (BCLK/).** BCLK/ is used to synchronize the exchange logic, with synchronization occuring on the trailing (high to low) edge of the

pulse. BCLK/ has a duty cycle of approximately 50 percent, a maximum frequency of 10MHz, and can be slowed, stepped, or stopped as called for by system design. There is no requirement for synchronization between BCLK/ and CCLK/, but they may be derived from the same source. The BCLK/ line is driven by a TTL clock driver.

2.4.1.2 BUS BUSY (BUSY/). BUSY/ is driven by the bus master in control of the bus. All other masters monitor BUSY/ to determine the state of the bus. This signal is bi-directional and is driven by an open collector gate. It is synchronized by BCLK/.

2.4.1.3 BUS PRIORITY IN (BPRN/). BPRN/ indicates to a master that no master of higher priority is requesting MULTIBUS control. BPRN/ is synchronized by BCLK/ and driven by TTL gates. In a serial resolution scheme, this is the master's input from the priority chain. In a parallel resolution scheme, this is the masters input from the parallel priority resolution circuit.

**2.4.1.4 BUS PRIORITY OUT (BPRO/).** The Bus Priority Out (BPRO/) line is only used in a serial resolution scheme. It is deactivated by a bus master when it requests the MULTIBUS interface, indicating to lower priority masters that a higher priority bus request exists. BPRO/ is driven by TTL gates. BPRO/ is synchronized by BCLK/.

2.4.1.5 BUS REQUEST (BREQ/). The Bus Request line (BREQ/) is used with the parallel priority resolution scheme, and is a request of a master for MULTIBUS control. The priorities of the BREQ/s from each master are resolved in a parallel priority resolution circuit. The highest priority request enables the BPRN/ input of that master, allowing it to gain control of the bus. BREQ/ is synchronized by BCLK/ and is a TTL output.

2.4.1.6 COMMON BUS REQUEST (CBRQ/) (optional). Any master which wants control of the MULTIBUS interface but does not control it, can activate CBRQ/ with an open collector gate. If CBRQ/ is high it indicates to the bus master that no other master is requesting the bus and therefore the present bus master can retain the bus. This saves the bus exchange overhead for the current master.

#### NOTE

All the bus exchange signals are synchronized by BCLK/.

#### 2.4.2 BUS EXCHANGE PRIORITY TECHNIQUES

Two bus exchange priority techniques are discussed, a serial technique or a parallel technique. Figures 2-13 and 2-14 illustrate these two techniques. The bus exchange implementation discussed in Section 2.5 is the same for both techniques.

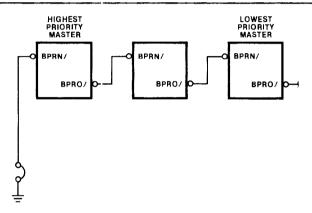

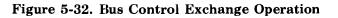

2.4.2.1 SERIAL PRIORITY TECHNIQUE. Serial priority resolution is accomplished with a daisy chain technique (see figure 2-13). The priority input (BPRN/) of the highest priority master is tied to ground. The priority output (BPRO/) of the highest priority master is then connected to the priority input (BPRN/) of the next lower priority master, and so on. Any master generating a bus request will raise the priority line to all the lower priority masters. In this implementation, the bus request line (BREQ/) is not used outside of the individual masters. A limited number of masters can be accomodated by this technique, due to the gate delays through the daisy chain.

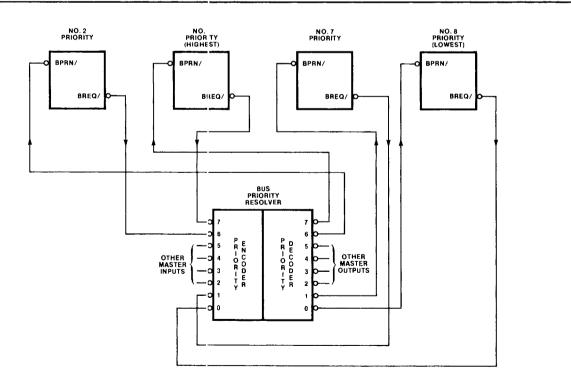

2.4.2.2 PARALLEL PRIORITY TECH-NIQUE. In the parallel priority technique, the priority is resolved in a priority resolution circuit in which the highest priority input is encoded at the chip outputs. This coded value is then decoded to activate the appropriate BPRN/ line. The BPRO/ lines are not used in the parallel priority scheme. Up to sixteen masters can be accomodated by the parallel priority technique.

#### 2.4.3 MULTIBUS EXCHANGE IMPLEMENTATION

The MULTIBUS exchange implementation is shown in figure 2-15. This implementation example uses a parallel resolution scheme, however the timing would be basically the same for the serial resolution scheme.

In this example, master A has been assigned a lower priority than master B. The bus exchange occurs because master B generates a bus request during a time when master A has control of the bus.

The exchange process begins when master B requires the bus to access some resource such as an I/O or memory module. This internal request is synchronized with the trailing edge (high to low) of BCLK/ to generate a bus request (BREQ/). The bus priority in signal (BPRN/) to master A is inactive. Master A

must first complete the current bus command if one is in operation. After it completes the command, BUSY/ goes inactive on the next trailing edge of BCLK/. This allows the actual bus exchange to occur, because master A has relinquished control of the bus, and master B has been granted its BPRN/. During this time, the drivers for master A are disabled. Master B must take control of the bus with the next trailing edge of BCLK/ to complete the bus exchange. Master B takes control by activating BUSY/ and enabling its drivers.

It is possible for master A to retain control of the bus and prevent master B from getting control. Master A

activates an internal signal called Override (or Bus Lock) which keeps BUSY/ active allowing control of the bus to stay with master A. This guarantees a master consecutive bus cycles for such software functions as Test and Set.

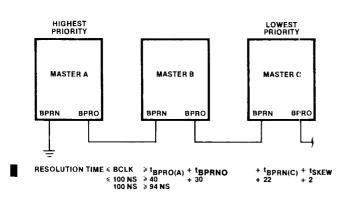

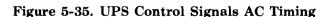

### 2.5 POWER FAILURE CONSIDERATIONS

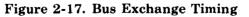

The MULTIBUS interface provides a means of handling power failures. The following sections, define the signals used for power failure handling, and the sequence of events followed when a power failure occurs. Figure 2-16 shows the timing of the power fail sequence.

#### NOTE

The power failure feature is optional. The signals used with this feature are on auxiliary connector P2.

#### 2.5.1 MULTIBUS POWER FAILURE SIGNALS

2.5.1.1 AC LOW (ACLO). This signal, generated by the power supply, goes high when the AC line voltage drops below a certain voltage\* indicating D.C. power will fail in a minimum of 3 msec. ACLO goes low when all D.C. voltages return to 95% of their indicated value. This line must be pulled up by the standby power source.

#### \*NOTE

The value used depends upon supply voltage, and power supply design. A typical value for 120V AC is 100V AC.

**2.5.1.2 POWER FAIL INTERRUPT (PFIN/).** This signal interrupts the processor when a power failure occurs, as indicated by ACLO.

**2.5.1.3 POWER FAIL SENSE (PFSN/).** This line is the output of a latch which indicates that a power failure has occurred. It is reset by Power Failure Sense Reset (PFSR/) and must be powerd by the standby power source.

2.5.1.4 POWER FAIL SENSE RESET (PFSR/). This line is used to reset the power fail sense latch (PFSN/)

Figure 2-18. Power Fail Timing Sequence

)

**2.5.1.5 MEMORY PROTECT (MPRO/).** Prevents memory operation during periods of uncertain DC power by inhibiting memory requests.

**2.5.1.6 INITIALIZE (INIT/).** The INIT/ line resets the entire system to a known internal state.

#### 2.5.2 POWER FAIL SEQUENCE

The power supply monitors the AC power level. When it drops below an acceptable value, the power supply raises ACLO which tells the power fail logic that a minimum of three milliseconds will elapse before power will fall below an operating level. The power fail logic sets a sense latch (PFSN/) and generates an interrupt to the processor so that it can store its environment. After a 2.5 millisecond timeout, the memory protect signal (MPRO/) is asserted, preventing any memory activity. As power falls, the memory goes on standby power. Note that the power fail logic must be powered from the standby source.

As the AC line revives, the power supply voltage level is monitored. After power has been at its operating level for one millisecond minimum, the signal ACLO goes low, beginning the restart sequence. First the memory protect line (MPRO/) then the initialize line (INIT/) become inactive. The bus master now starts running. The bus master(s) checks the power fail latch (PFSN/) and, if it finds it set, branches to a power up routine which resets the latch (PFSR/), restores the environment, and resumes execution.

Note that INIT/ is activated until power has risen to some operable level and must stay low for five milliseconds minimum before the system is allowed to restart. Alternatively, INIT/ may be held low through an open collector device by MPRO/.

How the power failure equipment is configured is left to the system designer. The backup power source may be batteries located on the memory boards or more elaborate facilities located off-board. The location of the power fail logic determines what lines appear on the MULTIBUS interface. Pins on the P2 connector have been specified for the power failure functions for use as needed.

## **3.0 INTRODUCTION**

All electrical specifications for the MULTIBUS are presented in this chapter.

Section 3.1 presents the general bus consideration of State Relationships, Signal Line Characteristics, and Power Supplies.

Section 3.2 contains the timing specifications for the MULTIBUS.

The final Section, 3.3, contains specifications for the signal line drivers and receivers, as well as the electrical termination requirements.

When electrical specifications indicate minimum or maximum values for the MULTIBUS, they must be measurable at any point on the bus.

Note that a particular implemented bus could have any amount of bus propagation delay and ringing (before setup times), as long as all bus parameters (e.g.; setup, hold, and other times) were met at all points on the bus. However, in order to facilitate the design of a compatible set of modules (masters and slaves) that use the bus, the standard maximum bus propagation delay will be specified as tpD (max).

Table 3-1 summarizes all of the key figures and tables in this chapter.

Table 3-1. Location of Key Information

|            | Summary Information                         | Section |

|------------|---------------------------------------------|---------|

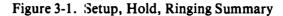

| Figure 3-1 | Setup, Hold, Ringing Summary                | 3.1.2   |

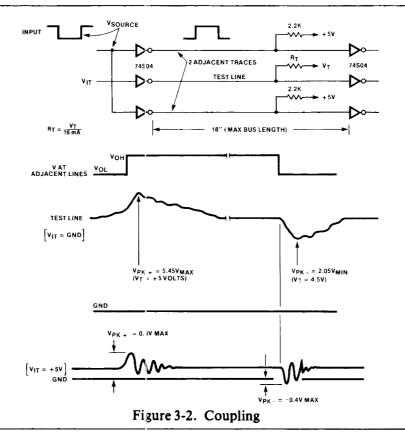

| Figure 3-2 | Coupling                                    | 3.1.2   |

| Table 3-2  | Power Supply Specifications                 | 3.1.3   |

| Table 3-3  | Timing Specifications Summary               | 3.2     |

| Table 3-4  | Receivers, Bus Drivers, and<br>Terminations | 3.3     |

## 3.1 GENERAL BUS CONSIDERATIONS

#### 3.1.1 LOGICAL AND ELECTRICAL STATE RELATIONSHIPS

Electrical state relationships apply to all bus signal lines as described functionally in Section 2.

The signal names indicate whether or not the signal lines on the MULTIBUS are active high or active low. If the signal name ends with a slash ("/"), then the logical-electrical state relationship for that signal is:

| <br>gical<br>ate | Electrical<br>Signal Level | At Receiver  | At Driver    |

|------------------|----------------------------|--------------|--------------|

| 0                | H = TTL high state         | 5.25V≥H≥2.0V | 5.25V≥H≧2.4V |

| 1                | L = TTL low state          | .8V≥L≥5V     | .5V≥L≥0V     |

If the signal name has no slash (no "/"), then the logical-electrical state relationship for that signal is:

| Logical<br>State | Electrical<br>Signal Level | At Receiver  | At Driver    |

|------------------|----------------------------|--------------|--------------|

| 0                | L = TTL low state          | .8V≥L≥5V     | .5V≥L≥0V     |

| 1                | H = TTL high state         | 5.25V≥H≥2.0V | 5.25V≥H≷2.4V |

These specifications are based on TTL where the power source is 5 volts  $\pm$  5%, referenced to logic ground (GND).

When specified, current flow into a node has a positive sign and out of a node a negative sign.

#### **3.1.2 SIGNAL LINE CHARACTERISTICS**

Described below are two types of requirements. The first includes the requirements on the signal line that are measured when the signal line is in use. The second type includes those that are measured under special test conditions.

**3.1.2.1 IN-USE SIGNAL LINE REQUIRE-MENTS**. During normal use the rise and fall times of the signals depend on which type of driver is used (refer to Table 3-4):

|                                    | Open Collector | Totem Pole | 3-State |

|------------------------------------|----------------|------------|---------|

| Rise Time<br>(from low<br>to high) | -              | 10ns       | 10 ns   |

| Fall Time                          | 10 ns          | 10ns       | 10ns    |

(where "high" is TTL high, minimum; and "low" is TTL low, maximum; see Section 3.1.1)

The typical signal propagation delay on the MULTI-BUS is  $t_{PD}(typ)$ . This is measured from the edge of any one board plugged into the MULTIBUS to any other board plugged into the MULTIBUS.

tpn(typ) = 3ns

These dynamic signal requirements can be tested for acceptance by using 74S20 gates as drivers.

#### NOTE

For all boards plugged into the MULTIBUS the Setup, Hold, and any other times are measured at the edge of the board where it is plugged into the MULTIBUS. This means that all board-internal delays must be taken into account while still providing for the Setup, Hold, and other times.

After Power-Up, the following specifications apply.

The bus termination required for each signal line is given in Table 3-4,. Referenced for each signal is the section in which specific termination, receiver, and driver requirements are given. For physical locations for bus terminators refer to Design Guidelines and System Application Section 5.7.

The settling time for all command line signals (see Section 2.2.5) after a transition, is zero. On these lines the ringing cannot go beyond the noise immunity levels-i.e., high, minimum; or low, maximum. This also applies to all Acknowledge and Inhibit lines.

For all address lines (see Section 2.2.2) the signals must be stable (settled) at least 50ns before any command line goes active (setup time). This settling requirement means there can be no ringing beyond the noise immunity levels (High, min; Low, max). These requirements also apply to the Data lines (Section 2.2.2) during any write operations.

For all data lines, during read operations, the setup time is Ons before the Transfer Acknowledge (XACK/) signal goes active; and the hold time is 0ns after the read-type command goes inactive.

The setup, hold, and command ringing is summarized and graphically presented in figure 3-1.

3.1.2.2 BACKPLANE SIGNAL TRACE CHARACTERISTICS. Requirements for line-toline coupling characteristics are shown in Figure 3-2. The specific test conditons under which the specifications are to be met are shown.

Refer to Section 4 for mechanical restrictions on trace characteristics.

#### 3.1.3 BUS POWER SPECIFICATIONS

Table 3-2 provides all Bus power specifications.

| Standard (P1)                              |                                      |                                   | Optional (P2) |              |          |          |                      |              |              |            |

|--------------------------------------------|--------------------------------------|-----------------------------------|---------------|--------------|----------|----------|----------------------|--------------|--------------|------------|

|                                            |                                      |                                   |               |              | Analo    | g Power  | Battery Power Backup |              |              | up         |

|                                            | Ground                               | +5                                | +12           | -12          | +15      | -15      | +5                   | +12          | -12          | -5         |

| Mnemonic                                   | GND                                  | +5V                               | +12V          | -12V         | +15V     | -15V     | +5B                  | +12B         | -12B         | -5B        |

| Bus Pins                                   | P1+1,2,<br>11,12,<br>75,76,<br>85,86 | P1+3,4<br>5,6,81,<br>82,83,<br>84 | P1+7,8        | P1+79,<br>80 | P2+23,24 | P2+25,26 | P2+3,4,<br>5,6       | P2+11,<br>12 | P2+15,<br>16 | P2-7,<br>8 |

| Nominal Output                             | Ref.                                 | +5.0V                             | +12.0V        | -12.0V       | +15.0V   | -15.0V   | +5.0V                | +12.0V       | -12.0V       | -5.0V      |

| Tolerance from Nominal <sup>1</sup>        | Ref                                  | ±5%                               | ±5%           | <u>+</u> 5%  | ±3%      | ±3%      | ±5%                  | ±5%          | ±5%          | ±5%        |

| Ripple<br>(Pk-Pk)²                         | Ref                                  | 50mV                              | 50mV          | 50mV         | 10mV     | 10m V    | 50m V                | 50mV         | 50mV         | 50mV       |

| Transient<br>Response<br>Time <sup>3</sup> |                                      | 500µs                             | 500µs         | 500µs        | 100µs    | 100µs    | 500µs                | 500µs        | 500µs        | 500µs      |

| Transient<br>Deviation⁴                    |                                      | ±10%                              | ±10%          | ±10%         | ±10%     | ±10%     | ±10%                 | ±10%         | ±10%         | ±10%       |

Table 3-2. Bus Power Specifications

NOTES:

Tolerance is worst case, including initial voltage setting, line and load effects of power source, ripple, temperature drift, and 1. any additional steady state influences.

2. As measured over any bandwidth not to exceed 0 to 5 MHz.

As measured from the start of a load change to the time an output recovers with  $\pm 0.1\%$  of final voltage (50% load change). 3

Measured as the peak deviation from the initial voltage.

All voltages not shown in table 3-2, that may be required on a board plugging into the MULTIBUS should be derived from one of the standard voltages  $(+5, \pm 12)$ .

See Section 5.4 for guidelines and examples of power failure circuitry. Section 5-6 describes on-board filter capacitors. Section 5.5 (Design Recommendation Summary) includes power supply guidelines.

Refer to Section 6.5.1 for power supply voltages that may exist in early MULTIBUS-type systems.

#### 3.1.4 TEMPERATURE AND HUMIDITY

All bus specifications should be met while the temperature and humidity are within the following ranges:

Temperature: 0-55°C (32-150°F) Free moving air across modules and bus.

Humidity: 90% Max Relative (No Condensation)

These represent a standard environment for the MULTIBUS. It may be desireable to create more (or less) severe environmental restrictions in some applications.

## 3.2 TIMING

This section describes all timing specifications on the MULTIBUS. It does not present descriptions or functional relationships (which are given in Section 2). This section does imply the functionality when relating two signals. Section 2 should be referred to for all ambiguities.

Table 3-3 summarizes all of the timing specifications in this section. For detailed descriptions refer to the specific sections indicated in the table.

The timing diagrams shown in this section usually show the MIN or MAX values required for each parameter. However, for clarity in the diagrams, parameters usually do not have MINIMUMS and MAXI-MUMS both indicated on the diagram. The Bus Timing Specification table (Table 3-3) should be referenced for completed MIN/MAX information. The timing diagrams show how all of the parameters are defined in relation to the signals involved. All timing is measured at 1.5V with loading capacitance C<sub>0</sub> and terminations as specified in Table 3-4.

| Parameter         | Description                             | Minimum               | Maximum               | Units | Sections<br>To<br>Reference |

|-------------------|-----------------------------------------|-----------------------|-----------------------|-------|-----------------------------|

| <sup>t</sup> BCY  | Bus Clock Period                        | 100                   | ~ (D C )              | ns    | 3.2.5                       |

| <sup>t</sup> BW   | Bus Clock Width                         | 0.35 t <sub>BCY</sub> | 0.65 t <sub>BCY</sub> | ns    | 3.2.5                       |

| <sup>I</sup> SKEW | BCLK/skew                               |                       | t <sub>PD</sub>       | ns    | 3.2.5                       |

| teD(tyb)          | Standard Bus<br>Propagation Delay       |                       | 3                     | ns    | 3.1.2,<br>3.2.5             |

| <sup>t</sup> AD   | Address Disable                         | 100                   |                       | ns    |                             |

| tas               | Address Set-Up Time<br>(at Slave Board) | 50                    |                       | ns    | 3.2.1,<br>3.2.2,<br>3.2.4   |

| <sup>t</sup> DS   | Write Data Set<br>Up Time               | 50                    |                       | ns    | 3.2.2                       |

| <sup>t</sup> AH   | Address Hold Time                       | 50                    |                       | ns    | 3.2.1,<br>3.2.2,<br>3.2.4   |

| <sup>t</sup> DHW  | Write Data Hold Time                    | 50                    |                       | ns    | 3.2.2                       |

| <sup>t</sup> DXL  | Read Data Set<br>Up Time To XACK        | 0                     |                       | ns    | 3.2.1,<br>3.2.4             |

| <sup>t</sup> DHR  | Read Data Hold Time                     | 0                     | 65                    | ns    | 3.2.1,<br>3.2.4             |

| <sup>t</sup> XAH  | Acknowledge Hold<br>Time                | 0                     | 65                    | ns    | 3.2.1,<br>3.2.2,<br>3.2.4   |

Table 3-3. Bus Timing Specifications Summary

| Parameter          | Description                                                                                                                              | Minimum                 | Maximum                               | UNITS | Sections<br>To<br>Reference |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------|-------|-----------------------------|

| <sup>t</sup> XACK  | Acknowledge Time                                                                                                                         | 0                       | 8                                     | μS    | 3.2.1,3.2.2,<br>3.2.4       |

| <sup>t</sup> CMD   | Command Pulse<br>Width                                                                                                                   | 100                     | t <sub>TOUT</sub>                     | ns    | 3.2.1,<br>3.2.2             |

| t <sub>ID</sub>    | Inhibit Delay                                                                                                                            | 0                       | 100<br>(Recommend <100 ns)            | ns    | 3.2.3                       |

| <sup>t</sup> XACKA | Acknowledge Time<br>of an Inhibited Slave                                                                                                | t <sub>IAD</sub> + 50ns | 1500                                  | ns    | 3.2.3                       |

| <sup>I</sup> XACKB | Acknowledge Time of<br>an Inhibiting Slave                                                                                               | 15                      | 8                                     | μS    | 3.2.3                       |

| <sup>t</sup> IAD   | Acknowledge Disable<br>from Inhibit (An<br>internal parameter on<br>an Inhibited slave;<br>used to determine<br><sup>1</sup> XACKA Min.) | 0                       | 100<br>(Arbitrary)                    | ns    | 2.3.2                       |

| <sup>I</sup> INTA  | INTA/ Width                                                                                                                              | 250                     |                                       | ns    | 3.2.4                       |

| ICSEP              | Command Separation                                                                                                                       | 100                     |                                       | ns    | 3.2.4,                      |

| <sup>t</sup> BREQL | +BCLK/ to BREQ/<br>Low Delay                                                                                                             | 0                       | 35                                    | ns    | 3.2.6<br>3.2.5              |

| <sup>t</sup> BREQH | ∔BCLK/ to BREQ/<br>High Delay                                                                                                            | C                       | 35                                    | ns    | 3.2.5                       |

| <sup>I</sup> BPRNH | BPRN/ to   BCLK/<br>hold                                                                                                                 | £,                      |                                       | ns    |                             |

| <sup>1</sup> BPRNS | BPRN/ to +BCLK/<br>Setup Time                                                                                                            | 22                      |                                       | ns    | 3.2.5                       |

| <sup>t</sup> BUSY  | BUSY/ delay<br>from +BCLK/                                                                                                               | ¢.                      | 70                                    | ns    | 3.2.5                       |

| BUSYS              | BUSY/ to +BCLK/<br>Setup Time                                                                                                            | 25                      |                                       | ns    | 3.2.5                       |

| <sup>t</sup> BPRO  | 4BCLK/ to BPRO/<br>(CLK to Priority Out)                                                                                                 | 0                       | 40                                    | ns    | 3.2.5                       |

| <sup>t</sup> BPRNO | BPRN/ to BPRO/<br>(Priority In to Out)                                                                                                   | 0                       | 30                                    | ns    | 3.2.5                       |

| <sup>t</sup> CBRO  | +BCLK/ to CBRQ/<br>(CLK to Common<br>Bus Request)                                                                                        | 0                       | 60                                    | ns    | 3.2.5                       |

| <sup>1</sup> CBRQS | CBRQ/ to +BCLK/<br>Setup Time                                                                                                            | 35                      |                                       | ns    | 3.2.5                       |

| Serial<br>Priority | See Section 3.2.5                                                                                                                        |                         |                                       |       |                             |

| txcD               | XACK, to Command'<br>Delay                                                                                                               | ::0                     |                                       | ns    | 3.21<br>3.2 2               |

| t <b>B</b> SYO     | CBRQ/i or BUSY/i<br>to BUSY/t Delay                                                                                                      | -                       | 12                                    | μS    | 3.2.5                       |

| tlckh              | LOCK hold time from Command -                                                                                                            | 100                     |                                       | ns    | 326                         |

| tloks.             | LOCK to Command<br>Setup Time                                                                                                            | 100                     |                                       | ns    | 326                         |

| tlock              | LOCK Width                                                                                                                               |                         | 12                                    | μs    | 326                         |

| tCPM               | Central Priority<br>Module Resolution<br>delay (Parallel Priority)                                                                       | )                       | tBCY-tBREO<br>-21PD -tBPRNS<br>-tskew |       | 325                         |

## Table 3-3. Bus Timing Specifications Summary (Cont'd.)

| Parameter          | Description                          | Minimum  | Maximum              | Units | Sections<br>To<br>Reference |

|--------------------|--------------------------------------|----------|----------------------|-------|-----------------------------|

| 1CCY               | C-clock Period                       | 100      | 110                  | ns    | 3.2.6                       |

| <sup>t</sup> cw    | C-clock Width                        | 0.35:CCY | 0.65t <sub>CCY</sub> | ns    | 3.2.6                       |

| <sup>t</sup> INIT  | INIT/ Width                          | 5        |                      | ms    | 3.2.6<br>3.2.7              |

| <sup>t</sup> INITS | INIT/ to MPRO/<br>Setup Time         | 100      |                      | ns    | 3.2.7                       |

| <sup>t</sup> PBD   | Power Backup<br>Logic Delay          | 0        | 200                  | ns    | 3.2.7                       |

| <sup>t</sup> PBDI  | Power Backup<br>Logic Delay          | 200      |                      | ns    | 3.2.7                       |

| <sup>t</sup> PFINW | PFIN/ Width                          | 2.5      |                      | ms    | 3.2.7                       |

| <sup>t</sup> MPRO  | MPRO/ Delay                          | 2.0      | 2.5                  | ms    | 3.2.7                       |

| <sup>t</sup> ACLOW | ACLO/ Width                          | 3.0      |                      | ms    | 3.2.7                       |

| <sup>t</sup> PFSRW | PFSR/Width                           | 100      |                      | ns    | 3.2.7                       |

| <sup>t</sup> TOUT  | Timeout Delay                        | 1        | ∞ (DC)               | ms    | -                           |

| <sup>t</sup> DCH   | D.C. Power Supply<br>Hold from ACLO/ | 3.0      |                      | ms    | 3.2.7                       |

| <sup>t</sup> DCS   | D.C. Power Supply<br>Setup to ACLO/  | 1        |                      | ms    | 3.2.7                       |

#### Table 3-3. Bus Timing Specifications Summary (Cont'd.)

\* = is maximum t<sub>XACK</sub> of all inhibited boards.

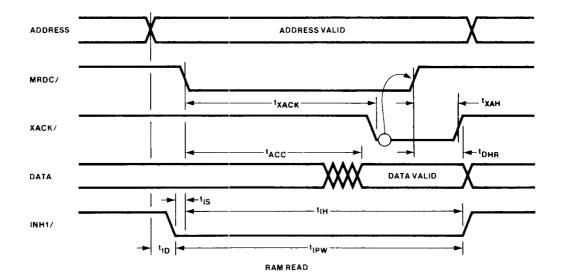

#### 3.2.1 READ OPERATIONS (I/O AND MEMORY)

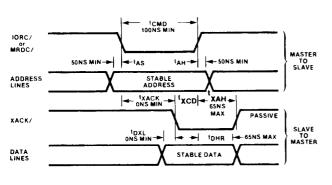

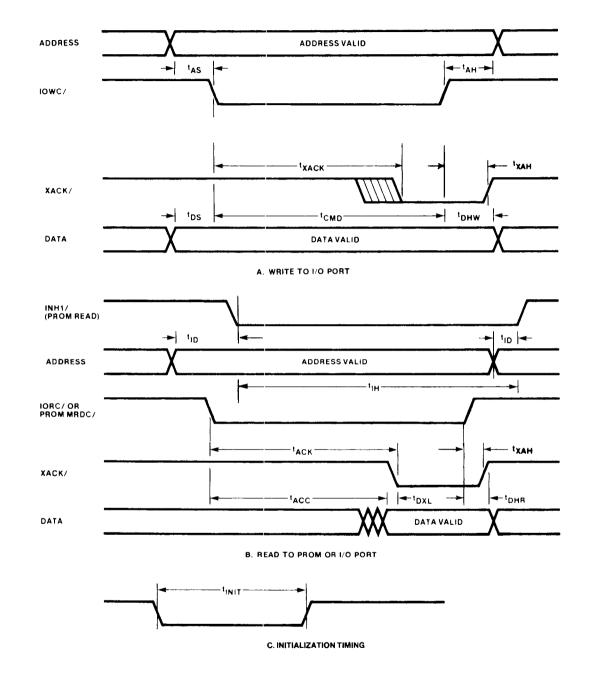

A Read operation transfers data from memory or from I/O to the master that is controlling the bus. For detailed functional descriptions refer to Section 2.2. The lines involved and timing specifications for a Read Operation are as follows (figure 3-3):

#### See Section 5.1 for guidelines and examples. See also the special inhibit operation in Section 3.2.3. For system anomalies with respect to read commands see Section 6.5.

#### 3.2.2 WRITE OPERATIONS (I/O AND MEMORY)

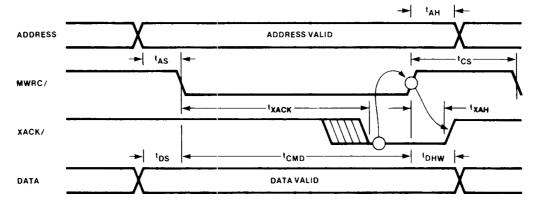

A Write Operation transfers data from the master (that is controlling the bus) to the memory or I/O. For detailed functional descriptions refer to Section 2.2. Timing for a Write Operation is as follows (figure 3-4):

Figure 3-4. Write AC Timing

See Section 5 for guidelines and examples, Section 6.5 for Write-related system anomalies, and Section 3.2.3 for inhibit operations.

#### 3.2.3 INHIBIT OPERATIONS