### INTERCONTINENTAL MICRO SYSTEMS CORP.

# **CPZ - 48000**

## SINGLE BOARD CENTRAL PROCESSOR

4015 Leaverton Court • Anaheim, California 92807 • (714) 630-0964 • Telex: 678401 - TAB-IRIN

#### TABLE OF CONTENTS

| C      | OI            | PY          | RI                        | [G]          | TE                   | N                         | 01         | <b>!I</b> ( | CE       | )    | ٠          | •          | •          | •          | • .  | •            | •          |                  | •            | •     | •   | •                | •     | ٠          | ٠            | •   | . • | ٠      | ٠          | •           | ٠          | •     | •              | •          | 1                |

|--------|---------------|-------------|---------------------------|--------------|----------------------|---------------------------|------------|-------------|----------|------|------------|------------|------------|------------|------|--------------|------------|------------------|--------------|-------|-----|------------------|-------|------------|--------------|-----|-----|--------|------------|-------------|------------|-------|----------------|------------|------------------|

| D      | )IS           | SC          | LA                        | II           | ME.                  | R                         | NC         | )T:         | IC       | E    |            |            |            | •          | •    | •            |            |                  | •            | •     | •   | •                | •     | •          | •            | •   | •   | •      | •          | •           | •          | •     | •              | •          | 1                |

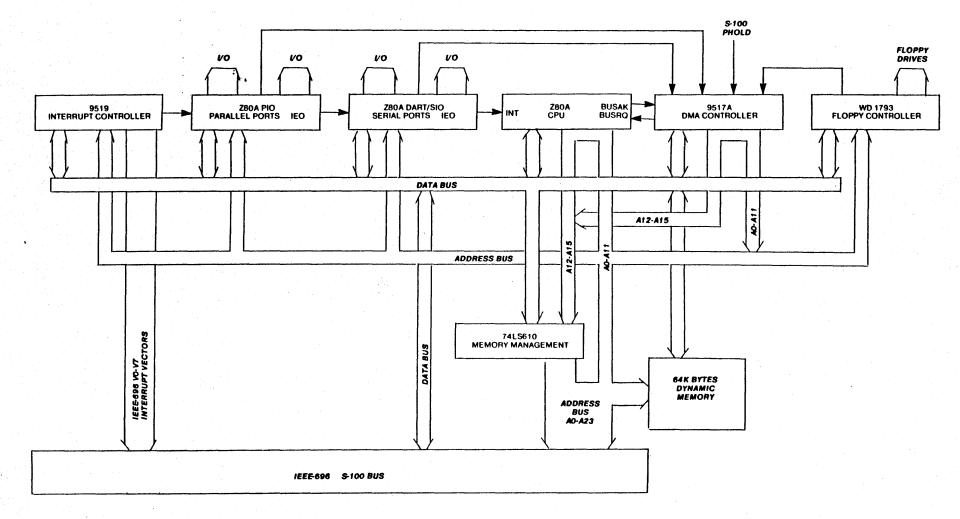

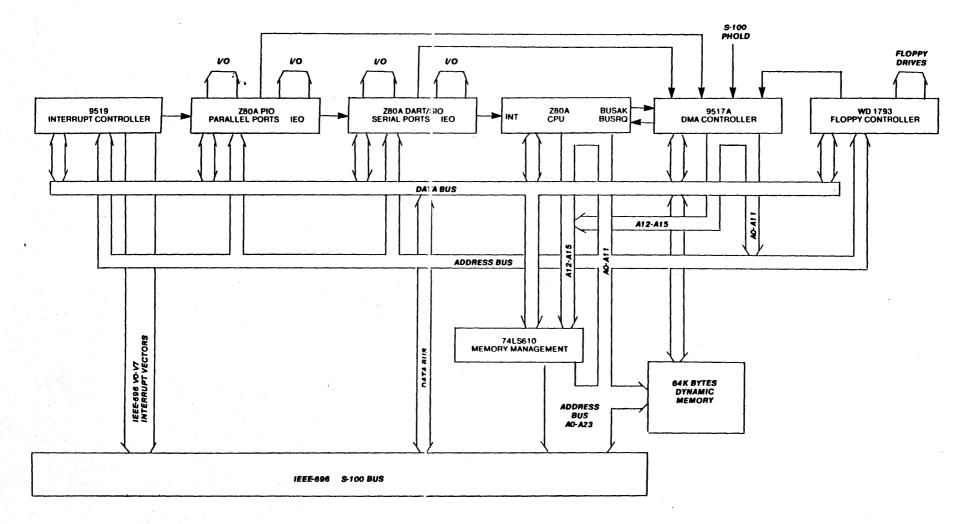

| T      | NT            | סי          | OT                        | TT/          | ገጠ                   | τn                        | N          |             |          |      |            |            |            |            |      |              |            |                  | _            |       |     | _                | _     |            |              |     |     |        |            |             | -          |       | -              |            | 2                |

|        | Ţ             | ٩٩          | et.                       | :11          | re                   | R                         |            |             | -        |      | -          |            |            | -          |      |              |            |                  |              |       |     |                  |       | -          |              | -   |     | -      |            | •           |            | •     | •              | •          | 2                |

| Ð      | זית           | <u>ה</u> על |                           | M            | A NU                 | -<br>T                    | ġ          | D           | -<br>-   |      | л.<br>Т    | n          | λ m·       | τr         | Ň    | 2            |            |                  |              |       |     | Ţ                | •     | . •        | •            |     | •   | •      | •          |             |            |       | Ţ              | •          | 2                |

| I<br>T | יוניב<br>אדדו | 17.<br>17.  | DI<br>m T                 | .01          | а.<br>Т. а. 1        | ند ب<br>۲                 | т.<br>Т.Т. |             |          |      | . T        |            | 1          | 10         | 111  | <b>,</b>     | •          |                  |              | •     | •   | •                | •     | •          | •            | ٠   | •   | •      | •          | • • • • • • | •          | •     | •              | •          | 223556667        |

| Г      | .OIV          |             | TI                        | נט.          | NA.                  | ч.                        | ות         | 50          | u n      | 11   | rT.        | τĊ         | ЛИ         |            | ٠    | •            | •          |                  |              | •     | •   | •                | •     | ٠          | ٠            | ٠   | ٠   | ٠      | ٠          | ٠           | ٠          | •     | ٠              | ٠          | 2                |

|        | 1             | .n          | pu                        | LT,          | 10                   | ut                        | pr         | lt          | ຼຽ       | TI   | ru         | .C1        | cu         | re         | )    | ٠            | •          |                  | •            | •     | ٠   | ٠                | ٠     | ٠          | ٠            | •   | ٠   | •      | ٠          | ٠           | •          | ٠     | ٠              | ٠          | 2                |

|        |               |             | 0f                        | f            | -B                   | oa                        | rĊ         |             | I/       | 0    | С          | 01         | 1t:        | rc         | )]]  | Le           | rε         | 5                |              | •     | ٠   | ٠                | ٠     | ٠          | ٠            | ٠   | ٠   | ٠      | ٠          | •           | ٠          | ٠     | ٠              | ٠          | 6                |

|        |               |             |                           | 5            | er:                  | 18                        | 1          | Т,          | /U       |      | 20         | <b>Г</b> 7 | 5          | υc         | n    | GT.          | 01         |                  |              | •     | •   | ٠                | ٠     | ٠          | ٠            | ٠   | ٠   | ٠      | ٠          | ٠           | •          | •     | •              | •          | 6                |

|        |               |             |                           | S            | er                   | ia                        | 1          | I           | /0       | ) (  | Co         | nt         | tr         | 01         | .10  | er           |            |                  |              | •     | •   | •                | •     | •          | •            | •   |     |        | •          | •           | •          | •     |                |            | 6                |

|        |               |             |                           | R            | ອາງ                  | a _                       | ٦R         | t           | e -      | CI   | 0          | cl         | r (        | Ge         | ne   | - 7          | คา         | 501              | •            |       |     |                  | -     | -          |              | -   | -   |        |            | •           |            |       | -              |            | 7                |

|        |               |             |                           | D            |                      | . 1                       | 7 6        | יי.<br>רי   | ŤΤ       | 11   | กั         | D          | -<br>      | +          | 6    | n n          | ++         | 50               |              | Tn    | +_  | . <del>.</del> 4 | · • • |            | •            | •   | •   | •      | •          | •           | •.         | •     | •              | •          |                  |

|        |               |             |                           | T I          | 1                    | 51<br>51                  | тс<br>Т    | -           | т.<br>-  |      | ).<br>74   | т (<br>    | -1<br>-1   | с<br>0     |      | ) 11<br>) 11 | ~ 4        | . U.             | L .          |       |     |                  | .a.   | 20<br>14 - | .1-          | ÷.  |     |        |            | •           | •          | ٠     | •              | •          | 8<br>9<br>9<br>9 |

|        |               |             |                           | יע           | ou                   | DT                        | e-         | ·_'         |          |      | 21         | nŧ         | ζT,        | e-         | .ne  | en           | 81         | LUJ              | <b>,</b>     | L.T   | oI  | ppy              | 1     | 118        | 3K           | CC  | nτ  | r      | 11         | ler         | •          | ٠     | ٠              | ٠          | 3                |

|        |               |             | On                        | -            | Bo                   | ar                        | d          | 1,          | /0       | ) (  | 20         | n          | t r        | 10         | 10   | er           | B          | •                |              | •     | •   | ٠                | •     | •          | ٠            | . • | ٠   | ٠      | ٠          | •           | ٠          | ٠     | ٠              | ٠          | 9                |

|        |               |             |                           | DI           | MA                   | С                         | or         | t           | ro       | 1]   | Le         | r          |            | •          | ٠    | ٠            | •          |                  | •            | •     | •   | ٠                | •     | •          | •            | •   | ٠   | •      | •          | •           | •          | •     | ٠              | •          | 9                |

|        |               |             |                           | D            | AM                   | 0                         | De         | era         | at       | ic   | on         | 8          |            | •          | •    | •            |            |                  | •            | •     | •   | •                | •     |            | •            | •   | •   | •      | •          | •           |            | •     | •              | •          | 10               |

|        |               |             |                           | D            | AN                   | Ċ                         | ĥe         | n           | ne       | 1    | ٨          | 88         | :1.        | ør         | me   | en.          | te         |                  | _            | _     |     |                  |       |            |              |     | -   | _      |            |             |            |       | •              | _          | 10               |

|        |               |             |                           | T,           | n+.                  | 0 T                       |            |             | +        | 2    | - <b>m</b> | +,         |            | ີ່         | Τ.   |              | <u>ج</u>   |                  |              | •     | •   | •                | •.    | •          | . •          | •   | •   | •      | •          | •           | •          | •     | •              | •          | 11               |

|        |               |             |                           | ÷.           |                      |                           | 1.6        | <u>.</u>    | U<br>L   | 200  | 511        |            | . 0.       | +<br>      | 10   | 19           | а.<br>т.   | , , ,<br>, , , , |              | •     | •   | •                | •     | •          | •            | •   | ٠   | •      | ٠          | •           | ٠          | •     | •              | ٠          | 11               |

|        |               |             |                           | 11           | nt                   | er                        | rι         | ι <u>p</u>  | U        | U    | on         | τı         | .0.        | Ϋ́Т        | .e.  | ۲ <i>۲</i>   | Se         | 516              | ec           | T.    | •   | •                | ٠     | ٠          | ٠            | •   | ٠   | ٠      | • 1        | ٠           | ٠          | •     | ٠              | ٠          | 11               |

|        | _             | _           |                           | M            | em                   | or                        | У          | M           | an       | a    | ge         | me         | en         | ţ          | Ui   | 11           | t          | •                | •            | •     | •   | ٠                | ٠     | •          | ٠            | ٠   | ٠   | ٠      | ٠          | •           | •          | ٠     | ٠              | •          | 14               |

|        | - 6           | 54          | K                         | [b]          | yt:                  | e                         | DJ         | m           | am       | ii   | 2          | R/         | ۱M,        | /I         | jo į | gi           | С          |                  | •            | •     | •   | •                | ٠     | ٠          | ٠            | • • | •   | •      | ٠          | •           | •          | •     | •              | ٠          | 15               |

|        | 2             | 2K          | /4                        | K            | E                    | PR                        | OŇ         | 1.          | •        | •    |            |            | •          | •          | •    | •            |            |                  |              | •     | •   | •                |       | •          | •            | •   | •   |        |            | •           |            | •     | •              |            | 16               |

|        | 1             | . /         | 'n                        | CI           | n i ·                | n                         | Ŝe         | 57          | e c      | ÷    | T          | 0.         | ว่         | C          | _    |              |            |                  |              | _     |     |                  | -     |            |              | _   | -   | _      |            |             | _          | -     |                |            | 16               |

|        | Ē             | > /<br>> ~  |                           | . m.         |                      | r<br>n                    | ~ ì        |             |          | . /ī | 2          |            | 2          | Ťτ         |      | ~ 4          | ~`         |                  |              | •     | •   | •                | •     | •          | •            |     | Ţ   | •      | •          | •           | •          | •     | - <b>-</b> - , | •          | 16               |

|        | 1             | . U         | WC                        |              | -0:                  |                           |            | . –         | -<br>-   | / 1  | 1 E        | D          | 50         | *          | 108  | 51           | C          | •                | <b>D</b> .4  | •     | ٠   | •                | •     | •          | ٠            | • . | •   | •.     | •          |             | •          | •     |                | •          | 10               |

|        | U<br>C        | 1           | 00                        | K.           | G                    | en                        | eı         | ·a          | το       | r    | . •        | _ (        | •          | •          | ٠    | .•           | •          |                  |              | •     | •   | •                | ٠     | ٠          | ٠            | •   | •   | ٠      | ٠          | •           | ٠          | ٠     | •              | •          | 17               |

|        | C             | P           | U                         | C            | on.                  | tr                        | 0]         | . i         | 51       | gı   | na         | 16         | 3 (        | Ge         | ene  | er           | <b>a</b> 1 | 101              | r            | •     | ٠   | ٠                | ٠     | ٠          | ٠            | •   | ٠   | ٠      | ٠          | ٠           | ٠          | ٠     | •              | •          | 17               |

|        | 5             | <b>}</b> -  | 10                        | 0            | B                    | us                        | 0          | 01          | nt       | TO   | 5l         |            | 3i,        | gr.        | a]   | ۱s           | Ģ          | }e1              | ne           | ra    | .tc | T                | •     | •          | •            | •   | •   | •      | •          | •           | •          | •     | •              | •          | 17               |

|        | ៍ទ            | 5-          | 10                        | 0            | B                    | us                        | ]          | 'n          | te       | ri   | fa         | .ce        | 3          | •          | •    |              |            |                  |              | •     | •   | •                | •     |            | •            | •   |     |        |            | •           | •          | •     | •              |            | 18               |

|        |               | h           | đτ                        | e            | 38                   | P                         | າງຮ        |             |          |      |            |            |            | -          |      | _            |            |                  | _            | _     | _   | -                |       | -          |              | _   | -   |        |            |             | -          | -     | -              |            | 19               |

|        | 7             |             | ***                       | +            | ה                    | -<br>+                    | 0          | ,<br>121    |          |      | •          | •          | •          | •          | •    | •            | •          |                  | •            | •     | •   | •                | •     | •          | •            | •.  | •   | •      | •          | •           | •          |       | • •            | •          | 19               |

|        |               | . 11        | pu<br>1                   |              | וע                   | 30                        | а<br>-     | ום.         | ue<br>D  | -    | •          | •          |            | •          | •    | ٠            | •          |                  | •            | •     | •.  | .•               | •     | •          | ٠            | •   | •   | •      |            | •           | ÷          | 0     | ÷.             | -          | 19               |

|        | C             | ju          | τŗ                        | u            | נס                   | va<br>_                   | τε         | 1           | Bu       | В    | ٠          | •          |            | •          | ٠    | ٠            | •          |                  | •            | •     | •   | •                | ٠     | •          | •            | •   | •   | •      | •          | •           | ٠          | ٠     | •              | ٠          | 19               |

|        | 5             | st          | at                        | u            | 5.                   | Bu                        | S          |             | •        | ٠    | ٠          | •          | •          | •          | ٠    | ٠            | : •        |                  | <b>b</b> - 4 | •     | ٠   | •                | ٠     | ٠          | ٠            | •   | ٠   | •      | •          | •           | •          | • '   | . •            | ٠          | 20               |

|        |               |             | вM                        | IEI          | MR                   | - (                       | Μe         | m           | or       | J    | R          | e          | ađ         | )          | •    | ٠            | •          |                  | •            | •     | •   | •                | ٠     | •          | •            |     | •   | •      | •          | •           | •          | •     | •              | •          | 20               |

|        |               |             | вM                        | [1           | ()                   | Dτ                        | ec         | bđ          | е        | Τe   | et         | cl         | <b>1</b> ) | •          |      |              |            |                  |              | •     |     | •                |       |            |              |     |     | •      |            | •           |            |       |                |            | 20<br>20<br>21   |

|        |               |             | вTа                       | N            | р`                   | (Ŧ                        | nT         | 117         | ŧ)       |      |            |            |            | _          |      | -            |            |                  |              |       |     | -                |       |            | -            | -   | -   |        | -          | -           | -          |       |                | -          | 20               |

|        |               |             | 20                        | 111          | r<br>n               | እት                        | ***        |             | +        | 1    | •          | •          | •          | •          |      | •            |            |                  |              | •     | •   | •                | •     | •          | •            | •   | •   | •      | •          | •           | •          |       | •              | •          | 21               |

|        |               |             | BU                        |              | L<br>L               | $\left( \sum_{i} \right)$ | u          | ייייי       | ui       | 1    | ٠          | - (        |            | •          | ٠    | •            | •          | •                |              | •     | •   | •                | •     | •          | •            | •   | •   | •      | •          | •           | •          | •     | ٠              | •          | 21               |

|        |               |             |                           |              |                      |                           |            |             |          |      |            |            |            |            |      |              |            |                  |              |       |     |                  |       |            |              |     |     | ٠      | ٠          | •,          | ٠          | ٠     | ٠              |            | 21               |

|        |               |             |                           |              |                      |                           |            |             |          |      |            |            |            |            |      |              |            |                  |              |       |     |                  |       |            |              | •   |     | ٠      | ٠          | ٠           | •          | •     | •              |            | 21               |

|        |               |             | вB                        | Ľ!           | ГA                   | - (                       | Ηε         | ıl.         | t        | Ac   | ck         | no         | )W         | le         | ed,  | ge           | )          |                  |              | •     | •   | •                | •     | •          | •            | •   | •   | •      | •          | •           | •          | •     | •              | •          | 21               |

|        | C             | 0           | nt                        | r            | <b>51</b>            | Î                         | n          | <u>.</u>    | t        | Bı   | າອ         |            |            | •          |      | -<br>-       | •          |                  |              | •     |     |                  |       | •          |              | •   | •   |        |            | •           | •          |       |                |            | 22               |

|        | F             | 2D          | Y                         | 1            | 37                   |                           | 2          | P.          |          | 21   | ÷1         |            |            | •          | •    | •            |            |                  |              | -     |     |                  |       |            | •            | •   | •   |        |            |             |            |       |                |            | 22               |

|        | - v           |             | +<br>ער                   |              | / a.                 | 2. 4                      | -          | 1           | 5 a<br>1 | n.   |            |            | - \        | •          | •    | •            | •          |                  | •            | •     | •   | •                | •     | •          | •            | •   |     | •      | ٠          |             | ٠          | ٠     | •              | · •        | 22               |

|        |               | .U          | m M<br>T C                |              | (S                   | pe                        | <b>C</b> ] | .a.         | T.       | ne   | 28         | .aj        | 7)         |            | •    | •            | _ (        |                  | • •          | • ,   | •   | ••               | •     | •          | ٠            | ٠   | -   | ٠      | ٠          | •           | ٠          | •     | .•             | •          | 22               |

|        | 1             | .N          | 23                        |              | $\sum_{i=1}^{M_{i}}$ | as                        | Kε         | LD.         | Te       |      | In         | te         | er         | rυ         | ιp   | Γ.           | Re         | ۶q١              | ıe           | 8T    | )   | ۰.               | •     | •          | •            | •   | ٠   | ,<br>• |            | • •         | •          | ٠     | •              | •          | 22               |

|        | N             | IM          | 1*                        |              | (N                   | on                        | -D         | 181         | sk       | al   | bl         | е          | 1          | nt         | ;e1  | C T          | uj         | ot.              | R            | eq    | ue  | est              | ;)    | ٠          | •            | •   | ٠   | ٠      | •          | ` é         | •          | •     | ÷              | •          | 23               |

|        | E             | [0          | LD                        | ) <b>*</b> . | ()                   | DM                        | A          | R           | ea       | ue   | 28         | t          | )          | •          | •    | . •          |            |                  |              | •     | •   | •                | •     | •          |              | •   | •   | ·      |            | <b>.</b>    | •          | •     |                | •          | 23               |

|        | C             | <b>`</b> 0  | nt                        | r            | oİ                   | 0                         | n 1        | ומ          | uf       | 1    | BIJ        | 8          |            |            | •    | -            |            |                  |              | · .   |     | •                |       |            |              | •   |     |        | : <u> </u> |             |            |       |                | ۰ <u>۲</u> | 23               |

|        |               | -           | DS                        | Y            | NC                   | Ĩ                         | C.         | re.         | Ĩe       |      | 3+         | 21         | +          | Ĩ.         | -    | -            |            |                  |              | - · . | -   | •                |       |            |              |     |     |        |            |             | ۰ <b>.</b> |       |                | <u> </u>   | 24               |

|        |               |             |                           |              | VA:                  |                           |            |             |          |      |            |            |            |            |      |              |            |                  |              |       |     |                  |       | •          | •            |     |     | -      | -          | -           |            | •     | •              |            | 24               |

|        |               |             | ~т<br>Т                   | 101          | ¥ №.<br>ТЪТ          | <u>п</u> ,                | <u>ہ</u>   | 5           | 이번<br>고  |      | 18         |            | 8          | / 1<br>/ 1 | . u  | /            | •          |                  |              |       |     |                  |       |            | ٠            | ٠   |     | ٠      | •          | °●          | •          | •     | •              | •          |                  |

|        |               |             | $\mathbf{b}_{\mathbf{r}}$ | Т            | т 1Л                 | <u>``</u>                 | ne         | B           | u,       | 21   | Γ          | 0          | be         | Ł          | ٠    | ٠            |            | •                | •            | •     | ٠   | •                | ٠     | -          | ٠            | ٠   | •   | •      |            | •           | •          | •     | •              | •          | 24               |

|        |               |             | DW                        | IR'          | <b>*</b>             | (W                        | rj         | t           | e        | S    | tr         | 01         | De         | )          | ٠    | •            |            |                  |              |       |     | •                | •     | •          | , <b>e</b> - | •   | •   | •      | •          | •           | •          | •● 1* | •              | •          | 25               |

|        |               |             | рE                        | L]           | DA                   | - (                       | Ηc         | 1           | đ        | A    | ck         | n          | ow:        | le         | ed į | ge           | )          |                  |              | •     |     |                  | ٠     | •          | •            |     |     | •      | •          | •           | •          | •     | •              | •          | 25               |

|        |               |             | pW                        | IA:          | IT                   | 1                         | We         | i           | t        | ſ    | ÓD         | t          | io         | ne         | il`  | 1)           |            |                  | •            | •     |     | •                | •     |            |              | •   |     |        | 1          |             |            |       |                | •          | 25               |

|        |               |             |                           | •            |                      | <b>.</b> .                |            |             |          | 7    | -          |            | -          |            |      |              |            |                  |              |       | 1   |                  | 9.51  |            |              |     |     |        |            |             |            | ್     |                | 3.1        |                  |

Information contained herein is Proprietary to I.C.M. Corp.

| 后,我们们的你们,你们们就是你们的你们,你们们就是你们的你们,你们们就是你们的你们,你们们的你们,你们们们就是你们的你们,你们就是你们的你们,你们们不是你们的你,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| DMA Control Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                                                                                         |

| Vector Interrupt Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

| Utility Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27                                                                                                                         |

| System Clock (Master Clock)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27                                                                                                                         |

| Clock (Clock)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27                                                                                                                         |

| System Clock (Master Clock)<br>Clock (Clock)<br>MWRITE (Memory Write)<br>POC* (Power-on Clear)<br>Slave CLR* (Slave Clear)<br>FPPOP* (Frace line)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27                                                                                                                         |

| MWRITE (Memory Write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21                                                                                                                         |

| POC* (Power-on Clear)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28                                                                                                                         |

| Slave CLR* (Slave Clear)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 28                                                                                                                         |

| ERROR* (Error line)<br>PWRFAIL* (Power Failure Line)<br>System Power<br>MANUFACTURER SPECIFIED LINES<br>IPROCESS* (Interrupt in Process line)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28                                                                                                                         |

| ERROR <sup>*</sup> (EFFOF line) • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20                                                                                                                         |

| PWRFAIL* (Power Failure Line)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28                                                                                                                         |

| System Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28                                                                                                                         |

| MANITEACHIDED ODECTRIED TINES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29                                                                                                                         |

| MANUFACTURER SPECIFIED LINES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                                                                                         |

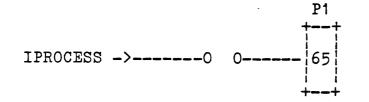

| IPROCESS* (Interrupt in Process line)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29                                                                                                                         |

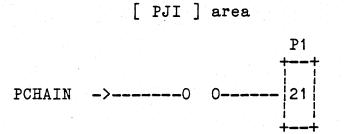

| PCHAIN (Interrupt Priority Line)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29                                                                                                                         |

| DECUT (Francis Monory Dofrach Idae)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30                                                                                                                         |

| RESE (External Memory Refresh Line)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20                                                                                                                         |

| Reserved Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30                                                                                                                         |

| OPERATING INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31                                                                                                                         |

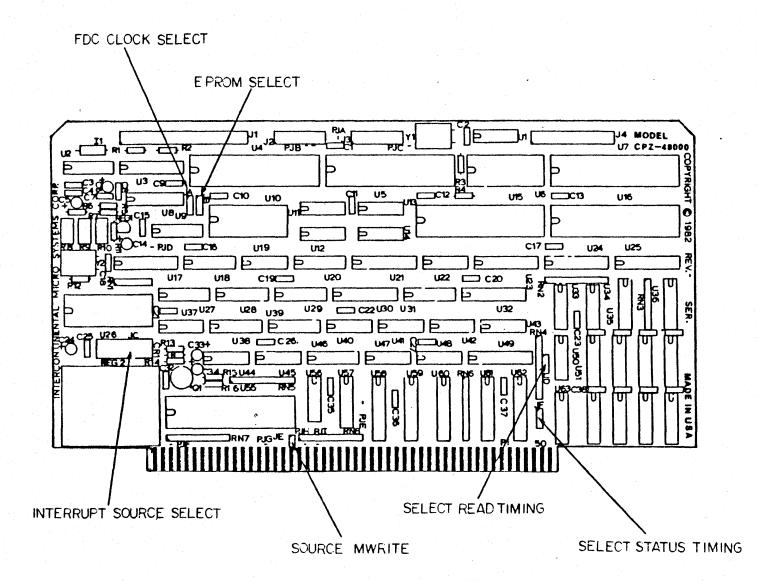

| HARDWARE SETUP INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21                                                                                                                         |

| JUMPER OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32                                                                                                                         |

| JUMPER OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32                                                                                                                         |

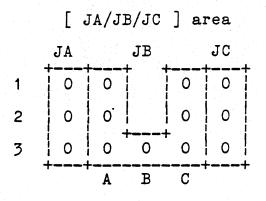

| TR = (TPR(M Soloot))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32                                                                                                                         |

| JB - (EPROM Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22                                                                                                                         |

| JC - (Interrupt Signal Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33                                                                                                                         |

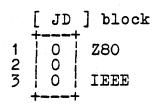

| JD - (IEEE/Z80 Timing Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35                                                                                                                         |

| IF = (Connect "MWPIMF" + c S = 100 Pusc)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35                                                                                                                         |

| $D = (O \cap O \cap D)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                                                                                                                         |

| JD - (IEEE/Z80 Timing Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36                                                                                                                         |

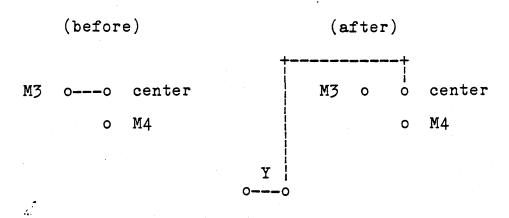

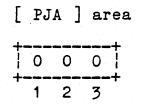

| SOLDER/TRACE CUT OPTIONS<br>PJA - (Enable Floppy Controller "Test" (Enable Fast Step) .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37                                                                                                                         |

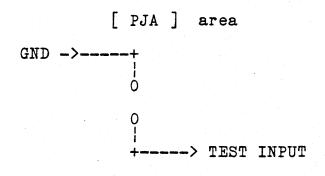

| PIA - (Enchle Florny Controller "Test" (Enchle Fest Sten)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38                                                                                                                         |

| DID (DID Det 1 1 2) och General Solat)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70                                                                                                                         |

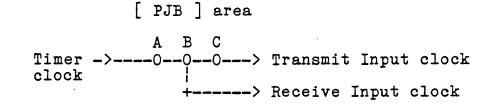

| rab = (bio rort & clock bource beleect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - 38                                                                                                                       |

| PJC - (SIO Port B Clock Source Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 38<br>39                                                                                                                   |

| PJC - (SIO Port B Clock Source Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 38<br>39<br>39                                                                                                             |

| PJB - (SIO Port A Clock Source Select)         PJC - (SIO Port B Clock Source Select)         PJD - (Connect Z80 Refresh To S-100 Bus)         PJE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38<br>39<br>39                                                                                                             |

| $PJE = (Connect pWAIT To S-100 Bus) \dots                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40                                                                                                                         |

| PJE - (Connect pWAIT To S-100 Bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40<br>40                                                                                                                   |

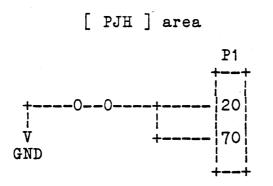

| PJE - (Connect pWAIT To S-100 Bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40<br>40                                                                                                                   |

| PJE - (Connect pWAIT To S-100 Bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40<br>40<br>41                                                                                                             |

| PJE - (Connect pWAIT To S-100 Bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40<br>40<br>41<br>41                                                                                                       |

| PJE - (Connect pWAIT To S-100 Bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40<br>40<br>41<br>41<br>42                                                                                                 |

| PJE - (Connect pWAIT To S-100 Bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40<br>40<br>41<br>41<br>42                                                                                                 |

| PJE - (Connect pWAIT To S-100 Bus)<br>PJF - (Connect S-100 Bus Ground To PCB Ground Plane(Pin 53)<br>PJG - (Connect Interrupt-In-Process to S-100 Bus)<br>PJH - (Connect S-100 Bus Ground to PCB Ground Plane<br>PJI - (Connect Interrupt Priority Chain to S-100 Bus<br>FLOPPY DRIVE JUMPER OPTIONS                                                                                                                                                                                                                                                                                                                                                              | 40<br>40<br>41<br>41<br>42<br>43                                                                                           |

| PJE - (Connect pWAIT To S-100 Bus)<br>PJF - (Connect S-100 Bus Ground To PCB Ground Plane(Pin 53)<br>PJG - (Connect Interrupt-In-Process to S-100 Bus)<br>PJH - (Connect S-100 Bus Ground to PCB Ground Plane<br>PJI - (Connect Interrupt Priority Chain to S-100 Bus<br>FLOPPY DRIVE JUMPER OPTIONS                                                                                                                                                                                                                                                                                                                                                              | 40<br>40<br>41<br>41<br>42<br>43                                                                                           |

| PJE - (Connect pWAIT To S-100 Bus)<br>PJF - (Connect S-100 Bus Ground To PCB Ground Plane(Pin 53)<br>PJG - (Connect Interrupt-In-Process to S-100 Bus)<br>PJH - (Connect S-100 Bus Ground to PCB Ground Plane<br>PJI - (Connect Interrupt Priority Chain to S-100 Bus<br>FLOPPY DRIVE JUMPER OPTIONS<br>Shugart Model 800/801<br>Shugart Model 850/851                                                                                                                                                                                                                                                                                                            | 40<br>40<br>41<br>42<br>43<br>43<br>43                                                                                     |

| PJE - (Connect pWAIT To S-100 Bus)<br>PJF - (Connect S-100 Bus Ground To PCB Ground Plane(Pin 53)<br>PJG - (Connect Interrupt-In-Process to S-100 Bus)<br>PJH - (Connect S-100 Bus Ground to PCB Ground Plane<br>PJI - (Connect Interrupt Priority Chain to S-100 Bus<br>FLOPPY DRIVE JUMPER OPTIONS<br>Shugart Model 800/801<br>Shugart Model 850/851<br>Oume Datatrack 8                                                                                                                                                                                                                                                                                        | 40<br>40<br>41<br>42<br>43<br>43<br>44                                                                                     |

| PJE - (Connect pWAIT To S-100 Bus)<br>PJF - (Connect S-100 Bus Ground To PCB Ground Plane(Pin 53)<br>PJG - (Connect Interrupt-In-Process to S-100 Bus)<br>PJH - (Connect S-100 Bus Ground to PCB Ground Plane<br>PJI - (Connect Interrupt Priority Chain to S-100 Bus<br>FLOPPY DRIVE JUMPER OPTIONS<br>Shugart Model 800/801<br>Shugart Model 850/851<br>Oume Datatrack 8                                                                                                                                                                                                                                                                                        | 40<br>40<br>41<br>42<br>43<br>43<br>44                                                                                     |

| PJE - (Connect pWAIT To S-100 Bus)<br>PJF - (Connect S-100 Bus Ground To PCB Ground Plane(Pin 53)<br>PJG - (Connect Interrupt-In-Process to S-100 Bus)<br>PJH - (Connect S-100 Bus Ground to PCB Ground Plane<br>PJI - (Connect Interrupt Priority Chain to S-100 Bus<br>FLOPPY DRIVE JUMPER OPTIONS<br>Shugart Model 800/801<br>Shugart Model 850/851<br>Oume Datatrack 8                                                                                                                                                                                                                                                                                        | 40<br>40<br>41<br>42<br>43<br>43<br>44                                                                                     |

| PJE - (Connect pWAIT To S-100 Bus)<br>PJF - (Connect S-100 Bus Ground To PCB Ground Plane(Pin 53)<br>PJG - (Connect Interrupt-In-Process to S-100 Bus)<br>PJH - (Connect S-100 Bus Ground to PCB Ground Plane<br>PJI - (Connect Interrupt Priority Chain to S-100 Bus<br>FLOPPY DRIVE JUMPER OPTIONS<br>Shugart Model 800/801<br>Shugart Model 850/851<br>Oume Datatrack 8                                                                                                                                                                                                                                                                                        | 40<br>40<br>41<br>42<br>43<br>43<br>44                                                                                     |

| <pre>PJE - (Connect pWAIT To S-100 Bus)<br/>PJF - (Connect S-100 Bus Ground To PCB Ground Plane(Pin 53)<br/>PJG - (Connect Interrupt-In-Process to S-100 Bus)<br/>PJH - (Connect S-100 Bus Ground to PCB Ground Plane<br/>PJI - (Connect Interrupt Priority Chain to S-100 Bus<br/>FLOPPY DRIVE JUMPER OPTIONS<br/>Shugart Model 800/801<br/>Shugart Model 850/851<br/>Qume Datatrack 8<br/>Tandon TM848-1<br/>Mitsubishi M2896-63 (Half Height)<br/>Mitsubishi M2894-63 (Full Height)</pre>                                                                                                                                                                      | 40<br>41<br>42<br>43<br>44<br>45<br>46<br>46                                                                               |

| <pre>PJE - (Connect pWAIT To S-100 Bus)<br/>PJF - (Connect S-100 Bus Ground To PCB Ground Plane(Pin 53)<br/>PJG - (Connect Interrupt-In-Process to S-100 Bus)<br/>PJH - (Connect S-100 Bus Ground to PCB Ground Plane<br/>PJI - (Connect Interrupt Priority Chain to S-100 Bus<br/>FLOPPY DRIVE JUMPER OPTIONS<br/>Shugart Model 800/801<br/>Shugart Model 850/851<br/>Qume Datatrack 8<br/>Tandon TM848-1<br/>Mitsubishi M2896-63 (Half Height)<br/>Mitsubishi M2894-63 (Full Height)</pre>                                                                                                                                                                      | 40<br>41<br>42<br>43<br>44<br>45<br>46<br>46                                                                               |

| <pre>PJE - (Connect pWAIT To S-100 Bus)<br/>PJF - (Connect S-100 Bus Ground To PCB Ground Plane(Pin 53)<br/>PJG - (Connect Interrupt-In-Process to S-100 Bus)<br/>PJH - (Connect S-100 Bus Ground to PCB Ground Plane<br/>PJI - (Connect Interrupt Priority Chain to S-100 Bus<br/>FLOPPY DRIVE JUMPER OPTIONS<br/>Shugart Model 800/801<br/>Shugart Model 850/851<br/>Qume Datatrack 8<br/>Tandon TM848-1<br/>Mitsubishi M2896-63 (Half Height)<br/>Mitsubishi M2894-63 (Full Height)</pre>                                                                                                                                                                      | 40<br>41<br>42<br>43<br>44<br>45<br>46<br>46                                                                               |

| <pre>PJE - (Connect pWAIT To S-100 Bus)<br/>PJF - (Connect S-100 Bus Ground To PCB Ground Plane(Pin 53)<br/>PJG - (Connect Interrupt-In-Process to S-100 Bus)<br/>PJH - (Connect S-100 Bus Ground to PCB Ground Plane<br/>PJI - (Connect Interrupt Priority Chain to S-100 Bus<br/>FLOPPY DRIVE JUMPER OPTIONS<br/>Shugart Model 800/801<br/>Shugart Model 850/851<br/>Qume Datatrack 8<br/>Tandon TM848-1<br/>Mitsubishi M2896-63 (Half Height)<br/>Mitsubishi M2894-63 (Full Height)<br/>Seimens FDD100-8D<br/>Tandon TM100-2 (5 1/4" drive)</pre>                                                                                                              | 40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>47                                                                         |

| <pre>PJE - (Connect pWAIT To S-100 Bus)<br/>PJF - (Connect S-100 Bus Ground To PCB Ground Plane(Pin 53)<br/>PJG - (Connect Interrupt-In-Process to S-100 Bus)<br/>PJH - (Connect S-100 Bus Ground to PCB Ground Plane<br/>PJI - (Connect Interrupt Priority Chain to S-100 Bus</pre>                                                                                                                                                                                                                                                                                                                                                                              | 40<br>41<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48                                                                   |

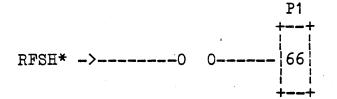

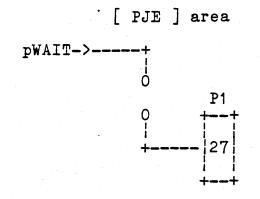

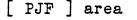

| <pre>PJE - (Connect pWAIT To S-100 Bus)<br/>PJF - (Connect S-100 Bus Ground To PCB Ground Plane(Pin 53)<br/>PJG - (Connect Interrupt-In-Process to S-100 Bus)<br/>PJH - (Connect S-100 Bus Ground to PCB Ground Plane<br/>PJI - (Connect Interrupt Priority Chain to S-100 Bus<br/>FLOPPY DRIVE JUMPER OPTIONS</pre>                                                                                                                                                                                                                                                                                                                                              | 40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49                                                                   |