# M48-000 UNIVERSAL CLOCK INSTRUCTION MANUAL

CONSISTS OF:

INSTALLATION SPECIFICATION MAINTENANCE SPECIFICATION PROGRAMMING SPECIFICATION SCHEMATIC 02-240A20 02-240R04A21 02-240R02A22 02-240R03D08

THIS MANUAL CONTAINS PROPRIETARY INFORMATION AND IS SUPPLIED BY INTERDATA FOR THE SOLE PURPOSE OF USING AND MAINTAINING INTERDATA SUPPLIED EQUIPMENT AND SHALL NOT BE USED FOR ANY OTHER PURPOSE UNLESS SPECIFICALLY AUTHORIZED IN WRITING.

Subsidiary of PERKIN-ELMER Oceanport, New Jersey 07757, U.S.A.

> (c) INTERDATA INC., 1971 All Rights Reserved Printed in U.S.A. May 1975

### UNIVERSAL CLOCK INSTALLATION SPECIFICATION

### 1. INTRODUCTION

This specification provides the necessary information for the installation of the 02-240 Universal Clock Module and the external clock option. The module assembly consists of one standard 35-398 half board and one 17-177 cable. The 35-398 half board must be strapped to a blank half board (INTERDATA 16-398 Half Board Kit) or an active half board (i.e. Memory Protect) to be installed in a chassis designed for full boards. The Universal Clock board may be used in either the right or left half position, as required. See Figure 1.

### 2. INSTALLATION

### 2.1

When the Universal Clock Module is shipped with a system, it is installed at the factory so there is no special unpacking procedure. It is only necessary to insure that the module is properly seated in its connectors. If the module assembly is purchased separately, it should be unpacked carefully and inspected for damage prior to installation.

### 2.2 Location

The 35-398 Universal Clock Module half board, strapped to a blank or active half board, may be installed in any I/O slot. However, it is preferable to use the highest priority position available. After installing the module, remove the RACK0/TACK0 strap located on the back panel between Terminals 222 and 122 of the selected slot.

### 2.3 Cables and Connectors

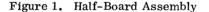

Connect the 17-177 cable as shown in Figure 2. Note that the cable is long enough to allow the 35-398 half board to operate on an extender.

CONNECT AT REAR OF CHASSIS TO TERMINALS INDICATED :

Figure 2. Cable Connections

### 3. EXTERNAL CLOCK OPTION

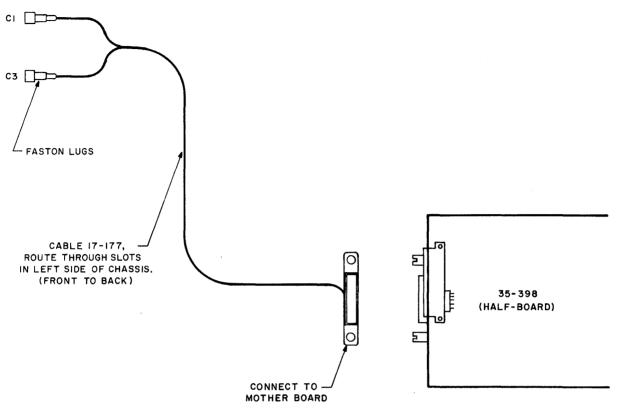

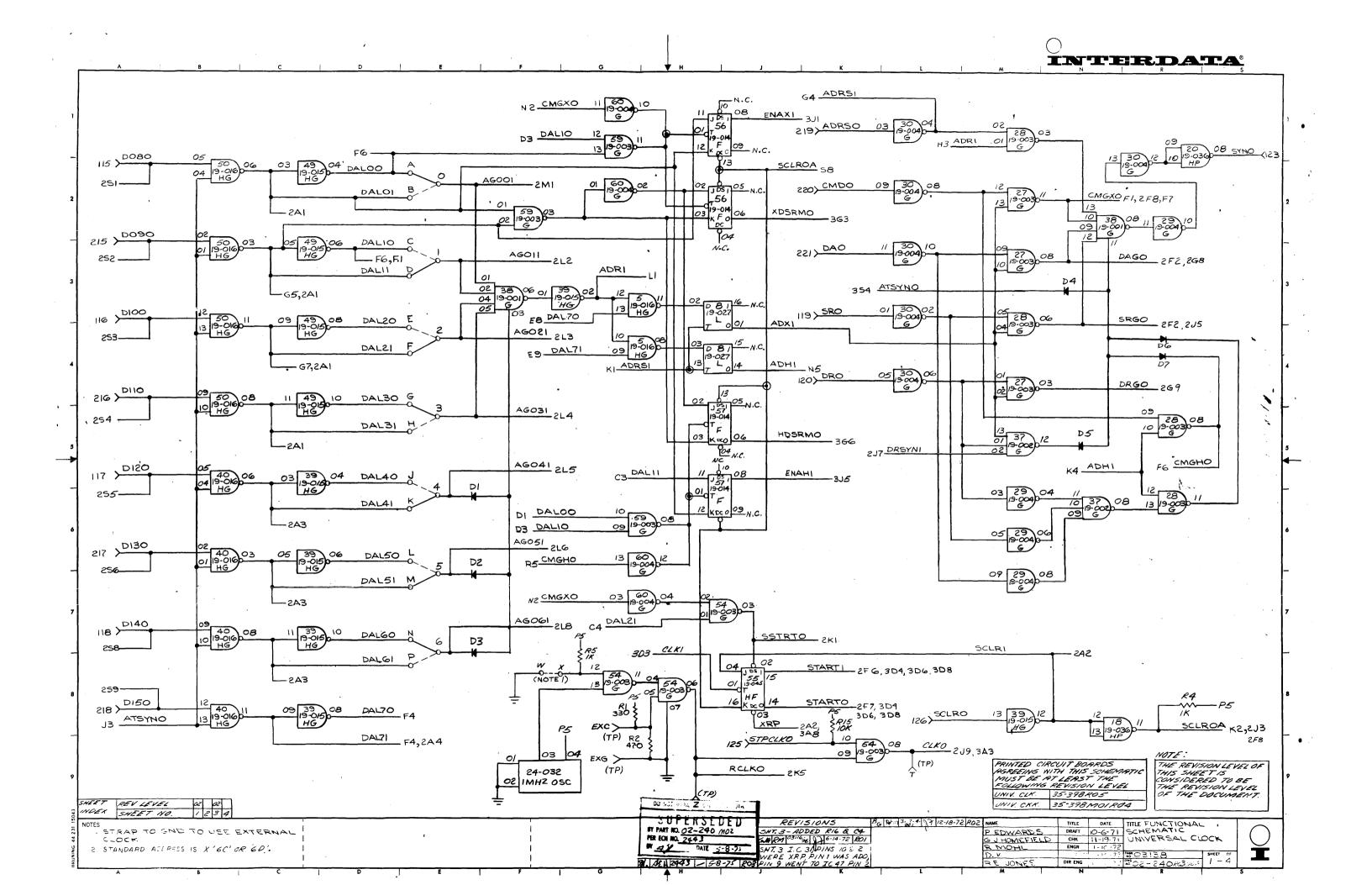

To use an external time base oscillator perform the following steps: (Refer to Schematics 02-240D08)

- 1. Strap Test Point (TP) A to Test Point (TP) B.

- 2. Connect the external oscillator, via twisted pair, to Test Point EXT and Test Point EXG (TP EXG is ground).

Internal termination of the Universal Clock Module is shown in Figure 3.

Figure 3. External Oscillator Connections, and Internal Termination

## UNIVERSAL CLOCK MAINTENANCE SPECIFICATION

#### 1. INTRODUCTION

The 02-240 Universal Clock Module consists of two I/O devices; 1. the programmable Precision Interval Clock (PIC), and 2. the AC Line Frequency derived Clock (LFC). The PIC provides the user with a Processor interrupt and a program accessible counter which is based on a dynamically variable (thru program control) Precision Resolution Clock and Interval Counter. The LFC is derived from the AC power line and provides the user with a Processor interrupt at twice the line frequency.

Since the PIC and LFC are completely independent of each other, they are covered in separate sections of this specification. Section 2 describes the PIC, and Section 3 describes the LFC. Both sections contain block diagram and functional schematic analysis, timing information, and sufficient notes to maintain this interface. A mnemonic list common to both sections is provided at the end of this specification.

### 2. PRECISION INTERVAL CLOCK

### 2.1 Block Diagram Analysis

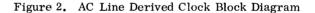

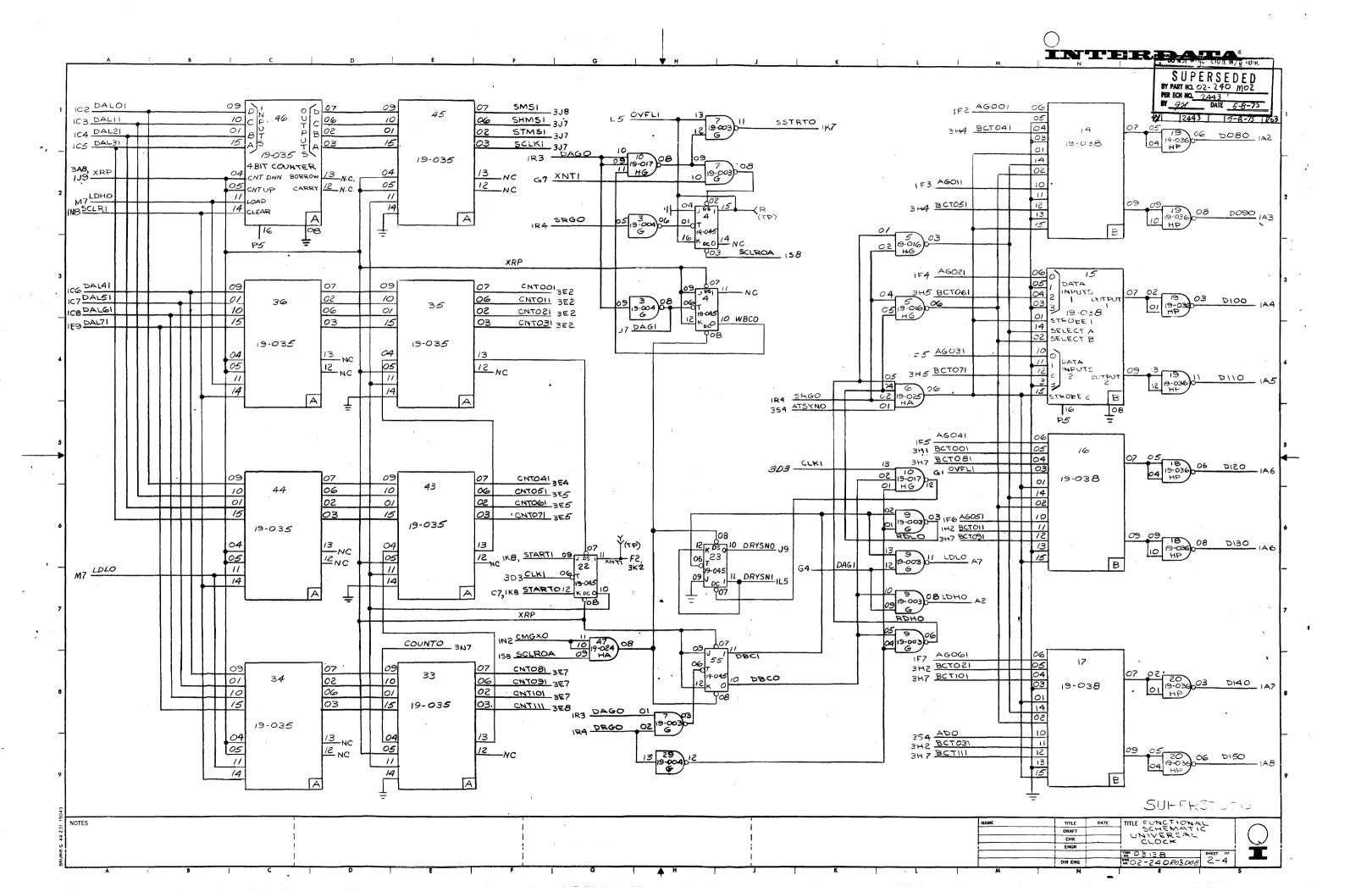

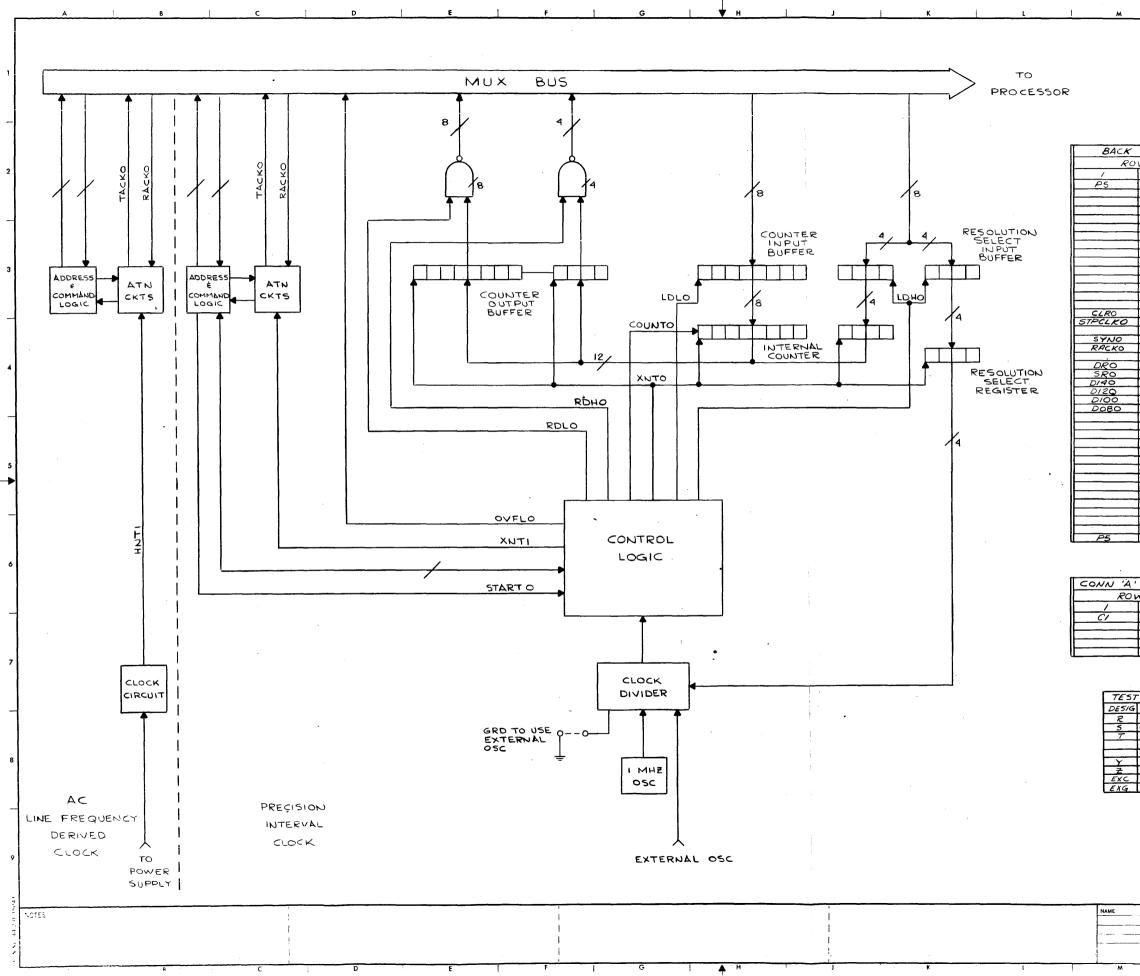

As shown in the PIC block diagram on Sheet 4 of Schematic 02-240D08, the Count Input Buffer and Resolution Select input Buffer are loaded from the Multiplexor Bus. Upon initial start up or at the end of an Interval period, this information is transferred to the Interval Counter and Resolution Select Register. The Resolution Select Register enables one of the four Resolution Clock rates available from the Clock Divider. The selected Clock Divider output Count Pulse (COUNT0) decrements the Interval Counter until it reaches zero, the next count pulse produces the PIC Interrupt (XNT1) which is sent to the attention circuits, and the process is repeated. The Interval Counter may be monitored through the Counter Output Buffer to the Multiplexor Bus.

### 2.2 Functional Diagram Analysis

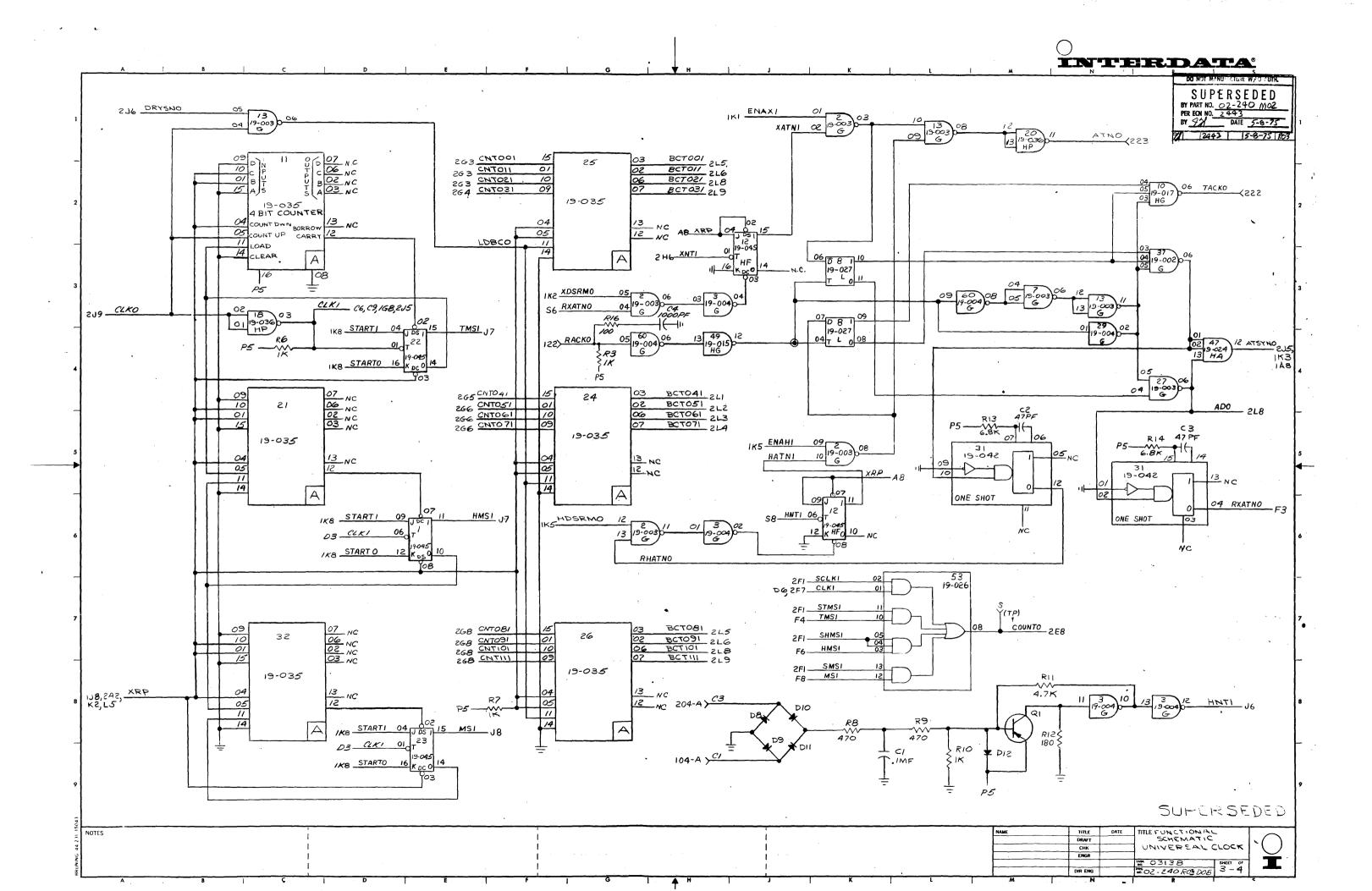

Refer to Functional Schematic 02-240D08 for the following analysis.

With the exception of common I/O bus buffering, the PIC logic is detached from the LFC. Status, Command, and Data Byte information is provided in the Programming Specification 02-240A22.

2.2.1 <u>Operation</u>. Initialization (SCLR0)(1L8) insures that the PIC is placed in the Disarm Mode by resetting the Enable PIC Interrupt (ENAX1)(1J1) and PIC Disarm (XDRM0)(1J2) flip-flops. The Resolution and Counter Input Buffers (2C1-9), and the Overflow (OVFL)(2H2), Data Byte Count (DBC1)(2H8), and Write Byte (WBC0)2H3) flip-flops are cleared.

The Resolution and Interval data is initially loaded into the PIC's Input Buffers (2E1-9) in two data bytes by Load Data Low (LDL0)(2M6) and Load Data High (LDH0)(2M7). A Start Command (CMGX0·DAL21) momentarily sets the START1 flip-flop (1J8), the next Raw Clock pulse resets it (RCLK0)(1H8). This action resets the PIC Interrupt flip-flop (XNT0) (2G7), and loads the Resolution Select Register (2E1-2) and the Interval Counter (2E3-9) from the Input Buffers. XANT1 (3J2) goes active if enabled.

The Resolution Register outputs (SMS1, SHMS1, STMS1, and SCK1) enable one of the Clock Divider outputs (3D1-9) to produce COUNT0 (3M7). COUNT0 starts to decrement the Interval Counter. When ZERO, the next count pulse activates the borrow output from the Interval Counter (2E3-9) and the XNT1 flip-flop (2G7) momentarily sets, it is reset by CLK1. This causes an interrupt to be queued in the PIC Attention flip-flop (XANT1)(3J1) if not in the Disarm Mode. Attention goes active (ATN0)(3N1), if enabled. The XNT0 pulse reloads the Resolution Select and Interval Counter Registers from the Input Buffers. Operation now proceeds as previously described.

During the Interval (Interval Counter has not reached zero), the Input Buffers may be altered by two data bytes containing a new Resolution and/or Interval. When the present Interval concludes, the new data will be loaded from the Input Buffer in place of the old. However, if the Interval times out between the start of the first data byte transferred and the end of the second data byte transferred, the Write Byte Count flip-flop (WBC)(2H3) causes the Overflow flip-flop to set (OVFL)(2H2). This stops the Clock by holding STARTO low (1J7). The clock will restart after the completion of the second data byte transfer or on receipt of a Start Command. OVFL remains set until the execution of a Sense Status, an Acknowledge Interrupt instruction, or Initialization.

The PIC is provided with an Output Buffer (3G1-9) so that the Interval Counter may be interrogated without disturbing its operation, by using two data byte transfers. The Output Buffer is normally loaded on every CLK1. The first Data Request gated (DRG0)(1R4) by Raw Clock (RCLK1)(1J9) latches up the Output Buffer by setting the Data Request Sync flip-flop (DRSYN1)(2J7), which in turn holds Load Buffered Count high (LDBC0)(2K7). The Read Data Low (RDL0)(2L6) is activated and SYN0 is returned. The falling edge of DRG1 sets the Read Byte Counter. The second DRG1 activates Read Data High (RDH0)(2L7) and SYN0 is returned. The falling edge of the second DRG1 resets the Read Byte Counter, which in turn resets the DRSYN1 flip-flop.

2.2.2 <u>Circuit Analysis</u>. It should be noted that numerous 19-035 four bit up-down counters are used as registers and perform no counting operations. The One-Shot (3R6) which resets the PIC Attention flip-flop (XATN1)(3J1) is set to produce a 175 nanosecond pulse (approximately).

2.3 Timing

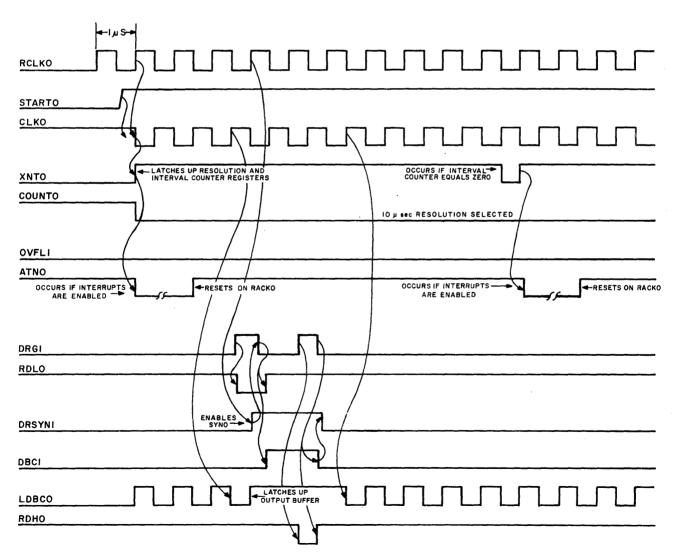

Refer to Figure 1.

Figure 1. Precision Interval Clock Timing Diagram

#### 2.4 Routine Maintenance, Adjustments, and Tests

The PIC requires no adjustments. The accuracy of the crystal oscillator should be checked with a digital frequency meter on RCLK0 (1J9) at Test Point Z (1MHZ  $\pm .01\%$ ).

### 2.5 Troubleshooting

The PIC may be reasonably tested using a static check. Refer to the Programming Specification, 02-240A22, for set up procedures. Test Program 06-133 provides a dynamic check which can be monitored by appropriate test equipment.

### 3. LINE FREQUENCY CLOCK

### 3.1 Block Diagram Analysis

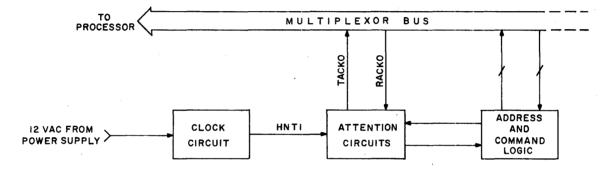

As shown in the LFC block diagram (Figure 2), the power supply provides a 12 VAC line from which the LFC Interrupt (HNT1)(3R8) is derived. Although shown separately for clarity, the LFC I/O logic (Address, Command and ATN circuits) is combined with that of the PIC. This is described in Section 4.

### 3.2 Functional Diagram Analysis

As shown on Sheet 3 of Functional Schematic 02-240D08, the clock circuit is driven by the 12 VAC output from the system power supply. A full wave bridge rectifier, followed by a ZERO voltage detector whose output is fed through two gates, produces the HNT1 pulse (3R8) at twice the line frequency. The LFC is placed in the Disarm Mode by SCLR0, resetting the Enable LFC Interrupt (ENAH1)(1J5) and the LFC Disarm (HDSRM0)(1J5) flip-flops. The LFC responds only to the Enable and Disable Commands. If the LFC is not in the Disarm Mode, HNT1 will toggle the LFC Attention flip-flop set (HATN1)(3K6) at twice the line frequency. Attention (ATN0)(3N1) is activated, if enabled.

#### 4. PIC AND LFC I/O FUNCTIONAL ANALYSIS

The Addresses of the PIC and LFC differ only by the state of Bit-7. The PIC address is always even (Bit-7 inactive), while the LFC address is always odd (Bit-7 active). The output of the PIC Address flip-flop (ADX1)(1J4) and LFC Address flip-flop (ADH1)(1J4) gates the control lines (DR0, DA0, SR0, and CMD0) to their respective logic.

The interrupt logic (Sheet 3) is arranged so that the PIC has the highest interrupt priority. Reference should be made to the <u>16 Bit Series Reference Manual</u>, Publication number 29-398 and the <u>32 Bit Series Reference Manual</u>, Publication number 29-365 for a description of standard I/O timing sequences. Refer to the Programming Specification, 02-240A22, for Command, Status, and Data Byte information.

### 5. MNEMONICS

The following list provides a brief description of each mnemonic found in the Universal Clock. The source of each signal on the Schematic Drawing, 02-240D08, is also provided.

| MNEMONIC                | MEANING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SCHEMATIC LOCATION |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| ΔD                      | Address - Bit-7 of device address returned on SRG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 354                |

| ADH                     | Address LFC - Active when the LFC address is recognized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1J4                |

| ADR                     | Address - Decoded address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1G3                |

| ADRS                    | Address - The Processor presents an Address Byte on Data<br>Lines D08:15. The device controller accepts the Address<br>Byte and responds with a SYN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1K1                |

| ADX                     | Address PIC - Active when the PIC address is recognized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1J4                |

| AG001:061               | Address Gate Lines - Selected straps which generate a unique device address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1F2-8              |

| ATN<br>(Test Point U)   | Attention - Any device desiring to interrupt the Processor<br>will activate the ATN line and hold this line until an ACK<br>is received from the Processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3N1                |

| ATSYN                   | Attention Synchronize - Strobes the address of the interrupting device to the Processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3S4                |

| BCT00-11                | Buffered Count Output - Output lines of Output Buffer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3H2-8              |

| CLK                     | Clock - Raw Clock gated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $1  \mathrm{L9}$   |

| CMD                     | Command - The Processor presents a Command Byte on<br>Data Lines D08:15. The device controller accepts the<br>Command Byte and responds with a SYN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 K2               |

| СМСН                    | Command Gated for LFC - Command gated by ADH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1R5                |

| CMGX                    | Command Gated for PIC - Command gated by ADX.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 R2               |

| CNT00-11                | Counter Output - Output lines from Interval Counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2F3-8              |

| COUNT<br>(Test Point S) | Count - Count pulse at selected Resolution Rate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3M7                |

| D080:150                | Data Lines - Data Lines D080:150 are used to transfer one<br>eight bit byte of data between the Processor and the device.<br>One byte of address or command is transferred from the<br>Processor to the device over Data Lines 8:15 (D08:15) when<br>accompanied by either an Address (ADRS) or a Command<br>(CMD) control line. One byte of data is transferred from<br>the Processor to the device when accompanied by the Data<br>Available (DA) control line. The device, in response to an<br>Acknowledge (ACK) control line or a Sense Status (SR) con-<br>trol line, sends one byte of address or status information<br>to the Processor over Data Lines D08:15. In response to a<br>Data Request (DR) control line, the device sends an eight<br>bit byte of data to the Processor. The device always sends<br>a Synchronize (SYN) signal to the Processor or that it<br>has either received the data from the Processor or that it<br>has sent the data to the Processor. The SYN signal is re-<br>moved immediately after the Processor removes the control line | 1 A2-8             |

| DA                     | Data Available - The Processor presents data on Data Lines D080:150 for transfer to the device. The device controller accepts the low byte and responds with a SYN.                                                                                                                                     | 1K3            |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| DAG                    | Data Available Gated - Data Available gated by ADX.                                                                                                                                                                                                                                                     | 1R3            |

| DAL00:70<br>01:71      | Data Available Lines - Data Lines D080:150 buffered double rail for data transfer to the device.                                                                                                                                                                                                        | 1D2-8          |

| DBC                    | Data Byte Count - Toggles on DAG or DRG.                                                                                                                                                                                                                                                                | 2J8            |

| DR                     | Data Request - The device controller presents data to<br>Data Lines 8:15 followed by a SYN.                                                                                                                                                                                                             | 1K4            |

| DRG                    | Data Request Gated - Data Request gated by ADX.                                                                                                                                                                                                                                                         | 1R4            |

| DRSYN                  | Data Request SYN - Enables SYN on DRG.                                                                                                                                                                                                                                                                  | 2J7            |

| ENAH                   | Enable LFC Interrupt - Gates HATN to ATN.                                                                                                                                                                                                                                                               | 1J5            |

| ENAX                   | Enable PIC Interrupt - Gates XATN to ATN.                                                                                                                                                                                                                                                               | 1J1            |

| EXC                    | External Clock - External time base oscillator connection.                                                                                                                                                                                                                                              | 1 H9           |

| EXG                    | External Ground - Ground for EXC.                                                                                                                                                                                                                                                                       | 1 H9           |

| HATN                   | LFC Attention - Queue flip-flop for LFC Interrupt.                                                                                                                                                                                                                                                      | 3K6            |

| HDSRM                  | LFC Disarm - Holds HATN reset, when active.                                                                                                                                                                                                                                                             | 1J5            |

| HMS                    | 100 microseconds - Clock Divider output for 100 microseconds.                                                                                                                                                                                                                                           | 3D6            |

| HNT<br>(Test Point V)  | LFC Interrupt - Pulsed at twice line frequency.                                                                                                                                                                                                                                                         | 3 <b>S</b> 8   |

| LDBC                   | Load Buffered Count - Loads Output Buffer.                                                                                                                                                                                                                                                              | 2K7            |

| LDH                    | Load Data High - Loads high byte of Input Buffer                                                                                                                                                                                                                                                        | $2\mathrm{L7}$ |

| LDL                    | Load Data Low - Loads low byte of Input Buffer                                                                                                                                                                                                                                                          | 2L7            |

| MS                     | 1 millisecond - Clock Divider output for one millisecond.                                                                                                                                                                                                                                               | 3D8            |

| OVFL<br>(Test Point R) | Overflow - Set on XNT. DBC                                                                                                                                                                                                                                                                              | 2 H2           |

| RACK                   | Receive Acknowledge - Control line activated by the Processor in response to an interrupt.                                                                                                                                                                                                              | 3G4            |

| RCLK<br>(Test Point Z) | Raw Clock - Buffered output of internal or external time base oscillator.                                                                                                                                                                                                                               | 1J9            |

| RDH                    | Read Data High - Enables High Byte from Output Buffer to data lines.                                                                                                                                                                                                                                    | 2L7            |

| RDL                    | Read Data Low - Enables Low Byte from Output Buffer<br>to data lines.                                                                                                                                                                                                                                   | 2L6            |

| SCLK                   | Select Clock - Enable Clock Divider output for one microsecond.<br>This information is proprietary and is supplied by INTERDATA for the sole<br>purpose of using and maintaining INTERDATA supplied equipment and shall<br>not be used for any other purpose unless specifically authorized in writing. | 2F1            |

| MNEMONIC              | MEANING                                                                                                                              | SCHEMATIC LOCATION |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| SCLR                  | System Clear - This is a metallic contact to ground that occurs during Power Fail, Power Up, or Initialize.                          | 1 L8               |

| SHMS                  | Select 100 microseconds - Enable Clock Divider output for 100 microseconds.                                                          | 2F1                |

| SMS                   | Select one millisecond - Enable Clock Divider output for one millisecond.                                                            | 2F1                |

| SR                    | Status Request - The device controller must present<br>device status to Data Lines D08:15 followed by a SYN.                         | 1K3                |

| SRG                   | Status Request Gated - Status Request gated by ADX.                                                                                  | $1\mathrm{R4}$     |

| SSTRT                 | Set Start - Sets Start flip-flop.                                                                                                    | 2 K1               |

| START                 | Start - Start Clock. Enables CLK1.                                                                                                   | 1K8                |

| STMS                  | Select 10 microseconds - Enable Clock Divider output for 10 microseconds.                                                            | 2 F1               |

| SYN                   | Synchronize - This signal is generated by the device<br>to inform the Processor that it has properly responded<br>to a control line. | 1S1                |

| ТАСК                  | Transmit Acknowledge - System daisy chain control line to the I/O system.                                                            | 3S3                |

| TMS                   | 10 microseconds - Clock Divider output for 10 microseconds.                                                                          | 3D4                |

| WBC                   | Write Byte Count - Toggles on DAG only.                                                                                              | 2H4                |

| XATN                  | PIC Attention - Queue flip-flop for PIC interrupt.                                                                                   | 3J1                |

| XDSRM                 | PIC Disarm - Holds XATN reset when active.                                                                                           | 1J2                |

| XNT<br>(Test Point T) | PIC Interrupt - Pulsed on completion of Interval Count.                                                                              | 2G6                |

| XRP                   | 1Kohm Resistor to Pt(+5).                                                                                                            | 2 F 9              |

### UNIVERSAL CLOCK PROGRAMMING SPECIFICATION

### 1. INTRODUCTION

The Universal Clock Module consists of two I/O devices; the programmable Precision Interval Clock (PIC), and the AC Line Frequency derived Clock (LFC). Since the PIC and LFC are completely independent of each other, they are covered in separate sections of this specification. Section 2 describes the PIC, and Section 3 describes the LFC.

### 2. PRECISION INTERVAL CLOCK

### 2.1 Description

The PIC provides the user with a Processor interrupt and a program-accessible counter which is based on a dynamically variable (thru program control) Precision Resolution Clock generator and Interval Counter.

As shown in Figure 1, PIC block diagram, the master time base for the PIC is provided by a one megahertz crystal oscillator. It should be noted that the internal oscillator can be disabled so that an external master time base oscillator may be used. See Installation Specification 02-240A20, for details.

### Figure 1. PIC Block Diagram

### 2.2 Operation

The basic PIC operation is:

- 1. The Resolution and Interval data is sent to the PIC by Write Data or Write Halfword instructions, and it remains in the Input Buffers until new data is supplied.

- 2. When the clock is started by an Output Command, the Resolution and Interval data in the Input Buffers is transferred to the Resolution Select Register and Interval Counter and an interrupt is generated if enabled. The Interval Counter begins to decrement at the selected resolution rate.

- 3. At the conclusion of the interval count (Interval Counter reaches zero) the next clock pulse causes the Interval Counter and Resolution Select Register to be reloaded from the Input Buffers. The clock continues to run and once again begins to decrement the Interval Counter.

- 4. The PIC generates an interrupt each time the Interval Counter and Resolution Select Register are reloaded from the Input Buffer if interrupts are enabled. Further, the PIC queues an interrupt if interrupts are disabled and not disarmed. Finally, the PIC neither generates nor queues an interrupt under the above circumstances if interrupts are disarmed.

- 5. The PIC is provided with an Output Buffer Register so that the Interval Counter may be interrogated at anytime without disturbing its operation. The contents of the Output Buffer does not change while it is being read by the Processor.

Note in Steps 2 and 3 that the Input Buffers are used by the PIC only at the beginning of each interval to reload the Resolution Select Register and Interval Counter. Hence, the Input Buffers are free to accept new data anytime during the remainder of the interval. Therefore, the user may output new Resolution and Interval data to the Input Buffers before the present interval concludes. When the present interval times out, the new data is loaded in place of the old and the PIC continues at the new Resolution and Interval.

If the present interval concludes during the time that the Input Buffers are being altered, an overflow condition exists causing the clock to pause until data transfer to the Input Buffers is completed or the PIC is issued a Command Start.

### NOTE

Overflow only resets on the execution of Sense Status or Acknowledge Interrupt instructions, or on Initialization. If Overflow occurs and is not reset by one of the above, the new clock interval will not be accurate.

### NOTE

If a ZERO is loaded, the clock duration equals the resolution.

Using the internal time base oscillator, the following resolutions and intervals may be obtained:

| RESOLUTION | INTERVAL           |

|------------|--------------------|

| lus        | 1us to 4,096us     |

| 10us       | 10us to 40,960us   |

| 100us      | 100us to 409,600us |

| 1ms        | 1ms to 4,096ms     |

2.3 Program Instructions

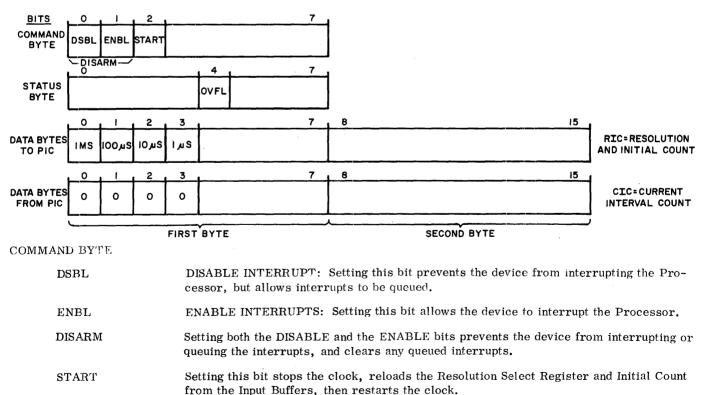

Command, Status and Data bytes for the PIC are shown on Table 1.

### 2.4 Program Sequences

Write instructions (WD, WDR, WH, or WHR) are used to initially set up or change the Resolution and Interval Count (RIC). To change the RIC, data transfers must be completed within the present clock interval or overflow status (OVFL) results.

When the interval times out, and the Interval Counter is reloaded, an interrupt is generated, if enabled; queued if disabled; and not queued if disarmed. Also, the RIC is loaded into the Resolution Select Register and Interval Counter, and the clock continues to run.

Command Start (OC or OCR with Bit-2 in the Command Byte set) is used to initially start or to reload the RIC and restart the clock.

Read instructions (RD, RDR, RH, or RHR) are used to interrogate the Current Interval Counter (CIC) during the count period.

Typical procedure for the PIC is:

- 1. Output two data bytes using the Write instructions to select the clock period.

- 2. Disarm device interrupts and start the clock using a Command instruction,

- 3. Enable device interrupts using a Command instruction.

- 4. Monitor the Interval Counter, if appropriate, by inputting two data bytes using the Read instructions.

- 5. If necessary, output new data bytes to change the RIC. Status can be checked for overflow condition, which would indicate that the new clock interval was not started on time.

- 6. To stop the PIC, output two bytes to the RIC with all Resolution bits ZERO, and issue a Command Start.

The PIC interrupts at the conclusion of each clock interval when the Interval Counter is reloaded, if enabled. It should be noted that the clock normally does not stop but merely creates an interrupt and restarts using the last selected RIC. This interrupt should be serviced with an Acknowledge Interrupt instruction, an Immediate Interrupt, or an appropriate Channel Command Block.

TABLE 1. PIC STATUS AND COMMAND BYTE CODING

This information is proprietary and is supplied by INTERDATA for the sole purpose of using and maintaining INTERDATA supplied equipment and shall not be used for any other purpose unless specifically authorized in writing.

The PIC either generates or queues an interrupt each time a START command is issued unless that command also sets (or a previous command has set) the PIC to the Disarm Mode.

### STATUS BYTE

OVFL

OVERFLOW: This bit is set if the interval times out during the time between the beginning of the first data byte transfer and the end of the second byte transfer to the device. If Overflow sets, counting stops. Counting resumes after a Command Start, or at the completion of the second data byte transfer. This bit resets on the execution of Sense Status or Acknowledge Interrupt instructions, or on Initialization.

DATA BYTES

Data Byte Transfers to PIC (Write). See Note 1.

| First Data Byte | Bits 0:3 specify Resolution.  | See Note 2.                                |

|-----------------|-------------------------------|--------------------------------------------|

|                 | Bits 4:7 specify the four mos | st significant bits of the Interval Count. |

Second Data Byte Bits 0:7 specify the eight least significant bits of the Interval Count.

Data Byte Transfers from PIC (Read). See Note 1.

| First Data Byte  | Bits 0:3 return as ZERO.<br>Bits 4:7 return the four most significant bits of the current Interval Count. |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Second Data Byte | Bits 0:7 return the eight least significant bits of the current Interval Count.                           |

- Note 1. The byte pointer is reset upon Initialization or any command; otherwise, it toggles on any data transfer (Read or Write).

- Note 2. If no Resolution bits are set, the count stops. If more than one Resolution bit is specified, the shortest Resolution is used.

- 2.6 Initialization

Initialization occurs on power up or when the Initialize button is depressed. After Initialization, the PIC is left in the Disarm Mode with the Resolution and OVFL bits reset.

2.7 Device Number

The INTERDATA preferred address is X'6C'. The PIC address must be even. Wire changes (see Maintenance Specification 02-240A21) can select any even number address for this device. See the sample program in Appendix 1.

### 3. AC LINE FREQUENCY DERIVED CLOCK

### 3.1 Description

The LFC interrupt rate is derived from the AC power line. The clock rate is twice the line frequency.

| POWER LINE FREQUENCY | CLOCK RATE           |

|----------------------|----------------------|

| 60Hz                 | 8.33ms per interrupt |

| 50Hz                 | 10 ms per interrupt  |

### 3.2 Program Instructions

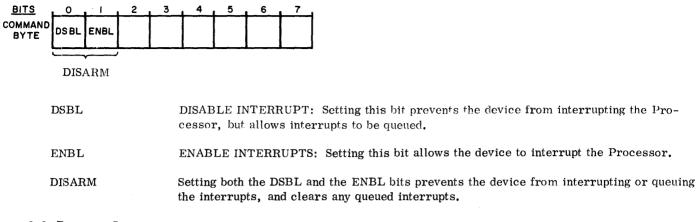

The Line Frequency Clock has only a Command Byte as shown in Table 2. All zero status is returned on any Sense Status instruction. Data transfer instructions have no effect on the device.

### NOTE

3.3 Program Sequence

The LFC has no set up procedure other than to enable interrupts with an Output Command instruction (OC or OCR).

3.4 Interrupts

The Line Frequency Clock, if enabled, interrupts at twice the line frequency. This interrupt should be serviced with an Acknowledge Interrupt instruction, an Immediate Interrupt, or an appropriate Channel Command Block. A status of all zeros is returned with Sense Status or Acknowledge Interrupt instructions.

### 3.5 Initialization

The LFC is initialized on power up or by depressing the Initialize button. After Initialization, the LFC is placed in the Disarm Mode.

### 3.6 Device Number

The INTERDATA preferred address is X'6D'. The LFC address must be odd. The most significant address bits are always the same as for the PIC.

| AP | $\mathbf{P}$ | ΕN | DI | Х | 1 |

|----|--------------|----|----|---|---|

|----|--------------|----|----|---|---|

| *<br>*<br>*<br>*        | THIS PI<br>OF THE                | C UNIVERSAL CLOCK MOD<br>RUPT EVERY 4MS AND 8MS | ECISION INTERVAL CLOCK<br>ULE TO CREATE A PROCESSOR<br>5 SEQUENTIALLY WITH 1MS |

|-------------------------|----------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------|

| DEVN                    | EQU                              | 13                                              |                                                                                |

| OVFL                    | EQU                              | 14                                              |                                                                                |

| R15                     | EQU                              | 15                                              |                                                                                |

| *                       |                                  |                                                 |                                                                                |

| ORG                     | LHI                              | DEVN, X'6C'                                     | LOAD DEVICE NUMBER                                                             |

|                         | $\mathbf{L}\mathbf{H}\mathbf{I}$ | R15, CLKINT                                     | SET UP SERVICE PNTR TABLE                                                      |

|                         | $\mathbf{STH}$                   | R15, X'D0'+X'D8'                                | FOR DEVICE NO. X'6C'                                                           |

| ORG1                    | WH                               | DEVN, FMS                                       | SET RIC FOR 4 MS                                                               |

|                         | SSR                              | DEVN, OVFL                                      |                                                                                |

|                         | BTC                              | 8, ORG1                                         |                                                                                |

|                         | OC                               | DEVN, START                                     |                                                                                |

| ORG2                    | WH                               | DEVN, EMS                                       | SET RIC FOR 8 MS                                                               |

|                         | SSR                              | DEVN, OVFL                                      |                                                                                |

|                         | BTC                              | 8, ORG2                                         |                                                                                |

|                         | OC                               | DEVN, ENB                                       |                                                                                |

|                         | LPSW                             | WAIT                                            |                                                                                |

| WAIT                    | DC                               | X'C800', ORG                                    |                                                                                |

| FMS                     | DC                               | X'8004'                                         | 1 MS RATE, 4 COUNTS                                                            |

| $\mathbf{E}\mathbf{MS}$ | DC                               | X'8008'                                         | 1 MS RATE, 8 COUNTS                                                            |

| START                   | DC                               | X'E000'                                         | DISARM START                                                                   |

| ENB                     | DC                               | X'4000'                                         | ENABLE                                                                         |

| *                       |                                  |                                                 |                                                                                |

|                         | JPT ROU                          | FINE                                            |                                                                                |

| *                       |                                  | •                                               |                                                                                |

| SAVE                    | DS                               | 6                                               | REGISTER SAVE AREA                                                             |

| CLKINT                  | DS                               | 4                                               | OLD PSW STORED HERE                                                            |

|                         | DC                               | 0                                               | NEW PSW STATUS                                                                 |

| •                       | STM                              | DEVN, SAVE                                      | SAVE 3 REGISTERS                                                               |

|                         | LHI                              | DEVN, X'6C'                                     | DEAD CIC                                                                       |

|                         | RHR                              | DEVN, R15                                       | READ CIC                                                                       |

|                         | C L'HI<br>BLS                    | R15,5                                           | CIC < 5 MEANS<br>CURRENT INTERVAL IS 4MS                                       |

| ORG3                    | BLS<br>WH                        | NEXT8<br>DEVN, FMS                              | NEXT INTERVAL 4MS                                                              |

| UNGD                    | SSR                              | DEVN, FMS<br>DEVN, OVFL                         | NEXT INTERVAL 4MS                                                              |

|                         | BTC                              | 8, ORG3                                         |                                                                                |

|                         | BIC<br>BS                        | TEST                                            |                                                                                |

| NEXT8                   | WH<br>WH                         | DEVN, EMS                                       | NEXT INTERVAL 8MS                                                              |

| 1117210                 | SSR                              | DEVN, EMS<br>DEVN, OVFL                         | ERROR STOP ON OVFL STATUS                                                      |

|                         | BTC                              | 8, NEXT8                                        |                                                                                |

| TEST                    | LM                               | DEVN, SAVE                                      | RESTORE REGISTER                                                               |

|                         | LPSW                             | CLKINT                                          | EXIT INTERRUPT ROUTINE                                                         |

|                         | END                              |                                                 |                                                                                |

|                         |                                  |                                                 |                                                                                |

This information is proprietary and is supplied by INTERDATA for the sole purpose of using and maintaining INTERDATA supplied equipment and shall not be used for any other purpose unless specifically authorized in writing.

A1-1/A1-2

INTERDATA

|   | S 、                                        |   |

|---|--------------------------------------------|---|

|   | DO NOT MANU CRUE W/DOUTH.                  |   |

|   | SUPERSEDED                                 |   |

|   | BY PART NO. 02-240 MOZ<br>PER ECH NO. 2443 |   |

|   | C 921 DAT 5-8-75                           | 1 |

| 1 | 2443 5-8-75 803                            |   |

|   | 2772 3.0.73 803                            |   |

| PANEL M               | 4 <i>P</i>       |  |

|-----------------------|------------------|--|

| $\mathcal{N}$         | TERM             |  |

| 2<br>GND              | NO.              |  |

| GNID                  | 41<br>40<br>39   |  |

|                       | 40               |  |

|                       | 39               |  |

|                       | 38               |  |

|                       | 37               |  |

|                       | 38<br>37<br>36   |  |

|                       | 35               |  |

|                       | 34               |  |

|                       | 33               |  |

|                       | <u>3</u> 3<br>32 |  |

|                       | 31               |  |

|                       | 30               |  |

|                       | 29               |  |

| ······                | 28               |  |

|                       | 27               |  |

|                       | 26               |  |

|                       |                  |  |

|                       | 24               |  |

| ATNO<br>TACKO         | 23               |  |

| TACKO                 | 22<br>21<br>20   |  |

| DAO                   | 21               |  |

| CMDO                  | 20               |  |

| ADR50<br>D150<br>D130 | 19               |  |

| 0/30                  | 18               |  |

| 0/30                  | 16               |  |

| D110<br>D090          | 15               |  |

| 0090                  | 12               |  |

|                       | 14               |  |

|                       | 12               |  |

|                       | 11               |  |

|                       | 10               |  |

|                       | 09               |  |

|                       | 08               |  |

|                       | 07               |  |

| 1                     | 06               |  |

| -                     | 05               |  |

|                       | 04               |  |

|                       | 03               |  |

|                       | 50               |  |

|                       | 01               |  |

| GND                   | 00               |  |

$\bigcirc$

| PIN ASSIGNMENT |     |  |

|----------------|-----|--|

| N TERM         |     |  |

| 2              | NO. |  |

| СЗ             | 04  |  |

|                | 03  |  |

|                | 02  |  |

|                | 01  |  |

|                | 00  |  |

| POINT  | INDEX |

|--------|-------|

| MNEM   | 200   |

| OVFL1  | ZHI   |

| COUNTO | 3M7   |

| CLKO   | 129   |

|        |       |

|        |       |

| XNTI   | 2F2   |

| RCLKO  | 149   |

|        | 168   |

|        | 169   |

| SUPERCEDED |

|------------|

|------------|

|   | TITLE   | DATE | TITLE FUNCTIONA | - SCHEMATIC | $\frown$ |

|---|---------|------|-----------------|-------------|----------|

|   | DRAFT   |      |                 |             | 1 ( )    |

|   | СНК     |      | UNIVERSAL       | CLOCK       |          |

|   | ENGR    |      |                 | -           |          |

|   |         |      | TASA 0313A      | SHEET OF    |          |

| 4 | бактик. | •    | 3               | 14 4        |          |

| 1 | N       |      | ¥               | sk          | •        |

### PUBLICATION COMMENT FORM

|•

| From                        | Date               |        |

|-----------------------------|--------------------|--------|

| Title                       | Publication Title  |        |

| Company                     | Publication Number |        |

| Address                     |                    |        |

|                             |                    |        |

|                             |                    |        |

| FOLD                        |                    | -<br>F |

| Check the appropriate item. |                    |        |

| Error Page No               | Drawing No         |        |

| Addition Page No.           | Drawing No         |        |

| Other Page No               | Drawing No         |        |

| Explanation:                |                    |        |

|                             |                    |        |

|                             |                    |        |

|                             |                    |        |

|                             |                    |        |

|                             |                    |        |

| FOLD                        |                    | 1      |

|                             |                    | ·      |

| 1                           |                    |        |

|                             |                    |        |

|                             |                    |        |

|                             |                    |        |

|                             |                    |        |

|                             |                    |        |

|        |                                                                 |   |                            | 1      |

|--------|-----------------------------------------------------------------|---|----------------------------|--------|

|        |                                                                 |   |                            |        |

|        |                                                                 |   |                            | 1      |

|        |                                                                 |   |                            |        |

|        |                                                                 |   |                            | I      |

| FOLD   |                                                                 |   |                            | FOLD   |

|        |                                                                 |   |                            |        |

|        |                                                                 | _ | FIRST<br>PERMIT<br>OCEANPC |        |

|        | BUSINESS REPLY MAIL<br>NO POSTAGE NECESSARY IF MAILED IN U.S.A. |   |                            |        |

|        | POSTAGE WILL BE PAID BY:                                        | - |                            |        |

|        |                                                                 |   |                            |        |

|        | INTERDATA                                                       | 3 |                            |        |

|        | Subsidiary of PERKIN-ELMER                                      |   |                            |        |

|        | Oceanport, New Jersey 07757, U.S.A.                             |   |                            |        |

|        |                                                                 |   |                            |        |

| TECH P | UBLICATIONS DEPT. MS 53                                         |   |                            |        |

| FOLD   |                                                                 |   |                            | FOLD   |

|        |                                                                 |   |                            |        |

|        |                                                                 |   |                            | 1      |

|        |                                                                 |   |                            | İ      |

|        |                                                                 |   |                            |        |

|        |                                                                 |   |                            |        |

|        |                                                                 |   |                            | 1      |

|        |                                                                 |   |                            | i<br>I |

|        |                                                                 |   |                            | 1      |

|        |                                                                 |   |                            | 1      |