# THE L-3050 COMPUTER SYSTEM FOR

**DATA SYSTEMS DIVISION** OF LITTON INDUSTRIES THE VSX PROGRAM DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES I DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES IN DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES IN DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES I DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES I DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES I DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES IN DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES I DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES III DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES TO DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES III DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES THE DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES I DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES IN DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES THE DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES TO DATA SYSTEMS DIVISION OF LITTON INDUSTRIES \* DATA SYSTEMS DIVISION OF LITTON INDUSTRIES III DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES III DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES III DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES IN DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES III DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES III DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES III DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES III DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF ENTTON INDUSTRIES III DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES III DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES III DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES I DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES III DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES TO DATA SYSTEMS DIVISION OF LITTON INDUSTRIES DATA SYSTEMS DIVISION OF LITTON INDUSTRIES TO DATA SYSTEMS DIVISION OF LITTON INDUSTRIES

# THE L-3050 COMPUTER SYSTEM FOR THE VSX PROGRAM

20 January 1967

Submitted to:

Naval Air Development Center Johnsville, Pennsylvania

This data shall not be disclosed outside the Government and shall not be duplicated, used, or disclosed in whole or in part for any purpose other than to evaluate the proposal; provided, that if a contract is awarded to this offeror as a result of or in connection with the submission of this data, the Government shall have the right to duplicate, use, or disclose the data to the extent provided in the contract. This restriction does not limit the Government's right to use information contained in the data if it is obtained from another source without restriction. All of the data submitted herein is subject to this restriction.

Prepared by:

Data Systems Division Litton Systems, Inc. 8000 Woodley Avenue Van Nuys, California

## TABLE OF CONTENTS

| Section |                             |                |                                                                                          | Page  |  |

|---------|-----------------------------|----------------|------------------------------------------------------------------------------------------|-------|--|

| I       | INTRO                       | ODUCTIO        | N                                                                                        | 1-1   |  |

| II      | L-3050 COMPUTER DESCRIPTION |                |                                                                                          |       |  |

|         | 2.1                         | FUNCT          | IONAL DESCRIPTION                                                                        | 2 - 1 |  |

|         |                             | 2.1.1          | System Organization                                                                      | 2 - 1 |  |

|         |                             | 2.1.2          | Special Features                                                                         | 2-4   |  |

|         |                             | 2.1.3          | L-3050 Instructions                                                                      | 2-10  |  |

|         |                             | 2.1.4          | Input/Output                                                                             | 2-36  |  |

|         | 2.2                         |                | CAL DESCRIPTION OF LABORATORY M UNIT                                                     | 2-46  |  |

|         |                             | 2.2.1          | General                                                                                  | 2-46  |  |

|         |                             | 2.2.2          | Processor and Memory Design                                                              | 2-46  |  |

|         | 2.3                         | PHYSIC<br>UNIT | CAL DESCRIPTION OF AIRBORNE L-3050                                                       | 2-50  |  |

|         |                             | 2.3.1          | General                                                                                  | 2-50  |  |

|         | ,                           | 2.3.2          | Computer Cabinet                                                                         | 2-50  |  |

|         |                             | 2.3.3          | Functional Drawers                                                                       | 2-53  |  |

|         |                             | 2.3.4          | The Multilaminate Board                                                                  | 2-53  |  |

|         |                             | 2.3.5          | Lead Joining                                                                             | 2-55  |  |

|         |                             | 2.3.6          | Cooling                                                                                  | 2-56  |  |

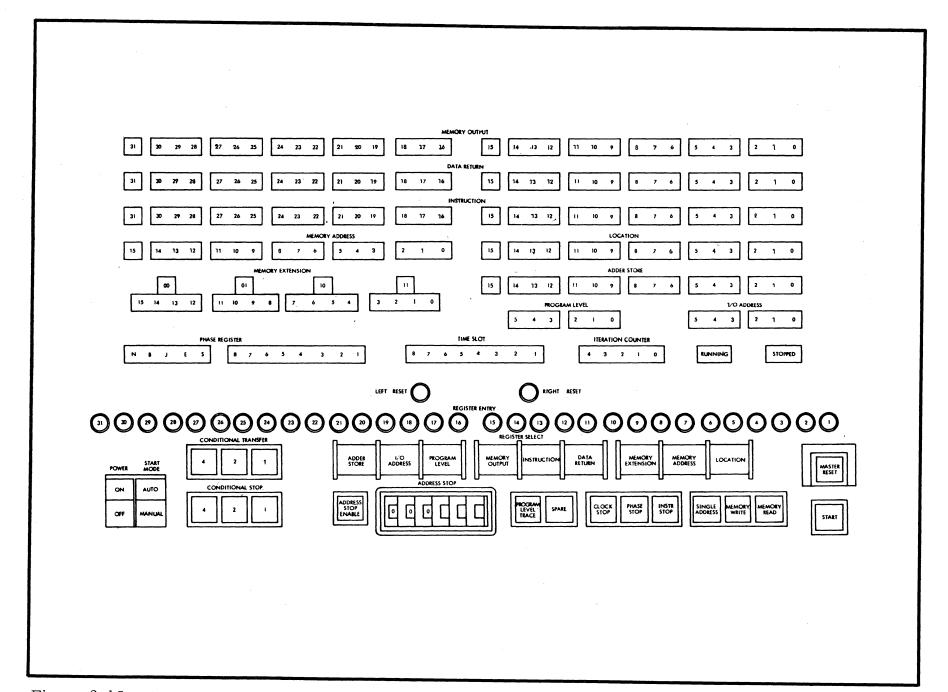

|         | 2.4                         | CONTR          | OL CONSOLE                                                                               | 2-58  |  |

|         |                             | 2.4.1          | Power and Start Mode Switches (Located<br>Lower Left-Hand Corner of Console<br>Keyboard) | 2-58  |  |

|         |                             | 2.4.2          | Master Reset (Located Middle of Right Side of Console Keyboard)                          | 2-60  |  |

|         |                             | 2.4.3          | Start (Located Lower Right Corner of Console)                                            | 2-61  |  |

|         |                             | 2.4.4          | Register Entry (Second Row of Buttons)                                                   | 2-61  |  |

|         |                             | 2.4.5          | Register Entry Reset (Two Top Buttons)                                                   | 2-61  |  |

|         |                             | 2.4.6          | Register Select (Center of Console)                                                      | 2-61  |  |

|         |                             | 2.4.7          | Single Address (Bottom Row, 4th Switch from Right)                                       | 2-62  |  |

|         |                             |                |                                                                                          |       |  |

# TABLE OF CONTENTS (Continued)

| Section | <u>.</u>      |          |                                                                   | Page        |

|---------|---------------|----------|-------------------------------------------------------------------|-------------|

|         |               | 2.4.8    | Memory Read (Bottom Row, 2nd Switch from Right)                   | 2-62        |

|         |               | 2.4.9    | Memory Write (Bottom Row, 3rd Switch from Right)                  | 2-63        |

|         |               | 2.4.10   | Instr Stop (Bottom Row, 5th Switch from Right)                    | 2-63        |

|         |               | 2.4.11   | Conditional Transfer (1, 2, 4) (Left End of Middle Row)           | 2-64        |

|         |               | 2.4.12   | Conditional Stop (1, 2, 4) (Left End of Bottom Row)               | 2-64        |

|         |               | 2.4.13   | Address Stop (Counter) (Center of Bottom Row)                     | 2-64        |

|         |               | 2.4.14   | Address Stop Enable (Bottom Row, Left of Center)                  | 2-64        |

|         |               | 2.4.15   | Clock Stop — Phase Stop                                           | 2-64        |

|         |               | 2.4.16   | Program Level Trace (Bottom Row, Right of Center)                 | 2-64        |

| III     | THE I         | -3050 IN | PUT/OUTPUT SYSTEM AS APPLIED TO VSX                               | 3-1         |

| -       | 3.1           | GENER    | ${f AL}$                                                          | 3-1         |

|         | 3.2           |          | NATE INPUT/OUTPUT SYSTEM<br>MENTATIONS                            | 3-1         |

|         |               | 3.2.1    | Two-Port Memory System                                            | 3-1         |

|         |               | 3.2.2    | Four-Port Memory System                                           | 3-1         |

|         | 3.3           | SUMMA    | ARY                                                               | 3-3         |

| IV      | PROG<br>L-305 |          | G CENTER REQUIREMENTS FOR THE VSX                                 | 4-1         |

|         | 4. 1          | GENER.   | $\mathtt{AL}$                                                     | 4-1         |

|         | 4.2           | PERIPH   | HERAL EQUIPMENT                                                   | <b>4-</b> 1 |

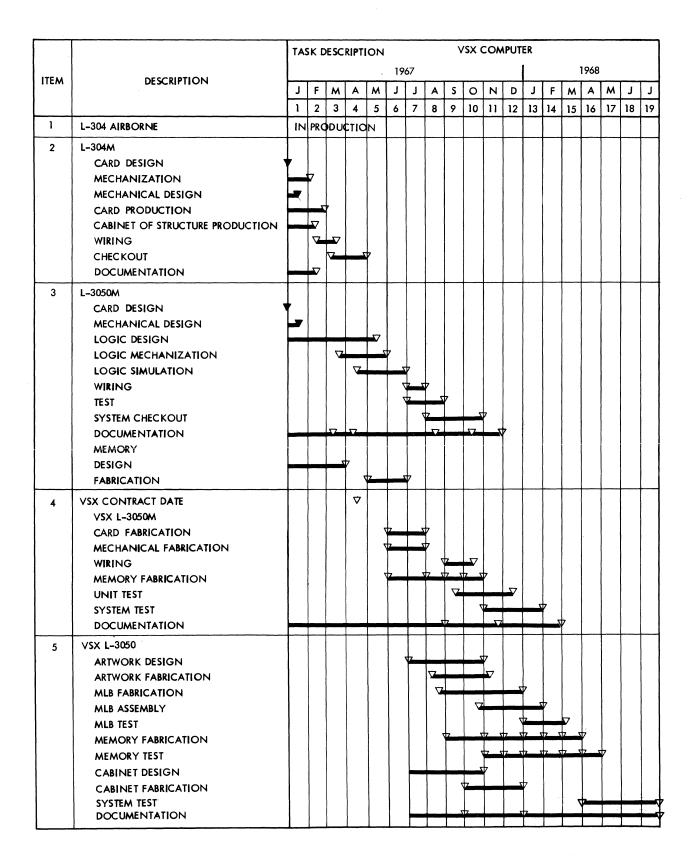

| V       |               |          | RY DELIVERY SCHEDULE FOR LITTON LINE OF MICROELECTRONIC COMPUTERS | 5 - 1       |

|         | 5.1           | INTROI   | DUCTION                                                           | 5-1         |

|         | 5.2           | DELIVE   | ERY SCHEDULE DEVELOPMENT                                          | 5-1         |

| •       |               |          |                                                                   |             |

| Append  | <u>lix</u>    |          |                                                                   |             |

| ٨       | EA CII        | TTV CAT  |                                                                   | A 7         |

| A       | LWOIT         | TII OAF  | PABILITY                                                          | <b>A-</b> 1 |

## LIST OF ILLUSTRATIONS

| Figure |                                                                                  | Page |

|--------|----------------------------------------------------------------------------------|------|

| 2-1    | L-3050 Data Processor System                                                     | 2-2  |

| 2-2    | Memory Map of Dedicated Locations                                                | 2-7  |

| 2-3    | L-3050 Data Word Formats                                                         | 2-11 |

| 2-4    | L-3050 Instruction Word Format                                                   | 2-11 |

| 2-5    | Address Extension Register                                                       | 2-14 |

| 2-6    | Move Instruction Word Format                                                     | 2-22 |

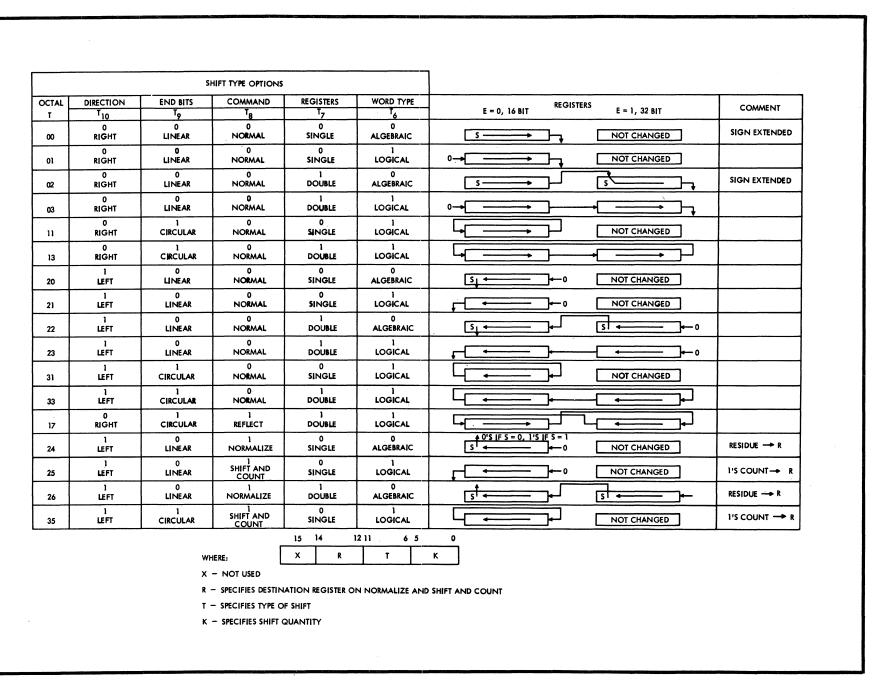

| 2-7    | L-3050 Shift Instructions                                                        | 2-30 |

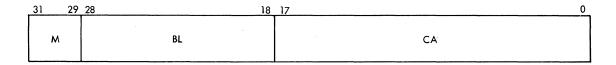

| 2-8    | Input/Output Key Word Format                                                     | 2-37 |

| 2-9    | Input/Output Termination Word                                                    | 2-38 |

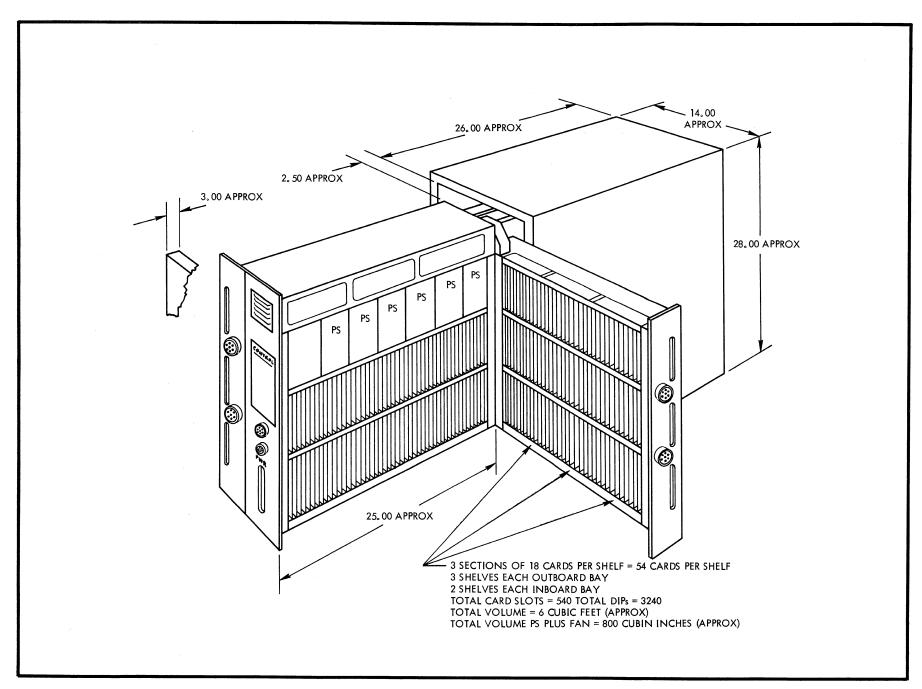

| 2-10   | Processor Configuration                                                          | 2-47 |

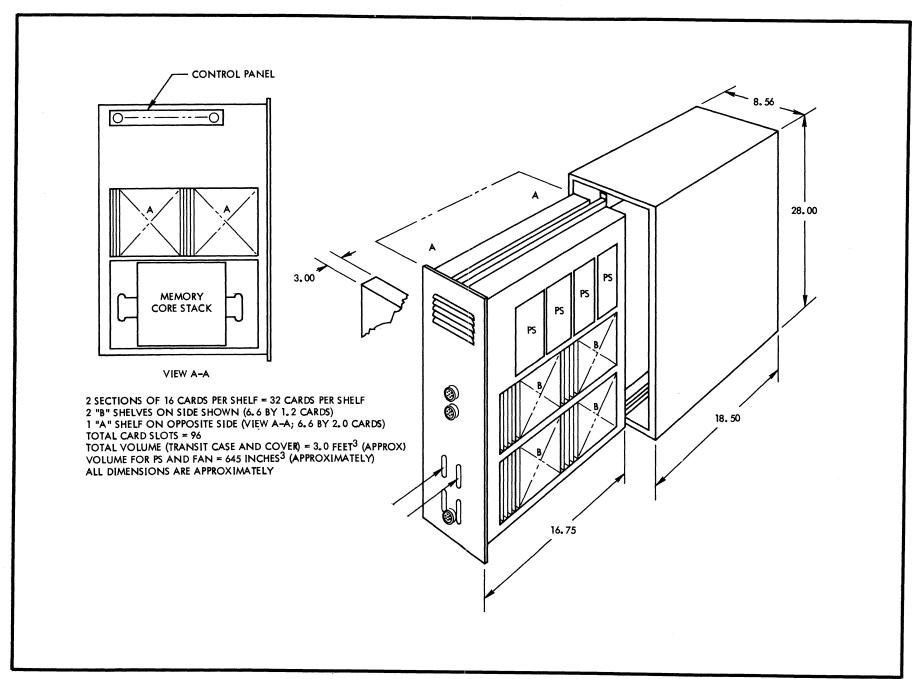

| 2-11   | Memory Unit                                                                      | 2-48 |

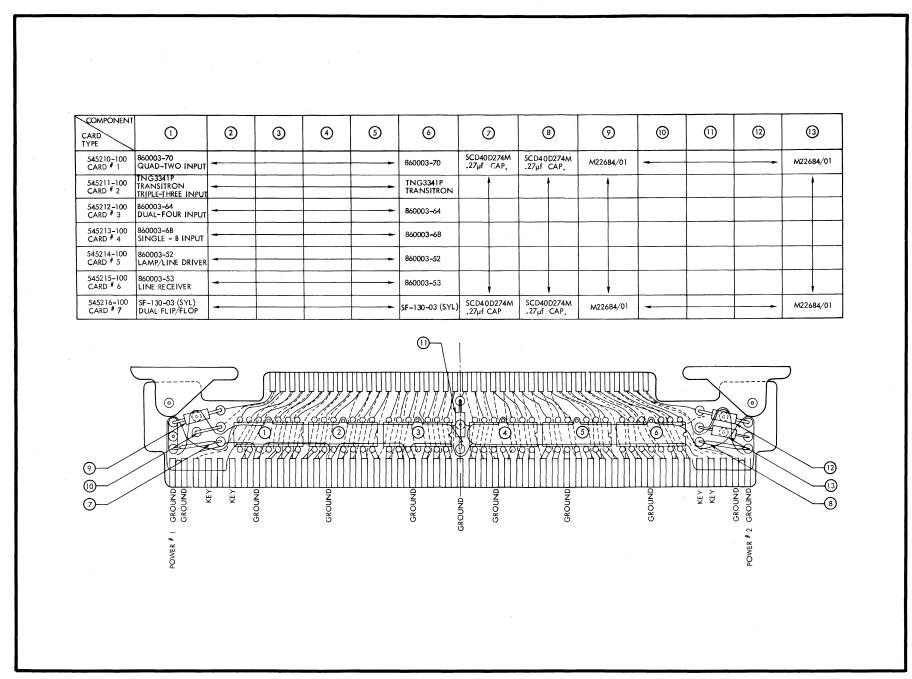

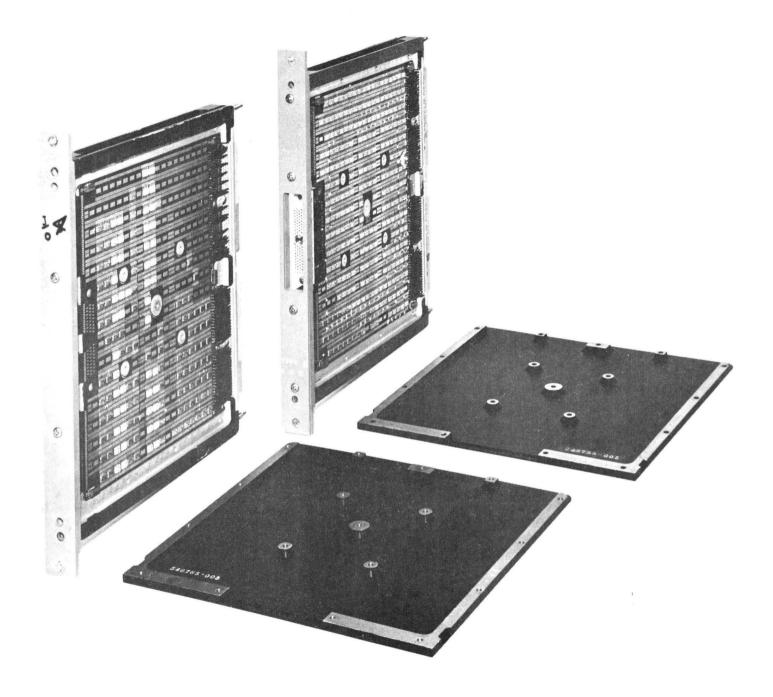

| 2-12   | Logic Card Assembly Information                                                  | 2-49 |

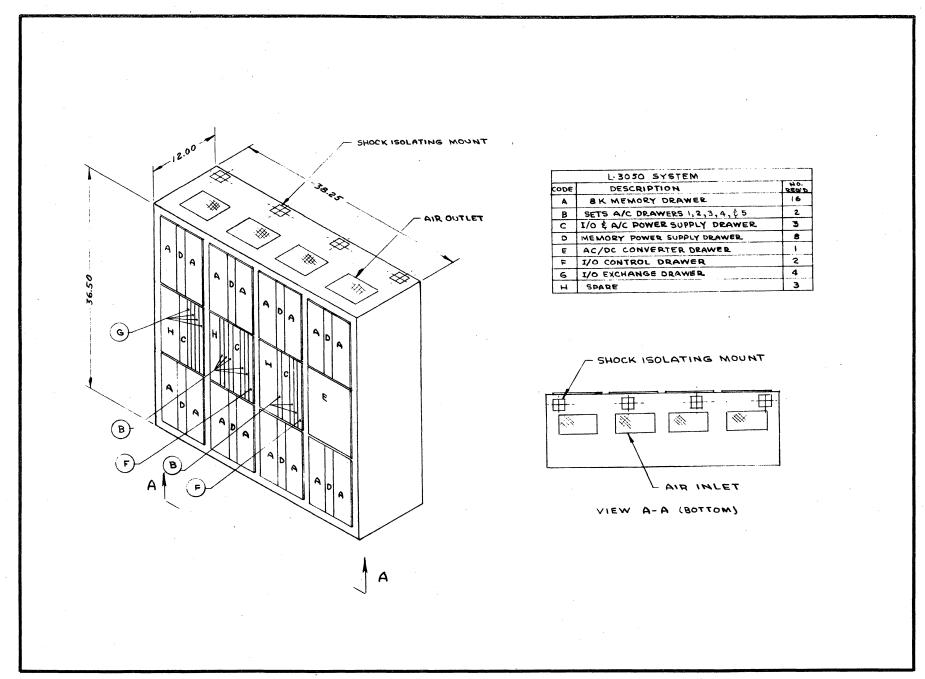

| 2-13   | L-3050 Computer                                                                  | 2-51 |

| 2-14   | Thermal Conductive Path in I/O and A&C Drawers                                   | 2-54 |

| 2-15   | Control Console                                                                  | 2-59 |

| 5-1    | Evolutionary Delivery Schedule for Litton L-304/L-3050 Microelectronic Computers | 5-2  |

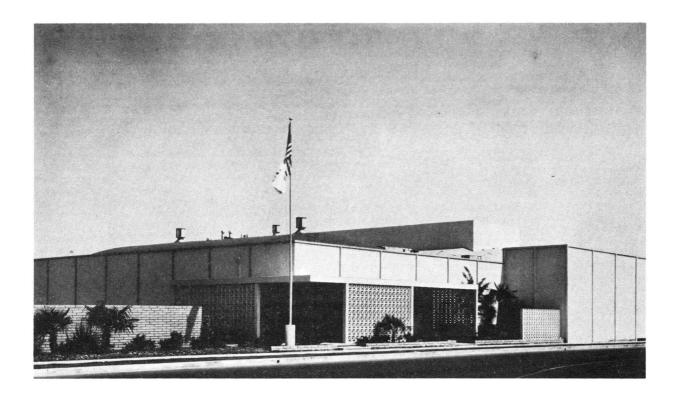

| A-1    | Building No. 45, Van Nuys                                                        | A-2  |

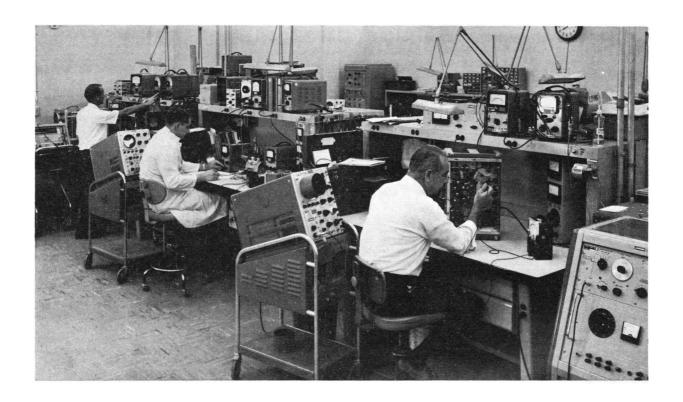

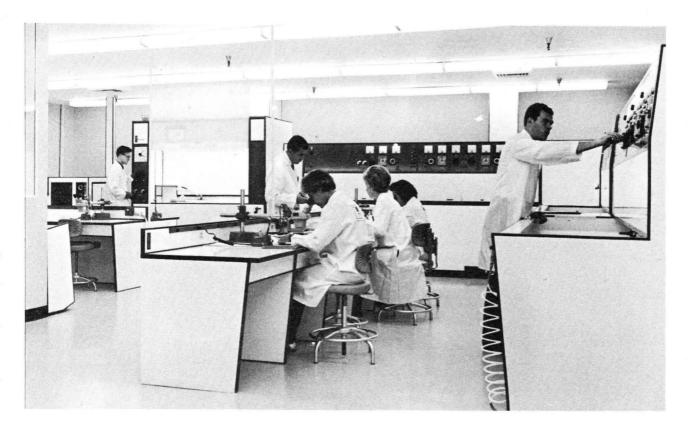

| A-2    | Typical Engineering Laboratory, Van Nuys                                         | A-2  |

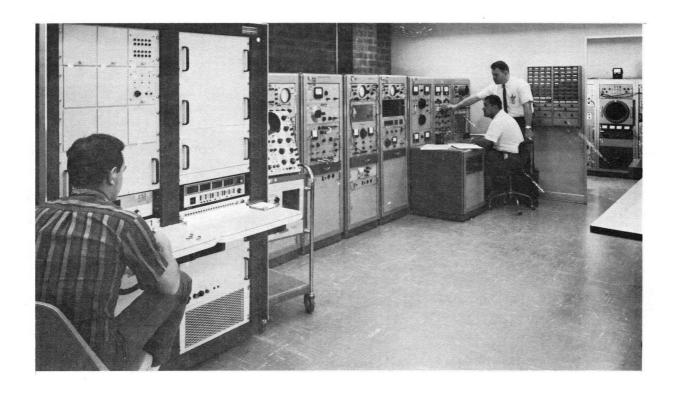

| A-3    | Receiving Inspection Area, Van Nuys                                              | A-3  |

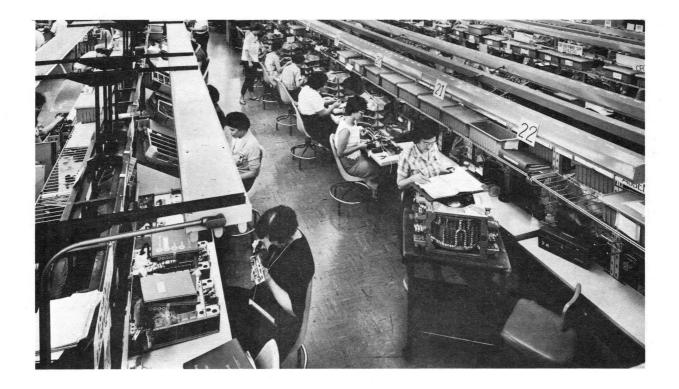

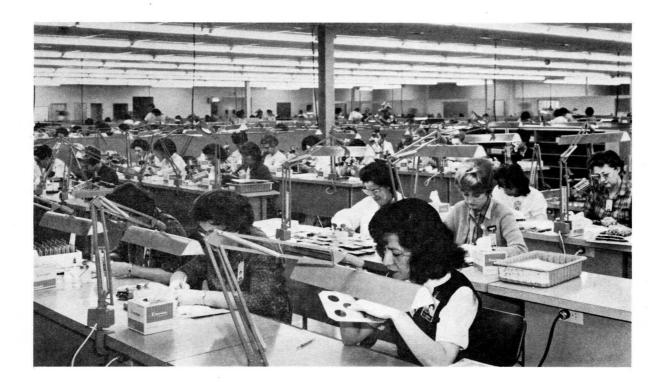

| A-4    | Electronics Assembly Area, Van Nuys                                              | A-3  |

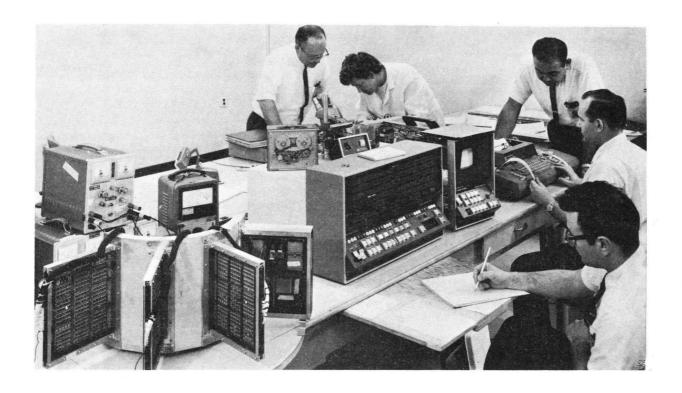

| A-5    | Microelectronic Cards Undergoing Automated Testing, Van Nuys                     | A-4  |

| A-6    | Salt Lake City Plant                                                             | A-4  |

| A-7    | Electronics Assembly Area, Salt Lake City Plant                                  | A-5  |

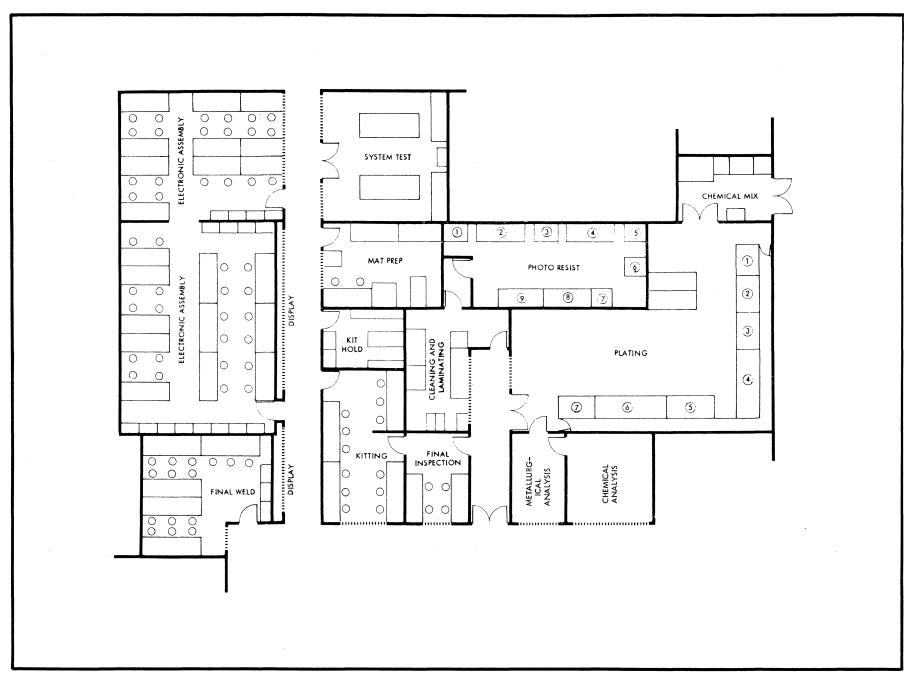

| A-8    | Floor Plan of Clean-Room Production Area, Van Nuys                               | A-7  |

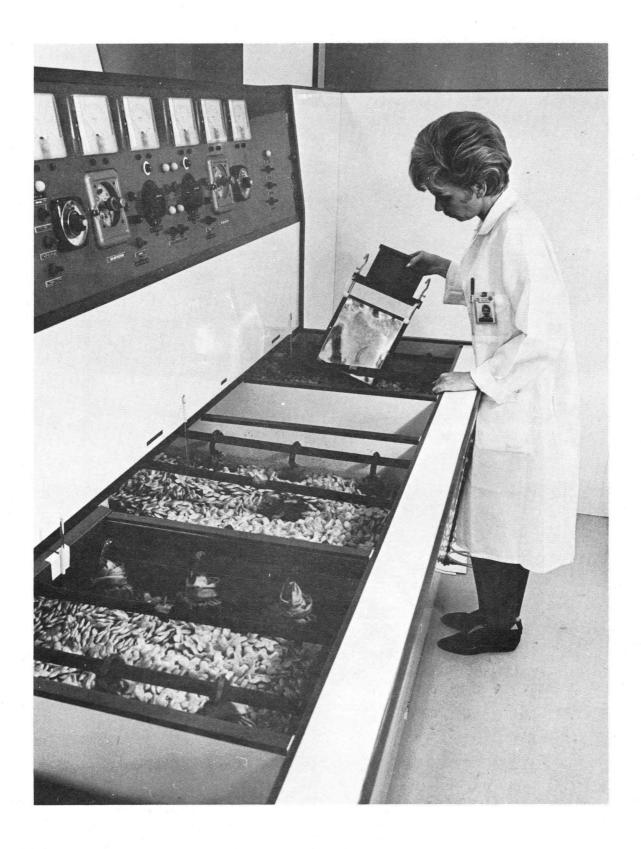

| A-9    | Plating Room                                                                     | A-8  |

| A-10   | Etching and Plating Area Designed for Maximum Efficiency                         | A-9  |

| A-,11  | Attachment of Components to Multilayer Laminated Boards, Using Microwelder       | A-10 |

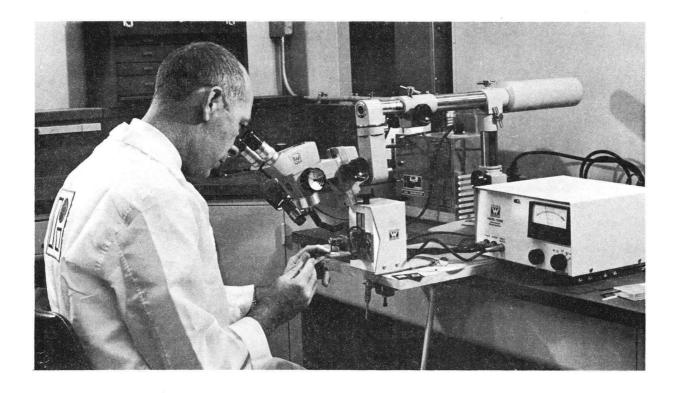

| A-12   | Inspection Area within the Microelectronic Production Area                       | A-10 |

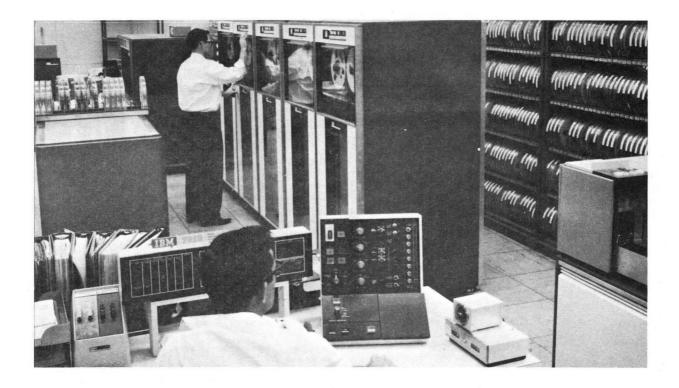

| A-13   | Van Nuys Data Processing Facility                                                | A-11 |

## LIST OF TABLES

| <u>Table</u> |                                               | Page  |

|--------------|-----------------------------------------------|-------|

|              |                                               |       |

| II-1         | Program Activity Register                     | 2 - 5 |

| II-2         | Special Operand Addresses                     | 2-8   |

| II-3         | Add Class Instruction Timing                  | 2-15  |

| II-4         | Summary of L-3050 Instructions                | 2-17  |

| II-5         | L-3050 Operand Addresses                      | 2-34  |

| II-6         | L-3050 Transfer Instruction Addresses         | 2-35  |

| II-7         | L-3050 Computer Physical Characteristics      | 2-52  |

| III-1        | Tactical Processor (Assuming Two-Port Memory) | 3-2   |

| III-2        | Sensor Processor (Assuming Two-Port Memory)   | 3-2   |

| IV-1         | List of Commercial Peripheral Equipments      | 4-2   |

| <b>A</b> - 1 | Environmental Test Equipment                  | A-12  |

#### SECTION I

#### INTRODUCTION

The L-3050 computer which is described in this proposal has been selected by Litton Data Systems Division as the computer which is ideally suited to solve the data processing problems encountered in the implementation of the VSX Program.

The L-3050 computer, latest member of the Litton Data Systems Division's L-300/L-3000 computer series, couples proven airborne construction techniques with advanced computer circuitry and organization to provide the highest speed, most versatile airborne computer in the industry. The multiple register, multiprogramming, multiprocessor and input/output systems featured by the L-300/L-3000 computer series have already proven effective in several real-time system applications. The implementation of these features in the L-3050 when combined with the timeliness of this computer development makes the L-3050 the ideal computer for the VSX Program.

The L-3050 is a high speed, parallel, binary computer specifically designed to meet the functional requirements of real-time command and control systems, and the environmental requirements of carrier-based airborne applications. The L-304, first member of the family, has been contracted for on three separate programs, one of which, the E2A retrofit development, involved a dual L-304 computer with up to 81,920 32-bit words of memory. The L-3050 uses virtually the identical memory with the exception that a 33rd bit per word has been added for parity. Simplified addressing to up to 131,072 32 bits is provided in all L-300 and L-3000 computers.

The processing capability of the L-3050 has been extended beyond that of the L-304 by increasing the number of instructions to 128, including 32-bit arithmetic as well as 16-bit arithmetic and adding to the number of registers to provide 8 16-bit process registers and 8 32-bit accumulators for each of the 64 program levels. Instruction execution times have been decreased appreciably from those of the L-304 by using "live" process registers and accumulators, taking maximum advantage of memory overlap and allowing instructions to be executed from the process registers or accumulators. The advantage gained by the latter step is shown in the execution times for the integration loop of the sample problem which shows an average execution time of less than 2.5 microseconds per instruction. The advantages of the basic computer organization are made apparent in the same problem where the inner loop of 5 instructions achieves two integrations for each pass through the loop.

The multiprogramming capabilities of the L-3050 are not demonstrated by the sample problems previously submitted to NADC, however, experience in the E2A application has shown that the savings in time and programming complexity in real-time processing is substantial with the L-300/L-3000 multiprogramming implementation. In that dual processor system which performs radar data processing, navigation, data link communication, and display and control processing, only 200 instructions are required for executive control.

The multiprocessing system, which has been proven in the E2A application, is, from the programmer's point of view, merely an extension of the multiprogram system of the single computer. The difference is that instead of one program operating, the highest priority program assigned to each processor is processed simultaneously. The net result is a virtual doubling of computer speed as maximum advantage is taken of each processor's capability.

The input/output system of the L-3050 provides the maximum in speed and flexibility. When the second processor is added to the system, the potential input/output speed and the number of possible system combinations is greatly increased. Each L-3050 is capable of controlling up to 64 input/output devices. Transfers may be either 8 bits in parallel or up to 32 bits in parallel at transfer rates of up to one word or character per memory cycle for each processor. Additional potential combinations are possible which allow input/output to proceed either with or without stealing memory cycles from the processor. It is also possible to arrange the I/O system as was done in the E2A retrofit program, so that peripheral units may be switched to either processor should the other fail.

The packaging used in the airborne L-3050 is the same as that which has successfully passed the rigors of a very extensive step-stress program. The multilayer boards used in the memory and logic portions of the computer makes for an extremely reliable package as well as one which is very compact and lightweight. The latter feature is of utmost importance for the VSX Program as the computer will be very limited in allowable cube and weight.

Finally, the Litton schedule for development of the L-3050 fits exactly the requirements of the NADC-VSX Program (see Section V). A plug-in card version is scheduled for completion in the latter part of 1967 with an airborne high-density version, using proven L-304 packaging, scheduled to follow within six months thereafter. This early development of the L-3050 assures that a proven product with the following unique features will be available for VSX needs:

#### USE OR DISCLOSURE OF PROPOSAL DATA IS SUBJECT TO THE RESTRICTION ON THE TITLE PAGE OF THIS PROPOSAL

- o Highest speed

- o Proven design concepts

- o Proven packaging

- o Simplified programming

- o Proven dual processor design

- o High speed, flexible I/O

- o Smallest size, lightest weight

- o High reliability

- o Fail-safe modes

- o Early availability of laboratory and airborne models

#### SECTION II

#### L-3050 COMPUTER DESCRIPTION

#### 2.1 FUNCTIONAL DESCRIPTION

#### 2.1.1 System Organization

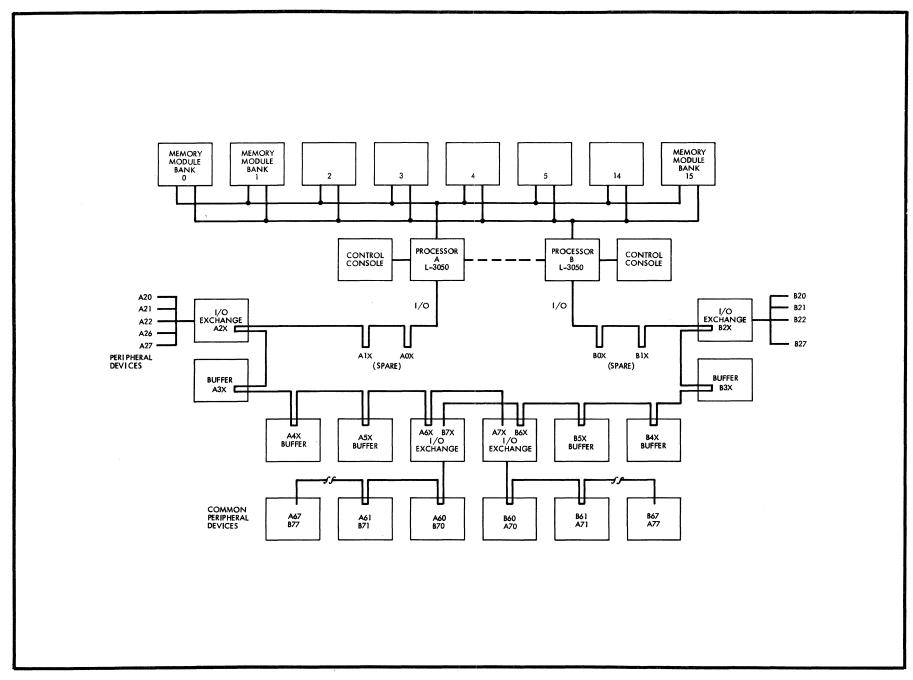

The L-3050 consists of a modular organization of basic system units. These units include: processors, memory modules, power supplies, control consoles, and input/output exchange units. Combinations of these basic units may be organized into systems that will meet the requirements of a wide variety of computer system applications. A typical L-3050 Dual Processor System is shown in Figure 2-1.

#### 2.1.1.1 Processor

A processor consists of the following functional units: arithmetic unit, instruction control unit, memory control unit, program level control unit, and input/output control unit. The arithmetic unit contains a 32-bit, parallel, full adder that is used to execute most instructions. The instruction control unit decodes the instruction and provides control signals to other functional units. It also provides the basic clock frequency to these units. The memory control unit controls traffic on a memory word bus and an address bus. The memory control unit processes requests for memory cycles from the other functional units of the processor and also provides memory parity check and generation functions.

The program level control unit determines which of up to 64 programs has the currently highest priority and provides program level switching control.

The processor contains an input/output control unit that is independent from the other functional units of the processor. This allows data communication to occur simultaneously with instruction computation. Each processor may control and communicate with up to 64 peripheral devices. This may be under instruction control or it may be independent of instruction control and under control of special "key words." Key words are accessed at a rate that is determined by the transmitting or receiving peripheral device. A key word contains block length, memory "running" address, and mode of operation. It is preset by the program prior to data communication.

The input/output control unit connects with peripheral devices via a common set of 33 bidirectional data lines (includes a parity line), control lines and three address lines. Data communication with all devices is controlled on these lines on a

Figure 2-1. L-3050 Data Processor System

"party line" basis. Eight separate "request" lines and eight separate "acknowledge" lines are provided to signal and respond to requests for data transmission over the common lines. When more than eight devices are required in the system, the three address lines are used to multiplex up to eight devices to a single request line. This is accomplished with an input/output exchange unit or a special buffer that controls more than one device.

#### 2.1.1.2 Memory Modules

Each memory module contains 8192 words and each word is 33 bits in length. Memory modules contain their own logic for the following: processing requests from two processors, memory protection under program control, bank address modification, and self-test. Memory timing is independent of processor timing and, therefore, may be a variable without modification to the processors. The standard L-3050 Memory Module can complete a full cycle in less than two microseconds. A processor can address up to 16 memory modules in one system.

Each memory module may be connected to two processors via independent address buses and word buses. A memory module is selected by the four most significant bits of one of its 17-bit address buses. This is a "bank address." The remaining 13 bits are used for word selection. Logic within a memory module will resolve a simultaneous request from two processors, otherwise, processors are serviced on a first come—first serve basis and the second processor is temporarily suspended if both processors are accessing the same memory module.

Memory protection from programmed modification is provided in 4096-word sizes. Special instructions are used to set one-half or all of the memory into a ''non-destructive'' mode. This control is provided for both processors and is independent for each processor.

A memory module is given a bank address under program control. A fourbit register in each module is used by both processors to contain a variable bank address. A memory module may also be set active or inactive under program control.

#### 2.1.1.3 Power Supplies

Each basic system unit contains its own microminiature power supply. Each power supply contains its own transient and fault detection hardware. Should a fault or line transient be detected, an automatic interrupt signal is transmitted to one or both of the processors. Action taken is a function of the system organization and which power supply has failed.

#### 2.1.1.4 Control Consoles

A control console is usually provided for each processor. This console contains features for program checkout, maintenance and automatic fault detection indicators. A control console does not normally connect via an input/output channel.

#### 2.1.1.5 Input/Output Exchange Units

An input/output exchange unit provides a multiplexing function for one of the eight main I/O stations. It provides an interface that is identical to the input/output control unit's interface. That is, it resolves priority control over eight request lines and controls sharing of common data and control lines just like the input/output control unit. An input/output exchange unit can be connected to two processors. A command from either processor will switch the I/O exchange unit from one processor to the other.

The I/O exchange unit also provides special long line drive capability for those devices that are located over 100 feet from the processor.

#### 2.1.2 Special Features

#### 2.1.2.1 Multiprogramming

Multiprogramming is a feature that allows the processor to execute up to 64 different programs, one at a time, on a priority demand basis. The control for switching from one program to another is built into the hardware.

2.1.2.1.1 Program Levels. Each of the 64 programs is assigned a program level number. This number corresponds to a bit position within a 64-bit register called the program status register. Bits are set or reset in this register by program or by the input/output control unit of the processor. There is also a second 64-bit register called the program enable register which provides a logical masking on the program status register. Bits in this register are set or reset by programmed instructions. Together, these two 64-bit registers are called the program activity register (PAR). The most significant (highest numbered) one-bit of the program status register which has a corresponding one-bit in the program enable register determines the currently active program.

The PAR is held in four, full word locations of the processor's 16 scratch pad registers. It is made available to the programmer with instructions that use half word, operand addresses: 004000 to 004070<sub>8</sub> (see Table II-1).

| OCTAL<br>ADDRESS | PROGRAM<br>ENABLE BITS             | OCTAL<br>ADDRESS | PROGRAM<br>STATUS BITS             |

|------------------|------------------------------------|------------------|------------------------------------|

| 4000             | 37 <sub>8</sub> TO 16 <sub>8</sub> | 4002             | 37 <sub>8</sub> TO 16 <sub>8</sub> |

| 4001             | 15 <sub>8</sub> TO 00 <sub>8</sub> | 4003             | 15 <sub>8</sub> TO 00 <sub>8</sub> |

| 4004             | 77 <sub>8</sub> 10 60 <sub>8</sub> | 4006             | 77 <sub>8</sub> TO 60 <sub>8</sub> |

| 4005             | 57 <sub>8</sub> TO 40 <sub>8</sub> | 4007             | 57 <sub>8</sub> TO 40 <sub>8</sub> |

Table II-1. Program Activity Register

A six-bit number that represents the active program level is logically generated and held in a register called the program level register. The contents of this register are available to the program by execution of normal instructions with special operand address  $004030_{\rm Q}$ .

Program levels 77<sub>8</sub> to 74<sub>8</sub> are reserved for special functions. Program level 77 is used for power-on and power-off functions. This level is automatically entered whenever a power transient is detected or power is initially turned on or off. All active registers of the L-3050 are automatically saved in memory each time a program level change is made: therefore, it is not necessary for the programmer to store these registers when a power transient is detected. During a power-off condition there is sufficient time to execute several instructions in level 77. The contents of the active registers on level 77 are lost when power is turned off. Program level 77 is the only program level that cannot be interrupted by the input/output control unit to process data requests. That is, no I/O communication can take place if the processor is executing a program at level 77. Program level 77 is always "enabled." That is, bit position 77 of the program enable register is wired to a "one."

Program level 76 is reserved for processing detected memory errors. The detection of a memory parity error by the memory control unit or the detection of an attempt to modify a protected area of memory will cause bit 76 of the program status register to be set and, if bit 76 of the program enable register is set, a program level change will occur. The bank address of the memory module that caused the error and the error type indication are automatically stored into the indicator word of program level  $76_{\rm g}$ .

Program level 75<sub>8</sub> is reserved for a program trace feature. If a console switch is depressed and a program level change occurs, program level 75 is entered (temporarily) in order to execute a program trace program.

Program level 74<sub>8</sub> is reserved for automatic entry due to detection of hard-ware faults. Special hardware is provided in all functional units to continually monitor for normal operation. Should abnormal operation be detected, program level 74 is entered.

Program level 00 is reserved for execution of a "bootstrap" routine after a program load operation.

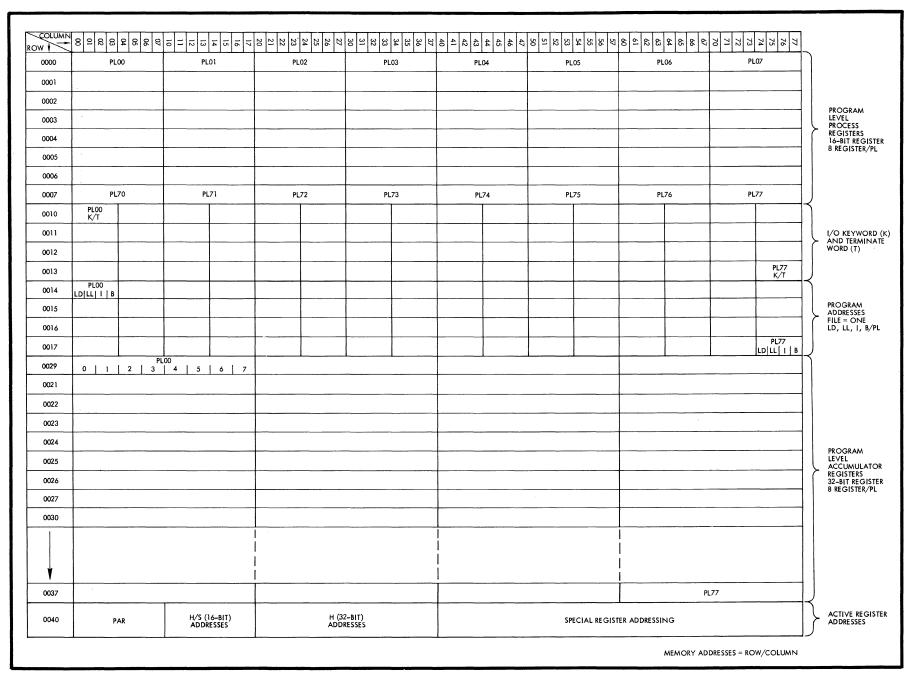

2. 1. 2. 1. 2 Program Level Registers. A set of fourteen, 32-bit words is assigned to each of the 64 program levels. These 896 words are assigned fixed addresses in the memory module that is selected by the base memory field of the memory extension register. These assigned addresses are shown in Figure 2-2. The set of fourteen words for the currently active program level are held in the processor's active registers. The remaining words are held in their fixed memory locations. Each time a program level change occurs, the old registers are written back into the base memory and the new registers are obtained from memory and are set into the processor's active registers. This operation requires less than 30 microseconds.

The fourteen words associated with each program level are as follows:

Eight Accumulators for full word instructions.

Four words that hold eight 16-bit process registers. These registers are used for index registers or half word accumulators.

Two words designated as the program address file, PAF. The PAF separates into four half words: the instruction location counter, LL; the memory address extension register, LD; the indicator word, IW; and the base address register, LB.

The eight active accumulators and 16 process registers are held in 12 of the processor's 16 scratch pad registers. The PAF is held in flip-flop registers for the currently active program.

These active registers, the program level register and program activity register, PAR, are available to the program by special operand addresses. Operand addresses 004000-0040378 are detected as special register addresses for most L-3050 instructions. Therefore, these memory locations in the processor's base memory are not available for data storage, however, they are available for instruction storage. Table II-2 lists the assigned special operand addresses.

Figure 2-2. Memory Map of Dedicated Locations

| HALF WORD<br>ADDRESS IN OCTAL | REGISTER NAME                                | REGISTER SYMBOL |

|-------------------------------|----------------------------------------------|-----------------|

| 004000                        | BITS 00-15 OF PROGRAM ENABLE REGISTER, PAR   | PE 15-00        |

| 004001                        | BITS 16-31 OF PROGRAM ENABLE REGISTER, PAR   | PE31-00         |

| 004002                        | BITS 00-15 OF PROGRAM STATUS REGISTER, PAR   | PS 1500         |

| 004003                        | BITS 16-31 OF PROGRAM STATUS REGISTER, PAR   | PS31-00         |

| 004004                        | BITS 32-47 OF PROGRAM ENABLE REGISTER, PAR   | PE47-32         |

| 004005                        | BITS 48-63 OF PROGRAM ENABLE REGISTER, PAR   | PE 63-48        |

| 004006                        | BITS 32-47 OF PROGRAM STATUS REGISTER, PAR   | PS47-32         |

| 004007                        | BITS 48-63 OF PROGRAM STATUS REGISTER, PAR   | PS 63-48        |

| 004010                        | HALF WORD PROCESS REGISTER, 0 (ACTIVE LEVEL) | H OR S-0        |

| 004011                        | HALF WORD PROCESS REGISTER, 1 (ACTIVE LEVEL) | H OR S-1        |

| 004012                        | HALF WORD PROCESS REGISTER, 2 (ACTIVE LEVEL) | H OR S-2        |

| 004013                        | HALF WORD PROCESS REGISTER, 3 (ACTIVE LEVEL) | H OR S-3        |

| 004014                        | HALF WORD PROCESS REGISTER, 4 (ACTIVE LEVEL) | H OR S-4        |

| 004015                        | HALF WORD PROCESS REGISTER, 5 (ACTIVE LEVEL) | H OR S-5        |

| 004016                        | HALF WORD PROCESS REGISTER, 6 (ACTIVE LEVEL) | H OR S-6        |

| 004017                        | HALF WORD PROCESS REGISTER, 7 (ACTIVE LEVEL) | H OR S-7        |

| 004020                        | FULL WORD ACCUMULATOR, 0 (ACTIVE LEVEL)      | н-0             |

| 004021                        | FULL WORD ACCUMULATOR, 1 (ACTIVE LEVEL)      | H-1             |

| 004022                        | FULL WORD ACCUMULATOR, 2 (ACTIVE LEVEL)      | H-2             |

| 004023                        | FULL WORD ACCUMULATOR, 3 (ACTIVE LEVEL)      | н-3             |

| 004024                        | FULL WORD ACCUMULATOR, 4 (ACTIVE LEVEL)      | H-4             |

| 004025                        | FULL WORD ACCUMULATOR, 5 (ACTIVE LEVEL)      | H-5             |

| 004026                        | FULL WORD ACCUMULATOR, 6 (ACTIVE LEVEL)      | H-6             |

| 004027                        | FULL WORD ACCUMULATOR, 7 (ACTIVE LEVEL)      | H-7             |

| 004030                        | PROGRAM LEVEL REGISTER, PAF                  | LP              |

| 004031                        | MEMORY EXTENSION REGISTER, PAF               | LD              |

| 004032                        | INDICATOR WORD, PAF                          | IW              |

| 004033                        | BASE ADDRESS REGISTER, PAF                   | LB              |

| 004034                        | RESERVED FOR FAULT ISOLATION                 |                 |

| 004035                        | RESERVED FOR FAULT ISOLATION                 |                 |

| 004036                        | RESERVED FOR FAULT ISOLATION                 |                 |

| 004037                        | RESERVED FOR FAULT ISOLATION                 |                 |

Table II-2. Special Operand Addresses

Registers of inactive programs are available by addressing their assigned locations in the base memory. The contents of the assigned memory locations of the active program's registers are set to all zeros at the time that the program is active.

The use of special register addresses for operands provide a convenient method of manipulating and controlling these registers. It also provides a method of programming register-to-register operations. Whenever the operand address field of an instruction selects a register as an operand, the instruction execution time is one microsecond less.

If a half word process register is used as an operand with a full word instruction, the 16-bit operand is assumed to be right justified. Sign extension is automatically provided on algebraic, full word instructions. If a full word accumulator is used as an operand with a half word instruction, the left or right half of the accumulator is selected according to the least significant bit of the operand address.

Transfer instructions (and others to be specified) do not use the special register address feature.

2.1.2.1.3 Program Address File. The program address file (PAF) contains four 16-bit fields that provide program address options and conditional status data for sequencing the current program. As stated in Subsection 2.1.2.1.2, there is a PAF for each of the 64 program levels. The four fields are: the instruction location register, LL; the memory extension register, LD; the base address register, LB; and the program indicator word, IW.

The instruction location register holds the address of the next instruction in normal sequence. It is a copy of the processor's instruction counter, LL, as it was when the associated program was last active.

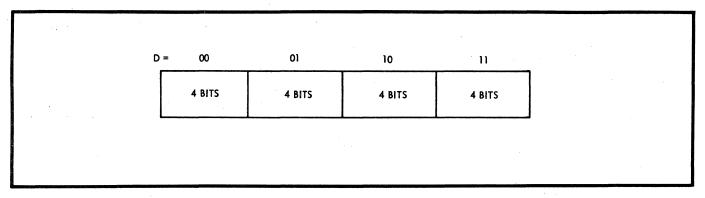

The memory extension register, LD, provides four fields of four bits each for expanded memory addressing. Each four-bit field represents a bank address. The LD register provides a convenient method of directly addressing up to 262, 144 16-bit words. Four of any 16 memory banks (16, 384 16-bit words per bank) are directly addressable on any program level for any one setting of the LD register (see Subsection 2.1.3.2).

An alternate method of extended memory addressing is also provided in the L-3050. This is provided with the base address register, LB, of the PAF. This 16-bit register may be added to the instruction's operand address or it may be added

to the instruction location register LL, at the option of the programmer. When this register is added to a 16-bit address, it is shifted left by 2-bit positions to yield an 18-bit address. The base address register provides a "dynamic relocatability" feature. It is described in more detail in Subsection 2.1.3.5. The option is controlled by three bits in the indicator word and by the least significant bit (W) of the "operand" address on transfer instructions.

The indicator word of the PAF also contains information bits that indicate the status of certain conditions of the assigned program. Three bit positions signify "less then," "greater than" or "equal to" as a result of compare instructions. These bits may be tested individually or in combination by a special transfer instruction. Two other bits indicate arithmetic overflow and floating point underflow. The remaining bits of the indicator word are used only in program levels 74<sub>8</sub> and 76<sub>8</sub>. If a memory error is detected, the bank address of the faulty memory is placed in the indicator word of program level 76. One of two bits are set to indicate a parity error or a protected area violation. If a functional unit is detected as failing, its code number is set into the indicator word of program level 74.

#### 2.1.3 L-3050 Instructions

#### 2.1.3.1 Data Word Formats

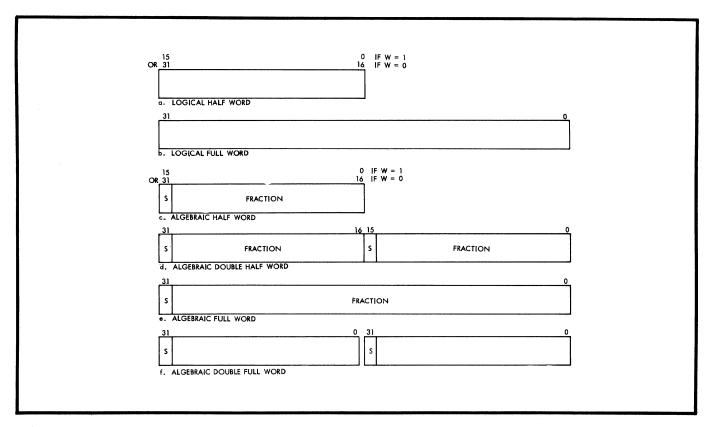

The L-3050 utilizes several data word formats depending upon the instruction's requirements. Data words may be logical or algebraic. Logical data words may be 16 bits or 32 bits in length. Algebraic words may be 16 bits or 32 bits in length. Certain algebraic operations may produce a double word result, such as the product on a fixed point multiply instruction. All algebraic words are treated as binary fractions with negative numbers represented in a two's complement form. The sign bit of algebraic numbers is located in the most significant bit position. A "one" represents a negative sign.

Figure 2-3 displays the L-3050 data word formats.

#### 2.1.3.2 Instruction Word Format

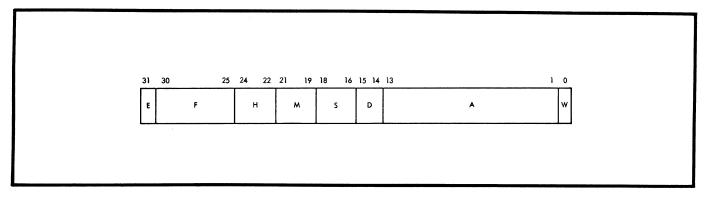

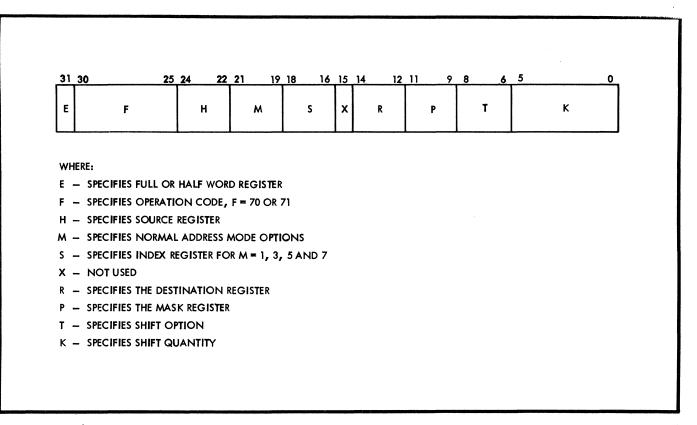

The L-3050 uses a 32-bit instruction format as shown in Figure 2-4. The fields of the instruction specify the following functions:

E, bit position 31 — This one-bit field generally specifies a half word (16-bits) operation or a full word operation (32-bits). If this bit is a one, a full word operation (as specified by the instruction's F field) occurs. On a few "interrupt control" type instructions, this bit (when set to a one) allows a program level change.

Figure 2-3. L-3050 Data Word Formats

Figure 2-4. L-3050 Instruction Word Format

1616-62

F, bit positions 30 to 25 — This six-bit field specifies the operation to be performed by the instruction. In the following instruction descriptions, a two-character octal number is used to specify this six-bit instruction code.

H, bit positions 24 to 22 — This three-bit field addresses the accumulator to be used with the instruction. If the E bit of the instruction is a one, the H field selects one of eight 32-bit accumulators for the operation. If the E bit is a zero, the H field selects one of eight 16-bit accumulators for the operation. There is a separate set of eight 32-bit accumulators and a separate set of eight 16-bit accumulators (a total of 12 full words) for each of the 64 program

- levels. These registers are held in memory for nonactive programs and are held in hardware registers for the active program.

- M, bit positions 21 to 19 This three-bit field provides nine operand addressing modes for the instruction as follows:

- $\underline{M} = 0$ , Direct Address The D, A, and W fields of the instruction word are not modified. The A and W fields specify an operand address in the memory bank that is indirectly selected by the D field. On full 32-bit operand addresses, W is assumed to be 0.

- $\underline{M}$  = 1, Direct Address with Indexing The D, A, and W fields of the instruction word are added to the content of the index register selected by the S field. Overflow on this addition is not detected. The sum replaces the D, A, and W fields within the instruction word register and is used as the new instruction address field as in M = 0.

- <u>M = 2, Literal</u> The D, A, and W fields represent a 16-bit word. A memory cycle to obtain this 16-bit word from memory is not required, thereby reducing instruction execution time. This word may be used as: an operand, a mask, an instruction address, a move instruction command, a shift instruction command, etc., depending upon the instruction's operation code. When this mode is used with full word accumulators, the 16-bit word is assumed to be right justified. That is, it is assumed to line up with the right half of the full word.

- $\underline{M} = 3$ , Literal with Indexing The D, A, and W fields represent a 16-bit half word as in mode 2. However, the process register that is selected by the instruction's S field is arithmetically added to this half word before the instruction operation (that is specified by the F field) takes place. This provides a useful double operation on many instructions. Overflow is detected on this addition, if it occurs the overflow indicator is set.

- $\underline{M}$  = 4, Indirect The contents of the memory word that is directly addressed by the D, A, and W fields is used as a 16-bit address. This "indirect" address replaces the D, A, and W fields within the instruction word register and is used as in M = 0.

- $\underline{M}$  = 5, Indexed, Indirect The D, A, and W fields of the instruction word are added to the index register that is selected by the S field. Overflow on this addition is not detected. The sum is used to address a 16-bit

word in memory that replaces the D, A, and W fields of the instruction in the instruction word register. This new address is then used as in M = 0.

- $\underline{M}$  = 6, Indirect, with Indexing The D, A, and W fields of the instruction select a 16-bit word in memory which is added to the index register selected by the S field of the instruction. No overflow detection occurs. The sum replaces the D, A, and W fields of the instruction in the instruction word register. This new address is then used as in  $\underline{M}$  = 0.

- <u>M = 7</u>, Relative with No Indexing The S field must be all zeros. The content of the current program's instruction location counter is added to the D and A fields of the instruction. The W bit is not modified. Overflow is not detected on this addition. The sum replaces the D and A fields of the instruction within the instruction word register. This operation yields an address that is relative to the address of the <u>next</u> instruction in sequence.

- $\underline{M}$  = 7, Relative with Indexing The S field must not be all zeros; it selects one of seven process registers. The D, A, and W fields of the instruction word are added to the content of this process register. The content of the current program's instruction location counter is then added to this indexed address. Overflow is not detected on either of the additions. The sum replaces the D and A fields of the instruction within the instruction word register. This operation yields an indexed address that is relative to the address of the next instruction in sequence.

- S, bit positions 18 to 16 This three-bit field selects one of eight 16-bit registers to be used for operand address indexing. These eight registers are the same registers as the 16-bit accumulators that are also selectable by the instruction's H field when the E bit is set to a zero. Because of their dual purpose, these registers are called "process registers." The S field is used on address modes M = 1, 3, 5, 6 and 7 with  $S \neq 0$ .

- <u>D</u>, bit positions 15 and 14 These two bits normally select one of four fields in the memory extension register, LD, as shown in Figure 2-5.

The selected four bits are used to select an 8192 word memory bank. Note that four banks, 32,768 words, are addressable with one setting of the memory extension register. This register is easily loaded with a special instruction or by special address to provide access of up to 131,072 full words of memory. The contents of this register may be different for each program level.

Figure 2-5. Address Extension Register

The D bits may also be used as normal memory address bits along with the instruction's A field. The D, A, and W fields represent a 16-bit address that is algebraically added to the contents of the base address register, LB. This option is selected by the program by the setting of two control bits that are located in the indicator word register, IW. The LB register is assumed to be shifted left by two-bit positions with respect to the D, A, and W fields. The algebraic sum yields an 18-bit address that can select up to 131,072 full words. These addresses are relative to the contents of the base address register.

A, bit positions 13 to 1 — These bits represent a full word address in the 8192 word memory bank that was selected either by the instruction's D field and memory extension register or the four most significant bits of the sum of the D and A fields and the base address register.

W, bit position 0 — This bit is used on half word operations (E bit set to 0) to select the left half or right half of the word to be used as the operand. If W is a one the right half of the word is used.

#### 2.1.3.3 Instruction Timing

Instruction execution time in the L-3050 is dependent upon the operant address mode selected by the instruction's M field and the location of instructions and operands in memory. If instructions and operands are located in separate memory banks, advantage of memory cycle overlap is taken.

Table II-3 displays the instruction execution times (in microseconds) for all operand address modes on an add type instruction. The memory overlap column assumes that instructions, indirect addresses and operands are located in different memory banks. The no overlap column displays the instruction timing as if only one memory bank were used for all storage. In addition, it should be noted that a still further reduction in instruction time is possible when the <u>operand</u> is located in the active scratch pad registers.

| OPERAND ADDRESS MODE      | MEMORY OVERLAP    | NO MEMORY OVERLAP |

|---------------------------|-------------------|-------------------|

| M = 0, DIRECT             | 2, 5 MICROSECONDS | 4.0 MICROSECONDS  |

| M = 1, DIRECT, INDEXED    | 3.0 MICROSECONDS  | 4.0 MICROSECONDS  |

| M = 2, LITERAL            | 2.0 MICROSECONDS  | 2.0 MICROSECONDS  |

| M = 3, LITERAL, INDEXED   | 2.0 MICROSECONDS  | 2.0 MICROSECONDS  |

| M = 4, INDIRECT           | 3.5 MICROSECONDS  | 6.5 MICROSECONDS  |

| M = 5, INDEXED, INDIRECT  | 4.0 MICROSECONDS  | 4.0 MICROSECONDS  |

| M = 6, INDIRECT, INDEXED  | 4.0 MICROSECONDS  | 4, 0 MICROSECONDS |

| M = 7, RELATIVE, NO INDEX | 3.0 MICROSECONDS  | 4.0 MICROSECONDS  |

| M = 7, RELATIVE, INDEXED  | 3, 5 MICROSECONDS | 4.0 MICROSECONDS  |

Table II-3. Add Class Instruction Timing

The most general case, for those instructions which require an operand, is the direct address mode (M = 0). The most common case for those instructions which use the instruction's address field for other than operand addresses (such as transfer instructions) is the literal mode (M = 2). These are the times that are quoted with the instruction descriptions in Subsection 2.1.3.4. It is also assumed that data and instructions are located in different memory banks in the quoted times of Subsection 2.1.3.4.

There is no difference in instruction timing between half word and full word operations except on multiply, divide and square root instructions.

When the relative address option (see Subsection 2.1.3.5) is used on operand addressing, instruction execution times are increased by one-half microsecond.

All instruction execution times that are shown in this document represent design goals. These times assume that a full memory cycle, including logic propagation times for addressing and control will require 2.0 microseconds. It is also assumed that memory access on a read operation will require 1.0 microseconds.

#### 2.1.3.4 Instruction Descriptions

In describing each L-3050 instruction (see Subsections 2.1.3.4.1 through 2.1.3.4.7) the following notations are used:

- E The instruction word's E bit.

- F The instruction word's F field.

- H The instruction word's H field.

- h The contents of the selected accumulator, selected by the instruction's H field. h may be a 16-bit or 32-bit accumulator.

- h+1 The contents of the next numbered accumulator that was selected by the instruction's H field.

- L Represents the contents of the instruction location register. This number is the address of the next instruction in normal sequence.

- n The number of bit positions shifted on a shift type instruction.

- Y A general representation for the instruction's operand address.

- () Parentheses represent the contents of the memory location that is addressed by the word within the parentheses.

- Absolute value.

- ✓ Logical inclusive OR function.

- Logical exclusive OR function.

- -- "Replaces."

Unless otherwise noted in the instruction descriptions, the interpretation of the instruction's E bit is to select a half or a full word operation, the H field selects an accumulator, the M field selects the operand addressing mode, and the S field selects an index register.

The term "process register" is used in most instruction descriptions. This term is used in place of "accumulators" because the register selected by the instruction's H field may be a 16-bit index register, a 16-bit accumulator or a 32-bit accumulator.

Table II-4 contains a summary of L-3050 instructions.

#### 2.1.3.4.1 Arithmetic Class.

| Add          | General: $h+(Y) \rightarrow h$              | 2.5 µsec |

|--------------|---------------------------------------------|----------|

| E = 0, ADH   | The operand (Y) is algebraically added to   |          |

| E = 1, $ADF$ | the process register h. If arithmetic over- |          |

| F = 10       | flow occurs, the overflow indicator is set. |          |

| E   | F          | NAME                                               | MNE        | E                                                | F        | NAME                                                        | MNE        |

|-----|------------|----------------------------------------------------|------------|--------------------------------------------------|----------|-------------------------------------------------------------|------------|

| 0 0 | 00         | HALT                                               | HLT        | 1                                                | 00       |                                                             |            |

| 0   | 01<br>02   | EXECUTE EXCHANGE HALF                              | EXE<br>EXH |                                                  | 01<br>02 | EXCHANGE FULL                                               | EXF        |

| Ö   | 03         | EXCHANGE DOUBLE HALF                               | EDH        | i                                                | 03       |                                                             | -          |

| 0   | 04         | LOAD HALF                                          | LSH        | !                                                | 04       | LOAD FULL                                                   | LSF        |

| 0   | 05<br>06   | STORE HALF LOAD DOUBLE, HALF                       | STH<br>LDH | <del>                                     </del> | 05<br>06 | STORE FULL LOAD DOUBLE FULL                                 | STF<br>LDF |

| 0   | 07         | STORE DOUBLE, HALF                                 | S DH       | l i                                              | 07       | STORE DOUBLE FULL                                           | SDF        |

| 0   | 10         | ADD HALF                                           | ADH        | 1 !                                              | 10       | ADD FULL                                                    | ADF        |

| 0   | 11<br>12   | SUBTRACT HALF ADD HALF REPLACE                     | SBH<br>RAH |                                                  | 11<br>12 | SUBTRACT FULL ADD FULL, REPLACE                             | SBF<br>RAF |

| ŏ   | 13         | SUBTRACT HALF REPLACE                              | RSH        | l i                                              | 13       | SUBTRACT FULL, REPLACE                                      | RSF        |

| 0   | 14         | ADD ABSOLUTE HALF                                  | AAH        | 1                                                | 14       | ADD ABSOLUTE FULL                                           | AAF        |

| 0   | 15<br>16   | SUBTRACT ABSOLUTE HALF LOAD ABSOLUTE HALF          | SAH<br>LAH | 1 1                                              | 15<br>16 | SUBTRACT ABSOLUTE FULL LOAD ABSOLUTE, FULL                  | SAF<br>LAF |

| 0   | 17         | LOAD COMPLEMENT, HALF                              | LCH        | l i                                              | 17       | LOAD ABSOLUTE, FULL                                         | LCF        |

| 0   | 20         | EXCLUSIVE OR HALF                                  | EOH        | 1                                                | 20       | EXCLUSIVE OR FULL                                           | EOF        |

| 0   | 21<br>22   | INCLUSIVE OR HALF LOGICAL AND HALF                 | IOH<br>ANH | 1                                                | 21       | INCLUSIVE OR FULL                                           | IOF        |

| 0   | 22         | MEMORY BANK DESIGNATE                              | MBD        | l i                                              | 22       | LOGICAL AND FULL BASE MEMORY DESIGNATE                      | ANF<br>MBB |

| Ö   | 24         | REPLACES EXCLUSIVE OR, HALF                        | REH        | i                                                | 24       | REPLACES EXCLUSIVE OR, FULL                                 | REF        |

| 0   | 25         | REPLACES INCLUSIVE OR, HALF                        | RIH        | !                                                | 25       | REPLACES INCLUSIVE OR, FULL                                 | RIF        |

| 0   | 26<br>27   | REPLACE LOGICAL AND, HALF MEMORY BANK ASSIGN       | RNH<br>MBA | 1                                                | 26<br>27 | REPLACE LOGICAL AND, FULL                                   | RNF        |

| 0   | 30         | MULTIPLY HALF                                      | MPH        | i                                                | 30       | MULTIPLY FULL                                               | MPF        |

| 0   | 31         | DIVIDE HALF                                        | DIH        | !                                                | 31       | DIVIDE FULL                                                 | DIF        |

| 0   | 32         | DECREMENT H BY TWO                                 | DIX        | 1                                                | 32<br>33 | INCREMENT H BY TWO                                          | ITX        |

| 0   | 33<br>34   | DECREMENT H BY ONE TRANSFER ON INDICATORS          | ITX<br>XFR | I                                                | 33       | INCREMENT H BY ONE                                          | IOX        |

| 0   | 35         | TRANSFER AND STORE LINK                            | XLK        | 11                                               | 35       |                                                             |            |

| 0   | 36         | TRANSFER ON CONSOLE SWITCH                         | XSW        | !                                                | 36       |                                                             |            |

| 0   | 37<br>40   | TRANSFER OF HALF = 0                               | XZH        | 1                                                | 37<br>40 | TRANSFER IF FULL = 0                                        | XZF        |

| 0   | 41         | TRANSFER OF HALF = 0                               | XNH        | i                                                | 41       | TRANSFER IF FULL # 0                                        | XNF        |

| 0   | 42         | TRANSFER IF HALF < 0                               | XLH        | 1                                                | 42       | TRANSFER IF FULL < 0                                        | XLF        |

| 0   | 43<br>44   | TRANSFER IF HALF ≥ 0 SHIFT HALF                    | SHH        | 1                                                | 43<br>44 | TRANSFER IF FULL > 0 SHIFT FULL                             | XPF<br>SHF |

| 0   | 44<br>45   | JULI UMPL                                          | DFP        | i                                                | 45       | JULI FOLL                                                   | эпг        |

| 0   | 46         |                                                    | MFP        | 1                                                | 46       |                                                             |            |

| 0   | 47         |                                                    | 1          | !                                                | 47<br>50 |                                                             |            |

|     |            |                                                    | SFR        | 1                                                | 52<br>53 |                                                             |            |

| 0   | 54         | GATED COMPARE HALF                                 | GCH        | 1                                                | 54       | GATED COMPARE FULL                                          | GCF        |

| 0   | 55         | COMPARE HALF                                       | CWH        | !                                                | 55       | COMPARE FULL                                                | CMF        |

| 0   | <b>5</b> 7 |                                                    | SFQ        | 1                                                | 56<br>57 | SQUARE ROOT FIXED                                           | SQP        |

| 0   | 5/<br>60   | SET LOWER BIT OF Y                                 | SBL        | i                                                | 60       | SET LOWER BIT AND INTERRUPT                                 | SLI        |

| 0   | 61         | SET UPPER BIT OF Y                                 | SBU        | 1                                                | 61       | SET UPPER BIT AND INTERRUPT                                 | SUI        |

| 0   | 62         | RESET LOWER BIT OF Y RESET UPPER BIT OF Y          | RBL        |                                                  | 62       | RESET LOWER BIT AND INTERRUPT RESET UPPER BIT AND INTERRUPT | RLI<br>RUI |

| 0   | 63<br>64   | TEST LOWER BIT FOR ZERO                            | TLZ        | i                                                | 64       | TEST AND SET LOWER BIT                                      | TLI        |

| Ó   | 65         | TEST UPPER BIT FOR ZERO                            | TUZ        | 1                                                | 65       | TEST AND SET UPPER BIT                                      | TZI        |

| 0   | 66         | TEST LOWER BIT FOR ONE<br>TEST UPPER BIT FOR ONE   | TLM<br>TUN | I<br>I                                           | 66<br>67 | TEST AND RESET LOWER BIT<br>TEST AND RESET UPPER BIT        | TNI<br>TUI |

| 0   | 67<br>70   | MOVE AND ZERO, HALF                                | MZH        | 1                                                | 70       | MOVE AND ZERO, FULL                                         | MZF        |

| ŏ   | 70<br>71   | MOVE AND INSERT, HALF                              | MIH        | i                                                | 71       | MOVE AND INSERT, FULL                                       | MIF        |

| 0   | 72         | STORE ALL ZEROS, HALF                              | SZH        | !                                                | 72       | STORE ALL ZEROS, FULL                                       | S ZF       |

| 0   | 74<br>75   | DEVICE COMMAND                                     | DEC<br>ITH | 1                                                | 74<br>75 | DEVICE COMMAND, SUICIDE<br>INPUT TO REGISTER, FULL          | DES<br>ITF |

| 0   | 75<br>76   | INPUT TO REGISTER, HALF OUTPUT FROM REGISTER, HALF | OFH        | l i                                              | 75<br>76 | OUTPUT FROM REGISTER, FULL                                  | OFF        |

| ŏ l | 76<br>77   | NO OPERATION                                       | NOP        | i                                                | 77       | DIAGNOSE                                                    | DIG        |

| •   |            | •                                                  |            |                                                  |          |                                                             |            |

| 1   |            |                                                    | ]          |                                                  |          |                                                             |            |

| 1   |            |                                                    | 1          |                                                  |          | 1                                                           |            |

| i   |            |                                                    |            |                                                  |          | l                                                           |            |

|     | ľ          |                                                    | 1          | 1                                                |          | 1                                                           |            |

|     |            |                                                    |            |                                                  |          | •                                                           |            |

|     |            |                                                    | , 1        |                                                  |          |                                                             |            |

| l   |            |                                                    |            |                                                  |          |                                                             |            |

|     |            |                                                    |            |                                                  |          |                                                             |            |

| 1   |            |                                                    | [          | [                                                | l        | l                                                           |            |

| 1   |            |                                                    |            |                                                  | l        |                                                             |            |

| 1   |            |                                                    |            |                                                  |          |                                                             |            |

| I   |            |                                                    |            |                                                  |          |                                                             |            |

| l   |            |                                                    | ļ i        |                                                  |          |                                                             |            |

|     |            |                                                    | [ [        |                                                  | ĺ        | 1                                                           |            |

| ł   |            |                                                    |            |                                                  |          |                                                             |            |

|     |            |                                                    |            |                                                  | 1        |                                                             |            |

|     |            |                                                    |            |                                                  |          |                                                             |            |

|     |            |                                                    |            |                                                  |          |                                                             |            |

Table II-4. Summary of L-3050 Instructions

# USE OR DISCLOSURE OF PROPOSAL DATA IS SUBJECT TO THE RESTRICTION ON THE TITLE PAGE OF THIS PROPOSAL

| Subtract                           | General: h - (Y)→h                                                                                                                                                                                                                                | 2.5 μsec |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| E = 0, SBH<br>E = 1, SBF<br>F = 11 | The operand (Y) is algebraically subtracted from process register h. If arithmetic overflow occurs, the overflow indicator is set.                                                                                                                |          |

| Replace Add                        | General: $(Y) + h \longrightarrow (Y)$                                                                                                                                                                                                            | 3.5 µsec |

| E = 0, RAH<br>E = 1, RAF<br>F = 12 | The process register h is algebraically added to the operand at address Y. h is not changed. If arithmetic overflow occurs, the overflow indicator is set.                                                                                        |          |

| Replace Subtract                   | General: $(Y) - h \rightarrow (Y)$                                                                                                                                                                                                                | 3.5 µsec |

| E = 0, RSH<br>E = 1, RSF<br>F = 13 | The process register h is algebraically subtracted from the operand at address Y. h is not changed. If arithmetic overflow occurs, the overflow indicator is set.                                                                                 |          |

| Add Absolute                       | General: $h +  (Y)  \rightarrow h$                                                                                                                                                                                                                | 2.5 µsec |

| E = 0, AAN<br>E = 1, AAF<br>F = 14 | The operand (Y) is algebraically added to process register h, if it is positive or it is algebraically subtracted from process register h if it is negative. If arithmetic overflow occurs, the overflow indicator is set.                        |          |

| Subtract Absolute                  | General: $h -  (Y)  \rightarrow h$                                                                                                                                                                                                                | 2.5 μsec |

| E = 0, SAH<br>E = 1, SAF<br>F = 15 | The operand (Y) is algebraically subtracted from process register h if it is positive or it is algebraically added to process register h if it is negative. If arithmetic overflow occurs, the overflow indicator is set.                         |          |

| Load Absolute                      | General: $ (Y)  \rightarrow h$                                                                                                                                                                                                                    | 2.5 μsec |

| E = 0, LAH<br>E = 1, LAF<br>F = 16 | The operand (Y) replaces the process register h if it is positive. If (Y) is negative it is converted to the equivalent positive number (two's complement) and replaces h. If the operand (Y) is a minus one, the overflow indicator will be set. |          |

- 10

| Load Complement                    | General: -(Y)→h                                                                                                                                                                                                                                                                                                                                 | 2.5 µsec         |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| E = 0, LCH<br>E = 1, LCF<br>F = 17 | If the operand (Y) is a negative number, the positive equivalent is loaded into process register h. If the operand (Y) is a positive number, the negative equivalent is loaded into process register h(Y) represents the two's complement of (Y). If the operand (Y) is a minus one (-1.0) the overflow indicator will be set.                  |                  |

| Multiply                           | General: $h \times (Y) \longrightarrow h$ , $h + 1$                                                                                                                                                                                                                                                                                             | if E = 0:6 μsec  |

| E = 0, MPH<br>E = 1, MPF<br>F = 30 | The operand (Y) is multiplied by process register h. The result is a double word product that replaces the process register pair, h and h + 1. Overflow may occur on the addition if minus one is multiplied times minus one. If overflow occurs, the overflow indicator is set.                                                                | if E = 1:10 μsec |

| Divide                             | General: h, h + l $\div$ (Y) $\longrightarrow$ h, REM $\longrightarrow$ h + l                                                                                                                                                                                                                                                                   | if E = 0:10 μsec |

| E = 0, DIH<br>E = 1, DIF<br>F = 31 | The process register pair, h, h + l is divided by the operand (Y). The quotient plus sign is stored into process register h. The remainder is stored into process register, h + l. The sign of the remainder equals the sign of the dividend. Overflow represents an illegal divide when the divisor (Y) is less than or equal to the dividend. | if E = 1:18 μsec |

| Square Root                        | General: $\sqrt{(Y)} \rightarrow h$                                                                                                                                                                                                                                                                                                             | 18 µsec          |

| E = 1, SQP<br>F = 56               | The square root of the full, fixed point word at address Y is extracted and stored into accumulator h. If the operand is negative, the overflow indicator is set.                                                                                                                                                                               |                  |

#### 2.1.3.4.2 Logical Class

General:  $h \forall (Y) \rightarrow h$ 2.5 µsec Exclusive OR E = 0, EONThe operand (Y) is logically matched with E = 1, EOF process register h. For every one bit in F = 20(Y) and corresponding zero bit in h a one is inserted into that bit position of h. For every one bit in (Y) and corresponding one bit in h a zero is inserted into that bit position of h. Zero bits in (Y) do not modify the corresponding bit positions in h. Inclusive OR General:  $h V (Y) \rightarrow h$ 2.5 µsec E = 0, IOH The operand (Y) is logically merged with the E = 1, IOF process register h. For every one bit in (Y) F = 21a one is inserted into that bit position of h, regardless of its original state. Zero bits in (Y) do not modify the corresponding bit position in h. Logical AND General:  $h \Lambda (Y) \rightarrow h$ 2.5 µsec E = 0, ANH The operand (Y) is logically masked with the E = 1, ANF process register h. For each zero bit in (Y) F = 22the corresponding bit position in h is reset to a zero. For each one bit in (Y) the corresponding bit position in h remains unchanged. General:  $(Y) \forall h \longrightarrow (Y)$ 3.5 µsec Replace Exclusive OR Process register h is logically matched with E = 0, REH operand (Y). For every one bit in h the corre-E = 1, REF sponding bit position of (Y) is set to a one if it F = 24was a zero or it is reset to a zero if it was a one. Zero bits in h will not change the corre-

sponding bit positions in (Y).

Replace Inclusive OR General:  $(Y) V h \longrightarrow (Y)$

3.5 µsec

E = 0, RIH E = 1, RIF

F = 25