# SBC M1 SERIES SINGLE BOARD COMPUTER

# **User Guide**

# **0. FIRST EDITION**

# M1 Single Board Computer User Guide Version 1.0

The material in this SBC M1 User Guide may be subject to modification. Notification of any modifications may not be given but copies of any such changes will be available. The following are trademarks or model numbers of Digital Equipment Corporation used in this document:

- DLV11 - LSI-11 - Q-BUS - DCJ11 - PDP-11

# Mentec Limited Mentec House,Dun Laoghaire Industrial Estate Dun Laoghaire Co. Dublin Ireland

| Telephone: | 353-1-2059797 |

|------------|---------------|

| Fax:       | 353-1-2059798 |

Mentec Limited assumes no responsibility for any errors, which may appear in this document

Copyright 1998 - Mentec Limited. All Rights Reserved

1

# CONTENTS

# PAGE

| PREFACE                              |     |

|--------------------------------------|-----|

| AUDIENCE                             | 0-6 |

| ORGANISATION                         | 0-6 |

| RELATED DOCUMENTS                    | 0-7 |

|                                      |     |

| CHAPTER 1 PRODUCT OVERVIEW           |     |

| 1.1 INTRODUCTION.                    | 1-1 |

| 1.2 PROCESSOR                        | 1-1 |

| 1.3 MEMORY                           | 1-1 |

| 1.4 LSI-BUS INTERFACE                | 1-1 |

| 1.5 SERIAL LINES.                    | 1-1 |

| 1.6 LINE TIME CLOCK                  | 1-2 |

| 1.7 BOOTSTRAPS.                      | 1-2 |

| 1.8 INTERRUPTS.                      | 1-2 |

| 1.9 LED DISPLAY                      | 1-2 |

|                                      |     |

| CHAPTER 2 SPECIFICATIONS             |     |

| 2.1 PHYSICAL.                        | 2-1 |

| 2.2 POWER REQUIREMENTS.              | 2-1 |

| 2.3 ENVIRONMENTAL                    | 2-1 |

| 2.3.1 Temperature                    | 2-1 |

| 2.3.2 Airflow                        | 2-1 |

| 2.3.3 Environment                    | 2-1 |

| 2.3.4 Relative Humidity              | 2-2 |

| 2.4 CONNECTORS AND CABLES            | 2-2 |

|                                      |     |

| CHAPTER 3 UNPACKING AND INSTALLATION |     |

| 3.1 INTRODUCTION.                    | 3-1 |

| 3.2 UNPACKING                        | 3-1 |

| 3.3 INSTALLATION.                    | 3-2 |

| 3.3.1 Introduction                   | 3-2 |

| 3.3.2 Bus Connections                | 3-2 |

| 3.4 USER CONNECTION                  | 3-3 |

| 3.5 DIAGNOSTIC LEDs AND POWER-UP     | 3-3 |

# CONTENTS

PAGE

| CHAPTER 4 SELECTABLE HARDWARE CONFIGUR      | ATION  |

|---------------------------------------------|--------|

| 4.1 INTRODUCTION                            | 4-1    |

| 4.1.1 Bus Grant Continuity Jumpers.         |        |

| 4.1.2 Fuse                                  | 4-1    |

| 4.1.3 Factory Hardware Default Switch       | 4-1    |

| 4.1.4 Rotary Baudrate Switch.               | 4-2    |

| CHAPTER 5 PROGRAMMABLE MODULE CONFIGU       | RATION |

| 5.1 INTRODUCTION.                           |        |

| 5.2 FUNCTIONAL OVERVIEW                     | 5-1    |

| 5.3 OPERATIONAL OVERVIEW                    | 5-1    |

| 5.4 AUTOMATIC BOOT MODE.                    | 5-2    |

| 5.5 DIALOGUE MODE                           | 5-2    |

| 5.5.1 BOOT - Boot from a specific device.   | 5-3    |

| 5.5.2 HELP - Provide a summary of commands. | 5-3    |

| 5.5.4 MAP - Display a map of address space. | 5-4    |

| 5.5.5 SETUP - Configure the SBC M1          | 5-4    |

| 5.5.5.1 Modify Hardware Setup               | 5-5    |

| 5.5.5.2 Modify Software Setup               | 5-10   |

| 5.5.5.3 Save Modified Setup.                |        |

| 5.5.5.4 Initialise To Factory Setup         | 5-13   |

| 5.5.5.5 Configure Autoboot List             | 5-13   |

| 5.5.5.6 Configure Device Translations       | 5-14   |

| 5.5.5.7 Exit Setup                          | 5-15   |

| 5.6 BOOTPROM MAPPING                        | 5-16   |

| 5.7 USAGE OF BOOTPROM WINDOWS               | 5-16   |

| 5.8 CODE OVERVIEW                           | 5-17   |

| 5.9 DEVELOPMENT UTILITIES                   | 5-18   |

#### CONTENTS

PAGE

#### SYSTEM ARCHITECTURE **CHAPTER 6** 6.1 INTRODUCTION ..... 6-1 6.2 PROCESSOR MODES ..... 6-1 6.3 GENERAL PURPOSE REGISTERS ..... 6-1 6.4 SPECIAL PURPOSE REGISTERS ..... 6-2 6.4.1 Internal Registers. 6-2 6.4.1.1 The Processor Status Word ..... 6-3 6.4.1.2 The CPU Error Register ..... 6-5 6.4.2 The System Registers ..... 6-7 6.4.2.1 The Maintenance Register. 6-7 6.4.3 The External Registers. 6-7 6.4.4 The Power-Up Register ..... 6-8 6.4.5 The Program Interrupt Request Register. 6-9 6.5 MEMORY MANAGEMENT 6-11 6.5.1 Active Page Registers ..... 6-11 6.5.1.1 Page Address Register ..... 6-11 6.5.1.2 Page Descriptor Register ..... 6-11 6.5.2 The Memory Management Registers ..... 6-13 6.5.2.1 Memory Management Register 0 ..... 6-13 6.5.2.2 Memory Management Register 1 ..... 6-14 6-14 6.5.2.4 Memory Management Register 3 ..... 6-15 6.5.3 Mapping from Virtual to Physical Memory ..... 6-16 6.5.4 Instruction and Data Space ..... 6-16 6.6 SBC M1 MEMORIES ..... 6-17 6.6.1 Main Memory ..... 6-17 6-17 6-17 6.7 EPROM STORAGE AND USE ..... 6-19 6.8 PROGRAM CONTROL OF THE LINE-TIME CLOCK 6-19 6.9 PAGE CONTROL REGISTER FOR BOOTPROM ..... 6-19 6.10 PARITY MEMORY CONTROL AND STATUS BIT ASSIGN. 6-20

SBC M1 USER GUIDE

*REF:M1UG ISSUE: REV V1.0.*

# CONTENTS

PAGE

| CHA    | PTER 7         | SERIAL I/O INTERFACE           |      |

|--------|----------------|--------------------------------|------|

| 7.1 IN | ITRODUCTI      | ON                             | 7-1  |

|        |                | RD                             | 7-1  |

|        |                | ARCHITECTURE                   | 7-2  |

|        |                |                                | 7-2  |

|        |                |                                | 7-2  |

| 7.3.3  | Serial Line In | terrupt Priorities             | 7-2  |

|        |                | REGISTERS                      | 7-3  |

|        |                | CABLES                         | 7-5  |

|        |                | S                              | 7-9  |

| 7.5.2  | User Cable C   | onstruction                    | 7-11 |

| APPE   | ENDIX A        | BACKPLANE PIN UTILISATION      |      |

| A      | APPENDD        | A - BACKPLANE PIN UTILISATION  | A-1  |

| APPE   | ENDIX B        | OP CODES & TRAPS               |      |

| B 1    | NUMERIC        | AL OP CODE LISTINGS            | B-1  |

| B.2    |                | PTS ASYNCHRONOUS & SYNCHRONOUS | B-4  |

| APPE   | ENDIX C        | I/O PAGE MEMORY MAP            |      |

| С      | APPENDIX       | C - I/O PAGE MEMORY MAP        | C-1  |

| APPE   | NDIX D         | DEVICE MNEMONICS               |      |

| D      | APPENDD        | <b>X D - DEVICE MNEMONICS</b>  | D-1  |

# PREFACE AUDIENCE

This document is intended for two specific types of user. Firstly, the engineer who needs to configure and install the SBC M1 Single Board Computer. Secondly, the programmer who wants to write applications software for the module. An overview of the architecture is given, but the document is not intended as a tutorial on PDP-11's.

# ORGANISATION

Configuration, programming and installation details are divided among the chapters as follows:

# **CHAPTER 1: PRODUCT OVERVIEW**

Chapter 1 describes the main functions and features of the SBC M1

#### **CHAPTER 2: SPECIFICATIONS**

Chapter 2 gives a quantitative description of the features of the SBC M1.

# **CHAPTER 3: UNPACKING AND INSTALLATION**

Chapter 3 outlines the steps a user must follow in order to successfully unpack and install the module.

# **CHAPTER 4: HARDWARE CONFIGURATION**

Chapter 4 explains how the user can alter the hardware configuration of the SBC M1.

# **CHAPTER 5: SELECTABLE SOFTWARE CONFIGURATION**

Chapter 5 describes the functionality and operation of the SBC M1 software.

# **CHAPTER 6: SYSTEM ARCHITECTURE**

Chapter 6 gives an overview of the architecture of the SBC M1 module. It describes how the PDP-11 architecture is implemented on the SBC M1.

#### **CHAPTER 7: SERIAL I/O INTERFACE**

Chapter 7 details the architecture, programming and cables of the serial-line sub-system.

#### **APPENDIX A: BACKPLANE PIN UTILISATION**

Appendix A lists the Q-Bus signals and indicates their positions on the module.

# **APPENDIX B: OP CODES & TRAPS**

Appendix B contains a list of PDP-11 OP Codes.

# APPENDIX C: I/O PAGE MEMORY MAP

Appendix C contains a memory map of the I/O page for the SBC M1.

# **APPENDIX D: DEVICE MNEMONICS**

Appendix D contains the device mnemonics as used in the boot prompts.

# **RELATED DOCUMENTS**

The following Digital Equipment Corporation publications provide additional information on DEC PDP-11. DCJ11 User Guide, Micro PDP-11 Hand Book and the Micro PDP-11 Interface Hand Book

# **1 PRODUCT OVERVIEW**

#### **1.1 INTRODUCTION**

The SBC M1 module is a high performance ASIC based PDP11 quad height QBUS card. The module contains 1 to 4Mb of RAM, four DLV11J compatible serial lines and 32 Kb of FLASH EPROM, and a 50Hz, 60Hz, 800Hz or BEVENT real-time clock. The SBC M1 also interfaces to the 22-bit Q-BUS and supports block mode DMA.

#### **1.2 PROCESSOR**

The M1 is a high performance PDP-11 similar in functionality to previous Mentec PDP11 CPU's. PDP11 instructions are implemented in "Microcode" a micro programmed subsystem based on an ASIC implementation. The Console ODT function is also performed in the M1's Microcode.

#### **1.3 MEMORY**

The module contains 1Mb/2Mb/3Mb/4Mb of Q-bus non-parity SRAM. The Module's SRAM is accessible by other system devices over the Q-bus using DMA.

#### **1.4 LSI-BUS INTERFACE**

The module interfaces to the extended LSI-11 bus and can address up to 4 MB of main memory and communicate with other bus devices, disk controllers or asynchronous serial line multiplexers. The 22-bit extended LSI-11 bus is completely downward compatible with the standard 18-bit LSI-11 bus.

#### **1.5 SERIAL LINES**

Contained on the module are four independent, full-duplex, asynchronous serial line units (SLUs) which are software compatible with the DLV11J Q-bus module. Channel number 3 is configurable as the system console. The interface transmits and receives data from the peripheral device over EIA lines, which support data leads only. The four independent lines are contained within a single FPGA chip.

#### **1.6 LINE TIME CLOCK**

The line time clock on the module is used by software systems to control events, such as operating system scheduling, software interrupts and system time.

#### **1.7 BOOTSTRAPS**

There are a number of primary bootstraps available on the module, which facilitate the loading of secondary bootstraps from storage devices, such as tape and disk drives.

#### **1.8 INTERRUPTS**

An interrupt allows the current code being executed by the processor to be suspended, while the requesting device is serviced. The interrupt source may be from either the LSI-11 bus or the SBC M1 processor. The interrupt facility of the LSI-11 bus, supported by the module, allows any I/O device to temporarily suspend the current program execution and divert the processor operation to service the requesting device.

# **1.9 LED DISPLAY**

The LED display indicates the power up status and operating status of the module i.e. is there power on the module, have all power-up diagnostics been passed, is the module in console ODT or executing software.

# **2. SPECIFICATION**

# 2.1 PHYSICAL

| Height - | 25 mm.  |

|----------|---------|

| Length - | 214 mm. |

| Width -  | 265 mm. |

| Weight - | 426 g.  |

#### 2.2 POWER REQUIREMENTS

| Power Supply - | +5.0 V +10%/-5% | 7A (typical). |  |  |

|----------------|-----------------|---------------|--|--|

|                | +12V +/- 5%     | 2A (max.).    |  |  |

| NOTE: | The M1 does not use 12V it only supplies it to |

|-------|------------------------------------------------|

|       | the Berg headers for use by external devices.  |

# 2.3 ENVIRONMENTAL

#### 2.3.1 TEMPERATURE

| Storage -          | -10 to 60 Degrees C. |

|--------------------|----------------------|

| <b>Operating</b> - | 0 to 50 Degrees C.   |

| NOTE: | The module should be brought into operating conditions and allowed to |

|-------|-----------------------------------------------------------------------|

|       | stabilise before commencing operation.                                |

# 2. 3.2 AIRFLOW

**Operating** - Adequate airflow must be provided to limit the inlet to outlet temperature rise across the module to 5 Degrees C when the inlet temperature is 35 Degrees C.

**NOTE:** These are design limits. Lower temperature limits will serve to increase the life of the product.

# 2. 3.3 ENVIRONMENT

**Operating** Air must be non-caustic.

# 2. 3 .4 RELATIVE HUMIDITY

| Storage -          | 10% to 90% | (no condensation). |

|--------------------|------------|--------------------|

| <b>Operating</b> - | 10% to 90% | (no condensation). |

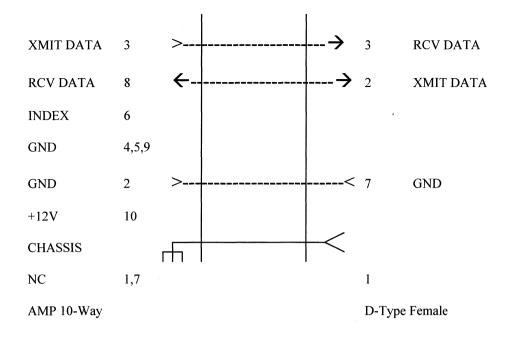

# 2. 4 CONNECTORS AND CABLES

| <b>Connectors:</b> | AMP 2x5 pin male                      |

|--------------------|---------------------------------------|

| J3 to J6:          | RS232 Null Modem - DEC BC20N-05       |

| Cables:            | [2x5 pin AMP female to RS-232C female |

|                    | (25-way Cannon D-type)].              |

# 3. UNPACKING AND INSTALLATION

# **3.1 INTRODUCTION**

This chapter explains how to unpack and install the SBC M1 module. It is advisable to leave the module in the factory configuration until its operation has been verified.

# 3.2 UNPACKING

The following four steps outline how the SBC M1 should be unpacked. (If there is visible damage to the shipping carton then the module should be unpacked in the presence of the delivering carriers agent).

# WARNING STATIC ELECTRICITY CAN DAMAGE COMPONENTS ON THE MODULE. PROPER PRECAUTIONS SHOULD BE TAKEN DURING ANY OPERATION WHICH INVOLVES HANDLING THE BOARD.

- 1). Ensure that an anti-static wrist-strap is being worn.

- 2). Lay the shipping carton on a flat surface and open out the flap.

- 3). Remove the module from the anti-static bubble-wrap. Allow a moment for any static to leak away to ground and then remove the module from the anti-static bag.

- 4). Inspect the module for damage.

If the module is damaged then no installation or repair should be undertaken. If the delivering carriers agent was not present during the unpacking then an insurance inspection claim should be called for. If the board is to be repaired then it should be returned to the distributor.

# **3.3 INSTALLATION**

# 3.3.1 Introduction

This section details the installation of the SBC M1. Bus connections and user connections are described. Full details of the LED display on the front of the module are also given since monitoring these is the first step in verifying the correct operation of the module.

# 3. 3.2 Bus Connections

The following must be verified before the module is installed in the backplane:

- 1). The backplane is a correct Q-Bus AB-AB or AB-CD backplane.

- 2). +5Vdc and +12Vdc are available at the correct points on the backplane Module damage will result if user power is incorrectly bussed (ref AppendixA).

- 3). There is adequate power reserve for the module and any other Q- Bus modules which are to be inserted in the backplane.

- 4). The backplane is adequately cooled and there is sufficient airflow.

- 5). The board is configured as required. It is advisable to leave the module in the factory configuration until its operation has been verified.

# WARNING MODULE DAMAGE WILL RESULT IF THE BOARD IS REMOVED FROM THE BACKPLANE WITH POWER APPLIED.

The SBC M1 may now be installed as follows.

- 1).Place the module in the backplane in the first most slot. The other cards should then be placed in the following slots. Ensure that grant continuity is maintained for all the NPR modules. The respective backplane documentation should give details.

- 2). Apply power to the backplane and observe diagnostic LEDs for correct operation.

# **3.4 USER CONNECTION**

The serial communications with the SBC M1 is by means of four AMP ten-way connectors on the front of the module (refer to figure 4.1). A suitable DEC cable is BC20N-05 (5 foot EIA RS-232C null modem cable). For initial module verification a single cable should be connected to J6.

# 3.5 DIAGNOSTIC LEDs AND POWER-UP

|          | J6 | J5 | J4 | J3 | Leds 12-6 | Sw2                               | Led 5 | Leds 4-1 | Sw1 | Led 13 |

|----------|----|----|----|----|-----------|-----------------------------------|-------|----------|-----|--------|

| <b>Q</b> |    | I  | I  |    |           | $\begin{bmatrix} 0 \end{bmatrix}$ |       |          |     |        |

#### **Led Indicators:**

| 1.<br>2. | Led 1 WCS Led 2 WCS |            | Red<br>Red |

|----------|---------------------|------------|------------|

| 3.       | Led 3 WCS           |            | Red        |

| 4.       | Led 4 WCS           | Load 4     | Red        |

| 5.       | Led 5 FP Ind        | licator    | Red        |

| 6.       | Led 6               | 12V        | Green      |

| 7.       | Led 7               | BDCOK      | Green      |

| 8.       | Led 8               | Run        | Green      |

| 9.       | Led 9               | ODT        | Red        |

| 10.      | Led 10              | Console    | Red        |

| 11.      | Led 11              | Memory     | Red        |

| 12.      | Led 12              | CPU        | Red        |

| 13.      | Led 13              | i960 Reset | Red        |

# Hardware Setup Switch SW1 operates as per manual page 4-1 M1 Board Power Up Indicators:

#### Rotary Switch SW2 operates as per manual page 4-3

On power up the M1 SBC differs from The M11 SBC in the following manner. The banner message,

Loading Microcode v1.\* 1 2 3 4 5

is replaced by the extinguishing of six LED indicators in the following sequence,

LED 13 extinguishes followed by Led 5. Then LED's 1,2,3,4 illuminate together and extinguish singularly in the sequence 1, 2, 3, 4. LED's 6 through 12 should be consistent with the SBCM11 LED indicators as described in Table 3.1 at the end of this chapter. This sequence of events indicates a correct power up procedure of the M1 SBC.

The LED display (6 through 12) on the front of the module should be observed while the power is being switched on. When power is applied, two bus signals, BDCOK-H and BPOK-H, are asserted. These signals indicate that the correct DC power and AC line power levels are available. The M1 then proceeds to execute a power-up diagnostic routine, which test the CPU, MEMORY and CONSOLE. When each diagnostic is passed the corresponding diagnostic LED is turned off. The action taken by the M1 at this point depends on the value of the power-up configuration register. If the module is in factory configuration, it will commence executing the boot code resident in the module's FLASH EPROMS.

| Led | Colour | Description                                                                                                                                                                                                           |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | Red    | CPU Test. Cleared on power-up if internal CPU diagnostic is passed.                                                                                                                                                   |

| 7   | Red    | Memory Test. Cleared on power-up if CPU receives<br>a reply from memory at address 0 and no reply from<br>memory at address 17777700 octal                                                                            |

| 8   | Red    | Console Test. Cleared on power-up if CPU receives<br>a reply from console DLART at address 17777560 octal                                                                                                             |

| 9   | Red    | Processor in ODT. Set if processor is running console ODT.                                                                                                                                                            |

| 10  | Green  | Processor Running. Set if the processor is executing code.                                                                                                                                                            |

| 11  | Green  | Power. This LED indicates the status of the signal BDCOK-H<br>on the Q-bus. BDCOK-H is a PSU generated signal that is asserted when<br>there is sufficient DC voltage available to sustain reliable system operation. |

| 12  | Green  | Communications Power. Set if fuse F1 and +/- 12V are operating correctly.                                                                                                                                             |

#### TABLE 3-1STATUS LED DESCRIPTION

# 4. SELECTABLE HARDWARE CONFIGURATION

#### 4.1 INTRODUCTION

Module hardware configuration is by means of selecting switch positions and component values, as described in this chapter, and by means of firmware which is user programmable through the console as described in chapter 5.

#### 4. 1.1 Bus Grant Continuity Jumpers

To confirm the installation of the grant jumpers on the module identify the back-plane and refer to table 4-1 for jumper configuration. Jumpers are located at W1 and W2.

#### **NOTE:-** Jumpers are installed in module on leaving factory.

| Backplane      | Bus Type | Jumpers |

|----------------|----------|---------|

| H9270 (4 slot) | Q/Q      | in      |

| H9275 (9 slot) | Q22/Q22  | in      |

| H9273 (4 slot) | Q/CD     | out     |

| H9276 (9 slot) | Q22/CD   | out     |

#### 4. 1.2 Fuse

If the current drawn by all external device powered via the modules communications connectors (J3 - J6) exceeds 2 amps, the modules fuse (F1) will have to be replaced. LED 12 will be extinguished if the fuse has blown or +/- 12V has failed. Replace the fuse with one of the same specification.

#### 4.1.3 Factory Hardware Default Switch

This switch allows the user to force the module's PROGRAMMABLE HARDWARE CONFIGURATION to factory standard. Switch, SW1 is usually set such that the module's configuration is loaded from the EPROM on power-up (Refer to section 5.5.5.1 for details on factory default).

Figure 4.1 SBC M1 Layout

# 4.1 4 Rotary Baud Rate Default Switch

Switch SW2 provides a hardware over ride switch for the baud rate on the console serial line. This switch effectively over rides the baud rate selected in the Hardware Setup Menu. Table 4-3 provides details of the Rotary Baud Rate switch settings.

| Position | Baud rate                  |  |

|----------|----------------------------|--|

| 0 to 7   | As per Hardware Setup Menu |  |

| 8        | 38400 Baud                 |  |

| 9        | <b>19200 Baud</b>          |  |

| Α        | 9600 Baud                  |  |

| B        | 4800 Baud                  |  |

| С        | 2400 Baud                  |  |

| D        | <b>1200 Baud</b>           |  |

| Е        | 600 Baud                   |  |

| F        | <b>300 Baud</b>            |  |

# 5. PROGRAMMABLE MODULE CONFIGURATION

# **5.1 INTRODUCTION**

This chapter is a guide for the boot/diagnostic and module configuration software. It describes the functionality and basic operation of the software. In addition some of the internal functioning of the software is described.

The bootstrap and diagnostic firmware is contained in one FLASH EPROM on the SBC M1. The EPROM is used both by the power-up circuitry and the boot/diagnostic software to retain setup information.

# **5.2 FUNCTIONAL OVERVIEW**

The bootstrap/diagnostic EPROM provides a set of diagnostics, bootstraps for standard devices, and configuration software for the board. The boot software can operate in two modes viz:

Automatic Mode: - The bootstrap attempts to boot in sequence from a pre-configured list of devices.

**Dialogue Mode:** - The user enters commands directly to configure or boot the system.

Dialogue mode is entered when an non-configured board is booted, when an automatic bootstrap fails, or when <CTRL/C> is entered during the execution of diagnostics or an auto-boot sequence. Therefore if a board is setup for automatic boot, with power-up testing disabled, it may be necessary to unload or disable all devices in the automatic boot list to gain access to the dialogue boot.

# **5.3 OPERATIONAL OVERVIEW**

The boot code supports both ANSI standard video terminals and dumb terminals. ANSI standard terminals use cursor position escape sequences whereas dumb terminals allow only standard ASCII control characters.

Both upper and lower case may be used interchangeably in all responses to the boot/ diagnostic code. Lowercase is converted to and echoed as uppercase.

As the SBC M1 does not have a display register, failures early in testing i.e. before the functionality of the console sub-system are established, are signalled by the processor halting with a failure code in R0.

#### The Failure codes are as follows:

- 0 bootPROM window 0, window number invalid.

- 1 bootPROM window 1, window number invalid.

- 2 bootPROM window 0, checksum invalid.

- 3 bootPROM window 1, checksum invalid.

- 4 Low 64kB memory failure.

- 5 bootPROM window number invalid, not window 0 or 1.

- 6 bootPROM window checksum invalid, not window 0 or 1.

- 7 Processor Trap to memory location 4 octal.

- 10 Processor Trap to memory location 10 octal.

- 11 Data parity error detected, trap location 114 octal.

# 5.4 AUTOMATIC BOOT MODE

Automatic boot mode is selected using the "Setup Option" in dialogue mode. In this mode the bootstrap will run processor and memory diagnostics and then attempt to boot the system from one or a series of devices. These devices may be selected using the "BOOT Option" also in dialogue mode. The diagnostics run during boot are configurable from the setup menu as described in section 5.5.5.

# 5.5 DIALOGUE MODE

Dialogue mode is intended for use in reconfiguring the system. The following is the initial dialogue mode menu:

| BOOT -  | BOOT FROM A SPECIFIC DEVICE.    |

|---------|---------------------------------|

| HELP -  | PROVIDE A SUMMARY OF COMMANDS.  |

| list -  | LIST BOOTSTRAPS PROVIDED.       |

| MAP -   | DISPLAY A MAP OF ADDRESS SPACE. |

| SETUP - | CONFIGURE THE SBC M1.           |

| TEST -  | ENTER A CONTINUOUS TEST MODE.   |

To invoke the required option, enter the associated command and a <CR>.

Note: - 'TEST' assumes that the hardware setup information is valid.

# 5. 5.1 BOOT - Boot from a specific device

To enter this option the user inputs "B<CR>" at the main menu and the SBC M1 responds with the prompt "BOOT>". The BOOT function invokes the SBC M1 device specific bootstrap to load a primary bootstrap from the selected boot device. The user must enter the boot device mnemonic and device unit number followed by "<CR>". The device number is only required in instances when more than one device of a certain type is resident in the system. Note the default device number is "0" e.g. to select a second RL02 drive the user enters DL1 followed by <CR>.

When the software has been loaded from the device, control is relinquished to the primary bootstrap, which normally proceeds to load a secondary bootstrap and then a possible tertiary bootstrap. Success of this operation is usually indicated by a "linefeed" at the console. The devices and the mnemonics that are supported by the SBC M1 are listed in table 5-1.

# TABLE 5-1 SUPPORTED DEVICES

| Mnemonic | Device                          |

|----------|---------------------------------|

| DB       | RM03 emulation                  |

| DD       | TU58                            |

| DL       | RL01/02                         |

| DU       | MSCP                            |

| DX       | RX01                            |

| DY       | RX02                            |

| EE       | CONCENTRATOR                    |

| MS       | TK25/TSV05                      |

| MU       | TK50                            |

| XQ       | DEQNA (Decnet boot)             |

| NL       | Delay for devices to come ready |

5. 5.2 HELP - Provide a summary of commands

This option redisplays the MAIN MENU and is selected by entering "H<CR>" at the above menu. This option is useful when the console is a dumb terminal and it is required to recall the available commands.

# 5. 5.3 LIST - List bootstraps provided

This option lists the mnemonics and corresponding devices that the SBC M1 module can boot from as shown in table 5-1 above. This option is selected by entering "L<CR>" at the MAIN MENU. <CR> returns the user to the main menu.

# 5. 5.4 MAP - Display a map of address space

When this option is selected the SBC M1 reads all locations in the 4Mb address space (0 to 17777777 octal), starting at location 0 and working upwards through the memory address space and then proceeding into the I/O address space. The SBC M1 continues reading until a location fails to reply at which stage it outputs the address it started from and the address of the last location that replied. This procedure is carried out until the complete address range has been read.

This operation reports all contiguous memory blocks and I/O device registers which respond to read commands in the system. The I/O space occupies the top 8 Kbytes of the total 4 Mbytes address space.

This option is selected by entering "M<CR>" at the MAIN MENU. <CR> returns the user back to the main menu.

For listing of fixed I/O page registers refer to Appendix C.

# 5. 5.5 SETUP - Configure the SBC M1

Setup mode allows the configuration of both the SBC M1 hardware and of the boot/diagnostic operation. Alterations to Software Setup take effect immediately, however they must be saved for retention. Hardware alterations only take effect if SW1 is in position "B" on power up. SW1 is used to force the module into factory hardware configuration (position 'A') or load hardware configuration from FLASH EPROM (position 'B'). Software configuration is reset to factory default by selecting option 4 of the Setup Menu.

#### The initial setup mode menu is shown below:

#### SETUP MENU

- 1 MODIFY HARDWARE SETUP

- 2 MODIFY SOFTWARE SETUP

- 3 SAVE MODIFIED SETUP

- 4 INITIALIZE TO FACTORY SETUP

- 5 CONFIGURE AUTOBOOT LIST

- 6 CONFIGURE DEVICE TRANSLATIONS

- 7 EXIT SETUP

To select an option, enter the associated number and press <CR>.

The first two options may be used to obtain a listing of the current setup. No changes are saved to the FLASH EPROM until a save is performed.

#### 5.5.5.1 Modify Hardware Setup

This option is selected by entering "1<CR>" at the "SETUP MENU". The following menu is then displayed indicating the configurable hardware. The various options for each hardware element are described below. "<CR>" returns the user to the "SETUP MENU".

Note that SW1 is only used to temporarily force the module to factory hardware configuration. Changes to the setup may be made with SW1 in either position but only take effect when SW1 is in position "B" and the board is powered up.

NOTE : Any devices which will conflict with the module's factory setups must be removed from the system when the module is being restored to default settings.

To alter a specific hardware element the user enters the corresponding number from the menu followed by <CR>. The menu below shows the factory hardware configuration for the SBC M1 module:

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | Base address of DLV11J emulation .<br>Base vector of DLV11J emulation<br>Serial line 0 baud rate<br>Serial line 1 baud rate<br>Serial line 2 baud rate<br>Serial line 3 baud rate<br>On-board console | 176500<br>300<br>9600<br>9600<br>9600<br>9600<br>Enabled |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 8                                    | On-board LTC                                                                                                                                                                                          | 60 HZ                                                    |

| 9                                    | On-board bootPROM                                                                                                                                                                                     | Enabled                                                  |

| 10                                   | Power-Up mode                                                                                                                                                                                         | 173000                                                   |

| 11                                   | Power-Up address                                                                                                                                                                                      | 000000                                                   |

| 12                                   | On-board parity CSR address                                                                                                                                                                           | 172100                                                   |

| 13                                   | Halt option                                                                                                                                                                                           | Cleared                                                  |

| 14                                   | On board parity enable                                                                                                                                                                                | Enabled                                                  |

| 15                                   | Console Halt enable                                                                                                                                                                                   | Enabled                                                  |

| 16                                   | Memory timeout select                                                                                                                                                                                 | 24uS                                                     |

Note 1 :- In order for a modification to the hardware configuration to take effect the configuration must be saved and the system turned off and on as the information is loaded only during initialisation.

# Note 2 :- Refer to section 5.5.5.4. Restore Factory Hardware Configuration for details on how to reset the SBC M11 module to factory hardware configuration.

The SBC M1 has four on-board serial lines that emulate the functionality of a DLV11J. The first 8 options in the hardware setup menu allow the user to configure most of the characteristics of this emulation. The serial (DL) lines do not support parity generation or the generation of more than one stop bit.

# 1. DLV11J Base Address

A DL module consists of four serial lines. Each serial line has four registers and as a result, the address space for the DL module requires sixteen contiguous locations. Therefore the base address for the DL module must increment in 40 octal bytes or 16 decimal words in the range 160000 octal to 177740 octal.

# NOTE:- That the I/O page addresses for these serial lines will occupy range of 30 octal if the on-board console is enabled and 40octal if it is disabled.

# 2. DLV11J Base Vector

Similarly the four interrupt vector addresses for use with the serial lines must be contiguous. The base interrupt vector for the DL lines is selectable in the range 0 to 340 octal. Note that bits [0:4] of the interrupt base address are always set to 0. The default base address is 300.

# Note:- The vectors for these serial lines will occupy a range of 30 octal if the onboard console is enabled and 40 octal if it is disabled.

# 3-6. Serial Line Baud Rate.

The baud rate for each of the four serial lines may be individually configured to any of 300, 600, 1200, 2400, 4800, 9600, 19200 or 38400 baud. When this option is selected, the user enters the number of the required baud rate as displayed on the screen followed by  $\langle CR \rangle$ .

# 7. On-Board Console

If this option is selected the CSR address for SLU3 is 177560 octal and the vector is 60 octal irrespective of the addresses assigned to the other serial lines. When using on-board console the base address for the DL module must be either 176500 octal, 176540 octal or 177500 octal . A warning is given on saving the setup if one of the above is not selected as the base address due to the configuration not being DLV11J compatible.

# 8. Line Time Clock

The on-board clock source may be configured as a 50, 60 or 800 Hz clock or the bus signal BEVENT can be used. The source is selected by entering the required option number as displayed on the screen followed by  $\langle CR \rangle$ .

# 9. On-Board BootPROM

This option allows the BootPROM to be disabled. If this option is used the hardware setup is still loaded from the FLASH EPROM when the system is initialised. The setup bypass switch SW1 must be used to regain access to the on-board FLASH EPROM to allow any further changes to be made to the on-board firmware. Note that the PCR resident at 177520 octal is also disabled if the on board BootPROM is disabled.

#### 10. Power-up Mode

There are four power-up modes which can be selected by entering one of the options from table 5-2 below.

# TABLE 5-2 POWER-UP MODE OPTIONS

- 0 Trap through location 24 octal

- 1 Enter console ODT

- 2 Power-up to location 173000 octal

- 3 Power-up to the user specified power-up address

# 11. Power-up Address

The user may configure the most significant 7 bits of the power-up address. In order for this address to apply, power-up mode option 3 must be selected. The address is entered as a sixteen bit octal number followed by <CR>. Note that the MMU is turned off on power-up and as a result the SBC M1 module has a sixteen bit address range.

# 12. On-Board Parity CSR Address

The parity CSR on the SBC M11 module allows program control of certain memory parity functions and contains diagnostic information if a parity error occurs in the on-board memory system. The on-board memory CSR may be assigned one of the word addresses in the range 172100 octal to 172136 octal which allows for sixteen memory CSR's. Since the on-board memory starts at location 0, the CSR is assigned as default the first address in this range. Additional Q-bus memory cards will have their parity CSR's in ascending order following their base address.

The user is prompted for an address in the range indicated above and the address is entered as a sixteen bit octal number followed by <CR>.

# 13. Halt Option

Indicates how a HALT instruction is executed in KERNEL mode. If clear the processor enters console ODT. If set the processor traps through location 4 and sets bit 7 of the CPU error register. This is selected by entering the required option as displayed on the screen followed by <CR>.

# **<u>14.</u>** On-board Parity Enable

This option allows the generation of parity interrupts and aborts to be enabled/disabled. If disabled, the error is still logged in the parity CSR. The disabling of aborts is not recommended except for special applications.

# 15. Console Halt Enable

This option allows the user to configure whether or not the system will halt on receipt of a break from the console.

# **16.** Memory Timeout Select

This option allows selection of memory timeout periods of 12.5us or 25 us. It should be set to 25 us if older Q-Bus devices cause bus timeouts at 12.5 us.

#### The following lists the module's factory hardware configuration:

Serial Line Base address -17776500 octal 1). 2). Serial Line Vector address -300 octal. Serial Line Baud Rate -3). 9600. Serial Line Baud Rate -4). 9600. Serial Line Baud Rate -9600. 5). 6). Serial Line Baud Rate -9600. 7). Onboard Console -Enabled. 8). Line Time Clock Frequency -60Hz. 9). BootPROM -Enabled. Power-up Mode-173000 octal. 10). User Power up Address -11) 000000 Parity CSR address -12). 17772100 octal. Halt option -13) Cleared On Board Parity -14) Enabled Console Halt Enable -Enabled 15) 16) Memory Timeout Select -24 us

#### 5.5.5.2 Modify Software Setup

This allows the configuration of power-up action, console type, diagnostics run at power-up, and non-standard device CSR assignments. When the software setups are modified they take effect immediately, however a save operation must be implemented to retain them. The displayed menu with the factory configured option settings is as shown below:

|   | BOOT OPTION                    |           |

|---|--------------------------------|-----------|

| 2 | AUTOBOOT LOOP/EXIT OPTION      | .Loop     |

| 3 | CONSOLE TYPE                   | .DUMB     |

| 4 | DISABLE ALL DIAGNOSTICS        | .NO       |

| 5 | ENABLE EXTENDED TESTING        | .NO       |

|   | ENABLE LINE TIME CLOCK         |           |

| 7 | ALLOW NON-STANDARD BOOT BLOCK. | .Disabled |

|   |                                |           |

To select an option, enter the required number followed by <CR>.

# 1. Boot Option

This allows the user to determine whether the SBC M1 will power-up in dialogue mode where the main menu is displayed or attempt to boot from devices listed in the auto-boot configuration table (refer to section 5.5.5.5).

#### 2. Console Type

With this option the user may determine the type of terminal with which the system is to interact. If ANSI mode is selected (Option 1) the bootstrap will use ANSI escape sequences for cursor positioning. Option 0 should be selected if the console terminal does not support ANSI escape sequences or is a hard-copy terminal. Factory default is dumb mode.

#### Note : VT100 terminals support ANSI escape sequences.

# 3. Disable All Diagnostics

Board diagnostics are executed at power-up. These diagnostics are intended to provide confidence in the operation of the board and are not for fault isolation.

#### The following tests are performed

- Low memory 0-64 K.

- Existence and operation of I/O page registers.

- Basic CPU functionality All GP registers etc.

- BootPROM checksums and PCR.

- MMU.

- Console SLU.

- Memory parity register.

- Basic memory test.

If the user requires no diagnostic tests to be performed the option "1" should be selected followed by <CR>. However, it is recommended that these tests be kept enabled.

# 4. Enable Extended Testing

When selected, this option provides an extended memory test, which is run in conjunction with the standard diagnostics. This test verifies the integrity of all available system memory and the existence and operation of the fixed I/O page registers. (Refer to Table 5-3).

SBC M1 USER GUIDE

| Address             | Register                                   |

|---------------------|--------------------------------------------|

| 172200 to<br>172376 | Page address and page descriptor registers |

| 172516              | MMR3                                       |

| 173000 to<br>173776 | BootPROMs                                  |

| 177546              | Line time clock                            |

| 177560 to<br>177566 | Console registers                          |

| 177520              | Page control register                      |

| 177572 to<br>177576 | Memory management registers                |

| 177600 to<br>177676 | Page address and page descriptor registers |

| 177744              | Memory system error register               |

| 177746              | Cache control register                     |

| 177750              | Maintenance register                       |

| 177752              | HIT/MISS register                          |

| 177766              | CPU Error register                         |

| 177772              | Program interrupt request                  |

| 177776              | Processor status word                      |

# TABLE 5-3 FIXED I/O PAGE REGISTERS

# 5. Enable Line Time Clock

This option allows the user to enable the line time clock on the SBC M1. The line time clock interrupts at PR6 while the bootstrap executes at PR7, therefore all LTC interrupts are ignored. When control is relinquished to the primary bootblock it must cater for LTC interrupts either by executing at or above PR6, disabling the LTC or providing an interrupt service routine at the LTC vector 100 octal.

# Note: DEC operating systems primary bootstraps execute at PR0, therefore the LTC must be disabled on booting these systems.

#### 6. Allow Non-standard Boot Block

When the standard boot block option is enabled, primary code is checked to ensure that the first instruction is NOP (240 octal). If this test fails an error message is displayed to indicate that the media cannot be booted. If the non-standard boot block option (option 1) is selected, this test is dispensed with and control is passed unconditionally to the primary bootstrap.

# 5.5.5.3 Save Modified Setup

This option must be selected in order to save any hardware or software modifications to the board. When selected, a message "SAVE IN PROGRESS PLEASE WAIT" is displayed after which control is returned to the setup menu. Software alterations take effect immediately. Modifications to hardware only take effect if the module has been powered-up again with SW1 in position 'B'.

# 5.5.5.4 Initialise To Factory Setup

The SBC M1 Programmable Hardware and Software configuration is restored to factory setting when this option is invoked. In order for this configuration to be retained on power-up it must be saved by selecting option 3 from the "SETUP MENU".

# 5.5.5.5 Configure Autoboot List

The user may configure a list of up to six devices in the order in which it is desired to attempt to boot them. If the list has not been configured all entries are shown as unused and the user is prompted to modify the list. The configuration menu is as shown below in table 5-4.

# TABLE 5-4 AUTOBOOT CONFIGURATION

| DE | VICE   | LOWEST UNIT | HIGHEST UNIT |

|----|--------|-------------|--------------|

| 1  | DU     | 0           | 10           |

| 2  | DL     | 0           | 2            |

| 3  | Unused |             |              |

| 4  | Unused |             |              |

| 5  | Unused |             |              |

| 6  | Unused |             |              |

In order to delete a device from the list it should be selected and <CR> alone entered as the response to the prompt for the device mnemonic.

Note : There is a NL mnemonic which may be used as the first device to provide a delay for some peripherals to come online after power up. The use of this device is not normally necessary. If needed it should be configured with a highest unit number of 0. The lowest unit number should be configured to specify the delay required. A unit number of 1 provides approximately 0.75 seconds delay (dependent on clock frequency) and a unit number of 30 provides 24 \* 0.75 seconds delay (Note unit numbers are octal). It may also be useful to use this device to allow users to enter <CTRL/C> before a real auto-boot is entered.

#### 5.5.5.6 Configure Device Translations

The boot software may be configured to allow for non-standard CSR addresses by use of the device translation table. This table contains a list by mnemonic of device types with the lowest and highest unit numbers to which the entry applies and the corresponding CSR address. When booting the software initially scans this table and if an entry is found corresponding to the device from which it is attempting to boot the CSR in the table is used, otherwise the default standard CSR is used. Only 6 entries are allowed in the table and the menu is similar to the auto-boot configuration.

| TABLE 5-5 DEVICE TRANSLATION TABLE |              |        |  |  |

|------------------------------------|--------------|--------|--|--|

| LOWEST UNIT                        | HIGHEST UNIT | CSR    |  |  |

| 0                                  | 10           | 172150 |  |  |

| 0                                  | 2            | 174400 |  |  |

|                                    |              |        |  |  |

|                                    |              |        |  |  |

|                                    |              |        |  |  |

|                                    |              |        |  |  |

|                                    | 0            | 0 10   |  |  |

To select a specific device, enter the appropriate device number followed by <CR>.To exit from this option, enter <CR>.

Note : The bootstrap device table contains an entry for the maximum number of devices per controller, if no entries for a mnemonic exist in the device translation table the unit number entered by a user is validated to be in the range 0 to n-1. If an entry exists in the device translation table for the unit number entered it is validated against the range given in the table entry.

As each device translation table entry is assumed to correspond to one controller with one CSR the lowest unit number in the table entry is subtracted from the unit number entered to give the device number within the controller before it is passed to the device specific bootstrap. The one slight exception to the above rule is that the standard bootstrap table supports 4 MS units as there are 4 sequentially assigned fixed CSRs in the I/O page.

#### 5.5.5.7 Exit Setup

Select this option to return to main menu.

5.5.6 Test - Enter A Continuous Test Mode.

In this mode it is assumed that the SBC M1 module is in a valid hardware configuration. Diagnostics are continuously executed until <CTRL C> is entered by the user. At this point control is returned to the main menu on completion of the current diagnostic.

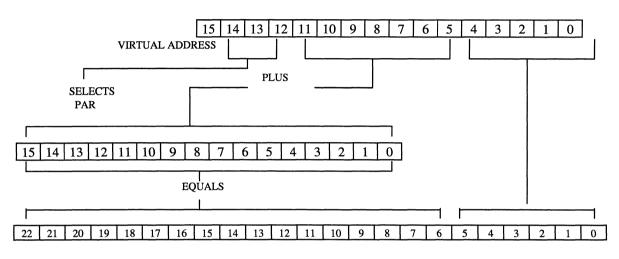

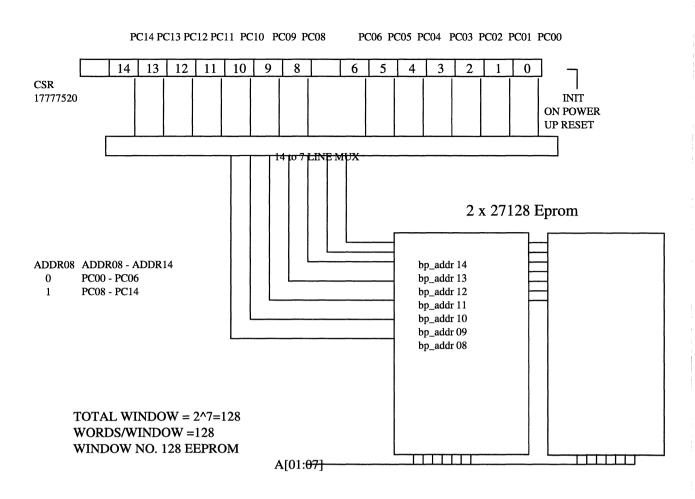

## 5.6 BOOTPROM MAPPING

The FLASH EPROM is mapped using a page control register at location 17777520 octal. The PCR functions as two separate halves. The low byte is used as bits 8 to 14 of the EPROM address for addresses in the range 173000 to 173377 and the high byte as bits 8 to 14 of the EPROM address for addresses in the range 173400 to 173777.

Bits 8 to 14 of the PCR provide a total of 128 windows of 256 bytes each. Of these 128 (0-127) are used to map the EPROM and one (127) is used to map the setup data. The setup data is byte wide with the least significant byte being valid. This provides 128 bytes of EPROM and 31.75 K bytes of BootPROM. The first 8 bytes of setup data are reserved for hardware configuration. These bytes are read by the SBC M1 power-up circuitry unless the configuration bypass switch (SW1) is on. The definition of these bytes is hardware defined and they must contain a valid configuration.

## 5.7 USAGE OF BOOTPROM WINDOWS

Windows 0 and 1 are allocated for use by the code, which relocates the remaining code to RAM. These two windows relocate the contents of all of the remaining windows. The format of the remaining windows is such that the first word contains the load address i.e. the address at which the code is to be loaded. In order to provide a degree of testability the last 2 bytes of each window in the BootPROMs are reserved locations for diagnostic purposes. Byte 377 octal is the window number, this is used to test the functioning of the PCR. Byte 376 octal is an exclusive-OR checksum to validate the integrity of the EPROMS.

As the setup data is mapped to the low byte only, the checksum is in byte 376 octal as normal and no block number is provided. The overheads in the windows mean that the effective window size is 252 bytes. As two windows are allocated for code relocation to RAM the effective upper limit on the actual code size for the main code is 124x252 = 31248 bytes or just over 30 Kb. The physically resident setup data and Boot Code are in one 29F010 device but the Boot Code is in hardware protected sectors and appears to be 16 Bits wide to the software.

## 5.8 CODE OVERVIEW

The operation of the boot software proceeds as follows:

1). A test is performed on low memory.

2). The basic trap vectors are set up.

3). 16 bit memory space is tested.

4). The EPROM code is transferred to RAM.

5). Control is transferred to the code in RAM.

6). If boot is selected the requested bootstrap is searched for and if found, it is invoked.

7). If the boot block is valid or the non standard boot block format is enabled control is passed to the boot block.

This method of operation requires that the first one or two windows of the Boot Code contain code specifically written for execution in those windows to perform basic testing and relocate the remaining code. The remaining code is transferred to RAM at address 10000 and control is transferred to this. The setup data cannot be relocated in the same manner as the remaining code as only the low byte is valid and it has a different format. It is therefore specifically unpacked into a formatted area of RAM.

## **5.9 DEVELOPMENT UTILITIES**

A utility program is used to process a number of RT11 load-able absolute binary files to a HEX ASCII PROM file. The boot code is developed and tested in RAM under RT11. It is transferred to VAX/VMS by using the VMS EXCHANGE utility. The Mentec PROM FORMAT utility is then used to format the code. This utility program is written in VAX FORTRAN.

## **6. SYSTEM ARCHITECTURE**

#### 6.1 INTRODUCTION

This chapter describes the architecture of the SBC M1 with special reference to how the M1 interfaces with other system components.

#### 6.2 PROCESSOR MODES

There are three processor modes - Kernel, Supervisor and User. Each one has a different degree of control over the operation of the M1. They are chosen by setting bits 14 and 15 in the Processor Status Word (PSW). The existence of different processor modes allows security to be implemented in a multi-programming environment. For example, WAIT, RESET and HALT statements can only be executed in Kernel mode. Certain bits in the PSW may only be written to in Kernel mode. (Refer to section 6.4.1.1). Thus, nonprivileged users are kept from having too much control over the system.

#### **6.3 GENERAL PURPOSE REGISTERS**

The M1 has sixteen general purpose registers. These registers do not reside in the address space. Twelve of the registers are true general purpose registers. These are arranged as two sets, R0 to R5 and R0' to R5'. Only one of these sets is available to the user at any one time. The choice is made by setting bit 11 in the Processor Status Word. These registers may be used as accumulators or as base or index registers for memory addressing. The existence of two sets means that fast context switching is possible. There are three registers used as stack pointers - one for each of the operating modes. Thus there is a kernel stack pointer (KSP), a supervisor stack pointer (SSP) and a user stack pointer (USP). The mode is chosen by setting bits 14,15 in the PSW and the stack pointer is then referred to as register R6.

The stack moves downwards in memory when items are pushed on to it. The stacks can be used to provide linkage information when the processor modes are switched. The M1 provides hardware stack protection for the Kernel stack. Yellow and Red stack traps are described in table 6-3. The final register is the program counter (instruction pointer). It is incremented by two every time a word is fetched from memory. It is accessed as register R7. R7 may also be used as a base or index registers for addressing. This has the effect of extending the power of the addressing modes.

#### 6.4 SPECIAL PUROSE REGISTERS

As well as the general purpose registers the SBC M1 module implements a set of special purpose registers. These registers are used by the user to set some of the operational features of the system or by the system to provide status information to the user.

There are four sub-divisions of special purpose registers. These are the internal registers, System registers, External Registers and Power-up Register. They all differ from the General Purpose Registers in that they have addresses in the 4K words of memory reserved for I/O addresses (the I/O Page).

#### 6.4.1 Internal Registers

The Internal Registers are so named because they are implemented in the logic of the M1 itself. Unlike the General Purpose Registers, however, the user accesses them by addressing locations in the I/O page. Table 6-1 lists the internal registers. The Processor Status Word and CPU Error Register are described here. Descriptions of the other registers are reserved until the relevant sections of the architecture are being described.

| Abbrv. | Register                          | Address   |

|--------|-----------------------------------|-----------|

| PSW    | Processor Status Word             | 177777768 |

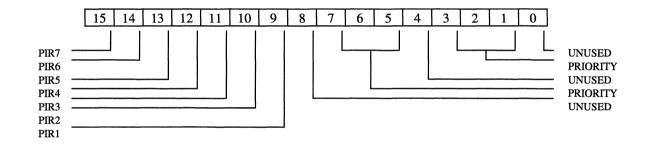

| PIRQ   | Program Interupt Request Register | 177777728 |

| CPUERR | CPU Error Register                | 177777668 |

| HMR    | Hit /Miss Register                | 177777528 |

| -      | Memory Management Registers       | *         |

| -      | Floating Point Registers          | **        |

#### TABLE 6-1INTERNAL REGISTERS

\* Refer to Appendix C.

\*\* Floating Point Registers do not have addresses they are referenced using special instructions.

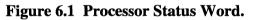

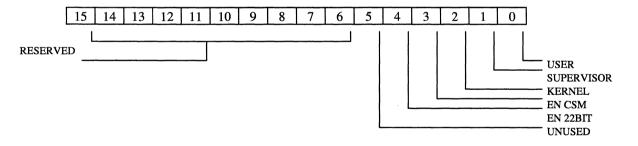

## 6.4.1.1 Processor Status Word

The Processor Status Word (PSW) contains information about current processor staus. It also contains information about the result of the current instruction. By writing to it the user can provide the M1 with information about how it is to run. Figure 6-1 gives a schematic of the PSW. Table 6-2 explains each bit in detail.

| Bit   | Name                      | Description                                                              |                                                                                                                   |  |

|-------|---------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

| 15:14 | Current Mode<br>(R/W)     | The Status Of these bits indicate the current processor mode as follows: |                                                                                                                   |  |

|       | $(\mathbf{W},\mathbf{W})$ | Bits                                                                     | Mode                                                                                                              |  |

|       |                           | 15 14                                                                    | Mode                                                                                                              |  |

|       |                           | 0 0                                                                      | Kernel                                                                                                            |  |

|       |                           | 0 1                                                                      | Supervisor                                                                                                        |  |

|       |                           | 1 0                                                                      | N/A                                                                                                               |  |

|       |                           | 1 1                                                                      | User                                                                                                              |  |

| 13:12 | Previous Mode<br>(R/W)    |                                                                          | e the previous processor<br>e same meanings as bits                                                               |  |

| 11    | Register Set              | If Bit 11 is 0 then                                                      | R0-R5 are used.                                                                                                   |  |

|       | (R/W)                     | If Bit 11 is 1 then                                                      | R0'-R5' are used.                                                                                                 |  |

| 10:09 | Unused<br>(Read Only)     | These bits are unu                                                       | used and read back as 0's                                                                                         |  |

| 08    | Reserved                  |                                                                          |                                                                                                                   |  |

| 07:05 | Priority                  | with bit 5 as the L interrupt needs a p                                  | d as a 3 bit binary numbe<br>east Significant Bit. An<br>priority greater than this<br>can interupt the processor |  |

#### TABLE 6-2 PROCESSOR STATUS WORD

Register set

Unused

Reserved

Trace

**Priority**

| 04       Trace Trap       If this bit is set then the processor traps to location 14 at the end of the instruction currently being executed. The bit may not be set directly - it must be set via an RTI or RTT instruction.         03       N       This bit is set if the result of the previous operation was negative.         02       Z       This bit is set if the result of the previous operation was 0.         01       V       This bit is set if the previous operation resulted in an arithmetic overflow.         00       C       This bit is set if the Most Significant Bit of result of the previous operation was carried | Bit               | Name       | Description                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| (Read Only)operation was negative.02ZThis bit is set if the result of the previous<br>operation was 0.01VThis bit is set if the previous operation<br>(Read Only)01CThis bit is set if the Most Significant Bit of                                                                                                                                                                                                                                                                                                                                                                                                                              | 04                | Trace Trap | to location 14 at the end of the instruction<br>currently being executed. The bit may not<br>be set directly - it must be set via an RTI or |

| (Read Only)operation was 0.01VThis bit is set if the previous operation<br>(Read Only)00CThis bit is set if the Most Significant Bit of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 03                | - · · ·    | -                                                                                                                                           |

| <ul> <li>(Read Only) resulted in an arithmetic overflow.</li> <li>00 C This bit is set if the Most Significant Bit of</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 02                |            | -                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 01                | •          | <b>A A</b>                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00                | •          |                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | it Mode  <br>Iode |            | Zero<br>Negati                                                                                                                              |

## TABLE 6-2 Contd. PROCESSOR STAUS WORD

6-4

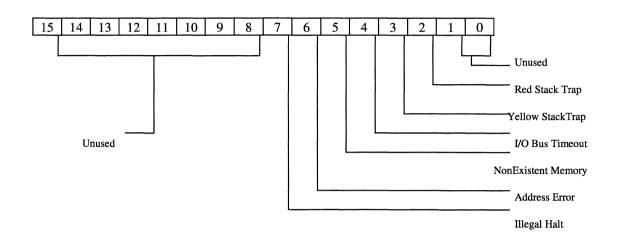

#### 6.4.1.2 The CPU Error Register

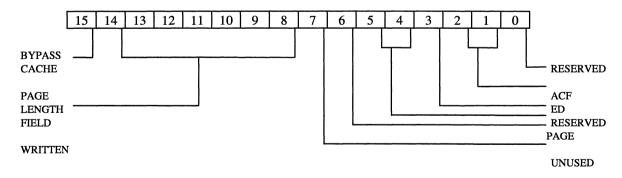

The M1 traps to location 4 when a CPU error occurs. The CPU error register is used to log the nature of the error. Only bits [7:2] of the CPU error register are used all of the other bits return 0's when read. The CPU error register is summarised in Table 6-3 and Figure 6.2.

Figure 6.2 CPU Error Register.

| Bit   | Name                       | Description                                                                                                                                                                                                                                          |

|-------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:08 | Unused                     | Return 0's when read.                                                                                                                                                                                                                                |

| 07    | Illegal<br>HALT            | A HALT instruction is illegal if<br>executed in user or supervisor mode. A trap 4 will<br>occur and this bit will be set. A HALT will<br>cause this sequence of events in all three modes<br>if bit 3 in the power-up configuration register is set. |

| 06    | Address<br>Error           | A trap to 4 will occur if an attempt is made to<br>address a word with an odd address or if an attempt<br>is made to fetch an address from an internal<br>register. Bit 6 in the CPU error register is set in<br>these instances.                    |

| 05    | Non-<br>Existent<br>Memory | An attempted access to a memory<br>location which does not exist will<br>cause a trap to 4. Bit 5 of the CPU<br>Error Register is set. If the location is in the I/O page the<br>bit 4 is set instead.                                               |

| 04    | I/O Bus<br>Timeout         | If a non-existent location is in<br>the I/O page then bit 6 is set.                                                                                                                                                                                  |

| 03    | Yellow<br>Stack Trap       | Set when a yellow zone stack trap<br>occurs i.e. when a Kernel stack<br>reference has a virtual address of less than octal 400                                                                                                                       |

| 02    | Red<br>Stack Trap          | If a Kernel stack abort occurrs<br>during an interrupt, trap or abort<br>sequence then a red stack trap is flagged<br>and locations 0 and 2 are used as an emergency<br>stack, vectoring through location 4.                                         |

| 01:00 | Unused                     | Return 0's when read.                                                                                                                                                                                                                                |

## TABLE 6-3CPU ERROR REGISTER

### 6.4.2 System Registers

The registers classed as system registers have addresses in the range 17777740<sup>8</sup> to 1777750<sup>8</sup>. The SBC M1 has three system registers; the Maintenance Register, the Memory Error Register, and the Cache Control Register. Table 6-4 gives the addresses of these registers.

The Cache Control Register, the Memory Error Register and Hit Miss Register are implemented for compatibility and have no effect on system operation and are not described further.

Some operating systems check for the existence of the Maintenance Register and this is the main reason for its inclusion. The Maintenance Register is described in section 6.4.2.1.

### 6.4.2.1 The Maintenance Register

The Maintenance Register (MR) has the same bit definitions as the Power-up and Configuration Register. The latter is equivalent to the DCJ11's external register and is described in section 6.4.4.

| TABLE 6-4        | SYSTEM REGISTERS                               |                                                                            |

|------------------|------------------------------------------------|----------------------------------------------------------------------------|

| Register         | Address                                        |                                                                            |

| Maintenance Reg  | ister 17777508                                 |                                                                            |

| Memory Error Ro  | egister 177777448                              |                                                                            |

| Cache Control Re | gister 177777468                               |                                                                            |

|                  | Register<br>Maintenance Reg<br>Memory Error Re | RegisterAddressMaintenance Register177777508Memory Error Register177777448 |

### 6.4.3 The External Registers

These are the Line-Time Clock Register, The Parity Control and Status Register (PCSR) and the Page Control Register (PCR). Table 6-5 lists the external registers.

| Abbrv. | Register                            | Address   |

|--------|-------------------------------------|-----------|

| LTC    | Line-Time Clock Register            | 177775468 |

| PCSR   | Parity Control and Status Register. | 177721XX8 |

| PCR    | Page Control Register               | 177775208 |

## TABLE 6-5EXTERNAL REGISTERS

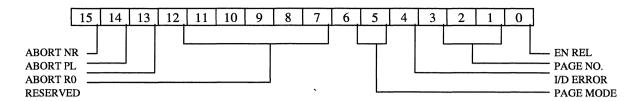

## 6.4.4 The Power-Up Register

As part of the M1 power-up diagnostic routine it reads the Power-Up register using a unique instruction. Table 6-6 describes the information relayed to the

|       | IADLE 0-0         | FOWER-OF REGISTER                                                                                                                                      |

|-------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Name              | Description                                                                                                                                            |

| 15:09 | Boot<br>Address   | These bits represent the address from which the M1 is to start executing boot code, bits 00:08 of the address are always logic zero.                   |

| 08    | Unused            | This bit is unused on the M1                                                                                                                           |

| 07    | -                 | Reserved for future use.                                                                                                                               |

| 06:04 | Processor<br>Type | These bits are read by operating<br>systems to determine the processor<br>type. (Maintenance Register)                                                 |

| 03    | Halt<br>Option    | This bit determines the action to be<br>taken by the M1 on receipt of a<br>halt instruction :<br>0 - Enter Console ODT<br>1 - Trap Through Location 4. |

## TABLE 6-6POWER-UP REGISTER

| Bit | Name     | Description                                 |

|-----|----------|---------------------------------------------|

| 2:1 | Power-up | The M1 uses these bits on                   |

|     | mode     | power-up to determine which of              |

|     |          | the following actions is to be taken        |

|     |          | Bits: Mode                                  |

|     |          | 2 1                                         |

|     |          |                                             |

|     |          | 00 - Trap through location 248              |

|     |          | 01 - Enter console ODT                      |

|     |          | 10 - Power-up to 1730008                    |

|     |          | 1 1 - Power-up to user specified            |

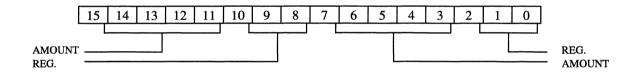

|     |          | address bits 15:09                          |